# SERVICE MANUAL

Friden

ELECTRONIC COMPUTER

# Model 21 Processor

Friden, Inc. SAN LEANDRO, CALIF

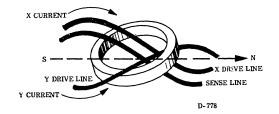

# SERVICE MANUAL

# MODEL 20/21 PROCESSOR

# SYSTEM TEN

Publication No. 43-0302-000 Sections 1-7, 9, 12 & Reference 43-0302-100 Sections 8, 10, 11 & 14-17 43-0302-200 Section 13 43-0302-300

January 1975

If additional copies of this manual are required, please order by publication no. on Form No. 5234 from:

Singer Business Machines Publications Distribution P.O. Box 2100 Sparks, Nevada 89431

PRINTED IN U.S.A.

### TABLE OF CONTENTS

# SECTION 1, INTRODUCTION

| 1-0.0     | GENERAL INTRODUCTION                                                                                                                           | 1-3                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 1-1.0     | EQUIPMENT DESCRIPTION<br>1-1.1 MAIN MEMORY<br>1-1.2 ARITHMETIC AND CONTROL UNIT<br>1-1.3 INPUT/OUTPUT CONTROLLERS<br>1-1.4 FILE ACCESS CHANNEL | 1-3<br>1-3<br>1-4<br>1-5<br>1-7                      |

| 1-2.0     | EQUIPMENT CONSTRUCTION<br>1-2.1 ACU MODULE<br>1-2.2 EXPANSION MODULES                                                                          | 1-7<br>1-7<br>1-7                                    |

| SECTION 2 | , MEMORY USE, INSTRUCTION AND DATA FORMATS                                                                                                     |                                                      |

| 2-1.0     | MEMORY USE, INSTRUCTION AND DATA FORMATS<br>2-1.1 CHARACTER USE AND STRUCTURE<br>2-1.2 DATA WORD AND FIELD<br>2-1.3 INSTRUCTION WORD           | 2-3<br>2-3<br>2-4<br>2-4                             |

| 2-2.0     | MEMORY ORGANIZATION<br>2-2.1 PROTECTED AREA<br>2-2.2 INDEX REGISTERS                                                                           | 2-6<br>2-7<br>2-10                                   |

| SECTION 3 | , ARITHMETIC & CONTROL UNIT                                                                                                                    |                                                      |

| 3-0.0     | ARITHMETIC & CONTROL UNIT                                                                                                                      | 3-3                                                  |

| 3-1.0     | DATA AND INSTRUCTION REGISTERS AND CONTROLS<br>3-1.1 TIMING AND SEQUENCING                                                                     | 3-3<br>3-6                                           |

| 3-2.0     | MEMORY ADDRESSING<br>3-2.1 ADDRESS ERROR<br>3-2.2 RELATIVE ADDRESSING<br>3-2.3 COMMON ADDRESSING<br>3-2.4 BASE ADDER                           | 3-14<br>3-14<br>3-15<br>3-15<br>3-15                 |

| 3-3.0     | LOGIC OPERATION<br>3-3.1 READ CONTROL (LOAD REQUEST)                                                                                           | 3-17<br>3-18                                         |

| 3-4.0     | HARDWARE FUNCTIONS<br>3-4.1 INTERRUPT<br>3-4.2 READ/WRITE<br>3-4.3 SWITCH<br>3-4.4 BEGIN<br>3-4.5 INDIRECT ADDRESS<br>3-4.6 INDEX              | 3-25<br>3-25<br>3-26<br>3-33<br>3-33<br>3-36<br>3-36 |

| SECTION 3 | , ARITHN | METIC & CONTROL UNIT                 | PAGE |

|-----------|----------|--------------------------------------|------|

| 3-5.0     | INSTRU   | CTION SET                            | 3-37 |

|           | 3-5.1    | READ                                 | 3-37 |

|           | 3-5.2    | WRITE                                | 3-42 |

|           | 3-5.3    | MOVE ADDRESS                         | 3-44 |

|           | 3-5.4    | ADD & SUBTRACT                       | 3-45 |

|           | 3-5.5    | DIVIDE                               | 3-49 |

|           | 3-5.6    | MULTIPLY                             | 3-53 |

|           | 3-5.7    | TRANSFER, MOVE NUMERIC, and EXCHANGE | 3-56 |

|           | 3-5.8    | BRANCH                               | 3-57 |

|           | 3-5.9    | EDIT                                 | 3-60 |

|           | 3-5.10   | FORM NUMERIC FIELD                   | 3-62 |

|           | 3-5.11   | COMPARE                              | 3-64 |

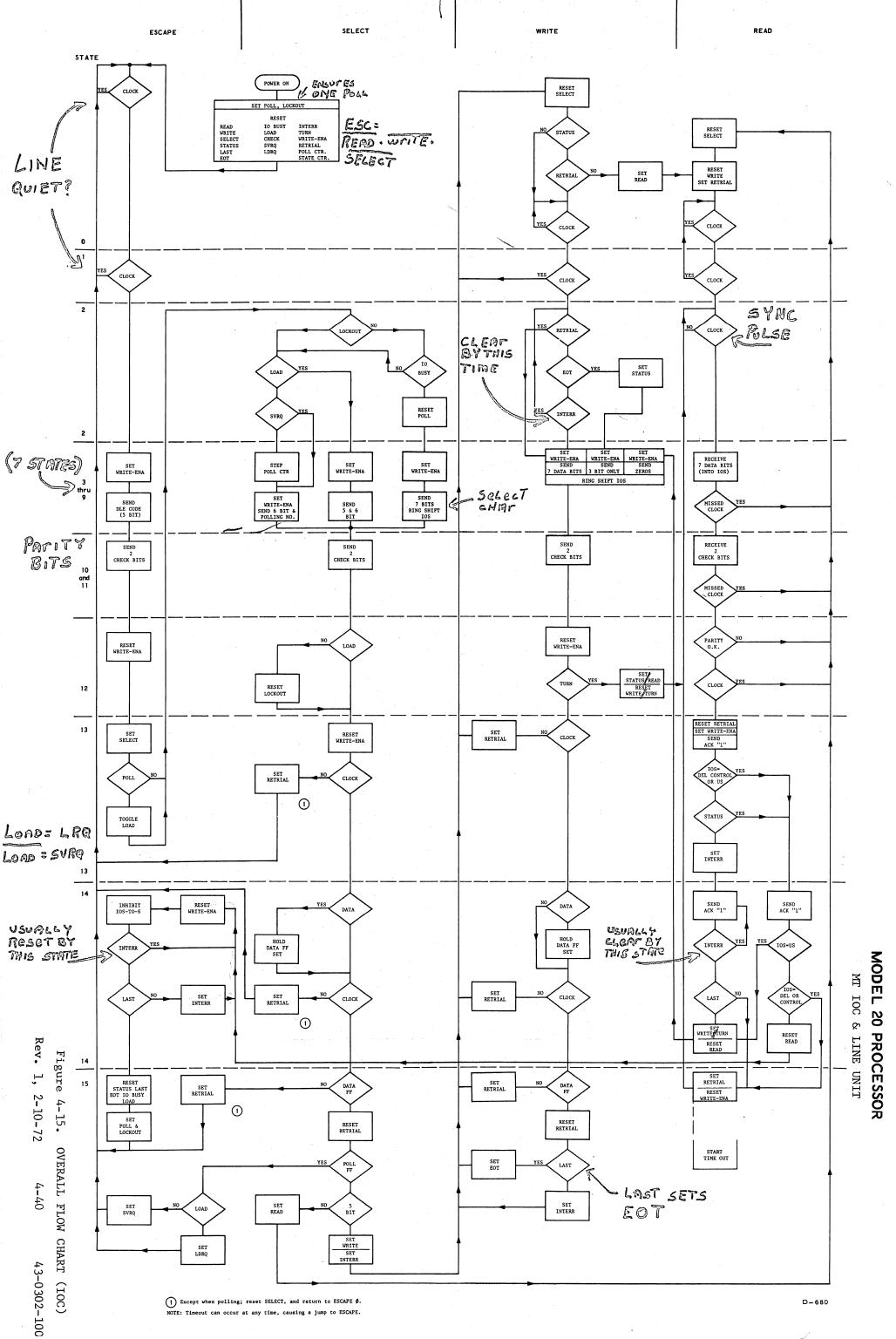

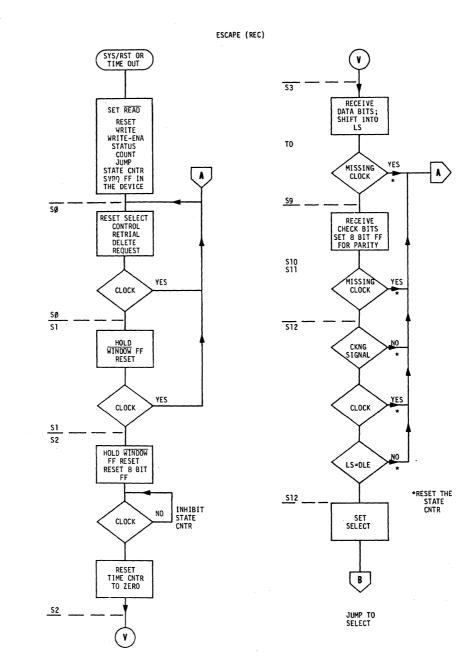

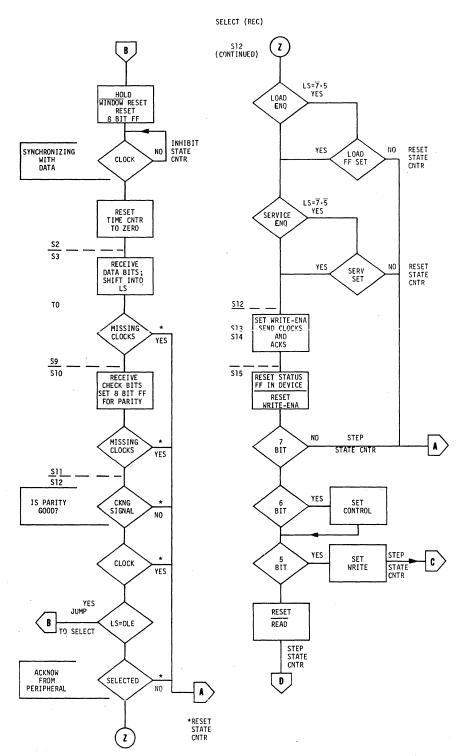

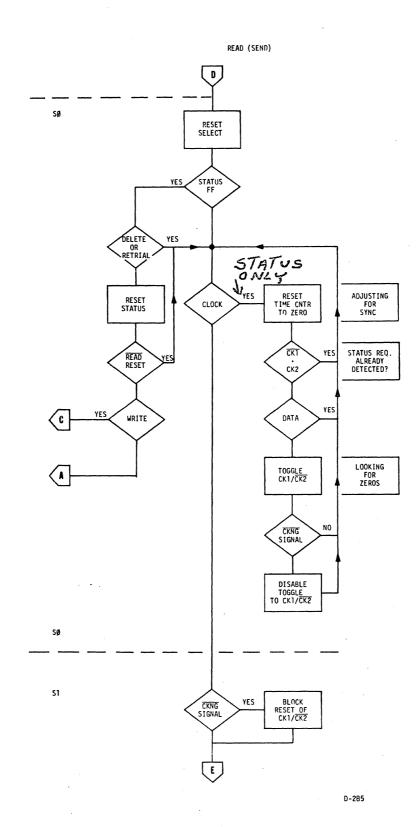

# SECTION 4, IOC/LINE UNIT

| 4-1.0 | INTRODUCTION                                                                                                                    | 4-3                             |

|-------|---------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

| 4-2.0 | DATA FORMAT<br>4-2.1 DATA TRANSFER                                                                                              | 4-4<br>4-5                      |

| 4-3.0 | POLLING & SELECTION<br>4-3.1 POLL COUNTER<br>4-3.2 RETRIAL<br>4-3.3 TIMEOUT<br>4-3.4 LOCKOUT                                    | 4-6<br>4-7<br>4-7<br>4-7<br>4-8 |

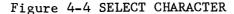

| 4-4.0 | IOC & LINE UNIT TIMING<br>4-4.1 TIME COUNTER<br>4-4.2 STATE COUNTER<br>4-4.3 SYNCHRONIZATION                                    | 4-9<br>4-9<br>4-11<br>4-11      |

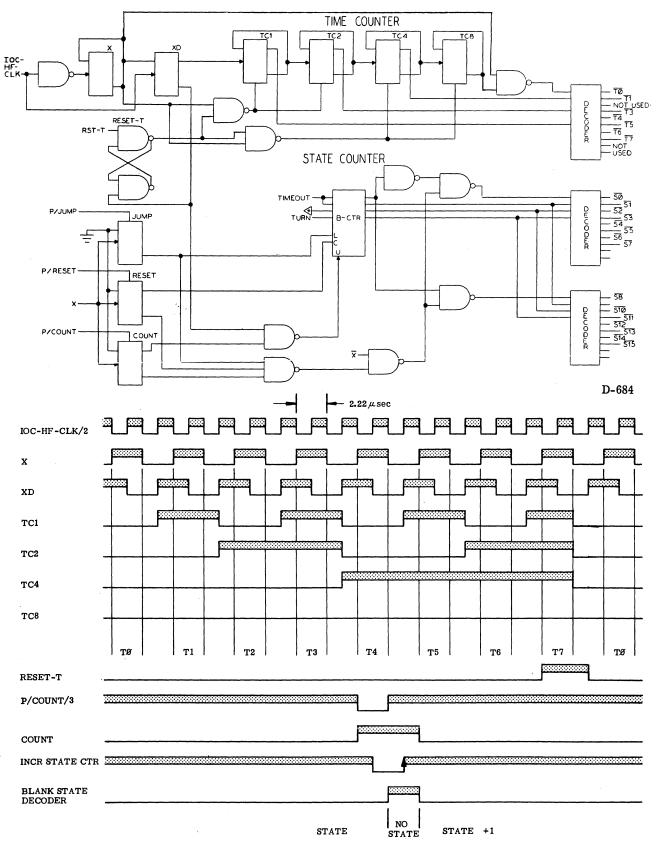

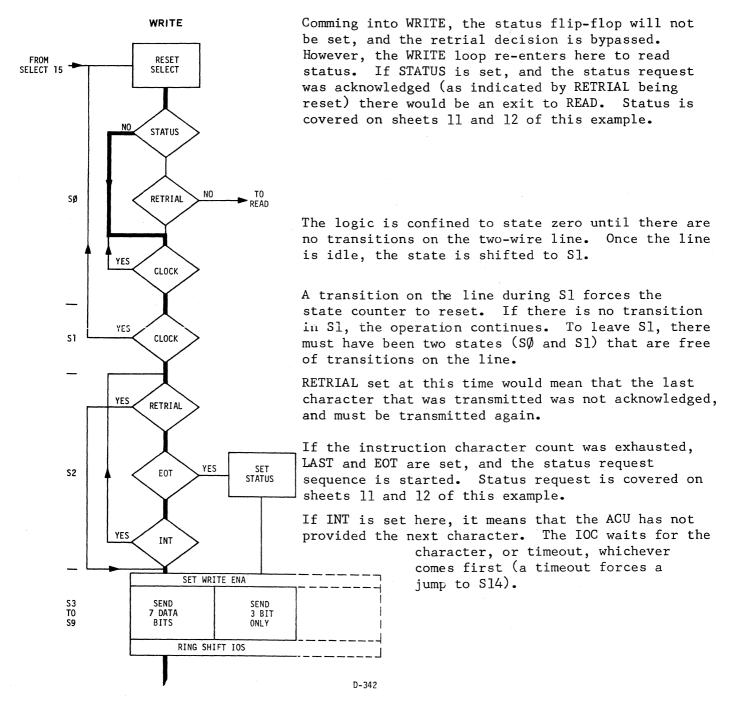

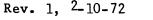

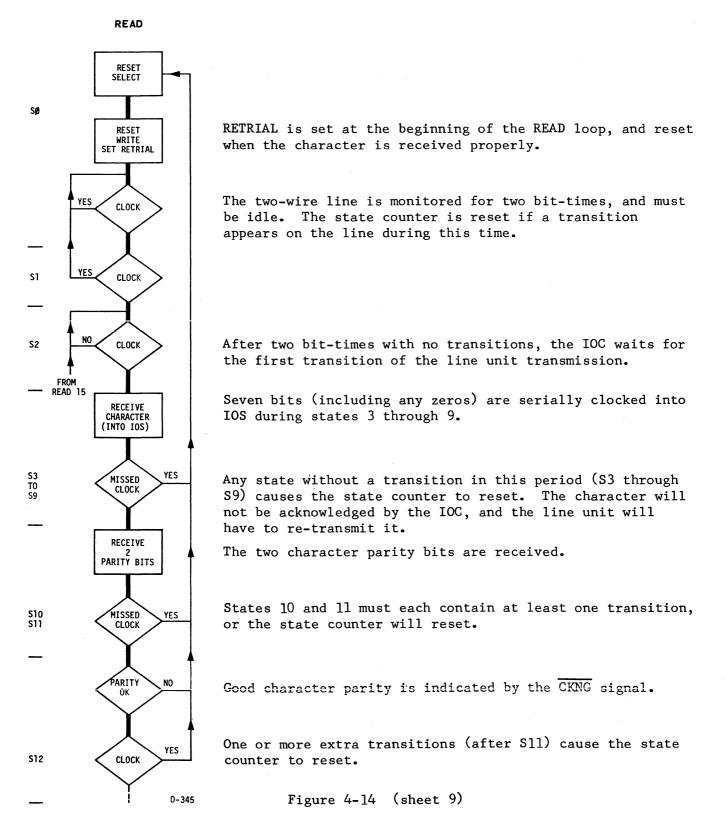

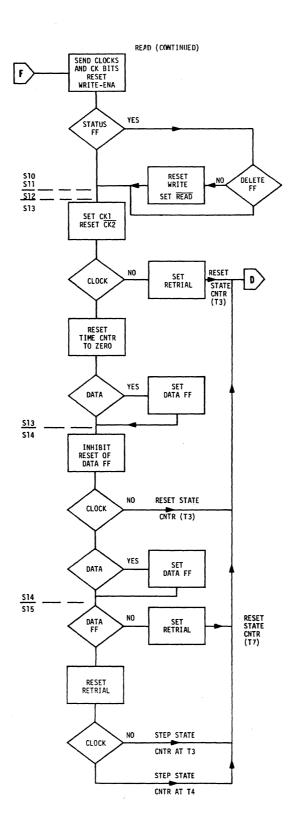

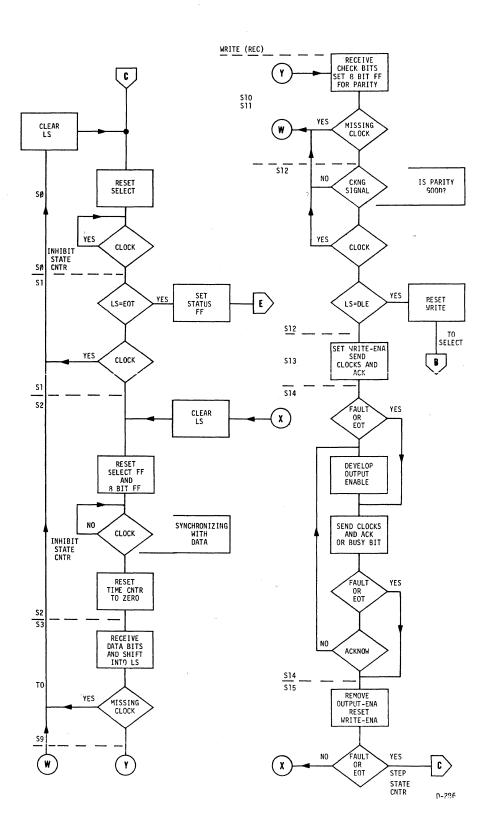

| 4-5.0 | READ/WRITE LOGIC<br>4-5.1 IOC WRITE & LINE UNIT READ LOGIC<br>4-5.2 IOC READ & LINE UNIT WRITE LOGIC<br>4-5.3 PARITY FLIP-FLOPS | 4-41<br>4-14<br>4-15<br>4-17    |

| 4-6.0 | STATUS                                                                                                                          | 4-17                            |

ii

SECTION 4, IOC/LINE UNIT (Continued)

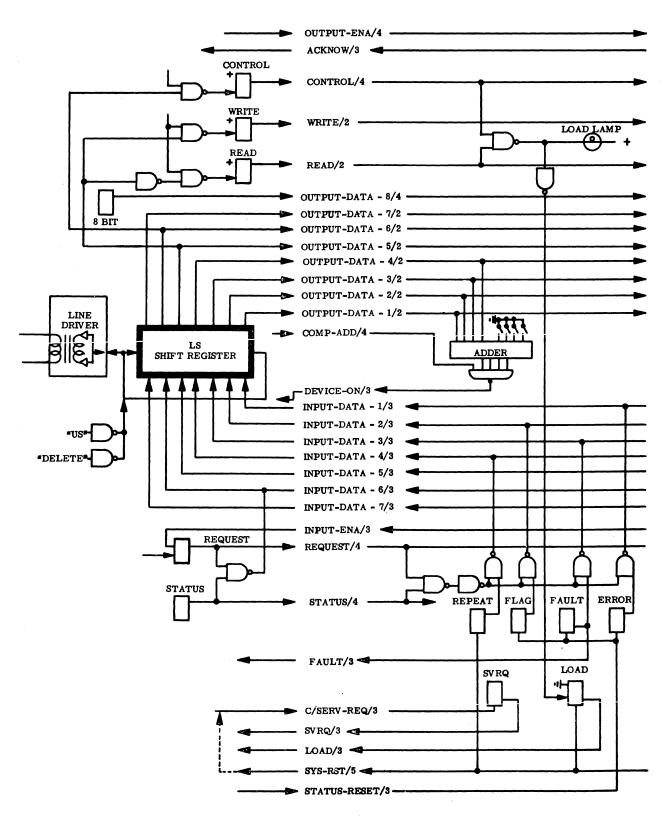

| 4-7.0  | INTERFACE SIGNALS<br>4-7.1 ACU/IOC SIGNALS<br>4-7.2 LINE UNIT/PERIPHERAL SIGNALS | <b>4-</b> 20<br><b>4-</b> 20<br><b>4-</b> 25 |

|--------|----------------------------------------------------------------------------------|----------------------------------------------|

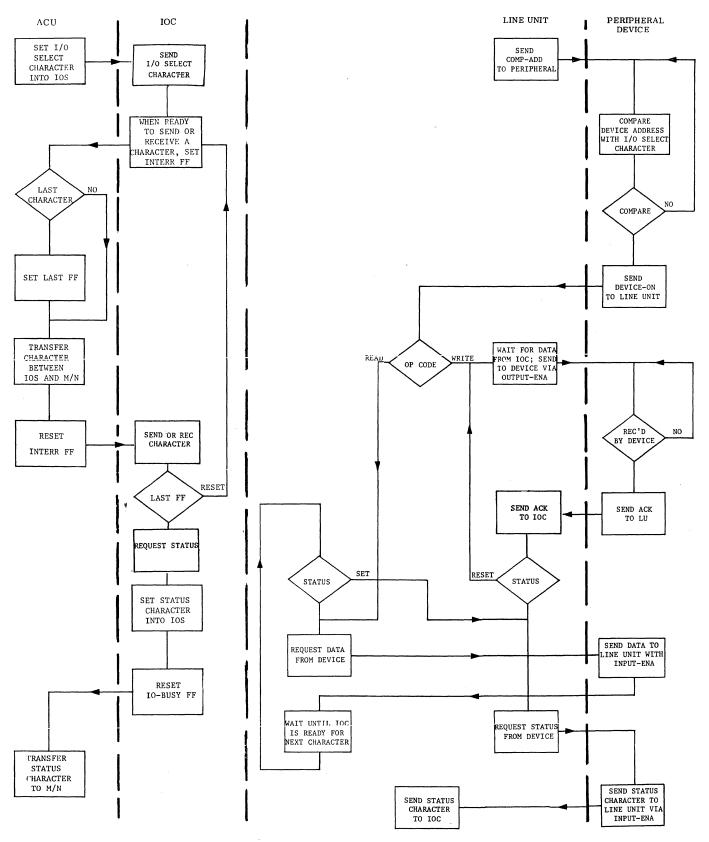

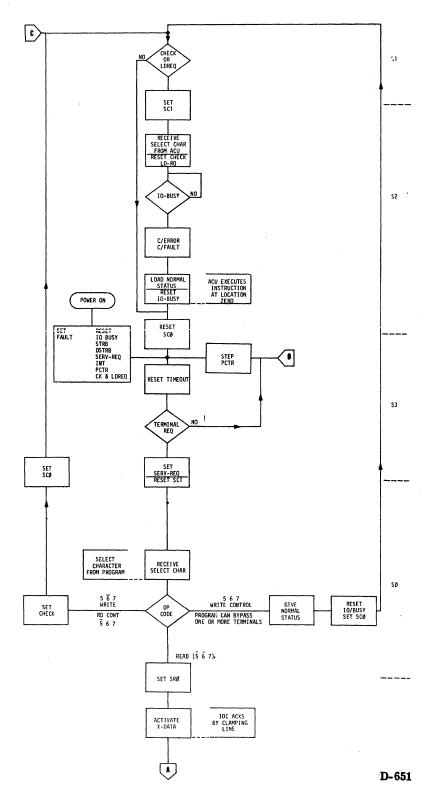

| 4-8.0  | SEQUENCE OF OPERATIONS<br>4-8.1 IOC OPERATION<br>4-8.2 LINE UNIT OPERATION       | 4-27<br>4-27<br>4-41                         |

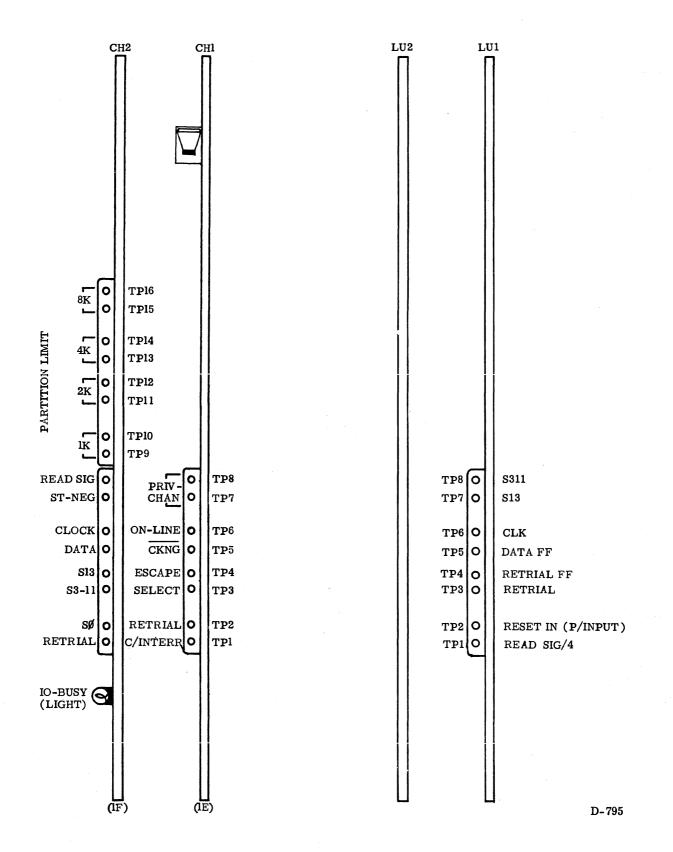

| 4-9.0  | TEST POINTS                                                                      | 4-49                                         |

| 4-10.0 | MT IOC/LINE UNIT GLOSSARY                                                        | 4-51                                         |

SECTION 5, MAIN MEMORY

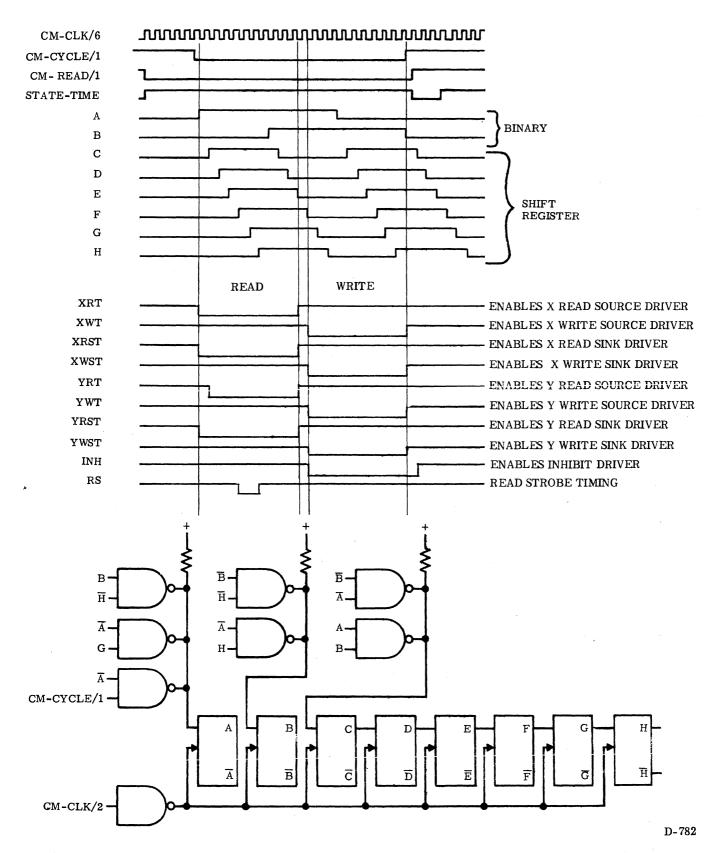

| 5-1.0 | GENERAL<br>5-1.1 CORE MEMORY CYCLES                                             | 5-3<br>5-4           |

|-------|---------------------------------------------------------------------------------|----------------------|

| 5-2.0 | CORE MAGNETS                                                                    | 5-5                  |

| 5-3.0 | CORE CYCLE OPERATION<br>5-3.1 READ/WRITE                                        | 5-7<br>5-7           |

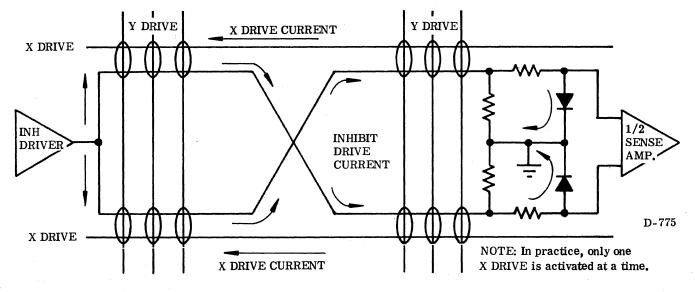

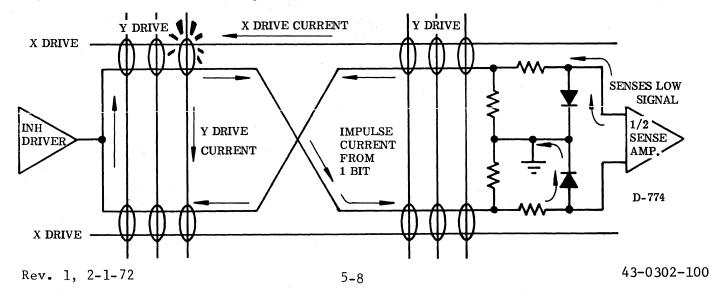

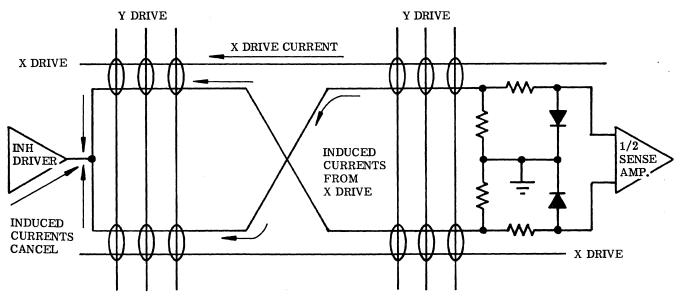

| 5-4.0 | SENSE/INHIBIT LINES                                                             | 5-8                  |

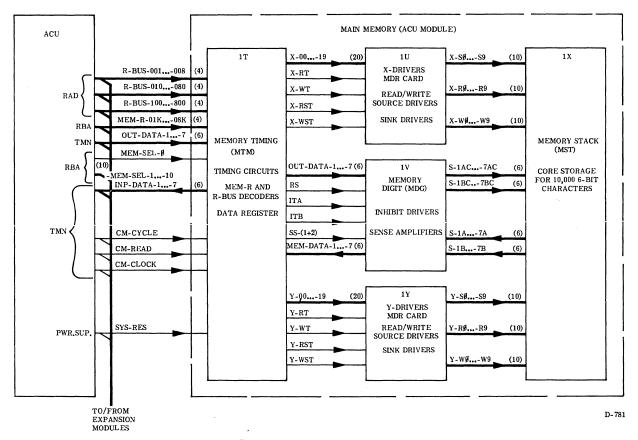

| 5-5.0 | MAIN MEMORY LOGIC<br>5-5.1 INTERFACE SIGNALS<br>5-5.2 MAIN MEMORY CIRCUIT CARDS | 5-10<br>5-10<br>5-12 |

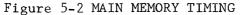

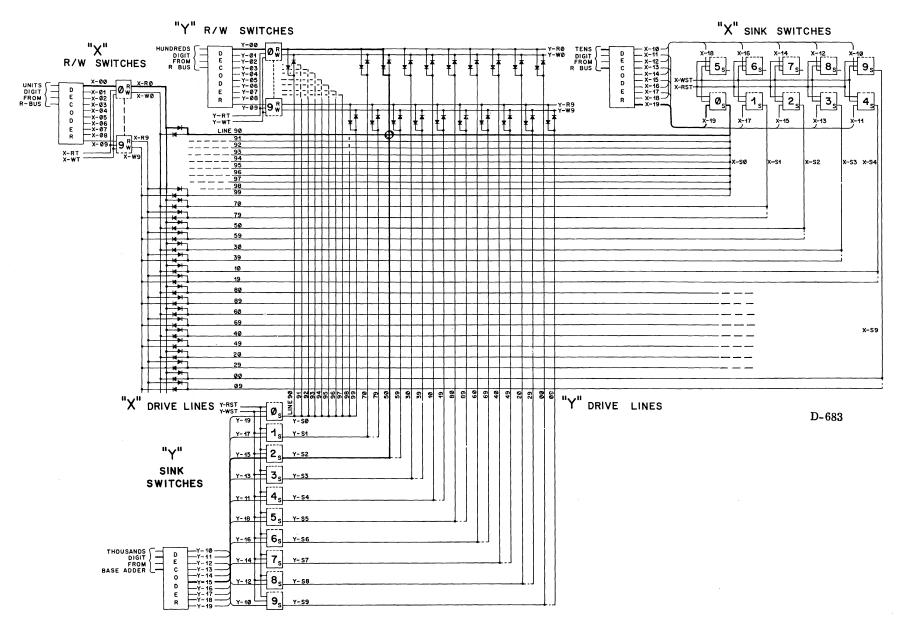

| 5-6.0 | ADDRESS SELECTION                                                               | 5-16                 |

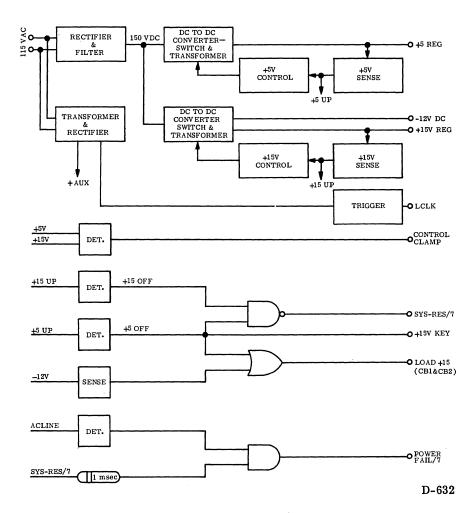

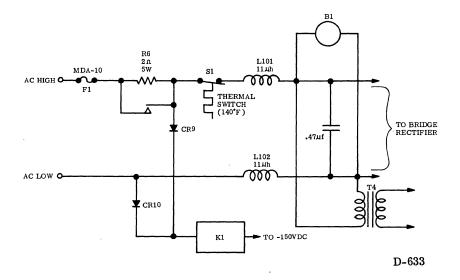

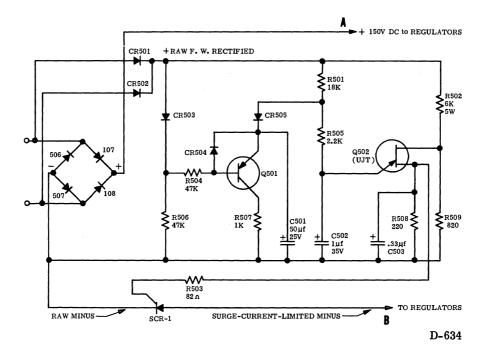

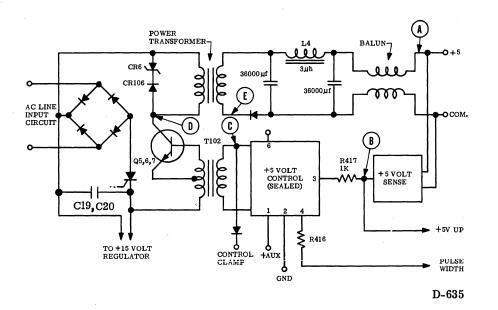

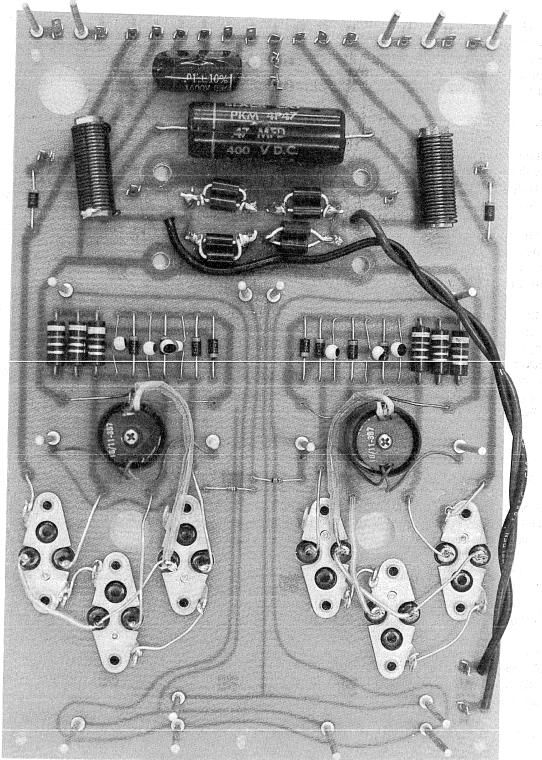

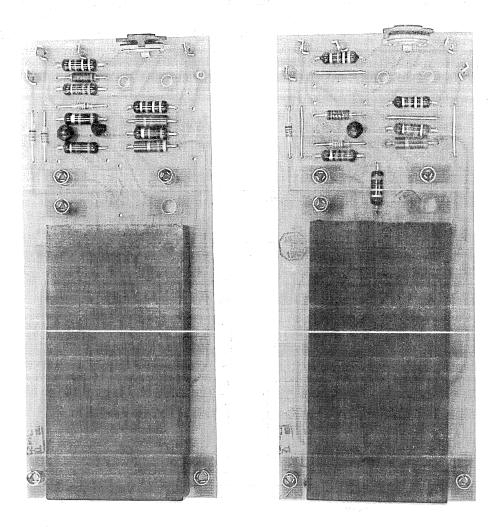

SECTION 6, 9001306 PROCESSOR POWER SUPPLY

| Α. | GENERAL DESCRIPTION                                                                                          | 6-3                               |

|----|--------------------------------------------------------------------------------------------------------------|-----------------------------------|

| B. | INPUT/OUTPUT SPECIFICATIONS                                                                                  | 6-3                               |

| С. | LOGIC SIGNALS                                                                                                | 6-4                               |

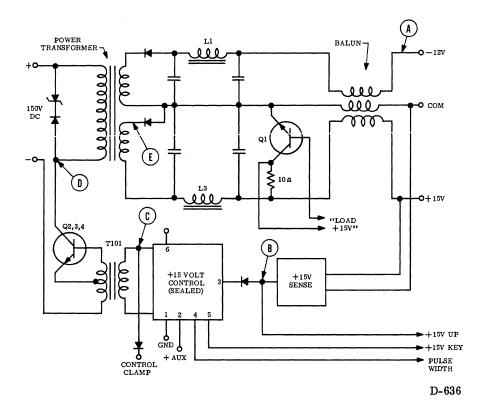

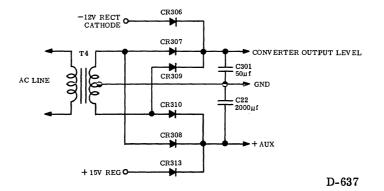

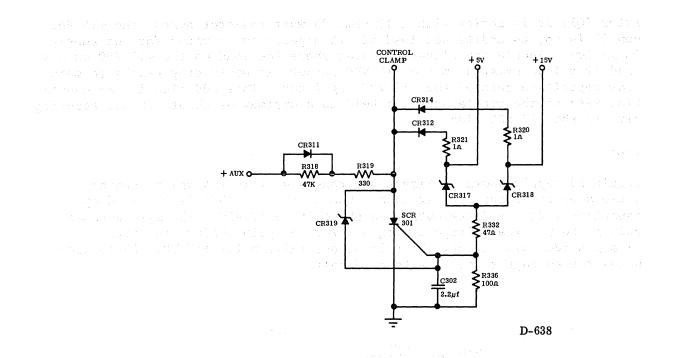

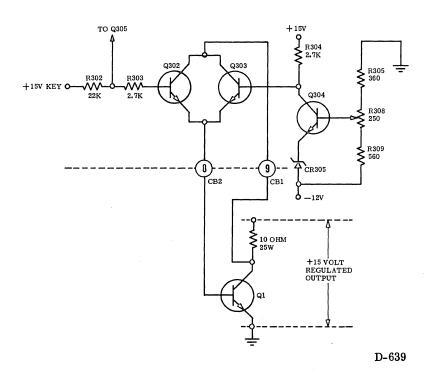

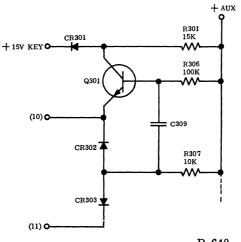

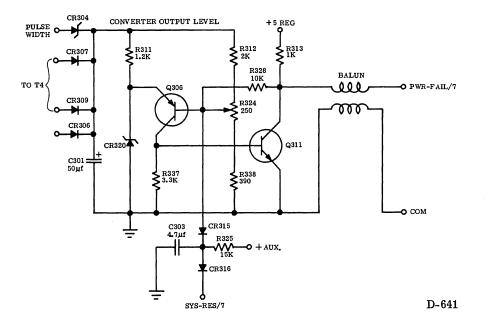

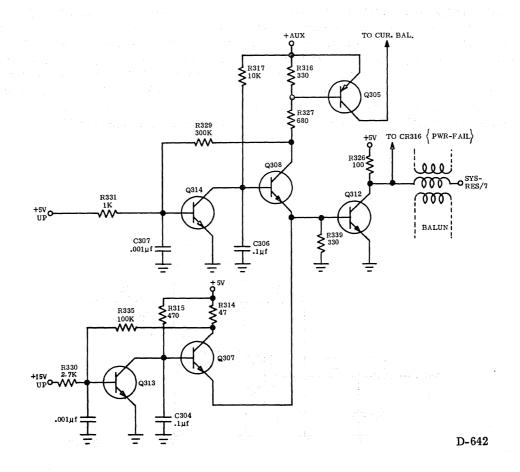

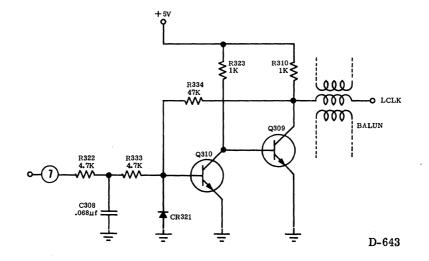

| D. | CIRCUIT DESCRIPTION<br>AC INPUT CIRCUIT<br>+5-VOLT REGULATOR<br>+15-VOLT AND -12-VOLT CIRCUIT<br>+AUX SUPPLY | 6-4<br>6-6<br>6-7<br>6-12<br>6-13 |

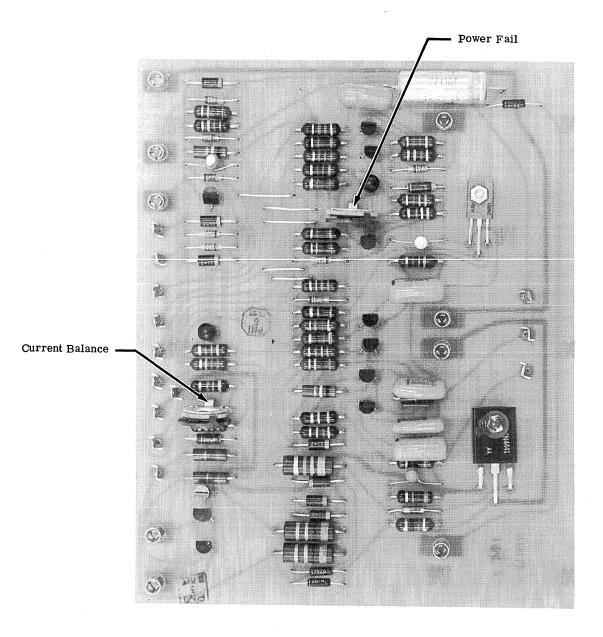

|    | OVER-VOLTAGE CROWBAR<br>CURRENT BALANCE                                                                      | 6-14<br>6-14                      |

|    | -12 VOLT CURRENT LIMIT<br>POWER FAIL DETECTOR                                                                | 6-15<br>6-16                      |

| SECTION | 6, 9001306 PROCESSOR POWER SUPPLY (Cont.)               | PAGE |

|---------|---------------------------------------------------------|------|

|         | SYSTEM RESET DETECTOR                                   | 6-19 |

|         | LINE CLOCK TRIGGER                                      | 6-21 |

|         | SEQUENCING                                              | 6-21 |

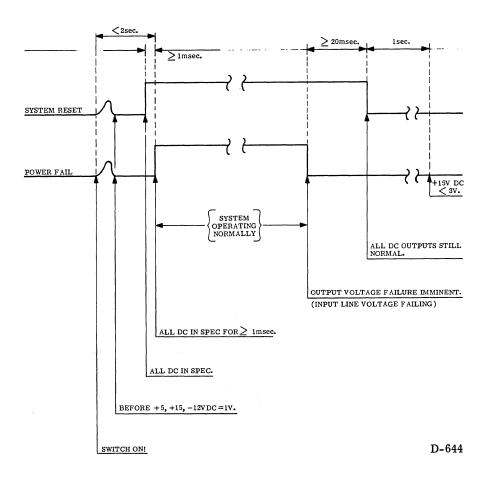

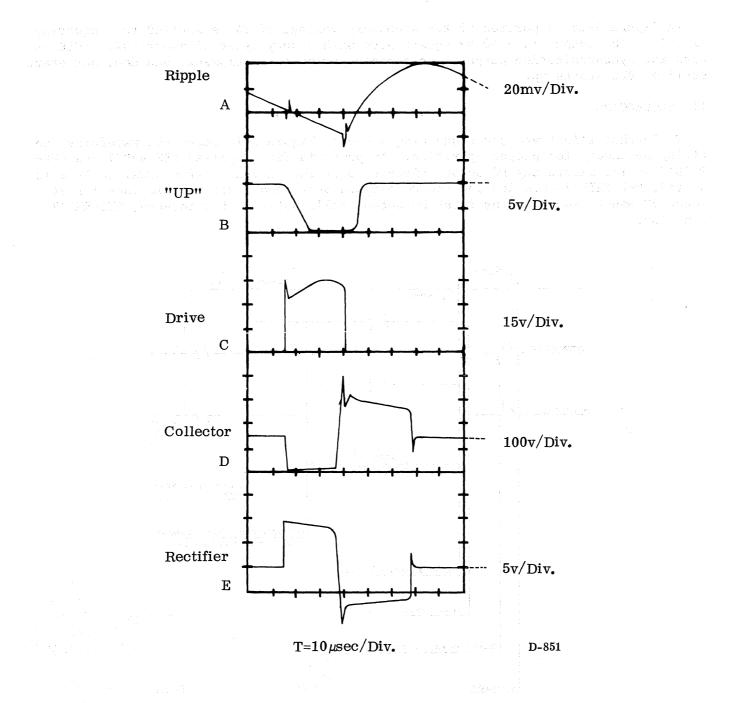

|         | POWER SUPPLY WAVEFORMS                                  | 6-22 |

|         | SUPPLEMENTARY POWER SUPPLY                              | 6-22 |

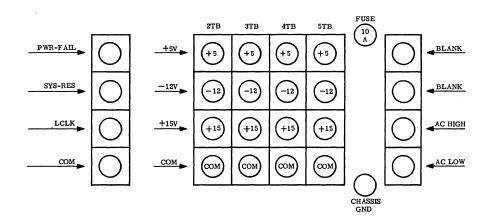

|         | MANIFOLD DESIGNATIONS                                   | 6-22 |

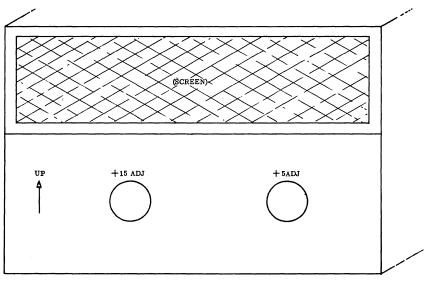

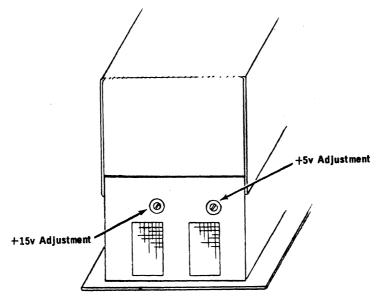

| E.      | INTERIM ADJUSTMENT PROCEDURE (PIONEER POWER SUPPLY)     | 6-24 |

|         | ADJUSTMENT LOCATIONS                                    | 6-24 |

|         | +5 VDC ADJUSTMENT                                       | 6-24 |

|         | +15 VDC ADJUSTMENT                                      | 6-24 |

|         | -12 VDC CURRENT BALANCE ADJUSTMENT                      | 6-26 |

|         |                                                         | 6-27 |

|         | FINAL ADJUSTMENT                                        | 6-27 |

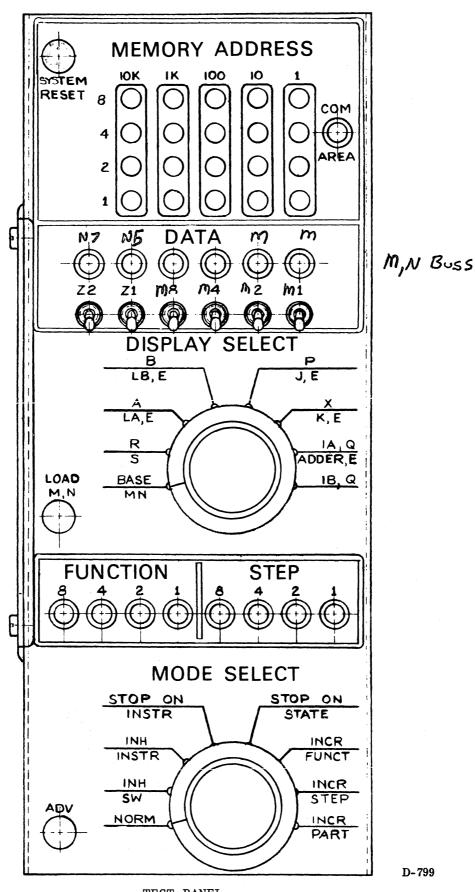

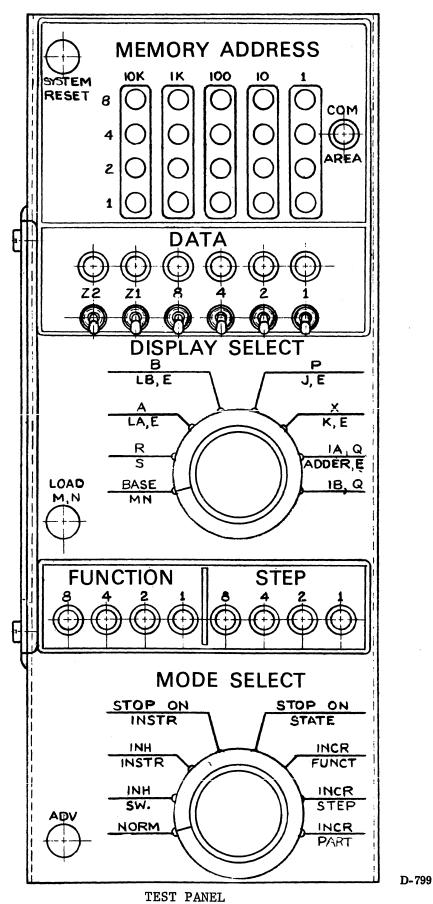

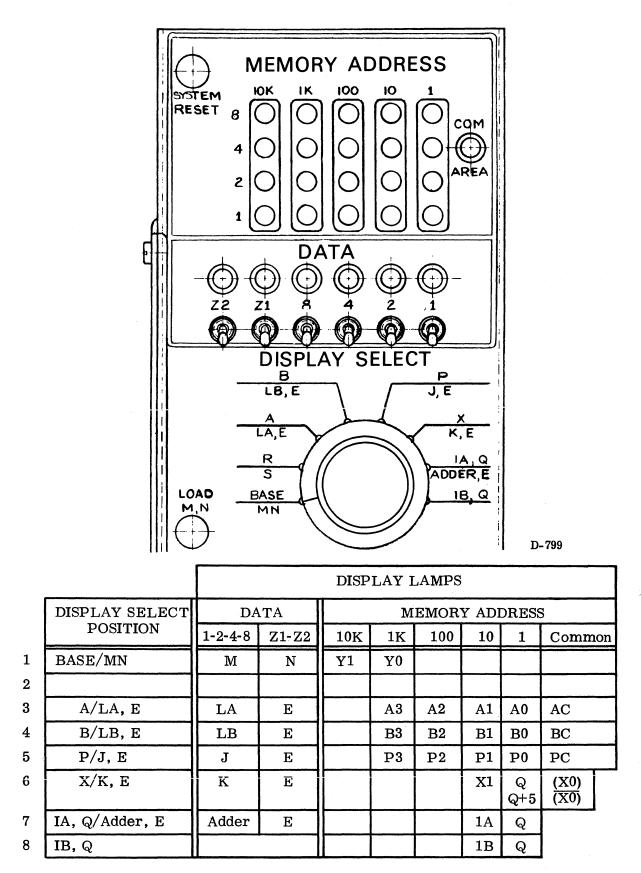

| SECTION | N 7, TEST PANEL                                         |      |

|         | CENEDAL DECONTORION                                     | 7-3  |

| Α.      | GENERAL DESCRIPTION<br>MODE SELECT AND ADVANCE SWITCHES | 7-3  |

|         | FUNCTION AND STEP INDICATORS                            | 7-5  |

|         | DISPLAY SELECT SWITCH, DISPLAY LAMPS                    | 7-7  |

|         | · · · · · · · · · · · · · · · · · · ·                   | 7-7  |

|         | LOAD M, N AND DATA SWITCHES<br>SYSTEM RESET SWITCH      | 7-7  |

|         | READ/WRITE PROCEDURE                                    | 7-8  |

| SECTION | 8, ON LINE COMMUNICATIONS ADAPTOR                       |      |

| Α.      |                                                         | 8-3  |

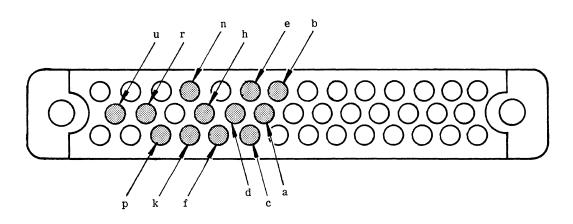

|         | PHYSICAL CHARACTERISTICS                                | 8-3  |

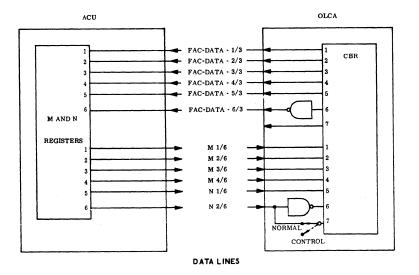

| в.      | INTERFACE                                               | 8-6  |

| D.      | INTERFACE SIGNALS                                       | 8-6  |

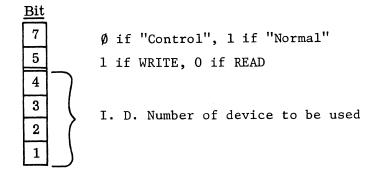

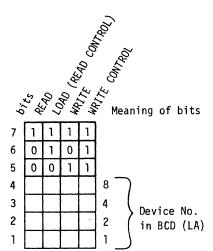

|         | DEVICE SELECTION                                        | 8-7  |

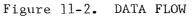

|         | DATA FLOW                                               | 8-7  |

|         | DATA FLOW                                               |      |

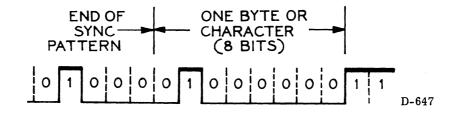

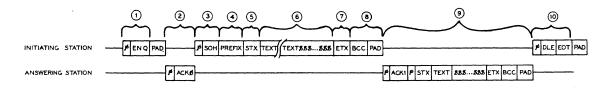

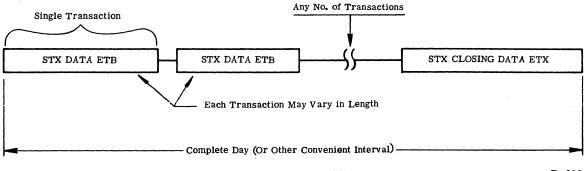

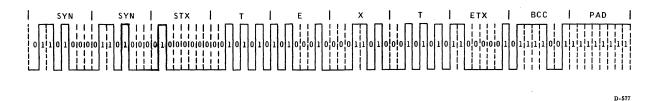

| С.      | BINARY SYNCHRONOUS COMMUNICATIONS                       | 8-9  |

|         | INTRODUCTION                                            | 8-9  |

|         | DATA LINK                                               | 8-9  |

| 4 A. J. | BSC OPERATION                                           | 8-10 |

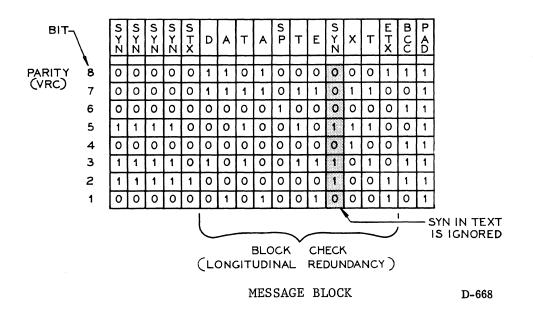

|         | ERROR CHECKING                                          | 8-11 |

|         | DATA-LINK CONTROL                                       | 8-12 |

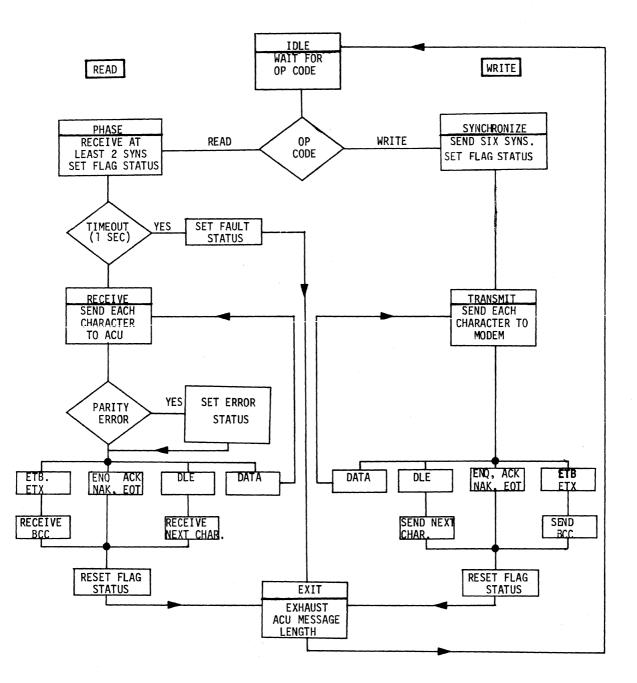

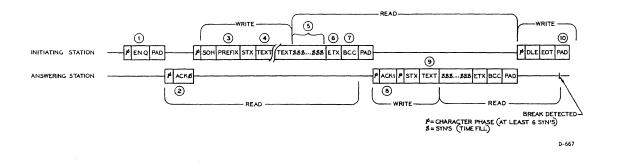

| D.      | OLCA GENERAL OPERATION                                  | 8-15 |

|         | IDLE                                                    | 8-15 |

|         | READ                                                    | 8-15 |

|         | WRITE                                                   | 8-15 |

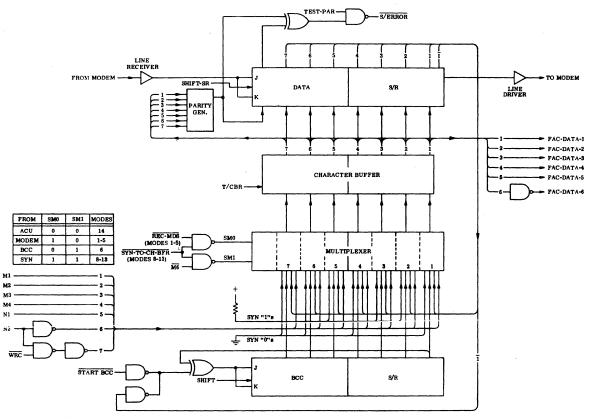

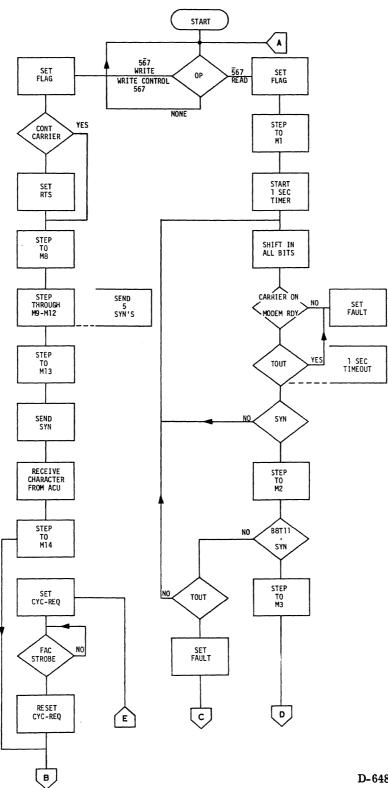

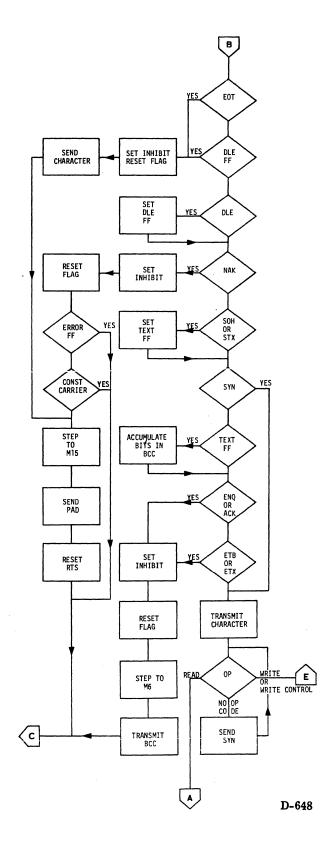

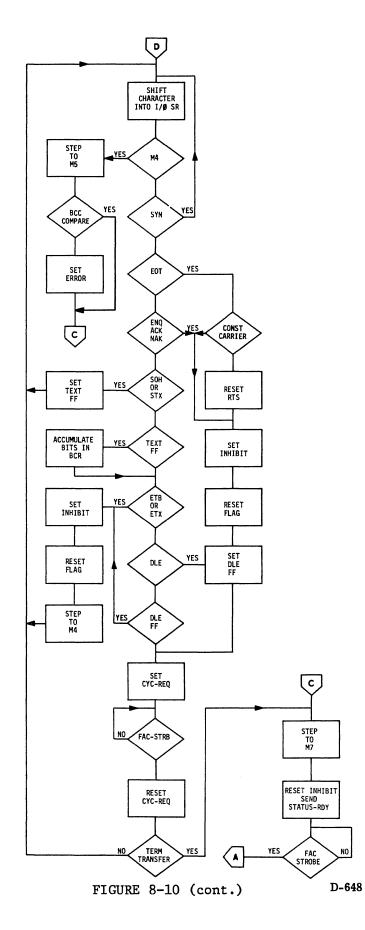

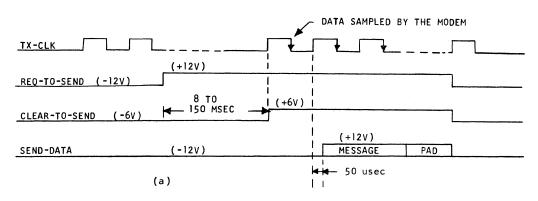

| E.      | DETAILED OPERATION                                      | 8-16 |

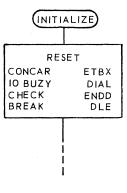

| •       | MØ, IDLE                                                | 8-16 |

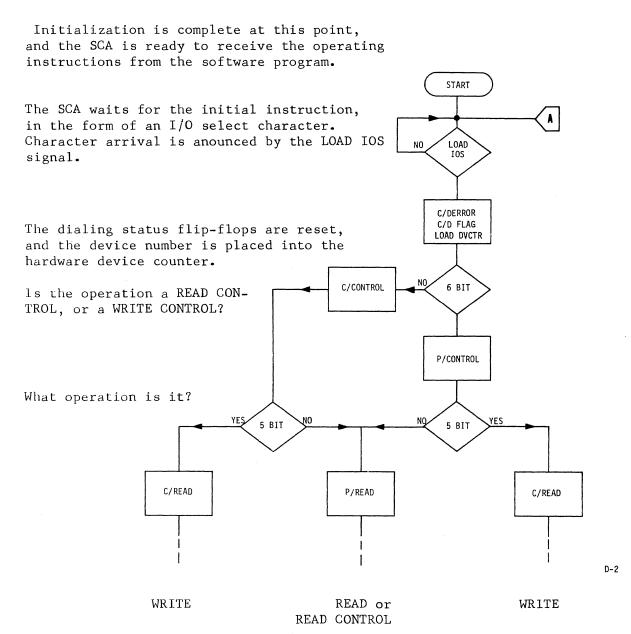

|         | M1, PHASE                                               | 8-20 |

|         | M2, CONFIRM PHASE                                       | 8-20 |

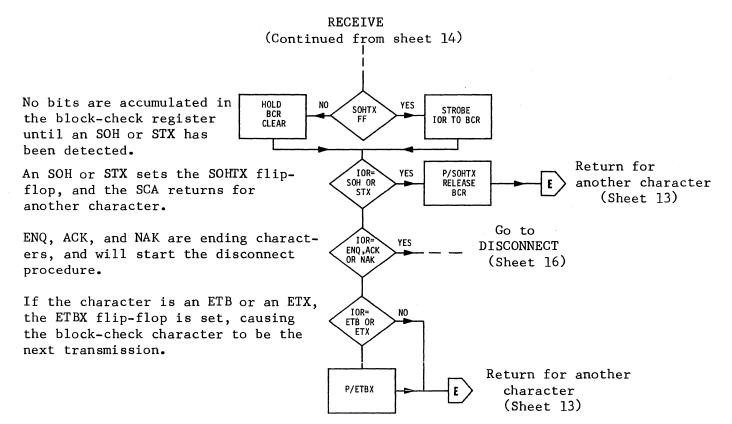

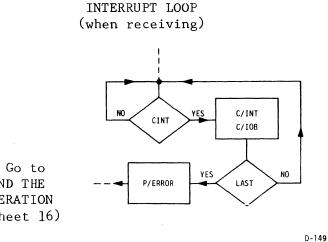

|         | M3, RECEIVE                                             | 8-20 |

|         | M4, RECEIVE BCC                                         | 8-20 |

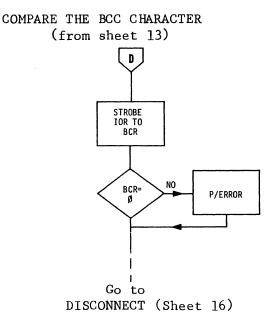

|         | M5, COMPARE BCC                                         | 8-20 |

|         | M8, THROUGH M12, SYNCHRONIZE                            | 8-21 |

| SECTIC  | N 8, ON LINE COMMUNICATIONS ADAPTER (Continued) | PAGE         |

|---------|-------------------------------------------------|--------------|

|         | M13, END SYNCHRONIZATION                        | 8-21         |

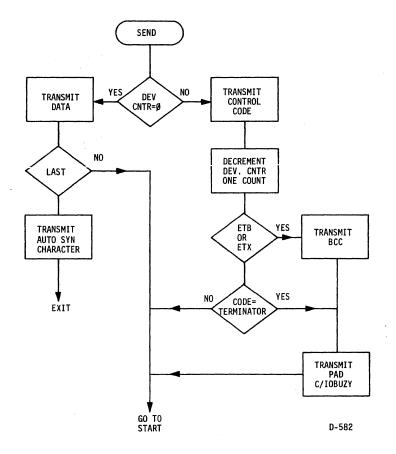

|         | M14, TRANSMIT                                   | 8-21         |

|         | M6, TRANSMIT BCC                                | 8-21         |

|         | M15, TRANSMIT PAD                               | 8-21         |

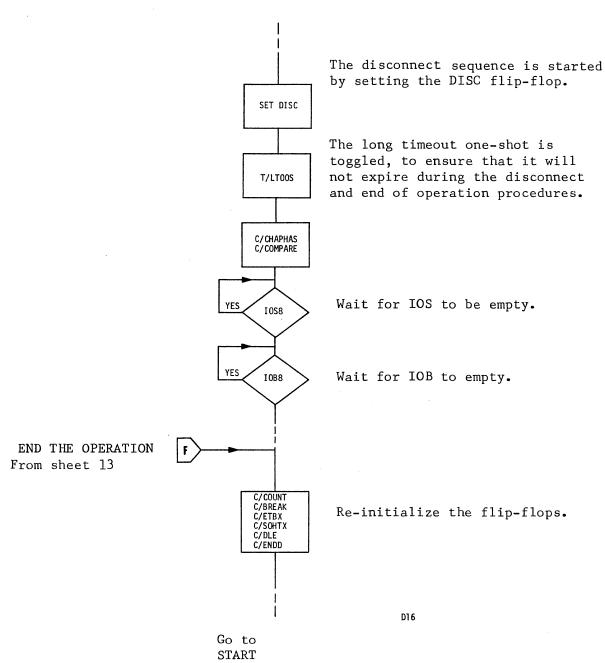

|         | M7, EXIT                                        | 8-21         |

|         | STATUS                                          | 8-22         |

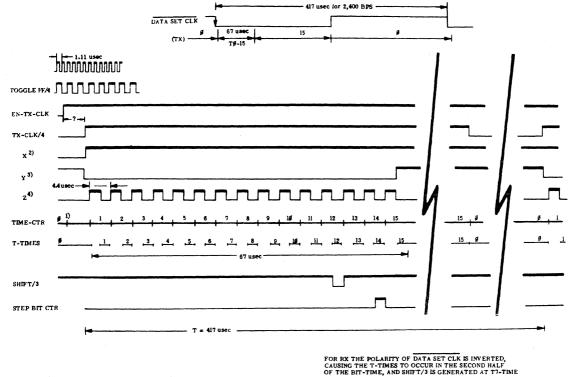

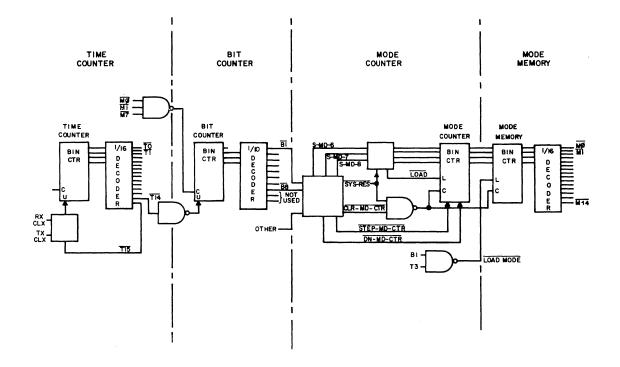

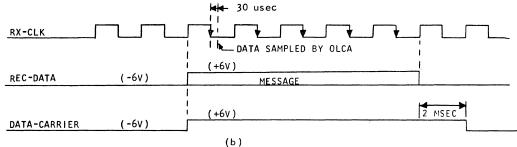

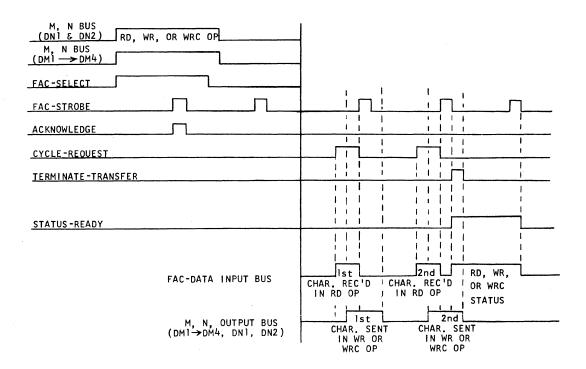

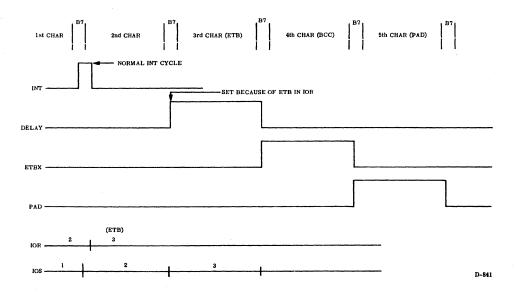

| ÷       | TIMING                                          | 8-23         |

|         |                                                 | 0 20         |

| F.      | GLOSSARY                                        | 8-25         |

| G.      | REFERENCE                                       | 8-27         |

| 0.      |                                                 | 0 27         |

| SECTION | N 9, MDTS IOC                                   |              |

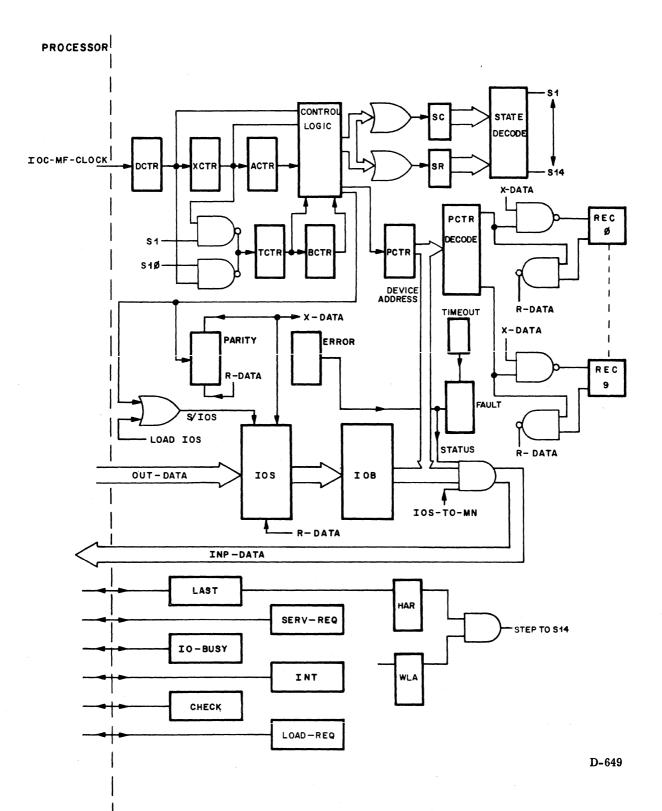

| Α.      | INTRODUCTION                                    | 9-3          |

|         |                                                 |              |

| Β.      | PROCESSOR/MDTS IOC COMMUNICATION                | 9-3          |

|         | INTERFACE SIGNALS                               | 9-5          |

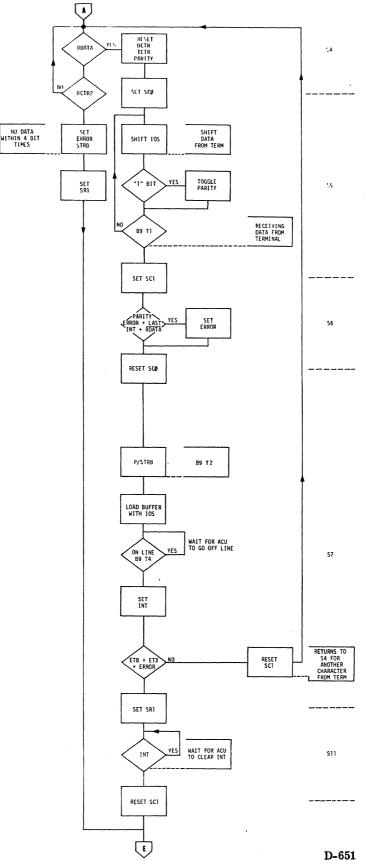

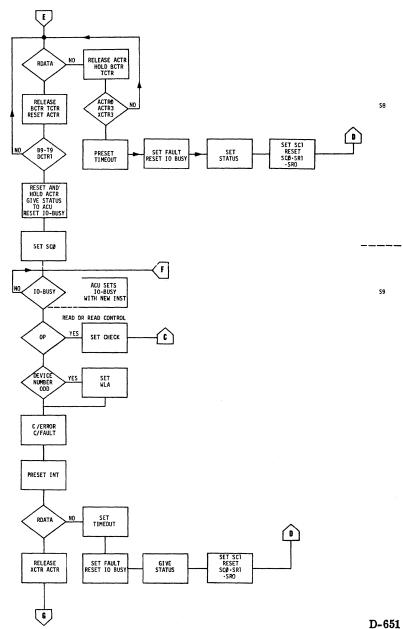

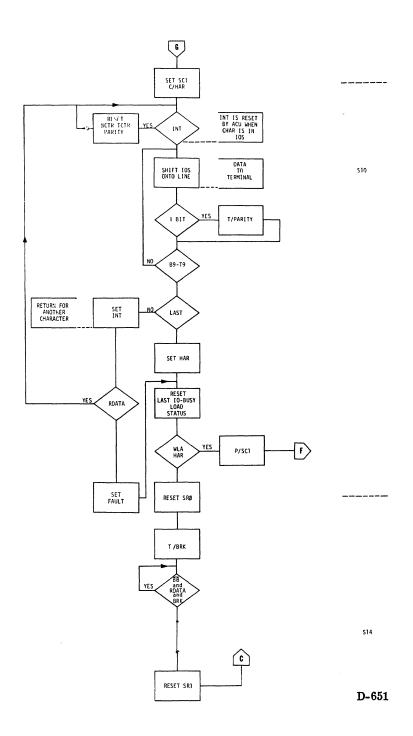

|         | MDTS IOC OPERATION                              | 9-6          |

|         | MANUAL CONTROLS                                 | 9-13         |

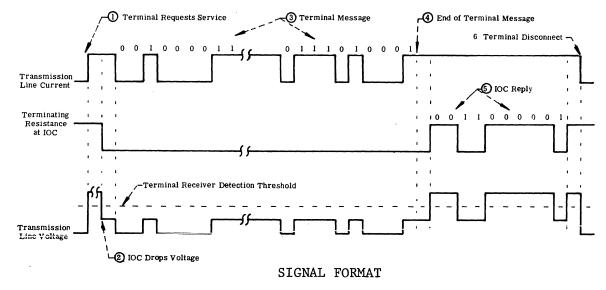

| C       | MDTS IOC/TERMINAL COMMUNICATION                 | 9-14         |

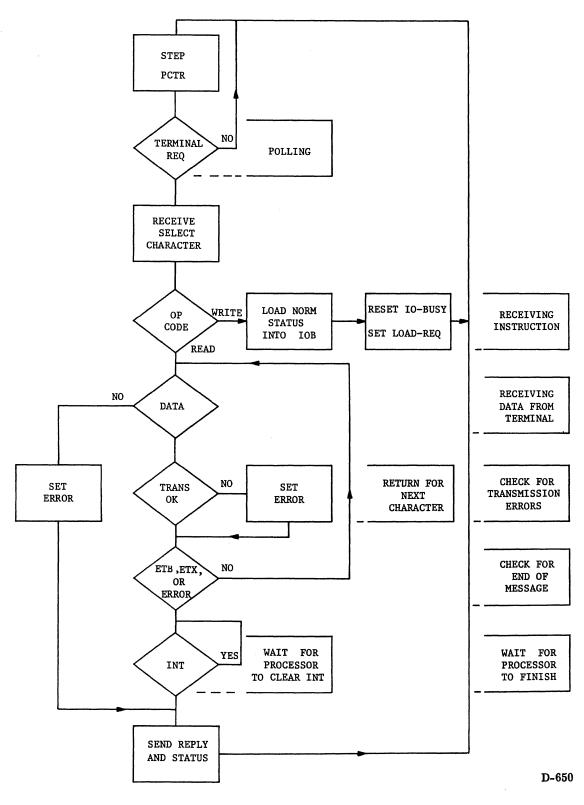

| 0.      | INTRODUCTION                                    | 9-14<br>9-14 |

|         | MESSAGE FORMAT                                  | 9-14<br>9-14 |

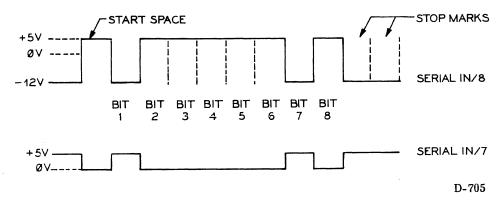

|         | CHARACTER TRANSMISSION                          | 9-16         |

|         | DATA TRANSFER                                   | 9-17         |

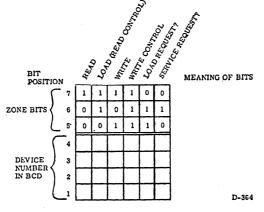

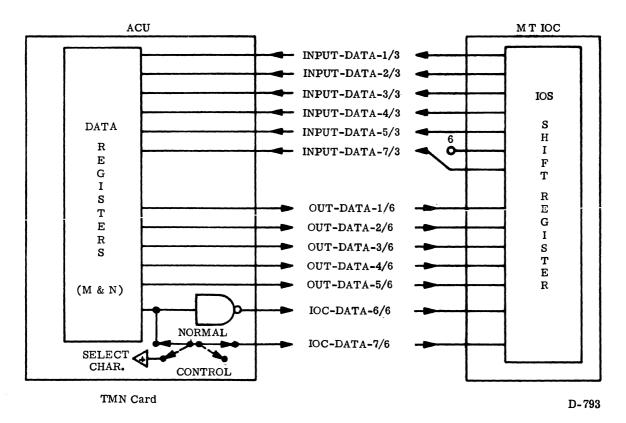

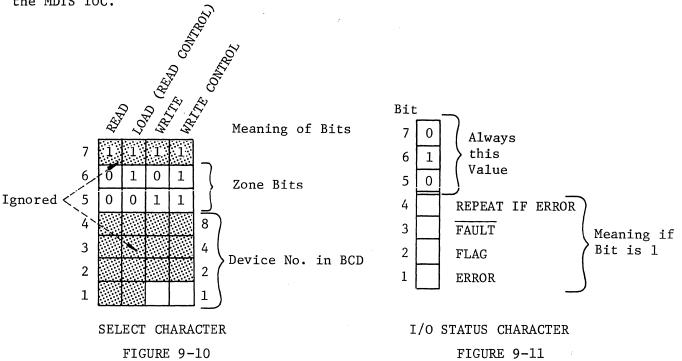

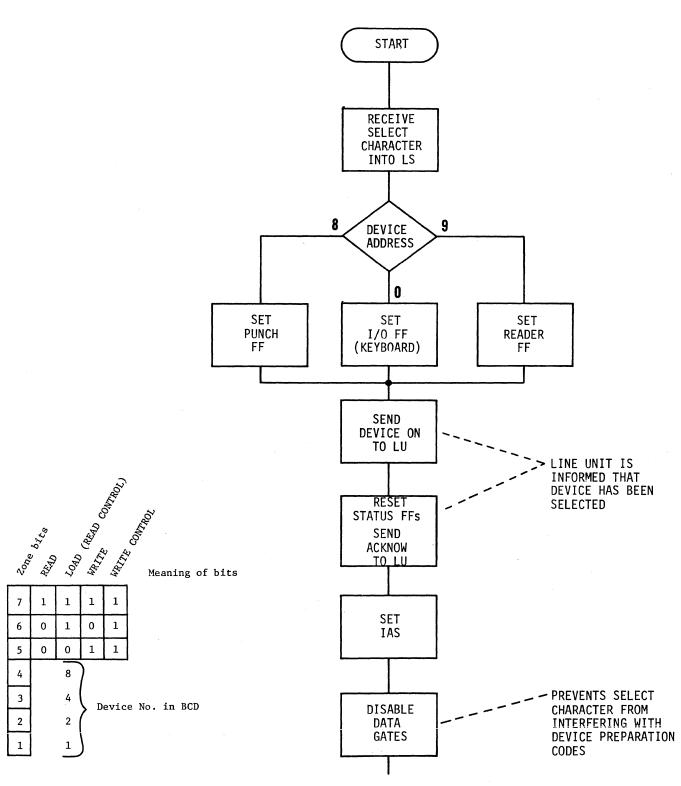

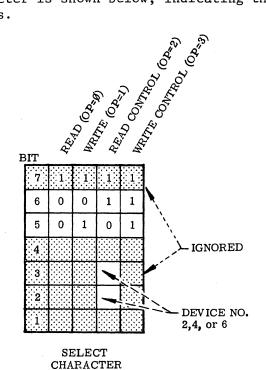

|         | SELECT CHARACTER                                | 9-18         |

|         |                                                 | 9-18         |

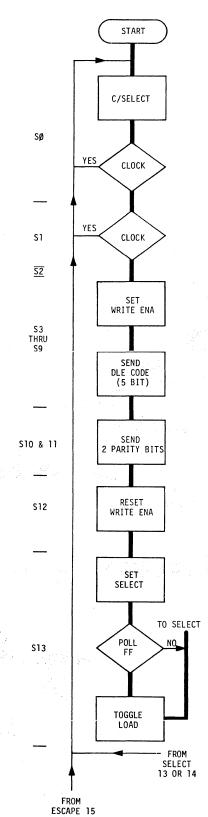

|         | STATUS<br>POLLING                               | 9-19<br>9-19 |

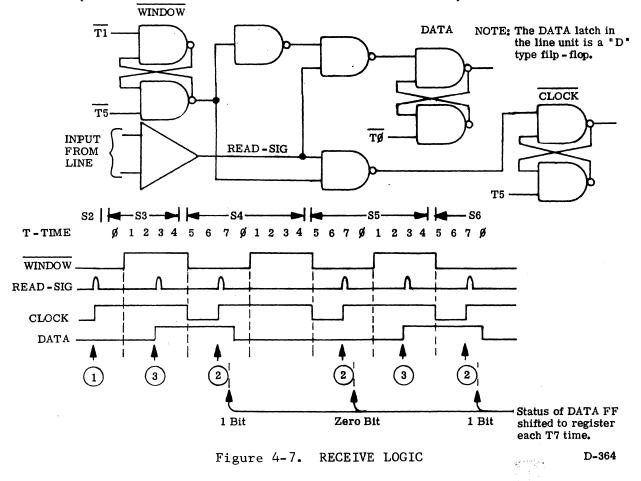

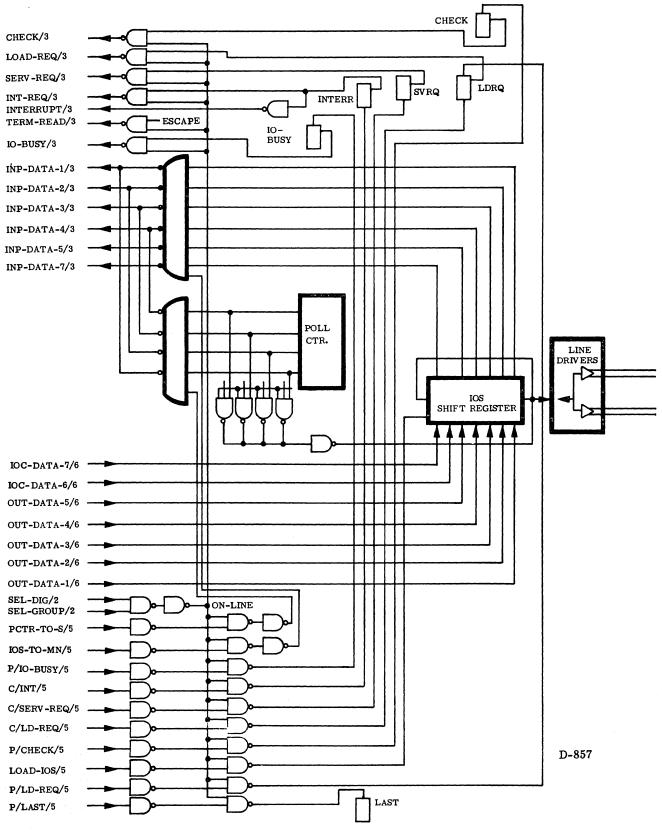

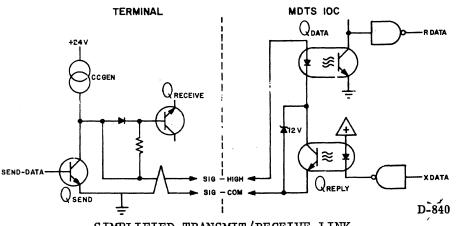

|         | TRANSMIT/RECEIVE LOGIC                          | 9-19         |

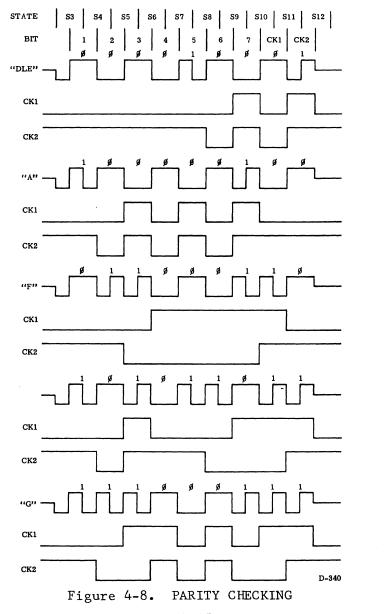

|         | PARITY                                          | 9-20         |

|         | STATE COUNTER                                   | 9-20         |

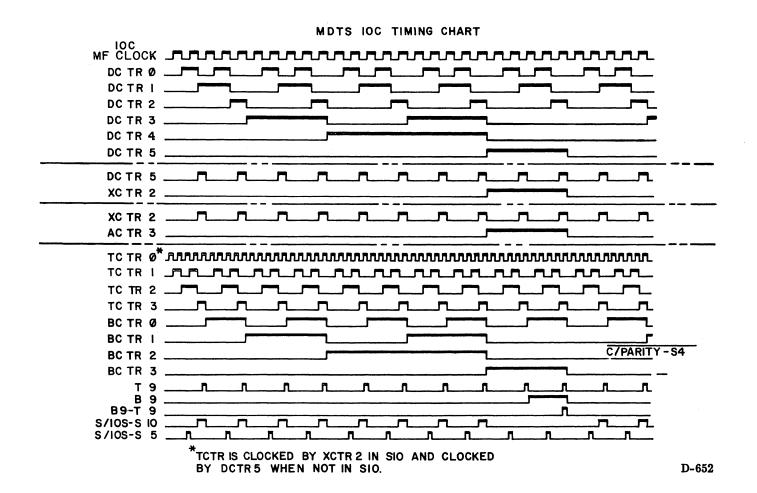

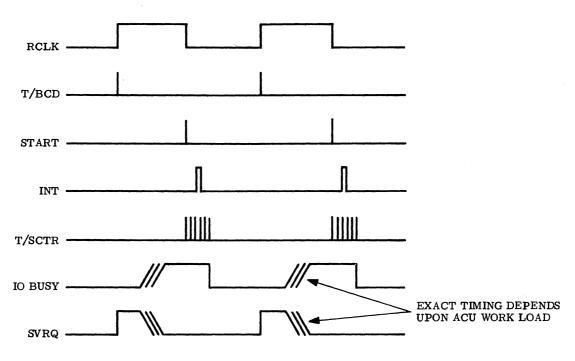

|         | TIMING                                          | 9-22         |

|         | LOGIC FUNCTION LOCATION                         | 9-24         |

|         |                                                 | 9-25         |

|         |                                                 |              |

| D.      | SIGNAL AND TERM GLOSSARY                        | 9-26         |

|         |                                                 |              |

| SECTIO  | N 10, COLLECTADATA 30 IOC AND TERMINATOR        |              |

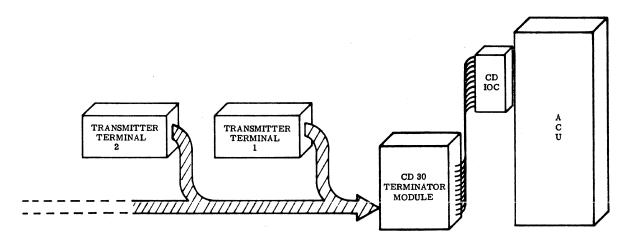

| Α.      | GENERAL DESCRIPTION                             | 10-3         |

|         |                                                 | 10 5         |

| В.      | PRIORITY SCHEME                                 | 10-5         |

| с.      | TERMINATOR INTERFACE                            | 10-7         |

| Ď.      | MEDICINATION MODILI E TROMALI ANTON CONTRACTOR  | 10-8         |

| D.      | TERMINATOR MODULE INSTALLATION/OPERATION        | 10-8         |

|         | INSTALLATION                                    | 10-8         |

|         | OPERATION                                       | 10 0         |

| Е.      | IOC LOGIC                                       | 10-9         |

| • •     |                                                 |              |

| F.      | TRANSMISSION FORMAT                             | 10-10        |

|         |                                                 |              |

| SECTIO | N 10, COLLECTADATA 30 IOC AND TERMINATOR (Cont.)                                                                                                                                                                                   | PAGE                                                                                                     |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| G.     | SELECTION                                                                                                                                                                                                                          | 10-11                                                                                                    |

| н.     | TIMING<br>LCTR<br>TIMER                                                                                                                                                                                                            | 10-13<br>10-13<br>10-13                                                                                  |

| I.     | INTERFACE SIGNALS<br>TERMINATOR/IOC INTERFACE                                                                                                                                                                                      | 10-14<br>10-14                                                                                           |

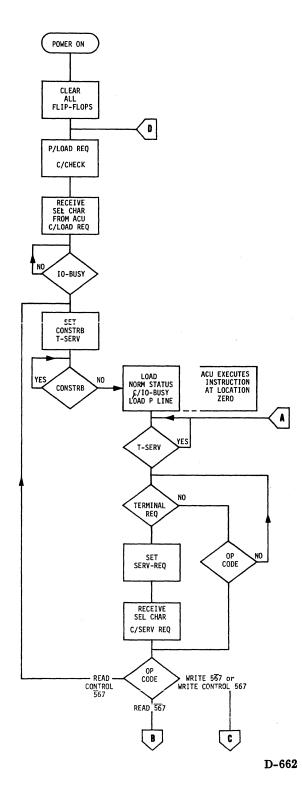

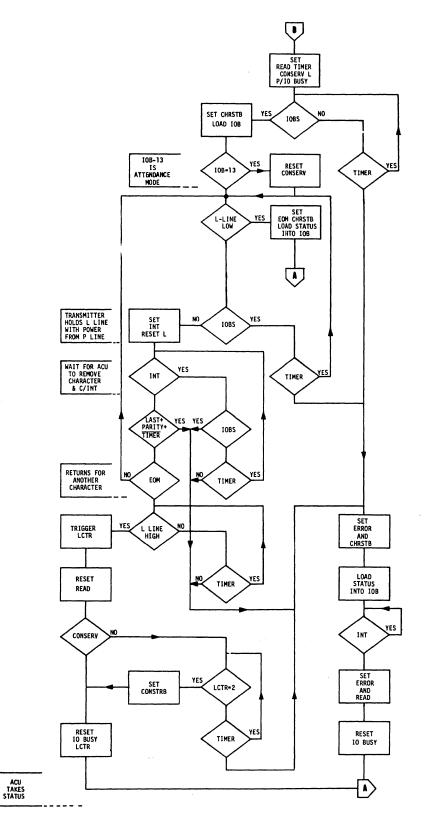

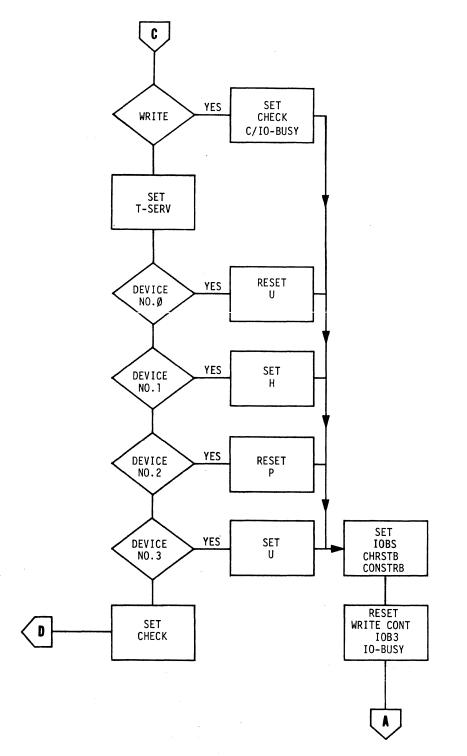

| J.     | OPERATION<br>READ CONTROL<br>WRITE CONTROL<br>READ                                                                                                                                                                                 | 10-16<br>10-16<br>10-16<br>10-16                                                                         |

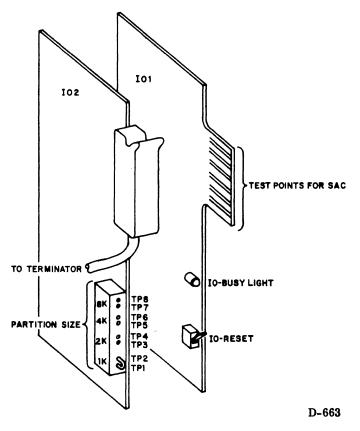

| К.     | MANUAL CONTROLS                                                                                                                                                                                                                    | 10-21                                                                                                    |

| L.     | GLOSSARY<br>INTERFACE SIGNALS                                                                                                                                                                                                      | 10-22<br>10-22                                                                                           |

| М.     | REFERENCE                                                                                                                                                                                                                          | 10-25                                                                                                    |

| SECTIO | N 11, SYNCHRONOUS COMMUNICATIONS ADAPTER                                                                                                                                                                                           | ·                                                                                                        |

| 11-1.0 | INTRODUCTION                                                                                                                                                                                                                       | 11-3                                                                                                     |

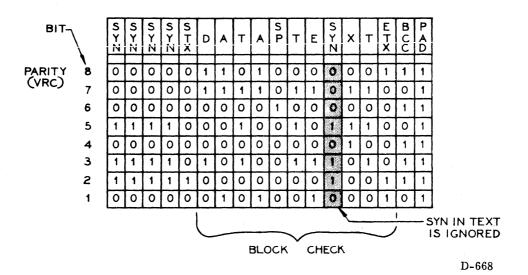

| 11-2.0 | BINARY SYNCHRONOUS COMMUNICATIONS<br>11-2.1 DATA LINK<br>11-2.2 BSC OPERATION<br>11-2.3 ERROR CHECKING                                                                                                                             | 11-6<br>11-6<br>11-9<br>11-10                                                                            |

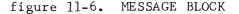

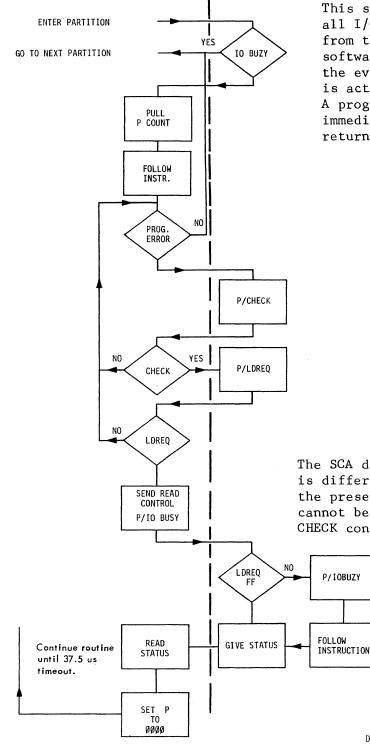

| 17-3.0 | PROCESSOR/SCA INTERFACE                                                                                                                                                                                                            | 11-11                                                                                                    |

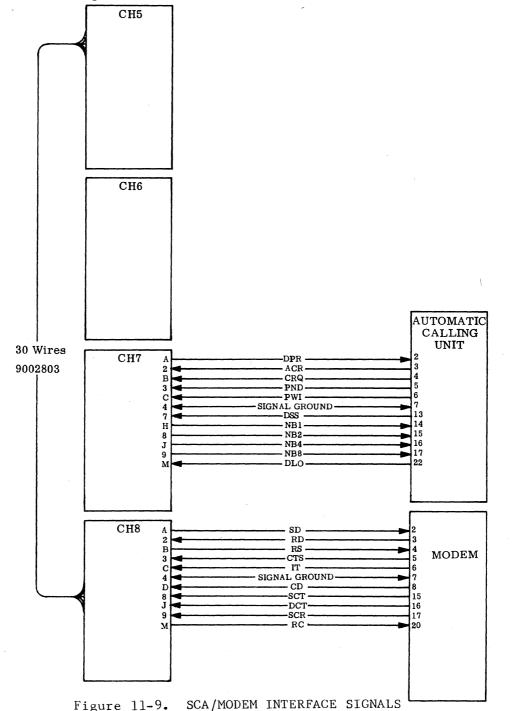

| 11-4.0 | SCA/DATA SET & AUTOMATIC CALLING UNIT INTERFACE                                                                                                                                                                                    | 11-13                                                                                                    |

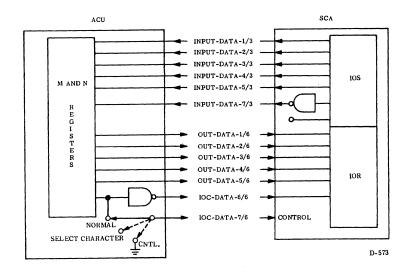

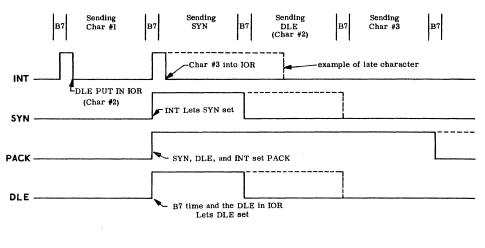

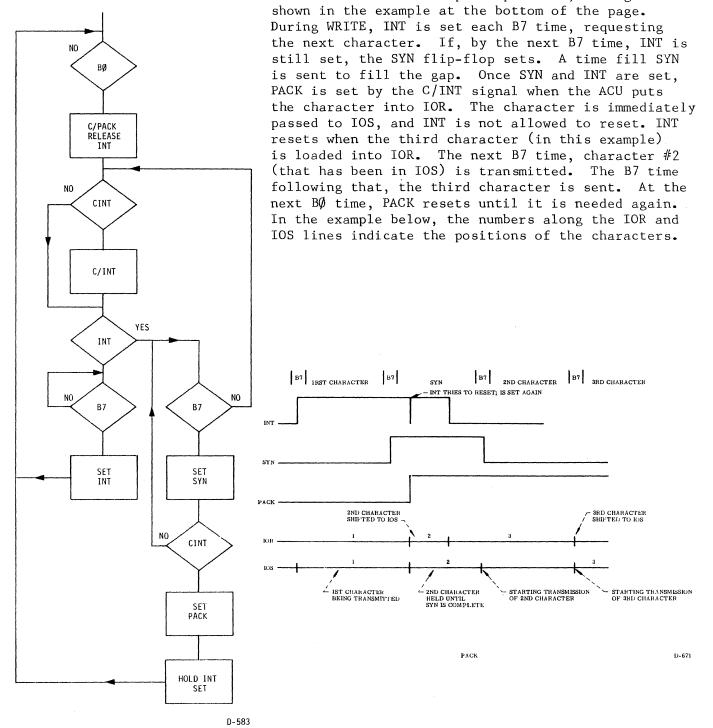

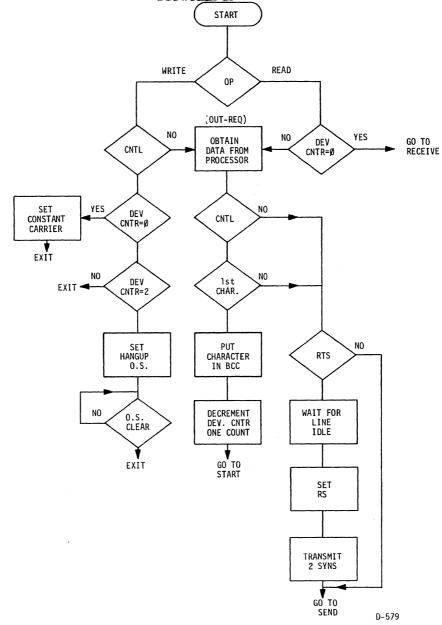

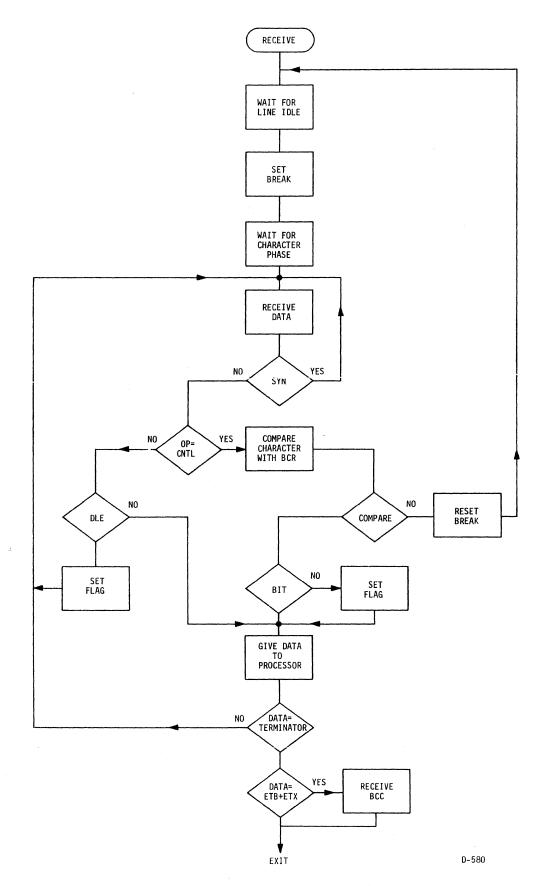

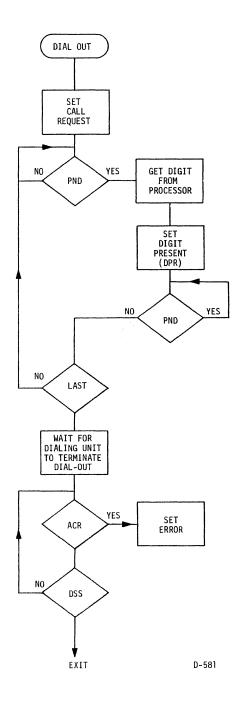

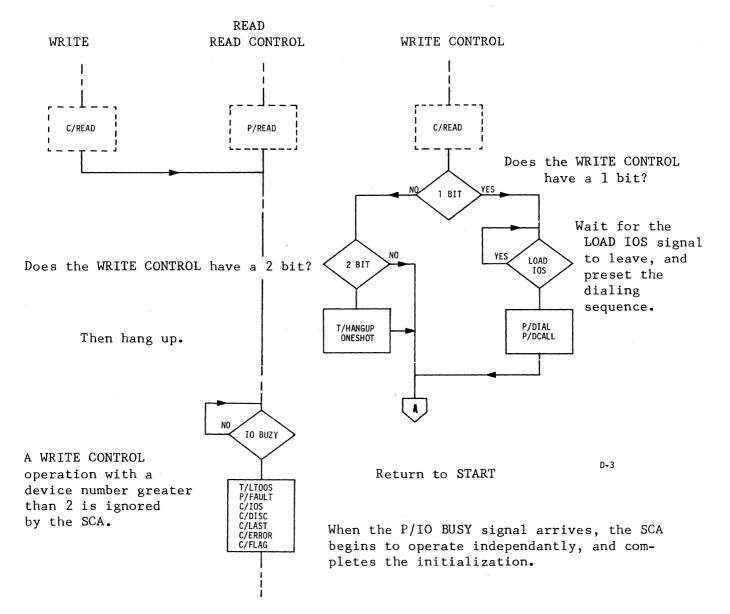

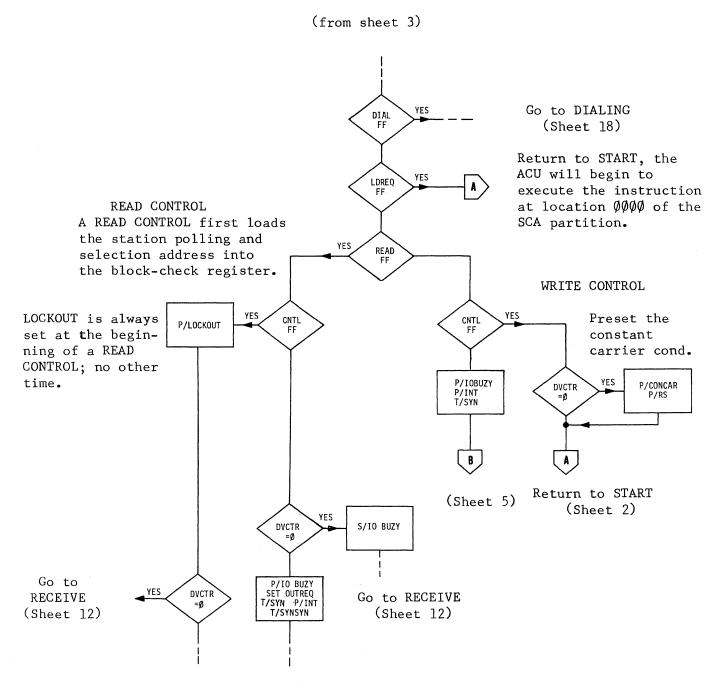

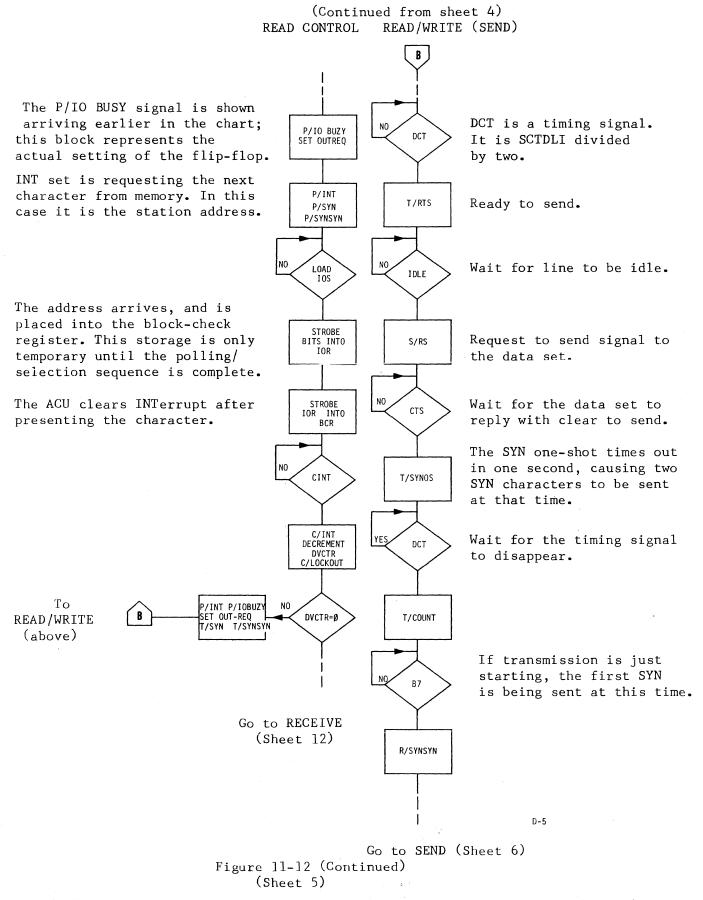

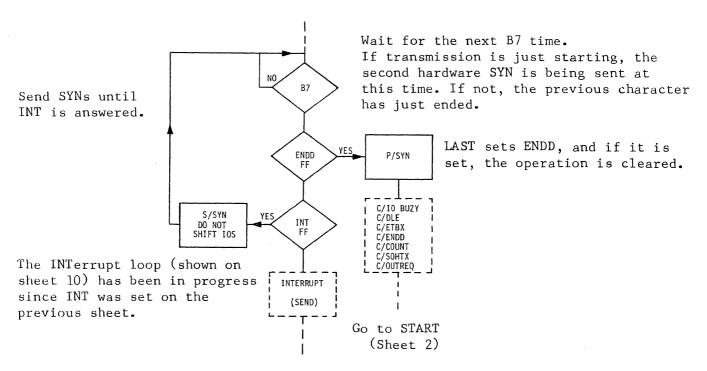

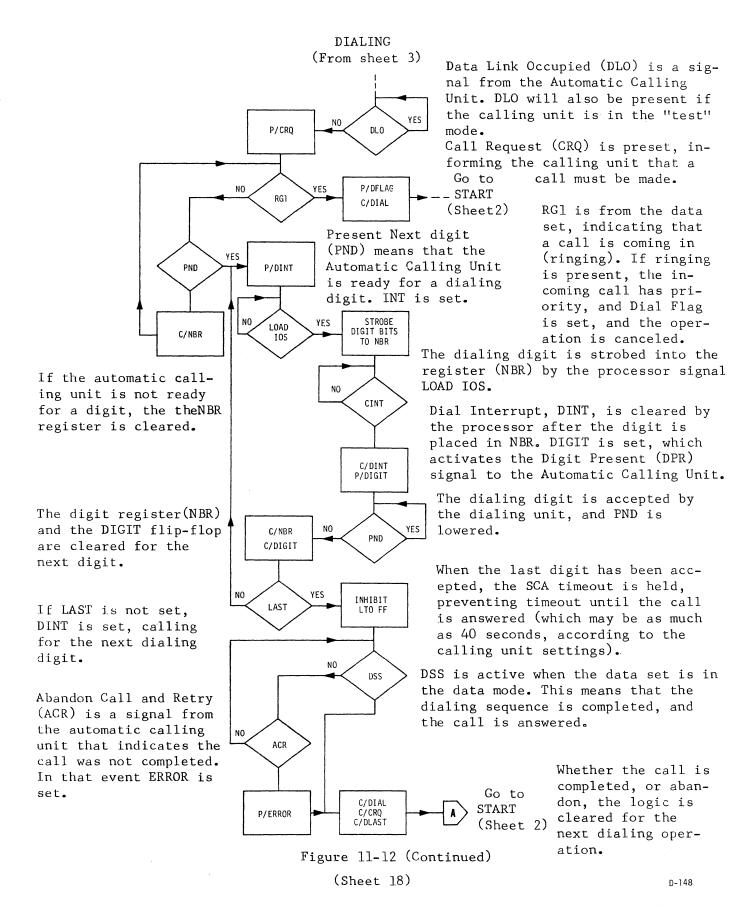

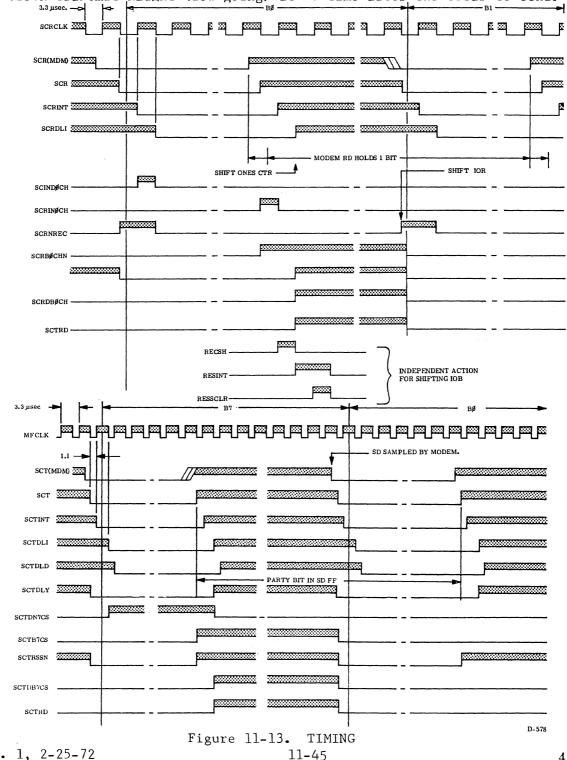

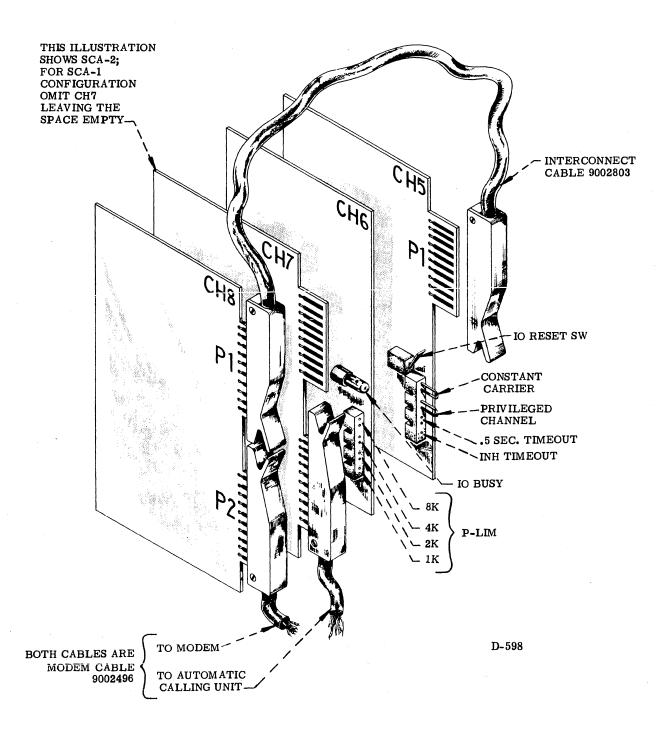

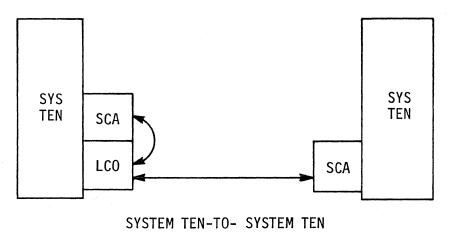

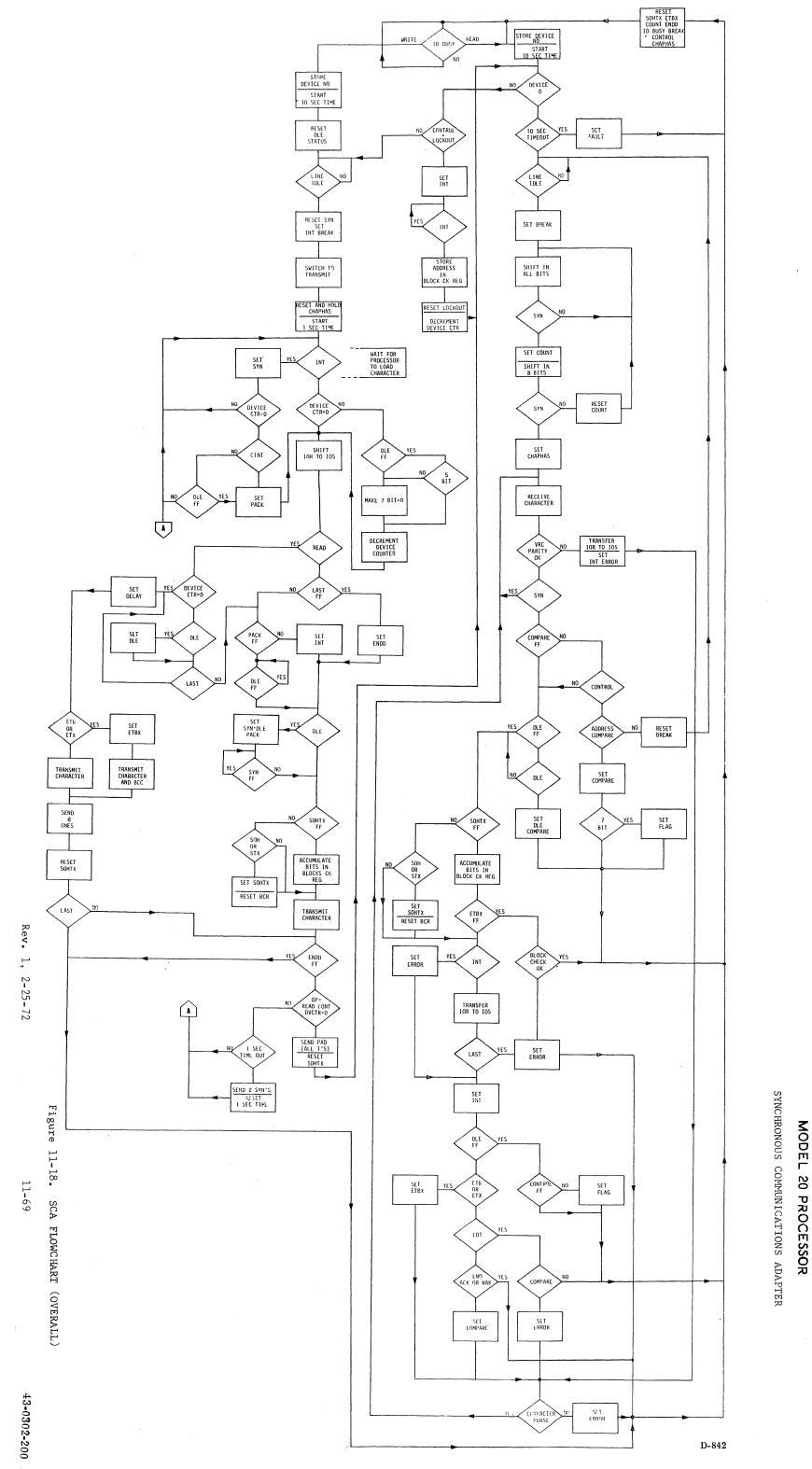

| 11-5.0 | SCA OPERATION<br>11-5.1 WRITE CONTROL<br>11-5.2 READ CONTROL<br>11-5.3 READ<br>11-5.4 WRITE<br>11-5.5 TIMEOUT<br>11-5.6 DLE<br>11-5.7 PACK<br>11-5.8 DELAY<br>11-5.8 DELAY<br>11-5.9 FLOWCHART<br>11-5.10 STATUS<br>11-5.11 TIMING | 11-14<br>11-14<br>11-15<br>11-16<br>11-16<br>11-17<br>11-18<br>11-19<br>11-20<br>11-21<br>11-44<br>11-45 |

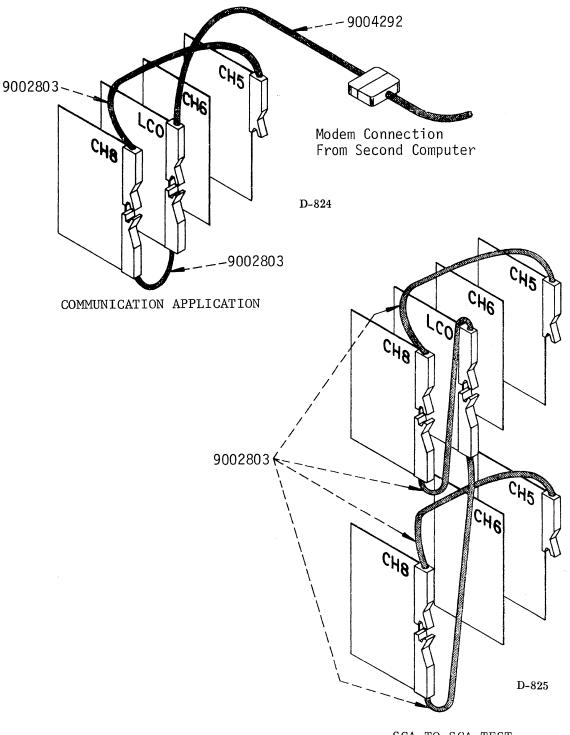

| 11-6.0 | REFERENCE<br>11-6.1 SUMMARY OF SCA FUNCTIONS<br>11-6.2 MANUAL CONTROLS<br>11-6.3 LCO<br>11-6.4 GLOSSARY<br>11-6.5 SCA EQUATIONS                                                                                                    | 11-46<br>11-46<br>11-47<br>11-49<br>11-53<br>11-60                                                       |

SECTION 12, DISC CONTROLLER

| 12-1.0  | INTRODUCTION                                                                                                                                                                                                            | 12-3                                                                 |  |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|--|

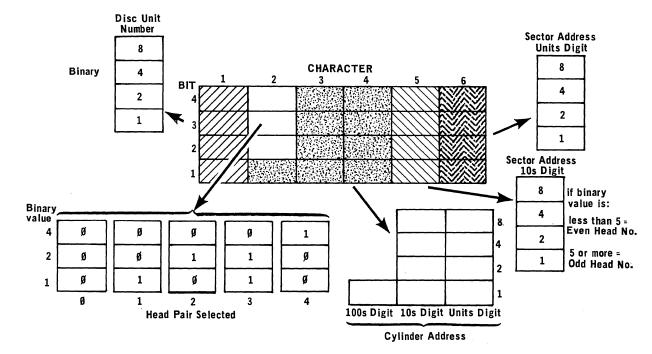

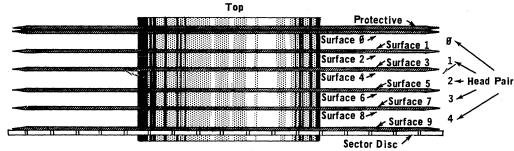

| 12-2.0  | DATA LOCATION                                                                                                                                                                                                           |                                                                      |  |

| 12-3.0  | INSTRUCTIONS                                                                                                                                                                                                            | 12-4                                                                 |  |

| 12-4.0  | STATUS                                                                                                                                                                                                                  | 12-5                                                                 |  |

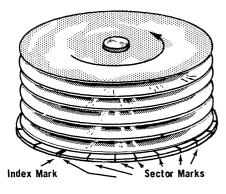

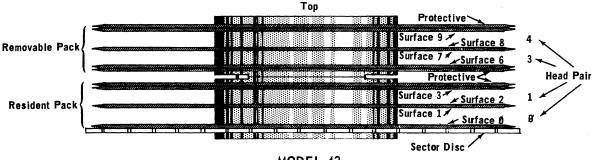

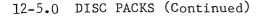

| 12-5.0  | DISC PACKS                                                                                                                                                                                                              | 12-6                                                                 |  |

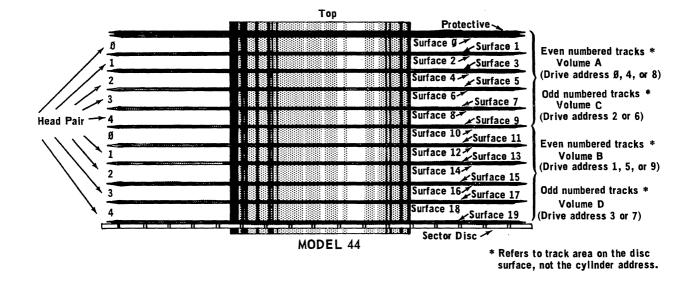

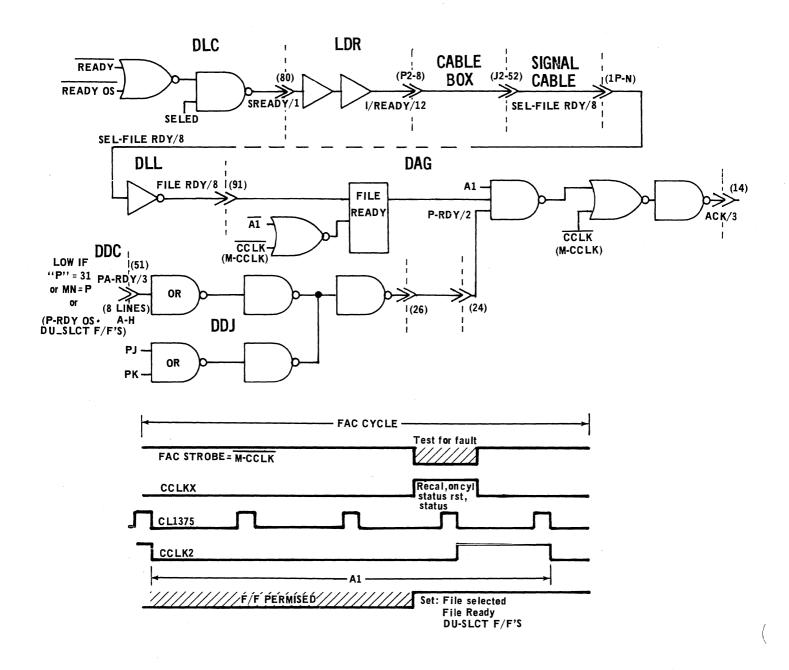

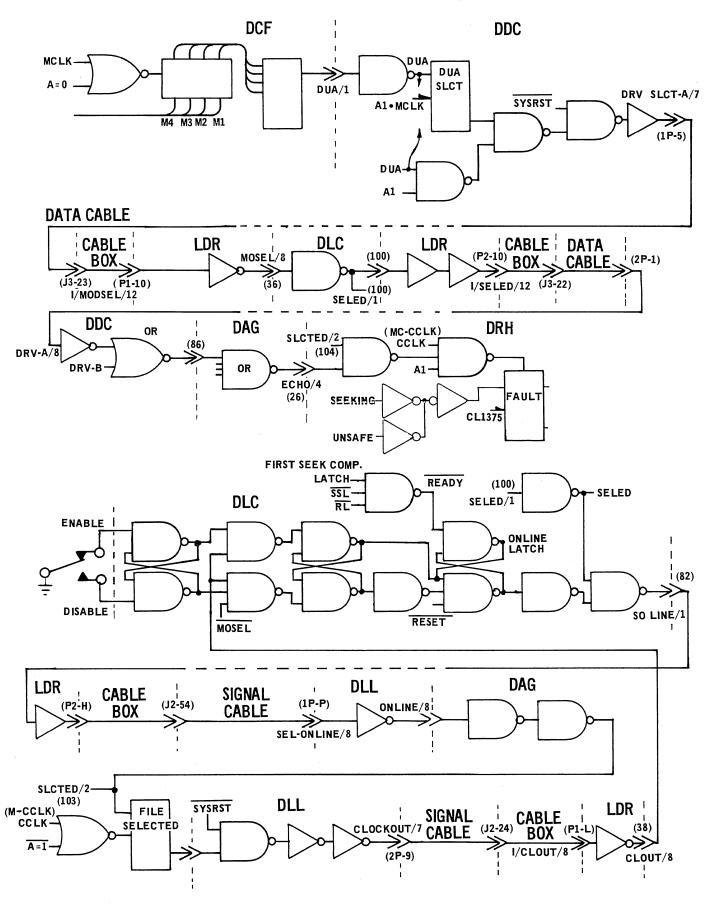

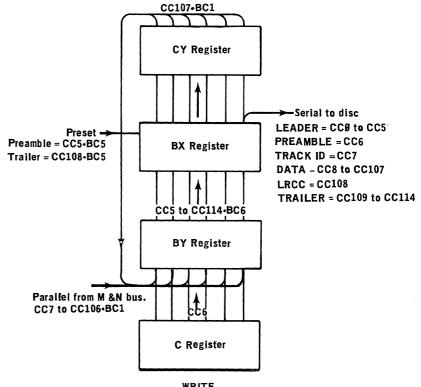

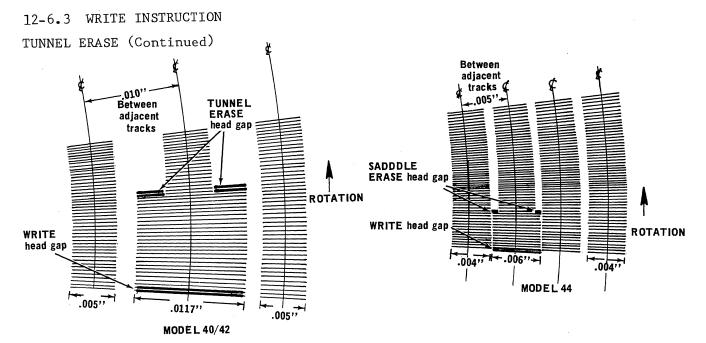

| 12-6.0  | DISC CONTROLLER OPERATION<br>12-6.1 FAC MODULE SELECTION<br>12-6.2 DEVICE SELECTION<br>12-6.3 WRITE INSTRUCTION<br>12-6.4 READ INSTRUCTION<br>12-6.5 CHECK READ<br>12-6.6 DXH READ-BEFORE-WRITE<br>12-6.7 WRITE CONTROL | 12-7<br>12-7<br>12-7<br>12-8<br>12-17<br>12-19<br>12-20<br>12-21     |  |

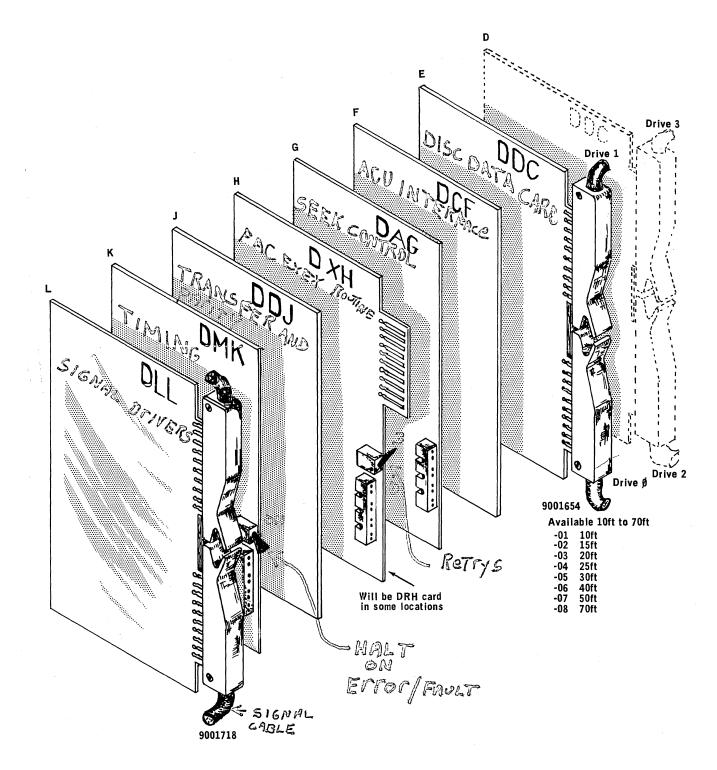

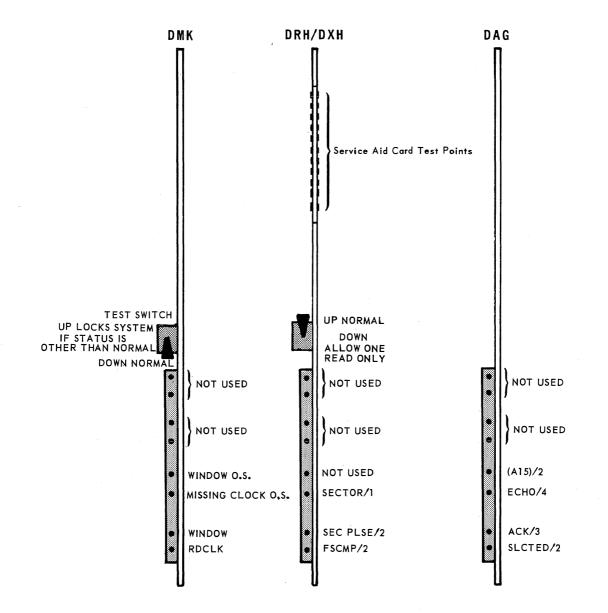

| 12-7.0  | LOGIC CARDS<br>12-7.1 DDC<br>12-7.2 DMK<br>12-7.3 DDJ<br>12-7.4 DAG<br>12-7.5 DRH/DXH<br>12-7.6 DCF<br>12-7.7 DLL                                                                                                       | 12-22<br>12-22<br>12-22<br>12-24<br>12-25<br>12-26<br>12-27<br>12-28 |  |

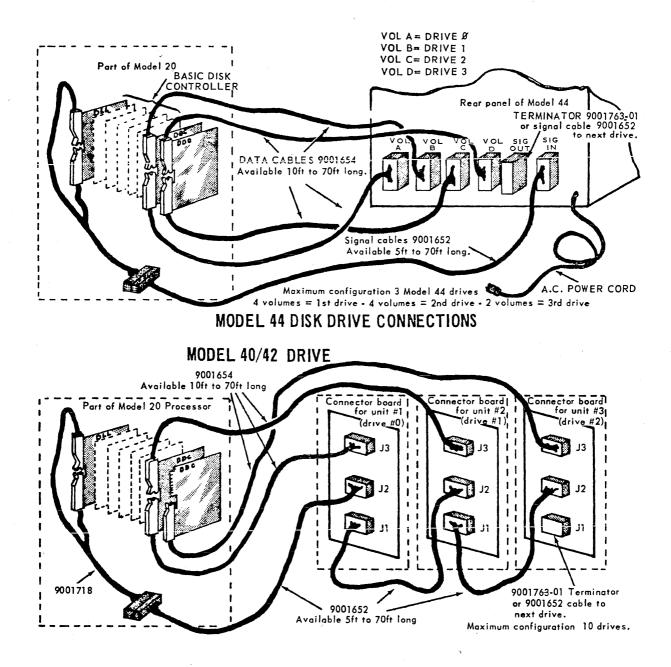

| 12-8.0  | INSTALLATION                                                                                                                                                                                                            | 12-28                                                                |  |

| 12-9.0  | GLOSSARY                                                                                                                                                                                                                | 12-30                                                                |  |

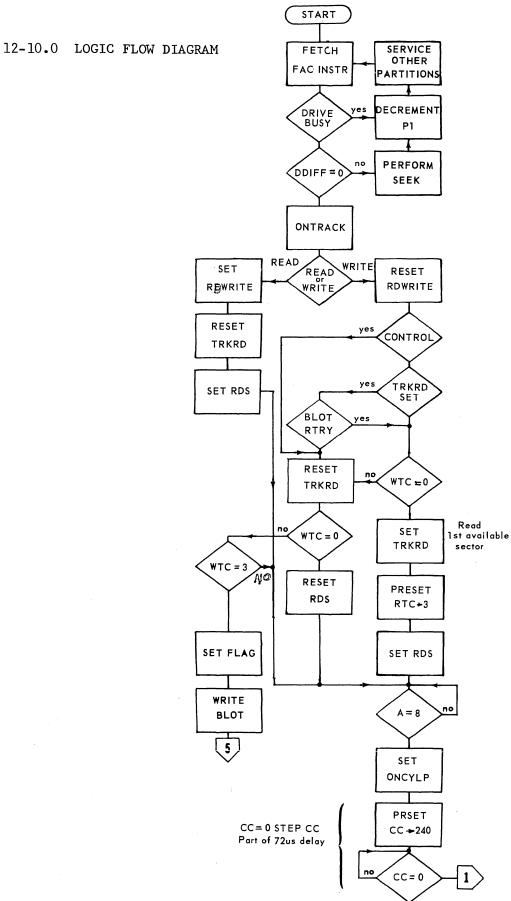

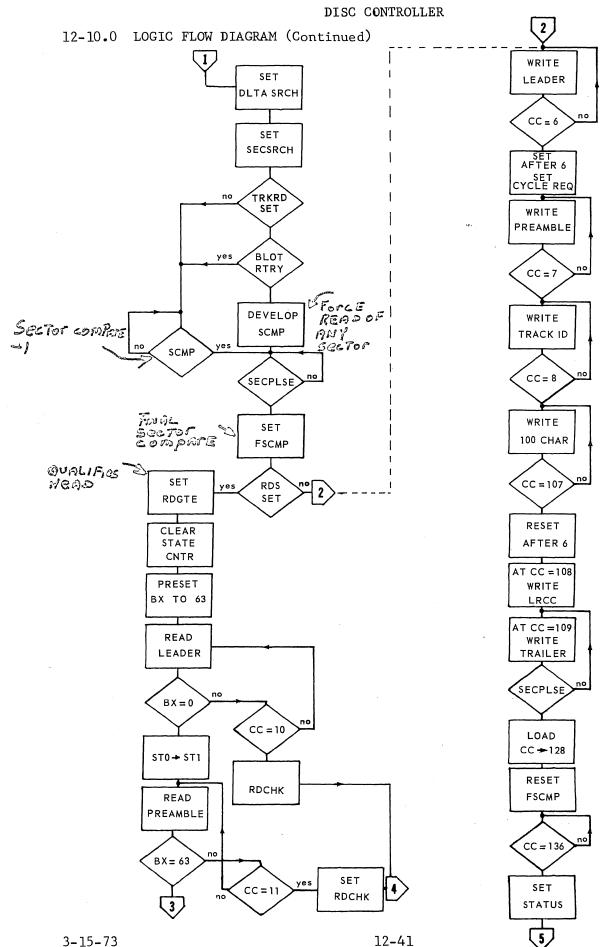

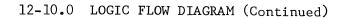

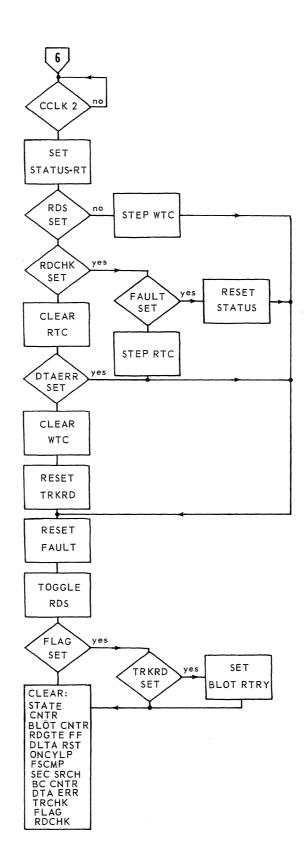

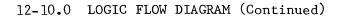

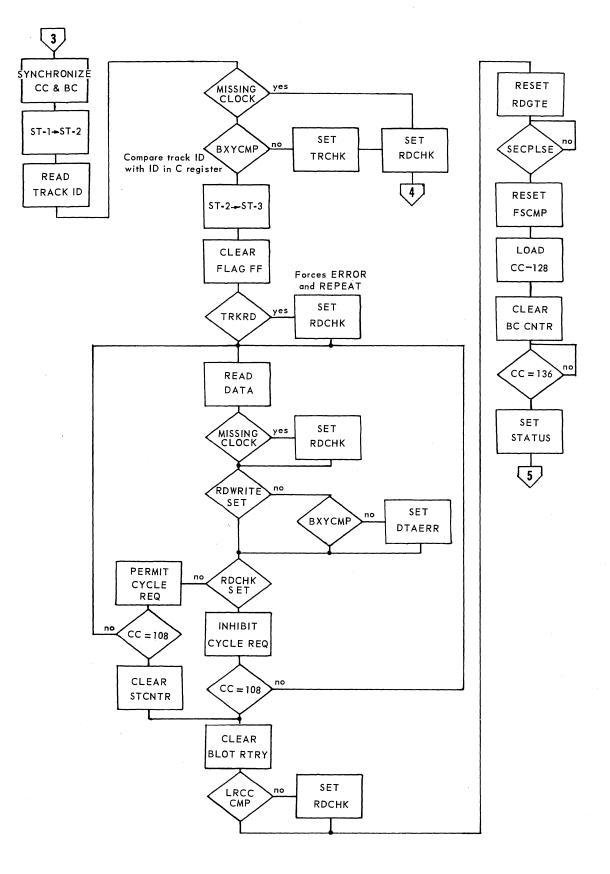

| 12-10.0 | LOGIC FLOW DIAGRAM                                                                                                                                                                                                      | 12-40                                                                |  |

| 12-11.0 | TEST POINTS                                                                                                                                                                                                             | 12-46                                                                |  |

|         |                                                                                                                                                                                                                         |                                                                      |  |

### SECTION 13, MTC CONVERSION

| 13-1.0 | INTRODU | CTION                  |  | 3 |

|--------|---------|------------------------|--|---|

|        | 13-1.1  | DESCRIPTION            |  | 3 |

|        | 13-1.2  | TAPE FORMAT            |  | 3 |

|        | 13-1.3  | PARITY CONSIDERATIONS  |  | 3 |

|        | 13-1.4  | TAPE TRACK ASSIGNMENTS |  | 4 |

| 13-2.0 | CODE CO | NVERSION               |  | 5 |

|        | 13-2.1  | 9-TRACK                |  | 5 |

|        | 13-2.2  | 7-TRACK                |  | 5 |

| 13-3.0 | OPERATI | ON                     |  | 6 |

|        | 13-3.1  | WRITE                  |  | 6 |

|        | 13-3.2  | READ                   |  | 6 |

|        |         |                        |  |   |

| SECTION 13 | , MTC CONVERSION (Continued)                 | PAGE     |

|------------|----------------------------------------------|----------|

|            | 13-3.3 WRITE CONTROL<br>13-3.4 STATUS        | 7<br>7   |

| 13-4.0     | LOGIC DESCRIPTION                            | 9        |

|            | 13-4.1 TC1 BOARD                             |          |

|            | 13-4.2 TCX BOARD                             | 10<br>11 |

|            | 13-4.3 TC3 BOARD                             | 11<br>12 |

|            | 13-4.4 ERAM BOARD<br>13-4.5 CONTROLLER CABLE | 12       |

|            | 13-4.6 TERMINATOR ASSEMBLY                   | 14       |

| 13-5.0     | LOGIC OPERATION                              | 14       |

|            | 13-5.1 TIMING                                | 14       |

|            | 13-5.2 GAP TIMING REQUIREMENTS               | 15       |

|            | 13-5.3 SELECT STATUS                         | 17       |

|            | 13-5.4 READ                                  | 18<br>21 |

|            | 13-5.5 WRITE<br>13-5.6 TAPE MOTION CONTROL   | 21       |

|            |                                              |          |

| 13-6.0     | INTERFACING SIGNALS                          | 23       |

|            | 13-6.1 FAC TO CONTROLLER, IN/OUT             | 24       |

|            | 13-6.2 TAPE DRIVE TO CONTROLLER, IN/OUT      | 25       |

| 2          |                                              |          |

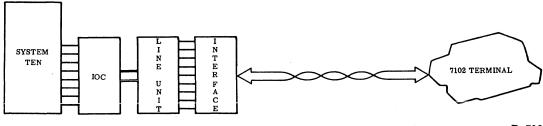

| SECTION 14 | , 7102 INTERFACE                             |          |

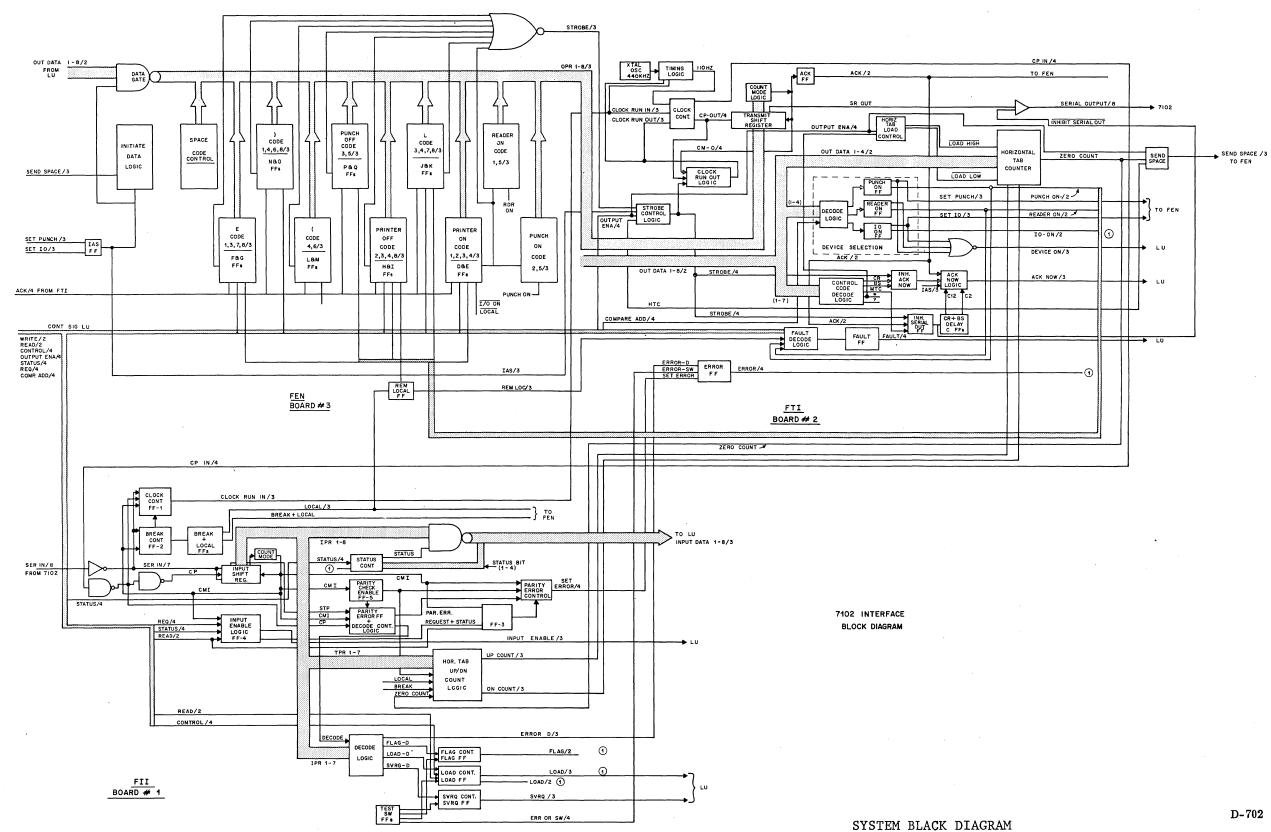

| A. INT     | RODUCTION                                    | 14-3     |

|            | INTERFACE 7102 TERMINAL COMMUNICATION        | 14-3     |

|            | 7102 INTERFACE/LINE UNIT COMMUNICATION       | 14-5     |

|            | INTERFACE SIGNALS                            | 14-6     |

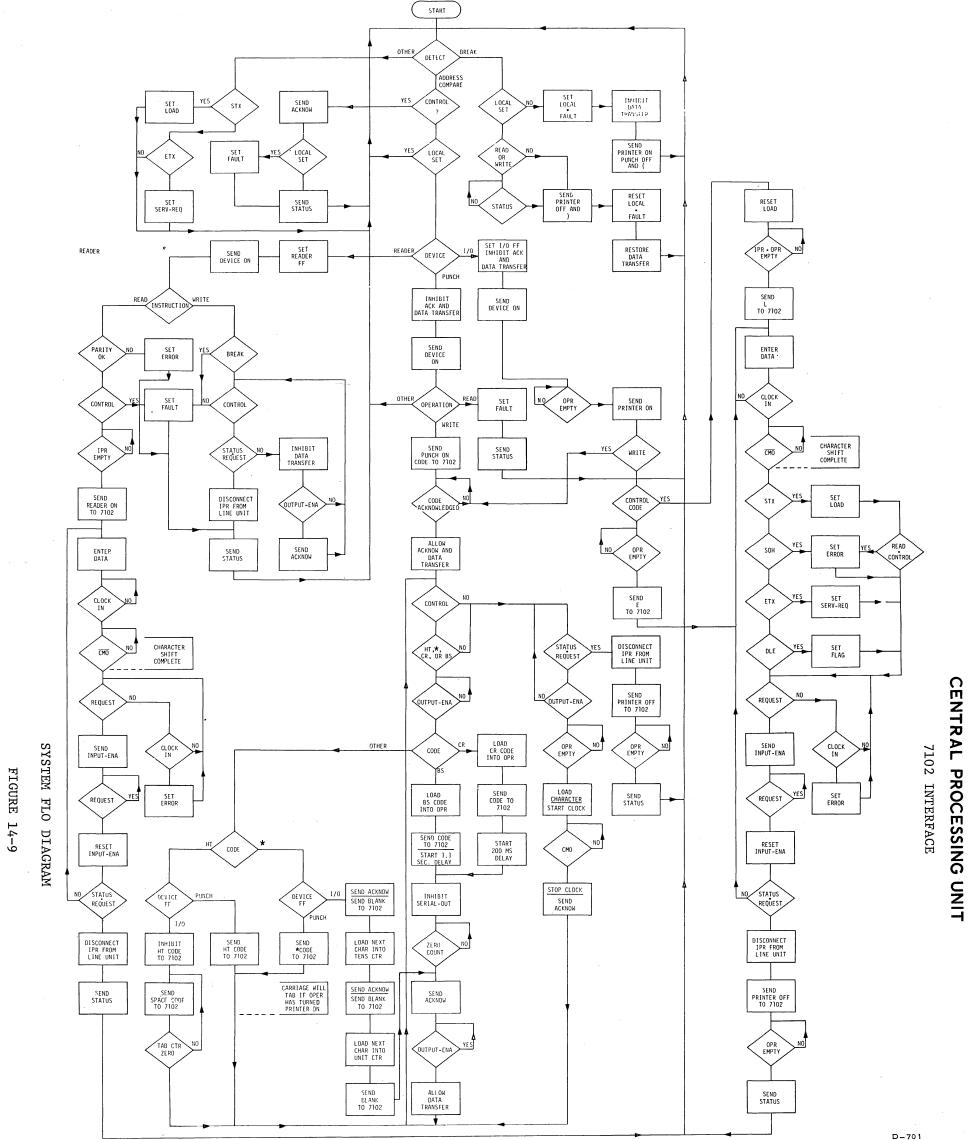

| B. OPE     | RATION                                       | 14-6     |

|            | BREAK AND LOCAL                              | 14-8     |

|            | PUNCH OR I/O (PRINTER AND KEYBOARD)          | 14-9     |

|            | READER                                       | 14-10    |

|            | RECEIVE                                      | 14-11    |

|            | TRANSMIT                                     | 14-12    |

|            | SPECIAL CODES                                | 14-14    |

|            | BACKSPACE AND CARRIAGE RETURN                | 14-16    |

|            | HORIZONTAL TAB                               | 14-16    |

|            | STATUS                                       | 14-17    |

| C. OPE     | RATOR REQUIREMENTS                           | 14-19    |

|            | POWER-ON                                     | 14-19    |

|            | LOCAL/NOT LOCAL                              | 14-19    |

|            | LOAD                                         | 14-19    |

|            | ENTER                                        | 14-19    |

|            | RESET                                        | 14–19    |

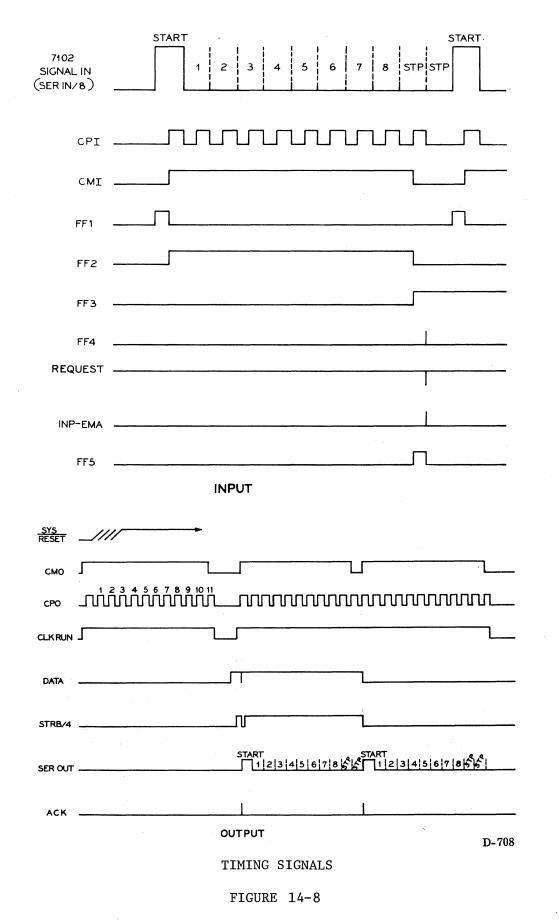

| D. TIM     | TNC                                          | 14-19    |

| D• TTN     | TIIQ                                         | 14-19    |

| SECTION 14, 7102 INTERFACE (Continued)                                                                            | PAGE                                      |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| E. LOGIC LOCATION<br>FII<br>FTI<br>FEN<br>HORIZONTAL TAB LOGIC LOCATION                                           | 14-20<br>14-20<br>14-20<br>14-20<br>14-20 |

| F. SIGNAL GLOSSARY                                                                                                | 14-21                                     |

| G. REFERENCE<br>7102 INTERFACE SIGNAL LIST                                                                        | 14-22<br>14-22                            |

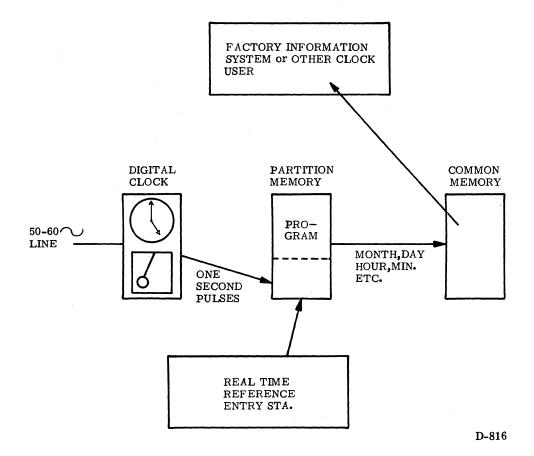

| SECTION 15, DIGITAL CLOCK                                                                                         |                                           |

| A. INTRODUCTION                                                                                                   | 15-3                                      |

| B. OPERATION<br>LOGIC ACTION                                                                                      | 15-3<br>15-4                              |

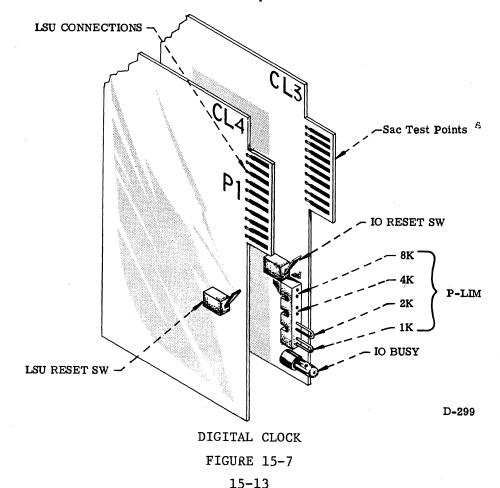

| C. MANUAL OPERATION                                                                                               | 15-13                                     |

| D. GLOSSARY                                                                                                       | 15-14                                     |

|                                                                                                                   |                                           |

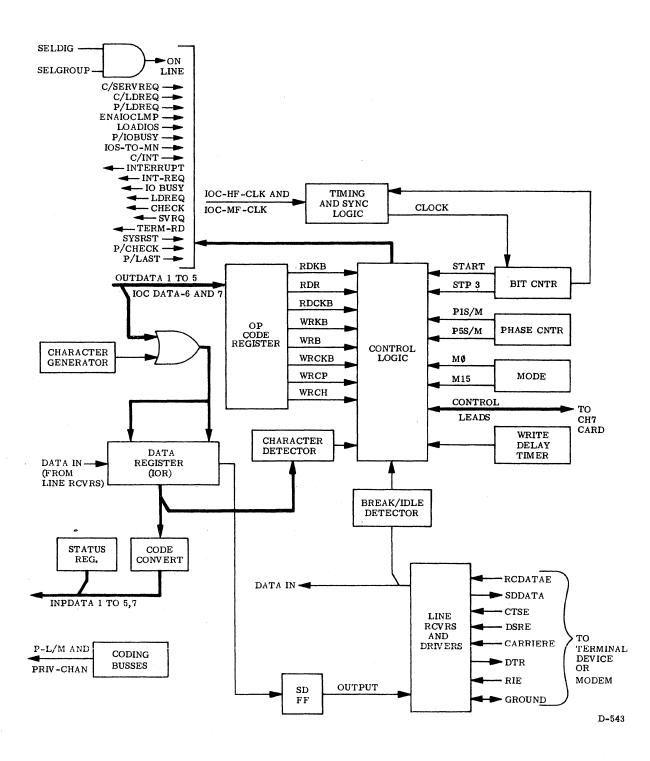

| SECTION 16, ASYNCHRONOUS TERMINAL ADAPTER                                                                         |                                           |

| 16-1.0 INTRODUCTION                                                                                               | 16-3                                      |

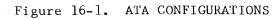

| 16-2.0 INSTALLATION<br>16-2.1 MANUAL SETTINGS                                                                     | 16-3<br>16-3                              |

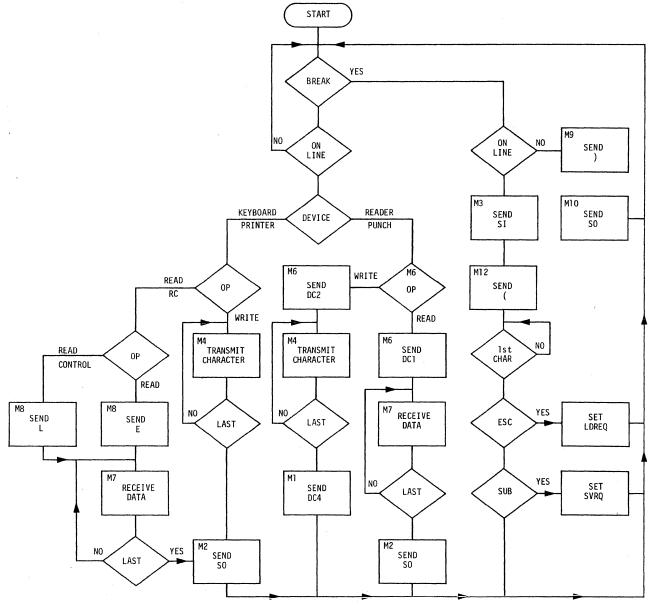

| 16-3.0 OPERATION<br>16-3.1 OPERATOR ENTRY<br>16-3.2 LOCAL/ONLINE<br>16-3.3 SERVICE REQUEST<br>16-3.4 LOAD REQUEST | 16-7<br>16-7<br>16-7<br>16-7<br>16-8      |

| 16-4.0 LOGIC SEQUENCES<br>16-4.1 TIMING<br>16-4.2 MODES<br>16-4.3 PHASES                                          | 16-9<br>16-9<br>16-9<br>16-11             |

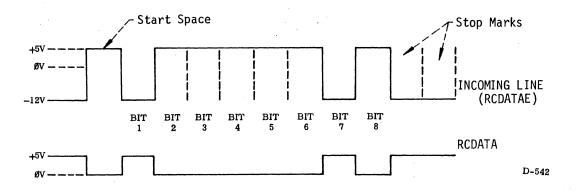

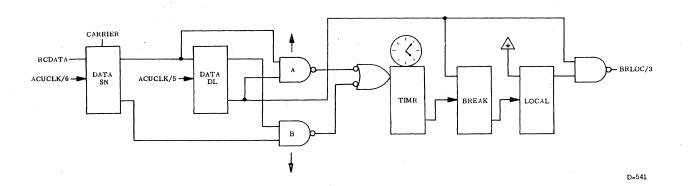

| 16-5.0 TTY TRANSMISSION<br>16-5.1 INTERFACE CONTROL LINES<br>16-5.2 BREAK DETECTOR                                | 16-12<br>16-12<br>16-12                   |

| 16-6.0 LOGIC OPERATION<br>16-6.1 SPECIAL CODES<br>16-6.2 STATUS INDICATIONS                                       | 16-15<br>16-17<br>16-18                   |

| 16-7.0 ATA GLOSSARY                                                                                               | 16-19                                     |

### REFERENCE

| Α.  | USASCII CODE                               | A-2              |

|-----|--------------------------------------------|------------------|

|     | CONTROL CHARACTERS                         | A-3              |

|     | GRAPHIC CHARACTERS                         | A-3              |

|     | DEFINITIONS                                | A-4              |

| B.  | GLOSSARY                                   | B-1              |

|     | TERMS                                      | B-1              |

|     | SIGNAL NAMES                               | B-3              |

| C-1 | L.O MODEL 20 PROCESSOR INSTALLATION        | C-1              |

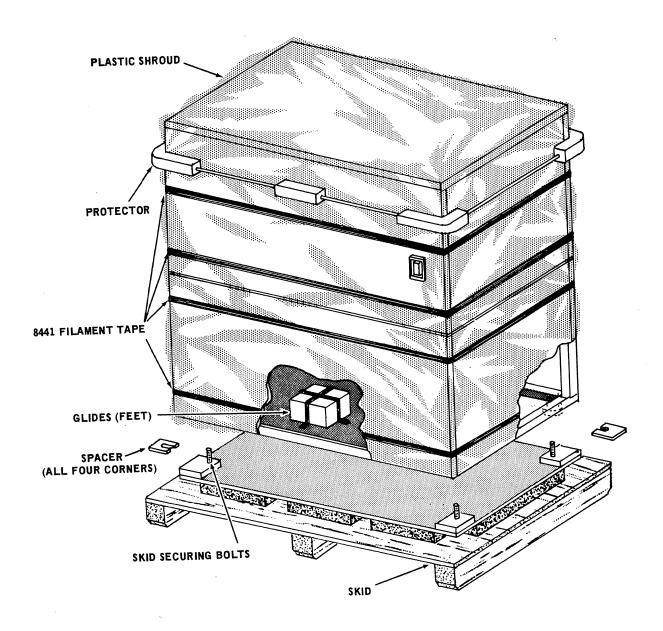

|     | C-1.1 DELIVERY INSPECTION                  | C-1              |

|     | C-1.2 UNPACKING                            | C-1              |

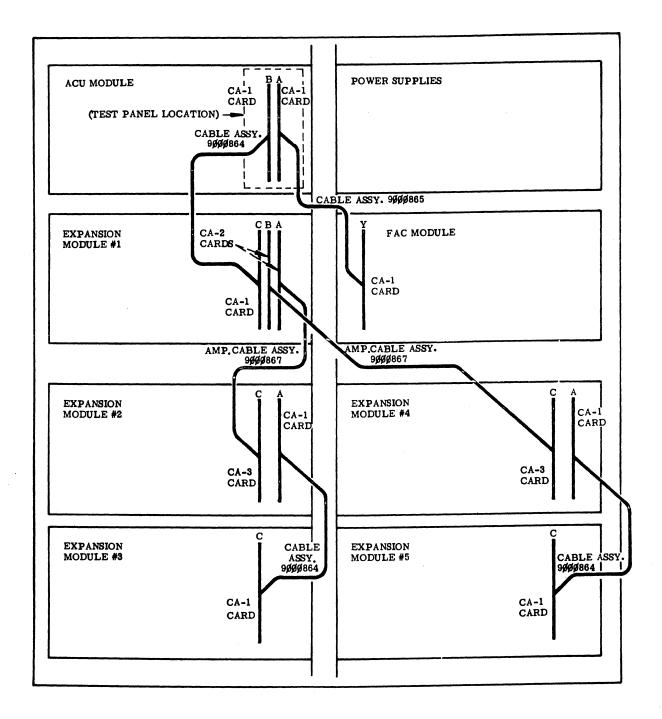

|     | C-1.3 INSTALLING EXPANSION MODULES         | C-1              |

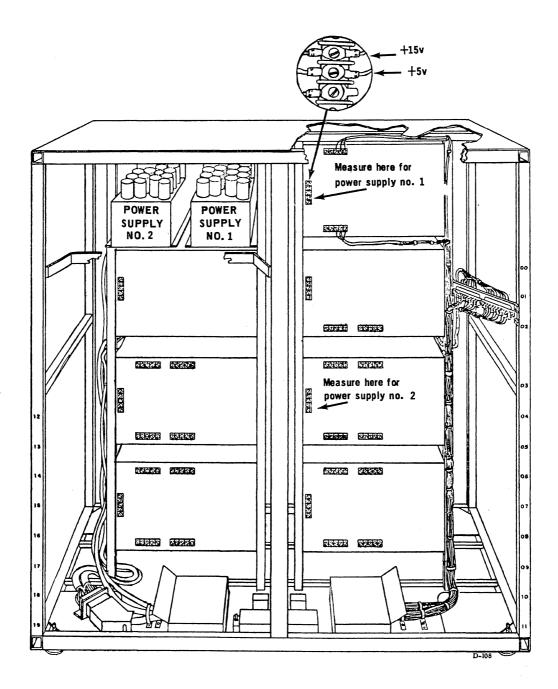

|     | C-1.4 INSTALLING POWER SUPPLY NO. 2        | C-6              |

|     | C-1.5 INSTALLING ADDITIONAL MEMORY MODULES | C-8              |

|     | C-1.6 INSTALLING ADDITIONAL IOC's          | C-8              |

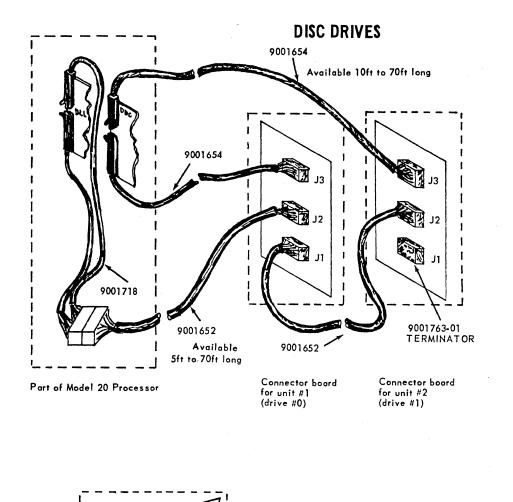

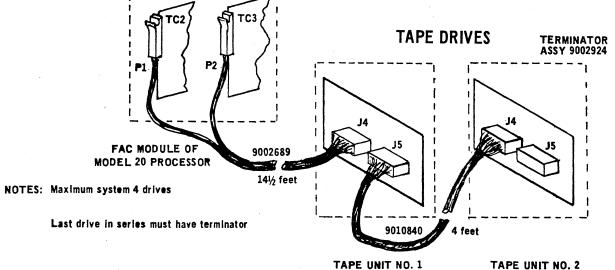

|     | C-1.7 CONNECTING FAC CABLES                | C-11             |

|     | C-1.8 PATCHING                             | C-13             |

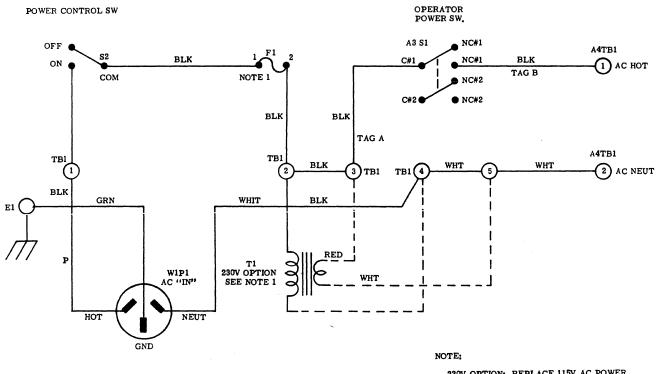

|     | C-1.9 POWER INPUT                          | C-14             |

|     | C-1.10 PRE ACTIVATION CHECKS               | C-14             |

| D.  | FIGURES AND TABLES                         | D-1              |

|     | INSTRUCTION WORD SUMMARY                   | D-1              |

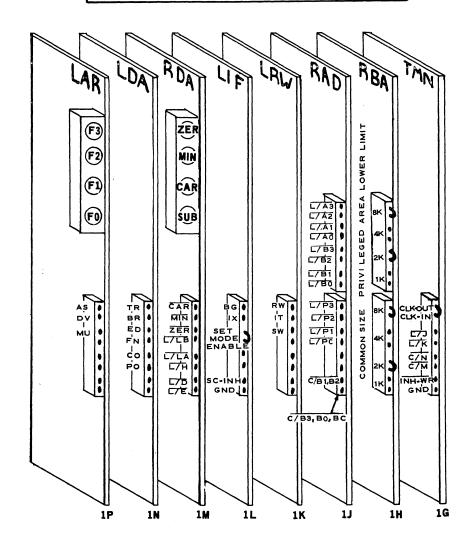

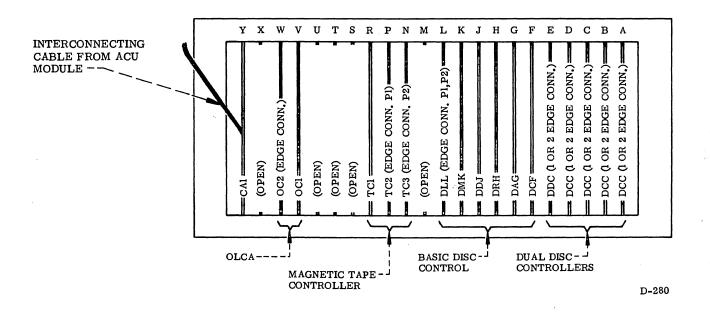

|     | ACU MODULE CIRCUIT CARD LOCATIONS          | D-2              |

|     | EXPANSION MODULE CIRCUIT CARD LOCATIONS    | D-2              |

|     | FAC MODULE CIRCUIT CARD LOCATIONS          | D-3              |

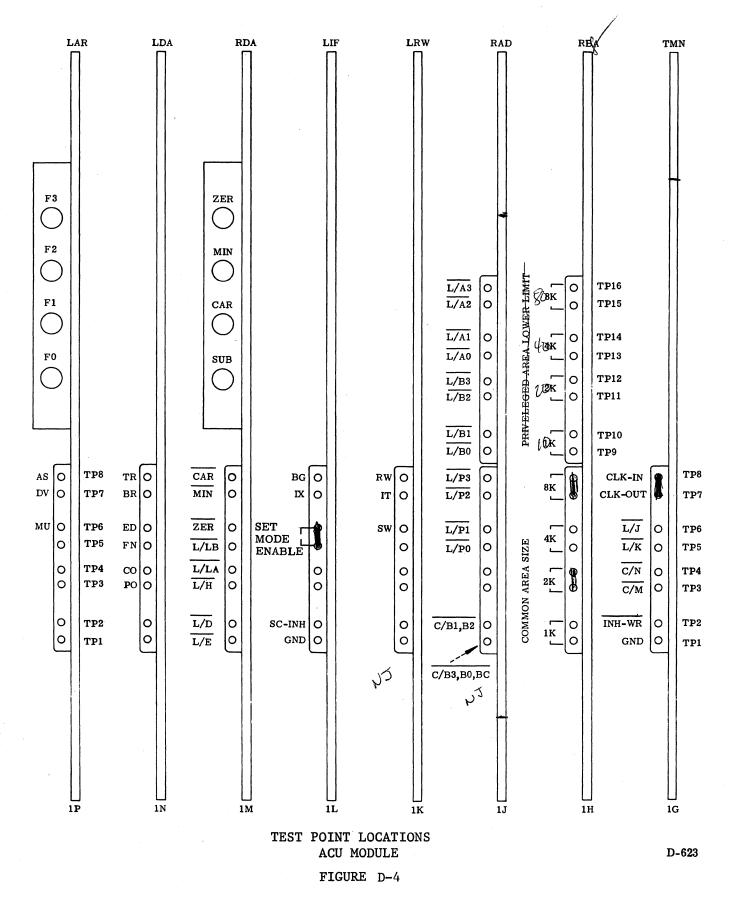

|     | TEST POINT LOCATIONS ACU MODULE            | D-6              |

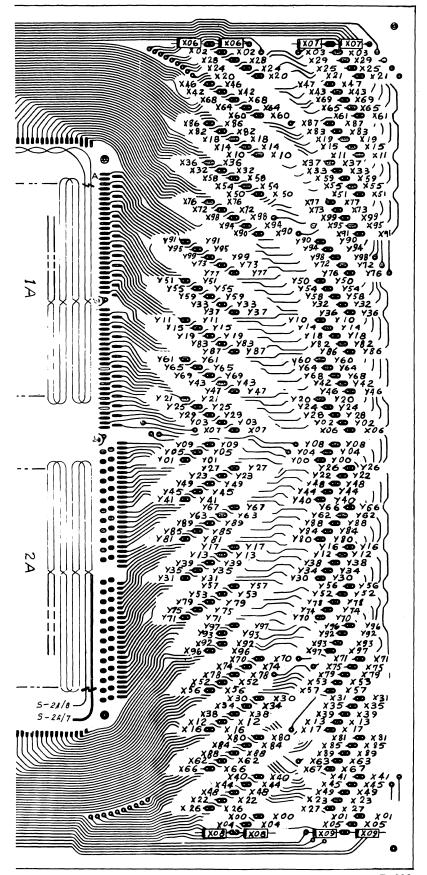

|     | MEMORY DIODE LOCATIONS                     | D <del>0</del> 7 |

| E.  | ENVIRONMENTAL REQUIREMENTS                 | E-1              |

|     | GENERAL REQUIREMENTS                       | E-1              |

|     | APPROXIMATE POWER DISSIPATIONS             | E-1              |

|     | FIRE PROTECTION                            | E-1              |

|     | THIRD GROUND WIRE                          | E-1              |

| F.  | ALGORITHMS                                 | F-1              |

|     | INTRODUCTION                               | F-2              |

|     | ADD/SUBTRACT (AS)                          | F-3              |

|     | BEGIN (BE)                                 | F-5              |

|     | BRANCH (BR)                                | F-9              |

|     | COMPARE (CO)                               | F-11             |

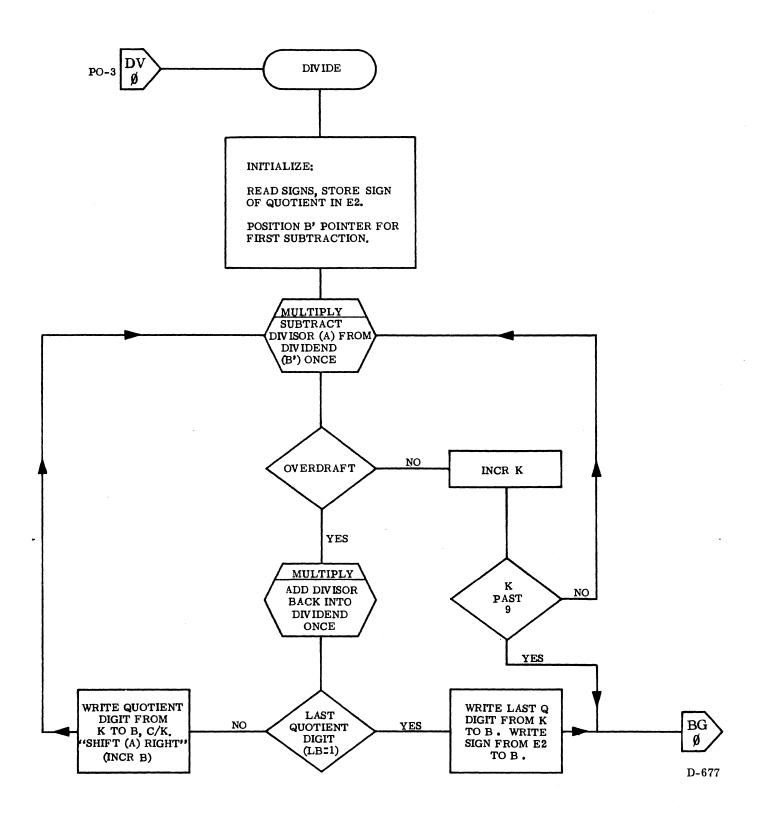

|     | DIVIDE (DV)                                | F-12             |

|     | EDIT (ED)                                  | F-15             |

|     | FORM NUMERIC FIELD (FN)                    | F-17             |

|     | INDEX (IX)                                 | F-18             |

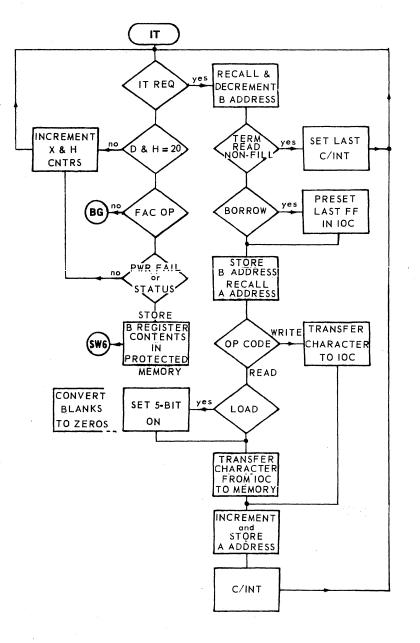

|     | INTERRUPT (IT)                             | F-20             |

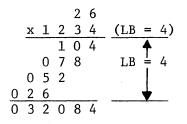

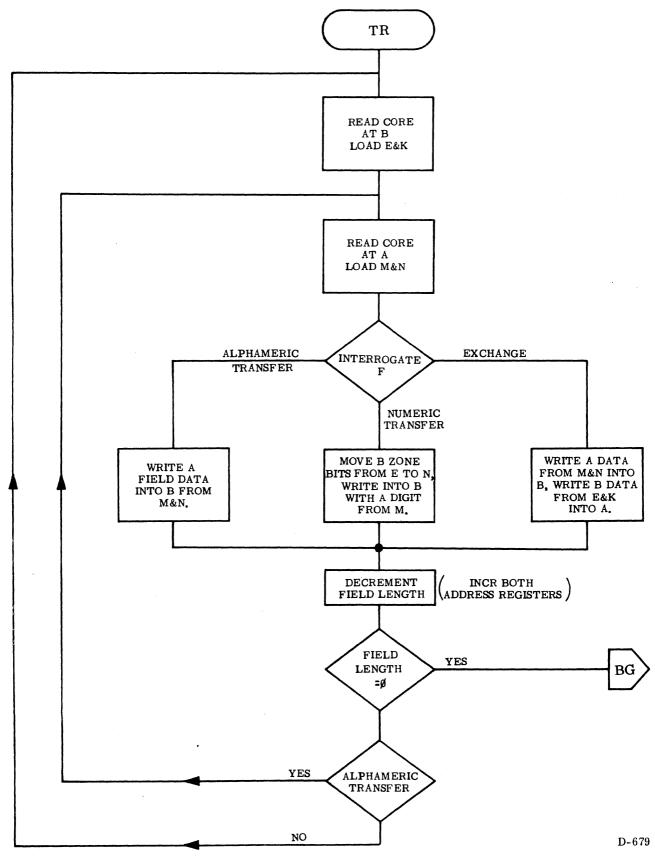

|     | MULTIPLY (MU)                              | F-24             |

|     | POSITIONING (PO)                           | F-27             |

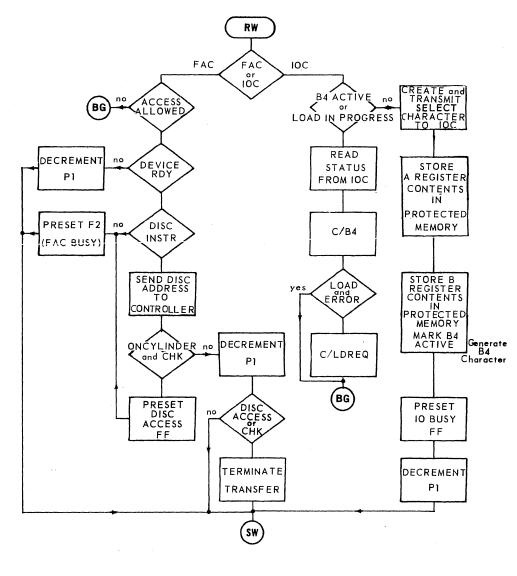

|     | READ/WRITE (RW)                            | F-28             |

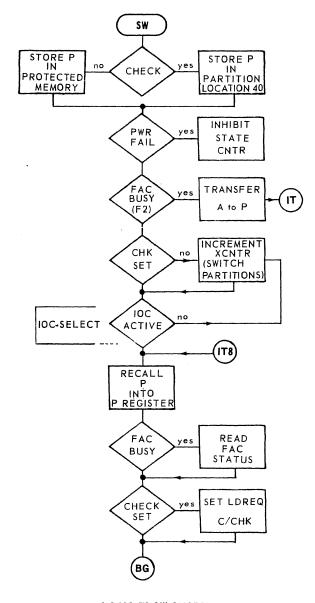

| 1   | SWITCH (SW)                                | F-32             |

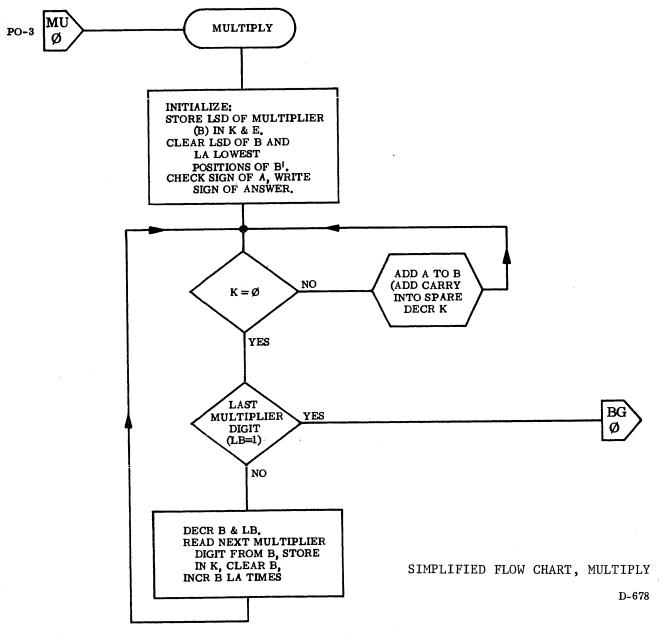

|     | TRANSFER (TR)                              | F-34             |

| REFERENCE (Continued)  | PAGE |

|------------------------|------|

| G. MAINTENANCE         | G-1  |

| REFERENCES             | G-1  |

| TOOLS REQUIRED         | G-1  |

| SAFETY PRECAUTIONS     | G-1  |

| PREVENTIVE MAINTENANCE | G-1  |

| CORRECTIVE MAINTENANCE | G-3  |

# INTRODUCTION

### SECTION 1

# CONTENTS

| 1-0.0 | GENERAL INTRODUCTION                                                                     | 1-3 |

|-------|------------------------------------------------------------------------------------------|-----|

| 1-1.0 | EQUIPMENT DESCRIPTION1-1.1MAIN MEMORY                                                    | 1-3 |

|       | 1-1.2ARITHMETIC AND CONTROL UNIT.1-1-3INPUT/OUTPUT CONTROLLERS.1-1.4FILE ACCESS CHANNEL. | 1-5 |

|       | EQUIPMENT CONSTRUCTION1-2.1ACU MODULE1-2.2EXPANSION MODULES                              | 1-7 |

INTRODUCTION

9-1-73

INTRODUCTION

### 1-0.0 GENERAL INTRODUCTION

This manual describes the organization and hardware operation of the Model 20, Model 21, 6800, and 101 processors. This section of the manual provides a general description of the equipment, its purpose, and relationship to other equipment. Later sections describe the principals of operation, installation, and maintenance information. Generally throughout this manual, the hardware portion of the Model 20, Model 21, 6800, and 101 is called the processor. Individual differences of the various models are described only where the differences affect the service of the equipment.

### 1-1.0 EQUIPMENT DESCRIPTION

The basic cabinet configurations of the Model 20/21, 6800, and 101 processors are shown in the artist's concept on the opposing page. The processors are businessoriented, stored program digital computers that combine small size, and medium performance, with the ability to service several independent users simultaneously.

The 6800 system and System Ten 101 are special versions of the basic Model 21 processor, and for service considerations, they can be treated as a Model 21 with limited memory and IOCs.

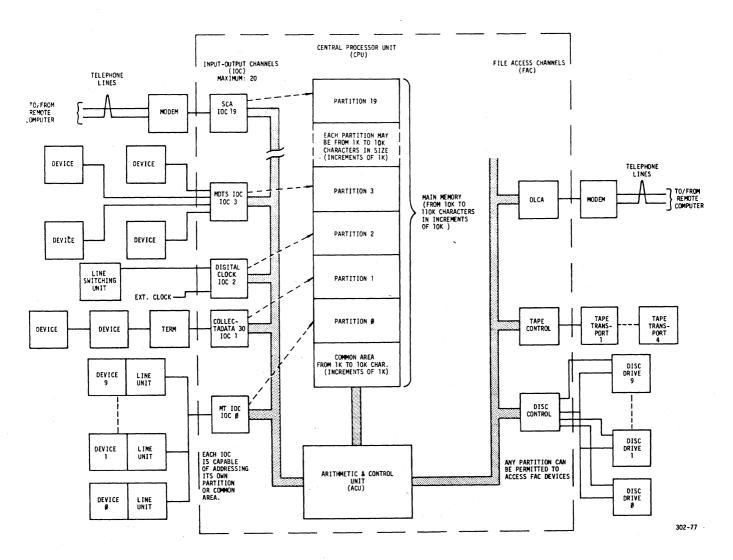

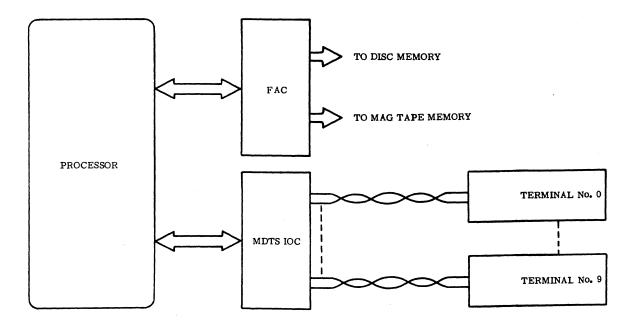

The processor hardware can be thought of as four seperate, but interworking units, Main Memory Arithmetic and Control Unit (ACU) File Access Channel (FAC) and Input/Output Controllers (IOC).

### 1-1.1 MAIN MEMORY

The main memory provides random access core storage for a minimum of 10,000 to a maximum of 110,000 6-bit characters (the 6800 system and 101 processor are limited to a maximum of 30,000 characters of storage in main memory). Memory modules can be added to a minimum system in increments of 10,000 characters each until the maximum capacity of the system is reached. Additional and/or redundant character storage is available through the file access channel to magnetic disc or tape units. All transfers into or out of the main memory are performed by the arithmetic and control unit.

The main memory is electrically divided into user areas (called partitions) that correspond to one IOC for each partition. The size of each partition is determined by hardware jumpers on its IOC card, and can be from 1000 characters to 10,000 characters each. However, the total of all memory allotments cannot exceed the amount of memory that is contained in the system.

In addition to user partitions, the main memory has a common portion that is available for use by any of the partitions (IOCs). The size of common memory is governed by jumpers on the RBA/RBX card within the ACU, and is adjustable from 1,000 characters to 10,000 characters for the Model 20, 29,000 characters for the 6800 and 101 systems, and 65,000 characters for the Model 21. The Model 21 can be patched for a greater number, but is limited by software standards to 65K. All partitions are serviced in sequence, and only one character at a time can enter or exit main memory.

### INTRODUCTION

### 1-1.2 ARITHMETIC AND CONTROL UNIT

The Arithmetic and Control Unit (ACU) fetches instruction and data from memory, operates on the data, and stores the results in main memory. The ACU also transfers data between main memory and the IOCs or FAC. All interface to main memory is through the ACU. Each user (IOC) is selected by the ACU in numerical sequence, and monopolizes the unit for a short time. The ACU limits this monoply to 37.5 ms, after which time, the first successful branch in the software program will cause a switch to the next partition. During power up and power down, the ACU stores the necessary information to allow normal processing to continue without re-loading program after each power interruption.

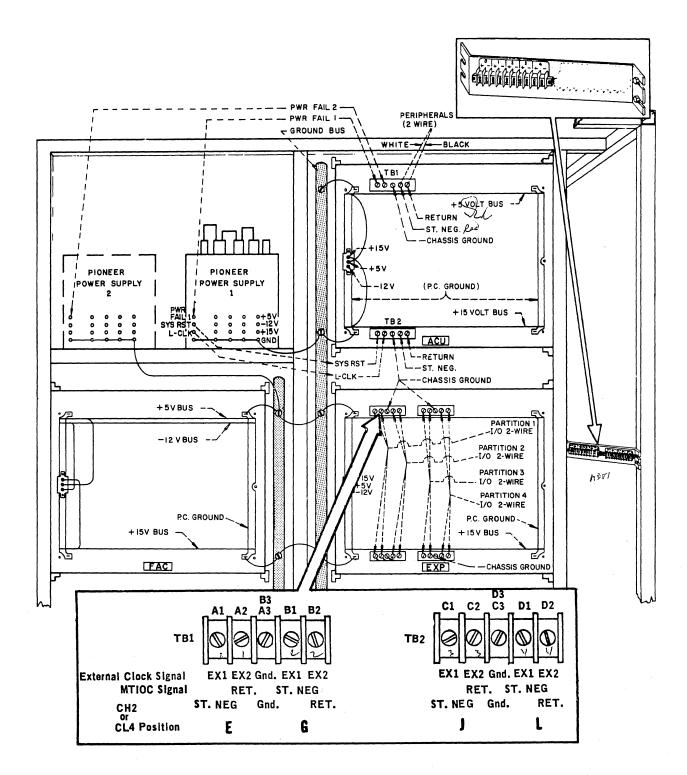

The block diagram below shows the relationship of the ACU to main memory, the IOCs, and the FAC. Each system will vary greatly in requirements, and only the general elements are shown in the illustration.

### EXAMPLE OF A SYSTEM CONFIGURATION

INTRODUCTION

### 1-1.3 INPUT/OUTPUT CONTROLLERS

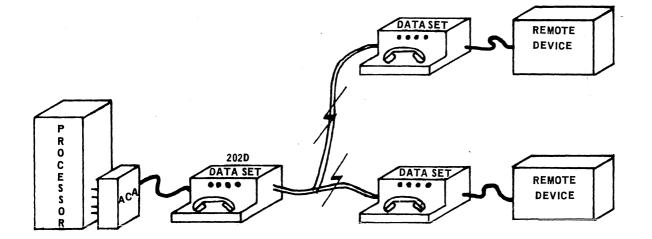

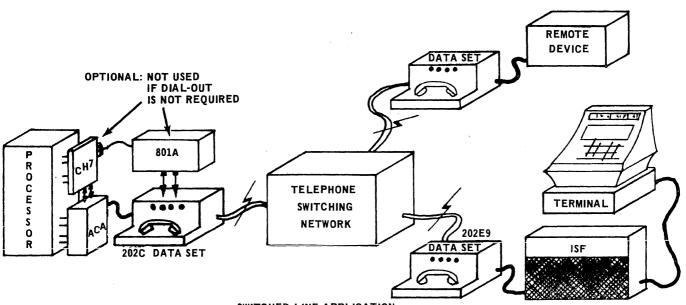

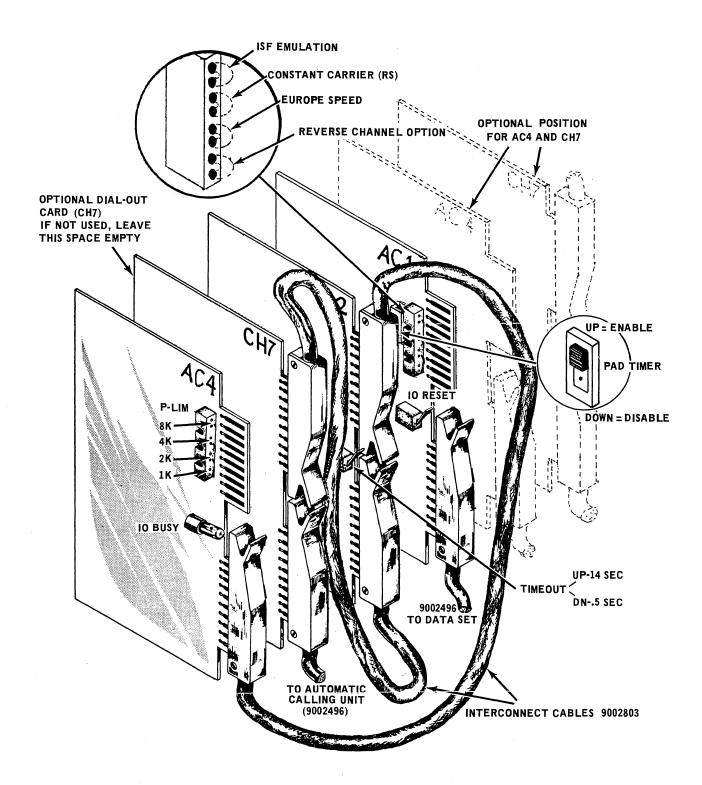

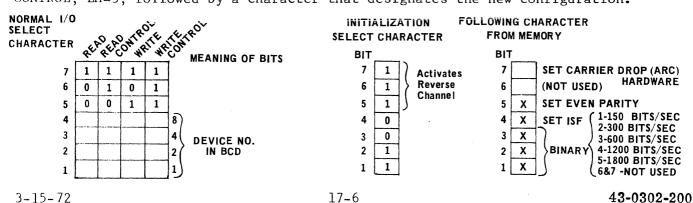

The input/output controllers (IOCs) provide communication between the ACU and the various peripheral devices, or through communication lines to remote computers. The type of IOC that is used for a partition depends upon the user device that is needed. A general list of the currently available IOCs is given below; a detailed description of each IOC is given in a later section of this manual.

| ІОС Туре                                       | Circuit Card<br>Identification      | User Device(s)                                                                                                          |

|------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| Multi-terminal<br>IOC (MTIOC)                  | СН1, СН2                            | Workstation (typebar printer or GRT), Card<br>Reader, Paper Tape Reader, Line Printer,<br>Card Punch, Paper Tape Punch. |

| MDTS IOC                                       | CX3, C <b>X</b> 4<br>(CH3, CH4)     | Retail Terminal, Manufacturing Information<br>System.                                                                   |

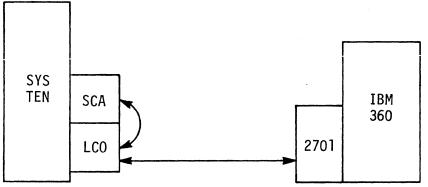

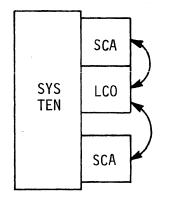

| Synchronous<br>Communication<br>Adapter (SCA)  | CH5, CH6, CH8<br>(CH7 if auto dial) | Remote computer or other synchronous device.<br>Must use modem if long distance is involved.                            |

| Asynchronous<br>Communication<br>Adapter (ACA) | ACl, AC2, AC4<br>(CH7 if auto dial) | Remote asynchronous devices, including<br>computers. Must use modem if long distance<br>is involved.                    |

| Asynchronous<br>Terminal<br>Adapter (ATA)      | TAl, TA2<br>(CH7 if auto dial)      | Model 7102 or similar OEM devices.<br><i>MoD 30, TTY 33</i>                                                             |

| Digital Clock                                  | CL3, CL4                            | External Clock Interface and/or Terminal switching Unit.                                                                |

| Collectadata<br>30 IOC                         | 101, 102                            | Collectadata 30 Terminals.                                                                                              |

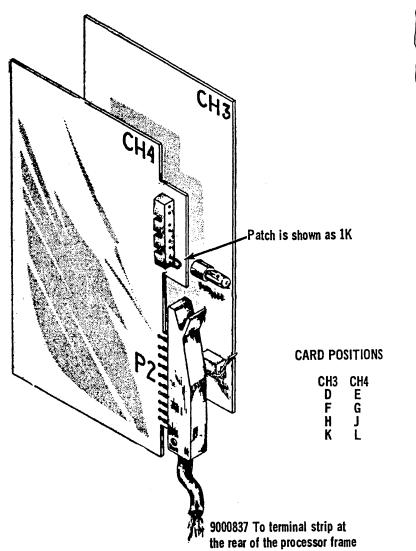

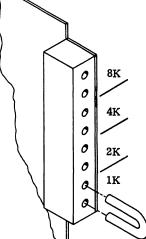

Each IOC is capable of addressing any character within its memory partition, or the common area of memory. IOC partition size is determined by hardware jumpers that are located on one of the IOC cards (see the individual IOC description for patching procedures). Partition size is always 1,000 to 10,000 characters, in IK increments. Common area in the Model 20 is limited to 10,000 characters, but the 6800, and 101 systems can have all memory as common, except for the minimum IK for each IOC that is installed. The Model 21 hardware follows the same rules, but because of software limitations, should not be patched for a common size that is greater than 65K.

The Model 20 has a Priveledged area of common memory that, if patched by jumpers on the RBA card, allows only those IOCs that are patched for Priveledged access into that portion of memory. This feature applies only to the Model 20, and does not apply to the Model 21, 6800, or 101 systems.

INTRODUCTION

### PROCESSOR MODULE ARRANGEMENT

### INTRODUCTION

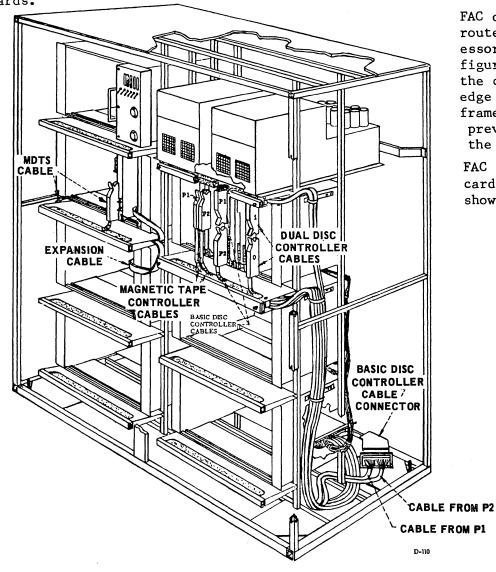

### 1-1.4 FILE ACCESS CHANNEL

The File Access Channel (FAC) provides interface to magnetic disc storage and magnetic tape storage. The FAC contains the controllers that direct and control the magnetic storage devices under direction of program and the ACU. Data is transferred to disc units in groups of 100 characters each, preceded by a leader and track ID, and followed by a trailer. Magnetic tape transfers are not limited to a specific number of characters, and may vary considerably in data field length, with controlling or identifying characters preceding and following the data.

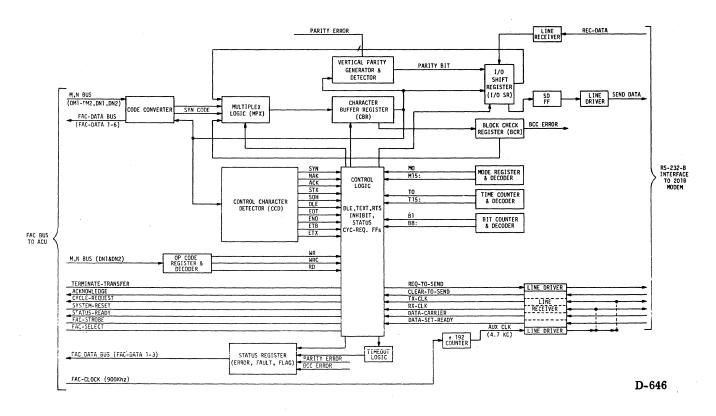

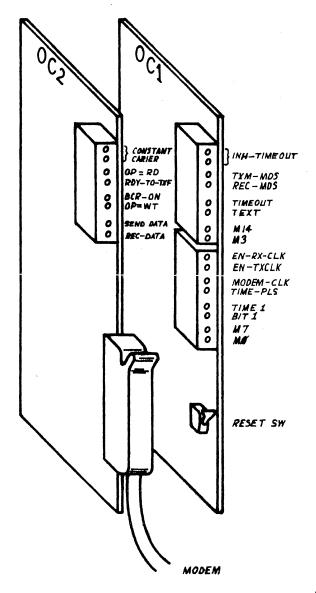

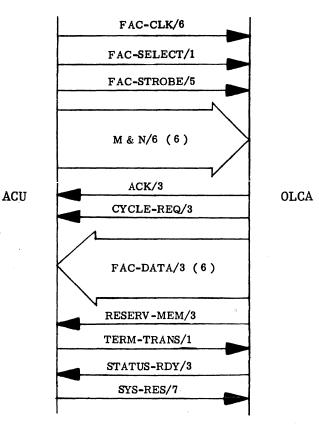

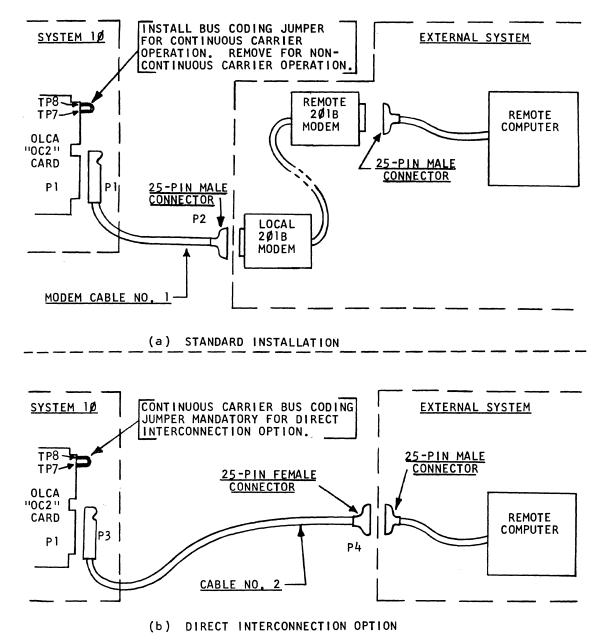

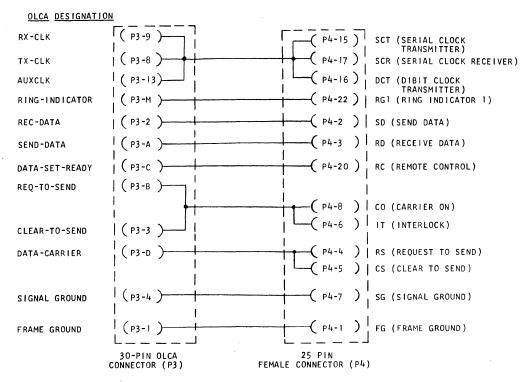

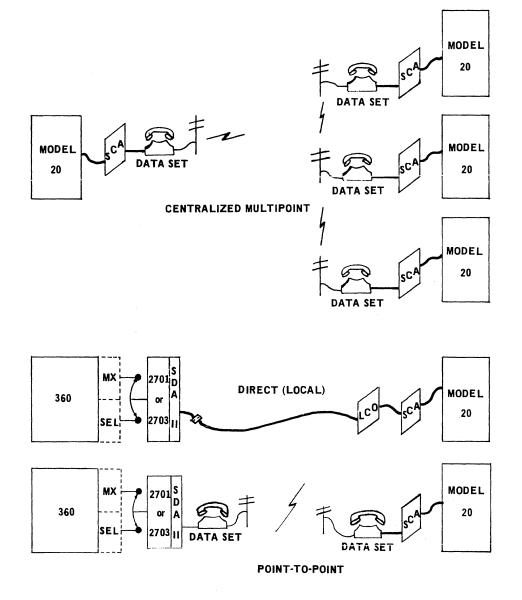

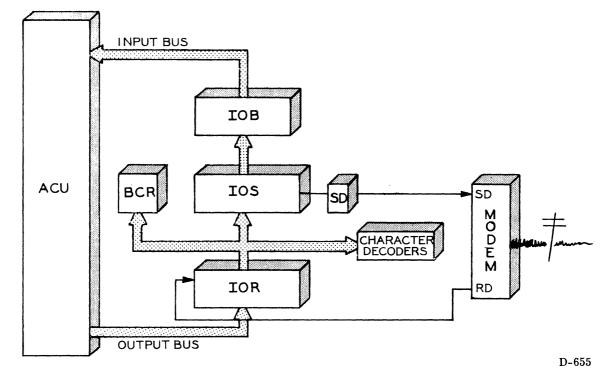

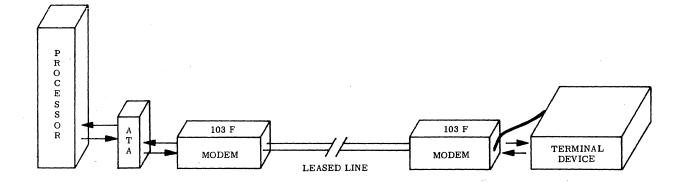

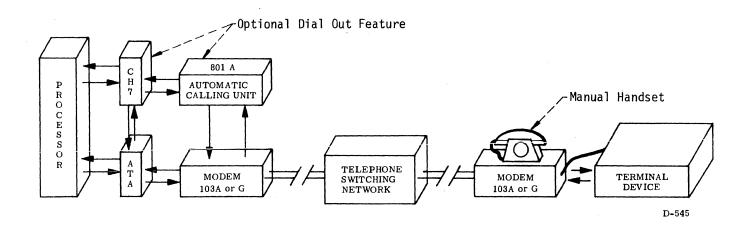

In some processors the FAC may also include an on-line communication adapter (OLCA) that is used for synchronous communication to another computer. This device may be cabled to the other computer if local, or it may have a modem that inter-faces to either a leased line or the dial telephone system.

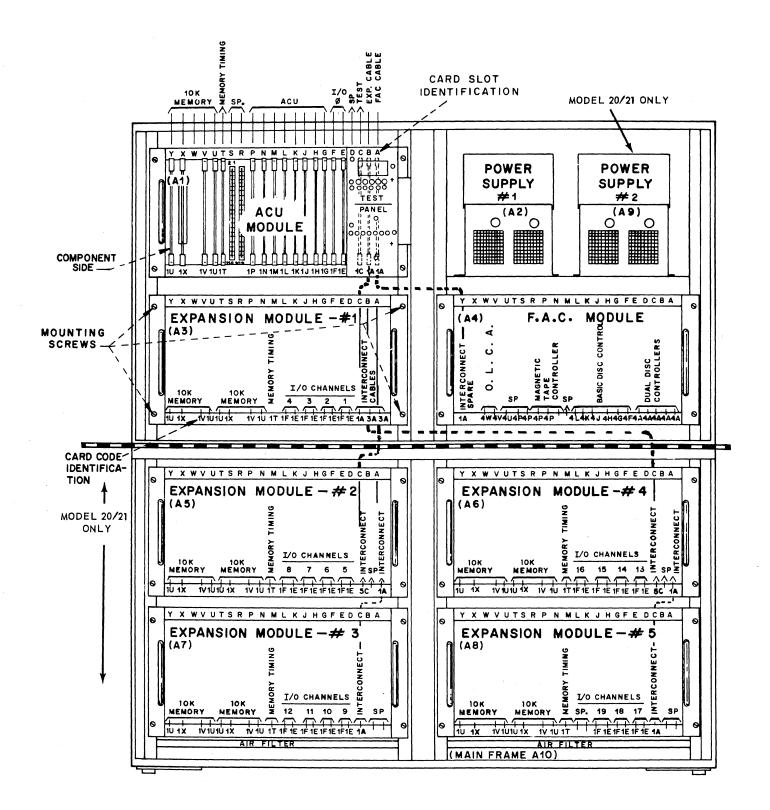

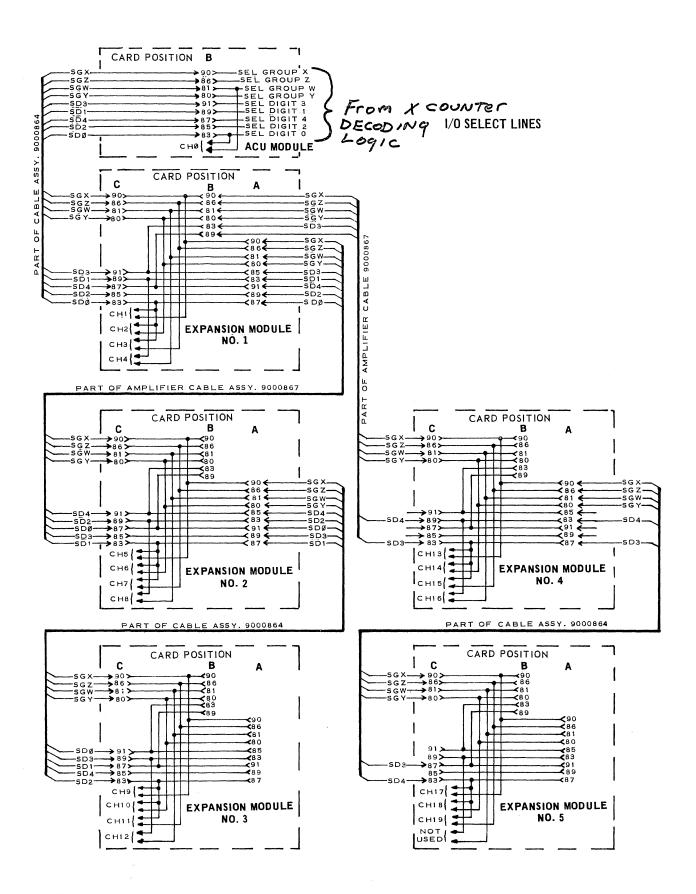

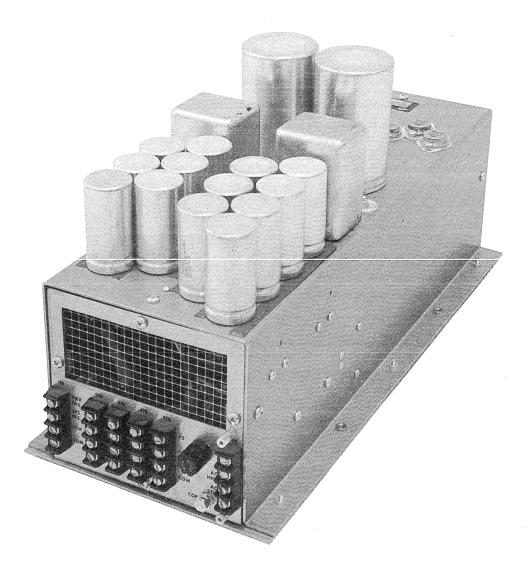

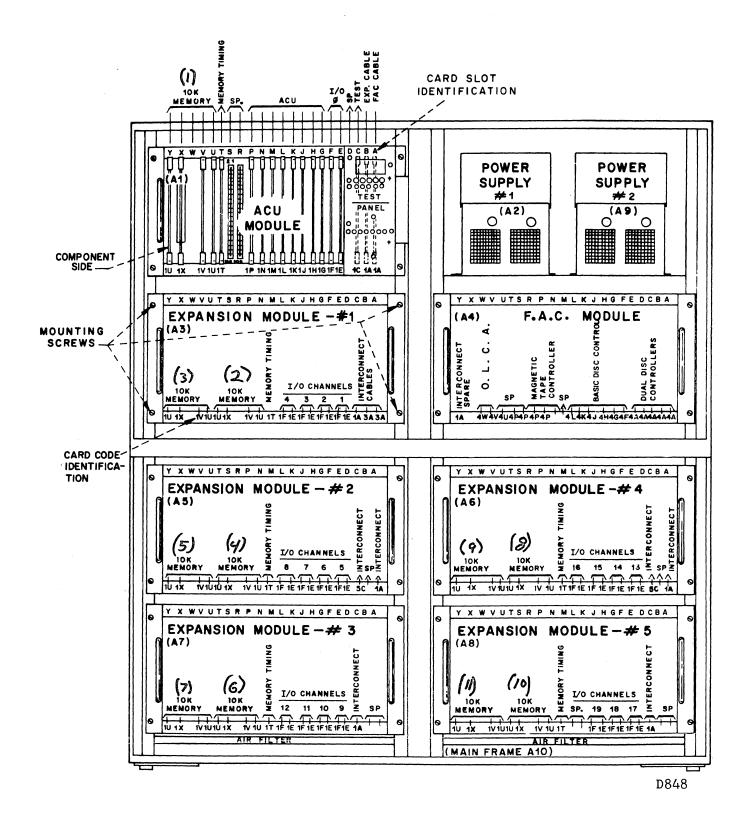

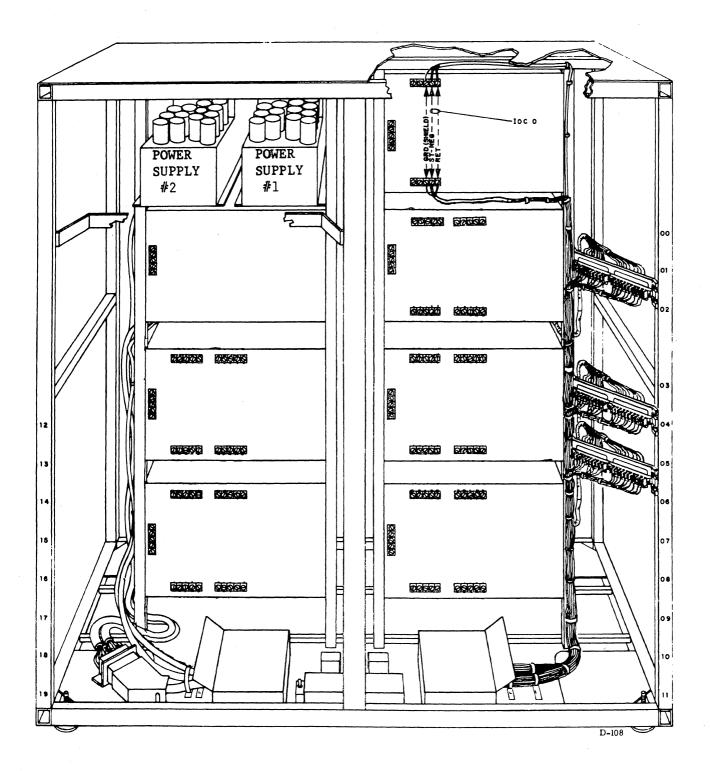

### 1-2.0 EQUIPMENT CONSTRUCTION

The Model 20/21 processor is physically a main frame that houses up to seven modules and two power supplies. The 6800 and 101 systems have only three modules and one power supply. The figure on the opposing page shows the module arrangement for the processor main frame. The 6800 and 101 processor modules are confined to the area above the large dotted line. And because of the limited need, the 6800 and 101 have only one power supply. The general construction of the modules provides for up to 22 circuit cards to be installed into rear connectors that directly interface to the motherboard. The modules are interconnected by cables that connect to designated card slots (shown by dotted lines on the illustration). The four basic modules are:

> ACU module Expansion module FAC module Power supply

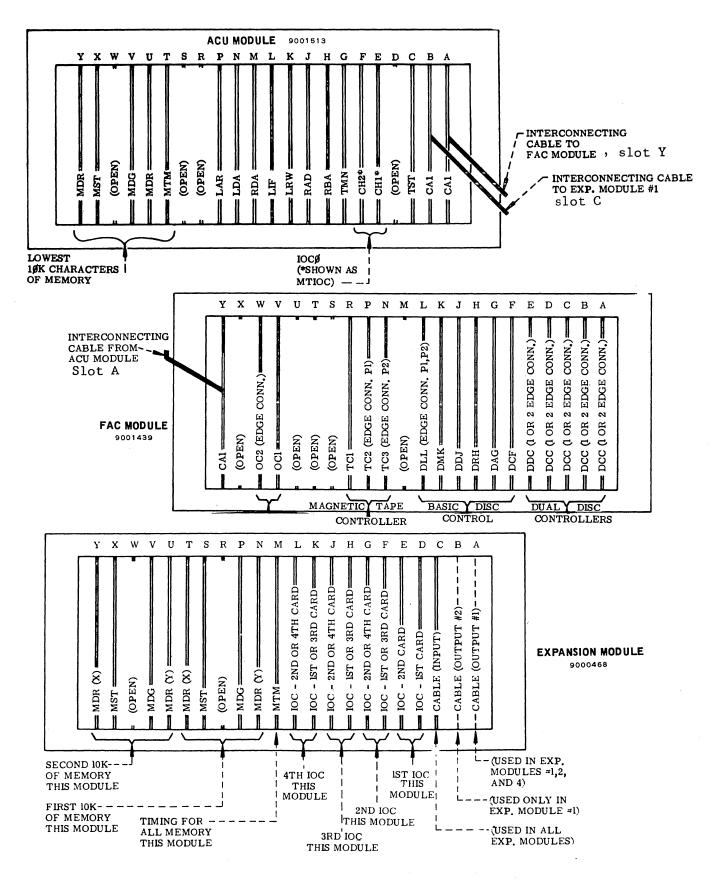

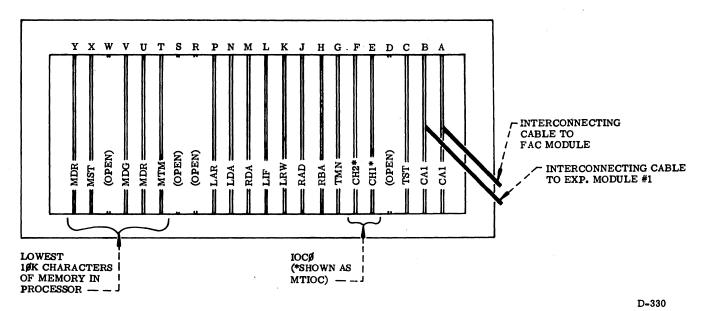

### 1-2.1 ACU MODULE

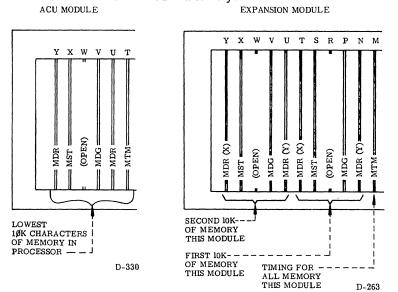

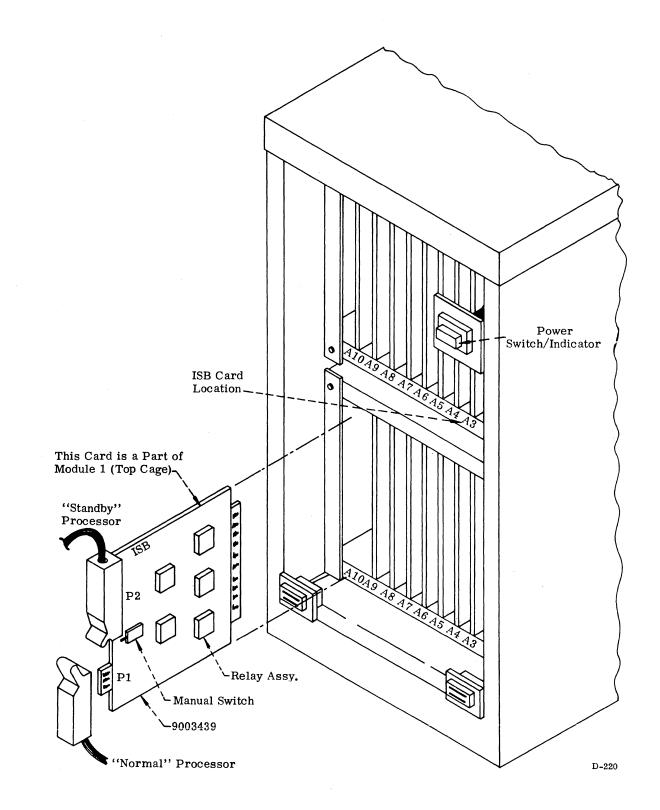

The ACU module contains nine circuit cards that comprise the ACU (including the Test Panel), five cards that make up the minimum memory (10K storage and the associated circuits), two expansion cable slots, and one IOC position (two slots). The IOC within the ACU module is partition zero, the only partition that is capable of performing the SET MODE instruction.

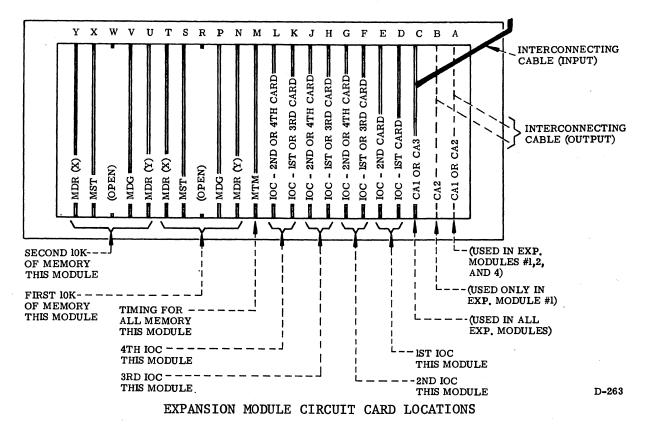

### 1-2.2 EXPANSION MODULES

Expansion modules are used to increase the total capacity of the processor. Each expansion module can add 20K more memory, and four IOCs. The memory capability can be added in 10K units, but should be placed in the lower addresses first (M,P, S,T and U). In the full size processor (model 20/21) the memory should be added to the lower numbered expansion modules first.

The IOCs have no direct effect on the memory expansion, and can be installed at random. However, the partition number that is assigned to an IOC is determined by the physical position within the processor. If an IOC position is left open, and filled at a later time, all higher partitions are moved up in memory, making it necessary to re-load the programs in those higher partitions.

MEMORY USE, INSTRUCTION AND DATA FORMATS

### SECTION 2

### CONTENTS

| 2-1.0 | MEMORY | USE, INSTRUCTION AND DATA FORMATS |

|-------|--------|-----------------------------------|

|       | 2-1.1  | CHARACTER USE AND STRUCTURE       |

|       | 2-1.2  | DATA WORD AND FIELD               |

|       | 2-1.3  | INSTRUCTION WORD                  |

| 2-2.0 | MEMORY | ORGANIZATION                      |

|       | 2-2.1  | PROTECTED AREA                    |

|       | 2-2.2  | INDEX REGISTERS                   |

### MEMORY USE, INSTRUCTION AND DATA FORMATS

INTERNAL CODE

### CHARACTER STRUCTURE

### ASCII CODE CHART

### MEMORY USE, INSTRUCTION AND DATA FORMATS

### 2-1.0 MEMORY USE, INSTRUCTION AND DATA FORMATS

The Arithmetic and Control Unit (ACU) performs arithmetic operations, manipulates data, and provides access to main memory by the IOCs and FAC. These operations are directed by instructions that are stored in memory and retrieved by the ACU. The instructions are executed in sequence except for branch instructions that may cause the ACU to begin operation at a different memory address. Under the control of a stored program and/or hardware, the ACU can commence or stop executing any program in storage, it may alter an instruction or replace the entire program, it may request additional inputs or perform subroutines called for by condition codes, or may provide abnormal condition indication (status). During the instruction fetching portion of the ACU operation, the ACU examines the contents of memory in groups of ten characters (actually two groups of five each). It is because of this that all instructions (words of ten characters each) must begin at an address that is evenly divisable by ten. Other than this restriction, program and/or data can reside anywhere in the IOC partition of memory, or anywhere in common memory, except the protected area.

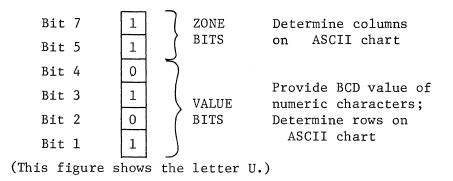

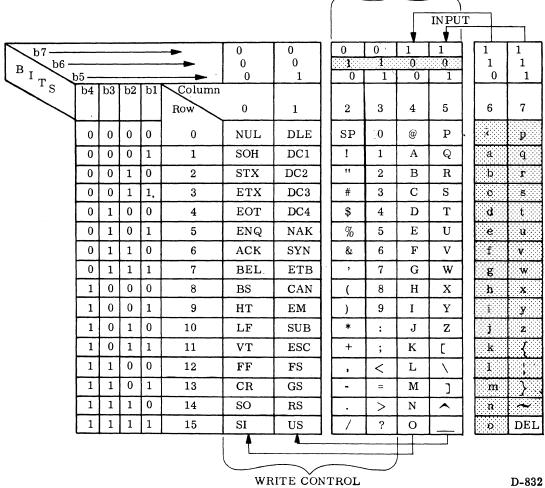

### 2-1.1 CHARACTER USE AND STRUCTURE

The ACU uses and stores in memory a six-bit character. Since the ASCII code is a seven bit code (plus parity), the IOC device must convert the incomming characters to the internal ASCII sub-set, and the outgoing characters back to the full ASCII equivalent. The ASCII chart on the opposing page has been modified to show the conversions that are made for the ACU hardware.

Normally, the 6- and 7- bits of the processor internal code are opposite for the alphabetic characters. Therefore, when characters are entered into main memory, the 6-bit is dropped. The result is the loss of distinction between upper and lower case letters, and the loss of the control characters in columns 0 and 1.

Characters that are transfered from memory to an IOC device are reconstructed by inverting the 7-bit from storage, and placing that bit in the 6-bit position. The 7-bit remains unchanged, and the character is recognized as the upper case letter of the ASCII code that was stored. When an instruction calls for a (WRITE) control code, the 6-bit is created as for a normal character, but then the 7-bit is forced to zero. This causes characters that were stored in memory as those in columns 4 and 5 to be recognized as the control codes from columns 0 and 1. (Example: a WRITE Control C transmits an ETX)

The lower four bits of a character provide a numeric value from 0 to 15, corresponding to the sixteen rows of the ASCII chart. The 5- and 7- bits determine the column within the chart, and are called zone bits.

The use of a character determines its structure and categorizes it into one of two types: data or instruction. A data character is the basic unit of a word or field that is meaningful to the operator; an instruction character is the basic unit of a ten-character word and/or a many word program that is meaningful to the ACU hardware. Data words may be entered at any selected location within the partition or common area of memory, and may vary greatly in length. Instruction words are always stored at an address that is evenly divisible by ten, and they are always ten characters long. All memory addressing is by character position. The six individual bits of the character are addressed simultaneously, and are considered as one memory location.

9-1-73

43-0302-100 © Singer Decisions Machines

MEMORY USE, INSTRUCTION AND DATA FORMATS

### 2-1.2 DATA WORD AND FIELD

A data word or field consists of one or more contiguous (continuously-adjacent) characters that are treated by an instruction as a single unit. A data field or word can be located anywhere in the memory that is available to the I/O device, and has no hardware restrictions that require an even or divisable-by-ten address. It is addressed by the leading character position which resides at the lowest numbered character position in memory. As the field is read (or written into) the ACU increments the internal addresing structure one count for each character. In an arithmetic instruction, the data word is a decimal number, with the leading character as the most significant digit. In that case, the ACU adjusts the addressing before the number is read so that the least significant digit is acted upon first. In an arithmetic instruction, the internal memory addressing is counted down as the word is read.

### 2-1.3 INSTRUCTION WORD

Instruction words are the basic units that comprise the computer program. The address of each instruction word must be evenly divisable by ten (this is unlike the data word which can have its leading character at any location). One other condition is imposed upon all instruction words: The lower four bits of any character within an instruction word must not represent a BCD value that is greater than a decimal nine. Specific details of the instruction word operation and conditions are given in section 3 of this manual.

An instruction word is always ten characters long, and causes the processor to perform the specified operation. To perform this operation, the ACU will step through hardware routines that resemble response to software instructions. However, these routines are internal, and are performed without the aid of external program. Each instruction word consists of modular groups of bits which identify data fields, define what is to be done with the fields, set up the conditions under which the operation will be performed, and specify the location into which the answer or result will be placed.

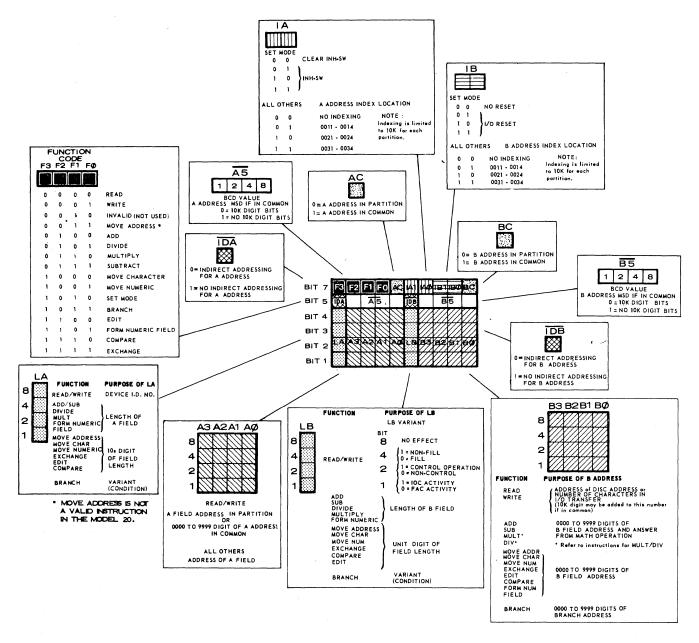

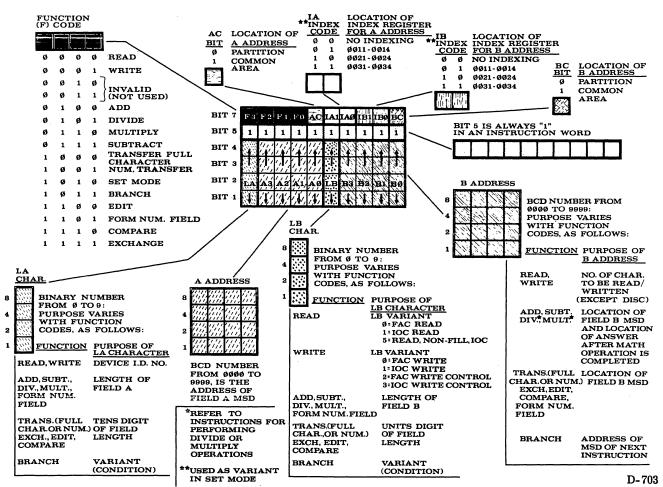

The figure at the right shows a composite block of the instruction word bits. The basic units of the instruction word are expanded upon in the surrounding blocks.

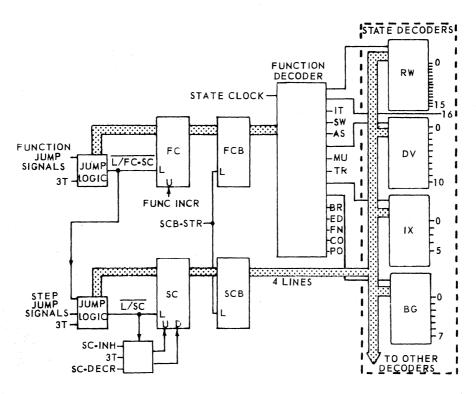

The basic portion of the instruction word is the Function Code (also called the Operation, or "Op" Code) that sets up the initial conditions for the operation that is to be performed. During the operation, the hardware sequencing will change the internal function code many times. Each ACU function, such as READ, WRITE, BRANCH, etc., is performed under hardware direction that is implimented by changing the internal function code. These internal changes are completely automatic, and depend upon the original function code, and the conditions that are encountered during the performance of the instruction.

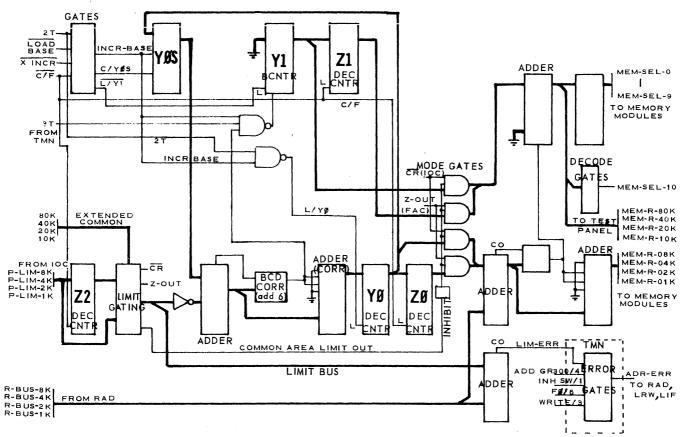

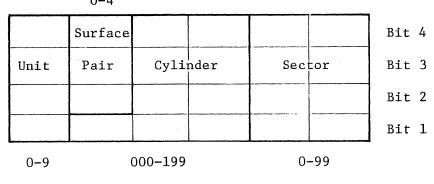

Data that is involved in the performance of an instruction is usually identified by the A and B addresses. The exception to this is the disc instruction, where the B address tells the location of the disc address in memory. The AC and BC bits indicate whether the A or B address is in partition memory or in common memory. In all of the processors except the model 20, there is the possibility of an A5 and B5 character. These are the MSD or 10K digit of the address, if the address is in the

MEMORY USE, INSTRUCTION AND DATA FORMATS

common area of memory. Notice that unlike the main portion of the address, the A5 and B5 characters are structured laterally within the instruction word.

The Model 20 processor is limited to 10K addressing, even in common, because of a requirement that the 5 bits of all characters in an instruction must be ls. The Model 20 hardware will set a data check condition if this requirement is not met. A data check will be set in all models if the lower four bits of any instruction character exceed a binary 9.

The LA and LB characters identify the device number when performing a READ or WRITE operation, specify BRANCH conditions, or the length of field for other instructions.

MEMORY USE, INSTRUCTION AND DATA FORMATS

### 2-1.3 INSTRUCTION WORD (Continued)

The index codes, IA and IB, direct the hardware to one of three automatically located addresses in memory. The numeric portion(lower four bits) of the four characters at the specified location are then added to the A and/or B address (as specified by IA and IB) before the A and B addresses are used. The four-character areas of memory that are located automatically by the IA and IB bits are considered to be registers, even though the area is not restricted by hardware to that use. The index register areas of memory can be used for data or instructions, without restrictions (other than the normal restrictions that apply to all memory).

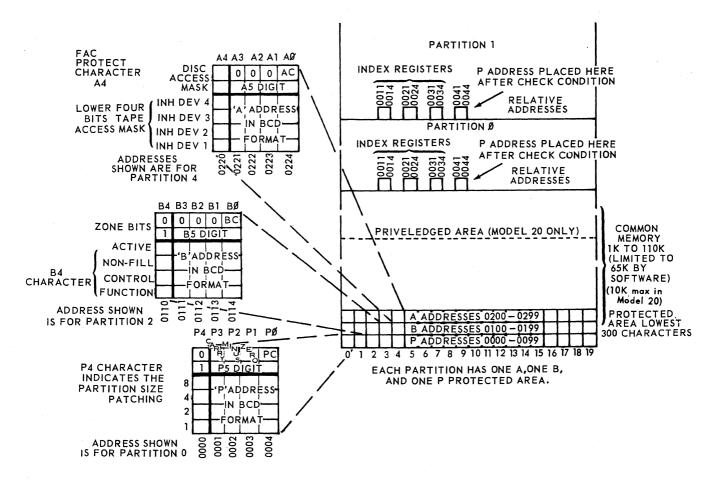

### 2-2.0 MEMORY ORGANIZATION

The figure below is a graphic representation of a portion of the processor memory. The large divisions represent the partitioning into common and individual user areas of memory. The small blocks within the individual partitions represent the index register areas of that partition. The address of these registers is hardware assigned relative to the zero address of the partition. For example, the first index register within a partition begins at the eleventh character position, and includes the characters to the fourteenth character position. If the size of a lower numbered partition is changed, or if the size of common is changed, the physical location of the index register is changed, but the relationship to the zero address of the partition remains the same.

### MEMORY USE, INSTRUCTION AND DATA FORMATS

### 2-2.1 PROTECTED AREA

The first three hundred character positions in memory are called the protected area. This area is contained within the Common area of memory, and is used by the ACU as a temporary storage area for pertinent information about the instruction that is in progress in each partition, or the instruction address that will be used when the partition is next serviced by the ACU.

The protected area can be examined by any partition, but can only be altered by entry from the Test Panel, or by partition zero under the SET MODE instruction. Normally the protected area is used only by the ACU as a placemarker for partitions that are not being serviced. If the processor power is failing, the information from the active partition is placed into protected memory. Because the program addresses for all the other, inactive, partitions are already stored, processing begins again after a power failure without a loss of data.

The A and B addresses are stored in the protected area during Read and Write operations. The stored A and B addresses are used by the ACU during Interrupt cycles of the Read or Write operation. Each time an A or B address is used in this way, it is advanced by one number, placing the next character address in position to be used for the next interrupt cycle. This procedure is explained in greater detail under Read and Write, in section 3 of this manual.

Each I/O channel is assigned a partition in memory (by the physical position of the I/O cards), and is also associated with one A address, one B address, and one P address in protected memory. The explanations that follow for the A, B, and P addresses describe the uses within one partition. The uses and restrictions apply equally to all partitions.

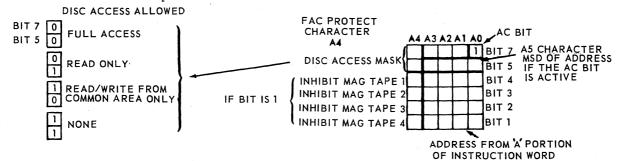

### A ADDRESS

The A address area (0200 to 0299) contains a series of five-character A addresses, one for each I/O. The A address, as mentioned above, is from the A portion of a READ or WRITE instruction word. However, the first character (A4) of the protected A address is the FAC Protect Character. This character (A4) is not altered by the ACU (except by special operator or program intervention) and controls which of the FAC magnetic tape or magnetic disc devices can be used by the associated partition. The A4 character can be examined by addressing a one character WRITE from: the partition number times five, plus 200 (with the AC bit active). The A4 character is entered into protected memory, either from the Test Panel, or from partition zero under a SET MODE instruction. If the A4 character is any other than a space code (all zero bits) one or more of the FAC devices is restricted from use by the partition. The example below shows the meaning and restrictions that are contained in the five-character A protected area.

MEMORY USE, INSTRUCTION AND DATA FORMATS

### 2-2.1 PROTECTED AREA

### A ADDRESS (Continued)

Most of the characters in the A protected area are from the instruction word, and follow the rule that the lower four bits cannot exceed a binary nine. The A4 character is an exception to this rule, and can be any value, and is not checked by the ACU for a data fault. A-protected is not used by an FAC instruction.

The A address example that is shown below illustrates the bits that might be

| 0120 1200 BIT |   |   |    |   |   |  |  |

|---------------|---|---|----|---|---|--|--|

| 0             | 0 | 0 | 0  | 1 | 7 |  |  |

| 0             | 1 | 1 | 1  | 1 | 5 |  |  |

| 1             | 0 | 1 | 0. | 0 | 4 |  |  |

| 1             | 0 | 0 | 1  | 0 | 3 |  |  |

| 0             | 1 | 0 | 0  | 0 | 2 |  |  |

| 1             | 1 | 1 | 0  | 1 | 1 |  |  |

used in a customer situation. From the location of the characters in the protected area, it is determined that the user, in this case, is partition 2. The device or devices on this partition are allowed full access to the disc storage within the system. However, only magnetic tape drive number 2 is available to this partition. The type of instruction cannot be determined from the A protected area, but the active data in the instruction is located at 3941 in the Common area of memory. Notice that

the 5 bits in the AO, A1, A2, and A3 characters are all ls. In the 6800, 101, and model 21, one or more of these bits may be zero. In that case, the zeros represent the binary value of the 10K digit of the A address (providing the AC bit is a 1 as it is in the example).

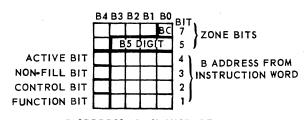

### **B** ADDRESS

The B address area (0100 to 0199) contains a series of five-character B addresses, one for each I/O. The B area of protected memory will accomodate 20 such addresses, but abbreviated systems such as the 6800 and 101 can only use a portion of these.

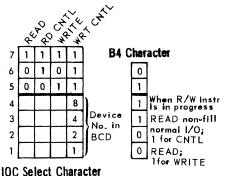

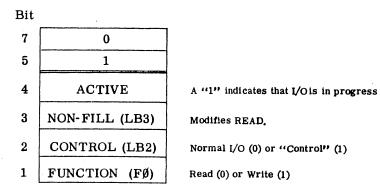

The B-protected area is used during an IOC READ or WRITE to store the remaining number of characters (less one) that are yet to be transfered. This number is decremented with each character transfer until a borrow condition is created, and the LAST flip-flop is set, terminating the operation. The conditions under which the characters are transfered are controlled by the B4 character of the B-protect area of memory.

The B4 character contains the I/O channel control bits. These bits are loaded from several sources, and are not the same as the B4, or LB, portion of the instruction word. Bit 1 comes from F0 (showing a READ or WRITE condition), bits 2 and 3 come from LB bits 2 and 3, and bit 4 is placed by the ACU as a status retrieval flag. Bit 4 causes status to be read by the ACU after an I/O instruction has been completed.

The B address area in protected memory is also used at the termination of an FAC Read or WRITE instruction to store any residual count (less one). A disc instruction that ends in normal status leaves a count of 9999 (one less than zero). A disc instruction that ends in FAULT leaves a residual count of 0099 (one less than 100).

**B ADDRESS BIT STRUCTURE**

|              | 5         | 501        | 6   |    | . ( | 5169 |

|--------------|-----------|------------|-----|----|-----|------|

|              | <b>B4</b> | <b>B</b> 3 | B 2 | Bl | B0  |      |

|              | 0         | 0          | 0   | 0  | 0   | 7    |

|              | 1         | 1          | 1   | 1. | 1   | 5    |

| ACTIVE BIT   | 1         | 0          | 1   | 0  | 0   | 4    |

| NON-FILL BIT | 0         | 0          | 0   | 0  | 0   | 3    |

| CONTROL BIT  | 0         | 1          | 0   | 0  | 0   | 2    |

| FUNCTION BIT | 0         | 0          | 0   | 1  | 0   | 1    |

2-8

F

EXAMPLE OF B ADDRESS

COMMON AREA ADDRESS

43-0302-100

C Singer Business Machines

### MEMORY USE, INSTRUCTION AND DATA FORMATS

### 2-2.1 PROTECTED AREA

### B ADDRESS (Continued)

The B-protected number that is recorded after a Mag Tape WRITE instruction (from memory to tape) is always 9999. A Mag Tape READ instruction that is filled or exceeded will also record 9999 in the B-protected area. A Mag Tape instruction that is terminated before the field is filled (the usual programming procedure) will leave a residual count in B-protected that is one count less than the number of characters that would be required to fill the remainder of the field.

The example shows that partition 9 is busy with a normal (not CONTROL) read instruction that needs 2811 additional characters to complete the specified field. If the operation is terminated before that number of characters is received, the rest of the field will be filled with blanks (SPace codes).

### P ADDRESS

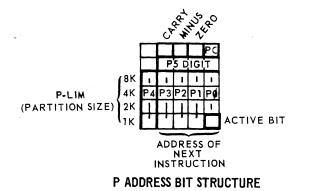

The P area of protected memory contains a series of five-character addresses that are mostly used to direct the ACU to the proper program location when the partition is serviced. The lower four bits of the P4 character are a read-out of the P-LIM jumper settings on the I/O card. The read-out is only an indication to the system operator, and is not used by the ACU in any other way.

The 7-bit in the PØ character is the PC bit, indicating that the P address is in the common area of memory if it is a l. The lowest order bit of the PØ character is set to a Ø each time the ACU begins to service the partition, and restored to a l when the ACU leaves the partition (except when the ACU leaves to service an INTerrupt on a cycle stealing basis). The 7-bits of the Pl, P2, and P3 characters indicate the status of the condition flip-flops when the ACU switched partitions. These bits are used to re-establish the states of the condition flip-flops when the partition is serviced again. The condition flip-flops are used to direct a conditional BRANCH, if that is the next instruction that is pulled.

The P address bit structure is shown in the illustration below, along with an example of a P address that could be found in memory. The example shows the address for partition 5, which has the P-LIM jumpers set to a partition size of 7K, or 7000 characters. The last instruction in that partition ended normally, and the next instruction to be used is at location 24060 in the common area of memory. The new instruction address does not include the active bit of the P $\emptyset$  character. This example would be impossible in a Model 20 processor, because the zero (the 10K digit) in the 5-bit area would have caused a data check, causing a program restart.

COMMON AREA ADDRESS

| S'S'S'S'S'S'BIT |   |   |    |   |   |

|-----------------|---|---|----|---|---|

| 0               | 0 | 0 | 1. | X | 7 |

| 1               | 1 | 0 | Ì  | 1 | 5 |

| 0               | 0 | 0 | 0  | 0 | 4 |

| 1               | 1 | 0 | 1  | 0 | 3 |

| 1               | 0 | 0 | 1  | 0 | 2 |

| 1               | 0 | 0 | 0  | 1 | 1 |

### EXAMPLE OF P ADDRESS

C Singer Business Hackins

### MEMORY USE, INSTRUCTION AND DATA FORMATS

### 2-2.2 INDEX REGISTERS

There are three locations of four characters each within each partition that can be automatically accessed as index registers. These index registers are not devices, but are character addresses at fixed positions within the relative partition location. Indexing bits within the instruction word cause the characters that are stored at the specified index register location(s) to be retrieved and temporarily added to the A and/or B address portion of the instruction. The index registers are relative to the partition, and are at the same relative positions within each partition. Indexing allows up to 9999 to be added to the instruction address, and can cause address errors if the modified address is greater than the partition size.

There is no restriction that reserves the index register area exclusively for indexing. Data and/or program instructions can be written into any or all of the index register areas in memory.

### LOCATION 40

Location 40 within each partition is essentially an error register for storing the P count when an error is detected. The P (program) count is the memory location of the next instruction, or the next character in a READ or WRITE transfer. When the ACU hardware detects an error, the CHECK flip-flop is set, causing the contents of the (hardware) P register to be stored along with the P-LIM value into locations 0040 through 0044 in partition memory, rather than into the P protected area of memory. The P-LIM value is a single digit from 1 to : (:=10K) representing the 1K increments of the partition size patching. If an error is made during the character transfer portion of an I/O (input/output) instruction, the P count will be one count greater than the address where the error occurred. Any other error will cause the P count to be eleven (one instruction word + 1) greater than the error causing instruction. In the case of a branch instruction to a location that is greater than the partition (or common) limit, the branch will be completed before the error is discovered, and the stored P count will only reveal the branch destination, and not the source of the error.

Normal data or program can be placed into the location 40 area with no restrictions other than the regular conditions of data and program entry. However it is not advisable to place data at this location, because it will be destroyed and replaced if an error is made. Detectable errors that will cause the P address to be stored at location 40 are of three basic types that are listed below.

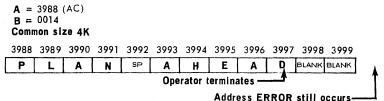

### Address Error

- An address that is greater than the partition size.

- An address that is greater than the alloted common size.

- In the Model 20 only, an attempt to address the priveledged area of memory from a partition that is not patched for priveledged entry.

- An attempt to change data in protected memory (except through SET MODE).

### Invalid Function Code

- Binary 3 (0011) used in an instruction word.

- Binary 2 (0010) used in a Model 20 instruction word.

- Binary 10 (1010) used when the SET MODE enable jumper is not installed (on the LIF card).

Data Fault

- Lack of a 1 in the 5-bit position of any character in a Model 20 instruction.

- Lack of a 1 in the 5-bit position of a disc address (the six-character data field at the B address).

- A binary value greater than 9 in the lower four bits of an instruction character, character used for indexing, or a disc address character (except for the disc unit number in all models other than Model 20).

ARITHMETIC & CONTROL UNIT

# SECTION 3

### CONTENTS

| 3-0.0 ARITHMETIC & CONTROL UNIT                                                                                                         | 3-3                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| 3-1.0 DATA AND INSTRUCTION REGISTERS AND CONTROLS<br>3-1.1 TIMING AND SEQUENCING                                                        | 3-3<br>3-6                                                                           |

| 3-2.0 MEMORY ADDRESSING<br>3-2.1 ADDRESS ERROR<br>3-2.2 RELATIVE ADDRESSING<br>3-2.3 COMMON ADDRESSING<br>3-2.4 BASE ADDER              | 3-14<br>3-14<br>3-15<br>3-15<br>3-15                                                 |

| 3-3.0 LOGIC OPERATION<br>3-3.1 READ CONTROL (LOAD REQUEST)                                                                              | 3-17<br>3-18                                                                         |

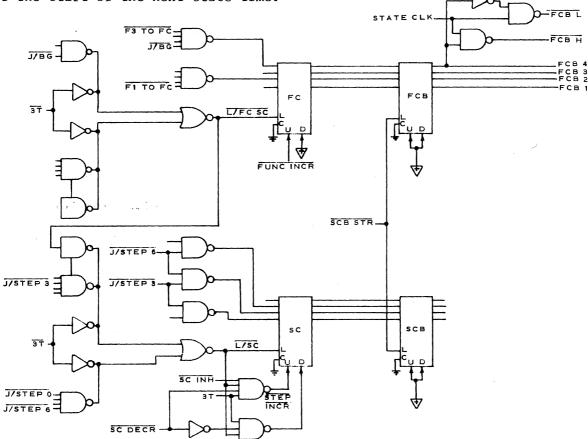

| 3-4.0 HARDWARE FUNCTIONS<br>3-4.1 INTERRUPT<br>3-4.2 READ/WRITE<br>3-4.3 SWITCH<br>3-4.4 BEGIN<br>3-4.5 INDIRECT ADDRESS<br>3-4.6 INDEX | 3-25<br>3-25<br>3-26<br>3-33<br>3-33<br>3-36<br>3-36                                 |

| 3-5.6 MULTIPLY<br>3-5.7 TRANSFER, MOVE NUMERIC, and EXCHANGE<br>3-5.8 BRANCH<br>3-5.9 EDIT<br>3-5.10 FORM NUMERIC FIELD                 | 3-37<br>3-37<br>3-42<br>3-44<br>3-45<br>3-49<br>3-53<br>3-56<br>3-57<br>3-60<br>3-62 |

| 3-5.11 COMPARE                                                                                                                          | 3-64                                                                                 |

]]-]-73

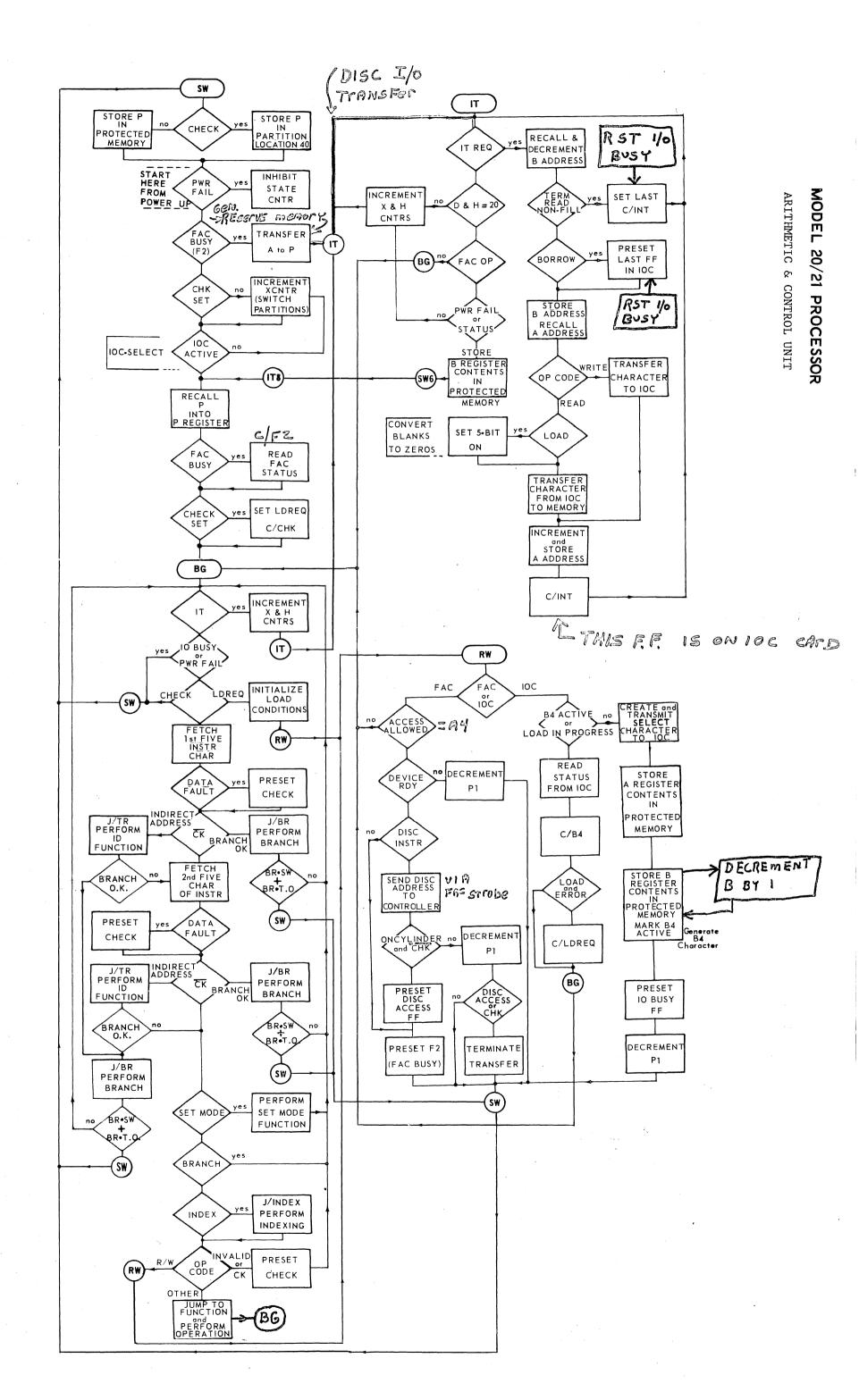

# MODEL 20/21 PROCESSOR ARITHMETIC & CONTROL UNIT

43-0302-100

3-2

### ARITHMETIC & CONTROL UNIT

### 3-0.0 ARITHMETIC & CONTROL UNIT

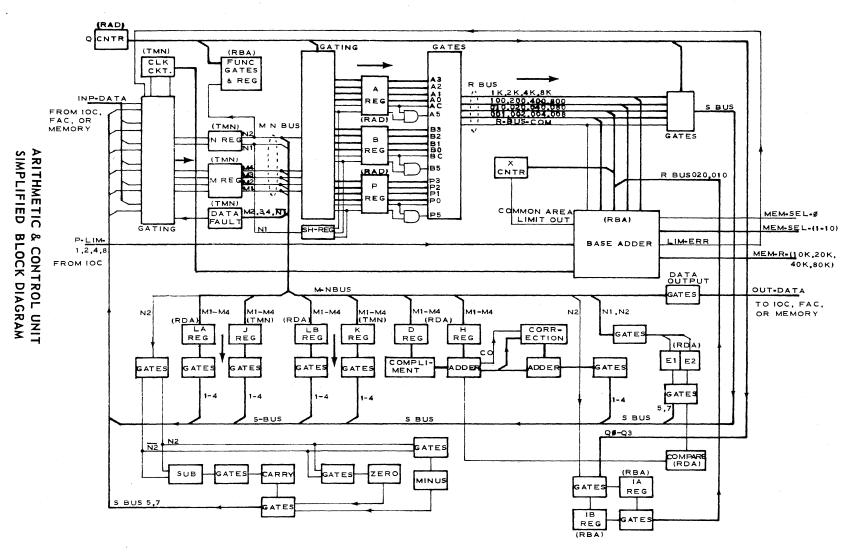

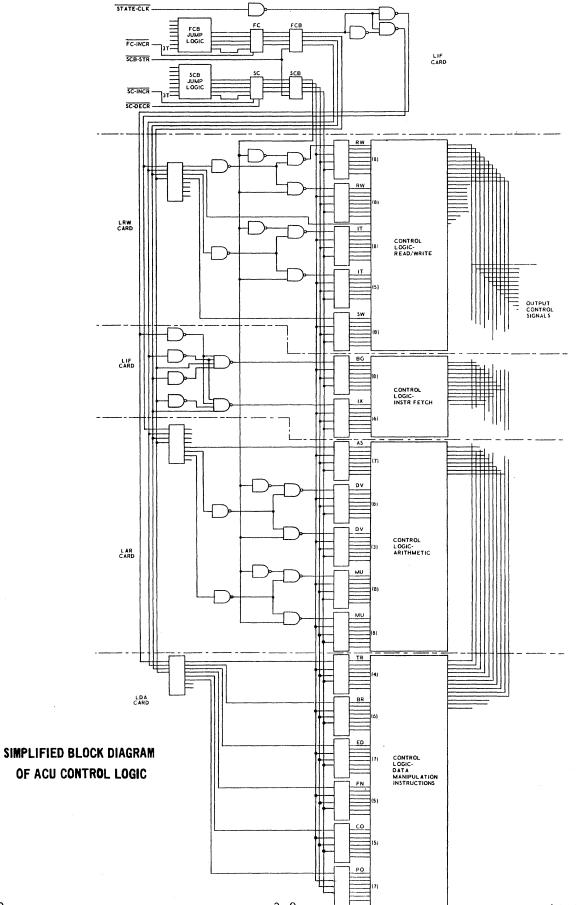

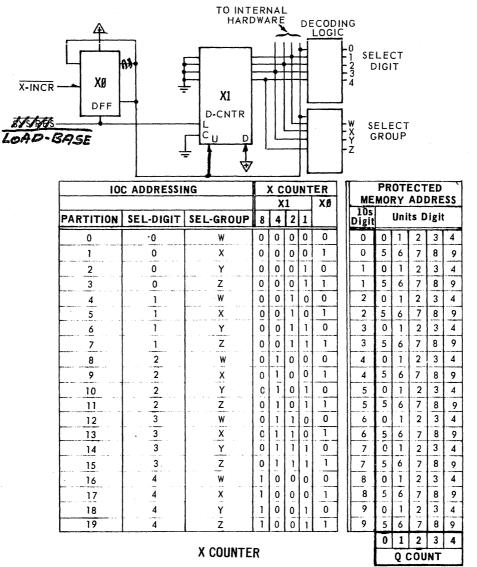

The Arithmetic and Control Unit (ACU) is the central logic and time sequencing for the entire processor. All program instructions and data manipulations (to and from memory) are processed by the ACU. Automatic operations that are caused by certain instructions and conditions are controlled by the ACU. User (partition) sequencing and time sharing is also controlled by the ACU.

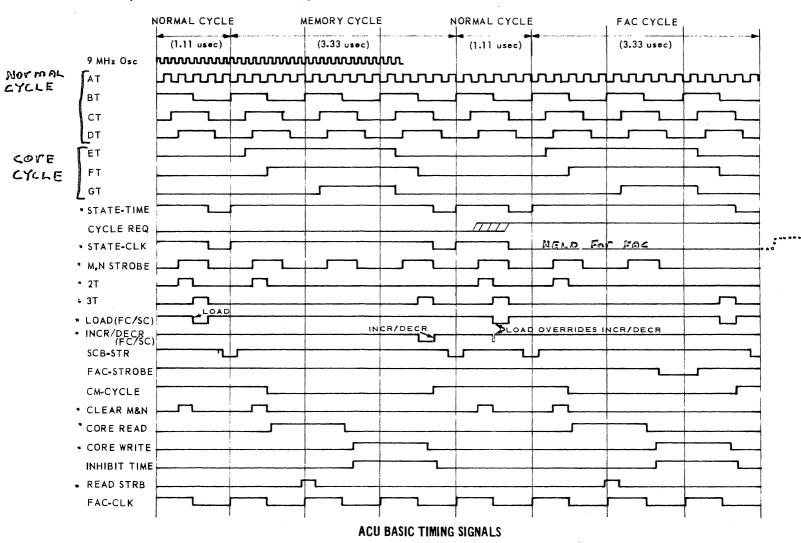

The ACU services information from only one user at a time, even though service appears to be simultaneous by quickly switching from one operation to the next. The ACU hardware is exclusively available to the partition that is being serviced, but may be released for short periods between instructions to allow INTerrupt memory cycles. Most I/O controllers process data transfers to and from peripheral devices (or communication lines) independantely from the ACU, requesting memory cycles on an INTerrupt basis. Before fetching a new instruction in the active partition, the ACU may momentarily leave the working partition to service these INTerrupt requests. Each operation, including the INTerrupt memory cycles, is performed in sequence, one at a time.

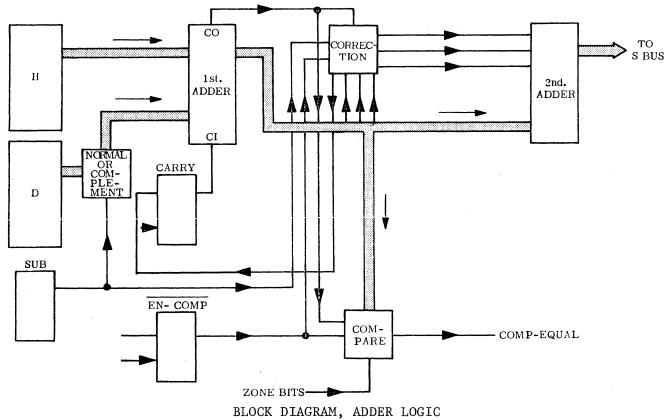

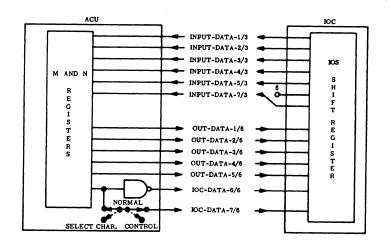

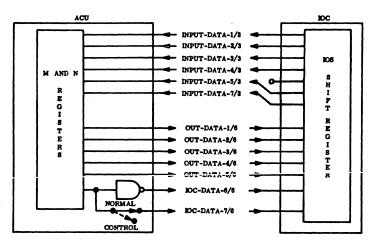

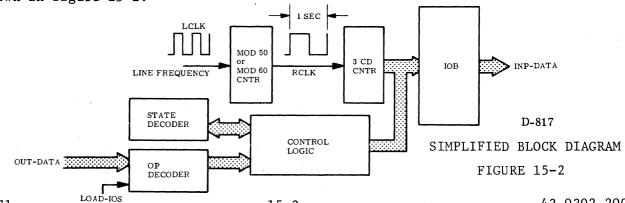

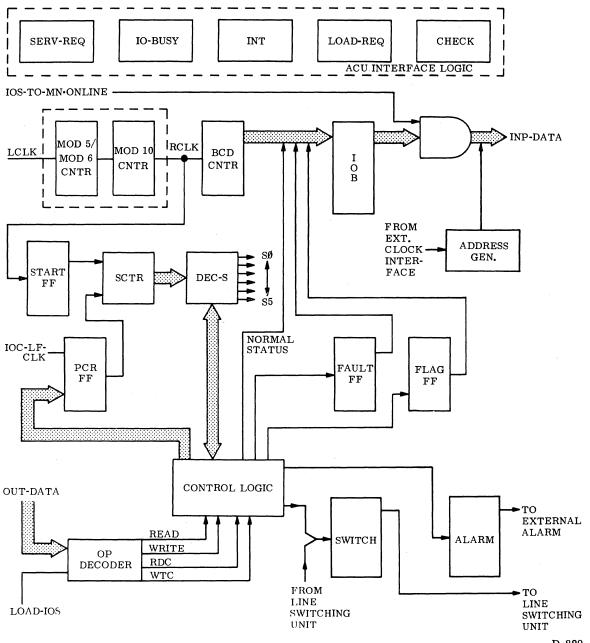

The ACU simplified block diagram on the opposing page shows the general organization and signal flow within the ACU. Data or instruction characters that come from either an I/O device, an FAC device, or from memory, enter the ACU on the INP-DATA lines. Timing signals from the ACU clock circuits gate the information from the INP-DATA lines into the M and N registers, one character at a time.

The M and N bus, a series of six data lines, routes each character to the inputs of the various registers within the ACU. As each character is entered into the M and N registers, ACU timing and enabling conditions cause the bits to enter the appropriate hardware registers (most of the timing and qualifying inputs for the registers are omitted from the block diagram). The general data flow of data within the ACU is summarized below.

- Characters are gated into the M and N registers, and thus onto the M and N bus.

- Each bit is gated into an appropriate register, where it will be acted upon or stored until required.

- The processed data is gated from the outputs of the registers, one character at a time, onto the S bus.

- Input gating clocks the characters from the S bus into the M and N registers, and onto the M and N bus.

- The data output gates are enabled, sending characters onto the OUT-DATA lines, and to an IOC device, an FAC device, or to memory.

### 3-1.0 DATA AND INSTRUCTION REGISTERS AND COUNTERS

The ACU contains many registers, flip-flops, and counters that temporarily store instruction and data bits, and provide sequencing for many of the ACU operations. Some of these registers and counters are named for the portions of the instruction word that they store or control. For example, the LA portion of the instruction word is stored in the LA register. Other registers are for data manipulation, and the names do not relate to their operation.

### ARITHMETIC & CONTROL UNIT

### 3-1.0 DATA AND INSTRUCTION REGISTERS AND COUNTERS (Continued)

The instruction word is literally taken apart as it is received from memory, and placed into hardware registers. The overall and specific content of the hardware registers determines the character, or operation, of the ACU for the duration of the instruction. The ACU will pass through many internal functions during the completion of an instruction, but is always guided and directed by the bit content of the instruction word, and the conditions that are encountered during the progress of the instruction.

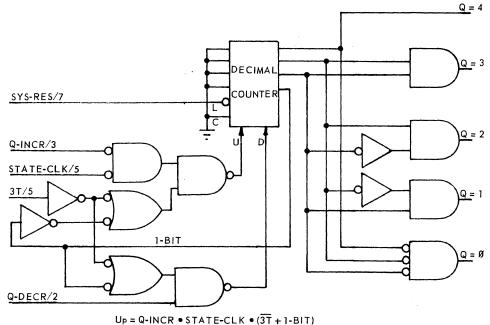

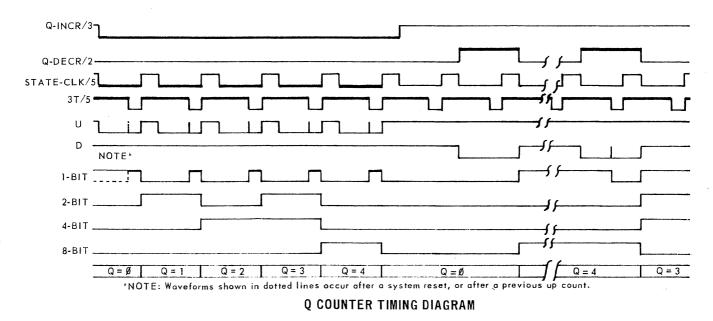

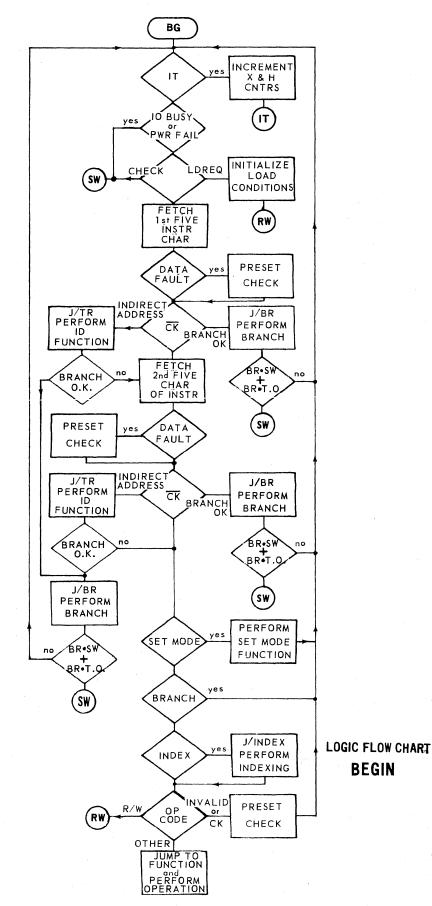

When service begins in a partition, the ACU is working under the internal function BEGIN. The P count is recalled from protected memory, and that position in memory is addressed. The first five characters are "pulled" from memory, one at a time. A series of checks for data fault, branch, etc. are made, and if none of these conditions are present, the second five characters of the instruction word are pulled. The Q counter is used as the clocking source for the instruction pulling routine. The Q counter is a five-count device (Q for quinary) and is described later in this section.