**Xerox BTM/BPM/UTS**

Sigma 5-9 Computers

Overlay Loader Technical Manual

D 8

XERUX

# Xerox BTM/BPM/UTS

Sigma 5-9 Computers

**Overlay Loader**

## **Technical Manual**

90 18 03B

June 1972

Price: \$5.00

### REVISION

The Overlay Loader described in this manual operates under the B00 version of UTS and the F01 version of BPM/BTM. Changes in the text marked by revision bars apply only to UTS. The previous (A) edition of this manual completely describes the loader operating under the F01 version of BPM/BTM.

## **RELATED PUBLICATIONS**

| Title                                                                                             | Publication No. |

|---------------------------------------------------------------------------------------------------|-----------------|

| Xerox Sigma 5 Computer/Reference Manual                                                           | 90 09 59        |

| Xerox Sigma 6 Computer/Reference Manual                                                           | 90 17 13        |

| Xerox Sigma 7 Computer/Reference Manual                                                           | 90 09 50        |

| Xerox Sigma 8 Computer/Reference Manual                                                           | 90 17 49        |

| Xerox Sigma 9 Computer/Reference Manual                                                           | 90 17 33        |

| Xerox Universal Time-Sharing System (UTS)/TS Reference Manual                                     | 90 09 07        |

| Xerox Universal Time-Sharing System (UTS)/SM Reference Manual                                     | 90 16 74        |

| Xerox Universal Time-Sharing System (UTS)/OPS Reference Manual                                    | 90 16 75        |

| Xerox Batch Processing Monitor (BPM)/System Technical Manual                                      | 90 15 28        |

| Xerox Batch Time-Sharing Monitor (BTM)/Edit Subsystem Technical Manual                            | 90 19 11        |

| Xerox Batch Time-Sharing Monitor (BTM)/Delta Subsystem Technical Manual                           | 90 18 79        |

| Xerox BPM/BTM/UTS/System Generation Technical Manual                                              | 90 18 77        |

| Xerox Batch Processing Monitor (BPM)/BP, RT Reference Manual                                      | 90 09 54        |

| Xerox Batch Processing Monitor (BPM) and Batch Time-Sharing Monitor (BTM)/OPS<br>Reference Manual | 90 11 98        |

| Xerox Batch Time-Sharing Monitor (BTM)/TS Reference Manual                                        | 90 15 77        |

|                                                                                                   |                 |

Manual Content Codes: BP – batch processing, LN – language, OPS – operations, RBP – remote batch processing, RT – real-time, SM – system management, TS – time-sharing, UT – utilities.

The specifications of the software system described in this publication are subject to change without notice. The availability or performance of some features may depend on a specific configuration of equipment such as additional tape units or larger memory. Customers should consult their Xerox sales representative for details.

## CONTENTS

| PREF | ACE                                                                                   | v            |

|------|---------------------------------------------------------------------------------------|--------------|

| GLC  | DSSARY                                                                                | vi           |

| 1.0  | environment                                                                           | 1            |

|      | <ul><li>1.1 Introduction</li><li>1.2 System Interface and General Operating</li></ul> | _ 1          |

|      | Characteristics<br>1.2.1 Loader Operation Under BPM                                   | _ 3<br>_ 2   |

|      | or UTS<br>1.2.2 Loader Entry/Exit<br>1.2.2 What the Sector Description the            | _ 3<br>_ 3   |

| ,    | 1.2.3 What the System Does with the<br>Loader's Output                                | _ 3          |

| 2.0  | GENERAL OPERATING CHARACTERISTICS                                                     | 6            |

|      | 2.1 Functional Overview                                                               |              |

|      | 2.1.1 Loader Terminology                                                              | _ 6          |

|      | 2.1.2 The First Pass                                                                  | _ 9          |

|      | 2.1.3 The Second Pass<br>2.1.4 Advantages of a Two-Pass Loader                        |              |

|      | 2.1.4 Advantages of a Two-rass Loader<br>2.2 Structure: The Major Pieces              |              |

|      | 2.2.1 LDR                                                                             |              |

|      | 2.2.2 The First Pass                                                                  | _ 19         |

|      | 2.2.2         The First Pass           2.2.3         The Second Pass                  |              |

|      | 2.2.4 Forming the Loader                                                              |              |

|      | 2.3 How the Loader Uses Memory                                                        |              |

|      | 2.3.1 Partitioning Core for the<br>First Pass                                         | _ 20         |

|      | 2.3.2 Partitioning Core for the<br>Second Pass                                        | _ 21         |

|      | 2.4 How the Loader Obtains Memory                                                     |              |

|      | 2.4.1 Loader Running Under BPM                                                        |              |

|      | 2.4.2 Loader Running Under UTS                                                        |              |

|      | 2.5. Maintaining the Loader, DEBUG Mode                                               | _ 2/         |

| 3.0  | INPUT, OUTPUT, LOADER-GENERATED<br>TABLES                                             | 29           |

|      | 3.1 Input                                                                             | _ 29         |

|      | 3.1.1 LOCCT, ROM, Tree Tables                                                         |              |

|      | 3.1.2       Files (ROMs and Load Modules)         3.1.3       Registers and JIT Input |              |

|      | 3.1.4 ASSIGN Record                                                                   |              |

|      | 3.1.5 Error Message File (ERRMSG)                                                     |              |

|      | 3.1.6 Modify File (idD)                                                               |              |

|      | 3.1.7 Core Libraries (UTS only)                                                       | _ 41         |

|      | 3.2 Output                                                                            |              |

|      | 3.2.1 Load Modules, Overall Format                                                    |              |

|      | 3.2.2 Library Load Modules                                                            | _ 44<br>/    |

|      | 3.2.3 REF/DEF Stack<br>3.2.4 Expression Stack                                         | _ 40<br>_ 50 |

|      | 3.2.5 Relocation Dictionary                                                           | _ 50<br>_ 52 |

|      | 3.2.6 Miscellaneous (Map, Diagnostics,                                                | _ 52         |

|      | Severity Level)                                                                       | _ 53         |

|      |                                                                                       |              |

|     | 3.3  | Loader-Generated Tables       | 58               |

|-----|------|-------------------------------|------------------|

|     |      | 3.3.1 Formats for the TCB     | and              |

|     |      | DCB Name Tab                  | le 58            |

|     |      | 3.3.2 TREE                    | 58               |

|     |      | 3.3.3 REF/BREF Tables         | 58               |

|     |      | 3.3.4 DCBs                    | 60               |

|     | 3.4  | Examples                      | 62               |

|     |      | 3.4.1 A Sample Program _      | 62               |

|     |      | 3.4.2 The ROM                 |                  |

|     |      | 3.4.3 The Load Module         |                  |

|     |      | 3.4.4 The Relationship Be     |                  |

|     |      | Expression Stac               |                  |

|     |      |                               | 66               |

|     |      | ,                             |                  |

|     |      |                               |                  |

| 4.0 | DES  | CRIPTION OF THE FIRST PA      | ASS 68           |

|     | 4.1  | INIT1 — Initialization for th | ne First Pass 68 |

|     |      | PASS1                         |                  |

|     |      | 4.2.1 The Main Loop           |                  |

|     |      | 4.2.2 Object Module Prod      | cessor           |

|     |      | (LP1-Pass One)                | 72               |

|     |      | 4.2.3 Load Module Proces      |                  |

|     |      |                               | ; One) 78        |

|     |      | 4.2.4 The Librarian (SATR     | (EF) 82          |

|     |      |                               |                  |

| 5.0 | PRE  | PARING TO FORM THE CO         | RE IMAGE 86      |

|     |      |                               |                  |

|     |      | IN2                           |                  |

|     | 5.2  | PS2 - The Driver for the Se   | cond Pass 88     |

|     | 5.3  | ALL – Memory Allocation _     | 88               |

|     |      |                               |                  |

| 6.0 | FO   | MING THE CORE IMAGE (         | EVL) 91          |

|     |      |                               |                  |

|     |      | EVEX PRS                      |                  |

|     | 6.2  | LOADSEG                       |                  |

|     |      | 6.2.1 The Main Loop           | 92               |

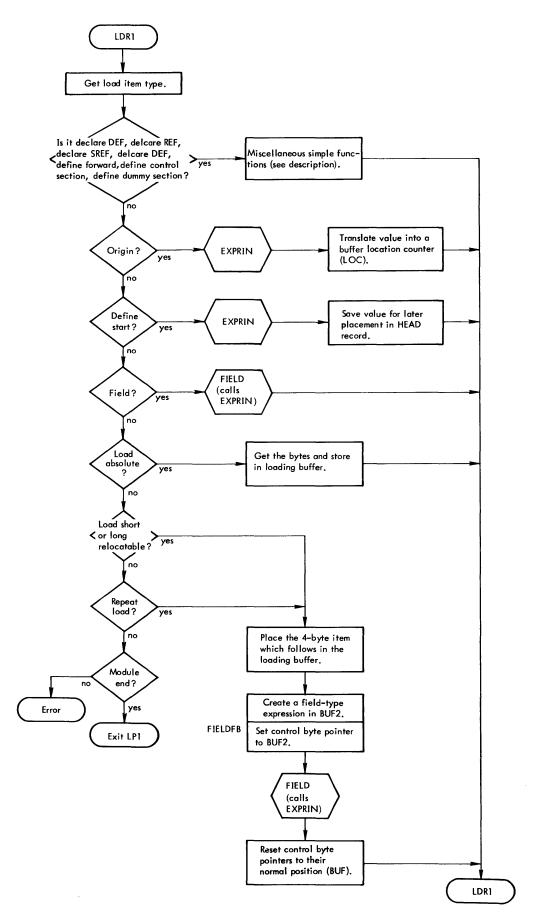

|     |      | 6.2.2 Object Module Prod      | cessor           |

|     |      | (LP1-Pass Two)                | 93               |

|     |      | 6.2.3 Load Module Proces      | ssor             |

|     |      |                               | s Two) 105       |

|     |      |                               |                  |

|     |      |                               |                  |

| 7.0 | WR]  | TING THE LOAD MODULE          | (WRT) 108        |

|     |      |                               |                  |

|     |      |                               | 110              |

| 8.0 | ΗN   | ISHING UP (FIN)               | 119              |

|     |      |                               | ,                |

|     |      | X A. LOADER-GENERATED         |                  |

| 1   | INTE | RNAL SYMBOL TABLES (UT        | S Only) 126      |

| م ۸ |      |                               |                  |

|     |      | X B. STORAGE LAYOUT           | 134              |

|     | Ur 3 | TUFF                          | 134              |

|     |      |                               |                  |

iii

ł

### FIGURES

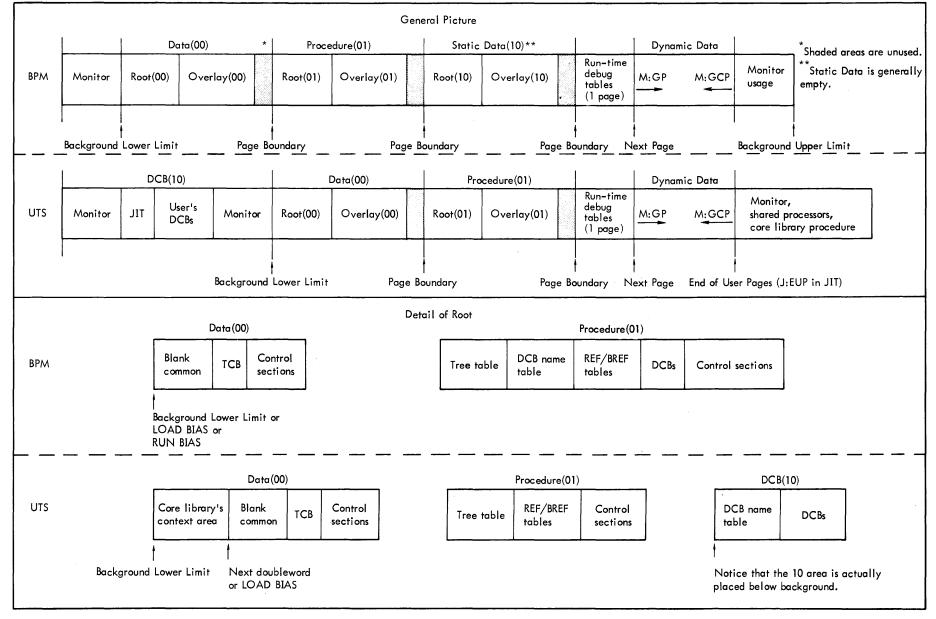

| 1.   | Load Module Layout at Run-Time                                                                           | . 5  |

|------|----------------------------------------------------------------------------------------------------------|------|

| 2.   | Segment Processing Sequence, Pass One                                                                    | . 11 |

| 3.   | The First Pass — General Flow                                                                            | 12   |

| 4.   | Segment Processing Sequence, Pass Two                                                                    | 14   |

| 5.   | The Second Pass – General Flow                                                                           | 15   |

| 6.   | Loader's DATA (00) Area (Within LDR)                                                                     | . 18 |

| 7.   | How the Loader Uses Memory: Pass One                                                                     | 21   |

| 8.   | How the Loader Uses Memory: Pass Two —<br>Nonextended Memory Mode                                        | 23   |

| 9a.  | How the Loader Uses Memory: Pass Two —<br>Extended Memory Mode, Construction<br>of Core Image Records    | 25   |

| 9b.  | How the Loader Uses Memory: Pass Two —<br>Extended Memory Mode, Concatena-<br>tion of Core Image Records | 26   |

| 10.  | Loader Control Command Table (LOCCT)                                                                     | 30   |

| 11.  | ROM Tables                                                                                               | 32   |

| 12.  | Tree Tables                                                                                              | 33   |

| 13.  | TREE Table Linking – in Relation to<br>the Overlay Structure                                             | 35   |

| 14.  | LOCCT, TREE, and ROM Table<br>Relationships                                                              | 36   |

| 15.  | ERRMSG File                                                                                              | 40   |

| 15b. | Variable Diagnostic Information                                                                          | 55   |

| 16.  | Recognized DCBs and Their Defaults                                                                       | 61   |

| 17.  | The Loader Driver (in LDR)<br>Flow Chart                                        | . 70 |

|------|---------------------------------------------------------------------------------|------|

| 18.  | INIT1 Flow Chart                                                                | . 71 |

| 19.  | Declaration Stack Format                                                        | . 73 |

| 20a. | PASS1 Object Module Processor (LP1)<br>Flow Chart                               | . 76 |

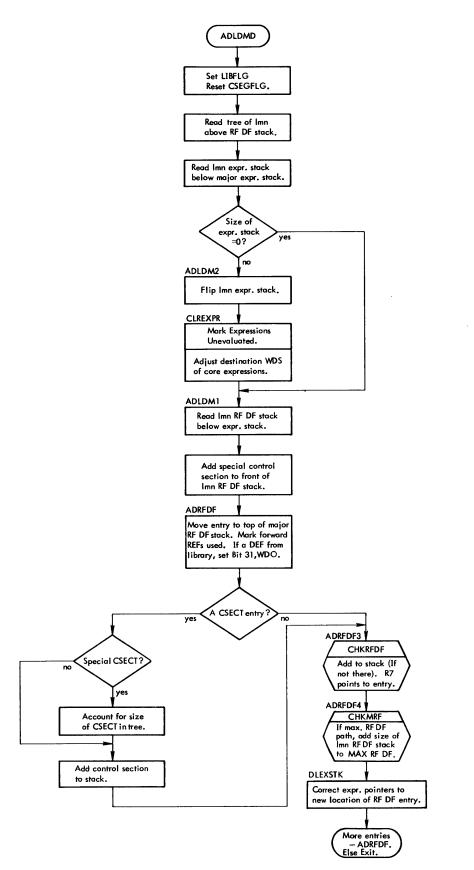

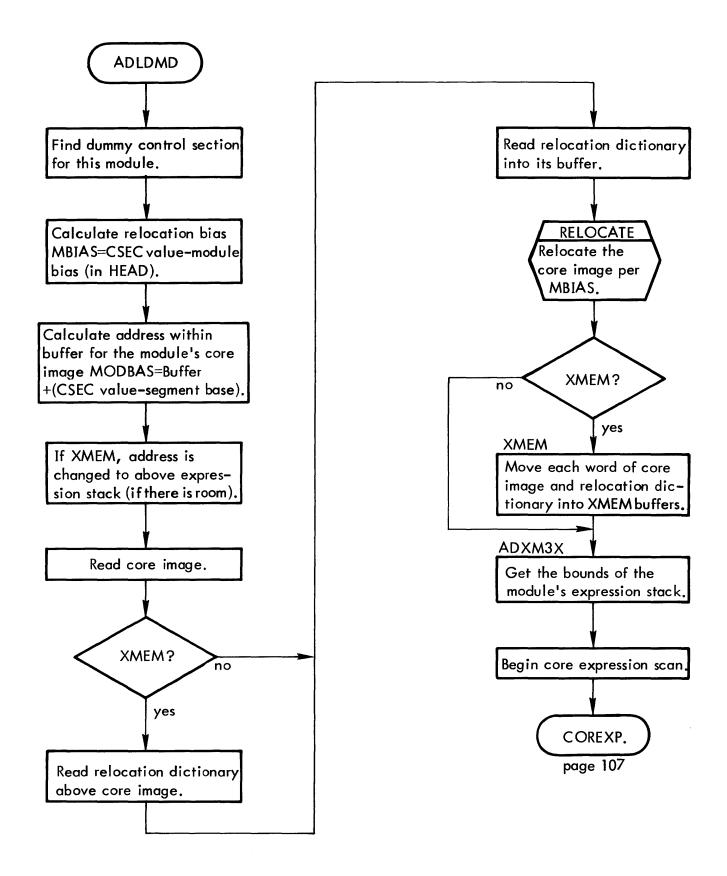

| 20b. | PASS1 Load Module Processor<br>(ADLDMD) Flow Chart                              | . 81 |

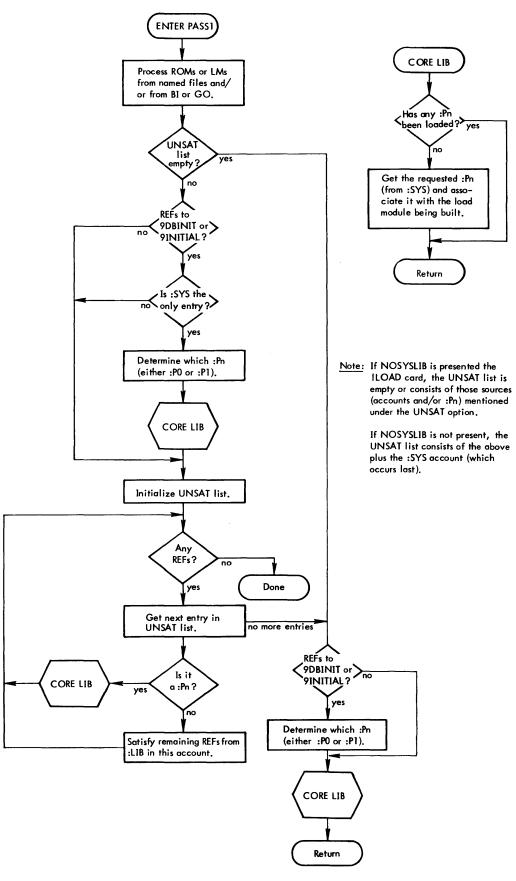

| 21.  | Core Library Association Flow Chart                                             | . 85 |

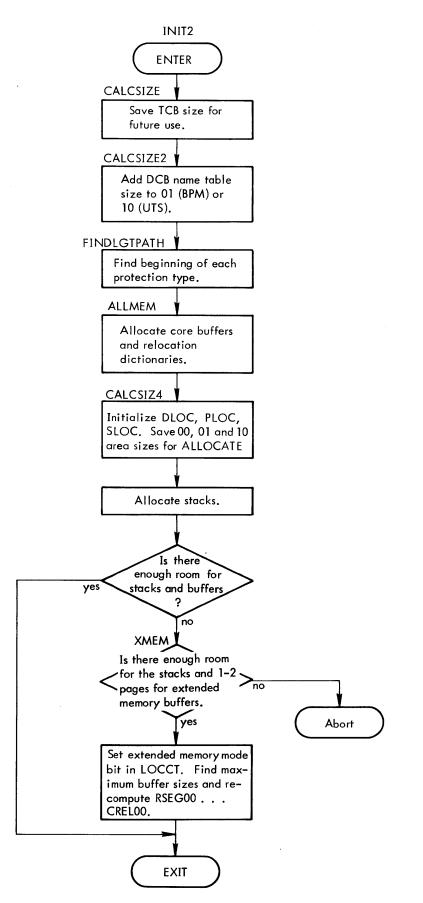

| 22.  | INIT2 Flow Chart                                                                | . 87 |

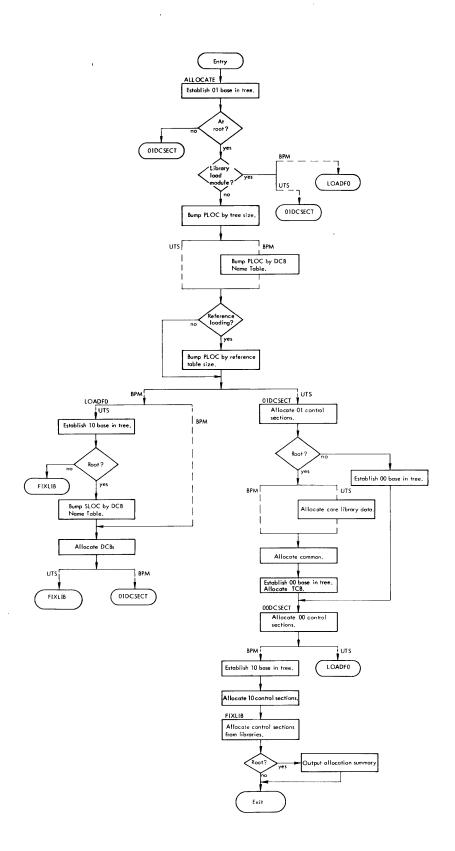

| 23.  | ALLOCATE Flow Chart                                                             | . 90 |

| 24.  | Format of the Keys of idX<br>(Extended Memory File for<br>Standard Load Module) | . 93 |

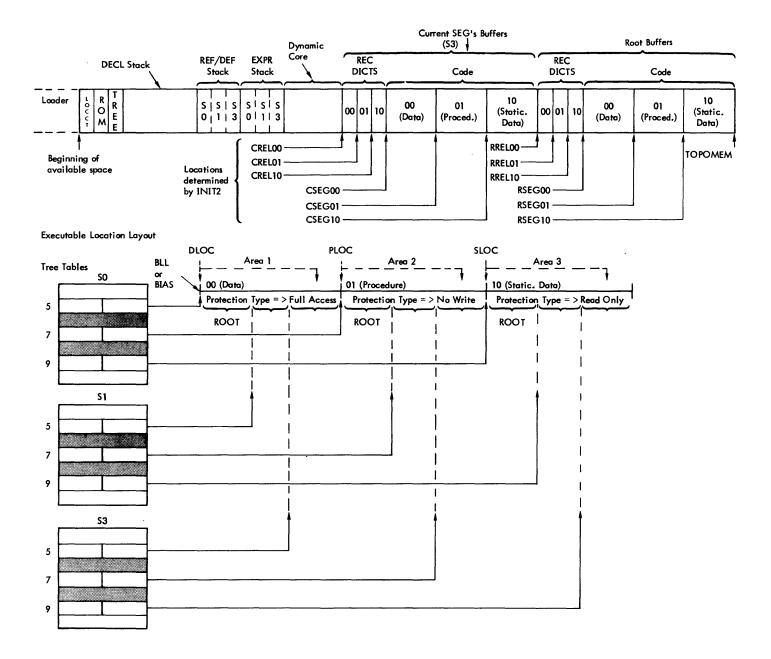

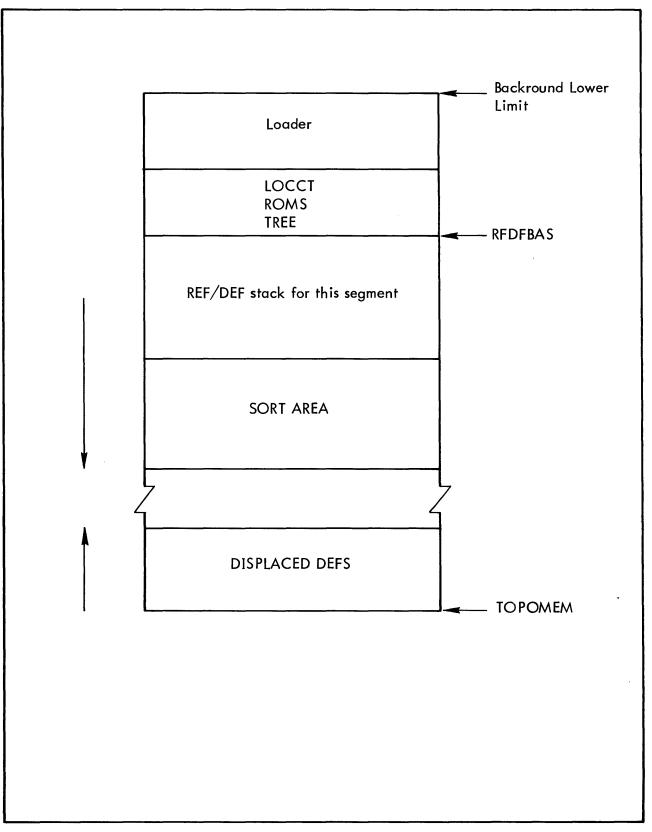

| 25.  | Snapshot of Core Usage During EVL                                               | . 94 |

| 26.  | PASS2 Object Module Processor<br>Flow Chart                                     | 101  |

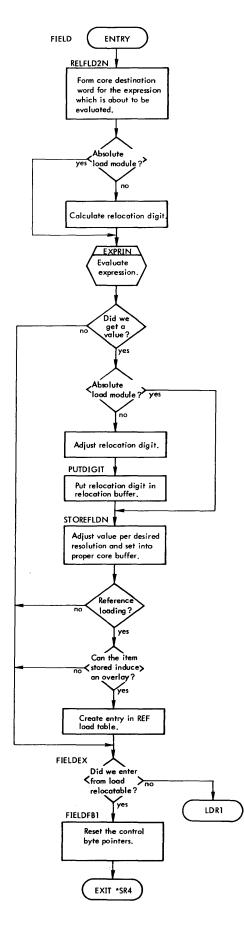

| 27a. | Field and Expression Logic Flow Chart                                           | 102  |

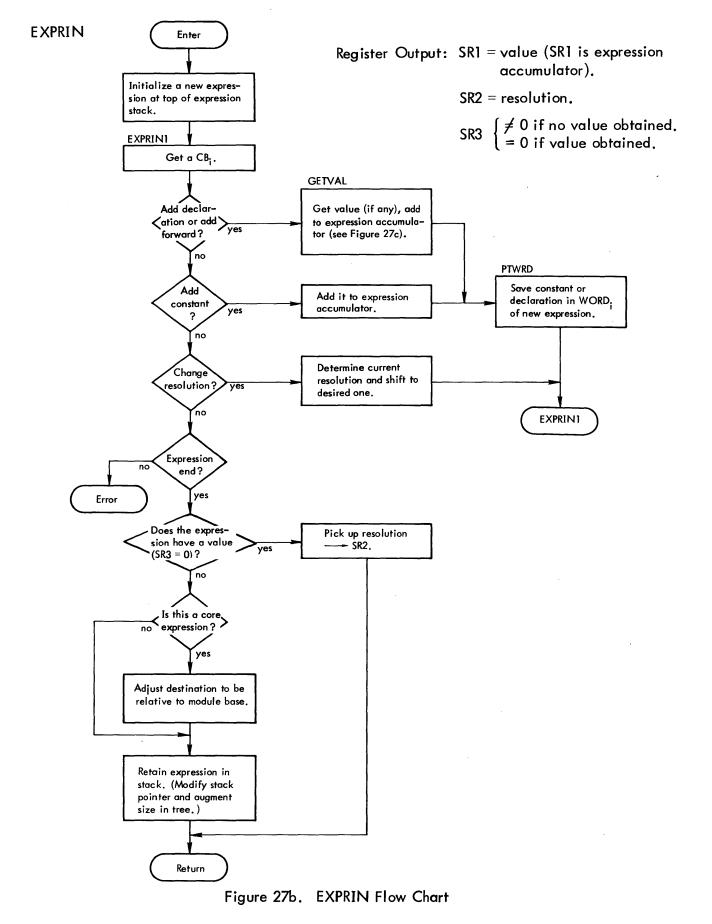

| 27b. | EXPRIN Flow Chart                                                               | 103  |

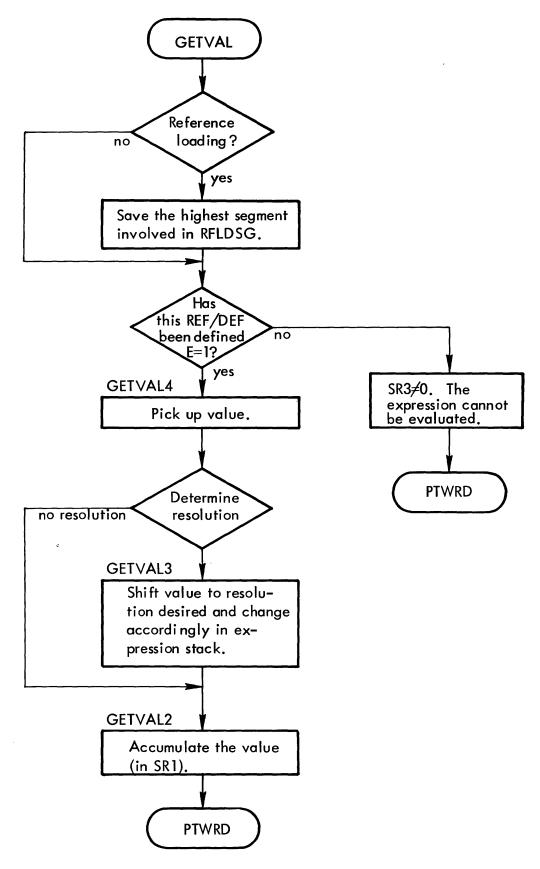

| 27c. | GETVAL Flow Chart                                                               | 104  |

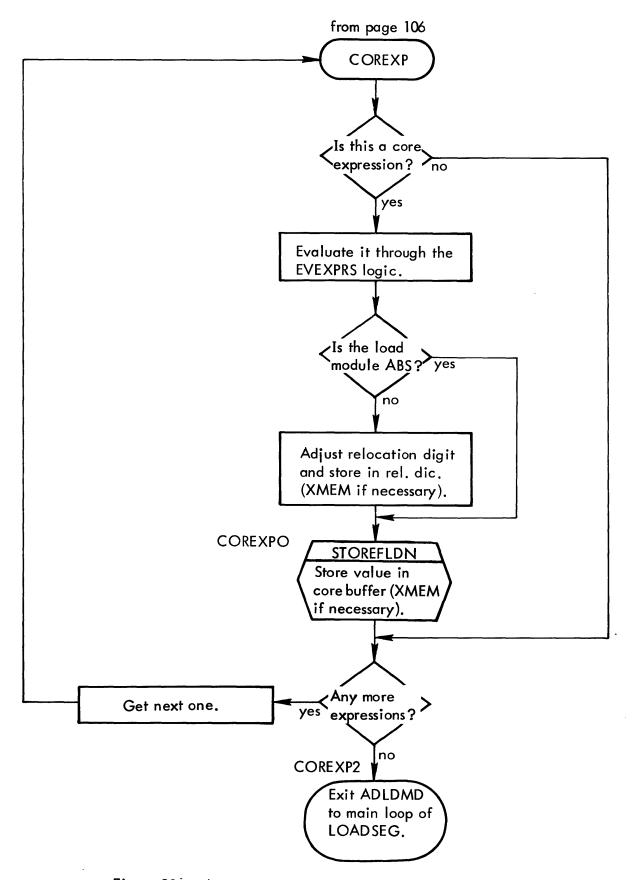

| 28.  | PASS2 Load Module Processor Flow Chart                                          | 106  |

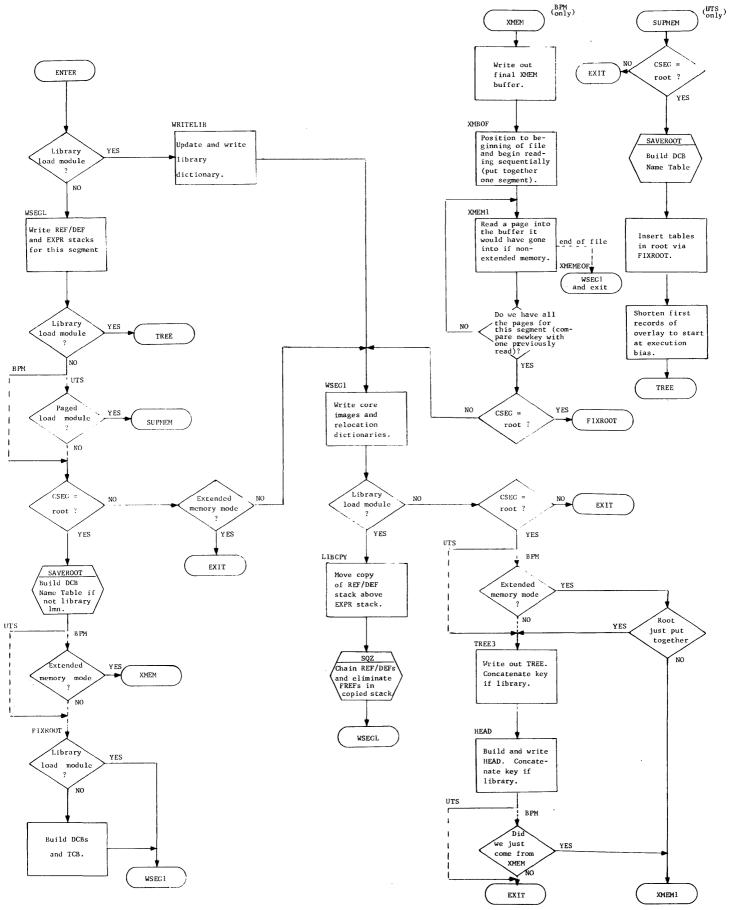

| 29.  | WRITESEG – Overall Flow                                                         | 109  |

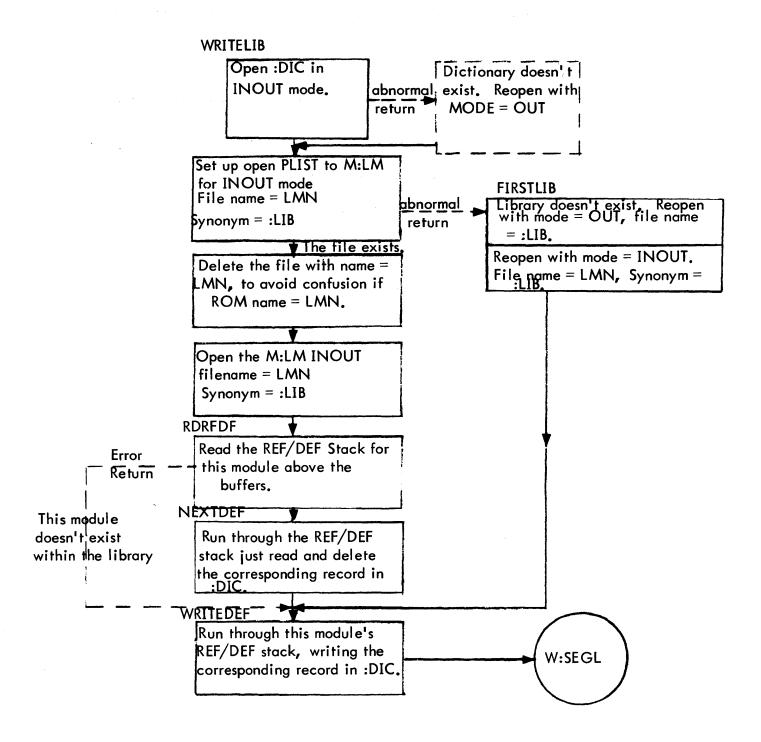

| 30.  | WRITELIB Flow Chart                                                             | 114  |

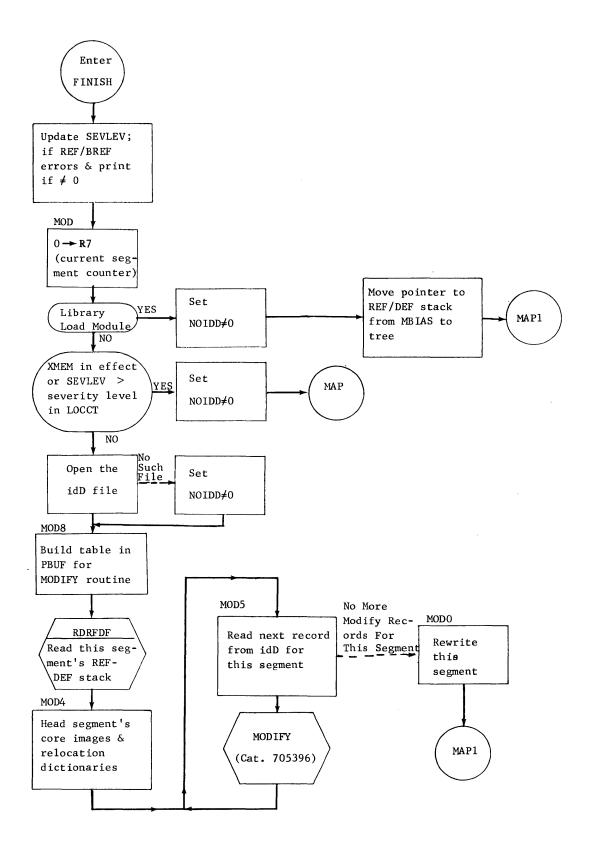

| 31.  | FINISH Flow Chart                                                               | 121  |

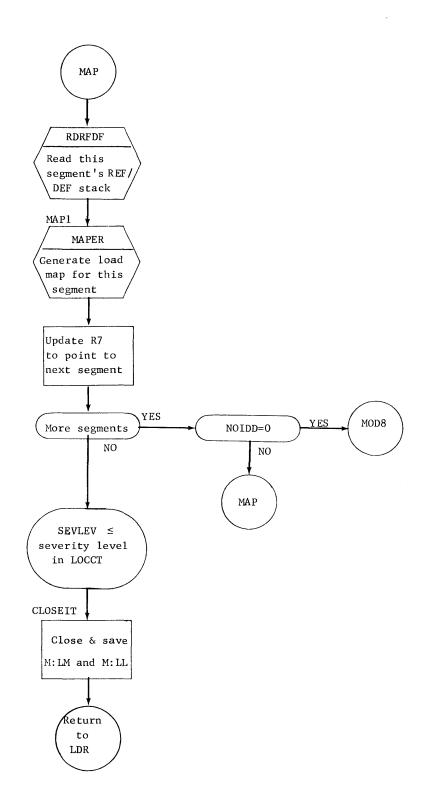

| 32.  | Memory Layout During MAPER<br>Routine                                           | 123  |

## PREFACE

This document describes the purpose and architecture of the Overlay Loader within the environment of BPM or UTS. It is assumed that the reader is familiar with the usage of BPM/UTS Monitor services as well as the Sigma Standard Object Language (see the BPM/BTM/SM Reference Manual, 90 17 41).

v

## GLOSSARY

- CCI (Control Command Interpreter): a processor (brought into core by the Monitor) which reads the ILOAD card and records the information in an LOCCT Table.

- core image: that part of a load module which is laid into core at execution time.

- core library: for UTS, a special collection of files under the :SYS account for association with FORTRAN programs.

- DCB (Device Control Block): a table for use by the Monitor in performing an I/O operation.

- DCB Name Table: a loader-built table which directs the Monitor to the location of a particular DCB within a program.

- declaration stack: a Loader stack which serves to keep track of the declarations made in a given ROM.

- DEFCOM: a processor which outputs a special type of load module.

- expression stack: for any segment, a collection of expressions defining DEFs and forward references and expressions whose values are to be placed in the segment's core image.

- extended memory mode: a mode in which the Loader builds core images and relocation dictionaries in page-sized records within a file on the RAD.

- HEAD: a key to one of the records of a load module file, the record containing basic size and source information.

- idB: a CCI-built table containing information from the BI device (when BI is specified on the LOAD card).

- idD: a file built by CCI on the basis of IMODIFY cards following the ILOAD card.

- idG: the file name the Loader uses to access information specified by the GO option.

- idL: the file name assigned to a load module if no name is specified via the LMN option.

- idX: the name of the intermediate file used during the extended memory mode to build standard (i.e., nonpaged) core image and relocation dictionary records (BPM only).

- JIT (Job Information Table): a Monitor table of information pertinent to the job currently in execution.

- library: the term ascribed to two files, :LIB and :DIC, which are constructed by the Loader.

- load item: a string of bytes representing a "clause" in object language.

- load module: a keyed file which is output by the Loader (and several other processors).

- LOCCT (Load Control Command Table): a table which the Loader must access for its own control card input.

- object language: the language generated by assemblers and compilers to convey information to the Loader.

- PASS3: a processor which calls the Loader to form a load module.

- path: a collection of segments of a program which can reside in core at the same time.

- REF/DEF Stack: a Loader-built stack for each segment whose entries contain values for control sections, external names (DEFs, REFs, SREFs), and forward references.

- relocation dictionary: a record constructed by the Loader which indicates how to relocate each word of a corresponding core image record.

- ROM (Relocatable Object Module): a type of input component to the Loader which was generated by an assembler or compiler.

- segment: a piece of a program which may be replaced in core by another piece of the program.

- stack path: the collection of REF/DEF or expression stacks belonging to the segments on a given path.

- system id: a job-oriented identification number determined by the Monitor and supplied to the Loader via the LOCCT Table.

- TCB (Task Control Block): a Loader-built table containing the user's temp stack and areas for system use.

- TREE: a collection of tables reflecting the overlay structure of a program.

#### 1.0 ENVIRONMENT

#### 1.1 INTRODUCTION

The purpose of any loader is to translate and unite its input (ROMs and libraries) into such a form that the output (a load module) may be executed under the target operating system. Accordingly, the Overlay Loader performs those functions which might be expected of any loader operating under BPM or UTS:

- a. Process ROMs producing continuous sections of data, procedure, and DCBs (or static data if BPM), insuring a page boundary for the three protection types (00, 01, 10, respectively).

- b. Satisfy REFs among the ROMs.

- c. Access "libraries" to satisfy PREFs.

- d. Build DCBs.

- e. Build a DCB Name Table for Monitor use.

- f. Build a TCB.

The special characteristics of the Overlay Loader are identified as follows:

a. Create Overlay Programs

An overlay program is one which has only one piece (segment) resident in core permanently. The other segments are called by the M:SEGLD procedure and brought into core as needed. These segments may reside (at different times) in the same core area, thus reducing the amount of core required to house the entire program.

Since, in general, a program may consist of three areas (one per protection type), each beginning on a page boundary, the Overlay Loader must have the ability to create the three trees, each beginning on a page boundary.

#### b. Reference Loading

If the user does not choose to maintain responsibility for calling the segments of an overlay program (by explicitly using M:SEGLD), he may direct the Loader to insert the M:SEGLD code into his program by specifying REF or BREF on the !LOAD card. This code is built, in the BREF mode, wherever there is a branch type instruction involving a REF to a higher segment. In the REF mode, it is built wherever there is any expression whatsoever involving a REF to a higher segment.

#### c. Load Module Libraries

It is desirable to maintain libraries of frequently used routines which are themselves already in load module form, since subsequent inclusion of a library module would be faster than processing the original ROM language.

d. Relocatable Load Modules

The Loader creates a relocation dictionary which allows subsequent placement of the load module into a core area other than the one at which it was originally biased. Relocation is accomplished via a BIAS option on the IRUN command for BPM. (<u>NOTE</u>: UTS does not allow a BIAS on the IRUN card; hence for UTS, the only use of the relocation dictionary is in the case of merging a library load module into another program.)

e. Dummy Sections

The Loader has the ability to recognize dummy sections of the same name in various modules and to allocate on the basis of the largest one encountered. This feature is generally used in large FORTRAN programs which rely heavily on COMMON (COMMON is a form of dummy sectioning).

#### 1.2 SYSTEM INTERFACE AND GENERAL OPERATING CHARACTERISTICS

#### 1.2.1 Loader Operation Under BPM or UTS

The Loader operates under BPM or UTS and produces either BPM or UTS load modules. These load modules are not interchangeable due to differences in the format of the HEAD record and in the allocation of the DCB area (see Section 3.2.1). Neither are the Loaders themselves interchangeable. That is, the UTS Loader will not operate under BPM and vice versa, due to differences in obtaining memory (see Section 2.4). An assembly parameter will select those areas of loader code which are unique to BPM or UTS. The parameter is MODE. At assembly time, in each source module except the last, this parameter must be set to 0 for BPM and 1 for UTS.

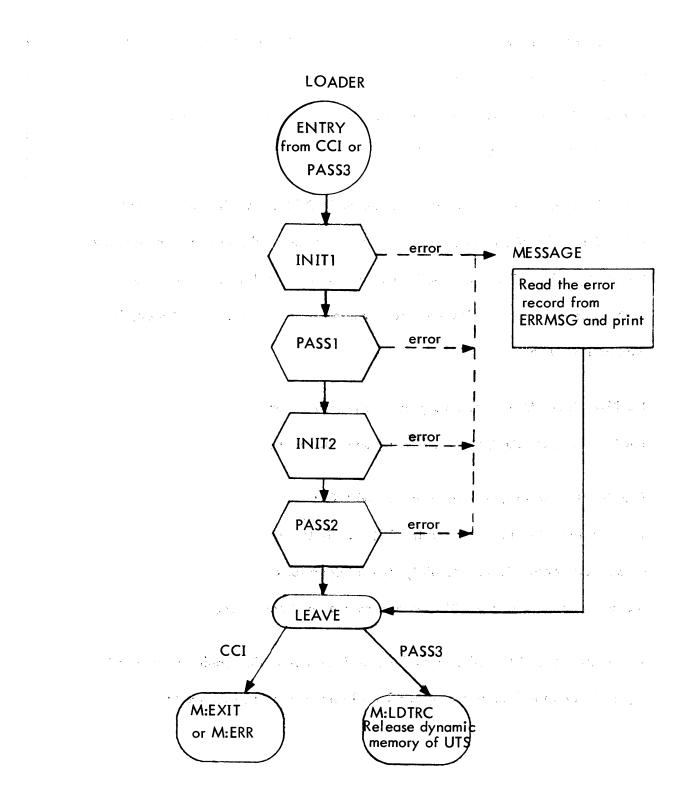

#### 1.2.2 Loader Entry/Exit

Loader entry/exit is via CCI or the SYSGEN PASS3 processor (as a result of !LOAD or !PASS3). If the Loader is entered via CCI, the !LOAD and !TREE cards and (optionally) the BI device are read by CCI and packaged into tables (see Tables, Section 3.1.1) prior to entry. If entry is through PASS3, these tables are accessed from a previously existing file (created by the !LOCCT processor) and presented to the Loader in the same form that CCI would have presented them. The Loader decides which return to execute (an M:EXIT to CCI or an M:LDTRC to PASS3) on the basis of register or JIT input. Also, for UTS, if the Loader is to exit to PASS3, it must first "release" all memory which it obtained (via M:GP or M:GCP or M:GVP).

#### 1.2.3 What the System Does With the Loader's Output

A !RUN command will cause the "Program Loader" (in BPM-PRGMLDR, in UTS-FETCH) to access the load module file, modify and/or relocate it, lay it into core per the dictates of its HEAD and TREE records and transfer control to the START address (whereupon the program is "in execution"). Figure 1 shows the user program as it sits in core during execution. If the program is overlaid, at some point it will issue an M:SEGLD call. (This was part of the user's code or was inserted by the Loader per the REF/BREF option.) Since a copy of the TREE is always a permanent part of the root segment (protection type 01), the segment loader has all the information it needs to access the desired segment, deposit it in its destination, and record the fact that the segment is now in core (to avoid unnecessary reloading in the future).

Branching between segments is the user's responsibility if he issued an explicit M:SEGLD. If REF or BREF is in effect, the branching is automated by the Loader-built table entry.

Figure 1. Load Module Layout at Run-Time

90 18 03B-1(8/72)

S

#### 2.0 GENERAL OPERATING CHARACTERISTICS

#### 2.1 FUNCTIONAL OVERVIEW

#### 2.1.1 Loader Terminology

At this point, it might be well to review some fundamentals of the object language and define some terminology relative to the Loader.

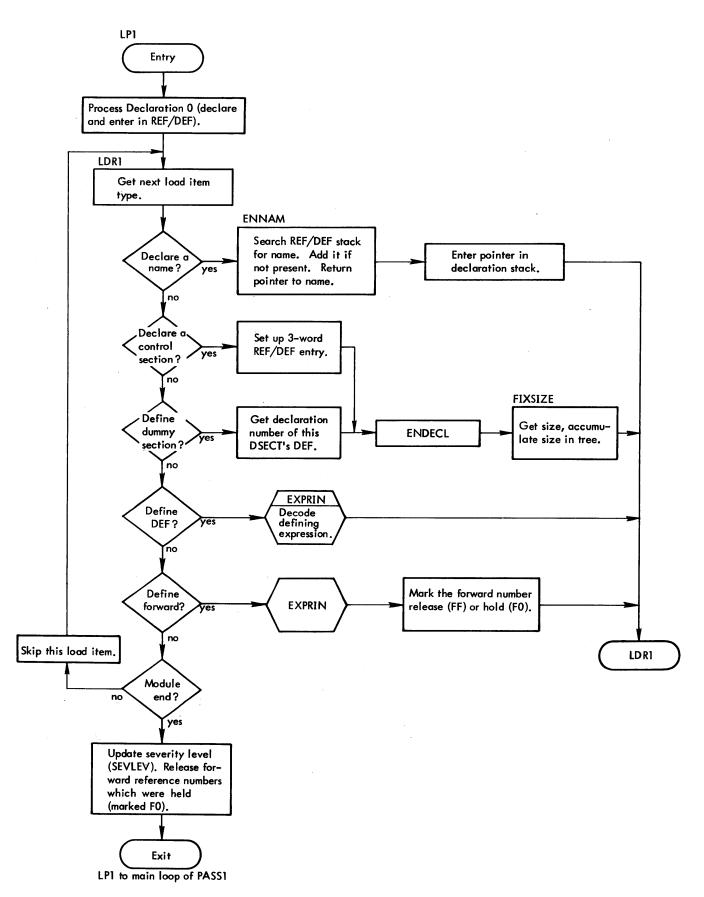

a. Declaration Numbers

Within a given ROM, all control sections, DEFs, PREFs, SREFs are declared; that is to say, each is assigned a "declaration number". (The ROM assigns declaration numbers consecutively.) In an expression which involves any of these items, the ROM refers to them via their declaration number. The Loader, therefore, must remember these numbers; it does so by building a declaration stack as the numbers are encountered within the module. (The stack is destroyed at module end since it has no meaning for the next module.) An entry in the declaration stack is simply a pointer to the proper entry in the segment's REF/DEF stack (which will eventually contain the complete story about that declaration).

b. Dummy Sections

Within a ROM, a dummy control section is treated as both a DEF and a control section. In particular, the ROM must first declare the dummy section's name (the label that is to be associated with the first location of the section) as an ordinary external definition. Subsequently, the ROM declares the dummy section itself as a control section (via 'Declare Dummy Section'). This declaration refers to the previously declared label, thereby associating the name with the dummy control section.

#### c. Expressions

The value of a DEF, Origin, Start or forward reference is given to the Loader from the ROM via an expression. Load items to be placed in the core image also involve expressions. An expression consists of operators (control bytes) which operate on constants, declarations, and forward reference numbers. Thus, an expression might say "add the value of declaration 5 with the constant X'10'". When the Loader wants to calculate the result of ("evaluate") this expression, it first looks in the fifth entry of the declaration stack to get a pointer to the proper REF/DEF stack entry. Next it adds the value word of that REF/DEF entry to the expression accumulator and then adds the value X'10' to the expression accumulator.

d. Forward Reference Numbers

Within a ROM we will encounter expressions involving forward references. These are referred to via random numbers. Therefore, the Loader must keep track of them in a similar way that it keeps track of declaration numbers. This is done by creating an entry in the REF/DEF stack containing the reference number. When a forward reference number is encountered in an expression, the Loader searches the REF/DEF stack for a match. If none is found, a new entry is created. Since the numbers are meaningless for the next module, the Loader "releases" them at module end.

Forward references are of two types: those which can be resolved by module end or sooner, and those which cannot be so resolved. The latter type consists of forward references whose defining expressions contain REFs or DSECTs. When the expression to define the forward reference is encountered, it will indicate which of the above was meant (define forward reference (DFREF) or define forward reference and hold (DFREFH)). A DFREF expression implies that the corresponding forward number is now closed and invalid;

a new expression involving that number refers to a new forward reference. The Loader must mark its REF/DEF entry as such ("release" it). On the other hand, a DFREFH expression implies that the number may occur within another expression. Therefore, it is still valid and cannot be released until module end. Notice that the number is always released at module end, even though the forward reference itself may not be resolved yet.

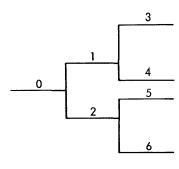

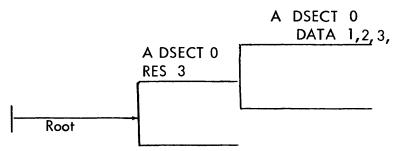

e. Files, Segments, and Paths

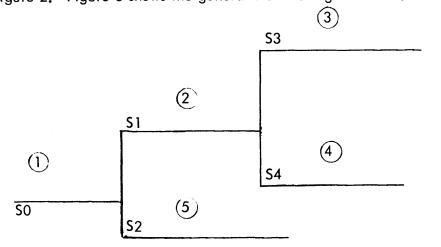

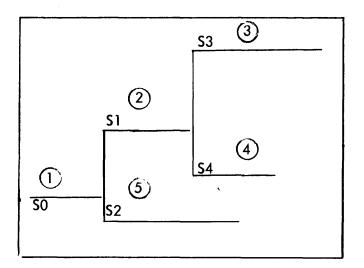

A <u>segment</u> is made up of files (ROMs or load modules) and is a piece of the target load module. A segment may be overlaid by another segment. A <u>path</u> of an overlay structure is a set of segments which reside in core at the same time. The <u>root</u> is the segment which is always in core. In Figure 2, there are three paths: S0-S1-S3, S0-S1-S4, and S0-S2. Given a segment we may speak of its <u>back-link</u>, <u>forward-link</u>, and <u>overlay-link</u>. (The forward-link is also called the "sublink".)

| 0  | r    | •   | •     |    | <b>F</b> • | <u> </u>   |

|----|------|-----|-------|----|------------|------------|

| ке | terr | ina | aaain | to | Figure     | <b>Z</b> : |

|    |      |     |       |    |            |            |

| Segment    | Back-Link  | Forward-Link | Overlay-Link |

|------------|------------|--------------|--------------|

| SO         | None       | <b>S</b> 1   | None         |

| S1         | SO         | <b>S3</b>    | S2           |

| S2         | SO         | None         | None         |

| <b>S</b> 3 | <b>S</b> 1 | None         | <b>S4</b>    |

| S4         | S1         | None         | None         |

f. Loader Stacks

The Loader forms three stacks: the declaration stack, REF/DEF stack, and expression stack. The declaration stack is created and destroyed for each ROM. An entry in the declaration stack is simply a pointer to that entry in the REF/DEF stack which describes the declaration. The REF/DEF stack is really a misnomer since it includes an entry for every declaration (control section, DEF, REF, SREF) as well as for forward references.

The expression stack contains defining expressions for DEFs and forward references, as well as expressions whose value is to be added to a word in the core image itself (core expressions).

The components of an expression are operators (control bytes) acting on declaration numbers, forward reference numbers, and constants. The value (result of performing the operations, e.g., add value of declaration, add constant, etc.) is either placed in the VALUE word of the REF/DEF stack or in the core image if it is a core expression. The Loader creates a REF/DEF and expression stack for each segment. These stacks are created along a path. The Loader's stack area will develop in the same way that the segments are overlaid. In Figure 2, if we are working on S4, then the stacks for S0 and S1 and S4 are in core. If stack S4 is in core, stack S3 will not be, since they are on different paths. (This implies, incidentally, that if one segment is to communicate with another via REFs and DEFs, they must lie on the same path.) We refer to a "stack path" as the set of stacks belonging to a given path.

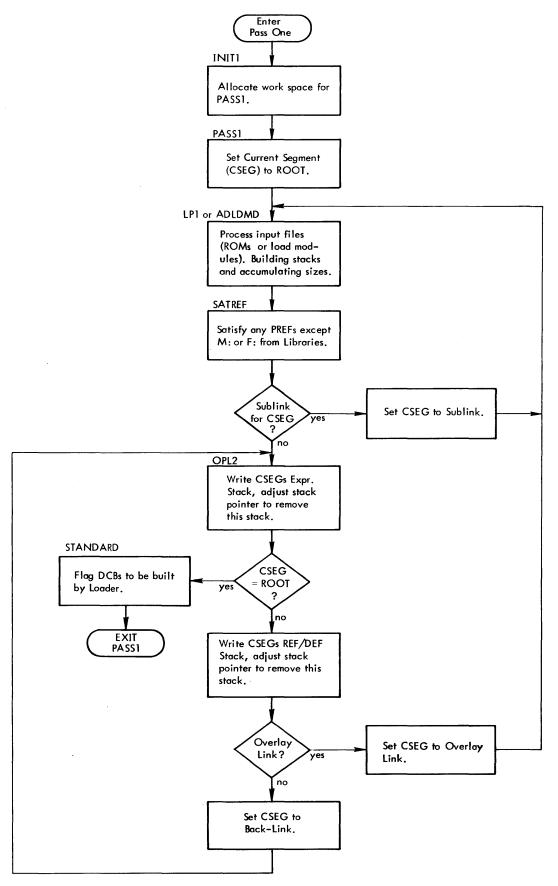

#### 2.1.2 The First Pass

The first pass gathers all information relative to the sizes of major pieces of the load module (i.e., the size of each protection type per segment and the stack sizes). Additionally, the first pass provides the second pass with an efficient means of developing the core image by constructing the REF/DEF and expression stacks. As it scans each input component (ROM or load module),

Pass One examines only that information necessary to accomplish these two functions; viz. size computation and stack construction. Any information not relevant to these functions is ignored until Pass Two.

If the component is a ROM, the sizes are to be found in the "declare control section" load items. Pass One accumulates each control section size in the appropriate protection type of the TREE. A REF/DEF entry is also built for each "declare control section" load item, as well as for load items which declare names as forward references. (For each name declaration, either a new entry is added to the REF/DEF stack or an old one is modified.) Expression stack entries result from load items which define external DEFs or forward references. (When a new entry is made in either the REF/DEF or expression stack, the size of that stack is updated in the TREE.) All load items dealing with the content of the core image (e.g., "load relocatable") are ignored.

If the component is a load module, the HEAD and TREE records contain the sizes of the core image and the stacks. These are added to the TREE. The load module's stacks are then merged with the ones being constructed. The core image and relocation dictionary records are ignored until Pass Two.

At the end of processing each segment's explicit element files, the REF/DEF stack is scanned for all PREFs except those having names starting with M: or F: (for which the Loader will build DCBs). For each PREF found, Pass One searches those libraries specified on the !LOAD card for a load module which will satisfy the PREF. If it finds one, the load module's name is added to the list of input files (ROM Tables), the size is recorded in the TREE and its stacks are merged with the ones being built.

The sequence of processing the overlay structure is from the root segment outward, as shown in Figure 2. Figure 3 shows the general flow during Pass One.

Figure 2. Segment Processing Sequence, Pass One

At the end of the first pass we have:

- a. sizes of the segments per protection type, including the sizes of modules obtained from the library. These sizes are in the Tree Tables.

- b. a REF/DEF and expression stack for each segment written to the RAD. The stacks are structurally complete. They include the merged library stacks. The value and resolution for each REF/DEF entry is not determined until the second pass.

- c. defining expressions for DEFs and FREFs in the appropriate expression stacks. The expression stacks also include expression stacks from library load modules.

- d. sizes for the REF/DEF and expression stacks in the Tree Tables.

- e. ROM Tables augmented by the names of library load modules pulled in as a result of satisfying PREFs.

Figure 3. The First Pass – General Flow

....

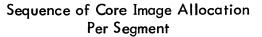

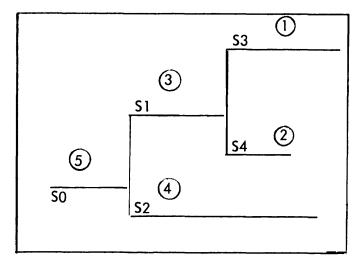

#### 2.1.3 The Second Pass

This pass develops the actual core images and relocation dictionaries and writes the load module to the RAD.

Based on the sizes known from PASS1, core is partitioned into the stack area and buffers for the core images and relocation dictionaries. If this partitioning is not possible, Pass Two goes into "extended memory mode", meaning that the core images and dictionaries will be developed within an intermediate RAD file, page by page.

The expression and REF/DEF stacks for an entire path are brought into core and, from the size and protection type of every control section, locations are assigned to all of the sections (the control sections are "allocated") along this path.

After evaluating and defining all possible DEFs and FREFs, Pass Two is now in a position to reread the input files (proceeding backwards along a path). As it reads, it places data in the core and relocation buffers (or into the extended memory mode file, as the case may be) as per the dictates of the load items. When a segment is complete, its REF/DEF stack, expression stack, core images, and relocation dictionaries are written out (unless we are in extended memory mode, in which case processing of the paged core image and relocation dictionary records is deferred until the root segment has been constructed).

The sequence of forming the core images for an overlay structure proceeds from the sublinks back toward the root, but, as mentioned, allocation occurs forward along a path (see Figure 4).

Sequence of Forming Core Image Per Segment

Figure 4. Segment Processing Sequence, Pass Two

Special attention comes into play when we reach the root segment at the end of the second pass. If extended memory mode is in effect, the load module must be reconstructed from the page records of the extended memory mode file which were created during the formation of the core image In any case, the TCB and DCBs are built, the HEAD and TREE records are written, necessary modifications per !MODIFY cards are made, the severity level is printed, and the Loader returns control to CCI or PASS3.

Figure 5 shows the general flow of Pass Two.

.

Figure 5. The Second Pass – General Flow

#### 2.1.4 Advantages of a Two-Pass Loader

- a. The primary advantage is accorded to FORTRAN programs which use Blank COMMON. A two-pass Loader has the ability to discover the largest dummy section of the same name (dummy sections are intrinsically externally defined) and to allocate accordingly. This would be, if not impossible, an extremely difficult matter for a one-pass Loader.

- A one-pass Loader has difficulty with overlaid load modules having more than one protection type. The problem arises in determining how many pages of memory should be allocated for the 00 protection type before allocating for the 01 protection type. A two-pass Loader can compute, in its first pass, the size each protection type requires and can allocate memory accordingly for the second pass.

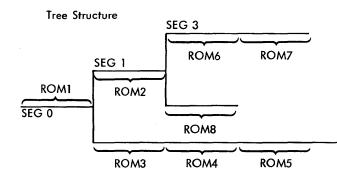

#### 2.2 STRUCTURE: THE MAJOR PIECES

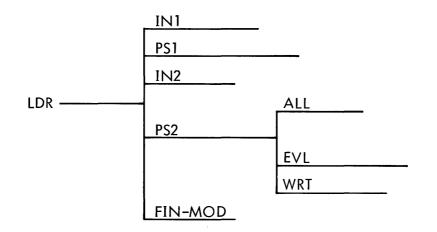

The Overlay Loader is a two-pass Loader; that is, the ROMs and load modules from which the target load module is constructed are read two distinct times. The Loader is composed of nine ROMs. These ROMs may be grouped according to their usage in the first or second pass.

| When Used                 | File Name  | Entry Points       | <u>Catalog No.</u>               |

|---------------------------|------------|--------------------|----------------------------------|

| Throughout<br>both passes | LDR        | LOADER             | 704724                           |

| First Pass                | IN1<br>PS1 | INITI<br>PASSI     | <b>704</b> 725<br><b>70</b> 4726 |

| Second Pass               | IN2        | INIT2              | 704728                           |

|                           | PS2<br>ALL | PASS2<br>ALLOCATE  | 704728<br>704729                 |

|                           | EVL        | LOADSEG, EVEXPRS   | 704730                           |

|                           | WRT<br>FIN | WRITESEG<br>FINISH | 704731<br>706258                 |

|                           | MOD        | MODIFY             | 705396                           |

#### 2.2.1 LDR

This ROM is a collection of frequently used subroutines, temp space, variable data, DCBs and a driver which contains the start address (LOADER) and which subsequently BALs to the first and second passes and exits.

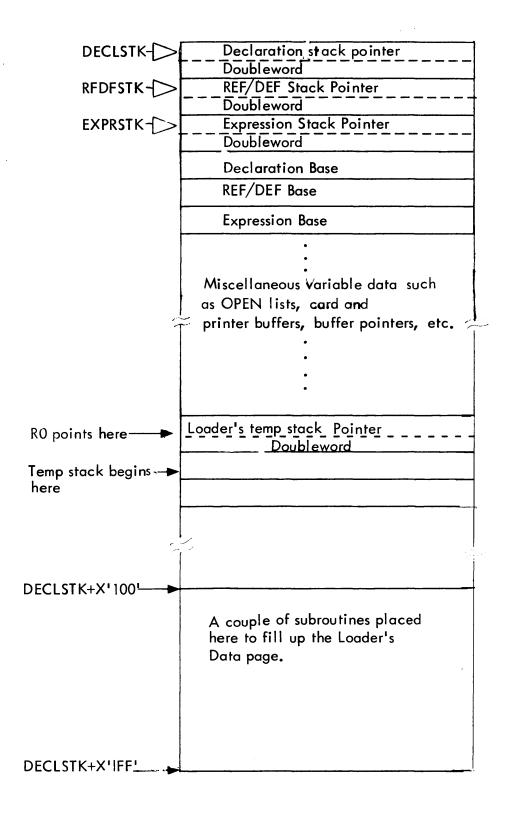

The LDR module contains the Loader's only DATA area (one page). This area is composed of two parts: a temp stack (pointer in R0) and a collection of variable data (stack pointer, doubleword buffer pointers, location counters, etc.). See Appendix B for a description of the use of the variable data cells in the loader's STUFF stack.

Figure 6 illustrates the format of this area.

Figure 6. Loader's DATA (00) Area (Within LDR)

#### 2.2.2 The First Pass

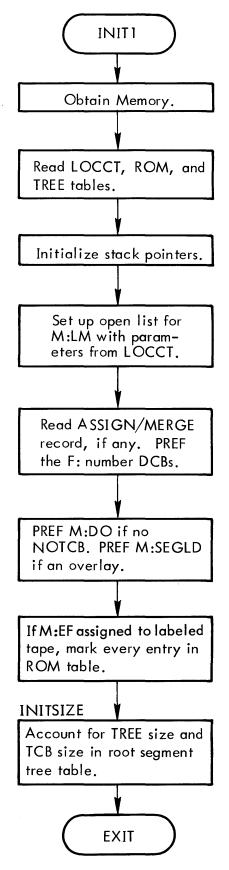

## IN1 - entry/exit from LDR.

- allocates the work space for PS1.

- reads the LOCCT, ROM, TREE Tables.

- reads and processes the ASSIGN record.

#### PS1 - entry/exit from LDR.

- reads and processes ROMs and load modules, collecting the information necessary to ascertain sizes of control sections and maximum stacks.

- satisfies PREFs from libraries.

- writes out interim stacks.

#### 2.2.3 The Second Pass

| IN2 | -                | entry/exit from LDR.<br>allocates the work space for the second pass, determining<br>if extended memory mode is necessary.                                                                                                                                                |

|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PS2 | -<br>-<br>-      | entry/exit from LDR.<br>a driver for the second pass.<br>calls ALL, EVL, and WRT.<br>reads current segment's stacks.                                                                                                                                                      |

| ALL | -<br>-<br>-      | entry/exit from PS2.<br>assigns locations to all control sections.<br>prints load module allocation summary.                                                                                                                                                              |

| E∨L | -<br>-<br>-      | has two entry points, EVEXPRS and LOADSEG, both from PS2.<br>evaluates expressions from PASS1 and core expressions from load modules.<br>forms core image and relocation dictionary going through extended<br>memory mode logic.<br>builds reference loading table.       |

| WRT | -<br>-<br>-<br>- | entry/exit from PS2.<br>creates TCB and DCBs, and the DCB Name Table.<br>concatenates the pages of the extended memory mode file for a<br>standard load module.<br>cleans up the paged core image records for a paged load module.<br>writes the load module to the file. |

| FIN | -<br>-<br>-      | entry/exit from LDR.<br>updates and prints severity level.<br>reads idD and calls MOD.<br>generates load map.                                                                                                                                                             |

| MOD | -                | entry/exit from FIN.<br>performs the modifications per !MODIFY cards which followed<br>the !LOAD.                                                                                                                                                                         |

#### 2.2.4 Forming the Loader

If the Loader is overlaid, it bears the following TREE structure:

ITREE LDR-(IN1, PS1, IN2, PS2-(ALL, EVL, WRT), FIN-MOD)

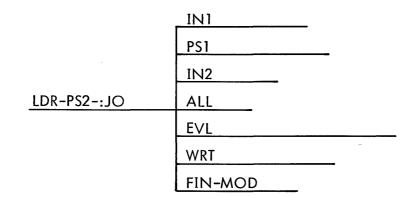

The UTS Loader is overlaid according to the following TREE structure:

!TREE LDR-PS2-: JO-(IN1, PS1, IN2, ALL, EVL, WRT, FIN-MOD)

The tree structure is such for the UTS Loader because, as a shared processor, the Loader is allowed only one level of overlay. Note also that the file :JO (in :SYS) must be listed as the last element file when forming the UTS version:

!LOAD (LMN, LOADER), (NOTCB), (NOSYSLIB), (SL, F), ;

! (EF, (LDR), (IN1), (PS1), (IN2), (PS2), (ALL), (EVL), (WRT), (FIN), (MOD), (JO, :SYS))

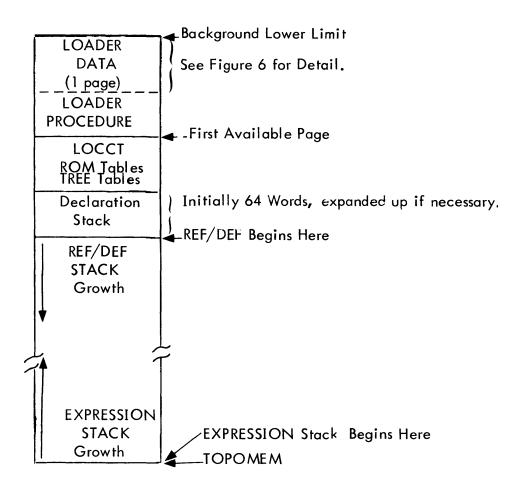

#### 2.3 HOW THE LOADER USES MEMORY

#### 2.3.1 Partitioning Core for the First Pass

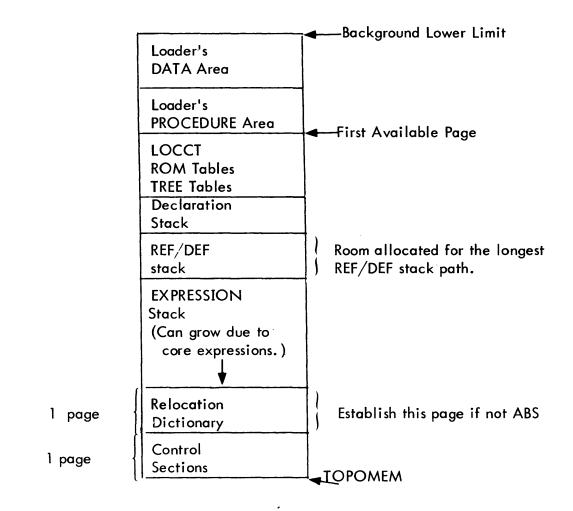

Recall that the first pass, after it has read the LOCCT, ROM, and TREE Tables, constructs the REF/DEF and expression stacks. (The declaration stack is volatile for each ROM.) Accordingly the partition concerns itself with only these areas. (Partitioning for the first pass is done by IN1.)

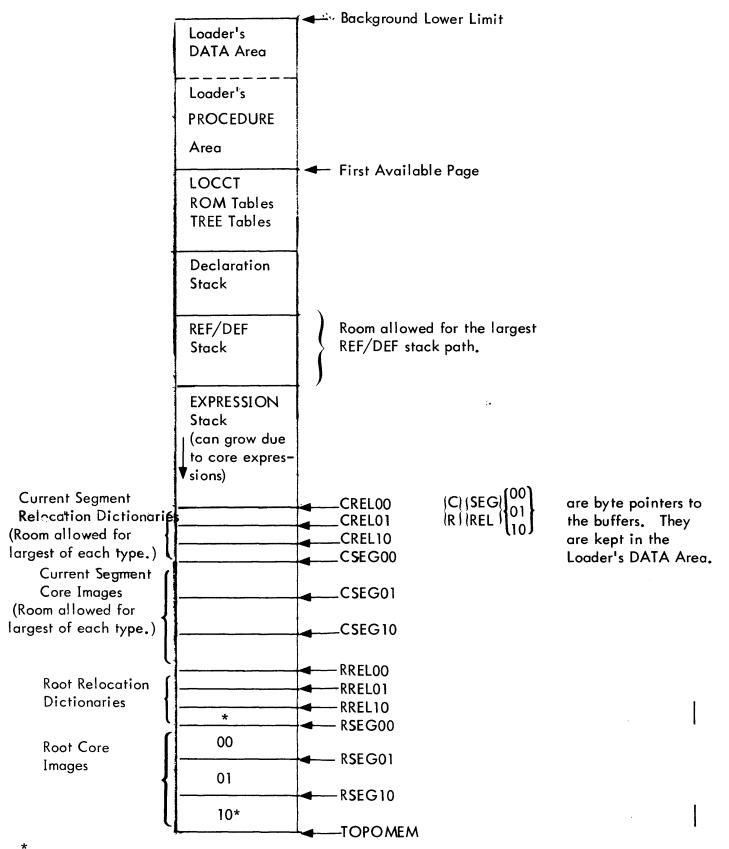

Figure 7. How the Loader Uses Memory: Pass One

If the REF/DEF and EXPRESSION Stacks meet during Pass One, processing is discontinued (JOB aborts).

#### 2.3.2 Partitioning Core for the Second Pass

The second pass is concerned with developing the core images and relocation dictionaries (unless ABS was specified, in which case there are no relocation dictionaries). Buffers are needed to house these.

There must also be room to hold the REF/DEF and EXPRESSION stacks for the largest path. The size of the REF/DEF stack is known from PASS1, but the expression stack can grow (due to unevaluatable core expressions). Maximum declaration stack size was also retained in PASS1.

There are two partitioning schemes: nonextended memory mode and extended memory mode. IN2 (which performs the partitioning) will select the former, if space permits.

#### a. Nonextended Memory Mode (Fig. 8)

Two buffers are reserved for each protection type; one for the core image and one for the relocation dictionary. Such buffers are reserved for the root and for the current segment. Hence, in a full-blown relocatable TREE, there would be 12 buffers. (The reason for the double buffers is to permit a higher segment with load items in a DSECT belonging to the root to store those items into the root.)

Since the expression stack can grow, the buffer allocation begins from TOPOMEM down. (Notice that the expression stack is growing in the opposite direction than it did in the first pass.)

.

For UTS, these buffers can grow due to rounding to prevent DCBs from overlapping page boundaries. If this occurs, all buffer pointers are shifted down accordingly. See Section 5.3.

Figure 8. How the Loader Uses Memory: Pass Two - Nonextended Memory Mode

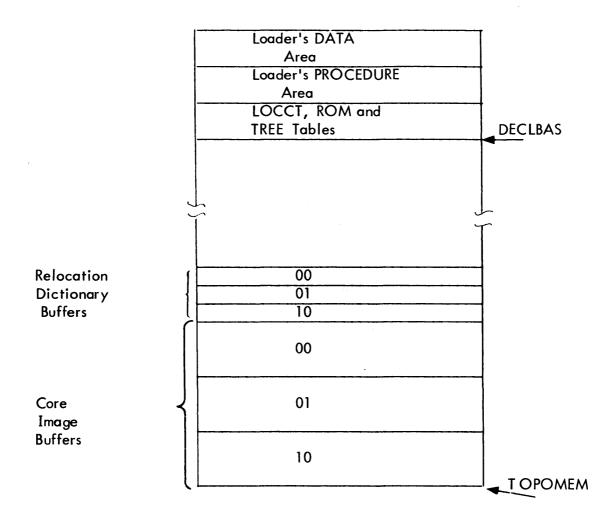

#### b. Extended Memory Mode (Figures 9a and 9b)

If the above partition is not possible, IN2 enters extended memory mode which consists of replacing the 12 buffers with page buffers (one if ABS is specified, two if not) at TOPOMEM down. All segments, including the root, are built within these buffers. The EVL module uses these buffers to construct page records of the core images and relocation dictionaries. The file used to develop these records is either a temporary (idX) file (for a standard load module) or the load module file itself (for a paged load module). Only one page buffer is required in the latter case since a paged load module is forced ABS. Figure 9a illustrates the use of memory during the construction of the page records.

If a standard load module is to be constructed in extended memory, memory is partitioned differently at the end of the second pass (in the module WRT). Six buffers (or three if ABS) are used to concatenate the page records, one segment at a time. Figure 9b illustrates memory usage during the concatenation (sometimes called "put-together" phase) of extended memory mode.

The above partition is not required for the paged load module; instead, room is needed only for those core image records belonging to the root which are to contain loader-built tables. These records are read in successive order above DECLBAS according to protection type.

Figure 9a. How the Loader Uses Memory: Pass Two – Extended Memory Mode, Construction of Core Image Records

Figure 9b. How the Loader Uses Memory: Pass Two – Extended Memory Mode, Concatenation of Core Image Records

#### 2.4 HOW THE LOADER OBTAINS MEMORY

#### 2.4.1 Loader Running Under BPM

IN1 simply does a M:GP requesting the maximum (256) number of pages.

#### 2.4.2 Loader Running Under UTS

Since memory must be obtained from both ends of the dynamic page area, and since UTS restricts the number of pages obtained, the above BPM technique does not suffice. IN1 initially gets four pages via M:GP. It then takes memory trap control (M:TRAP) such that "demand paging" is in effect. That is, whenever a memory violation occurs due to access of an unauthorized page, the Loader's TRAP routine (in the LDR module) is entered. TRAP computes the virtual page address requested and obtains the page via M:GVP.

#### 2.5 MAINTAINING THE LOADER, DEBUG MODE

The Loader program, as a processor, cannot be executed as a user's program since it does not read its own control card. However, a special version of the Loader (called the "debug version") can run as a user's program, thus making Loader maintenance and modification an easier task. The debug version of the Loader is obtained by assembling LDR, IN1, and PS2 with the assembly parameter DEBUG EQU'd to 1. This causes code to be assembled which will read the LOCCT, ROM, and Tree Tables from a file (created by the LOCCT processor). It also causes the M:BI and M:DO DCBs to be built for reading the LOCCT and for handling !SNAPs, !MODIFYs, and !PMDs. A debug Loader can be assembled for either UTS or BPM, as determined by the parameter MODE.

#### Example:

- 1 **!**ASSIGN M: BI, (FILE, LOCCTTEST)

- 2 IRUN (LMN, DELOAD), (XSL, F)

- 3 **!**MODIFY .....

- : ISNAP MESSAGE, MSG, (DECLSTK, DECLSTK+100), (+E200, +E600)

- n **!**PMD (00)

- Card 1. The file must have been created by the LOCCT processor (see BPM Reference Manual, 90 09 54).

- Card 2. The Loader (DELOAD in this example) must have been formed with LDR, IN1, and PS2 assembled in the DEBUG EQU 1 mode.

- Card 3-n MODIFYs and debug commands.

In this mode the Loader may also be executed from the terminal under the RUN subsystem for BPM.

#### 3.0 INPUT, OUTPUT, LOADER-GENERATED TABLES

#### 3.1 INPUT

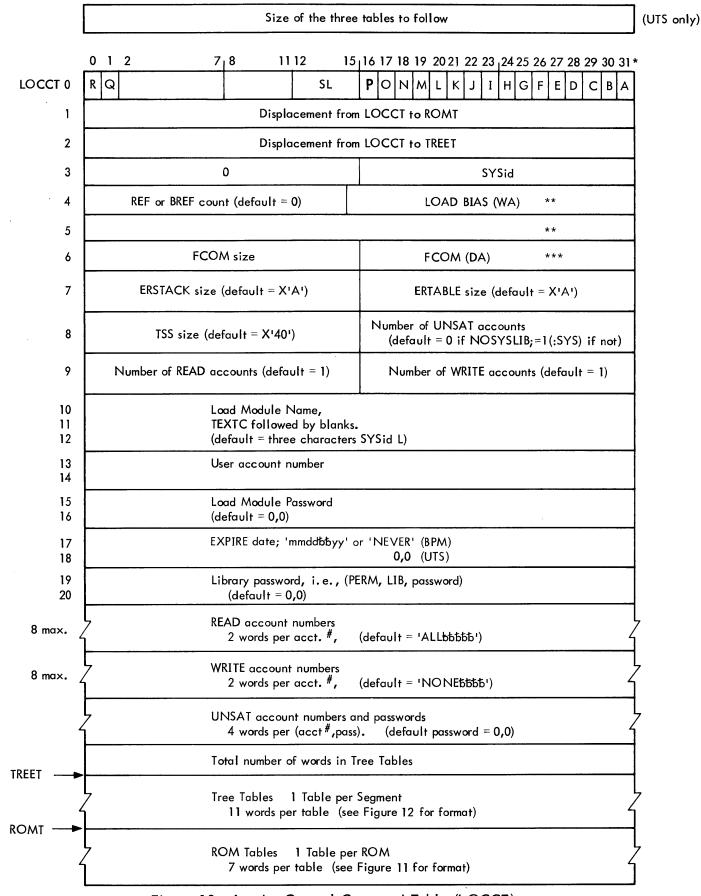

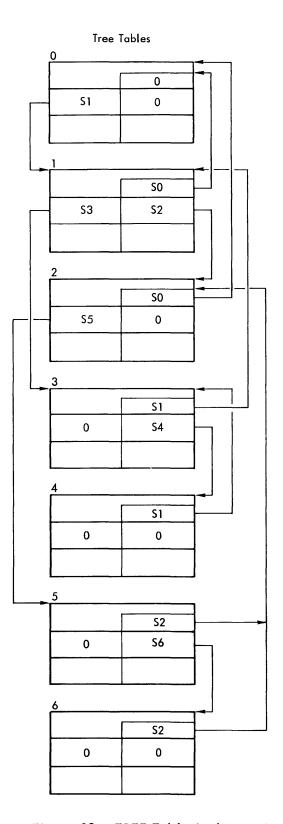

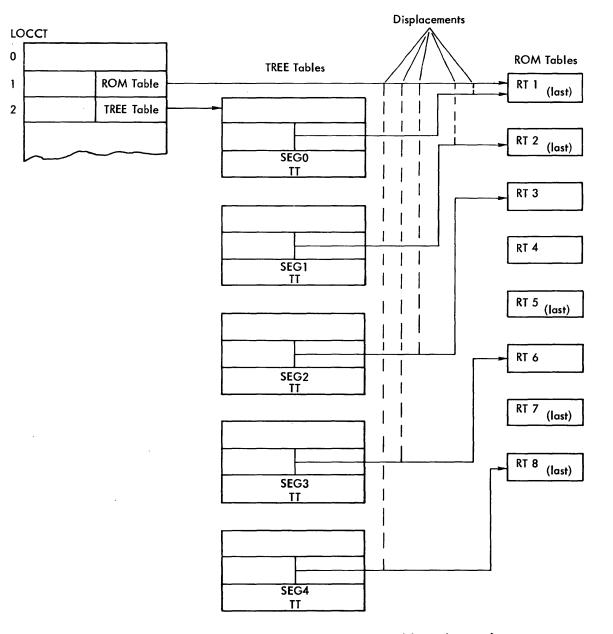

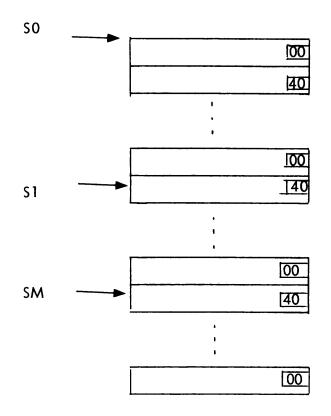

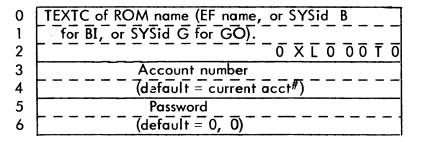

#### 3.1.1 LOCCT, ROM, Tree Tables

Based on the !LOAD and !TREE cards, three related and contiguous tables are presented to the Loader upon entry: the Load Control Command Table (LOCCT), the Tree Table, and the ROM Table. If BPM is operating, the tables reside on sector 36 of the absolute area of the disk. Total size is contained in R6 upon entry to the Loader. If UTS is operating, the tables are left in core preceded by a word containing the size. A pointer to this area is in word JB:BCP of the JIT.

In either case, the Loader moves these tables into its first dynamic page (M:GP) during initialization.

Figure 10. Loader Control Command Table (LOCCT)

```

Tree Tables

```

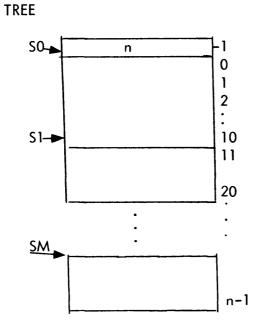

Overall picture for M segments (S0, ... SM)

n = total size of the tables

Tree Table Format (one 11-word Table per Segment)

| ļ                  | - 0            |                |      |         |

|--------------------|----------------|----------------|------|---------|

| Displacement 🔨     | !L             | XTC Format     | - 2  |         |

| from the beginning | ROM Pointer    | Back Link **   | 3    |         |

| of the ROM Tables  | Forward Link** | Overlay Link** | 4    |         |

| to the first ROM   | 00 Size *      | 00 Loc*        | 5    | Init    |

| Table for this     | REF/DEF Size   | REF/DEF Loc*   | 6    | ially   |

| segment            | 01 Size*       | 01 Loc*        | 7    | Clear - |

|                    | Expr. Size     | Expr. Loc*     | 8    | ed      |

|                    | 10 Size*       | 10 Loc*        | 9    | eu      |

|                    |                |                | 10 / | /       |

Figure 12. Tree Tables

Segment name is determined by the name of the first file in the segment. (If the load module has only one segment, i.e., the root, the keys begin with load module name. If no load module name was supplied, the name is idL.

Words 5-10 of each Tree Table are computed by the Loader.

Word 10 of the ROOT Tree Table is used to monitor the size of the REF/BREF Tables.

\*Doubleword address or # of doublewords

\*\* Displacements from TREE

Tree Structure

#### Tree Table Link Pointers

|           | back    | 3 |

|-----------|---------|---|

| sub (fwd) | overlay | 4 |

|           |         |   |

•

Figure 13. TREE Table Linking – in Relation to the Overlay Structure

•

Figure 14. LOCCT, TREE, and ROM Table Relationships

#### 3.1.2 Files (ROMs and Load Modules)

The Loader will access ROM files and load module files. All file names specified on the !LOAD card under the EF option appear in the ROM Table. Additionally, the files idB and idG may appear in the ROM Table if the user specified (BI) or (GO), respectively. During Pass One processing, the Loader augments the ROM Table by those library load modules which are to be included. Note that the Loader is entirely file-oriented. That is, ROMs coming from cards on BI will be read by CCI which creates a file by the name of idB. (Exception: M:EF may be assigned to labeled tape.)

a. ROM Files

A ROM file consists of one or more ROMs produced by an assembler or compiler (see the BPM Reference Manual (90 09 54) for a description of the ROM language). ROM files are accessed either from the accounts specified in the EF list (which the Loader sees in the ROM Table) or from the files idB and idG. (If a !TREE card has been included, idB and idG would appear in the ROM Tables for the root segment.)

b. Load Module Files

Load modules acceptable for combination with ROMs to form a new load module are built either by

- the Loader itself, in which case they are library load modules (see Output Section, 3.2, for format);

- 2) PASS2 of SYSGEN; or

- 3) DEFCOM processor.

The HEAD of the input load module indicates one of the above sources in order that any attributes may be handled correctly. Any such load module must be of one protection type, relocatable, and not overlaid. Furthermore, if such a load module contains a DSECT, then the entire load module consists of that DSECT alone.

### BPM

R6 = word size of LOCCT, ROM, and Tree Tables

R7 = xx id

- SR1 = information needed by CCI or PASS3. This is simply stored and restored upon exit.

- D4 = foreground COMMON bias

### UTS

| J:EUP          | = | page number of the last user page                      |

|----------------|---|--------------------------------------------------------|

| J:JIT, byte 3  | = | id                                                     |

| JB:BCP, byte 1 | = | page pointer to LOCCT Table –1.<br>This word contains: |

xx n

which is followed by the LOCCT, ROM, and Tree Tables.

SR1, D4 = same as BPM

xx = 0, if CCI called the Loader.  $\neq 0$ , if PASS3 called the Loader.

n = size of LOCCT, ROM, and Tree Tables

id = system id (see Glossary)

.

.

#### 3.1.4 ASSIGN Record

CCI builds a record of all ASSIGN information encountered during a job. The Loader examines this record to see if any F: number DCBs have been entered and, if so, will generate those DCBs with default entries (if they are PREFs within the user program). In UTS this record is read via an FPT code = X'2D'. In BPM the record is in section 35 of absolute area of the RAD and is read with an FPT code of X'16'. (See Section 16 of the F00 BPM Technical Manual for formats.)

#### 3.1.5 Error Message File (ERRMSG)

This is a keyed file under the :SYS account. Its keys are of the form:

# 03 02 error number

The records are the text error messages. To alter the file, one uses the programs ERROM (Cat. No. CN706106) and ERRDATA (Cat. No. SI706107) for BPM, and the program ERRMWR for UTS.

When an error occurs, the Loader transfers control to MESSAGE (in LDR) with the error number in R3. MESSAGE builds the key, reads and prints the associated record.

Figure 15 is a listing of ERRMSG (to date).

| KEY    | MESSAGE                                               |      |

|--------|-------------------------------------------------------|------|

| 020001 | UNEXPECTED EOF                                        |      |

| 020002 | ILLEGAL RECORD I. D.                                  |      |

| 020002 | SEQUENCE ERROR                                        |      |

| 020004 | ILLEGAL RECORD SIZE                                   |      |

| 020005 | CHECKSUM ERROR                                        |      |

| 020006 | ABNORMAL I/O                                          |      |

| 020007 | CANNOT OPEN E. F.                                     |      |

| 020008 | STACK OVERFLOW                                        |      |

| 020009 | BIAS TOO LARGE                                        |      |

| 02000A | ILL. ROM LANGUAGE                                     |      |

| 02000B | BAD START ADDRESS                                     |      |

| 02000C | UNEXPECTED ROM END                                    |      |

| 02000D | REPEAT LOAD IS ZERO                                   |      |

| 02000E | IMPROPER BOUND                                        |      |

| 02000F | ILLEGAL ORG                                           |      |

| 020010 | BAD I/O RETURN FROM M:LM DCB                          |      |

| 020011 | SEV. LEV. EXCEEDED                                    |      |

| 020012 | ILL. LIB. LOAD MOD.                                   |      |

| 020013 | NO ROOM TO ROUND DCBS TO PAGE BOUNDARIES. TRY FORCING | XMEM |

| 020014 | ILL. DSECT                                            |      |

| 020015 | ROOT SEGMENT TOO LARGE TO LOAD                        | IN2  |

| 020016 | NEW UTS ERR FROM XMEM                                 | IN2  |

| 020017 | CANNOT ENTER XMEM. STACKS TOO LARGE.                  | IN2  |

| 020018 | NOT ENOUGH ROOM TO CONCATENATE XMEM PAGES             | IN2  |

| 020019 | NO ROOM TO READ LIBRARY CORE IMAGE                    | EVL  |

| 02001A | NO ROOM TO READ LIBRARY RELOCATION DICTIONARY         | WRT  |

| 02001B | NO ROOM FOR NEW EXPRESSION                            | WRT  |

| 02001C | NO ROOM TO BUILD DCB TABLE. TRY FORCING XMEM          | WRT  |

| 02001D | NO ROOM TO BUILD DCB TABLE                            | WRT  |

| 02001E | LIBRARY LOAD MODULE REF/DEF STACK TOO LARGE TO UPDATE | WRT  |

| 02001F | INSUFFICIENT PHYSICAL MEMORY                          |      |

| 020020 | BAD ASSIGN/MERGE RECORD                               |      |

| 020021 | NO ROOM TO ADD LIBRARY LOAD MODULE TO ROM TABLE       |      |

| 020022 | NO ROOM TO READ LIBRARY REF/DEF STACK                 |      |

| 020023 | NO ROOM TO UPDATE LIBRARY                             |      |

| 020024 | INVALID KEY SUPPLIED FOR DELETE RECORD ON M:DIC       |      |

| 020025 | I/O ERROR ON M:DIC IN WRITESEG                        |      |

| 020026 | ILLEGAL LIBRARY LOAD MODULE NAME                      |      |

| 020027 | ABNORMAL I/O ON OPEN OR READ TO CORE LIBRARY          |      |

| 020028 | INVALID DECLARATION NUMBER REFERENCE (BAD ROM).       |      |

| 020029 | INVALID KEY SUPPLIED FOR WRITE RECORD ON M:DIC        |      |

| 02002A | ILLEGAL LOADER TRAP                                   |      |

#### MESSAGE

02002B ABNORMAL I/O IN WRITELIB 02002C CANNOT FIND REF/DEF NAME IN STACK 02002D LIB LOAD MODULE TOO BIG - CANNOT USE EXTENDED MEMORY 02002E LIB LMN IS NOT ALLOWED ON A PRIVATE VOLUME

Figure 15. ERRMSG File (cont.)

#### 3.1.6 Modify File (idD)

This keyed file is built by CCI in the user's account on the basis of the !MODIFY cards.

Its keys are of the form:

TEXTC segment name concatenated with xx, where  $0 \le xx \le n$  and n = the hexadecimal number of !MODIFY cards.

See Section 16 of the FOO BPM Technical Manual for a more detailed format.

#### 3.1.7 Core Libraries (UTS only)

Core libraries exist only under the :SYS account. An absolute copy of a core library's procedure area exists on swap storage associated with the name :Pnnn and is placed at run-time into a fixed area. The DEFs for :Pnn which relate the core library's context area (preceding the user's blank COMMON) with the user and the library procedure are contained in a load module (formed by DEFCOM) named :Pn. The Loader's job is to read :Pn, merge the DEFs into the REF/DEF stack of the target load module, and signal the !RUN processor that it is to associate :Pnn with this program. The signal consists of placing the text :Pnnn in the HEAD record of the load module.

:PO is the name of the FORTRAN core library with debug.

:P1 is the name of the FORTRAN core library without debug.

See Chapter 6 of the UTS System Management Guide for details on core libraries.

#### 90 18 03B-1(8/72)

41

KEY

#### OUTPUT 3.2

# 3.2.1 Load Modules, Overall Format

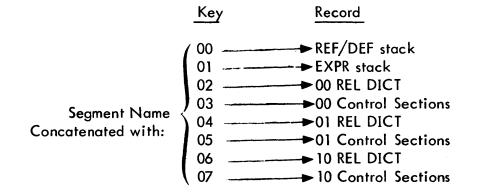

A load module is a keyed file whose name was supplied on the !LOAD card (default = idL). The keys and records are as follows:

# Record

# BPM

# a. Key = HEAD

|   | 0                      |           | 8                    | 16                   | 24 3  |

|---|------------------------|-----------|----------------------|----------------------|-------|

| 0 |                        | 8X        | 00                   | FF                   | n     |

|   | AB                     | SL        |                      | START add            | dress |

| 2 | TCB*                   |           | Module Bias*         |                      |       |

| 3 | DATA (00) Base*        |           | Base*                | PROCEDURE (01) Base* |       |

| 4 | STATIC DATA (10) Base* |           | Next Available Page* |                      |       |

| 5 |                        | MAX RF/DF | SIZE                 | TREE Size            |       |

# UTS

| 0  | 8X         | 00     | FF        | n             |            |

|----|------------|--------|-----------|---------------|------------|

| 1  | A B SL     | ·      | START add | lress         |            |

| 2  | TCB*       |        | Module Bi | as*           |            |

| .3 | DATA Size* |        | DATA (00) | Base*         |            |

| 4  | PROCEDUR   | SIZE * | PROCEDU   | RE (01) Base* |            |

| 5  | MAX RF/DF  | Size   | TREE Size |               |            |

| 6  | DCB Size*  |        | DCB Base  | (10)*         |            |

| 7  |            | 0      |           | 0             | **         |

| 8  |            | 0      |           | 0             |            |

| 9  |            | 0      |           | 0             |            |

| A  |            | 0      |           | 0             | ***        |

| В  |            | 0      |           | 0             |            |

|    |            |        |           |               | ' <b>/</b> |

(Footnotes are on next page.)

Footnotes to keys and records shown on previous page:

\*Doubleword address

| n<br>A | n byte 0, word 0<br>= number of bytes in<br>= 1, abs module<br>= 1, NOTCB | X = 0, load module produced by Loader.<br>= 1, load module produced by SYSGEN.<br>= 2, library load module produced by Loader.<br>= 3, load module produced by DEFCOM (con-<br>sists of HEAD, TREE, and REF/DEF (Stack).<br>= 5, pages load module produced by Loader.<br>the HEAD record. For UTS, n = X'30'; for BPM, n = X'18'. |

|--------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | = Final Severity Lev                                                      | el                                                                                                                                                                                                                                                                                                                                 |

|        | Word 7<br>Words 9, A, B                                                   | If DEFCOM output, this word = byte size of DATA area.<br>If the LMN is associated with a core library, these words<br>are :Pnnn in TEXTC format.                                                                                                                                                                                   |

- b. Key = TREE Record is the Tree Tables (see Figure 12).

- c. Segment Components Standard Load Module

For each segment, the following records are built:

d. Segment Components - Paged Load Module

For each segment, the expression stack and REF/DEF stack records have the same format as those for the standard load module. Relocation dictionary records are not constructed.

The core images are partitioned into records of at most 512 words in length with 3-byte keys of the following format:

where SEG = the TREE segment number of the segment containing the core image. PAGE = the page number of the virtual page that will contain this record at execution time.

All core image records are one page in length except for the first record of an overlay segment's 00, 01, and 10 areas. The length of this record satisfies the following: at execution time, the record begins at the execution bias for this protection type and ends at the next page boundary.

### 3.2.2 Library Load Modules

A library constructed by the Overlay Loader consists of two keyed files, :LIB and :DIC. The library load modules actually reside in one file (:LIB). :DIC is a dictionary whose keys are the text names of DEFs. The record associated with a dictionary key is the text name of the load module (within :LIB) in which that DEF is defined. Thus, in order to locate the unique group of records within :LIB which pertain to a given PREF, the Loader does a keyed READ to :DIC, the key being the PREF which is being satisfied. This keyed READ returns the library load module name within :LIB. With this information the Loader can then read the library load module records into core and merge them with the target load module.

The keys and records in :LIB are identical to those of non-library load modules (see above) except that the keys "HEAD" and "TREE" are concatenated with the TEXT load module name (to keep them unique). Each individual library load module name is "synonymous" (in a file sense) with the name :LIB.

A slight difference also exists in the REF/DEF and expression stack formats. The VALUE word of an entry in the REF/DEF stack is actually the head of a chain through the expression stack of all those entries which involve that REF/DEF. (This expedites subsequent merging of the stacks when the library is included in a user program.)

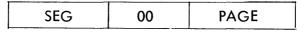

# 3.2.3 REF/DEF Stack

There is one REF/DEF stack for each segment. A REF/DEF stack is composed of entries for every control section and forward reference in the segment. It also contains an entry for every name (DEF, REF, SREF) in the segment which does not occur in this segment's backward path.

Before a name is added to a segment's REF/DEF stack, the segment's stack and the REF/DEF stacks for this segment's backward path are searched. If the name is not in these stacks, a new entry is added to the segment's stack. If the name already exists, the entry in which the name appears is treated as follows:

| New Name | Type of Existing<br>REF/DEF Entry | Modification of<br>Existing REF/DEF Entry |

|----------|-----------------------------------|-------------------------------------------|

| DEF      | DEF                               | Double DEF                                |

| DEF      | REF                               | DEF                                       |

| DEF      | SREF                              | DEF                                       |

| REF      | DEF                               | Used DEF                                  |

| REF      | REF                               | No change                                 |

| REF      | SREF                              | REF                                       |

| SREF     | DEF                               | Used DEF                                  |

| SREF     | REF                               | No change                                 |

| SREF     | SREF                              | No change                                 |

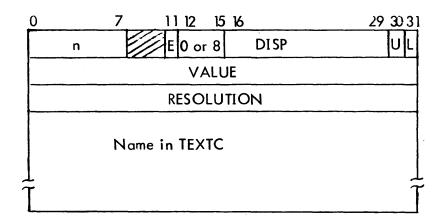

### GENERAL REF/DEF STACK FORMAT

where:

n = number of words in this entry.

E = 1, if the entry has a VALUE

TYPE = 0 or 8 DEF 1 SREF 2 PREF 3 or B Dummy Section 4 or 6 Control Section

- 5 or 7 Forward Reference

- VALUE = constant or address if the load module is not a library

or

head of a chain in the expression stack if the load module is a library (see SQZ, Section 7.0).

RESOLUTION = the resolution in which the VALUE is expressed. Resolution is of the form:

| 0  |    | 16   |      |        |  |

|----|----|------|------|--------|--|

| by | te | half | word | double |  |

If the VALUE is a constant, the RESOLUTION word is 0.

If the VALUE is an address, one and only one byte of the RESOLUTION word is nonzero (viz., the appropriate byte = X'01').

If the RESOLUTION assumes a form different from either of the above, the VALUE is of mixed resolution. (In this case the load module cannot be relocated and is forced ABS.)

# TYPE = 0 or 8 (DEF)

where:

TYPE = 0, this entry is a DEF.

= 8, this entry is a double DEF.

E = 1, the DEF has a value.

DISP = Displacement to the segment in the Tree Table where the DEF is located.

U = 1, used DEF (the DEF has been referenced).

L = 1, the DEF was defined in a library.

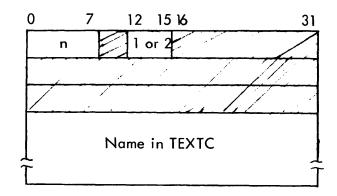

# TYPE = 1, 2 (SREF or REF)

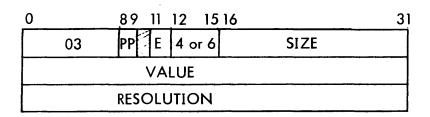

TYPE = 1, SREF = 2, PREF TYPE = 4 or 6 (Control Section)

where:

TYPE = 4, when first declared in PASS1 (LP1).

- = 6, after rereading the declaration in PASS2 (LP1 of EVL).

- E = protection type

- SIZE = size of the control section in doublewords.

- NOTE: A special entry is created by the Loader and inserted in front of a library load module's REF/DEF stack. It has a TYPE = 4, but can be detected (in PASS2) because all previous control sections would have been changed to 6 by this time.

| 0        | 8 9 11 | 12 1. | 516 3    |  |  |

|----------|--------|-------|----------|--|--|

| 03       | PP E   | 4     | SIZE     |  |  |

| VALUE    |        |       |          |  |  |

| EXP SIZE |        |       | EXP DISP |  |  |

where:

| SIZE =    | Size of the load module's core image in doublewords. |

|-----------|------------------------------------------------------|

| VALUE =   | Location of this load module's core image (within    |

|           | the target load module).                             |

| EXP SIZE= | Word size of the load module's expression stack.     |

| EXP DISP= | Displacement of load module's expression stack       |

|           | within this segment's expression stack.              |

# TYPE = 3 or B (Dummy Control Section)

|   |               |          | ,             |       |    |

|---|---------------|----------|---------------|-------|----|

| 0 |               | 7 8.9 10 | 0 11 12 15 16 |       | 31 |

|   | n             | PP       | E 3orB        | SI ZE |    |

|   |               |          | VALUE         |       |    |

|   |               | R        | esolution     |       |    |

|   | Name of DSECT |          |               |       |    |

|   |               | (or DC   | B) in TEXTC   |       |    |

| ł |               |          |               |       | 1  |

where:

- TYPE = 3, Dummy Control Section

- = B, At the end of PASS1, all PREFs (TYPE2) with names beginning with M: or F: are changed to TYPE B, indicating that the Loader is to build them at the end of the second pass.

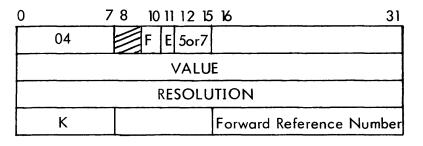

### TYPE = 5 or 7 (Forward Reference)

where:

Κ

TYPE = 5, Forward Reference.

- = 7, Forward Reference is defined from a library.

- = 0, Until the forward reference is defined.

- =FF, Define forward REF and "release" the reference number.

- =F0, Define forward REF and hold the reference number until module end.

- F = 1, the forward reference is used in a "Define forward reference and hold" expression.

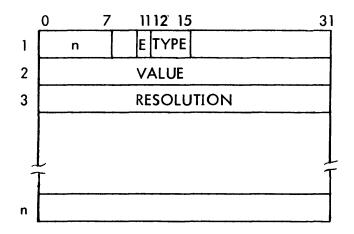

#### 3.2.4 Expression Stack

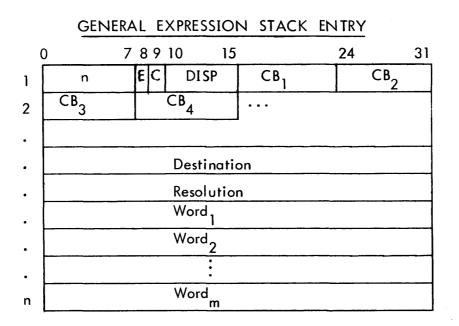

The Loader builds an entry in the expression stack by re-formatting a ROM expression. This re-formatting process consists of grouping all of the control bytes together in one part of the entry, and all of the operands in another. If the ROM operand is a constant, it is transferred verbatim from the ROM to the operand portion of the entry. If the ROM operand is a declaration number, the REF/DEF stack pointer is accessed from the declaration stack and placed in the operand portion of the expression entry. If the ROM operand is a forward reference number, the corresponding REF/DEF stack pointer is transferred to the operand portion of the entry. Some control bytes have no operands (viz., expression end or change resolution) and therefore, have no corresponding item in the operand portion. Thus, the control byte portion of the entry is related sequentially to the operand portion, except in the case where no operand exists.

The value of an expression is deposited either in a REF/DEF stack entry or in a field in the core image of the target load module. (See Section 2.1.1f). In the first case, the destination of the expression's value is described by a pointer to the entry in the REF/DEF stack. In the second case, the destination is described by a <u>core expression</u>. A core expression contains the field size, in bits (which can cross up to eight words of the core image); the address of the last word in the core image to be changed; and the terminal bit position of the field.

where:

n = number of words in entry

E = 1, this entry has been evaluated.

= 0, this entry has not been evaluated.

C = 0, this entry's Destination is a pointer to the REF/DEF stack.

= 1, this entry's Destination is a core expression.

DISP = number of words to Word 1.

Destination: (where the value of the entry is to be deposited) =

one of the following forms, depending upon the value of C.

# **REF/DEF** Pointer

015 1631If C = 0Segment's Displacement<br/>in Tree TableDisplacement within<br/>segment's REF/DEF stack

#### Core Expression

|            | 0          | 78 | 14                       | 15 | 3            | 31 |

|------------|------------|----|--------------------------|----|--------------|----|

| If $C = 1$ | Field Size |    | Terminal<br>Bit Position |    | Word Address |    |

Resolution:Same as REF/DEF stack.CB; =a control byte of the expression.Word; =is referenced by a control byte and is a constant<br/>or pointer to the segment's REF/DEF stack (same<br/>form as Destination where C=0).

### 3.2.5 Relocation Dictionary

If ABS is not specified on the !LOAD card, each segment will have records of relocation dictionaries (one per protection type). One relocation digit is developed for each word in the protection area.

Relocation Dictionary Digits

| Digit | Type of Relocation                                            |

|-------|---------------------------------------------------------------|

| 0     | relocate the word at byte resolution.                         |

| 1     | relocate the word at halfword resolution.                     |

| 2     | relocate the word at word resolution.                         |

| 3     | relocate the word at doubleword resolution.                   |

| 8     | relocate the left half of the word at doubleword resolution.  |

| 9     | relocate the right half of the word at doubleword resolution. |

| Α     | relocate both halves of the word at doubleword resolution.    |

| Ε     | absolute.                                                     |

1

Notice that relocation digits exist only for items that terminate on halfword boundaries.

A load module which has an item not amenable to one of these digits is set to ABS. Example: BOUND 4

ZAP EQU DA(\$) GEN, 8, 16, 8 0, ZAP, 0

or

|     | BOUND   | 4      |           |

|-----|---------|--------|-----------|

| ZAP | EQU     | \$     |           |

|     | GEN, 3, | 17, 12 | 0, ZAP, 0 |

Either of these would cause the module to be set ABS since ZAP does not terminate on

a halfword boundary.

# 3.2.6 Miscellaneous (Map, Diagnostics, Severity Level)

The map, diagnostics, and the severity level of the load module are output via the M:LL DCB (normally the printer):

a. Load Map

The load map is generated at the end of the load process. For each segment, the map includes:

- i) A header consisting of the segment name and size. For the root segment, the load module name, account number, start address, and bias are also listed.

- ii) A summary of the segment's protection type boundaries and sizes of the format: \*\*\*\*PROTECTION TYPES: 00 DATA 01 PROCEDURE 10 STATIC

| SEGHI–0 valhi | SEGHI-0 valhi | SEGHI-2 valhi |

|---------------|---------------|---------------|

| SEGLO-0 vallo | SEGLO-1 vallo | SEGLO-2 vallo |

| 00SIZE=size   | 01 SIZE=size  | 10 SIZE=size  |

where valhi = the high word address for this protection type.

vallo = the start address (word resolution) for this protection type. size = the size, in words, of the protection type area.

- iii) A list of any unsatisfied primary references (PREFs).

- iv) A list of any unsatisfied secondary references (SREFs).

- v) A list of any multiply-defined definitions (DDEFs).

- vi) A list of definitions with absolute values (ADEFs).