CSP-007

**Prepared** for

SDS Data Systems

Beverly Hills, California

10 March 1966

# CONTENTS

|      |         |                                           | Page |

|------|---------|-------------------------------------------|------|

| SECT | ION I:  | GENERAL                                   | 1-1  |

| 1.0  | DIFFE   | ERENT TYPES OF INPUT/OUTPUT               | 1-1  |

|      | 1.1     | RWD Interface                             | 1-1  |

|      | 1.2     | Eight-Bit Data Path                       | 1-2  |

|      | 1.3     | Memory Bus                                | 1-4  |

|      | 1.4     | Testing of External Signals               | 1-5  |

| 2.0  | SIGN    | A COMPATIBILITY                           | 1-5  |

| 3.0  | ELEC    | TRICAL DESCRIPTION OF INTERFACES          | 1-6  |

| 4.0  | EXPA    | NSIÓN                                     | 1-8  |

| SECT | ION II: | READ-WRITE-DIRECT INTERFACE               | 2-1  |

| 1.0  | INST    | RUCTIONS IN THE COMPUTER                  | 2-1  |

|      | 1.1     | Data Input                                | 2-1  |

|      | 1.2     | Data Output                               | 2-1  |

|      | 1.3     | Effective Address Assignments             | 2-2  |

| 2.0  | INTE    | RFACE SIGNAL LINES AND CABLING            | 2-3  |

| 3.0  | LOG     | IC DESIGN AT THE INTERFACE                | 2-4  |

|      | 3.1     | Circuitry for Function Strobe Acknowledge | 2-4  |

|      | 3.2     | Read Direct Timing                        | 2-4  |

|      | 3. 3    | Write Direct Timing                       | 2-5  |

|      | 3.4     | Hanging Up the RWD Interface              | 2-5  |

|      | 3.5     | Decoding                                  | 2-6  |

| 4.0  | RECO    | MMENDED METHOD FOR ACHIEVING SIGMA 2      |      |

|      | COM     | PATIBILITY                                | 2-6  |

i

|       |         |                                                           | •*<br>• |

|-------|---------|-----------------------------------------------------------|---------|

|       |         |                                                           | Page    |

| SECTI | ON III: | IOP INTERFACE                                             | 3-1     |

| 1.0   | INSTR   | UCTIONS IN THE COMPUTER                                   | 3-1     |

|       | 1.1     | General Description                                       | 3-1     |

|       | 1.2     | SIO Instruction                                           | 3-2     |

|       | 1.3     | Operational Sequence After SIO                            | 3-5     |

|       | 1.4     | Data and Command Chaining                                 | 3-9     |

|       | 1.5     | Command Word Format                                       | 3-11    |

|       | 1.6     | HIO, TIO, and TDV Instructions                            | 3-14    |

|       | 1.7     | Interrupt Structure and AIO Instruction                   | 3-15    |

| 2.0   | INTER   | FACE SIGNAL INTERACTION AND TIMING                        | 3-17    |

|       | 2.1     | Pfiority Determination                                    | 3-17    |

|       | 2. 2    | Leading and Trailing Acknowledgement                      | 3-20    |

|       | 2.3     | Processing Computer Instructions                          | 3-21    |

|       | 2.4     | Service Calls and Acknowledgement                         | 3-23    |

|       | 2.5     | Request Strobes and Acknowledgement (Data Input & Output) | 3-25    |

|       | 2.6     | Order Output                                              | 3-28    |

|       | 2.7     | Order Input                                               | 3-30    |

| ·     | 2.8     | Terminal Orders                                           | 3-31    |

|       | 2.9     | Interrupt Calls and Acknowledgement                       | 3-32    |

| 3.0   | DEVIC   | E SUBCONTROLLER                                           | 3-34    |

|       | 3.1     | General                                                   | 3-34    |

|       | 3. 2    | Subcontroller Component Parts                             | 3-34    |

|       | 3.3     | Subcontroller Usage                                       | 3-35    |

|       | 3.4     | Subcontroller Summary Description                         | 3-35    |

| 4.0   | DIFFER  | RENCES ON SIGMA 2                                         | 3-38    |

| 5.0   | INTER   | FACE SIGNAL LINES AND CABLING                             | 3-39    |

|        |           |                                                           | Page |

|--------|-----------|-----------------------------------------------------------|------|

| SECTI  | ON III:   | IOP INTERFACE (Continued)                                 |      |

| 6.0    | LOGI      | C DESIGN OF DEVICE CONTROLLERS (DESIGN TIPS)              | 3-40 |

|        | 6.1       | General                                                   | 3-40 |

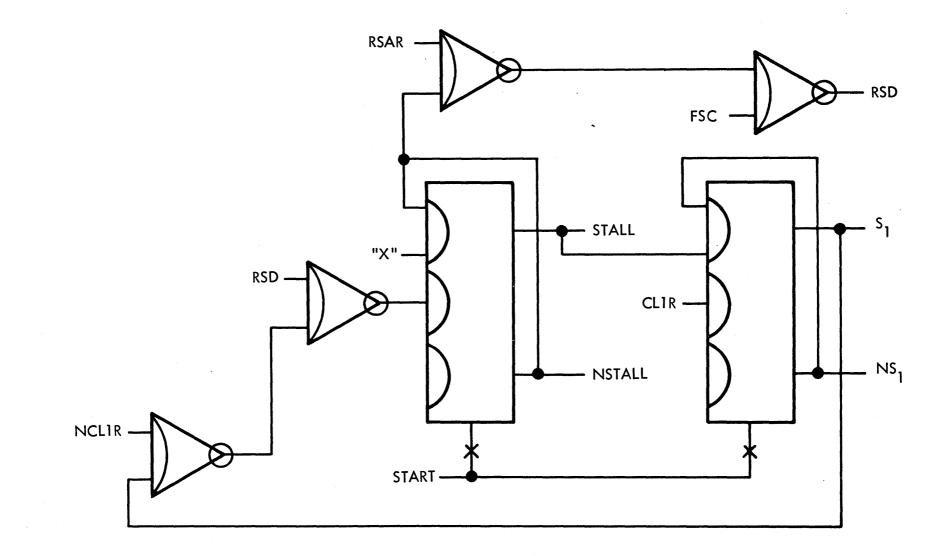

|        | 6.2       | "START" Flip-Flop and Control Flip-Flop Initialization    | 3-41 |

|        | 6.3       | Terminal Order Control Flip-Flop                          | 3-42 |

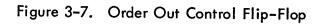

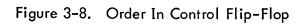

|        | 6.4       | Order Out Control Flip-Flop                               | 3-43 |

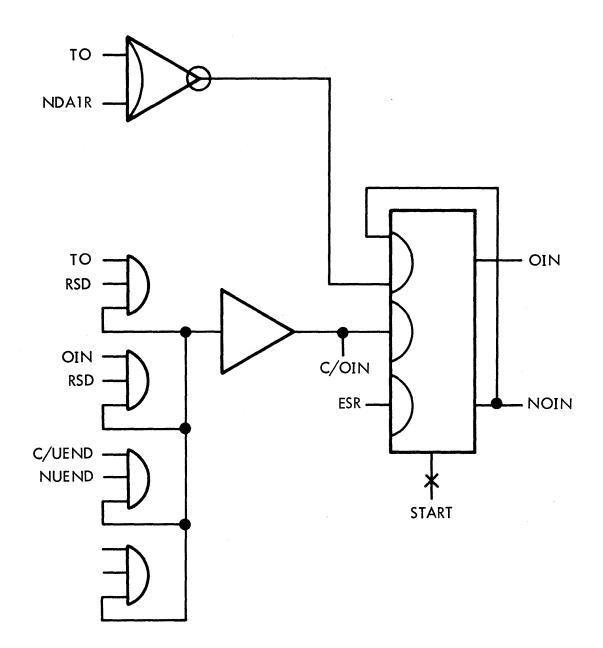

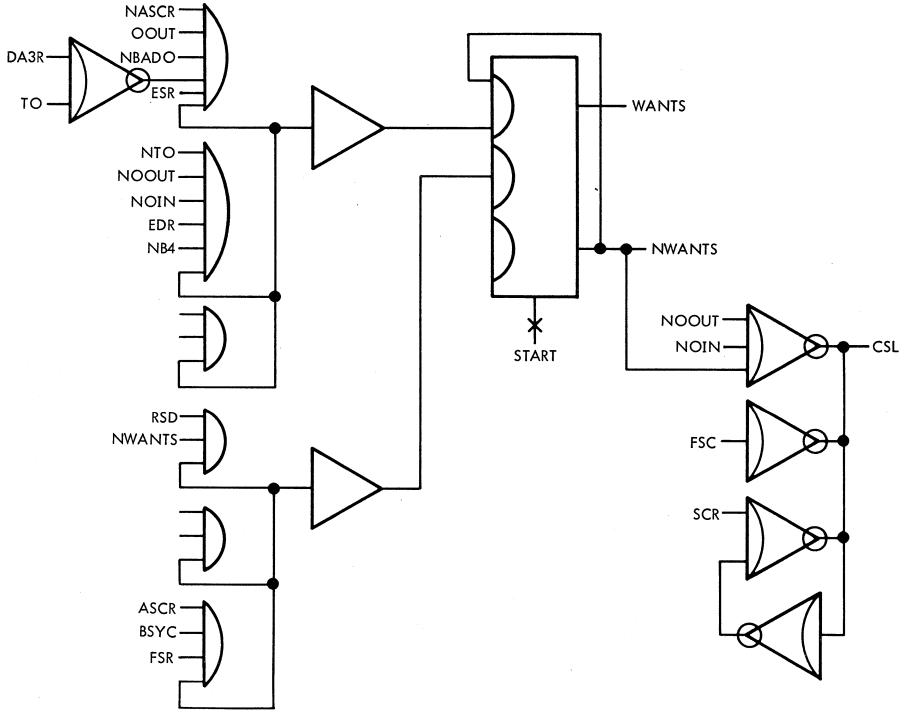

|        | 6.5       | Order In Control Flip-Flop                                | 3-44 |

|        | 6.6       | "WANT SERVICE" Control Flip-Flop                          | 3-45 |

|        | 6.7       | Request Strobe and Acknowledgement                        | 3-46 |

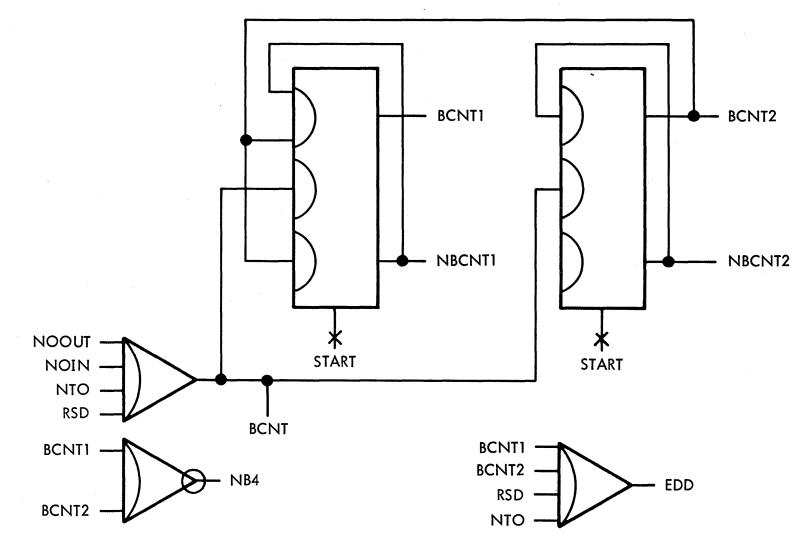

|        | 6.8       | Quantity of Data Bytes per Service Cycle                  | 3-47 |

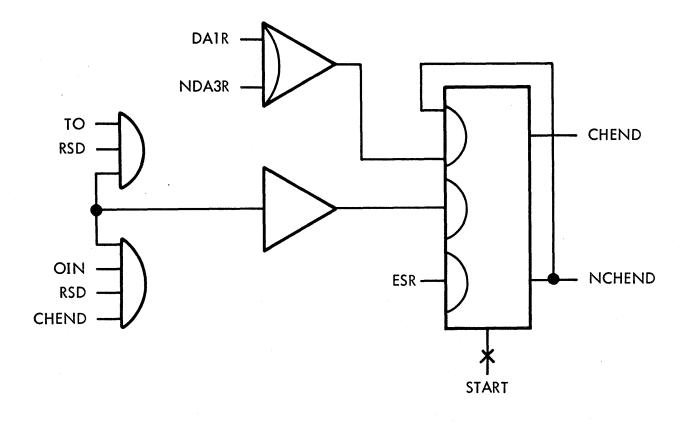

| •<br>• | 6.9       | Channel End                                               | 3-48 |

|        | 6.10      | "Bad Order" Detection                                     | 3-49 |

|        | 6.11      | Unusual End                                               | 3-50 |

|        | 6.12      | "WANT INTERRUPT" Control Flip-Flop                        | 3-51 |

|        | 6.13      | State Flip-Flops                                          | 3-52 |

| SECTI  |           | MEMORY BUS INTERFACE                                      | 4-1  |

| 52011  |           |                                                           |      |

| APPEI  | NDIXES:   |                                                           |      |

|        | A.        | Cable Characteristics                                     | A-1  |

|        | <b>B.</b> | Summary of Bit Coding for Various Data Exchanges          | B-1  |

|        | C.        | Summary of Cable Signals                                  | C-1  |

|        | D.        | Reference Specifications                                  | D-1  |

|        | E.        | Dictionary of IOP/Device Controller Terms & Abbreviations | E-1  |

|        | · F.      | Subcontroller Module Locations                            | F-1  |

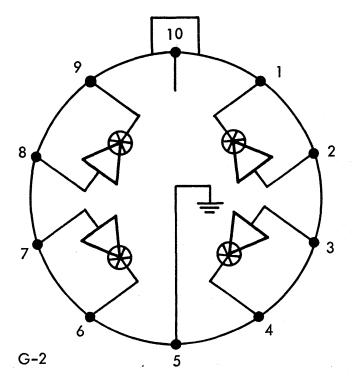

|        | G.        | T-Series Circuits, Specifications and Schematics          | G-1  |

FIGURES

|       |                                                        | Page          |

|-------|--------------------------------------------------------|---------------|

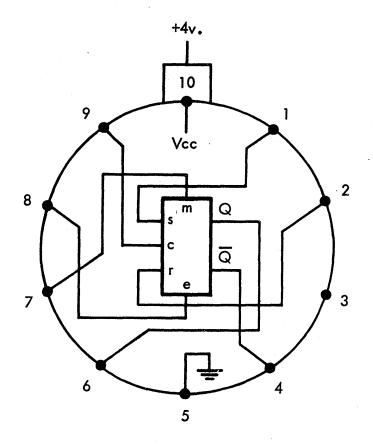

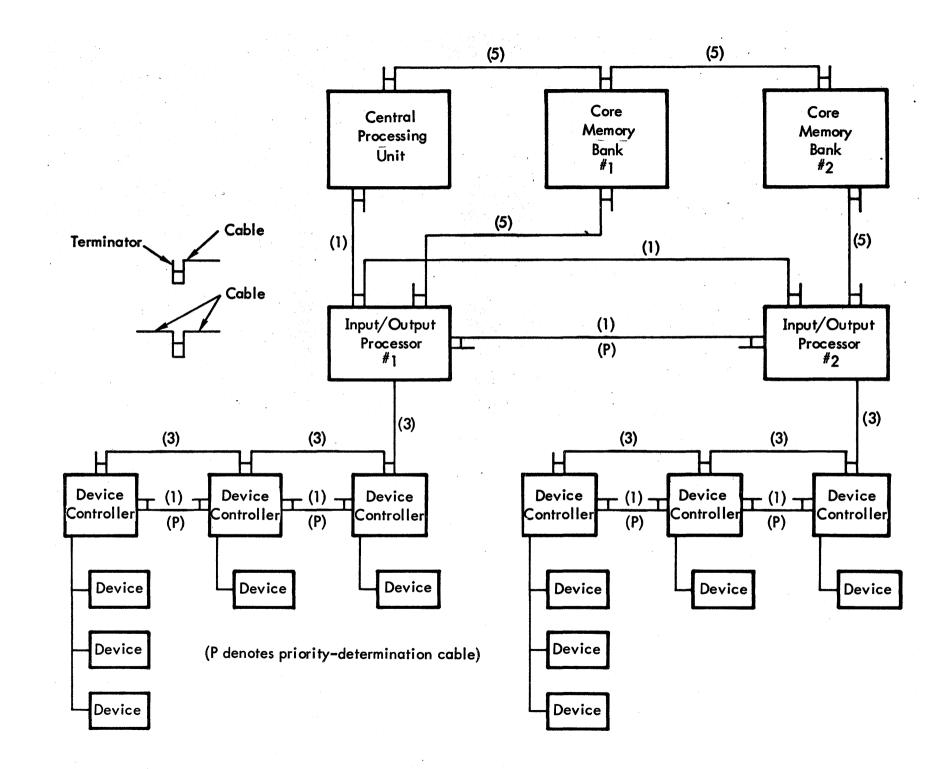

| 1-1.  | SIGMA 7 Cabling Scheme                                 | 1-6a          |

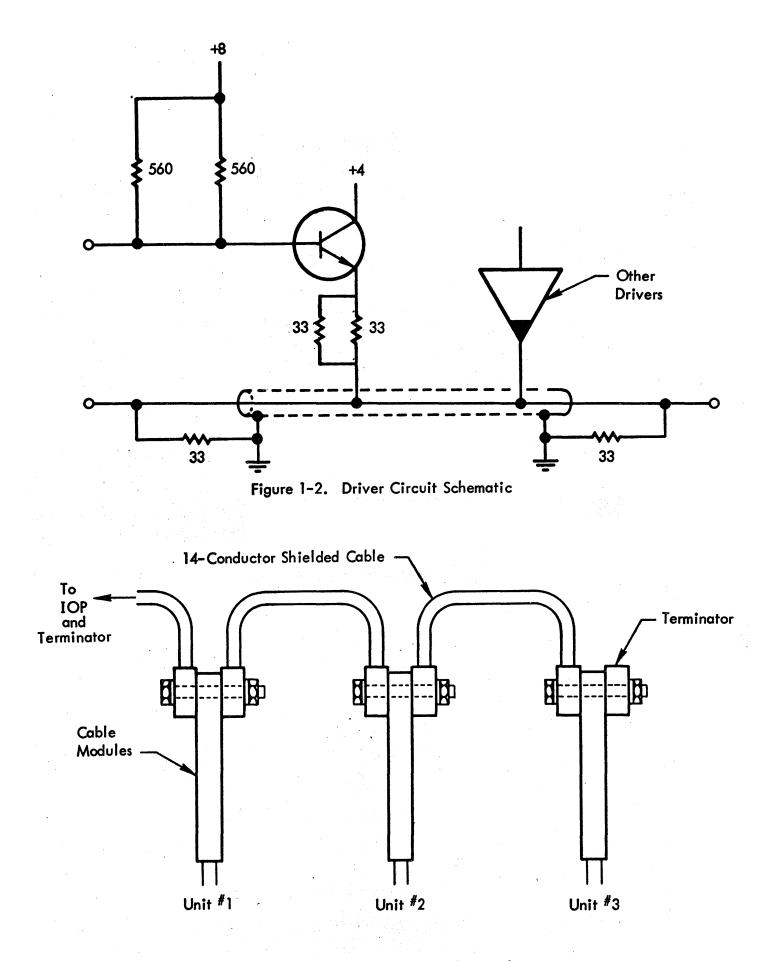

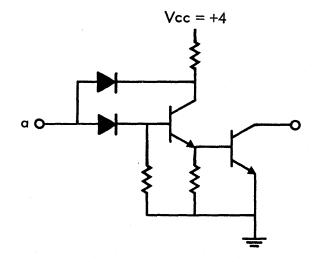

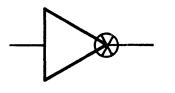

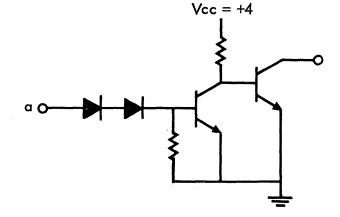

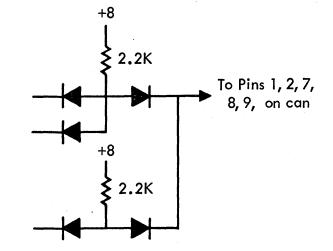

| 1-2.  | Driver Circuit Schematic                               | 1-7a          |

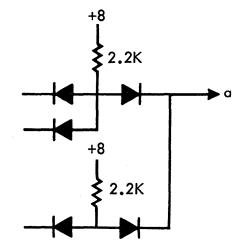

| 1-3.  | Cable and Terminator Connections                       | 1-7a          |

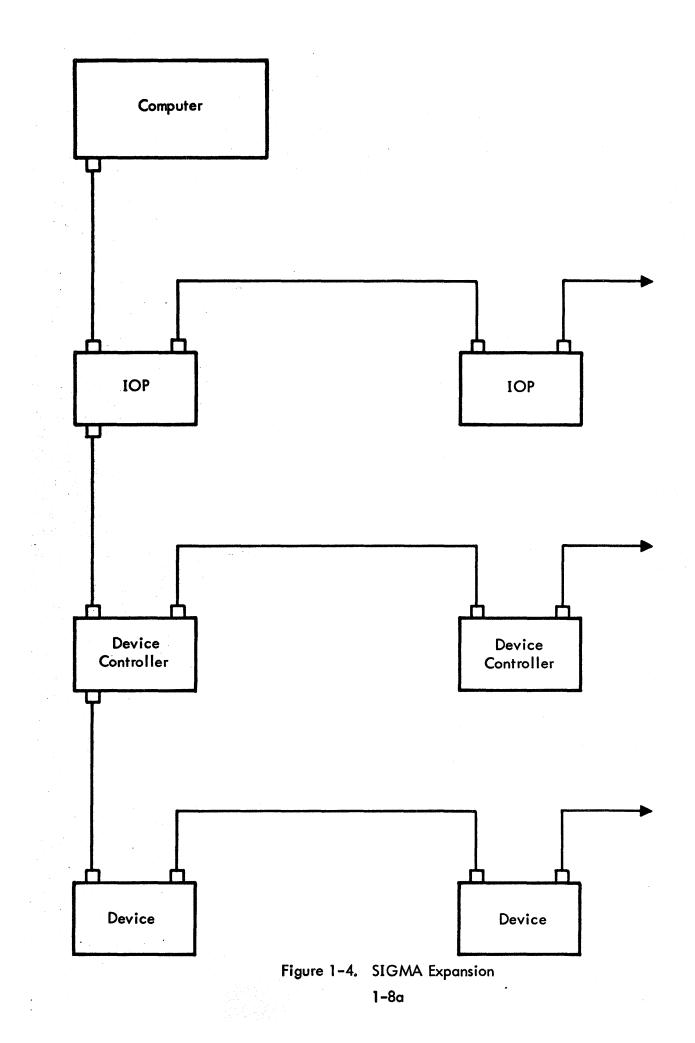

| 1-4.  | SIGMA Expansion                                        | 1-8a          |

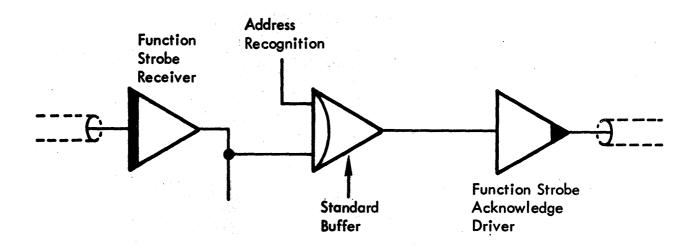

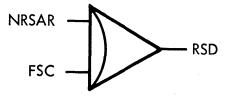

| 2-1.  | Function Strobe Acknowledge Circuit                    | <b>2-4</b> a  |

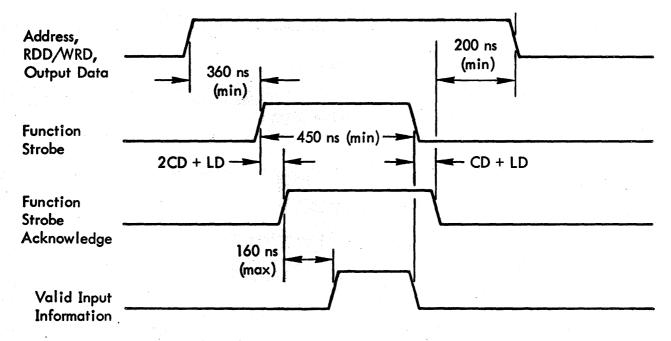

| 2-2.  | Read Direct Timing and Write Direct Timing             | <b>2-4</b> a  |

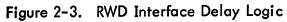

| 2-3.  | RWD Interface Delay Logic                              | <b>2-</b> 5a  |

| 2-4.  | SIGMA 2, RWD Compatibility                             | <b>2-</b> 7a  |

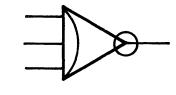

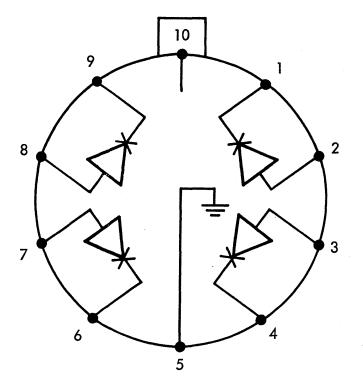

| 3-1.  | Priority Chain Implementation                          | 3-20a         |

| 3-2.  | Function Strobe Acknowledgement                        | 3-21a         |

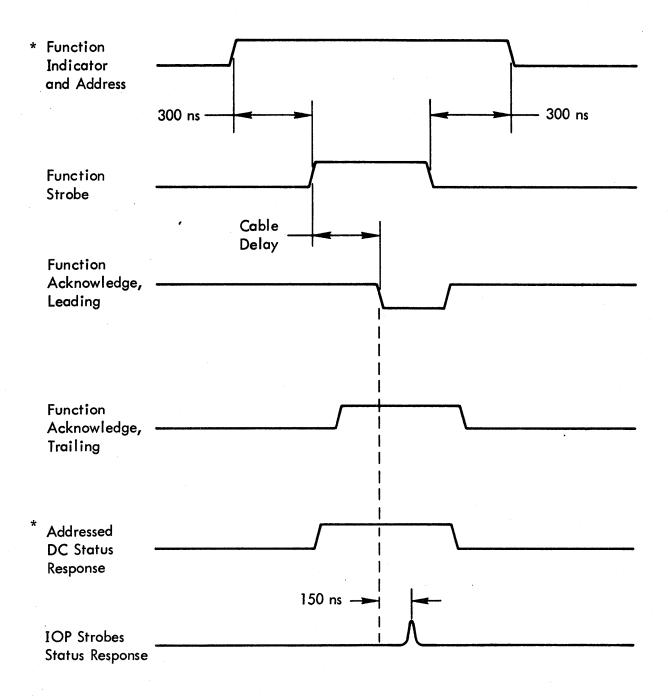

| 3-3.  | Instruction Execution Timing                           | 3-22a         |

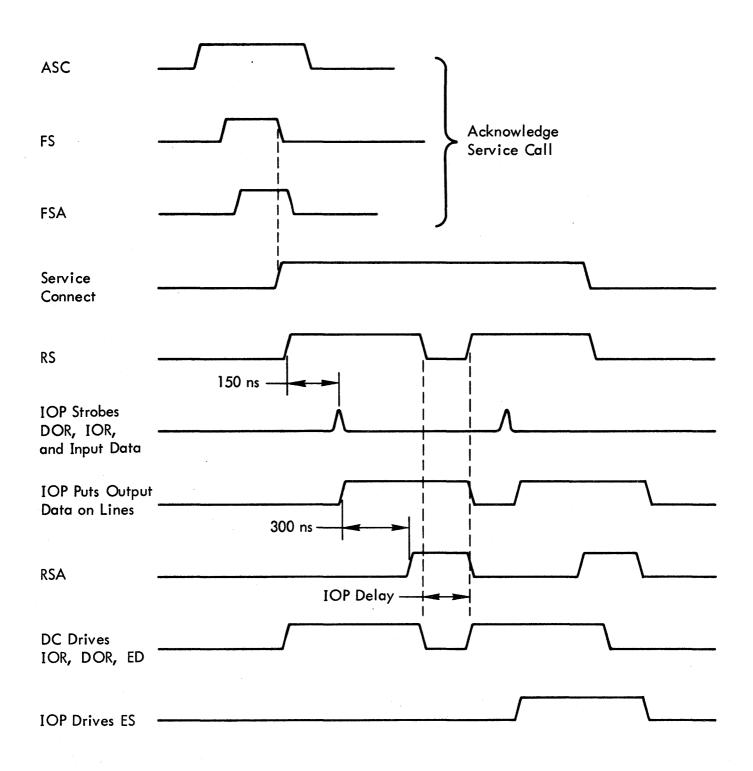

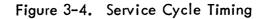

| 3-4.  | Service Cycle Timing                                   | 3-24a         |

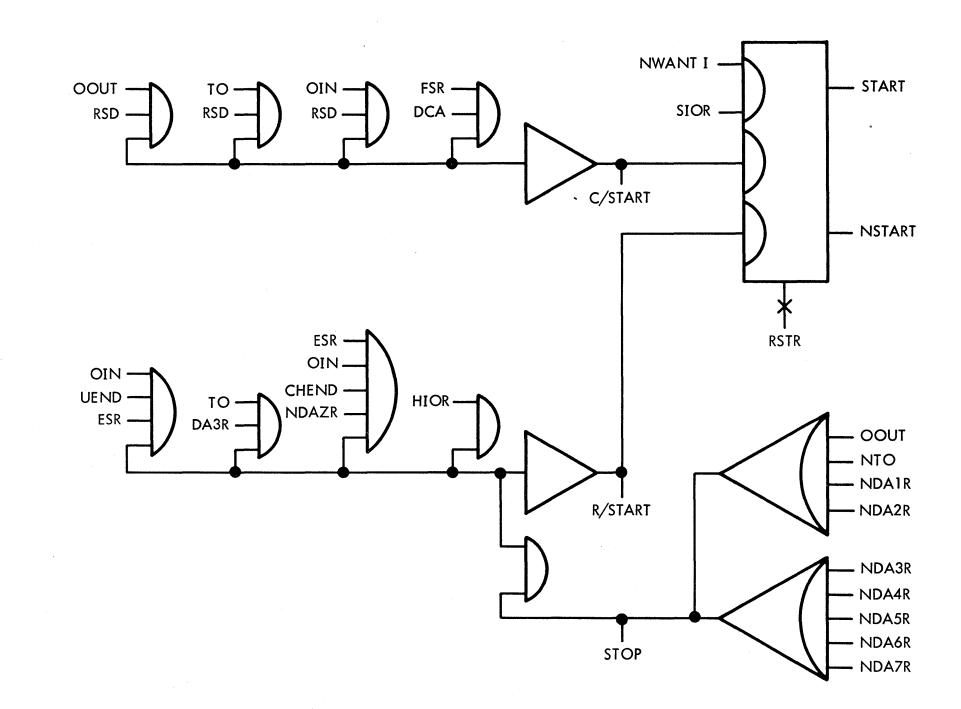

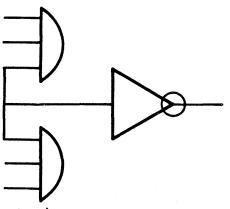

| 3-5.  | "START" Flip-Flop and Control Flip-Flop Initialization | 3-41a         |

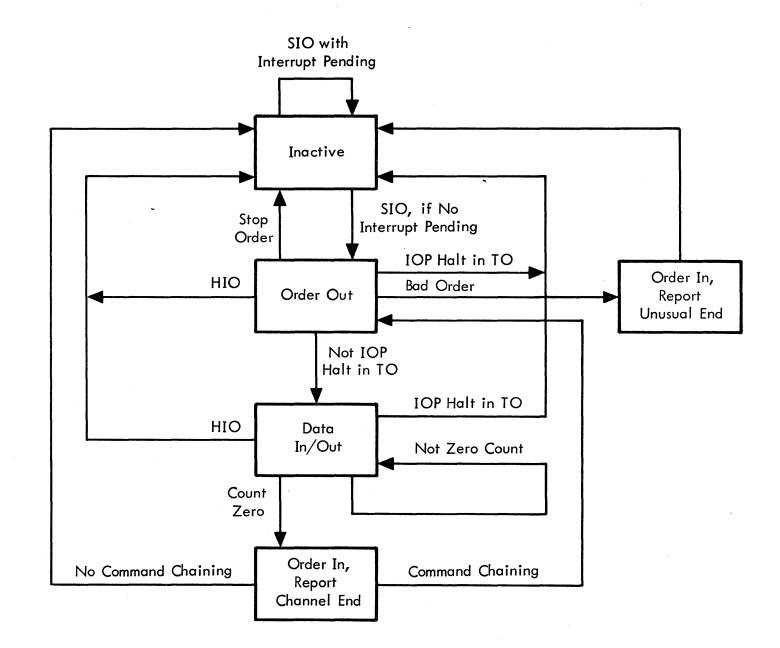

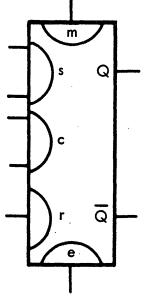

| 3-6.  | Terminal Order Control Flip-Flop                       | 3-42          |

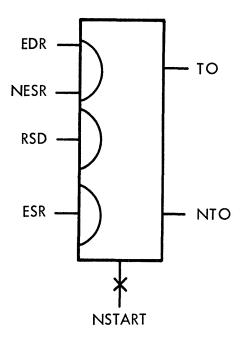

| 3-7.  | Order Out Control Flip-Flop                            | 3-43a         |

| 3-8.  | Order In Control Flip-Flop                             | 3-44a         |

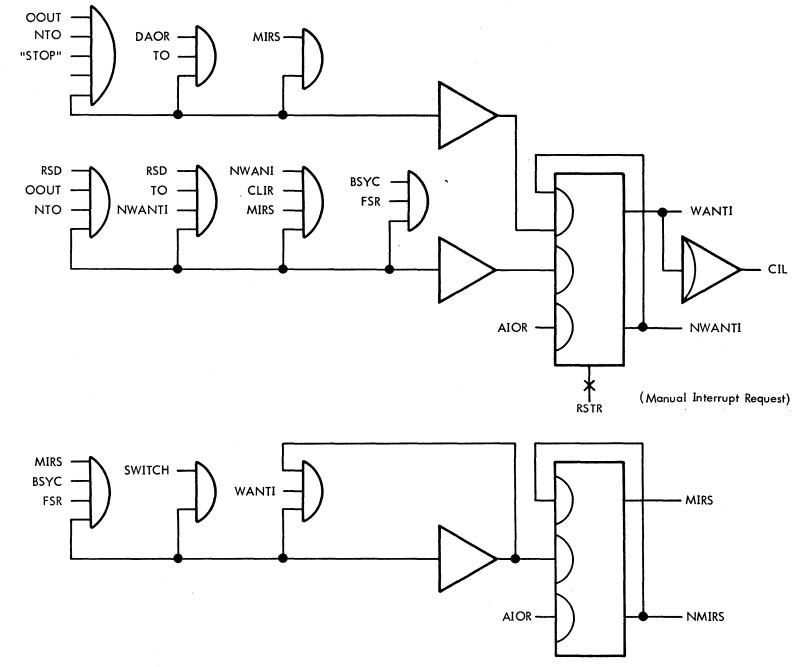

| 3-9.  | "WANT SERVICE" Control Flip-Flop                       | <b>3-4</b> 5a |

| 3-10. | Request Strobe and Acknowledgement                     | <b>3-46</b> a |

| 3-11. | Typical Byte Counter                                   | <b>3-47</b> a |

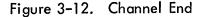

| 3-12. | Channel End                                            | 3-48          |

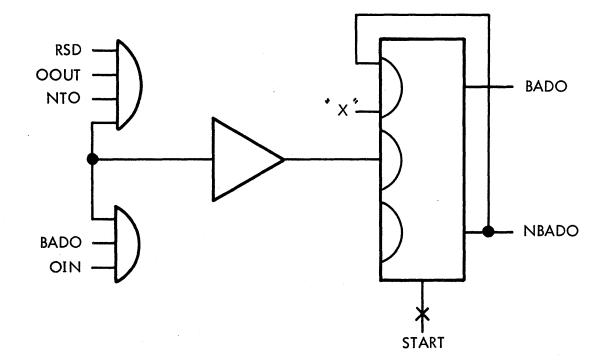

| 3-13. | "Bad Order" Detection                                  | 3-49          |

| 3-14. | Unusual End                                            | 3-50          |

| 3-15. | "WANT INTERRUPT" Control Flip-Flop                     | 3-51a         |

| 3-16. | State Flip-Flops                                       | <b>3-52</b> a |

| •     |                                                        |               |

#### 1.0 DIFFERENT TYPES OF INPUT/OUTPUT

1.1 RWD Interface

The Read-Write-Direct interface gets its name from the two SIGMA instructions that control this interface: Read Direct (RDD), and Write Direct (WRD). This interface is similar in a sense to the POT/PIN interface on the SDS 900 Series computers; RDD is analogous to an EOM/PIN sequence of instructions, while WRD is analogous to an EOM/POT sequence. There is no analogy for the SKS instruction. This function is accomplished in another way, described in Section I-1.4.

Each instruction (RDD or WRD) presents 16 bits of effective address at the interface, along with a control signal designated Function Strobe. The external unit must provide a signal called Function Strobe Acknowledge which, like Rt in the 900 Series computers, allows the RDD or WRD instruction to be executed.

During RDD, the external unit may provide 32 bits of data for storage in a computer register; this data is provided in conjunction with Function Strobe Acknowledge. During WRD, the computer provides 32 bits of data to the external unit (in conjunction with Function Strobe) on the same 32 lines that are used to transmit input data during RDD. Thus the 32 data lines are time-shared for the two different instructions.

Additional signals provided at the interface are:

- a line that differentiates between RDD and WRD for the external user (since they appear identical in all other respects),

- two additional data lines for input (they are input lines even during WRD), which set the computer's condition code bits 3 and 4,

an I/O Reset signal, and

. •

a 1-Mc clock signal (not synchronized in any way with instruction execution.

On SIGMA 2, the RWD interface is identical, scept that the data path is only 16 bits wide. Thus, only three cables are required for SIGMA 2, rather than the four cables on SIGMA 7 and SIGMA 5, since each SIGMA cable contains 14 conductors.

## 1.2 Eight-Bit Data Path

The eight-bit data path, referred to as the Input/Output Processor (IOP) interface, is analogous to the TMCC/DACC interfaces in the SDS 900 Series computers. One eight-bit data path is associated with each IOP in a system (there may be up to eight IOP's). Each path is logically and electrically independent of every other path, in every respect. Device Controllers (peripheral control units) are attached to this interface in a completely parallel manner, requiring only one set of four cables to be connected to the IOP; each Device Controller is connected to the one before it (nearer physically to the IOP). Section I-3 gives a complete description of the electrical characteristics of this interface, and Section II-3 describes the cabling.

Up to 32 Device Controllers may be attached to any IOP interface. All Device Controllers time-share the single eight-bit data path. Operation resembles interlaced operation on the 900 Series, except that the interlace word count and each main memory address are stored in an IOP private fast memory for each Device Controller attached to the bus. Since the private fast memory also contains other control information associated with each Device Controller, 56 bits of storage in the IOP are assigned exclusively to each possible device address. Each device connects to the IOP through a Device Controller (DC).

Once a device has been "started" by the main computer program, the general scheme of I/O interaction is as follows:

- Any number of Device Controllers may request "service" simultaneously from the IOP.

- 2. The IOP brings up certain signals that activate a hard-wired priority chain between Device Controllers. The highest priority Device Controller that has requested service puts its own device address on some return lines, along with an acknowledge signal, and is then "connected" to the IOP for a short time.

1-2

- 3. While it is connected to the IOP, a Device Controller makes its request: Data Out, Data In, control information from the CPU memory, or transfer of control information into the IOP fast memory.

- 4. While it is connected to an IOP, a Device Controller can transmit or receive up to four (8-bit) bytes of data or one byte of control information, plus, in some cases, an additional byte of control information known as a Terminal Order.

It should be noted that up to 32 devices on a given IOP may request service simultaneously. They are serviced in sequence by the IOP, based on the hard-wired priority chain. The brief description abive is intended to serve only as an introduction; Section III describes the IOP interface in greater detail.

This interface is compatible on SIGMA 2, SIGMA 5, and SIGMA 7, except for some differences in bit coding for certain exchanges of control information and in the handling of Order In, Order Out, and Terminal Orders. These differences are discussed in III-4.

The different types of IOP's that may be utilized with a SIGMA system include:

| M/IOP  | Multiplexor IOP (basic unit) |

|--------|------------------------------|

| S/IOP  | Selector IOP                 |

| S'/IOP | Selector Piggyback IOP       |

Throughout this manual, the letters IOP generally refer to the M/IOP interface.

All IOP's present the same interface and general signal interaction to a Device Controller. Any device designed to operate on the IOP interface described in this manual may connect to any of the specified types of IOP's. However, the S/IOP is designed to allow much higher data rates (up to 1.5 million bytes per second) versus a maximum of approximately 0.3 million for an M/IOP. Also, the S/IOP permits only one device to be active at any given time, as compared to up to 32 active devices for the M/IOP.

1-3

The S'/IOP is an additional S/IOP that shares the same bus as its parent S/IOP. It is identical in all other respects. The S/IOP and S'/IOP also permit Device Controllers that operate with a 32-bit data interface, whose control signals are identical with the M/IOP. Obviously, such a Device Controller cannot be used on the 8-bit M/IOP.

Due to cabling and port access restrictions, the following formulas apply to system IOP configurations:

$$M + S \leq 5$$

$$M + S + S' \leq 8$$

where M = number of M/IOP's

S = number of S/IOP's

S' = number of S'/IOP's

### 1.3 Memory Bus

The IOP itself connects to the computer, as well as to the memory bus for some memory module. Although it is seldom necessary for system requirements, an external device can connect directly to this memory bus.

The memory bus comprises 32 data lines (time-shared for input and output), 17 address lines, a Memory Request signal, a Data Release line, an Address Release line, an Address Here signal, and a Parity Error signal. There are also four Write Byte control lines that are used during partial write operations to specify which of the four bytes in a memory cell are to be altered during that operation.

The memory bus is described in detail in Section IV.

### 1.4 Testing of External Signals

SIGMA systems do not have any explicit instructions to allow external signals to be tested through the RWD interface, analogous to the SKS instruction in 900 Series computers. However, this function can be accomplished quite readily by means of an RDD instruction (which stores up to 32 bits in a specified register), followed by a Compare Selective (CS) instruction, and then a test of the condition code bits (whose settings are based on the results of the CS). Single or multiple bits may be tested by this procedure. The SIGMA 5 and SIGMA 7 reference manuals describe how these instructions operate.

# 2.0 SIGMA COMPATIBILITY

SIGMA 5 and SIGMA 7 are completely identical with respect to all interfaces. SIGMA 2 has certain differences on the various interfaces.

On the RWD interface, the only difference of consequence to the external-unit designer is the word size: 16 bits on SIGMA 2 versus 32 bits on SIGMA 5 and SIGMA 7. The means to accommodate this difference for standard products are discussed in Section II-5.

On the IOP interface, it is an unbreakable rule that all units must be capable of operating equally well on SIGMA 7, SIGMA 5, or SIGMA 2. This will affect design with respect to the means of identifying certain conditions. For instance, on SIGMA 5 and SIGMA 7, Terminal Orders always follow an Order Out cycle; on SIGMA 2 they may not. Thus, the logic conditions that cause a Terminal Order state must be derived from identifying signals provided by the computer, rather than directly from the occurrence of the Order Out cycle itself. This issue is discussed in Section III, and particularly in Section III-4.

### **3.0 ELECTRICAL DESCRIPTION OF INTERFACES**

All interfaces – RWD, IOP, and memory bus – utilize the same cable driver/receiver scheme, and the same means of inter-unit cabling. All inter-unit cabling consists of several cables. Each cable consists of 14 shielded wires, whose characteristics are given in Appendix A. Each shielded wire is used as a transmission line which is terminated with its 33-ohm characteristic impedance at each end. Connection to this line is by virtually tapping the line without unduly affecting its characteristic impedance. A number of cables are used to handle all signals associated with each interface. These are:

RWD Interface

4 cables for SIGMA 5 and SIGMA 7 3 cables for SIGMA 2

3 cables for all

IOP Interface to Device Controller

(There is, in addition, a single prioritydetermination cable running only between Device Controllers; it does not connect to the IOP.)

IOP Interface to Memory5 cables for allIOP Interface to Computer1 cable for allMemory Bus5 cables for all

Figure 1-1 on the following page shows the cabling scheme.

For all signals except those associated with priority determination among Device Controllers, each unit may tap any line with both a driver and a receiver. The following conventions have been adopted:

| Logic One  | +2 volts | driver output | H | low impedance  |

|------------|----------|---------------|---|----------------|

| Logic Zero | 0 volts  | driver output | = | high impedance |

It should be noted that this reverses the conventions in the SDS 900 Series equipment, where a logical one was the high impedance state and logical zero was the low impedance state. Thus, the quiescent state of time-shared lines must be altered: the

1-6a

quiescent state of any time-shared line must be high impedance from the driver (logical zero). Any single unit whose driver is active (turned on) on a given line may bring that line to the logical-one state. This is accomplished by the driver circuit shown in Figure 1-2 on the following page.

Receiver circuits similarly tap the common line for each signal; they consist of highnoise-rejection discriminator circuits.

There is no inversion in either drivers or receivers. If the input to a driver is a logical one (+4 volts), the line driven goes to logical one (+2 volts). If a line is at logical one (+2 volts), the receiver output is at logical one (+4 volts).

The priority determination signals are carried by exactly the same sort of scheme, except that normally only one driver and one receiver are attached to each line. Signals are received by each unit, passed through decision-making ordinary logic elements, and then they may or may not be passed on to the next unit.

Except for length, inter-unit cabling is all physically identical. There are no special components or circuits on the cables themselves. Cables are attached to the back of cable driver/receiver modules (AT10, AT11, AT12, AT17). These modules may be plugged into any slot on a standard SIGMA chassis; however, there are standard slots, for standard interfaces, into which they should be wired so they can be identified easily by Customer Service personnel.

Each such module can accommodate two cables, which are bussed (by etching on the module) directly to each other, as well as to the active circuits on the module (drivers and/or receivers). Thus, inter-unit cabling comprises one long transmission line, with drivers and receivers attached at each unit. The "last" unit on the transmission line (at both ends) must have a terminating network attached to the line in place of the cable that would ordinarily run out from that point, as shown in Figure 1-3.

1-7

Figure 1–3. Cable and Terminator Connections

# 4.0 EXPANSION

The philosophy of design for the SIGMA input/output system dictates that elements in the system should be separable and easily connected. Therefore the following design goals should be noted carefully:

All cables should be identical except for length.

Cable receptacle locations should occur in the same place within each chassis assembly.

Similar assemblies should be connected in similar fashion.

Cables are trunk to tail, and there should be no ambiguity as to the means by which interconnection or expansion of assemblies is mechanized.

Figure 1-4 on the following page exemplifies these ideas and demonstrates how expansion is physically realizable.

## SECTION II: READ-WRITE-JIRECT INTERFACE

# 1.0 INSTRUCTIONS IN THE COMPUTER

### 1.1 Data Input

In SIGMA 5 and SIGMA 7 the Read Direct (RDD) instruction presents the low-order 16 bits of its effective address on the RWD interface address lines, along with a signal that indicates the execution of the RDD instruction. The selected external device must generate an acknowledge signal and may present up to 32 bits of data on the RWD interface data lines, as well as two bits of condition code information on two other lines to set CC3 and CC4. If R (the register-specifying field in the instruction) is not equal to zero, the 32 data bits are stored in the specified register. If R equals zero, the 32 data lines are ignored, but CC3 and CC4 are still set as specified by the external device.

In SIGMA 2 Read Direct (RD) is the same as RDD in SIGMA 5 and SIGMA 7, except that only 16 bits of data are accepted, and they are stored in the SIGMA 2 accumulator. The condition code input lines are stored in the SIGMA 2 carry and overflow indicators.

# 1.2 Data Output

In SIGMA 5 and SIGMA 7 Write Direct (WRD) presents the low-order 16 bits of its effective address on the RWD interface address lines, along with a signal that indicates the execution of the WRD instruction. The selected external device must generate an acknowledge signal, and may accept 32 bits of data from the RWD interface data lines; the computer simultaneously accepts two bits of condition code information on two other lines to set CC3 and CC4. If R (the register-specifying field in the instruction) is not equal to zero, the 32 bits of the specified register are transmitted on the 32 data lines. If R equals zero, the 32 data lines are set at logical zero regardless of the contents of any register, but CC3 and CC4 are still set as specified by the external device. On SIGMA 2 Write Direct (WD) is the same as WRD for SIGMA 5 and SIGMA 7, except that only 16 bits of data are transmitted; they are taken from the SIGMA 2 accumulator. The condition code input lines are stored in the carry and overflow indicators in SIGMA 2.

### 1.3 Effective Address Assignments

The general area that is controlled by any RDD, WRD, RD, or WD instruction is specified by the high-order four bits of the effective address, and is designated as the control mode. The effective address bits are designated numerically as 16-31 in SIGMA 5 and SIGMA 7. Control mode assignments have been made as follows:

| Hexadecimal | Definition                |

|-------------|---------------------------|

| 0           | Internal Computer Control |

|             | Interrupt Control         |

| <b>2-B</b>  | Presently Unassigned      |

| С-Е         | Systems Standard Products |

|             | Systems Special Units     |

A list of effective address assignments for control modes C to E is to be maintained by the Systems Engineering secretary. If a unit which might be applicable to future systems is to be designed, approval must be obtained from the Director of Systems Engineering for assignment of a standard WRD effective address coding. No central record will be kept for effective address assignments with control mode F.

For all standard product effective address assignments, the reservation of a particular code will apply to both SIGMA 5/SIGMA 7 and SIGMA 2, even if the standard product is designed to operate primarily on only one of the systems. It should be emphasized, however, that standard products should be designed, whenever possible, with a view towards effective operation on any SIGMA computer. Suggested means of accomplishing this are discussed in Section II-5. 2.0

# INTERFACE SIGNAL LINES AND CABLING

The following cables are involved in the RWD interface:

| Cable No. | Connects to                                       | Transmits                       |  |  |  |  |  |

|-----------|---------------------------------------------------|---------------------------------|--|--|--|--|--|

| 1         | AT11 cable driver/receiver<br>module (235 in CPU) | data input/output bits 00–13    |  |  |  |  |  |

| 2         | AT11 cable driver/receiver<br>module (27Q in CPU) | data input/output bits 14-27    |  |  |  |  |  |

| 3         | AT11 cable driver/receiver                        | data input/output bits 28–31;   |  |  |  |  |  |

|           | module (30P in CPU)                               | Function Strobe;                |  |  |  |  |  |

|           |                                                   | Function Strobe Acknowledge;    |  |  |  |  |  |

|           |                                                   | RDD/WRD; and                    |  |  |  |  |  |

|           |                                                   | Address Lines 5–7 and 12–15     |  |  |  |  |  |

| 4         | AT10 cable receiver module                        | CC3 and CC4;                    |  |  |  |  |  |

|           | (29N in CPU)                                      | I/O Reset;                      |  |  |  |  |  |

|           |                                                   | 1-Mc Clock;                     |  |  |  |  |  |

|           |                                                   | Address Lines 0-4 and 8-11; and |  |  |  |  |  |

|           |                                                   | One Spare.                      |  |  |  |  |  |

The following items should be noted:

Cable No. 1 is not needed for a SIGMA 2 system.

The designer must ground inputs to drivers for Function Strobe, RDD/WRD, I/O Reset, the 1-Mc Clock, Address Lines 14 and 15, and any unused data lines (including CC3 or CC4 if they are unused).

Appendix C gives module pin numbers for these cables.

RDD/WRD is true for WRD.

# **3.0** LOGIC DESIGN AT THE INTERFACE

Cable drivers may be driven by any standard logic circuit, including flip-flop outputs. However, the cable driver circuit takes eight unit loads. The nominal output of standard SIGMA logic elements is 16 unit loads. Pull-up resistors consume two unit loads, and terminating resistors consume five unit loads. Terminating resistors are not ordinarily needed on circuits that feed cable driver inputs; thus any circuit is apparently allowed to feed one cable driver and six other loads. It is recommended that, where possible, circuits feeding cable drivers not drive any other points.

### 3.1 Circuitry for Function Strobe Acknowledge

The circuitry for acknowledging the Function Strobe signal is shown in Figure 2–1 on the following page.

## **3.2** Read Direct Timing

The timing for the Read Direct instruction is shown in Figure 2–2. For this instruction, the following operations take place.

1. The CPU puts the effective address on the Address Lines and holds RDD/WRD at ground for at least 360 nanoseconds, then brings up Function Strobe.

2.

The external unit that can properly decode the Address Lines uses Function Strobe as a gate to put the following signals on their proper lines:

Data Bits

CC3 and CC4

Function Strobe Acknowledge

- 3. After seeing Function Strobe Acknowledge, the CPU delays for a short period (whose duration is not germane to the proper operation of external units) and accepts the data and CC3 and CC4; then it drops Function Strobe, after a delay of 300 nanoseconds minimum (no maximum).

- 4. When the addressed external unit sees Function Strobe drop, it immediately releases the data lines, CC3, CC4, and Function Strobe Acknowledge.

5. The CPU does not drop the address lines until (200 nanoseconds minimum) it sees Function Strobe Acknowledge released.

Figure 2-1. Function Strobe Acknowledge Circuit

Figure 2-2. Read Direct Timing and Write Direct Timing

### 3.3 Write Direct Timing

The timing for the Write Direct instruction is shown in Figure 2–2. For this instruction, the following operations take place:

- 1. The CPU puts the effective address on the Address Lines and holds RDD/WRD at a true state for at least 360 nanoseconds, then brings up Function Strobe.

- 2. The external unit that can properly decode the Address Lines accepts the information on the data lines and uses Function Strobe as a gate to put CC3, CC4, and Function Strobe Acknowledge on their lines. The output data may be accepted either by using Function Strobe as a dc gate (two-sided loading), or by ac clocking at the trailing edge of Function Strobe. The latter approach is recommended.

- After seeing Function Strobe Acknowledge, the CPU delays for a short period (whose duration is not germane to the proper operation of the external unit), and accepts CC3 and CC4. Then it drops Function Strobe, after a delay of 300 nanoseconds minimum (no maximum).

- 4. When the addressed external unit sees Function Strobe drop, it immediately releases CC3, CC4, and Function Strobe Acknowledge.

- The CPU does not drop the address lines, the data lines, or RDD/WRD, until it sees Function Strobe Acknowledge released (200 nanoseconds minimum).

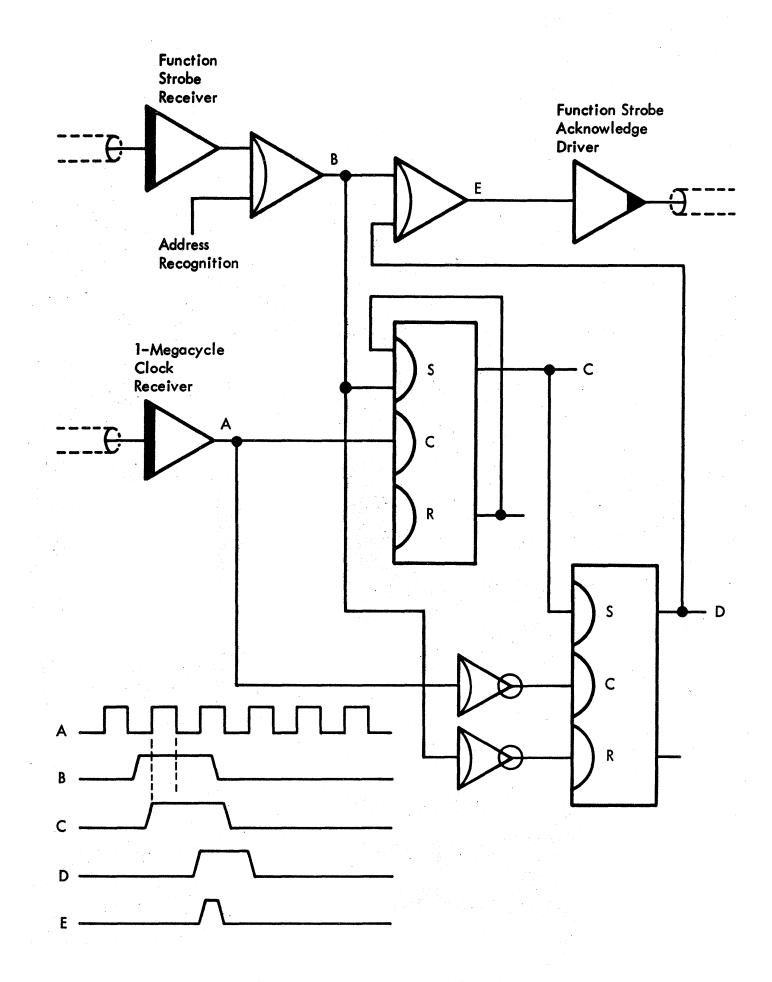

3.4 Hanging Up the RWD Interface

It is a Systems Engineering policy not to hang up the RWD interface for any duration longer than 1.6 µsec, and only then in cases where there is clearly an engineering or economic advantage to be gained by doing so (for instance, to avoid the use of oneshots or unnecessary buffer storage). The recommended logic for accomplishing this is shown in Figure 2-3 on the following page, along with timing diagrams. Point B is true for 0.6 to 1.6 µsec.

### 3.5 Decoding

All units designed by Systems Engineering must completely decode all 16 bits of the RDD and WRD effective address. There should be absolutely no exceptions to this rule.

# 4.0 RECOMMENDED METHOD FOR ACHIEVING SIGMA 2 COMPATIBILITY

Special units designed expressly for SIGMA 2 need not give any consideration to potential usage on SIGMA 5 or SIGMA 7. In the event that they were so used, the only disadvantage would be a reduction in efficiency, since only half of each SIGMA 5 or SIGMA 7 word would be used. There are no engineering barriers to such interchange.

Special units designed expressly for SIGMA 5 or SIGMA 7 should give some consideration to potential usage on SIGMA 2. If such units are optimized for operation on SIGMA 5 and SIGMA 7, they will, in general, not be able to operate effectively on SIGMA 2 unless the usage of each half of each data word is independent of the usage of the other half. The information in the following paragraphs regarding compatibility for standard units should be considered in designing special units for SIGMA 5 and SIGMA 7, since it may be profitable in some cases to make even such special units compatible with SIGMA 2.

All standard units must be capable of efficient operation on either SIGMA 2 or SIGMA 5 and SIGMA 7, unless quite strong economic or operational disadvantages can be shown. The scheme used in the JB30/JB31/JB32 Digital Junction Boxes to ensure this compatibility is described below.

Two bits are reserved in the effective address of each RDD or WRD instruction to specify whether the operation should be only on the high half of the word, only on the low half, or on the full word (both bits true). In general, the mechanics of implementation have shown that there is small incremental cost increase associated with this approach. A slot is reserved in each chassis, to which all 32 data receiver outputs (the output data from the CPU) are brought. When the unit is used on SIGMA 2, a special jumper module is inserted in this slot. The module connects bits 00 and 16, 01 and 17, etc. Thus any output operation in SIGMA 2 involves the proper 16 bits from the CPU, whether high-half or low-half operation is specified in the instruction.

Figure 2-4 on the following page illustrates how the same operation is accomplished for a typical application — namely digital inputs. The example shows bits 00 and 16; the remaining pairs of bits up to 15 and 31 are similar.

Figure 2-4 shows the normal implementation for SIGMA 5 and SIGMA 7. When the unit is used on SIGMA 2, the circuits designated "A" are replaced by inverting (rather than buffering) circuits with identical gating structures. Most SIGMA logic modules come in pairs like this. The special module designated "B", which has only jumpers in SIGMA 5 and SIGMA 7, is replaced for SIGMA 2 by one that contains inverters, as shown in Figure 2-4. Thus, no wiring changes of any kind are required.

Figure 2-4. SIGMA 2, RWD Compatibility

### SECTION III: IOP INTERFACE

### **1.0** INSTRUCTIONS IN THE COMPUTER

### 1.1 General Description

SIGMA 5 and SIGMA 7 require different CPU programming than SIGMA 2 to handle the IOP interface. The description that follows refers to SIGMA 5 and SIGMA 7. The SIGMA 2 description is presented in Section III-4.

SIGMA 5 and SIGMA 7 actually communicate only with the IOP. The IOP then handles communication with each Device Controller, including order and control information as well as data transfers. To perform these functions, the IOP utilizes the system's main memory, as well as its own internal fast memory. The internal fast memory in the IOP, which is organized in such a manner that there are a certain number of bits reserved for each possible I/O channel (Device Controller), is not directly accessible to the programmer. However, certain information in this fast memory can be transferred to fast memory or CPU registers by means of the instructions described in this section.

To initiate data transfers with any Device Controller, the programmer may issue a Start I/O (SIO) instruction. This instruction activates the selected Device Controller and provides information regarding how much data is to be transferred and the main memory locations involved in the transfer. It also provides control information that tells the IOP what to do in the event of certain conditions, such as running out of data, various errors, or acting on special control information provided by the Device Controller itself.

The Start I/O instruction does not itself provide any information except an IOP address, a device address, and a memory location that defines the starting point for the actual list of commands stored in main memory. This command list in main memory consists of pairs of words (called command pairs), each of which contains a byte address, a byte count, a command (read, write, read backward, etc.), and various control flags that influence IOP operation. The IOP operates in such a manner that it can read through

3-1

this sequence of command words in main memory, executing the functions required by each command pair in turn. The command word format is described in detail in Section III-1.5.

### 1.2 SIO Instruction

The Start I/O instruction has the following format in a computer program:

| IA | Ô | 0 | 1 | 0 | 0 | 0 | 0 | R        | X      | Address                                            |

|----|---|---|---|---|---|---|---|----------|--------|----------------------------------------------------|

| 0  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 9 10 1 | 121314 | 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

IA = indirect addressing bit

R =, register on currently selected page

X = index register (none if X = 0)

First, indirect addressing is performed, if IA = 1, to obtain a new address. If indexing is also specified, the contents of the specified index register are added to this new address to form the effective address for the instruction. The low-order eleven bits of this effective address are now interpreted as an I/O address, in the following manner:

| ſ | T  | OP N | _  | 0  |      |       | Devic | e Con | trolle | er.  |    | Form 1 |

|---|----|------|----|----|------|-------|-------|-------|--------|------|----|--------|

|   | 1  |      | 0. | 1  | D. ( | Contr | oller |       | Dev    | /ice |    | Form 2 |

|   | 21 | 22   | 23 | 24 | 25   | 26    | 27    | 28    | 29     | 30   | 31 |        |

The second form, where bit 24 = 1, is used for Device Controllers that may have many devices attached to them, only one of which can be engaged in data exchanges at any given time. A tape controller and individual tape transports exemplify this type of unit.

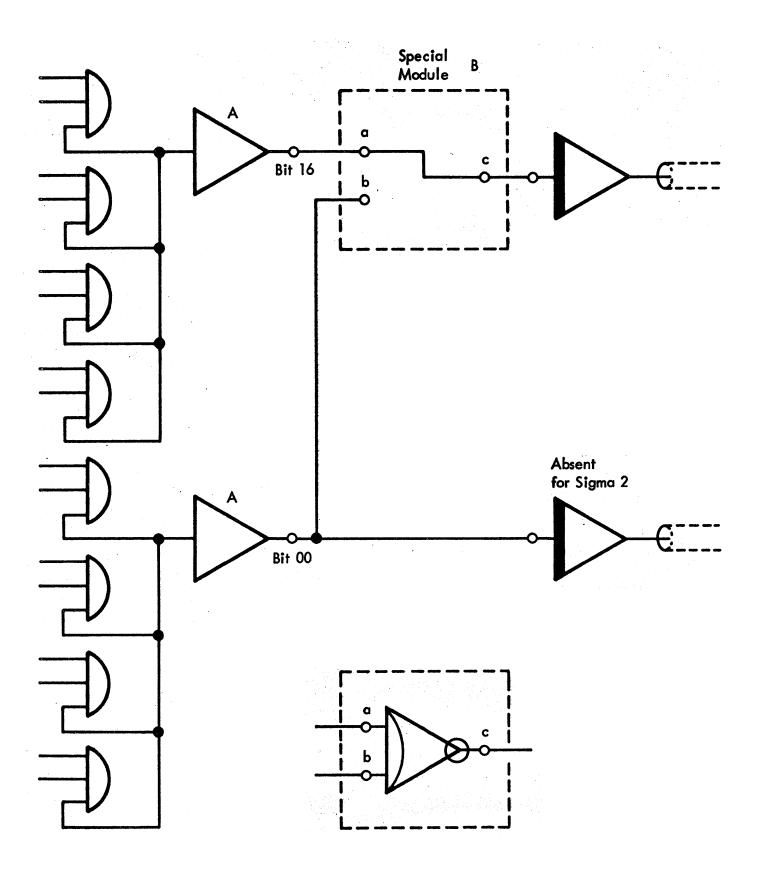

SIO assumes that the programmer has previously set up main memory cell 20\* with a word having the following format:

| 0   |    | -  | - | - | - | æ | <b>.</b> |   | - | -  |    | -  | -  | -  | 0  |    |    | C  | om | ma | nd | Do | out | lev | vor | d / | Add | dre | SS   | -    |    |

|-----|----|----|---|---|---|---|----------|---|---|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-----|-----|-----|------|------|----|

| 0   | 1  | 2  | 3 | 4 | 5 | 6 | 7        | 8 | 9 | 10 | 1] | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21 | 22 | 23  | 24  | 25  | 26  | 27  | 28  | 3 29 | 30 3 | 31 |

| *bo | se | 16 |   |   |   |   |          |   |   |    |    |    |    |    |    |    |    |    |    |    |    |    |     |     |     |     |     |     |      |      |    |

The SIO instruction now takes the I/O address, as previously determined, and the nature of the R field, and merges them into cell 20 to produce a word in cell 20 having the following format:

|      | Address<br>t 8 Bits) | R  | 0 -  | 0        | Command Doubleword Address                      |

|------|----------------------|----|------|----------|-------------------------------------------------|

| 0123 | 4 5 6 7              | 89 | 1011 | 12131415 | 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

The IOP interprets bits 8 and 9 above in the following manner:

| 00 | The IOP only sets the condition code bits based on the response from the addressed Device Controller (R was 0).        |  |  |

|----|------------------------------------------------------------------------------------------------------------------------|--|--|

|    |                                                                                                                        |  |  |

| 01 | The IOP sets the condition code bits as for 00, but also writes status information in main memory cell 21 (R was odd). |  |  |

| 10 | The IOP sets the condition code bits as for 00, but also writes                                                        |  |  |

|    | status information in main memory cells 20 and 21, replacing                                                           |  |  |

|    | the original contents above of cell 20 (R was even and non-zero).                                                      |  |  |

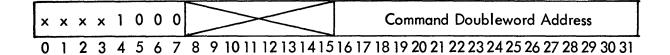

The information that the IOP may write back into condition code bits 1 and 2, and cells 20 and 21 (if directed as above to do so), has the following format:

CC1 If set, the I/O address was not recognized by any device.

CC2 If set, the SIO instruction was unsuccessful (i.e., it was rejected by the Device Controller for one of a variety of reasons that are discussed later).

| Cell 20* | Command Doubleword Address                                                   |        |                                              |  |  |  |

|----------|------------------------------------------------------------------------------|--------|----------------------------------------------|--|--|--|

|          | 0 1 2 3 4 5 6 7 8 9 10 11 12 13                                              | 141516 | 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |  |  |  |

| Cell 21* | Status                                                                       | 0      | Byte Count                                   |  |  |  |

|          | 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 |        |                                              |  |  |  |

The command doubleword address that is returned to cell 20 is the one associated with the previous order or I/O function to the addressed channel. This is undefined if the instruction is the first SIO since power-on. The byte count returned to cell 21 is the byte count stored in the IOP fast memory word associated with the addressed channel. It is also undefined if this is the first SIO since power-on. The status bits in cell 21, as returned by the IOP (which generates them itself or receives them from the Device Controller), have the following significance:

| Bit O      | device interrupt pending                                        |

|------------|-----------------------------------------------------------------|

| Bits 1 & 2 | 00 = device ready                                               |

|            | 01 = device not operational                                     |

|            | 10 = device unavailable                                         |

|            | 11 = device busy                                                |

| Bit 3      | device automatic                                                |

| Bit 4      | device unusual end                                              |

| Bits 5 & 6 | 00 = Device Controller, ready                                   |

|            | 01 = Device Controller not operational                          |

|            | 10 = Device Controller unavailable                              |

|            | 11 = Device Controller busy                                     |

| Bit 7      | undefined                                                       |

| Bit 8      | incorrect length (via order-in from Device Controller)          |

| Bit 9      | transmission data error (data-in, parity, or order-in error)    |

| Bit 10 .   | transmission memory error (data parity)                         |

| Bit 11     | memory address error (non-implemented memory address)           |

| Bit 12     | IOP memory error (memory parity error while fetching command)   |

| Bit 13     | IOP control error (two successive Transfer in Channel commands) |

| Bit 14     | IOP halt                                                        |

3-4

Since the IOP might be busy with a Device Controller (exchanging data) when the SIO is issued by the CPU, it is possible for the system to "stall" for a short time until the IOP is free to process the SIO. However, this time cannot, even in the worst case, exceed the time required to finish servicing the currently connected Device Controller, since the CPU then has higher priority (for IOP usage) than any Device Controller that needs service.

After this phase of the SIO instruction is completed, including status exchange with the Device Controller, the CPU copies cell 21 (only if it was written into by the IOP) into register Rul (If R is even, Rul = R + 1; if R is odd, Rul = R). The CPU also copies cell 20 (only if it was written into by the IOP) into register R. If R is odd (making R = Rul), R will then contain the original contents of cell 21, and cell 20 will not be in any of the registers.

#### 1.3 Operational Sequence after SIO

Once a Device Controller has been activated by an SIO instruction, and until it either halts itself or is halted by an HIO instruction, it may make service calls to the IOP. A Device Controller makes a service call by activating a specified line in one of the cables to the IOP, and it may do this at any time, without regard to the state of the IOP. For example, when a Device Controller makes a service call the IOP may be occupied at the time in communicating with the CPU, main memory, or some other Device Controller. A single line is used by all Device Controllers to make their service calls, i.e., they all use the same line.

As soon as the IOP has completed its previous activity, it continues scanning the service call line until it detects activation by some Device Controller. At this time, the IOP does not know which Device Controller is requesting service – any number of Device Controllers might be requesting service simultaneously. The IOP then issues a signal called Function Strobe, in conjunction with a function indicator called Acknowledge Service Call (ASC), which is transmitted to all units attached to the IOP.

A separate, hard-wired priority determination chain runs from controller to controller (this is discussed in detail in Section III-3. 1). This chain is important primarily when more than one controller has called for service. The highest priority controller that has requested service then places its device address on the eight function response lines of the interface, and acknowledges the function strobe. All other units must stay off all lines. The active unit is then connected to the IOP for service, and goes through a service cycle which may involve the transfer of one to five bytes of information.

The IOP uses the address that is returned on the function response lines to select the fast memory location from which required information will be obtained for the subsequent service cycle to the connected controller. The connected controller then initiates data transfers by activating a line designated "Request Strobe". During Request Strobe activation, the Device Controller must also control two lines called Data-Order Request (DOR) and Input/Output Request (IOR). These two lines are decoded by the IOP to select one of four possible functions that may be performed by the IOP during that cycle:

| DOR | IOR | Function     |

|-----|-----|--------------|

| 0   | 0   | Data Input   |

| 0   | 1   | Data Output  |

| 1   | 0   | Order Input  |

| 1   | 1   | Order Output |

The operation of the IOP while performing these functions is discussed later in this section. The manner in which a service cycle is terminated is controlled by two additional signals: End Data (ED) and End Service (ES), coded as follows:

#### Meaning

The controller must generate another Request Strobe and accept or provide another byte of data.

This is the last data byte; the controller must disconnect itself and not generate any more Request Strobes.

This is the last data byte; however, the controller must not disconnect itself yet and must generate one more Request Strobe. During the next Request Strobe, the IOP will output certain control information to the controller. This is known as a Terminal Order.

X

ED

0

1

1

ES

0

1

0

1

This configuration defines the Terminal Order when preceded by "10"; the controller must disconnect itself and not generate any more Request Strobes.

In response to each Request Strobe generated by the Device Controller, the IOP generates a signal called Request Strobe Acknowledge. Along with Request Strobe Acknowledge, the IOP either provides data (if the subcycle is for Data Out, Order Out, or Terminal Order) or accepts the data provided by the controller (if the subcycle is for Data In or Order In).

The ED line may be driven by either the IOP or the Device Controller. The Device Controller normally drives this line, at the same time it activates Request Strobe, when it has received all the data necessary (or input all the data called for during the current service cycle). It may also drive this line because an error has been detected in data transmission and the Device Controller therefore wishes to terminate operations.

The IOP may drive the ED line true for one of three reasons:

An error of some sort has been detected, and the IOP has been conditioned to terminate operations when this error is detected.

- 2. A word boundary has been reached during data transfers, and the IOP would have to go back to main memory to get more data bytes. Activating ED and ending the service cycle permits other operations, such as service to the CPU or other Device Controllers, to take place.

- 3. The service cycle was for either Order Out or Order In; each consists of a one-byte transfer.

The ES line, on the other hand, may be driven only by an IOP. It is driven under precisely two circumstances:

- 1. Either the IOP or the Device Controller has signalled ED, and there is no necessity for a Terminal Order.

- 2. It is driven during the Terminal Order.

In the first case, ES is driven during the same subcycle that ED was driven, so they both appear together back at the Device Controller. The Device Controller should use the trailing edge of Request Strobe to inspect the state of ED and ES and decide whether or not additional Request Strobes will be required and if one is required, whether it should be for a Terminal Order or for more data transfer.

In SIGMA 5 and SIGMA 7, Order In is always followed by a Terminal Order, even though there may sometimes be no important information to be transmitted in the Terminal Order.

It should be noted that in SIGMA 5 and SIGMA 7, precisely seven different types of service cycles can occur:

- 1. one, two, three, or four data bytes out

- 2. one, two, three, or four data bytes out and a Terminal Order

- 3. one, two, three, or four data bytes in

- 4. one, two, three, or four data bytes in and a Terminal Order

- 5. Order Out (one byte)

- 6. Order In (one byte) and a Terminal Order

- 7. Order Out and a Terminal Order

The following points should be noted carefully:

- The coding of DOR and IOR by the Device Controller need only be given during the first byte of each service cycle, even in the cycle is five bytes long; the state of these lines is ignored after the first byte of each service call.

- The Device Controller, if it wishes to end the service cycle, drives ED while the last data byte is being input or output; the Device Controller should not drive ED during the Terminal Order.

- The Device Controller must disconnect following the subcycle in which it sensed ES true, and must generate an additional Request Strobe following any subcycle in which it sensed ES false.

#### 1.4 Data and Command Chaining

"Data chaining" is the term used to describe a particular IOP reaction to "running out of data", i.e., the byte count in IOP fast memory for a particular channel goes to zero. If the programmer has specified data chaining with bit 0 of the odd command word, then the IOP performs the following sequence of actions when the byte count goes to zero:

- The IOP fast memory is accessed to determine the last command doubleword address.

- 2. This address is incremented by two, to produce a new command doubleword address.

- The IOP accesses two main memory cells (the command doubleword) and stores in its own fast memory a new byte count, a new memory byte address, and a

new set of eight IOP control flags. The "order" bits in the command doubleword are ignored, and not passed on to the Device Controller.

4. The IOP then continues data exchanges with the Device Controller, based on further service requests from that Device Controller. The Device Controller has no knowledge of the occurrence of data chaining.

"Command chaining" is caused by the Device Controller, in response to orders from the programmer. Its net effect is similar to that of data chaining, except that the IOP also passes along a new "order" (the highest eight bits of the first command word) to the Device Controller. Command chaining only occurs as a result of the following sequence of operations:

- 1. The Device Controller signals "channel end" by means of an Order In.

- 2. If command chaining was called for by bit 2 of the second command word of the last executed command doubleword, the IOP sets the command chaining bit in the Terminal Order that follows Order In.

- 3. The Device Controller recognizes this condition and requests an Order Out cycle. At this time the IOP determines the new doubleword address and accesses main memory to get a new command doubleword, just as it did in the data chaining operations described above.

Data chaining is used for scatter-read or gather-write operations, where the external device is operating with continuous data that may come from or be delivered to non-contiguous areas of memory, in sub-blocks of any size specified by the programmer. Command chaining provides a means of writing a sub-program (a sort of subroutine) whose execution and sequencing can be under control of the IOP and/or the Device Controller. It avoids the necessity for active program intervention in many cases, thus saving time and programming effort.

The IOP does not ordinarily take any action based on the particular order in the command doubleword, except for a Transfer in Channel command. This command is not passed on to the Device Controller. Instead, the IOP alters the current command doubleword address to the new location specified by the Transfer in Channel (TIC) command. When TIC is used in conjunction with the chaining modifier bit (which the Device Controller can signal in an Order In), it allows selective branching within the CPU command list, under control of the Device Controller.

1.5 Command Word Format

The IOP accesses main memory to obtain command words under two conditions:

- . The Device Controller has made a request for Order Out.

- During data exchange (input or output), the IOP determines that the byte count has gone to zero, and the data chaining bit in the previous command word was set.

The request for Order Out in the first case above can be generated by the Device Controller for one of two reasons:

- An SIO instruction was issued to and accepted by the Device Controller. The Order Out is thus issued to obtain the first command doubleword from main memory, in order to inform the Device Controller regarding the exact nature of the operations it is to perform and to allow the IOP to store the required control information (byte count, memory byte address, control flags).

- The Device Controller had issued an Order In specifying "channel end", and in the Terminal Order following that Order In, the IOP had indicated that the programmer had called for command chaining.

The general format for command words is as follows:

|   |   |   | С | )rd | er |   |   |   |   | > | $\sim$ | <     | <u> </u> | 1 |    |    |    |    |    |    | ٨  | ٨er | noı | ſY | Byt  | е  | Ad | dre | ess |    |    |    |      |      |    |  |

|---|---|---|---|-----|----|---|---|---|---|---|--------|-------|----------|---|----|----|----|----|----|----|----|-----|-----|----|------|----|----|-----|-----|----|----|----|------|------|----|--|

| ( | 0 | 1 | 2 | 3   | 4  | 5 | 6 | 7 | 8 | 9 | 10     | ) ] ] | 11       | 2 | 13 | 14 | 41 | 51 | 16 | 17 | 18 | 19  | 20  | 2  | 1 22 | 22 | 32 | 42  | 526 | 52 | 27 | 28 | 29 : | 30 3 | 31 |  |

#### For Transfer in Channel commands, the format is:

Odd command words have the following format:

The coding of the Order bits in the even command word is:

MMMMMM11 = ControlMMMMMM01 = WriteMMMMMM10 = ReadMMMM1100 = Read BackwardMMMM0100 = SenseXXXX1000 = Transfer in ChannelI0000000 = Stop

where

M denotes a modifier bit unique to the particular Device Controller X denotes "don't care"

I denotes interrupt condition

The coding of the IOP flag bits in the odd command word is shown in Table 3–1 on the following page.

Table 3-1, IOP Flag Bit Coding

| Bit | Name | Function                                                                                                                                                                                                                                                                                                                |

|-----|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | DC   | Data Chain: if this bit is true, then when the byte count goes to zero the IOP accesses memory for the next command pair but does not pass the Order along to the Device Controller.                                                                                                                                    |

| 1   | IZC  | Interrupt on Zero Count: if this bit is true, then when the byte count goes to zero the IOP generates a Terminal Order to the Device Controller, in which the interrupt bit (data line 0) is set.                                                                                                                       |

| 2   | сс   | Command Chain: if this bit is true, then when the Device Controller sig-<br>nals "channel end" to the IOP (by setting data line 3 in an Order In), the<br>IOP signals command chaining to the Device Controller in the Terminal<br>Order which follows the Order In (by setting data line 2 in that Terminal<br>Order). |

| 3   | ICE  | Interrupt at Channel End: if this bit is true, then when "channel end" is<br>signalled to the IOP by the Device Controller (by setting line 3 in an<br>Order In), the IOP sets the interrupt bit in the Terminal Order which<br>follows that Order In.                                                                  |

| 4   | HTE  | Halt on Transmission Error: if this bit is true, then the IOP signals "IOP halt" to the Device Controller by setting bit 3 in a Terminal Order, if any of the following conditions occur:                                                                                                                               |

|     |      | . A parity error is detected by the IOP during communication between the IOP and main memory.                                                                                                                                                                                                                           |

|     |      | . The Device Controller signals Transmission Error to the IOP by means of bit 0 set in an Order In.                                                                                                                                                                                                                     |

|     |      | . The Device Controller signals Incorrect Length to the IOP by means of bit 1 set in an Order In <u>and</u> the SIL flag is not set.                                                                                                                                                                                    |

| 5   | IUE  | Interrupt at Unusual End: if this bit is true, then when Unusual End is signalled to the IOP by the Device Controller in an Order In, the IOP sets the interrupt bit in the Terminal Order that follows the Order In.                                                                                                   |

| 6   | SIL  | Suppress Incorrect Length: if this bit is true, then Incorrect Length indica-<br>tions from the Device Controller during Order In are ignored. Otherwise,<br>Incorrect Length indications may cause an IOP Halt to be issued to the<br>Device Controller if the HTE flag is set (see above).                            |

| 7   | S    | Skip: if this bit is true, the IOP performs all actions usually associated with the command except memory accesses.                                                                                                                                                                                                     |

2

It should be noted that, for each channel (Device Controller), the IOP must store and maintain in its own fast memory the following information:

- Memory Byte Address (19 bits), which is incremented or decremented after each data exchange with the Device Controller (decremented only when Order was Read Backward).

- Command Doubleword Address (16 bits), which is incremented by two prior to the extraction of each new command doubleword from main memory. It is ordinarily changed only by an SIO instruction or this incrementing, but a TIC command may also change it.

- Byte Count (16 bits), which is incremented by one after the exchange of

each 8-bit byte with the Device Controller.

- IOP Control Flags (8 bits), which may be altered only by a new command word other than TIC or Stop.

It should also be noted that Order does not have to be preserved in IOP fast memory. The Order is transmitted directly to the Device Controller, if required, at the time the command word is read from main memory by the IOP, and is not needed thereafter.

# 1.6 HIO, TIO, and TDV Instructions

The format for Halt I/O (HIO), Test I/O (TIO), and Test Device (TDV) instructions is similar to that for SIO.

| HIO |    | 0 | 0 | 1 | 0 | 0 | 1 | 1 |            | ſ      |                                                   |

|-----|----|---|---|---|---|---|---|---|------------|--------|---------------------------------------------------|

| TIO | IA | 0 | 0 | 1 | 0 | 0 | 0 | 1 | R          | X      | Address                                           |

| TDV |    | 0 | 0 | 1 | 0 | 0 | 1 | 0 |            |        |                                                   |

|     | 0  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 9 10 1 1 | 121314 | 1516 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

The low-order eleven bits of the effective address, after indirect addressing and indexing (if specified), are also interpreted (as for SIO) as specifying an IOP number and an 8-bit device address. Memory cell 20\* does not have to contain a command doubleword address, as for SIO.

\*base 16

However, the R field is still used to specify the locations to which the IOP returns data (20 only, 20 and 21, or neither). The format of cell 20 before the execution of HIO, TIO, or TDV is the same as for SIO (device address and R bits), without the command doubleword address.

The contents of cells 20 and 21 after HIO, TIO, or TDV has been executed are similar to the format after SIO, described in Section II-1.2. The status bits (0-14 of cell 21) have exactly the same meaning for SIO, HIO, and TDV. For TDV, the high-order eight status bits represent status information unique to the particular Device Controller that is being tested. Descriptions of this status are contained in the individual specifications for each controller.

# 1.7 Interrupt Structure and AIO Instruction

The IOP has its own priority interrupt structure which is completely independent of the normal external priority interrupt structure, except that the relative priority of the two groups may be altered by hard-wiring. All interrupts from Device Controllers attached to IOP's come through a single memory cell. This is equivalent to a situation where all peripheral equipment interrupts (including IOP interrupts such as Count Equals Zero) are bussed to a common priority interrupt, whose place in the priority chain is variable (hard-wired only). There must, therefore, be some way to determine which of many possible devices has actually caused the common interrupt; in fact, there may be at any given time active interrupt requests from many controllers, but only one interrupt occurs.

The Acknowledge Input/Output Interrupt (AIO) instruction is used to determine the source of such an interrupt request. This instruction is not addressed to a particular device, since one of its results is to determine which device caused an interrupt. Thus, the instruction format is somewhat different from SIO et al:

| IA | 0 | 1 | 1 | 0 | 0 | 1 | 1 |   | R         | X      | Address                                            |

|----|---|---|---|---|---|---|---|---|-----------|--------|----------------------------------------------------|

| 0  | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 11 1 9 10 | 121314 | 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 |

The difference from SIO is primarily in the interpretation of the effective address: only bits 21 to 23 are significant. These bits establish the type of interrupt being acknowledged. For standard I/O interrupts, these bits should be coded 000. The remainder of the address field is not used.

When an AIO instruction is issued, various control signals are sent out to the IOP's (up to eight in a system). Each IOP passes the control signals on to the next IOP, unless one of the controllers connected to it has an active interrupt. The IOP with the interruptrequesting controller then passes the control signals on to its Device Controllers, where the controllers themselves establish priority in a similar manner. The highest priority interruptrequesting Device Controller sends its own address to the IOP, along with some status information regarding its interrupt request. The IOP appends its own IOP number, and passes this information to the CPU, which writes into cell 20 a word of the following form:

| Status                                | 0 0 0 0 0 IOP # Device Controller<br>(and Device) |

|---------------------------------------|---------------------------------------------------|

| 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 | 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31   |

Status bits 0-7 represent interrupt status information unique to the Device Controller whose interrupt was acknowledged. The significance of these bits is described in the specifications for each device. Bits 8-15 have standard meaning for all IOP's and controllers:

- . Bit 8 Incorrect Length, as defined for SIO

- . Bit 9 Transmission Data Error, as defined for SIO

- Bit 10 Zero Byte Count Interrupt (set only if the IZC flag in the last command doubleword was true and the byte count equals zero)

- Bit 11 Channel End Interrupt (set only if the ICE flag in the last command doubleword was true and the device has signalled "channel end" to the IOP via an Order In)

- Bit 12 Unusual End Interrupt (set only if the IUE flag in the last command doubleword was true, and the IOP has signalled the controller to halt by means of a Terminal Order)

This word is then moved to the register specified in the AIO instruction.

There are two basic reasons for which a Device Controller may issue an interrupt request:

- . In a Terminal Order from the IOP, the interrupt bit (bit 0 in the Terminal Order) was true.

- . An internal condition in the controller calls for an interrupt, based on the design specifications for the Device Controller. In some cases the Device Controller might need or accept control information from the IOP (and hence the CPU and programmer) which conditions this interrupt, or it might be generated internally, by such an event as the depression of a manual push-button.

### 2.0 INTERFACE SIGNAL INTERACTION AND TIMING

# 2.1 Priority Determination

Three cables run from the IOP to the first Device Controller, from the first to the second Device Controller, etc., as described in Section I-3. In addition, a priority determination cable runs only from Device Controller to Device Controller, and does not connect to the IOP. The signals on this cable are used to determine which Device Controller reacts to stimuli for two different sets of conditions:

> When more than one Device Controller has made a service request at nearly the same time, only one may be connected for service. When the IOP acknowledges the service call, the highest priority requesting Device Controller responds to the IOP's acknowledgement. The other waits until some subsequent service call acknowledgement comes from the IOP.

When more than one Device Controller has made an interrupt request, and the AIO instruction is executed by the CPU and IOP, only the highest priority Device Controller may respond to this function; the others must wait until the CPU executes some subsequent AIO instruction. It should be noted that the physical routing of the priority determination cables, which determine the relative priority of units in the event of simultaneous interrupts or service calls, is completely independent of the physical routing of the three ordinary data transmission cables. These three cables are normally installed according to the physical placement of Device Controllers, in order to minimize total cable length. Maximum allowable cable length is 100 feet. The routing of the priority determination cable is based on the desired sequence of responses in the event of simultaneous requests, and 160 feet is the maximum allowed. The desired sequence of responses is influenced by the likelihood of rate overruns, the frequency of service requests, and the degree of difficulty involved in correcting rate overruns. One proposed approach is that devices which require manual intervention to correct rate overruns (such as punched card devices) should have highest priority for service; it should be noted that rate overruns on magnetic tape and discs can be corrected entirely under program control.

Five signals are carried on the priority determination cable:

| • HPI High Priority Inte | •    |

|--------------------------|------|

| . HPS High Priority Ser  | vice |

| . BSY Busy               |      |

| . AVI Available Input    |      |

| . AVO Available Outpu    | t    |

The first three of these signals each constitute a bus which is tapped and driven by each unit, just like all signals on the ordinary data transmission cables. AVI and AVO are unique in that they are not busses; AVO is an output signal from each Device Controller, sent to the next one down the line; it is a logical function of AVI (an input signal), BSY, HPI, HPS, and the internal state and design specifications of the Device Controller.

When the IOP detects a service request (which may be from one or any number of Device Controllers), it activates a strobe that is fed to all Device Controllers in parallel and an indicator that defines the Acknowledge Service Call function. Only the highest priority device must respond actively, while lower priority devices respond passively. Section III-2. 2 describes this response in more detail. AVI is always true for the first Device Controller in the priority determination chain. AVI for each subsequent Device Controller is equal to AVO from the preceding Device Controller in the chain. Each Device Controller must look at the required lines and at its own internal signals and produce the following reactions:

- 1. If a Device Controller has no service request pending, it must pass on AVO as soon as it sees AVI.

- 2. If a Device Controller has a service request pending, it passes on AVO when it sees AVI only if the following conditions are met:

- . HPS is true, and

- that unit's service request is low priority (i.e. the unit has not generated HPS itself.

- 3. If a Device Controller has a service request pending, it does not pass on AVO when it sees AVI if either of the following conditions are true:

- . it has generated HPS itself, or

- . HPS is not true.

When it does not pass on AVO, it must generate BSY instead.

- 4. Every unit must perform the required passive acknowledgement (see Section III-2. 2) for each of the mutually exclusive possibilities:

- . BSY is seen to go true

- . AVI is passed on as AVO

- . BSY is generated by the unit

- 5. The unit which causes BSY to go true is then connected to the IOP for service, and may engage in data exchanges; all other units must await their turn at some subsequent time.

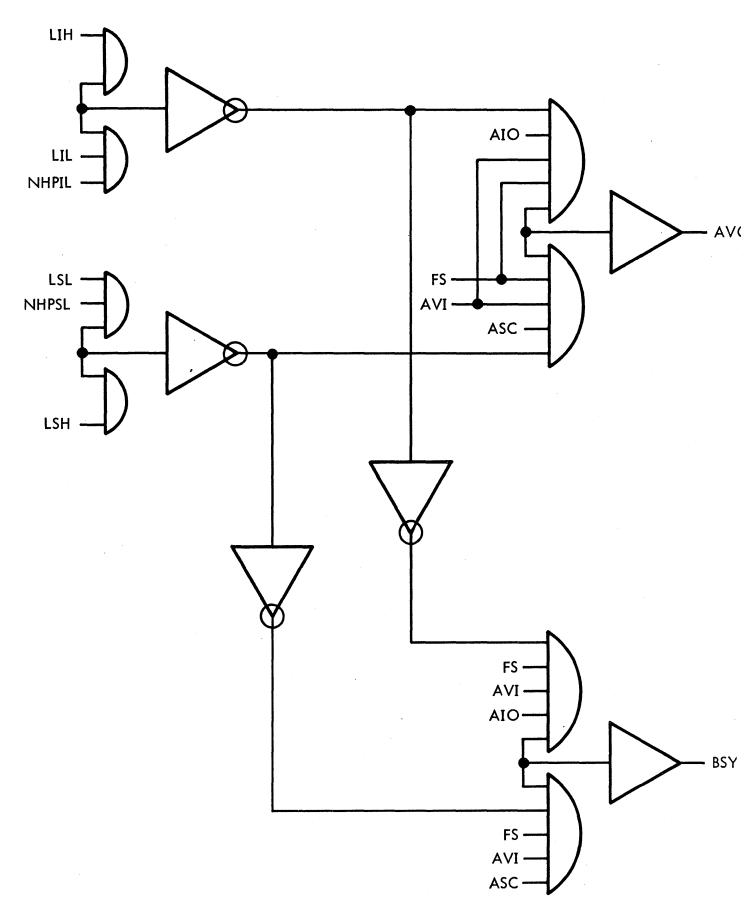

The same priority chain is used in connection with response to the AIO instruction, except that a different function indicator occurs (AIO instead of ASC), and HPI is used in place of HPS in the logic. Figure 3-1 on the following page shows schematically the logic implementation for a typical unit. However, the designer will not generally have to implement this, since it is included as a part of the Subcontroller (see Section III-3).

# 2.2 Leading and Trailing Acknowledgement

Device Controllers in a SIGMA system time-share a single bus for most control and data signals. Obviously, the cable length of this bus is a variable from system to system. To permit completely asynchronous operation on this bus, and therefore to obtain maximum operating rates (IOP bandwidth) for each system, a scheme for positive acknowledgement of both the leading and trailing edges of IOP-generated strobe pulses has been devised.

The IOP issues a Function Strobe during the execution of each of the five computer instructions, and also for the Acknowledge Service Call function. This strobe must be acknowledged by every device, even though only the device that recognizes its own address is involved in active communication with the IOP, in order to allow execution of the instruction. The IOP observes the acknowledgement, and uses this to drop the Function Strobe. Each device must indicate that it has seen the release of Function Strobe (and is therefore finished with its required reactions) before the IOP completes and exits the instruction.

Due to delays in signal transmission over long cables, devices that are physically closest to the IOP sense state changes in Function Strobe (and other IOP signals) sooner than those devices that are farther away. This would ordinarily cause IOP counter-reactions before the Function Strobe signal had propagated to the end of a long cable. Hence, the IOP could possibly enter the execution phase of an instruction before the farthest device in a system had even seen Function Strobe; this would obviously be improper, and could lead to errors.

To avoid this situation, a scheme has been devised to notify the IOP of receipt of both the leading and trailing edges of Function Strobe by the last (farthest) unit on a line.

Figure 3-1. Priority Chain Implementation

.

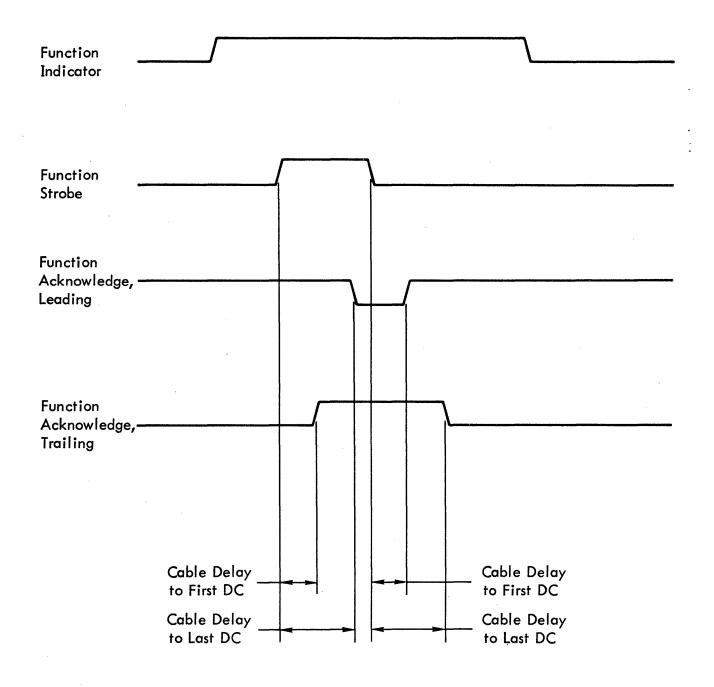

Two signal lines are required, designated Function Strobe Acknowledge Leading (FSL) and Function Strobe Acknowledge Trailing (FST). Each device, when it senses Function Strobe (FS), must release FSL, which is normally true, and drive FST (normally false). The IOP senses FST to be true as soon as the closest device has driven it, based on the cable-driving scheme described in Section I-3. However, the IOP cannot sense FSL false until all devices (hence the last one, which is presumably the farthest) have released it. Thus the IOP correctly assumes that the true-to-false transition of FSL indicates that all devices have seen FS.

When the IOP has released FS (after it has seen FSL go true), each device then drives FSL again, and releases FST. As soon as the first device drives FSL, the IOP senses it. However, that is valueless for determining when the last device on the cable has seen FS go low. On the other hand, FST cannot go low until every device, including the last, has released it, since any one driver true would hold the line true. Thus the IOP correctly assumes that the true-to-false transition of FST indicates that all devices have properly sensed the false state of FS.

Figure 3-2 shows a timing diagram for the interaction of FS, FST, and FSL. It should be noted that if there is not a device present with the specified address, neither the IOP nor the CPU hangs up, since all devices are controlling FST and FSL (whether or not they are addressed) to allow this operational sequence to take place. One of the condition code lines is also driven only by the device which recognizes its own address. Thus, the absence of a device is signalled by the failure of any device to drive this condition code line.

2.3 Processing Computer Instructions

The four instructions SIO, HIO, TIO, and TDV are quite similar. Their primary characteristics and differences are listed below: