## CARTRIDGE DISK CONTROLLER MODEL 7250A01 ASSEMBLY NO. 202624

# CARTRIDGE DISK CONTROLLER MODEL 7250A01

## ASSEMBLY NO. 202624

Specifications, equipment descriptions, and procedures contained herein are subject to change without notice.

February 1974

Prepared by Service Education, Western Operations

701 So. Aviation Blvd., El Segundo, Calif. 90245, 213 679-4511

#### PREFACE

The purpose of a Field Engineering Maintenance Manual (FEMM) is to provide, under one cover, Development Engineering-produced documentation which is relevant to the maintenance of Xerox Computer equipment.

#### ENGINEERING SUPPORT INDEX (ESI)

The Engineering Support Index is a table of contents indicating the drawings contained in this manual and reflects the revision level of each individual drawing to the Top Assembly drawing.

#### UPDATING

When Engineering Orders (EO) to Top Assemblies are released, documentation is updated and distributed to appropriate installations by Xerox Computer Field Engineering through the method of Field Modification Kits (FMK's). If Xerox is responsible for maintaining the affected equipment, the EO and the documentation Update Package is sent to the appropriate customer Service District office. The Customer Engineer is then responsible for prompt EO installation and manual updating. If the Xerox customer is responsible for equipment maintenance, a notification of the EO and the documentation Update Package is sent to the customer address that the customer has provided.

The Update Package typically includes a revised title page, revised Engineering Support Index page, and all pages that have been revised.

#### CHANGES

Changes to a FEMM drawing can only be brought about by the submission of a Drawing Change Request (DCR). To effect a drawing change, field personnel must submit a Technical Action Request (TAR). A DCR may then be submitted by Maintenance Engineering after the TAR is reviewed. Customers who wish to notify Xerox of any discrepancies within the FEMM may submit their comments on the Reader Survey sheet in the back of the manual and forward it to Xerox Computer Field Engineering Publications.

A

903059

-

|         |                            |             | ERING SUPPORT INDEX                                                                                                      |                            |              |

|---------|----------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------|--------------|

| MO      | DEL72                      | 50A01       | TOP ASSEMBLY LEVEL                                                                                                       | <u> </u>                   |              |

|         |                            |             |                                                                                                                          |                            |              |

|         | MECA                       |             |                                                                                                                          |                            |              |

| Section | Drawing No.                | Level       | Title                                                                                                                    | Page                       | es -         |

| 1       | THEORY OF                  | OPERATIC    | INS                                                                                                                      |                            |              |

|         | 104262                     | Α           | Theory of Operations, Cartridge Disk Controller                                                                          | 1 thru                     | 90           |

| 11      | FIELD MAIN                 | NTENANCE    | PROCEDURES                                                                                                               |                            |              |

|         | Maintenance                | Procedures  | ,                                                                                                                        | 1 thru                     | 8            |

| 111     | ENGINEERI                  | NG TECHNI   | CAL INFORMATION                                                                                                          |                            |              |

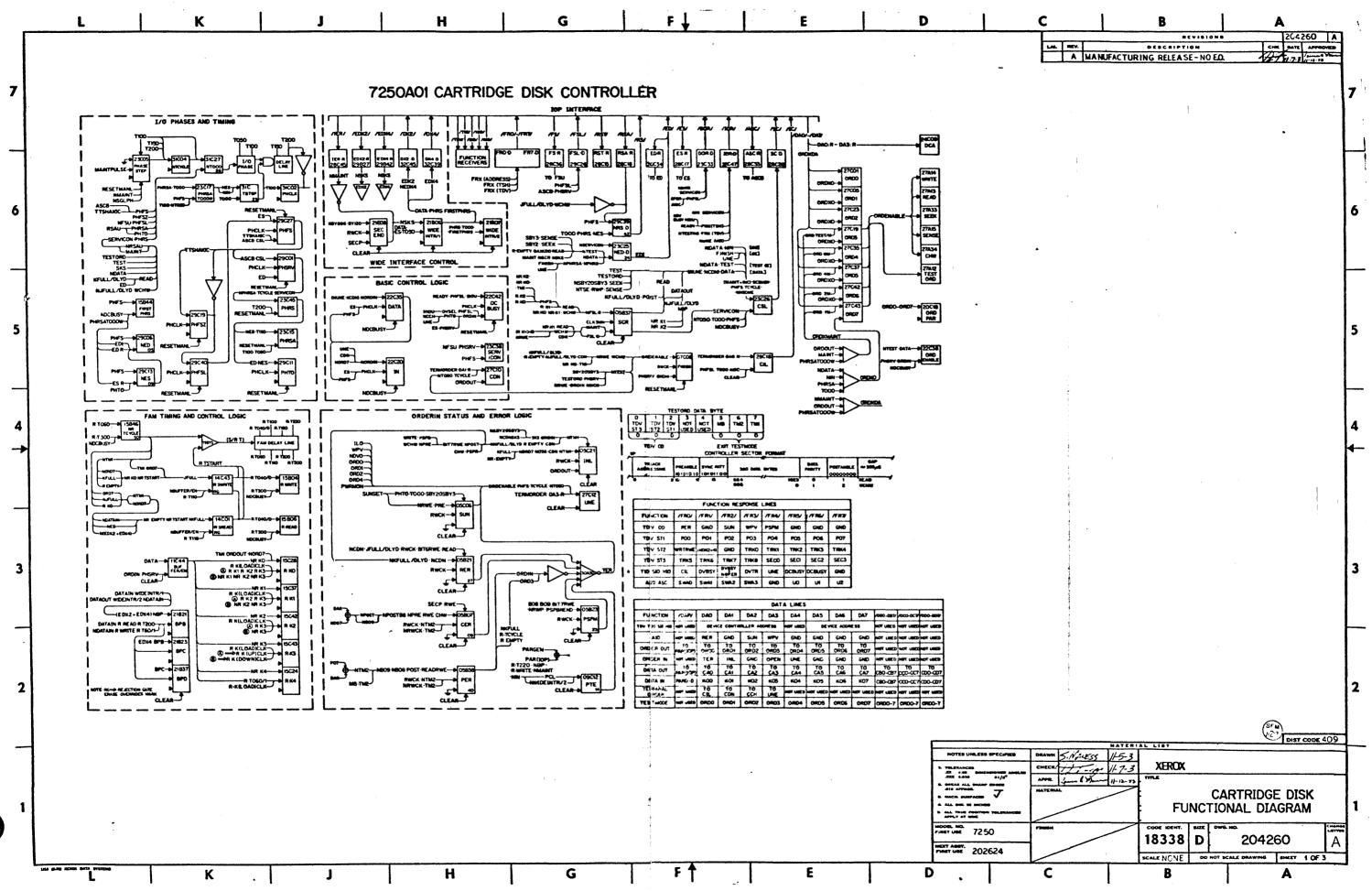

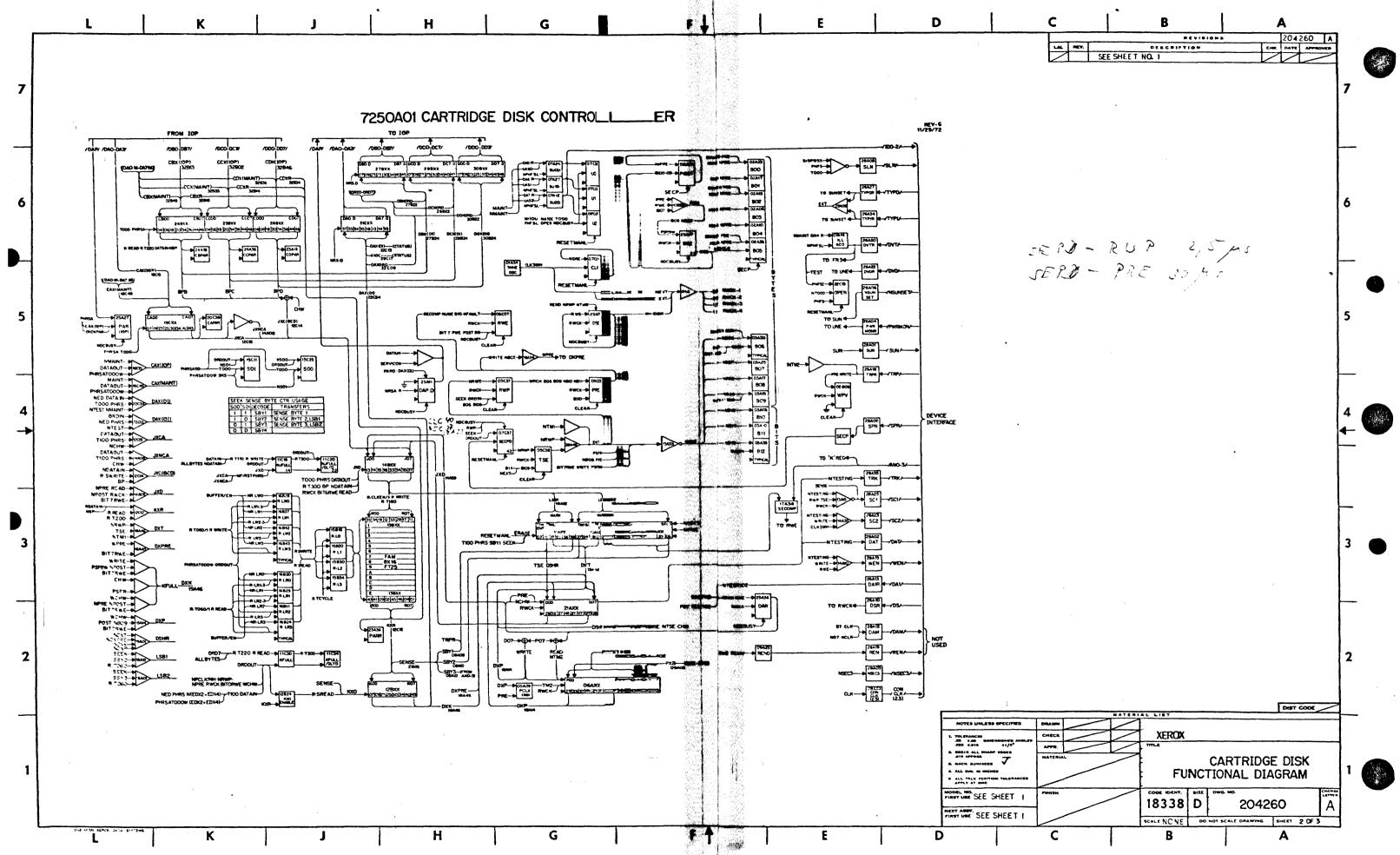

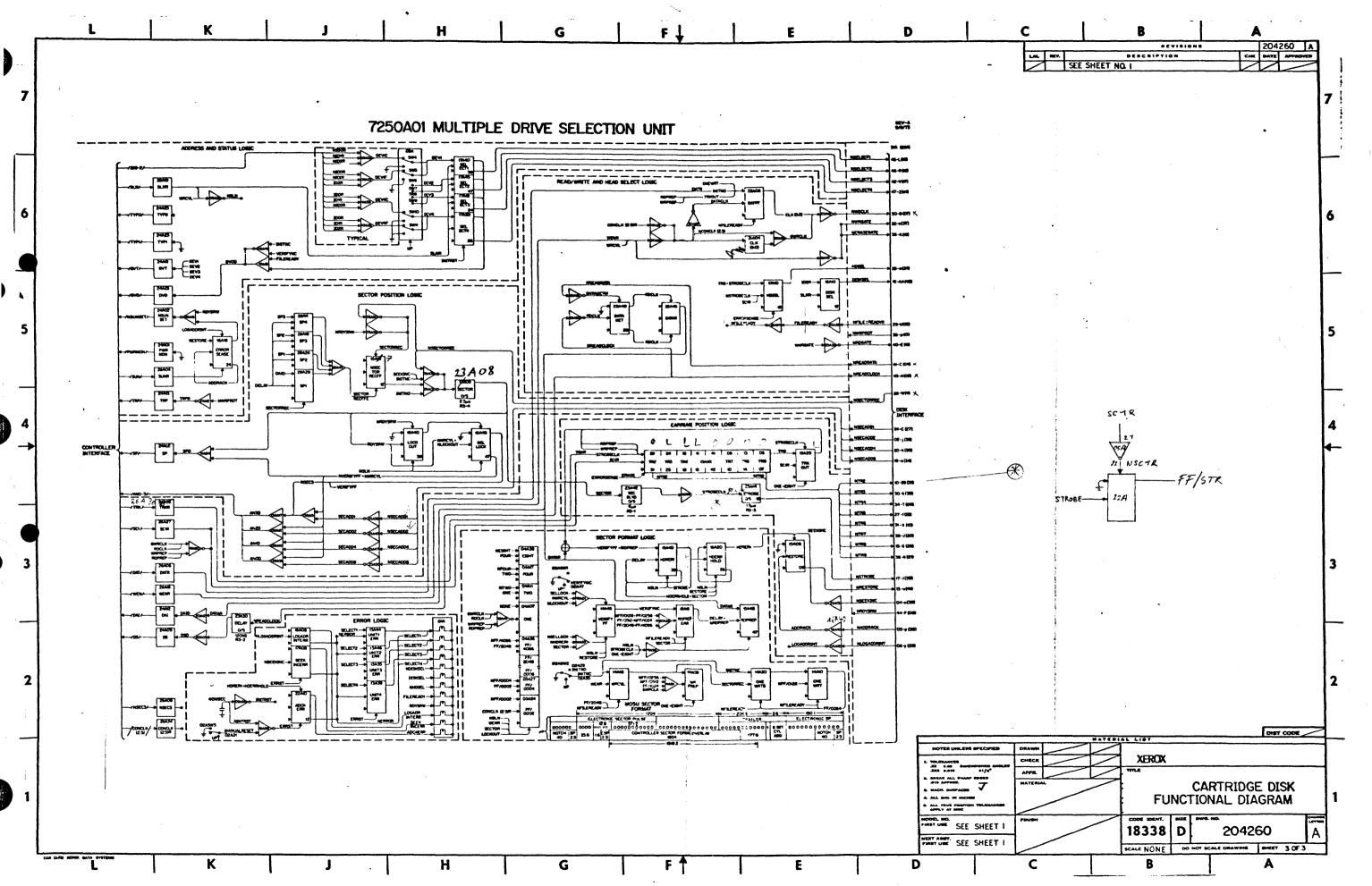

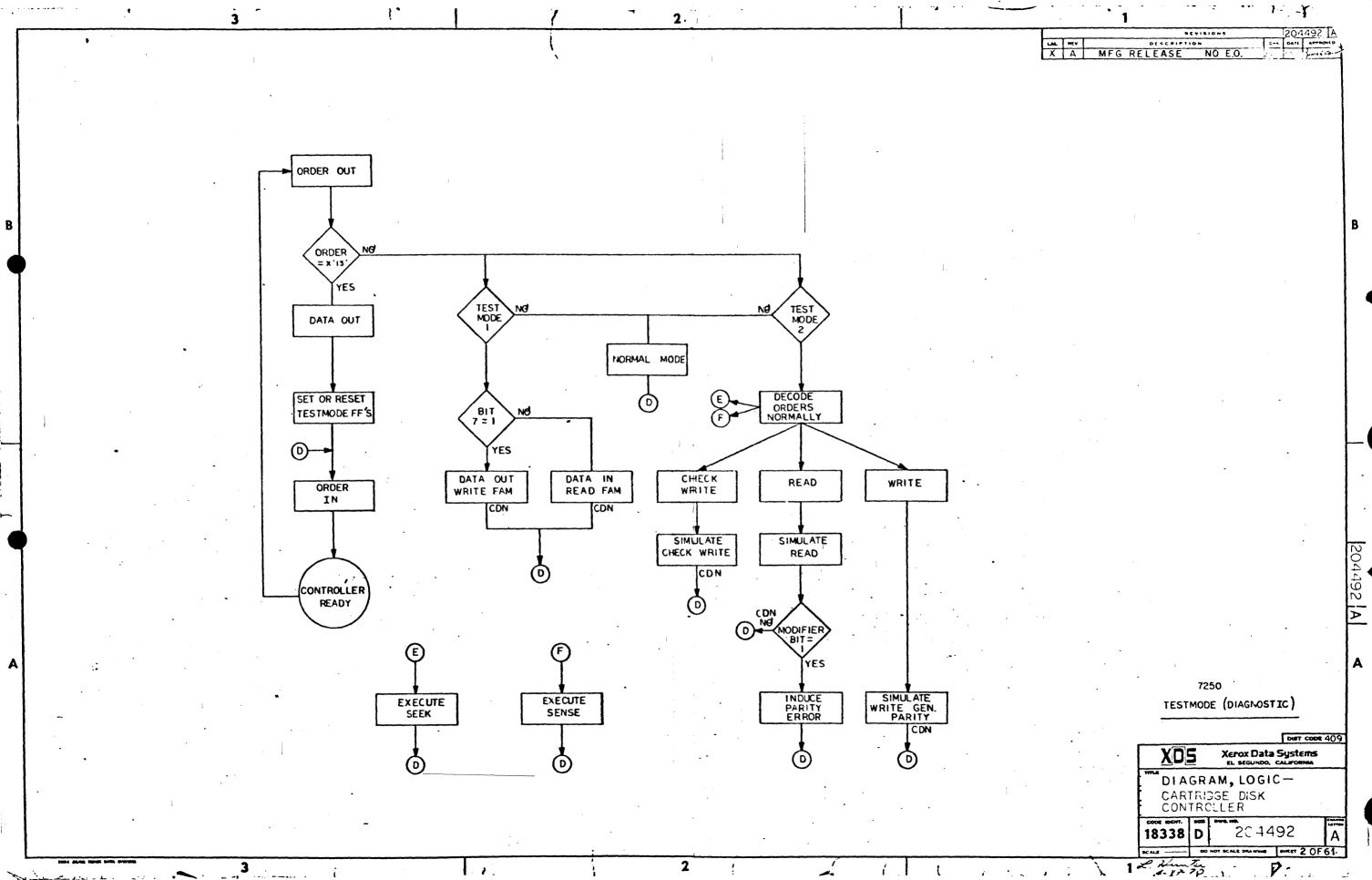

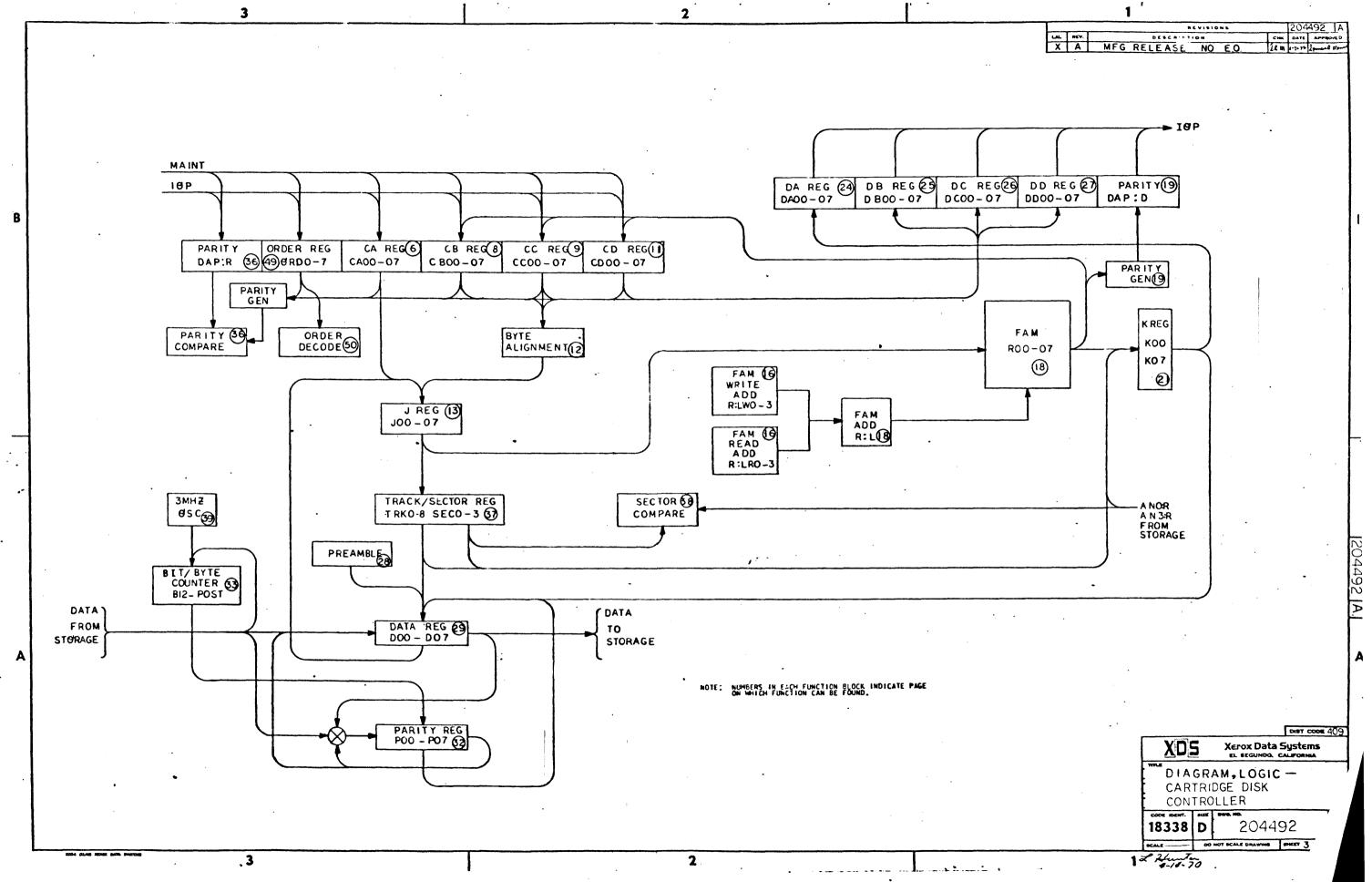

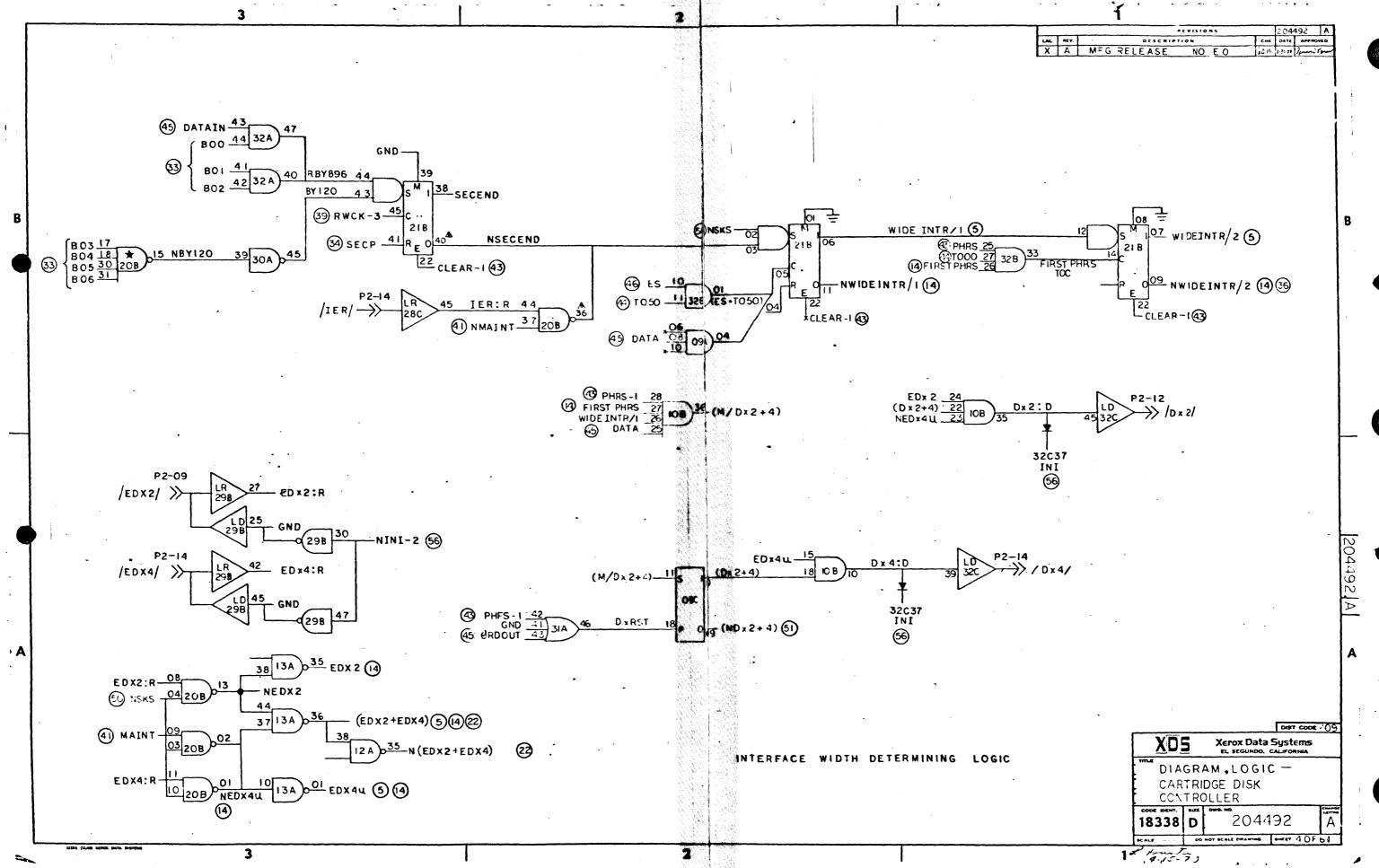

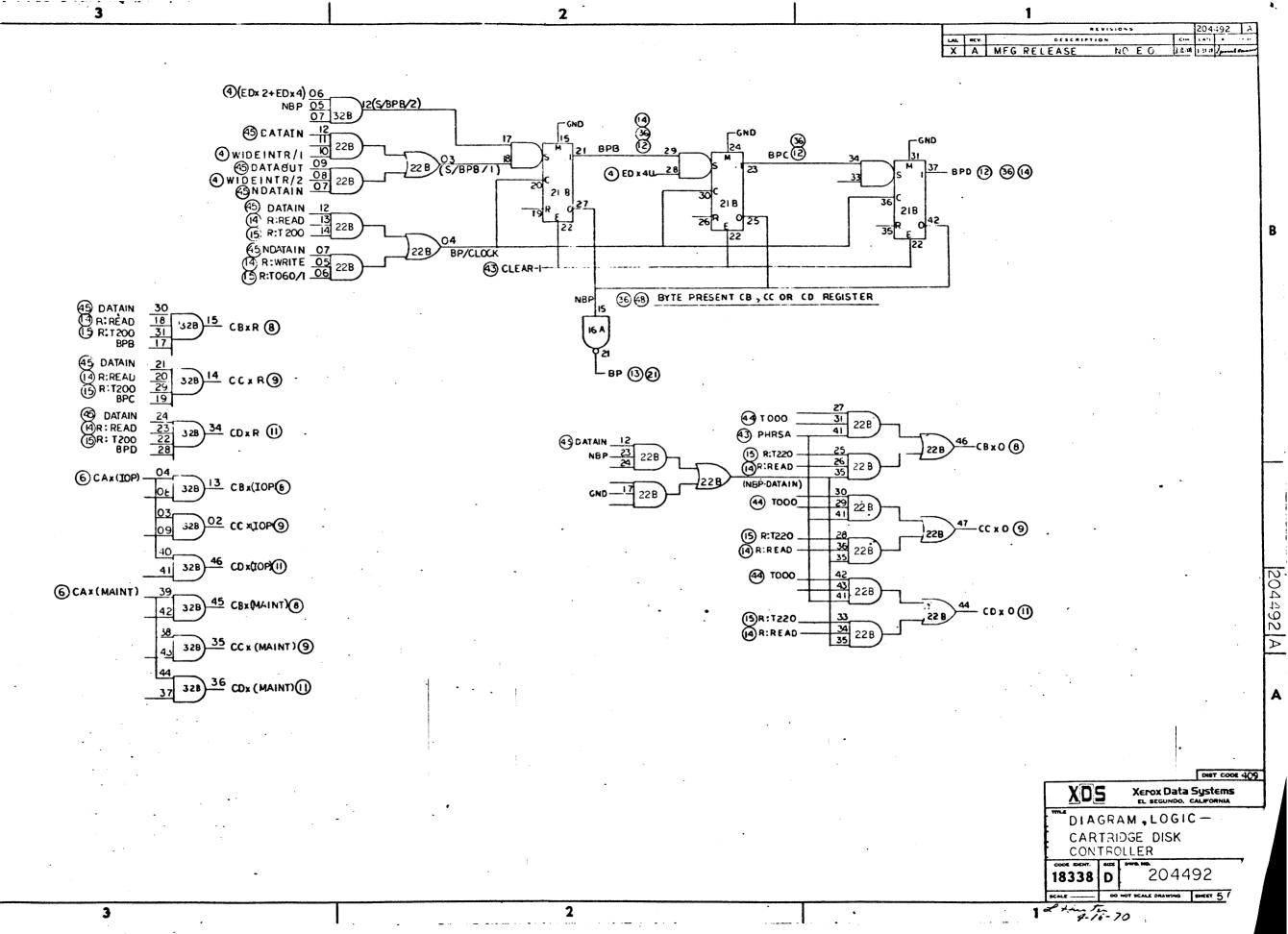

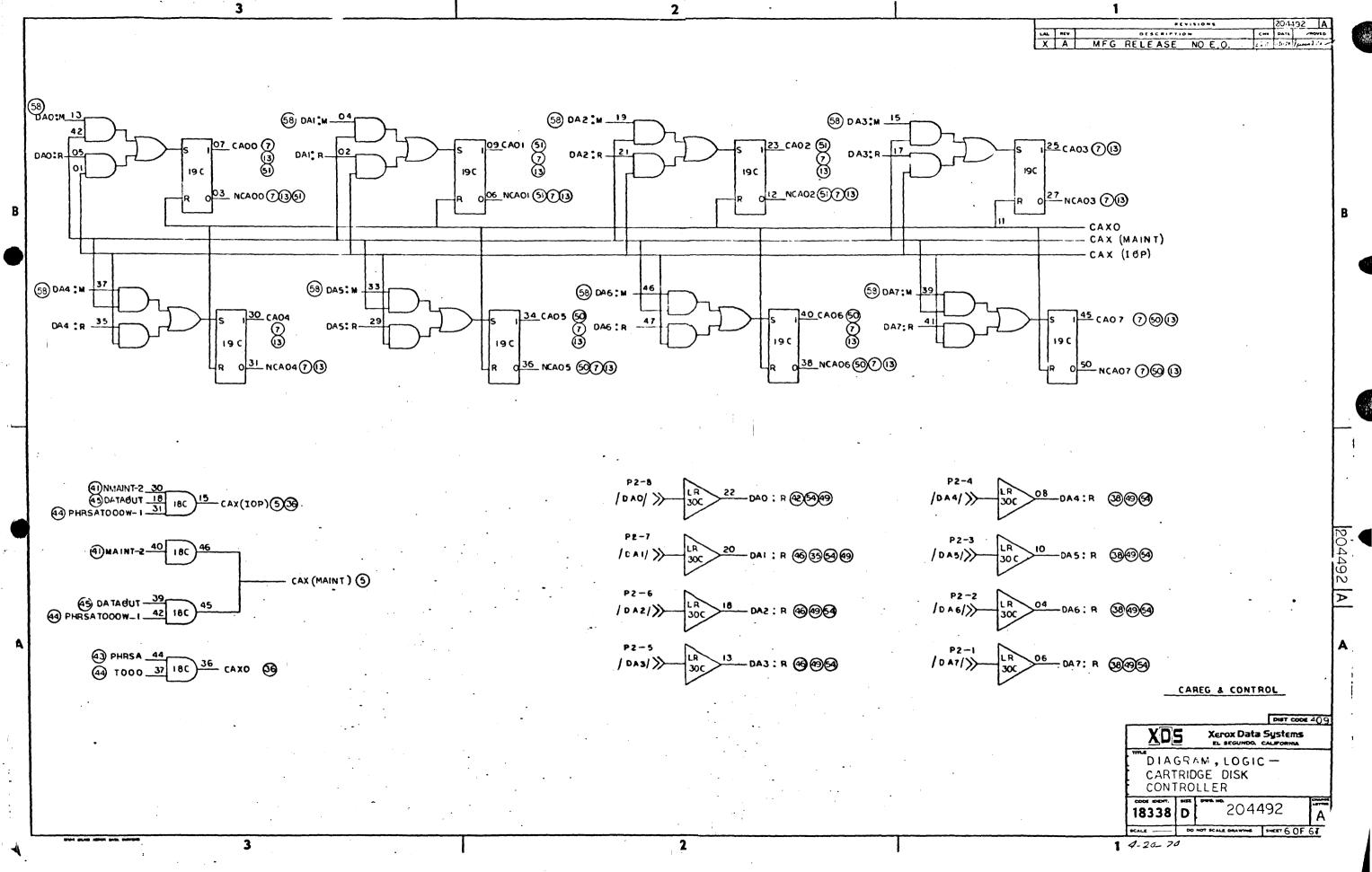

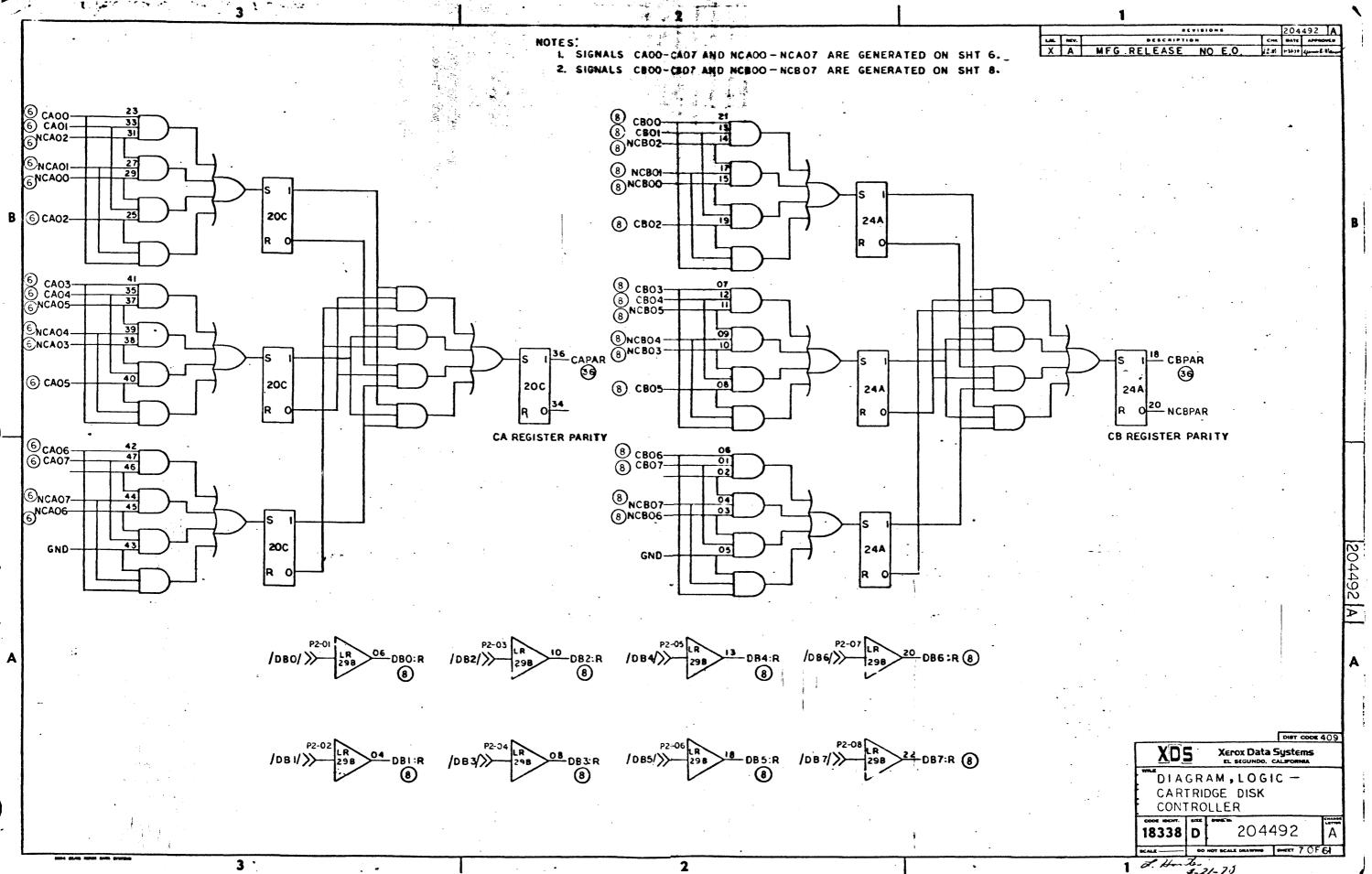

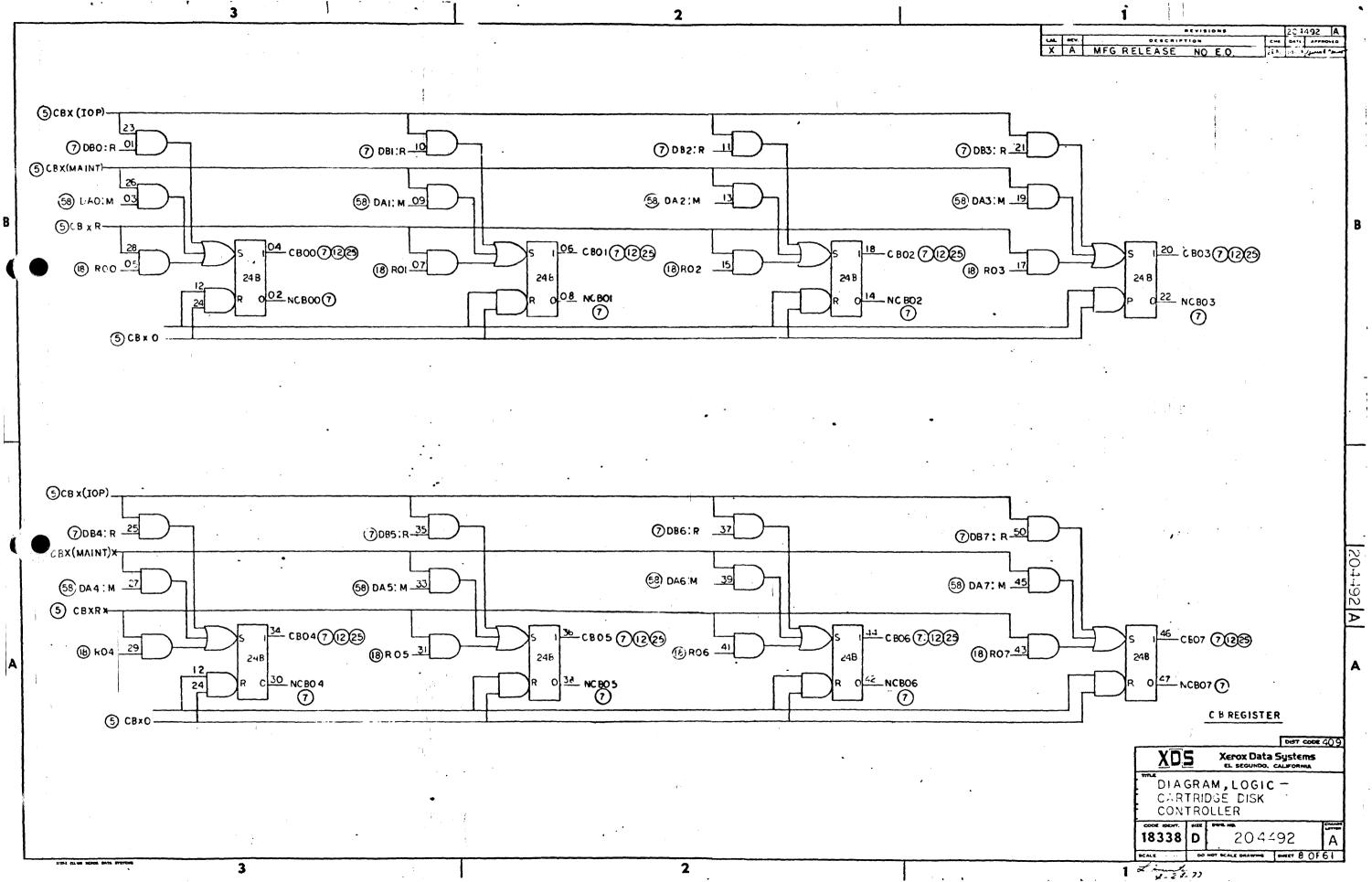

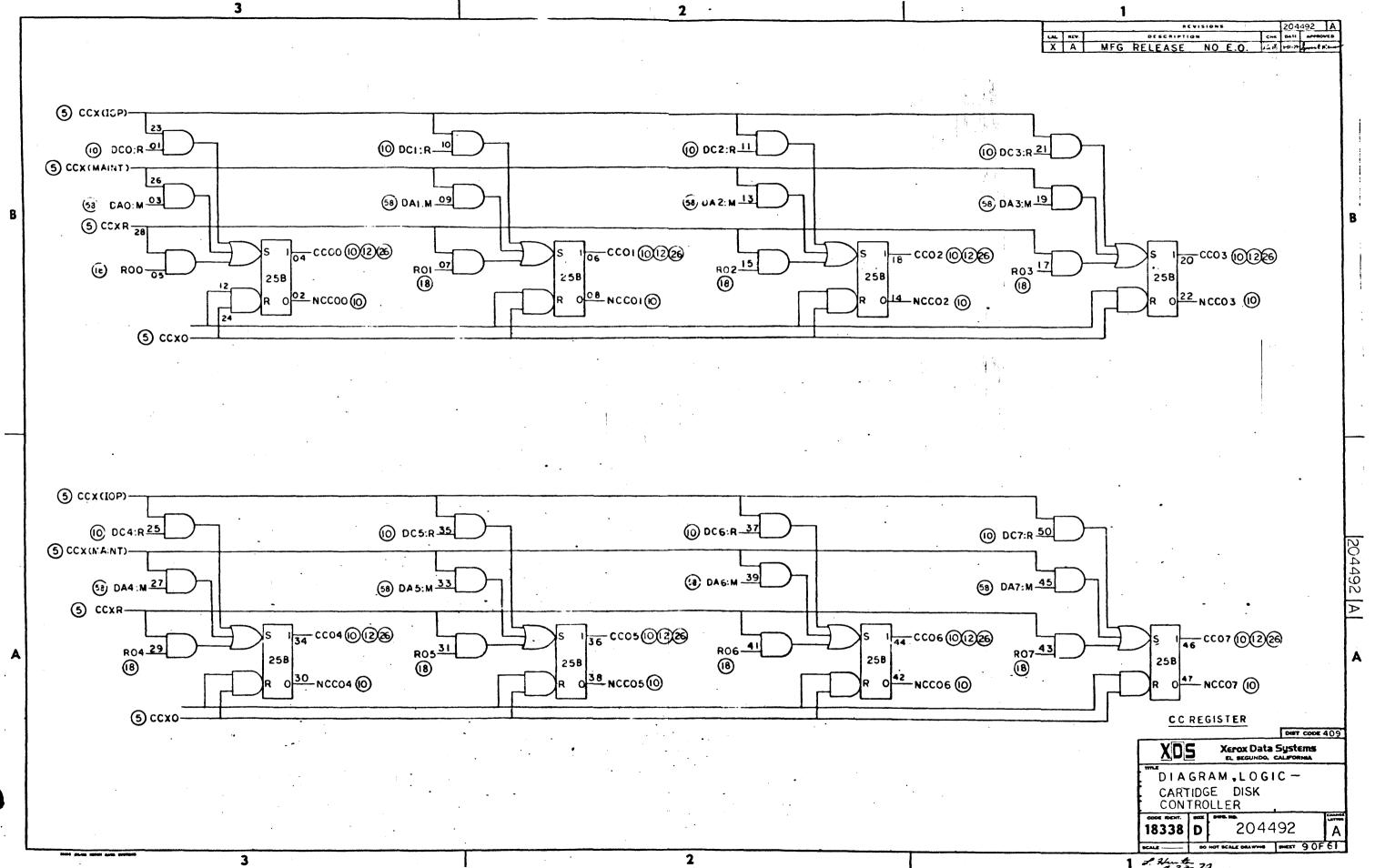

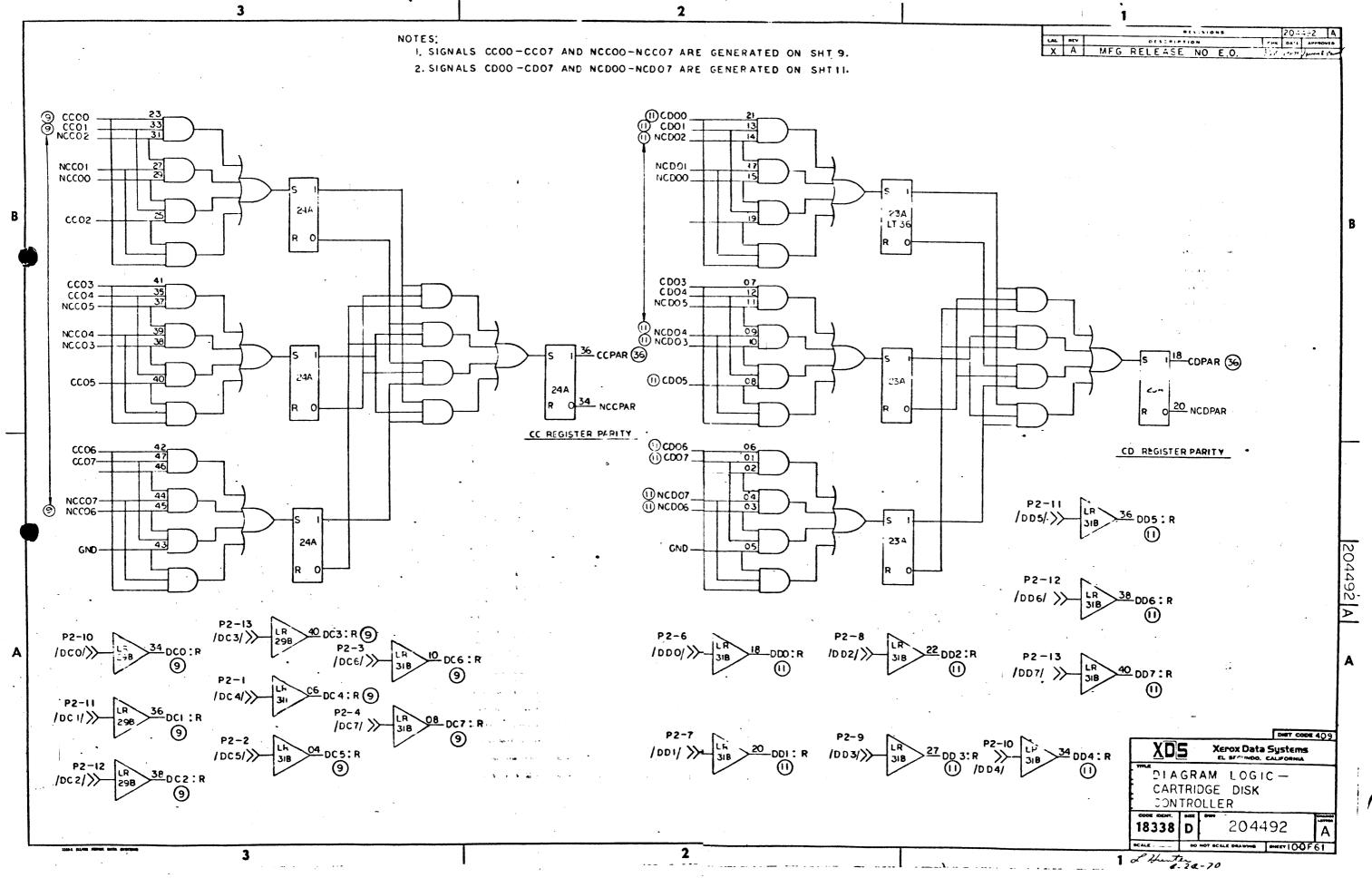

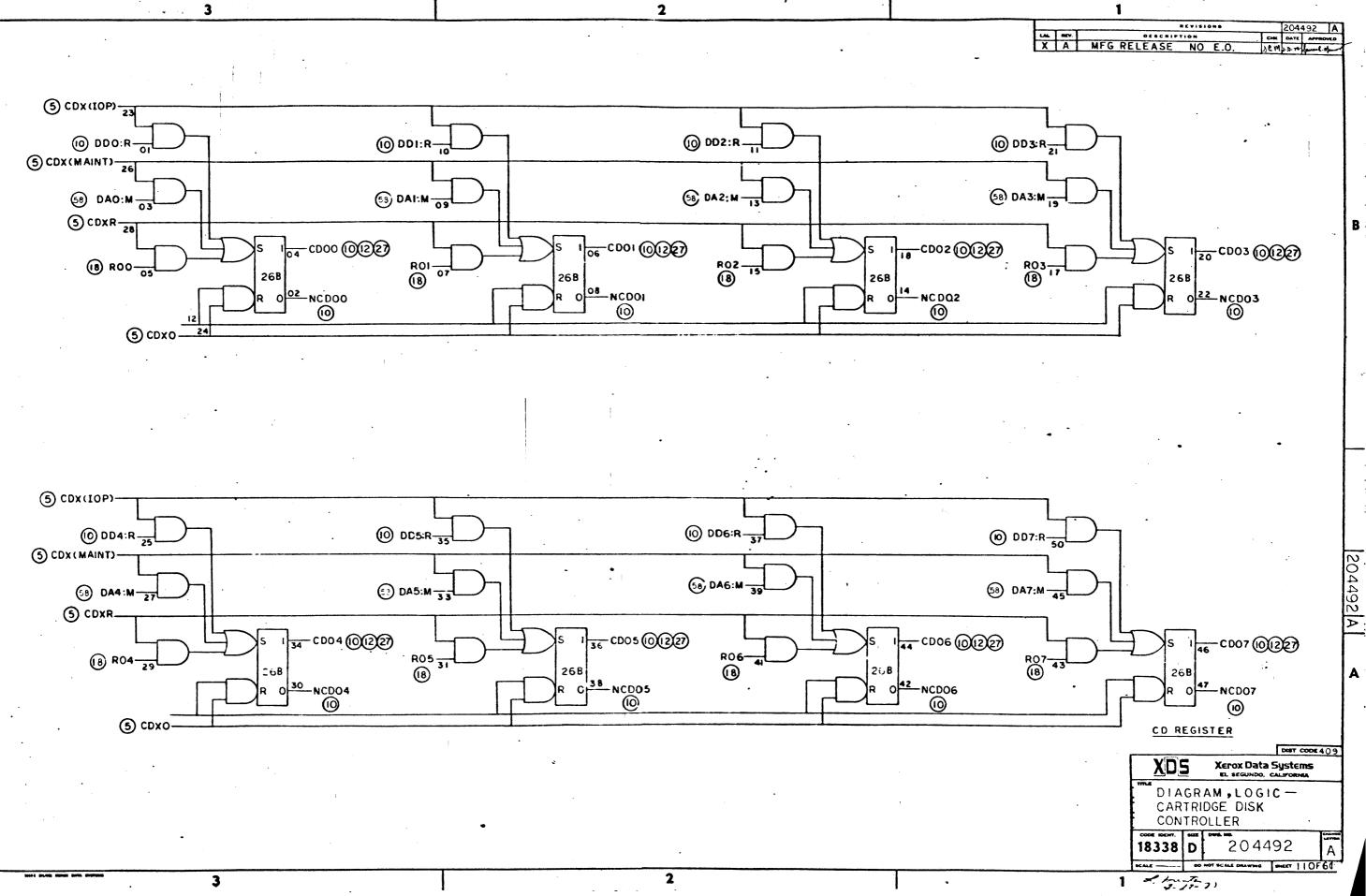

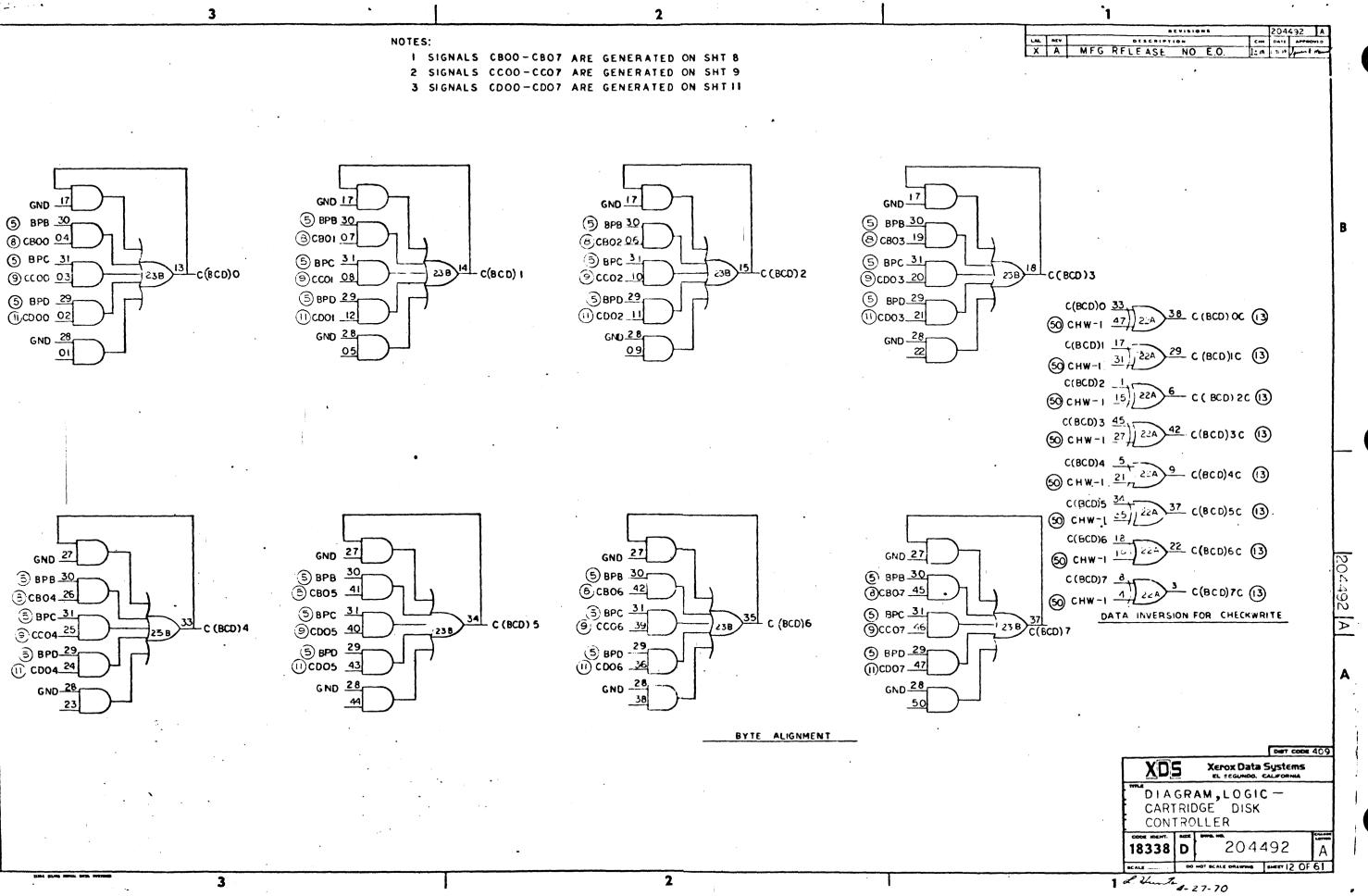

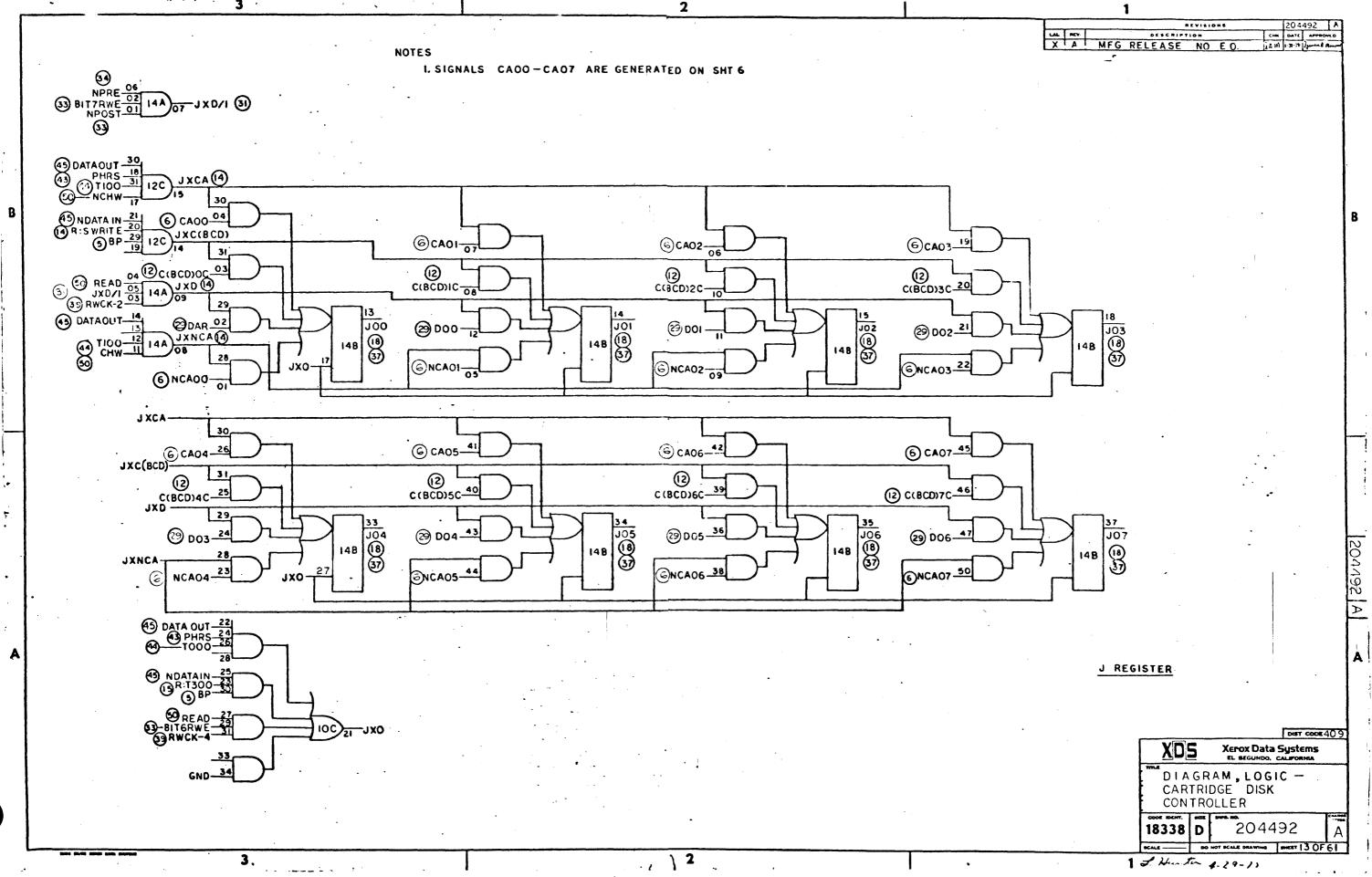

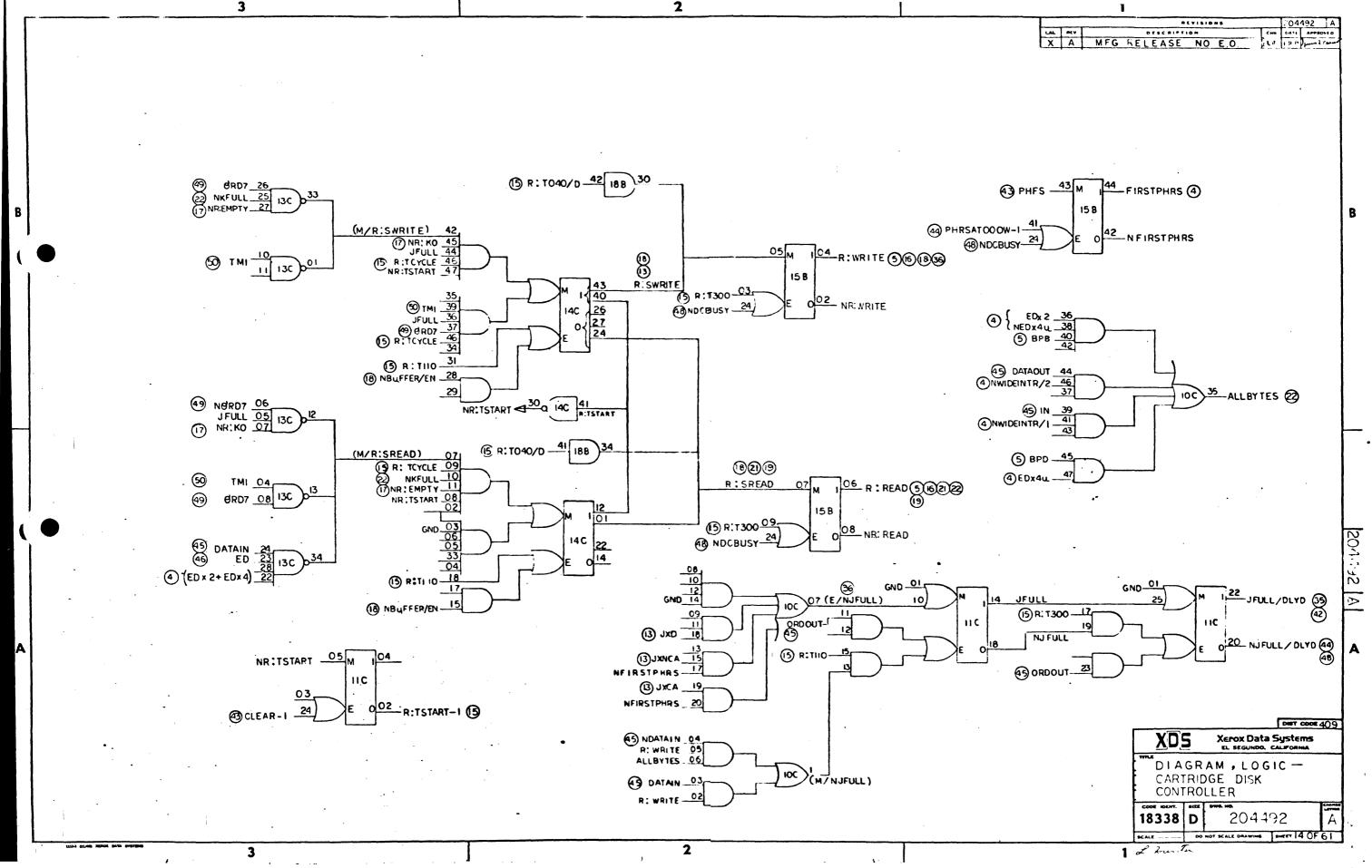

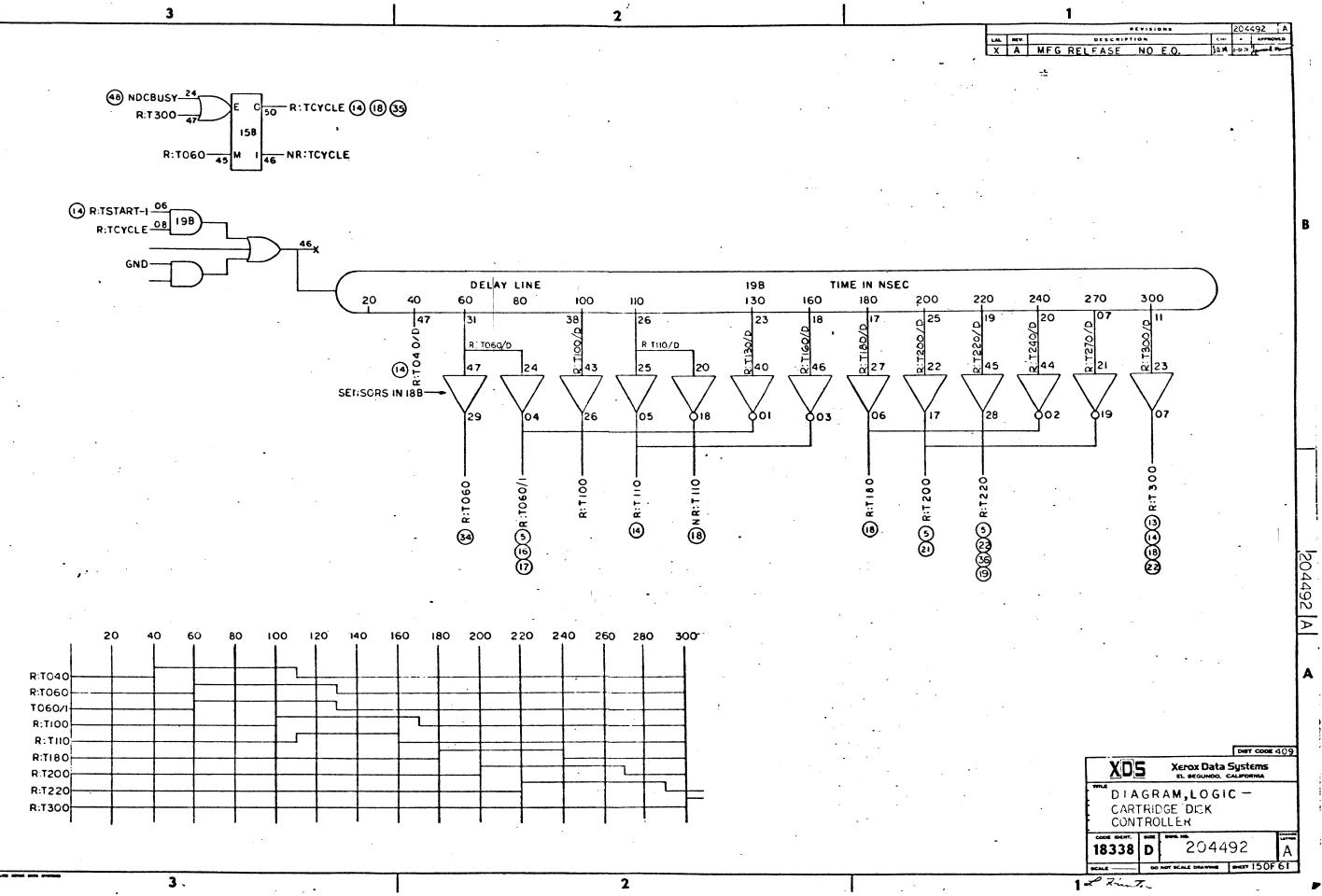

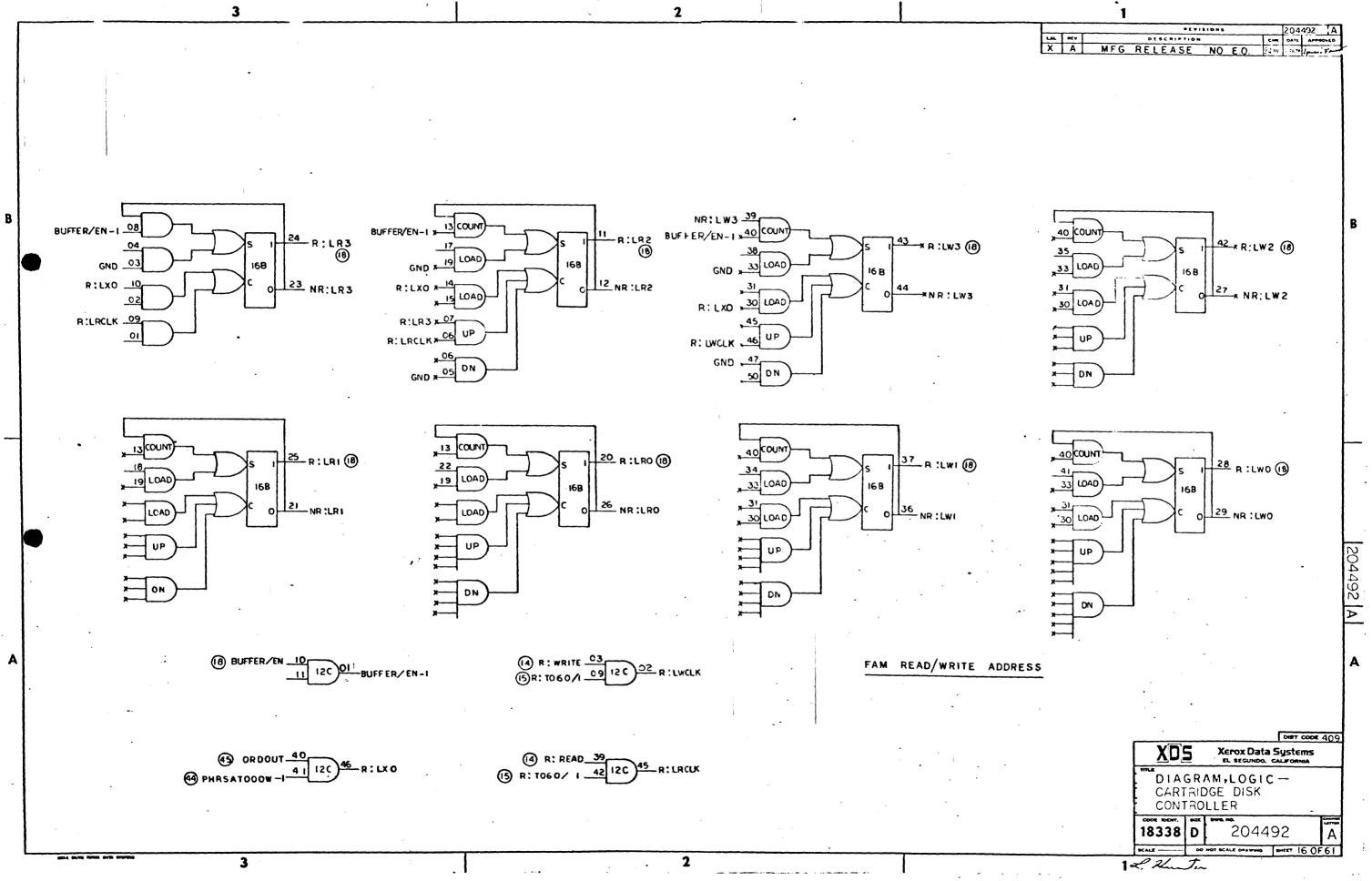

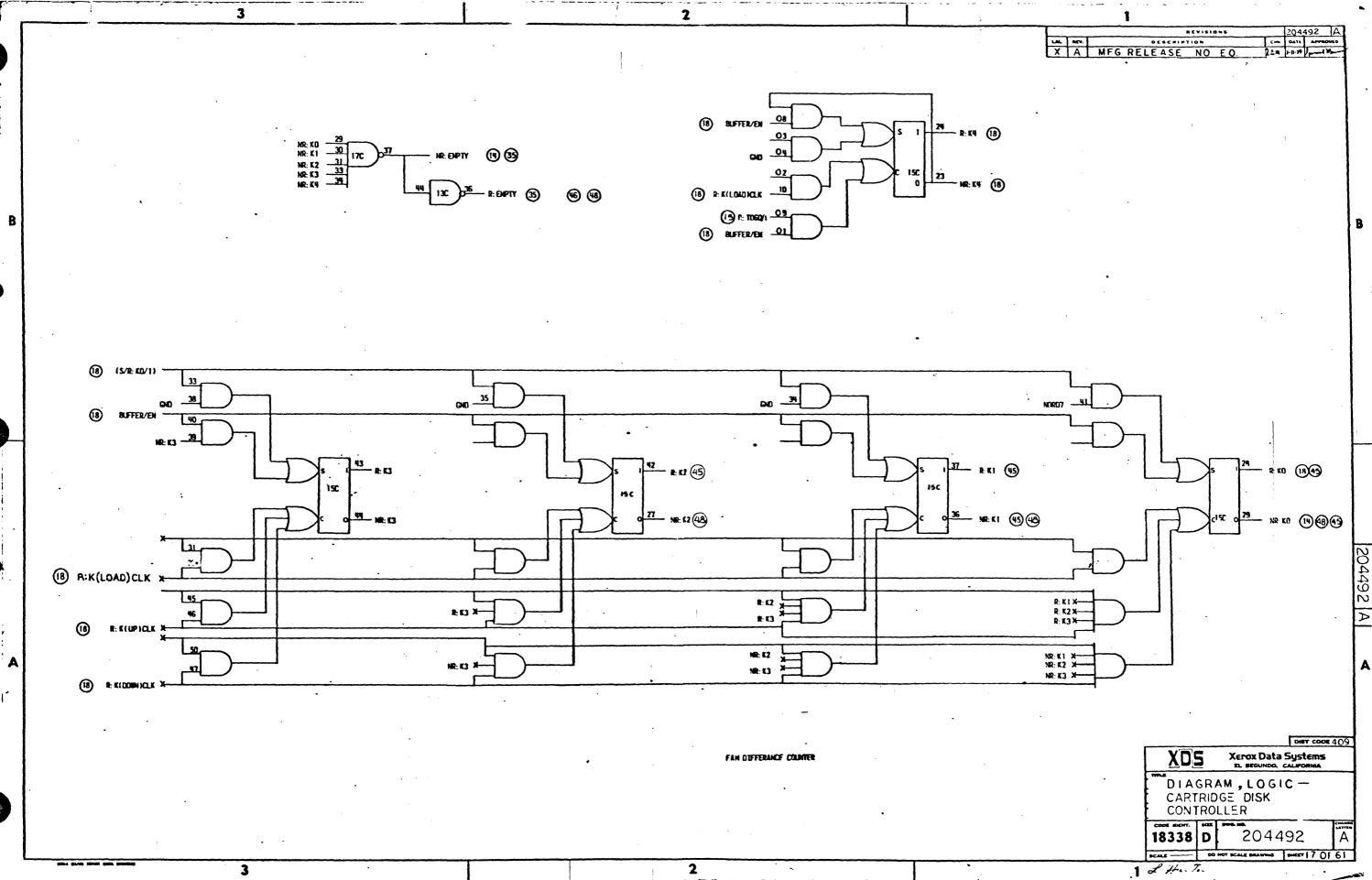

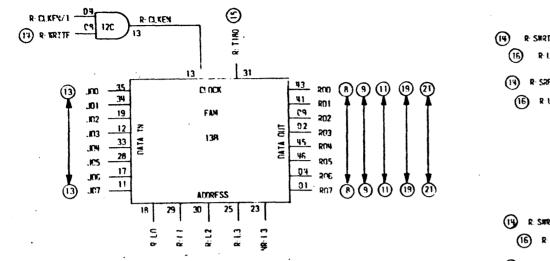

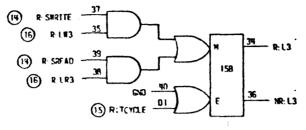

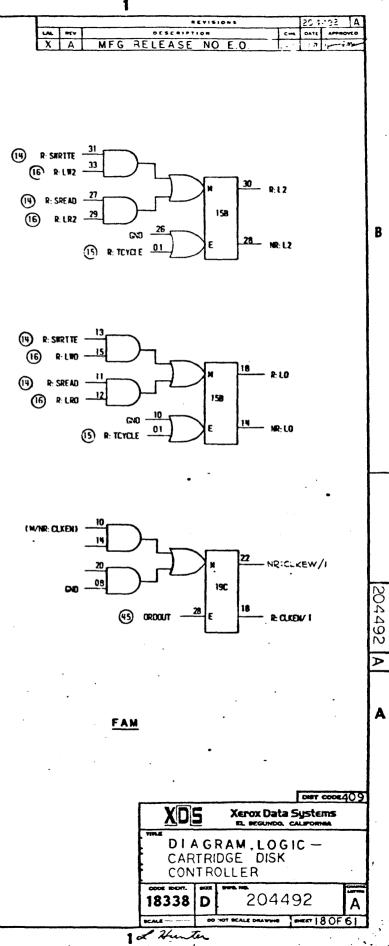

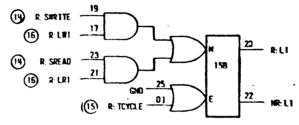

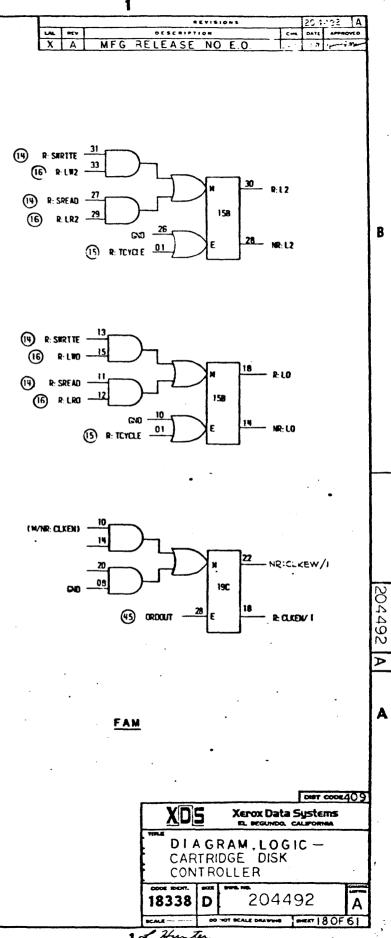

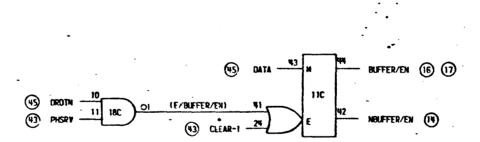

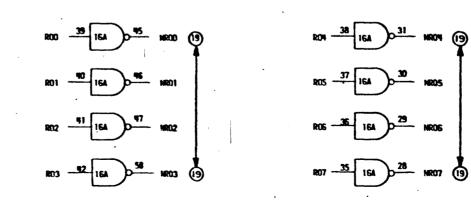

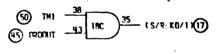

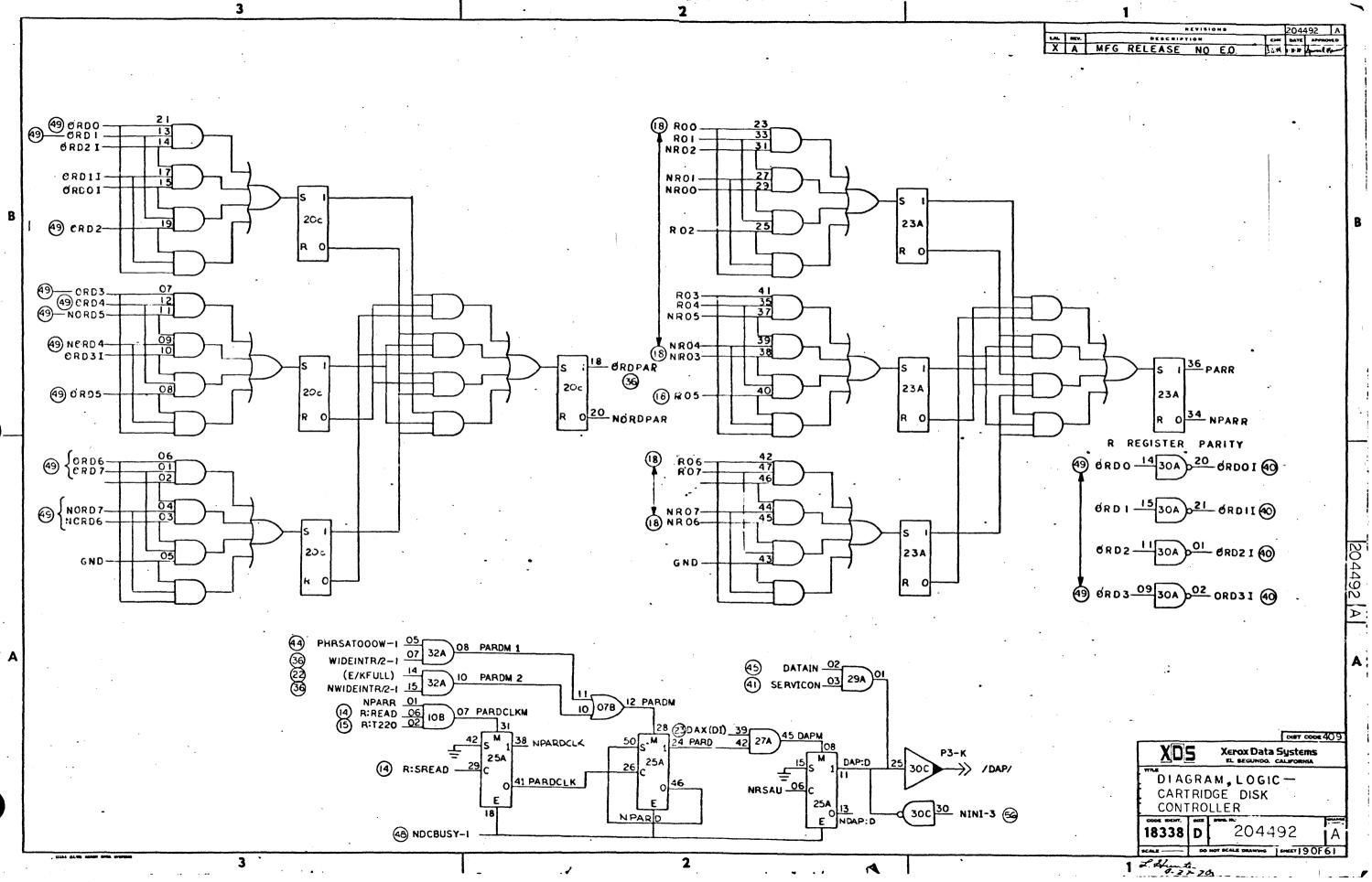

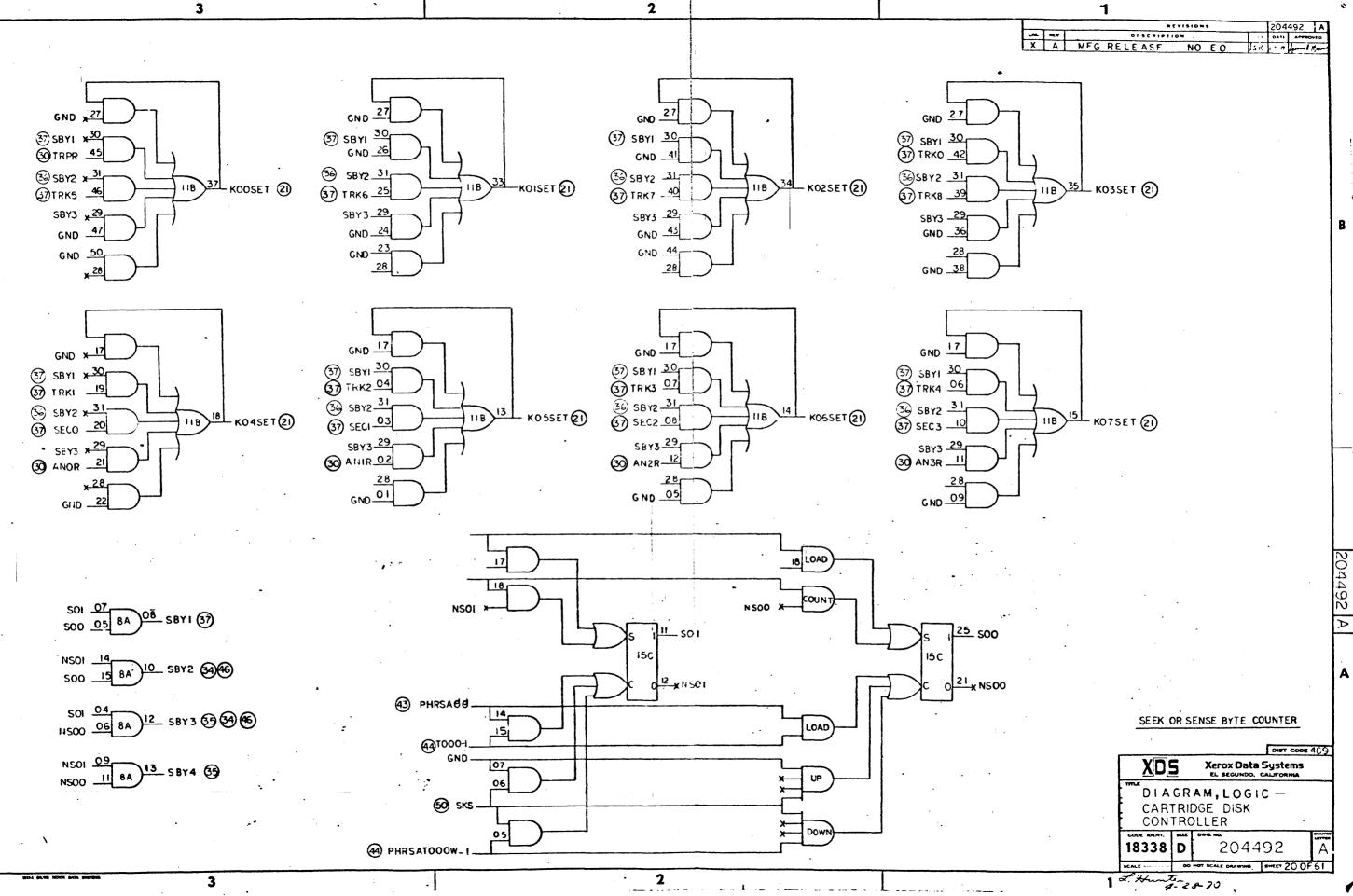

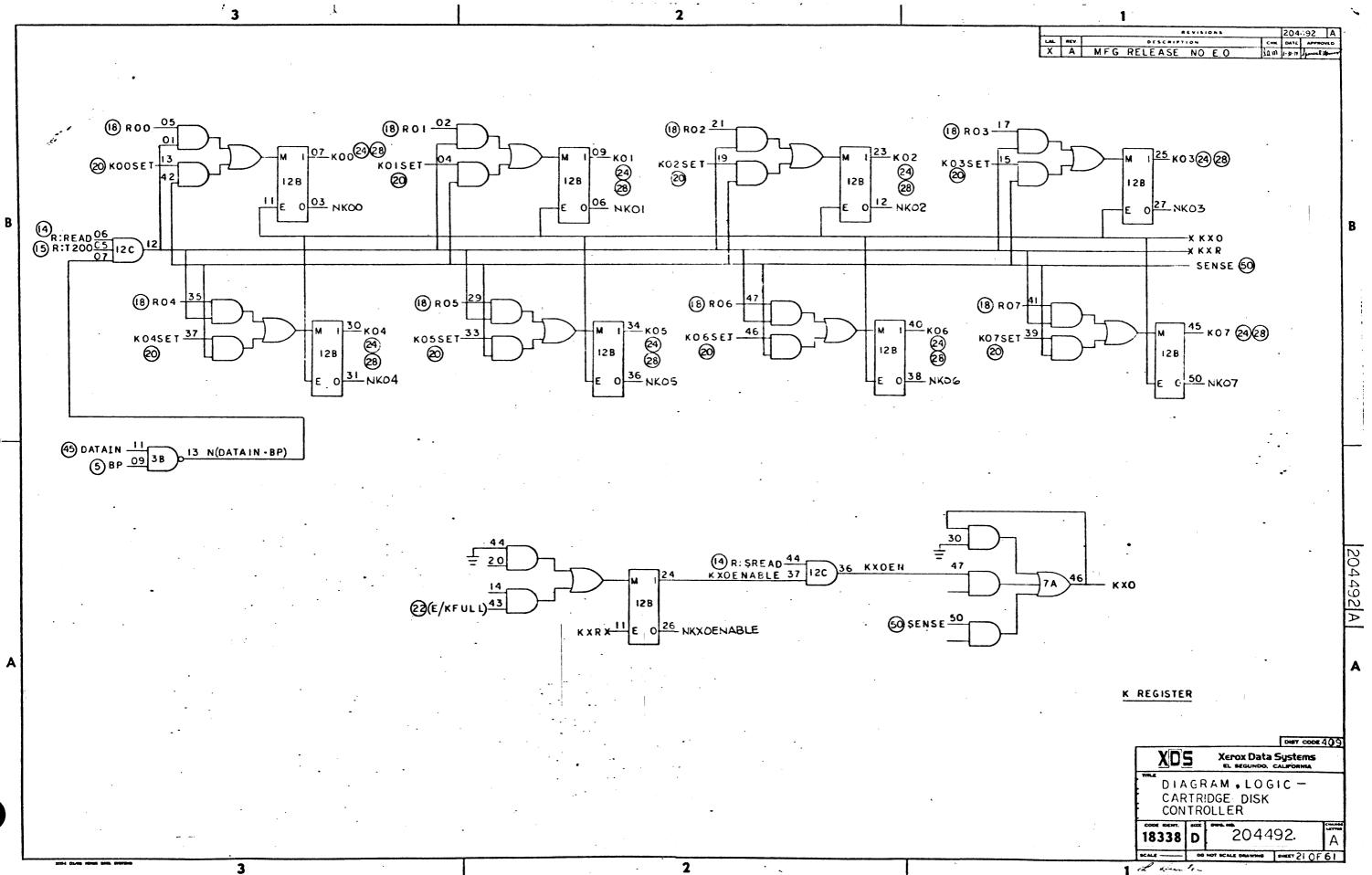

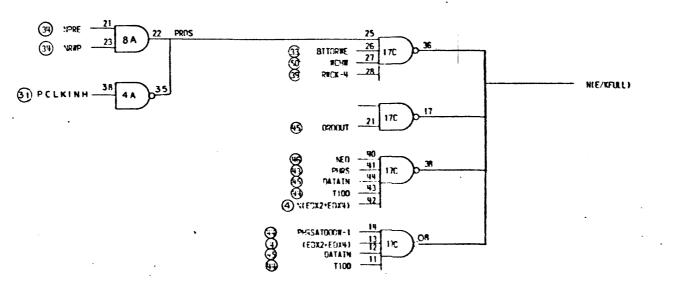

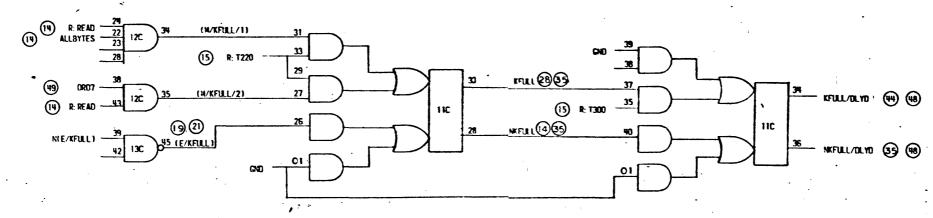

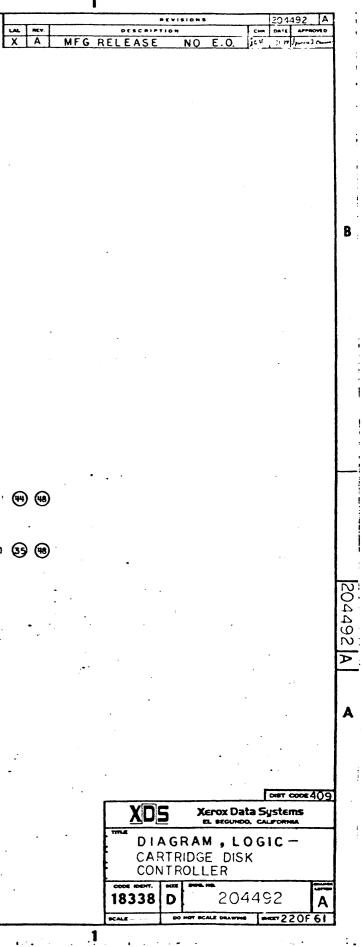

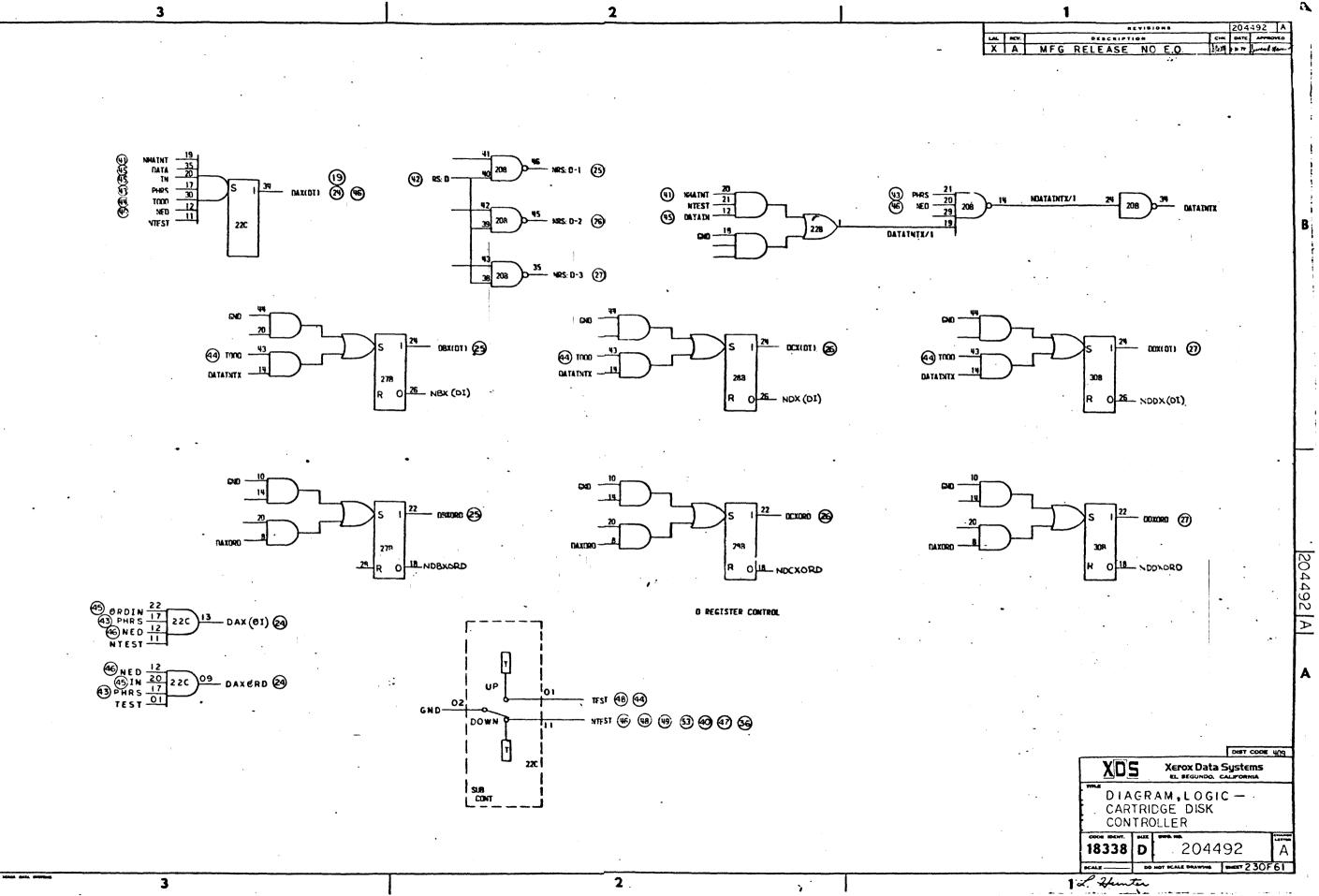

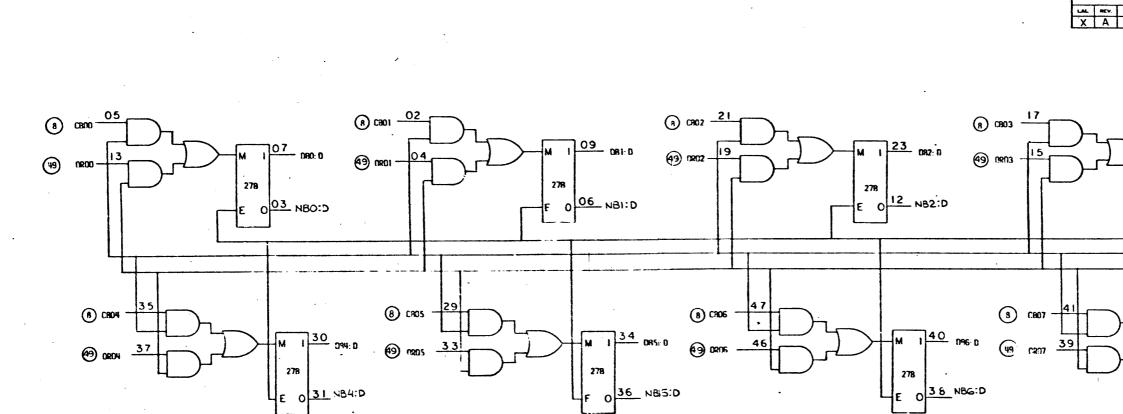

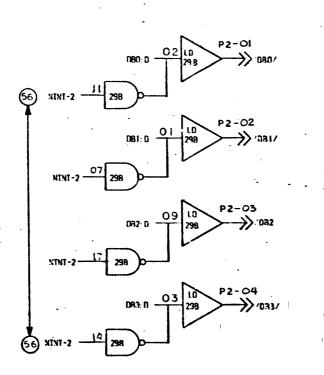

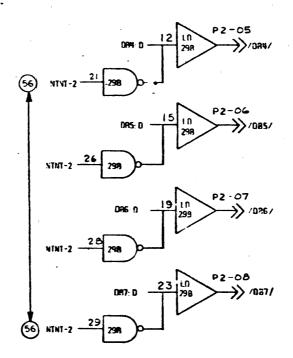

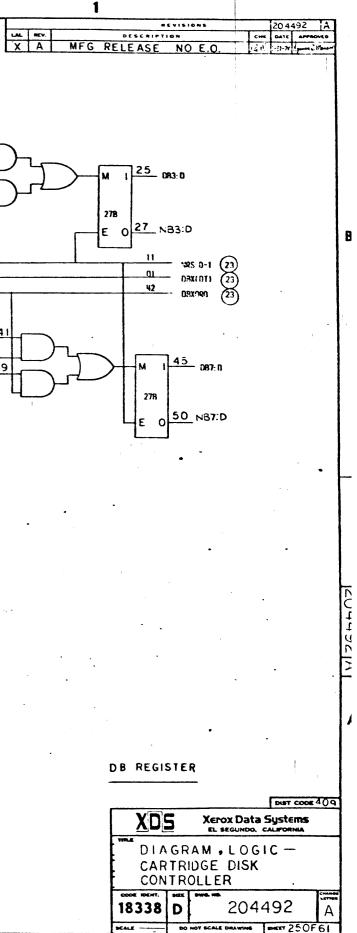

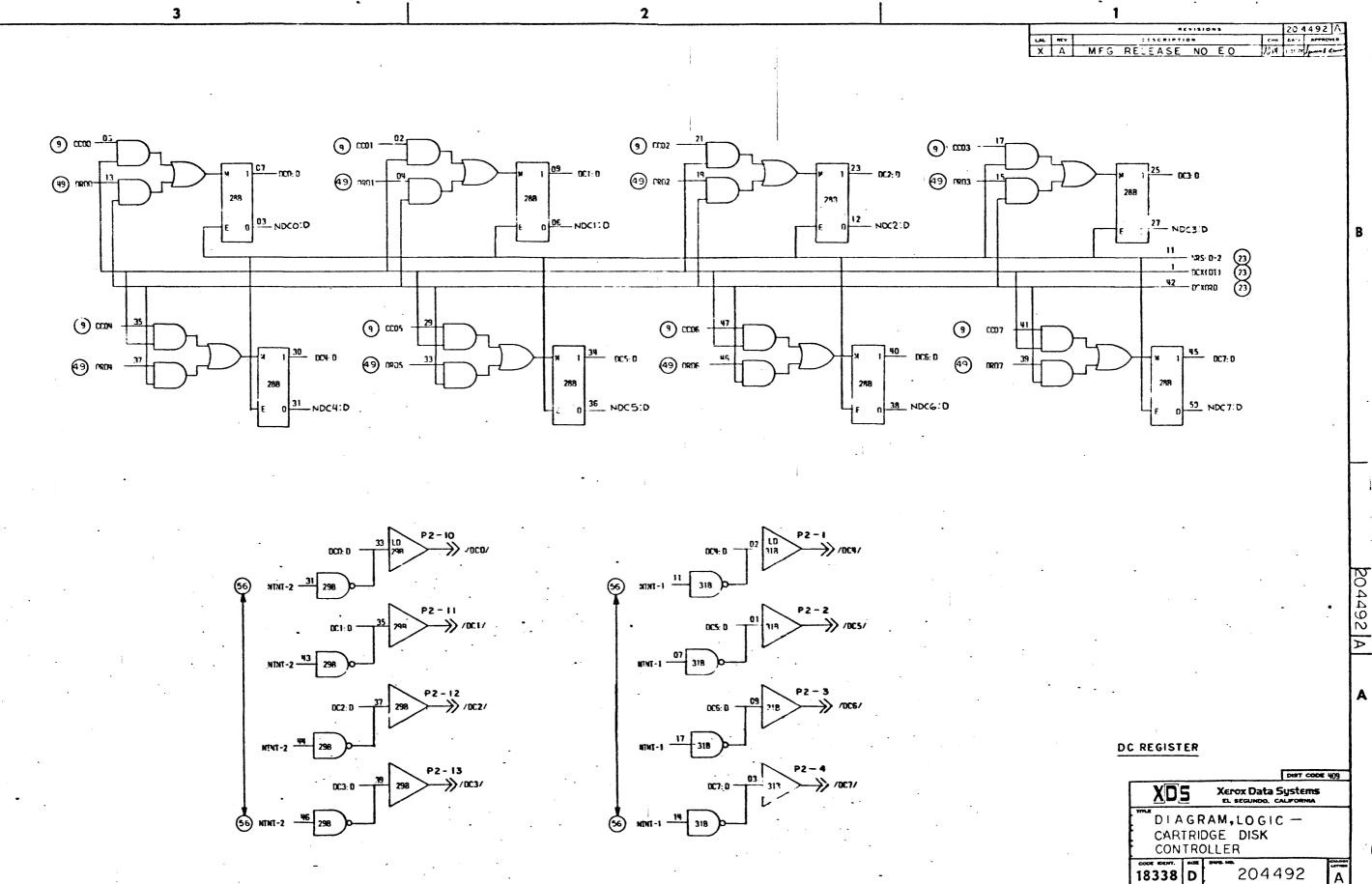

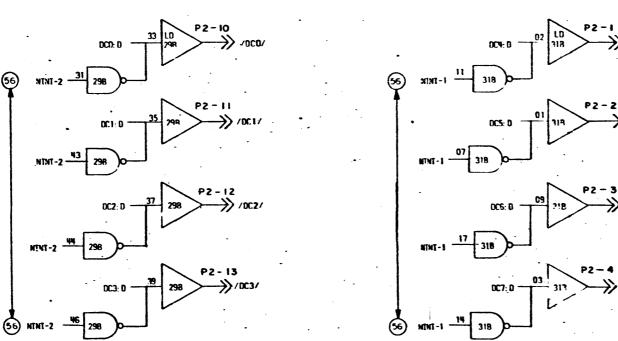

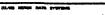

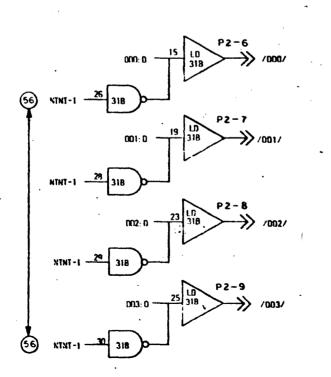

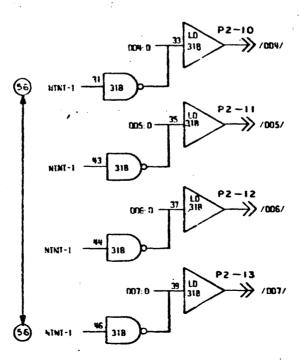

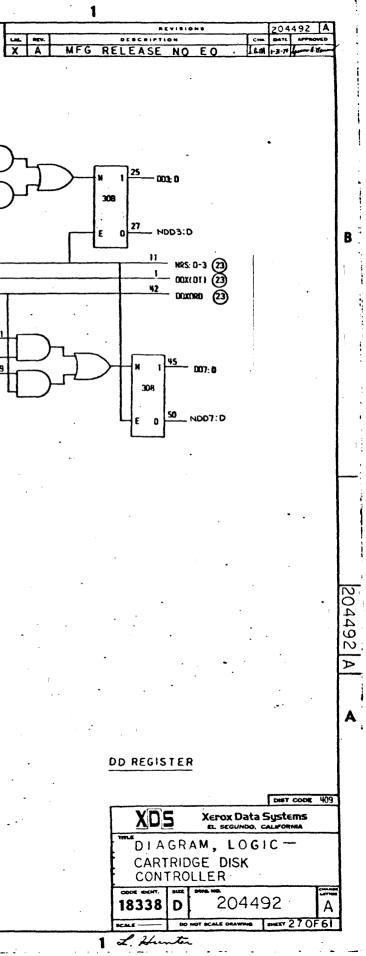

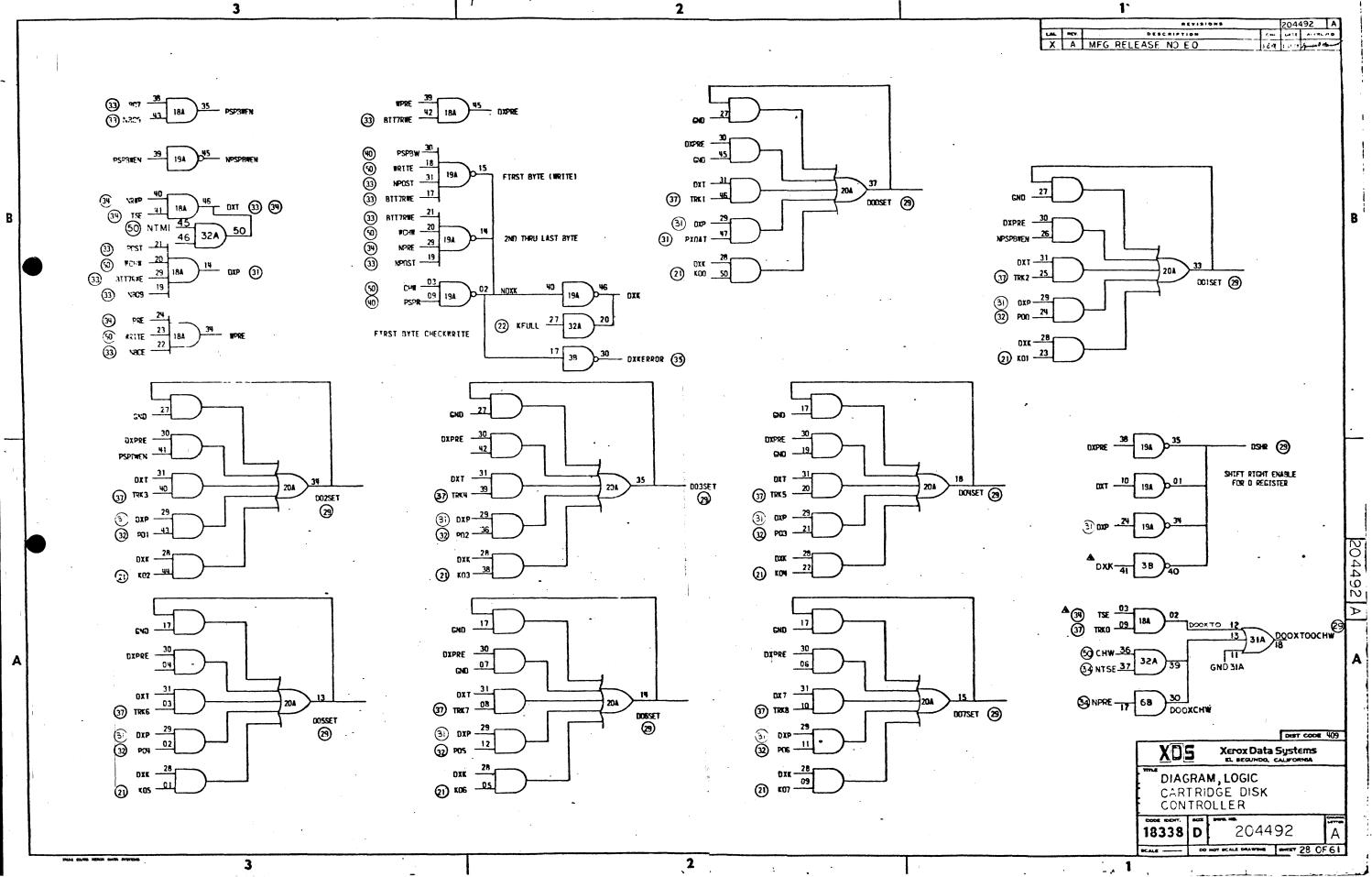

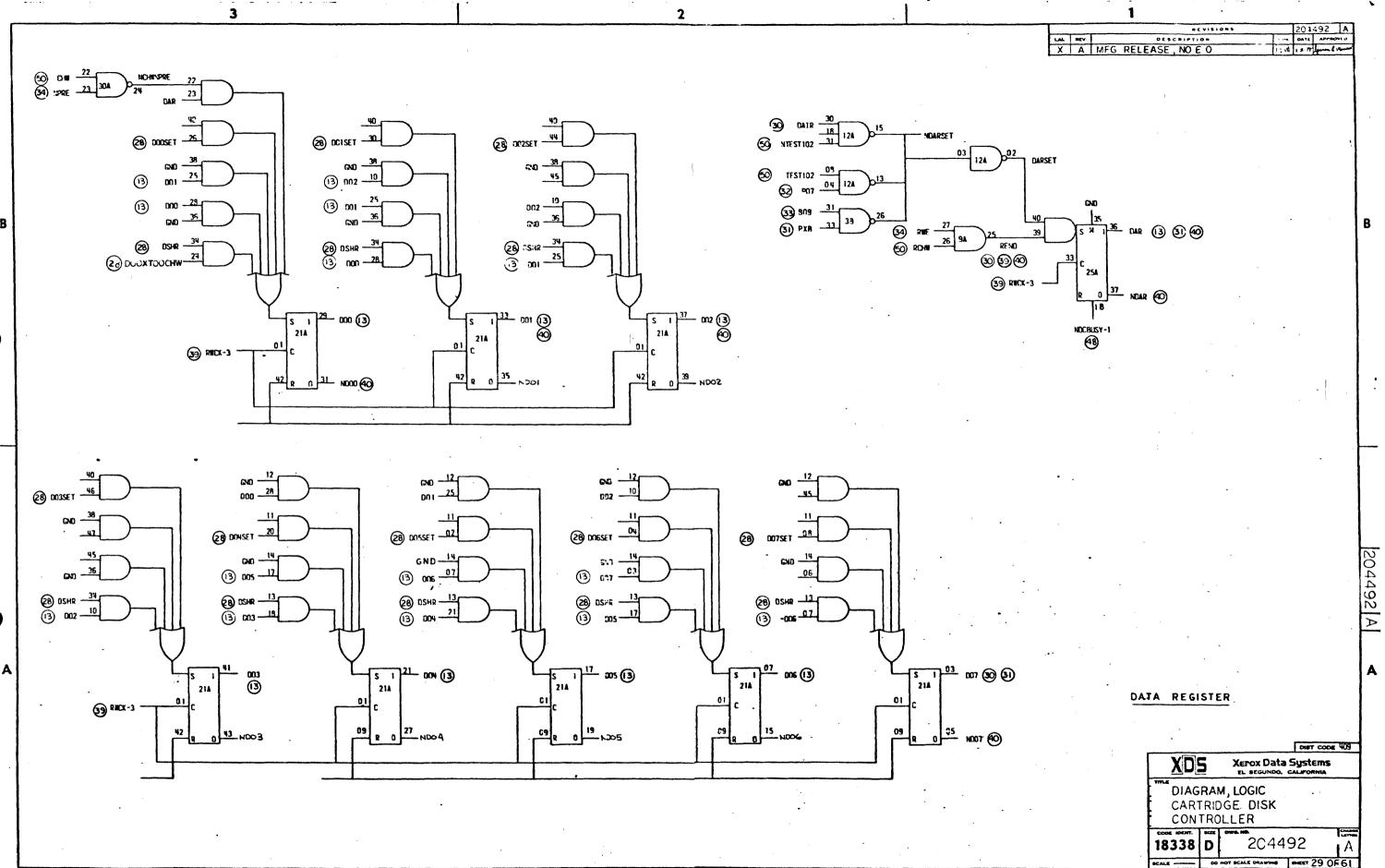

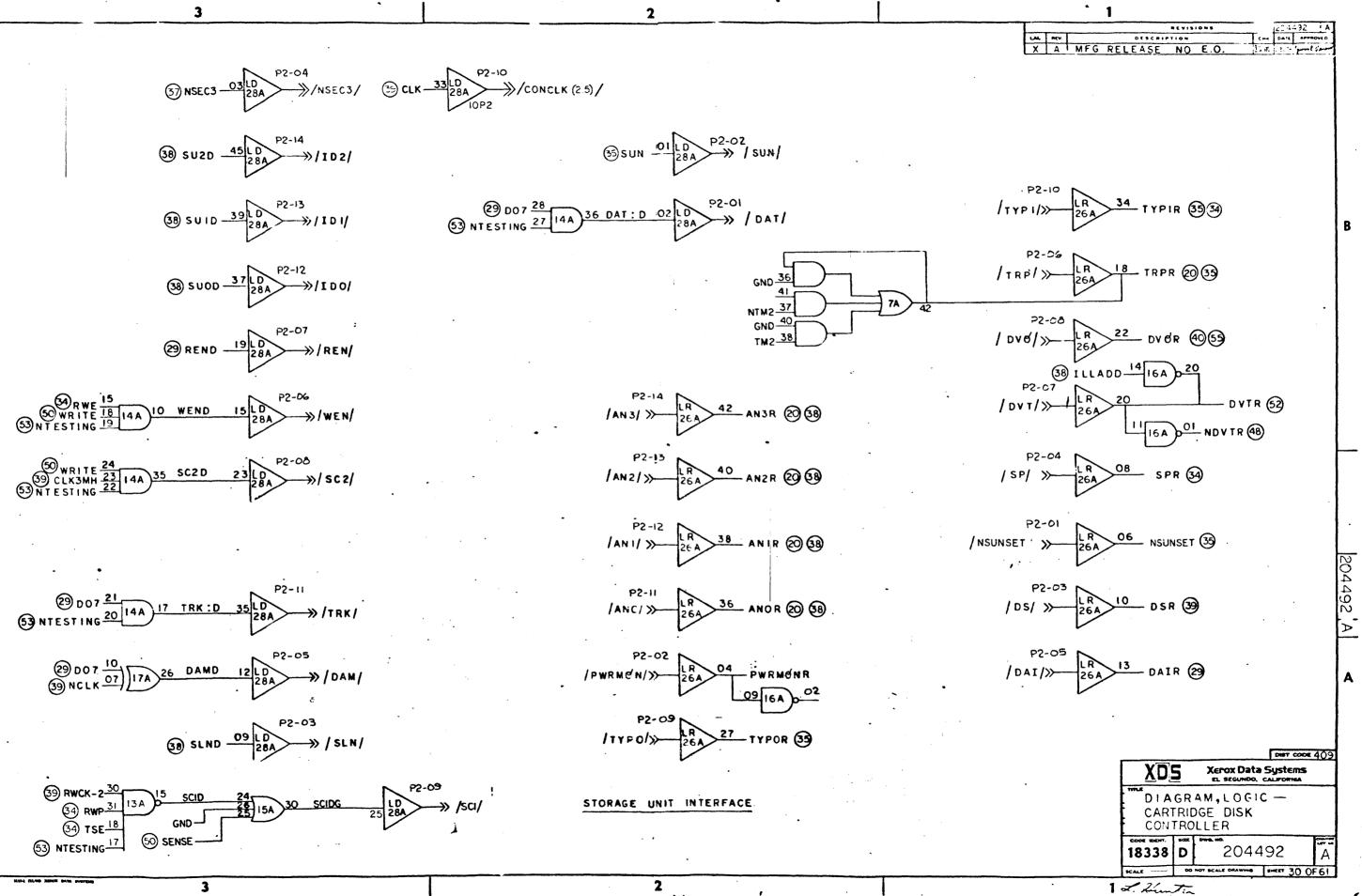

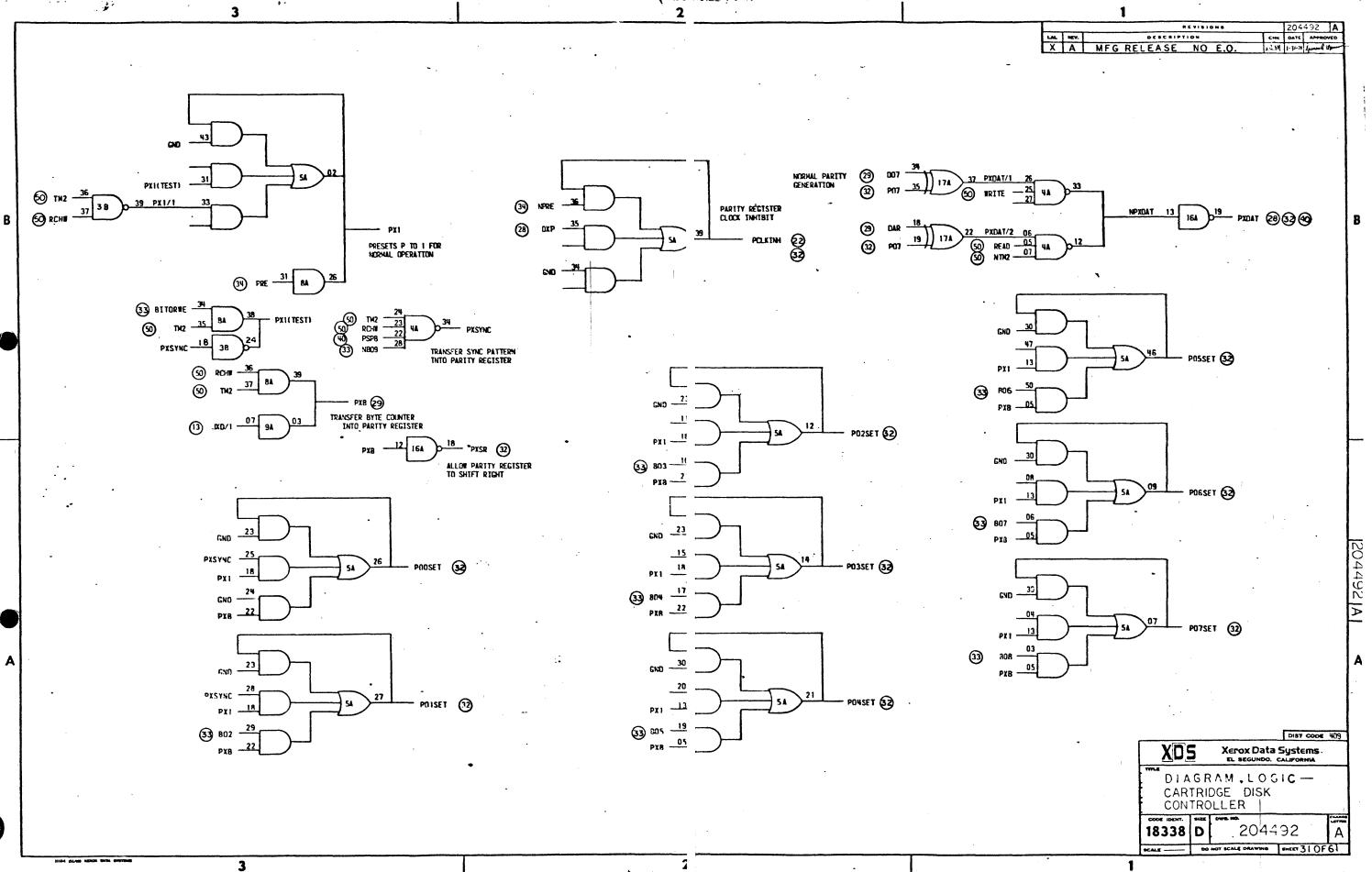

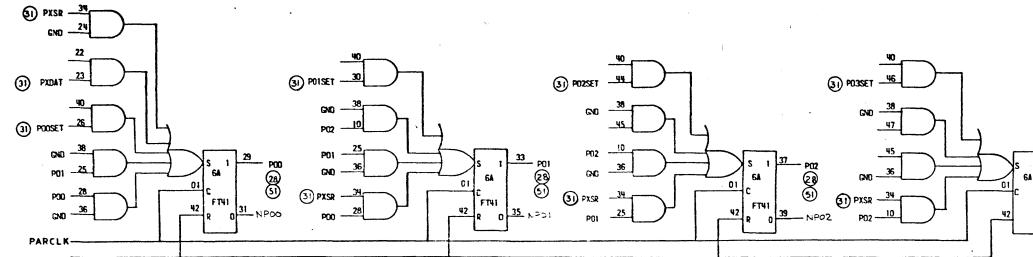

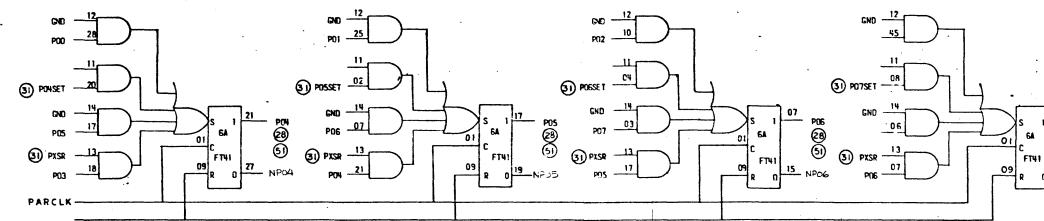

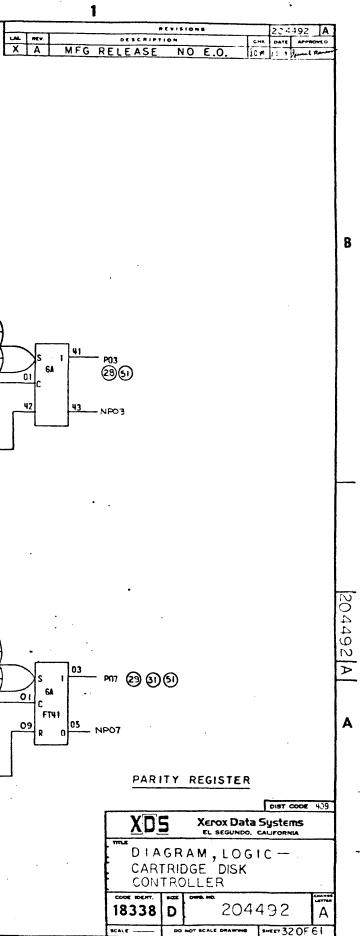

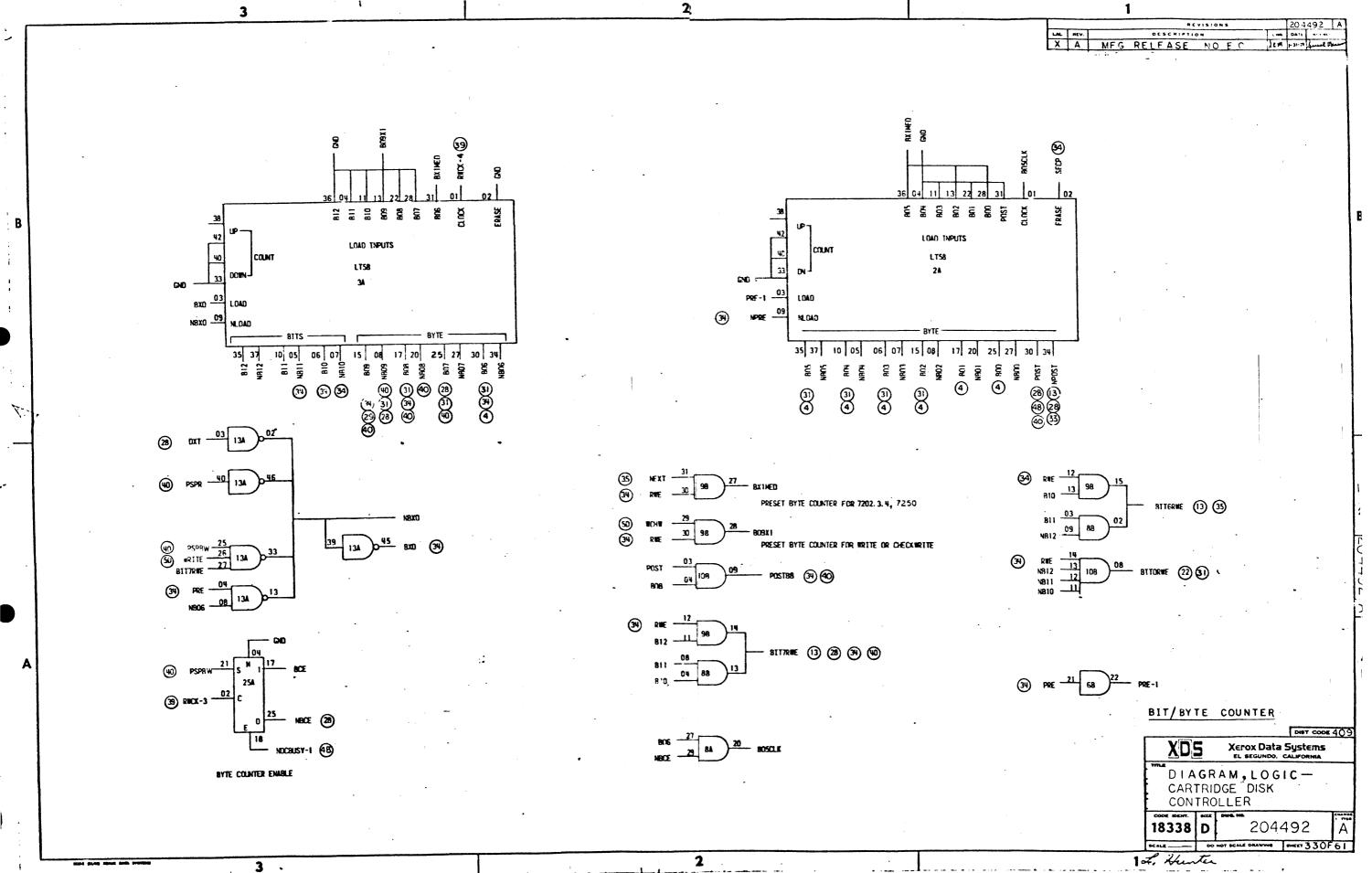

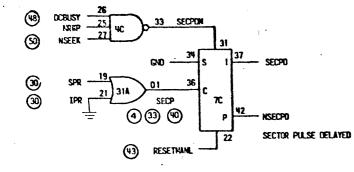

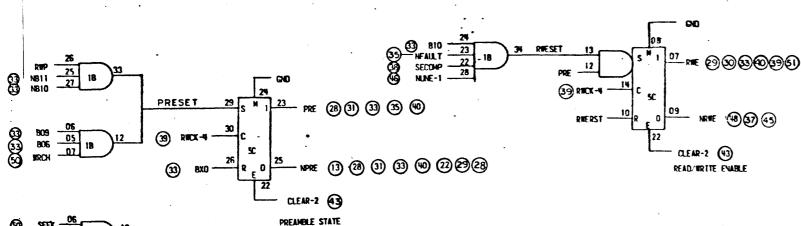

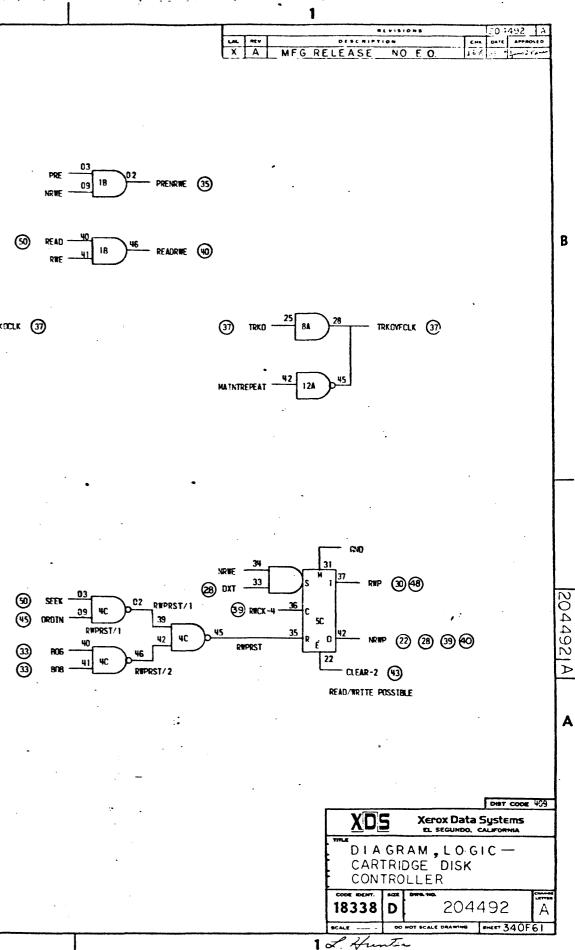

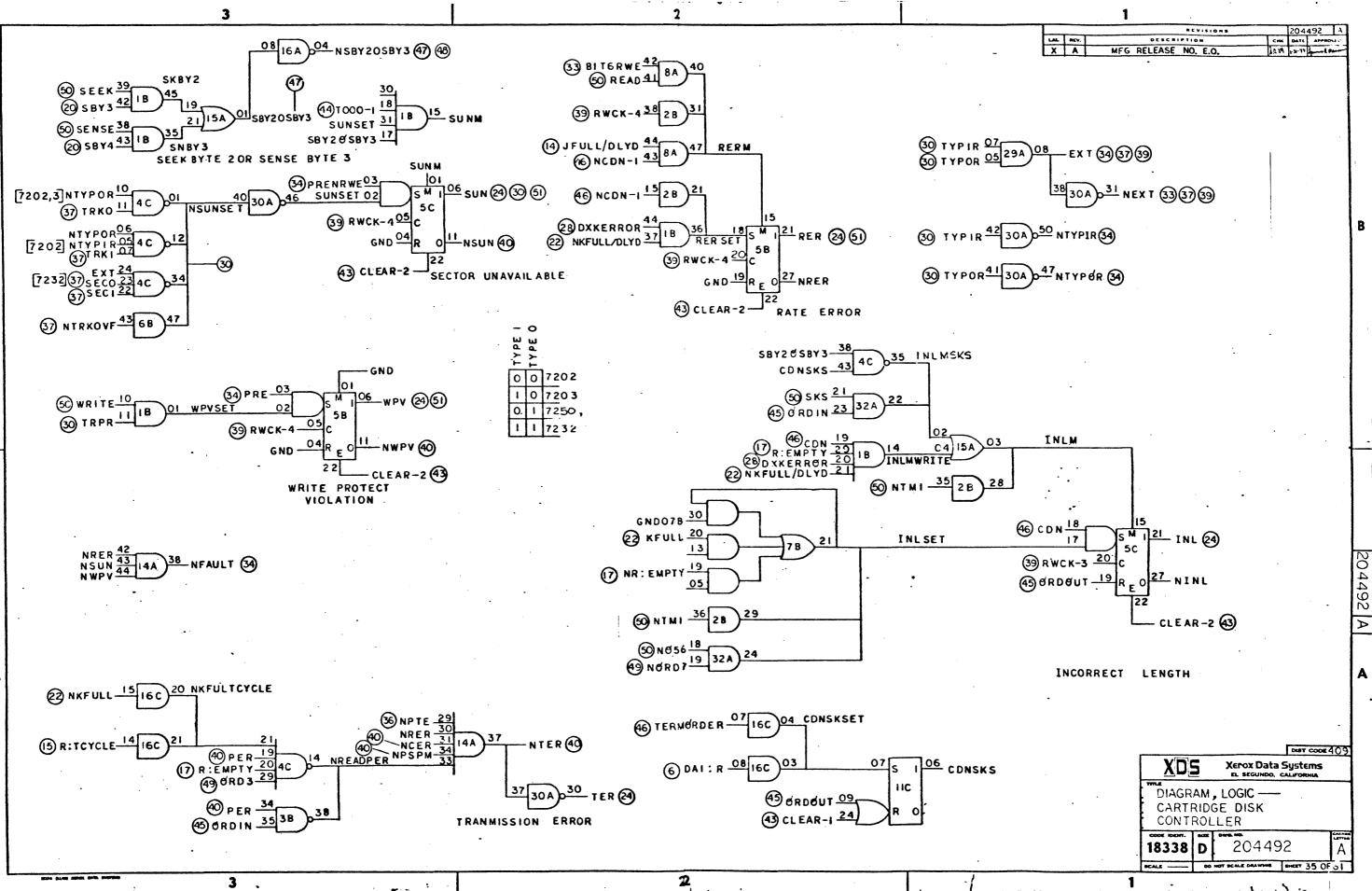

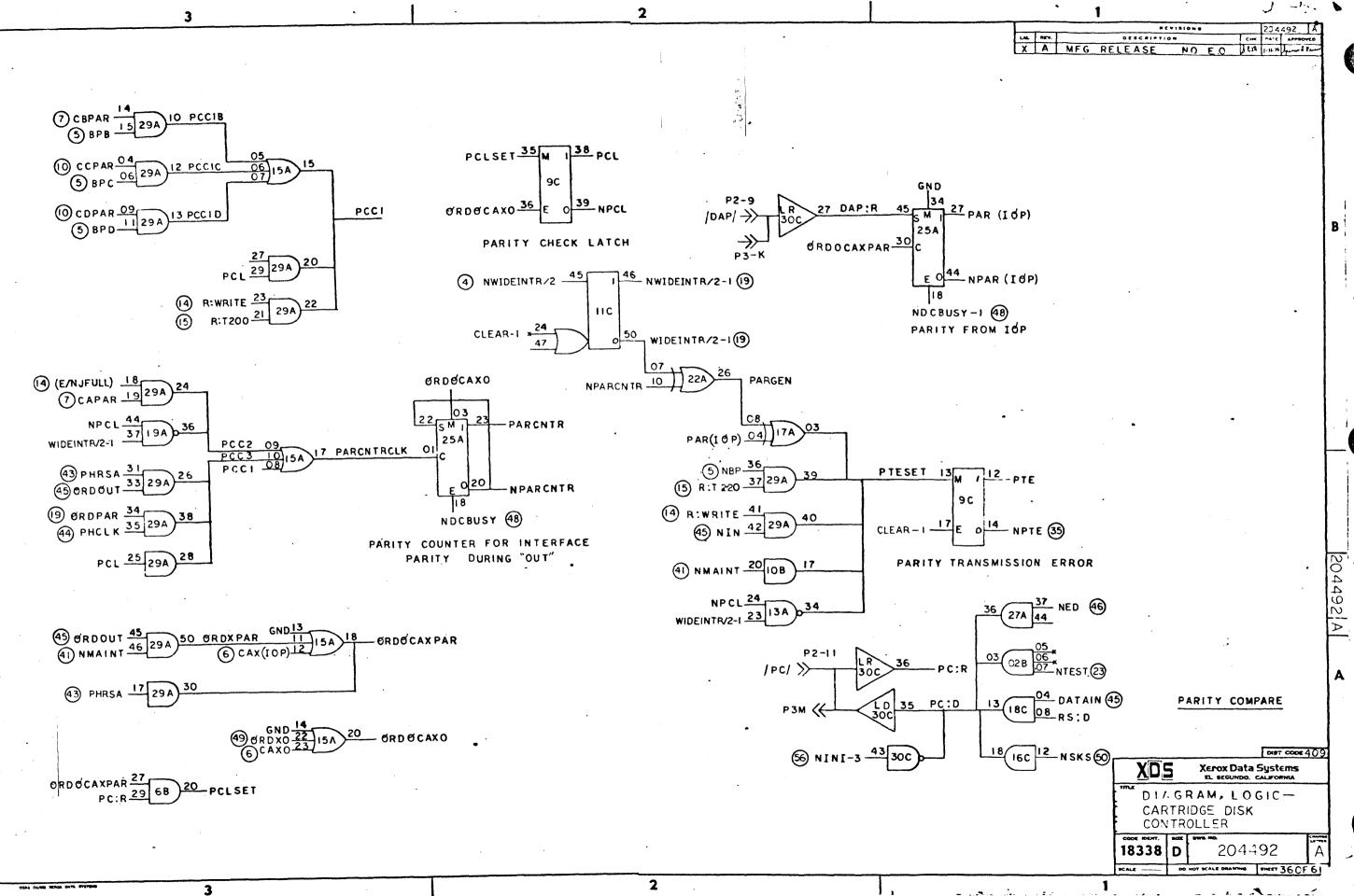

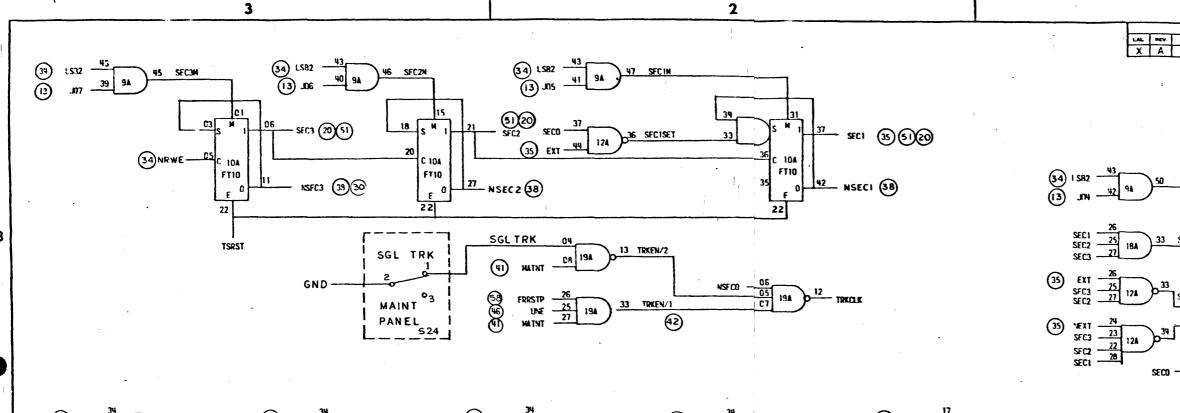

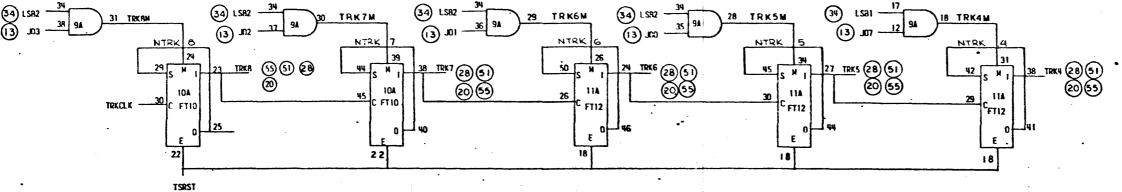

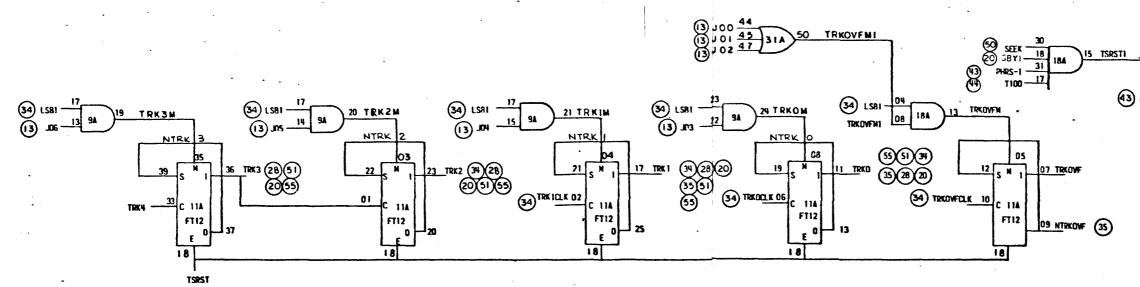

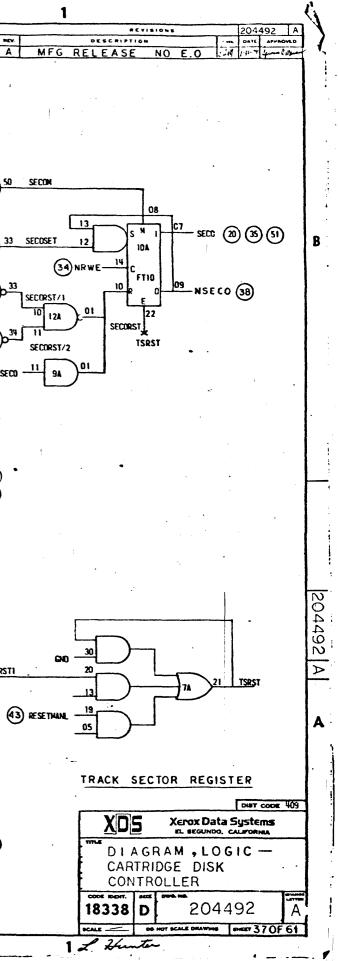

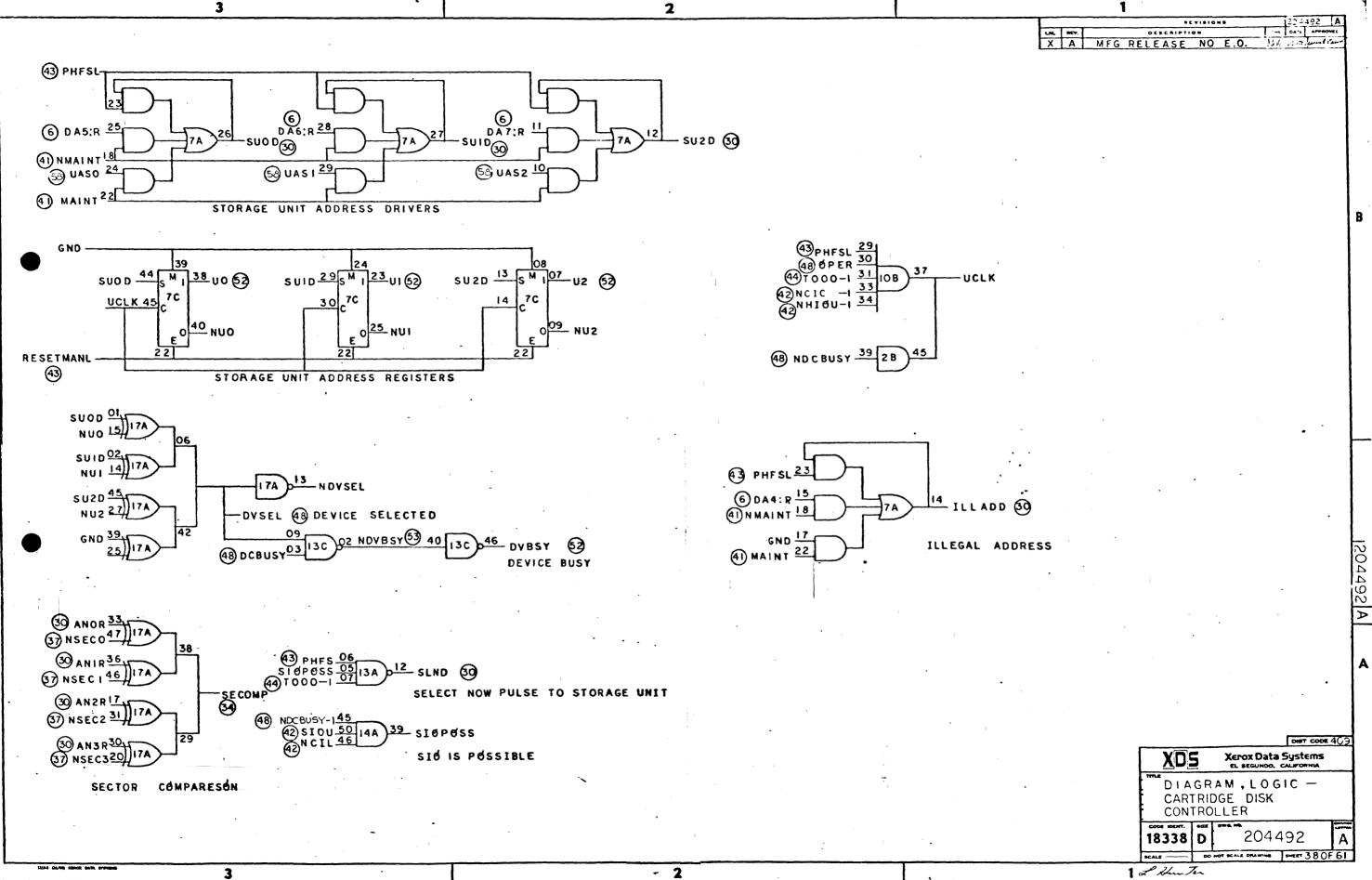

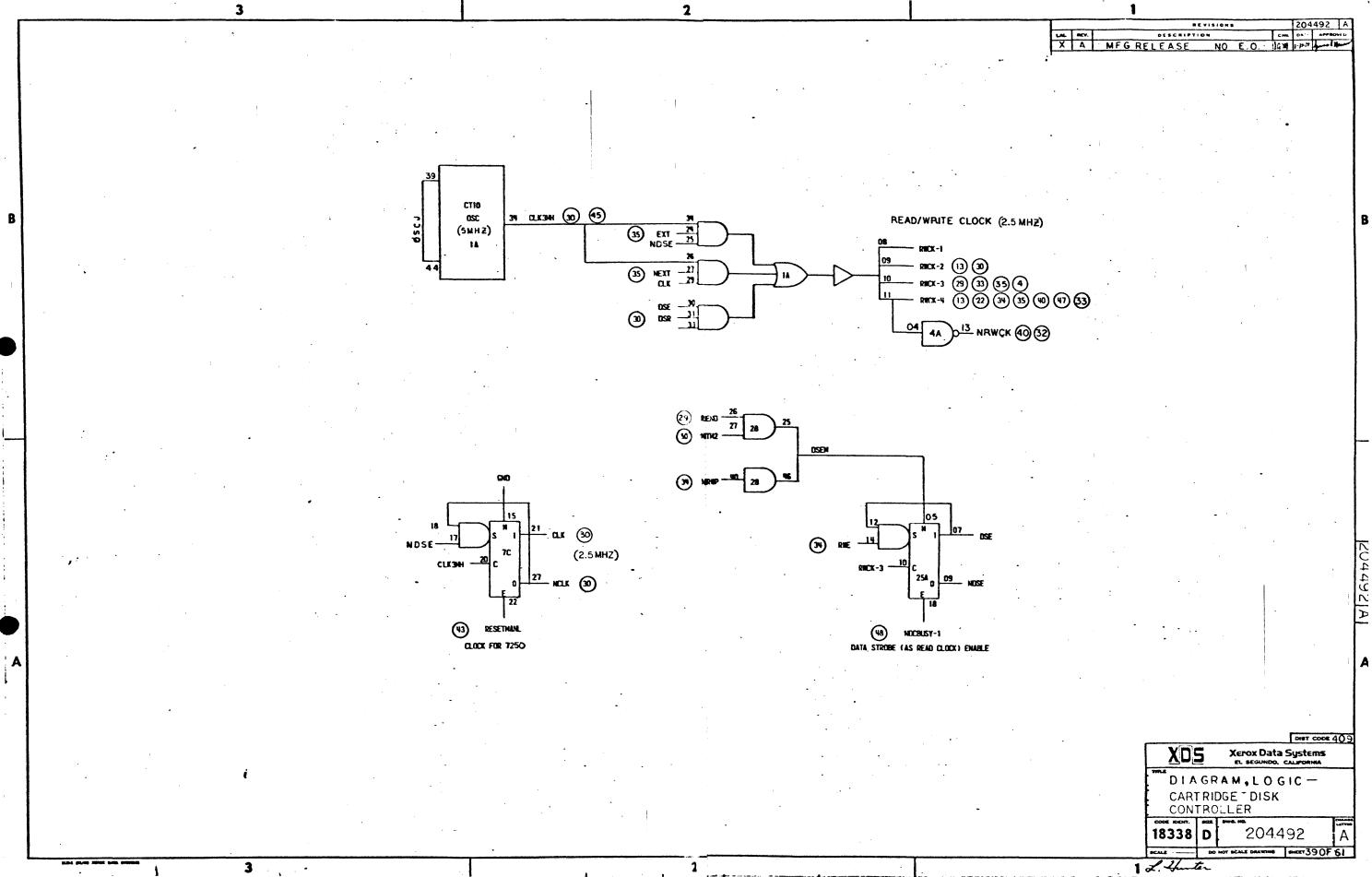

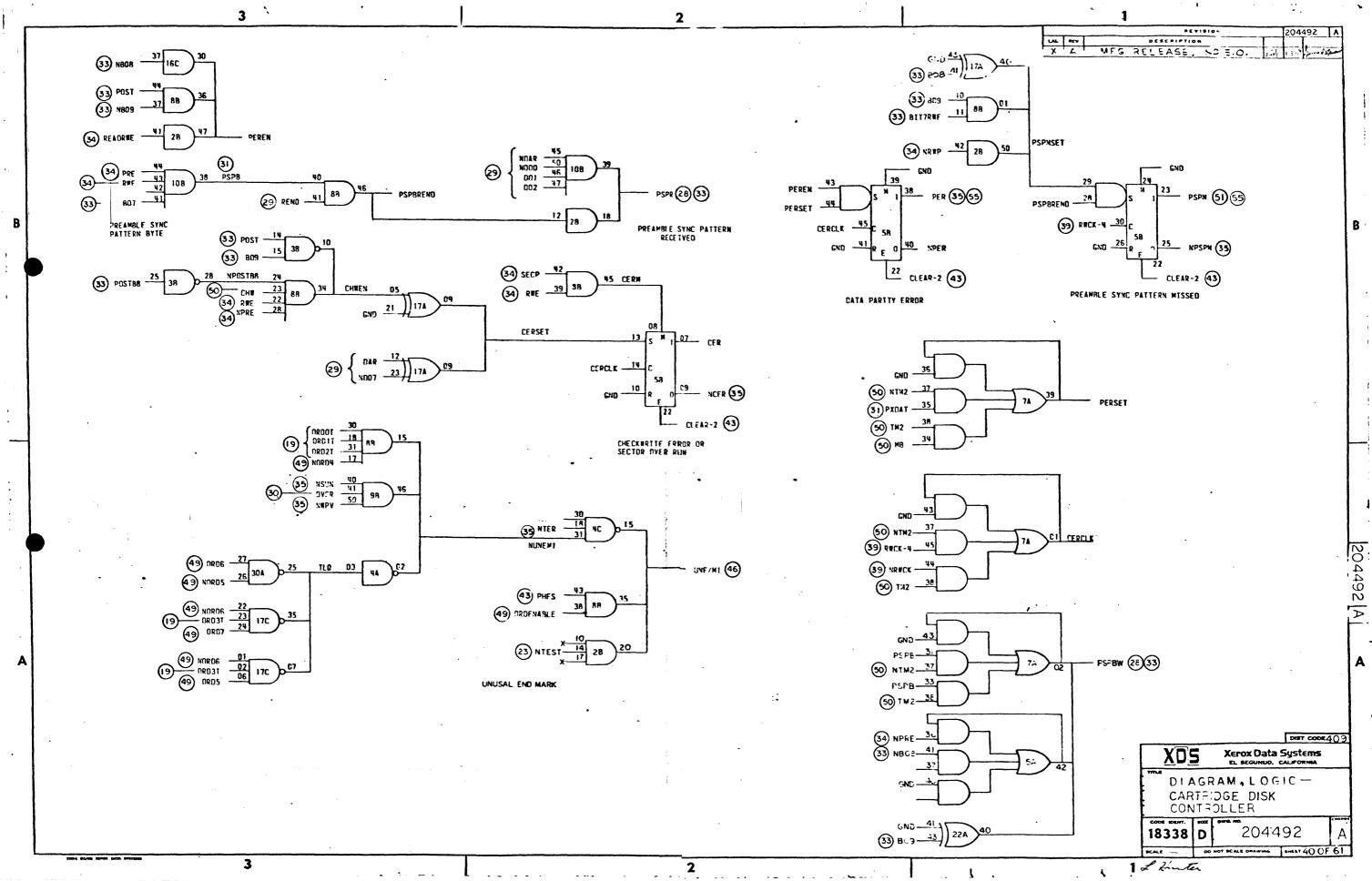

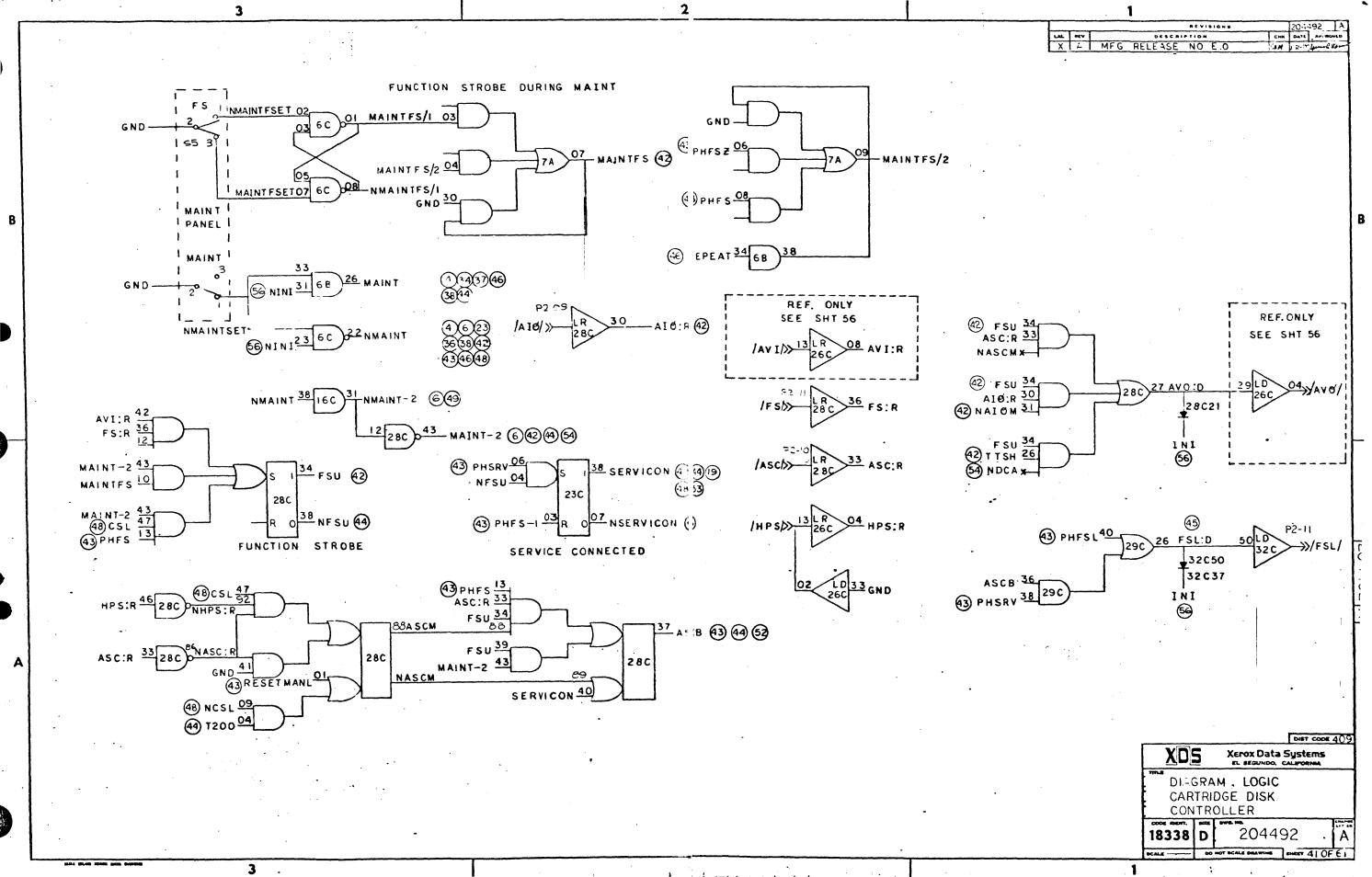

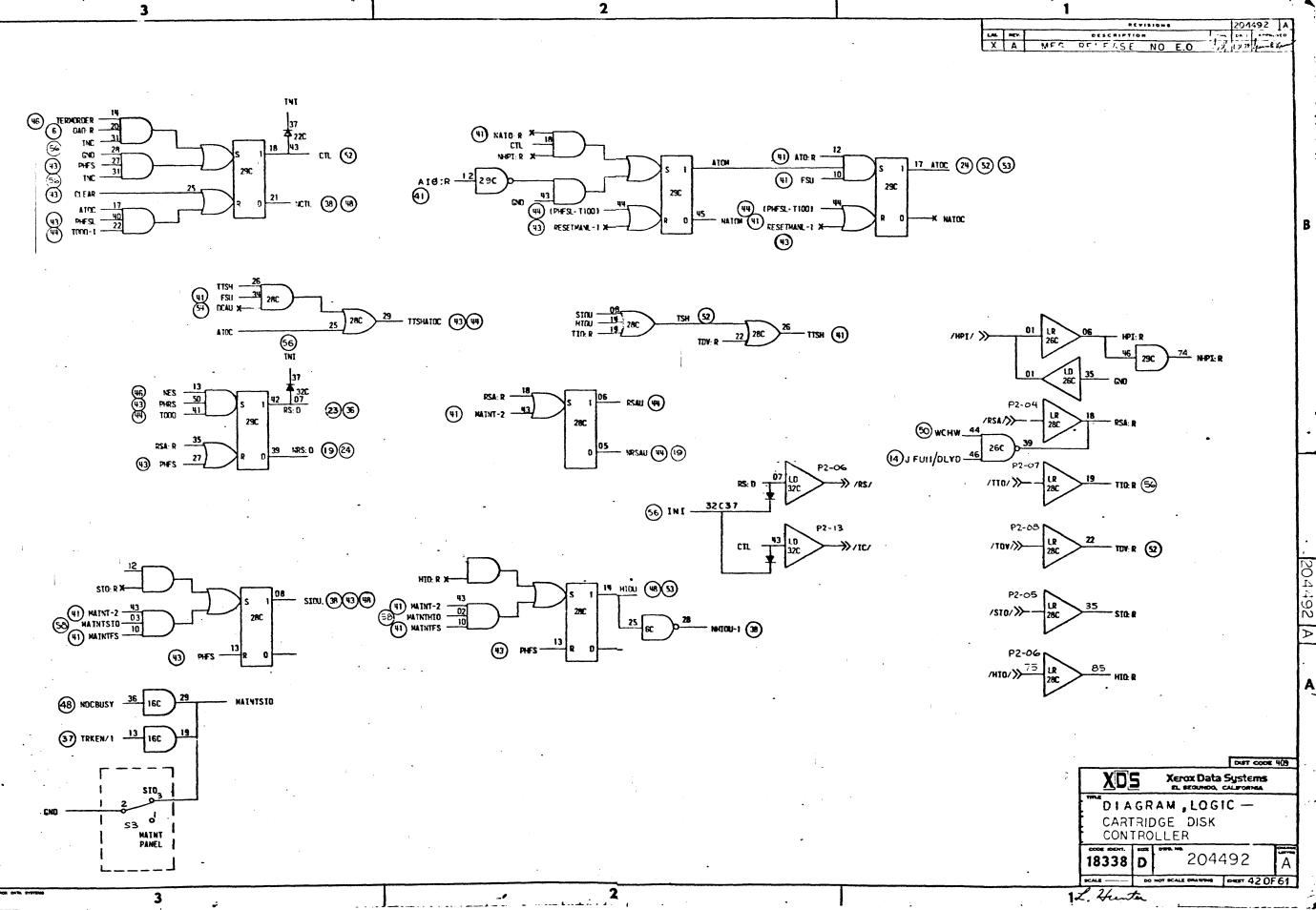

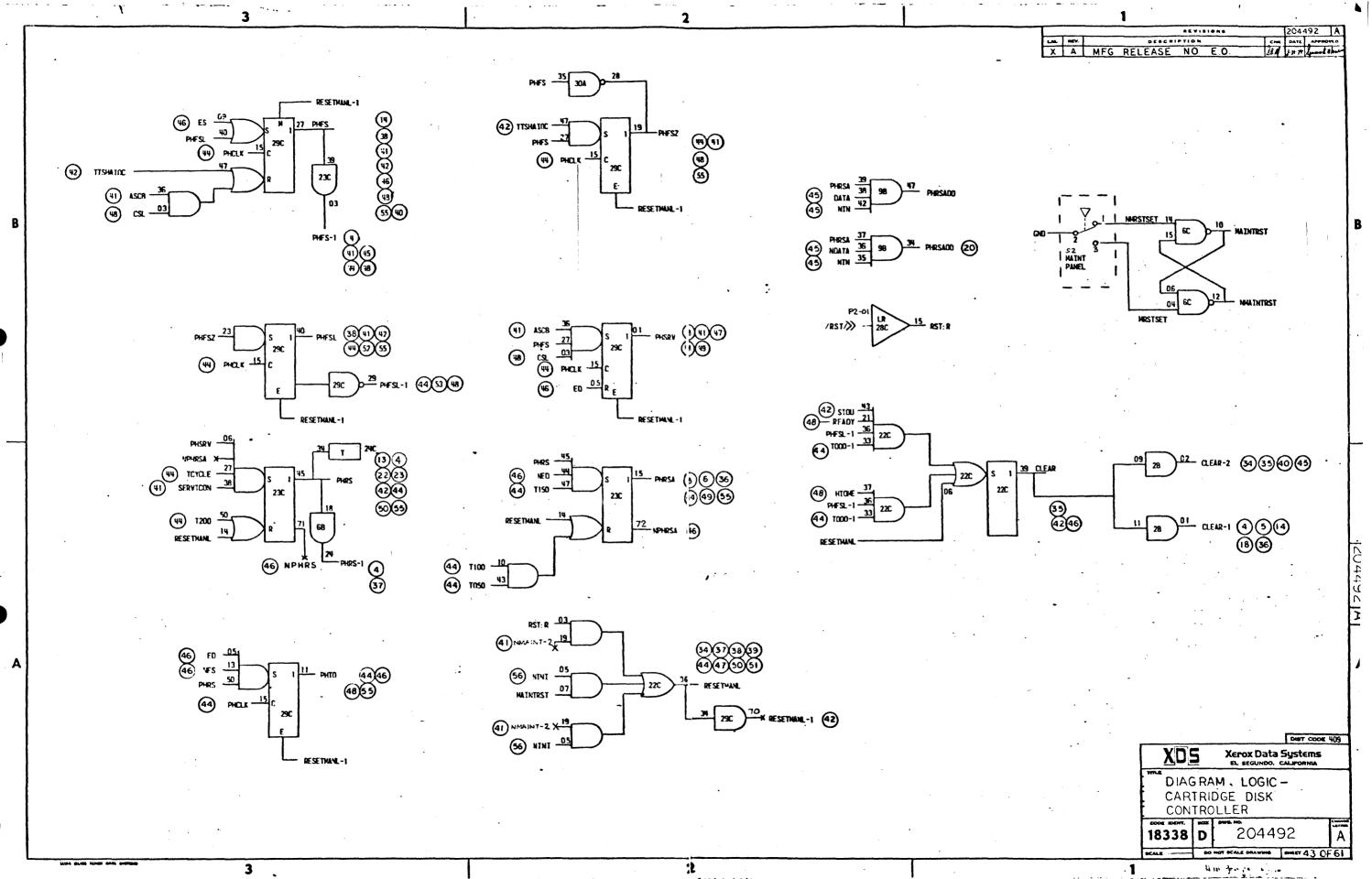

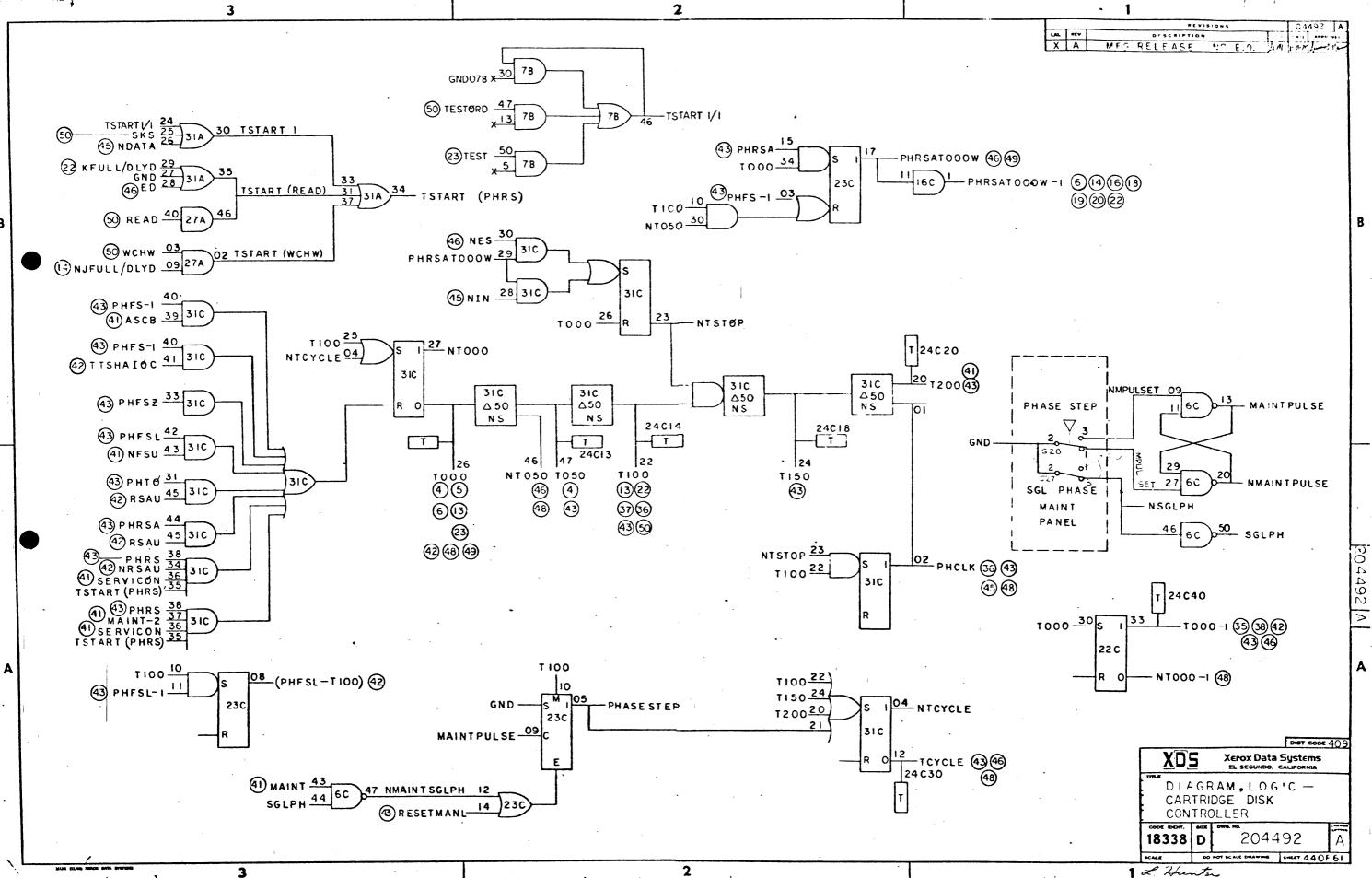

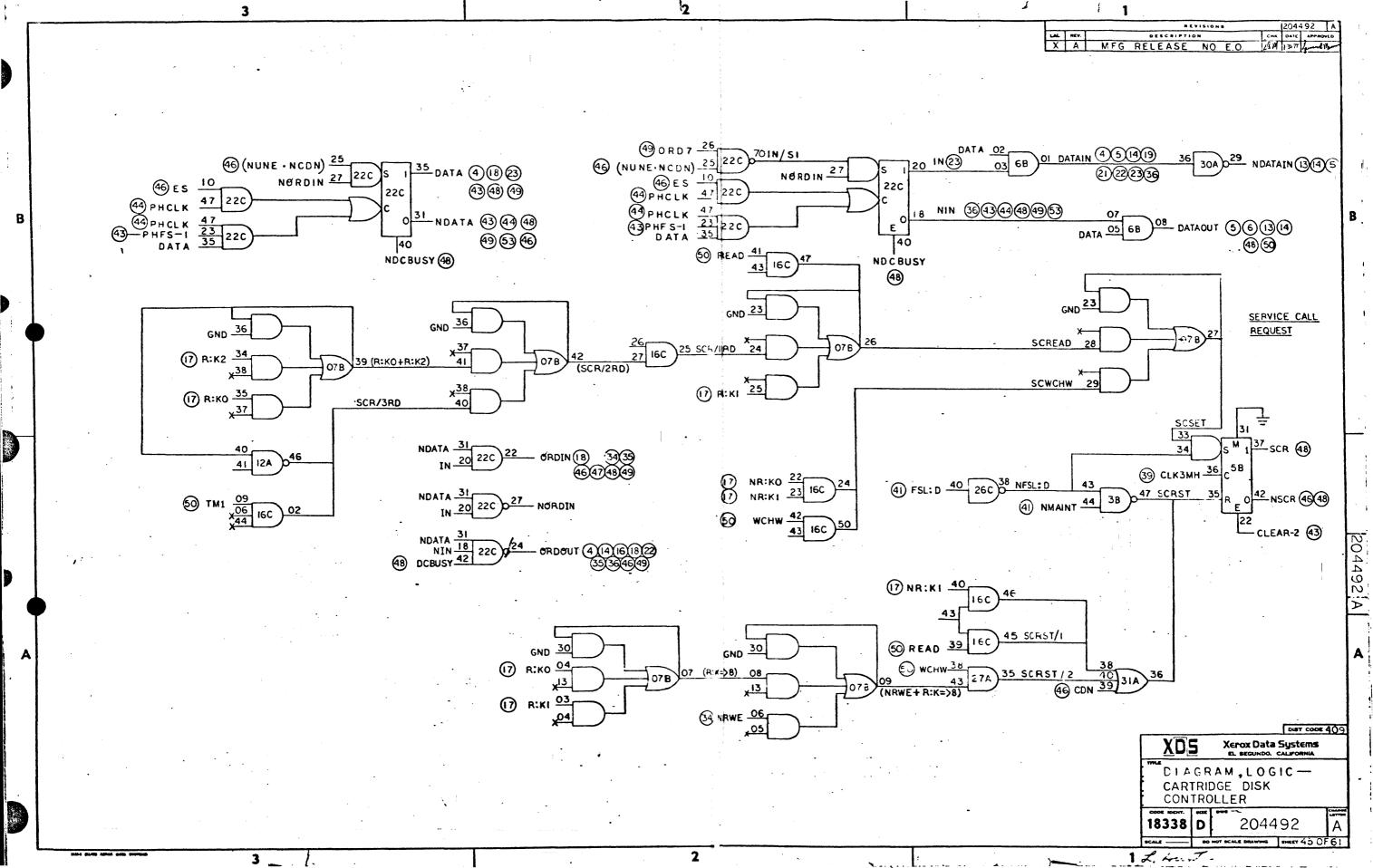

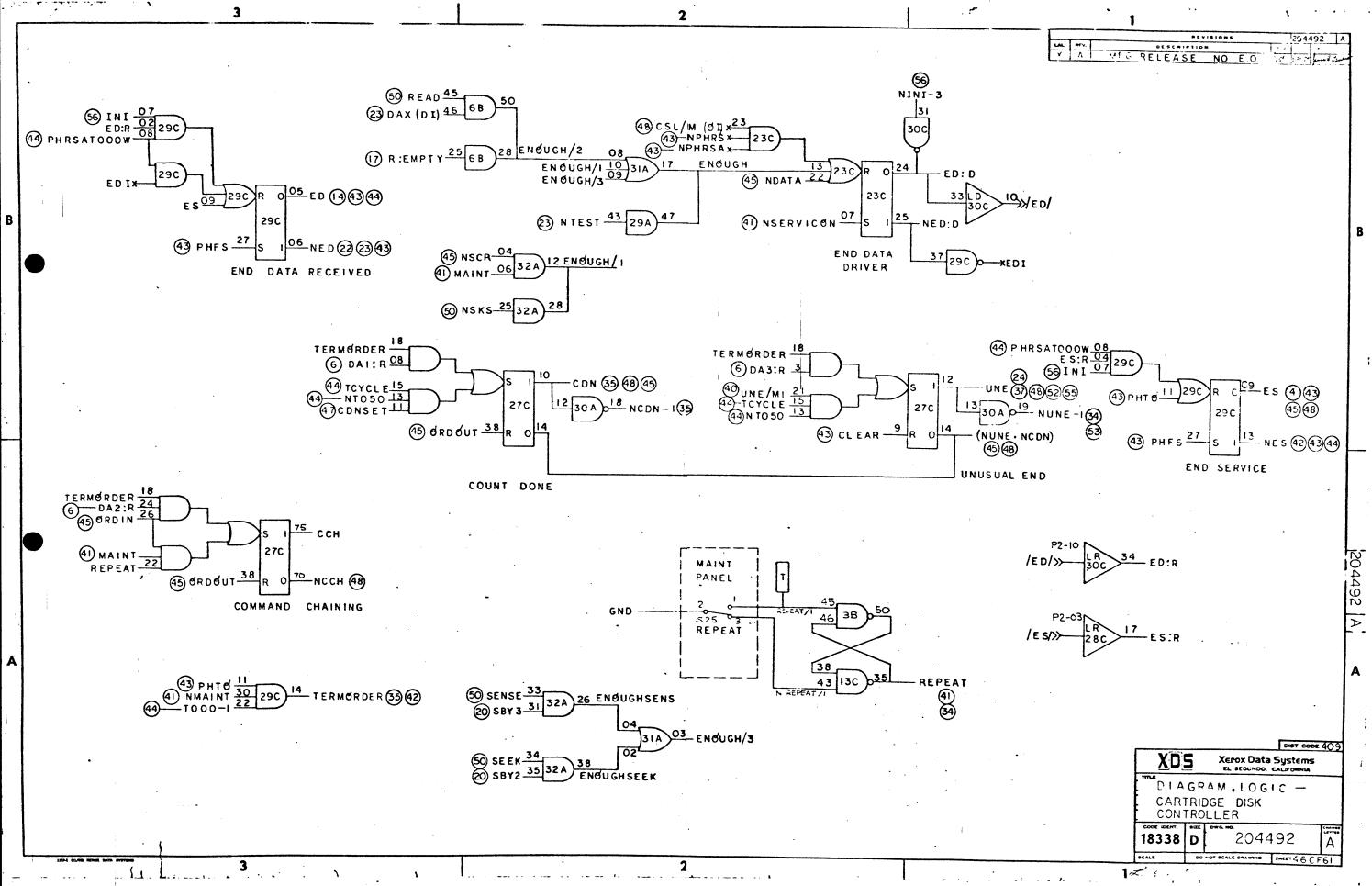

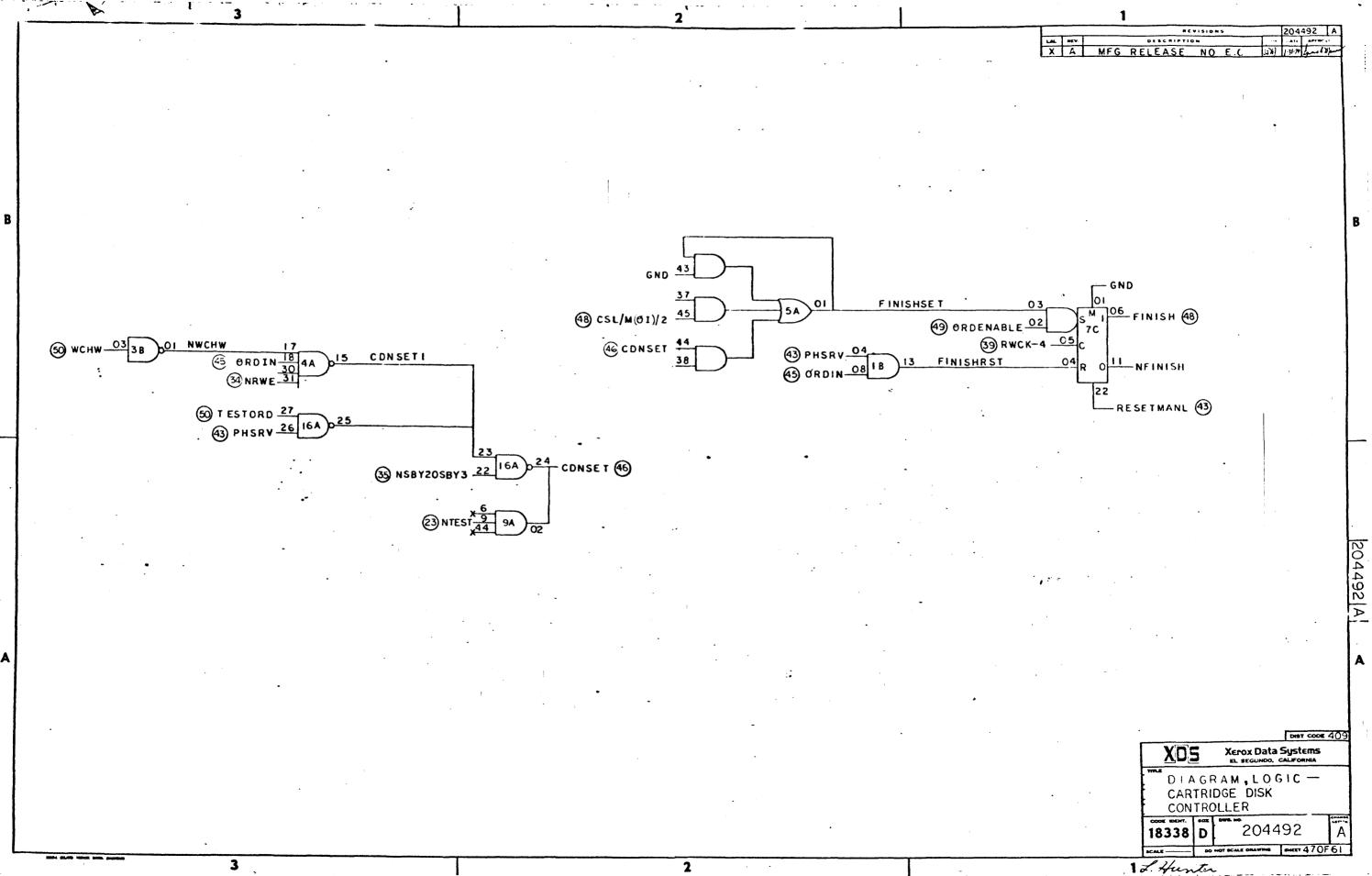

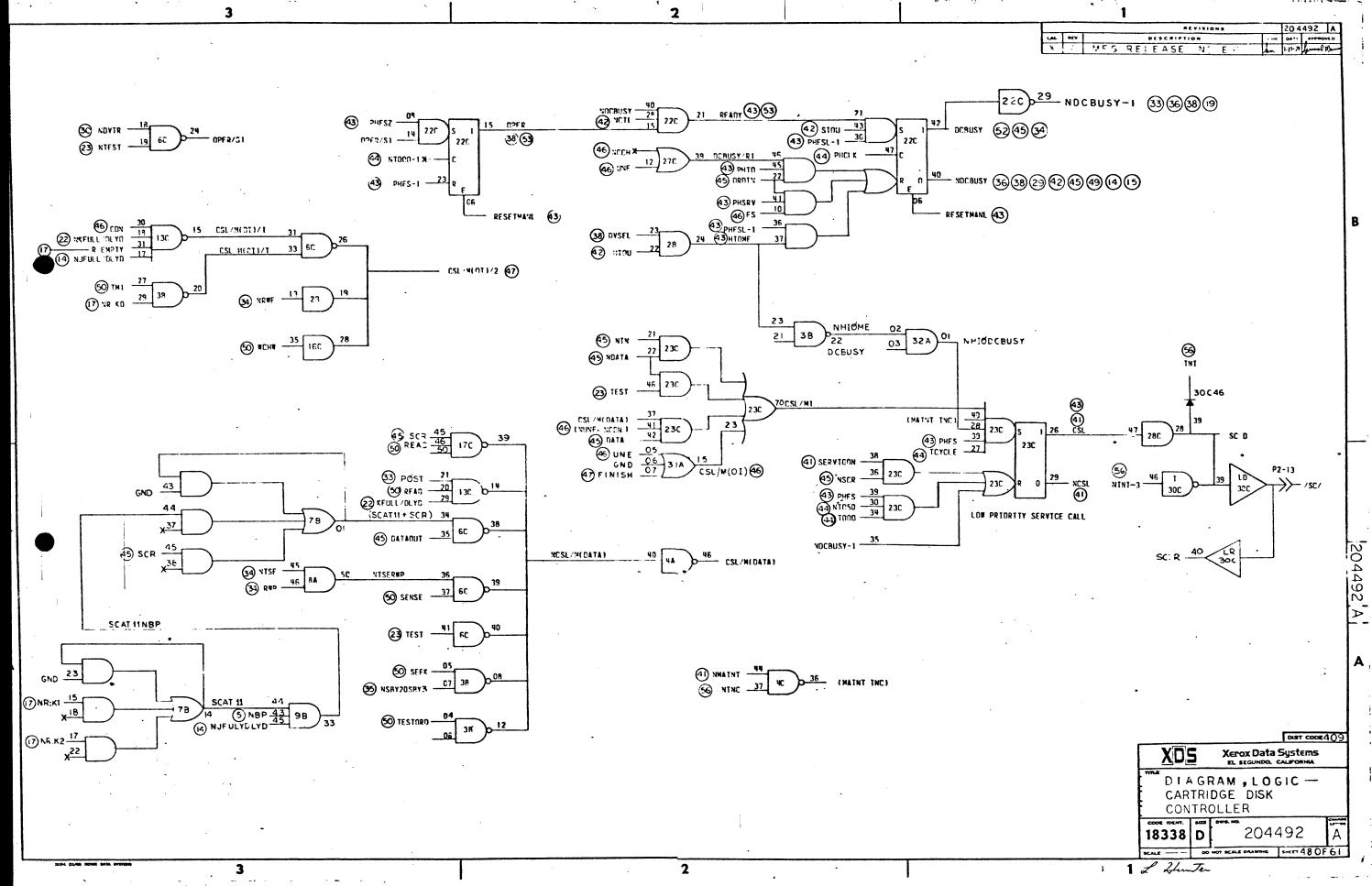

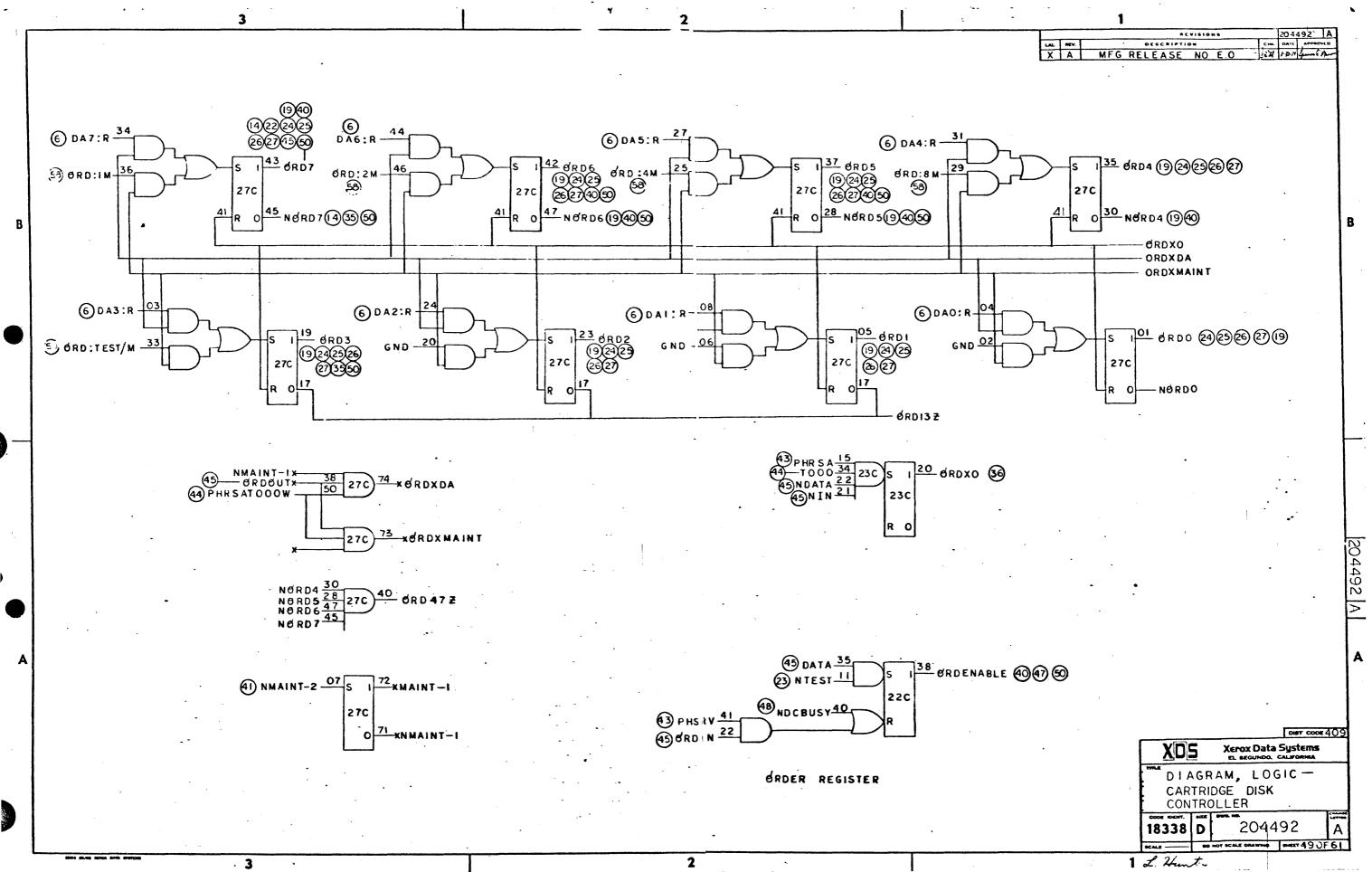

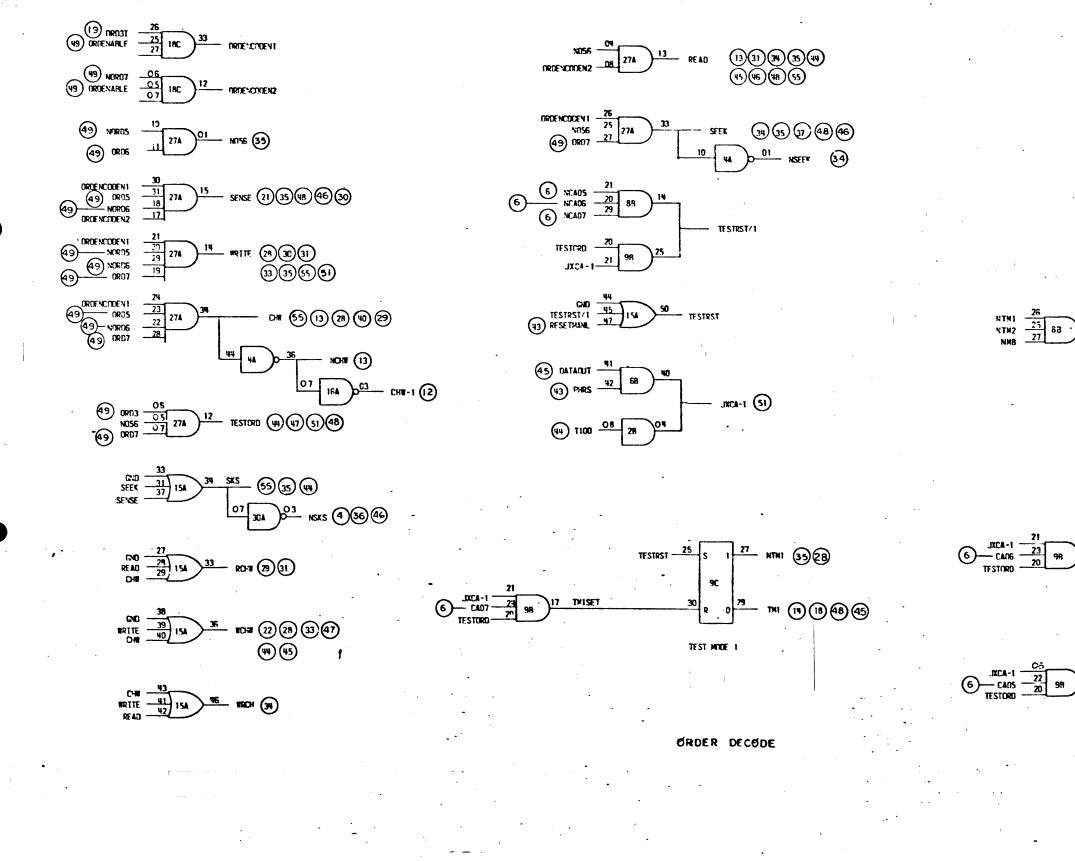

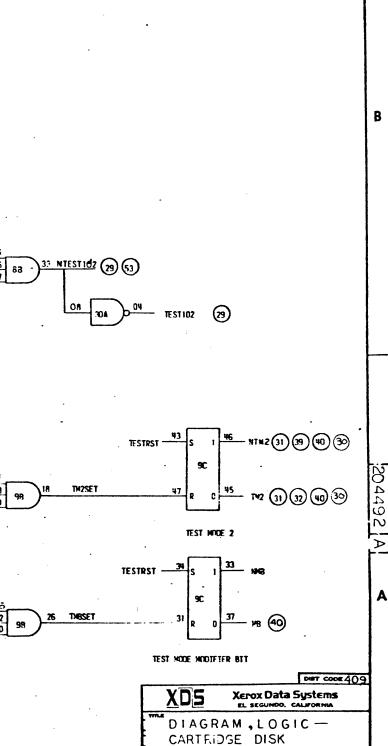

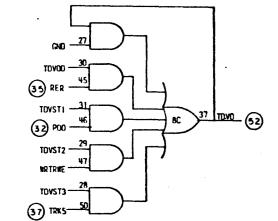

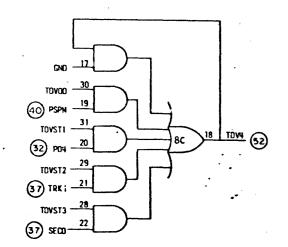

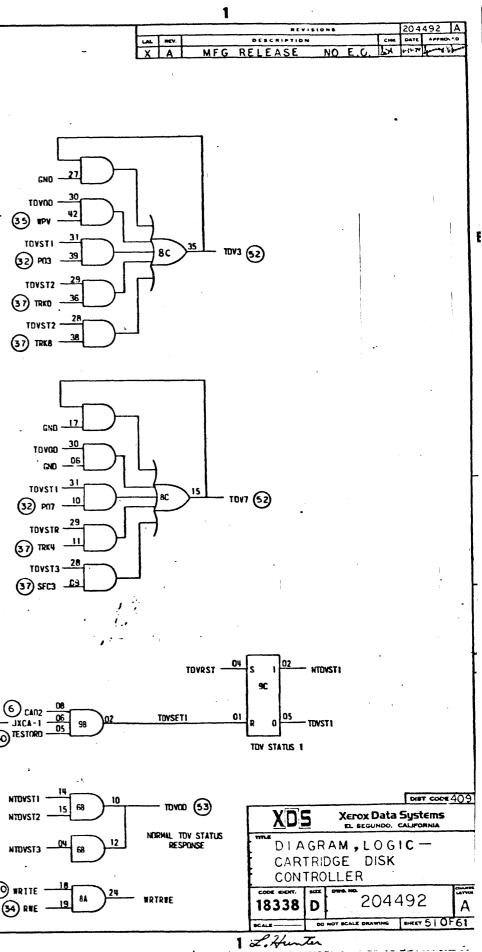

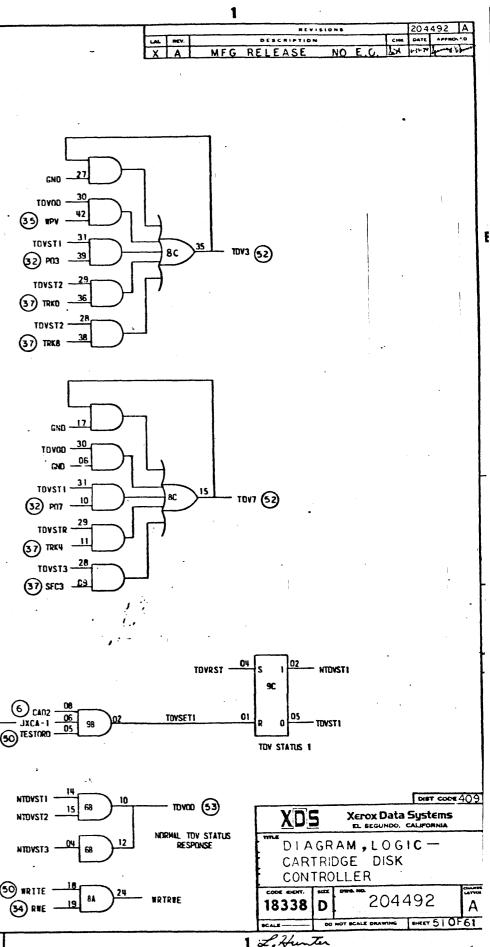

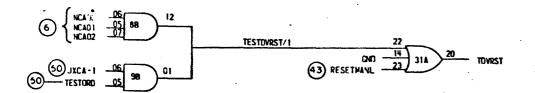

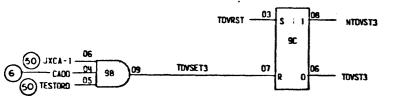

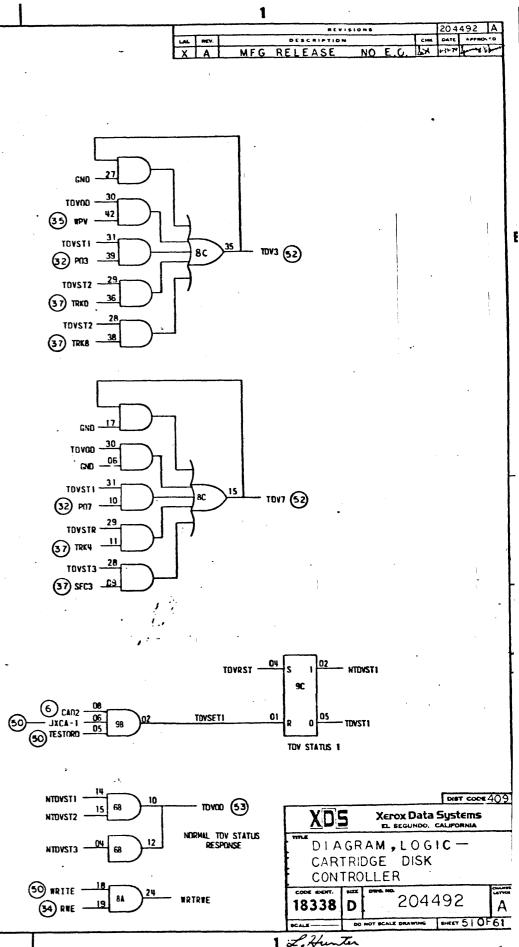

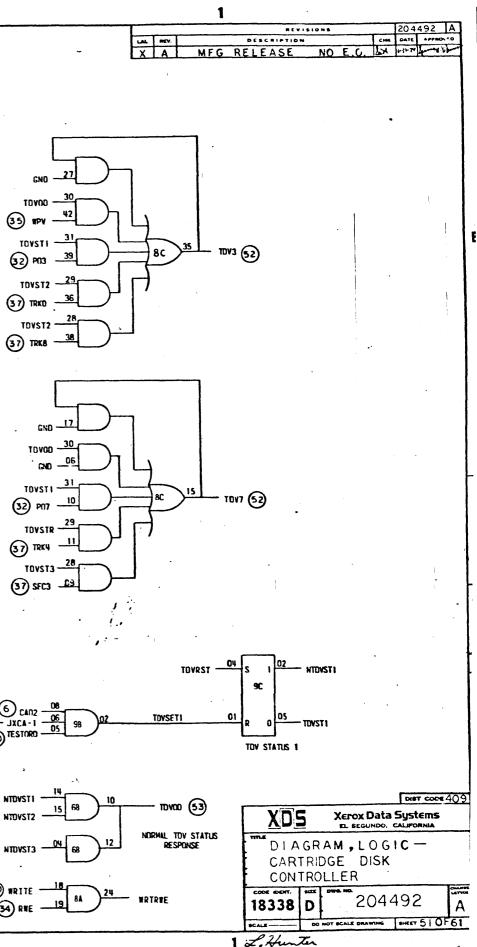

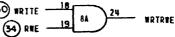

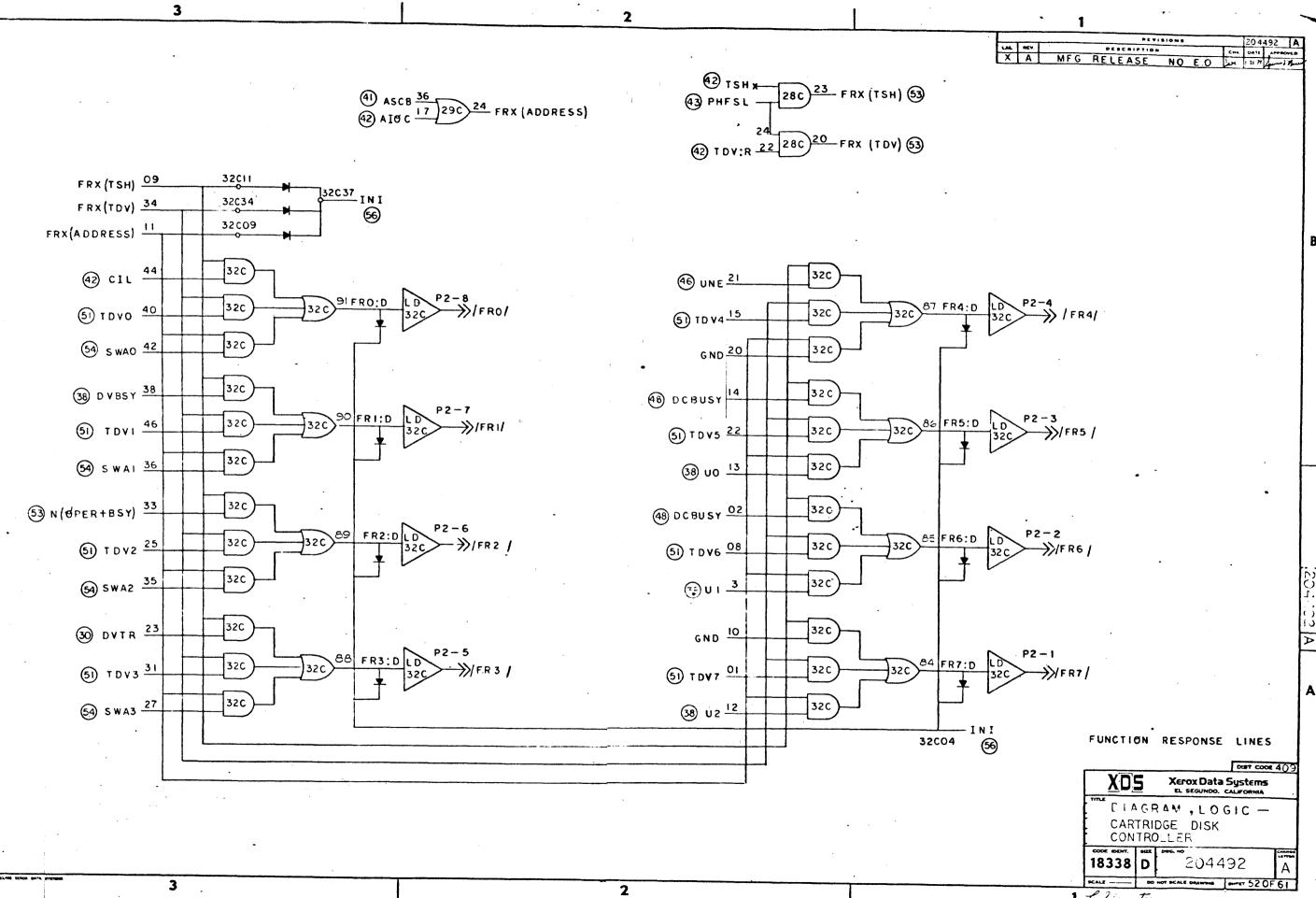

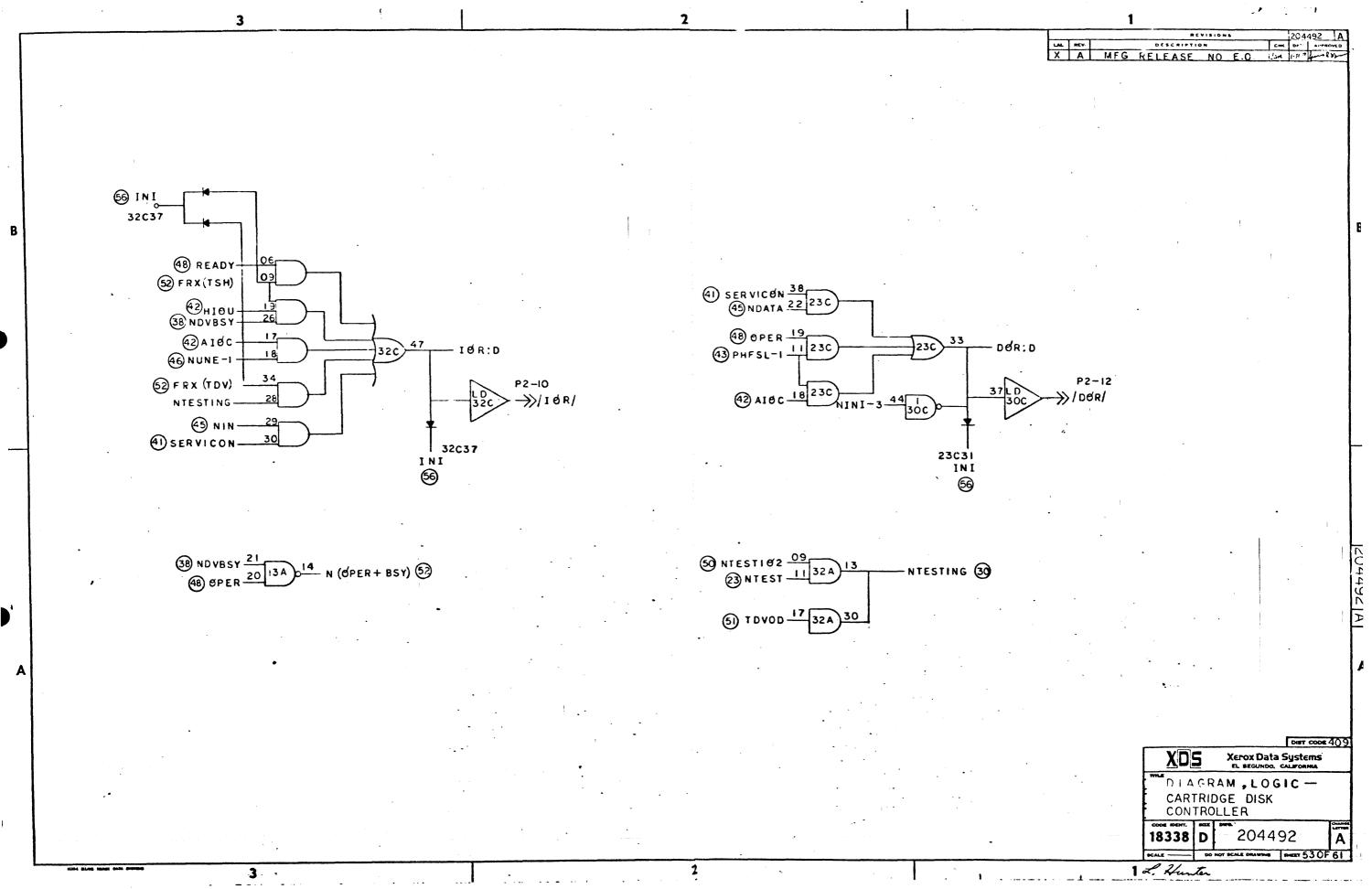

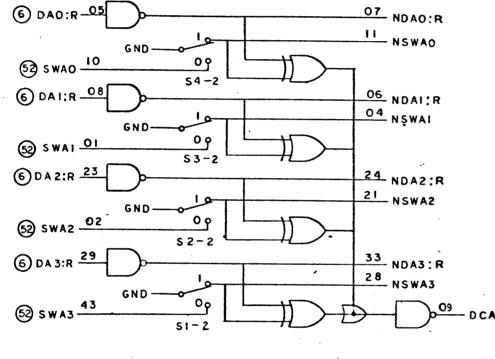

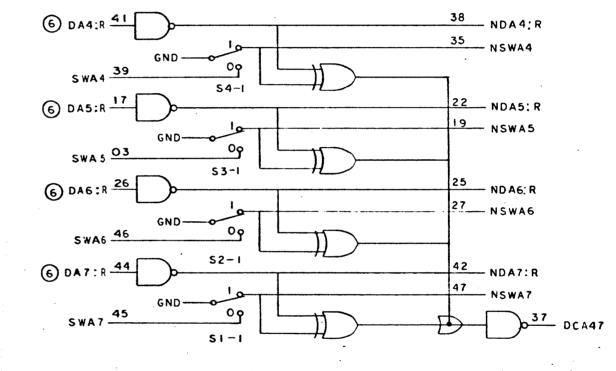

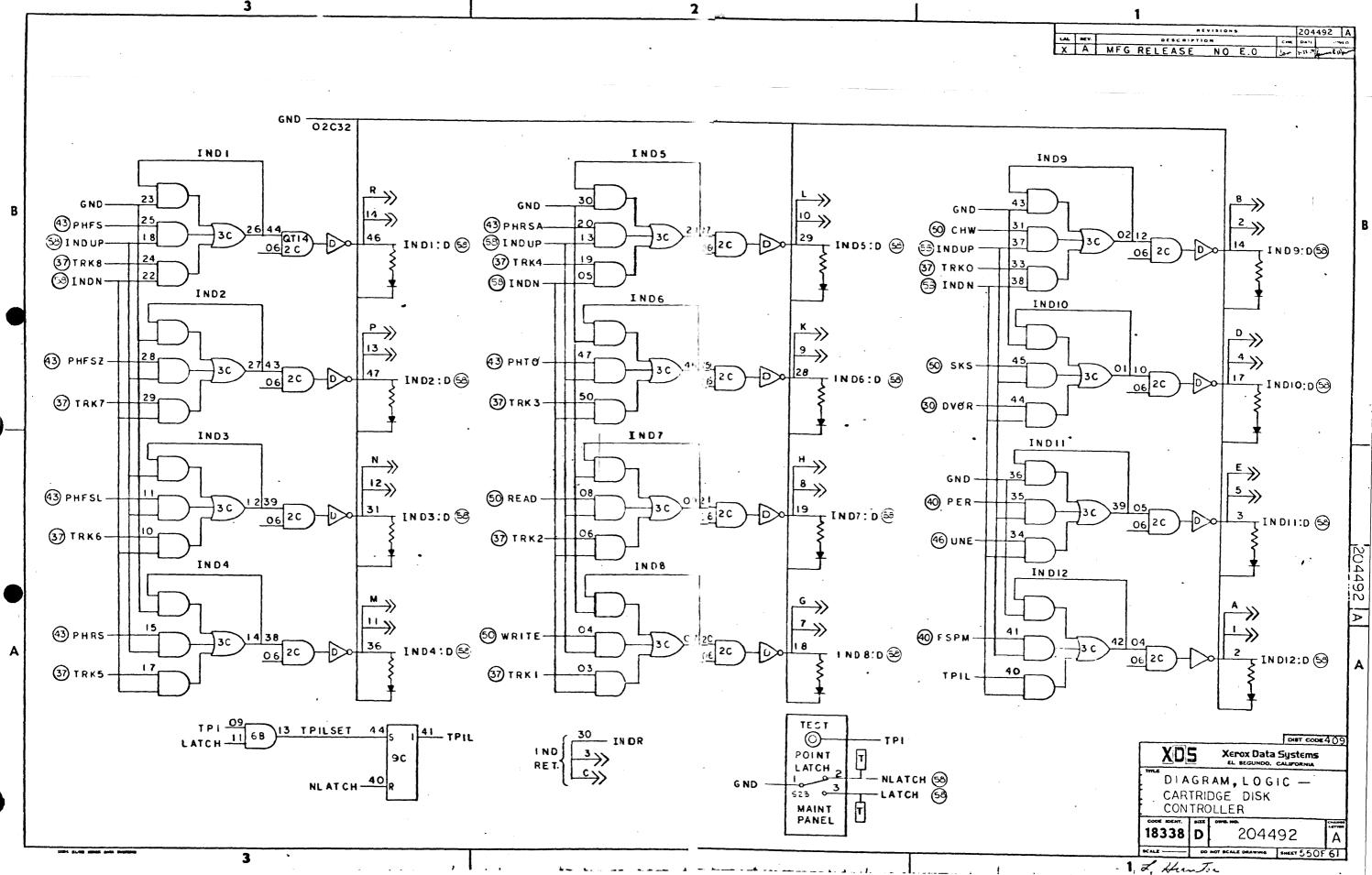

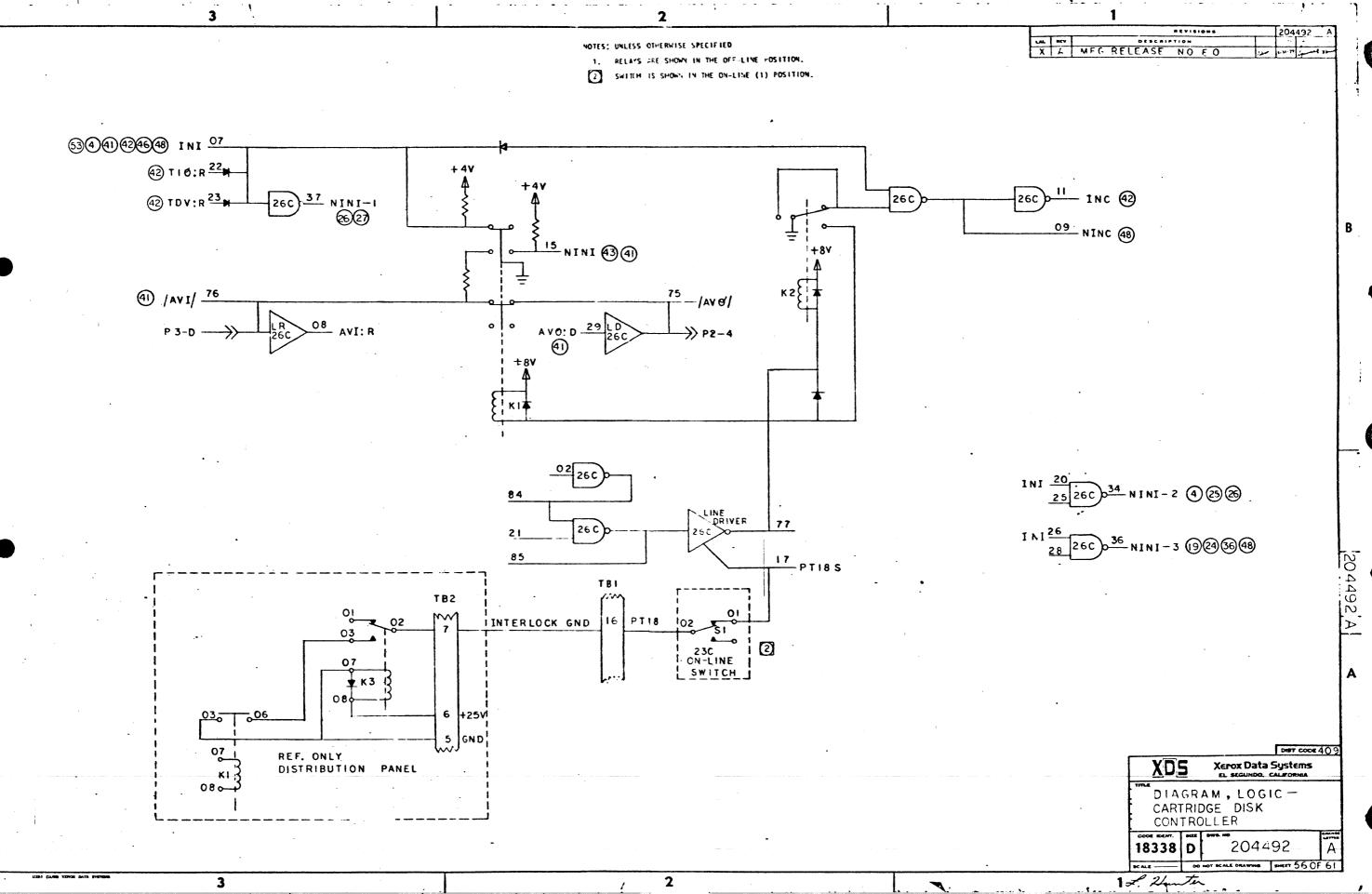

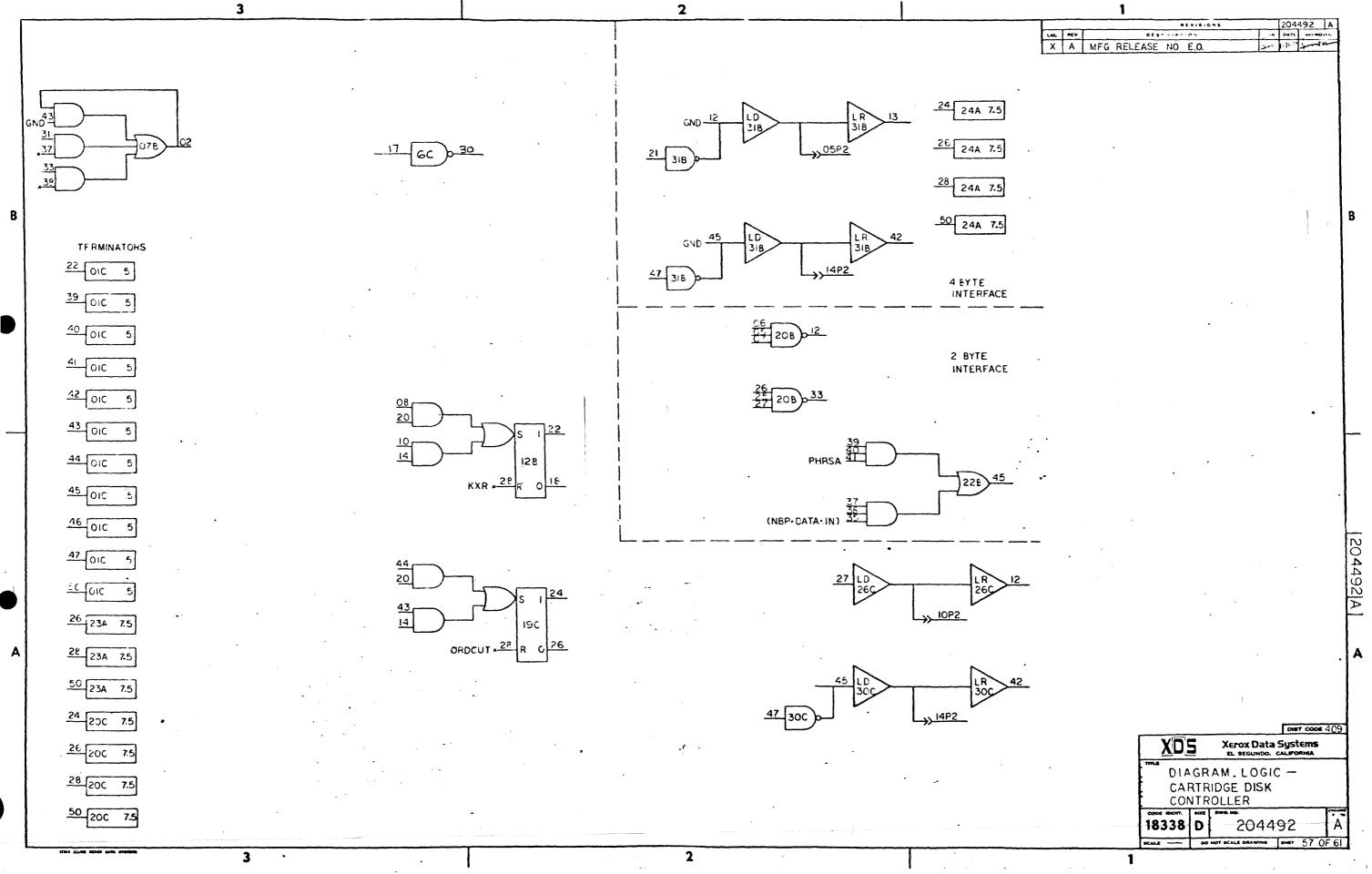

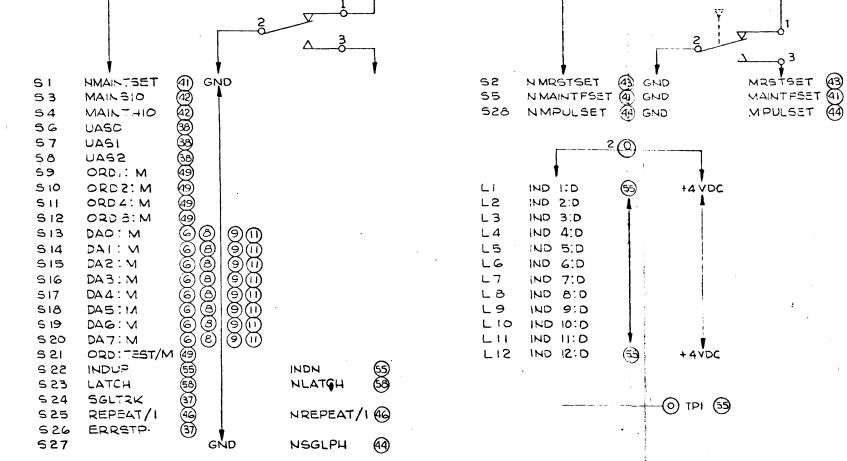

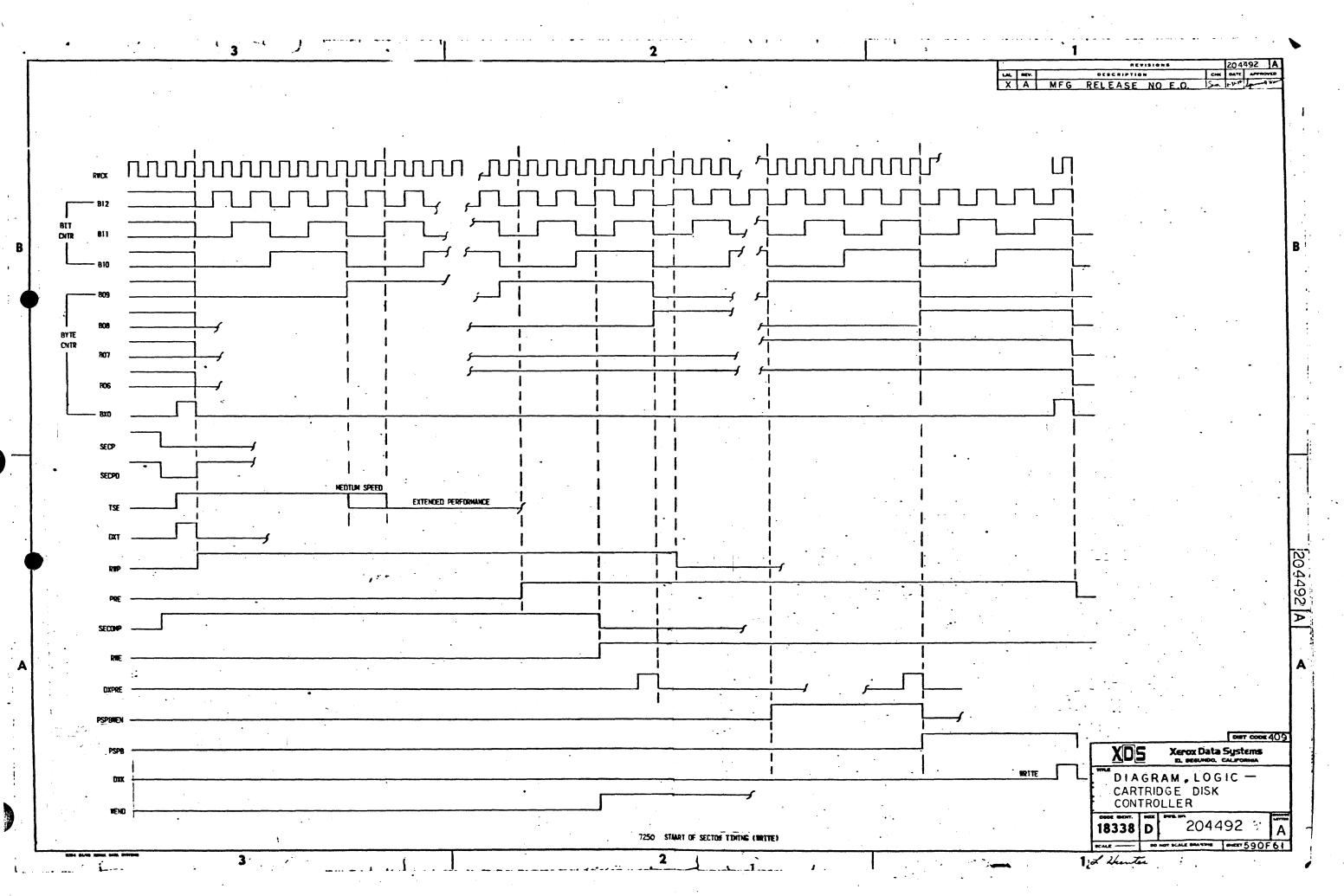

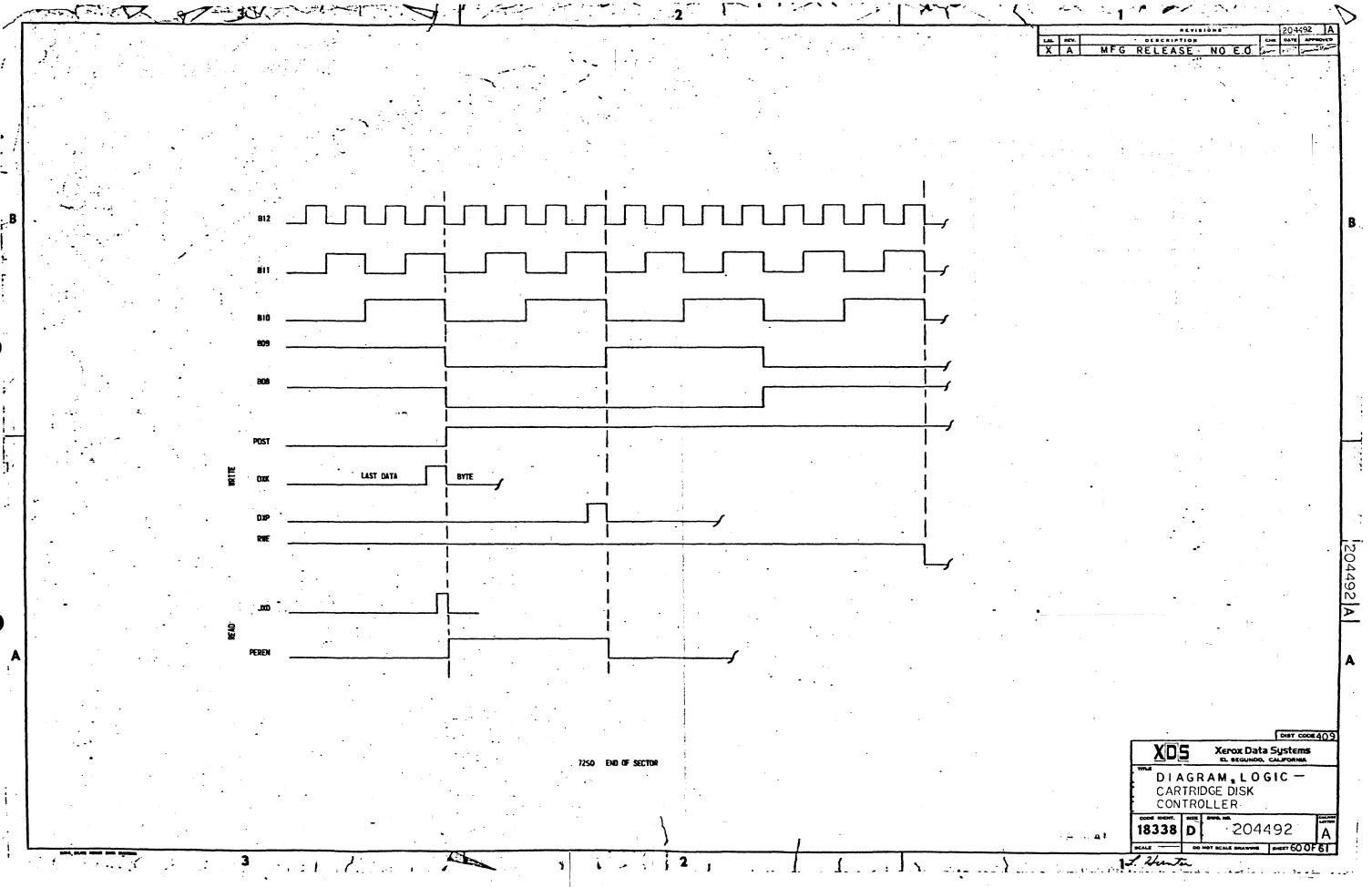

|         | 204260<br>204493<br>204492 | A<br>A<br>A | Cartridge Disk Functional Diagram<br>Assembly, Module Kit and Location Chart<br>Diagram, Logic–Cartridge Disk Controller | 1 thru<br>1 thru<br>1 thru | 3<br>3<br>61 |

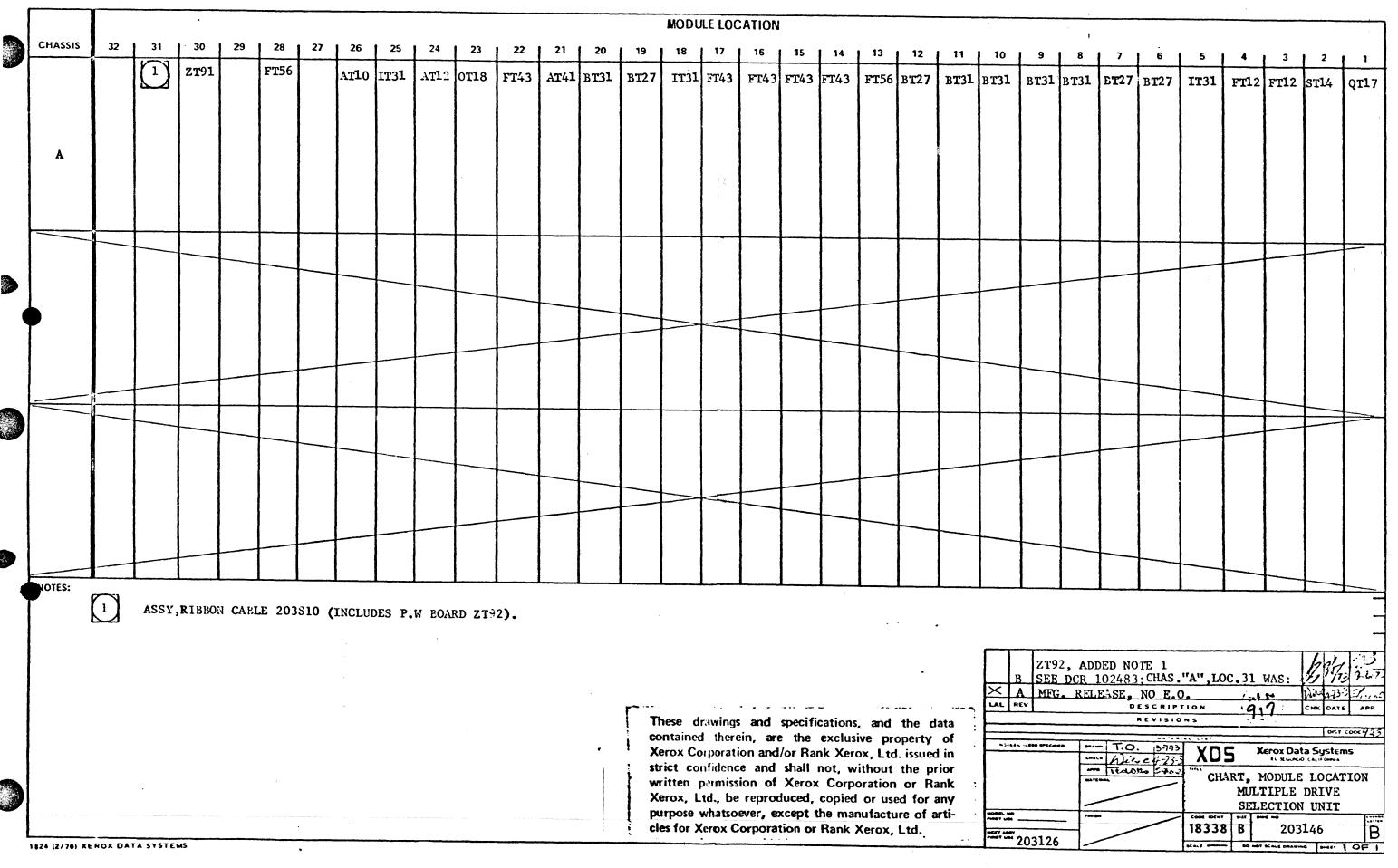

|         | 203146                     | В           | Module Location Chart, Multiple Drive<br>Selection Unit                                                                  | 1 of 1                     | -            |

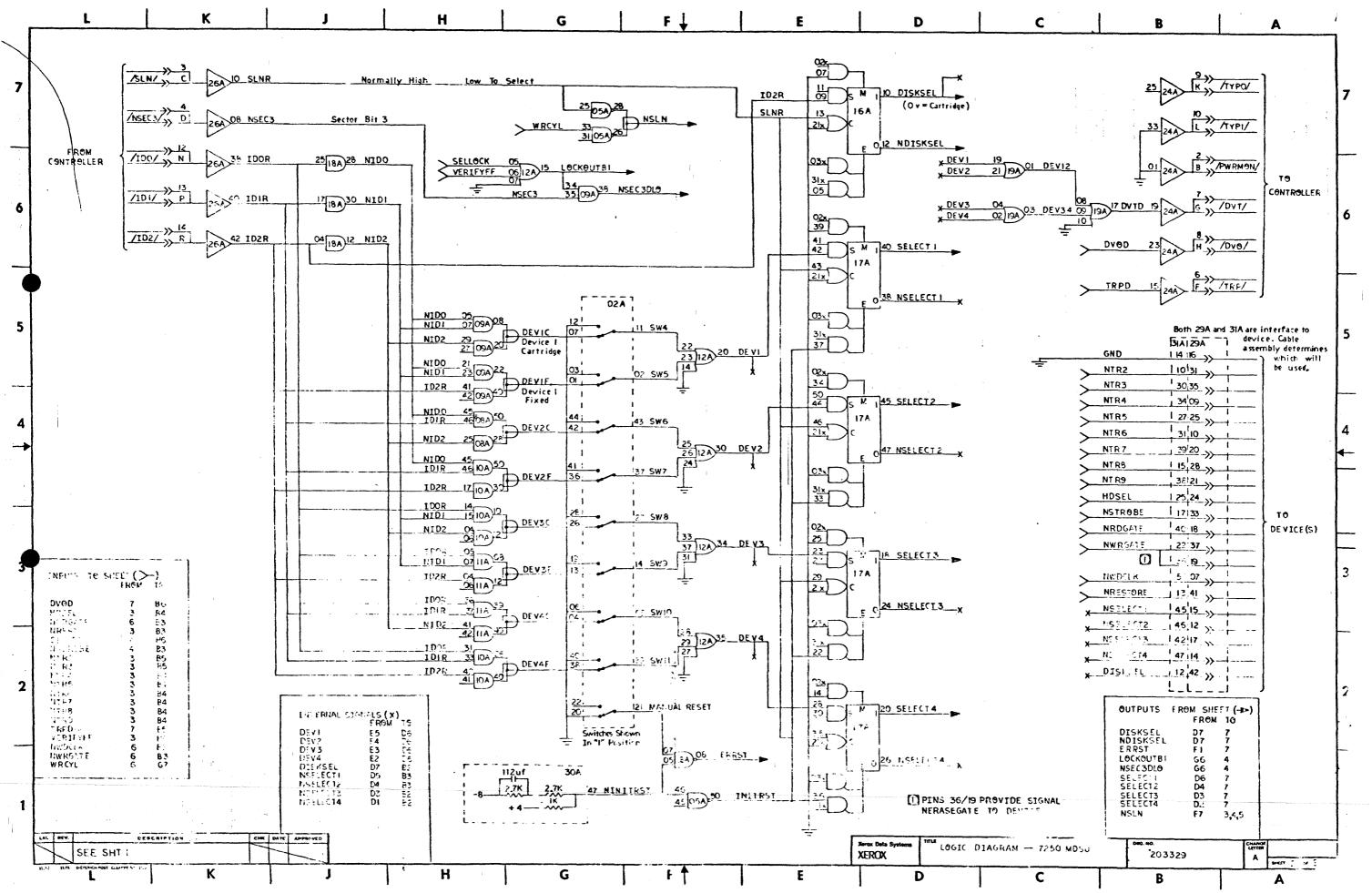

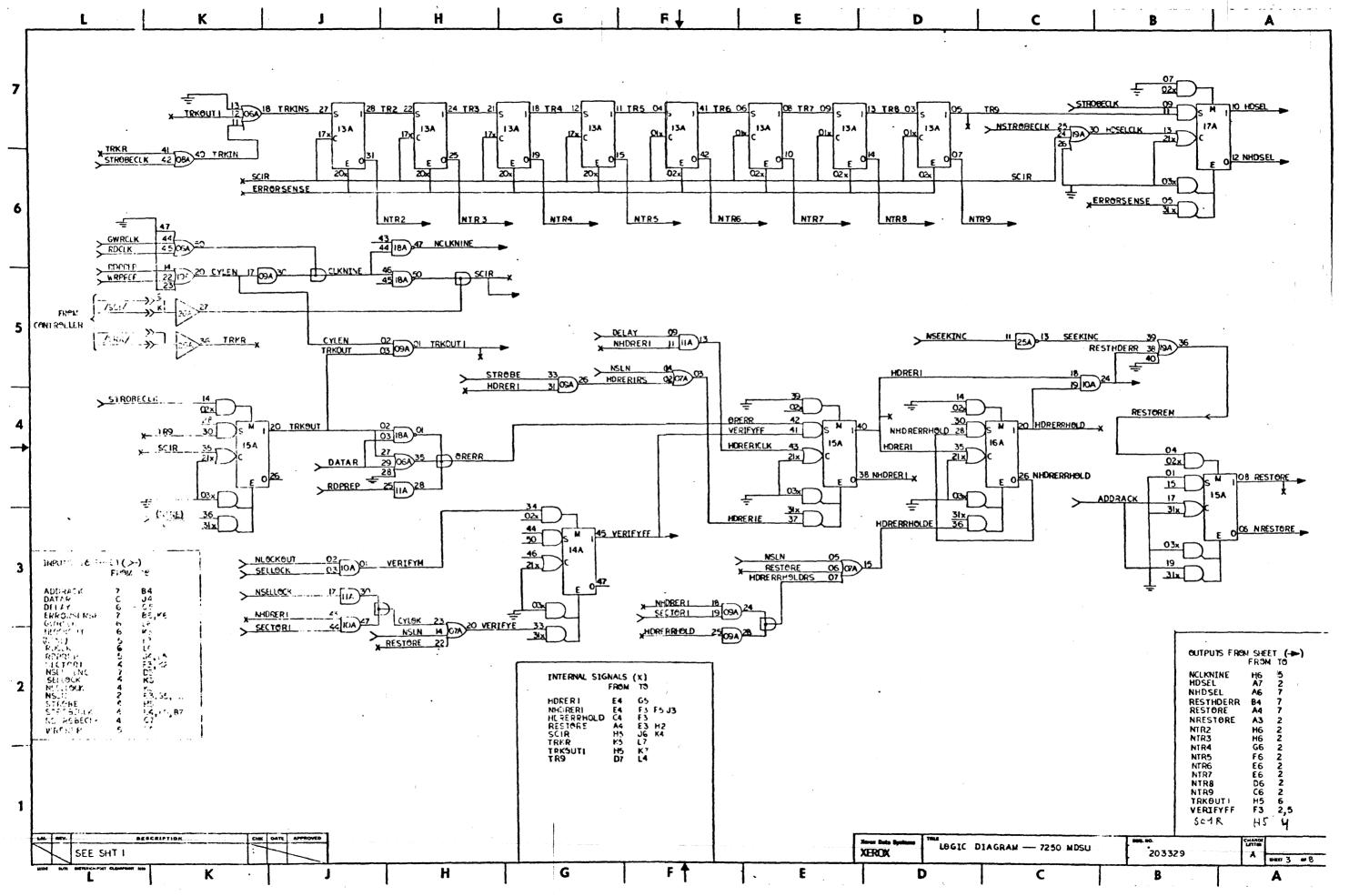

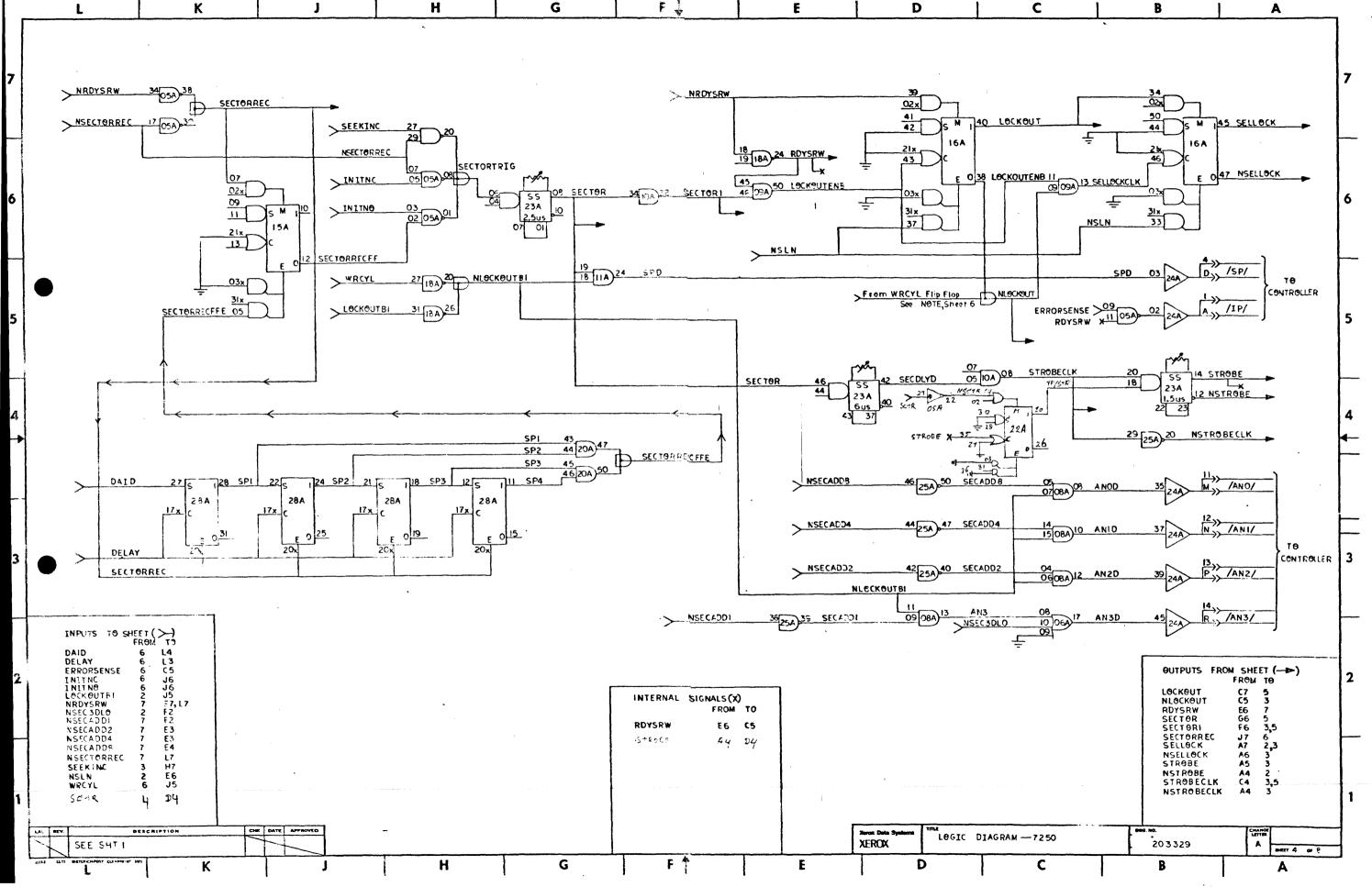

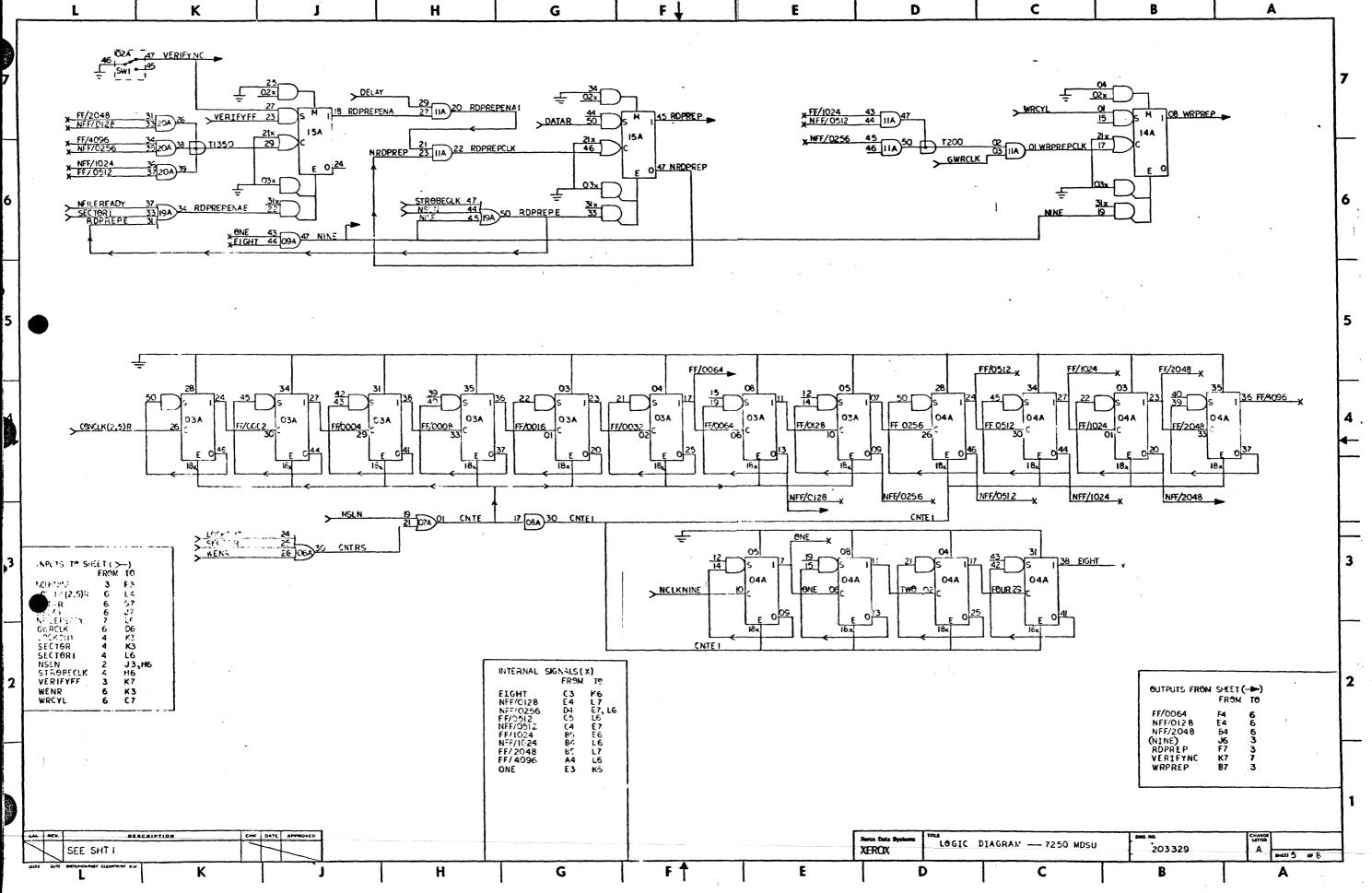

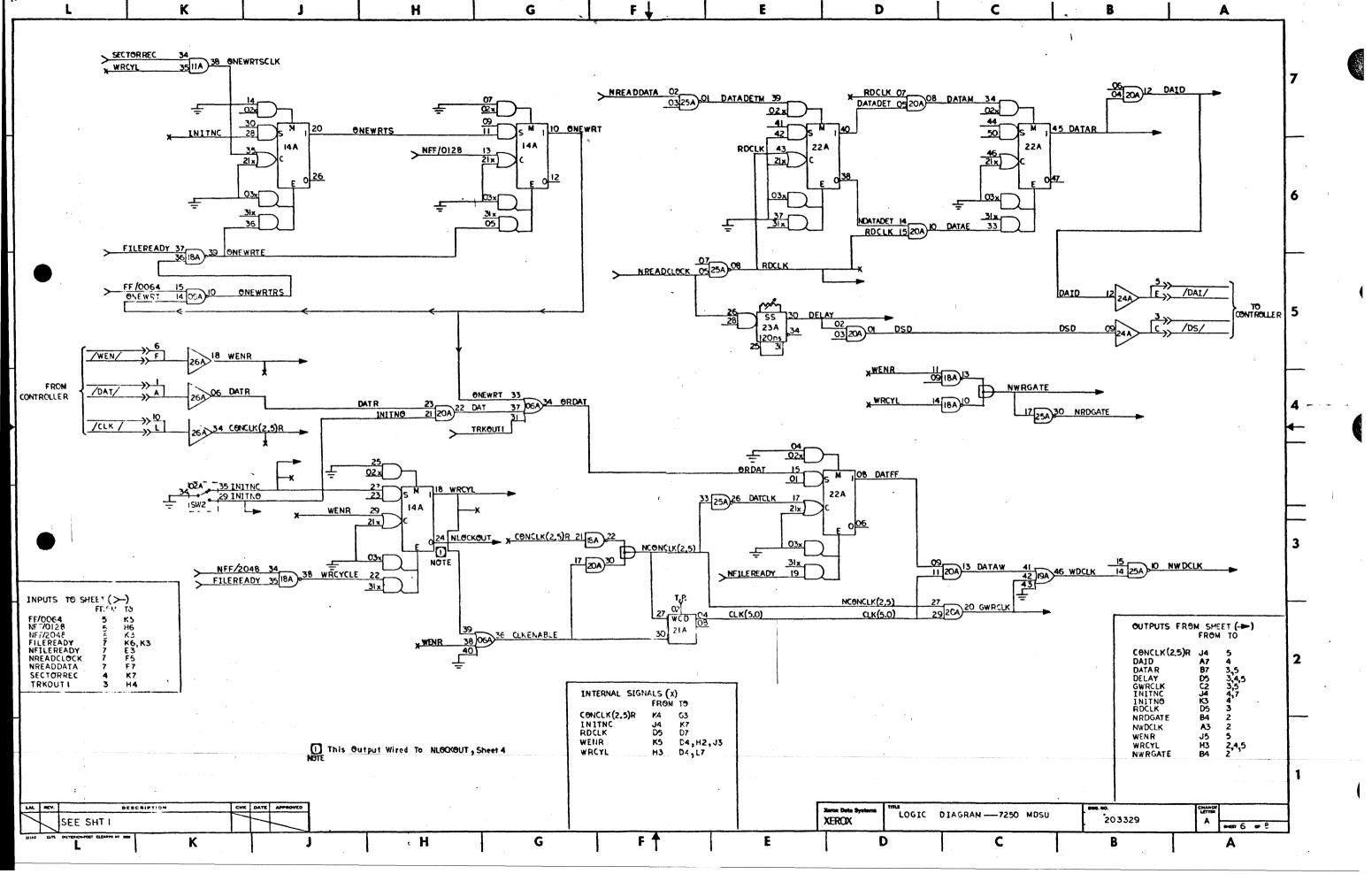

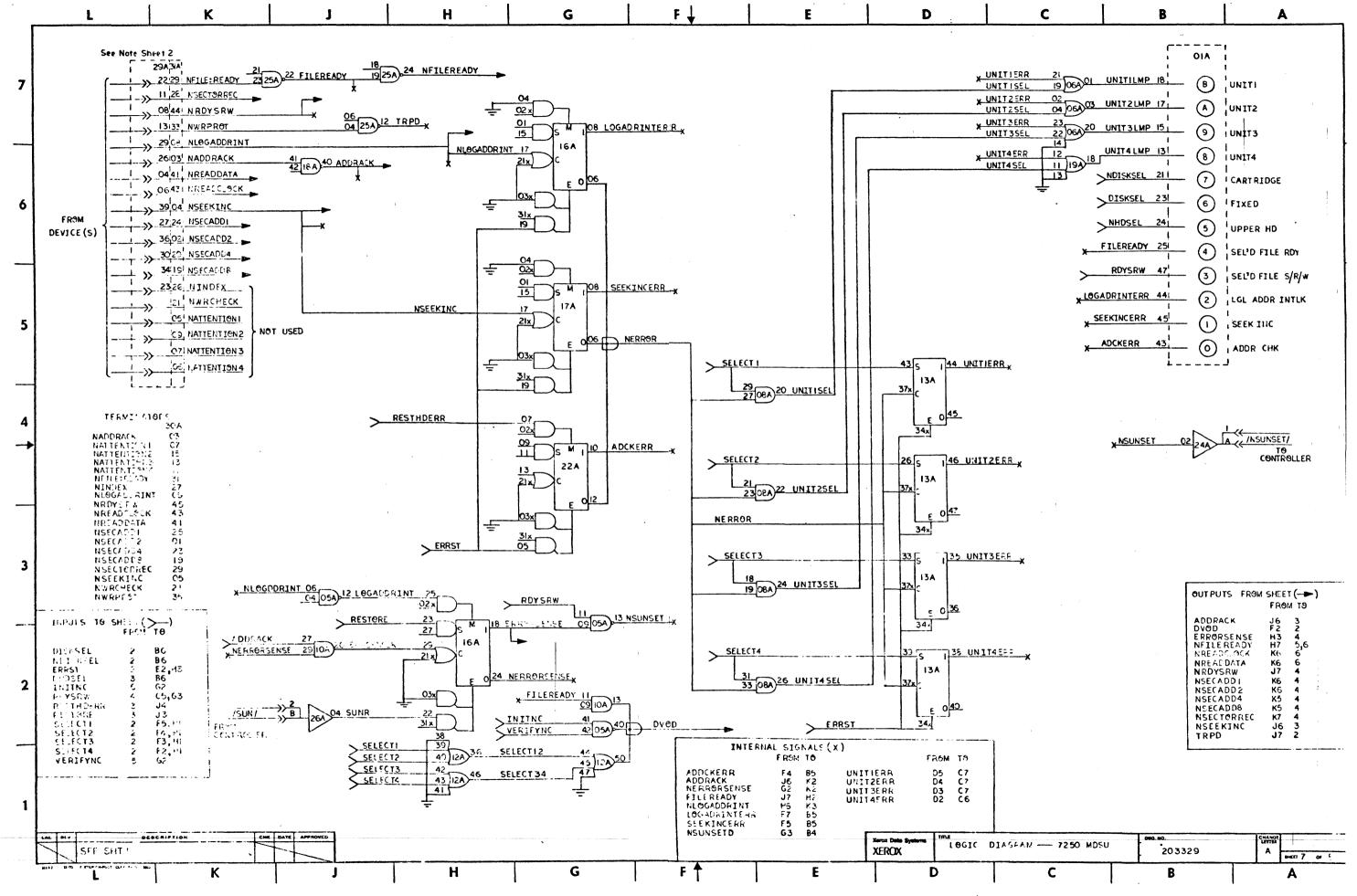

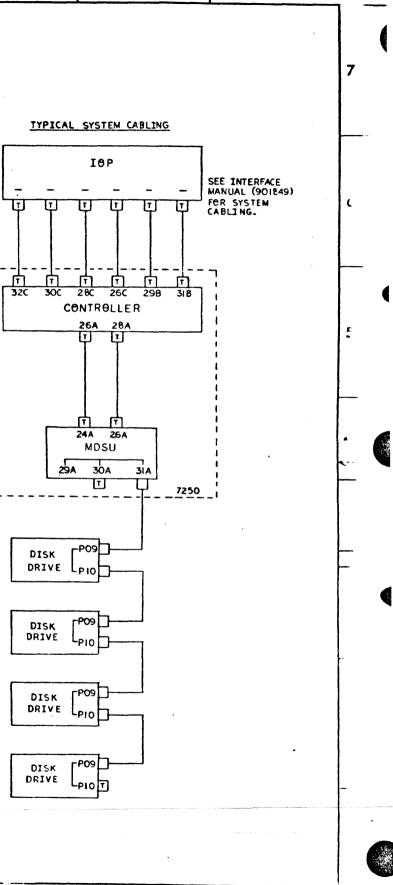

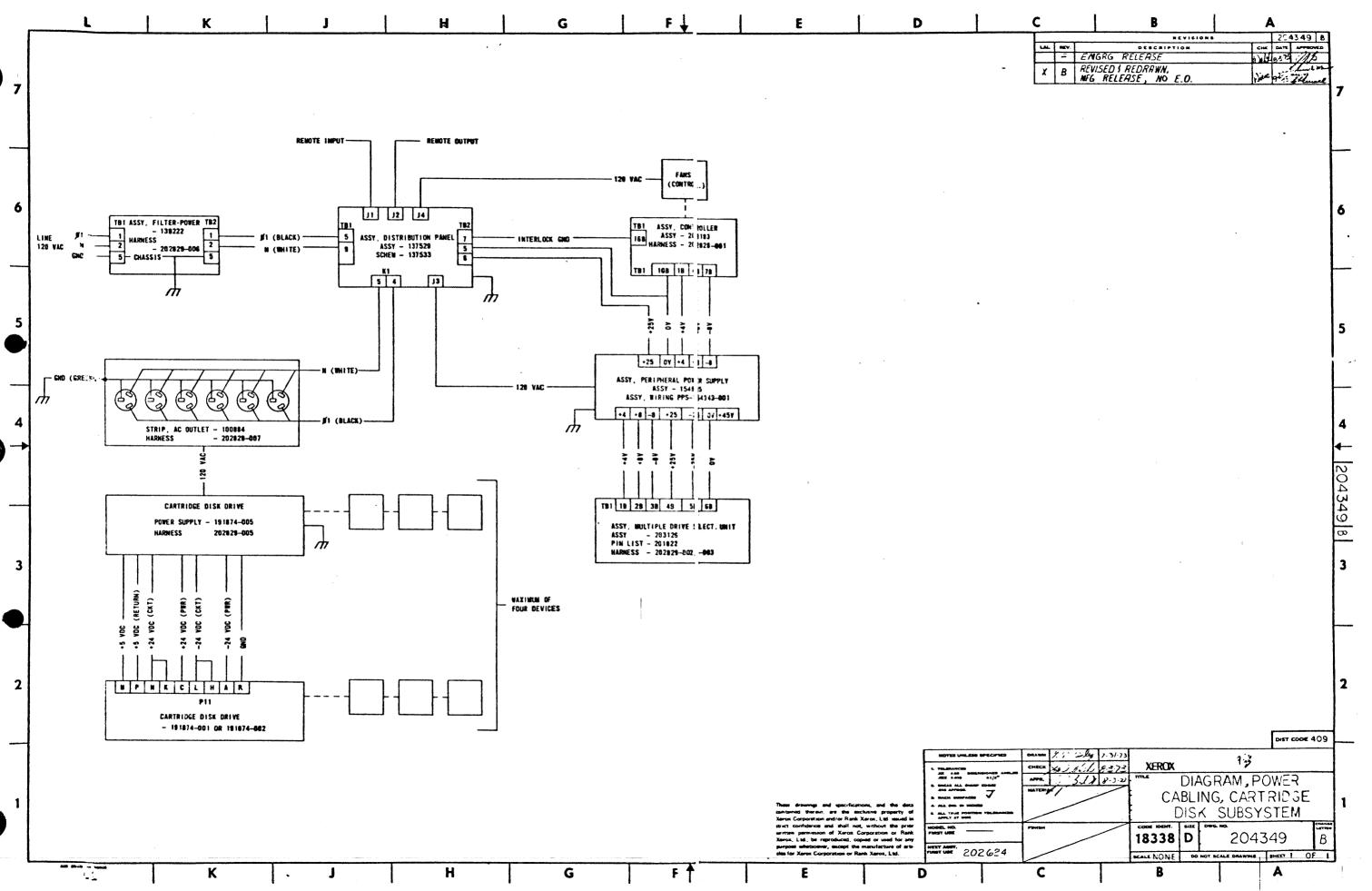

|         | 203329<br>204349           | A<br>B      | Diagram, Logic-Multiple Drive Selection Unit<br>Diagram, Power Cabling, Cartridge Disk<br>Subsystem                      | 1 thru<br>1 of 1           | 8            |

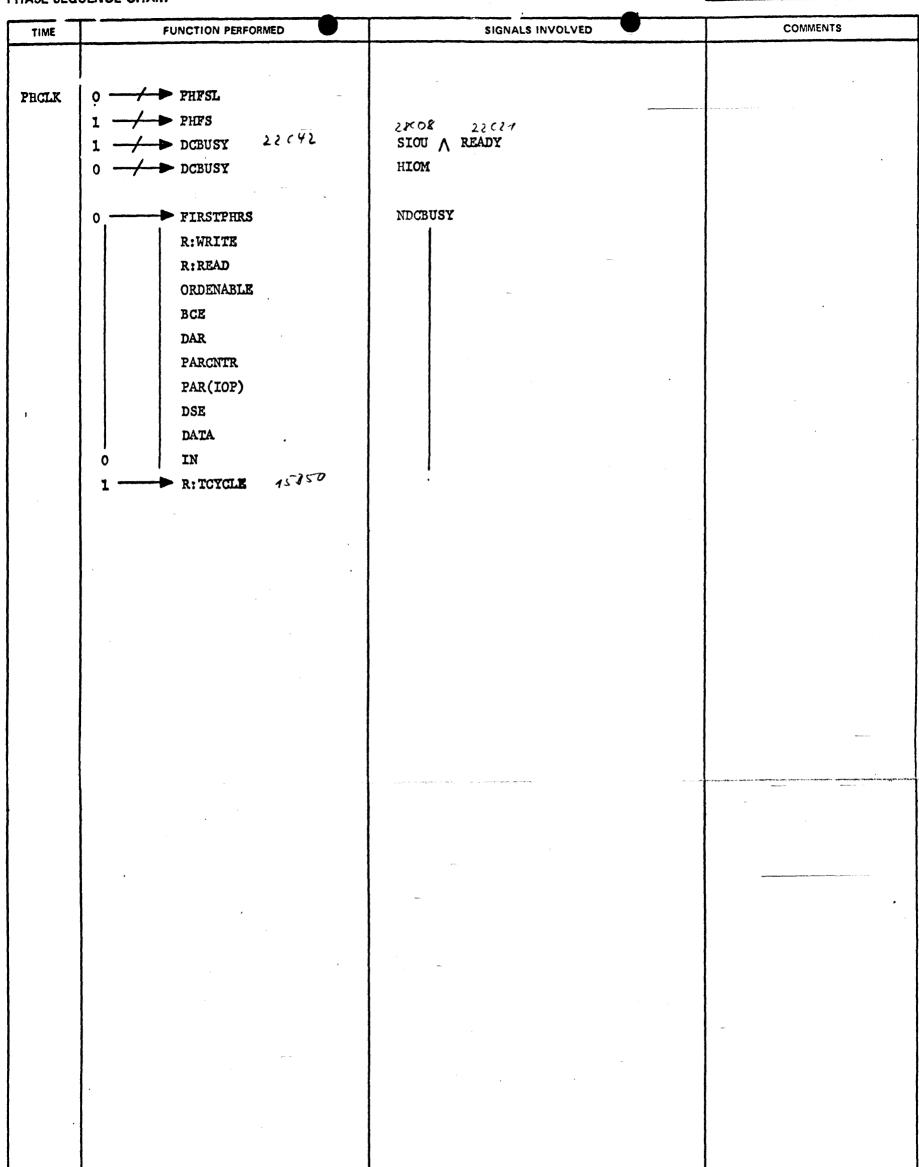

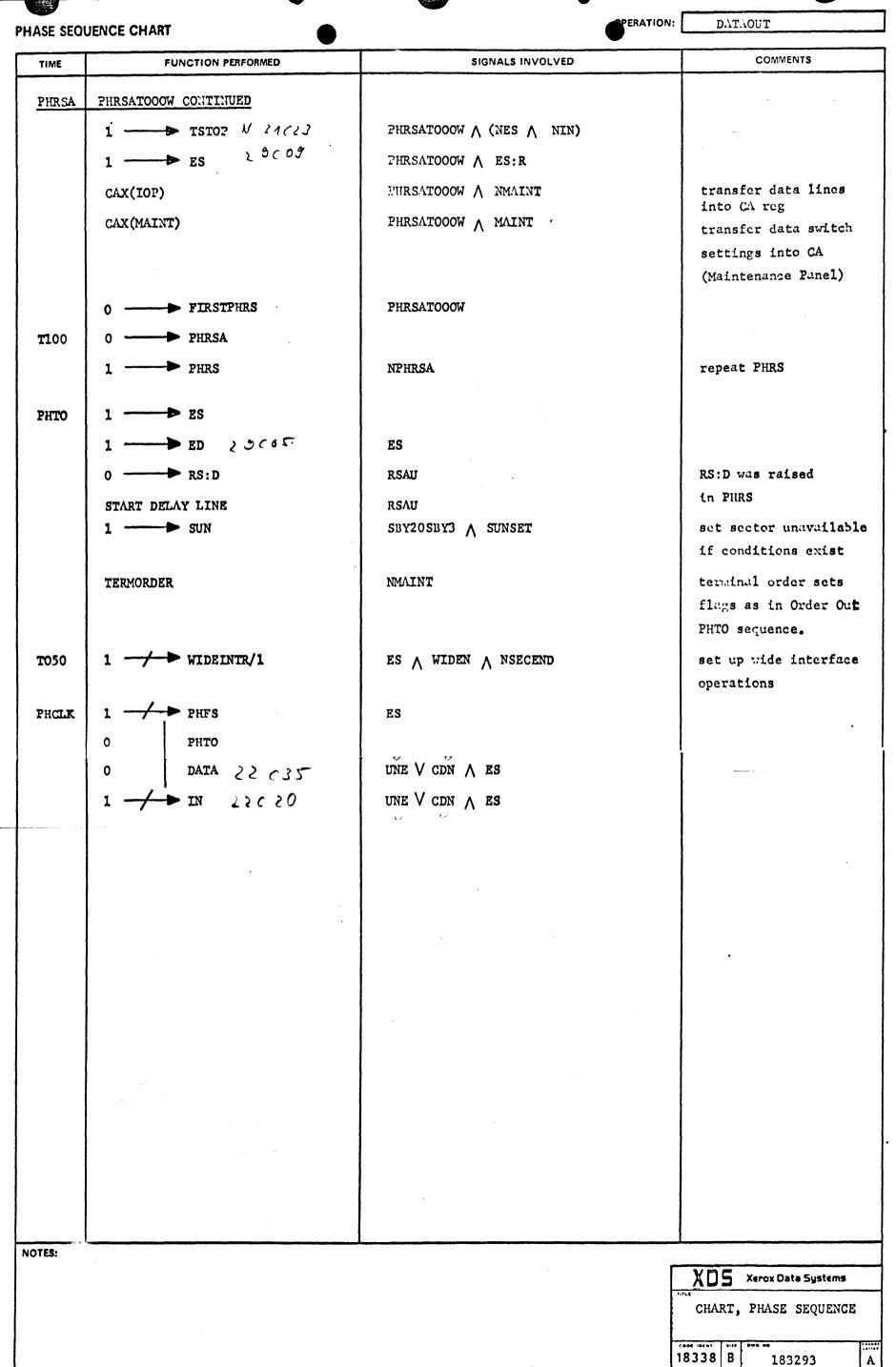

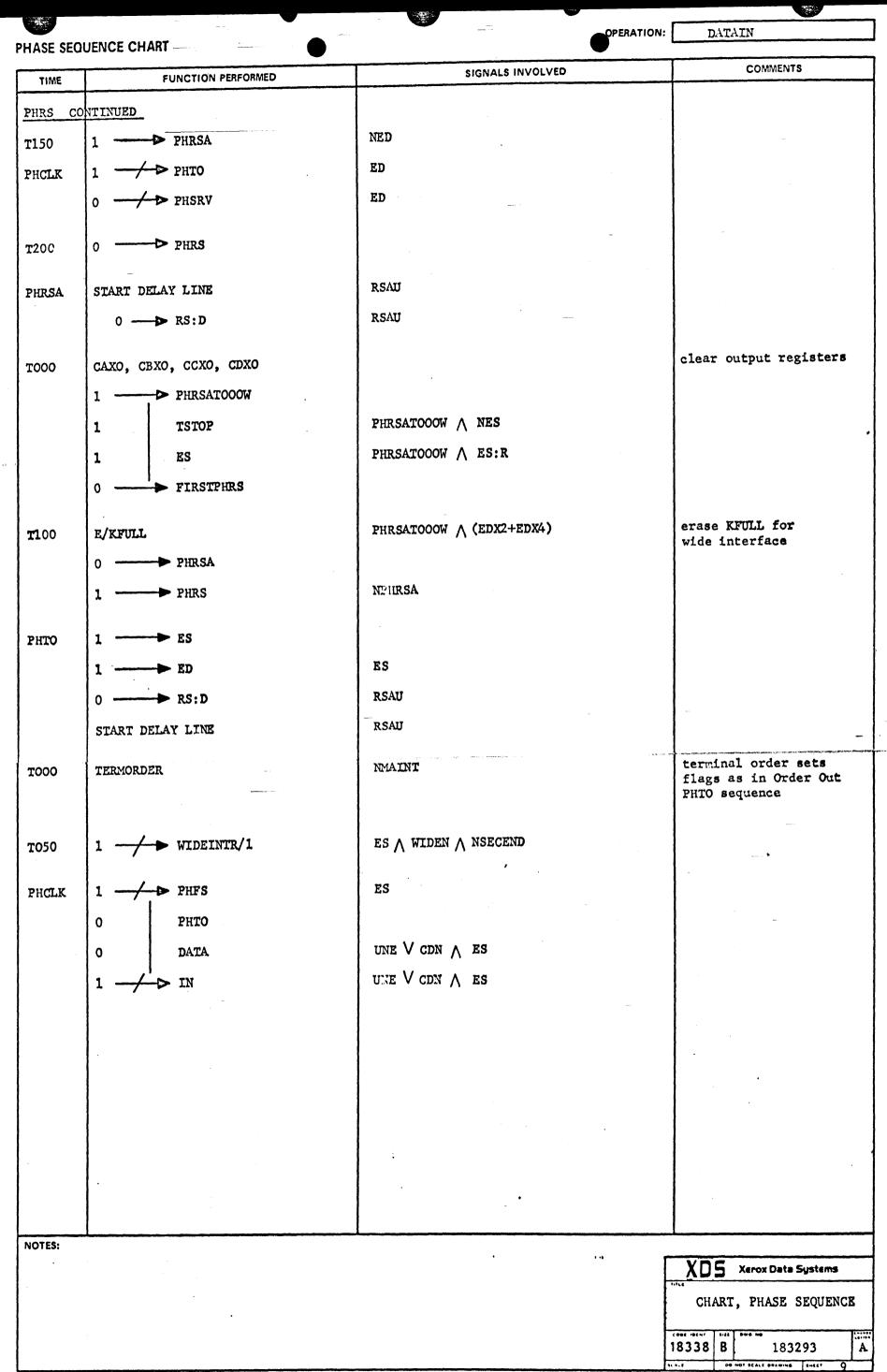

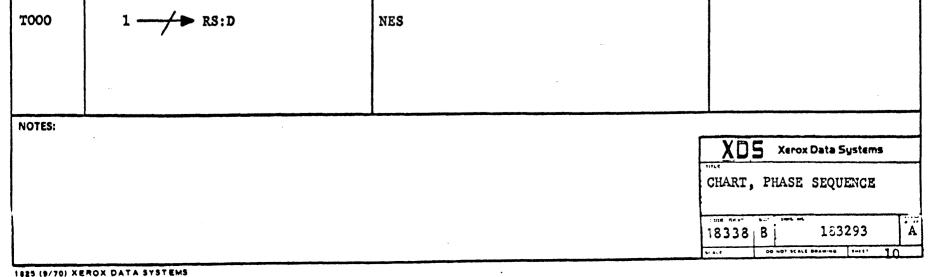

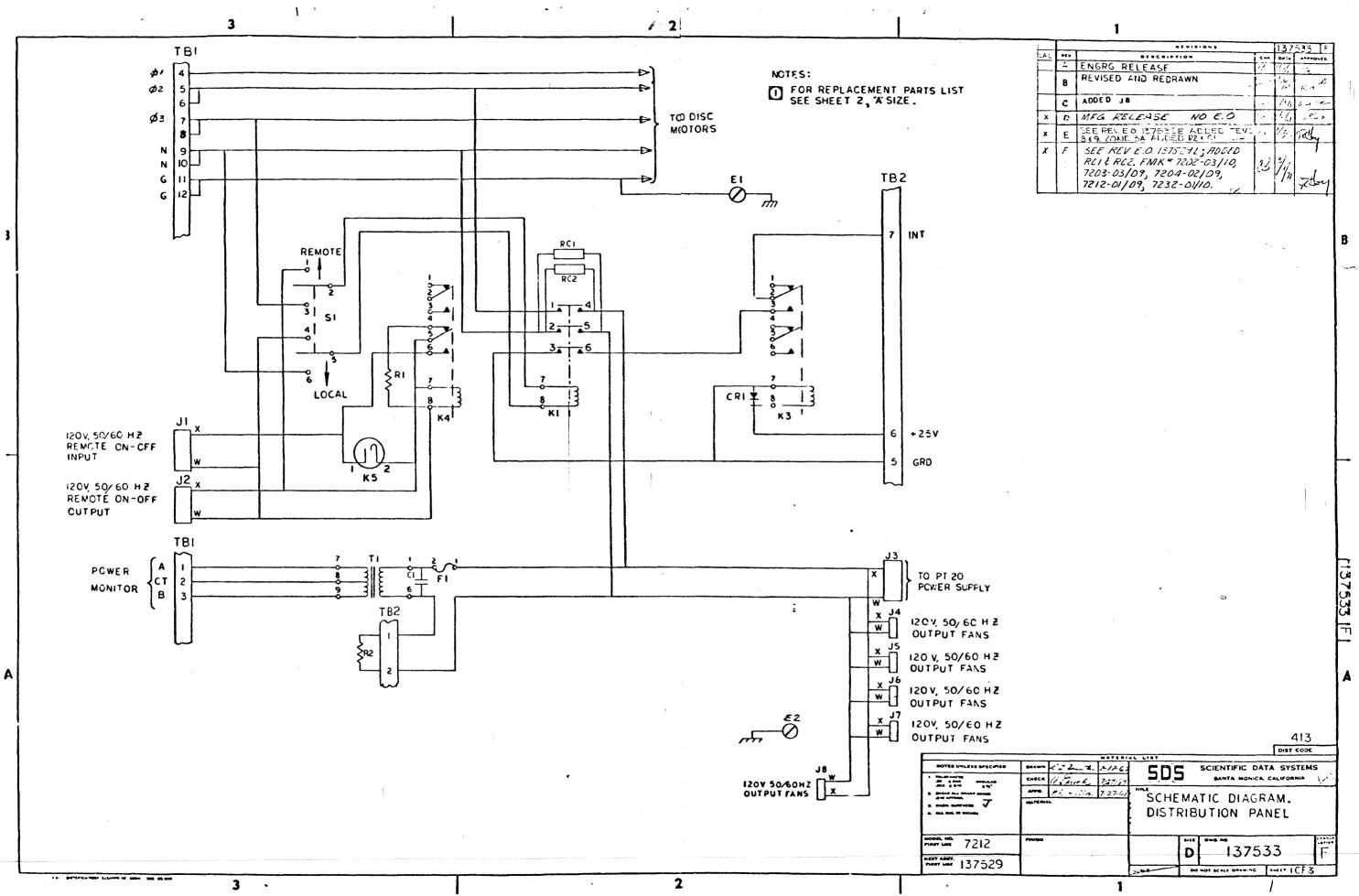

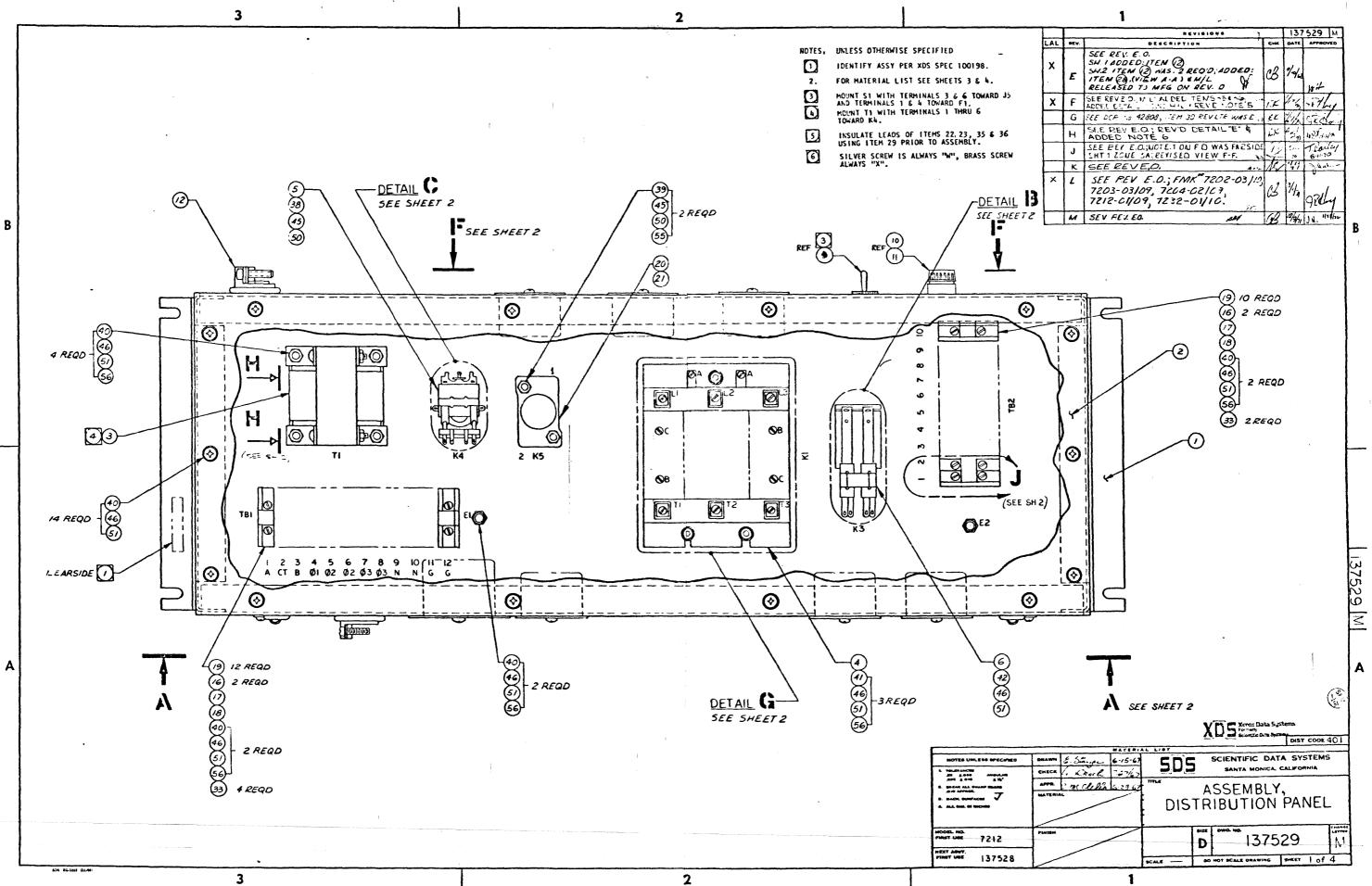

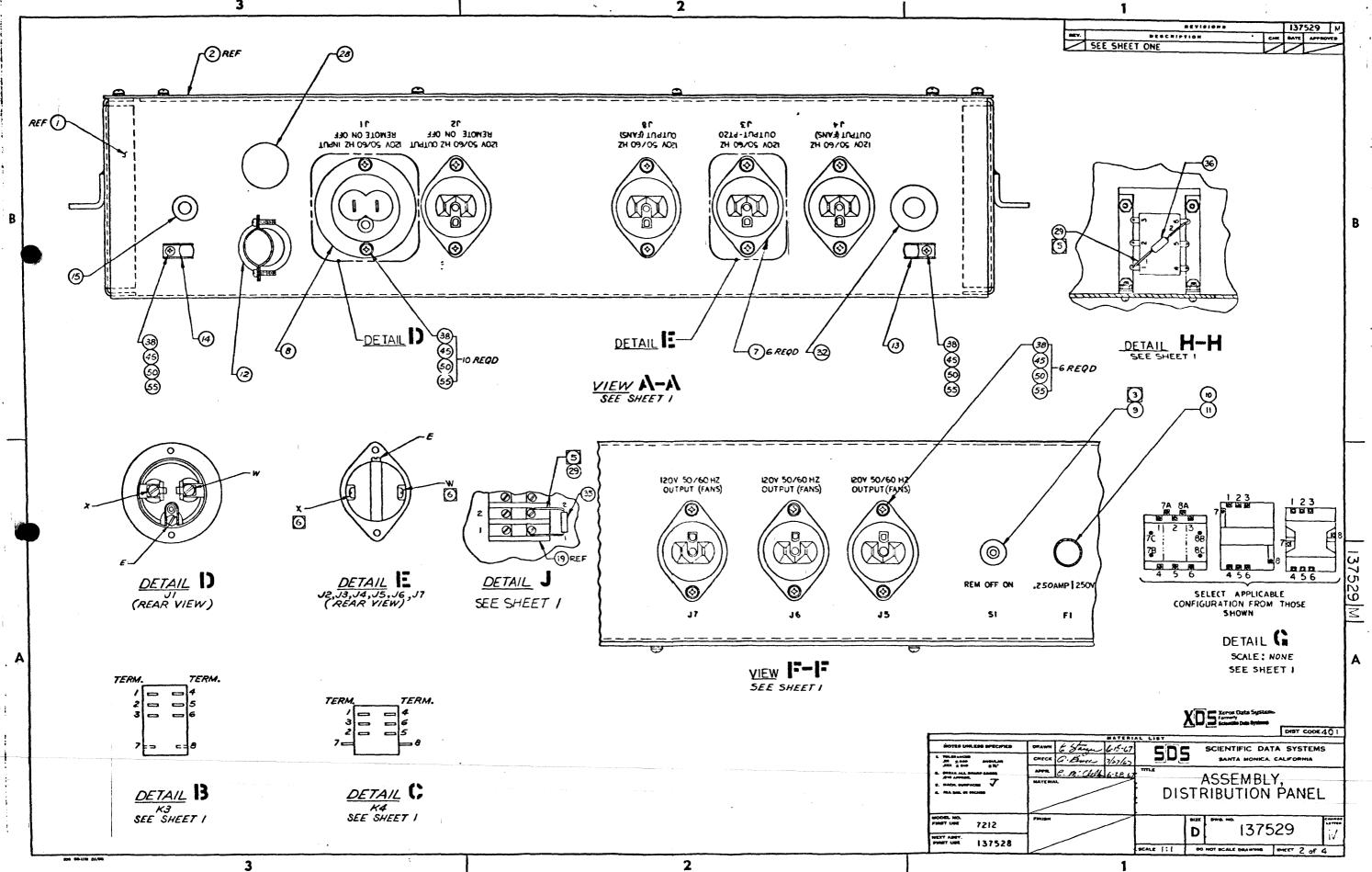

|         | 1375 <b>33</b><br>183293   | F<br>A      | Schematic Diagram, Distribution Panel<br>Chart, Phase Sequence                                                           | 1 thru<br>1 thru           | 3<br>11      |

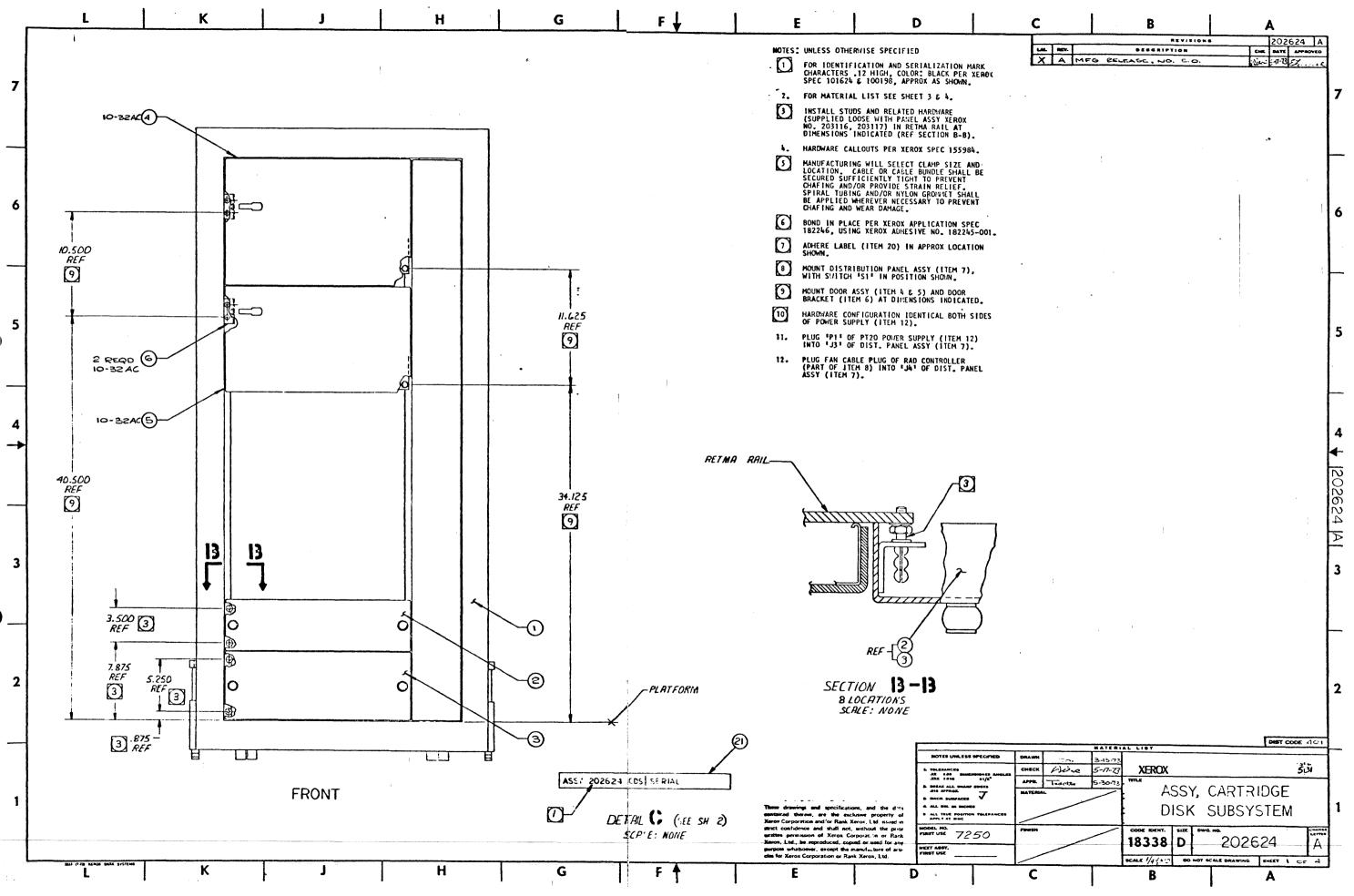

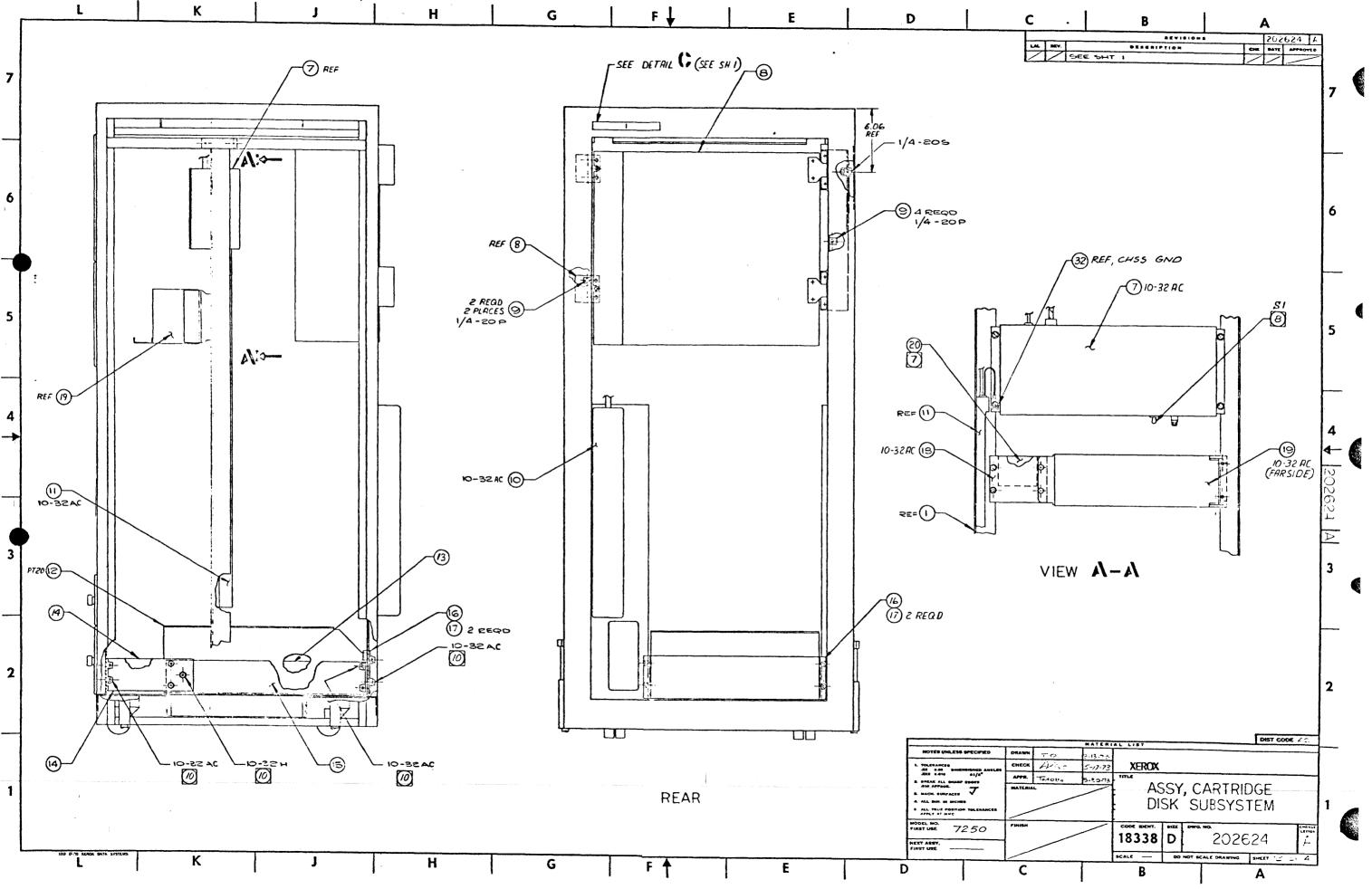

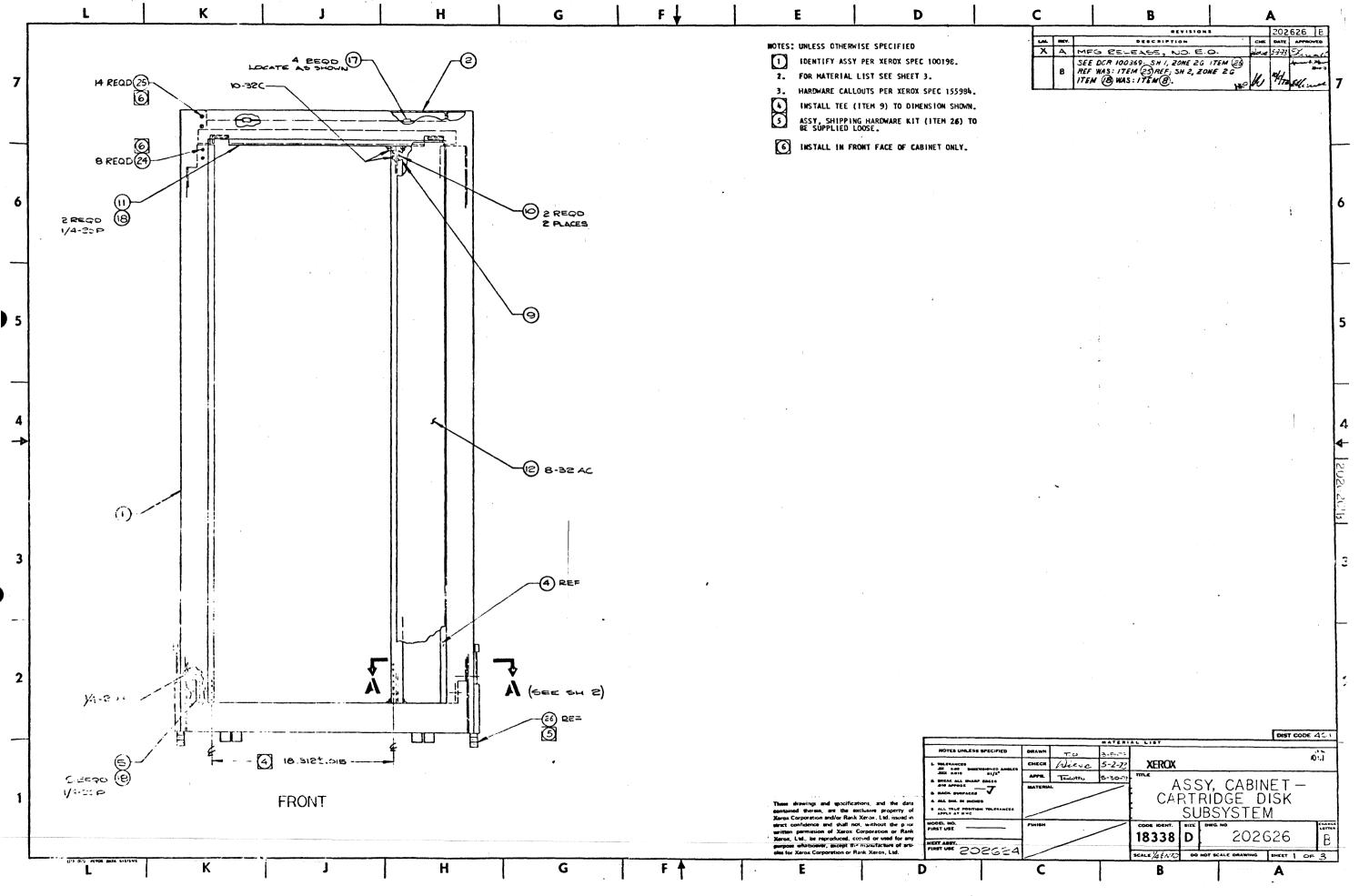

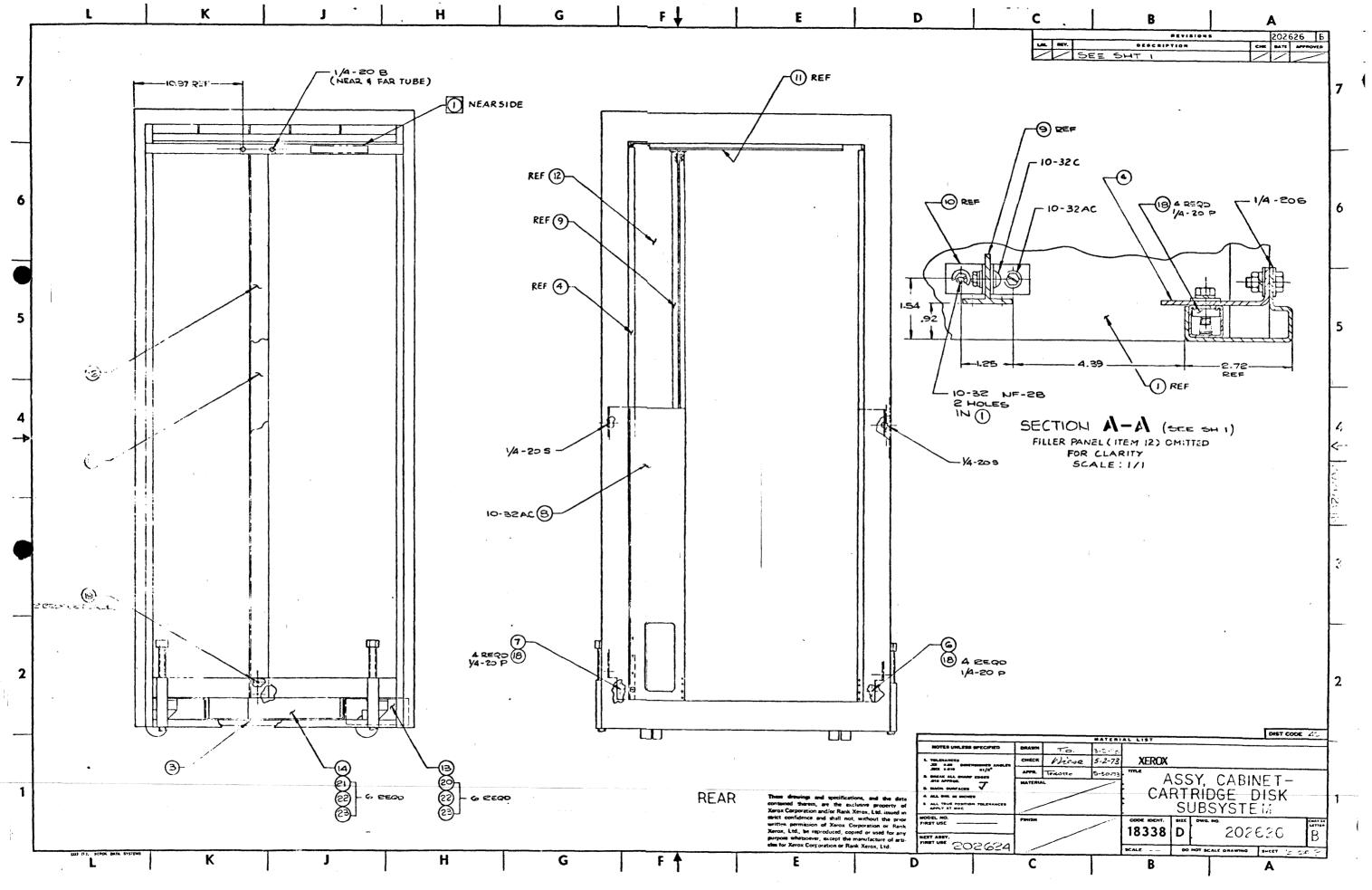

|         | 202624<br>202626           | A<br>B      | Assembly, Cartridge Disk Subsystem<br>Assembly, Cabinet–Cartridge Disk Subsystem                                         | 1 thru<br>1 thru           | 4<br>3       |

|         | 137529<br>139222           | M<br>K      | Assembly, Distribution Panel<br>Assembly, Filter-Power                                                                   | 1 thru<br>1 thru           | 4<br>2       |

|         | 203183<br>202829           | D           | Assembly, Controller–Cartridge Disk Drive<br>Assembly, Harness–Cartridge Disk Subsystem                                  | 1 thru<br>1 thru           | 4<br>16      |

|         | 203126<br>204497           | BA          | Assembly, Multiple Drive Selection Unit<br>Assembly, Maintenance Panel–Controller                                        | 1 thru<br>1 thru           |              |

|         | 203116<br>203117           | A<br>A      | Assembly, Panel, Push-On<br>Assembly, Panel, Push-On                                                                     | 1 thru<br>1 thru           | 2            |

|         | 203123<br>203888           | BB          | Assembly, Kit–Cartridge Disk Subsystem<br>Assembly, Kit, Conversion Full to Half<br>Capacity Cartridge Disk Drive        | 1 thru<br>1 thru           | 4<br>3       |

|         | 203702<br>137113           | BU          | Assembly, Kit-Cartridge Disk Subsystem<br>Integration Drawing, Sigma I/O Interface                                       | 1 thru<br>1 thru           | 4<br>18      |

|         | 203777                     | D           | Subsystem<br>Installation Drawing, Cartridge Disk<br>and Controller                                                      | 1 thru                     | 21           |

|         | 203825<br>204486           | D<br>A      | Installation Drawing, Cartridge Disk<br>Configuration Control List–Cartridge Disk                                        | 1 thru<br>1 thru           | 16<br>2      |

|         | 204487                     | В           | Subsystem<br>Configuration Control List–Cartridge                                                                        | 1 thru                     | 2<br>5       |

|         | 204488                     | A           | Disk Drive<br>Configuration Control List—Cartridge                                                                       | 1 thru                     | 5            |

|         | 204731                     | В           | Disk Drive<br>Module—Sr, Modification                                                                                    | 1 thru                     | 4            |

|         |                            |             | an a                                                                                 |                            |              |

i

Ι,

|         |                                                                                                              | NEERIN     | NG SUPPORT                                                                                                            |           | -     |                                                                                                        |

|---------|--------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------|-----------|-------|--------------------------------------------------------------------------------------------------------|

| MO      |                                                                                                              |            | TOP ASSEMBLY                                                                                                          | 202624    | LEVEL | A                                                                                                      |

| NAN     | AE <u>CARTRIE</u>                                                                                            | DGE DISK ( | CONTROLLER                                                                                                            |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

| Section | Drawing No.                                                                                                  | Level      |                                                                                                                       | Title     |       | Pages                                                                                                  |

| IV      | DESIGN AUTO                                                                                                  |            | DATA                                                                                                                  |           |       |                                                                                                        |

|         | 204432-001<br>204432-100<br>204431-001<br>204431-903<br>201823-100<br>201823-001<br>201822-001<br>201822-901 | BB         | Logic Dictionary<br>Logic Equations<br>Pin List<br>Pin Index<br>Logic Dictionary<br>Pin List<br>Pin List<br>Pin Index |           |       | 1 thru 179<br>1 thru 41<br>1 thru 124<br>1 thru 95<br>1 thru 12<br>1 thru 44<br>1 thru 31<br>1 thru 31 |

|         |                                                                                                              |            |                                                                                                                       |           | ,     |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       | 1.                                                                                                     |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       | 1         |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            | -                                                                                                                     |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            | •                                                                                                                     |           |       | :                                                                                                      |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              |            |                                                                                                                       |           |       |                                                                                                        |

|         |                                                                                                              | -          |                                                                                                                       | • • • • • |       |                                                                                                        |

,

#### 903059

#### RELATED PUBLICATIONS

The following Xerox publications contain information not included within this manual. These publications must be available as part of Site Documentation in order for the user of this manual to learn, install, operate, and maintain the equipment.

| Publication Title                                       | Do | cument No. |

|---------------------------------------------------------|----|------------|

| Cartridge Disk Reference Manual                         |    | 903024     |

| Cartridge Disk Drive Maintenance Manual Modes 7251/7252 |    | 903042     |

| Sigma 2/3 Diagnostic Program Monitor Manual             |    | 901650     |

| Sigma 2/3 Comprehensive RAD Diagnostic Manual           |    | 901721     |

| Sigma 5/7 Diagnostic Program Monitor Manual             |    | 901649     |

| Sigma 5/7 Comprehensive RAD Diagnostic Manual           |    | 901678     |

903059

## SECTION I

• 1

## THEORY OF OPERATIONS

|     |      | Revisions                      |       | 204     | 262 A         |

|-----|------|--------------------------------|-------|---------|---------------|

| LAL | Rev. | Description                    | Chk   | Date    | Approved      |

| X   | A    | MANUFACTURING RELEASE, NO E.O. | hiere | 1-30 74 | Ipener A. War |

Scale NONE

Do Not Scale Drawing

Sheet

1

202624

Α

### TABLE OF CONTENTS

| Sec                                                                               | tion                          |                                                                                                                |                                                                                                                                                                             |                                                                         | Title             |            |       | •                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                             | n.,,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | •       |     |                             | Shee                                                                                                           | t |

|-----------------------------------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------|------------|-------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------|-----|-----------------------------|----------------------------------------------------------------------------------------------------------------|---|

| ••••••                                                                            | 1.0                           | INTRO                                                                                                          | DUCTION                                                                                                                                                                     |                                                                         |                   |            |       |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |         |     | •                           |                                                                                                                |   |

|                                                                                   |                               | 1-1<br>1-2                                                                                                     | Purpose                                                                                                                                                                     |                                                                         | • •               | ••         | •••   | •                           | •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                             | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •           | •       | • • | •                           | . 5                                                                                                            |   |

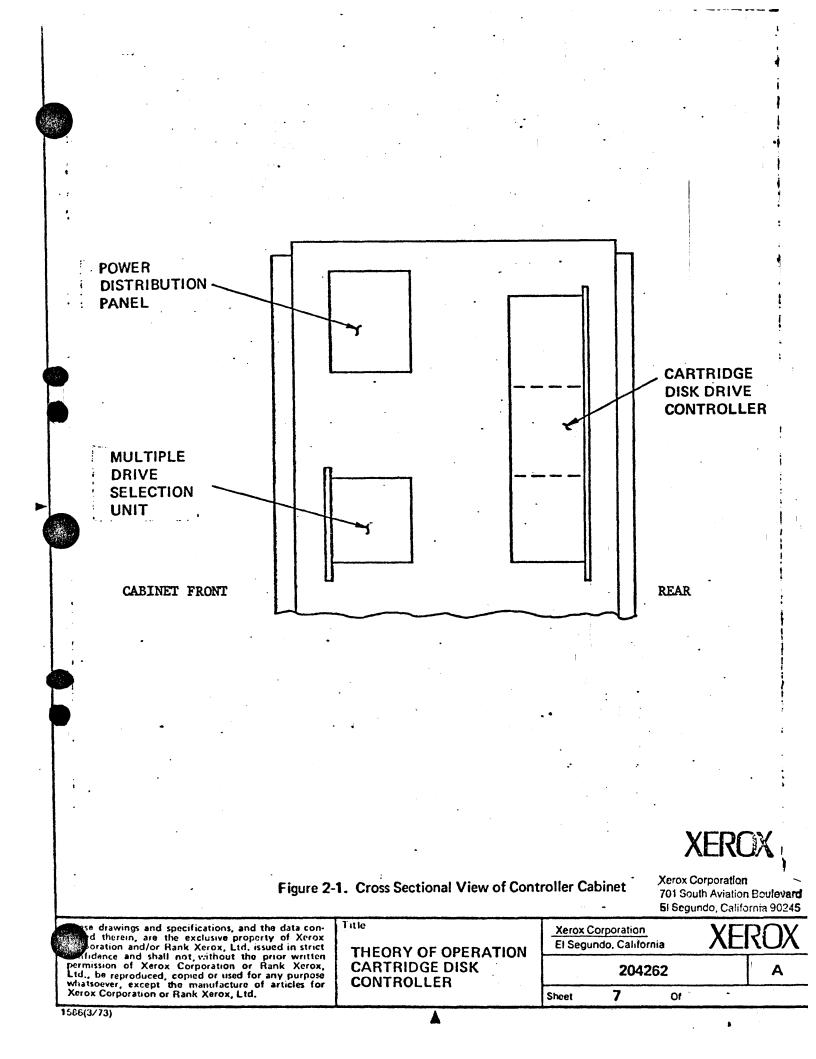

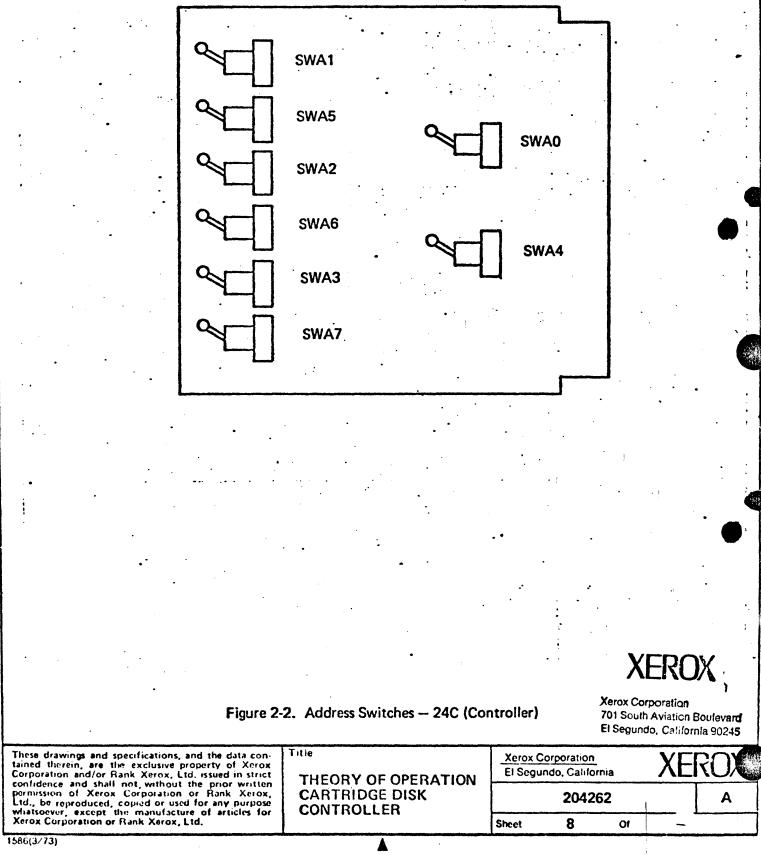

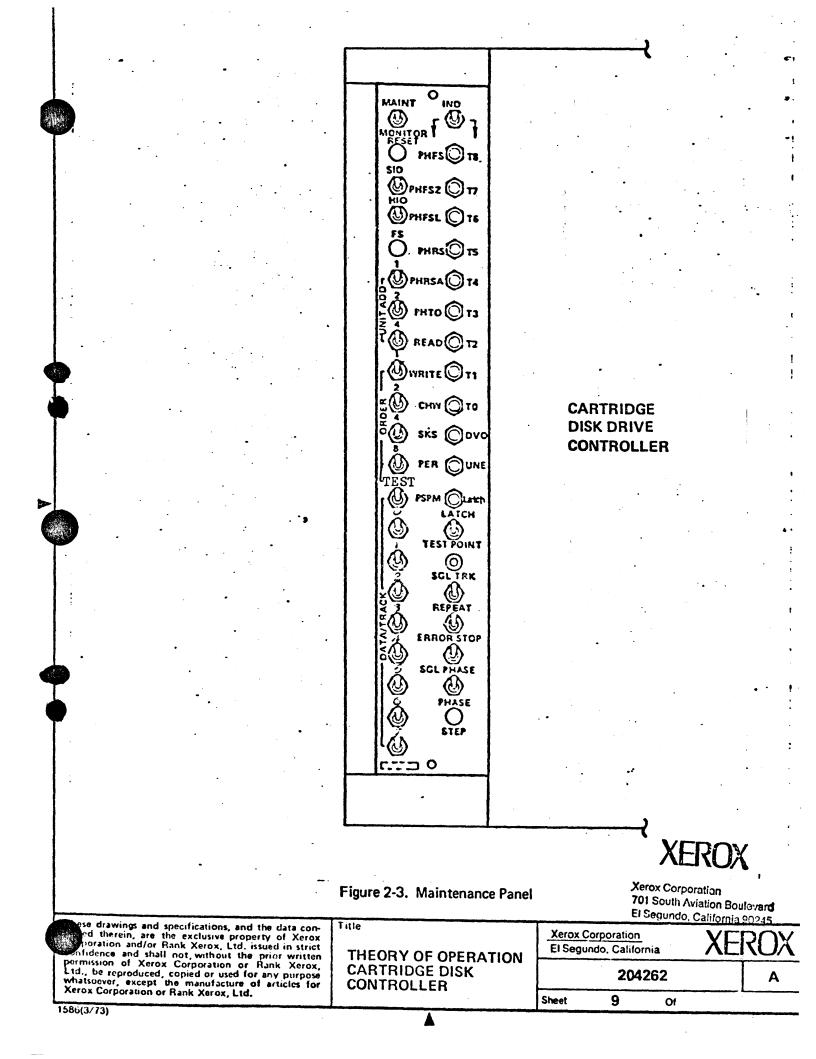

| 2                                                                                 | 2.0                           | EQUIP                                                                                                          | MENT PHYSICAL D                                                                                                                                                             | ESCRIPTI                                                                | ON                |            |       |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |         |     |                             |                                                                                                                |   |

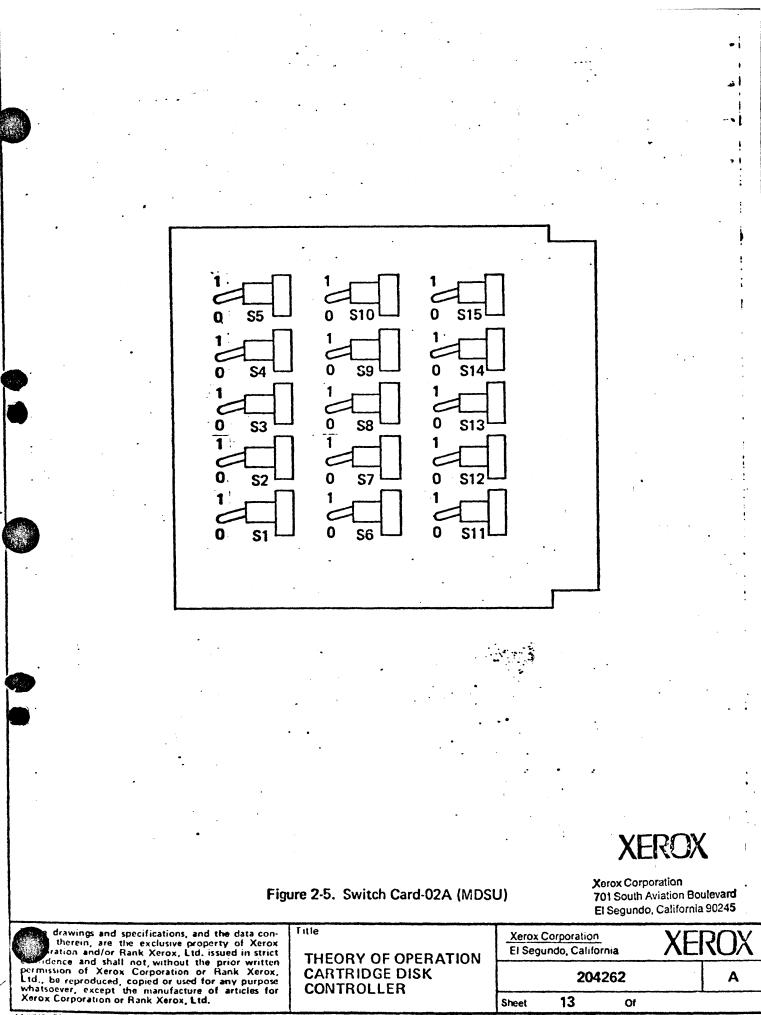

|                                                                                   | -                             | 2-1<br>2-2<br>2-3<br>2-4<br>2-5<br>2-6                                                                         | General<br>Controls and Indicat<br>Subcontroller Sw<br>Maintenance Pane<br>Selection Unit<br>Power Requirement                                                              | ors<br>itches                                                           | • •<br>• •<br>• • | • •<br>• • | · ·   | •<br>•<br>•                 | • •<br>• •<br>• •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • •<br>• •<br>• •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •<br>•<br>•                   | • •<br>• •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •<br>•<br>• | • •     | • • | •<br>•<br>•                 | 6<br>6<br>6<br>11<br>14                                                                                        |   |

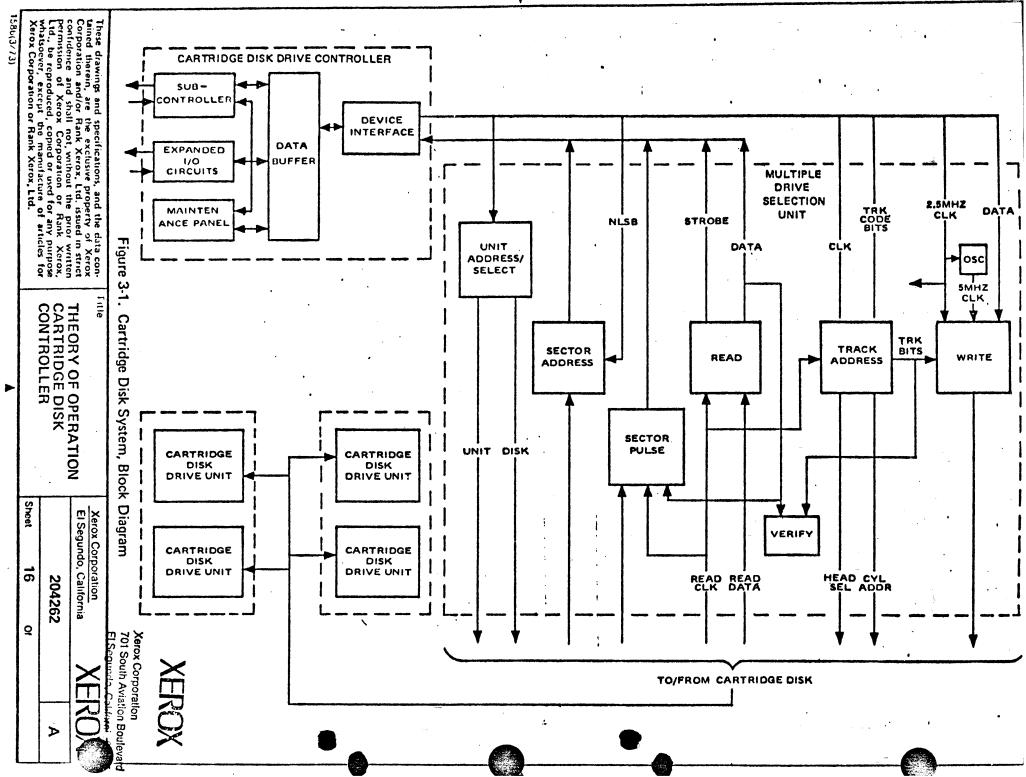

| ;                                                                                 | 3.0                           | GENE                                                                                                           | RAL FUNCTIONAL                                                                                                                                                              | DESCRIPT                                                                | <b>FION</b>       |            |       |                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |         |     |                             |                                                                                                                |   |

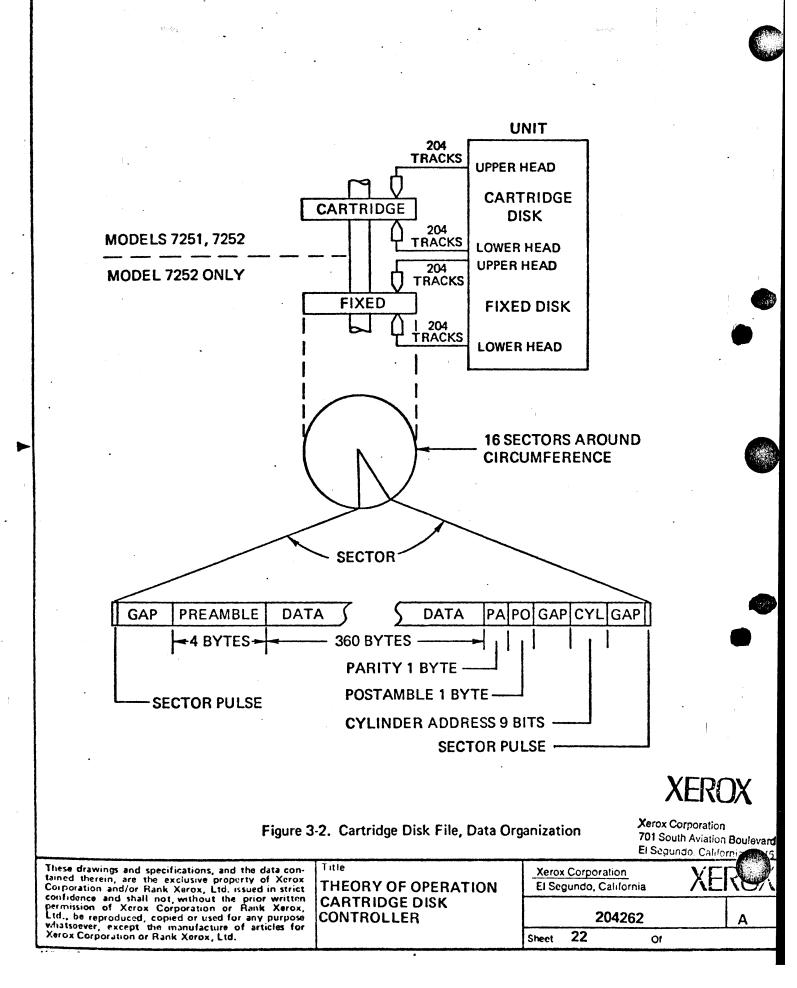

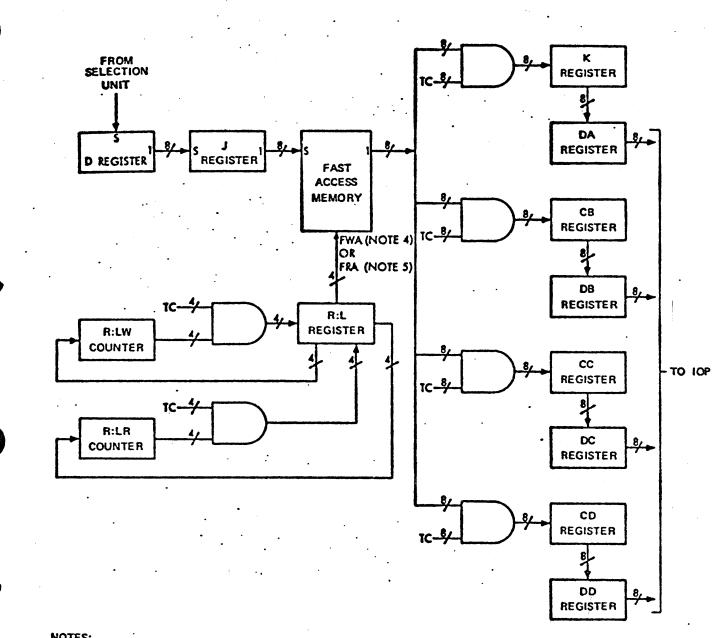

|                                                                                   |                               | 3-1<br>3-2<br>3-3<br>3-5<br>3-7<br>3-9<br>3-11<br>3-13<br>3-15<br>3-16<br>3-17<br>3-10<br>3-20<br>3-21<br>3-22 | General                                                                                                                                                                     | torage                                                                  |                   |            |       | • • • • • • • • • • • • • • |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | • • • • • • • • • • • • • • • |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             |         |     | • • • • • • • • • • • • • • | 15<br>15<br>17<br>21<br>24<br>24<br>24<br>24<br>24<br>24<br>25<br>26<br>28<br>31<br>32<br>33<br>33<br>33<br>34 |   |