Scientific Data Systems A XEROX COMPANY

# **5D5 SIGMA** 100 CARD/MINUTE CARD PUNCH MODEL 7165

**Reference Manual**

# **CARD PUNCH ORDER CODES**

| Code<br>(Hexadecimal) | )<br>) | Function                             |

|-----------------------|--------|--------------------------------------|

| 01                    |        | Punch Binary (stack card normally)   |

| 05                    |        | Punch EBCDIC (stack card normally)   |

| 09                    |        | Punch Binary (offset stack on error) |

| 0D                    |        | Punch EBCDIC (offset stack on error) |

| 11                    |        | Punch Binary (offset stack)          |

| 15                    |        | Punch EBCDIC (offset stack)          |

| 19                    |        | Punch Binary (offset stack)          |

| 1D                    |        | Punch EBCDIC (offset stack)          |

| 41 <sup>†</sup>       |        | Punch Binary (stack card normally)   |

| 45 <sup>†</sup>       |        | Punch EBCDIC (stack card normally)   |

| 49 <sup>†</sup>       |        | Punch Binary (offset stack on error) |

| 4D <sup>†</sup>       |        | Punch EBCDIC (offset stack on error) |

| 51 <sup>†</sup>       |        | Punch Binary (offset stack)          |

| 55 <sup>†</sup>       |        | Punch EBCDIC (offset stack)          |

| 59 <sup>t</sup>       |        | Punch Binary (offset stack)          |

| 5D <sup>†</sup>       |        | Punch EBCDIC (offset stack)          |

<sup>t</sup>Interrupt at Data Transmission Complete (i.e., device-initiated interrupt occurs at zero byte count).

PRICE: \$1.00

# **100 CARD/MINUTE CARD PUNCH**

# MODEL 7165

# **REFERENCE MANUAL**

for

# SDS SIGMA COMPUTERS

PRELIMINARY EDITION

90 15 67A

July 1969

SCIENTIFIC DATA SYSTEMS A XEROX COMPANY/701 South Aviation Boulevard/El Segundo, California 90245

# **RELATED PUBLICATIONS**

| Title                                           | Publication No. |

|-------------------------------------------------|-----------------|

| SDS Sigma 7 Computer Reference Manual           | 90 09 50        |

| SDS Sigma 5 Computer Reference Manual           | 90 09 59        |

| SDS Sigma 2 Computer Reference Manual           | 90 09 64        |

| SDS 5/7 Symbol and Meta-Symbol Reference Manual | 90 09 52        |

| SDS Sigma 2 Symbol Reference Manual             | 90 10 51        |

ALL SPECIFICATIONS SUBJECT TO CHANGE WITHOUT NOTICE

# CONTENTS

| 1. | GENERAL DESCRIPTION               | 1   |

|----|-----------------------------------|-----|

|    | Introduction                      | 1   |

|    |                                   |     |

| 2. | FUNCTIONAL DESCRIPTION            | 2   |

|    | Physical Description              | 2   |

|    | Data Presentation                 | 2   |

|    | EBCDIC Format                     | 2   |

|    | Binary Format                     | 2   |

|    | Card Punch States                 | 3   |

|    | Operational States                | ্ত  |

|    | Ready Condition                   | 3   |

|    | Busy Condition                    | 3   |

|    | Manual Mode                       | 3   |

|    | Automatic Mode                    |     |

|    |                                   | -   |

|    | Data Transfer                     | 3   |

| 3. | PROGRAM INTERFACE                 | 5   |

|    | Punch Orders<br>Punch Card EBCDIC |     |

|    | Punch Card EBCDIC                 | 5   |

|    | Punch Card Binary                 | 5   |

|    | Key Events                        | 5   |

|    | Start Input/Output                | 5   |

|    | Unusual End Conditions            | 5   |

|    | Channel End Condition             | 6   |

|    | Fault Conditions                  | 6   |

|    | Error Conditions                  |     |

|    | Card Punch Status Response        | 6   |

|    | I/O Instruction Status Bits       | 6   |

|    | Device Status Byte                | 6   |

|    | Operational Status Byte           | 6   |

|    | Programming Considerations        | 6   |

|    |                                   | . 0 |

| 4. | OPERATIONS                        | 12  |

|    | Operator Controls                 | 12  |

|    | Power                             | 12  |

|    | Start                             | 12  |

|    | Stop                              | 13  |

|    | Manual Feed                       | 13  |

|    | Reset                             | 13  |

|    | Hopper/Stacker                    |     |

|    | Punch Error                       | 14  |

|    | Chips/Jam                         | 14  |

|    | Input Hopper                      | 14  |

|    | Output Stacker                    | 14  |

|    | Cover Interlock                   | 14  |

|    | Operating Instructions            |     |

|    | Operating Preparation             | 14  |

|    | Turn-On Procedure                 | 14  |

|    | Continuous Operation              | 14  |

|    | Momentary Halt                    | 14  |

|    | Automatic Recoverable Halt        | 14  |

|    |                                   | -   |

| Clearing Card Jams | 15 |

|--------------------|----|

| Pick Jam           | 15 |

| Throat Jam         | 15 |

| Registration Jam   | 15 |

| Eject Jam          | 16 |

| Punch Head Jam     | 16 |

# APPENDIXES

| Α. | SDS STANDARD SYMBOLS, CODES, AND CORRESPONDENCES | 17 |

|----|--------------------------------------------------|----|

| Β. | PROGRAMMING EXAMPLES                             | 23 |

|    | Sigma 5/7 Programming Example                    | 23 |

|    | Sigma 2 Programming Example                      | 24 |

# ILLUSTRATIONS

|    | Model 7165 Card Punch                          | _ iv |

|----|------------------------------------------------|------|

| 1. | Card Rate (cards per minute)                   | 1    |

| 2. | EBCDIC Card Punch Operation                    | 2    |

| 3. | Binary Card Punch Operation                    | _ 2  |

| 4. | Card Punch Timing                              | 9    |

| 5. | Controlling System and Card Punch Actions      | 10   |

| 6. | Model 7165 Card Punch                          | 12   |

| 7. | Control Panel                                  | 13   |

| 8. | Card Punch Mechanism with Access Cover<br>Open | _15  |

| 9. | Card Punch Mechanism, Left View                | 16   |

# TABLES

| 1. | Characteristics                               | 1 |

|----|-----------------------------------------------|---|

| 2. | Card Punch State Transitions                  | 4 |

| 3. | Card Punch I/O Instruction Execution Response | 6 |

| 4. | Device Status Response for SIO, TIO, and HIO  | 7 |

| 5. | Device Status Response for TDV and AIO        | 8 |

| 6. | Operational Status Byte                       | 8 |

Model 7165 Card Punch

# **1. GENERAL DESCRIPTION**

# **INTRODUCTION**

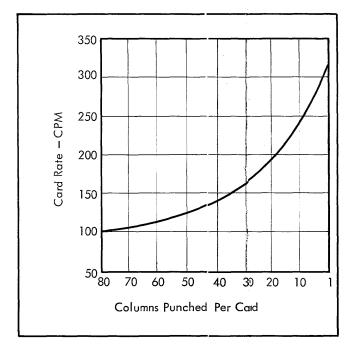

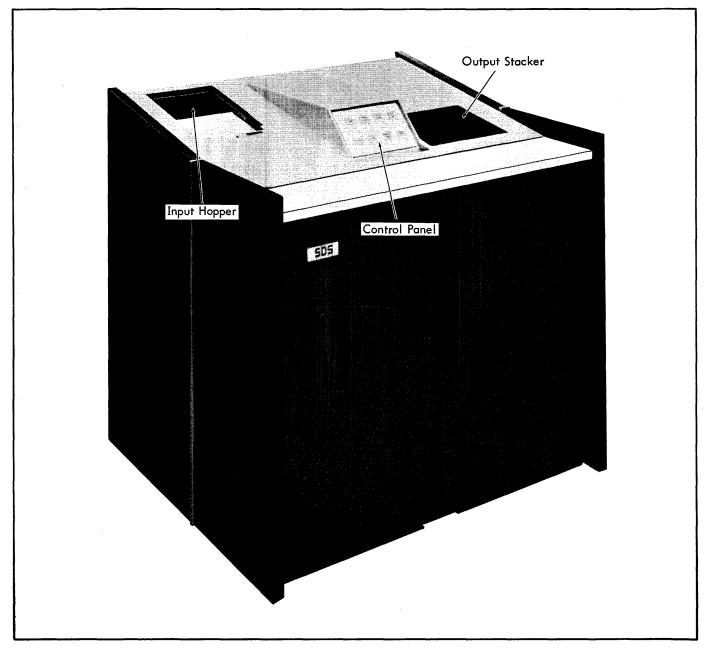

SDS Model 7165 Card Punch permits Sigma computer users to punch a standard 80-column card serially, column by column, at a rate of 100 cards per minute. When punching fewer than 80 columns, the rate increases up to a maximum of 300 cards per minute. Data is punched in either binary or EBCDIC format; an automatic check detects erroneously punched cards. An input hopper provides for card loading, and an output stacker for unloading. A card offset feature allows a selected card to be offset (raised) from the stack upon command. This feature may be used for card deck separation, for example.

When the card punch is operating, a card is picked from the input hopper and transported to the registration station where it is stopped and registered for column one data. After column one, the card is incrementally stepped, has as many columns punched as required, and then is transported to the output stacker. Phot o-electric diodes monitor card progress through the transport and provide signals for transport control and card-handlling matunctions.

Figure 1. Card Rate (carcls per minute)

Table 1. Characteristics

| Operating Characteristics               |                                              |  |  |  |

|-----------------------------------------|----------------------------------------------|--|--|--|

| Punch Speed                             | 100 cards per minute (all                    |  |  |  |

| (See Figure 1)                          | 80 columns)                                  |  |  |  |

|                                         | 300 cards per minute (sin–<br>gle column)    |  |  |  |

| Hopper capacity                         | 1000 cards                                   |  |  |  |

| Stacker capacity                        | 1000 cards                                   |  |  |  |

| Card type                               | EIA standard RS-292,<br>media I.             |  |  |  |

| Physical C                              | haracteristics                               |  |  |  |

| Height                                  | 40 in.                                       |  |  |  |

| Width                                   | 37.5 in.                                     |  |  |  |

| Depth                                   | 33 in.                                       |  |  |  |

| Weight (approximate)                    | 480 lb                                       |  |  |  |

| Cable length (Con-<br>troller to punch) | 40 ft (standard)<br>200 ft (optional)        |  |  |  |

| Environment                             | al Characteristics                           |  |  |  |

| Power requirements                      | 120 vac±10%, 50 or<br>60 Hz±1%, single-phase |  |  |  |

| Initial surge                           | 36 amp for 150 ms                            |  |  |  |

| Steady state                            | 9.5 amp, idle; 16 amp,<br>punching           |  |  |  |

| Temperature                             |                                              |  |  |  |

| Operating                               | 50° F to 95° F                               |  |  |  |

| Shipping or storage                     | –40° F to 150° F                             |  |  |  |

| Humidity                                |                                              |  |  |  |

| Operating                               | 20% to 75%                                   |  |  |  |

| Shipping or storage                     | 20% to 95% (provided no condensation occurs) |  |  |  |

| Shock                                   | 5Gs for $11 \pm 1$ ms                        |  |  |  |

| Vibration                               | 1G from 15 to 500 Hz                         |  |  |  |

# 2. FUNCTIONAL DESCRIPTION

# PHYSICAL DESCRIPTION

This card punch system consists of a card punch device with an electronics chassis assembly and a punch controller assembly (mounted in a standard SDS I/O rack). The controller interfaces the electronics chassis to the Sigma IOP or I/O channel.

The card punch is a free-standing unit, mounted on casters. The card-handling mechanism is supported on a rigid frame by vibration mounts. The front and rear doors and cover are hinged for easy access.

# DATA PRESENTATION

An 80-column card may be used to record data in either of two formats, EBCDIC or binary.

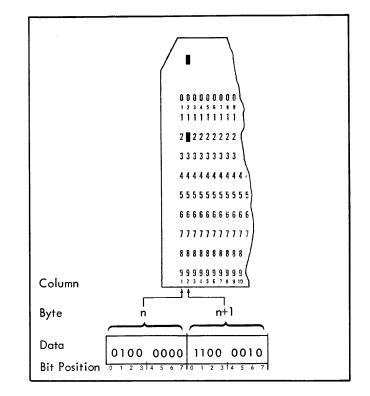

#### EBCDIC FORMAT

In the EBCDIC format, a card image consists of from 1 to 80 bytes of data. Each byte of this image is an 8-bit code in the range  $0 - 255_{10}$  ( $00_{16} - FF_{16}$ ), each of which corresponds to a punch configuration for a single column (see Appendix A). This card image, when transmitted to the card punch, is recorded on the card column by column with the punch configuration in column 1 corresponding to the first transmitted byte of the card image and the punch configuration in the last column corresponding to the last byte of the card image.

Figure 2 illustrates how the first two bytes of an EBCDIC card image are presented to the card punch by the controlling system. Note that EBCDIC code 4016 produces a blank (no punch) card column.

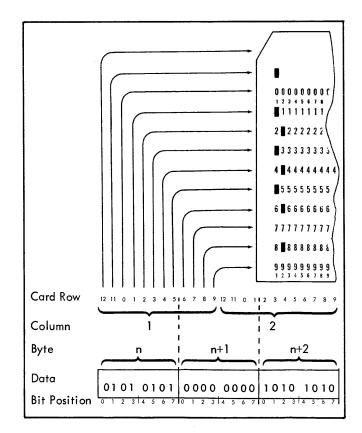

#### BINARY FORMAT

In the binary format, a card image consists of from 1 to 120 bytes of data. The binary card image, when received by the card punch, is reassembled as 12-bit codes and each 12-bit code is punched in the corresponding card column.

Figure 3 illustrates how the first three bytes of a binary card image are punched. Note that the first byte of the binary card image is punched in column 1, rows 12-5, with a 1 in the byte corresponding to a punch in the appropriate row. The second byte of the card image is separated so that bits 0-3 of the byte correspond to punches in rows 6-9 of column 1, and bits 4-7 of the byte correspond to rows 12-1 of column 2. The third byte of the card image is punched in rows 2-9 of column 2.

Figure 2. EBCDIC Card Punch Operation

Figure 3. Binary Card Punch Operation

# **CARD PUNCH STATES**

The initial state of the card punch depends on its power status. Complete absence of power removes the card punch from the controlling system. If power is applied to the controller, address recognition takes place when an I/O instruction is issued. If no power is applied to the punch when an I/O instruction is issued. If no power is applied to the punch when an I/O instruction is issued, status information is returned to the computer indicating the device is "not operational".

#### **OPERATIONAL STATES**

The card punch is in one of the four operational states explained below and summarized in Table 2 if the following conditions are satisfied.

- 1. Power is present.

- 2. No transport mechanism fault exists.

- 3. Interlock is closed.

- 4. No manual card feed is in process.

The condition and mode status of the card punch at any given time is returned to the central processor in response to such I/O instructions as SIO, HIO, and TIO. Other I/O instructions, such as AIO and TDV, obtain more specific indications of punch status.

#### **READY CONDITION**

In the "ready" condition, the punch can accept an SIO instruction, provided that no interrupt is pending. To be in the "ready" condition, the punch must be "operational" and the execution of an order to punch a card must not be pending.

#### **BUSY CONDITION**

In the "busy" condition, the punch has accepted an SIO instruction. It will not accept a new order until the current order (or orders) is completed and no interrupt is pending.

#### MANUAL MODE

The punch is in the "manual" mode when any condition requiring operator intervention arises before the punch can function normally (e.g., stacker full, hopper empty, or chip box full). The "manual" mode is forced by the operator pressing the STOP switch on the card punch control panel. The punch can accept an SIO instruction in this mode but does not act on it until the "automatic" mode is entered.

#### AUTOMATIC MODE

When all conditions for successful card punch operation are present, the punch enters the "automatic" mode when the START switch is pressed.

#### TRANSITION BETWEEN STATES

The card punch state transitions and the conditions causing the punch to change from one operational state to another are summarized in Table 2.

### **DATA TRANSFER**

A card punch operation is initiated from the controlling system by an SIO instruction if the following conditions are satisfied.

- 1. I/O address recognition exists.

- 2. Punch is in "ready" condition.

- 3. No interrupt is pending.

If the card punch is in the "automatic" mode, it requests an order from the controlling system to punch one card. After receiving a valid punch order, the card punch begins to accept the card image, column by column, from the controlling system. Data for column 1 is received and punched, then data for column 2, and so on, for the entire card image until the punch receives a "count done" or "halt" signal or a fault condition is encountered. The byte count in the I/O command doubleword controls the number of columns to be punched. Normal or offset stacking is specified in the punch order. (See Chapter 3 for detailed information.)

|  | Table 2. | Card | Punch | State | Transitions |

|--|----------|------|-------|-------|-------------|

|--|----------|------|-------|-------|-------------|

| Next<br>State<br>Present<br>State | Ready Manual                                                                                                                                                                                                                           | Busy Manual                                                                                                                                                                            | Ready Automatic                                                                                                                                           | Busy Automatic                                                                        |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Ready Manual                      |                                                                                                                                                                                                                                        | SIO accepted,<br>manual card feed<br>in progress                                                                                                                                       | START switch operated<br>with no operator inter-<br>vention <sup>t</sup> required                                                                         | Not possible                                                                          |

| Busy Manual                       | <ul> <li>I/O reset</li> <li>HIO received</li> <li>Device RESET<br/>switch operated</li> <li>Invalid order</li> <li>Manual feed<br/>complete</li> </ul>                                                                                 |                                                                                                                                                                                        | Not possible                                                                                                                                              | START switch<br>operated with<br>no operator<br>intervention <sup>t</sup><br>required |

| Ready<br>Automatic                | STOP or device<br>RESET switch<br>operated                                                                                                                                                                                             | Not possible                                                                                                                                                                           |                                                                                                                                                           | SIO accepted                                                                          |

| Busy<br>Automatic                 | <ul> <li>STOP switch<br/>operated and<br/>no order pending</li> <li>Device RESET<br/>switch operated</li> <li>Operation com-<br/>pleted and no<br/>order pending<br/>but operator<br/>intervention<sup>†</sup><br/>required</li> </ul> | <ul> <li>STOP switch<br/>operated with<br/>order pending</li> <li>Operation com-<br/>pleted with order<br/>pending but opera-<br/>tor intervention<sup>†</sup><br/>required</li> </ul> | <ul> <li>I/O reset</li> <li>HIO received</li> <li>Invalid order</li> <li>Operation completed and no operator intervention<sup>t</sup> required</li> </ul> |                                                                                       |

.

# **3. PROGRAM INTERFACE**

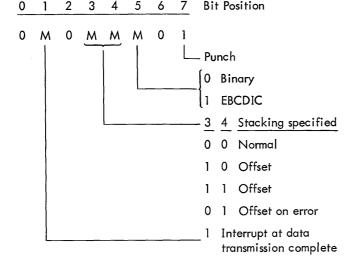

### PUNCH ORDERS

The 8-bit punch order specifies the binary or EBCDIC punch mode and whether normal or offset stacking is required. The specified punch mode applies to the entire card image; punch modes may not be changed for a given card. Cards proceed through the punch station one column at a time, column 1 first. In the EBCDIC mode, 1-byte service is requested per column. In the binary mode, 2-byte service is requested for all odd columns and 1-byte service for all even columns. In either mode, the image is transmitted once per card.

The following illustration indicates the required and optional bit configurations of the basic punch order. Bit positions 1 and 3-5 have indicated options. To be a valid order, bit 7 must be a "1".

#### PUNCH CARD EBCDIC

The following table lists the valid orders (hexadecimal code) to feed and punch a card in the EBCDIC mode.

| Order              | Action                |

|--------------------|-----------------------|

| X'05'              | Stack card normally   |

| <sup>†</sup> י45'X | Stack card normally   |

| X'0D'              | Offset stack on error |

| X'4D' <sup>†</sup> | Offset stack on error |

| X'15'              | Offset stack          |

| יסויא              | Offset stack          |

| X'55' <sup>†</sup> | Offset stack          |

| X'5D' <sup>†</sup> | Offset stack          |

|                    |                       |

<sup>&</sup>lt;sup>1</sup>Interrupt at Data Transmission Complete (i.e., deviceinitiated interrupt occurs at zero byte count)

#### PUNCH CARD BINARY

The following table lists the valid orders (hexadecimal code) to feed and punch a card in the binary mode.

| Order              | Action                |

|--------------------|-----------------------|

| X'01'              | Stack card normally   |

| X'41' <sup>†</sup> | Stack card normally   |

| X'09'              | Offset stack on error |

| X'49' <sup>†</sup> | Offset stack on error |

| יוויא              | Offset stack          |

| X'19'              | Offset stack          |

| <sup>†</sup> 'ו5יX | Offset stack          |

| X'59' <sup>†</sup> | Offset stack          |

# **KEY EVENTS**

The key events that occur during a card punch operation follow. No chronological order should be assumed from the order of presentation. Timing information is under "Programming Considerations".

#### START INPUT/OUTPUT

A card punch operation begins with the execution of a START INPUT/OUTPUT (SIO) instruction. If I/O address recognition exists and the punch is in the "ready" condition with no interrupt pending, the controlling system sets its "I/O address recognition" and "SIO accepted" indicators. The card punch advances from the "ready" to the "busy" condition, requests an order from the controlling system, and then waits for the order to arrive. In the manual mode, "SIO accepted" does not mean that the punch has started to feed and punch a card, only that it has acknowledged the I/O address and is in the "ready" condition with no interrupt pending.

#### UNUSUAL END CONDITIONS

Upon detecting any of the following conditions, after an order is received, the card punch returns an "unusual end" indication to the controlling system.

- 1. Invalid order code.

- 2. Transport mechanism malfunction (jam) while punching.

- 3. Power failure while punching.

- 4. RESET switch activated while punching.

- 5. Punch error (echo check).

- 6. Data overrun (rate error) while punching.

- 7. Access cover interlock opened while punching.

- 8. IOP halt during data transmission (not applicable to Sigma 2).

- 9. TEST switch (on maintenance panel) moved to TEST position while punching.

- 10. POWER switch pressed while punching.

#### CHANNEL END CONDITION

After receiving a valid order, the card punch signals "channel end" to the controlling system when a card being punched leaves the punch station or an "unusual end" condition occurs. A card may leave the punch station after punching any number of columns from 1 through 80, that is, after punching the byte preceding "count done".

### FAULT CONDITIONS

A "fault" condition is any condition that causes a device to report a "not operational" condition in response to an SIO, HIO, or TIO instruction. The following conditions cause the card punch to become "not operational".

- 1. Transport mechanism malfunction (jam).

- 2. Interlock open.

- 3. TEST switch (on maintenance panel) in TEST position.

- 4. Absence of ac or dc power.

- 5. Pressing RESET switch.

- 6. Pressing POWER switch.

### ERROR CONDITIONS

An error condition is any condition that results in invalid data being recorded, but does not cause the device to become "not operational"; thus, program recovery is possible. The card punch can detect and report the following error conditions to the controlling system:

Data Overrun (rate error). Data overrun will be reported if the data required for a given column is not received by "column advance" time. This will cause offset stacking if indicated by the order that caused this card feed. "Unusual end" will be reported at normal "channel end" time.

Punch Error (echo check). Punch error will be reported when the punch validation (echo check) circuitry detects a difference between the data punched and the data received. This error will cause offset stacking if indicated in the order that caused this card feed. "Unusual end" will be reported at normal "channel end" time.

Incorrect Length. Incorrect length will be reported if "count done" is not coincident with column 80 in either format. (This is not considered an error for stack on error.) It is valid to transmit fewer than 80 bytes in EBCDIC or 120 bytes in binary.

# **CARD PUNCH STATUS RESPONSE**

The card punch can return status information in response to computer-executed I/O instructions. Detailed explanations of the I/O instructions are in the Sigma computer reference manuals.

### **I/O INSTRUCTION STATUS BITS**

Execution of an I/O instruction provides two bits of information pertaining to the general status of the addressed I/O device and its controller. Table 3 lists the I/O instructions, status bit settings, and the significance of each setting.

### DEVICE STATUS BYTE

Eight bits of information are made available to the controlling system in the Device Status Byte in response to the execution of an I/O instruction, as shown in Tables 4 and 5.

### **OPERATIONAL STATUS BYTE**

In addition to the information contained in the Device Status Byte, the Operational Status Byte generated at the end of each I/O operation also provides indicators to the controlling system (see Table 6).

# **PROGRAMMING CONSIDERATIONS**

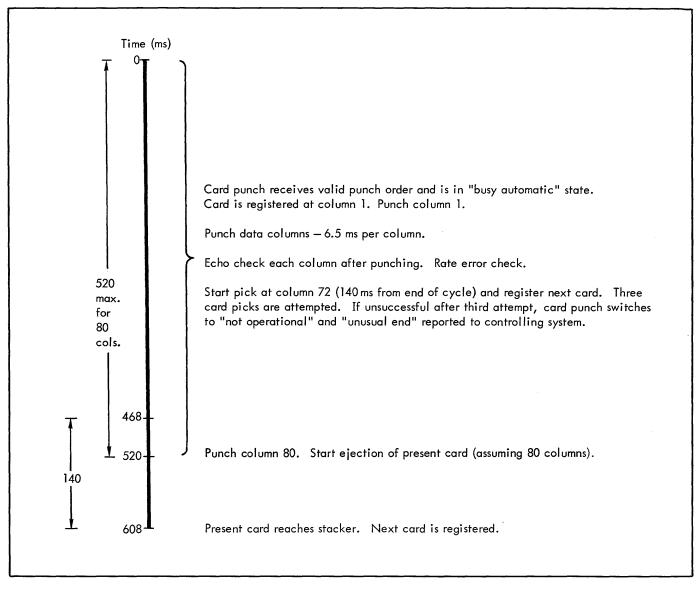

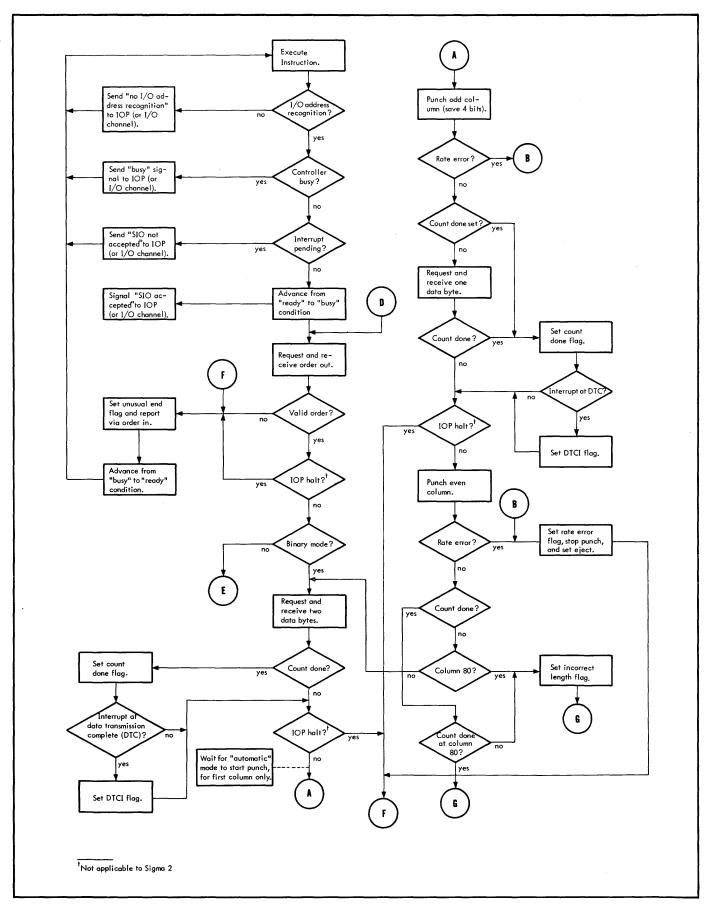

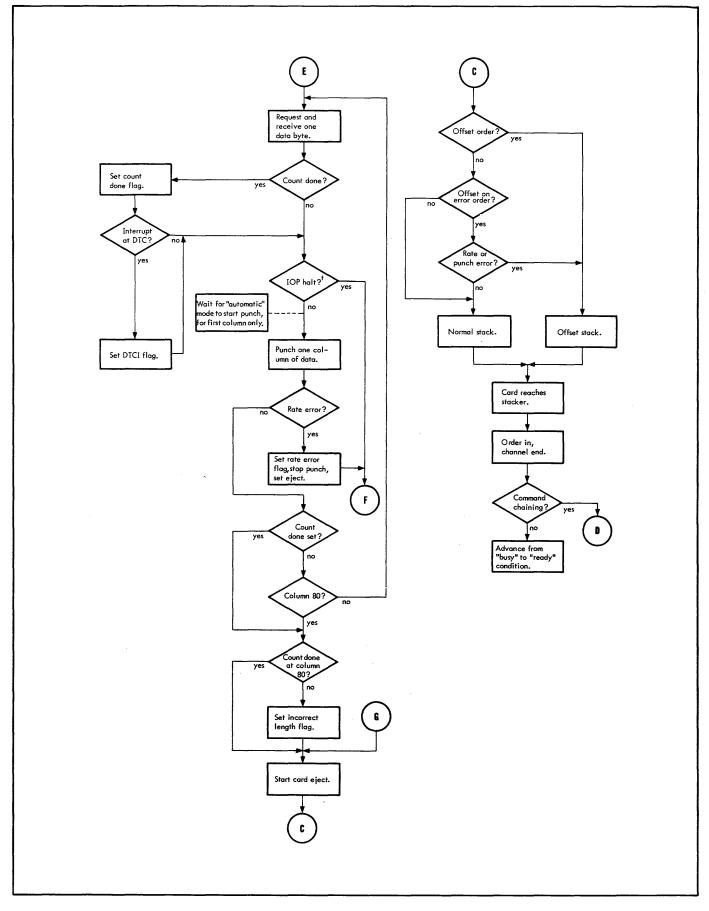

Figure 4 illustrates card punch timing. Figure 5 illustrates the sequential relationship of the key events that occur during a card punch operation.

|             | Status Bits <sup>†</sup> |          |                                                                                                      |

|-------------|--------------------------|----------|------------------------------------------------------------------------------------------------------|

| Instruction | CC1 or O                 | CC2 or C | Significance                                                                                         |

| SIO         | 0                        | 0        | I/O address recognized and SIO accepted.                                                             |

|             | 0                        | 1        | I/O address recognized but SIO not accepted.                                                         |

|             | 1                        | 0        | Selector IOP is "busy" (not applicable to Sigma 2).                                                  |

|             | 1 1                      |          | I/O address not recognized.                                                                          |

|             |                          |          | ndition code bits in Sigma 5/7 computers. The symbols O and C refer, respectively, igma 2 computers. |

Table 3. Card Punch I/O Instruction Execution Response

Table 3. Card Punch I/O Instruction Execution Response (cont.)

|                         | Status Bits <sup>†</sup> |                 |                                                                                    |

|-------------------------|--------------------------|-----------------|------------------------------------------------------------------------------------|

| Instruction             | CC1 or O                 | CC2 or C        | Significance                                                                       |

| HIO                     | 0                        | 0               | I/O address recognized and punch "not busy" when halt occurred.                    |

|                         | 0                        | 1               | I/O address recognized and punch "busy" when halt occurred.                        |

|                         | - 1                      | 0               | Invalid code.                                                                      |

|                         | 1                        | 1               | I/O address not recognized.                                                        |

| TIO                     | 0                        | 0               | I/O address recognized and SIO can currently be accepted.                          |

|                         | 0                        | 1               | I/O address recognized but SIO cannot currently be accepted.                       |

|                         | 1                        | 0               | Selector IOP is "busy" (not applicable to Sigma 2).                                |

|                         | 1                        | 1               | I/O address not recognized.                                                        |

| TDV                     | 0                        | 0               | I/O address recognized.                                                            |

|                         | 0                        | 1               | I/O address recognized and subcontroller is in test mode.                          |

|                         | 1                        | 0               | Selector IOP is "busy" (not applicable to Sigma 2).                                |

|                         | 1                        | 1               | I/O address not recognized.                                                        |

| AIO                     | 0                        | 0               | Normal interrupt condition present.                                                |

|                         | 0                        | 1               | Previous operation terminated in an "unusual end" condition.                       |

|                         | 1                        | 0               | Invalid code.                                                                      |

|                         | 1                        | 1               | No interrupt condition present.                                                    |

| <sup>t</sup> The symbol | s CC1 and C              | C2 refer to cor | ndition code bits in Sigma 5/7 computers. The symbols O and C refer, respectively, |

'The symbols CC1 and CC2 refer to condition code bits in Sigma 5/7 computers. The symbols O and C refer, respectively, to Overflow and Carry indicators in Sigma 2 computers.

| Bit<br>Position | Function                 | State | Meaning                                                                                                                                                                                                                                           |  |

|-----------------|--------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 0               | Device Interrupt Pending | 1     | Device interrupt is pending (issued, but not yet acknowledged by<br>an AIO instruction). A new order will not be accepted until the<br>interrupt is cleared by an AIO or HIO instruction, or manually (I/O<br>reset from computer control panel). |  |

| 1,2             | Card Punch Condition     |       | A combination of these two bits indicates the current card punch condition:                                                                                                                                                                       |  |

|                 |                          | 00    | Card Punch Ready.                                                                                                                                                                                                                                 |  |

|                 |                          | 01    | Card Punch Not Operational. Manual intervention required to clear<br>"not operational" condition.                                                                                                                                                 |  |

|                 |                          | 10    | Device Unavailable – Not applicable.                                                                                                                                                                                                              |  |

|                 |                          | 11    | Card Punch Busy.                                                                                                                                                                                                                                  |  |

| 3               | Mode-Automatic or        | 0     | Manual mode.                                                                                                                                                                                                                                      |  |

|                 | Manual                   | 1     | Automatic mode.                                                                                                                                                                                                                                   |  |

| 4               | Unusual End              | 1     | Execution of previous punch order terminated due to abnormal condition, as listed under "Unusual End Conditions".                                                                                                                                 |  |

| 5,6             | Controller Condition     |       | Same configurations as bits 1, 2.                                                                                                                                                                                                                 |  |

| 7               | Unassigned               | 0     | Currently unassigned and always reset to zero.                                                                                                                                                                                                    |  |

Table 4. Device Status Response for SIO, TIO, and HIO

Table 5. Device Status Response for TDV and AIO

| Bit<br>Position | Function                                      | State | Meaning                                                                                                                                                                                                                                                                   |

|-----------------|-----------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | Data Overrun                                  | 1     | Data overrun (rate error) reported if data required for a given column<br>not received by "column advance" time. This causes offset stacking<br>if indicated by order that caused this card feed. "Unusual end" re-<br>ported at "channel end".                           |

| 1               | Unassigned – TDV                              | 0     | Currently unassigned and always reset to zero.                                                                                                                                                                                                                            |

|                 | Data Transmission<br>Complete Interrupt – AIO | 1     | Data Transmission Complete interrupt occurred.                                                                                                                                                                                                                            |

| 2               | Punch Error                                   | 1     | Punch error reported when punch validation (echo check) circuitry<br>detects difference between data punched and data received. This<br>error causes offset stacking if indicated in the order that caused this<br>card feed. "Unusual end" is reported at "channel end". |

| 3-7             | Unassigned                                    | 0     | Currently unassigned and always reset to zeros.                                                                                                                                                                                                                           |

|                                   |                                           | Tuble     | Q. Operational status byte                                                                                                                                                                                                                                                               |

|-----------------------------------|-------------------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bit<br>Position                   | Function                                  | State     | Meaning                                                                                                                                                                                                                                                                                  |

| 0                                 | Transmission Data<br>Error (data overrun) | 1         | See Table 5, Bit Position 0.                                                                                                                                                                                                                                                             |

| 1                                 | Incorrect Length                          | 1         | Byte counts are 80 for EBCDIC and 120 for binary. If any other<br>count used, incorrect length reported at channel end. If less than<br>these counts used, card rate is increased as shown in Figure 1. If<br>more than these counts are used, punching is terminated with<br>column 80. |

| 2                                 | Chaining Modifier                         | 0         | Not used and always reset to zero.                                                                                                                                                                                                                                                       |

| 3                                 | Channel End                               | 1         | I/O operations have been terminated for any reason listed under<br>"Channel End Conditions".                                                                                                                                                                                             |

| 4                                 | Unusual End                               | 1         | Execution of previous order terminated due to abnormal condition (see "Unusual End Conditions").                                                                                                                                                                                         |

| 5-7                               | Unassigned                                | 0         | Currently unassigned and always reset to zero.                                                                                                                                                                                                                                           |

| <sup>†</sup> For Sigma<br>manual. | a 2 computers. For Sigma 5/7              | computers | , see the "Operational Status Byte" in the applicable computer reference                                                                                                                                                                                                                 |

Table 6. Operational Status Byte<sup>†</sup>

Figure 4. Card Punch Timing

Figure 5. Controlling System and Card Punch Actions (cont.)

# 4. OPERATIONS

### **OPERATOR CONTROLS**

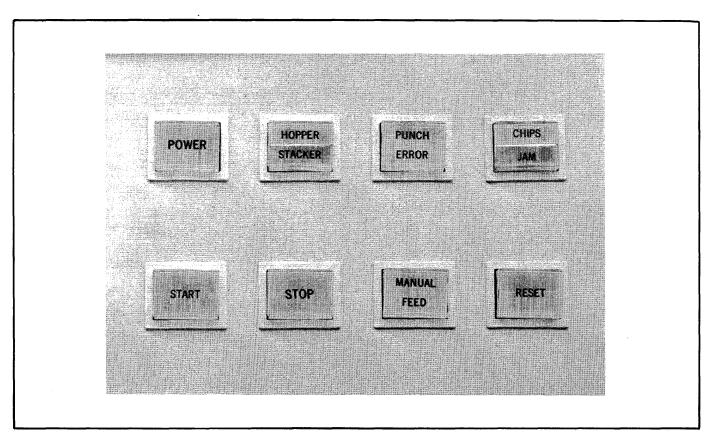

The control panel, which is located in the access (top) cover, contains eight switches and indicators (see Figures 6 and 7).

#### POWER

This push-on/push-off switch-indicator controls ac power to the card punch motor. The switch does not control dc power to the punch unit. The indicator is illuminated when the switch is on.

#### START

When this switch-indicator is activated, the punch enters the automatic mode provided that it is operational and operator intervention is not required. The indicator is illuminated when the punch is in the automatic mode. The card punch is "operational" if the following conditions are satisfied.

- 1. Power is applied.

- 2. Cover interlock is closed.

- 3. Transport fault not present.

Figure 6. Model 7165 Card Punch

- 4. RESET switch on control panel not activated.

- 5. TEST switch (on maintenance panel) is off.

Operator intervention is required if

- 1. Hopper is empty.

- 2. Stacker is full.

- 3. Chip box is full or out of place.

- 4. Manual feed is required.

- <u>Note:</u> Pressing the START switch when manual feed is required causes the MANUAL FEED indicator to illuminate.

### STOP

When this switch-indicator is activated, the punch completes the operation on the card being processed before stopping and entering the manual mode. The indicator is illuminated when the punch is in the manual mode.

#### MANUAL FEED

Activating this switch-indicator causes a single card-feed cycle to occur provided that the punch is in the manual

mode and all current card cycles are completed. A cardfeed cycle is as follows:

- 1. If a card is present in the punch station, it is transported to the output stacker.

- 2. If the hopper is not empty, a card is picked and transported to the punch station and registered for punching.

The indicator is illuminated while the switch is activated.

#### RESET

Activating this switch-indicator clears the punch error and jam indicators. If the punch is "busy", an "unusual end" condition will be reported. The indicator is illuminated while the switch is activated.

If the RESET switch is pressed during any program-controlled operation, the program must be restarted since all punch data will have been eradicated.

### HOPPER/STACKER

The HOPPER portion of this split-field indicator illuminates when the hopper becomes empty. The HOPPER field remains on until the operator places cards in the hopper and activates the START or MANUAL FEED switch.

The STACKER field illuminates when the stacker becomes full; it remains on until the operator removes cards from the stacker and activates the START or MANUAL FEED switch.

#### PUNCH ERROR

This indicator illuminates when a punch error is detected. It remains on until the START, MANUAL FEED, or RESET switch is activated.

#### CHIPS/JAM

The CHIPS field of this split-field indicator illuminates when the chip box is full or not properly in place. It remains on until the operator properly replaces the empty chip box and activates the START or MANUAL FEED switch. (The chip box is located behind the left front door.)

The JAM field illuminates when a transport fault is detected. After the fault is remedied, the operator presses the RESET switch to turn off the indicator. Transport faults are defined as:

- 1. A pick failure, occurring when three attempts to pick and deliver a card into the transport have been made without success.

- 2. A registration failure, occurring when a picked card fails to register at the punch station.

- 3. A punch station exit failure, occurring when a card fails to exit the punch station or is not delivered to the stacker.

- Note: The motor is shut off immediately if a transport fault (jam) is detected.

### **INPUT HOPPER**

The input hopper (see Figure 6) is located on the left side of the upper cabinet. Its capacity is 1000 cards. The wheeled card weight rests against cards in the hopper. Since the bed of the hopper is inclined toward the picker assembly, cards are gravity fed to the pick roller. A switch senses when the hopper is empty.

### **OUTPUT STACKER**

The output stacker (see Figure 6) is located at the right side of the cabinet. Its capacity is 1000 cards. Cards enter the stacker aided by the output stacker rollers. The springloaded follower plate maintains the cards in proper position. A switch (actuated by the follower plate) senses when the stacker is full.

Associated with the stacker is an offset assembly that raises a selected card approximately one-halfinch upon command. This feature is used for identifying error cards or separating decks. It must not be used continuously for large groups of cards; otherwise, card damage will occur.

# **COVER INTERLOCK**

An interlock switch, located under the top cover, is closed when the cover is in place. When the cover is raised, the spring-loaded switch opens and disables the punch.

### **OPERATING INSTRUCTIONS**

This section describes operating, turn-on, halt, and jamclearing procedures.

#### **OPERATING PREPARATION**

Before operating the card punch, use the following procedures:

- Check the hopper and stacker to see that they are free of foreign matter.

- 2. Check the chip box.

- 3. Prepare the cards for use by ruffling and flexing them. Tamp the cards so that the deck is square.

- 4. Inspect edges of cards for irregularities.

- 5. With nine-edge up and column one to the right, place cards in the hopper. Put the card weight against the cards.

#### **TURN-ON PROCEDURE**

- 1. Press the POWER switch on the control panel. The POWER and STOP indicators will illuminate.

- 2. Press the MANUAL FEED switch. The MANUAL FEED indicator will illuminate. One card will be transported to the registration station.

- 3. Press the START switch. The START indicator will illuminate.

The card punch is now ready for operation under program control.

#### CONTINUOUS OPERATION

The card punch may be operated continuously provided that the operator adheres to the following practices:

- Do not remove card weight from the cards in the hopper when there are less than three inches of cards remaining (this may cause a jam).

- 2. Add cards to hopper before the card deck is less than three inches high.

- 3. Remove cards from stacker before it is full.

#### MOMENTARY HALT

The following procedure enables the operator to interrupt the operation of the card punch and restart it at the point of interruption.

- 1. Press the STOP switch.

- 2. Perform the required task.

- 3. Press the START switch.

### AUTOMATIC RECOVERABLE HALT

The following conditions cause the punch to enter the "manual" mode. Performing the required task and pressing the START switch will restart the punch with no loss of information.

- 1. Hopper empty

- 2. Stacker full

- 3. Chip box full

# **CLEARING CARD JAMS**

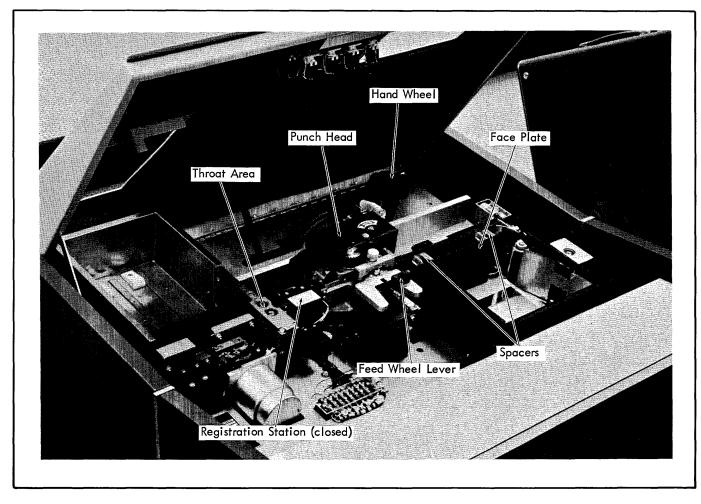

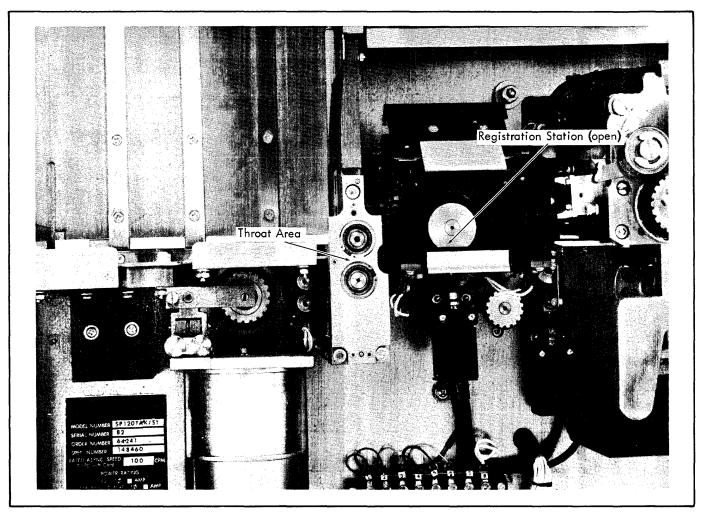

When a transport jam is sensed, the JAM field of the CHIPS/JAM indicator on the control panel will illuminate. Also, the appropriate FAULT INDICATOR on the maintenance panel (inside the right front door) will illuminate. In case of repeated failures, call Customer Engineering maintenance personnel. The procedures for clearing card jams are outlined below (see Figures 8 and 9).

<u>Note:</u> Be careful in clearing a card jam to avoid damage to the mechanism.

#### PICK JAM

- 1. Remove cards from input hopper and transport mechanism.

- 2. Check leading edges of cards for irregularities. Remove damaged cards.

- 3. Ruffle and flex the card deck. Tamp the cards so that the deck is square. Replace cards in hopper.

- 4. Press RESET switch to clear all indicators and then resume operation.

#### THROAT JAM

- 1. Remove cards from input hopper and transport mechanism.

- 2. Open registration station by lifting hinged cover catch and pressing it (toward rear of unit).

- 3. Turn hand wheel until the jammed card can be removed. Remove all pieces of the card.

- 4. Close registration station.

- 5. Replace cards in hopper.

- 6. Press RESET switch to clear all indicators and then resume operation.

#### **REGISTRATION JAM**

- 1. Press RESET switch and then MANUAL FEED switch. This may eject the irregular card.

- 2. If step 1 is unsuccessful, open registration station.

- Apply thumb pressure (toward back of machine) to the feed wheel lever on the punch head to disengage pressure roller from feed wheel. Remove card.

- 4. Close registration station.

- 5. Press RESET switch to clear all indicators and then resume operation.

Figure 8. Card Punch Mechanism with Access Cover Open

Figure 9. Card Punch Mechanism, Left View

# EJECT JAM

- 1. Remove face plate by placing fingers under the clear plastic spacers and lifting up.

- <u>Note:</u> If jammed card is in stacker area, it is unnecessary to remove face plate.

- 2. Turn the hand wheel until the jammed card can be removed.

- 3. Replace face plate carefully, ensuring that no damage occurs to the alignment pins.

- 4. Press RESET switch to clear all indicators and then resume operation.

### PUNCH HEAD JAM

If the card jam is in the punch head area, do not attempt to clear the jam. Call Customer Engineering maintenance personnel.

# **APPENDIX A.** SDS STANDARD SYMBOLS, CODES, AND CORRESPONDENCES

This appendix contains the following reference material:

Title

SDS Standard Symbols and Codes

- Standard 8-Bit Computer Codes (EBCDIC Extended Binary-Coded-Decimal Interchange Code)

- SDS Standard 7-Bit Communication Codes (USASCII United States of America Standard Code for Information Interchange)

- SDS Standard Symbol-Code Correspondences

# SDS STANDARD SYMBOLS AND CODES

The symbol and code standards described in this publication are applicable to all SDS products, both hardware and software. They may be expanded or altered from time to time to meet changing requirements.

The symbols listed here include two types: graphic symbols and control characters. Graphic symbols are displayable and printable; control characters are not. Hybrids are SP (the symbol for a blank space), and DEL (the delete code) which is not considered a control command.

Three types of code are shown: (1) the 8-bit SDS Standard Computer Code, i.e., the SDS Extended Binary-Coded-Decimal Interchange Code (EBCDIC); (2) the 7-bit United States of America Standard Code for Information Interchange (USASCII); and (3) correspondence between these two codes.

# SDS STANDARD CHARACTER SETS

1. EBCDIC

57-character set: uppercase letters, numerals, space, and & - / . < > ( ) + | \$ \* : ; , % # @ ' =

63-character set: Same as above plus ¢ ! \_ ?

89-character set: same as 63-character set plus lowercase letters

2. USASCII

95-character set: same as above plus lowercase letters and  $\{\}$   $\stackrel{1}{\downarrow} \sim 1$

# **CONTROL CODES**

In addition to the standard character sets listed above, the SDS symbol repertoire includes 37 control codes and the hybrid code DEL (hybrid code SP is considered part of all character sets). These are listed in the table titled SDS Standard Symbol-Code Correspondences.

### SPECIAL CODE PROPERTIES

The following two properties of all SDS standard codes will be retained for future standard code extensions:

- 1. All control codes, and only the control codes, have their two high-order bits equal to "00". DEL is not considered a control code.

- No two graphic EBCDIC codes have their seven loworder bits equal.

# SDS STANDARD 8-BIT COMPUTER CODES (EBCDIC)

|                          |      |          |           |          |            |      |      |       | Most   | Signif | icant    | Digits |      |                |      |         |          |      |

|--------------------------|------|----------|-----------|----------|------------|------|------|-------|--------|--------|----------|--------|------|----------------|------|---------|----------|------|

| ſ                        | Hexo | adecimal | 0         | 1        | 2          | 3    | 4    | 5     | 6      | 7      | 8        | 9      | Α    | В              | с    | D       | Е        | F    |

|                          |      | Binary   | 0000      | 0001     | 0010       | 0011 | 0100 | 0101  | 0110   | 0111   | 1000     | 1001   | 1010 | 1011           | 1100 | 1101    | 1110     | 1111 |

|                          | 0    | 0000     | NUL       | DLE      | ds         |      | SP   | &     | -      |        |          |        |      |                | -    |         |          | 0    |

|                          | 1    | 0001     | SOH       | DC1      | <b>S</b> 5 |      |      |       | 1      |        | a        | j      |      | $\backslash^1$ | А    | J       |          | 1    |

|                          | 2    | 0010     | STX       | DC2      | fs         |      |      |       |        |        | Ь        | k      | s    | {1             | В    | к       | S        | 2    |

|                          | 3    | 0011     | ETX       | DC 3     | si         |      |      |       |        |        | с        | I      | t    | }1             | с    | L       | Т        | 3    |

|                          | 4    | 0100     | EOT       | DC4      |            |      |      |       |        |        | d        | m      | υ    | ['             | D    | м       | υ        | 4    |

| "                        | 5    | 0101     | нт        | LF<br>NL |            |      | Wil  | not b | e assi | gned   | е        | n      | v    | ]1             | E    | N       | v        | 5    |

| Digit                    | 6    | 0110     | АСК       | SYN      |            |      |      |       |        |        | f        | o      | w    |                | F    | 0       | w        | 6    |

| cant                     | 7    | 0111     | BEL       | ETB      |            |      |      |       |        |        | g        | р      | ×    |                | G    | Р       | х        | 7    |

| Least Significant Digits | 8    | 1000     | EOM<br>BS | CAN      |            |      |      |       |        |        | h        | ٩      | у    |                | н    | Q       | Y        | 8    |

| east S                   | 9    | 1001     | ENQ       | EM       |            |      |      |       |        |        | i        | r      | z    |                | I    | R       | Z        | 9    |

| Ľ                        | A    | 1010     | NAK       | SS       | -          |      | ¢ 2  | !     | ~1     | :      |          |        |      |                |      |         |          |      |

|                          | В    | 1011     | VT        | ESC      |            |      |      | \$    | ,      | #      |          |        |      |                |      |         |          |      |

|                          | с    | 1100     | FF        | FS       |            |      | <    | *     | %      | @      |          |        |      |                | Wil  | I not b | be assig | gned |

|                          | D    | 1101     | CR        | GS       |            |      | (    | )     | _      | •      |          |        |      |                |      |         |          |      |

|                          | E    | 1110     | so        | RS       |            |      | +    | ;     | >      | =      |          |        |      |                |      |         |          |      |

|                          | F    | 1111     | SI        | US       | PE         |      | 2    | 2     | ?      | u      |          |        |      |                |      |         |          | DEL  |

|                          |      |          |           | 3        | ,          |      |      |       | 4      |        | <u> </u> |        | 5    |                |      |         |          |      |

#### NOTES:

- The characters ^ \ { } [ ] are USASCII characters that do not appear in any of the SDS EBCDIC-based character sets, though they are shown in the EBCDIC table.

- 2 The characters ≠ | → appear in the SDS 63- and 89-character EBCDIC sets but not in either of the SDS USASCII-based sets, However, SDS software translates the characters ≠ | → into USASCII characters as follows:

| EBCDIC | = | UASCII         |

|--------|---|----------------|

| ¢      |   | <b>`</b> (6-0) |

| 1      |   | ¦ (7-12)       |

| _      |   | ~ (7-14)       |

- 3 The EBCDIC control codes in columns 0 and 1 and their binary representation are exactly the same as those in the USASCII table, except for two interchanges: LF/NL with NAK, and HT with ENQ.

- 4 Characters enclosed in heavy lines are included only in the SDS standard 63and 89-character EBCDIC sets.

- 5 These characters are included only in the SDS standard 89-character EBCDIC set.

# SDS STANDARD 7-BIT COMMUNICATION CODES (USASCII)<sup>1</sup>

|                          |                             |          |          |      | Most       | Signif | icant | Digits      |      |      |

|--------------------------|-----------------------------|----------|----------|------|------------|--------|-------|-------------|------|------|

|                          | Decimal<br>(rows) (col's.)→ |          | 0        | 1    | 2          | 3      | 4     | 5           | 6    | 7    |

|                          | ļ                           | Binary 1 | ×000     | ×001 | ×010       | ×011   | ×100  | ×101        | ×110 | ×111 |

|                          | 0                           | 0000     | NUL      | DLE  | SP         | 0      | @     | P           | ``   | Р    |

|                          | 1                           | 0001     | sон      | DCI  | . 5<br>!   | 1      | А     | Q           | a    | q    |

|                          | 2                           | 0010     | STX      | DC2  | Ĥ          | 2      | В     | R           | Ь    | r    |

|                          | 3                           | 0011     | ETX      | DC3  | #          | 3      | с     | S           | c    | s    |

|                          | 4                           | 0100     | EOT      | DC4  | \$         | 4      | D     | т           | d    | t    |

| s                        | 5                           | 0101     | ENQ      | NAK  | %          | 5      | E     | υ           | е    | U    |

| Least Significant Digits | 6                           | 0110     | АСК      | SYN  | &          | 6      | F     | v           | f    | v    |

| icant                    | 7                           | 0111     | BEL      | ETB  | ı          | 7      | G     | w           | g    | w    |

| Signif                   | 8                           | 1000     | BS       | CAN  | (          | 8      | н     | x           | h    | ×    |

| east S                   | 9                           | 1001     | нт       | EM   | )          | 9      | I     | Y           | i    | у    |

| -                        | 10                          | 1010     | LF<br>NL | SS   | *          | :      | J     | z           | j    | z    |

|                          | n                           | 1011     | VΤ       | ESC  | +          | ;      | к     | [5          | k    | {    |

|                          | 12                          | 1100     | FF       | FS   | ,          | <      | L     | $\setminus$ | 1    | -    |

|                          | 13                          | 1101     | CR       | GS   | -          | =      | м     | ] 5         | m    | }    |

|                          | 14                          | 1110     | so       | RS   | •          | >      | N     | 4~5         | n    | ~ 4  |

|                          | 15                          | 1111     | SI       | US   | 1          | ?      | 0     | -4          | o    | DEL  |

|                          |                             |          |          | 2    | ~ <u> </u> |        |       | 3           |      |      |

NOTES:

- Most significant bit, added for 8-bit format, is either 0 or an odd-parity bit for the remaining 7 bits.

- 2 Columns 0-1 are control codes.

- 3 Columns 2-5 correspond to the SDS 64-character USASCII set. Columns 2-7 correspond to the SDS 95-character USASCII set.

- 4 On many current teletypes, the symbol

- ~ is † (5-14)

- \_\_\_\_\_ is --\_\_\_\_ (5-15)

- ~ is ESC or ALTMODE control (7-14)

and none of the symbols appearing in columns 6-7 are provided. Except for the three symbol differences noted above, therefore, such teletypes provide all the characters in the SDS 64-character USASCII set. (The SDS 7015 Remote Keyboard Printer provides the 64-character USASCII set also, but prints ^ as ^ .)

5 On the SDS 7670 Remote Batch Terminal, the symbol

| is | 1        | (2-1)        |

|----|----------|--------------|

| is | ¢        | (5-11)       |

| is | 1        | (5–13)       |

| is | _        | (5-14)       |

|    | is<br>is | is ¢<br>is ! |

and none of the symbols appearing in columns 6-7 are provided. Except for the four symbol differences noted above, therefore, this terminal provides all the characters in the SDS 64-character USASCII set.

# SDS STANDARD SYMBOL-CODE CORRESPONDENCES

| EBCDIC                                                                                                                     | Symbol                                                                                                       | Card Code                                                                                                                                                                                              | USASCII <sup>††</sup>                                                                                               | Meaning                                                                                                                                                                                                                                                                                                     | Remarks                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07<br>08<br>07<br>08<br>07<br>08<br>09<br>0A<br>0B<br>0C<br>0D<br>0E<br>0F       | NUL<br>SOH<br>STX<br>ETX<br>EOT<br>HT<br>ACK<br>BEL<br>BS or EOM<br>ENQ<br>NAK<br>VT<br>FF<br>CR<br>SO<br>SI | 12-0-9-8-1<br>12-9-1<br>12-9-2<br>12-9-3<br>12-9-4<br>12-9-5<br>12-9-6<br>12-9-7<br>12-9-8<br>12-9-8-1<br>12-9-8-1<br>12-9-8-2<br>12-9-8-3<br>12-9-8-3<br>12-9-8-4<br>12-9-8-5<br>12-9-8-6<br>12-9-8-7 | 0-0<br>0-1<br>0-2<br>0-3<br>0-4<br>0-9<br>0-6<br>0-7<br>0-8<br>0-5<br>1-5<br>0-11<br>0-12<br>0-13<br>0-14<br>0-15   | null<br>start of header<br>start of text<br>end of text<br>end of transmission<br>horizontal tab<br>acknowledge (positive)<br>bell<br>backspace or end of message<br>enquiry<br>negative acknowledge<br>vertical tab<br>form feed<br>carriage return<br>shift out<br>shift in                               | 00 through 23 and 2F are control codes.<br>EOM is used only on SDS Keyboard/<br>Printers Models 7012, 7020, 8091,<br>and 8092.                                                                                              |

| 10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>1A<br>18<br>19<br>1A<br>1B<br>1C<br>1D<br>1E<br>1F             | DLE<br>DC1<br>DC2<br>DC3<br>DC4<br>LF or NL<br>SYN<br>ETB<br>CAN<br>EM<br>SS<br>ESC<br>FS<br>GS<br>RS<br>US  | 12-11-9-8-1<br>11-9-1<br>11-9-2<br>11-9-3<br>11-9-4<br>11-9-5<br>11-9-6<br>11-9-7<br>11-9-8<br>11-9-8-1<br>11-9-8-3<br>11-9-8-3<br>11-9-8-4<br>11-9-8-5<br>11-9-8-6<br>11-9-8-7                        | 1-0<br>1-1<br>1-2<br>1-3<br>1-4<br>0-10<br>1-6<br>1-7<br>1-8<br>1-9<br>1-10<br>1-11<br>1-12<br>1-13<br>1-14<br>1-15 | data link escape<br>device control 1<br>device control 2<br>device control 3<br>device control 4<br>line feed or new line<br>sync<br>end of transmission block<br>cancel<br>end of medium<br>start of special sequence<br>escape<br>file separator<br>group separator<br>record separator<br>unit separator |                                                                                                                                                                                                                             |

| 20<br>21<br>22<br>23<br>24<br>25<br>26<br>27<br>28<br>29<br>2A<br>28<br>29<br>2A<br>28<br>2C<br>2D<br>2E<br>2F             | ds<br>ss<br>fs<br>si                                                                                         | 11-0-9-8-1<br>0-9-1<br>0-9-2<br>0-9-3<br>0-9-4<br>0-9-5<br>0-9-6<br>0-9-7<br>0-9-8<br>0-9-8-1<br>0-9-8-1<br>0-9-8-3<br>0-9-8-4<br>0-9-8-5<br>0-9-8-5<br>0-9-8-6<br>0-9-8-7                             |                                                                                                                     | digit selector<br>significance start<br>field separation<br>immediate significance start<br>parity error                                                                                                                                                                                                    | <ul> <li>20 through 23 are used with<br/>Sigma 7 EDIT BYTE STRING (EBS)<br/>instruction – not input/output con-<br/>trol codes.</li> <li>24 through 2E are unassigned.</li> <li>If parity checking is requested.</li> </ul> |

| 30<br>31<br>32<br>33<br>34<br>35<br>36<br>37<br>38<br>37<br>38<br>39<br>3A<br>38<br>37<br>3A<br>3B<br>3C<br>3D<br>3E<br>3F |                                                                                                              | 12-11-0-9-8-1<br>9-1<br>9-2<br>9-3<br>9-4<br>9-5<br>9-6<br>9-7<br>9-8<br>9-8-1<br>9-8-2<br>9-8-3<br>9-8-3<br>9-8-4<br>9-8-5<br>9-8-6<br>9-8-7                                                          |                                                                                                                     |                                                                                                                                                                                                                                                                                                             | 30 through 3F are unassigned.                                                                                                                                                                                               |

# SDS Standard Symbol-Code Correspondences (cont.)

| EBCDIC                                                                                                         | Symbol                                     | Card Code                                                                                                                                                                             | USASCII <sup>††</sup>                             | Meaning                                                                                                        | Remarks                                                                                                                                                                                                                                               |

|----------------------------------------------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>47<br>48<br>49<br>4A<br>4B<br>4C<br>4D<br>4E<br>4F       | SP<br>¢ or '<br><<br>(<br>† or             | blank<br>12-0-9-1<br>12-0-9-2<br>12-0-9-3<br>12-0-9-4<br>12-0-9-5<br>12-0-9-6<br>12-0-9-7<br>12-0-9-8<br>12-8-1<br>12-8-2<br>12-8-3<br>12-8-3<br>12-8-4<br>12-8-5<br>12-8-6<br>12-8-7 | 2-0<br>6-0<br>2-14<br>3-12<br>2-8<br>2-11<br>7-12 | blank<br>cent or accent grave<br>period<br>less than<br>left parenthesis<br>plus<br>vertical bar or broken bar | <ul> <li>41 through 49 will not be assigned.</li> <li>Accent grave used for left single quote. On model 7670, ` not available, and ¢ = USASCII 5-11.</li> <li>On Model 7670, <sup>1</sup>/<sub>1</sub> not available, and 1 = ASASCII 2-1.</li> </ul> |

| 50<br>51<br>52<br>53<br>54<br>55<br>56<br>57<br>58<br>59<br>58<br>59<br>5A<br>58                               | &<br>!                                     | 12<br>12-11-9-1<br>12-11-9-2<br>12-11-9-3<br>12-11-9-4<br>12-11-9-4<br>12-11-9-5<br>12-11-9-6<br>12-11-9-7<br>12-11-9-8<br>11-8-1<br>11-8-2                                           | 2-6<br>2-1                                        | ampersand<br>exclamation point                                                                                 | 51 through 59 will not be assigned.                                                                                                                                                                                                                   |

| 5B<br>5C<br>5D<br>5E<br>5F                                                                                     | S<br>*<br>)<br>;<br>~ or ¬                 | 11-8-3<br>11-8-4<br>11-8-5<br>11-8-6<br>11-8-7                                                                                                                                        | 2-4<br>2-10<br>2-9<br>3-11<br>7-14                | dollars<br>asterisk<br>right parenthesis<br>semicolon<br>tilde or logical not                                  | On Model 7670,∼is not available,<br>and ¬= USASCII 5-14.                                                                                                                                                                                              |

| 60<br>61<br>62<br>63<br>64<br>65<br>66<br>67<br>68<br>69                                                       | 7                                          | 11<br>0-1<br>11-0-9-2<br>11-0-9-3<br>11-0-9-4<br>11-0-9-5<br>11-0-9-6<br>11-0-9-7<br>11-0-9-8<br>0-8-1                                                                                | 2-13<br>2-15                                      | minus, dash, hyphen<br>slash                                                                                   | 62 through 69 will not be assigned.                                                                                                                                                                                                                   |

| 6A<br>6B<br>6C<br>6D<br>6E<br>6F                                                                               | ~<br>, %<br>- ><br>?                       | 12-11<br>0-8-3<br>0-8-4<br>0-8-5<br>0-8-5<br>0-8-6<br>0-8-7                                                                                                                           | 5-14<br>2-12<br>2-5<br>5-15<br>3-14<br>3-15       | circumflex<br>comma<br>percent<br>underline<br>greater than<br>question mark                                   | On Model 7670 ^ is ¬. On Model<br>7015 ^ is ^ (caret).<br>Underline is sometimes called "break<br>character"; may be printed along<br>bottom of character line.                                                                                       |

| 70<br>71<br>72<br>73<br>74<br>75<br>76<br>77<br>78<br>79<br>7A<br>78<br>79<br>7A<br>7B<br>7C<br>7D<br>7E<br>7F | :<br>#<br>@<br>'<br>=<br>"<br>nal notation | 12-11-0<br>12-11-0-9-1<br>12-11-0-9-2<br>12-11-0-9-3<br>12-11-0-9-4<br>12-11-0-9-5<br>12-11-0-9-6<br>12-11-0-9-7<br>12-11-0-9-8<br>8-1<br>8-2<br>8-3<br>8-4<br>8-5<br>8-6<br>8-7      | 3-10<br>2-3<br>4-0<br>2-7<br>3-13<br>2-2          | colon<br>number<br>at<br>apostrophe (right single quote)<br>equals<br>quotation mark                           | 70 through 79 will not be assigned.                                                                                                                                                                                                                   |

| EBCDIC <sup>†</sup>                                                                                                        | Symbol                               | Card Code                                                                                                                                                                                                   | USASCII <sup>††</sup>                                              | Meaning                                                                 | Remarks                                                                                                                                                                                               |