# XD5 SIGMA COMPUTER SYSTEMS/Interface Design Manual

900973D-1

December 1969 (Revised June 1970)

Xerox Data Systems 701 South Aviation Blvd., El Segundo, California 90245 (213) 772-4511, 679-4511

| ST OF EFFECTIVE PAGES                               | <u> </u>                 |                       |      |

|-----------------------------------------------------|--------------------------|-----------------------|------|

|                                                     |                          |                       |      |

|                                                     | Total number of page     | æ is 100, as follows: |      |

| Page No.                                            | Issue                    | Page No.              | Issu |

| Title · · · · · · · · · · · · · · · · · · ·         | · · · · · · · Original   |                       |      |

| A                                                   |                          |                       |      |

| Foreword                                            |                          |                       |      |

| i thru iv                                           | •                        |                       |      |

| v thru vi                                           | •                        | )                     |      |

| 1-1 thru 1-8 · · · · · · · · · · · · · · · · · · ·  | · · · · · · · · Original |                       |      |

| 2.1                                                 |                          |                       |      |

| 2-2                                                 | -                        | )                     |      |

| 2-3 thru 2-6                                        | · · · · · · · · Original |                       |      |

| 3-1 thru 3-24 · · · · · · · · · · · · · · · · · · · | · · · · · · · Original   |                       |      |

| 4-1 thru 4-6                                        | · · · · · · · · Original |                       |      |

| 5-1 thru 5-3                                        | ····· Original           |                       |      |

| 5-4                                                 | ····· Revised June 1970  | )                     |      |

| 5-5                                                 | · · · · · · · · Original |                       |      |

|                                                     | ····· Revised June 1970  | )                     |      |

| 5-8 thru 5-9                                        | •••••• Original          |                       |      |

| 5-10                                                | ····· Revised June 1970  | )                     |      |

|                                                     | · · · · · · · · Original |                       |      |

|                                                     | · · · · · · · · Original |                       |      |

|                                                     | ····· Original           |                       |      |

|                                                     | ····· Original           |                       |      |

|                                                     | · · · · · · · Original   |                       |      |

| PUBLICATION                       | PDQ NO. <u>72-001</u><br>PUBLICATION NO. <u>XDS 900973D</u> |

|-----------------------------------|-------------------------------------------------------------|

| DATA                              | DATE19 January 1972                                         |

| QUICK                             | Page1 of2                                                   |

| TO: ALL HOLDERS OF XDS Sigma Comp | uter Systems/Interface Design Manual                        |

TO: ALL HOLDERS OF XDS <u>Sigma Computer Systems/Interface</u> Design Manual SUBJECT: TEMPORARY CHANGES TO TECHNICAL MANUAL

The following changes to Technical Manual <u>900973D</u> are necessary to reflect the latest technical information. The changes are released in this manner for purposes of expediency. The next scheduled revision to the manual will incorporate these changes formally.

PURPOSE: The purpose of this PDQ is to correct the information contained in table 7–2, Sigma 2 or 3 Integral Priority Interrupt and Clock Cable Signals.

## INSTRUCTIONS:

- 1. Page 7-9: Cross out existing table 7-2.

- 2. Insert page 2 of this PDQ (marked page 7–8a) between pages 7–8 and 7–9.

- 3. Insert his PDQ instruction sheet between the cover and title page of technical manual 900973D. Do not remove it until the above change has been incorporated in a released revision or re-issue of the technical manual.

**APPROVED**

ANAGER, PUBLICATIONS DEVELOPMENT

## FOREWORD

This D-1 revision supersedes XDS 900973D and incorporates information previously supplied by PDQ 70-020 and PDQ 70-024.

.

## CONTENTS

| Section | Title                                                       | Page       |

|---------|-------------------------------------------------------------|------------|

| I       | GENERAL INFORMATION                                         | 1-1        |

|         | Introduction                                                | 1-1        |

|         | DIO Interface                                               | 1-1        |

|         | IOP Interface                                               |            |

|         | 16-Bit and 32-Bit Memory Interfaces                         | 1-1<br>1-1 |

|         |                                                             | 1-2        |

|         | Selection of Components                                     |            |

|         | Cable Layout                                                | 1-2        |

|         | Driver-Receiver Circuits                                    | 1-2        |

|         | Cable-to-Module Connections                                 |            |

|         | Testing External Signals                                    |            |

|         | Design Aids                                                 | 1-7        |

|         |                                                             | ~ 1        |

| н       | DIO INTERFACE                                               | 2-1        |

|         | Introduction                                                | 2-1        |

|         | Interface Description                                       |            |

|         | Data Lines                                                  |            |

|         | Address Lines (A00R-A15R)                                   | 2-1        |

|         | Read Direct/Write Selection Line (RWDR)                     | 2-1        |

|         | Function Strobe and Acknowledgement Lines (RFSR and RFSAD)  | 2-2        |

|         | Status Lines (CC3D and CC4D)                                | 2-3        |

|         | I/O Reset Line (RSTR)                                       |            |

|         | 1.024-MHz Clock (CL1R)                                      |            |

|         | Basic Instructions                                          |            |

|         | Data Input                                                  |            |

|         | Data Output                                                 |            |

|         |                                                             |            |

|         | Cable Drivers                                               |            |

|         | Circuitry for Function Strobe Acknowledge                   |            |

|         | External Device Inputs                                      |            |

|         |                                                             |            |

| 111     | IOP INTERFACE                                               | 3-1        |

|         | Introduction                                                | 3-1        |

|         | Device Controllers                                          | 3-1        |

|         | I/O Sequence                                                | 3-1        |

|         | IOP Interface Line Description                              |            |

|         | Data Lines                                                  | 3-1        |

|         | Function Indicator Lines                                    |            |

|         | Function Strobe, Function Strobe Acknowledge, AVI/AVO Lines |            |

|         | Function Response Lines                                     |            |

|         | Service Call and High Priority Service Lines                |            |

|         | Interrupt Call and High Priority Interrupt Lines            |            |

|         | Request Strobe and Request Strobe Acknowledge Lines         |            |

|         | End Data and End Service Lines                              |            |

|         | Data Parity and Parity Check Lines                          |            |

## **CONTENTS** (Cont.)

| Section | Title                                                          | Page  |

|---------|----------------------------------------------------------------|-------|

|         | Enable Extended Interface and Extended Interface Request Lines | 3-7   |

|         | Word-Aligned Data Required Line                                | 3-7   |

|         | Inhibit Extended Interface Request                             | 3-7   |

|         | Fast Device Controller and Zero-Byte Count Interrupt Lines     | 3-7   |

|         | I/O Reset and 1.024-MHz Clock Lines                            | 3-7   |

|         | IOP Interface Functions                                        | 3-7   |

|         | Priority Determination                                         | 3-7   |

|         | Data Transmission and Priority Cables                          | 3-7   |

|         | Priority Cable Function                                        |       |

|         | Priority Signals                                               | 3-7   |

|         | Strobe Acknowledgement                                         | 3-8   |

|         | Instruction Execution                                          | 3-8   |

|         | SIO, HIO, TIO and TDV Instructions                             | 3-8   |

|         |                                                                | 3-10  |

|         | Service Calls and Acknowledgement                              | 3-10  |

|         | Service Cycles                                                 | 3-10  |

|         | Data In Service Cycle                                          | 3-13  |

|         | Data Out Service Cycle                                         | 3-13  |

|         | Order Output Service Cycle                                     | 3-13  |

|         | Order Input Service Cycle                                      |       |

|         | Service Cycle Signal Interaction                               |       |

|         | Terminal Orders                                                |       |

|         | Input/Output Processors                                        |       |

|         | Sigma 2 Integral IOP                                           |       |

|         | Sigma 3 Integral IOP                                           |       |

|         | Sigma 3 External IOP                                           |       |

|         | Sigma 2 and 3 Differences                                      |       |

|         | Sigma 5 Integral IOP                                           |       |

|         | Eight-Bit Multiplexer IOP                                      |       |

|         | Thirty-Two-Bit Multiplexer IOP                                 |       |

|         |                                                                |       |

|         |                                                                |       |

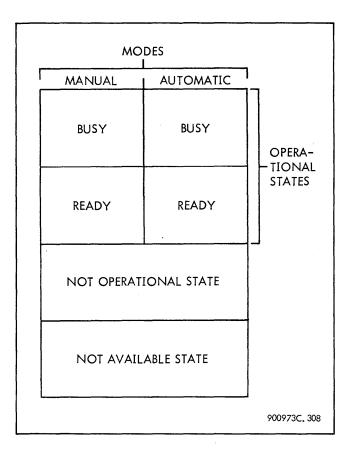

|         | Device Operatonal States and Controls                          |       |

|         | States and Modes                                               |       |

|         | Controls and Indicators                                        |       |

|         | DC Ready Condition                                             |       |

|         | Device Subcontroller                                           |       |

|         | Subcontroller Description                                      |       |

|         | Subcontroller Signals                                          |       |

|         | Interface Connect/Disconnect Description                       | ••••• |

|         | Connect Principles of Operation                                |       |

|         | Disconnect Principles of Operation                             |       |

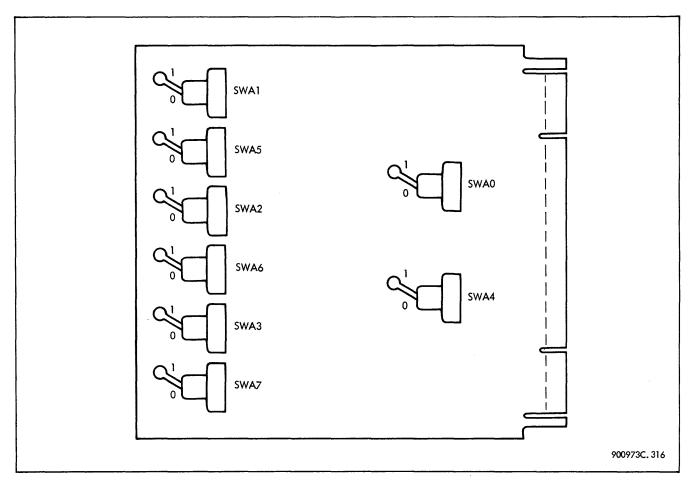

|         | Switch Comparator Module                                       | 0.04  |

|         |                                                                |       |

|         |                                                                |       |

|         | IOP-DC Service Cycles                                          |       |

|         | Terminal Order                                                 |       |

|         | Continuous Service Call DC                                     |       |

|         | Special Considerations for Multidevice Controllers             |       |

|         | Optional UEND Generators                                       |       |

|         | DC-Generated Interrupt                                         |       |

| IV      |                                                                | 4-1   |

| IV      | SIGMA 2 16-BIT MEMORY INTERFACE                                |       |

|         | Introduction                                                   |       |

|         | Memory Communication                                           |       |

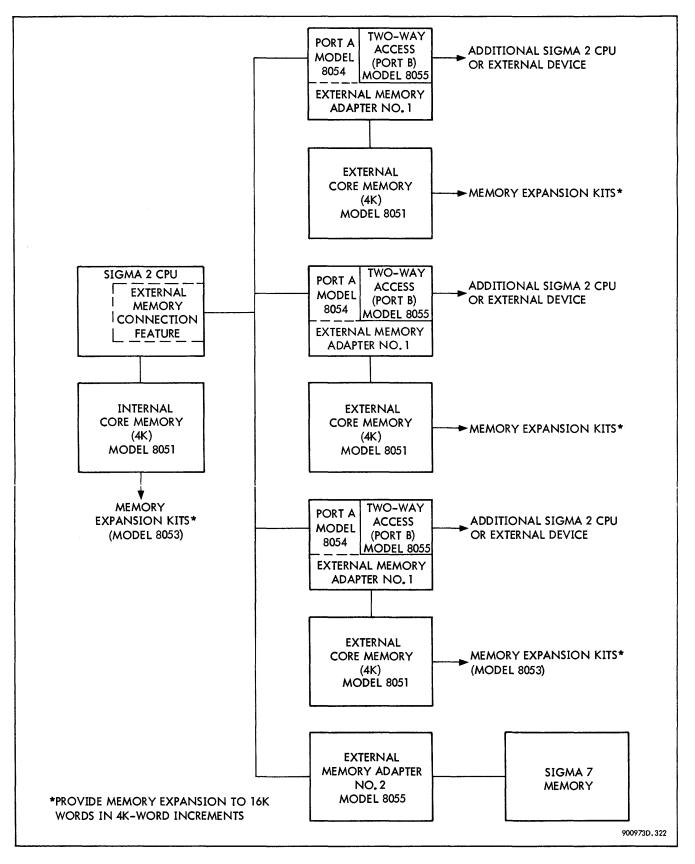

|         | Sigma 2 External Memory Ports                                  |       |

|         | Address Range and Starting Address Switches                    |       |

|         | Data Signals                                                   |       |

|         | Control Signals                                                | 4-1   |

•

## **CONTENTS (Cont.)**

| Section | Title                                       | F           | oage       |

|---------|---------------------------------------------|-------------|------------|

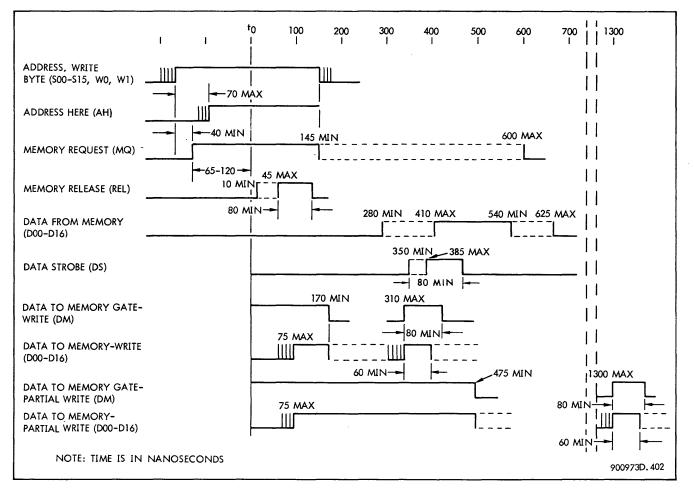

|         | Signal Lines and Timing                     |             | 4-1        |

|         | Address, Data, Control Signal Sequence      |             | 4-1        |

|         | Timing                                      |             | 4-5        |

|         |                                             |             |            |

| v       | SIGMA 3 16-BIT MEMORY INTERFACE             |             | 5-1        |

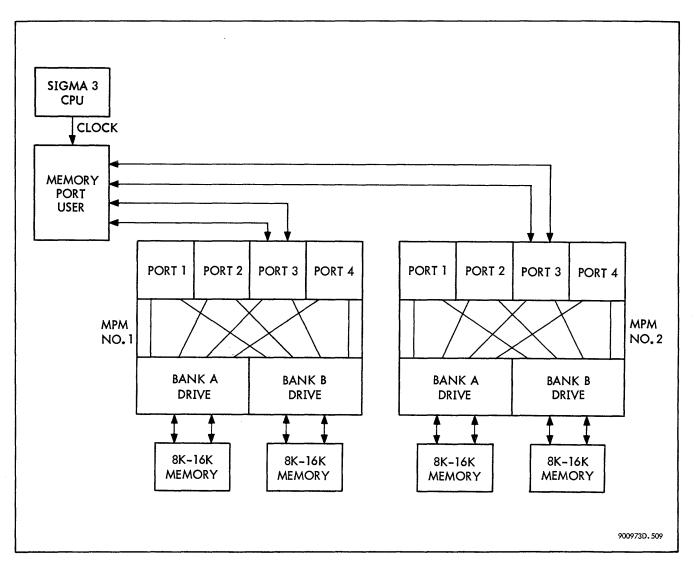

|         | Introduction                                |             | 5-1        |

|         | Memory Communication                        |             | 5-1        |

|         | Clocking                                    |             | 5-1        |

|         | Port Cabling                                |             | 5-1        |

|         | Addressing                                  |             | 5-1        |

|         | Parity                                      |             | 5-1        |

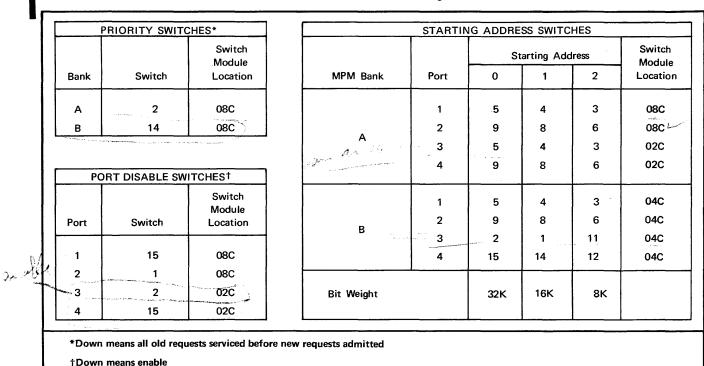

|         | Port Priority                               |             | 5-4        |

|         | Port Disable                                |             | 5-4        |

|         | Signal Description                          |             | 5-4        |

|         |                                             |             | 5-4        |

|         | Detailed Signal Description                 |             | 5-5        |

|         | External Memory Adaptor                     | • • • • • • | 5-6        |

|         | Design Aids                                 |             | 5-6        |

|         |                                             |             | 5-6        |

|         | Module AT59                                 |             | 5-6        |

|         | Mechanization Example                       |             | 5-6        |

| VI      | SIGMA 5 AND 7 32-BIT MEMORY INTERFACE       | •••••       | 6-1        |

|         | Introduction                                |             | 6-1        |

|         | Memory Communication                        |             | 6-1        |

|         | Port Concept                                |             | 6-1        |

|         | Memory Port Sequence                        |             | 6-1        |

|         | Signal Description                          |             | 6-2        |

|         | Memory Request (MQ)                         |             | 6-3        |

|         | Address (L15-L31)                           |             | 6-3        |

|         | Address Here (AH)                           |             | 6-3        |

|         | Data to Memory (M00-M31)                    |             | 6-3        |

|         | Data from Memory (M00-M31)                  |             | 6-3        |

|         | Write Byte (MW0-MW3)                        |             | 6-3        |

|         | Abort (ABO)                                 |             | 6-3        |

|         | Memory Request Release (MQR)                |             | 6-3        |

|         | Data Release (DR)                           |             | 6-3        |

|         | Early Data Release (EDR)                    |             | 6-3        |

|         |                                             |             | 6-3        |

|         | Second Request Allowed (SRA)                |             | 6-3        |

|         | Parity Error and Parity OK (PE and POK)     |             | 6-7        |

|         | High Speed Operaton                         |             | 6-7<br>6-7 |

|         | Accessing Data from One Memory Module       |             | 6-7        |

|         | Accessing Data from Multiple Memory Modules |             |            |

|         | ······································      |             |            |

| VII     | INTERRUPT AND CLOCK INTERFACE               |             | 7-1        |

|         | Introduction                                |             | 7-1        |

|         | External Priority Interrupts                |             | 7-1        |

|         | Sigma 2 or 3 Integral Priority Interrupts   |             | 7-2        |

|         | Interrupt Interface Service Modules         |             | 7-2        |

|         | Module AT11                                 |             |            |

|         | Module AT39                                 |             | 7-3        |

|         | Module LT55                                 |             | 7-3        |

## **CONTENTS** (Cont.)

| Section | Title                                  | Page                                                        |

|---------|----------------------------------------|-------------------------------------------------------------|

|         | Module ST29                            | . 7-3<br>. 7-3<br>. 7-3<br>. 7-3<br>. 7-3<br>. 7-3<br>. 7-3 |

| VIII    | CABLE AND SIGNAL DATA                  | . 8-1                                                       |

|         | Peripheral Equipment Tester Model 7901 | . 8-2<br>. 8-2<br>. 8-2<br>. 8-2                            |

| іх      | FLOW DIAGRAMS                          | . 9-1                                                       |

| x       | SIGNAL DICTIONARY                      | . 10-1                                                      |

## LIST OF ILLUSTRATIONS

# Figure

1-2

1-3

1-4

1-5

1-6

1-7

2-1

2-2

2-3

3-1

3-2

3-3

34

3-5

3-6

3-7 3-8

3-9

3-10

3-11 4-1

4-2

5-1

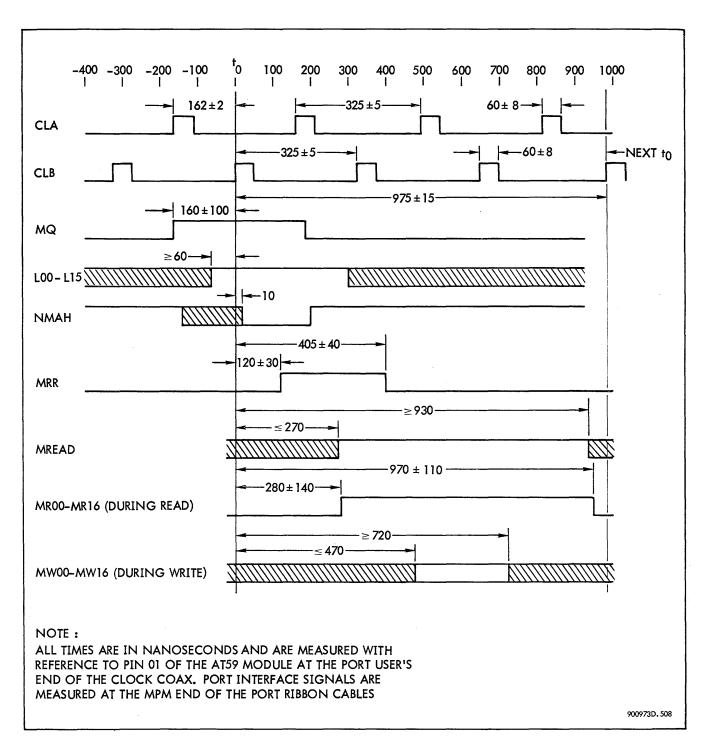

5-2

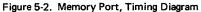

5-3

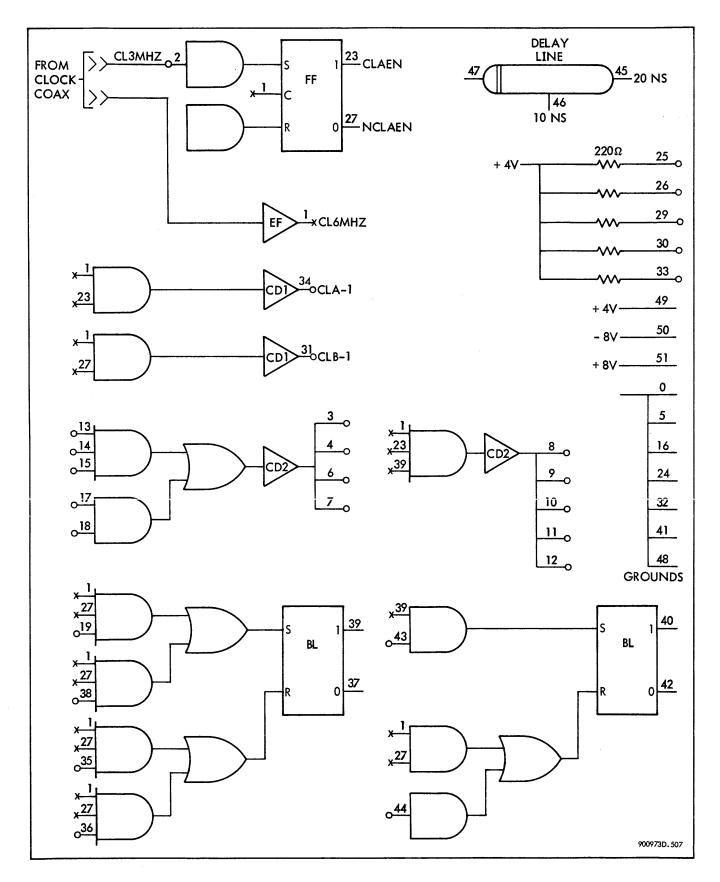

5-4

#### Title

Page

5-9

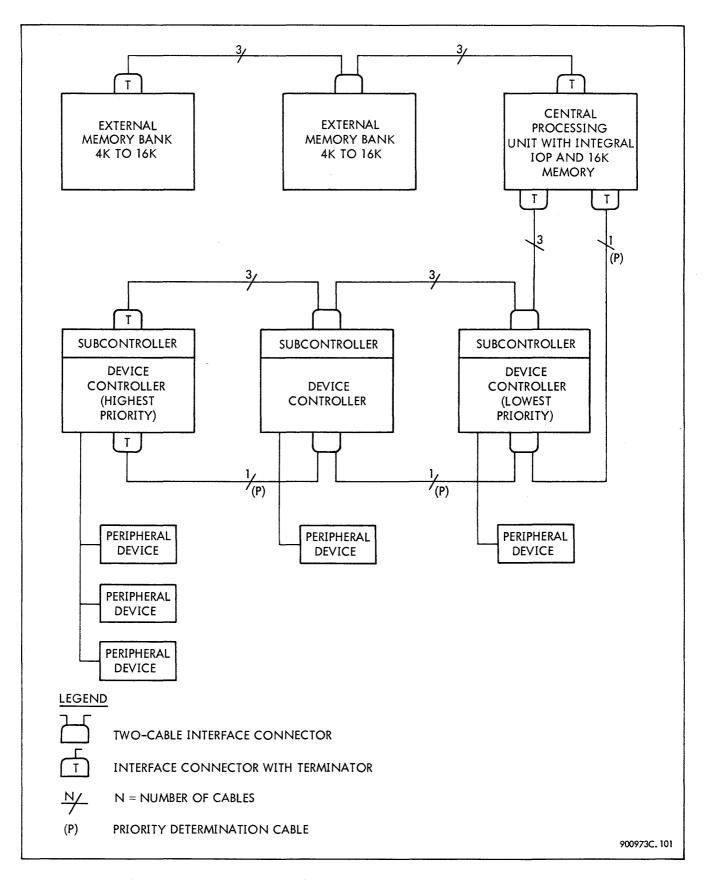

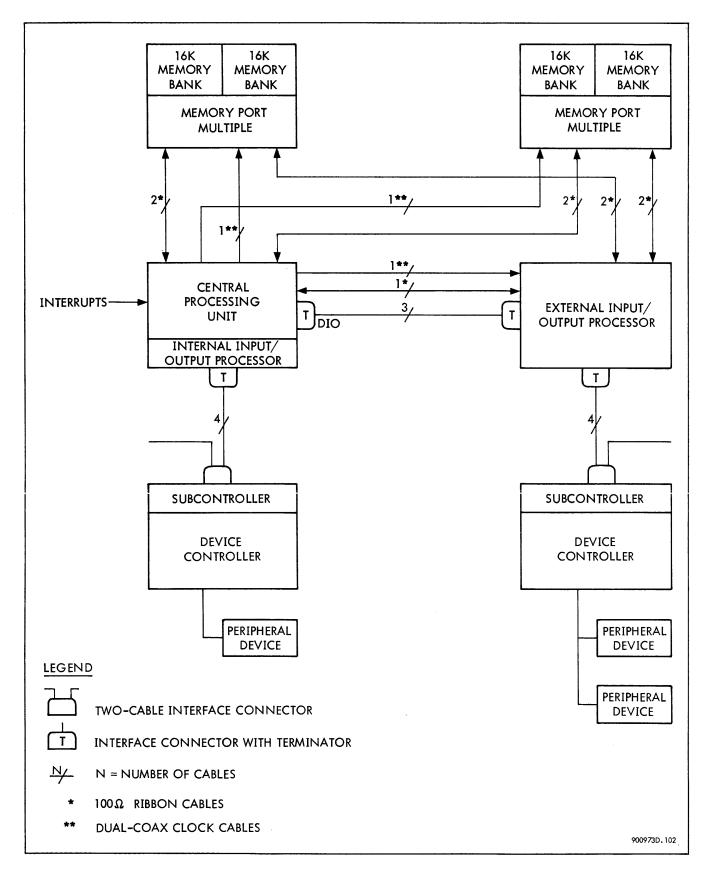

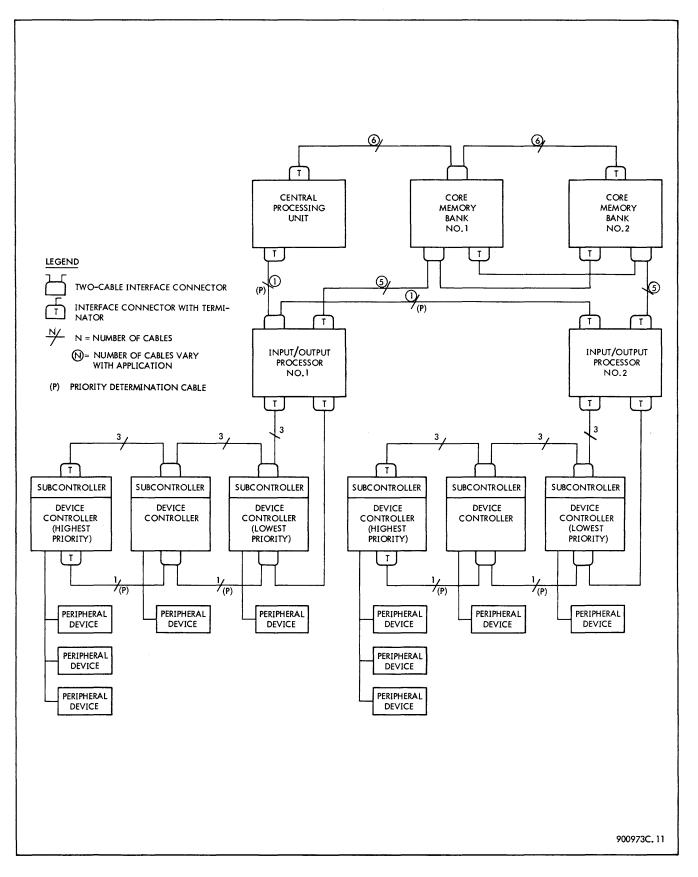

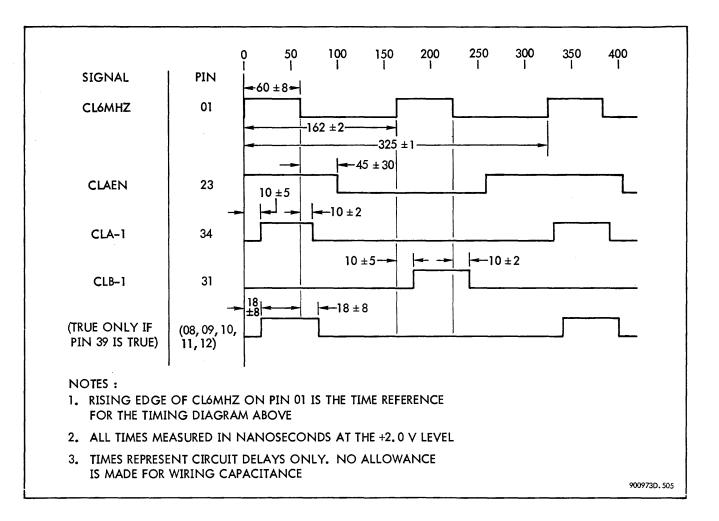

#### Typical Sigma 2 Cabling Scheme 1-3 Typical Sigma 3 Cabling Scheme 1.4 Typical Sigma 5 and 7 Cabling Scheme 1-5 Typical Transmission Line Connections 1-6 Cable Driver Circuit, Simplified Schematic Diagram 1-6 Interface Cable Connectors 1-7 Cable and Terminator Connections 1-8 DIO Interface Diagram 2-1 RD/WD (External Mode), Timing Diagram 2-2 Function Strobe Acknowledge, Logic Diagram 2-4 IOP Interface Signal Lines Diagram 3-2 Typical I/O Interconnections 3-4 Data Transmission Cable Twin Installation 3-8 3-9Strobe Acknowledge, Interface Diagram 3-9 Sigma 2 External Memory, Timing Diagram 4-6 5-3 Memory Port, Timing Diagram 5-5 AT59 Module Logic Diagram 5-8

AT59 Module Timing Diagram.....

## XDS 900973

## LIST OF ILLUSTRATIONS (Cont.)

## Figure

## Title

## Page

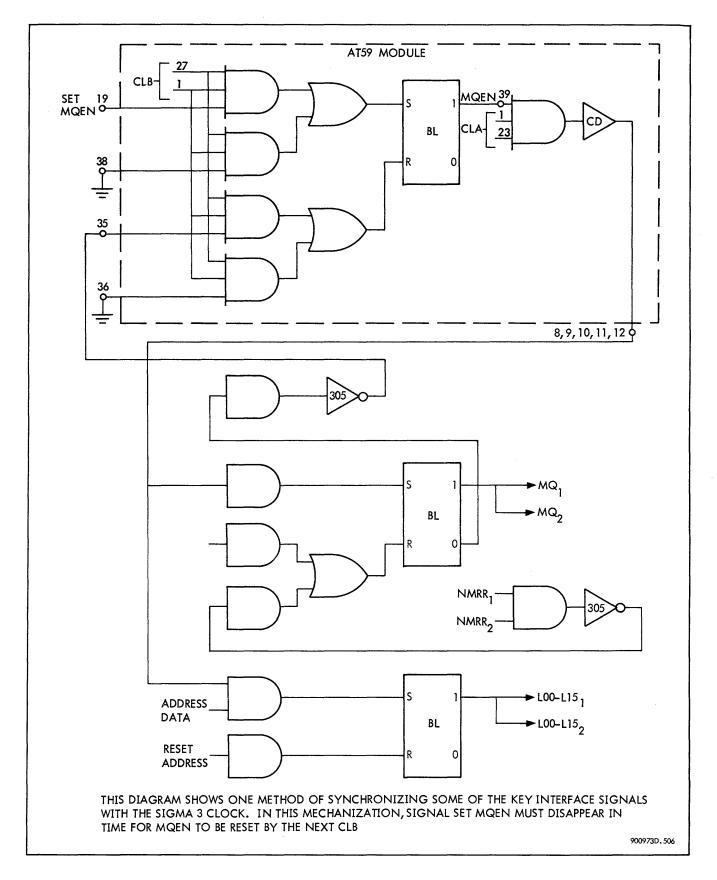

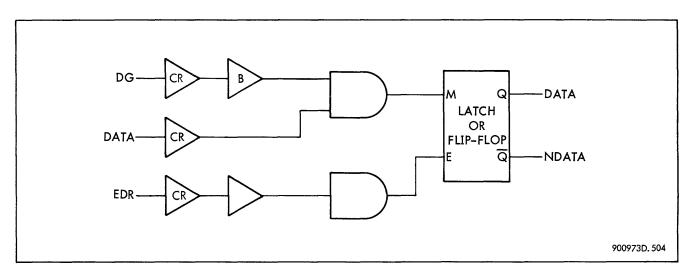

| 5-5 | Control Logic Mechanization, Logic Diagram                  |

|-----|-------------------------------------------------------------|

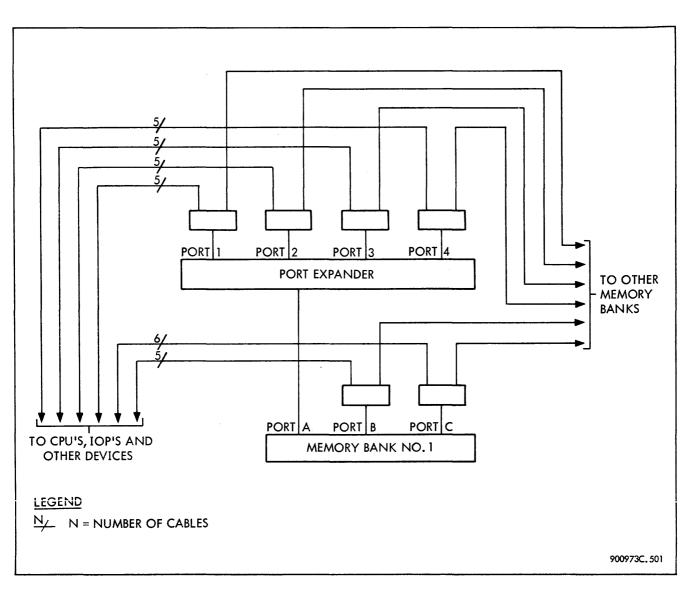

| 6-1 | Memory Port Expander, Installation Block Diagram            |

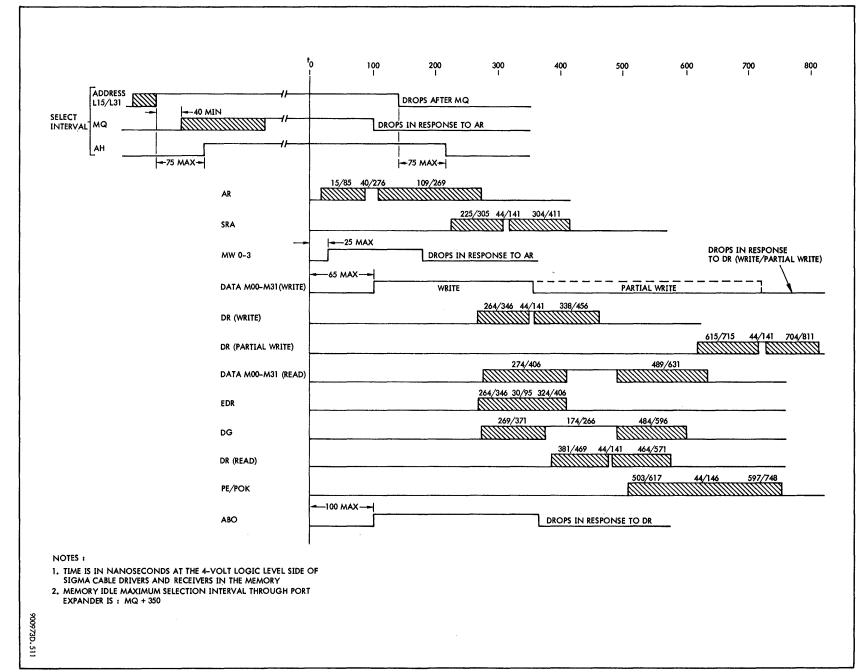

| 6-2 | Ports A, B, and C, Timing Diagram                           |

| 6-3 | Ports 1, 2, 3, and 4, Timing Diagram                        |

| 6-4 | Read and Hold Memory Data, Logic Diagram                    |

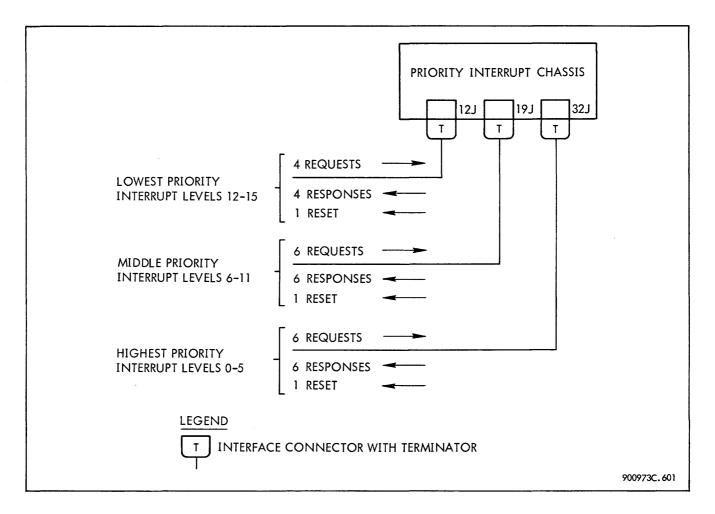

| 7-1 | External Priority Interrupt Chassis, Interface Diagram      |

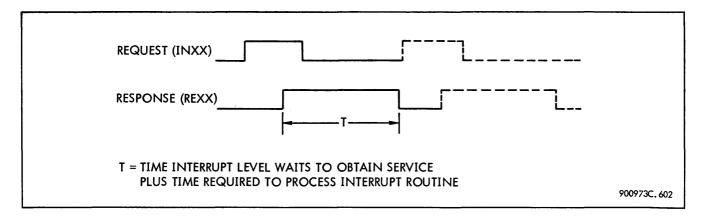

| 7-2 | External Interrupt Request and Response, Timing Diagram     |

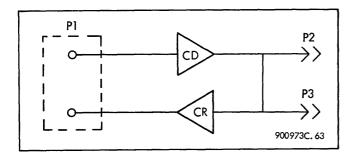

| 7-3 | AT11 Cable Driver-Cable Receiver Circuit, Schematic Diagram |

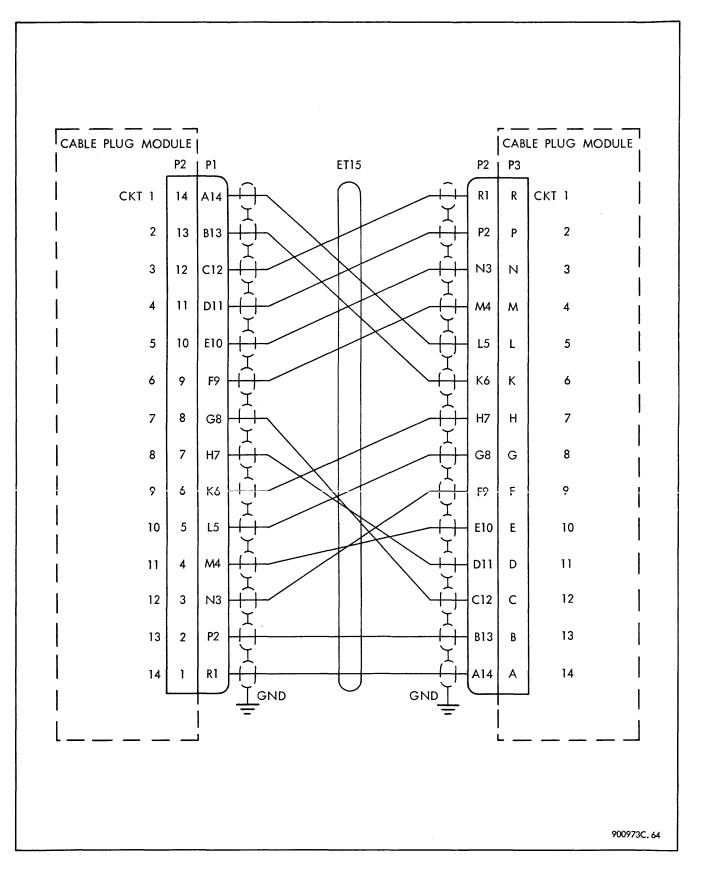

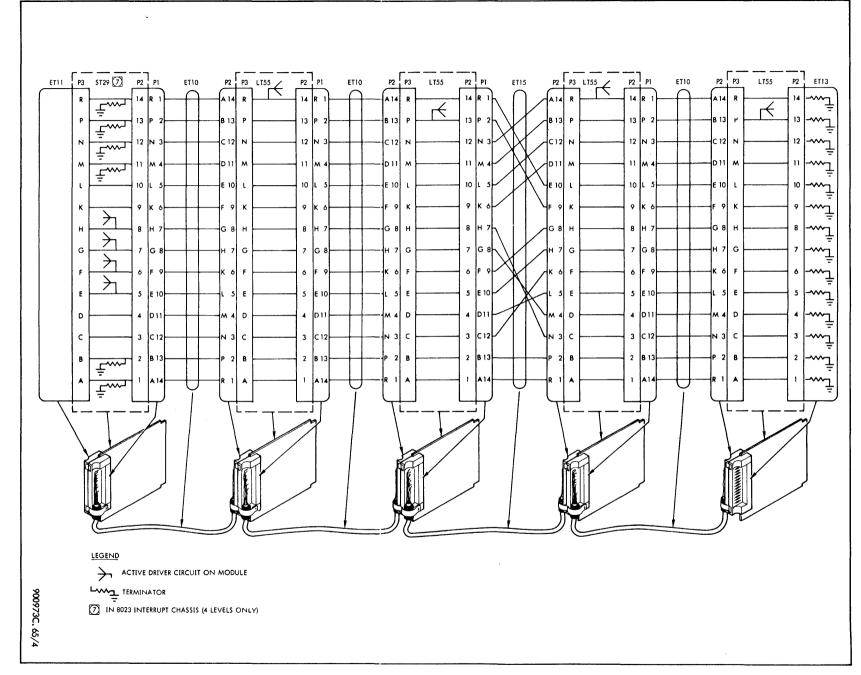

| 7-4 | ET15 Priority Interrupt, Cable Diagram                      |

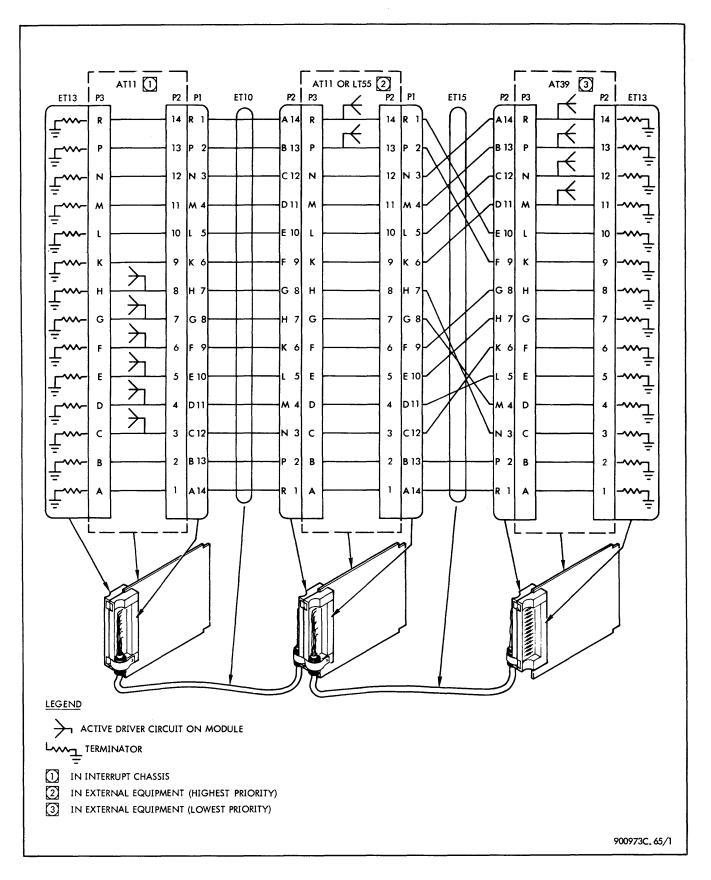

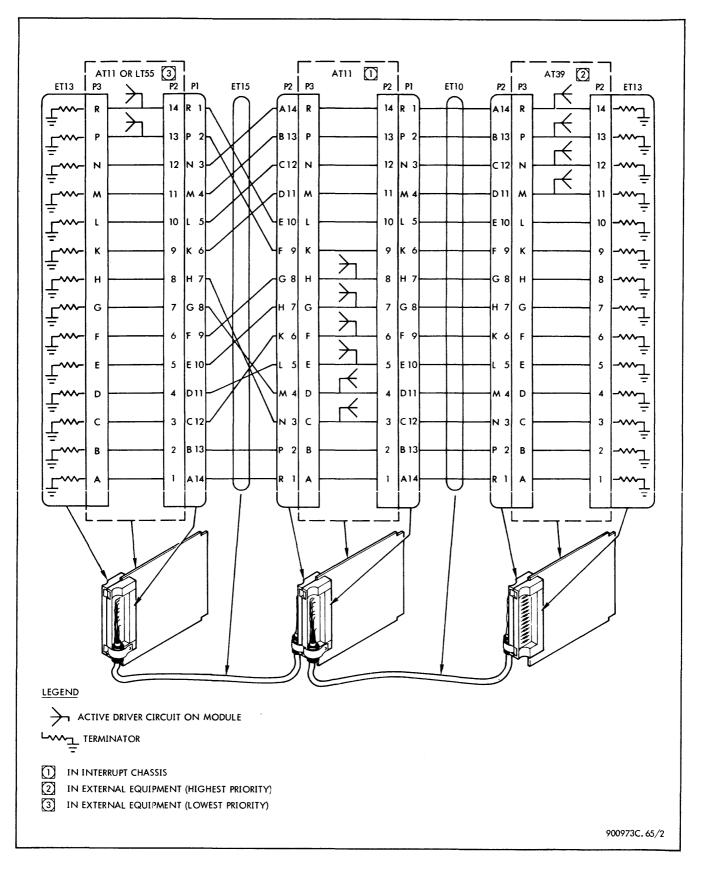

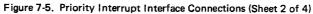

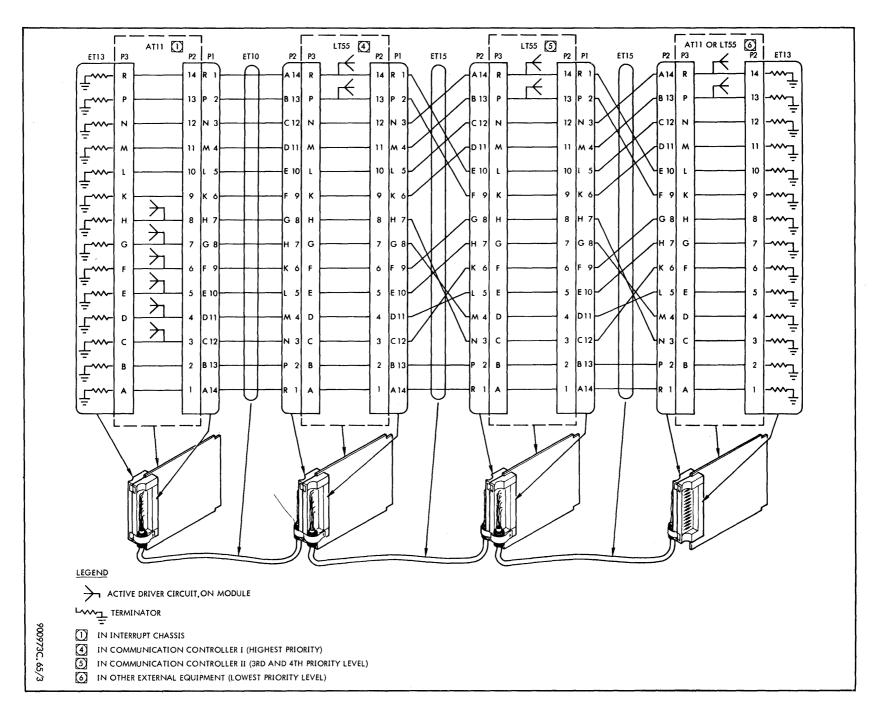

| 7-5 | Priority Interrupt Interface Connections (4 Sheets)         |

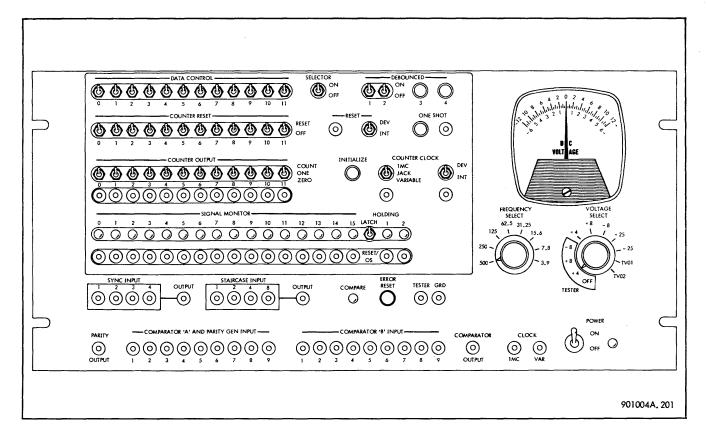

| 8-1 | Peripheral Equipment Tester Control Panel                   |

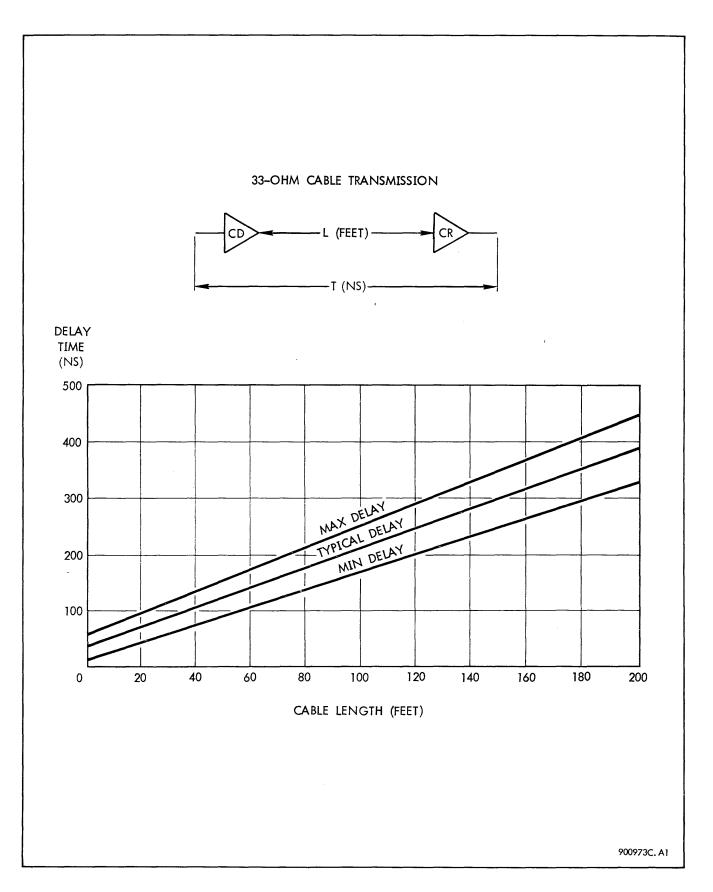

| 8-2 | Delay as a Function of Cable Length                         |

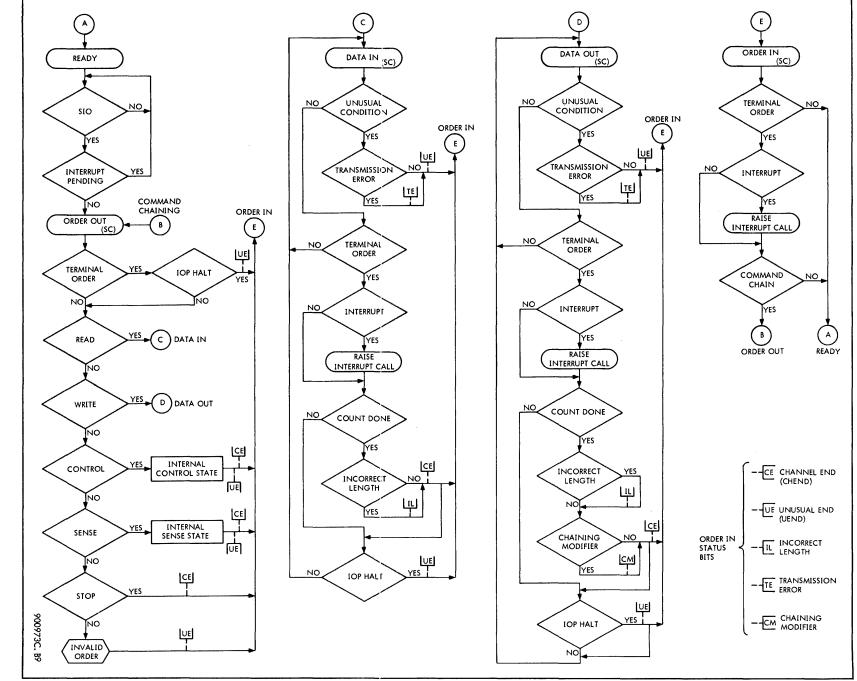

| 9-1 | Eight-Bit I/O Operatonal State, Flow Diagram                |

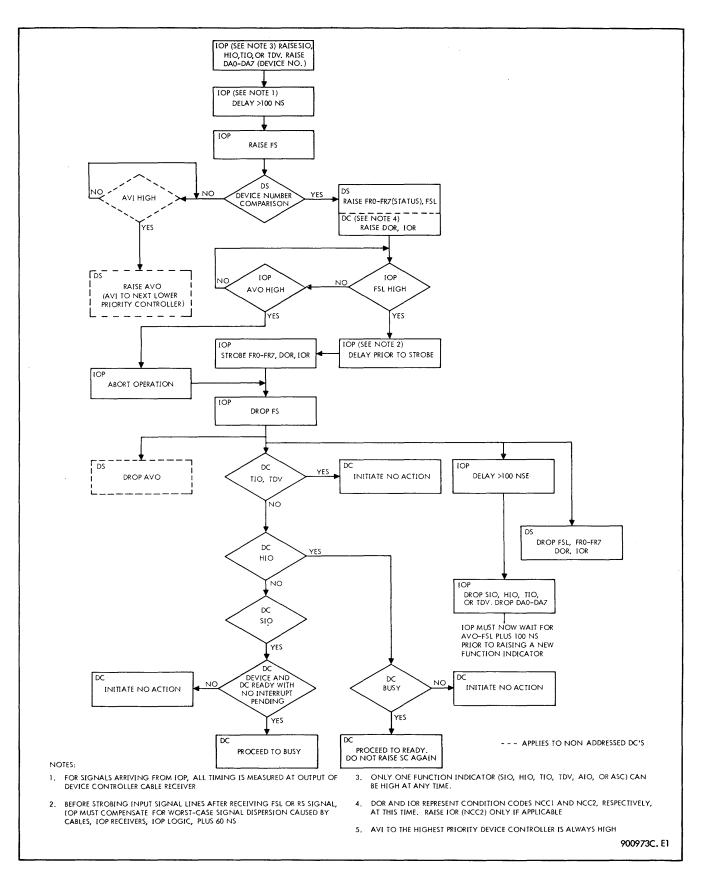

| 9-2 | SIO, HIO, TIO, and TDV, Flow Diagram                        |

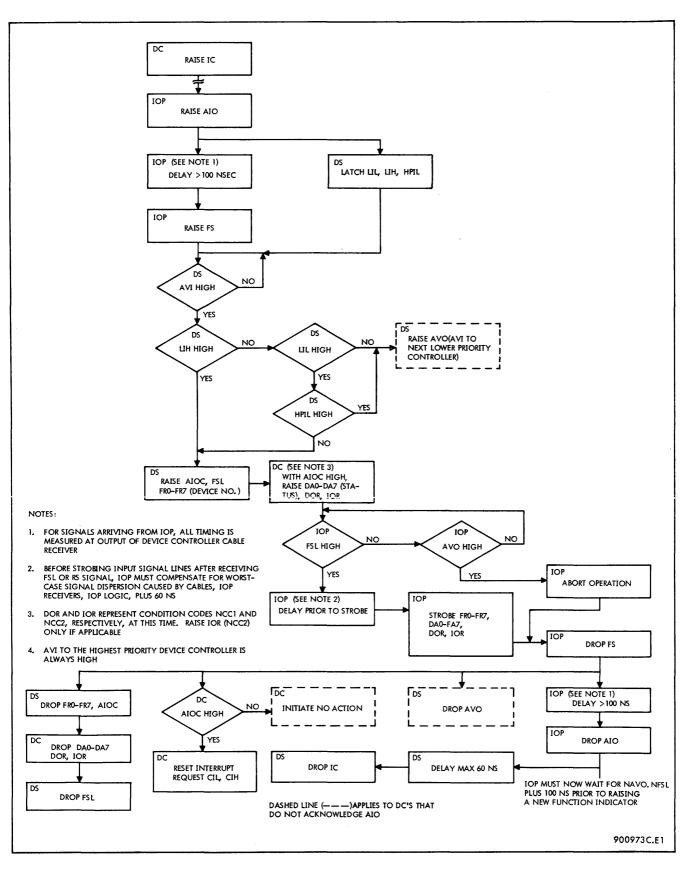

| 9-3 | AIO, Flow Diagram                                           |

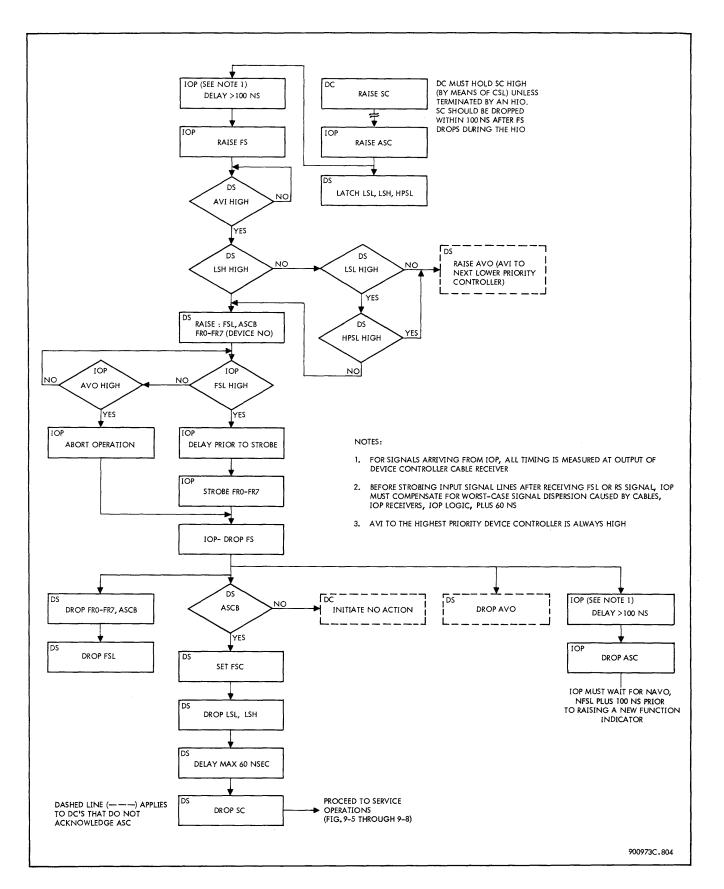

| 9-4 | ASC (Prior to Service Connection), Flow Diagram             |

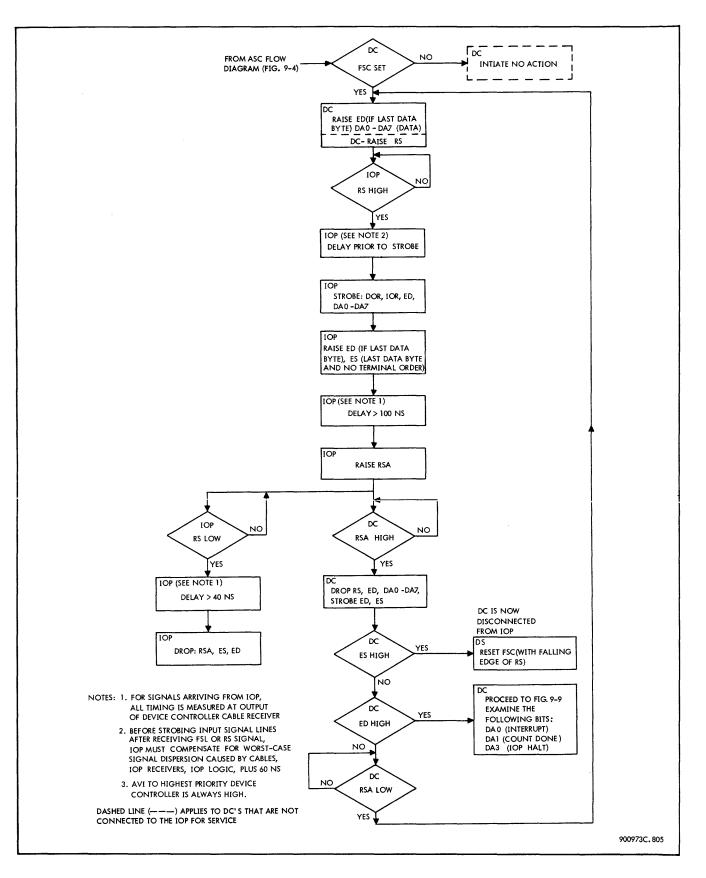

| 9-5 | Service — Data Input, Flow Diagram                          |

| 9-6 | Service — Data Output, Flow Diagram                         |

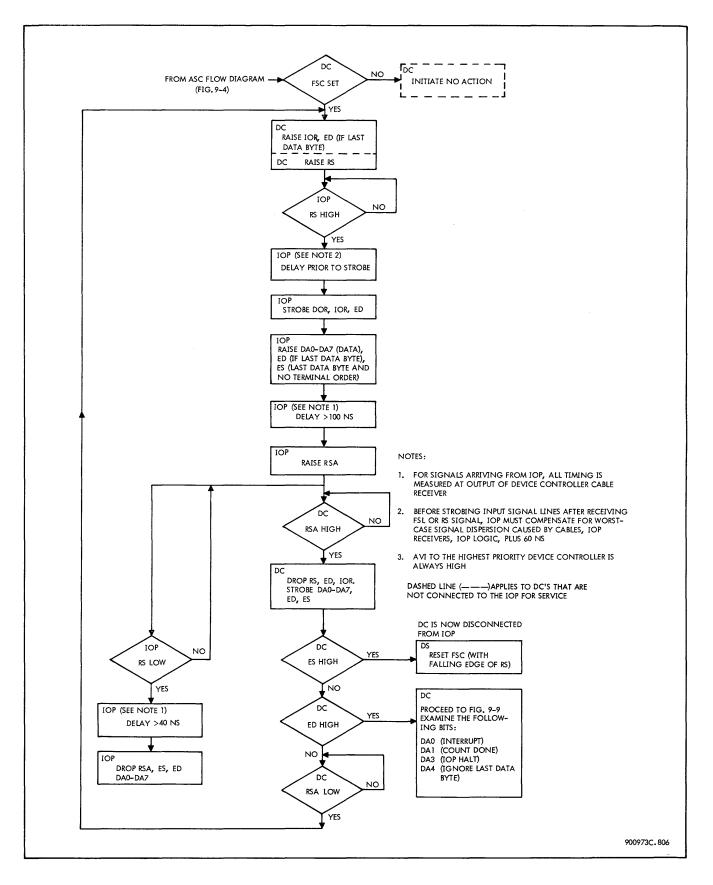

| 9-7 | Service – Order Output, Flow Diagram                        |

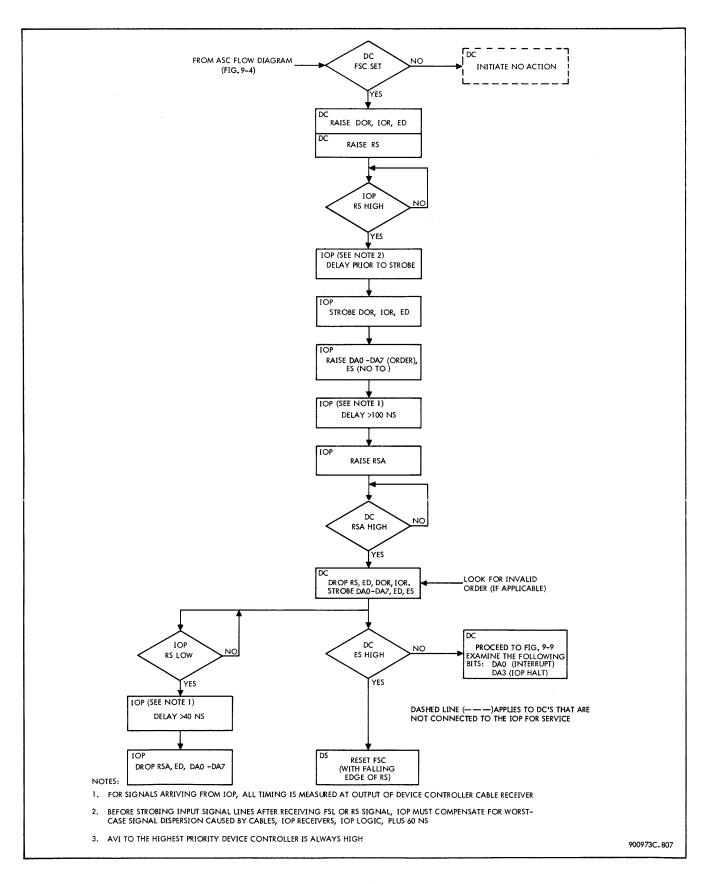

| 9-8 | Service – Order Input, Flow Diagram                         |

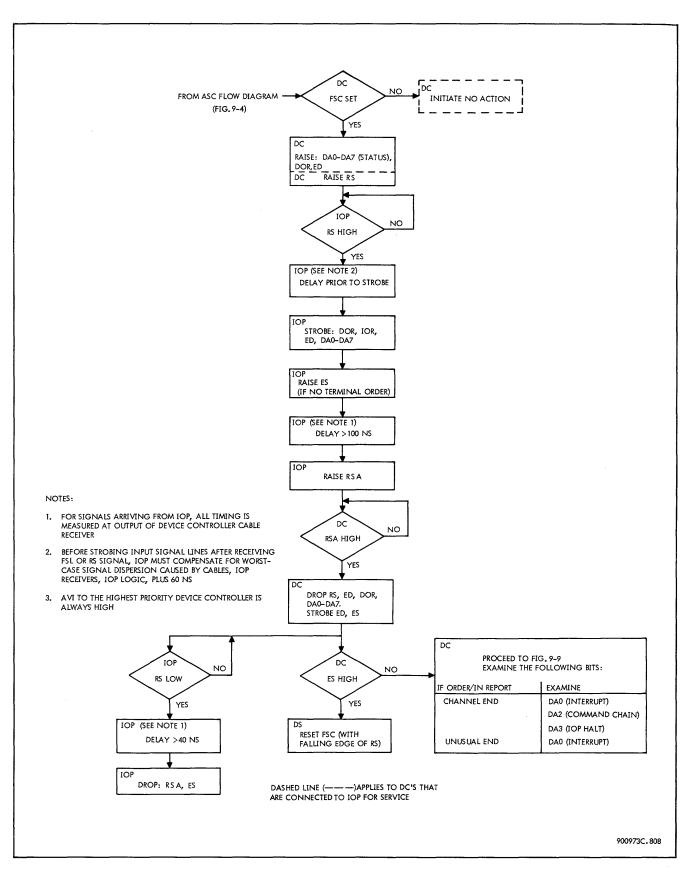

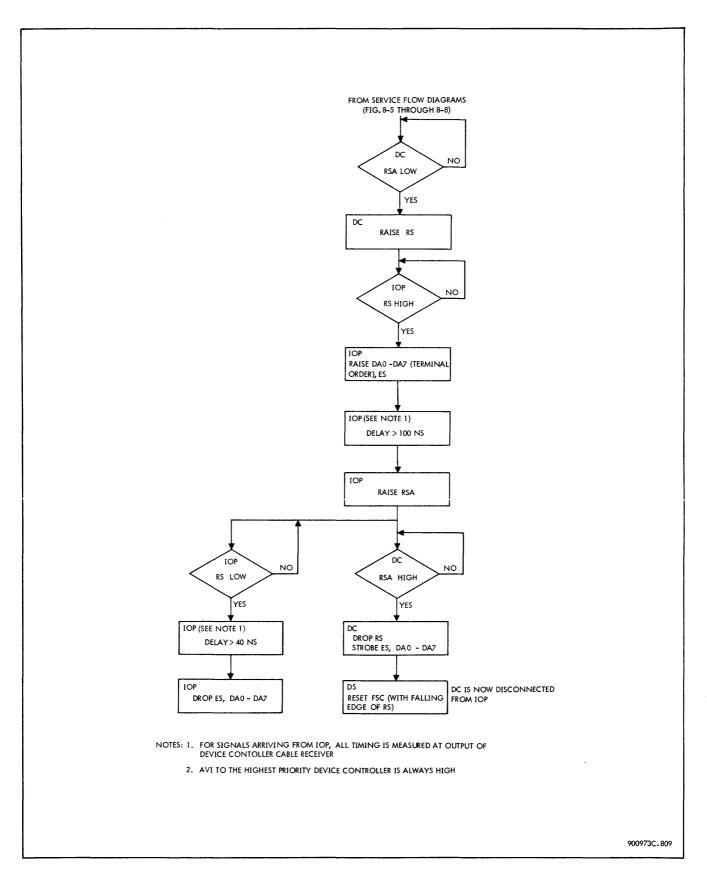

| 9-9 | Terminal Order, Flow Diagram                                |

## LIST OF TABLES

## Table

## Title

## Page

| 2-1          | DIO Interface Signals                                            |

|--------------|------------------------------------------------------------------|

| 3-1          | IOP Interface Cable Signals at Device Controller                 |

| 3-2          | Summary of Bit Codings for Data Exchanges                        |

| 3-3          | SIO, HIO, and TIO Status Response                                |

| 3-4          | IOP Service Cycle Lines Description                              |

| 3-5          | Order Input Bit Significance                                     |

| 3-6          | Subcontroller Connector/Cable/Module Relationship                |

| 3-7          | Device Subcontroller Model 7900, Reference Documents             |

| 4-1          | Sigma 2 External Memory Switch Settings                          |

| ´ <b>4-2</b> | Interface Signals for 16-Bit Memory                              |

| 4-3          | Cable and Connector Pin Assignment for Sigma 2 Port Cables       |

| 4-4          | Connector Locations for 16-Bit Memory Interface 4-4              |

| 5-1          | Format of Memory Port Cable No. 1                                |

| 5-2          | Format of Memory Port Cable No. 2                                |

| 5-3          | Drive Requirements for Signals to an MPM                         |

| 5-4          | MPM Switch Settings                                              |

| 5-5          | AT59 Module Signal Characteristics                               |

| 5-6          | Sigma 3 Memory Port Calbe Locations                              |

| 6-1          | Sigma 5 or 7 Memory Starting Address, Toggle Switch Settings     |

| 6-2          | Sigma 5 or 7 Memory Cables for Signals                           |

| 6-3          | Sigma 5 or 7 Memory Cable Location Chart                         |

| 7-1          | Interrupt Interface Signals                                      |

| 7-2          | Sigma 2 or 3 Integral Priority Interrupt and Clock Cable Signals |

| 7-3          | Sigma 5 or 7 Clock Cable Signals                                 |

| 7-4          | Sigma 2 or 3 External Priority Interrupt Cable Signals           |

| 8-1          | Byte and Cable Signal Relationship                               |

| 10-1         | Signal Logic Dictionary                                          |

|              |                                                                  |

## SECTION I GENERAL INFORMATION

#### INTRODUCTION

The Interface Design Manual (IDM) was prepared to assist engineers in connecting external equipment to Xerox Data Systems Sigma computers. It describes compatible interfaces for all configurations of Sigma series equipment.

For information on the use of XDS T-Series integrated circuit modules, see XDS T-Series Integrated Circuit Logic Modules Description and Specifications Bulletin 64-51-03R, which can be obtained from the local XDS representative or directly from corporate headquarters.

#### Note

Timing information, signal nomenclature, and systems cabling descriptions included in the IDM are not authorized for use as maintenance data.

The Sigma interface line-up consists of:

1. Direct Input/Output (DIO), also called Read Direct/Write Direct Interface

- 2. Input/Output Processor (IOP) Interface

- 3. Sigma 2 16-Bit Memory Interface

- 4. Sigma 3 16-Bit Memory Interface

- 5. 32-Bit Memory Interface

- 6. Interrupt and External Real-Time Clock Interface

#### **DIO INTERFACE**

The DIO interface provides input or output paths for central processing unit (CPU) communication with external devices to transmit or to receive data and control information.

The DIO interface is controlled by the Read Direct (RD) or by the Write Direct (WD) instructions. Each RD or WD instruction presents the 16 least significant bits of the effective address at the interface together with a control signal. The external unit addressed must then acknowledge the call to enable instruction execution. Direct input/output is the simplest means of transferring data or control information between the CPU and any unit. A unit requires less control logic to connect to the DIO interface than to connect to an IOP or directly to memory.

However, a CPU instruction is necessary for every word transferred. Therefore a unit on the DIO interface generally requires more CPU time than when other methods are used. Also, a unit on the DIO interface may need an interrupt level to call in the CPU. The DIO interface consists of data lines, address lines, RD/WD selection line, function strobe line, function strobe acknowledge line, status lines, I/O reset line, and 1.024-MHz clock line.

Most XDS equipment designed to operate on the DIO interface will function satisfactorily with the Sigma 2, 3, 5, or 7 computer. For specific information, refer to the applicable computer reference manual.

## **IOP INTERFACE**

The IOP interface provides lines through which peripheral units are controlled by a Sigma CPU and lines for data exchange between peripherals and core memories. The IOP interface is characterized by automatic operation. Following program initiation, data transfers occur automatically and without further direct program intervention.

The IOP interface consists of data lines, function lines, status lines, control lines (strobes, acknowledgments, and so forth), priority determination lines, service request lines, miscellaneous lines.

#### **16-BIT AND 32-BIT MEMORY INTERFACES**

The 16-bit memory interfaces in Sigma 2 and Sigma 3 and the 32-bit Sigma 5 and 7 memory interfaces provide direct data interchange between external devices and the Sigma memories. The Sigma 2 and 3 memory systems store 64K words maximum; Sigma 5 and 7 each store 128K words maximum. The memory interfaces are characterized by simplicity, a high data transfer rate, and a maximum flexibility of control.

The memory interfaces consist of data lines, address lines, control lines (request, acknowledge, and so on) and miscellaneous lines.

Each standard device, CPU, IOP, or special device which requires a direct connection to memory communicates with memory on its own bus. Although seldom necessary, special external devices can share a memory bus if related logic is included to resolve access conflicts.

## **INTERRUPT AND CLOCK INTERFACE**

The external interrupt interface provides peripheral devices with the means of notifying the CPU of the need for service. The several external interrupt chassis can be located in the CPU or elsewhere. The real-time clock interface is located at the CPU and enables users to run real-time programs at desired rates.

Sigma 5 and 7 computers accept a maximum of 14 interrupt chassis with each chassis providing up to 16 interrupt levels. In Sigma 2, one group of four integral levels and eight external chassis of 16 levels are available. In Sigma 3, one group of four integral levels and six internal chassis of 16 levels each are available. Three cables are used to interface a priority (external) interrupt control chassis and user equipment.

The interrupt and clock interface consists of:

Interrupt request lines Interrupt acknowledge lines I/O reset line External real-time clock input lines

#### CABLING

#### SELECTION OF COMPONENTS

The use of XDS cabling, cable drivers, and cable receivers as tie-ins to power supplies is essential for the following reasons:

1. Design, fit, and function of XDS cables, cable drivers, and cable receivers are matched to the usage.

2. XDS components provide verified efficiency and reliability.

3. No effort need be expended in converting data in the interface design manual (IDM).

A monetary loss would result if substitute components failed to perform all required functions or fell short of XDS performance criteria.

5. XDS must disclaim a responsible supplier interest in interface installations where substitute cabling, cable drivers, or cable receivers have been employed.

#### CABLE LAYOUT

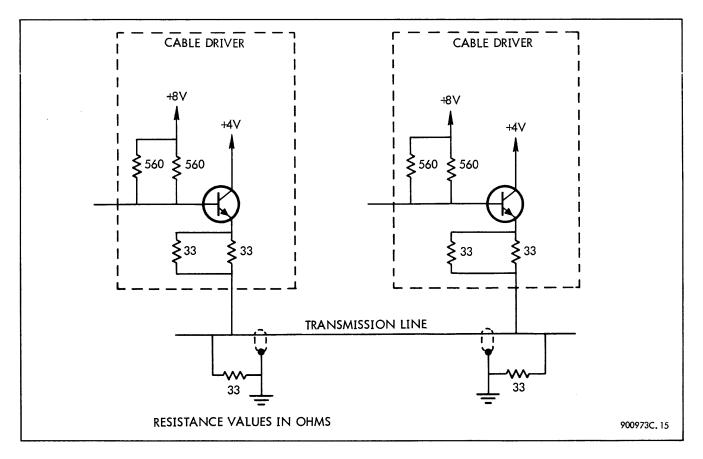

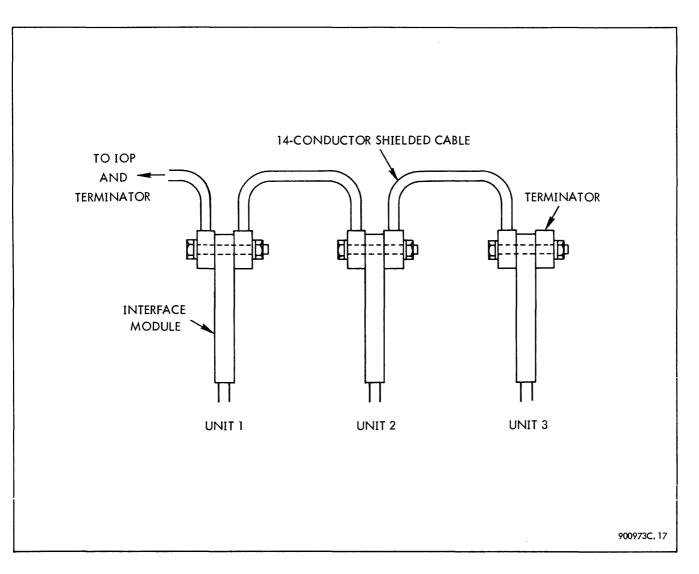

All interfaces described in this manual, except the Sigma 3 memory interface, use the same cable driver- receiver scheme and the same means of interunit cabling (figures 1-1 through 1-3). Interunit cabling consists of several cables, with each cable consisting of 14 shielded wires (for characteristics refer to section VIII). Each shielded wire used as a transmission line is terminated with a 33-ohm characteristic impedance at each end (figure 1-4). Connection to this line is made by tapping the line without unduly affecting the characteristic impedance. A number of cables are used to handle all signals associated with each interface. These are:

| DIO interface                                                 | Three cables for Sigma 2 or 3                                                        |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------|

|                                                               | Four cables for Sigma 5 or 7                                                         |

| IOP interface to<br>device controller —<br>one-byte interface | Four cables for all (three signal cables plus a single priority-determination cable) |

| IOP interface to<br>device controller<br>four-byte interface  | Six cables for all (five signal cables plus priority determination cable)            |

| Memory interface                                              | Three cables for Sigma 2                                                             |

|                                                               | Two ribbon cables for Sigma 3                                                        |

|                                                               | Five cables for Sigma 5                                                              |

|                                                               | Five cables for Sigma 7                                                              |

Interrupt interface

One, two, or three cables for all (depending on the number of interrupts)

For all signals on 33-ohm cables (except device controller priority determination signals), each unit may tap any line with both a cable driver and a cable receiver. The following conventions are used:

Logical one, +2 volts - Driver output = low impedance

Logical zero, 0 volts - Driver output = high impedance

### DRIVER-RECEIVER CIRCUITS

The quiescent state of any time-shared line is high impedance from the driver (logical zero). A unit whose driver is active on a given line may bring that line to the logical one state using the driver circuit shown in figure 1-5. Receiver circuits similarly tap the common line for each signal. Receivers incorporate high-noise-rejection discriminator circuits. No inversion exists in either drivers or receivers. If the input to a driver is a logical one (+4 volts), the line driven goes to logical one (+2 volts). If a line is at logical one (+2 volts), the receiver output is at logical one (+4 volts).

Priority determination signals are similar except that only one driver and one receiver are normally connected to each line. Signals are received by each unit through standard logic elements and then may or may not be routed to the next unit.

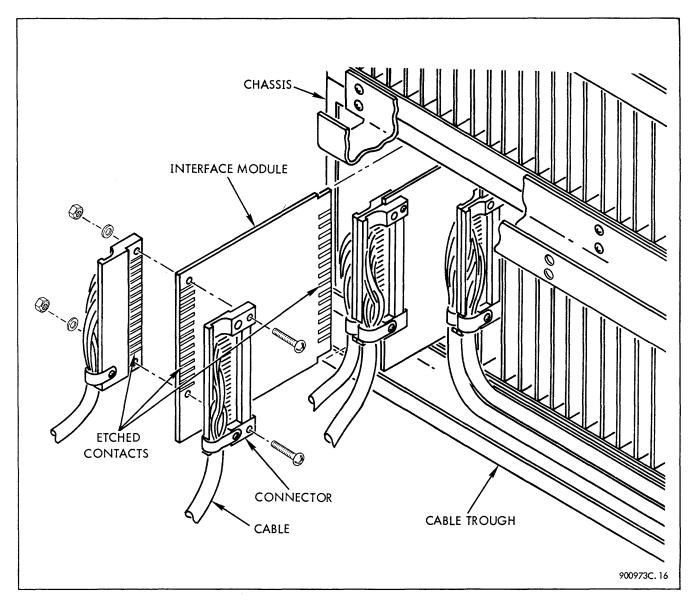

#### CABLE-TO-MODULE CONNECTIONS

Except for length and the special offset cable described in section VII, all interunit cabling is physically identical. The cables do not include special components or circuits and are directly connected to edge contacts on the various cable driver-receiver modules. The cable driver-receiver modules can be inserted in any slot (except adjacent slots) in a standard Sigma chassis. Standard slots are provided for standard interfaces. The modules should be wired into these slots for ease of identification by customer servicemen. Cable driver-receiver modules cannot be located in adjacent module slots because of space limitations. At least one module of some other type or an unused connector slot must be provided between cable driver-receiver modules.

Each driver-receiver module can accept two cables mechanically sandwiched to the module (figure 1-6). Thus, interunit cabling comprises one long transmission line with drivers and receivers connected at each unit. The last unit on the transmission line at each end must have a terminator attached to the line in place of the cable that would otherwise start from that point (as shown in figure 1-7).

## **TESTING EXTERNAL SIGNALS**

Either RD or WD instructions can be used to select and to test an external condition and to transmit the results of that test on two sense lines at the interface. Test results are stored in condition code bits 3 and 4 in Sigma 5 or 7, or in the overflow and carry bits in Sigma 2 or 3. Program instructions permit these flags to be tested with branching based on their state.

Figure 1-1. Typical Sigma 2 Cabling Scheme

XDS 900973

XDS 900973

Figure 1-4. Typical Transmission Line Connections

Figure 1-5. Cable Driver Circuit, Simplified Schematic Diagram

Figure 1-6. Interface Cable Connectors

## **DESIGN AIDS**

The Sigma input/output system design concept emphasizes ease of component connection and separation. The interface design engineer should therefore ascertain that he has followed the following basic considerations:

1. All cables (except the special offset cable described in section VI) should be identical except for length.

2. Cable receptacles should be located in the same place in each chassis assembly.

3. Similar assemblies should be connected in similar manner.

4. Cables should be connected in a trunk-to-tail manner.

5. Cable length restrictions (as stated in the IDM) should not be exceeded.

6. No more than 25 receivers or 25 drivers should be connected to one line.

7. No more than one transmitter should drive a given line to its positive level at a given time.

8. The end of each line is terminated by a 33-ohm resistor to ground.

Figure 1-7. Cable and Terminator Connections

## SECTION II

## **DIO INTERFACE**

### INTRODUCTION

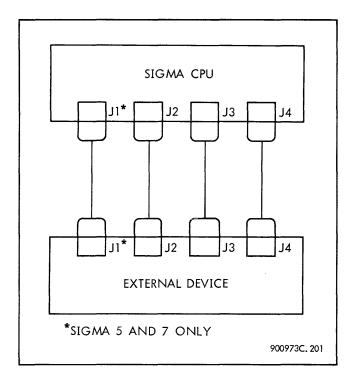

The Direct Input/Output (DIO) interface (figure 2-1) is controlled by the Read Direct (RD) and the Write Direct (WD) instructions. Each RD or WD instruction presents the 16 least significant bits of the effective address at the interface together with an FS (function strobe) control signal. The external unit must provide a function strobe acknowledge (FSA) signal to enable complete execution of the RD or the WD instruction.

During the RD instruction, the external unit may provide data (32 bits in Sigma 5 or 7 and 16 bits in Sigma 2 or 3) for storage in a computer register. This data is provided in conjunction with signal FSA. During the WD instruction, Sigma 5 or 7 presents 32 bits and Sigma 2 or 3 presents 16 bits of data to the external unit with signal FS. WD is transmitted on the same lines used to transmit input data during the RD instruction. The data lines are thus bidirectional and are time-shared for the two instructions.

Additional signals provided at the DIO interface are:

1. A signal that differentiates between RD and WD instructions for the external user (since RD and WD appear identical in all other respects).

Figure 2-1. DIO Interface Diagram

2. Two input status lines. During either RD or WD instructions, these data lines set condition code bits 3 and 4 (CC3 and CC4) in Sigma 5 or 7 or set the overflow and carry bits in Sigma 2 or 3 (O and C).

3. An input/output reset signal.

4. A 1.024-MHz clock signal (not synchronized with instruction execution).

For a listing of DIO interface signals, refer to table 8-2.

## **INTERFACE DESCRIPTION**

#### DATA LINES

Thirty-two bidirectional data lines are available on Sigma 5 or 7 and 16 lines on Sigma 2 or 3. When an RD or a WD instruction is not being executed, these data lines are in an undefined state, that is, the lines may be high, low, or changing.

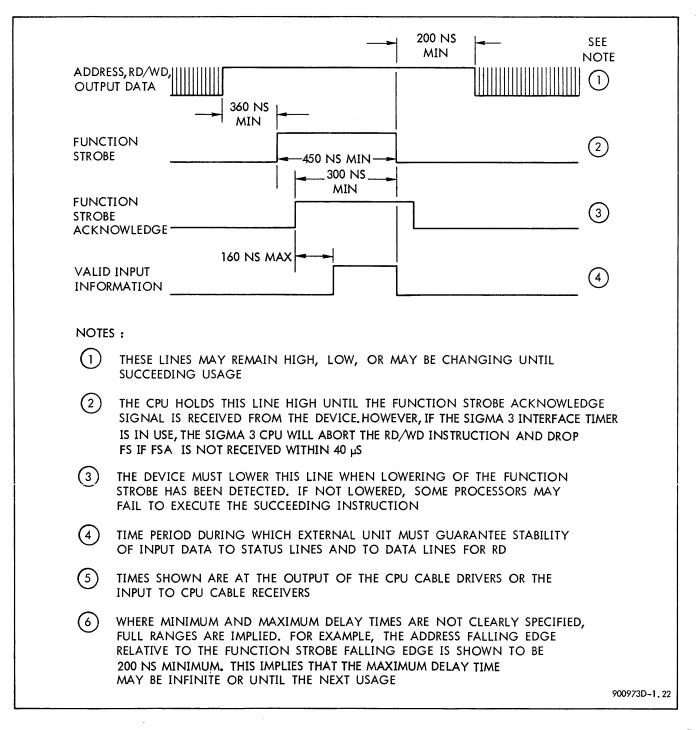

During execution of a WD instruction, the CPU puts data on the lines to obtain stability for at least 360 nanoseconds (ns) before the function strobe is raised. The date lines remain stable for at least 200 ns after the CPU lowers the function strobe. (The times given are at the CPU driver outputs.)

During execution of an RD instruction, the addressed external unit places data on the lines with the FSA response signal. Data must be steady at the CPU receiver input no later than 160 ns after FSA reaches the CPU receiver input. The external device must continue to hold the data lines stable until the falling edge of the function strobe has been detected.

All timing is measured at the output of the CPU cable drivers for signals arriving from the CPU. All timing is measured at the input to the CPU cable receiver for signals being sent to the CPU. When measuring delays between signals, all measurements are made at the 50-percent point of the voltage waveforms. Figure 2-2 is a diagram of RD/WD timing.

#### ADDRESS LINES (A00R-A15R)

The 16 address lines are driven only by the CPU. Timing is identical to that of the data lines during a WD instruction (figure 2-2). Address line information consists of the effective address (16 least significant bits) of the WD or RD instruction.

#### **READ DIRECT/WRITE DIRECT SELECTION LINE (RWDR)**

The CPU drives one line to enable external devices to distinguish between a WD (output) and an RD (input) instruction. Timing is the same as for the address lines and the data lines during output. The selection line is driven high for WD and low for RD.

## FUNCTION STROBE AND ACKNOWLEDGMENT LINES (RFSR AND RFSAD)

The DIO interface is alerted and synchronization is obtained by means of the FSS and the FSA signals. Upon executing a WD or a RD instruction, the CPU sets address lines, the RD/WD selection

line, data lines (for a WD instruction) and then raises FS after a minimum delay of 360 ns at the driver output. The external device which recognizes the address responds by raising FSA. Upon detecting FSA, the CPU lowers FS after a minimum delay of 300 ns. The external device should then respond to the falling edge of FS by removing all signals from the interface without delay.

#### STATUS LINES (CC3D AND CC4D)

Two lines allow the external device to send two status bits to the CPU for either WD or RD instructions. The timing requirement for these two signals is the same as for input data during an RD instruction. Only the device addressed may raise these lines.

#### I/O RESET LINE (RSTR)

The I/O reset line is raised in response to manual setting of the applicable control panel switches or during a power-on or a power-off sequence. The applicable control panel switches are the I/O RESET and SYS RESET on Sigma 5 and 7, the INITIALIZE switch on Sigma 2, and the RESET switch on Sigma 3.

#### 1.024-MHz CLOCK (CL1R)

A 1.024-MHz clock signal is available for use by devices connected to the DIO interface. The line is continuously driven by the CPU regardless of the CPU function in progress. The signal is a square wave of approximately 50 percent duty cycle with a crystal-controlled frequency of 1.024 MHz ( $\pm 0.02$  percent long-term stability).

## **BASIS INSTRUCTIONS**

#### DATA INPUT

The RD instruction presents the 16 low-order effective address on the DIO interface address lines together with a signal that indicates execution of the RD instruction. The selected external device generates an acknowledge signal and presents data on the DIO interface data lines, as well as two bits of status information on the two status lines. In Sigma 5 or 7, if the R-field (the registerspecifying field in the instruction) is not equal to zero, the 32 data bits are stored in the specified register. If the R-field equals zero, the 32 data lines are disregarded, but bits CC3 and CC4 are still set as specified by the external device. In Sigma 2 or 3, the RD instruction is the same as in Sigma 5 or 7 except that only 16 bits of data are accepted and are stored in the accumulator. The status input lines are stored in the Sigma 2 or 3 overflow and carry indicators.

#### DATA OUTPUT

In Sigma 5 and 7, the WD instruction presents the 16 low-order bits of effective address on the DIO interface address lines together with a signal that indicates execution of the WD instruction. The selected external device generates an acknowledge signal and may accept 32 bits of data from the DIO interface data lines. The computer simultaneously accepts two bits of status information on two other lines to set bits CC3 and CC4. If the R-field is not equal to zero, the 32 bits of the specified register are transmitted on the 32 data lines. If the R-field equals zero, the 32 data lines are set at logical zero regardless of the contents of any register, but bits CC3 and CC4 are still set as specified by the external device.

On Sigma 2 or 3, the WD instruction is the same as Sigma 5 and 7 except that only 16 bits of data are transmitted from the accumulator. The status input lines are stored in the overflow and carry indicators.

#### EFFECTIVE ADDRESS ASSIGNMENTS

The general area controlled by an RD or WD instruction is specified by the four high-order bits of the address which appear on the I/O

bus. These bits designate the control mode. Control mode assignments are as follows:

| Hexadecimal | Definition                                                                 |  |  |

|-------------|----------------------------------------------------------------------------|--|--|

| 0           | Internal computer control                                                  |  |  |

| 1           | Interrupt control (WD instruction only)                                    |  |  |

| 2           | XDS testers                                                                |  |  |

| 3 through E | Reserved for assignment by XDS for use in standard products                |  |  |

| F           | Systems special units (for customer use with specially designed equipment) |  |  |

A list of effective address assignments for control modes 0 through E is maintained by the XDS Product Planning Department. For detailed coverage of effective address assignments, refer to the applicable Sigma reference manual. For all standard product effective address assignments, the reservation of a particular code applies to all Sigma computers.

#### **DESIGN AIDS**

#### **CABLE DRIVERS**

Cable drivers may be driven by any standard XDS logic circuit, including flip-flop outputs. However, the following considerations should be noted:

1. The cable driver circuit takes nine unit loads (one unit load equals 3.8 MA).

2. The nominal output of standard Sigma logic elements is 16 unit loads.

3. Pull-up resistors draw two unit loads.

4. Terminating resistors draw five unit loads.

5. Terminating resistors should not be used on circuits that feed cable driver inputs (any circuit can feed one cable driver and five other loads).

6. The driving source should use no pull-up resistors for a cable driver input.

Insofar as possible, circuits feeding cable drivers should not be used to drive other points.

#### CIRCUITRY FOR FUNCTION STROBE ACKNOWLEDGE

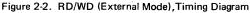

Figure 2-3 shows a circuit for obtaining the FSA signal.

#### **EXTERNAL DEVICE INPUTS**

An external unit should utilize the DIO interface for the shortest possible period needed for information transfer. This guideline may be modified for an engineering or an economic tradeoff. During the period that an external unit employs the DIO interface, the CPU cannot execute additional instructions. Also, a watchdog timer trap may occur on some processors.

The designer of external equipment must ground inputs to drivers for the function strobe, RD/WD, I/O reset, the 1.024-MHz clock, address lines 0-15, unused data lines, and CC3 and CC4 if not used (refer to table 2-1). Failure to release FSA may delay completion of instruction execution. Good design practice therefore is that the external unit release FSA as soon as the CPU has released FS.

Note that RD/WD is true for the WD instruction.

Figure 2-3. Function Strobe Acknowledge, Logic Diagram

| CABLE                                 | BACKPANEL     |              | SIGNAL NAME    |                |           |  |  |

|---------------------------------------|---------------|--------------|----------------|----------------|-----------|--|--|

| CONNECTOR PIN                         | CONNECTOR PIN | Cable J1     | Cable J2       | Cable J3       | Cable J4  |  |  |

| 1, A                                  | 2             | DB1D         | DB15D          | DB29D          | *         |  |  |

|                                       | 6             | DB1R         | DB15R          | DB29R          | A03R      |  |  |

| 2, B                                  | 1             | DB0D         | DB14D          | DB28D          | *         |  |  |

|                                       | 4             | DB0R         | DB14R          | DB28R          | A02R      |  |  |

| 3, C                                  | 9<br>10       | DB3D<br>DB3R | DB17D<br>DB17R | DB31D<br>DB31R | Unassigne |  |  |

| 4, D                                  | 3             | DB2D         | DB16D          | DB30D          | *         |  |  |

|                                       | 8             | DB2R         | DB16R          | DB30R          | A04R      |  |  |

| 5, E                                  | 12            | DB4D         | DB18D          | *              | *         |  |  |

|                                       | 13            | DB4R         | DB18R          | FSR            | A00R      |  |  |

| 6, F                                  | 15            | DB5D         | DB19D          | FSAD           | *         |  |  |

|                                       | 18            | DB5R         | DB19R          | — —            | A01R      |  |  |

| 7, G                                  | 19            | DB6D         | DB20D          | *              | *         |  |  |

|                                       | 20            | DB6R         | DB20R          | RWDR           | A08R      |  |  |

| 8, H                                  | 23            | DB7D         | DB21D          | *              | *         |  |  |

|                                       | 22            | DB7R         | DB21R          | A05R           | A09R      |  |  |

| 9, K                                  | 25            | DB8D         | DB22D          | *              | *         |  |  |

|                                       | 27            | DB8R         | DB22R          | A06R           | A10R      |  |  |

| 10, L                                 | 33            | DB9D         | DB23D          | *              | *         |  |  |

|                                       | 34            | DB9R         | DB23R          | A07R           | A11R      |  |  |

| 11, M                                 | 35            | DB10D        | DB24D          | *              | CC3D      |  |  |

|                                       | 36            | DB10R        | DB24R          | A12R           |           |  |  |

| 12, N                                 | 37            | DB11D        | DB25D          | *              | CC4D      |  |  |

|                                       | 38            | DB11R        | DB25R          | A13R           |           |  |  |

| 13, P                                 | 39            | DB12D        | DB26D          | *              | *         |  |  |

|                                       | 40            | DB12R        | DB26R          | A14R           | RESR      |  |  |

| 14, R                                 | 45            | DB13D        | DB27D          | *              | *         |  |  |

|                                       | 42            | DB13R        | DB27R          | A15R           | 1MHZR     |  |  |

|                                       |               | Cable J1     | Cable J2       | Cable J3       | Cable J4  |  |  |

| · · · · · · · · · · · · · · · · · · · | Sigma 2       |              | 28A            | 30A            | 32A       |  |  |

| MODULE                                | Sigma 3       |              | 24A            | 26A            | 28A       |  |  |

| LOCATOR                               | Sigma 5       | 09M          | 220            | 260            | 290       |  |  |

|                                       | Sigma 7       | 235          | 27Q            | 30P            | 29N       |  |  |

Table 2-1. DIO Interface Signals

\*Must be hard-wired to ground

Notes

Data lines 0 through 15 not available on Sigma 2 and 3 Table listing is in relation to an AT11 type module

## SECTION III

## **IOP INTERFACE**

### INTRODUCTION

Peripheral devices connect to Sigma series hardware through the following Input/Output Processor (IOP) interfaces:

Sigma 2 integral IOP

Sigma 3 integral IOP

Sigma 3 external IOP (EIOP)

Sigma 5 integral IOP

Sigma 5 or 7 multiplexer IOP (MIOP)

Sigma 5 or 7 selector IOP (SIOP)

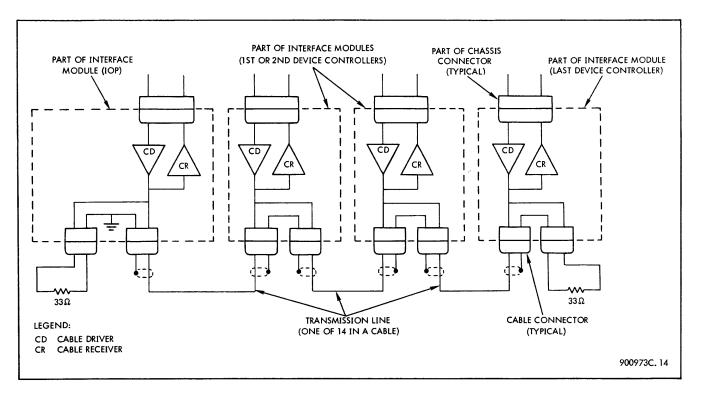

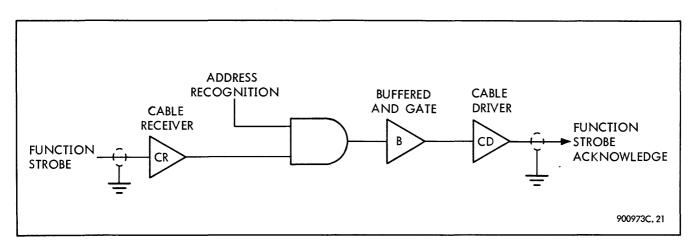

The IOP interface provides lines through which peripherals are controlled by a CPU and provides lines for data exchange between peripherals and Sigma core memories. As shown in figure 3-1, a peripheral can be connected to the IOP interface with four, five, or six cables for the one byte, two byte or four byte data path, respectively. Table 3-1 is a listing of IOP interface cable signals at the device controller.

## **DEVICE CONTROLLERS**

With the exceptions listed under Input/Output Processors in this section, all IOP's present the same interface and general signal interaction to a device controller (DC). Any peripheral device designed to operate on the eight-bit (one-byte) IOP interface described in this manual can connect to any type of IOP (subject to rate capabilities).

The IOP-DC interface uses an 8, 16 or 32-bit data path, which corresponds to one, two and four bytes, respectively. One data path is associated with each IOP in a system. Each data path is logically and electrically independent of other paths. If more than one DC is used, the additional DC's are interconnected to the first DC in a trunk-tail manner (see figure 3-2). All DC's time-share the single data path. Each peripheral device connects to the IOP through a device controller.

## **I/O SEQUENCE**

A typical DC operational state flow diagram is shown in figure 9-1. Once a peripheral device has been started by the main computer program, the general I/O sequence is as follows:

1. All DC's in the busy state may request service simultaneously from the IOP. In an SIOP installation, only one DC can be busy per given instant.

2. The IOP brings up signals to activate a hard-wired priority chain between DC's. The highest priority DC that has requested

service puts its device address on return lines together with an acknowledge signal and is then connected to the IOP.

3. A DC makes one of the following requests while connected to the IOP:

a. Data out (DOUT) — data transfer from memory to the DC  $\,$

b. Data in (DIN) - data transfer from the DC to memory

c. Order out (OOUT) - control information transfer from the IOP to the DC

d. Order in (OIN) - control information transfer from the DC to the  $\ensuremath{\mathsf{IOP}}$

4. While connected to an IOP, a DC can transmit or receive up to four bytes of data (a record if it is connected to an SIOP) or one byte of control information and, in some cases, an additional byte for the terminal order. Each device is serviced in sequence by the IOP based on the hard-wired priority chain.

### **IOP INTERFACE LINE DESCRIPTION**

Figure 3-1 shows IOP interface lines.

#### DATA LINES

The data lines (DA0-DA7, DB0-DB7, DC0-DC7, DD0-DD7) are multipurpose lines driven by either the IOP or the DC. The data lines transmit information during the following operations:

1. During execution of Start Input/Output (SIO), Halt Input/Output (HIO), Test Input/Output (TIO), and Test Device (TDV) instructions when the IOP sends a DC address (DA0-DA7 only)

2. Execution of Acknowledge Interrupt (AIO) instructions when a DC sends status to the IOP (DA0-DA7 only)

3. An order-out sequence when the IOP sends an order to a DC (DA0-DA7 only)

4. An order-in sequence when a DC sends an operational status byte to the IOP (DA0-DA7 only)

5. Data-out sequences when the IOP sends data to the DC (DA0-DA7, DB0-DB7, DC0-DC7, DD0-DD7)

6. Data-in sequences when a DC sends data to the IOP (DA0-DA7, DB0-DB7, DC0-DC7, DD0-DD7)

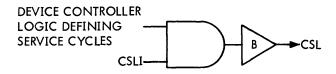

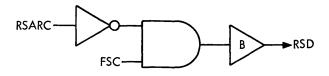

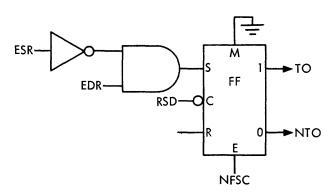

HIGHEST PRIORITY LOWEST PRIORITY IOP NO. WIRES DEVICE CONTROLLER DEVICE CONTROLLER SIGNAL PURPOSE SIGNAL DIRECTION FRO-FR7 (8) FUNCTION RESPONSE LINES RS (1) REQUEST STROBE IOR (1) INPUT OUTPUT REQUEST FSL (1) FUNCTION STROBE ACKNOWLEDGE IC (1) INTERRUPT CALL DX2, DX4 (2) TWO-BYTE, FOUR-BYTE INTERFACE REQUEST \_\_\_\_ JŹ DAO-DA7, DAP (9) DATA LINES, BYTE 0 ODD PARITY ED (1) END DATA PC (1) PARITY CHECK DOR (1) DATA/ORDER REQUEST SC (1) SERVICE CALL (1) SPARE 13 RST (1) RESET I/O CLI (1) 1.024 MHZ CLOCK ES (1) END SERVICE RSA (1) REQUEST STROBE ACKNOWLEDGE SIO (1) START I/O HIO (1) HALT I/O TDV (1) TEST DEVICE AIO (1) ACKNOWLEDGE INTERRUPT ACKNOWLEDGE SERVICE ASC (1) FS FUNCTION STROBE (1) TIO (1) TEST L/O (1) ZERO-BYTE COUNT INTERRUPT ZBCI WADR (1) WORD-ALIGNED DATA REQUIRED 1ER (1) INHIBIT EXTENDED INTERFACE REQUIRED J4 SEE AVI (1) ALWAYS HIGH NOTE 2 AVI (1) ALWAYS HIGH - HPS (1) HIGH PRIORITY SERVICE -HPI (1) HIGH PRIORITY INTERRUPT (1) FAST DEVICE CONTROLLER FAST AVO (1) ABORT I/O OPERATION CI ، رجد د L DBO-DB7 (8) DATA LINES, BYTE 1 LEGEND (1) ENABLE TWO-BYTE INTERFACE EDX2 CR CABLE RECEIVER DC0-DC3 (4) DATA LINES, BYTE 2 CD CABLE DRIVER EDX4 (1) ENABLE FOUR-BYTE INTERFACE NOTES : SEE NOTE 3 -J6 1. FOR CLARITY, CABLE TERMINATORS ARE DC4-DC7 (4) DATA LINES, BYTE 2 NOT SHOWN 2. PRIORITY CABLE IS SHOWN IN DASHED DD0-DD7 (8) DATA LINES, BYTE 3 LINE (----) 900973D.302 SPARE (2) 3. J5 REQUIRED FOR 2 AND 4 BYTE INTERFACE. J6 REQUIRED FOR 4 BYTE INTERFACE

Figure 3-1. IOP Interface Signal Lines Diagram

3-2

XDS 900973

#### XDS 900973

| CABLE     | BACKPANEL | SIGNAL NAME AT BACKPANEL |                   |                   |                    |                   |                   |

|-----------|-----------|--------------------------|-------------------|-------------------|--------------------|-------------------|-------------------|

| CONNECTOR | CONNECTOR | J1<br>AT12 Module        | J2<br>AT11 Module | J3<br>AT10 Module | J4*<br>AT17 Module | J5<br>AT11 Module | J6<br>AT11 Module |

| A, 1      | 2         | FR7D                     | DA7D              |                   | (35) HPID          | DB0D              | DC4D              |

|           | 6         |                          | DA7R              | RESTR             | (06) HPIR          | DBOR              | DC4R              |

| В, 2      | 1         | FR6D                     | DA6D              |                   | (33) HPSD          | DB1D              | DC5D              |

|           | 4         |                          | DA6R              | CL1R              | (04) HPSR          | DB1R              | DC5R              |

| C, 3      | 9         | FR5D                     | DA5D              |                   | (31) FASTD         | DB2D              | DC6D              |

|           | 10        |                          | DA5R              | ESR               |                    | DB2R              | DC6R              |

| D, 4      | 3         | FR4D                     | DA4D              |                   | (29) AVOD          | DB3D              | DC7D              |

|           | 8         |                          | DA4R              | RSAR              | (08) AVIR          | DB3R              | DC7R              |

| E, 5      | 12        | FR3D                     | DA3D              |                   | **                 | DB4D              | t                 |

|           | 13        |                          | DA3R              | SIOR              |                    | DB4R              | †                 |

| F, 6      | 15        | FR2D                     | DA2D              |                   | **                 | DB5D              | DD0D              |

|           | 18        |                          | DA2R              | HIOR              |                    | DB5R              | DD1R              |

| G, 7      | 19        | FR1D                     | DA1D              |                   | **                 | DB6D              | DD1Đ              |

|           | 20        |                          | DA1R              | TIOR              |                    | DB6R              | DD1R              |

| Н, 8      | 23        | FR0D                     | DA0D              |                   | **                 | DB7D              | DD2D              |

|           | 22        |                          | DAOR              | TDVR              |                    | DB7R              | DD2R              |

| К, 9      | 25        | RSD                      | DAPD              |                   | **                 |                   | DD3D              |

|           | 27        |                          | DAPR              | AIOR              |                    | EDX2R             | DD3R              |

| L, 10     | 33        | IORD                     | EDD               |                   | **                 | DC0D              | DD4D              |

|           | 34        |                          | EDR               | ASCR              |                    | DCOR              | DD4R              |

| M, 11     | 35        | FSLD                     | PCD               |                   | **                 | DC1D              | DD5D              |

|           | 36        |                          |                   | FSR               |                    | DC1R              | DD5R              |

| N, 12     | 37        | DX2D                     | DORD              |                   | **                 | DC2D              | DD6D              |

| -         | 38        |                          |                   | ZBCIR             |                    | DC2R              | DD6R              |

| P, 13     | 39        | ICD                      | SCD               |                   | **                 | DC3D              | DD7D              |

|           | 40        |                          | SCR               | WADRR             |                    | DC3R              | DD7R              |

| R, 14     | 45        | DX4D                     | †                 |                   | **                 |                   | t .               |

|           | 42        |                          | t                 | IERR              |                    | EDX4R             | t                 |

## Table 3-1. IOP Interface Cable Signals at Device Controller

\*Backpanel connector pin for AT17 only

<sup>†</sup>Spare

\*\*No cable driver-receiver available

Figure 3-2. Typical I/O Interconnections

Ċ

7. When the IOP sends a terminal order to the DC in response to a DC request (DA0-DA7 only)

During data-in or data-out operations the data path may be one, two or four bytes wide depending on the IOP in use and the state of the EDX-DX control lines. Table 3-2 includes a summary of bit codes used on the data lines.

#### FUNCTION INDICATOR LINES

Function indicator lines SIO, HIO, TIO, TDV, AIO, and ASC are controlled by the IOP. These lines let the device know which I/O instruction the CPU is currently executing (SIO, HIO, TIO, TDV, or AIO), or that its service call (SC) is being acknowledged by an Acknowledge Service Call (ASC). Only one of the function indicator lines may be true at one time. These lines are driven for SIO, HIO, TIO, TDV, and AIO based on the instruction executed by the computer. The ASC function indicator is generated by the IOP in response to a service call from a device and is not controlled directly by the CPU or by CPU instruction. Generation of the function indicators is also controlled by the internal IOP address selection logic and timing signals from the phase flip-flops and delay lines.

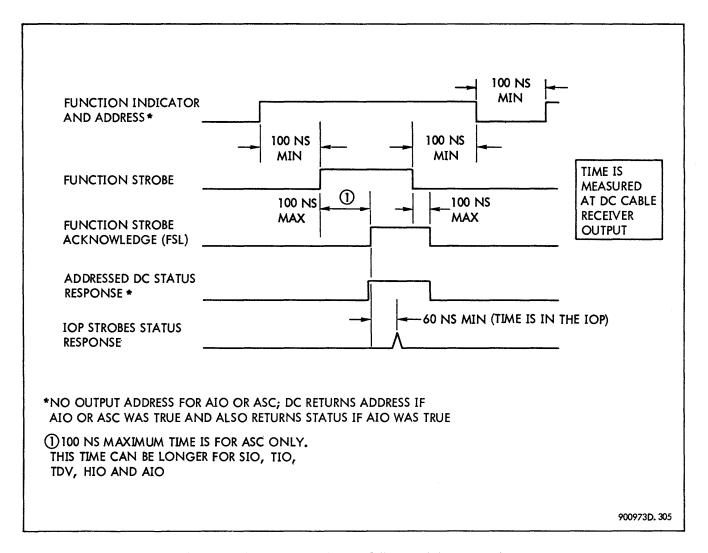

## FUNCTION STROBE, FUNCTION STROBE ACKNOWLEDGE, AVI/AVO LINES

When logic power is on, the IOP provides a continuous available input (AVI) signal input to the highest priority DC connected to the IOP. The IOP raises a function indicator line and the function strobe (FS) line in response to a CPU request to perform I/O instructions or in response to a DC service request. The DC's respond to FS by raising either the function strobe acknowledge (FSL) line or the available output (AVO) line at the IOP interface.

The addressed DC answers an FS (accompanied by an SIO, HIO, TIO, or TDV function indicator) by raising the FSL line if the DC is connected. If DC is not connected, the DC raises AVO.

In response to an FS accompanied by an AIO function indicator, the highest priority DC with an interrupt call pending responds by raising the FSL line. If no interrupt call is pending, the AVO line is raised. In response to an FS accompanied by an ASC function indicator, the highest priority DC with a service call pending responds by raising the FSL line. If no service call is pending, the AVO line is raised.

#### FUNCTION RESPONSE LINES

The multipurpose function response lines (FR0-FR7) are DC controlled. When responding to an FS accompanied by an SIO, HIO, TIO, or TDV function indicator, the DC places status information on the function response lines. The DC places its address on the FR lines when responding to an FS accompanied by an AIO or ASC function indicator. Table 3-2 includes a summary of bit codes used on the function response lines.

#### DATA/ORDER AND INPUT/OUTPUT REQUEST LINES

The multipurpose data/order (DOR) and input/output request (IOR) lines are DC controlled. When responding to an FS accompanied by an SIO, HIO, TIO, TDV, or AIO function indicator, the DC places condition code data on the DOR and the IOR lines. When responding to an FS accompanied by the ASC function indicator, the DC codes the DOR and the IOR lines to inform the IOP whether an order out/order in or data out/data in operation is to be performed. A summary of bit codes used in conjunction with DOR and IOR is included in table 3-2. The bit code responses (IOR, DOR) to FS accompanied by ASC are shown under Service Cycles in this section.

#### SERVICE CALL AND HIGH PRIORITY SERVICE LINES

The service call (SC) and the high priority service (HPS) lines are DC controlled. Only the IOP responds to the SC line. Only DC's respond to the HPS line. Device controllers raise the SC line to request order out-order in data out-data in operation by the IOP.

The IOP responds to an SC by raising the ASC function indicator and FS. The subsequent response of a device controller to FS depends on whether or not the particular DC has an SC pending.

A DC which does not have an SC pending raises the AVO line when AVI goes true. The DC takes no action if the AVI line does not go true (indicating that a higher priority DC has an SC pending).

A DC with an SC pending determines the status of the AVI and the HPS lines. The DC raises the FSL line if AVI is true and HPS false (or if the DC is driving HPS). Otherwise, the DC raises the AVO line to the next lower priority DC. If the AVI line does not go true, the DC takes no action in response to FS and ASC.

#### INTERRUPT CALL AND HIGH PRIORITY INTERRUPT LINES

The interrupt call (IC) and the high priority interrupt (HPI) lines are DC controlled. Only the IOP responds to the IC line. Only DC's respond to the HPI line. DC's raise the IC line to generate an input/output interrupt call to the CPU.

The IOP responds to an IC during execution of an AIO instruction by raising the AIO function indicator and FS. The subsequent response of a device controller to FS depends on whether or not the particular DC has an IC pending.

A DC which does not have an IC pending raises the AVO line when AVI goes true. The DC takes no action if the AVI line does not go true (indicating that a higher priority DC has an IC pending).

A DC with an IC pending determines the status of the AVI and the HPI lines. The DC raises the FSL line if AVI is true and if HPI false (or if the DC is driving HPI). Otherwise, the DC raises the AVO line to the next lower priority DC. If the AVI line does not go true, the DC takes no action in response to FS and AIO.

## REQUEST STROBE AND REQUEST STROBE ACKNOWLEDGE LINES

The request strobe (RS) line is DC controlled and the request strobe acknowledge (RSA) line is IOP controlled in response to an RS signal from the DC. These lines operate in a closed-loop mode; that is, upon sensing that the DC has driven the RS line, the IOP delays and then drives the RSA line. Upon sensing that the RS line has dropped, the IOP immediately drops the RSA line. After connecting for service, the DC sends a succession of RS signals to the IOP until the IOP signals RSA and end service.

#### END DATA AND END SERVICE LINES

The end data (ED) line is driven by either the DC or the IOP. The end service (ES) line is driven by the IOP only. The ED line is

| Function                                                                                      | Lines* | 0                     | 1                                                     | 2                       | 3                     | 4                                            | 5                                                    | 6                            | 7                          | DOR<br>(NCC1)          | IOR<br>(NCC2)                                                                                   |

|-----------------------------------------------------------------------------------------------|--------|-----------------------|-------------------------------------------------------|-------------------------|-----------------------|----------------------------------------------|------------------------------------------------------|------------------------------|----------------------------|------------------------|-------------------------------------------------------------------------------------------------|

| sio, hio, tio, tdv                                                                            | DA     |                       |                                                       |                         | Device con            | troller address                              |                                                      |                              |                            |                        |                                                                                                 |

| SIO, HIO, TIO                                                                                 | FR     | Interrupt<br>pending  | 00 = D read<br>01 = D not<br>10 = D una<br>11 = D bus | operational<br>vailable | Device<br>automatic   | Device<br>unusual<br>end (last<br>operation) | 00 = DC re<br>01 = DC no<br>10 = DC ur<br>11 = DC bu | ot operational<br>navailable | 0                          | Address<br>recognition | SIO: SIO successful<br>HIO: DC was not busy<br>when HIO occurred<br>TIO: SIO can be<br>accepted |

| ΤΟν                                                                                           | FR     | Rate error            |                                                       |                         |                       |                                              |                                                      |                              |                            | Address<br>recognition | Abnormal condition<br>does not exist                                                            |

| AIO                                                                                           | DA     |                       | Device end                                            |                         |                       |                                              |                                                      |                              |                            | AIO<br>acknowledged    | DC error or fault<br>does not exist                                                             |

| AIO, ASC                                                                                      | FR     |                       |                                                       |                         | Device con            | troller address                              | 1                                                    |                              |                            |                        |                                                                                                 |

| Order in                                                                                      | DA     | Trans.<br>error       | Incorrect<br>length                                   | Chaining<br>modifier    | Channस<br>end         | Unusual<br>end                               |                                                      |                              |                            | 1                      | O                                                                                               |

| Terminal order                                                                                | DA     | Interrupt             | Count<br>done                                         | Command<br>chain        | IOP<br>halt           |                                              |                                                      |                              |                            |                        | · · · · · · · · · · · · · · · · · · ·                                                           |

| Order out Control<br>(even Write<br>command Read<br>word bits Read back<br>0-7) Sense<br>Stop | DA     | M<br>M<br>M<br>M<br>1 | M<br>M<br>M<br>M<br>0                                 | M<br>M<br>M<br>M<br>0   | M<br>M<br>M<br>M<br>0 | M<br>M<br>1<br>0                             | M<br>M<br>1<br>1<br>0                                | 1<br>0<br>1<br>0<br>0<br>0   | 1<br>1<br>0<br>0<br>0<br>0 | 1                      | 1                                                                                               |

XDS 900973

မှ ဂ

.

always driven by the DC with the initial RS of an order out-order in sequence. During a data out-data in sequence, either the DC or the IOP may raise the ED line to signify that no additional data is to be exchanged.

The IOP drives the ES line together with the RSA line to signify that the service sequence is to terminate. If the ES line is held false when the ED line is initially driven, the DC must request a terminal order from the IOP before termination. Otherwise, the DC concludes the sequence with the last data exchange.

#### DATA PARITY AND PARITY CHECK LINES

The data parity (DAP) line is driven by either the IOP or the DC. The parity check (PC) line is driven only by the DC. The IOP generates an odd parity bit for the data byte on data lines DA0 through DA7 for all data-out exchanges. A device controller (such as a magnetic tape controller) may record this bit.

On data input exchanges, the DC may send the DAP bit to the IOP together with the data byte on lines DA0 through DA7. The DC can also request the IOP to check the odd parity by raising the PC line. (The IOP does not check odd parity if EDX4 and DX4 are true.)

#### ENABLE EXTENDED INTERFACE AND EXTENDED INTER-FACE REQUEST LINES

The enable four-byte (EDX4) and the enable two-byte (EDX2) interface lines are IOP controlled. The four-byte request (DX4) and the two-byte request (DX2) lines are DC controlled.

An IOP that is capable of exchanging data during data in-data out sequences over an extended data path drives the EDX4 or EDX2 line true.

A DC connected to an IOP that is signaling extended data path capability (EDX4 or EDX2) may request extended data path exchanges by raising DX4 or DX2, whichever corresponds to the signaled capability of the IOP.

#### WORD-ALIGNED DATA REQUIRED LINE

The word-aligned data required (WADR) line is IOP controlled. This line is always false in IOP's with only a one-byte data path. A true signal on the WADR line indicates that each data word on the expanded width data path must correspond to a full word and must be aligned on a word boundary for exchanges between an IOP and memory. The WADR line normally does not generate additional DC functions. In a specialized DC application (such as a data systems design integration), the WADR line could be made available to the program through routing to an unused TDV status bit.

#### INHIBIT EXTENDED INTERFACE REQUEST

The inhibit extended interface request (IER) line is driven by the IOP with the same timing as ES to signal to the DC that the next I/O service call sequence must be in the one-byte mode.

The DC monitors IER only at ES with the last RSA. If IER is false, the DC may enter an extended mode of operation when again connected for service. If IER is true at ES with the last RSA, the DC is forced to operate in the one-byte data path mode when reconnected for service.

## FAST DEVICE CONTROLLER AND ZERO-BYTE COUNT INTERRUPT LINES

The fast device controller (FAST) line is DC controlled, and the zero-byte count interrupt (ZBCI) line is IOP controlled. If a DC drives the FAST line during service sequences, the IOP does not terminate to send ZBCI to the DC during data chaining. However, certain IOP's drive the DC ZBCI line to signify that the DC should request a ZBCI.

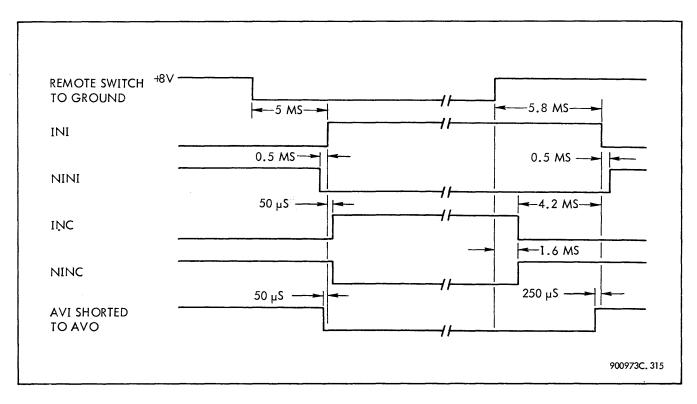

#### I/O RESET AND 1.024-MHz CLOCK LINES

The I/O reset (RST) and the 1.024-MHz clock (CL1) lines are IOP controlled. The RST signal is generally used for initializing a DC. The CL1 line is driven continuously at a 1.024 MHz rate and may be used by DC's as a flip-flop clock.

#### **IOP INTERFACE FUNCTIONS**

#### PRIORITY DETERMINATION

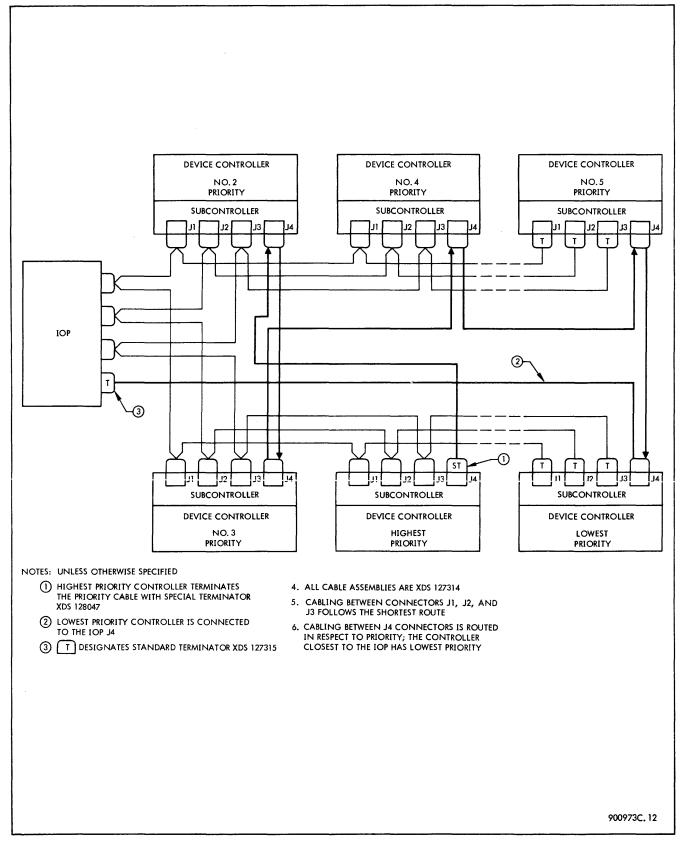

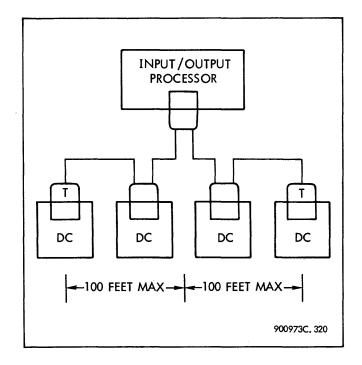

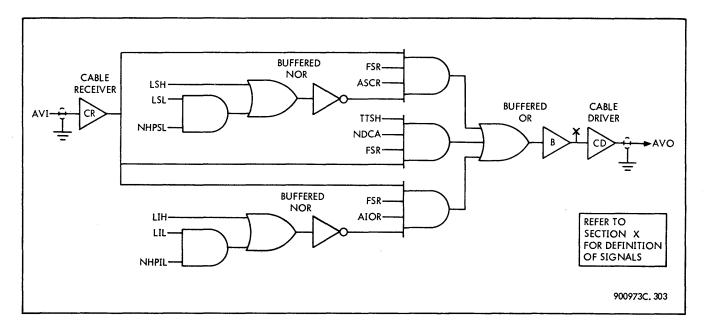

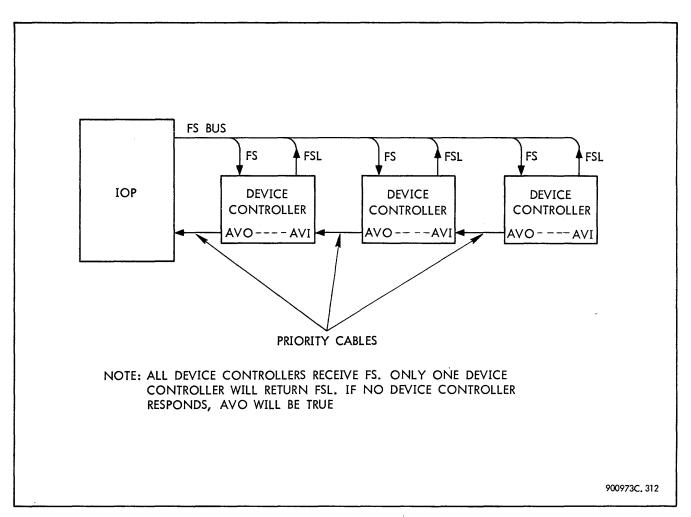

#### Data Transmission and Priority Cables (See figure 3-2)