|     |      |                     | 1549       | 91 B     |                 |

|-----|------|---------------------|------------|----------|-----------------|

| LAL | REV. | DESCRIPTION         | СНК        | DATE     | APPROVED        |

|     | A    | ENGR RELEASE        | B2         | 8/13/69  | In state.       |

| X   | B    | MFG RELEASE NO E.O. | BZ         | 10/15/69 | Rististiq gomit |

| 1   | 1~~  |                     | <u>v</u> e | /0/      |                 |

CONTROL DRAWING 131

| DRAWING NO.              |                                                                                                                              | DESCI                                                                                                        | RIPTION                                                                                                                     |                                                                                                                                                                                                          | R                                                                                                                                                                                                                                                                                                                                                                               | EFERENCE DESIG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | NATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ITEM<br>NO,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                                                                                                                              |                                                                                                              | MATERIA                                                                                                                     | AL LIST                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TES UNLESS SPECIFIED     | DRAWN                                                                                                                        | I. Linkous                                                                                                   | 8-11-69                                                                                                                     |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                 | SNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TRANCES<br>±.030 Angular | CHECK                                                                                                                        | Brille                                                                                                       | 8-13-69                                                                                                                     |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                 | EL SEGUNDO, CALIFORNIA                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | <i>*</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| AK ALL SHARP EDGES       | APPR.                                                                                                                        | JWALL                                                                                                        | 813 BA                                                                                                                      | TITLE                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| APPROX.<br>H. SURFACES V |                                                                                                                              | V                                                                                                            | Terra da Astan                                                                                                              |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PLEXING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| DIM. IN INCHES           | A to g ben X                                                                                                                 | <ul> <li>A second state</li> </ul>                                                                           | · · · · · · · · · · · · · · · · · · ·                                                                                       | • • • • • • • • • • • • • • • • • • •                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| NO.                      |                                                                                                                              |                                                                                                              |                                                                                                                             |                                                                                                                                                                                                          | SIZE                                                                                                                                                                                                                                                                                                                                                                            | DWG. NO.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CHANGE<br>LETTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                          |                                                                                                                              | ومد                                                                                                          |                                                                                                                             | CODE IDENT.<br>NO. 18338                                                                                                                                                                                 | A                                                                                                                                                                                                                                                                                                                                                                               | 154991                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | В                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <b>ISY.</b>              |                                                                                                                              |                                                                                                              |                                                                                                                             |                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 154560                   |                                                                                                                              |                                                                                                              | -                                                                                                                           | SCALE                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                 | NOT SCALE DRAWING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | SHEET 1 of g                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3 · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                          | RANCES<br>±.030 ANGULAR<br>±.010 ±½°<br>NK ALL SHARF EDGES<br>APPROX.<br>H. SURFACES J<br>DIM. IN INCHES<br>NO.<br>8273/8473 | RANCES<br>±.030 ANGULAR<br>±.010 ±½*<br>APPROX.<br>H. SURFACES<br>DIM. IN INCHES<br>NO.<br>8273/8473<br>ISY. | RANCES<br>±.030 ANGULAR<br>±.010 ± ½°<br>NK ALL SHARP EDGES<br>APPROX.<br>H. SURFACES<br>DIM. IN INCHES<br>NO.<br>8273/8473 | FES UNLESS SPECIFIED     DRAWN     I. Linkous     8-11-69       RANCES     ±.030     ANGULAR     CHECK     CHECK     8-13-69       ±.010     ±½°     APPR.     W. S. | RANCES     LOS     OFFICE       ±.030     ANGULAR     CHECK     Gille     8-13-69       ±.010     ±½*     APPR.     Wille     TITLE       NK ALL SHARP EDGES     APPR.     Wille     TITLE       APPROX.     TITLE     PR       M. SURFACES     TITLE     PR       DIM. IN INCHES     TITLE     PR       NO.     8273/8473     CODE IDE NT.       ISY.     SY.     CODE IDE NT. | TES UNLESS SPECIFIED     DRAWN     I. Linkous     8-11-69       ±.030     ANGULAR     ±.010     ±.02     B     2.12-69       ±.010     ±.02     APPR.     J.116     8-12-69       NK ALL SHARP EDGES     APPR.     J.116     8-12-69       APPROX.     J.116     8-12-69     TITLE       NK ALL SHARP EDGES     APPR.     J.116     8-12-69       NR. SURFACES     J.116     S.116     S.116       JIM. IN INCHES     J.116     S.116     S.116       NO.     8273/8473     S.273/8473     S.200 | TES UNLESS SPECIFIED       DRAWN       I. Linkous       8-11-69       SDS         RANCES       ±.030       ANGULAR       CHECK       Jilk       8-15-69       EL SEGUNDO, CALIFORNIA         ±.010       ±.14*       APPR.       Jilk       8-15-69       TITLE         NK ALL SMARP EDGES       APPR.       Jilk       8-15-69       FRODUCT DESIGN SPECIFICATION         M. SURFACES       J       Jilk       NO.       NO.       NO.       S273/8473         SSY.       B273/8473       Journal State       CODE IDE NT.       A       A | TES UNLESS SPECIFIED     DRAWN     I. Linkous     8-11-69       RANCES<br>±.030     Angular<br>±.030     CHECK     2:11/2     8-15-69       KALL SHARP EDGES     APPR.     Workwark     5:11/4       APPROX.     FRODUCT DESIGN SPECIFICATION     INPUT/OUTPUT PROCESSOR, MULTIPLEXING       INPUT/OUTPUT PROCESSOR, MULTIPLEXING     State     0:000 100 100 100 100 100 100 100 100 10 |

| T | Ά | B | L | E | 0 | F | С | 0 | 1 | 11 | E | N | T | S |  |

|---|---|---|---|---|---|---|---|---|---|----|---|---|---|---|--|

|   |   |   |   |   |   |   |   |   |   |    |   |   | - |   |  |

|   |   |   |   |   |   |   |   |   |   |    |   |   |   |   |  |

| 1_0        | Introduction                                     |

|------------|--------------------------------------------------|

| 1.1        | Scope                                            |

| 1.2        | Related Documents                                |

| 1.3        | General Description: Features, Function          |

|            |                                                  |

| 2.0        | Detailed Description                             |

| 2.1        | System Interconnection                           |

| 2.2        | Interface Signal Transmission                    |

| 2.3        | Memory Interface                                 |

| 2.4        | CPU Interface                                    |

| 2.5<br>2.6 | Device Controller Interface<br>Display Interface |

| 2.7        | IOP Internal Operation                           |

| 2.8        | CPU Service Calls                                |

| 2.9        | DC Service Calls                                 |

| 2.10       | Memory Bus-Sharing                               |

| 2.11       | Display Operation                                |

|            |                                                  |

| TITLE                                                   | SDS   |       |    | ı  |   |

|---------------------------------------------------------|-------|-------|----|----|---|

| PRODUCT DESIGN SPECIFICATION<br>INPUT/OUTPUT PROCESSOR, |       | 15499 | 1  |    | В |

| MULTIPLEXING                                            | SHEET | 2     | OF | 83 |   |

24.

INTRODUCTION

Scope

1.0

1.1

This specification defines the design requirements for a free-standing multiplexer IOP (MIOP) with optional four-byte data path, memory-bus sharing, and display option to be used with Sigma 5 or Sigma 7 systems. This specification includes the actions and responses required by the MIOP at the CPU interface, the device controller (DC) interface, the core memory interface, and the maintenance subcontroller (MS) display interface. In addition, this specification defines the various required internal IOP operations and sequences.

| TITLE                                                   | 5DS   |     |     | - 1<br>- |      |

|---------------------------------------------------------|-------|-----|-----|----------|------|

| PRODUCT DESIGN SPECIFICATION<br>INPUT/OUTPUT PROCESSOR, |       | 154 | 991 |          | B    |

| MULTIPLEXING                                            | SHEET | · 3 | OF  | 83       | <br> |

|                                                         |       |     |     |          | <br> |

**Related** Documents

1.2

Product Planning Specifications:

Sigma Document 316, Planning Specification: Multiplexor IOP with Optional Four-Byte Data Path

and Optional Memory Bus-Sharing.

Product Design Specifications:

| 117336 | Specification, Central Processing Unit   |

|--------|------------------------------------------|

| 117653 | Specification, Sigma Memory              |

| 123382 | Specification, Eight-Bit Data Path       |

| 137556 | Specification, Four-Byte Data Path       |

| 154169 | Specification, Maintenance Subcontroller |

| TITLE<br>PRODUCT DESIGN SPECIFICATION | 5DS     |       |   |

|---------------------------------------|---------|-------|---|

| INPUT/OUTPUT PROCESSOR,               | 154991  |       | В |

| MULTIPLEXING                          | SHEET 4 | OF 93 |   |

## 1.3 General Description

## 1.3.1 Basic Features

The basic MIOP, model number 8273/8473, provides for coupling Sigma peripheral units to a Sigma 5 or Sigma 7 CPU and core memory. The MIOP responds to service requests from either the CPU or DC's in a time multiplexed fashion. Capability is built into the MIOP which allows it to direct and control I/O operations by executing a command list prepared by the CPU.

The basic MIOP provides 8 sub-channel positions to accomodate 8 DC's. Each DC that utilizes the basic 8 sub-channel positions may have as many as 16 devices connected. The data path interconnecting the basic MIOP with DC's is one-byte (8-bits) wide.

At the core memory interface, the MIOP has the capability for addressing memories as large as 131,072 words (524,288 bytes).

1.3.2 Optional Features

A model 8273/8473 MIOP may be supplied with the following optional features:

Model 8274/8474 Bus-sharing feature

Model 8275/8475 Four-Byte interface feature

Model 8276/8476 Additonal eight sub-channels.

Авву. 154999

Display Option. This option is useful only when a Maintenance Subcontroller (154543) is connected to the MIOP.

| TITLE<br>PRODUCT DESIGN SPECIFICATION | SDS       |      |

|---------------------------------------|-----------|------|

| INPUT/OUTPUT PROCESSOR,               | 154991    | В    |

| MULTIPLEXING                          | SHEET 5 0 | F 83 |

SDS-E-112(4/65)

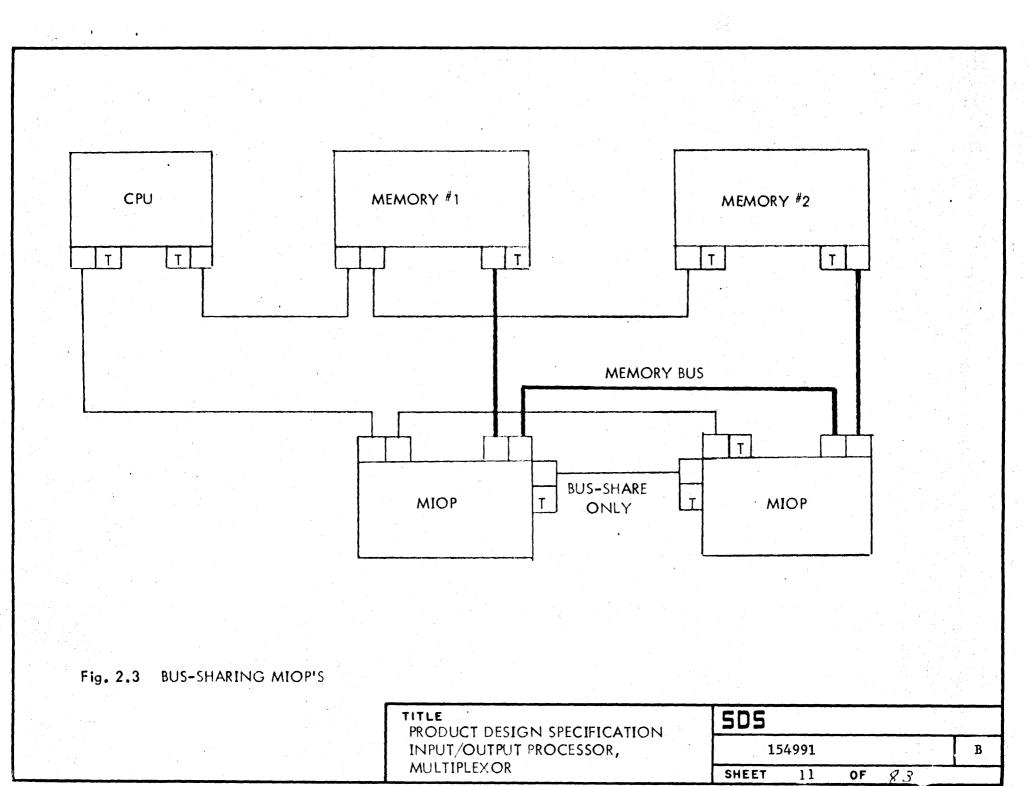

The model 8274/8474 bus-sharing feature permits two model 8273/8473 MIOP's to share a core memory bus on a time-shared basis. This optional feature consists of a group of modules that are installed into the two MIOP's that are to share the core memory bus.

The model 8275/8475 four-byte interface feature consists of a group of modules that extends the width of the data path at the DC interface from one-byte to four-bytes. This feature enables those DC's that also contain a four-byte wide data path to transmit data at a higher rate than is possible via the one-byte path and thus improve the data throughput for the I/O system.

The model 8276/8476 option consists of a group of modules that provides an additional eight subchannels to the basic model 8273/8473 MIOP. The MIOP will accommodate a maximum of 24 sub-channels. That is, in addition to the basic eight sub-channel positions a maximum of 16 optional sub-channel positions may be provided in groups of eight. The basic eight sub-channel positions only (addressed 0 through 7) may be used for servicing DC's with multiple devices.

The IOP display option (154999) contains a group of modules that provides the display interface for maintenance purposes. When the option is installed, the MIOP, under program control, can be operated in single phase mode and can send the states of 112 internal signals (16 at a time) to a CPU general register using Read Direct and Write Direct instructions via the DIO interface and the Maintenance Subcontroller, MS. 1.3.3 Functional Requirements

The MIOP responds to service requests from either the CPU or from DC's. In response to service requests from the CPU the MIOP performs operations related to the execution of SIO, TIO, HIO, TDV, and AIO instructions. In response to service requests from DC's the MIOP performs operations designated as Data Out,

> TITLE PRODUCT DESIGN SPECIFICATION INPUT/OUTPUT PROCESSOR, MULTIPLEXING

| SD5   |        |    | -  |  |

|-------|--------|----|----|--|

|       | 154991 | ·  |    |  |

| SHEET | 6      | OF | 83 |  |

B.

SDS-E-112(4/65)

Data In, Order Out, and Order In. During the responses mentioned above the MIOP may perform or control

certain operations required by the I/O system as follows:

Generation and Transmittal of Terminal Orders

Data Chaining

Command Chaining

Transfer in Channel

Retrieval, Generation, and Storage of Status

Error Checking

TITLE PRODUCT DESIGN SPECIFICATION INPUT/OUTPUT PROCESSOR, MULTIPLEXING

| SHEET | 154991<br>7 | OF | 83 | <u>а</u> |  |

|-------|-------------|----|----|----------|--|

|       |             |    |    | В        |  |

| 5D5   |             |    |    |          |  |

#### 2.0 DETAILED DESCRIPTION

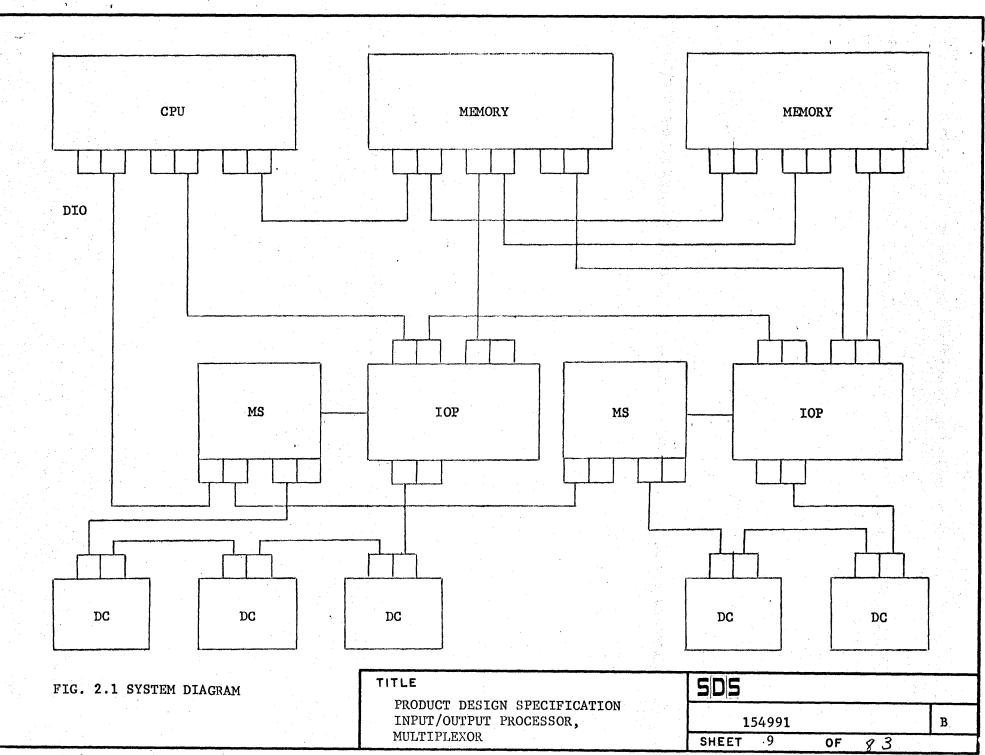

## 2.1 System Interconnection

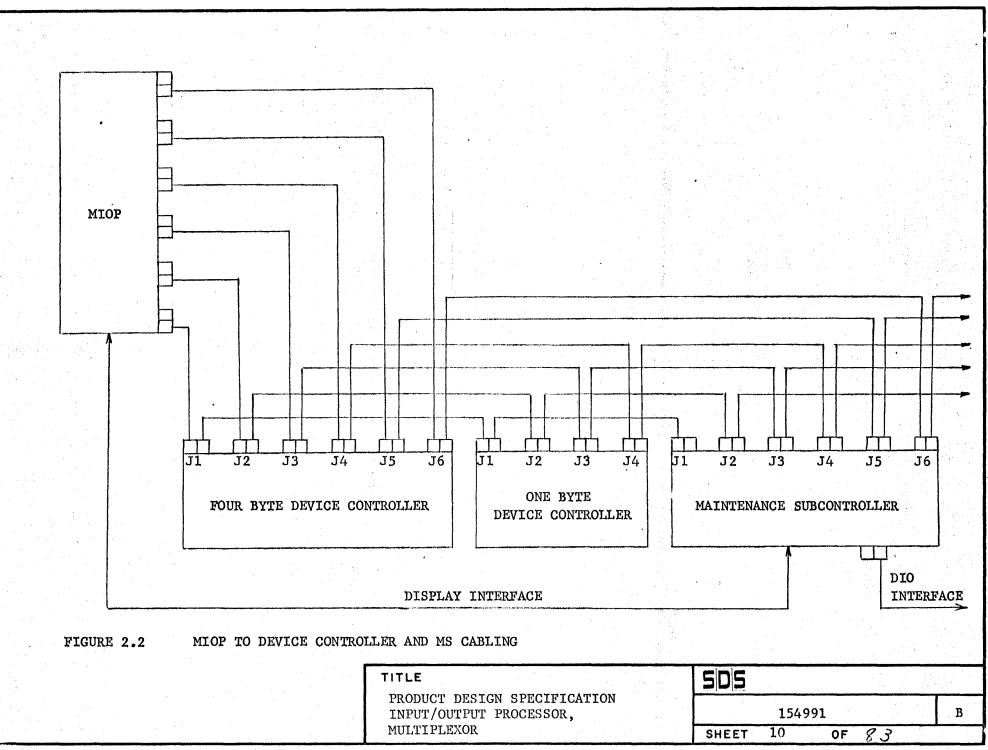

The IOP's interconnect with the CPU, Memories, Device Controllers, and Maintenance Subcontrollers, as shown in Figure 2.1. IOP's shall be connected by cables to the CPU in a trunk-tail fashion for the purpose of interrupt priority determination. Addressing of eight IOP's is permitted. All IOP's connected to a given CPU shall be connected to the memory bank containing address X'20" and X'21' for that CPU. However, all IOP's need not be connected to all memories. Device Controllers shall be connected to the IOP at the Display Interface through a 100  $\Omega$  ribbon cable.

The MIOP may be connected to the Device Controllers and MS with a one byte, or a four byte data path (I/O interface). Also, the MIOP shall be connected by priority cable to the Device Controller and MS for the purposes of service priority determination. The rules of priority assignments to the Device Controllers are described in 123382 and 137556.

| TITLE<br>PRODUCT DESIGN SPECIFICATION |       | 5D5   |      |    |    |   |

|---------------------------------------|-------|-------|------|----|----|---|

| INPUT/OUTPUT PROCESSOR,               |       |       | 1549 | 91 |    | В |

| MULTIPLEXING                          | · · · | SHEET | 8    | OF | 83 |   |

SDS-E-112(4/65)

SDS-E-112(4/65)

S 2 1

SDS-E-112(4/65)

SDS-E-112(4/65)

ng sa katalan Karalan Interface Signal Transmission (Except Display Interface)

All interface signal exchange shall be via AT10 Cable Receiver Module (SDS Part No. 123018), AT11 Cable Driver/Receiver Module (SDS Part No. 123019), AT12 Cable Driver Module (SDS Part No. 124629), AT13 Cable Driver/Receiver Module (SDS Part No. 125260), AT61 Cable Driver Module (SDS Part No. 149481), or AT70 Cable Driver/Receiver Module (SDS Part No. 152815) as used throughout the Sigma system.

Communication shall be via terminated shielded conductors having a nominal impedance of 33 ohms. The signal transmission cable consists of 14 shielded conductors as specified under SDS Part No. 101787. Cable connectors are SDS Part No. 115833. These connectors provide for mating with 14 printed wiring contacts on cable plug modules. Cables shall be terminated at the extremities with 33 ohm resistors to ground. The terminating plug assemblies (containing the 33 ohm resistors) are SDS Part No. 127315.

The signal characteristics on the cable shall be as follows:

Logical One = + 2 volts Logical Zero = 0 volts

| TITLE<br>PRODUCT DESIGN SPECIFICATION   | SD5            |    |

|-----------------------------------------|----------------|----|

| INPUT/OUTPUT PROCESSOR,<br>MULTIPLEXING | 154991         | B. |

|                                         | SHEET 12 OF 93 |    |

2.2

#### 2.3 MEMORY INTERFACE

2.3.1 Signal Convention

> Signal exchange shall be via AT11 Cable Driver/Receiver, AT12 Cable Driver, AT61 Cable Driver, and AT70 Cable Driver/Receiver Modules. The signals will use a convention of +2 volts as true logic.

#### 2.3.2

Busses

Each MIOP shall have a bus for interfacing with core memories. Two MIOP's may, however, share a core memory bus if the Bus Share option is present in both.

An IOP shall use only a single memory bus and shall not make a memory request before receiving an Address Release signal or an Address Here false signal from the prior request.

2.3.3 Cells 20 and 21

Ports

The MIOP uses memory cells 20\* and 21\* when responding to CPU requests for service. It shall be a requirement that the memory (memories if interleaving is used) that possess IOP memory cells 20\* and 21\*, must also possess CPU memory cells 20\* and 21\*. This requirement shall also be true for an IOP which is to provide the CPU with its initial information during a bootstrap load operation.

## 2.3.4

The IOP shall normally be connected either to memory port A or memory port B (memory port A having highest priority). However, there shall be no special form of implementation which would preclude the IOP from using port C.

#### 2.3.5

## Signal Lines Interconnecting IOP and Memory.

The lines tabulated below interconnect the IOP and memory: (In the table, X refers to one of memory port A, B. or C.)

| <br>TITLE<br>PRODUCT DESIGN SPECIFICATION | SDS            |   |  |  |

|-------------------------------------------|----------------|---|--|--|

| INPUT/OUTPUT PROCESSOR<br>MULTIPLEXING    | 154991         | В |  |  |

|                                           | SHEET 13 OF 83 |   |  |  |

## \* Base 16

SDS-E-112(4/65)

2,3.5 (cont'd)

| Description        | Designation        | Number<br>of Lines | Direction of Signal Flow<br>IOP to Memory Memory to IOP |                            |  |  |

|--------------------|--------------------|--------------------|---------------------------------------------------------|----------------------------|--|--|

|                    |                    | of Lines           | IOF to Memory                                           | Memory to IOP              |  |  |

| Data Signals       | /MX0/ thru /MX31/  | 32                 | x                                                       | x                          |  |  |

| Address Signals    | /LX15/ thru /LX31/ | 17                 | x                                                       |                            |  |  |

| Address Here       | /AHX/              | 1                  |                                                         | ×                          |  |  |

| Address Release    | /ARX/              | 1                  |                                                         | x                          |  |  |

| Data Gate          | / DGX/             | 1                  |                                                         | x                          |  |  |

| Parity Error       | /PEX/              | 1                  |                                                         | x                          |  |  |

| Parity O.K.        | /POKX/             | 1                  |                                                         | та станата<br>х на станата |  |  |

| Write Byte Signals | /MW0X/ thru /MW3X/ | 4                  | x                                                       |                            |  |  |

| Memory Request     | /MQX/              | 1                  | x                                                       |                            |  |  |

| Data Release       | /DRX/              | 1                  |                                                         | <b>X</b>                   |  |  |

2.3.6 Signal Timing

Timing of the signals described in 2.3.5 shall conform to the following: (All times as measured at IOP/Cable interface).

2, 3, 6, 1

Data Lines

Data Input to Memory

During a core memory write operation signals on the data lines (MXO thru MX31) shall be present and stable within 120 nanoseconds after the Memory Request (MQX) is given. The data lines shall remain stable for a minimum of 160 nanoseconds after the Address Release signal is received by the IOP for a full write operation or the Parity OK or Parity Error signal is

| TITLE<br>PRODUCT DESIGN SPECIFICATION  | SDS .    |       |   |

|----------------------------------------|----------|-------|---|

| INPUT/OUTPUT PROCESSOR<br>MULTIPLEXING | 154991   |       | В |

| MULTIFLEXING                           | SHEET 14 | OF 83 |   |

received by the IOP for a partial write operation.

#### Data Output from Memory

During a core memory read operation, signals on the data lines are strobed by the Data Gate Signal into the IOP memory Interface register. The data signals shall not change during the interval 80 nanoseconds before Data Gate falls until 65 nanoseconds after Data Gate falls.

#### 2.3.6.2 Address Lines

Signal on the Address Lines (LX15 thru LX31) shall be stable not less than 90 nanoseconds before the Memory Request signal rises and shall remain stable until 20 nanoseconds after the Memory Request signal has been dropped by the IOP.

#### 2.3.6.3 Data Gate Signal

The Data Gate signal strobes data into the IOP memory interface register during a core memory read operation. The Data Gate signal shall be a positive-going pulse not less than 80 nanoseconds in duration.

## 2.3.6.4 Parity Error and Parity OK

The Parity Error (PEX) and the Parity OK (POKX) signals shall be positive-going pulses not less than 70 nanoseconds wide and shall indicate the result of the parity check performed during a memory read or partial write operation by the memory.

## 2.3.6.5 Write Byte Signals

During a Memory full-write or partial write operation, the Write Byte (MW0X thru MX3X) signals shall designate the memory byte or byte into which data is to be written. These signals shall be present and stable within 120 nanoseconds after the Memory Request signal. They shall be present until the Address Release Signal is received at the IOP.

|     | TITLE<br>PR( DUCT DESIGN SPECIFICATION | 505      | r     | 1 |

|-----|----------------------------------------|----------|-------|---|

|     | INPUT/OUTPUT PROCESSOR,                | 154991   |       | В |

| · · | MULTIPLEXING                           | SHEET 15 | OF 83 |   |

2.3.6.6 Memory Request Signal

The Memory Request signal shall come true when the IOP wishes to make a memory access. This signal shall remain true until the IOP receives the Address Release signal or the Address Here signal is false when strobed.

2.3.6.7 Address Release Signal

The Address Release shall be a positive-going pulse not less than 80 nanoseconds in duration that designates to the IOP that the address lines may be changed and that the Memory Request line may go false.

## 2.3.6.8 Address Here

The Address Here line when true shall designate to the IOP that the address coded on lines LX15 thru LX31 is an address implemented in the memory or memories to which the IOP is attached. The Address Here line shall be strobed no sooner than 260 nanoseconds after the Address Lines have settled.

#### 2.3.6.9 Data Release Signal

The Data Release signal shall be a positive-going pulse not less than 80 nanoseconds in duration. During a core memory full write cycle initiated by the IOP the Data Release signal shall signify that the memory data lines may be released and that another memory cycle may be initiated.

#### 2.3.7

#### CABLE LENGTH

The total IOP/Memory cable length shall not exceed 64 feet to the furthest Memory port, (with 8274/8474 Bus-sharing feature cable length shall not exceed 40 feet). The IOP may drive cables in two directions in order to minimize the cable length. All cables in the bus interconnecting an IOP with a particular Memory port shall be of the same nominal length.

## 2.3.8

### CABLE AND CONNECTOR PIN ASSIGNMENT

Five cables are required to interconnect the IOP and memory. The pin assignment of signals in thos cables at the Cable Driver/Receiver and Cable Connector interface shall be as

SDS

SHEET

154991

16

В

83

OF

specified below:

| TITLE          |                |

|----------------|----------------|

| PRODUCT DESIGN | SPECIFIC ATION |

| INPUT/OUTPUT P | ROCESSOR,      |

| MULTIPLEXING   |                |

|                |                |

| ~ ~ | -  |     |    | - 4 | <br>~ | ۰. |  |

|-----|----|-----|----|-----|-------|----|--|

| nc  | L. | + * | ,, |     | ь.    | ۱. |  |

|     |    |     |    |     |       |    |  |

| Ca   | 11.      | - | 1 |

|------|----------|---|---|

| 1,74 | <b>D</b> |   | 1 |

# AT11 Cable Driver/Receiver Module

| Connector Pin | Signal Desig. at Connector | Signal | Fur | ctiona   | l Desc | ription                            |

|---------------|----------------------------|--------|-----|----------|--------|------------------------------------|

| 2             | / MX 0 /                   | Da     | ata | Line,    | Port 2 | x                                  |

| 1             | /MX1/                      |        |     | 1) · · · |        |                                    |

| 4             | /MX2/                      | · ·    |     | 11 -     |        | n an Angeler<br>Angeler an Angeler |

| 3             | /MX3/                      |        |     | 11       |        |                                    |

| 5             | /MX4/                      |        |     | 11       |        |                                    |

| 6             | /MX5/                      |        |     | 11       | •      |                                    |

| 7             | /MX6/                      |        |     | 11       |        |                                    |

| 8             | /MX7/                      |        |     | ti je s  |        | •                                  |

| 9             | /MX8/                      |        |     | 11       |        |                                    |

| 10            | /MX9/                      |        |     | н        |        |                                    |

| 11            | /MX10/                     |        | :   | 11       |        |                                    |

| 12            | /MX11/                     |        |     |          |        |                                    |

| 13            | /MX12/                     |        |     | 11 . j   | :      |                                    |

| 14            | /MX13/                     |        |     | н.       |        |                                    |

|               |                            | •      |     |          |        |                                    |

|   | TITLE                                                  | SDS    |       |    |            |

|---|--------------------------------------------------------|--------|-------|----|------------|

|   | PRODUCT DESIGN SPECIFICATION<br>INPUT/OUTPUT PROCESSOR | 154991 |       |    | <b>B</b> - |

| · | MULTIPLEXING                                           | SHEET  | 17 OF | 83 |            |

Cable 2

# ATII Cable Driver/Receiver Module

|                | Connector Pin | Signal Desig. at Connector              | Signal Functional Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------|---------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 2             | /MX14/                                  | Data Line, Port X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 1             | /MX15/                                  | <b>H</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 4             | /MX16/                                  | tt in the second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                | 3             | /MX17/                                  | n an                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 5             | /MX18/                                  | $\mathbf{H} = \{\mathbf{u}_{i}, \dots, \mathbf{u}_{i}\}  \mathbf{H} = \{\mathbf{u}_{i}, \dots, \mathbf{u}_{i}\}  \mathbf{H} = \{\mathbf{u}_{i}, \dots, \mathbf{u}_{i}\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 6             | /MX19/                                  | <b>11</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                | 7             | //MX20/                                 | $\mathbf{u}_{i} = \mathbf{u}_{i}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                | 8             | /MX21/                                  | $\mathbf{H} = \{\mathbf{u}_{1}, \dots, \mathbf{u}_{n}\}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                | 9             | /MX22/                                  | n na star star star star star star star sta                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |