| an a   | in gestioned with the strength and |      |    | j£dangang ngang magkansigani a s | r, a (Lazan Aliman dan                              | nde ster ange andere de stander (* 1996) de s        | n an                                  | REVIS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 510 N 5                                                                                                                                                                                                                            | 4      | 1339    | 91           | 62.*                              |

|--------------------------------------------|------------------------------------|------|----|----------------------------------|-----------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|--------------|-----------------------------------|

|                                            |                                    | L    | AL | REV.                             |                                                     |                                                      | DESCRI                                                                    | PTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                    | снк    | DATE    | Арри         | OVED                              |

|                                            |                                    |      |    | Α                                | ENG                                                 | R. REL                                               |                                                                           | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                    | PMA    | 8-19-6  | PMA          | ەرچىنى بۇلەرمىڭ ئانىلەنغ بەردا بى |

|                                            |                                    | x    | :  | В                                |                                                     |                                                      | DRAWN, MFG. R                                                             | ELEASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                    | BZ.    | 9-14-7  | R.R.         | ush                               |

|                                            |                                    |      |    |                                  |                                                     |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | , 7.3.1, 7.3.2.3,                                                                                                                                                                                                                  | СВ     | 4-3-8   |              | LMK                               |

|                                            |                                    |      |    | С                                | CAB                                                 | LE 2 & 5                                             |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ., 7.4.3, 7.5                                                                                                                                                                                                                      |        |         |              | KDB                               |

|                                            |                                    | X    |    | D                                | SEE<br>Re                                           | REV. E.O                                             | .; REVISED PA                                                             | RA. 6.2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 2.6, SH. 29.<br><u>Blg</u><br>ARA 5.7, SH 19                                                                                                                                                                                       | Bis    | 6/9/69  | $\eta R_{g}$ |                                   |

|                                            |                                    |      | X  | E                                | SE                                                  | EREV                                                 | E.O.; REVIS                                                               | SED P                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ARA 5.7, SH 19                                                                                                                                                                                                                     | OB     | 9/18/33 | NR -         | 1/2.2/4-7<br>                     |

|                                            | · .                                |      |    |                                  | a Mandon <b>Mandon Son</b> a (Construction de la Re | ουλακτοβητικό το | n n derme Brack – Laffer Zonkonske en roch uf ur frieden Brack in der son | <ul> <li>To a second parameter of the second seco</li></ul> |                                                                                                                                                                                                                                    |        |         |              |                                   |

|                                            |                                    |      |    |                                  |                                                     |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

|                                            |                                    |      |    |                                  |                                                     |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

|                                            |                                    |      |    |                                  |                                                     |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              | -<br>-<br>                        |

|                                            |                                    |      |    |                                  |                                                     |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

|                                            |                                    |      |    |                                  | a.                                                  |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

|                                            | ·                                  |      |    |                                  |                                                     |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              | 131                               |

| NO. DRAWING NO                             | o.                                 |      |    | D                                | ESCR                                                | IPTION                                               | ak ka ja kan ng minang mang mang mang mang mang mang mang                 | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EFERENCE DES                                                                                                                                                                                                                       | IGNA   | TION    |              | ITEM<br>NO.                       |

|                                            | <i>L</i>                           |      | ·  |                                  | ****                                                | MATERI                                               | AL LIST                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | ۵۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲<br>۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - ۲۰۰۵ - |        |         |              |                                   |

| NOTES UNLESS SPECIFIED                     |                                    | RAWN | Р. | MC AF                            | EE                                                  | 8-18-66                                              | -66                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

| 1, TOLERANCES<br>,XX ±.030 ANGULAR         | C                                  | HECK | Р. | Mc Af                            | ee                                                  | 8-19-66                                              |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | SANTA MONICA. CALIFO                                                                                                                                                                                                               | RNIA   |         |              |                                   |

| .XXX ±.010 ±½°<br>2. Break all sharp edges | A                                  | PPR. | I  | M.And                            | erson                                               | 8-19-66                                              | TITLE                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

| .010 APPROX.<br>3. MACH, SURFACES          |                                    |      | -  |                                  | nuled (67 a' 8' 46' 10'                             |                                                      | PRODUCT DESIGN SPECIFICATION                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

| 4. ALL DIM, IN INCHES                      |                                    |      |    |                                  |                                                     |                                                      | -                                                                         | INPUT/OU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | JTPUT PROCESSOR, SI                                                                                                                                                                                                                | ELECTO | 2       |              |                                   |

|                                            |                                    |      |    |                                  |                                                     |                                                      | <b>-</b>                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

| MODEL NO.                                  |                                    |      |    |                                  | <b>.</b>                                            |                                                      |                                                                           | SIZE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DWG. NO.                                                                                                                                                                                                                           |        |         |              | CHANOE<br>LETTER                  |

| 8485                                       |                                    |      |    |                                  |                                                     |                                                      |                                                                           | A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 133991                                                                                                                                                                                                                             |        |         |              | E                                 |

| NEXT ASSY.                                 |                                    |      |    |                                  |                                                     |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <u>†</u>                                                                                                                                                                                                                           |        |         |              | - k                               |

| 117620                                     |                                    |      |    |                                  |                                                     |                                                      | SCALE                                                                     | DC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | NOT SCALE DRAWING                                                                                                                                                                                                                  | SH     | EET 1   | of 70        |                                   |

| SDS-E-564 (4/65)                           |                                    |      |    |                                  |                                                     |                                                      |                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                    |        |         |              |                                   |

# Table of Contents

| Section |                               |

|---------|-------------------------------|

| 1.0     | Scope                         |

| 2.0     | Applicable Documents          |

| 3.0     | Requirements                  |

| 4.0     | Interface Signal Transmission |

| 5.0     | Memory Interface              |

| 6.0     | CPU Interface                 |

| 7.0     | Device Controller Interface   |

| 8.0     | Bus-Sharing Option            |

| ſ |                                                                  | SDS   |   |        |    | <u>, and a style yn de star yn a s</u> |

|---|------------------------------------------------------------------|-------|---|--------|----|----------------------------------------|

|   | PRODUCT DESIGN SPECIFICATION<br>INPUT/OUTPUT PROCESSOR, SELECTOR |       |   | 133991 |    | E                                      |

|   |                                                                  | SHEET | 2 | OF     | 70 |                                        |

1.0 SCOPE

SDS-E-112(4/65)

1.1 This specification covers the actions and responses required at the DC/IOP, CPU/IOP, and Memory/IOP interfaces and the design requirements of the free standing selector IOP to be used with the Sigma computer series.

2.0 APPLICABLE DOCUMENTS

2.1 Selector IOP Planning Specification, Sigma Document 182

2.2 I/O System Product Planning Specification, Sigma Document 156

2.3 Specification, Central Processing Unit, Dwg. No. 117336

- 2.4 Specification, Design 8-Bit Data Path Interface, Dwg. No. 123382

- 2.5 Specification, Sigma/Delta Core Memory, Dwg. No. 117653

- 2.6 Specification, Design, Four Byte Data Path Interface, Dwg. No. 137556

- 2.7 Selector, IOP Specification Addendum, Sigma Document 256

- 2.8 Revised Selector IOP Product Factoring, Sigma Document 260

| TITLE<br>PRODUCT DESIGN SPECIFICATION | 505   |   |       |     |   |

|---------------------------------------|-------|---|-------|-----|---|

| INPUT/OUTPUT PROCESSOR, SELECTOR      |       | 1 | 33991 |     | E |

|                                       | SHEET | 3 | OF    | 570 |   |

### 3.0 REQUIREMENTS

3.1 IOP Functional Requirements

3.1.1 CPU I/O Instructions

On command from the CPU, the IOP shall perform the required operations associated with the SIO, TIO, HIO, TDV, and AIO instructions.

### 3.1.2 Device Controller Servicing

The IOP shall perform the operations for the following types of Device Controller service operations:

Service Call Data Out Data In Order Out Order In Interrupt

### 3.1.3 Operating Speed

The Selector IOP shall be capable of exchanging data with a non-interleaved core memory at maximum memory rate (one cycle every 850 nanoseconds). The S/IOP shall be capable of transferring data to and from a device controller at a maximum rate of 1.25 million transfers a second, a transfer may be 1, 2, or 4 bytes wide.

| TITLE<br>PRODUCT DESIGN SPECIFICATION | 505   |   |       |    |                                                   |  |

|---------------------------------------|-------|---|-------|----|---------------------------------------------------|--|

| INPUT/OUTPUT PROCESSOR, SELECTOR      |       |   | 33991 |    | $\int_{1}^{1} \frac{\partial  w }{\partial x} dx$ |  |

|                                       | SHEET | 4 | OF    | 20 |                                                   |  |

### 3.2 BASIC FEATURES

The Selector IOP provides for the coupling of the CPU and memories to very high speed peripheral devices. These devices may have data rates that would exceed the bandwidth of the Multiplexing IOP or would use up such a large percentage of that band width as to make it impractical to run any other device concurrently. Capability is built into the IOP which allows it to direct and control I/O operations by executing a command list prepared by the CPU.

The IOP has memory addressing format capability for working with memories as large as 1,048,576 words. However, it will be mechanized to handle memories only as large as 131,072 words (524,288 bytes).

The basic DC/IOP interface has I/O unit addressing capability for up to 136 Device Controllers. However, 32 Device Controllers may be connected and only one Device Controller may be in operation at a time. Concurrent operation of two or more Device Controllers on a single S/IOP is not permitted.

The Selector IOP may operate with Device Controllers having a one-byte, two-byte, or four-byte wide data path.

#### 3.3 OPTIONAL FEATURES

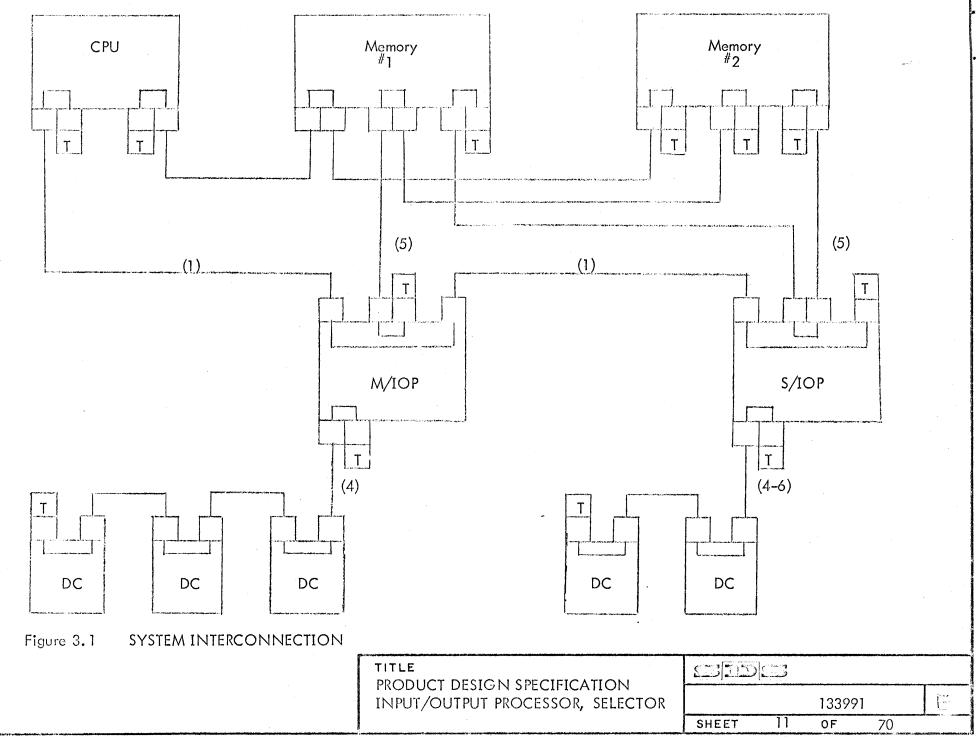

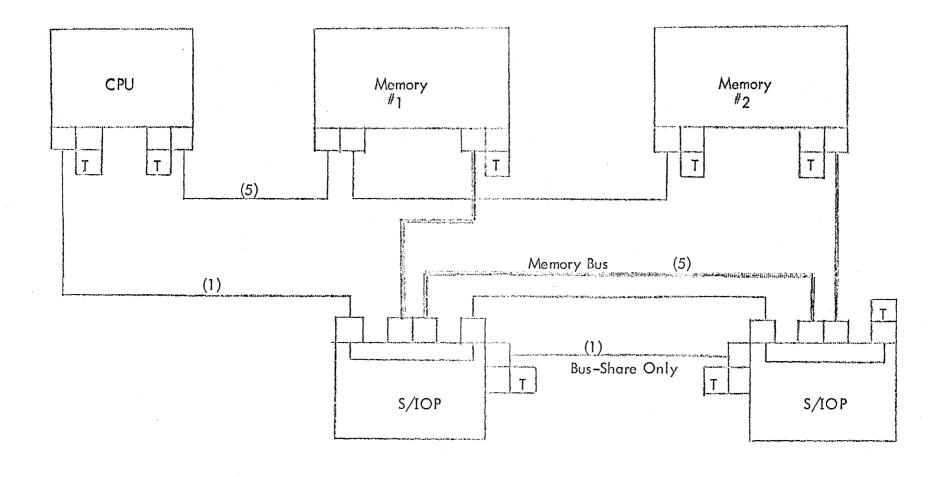

A Selector IOP may be supplied with an optional core memory bus-sharing feature. This optional feature, when installed in the IOP, enables the IOP to time-share a core memory bus with another Selector IOP if the other Selector IOP also has the optional bus-sharing feature.

#### 3.4 IOP INTERNAL OPERATION

The Selector IOP is a passive link between core memory and the Device Controllers connected to the IOP.

Once an I/O operation has been initiated by the CPU, the operation is performed to completion, independently, by the IOP, Device Controller, and Core Memory. The IOP will perform core memory accesses, as required by the Device Controller, and update current

| TITLE<br>PRODUCT DESIGN SPECIFICATION | sdi   |   |        |    |    |

|---------------------------------------|-------|---|--------|----|----|

| INPUT/OUTPUT PROCESSOR, SELECTOR      |       |   | 133991 |    | Y. |

|                                       | SHEET | 5 | OF     | 70 |    |

command information. The IOP will also record IOP status for future interrogation by the CPU. During a record, a new command may be loaded by the IOP - making scatter reads and gather writes possible (data chaining). At the end of a record, a new command may be loaded by the IOP and an order sent to the Device Controller - allowing multiple record operations to occur without CPU reinitiation (command chaining). The maximum number of devices that may be attached to a Selector IOP is 32. A Selector IOP allows only one of the several possible devices attached to it to be in transmission operation at a given time. The Selector IOP also allows a Device Controller to exchange a complete record with core memory as the result of a single service request from the Device Controller. The Selector IOP will exchange data with a Device Controller until the Device Controller terminates the exchange or until the entire record has been transmitted as indicated by count done. Limitations on data chaining and number of device controllers that may be connected are functions of device speed, interface width, and cable lengths.

.

The IOP shall perform the operations described in this section in response to service calls from the CPU or from Device Controllers. Specific interface responses are described in Sections 5.0, 6.0 and 7.0.

#### 3.4.1 **CPU** Service Calls

The IOP shall respond to service calls from the CPU and perform the following operations: SIO, HIO, TIO, TDV, and AIO. The IOP shall respond in a manner dependent on the state of the IOP such that CPU interference to data transfer between the IOP and core memory is minimized. Each IOP shall have the facility for assignment of the IOP address by the setting of switches on a switch module type LT26 (SDS Part No. 126982), located within the IOP.

#### SIO

The IOP shall decode and recognize the SIO function and shall decode the IOP address lines. If no address recognition, the IOP's shall pass the Control Strobe along to the last IOP and the Control Strobe shall be returned to the CPU on the Proceed line. If the addressed Selector IOP is busy, (whether or not engaged in service) with a Device Controller as the result of a

| TITLE                            |

|----------------------------------|

| PRODUCT DESIGN SPECIFICATION     |

| INPUT/OUTPUT PROCESSOR, SELECTOR |

| 505   |    |      |    |    |

|-------|----|------|----|----|

|       | 13 | 3991 | -  | 15 |

| SHEET | 6  | OF   | 70 |    |

and the state of the

previous SIO, the instruction shall be partially executed. (the condition codes shall be sent signifying that the IOP was busy).

If the IOP address is recognized and the IOP is not Busy, the IOP shall access cell 20\* for the Device address and the command address. If a memory parity error is detected at this point, the IOP shall terminate the operation and send the Proceed signal with appropriate condition codes. If there is no memory parity error, the IOP transmits the SIO function Indicator and Device address at the Device Controller interface and waits for a response. After receiving the response from the Device Controller the IOP loads cells 20\* and 21\* if requested by the CPU and sends the appropriate condition codes and Proceed signal to the CPU.

#### TIO, TDV

These operations are performed in a manner similar to the SIO operation. If the IOP is Busy and currently responding to a Device Controller service request then the IOP partially executes the operation (condition codes are sent signifying the IOP busy state ); otherwise, the TIO or TDV operation is normally executed.

#### HIO

The HIO operation is performed in a manner similar to the SIO operation and is always normally executed. If, when the CPU requests the IOP to perform an HIO operation, the IOP is currently servicing a Device Controller service request then the IOP terminates the Device Controller service and then responds to the CPU request.

#### AIO

The IOP shall decode and recognize the function. If no interrupt is pending, the IOP's shall pass the Control Strobe along to the last IOP which shall return the strobe to the CPU on the Proceed line with the appropriate condition code settings. The IOP with the highest priority and an interrupt pending shall terminate an ongoing Device Controller service and then pass the AIO function indicator along to the Device Controllers. The IOP shall then wait for the highest-priority Device Controller with interrupt pending to respond with Device/Device Controller address and status. The IOP shall then complete the AIO operation by writing the IOP/Device

\*Base 16

| TITLE        |              |          |

|--------------|--------------|----------|

| PRODUCT DESI | GN SPECIFICA | TION     |

| INPUT/OUTPUT | PROCESSOR,   | SELECTOR |

| 505 |        |

|-----|--------|

|     | 133991 |

7

OF

70

SHEET

| ς | D   | ς | -E- | 1 | 1 | 5 | ļ | 1.    | 18  | 5 | ١ |

|---|-----|---|-----|---|---|---|---|-------|-----|---|---|

| 1 | 1,1 |   |     | 1 | â |   | 3 | * : Z | 1.3 | 1 | J |

Controller/Device address and status in cell 20\* and sending condition codes and Proceed signal to the CPU.

### 3.1.3.2 Device Controller Service Calls