# **SIGMA BASICS**

**JUNE 1968**

(Revision I)

# FOR TRAINING PURPOSES ONLY

#### **PREFACE**

The development of the Sigma Product Line resulted in the generation of a huge mass of supporting documentation. This training document is an attempt to combine information from many different documents which pertain to the understanding and maintenance of all Sigma products. It is also an attempt to supply explanations and carifications on the interpretation and use of these documents; explanations which are not presently found elsewhere.

This document is aimed at giving the user the basic knowledge of Sigma hardware structures so that he can assume the study of specific Sigma equipment armed with a solid background of the fundamental principles involved in the operation of any Sigma device.

This document assumes that the reader is thoroughly familiar with digital electronic circuitry and Boolean algebra. Experience on other digital computers will allow the reader to assimilate some of the information easier, however, it is not a prerequisite.

Our appreciation is extended to Robert J. Spinrad, Vice-President of Programming, for his permission to include his excellent article on software, written while he was a member of the Brookhaven National Laboratory Staff.

SCIENTIFIC DATA SYSTEMS TECHNICAL TRAINING STAFF

# TABLE OF CONTENTS

| Pref | ace  |               | • • •       |        |        | • •  |     | •  | •   |     |     |     |            | • | • | • | • |   |   | PAGE  |

|------|------|---------------|-------------|--------|--------|------|-----|----|-----|-----|-----|-----|------------|---|---|---|---|---|---|-------|

| SECI | ION  | I             |             |        |        | •    |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

|      |      |               | Sigma       | 1?     | • •    | • •  |     | •  | •   | •   | •   | •   | •          | • | • | • | • | • | • | .1-1  |

| SECI | CION | II            |             |        |        |      |     | ·  |     |     |     |     |            |   |   |   |   |   |   |       |

|      | Sign | na Pi         | roduct      | Line   | · .    | • •  |     | •  | •   | •   | •   | •   | •          | • | • | • | • | • | • | .2-1  |

| SECI | ION  | III           |             |        |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

|      | T Se | eries         | s Logi      | c Mod  | lu1es  |      |     |    | •   | •   |     |     |            |   |   |   |   |   |   | .3-1  |

|      |      |               | Speci       |        |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

|      |      |               | -<br>ted Ci |        |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

|      | SDS  | 304           | 8-Bit       | Memo   | ry E   | leme | nt. |    |     | •   |     |     | •          | • |   |   |   |   |   | .3-8  |

|      | SDS  | 305           | Inver       | ter .  |        |      | •   |    | •   | •   | •   |     |            |   |   |   |   |   |   | .3-13 |

|      | SDS  | 306           | Buffe       | er     |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

|      | SDS  | 307           | Flip-       | Flop   |        |      |     |    | •   |     | 0   |     |            |   |   |   |   |   |   | .3-15 |

|      | SDS  | 308           | Discr       | imina  | tor    |      |     |    |     |     |     | •   |            |   |   |   |   |   |   | .3-20 |

|      | SDS  | 311           | Flip-       | Flop   |        |      |     | •  | •   | •   | •   | •   | •          | • | • | • | • | • | • | .3-23 |

| SECT | ON   | IV            |             |        |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

|      | Sign | na Lo         | ogic S      | ymbo]  | ogy    |      |     |    | •   |     |     |     |            |   |   |   |   |   |   | .4-1  |

|      |      | 9 <b>-</b> Se | eries       | Symbo  | logy   |      |     |    |     | •   |     |     |            |   |   |   |   |   |   | .4-3  |

|      |      | MIL-          | -STD-8      | 806B S | ymbo   | logy |     | •  | •   | •   | •   | •   | •          | • | • | • |   | • | • | .4-18 |

| SECT | ON   | v             |             |        |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

|      | Logi | lc In         | npleme      | ntati  | on.    |      |     | •  |     | •   |     |     |            |   |   |   |   |   |   | .5-1  |

|      |      | Auto          | mated       | Logi   | .c Sy  | stem |     | •  |     |     |     |     |            |   |   |   |   |   |   | .5-1  |

|      |      | How           | The A       | utoma  | ted 1  | Logi | c S | ys | ten | n W | loi | cks | 3 <b>.</b> |   |   |   |   |   |   | .5-5  |

|      |      | Auto          | oma ted     | Logi   | .c Equ | ati  | ons | •  |     | •   | •   |     |            | • |   |   |   |   |   | .5-9  |

|      |      | Auto          | omated      | Wire   | Lis    | ts.  |     |    |     | •   |     | •   |            |   |   |   |   | • |   | .5-63 |

|      |      |               | List.       |        |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

|      |      | Pin           | Index       |        |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   | .5-74 |

|      | App1 |               | ions        |        |        |      |     |    |     |     |     |     |            |   |   |   |   |   |   |       |

| SECTION VI PAGE                            | ;        |

|--------------------------------------------|----------|

| Maintenance Documents                      |          |

| Reference Manual                           | :        |

| Technical Manual                           | }        |

| Customer Service Tek-Tip                   | ŀ        |

| Engineering Drawings                       | . 1      |

| Diagnostics                                | .3       |

| Installation Documents                     | . 7      |

| Training Documents                         | 7        |

| Literature Request Form                    | 8        |

| Reproduction/Drawing Pull Request Form 6-3 | 9        |

|                                            |          |

| SECTION VII                                |          |

| Software Primer                            | -        |

| Programs that Produce Programs             | j,       |

| Programs that Run Programs                 | <u>;</u> |

| Complex Systems                            | <u>,</u> |

|                                            |          |

| SECTION VIII                               |          |

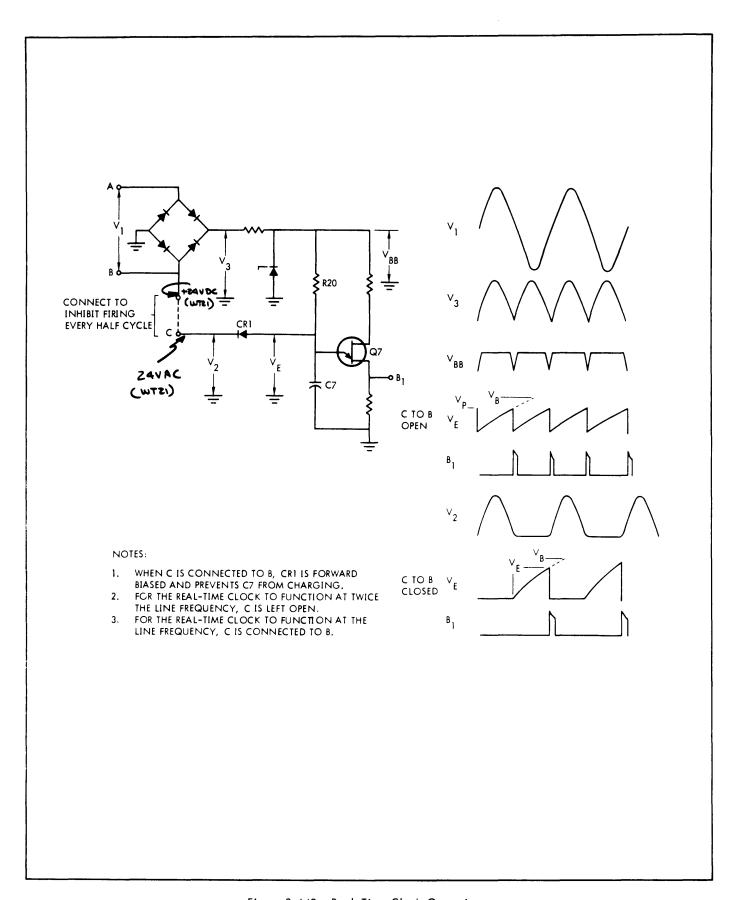

| Power Monitor Theory                       | _        |

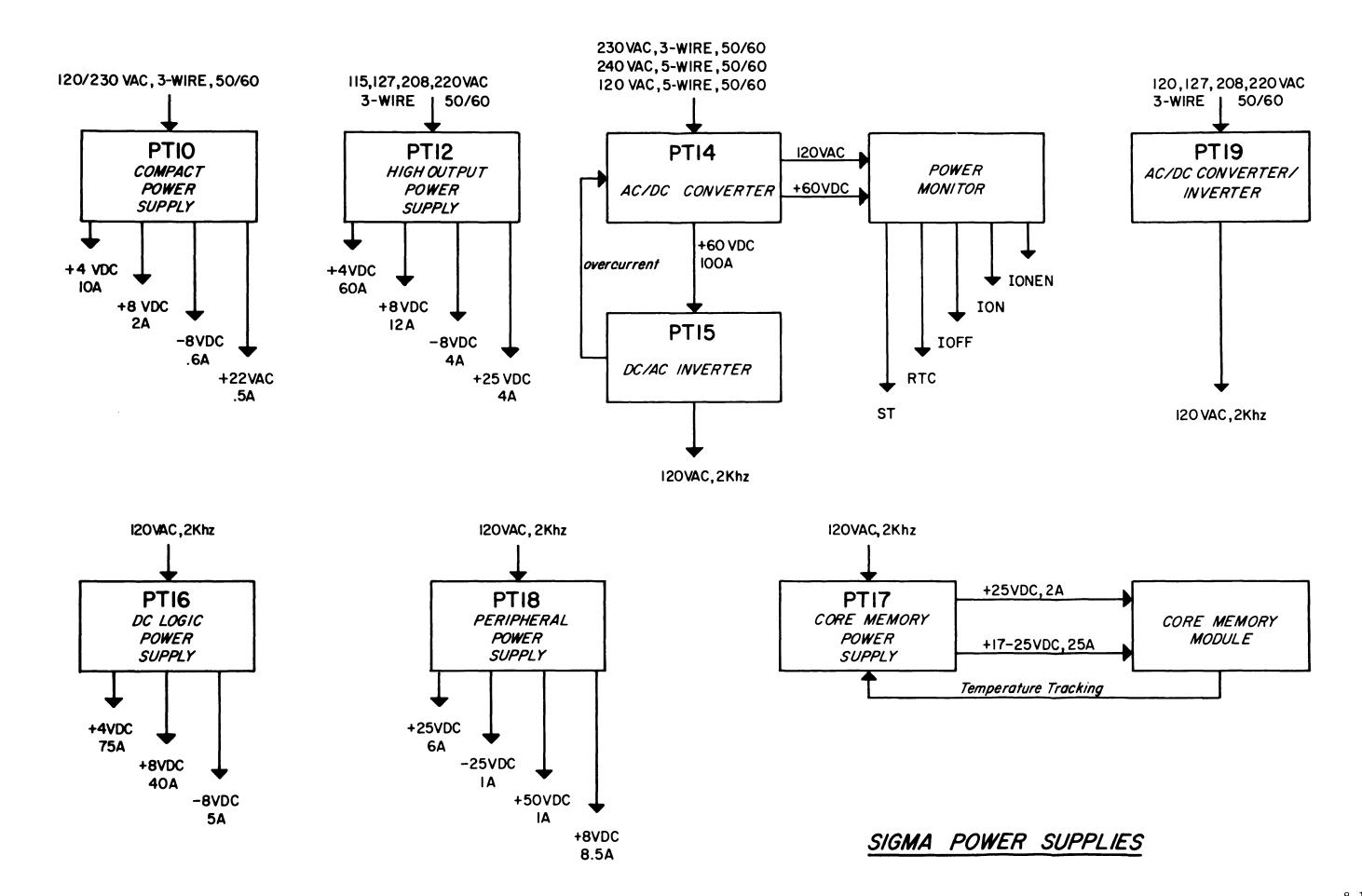

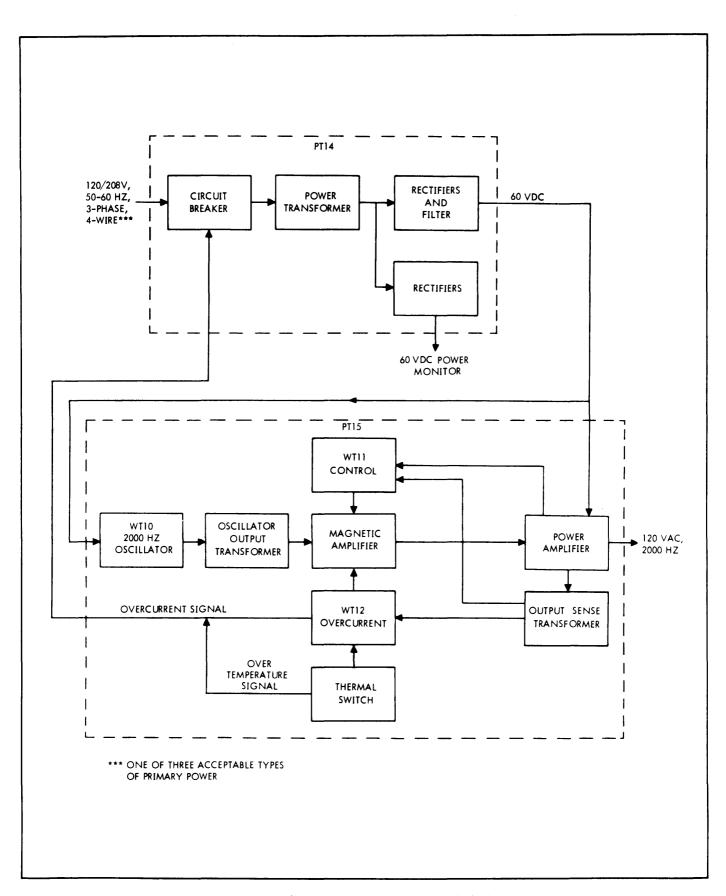

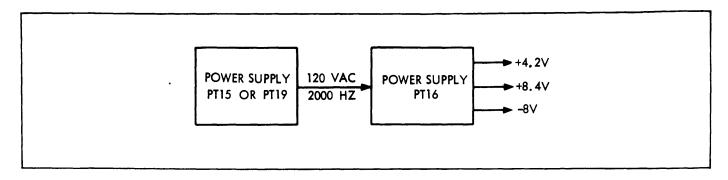

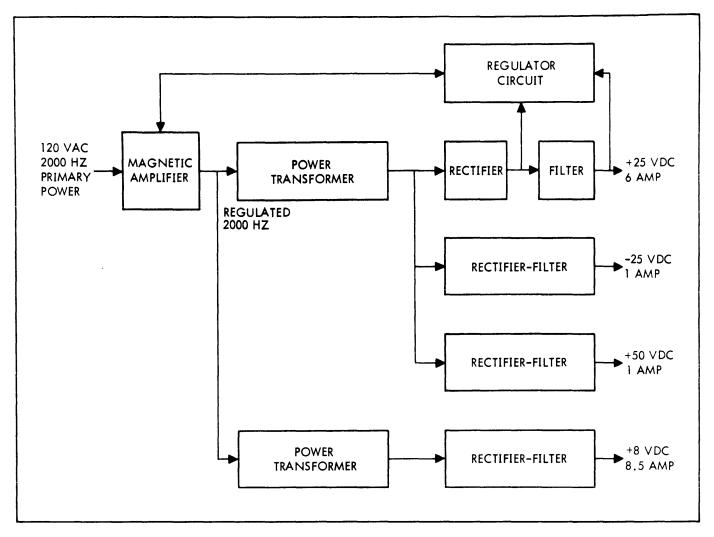

| Power Supply Diagram                       | .3       |

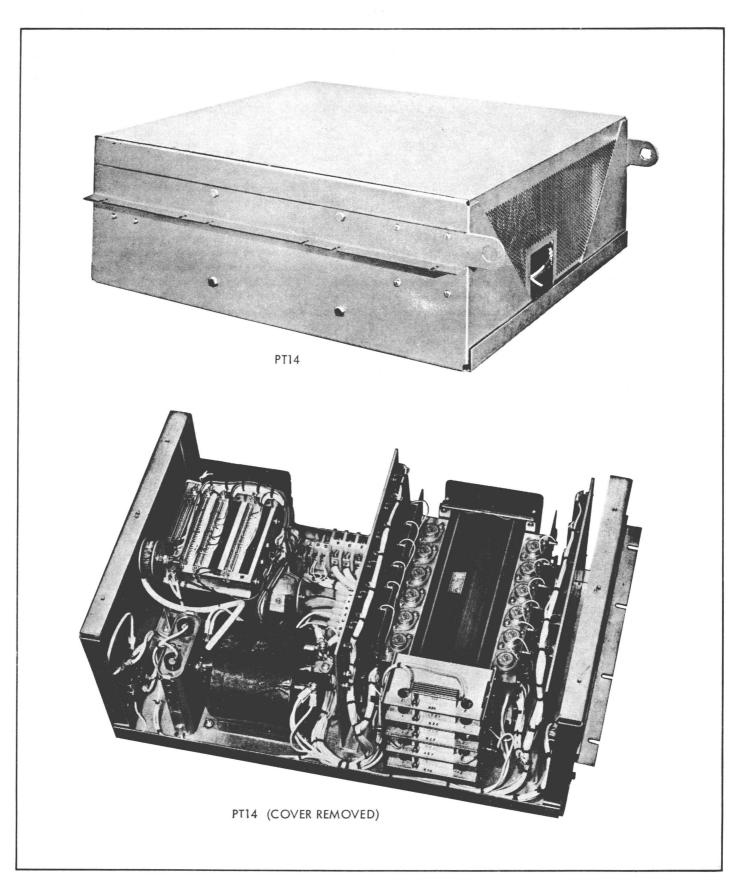

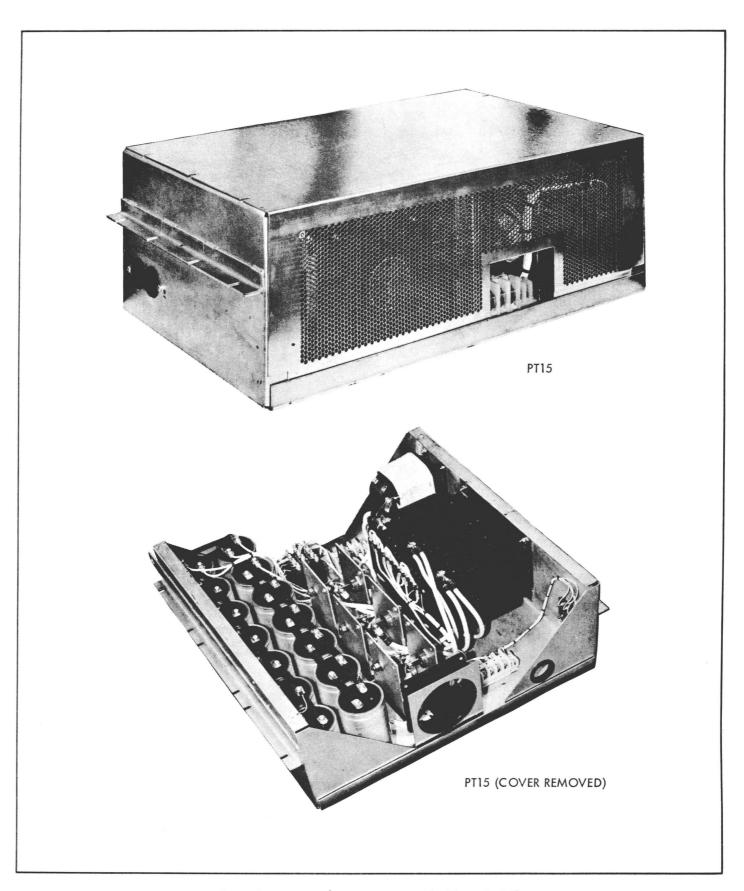

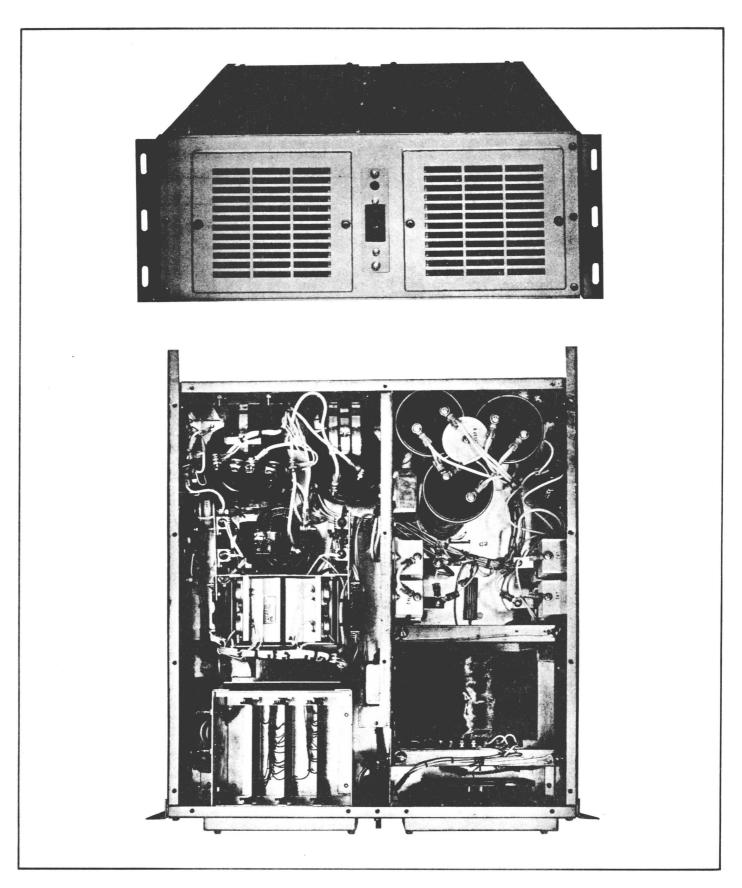

| PT14/PT15 Power Supply                     | .5       |

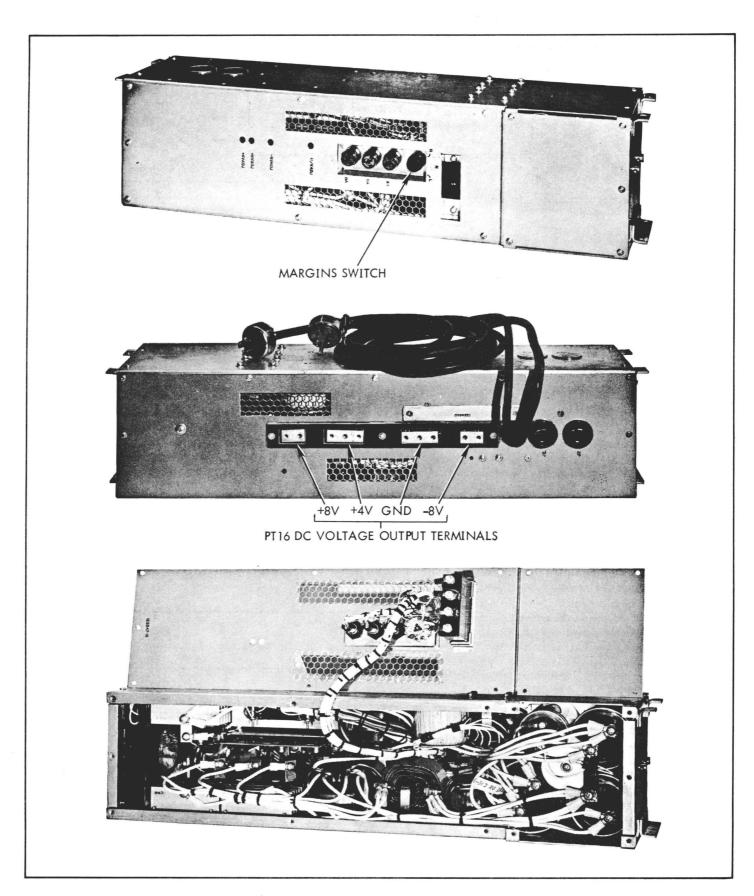

| PT16 Power Supply                          | 23       |

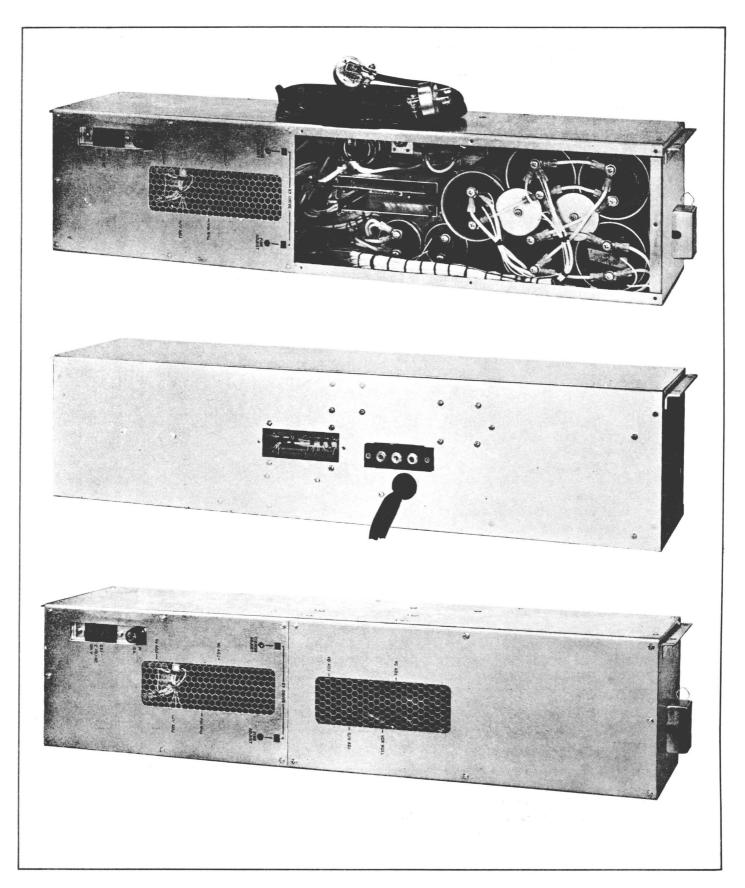

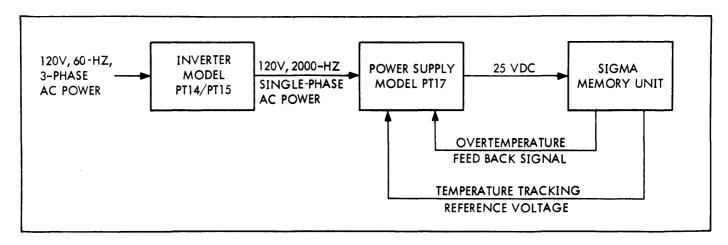

| PT17 Power Supply                          | 29       |

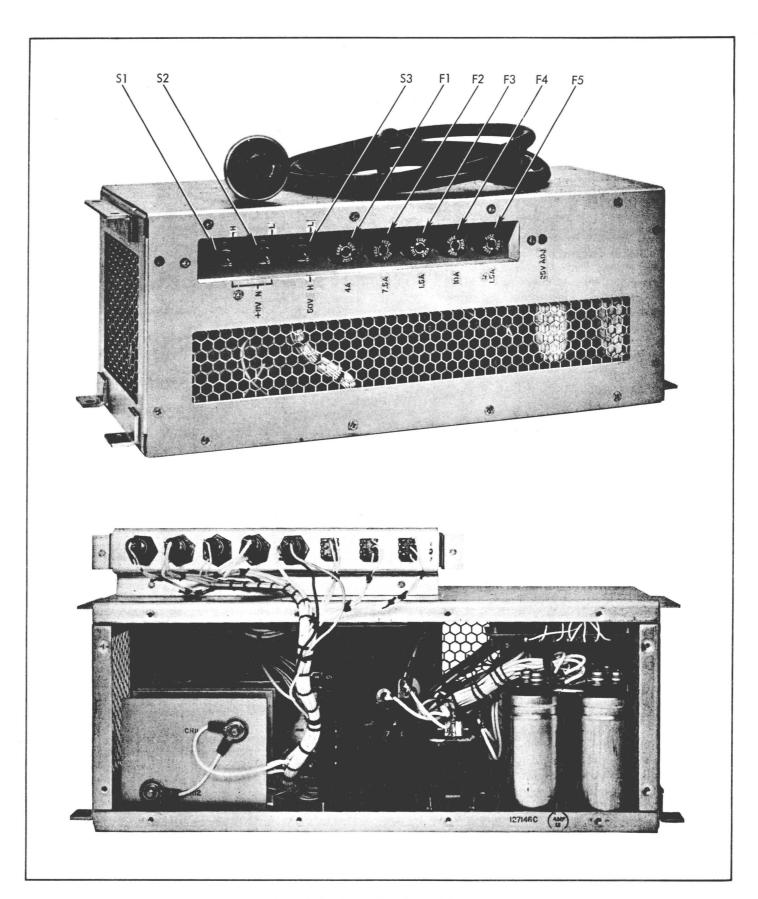

| PT18 Power Supply                          | 37       |

| PT19 Power Supply 8-4                      | ١3       |

WHAT IS SIGMA?

SECTION I

#### WHAT IS SIGMA?

In March 1966, SDS announced Sigma 7, marking the eight introduction by SDS of a computer offering greater capability and reliability than competitively priced machines.

The success of the Sigma line since then underscores the company's ability to develop advanced equipment by devising and putting into practice new development techniques such as:

- \* Critical-path charting methods in the design, programming, manufacturing, and documentation efforts to insure on-time delivery;

- \* Extensive use of standardized elements to make up the computer system, thereby minimzing manufacturing costs;

- \* Special computer programs to expedite the design of integrated circuits and computer logic;

- \* Automated logic implementation, including logic equations, wire lists, and wire verification, to speed the manufacturing process, and;

- \* Computer-controlled and semi-automatic testing methods at every level of assembly to insure maximum interface efficiency and customer satisfaction.

The specific techniques that led to the development of the Sigma 7 were established several years ago when SDS engineers saw that new developments in computer technology made possible radically new approaches in design.

Therefore, in undertaking a new computer development program, SDS planners set themselves these goals:

- \* To use the most advanced techniques that would be economically feasible by the time manufacturing began;

- \* To meet the needs of the users by looking ahead to the time when the new computers would be coming into use;

- \* To integrate hardware with software in a fully coordinated design that would offer more computation per dollar, and;

- \* To make both hardware and software modular and expandible to satisfy a wide range of requirements.

The result, announced two years later, was Sigma 7, first in a family of third-generation SDS computers. Sigma 7 is a fast, medium-size computer system that can simutaneously control real-time operations, interact with a large number of time-shared user stations, solve scientific problems, and process business data.

Sigma 7 was followed by Sigma 2, a small, low-cost computer system, in August 1966. Sigma 5 was then announced in the spring of 1967 as a fast, medium-size system which filled the capability and application gap between the Sigma 2 and Sigma 7.

Along with the three computer systems, SDS announced the availibility of many Sigma peripheral devices such as Card Readers and Punches, Teletypes, Line Printers, RAD Files, Magnetic Tape Transports, Paper Tape Systems, Keyboard Displays, and Communications equipment.

Other devices were concurrently announced which operate with a Sigma computer, such as D-A Converters, Multiplexors, and other Systems devices.

The Sigma Product Line is far from completed. Other computers will be announced, as well as peripherals, as the market dictates. Plans are in progress to create a computer system which fills the gap between the Sigma 2 and Sigma 5 computers. Many of the Sigma 5 and 7 computers are being shipped as a multiprocessor computer system, therefore, designers are looking ahead to the design of a fully integrated multi-processor computer system to more fully meet the needs of that market.

When the Sigma Product Line is completed it should represent a formidable array of computer hardware and software systems which can effectively compete in any computer system environment.

Sigma is a state-of-the-art computer system. Techniques and methods developed for Sigma will be with the industry for many years to come, even in an industry noted for its changing technology.

Therefore, the knowledge you will be gaining in the Sigma courses you are entering will be invaluable in your immediate needs, and profitable in your long-range career goals. Keep this in mind as you attend the training here at SDS in the Sigma Product Line equipment, and devote all of your energy to learning. Knowledge is a very salable and indispensable part of your career; appreciate the opportunity, and take advantage of it.

SIGMA PRODUCT LINE

**SECTION II**

# THE SIGMA PRODUCT LINE

# SIGMA 2

| Model Number | Description                            |

|--------------|----------------------------------------|

| 8001         | Sigma 2 Central Processor Unit         |

| 8011         | 2 Real Time Clocks                     |

| 8012         | Memory Parity Interrupt                |

| 8013         | Power Fail Safe                        |

| 8014         | Protection Feature                     |

| 8020         | Multiply/Divide Option                 |

| 8021         | Interrupt Control Chassis              |

| 8022         | Priority Interrupts, 2 levels          |

| 8023         | Integral Priority Interrupts, 2 levels |

| 8050         | External Memory Adapter, Model II      |

| 8051         | Basic Core Memory, 4096 words          |

| 8053         | Memory Increment, 4096 words           |

| 8054         | External Memory Adapter, Model I       |

| 8055         | Memory 2-Way Access                    |

| 8070         | External Interface Feature             |

| 8071         | Additional 4 I/O Channels              |

| 8072         | Watchdog Timer                         |

| 8091         | Integral KSR Teletype                  |

| 8092         | Integral ASR Teletype                  |

# SIGMA 5

| Model Number | Description                                              |

|--------------|----------------------------------------------------------|

|              |                                                          |

| 8201         | Sigma 5 Central Processor Unit                           |

| 8202         | Sigma 5 Central Processor Unit without Integral IOP      |

| 8203         | Integral IOP                                             |

| 8211         | 2 Additional Real Time Clocks                            |

| 8213         | Power Fail Safe                                          |

| 8214         | Memory Protect                                           |

| 8216         | Additional Register Block (16 General Purpose Registers) |

| 8218         | Floating Point Arithmetic Unit                           |

| 8221         | Interrupt Control Chassis (16 Priority Interrupt levels) |

| 8222         | Priority Interrupts, 2 levels                            |

| 8251         | Basic Core Memory, 4096 words                            |

| 8252         | Memory Increment, 4096 words                             |

| 8255         | Memory 2-Way Access                                      |

| 8256         | Memory 3-Way Access                                      |

| 8257         | Memory 6-Way Access                                      |

| 8270         | External Interface Feature                               |

| 8271         | Multiplexor I/O Processor with 8 Channels                |

| 8272         | Additional 8 Channels for MIOP                           |

| 8285         | Selector I/O Processor, Model II                         |

| 8291         | CFE-3 Control Unit                                       |

| 8292         | 2 CFE-3 Multiply/Add Units                               |

# SIGMA 7

| Model Number | Description                                              |

|--------------|----------------------------------------------------------|

|              |                                                          |

| 8401         | Sigma 7 Central Processor Unit                           |

| 8411         | 2 Additional Real Time Clocks                            |

| 8413         | Power Fail Safe                                          |

| 8414         | Memory Write Protection                                  |

| 8415         | Memory Map and Access Protection                         |

| 8416         | Additional Register Block (16 General Purpose Registers) |

| 8418         | Floating Point Arithmetic                                |

| 8419         | Decimal Arithmetic Unit                                  |

| 8421         | Interrupt Control Chassis (16 Priority Interrupt levels) |

| 8422         | Priority Interrupts, 2 levels                            |

| 8451         | Basic Core Memory, 4096 words                            |

| 8452         | Memory Increment, 4096 words                             |

| 8456         | Memory 3-Way Access                                      |

| 8457         | Memory 6-Way Access                                      |

| 8471         | Multiplexor I/O Processor with 8 Channels                |

| 8472         | Additional 8 Channels for MIOP                           |

| 8485         | Selector I/O Processor, Model II                         |

| 8491         | CFE-3 Control Unit                                       |

| 8492         | 2 CFE-3 Multiply/Add Units                               |

| 8495         | System Supervisory Console (Free-Standing)               |

# SIGMA PERIPHERAL DEVICES

| Model Number | Description                                                              |

|--------------|--------------------------------------------------------------------------|

| 7010         | KSR Teletype with Controller, 10CPS                                      |

| 7011         | KSR Teletype without Controller, 10CPS                                   |

| 7014         | KSR Teletype without Sigma 2 Integral Controller, 10CPS                  |

| 7020         | ASR Teletype with Controller, 10CPS                                      |

| 7021         | ASR Teletype without Controller, 10CPS                                   |

| 7060         | Paper Tape System with Controller and Rack (Reader, Punch, and Spooler). |

| 7061         | Paper Tape System Cabinet and Controller                                 |

| 7062         | Paper Tape Reader, 300CPS                                                |

| 7063         | Paper Tape Punch, 120CPS                                                 |

| 7064         | Paper Tape Spooler                                                       |

|              |                                                                          |

| 7120         | Card Reader, 400CPM                                                      |

| 7140         | Card Reader, 1500CPM                                                     |

| 7160         | Card Punch, 300CPM                                                       |

|              |                                                                          |

| 7201         | RAD Controller                                                           |

| 7202         | RAD Storage Unit, .75MB; 188,000 bytes/second                            |

| 7204         | RAD Storage Unit, 3.0MB; 188,000 bytes/second                            |

|              |                                                                          |

| 7321         | Magnetic Tape Controller                                                 |

| 7322         | 60KB Magnetic Tape Station (75 IPS, 9-Track)                             |

| 7323         | 120KB Magnetic Tape Station (150IPS, 9-Track)                            |

| 7361         | 20KC Magnetic Tape Controller                                            |

| 7362         | 20KC Magnetic Tape Station (37.5 IPS, 7-Track)                           |

| 7365         | BCD Option                                                               |

| 7371         | Magnetic Tape Controller                                                 |

| 7372         | 60KC Magnetic Tape Station (75 IPS, 7-Track)                             |

| 7374         | Binary Packing Option                                                    |

| 7440         | Buffered Line Printer, 600LPM        |

|--------------|--------------------------------------|

| 7445         | Buffered Line Printer, 1000LPM       |

|              |                                      |

| 7530         | Graph Plotter (11 Inch)              |

| 7531         | Graph Plotter (30 Inch)              |

|              |                                      |

| 7550         | Keyboard Display, Model I            |

| 7551         | Message Mode Feature                 |

| 755 <b>3</b> | Hard Copy Output Feature             |

| 7555         | Keyboard Display, Model II           |

| 7556         | High Speed Transmission Feature      |

|              |                                      |

| 7601         | Data Set Controller                  |

| 760 <b>2</b> | Full Duplex Feature                  |

| 7603         | Automatic Dialling Feature           |

| 7611         | Communications Controller            |

| 76 <b>12</b> | Format Group Timing Unit             |

| 76 <b>13</b> | Line Interface Unit                  |

| 7614         | High Speed Feature                   |

| 7615         | Send Module                          |

| 7616         | Receive Module                       |

| 7617         | DC Telegraph Interface               |

| 7618         | Automatic Dialing Unit               |

| 7619         | Additional Dialing Position          |

| 7650         | Channel Interface Unit               |

|              |                                      |

| 7700         | Inter-processor Interrupt Feature    |

| 7710         | Direct I/O Bus-Sharing Adapter       |

| 7720         | Multi-Controller Peripheral Switch   |

| 7721         | Manual Control for Peripheral Switch |

|              |                                      |

# SYSTEMS INTERFACE UNITS

| Model Number | Description                                 |

|--------------|---------------------------------------------|

|              |                                             |

| 7900         | Device Subcontroller                        |

| 7901         | Peripheral Equipment Tester                 |

| 7910         | Analog Output Controller                    |

| 7914         | Analog Input Controller                     |

| 7922         | Analog and Digital Adapter                  |

| 79 <b>29</b> | IOP to DIO Adapter                          |

| 7920         | DIO Adapter                                 |

| 7931         | DIO Adapter Expander                        |

| 7950         | 8 Stored Digital Outputs                    |

| 7951         | 16 Digital Inputs                           |

| 7952         | 8 Pulsed Digital Outputs (Quiescent +4 VDC) |

| 7953         | 8 Pulsed Digital Outputs (Quiescent 0 VDC)  |

| 7954         | 8 Relay/Lamp Drivers                        |

| 7969         | Frequency Control Basic                     |

| 7970         | Frequency Source Unit, Manual               |

| 7971         | Program Control Basic                       |

| 7972         | Frequency Source Unit, Programmed           |

# ACCESSORIES

| Model Number | Description                     |

|--------------|---------------------------------|

| 8901         | Cabinet Side Panel              |

| 8902         | Front Door                      |

| 8905         | Ut <b>ili</b> ty T <b>a</b> ble |

| 8910         | 19" Sigma Basic Cabinet         |

| 8920         | 24" Sigma Basic Cabinet         |

"T" SERIES LOGIC MODULES

SECTION III

#### T SERIES LOGIC MODULES

Experience with the successful SDS Sigma computers has shown that at the present state of component development the best performance, coupled with lower costs, is obtained when monolithic DTL (Diode-Transistor Logic) integrated circuit flipflops, inverters, and buffer amplifiers are combined with close tolerance, discrete diode-resistor gates and output pull-up resistors.

Integrated circuits cut costs, save space, improve reliability, and improve performance, by replacing repetitive clusters of transistor circuitry.

Diode gates retain flexibility where needed, in the gating structures, and help provide a very high noise rejection of 1.5 volts.

Discrete pull-up resistors (resistors connected between the output transistor and the DC voltage supply) allow the use of high current drive by keeping most power dissipation outside the IC package.

High current drive makes fan-out large, up to 14 gates per output, and easily permits use of clock frequencies up to 10 Mhz because logic line capacitance can be charged quickly.

All of these circuits are placed on the same size epoxy-glass etched circuit card, 4.5 inches high by 4.75 inches deep. The card has 52 gold-plated connector contacts to maintain circuit accessibility and still provide dense packing.

The cards plug into connectors which have reliable gold-plated, spring-loaded, bifurcated (2-pronged) contacts. Thirty-two modules can be placed side-by-side in 19" wide mounting cases, which are available in a wide variety of fixed-mount and hinged models having either wire-wrap or solder tail back panel pins.

Each mounting case incorporates a ground plane for noise immunity, and includes built-in voltage buses. Ninety-module tilting drawer cases are also offered. Any of the cases can be mounted in one of two types of cabinets which have 19" RETMA rails, doors, AC power wiring, swing-out frames, and optional side panels. a 300 cfm blower is available for cooling. An extender card is provided for troubleshooting.

Jumper wire kits, spooled wire, and wiring tools are available to further simplify mechanical assembly. Blank cards and drilled breadboards with circuit etch are also available.

Further wiring information can be obtained in Section V.

#### GENERAL SPECIFICATIONS

#### SUPPLY VOLTAGES

+4 VDC, + 10%

+8 VDC, + 10%

-8 VDC, + 10%

#### LOGIC LEVELS

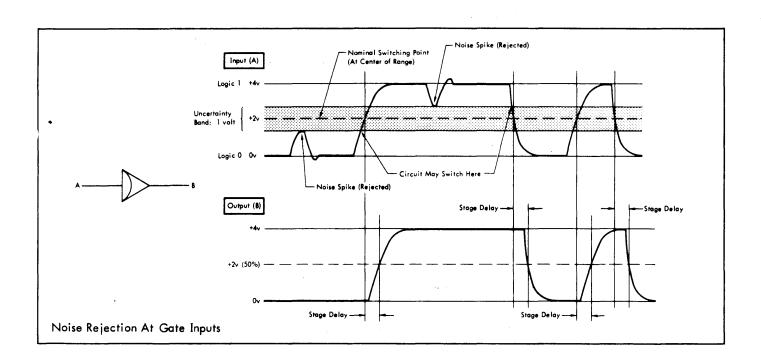

LOGIC "1": +4 VDC, nominal; +3.6 VDC to +10 VDC acceptable as inputs.

+3.6 VDC to +4.4 VDC maximum output variation.

LOGIC "O": 0 VDC nominal; +1.0 to -3 VDC acceptable as inputs.

0 VDC to +0.5 VDC maximum output variation.

#### NOISE THRESHOLDS

At Logic "0" - +1.5 VDC (greater may trigger True)

At Logic "1" - +2.5 VDC (lower may trigger False)

#### LOADING

1 Unit fan-out load is defined as 3.8 ma max., at the conducting logic level (0 VDC).

<u>Input Loading</u>: Any logic input applies 1 Unit Load to the preceding signal source, unless otherwise noted.

Output Loading: Buffer Amplifier, inverter amplifier, or one flip-flop output can drive 14 unit loads. (One flip-flop can be said to drive 28 unit loads, 14 for each output).

When buffer, inverter, or flip-flop outputs are wired together to form a wired logic function, each output attached to the node absorbs 2 unit loads due to the additional pull-up resistor placed at the node.

#### **TIMING**

| Stage Delay:  | Typical | Worst-case |

|---------------|---------|------------|

| Buffered gate | 18 nsec | 30 nsec    |

| Flip-Flop     | 40 nsec | 60 nsec    |

Frequency Range of Clock: DC to 10 Mhz

Minimum Input Timing: Flip-Flop DC inputs (Set or Reset) must be true for at least 40 nsec. AC Inputs (Set or Reset) must be true for 30 nsec. before clock changes from true to false, and 5 nsec thereafter.

Minimum Clock Duration: Clock must be true for 30 nsec., false for 60 nsec. Triggering takes place on falling edge when clock reaches +2 VDC (nominal) switching point.

#### TEMPERATURE

Ambient Operating Temperature: 5'C to 71 C (41'F to 160'F)

Storage Temperature: -55'C to +150'C

Further loading and wiring information can be found in Section V.

#### INTEGRATED CIRCUIT BUILDING BLOCKS

Only 6 basic IC components are used throughout the entire T Series Logic Module line to implement the various active circuits. They are:

| SDS Number | <u>Description</u>           |

|------------|------------------------------|

| 304        | 8-bit Memory Element         |

| 305        | Inverting Amplifier          |

| 306        | Buffer Amplifier             |

| 307        | Flip-Flop                    |

| 308        | Discriminator                |

| 311        | Flip-Flop with Delay Control |

SDS is currently producing a seventh IC circuit, the SDS 309 Buffer Latch, which will be used on newly-designed equipment. No information is available at this time on the SDS 309.

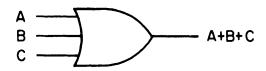

#### IC Diode-Resistor Gating

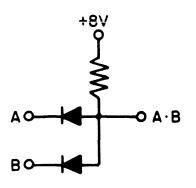

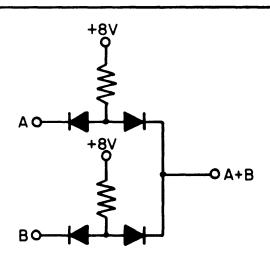

All IC components utilize external diode-resistor input gating when required. The diodes are 1N4154 Silicon diodes, and the gate load resistors are typically 2.2K-ohm, ± 5%, ½-watt film resistors, returned to the +8 VDC power supply voltage. The gating structures are of three types: logical AND, OR, and a logical AND/OR combination:

# LOGICAL-AND -NO ISOLATION

# LOGICAL-AND - WITH ISOLATION

# LOGICAL-OR

# LOGICAL - AND/OR COMBINATION

Note: either symbolic form is correct; the top is preferred.

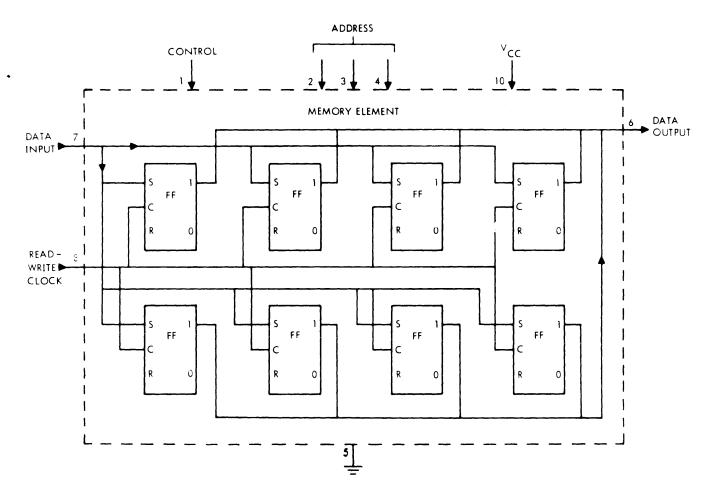

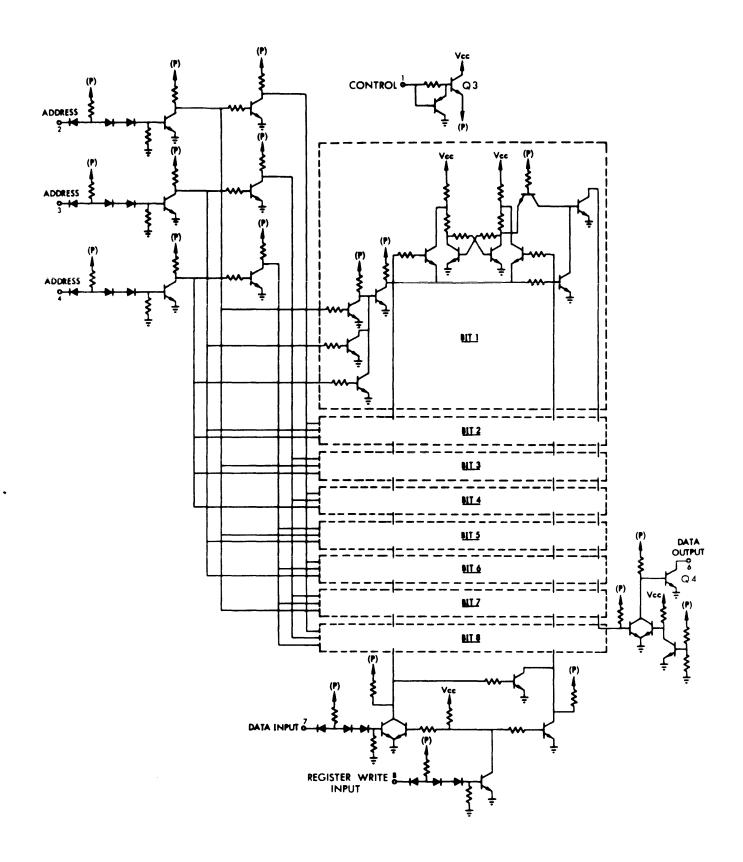

#### SDS 304 8-BIT MEMORY ELEMENT

The SDS 304 Memory Element is the heart of what are referred to as "Fast-Access" or "Scratchpad" memory. This Memory Element consists of 8 bistable multivibrators, control logic, 3-bit address decode logic, and input/output logic within a 10-lead TO-5 can. The circuit is fabricated as a semiconductor monolithic integrated circuit. Each Memory Element can be thought of as 8, 1-bit registers, each register being uniquely addressed by a 3-bit address.

#### SIMPLIFIED LOGIC DIAGRAM

SDS 304 Memory Element, Simplified Diagram

#### THEORY OF OPERATION

The Control Line (pin 1) enables the Memory Element to be either sensed or changed, and is usually a function of another address bit. When this line is +4 VDC, data can be "read" on pin 6 from the flip-flop currently being addressed by the Address Lines, pins 2, 3, & 4.

If the Read/Write Clock (pin 8) Line is also at +4 VDC, the flip-flop currently being addressed will assume the state of the Data Input Line (pin 7).

If the Data Input Line is at +4 VDC, the currently addressed flip-flop will Set. If the Data Input Line is at 0 VDC, the currently addressed flip-flop will Reset. This action occurs only if the Read/Write Clock Line is at +4 VDC.

Therefore, to "read" from the Memory Element, the Control Line must be at +4 VDC, and the Address Lines will be decoded to select the unique flip-flop to be read.

To change a flip-flop within the Memory Element, the Control Line and the Read/Write Clock must be at +4 VDC. The uniquely addressed flip-flop will then assume the state of the Data Input Line.

The Memory Element is volatile since the removal of DC power will destroy the contents of the 8, 1-bit registers. When power is applied, the 8 flip-flops may assume either a Set or Reset condition.

#### APPLICATION

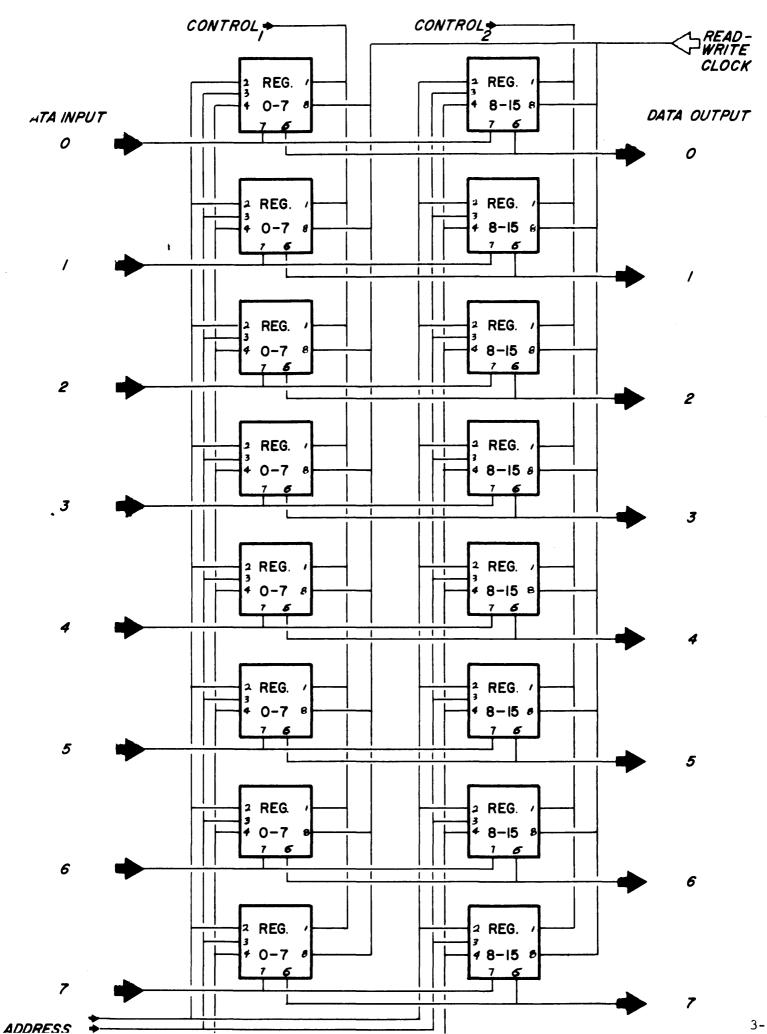

The SDS 304 is implemented to form "Fast-Access" registers of various lengths, and never as a stand-alone flip-flop. The diagram on the next page represents how 16 of the SDS 304 Memory Elements are used to form 16 8-bit registers which can operate with parallel input/output data.

In this application, the Control Lines are common to eight SDS 304 Memory Elements, and are controlled by the most significant address bit of a 4-bit address field. The 3 least significant bits of the address field are common to all 16 of the Memory Elements. Control Line 1 is equal to the address binary weight of  $2^3$ , and Control Line 2 is equal to  $2^3$ . Pin 2 of all cans is equal to the binary weight  $2^2$ ; pin 3 of all cans is equal to  $2^1$ , and pin 4 of all cans is equal to  $2^0$ . Thus, when the address field is equal to 0000, Control Line 1 will be true, and will enable the left-hand set of cans. The address lines, pins 2, 3, & 4 will then select one flip-flop from each of these 8 cans, allowing 8 bits of data to be read from pin 5 of these 8 cans in parallel.

The Data Output Lines (pin 6) of the left-hand set of cans are tied to the same lines from the right-hand set of cans, forming a wired "AND". All unselected cans will have a "1" output.

As the address field changes through its 4-bit structure, it can be seen that addresses in the range 0000 through 0111 will cause data to be accessed from the left-hand set of cans since Control Line 1 will be true. Thus, the left-hand set of cans could be referred to as registers 0-7. When the address swings into the range 1000 through 1111, Control Line 2 will be true, and the right-hand set of cans will be accessed. These could then be referred to as registers 8-15.

3-11

SDS304 Memory Element Schematic Diagram

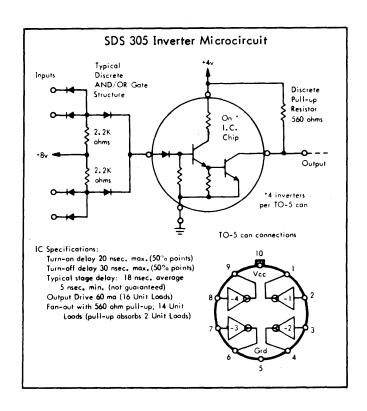

#### SDS 305 INVERTER

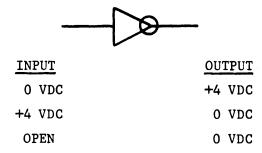

The SDS 305 contains 4 microcircuit Inverter Amplifiers housed in a 10-lead TO-5 can. The circuit is fabricated as a semiconductor monolithic integrated circuit. Each Inverter circuit presents the logical inversion of the input signal at the output. The Inverters will drive, and must be driven by, dioderesistor AND/OR gates.

#### LOGIC SYMBOL (1 of 4)

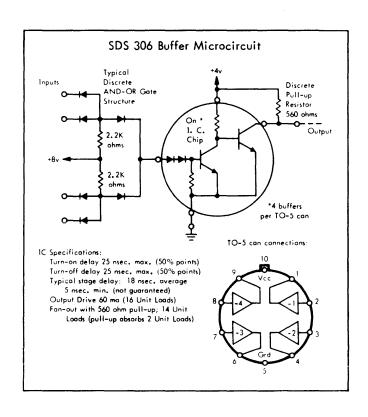

#### SDS 306 BUFFER

The SDS 306 contains 4 microcircuit Buffer Amplifiers housed in a 10-lead TO-5 can. The circuit is fabricated as a semiconductor monolithic integrated circuit. Each Buffer presents the logical equivalent of the input signal at the output, current-amplified. The Buffer will drive, and must be driven by, diode-resistor AND/OR gates.

### LOGIC SYMBOL (1 of 4)

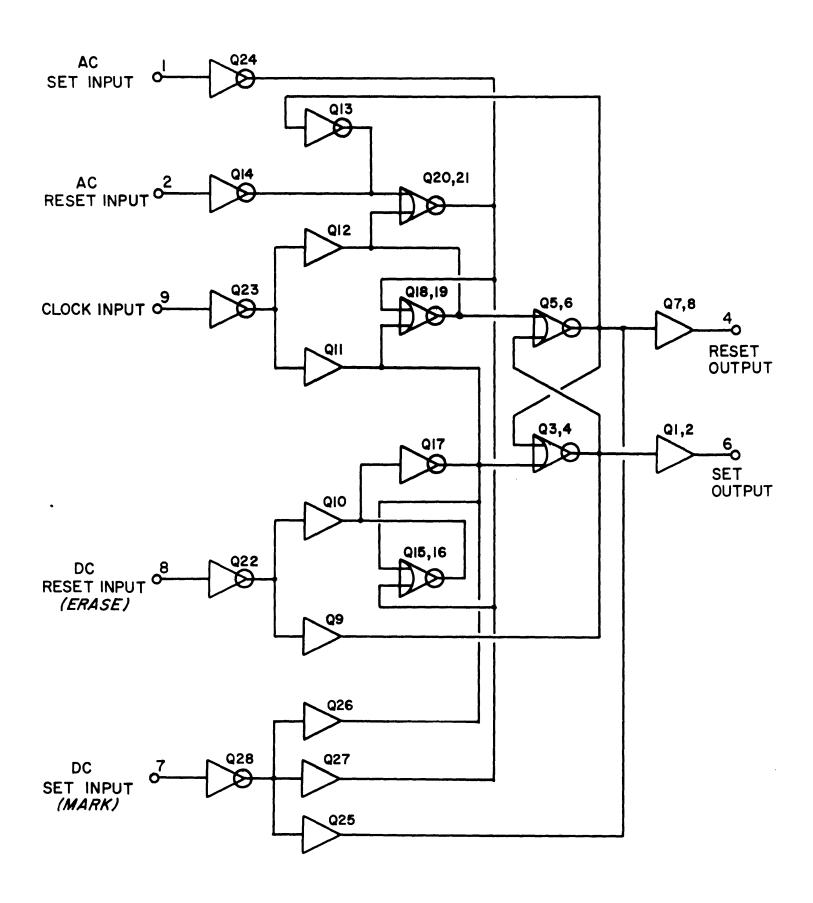

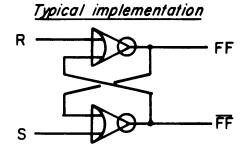

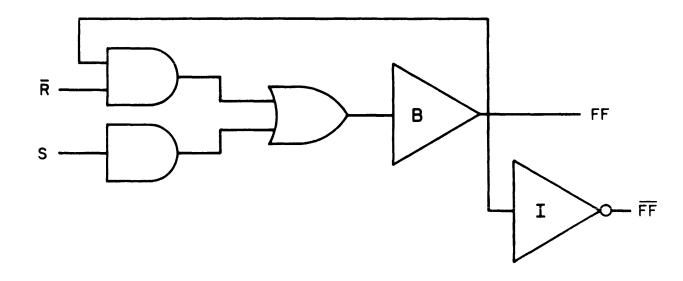

#### SDS 307 FLIP-FLOP

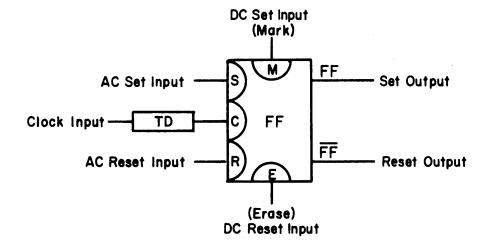

The SDS 307 is a microcircuit flip-flop housed in a 10-lead TO-5 can. The circuit is fabricated as a semiconductor monolithic integrated circuit. The SDS 307 is capable of being used as a DC flip-flop (no clock), an AC flip-flop (clocked), or both.

#### LOGIC SYMBOL

#### CIRCUIT DESCRIPTION

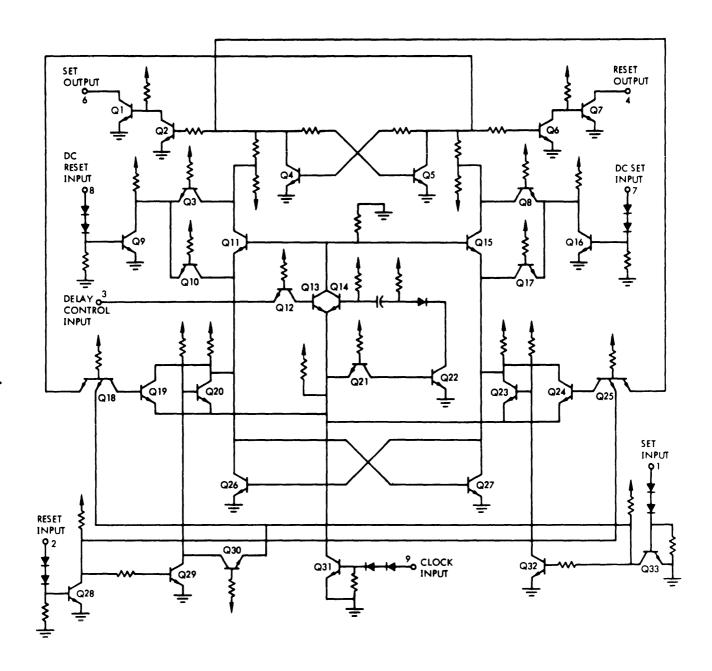

The operation can best be described by the logic diagram shown on the next page, which breaks the flip-flop into various subcircuits. The circuitry consists of 28 transistors, 36 resistors, and 10 diodes.

As can be seen from the logic diagram, the flip-flop is essentially a structure of NOR elements.

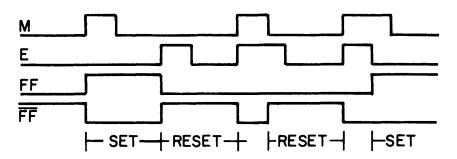

The flip-flop has a pair of DC inputs (called MARK for DC Set Input and ERASE for DC Reset Input. MARK is also referred in the equations as the FORCE input.) which can be used to make the flip-flop behave like a simple DC flip-flop. Their primary use is to override the AC Set and Reset Inputs, so that the flip-flop can be preset or cleared between clock trailing edges.

SIMPLIFIED LOGIC DIAGRAM, SDS 307

When the MARK input becomes True, the Set Output becomes True and stays True regardless of the state of the MARK input, and the Reset Output becomes False. When the ERASE input becomes True, the Reset Output becomes True and stays True, and the Set Output becomes False. If both DC inputs become True simultaneously, both Set and Reset Outputs will become False, and will stay False as long as both DC inputs are True. If one DC input then becomes False the flip-flop assumes the state determined by the other input, providing it remains True at least 40 nsec.

The gating of the flip-flop inputs is external to the IC, just as with the Buffer and Inverter IC's. The output pull-up resistor is also external to the IC. Gates are normally placed on the same module as the flip-flop IC and are not available at one of the 52 connector pins since the wiring from the gate output to the flip-flop input is via etch. On many modules the AC Reset Input is wired True by connecting the AC Reset input through a resistor to +8 VDC. This eliminates external wiring to the AC Reset Input in many applications. It is possible to wire the SDS 307 in this fashion since the AC Set Input always overrides the AC Reset Input if both inputs are simultaneously True.

The Set Override mechanism and the other SDS 307 features can be understood by an inspection of the logic diagram. The flip-flop is a dual-rank configuration of NOR elements. The second rank (Q3, Q4, Q5, and Q6) is a simple NOR flip-flop, coupled to the output pins through buffers that each provide 60 ma (16 unit loads), normally connected to external pull-up resistors.

The first rank (Q15 through Q21) consists of two flip-flops, one for Set (Q18-Q21), and one for Reset (Q15-Q17). The two internal lines which couple the first rank to the second rank also connect to the Clock Input logic. When the Clock goes True, these two lines are clamped to ground, isolating the first rank from the second rank, so that the second rank holds its original state. During this time, while Clock is True, the Set and Reset flip-flops are primed to the states of the AC Set and Reset Inputs. When the Clock Input goes False (Trailing Edge) they assume the new states and regain control of the second rank flip-flop. Note that the outputs change to the new state on the Clock Trailing Edge. AC Inputs must be steady for 30 nsec before the Clock falls, and for 5 nsec after the Clock falls to permit the first rank flip-flops to stabilize.

The Set Inverter (Q24) always overrides inputs to the Reset Inverter (Q14) when the AC Set Input is True because it is coupled to an output of the Set flip-flop, forming a wired AND, while the Reset Inverter is coupled to an input of the Set flip-flop. This is the basis for the Set Override feature.

The second rank output is fed back to the first rank so that outputs remain unchanged when clock pulses occur and both AC inputs are False.

Note that the DC Set (MARK) and DC Reset (ERASE) inputs essentially bypass the first rank, activating the second rank directly, thus overriding the entire AC Set-Reset structure.

SDS307 Flip-Flop Schematic Diagram

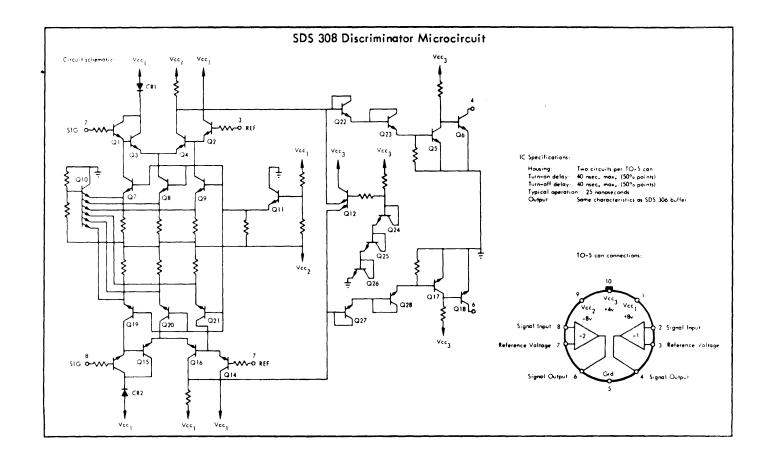

#### SDS 308 DISCRIMINATOR

The SDS 308 comprises 2 microcircuit discriminators housed in a 10-lead TO-5 can. The circuit is fabricated as a semiconductor monolithic integrated circuit. It forms an integral part of Cable Receiver modules (AT10, AT11). Each discriminator circuit produces a logical "1" (+4 VDC) at the output if the input signal is greater than the Reference Voltage. On the AT10 and AT11 modules, the Reference Voltage (RV) is fixed at approx. +0.54 VDC. If the input is less than the RV, or is open (floating) the output will be a logical "0" (0 VDC).

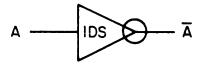

#### LOGIC SYMBOL (1 of 2)

| INPUT | OUTPUT |

|-------|--------|

| > RV  | +4 VDC |

| ≤ RV  | O VDC  |

| OPEN  | 0 VDC  |

#### APPLICATION

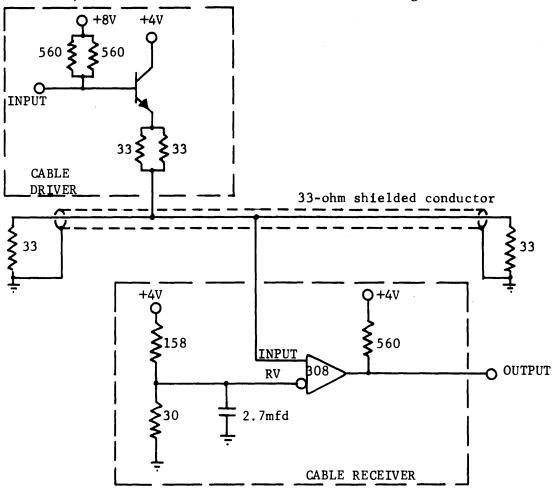

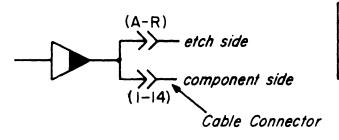

As stated before, the SDS 308 was designed primarilly to be used as part of Cable Receiver circuits, and are part of the AT10 and AT11 Cable Receiver modules. In this application, the input signal to the SDS 308 comes from a cable connector, 33-ohm cable, and a Cable Driver module in the following manner:

The input to the SDS 308 represents a high impedance to the line, causing a load of approx. 50 microamps to be absorbed. One Cable Driver can drive up to 25 Cable Receivers, however, the limit of 200 feet lengths for the 33-ohm cable normally is reached before this number of Cable Receivers can be connected to the cable.

The Cable Driver output is +2 VDC (logical "1") and 0 VDC (logical "0"). When more than 1 Cable Driver is connected to a line, the voltage on the line raises exponentially due to the decrease in emitter-follower series resistance versus the 33-ohm termination loads; this does not affect the Cable Receiver(s) performance, however, if this line is driving other, non-standard, logic, the rising line potential may be intolerable. The maximum line potential would be the collector potential of the Cable Driver emitter-follower (+4 VDC).

#### SDS 311 FLIP-FLOP

The SDS 311 is basically the same as the SDS 307, with the exception of the Delay Control Input, which is connected to pin 3 of the TO-5 can. This input provides a delayed Set and Reset Output of 80 to 200 nsec, after the fall of the Clock Input. This feature is only functional if the Delay Control Input (pin 3) is grounded. If left ungrounded, the SDS 311 operates identically to the SDS 307. The Delay Control Input affects only the Clock Input's negative transistion.

DC Set (MARK) and Reset (ERASE) inputs are unaffected. The SDS 311 is an integral part of modules FT30, FT31, and FT32, and is used for serial register operations.

#### LOGIC SYMBOL

SDS311 Flip-Flop Schematic Diagram

LOGIC Symbology

SECTION IV

#### SIGMA LOGIC SYMBOLOGY

Recently, the company decided to use logic symbology defined by the Defense Department, MIL-STD-806B, with some minor deviations. The implementation of MIL-STD-806B logic symbology affects logic diagrams for units currently undergoing documentation, and will not be retroactive.

Prior to this recent decision, logic diagrams produced by Technical Publications as part of their Technical Manuals have been drawn to a standard called ASA Y32.16-1965 which conformed roughly to what was to have been line printer-drawn diagrams. The idea of line printer-generated diagrams was short-lived, and no effort is being made to pursue the idea. Consequently, there are manuals in existence which have logic diagrams drawn to that standard. No attempt will be made here to explain that type of logic symbology since those manuals include an adequate explanation.

When drawings first started appearing for Sigma equipment which were drawn by the designers and engineers they conformed to the standard set up by the company for the older 9-Series product line, and is generally referred to as "9-Series Logic Symbology". Training adopted this standard partly because the designers and engineers adopted it, but mainly because Training felt that the 9-Series symbology was adequate for expressing Sigma logic implementation with only a few additional symbols, and that Customer Engineers who had worked on the 9-Series equipment would find it easier to learn Sigma equipment using familiar symbology. Further, some of the peripheral devices developed for Sigma utilized some 9-Series hardware, therefore, it was thought desireable to keep the supporting documentation compatible.

It is obvious that in learning and troubleshooting Sigma equipment you are going to be faced with at least 2 different logic symbology standards, the older 9-Series Symbology and MIL-STD-806B Symbology, until revisions and updating of material causes the 9-Series Symbology to phase out.

In the following pages are representative diagrams for both 9-Series and MIL-STD-806B Symbology, presented in two separate parts with an explanation as to their use (when necessary) and conventions. These two parts of this section should be considered as a reference area when you are in doubt as to the interpretation of a logic symbol; you are not expected to study these symbols at this time and commit them to memory.

Before you look the symbols over, keep in mind that the emphasis placed on logic diagrams as a maintenance aid only survives in isolated areas within the total Sigma Product Line, usually restricted to certain peripheral devices where the number of logic structures is small.

Logic diagrams, because they carry a strong visual impact, are drawn primarily for use in training, whether they appear in Technical Manuals or in Training Documents, and it is for this use, while you are learning the equipment, that familiarity with logic symbols really is important.

#### 9-Series Symbology

In applying 9-Series Symbology to Sigma circuit elements, many of the conventions have been retained as to the symbol shapes. Since the Sigma modules do have circuits not found in the 9-Series equipment, some new symbols have been added.

Each of the symbols is defined by a Boolean truth table when applicable. Sigma uses "positive logic", which means that a logic "1" equals a relatively high level (+4VDC, unless otherwise noted), and a logic "0" equals a relatively low level (0 VDC).

9-Series Symbology is based on a relationship between symbol shape and the type of hardware curcuitry it is trying to represent. This characteristic will be important when you are trying to see the differences between the 9-Series Symbology and MIL-STD-806B Symbology.

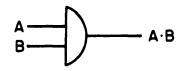

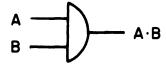

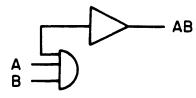

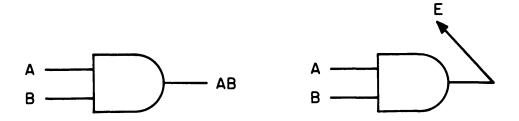

### AND GATE

(no isolation diode)

(with isolation diode)

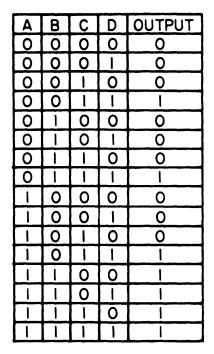

| Α | В | OUTPUT |  |  |

|---|---|--------|--|--|

| 0 | 0 | 0      |  |  |

| 0 |   | 0      |  |  |

|   | 0 | 0      |  |  |

|   |   |        |  |  |

note: an open input has same effect as +4VDC

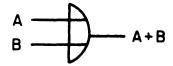

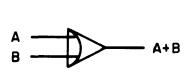

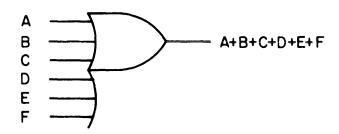

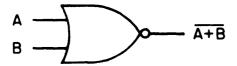

### INCLUSIVE OR GATE

| Α | В | OUTPUT |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | - |        |

|   | 0 |        |

| ı | 1 | 1      |

note: an open input has same effect as +4VDC

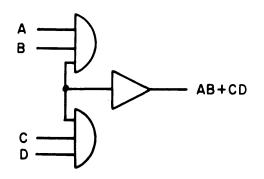

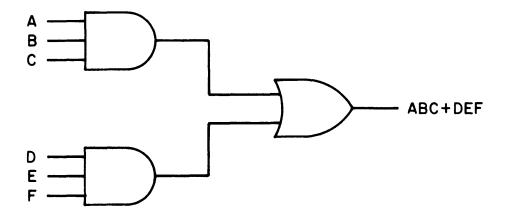

### AND/OR COMBINATION

(identical circuits)

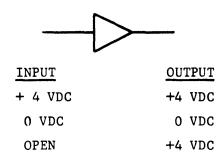

### BUFFER

| INPUT | OUTPUT |

|-------|--------|

| 0     | 0      |

|       |        |

| OPEN  |        |

L(no pull-up resistor provided for output transistor)

# <u>BAND</u>

(input to buffer not available at connector, and few inputs)

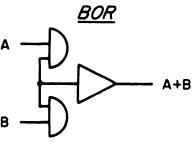

### BAND/BOR

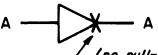

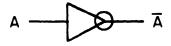

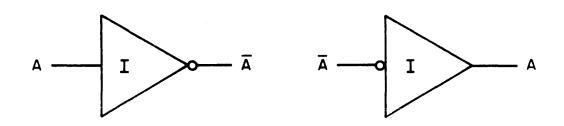

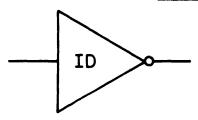

# INVERTER

| INPUT | OUTPUT |

|-------|--------|

| 0     |        |

|       | 0      |

| OPEN  | 0      |

| Α |  | Ā |

|---|--|---|

|---|--|---|

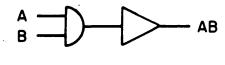

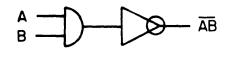

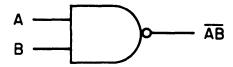

# <u>NAND</u>

# NAND/NOR

# WIRED OUTPUT — EXAMPLES

### CLOCK DRIVER

| INPUT | OUTPUT |

|-------|--------|

| OV    | OV     |

| +4V   | +4V    |

| OPEN  | +4V    |

### <u> 2 - INPUT</u>

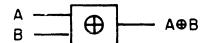

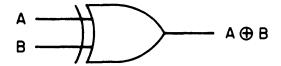

# EXCLUSIVE OR GATE

| Α | В | OUTPUT |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | İ | 1      |

| - | 0 |        |

| - | 1 | 0      |

(Explicit)

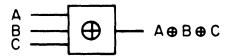

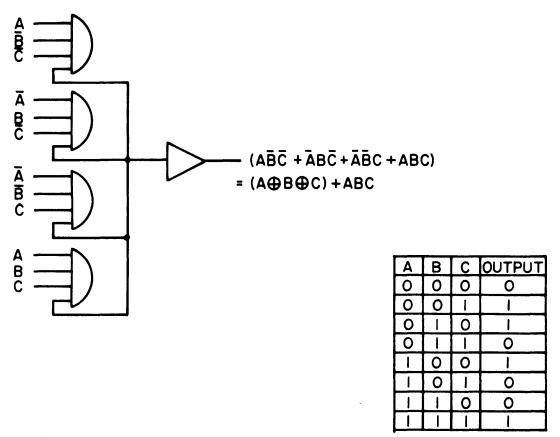

### 3-INPUT

| Α | В | С | OUTPUT |

|---|---|---|--------|

| 0 | 0 | 0 | 0      |

| 0 | 0 | _ |        |

| 0 |   | 0 |        |

| 0 |   |   | 0      |

|   | 0 | 0 |        |

|   | 0 |   | 0      |

| 1 |   | 0 | 0      |

| 1 |   |   | 0      |

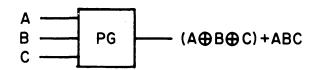

### (Implicit)

### (Explicit)

Note: the Parity Generator has a true output when an odd number of trues are present at the inputs.

# CABLE DRIVER

| INPUT | OUTPUT |

|-------|--------|

| +4V   | +2V    |

| OV    | OPEN   |

| OPEN  | +2V    |

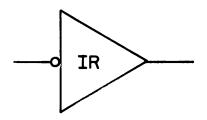

### CABLE RECEIVER

| INPUT | OUTPUT |   |

|-------|--------|---|

| OV    | OV     |   |

| +2V   | +4V    | * |

| OPEN  | OV     |   |

\* Input threshold is +0.54VDC

### 8-VOLT INTERFACE DRIVER

| INPUT | OUTPUT |

|-------|--------|

| OV    | +8V    |

| +4V   | OV     |

| OPEN  | +8V    |

# 8-VOLT INTERFACE RECEIVER

| INPUT | OUTPUT |   |

|-------|--------|---|

| OV    | +4V    |   |

| +8V   | OV     | * |

| OPEN  | OV     |   |

# Input threshold is + 4VDC

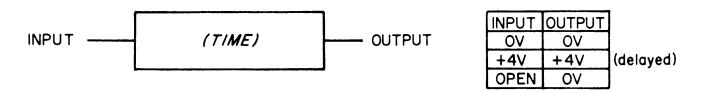

| INPUT | OUTPUT |           |

|-------|--------|-----------|

| OV    | -47    |           |

| +4V   | +4V    | (delayed) |

| OPEN  | -4V    |           |

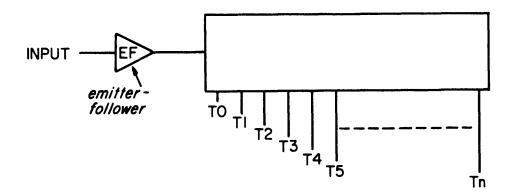

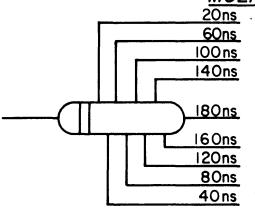

The Multi-Tap Delay Lines are tapped at fixed increments for their entire length, the increment being 20 nsec for the 600 nsec DT11 module, and 10 nsec for the 300 nsec DT14 module. The voltage levels at the delay line taps are nominally +4 VDC (Logic "1"), and -4 VDC (Logic "0"). Consequently, they require special sensor circuits to operate from the taps which have a high impedance input, to avoid loading down the delay line. Several sensor circuits may be connected to a tap, however, the interconnecting wire should be as short as possible to minimize the capacitive load on the delay line.

The Emitter-follower circuit at the input accepts 0 VDC to +4 VDC excursions and drives the delay line with +4 VDC to -4 VDC excursions. The Emitter-follower is normally gated by an AND/OR COMBINATION input gate.

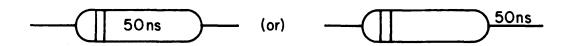

### DELAY ELEMENT

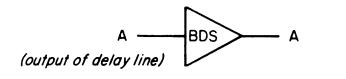

### BUFFER DELAY LINE SENSOR

| INPUT | OUTPUT |   |

|-------|--------|---|

| -4V   | OV     |   |

| +4V   | +4V    | * |

| OPEN  | +4V    |   |

# Input threshold is OVDC

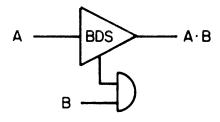

### GATED BUFFER DELAY LINE SENSOR

| Α  | В  | OUTPUT |

|----|----|--------|

| -4 | OV | OV     |

| -4 | +4 | OV     |

| +4 | OV | OV     |

| +4 | +4 | +4٧    |

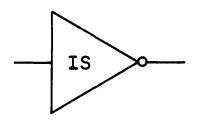

### INVERTER DELAY LINE SENSOR

| INPUT | OUTPUT |   |

|-------|--------|---|

| -4V   | +4V    |   |

| +4V   | OV     | 4 |

| OPEN  | OV     |   |

# Input threshold is OVDC

Note: IDS circuits are not gated.

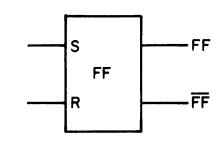

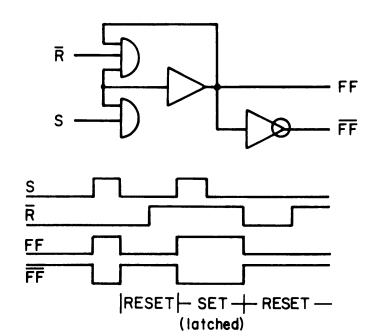

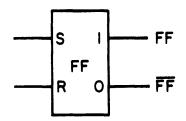

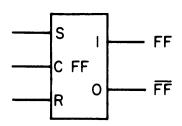

#### DC FLIP-FLOPS

S = DC Set Input

R = DC Reset Input

FF = Set Output

FF = Reset Output

DC Flip-Flops may also be implemented and shown as BUFFER LATCH circuits:

S = Set Input

R = Latch Control

FF = Set Output

FF = Reset Output

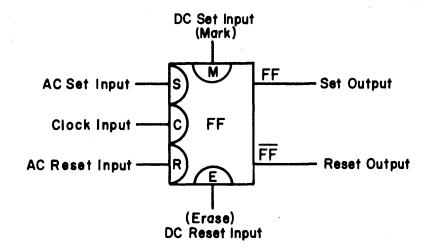

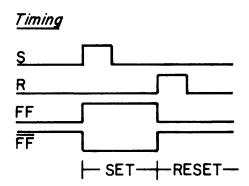

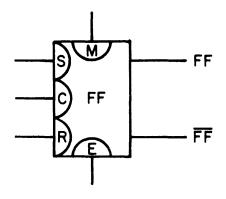

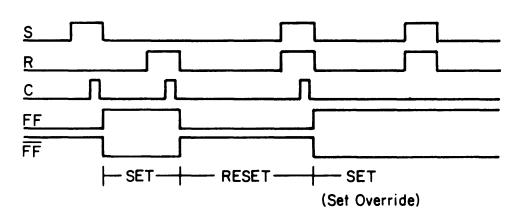

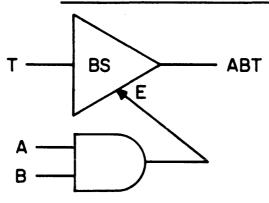

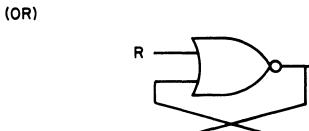

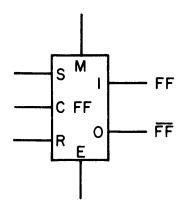

### AC FLIP-FLOP (using SDS 307 or 311 IC)

S = AC Set Input

C = AC Clock Input

R = AC Reset Input

M = DC Set Input - MARK (FORCE)

E = DC Reset Input - ERASE

FF = Set Output

FF = Reset Output

### AC MODE TIMING

Note: An open input is a True input.

### DC MODE TIMING

### OTHER SYMBOLS

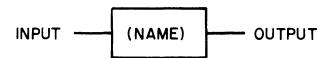

The symbology for other (specialized) logic or non-logic functions are usually as a rectangle with an associative mnemonic (name) within the rectangle:

#### MIL-STD-806B Symbology

MIL-STD-806B logic symbology is an attempt to standardize all logic diagrams used by the Defense Department. Their reasons for creating such a standard is obvious, since they purchase equipment from many different manufacturers.

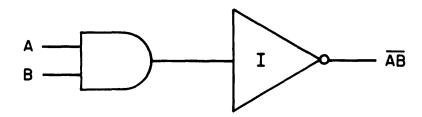

This standard is essentially <u>hardware-independent</u> and <u>function-oriented</u>. This means that the symbology attempts to represent Boolean functions rather than trying to differentiate between different types of circuitry, as is done in the 9-Series. No difference in symbology exists, for instance, between a passive (diode-resistor) circuit which produces an AND function, and an active circuit (diode-resistor-transistor) which also produces an AND function. The essential information is that an AND function is produced at a certain point.

MIL-STD-806B is also logic convention-independent in that the standard applies to both "positive" and "negative" logic conventions. SDS uses the positive logic convention as mentioned earlier.

The symbols available in MIL-STD-806B are capable of representing the bulk of logic functions found in most digital systems, however, most companies have found a need to modify or add some symbols to represent proprietary logic functions.

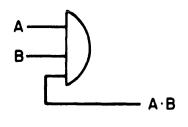

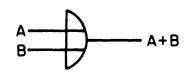

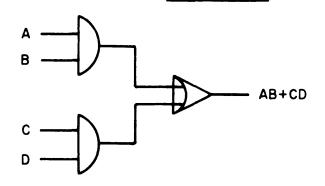

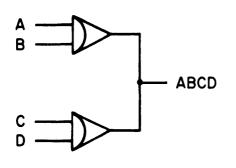

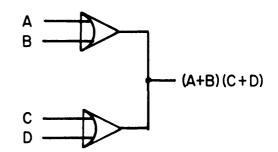

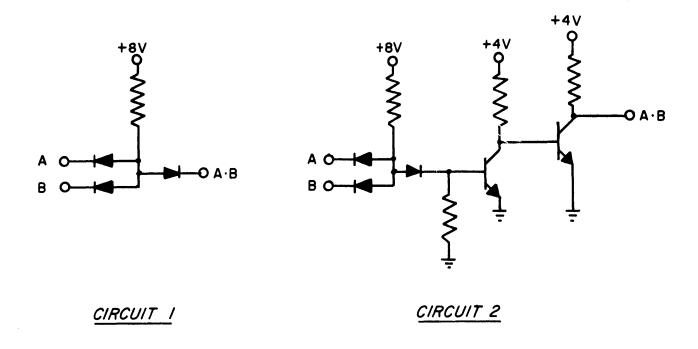

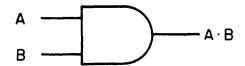

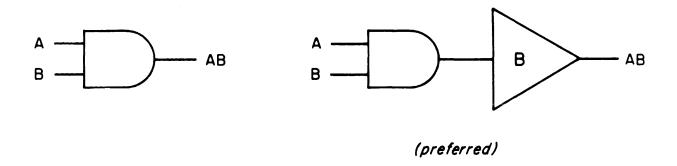

#### Hardware-Indiependence

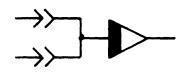

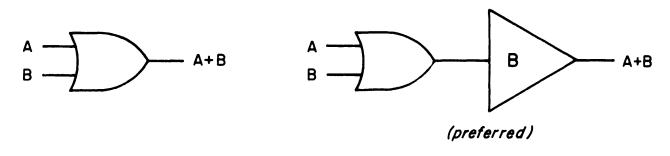

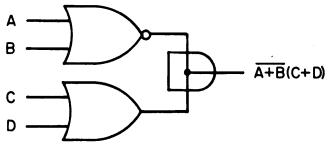

There are many ways to implement any given Boolean function. A simple AND gate could be implemented using either just dioderesistor logic, or dioderesistor gating feeding transistor circuitry for buffering and current gain. The resultant Boolean function is the same in both cases. Thus:

are both AND gates, capable of being represented by the same logic symbol:

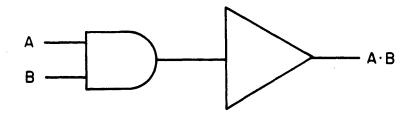

unless, in circuit #2, the transistor logic section was located on a different module or on the same module with unique pin numbers. In this case the logic symbology could be shown as:

so that module and pin information could be called out in detailled logic diagrams.

The basic assumption in representing functions rather than circuitry is that in troubleshooting it is more important to understand and verify the relationship between input and output signal(s) than to know what kind of circuitry is involved.

This assumption is argumentative in that active elements (transistor logic) insert stage delays (typically 18 nanoseconds in Sigma) whereas passive elements (diode-resistor logic) do not insert any significant delay. This difference could be important in high-speed logic analysis. This can be overcome, however, by representing active elements which have input gating as two separate symbols as shown above.

The following pages reflect the logic symbols used in MIL-STD-806B for the various Boolean functions. No attempt is made to analyze these symbols in the detail used by the actual MIL-STD-806B document. Truth tables are not shown, but can be related to those truth tables shown for the 9-Series symbols.

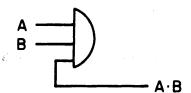

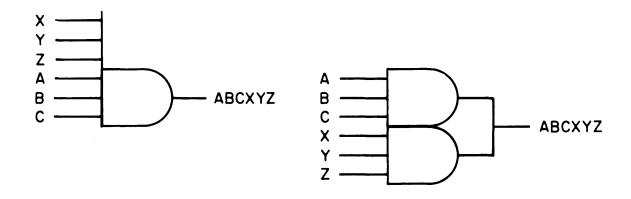

### AND GATE

"E" means that the output of this circuit is an extension to the input of another circuit at some point other than its "normal" input.

"R" means that an output resistor is not supplied as part of the etch circuitry, and must be supplied externally.

EXTENDED INPUTS

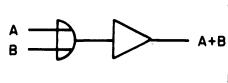

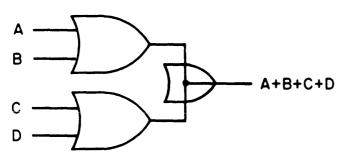

# INCLUSIVE-OR GATE

EXTENDED INPUTS

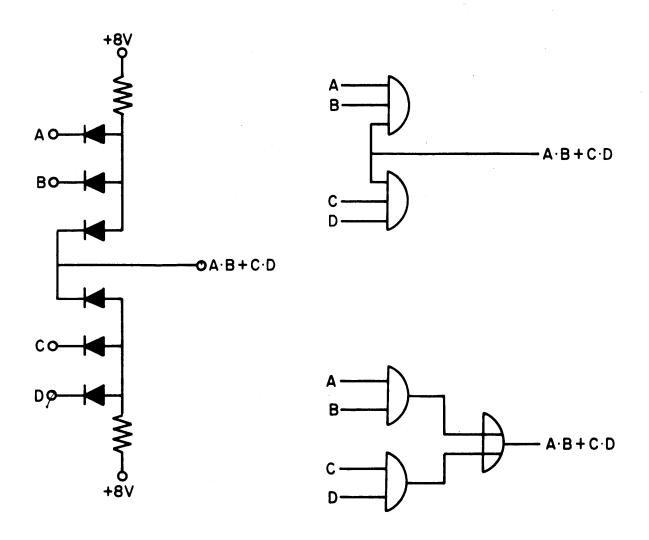

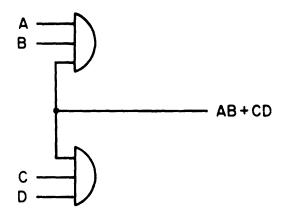

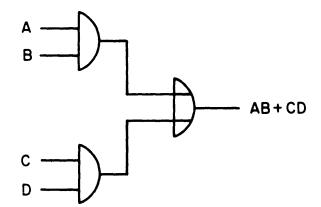

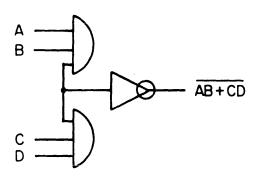

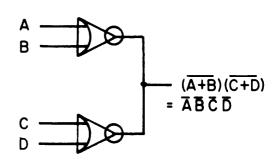

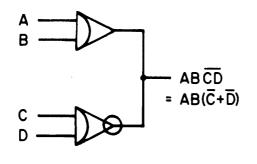

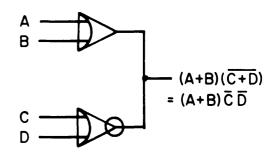

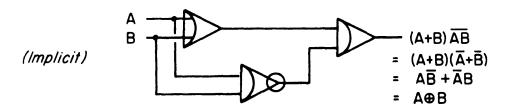

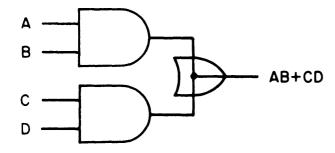

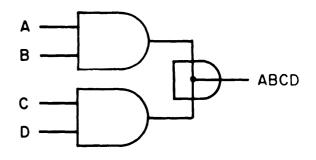

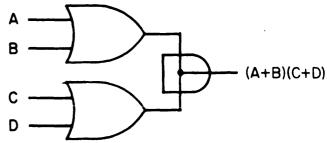

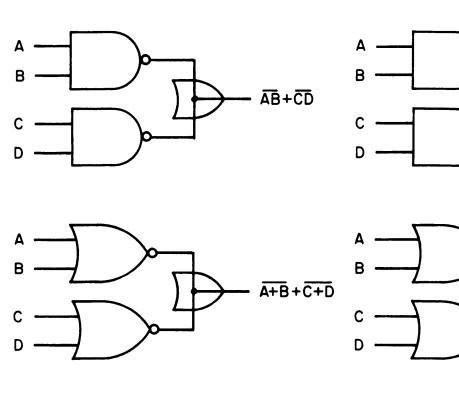

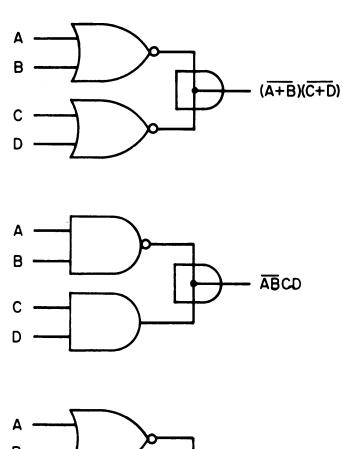

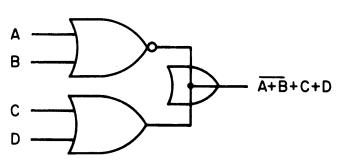

### AND/OR COMBINATION

# EXCLUSIVE - OR

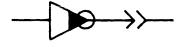

### **BUFFER**

"O" symbol indicates a logic "O" (OVDC), its absence indicates a logic "I" (+4VDC)

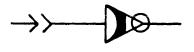

### *INVERTER*

# BAND

### (identical circuits)

### (identical circuits)

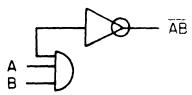

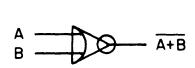

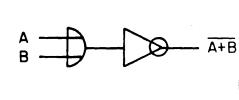

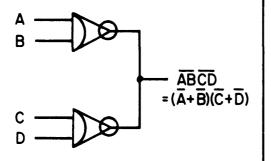

# NAND

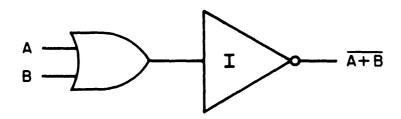

# <u>NOR</u>

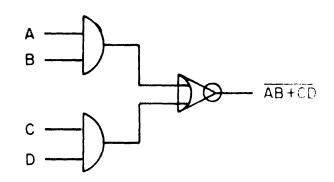

# WIRED OUTPUTS

AB+CD

- AB CD

# CLOCK DRIVER

# CABLE DRIVER

# CABLE RECEIVER

# 8-VOLT INTERFACE DRIVER

### 8-VOLT INTERFACE RECEIVER

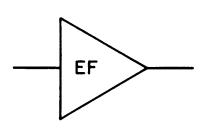

# EMITTER FOLLOWER

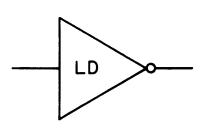

# LAMP DRIVER

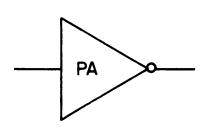

# PREAMPLIFIER

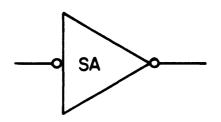

### SENSE AMPLIFIER

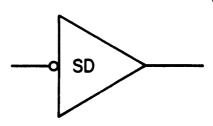

### SENSE DISCRIMINATOR

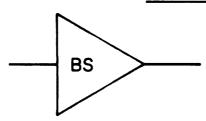

### BUFFER DELAY LINE SENSOR

### GATED BUFFER DELAY LINE SENSOR

### INVERTER DELAY LINE SENSOR

# MULTI-TAP DELAY LINE

### DELAY ELEMENT

# DC FLIP-FLOPS

## BUFFER LATCH

- FF

# AC FLIP-FLOPS

(or)

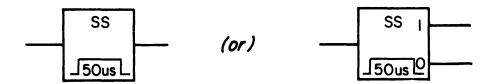

## SINGLE-SHOT

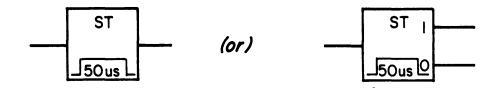

# SCHMITT TRIGGER

## OTHER SYMBOLS

LOGIC IMPLEMENTATION

**SECTION V**

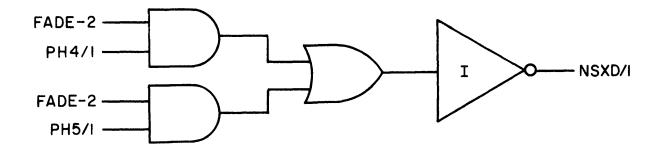

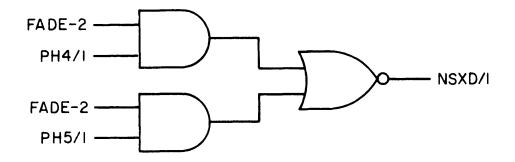

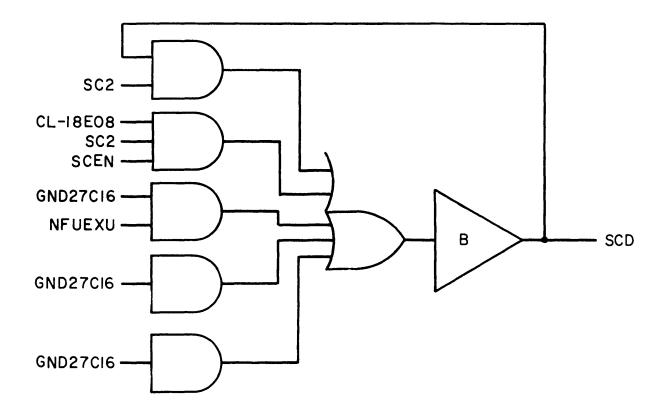

Through the Automated Logic System, used in the Sigma product development, SDS shifted the emphasis away from logic diagrams as a source for troubleshooting documentation and concentrated rather on the use of logic equations.

Using logic equations in lieu of diagrams is not a new idea in the industry. Other companies have been operating under this concept for years

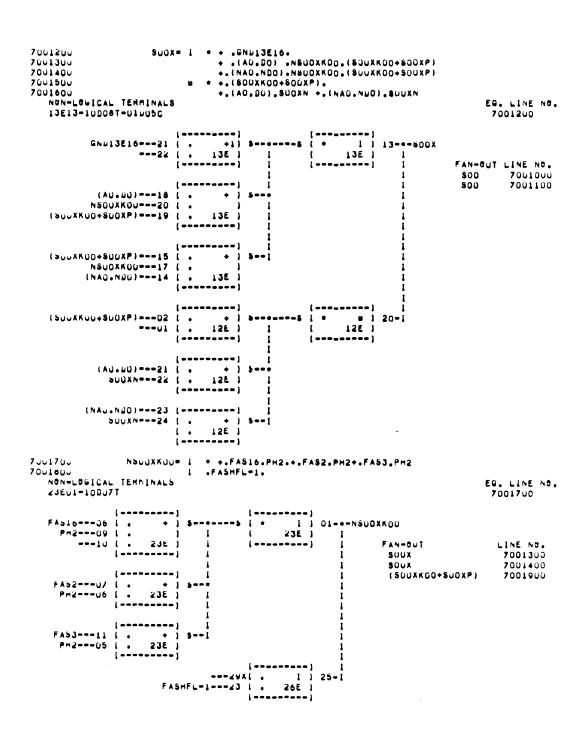

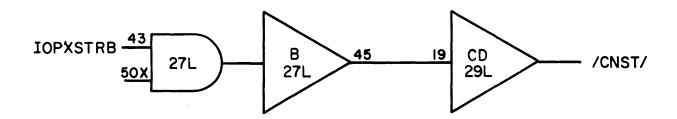

One of the plans for the Automated Logic System was to produce automated logic diagrams from the same program (LOTRAN) that produced the equations. The idea was to use the automated (implemented) equations as an input to a routine which would convert the equation format into a diagram format suitable for line printer output. The diagrams would use the standard line printer character set. The following page contains an example of this type of print out.

In the print out, all logic symbols are blocks. The logic function is denoted by an appropriate tag within the block, along with module location data. Pin numbers are shown, as well as the amount of loading (number of circuits being driven by an element).

The idea of automated logic diagrams was enormously appealing, since it would reduce the time needed to draw the diagram, and also would produce a quick, simple method of updating and correcting diagrams. Theoretically, the diagrams would also be more accurate.

Three factors were subsequently introduced which caused this idea to be abandoned, at least on a widespread basis. First, the print out itself proved to be inadequate in that the use of standard

Automated Logic Diagram - Sample

line printer characters created confusion in many complex logic structures. An example is the use of the character "I" to indicate an inverting function within a block, and also used as a means of drawing vertical lines outside of a block. Secondly, when logic structures are reduced to blocks one of the most valuable characteristics of a logic diagram is negated; the association of symbol shapes with logic functions. Lastly, reproduction of the print outs proved to be generally poor unless the line printer ribbon was changed frequently and the printer mechanism kept in optimum operating condition.

Because of these drawbacks, engineering decided to cancel the project. The program, however, is still existent, and some departments are using the print outs for internal use. No mass production of these diagrams are currently in progress, nor is there any likelihood that this project will be reinstituted at some later time. Further, hand-drawn logic diagrams will not be available for trouble-shooting as part of the standard equipment documentation.

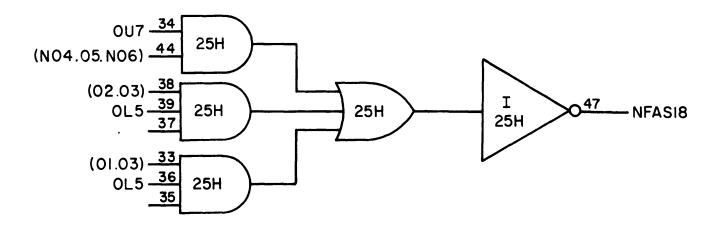

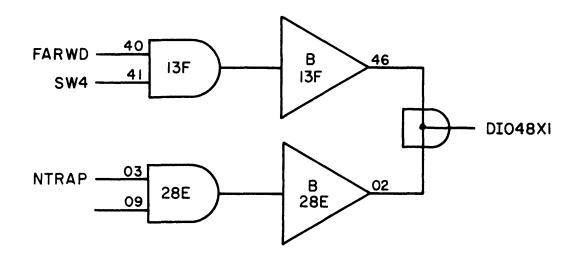

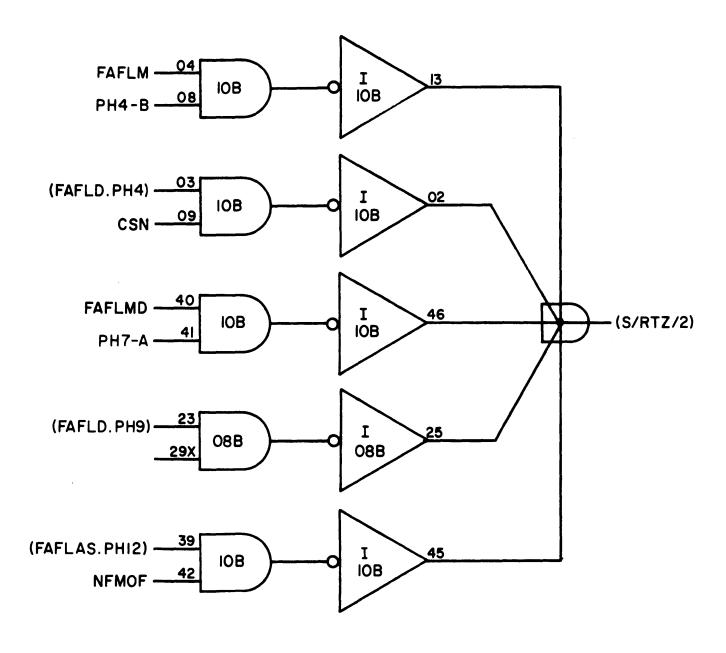

You will, however, be exposed to some "unofficially" drawn logic diagrams, either in a simplified manner, or completely implemented. These diagrams are being used in Technical Manuals and Training documents to clarify logic structures where necessary.

The company's decision to have Test and Maintenance personnel rely heavily on the use of logic equations for troubleshooting has been met by generally wide acceptance. Equations are easier to update, consume less space, and contain the same information as logic diagrams, except for forward references. On very large logic structures, such as found in a central processor, the equations represent a much more usable document than diagrams since they are much easier to work with than a large, combersome set of logic diagrams which would fill many pages.

Those who are used to troubleshooting with diagrams are the most resistive to working with equations. This is understandable. However, after becoming familiar with how to read and use the logic equations, they frequently find that equations are just as meaningful as the diagrams. Some logic structures, however, are very complex, and a logic diagram does aid in understanding these complex networks. In the electro-mechanical area, where mechanics are controlled by logic circuits, diagrams are useful. In core memory, where many non-logical functions are performed, diagrams are useful. You will find that some logic diagrams have been generated by either Technical Publications or Technical Training to assist in the understanding of certain structures in these areas.

Whether you prefer to use equations or diagrams is really a moot point since diagrams are not officially available. The ability to read and use the logic equations as published by SDS is the basic ability you must acquire to maintain and understand Sigma equipment. This ability overshadows everything else in importance, since without it you cannot effectively perform your job.

The following information relates to how the Automated Logic System works, how logic equations are produced, as well as wire lists, what they say, and how to use them in maintaining Sigma equipment. This information is very important to you and should be studied carefully.

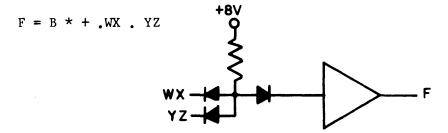

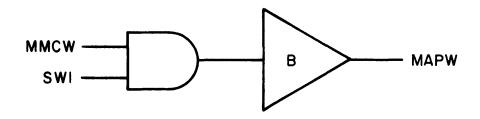

The symbol "B" to the right of the equality is a standard symbol for a Buffer Amplifier. This symbol is called an "Element Designator" and designates what kind of circuit is driving the function, F. Thus, a Buffer Amplifier is the hardware element being used to generate the function, F. Because F is an output logic term, "B" is an output Element Designator.

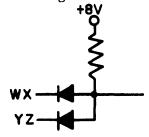

The two input terms, WX and YZ, are preceded by dots, or "period" symbols which indicate that WX is an input to an AND-facing diode, and YZ is also an input to an AND-facing diode. Further, it implies that WX and YZ are ANDed together. Schematically:

Since the AND symbols (.) precede the input terms in the logic equation, the "." symbol is called an Input Element Designator.

Thus, from the implemented equation a person can find not only the logic function performed, but also how it is implemented.

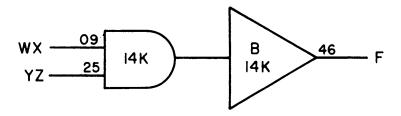

The physical location of this logic is important to know for troubleshooting. When the designer assigns the module to a location within the equipment, he will then write the module location and pin numbers beneath the implemented equations in this manner:

> F = B .WX .YZ (Logic Line) 14K46, 09, 25 (Pin Line)

The Pin Line expresses the module and pins where the logic terms can be found. In this example, "14K" indicates the Buffer and the input AND gate are located in module 14 of chassis (row) K. The number "46" following "14K" indicates that the Buffer output is pin 46. This is where the logic term, F, can be found. The comma symbol is just a separator, and has no logic relationship. The number "09" indicates that the first AND diode can be found on pin 09, and the number "25" indicates that the second AND diode can be found on pin 25. Since WX and YZ are the input terms to these diodes, they can be found on pins 09 and 25. If a drawing were to be shown of this logic structure, it would appear as:

The destination of the logic term, F, is the only important piece of information lacking. This information is not available in the implemented equation, but is available in another document, the Pin List.

When the designer has all of his logic functions defined as implemented equations, he submits them to key punching and inputs this into the computer under the control of the LOTRAN program. The program formalizes his equations into a standard format, and provides the designer with these formalized equations, a load list (pin list) showing how many elements each output term is driving, and an error list showing him any mistakes he might have made in assigning module or pin information, or errors in his syntax.

After several passes through this cycle, during which mistakes are corrected, the LOTRAN program would provide a set of documents which include:

- 1. Automated Logic Equations

- 2. Pin List

- 3. Pin Index

- 4. Module Map

- 5. Wiring Verification List (on magnetic tape)

- 6. Manufacturing Wiring Book

The Wiring Verification List is used by the Automatic Wiring Verification (AWV) test stations to test all point-to-point wiring under computer control.

The Manufacturing Wiring Book is used on the assembly line to perform the actual wiring of the backpanels.

The Automated Logic Equations, Pin List, Pin Index, and Module Map documents are the only documents which are of use to the Customer Engineer, and will be discussed in detail in the following pages.

#### Automated Logic Equations

The Automated Logic Equations contain all the Logic and Pin Lines that pertain to a functional unit of logic, which could be either a chassis of plug-in modules, or a complete Frame (9 rows) of plug-in modules, depending upon the equipment type.

The Automated Equations are presented in three distinct Sections:

- 1. Glossary of Element Designators

- 2. Logic Listing

- 3. Dictionary

The Glossary of Element Designators is placed towards the beginning of the Automated Equation book, immediately preceding the Logic Listing. It contains definitions for all the Element Designators used in the Logic Listing.

The Logic Listing contains all of the logic and pin lines that make up the functional unit. It is arranged numerically by Line Numbers.

The Dictionary is an alphabetical listing of all output logic terms which provides a cross reference to the appropriate Line Number, which can then be used to find the logic term in the listing. The Dictionary does not define the meanings of logic terms. The Dictionary is located either at the beginning or the end of the equation book.

The following three pages are examples of these three Sections.

SIGMA 7 CPU FRAME 2

1 131972-001 G 11/29/67

| CODE |       |                                                                                                                                                                                                                            |              |  |  |  |  |  |  |

|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|--|--|--|--|

|      |       | LOGIC EQUATIONS / PINS / REMARKS 9 10 22 2 4 15 16 22 4 19 20 7 12 22 25 76 72 28 29 30 2 22 23 24 35 16 27 28 29 40 40 40 40 40 44 44 45 46 47 48 25 00 19 23 23 24 55 36 27 38 29 60 60 67 68 66 67 68 67 68 67 70 67 70 | <b>C</b> /I  |  |  |  |  |  |  |

|      |       | 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 -                                                                                                                                                                                    |              |  |  |  |  |  |  |

| I    | •     | AND                                                                                                                                                                                                                        |              |  |  |  |  |  |  |

| I    | *     | DIRECT INPUT                                                                                                                                                                                                               |              |  |  |  |  |  |  |

| I    | CI    | CABLE INPUT                                                                                                                                                                                                                |              |  |  |  |  |  |  |

| O    | +     | OR                                                                                                                                                                                                                         |              |  |  |  |  |  |  |

| 0    | В     | BUFFER AMPLIFIER                                                                                                                                                                                                           |              |  |  |  |  |  |  |

| 0    | -BCD  | BUFFERED CABLE DRIVER                                                                                                                                                                                                      |              |  |  |  |  |  |  |

| 0    | -BCR  | BUFFERED CABLE RECEIVER                                                                                                                                                                                                    |              |  |  |  |  |  |  |

| 0    | СО    | CABLE OUTPUT                                                                                                                                                                                                               | CABLE OUTPUT |  |  |  |  |  |  |

| •    | - CON |                                                                                                                                                                                                                            |              |  |  |  |  |  |  |

| 0    | FB    | BUFFER FLIP-FLOP (SET)                                                                                                                                                                                                     |              |  |  |  |  |  |  |

| 0    | FF    | STANDARD J/K FLIP-FLOP (SET)                                                                                                                                                                                               |              |  |  |  |  |  |  |

| 0    | FN    | NAND FLIP-FLOP (SET)                                                                                                                                                                                                       |              |  |  |  |  |  |  |

| 0    | FR    | REPEATER FLIP-FLOP (SET)                                                                                                                                                                                                   |              |  |  |  |  |  |  |

| 0    | -GND  | GROUND INDICATOR                                                                                                                                                                                                           |              |  |  |  |  |  |  |

| 0    | -HSM  | HIGH SPEED MEMORY                                                                                                                                                                                                          |              |  |  |  |  |  |  |

| 0    | I     | INVERTING AMPLIFIER                                                                                                                                                                                                        |              |  |  |  |  |  |  |

| o    | -LD   | LAMP DRIVER                                                                                                                                                                                                                |              |  |  |  |  |  |  |

| 0    | NFF   | STANDARD J/K FLIP-FLOP (RESET)                                                                                                                                                                                             |              |  |  |  |  |  |  |

| 0    | NFN   | NAND FLIP-FLOP (RESET)                                                                                                                                                                                                     |              |  |  |  |  |  |  |

| О    | NFR   | REPEATER FLIP-FLOP (RESET)                                                                                                                                                                                                 |              |  |  |  |  |  |  |

| o    | -NS   | NO SOURCE INDICATOR                                                                                                                                                                                                        |              |  |  |  |  |  |  |

| 0    | - TD  | TIMING DELAY                                                                                                                                                                                                               |              |  |  |  |  |  |  |

| 1    | -VSP  | SPECIAL VOLTAGE                                                                                                                                                                                                            |              |  |  |  |  |  |  |

120

131971-001

11/29/67

SIGMA 7 CPU FRAME 1

.15 . . . 20

LOGIC EQUATIONS PINS REMARKS C/L CODE LINE NO. 12 3 14 15 16 17 14 19 20 21 22 22 24 25 26 27 28 28 30 31 32 33 34 35 36 37 34 39 40 41 42 42 44 45 46 47 44 49 50 51 52 35 36 55 56 57 34 59 60 61 67 67 64 69 70 MMCW =B\* +.FUMMC-1.PH5-B 6105400 A P 6105400 12B36, \$,\$,26, 25,36-23C45T A +.FUMMC-1.PH4-B.N(NP32.NP33) 6105402 A 6105402 12B\$,29, 28, 27 Α 6175050 MP19 =FFΑ P 03E04, 04-01B25C-03C15C-03D15C 6175050 Α 6175052 =NFF NMP19 A P 6175052 03E05 Α 6175054 S/MP19 +.BCON .(S/MP19/1) A Ρ 6175054 03E03, 03,10X, 24 A +.GND03E16 6175056 Α P 6175056 03E03,17X Α 6175060 R/MP19 Α Ρ 6175060 03E22 Α 6175064 C/MP19 = .CL-18E40Α 03E01X Ρ 6175064 Α 6175150 (S/MP19/1)=B .MIT .NMITEX .NMP19 Α P 02E37,46 6175150 50, 41,37-09E24T Α 6178000 MPP =B\* +.PH3-4 . CSN Α Ρ 6178000 12E42,\$,\$,40,50,39X,42-31C19C-31D19C-14F03C-14G03C-19H02T D 6178002 +.PH5-D .CSN A 29 6178002 12E\$,28X, A 6178004 . FAFLMD +.PH7-F A Ρ 6178004 12E\$,43, 44X Α 6178008 B FAFLM .ASN Α 6178008 11E46,41, 40 Α 6196000 (MAR+MRQ/1)=I .NMRQ .NMRQ/1 A Ρ 6196000 07C17, 20, 21, 17-02B11C

SIGMA 7 CPU FRAME 1

22 131971-100 N 11/29/67

| 1        | LINE NO.           | СНС         | LOGIC  |       | EQUA' |    | /             |       | PINS       | ,<br>, | REMA                  |            | , .           |

|----------|--------------------|-------------|--------|-------|-------|----|---------------|-------|------------|--------|-----------------------|------------|---------------|

| $\vdash$ | 2 8                | 9 10 . 15   | . 20 · | 25 ./ | 30    | 35 | 16 17 18 19 1 | 40    | 45 47 47 4 | 50     | 11 54 <b>55</b> 56 12 | 08 XV 60 A | 65            |

|          | 6105202            | NMITEX      |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6105204            | S/MITEX     |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6105214            | R/MITEX     |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6105218            | C/MITEX     |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6105400            | MMCW        |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6175050            | MP19        |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6175050            | NMP19       |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6175054            | S/MP19      |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6175060            | R/MP19      |        |       |       |    |               |       |            |        |                       |            |               |

| 1        | 6175064            | C/MP19      |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6175150            | (S/MP19/1)  |        |       |       |    |               |       |            |        |                       |            |               |

| 1        | 6178000            | MPP         |        |       |       |    |               |       |            |        |                       |            |               |

|          |                    | NMR Q       |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6196100<br>6196000 | (MRQ+MRQ/1) |        |       |       |    |               |       |            |        |                       |            |               |

| 1        |                    |             |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6197000            | MRQ/1       |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6196900            | NMRQ/1      |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6197580            | (S/MRQ/M)   |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6224000            | MULC        |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6224002            | NMULC       |        |       |       |    |               |       |            |        |                       |            |               |

| 1        | 6224004            | S/MULC      |        |       |       |    |               |       |            |        |                       |            |               |

| ١.       | 6224010            | R/MULC      |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6224014            | C/MULC      |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6224050            | (S/MULC/1)  |        |       |       |    |               |       |            |        |                       |            |               |

| ł        | 6224500            | MUSIC       |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6224502            | NMUSIC      |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6224504            | S/MUSIC     |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6224508            | R/MUSIC     |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6224510            | C/MUSIC     |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6240000            | MW          |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6240100            | NMW         |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6242100            | MWB         |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6242200            | NMWB        |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6242800            | MWH         |        |       |       |    |               |       |            |        |                       |            |               |

|          | 6242900            | NMWH        |        |       |       |    |               |       |            |        |                       |            |               |

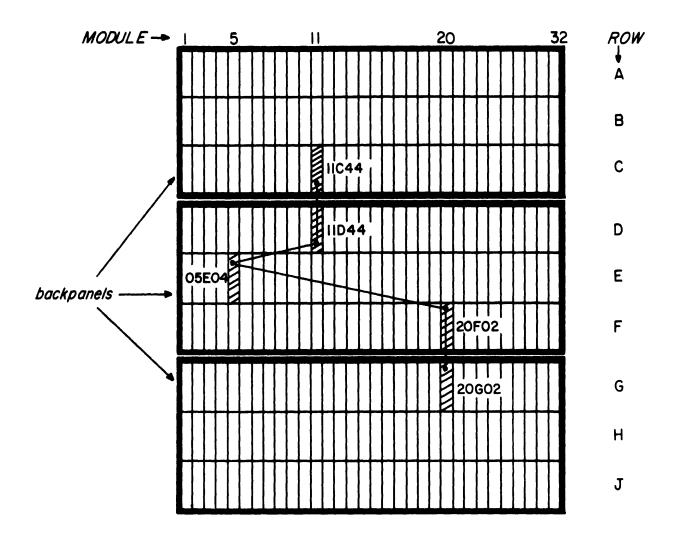

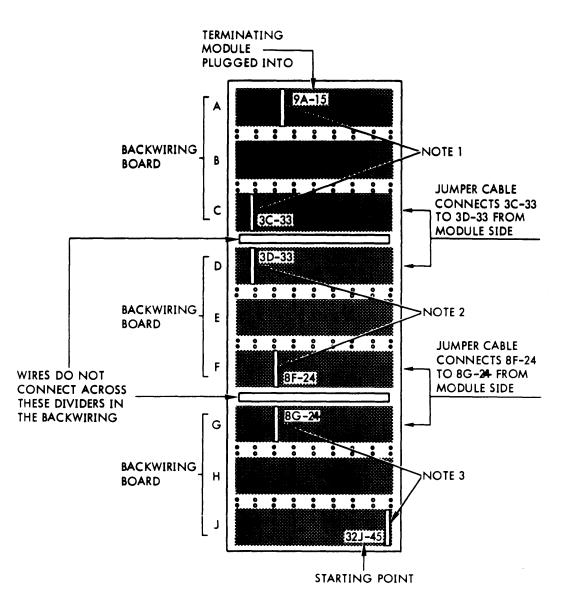

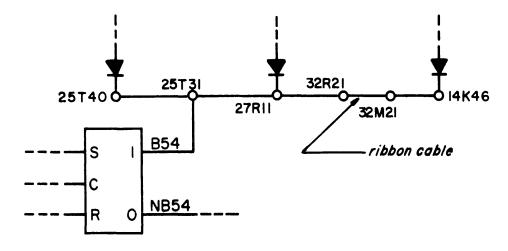

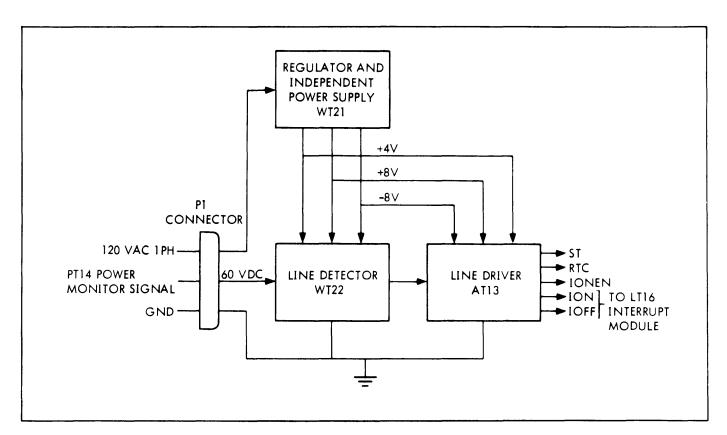

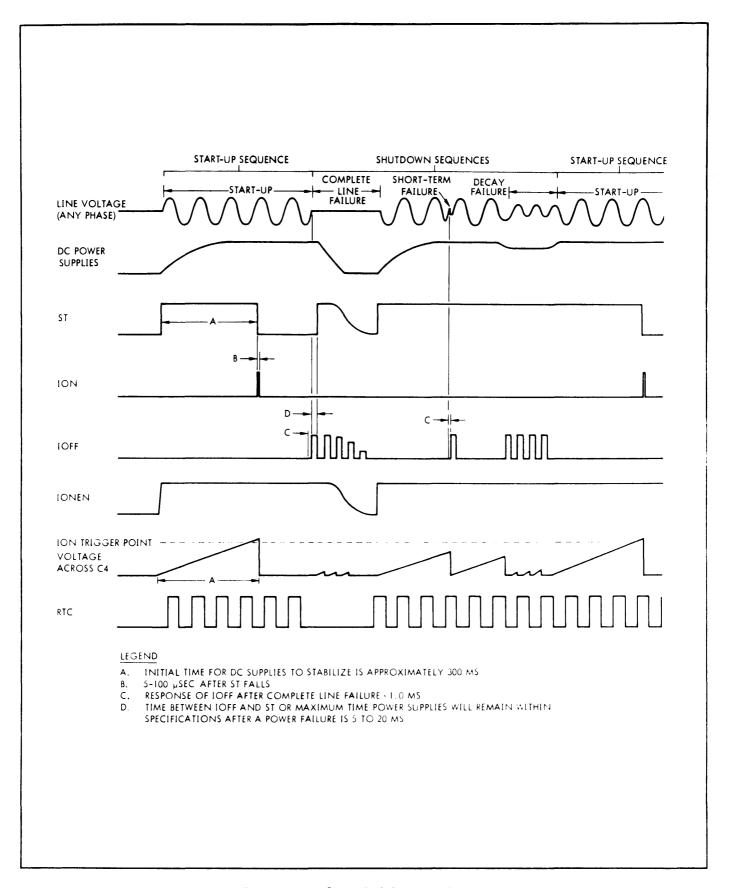

|          | 6244011            | MWN         |        |       |       |    |               |       |            |        |                       |            |               |