# **Ridge Hardware Reference Manual**

9007

## Hardware Reference Manual

second edition: 9007-B (APR 84) first update: 9007-B1 (MAY 85)

## PUBLICATION HISTORY

Manual Title: Hardware Reference Manual

First Edition: 9007 (AUG 82) Second Edition: 9007-B (APR 84) First Update 9007-B1 (MAY 85)

#### NOTICE

No part of this document may be translated, reproduced, or copied in any form or by any means without the written permission of Ridge Computers.

The information contained in this document is subject to change without notice. Ridge Computers shall not be liable for errors contained herein, or for incidental or consequential damages in connection with the use of this material.

#### MANUAL UPDATE

Document Title: Second Edition: First Update: Ridge Hardware Reference Manual 9007-B (APR 84) 9007-B1 (MAY 85)

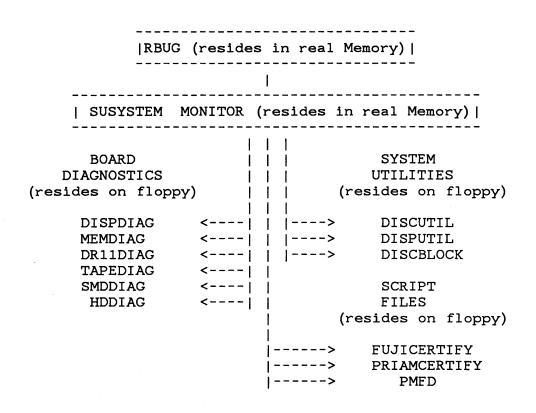

We are currently updating the entire Ridge Hardware Reference Manual. Until we complete our update, we are providing the SYSTEM DIAGNOSTICS section for you to add to your present copy of the manual.

To bring your Hardware Reference Manual up to date, replace pages i and ii with the updated pages supplied here, and add the SYSTEM DIAGNOSTICS section after the DR11 INTERFACE CONTROLLER section.

## TABLE OF CONTENTS

| SECTION 1 - THE RIDGE 32 SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standard Boards<br>Ridge 32 Card Cage<br>Front Panel Switches<br>Clock Board Control Switches<br>Clock Board Indicator Lights<br>System Boot<br>Self-Test<br>Controller Boards                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | $1-1 \\ 1-1 \\ 1-3 \\ 1-3 \\ 1-4 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 \\ 1-5 $ |

| SECTION 2 - FLOPPY DISC / LINE PRINTER CONTROLLER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Switches, Indicators, Pins<br>Board Layout<br>Board Cabling<br>P4 Connector<br>P3 Connector<br>P2 Connector Floppy Drive Interface<br>P1 Connector (test port - not normally used)<br>RS-232 Ports on Junction Panel Assembly (JPA)<br>Centronics Printer Cable<br>Data Products Cable (old style Winchester)<br>Data Products Cable (new style 50 pin D-sub)<br>Theory of Operation<br>Introduction<br>Board Layout<br>I/O Read, I/O Write, and I/O Interrupt Logic<br>DMA logic<br>Z80 CPU<br>Z80 Memory System<br>Z80 DMA Chip<br>Floppy Disc Chip<br>Z80 SIO Chips<br>Line Printers<br>Programming<br>Overview<br>Programming for Terminals<br>Terminal Write DCB's<br>Terminal Read DCB's<br>Terminal Control DCB's<br>Programming for the Floppy Disc Drive<br>Floppy Disc Device Control Block (DCB)<br>Versatec and Printer Device Control Block (DCB)<br>FDLP Monitor Program<br>Diagnostics (Not Yet Available) | 2-1<br>2-2<br>2-2<br>2-2<br>2-3<br>2-5<br>2-5<br>2-5<br>2-7<br>2-9<br>2-9<br>2-11<br>2-14<br>2-14<br>2-15<br>2-17<br>2-20<br>2-21<br>2-22<br>2-22<br>2-24<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25<br>2-25                                                                                                                                                                                                                                                                                                                                                          |

| SECTION 3 - HARD DISC CONTROLLER BOARD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

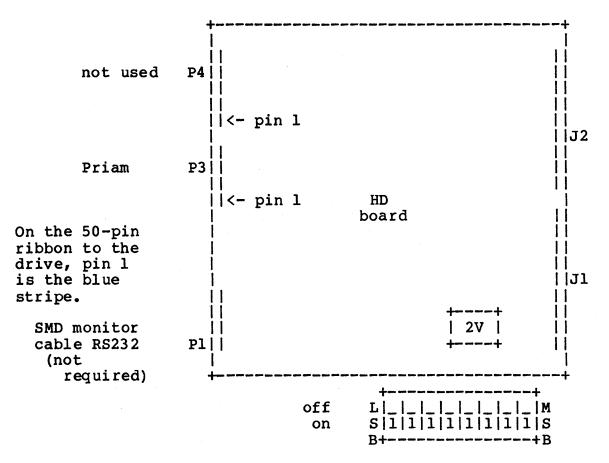

| Switches, Indicators, | Pins | 3-1 |

|-----------------------|------|-----|

| Board Layout          |      | 3-1 |

| Board Cabling         |      | 3-2 |

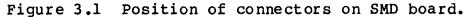

| P4 Connector - ANSI (not normally used)<br>P3 Connector - Priam<br>P1 Connector<br>Theory of Operation<br>Functional Description<br>Introduction<br>Layout<br>I/O Read, Write, and Interrupt Logic<br>DMA Logic<br>SERDES / Sync Detector / Comparator<br>ECC Circuits<br>Z80 Section<br>Bit Machine<br>Parallel Interface<br>Hard Disc Programming<br>Device Control Block (DCB)<br>Monitor Program<br>Diagnostics (Not Yet Available)<br>SECTION 4 - SMD CONTROLLER BOARD | 3-3<br>3-4<br>3-5<br>3-6<br>3-6<br>3-6<br>3-8<br>3-9<br>3-10<br>3-11<br>3-11<br>3-11<br>3-13<br>3-15<br>3-21                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

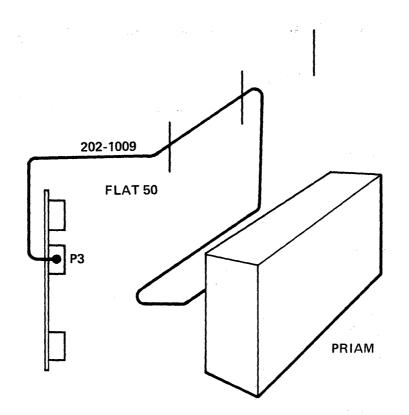

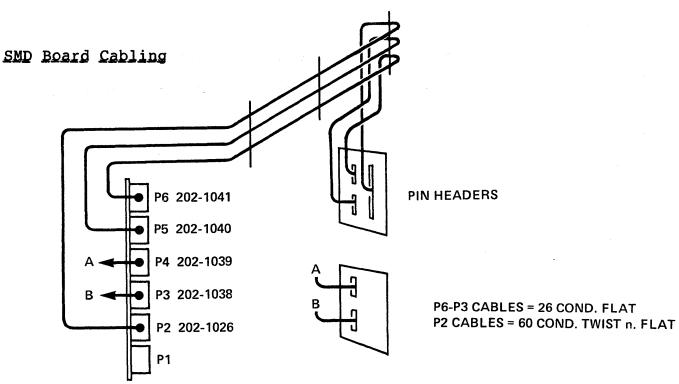

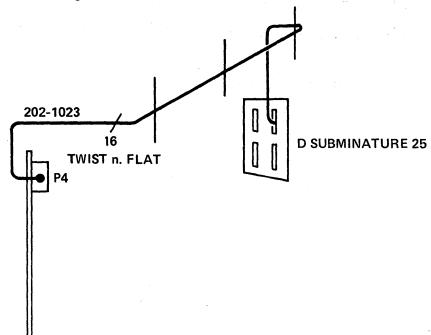

| Switches, Indicators, Pins<br>SMD Board Layout<br>Board Cabling<br>Board Switches<br>"A" Cable<br>"B" Cable<br>Monitor Cable<br>Theory of Operation<br>Functional Description<br>Introduction<br>Layout<br>I/O Read, Write, and Interupt Logic<br>DMA Logic<br>SERDES / Sync Detector / Comparator<br>ECC Circuits<br>Z80 Section<br>Bit Machine<br>Parallel Interface<br>Programming<br>SMD Controller Device Control Block<br>Ridge SMD Diagnostics (Not Yet Available)   | $\begin{array}{c} 4-1\\ 4-2\\ 4-2\\ 4-2\\ 4-2\\ 4-3\\ 4-5\\ 4-5\\ 4-5\\ 4-5\\ 4-6\\ 4-7\\ 4-8\\ 4-10\\ 4-11\\ 4-11\\ 4-12\\ 4-13\\ 4-15\\ 4-18\end{array}$ |

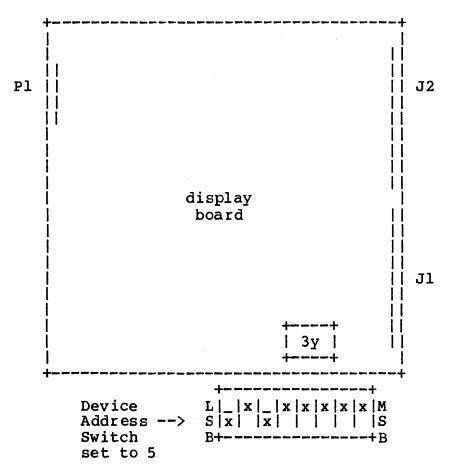

| SECTION 5 - MONOCHROME GRAPHIC DISPLAY INTERFACE B                                                                                                                                                                                                                                                                                                                                                                                                                          | OARD                                                                                                                                                       |

| Switches, Indicators, Pins<br>Board Layout<br>Board Cabling                                                                                                                                                                                                                                                                                                                                                                                                                 | 5-1<br>5-1<br>5-2                                                                                                                                          |

| Board Layout          |     |     |            |   | 5-1 |

|-----------------------|-----|-----|------------|---|-----|

| Board Cabling         |     |     |            |   | 5-2 |

| Theory of Operation ( | Not | Yet | Available) |   | 5-3 |

| Programming           |     |     |            |   | 5-4 |

| Diagnostics           |     |     |            | 1 | 5-9 |

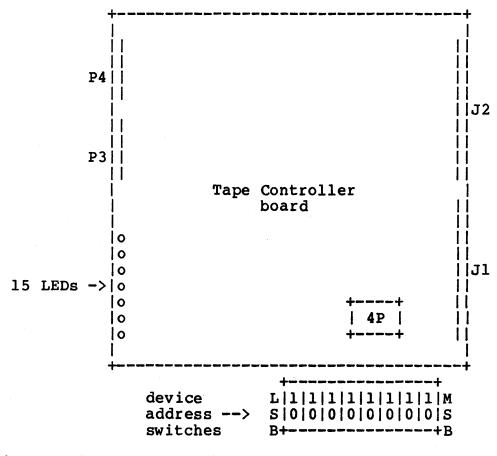

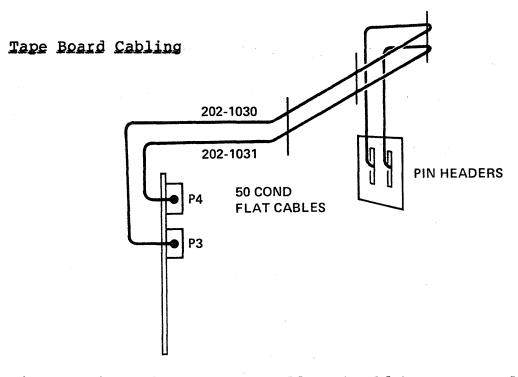

SECTION 6 - RIDGE 32 TAPE CONTROLLER BOARD

Switches, Indicators, Pins

6-1

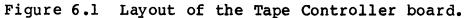

| Board Layout               | 6-1  |

|----------------------------|------|

| Board Cabling              | 6-2  |

| Jumpers                    | 6-2  |

| Switches                   | 6-2  |

| Indicators                 | 6-3  |

| Tape Board Pin Assignments | 6-3  |

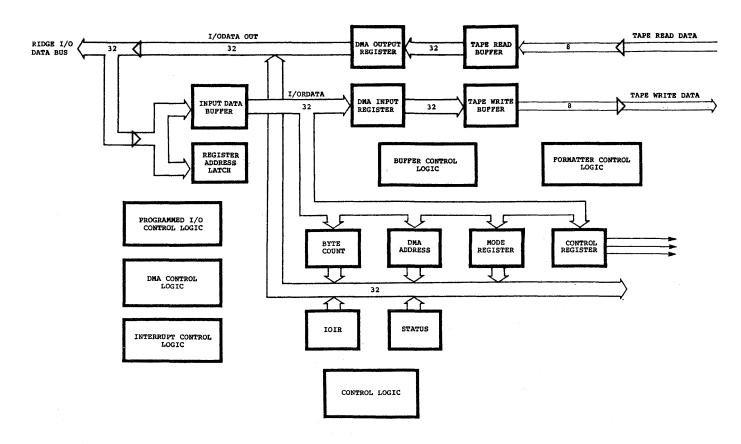

| Theory of Operation        | 6-5  |

| Programming                | 6-10 |

| Register Definitions       | 6-10 |

| Address Word               | 6-10 |

| Control Register           | 6-10 |

| Mode Register              | 6-11 |

| Status                     | 6-11 |

| DMA Address                | 6-12 |

| Byte Count                 | 6-12 |

| Interrupts                 | 6-13 |

| Diagnostics                | 6-14 |

| Auto Debug Mode            | 6-14 |

| Manual Debug Mode          | 6-18 |

## SECTION 7 - DR11 INTERFACE CONTROLLER

| Ridge DRll Interface Specifications  | 7-1  |

|--------------------------------------|------|

| Introduction                         | 7-1  |

| Interface Definition                 | 7-1  |

| DATA TRANSFERS                       | 7-3  |

| NORMAL MODE DMA CYCLES               | 7-3  |

| NORMAL MODE PROGRAMMED I/O TRANSFERS | 7-3  |

| LINK MODE                            | 7-3  |

| Switches, Indicators, Pins           | 7-4  |

| Board Layout                         | 7-4  |

| Board Cabling                        | 7-5  |

| Jumpers                              | 7-5  |

| Switches                             | 7-5  |

| Connectors                           | 7-6  |

| Indicators                           | 7-7  |

| DR11 Pin Assignments                 | 7-8  |

| Theory of Operation                  | 7-10 |

| DR11W Interface                      | 7-10 |

| RIDGE Controller                     | 7-14 |

|                                      | 7-14 |

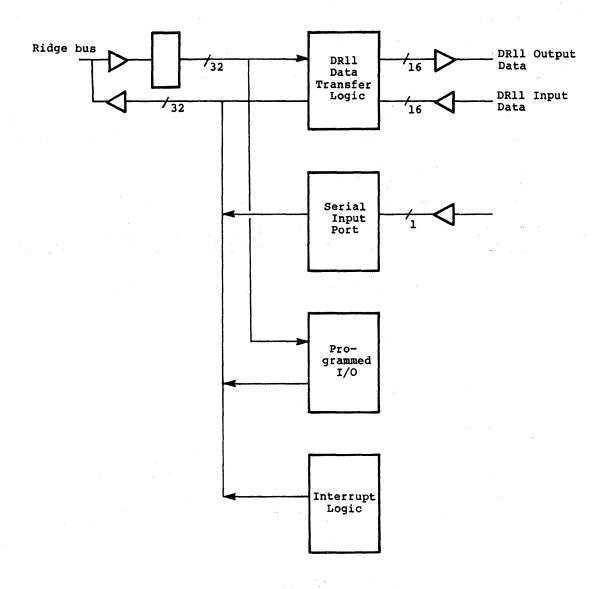

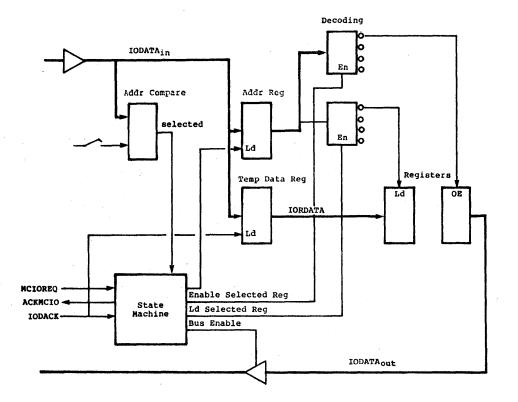

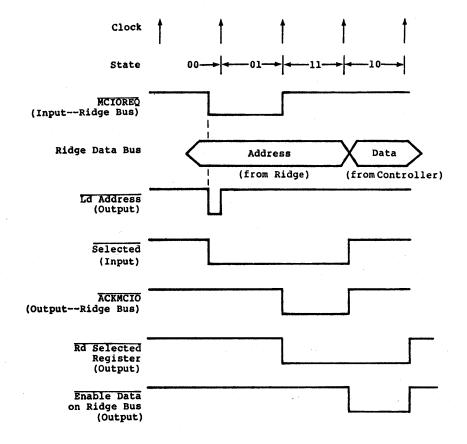

| Programmed I/O Logic                 | 7-15 |

| DATA Transfer Logic                  |      |

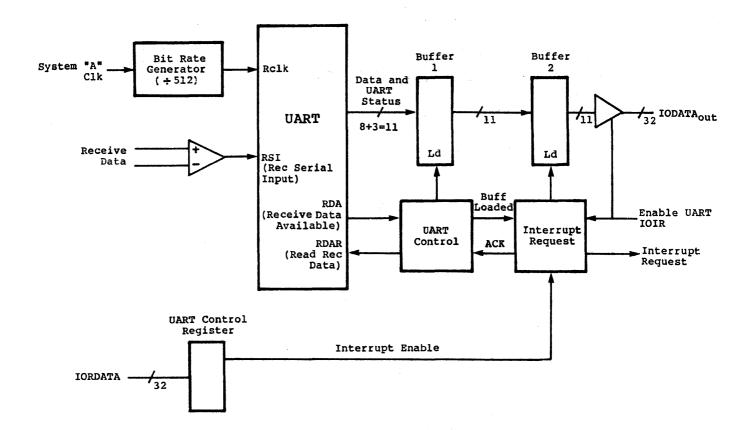

| Serial Input Port                    | 7-27 |

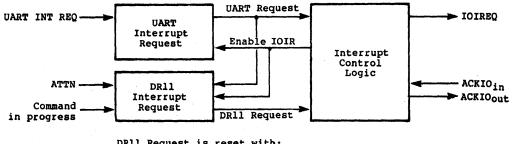

| Interrupt Logic                      | 7-27 |

| Programming                          | 7-29 |

| DR11 Register Definitions            | 7-29 |

| I/O Address Word                     | 7-29 |

| Control Register                     | 7-30 |

| Status                               | 7-30 |

| Word Count                           | 7-31 |

| DMA Address                          | 7-31 |

| DR11 Interrupts                      | 7-31 |

| Programmed I/O Data Registers        | 7-32 |

| Serial Port Register Definitions     | 7-32 |

| I/O Address Word                     | 7-32 |

| Control Register                     | 7-32 |

| Status Register                      | 7-32 |

|                                      |      |

| IOIR                   |      | 7-32 |

|------------------------|------|------|

| Diagnostics            | •    | 7-34 |

| Register Test          | -    | 7-34 |

| LoopBack Test          | -    | 7-35 |

| Metheus Test           | -    | 7-37 |

| Keyboard Test          |      | 7-38 |

| Ungermann-Bass NIU-150 | Test | 7-39 |

| -                      |      |      |

## APPENDIX A - Z80 REGISTERS

| SMD Writes                 | A-1 |

|----------------------------|-----|

| SMD Register Reads/Strobes | A-2 |

| HD I/O Ports (Writes)      | A-3 |

| HD I/O Ports (Reads)       | A-4 |

| HD I/O Ports (others)      | A-5 |

| FD/LP I/O Ports (Writes)   | A-6 |

| FD/LPD I/O Ports (Reads)   | A-7 |

| FD/LPD I/O Ports (Chips)   | A-8 |

SECTION 1 - RIDGE 32 SYSTEM

Standard Boards

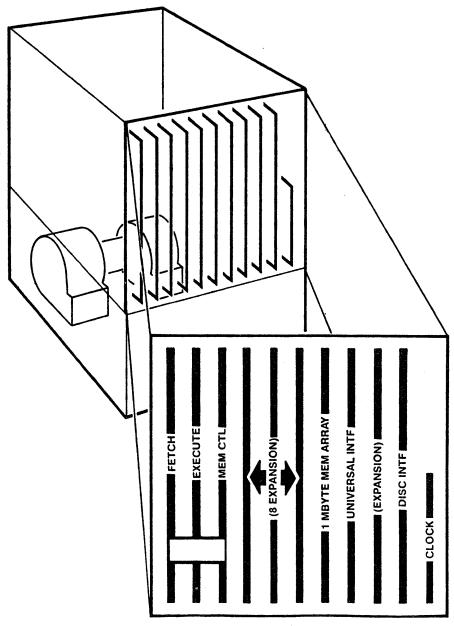

Ridge 32 Card Cage

Figure 1.1 Placement of boards in Ridge 32 card cage

1-2

#### Front Panel Switches

| Switch | Function                     |

|--------|------------------------------|

|        | الحي جين منت بين حيد جين جين |

Power On/Off Controls AC power.

- Device 1/2 When in the rest position (position 1), system software will be loaded from the hard disc at load time. If pressed and held in position 2 at load time, the floppy disc drive is selected as the source of the system software.

- Load This is a momentary switch, and when depressed resets the CPU and loads memory from device "1" or "2". In order to load from the floppy drive, depress and hold the device switch in the "2" position. Depress and release the load switch. After two seconds the floppy disc drive head loads, lighting the activity light on the floppy disc drive. Once the floppy disc drive begins loading, the device switch may be released.

#### Clock Board Control Switches

The Ridge clock board is a proprietary device which is not explained in detail in this book. The clock board is inserted in the Ridge card cage at the far right.

The six switches on the clock board, however, are described in the order that they are mounted on the board, from high to low position:

Switch Function

الله والله المراجع المر

- Single-Clock This momentary switch supplies the system with one clock pulse when depressed, if either the main clock switch or never-frozen clock switch is set to the frozen position.

- Main Clock During normal operation this switch is set to the left position. When set to the right, the main system clock is frozen. Single clocks may be supplied by depressing the single-clock switch.

- Never-Frozen During normal operation this switch is set to the Clock left position. When set to the right, clock pulses supplied to refresh main memory are frozen. Single never-frozen clocks may be supplied by depressing the single clock switch.

- Reset This momentary switch resets the system hardware and loads memory from the device selected on the front panel. This switch differs from the front panel load switch in that never-frozen clocks are still provided, preserving main memory while still resetting system hardware.

- Load Enable During normal operation, this switch is set to the left. The position of this switch can be tested by the software ELOGR instruction. This switch is used by microcode when recovering from a power glitch. When set to the left, "load is enabled" and the CPU resumes executing. When set to the right, "load is disabled" and the CPU begins executing at the switch 0 interrupt location in the CCB.

- Switch 0 This momentary switch interrupts the CPU, causing execution to begin at the location of the switch 0 interrupt in the CCB.

The system is reset whenever AC power is applied, or the reset switch or load switch is depressed.

#### Clock Board Indicator Lights

The clock board contains six light-emitting diodes (LED's) that indicate system status. The LED's are located below the set of switches. The LED's and their functions:

| LED  | Function                                                                                                                                                  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

|      |                                                                                                                                                           |

| Sync | Indicates that the clock board is generating<br>clock signals. When the system is reset, this<br>LED goes off for one-half second, then is<br>re-lighted. |

```

Lost DC Indicates that DC power was interrupted some

time previously. When the system is reset,

this LED lights until the boot command from

CPU microcode is issued.

o } Group

o } Group

o } Of four

o }

```

In addition to the above switches and indicators, there is a jumper which disables the timekeeping facilities. Timer 1 and timer 2 interrupts are inhibited by placing a jumper across pins 37 and 38 of the edge connector on the clock board. The jumper is placed horizontally on the seventh from the top pair of pins.

#### System Boot

The system is booted whenever it is reset: by turning on the power, or by pressing the the front panel load button or the reset button on the clock board. When the system is booted, the CPU microcode sends a boot command to the selected I/O device. If the hard disc drive is selected, 4096 bytes are read from page 1 of the disc (0origin) and placed in memory at location 3E000H. When the floppy disc drive is selected, the entire double density track of 8192 bytes is read from head 0, track 2 and placed in memory at locat on 3E000H. After loading memory, the booting device interrupts the CPU, and the CPU begins executing in kernel mode at location 3E000H. SRll (the CCB pointer) is set to 1, disabling timer 1 and timer 2 interrupts.

When loading from the floppy disc, turn on the power with the floppy door open. If a floppy error occurs during loading, the floppy disc controller will retry up to three times.

#### Self-Test

Any time the system is reset, the CPU self-test microcode is executed. When the system is working properly, the eight LED's mounted on the edge of the execute board flash in sequence, from bottom to top. (The execute board is customarily inserted at the far left of the Ridge card cage.) All LED's then go out, and the self-test continues. If there are no errors, the boot command is issued to the disc drive. If there is an error, the top LED goes on and stays on.

#### Controller Boards

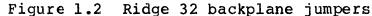

The Ridge processor communicates to I/O interfaces using the WRITE and READ instructions, and the I/O Interrupt Read (IOIR) word on interrupts. The WRITE instruction sends an address word and a data word to a device in the following format:

The most significant byte of the address word is the device number, from 0-255. The remainder of the address word and data word contains device-dependent data. The READ instruction sends an address word to the device and receives a data word from the device on reply. If the device specified in the READ or WRITE instruction does not respond in two microseconds, an I/O timeout occurs and a 1 is placed as a return indication in R1.

When an I/O device interrupts, the CPU microcode issues an I/O Interrupt Read, and receives an IOIR word. This word is placed in Special Register 0 (SR0) upon entry to the kernel. The format of the IOIR is below:

|      | 0      | 7 | 8   |           | 31   |

|------|--------|---|-----|-----------|------|

|      |        |   | +   |           |      |

| IOIR | device | # | dev | dependent | data |

| Word | +      |   | +   | ~~        | +    |

## SECTION 2 - FLOPPY DISC / LINE PRINTER CONTROLLER

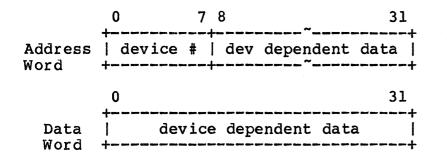

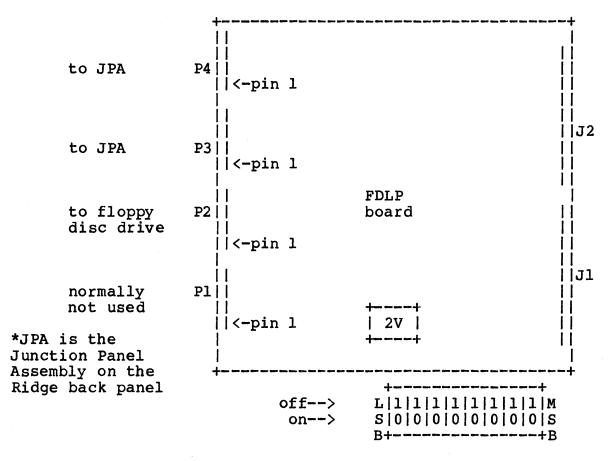

FDLP Control Switches, Indicator Lights, and Pin Assignments FDLP Board Layout

Figure 2.1 Position of connectors on FDLP board.

## FDLP Board P4 Connector

| Pin                        | Signal Name               | Pin | Signal Name               |

|----------------------------|---------------------------|-----|---------------------------|

| 1                          | ground                    | 26  | ground                    |

| 1<br>2<br>3                | + DP online               | 27  | received data portl       |

| 3                          | + DP ready                | 28  | ground                    |

| 4                          | + DP top of form          | 29  | transmit data             |

| 5                          | - Centronics fault        | 30  | ground                    |

| 6                          | - Centronics select       | 31  | ring port2                |

| 4<br>5<br>6<br>7<br>8<br>9 | + Centronics paper out    | 32  | clear to send port2       |

| 8                          | - Versatec online         | 33  | data carrier detect port2 |

| 9                          | + Versatec paper out      | 34  | request to send port2     |

| 10                         | ground                    | 35  | data terminal ready port2 |

| 11                         | ring port0                | 36  | ground                    |

| 12                         | clear to send port0       | 37  | received data port2       |

| 13                         | data carrier detect port0 | 38  | ground                    |

| 14                         | request to send port0     | 39  | transmit data port2       |

| 15                         | data terminal ready port0 | 40  | ground                    |

| 16                         | ground                    | 41  | ring port3                |

| 17                         | received data port0       | 42  | clear to send port3       |

| 18                         | ground                    | 43  | data carrier detect port3 |

| 19                         | transmit data port0       | 44  | request to send port3     |

| 20                         | ground                    | 45  | data terminal ready port3 |

| 21                         | ring portl                | 46  | ground                    |

| 22                         | clear to send portl       | 47  | received data port3       |

| 23                         | data carrier detect portl | 48  | ground                    |

| 24                         | request to send port1     | 49  | transmit data port3       |

| 25                         | data terminal ready portl | 50  | ground                    |

## FDLP Board P3 Connector

| Pin                                  | Signal Name                | Pin | Signal Name                                     |

|--------------------------------------|----------------------------|-----|-------------------------------------------------|

|                                      |                            |     | this win gan an the and the and the gan the set |

| 1                                    | ground                     | 26  | Versatec Remote Form Feed                       |

| 2                                    | - Centronics acknowledge   | 27  | ground                                          |

| 3                                    | ground                     | 28  | Versatec Remote EOT                             |

| 4                                    | + Centronics busy          | 29  | ground                                          |

| 5                                    | ground                     | 30  | Vers Remote Line Terminate                      |

| 6                                    | + DP demand                | 31  | ground                                          |

| 7                                    | ground                     | 32  | Versatec Bit l (lsb)                            |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | + Versatec busy            | 33  | Versatec bit 2                                  |

| 9                                    | ground                     | 34  | Versatec bit 3                                  |

| 10                                   | + Versatec P.I. clock      | 35  | Versatec bit 4                                  |

| 11                                   | ground                     | 36  | Versatec bit 5                                  |

| 12                                   | + DP strobe                | 37  | Versatec bit 6                                  |

| 13                                   | ground                     | 38  | Versatec bit 7                                  |

| 14                                   | - DP/C strobe              | 39  | Versatec bit 8 (msb)                            |

| 15                                   | ground                     | 40  | ground                                          |

| 16                                   | - DP/C clear               | 41  | ground                                          |

| 17                                   | ground                     | 42  | DP/C bit 1 (lsb)                                |

| 18                                   | - Versatec print           | 43  | DP/C bit 2                                      |

| 19                                   | ground                     | 44  | DP/C bit 3                                      |

| 20                                   | Vers simultan'us plot/prnt |     | DP/C bit 4                                      |

| 21                                   | ground                     | 46  | DP/C bit 5                                      |

| 22                                   | Versatec clear             | 47  | DP/C bit 6                                      |

|                                      | ground                     | 48  | DP/C bit 7                                      |

|                                      | Versatec reset             | 49  | DP/C bit 8 (msb)                                |

| 25                                   | ground                     | 50  | ground                                          |

| 23                                   | ground                     | 20  | yr o unu                                        |

## FDLP Board P2 Connector Floppy Drive Interface

| Pin                                  | Signal Name | Pin | Signal Name     |

|--------------------------------------|-------------|-----|-----------------|

| 1                                    | ground      | 26  | unit select 0   |

|                                      | low current | 27  | ground          |

| 3                                    | ground      | 28  | unit select l   |

| 4                                    | fault reset | 29  | ground          |

| 2<br>3<br>4<br>5<br>6<br>7<br>8<br>9 | ground      | 30  | unit select 2   |

| 6                                    | fault       | 31  | ground          |

| 7                                    | ground      | 32  | unit select 3   |

| 8                                    | not used    | 33  | ground          |

| 9                                    | ground      | 34  | direction       |

| 10                                   | two-sided   | 35  | ground          |

| 11                                   | ground      | 36  | step            |

| 12                                   | not used    | 37  | ground          |

| 13                                   | ground      | 38  | write data      |

| 14                                   | side select | 39  | ground          |

| 15                                   | ground      | 40  | write enable    |

| 16                                   | head load l | 41  | ground          |

| 17                                   | ground      | 42  | ťrack O         |

| 18                                   | head load 0 | 43  | ground          |

| 19                                   | ground      | 44  | write protected |

| 20                                   | index       | 45  | ground          |

| 21                                   | ground      | 46  | read data       |

| 22                                   | ready       | 47  | ground          |

| 23                                   | ground      | 48  | ĥead load 2     |

| 24                                   | not used    | 49  | ground          |

| 25                                   | ground      | 50  | head load 3     |

| FDLP | <u>Board</u> | <u>P1</u> | Connector | (test | port - | not | normally | used) |  |

|------|--------------|-----------|-----------|-------|--------|-----|----------|-------|--|

|------|--------------|-----------|-----------|-------|--------|-----|----------|-------|--|

| Pin    | Signal Name    |

|--------|----------------|

|        |                |

| 1      | ground         |

| 2      | ground         |

| 2<br>3 | switch 3       |

| 4      | ground         |

| 5      | switch 2       |

| 6      | ground         |

| 7      | switch l       |

| 8      | ground         |

| 9      | switch 0       |

| 10     | ground         |

| 11     | external reset |

| 12     | ground         |

| 13     |                |

| 14     | ground         |

FDLP RS-232 Ports on Junction Panel Assembly (JPA)

The active pins on the four Ridge RS-232 ports are:

| Name                 |

|----------------------|

|                      |

| Ground.              |

| Transmit data.       |

| Receive data.        |

| Request to send.     |

| Clear to send.       |

| Signal ground.       |

| Carrier detect.      |

| Data terminal ready. |

| Ring indicator.      |

|                      |

For instructions on modifying the baud rates, parity, etc. of the RS-232 ports, see the Ridge Operating System Reference Manual (part 9010), section 1, stty(1) utility program.

## Centronics Printer Cable

| signal                      | Ridge end<br>(on JPA) | wire                     | printer<br>end |

|-----------------------------|-----------------------|--------------------------|----------------|

| bitl                        | 1                     | red                      | 2              |

| bitl return                 | 20                    | black                    | 20             |

| bit2                        | 2                     | white                    | 3              |

| bit2 return                 | 21                    | black                    | 21             |

| bit3                        | 3                     | green                    | 4              |

| bit3 return                 | 22                    | black                    | 22             |

| bit4                        | 4                     | blue                     | 5              |

| bit4 return                 | 23                    | black                    | 23             |

| bit5<br>bit5 return         | 5<br>24<br>6          | yellow<br>black          | 6<br>24<br>7   |

| bit6<br>bit6 return<br>bit7 | 25<br>7               | brown<br>black<br>orange | 25<br>8        |

| bit7 return                 | 26                    | black                    | 26             |

| bit8                        | 8                     | white                    | 9              |

| bit8 return                 | 27                    | red                      | 27             |

| clear                       | 9                     | green                    | 31             |

| clear return                | 28                    | red                      | (30)           |

| cstrobe                     | 10                    | blue                     | 1              |

| cstrobe return              | 29                    | red                      | 19             |

| cbusy                       | 11                    | yellow                   | 11             |

| cbusy return                | 30                    | red                      | 29             |

| cpaper                      | 12                    | brown                    | 12             |

| cpaper return               | 31                    | red                      | (30)           |

| cselect                     | 14                    | orange                   | 13             |

| cselect return              | 33                    | red                      | (33)           |

| cack                        | 19                    | white                    | 10             |

| cack return                 | 37                    | green                    | 28             |

| cfault                      | 32                    | blue                     | 32             |

Connect 2 grounds together to pins 30 and 33.

Ridge end connector is 37 pin D-sub male.

Printer end is Amphenol 57-30360.

| Data | Products | <u>Cable</u> | (old | style | Winchester) |

|------|----------|--------------|------|-------|-------------|

|------|----------|--------------|------|-------|-------------|

|                                           | Ridge end | wire   | printer                   |

|-------------------------------------------|-----------|--------|---------------------------|

| signal                                    | (on JPA)  | wire   | end                       |

| والته فبست وتعت فيته فتتك فتتب فلده فالته |           |        | میں سن سن من من اس می شد: |

| bitl                                      | 1         | red    | В                         |

| bitl return                               | 20        | black  | D                         |

| bit2                                      | 2         | white  | F                         |

| bit2 return                               | 21        | black  | J                         |

| bit3                                      | 3         | green  | L                         |

| bit3 return                               | 22        | black  | N                         |

| bit4                                      | 4         | blue   | R                         |

| bit4 return                               | 23        | black  | т                         |

| bit5                                      | 5         | yellow | V                         |

| bit5 return                               | 24        | black  | Х                         |

| bit6                                      | 6         | brown  | Z                         |

| bit6 return                               | 25        | black  | b                         |

| bit7                                      | 7         | orange | n                         |

| bit7 return                               | 26        | black  | k                         |

| bit8                                      | 8         | white  | P                         |

| bit8 return                               | 27        | red    | S                         |

| clear                                     | 9         | green  | А                         |

| clear return                              | 28        | red    | С                         |

| dptof                                     | 12        | blue   | S                         |

| dptof return                              | 29        | red    | U                         |

| dpbof                                     | 13        | yellow | M                         |

| cbusy return                              | 30        | red    | Р                         |

| dpready                                   | 15        | brown  | CC                        |

| dpready return                            |           | red    | EE                        |

| dponline                                  | 16        | orange | У                         |

| dpdmd return                              | 35        | red    | AA                        |

| dpdmd                                     | 17        | white  | E                         |

| dpdmd return                              | 36        | green  | H                         |

| dpstrobe                                  | 18        | blue   | j                         |

| dpstrobe return                           | 37        | green  | m                         |

Ridge end connector is 37-pin D-sub male

printer end connector is 50-pin Winchester MRAC50P-JTDH 8

| FDLP Board Data | Products Cable        | (new style 50 pi  | n D-sub)       |

|-----------------|-----------------------|-------------------|----------------|

| signal<br>name  | Ridge end<br>(on JPA) | wire<br>color<br> | printer<br>end |

| bitl            | 1                     | red               | 19             |

| bitl return     | 20                    | black             | 3              |

| bit2            |                       | white             | 20             |

| bit2 return     | 21                    | black             | 4              |

| bit3            |                       | green             | 1              |

| bit3 return     | 22                    | black             | 2              |

| bit4            | 4                     | blue              | 41             |

| bit4 return     |                       | black             | 40             |

| bit5            | 5                     | yellow            | 34             |

| bit5 return     | 24                    | <b>black</b>      | 18             |

| bit6            | 6                     | brown             | 43             |

| bit6 return     | 25                    | black             | 42             |

| bit7            | 7                     | orange            | 36             |

| bit7 return     | 26                    | black             | 35             |

| bit8            | 8                     | white             | 28             |

| bit8 return     | 27                    | red               | 48             |

| clear           | 9                     | green             | 31             |

| clear return    | 28                    | red               | 15             |

| dptof           | 12                    | blue              | 24             |

| dptof return    | 29                    | red               | 8              |

| dpbof           |                       | yellow            | 25             |

| cbusy return    |                       | red               | 9              |

| dpready         | 15                    | brown             | 22             |

| dpready return  |                       | red               | 6              |

| dponline        | 16                    | orange            | 21             |

| dpdmd return    | 35                    | red               | 5              |

| dpdmd           | 17                    | white             | 23             |

| dpdmd return    | 36                    | green             | 7              |

| dpstrobe        | 18                    | blue              | 38             |

| dpstrobe return | 37                    | green             | 37             |

| <b>PJ</b> I | Board | Data | Products | Cable | (new  | style | 50 | pin | D-sub) |  |

|-------------|-------|------|----------|-------|-------|-------|----|-----|--------|--|

| <u> </u>    | Dourd | Pulu | TTOOGCCO |       | (1104 |       | 20 | P   |        |  |

Ridge end connector is 37-pin D-sub male.

Printer end connector is 50-pin D-sub male.

#### Theory of Operation

#### FDLP Introduction

The FDLP board controls four RS-232 ports, two line printer ports, and is capable of controlling two 8-inch floppy disc drives. It has a local Z80 processor with its own local memory and various circuits and chips to interface to the various devices. All data passes through the local memory before going to or from the devices. The devices are serviced by the Z80 in a variety of ways: the serial terminal ports are interrupt-driven; the floppy disc has a Z80 DMA chip associated with it, so that the Z80 may service other devices while those transfers are in progress; the line printers are interfaced with Z80 OUT instructions supported with special logic to check the printer handshaking.

The software organization of the Z80 code is task oriented. Each unit has a task control state. Although interrupts are enabled at most times (for instance the SIO chips handling the RS-232 ports interrupt and are serviced), tasks are scheduled and run to a certain state, the state is recorded and a mechanism is enabled to reschedule the task, the task relinquishes control of the Z80, and a Z80 dispatcher chooses the next task to run. Normally, an interrupt occurs and the interrupt procedure inserts a request in a queue to re-start a task at the recorded state.

The communication between the Ridge CPU and the board is:

I/O Write instructions start an operation

the Z80 usually requests further information about the request which it obtains from a dedicated area in Ridge memory called a Device Control Block (DCB)

if the operation is a device write, the Z80 will copy the data to its local memory

the operation is performed

if the operation is a device read, the data is moved from the local memory to Ridge memory

a Ridge interrupt is generated and the I/O Interrupt Read that the Ridge CPU will perform will return the board's device number, the unit on the board, and an indication of the success of the requested operation.

#### FDLP Board Layout

The primary logical parts of the board are :

I/O Read, I/O Write, and I/O Interrupt logic

a DMA sequencer to copy data in both directions between Ridge memory and Z80 memory. It has one word count register and two address registers: one for the Ridge address and one for the Z80 address

3) the Z80 CPU and its I/O decoders

4) 16 K bytes of dynamic ram

#### 5) 8 K bytes of EPROM

6) a DMA chip to service the floppy disc chip 7) an NEC uPD765 floppy disc chip with associated buffer and an analog phase-locked loop (PLL) to generate a read clock for the floppy disc chip to decode the read data from the floppy drive 8) two Z80 SIO chips for the RS-232 ports and Z80 CTC chips for generating the baud rate clocks for the SIO's. Also RS-232 drivers and receivers to translate to/from TTL levels 9) two sets of line printer logic that checks the line printer handshaking protocol as the Z80 writes to the printers. If the 280 writes before the last data operation is complete, the operation is aborted before the point where the printers would see it, and the Z80 is interrupted. The Z80 interrupt procedure the path of instruction flow of the interrupted alters procudure. The printer logic also has the capability of monitoring the state of printer "ready" lines and generating interrupts on changes.

#### I/O Read, I/O Write, and I/O Interrupt Logic

The I/O Read, Write, and Interrrupt sections are small state machines with four states.

#### INTERRUPT STATE MACHINE

The Interrupt State Machine is normally in the idle state. The Z80 sets a bit in a register it can write to; this advances the state. When the Z80 resets that bit, the state machine advances the state again and asserts IOIREQ1 or IOIREQ2. It also blocks ACKIOIout so that when multiple devices request an interrupt at the same time (or before the first device is acknowledged), any lower priority devices (further down the daisy-chain) will not see the ACKIOI signal, and will not gate their device numbers, but will continue to assert IOIREQ1 or IOIREQ2. When the board finally sees ACKIOIin, it advances the state once more and asserts its device number and the status register on the I/O bus. The state advances to the null state on the next clock unconditionally.

#### I/O READ STATE MACHINE

The I/O Read state machine is normally in the 0 (null) state. It enters state 1 on an MCIOREQ signal from the memory controller. From state 1, it advances to state 3 if three conditions are true at the clock edge:

- 1) MCIOREQ has remained true

- 2) MCIOWT is false (an I/O Read in progress) and

- 3) the high order byte on the Ridge I/O bus matches the value set in this board's device number switch.

If MCIOREQ is removed, th I/O Read state machine returns to state 0. If it reaches state 3, this board has been addressed with an I/O Read and the signal ACKMCIO is returned to the memory controller. From state 3, the state machine unconditionally advances to state 2 which gates the device number in the high order byte, the STATUS register in the next byte, and the low 16 address bits onto the Ridge I/O bus. After state 2, it advances to state 0.

#### I/O WRITE STATE MACHINE

The I/O Write state machine leaves its null state when it sees an MCIOREQ signal from the memory controller and enters state 1. From this state it will advance to state 3 if four conditions are true:

- 1) MCIOREQ has remained true

- 2) MCIOWT is true (an I/O Write is in progress

- 3) the high order byte on the Ridge I/O bus matches the value

- set in this board's device number switch

- 4) CMDINT is false.

If MCIOREQ is removed, this state machine returns to state 0. If it reaches state 3, this board has been addressed with an I/O WRITE and the signal ACKMCIO is returned to the memory controller. From state 3, the state machine unconditionally advances to state 2 which continues to load the COMMAND register with the contents of the I/O bus. It will remain in this state until the signal IODACK is asserted by the memory controller. It will then return to state 0. The effect of this is that the COMMAND register will contain the contents of the high order byte of the I/O bus when the IODACK was issued (which is the I/O Write Data Word). State 2 also sets the CMDINT bit which prevents further (successful) I/O Writes until it is reset and which interrupts the Z80 through the NMI pin.

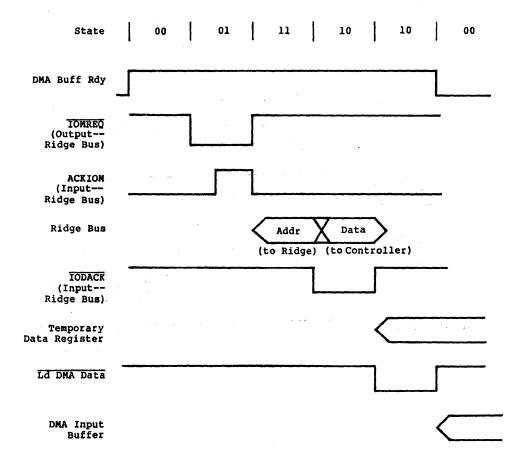

#### DMA logic

The DMA section contains a Word Count Register, a Ridge Address Register, and a Z80 Address Register. The transfers to or from Ridge memory are converted between 4-byte word format and singlebyte data by a 74S194 universal shift register.

EXAMPLE: When reading from Ridge memory, the data is loaded into the eight 74S194's on the parallel inputs. The high order byte is available immediately for transfer to the Z80 local memory and successive bytes are available after one shift command because of the arrangement of bits in the shift register chips. Each chip has four bits of the 32 bit word which are 8 bit positions apart (e.g., one chip has bits 0, 8, 16, 24; another has 1, 9, 17, 25). When the transfer is from Z80 memory to Ridge memory, the shift register is loaded by shifting a bit serially from each of the 8 bits of the byte wide Z80 bus into each of the eight 74Sl94's. Again, only four shifts are required for the conversion between byte and word. The Z80 memory transfers are co-ordinated with the Z80 CPU and Z80 DMA chip by obeying the conventions of BUSRQ and BUSAK defined for the Z80 family. When the state machines have control of the Z80 bus, they transfer four bytes at a time.

The DMA section has three inter-related state machines to control it:

a four-state sequencer called "MAIN" in the state diagrams which co-ordinates the startup process;

an eight-state sequencer called "RSM" which is the main generator of Ridge I/O bus memory signals; a four state sequencer called "ZREQ" which follows the Z80 BUSRQ and BUSACK rules;

and an eight-state sequencer called "DMA" which generates the Z80 memory strobes while doing a Z80 DMA cycle.

Before a DMA sequence begins, the Z80 program must set the direction of the transfer by setting the "Z'Write" bit. The addresses and word count registers also must be set. The Z80 then sets and then clears the "MSTART" bit to begin the DMA process.

When the "MSTART" bit is set, the "MAIN" state machine advances from state 0 to 1. On the next 125-ns clock cycle, the "RSM" advances from state 0 to 5. Normally, certain logic signals would be generated in state 5 but they are blocked because "MAIN" is still in state 1. While "MAIN" is in state 1, the "Z'Write" bit is copied to the "RWT" bit (Ridge Memory Write bit). By now, the DMA process has initiated, but is waiting for the Z80 to clear the "MSTART" bit. On the next cycle after the "MSTART" bit is cleared, the "MAIN" state machine advances to state 3 for one cycle and then remains in state 2 until the whole DMA transfer is complete. "MAIN" state 2 is a condition in many request signals that originate in "RSM"; until it is true, very little happens. The "MAIN" state 3, which is only true for one cycle, advances the "RSM" state to 7 if "RWT" is clear (the DMA transfer will be from Ridge memory to Z80 memory) so that on the cycle where "MAIN" state 2 first enables everything, "RSM" will be either in state 5 if RWT is set, or in state 7 if RWT is clear.

RIDGE TO Z80 MEMORY TRANSFERS

In this case, RWT is clear and the "RSM" begins its work in state In this state, the signal IOMREQ is generated and the daisy-7. chain signal ACKIOMout is blocked from continuing to lower priority When the board detects ACKIOMin become true, it advances boards. its state to 6, where it removes IOMREQ but asserts the Ridge Memory Address on the bus. On the next cyle, the RSM enters state 2, where it will stay until the memory controller asserts IODACK. In this state, the 74S194's are given a command to parallel load the Ridge I/O bus. For several cycles, they will be loading zeros (the state of the un-driven bus), but on the cycle where IODACK is asserted they will have loaded the data returned by the memory controller. With IODACK, the RSM enters state 3 which is named "UNLOAD". In this state, the RSM generates a signal "I WANT" (service from the Z80 section of the DMA machines). It will remain in this state until it sees a signal called "INC WC" which comes from the "DMA" state machine. During the cycle where "INC WC" is asserted, two other signals are examined: the carry-out from the Word Counter and the "ZERO" bit (the most significant bit of the Word Counter). If either "CARRY" or "ZERO" is set, the next state will be state 1 which asserts no signals and is followed immediately by state 0, the null state. Otherwise, the next state is 7 which was discussed in the beginning of this paragraph. The consequences of the signal "I WANT" will be discussed in following paragraphs.

**Z80 TO RIDGE MEMORY TRANSFERS**

In this case, the "RSM" remains in state 5 and various signals become active as "MAIN" reaches state 2. In particular, the signal "I WANT" is generated; this will cause activity in the two remaining state machines ("ZREQ" and "DMA") and will be discussed in the next paragraph. The "RSM" machine will stay in state 5 (named "load-up") until it sees the signal "INC WC". When it does (and the 74LS194's are loaded with a word of data for Ridge memory), the state will progress to state 7 where IOMREQ is generated and ACKIOMout is blocked. It will stay in this state until ACKIOMin reaches this board at which time the state will advance to state 6, also named the MADDR state. Here, the Ridge Memory address will be gated on the Ridge I/O bus. The next clock advances the state the MDATA state (state 4) where the contents of the 74S194's are gated onto the Ridge I/O bus. If the "ZERO" signal (the most significant bit of the Word Counter) is true, the next state will be state 0, the null state. If it is not, the next state is state 5 which was discussed at the beginning of this paragraph.

The "I WANT" signal causes the "ZREQ" state machine to advance from its null state (assuming that the Z80 DMA chip isn't currently asserting BUSREQ) to state 1, where it asserts BUSREQ to the Z80 CPU and Z80 DMA. If it sees BAO (Bus Acknowlege Out) for two cycles, it knows the Z80 CPU is ready to release the Z80 bus and that the Z80 DMA chip isn't currently requesting the bus. The "BAO" signal is the "BUSAK" signal from the Z80 CPU chainned through the Z80 DMA chip. "BUSREQ" continues to be asseted and, until it sees "INCWC", the "ZREQ" machine remains in state 2 (where it takes control of the Z80 bus and memory control signals by asserting "ALTernateENable". When "INCWC" is asserted, the ZREQ machine returns to its null state.

The "DMA" machine generates the Z80 memory control signals required to read or write data into the local memory and the "INCBC" and "INCWC" signals which control the address and word counters. It also generates the 74S194 "Shift Left" signal which converts between word and byte data formats. On the next cycle after it sees "ALTernate ENable", it leaves its null state and, in state 1, asserts an alternate "MREQ" signal to the Z80 memory system. If "RWT" is true, it also asserts an alternate "RD" signal to the Z80 memory system. It advances to state 3 and asserts the same signals as state 1. On the next 125ns clock, it advances to state 7 and asserts an alternate "WT" signal to the Z80 memory system if "RWT" is false. On the next clock edge, it advances to state 6 and asserts the same signals as it did in state 7, and also the 74S194 "Shift Left" signal if "RWT" is set. On the next clock edge, in state 4, it asserts the 74S194 "Shift Left" signal if "RWT" is false, and asserts the "INCBC" signal to advance the address registers. If "INCBC" is true and the two least significant Ridge Address Register bits are both ones (this register contains the full byte address), the "INCWC" signal is generated which which advances the "ZREQ" and "RSM" state machines as well as incrementing the Word Counter. On the next clock cycle, the "DMA" state machine advances to its null state. Each time the "DMA" machine is started up, it loops through its states four times and transfers four bytes before the "INCWC" signal is generated, which causes the "ZREQ" state machine to change state back to its null state and remove "ALTernate ENable", which leaves the "ZREQ"

#### <u>Z80 CPU</u>

The Z80 section is fairly conventional, with the exception that most of the I/O Write strobes are "shaped" by a pair of flip-flop bits that detect the first full cycle of the WT signal and generate pulses that are 125 or 250 ns wide.

#### Z80 Memory System

There are four 2732 EPROM chips on the board and a fairly conventional implementation of a 16K-byte dynamic ram subsystem for the Z80. Its unusual aspect is the "alternate" control signals which can come from the DMA machine described previously.

#### Z80 DMA Chip

The Z80 DMA chip's Bus Acknowledge In and Out signals (BAI and BAO) are part of the chain between the Z80 CPU and the "DMA" state machine described earlier. The DMA chip's INT pin is decoded to provide the Terminal Count (TC) signal to the Floppy Disc Chip described next.

#### Floppy Disc Chip

The floppy disc chip is a NEC uPD765 (Intel 8272). It provides most functions other than buffering, write pre-compensation, and read clock/data separation.

Write pre-compensation is performed by a shift register that delays Write Data from the chip by 82.5 ns per stage. The NEC 765 provides Early and Late signals that select betwen early, normal, and late data. The pre-compensation selected also depends on the track (the outer tracks are not pre-compensated) and whether a single- or double-density operation is taking place (only double-density is pre-compensated). The normal pre-compensation time is 250 ns.

Read data/clock separation is done with a phase-locked loop. The raw read data is fed to the first one-shot, whose time period is set to one of two values selected by transistor T401, depending on whether double-density (MFM) or single-density (FM) is selected. In either case, the one-shot's value is set to half the nominal window size for the density selected (0.5 microseconds for MFM and 1.0 microsecond for FM). The output of the Voltage Controlled Oscillator (VCO) is divided by an appropriate constant to generate a square wave with an on-time similar to that of the one-shot. Two flip-flops, with their clocks and clears cross-coupled to the shaped read data and VCO divided reference clock generate "pump up" "pump down" signals which are summed and integrated by an and operational amplifier to adjust the frequency and phase of the VCO. The further divided VCO clock becomes the Read Window signal to the NEC 765. A one-shot with a short (20 ns) value triggered off the negative edge of the first one-shot's output is used as the Read Data input to the NEC 765.

The floppy disc chip's interrupt request pin is connected to one of the CTC channels to generate the correct Z80 interrupt responses.

Z80 SIO Chips

Two Z80 SIO chips are used in a conventional manner to provide four serial channels. The baud rate clocks are derived from the outputs of four channels of the channels of two Z80 CTC chips. They are used as programmable dividers of a 1.22825 M Hz signal obtained from an oscillator chip.

#### Line Printers

The line printer logic includes one four-state sequencer which contains the protocol for the Versatec printers, and one which can be configured to either follow the Data Products or the Centronics protocol. In both cases, when the Z80 attempts to write to the line printer port with a OUT instruction, the state machine is checked to be sure that it is in its null state and that the line printer is not busy. If either of those two conditions are false, no data strobe gets through to the printer. Instead, a signal to a CTC channel is generated and a wait state for the OUT (which is always at least one cycle long) is extended to eight cycles to allow the CTC time to interrupt. The next instruction executed will be that of some interrupt procedure (most likely that of the CTC channel just mentioned). In any case, the OUT is stopped and a stack marker laid down. The interrupt procedure sets various flags and alters the return address to point beyond the OUT instruction. The Z80 code that generates the OUT's expects that to happen, and checks the flags and the "B" register to determine how many bytes were transfered. This circuitry allows the printers' buffers to be filled at the rate of OTIR instructions rather than a Z80 software loop that would test the printer state machines. The two CTC channels used for the two state machines can also be used generate interrupts when the printers become ready so that, perhaps, a software task to write more data to the printers can be scheduled and eventually run.

#### FDLP Board Programming Overview

The Floppy Disc / Line Printer (FDLP) controller can control two floppy disc drives, four RS-232 ports, a DataProducts/Centronicstype printer port, and a Versatec-type printer/plotter port.

There are 16 units. Terminals have 3 units each.

| unit(s) | use                             |

|---------|---------------------------------|

|         |                                 |

| 0 - 3   | Terminal Writes                 |

| 8 - 11  | Terminal Reads                  |

| 12 - 15 | Terminal Control and Status     |

| 4       | Versatec Printer/Plotter        |

| 5       | DataProducts/Centronics Printer |

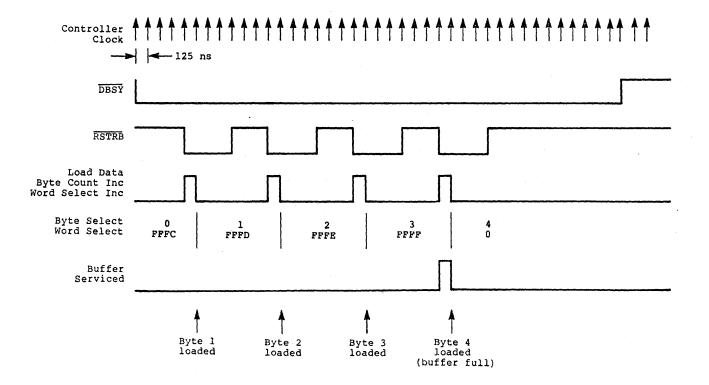

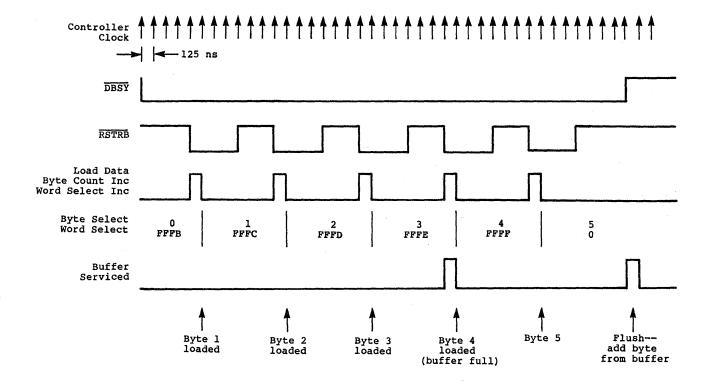

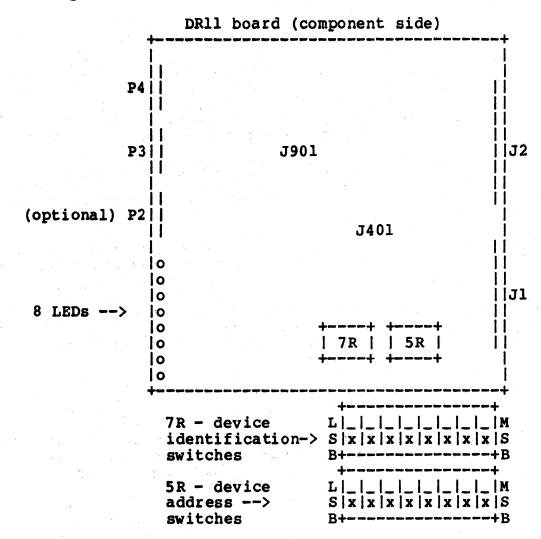

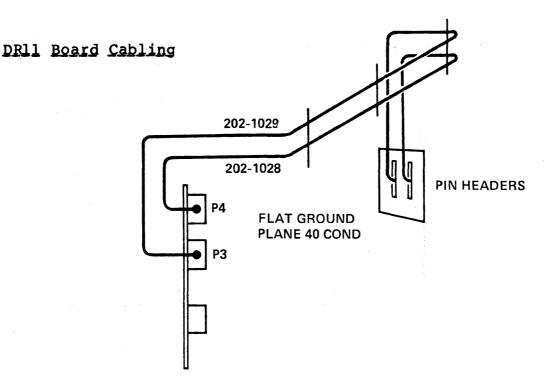

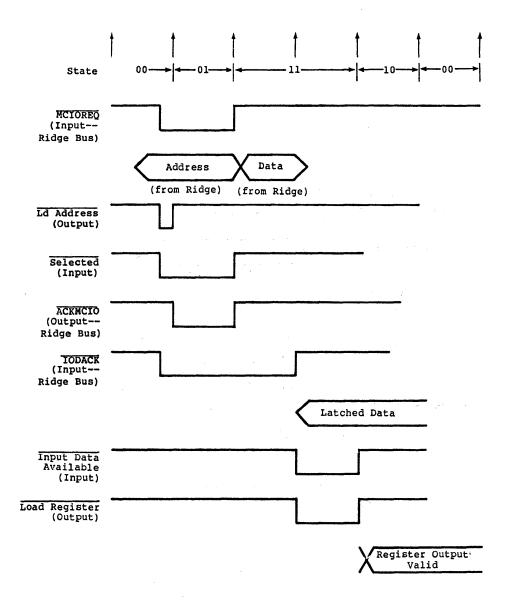

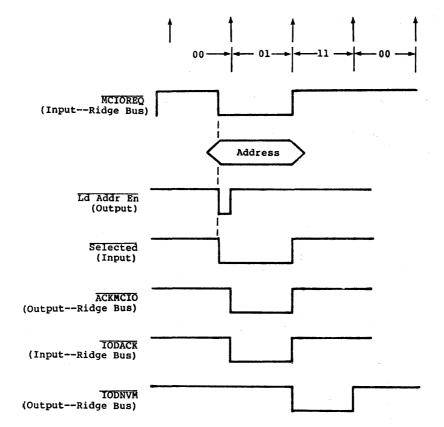

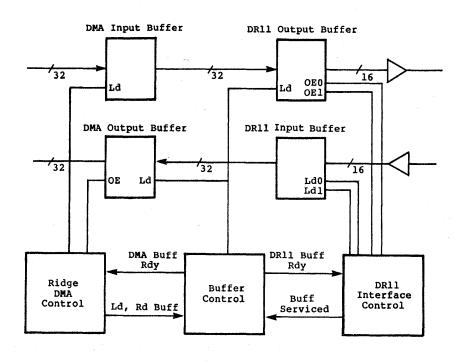

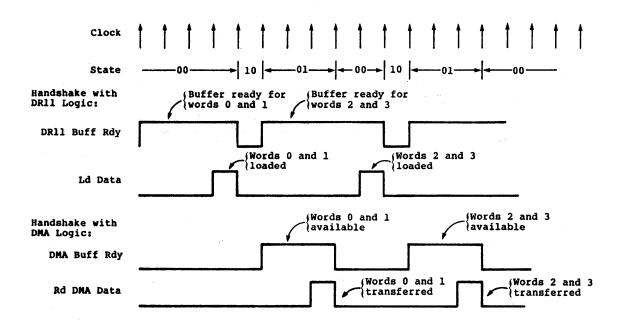

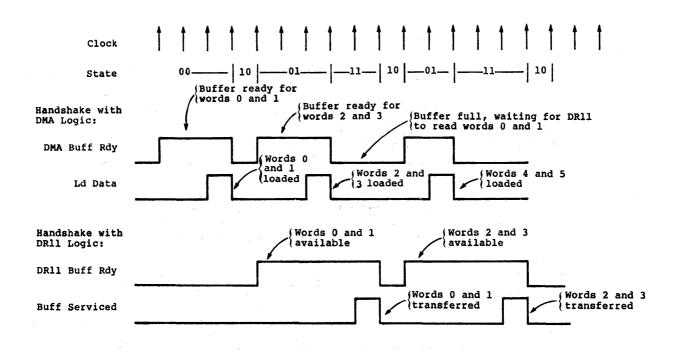

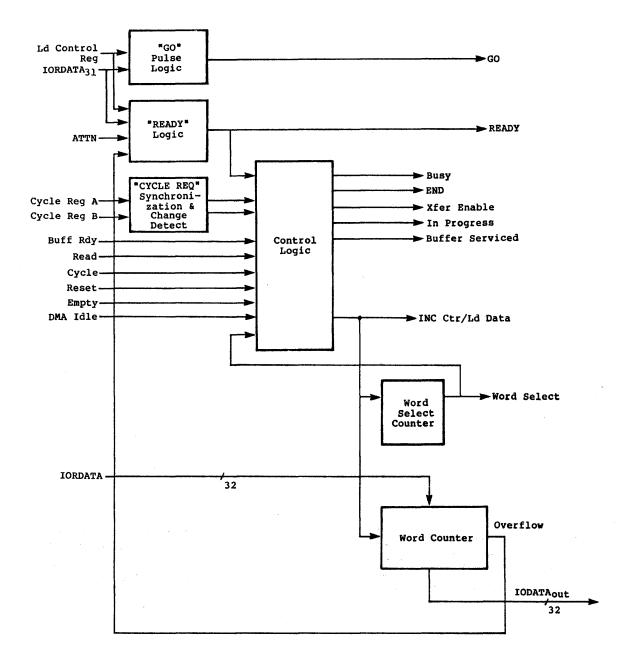

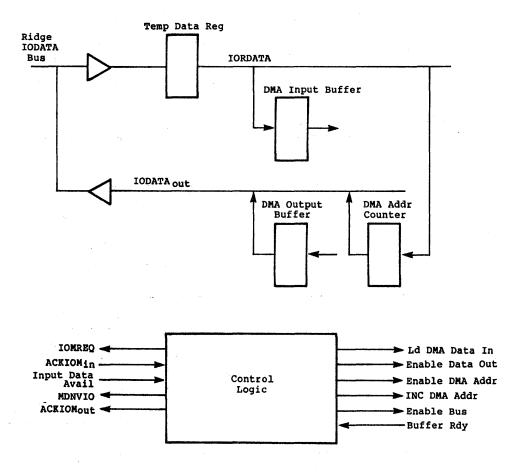

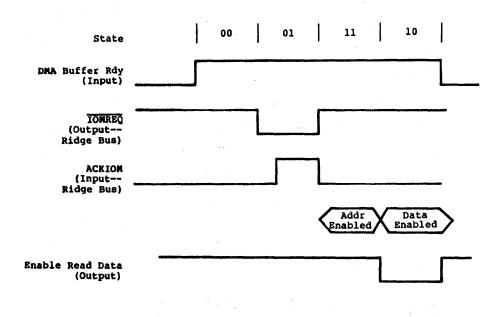

| 6       | Floppy Disc                     |