# SPECTRA 70

70/46

# Processor Reference Manual

70-46-601 March 1968 The information contained herein is subject to change without notice. Revisions may be issued to advise of such changes and/or additions.

First Printing: April 1967 Reissued: March 1968

## CONTENTS

|                   |                                                      | Page     |

|-------------------|------------------------------------------------------|----------|

| INTRODUCTION      | RCA Model 70/46 Processor                            | 1        |

|                   | Organization of Data                                 | 3        |

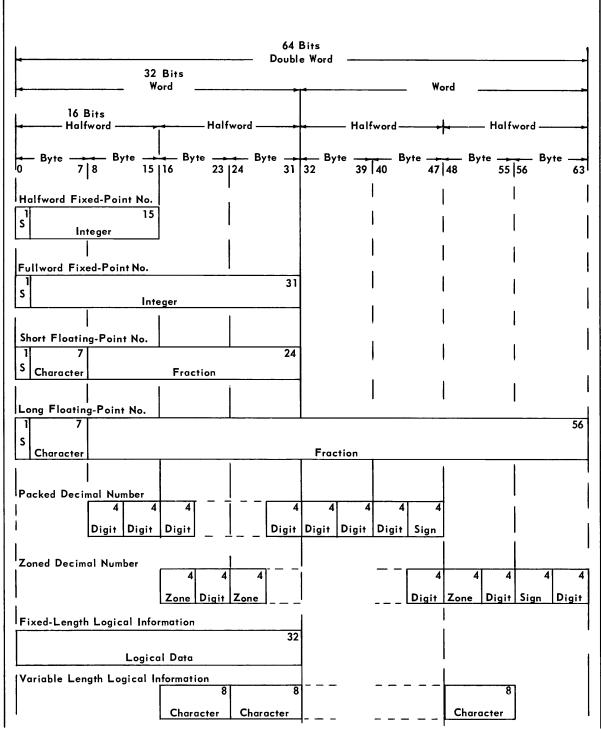

|                   | Data Formats                                         | 3        |

|                   | Numbering System                                     | 3        |

| SYSTEM STRUCTURE  | Main Memory                                          | 4        |

| STSTEM STRUCTURE  | Non-Addressable Main Memory                          | 4        |

|                   | Scratch-Pad Memory                                   | 4        |

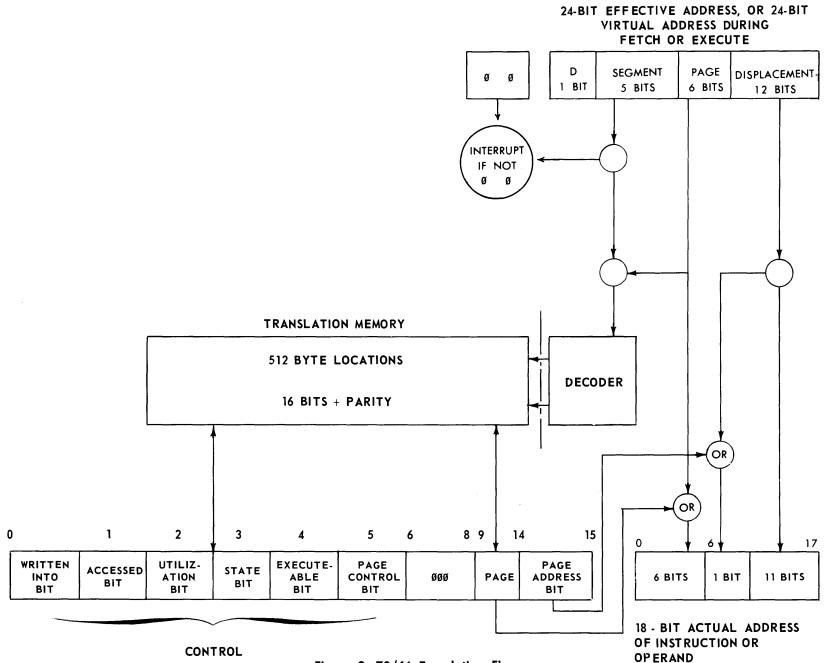

|                   | Translation Memory                                   | 5        |

|                   | Read-Only Memory                                     | 6        |

|                   | Program Control and Arithmetic Unit                  | 6        |

|                   | Input/Output Control                                 | 8        |

|                   | Interval Timer                                       | 8        |

|                   |                                                      |          |

| INSTRUCTION       | RR Format                                            | 9        |

| FORMATS           | RX Format                                            | 9<br>9   |

|                   | RS Format       SI Format                            | 9<br>10  |

|                   | SS Format                                            | 10       |

|                   |                                                      | 10       |

| ADDRESSING        | Memory Address Translation                           | 12       |

| PROGRAM INTERRUPT | Introduction                                         | 16       |

|                   | Processor States                                     | 16       |

|                   | Processing State $P_1$                               | 16       |

|                   | Interrupt Response State P <sub>2</sub>              | 16       |

|                   | Interrupt Control State P <sub>3</sub>               | 16       |

|                   | Machine Condition State P <sub>4</sub>               | 16       |

|                   | Processor State Registers                            | 17       |

|                   | Program Counter                                      | 17       |

|                   | General Registers                                    | 18       |

|                   | Floating-Point Registers                             | 18       |

|                   | Interrupt Status Registers                           | 18<br>20 |

|                   | Interrupt Mask Registers                             | 20<br>20 |

|                   | Program Mask Registers                               | 20<br>21 |

|                   | Register Addressing          Interrupt Flag Register | 21       |

|                   | Interrupt Conditions                                 | 23       |

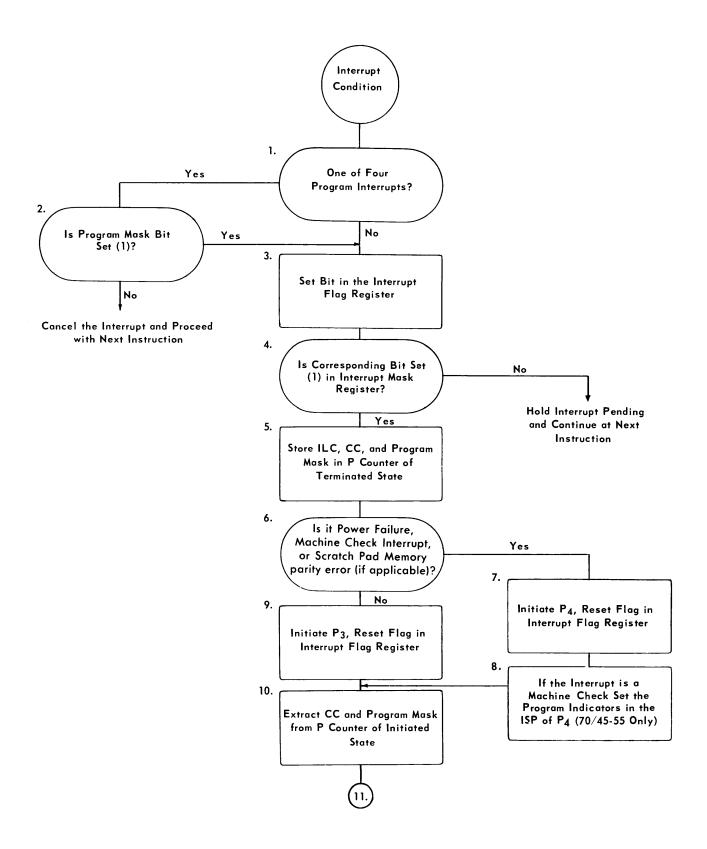

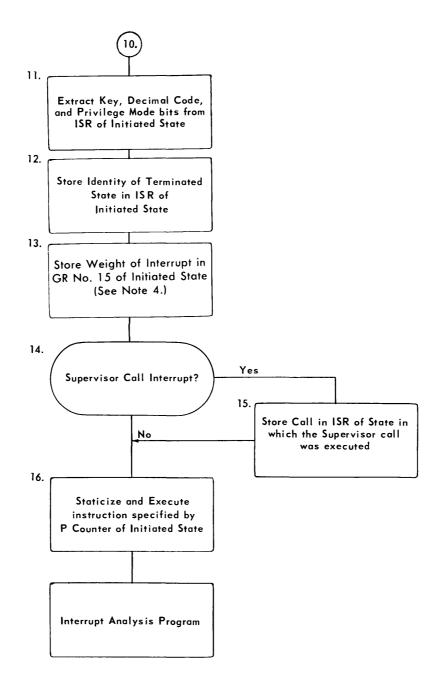

|                   | Interrupt Mechanization                              | 23       |

|                   | Automatic Interrupt                                  | 23       |

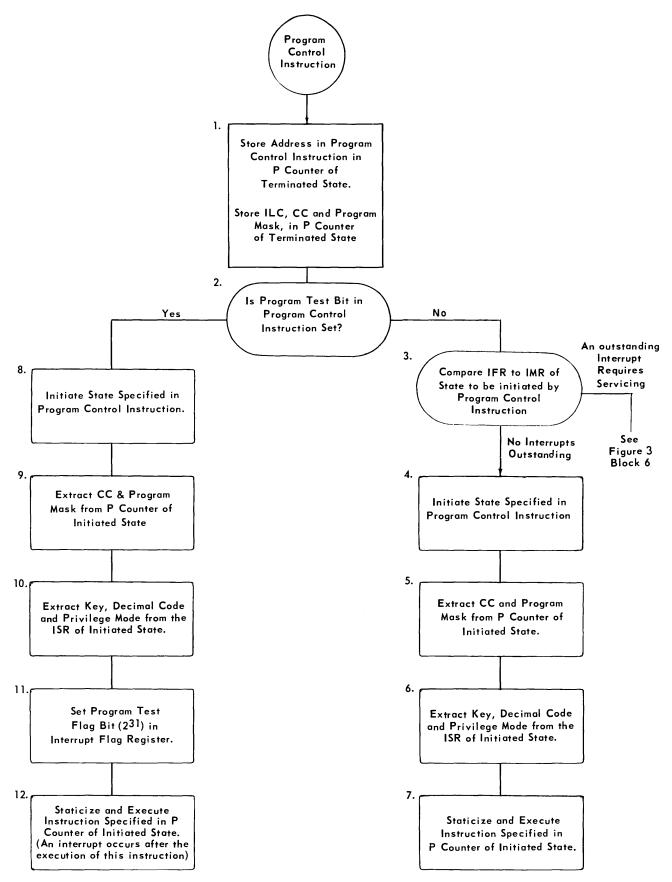

|                   | Program Controlled Interrupt                         | 33       |

|                   |                                                      |          |

|                   | Introduction                                         | 36       |

| OPERATION         | Input/Output Channels                                | 36       |

|                   | Selector Channels                                    | 36       |

|                   | Multiplexor Channel                                  | 37       |

## Page

| INPUT/OUTPUT<br>OPERATION | Input/Output Operational Control<br>Programming Considerations Prior to Input/Output Initiation | 38<br>38   |

|---------------------------|-------------------------------------------------------------------------------------------------|------------|

| (Cont'd)                  | Input/Output Initiation                                                                         | 38         |

|                           | Channel Servicing                                                                               | 38         |

|                           | Channel Address Word (CAW)                                                                      | 40         |

|                           | Channel Block Address (CBA)                                                                     | 40         |

|                           | Channel Command Word (CCW)                                                                      | 40         |

|                           | Input/Output Channel Registers                                                                  | 45         |

|                           | Channel Address Register (CAR)                                                                  | 45         |

|                           | Channel Command Register-II (CCR-II)                                                            | 45         |

|                           | Channel Command Register-I (CCR-I)                                                              | 46         |

|                           | Assembly/Status Register                                                                        | 47         |

|                           | CBA Register                                                                                    | 47         |

|                           | Input/Output Instructions                                                                       | 47         |

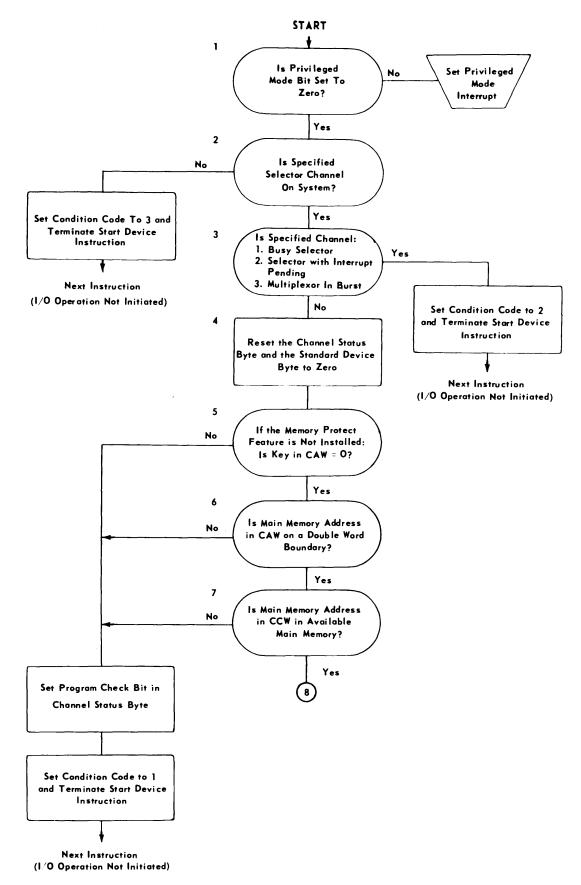

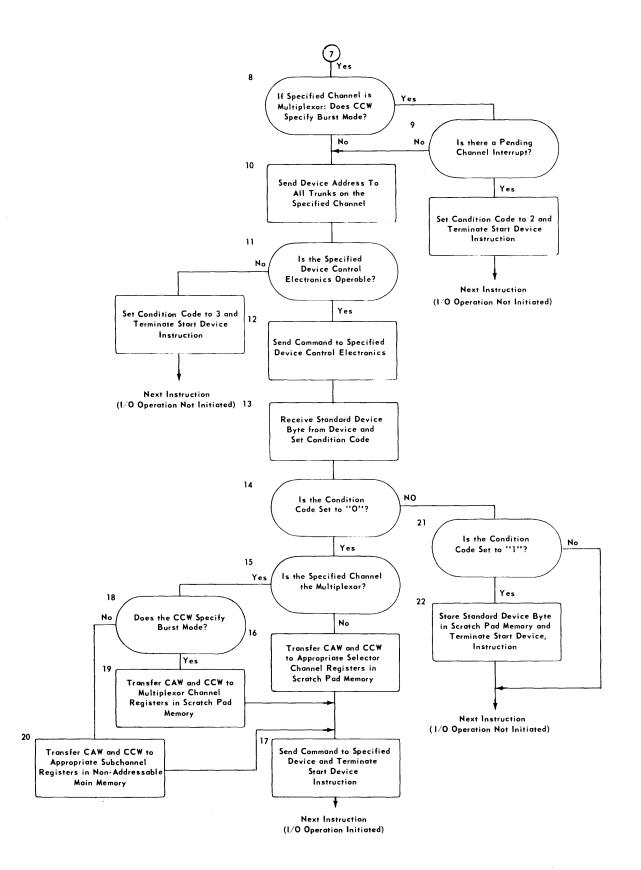

|                           | Start Device Instruction                                                                        | 47         |

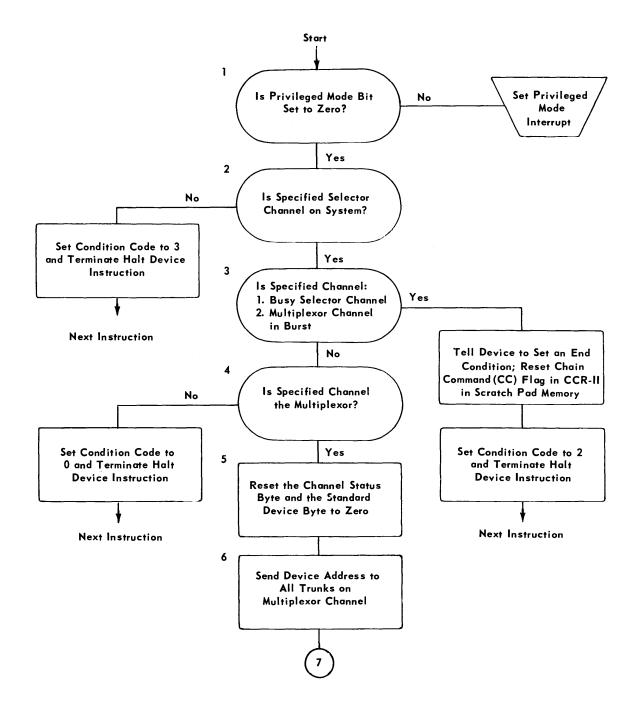

|                           | Halt Device Instruction                                                                         | 52         |

|                           | Test Device Instruction                                                                         | 5 <b>6</b> |

|                           | Check Channel Instruction                                                                       | <b>6</b> 0 |

|                           | Input/Output Status Indicators                                                                  | <b>6</b> 0 |

|                           | Condition Code                                                                                  | 61         |

|                           | Channel Status Byte                                                                             | <b>6</b> 3 |

|                           | Standard Device Byte                                                                            | 65         |

|                           | Sense Bytes                                                                                     | 66         |

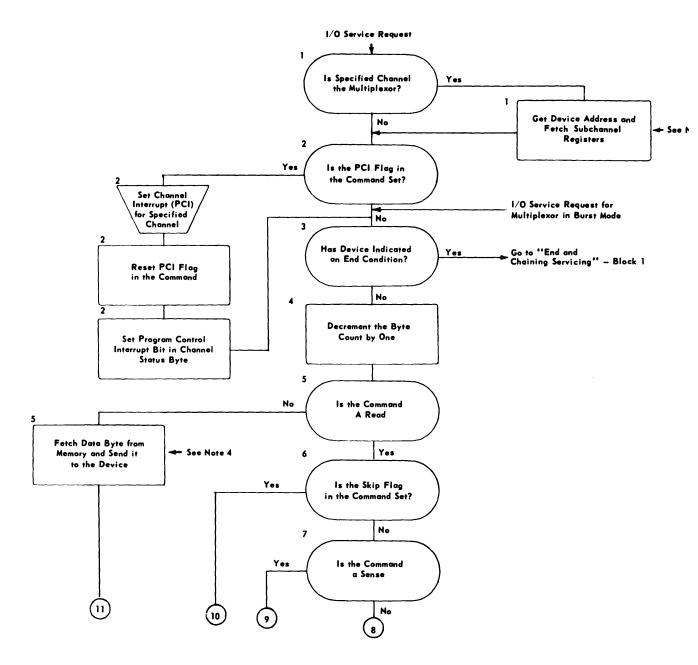

|                           | Channel Servicing                                                                               | 66         |

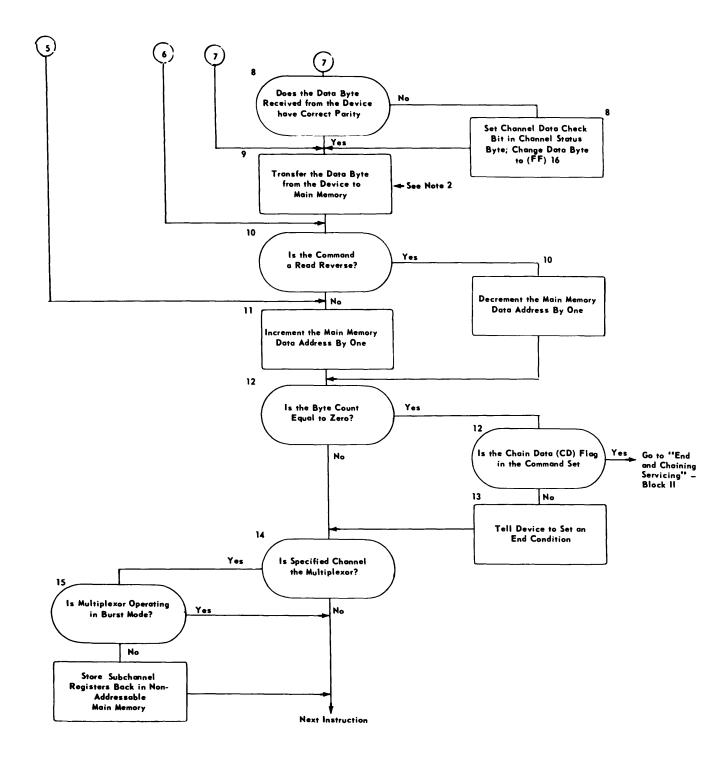

|                           | Servicing a Data Transfer                                                                       | 67         |

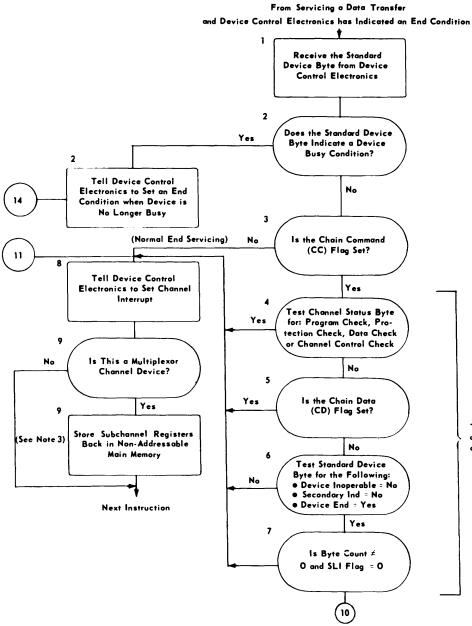

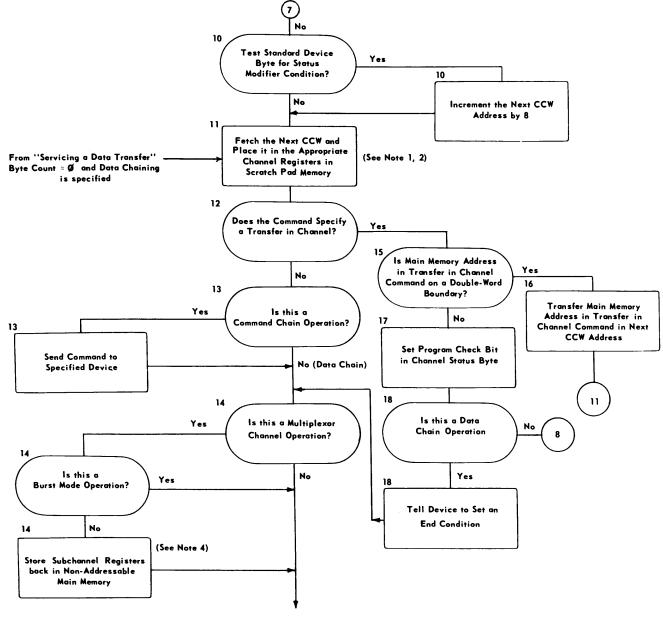

|                           | End and Chaining Servicing                                                                      | 72         |

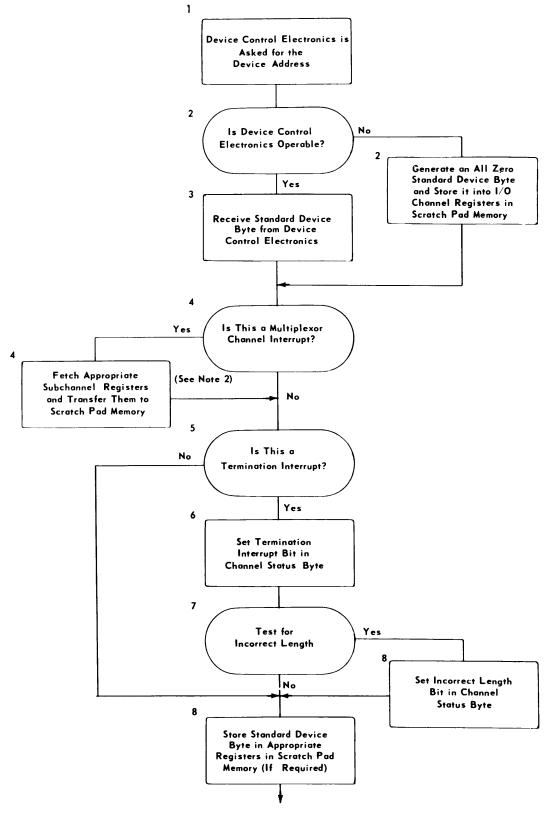

|                           | Interrupt Servicing                                                                             | 77         |

|                           |                                                                                                 |            |

| MULTI-PROCESSOR           | Introduction                                                                                    | 81         |

| INSTALLATION              | Operational Characteristics                                                                     | 81         |

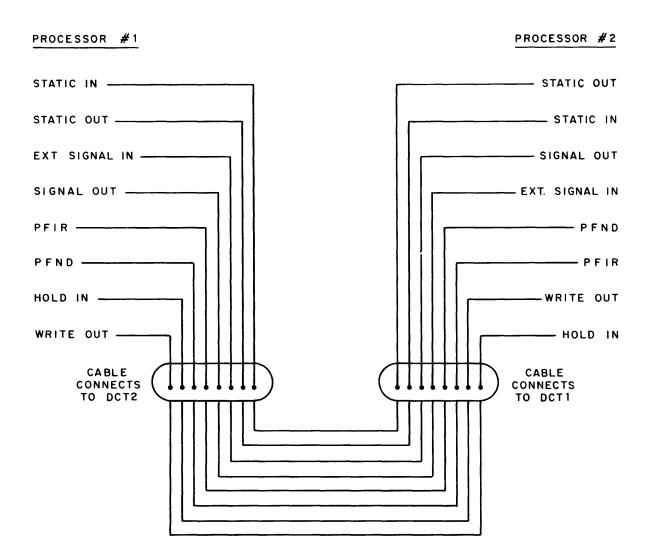

|                           | Direct Control Interface                                                                        | 82         |

|                           | Static Out Lines                                                                                | 82         |

|                           | Static In Lines                                                                                 | 82         |

|                           | Signal Out Line                                                                                 | 82         |

|                           | External Signal In Line                                                                         | 82         |

|                           | Power Failure Line (PFND)                                                                       | 82         |

|                           | Power Failure Inhibit In Line (PFIR)                                                            | 82         |

|                           | Dual Processor Complex                                                                          | 83         |

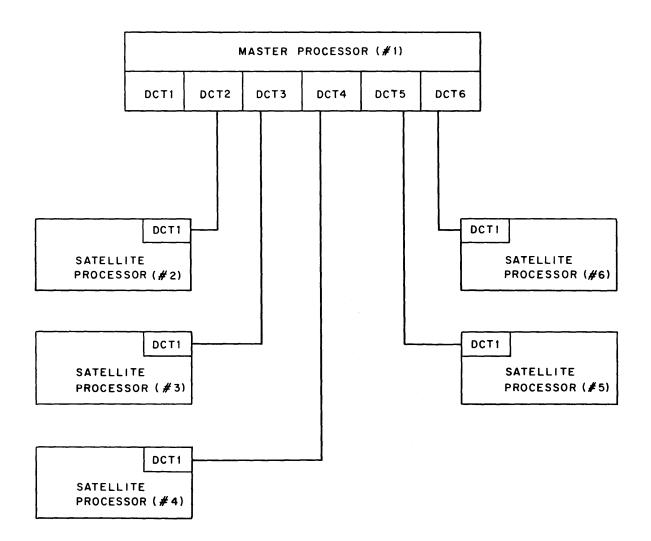

|                           | Master/Satellite Complex                                                                        | 84         |

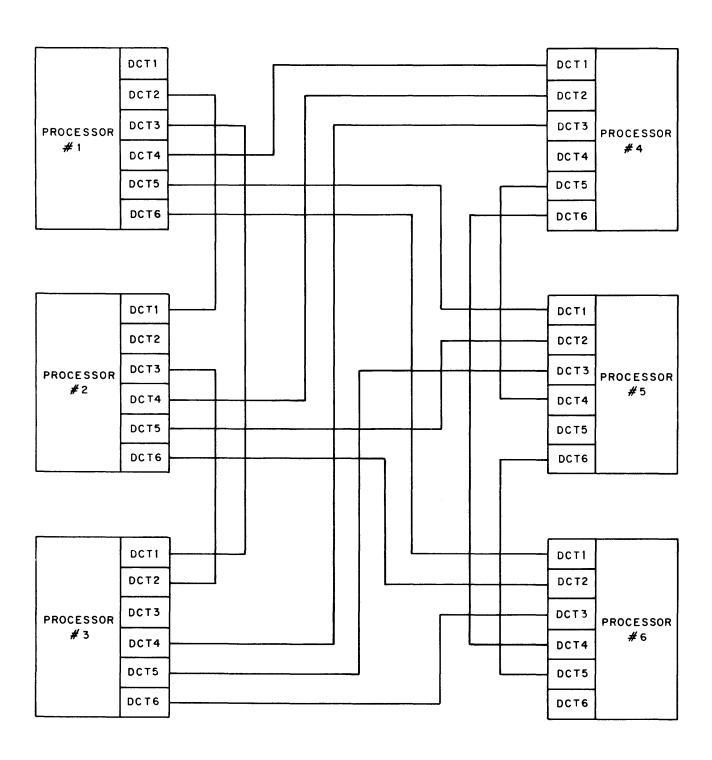

|                           | Maximum Multi-Processor Complex                                                                 | 85         |

|                           | Operational Procedures                                                                          | 86         |

|                           | Transmission Procedure                                                                          | 86         |

|                           | Response Procedure                                                                              | 86         |

|                           |                                                                                                 | 00         |

| PRIVILEGED                | Introduction                                                                                    | 88         |

| INSTRUCTIONS              | Introduction                                                                                    |            |

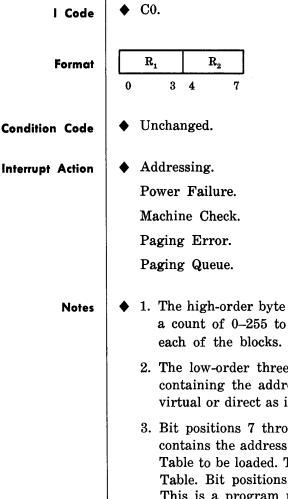

|                           | Instruction Formats                                                                             | 88         |

|                           | Interrupt Action                                                                                | 88         |

|                           | Function Call (FC)                                                                              | 90<br>92   |

|                           | Special Function #1 Load Translation Memory (LTM)                                               |            |

|                           | Special Function #2 Scan Translation Memory and Store (STMS)                                    | 94         |

|                           | Special Function #3 Store Translation Memory (STM)                                              | 96         |

|                           | Special Function #4 Load Interval Timer (LIT)                                                   | 97         |

|                            |                                                                                                               | Page  |

|----------------------------|---------------------------------------------------------------------------------------------------------------|-------|

| PRIVILEGED<br>INSTRUCTIONS | Special Function #5 Store Interval Timer (SIT)<br>Special Function #6 Paging Queue and Paging Error Interrupt | 98    |

| (Cont'd)                   | Service                                                                                                       | 99    |

|                            | Load Scratch-Pad (LSP)                                                                                        | 102   |

|                            | Store Scratch-Pad (SSP)                                                                                       | 103   |

|                            | Program Control (PC)                                                                                          |       |

|                            | Idle (IDL)                                                                                                    | 106   |

|                            | Diagnose (DIG)                                                                                                | 107   |

|                            | Start Device (SDV)                                                                                            |       |

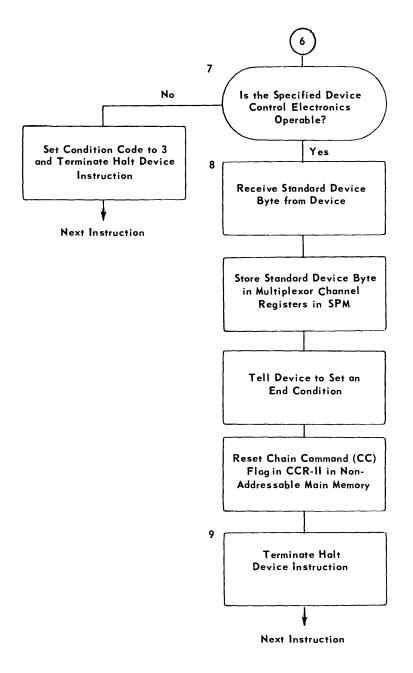

|                            | Halt Device (HDV)                                                                                             |       |

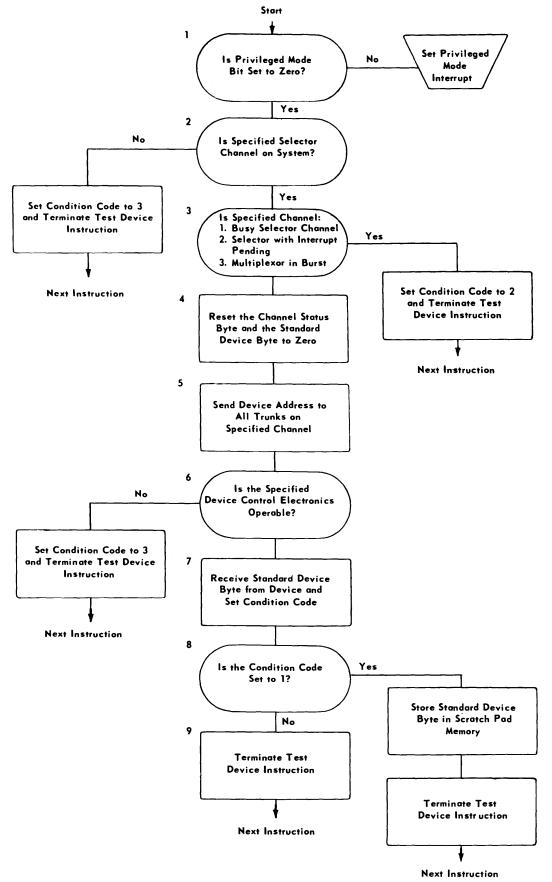

|                            | Test Device (TDV)                                                                                             |       |

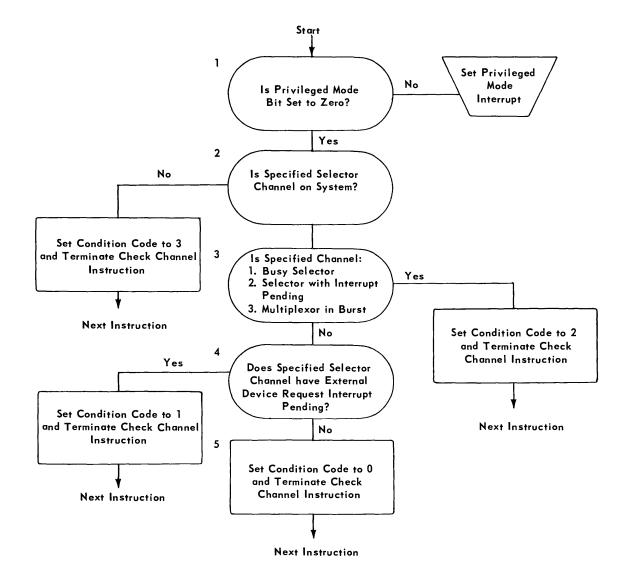

|                            | Check Channel (CKC)                                                                                           |       |

|                            | Insert Storage Key (ISK)                                                                                      |       |

|                            | Set Storage Key (SSK)                                                                                         |       |

|                            | Write Direct (WRD)                                                                                            |       |

|                            | Read Direct (RDD)                                                                                             |       |

|                            |                                                                                                               |       |

| PROCESSOR STATE            | Introduction                                                                                                  |       |

| CONTROL                    | Instruction Format                                                                                            |       |

| INSTRUCTIONS               | Condition Code Utilization                                                                                    | . 120 |

|                            | Interrupt Action                                                                                              | . 120 |

|                            | Supervisor Call (SVC)                                                                                         | . 121 |

|                            | Set Program Mask (SPM)                                                                                        | . 122 |

|                            |                                                                                                               | 100   |

| FIXED-POINT                | Introduction                                                                                                  |       |

| INSTRUCTIONS               | Data Format                                                                                                   |       |

|                            | Representation of Numbers                                                                                     |       |

|                            | Instruction Formats                                                                                           |       |

|                            | Condition Code Utilization                                                                                    |       |

|                            | Interrupt Action                                                                                              |       |

|                            | Load Word (LR) (L)                                                                                            |       |

|                            | Load Halfword (LH)                                                                                            |       |

|                            | Load and Test (LTR)                                                                                           | . 129 |

|                            | Load Complement (LCR)                                                                                         | . 130 |

|                            | Load Positive (LPR)                                                                                           |       |

|                            | Load Negative (LNR)                                                                                           | . 132 |

|                            | Load Multiple (LM)                                                                                            | . 133 |

|                            | Add Word (AR) (A)                                                                                             | . 134 |

|                            | Add Halfword (AH)                                                                                             | . 135 |

|                            | Add Logical (ALR) (AL)                                                                                        | . 136 |

|                            | Subtract Word (SR) (S)                                                                                        | . 137 |

|                            | Subtract Halfword (SH)                                                                                        | . 138 |

|                            | Subtract Logical (SLR) (SL)                                                                                   |       |

|                            | Compare Word (CR) (C)                                                                                         |       |

|                            | Compare Halfword (CH)                                                                                         |       |

|                            | Multiply Word (MR) (M)                                                                                        |       |

|                            | Multiply Halfword (MH)                                                                                        |       |

|                            | Divide (DR) (D)                                                                                               |       |

|                            | Convert to Binary (CVB)                                                                                       |       |

|                            | Convert to Decimal (CVD)                                                                                      |       |

|                            | Store Word (ST)                                                                                               |       |

|                            |                                                                                                               |       |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Page |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| FIXED-POINT             | Store Halfword (STH)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 148  |

| INSTRUCTIONS            | Store Multiple (STM)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 149  |

| (Cont'd)                | Shift Left Single (SLA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |

| · · ·                   | Shift Right Single (SRA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 151  |

|                         | Shift Left Double (SLDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 152  |

|                         | Shift Right Double (SRDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 153  |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |

| DECIMAL                 | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| ARITHMETIC              | Data Formats                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |

| INSTRUCTIONS            | Representation of Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |

|                         | Instruction Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|                         | Condition Code Utilization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |

|                         | Interrupt Action                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|                         | Add Decimal (AP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |

|                         | Subtract Decimal (SP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|                         | Zero and Add (ZAP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |

|                         | Compare Decimal (CP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |

|                         | Multiply Decimal (MP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |

|                         | Divide Decimal (DP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |