# ALL APPLICATIONS DIGITAL COMPUTER

DATA PROCESSING ELEMENT (DPE)

#### PROGRAMMER'S REFERENCE MANUAL

Ċ

BR-8184

30 SEPTEMBER 1974

# UNCLASSIFIED

ALL APPLICATIONS DIGITAL COMPUTER (AADC) DATA PROCESSING ELEMENT (DPE) PROGRAMMERS REFERENCE MANUAL

BR-8184

30 September 1974

Prepared for

Naval Air Development Center Warminster, Pennsylvania 18974

PREPARED BY

For a construction on the total of

RAYTHEON COMPANY MISSILE SYSTEMS DIVISION BEDFORD, MASSACHUSETTS

BLANK

# TABLE OF CONTENTS

| PA | GE |

|----|----|

| PREF | ACE   |              |           |                                | xviii |

|------|-------|--------------|-----------|--------------------------------|-------|

| 1.0  | INTRO | INTRODUCTION |           |                                | 1-1   |

| 2.0  | SYSTI | EM ARCHI     | ITECTURE  |                                | 2-1   |

|      | 2.1   | System       | Componen  | ts                             | 2-1   |

|      | 2.2   | Data Pr      | rocessing | Element Components             | 2-5   |

|      |       |              |           |                                | •     |

| 3.0  | DATA  | FLOW         |           |                                | 3-1   |

|      | 3.1   | Primar       | y Bus     |                                | 3-1   |

|      |       | 3.1.1        | Transmis  | sion Types                     | 3-6   |

|      |       | 3.1.2        | Sequence  | Number Field                   | 3-9   |

|      |       | 3.1.3        | Data/Ins  | truction Field                 | 3-9   |

|      |       | 3.1.4        | Source/D  | estination Field               | 3-10  |

|      | 3.2   | Channe       | 1         |                                | 3-11  |

|      |       | 3.2.1        | Input Qu  | eue                            | 3-12  |

|      |       | 3.2.2        | Output Q  | ueue                           | 3-13  |

| 4.0  | PROG  | RAM MANZ     | AGEMENT U | NIT (PMU)                      | 4-1   |

|      | 4.1   | PMU Red      | gisters   |                                | 4-1   |

|      |       | 4.1.1        | Addressa  | ble Registers                  | 4-1   |

|      |       |              | 4.1.1.1   | General Scratchpad Registers   | 4-1   |

|      |       |              | 4.1.1.2   | Program Address Register       | 4-2   |

|      |       |              | 4.1.1.3   | Interval Timer Register        | 4-3   |

|      |       |              | 4.1.1.4   | Source Registers               | 4-3   |

|      |       |              | 4.1.1.5   | Halt Indicator                 | 4-4   |

|      |       |              | 4.1.1.6   | Trap Level Register            | 4-4   |

|      |       |              | 4.1.1.7   | Parity Error Inhibit Indicator | 4-4   |

|      |       |              | 4.1.1.8   | Procedure Kernel Register      | 4-4   |

|      |       |              | 4.1.1.9   | Data Kernel Register           | 4-5   |

|      |       |              |           |                                |       |

-

|     |        | 4.1.1.10   | Upper Bound Register                   | 4-5           |

|-----|--------|------------|----------------------------------------|---------------|

|     |        | 4.1.1.11   | Lower Bound Register                   | 4-5           |

|     |        | 4.1.1.12   | Executive Mode Indicator               | 4-5           |

|     |        | 4.1.1.13   | Data Addressing Mode Indicator         | 4-6           |

|     |        | 4.1.1.14   | Replacement Algorithm Register         | 4-6           |

|     | 4.1.2  | Non Addre  | essable Registers                      | 4-6           |

|     |        | 4.1.2.1    | Procedure Page Register                | 4-6           |

| 4.2 | Modes  | of Operat: | ion                                    | 4-7           |

|     | 4.2.1  | Problem S  | Solving                                | 4-7 `         |

|     | 4.2.2  | Executive  | e Mode                                 | 4-7           |

|     |        | 4.2.2.1    | Entrance Into Executive Mode           | 4-7           |

|     |        |            | 4.2.2.1.1 Programmed                   | 4-8           |

|     |        |            | 4.2.2.1.2 Channel Interrupt            | 4-9           |

|     |        | 4.2.2.2    | Executive Mode Capabilities            | 4-10          |

|     |        |            | 4.2.2.2.1 Emergency<br>Commands        | 4-10          |

|     |        |            | 4.2.2.2.2 Security System              | 4-11          |

|     | •      | 4.2.2.3    | Exit From Executive Mode               | 4-11          |

| 4.3 | Detail | ed Instruc | ction Performance                      | 4-12          |

|     | 4.3.1  | External   | Instructions                           | 4-12          |

|     | 4.3.2  | Emergency  | y Commands                             | 4-13          |

|     | 4.3.3  | Internal   | Instructions                           | 4-14          |

|     |        | 4.3.3.1    | Virtual Addressing<br>Modification     | 4-15          |

|     |        | 4.3.3.2    | Normal Instruction Fetch               | 4-16          |

| ,   |        |            | 4.3.3.2.1 Program Counter<br>Operation | 4-16          |

|     |        |            | 4.3.3.2.2 Page Carry                   | 4-17          |

|     |        | 4.3.3.3    | Procedure Page Fetch                   | 4-17          |

|     |        |            | 4.3.3.3.1 Kernel Entry Word            | 4-18          |

|     |        |            | 4.3.3.3.2 Resident Procedure           | 4-20          |

|     |        |            | 4.3.3.3.3 Non Resident<br>Procedure    | 4 <b>-2</b> 0 |

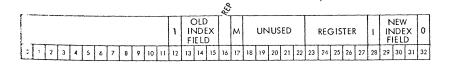

|     |        |            | 4.3.3.3.4 Replacement Algorithm        | 4-21          |

|     |        |            |                                        |               |

iv

•

|       | 4.3.3.4  | Non Standa:<br>Page Fetch | rd Procedure                                           | 4-23 |

|-------|----------|---------------------------|--------------------------------------------------------|------|

|       | 4.3.3.5  | Examples o:<br>Fetch      | f Instruction                                          | 4-23 |

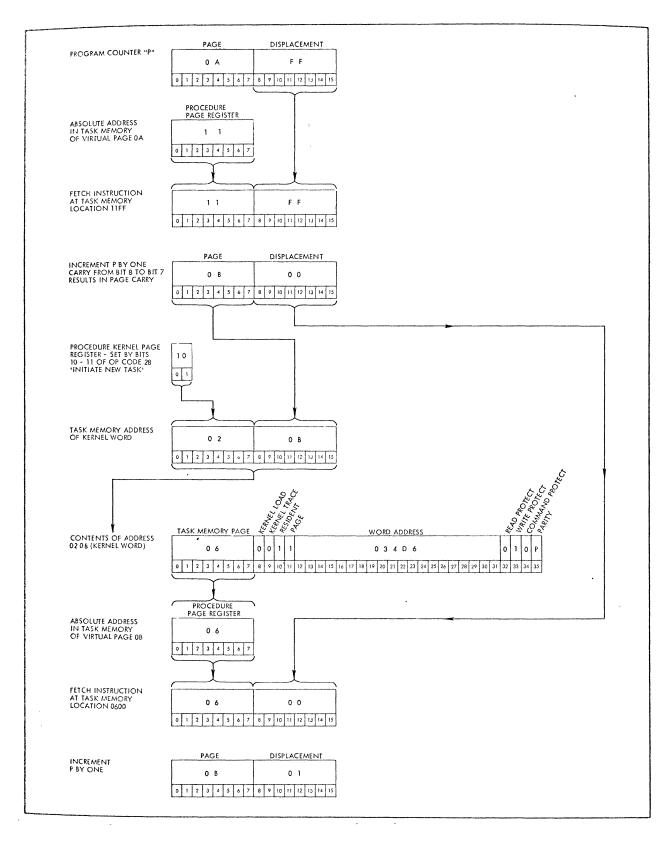

|       |          | 4.3.3.5.1                 | Resident Paged<br>Procedure                            | 4-24 |

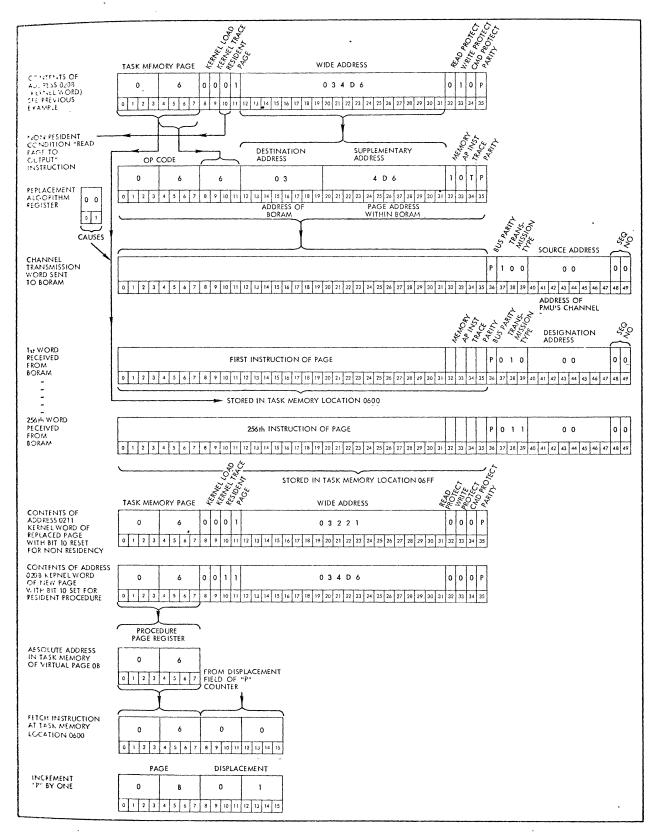

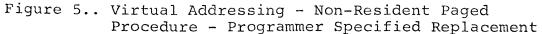

|       |          | 4.3.3.5.2                 | Non Resident Paged<br>Procedure                        | 4-24 |

| 4.3.4 | Instruct | ion Word Int              | terpretation                                           | 4-28 |

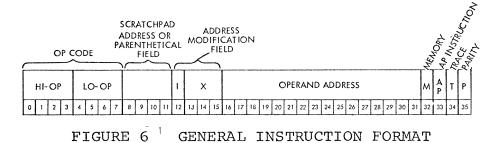

|       | 4.3.4.1  | Instruction               | n Format                                               | 4-28 |

|       | 4.3.4.2  | Parity                    |                                                        | 4-30 |

|       | 4.3.4.3  | Addressing                | Modification                                           | 4-30 |

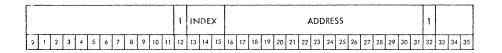

|       |          | 4.3.4.3.1                 | Indexing                                               | 4-30 |

|       |          | 4.3.4.3.2                 | Indirect Addressing                                    | 4-30 |

|       |          | 4.3.4.3.3                 | Chaining of Address<br>Modification                    | 4-32 |

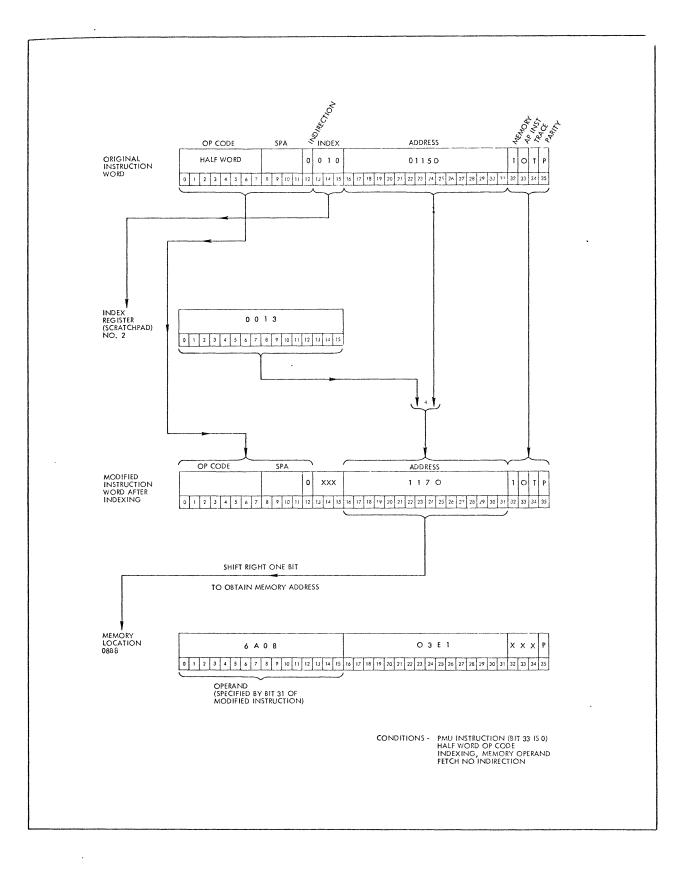

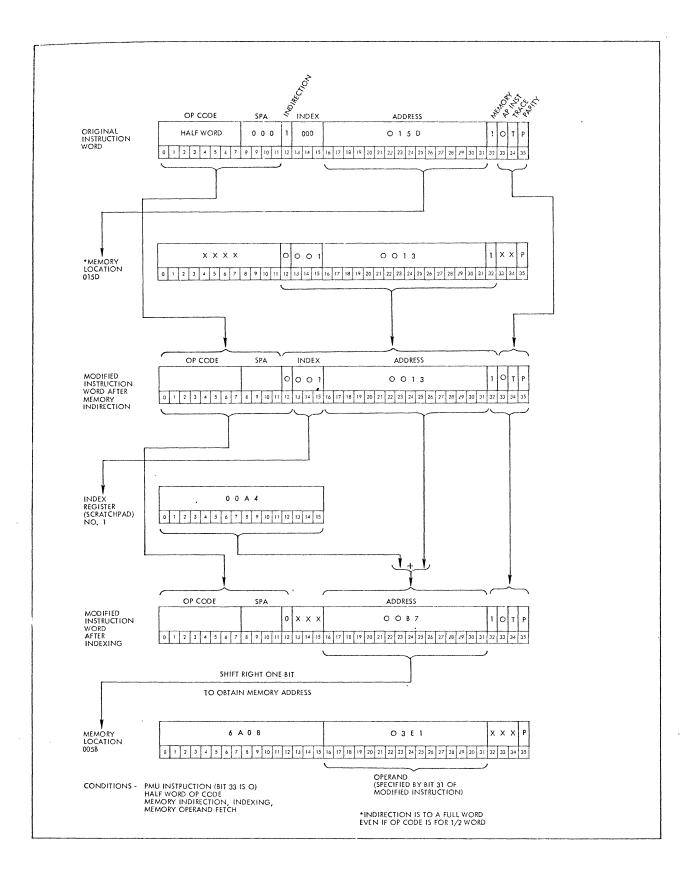

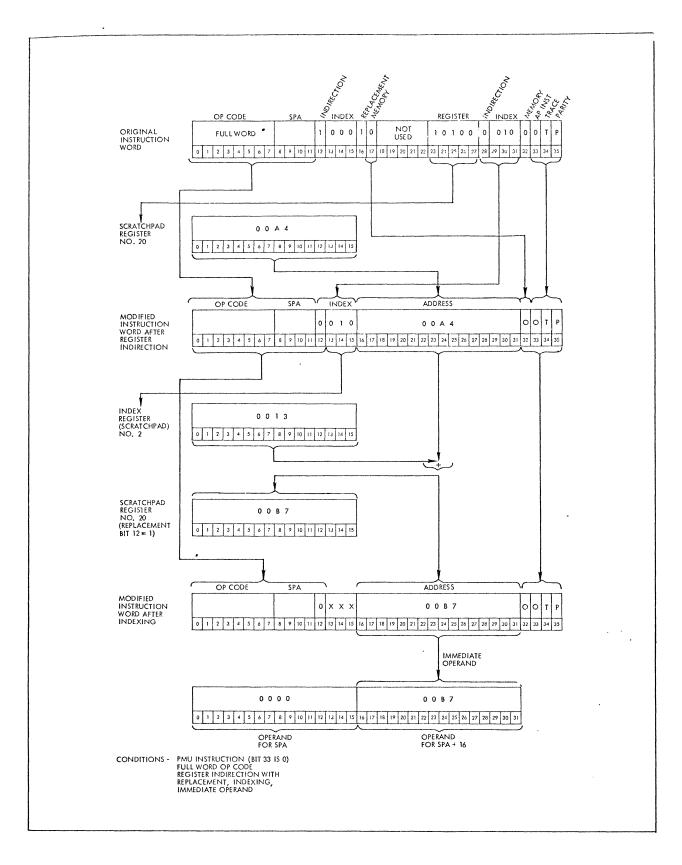

|       |          | 4.3.4.3.4                 | Examples of Address<br>Modification                    | 4-32 |

|       | 4.3.4.4  | Operand Cy                | cle                                                    | 4-38 |

|       |          | 4.3.4.4.1                 | Memory Operand<br>Fetch                                | 4-39 |

|       |          | 4.3.4.4.2                 | Non Memory Operand<br>Fetch                            | 4-44 |

|       |          | 4.3.4.4.3                 | Instruction Trace                                      | 4-45 |

|       |          | 4.3.4.4.4                 | Examples of Non<br>Resident Full Word<br>Operand Fetch | 4-45 |

|       |          | 4.3.4.4.5                 | -                                                      | 4-45 |

| 4.3.5 | Instruct | ion Executio              | -                                                      | 4-51 |

|       | 4.3.5.1  | Operand De                | stination                                              | 4-51 |

|       |          | 4.3.5.1.1                 | Destination is AP                                      | 4-51 |

|       |          | 4.3.5.1.2                 | Destination is PMU                                     | 4-52 |

|       | 4.3.5.2  | PMU Word F                | ormats                                                 | 4-53 |

|       |          | 4.3.5.2.1                 | Half Word Arithmetic<br>Format                         | 4-53 |

|       |          | 4.3.5.2.2                 | Full Word Arithmetic<br>Format                         | 4-53 |

v

| P. | A | GE |  |

|----|---|----|--|

|    |   |    |  |

|     |       | 4.3.5.2.3                      | Half Word Logical<br>Format      | 4-53 |

|-----|-------|--------------------------------|----------------------------------|------|

|     |       | 4.3.5.2.4                      | Full Word Logical<br>Format      | 4-53 |

|     |       | 4.3.5.2.5                      | Shift Count Format               | 4-54 |

|     |       | 4.3.5.2.6                      | Data Transmission<br>Word Format | 4-54 |

|     |       | 4.3.5.2.7                      | Transmission Word                | 4 55 |

|     | 4 2 6 |                                | Format                           | 4-55 |

|     | 4.3.6 | Operand Types                  |                                  | 4-55 |

|     |       | Overlapped Fetch Cy            |                                  | 4-57 |

| 4.4 |       | struction Definition           |                                  | 4-60 |

|     | 4.4.1 | PMU Arithmetic Inst            | ructions                         | 4-62 |

|     |       | (BO) Add                       |                                  | 4-62 |

|     |       | (B4) Add Full                  |                                  | 4-64 |

|     |       | (B3) Subtract                  |                                  | 4-66 |

|     |       | (B7) Subtract Full             |                                  | 4-68 |

|     |       | (CO) Multiply Half             | to Half                          | 4-70 |

|     |       | (C3) Multiply Half             | to Full                          | 4-72 |

|     | •     | (D3) Divide Half b             | y Half                           | 4-74 |

|     |       | (D2) Divide Full by            | Half                             | 4-76 |

|     | 4.4.2 | PMU Logical Instruc            | tions                            | 4-78 |

|     |       | (AO) AND                       |                                  | 4-78 |

|     |       | (A4) AND Full                  |                                  | 4-80 |

|     |       | (90) D And R                   |                                  | 4-82 |

|     |       | (94) D And R Full              |                                  | 4-84 |

|     |       | (C2) D And $\overline{R}$      |                                  | 4-86 |

|     |       | (C6) D And $\overline{R}$ Full |                                  | 4-88 |

|     |       | (B2) OR                        |                                  | 4-90 |

|     |       | (B6) OR Full                   |                                  | 4-92 |

|     |       | (B1) D Or R                    |                                  | 4-94 |

|       |                                | PAGE    |

|-------|--------------------------------|---------|

|       | (B5) D Or R Full               | 4-96    |

|       | (A3) D Or R                    | 4-98    |

|       | (A7) D Or R Full               | 4-100   |

|       | (93) NAND                      | 4-102   |

|       | (97) NAND Full                 | 4-104   |

|       | (Cl) NOR                       | 4-106   |

|       | (C5) NOR Full                  | 4-108   |

|       | (92) XOR                       | 4-110   |

|       | (96) XOR Full                  | 4-112   |

|       | (Al) XNOR                      | 4-114   |

|       | (A5) XNOR Full                 | 4-116   |

| 4.4.3 | PMU Shift Instructions         | 4-118   |

|       | (EO) Shift ARHO                | 4-118   |

|       | (El) Shift ARFO                | 4-120   |

|       | (E2) Shift ALHO                | 4-122   |

|       | (E3) Shift ALFO                | 4-124   |

|       | (FO) Shift LRHO                | 4-126   |

|       | (Fl) Shift LRFO                | 4-128   |

|       | (F2) Shift LLHO                | 4-130   |

|       | (F3) Shift LLFO                | . 4-132 |

|       | (DO) Shift LRHC                | 4-134   |

|       | (D1) Shift LRFC                | 4-136   |

| 4.4.4 | PMU Skip Instructions          | 4-138   |

|       | (62) Skip If Equal To          | 4-138   |

|       | (66) Skip If Equal To Full     | 4-140   |

|       | (71) Skip If Not Equal To      | 4-142   |

|       | (75) Skip If Not Equal To Full | 4-144   |

|       | (61) Skip If Greater Than      | 4-146   |

|       | (65) Skip If Greater Than Full | 4-148   |

|       | (72) Skip If Not Greater       | 4-150   |

.

, .

.

(76) ·Skip If Not Greater Than Full  $4 - 15_{2}$ (70) Skip If Less Than 4 - 154(74) Skip If Less Than Full 4-156 (63) Skip If Not Less Than 4 - 158(67) Skip If Not Less Than Full 4-160 (83) Skip On Bit N 4 - 162PMU Data Instructions 4.4.5 4-164 (91) Convert 2's To SM 4 - 164(95) Convert 2's To SM Full 4-166 (A2) Convert SM To 2's 4 - 168(A6) Convert SM To 2's Full 4 - 170(D6) Round 4 - 172(D7) Binary Normalize 4-173 4.4.6 PMU Transfer Instructions 4-175 (40) Transfer Unconditional 4-175 (42) Transfer If R Is Zero 4-176 (46) Transfer If R Zero Full 4-178 (41) Transfer If R Negative 4-180 (45) Transfer If R NEG Full 4-182 (43) Transfer If Not Equal 4-184 (50) Transfer On Incremented SP 4 - 186(37) Transfer To Executive 4-188 (51) Transfer And Stack 4 - 192(54) Transfer And Stack Kernel 0 4-196 (55) Transfer And Stack Kernel 1 4-196 (56) Transfer And Stack Kernel 2 4 - 196(57) Transfer And Stack Kernel 3 4 - 196(E4) Escape 0 4-197 (E5) Escape 1 4-197 (E6) Escape 2 4-197

PAGE

viii

|       | (E6)          | Escape 2                | 4-197 |

|-------|---------------|-------------------------|-------|

|       | <b>(</b> E7)  | Escape 3                | 4-197 |

|       | <b>(</b> F4)  | Escape 4                | 4-197 |

|       | (F5)          | Escape 5                | 4-197 |

|       | <b>(</b> F6)  | Escape 6                | 4-197 |

|       | (F7)          | Escape 7                | 4-197 |

| 4.4.7 | PMU           | Load/Store Instructions | 4-198 |

|       | <b>(</b> 12)  | Load SP                 | 4-198 |

|       | <b>(</b> 10)  | Load High SP            | 4-200 |

|       | <b>(</b> 16)  | Load SP Full            | 4-202 |

|       | (20)          | Load Left Byte          | 4-204 |

|       | <b>(</b> 22)  | Load Right Byte         | 4-206 |

|       | <b>(</b> 30)  | Load Absolute Value     | 4-207 |

|       | (34)          | Load Absolute Full      | 4-209 |

|       | (31)          | Load Negative           | 4-211 |

|       | <b>(</b> 35)  | Load Negative Full      | 4-212 |

|       | <b>(</b> 80)  | Mask Load               | 4-214 |

|       | <b>(</b> 84)  | Load Control Bits       | 4-216 |

|       | (86)          | Load Multiple           | 4-217 |

|       | <b>(</b> 44)  | Load Data Kernel        | 4-218 |

|       | <b>(</b> 64') | Load Page               | 4-221 |

|       | (13)          | Store SP                | 4-223 |

|       | (11)          | Store High Scratchpad   | 4-225 |

|       | <b>(</b> 17)  | Store SP Full           | 4-227 |

|       | (21)          | Store Byte Left         | 4-228 |

|       | (23)          | Store Byte Right        | 4-230 |

|       | <b>(</b> 85)  | Store Control Bits      | 4-232 |

|       | <b>(</b> 87)  | Store Multiple          | 4-233 |

|       | (77)          | Store Page              | 4-235 |

|       | <b>(</b> 19)  | Move Half to Half       | 4-237 |

|       | (lD)          | Move Full To Full       | 4-239 |

|       | (lF)          | Move Full And Stack     | 4-241 |

| P | PZ | Ŧ | GE |

|---|----|---|----|

|   |    |   |    |

| 4.4.8 | PMU Control Instructions                       | 4-243   |

|-------|------------------------------------------------|---------|

|       | (01) Proceed                                   | 4-243   |

|       | (27) Execute                                   | 4-244   |

|       | (32) Interval Timer Control/Halt               | 4-245   |

|       | (33) Store Interval Timer                      | 4-247   |

|       | (52) Return Stack to P                         | 4-248   |

|       | (53) Return Stack to P And Proceed             | 4-25.0  |

|       | (81) Reset Bit N                               | 4-252   |

|       | (82) Set Bit N                                 | 4-254   |

|       | (29) Set Task Parameters                       | 4-256   |

|       | (25) Set System Parameters                     | 4-258   |

|       | (28) Initiate New Task                         | 4–263   |

|       | (36) Test and Reset                            | 4-266   |

|       | (47) Command Subsystem/Address<br>Modification | 4-268   |

|       | (4F) Command Subsystem/Immediate<br>Execution  | 4-272   |

| 4.4.9 | PMU Input/Output Instructions                  | 4-276   |

|       | (00) Test And Reset To Output                  | 4-276   |

|       | (02) Read Word To Output                       | . 4-277 |

|       | (03) Write Word From Input                     | 4-278   |

|       | (60) Single Word I/O Command                   | 4-279   |

|       | (73) Two Word I/O Command                      | 4-281   |

|       | (7B) Two Word I/O with Indexing                | 4-284   |

|       | (04) Read Operand To Output                    | 4-287   |

|       | (06) Read Page To Output                       | 4-289   |

|       | (OC) Read Array To Output                      | 4-290   |

|       | (OE) Read Indirect Word To Output              | 4-291   |

|       | (05) Write Operand From Input                  | 4-292   |

|       | (07) Write Page From Input                     | 4-294   |

|       | (OD) Write Array From Input                    | 4-296   |

| 5.0 | THE ARITHMETIC PROCESSOR                    | 5-1  |

|-----|---------------------------------------------|------|

|     | 5.1 AP System Components                    | 5-1  |

|     | 5.1.1 The AP Fanout Box                     | 5-3  |

|     | 5.1.2 AP Input Formats                      | 5-6  |

|     | 5.1.3 AP Input Instruction/Data Queue (APQ) | 5-8  |

|     | 5.1.4 The AP Arithmetic Unit (APAU)         | 5-10 |

|     | 5.2 Basic AP Instruction Sequence           | 5-14 |

|     | 5.3 Basic AP Instruction Set                | 5-15 |

|     | 5.3.1 AP Arithmetic Instructions            | 5-16 |

|     | (Cl) Addition                               | 5-16 |

|     | (C4) Reverse Subtract                       | 5-19 |

|     | (C2) Subtract                               | 5-21 |

|     | (EO) Multiply                               | 5-23 |

|     | (D8) Reverse Divide                         | 5-25 |

|     | (DO) Divide                                 | 5-27 |

|     | (D4) Divide Residue                         | 5-29 |

|     | (DC) Reverse Divide Residue                 | 5-31 |

|     | (D2) Divide Short                           | 5-33 |

|     | (DA) Reverse Divide Short                   | 5-35 |

|     | (C5) Load Accumulator                       | 5-37 |

|     | (CA) Load Negative                          | 5-38 |

|     | (CC) Negation                               | 5-39 |

|     | (CF) Absolute Value                         | 5-40 |

|     | (BO) Signum                                 | 5-41 |

|     | (E4) Floor                                  | 5-42 |

|     | (E5) Ceiling                                | 5-43 |

|     | (E2) Square Root                            | 5-44 |

|     | (F4) Normalize                              | 5-45 |

|       |              |                                                  | PAGE  |

|-------|--------------|--------------------------------------------------|-------|

| 5.3.2 | LOAD,        | STORE Instructions                               | 5-46  |

|       | (E8)         | Store and Halt                                   | 5-56  |

|       | (EA)         | Store and Proceed                                | 5-47  |

|       | (31)         | Load Memory Word                                 | 5-48  |

|       | (32)         | Store Packed                                     | 5-49  |

|       | (33)         | Load Deferral                                    | 5-50  |

|       | (34)         | Store Deferral                                   | 5-51  |

|       | (B8)         | Unpack                                           | 5-52  |

|       | (B9)         | Load Word to Accumulator                         | 5-54  |

|       | (35)         | Push Data                                        | 5-55  |

|       | (36)         | Store Operand                                    | 5-56  |

| 5.3.3 | Compa        | are and TVD Instructions                         | ·5-58 |

|       | (92)         | Compare Less Than Destructive                    | 5-58  |

|       | (91)         | Compare Equal Non Destructive                    | 5-59  |

|       | (93)         | Compare Less Than or Equal<br>Non Destructive    | 5-60  |

|       | <b>(</b> 94) | Compare Greater Than Destructive                 | 5-61  |

|       | (95)         | Compare Greater Than or Equal<br>Non Destructive | 5-62  |

|       | (96)         | Compare Not Equal Destructive                    | 5-63  |

|       | (97)         | Set TVD Non Destructive                          | 5-64  |

|       | (98)         | Reset TVD Non Destructive                        | 5-65  |

|       | (99)         | Compare Equal Destructive                        | 5-66  |

|       | (9A)         | Compare Less Than Non Destructive                | 5-67  |

|       | <b>(</b> 9B) | Compare Less Than or Equal<br>Destructive        | 5-68  |

|       | (9C)         | Compare Greater Than Non Destructive             | 5-69  |

|       | (9D)         | Compare Greater Than or Equal<br>Destructive     | 5-70  |

|       | (9E)         | Compare Not Equal Non Destructive                | 5-71  |

|       | (9F)         | Set TVD Destructive                              | 5-72  |

|       | (90)         | Reset TVD Destructive                            | 5-73  |

|       | (B2)         | Minimum                                          | 5-74  |

|       | (B4)         | Maximum                                          | 5-75  |

.

| 5.3.4 | Tran         | sfer Instructions                                    | 5-76  |

|-------|--------------|------------------------------------------------------|-------|

|       | (AO)         | or (A8) No Transfer                                  | 5-76  |

|       | (Al)         | or (A9) Transfer on Equal To Zero                    | 5-77  |

|       | (A2)         | or (AA) Transfer on Greater<br>Than Zero             | 5-78  |

|       | <b>(</b> A3) | or (AB) Transfer on Greater Than<br>or Equal to Zero | 5-79  |

|       | (A4)         | or (AC) Transfer on Less Than Zero                   | 5-80  |

|       | (A5)         | or (AD) Transfer on Less Than or<br>Equal to Zero    | 5-81  |

|       | <b>(</b> A6) | or (AE) Transfer on Not Equal<br>to Zero             | 5-82  |

|       | (A7)         | or (AF) Unconditional Transfer                       | 5-83  |

|       | (BC)         | Transfer on Test Valid Set                           | 5-84  |

|       | (27)         | Execute                                              | 5-85  |

| 5.3.5 | Shif         | t Instructions                                       | 5-86  |

|       | (FO)         | Shift Open                                           | 5-86  |

|       | (Fl)         | Shift Cyclic                                         | 5-87  |

|       | (F8)         | Shift Single Open                                    | 5-88  |

|       | (F9)         | Shift Single Closed                                  | 5-89  |

| 5.3.6 | Boole        | ean and Logical Instructions                         | 5-90  |

|       | (70)         | Boolean Zero                                         | 5-90  |

|       | (71)         | Boolean AND                                          | 5-91  |

|       | (72)         | Boolean Less Than                                    | 5-92  |

|       | (73)         | Boolean Odd Even                                     | 5-93  |

|       | (74)         | Boolean Greater Than                                 | 5-94  |

|       | (75)         | Boolean Load                                         | 5-95  |

|       | (76)         | Boolean Not Egual                                    | 5-96  |

|       | (77)         | Boolean Inclusive OR                                 | 5-97  |

|       | (78)         | Boolean NOR                                          | 5-98  |

|       | (79)         | Boolean Equals                                       | 5-99  |

|       | (7A)         | Boolean Load Complement                              | 5-100 |

|       | (7B)         | Boolean Less Than or Equal                           | 5-101 |

|       | (7C)         | Boolean NOT                                          | 5-102 |

|        | (7D) Boolean Greater or Equal   | 5-103 |

|--------|---------------------------------|-------|

|        | (7E) Boolean NAND               | 5-104 |

|        | (7F) Boolean One                | 5-105 |

|        | (80) Logical Zero               | 5-106 |

|        | (81) Logical AND                | 5-107 |

|        | (82) Logical Less Than          | 5-108 |

|        | (83) No Operation               | 5-109 |

|        | (84) Logical Greater Than       | 5-110 |

|        | (85) Logical Load               | 5-111 |

|        | (86) Logical Not Equal          | 5-112 |

|        | (87) Logical Inclusive OR       | 5-113 |

|        | (89) Logical Equals             | 5-114 |

|        | (88) Logical NOR                | 5-115 |

|        | (8A) Load Complement            | 5-116 |

|        | (8B) Logical Less Than or Equal | 5-117 |

|        | (8C) Logical NOT                | 5-118 |

|        | (8D) Logical Greater or Equals  | 5-119 |

|        | (8E) Logical NAND               | 5-120 |

|        | (8F) Logical Set                | 5-121 |

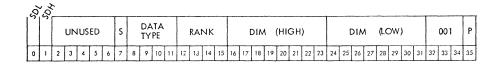

| 5.3.7  | Array Storage                   | 5-122 |

| 5.3.8  | Array Operations                | 5-124 |

| 5.3.9  | Parenthetical Control           | 5-125 |

| 5.3.10 | Arrays                          | 5-126 |

| 5.3.11 | Array Storage Area              | 5-127 |

| 5.3.12 | Dimension Word                  | 5-127 |

| 5.3.13 | Indirect Dimension Words        | 5-129 |

| 5.3.14 | Complex Numbers                 | 5-131 |

| 5.3.15 | Array Instructions              | 5-132 |

|        | (37) Load Op Code               | 5-133 |

|        | (61) Polynomial                 | 5-135 |

|        |                                 | . *   |

|      | (51) Dimension                      | 5-137 |

|------|-------------------------------------|-------|

|      | (60) Index Generator                | 5-138 |

|      | (50) Ravel                          | 5-139 |

|      | (62) Outer Product Reduction        | 5-140 |

|      | (63) Expand Along Column            | 5-142 |

|      | (64) Catenate Rows                  | 5-144 |

|      | (65) Transpose                      | 5-146 |

|      | (66) Reversal Along Rows            | 5-147 |

|      | (67) Laminate Rows                  | 5-148 |

|      | (68) Rotate Row                     | 5-150 |

|      | (69) Reshape                        | 5-152 |

|      | (6A) Take                           | 5-153 |

|      | (6B) Drop                           | 5-156 |

|      | (6C) Inner Product                  | 5-157 |

|      | (6D) Outer Product                  | 5-160 |

|      | (6E) Reduction Along Row            | 5-162 |

|      | (6F) Compression Along Columns      | 5-165 |

|      | 5.3.16 Generalized Array Operations | 5-167 |

|      | 5.3.17 Reductions on Null Elements  | 5-169 |

| TRAP | STRUCTURE                           | 6-1   |

|      | Trap Levels                         | 6-2   |

|      | Trap Mechanism                      | 6-3   |

| 6.3  | Parity Error Trap (No. 19)          | 6-5   |

| 6.4  | Interval Timer Trap (No. 18)        | 6-5   |

| 6.5  | AP Deferral Overflow Trap (No. 17)  | 6-5   |

| 6.6  | AP Deferral Underflow Trap (No. 16) | 6-5   |

| 6.7  | Kernel Protect Trap (No. 15)        | 6-6   |

| 6.8  | Read Protect Trap (No. 14)          | 6-6   |

| 6.9  | Write Protect Trap (No. 13)         | 6-6   |

| 6.10 | Command Protect Trap (No. 12)       | 6-7   |

| 6.11 | Page Error Trap (No. 11)            | 6-7   |

| 6.12 | Kernel Out of Bounds Trap (No. 10)  | 6-7   |

xv

| 6.13 Illegal Instruction Trap (No. 9)     | 6-8  |

|-------------------------------------------|------|

| 6.14 AP Underflow Trap (No. 8)            | 6-8  |

| 6.15 AP Overflow Trap (No. 7)             | 6-8  |

| 6.16 AP Store Error Trap (No. 6)          | 6-9  |

| 6.17 PMU Arithmetic Overflow Trap (No. 5) | 6-9  |

| 6.18 AP Domain Error Trap (No. 4)         | 6-9  |

| 6.19 AP Length Error Trap (No. 3)         | 6-9  |

| 6.20 Instruction Trace Trap (No. 2)       | 6-10 |

| 6.21 Kernel Trace Trap (No. 1)            | 6-10 |

| 6.22 Instruction Abort                    | 6-10 |

| 6.23 Computer Failure Signal              | 6-11 |

| Appendix | A – | Glossary                             | A-1 |

|----------|-----|--------------------------------------|-----|

| Appendix | в – | Numerical Listing of PMU Op Codes    | B-1 |

| Appendix | с – | Numerical Listing of AP Op Codes     | C-1 |

| Appendix | D - | Alphabetical Listing of PMU Op Codes | D-1 |

| Appendix | Е – | Alphabetical Listing of AP Op Codes  | E-1 |

| Appendix | F - | Considerations in Preparing Programs |     |

|          | •   | for the DPE                          | F-1 |

| Appendix | G - | PMU Instruction Attributes           | G-1 |

| Appendix | н – | AP Instruction Attributes            | H-1 |

| Appendix | I - | Channel Interrupt Conditions         | I-1 |

## LIST OF ILLUSTRATIONS

| Figure | l - AADC Baseline Configurat:              | ion                  | 2-2  |

|--------|--------------------------------------------|----------------------|------|

| Figure | 2 - Data Processing Element                |                      | 2-6  |

| Figure | 3 - Bus Word Format                        |                      | 3-7  |

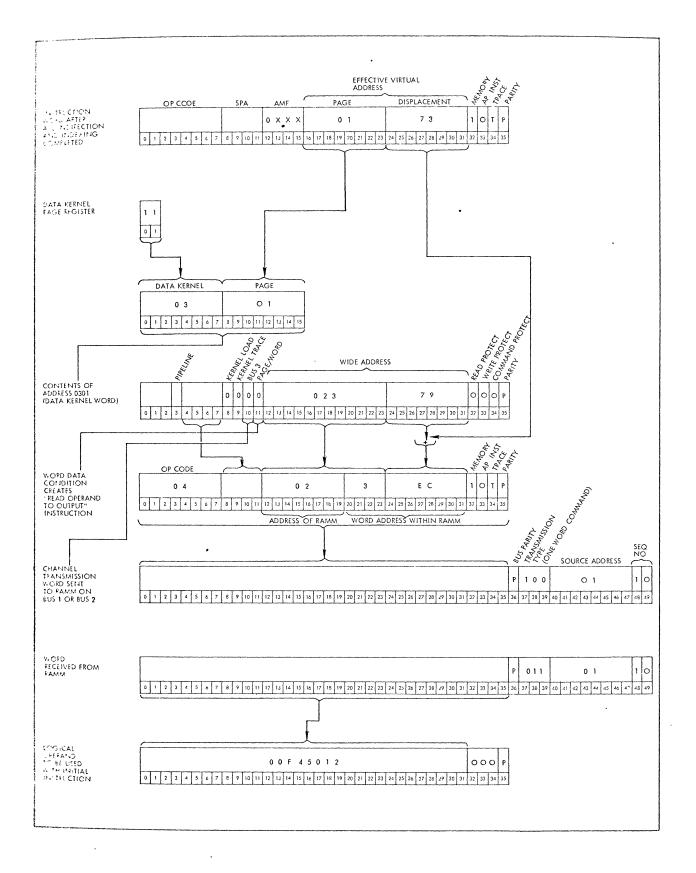

| Figure | 4 - Virtual Addressing - Res:<br>Procedure | ident Paged          | 4-25 |

| Figure | 5 - Virtual Addressing - Non<br>Procedure  | Resident Paged       | 4-26 |

| Figure | 6 - General Instruction Forma              | at                   | 4-28 |

| Figure | 7 - Address Mod EXl                        |                      | 4-34 |

| Figure | 8 - Address Mod EX2                        |                      | 4-36 |

| Figure | 9 - Address Mod EX3                        |                      | 4-37 |

| Figure | 10 - Virtual Addressing - Nor<br>Operand   | n Resident Full Word | 4-46 |

| Figure | ll - AP Block Diagram                      |                      | 5-2  |

| Figure | 12 - Instruction Look-Ahead M              | Mechanism (APQ)      | 5-10 |

| Figure | 13 - The Deferral Mechanism                |                      | 5-12 |

#### PREFACE

This reference manual is intended to satisfy the contractual requirements for Contract N62269-73-C-0660 for the Naval Air Development Center, Warminster, Pennsylvania. It is expected that the material contained in this document will become a substantial part of a future document to be entitled "Principles of Operation."

This manual is the reference manual for the Data Processing Element (DPE) of the All Application Digital Computer System (AADC). It provides a comprehensive description of the system and of the DPE instruction set. Because the DPE is comprised of two computational elements, the PMU and AP, that have separate instruction sets, a prefix, A-, will be used with the op code number of an AP instruction for purposes of differentiation within this manual. This manual is intended to be self-teaching for a reader that has a basic knowledge of data processing systems.

xviii

#### 1.0 INTRODUCTION

The AADC System employs an advanced, powerful general purpose digital system concept. Its concept embraces the computer applications spectrum from the minicomputer at one end to the powerful multiprocessor system at the other end. To accomplish this, the AADC defines modular elements which may be combined to whatever complexity is required by a given application. The modularity is not confined to the assembly of Processing Elements, Memories and I/O Controllers. The Data Processing Element (DPE) itself is separable into two components. One component is a stand alone mini-computer (Program Management Unit) while the other is a powerful Arithmetic Unit.

Salient features of the DPE are:

- Data Insensitive Arithmetic Structure

- Stack oriented accumulator structure to directly execute expressions in infix notation (parenthetical control)

- Implementation of APL primitives

- Virtual Addressing Support

- Pipeline Architecture

- Debugging and Performance Monitoring

- · Executive and Security Support

- Efficient Interprocessor Communications

BLANK

#### 2.0 SYSTEM ARCHITECTURE

#### 2.1 System Components

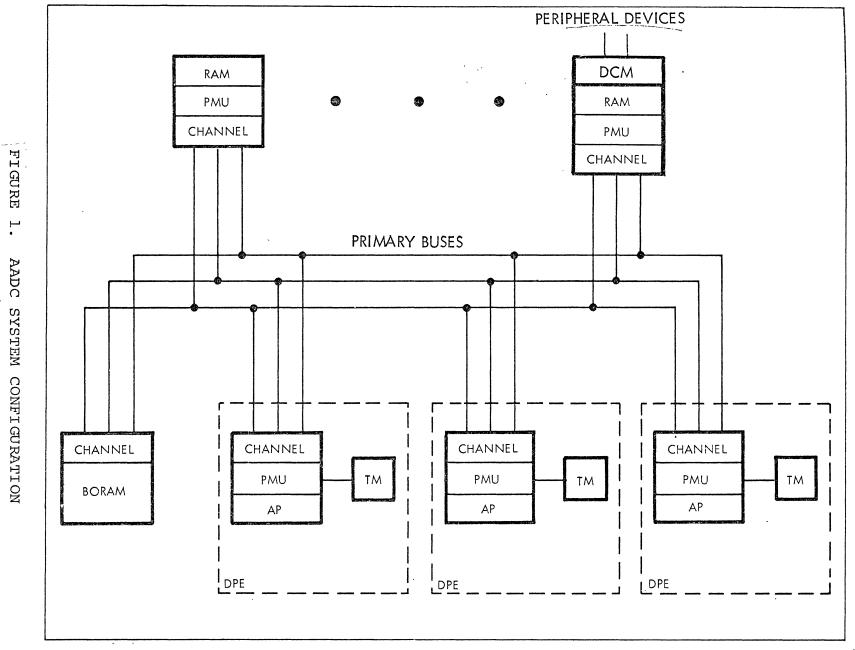

The block diagram (Figure 1) of an AADC configuration shows the system concept and the manner in which the elements interrelate. It should be noted that this is not the only configuration of an AADC.

There are three types of memories available in an AADC, the Block Oriented Random Access Memory (BORAM) which is used for storage of procedure, the Random Access Main Memory (RAMM) which is used for the storage of variables, and the Task Memory (TM) which is used as the local DPE memory.

There are two types of interface units available, the channel which is an AADC internal interface unit, and the Data Communicator Module (DCM) which is an external interface unit.

There are two additional AADC components. One component is a stand alone mini-computer (Program Management Unit) and the other is a powerful Arithmetic Unit (AP).

1) BORAM (Block Oriented Random Access Memory) -Stores procedure and constants for all programs in pages of 256 words each. Each program segment (or task) may require a number of pages of storage which may or may not be consecutively located in memory. During execution of a particular task, pages will be transferred to the TM of the executing DPE as needed on a demand basis. Transfers are via the primary bus at an uninterrupted rate of 150 nanoseconds per word. Access to the first word of a page is a maximum of two microseconds. In tactical operational use, this memory will function in the read only mode. The write mode will be provided for non-tactical or non-critical applications,

2) RAMM (Random Access Main Memory) - Constitutes the main data storage for the system. The RAMM typically consists of a series of modules, each 8 or 16K words (K=1024), 36 bits per word. Each RAMM has an associated PMU and channel unit which interfaces it with the remainder of the AADC subsystems. Data contained in RAMM can be addressed by any DPE on a single word or multi-word basis. The DPE can use this data directly, or hold it for later use in the TM. Data access time is 250 nsec though transfers are made over the primary bus at 150 nsec per word rate, and access time per word for blocks of data is 150 nsec.

3) TM (Task Memory) - Is a local direct access memory to the mini-computer (PMU) and is considered part of the DPE. The TM typically has 4K of 36 bit words, but could be as large as 64K words. Data transfers are made at 150 nsec per word rate.

4) Channel Unit - Is the common interface between elements of the AADC and the primary bus. It performs the queueing and transfer of information, and coordinates all internal bus transfers.

5) DCM (Data Communicator Module) - Is the interface unit to external devices. It contains serial to parallel converters, and packing and unpacking circuitry. It acts through the channel in the DPE configuration for communications with the computer.

DPE (Data Processing Element) - Is a general 6) purpose, programmable processor capable of performing logic and arithmetic operations necessary for handling sequentially organized tasks. The DPE contains a PMU (Program Management Unit), an AP (Arithmetic Processor), a channel and a TM (Task Memory). Procedure pages of program segments or tasks are stored in the TM for execution. Part of the TM is also used for temporary data storage. Control functions of the DPE, including normal instruction and operand fetching, executions of program management type instructions, and interfacing with the other elements via the channel and the primary bus, are handled by the PMU. Arithmetic and logical computations are performed in the AP. This separation of computational functions and control functions permits a highly parallel operation of the two subsystems. Additionally, the PMU is used as a front end memory controller for the RAMM.

#### 2.2 Data Processing Element Components

As indicated earlier, the DPE is a powerful general purpose digital computer which has the property that its sophisticated arithmetic logic may be separated from the computer proper leaving a simple mini-computer. Some factors which highlight the advantages of the DPE over other powerful data processors are:

1) The DPE handles fixed point, floating point and complex arithmetic automatically.

2) The DPE operates on arrays and matrices automatically.

3) The DPE solves algebraic expressions automatically through its ability to interpret parenthetical notation.

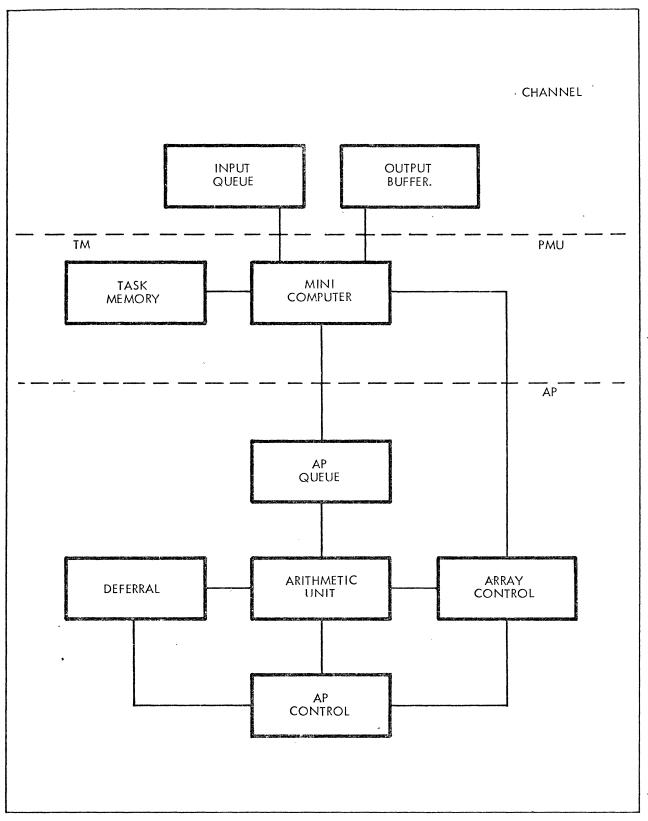

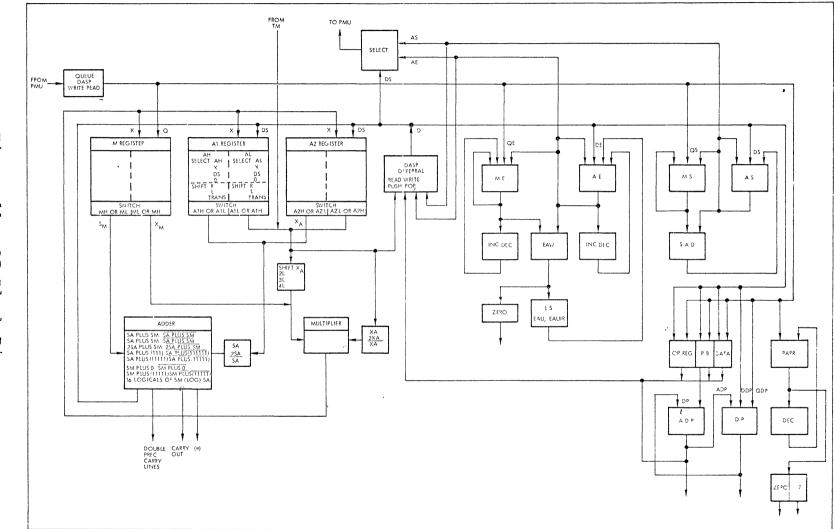

The block diagram in Figure 2 shows the DPE internal structure. The DPE contains four major components. They are the arithmetic processor (AP), the Program Management Unit (PMU), the Task Memory (TM) and the Channel.

FIGURE 2. DATA PROCESSING ELEMENT

#### The AP

The AP or Arithmetic Processor, is a data insensitive execution unit which performs arithmetic operations requiring full word precision at high speed. These instructions include Add, Subtract, Multiply, Divide, and Square Root. A11 operations are performed in floating point. The AP responds The first type involves receipt of to inputs of two kinds. an operation code and operand on which the AP acts according to its instruction set. A second is used in array operations and places the PMU under control of the AP Array Controller, addressing operands and operating as instructed by the AP. Additionally, the AP may interrupt the PMU during scalar-real instruction sequencing for servicing of store conditional transfer instructions, and exception conditions (e.g., exponent overflow).

To implement parenthetical notation, the AP contains a last-in/first-out (LIFO) deferral unit in which information is held for later operation. The operation of this deferral stack will be discussed in section 6.3.9 "Parenthetical Control."

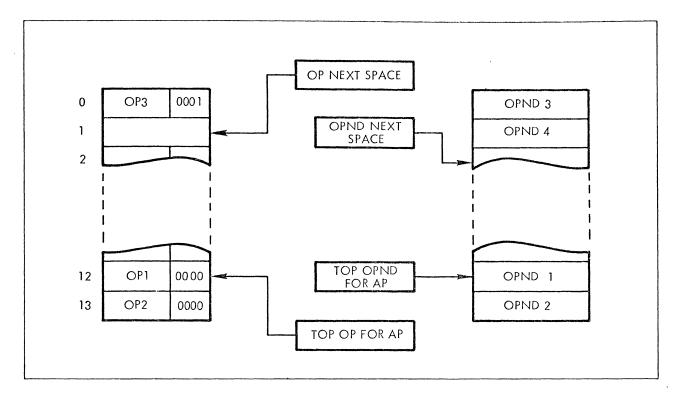

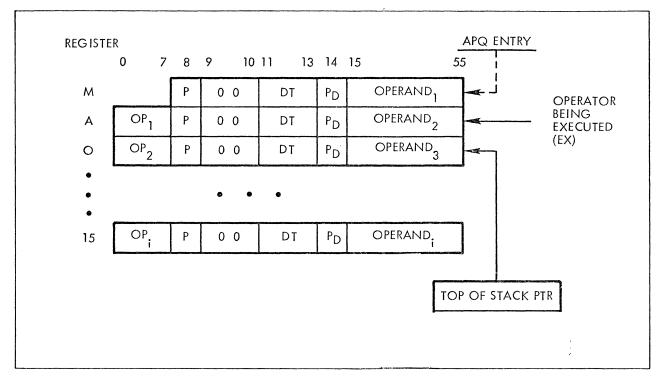

To permit the PMU and AP to run asynchronously in normal operations, a queue (AP Queue) is placed between them. This Queue is a simultaneous read/write scratchpad element that operates on a first-in/first-out basis. It is wide enough to contain an operation code, an operand, and certain necessary control and sequencing information. The queue length visible to the programmer is 13 words in length.

In normal operation, the PMU fetches an instruction (from TM) and an associated operand (from RAMM), and places the necessary data into the Queue. At the other side of the

Queue, the AP sequentially removes these instructions, and executes them. The AP can perform some instructions, such as ADD, faster than the PMU can complete a full fetch; certain other instructions, such as MULTIPLY, take longer than the fetch takes. Use of a Queue tends to average out these differences by permitting the PMU to stockpile instructions during periods when the AP is executing long instructions against the time when a series of short instructions will begin to deplete the queue.

#### The PMU

The PMU is a mini-computer in that it has its own arithmetic logic and instructions, and may in some applications be a stand alone machine. In the DPE, the PMU acts as the controlling subsystem. It fetches all instructions, performs address translation when necessary and obtains an appropriate operand. It executes its own instruction set and prepares others for transmission to the AP. It formats data requests to outside devices if required and controls the TM. During array processing, the PMU is controlled by the AP.

#### The TM

Task Memory is a small high speed memory which forms part of the DPE. This memory contains 4096 words of 36 bit length and provides the program which is executed by the DPE. The TM is subdivided into 16 pages of 256 words each. All programs are executed in modules of up to 256 words each.

As program pages are executed and new pages are required, they are brought in as needed and written over current pages. The decision as to which of the current pages are to be written over is decided in accordance with a number of algorithms which are mechanized by the PMU hardware.

#### The Channel

The Channel is the common interface between elements of the AADC and the primary bus. It performs the queueing and transfer of information, and coordinates the primary bus transfers. The primary buses are bi-directional buses which handle all data and control information transfers between the various computer system elements on a 50 bit parallel basis. Each word is transferred during a 150 The primary bus control scheme nanosecond time slot. assigns non-dedicated time slots on a rotational priority Each channel in the system contains a circuit which, basis. when tied in a closed chain, provides the rotational priority control. A channel desiring the bus, raises an internal demand line and waits notification of bus assignment. Channels having no demand are skipped so all time slots can be used. No element, except when specifically programmed to do so (i.e., BORAM), is permitted to hold on to the bus for more than two time slots. The BORAM locks the bus for one whole page transfer (256 words). Three buses are used to allow for efficient communication between channels as well as to provide redundancy. Two buses are programmatically identical while the third bus is not normally attached to a

DPE channel. This third bus is dedicated to other system functions. Any element desiring to communicate with another can use either bus when free. To make most efficient use of the primary buses, each channel contains an input queue on its input interface with the bus. This makes the destination channel effectively always available to receive data for it on the bus.

#### 3.0 DATA FLOW

The internal flow of data and procedures within an AADC is between the DPE, primary buses and other components. Each of these facets of the system can be explained somewhat independently, but will not be clear outside of the context of a complete system description. The following sections describe the operation and data flow between the primary bus, DPE, and other AADC system components.

### 3.1 Primary Bus

The system employs a time slotted bus. The time slots are non-dedicated. A distributed equal priority bus controller is used. The system is provided with automatic error retry. In order to allow this system to operate efficiently, the channels in the system are designed with a wide address and are almost always available to receive information.

Bus usage is assigned by the bus controller to a channel. This channel puts its information on the bus for a fixed period of time and then releases it unless the bus has been re-assigned to the same channel. A synchronizing clock is provided which is common to all channels. The time slots are said to be nondedicated because they are assigned to channels which have asked to send a word, as the requests occur, rather than in a fixed sequence.

The bus controller decides which channel will use a certain time slot during the preceeding one, so that no time is lost for this determination. The 'assignment is said to be equal priority because no

channel has easier access to the bus than any other. Some channels may send more words in consecutive slots than others according to fixed rules, but do not have any greater ability to obtain the bus.

The controller is distributed among the channels in a daisy chain fashion. That is, each channel receives a signal representing status of channels physically before it in the chain. According to preset logic, this signal is passed on to remaining channels. Other information on the bus is in a party line form. That is, the same wires are used for input to and output from every channel in the system. This type of bus is bi-directional.

Each channel which is capable of receiving information is supplied with an input queue buffer which is eight instruction words in length.

This means that all information sent to a channel will almost always be accepted by the receiver. In fact, the receiver can be executing an instruction while receiving and accepting a group of others which will wait their turn to be processed. The receiving channel is said to be essentially "always available". Sending channels will ordinarily await an indication of its instruction's being processed before attempting to continue sending to the same channel.

In order to ensure correctness of receipt of the information, parity checking is performed by the receiver on received words, but in order to avoid overly long time slots, this checking is done during the next

time slot after receipt. The error, if one occurred, is signaled in the second time slot after receipt on a separate cable. Correct receipt is acknowledged, to account for the absence of the indicated receiving unit. That is, correct receipt is positively signaled. Furthermore, irregular, but possible conditions such as receiver input queue full can be signaled.

When an error or receiver busy is signalled, the sender, which is constrained to maintain sent information in its Output Queue, retries the transfer. In order to maintain proper sequencing of messages, a receiving channel once it has rejected a word due to parity error or busy condition, it will reject with the 'busy' code all the words that may be received by it in the two time slots following the arrival of the first rejected word.

When the first rejected word is retried, if a second parity error is detected by the receiving channel, an emergency Transfer and Stack Kernel 0 (Op Code 54) instruction addressed to the Executive will be generated by the receiving channel and sent through its Output Queue to the Internal Bus.

A transmitting channel receiving a parity error Status Return for the second time for the same word will:

send an emergency Transfer and Stack

Kernel 0 (Op Code 54) instruction addressed

to the Executive, passing through its Output

Queue to the Primary Bus.

Keep retrying the transmission of the rejected word until either the word is accepted or the channel receives an emergency reset command from the Executive.

In the system described, a channel wishing to send information raises an internal control line indicating this and signalling its portion of the bus controller. Some time later, this channel is granted the bus. It sends its information during the indicated time slot, then releases the bus if required.

A channel maintains three address counters associated with its output queue.

- 1) the next queue location to be filled

- 2) the next queue location to be transmitted

- 3) the queue location after the last validated transmission

When an error or busy signal is received, no further transmission is permitted. If the channel continues to possess the bus, it transmits the No Transmission Code.

The channel may now obtain the bus for purposes of error or busy retry. Retry is made for only one word at a time. A second parity error Status Return received is signalled to the executive. Busy signals repeat the retry until accepted. When the queue validation counter equals the next queue location to be transmitted counter, normal continuous operation may be resumed. The Error Retry bit is set if the nature of the error was parity error.

If several words were sent with one having an error, only the incorrect or busy words need to be retried. If one word of a two word instruction which was sent is signalled as being an error, both words must be retried. Thus, the first word of a two word instruction is only considered as sent and validated when the second word of the instruction has also been received and validated.

Channels are provided as three bus units or as two bus units with extension capability to three buses.

The bus system described can run continuously with a transfer taking place in each time slot and will sometimes only degrade temporarily, when errors occur.

A further enhancement to the bus system is the AADC wide address. In this system, instructions placed on the bus are steered by their address field to the proper receiving element. The source element identifies itself using the source field provided as part of each transmission. Thus, any command request to an element may be placed on the bus with a destination address, and be certain that the element will pick up the request and process it. The element addressed can be anything from a main memory to a simple peripheral. The word addressed can be a register, a bank of switches or a word in a memory.

As an additional possibility, some elements may be designed so that they can be instructed to request channel transmission on only some of the available buses, so that an element can be given a bus

continuously or so that a bad bus can be removed from the system, allowing further error free operation with reduced total throughput.

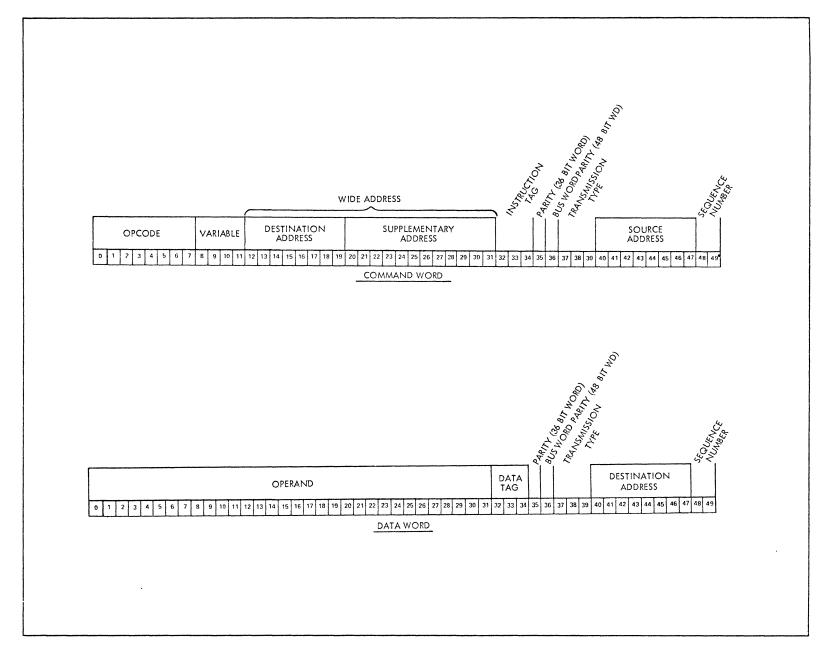

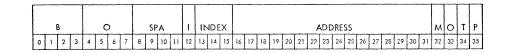

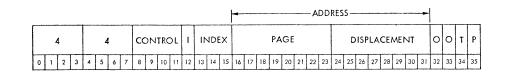

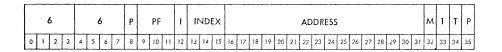

The word formats for the two word types, command and data, which are transmitted on the bus are illustrated in Figure 3 and are discussed in the following paragraphs.

### 3.1.1 Transmission Types (Commands and Data) (Bits 37-39)

The channels use the bus to transmit both commands and data to other subsystems. Presently, the bus system can specify the following types of transmission through 3 coded lines.

| Bit | Pattern |

|-----|---------|

| 000 |         |

0 No Transmission

There is no valid transmission on the bus. Receivers are to ignore the remainder of the bus content. The transmitting device possesses the bus, but did not want it.

1 Continue Interrupted Process 001

This is a special transmission code which will be discussed elsewhere in detail. The command normally causes immediate activation of the receiving device to initiate an operation previously suspended.

```

2 Data 010

```

The bus contains data. The receiving subsystem must be expecting this data. It is placed in the data queue.

Figure 3. Bus Word Format

.

3 Data and End of Block 011

Same as 2, with the additional information that is the last word of a variable block transfer. This code is generated by a transmitting subsystem under defined conditions.

4 Single Word Command 100

This indicates an instruction interrupt is on the bus.

5 Two Word Command 101

This code identifies the next word on the bus as being destined for the same device as this one. All other devices must unconditionally refuse the next word. Similarly, this device must unconditionally accept the next word and place it in the input instruction queue.

6 Single Word Emergency Command 110

This code identifies that this command is to be the next to be executed. Normal processing is interrupted and will not necessarily continue correctly.

7 Two Word Emergency 111

This code identifies that this command is to be the next to be executed. As with 5, the next word should be accepted as well. As with 6, normal processing is interrupted.

## 3.1.2 Sequence Number Field (Bits 48 and 49)

This 2-bit field can be set at 00, 01 or 10 and must be returned with the data requested by the source element. The source channel transmits this number any time its controlling element expects a data reply. When the source element does not expect a reply, as in the case of a single word write command, the channel transmits the currently valid transmission number. This means that a channel can issue up to 3 commands with data returns pending, and properly sequence the returns. If the returned data has the correct transmission number, the data is accepted. If the data has the correct number and is also EOB, then the expected sequence number register contained in the channel may be moved up to the next expected sequence number. Any data received in the incorrect sequence will be rejected by the channel with a busy signal. The fourth combination of the sequence number bits (11) is used only by elements placing commands in the channel output queue to indicate to the channel that the element is expecting a reply. The current sequence number incremented by one is to be used as the sequence number when this command is sent out on the AADC Internal Bus.

## 3.1.3 Data/Instruction Field (Bits 0-35)

The format of the 36 bits correspond to the Data or Instruction formats of the DPE.

#### 3.1.4 Source/Destination Field (Bits 40-47)

Elements are specified by an 8 bit number. The 8 bit number is identical to the high order 8 bits of a standard AADC 20 bit wide address. When commands are sent to an element, the address information contained within the 36 bit instruction word contains the Destination information to specify the Receiving element. The element address is specified by bits 12-19 in the command word.

Since commands require an eventual return of information to the originating element, the 8 bit field associated with a transmission command specifies the Source Subsystem in bits 40-47.

Data is transmitted only to an element which requested the data. Elements which request data from other elements must be ready to receive the returned data when it is provided. When a bus contains data, the associated 8 bit field contains the destination information (bits 40-47).

Each channel has two names, physical and logical. The physical name is wired in by the channels physical position in the AADC housing. Upon system reset, the logical name is made to be the physical name. The AADC Executive can, via the Set System Parameter (Op Code 25) instruction, determine the logical name of the channel. Independent of the logical name, all Emergency Commands are sent to the physical name of the channel.

One channel code has been reserved for specifying the executive system wherever it resides in the system. This is code FF (hexadecimal notation).

3.2 Channel

The channel control must perform sequencing of queue addressing output buffer selection, as well as decisions about the function to be performed as a result of information sent on the bus.

The channel unit contains four major parts which are the bus itself including the drivers, a bus controller circuit, the input queue, and an output queue. The bus and bus controller were discussed in Section 3.1. The Input and Output Queues will be discussed in the following sections.

## 3.2.1 Input Queue

The input queue is divided into two parts conceptually. These are Command and Data. The physical component is 16 words in length, with commands using 8 words and data using 8 words.

Information is stored into these queues in a first-in/first-out fashion. Of the information on the bus only the retried bit is stripped off. All other information is placed into the queue.

The queue will be considered empty when the next word to be read equals the next word to be written and the last operation was a read from the queue. The queue will be considered full when the next word to be read equals the next word to be written and the last operation was a write into the queue.

The queue full signal is used to refuse further information from the internal buses.

The routing of data and command is a function of the transmission field. In the case of the second word of a two word command, the information is always placed in the command queue.

Two deviations from this are the no transfer and continue bus tags. No transfer indicates that the device which has the bus has nothing to send. This word is ignored by the receiving channel unit.

Continue, when received, should be used by the element to format as a data word and is placed in the data queue.

An Emergency command is allowed to interfere with any operation in progress and will be passed through after validation.

Emergency commands bypass all commands presently waiting in the input queue, appearing immediately at the front of the queue.

As soon as the words received by the channel are validated and placed in the Input Queue attempts are made to send them out to the DPE one after another.

### 3.2.2 <u>Output Queue</u>

Before sending the information out on the AADC Internal Bus, the channel unit first places all command words and data words received from the DPE into the Output Queue. Up to 16 words mixed, command and/or data, can be entered into the queue in the sequence of arrival. The main purpose of the Output Queue is to provide a variable depth word buffer between the DPE, capable of sending a continuous stream of data words during burst mode, and the AADC Primary Bus with its automatic error retry requirement.

٠,

## 4.0 PROGRAM MANAGEMENT UNIT (PMU)

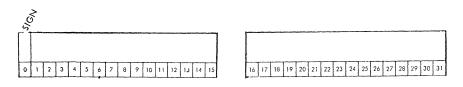

The PMU is a digital data processor with a 36 bit word length. It is capable of performing operations using half-word (16 bit), and full word (32 bit) operands. It performs arithmetic operations using sign magnitude integer arithmetic. The most significant bit of an operand is the sign bit: 0 means positive, 1 means negative.

## 4.1 <u>PMU Registers</u>

## 4.1.1 Addressable Registers

The registers in the following subparagraphs are addressable for the specified PMU operations.

### 4 1.1.1 General Scratchpad Registers

The PMU has one general scratchpad register set, consisting of 32 16-bit registers designated SP [0] through SP [3]]. Each SP register is capable of holding a half-word operand for arithmetic, shift and logical functions, and as temporary storage. SP [0] - SP [15] are directly addressable by designators in the instruction words. SP [1] through SP [7] may also be used as index registers, addressable by another set of designators in the instruction words.

For half-word operations SP [0] - SP [15] are each selectable as a 16-bit accumulator. For those operations in which a full word accumulator is required. a 32 bit register is made available by concatenating one register selected from SP [0] - SP [15] with the corresponding register selected from SP [16] - SP [31], respectively. The low bank of 16 registers will contain the most significant portion of the operand while the high bank, SP [16] - SP [31], will contain the least significant portion of the operand.

Within the general scratchpad set, all are available as pointers and operand registers. However, the following registers are dedicated to automatic functions in the DPE configuration and any programmatic contents may be destroyed.

| SP                                           | [15]                         | Interrupt Stack Pointer                         |

|----------------------------------------------|------------------------------|-------------------------------------------------|

| SP<br>SP<br>SP<br>SP<br>SP<br>SP<br>SP<br>SP | [21]<br>[22]<br>[23]<br>[24] | Used for Array Control in DPE<br>Configurations |

| SP                                           | [26]                         | Array Stack Deferral Pointer                    |

| SP                                           | [27]                         | Deferral Overflow/Underflow Stack Pointer       |

| SP                                           | [28]                         | Address of Indirect Dimension Word              |

| SP                                           | [29]                         | P Counter Temporary Storage                     |

| SP                                           | [30]                         | Internal Registers Temporary Storage            |

| SP                                           | [31]                         | Parameter Stack Linkage                         |

### 4.1.1.2 Program Address Register

The PMU has a 16 bit program address register which is designated P. The contents of P specify the address of the next instruction. The computer increments by one the contents of P for each instruction. Instructions which cause program jumps enter P with the address of the instruction to which program control is transferred. When the operations specified by the current instruction are completed, the contents of P are then used to obtain the next instruction.

#### 4.1.1.3 Interval Timer Register

The PMU has a 16 bit Interval Timer Register. When enabled, the contents of the Interval Timer Register decrement at an interval of 307.2 microseconds. The Interval Timer Trap Signal is generated when the contents of the Interval Timer Register equals zero. The Interval Timer Register is loaded and the decrementing sequence is enabled under program control. The total elapsed time capacity for the Interval Timer Register is approximately 20.1314 seconds.

#### 4.1.1.4 Source Registers

The PMU contains two source registers. The Program Source register (P-source) contains the 8 bit code of the external system element that requested the presently running program. The Interrupt Source register (I-source) contains the 8 bit code of the external system element that supplied the most recent external instruction. If the PMU is processing an external instruction, the I-source register is defined as containing the active source for that instruction. If the PMU is processing an internal instruction, the P-source register holds the active source.

## 4.1.1.5 <u>Halt (HALT) Indicator</u>

When the Halt Indicator is set (HALT = 1), the PMU will not perform program operations, but will only respond to externally generated instructions or internal traps. The Halt Indicator is set when bit 11 in either an Interval Timer Control/Halt instruction (Op Code 32) or a Transfer to Executive instruction (Op Code 37) is set and the instruction is executed, or the indicator is set by the Reset line. The Halt Indicator is reset (HALT = 0) by the execution of a Proceed instruction (Op Code 01), or a Return Stack to P and Proceed instruction (Op Code 53), or a Transfer and Stack instruction (Op Code 51).

#### 4.1.1.6 Trap Level Register

The PMU contains a five bit register which maintains the trap priority level of the presently running program (see section 6.0).

## 4.1.1.7 Parity Error Inhibit (PEI) Indicator

When this indicator is set (PEI = 1), the parity error trap signal will not be generated and no response will be made to a parity error. This indicator is set or reset by bit 9 of the Set System Parameter instruction (Op Code 25).

#### 4.1.1.8 Procedure Kernel Register

This two-bit register indicates which of the four lowest page areas of memory that the current program is referenced in.

### 4.1.1.9 Data Kernel Register

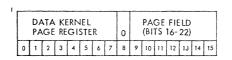

This two-bit register indicates which of the four lowest page areas of memory that is referenced for the data being used for current program.

## 4.1.1.10 Upper Bound Register

This four-bit register is used to designate the highest page area, within the 16 least significant page areas of local memory which are subject to automatic page replacement (see Section 4.3.3.2). This register is set with bits 8-11 of the Set Task Parameters instruction (Op Code 29).

### 4.1.1.11 Lower Bound Register

This two-bit register is used to designate the highest page area, within the four page areas normally reserved for kernel information, which are not subject to automatic page replacement (see Section 4.3.3.2). This register is set with the least significant bits (bits 14-15) of the Lower Bound field (bits 12-15) of the Set Task Parameters instruction (Op Code 29).

## 4.1.1.12 Executive Mode Indicator

This indicator, when set (= 1), designates that the PMU is in the executive mode and capable of performing all privileged functions. When this indicator is clear (= 0), the PMU is not in the executive mode. (See Section 4.2.2.)

## 4.1.1.13 Data Addressing Mode Indicator

This indicator, when set (= 1), designates that the data is to be accessed virtually, through references located in the Data Kernel. When clear (= 0), this indicator designates that the data is to be accessed directly from local memory. This indicator is set or reset by bit 23 of the Set Task Parameters instruction (Op Code 29).

## 4.1.1.14 Replacement Algorithm Register

This two-bit register contains the code for the presently operational replacement algorithm (see Section 4.3.3.2). This register is set with the contents of bits 18-19 of the Set Task Parameters instruction (Op Code 29).

## 4.1.2 <u>Non-Addressable Registers</u>

The register in the following subparagraph is not directly addressable by the programmer, but is included here for definition. It is referenced later in the manual in the discussion of virtual addressing.

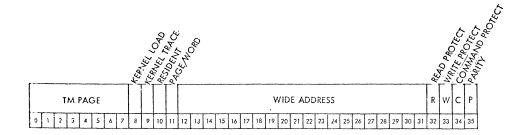

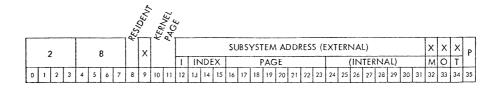

## 4.1.2.1 Procedure Page Register

This non-addressable eight-bit register contains the direct local memory address of the page of procedure currently being executed. The contents of this register are appended to the eight least significant bit of the program counter P, the displacement field, to obtain the direct local memory

address of the next instruction to be executed. This register is set with the contents of bits 0-7 of the procedure kernel word during a procedure page fetch. (See Section 4.3.3.2.)

#### 4.2 Modes of Operation

A DPE can operate in either one of two modes, Problem or Executive.

#### 4.2.1 Problem Mode

In this mode of operation, the Executive Mode Indicator is cleared to zero. This is the normal mode for interpreting procedure. All security protect mechanisms involved with virtual addressing are invoked. (See Section 4.2.2.2.2).

## 4.2.2 <u>Executive Mode</u>

In this mode of operation, Executive Mode Indicator set to one, a DPE possesses capabilities that would otherwise be illegal when there is an attempt to use them. The following description is in three parts.

- Entrance to Executive Mode

- Executive Mode Capabilities

- Exit from Executive Mode

## 4.2.2.1 Entrance into Executive Mode

There is only one way to enter the Executive Mode, the receipt of an external Transfer and Stack Kernel 0 instruction (Op Code 54) addressed to the channel which

recognizes the resource name hex "FF." The Transfer and Stack Kernel O instruction in this structure is a two word bus command. The first word, the instruction itself, invokes the Executive at a fixed entry point, a transfer to the instruction located at the virtual address hex "FFOO." The Executive, once invoked, must obtain the interrupt mask data word from its channel by executing a Write Word From Input instruction (Op Code O3). This mask word contains the necessary information for the Executive to determine what actions to perform. (Note: Further interrupts are inhibited until the interrupt mask word is fetched.)

The two word Transfer and Stack Kernel 0 instruction is transmitted to the Executive in the normal course of computation by one of two possible mechanisms: programmed or channel interrupt.

## 4.2.2.1.1 Programmed

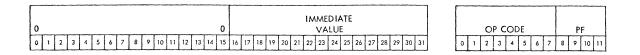

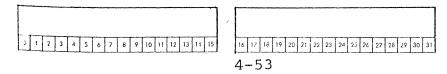

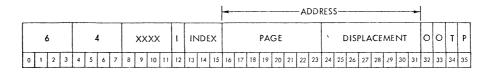

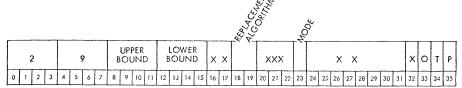

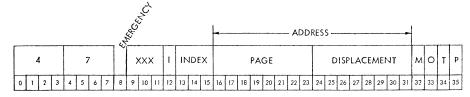

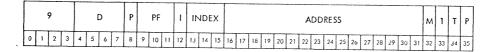

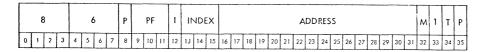

When a DPE wishes to interrupt the Executive, it executes a Transfer to Executive instruction (Op Code 37). This instruction causes the creation of the two word Transfer and Stack Kernal 0 command. The first word of the Transfer and Stack Kernel 0 instruction has been described in Section 4.2.2.1. The second word has the following format:

|   |   | RE |   | UR |   |   |   |   |   | 0  |    | 0  |    |    |    |    |    |    |    | I  | INT | ERI | RUF | Y T M | ۸AS | δĸ |    |    |    |    |    |

|---|---|----|---|----|---|---|---|---|---|----|----|----|----|----|----|----|----|----|----|----|-----|-----|-----|-------|-----|----|----|----|----|----|----|

| 0 | 1 | 2  | 3 | 4  | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 21  | 22  | 23  | 24    | 25  | 26 | 27 | 28 | 29 | 30 | 31 |

Bits 0-7 contain the resource name of the resource performing the Transfer to Executive instruction. The contents of this field are derived from the Resource Name field (bits 16-23) of the Set System Parameter instruction (Op Code 25).

Bits 8-15 are cleared to zeroes, which indicates that this interrupt was due to the execution of a Transfer to Executive instruction.

Bits 16-31, the interrupt mask, are the effective address field of the Transfer to Executive instruction (normally instruction bits 16-31 as an immediate). The meaning of the interrupt mask will be established by system software conventions.

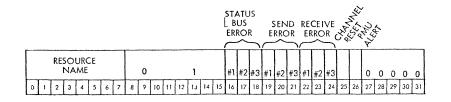

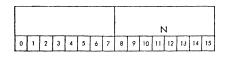

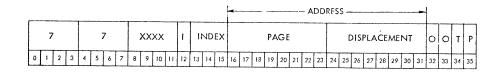

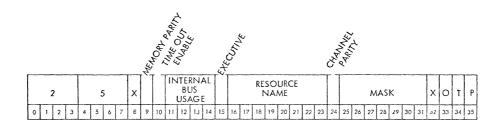

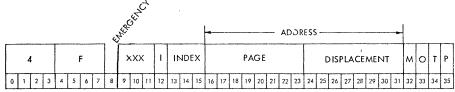

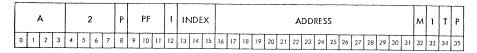

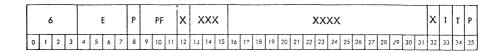

4.2.2.1.2 Channel Interrupt

The channel, in response to certain conditions that are described below, sends an interrupt to the executive. The channel creates a two word Transfer and Stack Kernel 0 command. The first word has the same format as an interrupt generated as a result of the execution of a Transfer to Executive instruction. The second word has the following format.

Bits 16-26 signify the occurrence of various interrupt conditions that the channel has detected. These conditions are independent and more than one may occur simultaneously. It should be noted that once a condition is detected by the channel and transmitted to the executive, subsequent occurrences of the same condition will not cause another executive interrupt unless the channel received a Set System Parameter instruction (Op Code 25) in the interim. (See Appendix I).

Bits 8-15 signify the interrupt originates from the channel. Bits 0-7 are the resource name for the originating channel.

It should be noted, nothing prevents an executive from sending an interrupt to itself.

## 4.2.2.2 Executive Mode Capabilities

When a DPE is in the executive mode of operation, it possesses capabilities not present in the problem mode. These capabilities involve two areas: the security system and emergency commands.

## 4.2.2.2.1 Emergency Commands

When a DPE is in the executive mode, two word emergency commands can be transmitted to an AADC resource via the Command Subsystem instructions (Op Codes 47 and 4F). If bit 8 of the Command Subsystem instruction is set to one, a two word command is transmitted that has a transmission tag designating emergency commands. See Section 4.3.2 for a description of emergency commands.

## 4.2.2.2.2 Security System

When the DPE is in the executive mode, all security violations involving the protection mechanisms for the kernel area cannot occur, i.e., read, write and command protect. Security violations that result due to an improper data structure still occur in the executive mode. For example, transferring to word data or attempting to execute the load page instruction with word data.

The kernel protect violations do not occur in the executive mode. It should be noted that this is true whether the executive is attempting to access the kernel in its own task memory, or is attempting to access a kernel area in a remote resource.

## 4.2.2.3 Exit From Executive Mode

The executive exits from the executive mode by executing a Return Stack to P instruction (Op Code 52) or a Return Stack to P and Proceed instruction (Op Code 53). Upon completion of this instruction, the DPE is either in the problem mode or a previous level of the executive. It is not possible to return to the executive mode when a return stack instruction is executed in the problem mode. There is a hardware override which leaves the DPE in the problem mode.

#### 4.3 Detailed Instruction Performance

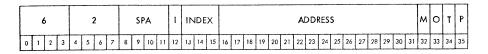

Instructions for the DPE are of three types: external. emergency, and internal. External instructions and emergency commands are received by the DPE over the primary bus system. Internal instructions are obtained from local memory, either as the result of a trap or a normal program counter instruction fetch or they are obtained from the primary bus specifically as the word following a Command Subsystem/Address Modifications (Op Code 47).

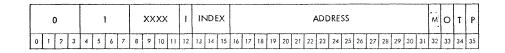

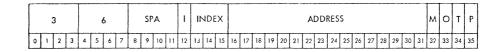

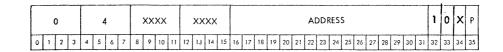

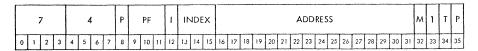

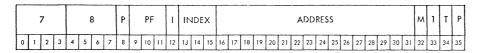

## 4.3.1 <u>External Instructions</u>

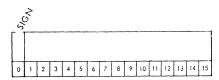

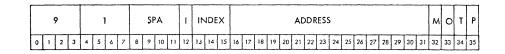

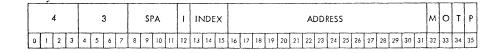

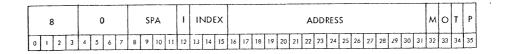

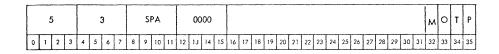

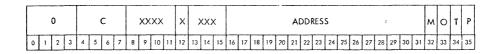

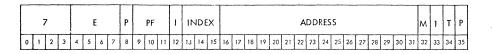

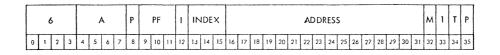

Any pending external instruction is processed immediately at the conclusion of the instruction currently being processed. External instructions are received over the primary bus system in a 50-bit format (see Section 3.1). The external instruction is the 36-bit high order (bit positions 0-35) portion of the incoming 50-bit transmission word, and has the following format.

| OP CODE         | SPA       | xxxx        | ADDRESS                                         | ΜΑΡ   | x x   |

|-----------------|-----------|-------------|-------------------------------------------------|-------|-------|

| 0 1 2 3 4 5 6 7 | 8 9 10 11 | 12 13 14 15 | 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 | 32 33 | 34 35 |

Bits 0-7 specify the operation to be performed.

Bits 8-11 specify a particular scratchpad register or specify a special purpose function depending upon the op code.

Bits 12-5 are unused.

Bits 16-31 specify the operand or the address of the operand.

Bit 32 define whether a memory reference is to be made or not.

Bit 33 define whether this is a PMU or an AP instruction.

Bit 34-35 are unused.

The above defined fields have the same meaning as for internal instructions (see Section 4.3.4.1 for further definition of these fields).

Address modification (bits 12-15) and parity (bit 35) checking are not performed by the PMU for external instructions. The instruction trace (bit 34) trap also is not generated for any external instruction.

## 4.3.2 <u>Emergency Commands</u>

An "emergency command" is a mechanism to enable the executive processor (or any other permitted device, such as the control panel) to interrupt a channel and cause the "emergency command" to be the next thing transmitted via its secondary bus.

Identified by the Transmission Code "lll" the emergency command is a two word instruction. Although any two-word instruction can theoretically be sent, the present AADC design contains a mechanism for producing the emergency transmission code only in conjunction with either of the COMMAND SUBSYSTEM instructions. This, the first word received by the channel will be a routing word, and the second will specify the action to be performed.

As previously mentioned, the channel, when receiving an emergency command addressed to one of its secondary bus devices, transmits the word, with it emergency code, as its next transmission. This is the only type of command information that takes precedence over data, and the integrity of the program of the addressed processor cannot be maintained -- the emergency command will interrupt an array being read or, in the case of the DPE, a pipeline of data requests. Recovery from these interruptions will probably be impossible. Sending a HALT command prior to the emergency command will not necessarily be effective in alleviating this problem unless sufficient time is allowed to ensure that the HALT was accepted.

Emergency commands may also effect other subsystems connected to the same channel. When the channel places the first word on the secondary bus, it begins to count the clock pulses. If 4096 clock pulses pass and the receipt of the command has not been acknowledged, the channel raises its SYSTEM MASTER RESET line and resets all the subsystems on the secondary bus.

When the Channel is known to be reset, the first subsequent instruction must not be an emergency instruction. After receipt of this first instruction, emergency instructions can be properly received.

## 4.3.3. Internal Instructions