## **TECHNICAL MANUAL**

# MODEL 402-2AM13 DISPLAY TERMINAL

#### TECHNICAL MANUAL

for

## $DIDS^*-400$

#### MODEL 402-2AM13

#### Digital Information Display

#### August 1968

Furnished under United States Government contract No. DAAB03-68-C-0451 Shall not be either released outside the Government, or used, duplicated, or disclosed in whole or in part for manufacture or procurement, without the written permission of Raytheon Company, except for: (i) emergency repair or overhaul work by or for the Government, where the item or process concerned is not otherwise reasonably available to enable timely performance of the work; or (i) release to a foreign government, as the interest of the United States may require; <u>provided</u> that in either case the release, use, duplication or disclosure hereof shall be subject to the foregoing limitations. This legend shall be marked on any reproduction thereof in whole or in part.

#### Prepared by

RAYTHEON COMPANY Equipment Division Wayland Laboratories Wayland, Massachusetts, U.S.A.

Printed in U.S.A.

\*A TRADEMARK OF RAYTHEON COMPANY

#### FOREWORD

This manual is published for the information and guidance of technical personnel responsible for the installation, operation, and maintenance of the Model 402-2AM13 Display Terminal, a unit of the DIDS\*-400 Digital Information Display System.

## TABLE OF CONTENTS

1

#### Title

Page

### CHAPTER 1. GENERAL INFORMATION

| 1-1    | Purpose of Equipment                         | 1-1   |

|--------|----------------------------------------------|-------|

| 1-2    | Description of Equipment                     | 1 - 1 |

| 1-2.1  | Keyboard Assembly All                        | 1-3   |

| 1-2.2  | Display Logic Board A13                      | 1-4   |

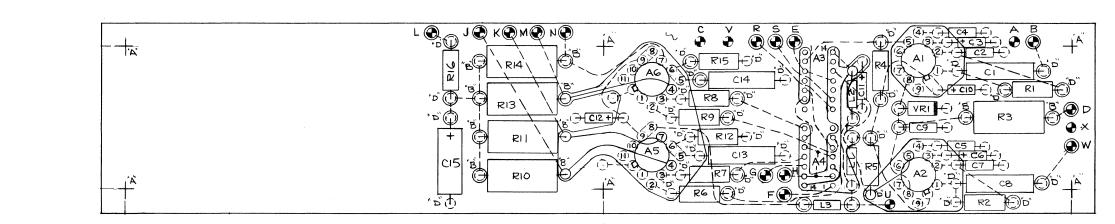

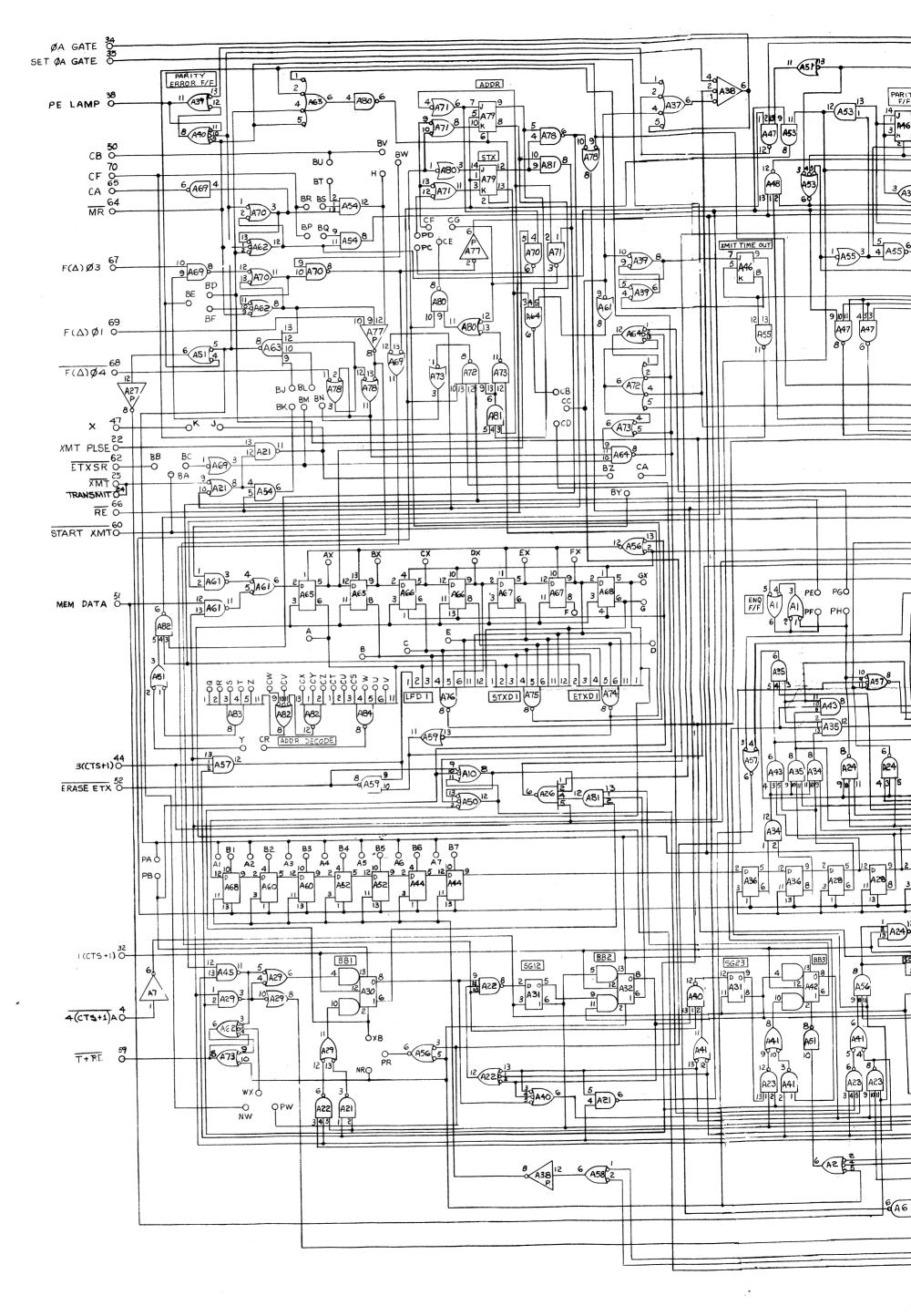

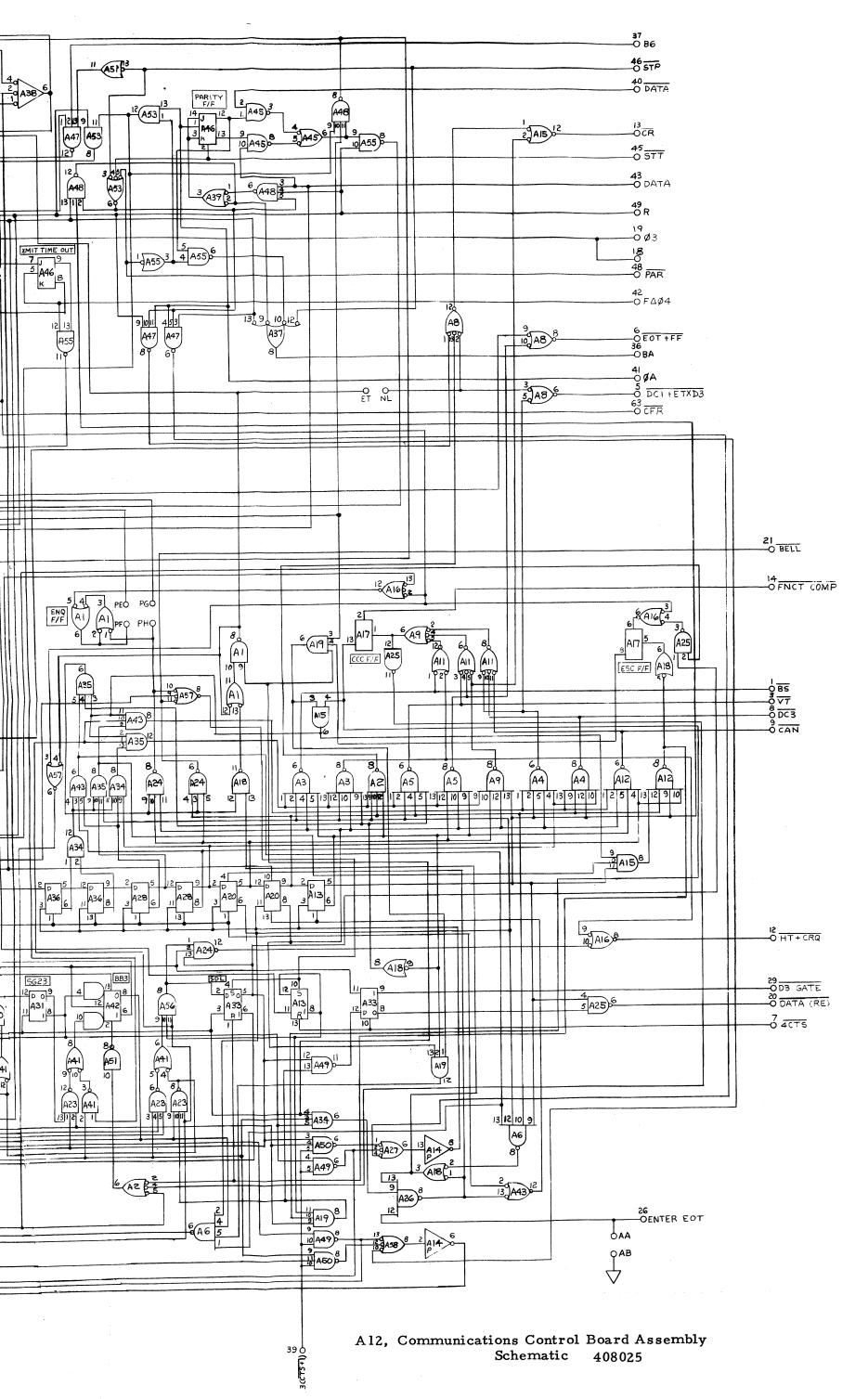

| 1-2.3  | Communications Control Board A12             | 1-4   |

| 1-2.4  | Timing and Discrete Board Al4                | 1-6   |

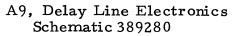

| 1-2.5  | Delay-Line Electronics A9                    | 1-7   |

| 1-2.6  | Delay Line A15                               | 1-7   |

| 1-2.7  | Monoscope Deflection Amplifier Assembly A3   | 1-7   |

| 1-2.8  | Monoscope Vl                                 | 1-7   |

| 1-2.9  | Video Preamplifier A7                        | 1-7   |

| 1-2.10 | Video Amplifier A8                           | 1-9   |

| 1-2.11 | Vertical and Horizontal Deflection Amplifier |       |

|        | Assembly A2                                  | 1-10  |

| 1-2.12 | Low Voltage Power Supply A4                  | 1-10  |

| 1-2.13 | High Voltage Power Supply A5                 | 1-11  |

| 1-2.14 | Cathode Ray Tube (CRT) V2                    | 1-11  |

| 1-3    | Information and Reference Tables             | 1-11  |

| 1-3.1  | Leading Particulars                          | 1-11  |

| 1-3.2  | Capabilities and Limitations                 | 1-12  |

| 1-3.3  | Wiring Options                               | 1-13  |

| 1-3.4  | Glossary of Terms                            | 1-14  |

## CHAPTER 2. INSTALLATION AND PREOPERATION

| 2 - 1   | Siting Requirements                             | 2 - 1        |

|---------|-------------------------------------------------|--------------|

| 2-1.1   | Location                                        | 2 - 1        |

| 2-1.2   | Primary Power Requirements                      | 2 - 1        |

| 2-2     | Installation Procedure                          | 2-2          |

| 2-2.1   | Receipt and Unpacking of Equipment              | 2-2          |

| 2-2.2   | Cable Requirements                              | 2-2          |

| 2-2.3   | Cable Fabrication                               | 2-2          |

| 2-3     | Preoperational Procedures                       | 2-2          |

| 2-3.1   | Visual Checkout                                 | 2-2          |

| 2-3.2   | Resistance and Voltage Measurements             | 2-3          |

| 2-3.3   | Alignment and Adjustments                       | 2-4          |

| 2-3.3.1 | Turn-On Procedure                               | 2-4          |

| 2-3.3.2 | Delay-Line Adjustment                           | 2 <b>-</b> 5 |

| 2-3.3.3 | Video Amplifier A8                              | 2-7          |

| 2-3.3.4 | Monoscope Deflection Amplifier A3               | 2 - 8        |

| 2-3.3.5 | Horizontal and Vertical Deflection Amplifier A2 | 2-11         |

| 2-4     | Reassembly                                      | 2-11         |

## TABLE OF CONTENTS (cont)

|                                                | Title                                                                                                                                                                           | Page                                                        |

|------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|                                                | CHAPTER 3. OPERATION                                                                                                                                                            |                                                             |

| 3-1<br>3-2<br>3-2.1<br>3-2.2<br>3-2.3<br>3-2.4 | Identification of Operating Controls and<br>Indicators<br>Operating Instructions<br>Preoperational Procedures<br>Turn-On Procedure<br>Operating Procedures<br>Turn-On Procedure | 3 - 1<br>3 - 8<br>3 - 8<br>3 - 8<br>3 - 8<br>3 - 8<br>3 - 8 |

|                                                | CHAPTER 4. THEORY OF OPERATION                                                                                                                                                  |                                                             |

| 4 - 1                                          | Introduction                                                                                                                                                                    | 4 - 1                                                       |

|                                                | Section I. FUNCTIONAL OPERATION                                                                                                                                                 |                                                             |

| 4-2                                            | Description of Section Contents                                                                                                                                                 | 4 - 1                                                       |

| 4-3                                            | System Description                                                                                                                                                              | 4 - 1                                                       |

| 4-4                                            | System Operation                                                                                                                                                                | 4-2                                                         |

| 4-5                                            | Optional Operation                                                                                                                                                              | 4 <b>-</b> 3                                                |

| 4-5.1                                          | Optional Communication Channel                                                                                                                                                  | 4-3                                                         |

| 4-5.2                                          | Optional Conversational Modes                                                                                                                                                   | 4-3                                                         |

| 4-5.3                                          | Address Options                                                                                                                                                                 | 4-3                                                         |

| 4-5.4                                          | Transmit Options                                                                                                                                                                | 4-3                                                         |

| 4-5.5                                          | Receive Options                                                                                                                                                                 | 4-4                                                         |

| 4-5.6                                          | Cursor Option                                                                                                                                                                   | 4-4                                                         |

| 4-6                                            | Interface Characteristics                                                                                                                                                       | 4-4                                                         |

| 4-6.1                                          | Request-to-Send                                                                                                                                                                 | 4-6                                                         |

| 4-6.2                                          | Clear-to-Send                                                                                                                                                                   | 4-6                                                         |

| 4-6.3                                          | Transmitted Data                                                                                                                                                                | 4-6                                                         |

| 4-6.4                                          | Received Data                                                                                                                                                                   | 4-6                                                         |

| 4-6.5                                          | Ground                                                                                                                                                                          | <br>4-6                                                     |

| 4-6.6                                          | Transmit/Receive Conditions                                                                                                                                                     | 4-6                                                         |

| 4-7                                            | Conversational Modes                                                                                                                                                            | 4-6                                                         |

| 4-7.1                                          | Enquiry-Response                                                                                                                                                                | 4-7                                                         |

| 4-7.2                                          | Polling                                                                                                                                                                         | 4-7                                                         |

| 4-8                                            | Character Representation                                                                                                                                                        | 4-7                                                         |

| 4-9                                            | Character Format                                                                                                                                                                | 4 - 8                                                       |

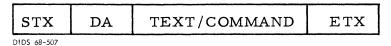

| 4-10                                           | Message Format                                                                                                                                                                  | 4-11                                                        |

| 4-11                                           | Message Format, Enquiry-Response                                                                                                                                                | 4-12                                                        |

| 4-11.1                                         | Enquiry Format                                                                                                                                                                  | 4-12                                                        |

| 4-11.2                                         | Response Format                                                                                                                                                                 | 4-12                                                        |

| 4-12                                           | Polling Message Format                                                                                                                                                          | 4-15                                                        |

| 4-12.1                                         | Polling Read Directive                                                                                                                                                          | 4-15                                                        |

| 4-12.2                                         | Polling Write Directive                                                                                                                                                         | 4-16                                                        |

| 4-12.3                                         | Polling ENQ Directive                                                                                                                                                           | 4-17                                                        |

|                                                | Section II. FUNCTIONAL DESCRIPTION                                                                                                                                              |                                                             |

| 4-13                                           | General Description of Section Contents                                                                                                                                         | 4-18                                                        |

## TABLE OF CONTENTS (cont)

## Title

|          | Title                                         | Page          |

|----------|-----------------------------------------------|---------------|

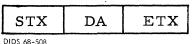

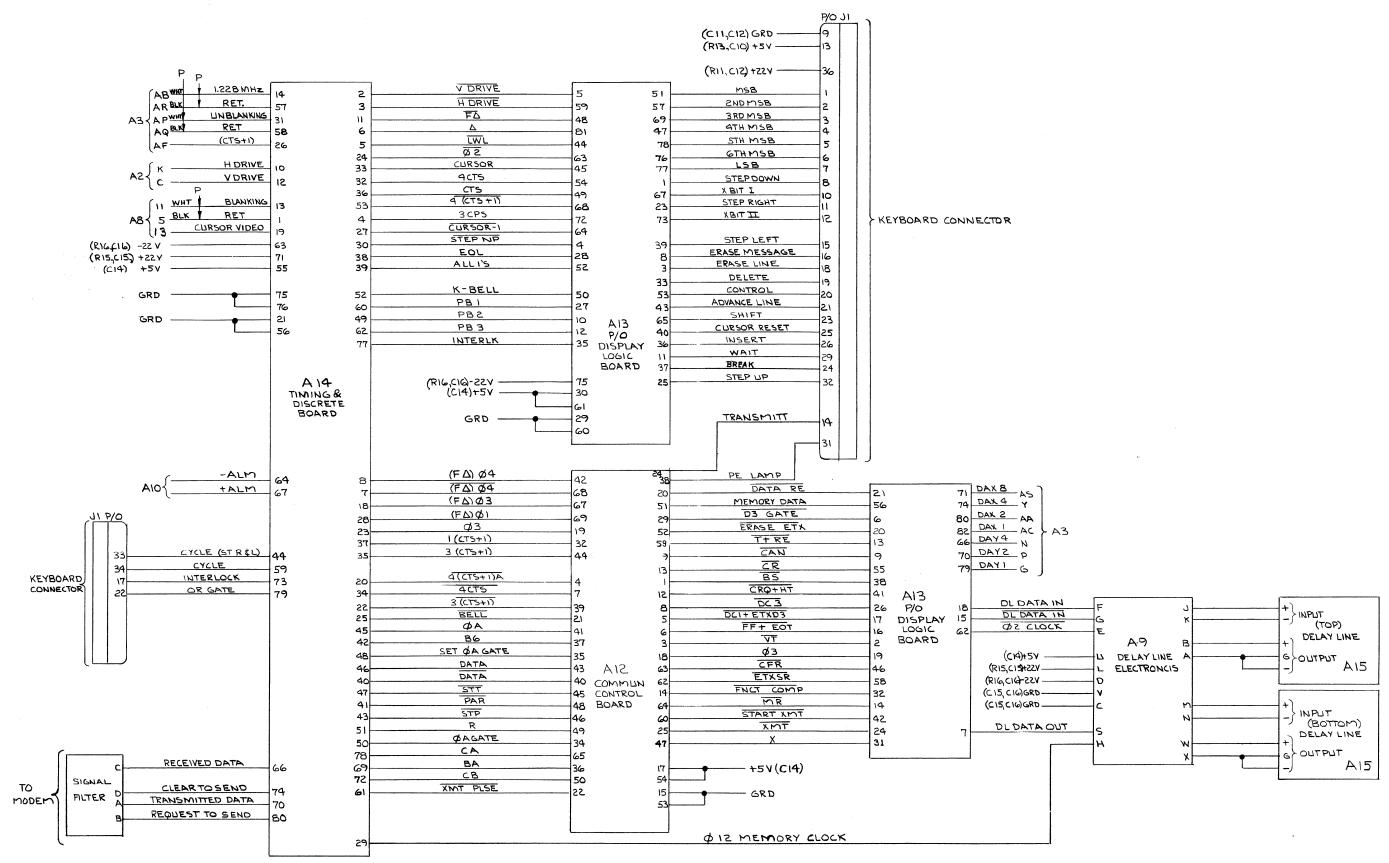

| 4-14     | Overall Block Diagram                         | 4 - 18        |

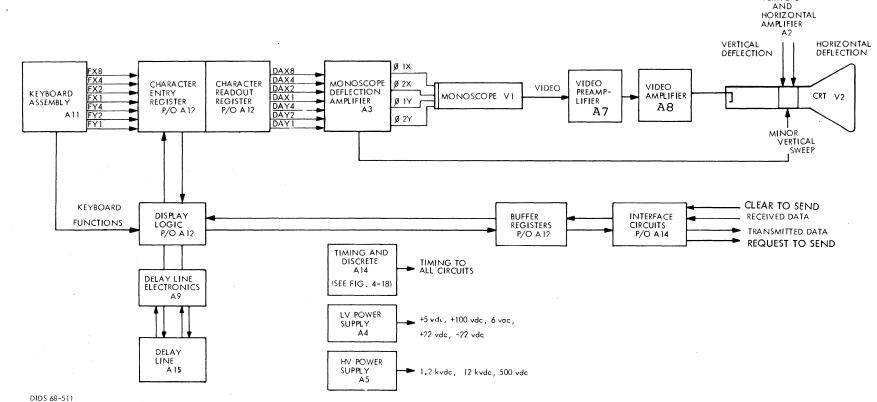

| 4-15     | Character Generation and Refresh              | 4-18          |

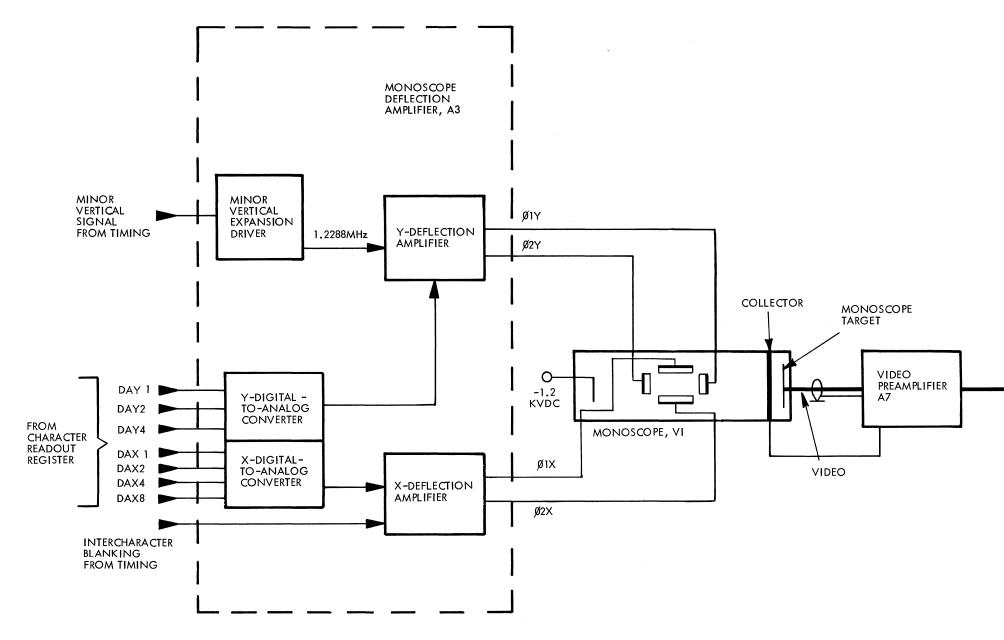

| 4-15.1   | Keyboard-Monoscope Circuits                   | 4-20          |

| 4-15.1.1 | Keyboard Assembly All                         | 4-20          |

| 4-15.1.2 | Character Entry Register                      | 4-30          |

| 4-15.1.3 | Character Readout Register                    | 4-30          |

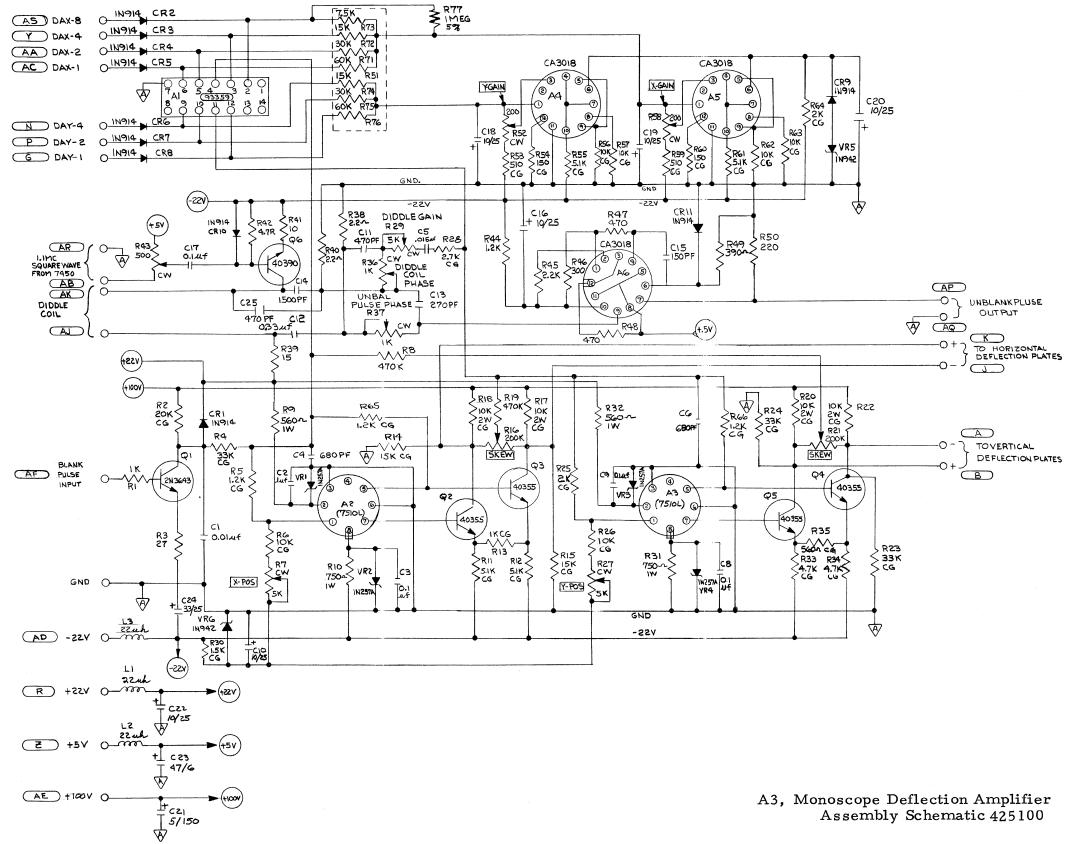

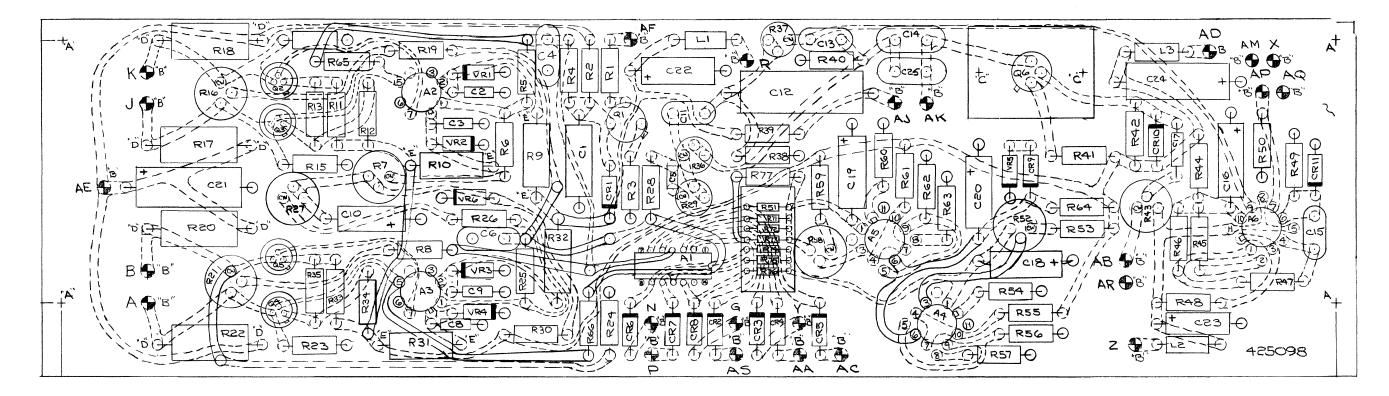

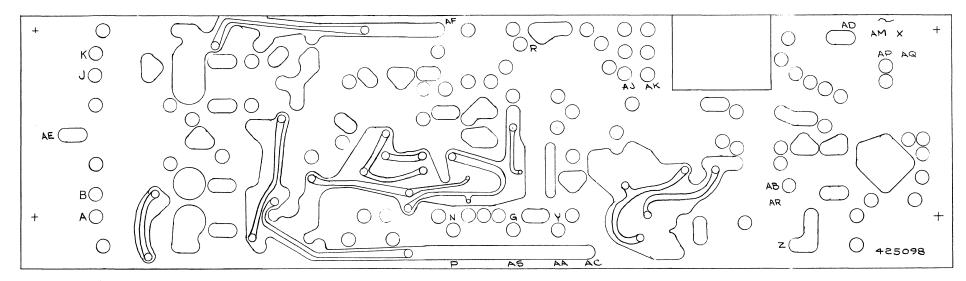

| 4-15.1.4 | Monoscope Deflection Amplifier A3             | 4-30          |

| 4-15.1.5 | Monoscope, Amplifiers, and CRT                | 4-31          |

| 4-15.1.6 | Summary                                       | 4-32          |

| 4-15.2   | Refresh-Memory Loop                           | 4-32          |

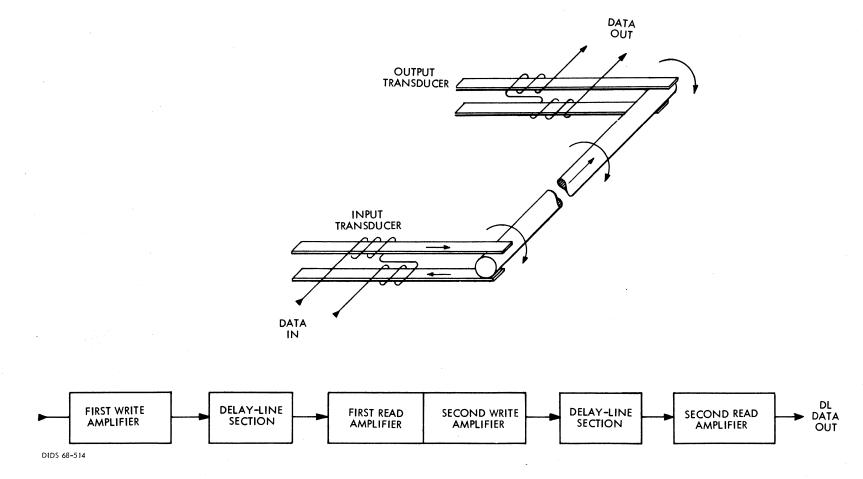

| 4-15.2.1 | Delay-Line Electronics A9                     | 4-33          |

| 4-15.2.2 | Delay Line A15                                | 4-33          |

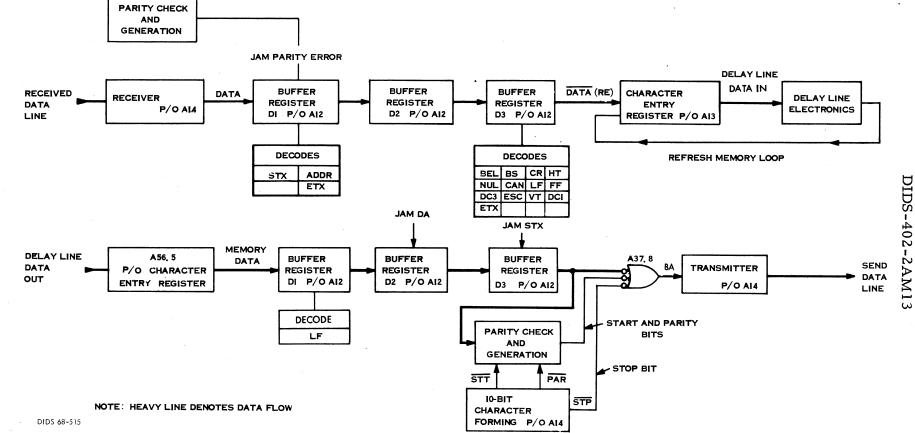

| 4-16     | Buffer Registers and Interface                | 4 <b>-</b> 35 |

| 4-16.1   | Transmit Mode                                 | 4-37          |

| 4-16.2   | Receive Mode                                  | 4-37          |

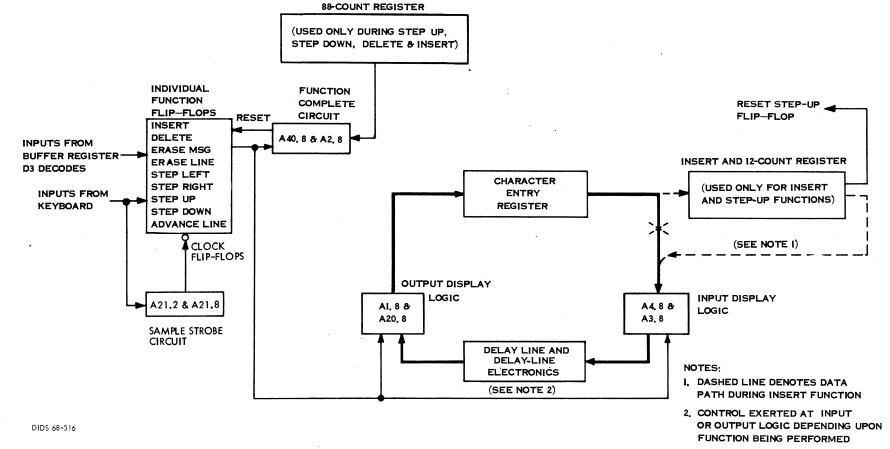

| 4-17     | Editing and Cursor Control Logic              | 4-38          |

| 4-17.1   | Individual Function Flip-Flops                | 4-41          |

| 4-17.2   | Sample Strobe Circuit                         | 4-41          |

| 4-17.3   | Input and Output Display Logic                | 4-41          |

| 4-17.4   | Insert and 12-Count Register                  | 4-42          |

| 4-17.5   | 88-Count Register                             | 4-42          |

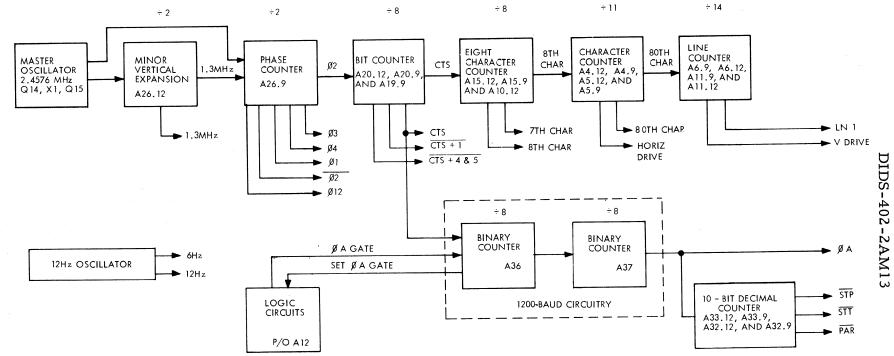

| 4-18     | Timing                                        | 4-42          |

| 4-18.1   | Master Oscillator                             | 4-44          |

| 4-18.2   | Minor Vertical Expansion                      | 4-44          |

| 4-18.3   | Phase Counter                                 | 4-44          |

| 4-18.4   | Bit Counter                                   | 4-45          |

| 4-18.5   | Eight-Character Counter                       | 4-46          |

| 4-18.6   | Character Counter                             | 4-46          |

| 4-18.7   | Line Counter                                  | 4-47          |

| 4-18.8   | 1200-Baud Circuitry                           | 4-47          |

| 4-18.9   | 10-Bit Decimal Counter                        | 4-48          |

| 4-18.10  | 12-Hz Oscillator                              | 4-48          |

| 4-19     | Raster Generation                             | 4-48          |

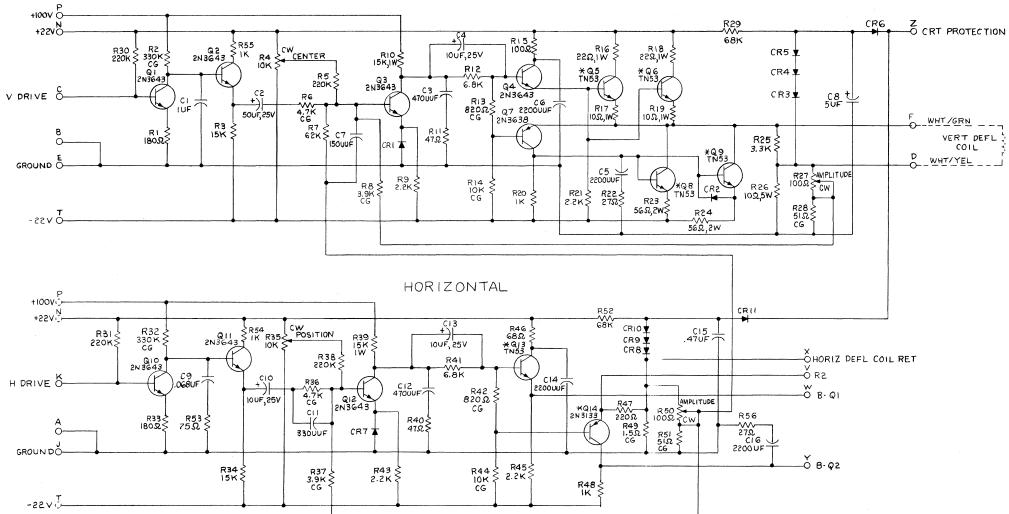

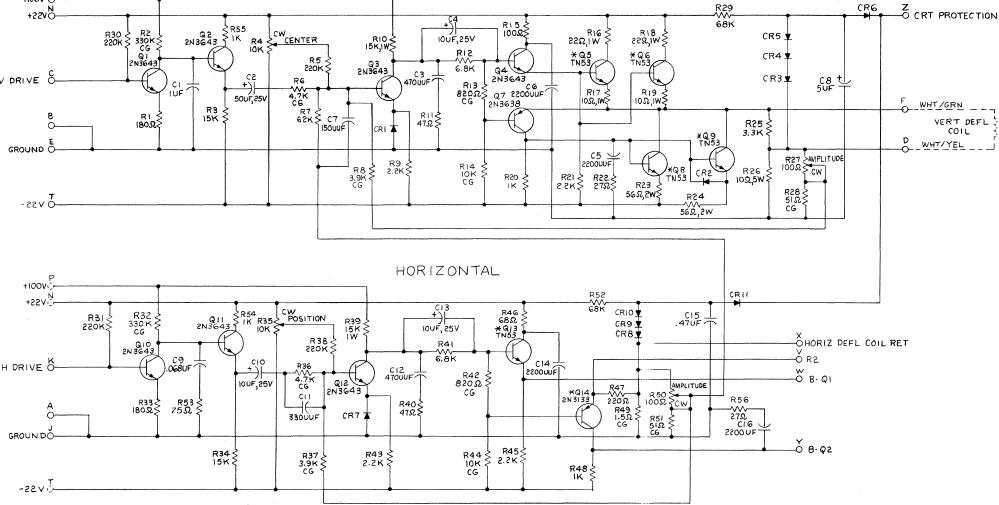

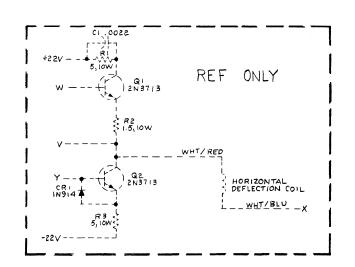

| 4-19.1   | Vertical and Horizontal Amplifier Assembly A2 | 4-49          |

| 4-19.1.1 | Horizontal Deflection Amplifier               | 4-49          |

| 4-19.1.2 | Vertical Deflection Amplifier                 | 4-50          |

| 4-19.1.3 | Minor Vertical Expansion Signal               | 4-50          |

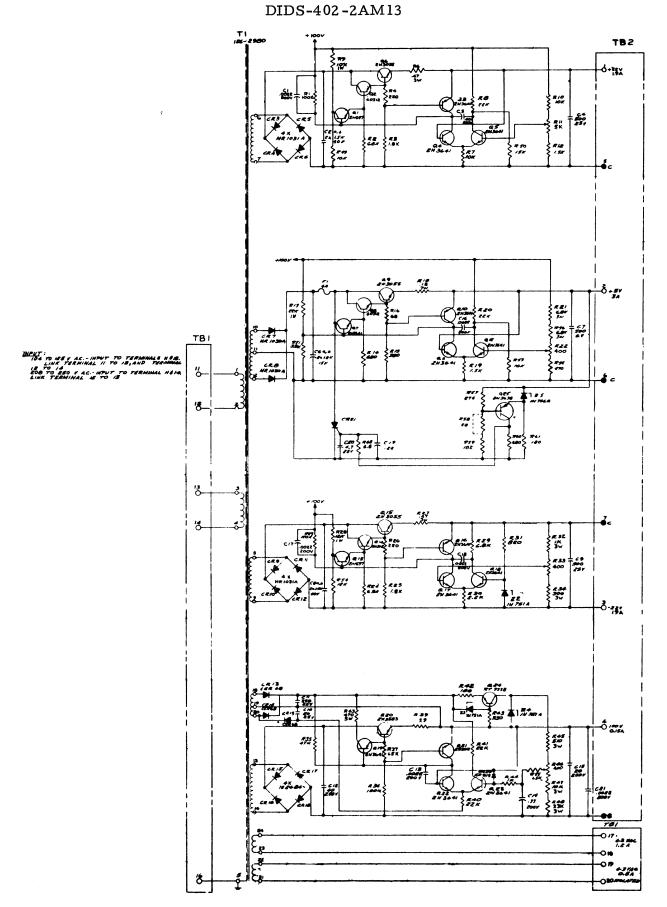

| 4-20     | Power Supplies                                | 4-51/4-52     |

| 4-20.1   | Low-Voltage Power Supply A4                   | 4-51/4-52     |

| 4-20.2   | High-Voltage Power Supply A5                  | 4-51/4-52     |

|          | Section III. CIRCUIT DESCRIPTION              |               |

| 4-21     | Description of Section Contents               | 4-53          |

| 4-22     | Communications Control Board A12              | 4-53          |

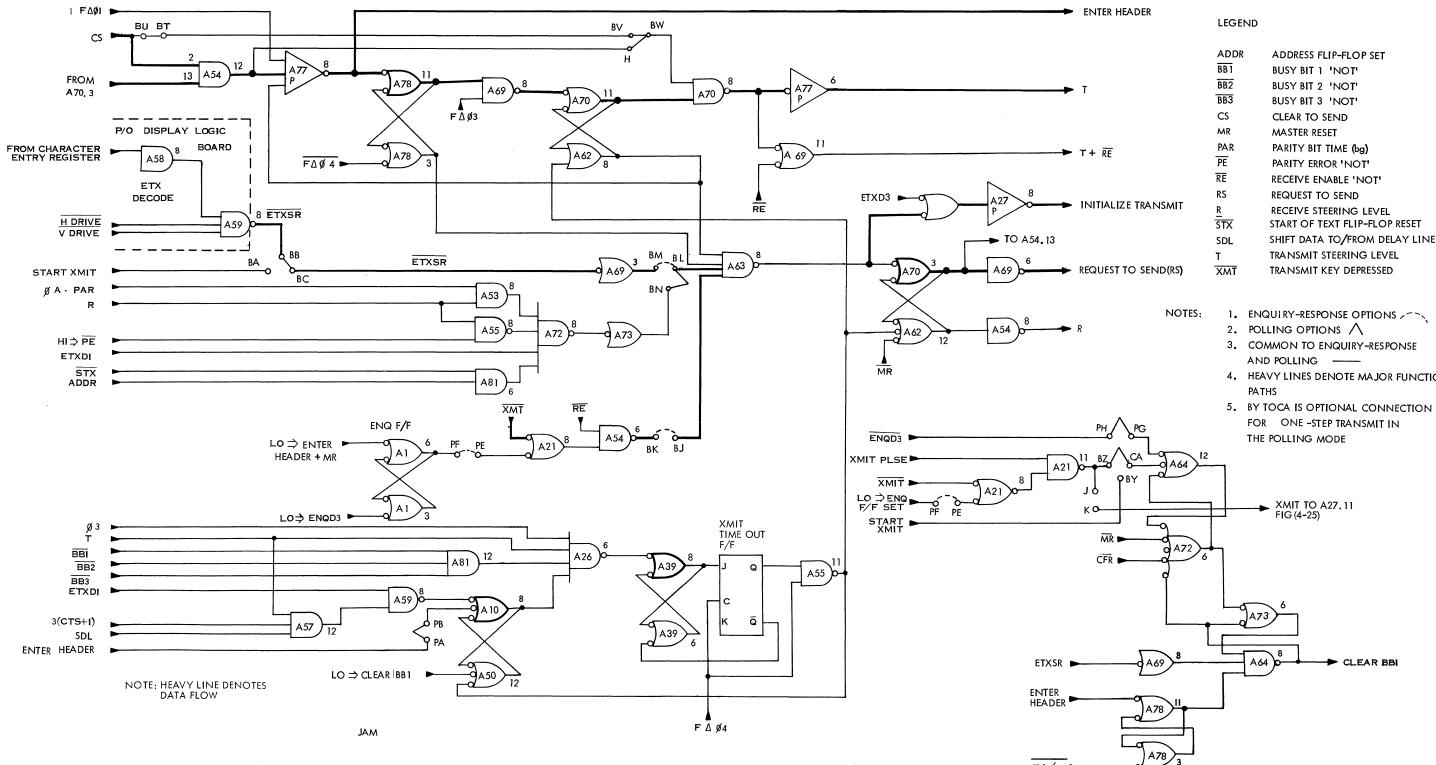

| 4-22.1   | Transmit Enable                               | 4-54          |

| 4-22.1.1 | Enquiry Response                              | 4-54          |

4-22.1.1 Enquiry Response

## TABLE OF CONTENTS (cont)

|                      | Title                                                       | Page               |

|----------------------|-------------------------------------------------------------|--------------------|

| 4-22.1.2             | Polling                                                     | 4-58               |

| 4-22.1.3             | Optional Operation                                          | 4-59               |

| 4-22.1.3.1           | Request-to-Send and Clear-to-Send                           | 4-59               |

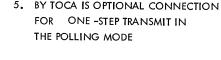

| 4-22.1.3.2           | One-Step Transmit                                           | 4-60               |

| 4-22.1.3.3           | Enquiry Option                                              | 4 -62              |

| 4-22.2               | Receive-Enable                                              | 4 <b>-</b> 63      |

| 4-22.2.1             | Enquiry-Response                                            | 4 <b>-</b> 63      |

| 4-22.2.2             | Polling                                                     | 4 <b>-</b> 65      |

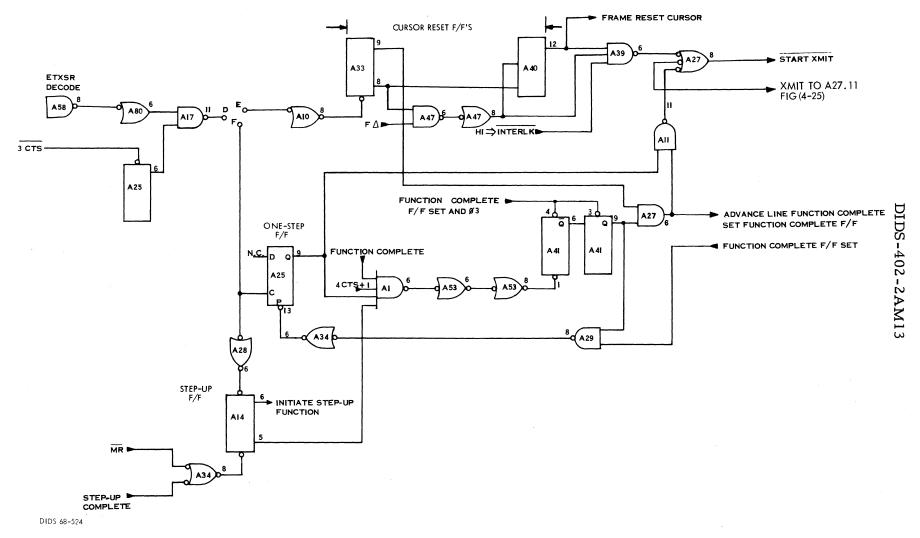

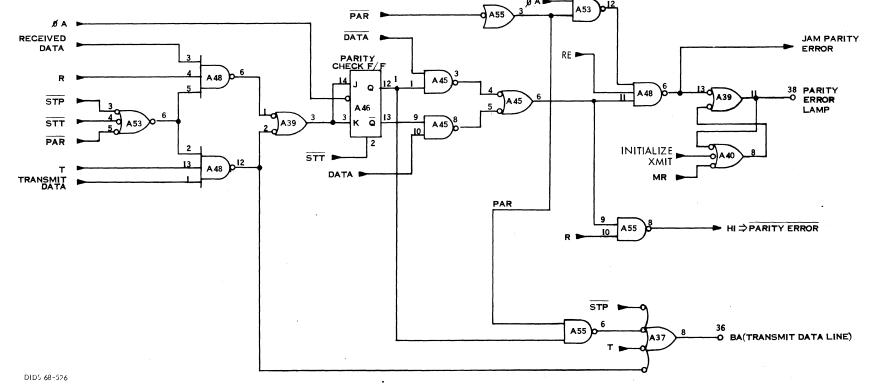

| 4-22.3               | Parity Check and Generation                                 | 4-66               |

| 4-22.3.1             | Receive                                                     | 4-66               |

| 4-22.3.2             | Transmit                                                    | 4-68               |

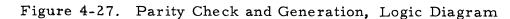

| 4-22.4               | Buffer Register Control Logic                               | 4-68               |

| 4-22.4.1             | Busy-Bit Flip-Flops                                         | 4-68               |

| 4-22.4.1.1           | Busy-Bit One                                                | 4-73               |

| 4-22.4.1.2           | Busy-Bit Two                                                | 4-73               |

| 4-22.4.1.3           | Busy-Bit Three                                              | 4-73               |

| 4-22.4.2             | Shift Gates                                                 | 4-74               |

| 4-22.4.2.1           | Shift Gate One-to-Two (SG12)                                | 4-74               |

| 4-22.4.2.2           | Shift Gate Two-to-Three (SG23)                              | 4-74               |

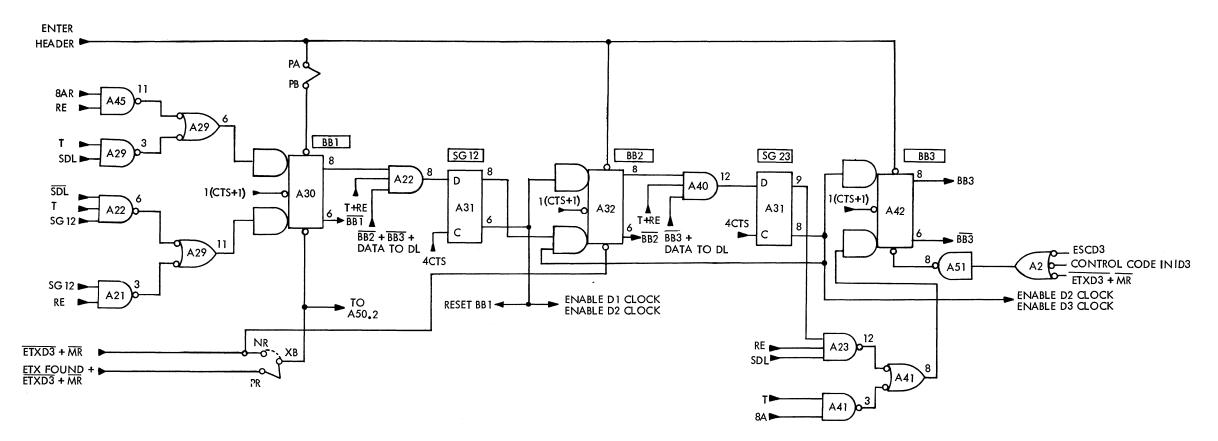

| 4-22.4.2.3           | Shift (to/from) Delay Line (SDL)                            | 4-75               |

| 4-22.4.2.3.1         | Receive Mode - Text Characters                              | 4-75               |

| 4-22.4.2.3.2         | Receive Mode - Control Characters When Pre-<br>ceded by ESC | 4 -76              |

| 4-22.4.2.3.3         | Receive Mode - Control Characters Not Pre-<br>ceded by ESC  | 4-76               |

| 4.22.4.2.3.4         | Receive Mode - Control Codes BELL, ENQ,                     | 4-70               |

|                      | and NULL                                                    | 4-77               |

| 4-22.4.2.3.5         | Transmit Mode - Text Character                              | 4-78               |

| 4-22.4.3             | Buffer Registers                                            | 4-80               |

| 4-22.4.3.1           | Buffer Register Dl                                          | 4-83               |

| 4-22.4.3.2           | Buffer Register D2                                          | 4 - 86             |

| 4-22.4.3.3           | Buffer Register D3                                          | 4 <b>-</b> 86      |

| 4-22.4.4             | Escape and Communications Control Code                      | 4 0 2              |

| 4 22 4 4 1           | Flip-Flops                                                  | 4-93               |

| 4-22.4.4.1           | CAN, DC3, DC1, CR, FF, VT, HT, BS Decodes                   | 4-94               |

| 4-22.4.4.2           | EN?, BELL, and NULL Decodes<br>ETX Decode                   | 4-94               |

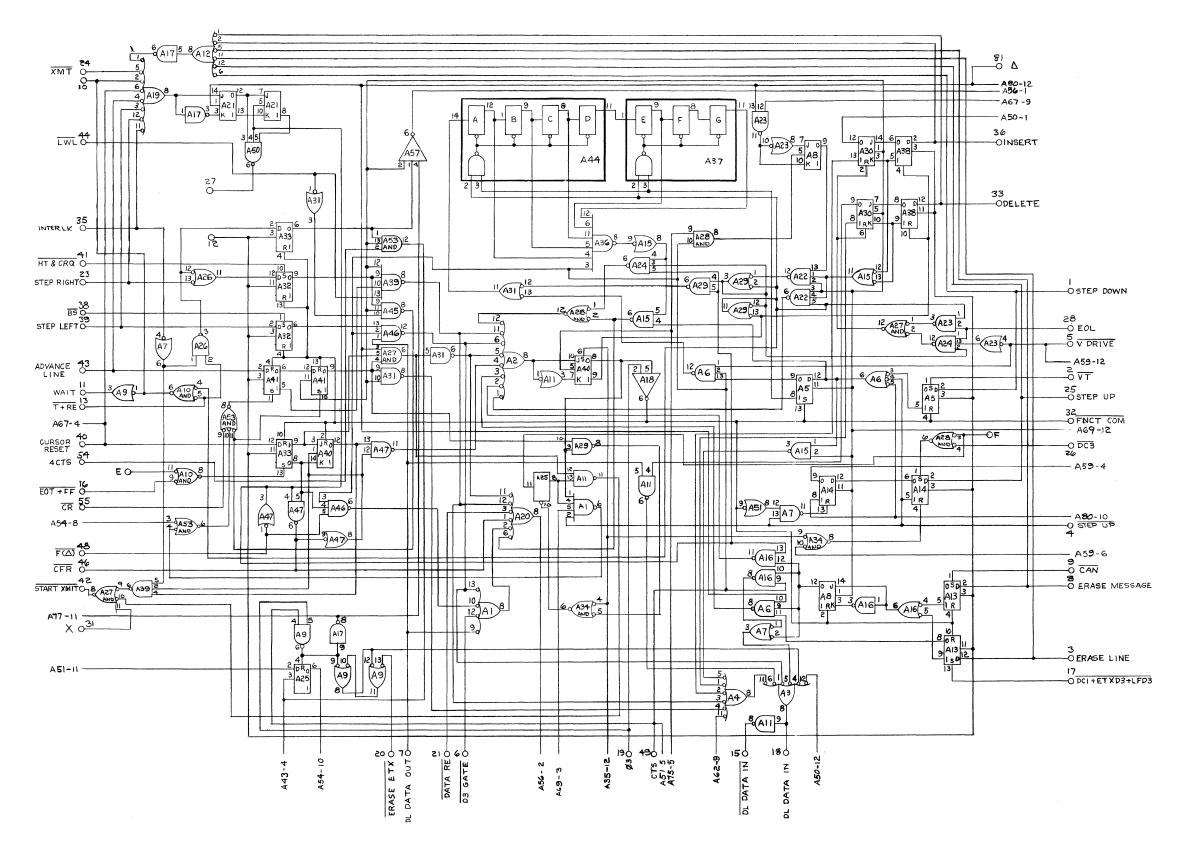

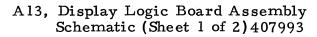

| 4-22.4.4.3<br>4-23   |                                                             | 4-96               |

|                      | Display Logic Board A13<br>Character Entry Register         | 4-96               |

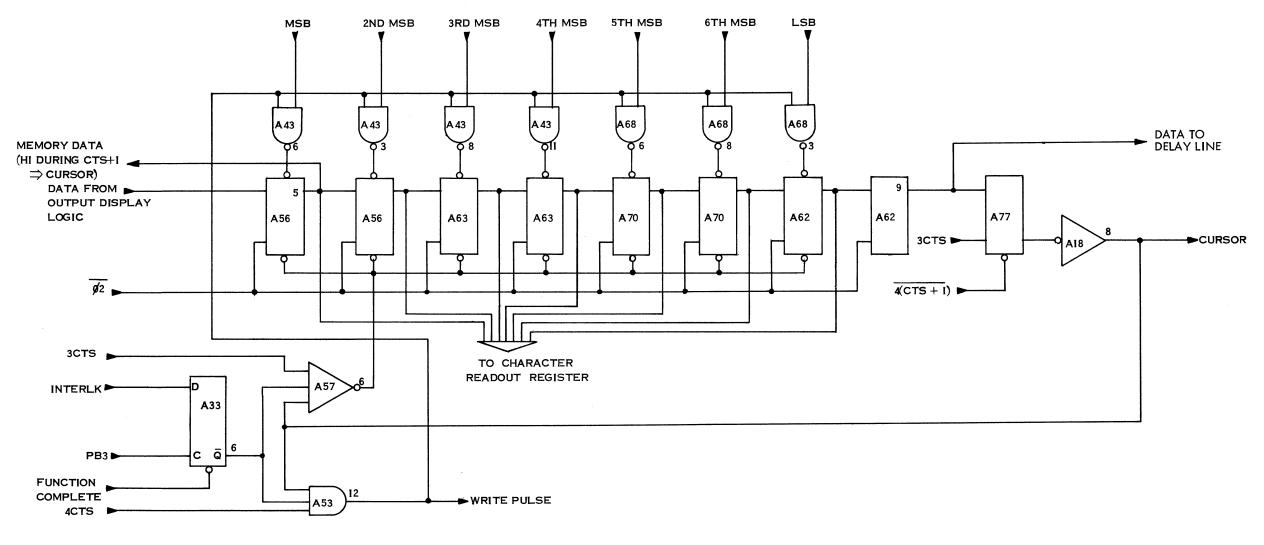

| 4-23.1               | Character Entry Register                                    | 4-96               |

| 4-23.1.1<br>4-23.1.2 | Data from Delay Line                                        | 4 <b>-</b> 96      |

| 4-23.1.3             | Data from Keyboard<br>Data from Buffor Register D3          | 4-99               |

| 4-23.1.4             | Data from Buffer Register D3                                | 4 - 100            |

| 4-23.1.5             | Data to Buffer Register D1                                  | 4-100<br>101/4-102 |

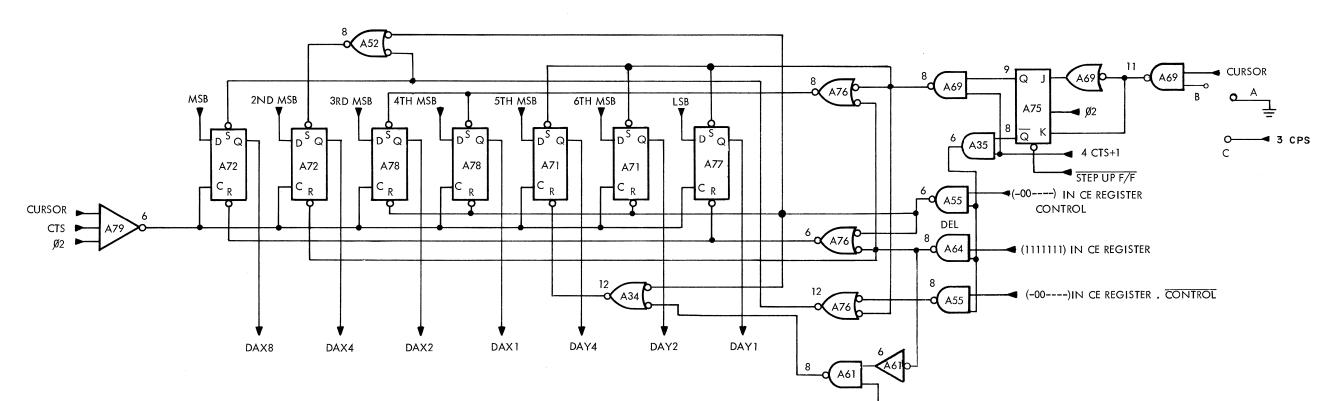

| 4-23.2               |                                                             | 101/4-102          |

| 4-23.3               | Character Readout Register 4-<br>Display Functions          | 4-106              |

| - <u>-</u>           |                                                             | 1 - 100            |

## TABLE OF CONTENTS (cont)

.

#### Title

|            | Title                                          | Page    |

|------------|------------------------------------------------|---------|

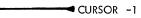

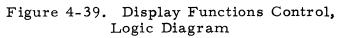

| 4-23.3.1   | Display Functions Clock                        | 4-106   |

| 4-23.3.2   | Step-Right Function                            | 4-108   |

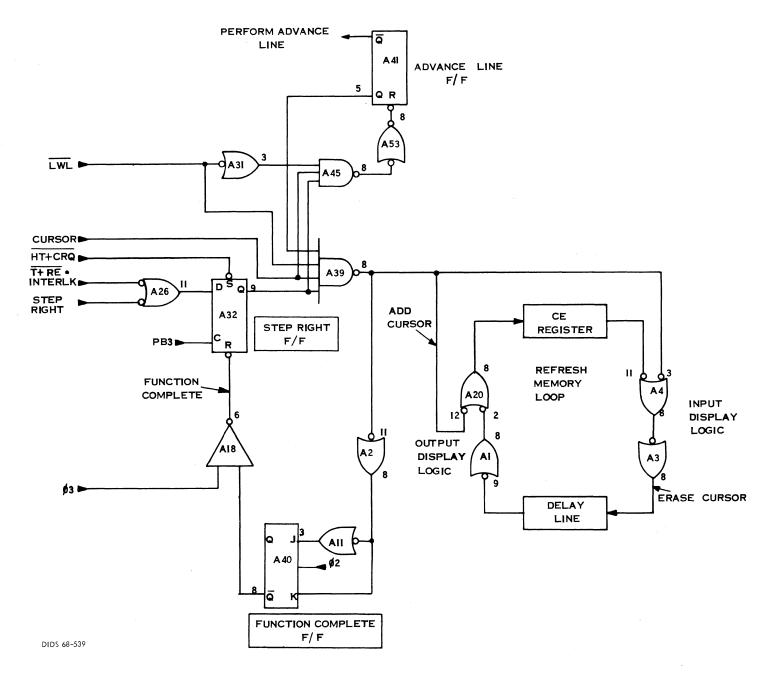

| 4-23.3.3   | Step-Left Function                             | 4-110   |

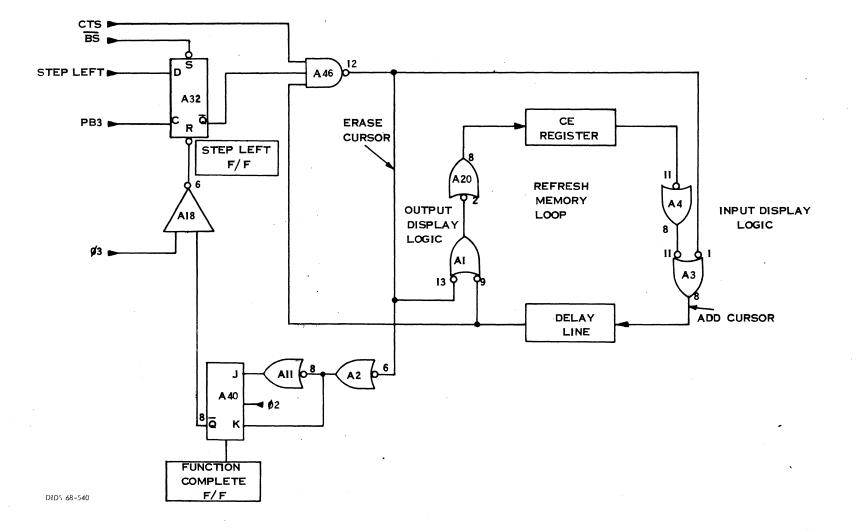

| 4-23.3.4   | Advance-Line Function                          | 4-112   |

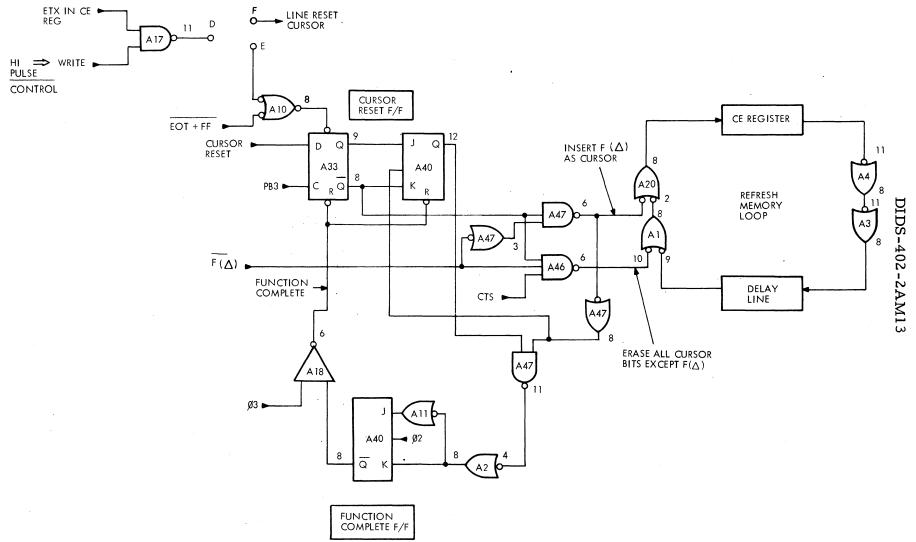

| 4-23.3.5   | Cursor Reset Function                          | 4-114   |

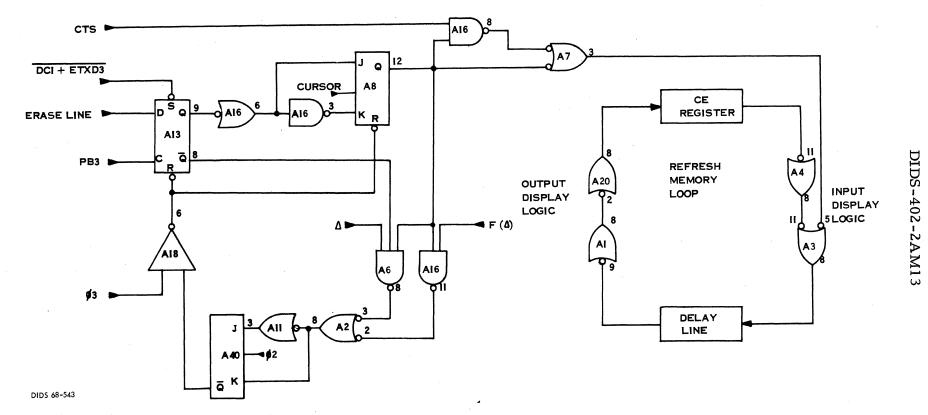

| 4-23.3.6   | Erase-Line Function                            | 4-117   |

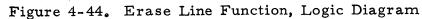

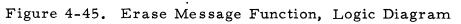

| 4-23.3.7   | Erase-Message Function                         | 4-117   |

| 4-23.3.8   | 12-Count and Insert Register                   | 4-120   |

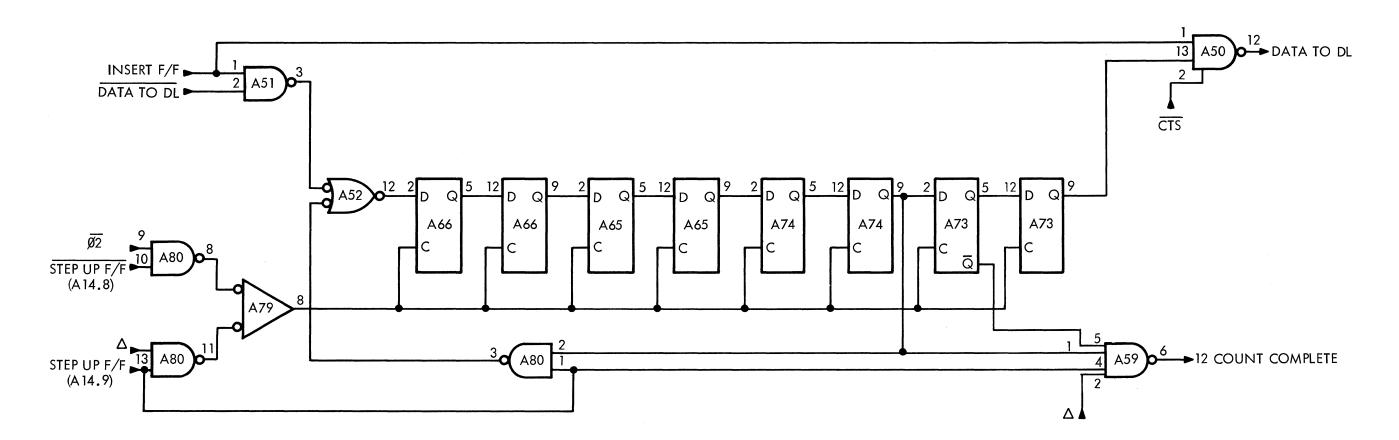

| 4-23.3.8.1 | 12-Count                                       | 4-123   |

| 4-23.3.8.2 | Insert Register                                | 4-123   |

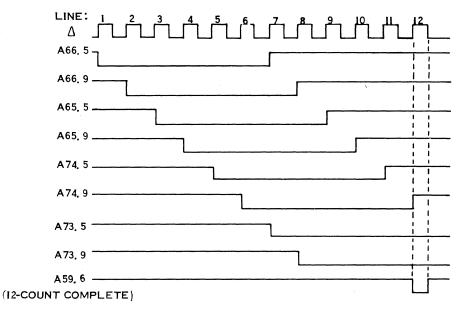

| 4-23.3.9   | 88-Count Circuit                               | 4-124   |

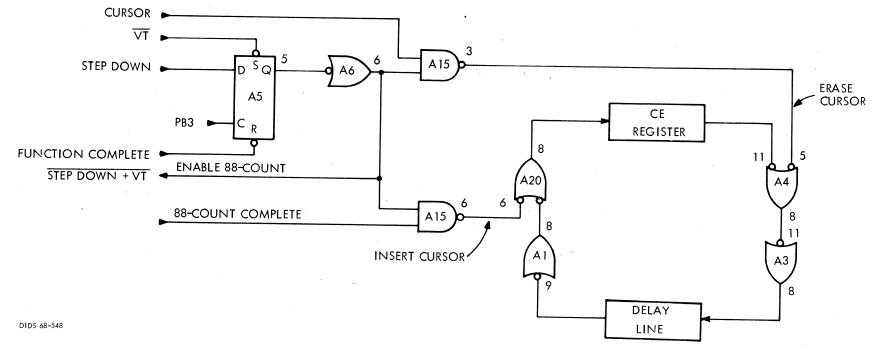

| 4-23.3.10  | Step-Down Function                             | 4-127   |

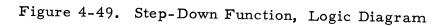

| 4-23.3.11  | Step-Up Function                               | 4-129   |

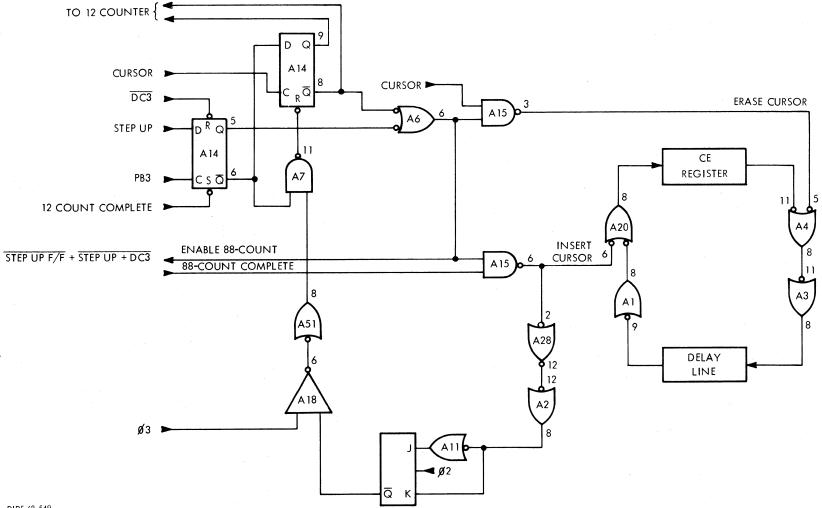

| 4-23.3.12  | Insert Character Function                      | 4-131   |

| 4-23.3.13  | Insert Line Function                           | 4-133   |

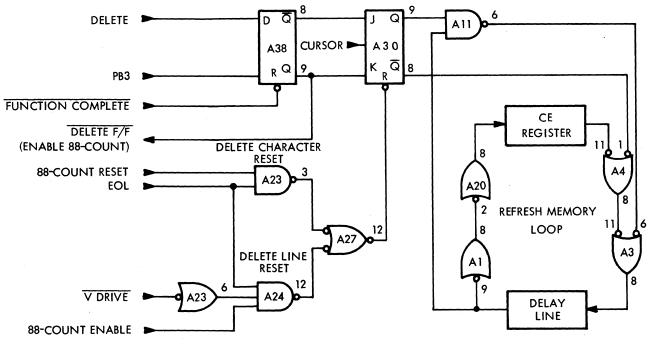

| 4-23.3.14  | Delete-Character Function                      | 4-134   |

| 4-23.3.15  | Delete -Line Function                          | 4-135   |

| 4-24       | Timing and Discrete Board Al4                  | 4-136   |

| 4-24.1     | Master Oscillator                              | 4-136   |

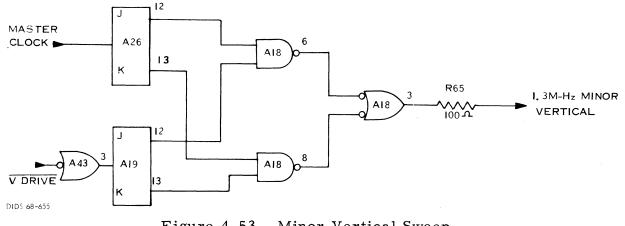

| 4-24.2     | Minor Vertical Sweep                           | 4-137   |

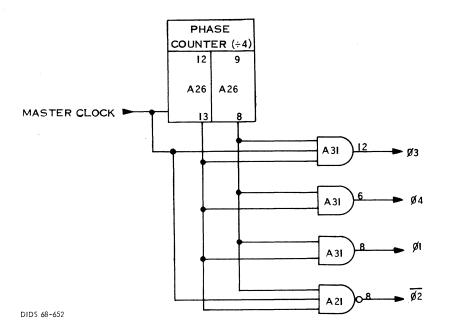

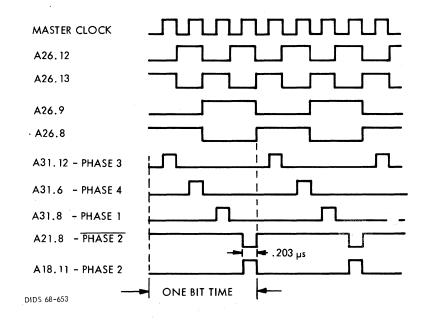

| 4-24.3     | Phase Counter                                  | 4-137   |

| 4-24.4     | Bit Counter                                    | 4-139   |

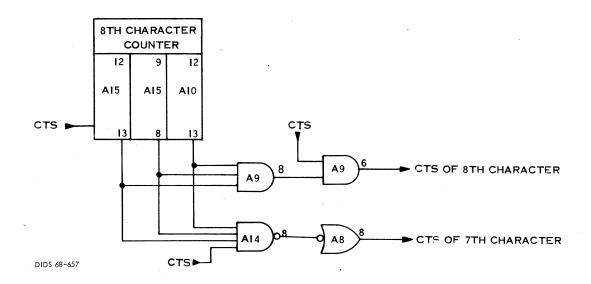

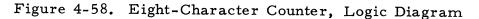

| 4-24.5     | Eight-Character Counter                        | 4-140   |

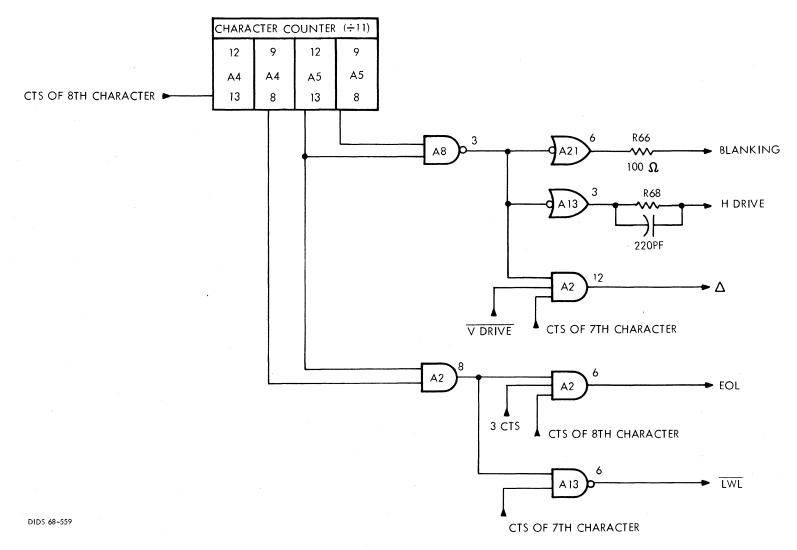

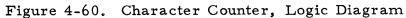

| 4-24.6     | Character Counter                              | 4-141   |

| 4-24.6.1   | LWL Pulse                                      | 4-144   |

| 4-24.6.2   | EOL Pulse                                      | 4-144   |

| 4-24.6.3   | Horizontal Drive and Blanking                  | 4-144   |

| 4-24.6.4   | First Word of Line ( $\Delta$ )                | 4-144   |

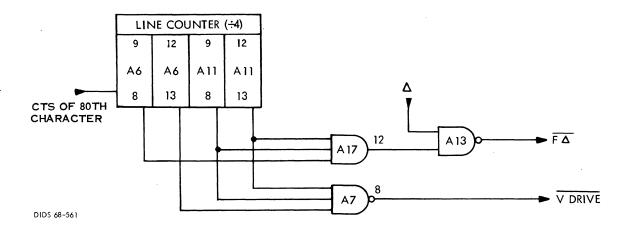

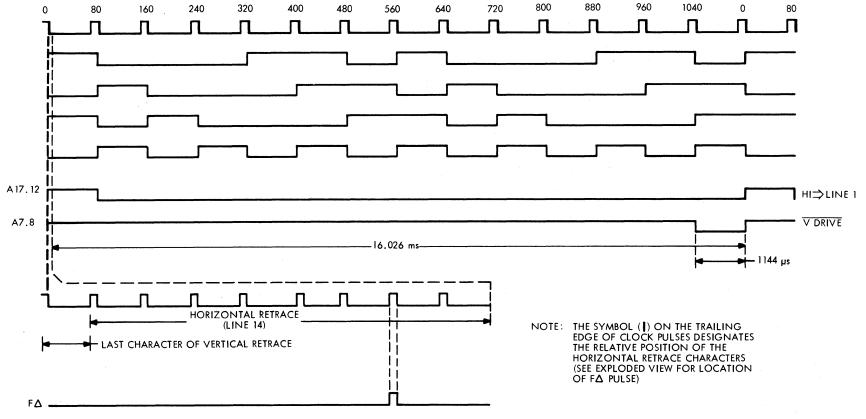

| 4-24.7     | Line Counter                                   | 4 - 144 |

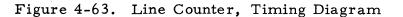

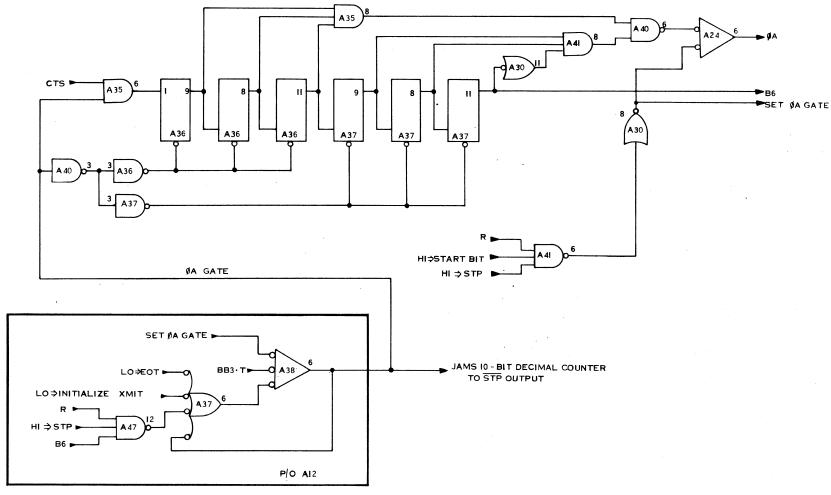

| 4-24.8     | 1200-Baud Circuitry                            | 4-145   |

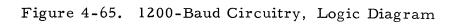

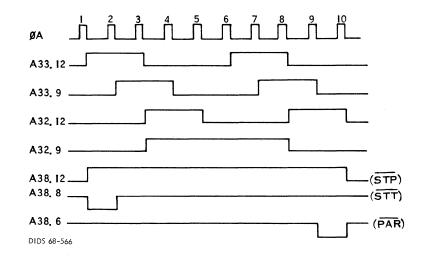

| 4-24.9     | 10-Bit Decimal Counter                         | 4 - 149 |

| 4-24.10    | Miscellaneous Circuits                         | 4-151   |

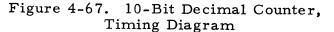

| 4-24.10.1  | Cursor Video                                   | 4-151   |

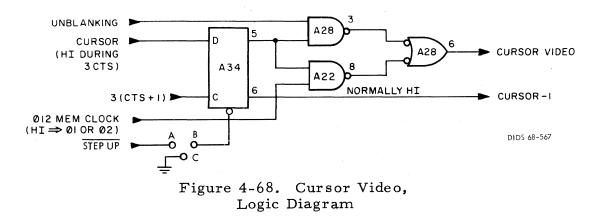

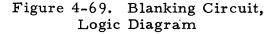

| 4-24.10.2  | Blanking                                       | 4-152   |

| 4-24.11    | Interface Circuits                             | 4-153   |

| 4-25       | Delay-Line Electronics A9 and Delay Line A15   | 4-153   |

| 4-26       | Monoscope Deflection Amplifier A3              | 4-154   |

| 4-26.1     | X and Y Digital-to-Analog Converters           | 4-154   |

| 4-26.2     | X-Deflection Amplifier and Associated Circuits | 4-155   |

| 4-26.3     | Y-Deflection Amplifier and Associated Circuits | 4-155   |

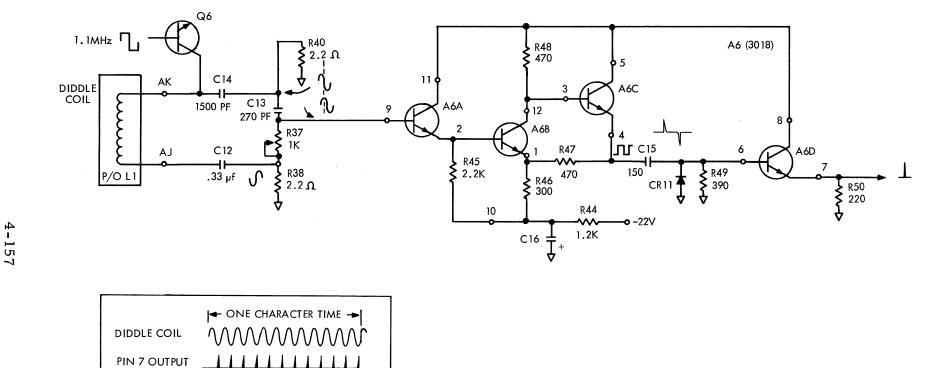

| 4-26.4     | Unblanking Pulse Generation                    | 4-156   |

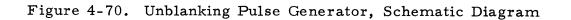

| 4-26.5     | Monoscope VI                                   | 4-156   |

| 4-27       | Video Preamplifier A7                          | 4-159   |

| 4-28       | Video Amplifier A8                             | 4-159   |

| 4-28.1     | Video Amplification                            | 4-159   |

| 4-28.2     | Blanking                                       | 4-160   |

## TABLE OF CONTENTS (cont)

#### Title

|        | Title                                           | Page    |

|--------|-------------------------------------------------|---------|

| 4-28.3 | CRT Protect                                     | 4 - 160 |

| 4-28.4 | Cathode Ray Tube V2                             | 4 - 160 |

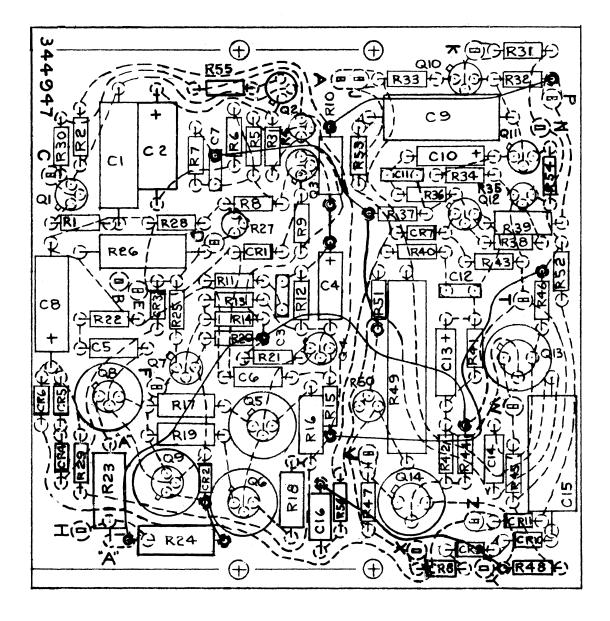

| 4-29   | Horizontal and Vertical Deflection Amplifier A2 | 4 - 162 |

| 4-29.1 | Horizontal Deflection Amplifier                 | 4 - 162 |

| 4-29.2 | Vertical Deflection Amplifier                   | 4 - 163 |

|        | Section IV. INTEGRATED CIRCUITS                 |         |

| 4-30   | General Description of Section Contents         | 4-163   |

| 4-31   | Integrated Circuits                             | 4-163   |

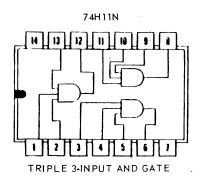

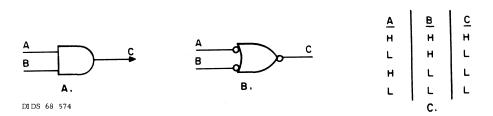

| 4-31.1 | AND Function                                    | 4-167   |

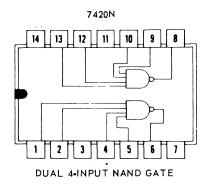

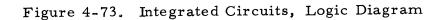

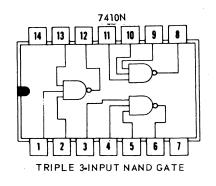

| 4-31.2 | NAND Function                                   | 4-167   |

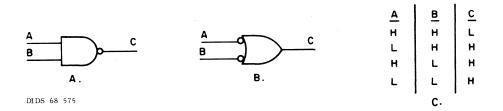

| 4-31.3 | Inverter/Driver Function                        | 4-167   |

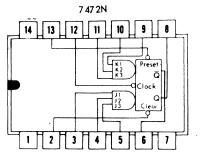

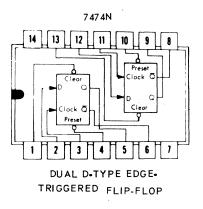

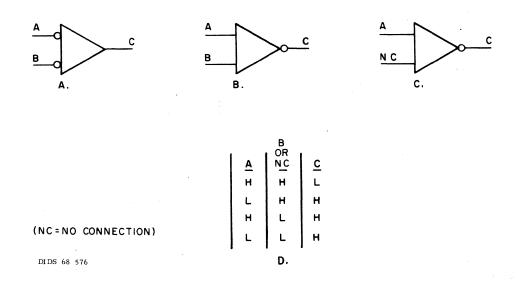

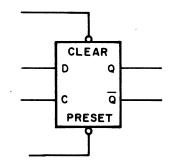

| 4-31.4 | Edge-Triggered Flip-Flop                        | 4-168   |

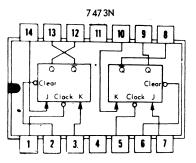

| 4-31.5 | J-K Master-Slave Flip-Flop                      | 4-168   |

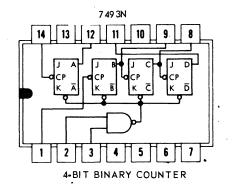

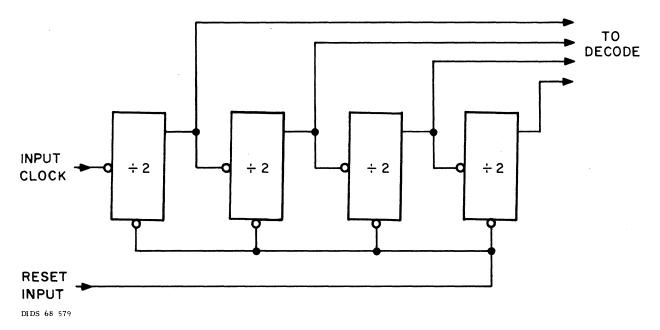

| 4-31.6 | 4-Bit Binary Counter                            | 4-170   |

#### CHAPTER 5. MAINTENANCE

| 5-1 | Maintenance Concept     | 5 -        | 1 |

|-----|-------------------------|------------|---|

| 5-2 | Test Equipment Required | 5 <b>-</b> | 1 |

### CHAPTER 6. PARTS LIST

#### CHAPTER 7. MASTER DRAWINGS

## LIST OF ILLUSTRATIONS

| Figure        |                                                      | Page           |

|---------------|------------------------------------------------------|----------------|

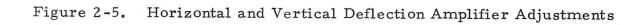

| 1 - 1         | Model 402-2AM13 Display Terminal                     | 1-2            |

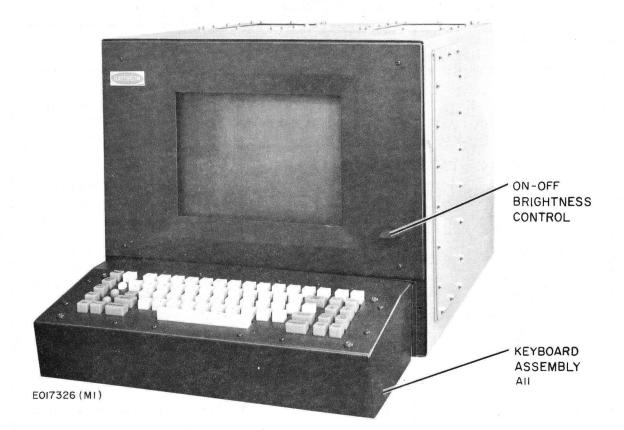

| 1-2           | Model 402-2AM13 Keyboard                             | 1-4            |

| 1-3           | Model 402-2AM13 Display Terminal, Right Side         |                |

|               | with Boards Open                                     | 1-5            |

| 1-4           | Model 402-2AM13 Display Terminal, Right View         | 1-6            |

| 1-5           | Model 402-2AM13 Display Terminal, Left Oblique       |                |

|               | Rear View with Logic Drawer Removed                  | 1-8            |

| 1-6           | Model 402-2AM13 Display Terminal, Left View          | 1-9            |

| 1-7           | Model 402-2AM13 Display Terminal, Rear View          | 1-10           |

| 2-1           | Display Terminal Outline Dimension Drawing           | 2 - 1          |

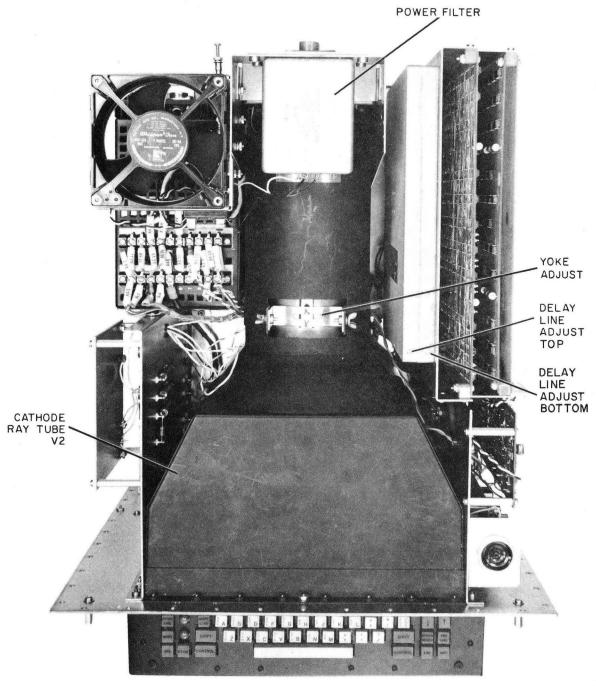

| 2-2           | Model 402-2AM13 Display Terminal, Top View           |                |

|               | with Cover Removed                                   | 2-6            |

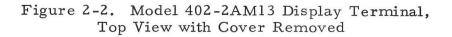

| 2-3           | Delay-Line Adjustment                                | 2-7            |

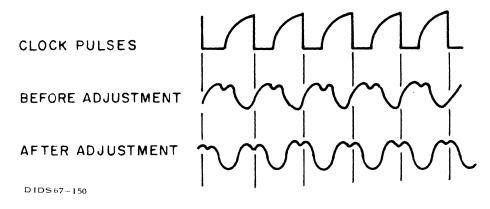

| 2-4           | Monoscope Deflection Amplifier Adjustments           | 2-10           |

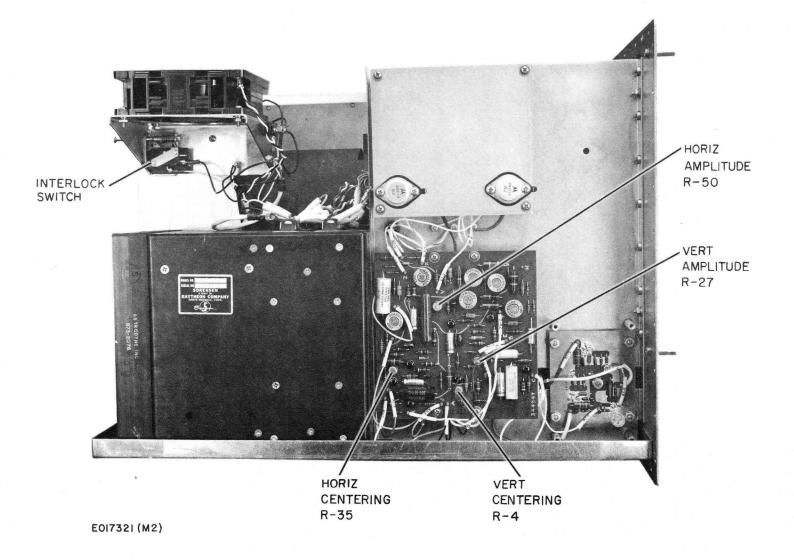

| 2-5           | Horizontal and Vertical Deflection Amplifier         |                |

|               | Adjustments                                          | 2 - 12         |

| 3 - 1         | Model 402-2AM13 Operating Controls and Indicators    | 3 - 1          |

| 3-2           | Keyboard Assembly Operating Controls and Indicators  | 3-2            |

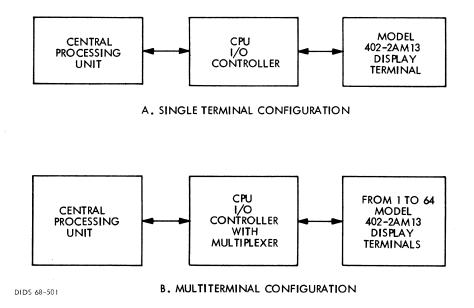

| 4-1           | Typical System Configuration                         | 4-2            |

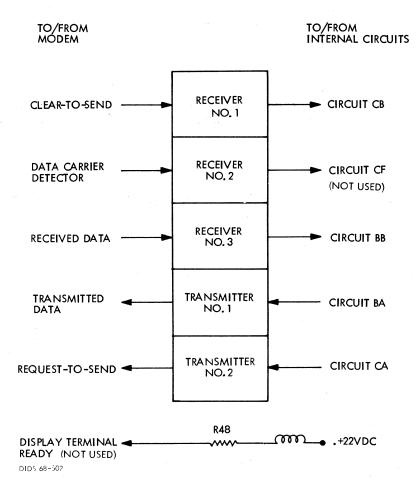

| 4-2           | Modem Interface Circuits                             | 4-5            |

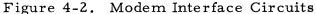

| 4-3           | ASCII Matrix                                         | 4-8            |

| 4-4           | Character Format                                     | 4 - 1 0        |

| 4-5           | Enquiry Message Format                               | 4-12           |

| 4-6           | Response Message Format                              | 4-12           |

| 4-7           | Polling Read Directive                               | 4-15           |

| 4-8           | Display Terminal Response to Read Directive if       |                |

|               | Message Available                                    | 4 - 16         |

| 4-9           | Display Terminal Response to Read Directive if       | 4 37           |

| 4 10          | No Message Available                                 | 4-16           |

| 4-10          | Polling Write Directive                              | 4-16           |

| 4-11          | Polling ENQ Directive                                | 4-17           |

| 4-12          | Model 402-2AM13 Display Terminal, Overall            | 4 10           |

| 4 10          | Block Diagram                                        | 4-19           |

| 4-13          | Character Entry and Readout Registers and Refresh    | 4 21/4 22      |

| 4 1 4         | Memory Loop                                          | 4-21/4-22      |

| 4-14          | Character Generation Circuitry                       | 4-23/4-24      |

| 4-15          | Delay-Line Memory Section, Simplified Diagram        | 4-34           |

| 4-16          | Buffer Registers and Interface                       | 4-36           |

| 4-17          | Editing and Cursor Control Logic, Block Diagram      | 4-40           |

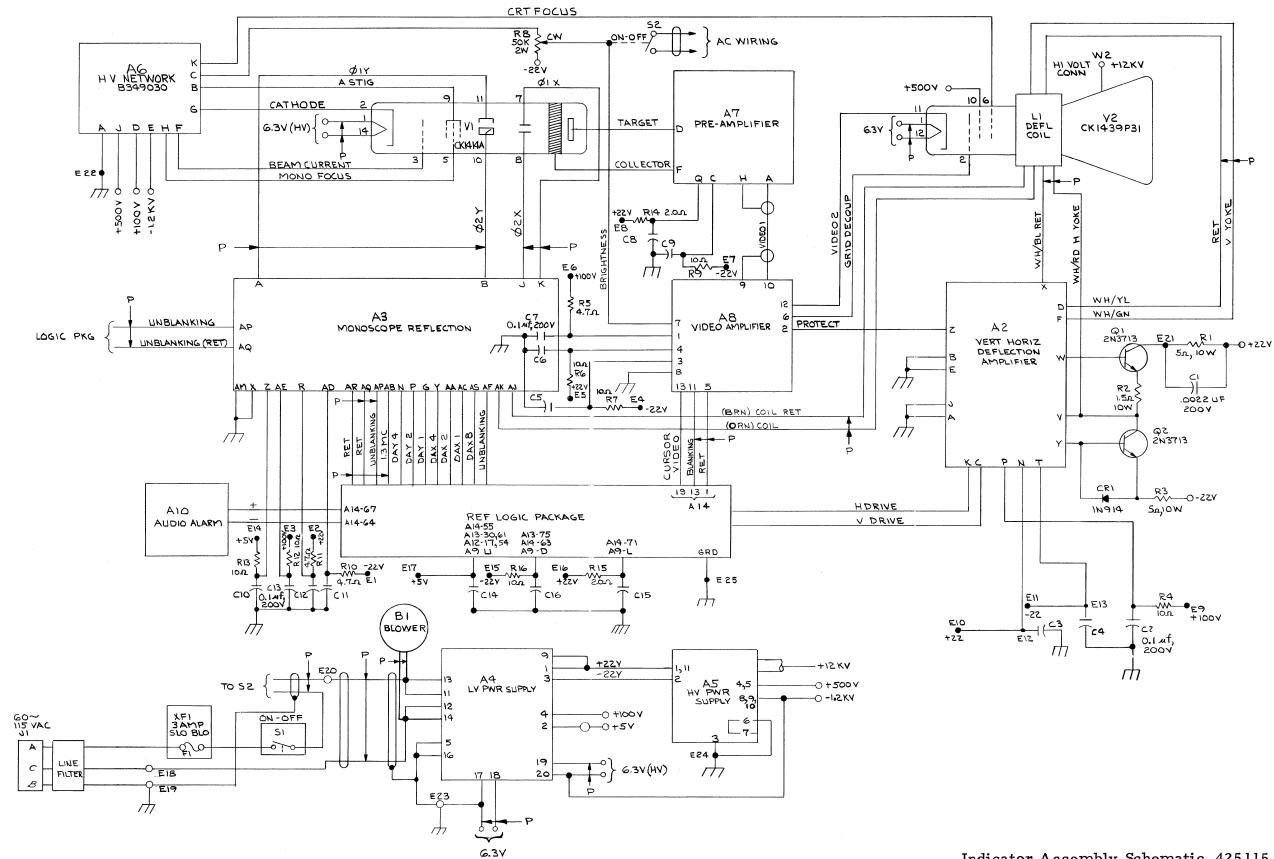

| 4-18          | Timing Circuits, Block Diagram                       | 4-43           |

| 4-19          | Phase Counter Outputs<br>Bit Counter Outputs         | 4-44           |

| 4-20          | Bit Counter Outputs and Memory Data Relationship     | 4-45           |

| 4-21          | Character Counter Outputs                            | 4-47           |

| 4-22          | Vertical and Horizontal Deflection Amplifier,        | 4-49           |

| 1 22          | Block Diagram                                        | 4-49           |

| 4 <b>-</b> 23 | Effect of Minor Vertical Expansion on CRT Scan Lines | <b>-+ -</b> 50 |

## LIST OF ILLUSTRATIONS (cont)

| Figure        |                                                 | Page          |

|---------------|-------------------------------------------------|---------------|

| 4-24          | Transmit Enable Circuitry                       | 4-55/4-56     |

| 4-25          | One-Step Transmit Option, Logic Diagram         | 4-61          |

| 4-26          | Receive Enable Circuitry, Logic Diagram         | 4-64          |

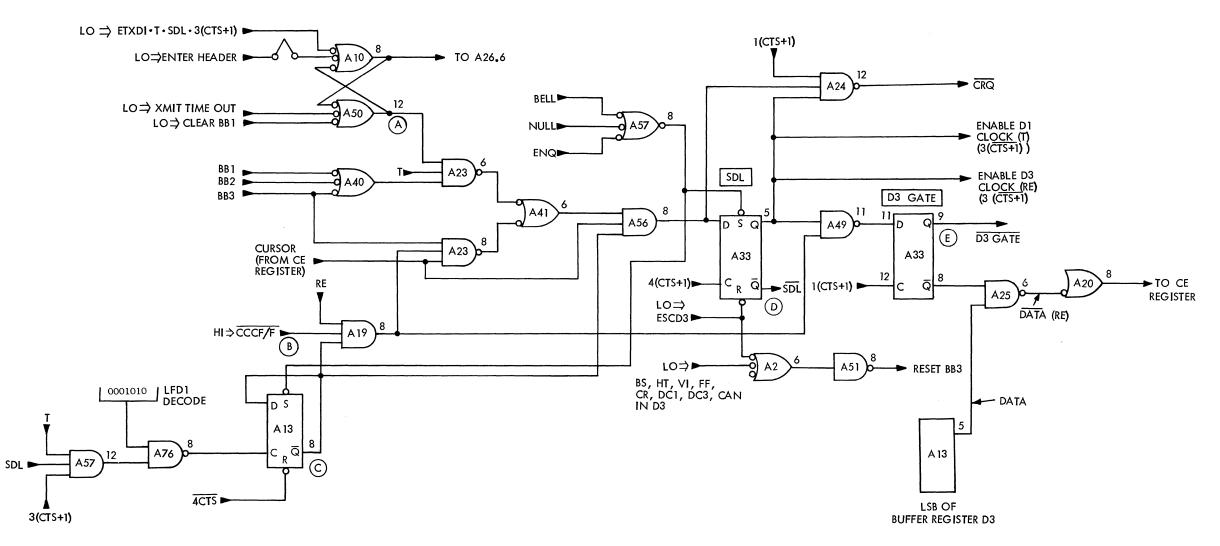

| 4-27          | Parity Check and Generation, Logic Diagram      | 4-67          |

| 4-28          | BB1, BB2, BB3, SG12, SG23 and Associated        |               |

|               | Circuits, Logic Diagram                         | 4-69/4-70     |

| 4-29          | SDL, D3 Gate and Associated Circuits, Logic     | <b>,</b> .    |

| /             | Diagram                                         | 4-71/4-72     |

| 4-30          | Use of NULL Control Codes                       | 4-78          |

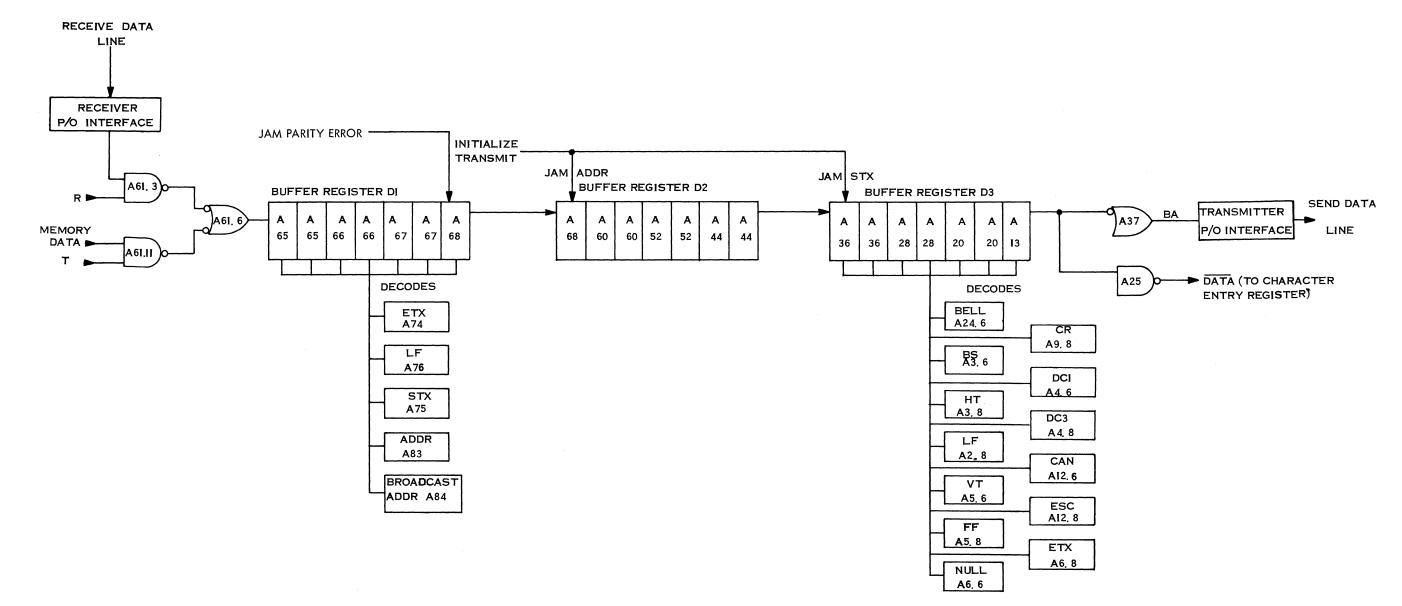

| 4-31          | Buffer Registers, Block Diagram                 | 4-81/4-82     |

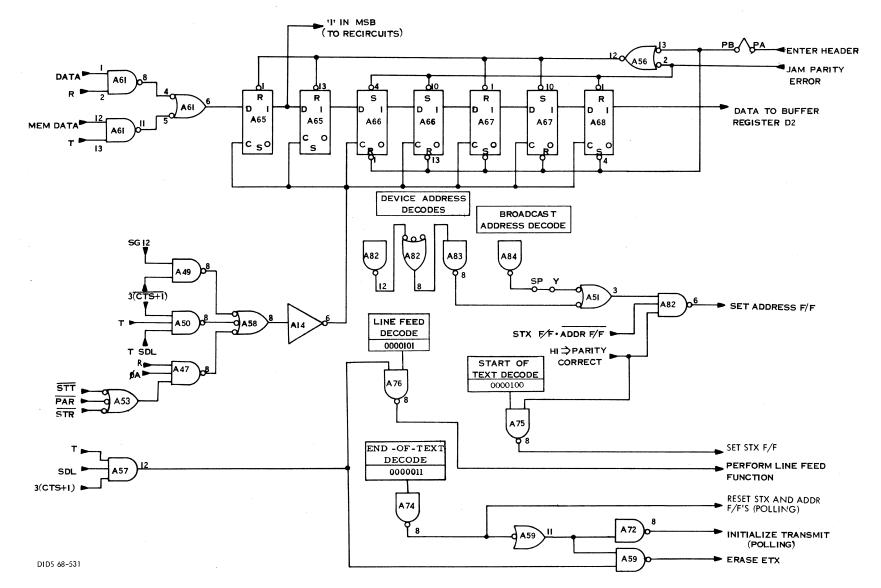

| 4-32          | Buffer Register Dl, Logic Diagram               | 4-84          |

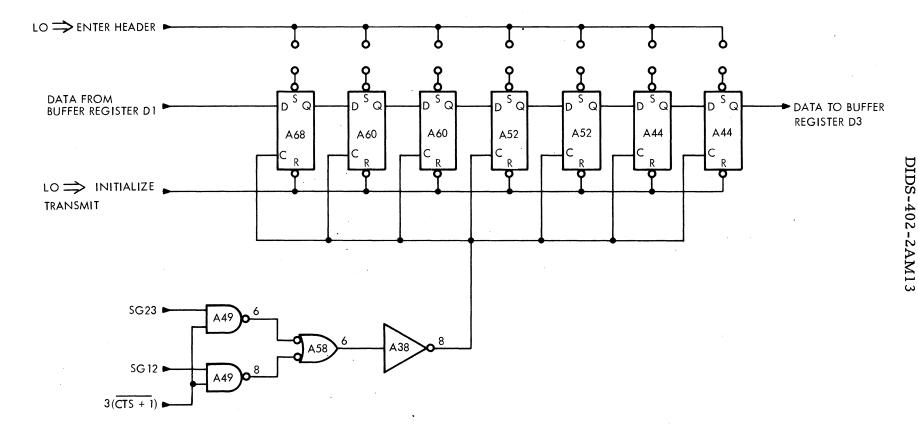

| 4-33          | Buffer Register D2, Logic Diagram               | 4-87/4-88     |

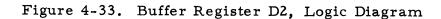

| 4-34          | Buffer Register D3, Logic Diagram               | 4-89/4-90     |

| 4-35          | ESC and CCC Flip-Flops and Associated Circuits, | , , .         |

|               | Logic Diagram                                   | 4-92          |

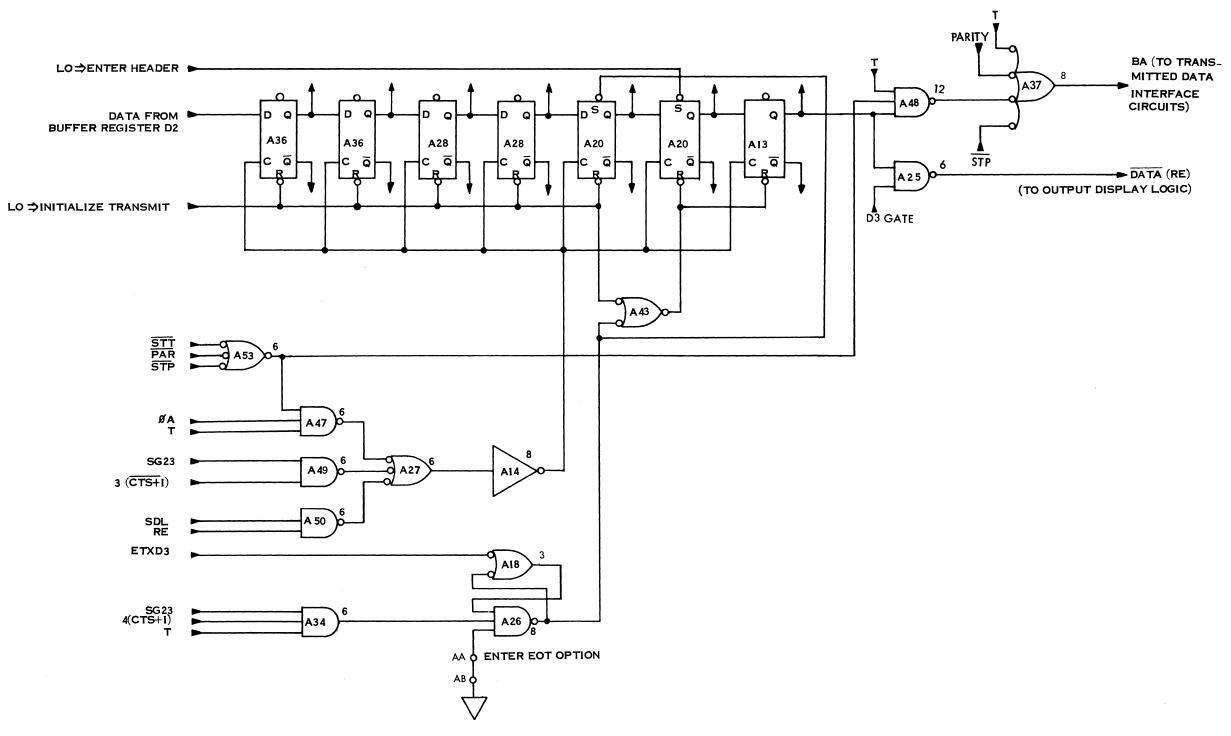

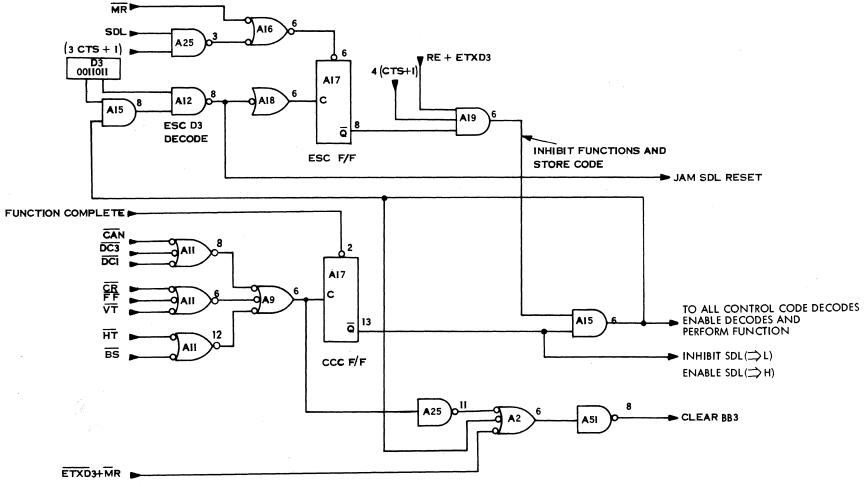

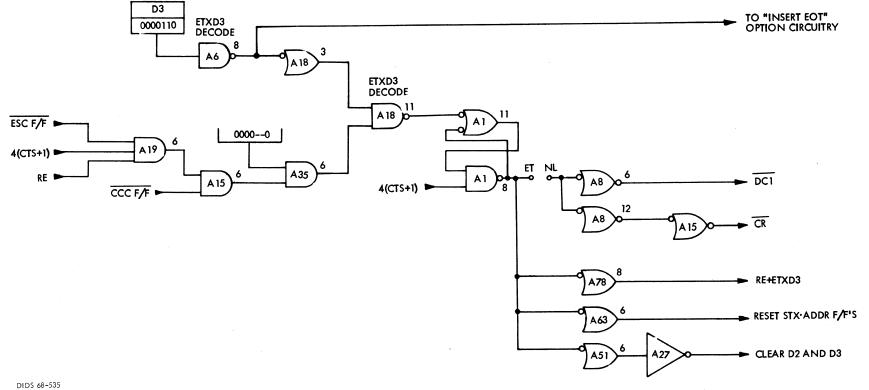

| 4-36          | ETX D3 Decode and Associated Circuits, Logic    | - /-          |

|               | Diagram                                         | 4 <b>-</b> 95 |

| 4-37          | Character Entry Register, Logic Diagram         | 4-97/4-98     |

| 4-38          | Character Readout Register, Logic Diagram       | 4-103/4-104   |

| 4-39          | Display Functions Control, Logic Diagram        | 4-107         |

| 4-40          | Step Right Function, Logic Diagram              | 4-109         |

| 4-41          | Step Left Function, Logic Diagram               | 4-111         |

| 4-42          | Advance Line Function, Logic Diagram            | 4-113         |

| 4-43          | Cursor Reset Function, Logic Diagram            | 4-115         |

| 4-44          | Erase Line Function, Logic Diagram              | 4-118         |

| 4-45          | Erase Message Function, Logic Diagram           | 4-119         |

| 4-46          | 12-Count and Insert Register, Block Diagram     | 4-121/4-122   |

| 4-47          | 12-Count Timing Diagram                         | 4-123         |

| 4-48          | 88-Count Circuit, Logic Diagram                 | 4-125/4-126   |

| 4-49          | Step-Down Function, Logic Diagram               | 4-128         |

| 4-50          | Step-Up Function, Logic Diagram                 | 4-130         |

| 4-51          | Insert Function, Logic Diagram                  | 4-132         |

| 4-52          | Delete Function, Logic Diagram                  | 4-134         |

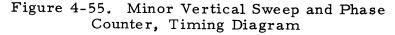

| 4 <b>-</b> 53 | Minor Vertical Sweep, Logic Diagram             | 4-137         |

| 4-54          | Phase Counter, Logic Diagram                    | 4-138         |

| 4 <b>-</b> 55 | Minor Vertical Sweep and Phase Counter, Timing  |               |

|               | Diagram                                         | 4-138         |

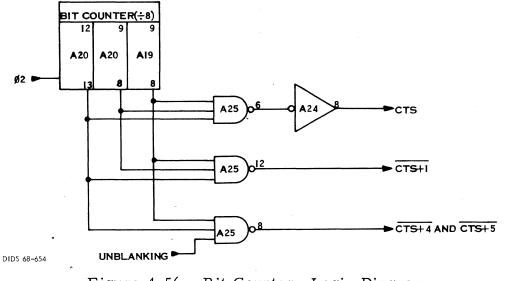

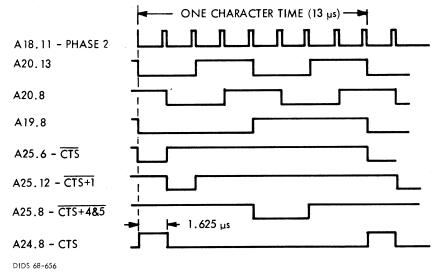

| 4-56          | Bit Counter, Logic Diagram                      | 4-139         |

| 4-57          | Bit Counter, Timing Diagram                     | 4-140         |

| 4 <b>-</b> 58 | Eight-Character Counter, Logic Diagram          | 4-140         |

| 4-59          | Eight-Character Counter, Timing Diagram         | 4-141         |

| 4-60          | Character Counter, Logic Diagram                | 4-142         |

| 4-61          | Character Counter, Timing Diagram               | 4-143         |

| 4-62          | Line Counter, Logic Diagram                     | 4 - 145       |

| 4-63          | Line Counter, Timing Diagram                    | 4-146         |

| 4-64          | High-Speed Timing Diagram                       | 4 - 147       |

## LIST OF ILLUSTRATIONS (cont)

| Figure |                                                    | Page           |

|--------|----------------------------------------------------|----------------|

| 4-65   | 1200-Baud Circuitry, Logic Diagram                 | 4-148          |

| 4-66   | 10-Bit Decimal Counter, Logic Diagram              | 4-150          |

| 4-67   | 10-Bit Decimal Counter, Timing Diagram             | 4-150          |

| 4-68   | Cursor Video, Logic Diagram                        | 4-151          |

| 4-69   | Blanking Circuit, Logic Diagram                    | 4-152          |

| 4-70   | Unblanking Pulse Generator, Schematic Diagram      | 4-157          |

| 4-71   | Monoscope and High Voltage Network, Schematic      |                |

|        | Diagram                                            | 4-158          |

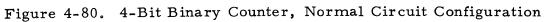

| 4-72   | CRT Indicator, Simplified Block Diagram            | 4-161          |

| 4-73   | Integrated Circuits, Logic Diagram                 | 4-165          |

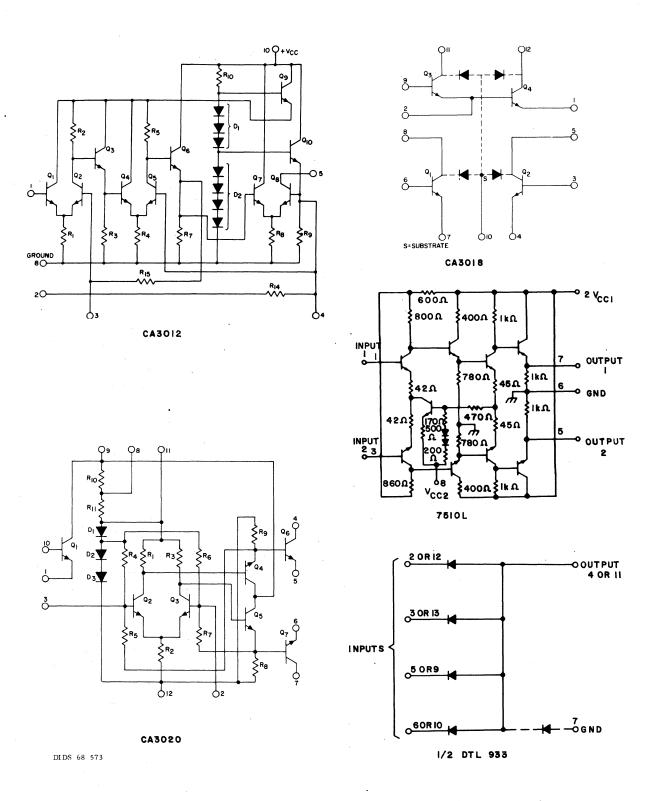

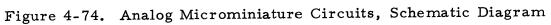

| 4-74   | Analog Microminiature Circuits, Schematic          |                |

|        | Diagram                                            | <b>4-</b> 166  |

| 4-75   | AND Function Logic Diagram and Truth Table         | 4-167          |

| 4-76   | NAND Function Logic Diagram and Truth Table        | 4-167          |

| 4-77   | Inverter/Driver Function, Logic Diagram and        |                |

|        | Truth Table                                        | 4 <b>-</b> 168 |

| 4-78   | Edge-Triggered Flip-Flop, Logic and Timing         |                |

|        | Diagram and Truth Table                            | 4-169          |

| 4-79   | J-K Master-Slave Flip-Flop, Logic Diagram and      |                |

|        | Truth Table                                        | 4-170          |

| 4-80   | 4-Bit Binary Counter, Normal Circuit Configuration | 4 - 17 1       |

|        |                                                    |                |

## LIST OF TABLES

| Table |                                              | Page          |

|-------|----------------------------------------------|---------------|

| 1-1   | Leading Particulars                          | 1-12          |

| 1-2   | Capabilities and Limitations                 | 1-12          |

| 1-3   | Wiring Options                               | 1-13          |

| 1-4   | Glossary of Terms                            | 1-14          |

| 3-1   | Operating Controls and Indicators            | 3-2           |

| 4-1   | ASCII Control Codes                          | 4-9           |

| 4-2   | Action of ASCII Control Codes During Receive | 4 - 13        |

| 4-3   | Keyboard Characters and Coding               | 4 <b>-</b> 25 |

| 4-4   | I-C Part Numbers and Cross-Reference         | 4-164         |

#### CHAPTER 1

#### GENERAL INFORMATION

#### 1-1 PURPOSE OF EQUIPMENT

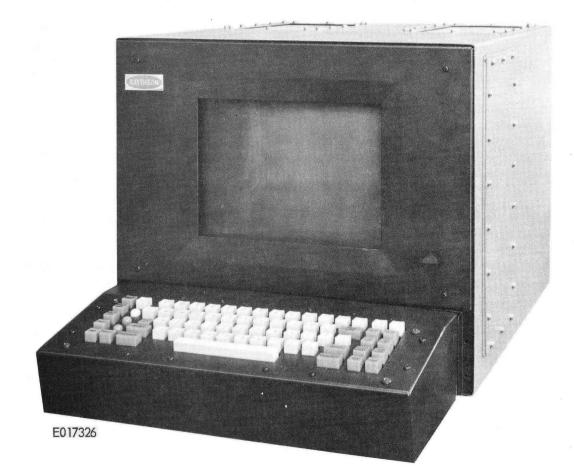

The Model 402-2AM13 Display Terminal (figure 1-1) is a radio frequency (rf) shielded display device designed to provide quick-action keyboard input and visual readout of information stored or processed by a central processing unit (CPU The Display Terminal operates in one of two separate modes: transmit or receive.

In the transmit mode, display terminal operators initiate messages by operating keys on the keyboard assembly. As each character key is depressed, a visual character corresponding to the particular key is produced on the cathode ray tube (CRT) screen. Simultaneously, a digital code corresponding to the particular character enters an internal memory device. When the operator has completed composing the message, the message is coupled through self-contained interface circuits to either a modem or a CPU Input/Output (I/O) device. This readout is non-volatile, and the message remains on the screen even though the data is transmitted.

In the receive mode, digital data messages arriving from the CPU are decoded by the Display Terminal and visual characters are produced on the CRT screen. Again, the data received is simultaneously stored in a memory device; if desired, the received message may be edited and returned to the CPU. In addition to receiving actual data characters, the Display Terminal recognizes several control codes. These codes produce a message which is formatted according to the CPU's programmed directives. Depending upon the nature of the information system, received data may be edited and returned to the CPU, or destroyed after noting the displayed information.

#### 1-2 DESCRIPTION OF EQUIPMENT

The Display Terminal is a compact, solid-state device completely selfcontained in an rf shielded cabinet. All interface connections conform to interface standard MIL-STD-188B and interfacing signals enter and exit through a single connector at the rear of the unit. Data transfer between the Display Terminal and the connected I/O device is asynchronous and occurs at a rate of 1200 bits/sec (baud).

The Display Terminal uses a monoscope character generator to produce 96 separate visual characters. These characters consist of the upper and lower case alphabet, numerals 0 through 9, and several special symbols. Up to 1040 high-resolution characters can be displayed on the CRT screen at any given moment in an 80 character/line, 13-line format. Extensive editing and cursor control increases operational flexibility by allowing operators to rapidly revise and update the information, correct errors, or arrange transmitted data messages in a particular format. All composition and editing of data messages is accomplished off-line; the Display Terminal is connected to the CPU only during the actual transfer of information.

Figure 1-1. Model 402-2AM13 Display Terminal

The Display Terminal consists of the following major circuits and components:

- a. Keyboard Assembly All

- b. Display Logic Board A13

- c. Communications Control Board A12

- d. Timing and Discrete Board Al4

- e. Delay Line Electronics A9

- f. Delay Line A15

- g. Monoscope Deflection Amplifier Assembly A3

- h. Video Preamplifier Assembly A7

- i. Video Amplifier Assembly A8

- j. Vertical and Horizontal Deflection Amplifier Assembly A2

- k. Low Voltage Power Supply A4

- 1. High Voltage Power Supply A5

- m. High Voltage Network Assembly A6

- n. Monoscope V1

- o. Cathode Ray Tube V2

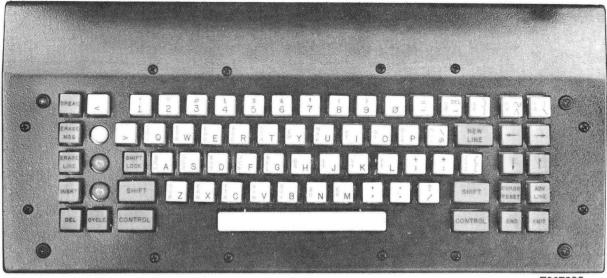

1-2.1 Keyboard Assembly All

The keyboard assembly (figure 1-2) provides a means of initiating and editing data messages, and controlling various display terminal operations. The 74 keys are arranged in an essentially USA Standard keyboard layout and have touch characteristics similar to a high-quality electric typewriter. Control keys are centralized at the right and left edges of the keyboard to prevent their unintentional depression during message composition. Noise-free operation is provided by magnetically actuated reed switches which enable current flow through a specific branch of a self-contained diode matrix. The code produced by the depression of a character key is used internally to produce a corresponding visual character on the CRT screen and externally to form a specific character of the transmitted message. In addition to the standard keys used for composing messages, the keyboard contains many special function keys. These keys (such as END, XMIT, ERASE MSG) are used for editing or control purposes.

E017325

#### Figure 1-2. Model 402-2AM13 Keyboard

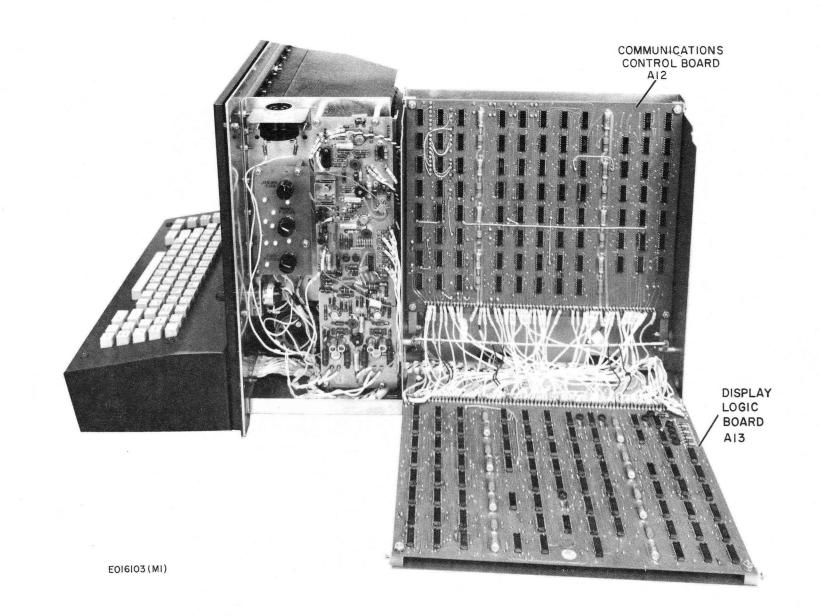

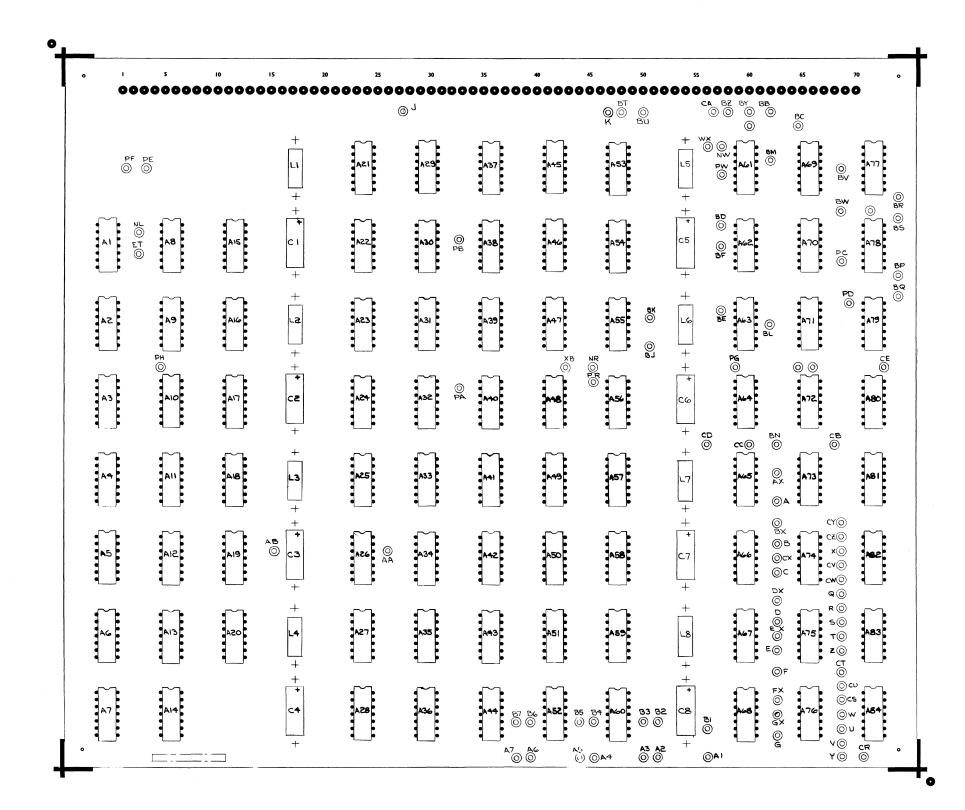

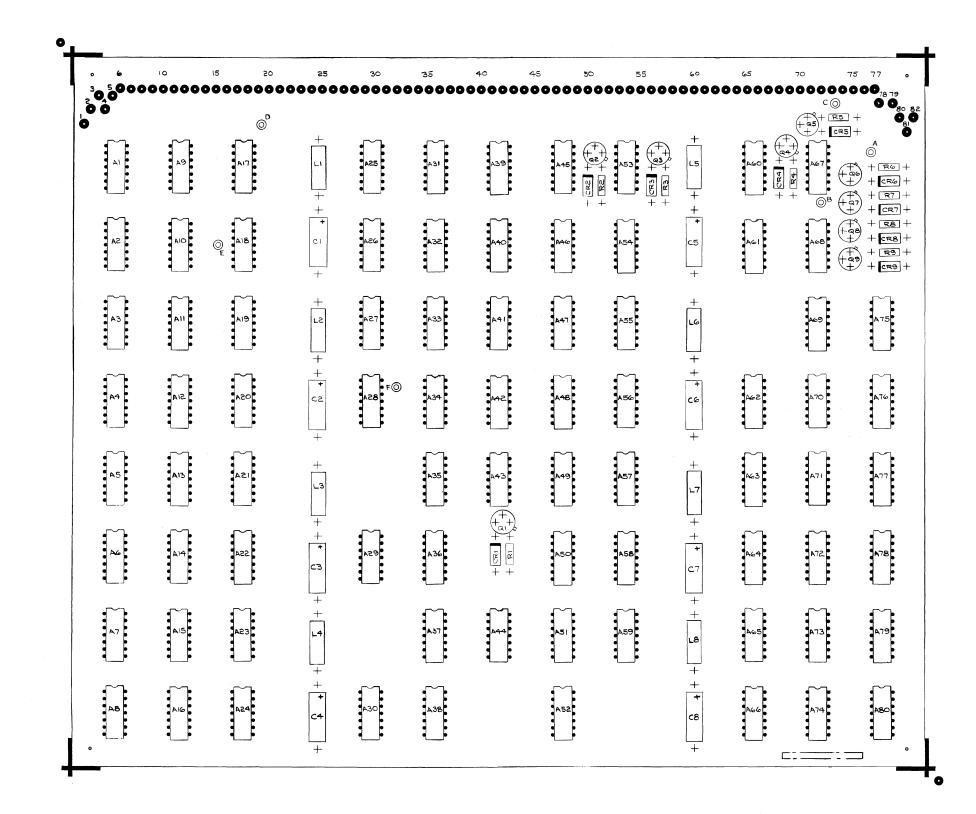

#### 1-2.2 Display Logic Board A13

The display logic board (see figure 1-3) is a hinged printed-circuit board located on the right side of the Display Terminal. Logic circuits contained on this board are formed by transistor-transistor-logic  $(T^2L)$  integrated circuits which are solder-connected to etched-copper printed circuits. The primary function of these circuits is to act as a keyboard interface by accepting 7-bit digital codes from the keyboard matrix. These coded characters are then transferred to the delay-line electronics and the monoscope deflection amplifier circuitry. In addition, numerous flip-flops on the display logic board are used to accomplish the various editing functions (such as step-left, step-right, erase line).

#### 1-2.3 Communications Control Board A12

The communications control board (see figure 1-3) is a hinged printedcircuit board located on the right side of the Display Terminal. Logic circuits contained on this board are formed by  $T^2L$  integrated circuits which are solderconnected to etched-copper printed circuits. The primary function performed by the communications control logic is to provide a three-character buffer storage for smoothly releasing data at the 1200-baud rate. Steering logic and decode circuits contained on this board determine whether the Display Terminal is in the transmit or the receive mode of operation.

1-5

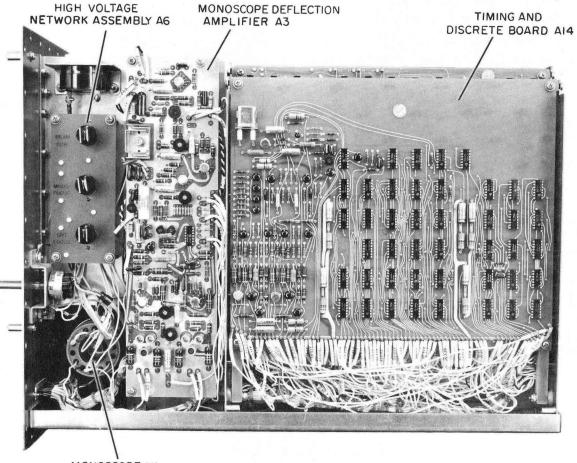

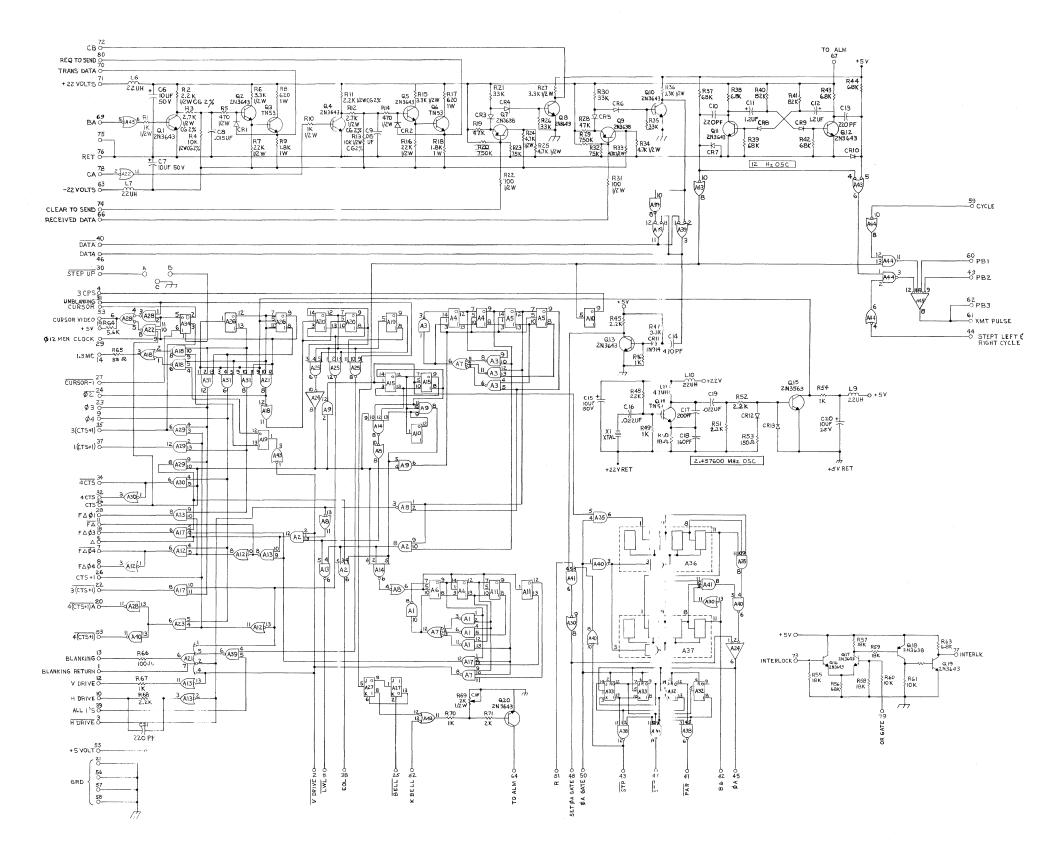

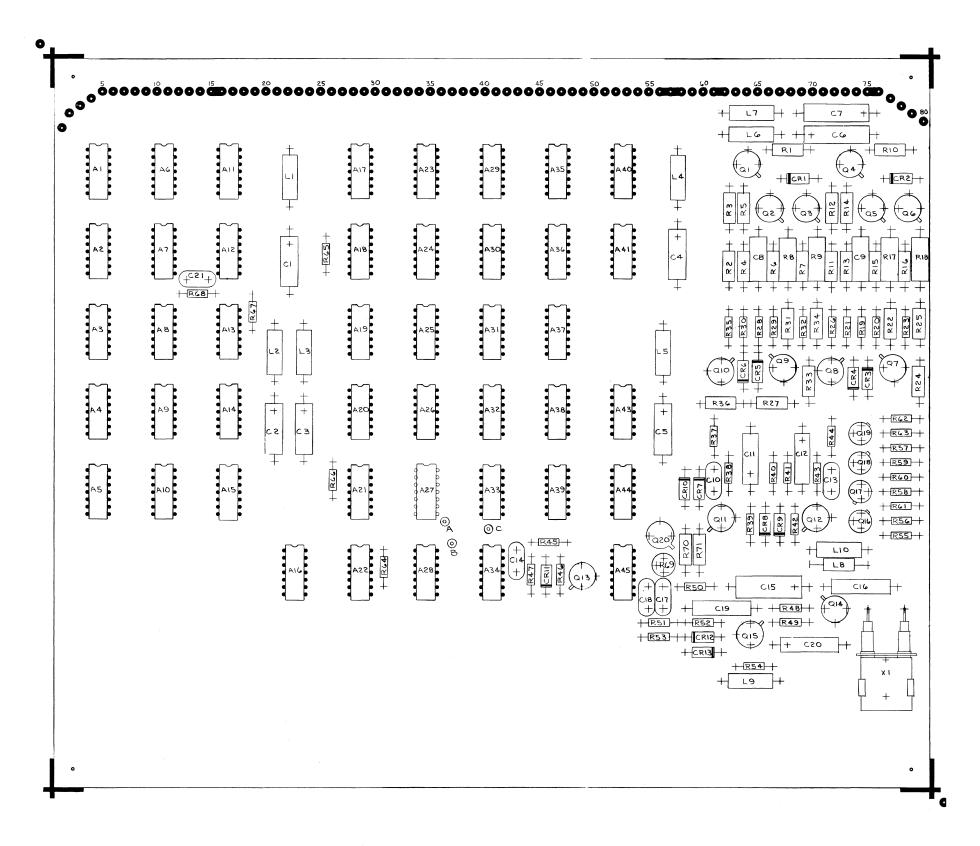

#### 1-2.4 Timing and Discrete Board A14

The timing and discrete board (figure 1-4) is a hinged printed-circuit board located on the right side of the Display Terminal. The circuits contained on the board perform a two-fold function: internal timing, and I/O signal interface.

The internal timing circuits consist of oscillators and counters which produce timing signals for: (1) controlling data to and from the Display Terminal (1200 Hz), (2) special functions (3 Hz and 6 Hz), (3) gating data within the Display Terminal, and (4) providing horizontal and vertical drive pulses.

The modem interface circuits consist of two receivers and two transmitters which amplify and level shift input and output interfacing signals.

MONOSCOPE VI

E017323 (MI)

Figure 1-4. Model 402-2AM13 Display Terminal, Right View

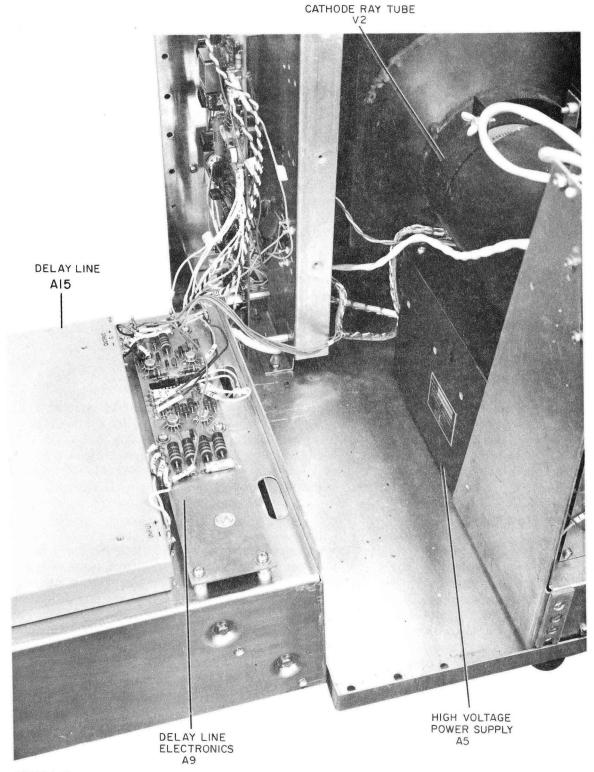

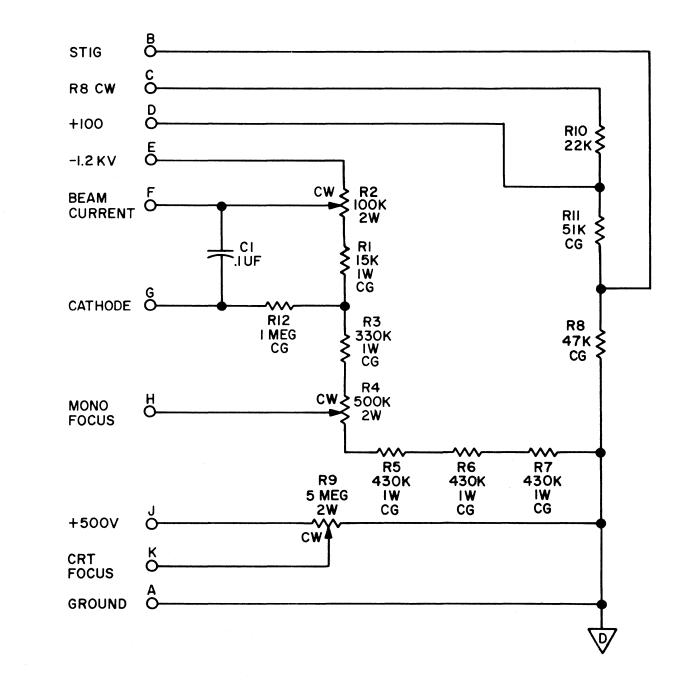

#### 1-2.5 Delay-Line Electronics A9

The delay-line electronics board (see figure 1-5) consists of two identical read-write amplifier circuits. These amplifiers amplify data coupled to and from the delay-line sections to compensate for any delay-line attenuation encountered by the data bits.

#### 1-2.6 Delay Line A15

The delay line (see figure 1-5) functions as an internal memory device for storing up to 1040 seven-bit data characters and retrace characters. Data characters circulating in the delay line are used to refresh the screen presentation every 16 ms (refresh-memory loop). The delay line also provides a storage capability for holding data characters during message composition for later transmission to the CPU.

Delay line A15 consists of two magnetostrictive delay-line sections which are series-connected between the read-write amplifiers on delay-line electronics board A9. The 1040 maximum character storage capacity (plus retrace) corresponds to the maximum number of displayable characters on the display terminal CRT screen.

#### 1-2.7 Monoscope Deflection Amplifier Assembly A3

The monoscope deflection amplifier (figure 1-4) is used to convert digital codes to analog voltages for positioning the monoscope beam to a specific character. Seven-bit digital codes are coupled from the display logic board and converted to produce two analog voltage outputs. These analog voltages are then amplified and applied to X and Y deflection plates for electrostatically deflecting the monoscope beam to a specific character on the monoscope target.

#### 1-2.8 Monoscope V1

The monoscope (see figure 1-4) provides a means of developing visual characters for display on the CRT screen. The monoscope font consists of 96 individual characters (numerals, letters, and symbols) which are etched onto the face of the monoscope. The electron beam is directed to a character by means of X and Y deflection voltages developed by the deflection amplifiers. As the beam scans a character, an output is produced by secondary emission. This video signal is then amplified and applied to the CRT for display.

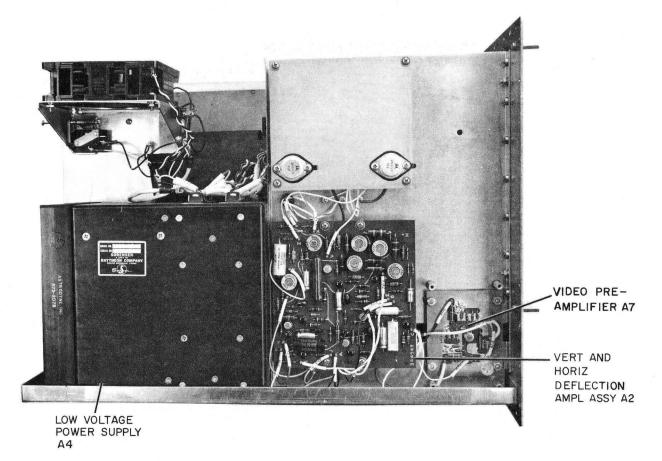

#### 1-2.9 Video Preamplifier A7

The video preamplifier circuit (figure 1-6) accepts relatively low-level video from the monoscope target and amplifies this video to a level suitable for driving the video amplifier.

E016101(MI)

Figure 1-5. Model 402-2AM13 Display Terminal, Left Oblique Rear View with Logic Drawer Removed

E017321 (MI)

#### Figure 1-6. Model 402-2AM13 Display Terminal, Left View

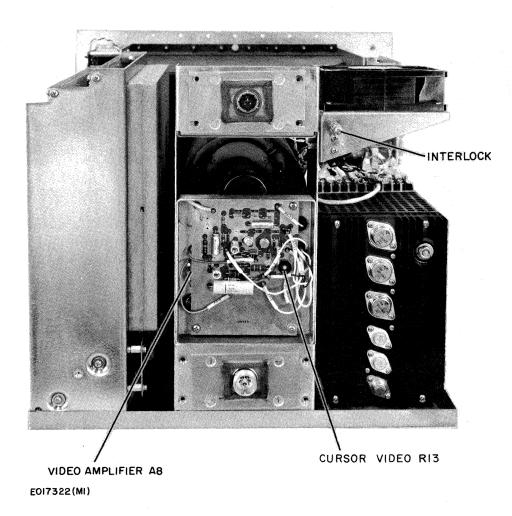

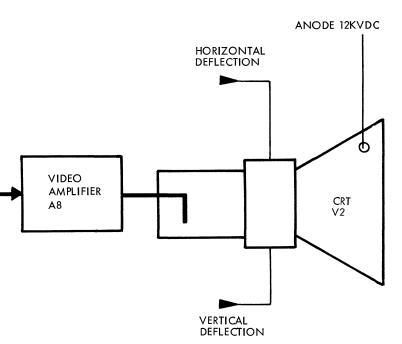

#### 1-2.10 Video Amplifier A8

The video amplifier (figure 1-7) accepts the amplified video output of the preamplifier and amplifies the video signal to a level suitable for driving the CRT cathode element. In addition to amplifying video signals, the video amplifier is responsible for blanking (cutting off) the CRT screen during horizontal and vertical retrace. This prolongs the life of the CRT and provides a clearer display presentation.

Figure 1-7. Model 402-2AM13 Display Terminal, Rear View

1-2.11 Vertical and Horizontal Deflection Amplifier Assembly A2

The vertical and horizontal deflection amplifier assembly (see figure 1-6) produces sweep voltages for scanning the CRT screen. Vertical and horizontal drive signals are developed by the timing circuits on timing and discrete board Al4. These drive signals are amplified by the deflection amplifier and two outputs are produced: vertical and horizontal sweep signals. The horizontal sweep signal causes the CRT electron beam to scan from left to right across the screen. The vertical sweep signal causes the CRT electron beam to scan from the top of the screen to the bottom. This electromagnetic deflection is accomplished by the vertical and horizontal windings of a deflection coil (yoke) mounted on the CRT neck between the cathode and anode elements.

1-2.12 Low Voltage Power Supply A4

The low voltage power supply (see figure 1-6) is a solid-state, fully regulated, ac-to-dc converter. The low voltage outputs are: +5 vdc, +22 vdc, -22 vdc, +100 vdc, 6 vac (isolated), and 6 vac (nonisolated). These voltages are used for the following functions:

| LV Output             | Function                                                                  |  |

|-----------------------|---------------------------------------------------------------------------|--|

| +5 vdc                | Display logic                                                             |  |

| +22 vdc and $-22$ vdc | High voltage power supply input,<br>interface circuits and sweep circuits |  |

| +100 vdc              | Power (driver) transistors                                                |  |

| 6 vac, isolated       | Monoscope filament                                                        |  |

| 6 vac, nonisolated    | CRT filament                                                              |  |

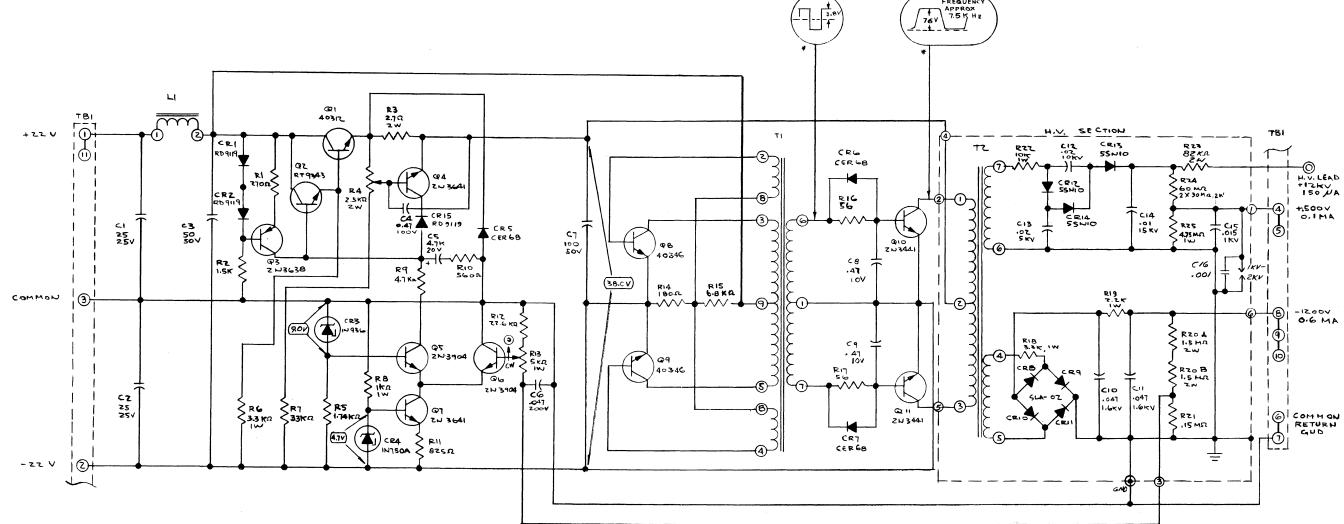

1-2.13 High Voltage Power Supply A5

The high voltage power supply (see figure 1-5) is a solid-state, fully regulated, dc-to-ac-to-dc converter. The high voltage outputs consist of: +500 vdc, -1200 vdc, and +12 kvdc. These voltages are used for the following functions:

| HV Output | Function                       |  |

|-----------|--------------------------------|--|

| -1200 vdc | Monoscope cathode              |  |

| +500 vdc  | Monoscope and CRT acceleration |  |

| +12 kvdc  | CRT anode                      |  |

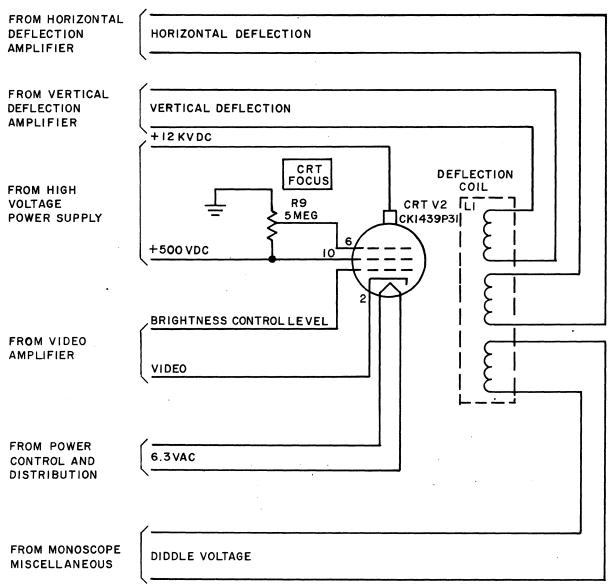

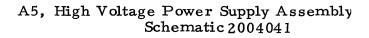

1-2.14 Cathode Ray Tube (CRT) V2

The CRT indicator (see figure 1-1) provides a 6-1/2 by 8-1/2 inch viewing surface for displaying a message of up to 1040 characters. The CRT screen is coated internally with a P31 (green) phosphor which emits light when scanned by the electron beam. When refreshed at a 63-Hz refresh rate, the CRT provides a flicker-free character presentation. A close-mesh screen stretched across the face of the screen cancels the effects of rf radiation and permits viewing in a lighted room without noticeable reflections.

#### 1-3 INFORMATION AND REFERENCE TABLES

The following pages contain tables which consolidate important reference data on the Model 402-2AM13 Display Terminal. The information contained in these tables is useful for installation planning and should be referenced before any changes are made at existing installations.

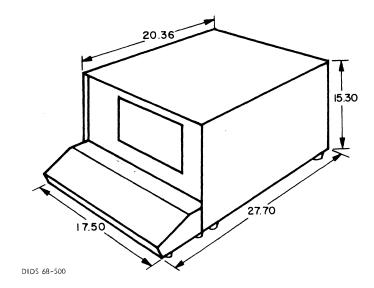

1-3.1 Leading Particulars

Table 1-1 lists the leading particulars of the Display Terminal. The information contained in this table should be referenced during initial planning to determine the operating requirements of the Display Terminal.

| Primary Power Requirements          | 105 to 125 vac, 50 to 60 Hz, single phase |

|-------------------------------------|-------------------------------------------|

| Power Dissipation                   | 150 W                                     |

| Environmental Conditions:           |                                           |

| Temperature Range<br>Humidity Range | 50° to 100°F<br>10 to 90% (relative)      |

| Dimensions:                         |                                           |

| Height<br>Width<br>Depth            | 15-1/2 in.<br>17-1/2 in.<br>27 in.        |

| Weight                              | 135-1/2 lb                                |

Table 1-1. Leading Particulars

## 1-3.2 Capabilities and Limitations

Table 1-2 lists the capabilities and limitations of the Display Terminal.

| Purpose of Equipment   | Provides quick-response on-line<br>communication with a central<br>processing unit (CPU) |

|------------------------|------------------------------------------------------------------------------------------|

| Mode of Operation      | Half-duplex                                                                              |

| Transmission Mode      | Asynchronous                                                                             |

| Conversational Mode    | Enquiry-Response or Polling                                                              |

| Transmission Rate      | 1200 baud                                                                                |

| Reception Rate         | 1200 baud                                                                                |

| Character Code         | ASCII                                                                                    |

| Display Presentation   | 1040 characters maximum arranged<br>in 13 lines of 80 characters each                    |

| Character Refresh Rate | 63 refresh-cycles/sec                                                                    |

| Character Format       | 10 bits/char.                                                                            |

| Parity                 | Even                                                                                     |

| Displayable Characters | 96, including numerals, upper and<br>lower case alphabetical, and<br>special symbols     |

Table 1-2. Capabilities and Limitations

## 1-3.3 Wiring Options

Table 1-3 lists and defines the design options available for changing the operating characteristics of the Display Terminal.

| <br><u>1able 1-5.</u>             |                                                                                                                                                                                                                    |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Conversational Mode               | Enquiry-Response or Polling                                                                                                                                                                                        |

| Broadcast Address                 | The Display Terminal recognizes<br>an address character other than<br>its own. This option permits the<br>CPU to broadcast to two or more<br>Display Terminals simultaneously.                                     |

| Frame Reset at End<br>of Transmit | The cursor is frame reset at the<br>end of a transmit sequence instead<br>of being advanced to the first<br>character position of the next line.                                                                   |

| One-Step Transmit                 | Two options are available:                                                                                                                                                                                         |

|                                   | <ol> <li>Depressing the END key inserts<br/>an ETX code, then frame<br/>resets the cursor and raises<br/>the Request-to-Send line.</li> </ol>                                                                      |

|                                   | 2) Depressing the END key<br>inserts an ETX code and<br>then moves the cursor to the<br>first character position of<br>the line it is on and initiates<br>automatic transmission to<br>the ETX.                    |

| End-of-Transmission<br>Character  | An EOT character code (0000100)<br>is substituted for the ETX<br>character code (0000011). This<br>option is usually employed in<br>polling sites where EOT signifies<br>the end of transmission from the<br>site. |

| Advance Line After Receive        | When an ETX character is decoded<br>in a received message, the cursor<br>is automatically advanced to the<br>first character position of the<br>next line.                                                         |

| Nonblinking Cursor                | A nonblinking cursor in the form of<br>a backward L ( $ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ $                                                                                                                      |

Table 1-3. Wiring Options

#### 1-3.4 Glossary of Terms

Throughout this manual, mnemonic words or symbols are used instead of cumbersome words or phrases, so that sentences can be shortened and long, repetitious phrases eliminated. Table 1-4 is an alphabetical listing of these mnemonic abbreviations and their definitions. Where applicable, the common name of the word is used for ease in reading the text and logic diagrams.

| Mnemonic Word<br>or Symbol | Meaning        | Definition                                                                                                                       |

|----------------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------|

| ВА                         |                | Transmitted data line which<br>couples serial bit data from<br>the display terminal to con-<br>nected CPU I/O device or<br>modem |

| baud                       |                | Bits/sec                                                                                                                         |

| ВВ                         |                | Received data line which<br>couples serial bit data from<br>the CPU I/O device to the<br>Display Terminal                        |

| BB1                        | Busy Bit One   | A flip-flop that reflects the<br>status (full, not full) of<br>buffer register Dl                                                |

| BB2                        | Busy Bit Two   | A flip-flop that reflects the<br>status (full, not full) of<br>buffer register D2                                                |

| BB3                        | Busy Bit Three | A flip-flop that reflects the<br>status (full, not full) of<br>buffer register D3                                                |

| BEL                        | Bell           | An ASCII control code which<br>causes an audible alarm to<br>be sounded                                                          |

| BS                         | Back Space     | An ASCII control code which<br>steps the cursor one position<br>to the left.                                                     |

| CA                         |                | Request-to-Send line                                                                                                             |

| CAN                        | Cancel         | An ASCII control code which<br>erases all characters from<br>the cursor position to the<br>end of the display terminal<br>screen |

Table 1-4. Glossary of Terms

| Mnemonic Word<br>or Symbol | Meaning                                    | Definition                                                                                                                                                                                                                        |

|----------------------------|--------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СВ                         |                                            | Clear-to-Send line                                                                                                                                                                                                                |

| CCC F/F                    | Communication<br>Control Code<br>Flip-flop | A flip-flop used to indicate<br>that a control code has been<br>received and the edit or<br>cursor control function is<br>in progress                                                                                             |

| CF                         |                                            | Data Carrier Detector line                                                                                                                                                                                                        |

| CFR                        | Cursor Frame<br>Reset                      | A pulse which resets the cursor<br>to the first character, first<br>line position of the display<br>terminal screen.                                                                                                              |

| CPU                        | Central<br>Processing<br>Unit              | A centralized computer that<br>forms the heart of the<br>digital display system                                                                                                                                                   |

| CR                         | Carriage Return                            | An ASCII control code which<br>moves the cursor to the first<br>character position of the next<br>line on the display terminal<br>screen.                                                                                         |

| CRQ                        | Cursor Right<br>Request                    | A pulse used to automatically<br>step the cursor one charac-<br>ter slot to the right. CRQ<br>is developed each time a<br>character is read into or<br>out of the delay line.                                                     |

| CTS                        | Cursor Time Slot                           | First bit of a character in<br>memory. This bit slot will<br>contain the cursor if a cursor<br>is attached to the character.<br>CTS is also a bit counter<br>output which is coincident<br>with the first bit of a charac-<br>ter |

| CTS +1                     | Cursor Time Slot<br>Plus One Bit           | Least significant bit (first<br>data bit) of a character                                                                                                                                                                          |

|                            |                                            | l                                                                                                                                                                                                                                 |

Table 1-4. Glossary of Terms (Cont)

| Mnemonic Word<br>or Symbol | Meaning                  | Definition                                                                                                                   |

|----------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------|

| Cursor                     |                          | A cursor ( ] ) used as a<br>reference point on the<br>Display Terminal screen<br>and in memory.                              |

| Cursor -1                  |                          | Cursor position on the screen<br>or in memory minus one<br>character position (the<br>character that precedes<br>the cursor) |

| DA                         | Device Address           | A 7-bit address code assigned<br>to any device                                                                               |

| DC1                        | Device Control<br>One    | An ASCII control code which<br>erases all visual characters<br>between the cursor position<br>and the end of the line        |

| DC3                        | Device Control<br>Three  | An ASCII control code which<br>steps the cursor to the same<br>character position of the<br>previous line                    |

| DL                         | Delay Line               | An internal memory device<br>which stores up to 1040<br>characters for display on<br>the display terminal screen.            |

| EOL                        | End of Line              | A timing pulse which is present<br>when the display terminal<br>scan has reached the end of<br>a line.                       |

| EOT                        | End of Trans-<br>mission | A character (optionally<br>provided) that signifies the<br>end of transmission from a<br>particular site                     |

| ENQ                        | Enquiry                  | An ASCII control code that<br>causes a transmit operation<br>to be initiated.                                                |

| ESC                        | Escape                   | An ASCII control code that<br>conditions the Display<br>Terminal to store the next<br>character of the message               |

## Table 1-4. Glossary of Terms (Cont)

| Mnemonic Word<br>or Symbol | Meaning                          | Definition                                                                                                                                                                             |

|----------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ETX                        | End of Text                      | The last character of a message                                                                                                                                                        |

| ETXD3                      | End of Text in D3                | A decoded output that is<br>present when an ETX charac-<br>ter is detected in buffer<br>register D3                                                                                    |

| ETXSR                      | End of Text in<br>Shift Register | A decoded output that is present<br>when an ETX character is<br>detected in the character<br>entry register.                                                                           |

| FF                         | Form Feed                        | An ASCII control code which<br>resets the cursor to the first<br>character position of the<br>first line.                                                                              |

| F/F                        | Flip-flop                        |                                                                                                                                                                                        |

| FNCT COM                   | Function<br>Complete             | An output which is present<br>when an editing or control<br>function is completed                                                                                                      |

| F ( <b>Δ</b> )             | Frame Pulse                      | A pulse that occurs when<br>1040 characters have been<br>counted by the line and charac-<br>ter counters; it is coincident<br>with the CTS of the first<br>character of the first line |

| H DRIVE                    | Horizontal Drive                 | Pulses used to develop a<br>sweep voltage for moving<br>the CRT beam across the<br>screen                                                                                              |

| нт                         | Horizontal Tab                   | An ASCII control code that<br>steps the cursor one<br>character position to the<br>right                                                                                               |

| INTERLK                    | Interlock                        | An output from the keyboard<br>which is present each time<br>a character key is depressed                                                                                              |

|                            |                                  |                                                                                                                                                                                        |

## Table 1-4. Glossary of Terms (Cont)

| Mnemonic Word<br>or Symbol | Meaning                  | Definition                                                                                                                             |

|----------------------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| I/O                        | Input/Output             | Any device or circuit that<br>provides an input signal<br>or output load                                                               |

| LF                         | Line Feed                | An ASCII control code which<br>advances the cursor to the<br>first character position of<br>the next line                              |

| LFD3                       | Line Feed in D3          | A decoded output which is<br>present when an LF<br>character is present in<br>buffer register D3                                       |

| LSB                        | Least Significant<br>Bit | Lowest order bit of a<br>character (b1)                                                                                                |

| LWL                        | Last Word of<br>Line     | A pulse that occurs during<br>CTS of the last character<br>of each line                                                                |

| MEM DATA                   | Memory Data              | Data line which couples<br>serial bit data from the<br>delay line to the character<br>entry register                                   |

| MSB                        | Most Significant<br>Bit  | Highest order bit of a character (b7)                                                                                                  |

| MR                         | Master Reset             | A logic level that resets the<br>Display Terminal logic                                                                                |

| PAR                        | Not Parity               | A decoded timing output<br>which indicates when the<br>count corresponding to the<br>parity bit (b <sub>10</sub> ) has been<br>reached |

| PE                         | Parity Error             | A logic level that goes high<br>when a parity error is<br>detected during the receive<br>mode                                          |

| R                          | Receive                  | During receive, R goes high<br>to enable the receive steering<br>logic.                                                                |

Table 1-4. Glossary of Terms (Cont)

| Mnemonic Word<br>or Symbol | Meaning                          | Definition                                                                                                                               |

|----------------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| RE                         | Receive Enable                   | A decode output which goes<br>high when certain characters<br>(STX and DA) are recognized<br>by the start of text and<br>address decodes |

| SDL                        | Shift (to or from)<br>Delay Line | A flip-flop that is set to enable<br>a serial data transfer to<br>(receive) or from (transmit)<br>the delay line                         |

| SG12                       | Shift Gate<br>One-to-Two         | A flip-flop that is set to enable<br>a serial data transfer from<br>buffer register Dl to buffer<br>register D2                          |

| SG23                       | Shift Gate<br>Two-to-Three       | A flip-flop that is set to enable<br>serial data transfer from<br>buffer register D2 to buffer<br>register D3                            |

| STP                        | Not Stop                         | A negative going pulse that is<br>in coincidence with the stop<br>bit of each 10-bit asynchron-<br>ous character                         |

| STT                        | Not Start                        | A negative going pulse that is<br>in coincidence with the start<br>bit of each 10-bit asynchronou<br>character.                          |

| STX                        | Start-of-Text                    | First character of any message                                                                                                           |

| Т                          | Transmit                         | During transmit, T goes high<br>to enable the transmit<br>steering logic                                                                 |

| V DRIVE                    | Vertical Drive                   | Pulses used to develop a<br>sweep signal for moving the<br>CRT beam downward<br>(vertical sweep)                                         |

| VT                         | Vertical Tab                     | An ASCII control code which<br>steps the cursor down to<br>the next line                                                                 |

## Table 1-4. Glossary of Terms (Cont)

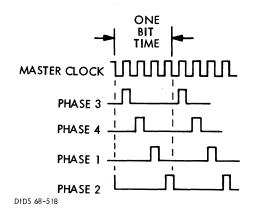

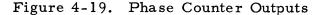

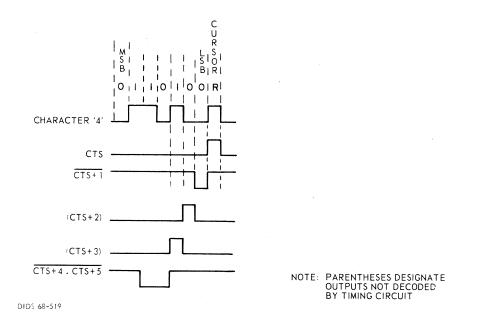

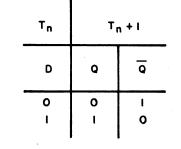

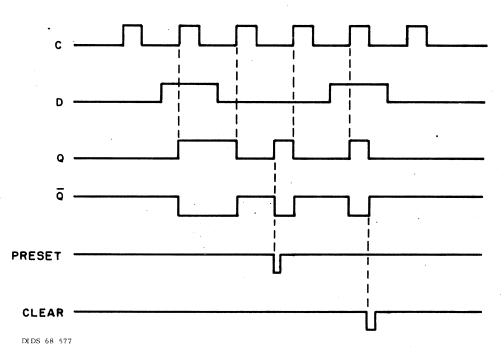

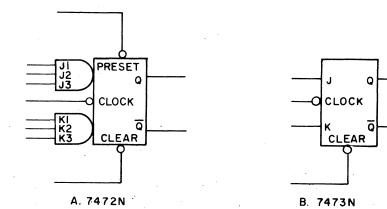

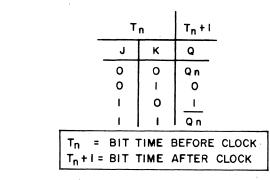

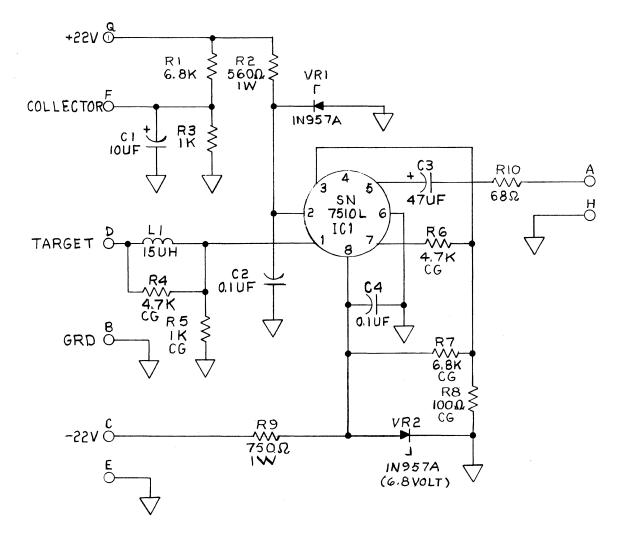

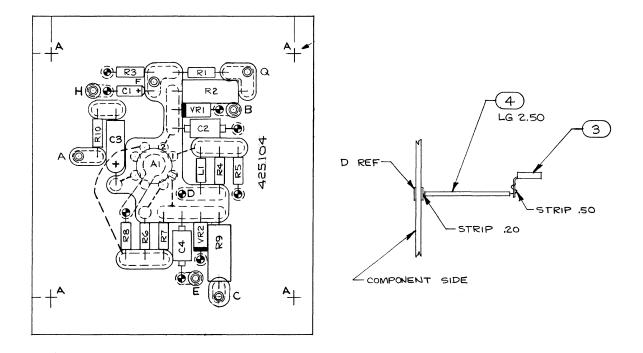

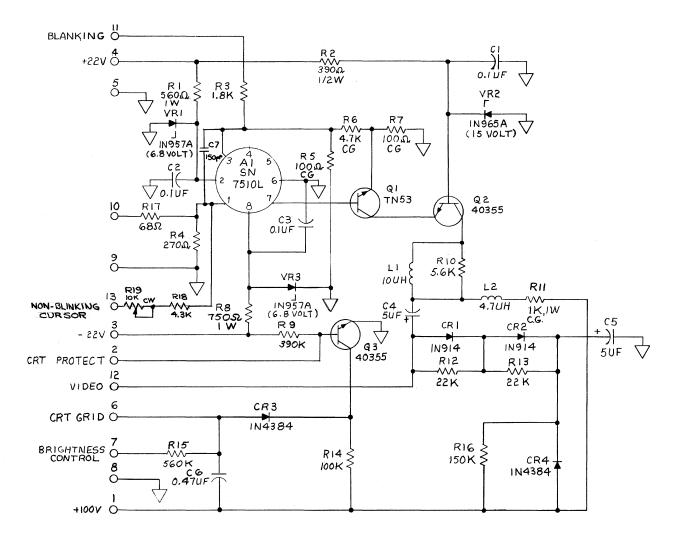

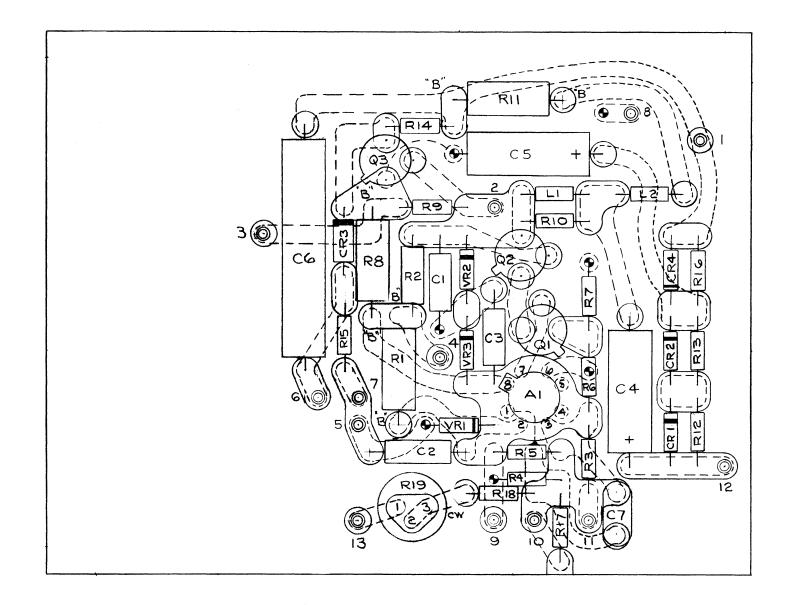

| Mnemonic Word<br>or Symbol | Meaning                               | Definition                                                                                        |