4150 Processor Functional Specification

Steve Small, Editor

PE-T-1440

August 16, 1988

## 4150 Processor Functional Specification

Steve Small, Editor

PE-T-1440

August 16, 1988

Copyright c 1988 by Prime Computer, Inc. Natick, Massachusetts 01760 All Rights Reserved 4150 Processor Functional Spec

**Date:** August 16, 1988

To: Prime Engineering

From: Steve Small, Editor

Subject: 4150 Processor Functional Spec

Reference: PE-TI-999 Fox Architecture Document

#### Abstract

This document defines the functional operation and hardware architecture for the 4150 and 4050 processors. The 4150 is the top of the line office environment machine as well as the entry level computer room machine. Both processors are TTL processors that support Prime's S, R, V, and I mode instruction sets.

Except where specifically noted in the text, all statements made in this document apply to both the 4150 and the 4050 processors.

I'd would like to take this opportunity to thank the writers of this document. Alphabetically:

Denise Chiacchia Tony Dorohov Tom Kinahan Mark Laird Brian Lefsky Tom O'Brien Stu Rae Sherri Root Steve Small

# Table of Contents

|    |       |                                                                        | Page     |

|----|-------|------------------------------------------------------------------------|----------|

| 1. | Syst  | em Overview                                                            | 1        |

|    | 1.1   | Introduction                                                           | 1        |

|    | 1.2   | System Packaging                                                       | 3        |

|    | 1.3   | Diagnostic Processor                                                   | 4        |

|    | 1.4   | System Power                                                           | 4        |

|    | 1.5   | Configuration Rules                                                    | . 5      |

|    |       | 1.5.1 Memory                                                           | 5        |

|    |       | 1.5.2 I/O<br>1.5.3 Power                                               | 6<br>7   |

|    | 1.6   | 9755 and 4050/4150 Comparisons                                         | 7        |

|    |       |                                                                        | · · ·    |

| 2. |       | essor Overview                                                         | 9        |

|    | 2.1   | General Description                                                    | 9        |

|    | 2.2   | Board Descriptions                                                     | 12       |

|    | 2.3   | VLSI Requirements                                                      | 12       |

|    | 2.4   | Major and Critical Paths                                               | 13       |

|    | 2.5   | Processor Physical Description                                         | 14       |

| 3. | Pipe  | line Control Unit Functional Overview                                  | 17       |

|    | 3.1   | Introduction                                                           | 17       |

|    |       | 3.1.1 Stage Clock Generation                                           | 19       |

|    | 3.2   | 9755 and 4150 Comparisons                                              | 20       |

|    | 3.3   | VLSI Requirements                                                      | 20       |

|    | 3.4   | Major and Critical Paths                                               | 20       |

| 4. | Cont  | rol Store Unit Functional Overview                                     | 21       |

|    | 4.1   | Introduction                                                           | 21       |

|    |       | <ul><li>4.1.1 Microsequencer</li><li>4.1.2 Control Store RAM</li></ul> | 23       |

|    |       | 4.1.2 Control Store RAM<br>4.1.3 Maintenance & Initialization Logic    | 23<br>23 |

|    |       | 4.1.4 Parity Checker                                                   | 23       |

|    |       | 4.1.5 BCYPDA                                                           | 23       |

|    | 4.2   | 9755 and 4150 Comparisons                                              | 23       |

|    | 4.3   | VLSI Requirements                                                      | 24       |

|    | 4.4   | Major and Critical Paths                                               | 24       |

| 5. | Insti | uction Decode/Effective Address Formation Functional Overview          | 25       |

|    | 5.1   | Introduction                                                           | 25       |

|    |       | 5.1.1 Instruction Decoding                                             | 25       |

### 4150 Functional Specification Page ii

|     |            | <ul><li>5.1.2 Effective Address Formation</li><li>5.1.3 Register File Collisions</li></ul> | 28<br>28 |

|-----|------------|--------------------------------------------------------------------------------------------|----------|

|     | 5.2        | -                                                                                          | 28       |

|     | 5.3        | VLSI Requirements                                                                          | 29       |

|     | 5.4        | Major and Critical Paths                                                                   | 29       |

| 6.  | Bran       | nch Cache Functional Overview                                                              | 31       |

|     | 6.1        | Introduction                                                                               | 31       |

|     |            | 6.1.1 Overview of Operation                                                                | 33       |

|     | 6.2        | 9755 and 4150 Comparisons                                                                  | 34       |

|     | 6.3        | VLSI Requirements                                                                          | 34       |

|     | 6.4        | Major and Critical Paths                                                                   | 34       |

| 7.  | Cach       | ne Functional Overview                                                                     | 35       |

|     | 7.1        | Introduction                                                                               | 35       |

|     |            | 7.1.1 Basic Cache Operation                                                                | 35       |

|     | <b>a</b> 0 | 7.1.2 Cache Writes and Operand Reads                                                       | 37       |

|     | 7.2        | 9755 and 4150 Comparisons                                                                  | 37       |

|     | 7.3        | VLSI Requirements                                                                          | 37       |

|     | 7.4        | Major and Critical Paths                                                                   | 38       |

| 8.  | Stor       | age Management Unit Functional Overview                                                    | 39       |

|     | 8.1        | Virtual Memory Concept                                                                     | 41       |

|     |            | 8.1.1 Introduction                                                                         | 41       |

|     |            | <ul><li>8.1.2 Segmentation</li><li>8.1.3 Protection Rings</li></ul>                        | 42<br>42 |

|     | 8.2        |                                                                                            | 43       |

|     | 0.2        | 8.2.1 Cache Address Sources                                                                | 43       |

|     |            | 8.2.2 Virtual to Physical Address Translation                                              | 43       |

|     |            | 8.2.3 Memory Traps                                                                         | 44       |

|     |            | 8.2.4 UNIX Support                                                                         | 45       |

|     | 8.3        | 9755 and 4150 Comparisons                                                                  | 45       |

|     | 8.4        | VLSI Requirements                                                                          | 45       |

|     | 8.5        | Major and Critical Paths                                                                   | 46       |

| 9.  | Exec       | ution Unit Functional Overview                                                             | 47       |

|     | 9.1        | Introduction                                                                               | 47       |

|     | 9.2        | 9755 and 4150 Comparisons                                                                  | 49       |

|     | 9.3        | VLSI Requirements                                                                          | 50       |

|     | 9.4        | Major and Critical Paths                                                                   | 50       |

| 10. | Me         | mory Controller Unit Functional Overview                                                   | 51       |

|     | 10.1       | Introduction                                                                               | 51       |

|      |      | 10.1.1 | Overview of Operation                       | 51  |

|------|------|--------|---------------------------------------------|-----|

|      |      |        | -                                           |     |

|      | 10.2 |        | and 4150 Comparisons                        | 53  |

|      | 10.3 | VLSI   | Requirements                                | 54  |

|      | 10.4 | Majo   | r and Critical Paths                        | 54  |

| 11.  | I/O  | Interf | ace Functional Overview                     | 55  |

|      | 11.1 | Intro  | duction                                     | 55  |

|      |      | 11.1.1 | Overview of Operation                       | 55  |

|      | 11.2 | 9755   | and 4150 Comparisons                        | 57  |

|      |      |        | Burst DMT Mode                              | 57  |

|      | 11.3 | VLSI   | Requirements                                | 57  |

|      | 11.4 |        | r and Critical Paths                        | 57  |

| 12.  | Svs  | tem Bu | sses Functional Overview                    | 59  |

|      | 12.1 |        | duction                                     | 59  |

|      | 12.1 | 12.1.1 |                                             | 59  |

|      |      | 12.1.1 |                                             | 5   |

|      |      |        | BVMA                                        | ź   |

|      |      |        | BPA, BPD                                    | e   |

|      |      |        | MA, MD                                      | Exe |

|      |      | 12.1.6 | BD Arbitration                              | 60  |

|      | 12.2 | 9755   | and 4150 Comparisons                        | 60  |

|      | 12.3 |        | Requirements                                | 61  |

|      | 12.4 |        | r and Critical Paths                        | 61  |

| 13.  | Pro  | cessor | Diagnostic Aid Functional Overview          | 63  |

| 1.5. | 13.1 |        | duction                                     | 63  |

|      | 13.1 |        | General                                     | 63  |

|      |      |        | Z80 Microprocessor                          | 65  |

|      |      |        | Stack                                       | 65  |

|      |      |        | Halts / Delays                              | 65  |

|      |      |        | Delay Counter                               | 65  |

|      |      |        | Sense Registers                             | 66  |

|      |      | 13.1.7 | Forcing Microcode Address                   | 66  |

|      |      | 13.1.8 | Reading/Writing Control Store               | 66  |

|      | 13.2 | 9755   | and 4150 Comparisons                        | 66  |

|      |      | 13.2.1 | Stand Alone / Self Diagnostic Mode          | 66  |

|      |      | 13.2.2 | Power Up Circuit                            | 66  |

|      |      | 13.2.3 | Sense Register 4                            | 67  |

|      |      | 13.2.4 |                                             | 67  |

|      |      | 13.2.5 | A                                           | 67  |

|      |      | 13.2.6 | -                                           | 67  |

|      |      | 13.2.7 | 66                                          | 67  |

|      |      | 13.2.8 |                                             | 68  |

|      |      | 13.2.9 | Bus Virtual Memory Address (BVMA) Interface | 68  |

|     | 13.3 VLSI Requirements                              | 68       |

|-----|-----------------------------------------------------|----------|

|     | 13.4 Major and Critical Paths                       | 68       |

|     | 13.4.1 Stack Write Cycle                            | 68       |

|     | 13.4.2 Halt Path                                    | 68       |

|     | 13.4.3 Trigger Path                                 | 69       |

| 14. | Microcode Functional Overview                       | 71       |

|     | 14.1 Introduction                                   | 71       |

|     | 14.1.1 Microcode Fields                             | 71       |

|     | 14.2 9755 and 4150 Comparisons                      | 73       |

|     | 14.2.1 Timing Changes                               | 73       |

|     | 14.2.2 Shift Instruction Implementation             | 73       |

|     | 14.2.3 Multiply Implementation                      | 73       |

|     | 14.2.4 Divide Implementation<br>14.2.5 I/O          | 74<br>74 |

|     |                                                     |          |

|     | 14.3 Microdiagnostics                               | 74       |

| 15. | VLSI Requirements                                   | 85       |

|     | 15.1 Introduction                                   | 85       |

|     | 15.2 Microsequencer                                 | 85       |

|     | 15.3 Cache Address                                  | 85       |

|     | 15.4 STLB Set Select                                | 86       |

|     | 15.5 Cache Set Select                               | 86       |

|     | 15.6 PEALU                                          | 86       |

|     | 15.7 Barrel Shifter                                 | 87       |

|     | 15.8 Write Buffer Address                           | 87       |

|     | 15.9 Register File Address                          | 87       |

| 16. | Diagnostic Processor Interface Detailed Description | 89       |

|     | 16.1 DP Two Way Communication                       | 91       |

|     | 16.2 DP One Way Communication                       | 92       |

|     | 16.2.1 PDA Acting as the DP                         | 93       |

|     | 16.3 VLSI Usage                                     | 93       |

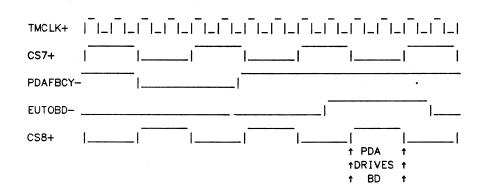

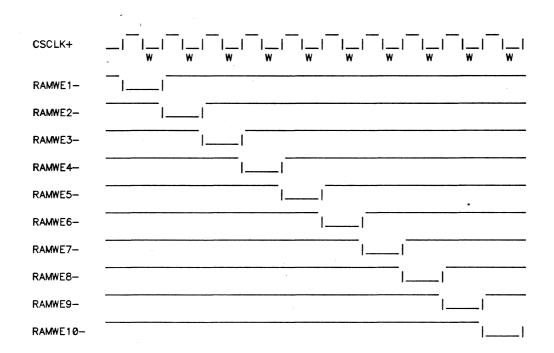

|     | 16.4 Timing Diagrams                                | 93       |

|     | 16.5 9755 Comparisons                               | 96       |

|     | 16.6 Critical Paths                                 | 97       |

|     | 16.7 Partitioning                                   | 97       |

| 17. | System Initialization Detailed Description          | 99       |

|     | 17.1 SYSVERIFY                                      | 99       |

|     | 17.1.1 Sysverify Overlays                           | 99       |

|     | 17.2 SYSCLR                                         | 134      |

| 18. | Pip  | eline Control Unit Detailed Description                                             | 135        |

|-----|------|-------------------------------------------------------------------------------------|------------|

|     | 18.1 | Instruction Flow Overview                                                           | 135        |

|     | 18.2 | PCU Operation                                                                       | 138        |

|     | 18.3 | PCU Control                                                                         | 139        |

|     |      | 18.3.1 Front End Control                                                            | 143        |

|     |      | 18.3.2 Back End Control                                                             | 143        |

|     | 18.4 | External PCU Hold Conditions                                                        | 144        |

|     |      | 18.4.1 Variable Length Microcode Step Timing                                        | 145        |

|     |      | 18.4.2 EHOLDs                                                                       | 147        |

|     |      | 18.4.3 Traps<br>18.4.4 Miscellaneous                                                | 147<br>150 |

|     | 18.5 | 9755 and 4150 Comparisons                                                           | 150        |

|     | 18.6 | -                                                                                   | 151        |

|     | 18.7 |                                                                                     | 151        |

|     | 18.8 |                                                                                     | 153        |

|     | 18.9 |                                                                                     | 153        |

|     | 1017 |                                                                                     | 100        |

| 19. | Con  | trol Store Unit Detailed Description                                                | 155        |

|     | 19.1 | Control Store Memory                                                                | 157        |

|     | 19.2 | Microinstruction Sequencing                                                         | 157        |

|     |      | 19.2.1 Normal Microinstruction Sequencing                                           | 158        |

|     |      | 19.2.2 Abnormal Microinstruction Sequencing                                         | 166        |

|     | 19.3 |                                                                                     | 167        |

|     | 19.4 | VLSI Usage                                                                          | 168        |

|     | 19.5 | Critical Paths                                                                      | 168        |

|     | 19.6 | Timing Diagrams                                                                     | 169        |

|     | 19.7 | 9755 Comparisons                                                                    | 169        |

|     | 19.8 | Partitioning                                                                        | 169        |

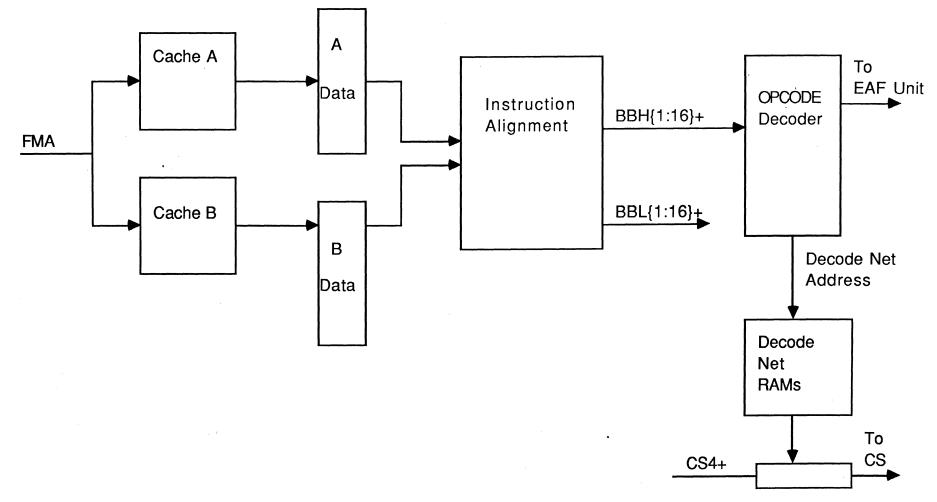

| 20. | Inst | ruction Decode Detailed Description                                                 | 171        |

|     | 20.1 | Instruction Fetch                                                                   | 171        |

|     | 20.2 | Instruction Stream Formats                                                          | 173        |

|     |      | 20.2.1 Aligned Short Instructions                                                   | 173        |

|     |      | 20.2.2 Aligned Long Instructions                                                    | 173        |

|     |      | 20.2.3 Unaligned Short Instructions                                                 | 174        |

|     |      | 20.2.4 Unaligned Long Instructions                                                  | 174        |

|     | 20.3 |                                                                                     | 174        |

|     |      | <ul><li>20.3.1 Decode Net</li><li>20.3.2 Register File Address Generation</li></ul> | 174<br>179 |

|     | 20.4 | VLSI Usage                                                                          | 179        |

|     | 20.4 |                                                                                     | 181        |

| •   |      | 9755 Comparisons                                                                    |            |

|     | 20.6 | Critical Paths                                                                      | 181        |

# 4150 Functional Specification

Page vi

|     | 20.7 Partitioning                                                                     | 181        |

|-----|---------------------------------------------------------------------------------------|------------|

| 21. | Effective Address Formation Detailed Description                                      | 183        |

|     | 21.1 Discussion of Basic Addressing Modes                                             | 183        |

|     | 21.2 Memory Reference Instruction Formats                                             | 185        |

|     | 21.3 EAF Decoding                                                                     | 186        |

|     | 21.4 Microcode Assisted EAF                                                           | 190        |

|     | 21.5 Hardware EAF                                                                     | 190        |

|     | 21.5.1 I Mode Immediate and Register to Register Instructions                         | 192        |

|     | 21.5.2 Indirect Support                                                               | 194        |

|     | 21.6 Register File Tracking/Collisions                                                | 195        |

|     | <ul><li>21.6.1 5-9 Register Collision</li><li>21.6.2 4-6 Register Collision</li></ul> | 196<br>197 |

|     | 21.0.2 4-0 Register Conston<br>21.7 VLSI Usage                                        | 199        |

|     | 21.8 9755 Comparisons                                                                 | 199        |

|     | 21.9 Major and Critical Paths                                                         | 199        |

|     | 21.10 Partitioning                                                                    | 200        |

|     | 21.10 Tartitioning                                                                    | 200        |

| 22. | Branch Cache Detailed Description                                                     | 201        |

|     | 22.1 VLSI Usage                                                                       | 204        |

|     | 22.2 9755 Comparisons                                                                 | 204        |

|     | 22.3 Major and Critical Paths                                                         | 205        |

|     | 22.4 Partitioning                                                                     | 205        |

| 23. | Cache Detailed Description                                                            | 207        |

|     | 23.1 Associative Memory Introduction                                                  | 207        |

|     | 23.2 Cache Organization                                                               | 210        |

|     | 23.3 Element Selection                                                                | 212        |

|     | 23.4 Cache Replacement                                                                | 213        |

|     | 23.5 Cache Reads and Writes                                                           | 214        |

|     | 23.5.1 Unaligned Cache Write                                                          | 215        |

|     | 23.5.2 Unaligned Cache Read                                                           | 219        |

|     | 23.6 Cache Miss                                                                       | 221        |

|     | 23.7 Error Detection and Reporting                                                    | 228        |

|     | 23.8 VLSI Usage                                                                       | 229        |

|     | 23.9 9755 Comparisons                                                                 | 229        |

|     | 23.10 Critical Paths                                                                  | 229        |

|     | 23.11 Partitioning                                                                    | 230        |

| 24. | Storage Management Unit Detailed Description                                          | 231        |

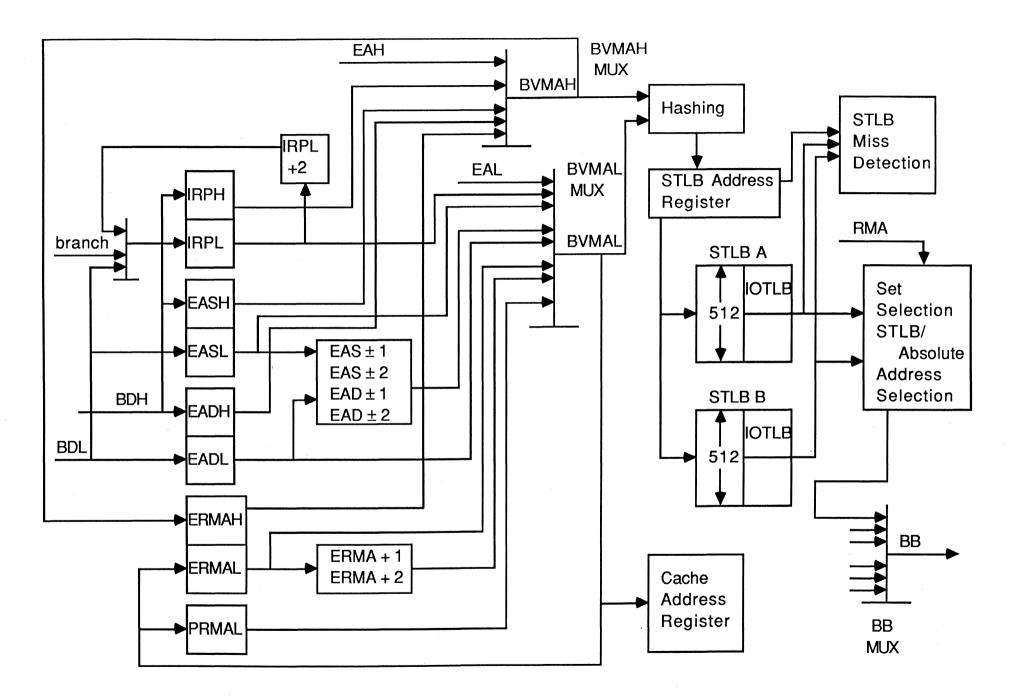

|     | 24.1 Cache and STLB Addressing                                                        | 231        |

|     | 24.1.1 IRP                                                                            | 233        |

|     |      | 24.1.2 EAS and EAD                                                                  | 233               |

|-----|------|-------------------------------------------------------------------------------------|-------------------|

|     |      | 24.1.3 ERMA and PRMA                                                                | 233               |

|     |      | 24.1.4 Feedback Paths                                                               | . 234             |

|     | 24.2 | STLB Organization                                                                   | 234               |

|     |      | 24.2.1 Shared Bit                                                                   | 235               |

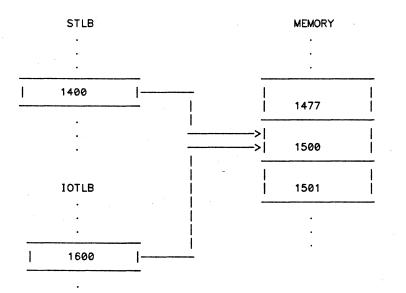

|     |      | 24.2.2 IOTLB Support                                                                | 236               |

|     | 24.3 | Traps                                                                               | 238               |

|     |      | 24.3.1 Read Address Trap                                                            | 238               |

|     |      | 24.3.2 STLB Miss                                                                    | 238               |

|     |      | 24.3.3 Access Violation                                                             | 239               |

|     |      | 24.3.4 Page Modified Trap                                                           | 239               |

|     |      | 24.3.5 Write Address Trap                                                           | 240               |

|     |      | 24.3.6 Flat Trap                                                                    | 240               |

|     |      | 24.3.7 Wrap Trap                                                                    | 240               |

|     | 24.4 | VLSI Usage                                                                          | 240               |

|     | 24.5 | Critical Paths                                                                      | 241               |

|     | 24.6 | 9755 Comparisons                                                                    | 241               |

|     | 24.7 | Partitioning                                                                        | 242               |

| 25. | Exe  | cution Unit Detailed Description                                                    | 243               |

|     | 25.1 | ALU Logic                                                                           | 246               |

|     |      | 25.1.1 ALU Modes                                                                    | 246               |

|     |      | 25.1.2 Carry                                                                        | 248               |

|     |      | 25.1.3 ALU Output                                                                   | 249               |

|     |      | 25.1.4 BA Mux                                                                       | 249               |

|     |      | 25.1.5 IBB Mux                                                                      | 249               |

|     |      | 25.1.6 RD and RS                                                                    | 250               |

|     | 25.2 | Barrel Shifter Logic                                                                | 250               |

|     |      | 25.2.1 BDI Encoding                                                                 | 251               |

|     |      | 25.2.2 Shift<br>25.2.3 BDI Output                                                   | 251<br>252        |

|     |      | 25.2.3 BDI Output                                                                   |                   |

|     | 25.3 | Register File                                                                       | 252               |

|     |      | <ul><li>25.3.1 Register File Bypass</li><li>25.3.2 Register File Tracking</li></ul> | 253<br>253        |

|     |      | 25.3.2 Register The Tracking<br>25.3.3 RP/REC                                       | 253<br>254        |

|     | 75 4 |                                                                                     |                   |

|     | 25.4 | Multiply<br>25.4.1 Booth's Algorithm                                                | <b>254</b><br>254 |

|     |      | 25.4.2 Multiply Implementation                                                      | 254               |

|     | 25.5 | Divide                                                                              | 262               |

|     | 23.5 | 25.5.1 Non-Restoring Divide Algorithm                                               | 262               |

|     |      | 25.5.2 Divide Implementation                                                        | 265               |

|     | 256  | Floating Point                                                                      | 267               |

|     | 23.0 | 25.6.1 Floating Add                                                                 | 267               |

|     |      | 25.6.2 Floating Subtract                                                            | 269               |

|     |      | 25.6.3 Floating Multiply                                                            | 20)               |

|     |      |                                                                                     |                   |

# 4150 Functional Specification

Page viii

| 25.6.4 Floating Divide                                       | 270               |

|--------------------------------------------------------------|-------------------|

| 25.6.5 Rounding                                              | 270               |

| 25.6.6 Quadruple Precision                                   | 272               |

| 25.7 Character and Decimal Instructions                      | 274               |

| 25.7.1 Introduction                                          | 274               |

| 25.7.2 Character Instructions<br>25.7.3 Decimal Instructions | 276<br>289        |

|                                                              | 306               |

| 25.8 System Timers                                           |                   |

| 25.9 Trap Logic                                              | <b>307</b><br>307 |

| 25.9.1 Fetch Cycle Traps<br>25.9.2 Non-Fetch Cycle Traps     | 308               |

| 25.10 Parity Reporting                                       | 308               |

| 25.11 VLSI Usage                                             | 301               |

| 25.12 Critical Paths                                         | 3                 |

| 25.12 Critical Fature<br>25.13 9755 Comparisons              | 3                 |

| -                                                            | 311               |

| 25.14 Partitioning                                           | 311               |

| 26. Memory Controller Unit Detailed Description              | 313               |

| 26.1 Overview                                                | 313               |

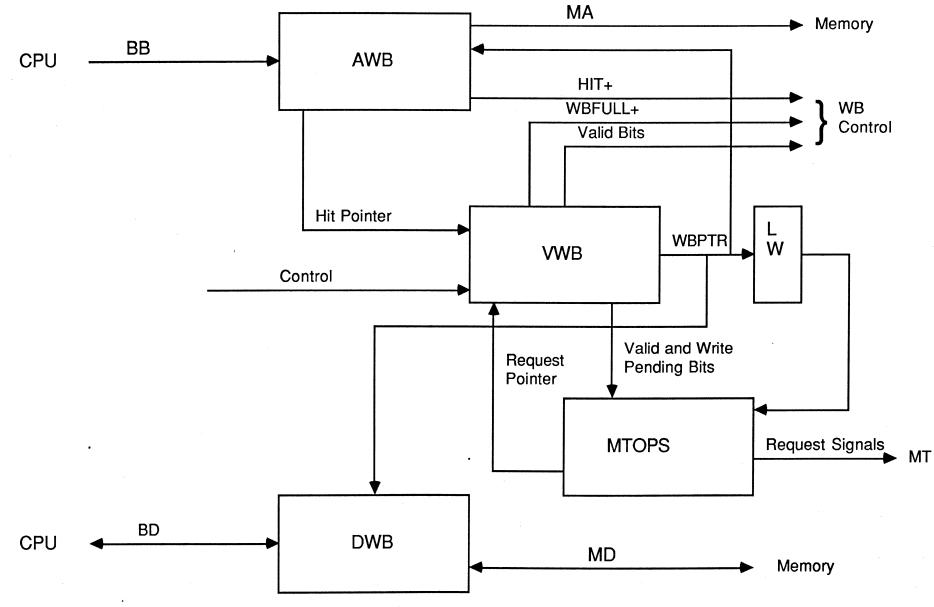

| 26.2 Write Buffer                                            | 315               |

| 26.2.1 Data Write Buffer                                     | 317               |

| 26.2.2 Address Write Buffer                                  | 318               |

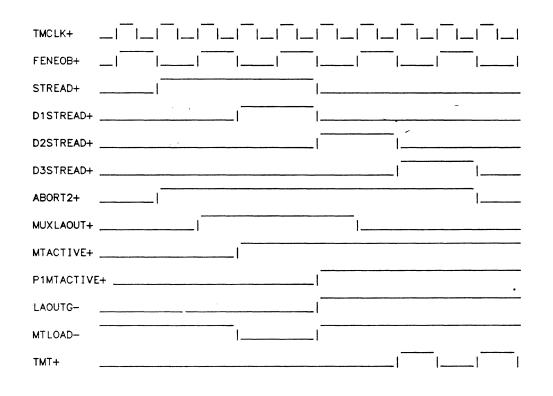

| 26.2.3 Valid Write Buffer<br>26.2.4 The WB as a Whole        | 319<br>320        |

| 26.2.4 Memory Timer OPeration Scheduler (MTOPS)              | 320               |

| 26.2.6 WB Diagnostics                                        | 325               |

| 26.3 CPU Request & Acknowledge                               | 326               |

| 26.3.1 CPU Write                                             | 327               |

| 26.3.2 CPU Read                                              | 328               |

| 26.4 Memory Timer                                            | 329               |

| 26.4.1 Read Status                                           | 334               |

| 26.4.2 MT Abort                                              | 336               |

| 26.4.3 MT Diagnostic Features                                | 336               |

| 26.5 Memory Configurations                                   | 336               |

| 26.6 Refresh                                                 | 338               |

| 26.7 Parity Checking/Generating                              | 339               |

| 26.8 Error Reporting                                         | 339               |

| 26.9 Battery Back Up                                         | 340               |

| 26.10 VLSI Usage                                             | 341               |

| 26.11 Critical Paths                                         | 341               |

| 26.12 Timing Diagrams                                        | 341               |

| 26.13 9755 Comparisons                                       | 342               |

|     | 26.14 Partitioning                                                    | 343             |

|-----|-----------------------------------------------------------------------|-----------------|

|     |                                                                       |                 |

| 27. | I/O Interface Detailed Description                                    | 345             |

|     | 27.1 DMx Control                                                      | 345             |

|     | 27.2 DMA/DMC/DMT/DMQ IN                                               | 348             |

|     | 27.3 DMA/DMC/DMT/DMQ OUT                                              | 349             |

|     | 27.4 Burst DMA Mode                                                   | 349             |

|     | 27.4.1 Burst DMA IN<br>27.4.2 Burst DMA OUT                           | 350<br>350      |

|     | 27.5 32-Bit Burst DMA Mode                                            | 350             |

|     | 27.6 Extended DMA                                                     | 351             |

|     | 27.7 Programmed I/O                                                   | <sup>2</sup> 51 |

|     | 27.8 Parity Checking                                                  | s.7 "A          |

|     | 27.9 Required I/O Controller Revision Levels                          |                 |

|     | •                                                                     |                 |

|     | 0 0                                                                   | 353             |

|     | <ul><li>27.11 9755 Comparisons</li><li>27.12 Critical Paths</li></ul> |                 |

|     |                                                                       | 353<br>354      |

|     | 27.13 Partitioning                                                    | 554             |

| 28. | Bus D Arbitration Detailed Description                                | 355             |

|     | 28.1 E Unit                                                           | 355             |

|     | 28.2 MC Unit                                                          | 355             |

|     | 28.3 S Unit                                                           | 355             |

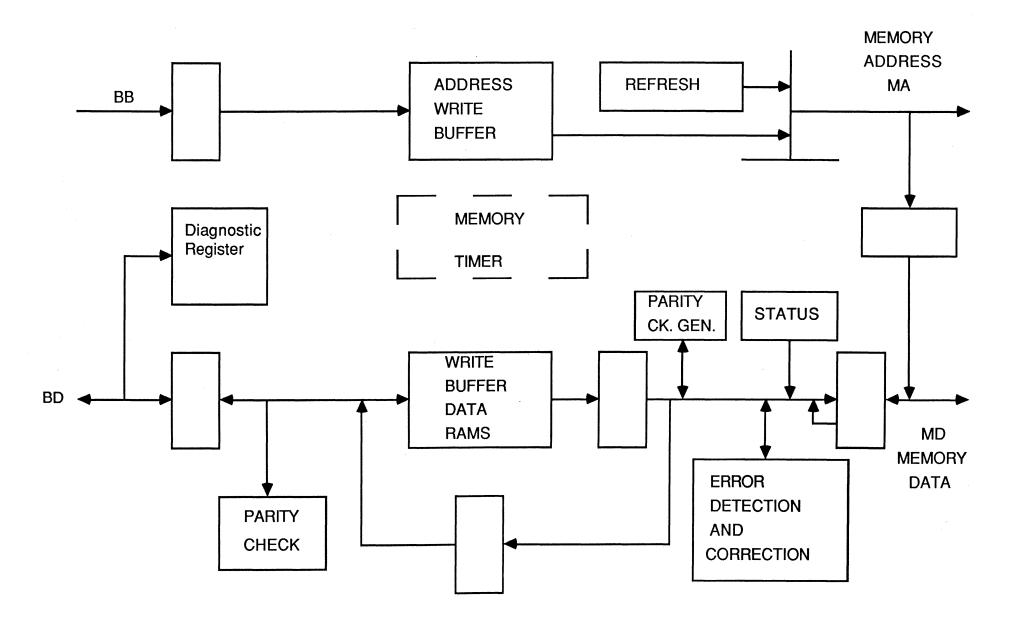

|     | 28.4 BPA                                                              | 356             |

|     | 28.5 PDA                                                              | 356             |

|     | 28.6 VLSI Usage                                                       | 357             |

|     | 28.7 Critical Paths                                                   | 357             |

|     | 28.8 9755 Comparisons                                                 | 357             |

|     | 28.9 Partitioning                                                     | 357             |

| 29. | Processor Diagnostic Aid Detailed Description                         | 359             |

|     | 29.1 Stack                                                            | 361             |

|     | 29.1.1 Inhibits                                                       | 361             |

|     | 29.1.2 Storing Data into the Stack                                    | 362             |

|     | 29.1.3 Reading Data from the Stack                                    | 362             |

|     | 29.2 Sense Registers                                                  | 362             |

|     | 29.2.1 SR1 and SR2<br>29.2.2 SR3                                      | 362<br>363      |

|     | 29.2.2 SR3<br>29.2.3 SR4                                              | 363<br>363      |

|     | 29.3 Halts and Delays                                                 | 363             |

|     | 29.3.1 Halts                                                          | 363             |

|     | 29.3.2 Delays                                                         | 363             |

# 4150 Functional Specification Page x

|     | 29.4 Event Counter                            | 364 |

|-----|-----------------------------------------------|-----|

|     | 29.4.1 Loading                                | 364 |

|     | 29.4.2 Reading                                | 364 |

|     | 29.4.3 Selecting Events to Count              | 364 |

|     | 29.5 Control Store Interface                  | 364 |

|     | 29.5.1 Reading/Writing Control Store          | 364 |

|     | 29.6 BDH Interface                            | 365 |

|     | 29.6.1 FORCEBCY                               | 366 |

|     | 29.6.2 Load Decode Net                        | 367 |

|     | 29.6.3 Load Memory                            | 367 |

|     | 29.7 Microprocessor                           | 367 |

|     | 29.8 PDA Configurations                       | 369 |

|     | 29.8.1 PDA Debug Configuration                | 369 |

|     | 29.8.2 Manufacturing CPU Debug Configuration  | 370 |

|     | 29.8.3 Customer or Field System Configuration | 370 |

|     | 29.9 How to Debug the PDA                     | 370 |

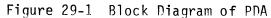

|     | 29.10 Timing Diagrams                         | 371 |

|     | 29.11 Critical Paths                          | 372 |

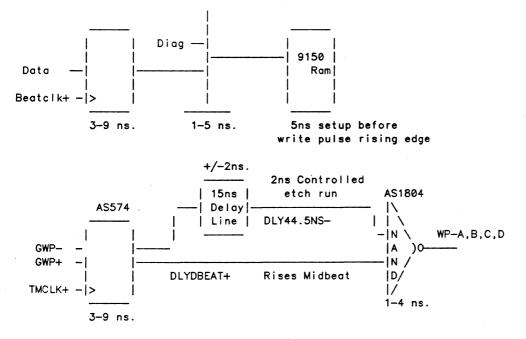

|     | 29.11.1 Stack Write Cycle                     | 372 |

|     | 29.11.2 Halt Path                             | 373 |

|     | 29.11.3 Trigger Path                          | 373 |

|     | 29.12 VLSI Usage                              | 373 |

|     | 29.13 9755 Comparisons                        | 373 |

|     | 29.13.1 Self Diagnostic Mode                  | 373 |

|     | 29.13.2 Stack                                 | 373 |

|     | 29.13.3 Trigger Conditions                    | 373 |

|     | 29.13.4 Event Counter                         | 374 |

|     | 29.13.5 Power Up Circuit                      | 374 |

|     | 29.13.6 BVMA Interface                        | 374 |

|     | 29.14 Partitioning                            | 374 |

| 30. | CMI Board Discussion                          | 375 |

|     | 30.1 4150 And 4050 Differences                | 377 |

|     | 30.2 Programmable Parts                       | 377 |

|     | 30.2.1 PALs                                   | 377 |

|     | 30.2.2 PROMs                                  | 379 |

|     | 30.3 Diagnostic Features                      | 380 |

|     | 30.4 Critical Paths                           | 381 |

|     | 50.4 Critical Faths                           | 301 |

| 31. | IS Board Discussion                           | 383 |

|     | 31.1 4150 And 4050 Differences                | 385 |

|     | 31.2 PALs                                     | 385 |

|     | 31.2.1 PCU PALs                               | 385 |

|     | 31.2.2 Parity Clocks                          | 385 |

32.

33.

|      | 31 2 3  | EAS, EAD, and INSTAT Clocks          | 385 |

|------|---------|--------------------------------------|-----|

|      |         | Branch Cache Control                 | 385 |

|      |         | Register Collisions                  | 385 |

|      |         | BVMA Select Control                  | 385 |

|      |         | Cache Write Control                  | 385 |

|      |         | RMA Clocks                           | 386 |

|      |         | Unaligned Read and Cache Data Clocks | 386 |

|      | 31.2.10 | •                                    | 386 |

|      | 31.2.11 | • · · • · ·                          | 386 |

|      |         | IRPL, IRPH, and RPST clocks          | 386 |

|      | 31.2.13 |                                      | 386 |

|      | 31.2.14 |                                      | 386 |

|      | 31.2.15 | -                                    | 386 |

|      | 31.2.16 |                                      | 386 |

|      | 31.2.17 | •                                    | 387 |

|      | 31.2.18 | 0                                    | 387 |

|      | 31.2.19 | 0                                    | 387 |

|      | 31.2.20 |                                      | 387 |

| 31.3 | PROM    |                                      | 387 |

| 51.5 | 31.3.1  | Destination                          | 387 |

|      |         | IAC                                  | 387 |

|      | 31.3.3  | Trap                                 | 387 |

| 31.4 |         | cal Paths                            | 387 |

|      |         |                                      |     |

| ΕB   | oard Di | iscussion                            | 389 |

| 32.1 | 4150    | And 4050 Differences                 | 391 |

| 32.2 | Progr   | ammable Parts                        | 391 |

|      | 32.2.1  | PALs                                 | 391 |

|      | 32.2.2  | PROMs                                | 393 |

| 32.3 | Diagn   | ostic Features                       | 394 |

|      | •       |                                      |     |

| 32.4 | Critic  | al Paths                             | 394 |

| PDA  | Board   | Discussion                           | 395 |

| 33.1 | 4150    | And 4050 Differences                 | 397 |

| 33.2 | Progr   | ammable Parts                        | 397 |

| 0012 |         | PALS                                 | 397 |

|      | 33.2.2  | PROMs                                | 398 |

| 33.3 |         | ostic Features                       | 398 |

| 33.4 | •       | al Paths                             | 398 |

| 55.4 | 33.4.1  | Stack Write Cycle                    | 398 |

|      | 33.4.2  | Halt Path                            | 399 |

|      |         | Trigger Path                         | 399 |

|      | 00.40   | 11660 1 Will                         | 577 |

### 4150 Functional Specification Page xii

# List of Figures

| FIG. | 1-1.  | System Diagram of 4150                           | 2   |

|------|-------|--------------------------------------------------|-----|

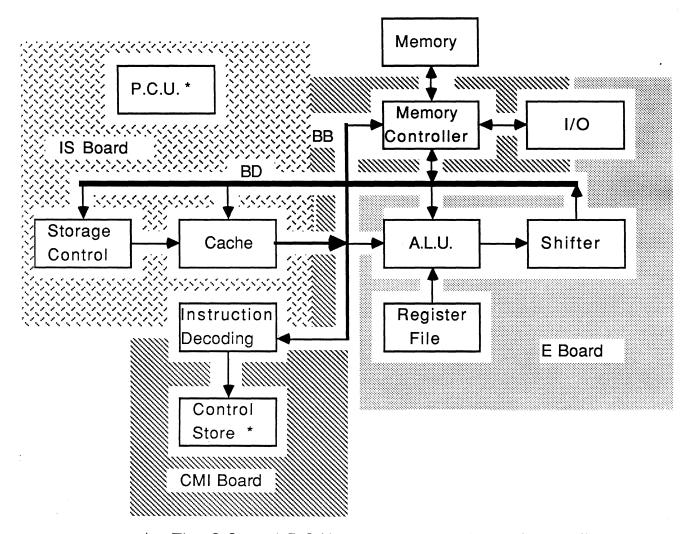

| FIG. | 2-1.  | Block Diagram of 4150 Processor                  | 10  |

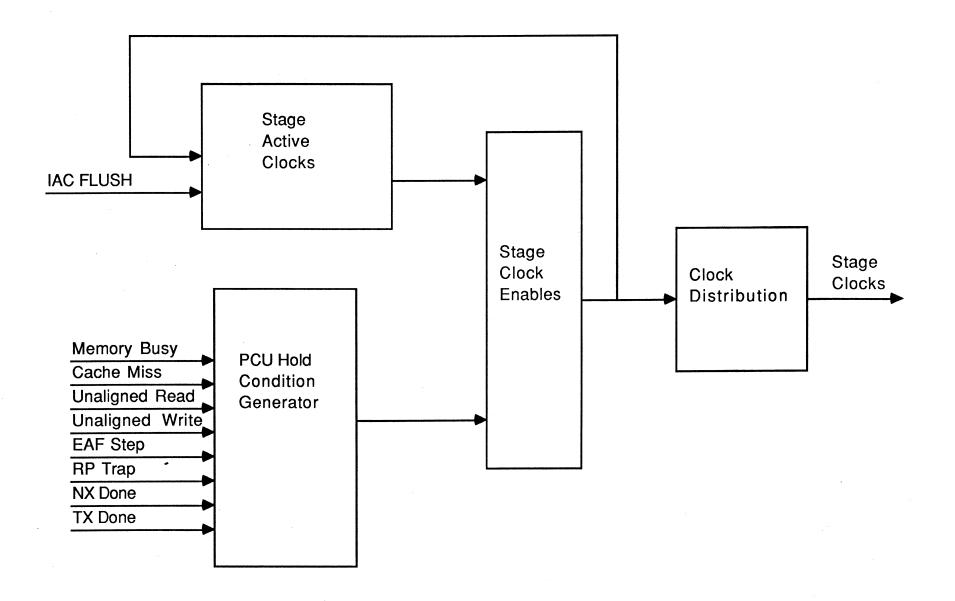

| FIG. | 3-1.  | Block Diagram of Pipeline Control Unit           | 18  |

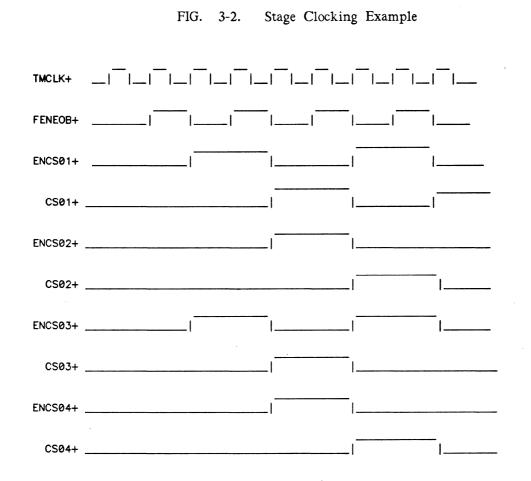

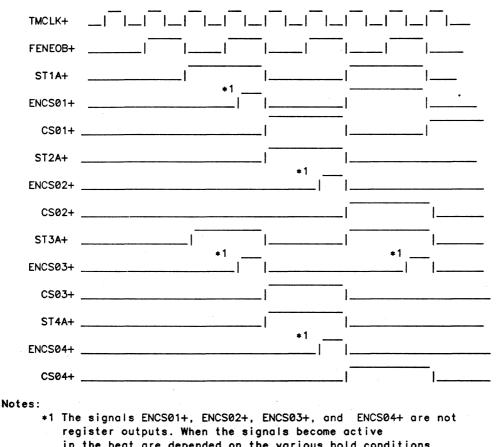

| FIG. | 3-2.  | Stage Clocking Example                           | 20  |

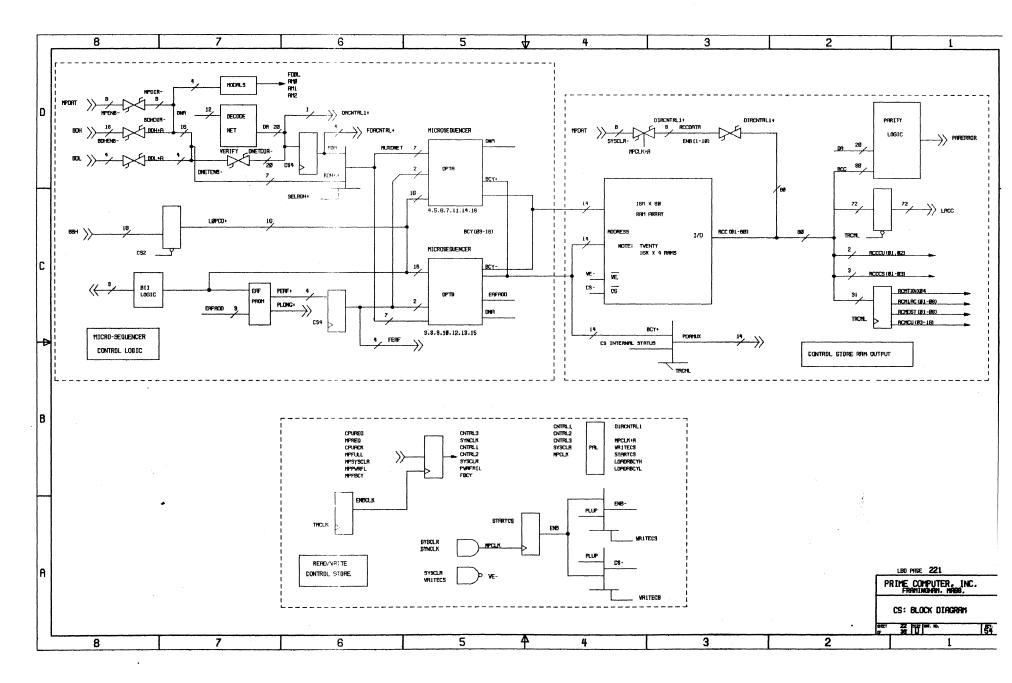

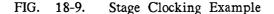

| FIG. | 4-1.  | Block Diagram of Control Store                   | 22  |

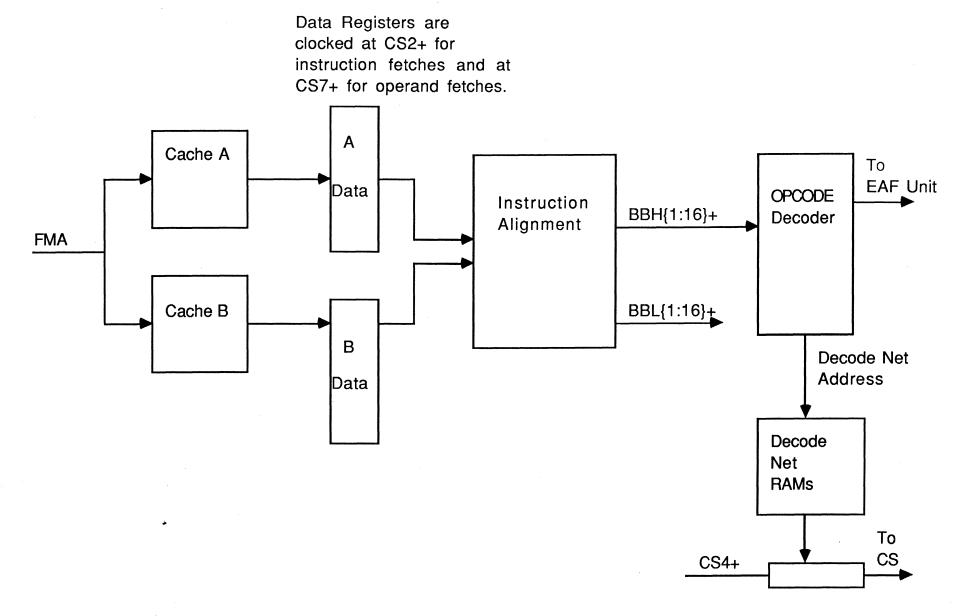

| FIG. | 5-1.  | Block Diagram of Instruction Decode Unit         | 26  |

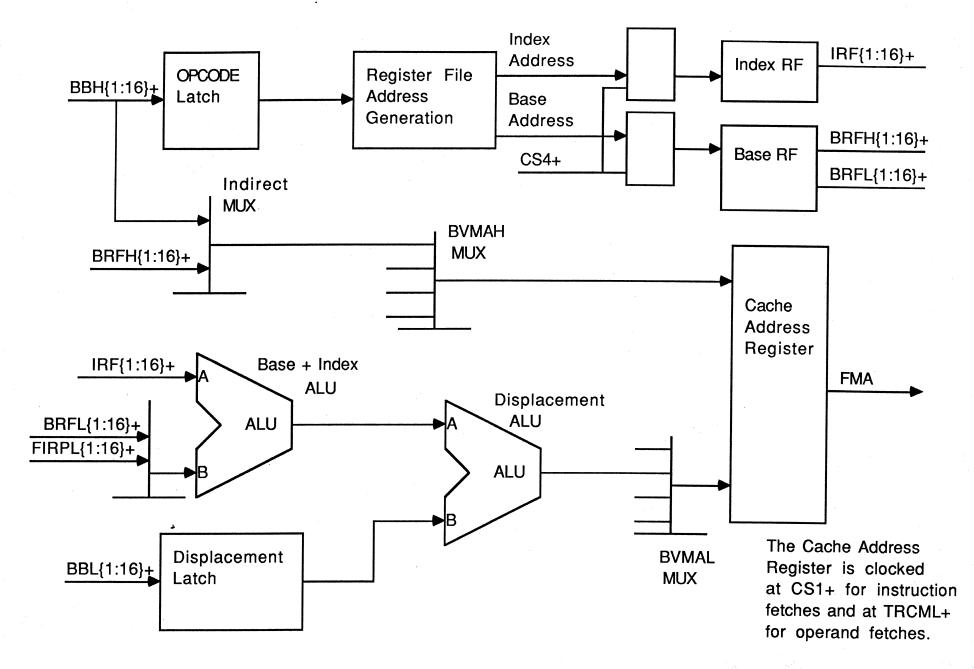

| FIG. | 5-2.  | Block Diagram of EAF Unit                        | 27  |

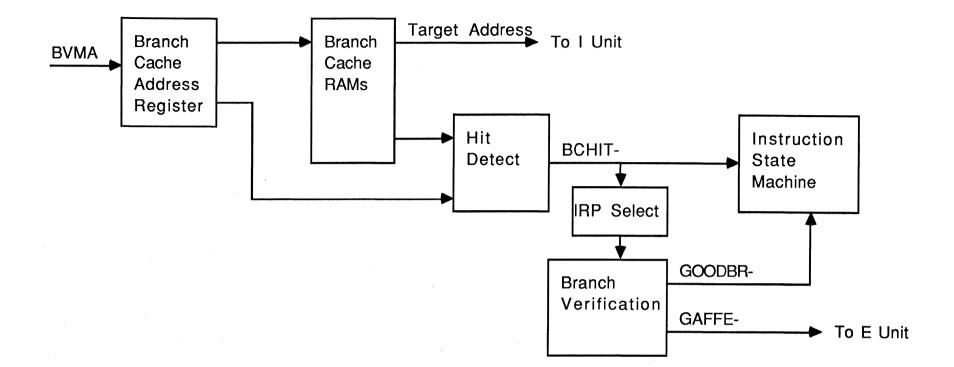

| FIG. | 6-1.  | Block Diagram of Branch Cache                    | 32  |

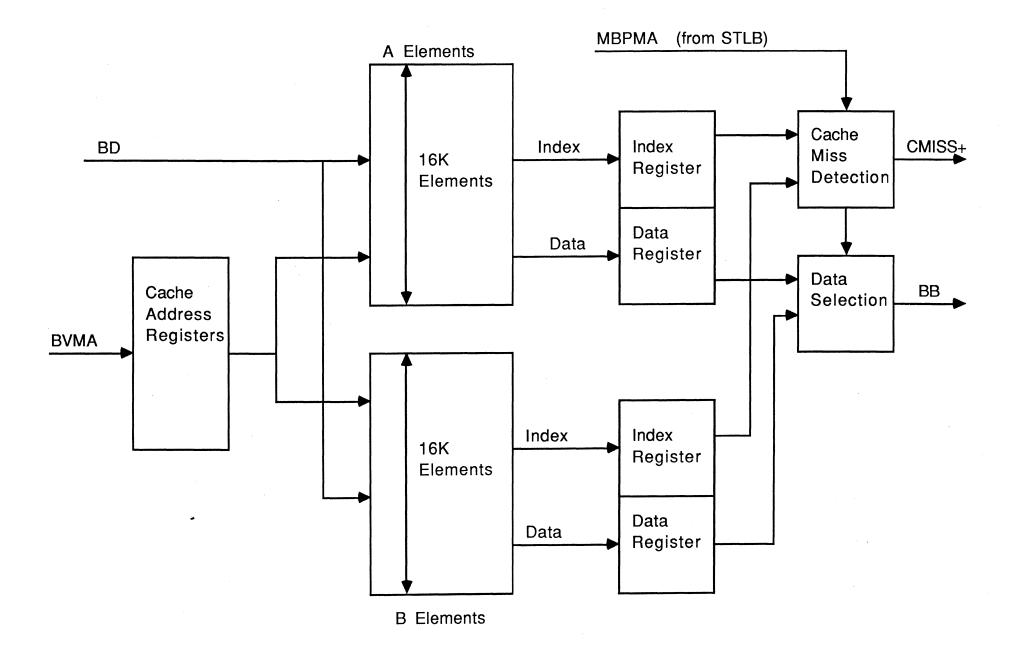

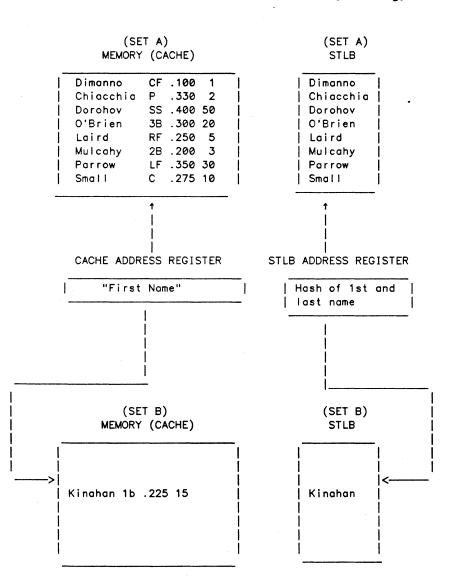

| FIG. | 7-1.  | Block Diagram of Cache                           | 36  |

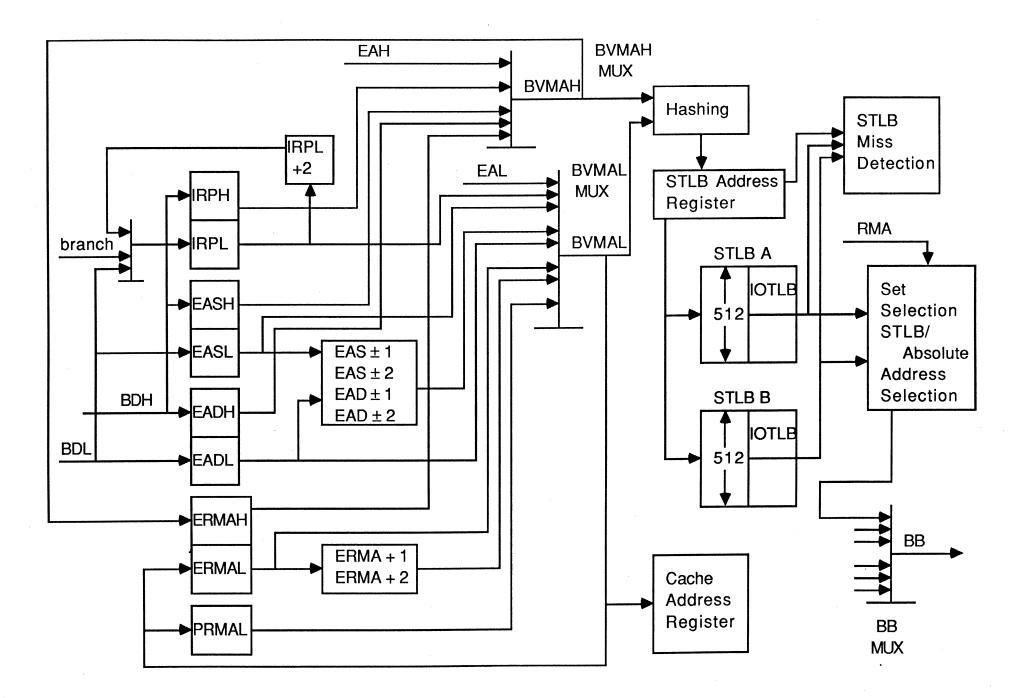

| FIG. | 8-1.  | Block Diagram of Storage Management Unit         | 40  |

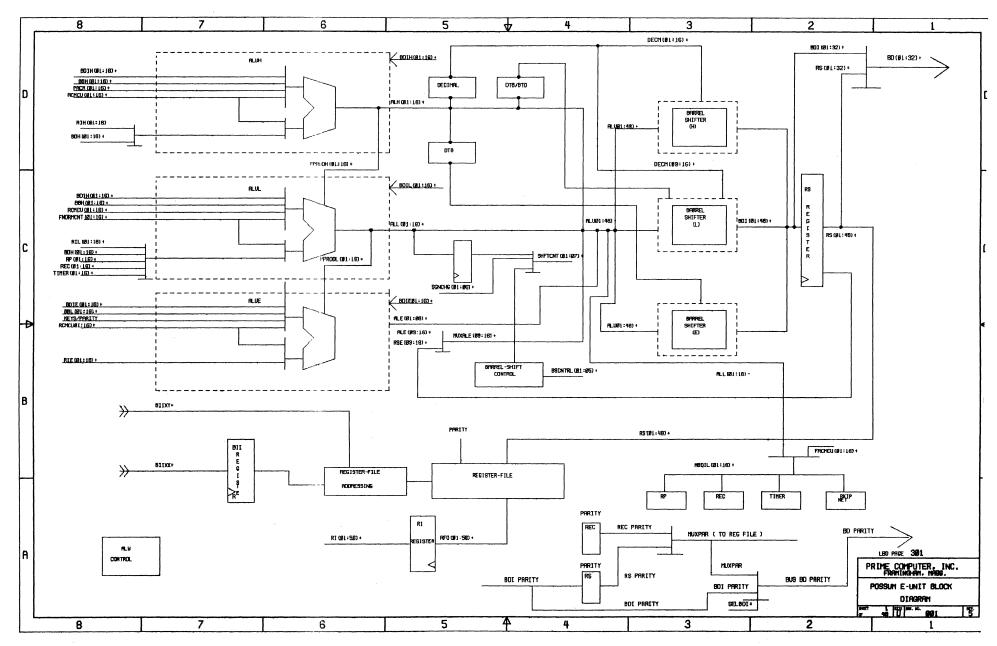

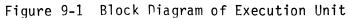

| FIG. | 9-1.  | Block Diagram of Execution Unit                  | 48  |

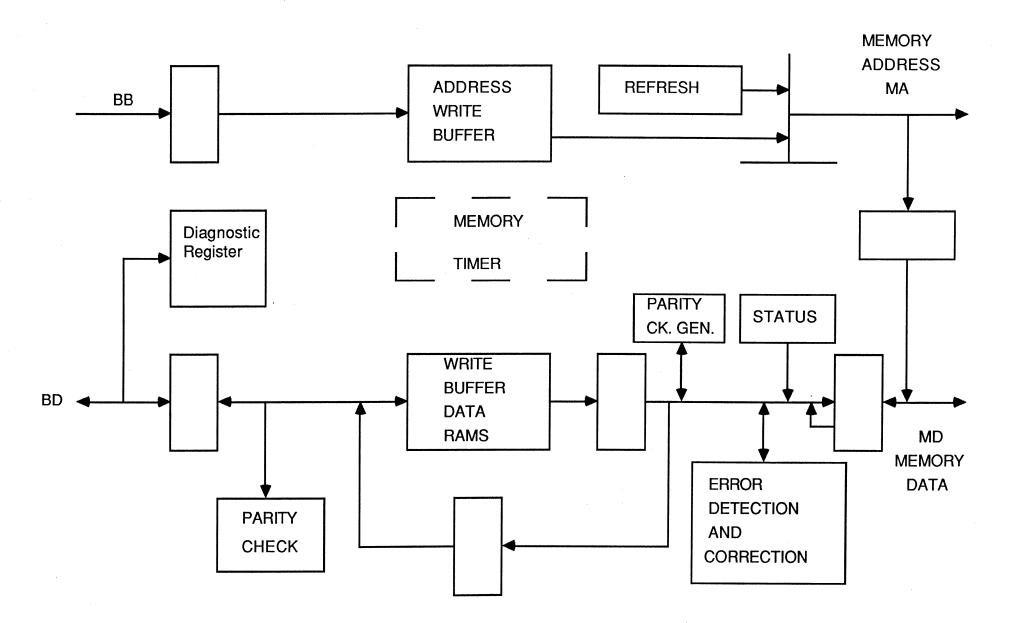

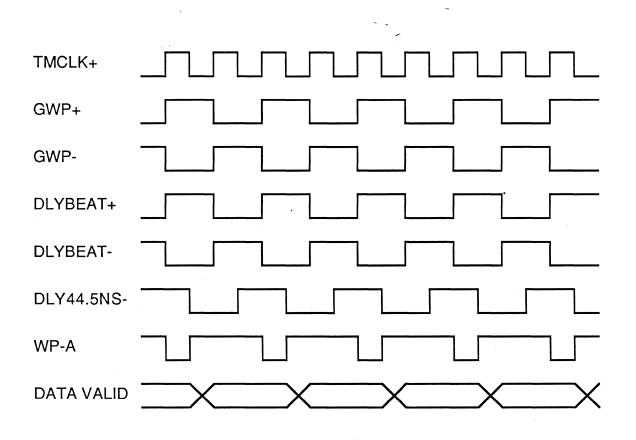

| FIG. | 10-1. | Block Diagram of Memory Controller               | 52  |

| FIG. | 11-1. | Block Diagram of I/O Interface                   | 56  |

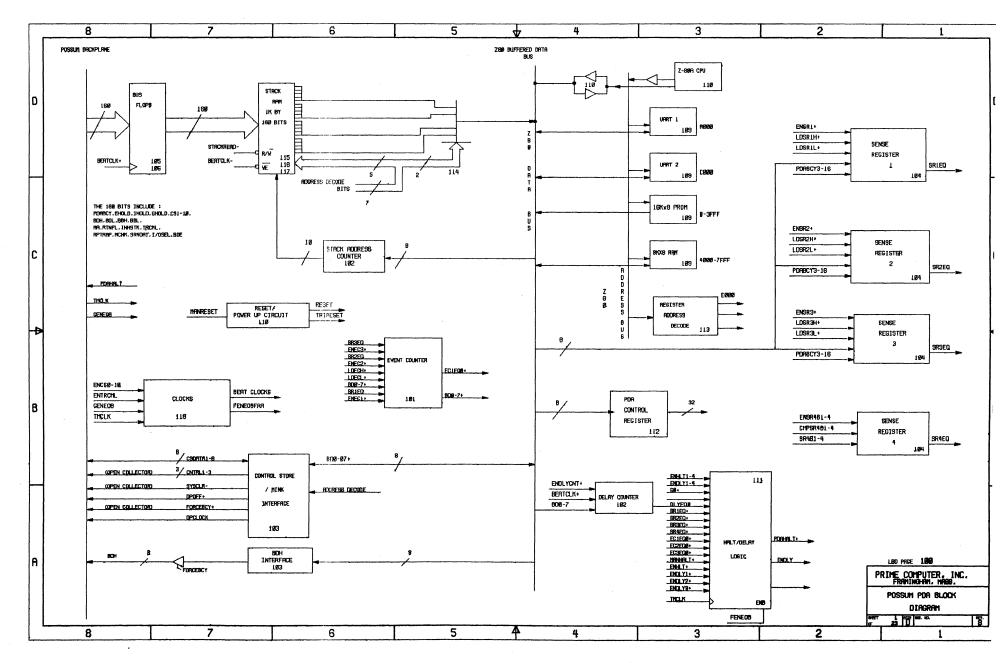

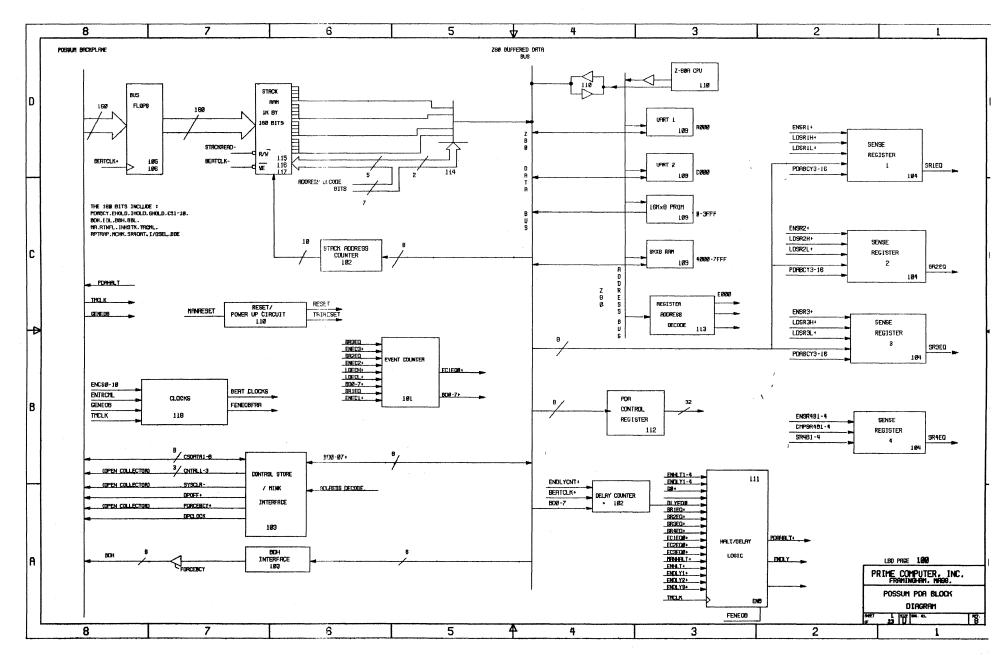

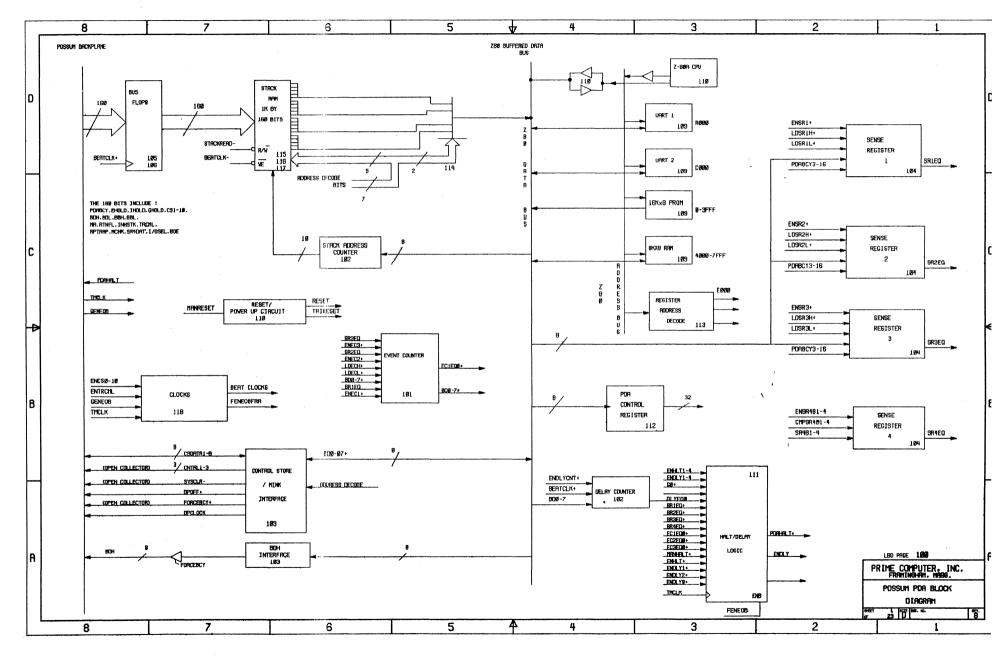

| FIG. | 13-1. | Block Diagram of PDA                             | 64  |

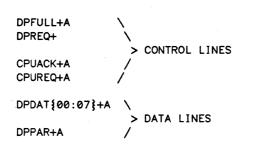

| FIG. | 16-1. | Diagnostic Processor Interface Signals           | 89  |

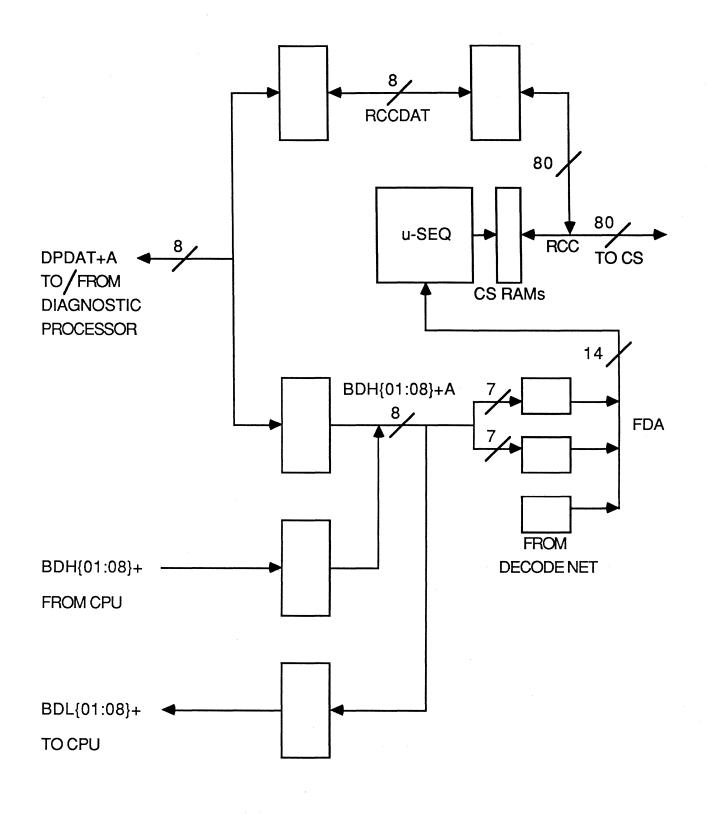

| FIG. | 16-2. | Diagnostic Processor Interface Block Diagram     | 90  |

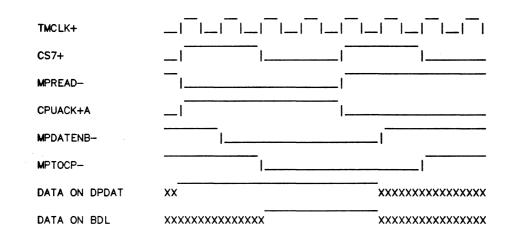

| FIG. | 16-3. | Read Data from DP to CPU                         | 94  |

| FIG. | 16-4. | Write Data from CPU to DP                        | 94  |

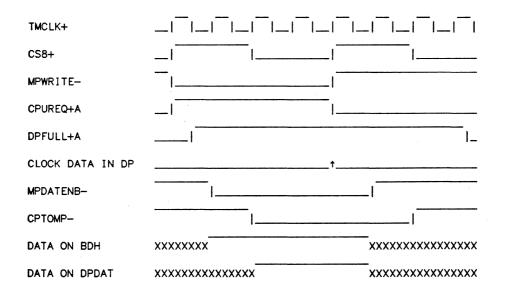

| FIG. | 16-5. | Load RBCYH & RBCYL                               | 95  |

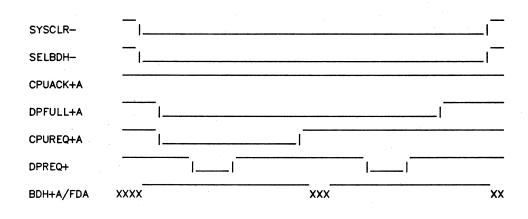

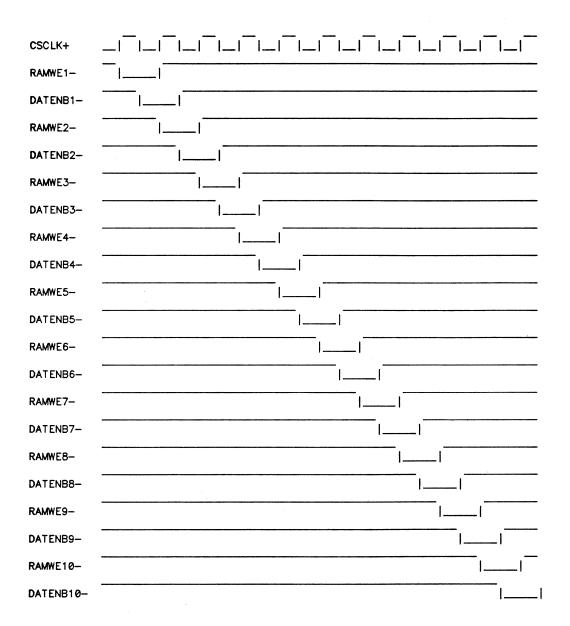

| FIG. | 16-6. | Write Control Store                              | 96  |

| FIG. | 18-1. | Conceptual Flow of Pipelined Instructions        | 135 |

| FIG. | 18-2. | Block Diagram of Pipeline Control Unit           | 136 |

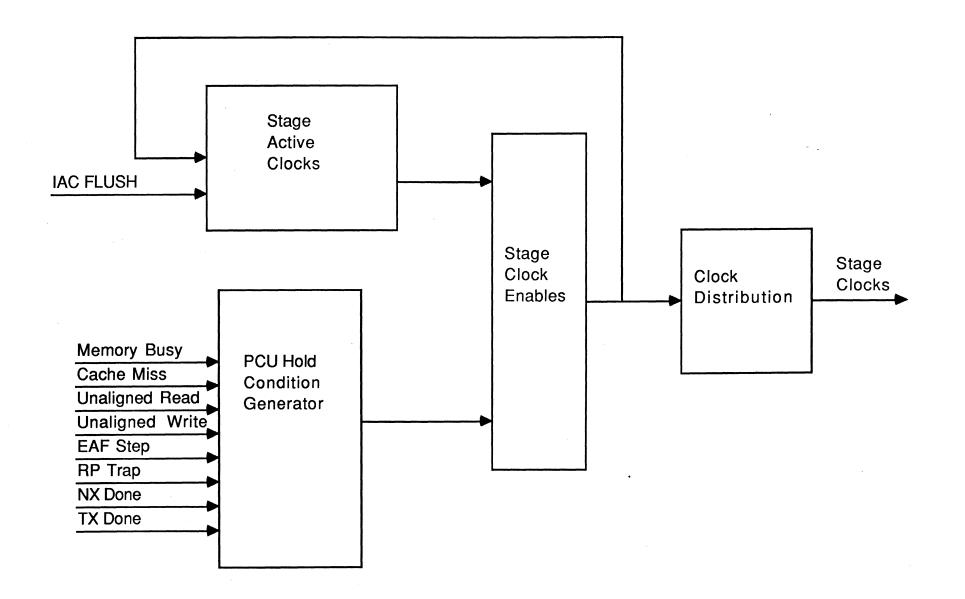

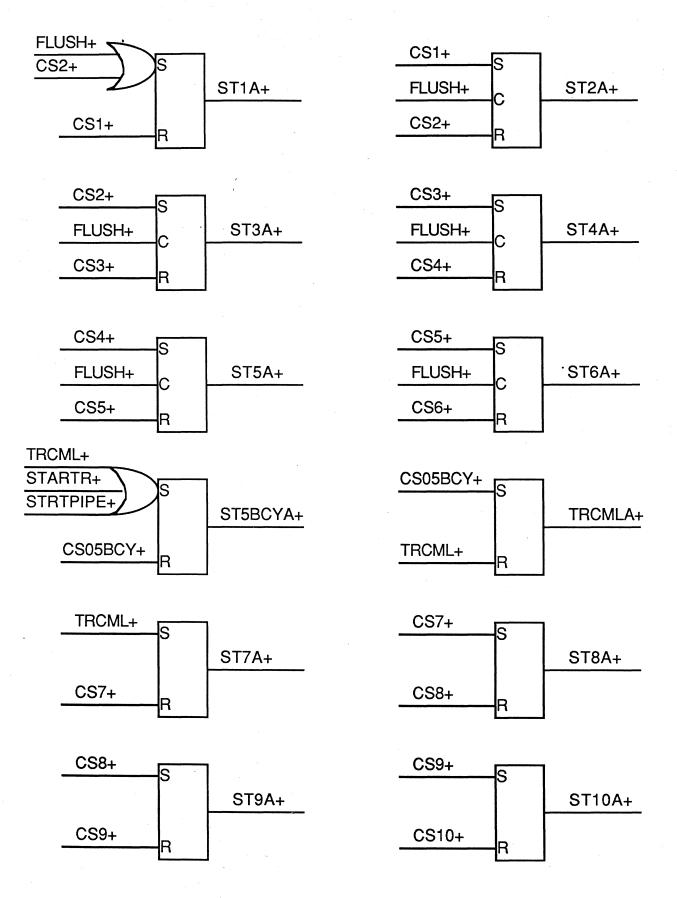

| FIG. | 18-3. | S-R Flip-Flop View of Stage Active Functionality | 141 |

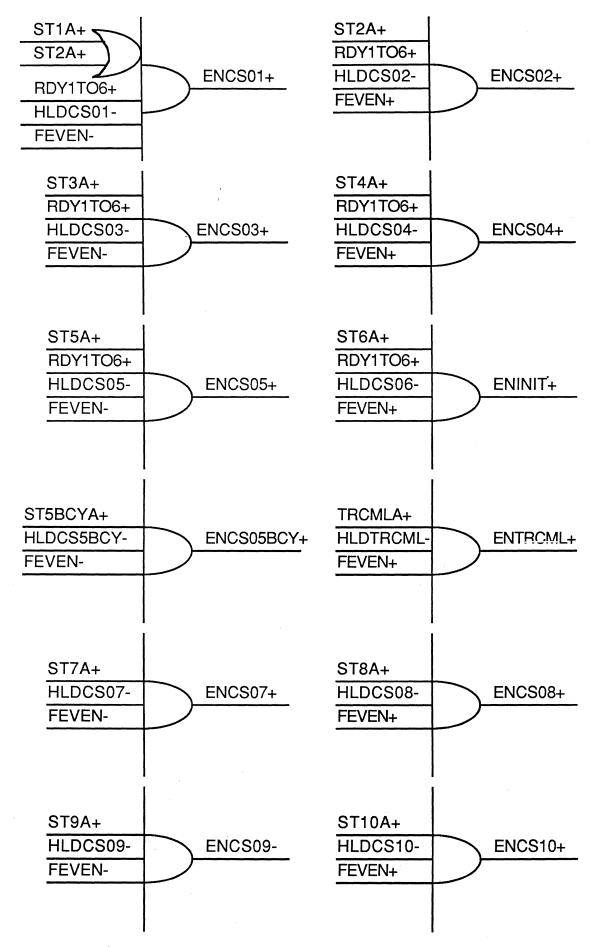

| FIG. | 18-4. | AND Gate View of Stage Clock Enables             | 142 |

| FIG. | 18-5. | Consecutive Odd Pipeline Stages Illustration     | 143 |

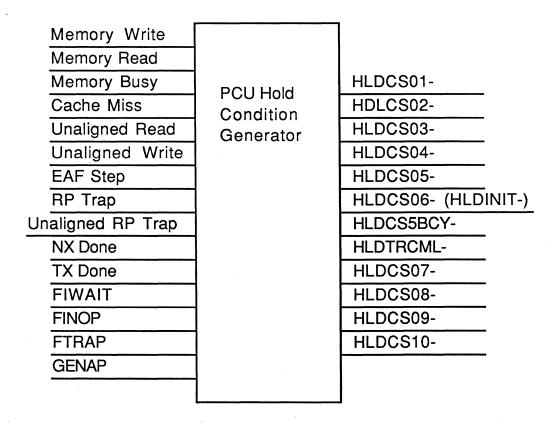

| FIG. | 18-6. | PCU Hold Condition Block Diagram                 | 144 |

| FIG. | 18-7. | TX NX Illustrations                              | 146 |

| FIG. | 18-8. | Pipeline Flow For RP Trap                        | 150 |

# 4150 Functional Specification Page xiv

| FIG. | 18-9.          | Stage Clocking Example                     | 153         |

|------|----------------|--------------------------------------------|-------------|

| FIG. | 19-1.          | Block Diagram of Control Store             | 156         |

| FIG. | 19-1.<br>19-2. | JUMP BCY Formation                         | 159         |

|      |                |                                            | 160         |

| FIG. | 19-3.          | DECODE and LDA BCY Formation               |             |

| FIG. | 19-4.          | BDH Branch BCY Formation                   | 160         |

| FIG. | 19-5.          | GOTO BCY Formation                         | 161         |

| FIG. | 19-6.          | EMIT BCY Formation                         | 162         |

| FIG. | 19-7.          | CRTN BCY Formation                         | 163         |

| FIG. | 19-8.          | CALL w/ JUMP Operation                     | 164         |

| FIG. | 19-9.          | CALL w/ GOTO Operation                     | 165         |

| FIG. | <b>19-1</b> 0. | PUSH w/ EMIT Operation                     | 166         |

| FIG. | 19-11.         | FORCEBCY Timing                            | 167         |

| FIG. | 19-12.         | Control Store Memory Write Cycle Timing    | 169         |

| FIG. | 20-1.          | Block Diagram of Instruction Decode Unit   | 172         |

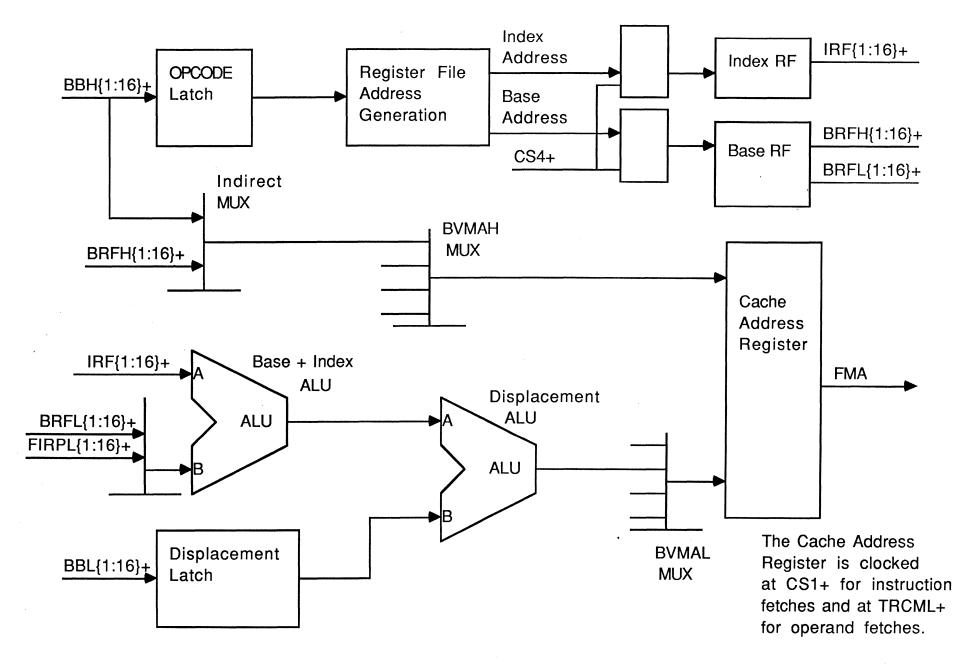

| FIG. | 21-1.          | Block Diagram of EAF Unit                  | 184         |

| FIG. | 21-2.          | Pipeline Flow During Indirect              | 194         |

| FIG. | 21-3.          | Generalized Pipeline Flow                  | 195         |

| FIG. | 21-4.          | 5-9 Register Collision Pipeline Flow       | 196         |

| FIG. | 21-5.          | 4-6 Register Collision Pipeline Flow       | 197         |

| FIG. | 21-6.          | 4-6 Register Collision Bypass              | 198         |

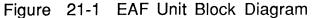

| FIG. | 22-1.          | Block Diagram of Branch Cache              | 202         |

| FIG. | 23-1.          | Direct Mapped Cache (Analogy)              | 208         |

| FIG. | 23-2.          | Two Set Associative Memory (Analogy)       | 209         |

| FIG. | 23-3.          | Block Diagram of Cache                     | 211         |

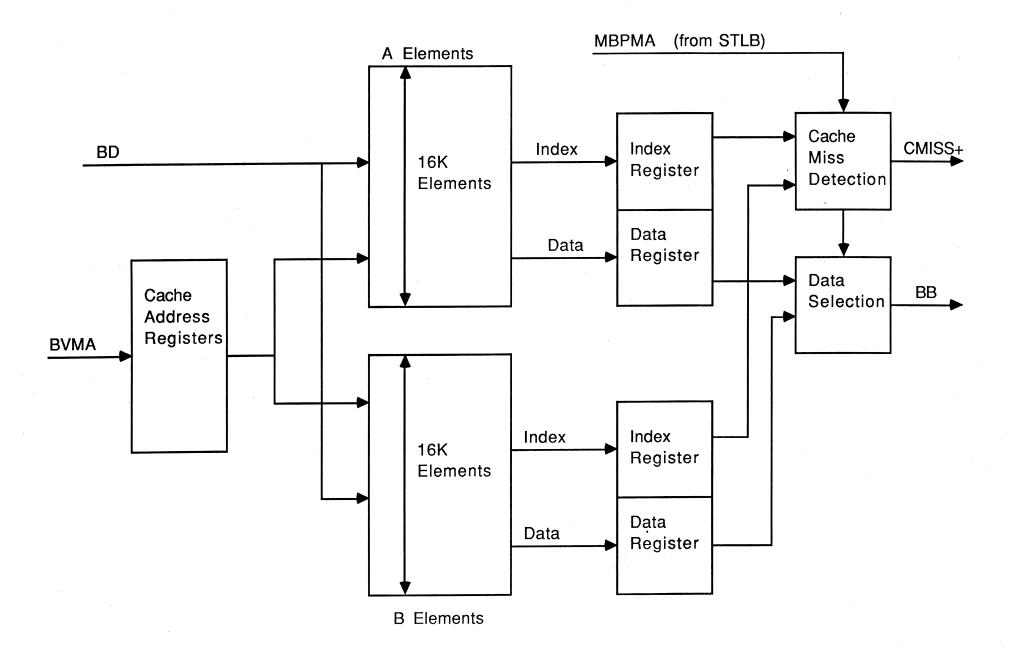

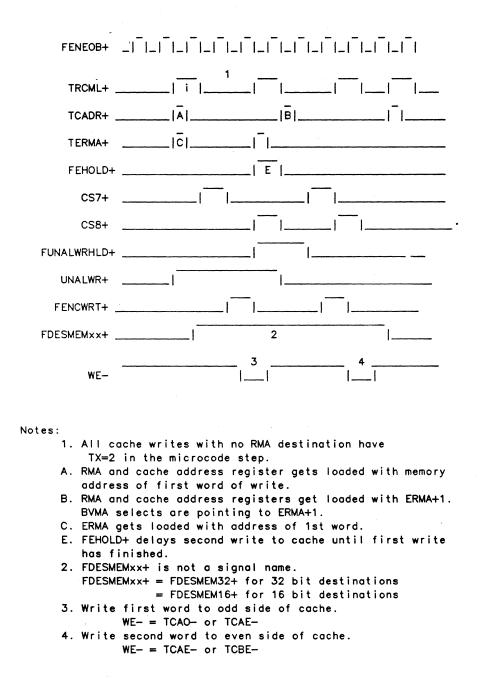

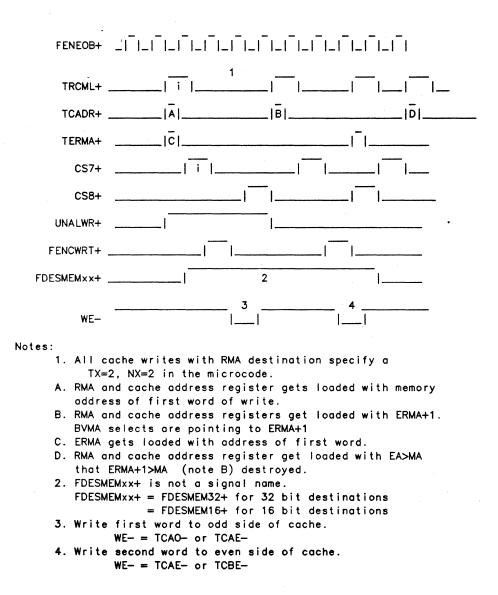

| FIG. | 23-4.          | Aligned Cache Writes                       | 215         |

| FIG. | 23-5.          | Unaligned Cache Writes: No RMA destination | 217         |

| FIG. | 23-6.          | Unaligned Cache Writes: RMA destination    | 219         |

| FIG. | 23-7.          | Unaligned Read Timing                      | <b>22</b> 0 |

| FIG. | 23-8.          | Unaligned Cache Miss: First Word only      | 223         |

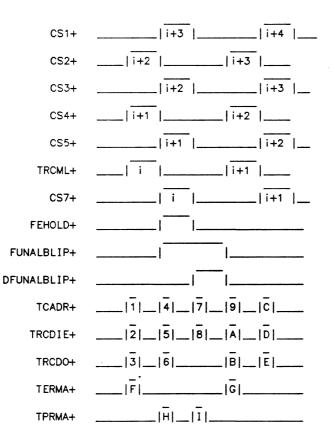

| FIG. | 23-9.  | Unaligned Cache Miss: Second Word only      | 225         |

|------|--------|---------------------------------------------|-------------|

| FIG. | 23-10. | Aligned Cache Miss                          | 227         |

| FIG. | 24-1.  | Block Diagram of Storage Management Unit    | 232         |

| FIG. | 24-2.  | STLB and IOTLB Mapping to the Same Location | 237         |

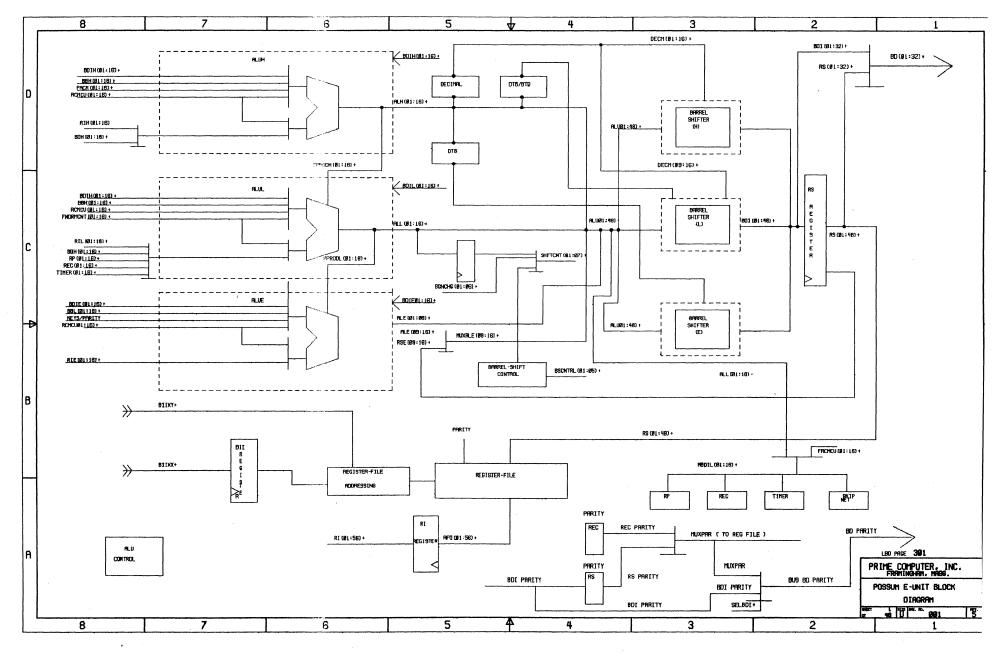

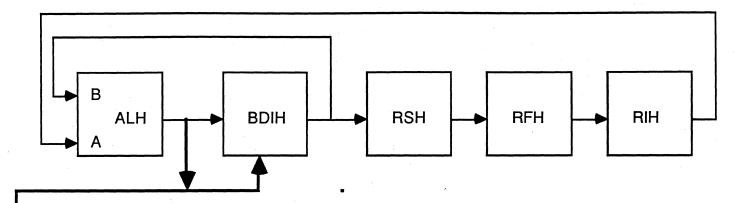

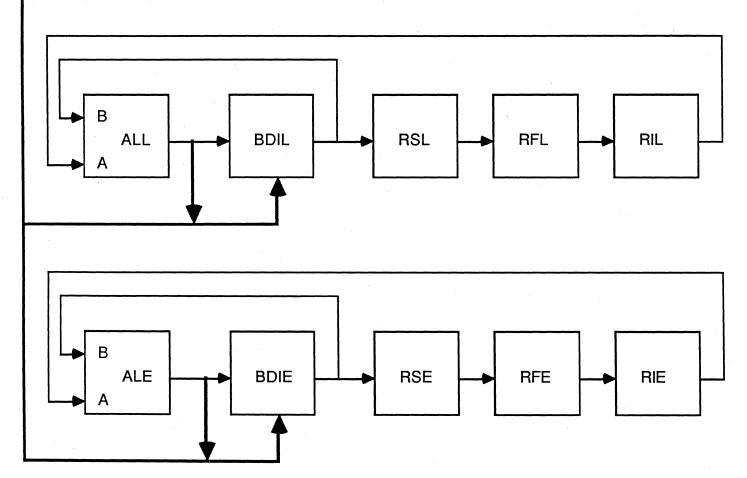

| FIG. | 25-1.  | Block Diagram of Execution Unit             | 244         |

| FIG. | 25-2.  | Execution Unit Data Flow Diagram            | 245         |

| FIG. | 25-3.  | Register File Location Layout               | 253         |

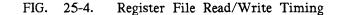

| FIG. | 25-4.  | Register File Read/Write Timing             | 253         |

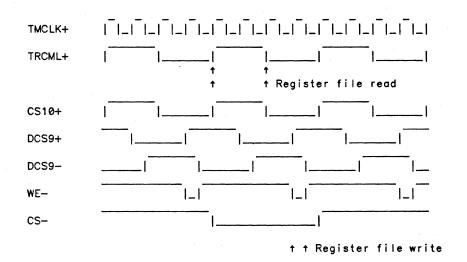

| FIG. | 25-5.  | Booth's Algorithm                           | 255         |

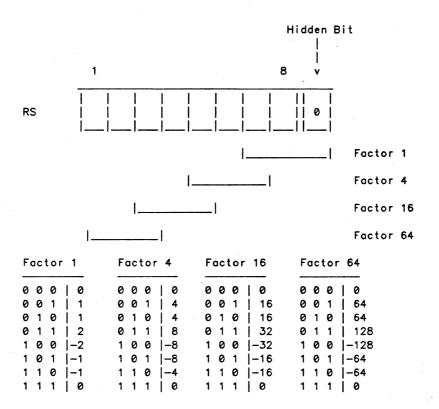

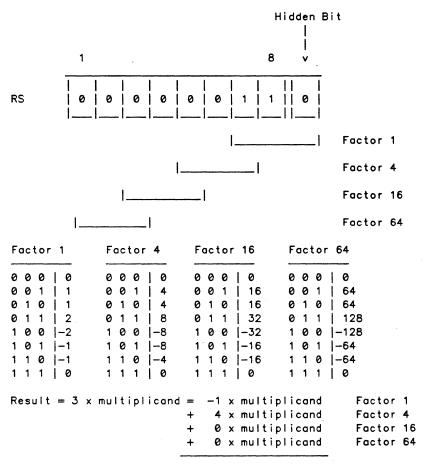

| FIG. | 25-6.  | Booth's Algorithm: Multiplier = 3 Example   | 256         |

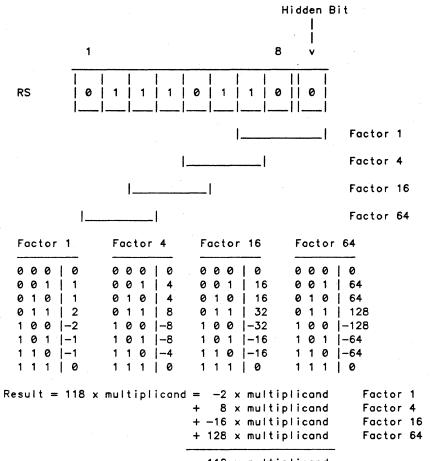

| FIG. | 25-7.  | Booth's Algorithm: Multiplier = 118 Example | 257         |

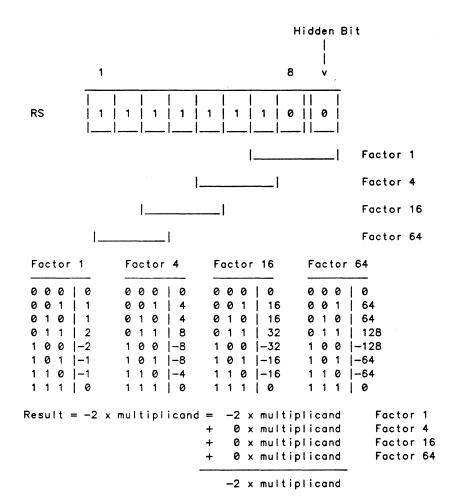

| FIG. | 25-8.  | Booth's Algorithm: Multiplier = -2 Example  | 258         |

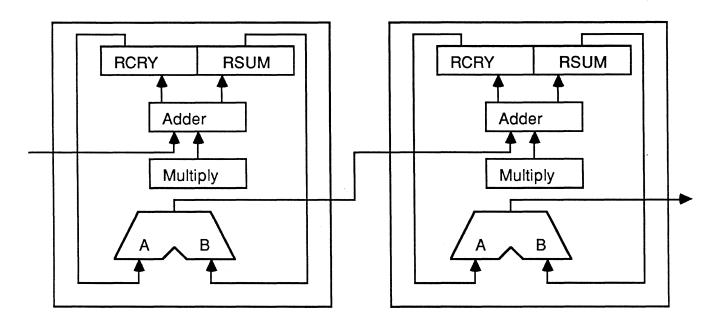

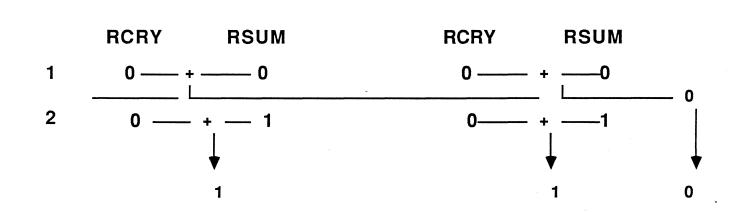

| FIG. | 25-9.  | Multiply Hardware Slicing                   | <b>26</b> 0 |

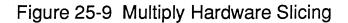

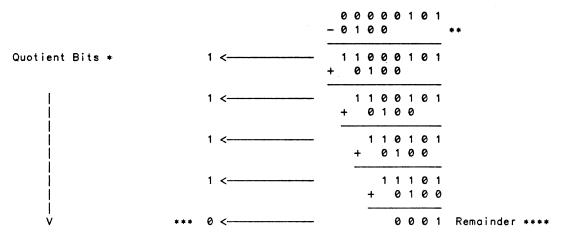

| FIG. | 25-10. | Non-Restoring Divide Example: 6 / 2         | 263         |

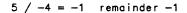

| FIG. | 25-11. | Non-Restoring Divide Example: 5 / -4        | 264         |

| FIG. | 25-12. | Non-Restoring Divide Example: 14 / 3        | 265         |

| FIG. | 25-13. | Quadruple Precision Normalize               | 273         |

| FIG. | 25-14. | Character and Decimal Alignment             | 275         |

| FIG. | 26-1.  | Block Diagram of Memory Controller          | 314         |

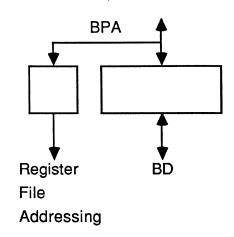

| FIG. | 26-2.  | Write Buffer Block Diagram                  | 316         |

| FIG. | 26-3.  | Data Write Buffer Organization              | 317         |

| FIG. | 26-4.  | VWB Location Format                         | 319         |

| FIG. | 26-5.  | Aligned Write VWB Patterns                  | 323         |

| FIG. | 26-6.  | Unaligned Write VWB Patterns (Examples)     | 324         |

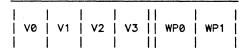

| FIG. | 26-7.  | WACK Timing Diagram                         | 341         |

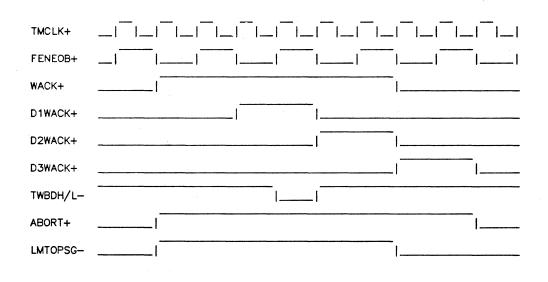

| FIG. | 26-8.  | STREAD Timing Diagram                       | 342         |

| FIG. | 27-1.  | Block Diagram of I/O Interface              | 346         |

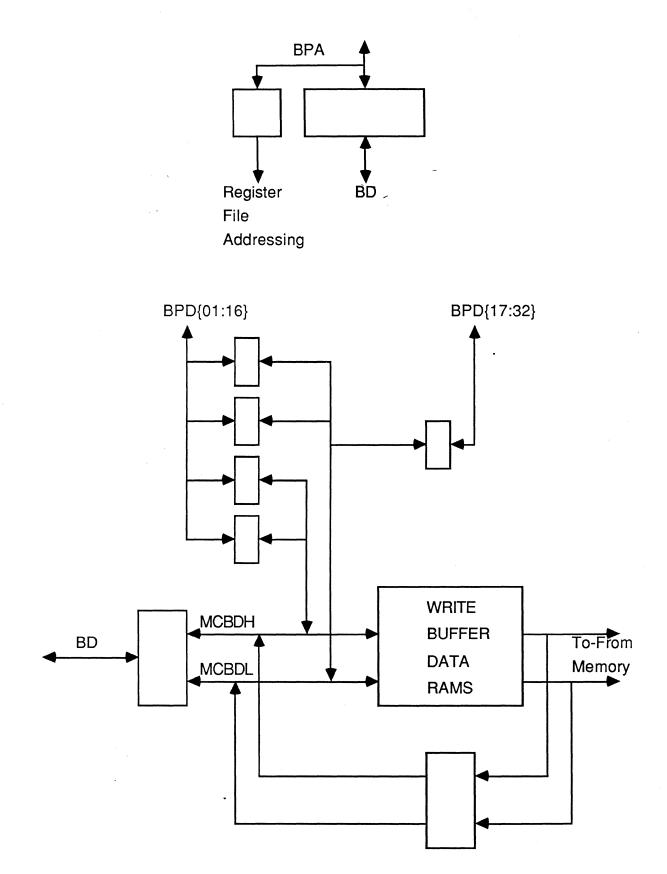

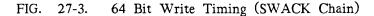

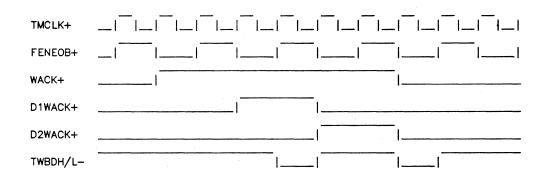

| FIG. | 27-2.  | BPCSTRB and BPCBSTRB Timing                 | 353         |

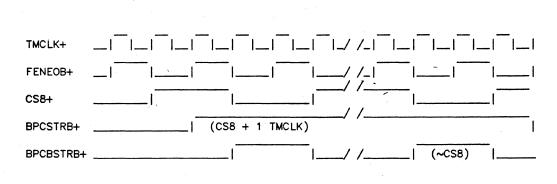

| FIG. | 27-3.  | 64 Bit Write Timing (SWACK Chain)           | 353         |

### 4150 Functional Specification Page xvi

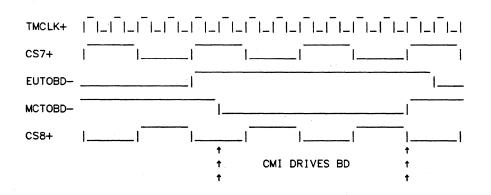

| FIG. | 28-1. | Transfer of BD Control, E to MC  | 355         |

|------|-------|----------------------------------|-------------|

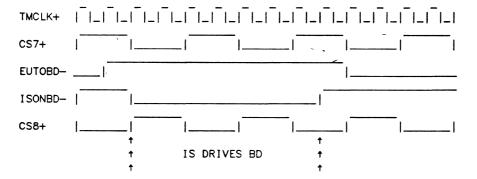

| FIG. | 28-2. | Transfer of BD Control, E to S   | 356         |

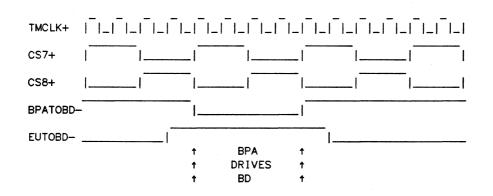

| FIG. | 28-3. | Transfer of BD Control, E to BPA | 356         |

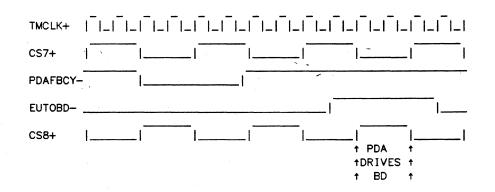

| FIG. | 28-4. | Transfer of BD Control, E to PDA | 357         |

| FIG. | 29-1. | Block Diagram of PDA             | <b>36</b> 0 |

| FIG. | 29-2. | PDA BDH Interface Fields         | 366         |

| FIG. | 29-3. | PDA Stack Write Pulse Timing     | 372         |

| FIG. | 30-1. | CMI Board Block Diagram          | 376         |

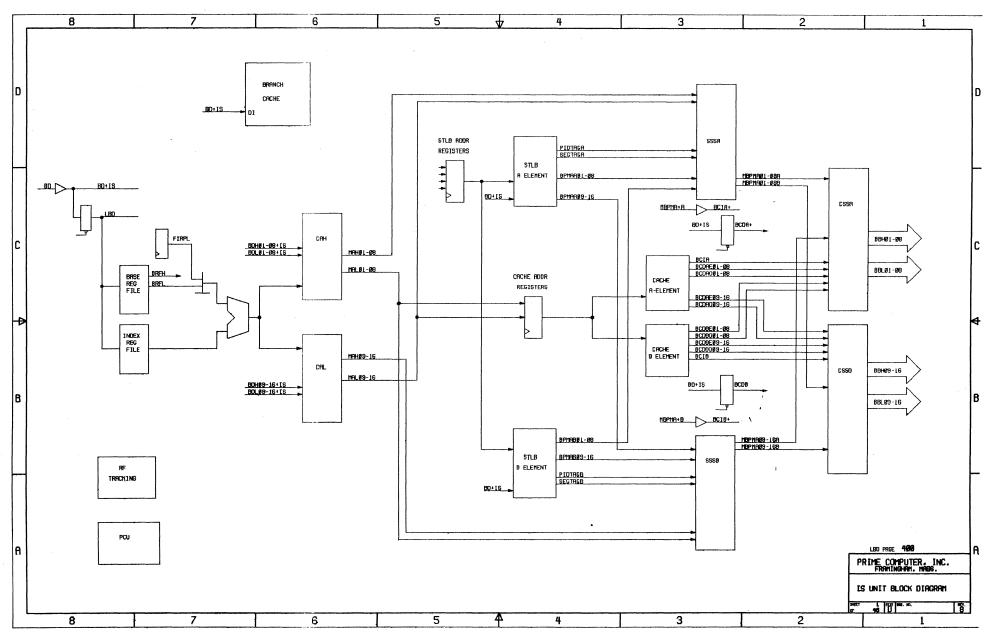

| FIG. | 31-1. | IS Board Block Diagram           | 384         |

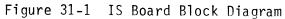

| FIG. | 32-1. | E Board Block Diagram            | <b>39</b> 0 |

| FIG. | 33-1. | PDA Board Block Diagram          | 396         |

# List of Tables

| TABLE | 1-1.  | Memory Configurations                                 | 6                        |

|-------|-------|-------------------------------------------------------|--------------------------|

| TABLE | 1-2.  | I/O Controller Required Revision Levels               | 7                        |

| TABLE | 5-1.  | BB Data During Different Pipeline Stages              | 28                       |

| TABLE | 9-1.  | ALU Data Sources                                      | 49                       |

| TABLE | 14-1. | 4150 Microcode Fields                                 | 71                       |

| TABLE | 14-2. | CS and CU Field Definitions                           | 72                       |

| TABLE | 16-1. | DP Interface One-Way Communication Commands           | 92                       |

| TABLE | 18-1. | Pipeline Hold Conditions                              | 145                      |

| TABLE | 19-1. | CS and CU Field Definitions                           | 158                      |

| TABLE | 19-2. | RCC/RCM Distribution Summary                          | 168                      |

| TABLE | 20-1. | BB Data During Different Pipeline Stages              | 173                      |

| TABLE | 20-2. | Decode Net Address Bit Generation                     | 176                      |

| TABLE | 20-3. | DNCNTRL{04:05}+ Interpretation                        | 178                      |

| TABLE | 20-4. | Base Register File Address Selection                  | 179                      |

| TABLE | 20-5. | 321 Mode Extended Base Register Selection             | <b>18</b> 0              |

| TABLE | 20-6. | I Mode Index Register Selection                       | <b>18</b> 0              |

| TABLE | 20-7. | Non-I Mode Index Register Selection                   | 181                      |

| TABLE | 21-1. | S or R Mode EAF Decoding                              | 187                      |

| TABLE | 21-2. | V Mode EAF Decoding                                   | 188                      |

| TABLE | 21-3. | I Mode EAF Decoding                                   | 189                      |

| TABLE | 21-4. | I Mode EAF Function Table                             | <b>19</b> 0              |

| TABLE | 21-5. | Register File ALU (ALUBX) Control                     | 192                      |

| TABLE | 21-6. | Displacement ALU (ALUD) Control                       | 192                      |

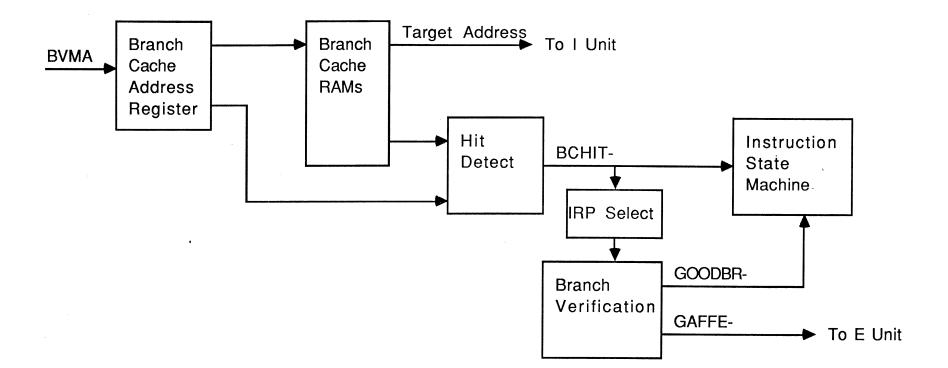

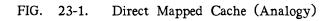

| TABLE | 23-1. | 4150 Baseball Team Statistics                         | 207                      |

| TABLE | 23-2. | FIFO Cache Replacement Algorithm                      | 214                      |

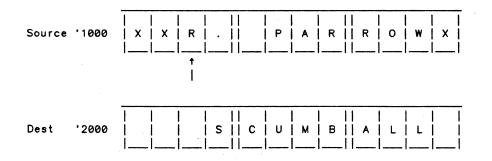

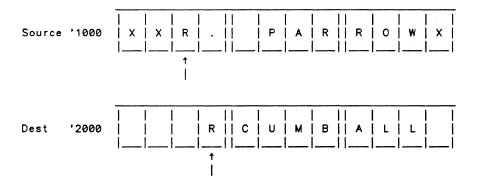

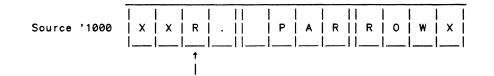

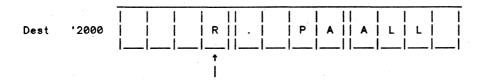

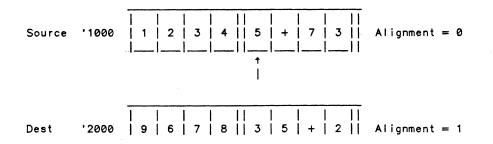

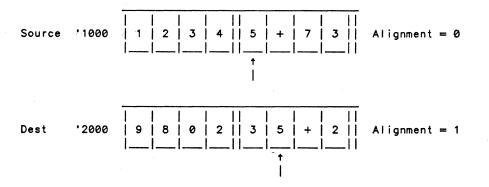

| TABLE | 23-3. | Memory Images for Figures 23-7, 23-8, 23-9, and 23-10 | <b>22</b> 0 <sup>°</sup> |

| TABLE | 23-4. | Notes for Figure 23-7                                 | 221                      |

| TABLE | 23-5. | Notes for Figure 23-8                                 | 224                      |

### 4150 Functional Specification Page xviii

| TABLE | 23-6.  | Notes for Figure 23-9                       | 226         |

|-------|--------|---------------------------------------------|-------------|

| TABLE | 23-7.  | Notes for Figure 23-10                      | 228         |

| TABLE | 24-1.  | STLB Entry Format                           | 234         |

| TABLE | 25-1.  | ALU Data Sources                            | 247         |

| TABLE | 25-2.  | ALU Modes                                   | 248         |

| TABLE | 25-3.  | BDI Modes                                   | 251         |

| TABLE | 25-4.  | ADJUST ALU Mode                             | 268         |

| TABLE | 25-5.  | ZFF IACs                                    | 275         |

| TABLE | 25-6.  | ZMV BDI Alignment                           | 277         |

| TABLE | 25-7.  | ZMSTRT ZBIT Jump Conditions for ZMV         | 278         |

| TABLE | 25-8.  | Other ZMSTRT Jump Conditions for ZMV        | 278         |

| TABLE | 25-9.  | ZMFAST Jump Conditions for ZMV              | 279         |

| TABLE | 25-10. | ZMSHRT Jump Conditions for ZMV, Part 1      | 279         |

| TABLE | 25-11. | ZMSHRT Jump Conditions for ZMV, Part 2      | <b>28</b> 0 |

| TABLE | 25-12. | ZMSHRT Jump Conditions for ZMV, Part 3      | 280         |

| TABLE | 25-13. | ZMEXIT Jump Conditions for ZMV, Part 1      | 281         |

| TABLE | 25-14. | ZMEXIT Jump Conditions for ZMV, Part 2      | 282         |

| TABLE | 25-15. | Character ALU Modes                         | <b>2</b> 83 |

| TABLE | 25-16. | ZMSTRT ALU Modes For Character Instructions | 283         |

| TABLE | 25-17. | ZMFAST ALU Modes For Character Instructions | 284         |

| TABLE | 25-18. | ZMSHRT ALU Modes For Character Instructions | 284         |

| TABLE | 25-19. | ZMEXIT ALU Modes For Character Instructions | 285         |

| TABLE | 25-20. | Decimal Instruction Control Word Format     | 291         |

| TABLE | 25-21. | Decimal Field Type Definitions              | 292         |

| TABLE | 25-22. | ADJUST Decimal Jump Conditions              | 294         |

| TABLE | 25-23. | OBTAIN Decimal Jump Conditions              | 294         |

| TABLE | 25-24. | UNLPCK Decimal Jump Conditions              | 295         |

| TABLE | 25-25. | UNLUNP Decimal Jump Conditions              | 295         |

| TABLE | 25-26. | XADP BDI mode                               | 297         |

| TABLE | 25-27.         | XADU BDI mode                           | 297         |

|-------|----------------|-----------------------------------------|-------------|

| TABLE | 25-28.         | DECMxNEQ- Link Bit Input                | 298         |

| TABLE | 25-29.         | UNLPCK ALU Mode, Unload Packed          | <b>29</b> 9 |

| TABLE | <b>25-3</b> 0. | UNLUNP ALU Mode, Unload Unpacked        | 299         |

| TABLE | 25-31.         | OBTAIN ALU Mode                         | 300         |

| TABLE | 25-32.         | ADJUST ALU Mode                         | 300         |

| TABLE | 25-33.         | E Unit Parity Error Codes               | 309         |

| TABLE | 26-1.          | WB Pointer Selection Chart              | 319         |

| TABLE | 26-2.          | MTOPS Decision Chart                    | 324         |

| TABLE | 26-3.          | ECC Check Bit Generation                | 333         |

| TABLE | 26-4.          | Syndrome Bits                           | 334         |

| TABLE | 26-5.          | Memory Configuration Slot Sizes         | 337         |

| TABLE | 26-6.          | Memory Configurations                   | 338         |

| TABLE | 27-1.          | BPC Mode Line Decoding                  | 347         |

| TABLE | 27-2.          | I/O Controller Required Revision Levels | 352         |

| TABLE | 29-1.          | Control Store Command Table             | 365         |

| TABLE | 29-2.          | Table of PDA BDH Commands               | 366         |

| TABLE | 30-1.          | CMI Diagnostic Register Layout          | 381         |

# 1. System Overview

#### 1.1 Introduction

The 4050 and 4150 are TTL super-minicomputers based on the 9755 pipeline. They are targeted as the high-end of Prime's office product line and as entry level computer room machines, replacing the 2755 and 9755 in the current product line.

These three board CPUs support S, R, V, and I mode addressing, including the latest enhancements such as ASCII8, "C" instructions, and 32IX mode. Additional major features include soft error recovery in the cache and STLB, a fully associative write buffer, a variable speed cooling system, and optional battery backed-up memory. The 4150 is designed to operate with at least Rev 20.2.5 of the PRIMOS operating system, although some features are not available until Rev 21. The 4050 requires at least Rev 20.2.6 or 21.0.2B.

UNIX support is being implemented and will be phased into newly built machines during 1988. The IS and CMI boards initially shipped will not provide the necessary hardware support for UNIX.

The 4050 and 4150 systems are very similar. They share hardware architecture, much microcode, use the same memory boards and diagnostic processor, and have identical mechanical features. They even share one CPU board. When only one system is mentioned throughout this document, it may be assumed that any comments are relevant for both systems, unless the two are being compared.

The 4050 system has an average performance of 2.7 MIPs, can also support up to 64 MB of main memory, supports up to 10 I/O controllers, and has a sustained I/O bandwidth of 5.8 MB/s.

The 4150 system is has an average performance of 3.6 MIPs, can support up to 64 MB of main memory, supports up to 10 I/O controllers, and has a sustained I/O bandwidth of 6.24 MB/s.

Major new features added to the 9755 design include:

- A 2-way set associative, 128KB cache with soft error recovery.

- A 2-way set associative, 1K entry STLB with soft error recovery

- A fully associative write buffer

- New floating point algorithms

- A new diagnostic processor

When the power shunt board is used in place of the BBU, power is shunted from P.S.#2 to the BBU power bus.

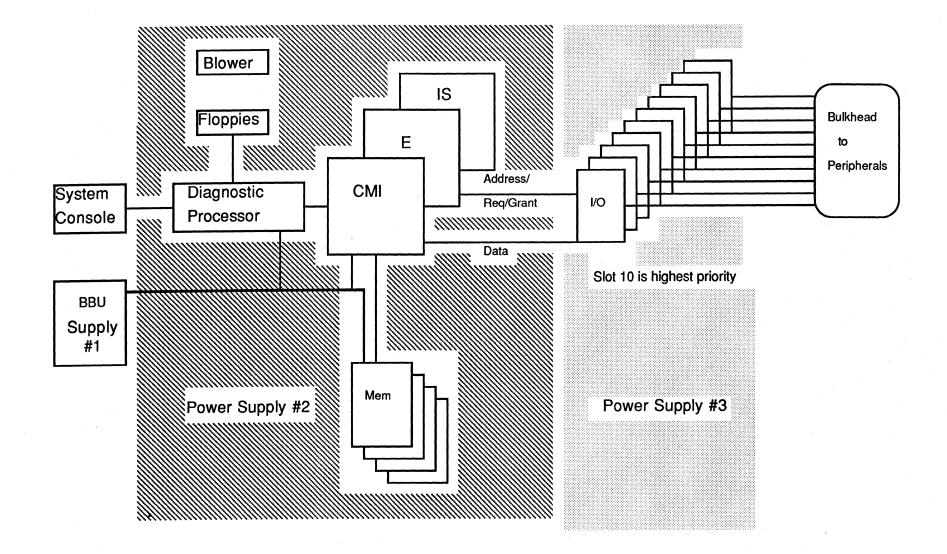

Figure 1-1 System Diagram of 4150

- A diagnostic history floppy disk

- Up to 32 MB memory with Abel memory boards (64 MB with Cain boards)

- Battery backed-up main memory

- Lower power

- Over 15 dBA quieter in most environments

- Smaller footprint

- Uses standard 208VAC power (not 3 phase)

#### 1.2 System Packaging

The system is packaged in a minimum of two cabinets. The first (main) cabinet contains the processor, memory, diagnostic processor, and I/O controllers. The main cabinet may optionally contain a battery backed-up power supply for memory protection and/or one Roadrunner (Sr.) for up to 64 asynchronous communications ports. The second and subsequent (peripheral) cabinets contain peripheral devices.

The main cabinet contains a single 22-slot backplane that integrates the diagnostic processor, power supplies, CPU, memory, and I/O. All boards and power supplies are mounted vertically and accessible from the front of the cabinet.

The main cabinet is the same height and depth as a 2755 (low-boy) cabinet, but is wider (24.5"). The cooling system draws air in from the bottom of the cabinet, across the boards, into the blower and out the back of the cabinet at the top. Besides providing a very efficient and relatively quiet cooling system, this design allows cabinets to be abutted at their sides, resulting in an overall floor space requirement equal to or less than that of the 2755 CPU cabinet. In fact, in typical configurations requiring no more than 64 asynchronous communications lines, no more than 1.5 GB of disk storage, and one tape drive, the 4050 or 4150 requires less space than a 2755.

Cables are routed from the front of the cabinet to the back across the top of the cabinet. They are guided by cable troughs and are easily accessible by removing the top panel and dropping the hinged rear panel.

The status panel is located at the top of the front panel. Below the status panel is a popopen panel which hides the floppy disks (2) and the key switch.

All external connectors are bulkheaded in the rear. All rear bulkheads, a portion of the exhaust duct, and the PDU hinge outward for service. In some configurations, a Roadrunner will be installed on the rear panel. It derives its cooling from exhaust air. Therefore, it is located just below the exhaust port and becomes a part of the exhaust port.

The peripheral cabinet(s) may contain disk drives, tape drives, communications ports, or some combination thereof. Each office peripheral cabinet may be considered to have an upper section and a lower section. Each section can house either 2 FSD disk drives, one streamer or quad density tape drive, or 64 asynchronous communication ports (Roadrunner Sr.). This cabinet is the same as the new 2755 peripheral cabinet. The standard 53" peripheral cabinet is used in the computer room, which has four sections.

Total main bay power dissipation and heat output are higher than those of the 2755. The 4050 and 4150 processors dissipate approximately 70% more power than the 2755 processor, resulting in approximately 135 Watts higher system power dissipation. The remaining power dissipation is configuration dependent and could also be higher due to new controllers and more slots.

Although greater cooling capacity is required, in a typical environment the main bay noise level is lower than that of the 2755. A new, higher efficiency, speed-controlled cooling system is employed to achieve much higher air flow without increasing noise levels.

#### 1.3 Diagnostic Processor

The Mink diagnostic processor provides a superset of the functionality of its 9755 equivalent, the Weasel. New DP functions implemented on the Mink include a high speed parallel interface to reduce control store loading time by at least 5:1, BBU support, analog voltage sensing of 5V supplies, voltage and frequency margining (using additional capabilities in the power supplies and in the clock generator in the processor), and support for the RAS bus. New higher density half-height floppy disks are used, with one for microcode storage and one available as a system log to maintain a record of major system events to support field service.

#### 1.4 System Power

Two Aphrodite power supplies are used. One powers the Mink, CPU, and memory, while the other powers the I/O. Power for the floppy disk and blower is taken from the processor's Aphrodite. Both supplies are required in all system configurations. The Roadrunner, if present, contains its own power supply.

A Daphne power supply with integral BBU can be installed directly into the system backplane for a low cost BBU solution. The supply blocks one memory slot and four I/O slots. In addition, the system can still support 24 MB of main memory with Abel memory boards or the full system maximum of 64 MB with Cain boards. The Daphne is capable of providing extensive ride-through of main memory, the Mink, and the dynamic memory refresh logic in the CPU. When the Daphne is in the system, the last displaced I/O slot must have a shield installed to prevent noise coupling from the power supply into adjacent logic. When the Daphne is not present, a shunt board must be plugged into the Daphne slot to pass power

and control signals from the CPU Aphrodite to the logic that would have been powered by the Daphne. All memory and I/O slots are usable with the shunt board in place.

Note that all 10 I/O slots are powered from one Aphrodite power supply, which must be considered in configuring the system in case there are a number of new controllers with excessive power consumption.

The system is configured for 208V 60Hz input power in domestic applications and 240V 50 Hz in international configurations. The internal power supplies and peripherals in domestic systems will be configured for 120V, which the PDU derives from the 208 V input. International systems will have all 240V power supplies and peripheral devices. The maximum operational configuration of the main bay will dissipate about 1800 W.

#### 1.5 Configuration Rules

#### 1.5.1 Memory

- 1. Only 8 MB Abel, 16 MB Cain, and 32 MB Cain boards may be used.

- 2. Always begin in slot #1 and do not skip slots unless the 32 MB Cain boards are used.

- 3. Always skip the next slot when using a 32 MB Cain board. 32 MB Cain boards may be placed only in slots 1 and 3. If there is one 32 MB Cain board, slot 2 may not be used. If there are two 32 MB Cain boards, no other boards may be used.

- 4. Always put the highest density remaining board in the next legal slot. Thus, exhaust the supply of 32 MB boards before inserting 16 MB boards and exhaust the supply of 16 MB boards before inserting 8 MB boards.

Table 1-1 shows the legal memory configurations.

and control signals from the CPU Aphrodite to the logic that would have been powered by the Daphne. All memory and I/O slots are usable with the shunt board in place.

Note that all 10 I/O slots are powered from one Aphrodite power supply, which must be considered in configuring the system in case there are a number of new controllers with excessive power consumption.

The system is configured for 208V 60Hz input power in domestic applications and 240V 50 Hz in international configurations. The internal power supplies and peripherals in domestic systems will be configured for 120V, which the PDU derives from the 208 V input. International systems will have all 240V power supplies and peripheral devices. The maximum operational configuration of the main bay will dissipate about 1800 W.

#### 1.5 Configuration Rules

#### 1.5.1 Memory

- 1. Only 8 MB Abel, 16 MB Cain, and 32 MB Cain boards may be used.

- 2. Always begin in slot #1 and do not skip slots unless the 32 MB Cain boards are used.

- 3. Always skip the next slot when using a 32 MB Cain board. 32 MB Cain boards may be placed only in slots 1 and 3. If there is one 32 MB Cain board, slot 2 may not be used. If there are two 32 MB Cain boards, no other boards may be used.

- 4. Always put the highest density remaining board in the next legal slot. Thus, exhaust the supply of 32 MB boards before inserting 16 MB boards and exhaust the supply of 16 MB boards before inserting 8 MB boards.

Table 1-1 shows the legal memory configurations.

#### TABLE 1-1. Memory Configurations

|      | 64 ME   | 3 Con | figur | ations     | 3         |      | 56 ME | 3 Con | figure | otions |      |      |    |

|------|---------|-------|-------|------------|-----------|------|-------|-------|--------|--------|------|------|----|

| Slot | 1       | 2     | 3     | 4          |           | Slot | 1     | 2     | 3      | 4      |      |      |    |

|      | 32      |       | 32    |            |           |      | 32    |       | 16     | 8      |      |      |    |

|      | 32      |       | 16    | 16         |           |      | 16    | 16    | 16     | 8      |      |      |    |

|      | 16      | 16    | 16    | 16         |           |      |       |       |        |        |      |      |    |

|      | 48 ME   | 3 Con | figur | ations     | 3         |      | 40 ME | 3 Con | figure | ations |      |      |    |

| Slot | 1       | 2     | 3     | 4          |           | Slot | 1     | 2     | 3      | 4      |      |      |    |

|      | 32      |       | 16    |            |           |      | 32    |       | 8      |        |      |      |    |

|      | 16      | 16    | 16    |            |           |      | 16    | 16    | 8      |        |      |      |    |

|      | 16      | 16    | 8     | <b>*</b> 8 | (See Note | 1)   | 16    | 8     | * 8    | * 8    | (See | Note | 1) |

|      | 32 ME   | 3 Con | figur | ations     | 3         |      | 24 MB | Conf  | igura  | tions  |      |      |    |

| Slot | 1       | 2     | 3     | 4          |           | Slot | 1     | 2     | 3      | 4      |      |      |    |

|      | 32      |       |       |            |           |      | 16    | 8     |        |        |      |      |    |

|      | 16      | 16    |       |            |           |      | 8     | 8     | 8      |        |      |      |    |

|      | 16      | 8     | * 8   |            | (See Note | 1)   |       |       |        |        |      |      |    |

|      | 8       | 8     | 8     | 8          |           |      |       |       |        |        |      |      |    |

|      | 16 MB   | Conf  | igura | tions      |           |      | 8 ME  | 3 Con | figuro | ations |      |      |    |

| Slot | 1       | 2     | 3     | 4          |           | Slot | 1     | 2     | 3      | 4      |      |      |    |

|      | 16<br>8 | 8     |       |            |           |      | 8     |       |        |        |      |      |    |

NOTE 1: 8 MB holes are created in memory where indicated by the asterisks in the configuration tables. These produce some additional Primos memory management overhead and should be avoided when possible.

#### 1.5.2 I/O

The highest priority slot is slot #10, the most distant slot from the processor. The other slots descend in priority from slot 10 down to slot 1.

Power available for I/O controllers is limited to that available from one Aphrodite, 130A + 5V, and 7A each from +12V and -12V.

If a Daphne BBU is present in the system, the number of I/O controllers is limited to six. The amount of power available for I/O controllers is not reduced.

#### 1.5.2.1 Required I/O Controller Revision Levels

Certain I/O controllers must be at a specified revision level to work in a 4150 or 4050 system. Table 1-2 shows these requirements.

TABLE 1-2. I/O Controller Required Revision Levels

| Board Name | Slang Name | Model Number | Part Number  | Revision |

|------------|------------|--------------|--------------|----------|

| IDC3       | Koala      | 6580         | TLA10019-001 | R        |

| MSTC       | Minnow     | 2382-003     | TLA10234-001 | R        |

| MPC4       | 1          | 7010T        | SPL91521-91  | ј н      |

| STSC       | Streamer   |              | 2301-901     | AA       |

| ASYNC LAC  | ICS3       | CLAC304      | ESA10063-001 | i c      |

| BMTC       | Marlin     |              | 2023-001     | N        |

| PNC II     | İ          |              | 2384-001     | G        |

#### 1.5.3 Power

Two Aphrodite power supplies are always required.

Either a shunt board or a Daphne power supply is required.

#### 1.6 9755 and 4050/4150 Comparisons

The 4050 and 4150 differ from the 9755 in technology, partitioning, packaging, and performance characteristics. The six 9755 boards have been compressed into three boards. The three backplanes of the 9755 have been replaced by one backplane that integrates the diagnostic processor, power supplies, CPU, memory, and I/O. Performance variations occur due to the 4050 and 4150's slower cycle times, VLSI enhancements (especially for floating point operations), new I/O microcode, larger set associative cache, larger set associative STLB, larger branch cache, associative write buffer, more efficient memory interface and increased main memory capability.

The 4050 and 4150 boards are all mounted vertically. All 9755 boards were mounted horizontally.

New higher density memory boards (Abel and Cain) support a new processor interface. New slot selection logic suppresses "holes" in memory for certain mixed memory configurations.

Although most 4050 and 4150 microcode is derived from 9755 microcode, substantial editing was performed to at least half of the code. The remaining code was rewritten to take advantage of special new hardware or machine dependent characteristics such as the new VLSI, I/O, and the DP interface. Some microcode fields have been redefined. New microdiagnostics have been written to enhance the coverage afforded by the 9755 diagnostics and cover new hardware.

The Mink DP provides the functionality of its 9755 equivalent, the Weasel, with the addition of a high speed parallel interface to reduce control store loading time by at least 5:1, BBU support, analog voltage sensing of 5V supplies, voltage and frequency margining (using additional capabilities in the power supplies and in the clock generator in the processor), and hardware support for the RAS bus. New higher density half-height floppy disks are used, with one for microcode storage and one available as a system log to maintain a record of major system events to support field service. Note that RAS bus support is being phased into the processor during 1988, requiring a different backplane than that originally shipped in the early systems.

I/O priority net arbitration has been moved into the processor.

The 4050 and 4150 have a larger set associative cache and STLB. Soft error recovery is implemented on both.

The major processor busses were converted to tristate buses. Therefore, special controls to eliminate clashes had to be implemented. Bus timing had to be altered to accommodate these changes.

The write buffer has been made fully associative in the 4050/4150 processors, so that it is no longer necessary to empty the write buffer before performing a main memory read operation. Writes can be merged more effectively so that fewer (and larger) main memory write operations are performed.