BUFFERED PE FORMATTER MODEL BF6X9

9600 IRONDALE AVE., CHATSWORTH, CALIF. 91311 PHONE (213) 882-0030 TWX (910) 494-2093

OPERATING AND SERVICE MANUAL NO. 101802

# **FOREWORD**

This manual provides operating and service instructions for the Buffered PE Formatter, Model BF6X9 — 0.5 K/1 K/2 K/4 K, manufactured by PERTEC Peripheral Equipment Division, Chatsworth, California.

The content includes a detailed description, specifications, and installation instructions. Also included is the definition of interface functions with regard to timing, levels, and interrelationships. Section VII contains photo parts lists and schematics.

#### SERVICE AND WARRANTY

This PERTEC product has been rigorously checked out by capable quality control personnel. The design has been engineered with a precise simplicity which should assure a new level of reliability. Ease of maintenance has been taken into consideration during the design phase with the result that all components (other than mechanical components) have been selected wherever possible from manufacturer's off-the-shelf stock. Should a component fail, it may be readily replaced from PERTEC or your local supplier. The unit has been designed for plug-in replacement of circuit boards or major components which will ensure a minimum of equipment down time.

PERTEC warrants products of its manufacture to be free from defect in design, workmanship, and material under normal use and service for a period twelve (12) months, or in the case of flexible disk products 120 days, after the date of shipment. PERTEC agrees to repair or replace at its authorized repair center, without charge, all defective parts in systems which are returned for inspection to said center within the applicable warranty period; provided such inspection discloses that the defects are as specified above, and provided further the equipment has not been altered or repaired other than with authorization from PERTEC and by its approved procedures, not been subjected to misuse, improper maintenance, negligence or accident, damaged by excessive current or otherwise had its serial number or any part thereof altered, defaced or removed. All defective items released hereunder shall become the property of seller. THIS WARRANTY IS IN LIEU OF, AND BUYER WAIVES, ALL OTHER WARRANTIES, EXPRESSED OR IMPLIED, INCLUDING THOSE OF MERCHANTABILITY OR FITNESS FOR PURPOSE.

Please read the instruction manual thoroughly as to installation, operation, maintenance, and component reference list. Should you require additional assistance in servicing this equipment, please contact the following conveniently located regional service centers — our trained service staff will be pleased to assist you.

iii

#### WESTERN REGION

PERTEC Service Center 17835 Ventura Blvd, Encino, California 91316 Phone (213) 996-1333 TWX (910) 493-2075

# **CENTRAL REGION**

PERTEC Service Center 6300 North River Road O'Hare International Transportation Center Rosemont, Illinois 60018 Phone (312) 696-2460 TWX (910) 253-5918

# **AUTHORIZED REPAIR CENTER**

PERTEC Repair Center 9600 Irondale Avenue Chatsworth, California 91311 Phone (213) 882-0030 TWX (910) 494-2093

#### **EASTERN REGION**

PERTEC Service Center 235 Bear Hill Road Waltham, Massachusetts 02154 Phone (617) 890-6230 TWX (710) 324-1154

### **EUROPEAN REGION**

PERTEC Service Center PERTEC International 10 Portman Road Reading, Berkshire RG3 1DU, England Phone Reading (734) 582-115 TWX (851) 847-101

# PROPRIETARY NOTICE

Information contained in this manual is disclosed in confidence and may not be duplicated in full or in part by any person without prior written approval of PERTEC Corporation. Its sole purpose is to provide the user with adequately detailed documentation so as to efficiently install, operate, maintain and order spare parts for the equipment supplied. The use of this document for all other purposes is specifically prohibited.

802B iV

# **TABLE OF CONTENTS**

|                                 | I                                                                                                                                                                                                   | Page                                                               |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| SECTION                         | I — GENERAL DESCRIPTION AND SPECIFICATIONS                                                                                                                                                          |                                                                    |

| 1.1<br>1.2<br>1.3<br>1.4<br>1.5 | Introduction . Purpose of Equipment . Physical Description of Equipment . Functional Description . Model Differences Mechanical and Electrical Specifications . 1.6.1 Interface Specifications .    | 1-1<br>1-1<br>1-2<br>1-3<br>1-4                                    |

| SECTION                         | II — INSTALLATION                                                                                                                                                                                   |                                                                    |

| 2.1<br>2.2<br>2.3<br>2.4<br>2.5 | Introduction Uncrating the Formatter Power Connections Rack Mounting the Formatter Interface Connections                                                                                            | 2-1<br>2-1<br>2-2                                                  |

| SECTION                         | III — OPERATION                                                                                                                                                                                     |                                                                    |

| 3.1<br>3.2                      | Introduction                                                                                                                                                                                        | 3-1                                                                |

| 3.3                             | Basic Operation 3.3.1 Preamble 3.3.2 Data 3.3.3 Postamble 3.3.4 Identification Burst 3.3.5 File Mark 3.3.6 Gaps 3.3.7 Parity 3.3.8 Dropout and Error Correction 3.3.9 Error Checking 3.3.10 Options | 3-1<br>3-3<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4<br>3-4<br>3-4        |

| 3.4<br>3.5                      | 3.5.11 Read Threshold Level 1 (ITHR1) 3.5.12 Read Threshold Level 2 (ITHR2) 3.5.13 Automatic (IAUTO) 3.5.14 Rewind (IREW) 3.5.15 Off-Line Command (IOFL)                                            | 3-5<br>3-5<br>3-5<br>3-6<br>3-6<br>3-6<br>3-7<br>3-7<br>3-7<br>3-7 |

# **TABLE OF CONTENTS (continued)**

|     |           |                                                              | Page          |

|-----|-----------|--------------------------------------------------------------|---------------|

|     | 3.5.17    | End of Operation (IEOO)                                      | 3-7           |

|     | 3.5.18    | Answer Strobe (IANS)                                         | 3-7           |

|     | 3.5.19    | Last Word (ILWDI)                                            | 3-8           |

|     | 3.5.20    | Write Parity, Write Data Lines (IWBP, IWB0 - IWB7)           | 3-8           |

|     | 3.5.21    | Buffer Configuration Control 0 (IBCC0)                       |               |

|     | 3.5.22    | Buffer Configuration Control 1 (IBCC1)                       | 3-8           |

|     | 3.5.23    | Buffer Configuration Control 2, 3 (IBCC2, IBCC3)             | 3-8           |

|     | 3.5.24    | Counter Reset Inhibit (ICAI, ICBI)                           | 3-8           |

| 3.6 | Interface | e Outputs (Buffered Formatter to Controller)                 | 3-9           |

|     | 3.6.1     | Formatter Busy (IFBY)                                        | 3-9           |

|     | 3.6.2     | Buffer Busy (IABSY, IBBSY)                                   | 3-9           |

|     | 3.6.3     | Buffer Overflow Indicators (IAOVFL, IBOVFL)                  | 3-9           |

|     | 3.6.4     | Data Busy (IDBY)                                             | 3-9           |

|     | 3.6.5     | Identification (IDENT)                                       | 3-9           |

|     | 3.6.6     | Hard Error (IHERI)                                           | 3-9           |

|     | 3.6.7     | Corrected Error (ICER)                                       | 3-10          |

|     | 3.6.8     | Transport Status and Configuration (IRDY, INRZ, I7TRK, ISGL, |               |

|     |           | ISPEED, IONL, IRWD, IFPT, IEOT, ILDP)                        |               |

|     | 3.6.9     | File Mark (IFMK)                                             |               |

|     | 3.6.10    | Request Strobe (IREQ)                                        |               |

|     | 3.6.11    | Buffer Last Word (IBLWD)                                     |               |

|     | 3.6.12    | Read Data Lines (IRBP, IRB0 - IRB7)                          |               |

| 3.7 |           | Interface — Buffer to Formatter                              |               |

|     | 3.7.1     | Formatter Address (IFAD)                                     |               |

|     | 3.7.2     | Transport Address (ITAD0, ITAD1)                             |               |

|     | 3.7.3     | Initiate Command (IGO)                                       |               |

|     | 3.7.4     | Command Lines                                                |               |

|     | 3.7.5     | Load and On-Line (ILOL) (Optional)                           | 3-12          |

|     | 3.7.6     | Rewind Command (IREW)                                        |               |

|     | 3.7.7     | Off-Line Command (IOFL)                                      |               |

|     | 3.7.8     | Formatter Enable (IFEN)                                      |               |

|     | 3.7.9     | Write Data Lines (IW0 - IW7, IWP)                            |               |

| 3.8 |           | Interface — Formatter to Buffer                              |               |

|     | 3.8.1     | Formatter Busy (IFBY)                                        | 3-13          |

|     | 3.8.2     | Data Busy (IDBY)                                             | 3-13          |

|     | 3.8.3     | Identification (IDENT)                                       |               |

|     | 3.8.4     | Hard Error (IHER)                                            |               |

|     | 3.8.5     | Corrected Error (ICER)                                       | 3-14          |

|     | 3.8.6     | File Mark (IFMK)                                             |               |

|     | 3.8.7     | Ready (IRDY)                                                 | 3-14          |

|     | 3.8.8     | On-Line (IONL)                                               | 3-14          |

|     | 3.8.9     | Rewinding (IRWD)                                             |               |

|     | 3.8.10    | File Protect (IFPT)                                          |               |

|     | 3.8.11    | Load Point (ILDP)                                            | 3-14          |

|     | 3.8.12    | End of Tape (IEOT)                                           | 3-15          |

|     | 3.8.13    | Transport Format (INRZ)                                      |               |

|     | 3.8.14    | Track Configuration (I7TRK)                                  | 3-15          |

|     | 3.8.15    | Head Configuration (ISINGLE)                                 |               |

|     | 3.8.16    | Tape Speed (ISPEED)                                          |               |

|     | 3.8.17    | Write Strobe (IWSTR)                                         | 0-10<br>2.15  |

|     | 3.8.18    | Read Strobe (IRSTR)                                          | 3-13<br>2 1 E |

|     | 3 8 19    | Bead Data Lines (IBP, IBU - IB/)                             | J-15          |

802B **Vİ**

# **TABLE OF CONTENTS**

|     |            |                             |                                                    | Page      |

|-----|------------|-----------------------------|----------------------------------------------------|-----------|

|     | 3.9        | Interfact<br>3.9.1<br>3.9.2 | e Outputs (Buffered Formatter to Transport)        | 3-16      |

|     |            | 3.9.3                       | Read Threshold 1 (IRTH1)                           |           |

|     |            | 3.9.4                       | Read Threshold 2 (IRTH2)                           |           |

|     |            | 3.9.5                       | Write Data (IWDP, IWD0 - IWD7)                     |           |

|     |            | 3.9.6<br>3.9.7              | Overwrite (IOVW)                                   |           |

|     |            | 3.9.7                       | Synchronous Reverse Command (ISRC)                 |           |

|     |            | 3.9.9                       | Rewind Command (IRWC)                              | 3-17      |

|     |            | 3.9.10                      | Set Write Status (ISWS)                            |           |

|     |            | 3.9.11                      | Off-Line Command (IOFC)                            |           |

|     |            | 3.9.12                      | Transport Select Lines (ISLT0, 1, 2, 3)            |           |

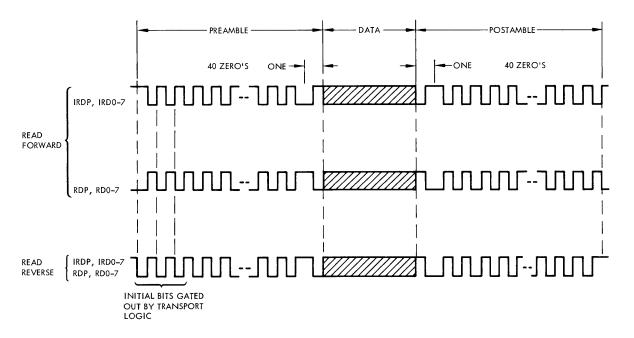

|     | 3.10       | Interfac                    | e Inputs (Transport to Buffered Formatter)         | 3-17      |

|     |            | 3.10.1                      | Read Data Lines (IRDP, IRD0 - IRD7)                |           |

|     |            | 3.10.2                      | Transport Format (INRZ)                            |           |

|     |            | 3.10.3                      | Single/Dual (ISGL) (Head Configuration) (Optional) |           |

|     |            | 3.10.4                      | Speed (ISPEED) (Tape Speed) (Optional)             |           |

|     |            | 3.10.5                      | On-Line (IONL)                                     | 3-18      |

|     |            | 3.10.6<br>3.10.7            | Rewinding (IRWD)                                   |           |

|     |            | 3.10.7                      | Load Point (ILDP)                                  |           |

|     |            | 3.10.9                      | End of Tape (IEOT)                                 |           |

|     | 3.11       |                             | Interface — Formatter to Formatter                 |           |

|     |            | 3.11.1                      | Reverse/Forward (IREV)                             |           |

|     |            | 3.11.2                      | Read Gate (IRGATE)                                 |           |

|     |            | 3.11.3                      | Test ID (ITESTID)                                  |           |

|     |            | 3.11.4                      | Identification Gate (IDG)                          |           |

|     |            | 3.11.5                      | Read End (IREND)                                   | 3-19      |

| SEC | TION       | IV — THI                    | EORY OF OPERATION                                  |           |

| OLC |            |                             |                                                    |           |

|     | 4.1<br>4.2 |                             | ction                                              |           |

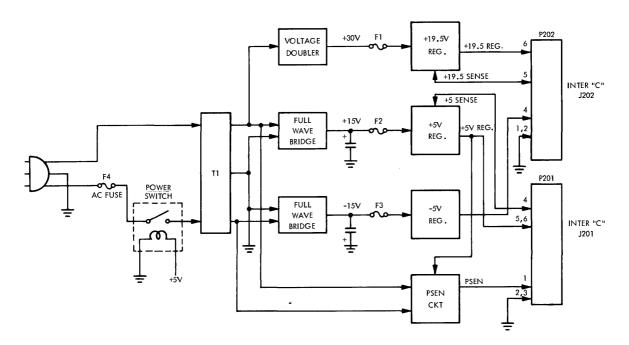

|     | 4.2        | 4.2.1                       | ration of the Formatter                            | 4-1<br>11 |

|     |            | 4.2.2                       | Power Supply                                       |           |

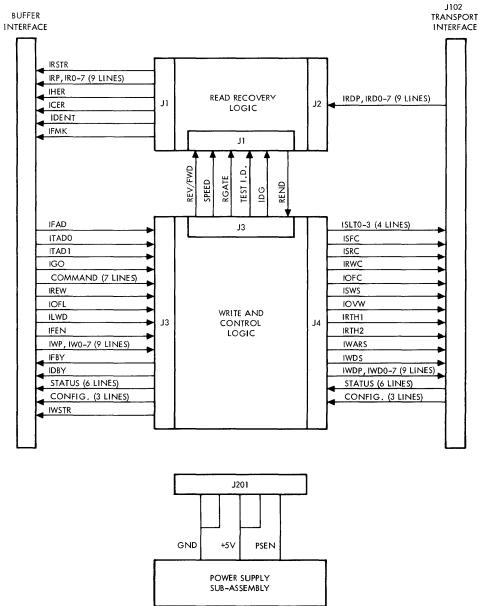

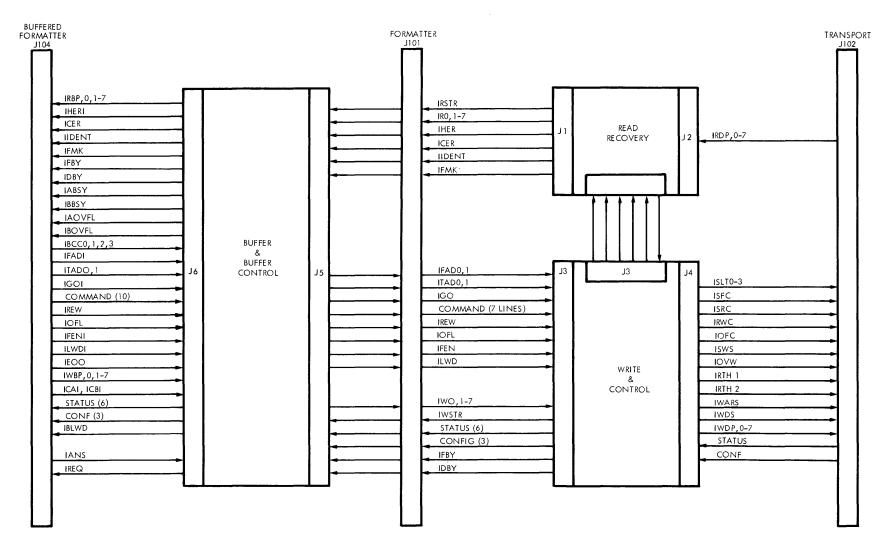

|     |            | 4.2.3                       | System Organization                                | 4-4       |

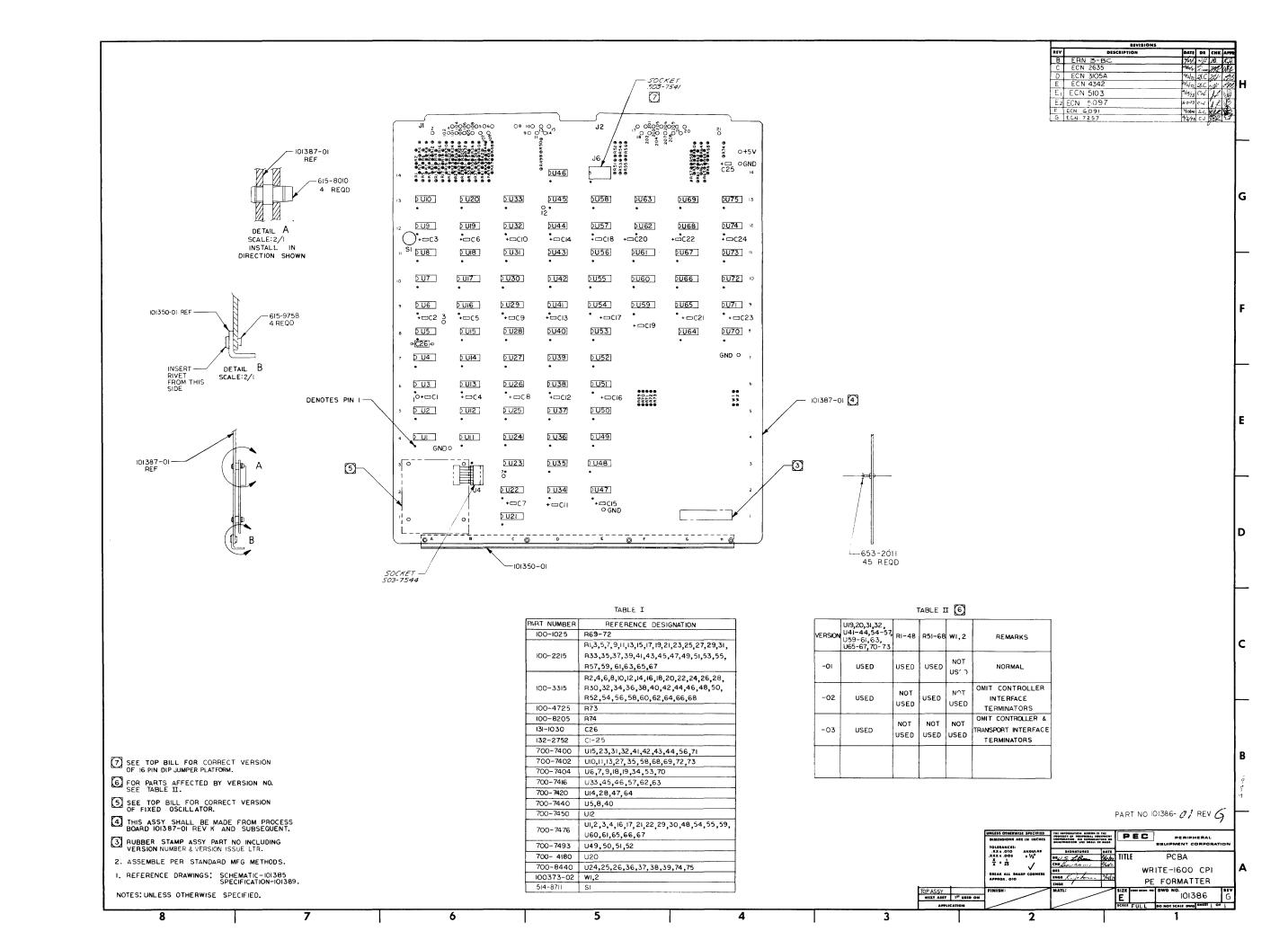

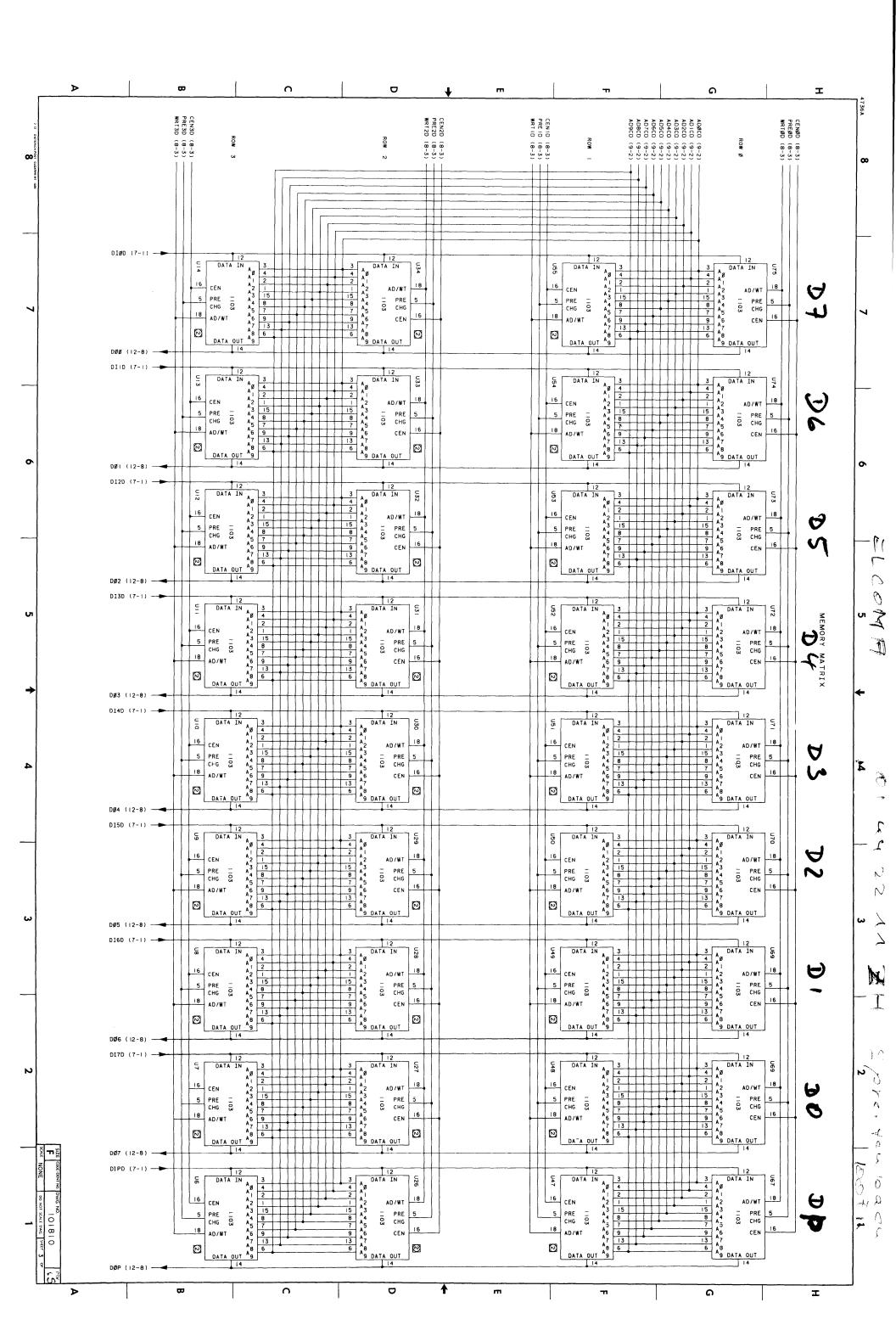

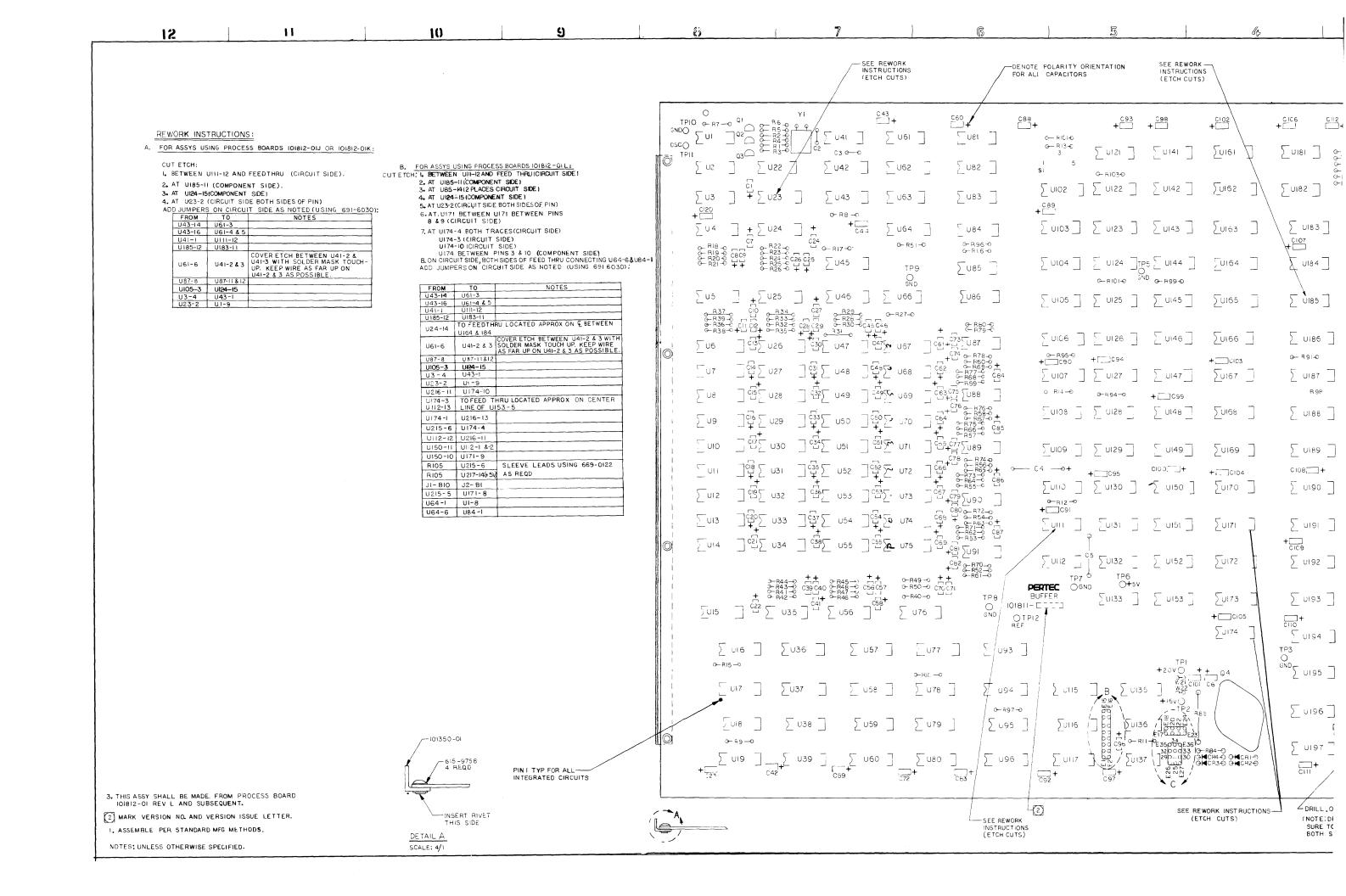

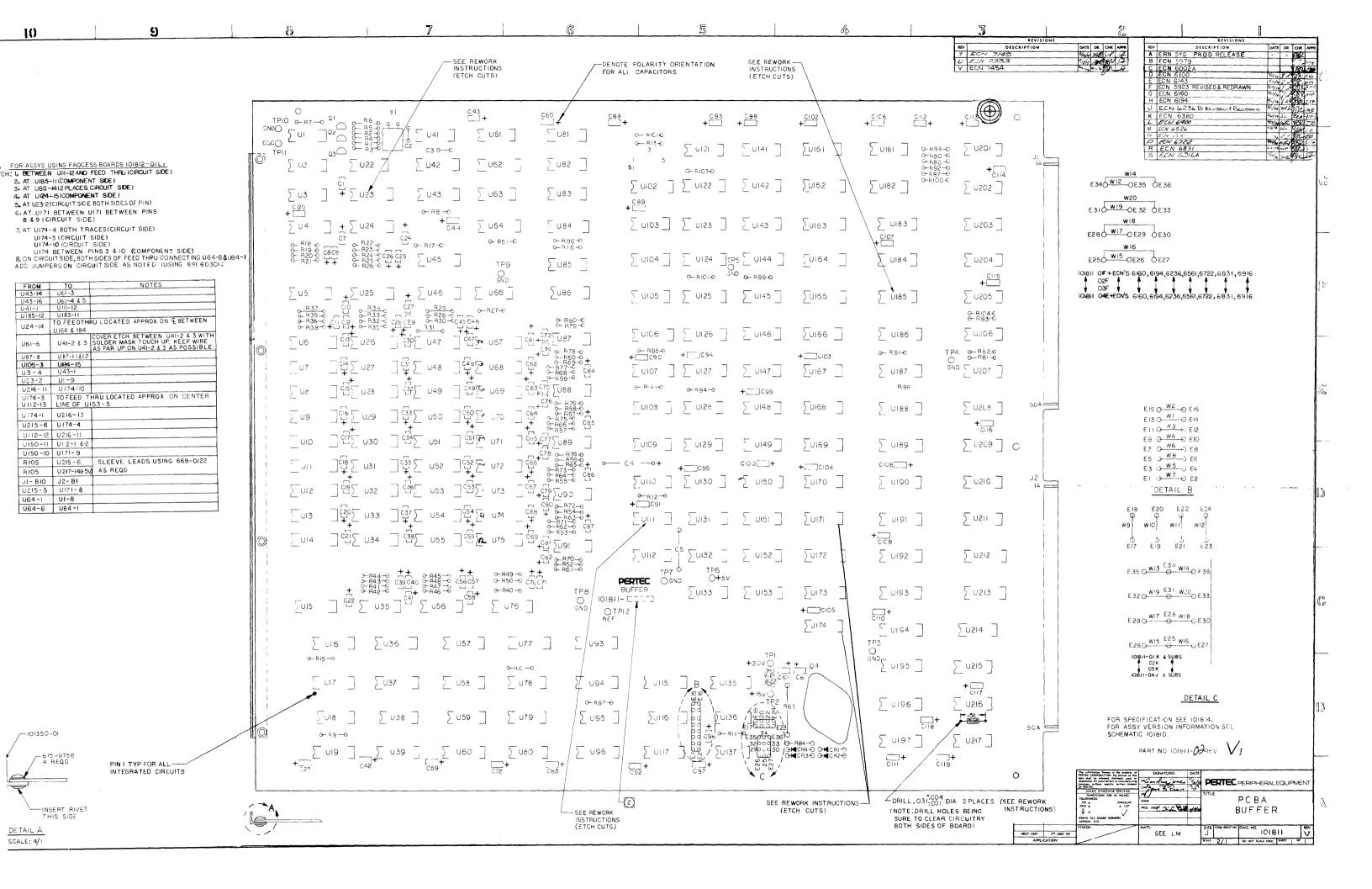

|     |            | 4.2.4                       | Buffer PCBA                                        | 4-4       |

|     |            | 4.2.5                       | PE Formatter PCBAs                                 |           |

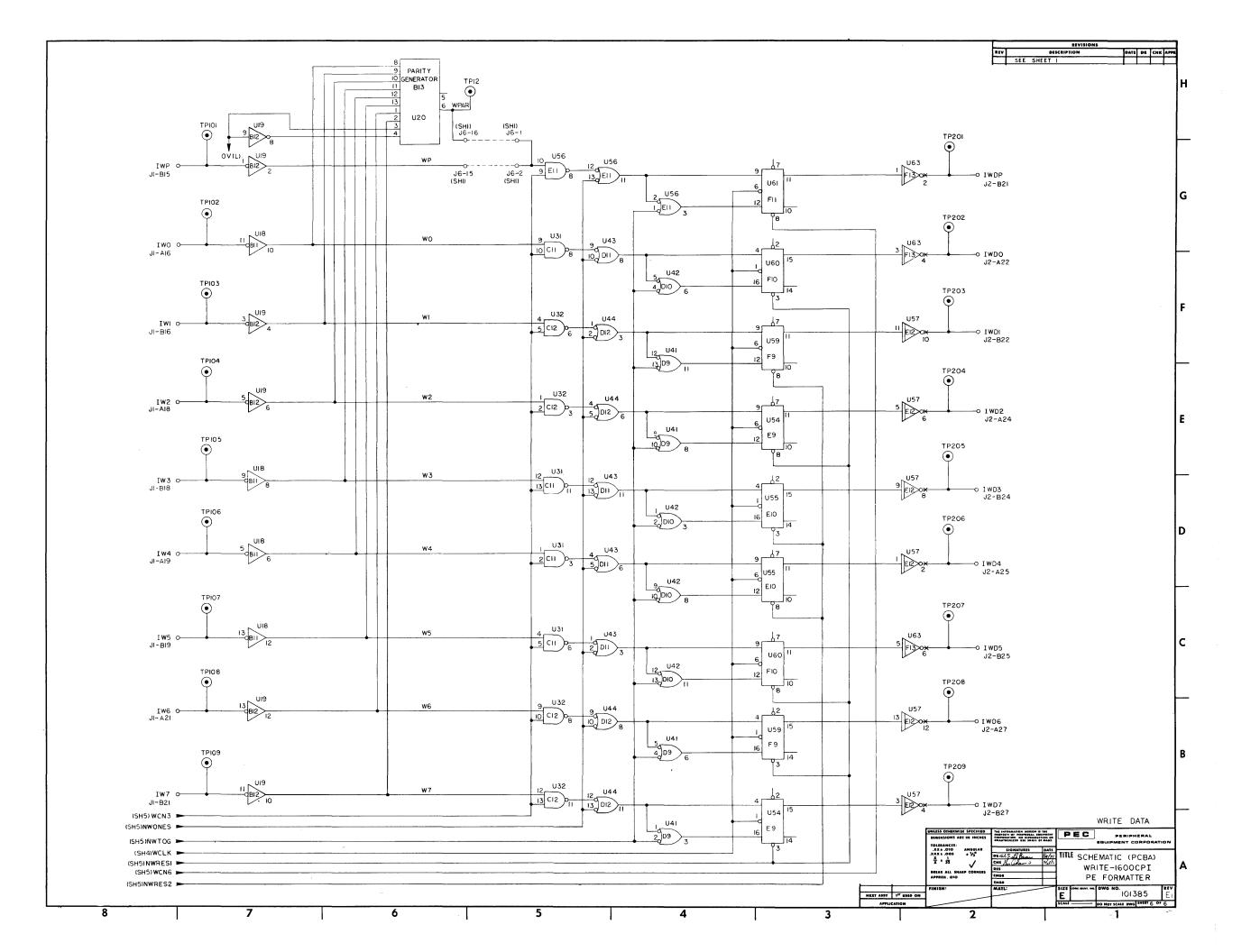

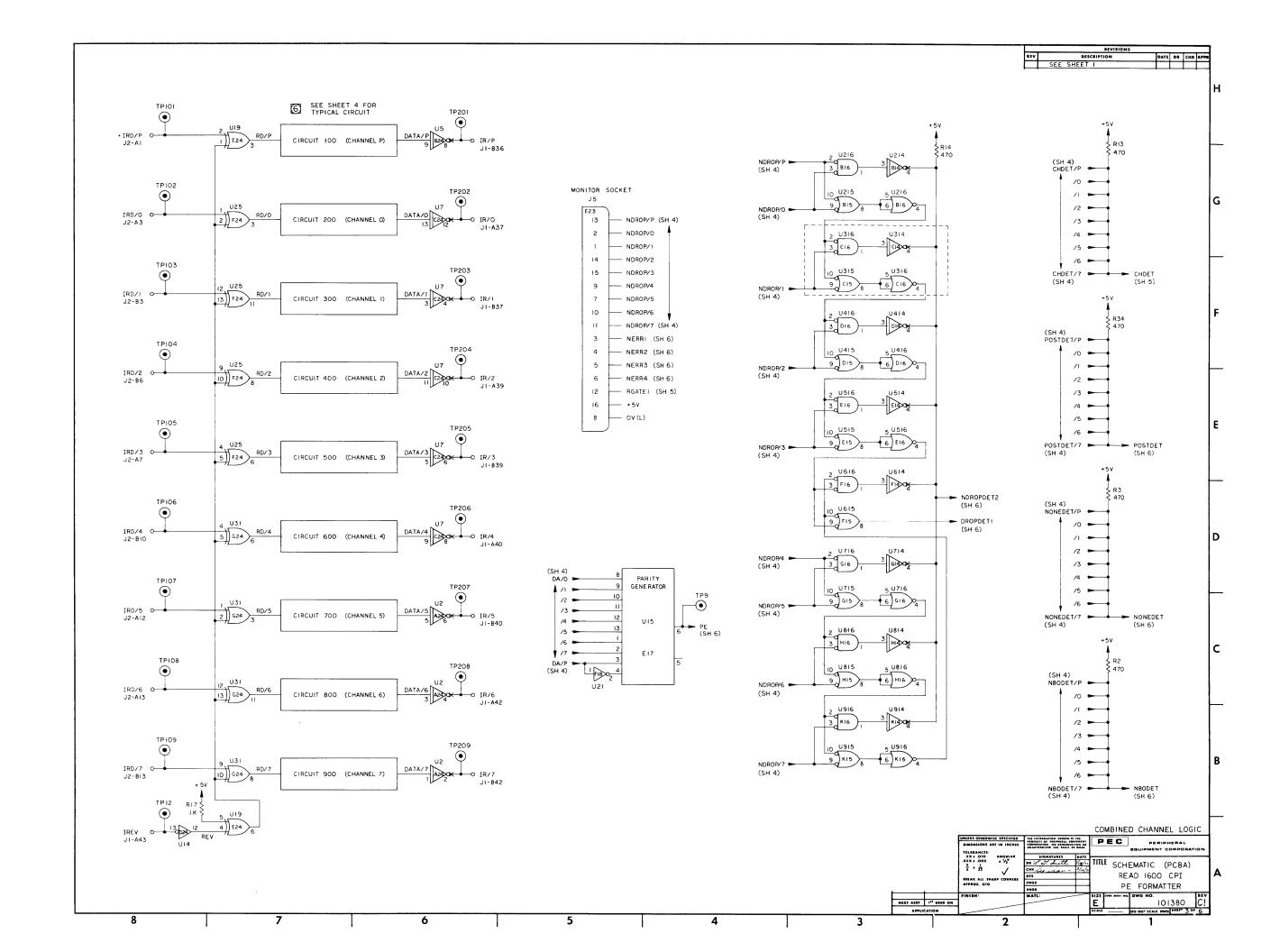

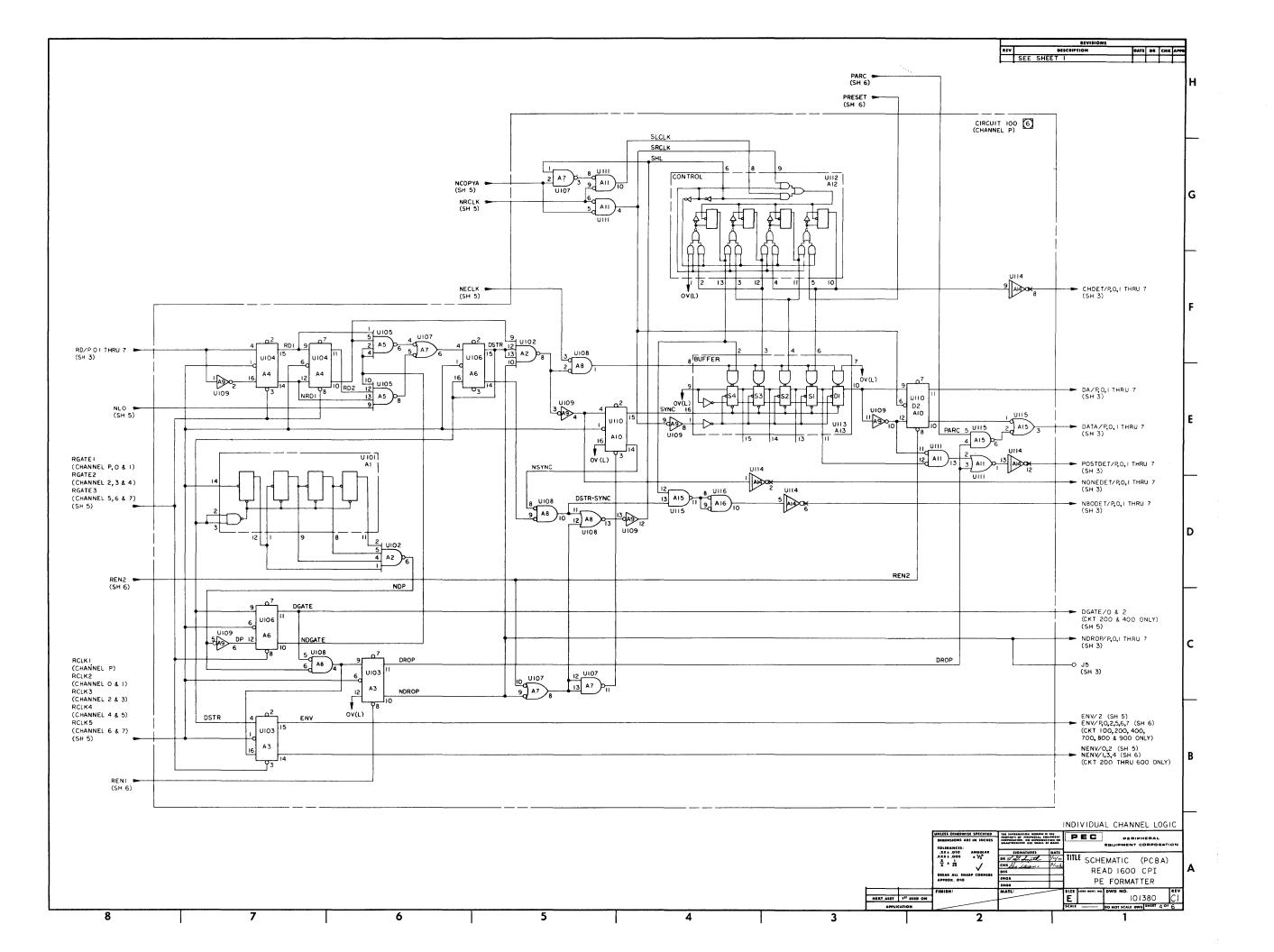

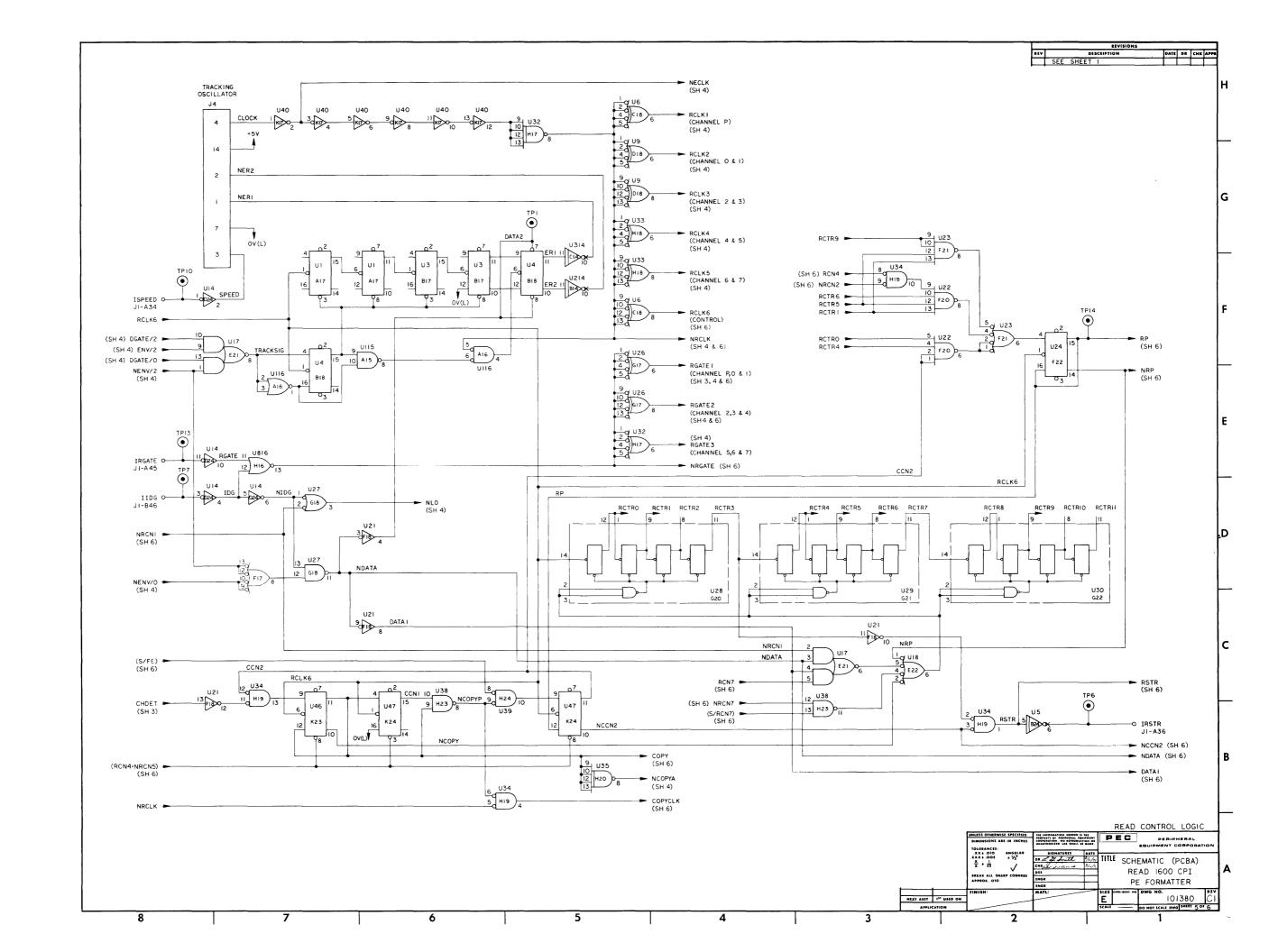

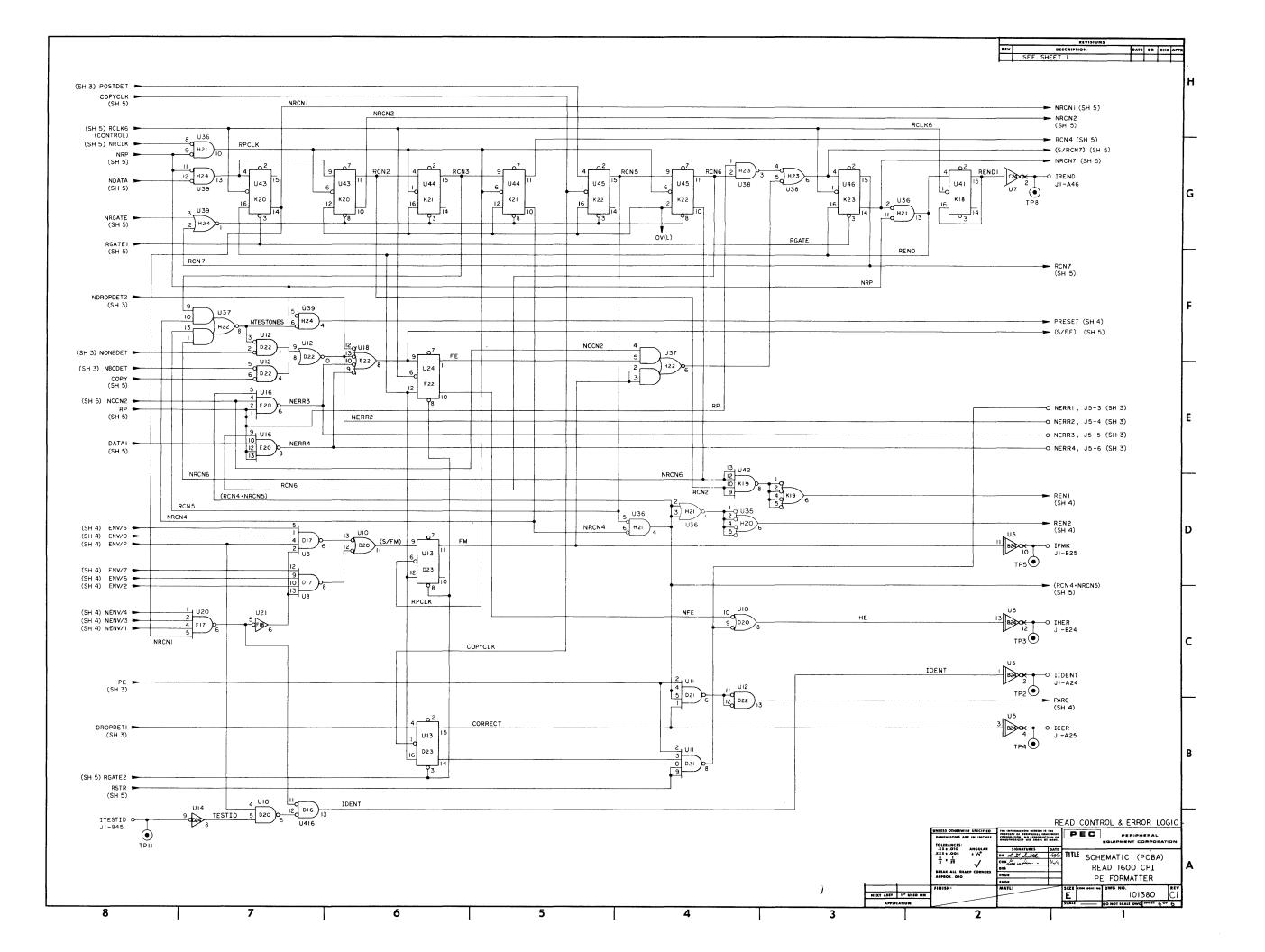

|     |            | 4.2.6                       | PE Write PCBA                                      |           |

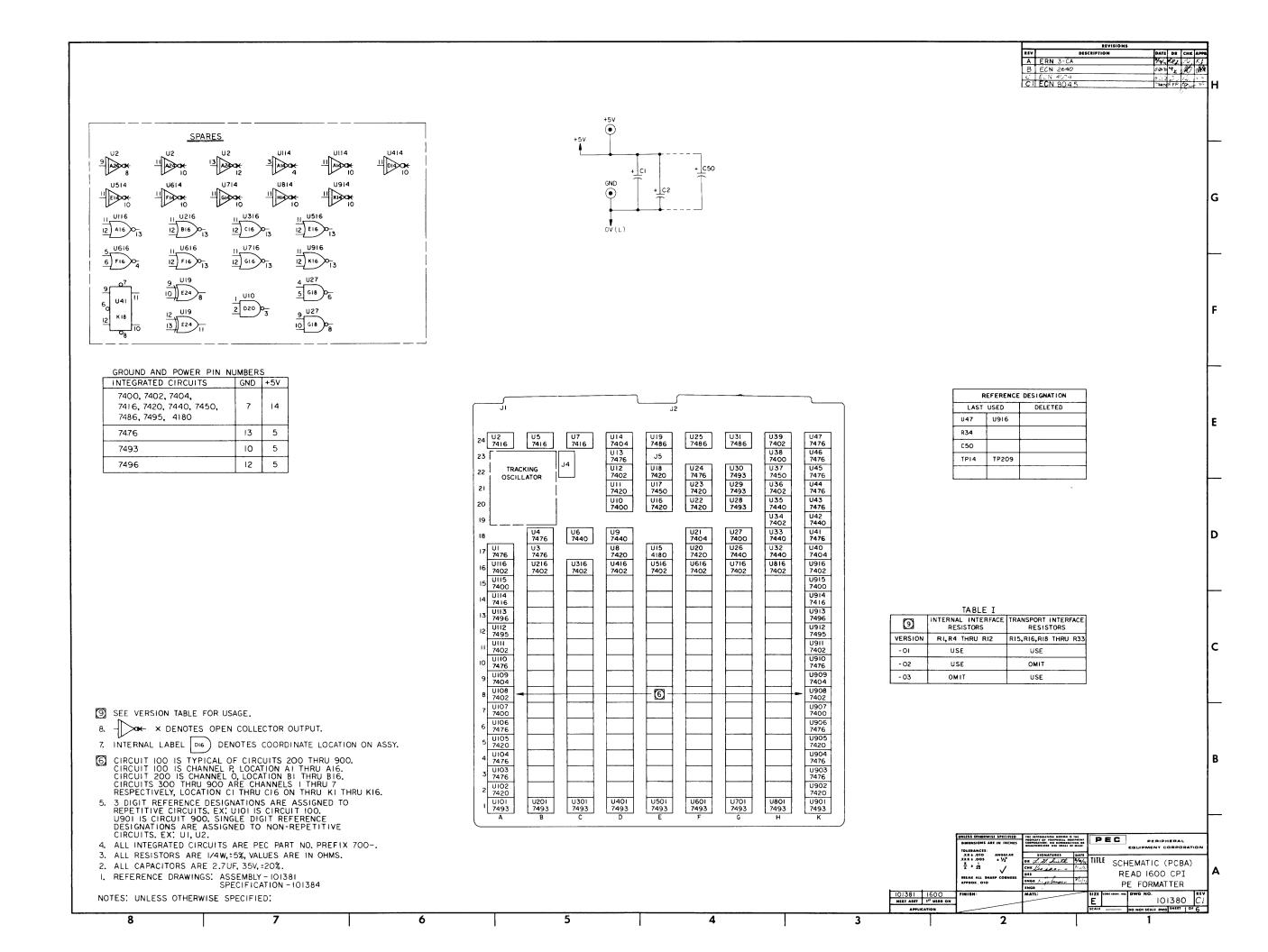

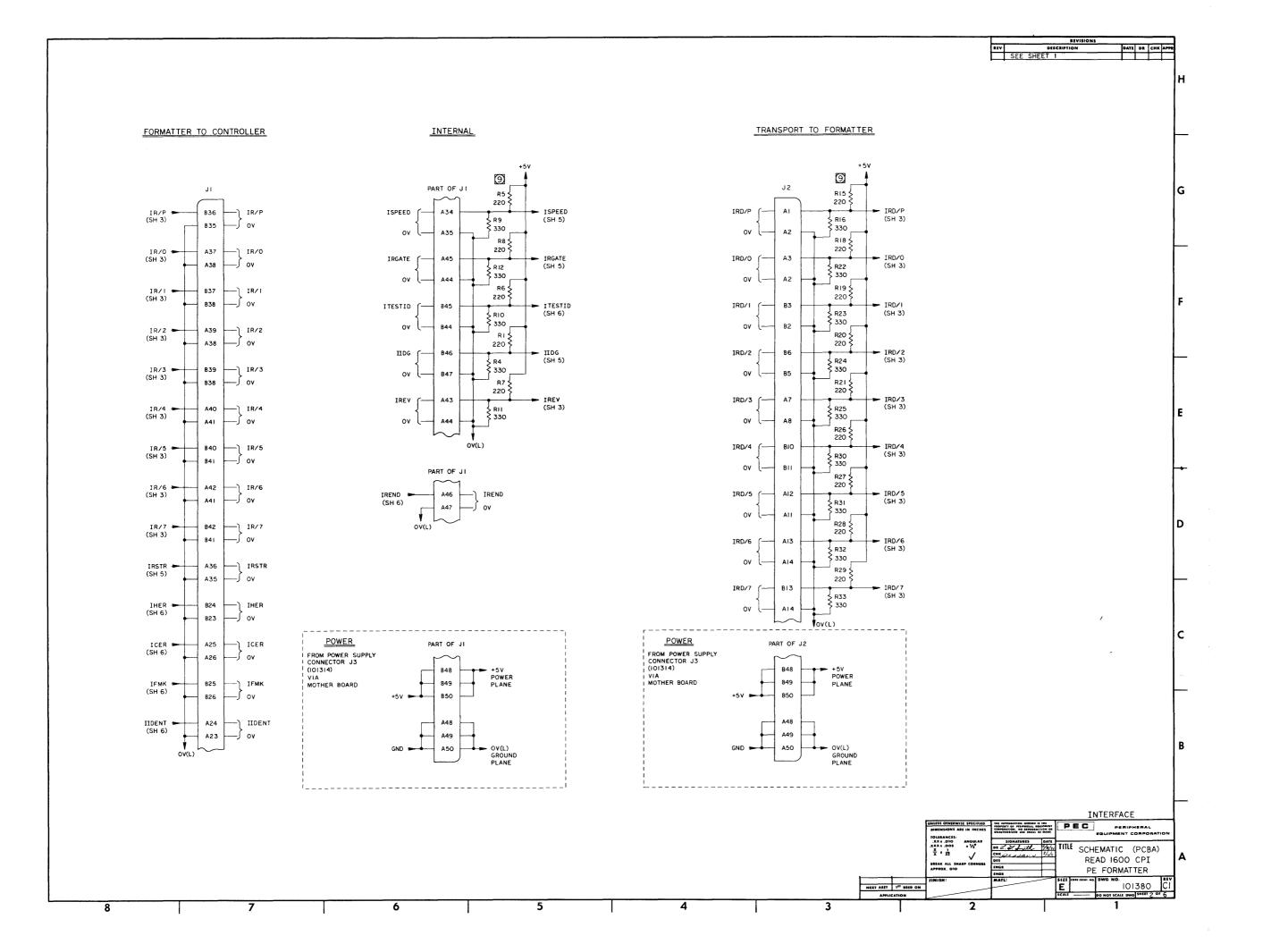

|     |            | 4.2.7                       | PE Read PCBA                                       | 4-23      |

| SEC | MOLT       | V DE1                       | TAILED ELECTRICAL AND LOGIC DESCRIPTIONS           |           |

| SEC |            |                             |                                                    |           |

|     | 5.1        |                             | ction                                              |           |

|     | 5.2        |                             | TTL Parameters and Circuits                        |           |

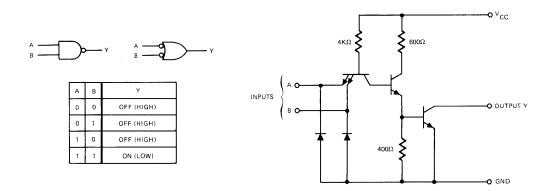

|     |            | 5.2.1<br>5.2.2              | 2-Input Nand Gate (Type 7400)                      |           |

|     |            | 0.4.4                       | - 2-111put 1901 Guto (1 ypo 1 702)                 | 0 1       |

VII 802B

# **TABLE OF CONTENTS (continued)**

|     |         |                                                                 | Page |

|-----|---------|-----------------------------------------------------------------|------|

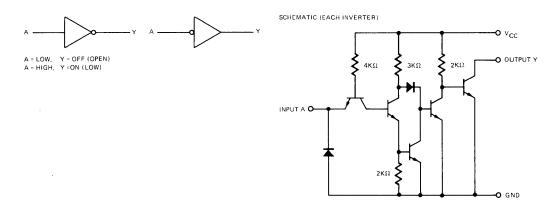

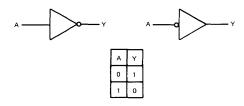

|     | 5.2.3   | Inverter (Type 7404)                                            | 5-1  |

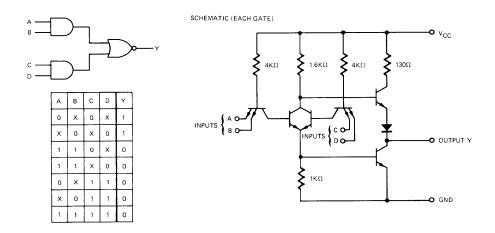

|     | 5.2.4   | 3-Input Nand Gate (Type 7410)                                   | 5-1  |

|     | 5.2.5   | Inverter Buffer / Driver (Type 7416)                            | 5-1  |

|     | 5.2.6   | 2-Input Nand Buffer (Type 7438)                                 | 5-1  |

|     | 5.2.7   | 2-Wide 2-Input And-Or-Invert Gate (Type 7450)                   |      |

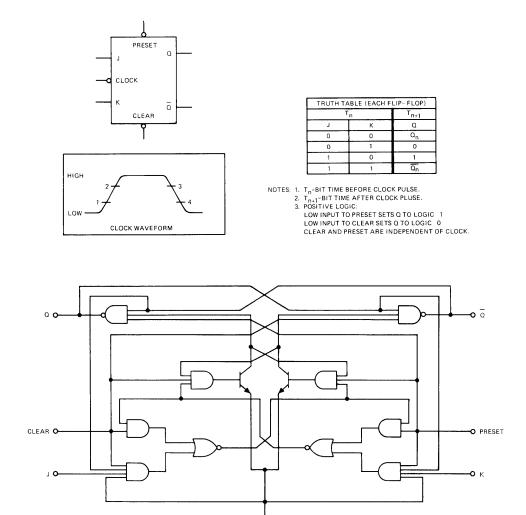

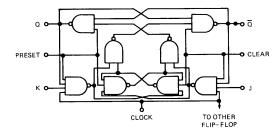

|     | 5.2.8   | J-K Master-Slave Flip-Flop (Type 7476)                          |      |

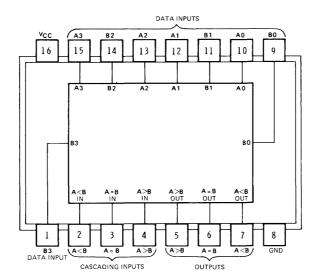

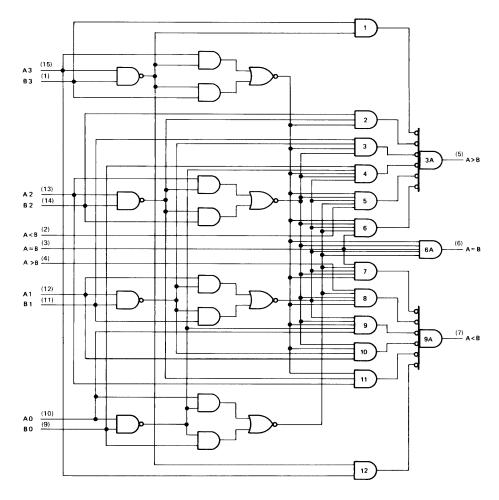

|     | 5.2.9   | 4-Bit Magnitude Comparator (Type 7485)                          |      |

|     | 5.2.10  | 2-Input Exclusive-Or Gate (Type 7486)                           | 5-6  |

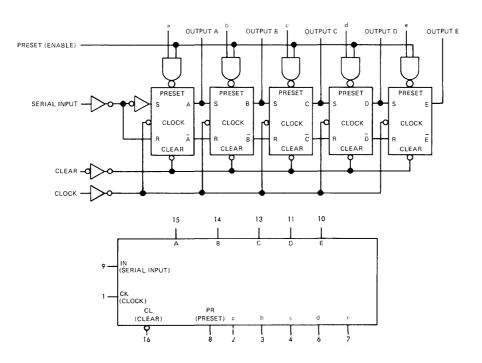

|     | 5.2.11  | 5-Bit Shift Register (Type 7496)                                | 5-8  |

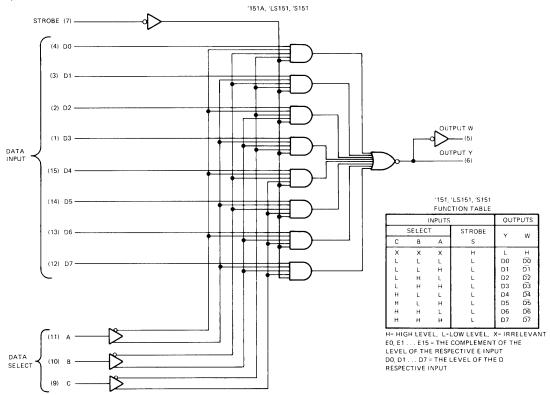

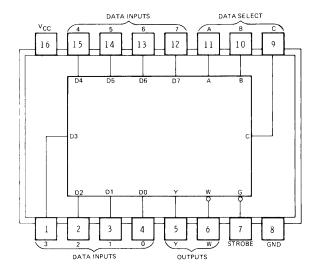

|     | 5.2.12  | Data Selector Multiplexer (Type 74151A)                         |      |

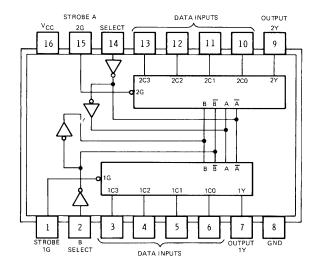

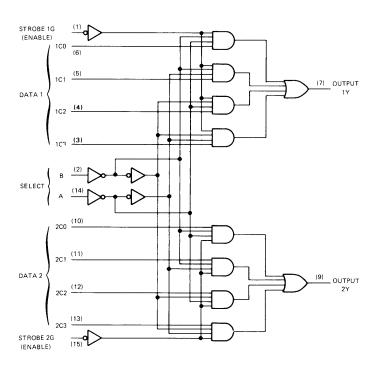

|     | 5.2.13  | Dual Data Selector/Multiplexer (Type 74153)                     | 5-10 |

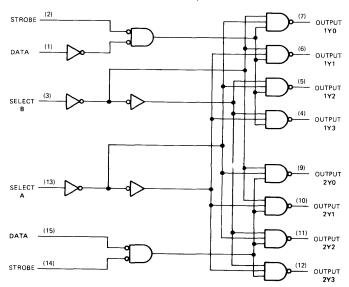

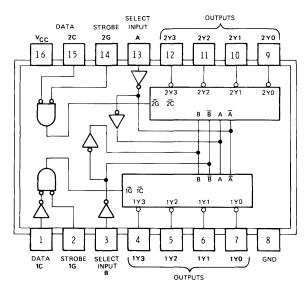

|     | 5.2.14  | Dual Decoder/Demultiplexer (Type 74155)                         |      |

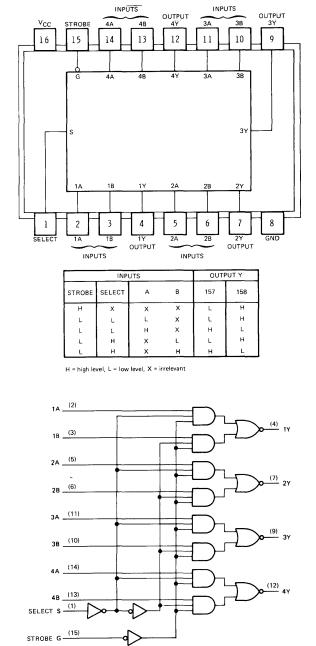

|     | 5.2.15  | Quadruple Data Selector/Multiplexer (Type 74157)                | 5-12 |

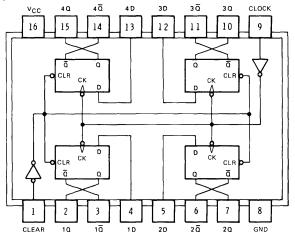

|     | 5.2.16  | Hex/Quadruple D-Type Flip-Flop (Type 74175)                     |      |

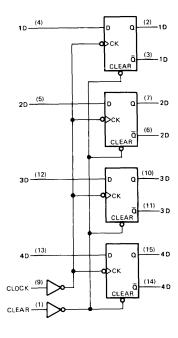

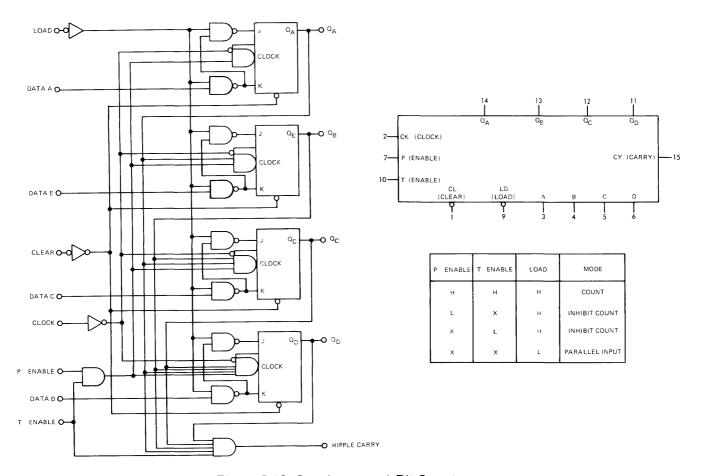

|     | 5.2.17  | Synchronous 4-Bit Counter (Type 74161)                          |      |

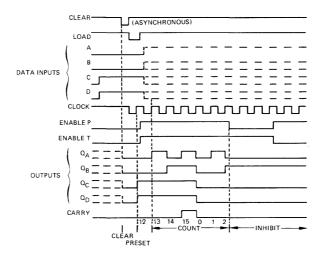

|     | 5.2.18  | Dual Line Receiver/Sense Amplifier (Type 75107)                 |      |

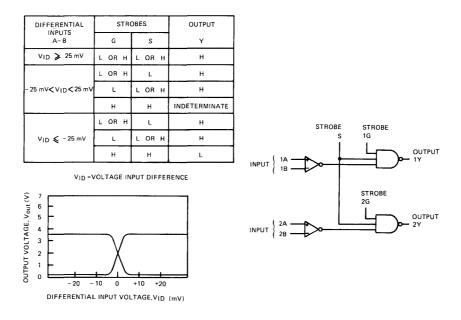

| F 2 | 5.2.19  | Operational Amplifier (Type 741)                                |      |

| 5.3 | 5.3.1   | peed TTL Parameters                                             | 5-16 |

|     | 5.3.1   | High-Speed Inverter (Type 74H04)                                |      |

|     | 5.3.3   | High-Speed J-K Master-Slave Flip-Flop (Type 74H76)              | 5-10 |

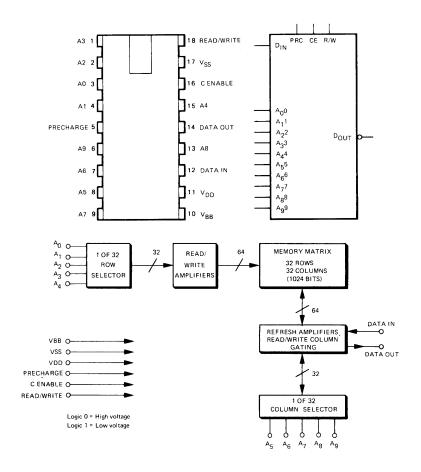

|     | 5.3.4   | MOS Silicon Gate (Type 1103)                                    | 5-18 |

|     | 5.3.5   | Schottky Bipolar-To-MOS Level Shifter and Driver (Type 3207A)   | 5-18 |

| 5.4 |         | Supply Assembly                                                 |      |

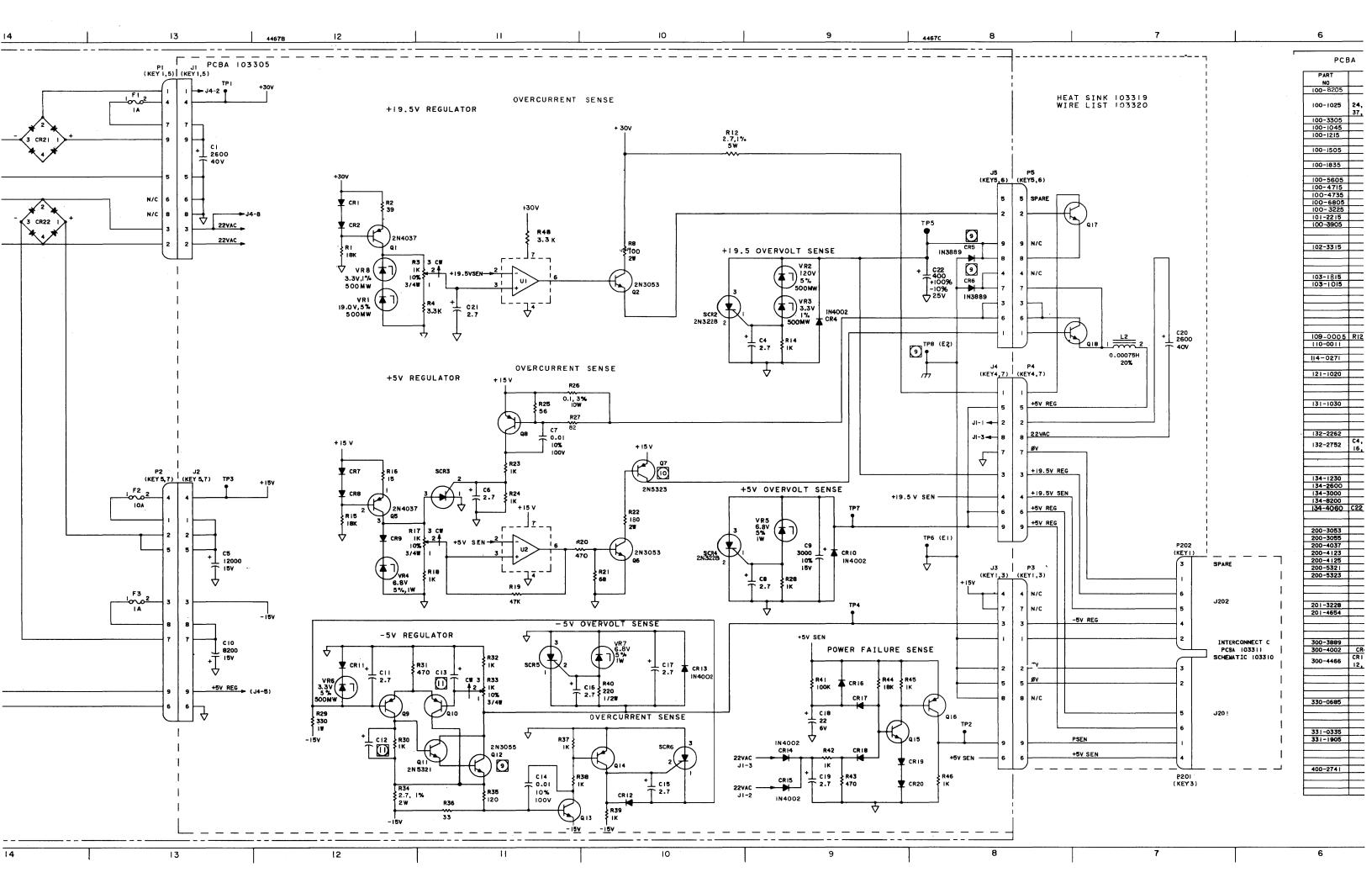

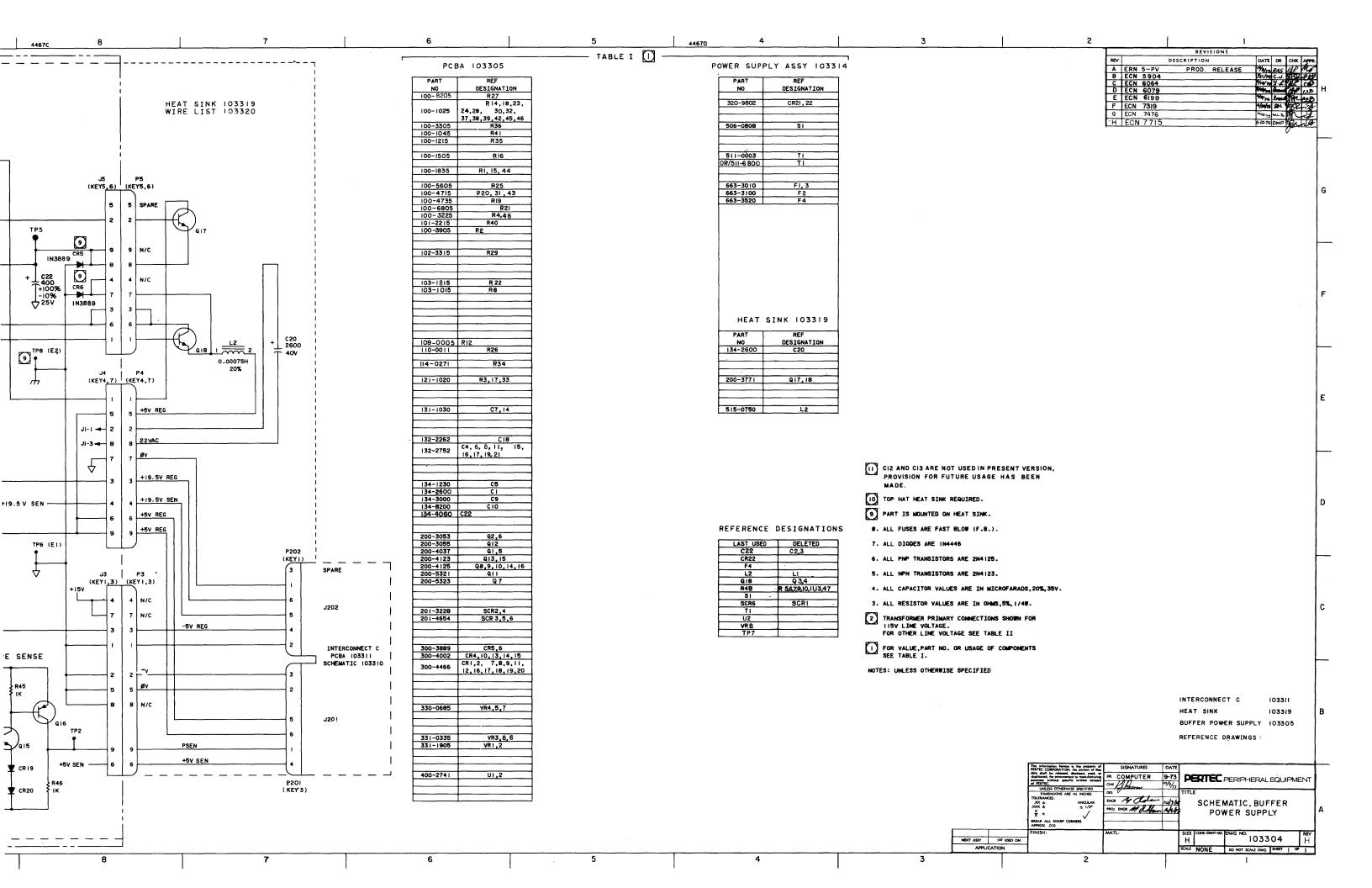

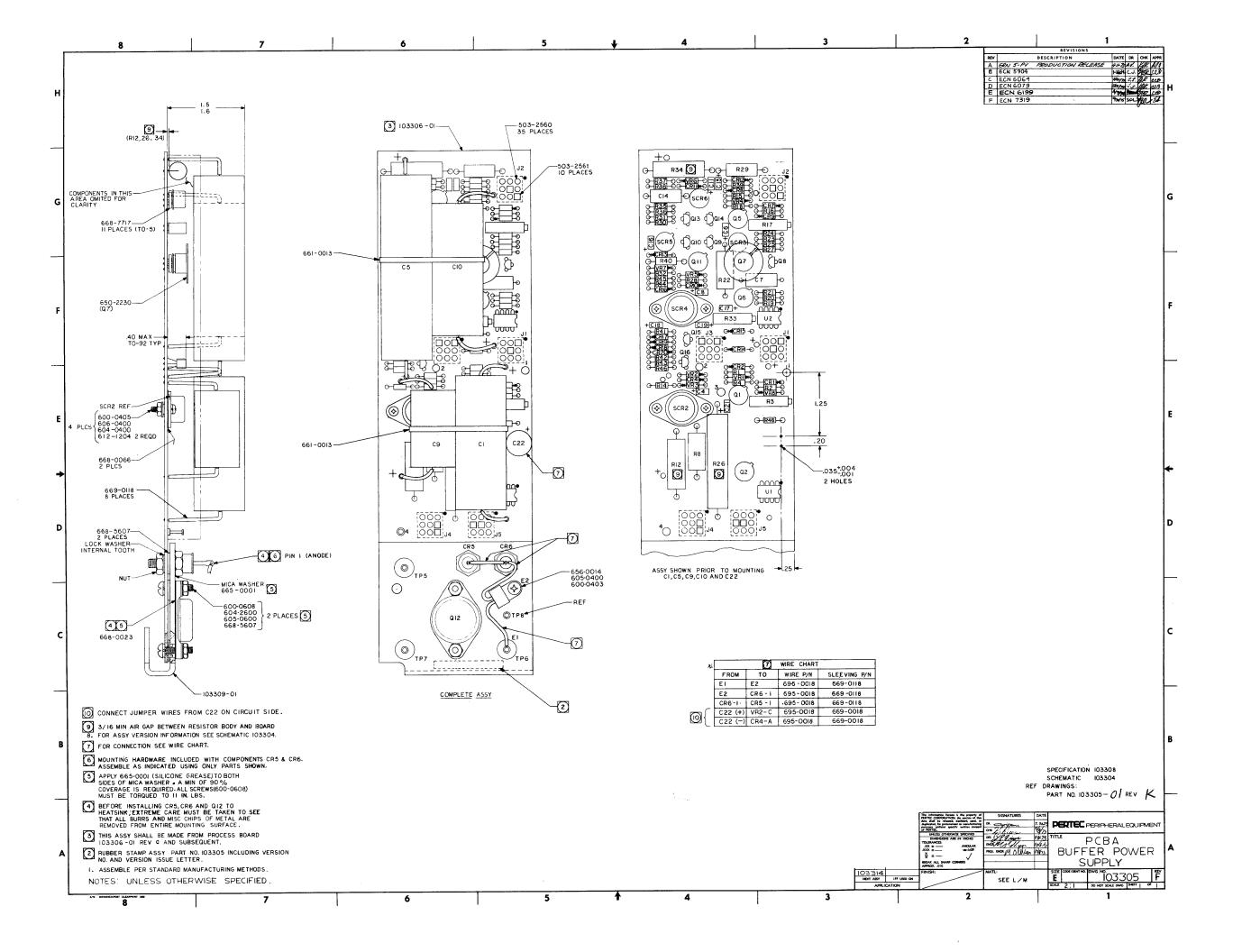

| 0.4 | 5.4.1   | Power Supply PCBA                                               |      |

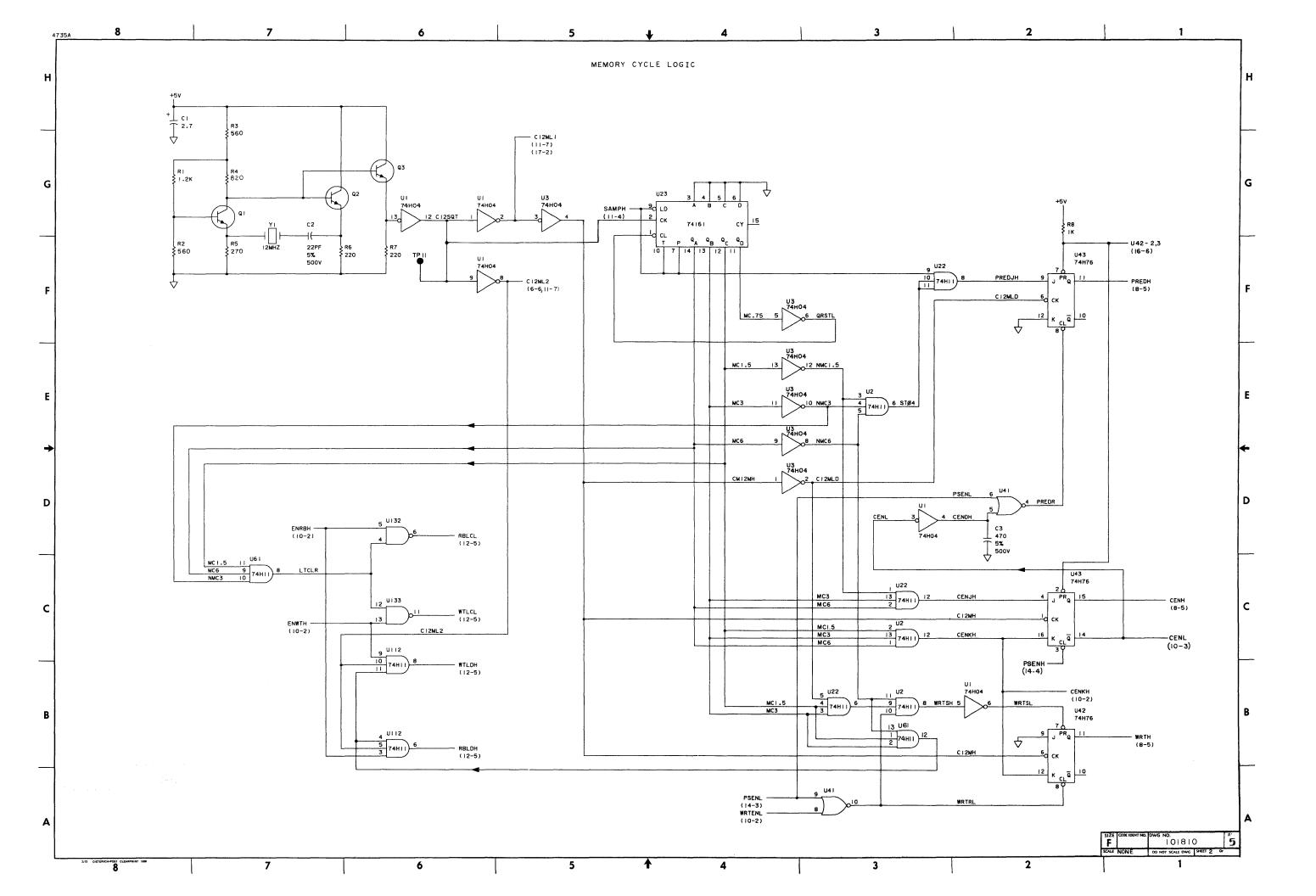

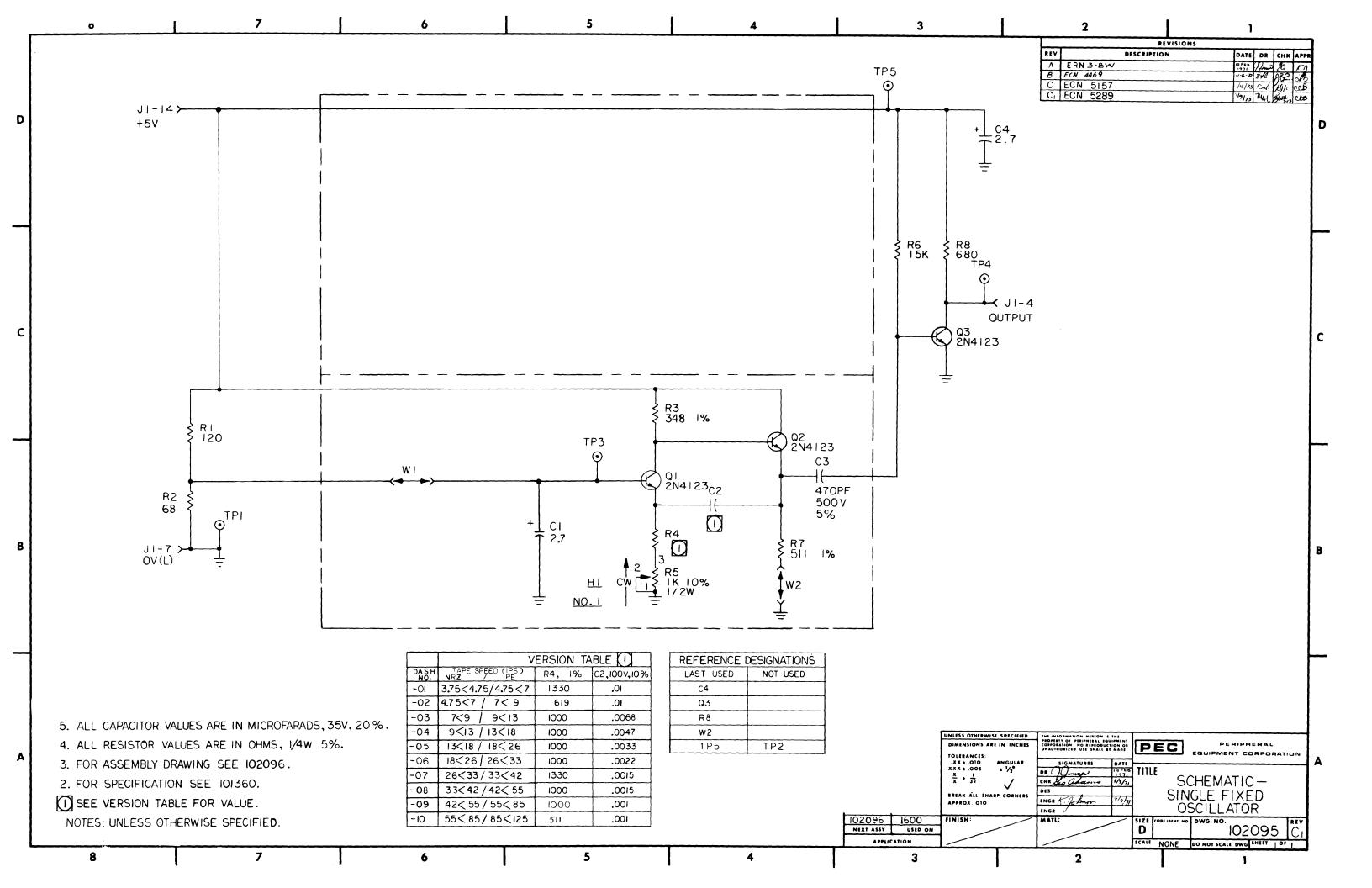

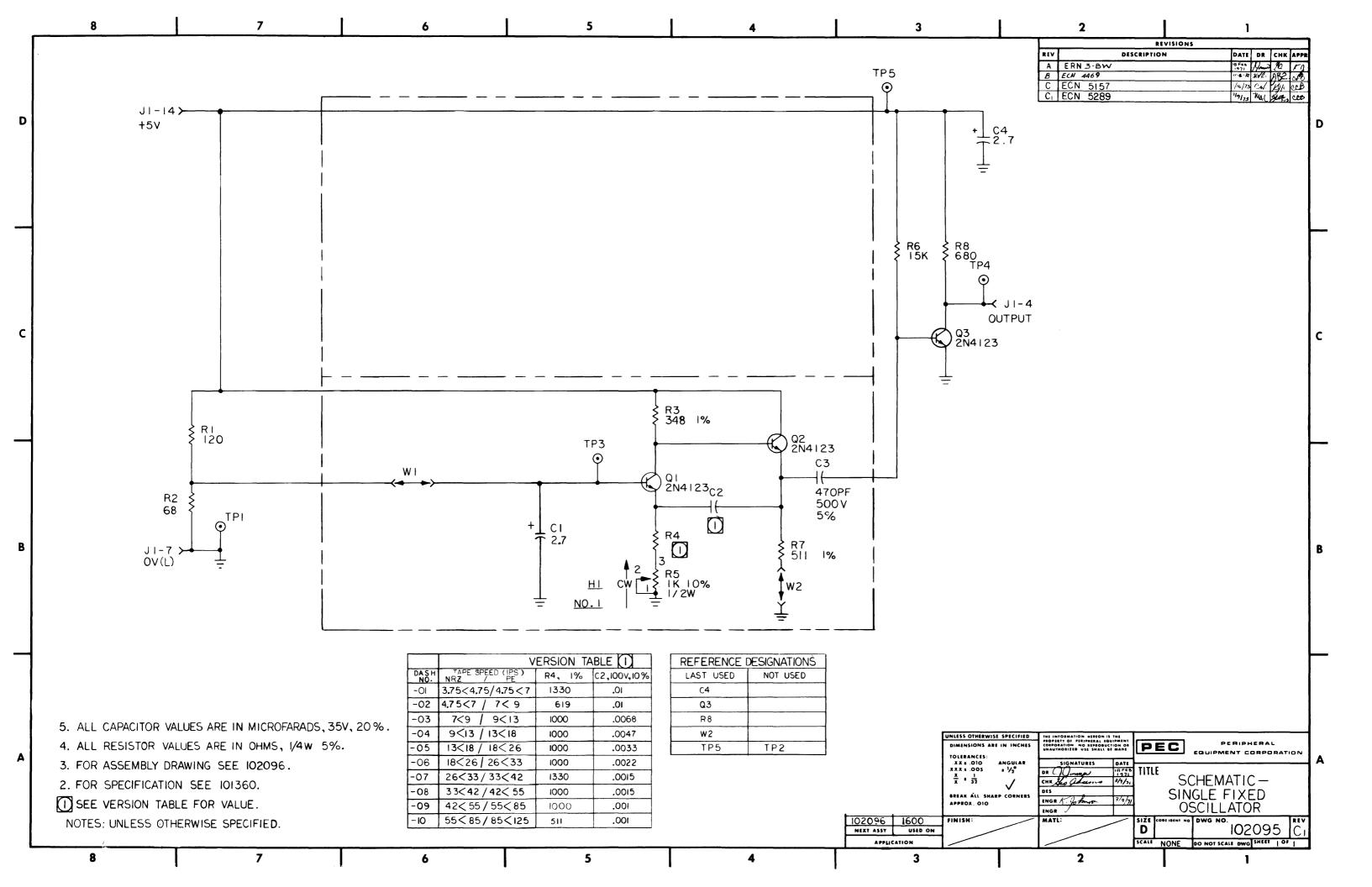

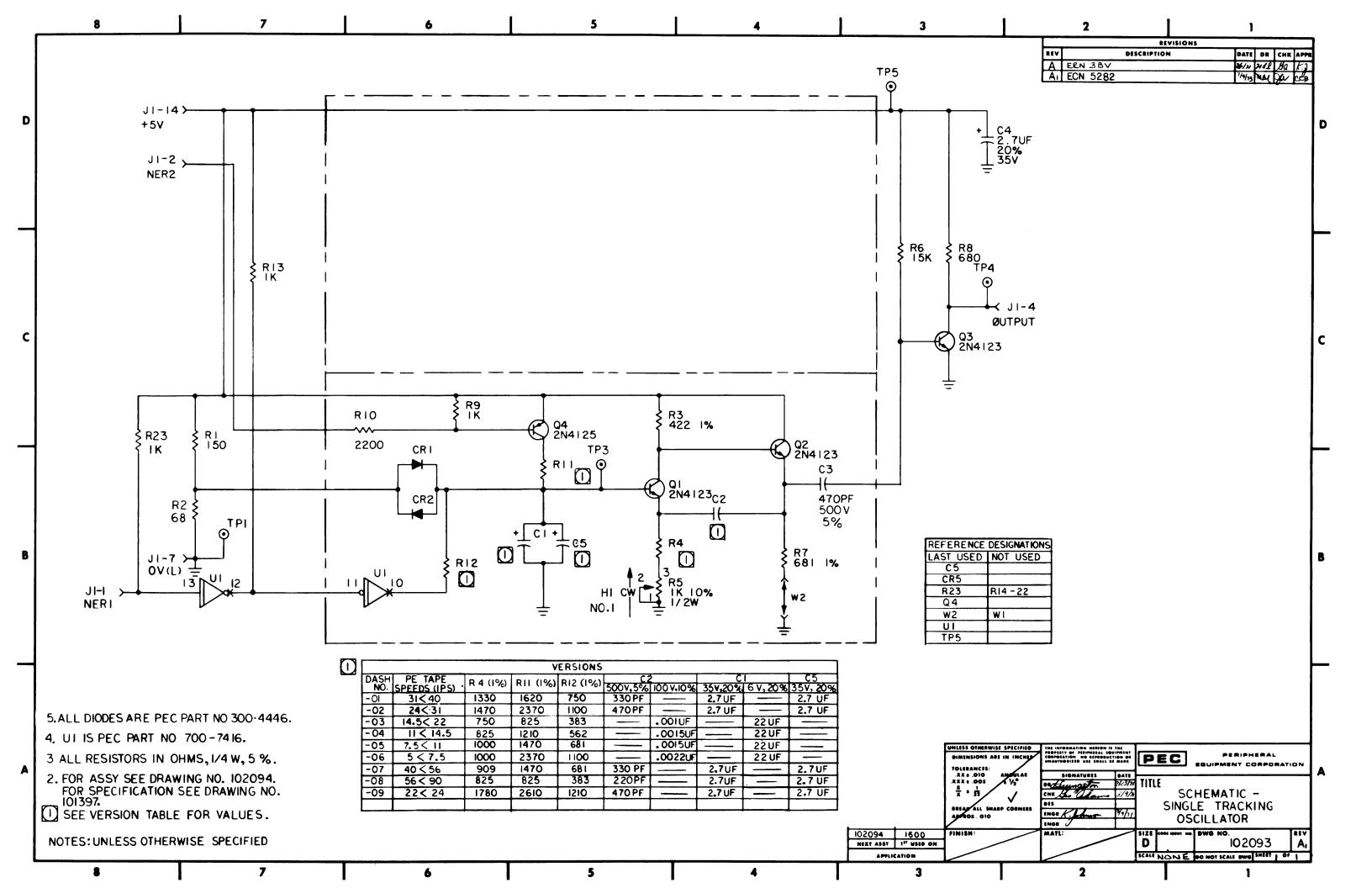

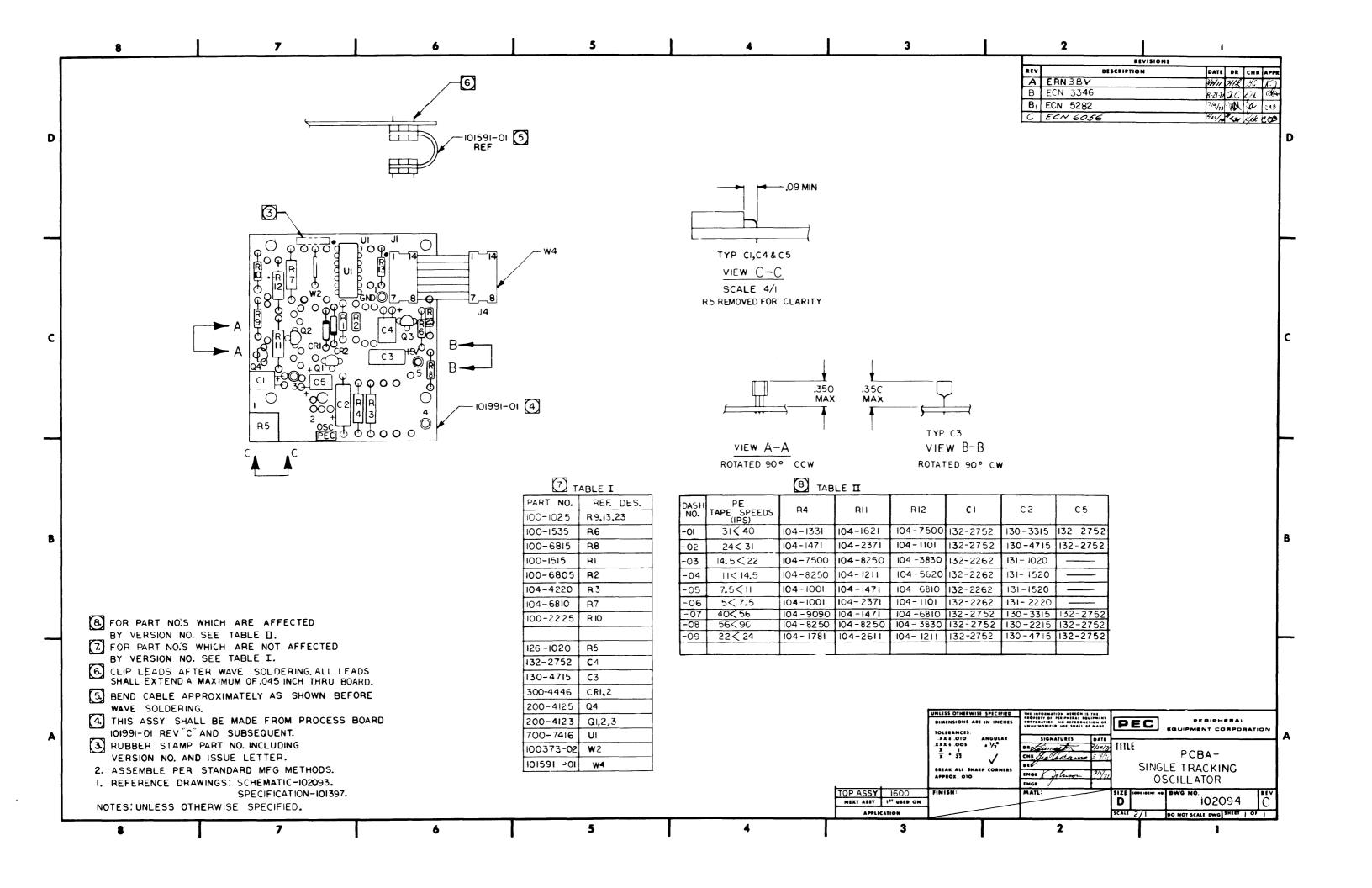

| 5.5 |         | scillator PCBAs                                                 |      |

| 5.6 |         | g Oscillator                                                    |      |

| 5.7 |         | e PCBA                                                          |      |

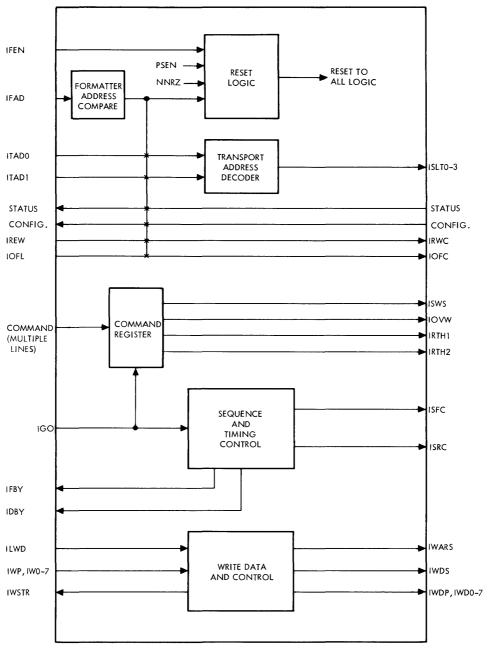

| 0.7 | 5.7.1   | Formatter and Transport Address Selection, Circuit Description. |      |

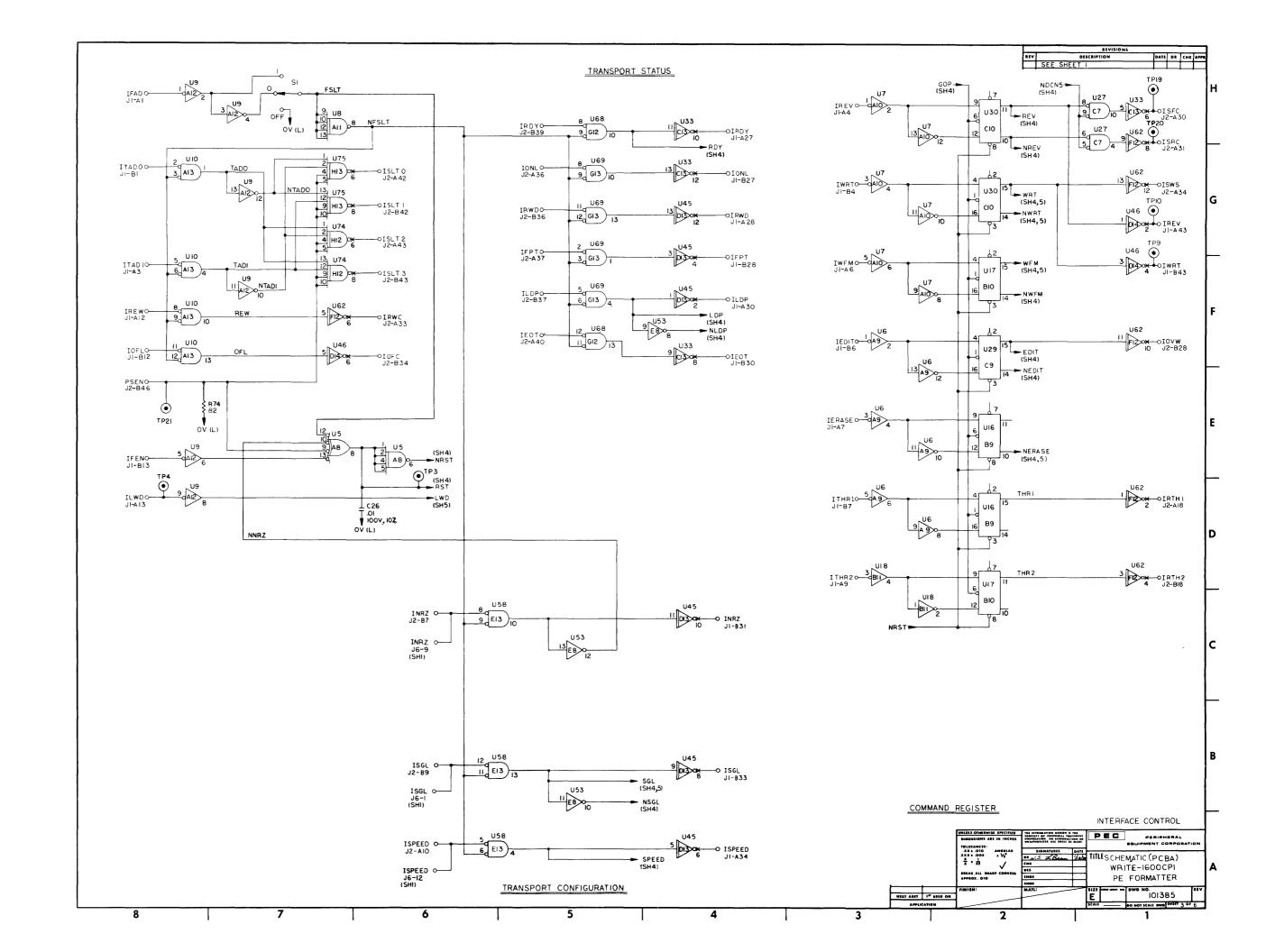

|     | 5.7.2   | Transport Status and Configuration Lines, Circuit Description   |      |

|     | 5.7.3   | Reset (RST)                                                     |      |

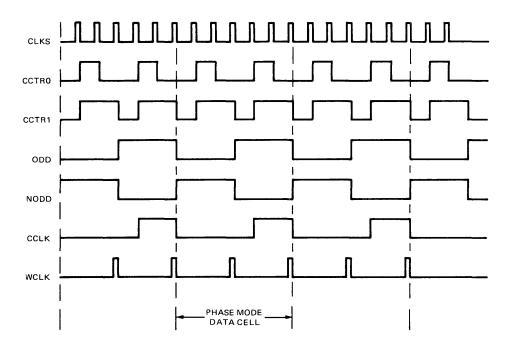

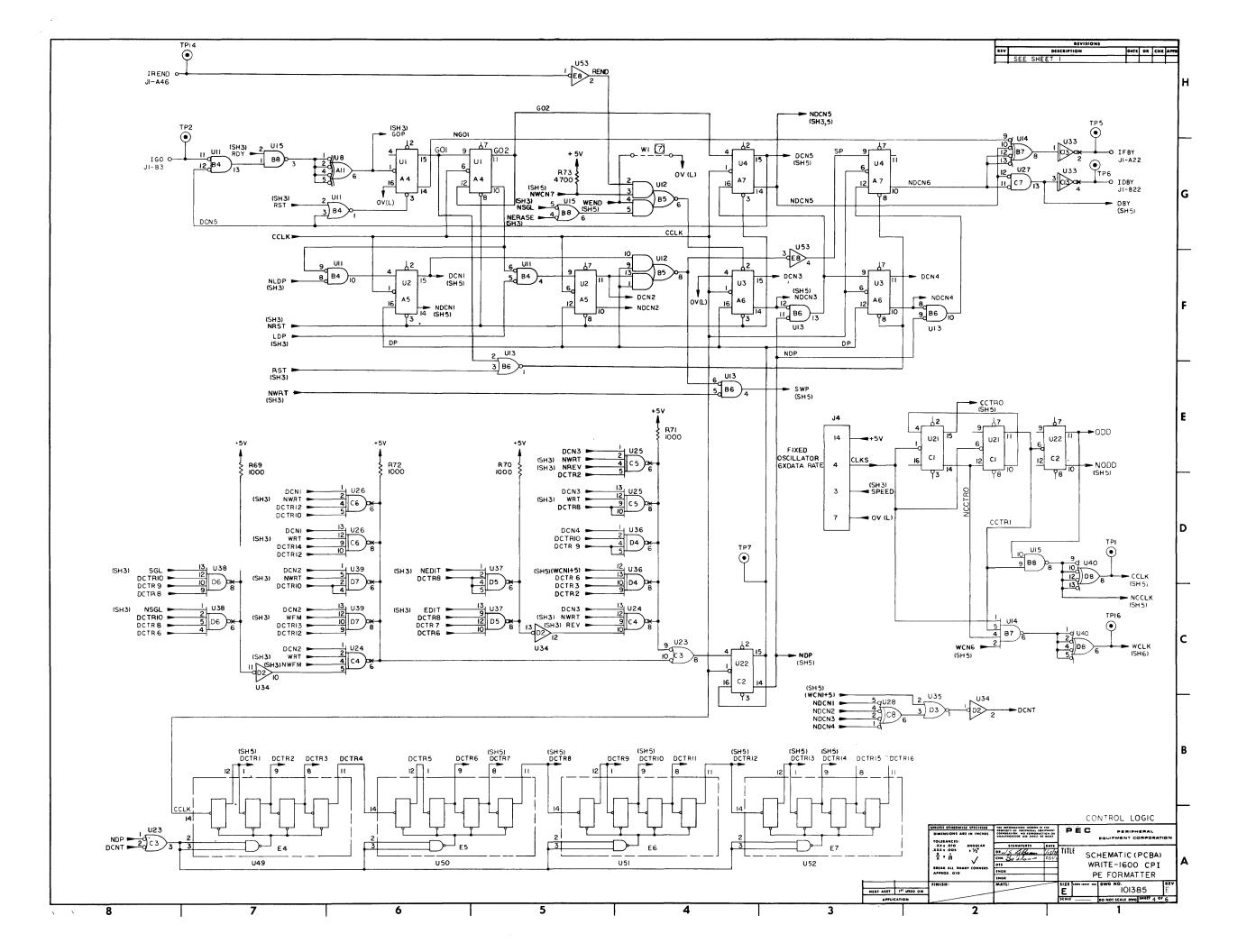

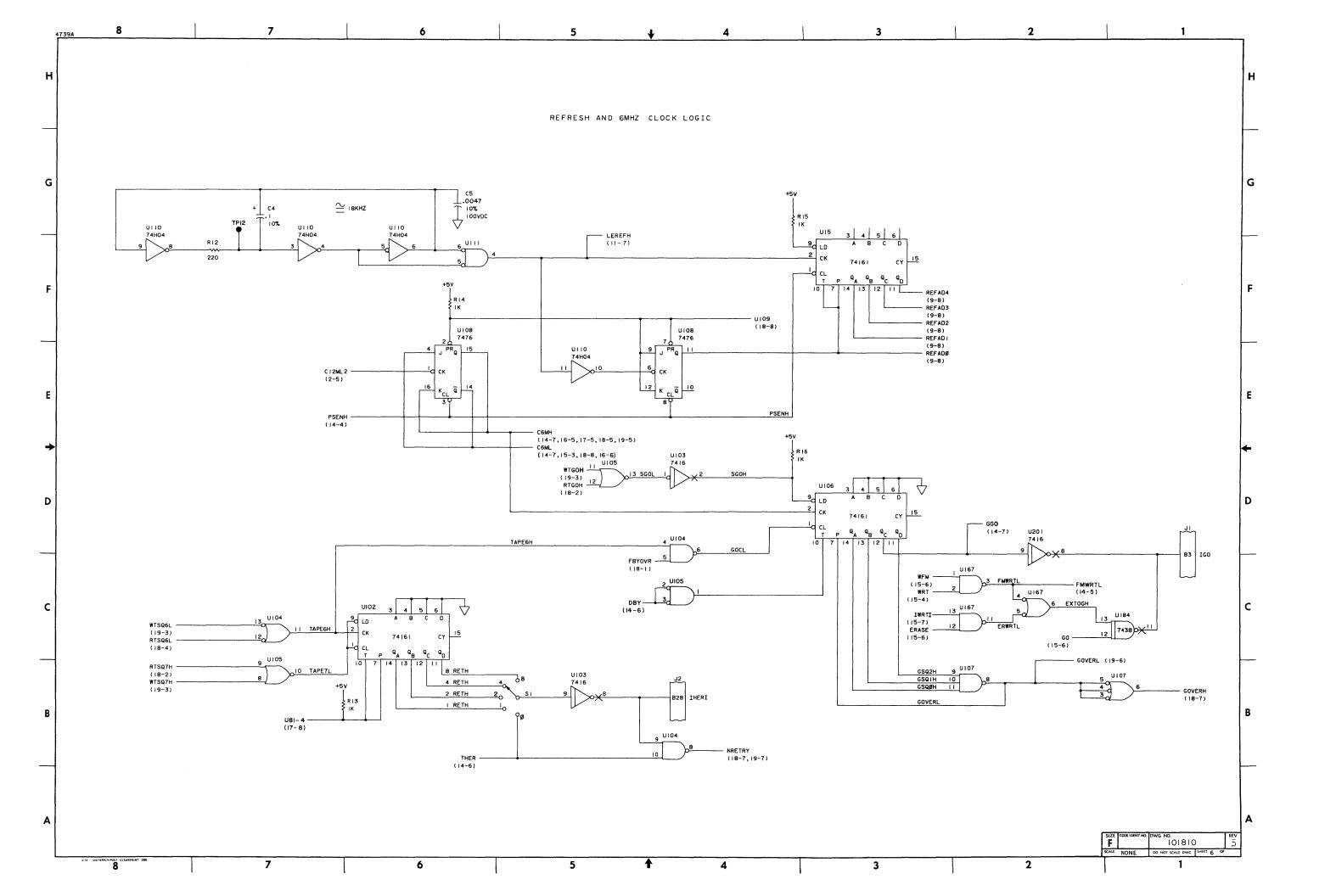

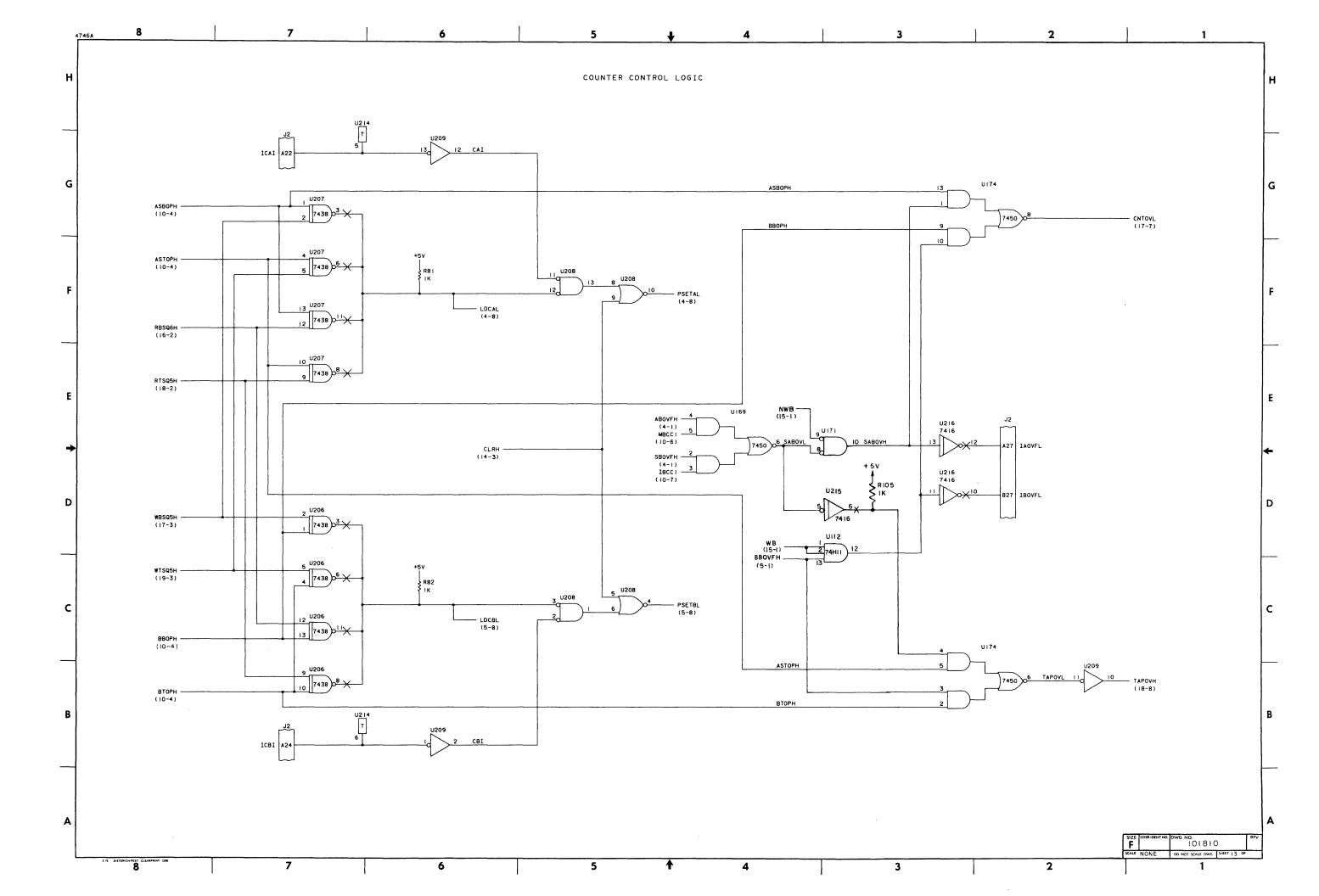

|     | 5.7.4   | Clock Logic                                                     |      |

|     | 5.7.5   | Formatter Commands                                              |      |

|     | 5.7.6   | Command Execution, Circuit Description                          |      |

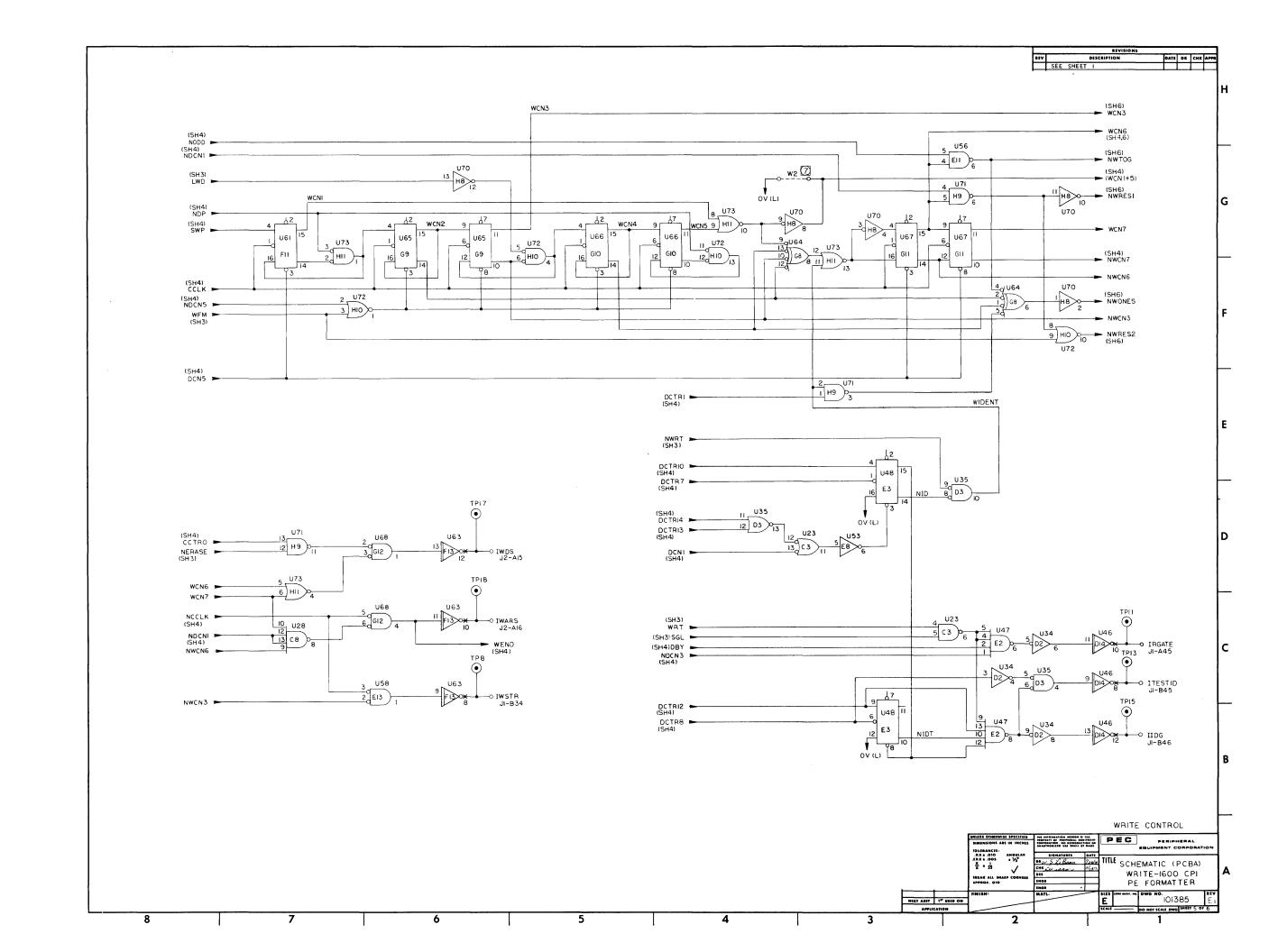

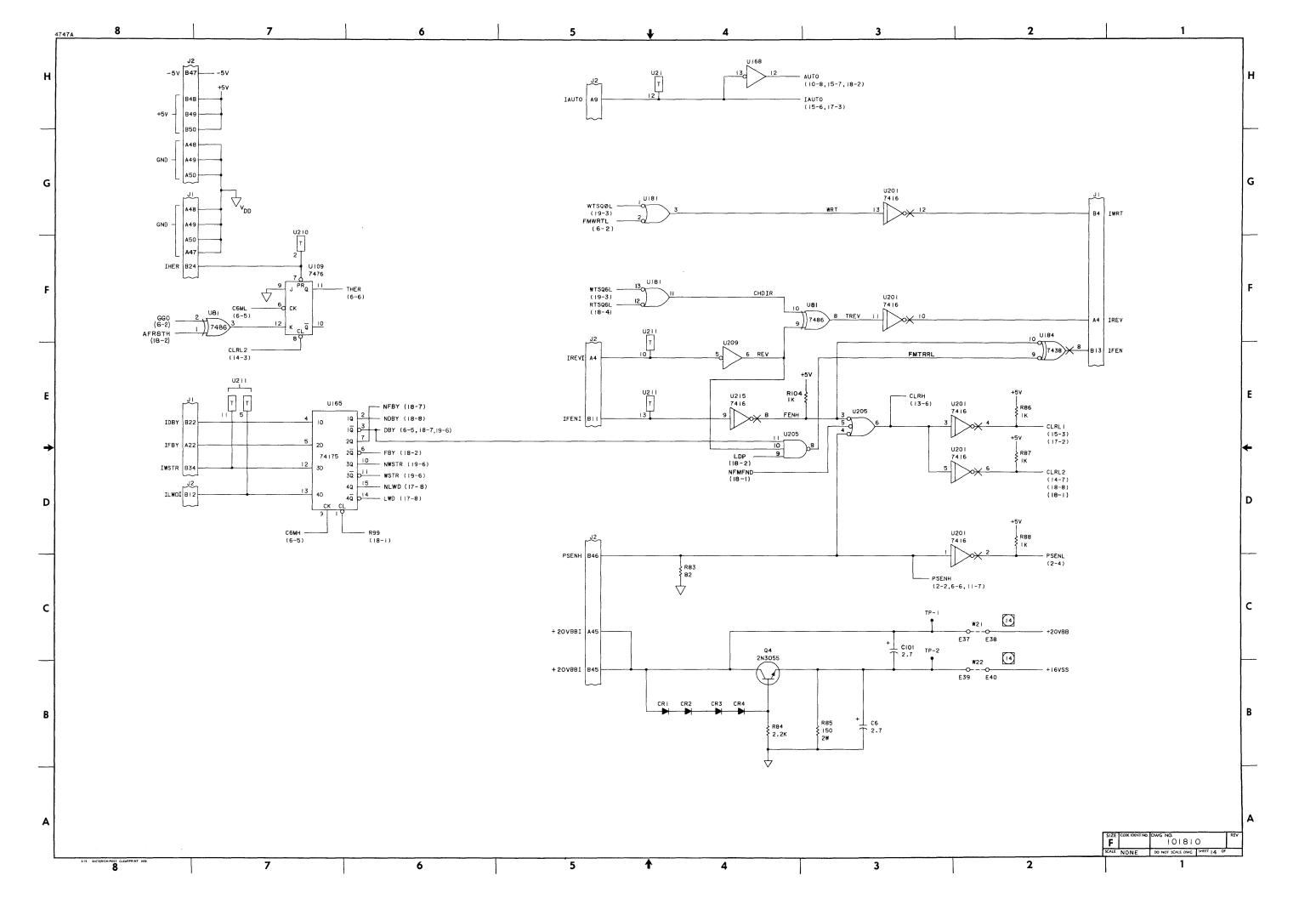

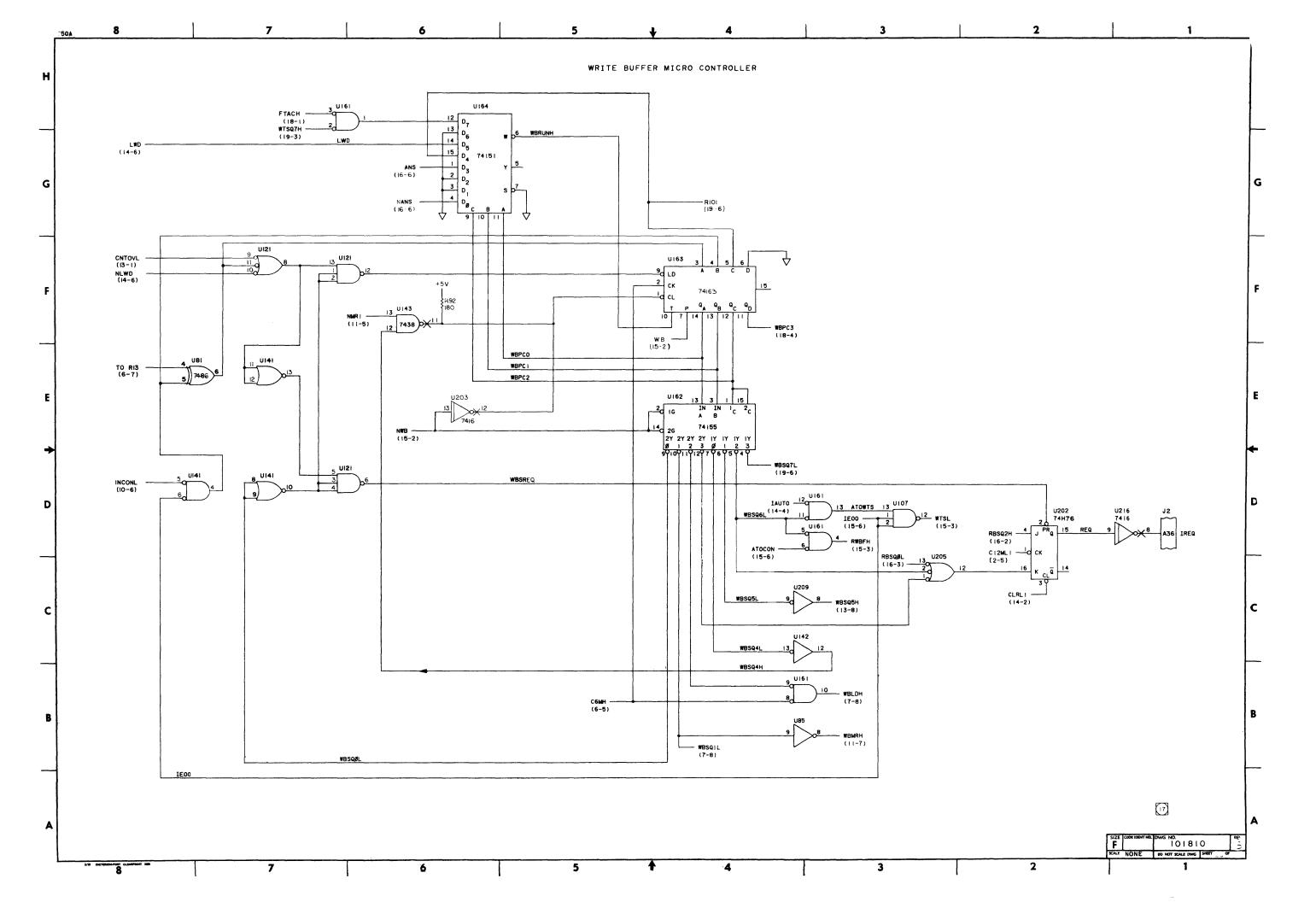

|     | 5.7.7   | Write Control Logic, Circuit Description                        |      |

|     | 5.7.8   | Write Data Logic, Circuit Description                           |      |

| 5.8 | PE Read | d PCBA                                                          |      |

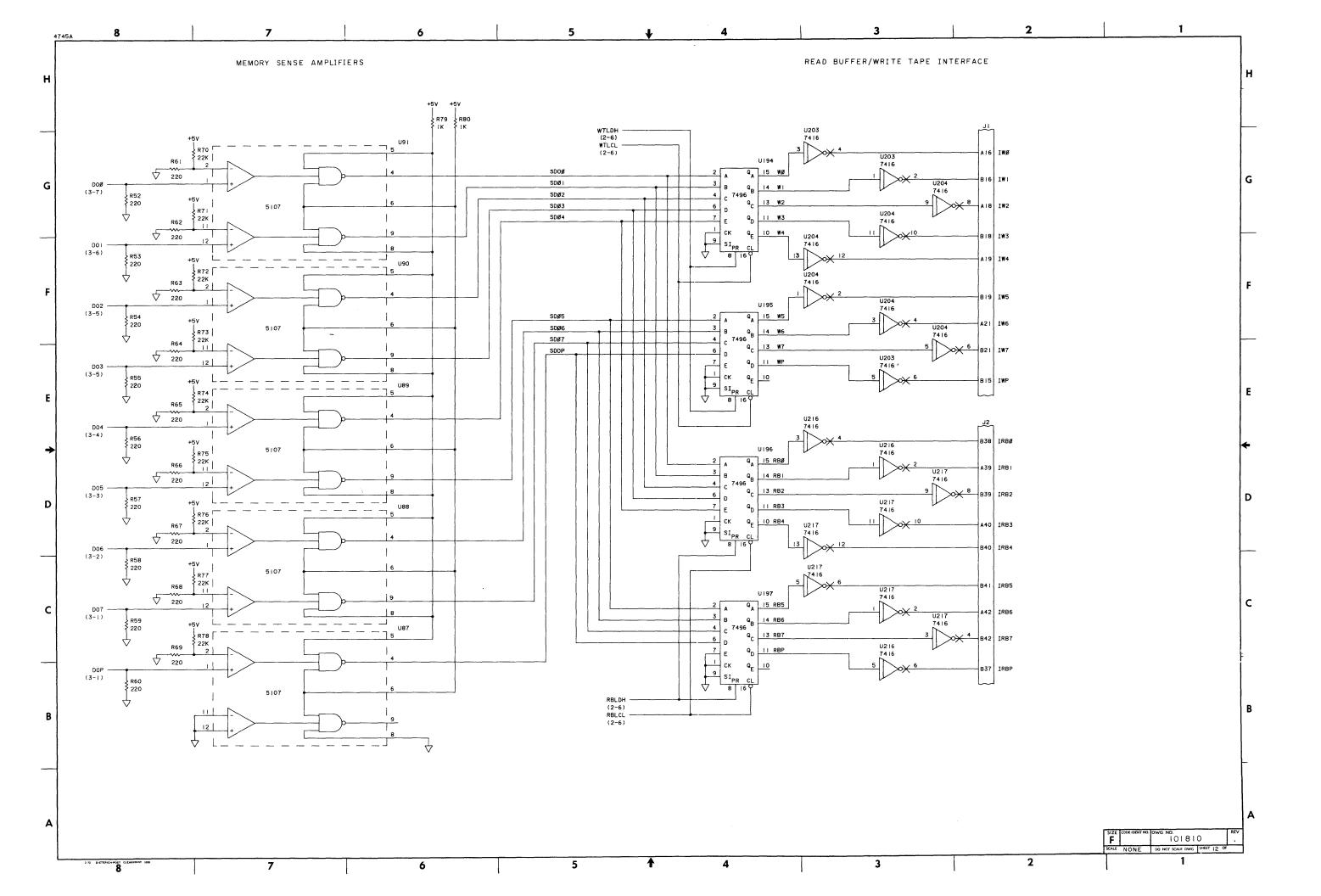

|     | 5.8.1   | Read Data Input                                                 | 5-46 |

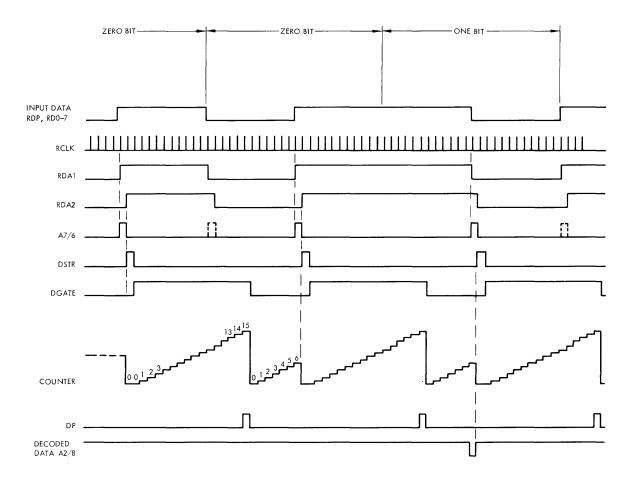

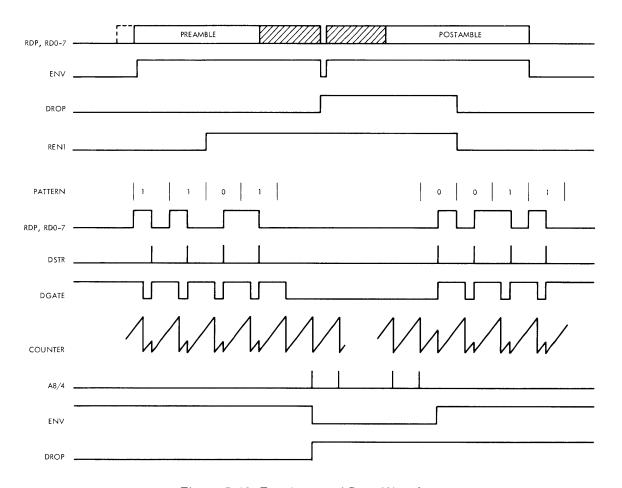

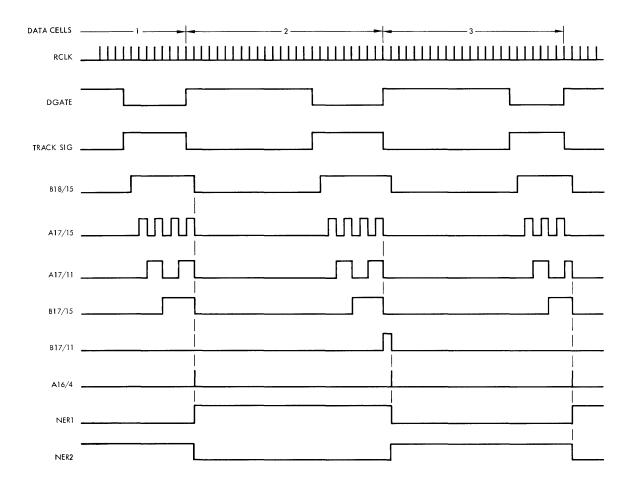

|     | 5.8.2   | Data Channel Logic, Circuit Description                         | 5-47 |

|     | 5.8.3   | Single/Multiple Track Dropout Detection                         | 5-53 |

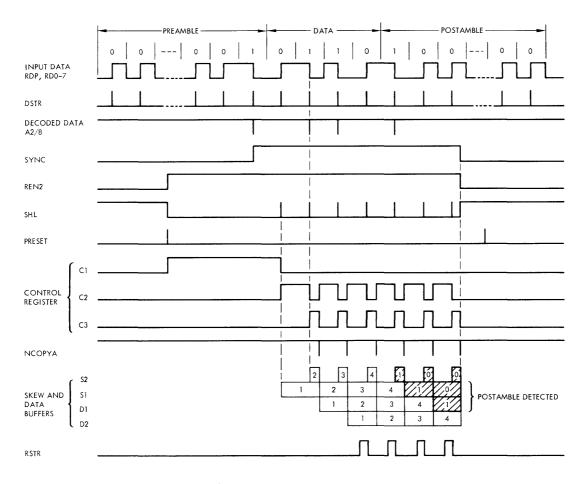

|     | 5.8.4   | Control Logic                                                   |      |

|     | 5.8.5   | File Mark                                                       |      |

|     | 5.8.6   | Identification Burst                                            |      |

|     | 5.8.7   | Error Detection                                                 |      |

| _   | 5.8.8   | Error Correction                                                |      |

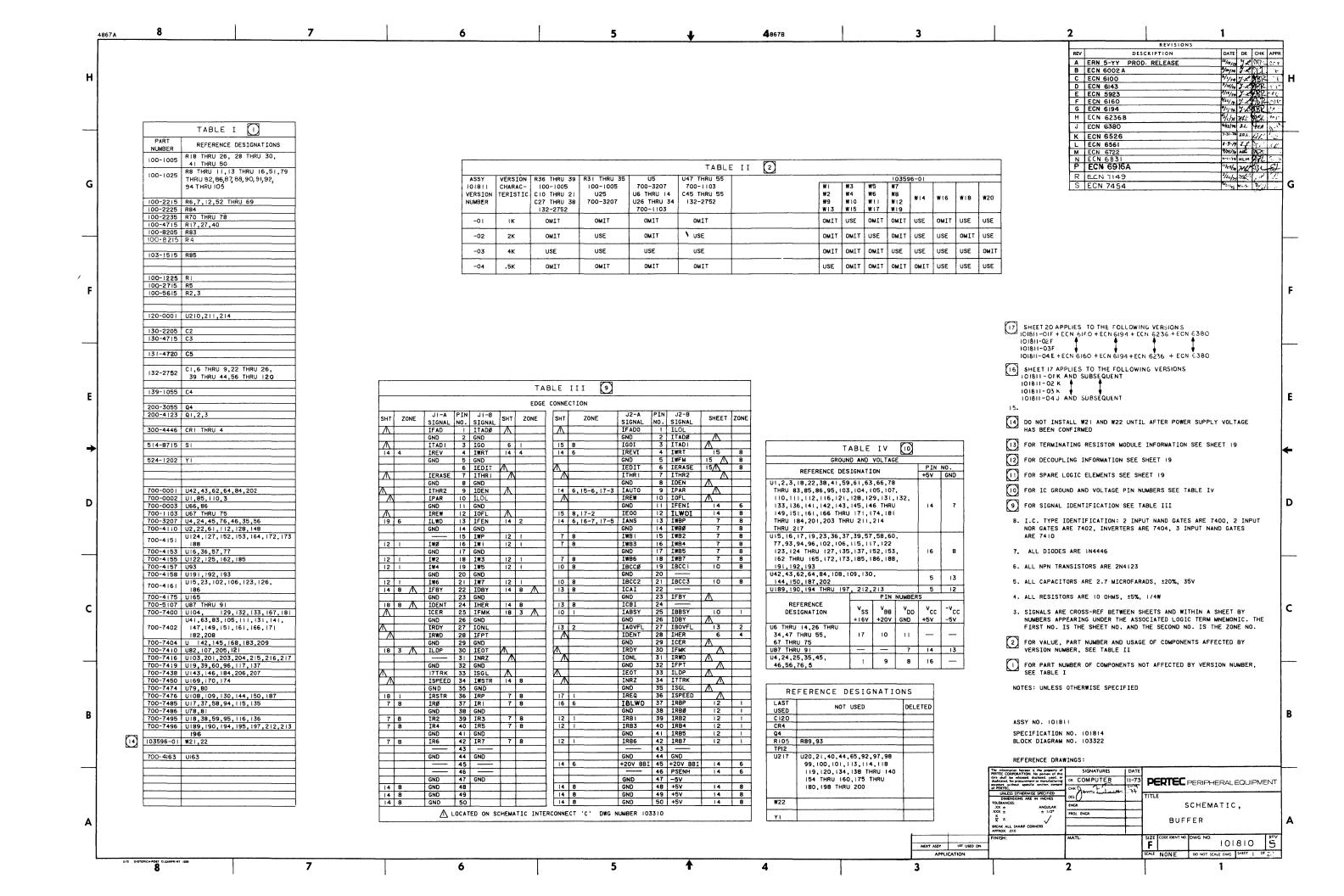

| 5.9 |         | PCBA                                                            |      |

|     | 5.9.1   | Circuit Description                                             | 5-61 |

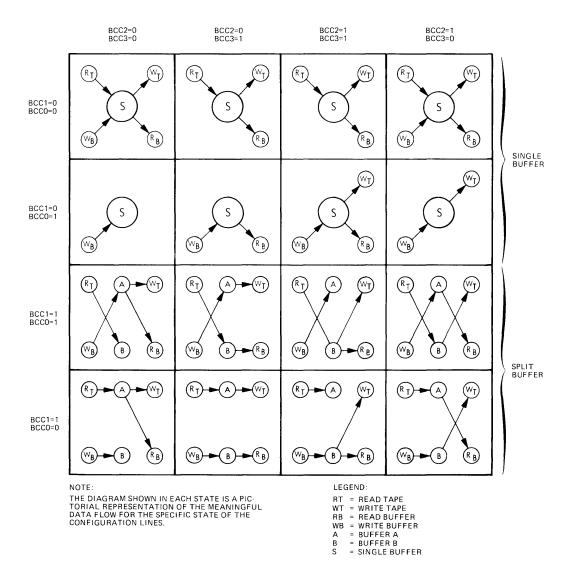

|     | 5.9.2   | Configuration Control Lines                                     | 5-67 |

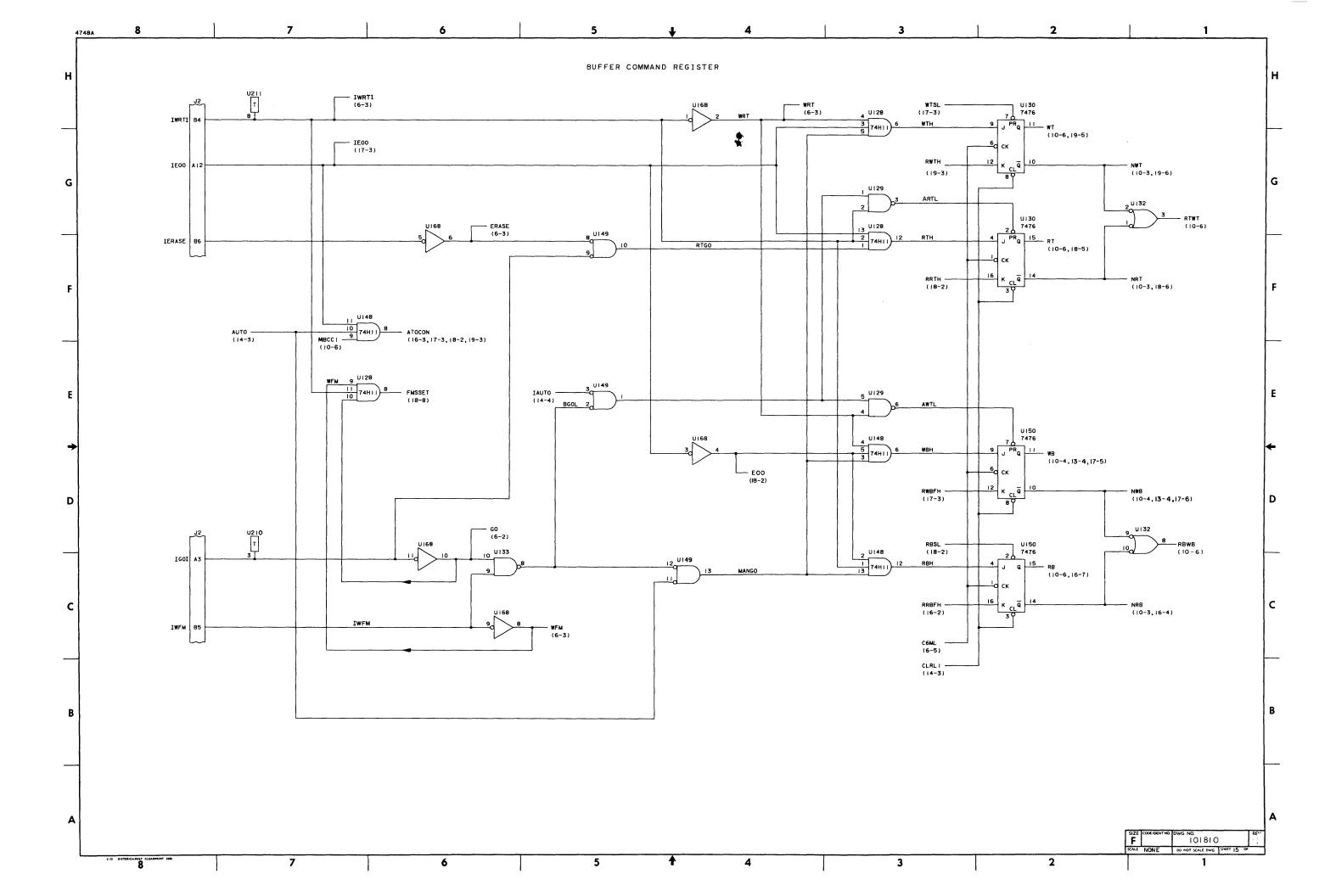

|     | 5.9.3   | Buffer/Controller Commands (Group 1)                            | 5-67 |

802B VIII

# **TABLE OF CONTENTS (Continued)**

|                                        |                                        |                                                                                                                                                                                                                                                                                                                                                               | Page                                                               |

|----------------------------------------|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

|                                        | 5.9.4<br>5.9.5<br>5.9.6                | Buffer/Formatter Commands (Group 2)                                                                                                                                                                                                                                                                                                                           | 5-71                                                               |

| SECTION                                | VI — M                                 | AINTENANCE ADJUSTMENTS                                                                                                                                                                                                                                                                                                                                        |                                                                    |

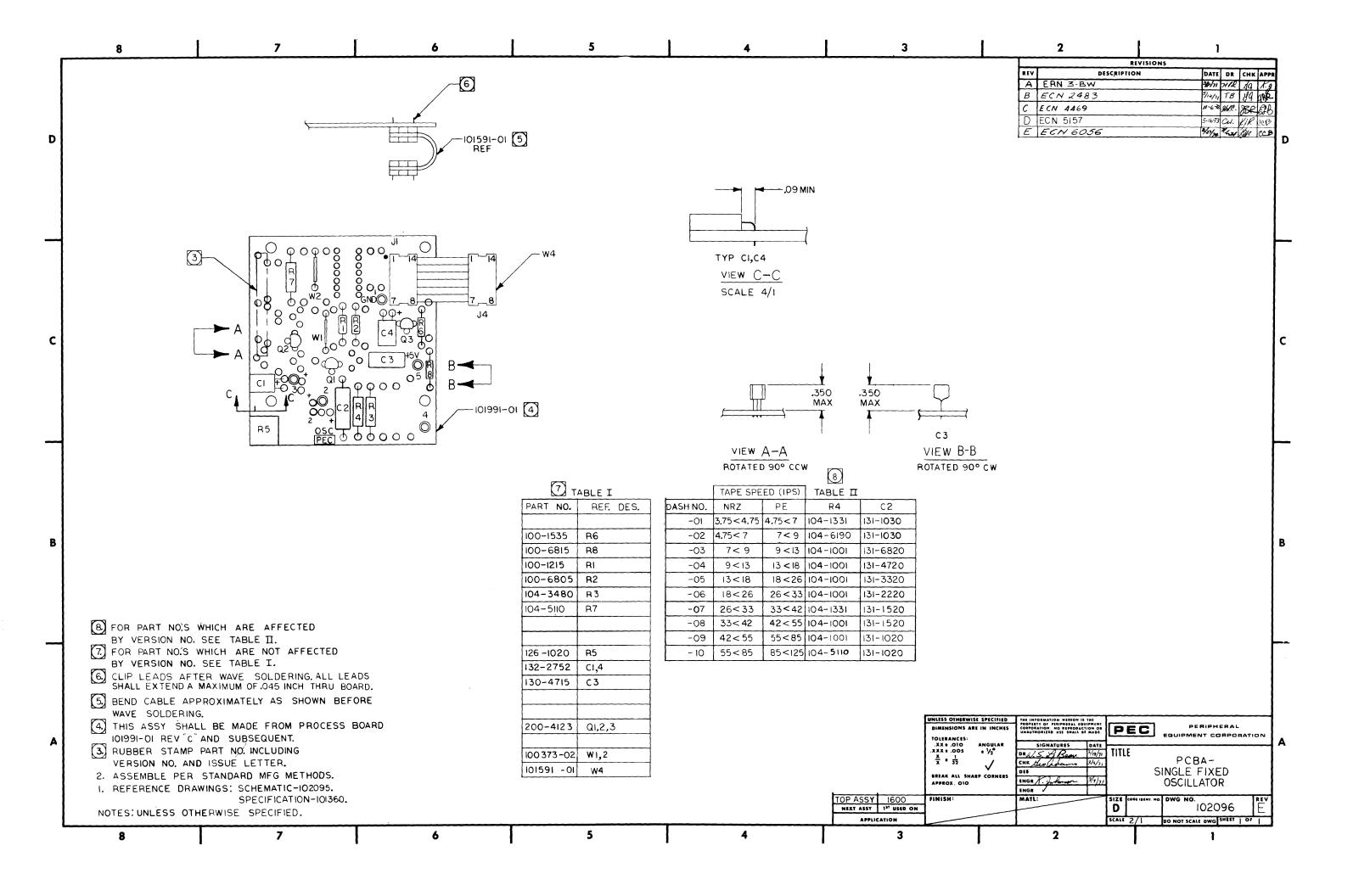

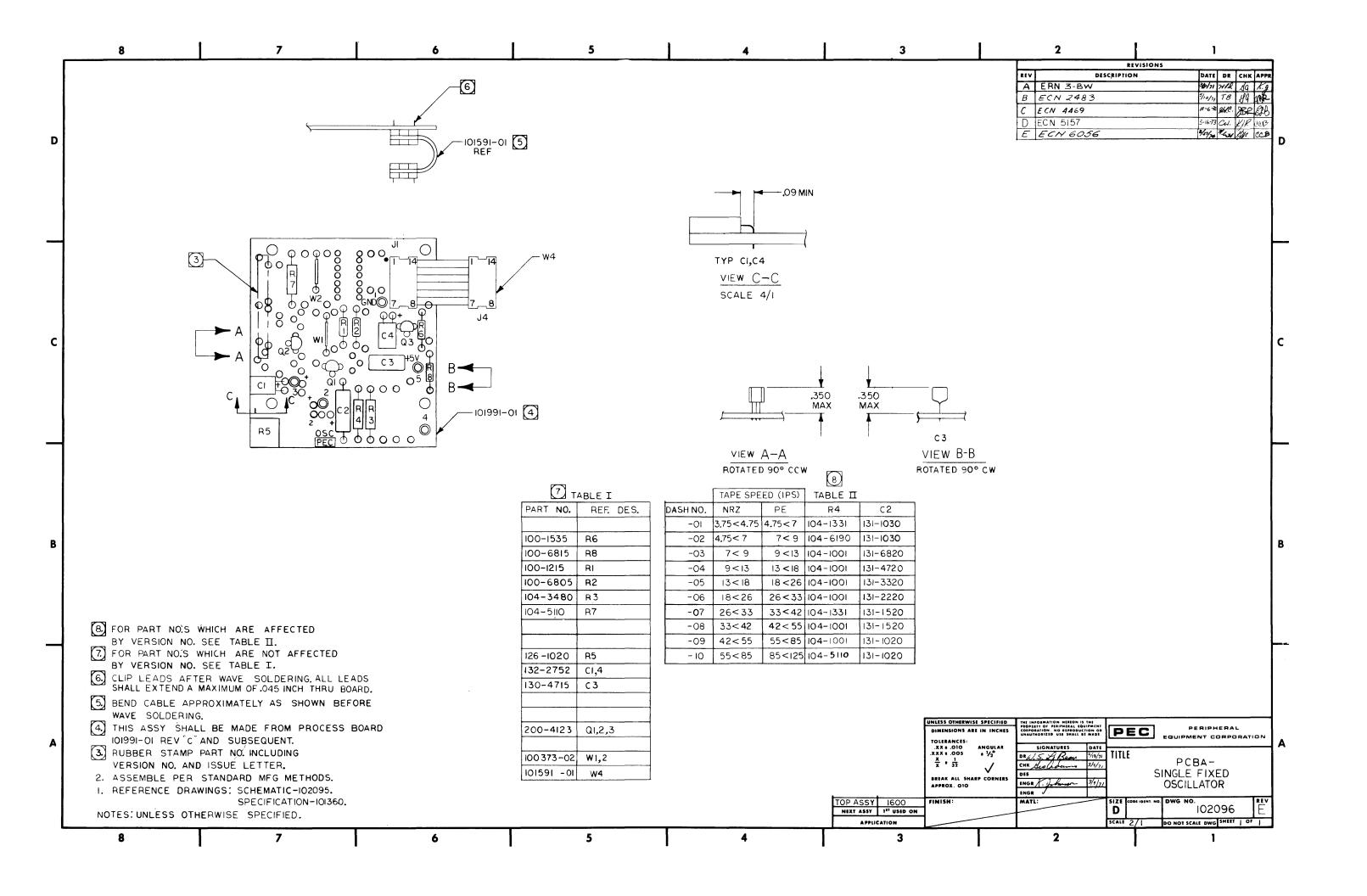

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6 | Fuse R<br>Schedu<br>Cleanii<br>Parts F | Replacement uled Maintenance ing the Formatter Replacement Adjustments cal Adjustments Adjustment Philosophy Power Supply PCBA (+5v) Power Supply PCBA (—5v) Power Supply PCBA (+20v) Fixed Oscillator (Single Speed Formatter) Fixed Oscillator (Dual Speed Formatter) Tracking Oscillator (Dual Speed Formatter) Tracking Oscillator (Dual Speed Formatter) | 6-1<br>6-1<br>6-1<br>6-1<br>6-1<br>6-2<br>6-2<br>6-3<br>6-4<br>6-5 |

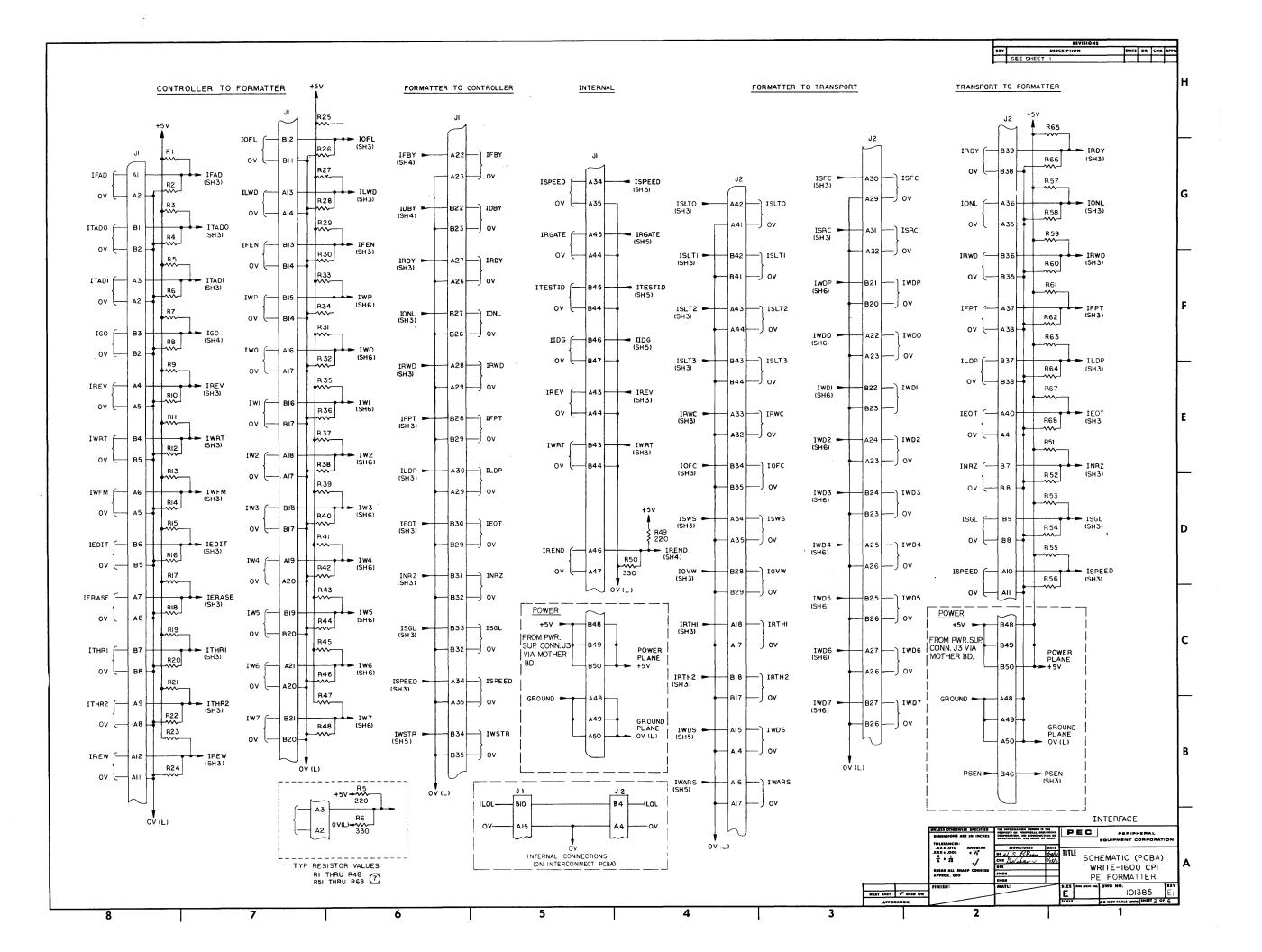

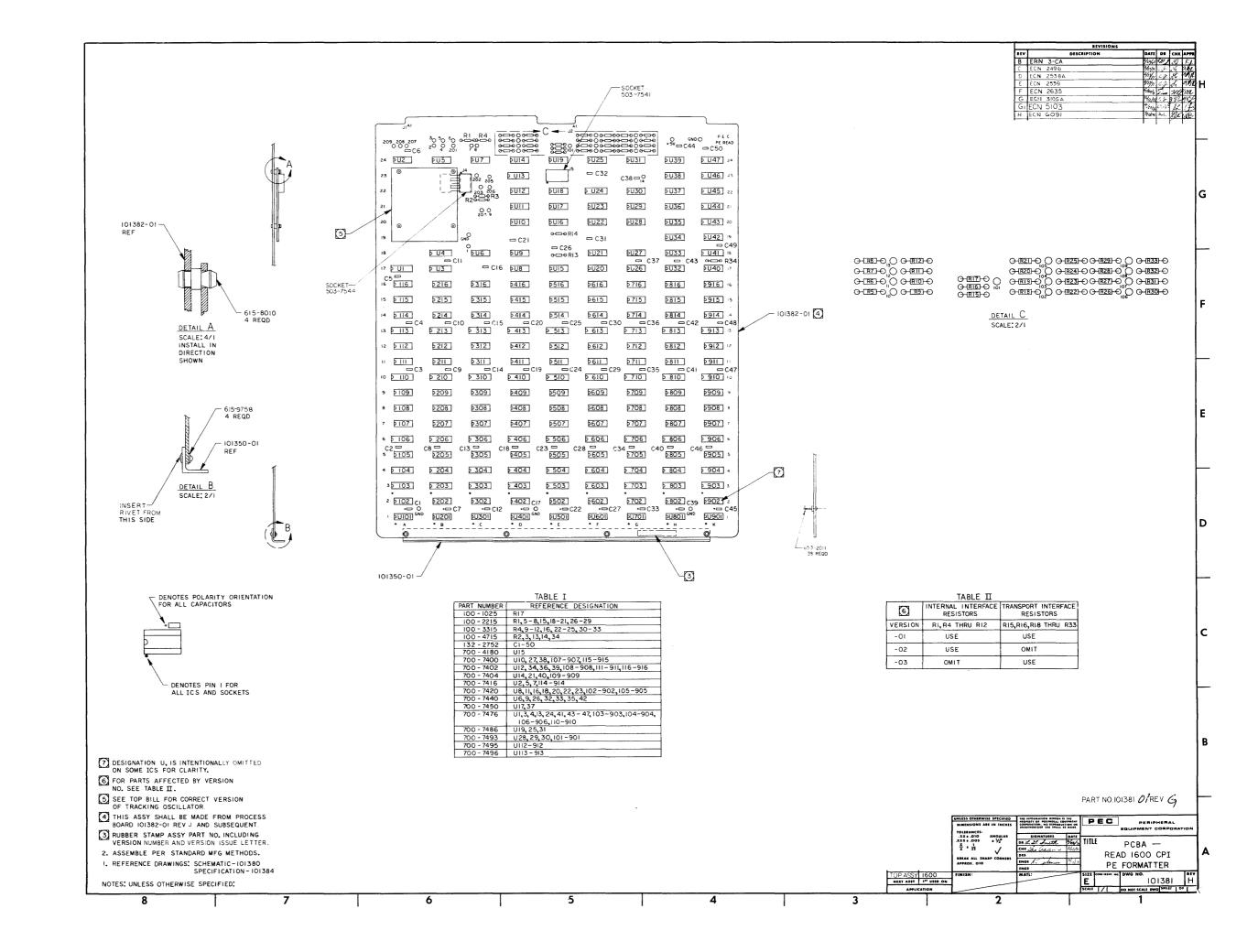

| SECTION                                | VII — P                                | ARTS LIST AND SCHEMATICS                                                                                                                                                                                                                                                                                                                                      |                                                                    |

| 7.1<br>7.2<br>7.3<br>7.4               | Illustra<br>Spare I                    | uction                                                                                                                                                                                                                                                                                                                                                        | 7-1<br>7-1                                                         |

# LIST OF ILLUSTRATIONS

| ì | Figure |                                                                         | Page |

|---|--------|-------------------------------------------------------------------------|------|

|   | 1-1    | Buffered PE Formatter                                                   | 1-2  |

|   | 1-2    | Typical System Configuration                                            | 1-3  |

|   | 1-3    | Interface Configuration                                                 | 1-4  |

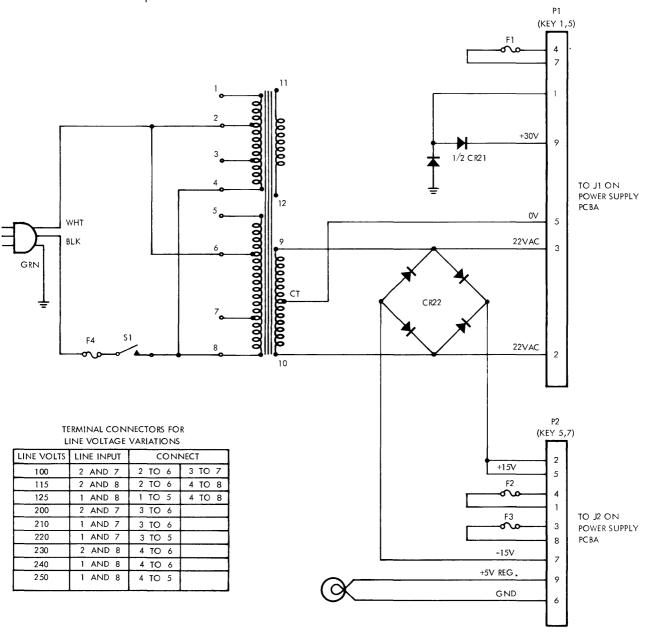

|   | 2-1    | Transformer Primary Connections                                         | 2-2  |

|   | 2-2    | Rack Mounting the Buffered Formatter                                    | 2-3  |

|   | 3-1    | 9-Track PE Tape Format                                                  | 3-2  |

|   | 4-1    | Relationship of Major Buffered Formatter Assemblies                     | 4-2  |

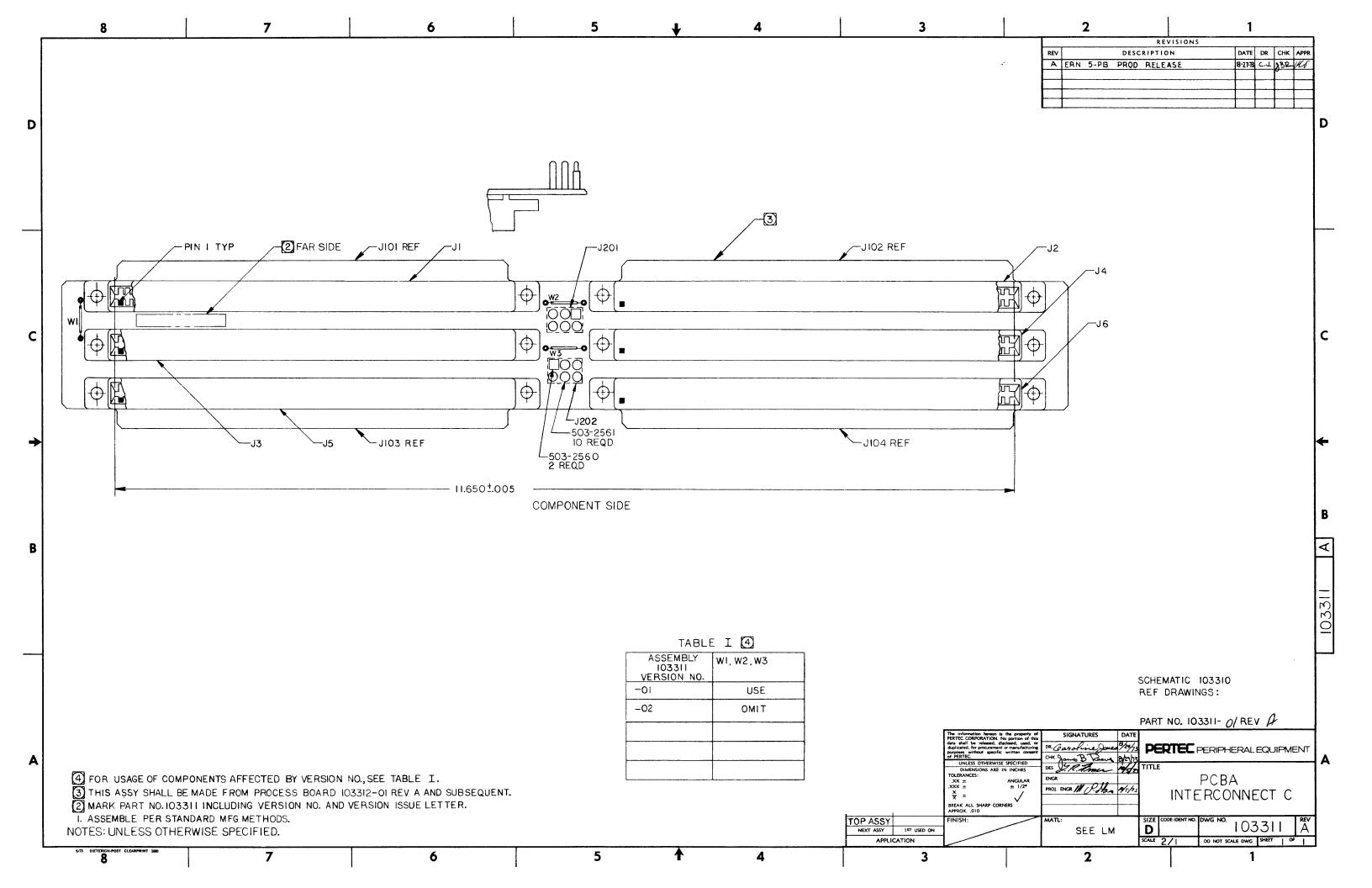

|   | 4-2    | Interconnect C Motherboard                                              | 4-3  |

|   | 4-3    | Power Supply Block Diagram                                              | 4-4  |

|   | 4-4    | PE Formatter Logic Organization                                         | 4-5  |

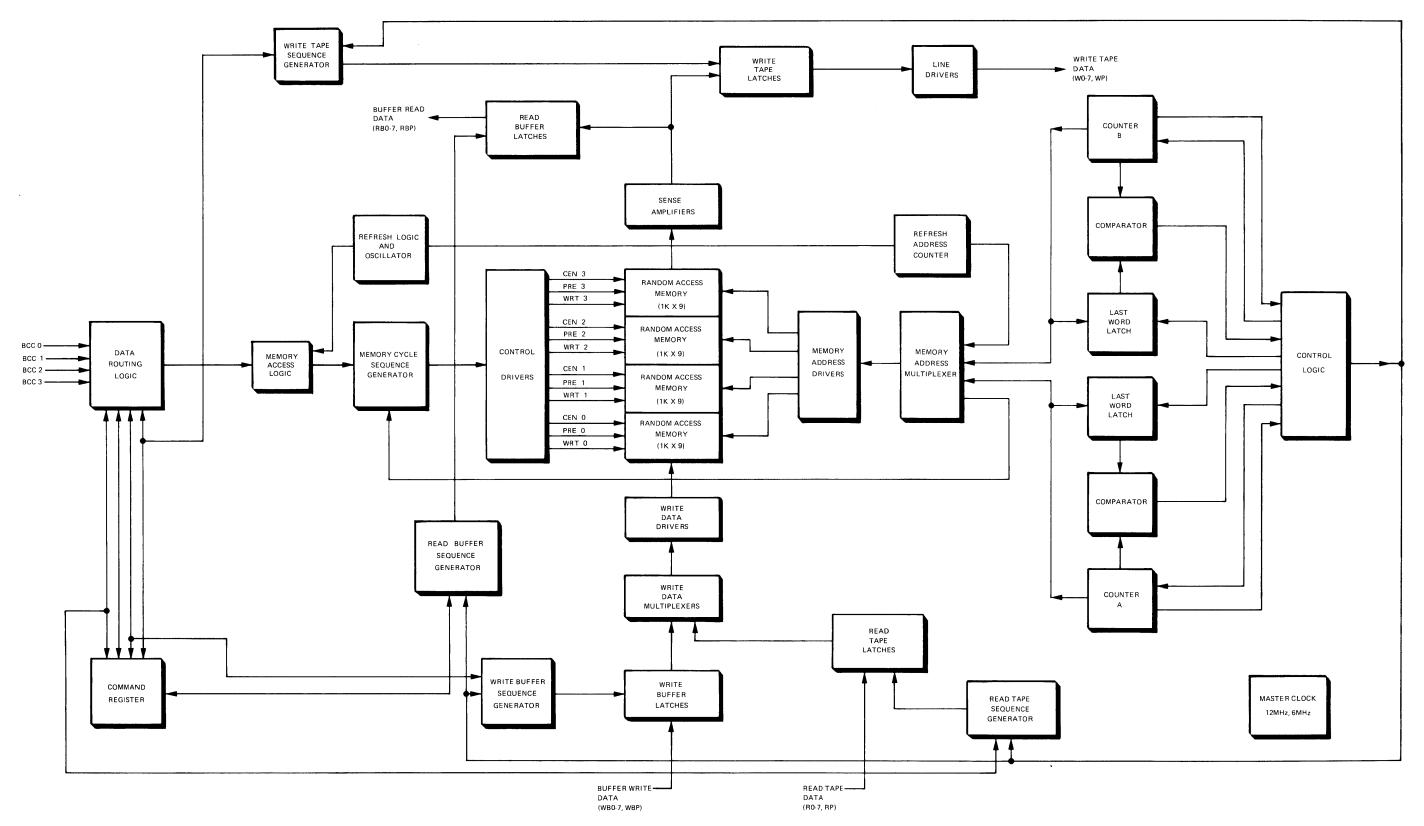

|   | 4-5    | Buffered PE Formatter Logic Organization                                | 4-6  |

|   | 4-6    | Buffer Organization Simplified Control Block Diagram                    | 4-29 |

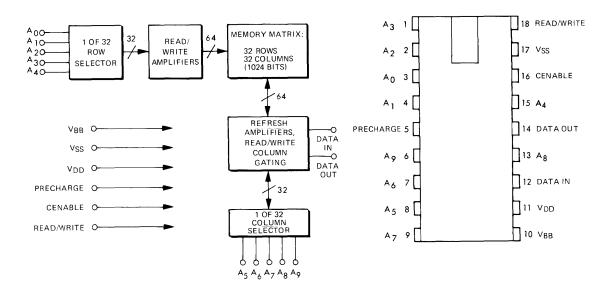

|   | 4-7    | Basic Memory Element                                                    | 4-9  |

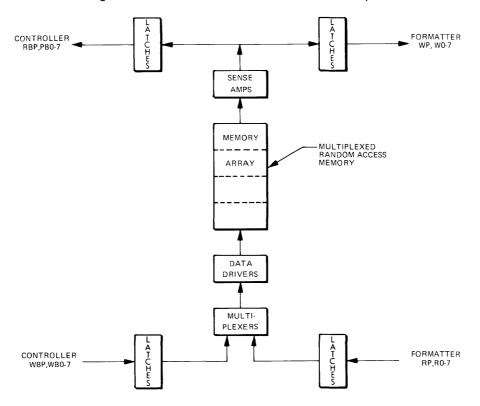

|   | 4-8    | Basic Data Flow                                                         | 4-10 |

|   | 4-9    | Configuration Control                                                   | 4-11 |

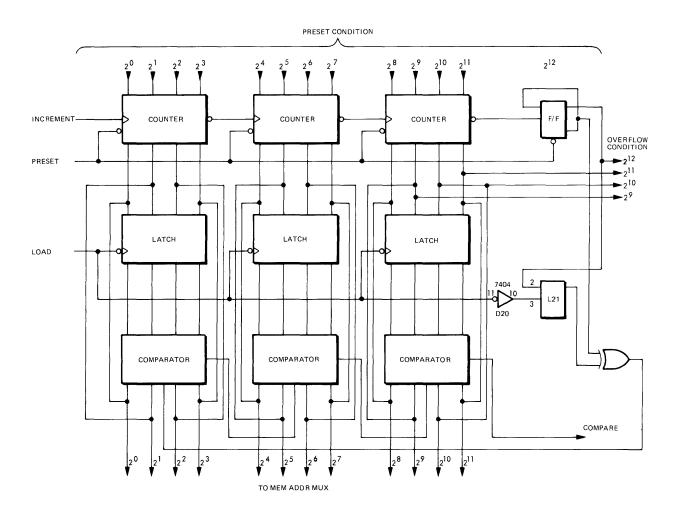

|   | 4-10   | Reference Counter Preset Conditions                                     | 4-12 |

|   | 4-11   | Overflow Conditions                                                     | 4-13 |

|   | 4-12   | Controller/Buffer Commands                                              | 4-14 |

|   | 4-13   | Buffer/Formatter Commands                                               | 4-15 |

|   | 4-14   | Buffered Formatter Transfer Function                                    | 4-16 |

|   | 4-15   | Write Logic, Simplified Block Diagram                                   | 4-19 |

|   | 4-16   | Phase Encoded Write Operation                                           | 4-21 |

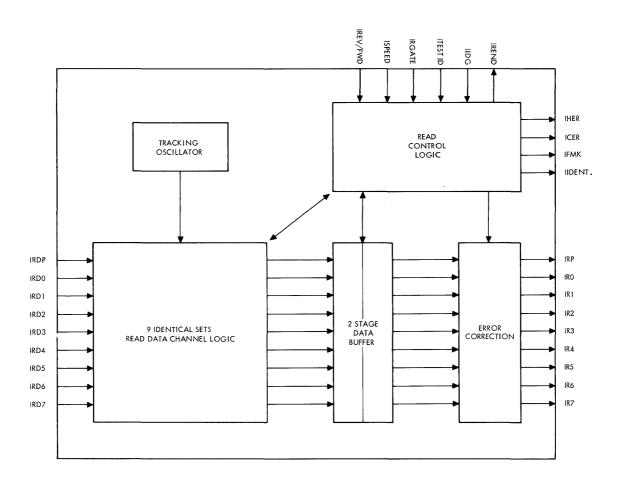

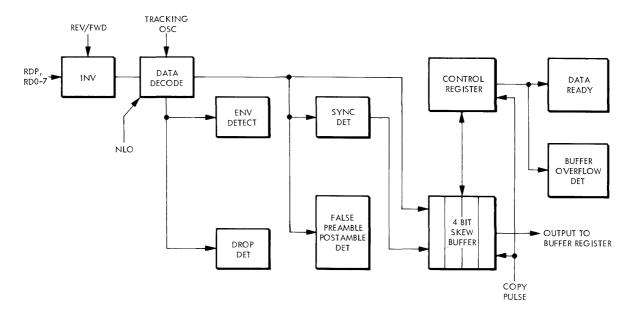

|   | 4-17   | PE Read PCBA, Simplified Block Diagram                                  | 4-24 |

|   | 4-18   | Read Data Channel Logic                                                 | 4-25 |

|   | 4-19   | PE Read Operation Illustrating Error Correction for Last Two Data Bytes | 4-27 |

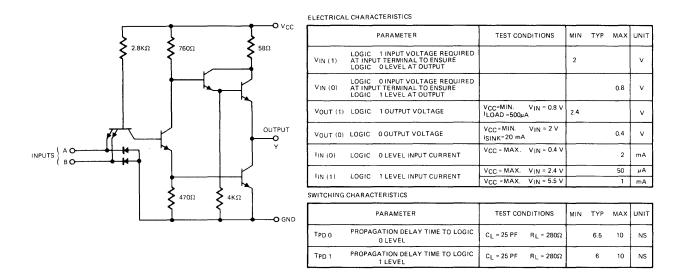

|   | 5-1    | Typical TTL Parameters                                                  | 5-2  |

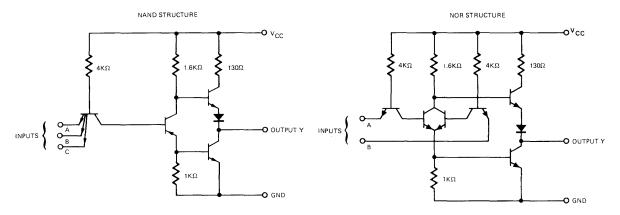

|   | 5-2    | 2-Input NAND Gate                                                       | 5-2  |

|   | 5-3    | 2-Input NOR Gate                                                        | 5-3  |

|   | 5-4    | Inverter (Type 7404)                                                    | 5-3  |

|   | 5-5    | 3-Input NAND Gate                                                       | 5-3  |

|   | 5-6    | Inverter Buffer / Driver                                                | 5-3  |

|   | 5-7    | 2-Input NAND Buffer                                                     |      |

|   | 5-8    | 2-Wide 2-Input AND-OR-INVERT Gate                                       | 5-4  |

802B X

# LIST OF ILLUSTRATIONS (continued)

| Figure |                                                                          | Page |

|--------|--------------------------------------------------------------------------|------|

| 5-9    | J-K Flip-Flop                                                            | 5-5  |

| 5-10   | 4-Bit Magnitude Comparator, Logic Symbol                                 | 5-6  |

| 5-11   | 4-Bit Magnitude Comparator, Logic Diagram                                | 5-7  |

| 5-12   | EXCLUSIVE-OR Gate                                                        | 5-7  |

| 5-13   | 5-Bit Shift Register                                                     | 5-8  |

| 5-14   | Data Selector Multiplexer                                                | 5-9  |

| 5-15   | Dual Data Selector/Multiplexer                                           | 5-10 |

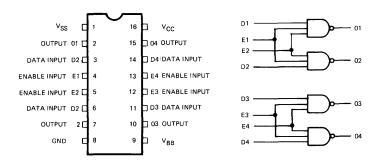

| 5-16   | Dual Decoder/Demultiplexer                                               | 5-11 |

| 5-17   | Quadruple Data Selector/Multiplexer                                      | 5-12 |

| 5-18   | Hex/Quadruple D-Type Flip-Flop                                           | 5-13 |

| 5-19   | Synchronous 4-Bit Counter                                                | 5-15 |

| 5-20   | Clear, Preset, Count, and Inhibit Sequences for Type 74161 4-Bit Counter | 5-15 |

| 5-21   | Dual Line Receiver/Sense Amplifier                                       | 5-16 |

| 5-22   | Operational Amplifier                                                    | 5-17 |

| 5-23   | Typical High-Speed TTL Parameters                                        | 5-17 |

| 5-24   | High-Speed 2-Input NAND Gate                                             | 5-17 |

| 5-25   | High-Speed Inverter                                                      | 5-18 |

| 5-26   | High-Speed J-K Master-Slave Flip-Flop                                    | 5-19 |

| 5-27   | MOS Silicon Gate                                                         | 5-19 |

| 5-28   | Schottky Bipolar Pin Configuration and Logic Symbol                      | 5-20 |

| 5-29   | Schottky Bipolar Waveforms and Switching Characteristics                 | 5-20 |

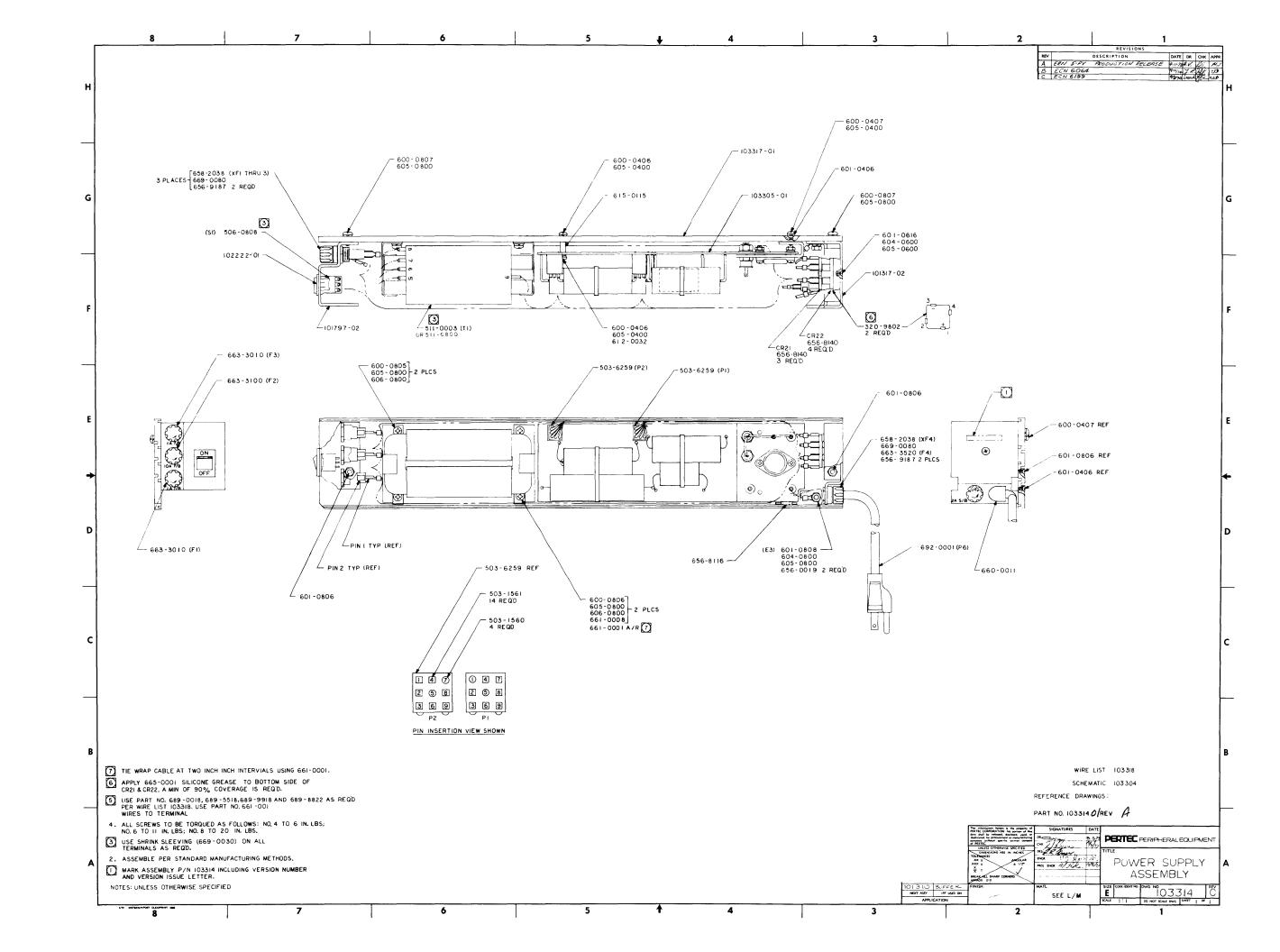

| 5-30   | Chassis Mounted Power Supply Components                                  | 5-21 |

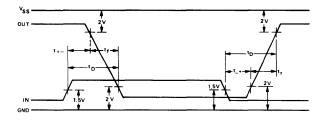

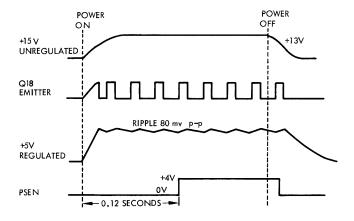

| 5-31   | Switching Regulator Waveforms                                            | 5-22 |

| 5-32   | Fixed Oscillator Waveforms                                               | 5-24 |

| 5-33   | Tracking Oscillator Control Waveforms                                    | 5-26 |

| 5-34   | Operation of Tracking Oscillator                                         | 5-27 |

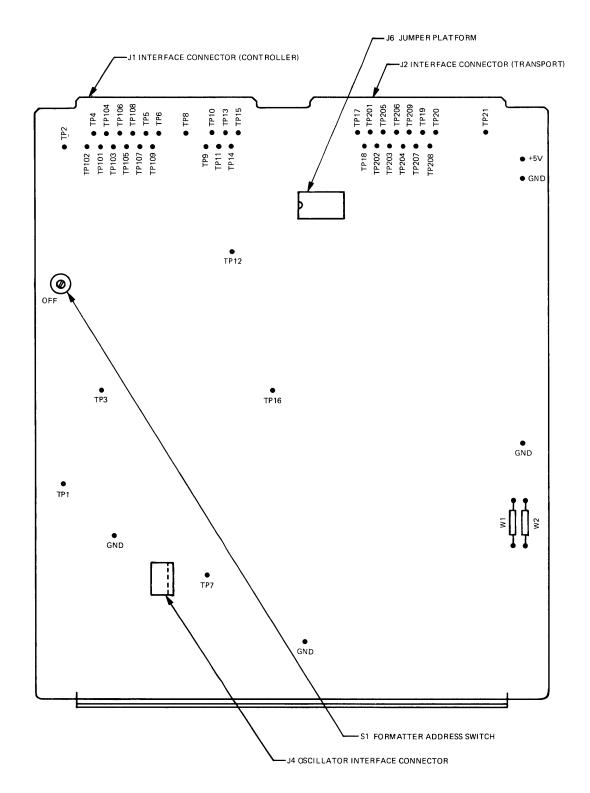

| 5-35   | PE Write PCBA, Test Point and Connector Placement                        | 5-29 |

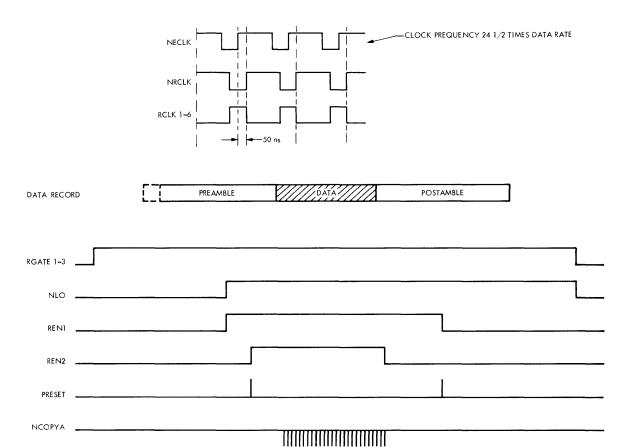

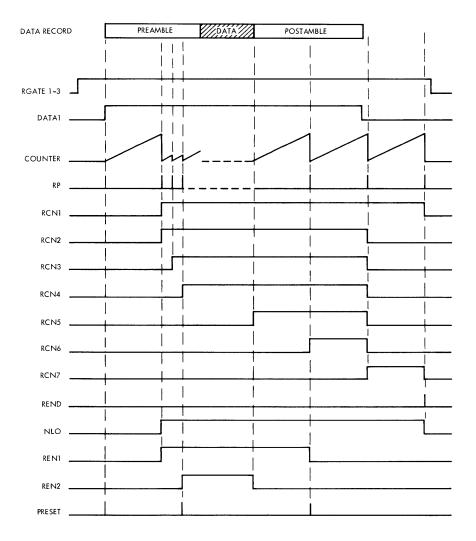

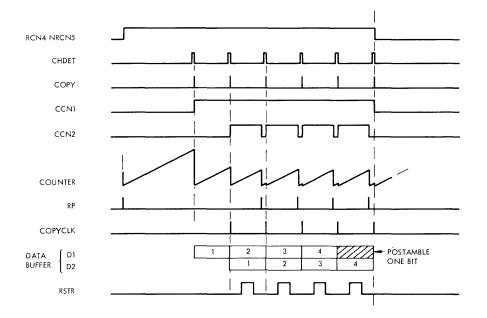

| 5-36   | Clock Waveforms                                                          | 5-32 |

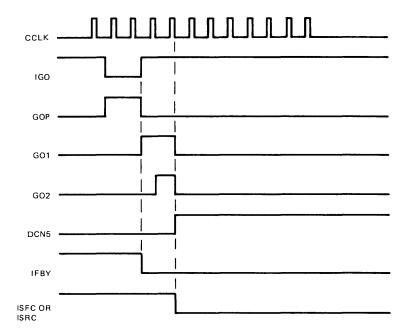

| 5-37   | Command Initiation Waveforms                                             | 5-33 |

| 5-38   | Command Timing                                                           | 5-35 |

| 5-39   | On-the-Fly Operation                                                     | 5-37 |

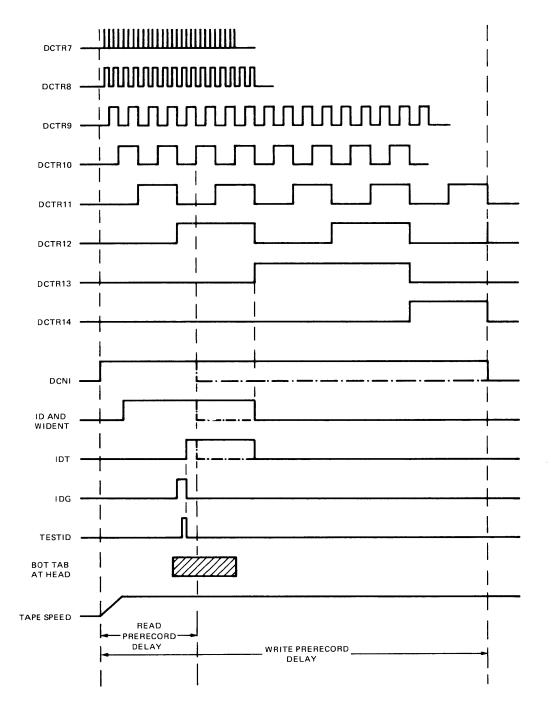

| 5-40   | Identification Timing, Read and Write                                    | 5-38 |

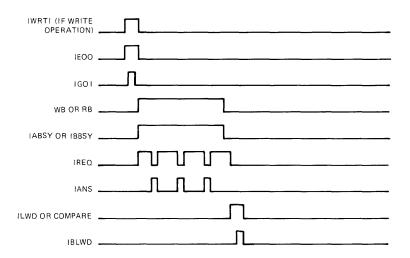

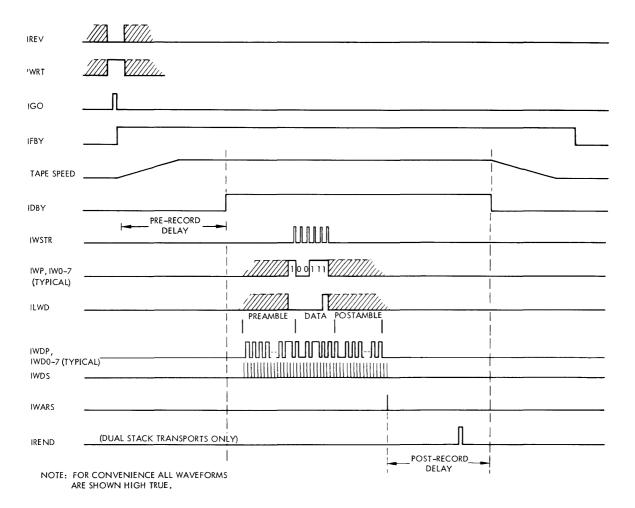

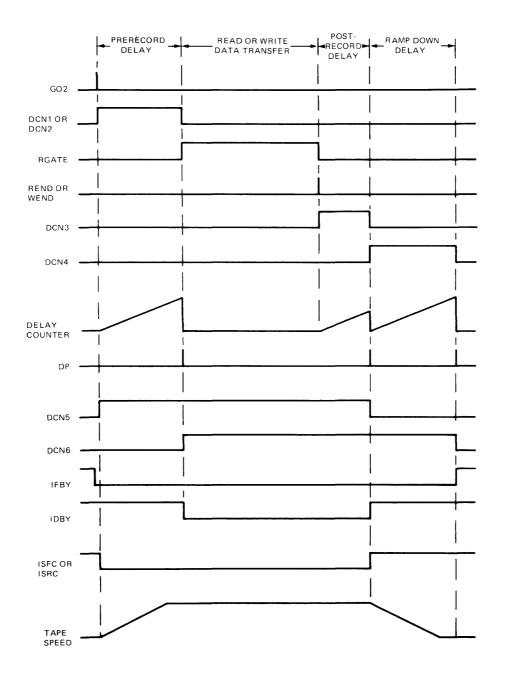

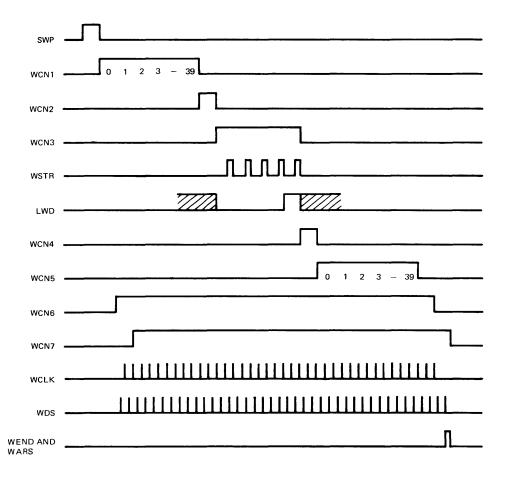

| 5-41   | Write Sequence                                                           | 5-40 |

| 5-42   | Write Data Encoding                                                      | 5-42 |

# LIST OF ILLUSTRATIONS (continued)

| Figure |                                                  | Page |

|--------|--------------------------------------------------|------|

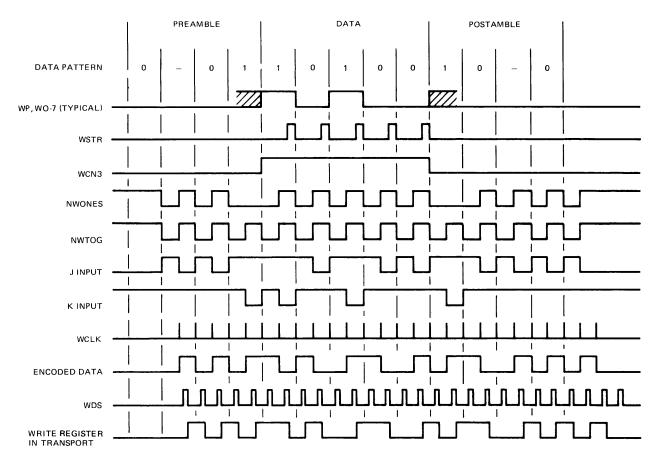

| 5-43   | PE Read PCBA, Test Point and Connector Placement | 5-45 |

| 5-44   | Read Input Signals                               | 5-46 |

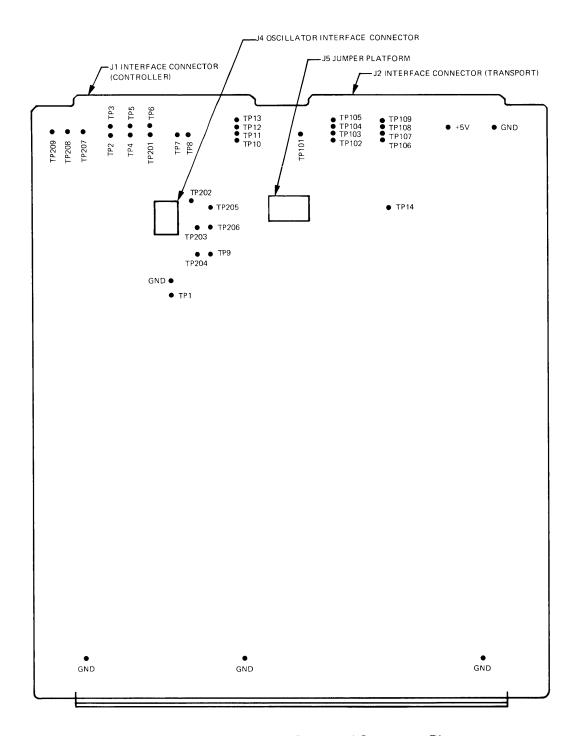

| 5-45   | Data Decoding Waveforms                          | 5-48 |

| 5-46   | Envelope and Drop Waveforms                      | 5-49 |

| 5-47   | Data Buffering                                   | 5-50 |

| 5-48   | Tracking Control Waveforms                       | 5-55 |

| 5-49   | Control Signals to Data Channels                 | 5-56 |

| 5-50   | Sequence Control                                 | 5-57 |

| 5-51   | Data Control                                     | 5-59 |

| 5-52   | File Mark Waveforms                              | 5-59 |

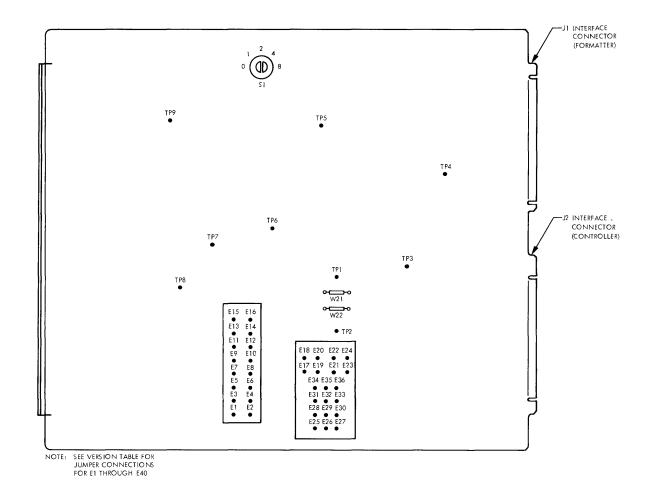

| 5-53   | Buffer PCBA, Test Point and Connector Placement  | 5-62 |

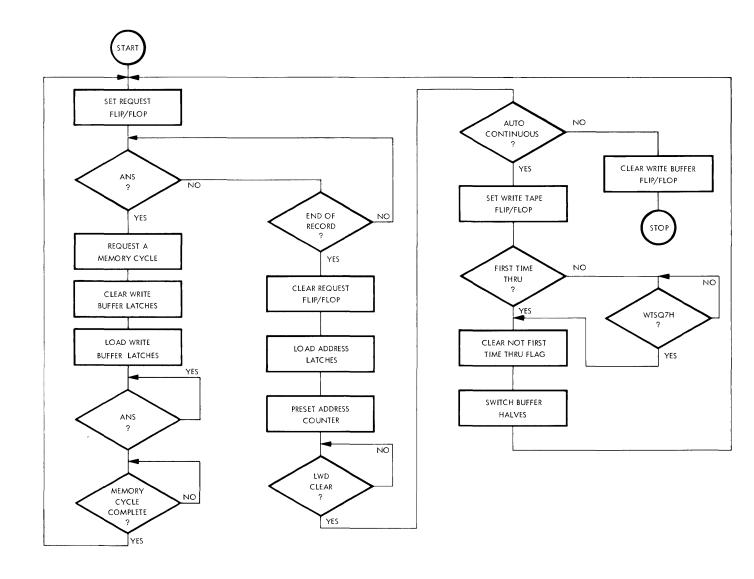

| 5-54   | Write Buffer, Simplified Flow Diagram            | 5-75 |

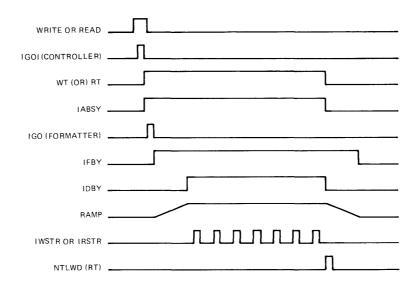

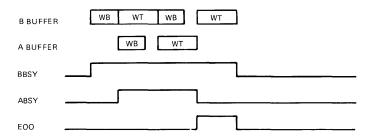

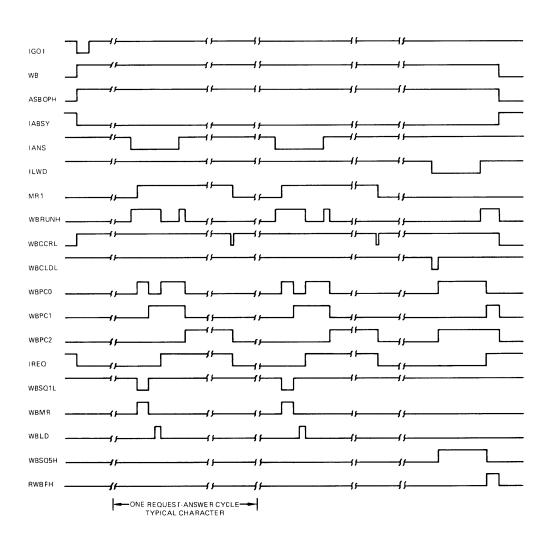

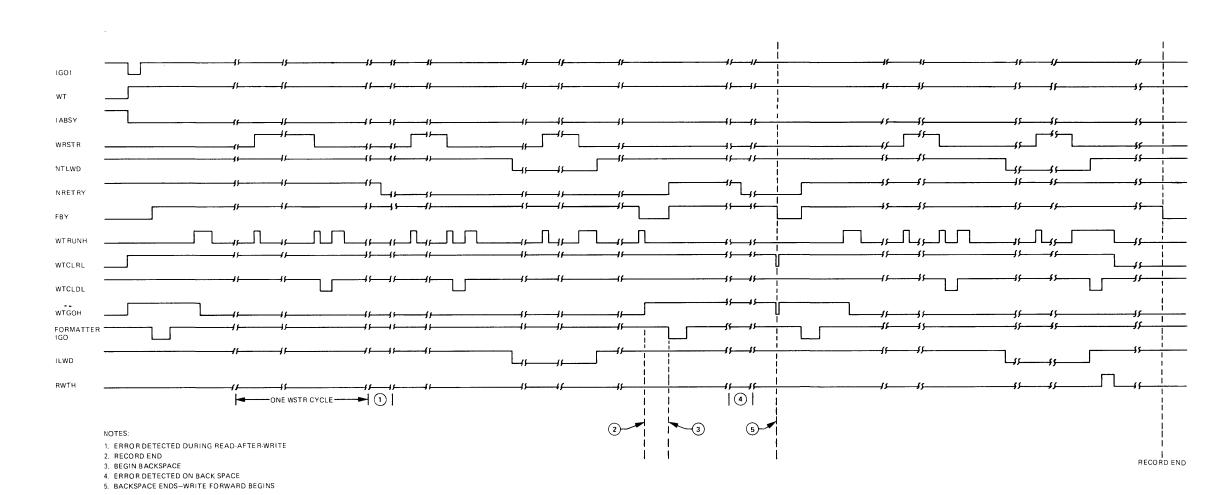

| 5-55   | Write Buffer, Timing Diagram                     | 5-77 |

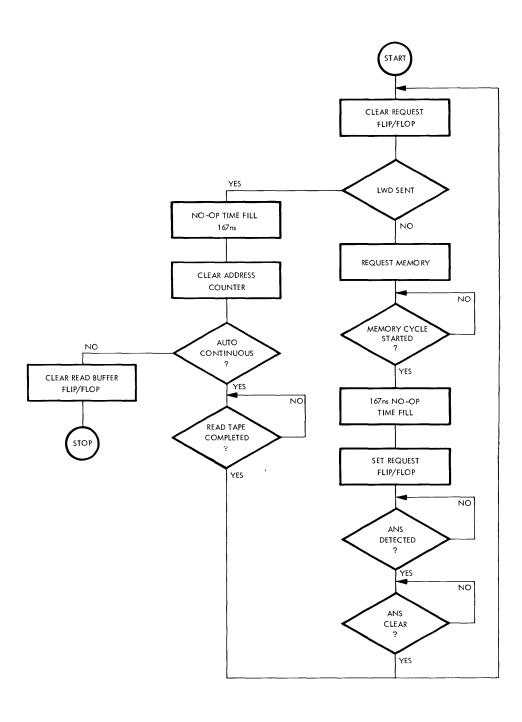

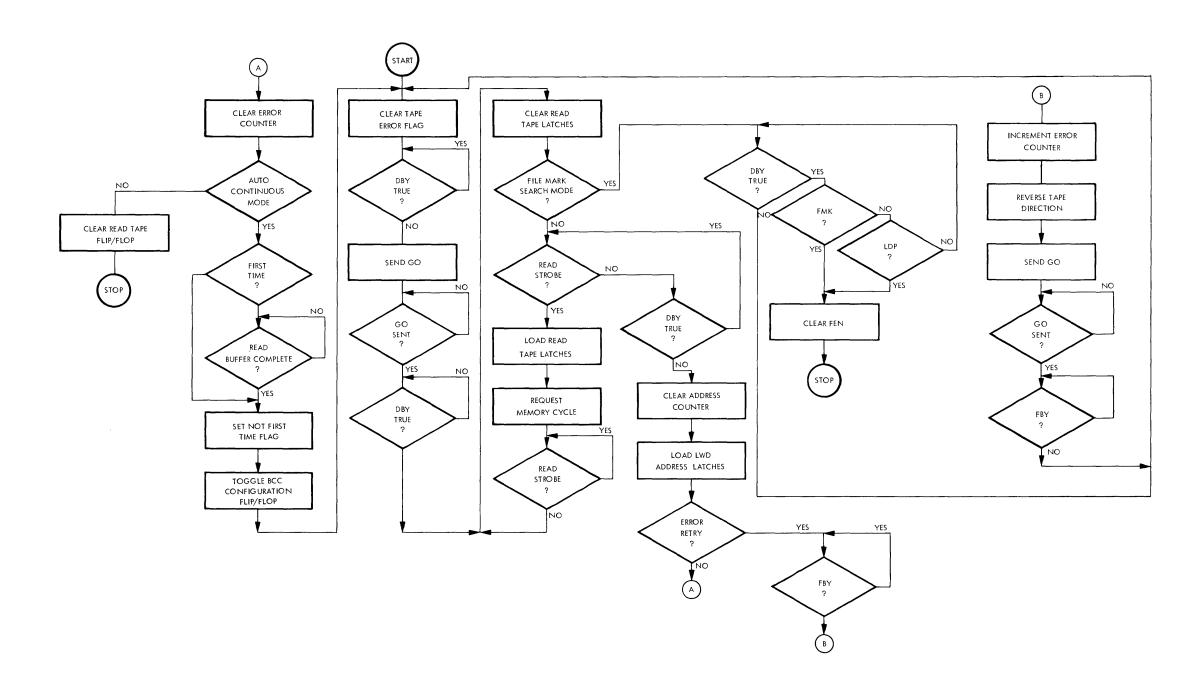

| 5-56   | Read Buffer, Simplified Flow Diagram             | 5-79 |

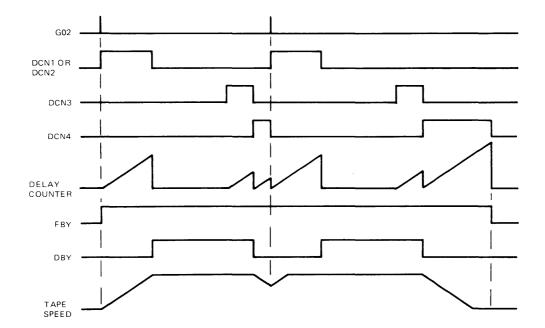

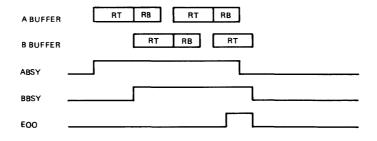

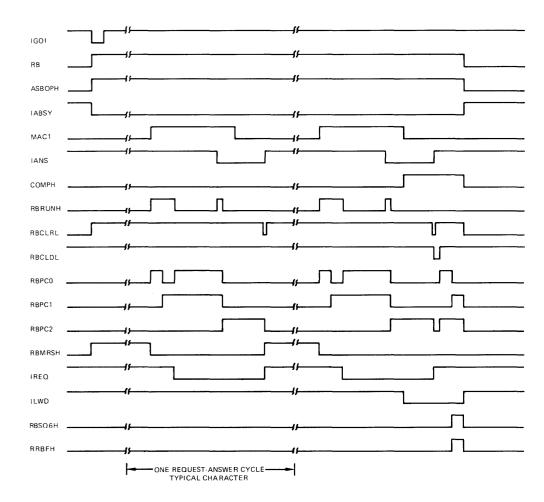

| 5-57   | Read Buffer, Timing Diagram                      | 5-81 |

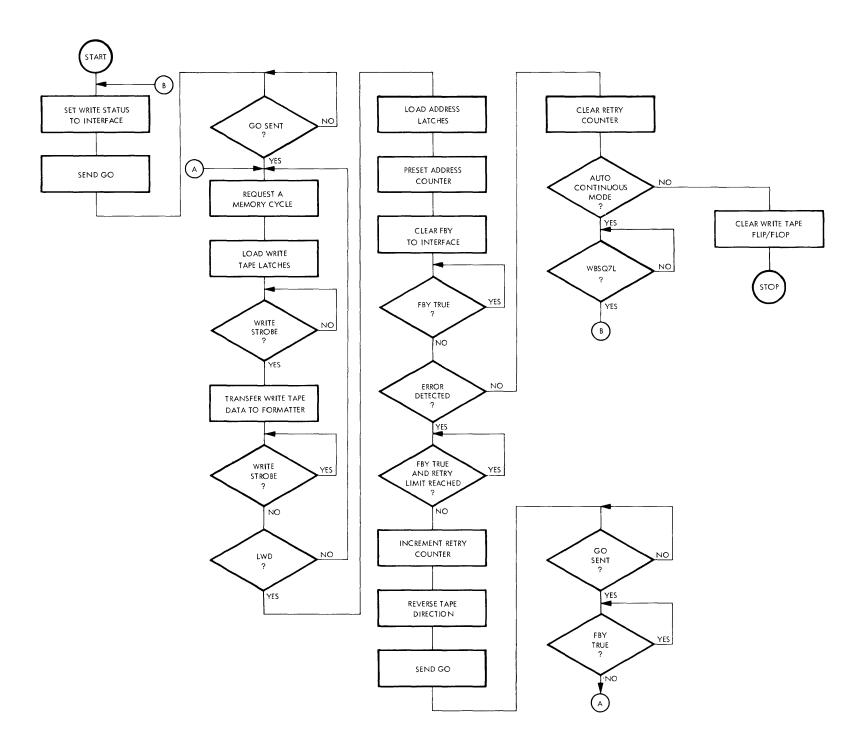

| 5-58   | Write Tape, Simplified Flow Diagram              | 5-83 |

| 5-59   | Write Tape, Timing Diagram                       | 5-85 |

| 5-60   | Read Tape Simplified Flow Diagram                | 5-87 |

| 5-61   | Automatic Write Continuous Transfer              | 5-72 |

| 5-62   | Automatic Read Continuous Transfer               | 5-73 |

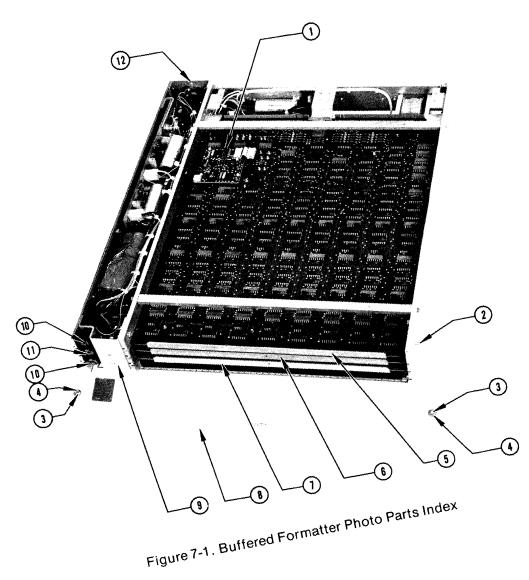

| 7-1    | Buffered Formatter Photo Parts Index             | 7-2  |

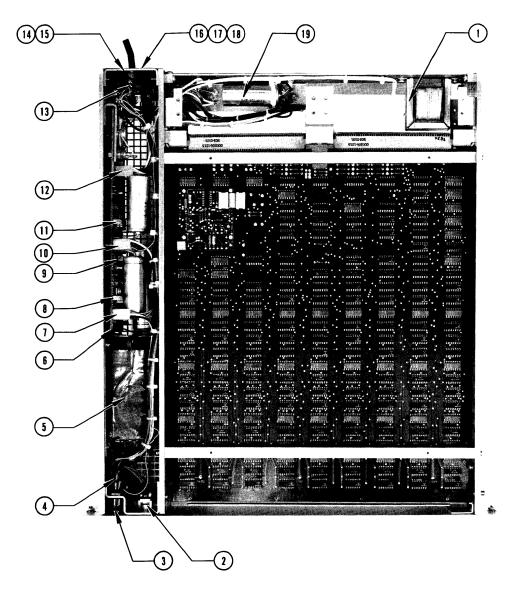

| 7-2    | Buffered Formatter Photo Parts Index             | 7-4  |

# LIST OF TABLES

| Table |                                                      | Page |

|-------|------------------------------------------------------|------|

| 1-1   | Mechanical and Electrical Specifications             | 1-5  |

| 2-1   | Interface Connections, Buffered Formatter/Transport  | 2-5  |

| 2-2   | Internal Connections Formatter/Buffer                | 2-5  |

| 2-3   | Interface Connections, Buffered Formatter/Controller | 2-5  |

| 3-1   | Command Coding                                       | 3-2  |

| 5-1   | Formatter Delays                                     | 5-34 |

| 5-2   | Buffer Version Identification                        | 5-62 |

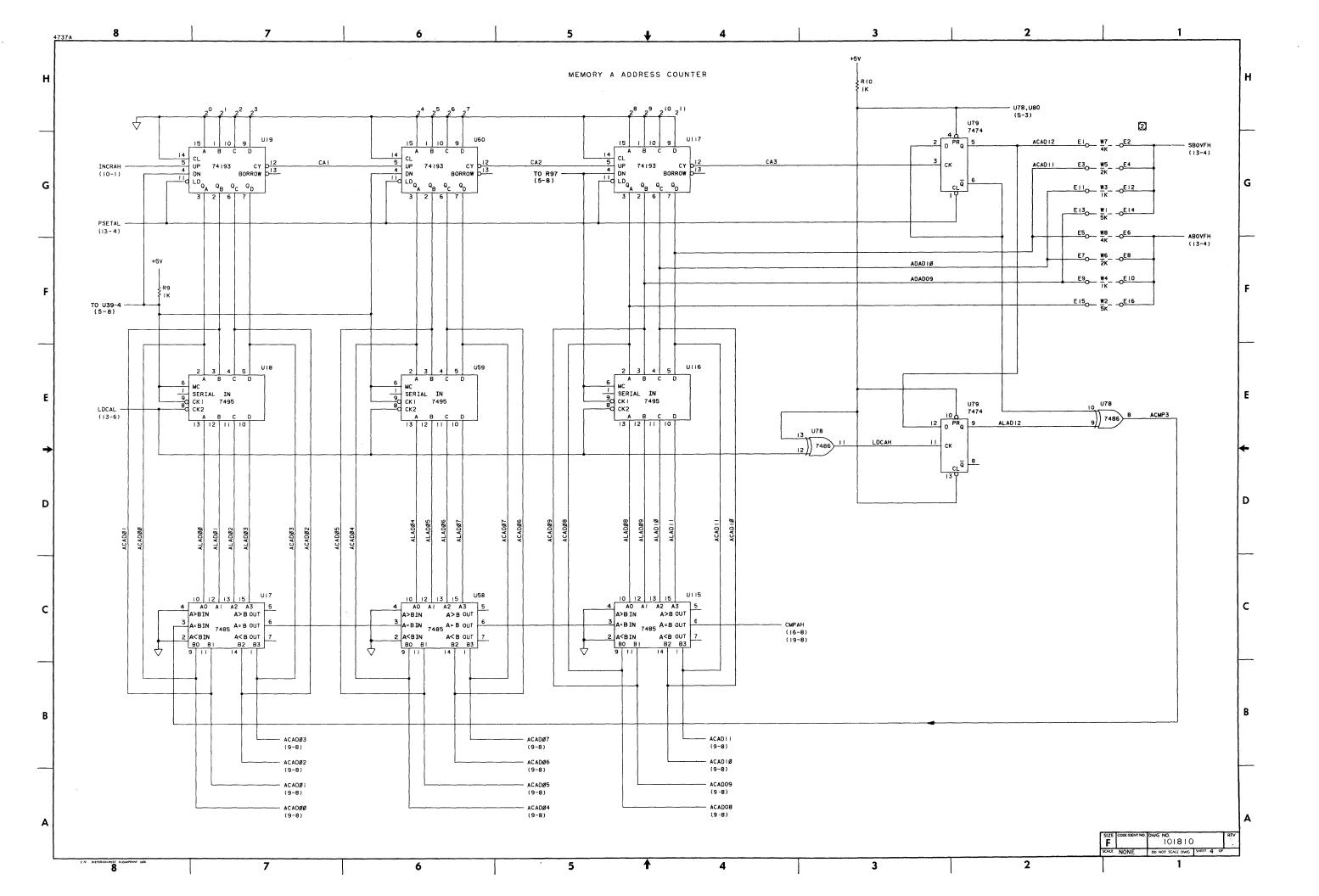

| 5-3   | Memory A Address Counter Jumper Connections          | 5-64 |

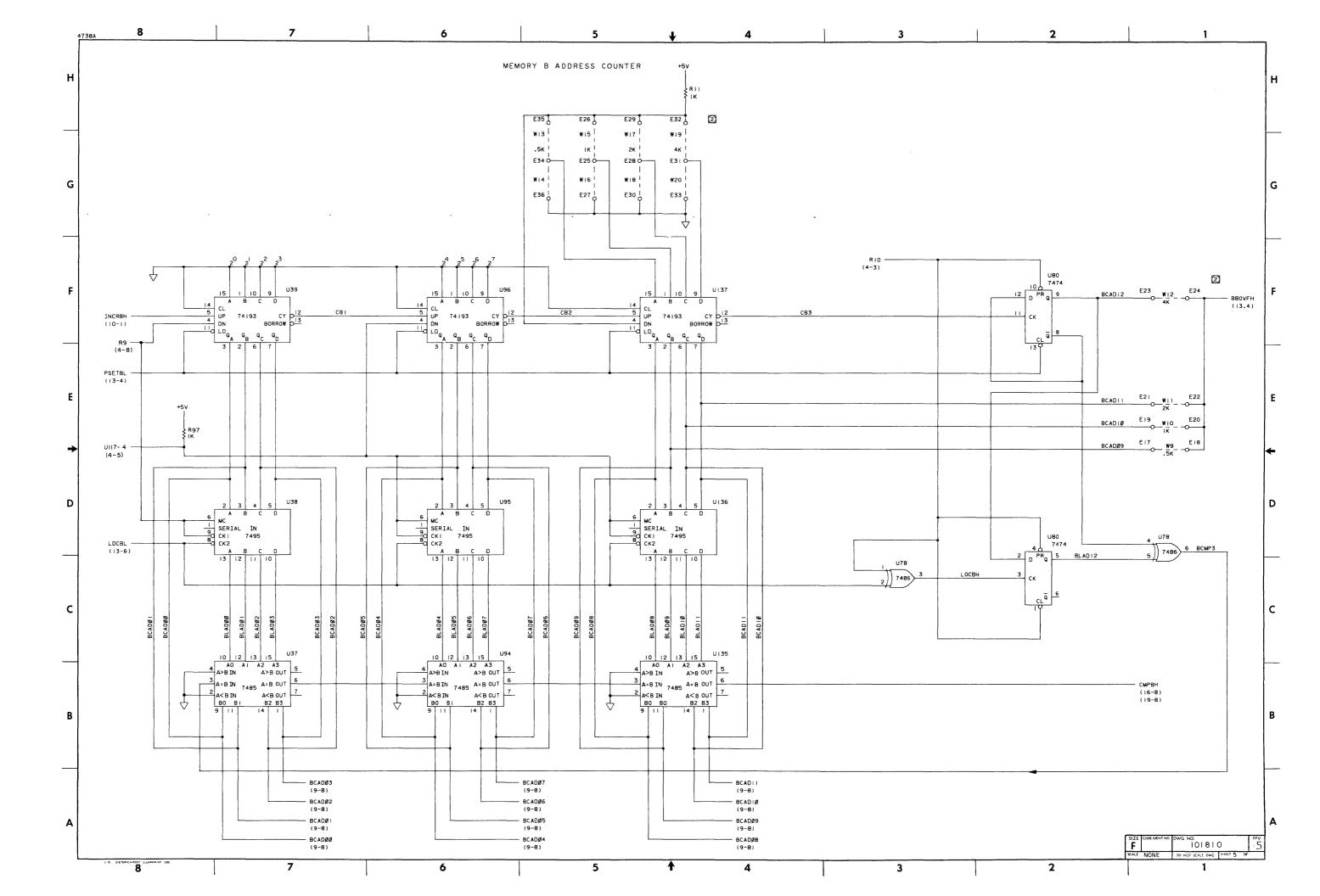

| 5-4   | Memory B Address Counter Jumper Connections          | 5-64 |

| 7-1   | Buffered Formatter Photo Parts Index                 | 7-3  |

| 7-2   | Buffered Formatter Photo Parts Index                 | 7-5  |

| 7-3   | Buffered PE Formatter Spare Parts List               | 7-6  |

| 7-4   | Part Number Cross Reference                          | 7-7  |

XIII 802B

802B XIV

# SECTION I GENERAL DESCRIPTION AND SPECIFICATIONS

#### 1.1 INTRODUCTION

This section provides a physical description, functional description, and specifications for the Buffered Phase Encoded Formatter, Model BF6X9, 0.5K/1K/2K/4K, manufactured by PERTEC Peripheral Equipment Division, Chatsworth, California.

#### 1.2 PURPOSE OF EQUIPMENT

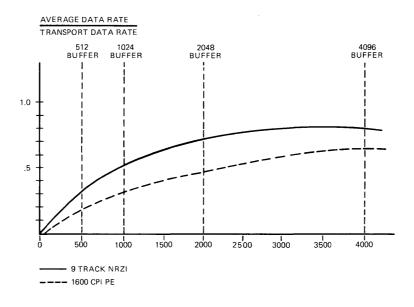

The Buffered Phase Encoded Formatter enables the asynchronous generation and reading of Phase Encoded (PE) ANSI and IBM compatible magnetic tapes when used in conjunction with PERTEC PE Magnetic Tape Transports. Data buffering, encoding, decoding, deskewing, error correction and tape motion control are provided by the formatter. The buffer portion of the formatter is 9 bits wide and may be one of four optional lengths. The ninth bit position may be used for flag data and is presented to the controller interface only. The buffer allows the data transfer to and from the customer's controller to be entirely asynchronous from 0 to 750 KHz.

Individual selection and operation with up to four *daisy-chained* PERTEC transports is provided. Normally, all transports attached to a formatter must be of the same speed. However, a dual speed option is available which allows the formatter to operate with any two different transport tape speeds. This option should be specified at the time of ordering.

The formatter section is capable of handling tape speeds in the range of 6.25 to 75.0 inches per second (ips).

The formatter operates directly from 100v ac to 250v ac, single phase, 48 to 400 Hz power. A tapped power transformer facilitates selection of the proper voltage.

#### 1.3 PHYSICAL DESCRIPTION OF EQUIPMENT

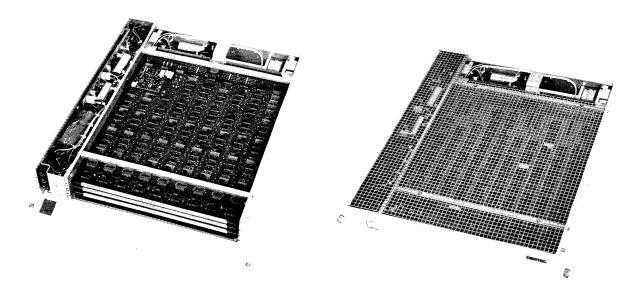

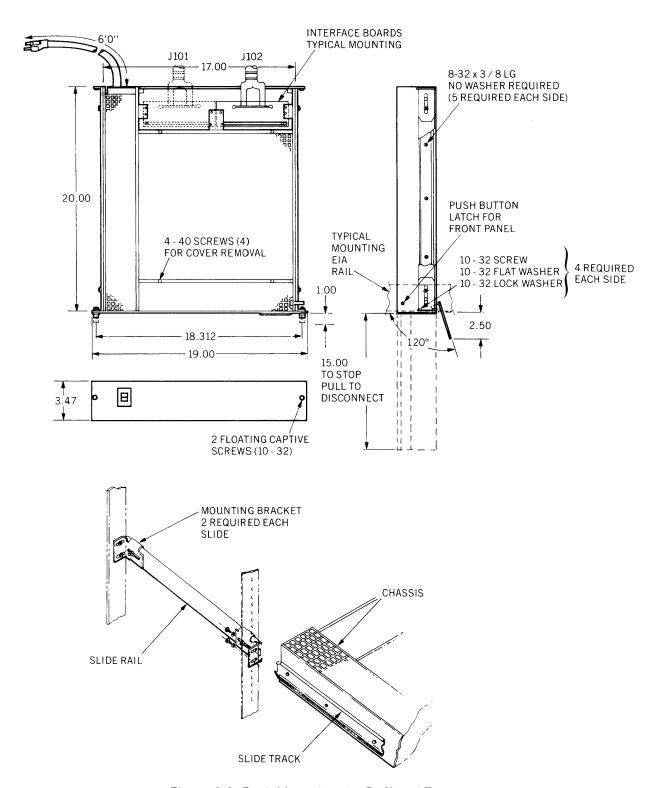

Two views of the Buffered PE Formatter are shown in Figure 1-1. The complete assembly is designed to be slide-mounted in a standard 19-inch EIA rack.

The formatter can be withdrawn from the rack to within three-quarters of its depth to facilitate servicing. The unit can be completely removed from the rack by increasing the withdrawing force.

The power supply and printed circuit boards are protected by a perforated panel which can be removed while the unit is extended. This provides access to the printed circuit boards from the top. A swing-down front panel (with cutouts to clear the power switch) provides access from the front.

A single operational control, the power switch, is located at the front of the power supply. Power is supplied through a 6-foot strain-relieved cord with a standard 3-pin plug.

Interface signals make connection to the formatter via edge connectors at the rear of the unit.

1-1

802B

Figure 1-1. Buffered PE Formatter

# 1.4 FUNCTIONAL DESCRIPTION

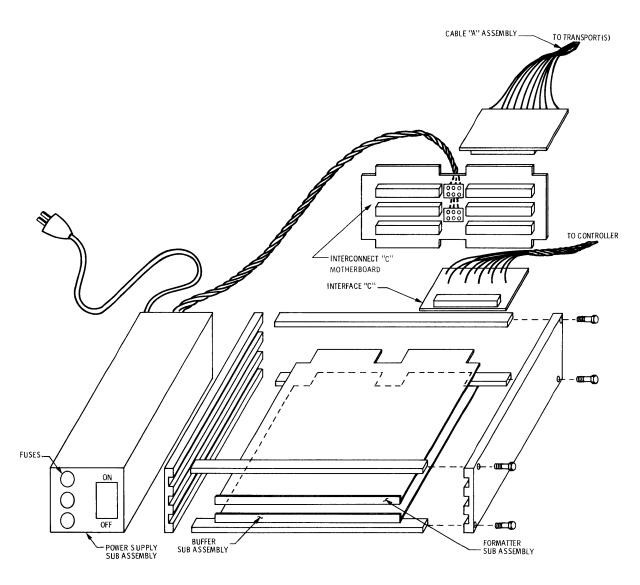

The Buffered PE Formatter contains all logic and functions associated with the reading and writing of IBM and ANSI compatible 1600 cpi magnetic tape.

All logic for the generation of preamble, postamble, phase encoding data, and file mark patterns for recording onto magnetic tape is included in the formatter. Also, logic for the complete recovery of read data, including data decoding, buffering, error and file mark detection, and error correction logic is included.

Additionally, the formatter includes the following features.

- (1) All timing necessary for the generation of IBM compatible IBGs and for correct head positioning between records.

- (2) Compatibility with transports having either single- or dual-stack heads.

- (3) Automatic recording of a Phase Mode identification burst prior to recording the first record on a tape.

- (4) Automatic testing for the Phase Mode identification burst when reading the first record on a tape.

- (5) Provision for fixed and variable length erase commands.

- (6) Facility for generation of special commands for the editing of previously recorded tapes.

- (7) Data buffering at optional lengths (512, 1024, 2048, or 4096) to be specified at time of order. Buffering can be performed either in a single- or split-buffer mode. Split, or double, buffering provides the customer with the option of continuous data flow at substantial throughput rates.

- (8) Switch selectable error recovery attempts during read/write tape operation.

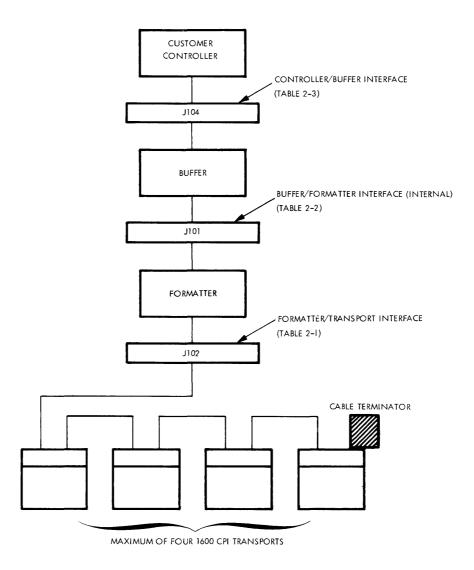

Two interfaces are provided, one to a controller and the other to the tape transports. Up to four transports may be daisy-chained on the transport interface. Figure 1-2 illustrates a typical system configuration.

Figure 1-2. Typical System Configuration

#### 1.5 MODEL DIFFERENCES

This manual covers the description of Models BF609, BF619, BF629, and BF649. The basic differences between the models are as follows.

(1) Model BF649 (Read After Write), Model BF629 (Read/Write)

These models are similar except that Model BF649 is designed to operate with transports having a dual stack head, and BF629 is designed for use with transports having a single stack head. Both models consist of four basic sections: control logic, write logic, read logic, and buffer logic.

(2) Model BF619 (Read Only)

This model is used in Read Only applications, and consists of three basic sections: control logic, read logic, and buffer logic.

# (3) Model BF609 (Write Only)

This model is used in Write Only applications, and consists of three basic sections: control logic, write logic, and buffer logic.

Each of the models described in Steps (1) through (3) can be configured to any of four optional buffer lengths. The length of the buffer can be 512, 1024, 2048 or 4096 and must be specified by the customer when the formatter is ordered.

#### 1.6 MECHANICAL AND ELECTRICAL SPECIFICATIONS

The mechanical and electrical specifications are shown in Table 1-1.

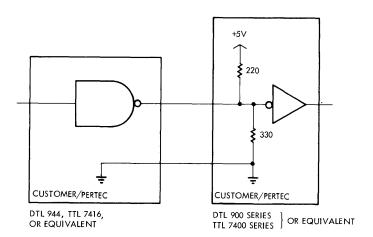

#### 1.6.1 INTERFACE SPECIFICATIONS

Levels: True = 0v (approximately)

False = +3v

Pulses: Levels as above. Minimum pulse width is 0.5 µsec. Edge transmission delay over

20 feet of cable is not greater than 100 nsec.

The interface circuits are designed so that a disconnected wire results in a false signal.

Figure 1-3 illustrates the configuration for which the transmitters and receivers have been designed.

Figure 1-3. Interface Configuration

Table 1-1

Mechanical and Electrical Specifications

| Buffer Lengths                                  | 512, 1024, 2048, or 4096*                                               |

|-------------------------------------------------|-------------------------------------------------------------------------|

| Recording Mode (IBM and ANSI Compatible)        | PE                                                                      |

| Packing Density                                 | 1600 cpi                                                                |

| Number of Channels                              | 9 (8 Data, 1 Parity)                                                    |

| Transport Tape Speed                            | 6.25 to 75 ips (15.87 to 190.5 cm/s)                                    |

| Data Rate Variation (Tracking Oscillator)       | ±10%                                                                    |

| Preamble                                        | 41 Characters                                                           |

| Postamble                                       | 41 Characters                                                           |

| ID Burst (1600 frpi)                            | Channel P                                                               |

| Tape Mark (3200 frpi)                           | Channels P, 0, 2, 5, 6, and 7                                           |

| Interblock Gap (IBG)                            | 0.6 inch (15.24 mm) (nominal)                                           |

| Parity                                          | Odd                                                                     |

| Dimensions<br>Height<br>Width<br>Depth          | 3.5 inches (8.89 cm)<br>19.0 inches (48.26 cm)<br>20.0 inches (50.8 cm) |

| Weight                                          | 25 pounds (11.34 kg) (maximum)                                          |

| Mounting — Standard 19-inch EIA Rack            | _                                                                       |

| Power Volts (ac) Watts (maximum) Frequency (Hz) | 100 — 250<br>150<br>48 — 400                                            |

| Electronics                                     | All Silicon, DTL, TTL, MOS                                              |

| Temperature<br>Operating<br>Non-Operating       | 2°C (35°F) to 50°C (122°F)<br>—45°C (—50°F) to 71°C (160°F)             |

| Altitude<br>Operating<br>Non-Operating          | 0 to 20,000 feet (0 to 6,096m)<br>0 to 50,000 feet (0 to 15,240m)       |

| Humidity (Operating)                            | 10 to 95% (Without Condensation)                                        |

| Error Retries (Switch Selectable)               | 0, 1, 2, 4, 8                                                           |

<sup>\*</sup>Optional Dual Buffer Lengths are 256, 512, 1024, 2048.

802B 1-6

# SECTION II INSTALLATION

#### 2.1 INTRODUCTION

This section contains a summary of interface lines, information for uncrating the formatter, as well as the procedure for electrically connecting the formatter.

#### 2.2 UNCRATING THE FORMATTER

The formatter is shipped in a protective container built to minimize the possibility of damage during shipping. The shipping container conforms to the National Safe Transit Committee Pre-Shipment Test Procedure.

The following procedure is used to uncrate the formatter unit.

- (1) Place the shipping container in the position indicated on the container.

- (2) Open the container by cutting the tape along the top joints of the container.

- (3) Remove four 4-inch square polyurethane corner blocks.

- (4) Remove the entire plywood shipping brace by lifting vertically.

- (5) Place the formatter (contained within the shipping brace) on a flat surface and remove four 1/4-inch steel bolts.

- (6) Remove the top plywood brace.

- (7) Lift the formatter from remaining plywood brace and place on a flat surface.

- (8) Remove the formatter from the plastic shipping bag.

- (9) Remove the cable and the manual from the shipping carton.

Check the contents of the shipping container against the packing slip; investigate for possible damage. Notify the carrier immediately if any damage is noted.

Access to the printed circuit boards is obtained by depressing the spring-loaded release button located on the right side of the formatter unit. The front panel, hinged at the bottom, will swing down to allow removal of the polyurethane foam pad placed inside the unit to prevent damage of the printed circuit boards during shipment.

Check the printed circuit boards and connectors for correct seating and installation.

Check that the identification label, located on the inside of the front panel, bears the correct model number and voltage requirement. If the actual line voltage at the installation site differs from that on the identification label, the power transformer taps should be changed as illustrated in Figure 2-1.

#### 2.3 POWER CONNECTIONS

A fixed, strain-relieved power cord is supplied for plugging into a polarized 115v ac outlet. For other power sockets, the supplied plug must be removed and the correct plug installed.

2-1

802B

| LINE<br>VOLTAGE | LINE<br>INPUT | CONNECT          |

|-----------------|---------------|------------------|

| 100             | 2 AND 7       | 2 AND 6, 3 AND 7 |

| 115             | 2 AND 8       | 2 AND 6, 4 AND 8 |

| 125             | 1 AND 8       | 1 AND 5, 4 AND 8 |

| 200             | 2 AND 7       | 3 AND 6          |

| 210             | 1 AND 7       | 3 AND 6          |

| 220             | 1 AND 7       | 3 AND 5          |

| 230             | 2 AND 8       | 4 AND 6          |

| 240             | 1 AND 8       | 4 AND 6          |

| 250             | 1 AND 8       | 4 AND 5          |

Figure 2-1. Transformer Primary Connections

# 2.4 RACK MOUNTING THE FORMATTER

The physical dimensions of the formatter, as illustrated in Figure 2-2, are such that it may be mounted in a standard 19-inch EIA rack; 3.5 inches of panel space is required. A depth of 20 inches behind the mounting surface is required.

To rack mount the formatter, proceed as follows.

- (1) Install the two side rails on the formatter using ten No. 8 screws (five per side). Refer to Figure 2-2 for correct positioning.

- (2) Install the two side rails in the EIA rack using eight No. 10 screws (four per rail). Refer to Figure 2-2 for correct positioning.

- (3) Taking care to align the side guides with the side rails, slide the formatter unit into the rack.

#### CAUTION

CARE SHOULD BE TAKEN TO ENSURE THAT THE POWER CORD AND INTERFACE WIRING BUNDLES ARE NOT DAMAGED DURING THE RACK MOUNTING OPERATION.

(4) Tighten the two captive retaining screws on the front of the formatter.

#### 2.5 INTERFACE CONNECTIONS

It is assumed that interconnection of PERTEC equipment and customer equipment uses a harness of individual twisted pairs, each with the following characteristics.

- (1) Maximum length of 20 feet.

- (2) Not less than one twist per inch.

- (3) 22- or 24-gauge conductor with minimum insulation thickness of 0.01 inch.

Ensure that the ground side of each twisted pair is grounded within a few inches of the signal source and destination.

Included with the formatter is a single input/output cable, five feet in length, which will connect to a transport. This cable is terminated with a strain-relieved edge connector.

Figure 2-2. Rack Mounting the Buffered Formatter

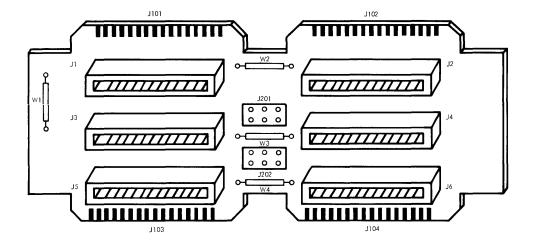

The signal connector is a 100-pin 0.1-inch center edge connector with a cable terminating board attached. Tables 2-1 and 2-3 list the input/output pin connections. Table 2-2 lists the internal formatter interface between the buffer and the formatter.

#### NOTE

Pins on the 100-pin connectors are numbered A1 through A50, and B1 through B50, where pin A1 is opposite B1, etc. Due to the topology of the motherboard, pin connections on the four external interface connectors are reversed at the PCBA connectors.

Table 2-1

Interface Connections, Buffered Formatter/Transport

| Connector<br>(Reference<br>Figure 2-2)           | Live<br>Pin                                                                                                        | Gnd<br>Pin                                                                                            | Signal*                                                                                                                                                                                                                                                                                                                                                                                                | Connector<br>(Reference<br>Figure 2-2)           | Live<br>Pin                                                                                                                              | Gnd<br>Pin                                                                                                                                             | Signal*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J102<br>Transport<br>to<br>Buffered<br>Formatter | A1<br>B1<br>B3<br>A6<br>B7<br>A7<br>B9<br>A9<br>B10<br>A10<br>B12<br>B13<br>A31<br>B36<br>A36<br>B37<br>A39<br>B40 | A2<br>B2<br>B2<br>A5<br>B8<br>B8<br>A8<br>B11<br>A11<br>B11<br>A14<br>A32<br>B35<br>B38<br>A38<br>B41 | READ DATA STROBE (IRDS)** READ DATA PARITY (IRDP) READ DATA 0 (IRDO) READ DATA 1 (IRD1) READ DATA 2 (IRD2) READ DATA 2 (IRD2) READ DATA 3 (IRD3) NRZI (INRZ) 7 TRACK (I7TR)** SINGLE (ISGL) SPEED (ISPEED) READ DATA 4 (IRD4) READ DATA 6 (IRD6) READ DATA 6 (IRD6) READ DATA 7 (IRD7) DENSITY INDICATOR (IDDI) ** ON-LINE (IONL) REWIND (IRWD) IFPT LOAD POINT (ILDP) READY (IRDY) END OF TAPE (IEOT) | J102<br>Buffered<br>Formatter<br>to<br>Transport | B15<br>B16<br>B18<br>A21<br>B22<br>B24<br>A22<br>B25<br>A25<br>B27<br>A27<br>A28<br>B30<br>A30<br>B31<br>B33<br>B34<br>B42<br>B43<br>A43 | B14<br>B17<br>B17<br>A17<br>A20<br>B23<br>A23<br>B23<br>A23<br>B26<br>A26<br>B26<br>A29<br>B32<br>B32<br>B32<br>B32<br>B35<br>A35<br>B41<br>B44<br>A44 | WRITE DATA STROBE (IWDS) WRITE AMPLIFIER RESET (IWARS) READ THRESHOLD Level 1 (IRTH1) READ THRESHOLD Level 2 (IRTH2) WRITE DATA PARITY (IWDP) WRITE DATA 1 (IWD0) WRITE DATA 1 (IWD1) WRITE DATA 2 (IWD2) WRITE DATA 3 (IWD3) WRITE DATA 3 (IWD4 WRITE DATA 4 (IWD4 WRITE DATA 6 (IWD6) WRITE DATA 6 (IWD6) WRITE DATA 7 (IWD7) OVERWRITE (IOVW) OVERWRITE (IOVW) SYNCHRONOUS FORWARD Command (ISFC) DENSITY SELECT (IDDS)** SYNCHRONOUS REVERSE Command (ISRC) REWIND Command (IRWC) SET WRITE STATUS (ISWS) OFF-LINE Command (IOFC) SELECT 0 (ISLT0) SELECT 1 (ISLT1) SELECT 2 (ISLT2) SELECT 3 (ISLT3) |

<sup>\*</sup>See Section III for definitions of interface functions.

<sup>\*\*</sup>Not applicable to this formatter.

Table 2-2 Internal Connections, Formatter/Buffer

| Connector<br>(Reference<br>Figure 2-2)                                                                                     | Gnd<br>Pin                                                                                                                     | Signal*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Connector<br>(Reference<br>Figure 2-2) | Live<br>Pin                                                                                                                                                                                           | Gnd<br>Pin                                                                                  | Signal*                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Buffer to B1 Formatter A3 B3 A4 B4 A6 B6 B6 A7 B7 A9 B10 B10 B10 A12 B12 A13 B13 A16 B16 B16 B16 B16 B16 B16 B16 B16 B16 B | A2<br>B2<br>A5<br>B5<br>A5<br>B5<br>A5<br>B8<br>A8<br>B8<br>A11<br>B11<br>A17<br>B17<br>A17<br>B17<br>A20<br>B20<br>A20<br>B20 | FORMATTER ADDRESS (IFAD) TRANSPORT ADDRESS (ITAD0) TRANSPORT ADDRESS (ITAD1) INITIATE Command (IGO) REVERSE/FORWARD (IREV) WRITE/READ (IWRT) WRITE FILE MARK (IWFM) EDIT (IEDIT) ERASE (IERASE) READ THRESHOLD Level 2 (ITHR2) DENSITY SELECT (IDEN)** LOAD AND ON-LINE (ILOL) REWIND (IREW) OFF-LINE (IOFL) LAST WORD (ILWD) FORMATTER ENABLE (IFEN) WRITE DATA 1 (IW1) WRITE DATA 2 (IW2) WRITE DATA 2 (IW2) WRITE DATA 4 (IW4) WRITE DATA 6 (IW6) WRITE DATA 6 (IW6) WRITE DATA 6 (IW6) WRITE DATA 7 (IW7) | Formatter<br>to<br>Buffer              | A22<br>B22<br>A24<br>A25<br>B25<br>A27<br>A28<br>B28<br>A30<br>B31<br>A33<br>A34<br>B33<br>A34<br>B36<br>B36<br>B37<br>A39<br>A40<br>B40<br>B40<br>B40<br>B40<br>B40<br>B40<br>B40<br>B40<br>B40<br>B | A23 B23 A23 B23 A26 B26 B26 A29 A29 A29 B32 A35 B35 B35 B35 B38 A38 B38 A38 B38 A41 B41 B41 | FORMATTER BUSY (IFBY) DATA BUSY (IDBY) IDENTIFICATION (IDENT) HARD ERROR (IHER) CORRECTED ERROR (ICER) FILE MARK (IFMK) READY (IRDY) ON-LINE (IONL) REWINDING (IRWD) FILE PROTECT (IFPT) LOAD POINT (ILDP) END OF TAPE (IEOT) NRZI (INRZ) 7 TRACK (I7TR)** SINGLE (ISGL) SPEED (ISPEED) WRITE STROBE (IWSTR) READ DATA OF (IRD) READ DATA OF (IRD) READ DATA 2 (IRD) READ DATA 3 (IR3) READ DATA 4 (IR4) READ DATA 5 (IR5) READ DATA 6 (IR6) READ DATA 6 (IR6) READ DATA 7 (IR6) |

Table 2-3 Interface Connections, Buffered Formatter/Controller

| Connector<br>(Reference<br>Figure 2-2)                         | Live<br>Pin                                                                                                                                                   | Gnd<br>Pin                                                                                                                                                                                                               | Signal*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Connector<br>(Reference<br>Figure 2-2)            | Live<br>Pin                                                                                                                                                                 | Gnd<br>Pin                                                                                                                               | Signal*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J104<br>Controller<br>to<br>Buffered<br>Formatter<br>Interface | A1<br>B1<br>A2<br>A3<br>B4<br>A5<br>B6<br>B10<br>A11<br>B13<br>A14<br>B15<br>B13<br>A16<br>A17<br>B18<br>A16<br>A17<br>B18<br>A18<br>B19<br>B21<br>B22<br>B24 | B2<br>B2<br>B2<br>B2<br>B5<br>B5<br>B5<br>B5<br>B5<br>B8<br>B8<br>B11<br>B11<br>B11<br>B11<br>B14<br>B14<br>B14<br>B14<br>B17<br>B17<br>B17<br>B17<br>B17<br>B17<br>B17<br>B20<br>B20<br>B20<br>B20<br>B23<br>B23<br>B23 | LOAD ON-LINE (ILOL) FORMATTER ADDRESS (IFADO) TRANSPORT ADDRESS (ITADO) TRANSPORT ADDRESS (ITADO) TRANSPORT ADDRESS (ITADO) TRANSPORT ADDRESS (ITADO) INITIATE Command (IGOI) REVERSE/FORWARD (IREVI) WRITE FRAD (IWRTI) WRITE FILE MARK (IWFM) EDIT (IEDIT) ERASE (IERASE) THRESHOLD LEVEL 1 (ITHR1) THRESHOLD LEVEL 2 (ITHR2) IDEN'* AUTOMATIC (IAUTO) REWIND (IREW) OFF-LINE (IOFL) FORMATTER ENABLE (IFENI) END OF OPERATION (IEOO) LAST WORD (ILWDI) ANSWER STROBE (IANS) PARITY (or FLAG) (IWBP) WRITE DATA 1 (IWB1) WRITE DATA 2 (IWB2) WRITE DATA 3 (IWB3) WRITE DATA 5 (IWB5) WRITE DATA 6 (IWB6) WRITE DATA 7 (IWB7) BUFFER CONFIGURATION CONTROL 0 (IBCC0) BUFFER CONFIGURATION CONTROL 1 (IBCC1) BUFFER CONFIGURATION CONTROL 2 (IBCC2) BUFFER CONFIGURATION CONTROL 3 (IBCC3) COUNTER B INHIBIT (ICBI) | J104<br>Buffered<br>Formatter<br>to<br>Controller | A23<br>B25<br>A25<br>A27<br>A26<br>B28<br>A29<br>A30<br>B31<br>A32<br>A33<br>A34<br>B33<br>A34<br>B33<br>A35<br>A36<br>B37<br>A38<br>B39<br>B40<br>A41<br>B42<br>B42<br>B37 | B23<br>B26<br>B26<br>B26<br>B26<br>B29<br>B29<br>B32<br>B32<br>B32<br>B35<br>B35<br>B35<br>B35<br>B35<br>B35<br>B35<br>B35<br>B35<br>B35 | FORMATTER BUSY (IFBY) BUFFER A BUSY (IABSY) BUFFER B BUSY (IBBSY) BUFFER B OVERFLOW (IAOVFL) BUFFER B OVERFLOW (IBOVFL) DATA BUSY (IDBY) IDENTIFICATION (IDENT) HARD ERROR (IHER) CORRECTED ERROR (ICER) (PE Only) FILE MARK (IFMK) READY (IRDY) ON-LINE (IONL) REWIND (IRWD) FILE PROTECT (IFPT) LOAD POINT (ILDP) END OF TAPE (IEOT) 7 TRACK/9 TRACK (17TRK)** NRZI/PHASE ENCODED (INRZ) SINGLE STACK/DUAL STACK (ISGL) HIGH SPEED/LOW SPEED (ISPEED) REQUEST DATA STROBE (IREQ) READ DATA 1 (IRB1) READ DATA 1 (IRB1) READ DATA 2 (IRB2) READ DATA 3 (IRB3) READ DATA 4 (IRB4) READ DATA 6 (IRB6) READ DATA 6 (IRB6) READ DATA 7 (IRB7) BUFFER LAST WORD (IBLWD) |

<sup>\*</sup>See Section III for details of interface functions.

<sup>\*\*</sup>Not applicable to this formatter.

<sup>\*\*</sup>Not applicable to this formatter.

802B

2-6

# SECTION III OPERATION

#### 3.1 INTRODUCTION

This section contains the functional specifications of the Buffered PE Formatter, a brief outline of the PE tape format, basic formatter operation, basic buffer operation, and a detailed definition of the various formatter interface lines.

#### 3.2 CONTROLS AND INDICATORS

The Buffered PE Formatter utilizes a single operational control located on the front panel.

#### 3.2.1 **POWER**

The ON/OFF switch is a rocker-type switch/indicator which connects line voltage to the power transformer. The indicator provides visual indication of the on/off status of the formatter.

When power is turned on, a reset signal is applied to all relevant flip-flops until the power supply voltages have been established.

When power is turned off or line voltage is lost, the formatter will reset all relevant flip-flops before the regulated power supplies decay, thus ensuring that no spurious signals are sent to the transports.

Three twist-lock fuses are provided adjacent to the power switch; a fourth fuse is located on the rear panel of the formatter. The front panel fuses consist of a 10-amp fast-blow fuse which protects the +5v circuits and two 1-amp fast-blow fuses which protect the +20v and —5v circuits. The rear panel fuse is a 2-amp slow-blow line fuse. Access to the front panel fuses is via the hinged front panel.

### 3.3 BASIC OPERATION

The Buffered PE Formatter is capable of executing the commands listed in Table 3-1. When a command is received from the customer's controller, the formatter goes busy and performs all control and timing functions necessary to execute the command. Any errors occurring during the command are reported to the controller. On completion of the command the formatter signals the controller and the controller is then free to issue a further command.

Two other command lines are provided which cause the transport to rewind, or to be switched off-line. These commands are routed directly to the selected transport and do not cause the formatter to go busy.

Note that for transports having a dual stack head, an automatic read-after-write data check is performed during each write command. Read-after-write errors are transmitted to the controller in the same manner as during read commands.

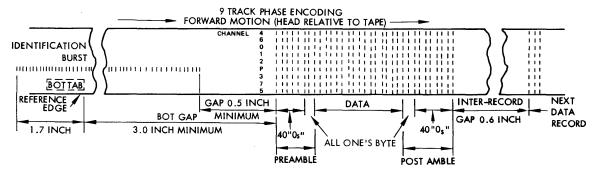

Figure 3-1 illustrates the 9-track PE tape format.

### 3.3.1 PREAMBLE

When writing, the formatter generates a preamble which precedes the data block. The preamble consists of 41 characters; the first 40 characters contain a zero (0) bit in each of

3-1 <sub>802B</sub>

Table 3-1 Command Coding

|                                                         | <i>]</i> :   |   |   | 12/2 |   |   |         |   |           |              |  |

|---------------------------------------------------------|--------------|---|---|------|---|---|---------|---|-----------|--------------|--|

| Read Tape Forward Into Buffer                           |              |   |   |      |   |   |         |   |           |              |  |

| 2. Read Tape Reverse Into Buffer                        | Π            | 1 |   |      |   | Γ | A/R     |   |           |              |  |

| 3. Read Tape Reverse Edit Into Buffer                   |              | 1 |   |      | 1 |   |         |   |           | A/R          |  |

| 4. Write Tape Forward From Buffer                       | T            |   | 1 |      |   |   |         | T |           |              |  |

| 5. Write Tape Forward Edit From Buffer                  | Π            |   | 1 |      | 1 |   | 1 1     |   |           |              |  |

| 6. Write File Mark Forward                              | Γ            |   | 1 | 1    |   |   | A/R*    |   | Any Level |              |  |

| 7. Erase Variable Length Tape                           |              |   | 1 |      |   | 1 |         |   |           |              |  |

| 8. Erase Fixed Length Tape                              |              |   | 1 | 1    |   | 1 |         |   |           |              |  |

| 9. Forward Space Tape                                   | $\Gamma^{-}$ |   |   |      |   | 1 |         |   |           |              |  |

| 10. Back Space Tape                                     |              | 1 |   |      |   | 1 | A/R     |   |           | Any<br>Level |  |

| 11. File Search Forward                                 |              |   |   | 1    |   |   |         |   | ]         |              |  |

| 12. File Search Reverse                                 | П            | 1 |   | 1    |   |   |         |   |           |              |  |

| 13. Write Bufer From Controller                         |              |   | 1 |      |   |   |         | 1 |           | A/R          |  |

| 14. Read Buffer To Controller                           |              |   |   |      |   |   | 1       |   | 1 A/H     |              |  |

| 15. Automatically Write Tape From Controller            | 1            |   | 1 |      |   |   | A / D*  |   | A         |              |  |

| 16. Automatically Write Tape Continuous From Controller | 1            |   | 1 |      |   |   | A/R*    |   | 7;        | 1 Any        |  |

| 17. Automatically Read Tape To Controller               | 1            |   |   |      |   |   | 4.15    |   | e         | Levél        |  |

| 18. Automatically Read Tape Continuously To Controller  | 1            |   |   |      |   |   | A/R V P |   | 1         |              |  |

| *As Required for Read-After-Write Units.                |              |   |   |      |   |   |         |   |           |              |  |

Figure 3-1. 9-Track PE Tape Format

the 9 tracks, and the subsequent single character contains a one (1) bit in each of the 9 tracks.

When performing a read operation, the formatter detects the preamble and separates it from the data block.

#### 3.3.2 DATA

When writing, the buffer accepts asynchronous data, character by character, through a Request/Answer handshake circuit. The buffer then initiates the formatter which converts the data into a PE signal in which:

- (1) A zero (0) bit is characterized by a transition in the middle of the bit cell away from the erase direction of magnetization.

- (2) A one (1) bit is characterized by a transition in the middle of the bit cell toward the erase direction of magnetization.

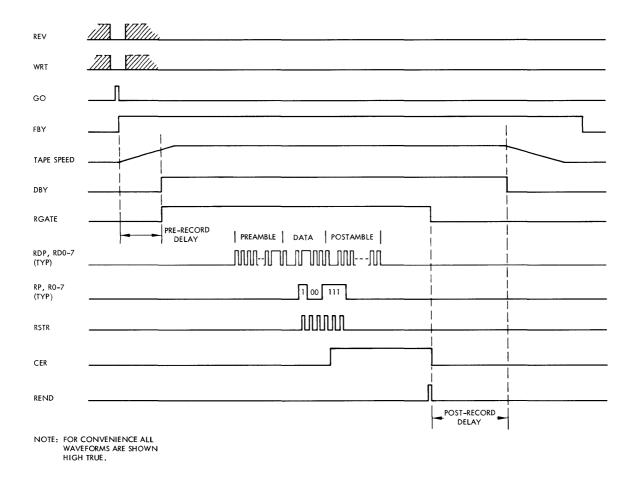

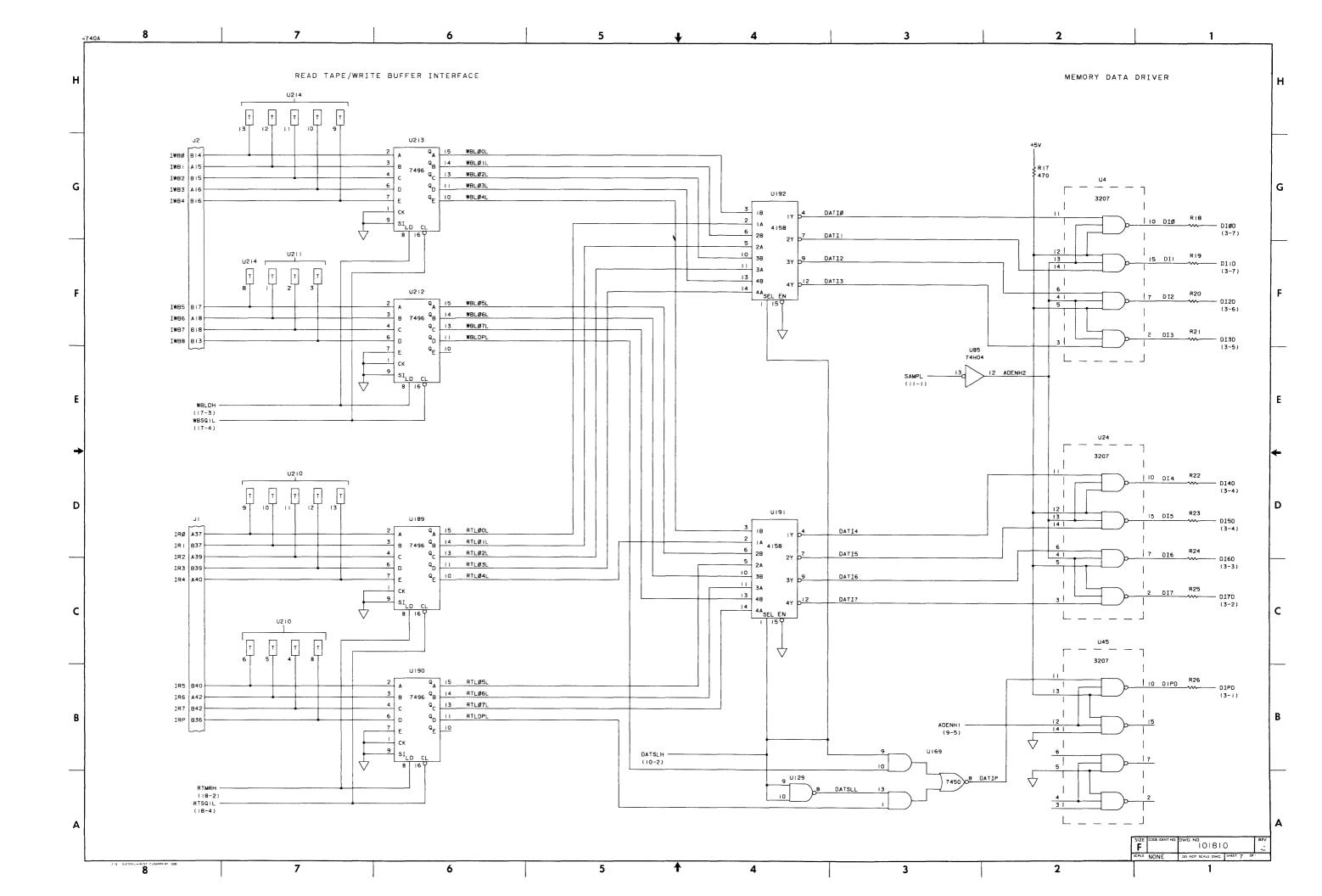

When reading, the formatter accepts 9 channels of digital phase encoded data from the transport, and provides 4 bits of buffer per channel for the purpose of deskewing. The read logic assembles these data into parallel form, performs various error checks, and transmits the data to the buffer on 8 read data lines together with the strobe waveform. The buffer then offers the data asynchronously to the controller via the same Request/Answer handshake circuitry that wrote the data.

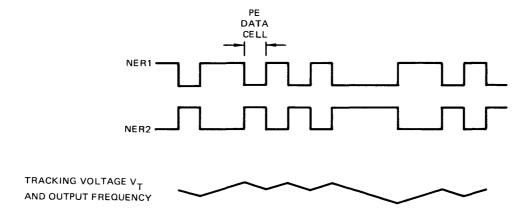

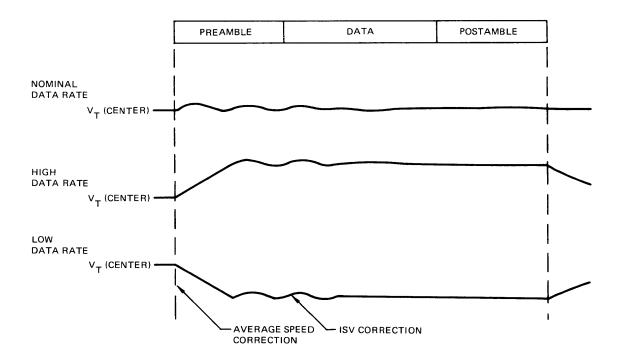

A tracking oscillator is provided in the formatter which can follow data rate variations of up to  $\pm 10$  percent over 35 character periods. Data rate variation results from the Instantaneous Speed Variation (ISV) in the transport reading the tape, plus the ISV in the transport on which the tape was written.

#### 3.3.3 POSTAMBLE

When writing, the formatter generates a postamble which follows the data and consists of 41 characters. The first character contains a one (1) bit in each of the 9 tracks; the subsequent 40 characters contain a zero (0) bit in each of the 9 tracks.

When performing a read operation, the formatter detects the postamble and separates it from the data block.

# 3.3.4 IDENTIFICATION BURST

When performing any write operation from BOT, the formatter automatically writes an IBM and ANSI compatible identification mark onto tape. This consists of a sequence of flux reversals at 1600 flux reversals per inch (frpi) in Channel P, with all other channels erased. A length of tape approximately 3 inches long is then erased before the first data record is written.

In the Read mode, the formatter samples the output of the parity channel as the BOT tab traverses the read head. If an identification burst is detected, the IDENT interface line is pulsed.

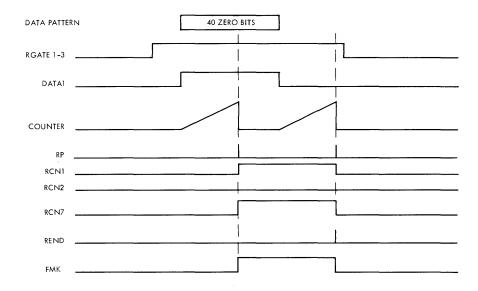

#### 3.3.5 FILE MARK

When writing, the formatter generates a phase encoded tape mark consisting of 80 flux reversals at 3200 frpi in Channels P, 0, 2, 5, 6, and 7. Channels 1, 3, and 4 are erased in the same direction as the IBG.

3-3

802B

When reading, the formatter will recognize a file mark if it contains at least 64 flux reversals in Channels P, 0, and 5, or Channels 2, 6, and 7 with Channels 1, 3, and 4 dc-erased.

#### 3.3.6 GAPS

The formatter provides the timing required to generate the following gaps.

(1) Interblock Gap (IBG)

Nominal: 0.6 inchMinimum: 0.5 inch

- Maximum: 25 feet (depends upon number of consecutive erasures, no restrictions placed by the formatter to limit this distance).

- (2) Initial Gap. When writing the first record from BOT, an ID burst is written followed by a gap of approximately 3 inches before the first data block.

When reading, the formatter can detect records written with an initial gap of 0.5 inch minimum between the end of the ID burst and the beginning of the first data block.

(3) File Mark Gap. A file mark is preceded by approximately 3.75 inches of tape with all tracks erased in the same direction as the IBG.

#### 3.3.7 PARITY

During a write operation, the formatter generates odd parity derived from the data present on the 8 data channels. An option is provided (jumper selectable) whereby the parity bit can be supplied externally.

When reading, the formatter checks that the parity of the 9 channels is odd. An error is signaled when the parity check fails.

### 3.3.8 DROPOUT AND ERROR CORRECTION

The formatter provides single and multiple track dropout detection. When a single track dropout occurs, the formatter performs error correction by use of the parity circuits and the data on the other 8 channels. A status line to the buffer indicates when error correction is taking place within the formatter.

After a track has experienced a dropout, the output of that track will be ignored for the remainder of that record, and no attempt will be made by the formatter to re-synchronize the data on that track.

# 3.3.9 ERROR CHECKING

A switch is provided on the Buffer PCBA to enable the automatic rewrite or reread of erroneous records. When selected, error retry is attempted in both the split- and single-buffer modes and during both a Write Tape or Read Tape operation in either direction. In the event that an error is detected, the buffer logic causes the formatter to command the selected tape transport to backspace and reread or, when used with read-after-write tape drives, rewrite the affected record. A maximum of 8 (switch selectable) attempts at writing a record can be made before the buffer logic flags the interface that a hard error (IHERI) exists. In the event of an IHERI after the maximum number of attempts, the tape transport is commanded to advance to the next record and perform the next operation.

## **3.3.10 OPTIONS**

The following features are available as options and must be specified at the time of ordering.

- (1) Formatter address 0 or 1.