## OSBORNE **16-Bit** Microprocessor Handbook

OSBORNE **16-Bit** Microprocessor Handbook

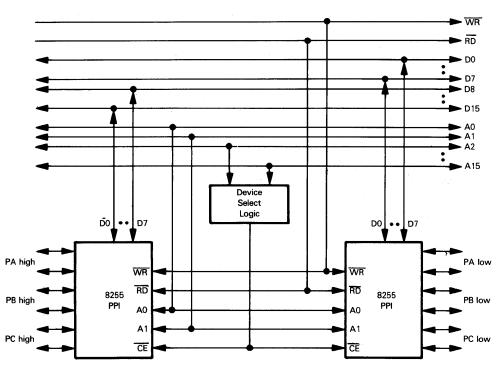

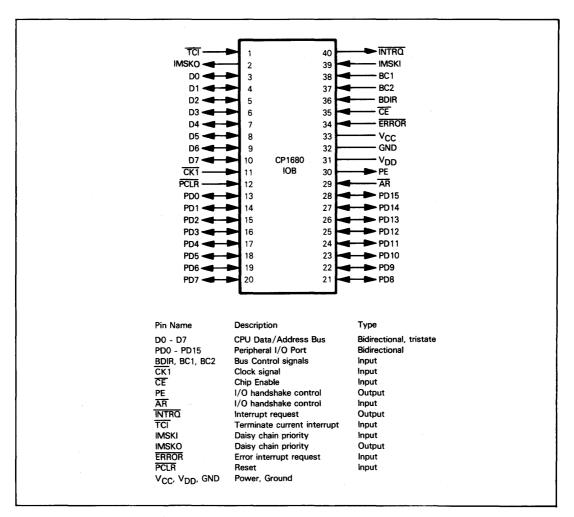

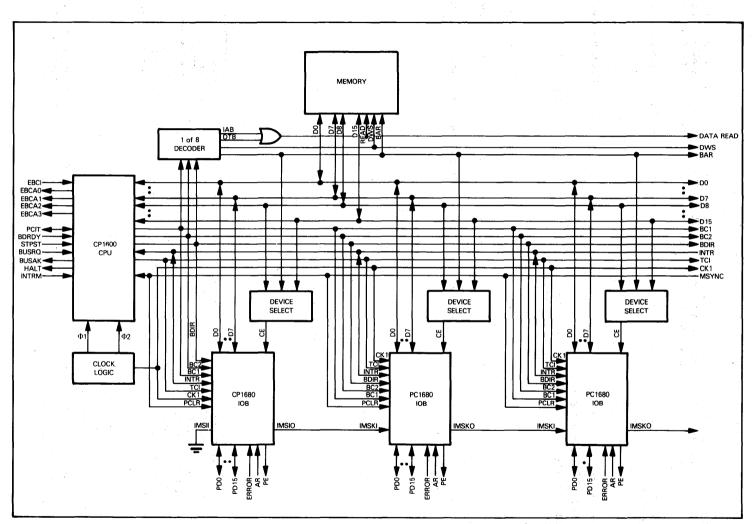

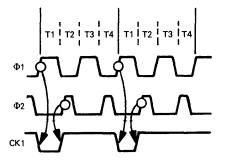

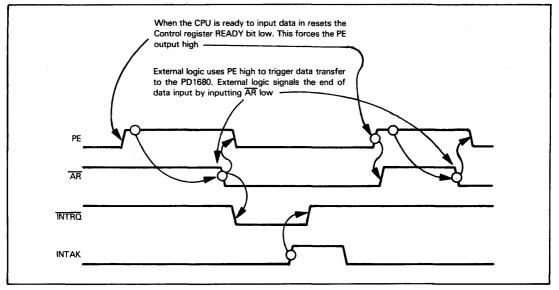

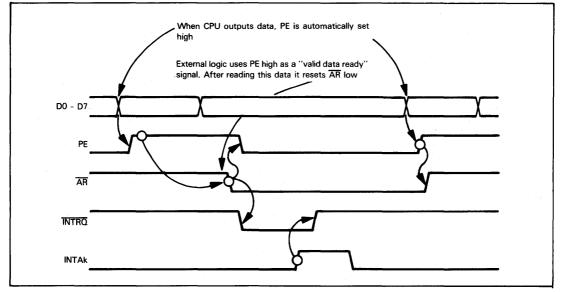

OSBORNE/McGraw-Hill Berkeley, California Copyright © 1981, 1979, 1978, 1976, 1975 by McGraw-Hill, Inc. All rights reserved. Printed in the United States of America. No part of this publication may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, recording or Otherwise without the prior written permission of the publishers.

Published by OSBORNE/McGraw-Hill 630 Bancroft Way Berkeley, California 94710 U. S. A.

For information on translations and book distributors outside of the U. S. A. , please write OSBORNE/McGraw-Hill at the above address.

123456789 KPKP 8987654321 ISBN 0-931988-43-8

Cover design by Marc Miyashiro.

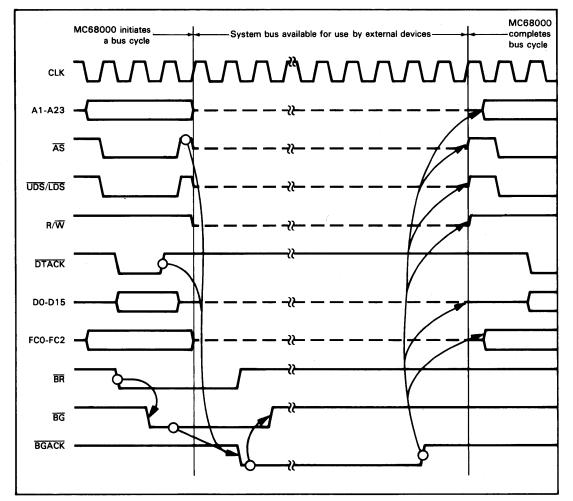

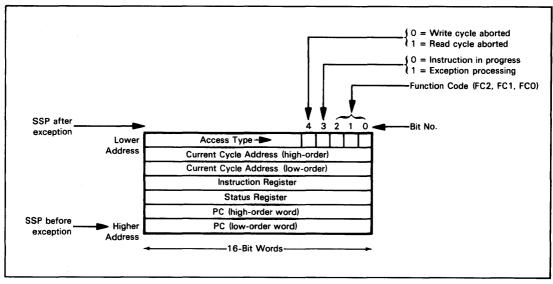

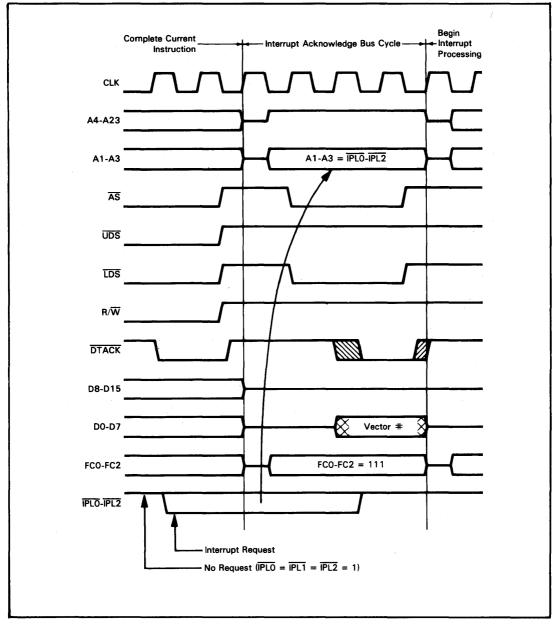

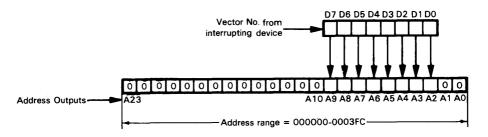

## **Contributing Authors**

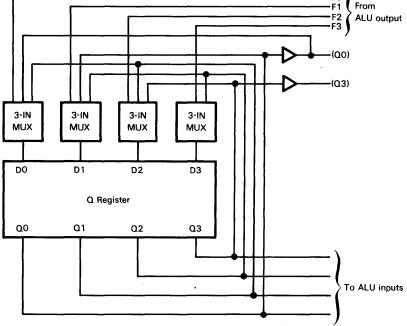

The following persons have contributed to the writing of sections of this book in addition to its principal authors.

> Bob Abramovitz Janice K. Enger Curtis A. Ingraham Susanna Jacobson Patrick L. McGuire

## Contents

- 1. The National Semiconductor PACE and INS8900 1-1 PACE and INS8900 Microcomputer System Overviews 1-2 INS8900 and PACE Timing and Instruction Execution 1-11 The INS8900 and PACE Instruction Set 1-11 The PACE DP8302 System Timing Element (STE) 1-35 The PACE Bidirectional Transceiver Element (BTE) 1-36 Using Other Microcomputer Support Devices with the PACE and INS8900 1-38 Data Sheets 1-D1

- 2. The General Instrument CP1600 2-1 CP1600 Instruction Timing and Execution 2-10 The CP1600 Instruction Set 2-16 Support Devices that may be used with the CP1600 2-27 The CP1680 Input/Output Buffer (IOB) 2-30 Data Sheets 2-D1

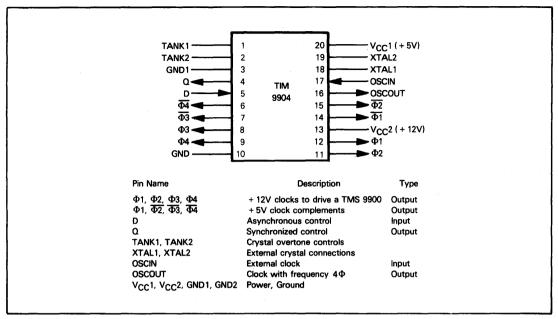

- 3. The Texas Instruments TMS 9900, TMS 9980, and TMS 9440 Products 3-1 The TMS 9900 Microprocessor 3-2 TMS 9900 Timing and Instruction Execution 3-15 The TMS 9900 Instruction Set 3-35 The TMS 9980A and the TMS 9981 Microprocessors 3-44 The TMS 9980A and the TMS 9981 Microprocessors 3-44 The TMS 9940 Single-Chip Microcomputers 3-52 The TIM 9904 Four-Phase Clock Generator/Driver 3-67 The TMS 9901 Programmable System Interface (PSI) 3-70 The TMS 9902 Asynchronous Communications Controller 3-82 The TMS 9903 Synchronous Communications Controller 3-95 Data Sheets 3-D1

- Single Chip Nova Minicomputer Central Processing Units 4-1

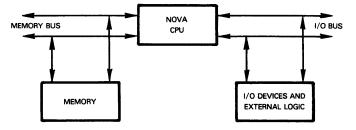

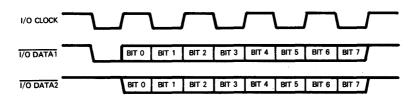

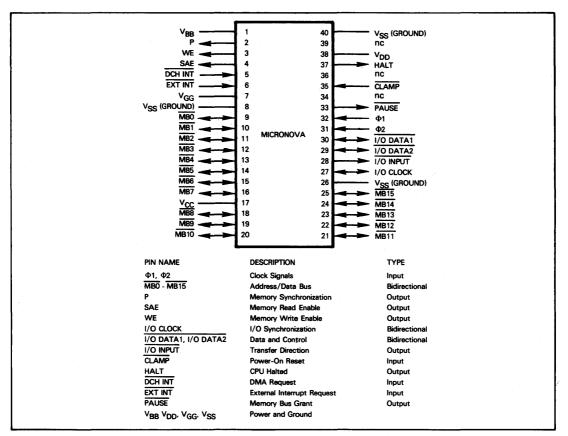

A Product Overview 4-2

CPU Logic and Instruction Execution 4-18

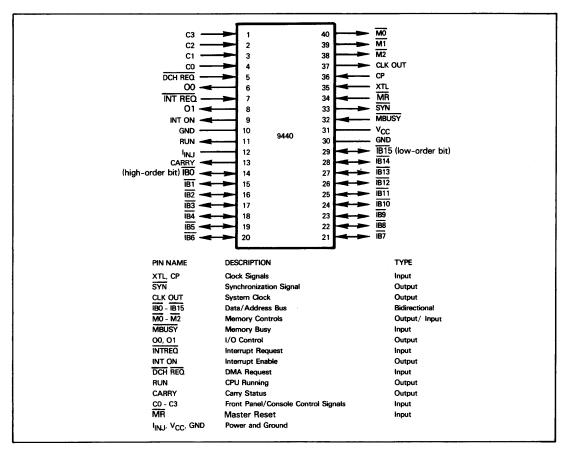

9440 Timing and Instruction Execution 4-24

The MicroNova and 9440 Instruction Sets 4-35

9440-Nova Bus Interface 4-77

Data Sheets 4-D1

#### 5. The Intel 8086 5-1

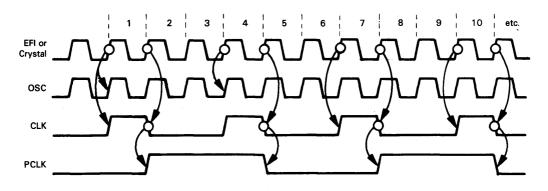

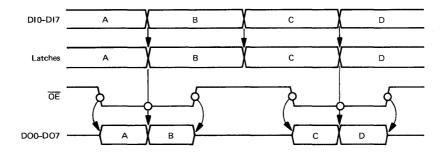

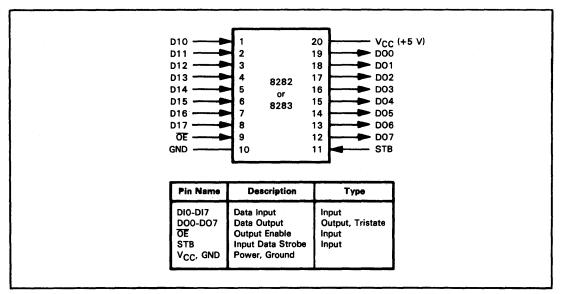

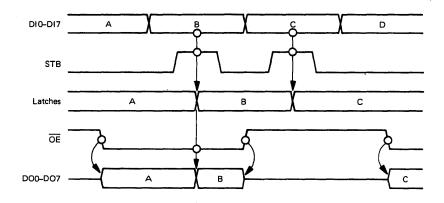

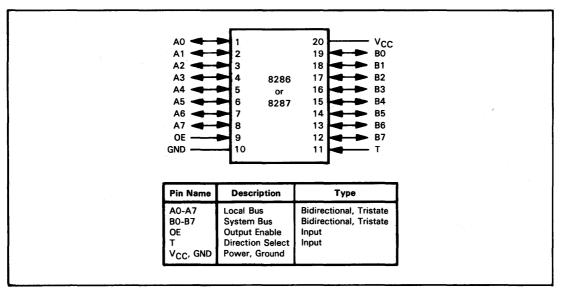

The 8086 CPU 5-4 8086 Timing and Instruction Execution 5-30 The 8086 Instruction Set 5-47 The 8088 CPU 5-87 The Intel 8284 Clock Generator/Driver 5-91 The Intel 8288 Bus Controller 5-98 The 8282/8283 8-Bit Input/Output Latch 5-102 The 8286/8287 8-Bit Bidirectional Bus Transceivers 5-104 Some 8086 Microprocessor Bus Configurations 5-105 Data Sheets 5-D1

#### 6. The Zilog Z8000 Series 6-1

The Z8001 and Z8002 CPUs 6-3 Z8001 and Z8002 Timing and Instruction Execution 6-23 The Z8000 Instruction Set 6-36 Data Sheets 6-D1

#### 7. The Motorola MC68000 7-1

MC68000 Pins and Signals 7-9 The MC68000 Instruction Set 7-38 Interfacing the MC68000 with 6800 Peripherals 7-44 Data Sheets 7-D1

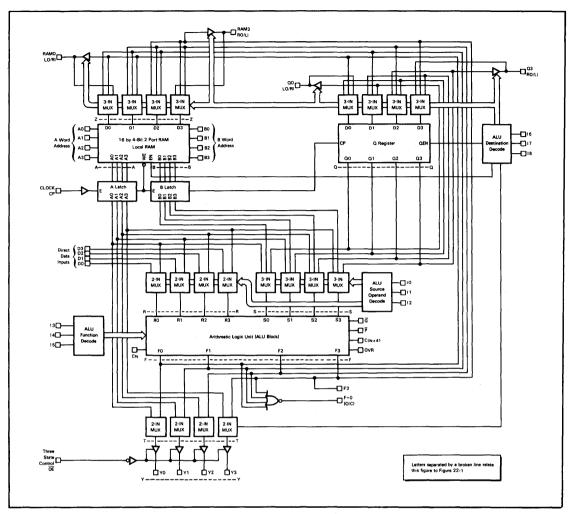

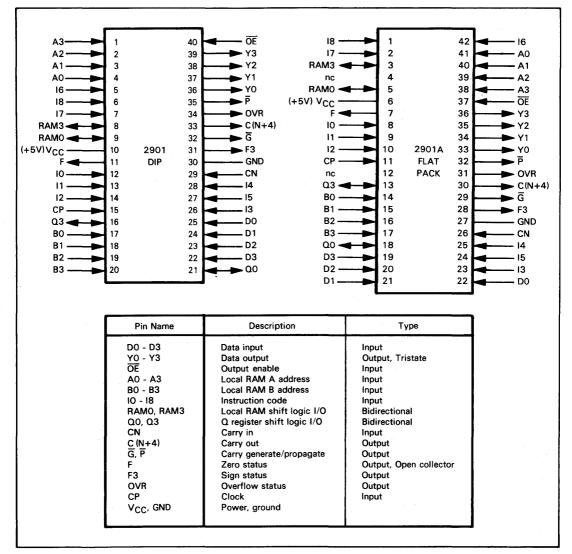

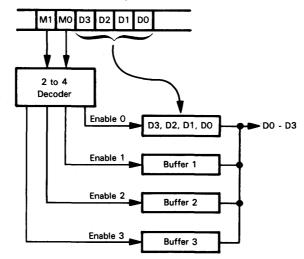

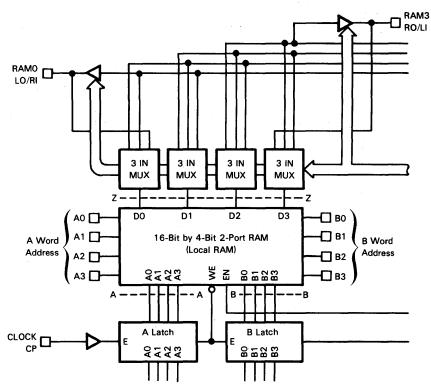

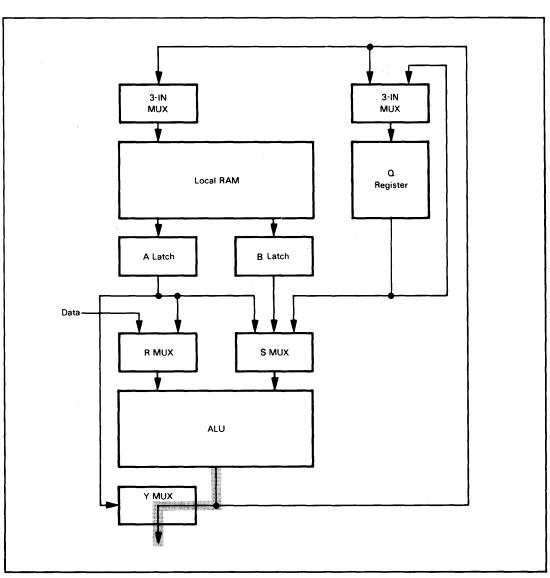

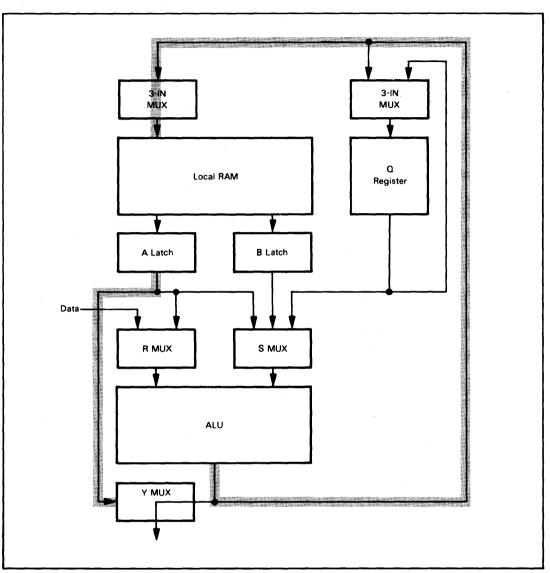

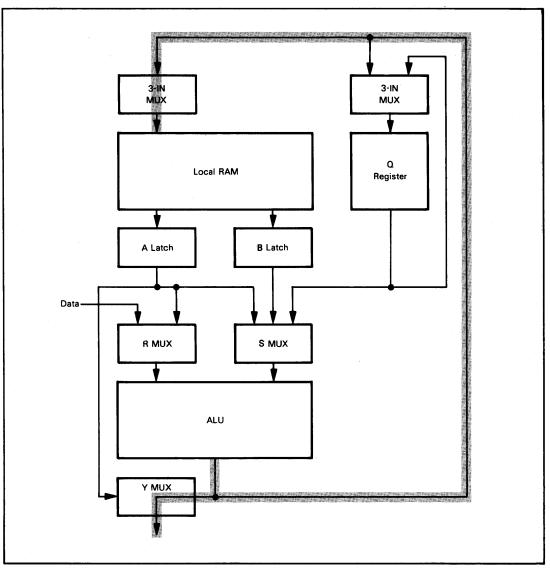

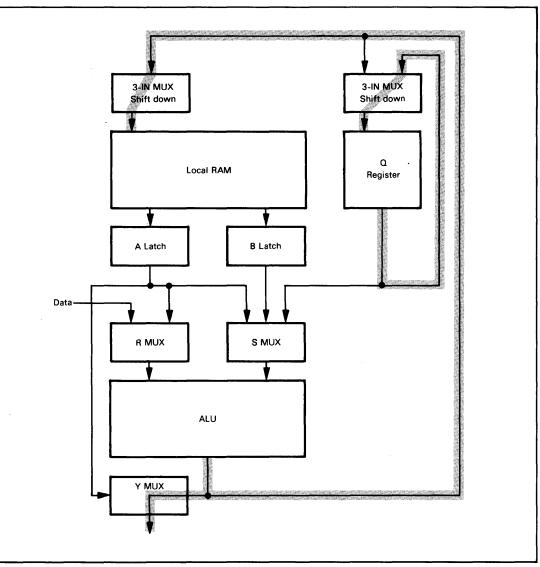

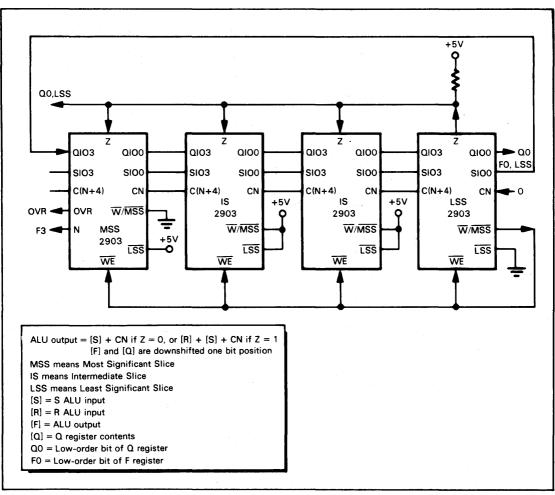

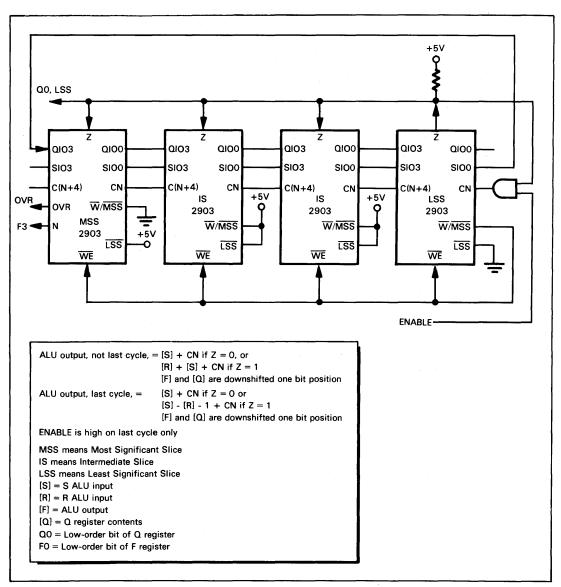

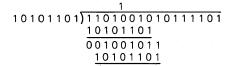

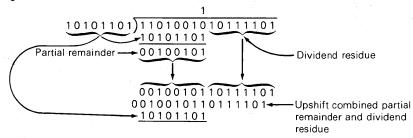

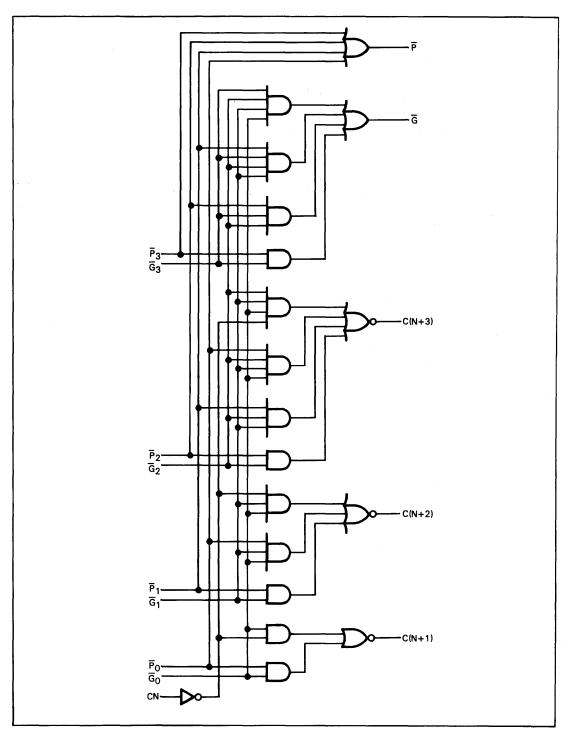

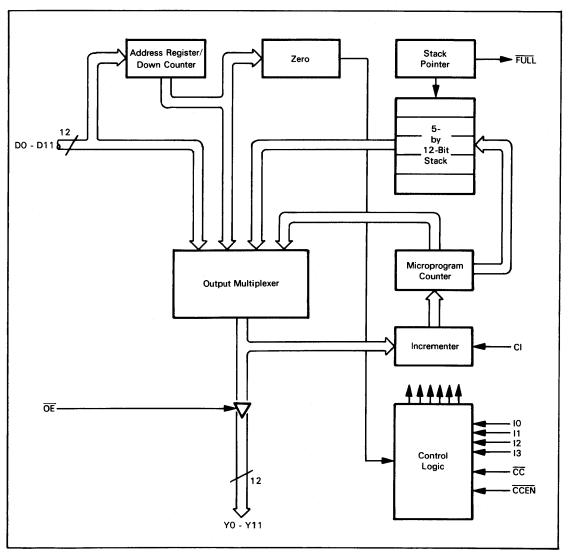

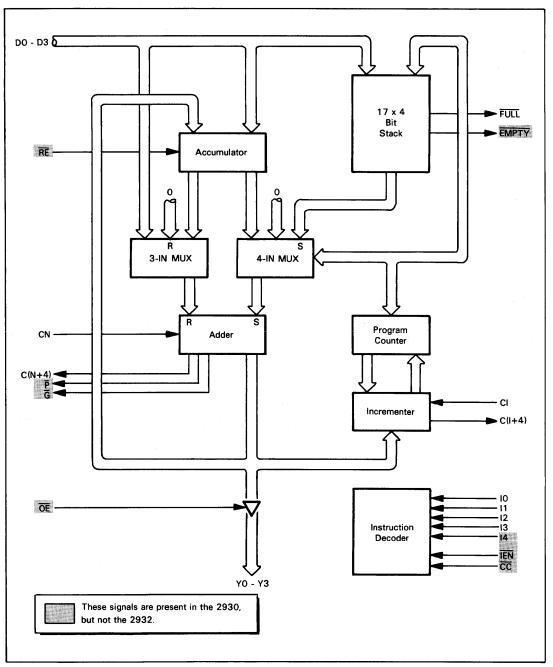

#### 8. 2900 Series Chip Slice Products 8-1 The 2901, 2901A, and 2901B Microprocessor Slice 8-2 The 2903 Microprocessor Slice 8-40 The 2902 Carry Look-Ahead Device 8-87 The 2909 and 2911 Microprogram Sequencers 8-92

The 2910 Microprogram Sequencer 8-110 The 2930 and 2932 Program Control Units 22-125 Data Sheets 8-D1

# INTRODUCTION

This is one of two books that replace *An Introduction to Microcomputers: Volume 2 – Some Real Microprocessors.* That volume went through several printings and in 1978 was printed loose-leaf. Six bimonthly updates to the loose-leaf version were published in 1979 and early 1980 to provide information on newly introduced microcomputer devices. The loose-leaf version proved, however, to be quite unpopular with bookstores because of packaging and handling considerations. It also became more and more difficult to maintain a timely flow of the bimonthly updates. For these reasons, *Volume 2* is being replaced by two bound paperback books: the *Osborne 4 & 8-Bit Microprocessor Handbook* and the *Osborne 16-Bit Microprocessor Handbook.* Together these handbooks include all of the information that was contained in *Volume 2* and the six updates. All known errors have been corrected and new data sheets have been added to the two handbooks. We have divided *Volume 2* into two separate handbooks because the single-volume version would be over 1800 pages in length and rather difficult to bind. In addition, the devices lend themselves to this grouping since the 16-bit microprocessors are generally much more powerful than the four- and eight-bit microprocessors, and thus are directed toward different applications.

Volume 2 was part of a four-volume Introduction to Microcomputers series:

- Volume 0 The Beginner's Book was written for readers who know nothing about computers.

- Volume 1 Basic Concepts provides a detailed explanation of microprocessor concepts including number systems, addressing modes, typical instruction sets, input/output techniques, and so on. The device descriptions in the 4 & 8-Bit Microprocessor Handbook and the 16-Bit Microprocessor Handbook assume that you have a working knowledge of the general concepts presented in Volume 1, and we will occasionally make references to material presented in Volume 1.

- · Volume 2 Some Real Microprocessors, which is being replaced by these handbooks.

- Volume 3 Some Real Support Devices, which describes general support devices that may be used with any microprocessor. Some dedicated support devices are the 4 & 8-Bit Microprocessor Handbook and the 16-Bit Microprocessor Handbook. We define a "dedicated" support device as one best used with its parent microprocessor. We define a "general" support device as one that can be used with any microprocessor. We will occasionally make reference in this book to some of the general support devices in Volume 3. When designing a system based on one of the microprocessors described in this handbook, you should not automatically assume that the dedicated support devices described in this book are the only ones or the best ones to use with a particular microprocessor: you should always check the functionally equivalent parts described in Volume 3.

In addition to this *Introduction to Microcomputers* series, we have begun publishing other individual handbooks. The first two handbooks of this series are: *The 8089 I/O Processor Handbook*, which includes the 8289 bus arbiter, and the *CRT Controller Handbook*, which describes five LSI CRT controller devices. This individual handbook approach will be used in the future to maintain a convenient flow of detailed, objective information on new microprocessors and related support devices.

## SIGNAL CONVENTIONS

Signals may be active high, active low or active in two states. An active high signal is one which, in the high state, causes events to occur, while in the low state has no significance. A signal that is active low causes events to occur when in the low state, but has no significance in the high state. A signal that has two active states will cause two different types of events to occur, depending upon whether the signal is high or low; this signal has no inactive state. Within this book a signal that is active low has a bar placed over the signal name. For example, WR identifies a "write strobe" signal which is pulsed low when data is ready for external logic to receive. A signal that is active high or has two active states has no bar over the signal name.

## TIMING DIAGRAM CONVENTIONS

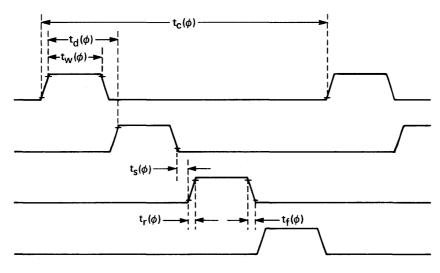

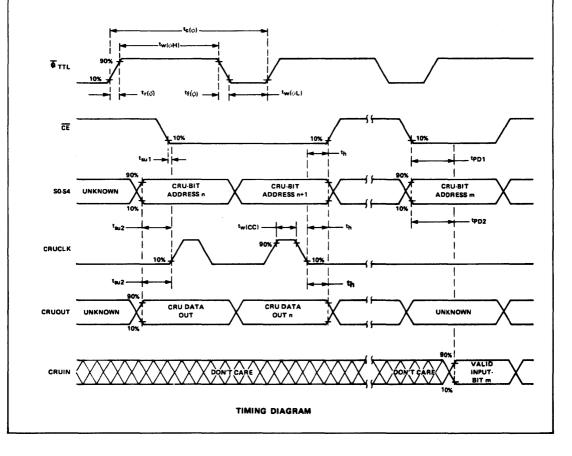

Timing diagrams play an important part in the description of any microprocessor or support device. Timing diagrams are therefore used extensively in this book. All timing diagrams observe the following conventions:

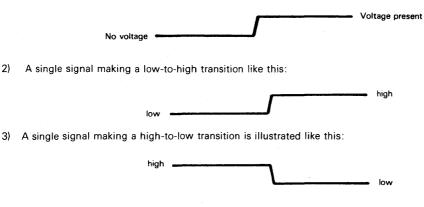

1) A low signal level is equivalent to no voltage. A high signal level is equivalent to voltage present:

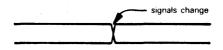

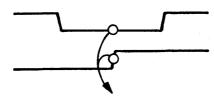

4) When using two or more parallel signals exist, the notation:

states that one or more of the parallel signals change level, but the transition (high-to low or low-to-high) is unspecified).

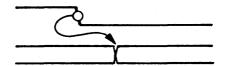

5) A three-state single signal is shown floating thus:

6) A three-state bus containing two or more signals is shown floating thus:

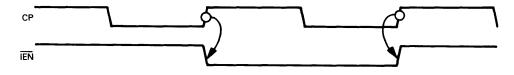

7) When one signal condition triggers other signal changes, an arrow indicates the relationship as follows:

Condition here Causes change here Thus a signal making a low-to-high transition would be illustrated triggering another signal making a high-to-low transition as follows:

A signal making a high-to-low transition triggering a bus change of state would be illustrated as follows:

8) When two or more conditions must exist in order to trigger another logic event, the following illustration is used:

Thus a low-to-high transition of one signal occurring while another signal is low would be illustrated triggering a third event as follows:

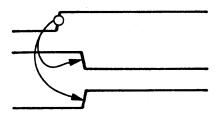

9) When a single triggering condition causes two or more events to occur, the following illustration is used:

Thus a low-to-high transition of one signal triggering changes in two other signal levels would be illustrated as follows:

10) All signal level changes are shown as square waves. Thus rise and fall times are ignored. These times are given in the data sheets which appear at the end of every chapter.

## **INSTRUCTION SET CONVENTIONS**

Every microcomputer instruction set is described with two tables. One table identifies the operations which occur when the instruction set is executed, while the second table defines object codes and instruction times.

Because of the wide differences that exist between one instruction set and another, we have elected not to use a single set of codes and symbols to describe the operations for all instructions in all instruction sets. We believe any type of universal convention is like to confuse rather than clarify; therefore each instruction set table is preceded by a list of symbols as used within the table alone.

A short benchmark program is given to illustrate each instruction set. Some comments regarding benchmark programs in general are, however, in order. We are not attempting to highlight strengths or weaknesses of different devices, nor does this book make any attempt to comparative analyses, since the criteria which make one microcomputer better than another are simply too dependent on the application.

Consider an application which requires relatively high speed processing. The only important criterion will be program execution speed, which may limit the choice to just one of the microcomputers we are describing.

Execution speeds of all of the microcomputers may, on the other hand, be quite adequate for a second application; in this case, price may be the only overriding factor. In a third application, a manufacturer may have already invested in a great deal of engineering development expense, using one particular microcomputer that was available in quantity earlier than any others; the advantages or disadvantages of using a different microcomputer, based on minor cost of performance advantages, will likely be overwhelmed by the extra expense and time delays involved with switching in midstream.

#### And what about benchmark programs?

There have been a number of benchmark programs in the literature, purporting to show the strengths or weaknesses of one microcomputer versus another; individual manufacturers

have added to the confusion by putting out their own competing benchmarks, aimed at showing their product to be superior to an immediate rival.

Benchmark programs are misleading, irrelevant and worthless for these reasons:

- 1) In a majority of microcomputer applications, program execution speed, and minor variations in program length, are simply overwhelmed by pricing considerations.

- 2) Even assuming that for some specific application, program length and execution speed are important, trivial changes in the benchmark program definition can profoundly alter the results that are obtained. This is one point we will demonstrate in this book, while describing individual instruction sets.

- 3) Benchmark programs are invariable written by the smartest programmers in an organization, and they take an enormous amount of time to ensure programming accuracy and excellence. This is not the level at which any user should anticipate "run of the mill" programmers working; indeed, a far more realistic evaluation of a microcomputer's instruction set could be generated by giving an average programmer too little time in which to implement an incompletely defined benchmark. This will more closely approximate the working conditions under which real products are developed. Of course, defining the "average programmer," "too little time" and an "incomplete specification" are all sufficiently subjective that they defy resolution.

BENCHMARK

COMPARATIVE

ANALYSIS

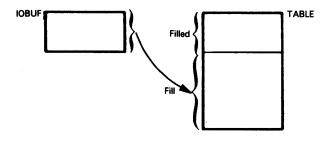

We will demonstrate the capriciousness of benchmark programs via the following benchmark program:

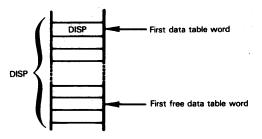

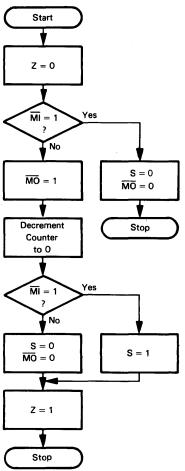

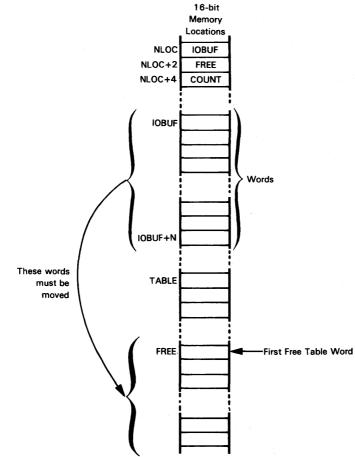

Raw data has been input to a general purpose input buffer, beginning at IOBUF. This raw data is to be moved to a permanent table, which may be partially filled; the raw data is to be stored in the data table starting with the first unfilled byte. The benchmark may be illustrated as follows:

## HOW THIS BOOK HAS BEEN PRINTED

Notice that text in this book has been printed in boldface type and lightface type. This has been done to help you skip those parts of the book that cover subject matter with which you are familiar. You can be sure that lightface type only expands on information presented in the previous boldface type. Therefore, only read boldface type until you reach a subject about which you want to know more, at which point start reading the lightface type.

# Chapter 1 THE NATIONAL SEMICONDUCTOR PACE AND INS8900

PACE was developed by National Semiconductor as a single-chip implementation of its multi-chip IMP-16. Since it was the first 16-bit, single-chip microprocessor, PACE is the first 16-bit microprocessor described in this book.

As might be expected of an early entry product. **PACE had a number of problems** — both in design and fabrication technology — which limited its acceptance. Therefore the INS8900 was recently introduced by National Semiconductor. The INS8900 is a redesigned, NMOS PACE, with internal logic problems resolved.

In this chapter we will describe both PACE and the INS8900. Specifically, we will identify the problems faced by a PACE user, which have been eliminated in the INS8900.

PACE and the INS8900 are 16-bit microprocessors because they handle data in 16-bit units. In many ways, however, the internal architecture of PACE and the INS8900 have an 8-bit orientation; this is something you should keep in mind while reading this chapter, because it does result in PACE and the INS8900 having program execution speeds that are comparable to, rather than being significantly faster than, the 8-bit microprocessors we have described in earlier chapters.

The only current manufacturer for PACE and the INS8900 is:

NATIONAL SEMICONDUCTOR, INC. 2900 Semiconductor Drive Santa Clara, CA 95050

There are agreements between Rockwell International and National Semiconductor and between Signetics and National Semiconductor to exchange microcomputer technical information and to produce each other's products. At the present time, neither Signetics nor Rockwell International has elected to second source PACE or the INS8900, and it is extremely unlikely that they will since both PACE and the INS8900 are products with limited futures. The amount of support that National Semiconductor provides is rapidly declining as newer, more powerful 16-bit microprocessors enter the marketplace.

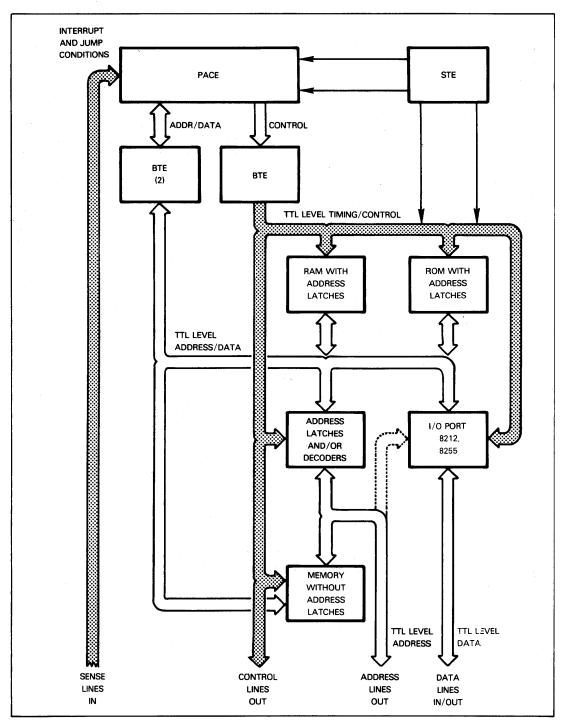

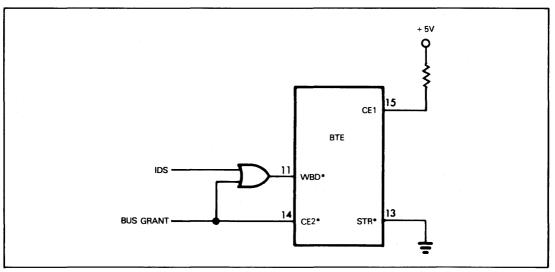

As shown in Figure 1-1, a typical PACE microcomputer will consist of a mixture of special-purpose PACE support devices and standard devices. The PACE microcomputer devices described in this chapter consist of:

#### The PACE CPU

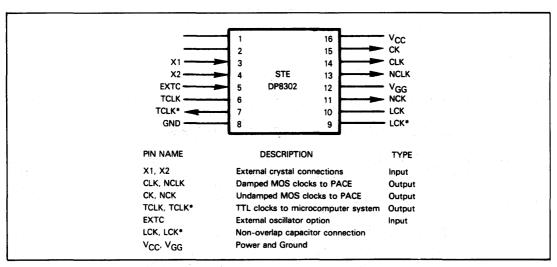

- The System Timing Element (STE), which generates clock signals for PACE and the system.

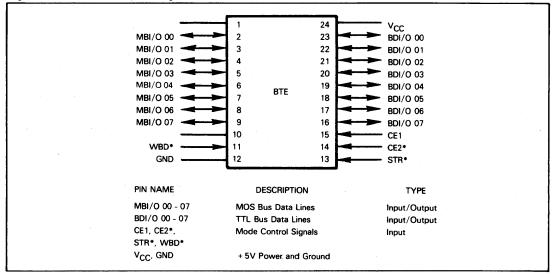

- The Bidirectional Transceiver Element (BTE), which converts the MOS-level PACE signals to TTL-level signals for other devices. The BTE is 8 bits wide.

The INS8900 needs a clock generator; a 2 MHz crystal and a 74C04 inverter are recommended. Otherwise, there are no special INS8900 support devices; in fact, you can easily use any NMOS support devices described in Volume 3 with the INS8900. Specifically, the STE and BTE devices cannot be used with the INS8900, because they provide MOS-to-TTL signal level conversions for PACE.

PACE requires +5V, +8V and -12V power supplies. The +8V is a substrate voltage requirement of the CPU and can be derived from the +5V power using a few discrete components. Therefore, a system can be implemented using only two primary power supplies: +5V and -12V. The INS8900 also uses three power supplies: +12V, +5V and -8V.

The INS8900 uses a 500 nanosecond clock to provide typical instruction execution times in the range of 8 to 20 microseconds. PACE (IPC-16A/520D) uses a 750 nanosecond clock to provide typical instruction execution times in the range of 12 to 30 microseconds.

Before making direct comparisons of these instruction execution times with those of other devices, however, note carefully that because of the 16-bit architecture of PACE and the INS8900, it may take many instructions on another microcomputer to perform the same operations as a single INS8900/PACE instruction.

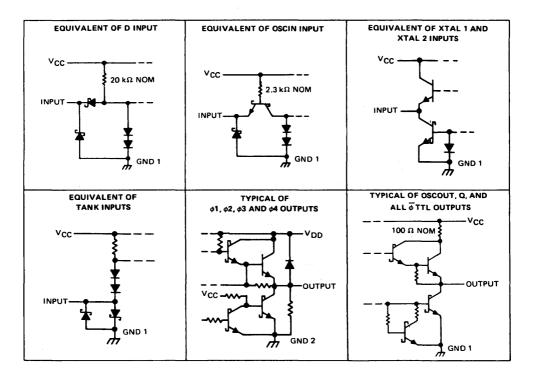

MOS level signals are input and output by PACE. TTL level signals are input and output by the INS8900.

P-channel silicon gate, MOS/LSI technology is used with PACE. N-channel MOS technology is used by the INS8900.

#### PACE AND INS8900 MICROCOMPUTER SYSTEM OVERVIEWS

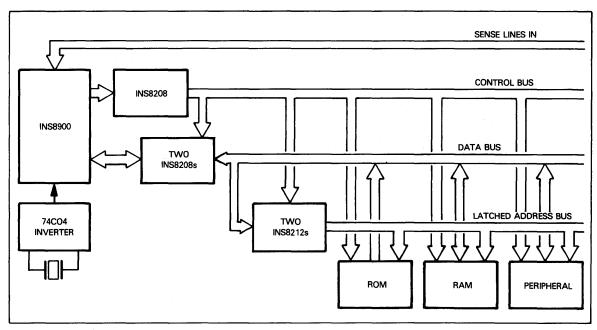

Figure 1-1 conceptually illustrates a PACE system. Figure 1-2 conceptually illustrates an INS8900 system.

As with any mini- or microcomputer system, the CPU outputs data, address, and control signals. In the case of PACE and the INS8900, the data and address signals use the same bus lines; therefore, they are said to be multiplexed.

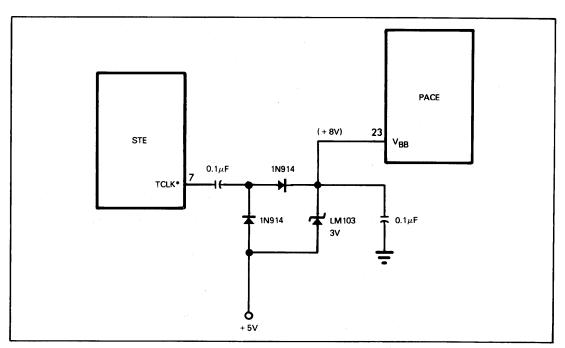

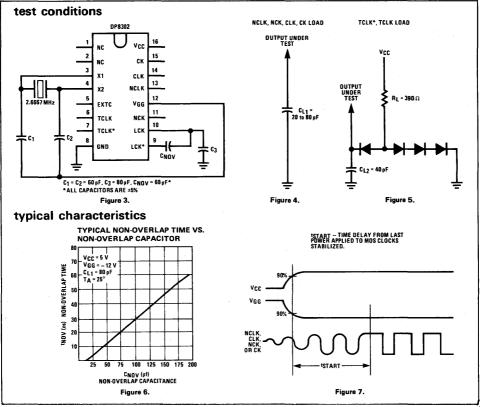

Timing signals needed by PACE are generated by the System Timing Element (STE). PACE signals are all MOS level; the STE therefore generates two sets of timing signals; one set are MOS level for PACE, the other set are TTL level for external logic.

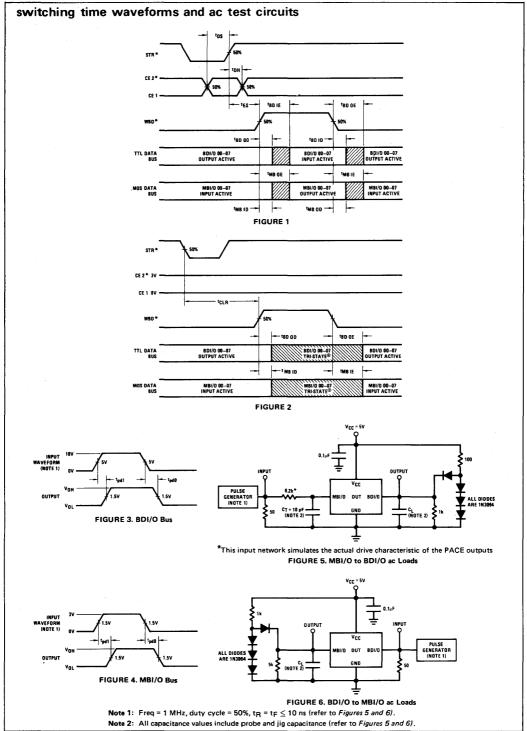

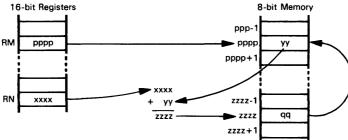

Since PACE signals are MOS level, Bidirectional Transceiver Elements (BTEs) must be present to translate outgoing signals from MOS to TTL levels, and to translate incoming signals from TTL to MOS levels. BTEs are quite indiscriminating in the signals they translate; in either direction, any signal arriving at an input pin is faithfully reproduced at the corres-

ponding output pin. Control signal options allow a BTE to operate bidirectionally, to drive output signals only, or to place both the MOS and TTL outputs in a high-impedance mode. Since the BTE is 8 bits wide, two BTEs operating bidirectionally provide buffering for the 16-bit Address/Data Bus. A third BTE, operating in the drive-only mode, provides buffering for the PACE control signals (NADS, ODS, IDS, and Flags).

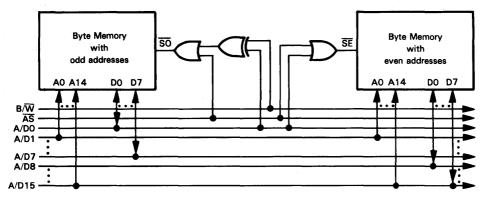

A complete TTL level bus is created by combining BTE outputs with the TTL level timing signals output by the STE. Remember, though, that the 16 address/data lines are multiplexed. External logic that can demultiplex these lines and that can respond to the PACE timing and con-

trol signal logic can connect directly to the TTL level address/data lines. For example, National Semiconductor provides ROM and RAM devices with on-chip address latches; these devices can interface directly to the TTL level bus.

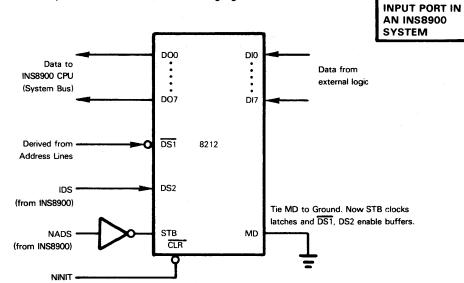

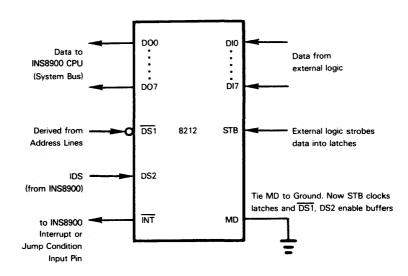

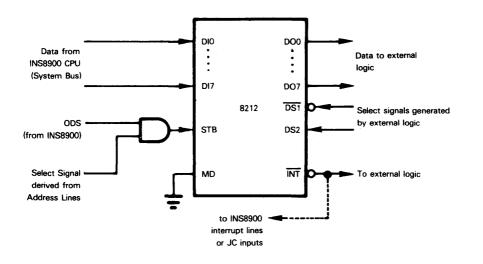

If memory devices or I/O ports are used that cannot demultiplex the address/data lines, you must provide separate logic to perform this function. No special PACE family devices are available for this purpose; however, standard logic devices can be used. For example, two hex flip-flop devices and a guad flip-flop device would provide a latched 16-bit Address Bus. Two 8212 I/O ports could also be used to latch the 16 bits of address information. The PACE Address Data Strobe (NADS)

signal can be used as the CLK input to the flip-flops or as the STB input to the 8212s. The PACE Address Data Strobe (NADS) signal can be used as the CLK input to the flip-flops. In many systems this is the most effective approach since a latched Address Bus allows you to use simpler address decoding techniques to generate memory chip enable and I/O port select signals.

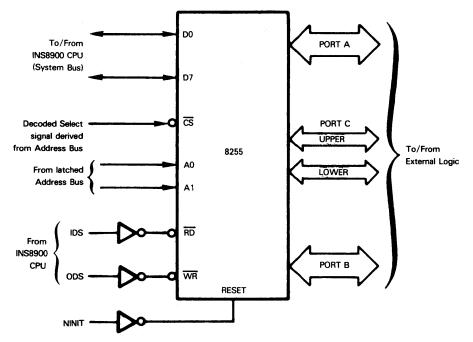

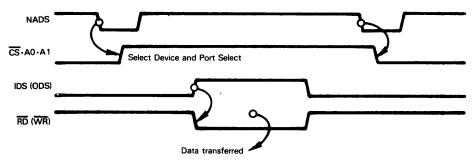

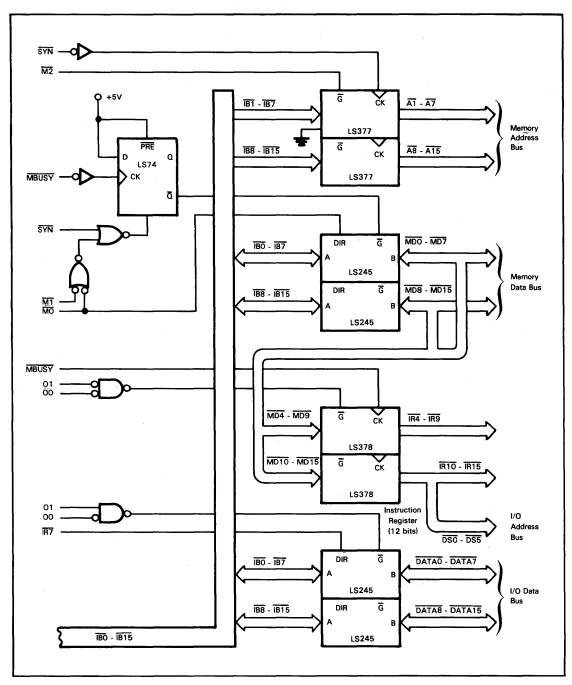

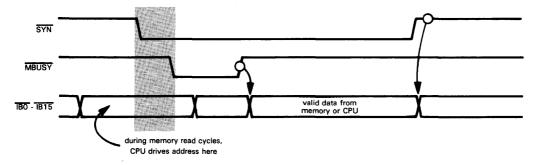

Figure 1-2 illustrates an INS8900 microcomputer system. Logic is quite elementary — and equivalent to that which you would expect with any other microcomputer. Control Bus, Data Bus, and Address Bus lines are buffered using INS8208 bidirectional buffers. These are National Semiconductor standard catalog devices, recommended by National Semiconductor and illustrated in their literature; however, any other buffer would do equally well. The Data/Address Bus is shown being demultiplexed by 8212s to create separate Data and Address Busses. This again is straightforward logic.

SYSTEM TIMING

PACE/INS8900

LOGIC LEVEL

ADDRESS

LATCHES

DECODERS

AND

Figure 1-1. A National Semiconductor PACE Microcomputer System

Figure 1-2. A National Semiconductor INS8900 Microcomputer System

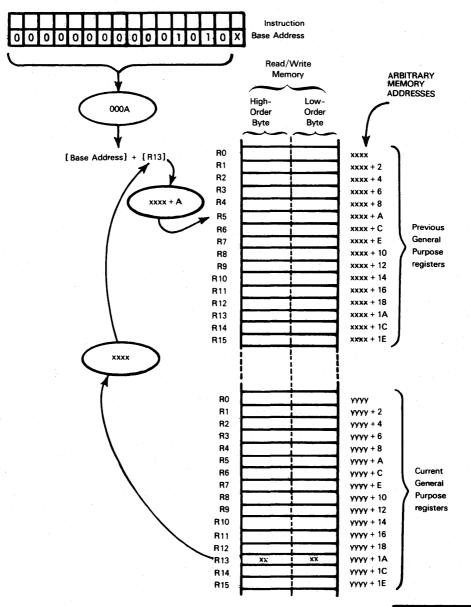

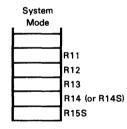

#### **INS8900 PROGRAMMABLE REGISTERS**

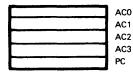

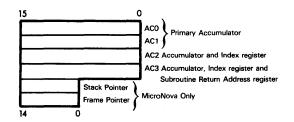

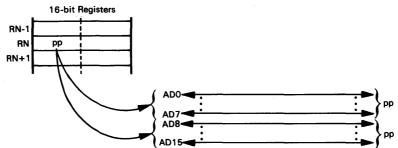

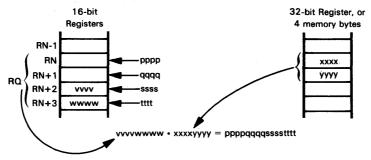

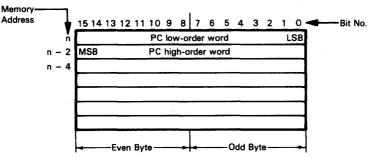

The INS8900 (and PACE) has four 16-bit Accumulators and a 16-bit Program Counter; these registers may be illustrated as follows:

Primary Accumulator Secondary Accumulator Secondary Accumulators and Index Registers Program Counter

# Accumulator AC0 may be likened to a primary Accumulator as described for our hypothetical microcomputer in Volume 1.

Accumulator AC1 is a secondary Accumulator.

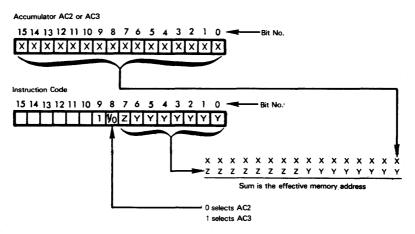

Accumulators AC2 and AC3 are equivalent to a combination of secondary Accumulators and Index registers.

Recall from Volume 1, Chapter 6 that an Index register differs from a Data Counter in that the Index register contents are added to a displacement (which is provided by a memory reference instruction) in order to determine the effective memory address.

The Program Counter serves the same function in an INS8900 system as it does in our hypothetical microcomputer described in Volume 1.

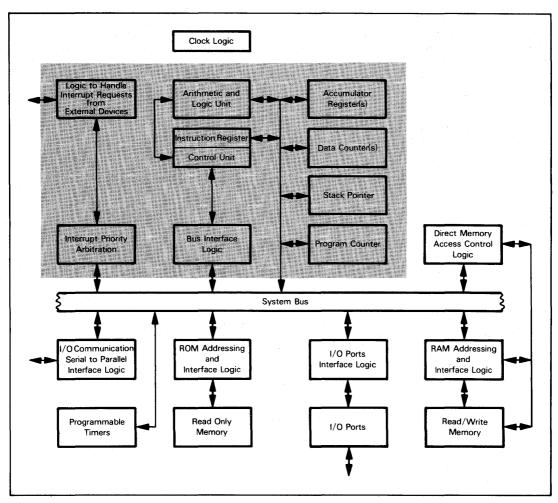

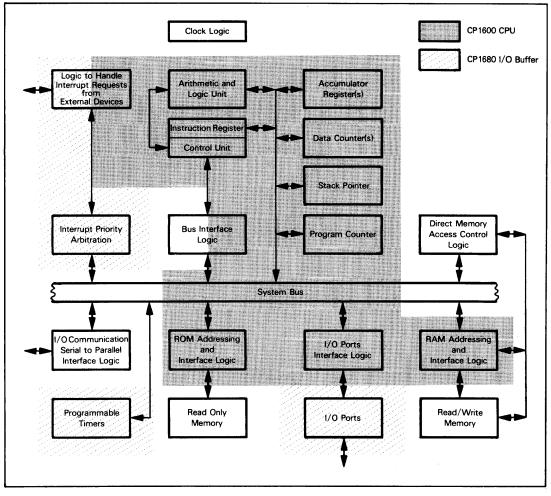

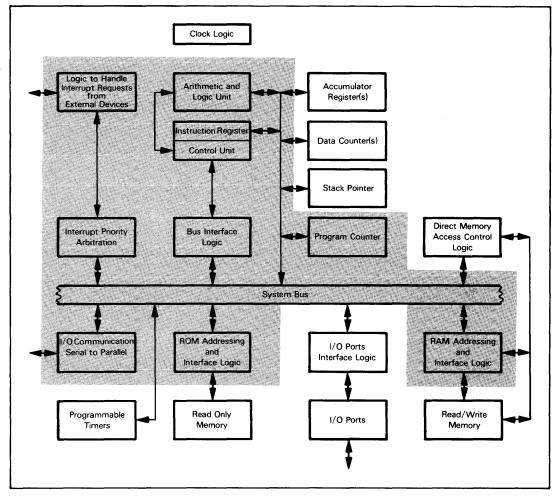

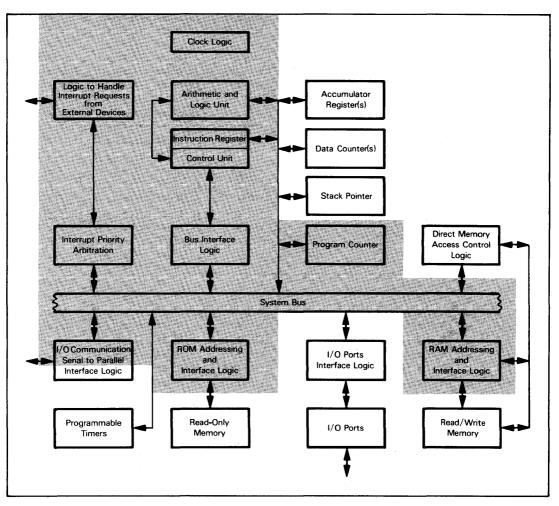

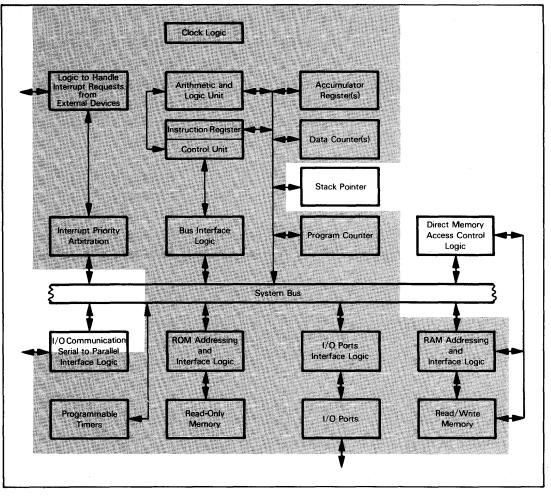

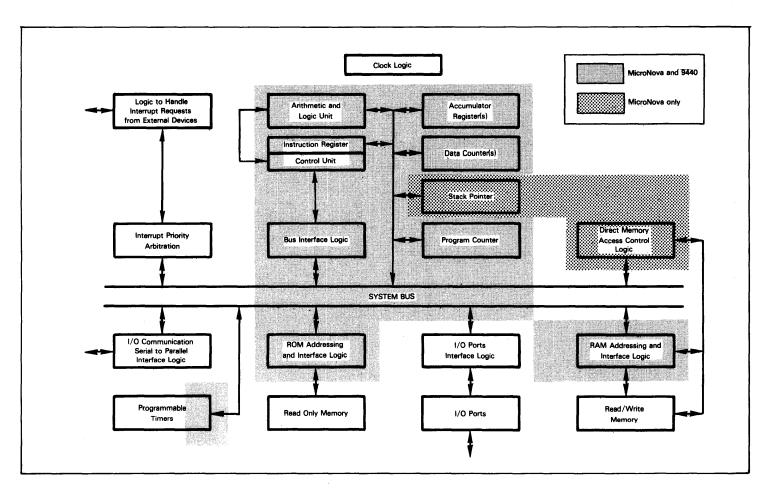

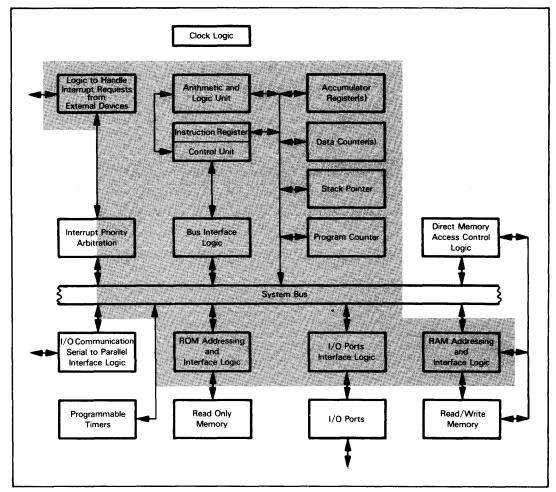

Figure 1-3 illustrates that part of our general microcomputer system logic which has been implemented in the INS8900 microprocessor.

Figure 1-3. Logic of the INS8900 Microprocessor

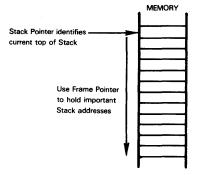

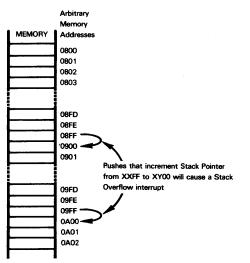

## **INS8900 STACK**

A Stack is provided on the INS8900 (and PACE) chip. The Stack is 16 bits wide and 10 words deep. The Stack is not a cascade stack, as described in Volume 1. Chapter 6: rather, chip logic maintains its own Stack Pointer to identify the next free Stack word. The Stack Pointer is automatically incremented and decremented in response to Push and Pull operations. Stack Push and Pull operations are initiated by CPU logic during execution of Jump-to-Subroutine (JSR) and Return-from-Subroutine (RTS) instructions, and during interrupt processing, to automatically save and restore the Program Counter.

In addition, the Stack can be used for temporary storage of data or status information. There are instructions which allow you to transfer words between the Stack and any Accumulator, or the Status and Control Flag register. This capability can significantly reduce the number of memory accesses required (thus increasing system speed) and can also reduce read/write memory requirements since intermediate values can be stored on the Stack.

Whenever the Stack becomes completely filled or emptied, an Interrupt Request is generated on the INS8900 chip. If you have enabled Stack Interrupts, program execution will be suspended, allowing you to deal with the situation. A Stack Full condition will indicate that it is time to dump data accumulated on the Stack out to read/write memory.

### **INS8900 AND PACE ADDRESSING MODES**

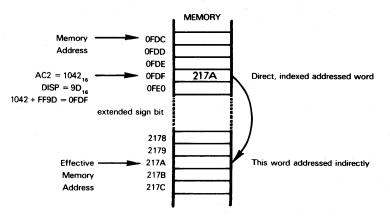

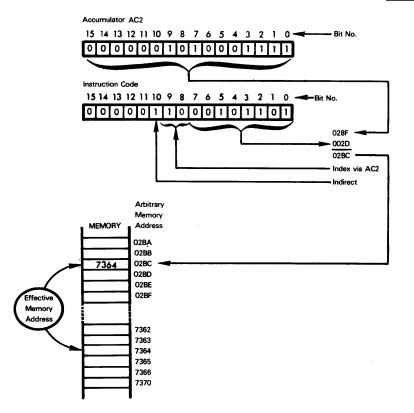

Most INS8900 (and PACE) memory reference instructions use either direct or direct, indexed addressing. A few instructions also offer indirect addressing and pre-indexed, indirect addressing. Refer to Volume 1. Chapter 6 for a description of these addressing modes.

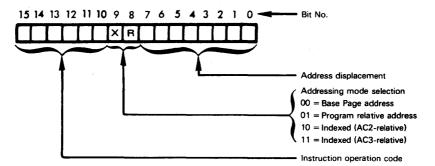

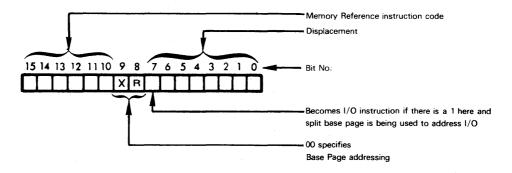

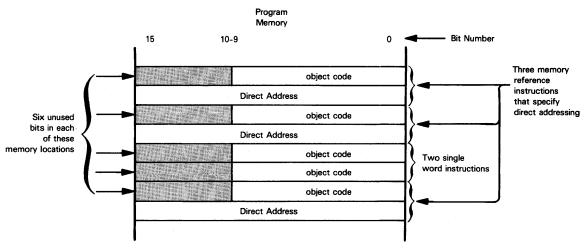

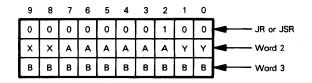

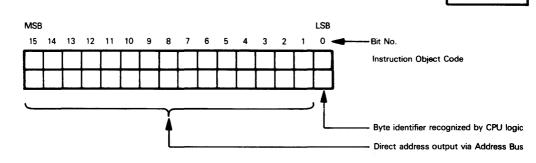

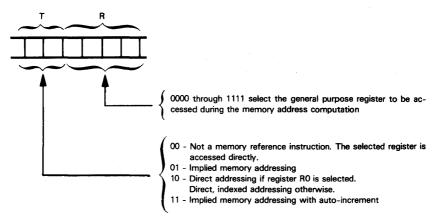

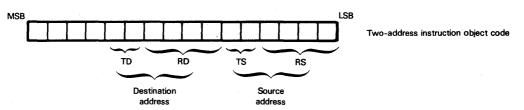

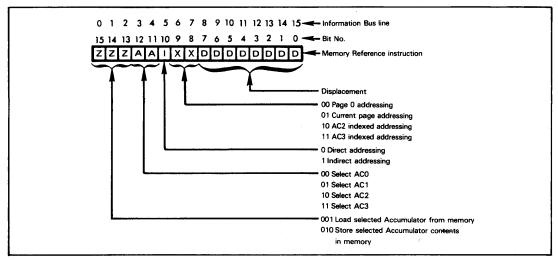

All memory reference instructions have the following object code format:

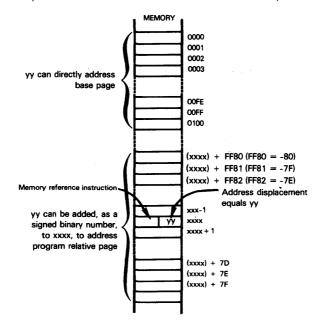

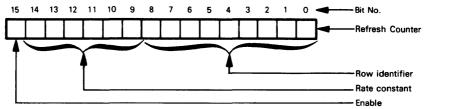

The 2-bit XR field lets you specify with each instruction the type of direct addressing you want used: base page, program relative or indexed (AC2- or AC3-relative). Since the address displacement is an 8-bit field in the instruction word, direct addresses are paged and each page consists of 256 words. Indexed and paged addressing variations have been described in Volume 1, Chapter 6.

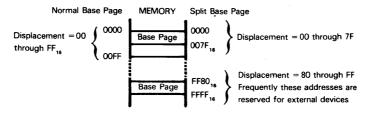

In addition, the INS8900 (and PACE) offers a variation of base page addressing, which is not described in Volume 1, Chapter 6. There is a control input signal (BPS) which allows the base page to be split between the top and bottom 128 words of memory, as follows:

BPS high splits the base page; BPS low keeps the base page as the bottom 256 words of memory.

Depending on how an INS8900 system has been configured, the base page may be permanently defined as split or as normal; or the base page may be varied between the two options under program control. There are a number of output control flags (which are described next) that may be set or reset under program control. If one of these flags is connected to the base page select pin, then setting or resetting this flag determines which base page option will be in effect:

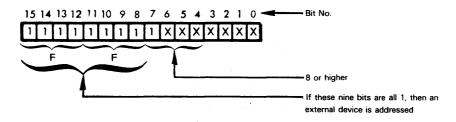

Splitting the base page between the top and bottom of memory is useful in an INS8900 microcomputer system because it simplifies external device addressing. If we reserve all memory addresses in the range FF80<sub>16</sub> - FFFF<sub>16</sub> for external devices, then external logic merely has to AND the top nine bits of an address and thus determine if an external device (rather than a memory location) is being addressed:

Splitting the base page also makes it easy to implement half of the base page in ROM, leaving the other half in RAM.

To a programmer, this scheme provides an easy way of generating 128 external device addresses. If the split base page option is in effect, then base page, direct addressing can be interpreted as external device addressing, so long as the high-order bit of the displacement is 1:

INS8900/PACE SPLIT BASE PAGE TO ADDRESS I/O

INS8900/PACE

DIRECT INDEXED ADDRESSING

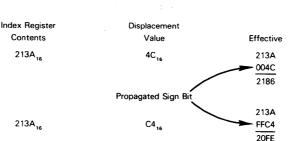

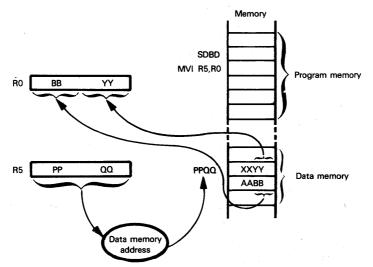

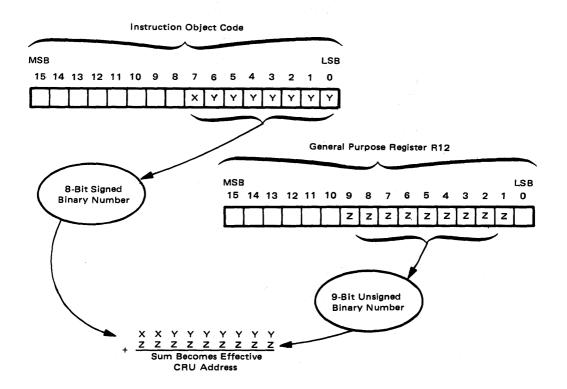

The base page and program relative options do not apply when the displacement is part of a direct, indexed address. When indexed addressing is specified, the INS8900 adds the contents of the displacement, as a signed binary number, to the contents of the identified Index register (AC2 or AC3). The sum becomes the effective address. Here are some examples:

Observe that the high-order bit of the displacement, being a sign bit, is propagated through the missing high-order displacement byte.

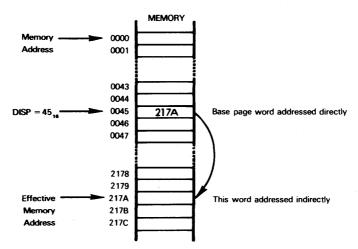

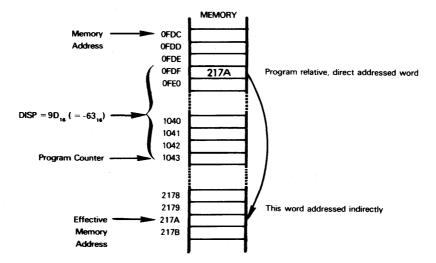

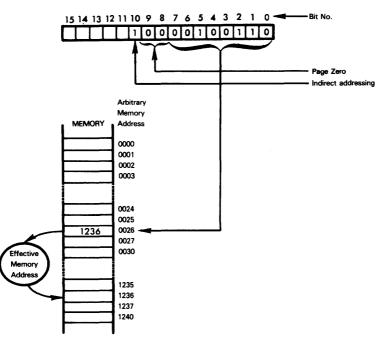

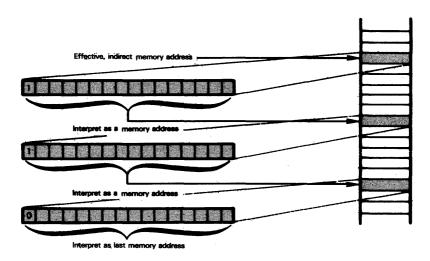

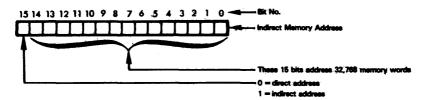

Instructions that allow indirect addressing simply superimpose indirect addressing logic on the preceding direct address generation logic. For example, if indirect addressing without indexing is specified, then a base page or program relative direct, address will be computed in the normal way, but the effective address is contained in the memory location identified by the direct address.

This illustration shows base page, indirect addressing; arbitrary memory addresses are used to make the illustration easier to understand:

This illustration shows program relative, indirect addressing, again using arbitrary memory addresses:

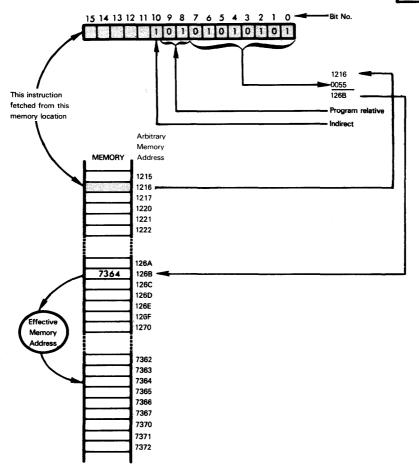

If indirect addressing with indexing is specified, then a direct address is first computed by adding the displacement, as a signed binary number, to the contents of the specified Index register; the direct indexed address thus computed provides the memory location where the indirect address will be found. This is illustrated as follows:

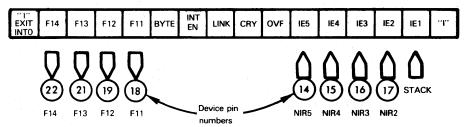

#### INS8900 AND PACE STATUS AND CONTROL FLAGS

The INS8900 has a 16-bit Status and Control Flag register. This register is on the CPU chip and is illustrated as follows:

# Fourteen of the 16 register bits are used. Three of the 14 bits are status flags as we define a status flag. These three flags are:

Overflow (OVF), which is a typical Overflow status.

**Carry (CRY)**, which is set and reset by arithmetic operations. as described for a typical Carry status.

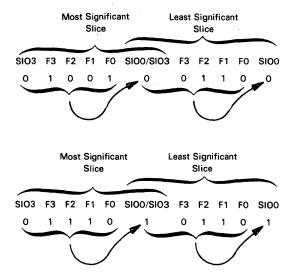

Link (LINK), which is set and reset by Shift and Rotate instructions, as described for the hypothetical microcomputer's Carry status in Volume 1. Chapter 7.

The separation of Carry into two statuses, one for shift and rotate operations, and the other for arithmetic operations, is a fairly common minicomputer feature; the advantage of separating these two statuses is that the results of arithmetic operations can be preserved across subsequent Shift and Rotate instructions.

BYTE causes data to be accessed in 8-bit lengths when this status is set to 1, or in 16-bit lengths when this status is set to 0.

Five bits (IE1 through IE5) are reserved for interrupt processing. These five bits selectively enable and disable five interrupt lines. One of these lines (IE1) is reserved for the Stack Overflow interrupt, the other four lines are available for external device interrupt requests. There is also a master interrupt enable and disable bit (INT EN).

Bits F11, F12, F13 and F14 are control flags which are output directly to INS8900 and PACE device pins; they can be used in any way to control external devices. One use, to select normal or split base page addressing, has already been described.

Only the three status flags OVF, CRY and LINK are automatically set or reset in the course of instruction execution. The remaining 11 bits of the Status and Control Flags register are set and reset by instructions or instruction sequences that read data into, or write data out of, the Status and Control Flags register.

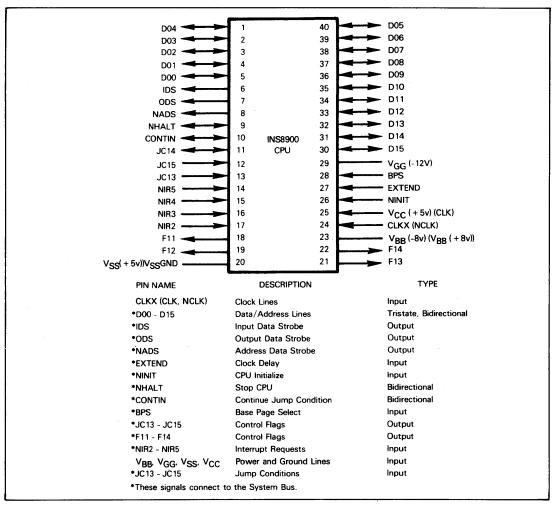

### **INS8900 AND PACE CPU PINS AND SIGNALS**

Pins and signals are illustrated in Figure 1-4 for the INS8900 and PACE devices. There are some small differences between the two sets of pin outs. These differences are shaded in Figure 1-4. Within the shaded areas, the INS8900 signal is shown closest to the arrow. The PACE signal is shown in brackets further out. Here is a summary of pins that differ:

#### INS8900 AND PACE SIGNAL DIFFERENCES

| Pin    | INS8900                | PACE                   |

|--------|------------------------|------------------------|

| Number | Signal                 | Signal                 |

| 20     | GND                    | V <sub>SS</sub> (+5V)  |

| 23     | V <sub>BB</sub> (-8V)  | V <sub>BB</sub> (+8V)  |

| 24     | CLKX                   | NCLK                   |

| 25     | V <sub>CC</sub> (+5V)  | CLK                    |

| 29     | V <sub>DD</sub> (+12V) | V <sub>GG</sub> (-12V) |

The pin out differences between PACE and the INS8900 are not surprising. Since PACE uses P-channel MOS technology, while the INS8900 uses N-channel MOS technology, we would expect power supply differences. Also, the INS8900, being a newer product, requires just one clock signal input (CLKX), compared to the two required by PACE (CLK and NCLK).

#### Let us examine the pins and signals in detail.

Figure 1-4. INS8900 and PACE CPU Signals and Pin Assignments

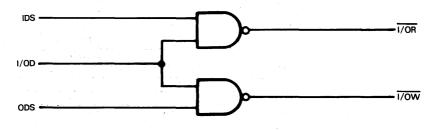

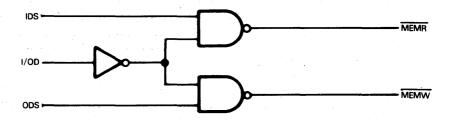

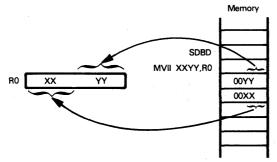

There are 16 data and address lines (D0 - D15), which are multiplexed for data input, data output and address output. Two control lines, ODS and NADS, identify output on the data and address lines as either data (ODS) or addresses (NADS). A further control line, IDS, is used to strobe data input.

The EXTEND control input is used by slow memories or external devices to lengthen an instruction's execution time by increasing the duration of a data input/output cycle; this extends the time available for memories or external devices to capture data output, or to present input data.

The NINIT input control initializes PACE; the Program Counter is set to 0. The Stack Pointer, the Stack and the Status and Control Flags register are cleared.

BPS has already been described; it is used to select either normal or split base page, for base page direct addressing.

**NHALT is** a bidirectional control signal **used by interrupt and halt logic.** As an input, NHALT can induce a Halt state, or in conjunction with CONTIN, it can generate a level 0 (highest priority) interrupt request. When the CPU executes a Halt instruction, NHALT is output high to identify the Halt state. The various uses of NHALT and its interaction with CONTIN are described in detail later in this chapter.

The CONTIN signal is used to terminate a Halt condition and is also used as an output interrupt acknowledge signal. When CONTIN is properly sequenced with the NHALT signal, it initiates a high priority interrupt, as we mentioned in the preceding paragraph. CONTIN can also be used as a Jump condition input in the same way as JC13, 14 and 15, which are described next.

JC13, 14 and 15 provide an interesting capability found in very few microcomputers discussed in this book; the condition of these three inputs can be tested by a Branch-on-Condition (BOC) instruction, thus allowing external control signals to directly manipulate PACE program instruction sequences.

F11, 12, 13 and 14 are the outputs for the corresponding flag bits in the Status and Control Flags register.

NIR2, 3, 4 and 5 are the external interrupt request lines. Interrupt priority arbitration logic is included on the INS8900 (and PACE) chip. NIR2 has the highest priority of the external interrupt lines, and NIR5 has the lowest priority.

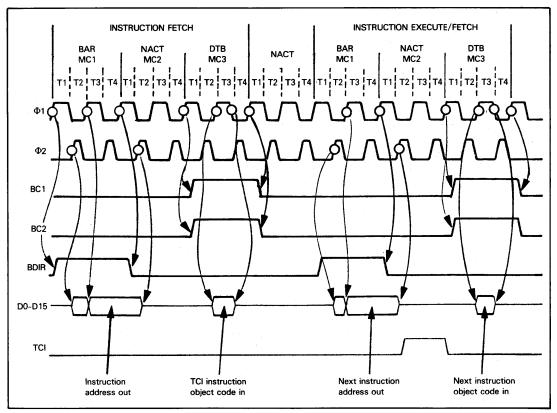

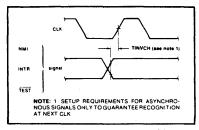

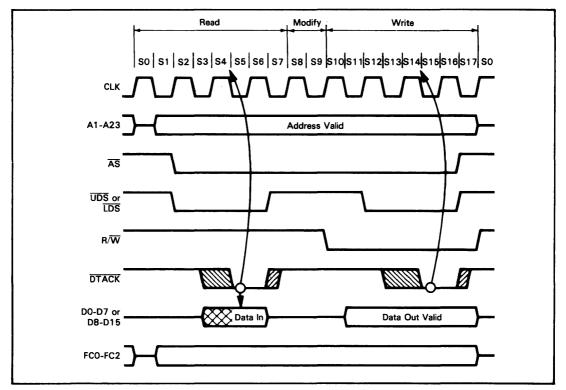

#### INS8900 AND PACE TIMING AND INSTRUCTION EXECUTION

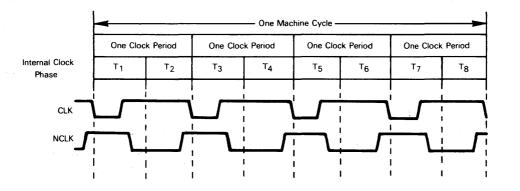

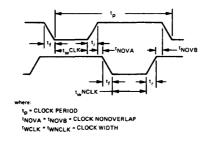

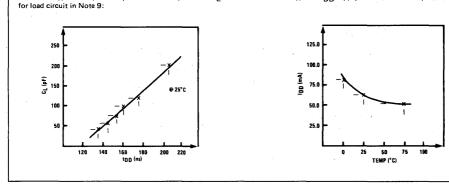

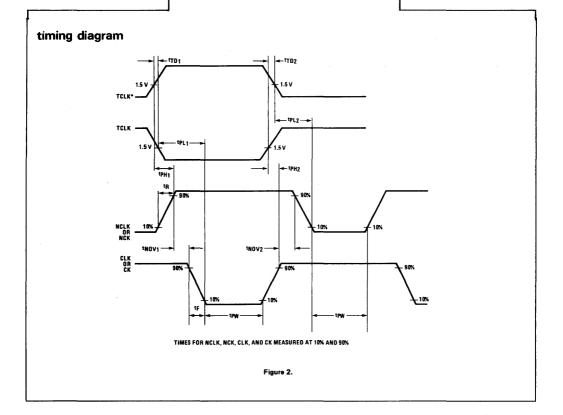

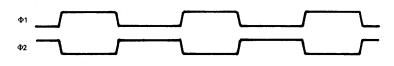

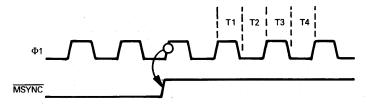

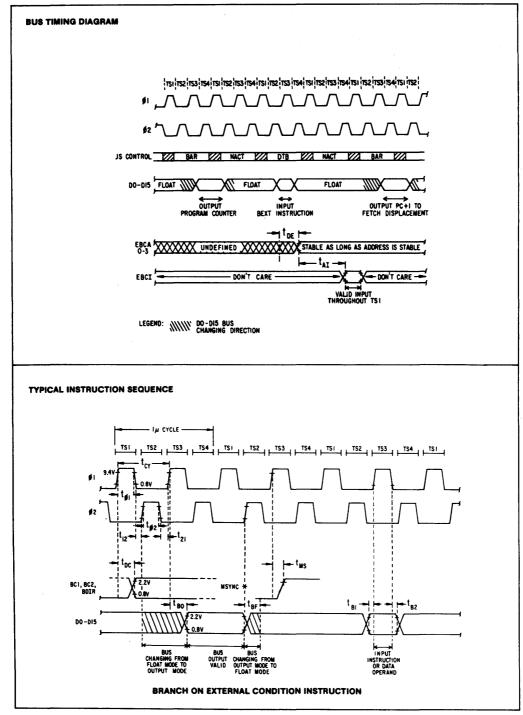

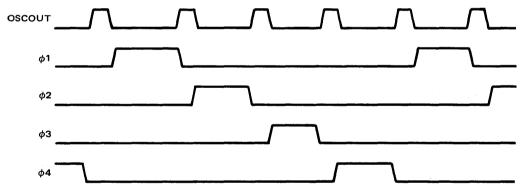

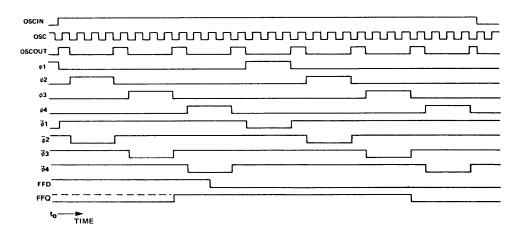

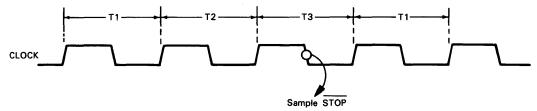

PACE uses a combination of two clock signal inputs to time events internally within the microprocessor CPU. The clock signals and the resultant internal clock phases can be illustrated as follows:

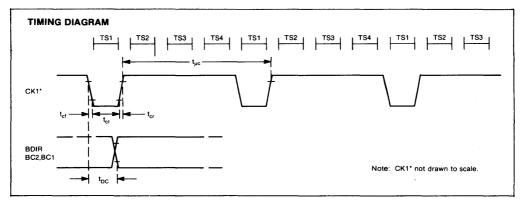

The INS8900 clock logic has been simplified. A single, uniform clock signal generates all timing as follows:

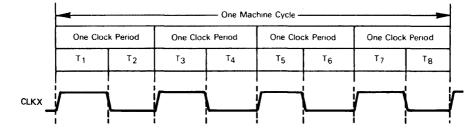

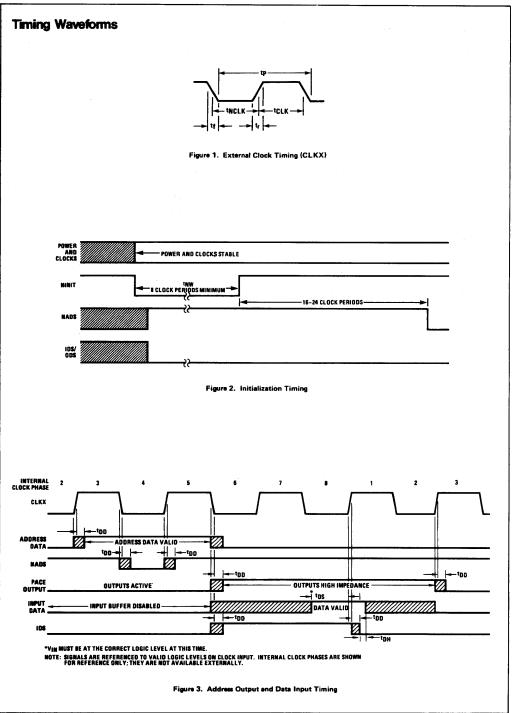

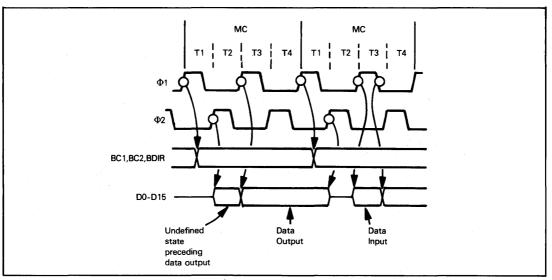

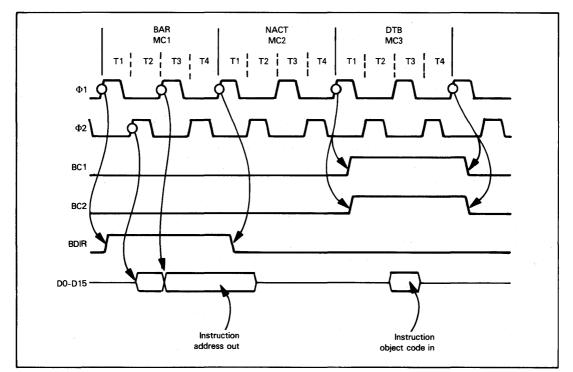

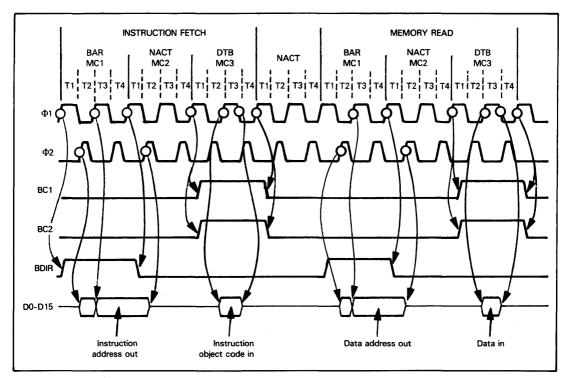

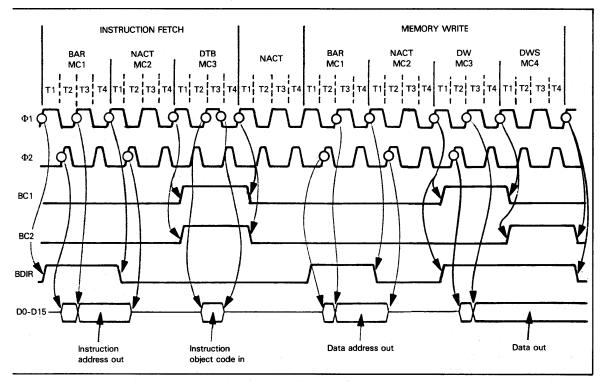

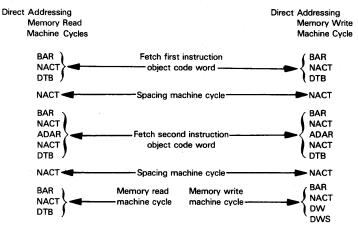

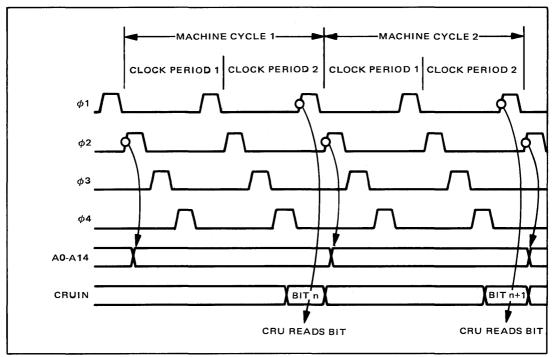

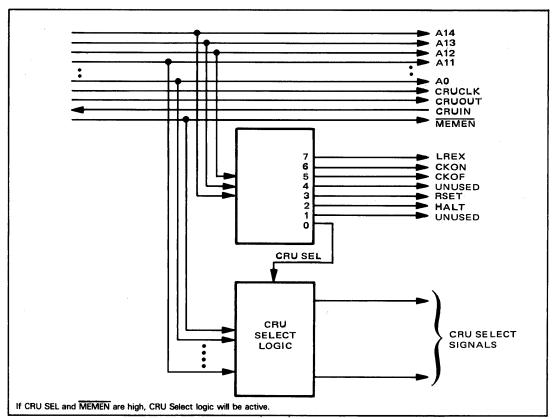

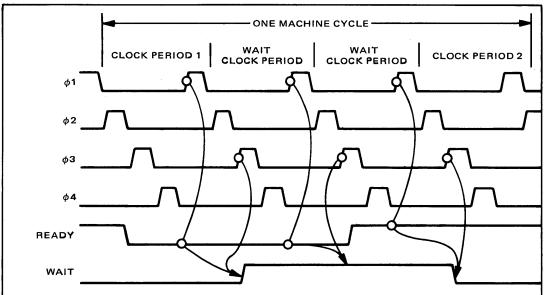

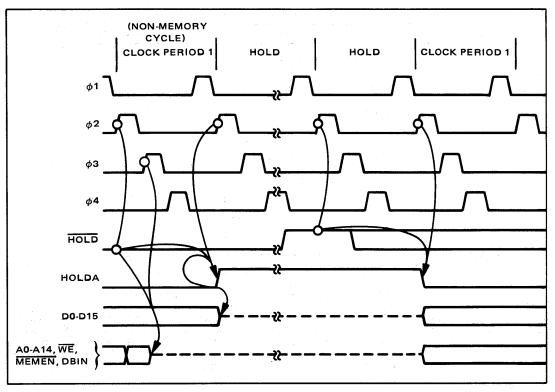

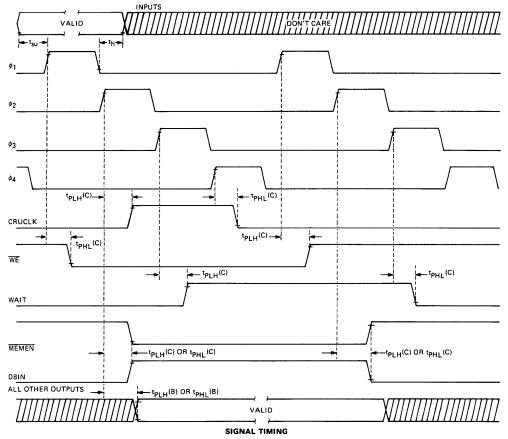

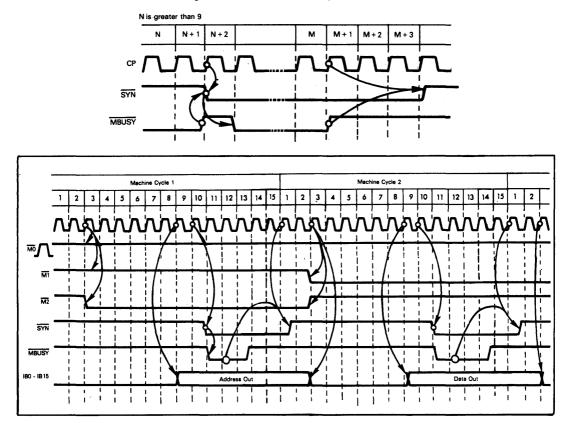

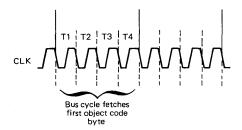

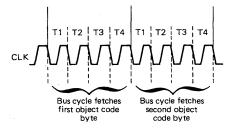

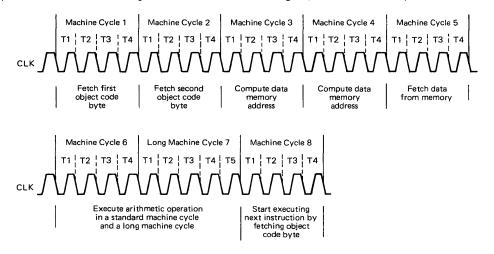

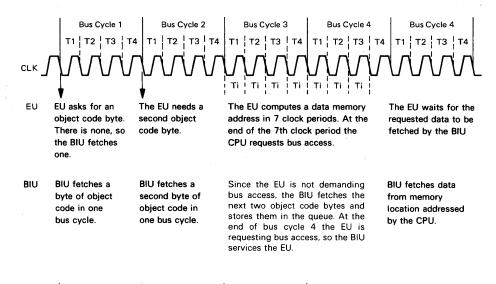

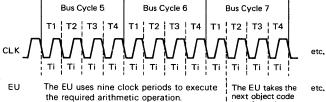

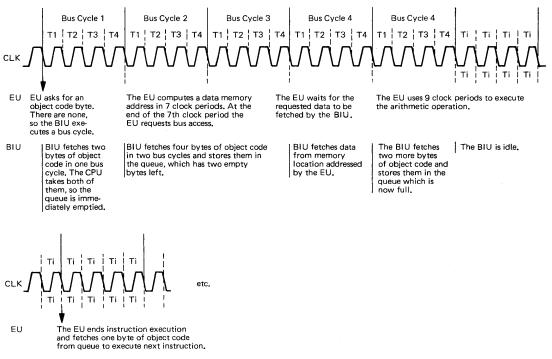

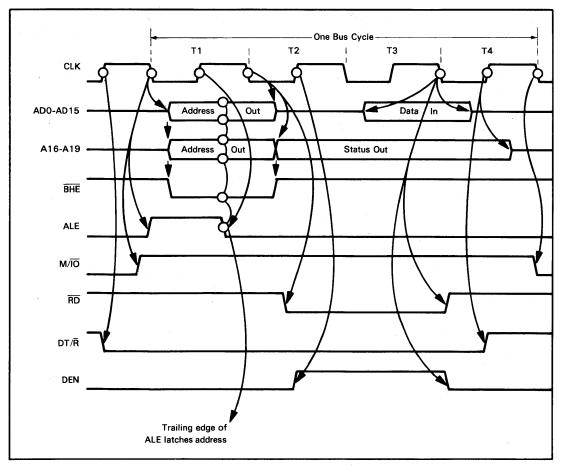

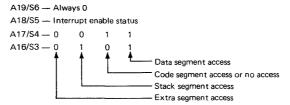

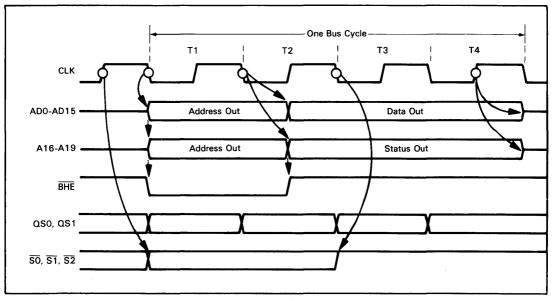

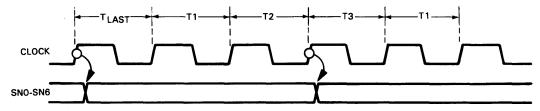

Several points should be noted regarding INS8900 and PACE timing. The internal clock phases (T1 through T8) are meaningless to external logic since they are not accessible, nor are they needed for any external synchronization purposes. We have shown them merely because they will simplify later discussions of data input/output operations. Four clock periods constitute a single machine cycle. Most instructions require between four and seven machine cycles for execution.

So far as external logic is concerned, there are only three types of machine cycles which can occur during execution of an instruction:

- 1) A data input operation (read) during which external logic must present a word of data to the CPU.

- 2) A data output operation (write) during which the CPU transmits a word of data to external logic.

- 3) An internal operation during which no CPU-initiated activity occurs on the System Bus.

All instructions include one or more data input machine cycles, and two or more internal operation machine cycles. Only a few instructions include data output machine cycles. The first machine cycle of any instruction's execution must, of course, be an instruction fetch operation — which to external logic is simply a data input cycle. Let us therefore begin by examining the data input machine cycle.

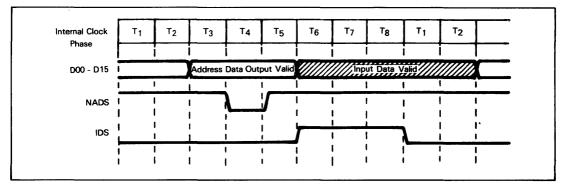

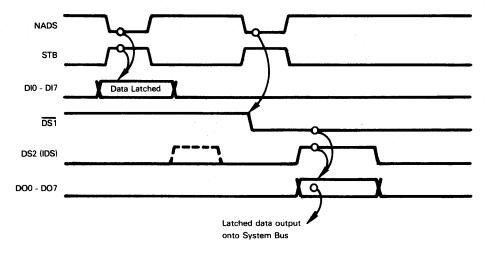

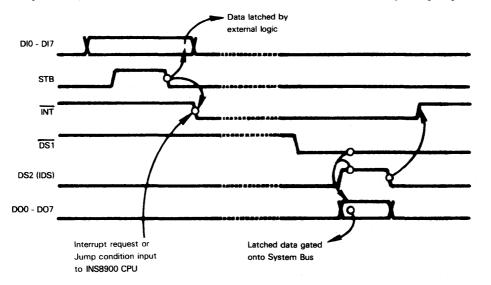

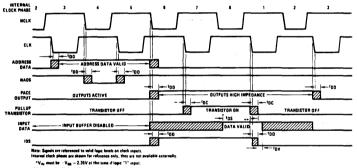

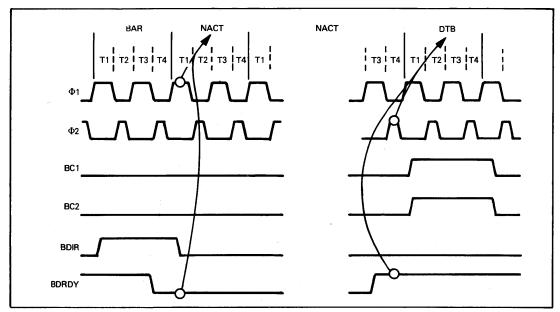

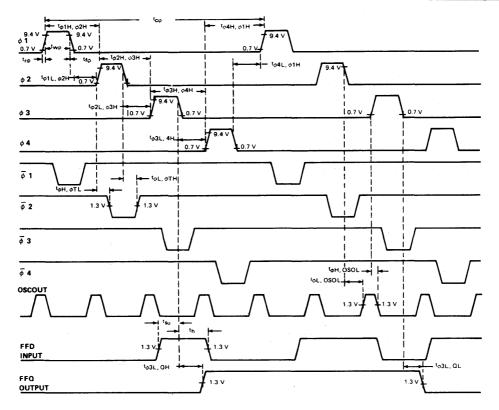

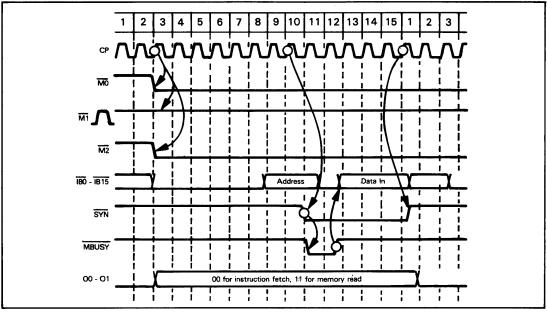

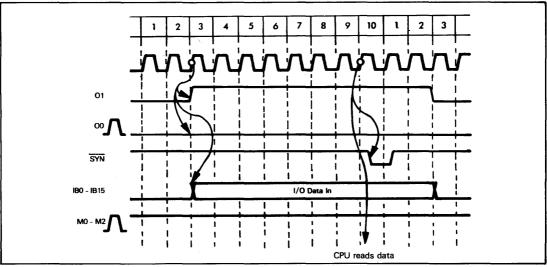

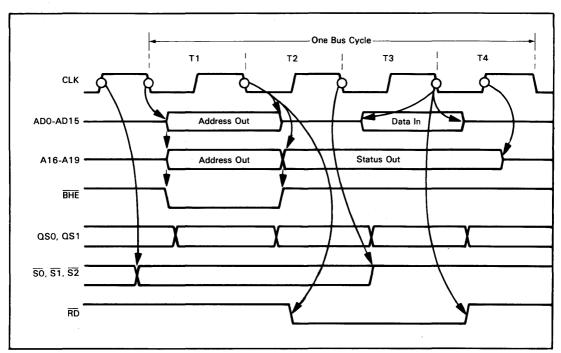

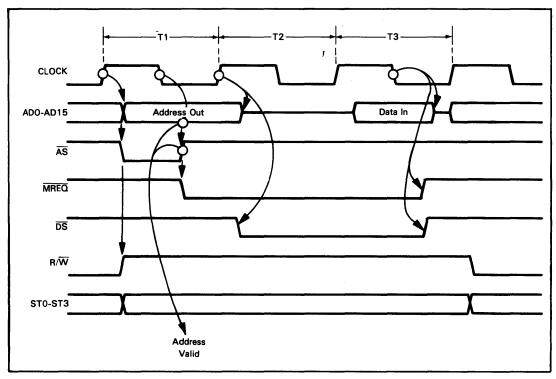

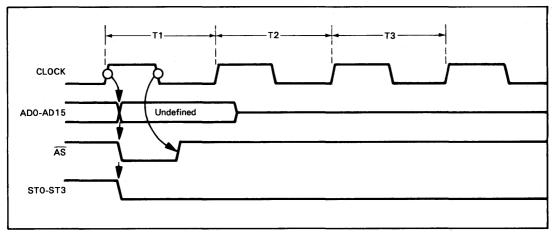

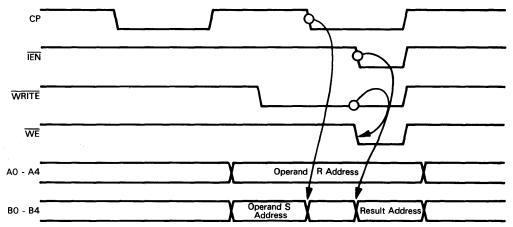

**Figure 1-5** illustrates timing for a standard data input machine cycle. Notice that the address is only present on the data lines for the first portion of the machine cycle. The NADS signal is sent out approximately in the center of the time interval during which the address data is valid; therefore, either the leading edge or trailing edge of NADS can be used to clock the address data.

The IDS signal is sent out at about the same time as the address information is taken off the data lines — well before the time when input data is expected by the CPU. This gives external logic time to prepare the input data. The input data needs to be valid only for a short time interval later in the machine cycle. Exact timing is given in the data sheets at the end of this chapter.

Figure 1-5. INS8900 and PACE Data Input Timing

MACHINE CYCLE INS8900 AND PACE

MACHINE

CYCLE

TYPES

INS8900

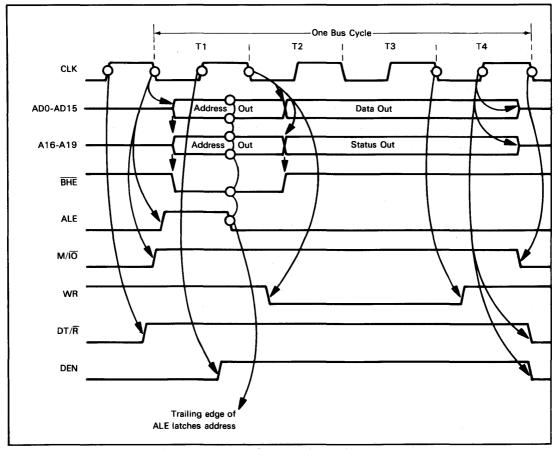

AND PACE

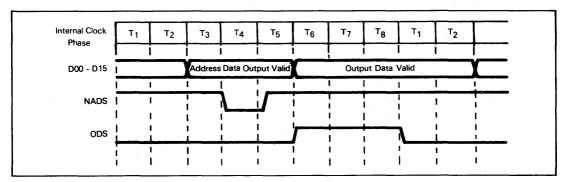

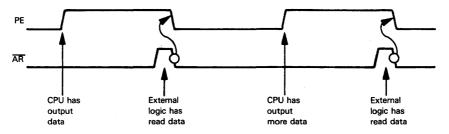

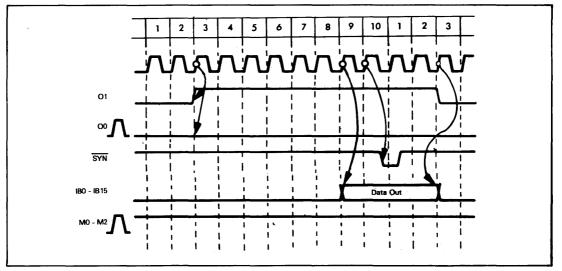

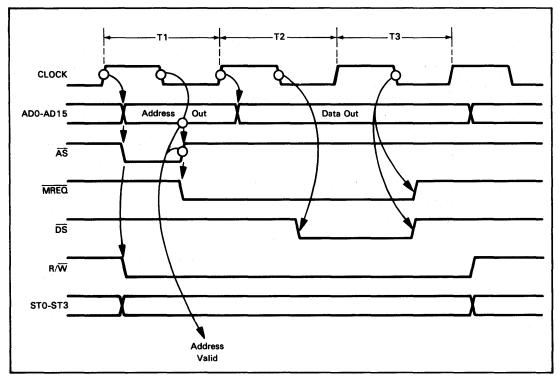

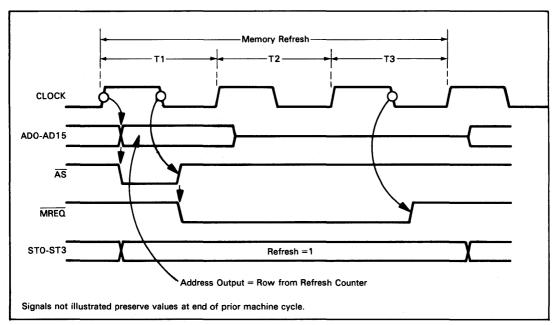

**Figure 1-6 illustrates timing for a standard data output cycle.** The address-output portion of the cycle is identical to that of the data input cycle just described; the ODS signal is sent out at the same part of the cycle as IDS was. At approximately the same time that ODS is sent out, the output data word is placed on the data lines. The output data remains valid beyond the end of the ODS signal so that the trailing edge of ODS can be used as the clock for external data latches.

INS8900 AND PACE DATA OUTPUT CYCLE

Figure 1-6. INS8900 and PACE Data Output Timing

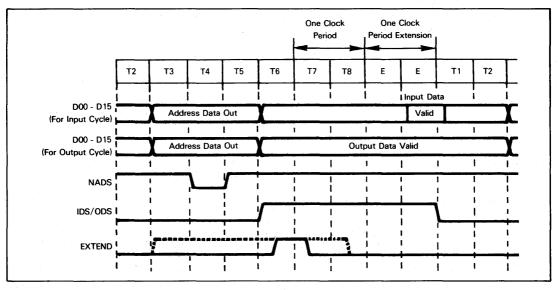

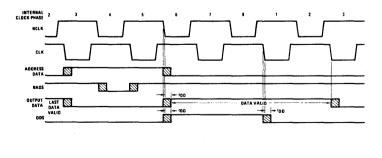

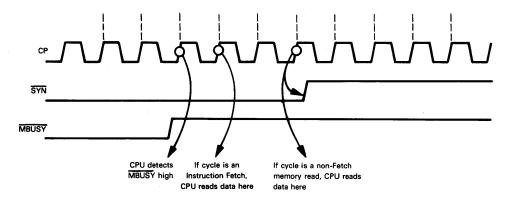

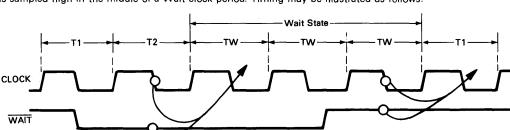

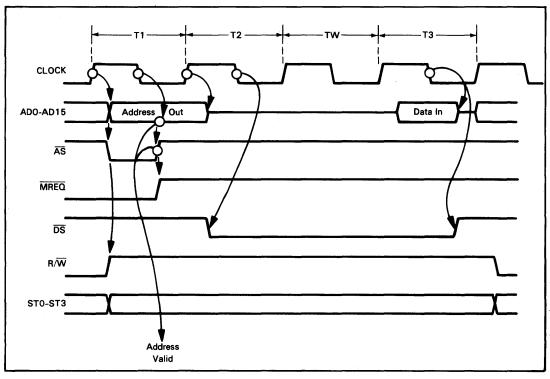

The data input/output cycles just described allow approximately two clock periods for external logic to respond. If this time interval is too short, the EXTEND signal input to the CPU can be used to lengthen the I/O cycle by multiples of the clock period (one clock period equals two internal clock phases). The EXTEND signal can be placed high during address time or immediately after the start of IDS or ODS, but it must be high before the end of internal clock phase 6 as shown in Figure 1-7.

INS8900 AND PACE EXTEND SIGNAL FOR SLOW I/O OPERATIONS

Figure 1-7. Using the EXTEND Signal to Lengthen I/O Cycles

The timing shown in Figure 1-7 provides the minimum I/O cycle extension of one clock period.

The maximum extension permitted by PACE is 2 microseconds; so with a clock period of 750 nanoseconds, this means that only two clock period extensions can be added to an input/output cycle. The second clock period extension is achieved by holding the EXTEND signal high for one additional clock period beyond the timing shown in Figure 1-7. The INS8900 has no maximum permitted extension.

Notice that the EXTEND signal does just what its name implies; it simply extends the duration of the data transfer portion of an I/O machine cycle. The trailing edge of the IDS or ODS signal is delayed and, for data input, the time until valid input data must be present is delayed. On data output cycles, the valid data is simply maintained on the data lines by the CPU for an extended period of time.

The EXTEND signal can also be used to suspend CPU input activity. This use of EXTEND will be described later under the heading of Direct Memory Access.

## THE INITIALIZATION OPERATION

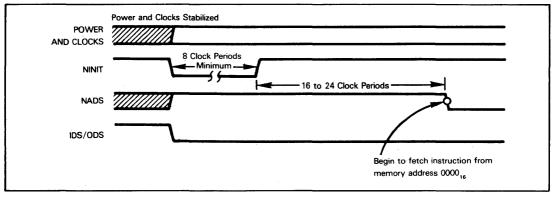

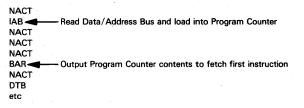

A NINIT low signal input to the CPU initializes the microprocessor. The NINIT signal is the equivalent of the Reset signal described for other microcomputers in this book. While NINIT is held low, CPU operations are suspended; IDS and ODS are reset low. NINIT must be held low for a minimum of eight clock periods to give the CPU time to respond. After NINIT goes high again, this is what happens:

- 1) The internal Stack Pointer is cleared.

- 2) All flags and interrupt enables are set low (except Level 0 Interrupt Enable which is set high).

- 3) The Accumulators contain arbitrary values.

- 4) The Program Counter is set to zero.

- 5) 16 to 24 clock periods after NINIT returns high, the NADS signal is output high. The first instruction is thus fetched from memory location zero (0000<sub>16</sub>).

Figure 1-8 illustrates the timing for the initialization operation. Note that the NINIT signal is shown going low after power and clocks are both stable. The NINIT signal must be applied whenever the CPU is powered-up; if NINIT is held low before clocks and/or power have stabilized, the NADS and NHALT output signals may have undefined states for eight clock pulses after the trailing edge of NINIT.

Figure 1-8. INS8900 and PACE Initialization Timing

### THE HALT STATE AND PROCESSOR STALL OPERATIONS

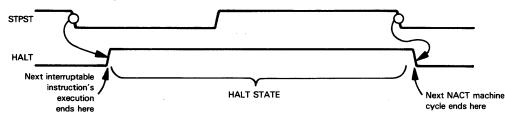

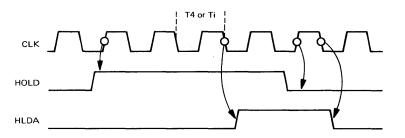

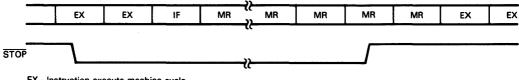

Most microprocessors described in this book have a Hold state, which typically describes a CPU condition during which there is no CPU-initiated activity on the System Busses; external logic can then perform Direct Memory Access operations. The INS8900 and PACE CPUs have an equivalent state that can be initiated under program control or by external logic. When this state is initiated under program control (by executing a Halt instruction) INS8900 and PACE literature calls it the Halt state; when initiated by external logic, it is called a Processor Stall.

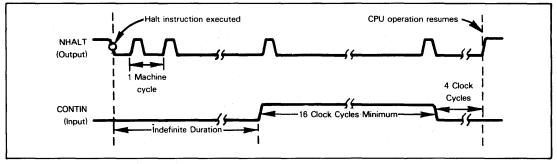

During normal program execution, the CPU NHALT control line provides a high output. When a Halt instruction is executed, the NHALT output is driven low to indicate that CPU activity is suspended. While in the Halt state, the NHALT output has a 7/8 duty cycle; that is, every eighth clock phase, the NHALT output goes high. If the NHALT output is merely used to drive an indicator on a

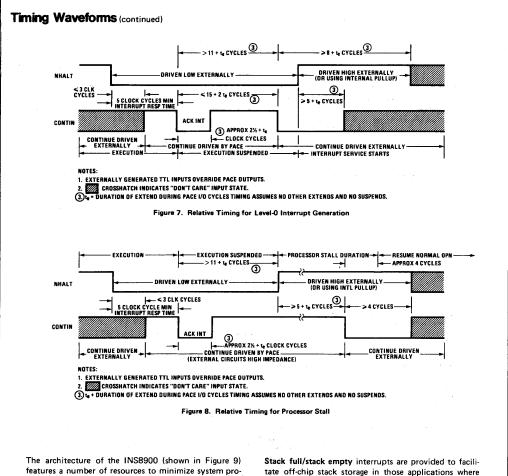

INS8900 AND THE PACE HALT STATE control panel, this 7/8 duty cycle is of little concern; but, if the NHALT signal is used as a logic signal, the 7/8 duty cycle must be accounted for. The Halt state is terminated by setting the CONTIN input signal high for a minimum of 16 clock cycles, and then resetting it low for at least four clock cycles, as shown in Figure 1-9. CPU operation then resumes by executing the next instruction, that is, the instruction that follows the Halt instruction.

Figure 1-9. Terminating INS8900 or PACE Halt State

As we have just seen, the PACE NHALT and CONTIN signals are interrelated. We mentioned earlier that these signals are also multifunctional. We will describe separately each of the functions that can be implemented with NHALT and CONTIN. Do not use these signals to implement more than one function unless your application absolutely

**requires the additional functions.** Critical and complicated timing relationships are required by the CPU to differentiate between various functions. For PACE, but not the INS8900, timing is further complicated by some circuit problems in the CPU's interrupt system, which we will describe later.

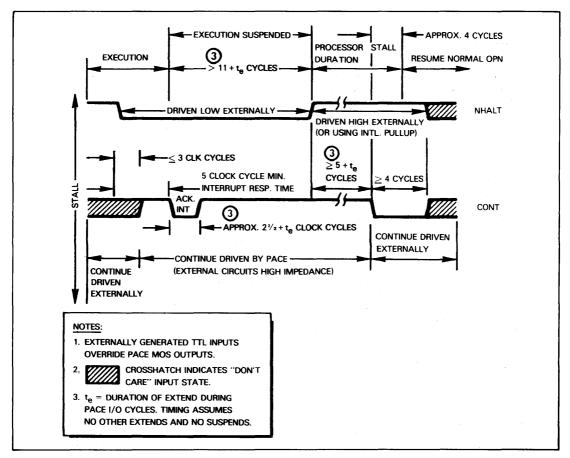

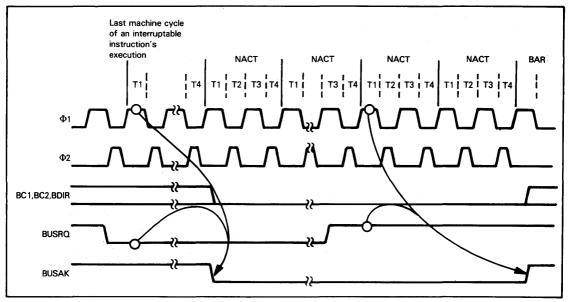

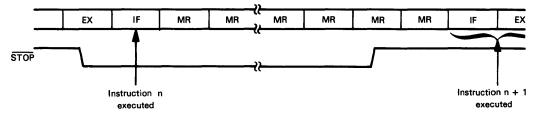

The INS8900 and PACE CPU can be forced into the Halt state by external logic. INS8900 and PACE literature defines this operation as a Processor Stall. A Processor Stall uses both NHALT and CONTIN as control signal inputs. Figure 1-10 shows the timing sequence required. The NHALT input must be driven low by external logic to initiate the sequence. CPU operation is then suspended after execution of the current instruction is completed. The minimum

response time is five clock cycles. The maximum response time is equal to the longest instruction execution time (refer to Table 1-2). There is no maximum time limit for a Processor Stall. The CPU simply remains in the Halt state until it is terminated by the CONTIN input signal, which must be properly sequenced with the removal of the NHALT input, as shown in Figure 1-10.

Let us take another look at the beginning of the Processor Stall timing sequence. Notice that when the CPU has completed the current instruction and recognized the stall request, the CONTIN output signal is briefly driven low by the CPU. This pulse is referred to as ACK INT (Acknowledge Interrupt) and can be used to let external logic know that the CPU is responding to the stall request. It may seem inappropriate for the CPU to provide an

Acknowledge Interrupt response when we are initiating a Processor Stall. However, as we shall see later in this chapter, a Level 0 Interrupt request begins with exactly the same timing sequence as a Processor Stall; in fact, the reaction of the CPU is the same for both operations until that point in the sequence where NHALT goes high. Therefore, the initial response of ACK INT is always sent out after NHALT is driven low.

## DIRECT MEMORY ACCESS OPERATIONS

At the beginning of our Halt state and Processor Stall discussion we mentioned that these are the equivalent of Hold states provided by other microprocessors. But there are some significant differences between the INS8900 and PACE Halt state, and the Hold state described for other microprocessors in this book. Because of these differences, Direct Memory Access operations with PACE or the INS8900 are not straightforward.

The INS8900 and PACE CPUs never float their Data or Control Busses. But remember that the design of any realistic INS8900 or PACE system is going to require buffer/drivers for the data lines and control signals. The BTE, which is part of the PACE microcomputer family, performs this buffering function.

Any bidirectional three-state buffer can be used to float INS8900 bus lines. In Figure 1-2, BUSSES INS8208 devices are shown performing this function. Thus it is the control signals input to the BTE by PACE or to the INS8208 by the INS8900 that actually float bus lines at the proper time, in order to allow DMA operations.

NHALT AND CONTIN

MULTIFUNCTIONAL

SIGNALS ARE

FLOATING

AND PACE SYSTEM

INS8900

Figure 1-10. Timing Diagram for Processor Stall Using NHALT and CONTIN Signals

But we must have a way of determining whether the CPU is going to be using the System Busses. There are several methods of making this determination; we will conceptually examine each of them within the context of three different DMA schemes:

- 1) DMA block data transfers initiated by the CPU

- 2) DMA block data transfers initiated by external logic

- 3) Cycle-stealing DMA transfers

From a hardware point of view, the simplest method of implementing DMA in a PACE or INS8900 system is to have the CPU initiate block transfers of data. Consider the following approach. The CPU will treat an external DMA controller as a peripheral device and will establish initial conditions such as starting address, word count, and direction (memory read or write). This information can be passed to the controller by treating its registers as memory

locations and using Store instructions to write into the registers. When the required information has been passed, the CPU simply executes a Halt instruction. As we described earlier, when a Halt instruction is executed, the NHALT control output line from the CPU is driven low (7/8 duty cycle). This signal could thus be used by the DMA controller as an indication that the CPU will not be using the System Bus and the DMA transfer can begin. When the transfer is completed, the DMA controller will use the CONTIN input to the CPU, as shown in Figure 1-9, to terminate the Halt instruction. Normal CPU operation will then resume.

Most microprocessors have a Bus Request input signal that can be used by external logic to request access to the System Busses. In a PACE or INS8900 system, the NHALT input signal can be used to force the CPU into a Processor Stall, as described earlier, and thus free the System Busses for DMA operations. The Acknowledge Interrupt (ACK INT) pulse on the CONTIN output line shown in Figure 1-10 is then equivalent to a Bus Grant signal, and the DMA controller may begin the data transfer. When the transfer is complete, the CONTIN line is used as a control input line to the CPU to terminate the Processor Stall.

Cycle-stealing DMA operations typically transfer a single word via the System Busses during a brief interval when the CPU is not using the busses. With this method, CPU operations need not be stopped; instead, they are only slowed down slightly, or in some cases not affected at all. In order to implement cycle-stealing DMA, external logic must have a way of detecting those time intervals when the CPU will not be using the System Busses. There are

two ways that this can be accomplished with the INS8900 or PACE CPU. The first method involves the use of the EX-TEND input signal to the CPU to suppress or suspend input/output operations; the second method uses a special technique to sense when the CPU is beginning an internal (non-I/O) machine cycle.

Earlier we described how to use the EXTEND input signal to lengthen the CPU input/output cycles. The EXTEND signal can also be used to prevent the CPU from beginning an I/O cycle, and thus ensure that the System Busses will be available to external devices for DMA operations.

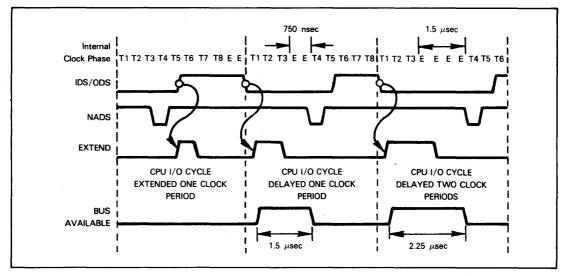

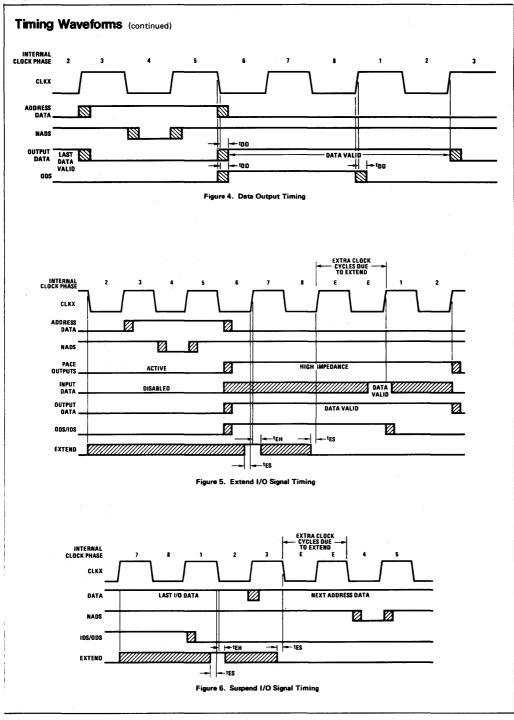

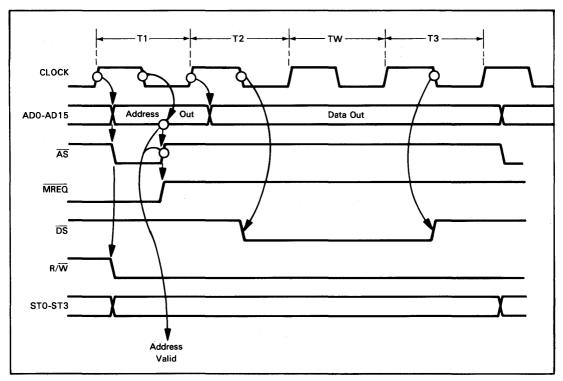

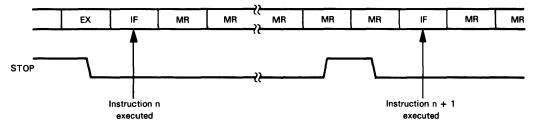

Figure 1-11 illustrates both uses of the EXTEND signal. The CPU looks at the EXTEND input signal at internal clock phases T1 and T6. Notice that during I/O cycles the IDS or ODS signal goes high at the beginning of T6 and low at the beginning of T1. If EXTEND is high during T6, then extra clock cycles are inserted after T8; this is the method that would be used to lengthen an I/O cy-

cle. If EXTEND is high during T1, then extra clock cycles are inserted between T3 and T4; this is the method we would use for DMA operations.

The trailing edge of IDS/ODS indicates that the CPU has just completed an I/O cycle and is therefore not using the System Busses at this instant. By setting EXTEND high at this time, we suppress the beginning of another I/O cycle while we use the busses for a DMA transfer.

Notice that we are merely lengthening the beginning of the machine cycle, and thus delaying that part of the machine cycle where the CPU might begin I/O activity. We do not know whether the current machine cycle will be an internal machine cycle or an I/O cycle, and we do not care. We have merely stolen the busses by slowing down the CPU.

Figure 1-11. Using PACE EXTEND Signal for Cycle-Stealing DMA

DMA BLOCK DATA TRANSFERS INITIATED BY EXTERNAL LOGIC IN PACE AND INS8900 SYSTEMS

CYCLE-STEALING DMA IN PACE AND INS8900 SYSTEMS

EXTEND USED

TO SUSPEND INS8900 AND

DURING DMA

**OPERATIONS**

PACE I/O

There are two drawbacks inherent in the EXTEND method of cycle-stealing DMA. First, whenever we use the System Busses for a DMA transfer, we slow down the operation of the CPU. Second, we must wait until the CPU has just completed an input/output cycle before we can perform the cycle steal. Since only about one-third of the CPU machine cycles are used for I/O, this means that bus access for DMA will be quite limited. Both of these drawbacks can be eliminated if we can find some technique for determining when the CPU is performing an internal (non-I/O) machine cycle. We could then use the System Busses any time that the CPU is not using them (which is more than 60% of the time) and we could perform the DMA transfer without slowing down CPU operations. We shall now describe just such a technique.

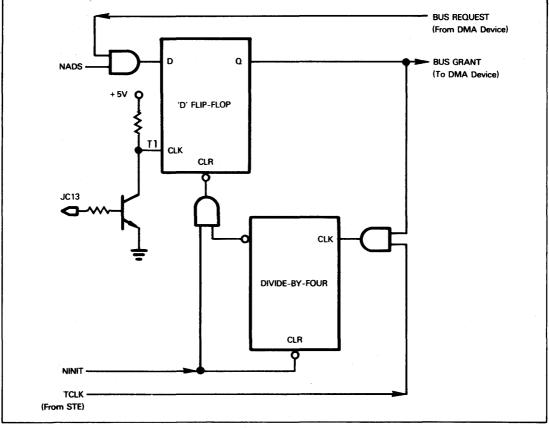

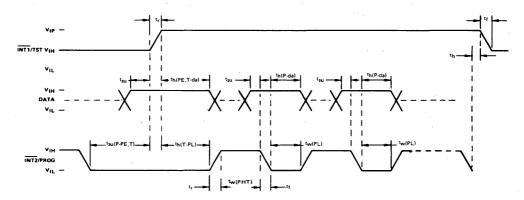

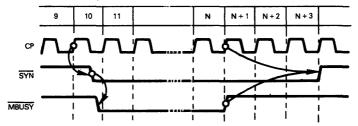

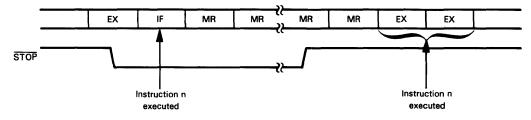

We stated earlier in this chapter that the internal clock phases (T1 through T8) are not available to external logic. However, National Semiconductor data sheets include a figure that shows circuits for internal drivers and receivers. A detailed examination of this figure reveals a very interesting and useful fact: the JC13 (Jump Condition 13) pin on the CPU is intended as an input signal; but, because of the way in which the receiver for this signal is designed, it also produces an output pulse on the JC13 pin during every machine cycle. The output pulse occurs

CYCLE-STEALING DMA DURING INS8900 AND PACE INTERNAL MACHINE CYCLES

during T4 of each machine cycle, and we can use this fact to design a very efficient cycle-stealing DMA arrangement.

Figure 1-12. Idealized Circuit for Cycle-Stealing DMA During INS8900 and PACE Internal Machine Cycles

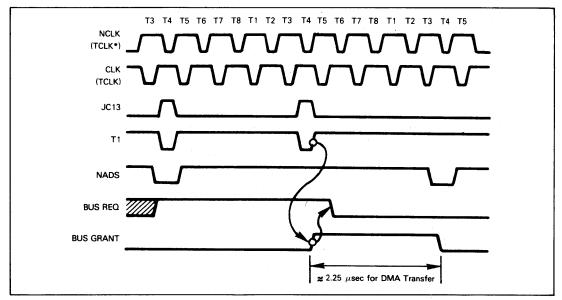

Figure 1-12 shows a circuit that uses the output pulse provided by JC13 to implement cycle-stealing DMA. Recall that the CPU sends out a negative-going NADS pulse at T4 of every input/output cycle. This NADS signal is ANDed in our circuit with an external device's DMA Bus Request and applied to the D input of a flip-flop. The JC13 output pulse, which also occurs at T4, is inverted via a transistor and applied to the clock input of the flip-flop. Thus, if NADS is high at T4 (indicating that the current CPU machine cycle is not an I/O cycle) the flip-flop will be set if there is a Bus Request present. The output of this flip-flop is then used by external logic as a Bus Grant signal and the DMA transfer can be in-

itiated. Since we do not know whether or not the next cycle will be a CPU I/O cycle, we must terminate DMA activity on the bus prior to the next T4 time. In Figure 1-12, this is accomplished using a divide-by-four counter.

The CLK input to the counter is a combination of the Bus Grant signal and the TCLK signal which is available from the PACE STE. This results in the timing shown in Figure 1-13. Notice that this scheme makes the bus available for about 7/8 of a machine cycle, or approximately 2.25 microseconds. If you refer back to Figure 14-10 you will notice that this is about the same length of time as was obtained by using the maximum duration of EXTEND. So, we have not increased the maximum time available for a DMA transfer. But, we have made two significant gains: DMA transfers can occur more frequently, and these transfers do not slow down CPU operations.

We must add a final note of caution to the description of this otherwise straightforward DMA technique. There are several critical timing paths in the idealized circuit shown in Figure 1-12. Both the JC13 pulse and the NADS signal occur at T4, although the trailing edge of NADS does occur slightly after the trailing edge of JC13. Therefore, the components used to provide CLK and D inputs to the flip-flop must be selected carefully to ensure that there is not a race condition. Additionally, we have shown the Bus Grant signal being reset at the end of T3. Since the leading edge of NADS occurs at T4, this timing relationship can be critical. However, if external devices such as address latches and decoders use the trailing edge of NADS, this timing should present no problems.

Figure 1-13. Timing for Cycle-Stealing DMA During INS8900 and PACE Internal Machine Cycle

### THE INS8900 AND PACE INTERRUPT SYSTEM

The INS8900 and PACE CPUs have complete on-chip interrupt systems. Six separate levels of interrupts are provided: one internal and five external interrupt request inputs, including a non-maskable input. Priority logic is provided on the CPU, and all interrupts are vectored, thus eliminating any polling requirements. Because of the various ways in which interrupts can be initiated, and also because of a few problems that exist in the PACE interrupt system, we will divide our description of the system into three parts:

- 1) Low priority external interrupts

- 2) Internal (Stack) interrupts

- 3) Non-maskable (Level 0) interrupts

But first, let us take an overview of the INS8900 and PACE interrupt system.

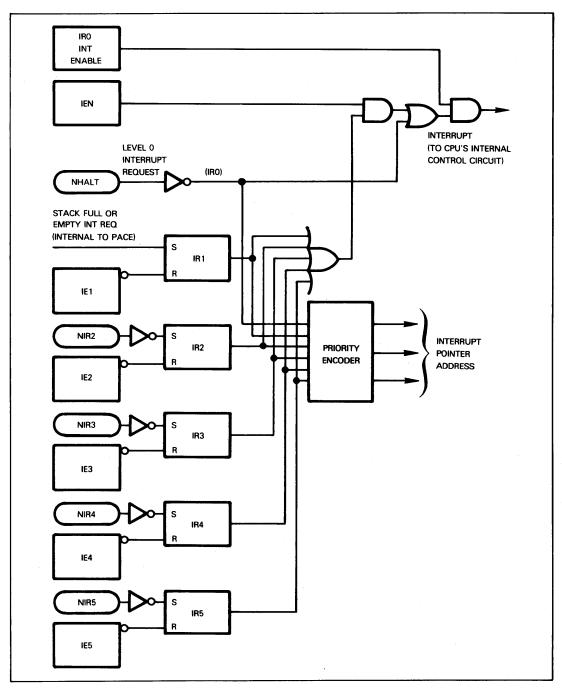

Figure 1-14. Internal View of INS8900 and PACE Interrupt System

Figure 1-14 depicts the interrupt logic that is contained on the CPU. The highest priority interrupt request is the non-maskable Level 0 interrupt request, which is initiated using the NHALT control input to the CPU. The lowest priority interrupt request is NIR5.

The Stack Interrupt and each of the four lower-priority external interrupt requests can be individually enabled or disabled by setting or clearing associated bits (IE1 - IE5) in the Status and Control Flag register. Notice in Figure 1-14 that these bits are shown as providing the 'R' input to a latch. The 'S' input to each of these latches is the actual interrupt request line. The significance of this is rather subtle. It means that an interrupt request need not supply a continuous low level until it is acknowledged. Instead, any pulse exceeding one PACE clock period will set the associated interrupt request latch: this allows narrow timing or control

pulses to be used as interrupt request inputs. Note, however, that the 'R' input to the latches overrides the 'S' input. Therefore, if the individual Interrupt Enable flag is reset, it not only prevents the latch from being set by interrupt requests, it will also clear a previously latched request that may or may not have been serviced. If this logic is not clear to you, you should study the characteristics of the RS flip-flop.

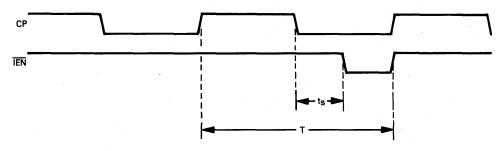

#### A master interrupt enable (IEN) flag is also provided in the Status and Control Flag register. IEN must be set true to allow any of the latched interrupt requests to be recognized by the CPU.

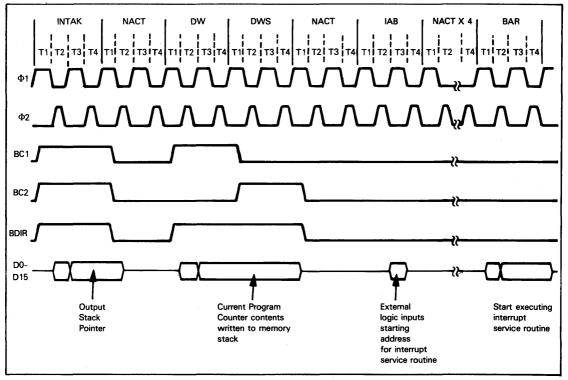

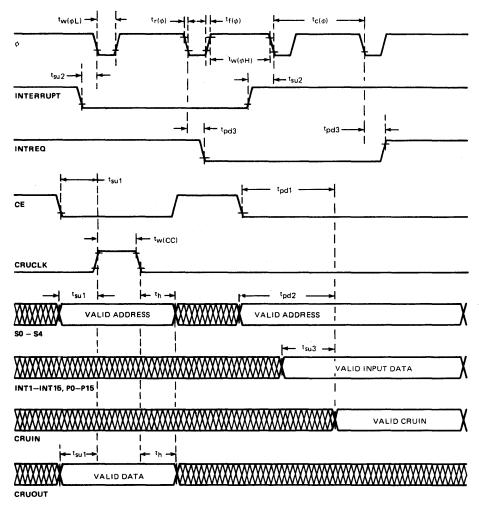

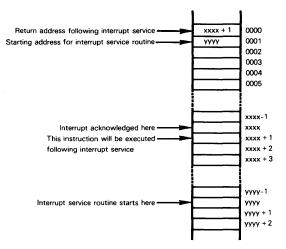

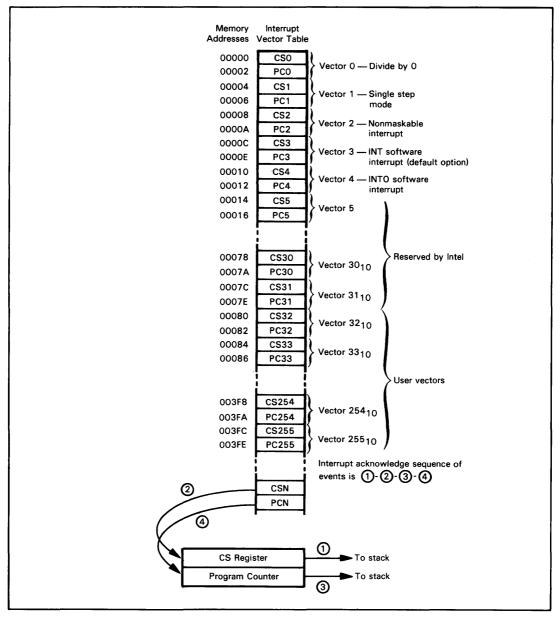

The CPU checks for interrupts at the beginning of every instruction fetch. If an interrupt request is present (and enabled), the instruction fetch is aborted, the contents of the Program Counter are pushed onto the Stack, and the master interrupt enable (IEN) is set low. The CPU then loads the Program Counter with the address vector for your interrupt service routine and executes the instruction contained at that address. (We'll describe the address vectors in the next paragraph.) The interrupt request just described requires a total of 28 clock cycles from the time the interrupt is recognized by the

CPU until the time when the first instruction of your interrupt service routine begins execution.

Memory locations 000216 through 000816 are used as pointer locations or address vectors. You load each of these locations with the starting address of the interrupt service routine for each interrupt as follows:

| MEMORY LOCATION | INTERRUPT POINTER FOR           |         |

|-----------------|---------------------------------|---------|

| 2               | Stack Interrupt                 |         |

| 3               | NIR2                            |         |

| 4               | NIR3                            |         |

| 5               | NIR4                            |         |

| 6               | NIR5                            |         |

| 7               | Level 0 Program Counter Pointer | Special |

| 8               | Level 0 Interrupt Origin        | case    |

#### The level 0 interrupt is a special case which we will describe on its own. But first let us look at interrupts in general.

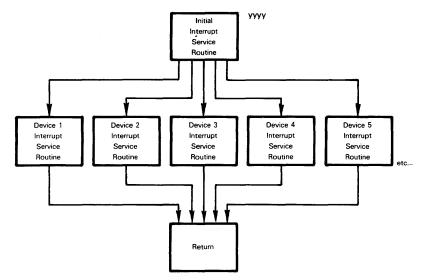

When the CPU responds to an interrupt, it loads the Program Counter with the contents of memory locations 2 through 6, depending on the specific level of interrupt that is being acknowledged. Control is thus vectored to the proper service routine. Suppose, for example, memory location 4 contains the value 2A3016. If an interrupt request occurring at pin NIR3 is acknowledged, then during the acknowledge process the contents of the Program Counter are saved on the Stack, following which the value 2A3016 is loaded into the Program Counter. Had the value 472816 been in memory location 4, then 472816 would have been loaded into the Program Counter instead of 2A3016. Thus, whatever memory address is stored in the memory location associated with the interrupt being acknowledged, this address will be loaded into the Program Counter, becoming the starting address for the specific interrupt service routine to be executed.

As part of the interrupt response we've just described, the CPU sends out a low-going pulse on the CONTIN line. Refer back to Figure 1-10 and associated text for a description of the ACK INT pulse. The last instruction executed by your interrupt service routine must be a Returnfrom-Interrupt (RTI) instruction. This instruction sets IEN high to re-enable interrupts, then pulls the top of the Stack into the Program Counter. This returns program control to the point where it was interrupted. The RTI instruction does not clear the internal Interrupt Request latch; therefore your interrupt service routine must reset the latch (using a Pulse Flag instruc-

tion), or the same interrupt request will still be present after the RTI instruction has been executed. Once the latch has been cleared, it can then be re-enabled for subsequent interrupt requests.

PACE INTERRUPTS

**INS8900**

that is, you want to leave behind a picture of the system as it looked immediately before the program termination occurred.

The interrupt sequence does not save the contents of any registers except the Program Counter. If the program that was interrupted requires that the contents of CPU registers be saved and then restored, your interrupt service routine must perform these operations.

The CPU's response to a Stack interrupt is as described for external interrupts. However, the interrupt request is generated internally by the CPU chip: it can be caused either by a Stack Full or a Stack Empty condition. Remember that the 10-word Stack is part of the CPU chip. It consists of an internal RAM and a pointer that can address Stack words 0 through 9. A Stack Empty interrupt request is generated whenever the pointer is at 0 and a Pull instruction is executed. A Stack Full interrupt request occurs when the pointer is at 7 (eight entries on the Stack) and a Push instruction is executed to fill the ninth word. The tenth word of the Stack will then be used as part of the interrupt response to store the Program Counter contents. Unless you intend to extend the Stack out

into main memory, your application program will not require a Stack Empty or Full interrupt. These interrupts become error conditions and can be avoided by careful programming.

If your program is treating the Stack Empty and Stack Full interrupts as error conditions, then you can disable Stack interrupts, in which case the full ten words of the Stack are available for nested interrupts and subroutines. Of course, this means that a Stack Full or Empty condition, should it occur, will become an undetected error, with unpredictable consequences.

When using PACE, but not the INS8900, there is an additional reason for not using the Stack interrupt capability unless you really need it. **PACE has an internal circuit problem that can cause improper interrupt response. If a Stack interrupt request occurs at the same time as an NIR3 or NIR5 interrupt request, the Stack interrupt address vector will be incorrectly accessed from location 0 instead of location 2.** The solution recommended in PACE literature is to load

both of these locations with the Stack interrupt vector. This apparently straightforward solution is complicated by the fact that location 0 also happens to be the initialization address; whenever the CPU is initialized, the first instruction executed is the one that is contained in location 0. Thus, the word in location 0 must serve a dual purpose:

- 1) It serves as an instruction whenever the CPU is initialized.

- 2) It serves as an address vector if a Stack interrupt occurs at the same time as NIR3 or NIR4.

Here's an example. The object code for a Copy Flags to Register (CFR) instruction is 0400<sub>16</sub>. So, if locations 0 and 2 both contain a value of 0400<sub>16</sub> the problem is solved. Your Stack interrupt service routine would have to begin at memory address 0400<sub>16</sub>, but you would be correctly vectored to that address regardless of whether or not the interrupt error we've just described occurs. On initialization, the first instruction executed would be the CFR instruction: this is not a very useful initialization instruction, but at least no damage is done.

## For a fuller discussion of this interrupt problem and the solution, refer to PACE literature. Also keep in mind that the problem has been fixed in the INS8900.

The non-maskable (Level 0) interrupt cannot be disabled and differs from the other interrupt levels both in the way it is initiated and in the way the CPU responds to it.

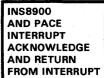

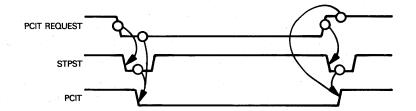

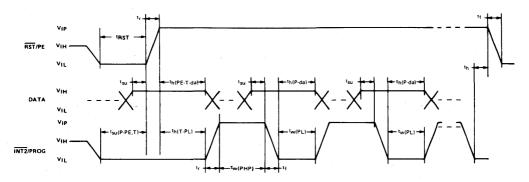

The Level 0 interrupt request is initiated using the NHALT control input signal in combination with the CONTIN input line. Figure 1-15 shows the timing relationships between NHALT and CONTIN that are required to initiate the non-maskable interrupt. If you compare this figure with Figure 1-10, you will notice that the Level 0 interrupt request and the Processor Stall begin in exactly the same way; NHALT is driven low by external logic and held low for some time after a low-going pulse (ACK INT) has been sent out on the CONTIN

line. The only difference between the two operations is towards the end of the timing sequence. For a Processor Stall, NHALT is allowed to return high while CONTIN is still high: for a Level 0 interrupt, the CONTIN line must be driven low by external logic before the NHALT line is allowed to go high. This critical timing sequence is the only way that the CPU has to differentiate between a Processor Stall and a Level 0 interrupt. Notice that this Level 0 interrupt timing sequence never requires external logic to drive CONTIN high. Therefore, if you're using the CONTIN line for any of its other multiple functions (including the ACK INT output pulse) you can merely tie CONTIN to ground and use NHALT to initiate the Level 0 interrupt.

The response of the CPU to the Level 0 interrupt is subtly different from its response to other interrupts. These subtle differences are related to the slightly different purpose of a non-maskable interrupt versus a normal program interrupt request. A non-maskable interrupt is typically used only when there is a catastrophic error or failure (such as loss of power) or to implement a control panel for program development or debug purposes. Both of these uses require that an asynchronous, unplanned program termination have a minimum effect upon system status;

Figure 1-15. Initiating INS8900 and PACE Level 0 Interrupt Using NHALT and CONTIN Signals

Remember that other levels of interrupts store the contents of the Program Counter or the Stack and reset the IEN flag in the Status and Control Flag register. This sequence obviously alters the "picture" of the CPU, since both Stack contents and Status and Control Flag register contents are changed. To avoid this, the Level 0 interrupt response by the CPU uses an external memory location to store the contents of the Program Counter. Memory location 000716 holds the address of the memory word where the Program Counter will be stored. The contents of the Status and Control Flag register are unaltered. CPU internal circuitry resets an "IRO INT ENABLE flag to prevent another interrupt from being recognized (refer to Figure 1-16), but this is not discernible to you. After the Program Counter has been saved in the designated memory location, the instruction contained in memory location 000816 is executed; this is the first instruction of your Level 0 interrupt service routine. Suppose, for example, that memory location 000716 contains the value FF0016. Following a Level 0 interrupt acknowledge, the actual instruction stored in memory location 000816 is executed.

Note that the Level 0 interrupt acknowledge sequence has not altered anything within the CPU that is discernible to you or to a program; the Stack, Accumulators, and Status and Control Flag register are all unchanged. Additionally, avoiding use of the Stack ensures that there will not be a Stack overflow — and in consequence a Stack interrupt will not be generated by this interrupt response sequence.

The normal Return-from-Interrupt (RTI) instruction that must be executed at the end of your interrupt service routine causes the Program Counter to be restored from the Stack. Since the Level 0 interrupt sequence does not utilize the Stack to store the Program Counter, a different technique must be used to return control to the interrupted program. First you must execute a Set

Flag (SFLG) or Pulse Flag (PFLG) instruction, referencing bit 15 in the Status and Control Flag register. This bit always appears to be set to a '1', but must be referenced in this case to enable lower levels of interrupts. Next you must ex-

ecute a Jump Indirect (JMP@) through the location pointed to by the contents of memory location 0007<sub>16</sub> to restore the original Program Counter contents.

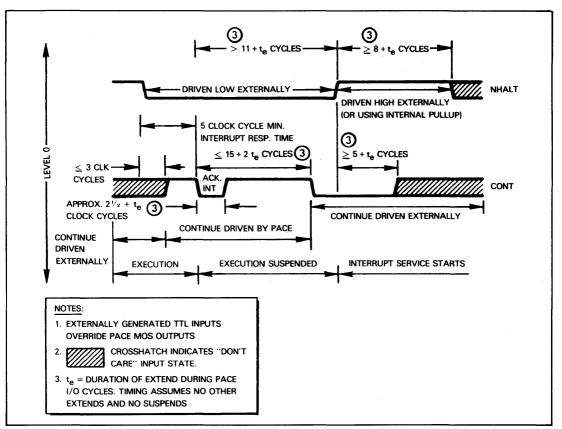

PACE, but not the INS8900, has some Level 0 interrupt circuit problems.

If a Level 0 interrupt occurs within the 12-clock-cycle period following the recognition of any other interrupt, PACE will either perform a Processor Stall (which we described earlier) or PACE will execute the Level 0 interrupt — but using the wrong pointer address. In short, you don't know what might happen under these circumstances. There is a solution for this prob-

INS8900

DIRECT

OPTIONS

AND PACE

ADDRESSING

lem. It requires that external logic allow NHALT to be applied to the PACE CPU only while the NADS signal is present, provided no Acknowledge Interrupt (ACK INT) has occurred since the last NADS pulse. ACK INT is accompanied by a negative-going pulse on the CONTIN line. Sound complicated? It is.

The circuit shown in Figure 1-16 is reproduced from PACE literature and solves the problem we've just described. We won't attempt to describe here how this circuit solves the problem. Note that this circuit only takes care of Level 0 interrupt problems; if you also want to use NHALT and CONTIN to cause a Processor Stall, you must design additional external logic.

Once again, we must advise that these interrupt system problems exist in PACE CPU chips. The INS8900 has none of these problems.

### THE INS8900 AND PACE INSTRUCTION SET

#### Table 1-1 summarizes the INS8900 and PACE instruction set.

The primary memory reference instructions have typical minicomputer addressing modes. These instructions will also be used as I/O instructions, since external devices are identified via selected memory addresses.

In Table 1-1, "direct addressing options" means the instruction can reference memory using any of the direct or direct indexed addressing options described earlier.

"Indirect addressing options" similarly specifies any of the indirect addressing options described earlier.

Both Branch and Skip instructions are provided, and each differs significantly from the philosophies described in Volume 1. Chapter 6.

There are 16 conditions that can cause a Branch, as shown in Table 1-3. Notice that three of the conditions are determined by external inputs JC13, 14, and 15. If a Branch-on-Condition is true, then the displacement which is added to the Program Counter is an 8-bit signed binary number as described in Volume 1, Chapter 6.

There are three varieties of Skip-on-Condition instructions. SKNE, SKG and SKAZ compare the contents of an Accumulator to a memory location which is addressed using direct or direct indexed addressing. Based on the results of the comparison, the instruction following the Skip may or may not be executed. These three instructions are therefore combined Skip and Memory Reference instructions.

ISZ and DSZ identify a memory location using direct or direct indexed addressing; the contents of the addressed memory location are incremented (ISZ) or decremented (for DSZ); if after the increment or decrement operation the memory location contains a 0 value, then the Skip is performed.

The AISZ instruction adds an 8-bit, signed binary number to the contents of an Accumulator; if the result is 0, a Skip is performed.

These Skip instructions will be very familiar to minicomputer programmers, and on most microcomputers are equivalent to a secondary Memory Reference or Immediate Operate instruction, followed by a Branch-on-Condition instruction.

Figure 1-16. Circuit to Prevent Conflicts Between PACE Level 0 Interrupts and Lower Priority Interrupts

| _             |                                                                                                                                                                                                                                                                                         |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|               | ing symbols are used in Table 1-1:                                                                                                                                                                                                                                                      |

| AC0           | Accumulator 0                                                                                                                                                                                                                                                                           |

| С             | Carry status                                                                                                                                                                                                                                                                            |

| СС            | 4-bit Condition Code described in Table 15-3                                                                                                                                                                                                                                            |

| D             | Any Destination register                                                                                                                                                                                                                                                                |

| DATA8         | 8-bit binary data unit                                                                                                                                                                                                                                                                  |

| DISP(X)       | Direct or indexed addressing operands as explained in the text.                                                                                                                                                                                                                         |

| @DISP(X)      | Indirect addressing operands as explained in the text.                                                                                                                                                                                                                                  |

| EA            | The effective address generated by the specified operands.                                                                                                                                                                                                                              |

| f             | 4-bit quantity selecting a bit in the Flag Word.                                                                                                                                                                                                                                        |

| FW            | Flag Word described in the text.                                                                                                                                                                                                                                                        |

| IEN           | Interrupt Enable status                                                                                                                                                                                                                                                                 |

| I             | A 1-bit unit determining whether LINK is included in the shift/rotate.                                                                                                                                                                                                                  |

| L             | Link status                                                                                                                                                                                                                                                                             |

| n             | Seven bits determining how many single bit shift/rotates are performed.                                                                                                                                                                                                                 |

| 0             | Overflow status                                                                                                                                                                                                                                                                         |

| PC            | Program Counter                                                                                                                                                                                                                                                                         |

| r             | Any register of the Accumulator: AC0, AC1, AC2 or AC3                                                                                                                                                                                                                                   |

| S             | Any Source register                                                                                                                                                                                                                                                                     |

| ST            | Top word of on-chip Stack.                                                                                                                                                                                                                                                              |

| x <y,z></y,z> | Bits y through z of the quantity x. For example, $r < 7.0 >$ is the low-order byte of the specified register.                                                                                                                                                                           |

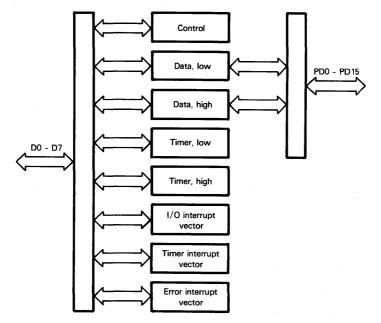

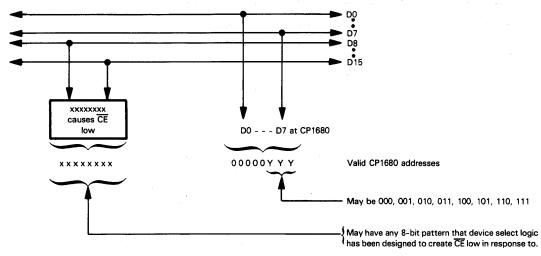

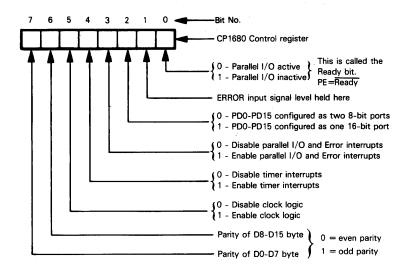

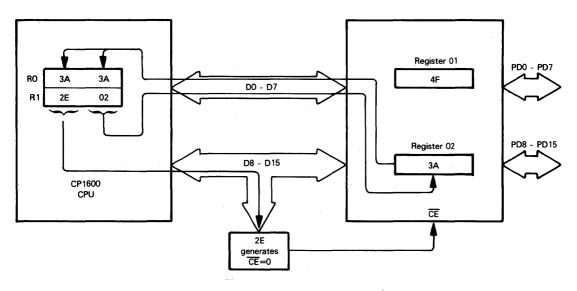

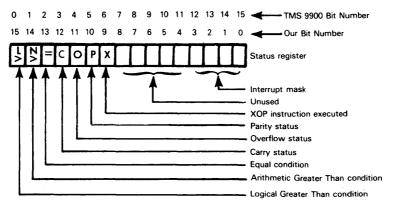

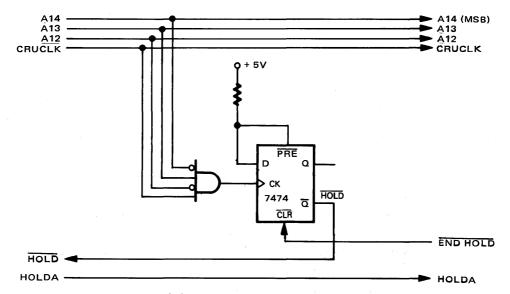

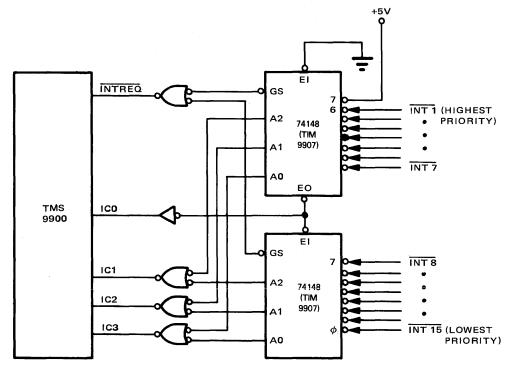

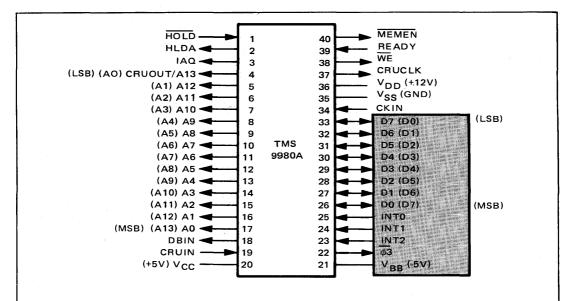

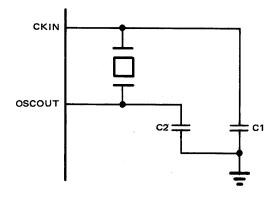

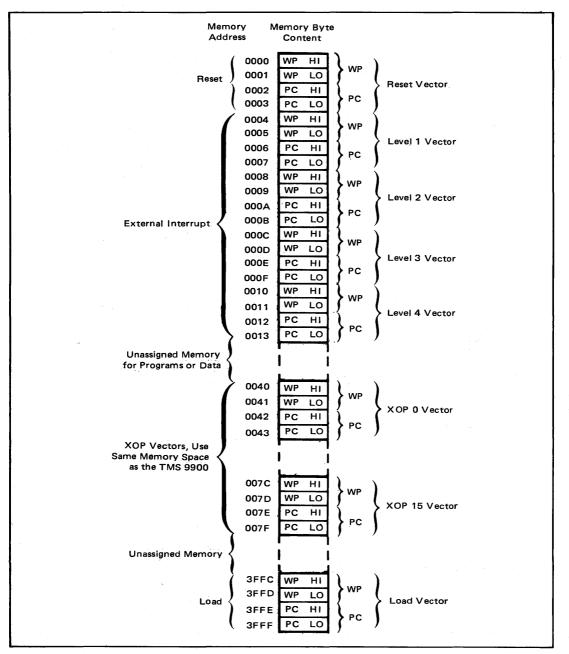

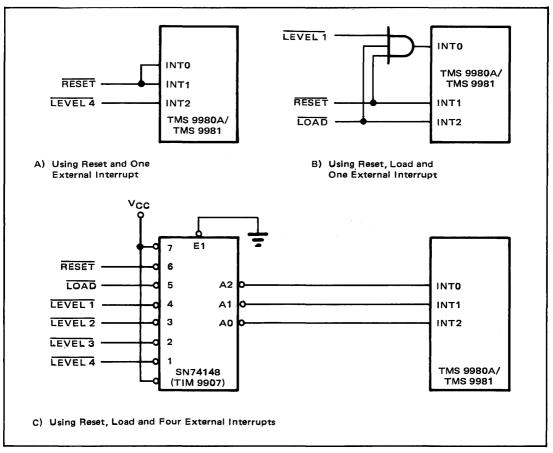

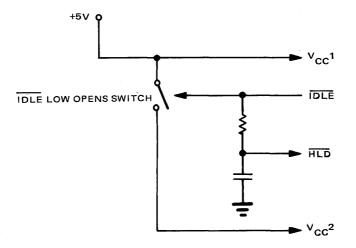

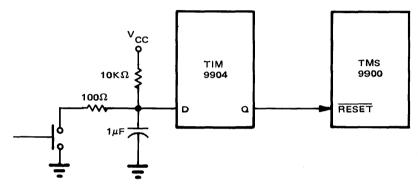

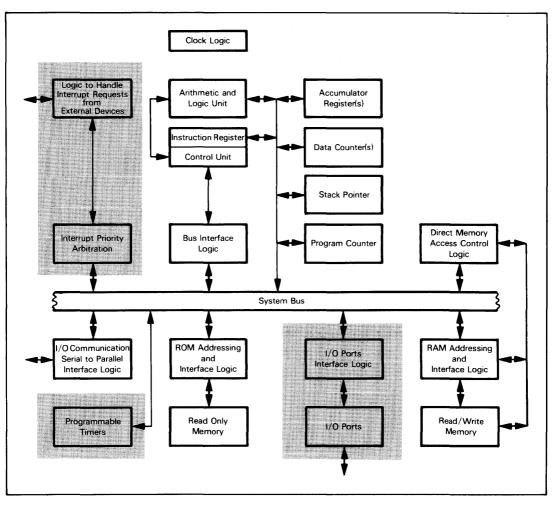

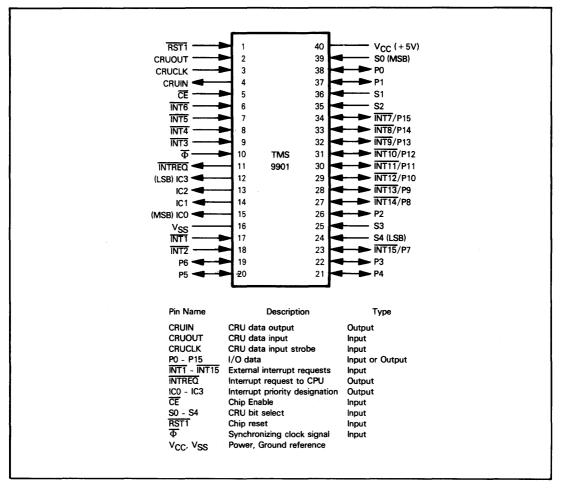

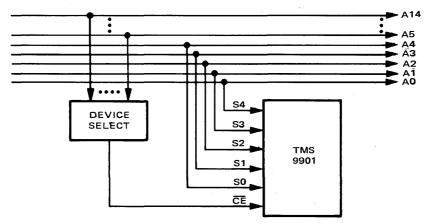

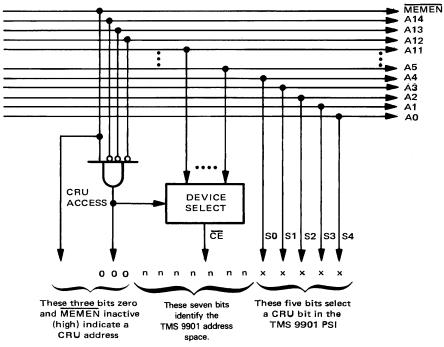

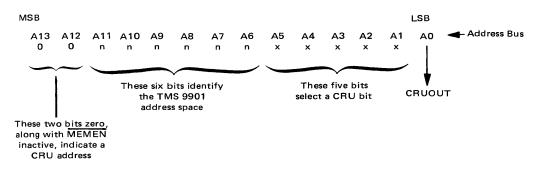

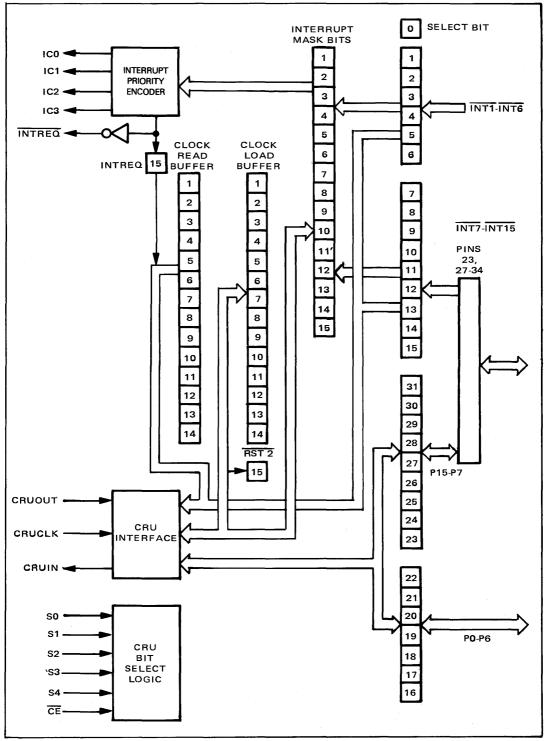

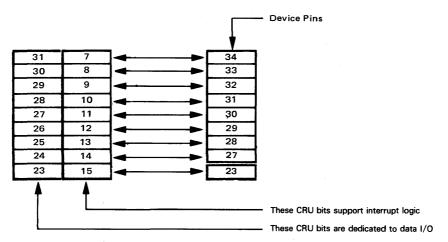

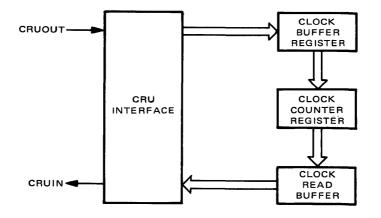

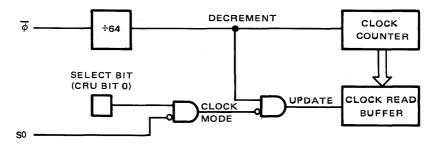

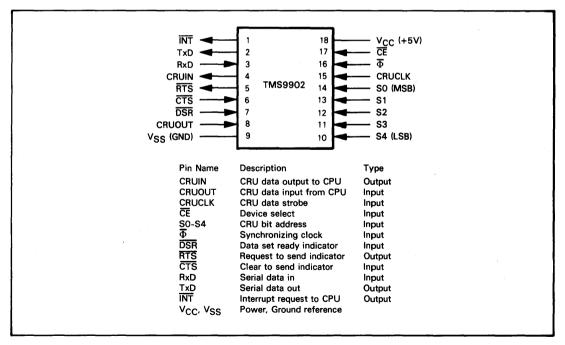

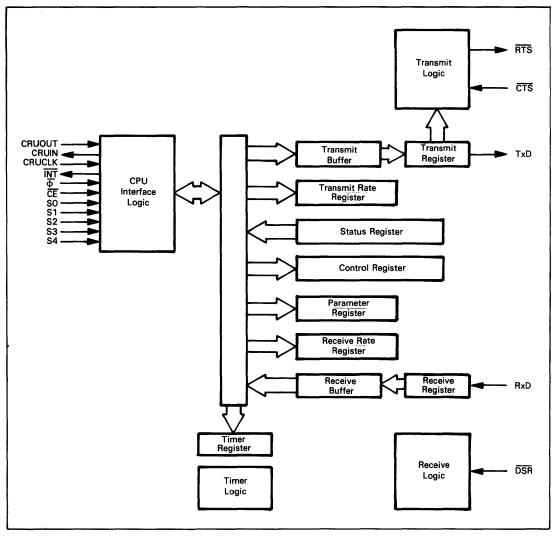

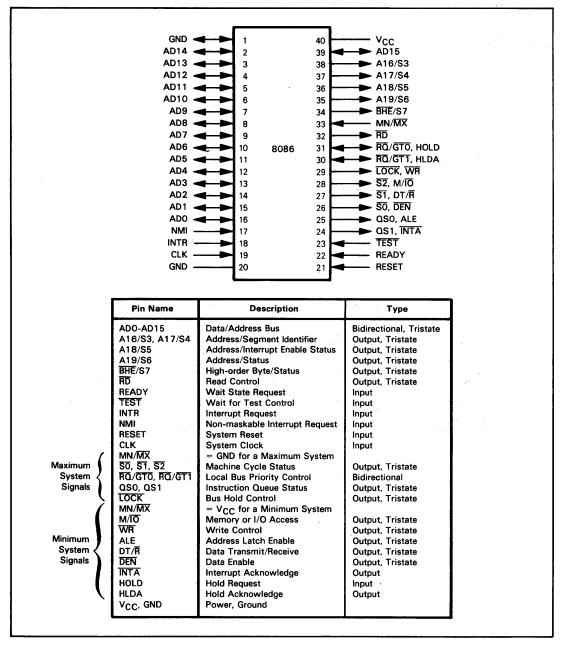

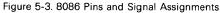

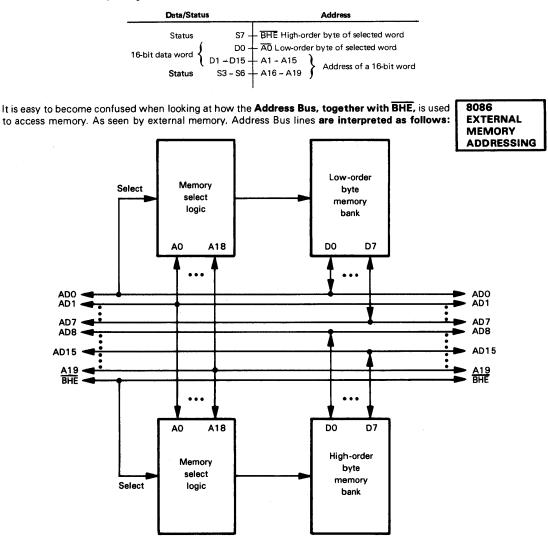

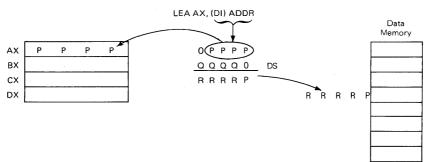

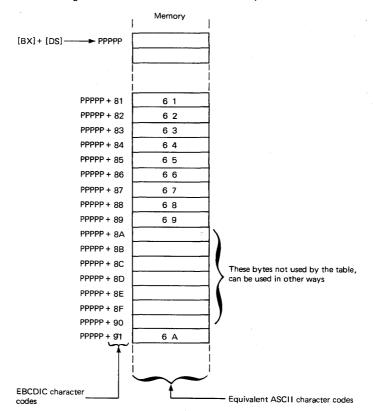

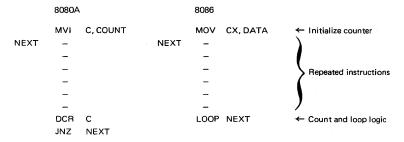

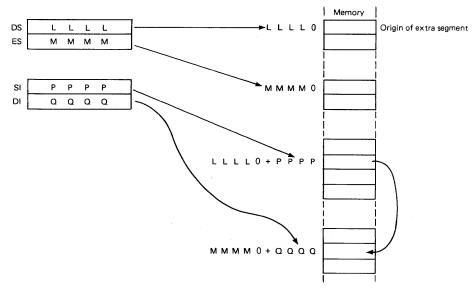

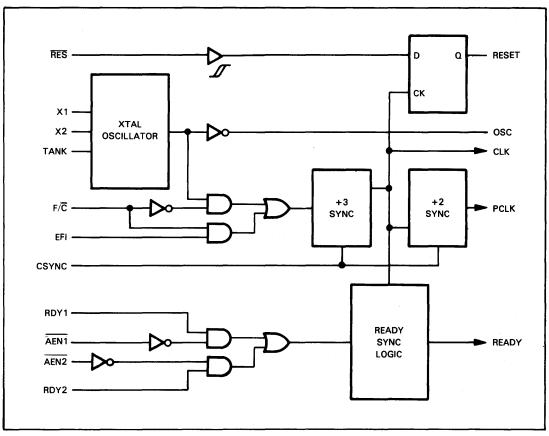

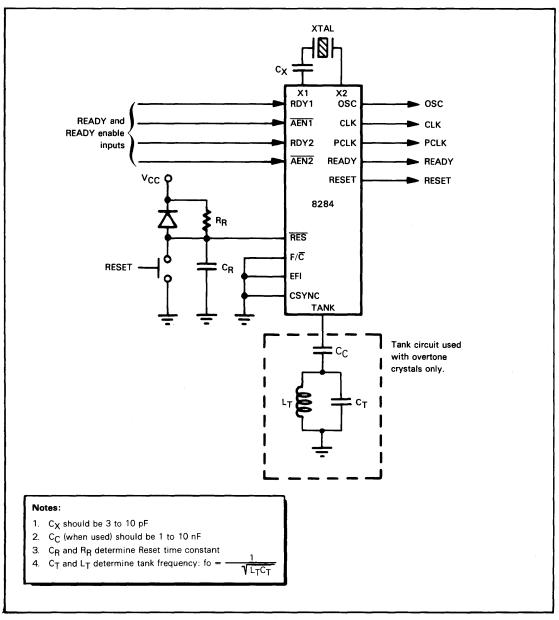

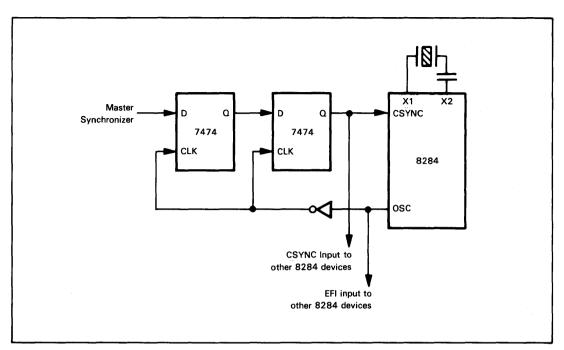

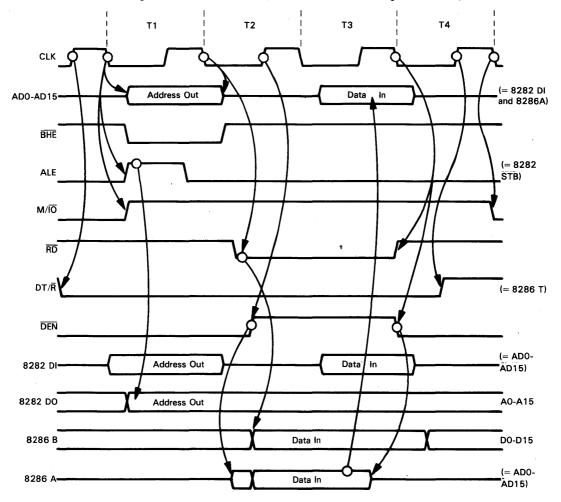

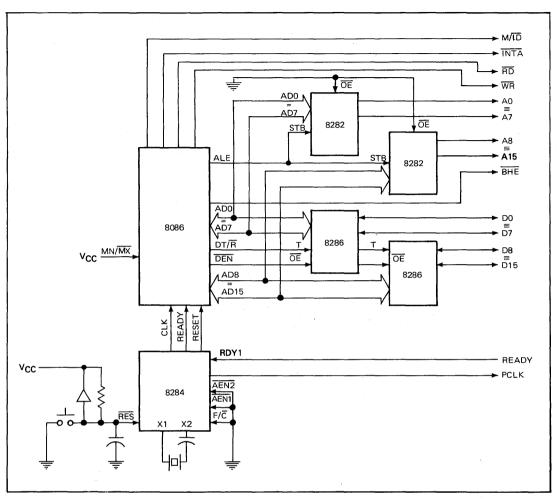

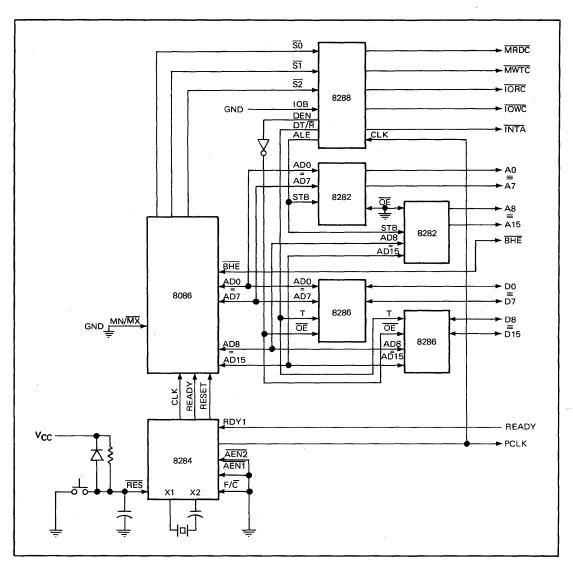

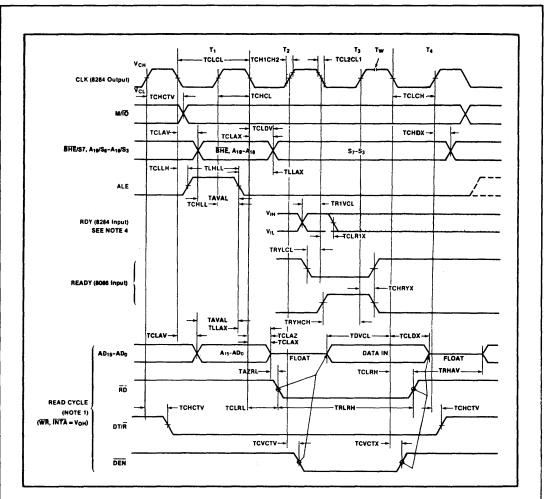

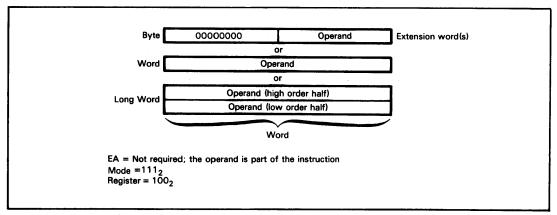

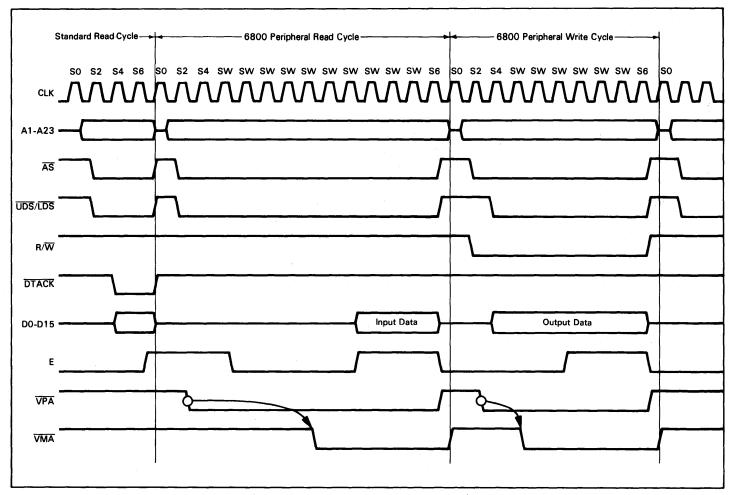

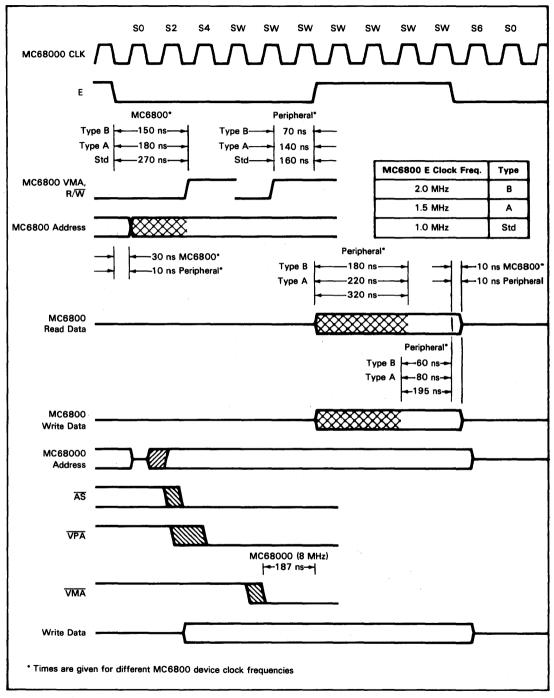

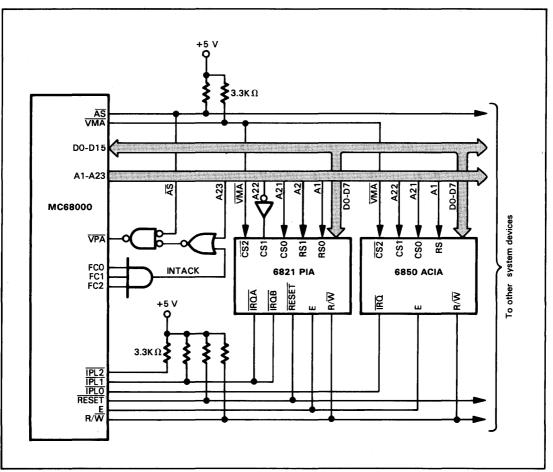

| []            | Contents of location enclosed within brackets. If a register designation is enclosed within the brackets, then the designated register's contents are specified. If a memory address is enclosed within the brackets, then the contents of the addressed memory location are specified. |