# **Theory of Operation**

# olivetti

## PREFACE

The Olivetti L1 M24/M21 Theory of Operation Manual contains the description of the circuit boards present in the basic module of the M24 and M21 Personal Computers. It also contains the description of some of the optional boards that can be used with the M24/M21 Personal Computers.

This manual is intended for field engineers, system specialists and laboratory engineers who need to maintain and repair the boards present in the M24 and M21 Personal Computers.

**DISTRIBUTION:** Internal (Z)

FIRST EDITION: November 1984

**REFERENCES:**

| M24/M21 | <ul> <li>Hardware Architecture and Function</li> </ul> | – code 4100710 W |

|---------|--------------------------------------------------------|------------------|

| M24     | – Service Manual                                       | - code 4100670 S |

| M21     | – Service Manual                                       | – code 4101680 C |

| M24     | – Schematics                                           | – code 4100750 S |

| M24     | – Spare Parts Catalogue                                | - code 4100740 Z |

|         |                                                        |                  |

**TRADEMARKS:**

**IBM** is a registered trade mark of International Business Machines Corp.

NEC is a registered trade mark of Nippon Electric Corp.

**Microsoft** and **MS-DOS** are registered trade marks of Microsoft Corp.

**Ethernet** is a registered trade mark of Digital Research and Rank Xerox Corp.

**Z8000** is a registered trade mark of Zilog Corp.

**Intel** is a registered trade mark of Intel Corp.

**INS** is a registered trade mark of National Semi-conductor Corp.

**CP/M-86** is a registered trade mark of Digital Research.

**OMNINET Transporter** is a registered trade mark of Corvus Systems Inc.

**DTC** is a registered trade mark of Data Technology Corp.

PUBLICATION ISSUED BY:

Copyright ⓒ 1984, by Olivetti All rights reserved Ing. C. Olivetti & C., S.p.A Direzione Documentazione 77, Via Jervis - 10015 IVREA (Italy)

M24/M21 Theory of Operation

# CONTENTS

PAGE

|      | 1. | SYSTEM DESCRIPTION             |

|------|----|--------------------------------|

| 1–1  |    | INTRODUCTION                   |

| 1–1  |    | CHARACTERISTICS                |

| 1-4  |    | CIRCUIT BOARDS                 |

|      | 2. | MOTHERBOARD                    |

| 2-1  |    | INTRODUCTION                   |

| 2-2  |    | MOTHERBOARD BLOCK DIAGRAM      |

| 2-6  |    | CENTRAL PROCESSOR UNIT         |

| 2-12 |    | NUMERIC DATA PROCESSOR         |

| 2–14 |    | DMA CONTROL LOGIC              |

| 2-21 |    | INTERRUPT CONTROL LOGIC        |

| 2-25 |    | CLOCK GENERATOR                |

| 2-28 |    | BUS ARBITER                    |

| 2-31 |    | BUS CONTROLLER                 |

| 2-33 |    | PROGRAMMABLE WAIT LOGIC        |

| 2-35 |    | RANDOM ACCESS MEMORY           |

| 2-42 |    | PROGRAMMABLE READ ONLY MEMORY  |

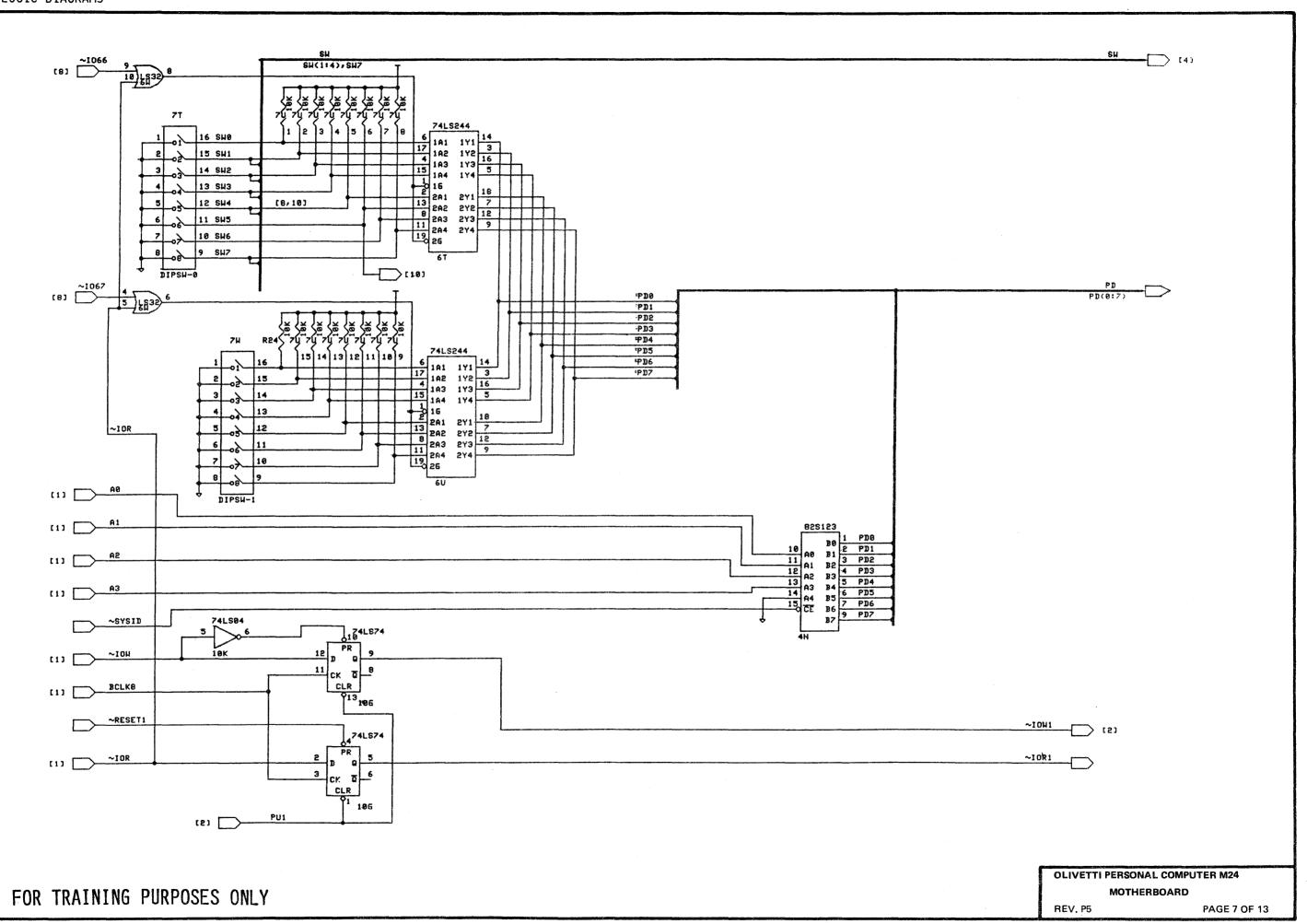

| 2-43 |    | INPUT/OUTPUT CHIP SELECT LOGIC |

| 2-47 |    | 1/0 ADDRESS MAP                |

| 2-48 |    | SYSTEM MEMORY ADDRESS MAP      |

| 2-49 |    | TIMER                          |

|      |    |                                |

- 2–52 REAL TIME CLOCK AND CALENDAR

- 2-53 SPEAKER INTERFACE

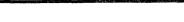

- 2–54 **KEYBOARD INTERFACE**

- 2-58 MINI-FLOPPY DISK INTERFACE

- 2-69 PARALLEL PRINTER INTERFACE

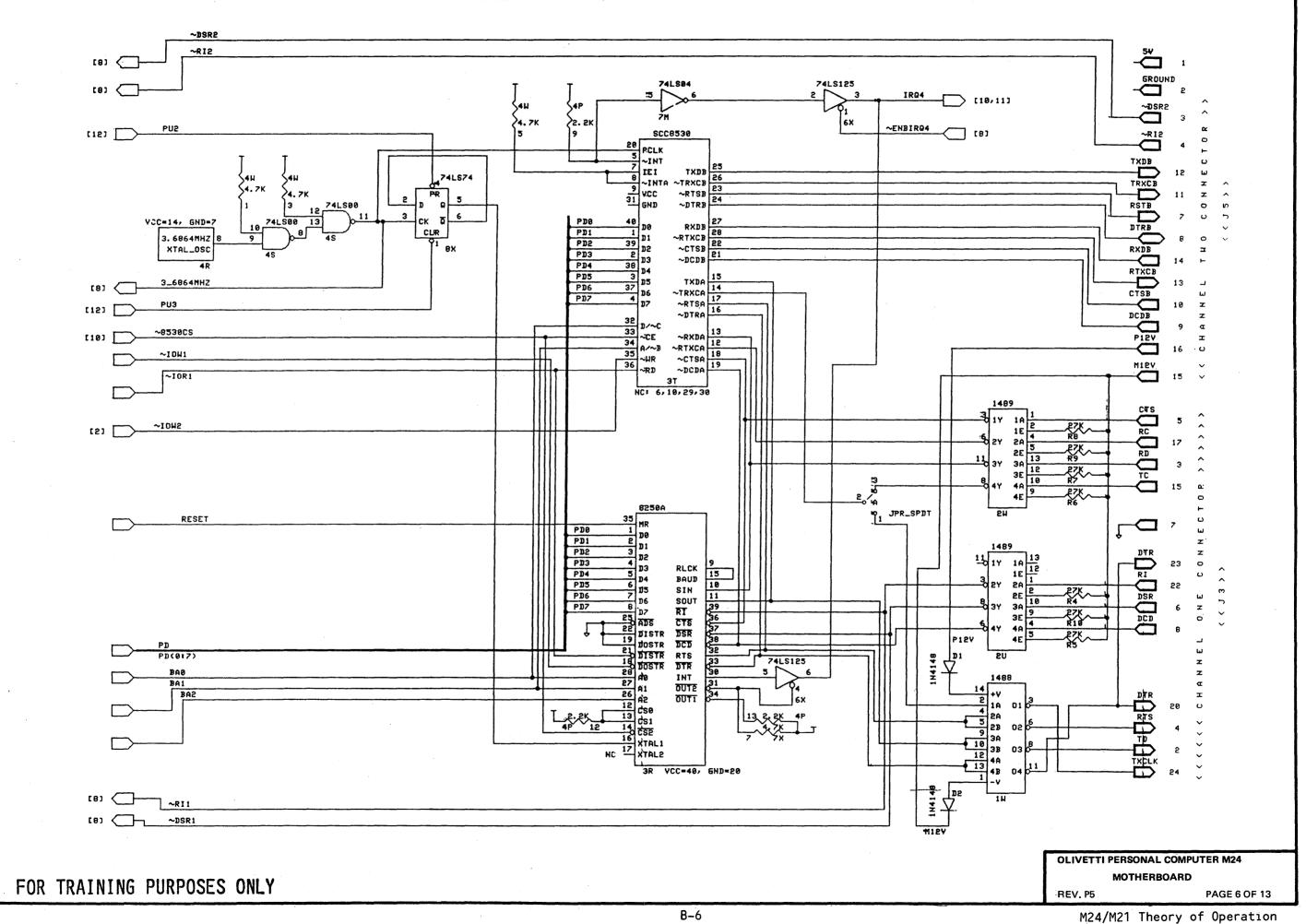

- 2-71 SERIAL COMMUNICATION INTERFACE

- 3. BUS CONVERTER BOARD

- 3–1 INTRODUCTION

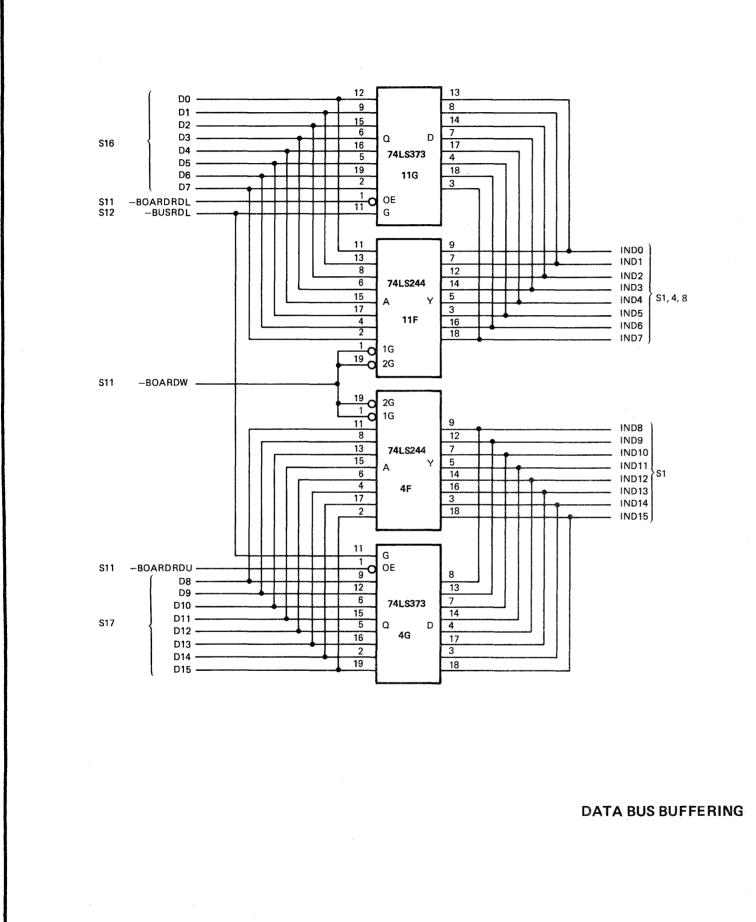

- 3–2 16 BIT DATA TRANSFERS

- 3-3 8 BIT DATA TRANSFERS

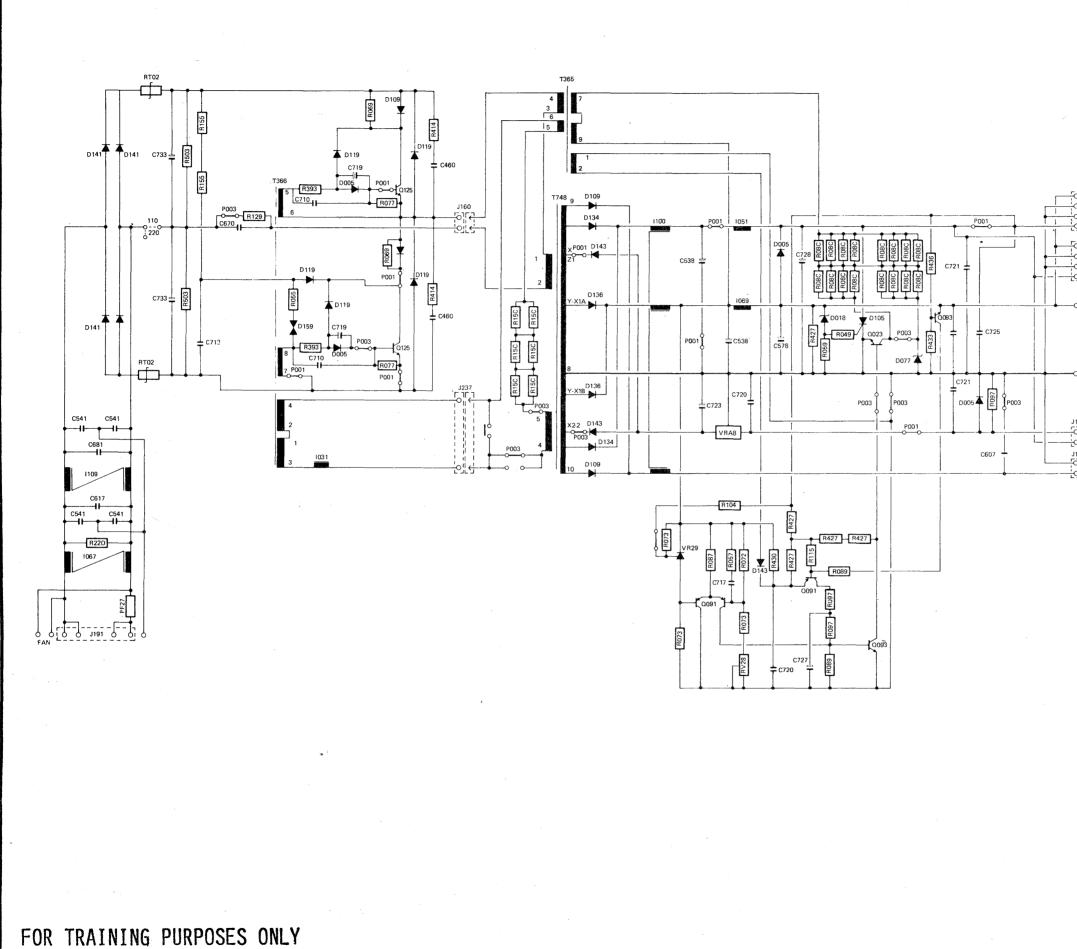

- 3-7 I/O EXPANSION BUS CONNECTORS

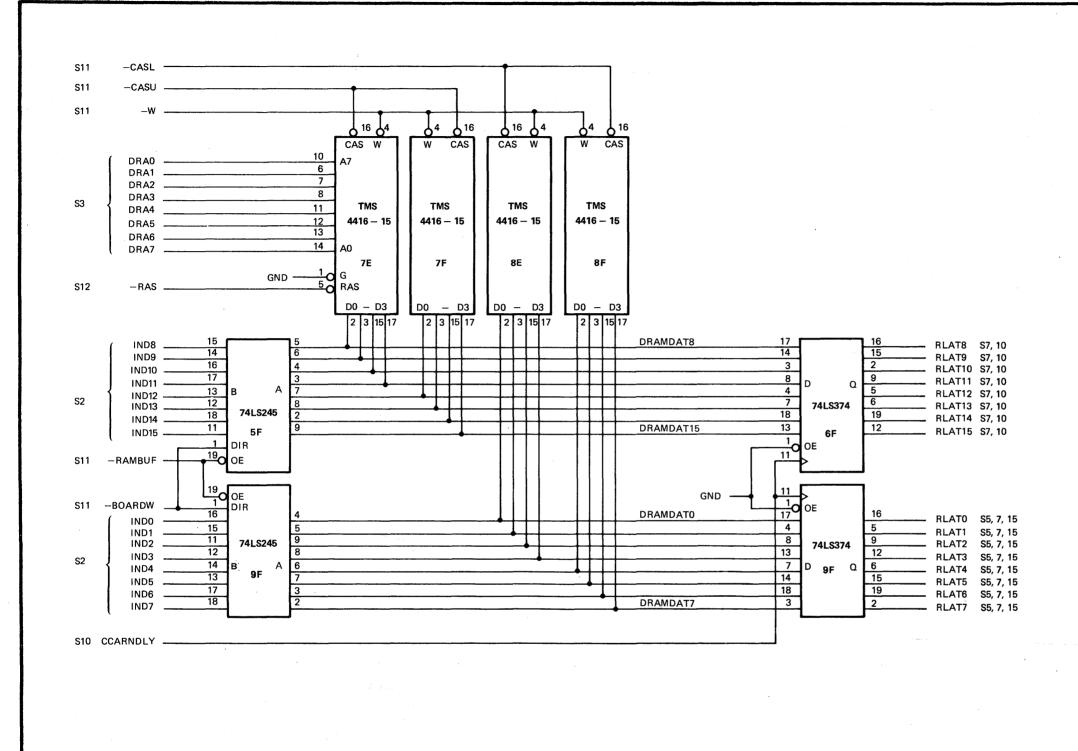

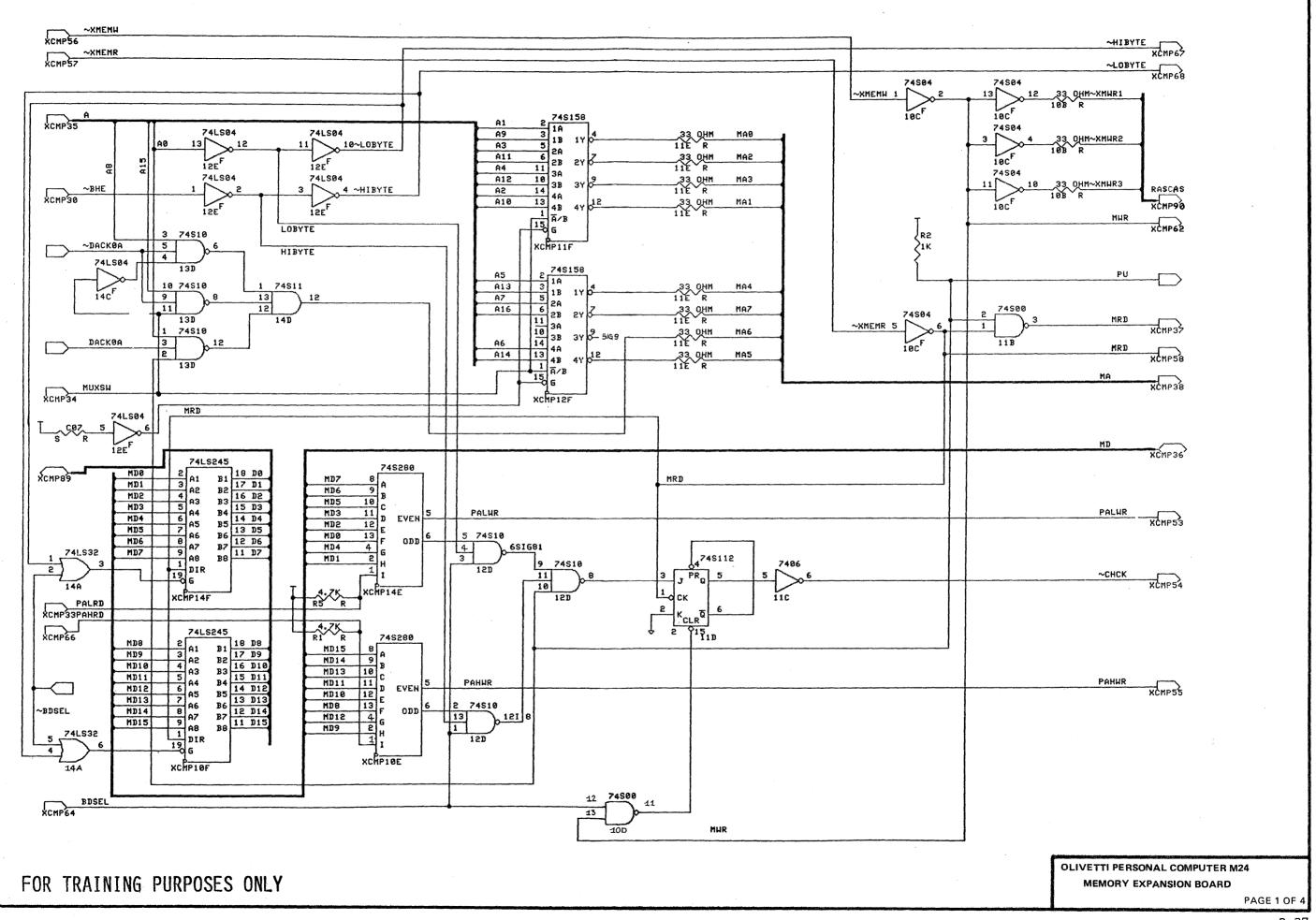

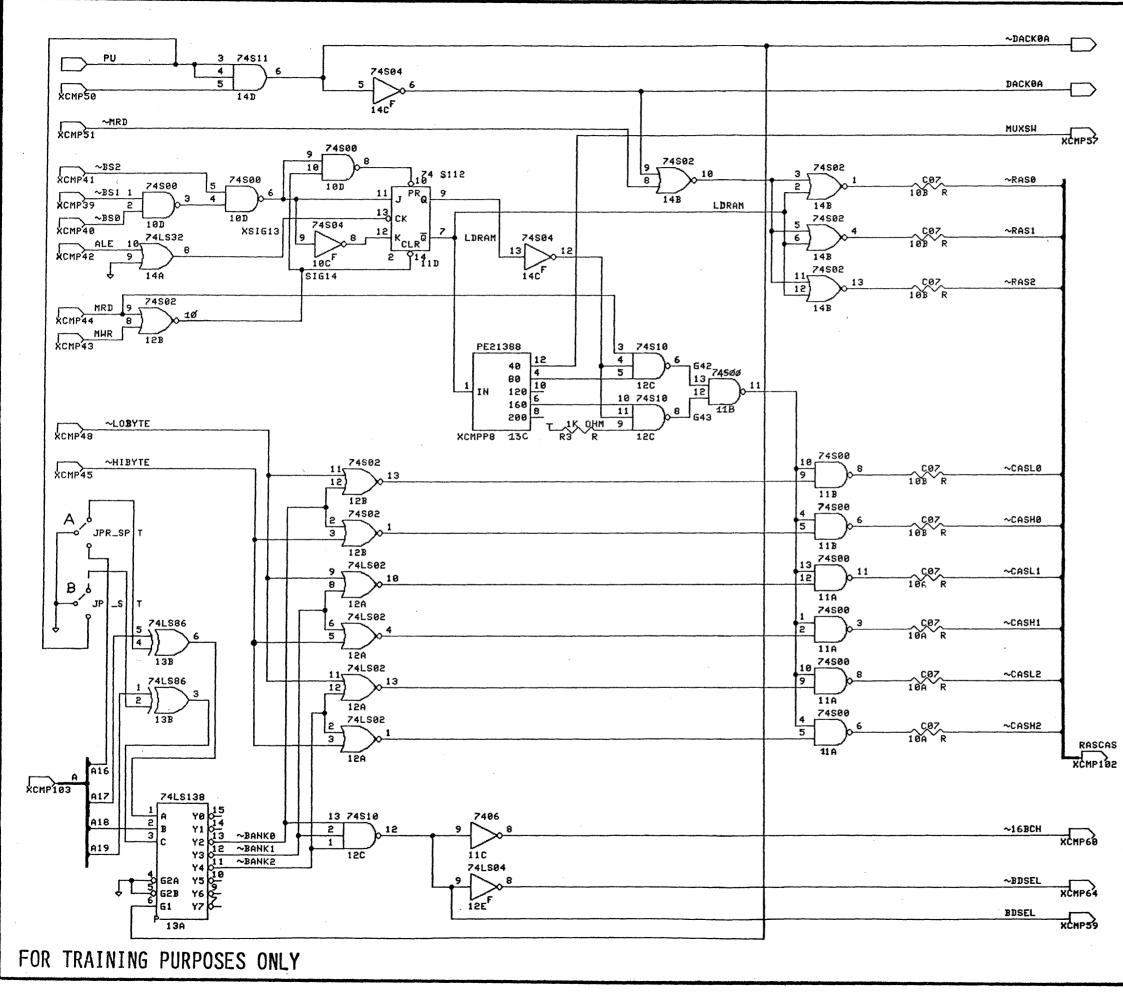

## 4. MEMORY EXPANSION BOARD

- 4–1 INTRODUCTION

- 4-1 MEMORY CONTROL LOGIC

- 4-3 MEMORY ADDRESSING

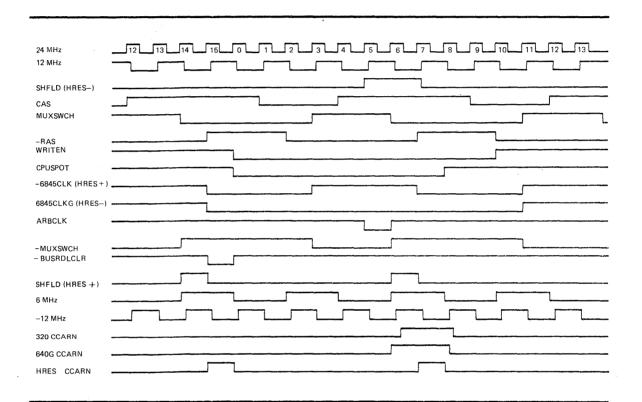

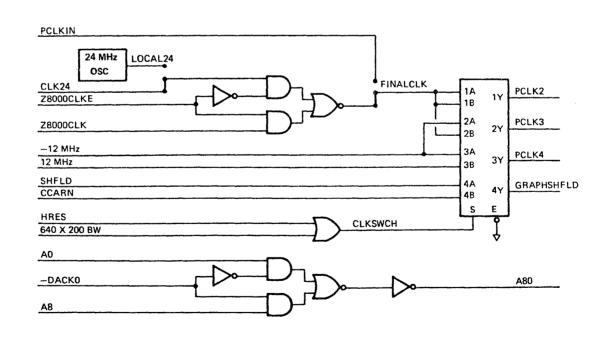

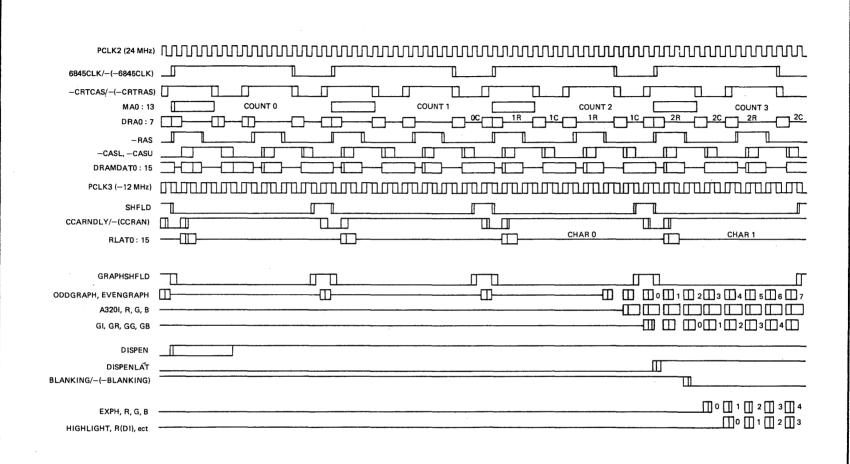

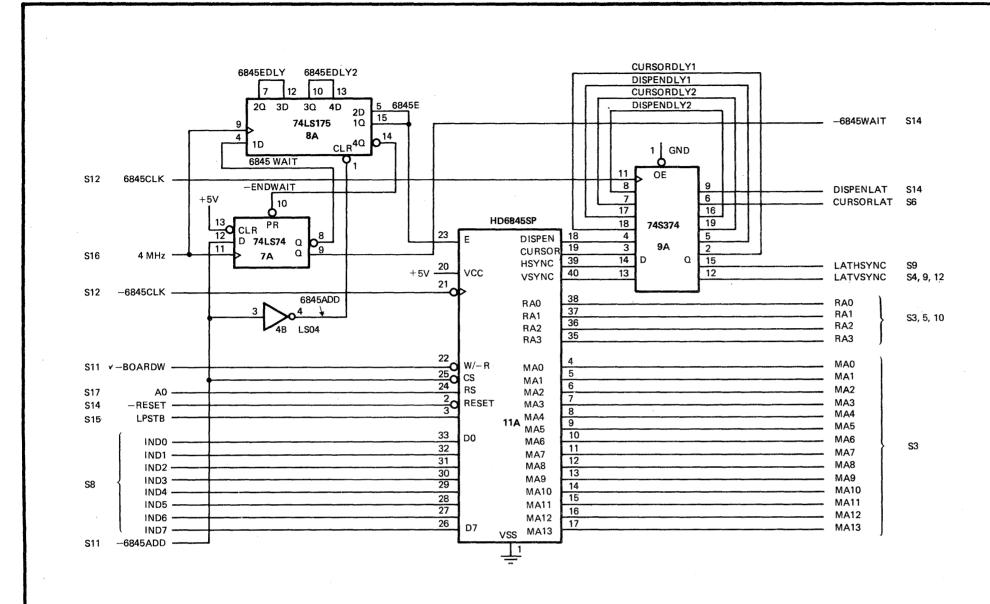

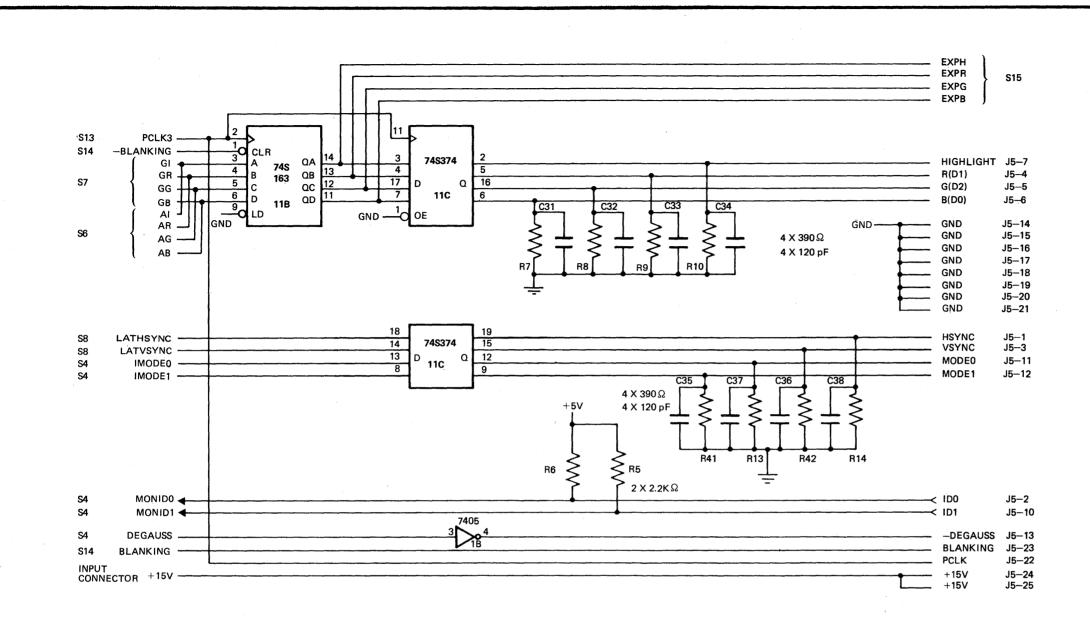

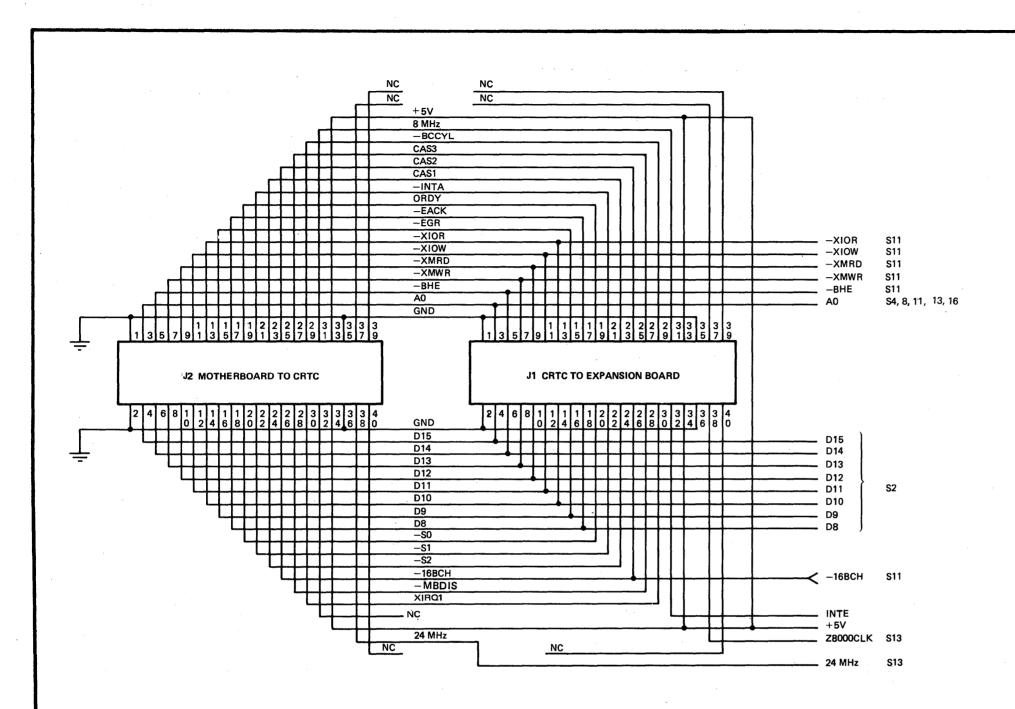

- 5. DISPLAY CONTROLLER

- 5-1 CHARACTERISTICS

- 5-2 OPTIONS DISPLAY BOARD

- 5-2 PRINCIPLES OF OPERATION

- 5–5 **FUNCTIONAL DESCRIPTION**

- 6. KEYBOARDS

- 6–1 INTRODUCTION

- 6–1 **FUNCTIONAL DESCRIPTION**

- 6–5 CHARACTERISTICS

- 7-1 7. POWER SUPPLY

- 7–1 INTRODUCTION

- 7-2 MECHANICAL CHARACTERISTICS

- 7-3 FUNCTIONAL DESCRIPTION

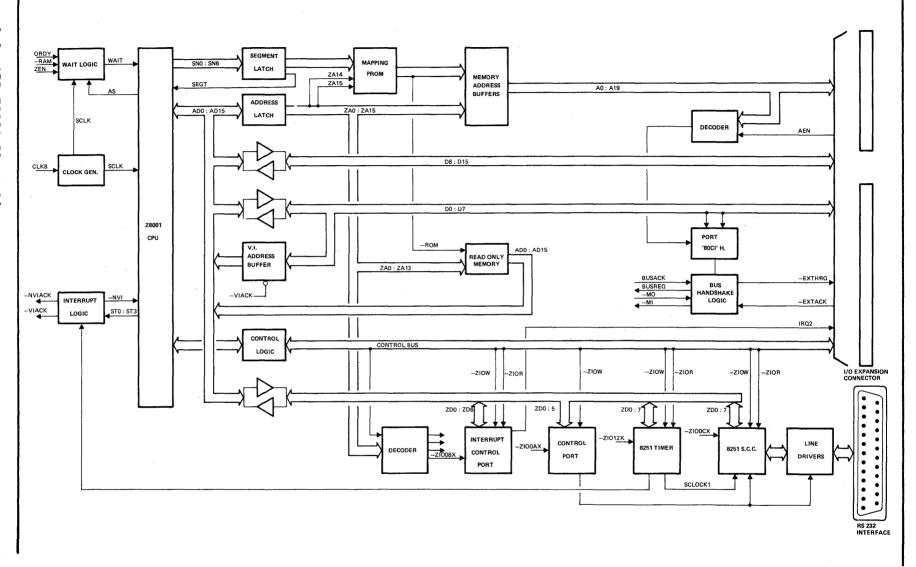

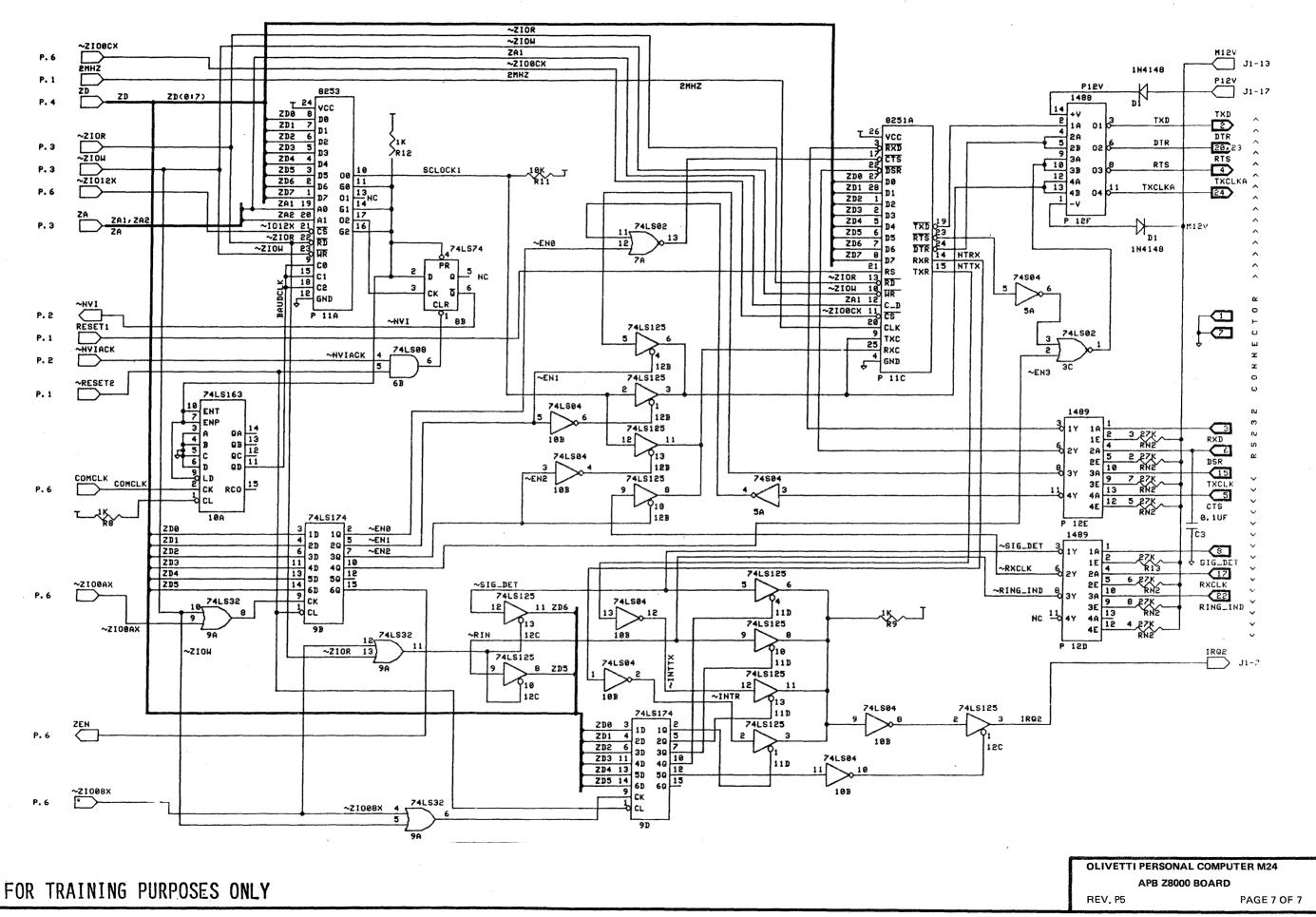

- 8. APB Z8000 BOARD (APB 2481)

- 8-1 OVERVIEW

- 8-1 GENERAL DESCRIPTION

- 8-3 FUNCTIONAL DESCRIPTION

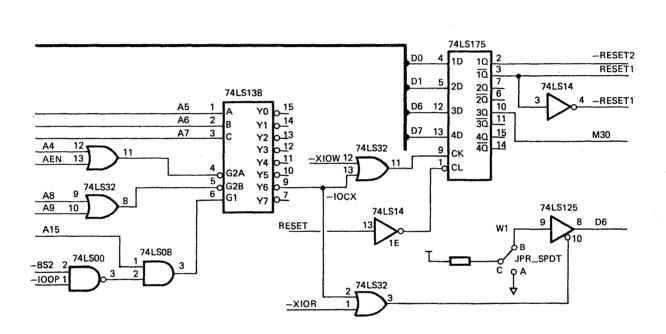

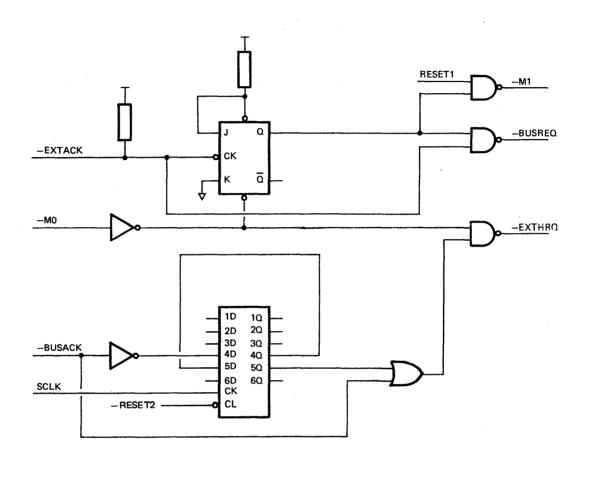

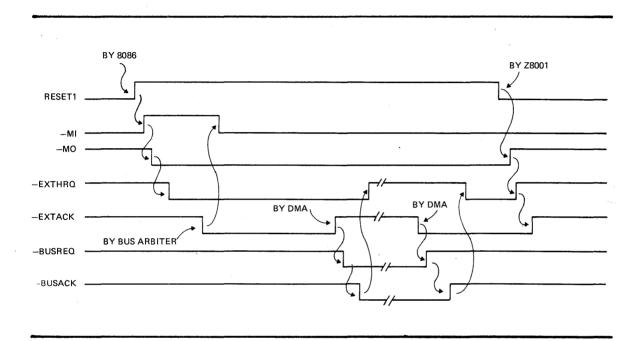

- 8-5 **BUS HANDSHAKING**

- 8-7 BUS HANDSHAKING TIMING

- 8-9 Z8001 PROCESSOR

- 8-12 PROGRAMMABLE READ ONLY MEMORY

- 8-13 RANDOM ACCESS MEMORY

- 8-22 **I/O DEVICES**

- 8-29 8251A SERIAL INTERFACE

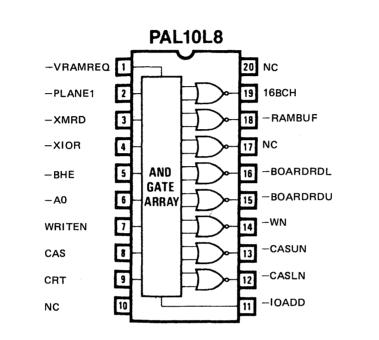

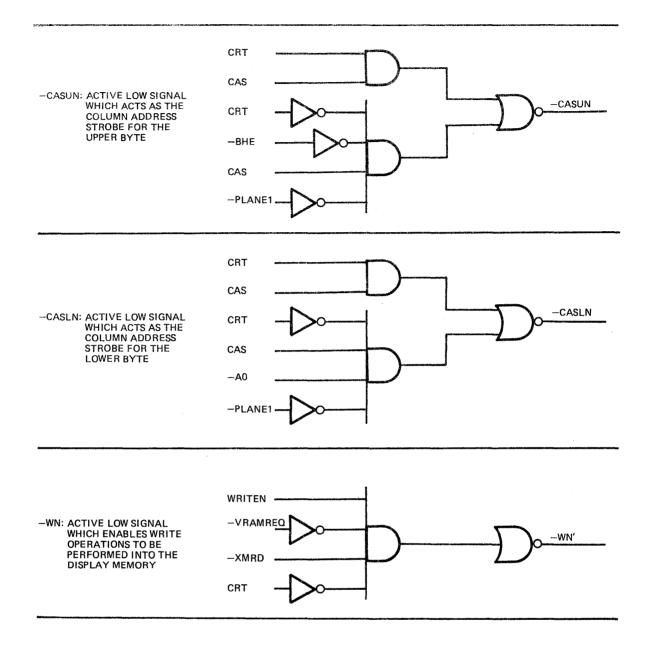

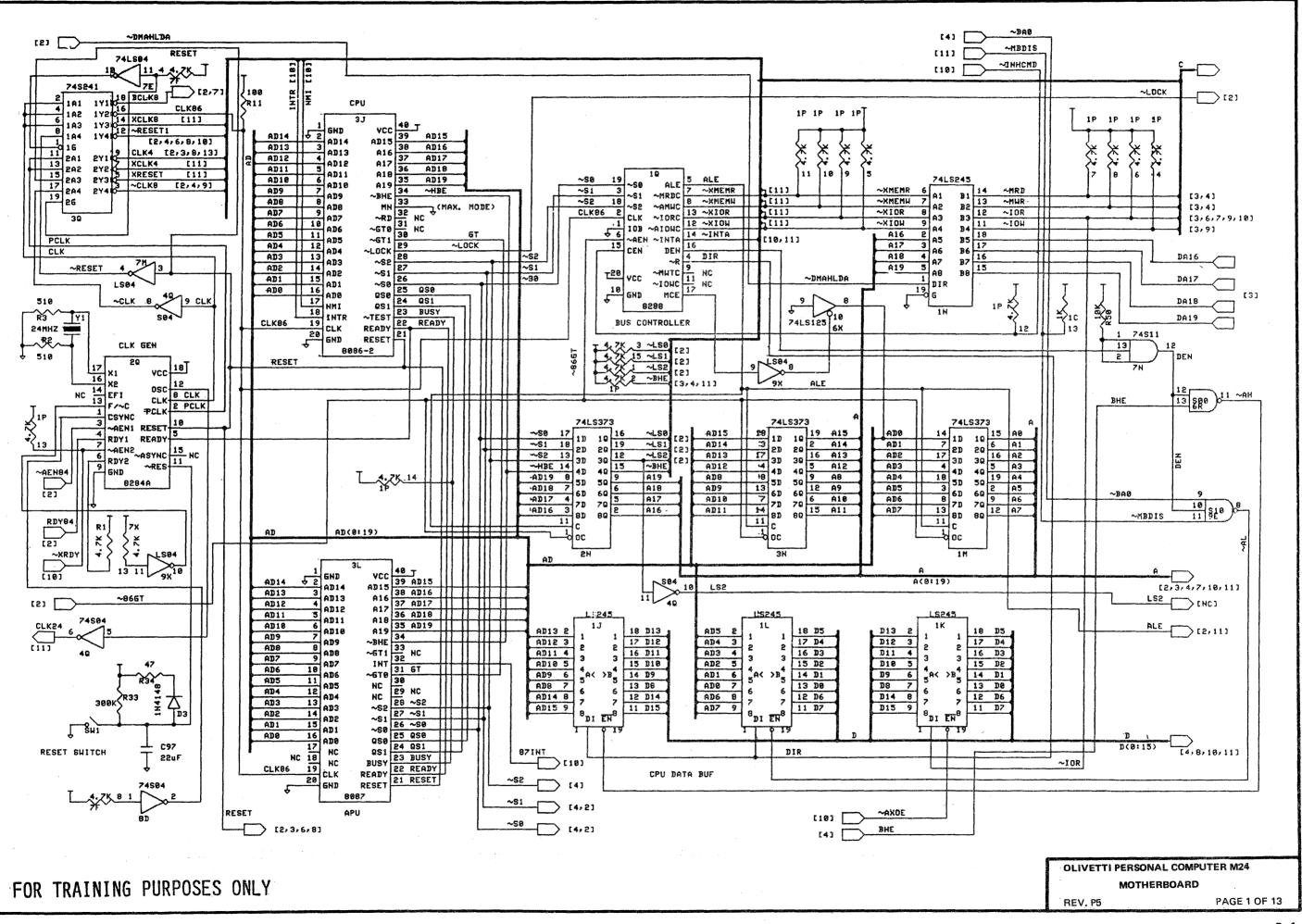

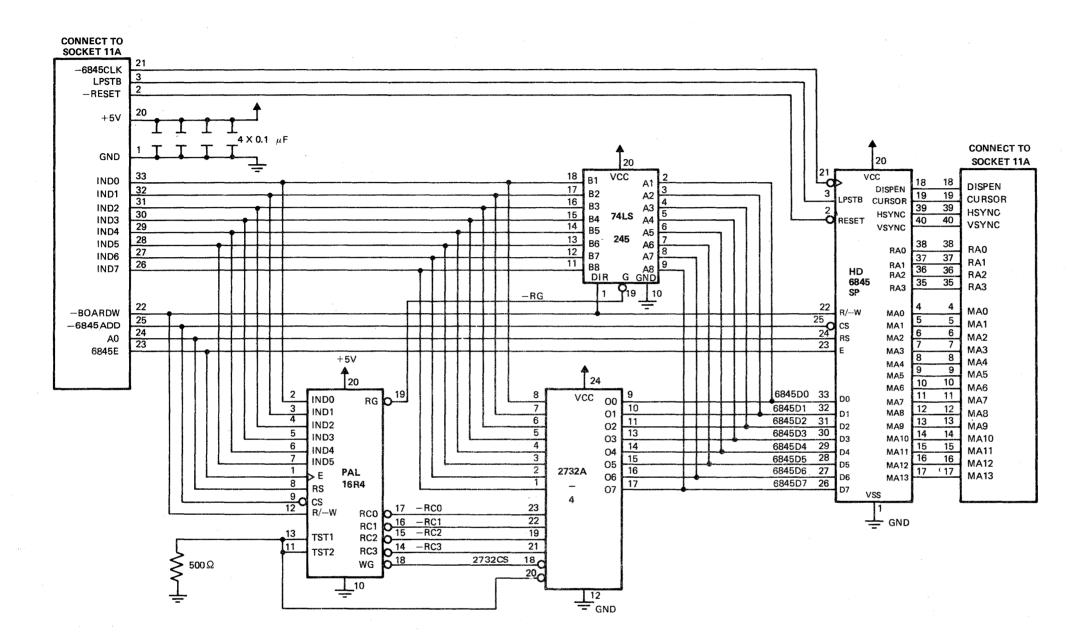

- A. DISPLAY CONTROLLER PAL AND ROM DESCRIPTIONS

- A-1 PAL 10L8 DESCRIPTION

- A-7 PROM 27S19A CONTENTS

- A-9 SCRAMBLER EPROM

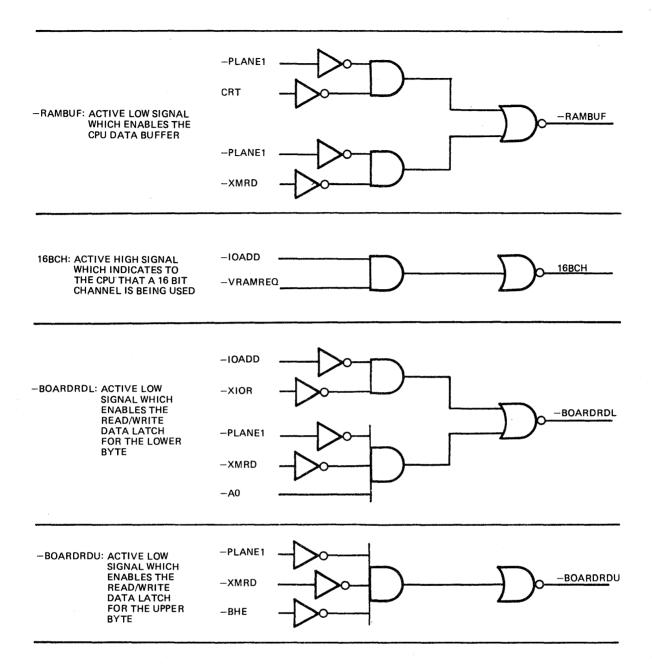

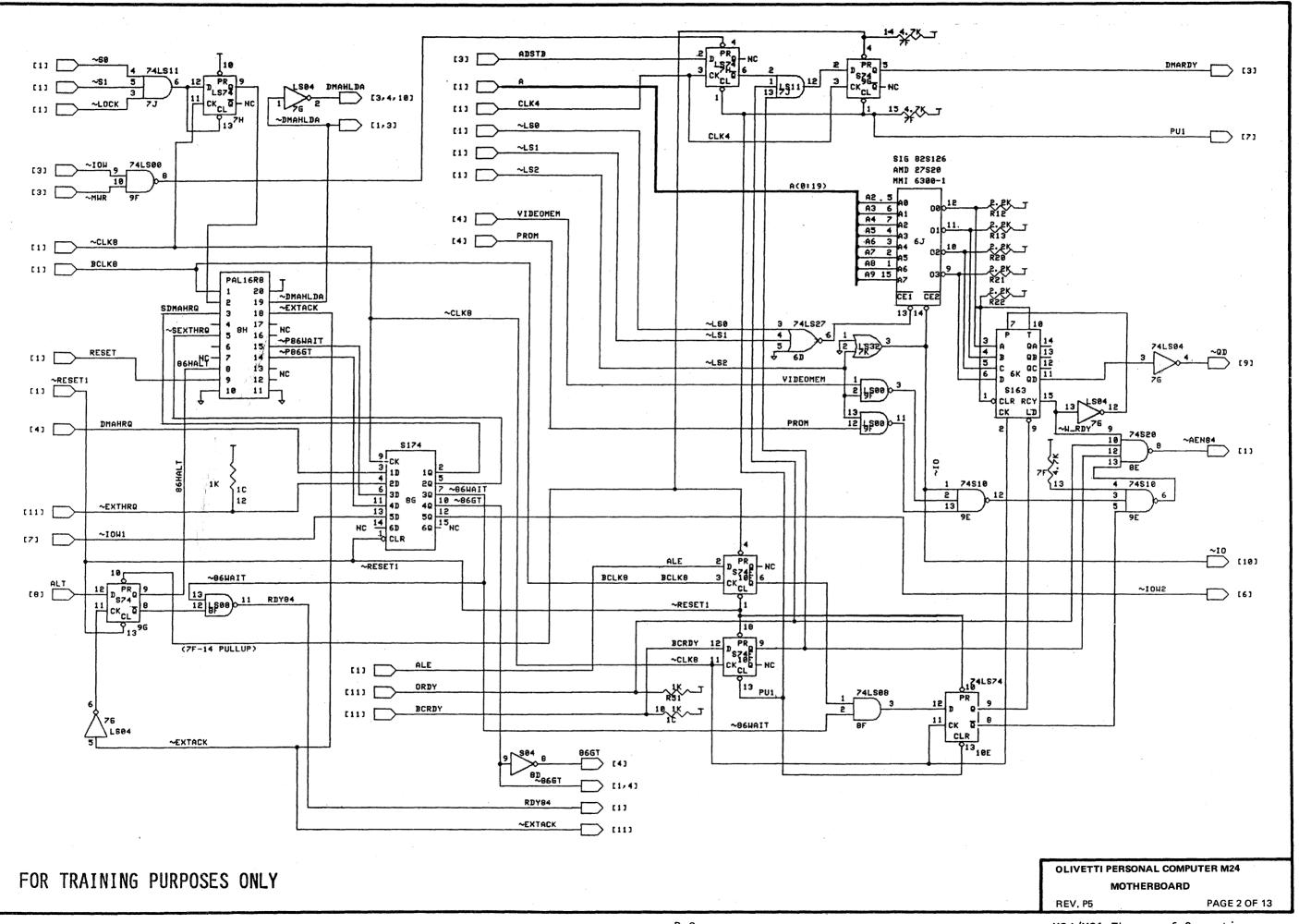

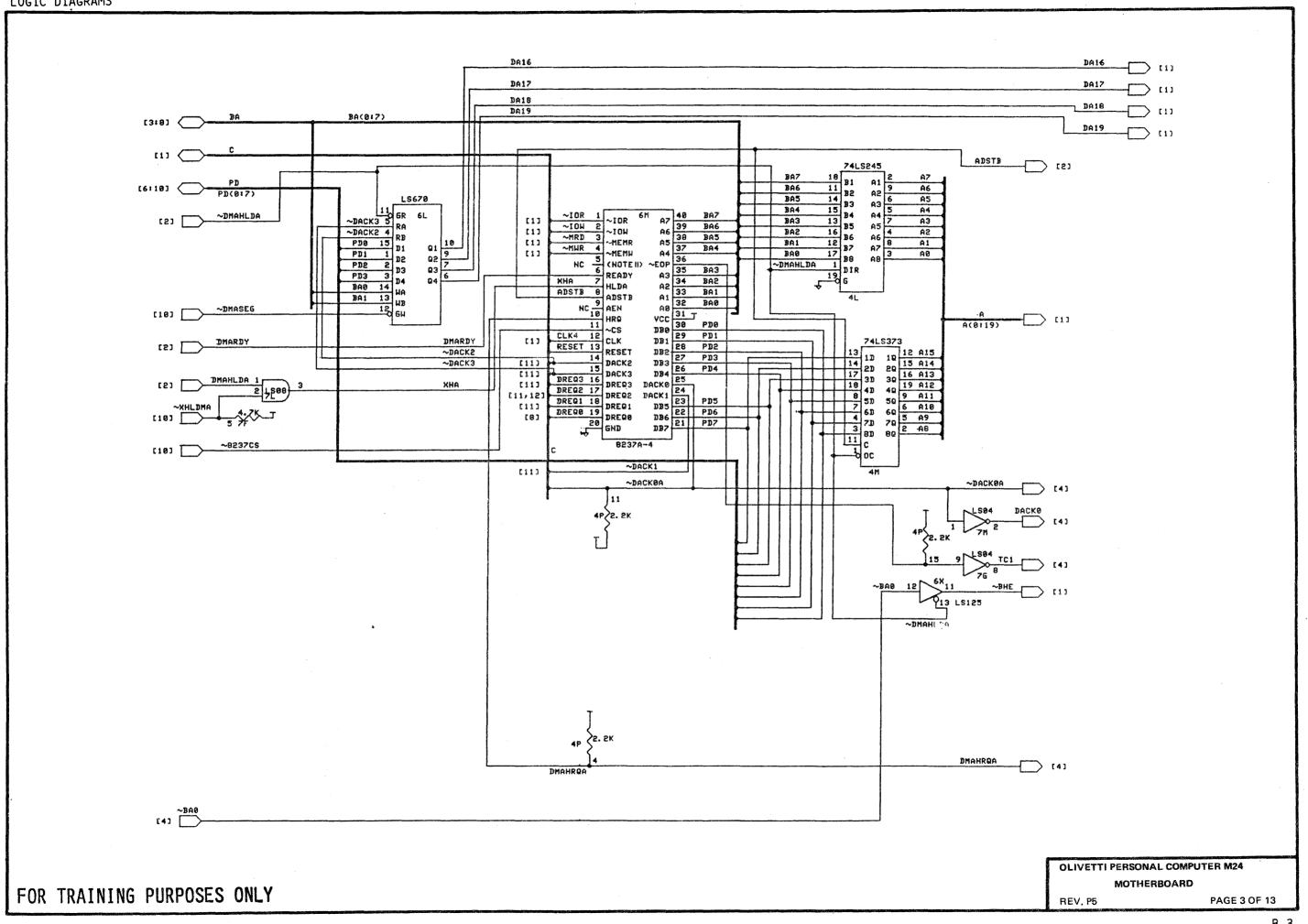

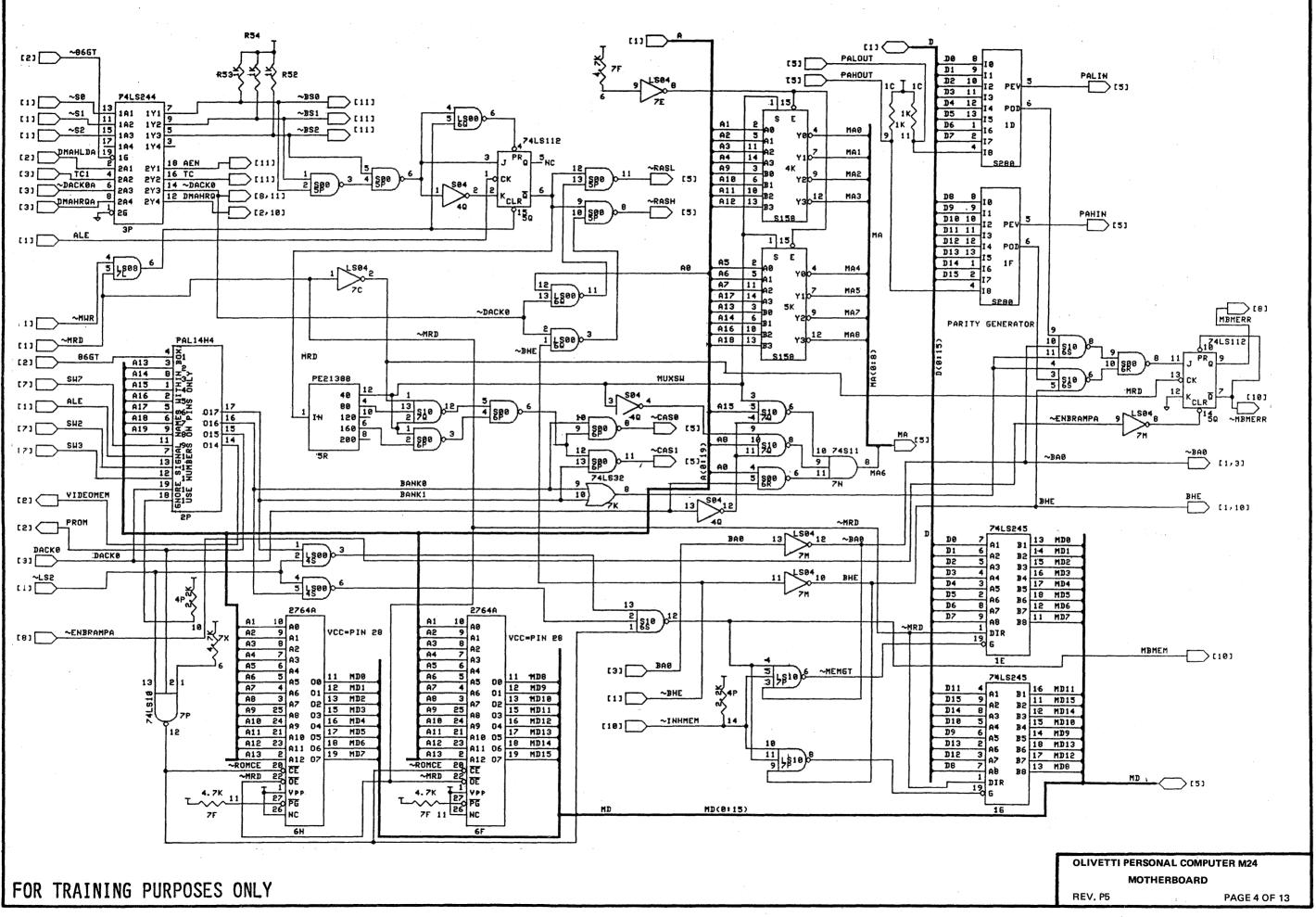

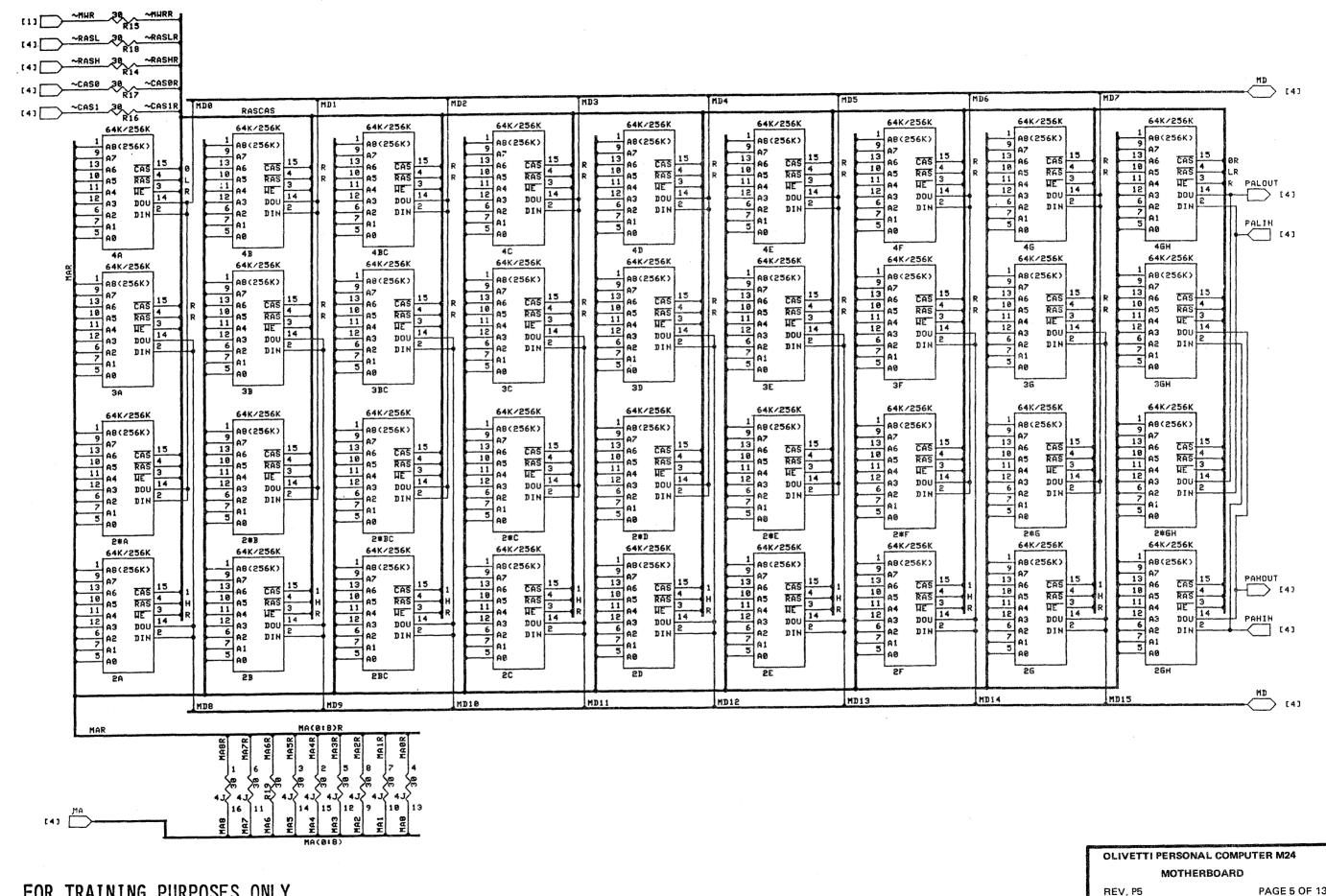

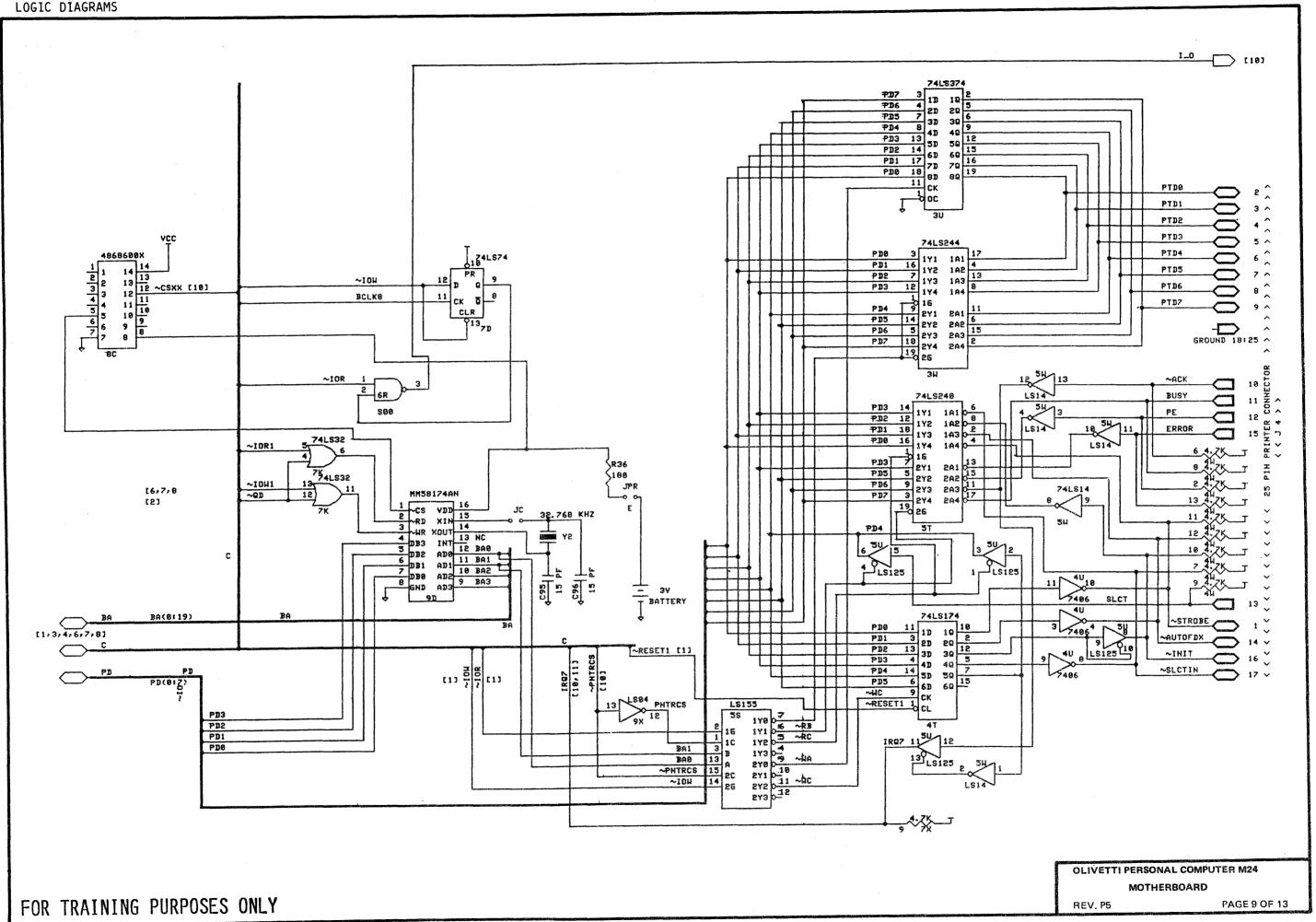

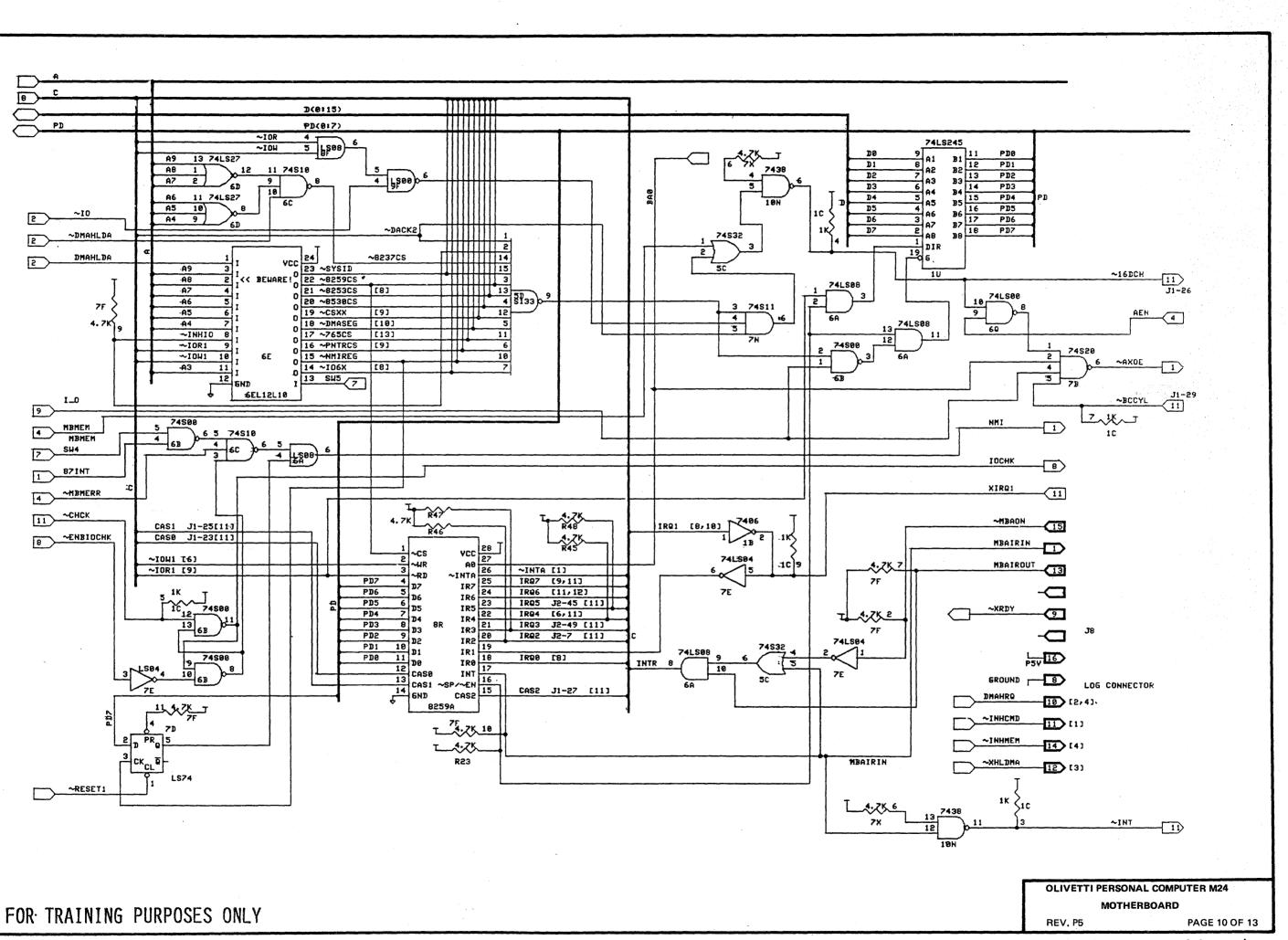

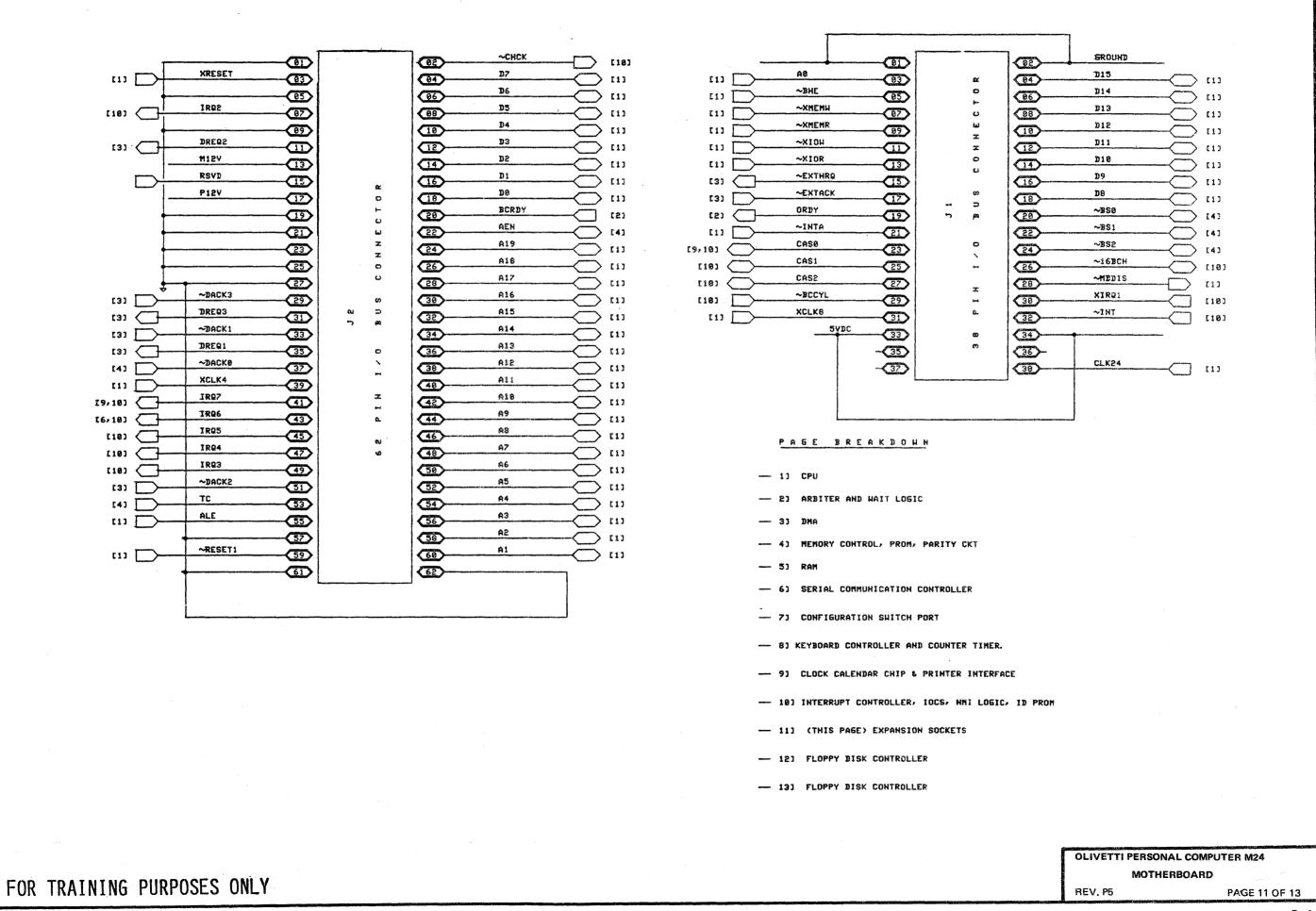

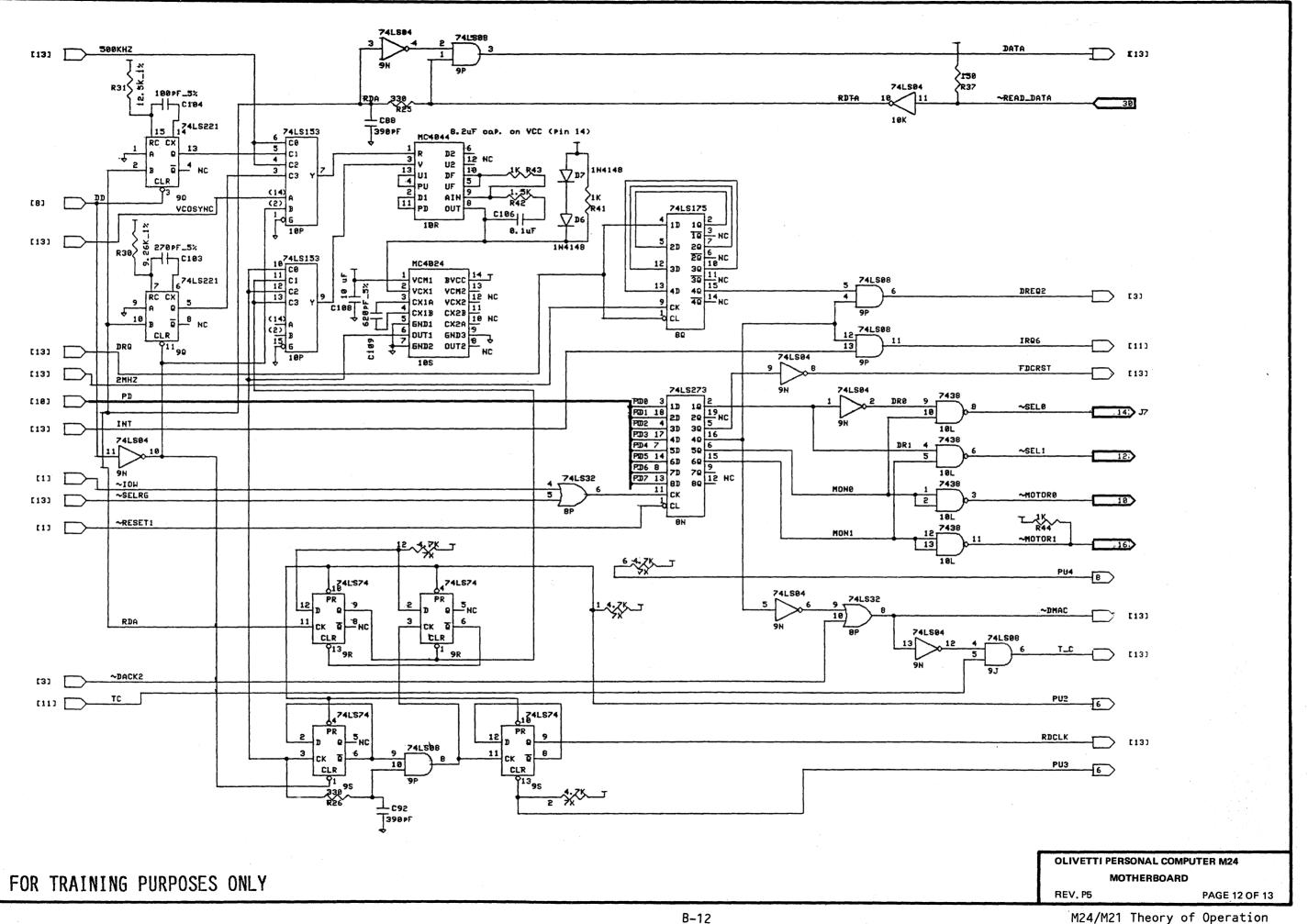

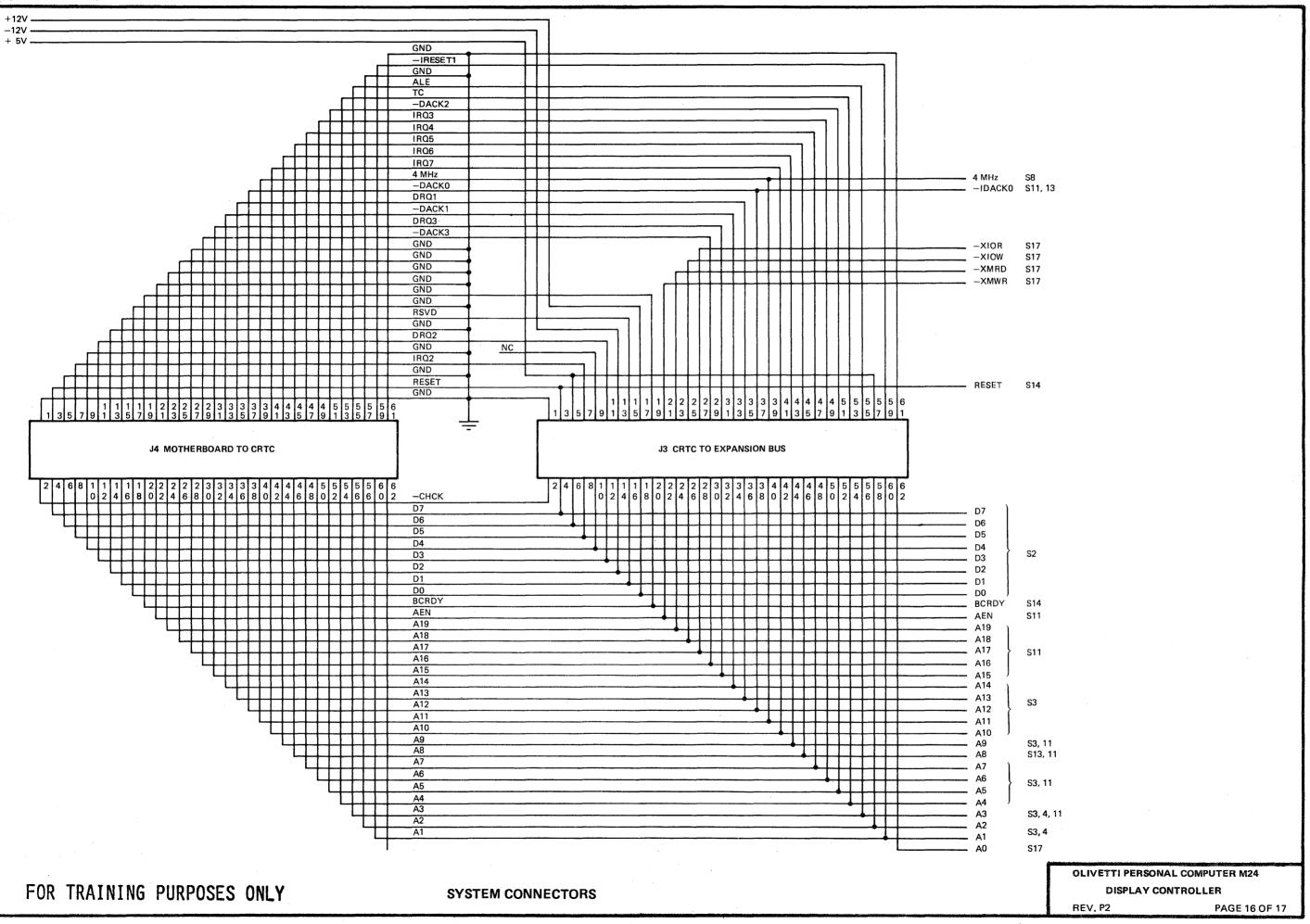

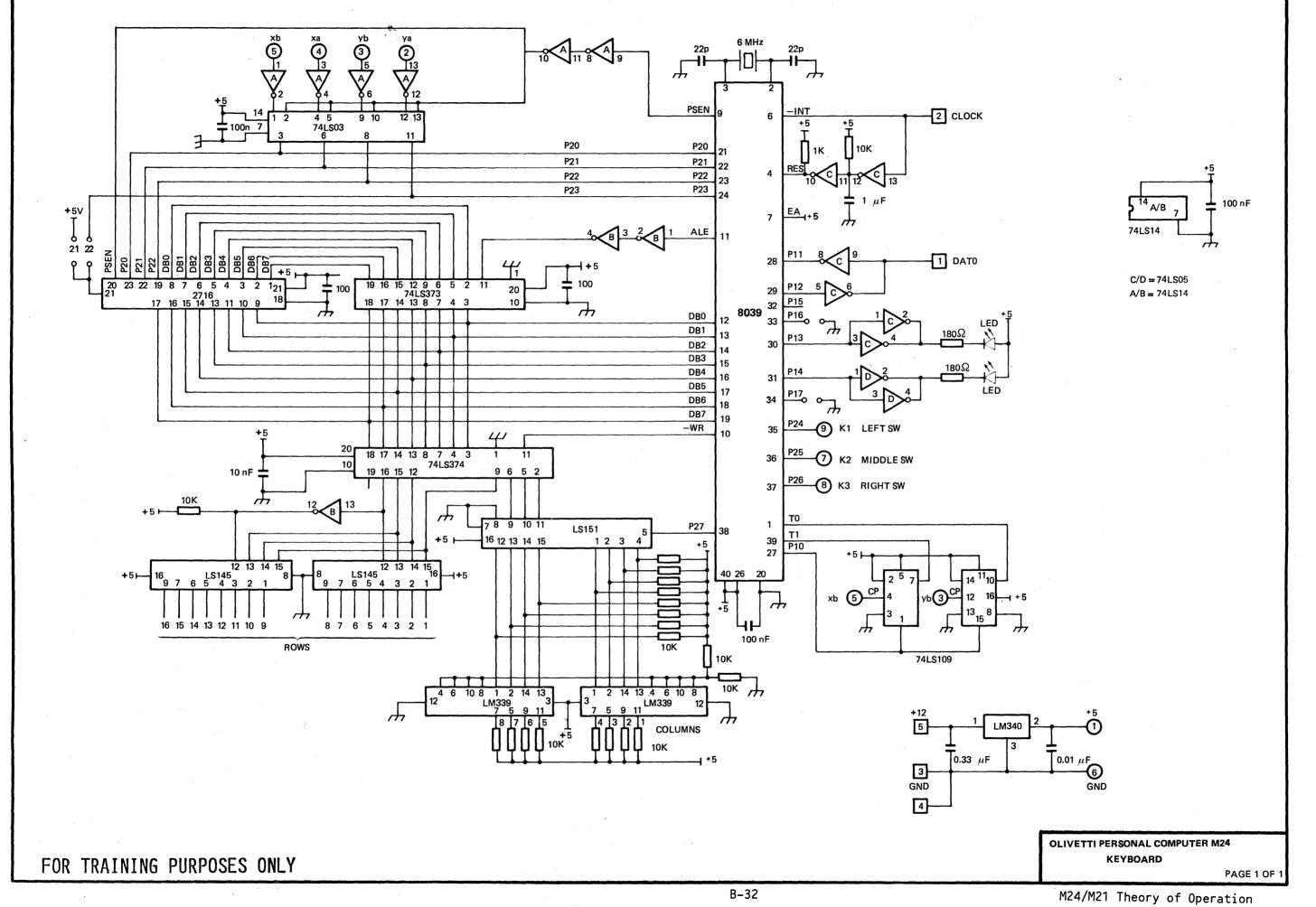

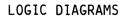

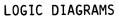

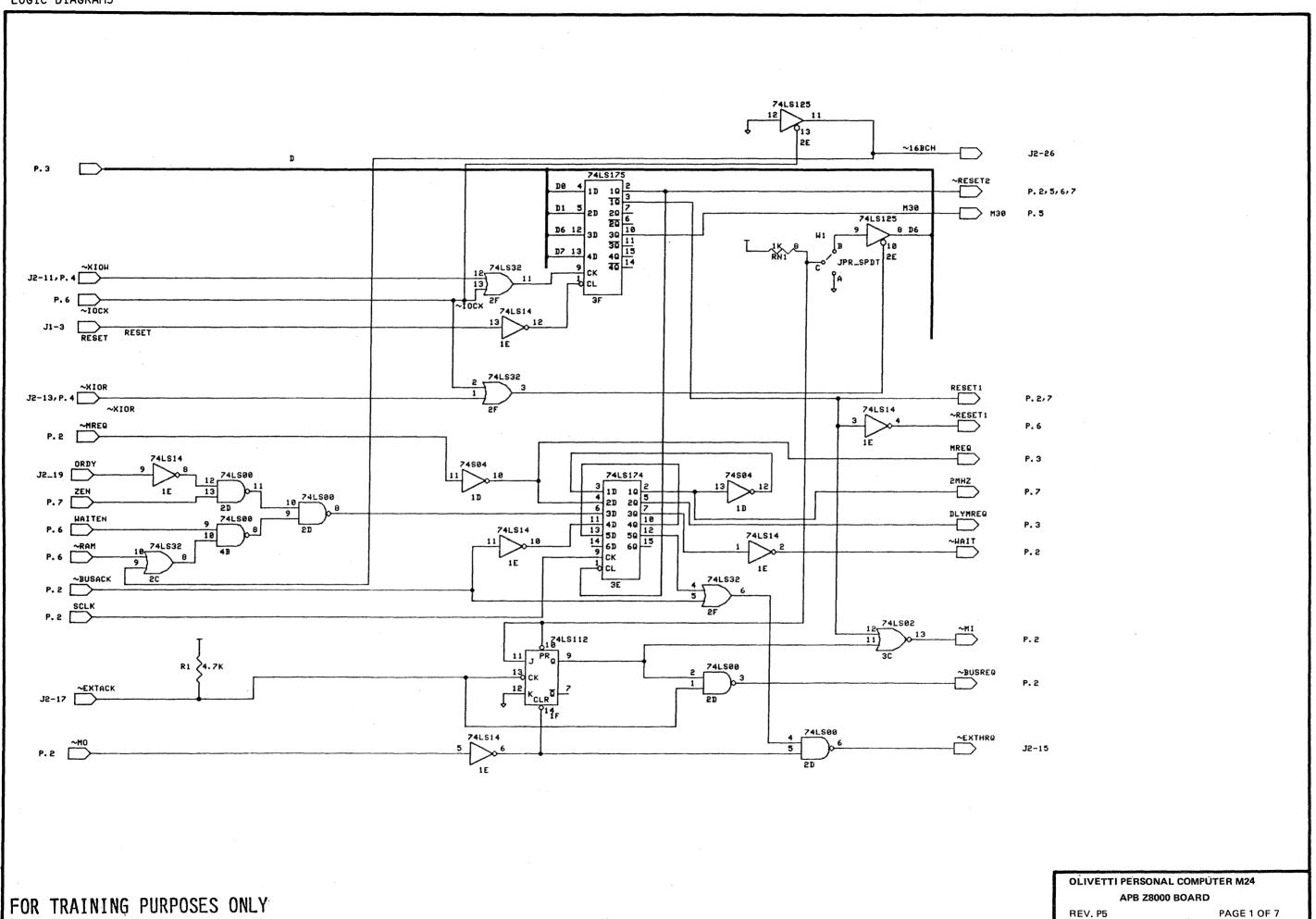

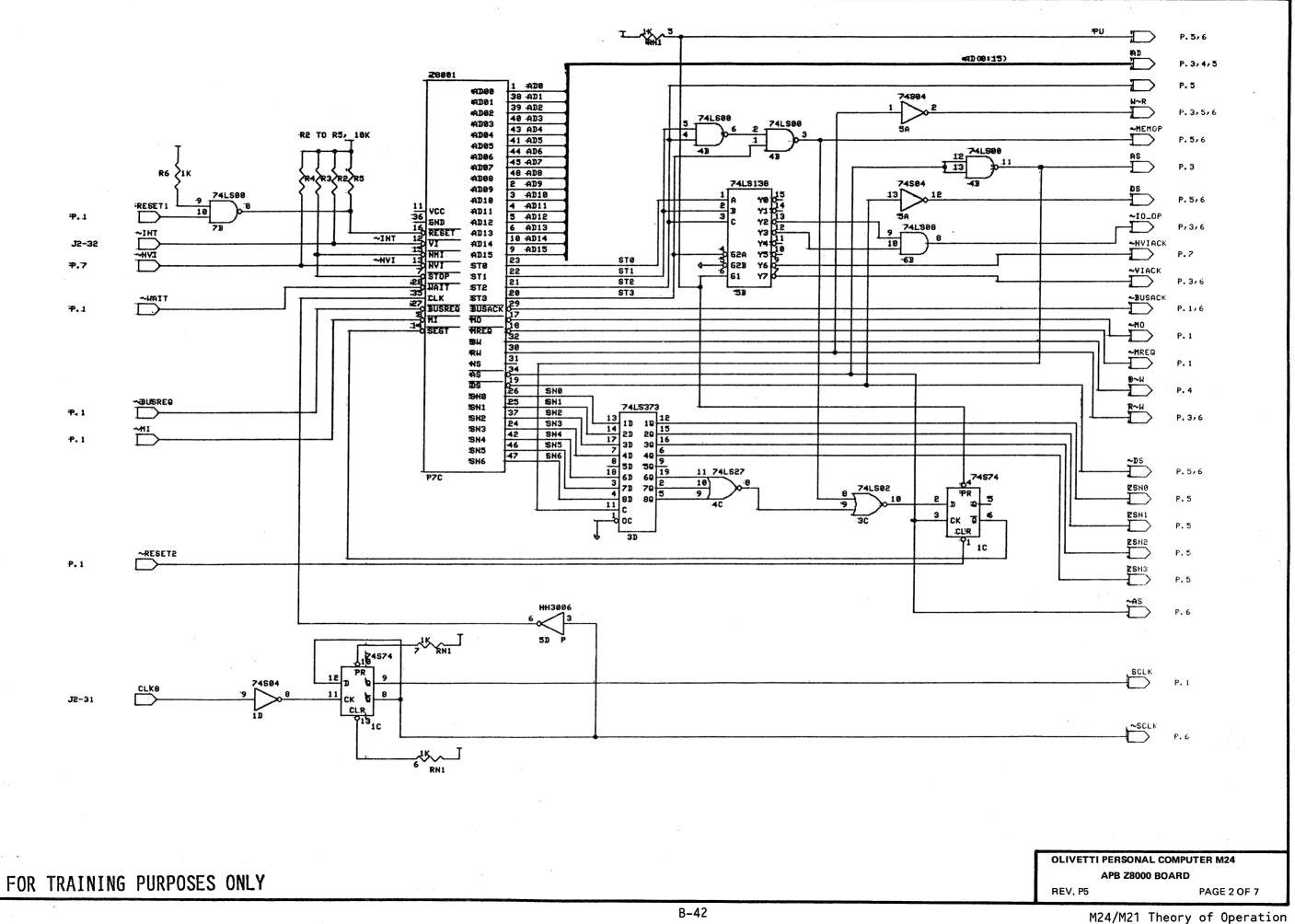

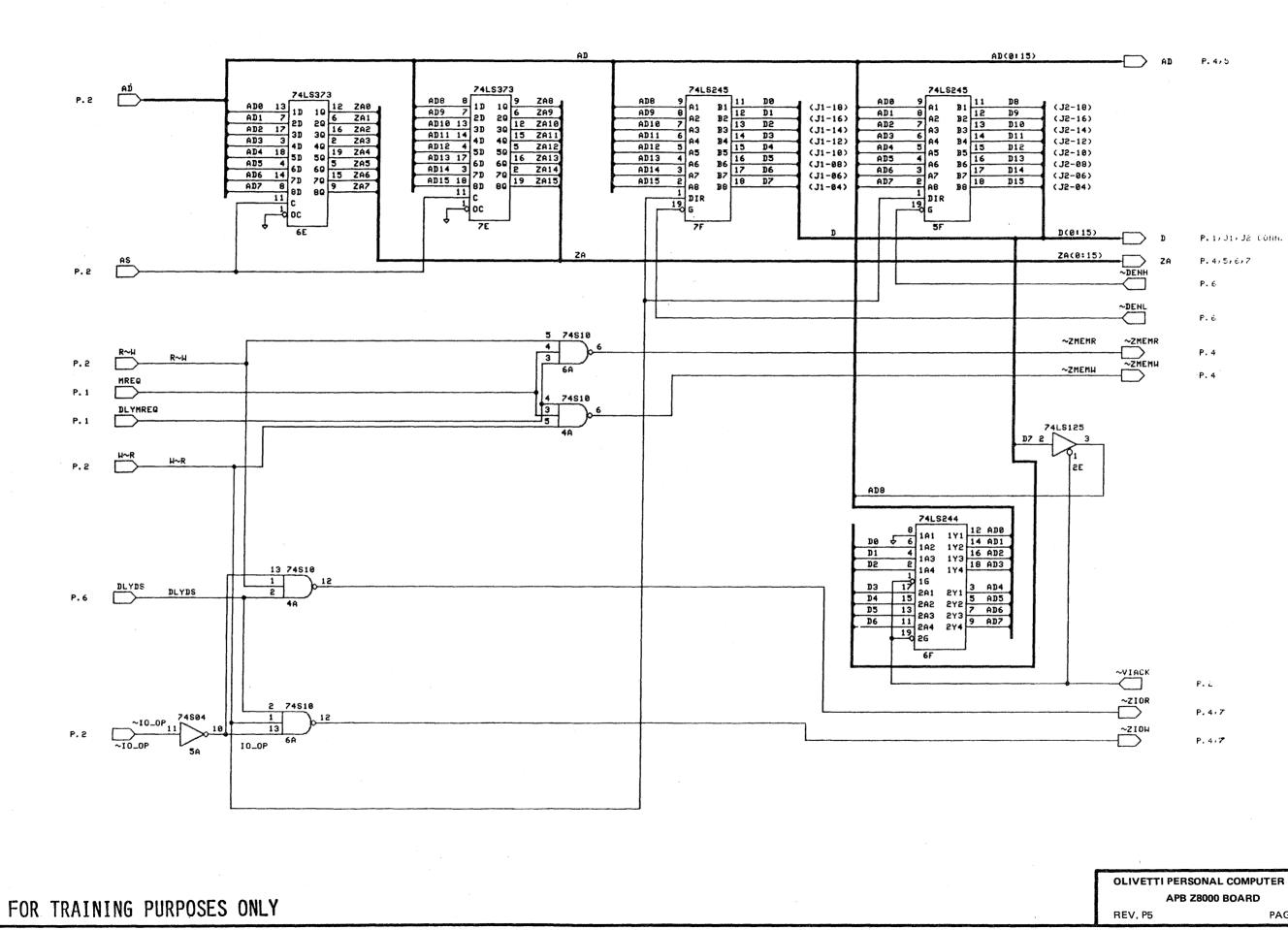

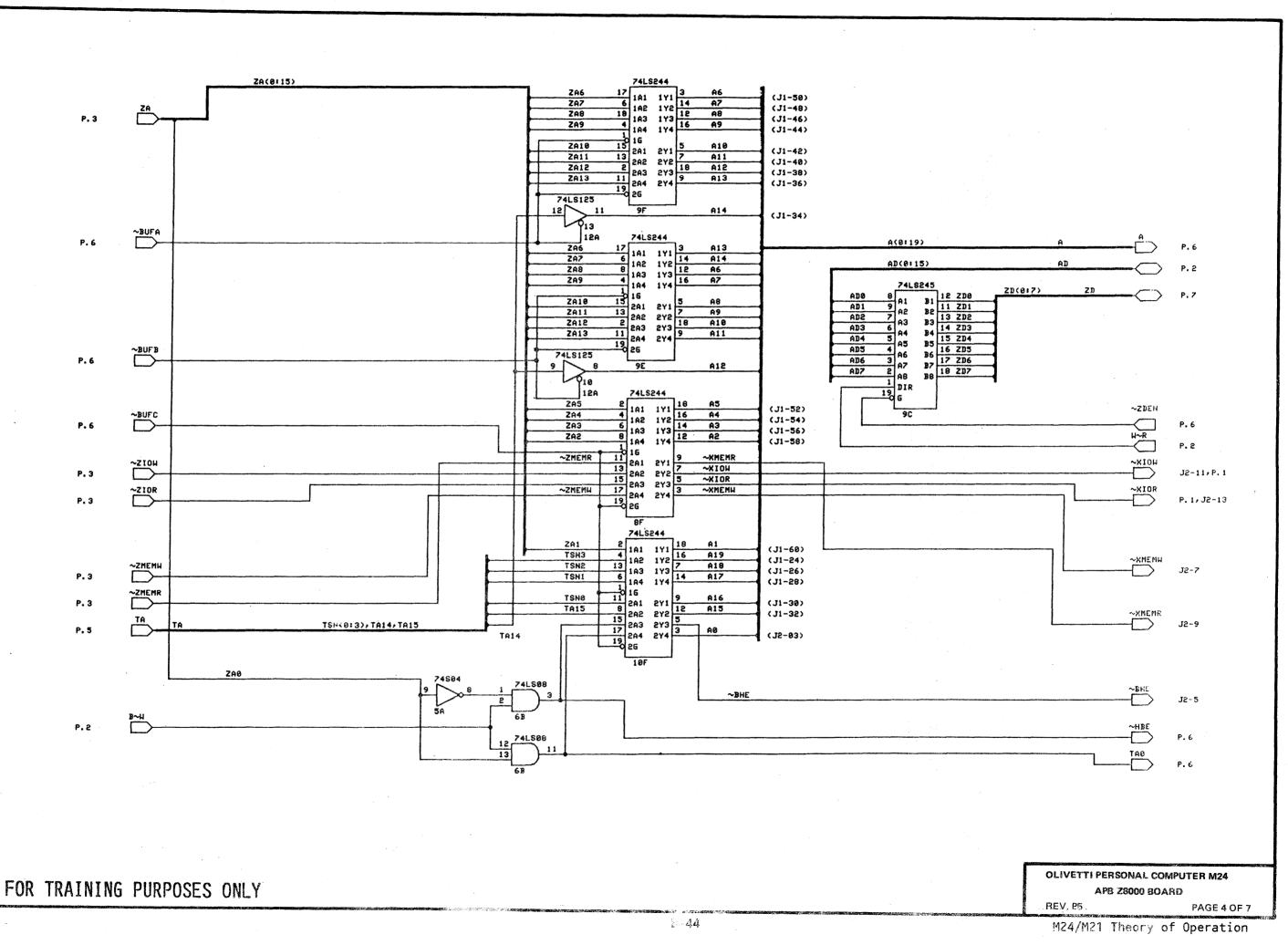

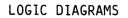

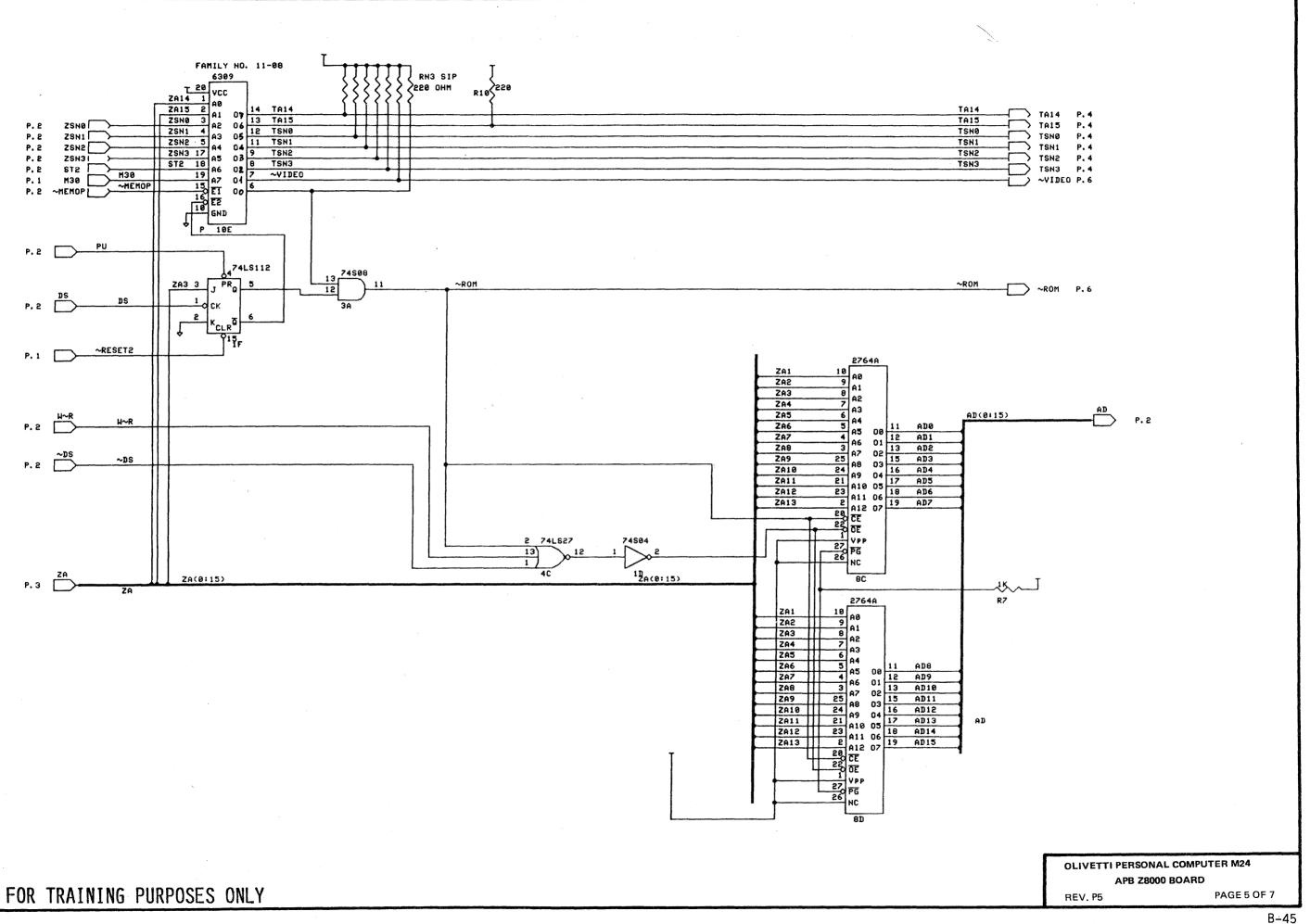

- B. LOGIC DIAGRAMS

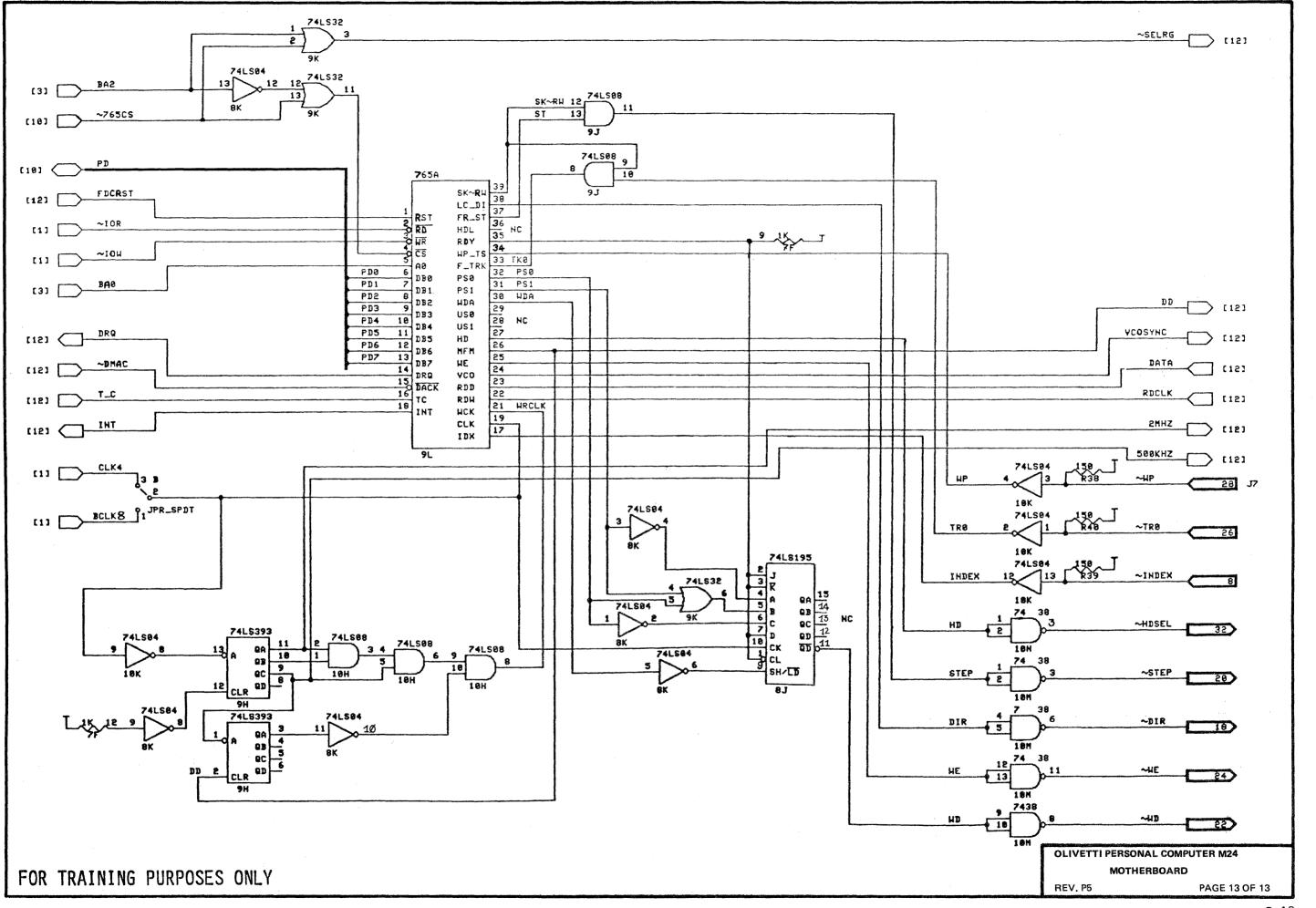

- B-1 MOTHERBOARD

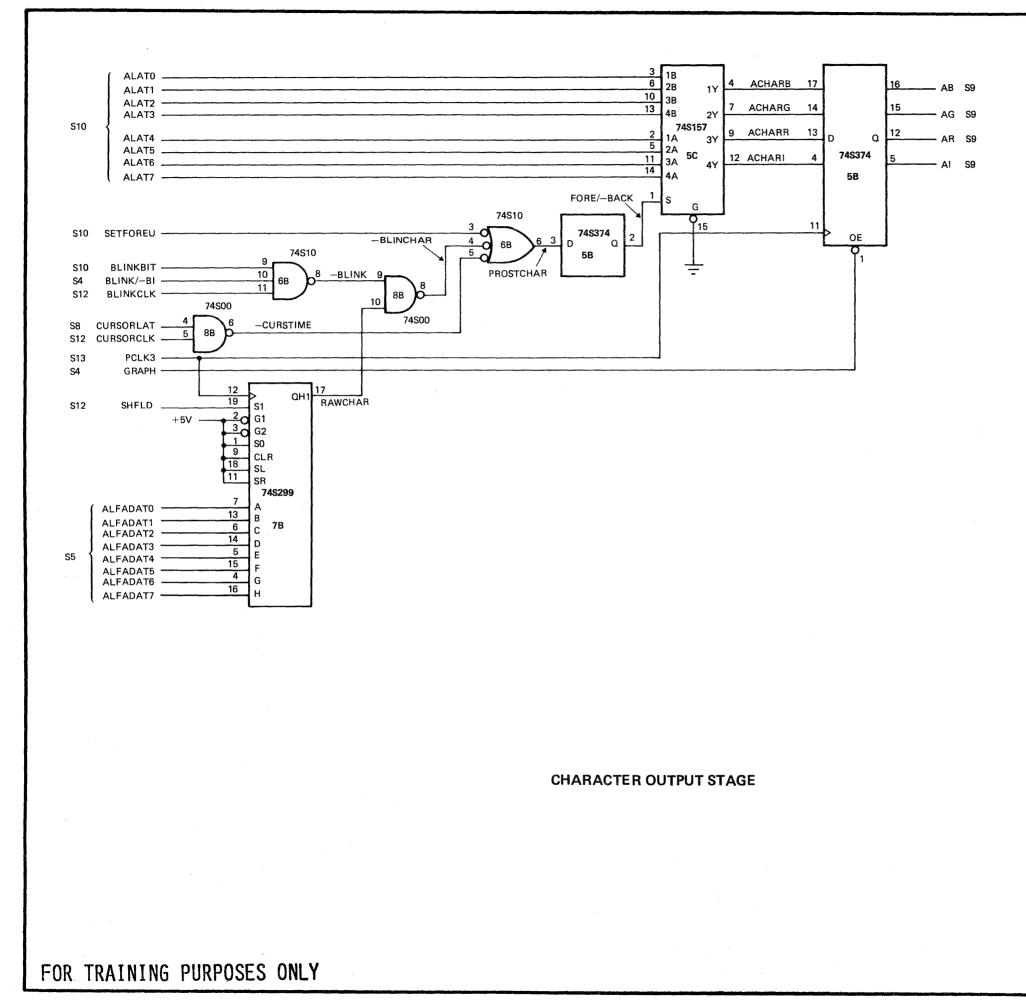

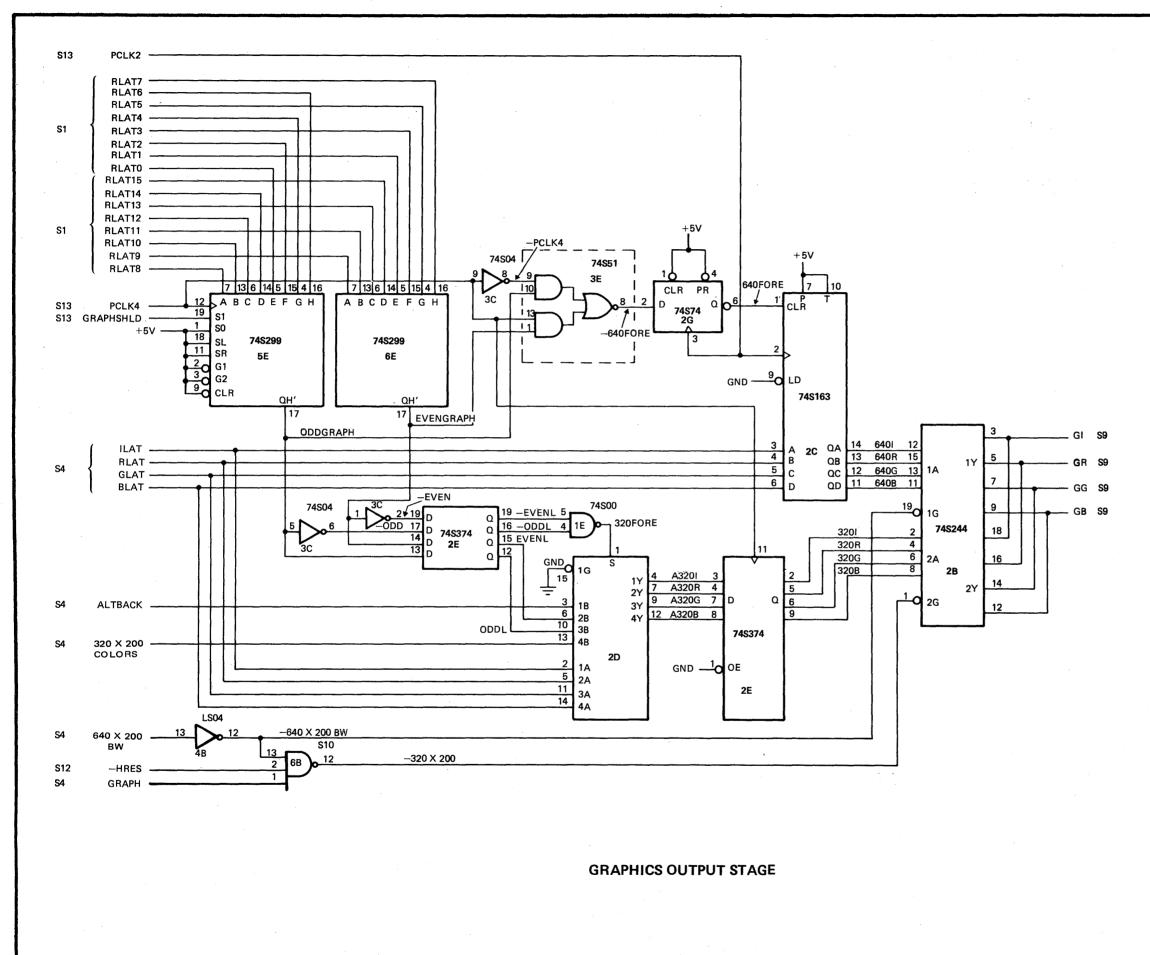

- B-14 DISPLAY CONTROLLER BOARD

- B-31 PIGGY BACK BOARD

- B-32 KEYBOARD

- B-33 POWER SUPPLY UNIT

- B-34 BUS CONVERTER BOARD

- B-37 MEMORY EXPANSION BOARD

- B-41 **APB Z8000 BOARD**

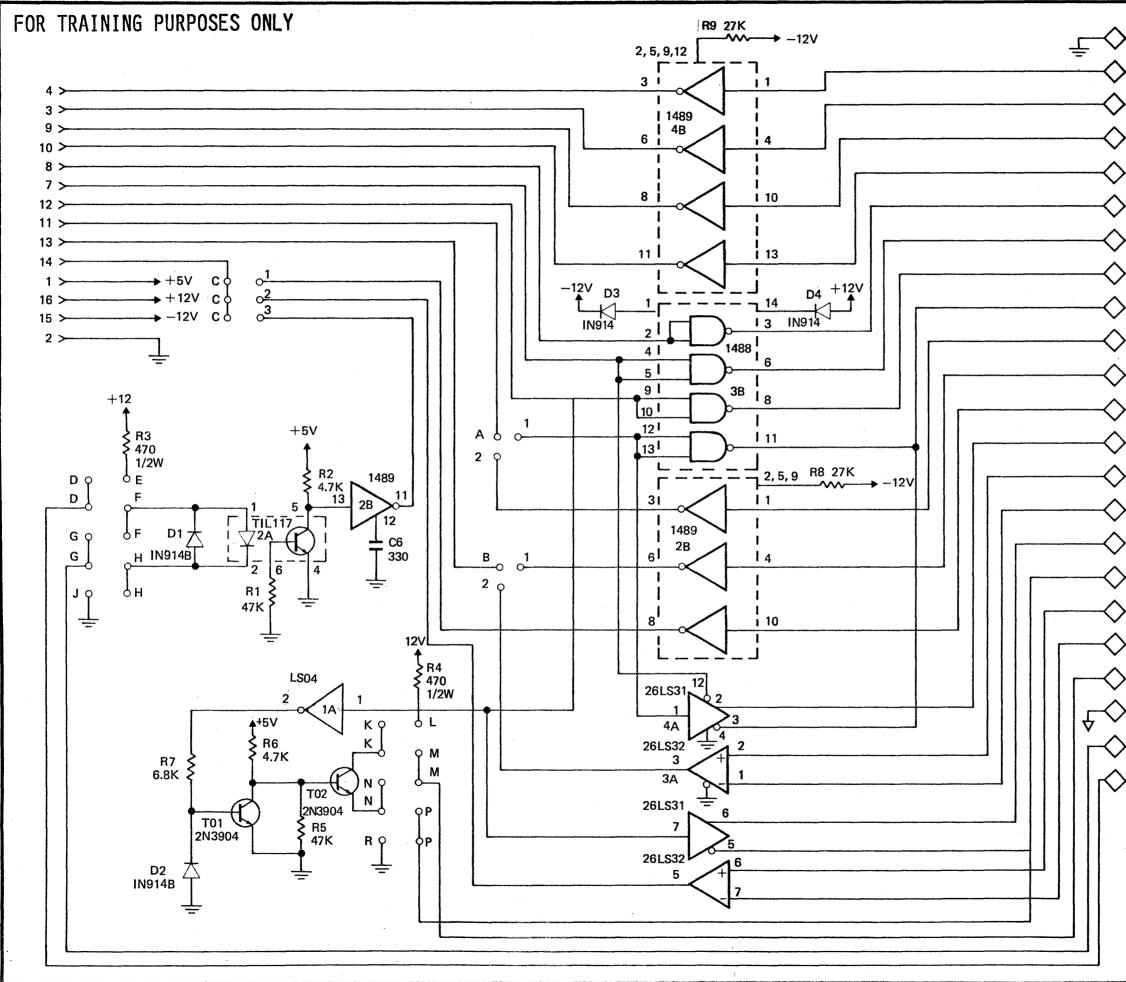

- B-49 MULTI-FUNCTION COMMUNICATION INTERFACE BOARD

1. SYSTEM DESCRIPTION

# CONTENTS

# PAGE

|      | 1. SYSTEM DESCRIPTION               |

|------|-------------------------------------|

| 1–1  | INTRODUCTION                        |

| 1–1  | CHARACTERISTICS                     |

| 1-4  | CIRCUIT BOARDS                      |

| 1-4  | MOTHERBOARD                         |

| 1-7  | INDIGENOUS DISPLAY CONTROLLER BOARD |

| 1-9  | POWER SUPPLY BOARDS                 |

| 1–10 | KEYBOARDS                           |

| 1–12 | BUS CONVERTER BOARD                 |

| 1–14 | MEMORY EXPANSION BOARD              |

| 1–15 | APB Z8000 BOARD (M24 Only)          |

| 1–16 | DISPLAY CONTROLLER OPTIONS BOARD    |

M24/M21 Theory of Operation

## INTRODUCTION

This manual gives a detailed functional description of the circuit boards which reside in the Olivetti M24/M21 Personal Computers. It also gives the functional description of the keyboard and some optional boards that can be inserted into the system.

#### CHARACTERISTICS

Basically the M24/M21 Personal Computers are made up of the processing unit and the associated peripheral units (that is, disk drives, display unit, printers, keyboard). The processing unit and the peripheral control circuits reside in the Basic Module.

The Basic Module always contains the following circuit boards:

- Motherboard

- Indigenous Display Controller

- Power Supply

The basic module can be expanded by the addition of the following circuit boards:

- Bus Converter Board

- Memory Expansion Board

- Display Controller Options Board

- APB Z8000 Board

The last three boards can only be added to the system if the Bus Converter Board is present. In fact, they are plugged into the dual row connectors expansion slots of the Bus Converter Board.

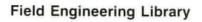

Fig. 1-1 System Block Diagram

With the Bus Converter Board present, other IBM compatible boards can be added to expand the system. These include:

- Hard Disk Controller

- Ethernet Transporter Board

- Ominet Transporter Board

- IEEE 488 Interface Board

- Twin RS232 Serial Interface Board

- Bisynchronous Communications Board

- Bit Oriented Communications Board

- Line Controller Unit Boards

These boards plug into the 62 pin connectors present on the Bus Converter Board.

## CIRCUIT BOARDS

#### MOTHERBOARD

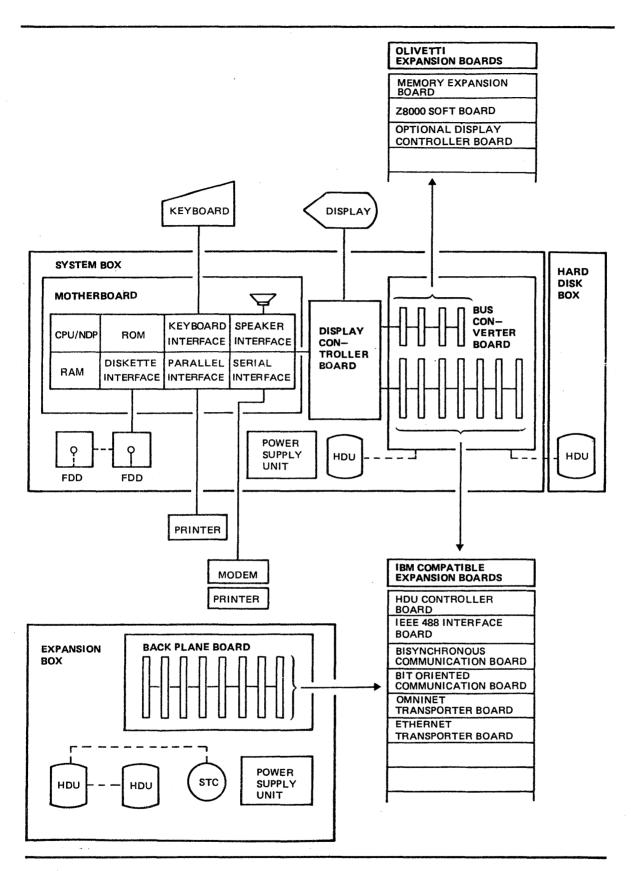

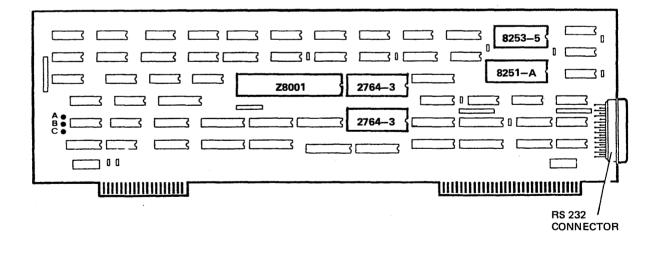

The motherboard is the main processing board of the M24/M21 systems. It is based on the 16 bit 8 MHz 8086 microprocessor and includes:

- Central Processing Unit (CPU): A 16 bit 8 MHz 8086 microprocessor which controls all the arithmetic and logic circuits within the system. It has a direct addressing capability up to 1 MB of memory, a 14 word by 16 bit register set and 24 operand addressing modes.

- Numeric Data Processor (NDP) Socket: This socket is available so that an 8087 Numeric Data processor can be installed as an option. This processor serves as a coprocessor attached to the 8086 CPU and effectively adds 80-bit floating point registers to the 8086 register set.

- 16KB of Read Only Memory (ROM): Two 8K ROM chips which contain the Power up Diagnostics, the Power on Bootstrap, the drivers for minifloppy disk drives, hard disk units and peripherals, and the initialization programs for Large Scale Integration chips.

- Random Access Memory (RAM): 128KB of RAM are available on the motherboard. These can be expanded up to 256KB with the insertion of 64K by 1 bit chips. When 256K by 1 bit chips are used the RAM can be expanded up to 512KB.

- **Memory Control Circuitry and Parity Checking:** This circuitry provides all the timing signals for the transfer of data to and from memory. It also multiplexes the addresses coming from the CPU and prepares them to address the particular memory location. The parity generation and checking circuitry generates a parity bit during a write operation and is then read back and checked for any parity error.

- Interrupt Handling Circuitry: It consists of an 8259 Interrupt Controller which is a programmable device that handles the priority interrupts to the CPU. It controls all the interrupts used in the system.

- Bus Arbiter Logic: The main component in this circuitry is the PAL

16R8 which handles the arbitration between the three bus masters namely the CPU, the DMA and an external processor.

- DMA Circuitry: This is based on the 8237 DMA controller and it allows the external 1/0 devices to transfer information to/from RAM memory directly without any CPU intervention.

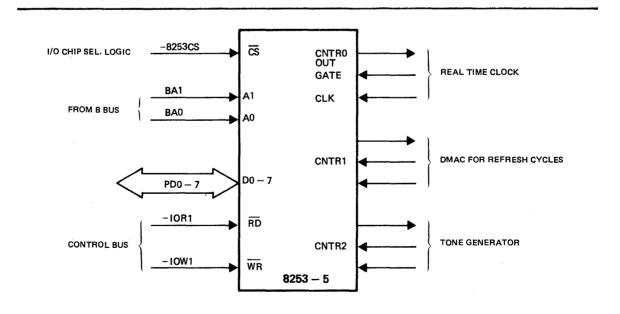

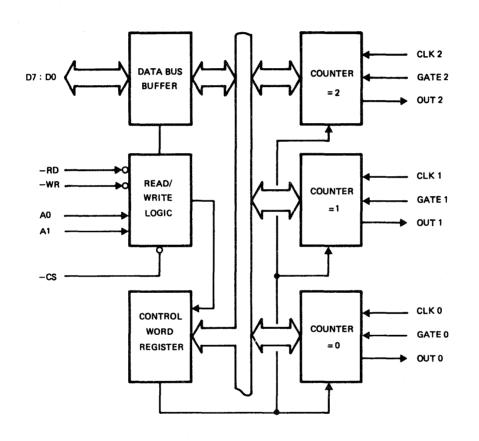

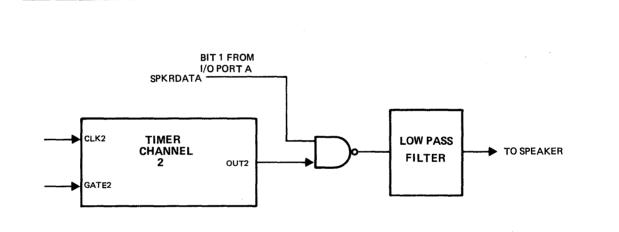

- **Timer:** This is an 8253 programmable device used to provide a real time clock, to time and request refresh cycles from the DMA channel, and to provide the tone generator for the audio speaker.

#### Fig. 1-2 Motherboard

۱

- Clock Calendar Chip with Battery Back Up: This chip is used to provide real time for the system. The battery back up is used to keep the device running even during a system power fail.

- **Parallel Interface:** This interface provides the system with one Centronics parallel port for connecting a printer.

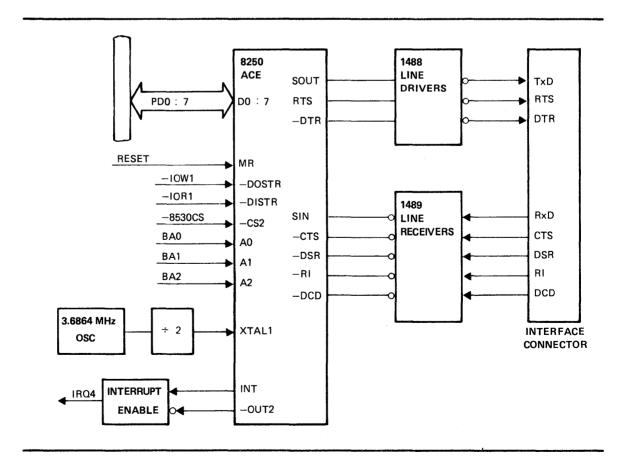

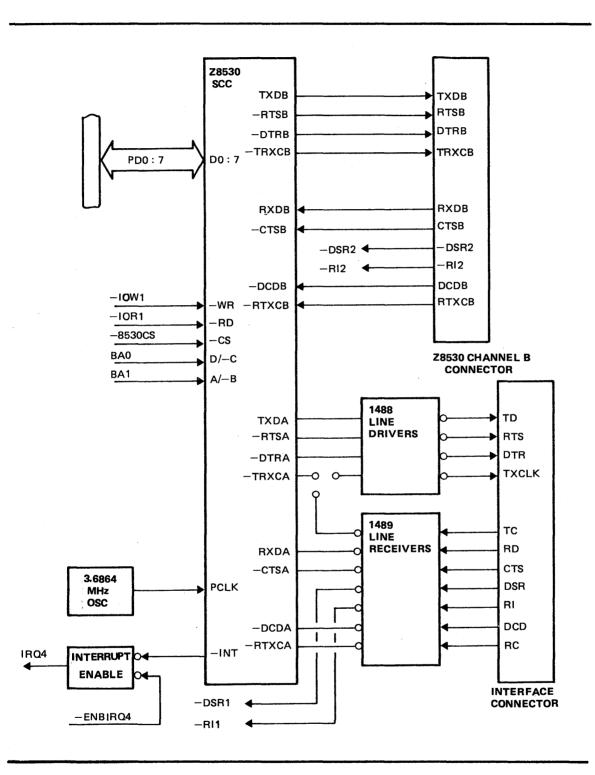

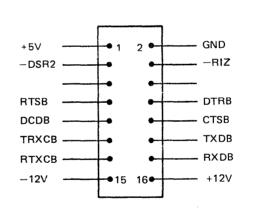

- Serial Interface: The motherboard uses an 8250 asynchronous communication controller to provide an RS-232-C channel. It is possible to remove this chip and replace it with an 8530 Serial Communications Controller. The 8530 SCC is a USART (Universal Synchronous Asysnchronous Receiver Transmitter) and provides two serial channels.

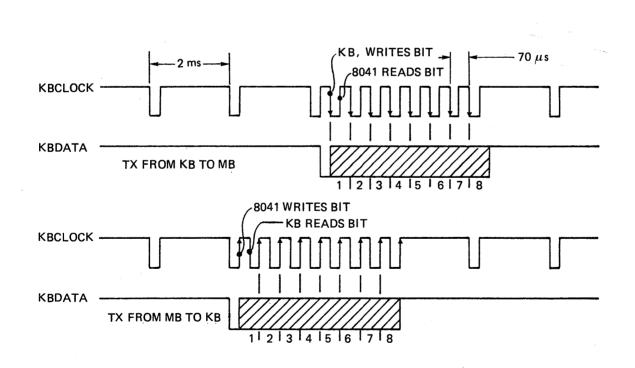

- Keyboard Interface: This interface is based on an 8041 microprocessor which is used to convert the system parallel data to serial data for the keyboard and vice-versa.

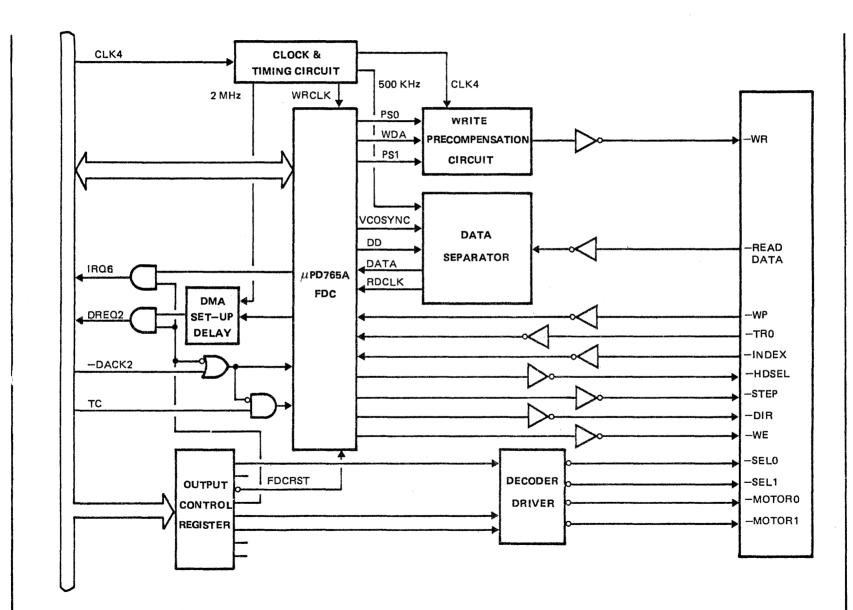

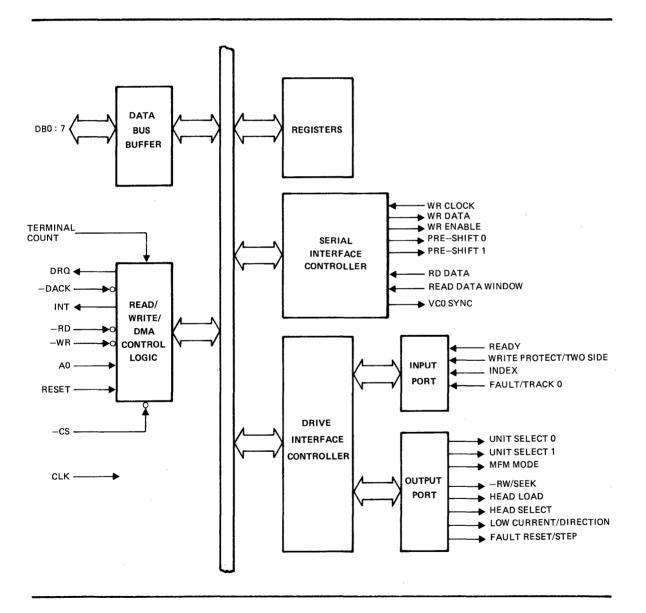

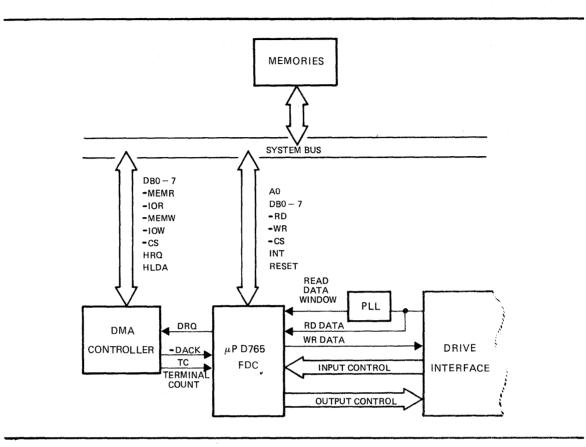

- Floppy Disk Interface: The floppy disk interface is based on the uPD765 controller and it provides the circuitry required to drive and control two 5.25 inch mini-floppy disk drives.

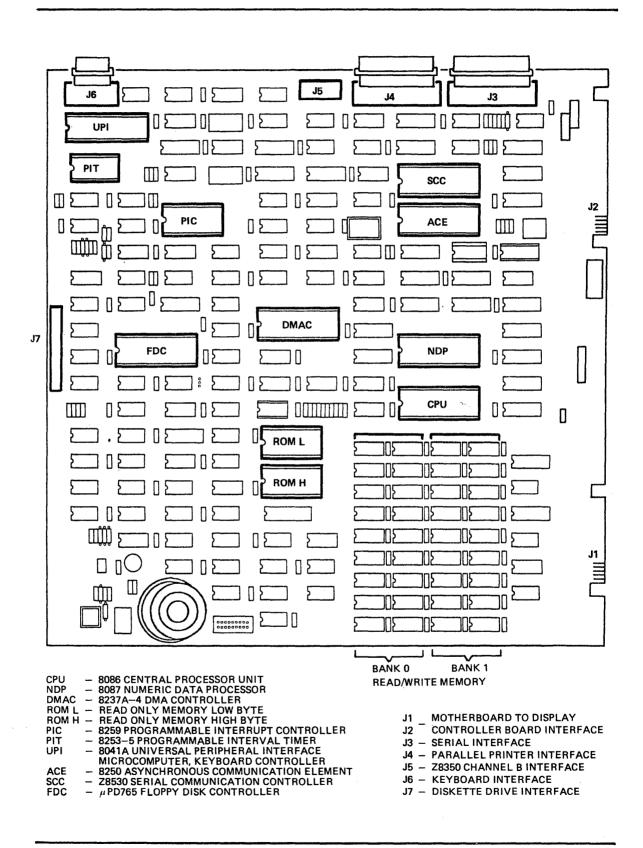

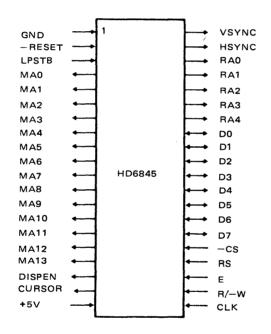

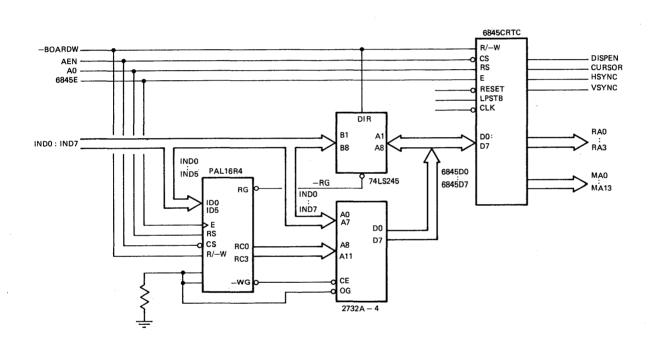

## INDIGENOUS DISPLAY CONTROLLER BOARD

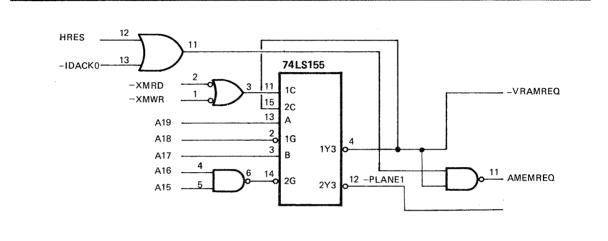

The Indigenous Display Controller circuit board is a microprocessor based interface board for controlling colour and monochrome display units. It is based on a 6845 CRT controller and contains 32KB of RAM. It has a 4K or an 8 K byte ROM. With a 4KB ROM only the IBM character set is provided while with an 8KB ROM a second character set can be implemented.

The Display Controller can support the following modes of operation:

- 40x25 Alphanumeric Mode

- 80x25 Alphanumeric Mode

- 640x400 Monochrome Graphics Mode

- 640x200 IBM compatible Monochrome Graphics Mode

- 320x200 IBM compatible Colour Graphics Mode (with 12" Display Unit)

- 512x256, M20 compatible, Monochrome Graphics Mode (with APB Z8000 Board and 12" Display Unit present)

When in a colour mode, this controller can display four colours simultaneously, chosen from a palette of 16. With a monochrome monitor, instead of the various colours, shades of grey are displayed.

This Display Controller contains the circuitry for providing the following character attributes:

- Reverse Video

- Blinking

- Highlight

- Hide

- Underline

Other characteristics of this display controller include Degaussing and paging.

Fig. 1-3 Indigenous Display Controller Board

1-8

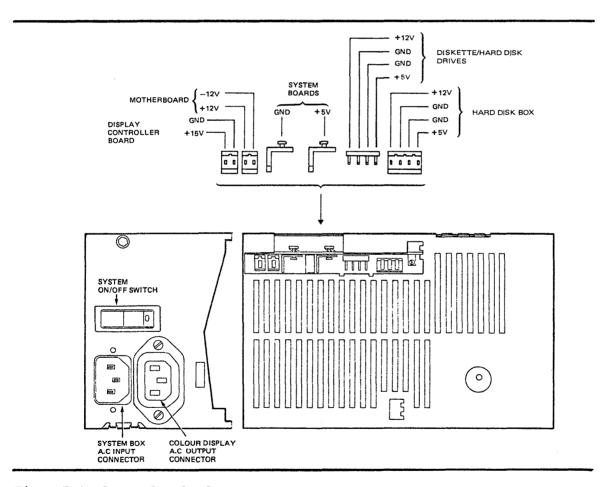

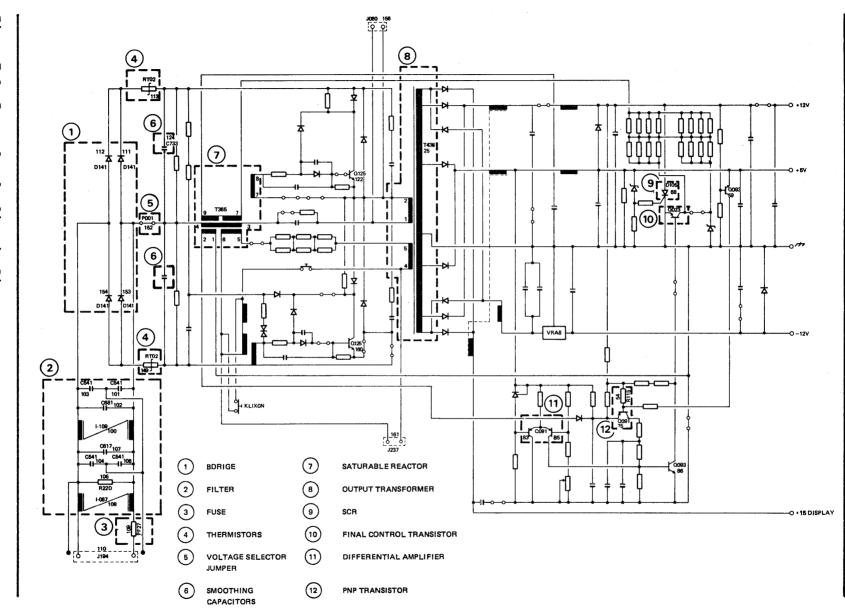

## POWER SUPPLY BOARDS

The Power Supply Unit provides the correct d.c. voltages for all the circuit boards resident in the Basic Module, the keyboard, the disk drives and the monochrome display unit.

The circuitry lies on two boards enclosed in a metal case. It is a switching type power supply with a line input of 110Vac or 220Vac selectable by an on board jumper. The voltage outputs are full wave rectified and include the +5Vdc, +12Vdc, +15Vdc, -12Vdc voltages. The power supply circuitry also include overload/overvoltage protection for all voltages.

#### **KEYBOARDS**

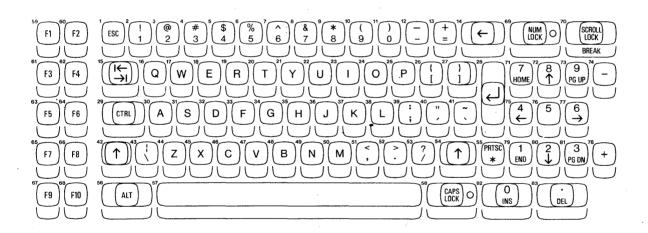

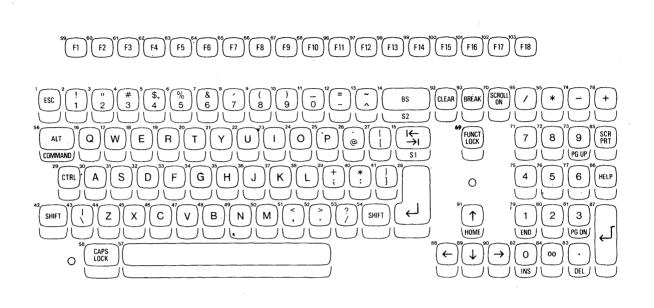

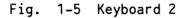

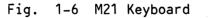

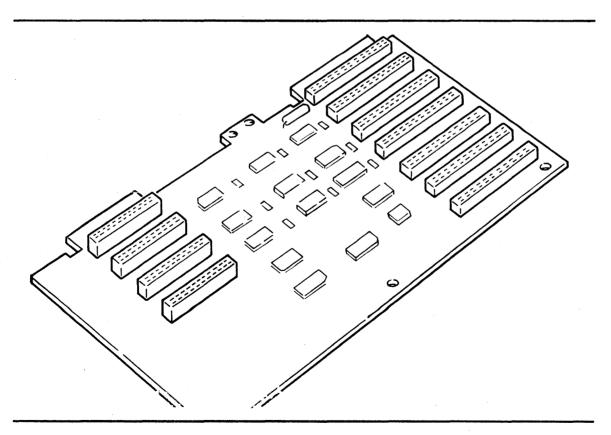

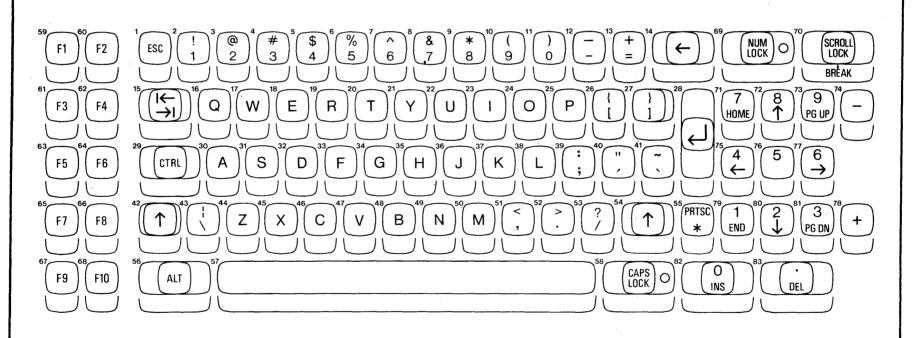

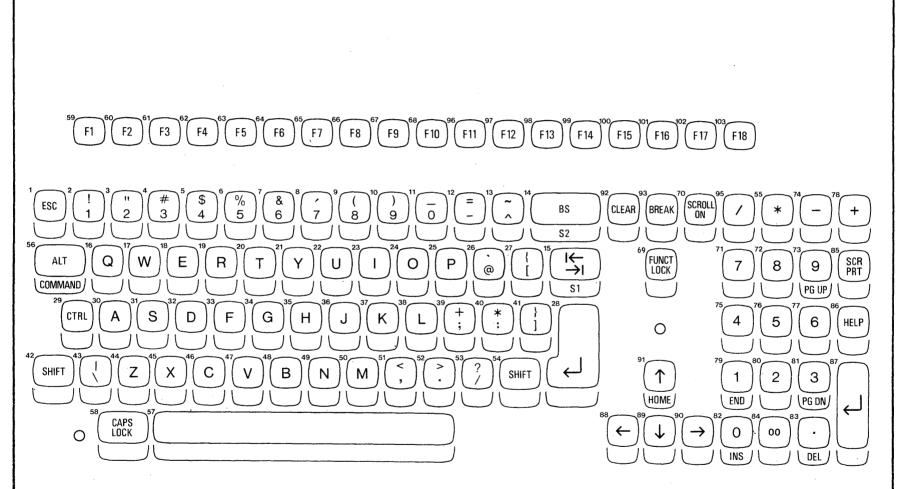

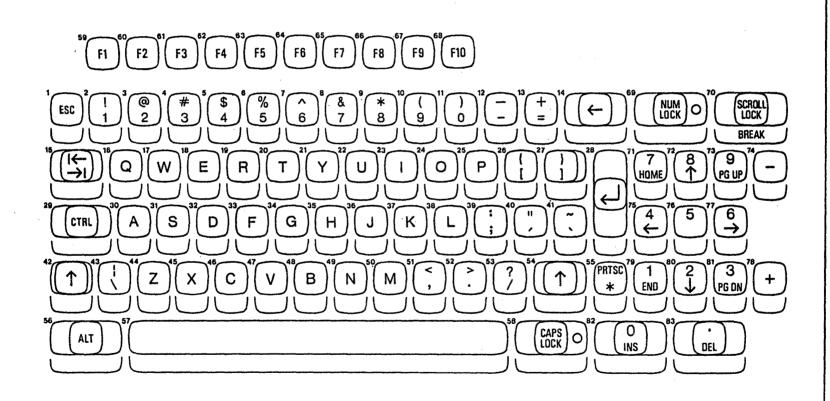

Three different kinds of keyboards are used on the M24 and the M21  $\,$  systems:

- Keyboard 1 IBM compatible keyboard for M24 system

- Keyboard 2 Native extended keyboard for M24 system

- M21 Keyboard IBM compatible keyboard for M21 system

The three keyboards have the same circuitry but differ in their layouts and in the number of function keys.

The keyboard circuitry is based on the 8039 microprocessor which is used with a 16K byte EPROM. This EPROM contains the keyboard self-test routine, the scan codes for all keyboard keys and a routine to test for stuck keys. A 9 pin connector is also available to permit the connection of a "mouse" to the keyboard.

Fig. 1-4 Keyboard 1

## **BUS CONVERTER BOARD**

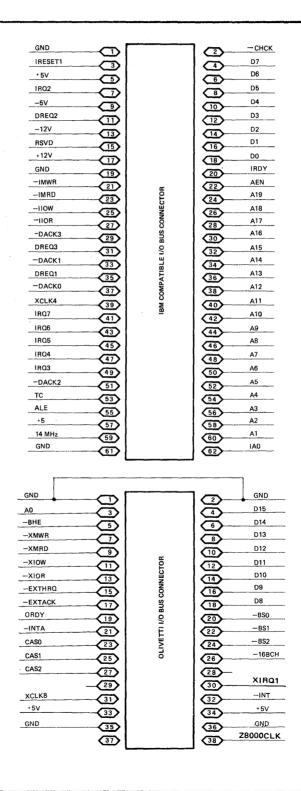

The Bus Converter Board is an optional board which when present provides 16 bit and 8 bit I/O expansion slots to the system. Thus it allows the simultaneous use of 16 bit Olivetti boards and 8 bit IBM compatible controllers.

It consists of an EPROM, addressed by a counter, which provides timing signals to enable and/or disable the required data buffers for I/O read or write operations to a controller.

This board contains two kinds of I/O bus connectors:

- 38 pin connectors to handle signals used by the 16 bit Olivetti boards.

- 62 pin connectors to handle signals used by both the 16 bit Olivetti boards and the 8 bit IBM compatible boards.

The M24 Bus Converter Board contains four 38 pin connectors and seven 62 pin connectors. The M21 Bus Converter Board contains one 38 pin connector and three 62 pin connectors.

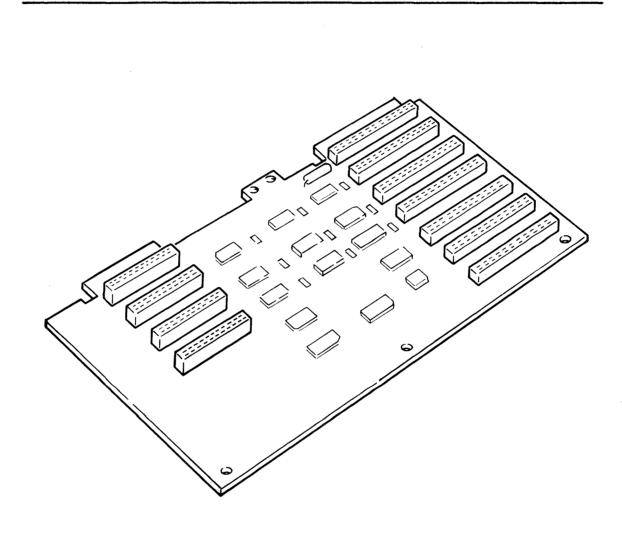

Fig. 1-7 M24 Bus Converter Board

## SYSTEM DESCRIPTION

Fig. 1-8 M21 Bus Converter Board

i

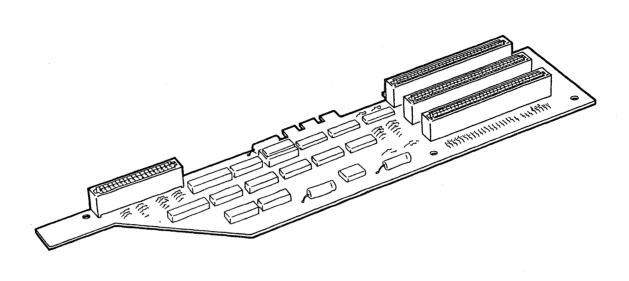

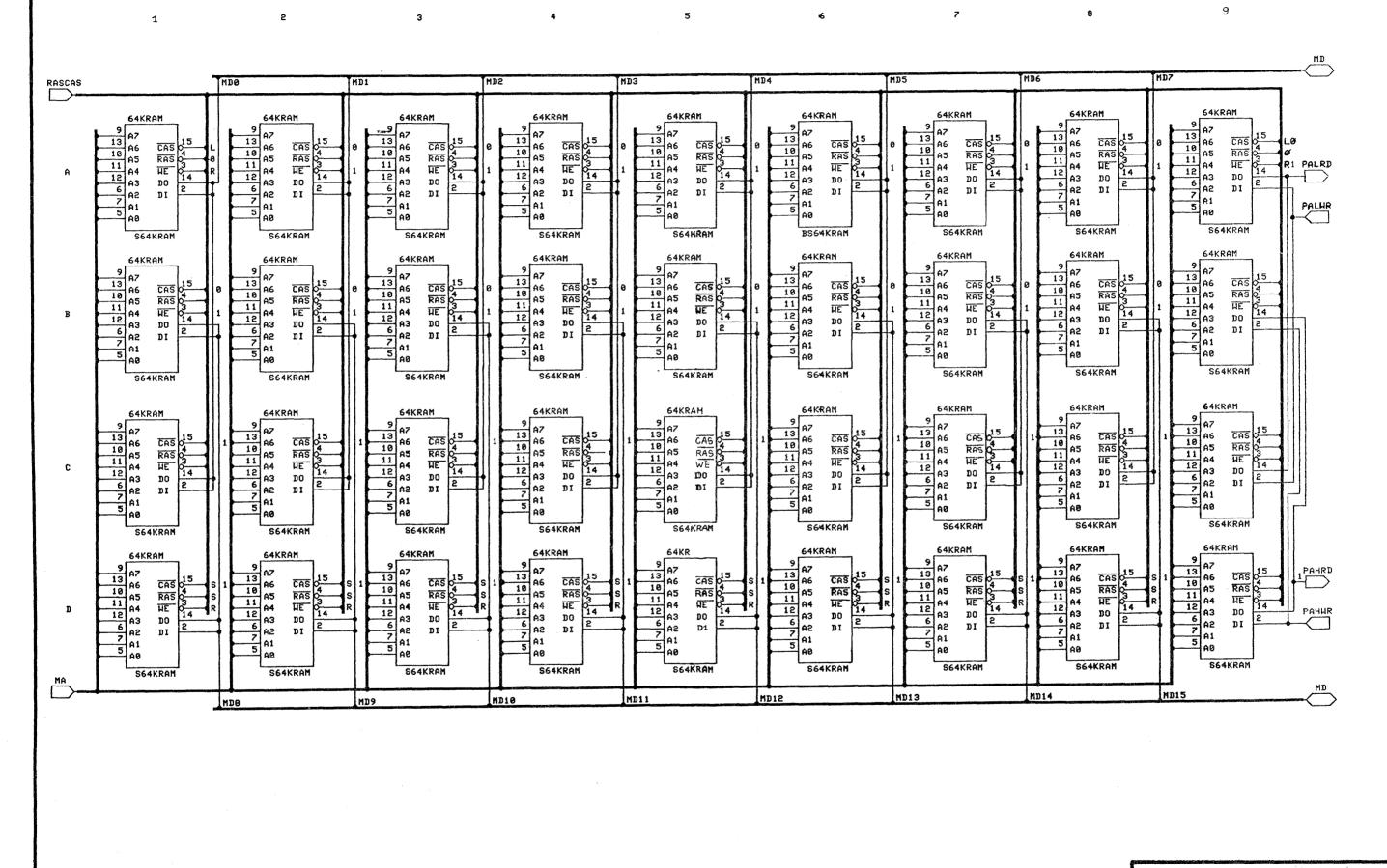

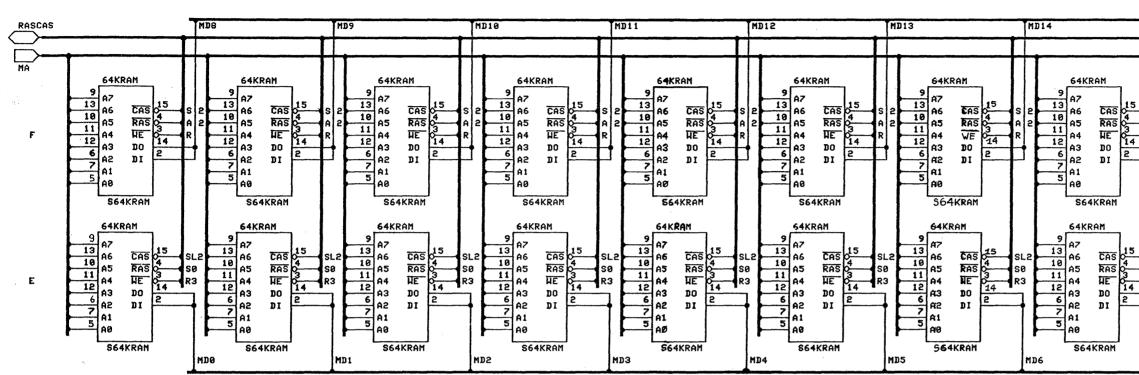

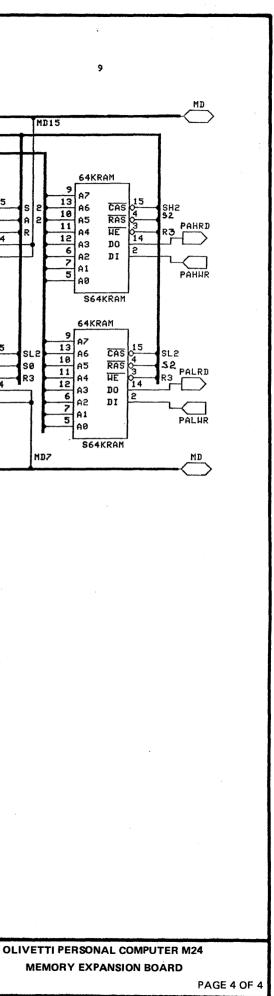

## MEMORY EXPANSION BOARD

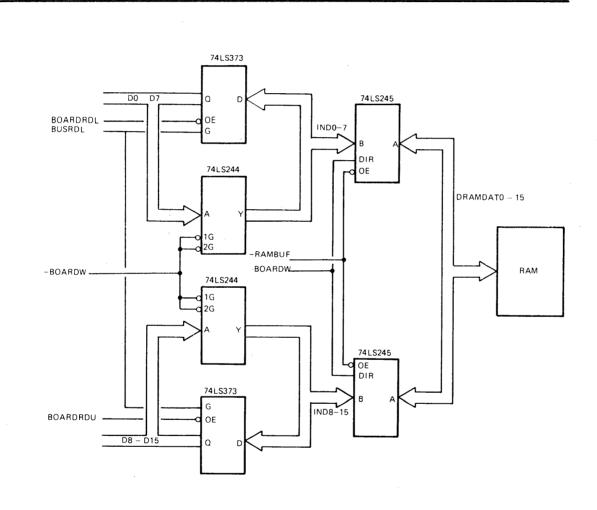

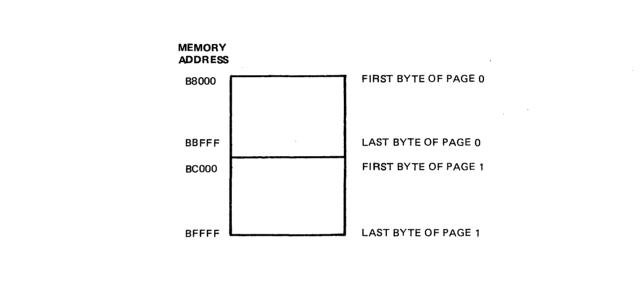

The Memory Expansion Board allows the expansion of the system RAM memory by a maximum of 384KB. It consists of 3 banks, each of 128KB, and each bank contains 2 groups of nine 64Kx1 RAM chips.

Besides the three RAM banks, this board also performs the memory control logic, address multiplexing, bus buffering and parity generation and checking required for the added RAM memory.

It is inserted in a slot on the Bus Converter Board and it is seen by the system as a 16 bit board and thus it can perform byte and word operations.

Fig. 1-9 Memory Expansion Board

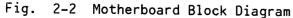

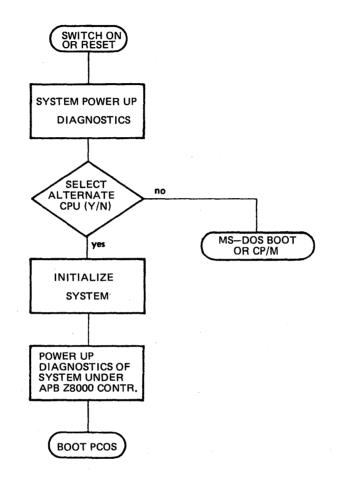

## APB Z8000 BOARD (M24 Only)

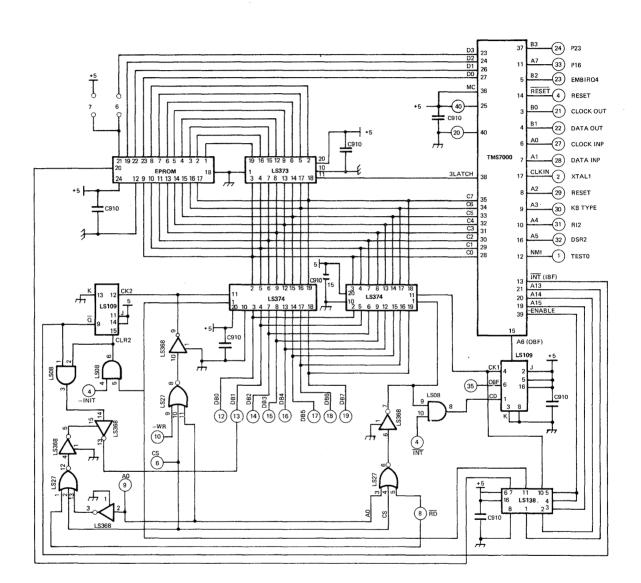

The APB Z8000 board is a 16 bit board which is inserted in the M24 Bus Converter Board. The function of this board is to allow the M24 system to operate in a PCOS (M20 operating system) environment instead of the M24 operating system. This permits M20 programs to be run on the M24 personal computer.

It is based on the Z8001 4MHz microprocessor and contains 8K bytes of resident ROMs used for bootstrap and diagnostic routines. It provides its own RS232 serial communication channel and uses the random access memory, the DMA circuitry and the peripheral controllers present on the mother-board.

The APB Z8000 board contains the bus handshaking circuitry which permits the system bus to be assigned either to the Z8001 processor or to the 8086 processor resident on the motherboard.

Also present on the APB Z8000 board is an address translation PROM which changes the Z8001 addresses to the physical memory addresses.

## Fig. 1-10 APB Z8000 Board

## DISPLAY CONTROLLER OPTIONS BOARD

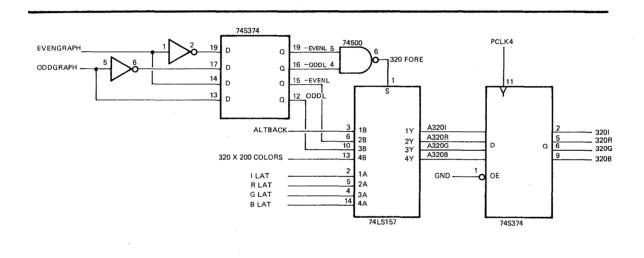

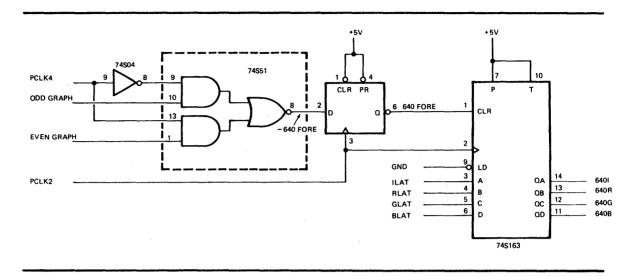

The Display Controller Options Board is an optional board which is inserted into the dual expansion slots on the Bus Converter Board. Its use is to upgrade the Indigenous Display Controller Board to a high performance display controller. It is connected to the indigenous display controller via a small flat cable while the Bus Converter Board acts as an interface between the options board and the M24 system.

This board provides additional display features to the M24 Indigenous Display Controller which include:

- up to three additional 640 x 400 bit planes

- software controlled Look Up Table

- ability to display 16 colours simultaneously

- ability to display characters and graphics simultaneously

- blinking pixels in graphics modes

- 4 colour, 8 colour PCOS compatibility (with Z8000 softcard present)

The presence of this board in this system permits the connection of more than one monitor. In fact the enhancement board outputs go on to a 25 pin D-type connector on the board itself. When only one monitor is present, it must be connected to the connector on this board. The monitor can be either colour or monochrome. A second monitor can be connected to the indigenous board.

2. MOTHERBOARD

# CONTENTS

## PAGE

|      | 2. | MOTHERBOARD                           |

|------|----|---------------------------------------|

| 2–1  |    | INTRODUCTION                          |

| 2-2  |    | MOTHERBOARD BLOCK DIAGRAM             |

| 2-6  |    | CENTRAL PROCESSOR UNIT                |

| 2-6  |    | CPU PIN FUNCTIONS                     |

| 2-8  |    | GENERAL OPERATION                     |

| 2-10 |    | CPU - MEMORY OPERATION                |

| 2–11 |    | CPU BUS OPERATION                     |

| 2–11 |    | CPU 1/0 OPERATION                     |

| 2-12 |    | NUMERIC DATA PROCESSOR                |

| 2–15 |    | DMA CONTROLLER FUNCTIONAL DESCRIPTION |

| 2–16 |    | DMA OPERATION                         |

| 2–16 |    | DMA CIRCUITRY                         |

| 2–19 |    | DMA – DEVICE SERVICE                  |

| 2-21 |    | INTERRUPT CONTROL LOGIC               |

| 2-21 |    | NON-MASKABLE INTERRUPT                |

| 2-22 |    | MASKABLE PRIORITY INTERRUPTS          |

| 2-25 |    | CLOCK GENERATOR                       |

| 2–28 |    | BUS ARBITER                           |

| 2-29 |    | DMA CONTROLLER CYCLE                  |

|      |    |                                       |

2-30 EXTERNAL CYCLE, CONCURRENT AND ALTERNATE

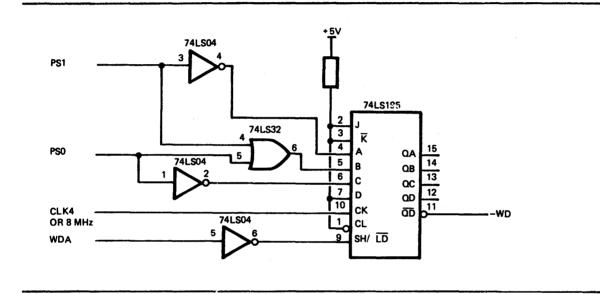

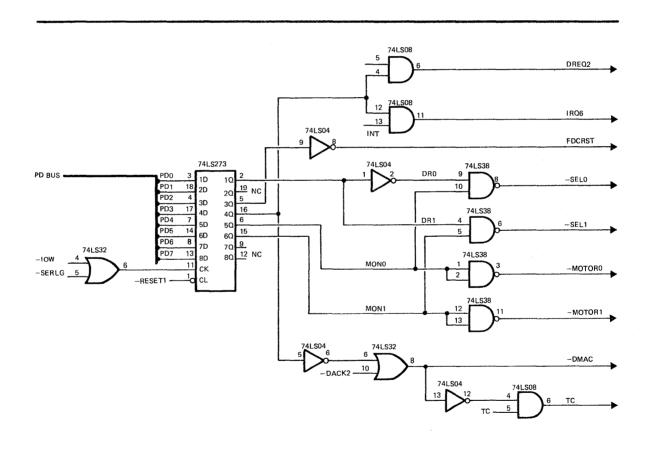

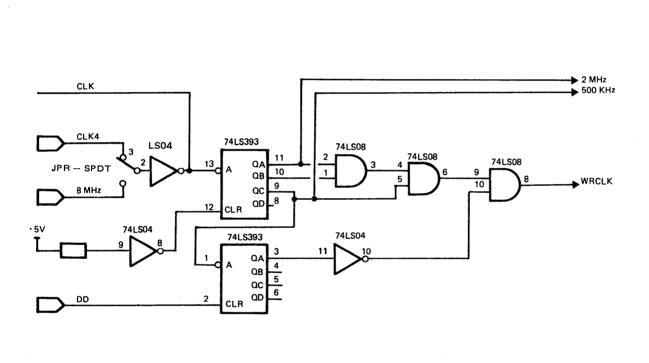

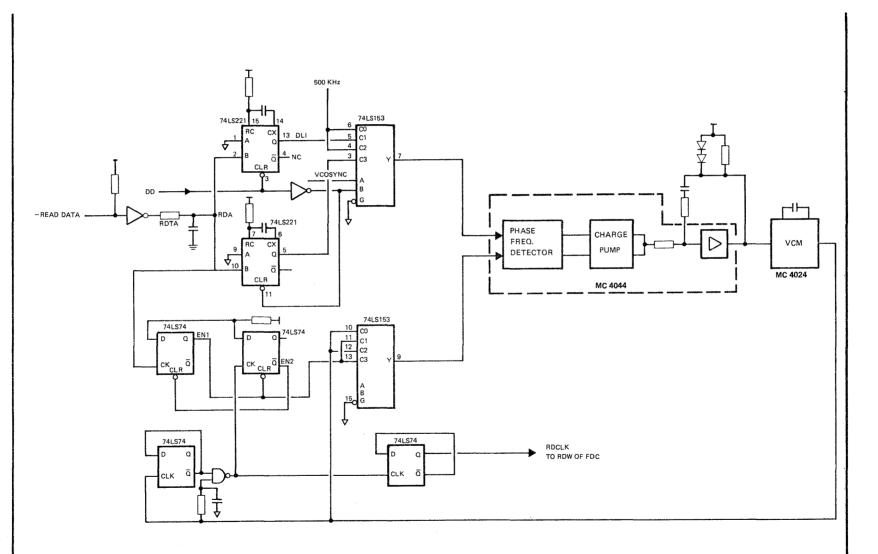

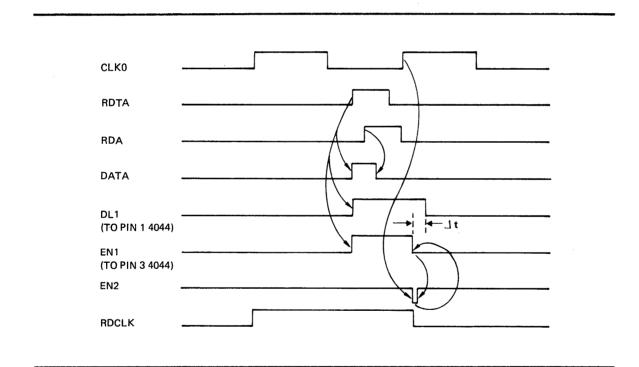

2-31 **BUS CONTROLLER** 2-33 PROGRAMMABLE WAIT LOGIC 2-35 RANDOM ACCESS MEMORY MEMORY CONTROL LOGIC 2-35 2-37 MEMORY ADDRESSING 2-40 MEMORY REFRESH 2-41 PARITY GENERATOR AND CHECKER 2-42 PROGRAMMABLE READ ONLY MEMORY 2-43 INPUT/OUTPUT CHIP SELECT LOGIC 2-44 INPUT/OUTPUT PORT SELECT LOGIC 2-45 SYSTEM CONFIGURATION PORT 66 2-46 SYSTEM CONFIGURATION PORT 67 2-47 1/0 ADDRESS MAP 2-48 SYSTEM MEMORY ADDRESS MAP 2-49 TIMER 2-52 REAL TIME CLOCK AND CALENDAR 2-53 SPEAKER INTERFACE 2-54 **KEYBOARD INTERFACE** 2-54 COMMUNICATION BETWEEN 8041 AND KEYBOARD 2-56 TMS7000 BOARD 2-58 MINI-FLOPPY DISK INTERFACE 2-60 FLOPPY DISK CONTROLLER 2-63 WRITE PRECOMPENSATION CIRCUITRY 2-65 DIGITAL CONTROL PORT AND DECODER 2-66 CLOCK AND TIMING CIRCUITRY 2-66 DATA SEPARATOR

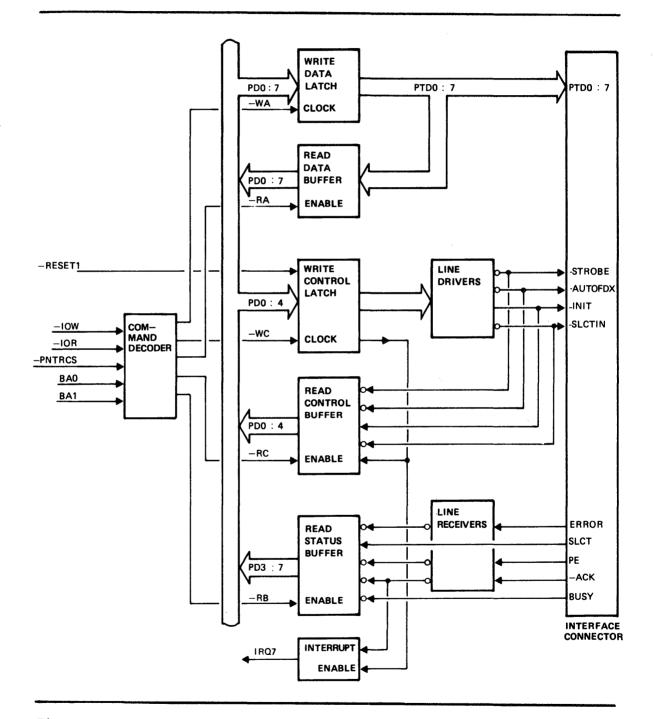

## 2-69 **PARALLEL PRINTER INTERFACE**

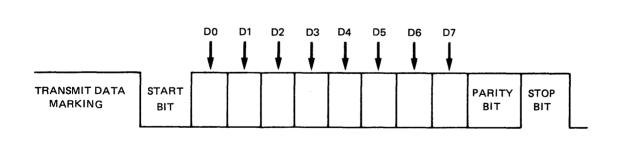

- 2-71 SERIAL COMMUNICATION INTERFACE

- 2-71 8250 ASYNCHRONOUS COMMUNICATIONS ELEMENT (ACE)

- 2-73 Z8530 SERIAL COMMUNICATION CONTROLLER

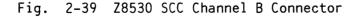

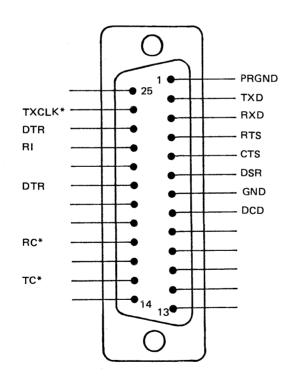

- 2-76 SERIAL INTERFACE SIGNALS AND CONNECTOR

- 2-78 MULTIFUNCTION COMMUNICATIONS INTERFACE

## INTRODUCTION

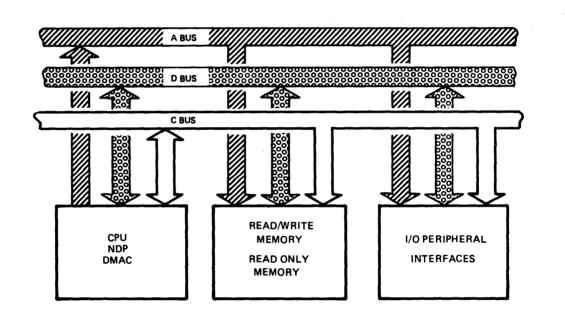

The motherboard is the large printed circuit board that sits at the bottom of the system box with the component side facing down. It consists of four major functional blocks.

- Processor/DMA Controller

- Memory (PROM and ROM)

- I/O peripheral interfaces

- 1/0 connectors

These functional blocks are connected by means of three system busses called A BUS, D BUS, and C BUS. Further busses are derived from these busses as explained later. Figure 2-1 shows the system Busses.

## Fig. 2-1 System Busses

The A Bus carries the address information generated by the CPU, NDP or DMA Controller.

The following busses are derived from the A Bus:

- MA Bus which addresses RAM Memory and EPROMS

- BA Bus which addresses DMA Controller

The D Bus carries the data information between the processor/DMA controller, the memory and the I/O peripheral interfaces. The following busses are derived from the D bus:

- MD Bus which carries data in and out of RAM memory and out of ROM memory

- PD Bus which carries data in and out of the DMA segment register, I/O peripheral interfaces and the Interrupt Controller.

The C Bus carries all the control signals.

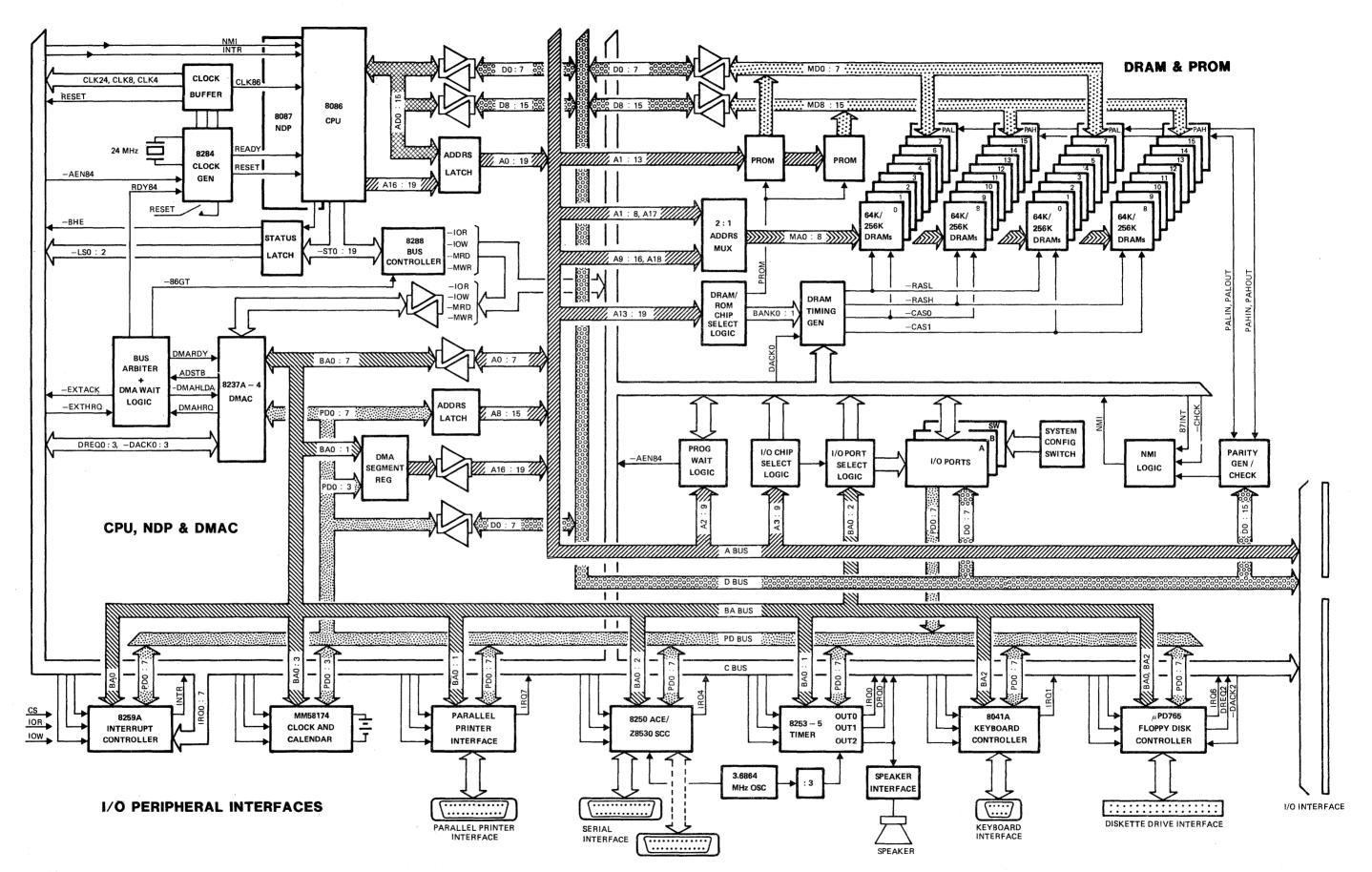

#### MOTHERBOARD BLOCK DIAGRAM

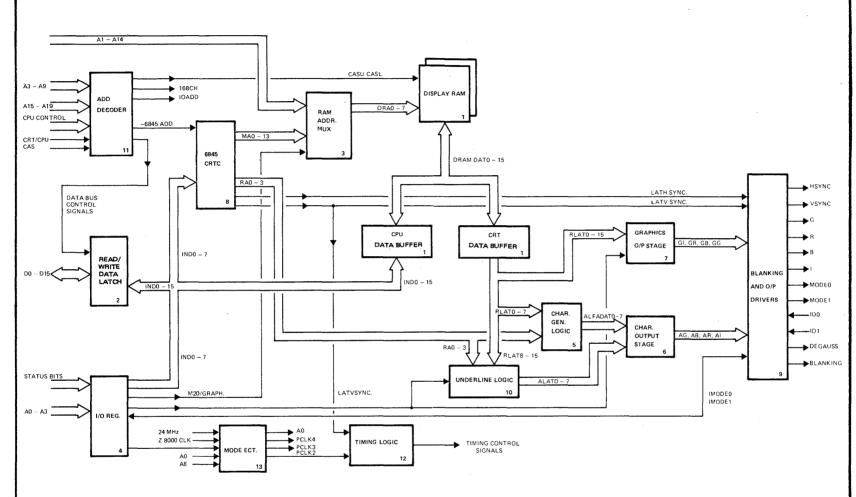

Figure 2-2 is a detailed block diagram of the motherboard. Below is a list of the various modules and their function.

#### CENTRAL PROCESSOR UNIT (CPU)

16 bit microprocessor chip that contains within itself the arithmetic and logic circuits which extract program instructions from memory, one at a time and execute them. The microprocessor used is the Intel 8086 which runs at a frequency of 8 MHz.

#### NUMERIC DATA PROCESSOR (NDP)

16 bit numeric data processor that provides the instructions and data types needed for high performance. It is available as an option.

#### **CLOCK GENERATOR**

The clock generator is a single chip clock generator/driver which supplies the system clock for the CPU (8MHz) and a 4MHz clock for the peripherals. The clock generator chip used is the Intel 8284A.

#### **CLOCK BUFFER**

Circuitry which receives the system and peripheral clocks from the clock generator, buffers them and repowers them. Clocks generated include: CLK86 used mainly by CPU, NDP and Bus Controller; BCLK8 used by other logic on the motherboard; XCLK8 used by the I/O expansion boards. The integrated circuit used is a 74LS241.

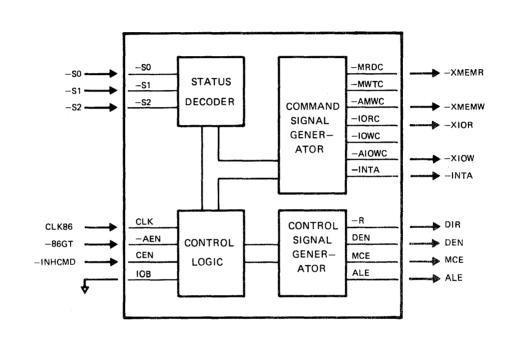

#### **BUS CONTROLLER**

The Bus Controller utilizes the status outputs from the CPU to generate and buffer control signals. The chip used is the Intel 8288.

#### DMA CONTROL BUFFER

The LS245 bidirectional buffer serves two purposes. The first is to repower commands from the bus controller so that there is enough driving power for these signals to the I/O connector. The second is to repower the commands from the DMA Controller to the I/O connector when DMA is in control.

#### CPU ADDRESS LATCHES

The CPU address is latched into the CPU Address Latches by the signal ALE (Address Latch Enable) from the Bus Controller. The Latch used is the 74LS373.

## CPU DATA BUFFER

The CPU Data Buffer repowers the CPU data to the system D Bus. The buffer used is the bidirectional LS245.

## BUS ARBITER CIRCUITRY

This circuitry arbitrates among the three system bus masters to access the system bus. The three system bus masters are: 8086 CPU, 8237 DMA Controller and an external processor (the Z8001 soft card for example). The main component of this circuitry is the Programmable Array Logic (PAL) 16R8 which handles this bus arbitration.

## WAIT LOGIC

Each processor bus cycle consists of at least 4 clock cycles. These are referred to as T1, T2, T3 and T4. In the event of a 'NOT READY' indication being given by the addressed device, WAIT states (Tw) are inserted between T3 and T4. These WAIT states are generated by the programmable wait logic which mainly consists of a PROM and a counter. These circuits insert the exact number of WAIT states needed for all devices, except for DMA ones (for DMA devices one WAIT state is automatically inserted).

#### DMA CONTROLLER

Direct Memory Access Controller is the device which allows external I/O devices to transfer information directly to/from RAM memory. The integrated circuit used is the Intel 8237.

#### DMA SEGMENT REGISTER

A 4 x 4 74LS670 register file which provides four upper address bits (A16-A19) so as to permit the DMA Controller to address up to 1MB of memory.

#### DMA ADDRESS LATCHES

Latches used to interface the DMAC to the system A bus. Latches used are the 74LS373 and 74LS245.

## RAM TIMING CIRCUITS

Circuitry which provides all the timing signals necessary to address memory and control the transfer of data or instructions to and from memory.

#### RAM ADDRESS MULTIPLEXER

Circuitry made up of multiplexers used to address RAM. The system memory can be addressed in bytes as well as in words addressing two bytes. The multiplexer used is the 74S158. This 2:1 multiplexer is used to switch either row address or column address to RAM at a certain required time.

#### RANDOM ACCESS MEMORY

Volatile memory which stores the Operating System, Interpreter, and all other user data and programs. Information stored in RAM may be altered. This Personal Computer uses 64K by 1 bit dynamic RAMs or 256K by 1 bit dynamic RAMs.

#### RAM PARITY GENERATOR AND CHECKER

Circuitry which generates the parity bit that gets written into memory during memory write operations. Parity is read back and checked against data to see if there is any parity error. If any parity error is detected, the parity error flip-flop is set and a CPU Non-Maskable Interrupt is generated. NMI is reserved for some event, as in this case, that cannot wait.

#### ERASABLE PROGRAMMABLE READ ONLY MEMORY (EPROM)

EPROM is used to store the power up diagnostics and bootstrap. It is a non-volatile type of memory and its capacity is 16KB

## INPUT/OUTPUT CHIP SELECT LOGIC

Circuitry used as motherboard I/O address decoder. A PAL12L10 is used as this decoder.

## MINI-FLOPPY DISK CONTROLLER

The circuitry which provides all the logic and control necessary to control and record data onto, or read from the 5.25 inch mini-floppy disks. It also initially formats new disks. The LSI component used is the uPD765.

## TIMER

Programmable device used to provide a real time clock, to time and request refresh cycles for DMA channel and to provide the tone generator for the audio speaker.

#### INTERRUPT CONTROL LOGIC

Programmable device that handles the priority interrupts to the CPU. It functions as an overall manager in the interrupt-driven system environment. The LSI component used is the Intel 8259.

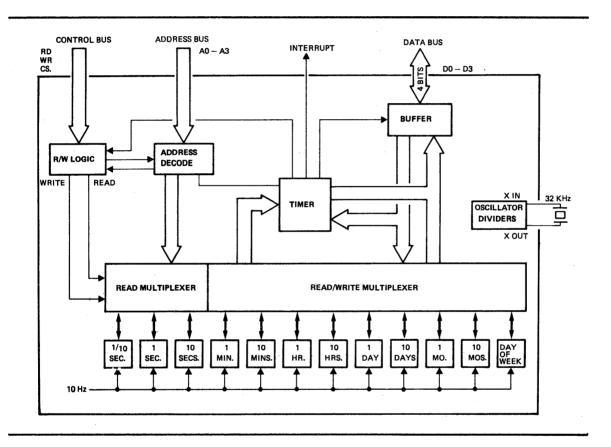

#### CLOCK CALENDAR CHIP

A battery backed-up clock calendar chip which provides real time such as seconds, minutes, hours, day of week, days and months for the system.

## SERIAL COMMUNICATION CONTROLLER

The 8250 Asynchronous Communication Element is used to support serial communication and is configured to have an RS232-C channel. The 8250 ACE can be replaced by the Z8530 SCC to have an asynchronous/ synchronous communication channel.

## PARALLEL PRINTER INTERFACE

Centronics-Like Parallel Printer Interface used to interface the personal computer to one of the parallel printers.

## **KEYBOARD CONTROLLER**

Circuitry that converts the system parallel data to serial data for the keyboard and vice-versa. The LSI component used is the Intel 8041.

## CENTRAL PROCESSOR UNIT

The central processor unit is the heart of the motherboard. Its function is to extract program instructions from memory and execute them. It consists of an Intel 8086 microprocessor chip, which contains internally the arithmetic and logic circuits required for executing the program instructions resident in memory.

The system can also use a Numeric Data Processor (NDP) which acts as a co-processor to the CPU. It provides other mathematical instructions for all data types needed for high performance computing. The NDP is an Intel 8087 chip and is an optional feature.

Externally, there are additional logic address decoding, timing and buffer elements which are necessary to address memory and to control data and instructions.

#### **CPU PIN FUNCTIONS**

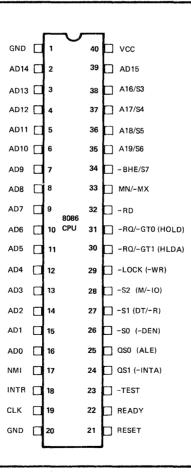

Figure 2-3 shows the pin functions for the Intel 8086 microprocessor in maximum mode and a brief description of each pin follows:

Fig. 2-3 8086 Pin Functions

## ADO-AD15 Address/Data Bus (Input/Output, active high)

These lines constitute the multiplexed memory/IO address and data bus. AO is used to enable data onto the least significant half of the data bus, DO-D7, in memory or I/O operations.

## A16/S3-A19/S6 Address/Status (Output, active high).

During T1 these are the four most significant address lines for memory operations. During memory and 1/0 operations, status information is available on these lines during T2,T3,Tw and T4. During 1/0 operations these status lines are low.

## MN/-MX Minimum/Maximum (Input)

This is the input used to select minimum or maximum mode for the 8086. In this case, maximum mode is used to support the 8087 NDP.

#### -BHE/S7 Bus High Enable/Status (Output, active low)

During T1 the -BHE signal is used to enable data onto the most significant half of the data bus D8-D15. The S7 status information is available during T2,T3, and T4.

## -S2 to -S0 Status Lines (Output, active low)

These are the status lines for memory/IO transactions, interrupt acknowledge, processor halt or passive state.

| -52 | -51 | -50 | Function              |

|-----|-----|-----|-----------------------|

| 0   | 0   | 0   | Interrupt Acknowledge |

| 0   | 0   | 1   | Read I/O port         |

| 0   | 1   | 0   | Write I/O Port        |

| 0   | 1   | 1   | Halt                  |

| 1   | 0   | 0   | Code Address          |

| 1   | 0   | 1   | Read Memory           |

| 1   | 1   | 0   | Write Memory          |

| 1   | 1   | 1   | Passive               |

## QSO-QS1 Queue Status (Output)

These lines are the status lines for the 8086 internal instruction queue.

#### -TEST Test (Input)

This input is examined by the "wait" instruction. If it is low, execution continues, otherwise the processor waits in an "idle" state.

## READY Ready (Input, active high)

This pin is used by addressed memory or I/O device to insert the required number of wait cycles. The READY signal from memory/IO is synchronized by the 8284A Clock Generator to form READY.

## -RQ/-GTO, -RQ/-GT1 Request/Grant (Input/Output)

These lines are used by other local bus masters to force the processor to release the local bus at the end of the processor's current bus cycle. -RQ/-GT0 has higher priority than -RQ/-GT1

## NMI Non-Maskable Interrupt (Input)

This is an edge triggered input which causes a type 2 interrupt. A transition from a low to a high initiates the interrupt at the end of the current instruction. The NMI interrupt has the highest priority over the other interrupts.

## INTR Interrupt Request (Input, active high)

This line is a level triggered input which is sampled during the last clock cycle of each instruction to determine if the processor should enter into an interrupt acknowledge operation.

#### -LOCK Lock (Output, active low)

This is to inform other system bus masters that the system bus won't be released while this pin is active.

## -RD READ (Output)

This read strobe indicates that the processor is performing a memory or I/O read cycle. This is not used in the this system.

## RESET Reset (Input, active high)

This causes the processor to terminate its present activity immediately.

#### CLK Clock (Input)

This provides the basic timing for the processor and bus controller.

#### **GENERAL OPERATION**

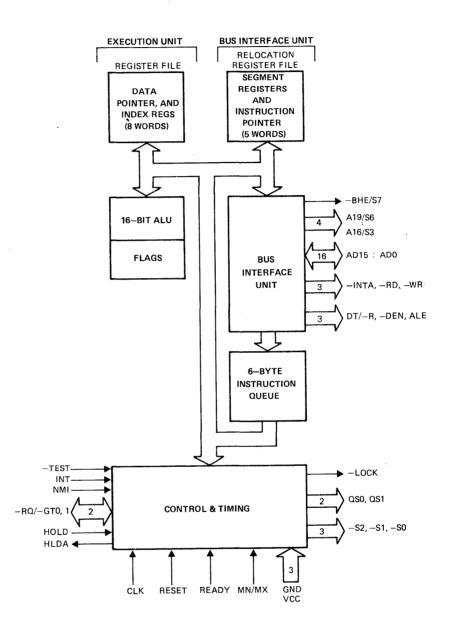

The internal functions of the Intel 8086 microprocessor are divided into two major functional units

- Execution/Control Unit (EU)

- Bus Interface Unit (BIU)

As shown in figure 2-4, these units can interact directly but for the most part perform their functions separately.

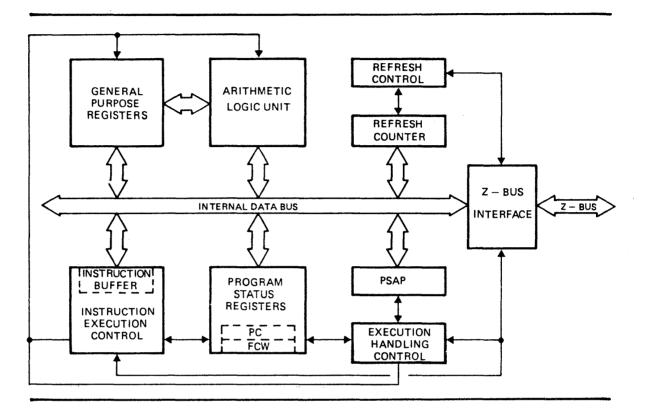

# Fig. 2-4 8086 Functional Block Diagram

The execution unit (EU) performs the basic processing functions, as it contains the data registers and the arithmetic logic unit (ALU). It accepts prefetched instructions from the BIU and returns unrelocated operand addresses to it. It then receives memory operands via the BIU, processes them, and passes the results to the BIU for storage. The Bus Interface Unit (BIU) first prefetches instructions before they are required by the EU. It buffers them in a queue that can contain up to six bytes of instruction stream, to wait for decoding and execution. The EU therefore does not need to wait for completion of a bus cycle before taking in a new instruction. The BIU also provides the functions related to operand fetch and store, address relocation, and bus control processing.

#### **CPU - MEMORY OPERATION**

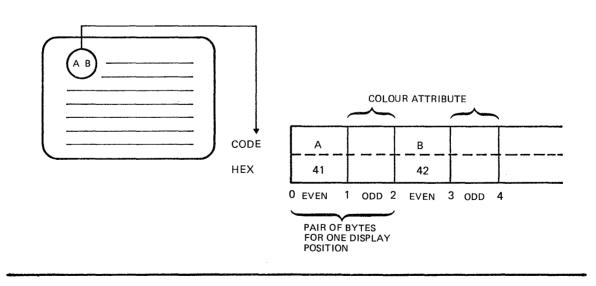

The 8086 processor employs a 20 bit address bus to access a byte or word in memory. The memory is logically organized as a linear array of 1 Mbyte addressed as 00000 to FFFFF (hex). Each location is an 8 bit byte.

Word (16 bit) operands consisting of consecutive bytes can fall on either even or odd address boundaries. The processor provides two signals, -BHE and AO, to select and enable an odd location, an even location or both.

For address and data operands, the least significant byte of the word will be stored in the lower valued address location and the most significant byte in the next highest address location.

The BIU automatically performs the proper number of memory accesses, one if the word operand is on an even byte boundary and two if it is on an odd byte boundary.

Physically the memory is organized as a high bank (D15-D8) and a low bank (D7-D0) which are addressed in parallel by the processor's address lines A19-A1. Byte data with even addresses is transferred on the D7 - D0 bus lines while odd addressed byte data (A0 high) is transferred on the D15-D8 bus lines.

| -BHE | <b>A</b> 0 |                                 |

|------|------------|---------------------------------|

| 0    | 0          | whole word                      |

| 0    | 1          | upper byte from/to odd address  |

| 1    | 0          | lower byte from/to even address |

| 1    | 1          | none                            |

# CPU BUS OPERATION

The 8086 microprocessor has a combined address and data bus called a time multiplexed bus. This bus is demultiplexed at the processor with a single set of address latches.

Each processor bus cycle consists of at least four CLK cycles referred to as T1,T2,T3 and T4. The address is emitted from the processor during T1 and transfer occurs on the bus during T3 and T4.

T2 is used for changing the direction during read operations. In the event of a "NOT READY" indication being given by the addressed device, "WAIT" states (Tw) are inserted between T3 and T4. Periods can occur between 8086 driven bus cycles referred to as "Idle" states. The processor uses them for internal housekeeping. During T1 of any bus cycle the ALE (Addressing Latch Enable) signal is emitted by the bus controller. At the trailing edge of this pulse, a valid address and certain status information for the cycle may be latched. Status bits -S0 to -S2 are used by the bus controller to identify the type of bus transaction.

## CPU I/O OPERATION

The 8086 microprocessor provides 64K addressable input or output ports. I/O space is addressable as if it were a single memory segment, without the use of segment registers. The I/O address appears in the same format as the memory address on bus lines A15-A0.

## NUMERIC DATA PROCESSOR

The 8087 Numeric Data Processor serves as a coprocessor attached to the 8086 CPU. It effectively adds eight 80-bit floating point registers to the 8086 register set. It uses its own instruction queue to monitor the 8086 instruction stream, executing only those instructions intended for it and ignoring the instructions needed for the 8086 CPU. The 8087 requires the same type of timing, power and bus structure as the 8086 in maximum mode. The 8087 NDP instructions include a full set of arithmetic functions as well as powerful exponential, logarithmic and trigonometric functions.

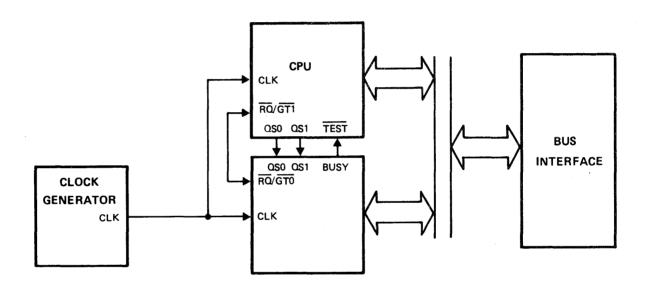

The 8087 NDP cannot run by itself as it needs the 8086 CPU to run the data, address and control busses which feed it instructions and operands. Figure 2-5 shows how the NDP is attached to the 8086 CPU. There are several lines running directly between the NDP and the CPU, namely:

- The test-busy signal

- A request/grant (RQ/-GTO) line

- Queue status (QS1, QS0) signals

The test input pin of the 8086 is connected to the BUSY output pin of the NDP. This allows the 8086 CPU to use the WAIT instruction before each NDP instruction and for the programmer to put an FWAIT instruction in the program following each NDP instruction which deposits data in memory for immediate use by the CPU. Then the numeric instruction gets translated to the indicated NDP numeric operation (with the preceding WAIT) and the FWAIT instruction is translated as the CPU WAIT instruction. While the 8087 NDP is executing a numeric operation, it puts a 1 on its busy pin (hence the test pin of the CPU is forced to a 1). While the 8086 CPU executes a WAIT instruction, it halts its activity until the test pin (pin 23) is returned to its normal state(0).

Thus the sequence of an NDP numeric instruction followed by a CPU WAIT will cause the CPU to call the NDP and then wait until the NDP has finished before proceeding.

The request/grant line RQ/-GTO is used by the NDP to gain control of the bus which is shared by the NDP and CPU. This request/grant on the NDP line is connected to the RQ/-GT1 of the 8086 CPU. This is a two way communication line. A signal (request) from the NDP to the CPU indicates that the NDP wants to use the bus. Before the NDP can take the bus it must wait for the return signal (grant) from the CPU. When the NDP finishes with the bus it sends a signal back to the CPU on the same line to indicate this. Thus, it is the NDP which requests the bus, and the CPU is the device which grants the bus as soon as it can after such a request.

There are two queue pins, QS1 and QS0, which help the NDP to keep its instruction queue synchronized with the CPU's. The two bits are used to encode the four possible states:

| struction         |

|-------------------|

|                   |

| of an instruction |

|                   |

Fig. 2-5 8087 NDP - 8086 CPU Connection

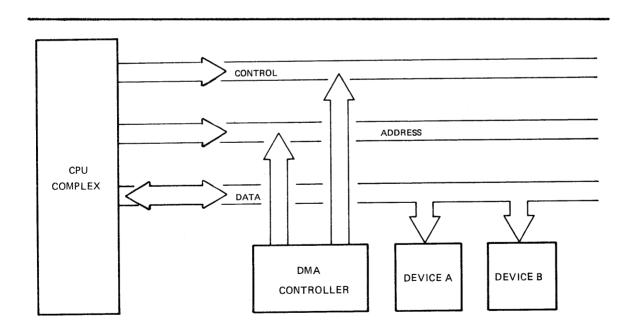

# DMA CONTROL LOGIC

DMA stands for Direct Memory Access and the main component of the DMA circuitry is the Intel 8237 DMA Controller. The DMA Controller is the device which takes over the system bus to transfer information directly from the I/O devices to the system memory and vice versa. This is necessary because blocks of data often have to be moved very rapidly.

The DMA circuitry is mainly made up of:

DMA Controller DMA Segment Register DMA Control Buffer DMA Data Buffer DMA Address Latches

A simple DMA transfer usually takes place as follows: The DMA Controller is told to make a transfer either by the CPU or other device; then the DMA Controller makes a request to gain control of the bus from the CPU, other processors, or controllers which might currently be using the bus; these other devices then relinquish control of the bus by putting their lines into the tri-state condition (electrically disconnecting the lines); they then grant the bus to the DMA Controller. Finally, the DMA Controller takes over the bus, generating its own address and control signals for the bus and causing the transfer of information.

Fig. 2-6 Simple DMA Transfer

# DMA CONTROLLER FUNCTIONAL DESCRIPTION

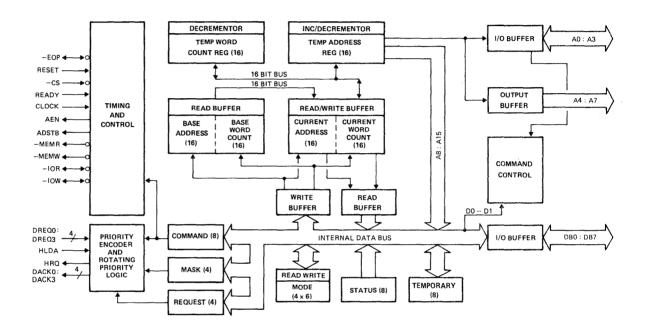

The DMA Controller used on the system is the Intel 8237. Figure 2-7 is a block diagram of the DMA Controller (DMAC).

Fig. 2-7 DMA Controller (8237) Block Diagram

. .

The DMA Controller (DMAC) contains three basic blocks of control logic.

The Timing Control Block that generates internal timing and external control signals for the DMAC.

The Program Command Control Block that decodes the various commands given to the DMAC by the microprocessor prior to servicing a DMA request. It also decodes the Mode Control word used to select the type of DMA during the servicing.

The Priority Encoder Block that resolves priority contention between DMA channels requesting service simultaneously. Channel 0 has the highest priority and channel 3 has the lowest priority.

Channel 0 is used to refresh the system dynamic memory. A channel of the timer is programmed to request periodically a dummy DMA transfer. This creates a memory-read cycle, which is available to refresh the dynamic memory on the motherboard as well as the memory expansion boards.

Channel 1 is connected to the I/O expansion bus to support high speed data transfer between I/O devices and memory.

Channel 2 is dedicated to the mini-floppy disk controller for transferring information to/from the minifloppy disk drive.

Channel 3 is connected to the I/O expansion bus to support high speed data transfer between I/O devices and memory.

## DMA OPERATION

The DMA is designed to operate in two major cycles, the idle cycle and the active cycle.

Each device cycle is made up of a number of states. The DMAC can assume seven separate states, each composed of one full clock period. State I (SI) is the inactive state. It is entered when the DMAC has no valid DMA requests pending. While in SI the DMAC is inactive but may be in the Program Condition, being programmed by the processor.

State 0 (SO) is the first state of the DMA service, when the DMAC has requested a hold but the processor has not yet returned an acknowledge. The DMAC may still be programmed until it receives HLDA (hold acknowledge) from the CPU. An acknowledge from the CPU indicates that DMA transfers may begin.

S1, S2, S3 and S4 are the working states of the DMA service. If more time is needed to complete a transfer than is available with normal timing, one WAIT cycle must be inserted. This is automatically inserted by part of the programmable WAIT logic

The WAIT state is inserted between S2 or S3 and S4 by the use of the READY line (DMARDY) on the DMAC. Note that the data is transferred directly from the I/O device to memory (or vice versa) with -IOR and -MEMW (or -MEMR and -IOW) being active at the same time. The data is not read into or driven out of the DMAC in I/O to memory or memory to I/O DMA transfers.

# DMA CIRCUITRY

The DMAC issues a DMA Hold Request Acknowledge DMAHRQA whenever there is at least one valid DMA request. DMAHRQA goes to an LS244 latch pin 8 and is output as DMAHRQ. DMAHRQ then inputs a 74S174 D latch which is clocked by the signal -CLK8. The output SDMAHRQ is one of the inputs to the Programmable Array Logic Chip PAL16R8. This PAL forms part of the Arbiter Logic explained in section 2-8.

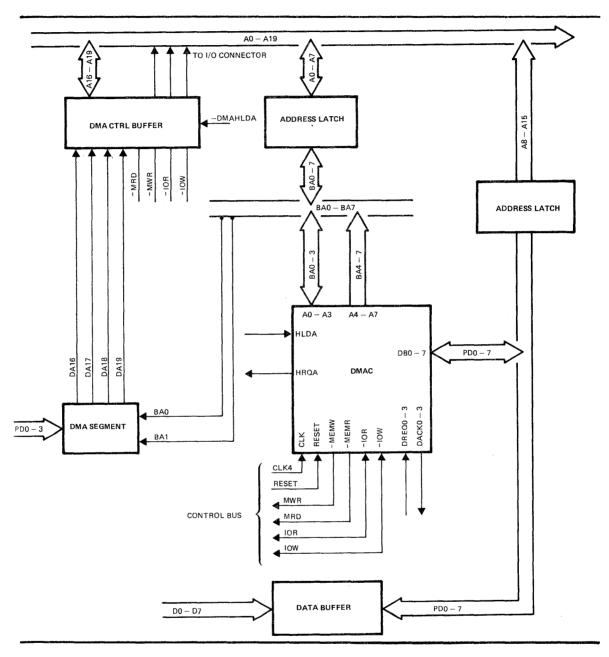

Figure 2-8 shows the DMA circuitry used on the system.

## Fig. 2-8 DMA Circuitry

The PAL outputs -DMAHLDA (DMA hold acknowledge) and -P86GT become active. The -DMAHLDA does a number of things:

It passes through an inverter (LSO4) to become DMAHLDA and then goes to the AND gate LSO8 where it is ANDed with a normally high signal (pull up resistor present on other input) to produce the signal XHA. This signal gives the DMAC the go-ahead to take control of the address bus, data bus and control bus. Also present on the AND input is -XHLDMA, which is the Hold Acknowledge signal for devices connected to the 1/0 connectors.

- It is input to pin 1 of the DMA Control Buffer and its effect is to change the direction of data flow through the buffer from B to A. This enables the DMAC to dialogue with devices such as expansion memory boards and I/O boards not on the motherboard.

- It enables the DMA address latch and the BA bus buffer to permit the DMA Controller to transfer bytes from the BA and DMA busses onto the A bus.

The generation of the signal -P86GT from PAL16R8 has the effect of disabling the CPU Address Latches and the CPU Data Buffers and the command lines from the Bus Controller. Hence the Address, Data and Control Busses are isolated from the CPU.

The DMAC now assumes control of the system busses.

The address for the first transfer operation comes out in two bytes. The least significant 8 bits (BAO-BA7) are output onto the the address bus via the BA bus buffer while the most significant 8 bits (PDO-PD7) are first strobed into the DMA address latch by the signal ADSTB before being output onto the address bus to complete the full 16 bits of the address bus. After the initial transfer takes place , the latch is updated only after a carry or borrow is generated in the least significant address byte.

DMAC supports 16 bit addresses which allow addressability to 64KB of memory. In order to make it able to address 1MB of memory as the CPU does, a 4 x 4 register file is used to provide the upper 4 bits DA16-DA19. This register file is named DMA segment register and is programmable by software to address any 64KB block within 1MB of memory space.

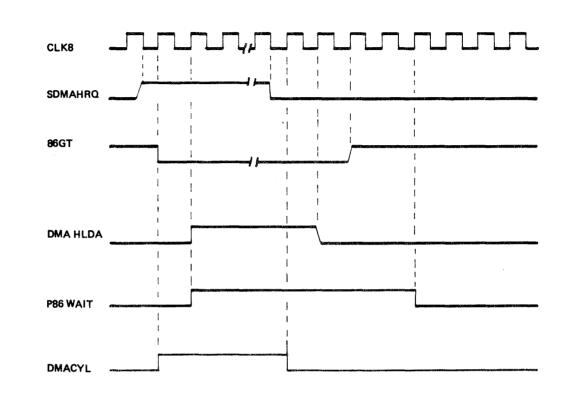

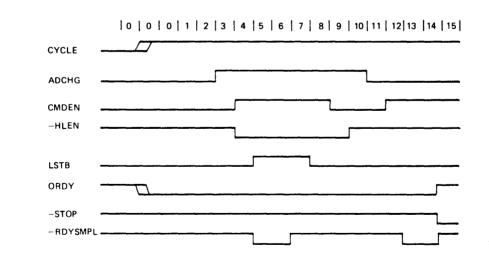

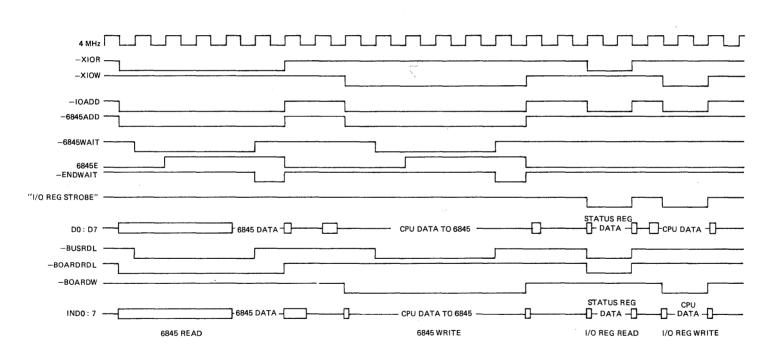

On the following page is a timing diagram showing the sequence of some of the signals used during a DMA operation.

Fig. 2-9 Timing Diagram

# DMA - DEVICE SERVICE

## Idle Cycle

When no channel is requesting service, the DMAC will enter the idle cycle and perform SI states. In this cycle the DREQ lines are sampled every clock cycle to determine if any channel is requesting a DMA service. When -CS is low and HLDA is low, the DMAC enters the program condition and address lines A0 to A3 address the control register to be loaded or read. The -IOR and -IOW lines are used to select and to time reads or writes.

## Active Cycle

When the DMAC is in the Idle Cycle and a channel requests a DMA service, the DMAC will output an HRQ and enter the active cycle. It is in this cycle that the DMA service will take place, in one of four modes:

#### Single Transfer Mode

In single transfer mode the device is programmed to make one transfer only. The word count will be decremented and the address decremented or incremented following each transfer. When the word count "rolls over" from zero to FFFF hex, a Terminal Count (TC) will cause an Autoinitialize if the channel has been programmed to do so. DREQ must be held active until DACK becomes active in order to be recognized. If DREQ is held active throughout the single transfer, HRQ will go inactive and release the bus to the system. It will go active again and, upon receipt of a new HLDA, another single transfer will be performed.

# Block Transfer Mode

In Block transfer Mode the device is activated by DREQ to continue making transfers during the service until a TC, caused by word count going to FFFF hex or an external -EOP (End of Process), is encountered. DREQ need only be held active until DACK becomes active. Again, an Autoinitialization will occur at the end of the service if the channel has been programmed for it.

## Demand Transfer Mode

In Demand Transfer mode the device is programmed to continue making transfers until a TC or external -EOP is encountered or until DREQ goes inactive. Thus transfers may continue until the I/O device has exhausted its data capacity. After the I/O device has a chance to catch up, the DMA service is re-established by means of DREQ. During the time between services when the CPU is allowed to operate, the intermediate values of address and word count are stored in the DMAC Current Address and Current Word Count registers. Only an -EOP can cause an Autoinitialize at the end of the service. -EOP is generated either by TC or by an external signal.

# INTERRUPT CONTROL LOGIC

Hardware interrupts are asynchronous events requiring CPU attention and are generally initiated by peripheral devices requiring service. The CPU is normally allowed to execute its main program until an interrupt request occurs. On receipt of an interrupt request, the CPU completes the instruction being executed, saves its current state (instruction pointer, code segment and flags) and fetches a new routine to service the interrupting device. Once the interrupting device has been serviced, the CPU resumes its main program at the point where it was interrupted.

The system has 9 interrupts in all: eight maskable priority interrupts and one non-maskable interrupt. The descending order of priority for these interrupts and associated devices are listed below.

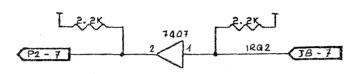

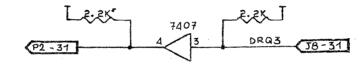

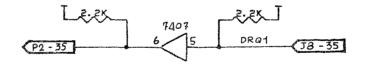

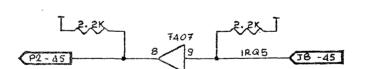

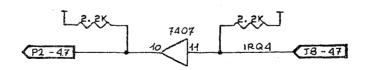

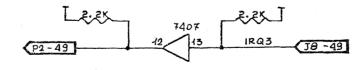

NMI non-maskable interrupt IRQ0 generated by Timer channel 0 IRQ1 generated by the Keyboard Controller IRQ2 generated by a board on one of the expansion slots IRQ3 generated by a board on one of the expansion slots IRQ4 generated by the Serial Controller IRQ5 generated by a board on one of the expansion slots IRQ6 generated by the Floppy Disk Controller IRQ7 generated by the Parallel Interface

NMI is handled by the NMI logic circuitry while IRQ0-7 are handled by the Interrupt Controller chip.

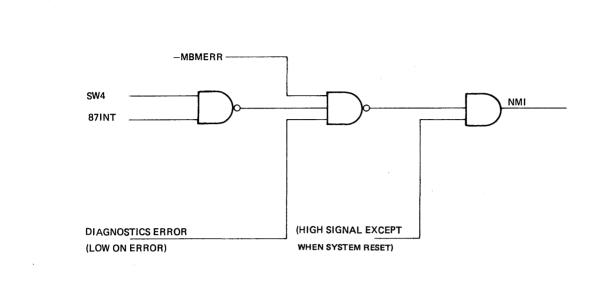

#### NON-MASKABLE INTERRUPT

The NMI has the highest priority. It is a hardware generated interrupt and is so called because the interrupt cannot be turned off by clearing the interrupt flag. The simplified NMI circuitry is shown in figure 2-10.

In this system an NMI is generated by any of the following events:

- Memory Parity Error (signal -MBMERR causes train of events to activate NMI)

- 2. 8087 NDP Interrupt (signals 87INT and SW004 cause train of events to activate NMI)

- 3. Failure in power-up diagnostics (signals -CHCK and -IOCHK cause train of events to activate NMI)

# Fig. 2-10 NMI Logic

The NMI is edge triggered into the CPU on a low to high transition. NMI is not synchronized to the clock but must have a duration of more than two CLK cycles in the high state. Any high going transition of NMI is latched on the 8086 CPU chip and is serviced at the end of the current instruction or between whole moves of a block-type instruction. The low going edge of NMI may occur before, during, or after the servicing of NMI. Another high going edge triggers another response if it occurs after the start of the NMI procedure.

## MASKABLE PRIORITY INTERRUPTS

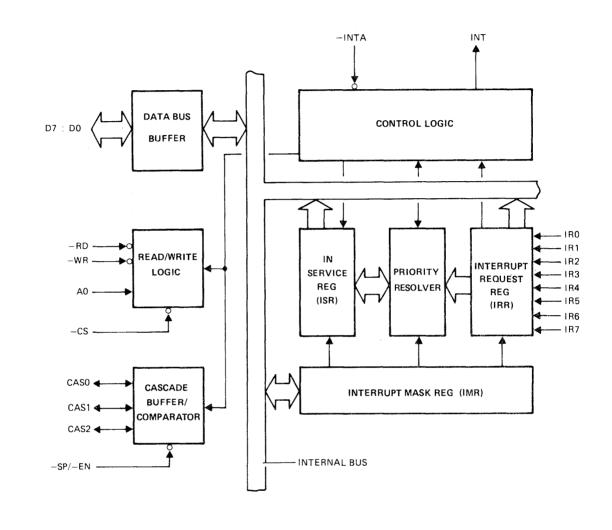

The circuitry that handles the maskable priority interrupts (IRQ00 - IRQ70) is the Intel 8259 Interrupt Controller chip. This Controller is a programmable device which functions as an overall manager in the interrupt-driven system environment. In other words, this controller has the task of only letting one device through to the CPU at a time, taking into consideration the fact that some devices have a higher priority than others. Fig. 2-11 is a block diagram of the 8259 Interrupt Controller.

## Fig. 2-11 Block Diagram of Interrupt Controller

Each device has an interrupt line which runs to one of the eight interrupt lines of the Programmable Interrupt Controller (PIC). The 8259 PIC can be programmed to ignore or to monitor any combination of these lines. This selection is determined via what is called the interrupt mask, a byte which is sent to the PIC by the CPU through a port located in the I/O space. This port is known as the control port. The 8 bits in this mask correspond to the eight devices. To turn off interrupts from a device, one has merely to set the corresponding bit in the mask equal to 1. Thus the 8259 will ignore all eight devices if a mask of FF hex is sent, and will respond to all of them if a mask of 00 hex is sent. If two or more devices (which are not masked out) signal the PIC for service at the same time, the PIC determines which goes first according to several user-selectable schemes. These include a fixed priority and a rotating priority scheme. The devices not yet serviced wait their turn in a waiting area which the PIC keeps track of. When a device begins to be serviced, the PIC moves out of this waiting area into the working area.

There is one interrupt line which runs from the PIC to the interrupt input line (INTRO) on the 8086 CPU. When the CPU gets a request on this line, it sends an acknowledge signal on the interrupt acknowledge line (INTA). The 8259 then sends a byte to the CPU telling it what type (location in the interrupt table) of interrupt should be executed. The value of the interrupt type is programmable. The eight devices are assigned eight consecutively numbered interrupt types starting at any multiple of 8.

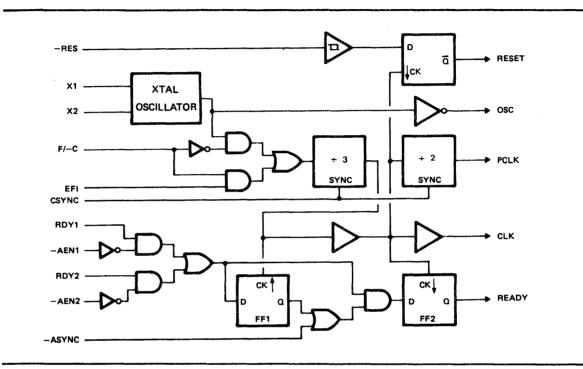

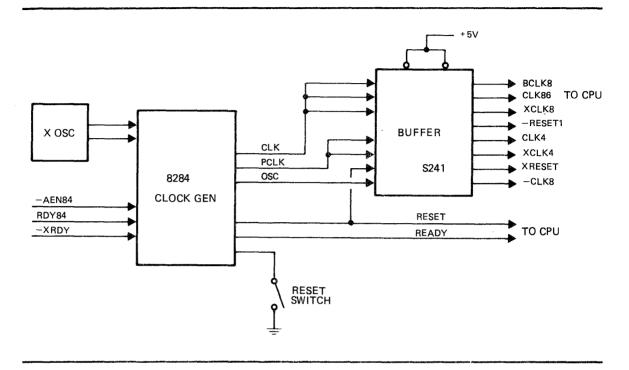

# CLOCK GENERATOR

The system uses the Intel 8284A as the Clock Generator chip. This is used in conjunction with a 24MHz crystal oscillator and a LS241 buffer to supply the timing for the entire system.

Fig. 2-12 8284 Clock Generator Block Diagram

The OSC output is a TTL level output of the internal oscillator circuitry. Its frequency is equal to that of the crystal. OSC is made available for use on the display controller board.

The clock signal CLK generated by the 8284 is an 8MHz clock with a 33% duty cycle and is used by the 8086 CPU. The 8284 also generates a 50% duty cycle 4MHz clock, PCLK, which is used by peripherals. In order to provide enough driving capability and to reduce the clock skew, these clocks are buffered and repowered by LS241.

The following are the outputs of LS241.

- CLK86 This is an 8MHz clock and used mainly by the 8086 CPU, 8087 NDP and 8288 bus controller.

- BCLK8 An 8MHz clock which travels on the C bus and is used by the Bus Arbiter, Programmable Wait Logic and I/O Chip and Port Select Logic.

- XCLK8 An 8MHz clock which is made available on the I/O expansion bus.

- CLK8 An 8MHz clock which is used by the Bus Arbiter, Progammable Wait Logic and Memory Control Logic.

- CLK4 A 4MHz clock used mainly by the DMA controller, Floppy Disk controller and keyboard controller.

- XCLK4 A 4MHz clock which is made available on the I/O expansion bus.

- -RESET1 This signal is used to reset various parts of the logic on the motherboard whenever the reset switch is pressed.

XRESET This is made available as a reset signal to the I/O expansion bus.

There are two signals which go to/from the 8284 Clock Generator to the 8086 processor and 8087 NDP. These are the RESET and READY signals. They are routed through the clock generator to synchronize them with the clock signals.

The function of the RESET signal is to restart the processor as if it had been turned off and on again. This is done in situations such as an infinite loop or a power glitch which has affected parts of the program in memory.

## Fig. 2-13 Clock Generator

The function of the READY signal is to insert the required number of "wait" states for slow memory or I/O devices. The READY signal goes from the external device through the clock generator to the processor. When the processor requests access to a device which is not ready to make a transfer, the device sends a low over the ready line and stops the processor until the READY signal goes high again. This is done by control-ling the inputs to the clock generator by the signals -AEN84 and RDY84.

The signal -AEN84 is normally low but goes high whenever "wait" states are to be inserted. The signal RDY84 goes low when either the DMA controller or an external processor require the CPU to stop.

Thus the READY output of the 8284 goes low when either the signal RDY84 is low (meaning that the DMA controller or the external processor are in command of the bus) or else the signal -AEN84 is high (meaning that one or more "wait" states need to be inserted).

The ready signal remains low until RDY84 and -AEN84 both go active. When both are active then READY goes high and the 8086 CPU starts functioning again.

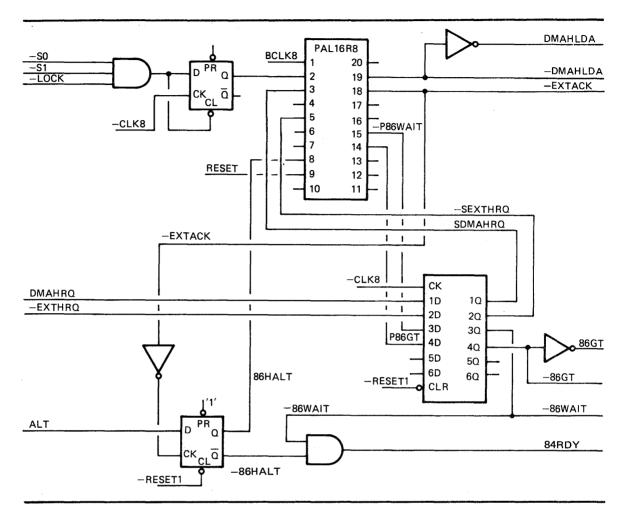

#### BUS ARBITER

The bus arbiter arbitrates between the three system bus masters. These masters are:

- 8086 CPU

- 8237 DMA Controller

- External Processor, Concurrent or Alternate

The bus arbitration is handled by the PAL16R8 which is used as a sequencer to sample the bus requests from the DMA controller and the external processor during the time that the CPU status is passive and not in the lock state. It then arbitrates the system bus to the DMA controller or an external processor, the DMA controller always taking priority over an external processor.

Once a bus request has been made by one of the above bus masters and is accepted by the bus arbiter, the appropriate address latches and data buffers are enabled and/or disabled, the CPU is put into the wait state and the new bus master acknowledged. The new bus master then takes control of the system busses.

When the new bus master has finished with the system bus, it removes its bus request and the bus arbiter gives control back to the CPU. The whole arbitration cycle is then repeated.

If the external processor is an alternate processor, once it has control of the system bus the CPU will not regain control until a hardware reset is performed. In this case the bus arbiter only arbitrates between the external processor and the DMA controller.

Fig. 2-14 Bus Arbiter

## DMA CONTROLLER CYCLE

The sequencer samples the DMA controller and external processor request lines DMAHRQ and EXTHRQ via the bus arbiter latch. If a DMA Controller request is present, irrespective of an external processor request, the bus arbiter issues the -P86GT signal. After passing through the bus arbiter latch, this signal changes to -86GT and is used to disable the CPU address latch, bus controller and data bus buffer. Thus the CPU address/data bus is isolated from the system address and data busses. The sequencer then starts the DMA controller cycle that issues the -P86WAIT signal together with -DMAHLDA and DMAHLDA.

The -P86WAIT signal becomes -86WAIT and is AND gated with -86HL1 to produce the RDY84 signal that acts on the ready input of the 8284 clock generator to make the CPU ready signal inactive. This puts the CPU into the wait state.

The -DMAHLDA signal changes the direction of transmission through the DMA control buffer, so that the expansion memory read and write signals and the address bits A16 to A19 are derived from the DMA controller. It

enables the DMA segment register and the DMA controller high byte address buffer LS373, and also changes the direction of the DMA controller low byte address latch so that the address bits AO-A16, which go on the A bus, are derived from the DMA controller.

The DMAHLDA signal indicates to the DMA controller that the CPU has released control of the system busses.

When the DMA Controller has finished with the system bus the DMAHRQ is removed. The sequencer then removes the DMAHLD signal followed by -P86GT and -P86WAIT so that control of the system bus is given back to the CPU.

## EXTERNAL CYCLE, CONCURRENT AND ALTERNATE

If an EXTHRQ is present, without a DMAHRQ being present, the bus arbiter issues the -P86GT signal to isolate the CPU address/data bus from the system address and data busses. The sequencer then starts the external processor cycle that issues the -P86WAIT signal together with EXTACK.

The -P86WAIT signal initiates a CPU wait state in the same manner as for the DMA controller cycle, and the -EXTACK signal clocks the ALT bit into the external processor latch to set the state of the 86HALT signal. The external processor is now able to take control of the system bus.

If the external processor is to act as a concurrent processor, the ALT bit will have been set low. This low, clocked into the external processor latch by the EXTACK signal, will maintain the 86HALT signal low and the sequencer treats the external processor as a concurrent processor.

When the external processor has finished with the system bus, the EXTHRQ is removed. The sequencer then removes the EXTACK signal followed by -P86GT and P86WAIT so that control of the system bus is given back to the CPU.

If the external processor is to act as an alternate processor, the ALT bit will have been set high. This high, clocked into the external processor latch by the EXTACK signal, sets the 86HALT signal high and the sequencer branches to the alternate processor cycle. The -86HALT signal, now set low, takes the RDY84 signal low and the CPU is put into the wait state. This maintains the ALT bit high and the CPU is held in the wait state until a hardware reset is performed.

In this case the bus arbiter only arbitrates between the external processor and the DMA controller.

## **BUS CONTROLLER**

The motherboard uses an Intel 8288 Bus Controller to perform the control of the various busses. This controller decodes the status output of the CPU in order to generate the bus command and control signals at the appropriate times. A block diagram of the Bus Controller is shown in Figure 2-15.

Fig. 2-15 8288 Bus Controller Block Diagram

| Stat<br>S2 | tus E<br>S1 | Sits<br>SO | Signal | 8288 Command Signals  |

|------------|-------------|------------|--------|-----------------------|

| 0          | 0           | 0          | -INTA  | Interrupt Acknowledge |

| 0          | 0           | 1          | -XIOR  | Read I/O              |

| 0          | 1           | 0          | -XIOW  | Write I/O             |

| 0          | 1           | 1          |        | none                  |

| 1          | 0           | 0          | -XMEMR | Read Memory           |

| 1          | 0           | 1          | -XMEMR | Read Memory           |

| 1          | 1           | 0          | -XMEMW | Write Memory          |

| 1          | 1           | 1          |        | none                  |

The command signals issued are as follows:

The control signals issued are as follows:

| 8288 Control Signals | Function                                                            |  |  |  |  |

|----------------------|---------------------------------------------------------------------|--|--|--|--|

| Address Enable (ALE) | to strobe the address onto the address latches                      |  |  |  |  |

| Data Enable (DEN)    | to enable the data buffers onto the data busses                     |  |  |  |  |

| Direction (DIR)      | to establish the direction of data flow through<br>the data buffers |  |  |  |  |

The Bus Controller outputs are enabled when the enable signal -86GT becomes active. Commands are only issued 115ns after this signal becomes active so that memory and I/O commands wait for bus arbitration. -86GT going inactive immediately tri-states the command outputs.

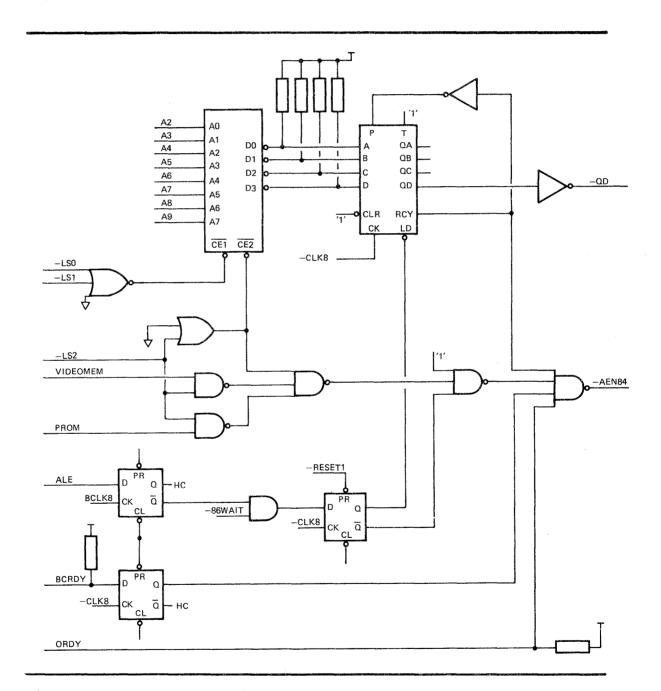

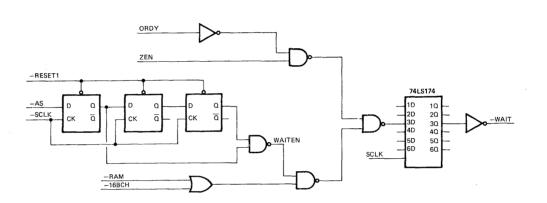

# PROGRAMMABLE WAIT LOGIC

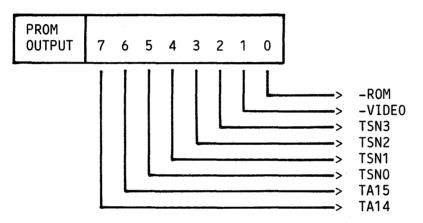

The programmable wait logic is used to insert the correct number of wait cycles required by the various memory and I/O circuits. It primarily consists of a PROM, that is essentially a look-up table for the number of wait cycles required for the various I/O circuits, and a divide-by-16 counter. Figure 2-16 shows the logic diagram of the programmable wait logic.

Fig. 2-16 Programmable Wait Logic

The PROM input consists of the I/O addresses A2 to A9. Its output, loaded into the counter by the ALE signal from the bus controller or by the -86WAIT signal from the bus arbiter, is 1's compliment of the number of wait cycles required.

Whenever the counter is loaded with F hex or the counter counts up to F hex, it generates a carry signal -WRDY. This carry signal is input to the clock generator enable NAND gate together with the ORDY and BCRDY signals from the expansion boards and the composit VIDEOMEM/PROM wait signal in order to produce the signal -AEN84. This signal acts on the address enable input -AEN1 of the 8284 Clock Generator to make the CPU ready signal active and maintain the CPU in the ready state. The carry output is fed back to the P enable input of the counter in order to inhibit the counter at F hex and maintain the CPU ready.

Loading the counter with a value other than F Hex, 1's compliment of number of wait cycles required, removes the carry signal and makes the CPU ready input inactive so that the CPU enters the wait state. The CPU then waits until the counter counts to F hex. In this manner the required number of wait cycles are inserted.

For memory access the wait logic PROM is disabled, the memory read and write statuses being decoded from the CPU status lines to produce the wait logic PROM enable signal. In order to insert wait cycles required for video memory access and system PROM access, signals VIDEOMEM and PROM are NAND gated with the status line -LS200 and the resultant signals are further NAND gated with the wait logic PROM enable signal in order to produce the composit VIDEO/PROM wait signal. This is NAND gated with the enable signal in order to the clock generator enable gate to produce signal -AEN84.

For the DMA cycle, one wait cycle is always inserted by the DMA wait logic. This wait logic acts on the DMA Controller ready input to extend the memory read and write pulses. The timing of the DMA ready signal is determined by the DMA address strobe ADSTB and the 4 MHz clock CLK4.

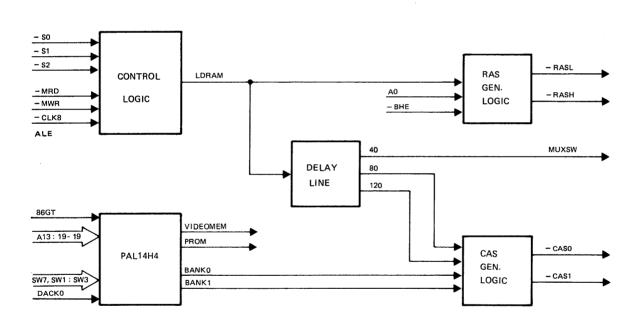

#### RANDOM ACCESS MEMORY

The motherboard RAM memory is organized in such a way that it could be addressed as bytes as well as words (2 bytes). It is divided in two banks namely bank 0 and bank 1 and each bank has an even byte bank and an odd byte bank. The motherboard has a minimum of 128K x 9 of read/write memory and is expandable up to a maximum of 640K x 9 of RAM with chip insertion.

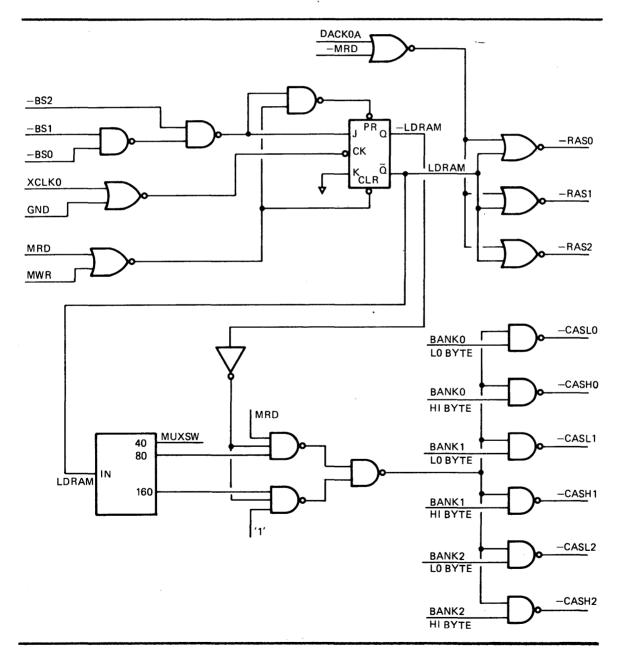

# MEMORY CONTROL LOGIC

As shown in figure 2-17 the signals required to address and access memory are:

| 0 |

|---|

| 1 |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

|   |

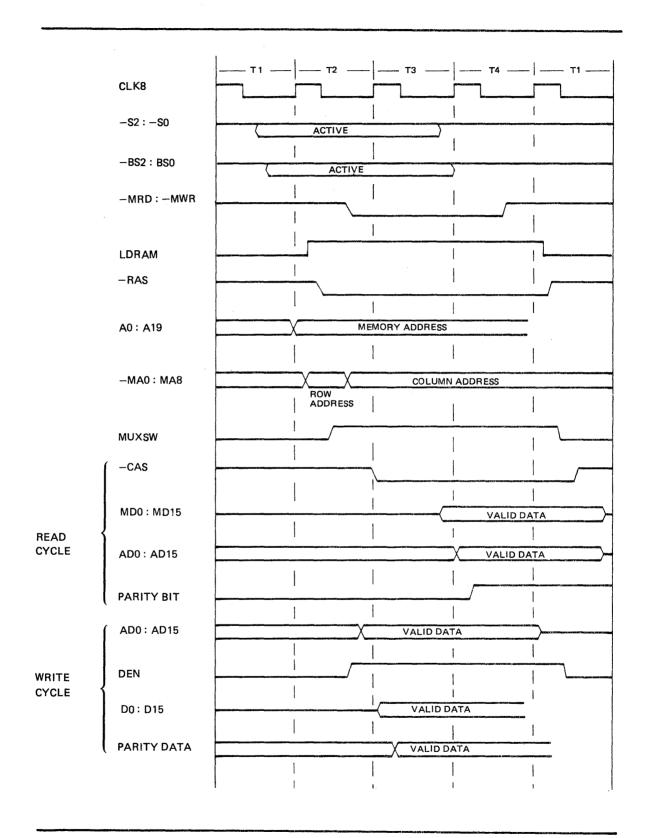

The memory cycle starts from the decoding of the CPU status lines -S0 to -S2. When these status lines are for memory read, memory write or code access, the input to the flipflop LS112 goes low. Thus when the flipflop is clocked the output signal LDRAM goes active high.

For the generation of -CASO and -CAS1 signals the LDRAM signal is delayed by the delay line PE21388 to allow the row address to be latched into the RAM memory.

For memory read or code access, -CASO and -CAS1 are delayed by 80ns while for a memory write -CASO and -CAS1 are delayed by 160ns to give time for the data to be latched into the memory data buffers.

PAL14H4 decodes whether the memory address is in bank 0, bank 1, in video memory or in the PROM. This is done from the system memory configuration switch SW0-SW3 and the address bits A13-A19.

If the memory address is for motherboard RAM memory the PAL generates either BANKO or BANK1 to select the corresponding column address strobe -CASO or -CAS1.

The selection of -RASL or -RASH is done by the signals AO and -BHE as seen in the table below.

|                                | -RASH | -RASL | AO | -BHE |

|--------------------------------|-------|-------|----|------|

| Word (2 bytes)                 | 0     | 0     | 0  | 0    |

| Upper byte from/to odd address | 0     | 1     | 1  | 0    |

| Lower byte from/to even addres | 1     | 0     | 0  | 1    |

| NONE                           | 1     | 1     | 1  | 1    |

This means that on a word operation both -BHE and AO are low and both -RASL and -RASH are activated. On a byte operation either -BHE is high for an even address selecting -RASL or AO is high for an odd address activating -RASH.

Fig. 2-17 Memory Control Circuitry

2-36

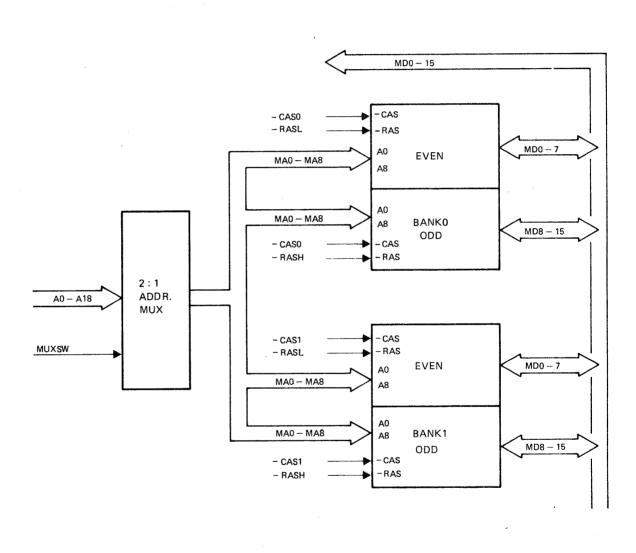

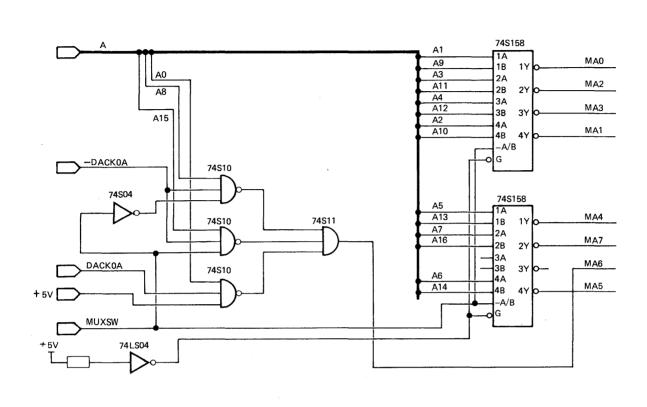

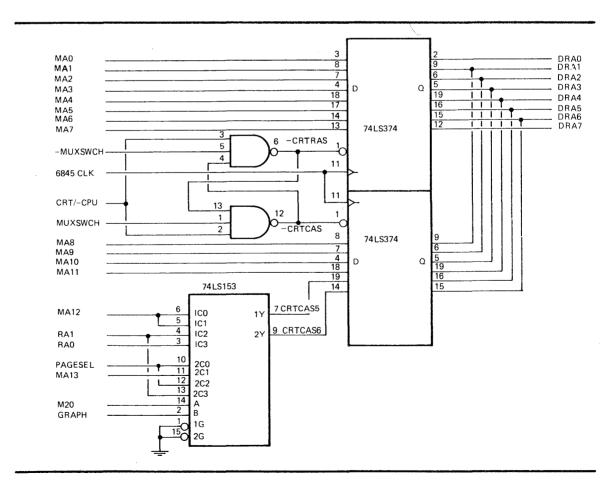

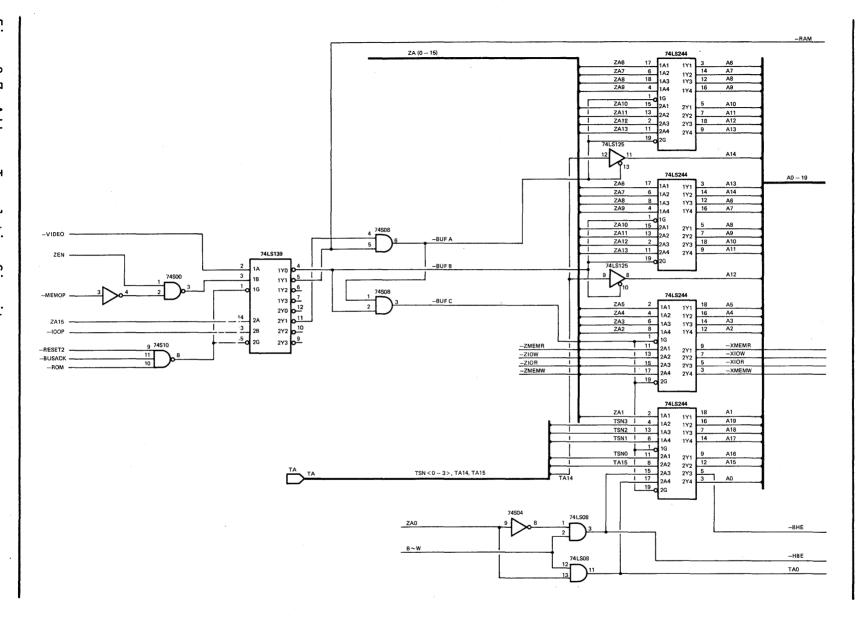

# MEMORY ADDRESSING

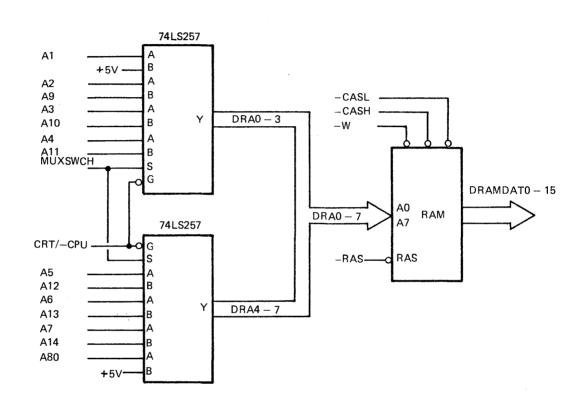

The addresses for the DRAM memory travel on the A bus. A1 to A8 go on to the RAM address multiplexer which consists of two 2 to 1 74S150 multiplexers and four AND gates.

# Fig. 2-18 Memory Addressing Logic

When the address bits arrive at the multiplexers, the select input pin 1 signal MUXSW is low and so the nine bits A1-A8,A17 go on to the output of the multiplexers. Thus when the -RASL or -RASH or both signals go active the outputs MAO-MA8 of the multiplexers are latched into the RAMs as the row address for the odd or even or both bytes (in the case of word addressing) for the particular bank.

40ns after -RASL or -RASH or both go active, MUXSW signal goes high, and so the address bits A9-A16, A18 go to the output of the multiplexers. Thus when the -CASO or -CAS1 signals go active, MAO-MA8 are latched into the RAMs as the column address for the even and odd bytes for either bank 0 or bank 1. In a read cycle -CASO or -CAS1 become active 80ns after -RASL or -RASH

Data from the addressed DRAMs passes through the 16 bit memory data buffer which consists of two bidirectional buffers (74LS245). This data buffer connect the MD bus to the D bus. Odd addressed data goes on MD8-MD15 while even addressed data goes on MD0-MD7.

Therefore on a word operation (16 bits to be accessed) two possibilities exist:

- First byte on even address

- First byte on odd address

and 160ns in a write cvcle.

If the first byte is on an even address only one memory cycle is required for accessing two bytes of data since both are on the same bank. But if the first byte being addressed is on an odd address, two cycles are required for word operation since the two bytes are on different banks.

Data is input or output from/to the MD bus according to the state of the write enable signal -MWR at the RAMs. If -MWR is low then a write operation occurs and data from the MD bus is input to the addressed RAMs. If -MWR is high then a read operation occurs and data from the addressed RAMs is output on the MD bus.

On a DMA memory cycle one wait state is inserted. This is generated by the circuitry consisting of the two D flipflops and an AND gate 74LS11. The address strobe ADSTB signal from the DMA controller, besides latching the upper address byte, is also input to the DMA wait logic. On a low to high transition of this signal the output Q of the first F/F, the output of the AND gate, and the output Q of the second F/F all go low. The latter Q output, called DMARDY, is used as an input to the DMA controller. Its function is to extend the memory read and write signals from the DMA controller.

DMARDY, as stated above, goes low and forces the DMAC to add wait states till the DMARDY goes high again. The timing in the system requires only one WAIT state to be inserted during a DMA memory cycle.

Fig. 2-19 Memory Timing Diagram

## MEMORY REFRESH

Refresh cycles are accomplished by programming channel 1 of the timer to request periodically a "dummy" DMA transfer. This action creates a memory read cycle which refreshes dynamic RAM both on the motherboard and expansion boards.

Timer channel 1 output periodically gives rise to DREQO (Data Request Signal). The DMA Controller (DMAC) then outputs DMAHRQ (hold request) to the 8086 CPU. When the XHA (hold acknowledge) is asserted, the DMAC gets control of the system busses and issues a -DACKO signal to both timer channel 1 and the memory control logic circuitry. At this stage the DMAC also issues the memory read signal -MRD. The signal -MRD active resets the F/F LS112 in the memory control logic putting the signal LDRAM high. This signal together with -DACKOB enable the two row address signals -RASL and -RASH.

The first row to be refreshed depends on the state of the memory address lines MAO-MA8. This address will be sequentially increased as the word count register in the DMAC is decremented. These sequential row addresses are latched with -RASL and -RASH and the internal row locations are hence refreshed.

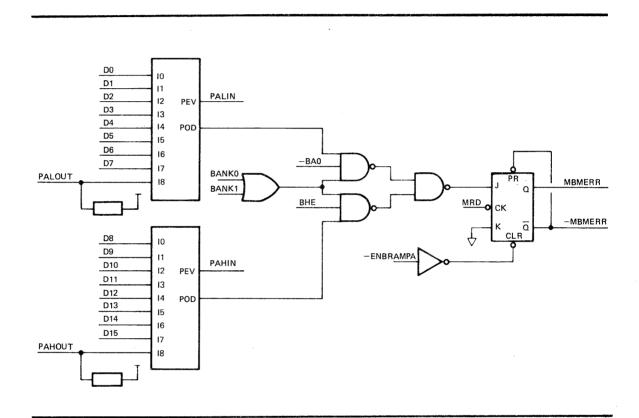

#### PARITY GENERATOR AND CHECKER

During a memory write cycle two parity bits are generated by the parity generator and checker and written to memory. These two bits are then read back from memory and checked against data for any parity errors during a memory read cycle. If a parity error exists, a non-maskable interrupt is generated the function of which is to stop the CPU operation immediately.

## Fig. 2-20 Parity Generator and Checker

During a write memory cycle the fifteen data bits DO-D15 together with the signals PALOUT and PAHOUT (which are high during a write memory cycle) are checked by the parity generators and two bits, PALIN and PAHIN, are generated low or high depending on whether the number of bits is even or odd. These bits are then written into memory.

During a read memory cycle these bits are read back from memory and checked against the data. If there has been no change in the data, then the input to the parity error flipflop is low and so when the MRD signal clocks the F/F, MBERR is low and no parity error is detected. But if there has been a change in the data, the input to the F/F goes high and the F/F is set when clocked. Thus -MBMERR goes low and an 8086 Non-Maskable Interrupt (NMI) is initiated.

#### PROGRAMMABLE READ ONLY MEMORY

Memory storage for the Power-on Bootstrap and Power-on diagnostics is provided by the EPROMS. Two 8K by 8 bit EPROMS provide 16KB of EPROM. The eight data outputs are connected to the bidirectional data bus MD and the EPROMs address lines are connected to the address bus BA. The chips are controlled by chip enable signal -ROMCE and the output enable signal -MRD. The EPROMs are only accessed by the CPU.

The EPROMs physically occupy addresses F0000 to FFFFF. Following power up or reset the 8086 CPU always begins execution at location FFFF0 where a jump instruction is located. This jump instruction directs the system to the initial program loading routine. When any EPROM location is addressed, PAL14H4 output, PROM, goes active. This in turn enables the PROM chips and also goes on to the wait logic circuitry and produces one wait state. PROM memory cycles require one wait state. The address lines AO-A12 are latched on to the PROMs with the chip enable signal. The desired location in PROM is addressed and the information stored in that location is gated on to the MD lines by the output enable signal -MRD.

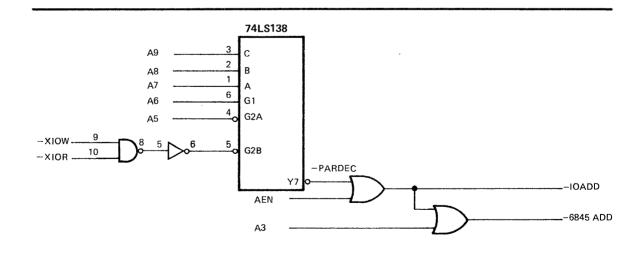

# INPUT/OUTPUT CHIP SELECT LOGIC

The I/O chip select logic uses a PAL as an address decoder to generate chip select signals from address bits A3 to A9. Chip selection is in accordance with the follow table.

| A9 | 8A | Α7 | A6 | A5 | Α4 | A3 | Function                   | Signal  |

|----|----|----|----|----|----|----|----------------------------|---------|

| 0  | 0  | 0  | 0  | 0  | 0  | Х  | DMA Controller             | -8237CS |

| 0  | 0  | 0  | 0  | 1  | 0  | Х  | Interrupt Controller       | -8259CS |

| 0  | 0  | 0  | 1  | 0  | 0  | Х  | Timer                      | -8253CS |

| 0  | 0  | 0  | 1  | 0  | 1  | Х  | SCC                        | -8530CS |

| 1  | 1  | 1  | 1  | 1  | 1  | 1  | ACE                        | -8530CS |

| 0  | 0  | 0  | 1  | 1  | 0  | Х  | 1/0 Port Select Logic      | -106X   |

| 0  | 0  | 0  | 1  | 1  | 1  | Х  | Clock Calendar             | -CSXX   |

| 0  | 0  | 1  | 0  | 0  | 0  | Х  | DMA Segment Register       | -DMASEG |

| 1  | 1  | 1  | 1  | 1  | 1  | 0  | Floppy Disk Controller     | -765CS  |

| 0  | 0  | 1  | 0  | 1  | 0  | Х  | NMI Register               | -NMIREG |

| 1  | 1  | 0  | 1  | 1  | 1  | 1  | Parallel Printer Interface | -PNTRCS |

| 0  | 0  | 1  | 1  | 1  | 1  | Х  | System I.D. Prom           | -SYSID  |

Note that the DMA controller chip select is not done by th |is PAL but by the logic consisting of the two NOR gates 74LS27 and the AND gate 74LS10.

The chip select signals are also used to generate the enable signal for the PD data bus buffer.

The address decoder is inhibited when the DMA Controller is in control of the system bus.

# INPUT/OUTPUT PORT SELECT LOGIC

The I/O port select logic uses a 3 to 8 line decoder LS138 which, when selected by the I/O chip select logic, generates I/O port select signals by decoding address bits AO to A2. Port selection is in accordance with the following table.

| A2 | A1 | A0 | Function                                | Signal |

|----|----|----|-----------------------------------------|--------|

|    | 2  |    | Keyboard 2011 Data Transfer Dead /Units | 10(0   |

| 0  | D  | U  | Keyboard 8041 Data Transfer Read/Write  | -1060  |

| 0  | 0  | 1  | Control Port A Read/Write               | -1061  |

| 0  | 1  | 0  | Control Port B Read                     | -1062  |

| 0  | 1  | 1  | Note Used                               | -1063  |

| 1  | 0  | 0  | Keyboard 8041 Command/Status            | -1064  |

| 1  | 0  | 1  | Communications Port Read                | -1065  |

| 1  | 1  | 0  | System Configuration Read               | -1066  |

| 1  | 1  | 1  | System Configuration Read               | -1067  |

For I/O read | operations the PD bus reads from the selec |ted port. For I/O write op |erations the PD bus writes to the selected |port. Read and wri |te operations are controlled by the Bus Con |troller. The signal -IOR1 controls the direction of the PD bus buffer. When this signal is low (read operation) the direction of data is from the PD bus to the D bus and when it is high (write operation) the direction of data is from the PD bus to the PD bus.

# SYSTEM CONFIGURATION PORT 66

This port determines the system configuration and is generated by means of the setting of the eight DIP switches in DIPSW-0 on the motherboard. These switches are set according to the following tables:

| SW4 | SW3 | SW2 | SW1 | BANK O | BANK 1 | EXPANSION<br>BOARD | TOTAL<br>MEMORY |

|-----|-----|-----|-----|--------|--------|--------------------|-----------------|

| ON  | ON  | ON  | 0FF | 128K   |        |                    | 128K            |

| ON  | ON  | OFF | ON  | 128K   | 128K   |                    | 256K            |

| ON  | ON  | OFF | OFF | 128K   | 128K   | 128K               | 384K            |

| ON  | 0FF | ON  | ON  | 128K   | 128K   | 256K               | 512K            |

| ON  | 0FF | ON  | 0FF | 128K   | 128K   | 384K               | 640K            |

| OFF | ON  | ON  | ON  | 512K   |        |                    | 512K            |

| OFF | ON  | ON  | OFF | 512K   | 128K   |                    | 640K            |

NOTE : SW4 = ON when 64Kx1 DRAM are used on the motherboard. SW4 = OFF when 256Kx1 DRAM are installed on the motherboard.

| SW NUMBER | OFF                | ON                 |

|-----------|--------------------|--------------------|

| SW8       | 2764 ROM installed | 2732 ROM installed |

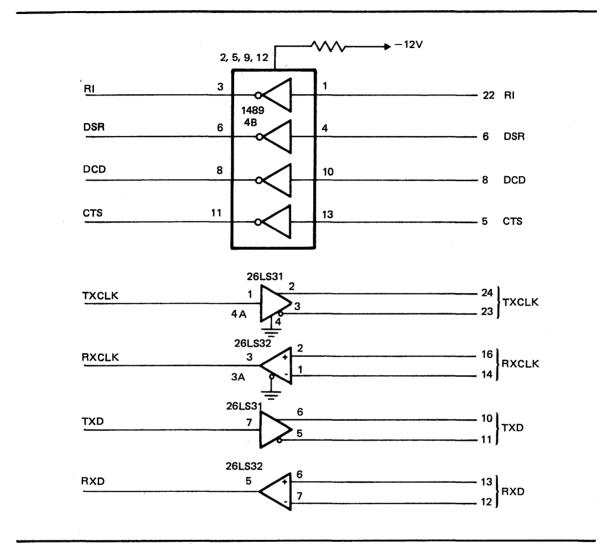

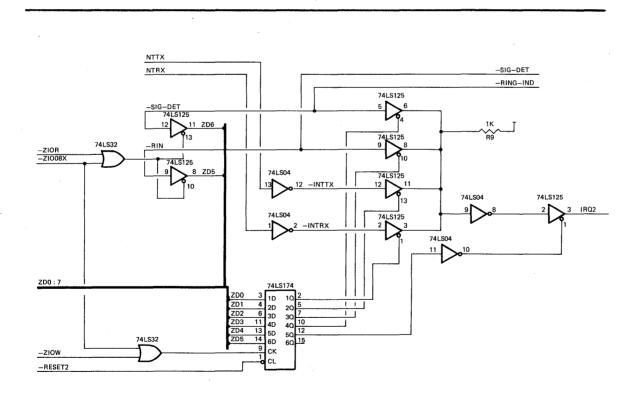

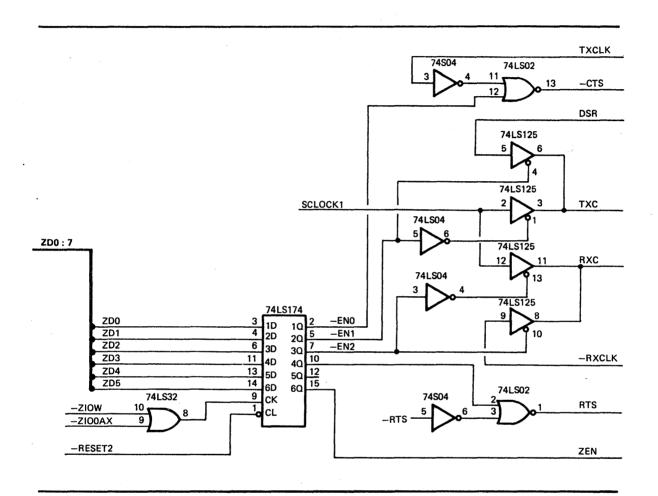

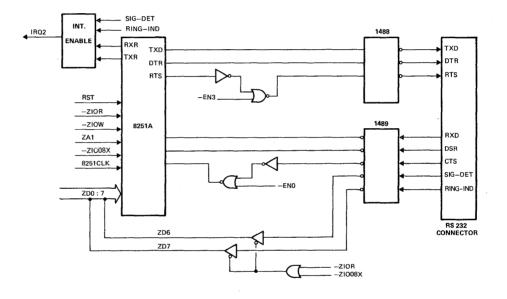

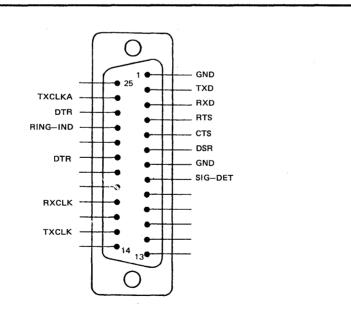

| SW7       | Not Used           | Not Used           |