2547 Ninth Street • Berkeley, California 94710 • (415) 549-0858

# North Star

# FLOATING POINT BOARD FPB-A

# Contents

| Parts List            | •  | • | • | • | •   | •   | • | •   | • | • | • | 3  |

|-----------------------|----|---|---|---|-----|-----|---|-----|---|---|---|----|

| Warranty              | •  | • | • | • | • . | . • | • | •   | • | • | • | 5  |

| Using the FPB         | •  | ė | • | • | •   | •   | • | •   | • | • | • | 6  |

| Theory of Operation   | •  | • | • | • | •   | •   | • | . • | • | • | • | 12 |

| Assembly and Check-or | ut | • | • | • | •   | •   | • | •   | • | • | • | 2Ø |

| Drawings              | •  | • | • | • | •   | •   | • | •   | • | • | ٠ | 24 |

Copyright, North Star Computers, Inc., 1978

**REVISION** 5

#### CAUTIONS

- 1. Correct this document from the errata before doing anything else.

- 2. Do NOT insert or remove the FPB from the computer while the power is turned on.

- 3. Do NOT insert or remove IC's from the board while the power is turned on.

- 4. Be sure the +5 volt regulators are generating +5 volt output voltages before installing any IC's.

- 5. Be careful to insert all IC's in correct positions and with correct orientation.

# PARTS LIST

| 1<br>2<br>2<br>1<br>2<br>1<br>3<br>3<br>1<br>3<br>1<br>1<br>1<br>1<br>1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | printed circuit board (5"<br>bolts, 6x32x1/2"<br>lock washers<br>nuts, 6x32<br>heat sink, 6805220<br>5 volt regulators, 7805 or<br>crystal, 8MHz<br>16-pin low profile IC sock<br>14-pin low profile IC sock<br>24-pin low profile IC sock<br>Documentation package<br>BASIC manual<br>BASIC paper tape | 340T-5<br>ets<br>ets                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Integrat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ed Circuits                                                                                                                                                                                                                                                                                             | Schematic Label                                                                                                                                              |

| 1<br>1<br>1<br>1<br>1<br>2<br>5<br>1<br>2<br>1<br>1<br>1<br>2<br>3<br>1<br>1<br>1<br>2<br>3<br>1<br>1<br>1<br>2<br>3<br>1<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>1<br>2<br>3<br>1<br>2<br>3<br>1<br>2<br>3<br>1<br>2<br>3<br>1<br>2<br>3<br>1<br>2<br>3<br>1<br>2<br>3<br>1<br>2<br>3<br>1<br>2<br>3<br>3<br>1<br>1<br>2<br>3<br>3<br>1<br>1<br>2<br>3<br>3<br>1<br>2<br>3<br>3<br>1<br>2<br>3<br>3<br>1<br>3<br>3<br>1<br>3<br>3<br>3<br>1<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3<br>3 | 74LS00<br>74LS02<br>74LS27<br>74LS27<br>74LS42<br>74LS51<br>74LS74<br>74LS75<br>74LS109<br>74LS132<br>74LS136<br>74LS151<br>74LS151<br>74LS157<br>74LS161<br>74LS169<br>74LS181<br>74LS258<br>7405<br>74109<br>74367 or 8097 or 8T97                                                                    | AN<br>NTR<br>3A<br>SN<br>SD<br>AOI<br>SY,CH<br>DTL,DIR,AL,BL,TL<br>DS<br>MN,ST<br>XR<br>BMX<br>EN<br>PCM,PCL<br>RB,LP,CNT<br>ALU<br>AMX<br>OC<br>GB<br>RD,LD |

| 1<br>1<br>4<br>11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 74SØØ<br>74SØ8<br>74S189<br>6301 or 74S287 or 82S129                                                                                                                                                                                                                                                    | FN<br>FA<br>LRAM, RRAM, DRAM, CRAM<br>CCOP, BAMP, BALP, BCSP, MSCP, CONP<br>ASRP, ACSP, STOP, BSRP, CADP                                                     |

# Capacitors

| 1  | 100uf electrolytic | C1    |

|----|--------------------|-------|

| 2  | 6.8uf tantalum     | C2,C3 |

| 1  | 330pf dipped mica  | C4    |

| 2  | 33pf dipped mica   | C5,C7 |

| 1  | 100pf dipped mica  | C6    |

| 15 | .047 ceramic disc  | *     |

|    |                    |       |

# Resistors

| 3 | 470 | ohm | R1,R2,R5 |

|---|-----|-----|----------|

| 2 | 2.2 | K   | R3,R6    |

| 1 | 1.2 | K   | R4       |

#### WARRANTY

North Star Computers, Inc. warrants the electrical and mechanical parts and workmanship of this product to be free of defects for a period of 90 days from date of purchase. If such defects occur, North Star Computers, Inc. will repair the defect at no cost to the purchaser. This warranty does not extend to defects resulting from improper use or assembly by purchaser, nor does it cover transportation to the factory. Also, the warranty is invalid if all instructions included in the accompanying documentation are not carefully followed. Should a unit returned for warranty repair be deemed by North Star Computers, Inc. to be defective due to purchaser's action, then a repair charge not to exceed \$30 without purchaser's consent will be assessed. Any unit or part returned for warranty repair must be accompanied by a copy of the original sales receipt. This warranty is made in lieu of all other warranties, expressed or implied, and is limited to the repair or replacement of the product.

#### USING THE FLOATING POINT BOARD (FPB-A)

#### ADDRESS SELECTION

Before using the floating point board, the memory addresses to which the FPB responds must be selected with jumper wires. The jumpers determine the four most significant bits of the addresses. The remaining 12 bits are fixed on the board. The jumper area is located just above IC XR. There are four pads labeled 15, 14, 13, and 12 associated with the four most significant address bits. The two pads at the ends provide ground(G) and high logic level(H). All address bits that should be "ones" should be daisy chain jumpered to G and all "zero" bits should be jumpered to H. The following table shows the RESTART and DATAIN addresses in hexadecimal corresponding to the 16 possible jumper combinations.

| 15 | 14 | 13 | 12 | RESTART     | DATAIN |

|----|----|----|----|-------------|--------|

| H  | Н  | н  | H  | ØFF2        | ØFF1   |

| H  | H  | H  | G  | lFF2        | lFFl   |

| Н  | H  | G  | Н  | 2FF2        | 2FF1   |

| H  | Н  | G  | G  | 3FF2        | 3FF1   |

| Н  | G  | H  | H  | 4FF2        | 4FF1   |

| H  | G  | H  | G  | 5FF2        | 5FF1   |

| H  | G  | G  | H  | 6FF2        | 6FF1   |

| H  | G  | G  | G  | <b>7FF2</b> | 7FF1   |

| G  | Н  | H  | Η  | 8FF2        | 8FF1   |

| G  | Н  | Н  | G  | 9FF2        | 9FF1   |

| G  | Н  | G  | Н  | AFF2        | AFF1   |

| G  | Н  | G  | G  | BFF2        | BFF1   |

| G  | G  | H  | H  | CFF2        | CFF1   |

| G  | G  | H  | G  | DFF2        | DFF1   |

| G  | G  | G  | Н  | EFF2        | EFF1   |

| G  | G  | G  | G  | FFF2        | FFF1   |

|    |    |    |    |             |        |

TO USE BASIC VERSION 5-FPB THE JUMPERS MUST BE WIRED TO USE ADDRESSES DFF2 AND DFF1. For proper operation no other memory in the computer can respond to addresses in the same block of sixteen as RESTART and DATAIN. For example, if RESTART and DATAIN are BFF2 and BFF1 then the FPB requires full use of addresses in the range BFFØ-BFFF.

#### PROGRAMMING

The 8080 or 280 program for causing the FPB to perform an arithmetic operation must perform the following steps in sequence.

- 1. Restart the FPB with a memory read of the RESTART address.

- Send the command byte which specifies the precision and operation to be performed. The command byte is the first data byte (i.e. not the first byte of an instruction) read after the RESTART.

- 3. Send the N bytes of the right operand. These are the N data bytes read after the command byte. No other data bytes may be read during the transmission of arguments.

- 4. Send the N bytes of the left operand. These are next N data bytes read. The FPB immediately starts performing the specified operation after the Nth data byte is read.

- 5. Wait for and receive the result status byte. The status byte is read by performing a read to the DATAIN address. If the sign bit of this value is zero then the FPB is still computing the result value. If the sign bit is one then the read byte is the status byte of the result.

- 6. Read the N bytes of the result value. The next N reads of the DATAIN address after reading the status byte provide the N bytes of the result value. After the last result byte is received at least 10 microseconds must elapse before another RESTART can be done. The result bytes must be read even after an error or else the next operation will not perform correctly.

The follwing sample program demonstrates the efficient use of the FBP.

IMPORTANT NOTE: After power-on a dummy operation must be performed to initialize the FPB. Subsequent operations will then perform corectly. The following program will initialize the FPB.

> LDA RESTART MVI A,2\*16 LDA Ø LDA Ø LDA Ø

\*SAMPLE USE OF THE NORTH STAR FPB \*FOR A DIVIDE OPERATION WITH 6 DIGIT PRECISION. \*IN THIS EXAMPLE ASSUME ARGUMENTS ARE IN MEMORY IN FORM: \* MOST SIGNIFICANT BYTE (MSB) DIGIT PAIR \* SUSEQUENT DIGIT PAIRS FOLLOW THE MSB \* EXPONENT+SIGN BYTE FOLLOWS LSB DIGIT PAIR. \*POINTERS ADDRESS THE EXPONENT+SIGN BYTE. \*BC HAS LEFT ARG POINTER. \*DE HAS RIGHT ARG POINTER. \*HL HAS RESULT POINTER.

\*THE FPB RECEIVES ITS ARGUMENTS BY "PEEKING" AT THE 8080 BUS \*WHEN THE ARGUMENT VALUES ARE LOADED TO ACCUMULATOR.

FDIV LDA RSTRT "WAKE UP" FPB MVI A,6\*16+DIVOP SPECIFY PRECISION AND OPERATION CODE LDAX D EXPONENT+SIGN BYTE OF RIGHT ARG ADVANCE POINTER TO NEXT BYTE DCX D LDAX D LEAST SIGNIFICANT DIGITS OF RIGHT ARG ADVANCE POINTER TO NEXT BYTE DCX D LDAX D DCX D LDAX D MOST SIGNIFICANT DIGITS OF RIGHT ARG LDAX B EXPONENT+SIGN BYTE OF LEFT ARG DCX B LDAX B LEAST SIGNIFICANT DIGITS OF LEFT ARG DCX B LDAX B DCX B LDAX B MOST SIGNIFICANT DIGITS OF LEFT ARG NOW THE FLOATING POINT BOARD IS PERFORMING THE OPERATION LXI D, DATAIN RECEIVE DATA ADDRESS FOR FPB FDIV1 LDAX D WAIT LOOP FOR COMPLETION SIGNAL ORA A SIGN BIT "1" MEANS FPB IS DONE LOOP IF SIGN BIT IS STILL "Ø" JP FDIV1 CHECK FOR ERROR, TESTED AT END ANI EBITS EXPONENT+SIGN OF RESULT LDAX D MOV M,A STORE EXPONENT+SIGN OF RESULT DCX H ADVANCE POINTER LDAX D LEAST SIGNIFICANT DIGITS OF RESULT MOV M,A DCX H LDAX D MOV M,A DCX H MOST SIGNIFICANT DIGITS OF RESULT LDAX D MOV M.A STORE IT RZ RETURN IF NO ERROR WAS DETECTED JMP ERROR GO REPORT ERROR

North Star Computers FPB

#### COMMAND BYTE FORMAT

| PREC | OPER |

|------|------|

| 4    | 4    |

PREC specifies the precision of the operand and result. It must be one of the following values.

Digits of Precision PREC (hexadecimal)

| 2   | 2 |

|-----|---|

| 4   | 4 |

| 6   | 6 |

| 8   | 8 |

| 10  | А |

| 12  | ¢ |

| 14  | E |

| N12 |   |

OPER specifies the operation to be performed. It must be one of the following values.

| OPER |

|------|

| 1    |

| 2    |

| 3    |

| 4    |

|      |

STATUS BYTE FORMAT

RD Ø Ø Ø OF UF DZ Ø

- RD if 1 indicates the operation is done and that the next N bytes read from the FPB will be the result. The other bits are valid only when RD is 1.

- OF if 1 indicates an overflow error, that is the magnitude of the result value would be too large to be represented.

- UF if 1 indicates an underflow error, that is the magnitude of the result value would be too smal to be represented.

DZ if l indicates a divide by zero error

North Star Computers FPB

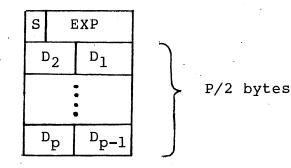

#### FLOATING POINT VALUE FORMAT

The first byte of a floating point value passed to the FPB contains the sign bit(S) and exponent(EXP). S=0 indicates a positive value and S=1 indicates a negative value. The exponent is represented in excess 64 binary. The exponent represented is to the base ten. Some examples of exponent values follow.

| Exponent | EXP(hexadecimal) |

|----------|------------------|

| -63      | Øl               |

| -1       | 3F               |

| Ø        | 4 Ø              |

| 1        | 41               |

| 10       | 4A               |

| 63       | <b>7 F</b>       |

The value zero is represented by a first byte with all zero bits (i.e.  $S=\emptyset$  and  $EXP=\emptyset$ ). If the precision is P digits then the fraction part is represented by P/2 bytes following the first byte. Two binary encoded decimal digits are packed per byte. The decimal point is assumed to be to the left of the most significant digit. D<sub>1</sub> is the least significant digit and D<sub>p</sub> is the most significant digit. All argument values must be normalized (i.e. D<sub>p</sub> non-zero). The FPB will always return a normalized value.

Examples in six digit precision:

| Value                 | Re               | epres | sent | tat | ion (ł | nexadecim | nal |

|-----------------------|------------------|-------|------|-----|--------|-----------|-----|

| Ø                     |                  | ØØ    | ØØ   | ØØ  | ØØ     |           |     |

| 1                     |                  | 41    | ØØ   | ØØ  | 10     | •         |     |

| .123456 x<br>987654 x | 108              | 48    | 56   | 34  | 12     |           |     |

| 987654 x              | 10 <sup>-9</sup> | В7    | 54   | 76  | 98     |           |     |

North Star Computers FPB

)

#### FPB-A BUS INTERFACE DESCRIPTION

The FPB-A is compatible with the S-100 bus, i.e. the bus used by ALTAIR and IMSAI computers. The following signals on the bus are used by the FPB-A. All signals are positive, high true, TTL logic levels.

- $DI_7-DI_{\emptyset}$  The 8 input data lines. The FPB reads operand bytes from these lines and tri-states result bytes onto these lines.

- $A_{15}-A_{\emptyset}$  The 16 address lines. The FPB decodes these lines to recognize the RESTART and DATAIN addresses.

- SMEMR Status line that indicates to the FPB that a bus cycle is memory read.

- SMl Status line that indicates to the FPB whether a memory read is a first byte of an instruction fetch or a data byte fetch.

- PDBIN Timing signal used by FPB to strobe result bytes onto DI bus and to indicate operand bytes have been strobed onto the DI bus by a memory module.

- PSYNC Used by the FPB to recognize the beginning of a memory cycle.

- Ø2 Used by the FPB to synchronize the memory reference control logic with the CPU.

- PRDY The logical AND of these two signals indicates that XRDY read data is stable on the DI bus. The FPB uses these signals when reading operand bytes.

- PHLDA Indicates that the memory reference is a DMA cycle. The FPB ignores DMA cycles while reading operand bytes.

#### THEORY OF OPERATION

#### HARDWARE

The FPB is a microprogram controlled processor designed specifically to perfrom high speed decimal floating point arithmetic operations. The unit is implemented entirely from medium and small scale TTL integrated circuits and PROM memory. All data paths in the microprocessor are 4 bits wide thus enabling processing one decimal digit at a time. The FPB is divided into four functional sections:

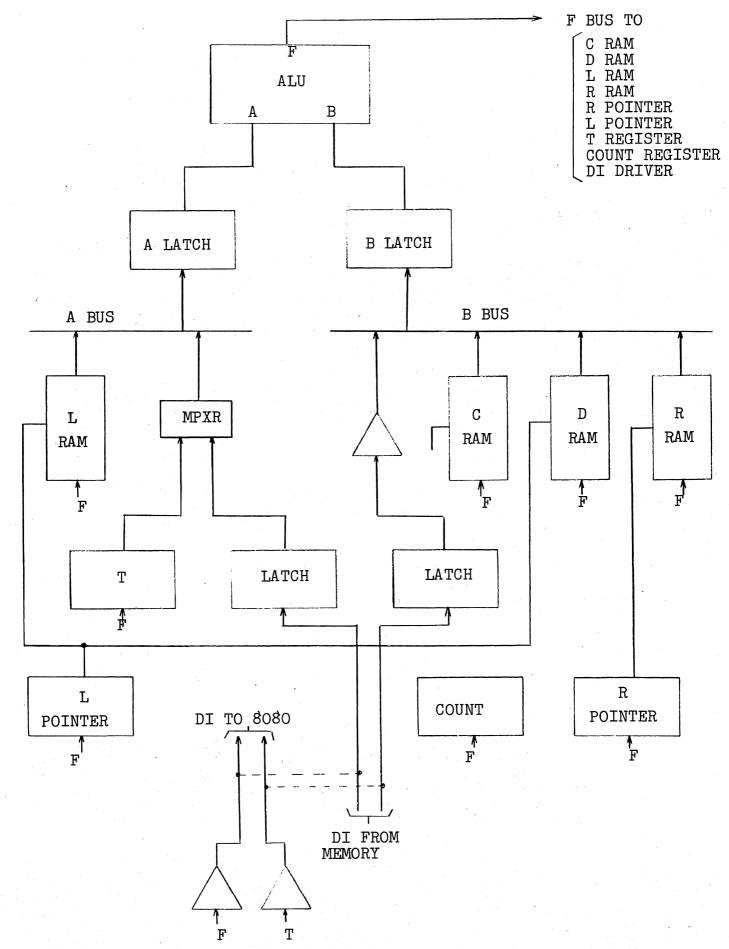

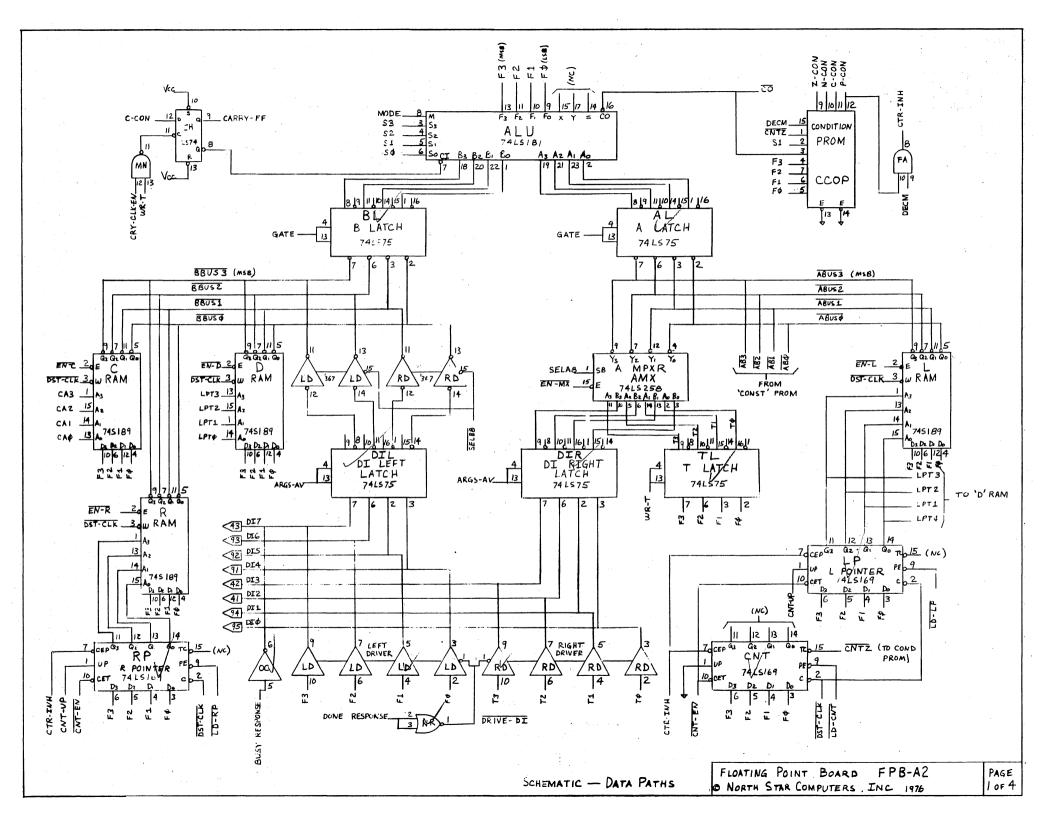

#### 1. Data Paths

The following diagram shows the microprocessor data paths. There are three main buses in the data paths: A, B, and F. During each instruction cycle of the microprocessor, values are gated onto the A and B buses which are latched at the end of the first half of the microcycle by the A and B latches. The latched A and B values serve as inputs to the ALU. The ALU output goes on the F-bus which is clocked into one of the RAM's or counters at the end of the microcycle. The T-LATCH is always loaded from the F-bus at the end of every microcycle. There are four 4 x 16 L-RAM and R-RAM generally hold the fraction part of the RAM's. left and right floating point operands and the D-RAM holds the result. C-RAM is used to hold the exponents, various constants and temporary results required during the calculation. There are three counters. L-PTR and R-PTR are used to address the L, R, and D RAM's. CNT is used to count the number of iterations through a program loop. The F-bus and T-LATCH together are used to gate an 8 bit result byte onto the DI bus. The two data input latches are used to catch operand bytes off the DI bus.

#### 2. Clock Circuit

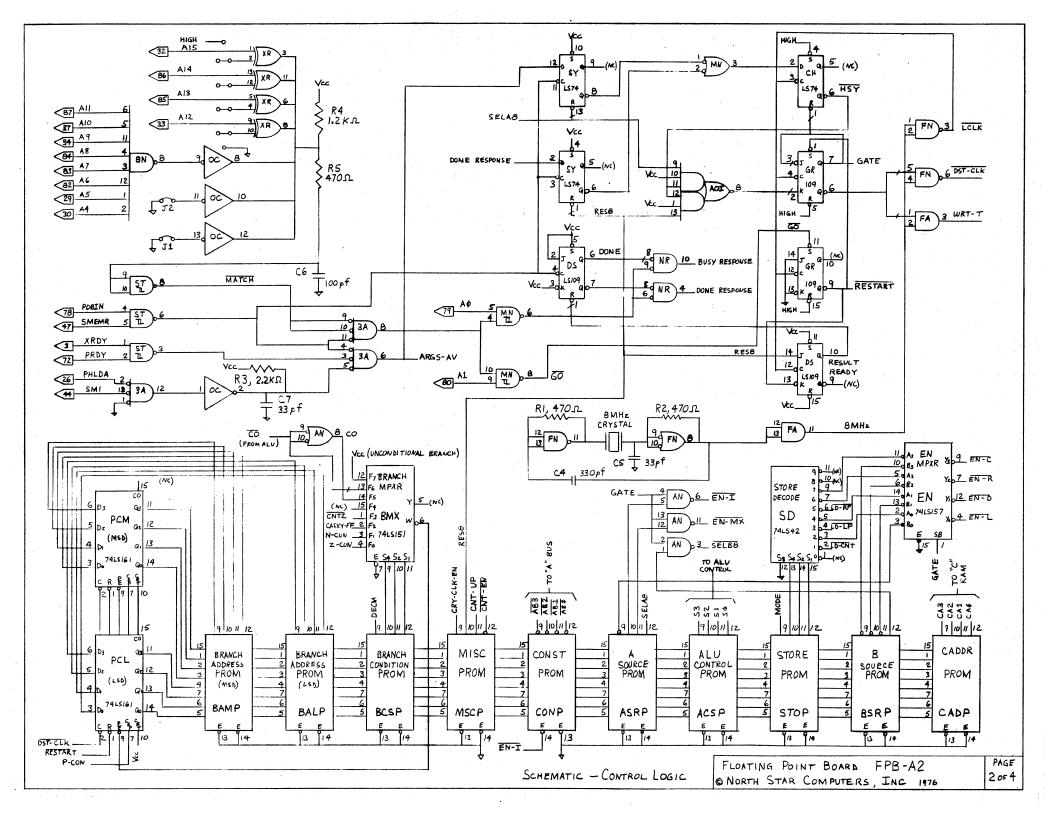

The clock circuit is a crystal controlled oscilator (IC's FN, FA). The generated 8 MHz signal is used to generate three clock signals. LCLK/ is a free running 8 MHz signal. DST-CLK and WRT-T are timing signals that operate at 4 MHz. These signals do not occur while the microprocessor is waiting for a bus memory cycle.

#### 3. Control Logic

The control logic is responsible for:

- a. sequencing the micro program counter. At the end of every microcycle the p-counter is either loaded causing a branch, incremented to address the next instruction, or left unchanged during loops. The branch multiplexor(BMX) determines which of seven conditions will cause a branch. The P-CON signal out of the condition PROM(CCOP) determines if the p-counter will increment.

- b. interfacing and decoding bus control lines. The ARGS-AV signal indicates when an operand byte is on the DI bus and is used to gate the DI latches. The GO signal indicates that a new floating point computation is to begin. After being sychronized to the microprocessor clock it is used to force the microprogram counter to zero. The BUSY RESPONSE and DONE RESPONSE signals indicate that a status or result byte should be gated onto the DI bus.

- c. synchronizing the microprocessor with memory references from the CPU. The bus synchronizing logic(IC's GR, CH, AOI, SY, DS) cause the microprocessor to hang if an expected memory read reference on the bus has not yet occurred. The SELA8 and RES8 microprogram conditions indicate that an argument byte is required by the microprogrm or that the CPU should take a result byte, respectively. The SY flip-flops catch the memory conditions with the CPU clock. HSY is the or of these conditions synchronized to the microprocessor clock. The signal is then used to generate GATE. GATE is used to enable DST-CLK and WRT-T and to enable A-LATCH and B-LATCH. GATE is kept high by the synchronizing logic to hang the microprocessor during the first half of a microcycle.

- 4. Microprogram Storage

The microprogram is stored in ten bipolar PROM's organized 4 bits by 256 words. A hexadecimal listing of the PROM contents follows. The meaning of each PROM is now given.

- a. Branch Address PROM (BAMP). Most significant 4 bits of the branch address.

- b. Branch Address PROM (BALP). Least significant 4 bits of the branch address.

- c. Branch Condition PROM (BCSP). bit 3 indicates arithmetic should be done in decimal mode. bits 2-Ø indicate one of eight branch conditions.

- d. Misc. PROM (MSCP).

- bit 3 enables clocking of the carry flip-flop at the end of a microcycle.

- bit 2 indicates that a result byte in the T-LATCH and on the F-bus is ready for the CPU.

- bit 1 indicates whether L-PTR and R-PTR should count up or down.

- bit  $\emptyset$  enables clocking of the three counters at the end of the microcycle.

- e. Const PROM (CONP). Contains the 4 bit constant to gate onto the A-bus.

- f. A Source PROM (ASRP). Specifies what to gate onto the Abus.

- g. ALU Control PROM (ACSP). Specifies the ALU function bits.

- i. Store PROM (STOP). bit 3 is the ALU mode bit bits 2-Ø specify which of seven destinations will get loaded from the F-bus at the end of the microcycle.

- j. B Source PROM (BSRP). Specifies what to gate onto the Bbus.

- k. C Address PROM (CADP). Specifies which word in the C-RAM to address.

CONST PROM AØ1Ø87ØF ØFØ877ØF ØCØFEDBØ FFF5BEF4 F7FFFFØØ ØØ0Ø07FØ ØFDFEFEØ AFFØEFFF 4FAØØFFF 7B77B7ØF ØFØFØEØØ EDFEFØØ5 F7FFØF5F FEØØF7FF ØFFFØFFF FFFØEFØF FØØFFØØØ ØEØØ1EFD ØØØDFØØF FØØØØØFF 7FØF7FØF FØØØØØFFF D7FFFDØF ØFEFFØØØ CADDR PROM E746514F FF320F1F 47FF777F FFFF8CB9 F15623E6 3B52AAA4 BBFFF14F FFFC32FC FFF4CF23 22FFFFA4 B6352BCB BFFF4EFF FØ4C4FF4 FC32FFFF 4FFFFF23 5647CFCF 4FECFF74 CFF77CC4 9BECF7C6 579E3223 210FF023 2C4FFF56 FF23C47C FCF4FEFF FC4FFEF7 C7FFC7CF FF657810 32FF0232 C4FFFFF1 0565F4FF F0000000 000000F STORE PROM FFFFFFID EEFFF8FB 18AA8889 EACFFFFF ØF8888808 ØF80F888 Ø9DEB814 408777CB Ø4483888 88888888 Ø8F8FØFF 1BAD9Ø44 ØF9BØ449 87778888 188ØCC88 888F3A7D 122B8478 438FF7B1 Ø223ØF7A A22Ø7788 88F888F8 83188Ø88 8888FØFB CB49DØ22 ØB9D2287 7FB87FBØ 44AA228F 77888F88 31880888 8F88D188 ØØØØØØØØ ØØØØØØØ BSOURCE PROM ASOURCE PROM ALU PROM FFBFBB9F FAFBBB6F 96FA666F FFFFFFF F6AAAA96 9F69FBA6 9AFFFA99 99A999FA 99969AAA BBFFFF6A 9AFAF9F6 9FFFA969 96AA969A A999FFFF 9FF9FAAA AAAF9F9F 999AA996 99FFF9A9 99999F9A A99999AA BAFFFAEA A99FF9AA FFAAF9FA FA9AF969 9AAF99F9 9FFA9FA9 996699AF 99FFAEAA 99AA9FFA 6EAAF9AA 90000000 0000000F BRADDR MSBITS PROM ØØØØØØØØ ØØØØØØØ1 171122A1 11111112 222A2E22 222224A3 A3333533 33333334 44444344 D44646E5 E5555555 55535565 66666666666667 77717776 76777788 88888778 88888889 99999999 99999A4 4AAAAAAA AAAAAIBB B6B6BBBB BBBBBCB BCCCCCCC BCCCCCCD DDDDDDDD D4DDDDE EEEE1EEE EEEEEEEE 10000000 0000007 BRADDR LSBITS PROM 12345678 98BCDEFØ 143221E8 9A8CDEFØ Ø2436578 9ABCDE3Ø 32335C79 7AFCDEFØ 63145B8C ACBEDE5Ø 52345678 9AA5DEØE 72345758 FAB8DEFØ 1217548C ACBCDE3Ø 13146FC8 9ACEDEFØ 33147638 9ABCDEØC 92345678 9ABCB722 1E4C5678 9ABCDEØE 92347479 7ABEDEF2 20345678 96BCDEF0 12327678 9ABCDEFE 70000000 0000008 MISC PROM 8808B8BB BBBFBFBB BBBBBBBB BB8BB880 BBBBB80A B3BABFBF B8CB88BB BBBBBBBB B8ØBB32B 3BBBBBB3 88ØB8B38 A8AB8BBB BBBBFBBB F3B8CBBB BFBBBBBB BBBBBB8Ø BBBB8ØB3 BBBBBB88 8Ø8A8ABB 8BBFBBBF 3B8CBBFB BBBFBB8C BBBBBBBB BBBBBBBB BRCOND PROM 7777777 73777777 70730007 77377777 77101077 77777117 57737179 3707777 68777110 Ø1777717 67777777 77377793 27777937 17737777 7737731Ø 1Ø777777 79370717 77077777 68773777 7777710 17777777 77773711 77107777 7777793 27779370 77707776 87777777 7777777 77737777 7777773 70000000 0000000

#### MICROPROGRAM

The FPB microprogram contains 256 instructions. The function of the program is now described. The common start up sequence starts at address zero and is executed when a RESTART memory read is performed by the CPU.

Common Start Up Sequence

- 1. Receive the command byte and save the precision and operation code.

- 2. Receive the right operand and save in the R-RAM

- 3. Receive the left operand and save in the L-RAM.

- 4. Dispatch to one of the four arithmetic routines based on the operation code.

ADD Routine

- Test for zero args. If the left argument is zero then return the right argument as the result. If the right argument is zero then return the left argument as the result.

- 2. Scaling. If the exponent difference is greater than the precision, then the argument with larger exponent is returned as the result. Otherwise, the argument with the smaller exponent is scaled right by the exponent difference. For example:

.1234 x  $10^3$  + .5678 x  $10^6$ after scaling becomes .00012 x  $10^6$  + .5678 x  $10^6$

Notice that an extra digit of precision is maintained internally.

3. Perform arithmetic. If the sign of the arguments are the same then the argument fraction parts are added. If the precision is P then P+2 digits are added, one lower order rounding digit and one higher order digit in case of overflow. For example if P=4 then the result of the previous example is Ø.56792. if the sign of the arguments are different then the fraction part of the right argument is subtracted from the fraction part of the left argument. An extra low order digit is included in the subtraction. If the right argument fraction part is larger than the left argument fraction part then the subtraction result must be complemented. For example:

> .1234 - .5678 = .55560 and after complementing becomes .44440

North Star Computers FPB

4. Normalize result. If an add was performed then the result is normalized right by one if the add caused an overflow. If a subtract was performed then the result must be normalized left for each high order zero digit in the result. For example, the following result must be normalized by two digits:

> $.5567 \times 10^{6}$  - .5511 x  $10^{6}$  = 0.00560 x  $10^{6}$ and after normalizing becomes .5600 x  $10^{4}$

If the result of the subtraction is all zero digits then a zero result value is returned.

5. Rounding. If the extra low order digit is greater than or equal to five then one is added to the fraction part of the result. If rounding causes an overflow then the result must be normalized right by one digit. For example,

> .99999 x 10<sup>6</sup> must be rounded to 1.0000 x 10<sup>6</sup> and now must be normalized to .1000 x 10<sup>7</sup>

6. Test and return result. If the operations generated a result with too large or small an exponent then a zero result value is returned and the overflow or underflow error flag is returned in the status byte. Otherwise, the result is returned without an error flag in the status byte.

SUBTRACT Routine

1. The sign of the right argument is complemented and then the ADD routine is performed.

MULTIPLY Routine

- 1. Zero test. If either argument is zero then a zero result is returned.

- 2. Perform multiply. The right argument is the multiplicand and the left argument is the multiplier. First, the result is set to zero. Then, the muliply is performed by doing a repeated add of the multiplicand for each digit of the multiplier. The add of the multiplicand is done to P+2 digit accuracy thus maintaining a rounding and overflow digit. The multiplicand is added D times where D is the value of the next digit of the multiplier. After each repeated add of the multiplicand, the result is shifted right. The multiplier is processed from least significant to most significant digit.

- 3. Normalize. If the result has a zero overflow digit, then the result must be normalized left by one digit.

- 4. Rounding. If the rounding digit is greater than or equal to five then one is added to the fraction part of the result.

- 5. Compute exponent. The exponents of the two arguments are added to get the result exponent.

- 6. Test and return result. The result is tested and returned as in the ADD routine.

DIVIDE Routine

- Test for zero. If the right arg is zero then a zero value is returned and the divide by zero error flag is set in the returned status byte. Otherwise, if the left arg is zero then a zero value is returned.

- 2. Perform divide. Division is done by performing repeated subtracts of the divisor from the dividend in a loop. The reapeat loop is done once for each digit of the dividend. The dividend is processed from most significant to least significant digit. After each digit is processed the dividend is shifted left. The repeated subtracts of the divisor continue until the dividend becomes negative, then the divisor is added back to make the dividend positive again. The successive digits of the result are the number of times the subtaction must be performed.

- 3. Normalize. If the first digit of the result is zero then then result must be normalized left by one digit.

- Round. If the rounding digit of the result is greater than or equal to five then one is added to the result value fraction part.

- Compute exponent. The result exponent is computed by subtracting the right arg exponent from the left arg exponent.

- 6. Test result and return. The result is tested and returned as in the ADD routine.

## ASSEMBLY AND CHECK-OUT INSTRUCTIONS

#### SOLDERING TIPS

For best results use a 15 watt soldering iron or an iron with a temperature regulated tip. The tip should be no wider than the solder pads on the printed circuit board. Use only a fine gauge, rosin core solder. When soldering, keep the soldering iron tip on the pad just long enough for the solder to completely flow. If the solder does not draw up the wire then more solder is required. Use less solder if it is overflowing the pad. If the solidified joint is not shiny it may be a cold solder joint and should be remelted. The soldering iron tip should be cleaned frequently by wiping on a damp sponge.

#### ASSEMBLY

For best results, assemble the FPB using the following steps. Between each step test that "ground" and "+5" are not shorted since it is very difficult to debug a short after all the components are installed.

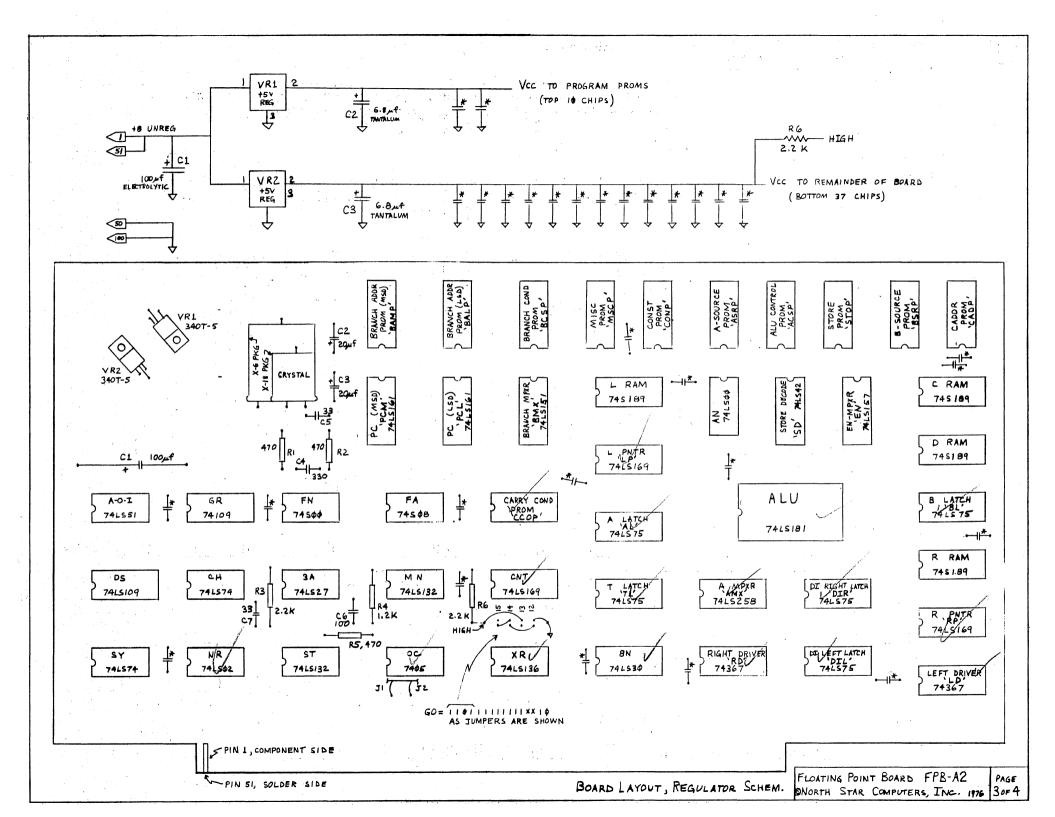

NOTE: Orient the board with the edge connector toward you and the heat sink area to the left. The component side is now up. The silk screen legend is on the component side. The solder side has the larger IC pads.

I. Install and solder the 33 sixteen-pin IC sockets. Orient them as shown on the layout sheet and on the silk screen legend.

NOTE: IC sockets can be installed by first stuffing them into the printed circuit board, then placing another flat board over the IC sockets and finally turning over this sandwich for soldering.

2. Similarly, install the 13 fourteen-pin IC sockets.

(3. Now install and solder the single twenty-four-pin IC socket.

4. Install and solder the six resistors in the locations indicated by the silk screen legend.

| 'R1         | 470 ohm | yellow-violet-brown | .4" spacing  |

|-------------|---------|---------------------|--------------|

| -R/2        | 470 ohm | yellow-violet-brown | .4" spacing  |

| <b>∕</b> R3 | 2.2 K   | red-red-red         | .6" spacing  |

| <b>A</b> 4  | 1.2 K   | brown-red-red       | .6" spacing  |

| (R5)        | 470 ohm | yellow-violet-brown | .5" spacing  |

| JR6         | 2.2 K   | red-red-red         | .55" spacing |

|             |         |                     |              |

NOTE: Save some of the snipped leads for use as jumpers.

5. Install and solder the 22 capacitors in the locations indicated by the silk screen legend.

| 1<br>vC2           | lØØuf | electrolytic | "+" toward edge of board |

|--------------------|-------|--------------|--------------------------|

| VC2                | 6.8uf | tantalum     | "+" of C2 and C3         |

| 12/3<br>10/4       | 6.8uf | tantalum     | toward each other        |

|                    | 330pf | dipped mica  |                          |

| <b>v</b> q5        | 33pf  | dipped mica  |                          |

| v\$6               | 100pf | dipped mica  |                          |

| √05<br>√06<br>↓∕C7 | 33pf  | dipped mica  |                          |

The remaining fifteen .Ø47uf ceramic disc capacitors are bypass capacitors and should be installed in the unlabeled oval capacitor locations on the silk screen legend (marked with asterisks on the layout drawing).

- 6. Install and solder the crystal. In addition to the two leads the top of the crystal case should be soldered flat against the PC board by soldering a piece of clipped resistor lead between the crystal case and the provided solder pad.

- . Place the heat sink on the PC board such that the pads for the / regulators show.

8. For both regulators, bend down the three regulator leads 90 degrees such that the leads go into the correct holes while the bolt holes line up. But don't solder yet.

9. Install the heat sink hardware so that the following sequence results from bottom to top: 6x32 bolt, PC board, heat sink, regulator, lock washer, and nut. Tighten the bolts so that the regulator leads are well separated from the heat sink and the heat sink is 1/8" away from the edge of the board for clearance with card guides. Now solder the regulator leads.

NOTE: Heat sink grease may be used though it is not generally needed. Don't tighten the bolts too tight to avoid cracking the PC board.

The board is now completely assembled except for inserting the IC's. Procede with the check-out procedure.

#### CHECK-OUT PROCEDURE

The following procedure should be followed for systematically checking-out the FPB. An oscilliscope is required for some steps in this procedure.

NOTE: It may be desireable to solder a piece of wire into the ground pad to the left of chip FA for clipping the scope ground.

DO NOT INSERT IC'S WITH THE POWER ON.

- 1. Check for +5 volts at the "+" side of each tantalum capacitor.

- Install IC's FN and FA. Check for an 8MHz square wave at FN-6 (i.e. pin 6 of IC FN).

- Install IC's PCM and PCL. Check that they count with a 2 microsecond period at PCL-11 and a 32 microsecond period at PCM-11.

- . Install the ten PROM's in the top row(note they are oriented upside down) and the IC AN. The contents of each PROM should now be sequencing at pins 9, 10, 11, and 12. This provides a way to verify the contents of PROM, should this be required.

- 5. Install IC's AL and ALU. There should be activity on ALU pins 2, 9, 10, 11, 13, 19, 21, and 23.

- 5. Install IC GR. Where previously there was an 8MHz signal at FN-6, now there should be 4MHz negative pulses with a 25% duty factor.

- 7. Install the address selection jumpers in the area between IC's XR and CNT. See the ADDRESS SELECTION description in the USING THE FLOATING POINT BOARD section for the details.

- 8. Install the following IC's: bottom row SY, NR, ST, OC, XR, 8N, next row DS, CH, 3A, MN, next row AOI. Now check the address comparison logic by referencing the jumper selected addresses using the front panel or using a program. When the RESTART address is referenced MN-8 should go low. When the DATAIN address is referenced MN-6 should go low.

9. Install all the remaining IC's. Now run the following test program.

| Address | Hex      | Symbolic    |                                       | ана стана стана<br>Конструкция стана стан |

|---------|----------|-------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| · .     |          |             |                                       | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                               |

| 1000    | 3A F2 XF | LDA RESTART | X depends on ad                       | ldress jumpers                                                                                                                                                                                                                      |

| 1003    | C3 ØØ 1Ø | JMP 1000    | · · · · · · · · · · · · · · · · · · · |                                                                                                                                                                                                                                     |

The following signals should now be observed.

a. "GO" low true pulses at GR-11

b. "RESTART" low true pulses at GR-9

- c. bursts of clock pulses at FN-6 (microinstructions being executed)

- d. pulses at SY-9 indicating the microcode waiting for an argument

e. activity at ALU pins 1,2,9,10,11,13,18,19,20,21,22,23

10. Run the add test program shown on page 4 of the drawings and verify that the results stored in memory bytes 5F5A, 5F5B, 5F5C, and 5F5D are correct.

| 0000         0000           0000         0000           0000         0000           0000         0000           0000         0000           0000         0000           0000         0000           0000         0000           0000         5F00         214ES           5F00         21         5F0           5F00         23         5F00           5F00         23         5F00           5F00         3EP         23           5F00         3EP         23           5F00         3EP         3EP           5F10         3EP         3EP           5F11         3EP         3EP           5F12         3D         5F12           3EP         3EP         3EP           5F22         7E         5F23           5F24         7E         5F28           5F36         3AF1D         5F38           5F38         3AF1D         5F38           5F38         3F48         23           5F44         23         5F44           5F48         3F48         77           5F38 <t< th=""><th>LDA FPGO<br/>NX H<br/>MOV A,M<br/>MOV A,M<br/>MOV A,M<br/>MOV A,M<br/>INX H<br/>MOV A,A<br/>INX H<br/>INX H<br/>MOV A,A<br/>INX H<br/>INX H<br/>IN</th><th>+ 4.321 = 103.1  NITIALIZE FPB CART INITIALIZE OWMAND AND PRECISION XPONENT IGITS IETUP DELAY LOOP IELAY LOOP</th><th>SEL88: (AN-3)     []     []     []     []       (MSCP - 10)    </th><th>HSY (CH-6)</th><th>GAFE UIUU UUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUU</th></t<> | LDA FPGO<br>NX H<br>MOV A,M<br>MOV A,M<br>MOV A,M<br>MOV A,M<br>INX H<br>MOV A,A<br>INX H<br>INX H<br>MOV A,A<br>INX H<br>INX H<br>IN | + 4.321 = 103.1  NITIALIZE FPB CART INITIALIZE OWMAND AND PRECISION XPONENT IGITS IETUP DELAY LOOP IELAY LOOP | SEL88: (AN-3)     []     []     []     []       (MSCP - 10) | HSY (CH-6) | GAFE UIUU UUUUUUUUUUUUUUUUUUUUUUUUUUUUUUUU |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|------------|--------------------------------------------|

| 1- 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |            |                                            |