#### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 1

INVENTORS --- P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L. J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J.D. LYONS, N.D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L.YOST & A. B. BRADEN, JR.

ΒY ù a en THEIR ATTORNEYS

Filed Dec. 15, 1959

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

3,112,394

Filed Dec. 15, 1959

#### P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

#### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 8

Vlin, des THEIR ATTORNEYS

THEIR ATTORNEYS

ŝ.

P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 12

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L. J. GOODRICK, E. Y. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J.D. LYONS, N.D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L.YOST & A. B. BRADEN, JR. BY

line onia a. b

THEIR ATTORNEYS

P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE 3,112,394

Filed Dec. 15, 1959

FIG.44A

INVENTORS - P. B. CLOSE, J.A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L.J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L.YOST & A.B. BRADEN, JR. BY line

THEIR ATTORNEYS

auen

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 17

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

THEIR ATTORNEYS

P. B. CLOSE ETAL

Nov. 26, 1963

INVENTORS -- P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, E. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

roa M. le

3,112,394

THEIR ATTORNEYS

P. B. CLOSE ETAL

Filed Dec. 15, 1959

ELECTRONIC COMPUTING MACHINE

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

THEIR ATTORNEYS

P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE 3,112,394

Filed Dec. 15, 1959

103 Sheets-Sheet 21

INVENTORS - P. B. CLOSE, J. A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L. YOST & A. B. BRADEN, JR. BY

cavender THEIR ATTORNEYS

#### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 22

BY

Duis a Kline Ø

THEIR ATTORNEYS

### P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE

3,112,394

Filed Dec. 15, 1959

THEIR ATTORNEYS

### P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE

3,112,394

Filed Dec. 15, 1959

103 Sheets-Sheet 24

Hauena THEIR ATTORNEYS

### P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE

3,112,394

Filed Dec. 15, 1959

THEIR ATTORNEYS

ELECTRONIC COMPUTING MACHINE

#### P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

#### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

THEIR ATTORNEYS

3,112,394

THEIR ATTORNEYS

15,

Filed Dec.

1959

Nov.

ELECTRONIC COMPUTING MACHINE σ Ξ CLOSE ETAL

3,112,394

103 Sheets-Sheet 33

26, 1963

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, R.P. MARVIN, W.L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L. YOST B. A. B. BRADEN, JR. BY

THEIR ATTORNEYS

P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE 3,112,394

Filed Dec. 15, 1959

103 Sheets-Sheet 35

INVENTORS --- P.B. CLOSE, J.A. COULTER, L.R. DITMER, R.P. FAHRENBRUCK, F.R. GOLDAMMER, L.J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J.D. LYONS, N.D. MANOR, R.P. MARVIN, W.L. MILLER, P.L. O'BRIAN, J.H. RANDALL, E.M. GARNER, R.O. SATHER, R.L.YOST & A.B. BRADEN, JR.

Juis a Kline

THEIR ATTORNEYS

Filed Dec. 15, 1959 [PIØ] 4186 Έ2 FIG. 59 .1058 oBdL 3104 -6030 Ild R 120 3096 41877 1059 JC 3105 o<u>Bc</u>L 6031 DÌ DI Ilc 120 人3097 ~1060 4188<sup>7</sup> BbL C 3106 6032 <sub>o</sub>Di DI) Ιb (120 -3098 4189 .IÕÕĬ CC 3107 BaL 6033 Ila\_\_\_\_O ۲3 (120) 3099 1062 4190 o<mark>BdL</mark> 3108 - 6034 o DØ DI IØd R (120) 3100 1063 419 o BcL ~3109 - 6035 o DØ D IØc Ô R **120** -3101 41927 1064 <u>о<mark>ВЫ</mark></u> Cr3110, 6036 D IØЬ R F3 (I2O) 3102 41937 -1065 BOL 6037 IØa R (120) -3103 4194>

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F.R.GOLDAMMER, L. J. GOODRICK, E.V.GULDEN, T. P. HOLLORAN, C. S. JENKINS, L.D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, BY R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

Kavend THEIR ATTORNEYS

ELECTRONIC COMPUTING MACHINE

INVENTORS- P.B. CLOSE, J.A. COULTER, L.R. DITMER, R.P. FAHRENBRUCK, F.R. GOLDAMMER, L.J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN C.S. JENKINS, L.D. KILLHEFFER, K.A. KINKER, J.D. LYONS, N.D. MANOR, R.P. MARVIN, W.L.MILLER, P.L. O'BRIAN, J.H. RANDALL E.M. GARNER, R.O. SATHER, R.L. YOST, & A.B. BRADEN, JR.

aues THEIR ATTORNEYS

ELECTRONIC COMPUTING MACHINE

INVENTORS P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. NILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR. BY HEIR ATTORNEYS

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

THEIR ATTORNEYS

#### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

INVENTORS — R. B. CLOSE, J. A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L. J. GOODRIGK, E.V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L. D. KILHEFFER, K.A. KINKER, J. D. HOLLORAN, MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L.YOST & A. B. BRADEN, JR.

n/ odvena

THEIR ATTORNEYS

P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

# P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE

3,112,394

lena THEIR ATTORNEYS

ELECTRONIC COMPUTING MACHINE

INVENTORS - P.B. GLOSE, J.A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W.L. MILLER, F.L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R.L. YOST & A. B. BRADEN, JR. BY

THEIR ATTORNEYS

P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, G.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L. O'BST & A. B. BRADEN, JR.

puis a Kline baues

THEIR ATTORNEYS

P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE 3,112,394

INVENTORS - P. B. CLOSE, J.A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, DWN I Kine R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR. BY

THEIR ATTORNEYS

P. B. CLOSE ETAL

103 Sheets-Sheet 51

ELECTRONIC COMPUTING MACHINE

1488

<u>MA</u>

CM

RI

SHF

0-

**FIG.73**

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

Carm.

THEIR ATTORNEYS

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 52

INVENTORS - P. B. CLOSE, J. A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINJ, L.D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARV.N, W. L. MILLER, P. L. O'BRIAN, J. H. RANDAL, E. N. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR. THEIR ATTORNEYS

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, G.S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W.L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L. YOST & A. B. BRADEN, JR. THEIR ATTORNEYS

Nov. 26, 1963

P. B. CLOSE ETAL

3,112,394

INVENTORS ----- P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M.GARNER, R.O. SATHER, R. L. YOST & A. B. BRADEN, JR. BY

THEIR ATTORNEYS

3,112,394

Nov. 26, 1963

ELECTRONIC COMPUTING MACHINE

INVENTORS - P.B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N.D. MANOR, R. P. MARVIN, W.L. MILLER, P. L. O'BRIAN, J. H. RANDALL E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR. THEIR ATTORNEYS

#### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Caven Ì THEIR ATTORNEYS

3,112,394

ELECTRONIC COMPUTING MACHINE

#### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

INVENTORS — P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR. THEIR ATTORNEYS

3,112,394

ELECTRONIC COMPUTING MACHINE

26, 1963

### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 65

Cavender THEIR ATTORNEYS

### P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 66

INVENTORS ----- P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A.B. BRADEN, JR. BY

Juie a Kline I Cavender

Ŭ THEIR ATTORNEYS

INVENTORS - P.B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P.L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

min en

THEIR ATTORNEYS

P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE 3,112,394

Filed Dec. 15, 1959

103 Sheets-Sheet 68

INVENTORS — P.B. CLOSE, J. A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A.B. BRADEN, JR.

Couis a R line вү 🖉 Haunder THEIR ATTORNEYS  $\not$

#### P. B. CLOSE ETAL

### 3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 69

INVENTORS

- NVENTORS P.B. CLOSE, J.A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L.J. GOODRICK, E.V. GULDEN, T.P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P.L. O'BRIAN, J. H. RANDALL, E.M. GARNER, R.O. SATHER, R. L.YOST & A. B. BRADEN, JR.

Arus a Kline Jour

THEIR ATTORNEYS

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 70

| the second se |    |

|-----------------------------------------------------------------------------------------------------------------|----|

| INVENTORS                                                                                                       |    |

| P. B. CLOSE, J.A. COULTER,                                                                                      |    |

| P. B. GLOSE, J.A. COULTER,<br>L.R. DITMER, R. P. FAHRENBRUG                                                     | к, |

| F. R. GOLDAMMER, L. J. GOODRIGK                                                                                 |    |

| E.V. GULDEN, T. P. HOLLORAN,                                                                                    |    |

| G. S. JENKINS, L.D. KILHEFFE                                                                                    | R. |

| K. A. KINKER, J. D. LYONS,                                                                                      |    |

| N.D. MANOR, R.P. MARVIN                                                                                         |    |

| W.L. MILLER, P.L. O'BRIAN,                                                                                      |    |

| J. H. RANDALL, E. M. GARNER                                                                                     |    |

| R. O. SATHER, R. L. YOST &                                                                                      | ., |

|                                                                                                                 |    |

| A. B. BRADEN, JR.                                                                                               |    |

| 1 -1                                                                                                            |    |

| Ani IVI                                                                                                         |    |

Ame Er avent

THEIR ATTORNEYS

BY

P. B. CLOSE ETAL

3,112,394

Nov. 26, 1963

mis a Kline ev. avender

3,112,394

THEIR ATTORNEYS

## P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 73

INVENTORS - P. B. CLOSE, J.A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L.J. GOODRICK, E.V. GULDEN, T.P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N.D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R.O. SATHER, R. L.YOST & A. B. BRADEN, JR.

Abuis a Kline avender

3,112,394

ELECTRONIC COMPUTING MACHINE

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

THEIR ATTORNEYS

ELECTRONIC COMPUTING MACHINE

INVENTORS ---- P. B. CLOSE, J.A. COULTER, L.R. DITMER, R. P.FAHRENBRUCK, F. R. GOLDAMMER, L.J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR. BY

ouis a and

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 88

INVENTORS — P. B. CLOSE, J.A. COULTER, L.R. DITMER, R. PFAHRENBRUCK, F.R. GOLDAMMER, L.J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J.D. LYONS, N.D. MANOR, R.P. MARVIN, W.L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M.GARNER, R.O. SATHER, R. L. YOST & A. B. BRADEN, JR.

INVENTORS ----- P. B. CLOSE, J.A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L.J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W.L. MILLER, P.L. O'BRIAN, J.H. RANDALL, E. M. GARNER, R.O. SATHER, R.L. YOST & A. B. BRADEN, JR.

P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 90

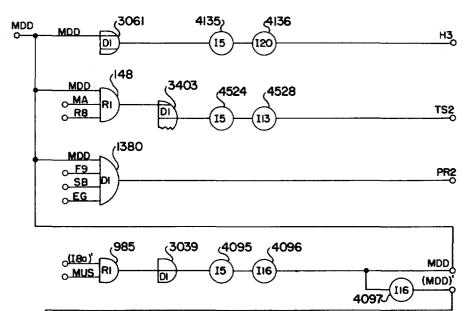

# **FIG. 101**

INVENTORS - P. B. CLOSE, J. A. COULTER, L.R. DITMER, R. P. FAHRENBRUCK, F.R. GOLDAMMER, L. J. GOODRICK, E.V. GULDEN, T. P. HOLLORAN, BY C.S. JENKINS, L.D. KILHEFFER, K. A. KINKER, J.D. LYONS, N.D. MANOR, R.P. MARVIN, W. L. MILLER, P.L. O'BRIAN, J.H. RANDALL, E.M. GARNER, R.O. SATHER, R.L. YOST & A.B. BRADEN, JR.

akline Ø Le. mun THEIR ATTORNEYS

ATTORNEYS

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 97

INVENTORS — P.B. CLOSE, J.A. COULTER, L.R. DITMER, R.P. FAHRENBRUCK, F.R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T.P. HOLLORAN, BY C.S. JENKINS, L.D. KILHEFFER, K.A. KINKER, J.D. LYONS, N.D. MANOR, R. P. MARVIN, W.L. MILLER, P.L. O'BRIAN, J.H. RANDALL, E. M. GARNER, R.O. SATHER, R. L. YOST & A.B. BRADEN, JR.

Souis a R liio nver

THEIR ATTORNEYS

P. B. CLOSE ETAL ELECTRONIC COMPUTING MACHINE 3,112,394

Filed Dec. 15, 1959

103 Sheets-Sheet 99

INVENTORS - P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, BY C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P. L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN

## P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 100

INVENTORS ---- P. B. CLOSE, J. A. COULTER, L. R. DITMER, R. P. FAHRENBRUCK, F. R. GOLDAMMER, L. J. GOODRICK, E. V. GULDEN, T. P. HOLLORAN, C. S. JENKINS, L. D. KILHEFFER, K. A. KINKER, J. D. LYONS, N. D. MANOR, R. P. MARVIN, W. L. MILLER, P.L. O'BRIAN, J. H. RANDALL, E. M. GARNER, R. O. SATHER, R. L. YOST & A. B. BRADEN, JR.

220 THEIR ATTORNEYS

P. B. CLOSE ETAL

ELECTRONIC COMPUTING MACHINE

2011 THEIR ATTORNEYS

## P. B. CLOSE ETAL

3,112,394

ELECTRONIC COMPUTING MACHINE

Filed Dec. 15, 1959

103 Sheets-Sheet 103

Sonial ender bai

20

60

## 1

#### 3,112,394

**ELECTRONIC COMPUTING MACHINE** Patrick B. Close and James A. Coulter, Dayton, Lowell R. Ditmer, Laura, Roy P. Fahrenbruck, Madeira, Freeland R. Goldammer and Le Roy J. Goodrick, Dayton, Ernest V. Gulden, Centerville, and Thomas P. Holloran, Dayton, Ohio, Charles S. Jenkins, Lexington, Ky., Lawrence D. Kilheffer, Karl A. Kinker, and James D. Lyons, Dayton, Neil D. Manor, Xenia, Richard P. Marvin, William L. Miller, Paul L. O'Brian, and James H. Randall, Dayton, and Edward M. Gar-<sup>10</sup> ner, Centerville, Ohio, Roy O. Sather, Dearborn, Mich., and Robert L. Yost and Arthur B. Braden, Jr., Dayton, Ohio, assignors to The National Cash Register Company, Dayton, Ohio, a corporation of Maryland Filed Dec. 15, 1959, Ser. No. 859,598 10 Claims. (Cl. 235-61.9) 15

The present invention relates generally to electronic computing devices and more particularly relates to a unique, low cost, general purpose type of electronic digital computing device.

With the ever-increasing enormity and complexity of record keeping and accounting systems in the business world of today, there is accordingly an ever-increasing demand, by necessity, for the adaptation and utilization 25of high-speed mechanization techniques compatible with such systems. Even though the installation of large scale data processors and electronic computing equipment has partially satisfied the needs of the larger business establishments, unfortunately they are not economically within the realm of practical usage by the smaller business 30 establishments. Consequently, the long-felt need by smaller businesses is yet to be satisfied.

Therefore, one of the principal objects of the present invention is to devise a new and improved low-cost electronic digital computer, which is of the general purpose 35 type in that it possesses substantially unlimited arithmetic and programming capabilities and yet is characterized by extreme simplicity of operation and compatibility with present-day record keeping and accounting systems.

Another object of the present invention is to devise a unique electronic computer having the characteristics aforesaid and which utilizes a commercially available accounting machine as one of its several input-output means in a manner such that the printing format is controlled  $\mathbf{45}$ almost entirely by the accounting machine and thereby minimizing memory space necessary for printing formatcontrol.

Still another object of the present invention is to devise a unique electronic computer having the characteristics 50aforesaid and which utilizes a serial-digit data-transfer technique and an addressable, random access, coincidentcurrent magnetic core memory synchronized to its several input-output devices in a novel manner to alleviate the necessity of extensive buffering to effect communication 55 with the devices.

A further object of the present invention is to devise an ambiguous-word type computer having the characteristics aforesaid and which is capable of utilizing, in an extremely simple manner, an address incrementing and decrementing format for an internally stored program whereby a single instruction of the program is capable of initiating a sequence of like operations on a multitude of word significations.

Another object of the present invention is to devise such 65a new and improved low-cost computer which is adapted to utilize input media in the form of data-carrying ledger cards, each having recorded thereon a combination of historical, current, and fixed data which is not only human-readable, but additionally is machine-readable and readily adaptable for computational purposes.

Still another object of the present invention is to devise a unique computer of the above-mentioned characteristics 2

which not only utilizes the data carried by the ledger card media and other input media in addition to key-board entry data to perform all calculations involved in a computing operation, but additionally, as an incident to the computing operation, updates the ledger card data in both its printed human-readable and its magnetically-recorded machine-readable sections and is thereby capable of producing a printed journal sheet and other output documents, if desired.

A further object of the present invention is to devise a novel low-cost computer which is capable of suppressing all insignificant digits while updating the ledger card data in both its printed human-readable and magneticallyrecorded machine-readable sections.

And another object of the present invention is to devise a new and improved low-cost transistorized computer which does not require air conditioning and which utilizes inexpensive resistor logic and transistor flipflop control circuitry which perform multiple functions and thus maintain the cost of the computer at a minimum.

The features of the present invention which are believed to be novel are set forth with particularity in appended claims. The organization and manner of operation of the invention, together with further objects and advantages thereof, may best be understood by reference to the following description taken in connection with the accompanying drawings, in the several figures of which like reference characters identify like elements, and in which:

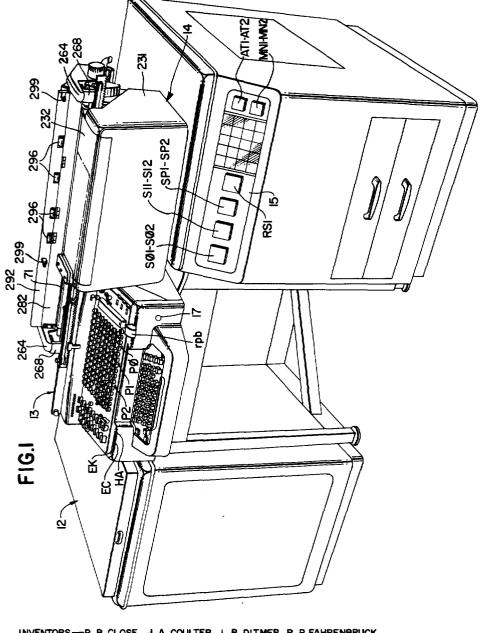

FIG. 1 is a perspective view of the novel computer constructed in accordance with the present invention;

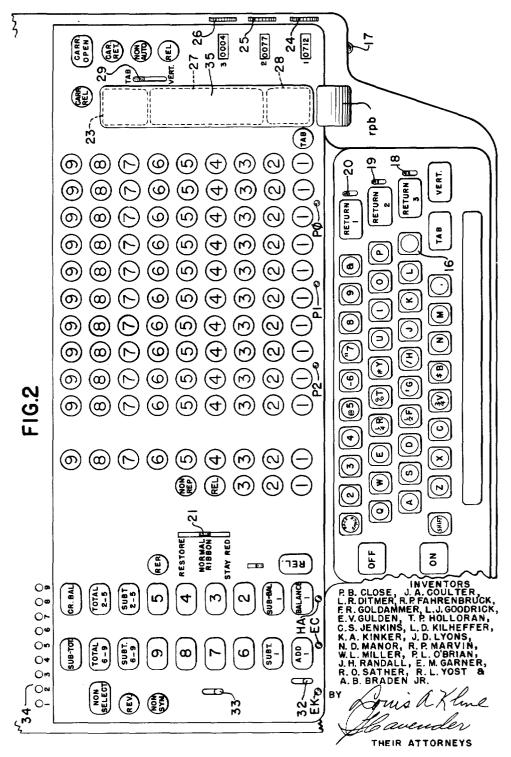

FIG. 2 is a plan view of the keyboard of the accounting machine portion of the computer;

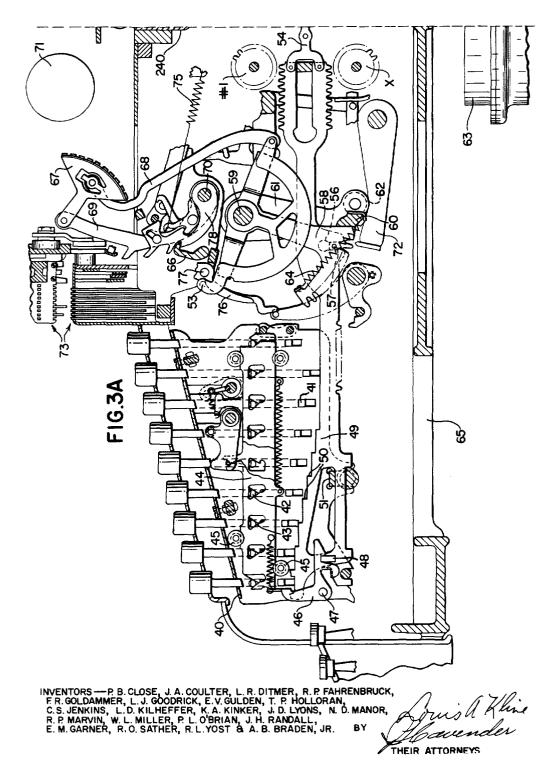

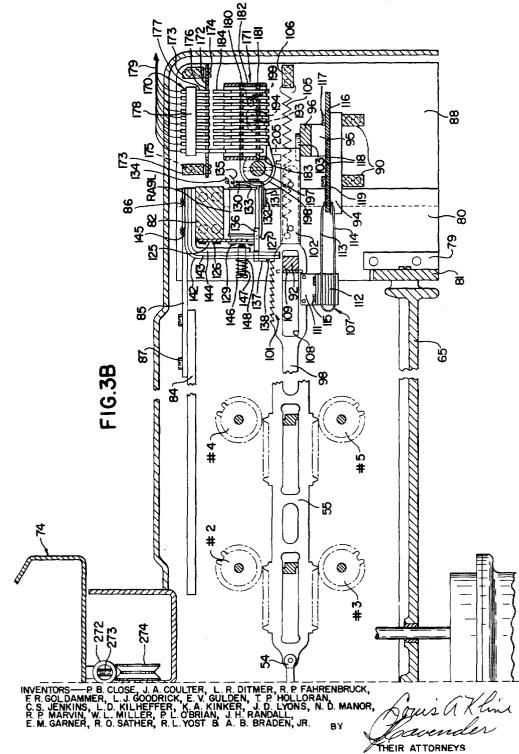

FIGS. 3A and 3B, when joined together at the dashed lines, form a longitudinal cross-sectional view of the accounting machine portion of the computer;

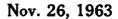

FIG. 4 is a plan view, partly in section, of the mechanism utilized in accordance with the present invention for stopping the amount racks of the accounting machine portion

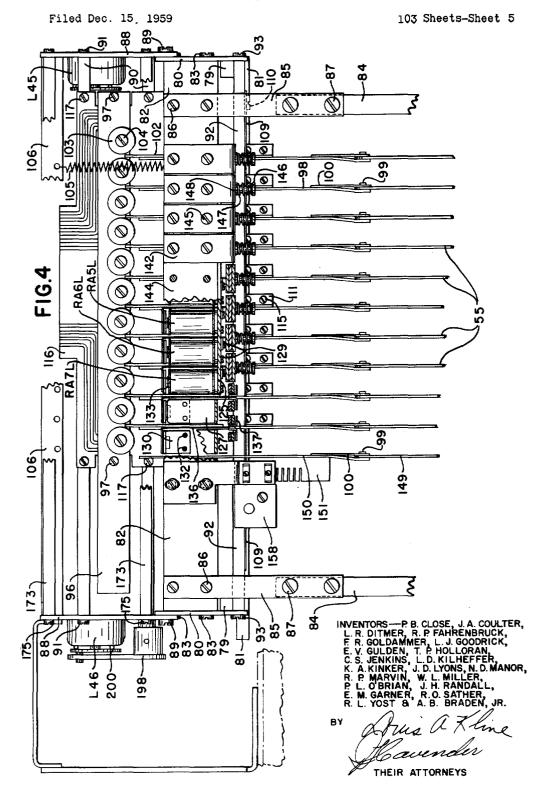

FIG. 5A is a plan view showing the conductor pattern disposed on the top surface of the printed-circuit board utilized for determining the stopped positions of the amount racks;

FIG. 5B is a plan view showing the conductor pattern disposed on the bottom surface of the printed-circuit board utilized for determining the stopped positions of the amount racks;

FIG. 5B is a plan view showing the conductor pattern disposed on the bottom surface of the printed-circuit board shown in FIG. 5A.

FIG. 6 is an exploded view of one of the various solenoid actuated mechanisms utilized for selectively stopping an amount rack;

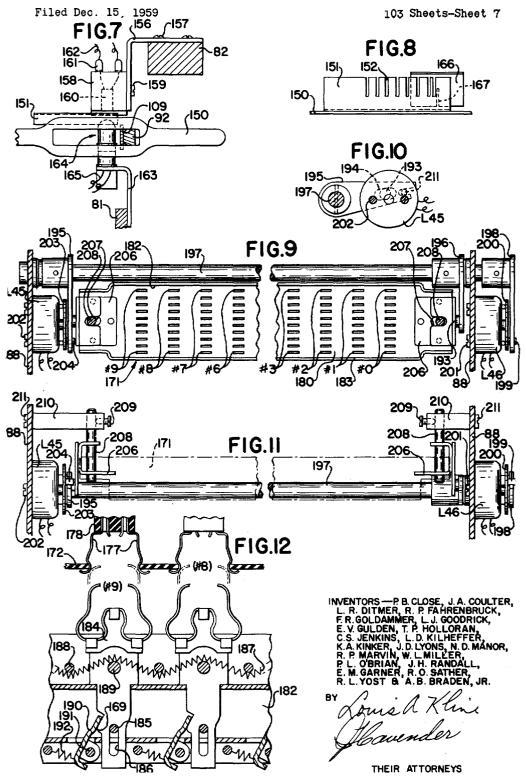

FIG. 7 is a fragmentary view of the photoelectric means utilized for indicating the instantaneous point-by-point digital positions of the various amount racks;

FIG. 8 is a plan view of the timing rack comb utilized by the photoelectric means of FIG. 7;

FIG. 9 is a plan view of the solenoid-actuated switch basket means utilized for determining the stopped positions of the various amount racks;

FIG. 10 is a partial end view of the mechanism shown in FIG. 9:

FIG. 11 is a partial front view of the mechanism shown in FIG. 9;

FIG. 12 is a fragmentary cross-sectional view of the basket portion of FIG. 9;

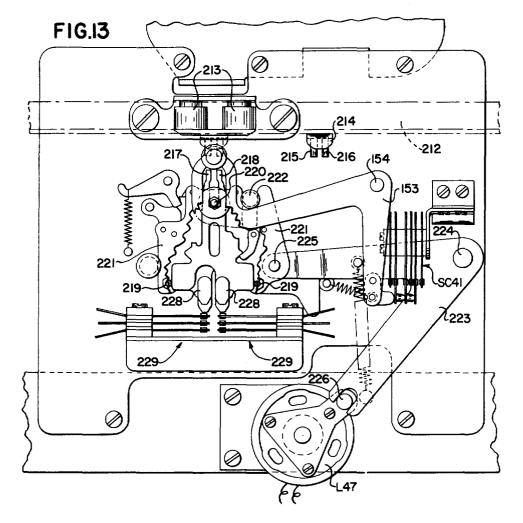

FIG. 13 is a plan view of the solenoid-actuated rear 70 form-bar readout mechanism utilized by the card and paper tape punching mechanisms for sensing the position of the accounting machine carriage;

20

50

75

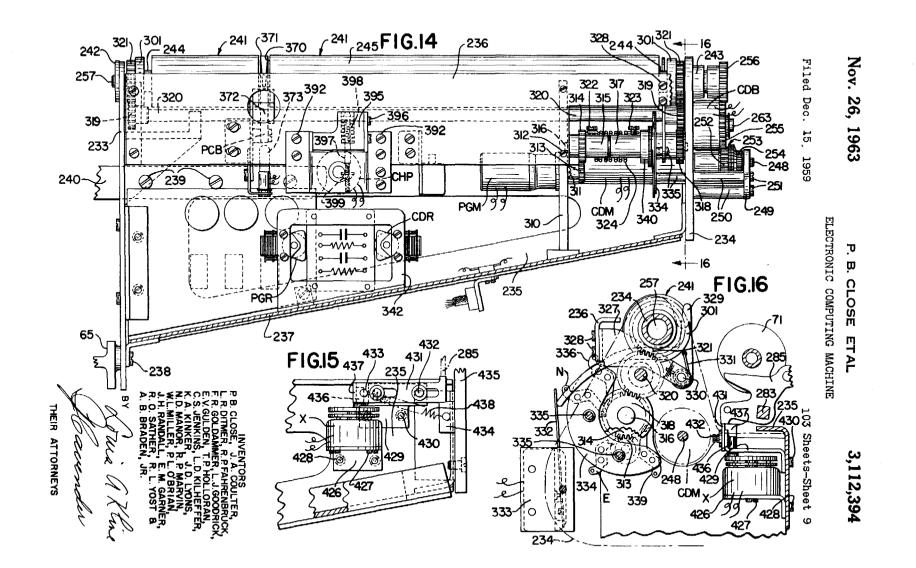

FIG. 14 is a front view of the ledger card handling mechanism shown in FIG. 1 with the cover and table portions thereof removed;

FIG. 15 is a partial front view of the solenoid-actuated mechanism shown in FIG. 16 which is utilized for selec-5tively preventing the lower compression rolls from being disengaged from the accounting machine platen;

FIG. 16 is a partly cross-sectional view taken along lines 16-16 of FIG. 14;

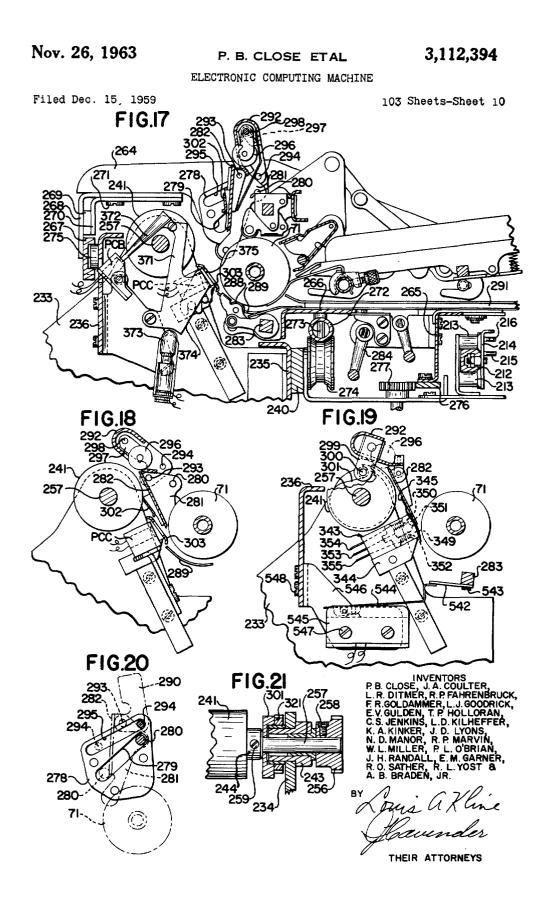

FIG. 17 is a partly cross-sectional view showing the 10 relationship between the ledger card handling equipment and the accounting machine carriage;

FIG. 18 is a partial view of FIG. 17 showing the relationship between the compression rollers, the cardhandling platen and the accounting machine platen when 15 the carriage of the accounting machine is open;

FIG. 19 is a partial view of FIG. 17 showing the compression rollers latched against the card-handling platen, and, additionally showing the relative position of the magnetic recording and reproducing heads;

FIG. 20 is a partial view of FIG. 17 showing the construction of the slotted side-plate portion of the accounting machine carriage;

FIG. 21 is a fragmentary cross-sectional view of a portion of the card-handling platen driving mechanism 25 riage stop; shown in FIG. 14;

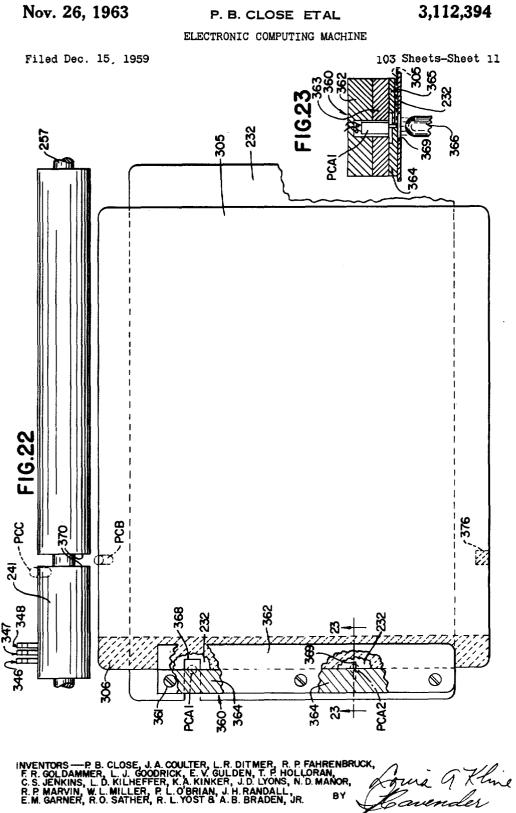

FIG. 22 is a plan view, partly in section, of a portion of the card-handling mechanism shown in FIG. 1;

FIG. 23 is a fragmentary cross-sectional view of the ledger card guide assembly shown in FIG. 22; 30

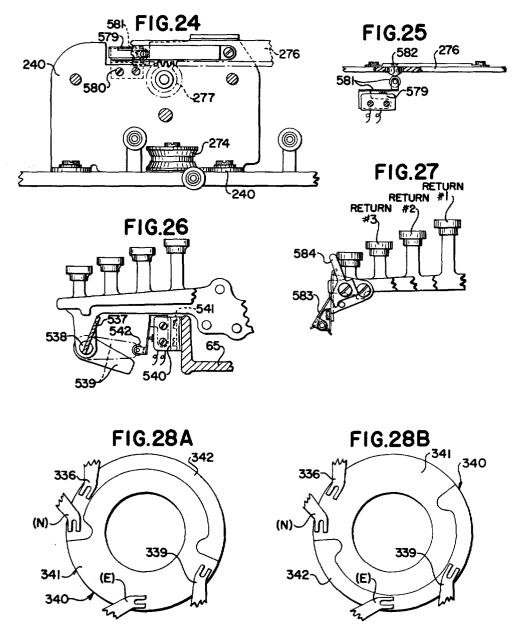

FIG. 24 is a partial plan view of the rear rack driving means shown in FIG. 17 which is utilized for effecting linear translation of the accounting machine carriage;

FIG. 25 is a fragmentary view, partly in section, of FIG. 24 showing the switching means utilized for detect- 35 lines, form a simplified block diagram of the computer ing home position of the accounting machine carriage;

FIG. 26 is a fragmentary view, partly in section, of the means utilized for preventing a typewriter key on the accounting machine keyboard from being depressed while the accounting machine is carrying-out a cycle of opera- 40 tion;

FIG. 27 is a fragmentary view of the means utilized for manually locking the typewriter carriage-return keys;

FIG. 28A illustrates the rotatable position of the commutator switching means, initially shown in FIG. 14, 45 when the compression rollers are latched with respect to the ledger card drive platen;

FIG. 28B illustrates the rotatable position of the commutator switching means when the compression rollers are unlatched from the ledger card drive platen;

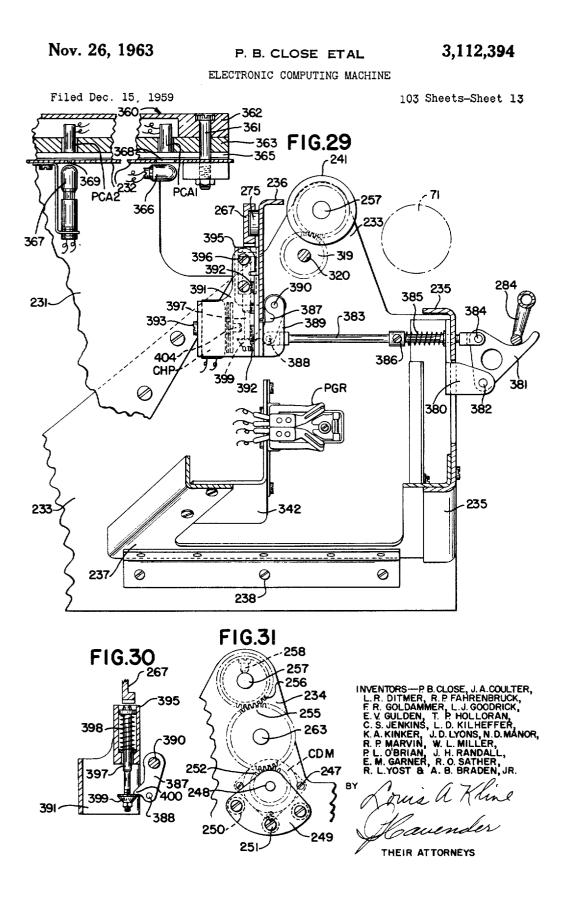

FIG. 29 is a fragmentary cross-sectional view longitudinally taken through the ledger card handling mechanism:

FIG. 30 is a fragmentary cross-sectional view of the 55solenoid-actuated means shown in FIG. 29 which is utilized for selectively locking the accounting machine carriage in home position;

FIG. 31 is a fragmentary view of the card-drive platenbraking means shown in FIG. 15;

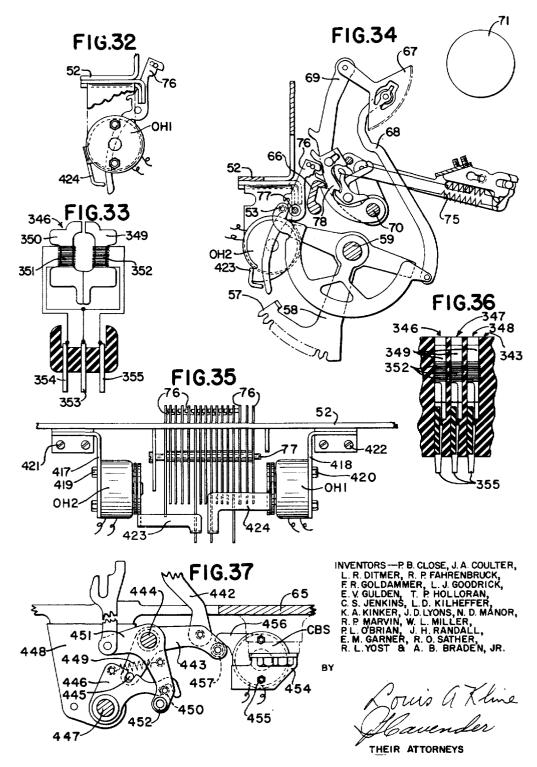

FIG. 32 is a fragmentary view of the solenoid means 60utilized for automatically unlatching selected low-order ones of the order-hooks of the accounting machine from their respective type-sectors;

FIG. 33 is a side view, partly in section, of one of the 65magnetic recording and reproducing heads utilized by the computer in accordance with the present invention;

FIG. 34 is a partial side view, partly in section, of the solenoid-actuated type-sector latching and unlatching mechanism;

FIG. 35 is a partial plan view of the solenoid-actuated type-sector latching and unlatching mechanism shown in FIG. 34;

FIG. 36 is a fragmentary cross-sectional view of the composite magnetic recording and reproducing head assembly utilized by the computer;

FIG. 37 is a fragmentary view, partly in section, of a portion of the linkage of the overdraft control mechanism of the accounting machine;

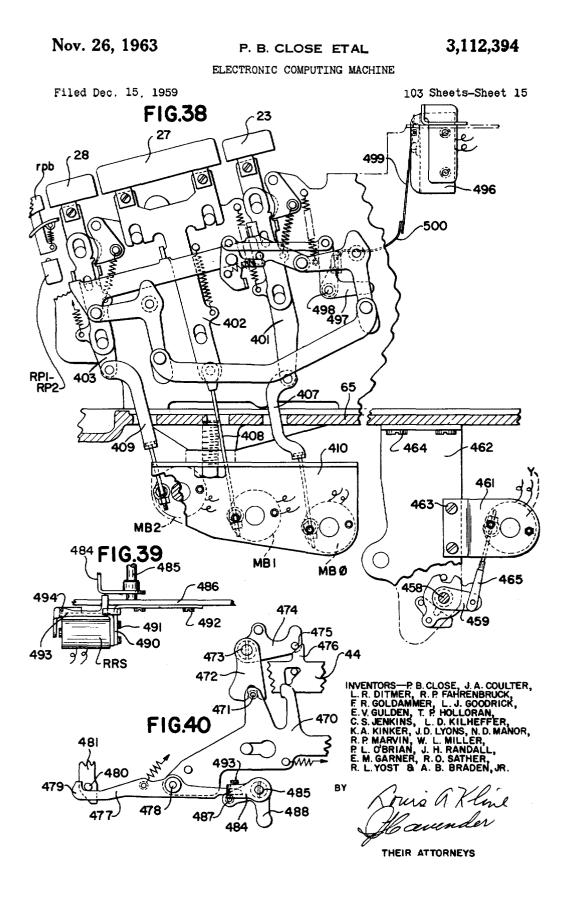

FIG. 38 is a side elevational view of a portion of the cycle-initiating motor-bar mechanism of the accounting machine and the solenoid-actuated means utilized for automatically effecting selective operation thereof;

FIG. 39 is a fragmentary view of the solenoid-actuated means which is utilized to selectively prevent an early release of a depressed amount key during an addition or

subtraction cycle of operation of the accounting machine; FIG. 40 is a fragmentary view of the portion of the accounting machine mechanism which is utilized in initiating a total-taking cycle of operation thereof;

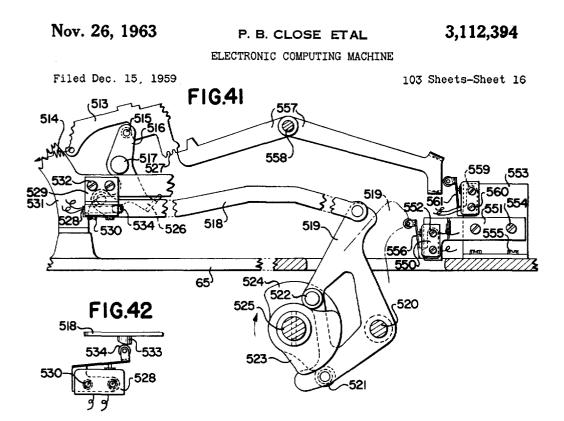

FIG. 41 is a fragmentary view of the reverse tabulation mechanism of the accounting machine;

FIG. 42 is a fragmentary view of the switching means shown in FIG. 41 which is utilized in detecting whether or not the accounting machine is in the process of carrying out a cycle of operation thereof;

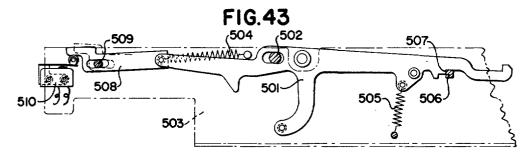

FIG. 43 is a fragmentary view of the accounting machine forward-tabulating lever and the switching means associated therewith utilized in detecting whether or not the accounting machine carriage is tabulating over a car-

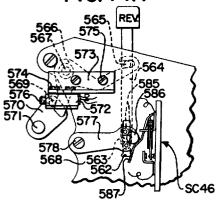

FIG. 44A is a fragmentary view of the totalizer reverse key and the mechanism associated therewith;

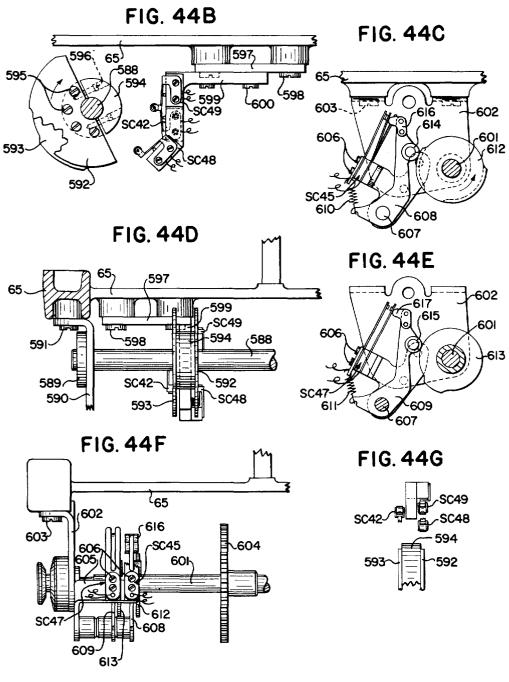

FIGS. 44B through 44G are fragmentary views of various cam actuated switching means which are utilized to effect selective energization of the paper tape punching mechanism shown in FIG, 44H;

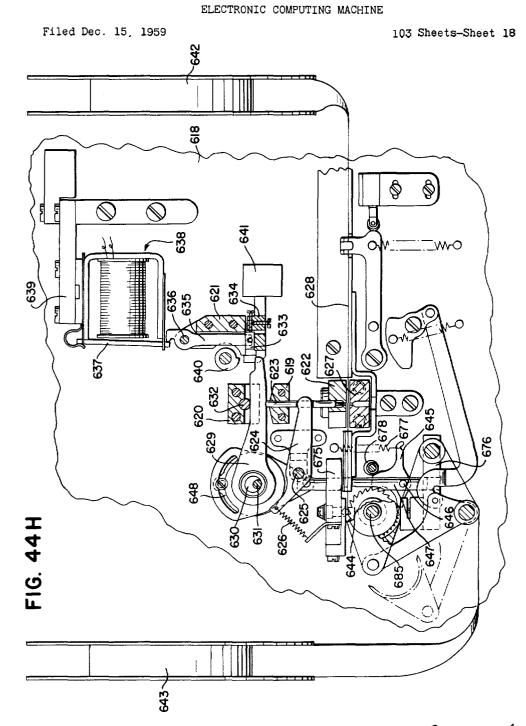

FIG. 44H is a partial side elevational view of the paper tape punching mechanism utilized by the computer;

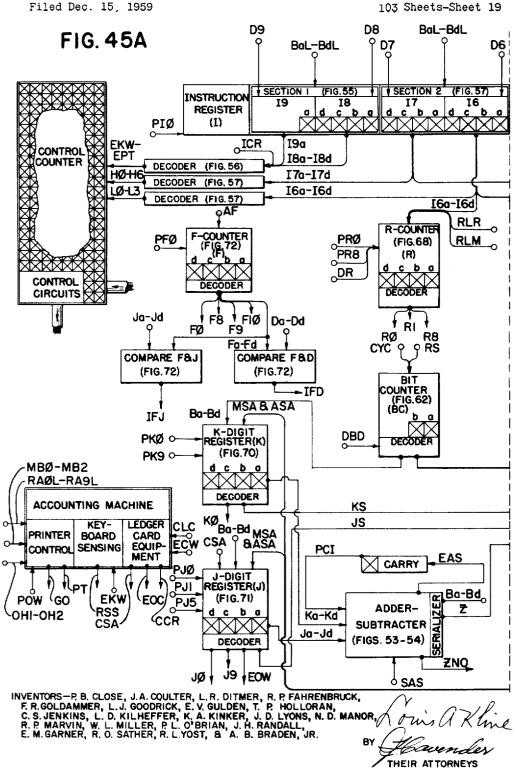

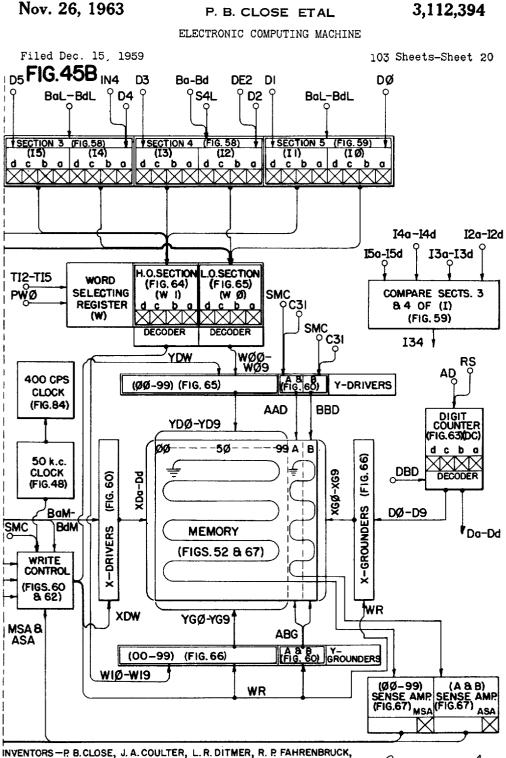

FIGS. 45A and 45B, when joined together at the dashed circuitry;

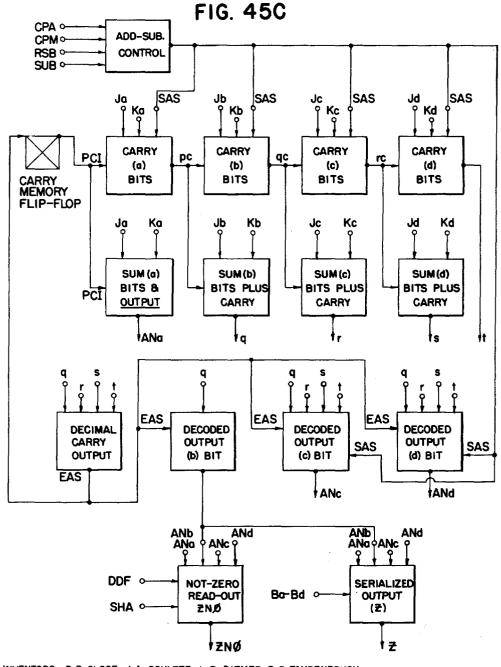

FIG. 45C is a simplified block diagram of the addersubtracter portion of the computer circuitry;

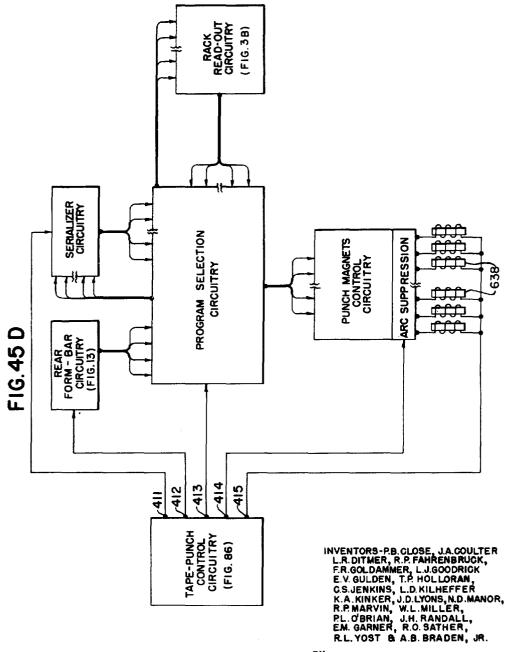

FIG. 45D is a simplified block diagram of the paper tape punch control circuitry;

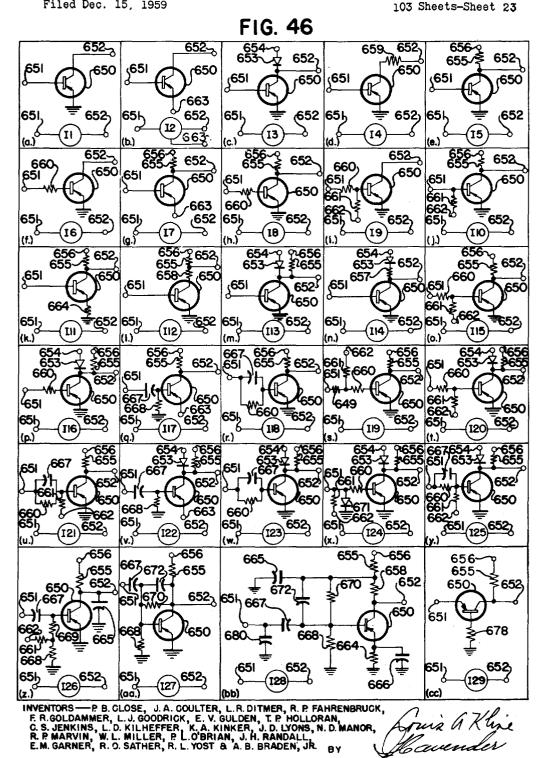

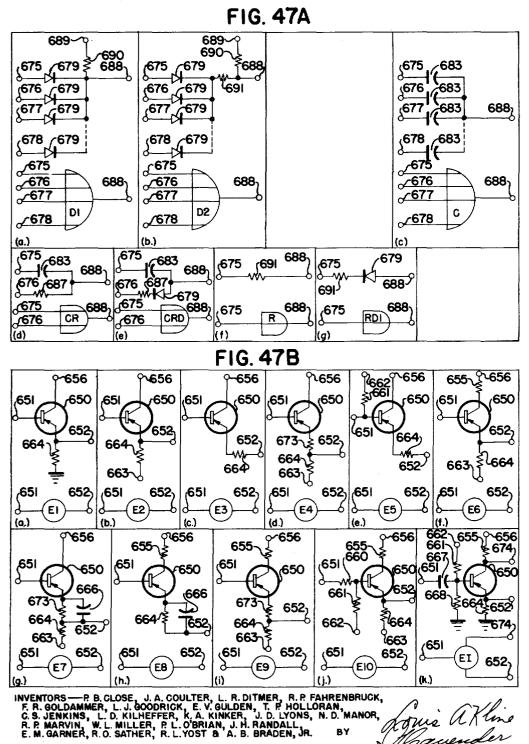

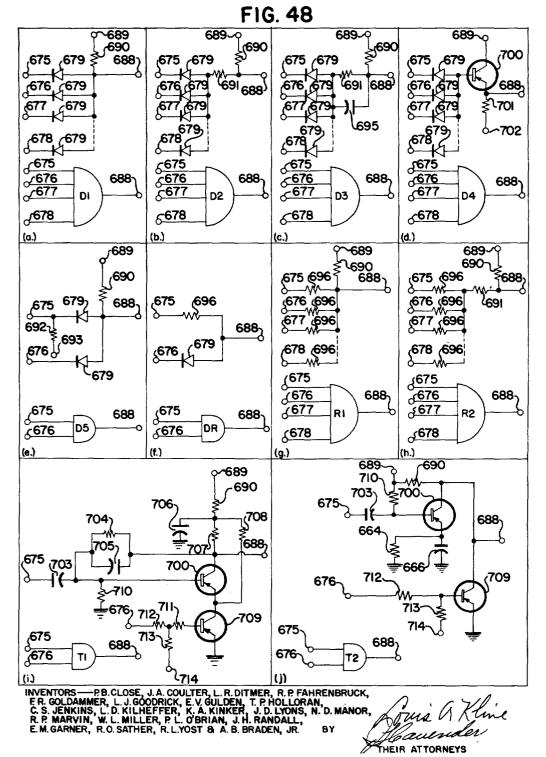

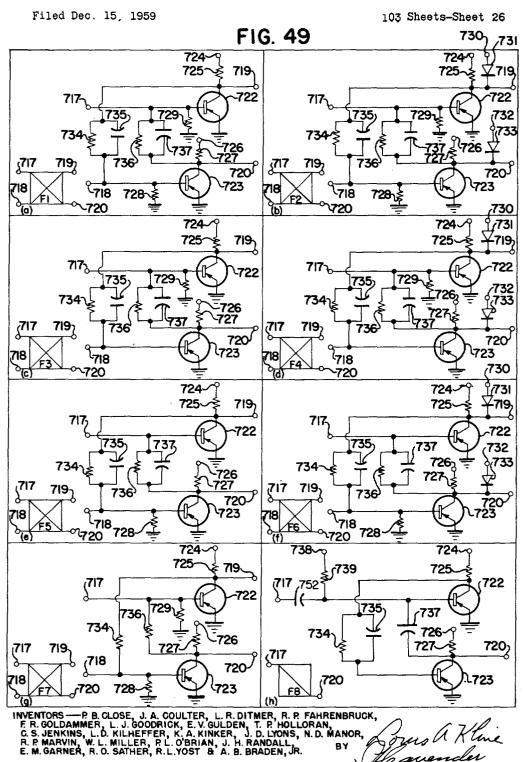

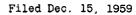

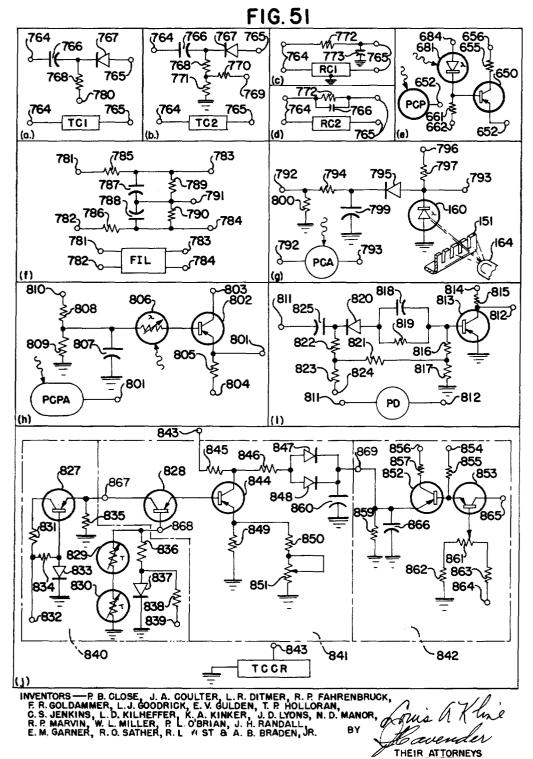

FIGS. 46 through 51 disclose the schematic circuit diagrams of all of the various building blocks utilized in constructing the circuitry portion of the computer;

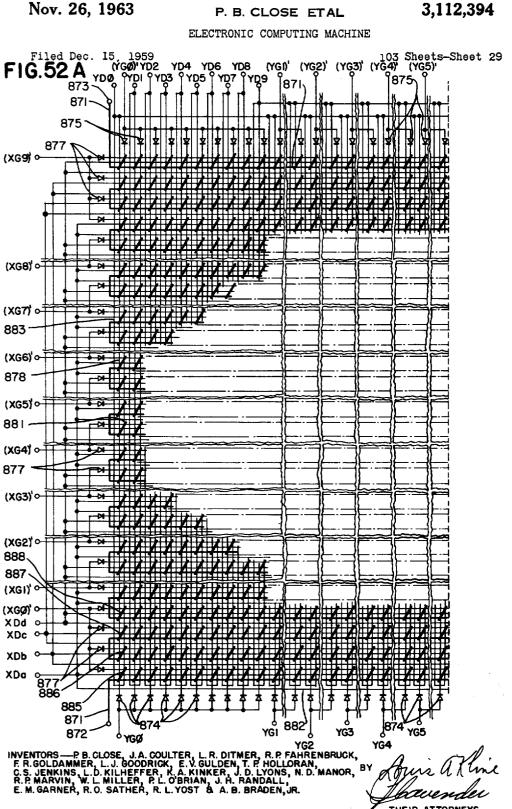

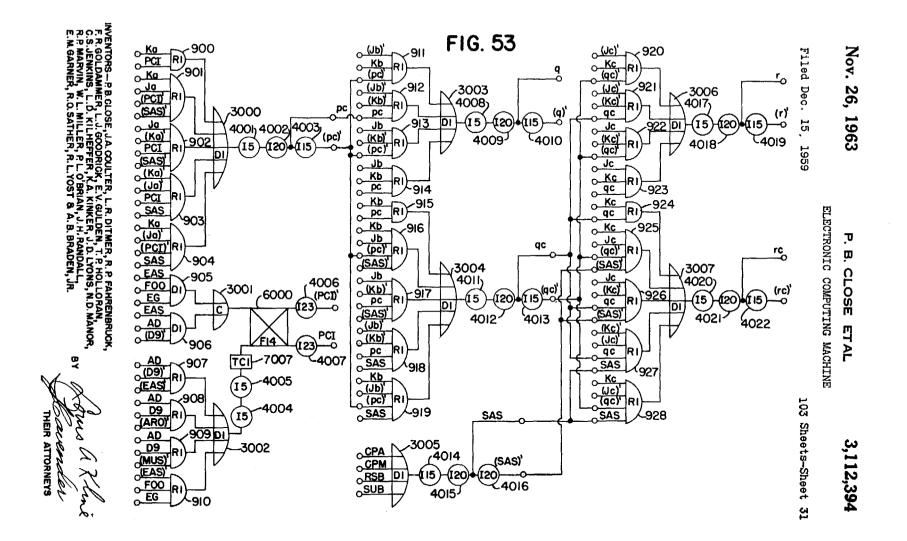

FIGS. 52A and 52B, when joined at the dashed lines, form a schematic circuit diagram of the coincident-current magnetic core memory;

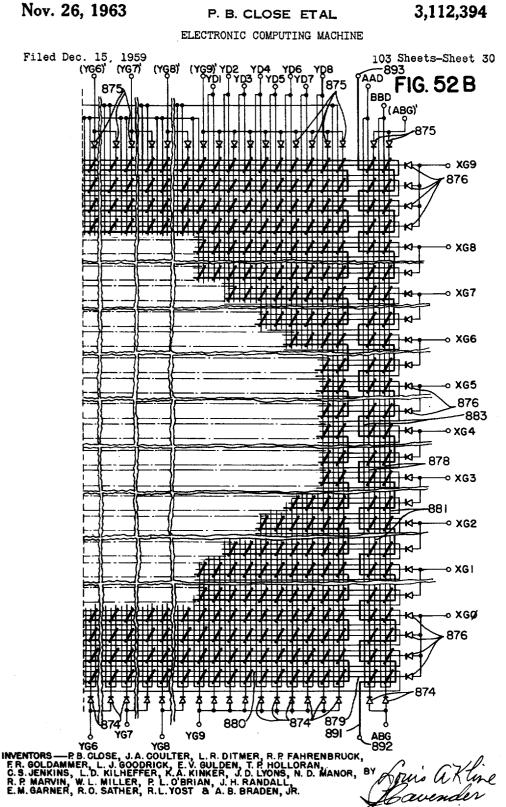

FIG. 53 is a portion of the logical diagram of the adder-subtracter circuitry;

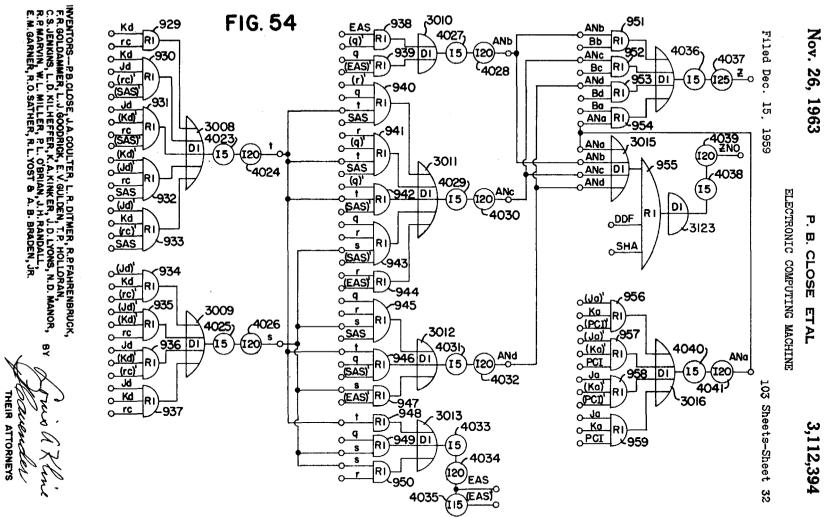

FIG. 54 is the remaining portion of the logical diagram of the adder-subtracter circuitry;

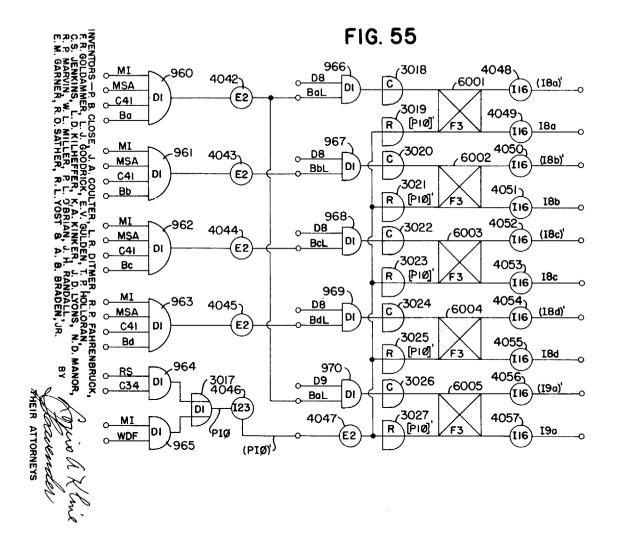

FIG. 55 is a logical diagram of section 1 of the instruction register;

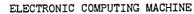

FIG. 56 is a logical diagram of the decoder portion of section 1 of the instruction register;

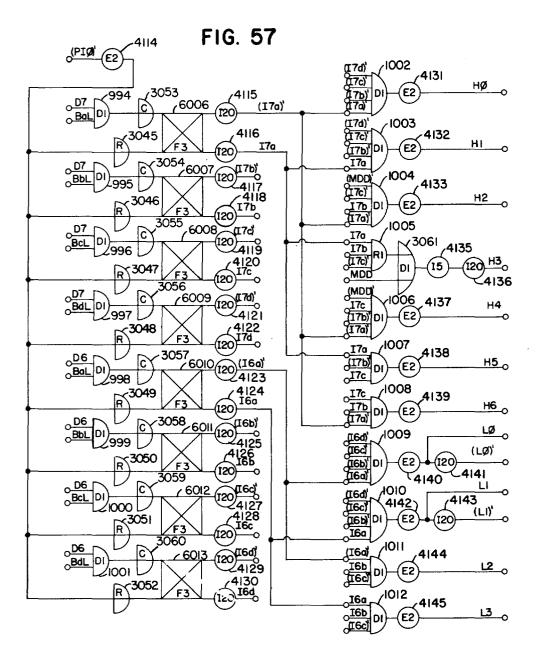

FIG. 57 is a logical diagram of section 2 of the instruction register;

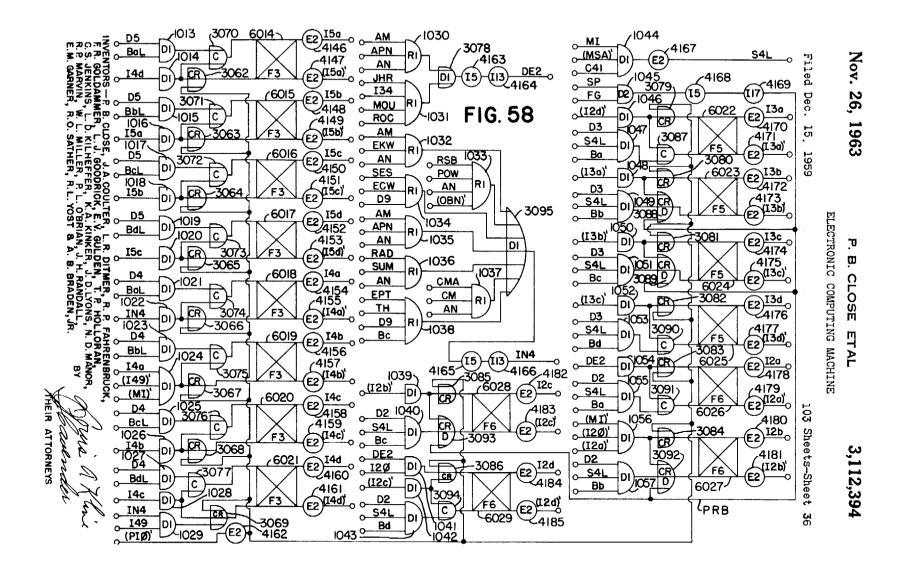

FIG. 58 is a logical diagram of sections 3 and 4 of the instruction register;

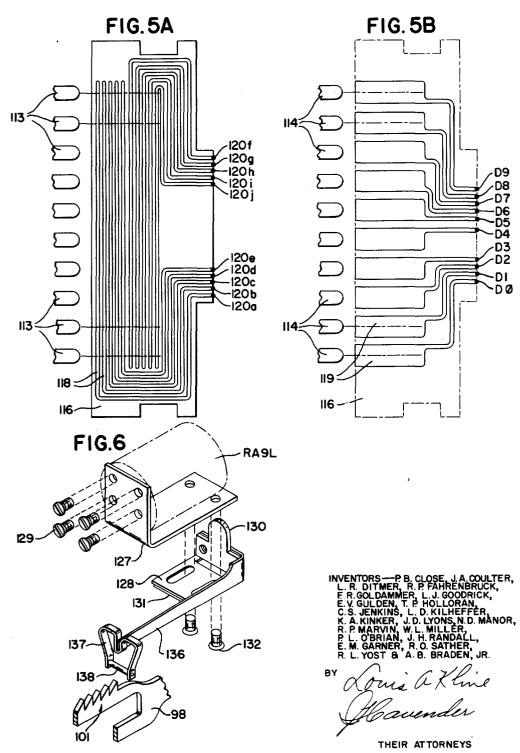

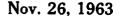

FIG. 59 is a logical diagram of section 5 of the instruction register and the compare circuitry relating to sections 3 and 4 of the instruction register;

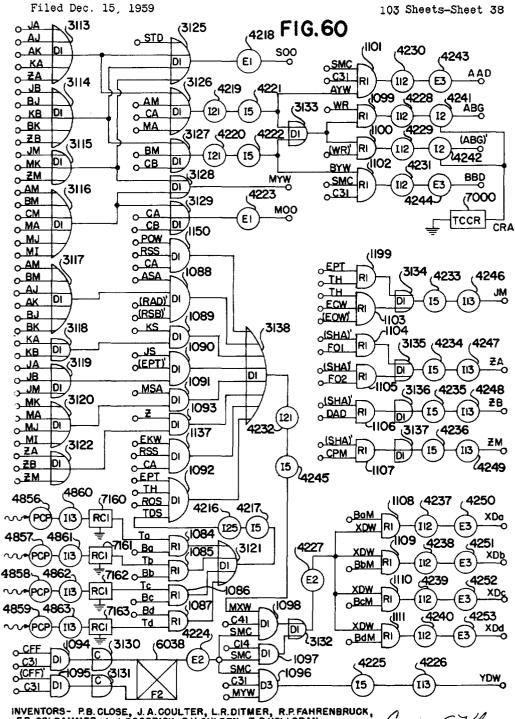

FIG. 60 is a portion of the logical diagram of the read-write, digit-cycle, word-cycle and subcommand initiating circuitry;

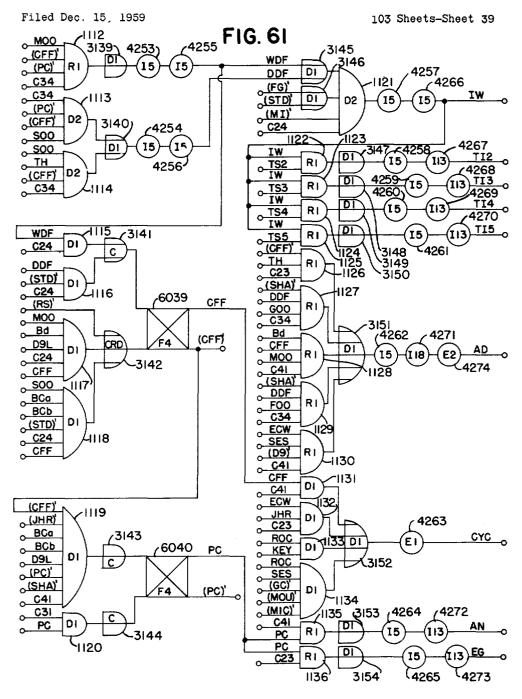

FIG. 61 is an additional portion of the logical diagram of the read-write, digit-cycle, word-cycle and subcommand initiating circuitry;

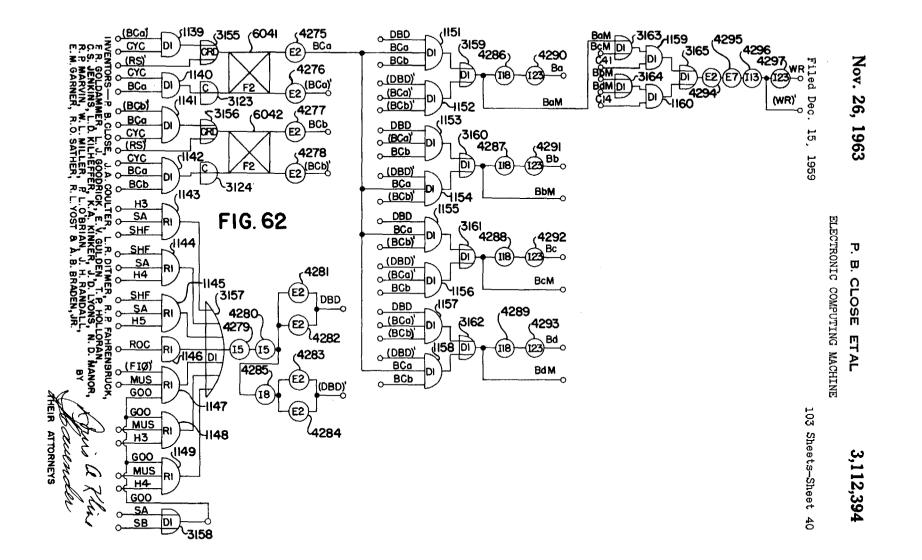

FIG. 62 is a logical diagram of the bit-counter;

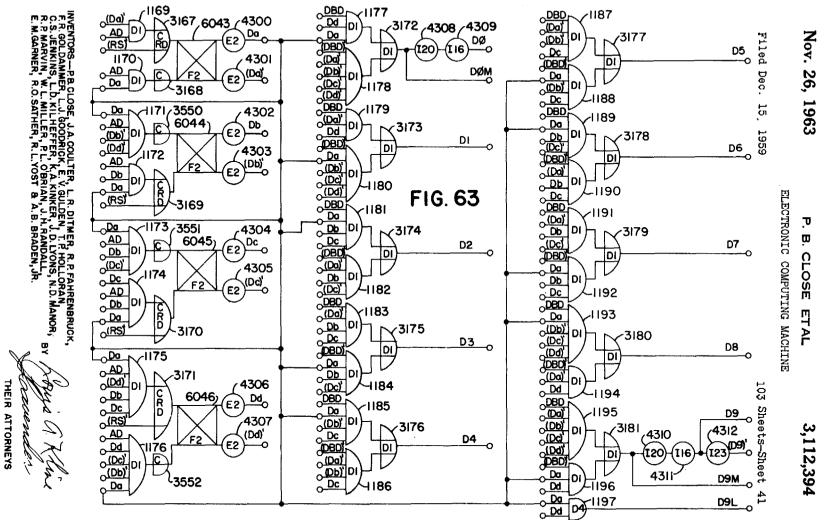

FIG. 63 is a logical diagram of the digit-counter;

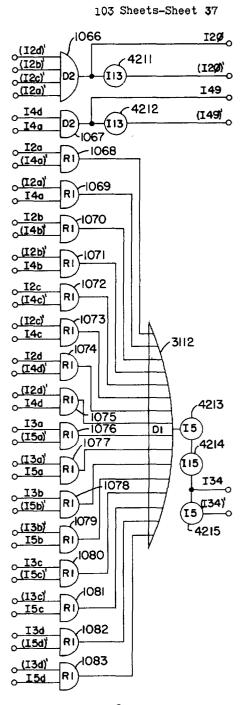

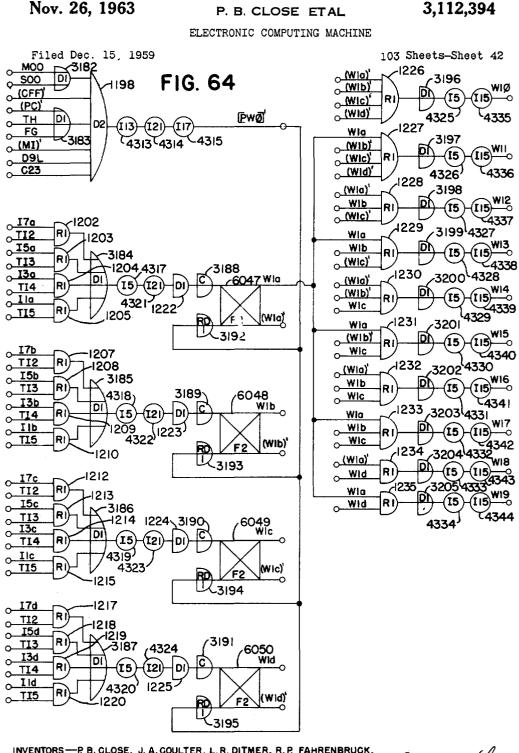

FIG. 64 is a logical diagram of the high-order section of the word-selecting register;

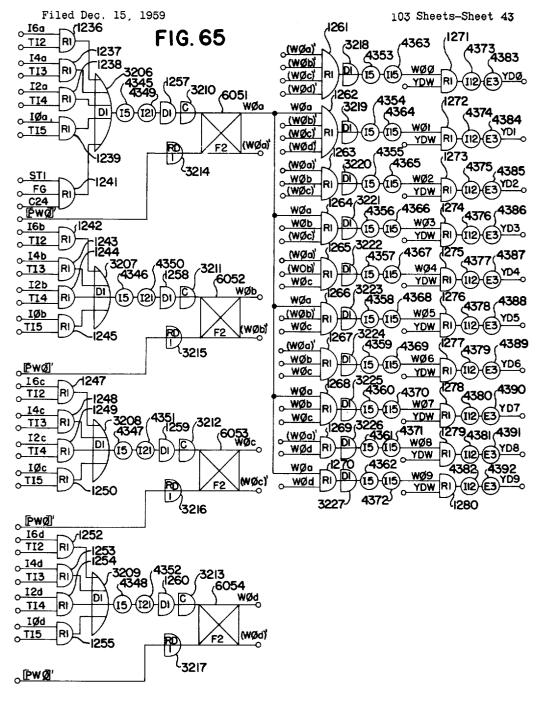

FIG. 65 is a logical diagram of the low-order section of the word-selecting register and a logical diagram of the Y-drivers;

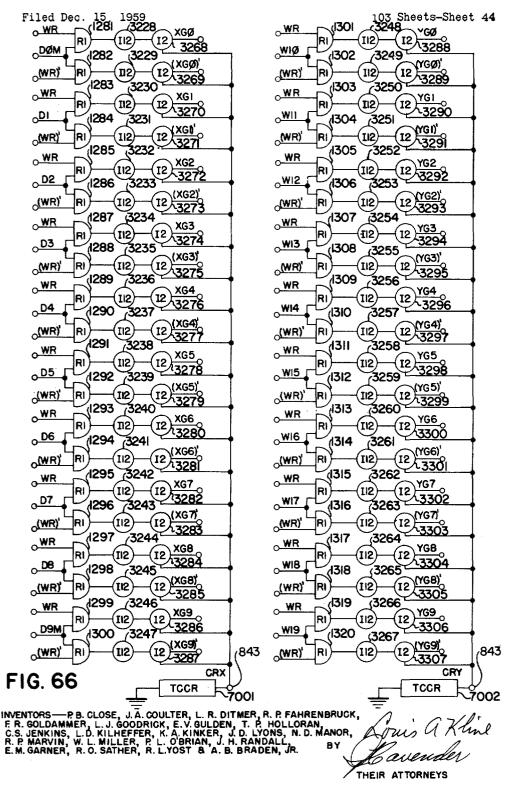

FIG. 66 is a logical diagram of the X and Y grounders;

$\mathbf{5}$

15

20

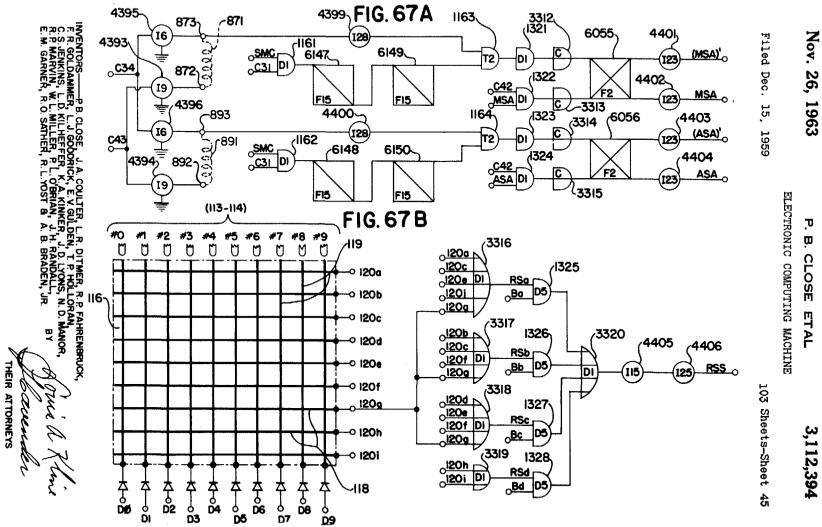

FIG. 67A is a logical diagram of the memory sense amplifiers;

FIG. 67B is a logical diagram of the rack-readout circuitry;

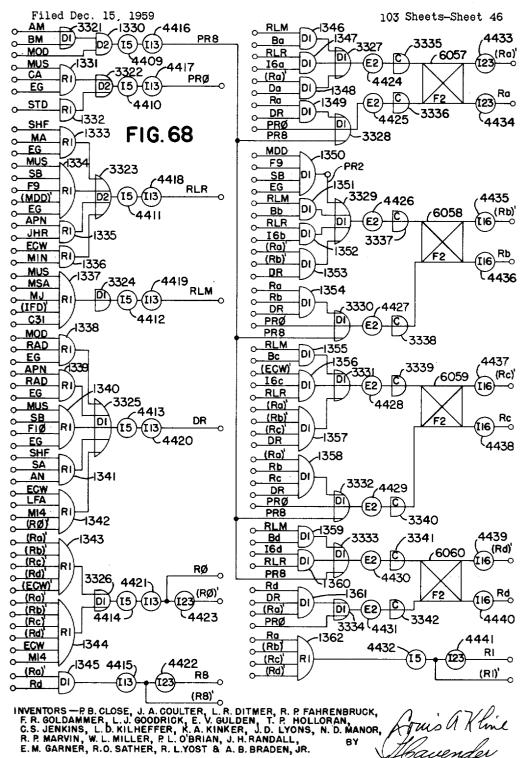

FIG. 68 is a logical diagram of the R-counter;

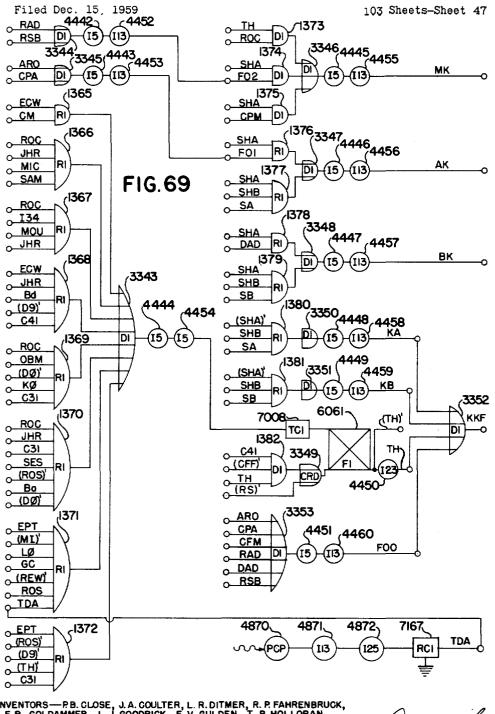

FIG. 69 is a logical diagram of a portion of the digitcycle initiating circuitry;

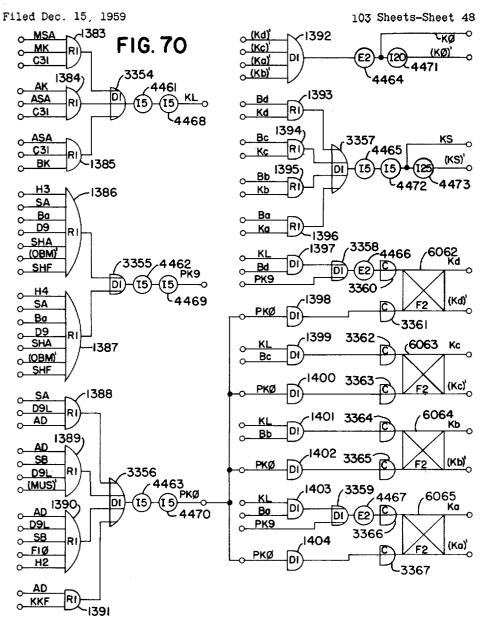

FIG. 70 is a logical diagram of the "K" digit-register and associated circuitry;

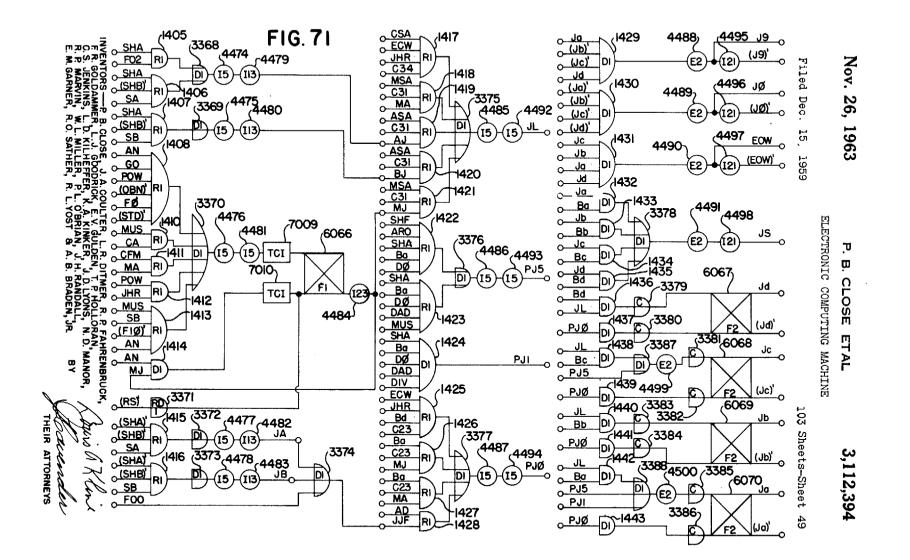

FIG. 71 is a logical diagram of the "J" digit-register 10and associated circuitry;

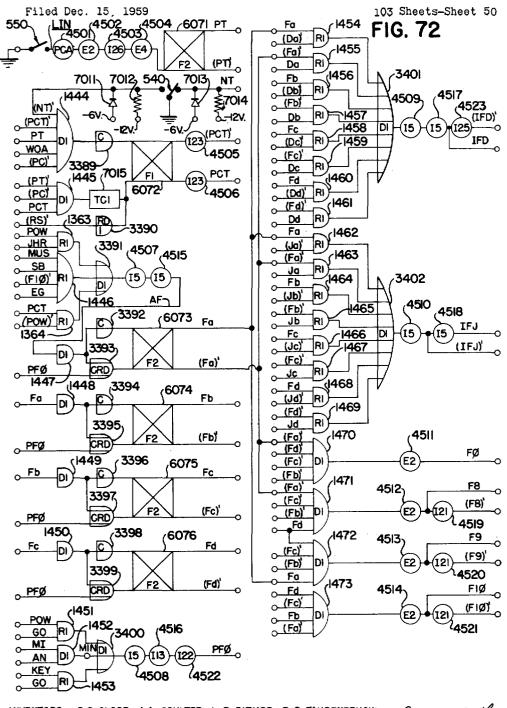

FIG. 72 is a logical diagram of the F-counter and compare circuitry;

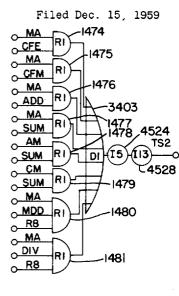

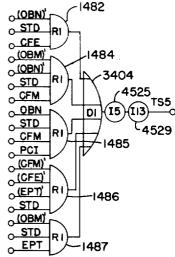

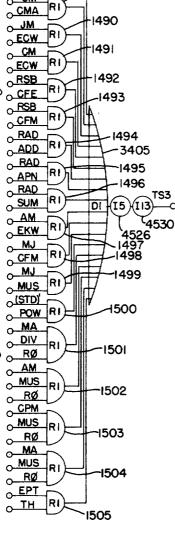

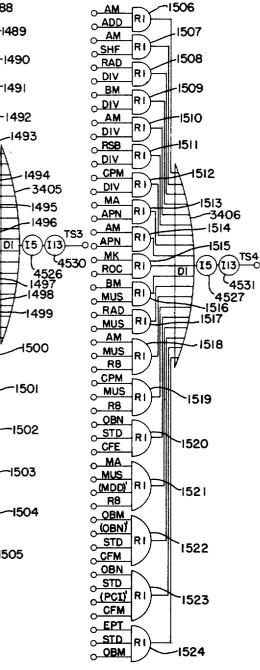

FIG. 73 is a logical diagram of the instruction register transfer circuitry;

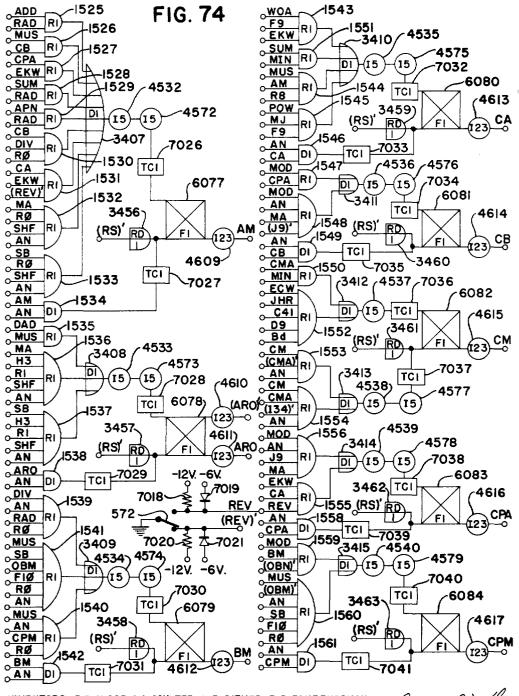

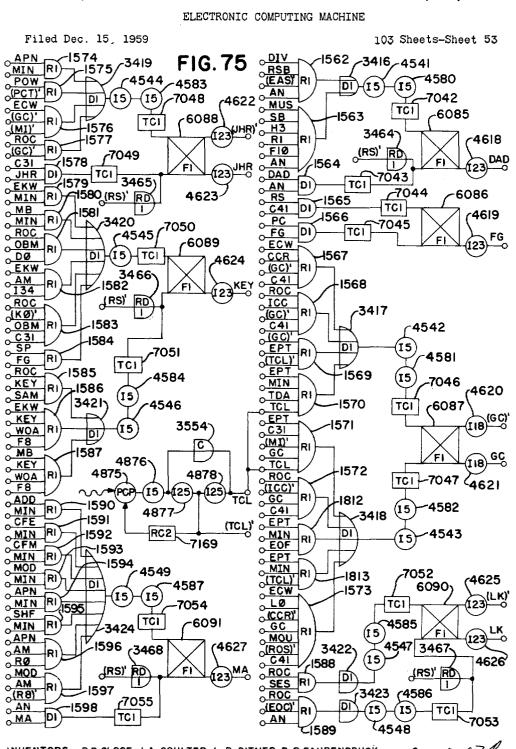

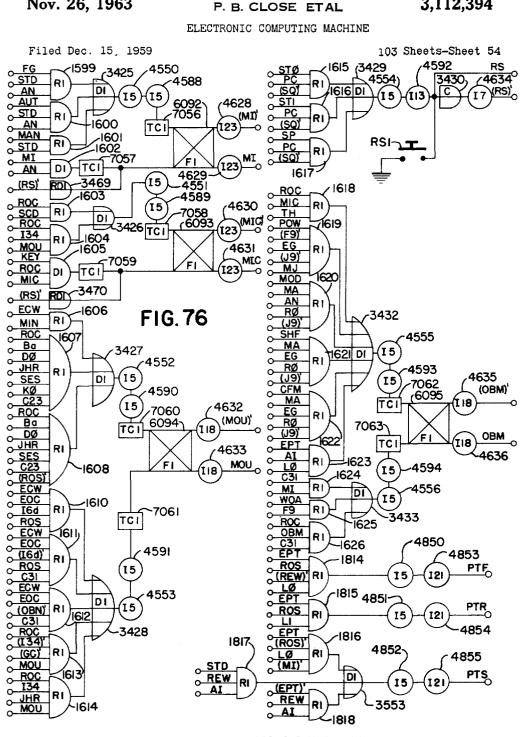

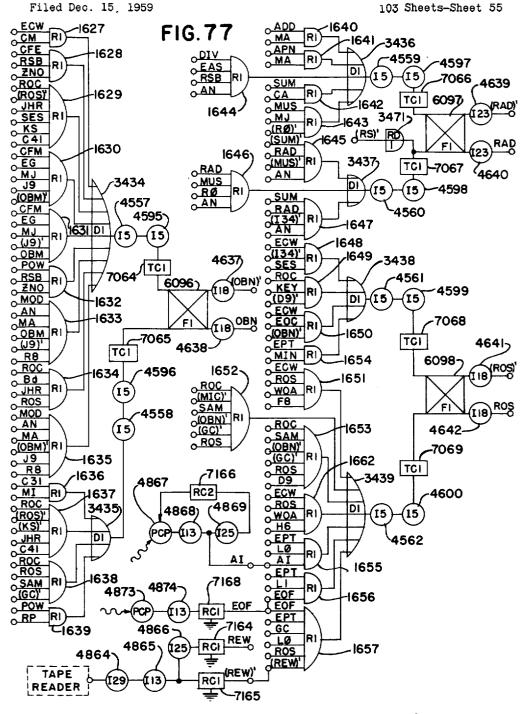

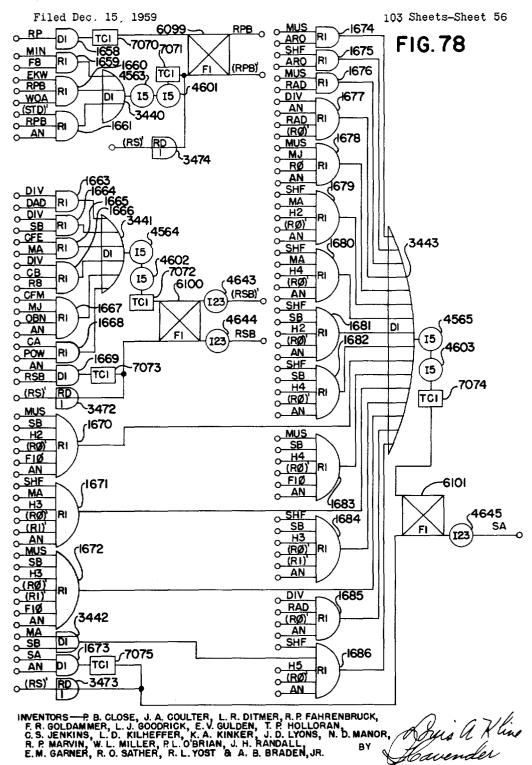

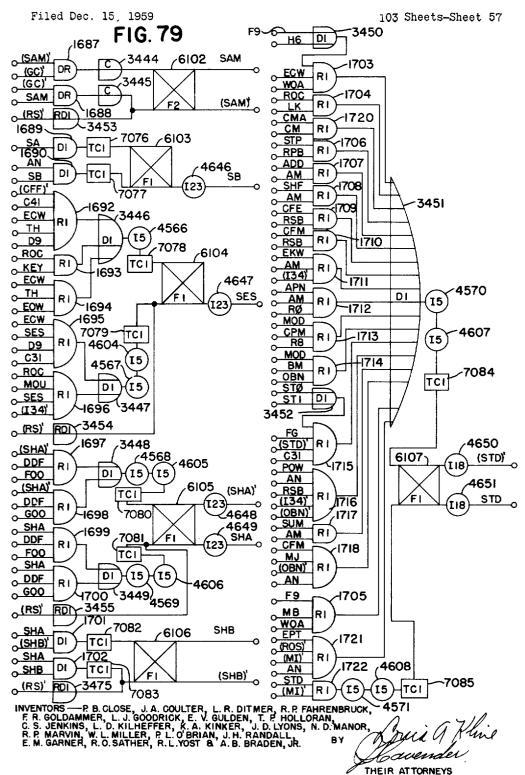

FIGS. 74 thru 79 are logical diagrams of the various word-cycle, time-delay and subcommand initiating flipflops:

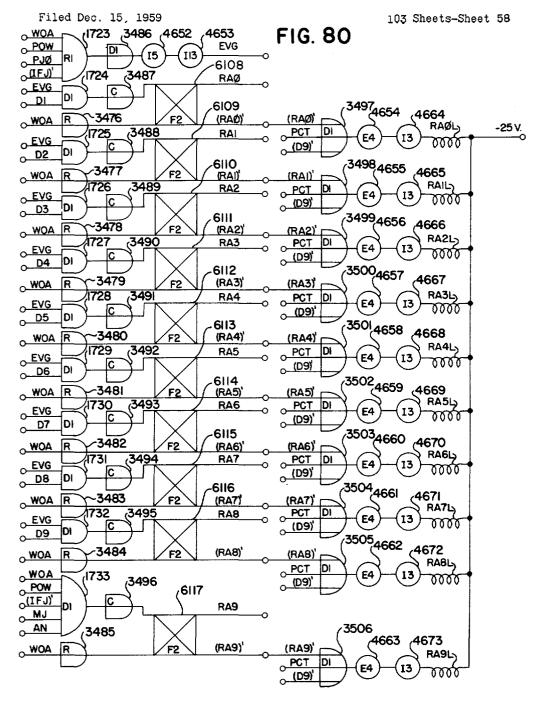

FIG. 80 is a logical diagram of the rack-stopping solenoids and flip-flops;

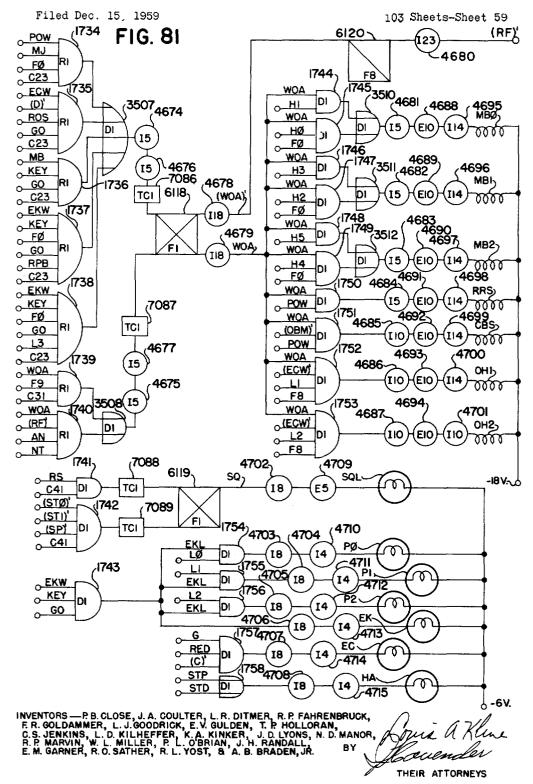

FIG. 81 is a logical diagram of various solenoid control and light indicating circuitry;

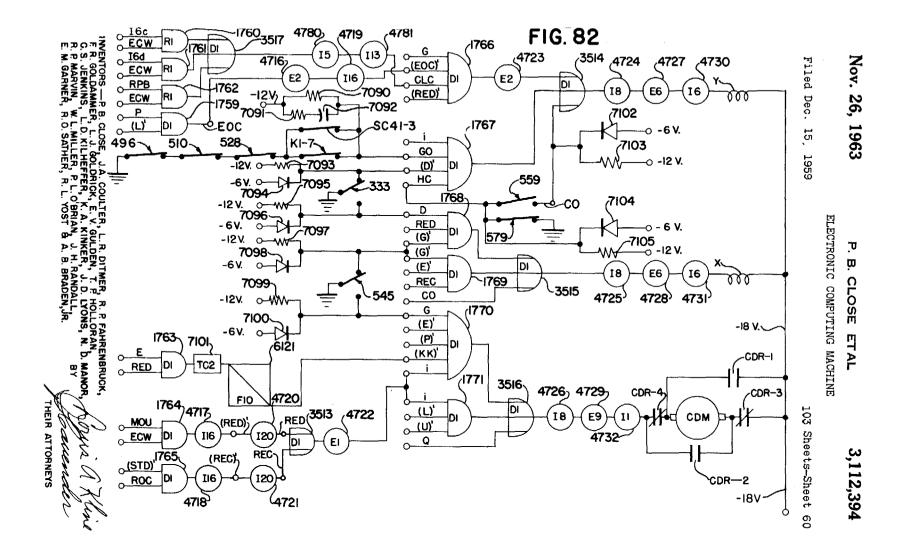

FIG. 82 is a portion of the logical diagram of the ledger card handling circuitry;

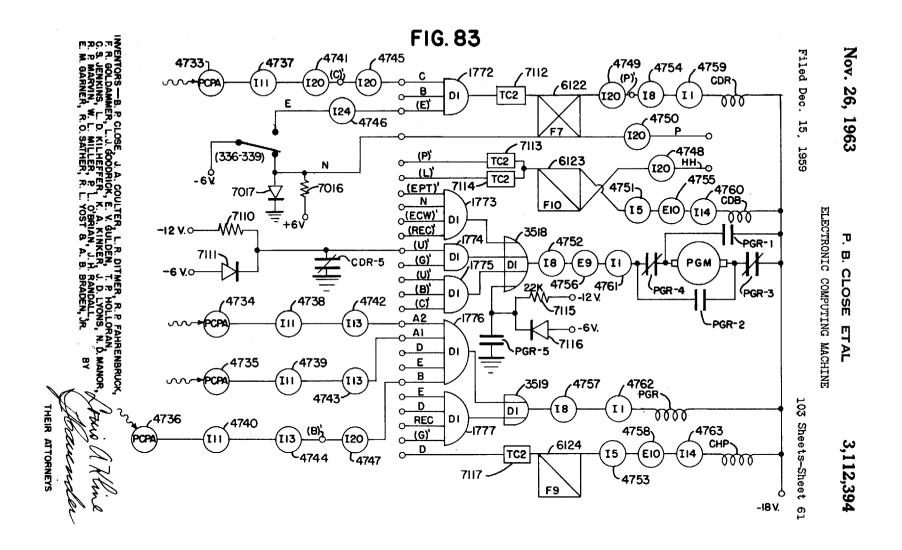

FIG. 83 is an additional portion of the logical dia- 25 gram of the ledger card handling circuitry;

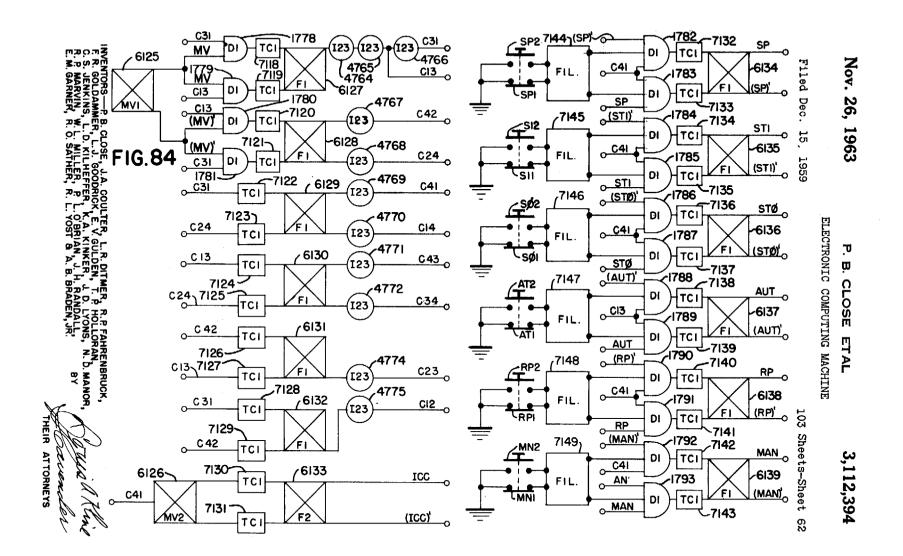

FIG. 84 is a logical diagram of the various timing clock and push-button control circuitry;

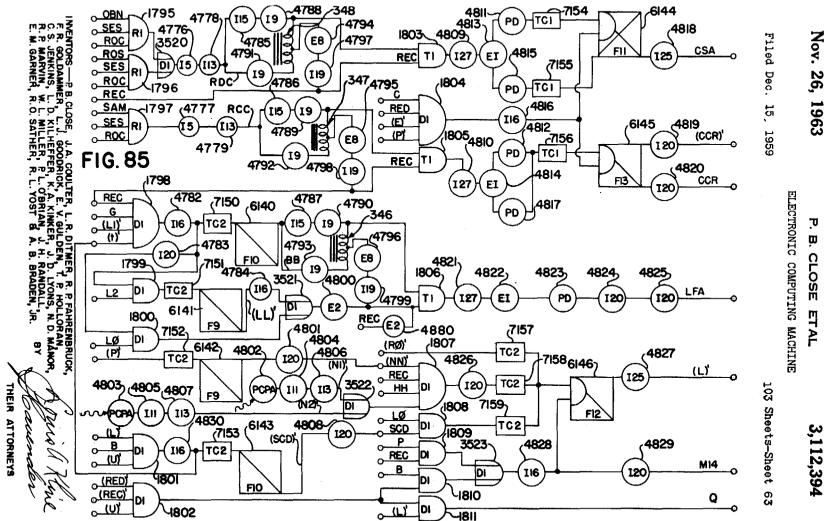

FIG. 85 is a logical diagram of the magnetic recording reproducing and control circuitry; 30

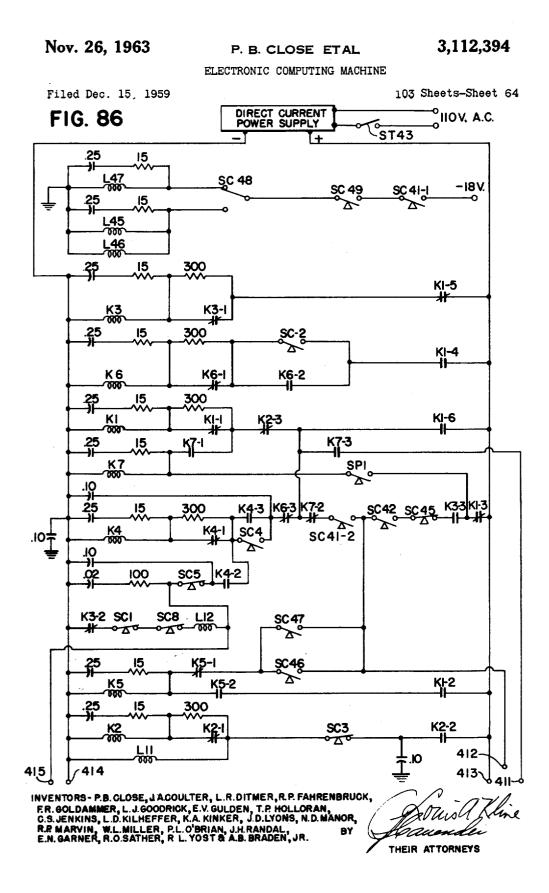

FIG. 86 is a schematic diagram of a portion of the tape punch control circuitry;

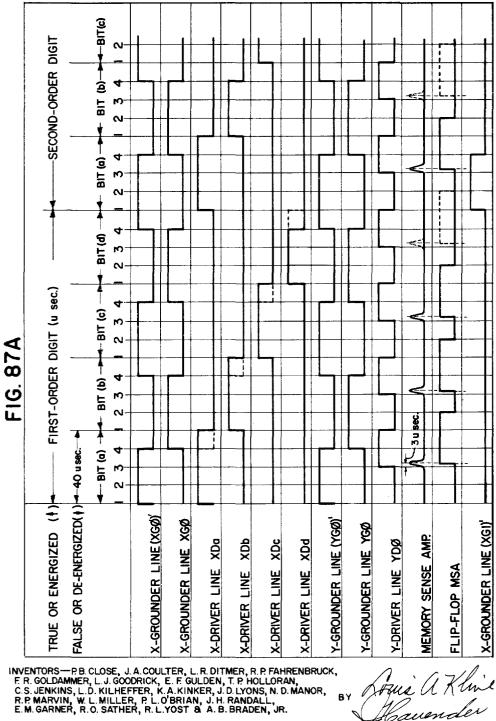

FIG. 87A is a timing chart illustrating the instantaneous logical states of the various control lines utilized during a memory read-write cycle of operation;

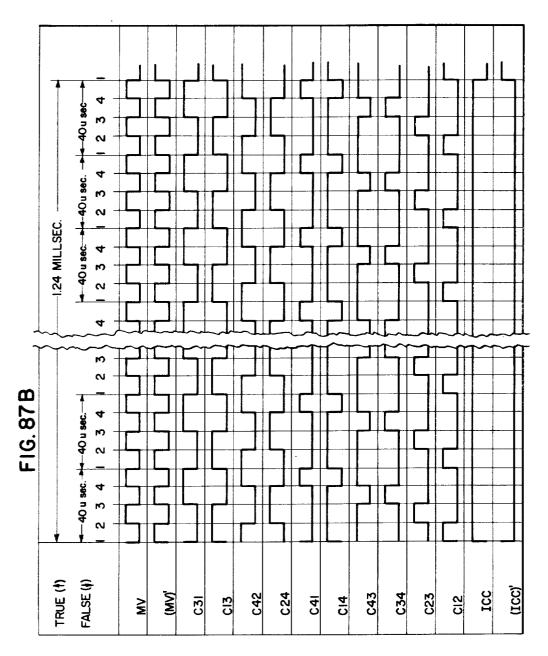

FIG. 87B is a timing chart illustrating the instantaneous logical states of the various synchronizing clock lines;

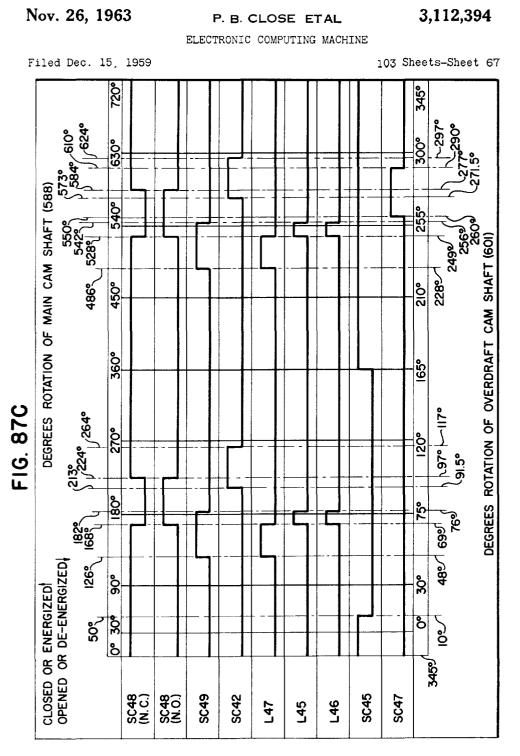

FIG. 87C is a timing chart illustrating the instantaneous conditions and states of energization of the various 40 switching and solenoid means utilized by the tape punch mechanism:

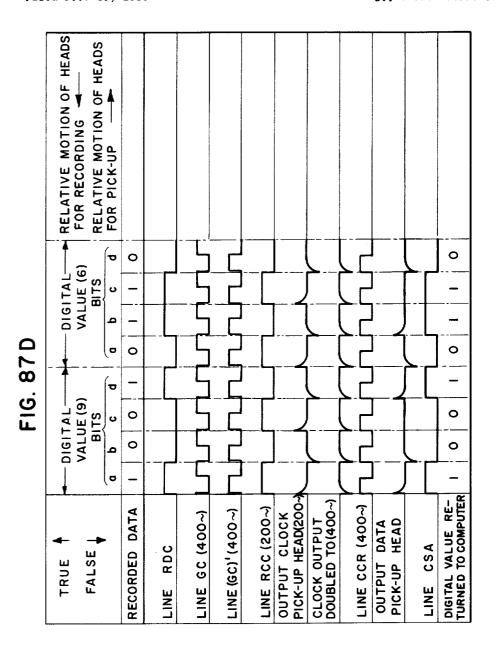

FIG. 87D is a timing chart illustrating the instantaneous logical states of the various control lines utilized during a magnetic recording and reproduction cycle of 45 operation;

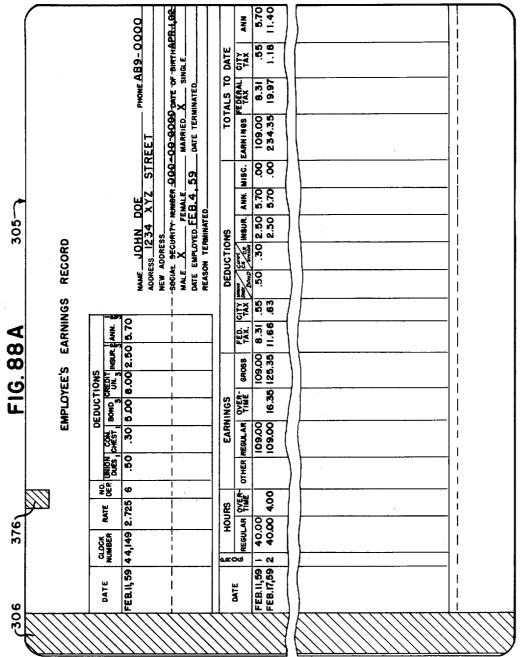

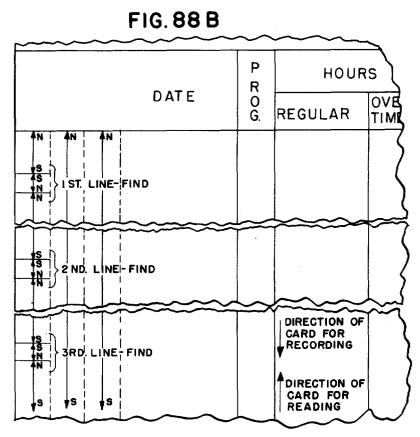

FIGS. 88A and 88B are diagrammatic illustrations of a portion of the magnetic ledger card utilized by the computer:

FIG. 88C is a diagrammatic illustration of a portion 50 tions executed in carrying out a CMA instruction; of the punched paper tape utilized by the computer;

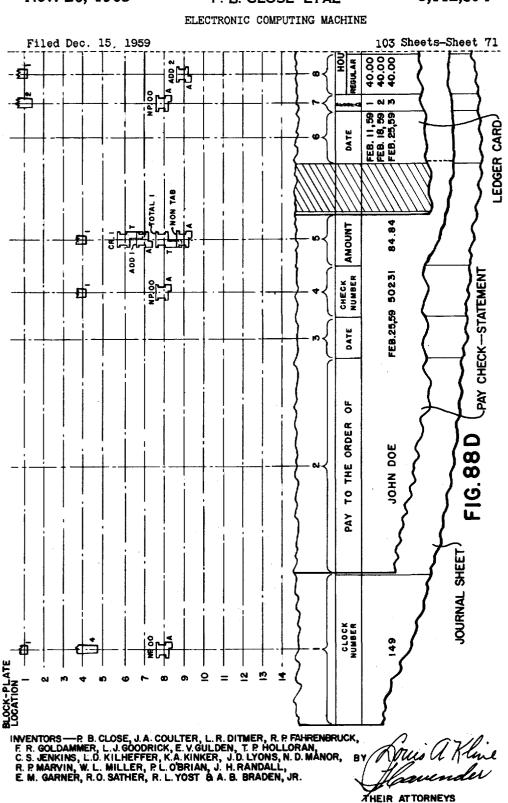

FIGS. 88D and 88E together form a diagrammatic illustration of a portion of the journal sheet and paycheck-statement combination properly placed in the accounting machine carriage, ready for a posting operation 55 thereon:

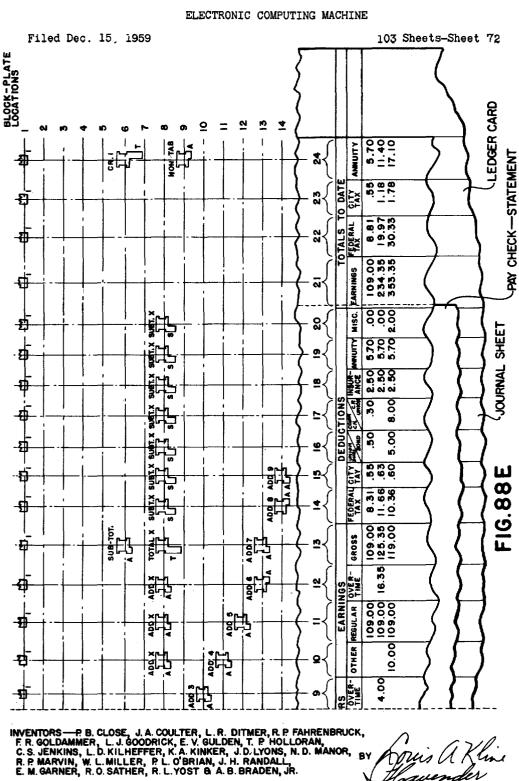

FIG. 88F is an illustration of a pay check;

FIG. 88G is an illustration of a statement form;

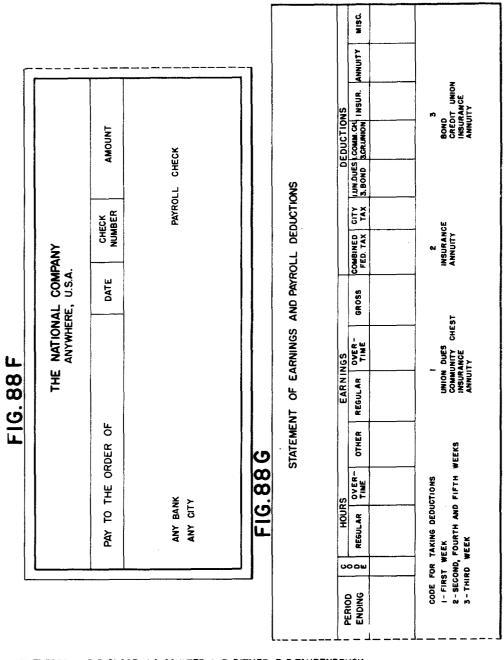

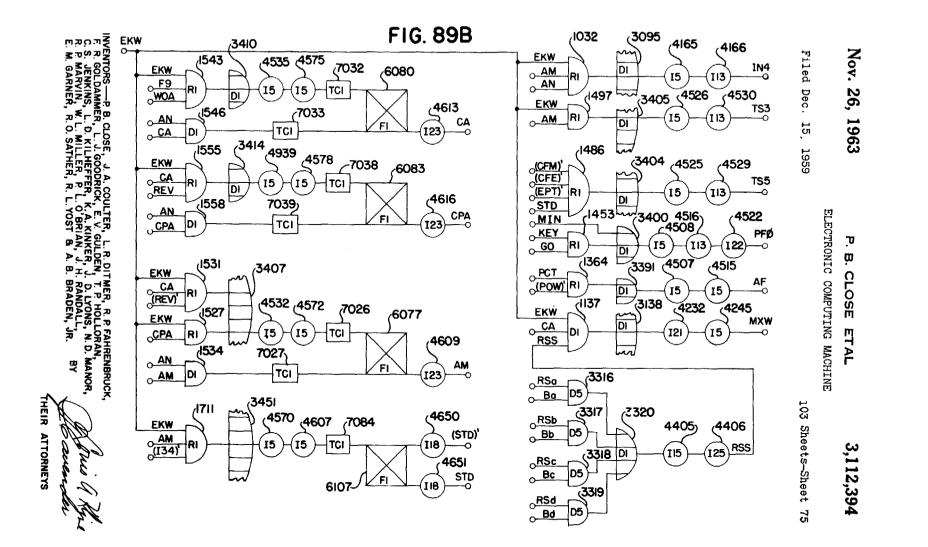

FIGS. 89A and 89B logically illustrate the various portions of the circuitry utilized by the computer in 60 tions executed in carrying out an SUM instruction; carrying out an enter-keyboard-words (EKW) instruction:

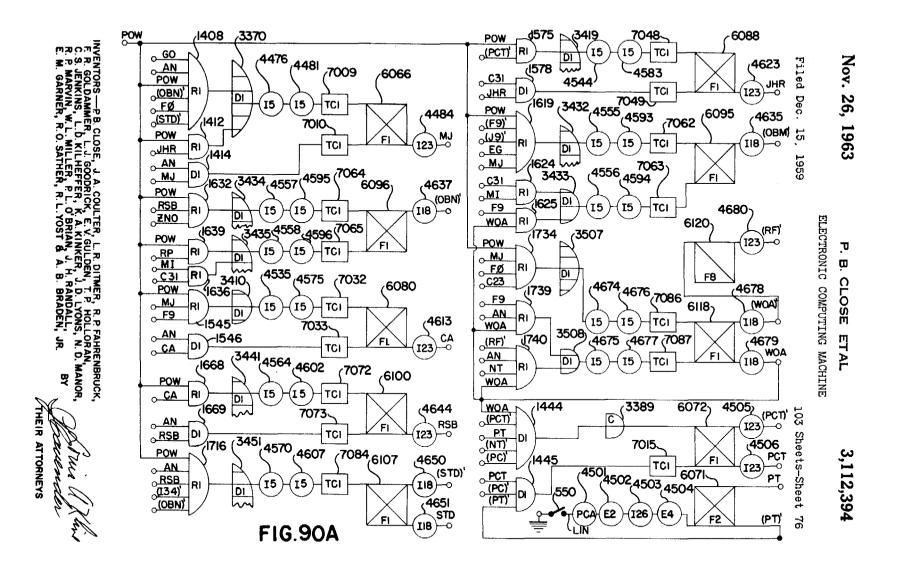

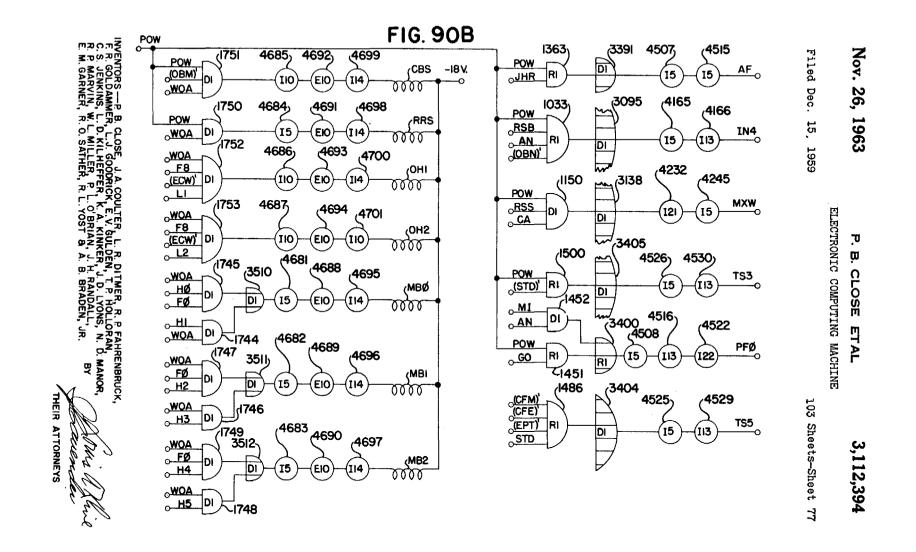

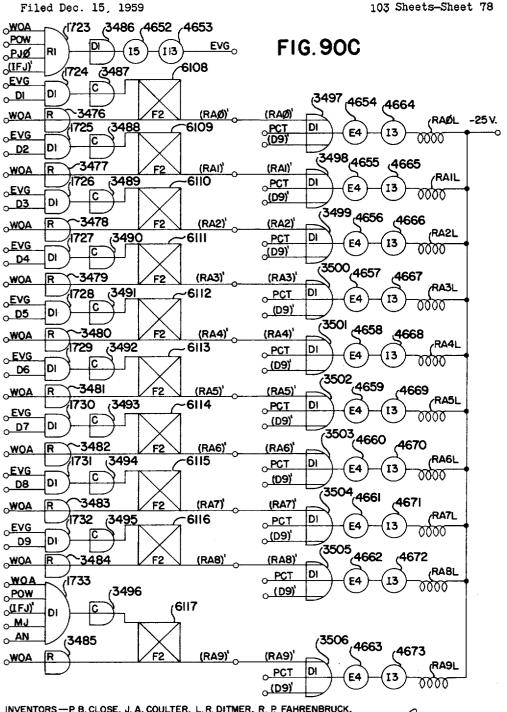

FIGS. 90A, 90B and 90C logically illustrate the various portions of the circuitry utilized by the computer in carrying out a print-out-words (POW) instruction;

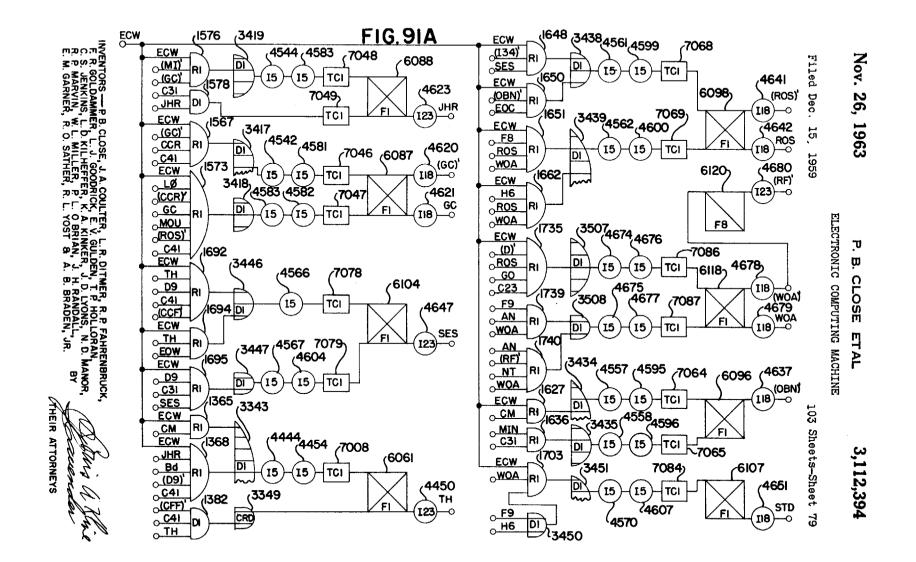

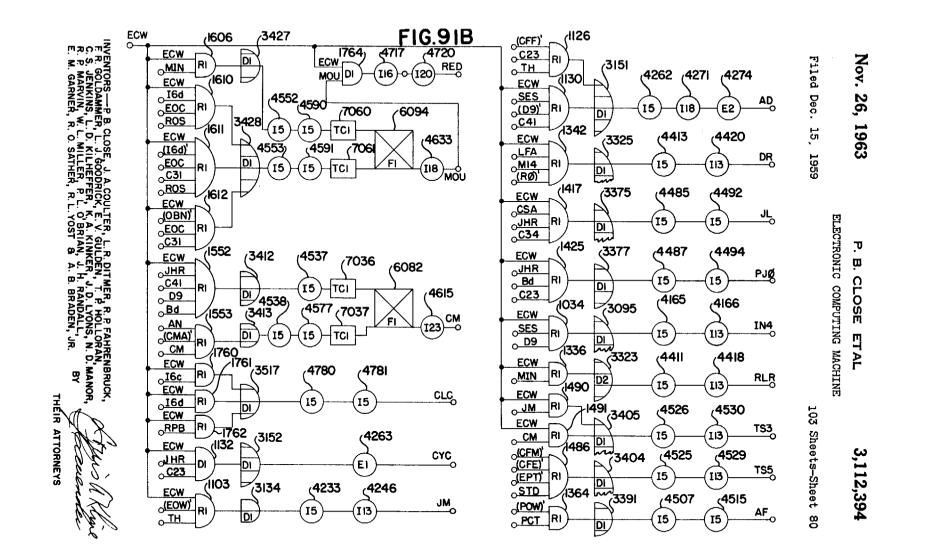

FIGS. 91A, 91B and 91C logically illustrate the various portions of the circuitry utilized by the computer in carrying out an enter-card-words (ECW) instruction;

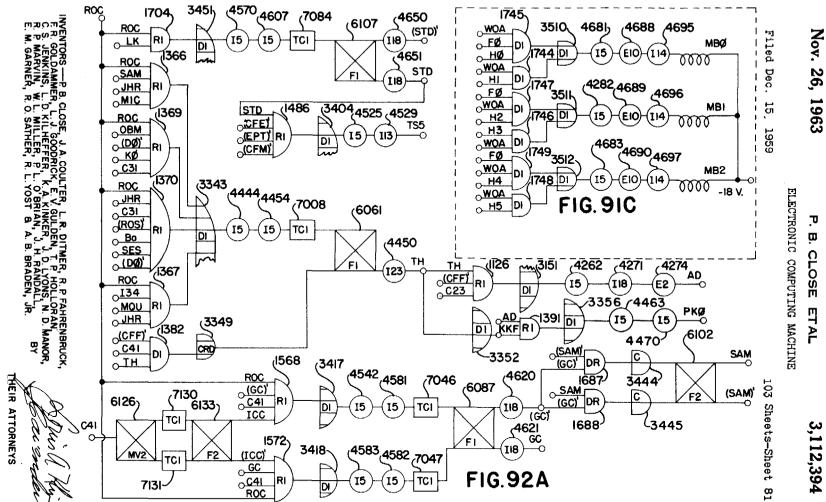

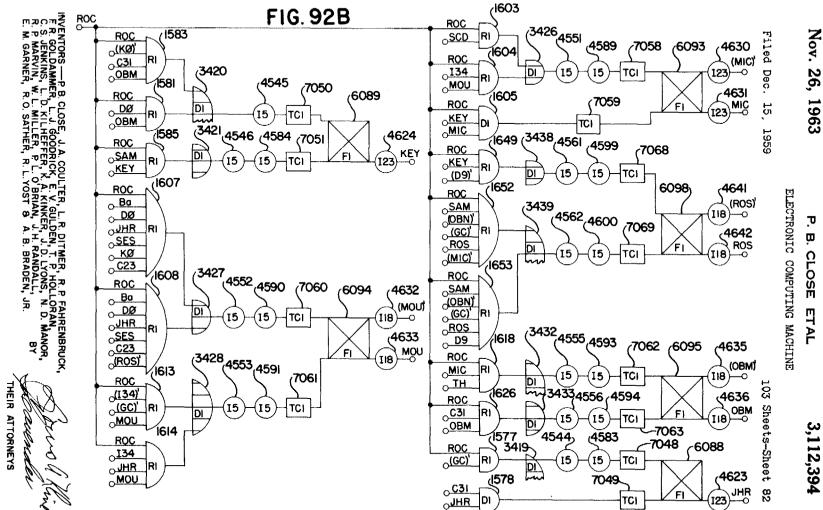

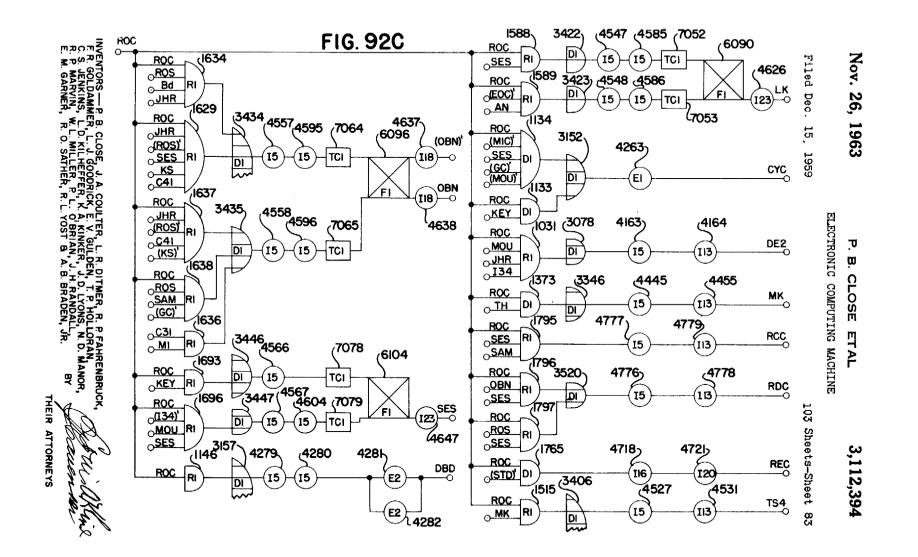

FIGS. 92A, 92B and 92C logically illustrate the various portions of the circuitry utilized by the computer in 70 tions executed in carrying out a CFM instruction; carrying out a record-on-card (ROC) instruction;

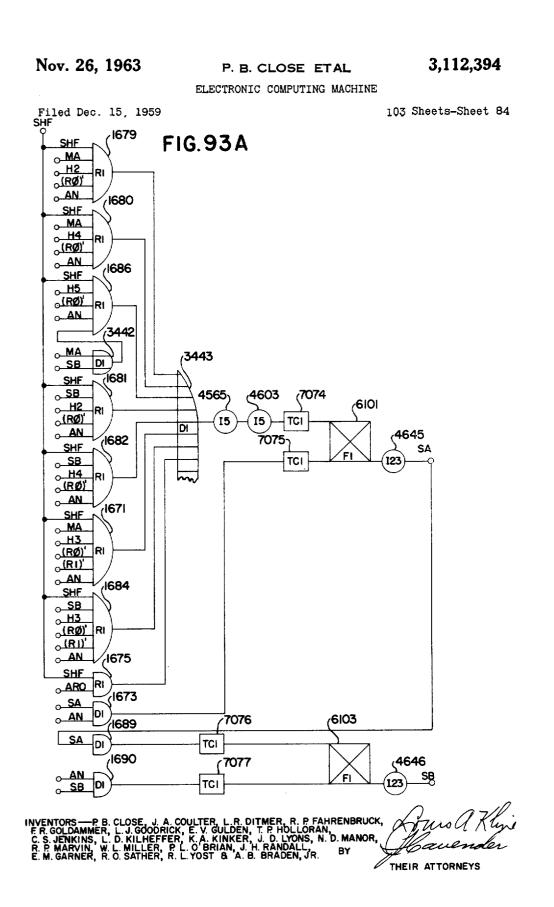

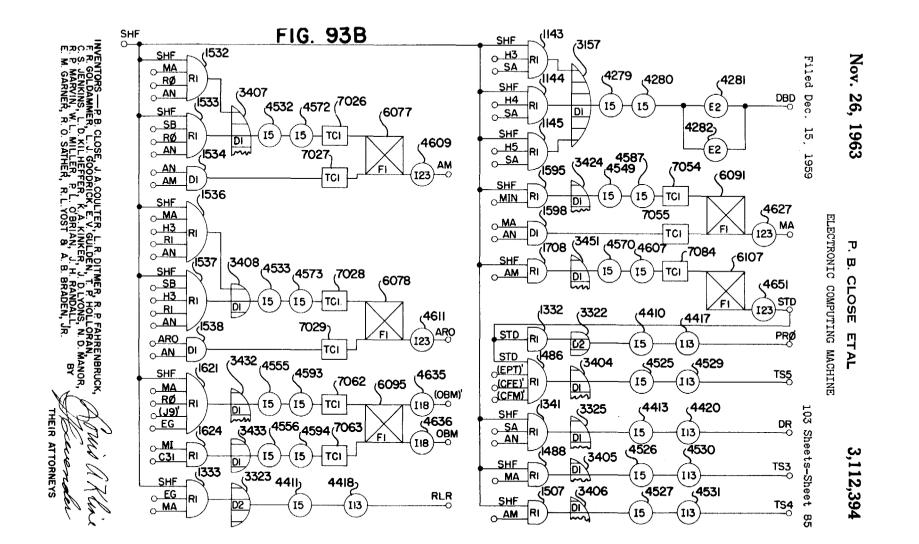

FIGS. 93A and 93B logically illustrate the various portions of the circuitry utilized by the computer in carrying out a shift (SHF) instruction;

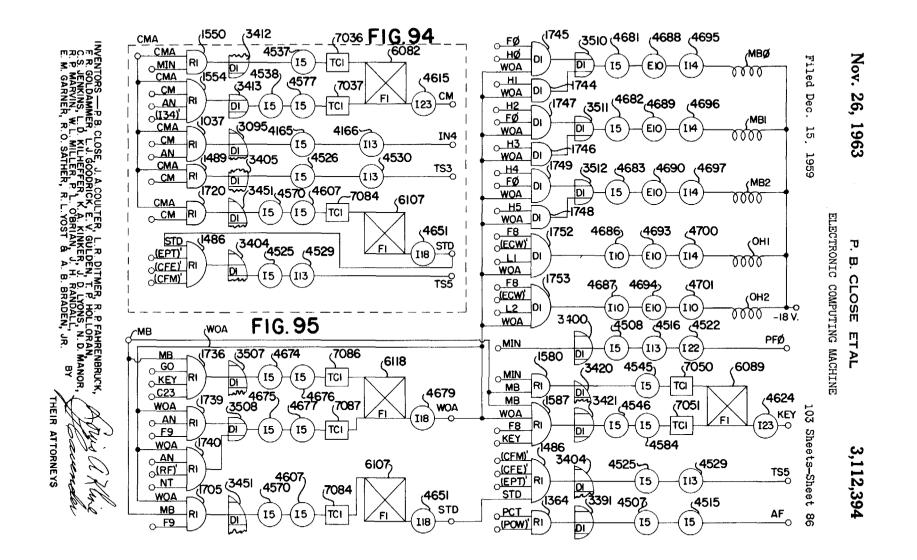

FIG. 94 logically illustrates the various portions of 75

the circuitry utilized by the computer in carrying out a clear-memory-addresses (CMA) instruction;

FIG. 95 logically illustrates the various portions of the circuitry utilized by the computer in carrying out a motor-bar (MB) instruction;

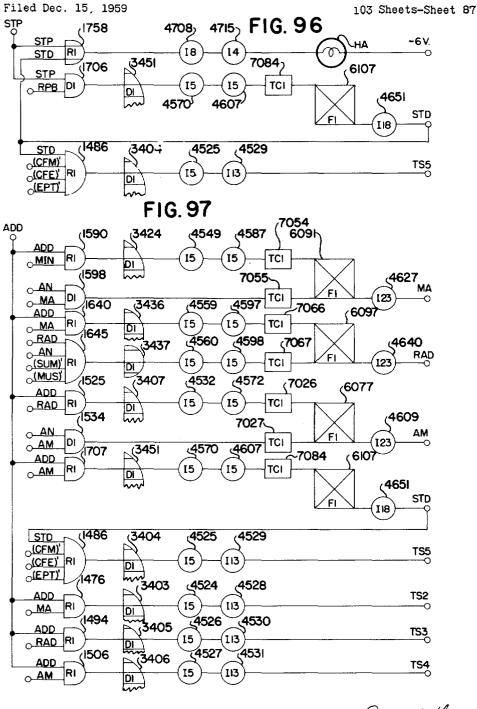

FIG. 96 logically illustrates the various portions of the circuitry utilized by the computer in carrying out a stop (STP) instruction;

FIG. 97 logically illustrates the various portions of the circuitry utilized by the computer in carrying out an add (ADD) instruction;

FIG. 98 logically illustrates the various portions of the circuitry utilized by the computer in carrying out a subtract (SUB) instruction;

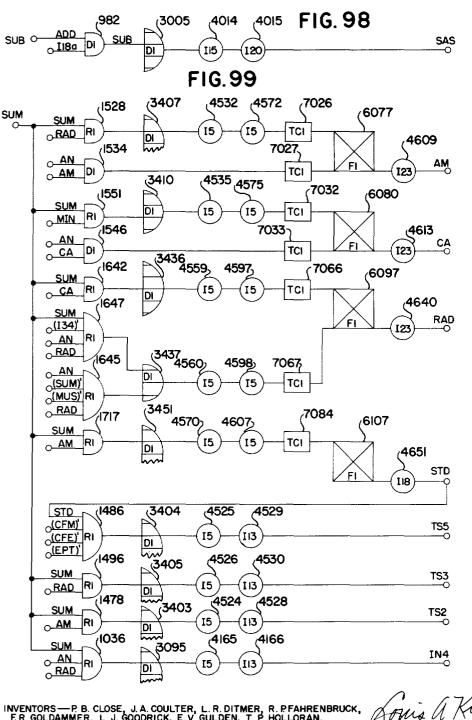

FIG. 99 logically illustrates the various portions of the circuitry utilized by the computer in carrying out a sum (SUM) instruction;

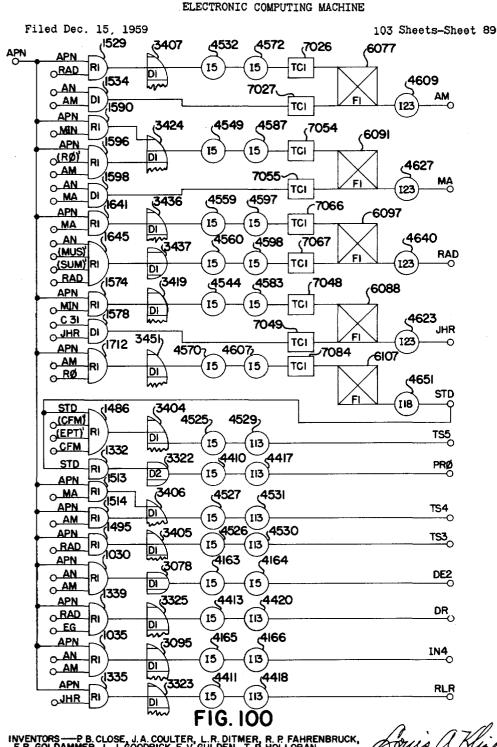

FIG. 100 logically illustrates the various portions of the circuitry utilized by the computer in carrying out an addpairs-of-numbers (APN) instruction;

FIG. 101 logically illustrates the various portions of the circuitry utilized by the computer in carrying out a multiply-dollar-decimal (MDD) instruction;

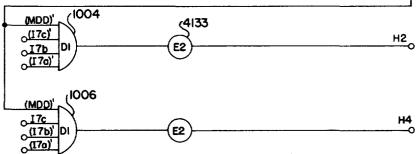

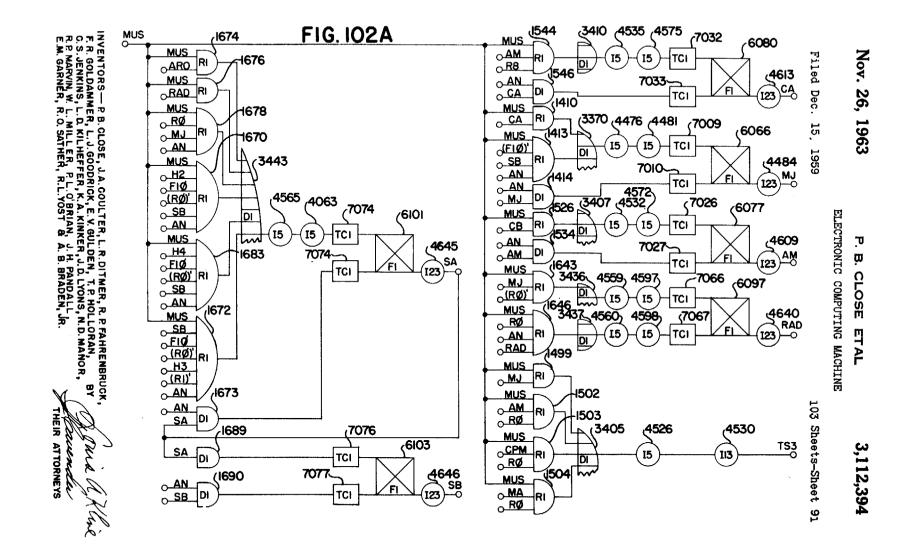

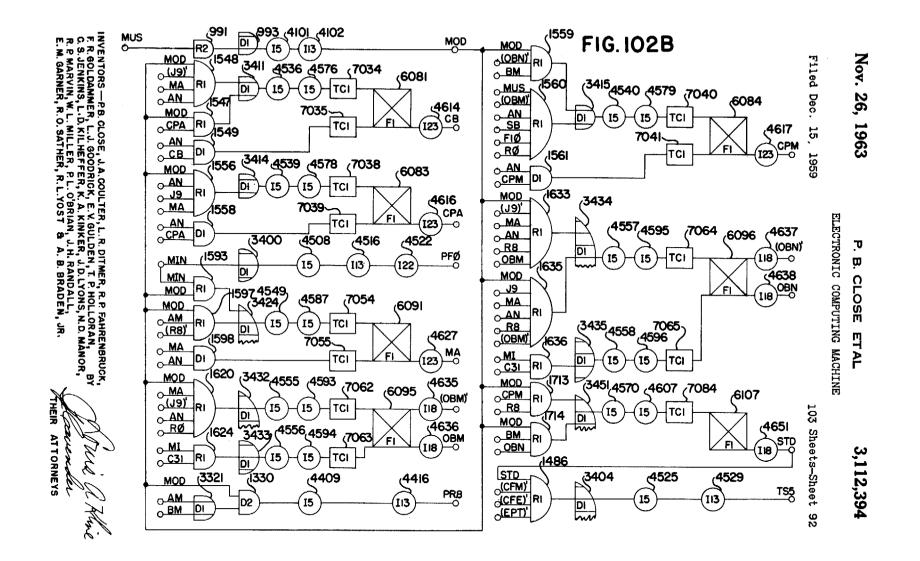

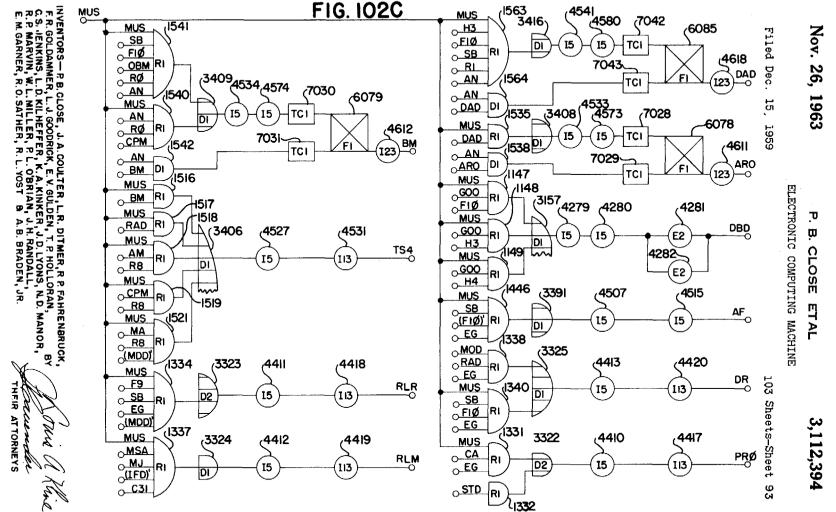

FIGS. 102A, 102B and 102C logically illustrate the various portions of the circuitry utilized by the computer

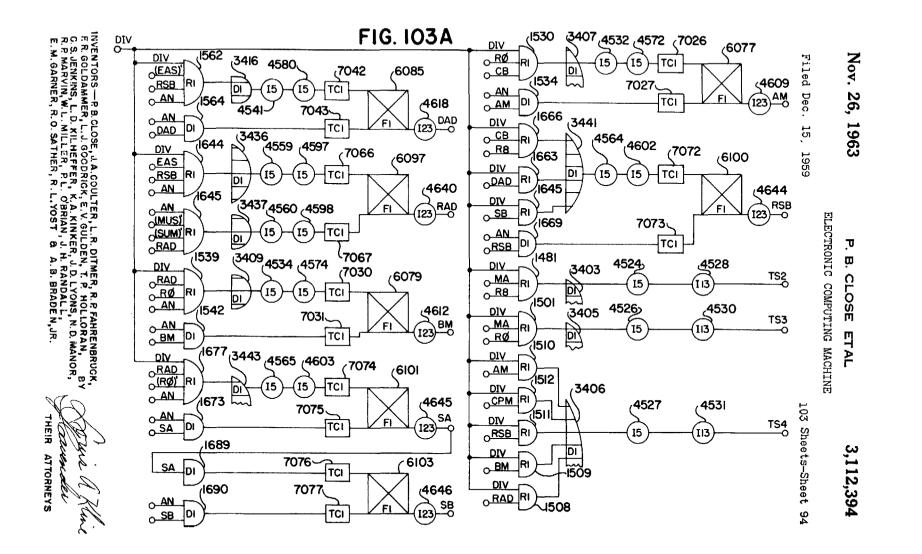

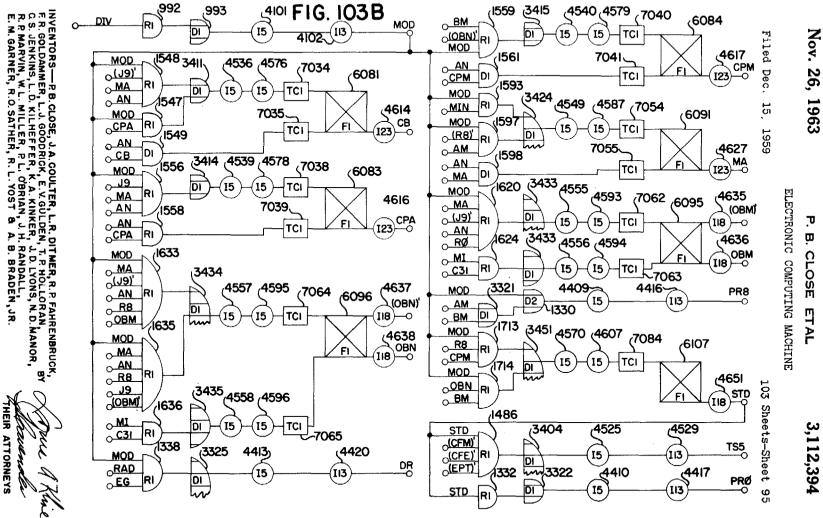

in carrying out a multiply-and-shift (MUS) instruction; FIGS. 103A and 103B logically illustrate the various portions of the circuitry utilized by the computer in carrying out a divide (DIV) instruction;

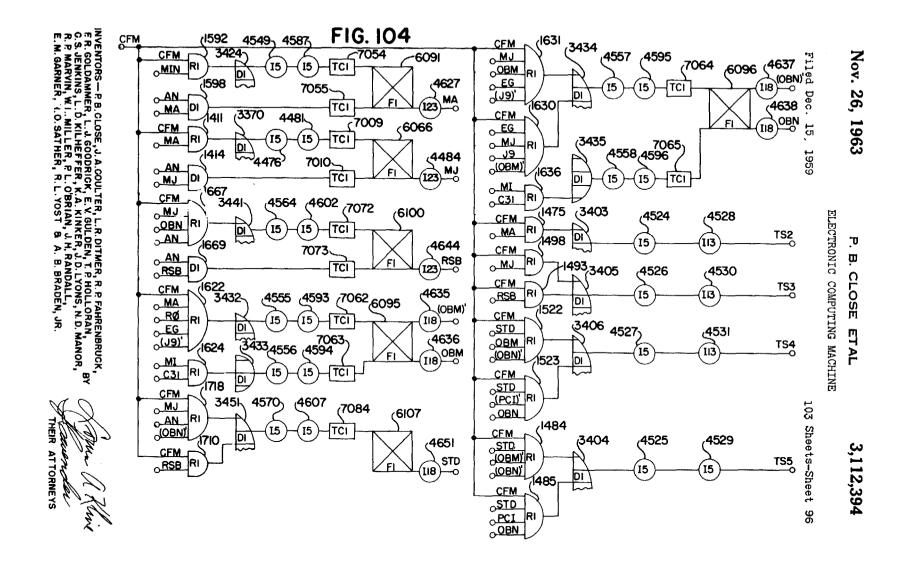

FIG. 104 logically illustrates the various portions of the circuitry utilized by the computer in carrying out a take-alternate-instruction (CFM) instruction;

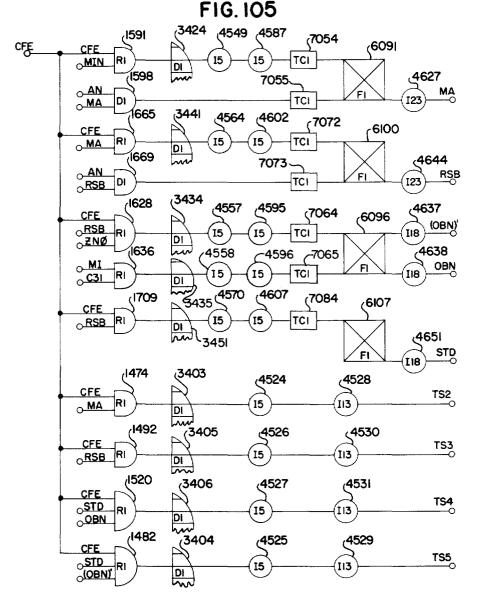

FIG. 105 logically illustrates the various portions of the circuitry utilized by the computer in carrying out a take-35 alternate-instruction (CFE) instruction;

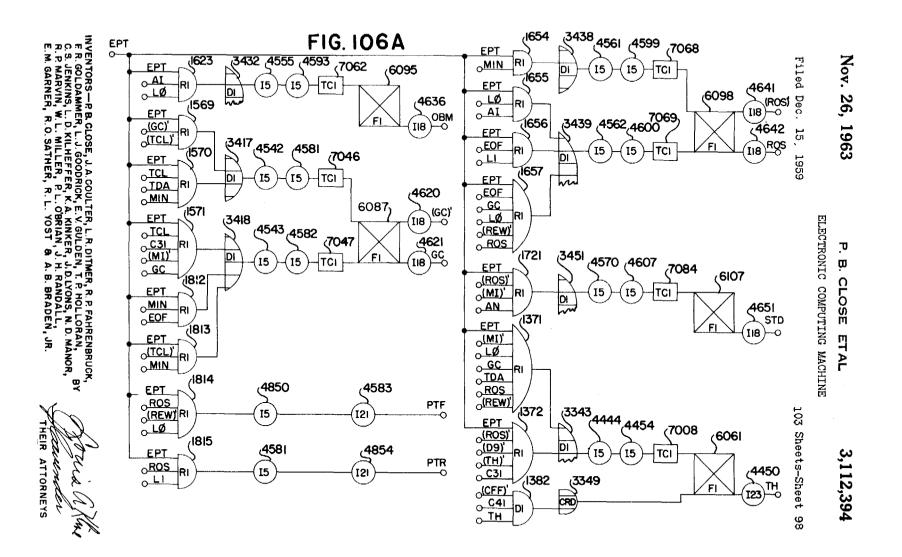

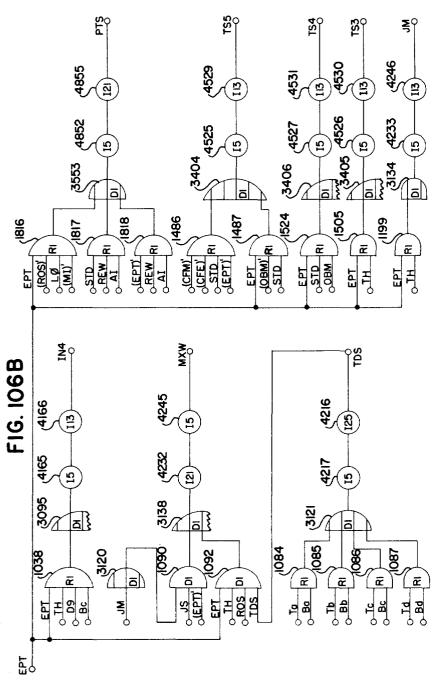

FIGS. 106A and 106B logically illustrate the various portions of the circuitry utilized by the computeer in carrying out an enter-punched-tape (EPT) instruction;

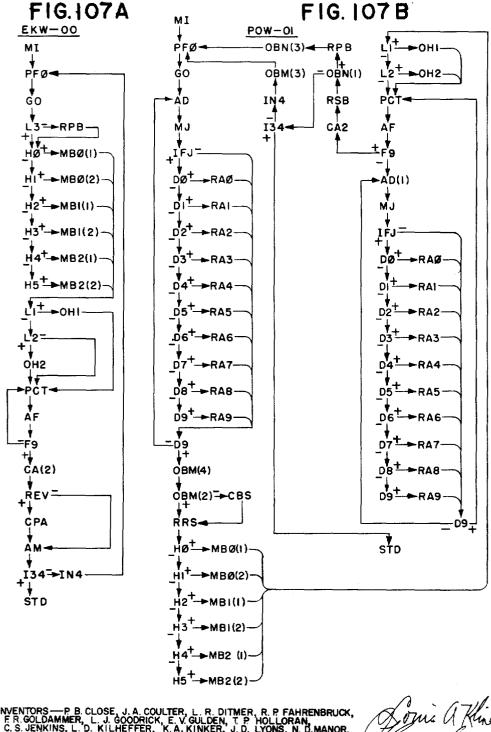

FIG. 107A is a flow diagram of the sequence of operations executed in carrying out an EKW instruction;

FIG. 107B is a flow diagram of the sequence of operations executed in carrying out a POW instruction;

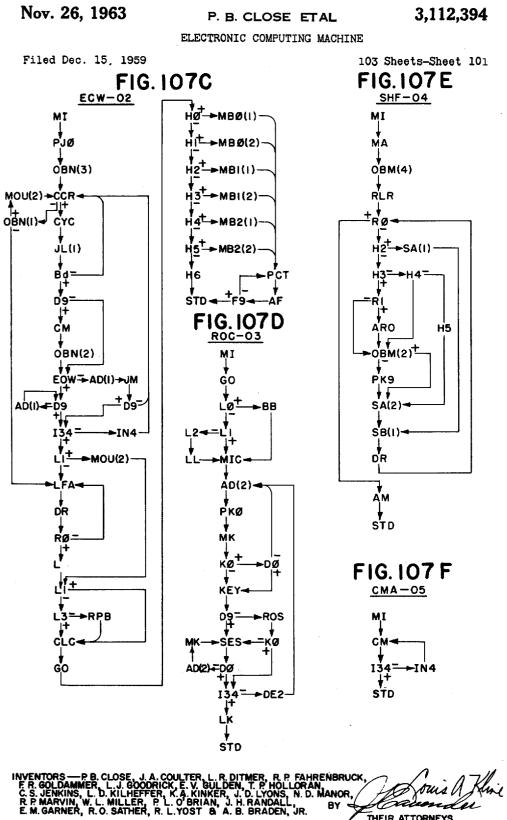

FIG. 107C is a flow diagram of the sequence of operations executed in carrying out an ECW instruction;

FIG. 107D is a flow diagram of the sequence of operations executed in carrying out an ROC instruction;

FIG. 107E is a flow diagram of the sequence of operations executed in carrying out an SHF instruction;

FIG. 107F is a flow diagram of the sequence of opera-

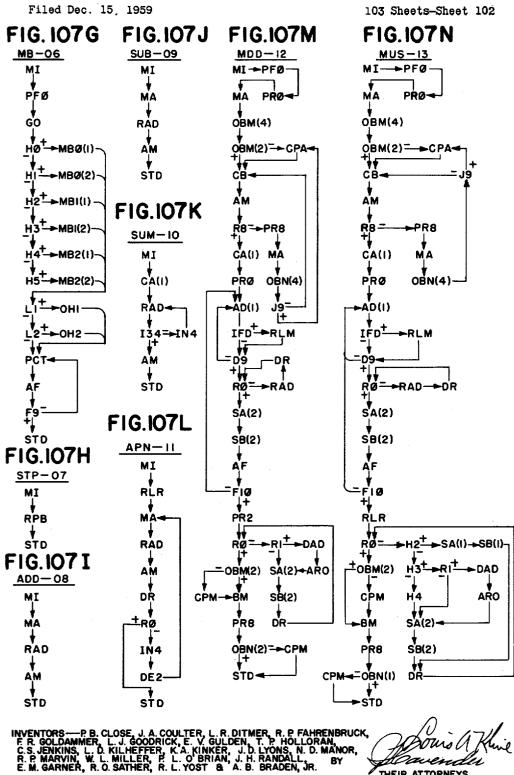

FIG. 107G is a flow diagram of the sequence of operations executed in carrying out an MB instruction;

FIG. 107H is a flow diagram of the sequence of operations executed in carrying out an STP instruction;

FIG. 107I is a flow diagram of the sequence of operations executed in carrying out an ADD instruction; FIG. 107J is a flow diagram of the sequence of opera-

tions executed in carrying out an SUB instruction; FIG. 107K is a flow diagram of the sequence of opera-

FIG. 107L is a flow diagram of the sequence of opera-

tions executed in carrying out an APN instruction; FIG. 107M is a flow diagram of the sequence of operations executed in carrying out an MDD instruction;

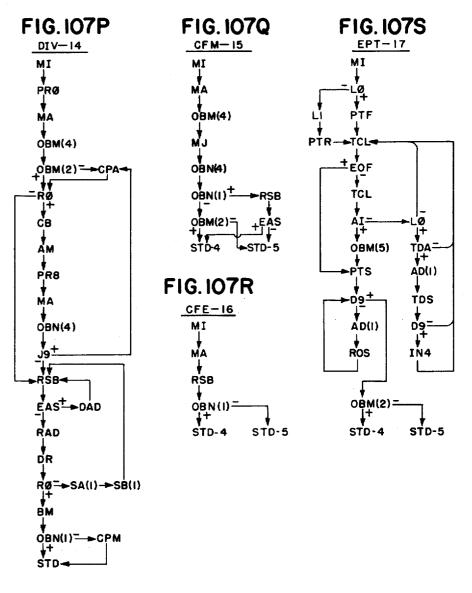

FIG. 107N is a flow diagram of the sequence of opera-65 tions executed in carrying out an MUS instruction; FIG. 107P is a flow diagram of the sequence of operations executed in carrying out a DIV instruction;

FIG. 107Q is a flow diagram of the sequence of opera-

FIG. 107R is a flow diagram of the sequence of operations executed in carrying out a CFE instruction; and FIG. 107S is a flow diagram of the sequence of opera-

tions executed in carrying out an EPT instruction.

Inasmuch as the following description of a physical

embodiment of the present invention is of considerable length and complexity, and is essentially divided into a multiplicity of separate sections, the various section headings are herein serially numbered and listed below in order to facilitate immediate reference to the various portions of the specification.

#### Column

3,112,394

| 1.<br>2.<br>3.    | General Description of Computer<br>Accounting Machine Portion of Computer (General)<br>Electric Tynowriter Portion of Accounting Machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8<br>8<br>8                                               |    |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|----|

| 4.<br>5.          | General Description of Computer<br>Accounting Machine Portion of Computer (General)<br>Electric Typewriter Portion of Accounting Machine<br>Amount Keyboard of Accounting Machine<br>Construction and Mode of Operation of Accounting Machine<br>of Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9<br>9<br>14                                              | 10 |

| 6.<br>7.          | of Computer<br>Paper Tape Punch Portion of Computer<br>Magnetic Ledger Card Handling Portion of Computer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 28<br>30                                                  |    |

| 8.<br>9.<br>10.   | Electromechanical Control Means.<br>Building Blocks Generally.<br>Inverter Building Blocks.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 47                                                        |    |

| $\frac{11.}{12.}$ | Inverter Building Blocks<br>Emitter-Follower Building Blocks<br>Logical OR Building Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | $\frac{49}{50}$                                           | 15 |

| 13.               | Logical OR Building Blocks<br>Logical AND Building Blocks<br>Flip-flop and Multivibrator Building Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | - 50<br>53                                                |    |

| 16.<br>17         | Miscellaneous Building Blocks<br>Magnetic Core Memory<br>X-Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 57<br>61<br>70                                            |    |

| 18.<br>19.        | X and Y Grounders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70<br>71                                                  | 20 |

| $\frac{20}{21}$   | Y-Drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $\frac{72}{73}$                                           |    |

| 22.<br>23.<br>24  | Word-Selecting Register<br>Summary of Word Selection<br>Synchronizing Clocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | $73 \\ 74 \\ 75$                                          |    |

| 25.<br>26.        | Detailed Read-Write Cycle<br>Sense-Amplifier Strobe                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 76<br>80                                                  | 25 |

| $\frac{27}{28}$ . | Format of Instruction Words Generally<br>Format of ENTER-KEYBOARD-WORDS Instruction Word<br>(FWW.00)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81<br>84                                                  |    |

| $29. \\ 30.$      | Summary of word Selection<br>Synchronizing Clocks.<br>Detailed Read-Write Cycle.<br>Sense-Amplifier Strobe.<br>Format of Instruction Words Generally.<br>Format of ENTER-KEYBOARD-WORDS Instruction Word<br>(EKW-00).<br>Format of PRINT-OUT-WORDS Instruction Word (POW-01).<br>Format of ENTER-CARD-WORDS Instruction Word (ECW-<br>02).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 56                                                        |    |

| $\frac{31}{32}$   | <ul> <li>Format of EXCORD-ON-CARD Instruction Word (ROC-63).</li> <li>Format of RECORD-ON-CARD Instruction Word (ROC-63).</li> <li>Format of SHIFT Instruction Word (SH 8-61).</li> <li>Format of CLEAR-MEMORY-ADDRESSES Instruction Word (CMA-05).</li> <li>Format of MOTOR-BAR Instruction Word (MB-06).</li> <li>Format of STOP Instruction Word (STP-67).</li> <li>Format of SDD Instruction Word (STP-69).</li> <li>Format of SUBTRACT Instruction Word (SUB-09).</li> <li>Format of SUBTRACT Instruction Word (SUB-09).</li> <li>Format of ADD PAIRS-of-NUMBERS Instruction Word (ADD-11).</li> <li>Format of MULTIPLY-DOLLAR-DECIMAL Instruction Word (MDD-12).</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 87<br>50<br>92                                            | 30 |