SUBJECT: MEMORY CORE HEATING BY SWITCHING AT HIGH FREQUENCIES

To: D. R. Brown

From: J. D. Childress

Date: January 31, 1956

John B. Goodenough Approved:

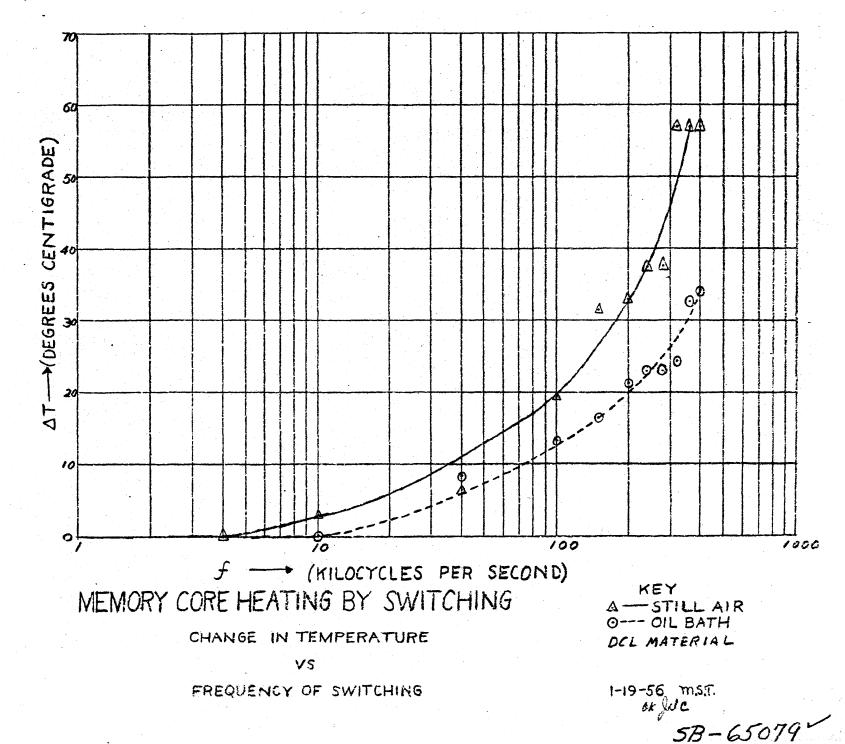

Abstract: The heating of a memory core caused by high frequency switching has been studied experimentally. For a switching frequency of 400 kilocycles(the maximum frequency possible in a coincident-current two-to-one selection memory of 5 microsecond cycle time)the temperature of the memory core (DCL material) may rise more than 57°C above ambient in still air or 34°C in an oil bath. At 200 kilocycles (the maximum reasonable switching frequency in the memory) the temperature rises are 33°C and 22°C, respectively. At 30°C above ambient (25°C), the memory core fails to hold information dependably. Thus, with forced air cooling the present memory should have no problem with heating; however, memories of shorter cycle time face serious heating problems.

Distribution: The following are to receive the complete memorandum:

| Best, R., B-131<br>Bradspies, S. | Sarles, F.W.<br>Smith, D.O. |

|----------------------------------|-----------------------------|

| Brown, D.R.                      | Zopatti, R.                 |

|                                  |                             |

| Childress, J.D.                  | Papian, W.N.                |

| Davidson, G.                     |                             |

| Ellis, D.H.                      |                             |

| Freeman, J.R.                    |                             |

| Goodenough, J.B.                 |                             |

| Guditz, E. A.                    |                             |

| Gurley, B.                       | į                           |

| Mitchell, J. L.                  |                             |

| Menyuk, N.                       |                             |

| Olsen, K.H.                      |                             |

| Pacl, R.A.                       |                             |

|                                  | 1 00 1 0                    |

Other staff in Group 63 are to receive abstracts only.

This document is issued for internal distribution and use only by and for Lincoln Laboratory personnel. It should not be given or shown to any other individuals or groups without express authorization. It may not be reproduced in whole or in part without permission in writing from Lincoln Laboratory. The research reported in this document was supported jointly by the Department of the Army, the Department of the Navy, and the Department of the Air Force under Air Force Contract No. AF 19(122)-458.

## Memorandum 6M-4137

Page 2 of 4

## Introduction:

The power P in ergs per second dissipated in a memory core switching at a frequency f in cycles per second is

$$P = f x lo^7 v \int_{-B_r}^{B_m} H_m dB \approx 5 x lo^6 x f_u v_l I_m \tau_s$$

(1)

where V is the volume of the core in cubic centimeters, where  $H_m$  is the maximum field in cersteds, B is in gauss,  ${}_{\rm u}V_{\rm l}$  is the output voltage signal in volts,  $I_m$  is the maximum current in amperes, and  $\tau_s$  is the switch time in seconds. Thus, for a memory core switching at f = 500 kc,

$$P \approx 3 \times 10^5 \frac{\text{ergs}}{\text{seconds}} \approx 3 \times 10^{-2} \text{ watt,}$$

(2)

an appreciable amount of power to be dissipated by an element the size of a memory core.

The heat energy dissipated by a memory core is a function of (1) the difference between the temperature of the core and the ambient temperature and (2) the nature of the medium into which the heat must go. Thus, as the frequency of switching is increased, the core temperature rises to effect the necessary additional dissipation.

Unfortunately, the properties of the core are dependent on the temperature. As the temperature increases, the switch time  $\tau_s$  decreases and the critical field  $H_d$  (the minimum amplitude of disturb pulses which cause disturb sensitivity) decrease. When  $H_d$  becomes equal to  $\frac{H_m}{2}$ , the memory core fails to hold information; thus  $T_{no}$ , the maximum operating temperature for the core, is defined as the temperature at which  $H_d = \frac{H_m}{2}$ .

The maximum temperature  $T_{no}$  depends on the type memory scheme in which the core must operate. For a perfect memory scheme (by "perfect" is meant that the only material requirement is that it be magnetic)  $T_{no} = T_c$ , the Curie temperature; for less ingenious schemes, the requirement on  $T_{no}$  is that it be higher than the maximum temperature a core can reach in normal memory operation.

## Experimental Procedure:

The heating by high frequency switching of a core of the DCL memory core composition was measured indirectly. First the undisturbed output voltage  $_{u_{l}}V_{l}$  for I = 0.9 amperes was measured as a function of temperature. Then  $_{u_{l}}V_{l}$  was measured as a function of the frequency of switching. By means of the first set of data, the increase in  $_{u_{l}}V_{l}$  caused by high frequency switching was translated into the equivalent change in temperature. The results are presented in Fig. 1.

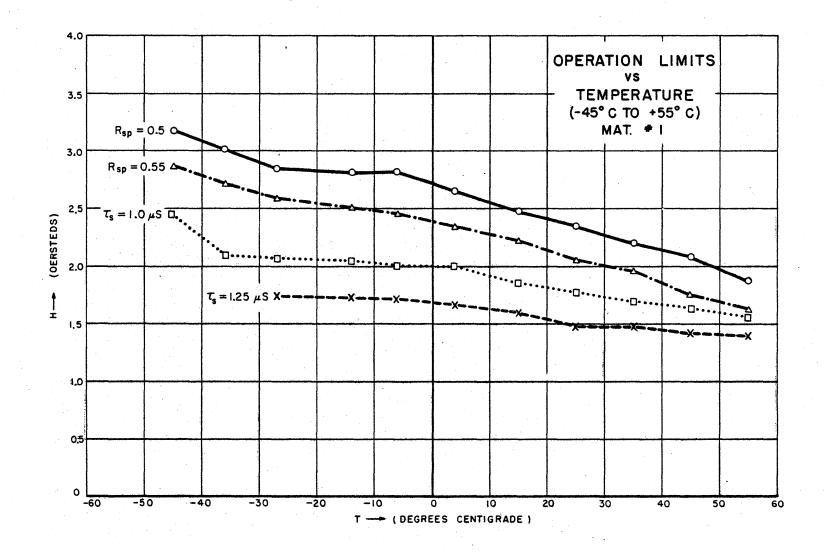

Fig. 2 is a plot of field amplitude margins as a function of temperature. The upper limit on  $H_m$  is given by

$$R_{sp} = \frac{H_d}{H_m} = 0.5,$$

(3)

the condition for operation in a coincident-current memory, two-to-one selection. An additional margin,  $R_{sp} = 0.55$  is also shown. The lower limit is determined by the minimum field for which the switching time  $\tau_s$  is

$$t_{2} = 1.25 \text{ microsecond},$$

(4)

the upper limit of  $\tau_s$  in the MTC type memory. An additional limit,  $\tau_s = 1.0$  microseconds, is also included.

## Discussion and Conclusions:

The memory operates at the point  $H_m = 1.9$  oersted and  $T_o = 25^{\circ}C$ on the Operation Limits plot, Fig. 2. Thus for these conditions  $T_{no} = 53^{\circ}C$ ; so a rise of temperature  $\Delta T = 28^{\circ}C$  is permissible.

If the memory were operated at  $H_m = 2.3$  oersteds and  $T_o = -30^{\circ}C$ , the maximum temperature would be  $T_{no} = 25^{\circ}C$  and  $\Delta T \approx 55^{\circ}C$ . Thus at the expense of higher driving power to the memory and refrigeration, wider temperature limits could be obtained.

The present MTC memory is cooled by forced air circulation. The cooling of the core by forced air circulation is better than that for still air and somewhat less than for immersion in an oil bath. The cooling would depend on the air velocity. An experiment with a fan

Page 4 of 4

blowing air over a core gave values almost midway between those for still air and those for oil immersion.

The maximum possible frequency at which a core in a memory of 5 microsecond cycle time could be switched is 500 kilocycles. This means that a single register is being continuously selected and at least one bit is having a ONE read out and rewritten continuously. This is a somewhat improbable occurrence -- and a useless one in terms of information handling. The reasonable occurrence is that a particular register be selected every other cycle resulting in a maximum switching frequency of 200 kilocycles.

From Fig. 1,  $\Delta T$  for a core switching at 400 kilocycles is greater than 57°C in still air or 34°C in an oil bath (Dow Corning 550 Silicone Oil); for 200 kilocycles,  $\Delta T$  is 33°C and 22°C, respectively. Since the maximum allowable temperature rise is about 28°C, it is evident that the memory may operate near the temperature limit but should not exceed the limit so long as the cooling system functions.

For very high-speed memories, heating is a serious problem. Two approaches suggest themselves:

- (1) Increase the surface area to volume ratio of the element;

- (2) Move the memory operating point to a lower temperature.

is & Childress

James D. Childress

JDC/md

Dwg. Numbers

SB-65079 - Figure 1 B-64423 - Figure 2 58-65079

B-64423