MASSACHUSETTS INSTITUTE OF TECHNOLOGY

# MIT/LCS/TR-556

# CONCURRENT TIMESTAMPING MADE SIMPLE

Rainer Gawlick

October 1992

545 TECHNOLOGY SQUARE, CAMBRIDGE, MASSACHUSETTS 02139

This blank page was inserted to preserve pagination.

# **Concurrent Timestamping Made Simple**

by

# **Rainer Gawlick**

B.A., Physics University of California - Berkeley (1989) Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

at the

## MASSACHUSETTS INSTITUTE OF TECHNOLOGY

June 1992

© Massachusetts Institute of Technology 1992

| Signature of Author |                                                                                 |

|---------------------|---------------------------------------------------------------------------------|

| 0                   | Department of Electrical Engineering and Computer Science<br>September 29, 1992 |

| Certified by        |                                                                                 |

| v                   | Nancy A. Lynch                                                                  |

|                     | Professor of Computer Science                                                   |

|                     | Thesis Supervisor                                                               |

| Certified by        |                                                                                 |

|                     | Nir Shavit                                                                      |

|                     | Assistant Professor of Computer Science, Tel Aviv University                    |

|                     | Thesis Supervisor                                                               |

| Accepted by         |                                                                                 |

|                     | Campbell L. Searle                                                              |

Chairman, Departmental Committee on Graduate Students

#### **Concurrent Timestamping Made Simple**

by

Rainer Gawlick

Submitted to the Department of Electrical Engineering and Computer Science

on September 29, 1992, in partial fulfillment of the

requirements for the degree of

Master of Science in Electrical Engineering and Computer Science

### Abstract

Concurrent Timestamp Systems (CTSS) allow processes to temporally order concurrent events in an asynchronous shared memory system. Bounded memory constructions of a CTSS are extremely powerful tools for concurrency control, and are the basis for solutions to many coordination problems including mutual exclusion, randomized consensus, and multiwriter multireader atomic registers. Unfortunately, known bounded CTSS constructions seem to be complex from the algorithmic point of view. Because of the importance of bounded CTSS, the rather involved original construction by Dolev and Shavit was followed by a series of papers that tried to provide more easily verifiable CTSS constructions.

In this paper, we present what we believe is the simplest, most modular, and most easily proven bounded CTSS algorithm known to date. The algorithm is constructed and its correctness proven by carefully reasoned use of several tools. Our algorithm combines the labeling method of the Dolev-Shavit CTSS with the atomic snapshot algorithm proposed in Afek et. al, in a way that limits the number of interleavings that can occur. To facilitate our correctness proof, we introduce a specially tailored intermediate CTSS specification using unbounded label values taken from the positive reals. Our correctness proof first shows that the real-number based specification meets the CTSS axioms. Using the forward simulation techniques of the I/O Automata model, we then show that our bounded algorithm implements the real-number based specification. Finally, we prove that any CTSS that meets the CTSS axioms can be used to implement multireader multiwriter atomic registers and first-some-first-serve (fcfs) mutual exclusion.

Thesis Supervisor: Nancy A. Lynch

Title: Professor of Computer Science

Thesis Supervisor: Nir Shavit

Title: Assistant Professor of Computer Science, Tel Aviv University

Keywords: Timestamps, Concurrent Algorithms, Distributed Systems, I/O Automata

# Contents

| 1  | Introduction                                 | 5  |

|----|----------------------------------------------|----|

| 2  | I/O Automata Model                           | 7  |

| 3  | Concurrent Timestamp System                  | 13 |

| 4  | An Unbounded Concurrent Timestamp System     |    |

| 5  | A Bounded Concurrent Timestamp System        | 23 |

| 6  | Invariants 2                                 |    |

| 7  | 7 Simulation Proof                           |    |

| 8  | Applications                                 | 46 |

|    | 8.1 Multireader Multiwriter Atomic Registers | 47 |

|    | 8.2 Mutual Exclusion                         | 55 |

| 9  | Formal Justification for Use of Snapshot     | 61 |

|    | 9.1 Theory                                   | 62 |

|    | 9.2 Proof                                    | 65 |

| 10 | Discussion and Future Work                   | 69 |

# Acknowledgements

First, I would like to thank my advisor Nancy Lynch and my co-advisor Nir Shavit. Without Nancy's incredible ability to read, correct, and improve numerous drafts of long and intricate proofs, this thesis would never have been finished. Because of Nancy, I now know what it means to have a *formal proof*. Nir's Ph.D thesis provides an important basis for the research in this thesis. Furthermore, Nir's help and advice was instrumental in the early stages of the thesis work.

Thanks also go to my office mates, Roberto Segala and Jørgen Søgaard-Andersen, for many helpful discussions.

This work was supported in part by the Office of Naval Research under Contract N00014-91-J-1046, by the Defense Advanced Research Projects Agency under Contract N00014-89-J-1988, and by the National Science Foundation under Contract 89152206-CCR.

## 1 Introduction

The paradigm of concurrent timestamping is at the heart of solutions to some of the most fundamental problems in multiprocessor concurrency control. Examples of such problems include *fcfs* mutual exclusion [19], construction of a multireader multiwriter atomic register[34], and randomized consensus [8]. A simple bounded construction of a CTSS implies simple bounded solutions to most of these extensively researched problems.

A timestamp system is somewhat like a ticket machine at an ice cream parlor. People's requests to buy the ice cream are timestamped based on a numbered ticket (label) taken from the machine. Any person, in order to know in what order the requests will be served, can scan through all the labels and establish the total order among them. A *concurrent* timestamp system (CTSS) is a timestamp system in which any process can either take a new ticket or scan the existing tickets simultaneously with other processes. Furthermore, a CTSS is *waitfree*, which means that a process is guaranteed to finish any of the two above mentioned tasks in a finite number of steps, even if other processes experience stopping failures. Waitfree algorithms are highly suited for fault tolerant and realtime applications (see [16]).

Israeli and Li, in [17], were the first to isolate the notion of bounded timestamping (timestamping using bounded size memory) as an independent concept, developing an elegant theory of bounded *sequential* timestamp systems. Sequential timestamp systems prohibit concurrent operations. This work was continued in several interesting papers on sequential systems with weaker ordering requirements by Li and Vitanyi [26], Cori and Sopena [9] and Saks and Zaharoglou [35]. Dolev and Shavit [11] were the first to define and construct a bounded *concurrent* timestamp system. However, to quote [12]: "Their algorithm is ingenious but its proof is long and involved."

Because of the importance of the bounded concurrent timestamping problem, the original solution by Dolev and Shavit has been followed by a series of papers directed at providing a simpler bounded CTSS algorithm. Israeli and Pinchasov [18] have simplified the [11] algorithm and its proof by modifying the labeling scheme of [11], introducing a new label scanning method, and simplifying the ordering-of-events based formal proof [23] by reasoning about global states (However, it still takes over 40 pages...). Dwork and Waarts [12] have taken a totally different approach, by having their bounded construction simulate a new and simpler type of unbounded CTSS construction in which processes choose from "local pools" of label values instead of a "global pool" as in [11, 18]. However, in order to bound the number of possible label values in the local pools, they are forced to introduce a form of amortized garbage collection. This greatly complicates their algorithm. (Their algorithm only has an informal operational proof.)

In this paper, we present a novel bounded algorithm that we believe is the simplest, most modular, and most easily proven CTSS algorithm known to date. Our basic approach is to decompose the problem into several distinct pieces.

- We base our algorithm on the atomic snapshot primitive introduced by Afek et. al [1] (we use it as a black box). This primitive is waitfree and allows a process to collect an "instantaneous" view of an array of shared registers. [1] gives an implementation of this primitive from atomic single writer multireader registers. By using a snapshot primitive, we limit the number of interleavings that can occur.

- The labeling operation, the operation of choosing a new label given a set of older ones, is very complex in all former algorithms. Based on the snapshot operation, we introduce a much simplified version of the labeling algorithm of [11].

- Proving that the bounded algorithm satisfies the CTSS specification has in the past led to long and involved inductive arguments. We overcome this problem by introducing a CTSS specification, that uses label values taken from the unbounded positive reals. Our correctness proof first shows that the real-number based specification meets the CTSS axioms of [11]. Using the forward simulation techniques of the I/O Automata model, we then show that our bounded algorithm implements the real-number based specification. (See [30] for references and a discussion of forward simulation techniques.)

The most efficient bounded CTSS implementations [12, 18] require O(n) time per operation. Though one might think that a high price in complexity must be paid for our algorithm's modularity and ease of proof, this is not the case. The size of the labels is O(n), and the time complexity of our algorithm is just that of the underlying atomic snapshot algorithm. The snapshot implementation of [3] requires  $O(n\sqrt{n})$  single writer multireader register operations per snapshot operation. Hence the complexity of our algorithm is  $O(n\sqrt{n})$  for each operation. The final section of this paper considers some applications of the CTSS primitive. We present specific algorithms for *fcfs* mutual exclusion and multireader multiwriter atomic registers and prove that any CTSS can be used as a primitive in these algorithms.

## 2 I/O Automata Model

We present our algorithm in the context of the I/O Automata model. This model, introduced by Lynch and Tuttle [29], represents algorithms as I/O Automata which are characterized by states, initial states, a set of actions called an action signature, state transitions called steps and an equivalence relation on some of the actions of the action signature called a partition. For a I/O Automaton A its five components are denoted by states(A), start(A), sig(A), steps(A), and part(A) respectively.

A step that results from an action is denoted by  $(s, \pi, s')$  where s is the original state,  $\pi$  is the action, and s' is the new state. If an action can be executed in a state s, it is said to be *enabled* in s. If an action is not enabled in state s, it is said to be *disabled* in s. Actions are classified into *external actions*, ext(A), those visible to user of the algorithm, and *internal actions*, int(A), which are not visible to the user. External actions are further classified into *input actions*, in(A), which are under the control of the user of the algorithm, and *output actions*, out(A), which are under the control of the algorithm. By definition input actions are enabled in all states. For an I/O Automaton A the tuple consisting of in(A) and out(A) is called A's *external action signature*, exsig(A). We now give a more precise definition for some of the elements of an I/O Automaton. Specifically, for an I/O Automaton A, sig(A) = (in(A), out(A), int(A)). Furthermore, part(A) defines an equivalence relation on the set of internal actions and output actions and output actions are states. For an I/O Automaton A, sig(A) = (in(A), out(A), int(A)).

An execution of an I/O Automaton is an alternating sequence of states and actions that could be produced if the algorithm is executed starting from an initial state. A state is called *reachable* is it is the final state of some execution. A fair execution,  $\alpha$ , of infinite length is one in which for all  $C \in part(A)$ , if some action from C (not necessarily always the same action) is continuously enabled,  $\alpha$  contains infinitely many actions from C. A fair execution of finite length is one in which for all  $C \in part(A)$  no actions of C are enabled in the final state. A schedule, sched( $\alpha$ ), is the projection of an execution  $\alpha$  onto the actions of the I/O Automaton. A fair schedule, fairsched( $\alpha$ ), is the projection of a fair execution  $\alpha$  on the actions of the I/O Automaton. A behavior, beh( $\alpha$ ), is the projection of an execution  $\alpha$  onto the external actions of the I/O Automaton. A fair behavior, fairbeh( $\alpha$ ), is the projection of a fair execution  $\alpha$  on the external actions of the I/O Automaton. The set of all possible behaviors of an I/O Automaton A is called behs(A). The set of all possible fair behaviors of an I/O Automaton A is called fairbehs(A).

In order to build complex I/O Automata from simple ones, the I/O Automata model defines the concept of *composition*. Composed I/O Automata interact using input and output actions that have the same name. Specifically, assume A and B are two composed I/O Automata. Let ACT be an output action of A and an input action of B. If A executes ACT this triggers the execution of ACT for B. In order to compose a set of I/O Automata, we must place certain restrictions on the action names the I/O Automata. Specifically, we require that none of the I/O Automata share any output actions, the internal actions of each I/O Automaton are not elements of the action sets of any other I/O Automaton, and no action can an element of the action sets of infinitely many I/O Automata (see [29] for a discussion of these restrictions). I/O Automata that satisfy these restrictions are said to be *strongly compatible*.

**Definition 2.1** Let  $I = \{1...n\}$ . A composition  $A = \prod_{i \in I} A_i$  of a countable collection of strongly compatible I/O Automata  $\{A_1...A_n\}$  is the I/O Automaton defined as follows<sup>1</sup>:

- $sig(A) = \left(\bigcup_{i \in I} in(A_i) \bigcup_{i \in I} out(A_i), \bigcup_{i \in I} out(A_i), \bigcup_{i \in I} int(A_i)\right),$

- $states(A) = \prod_{i \in I} states(A_i),$

- $start(A) = \prod_{i \in I} start(A_i),$

- steps(A) is the set of triples (s

<sub>1</sub>, π, s

<sub>2</sub>) such that for all i if π ∈ acts(A), then (s

<sub>1</sub>[i], π, s

<sub>2</sub>[i]) ∈ steps(A) and if π ∉ acts(A) then s

<sub>1</sub>[i] = s

<sub>2</sub>[i].

- $part(A) = \bigcup_{i \in I} part(A_i),$

<sup>&</sup>lt;sup>1</sup>The  $\prod$  symbol used to define states(A) and start(A) represents the normal Cartesian product. The notation  $\bar{s}[i]$  denotes the  $i^{th}$  component of the state vector  $\bar{s}$ .

We sometimes do not want the actions that constitute the interface between two composed I/O Automata to be visible to the environment. Therefore, the I/O Automata Model makes it possible to reclassify output actions to be internal actions. Such reclassified actions are said to be *hidden*.

The I/O Automata model represent a problem specification, P, as an external action signature, exsig(P), along with set of allowable behaviors, behs(P), on the actions in exsig(P). An I/O Automaton A is said to solve a problem specification P if exsig(A) = exsig(P) and  $fairbehs(A) \subseteq behs(P)$ . We say that an I/O Automaton A implements another I/O Automaton B if the fairbehs(A)  $\subseteq$  fairbehs(B). Our correctness proof uses the following theorem on simulation proofs which is a restricted version of a theorem in [29].

**Theorem 2.1** Let A and B be I/O Automata with sig(A) = sig(B), part(A) = part(B), and R a relation over the states of A and B. Suppose:

- 1. If a is an initial state of A, then there exists an initial state b of B such that  $(a,b) \in \mathbb{R}$ .

- Suppose a is a reachable state of A and b is a reachable state of B such that (a, b) ∈ R. If

(a, π, a') is a step of A then there exists a state b' of B such that (b, π, b') is a step of B

and (a', b') ∈ R.

- 3. If action  $\pi$  is enabled in state b of B and  $(a, b) \in \mathbb{R}$  then action  $\pi$  is enabled in state a of A.

Then  $fairbehs(A) \subseteq fairbehs(B)$ .

The I/O Automata model, while providing efficient techniques for reasoning about the correctness of algorithms, is much more general than the shared memory model [23] for which our timestamp algorithm is designed. Consequently, we introduce some added structure to the I/O Automata model. This section describes the basics needed to understand our correctness proof. Section 9 provides a more sophisticated development of shared memory concepts in the I/O Automata model. Some of the concepts in this section and most of the concepts in Section 9 are due to Goldman, Lynch and Yelick [15]. (See [28] for discussion of similar issues.)

We first introduce a type of interface which will be used to characterize the external action signature of I/O Automata and problem specifications for the shared memory model. The

interface captures the intuitive notion of a set of processes that perform operations on behalf of some user. Typically, any process might be able to perform several types of operations.

**Definition 2.2 (operational interface)** An operational interface is an external action signature S that partitions its actions into disjoint sets called operation types. The set of operation types of S is denoted by ops(S). Each operation type consists of at least one input and one output action.

As a short hand, we will sometime use the term *operation* instead of operation type. Notice that an operational interface only describes an external action signature. Hence an operational interface can be used to describe both I/O Automata and problem specifications. If we compose two I/O Automata which have an operational interface, the set of operation types of the composed I/O Automaton is the union of the sets of operation types of each of the constituent I/O Automata. Again, we must add some restrictions on a set of I/O Automata being composed. Assume that we wish to compose I/O Automaton A and I/O Automaton B. We require that each action in  $acts(A) \cap acts(B)$  be an element of the same operation type in A and B. Furthermore, if one action of an operation type of A or B is in  $acts(A) \cap acts(B)$  then all actions of that operation type are in  $acts(A) \cap acts(B)$ . An operation instance is defined as follows:

**Definition 2.3 (operation instance)** Let  $\beta$  be a behavior of an operational interface. Let *a* be an operation type of the operational interface. An *operation instance* is the occurrence of an input action of *a* and the first output action of *a* that follows the input action of *a* in the behavior  $\beta$ .

We now introduce a set of notational conventions. Let S be an operational interface. For an operation type  $a \in ops(S)$  we refer to the input actions of a by INVOKE(a, v) and the output actions of a by RESPONSE(a, r). The symbols v and r are syntactic placeholders for any arguments<sup>2</sup> that are used by this operation type. The I/O Automata and problem specifications that we consider typically allow several concurrent operations. We model concurrent operations with I/O Automata whose operational interfaces are structured as follows. Assume that A is an

<sup>&</sup>lt;sup>2</sup>Formally, v and r are used to uniquely identify the actions of operation type a. Intuitively, v and r represent arguments. The arguments v and r are syntactic placeholders since the I/O Automata Model does not have the concept of an argument. Arguments are implemented by having a separate action for each possible argument value.

I/O Automaton with an operational interface that can handle up to *n* concurrent operations. Then for each  $i \in \{1...n\}$  there exists a non empty set of operation types  $S_i \subset ops(exsig(A))$ .  $S_i$  and  $S_j$  are disjoint when  $i \neq j$ . For each operation type  $a_i \in S_i$  we refer to the input actions of  $a_i$  by INVOKE<sub>i</sub> $(a_i, v)$  and the output actions of  $a_i$  by RESPONSE<sub>i</sub> $(a_i, r)$ . Intuitively there is a process,  $p_i$ , associated with all actions whose names include the index *i*. For the remainder of the section, assume that all I/O Automata have an operational interface as described above.

We now define a set of concepts with which we can characterize the behaviors of I/O Automata and problem specifications that have operational interfaces. Let A be an I/O Automaton or a problem specification with an operational interface. If  $\beta$  is a behavior of A, then  $\beta_i$  is the projection of  $\beta$  onto the actions that have the index *i* as part of their name.

**Definition 2.4 (well-formed)** Let A be an I/O Automaton or a problem specification with an operational interface. A behavior  $\beta$  of A is *well-formed* if, for all  $\beta_i$ ,  $\beta_i$  consists of an alternating sequence of input and output actions, starting with an input action, such that each output action is immediately preceded by an input action of the same operation type. Specifically, if  $a_i \in ops(exsig(A))$ , each RESPONSE<sub>i</sub> $(a_i, r)$  action is immediately preceded by an INVOKE<sub>i</sub> $(a_i, v)$  action.

**Definition 2.5 (well-formed-input)** Let A be an I/O Automaton or a problem specification with an operational interface. A behavior  $\beta$  of A has a *well-formed-input* if, for all  $\beta_i$ , there exist no two consecutive input actions.

**Definition 2.6 (well-formed-preserving)** Let A be an I/O Automaton or a problem specification with an operational interface. Let  $\beta$  be a behavior of A.  $\beta$  is *well-formed-preserving* if, for all prefixes  $\beta'$  of  $\beta$  that have a well-formed-input,  $\beta'$  is well-formed.

We say that an I/O Automaton is well-formed-preserving if all of its behaviors are well-formedpreserving. Similarly, a problem specification is well-formed-preserving of all of its behaviors are well-formed-preserving. In addition to the safety properties described by the well-formedness concepts, we require the following liveness property.

**Definition 2.7 (response-live)** Let A be an I/O Automaton or a problem specification with an operational interface. Let  $\beta$  be a well-formed behavior of A. Then  $\beta$  is *response-live* if each INVOKE<sub>i</sub> $(a_i, v)$  action is eventually followed by a RESPONSE<sub>i</sub> $(a_i, r)$  action. We say that an I/O Automaton is response-live if all of its fair behaviors are response-live. Similarly, a problem specification is response-live of all of its behaviors are response-live. We can now define the following partial order on the operation instances of any well-formed and response-live behavior.

**Definition 2.8** ( $\longrightarrow$  order) Let  $\beta$  be a well-formed and response-live behavior of an I/O Automaton or problem specification with an operational interface. Let  $a_i$  and  $b_j$  be any two operation instances<sup>3</sup> in  $\beta$ . In general  $a_i$  and  $b_j$  can be instances of the same operation type. We say that  $a_i \longrightarrow b_j$  if and only if in the behavior  $\beta$  the RESPONSE<sub>i</sub> $(a_i, r)$  action associated with  $a_i$  precedes the INVOKE<sub>j</sub> $(b_j, v)$  action associated with  $b_j$ .

The order  $\rightarrow$  is the same as the *precedes* relation of [22, 23]. Since  $\beta$  is a well-formed behavior, all operations with same index are totally ordered by  $\rightarrow$ .

An important type of I/O Automaton is called an *atomic* I/O Automaton. Before defining an *atomic* I/O Automaton we introduce the notion of a *serial specification* [38].

**Definition 2.9 (serial specification)** A *serial specification* is a set of finite and/or infinite sequences of operations.

Intuitively, a serial specification characterizes a behavior consisting of a set of sequentially executed operations.

**Definition 2.10 (atomic I/O Automata)** An I/O Automaton A is *atomic* for a serial specification S if A has an operational interface, is well-formed-preserving, and is response-live. Furthermore, for any behavior  $\beta \in fairbehs(A)$  there exists a total order  $\implies$  on the operation instances in  $\beta$  such that:

- 1.  $\implies$  is consistent with  $\longrightarrow$ .

- 2. The sequence consisting of the operation instances in  $\beta$  ordered by  $\implies$  is in S.

$<sup>^{3}</sup>$ We sometimes use the same name for operation instances and operation types. The meaning of a name will always be clear from context.

## **3** Concurrent Timestamp System

The following is a formal definition of a CTSS due to Dolev and Shavit [11]. It uses the axiomatic specification formalism of Lamport [22, 23].

A CTSS is a problem specification with an operational interface. A CTSS that permits n concurrent operations has 2n operation types, specifically LABEL<sub>i</sub> and SCAN<sub>i</sub> for  $i \in \{1...n\}$ . Each of these operation types consists of the following actions: LABEL<sub>i</sub> consists of the input action BEGINLABEL<sub>i</sub>( $val_i$ ) and the output action ENDLABEL<sub>i</sub>. SCAN<sub>i</sub> consists of the input action BEGINSCAN<sub>i</sub> and the output action ENDSCAN<sub>i</sub>( $\bar{o}, \bar{v}$ ). A LABEL<sub>i</sub> operation associates a value,  $val_i$ , taken from any domain, V, with a label. In order correctly handle initial conditions the value domain V must specify some initial value  $v_o$ . A SCAN<sub>i</sub> operation returns a pair ( $\bar{o}, \bar{v}$ ), where  $\bar{v} = (v_1 \dots v_n)$  is an indexed set of values (one per process), and  $\bar{o}$  is an total order on these indexes.

We now introduce some notation. In a particular behavior  $\beta$ ,  $L_i^{[k]}$  denotes the  $k^{th}$  instance of a LABEL<sub>i</sub> operation, and  $S_i^{[k]}$  denotes the  $k^{th}$  instance of a SCAN<sub>i</sub> operation. Furthermore,  $val_i^{[k]}$  denotes the value passed to operation  $L_i^{[k]}$ . (The superscript [k] is used only for notation, and is not visible to the I/O Automaton). We call the superscript [k] an *execution number*. The domain of execution numbers is  $E = \{1, 2, \ldots\}$ . Finally, we define a *choice function*, c, as a function mapping  $\{1 \ldots n\} \times E \times \{1 \ldots n\}$  to  $E \cup \{0\}$ . Intuitively, the choice function provides a way to determine which operation wrote a value returned by a SCAN operation. Specifically, if  $c(i, a, k) \neq 0$ , the value  $v_k$  returned by operation  $S_i^{[a]}$  was written by the operation  $L_k^{[c(i,a,k)]}$ . If c(i, a, k) = 0, then the value  $v_k$  returned by operation  $S_i^{[a]}$  is the initial value  $v_a$ .

The set of behaviors of a CTSS, *behs*(CTSS), is defined as follows:

#### **Definition 3.1** $\beta \in behs(\text{CTSS})$ if and only if:

- 1. If  $\beta$  has a well-formed-input, then  $\beta$  is well-formed.

- 2. If  $\beta$  has a well-formed-input, then  $\beta$  is response-live.

- 3. If  $\beta$  is well-formed, then there exists a total order  $\implies$  on the set of all LABEL operations and a choice function c such that  $\beta$ ,  $\implies$  and c satisfy axioms PO-P4 given below.

Note: if  $\beta$  does not have a well-formed-input, then  $\beta$  can be arbitrary.

In order to handle initial conditions, we let  $val_i^{[0]} = v_o$  for all *i*, where  $v_o$  is the initial value of the value domain *V*. Recall that execution numbers start with 1.

**P0** choice function: For any value  $v_k$  in  $\bar{v}$  of  $S_i^{[a]}$ ,  $v_k = val_k^{[c(i,a,k)]}$  where  $val_k^{[0]} = v_o$ .

- **P1** ordering:  $\implies$  is a total order on the set of all LABEL operation instances in  $\beta$ , such that:

- **a**. precedence: For any pair of LABEL operation instances  $L_i^{[a]}$  and  $L_j^{[b]}$  (where possibly *i* and *j* are the same index), if  $L_i^{[a]} \longrightarrow L_j^{[b]}$ , then  $L_i^{[a]} \implies L_j^{[b]}$ .

**b.** consistency: For any SCAN operation instance  $S_i^{[a]}$  that returns  $\bar{v}$  and  $\bar{o}$ , if  $v_j, v_k \in \bar{v}$ :

c(i, a, j) > 0 and c(i, a, k) > 0: j < k in  $\bar{o}$  if and only if  $L_j^{[c(i, a, j)]} \implies L_k^{[c(i, a, k)]}$ .

- c(i,a,j) = 0 and c(i,a,k) = 0: j < k in  $\bar{o}$  if and only if j < k.

- c(i,a,j) = 0 and c(i,a,k) > 0: j < k in  $\overline{o}$ .

- c(i,a,j) > 0 and c(i,a,k) = 0: k < j in  $\overline{o}$ .

The above property implies that there is a unique total ordering on LABEL operation instances of all processes, which is a serialization order (part a), and with which all SCAN operations are consistent (part b).

**P2** regularity: Let  $S_j^{[a]}$  be a SCAN operation instance. If c(j, a, i) > 0, then  $S_j^{[a]} \not\rightarrow L_i^{[c(j,a,i)]}$ and there is no  $L_i^{[b]}$  such that  $L_i^{[c(j,a,i)]} \longrightarrow L_i^{[b]} \longrightarrow S_j^{[a]}$ . If c(j, a, i) = 0, then there exists no  $L_i^{[b]}$  such that  $L_i^{[b]} \longrightarrow S_j^{[a]}$ .

Though a regular CTSS (having properties P0-P2) would suffice for some applications (for example Lamport's "Bakery Algorithm" [19]), a more powerful concurrent timestamp system is needed in applications such as the multireader multiwriter atomic register construction (see [24, 34]). To this end the following third and fourth axioms are added:

**P3** monotonicity: Let  $S_i^{[a]}$  return  $v_k = val_k^{[c(i,a,k)]}$  and  $S_j^{[b]}$  return  $v_k = val_k^{[c(j,b,k)]}$  (where possibly i = j). Then,  $S_i^{[a]} \longrightarrow S_j^{[b]}$  and  $c(i, a, k) \neq c(j, b, k)$  imply c(i, a, k) < c(j, b, k).

Note that c(i,a,k) < c(j,b,k) implies that  $L_k^{[c(i,a,k)]} \implies L_k^{[c(j,b,k)]}$  when c(i,a,k) > 0 and c(j,b,k) > 0. Monotonicity is the property that in a unbounded real number CTSS can be

described by saying that the labels of any one process, as read by increasingly later SCAN operations, are "monotonically non-decreasing." It is important to note that P3 does not imply that one can serialize all LABEL and SCAN operation instances. It does however imply the serializability of the SCAN operation instances of all processes relative to the LABEL operation instances of any *one* process [37]. P4<sup>4</sup> is an extension of part of the regularity property to the  $\Rightarrow$  order. The properties P3 and P4 together imply that all SCAN operations that consider only the "largest" value, where "largest" is based on the  $\bar{o}$  ordering, can be serialized with respect to all LABEL operations.

**P4**  $\implies$  regularity: Let  $S_i^{[a]}$  be a SCAN operation instance. If c(i, a, k) > 0, then  $S_i^{[a]} \longrightarrow L_j^{[b]}$  implies that  $L_k^{[c(i,a,k)]} \implies L_j^{[b]}$ .

## 4 An Unbounded Concurrent Timestamp System

This section introduces a particular implementation of a concurrent time stamp system, UCTSS, that uses timestamps from  $\Re^+$ . UCTSS is introduced as an intermediary I/O Automaton whose purpose is to simplify the correctness proof of our bounded CTSS.

The code for the operations of UCTSS is presented in two forms. Figure 1 presents the code in the precondition-effect notation commonly used to describe I/O Automata<sup>5</sup>. Figure 2 uses psuedocode. We use the precondition-effect notation as the basis for the correctness proof and include the compact and intuitive psuedocode only for clarity.

The system models *n* processes indexed by  $\{1...n\}$ . Each process  $p_i$  in UCTSS can perform a SCAN<sub>i</sub> and LABEL<sub>i</sub> operation. A LABEL<sub>i</sub> operation allows process  $p_i$  to associate a label (timestamp) with a given value. A SCAN<sub>i</sub> operation allows process  $p_i$  to determine the order among values based on their associated labels. The function NEWLABEL<sub>i</sub>, which is used by LABEL<sub>i</sub> is defined in Figure 3. A SNAP<sub>i</sub> operation, which is defined by Afek et al. in [1], atomically reads an array of single writer multireader registers. A UPDATE<sub>i</sub> operation, also defined by [1], writes a value to a single register in the array of single writer multireader registers

<sup>&</sup>lt;sup>4</sup>A more powerful CTSS satisfying P4 is needed in applications such as the multireader multiwriter atomic register construction of [24, 34]. P4 is included in the journal version of [11], but is not included in the conference version of [11] or in [37].

<sup>&</sup>lt;sup>5</sup>BCTSS is the name for our bounded CTSS implementation. The name is included in the caption since the code in the figure is shared by BCTSS and UCTSS. BCTSS is introduced in Section 5.

Shared State:  $t_i$ : The current label associated with process  $p_i$ ; initially 0. The current value associated with process  $p_i$ ; initially  $v_o$ .  $v_i$ : Local State:  $nt_i$ : The new label for  $p_i$  determined by function MAKELABEL<sub>i</sub>; initially 0.  $val_i$ : The new value for  $p_i$  passed to LABEL<sub>i</sub>; initially  $v_o$ .  $\bar{t_i}$ : An array of labels returned by  $SNAP_i$ ; initially (0...0). An array of values returned by SNAP<sub>i</sub>; initially  $(v_o \dots v_o)$ .  $\bar{v_i}$ : An array of process indexes ordered based on the  $\ll$  order; initially  $(1 \dots n)$ .  $\bar{o_i}$ : The non-input action currently enabled; initially NIL.  $pc_i$ : The current operation; initially NIL.  $op_i$ : SCAN<sub>i</sub>: *Eff:*  $op_i \leftarrow SCAN_i$ BEGINSCANi  $pc_i \leftarrow SNAP_i(\bar{t}_i, \bar{v}_i)$  $\text{SNAP}_{i}(\bar{t}_{i}, \bar{v}_{i})$ Pre:  $pc_i = SNAP_i(\bar{t}_i, \bar{v}_i)$ Eff: If  $op_i = SCAN_i$  then  $\bar{o_i} \leftarrow$  the sequence of indexes where j appears before k in  $o_i$  iff  $(t_i, j) \ll (t_k, k)$  $pc_i \leftarrow \text{ENDSCAN}_i(\bar{o_i}, \bar{v_i})$ If  $op_i = LABEL_i$  then  $nt_i \leftarrow \text{NEWLABEL}_i(\bar{t_i})$  $pc_i \leftarrow UPDATE_i((t_i, v_i), (nt_i, val_i))$ ENDSCAN<sub>i</sub> $(\bar{o_i}, \bar{v_i})$ *Pre:*  $pc_i = ENDSCAN_i(\bar{o}_i, \bar{v}_i)$ *Eff:*  $pc_i \leftarrow \text{NIL}$ LABEL<sub>i</sub>: *Eff:*  $op_i \leftarrow LABEL_i$ BEGINLABELi  $pc_i \leftarrow \text{SNAP}_i(\bar{t}_i, \bar{v}_i)$ UPDATE<sub>i</sub>( $(t_i, v_i), (nt_i, val_i)$ ) Pre:  $pc_i = UPDATE_i((t_i, v_i), (nt_i, val_i))$ *Eff:*  $pc_i \leftarrow \text{ENDLABEL}_i$ ENDLABELi *Pre:*  $pc_i = \text{ENDLABEL}_i$ *Eff:*  $pc_i \leftarrow NIL$

Figure 1: Precondition-Effect code for UCTSS and BCTSS

SCAN<sub>i</sub> SNAP<sub>i</sub>( $\bar{t}_i, \bar{v}_i$ )  $\bar{o}_i \leftarrow$  the sequence of indexes where j appears before k in  $o_i$  iff  $(t_j, j) \ll (t_k, k)$ return  $(\bar{o}_i, \bar{v}_i)$ LABEL<sub>i</sub>(val<sub>i</sub>) SNAP<sub>i</sub>( $\bar{t}_i, \bar{v}_i$ )  $nt_i \leftarrow \text{NEWLABEL}_i(\bar{t}_i)$ UPDATE<sub>i</sub>( $(t_i, v_i), (nt_i, val_i)$ )

#### Figure 2: Psuedocode for UCTSS and BCTSS

read by  $SNAP_i$ .  $SNAP_i$  and  $UPDATE_i$  are waitfree, therefore their use does not compromise the waitfree properties of our timestamp algorithm.

| NEWLABEL <sub>i</sub> $(\bar{t_i})$ |                                                          |

|-------------------------------------|----------------------------------------------------------|

| if $i \neq i_{max}$                 |                                                          |

|                                     | where X is nondeterministically selected from $\Re^{>0}$ |

| ( 1162 1                            |                                                          |

Figure 3: Code for  $NEWLABEL_i$  of UCTSS

The state of UCTSS is defined by the shared state and the local state of each of the *n* process. The shared and local state of each process, along with the initial values are defined in Figure 1. The state of UCTSS also has derived variables  $t_{max}$  and  $i_{max}$ .  $t_{max} = MAX(t_1...t_n)$  and  $i_{max}$  is the largest process index *i* such that  $t_i = t_{max}$ .

In terms of the I/O Automata model, UCTSS is an I/O Automaton with an operational interface. UCTSS is a composition of n I/O Automata called  $p_1, \ldots, p_n$ . Each  $p_i$  is an I/O Automaton with an operational interface that consists of the operation types LABEL<sub>i</sub> and SCAN<sub>i</sub>. The LABEL<sub>i</sub> operation type consists of the input action BEGINLABEL<sub>i</sub>(val<sub>i</sub>) and the output action ENDLABEL<sub>i</sub>. The operation type SCAN<sub>i</sub> consists of the input action BEGINSCAN<sub>i</sub> and the output action ENDSCAN<sub>i</sub>( $\bar{o}_i, \bar{v}_i$ ). The internal actions of  $p_i$  are SNAP<sub>i</sub>( $\bar{t}_i, \bar{v}_i$ ) and UPDATE<sub>i</sub>(( $t_i, v_i$ ), ( $nt_i, val_i$ )). The set  $steps(p_i)$  is characterized by the *precondition* clause in each action. The set  $part(p_i)$ consists of a single equivalence classes  $C_i$  where the elements of  $C_i$  are the actions SNAP<sub>i</sub>( $\bar{t}_i, \bar{v}_i$ ), ENDSCAN<sub>i</sub>( $\bar{o}_i, \bar{v}_i$ ), UPDATE<sub>i</sub>(( $t_i, v_i$ ), ( $nt_i, val_i$ )), and ENDLABEL<sub>i</sub>. The set  $states(p_i)$  is the set of all possible states of  $p_i$  where each state is defined by the values of the variables of the shared and local state. The set  $start(p_i)$  is the set consisting of the state defined by the initial values of the variables of the shared and local state.

The shared state is accessed only using the atomic  $SNAP_i$  and the UPDATE<sub>i</sub> actions. Since  $SNAP_i$  and  $UPDATE_i$  are atomic, each action of UCTSS is atomic. Notice that the  $SNAP_i$  action makes references to the elements of the vector  $\bar{t}_i$  indirectly through the use of  $i_{max}$  and  $t_{max}$  and in order to calculate  $\bar{o}_i$ . Since  $SNAP_i$  is atomic, the labels in  $\bar{t}_i$  are the same as the corresponding labels in the shared state. In other words,  $t_{ij} = t_j$  during the action. Consequently, we refer directly to the shared variables  $i_{max}$ ,  $t_{max}$ , and  $t_i$  rather than their copies  $i_{i_{max}}$ ,  $t_{i_{max}}$ , and  $t_{i_i}$  when analyzing the  $SNAP_i$  action.

UCTSS uses labels that are non-negative real numbers. The ordering between labels is the usual < order of  $\Re^+$ . The ordering  $\ll$  used in the ORDER<sub>i</sub> action is a lexicographical order between label and process index pairs.

**Definition 4.1** (

$$\ll$$

order)  $(\ell_i, i) \ll (\ell_j, j)$  iff  $\ell_i < \ell_j$  or  $\ell_i = \ell_j$  and  $i < j$ .

We now prove some characteristics of  $\ll$  that will be used to prove that UCTSS solves CTSS. First consider the following notation:  $t_i^{[a]}$  is the label written as a consequence of the  $L_i^{[a]}$ operation. When a = 0, then  $t_i^{[a]}$  is equal to the initial value for labels, which for UCTSS is 0.  $L_i^{[a]}(\text{UPDATE})$  refers to the UPDATE<sub>i</sub> action executed as a consequence of the  $L_i^{[a]}$  operation and  $L_i^{[a]}(SNAP)$  refers to the SNAP, action executed as a consequence of the  $L_i^{[a]}$  operation. Similarly,  $S_i^{[a]}(SNAP)$  refers to the SNAP<sub>i</sub> action executed as a consequence of the  $S_i^{[a]}$  operation. The SNAP and UPDATE actions model two atomic operations. In the usual model for atomic operations [23], each operation is separated into a request (input) action and a response (output) action, concurrent operations executions are allowed, and it is assumed that every request eventually terminates in a matching response, in such a way as to produce the *illusion* of instantaneous operations. Consequently, we model SNAP and UPDATE as single actions rather than separate input and output actions. We present a formal justification for treating SNAP and UPDATE operations as single actions rather than separate input and output actions in Section 9. Since SNAP and UPDATE are single actions, there exists a total order on all SNAP and UPDATE actions. We represent this order by  $\Longrightarrow'$ . If a SNAP action returns the set of values,  $\bar{v}$ , and labels,  $\bar{t}$ , then  $v_k$  and  $t_k$  are the value and label written by the UPDATE<sub>k</sub> action that immediately proceeds the SNAP action in the  $\implies$ ' ordering. If a SNAP action is not proceeded by an UPDATE<sub>k</sub> action,

then  $v_k$  and  $t_k$  are equal to their initial values.

Lemma 4.1 Consider any well-formed, response-live behavior  $\beta$  where  $\beta \in fairbehs(UCTSS)$ . For any *i*, *a* and SNAP operation  $L_j^{[b]}(SNAP)$ , if either a > 0 and  $L_i^{[a]}(UPDATE) \Longrightarrow' L_j^{[b]}(SNAP)$ in  $\beta$ , or a = 0 then:

1.  $(t_i^{[a]}, i) \ll (t_j^{[b]}, j)$  when  $i \neq j$ . 2.  $(t_i^{[a]}, i) = (t_j^{[b]}, j)$  or  $(t_i^{[a]}, i) \ll (t_j^{[b]}, j)$  when i = j.

**Proof:** Let  $\overline{t_{max}}$  and  $\overline{i_{max}}$  be the  $t_{max}$  and  $i_{max}$  used in NEWLABEL<sub>j</sub> for  $L_j^{[b]}$ . Since  $\beta$  is wellformed, each process must read its current label when determining its new label. This fact, along with the fact that X in NEWLABEL<sub>i</sub> is in  $\Re^{>0}$ , shows that the labels for all process are nondecreasing. In other words, a label for some process in a particular state of  $\beta$  is never larger than the label for the same process in a subsequent state of  $\beta$ . Thus  $t_i^{[a]} \leq \overline{t_{max}}$  when a = 0. When a > 0,  $L_i^{[a]}(\text{UPDATE}) \Longrightarrow' L_j^{[b]}(\text{SNAP})$  shows that  $t_i^{[a]} \leq \overline{t_{max}}$ . Consider the following cases:

- $\underbrace{j = \overline{i_{max}} \text{ and } i \neq j}_{i}: \text{ When } j = \overline{i_{max}}, \text{ then } \overline{t_{max}} = t_j^{[b-1]}. \text{ Recall that } t_i^{[a]} \leq \overline{t_{max}}. \text{ Consider the cases } t_i^{[a]} = \overline{t_{max}} \text{ and } t_i^{[a]} < \overline{t_{max}} \text{ separately. When } t_i^{[a]} = \overline{t_{max}}, \text{ then, since } \overline{t_{max}} = t_j^{[b-1]}, \\ t_i^{[a]} = t_j^{[b-1]}. \text{ Furthermore, since } i \neq j \text{ and } j = \overline{i_{max}}, i \neq \overline{i_{max}}. \text{ Since } j = \overline{i_{max}}, i \neq \overline{i_{max}}, \\ and t_i^{[a]} = t_j^{[b-1]}, \text{ the definition of } i_{max} \text{ shows that } i < j. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence, } t_i^{[a]} = t_j^{[b]} \text{ and } i < j \text{ which implies that } (t_i^{[a]}, i) \ll (t_j^{[b]}, j). \text{ Now consider the case } t_i^{[a]} < \overline{t_{max}}. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence, } t_i^{[a]} < \overline{t_{max}}. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence, } t_i^{[a]} < \overline{t_{max}}. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_{max}}. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_{max}}. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_{max}}. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_{max}}. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_{max}}. \text{ As a result of the action } L_j^{[b]}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_j}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_j}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_j}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[b]} < \overline{t_j}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[a]} < \overline{t_j}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[b]} < \overline{t_j}, \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[b]} < \overline{t_j} < \overline{t_j}. \\ t_j^{[b]} = \overline{t_{max}}. \text{ Hence } t_i^{[b]} < \overline{t_j} < \overline{t_j}. \\ t_j^{[b]} = \overline{t_j} < \overline{t_j} < \overline{t_j} < \overline{t_$

- $\underline{j = \overline{i_{max}} \text{ and } i = j}: \text{ As a result of the action } L_j^{[b]} \text{ and the fact that } j = \overline{i_{max}}, t_j^{[b]} = \overline{t_{max}}. \text{ Since } t_i^{[a]} \leq \overline{t_{max}}, \text{ it must now be the case that } t_i^{[a]} \leq t_j^{[b]}. \text{ This implies that } (t_i^{[a]}, i) = (t_j^{[b]}, j) \text{ or } (t_i^{[a]}, i) \ll (t_j^{[b]}, j).$

- $\underline{j \neq \overline{i_{max}}}$ : As a result of the action  $L_j^{[b]}$  and the fact that  $j \neq \overline{i_{max}}, \overline{t_{max}} < t_j^{[b]}$ . Since  $t_i^{[a]} \leq \overline{t_{max}}, \overline{t_{max}}$  it must now be the case that  $t_i^{[a]} < t_j^{[b]}$ . This implies that  $(t_i^{[a]}, i) \ll (t_j^{[b]}, j)$ .

**Corollary 4.2** Consider any well-formed, response-live behavior  $\beta$  where  $\beta \in fairbehs(UCTSS)$ . For any two LABEL operations  $L_i^{[a]}$  and  $L_j^{[b]}$ , if  $L_i^{[a]} \longrightarrow L_j^{[b]}$  in  $\beta$ , then:

1.  $(t_i^{[a]}, i) \ll (t_j^{[b]}, j)$  when  $i \neq j$ . 2.  $(t_i^{[a]}, i) = (t_i^{[b]}, j)$  or  $(t_i^{[a]}, i) \ll (t_i^{[b]}, j)$  when i = j.

**Proof:** If  $L_i^{[a]} \to L_j^{[b]}$ , then  $L_i^{[a]}(UPDATE) \Longrightarrow' L_j^{[b]}(SNAP)$ . Now Lemma 4.1 proves the corollary.

Consider any well-formed, response-live behavior  $\beta$  where  $\beta \in fairbehs(UCTSS)$ . Define  $\Longrightarrow'$ , a total order on all the SNAP and UPDATE operations of  $\beta$ , as before. We now define a total order<sup>6</sup>  $\Longrightarrow$  on the LABEL operations in  $\beta$  and a choice function c. Recall from Definition 2.8 that  $\longrightarrow$  defines a partial order on the operation instances of a well-formed, response-live behavior.

**Definition 4.2** (

$$\Rightarrow$$

order)  $L_i^{[a]} \Rightarrow L_j^{[b]}$  iff either  $L_i^{[a]} \rightarrow L_j^{[b]}$  or  $(t_i^{[a]}, i) \ll (t_j^{[b]}, j)$ .

**Definition 4.3 (choice function** c) If  $S_i^{[a]}$  returns  $\bar{v}$  and  $L_j^{[b]}(UPDATE)$  is the UPDATE<sub>j</sub> action that immediately proceeds  $S_i^{[a]}(SNAP)$  in  $\Longrightarrow$ ', then c(i, a, j) = b. If no such UPDATE<sub>j</sub> action exists, then c(i, a, j) = 0.

For the following lemmas assume that  $\beta$  is well-formed, response-live,  $\beta \in fairbehs(UCTSS)$ , and  $\rightarrow$  is defined as in Definition 2.8. Furthermore,  $\Rightarrow$  and c are defined as in Definition 4.2 and Definition 4.2 respectively.

#### **Lemma 4.3** The order $\implies$ is a total order on all LABEL operation instances in $\beta$ .

**Proof:** In order to simplify the notation in this proof, we write  $L_i^{[a]} \ll L_j^{[b]}$  instead of  $(t_i^{[a]}, i) \ll (t_j^{[b]}, j)$ . Since  $\longrightarrow$  is a partial order, it is irreflexive, antisymmetric, and transitive. By definition,  $\ll$  is irreflexive, antisymmetric, and transitive.

*irreflexive*: This follows immediately from the fact that  $\rightarrow$  and  $\ll$  are irreflexive.

<u>antisymmetric</u>: To reach a contradiction assume that  $L_i^{[a]} \implies L_j^{[b]}$  and  $L_j^{[b]} \implies L_i^{[a]}$ . Since  $\longrightarrow$  and  $\ll$  are antisymmetric, we can assume without loss of generality that  $L_i^{[a]} \longrightarrow L_j^{[b]}$  and

<sup>&</sup>lt;sup>6</sup>Lemma 4.3 proves that  $\implies$  is a total order.

$L_j^{[b]} \ll L_i^{[a]}$ . Using the fact that  $L_i^{[a]} \longrightarrow L_j^{[b]}$  along with Corollary 4.2 we can conclude that  $L_i^{[a]} \ll L_j^{[b]}$  or  $L_i^{[a]} = L_j^{[b]}$ . However, this contradicts the fact that  $L_j^{[b]} \ll L_i^{[a]}$ .

<u>transitive</u>: For a contradiction assume that  $L_i^{[a]} \Longrightarrow L_j^{[b]}$  and  $L_j^{[b]} \Longrightarrow L_k^{[c]}$  but  $L_i^{[a]} \nrightarrow L_k^{[c]}$ . Consider the case where  $L_i^{[a]} \longrightarrow L_j^{[b]}$  and  $L_j^{[b]} \ll L_k^{[c]}$  but  $L_i^{[a]} \nleftrightarrow L_k^{[c]}$  and  $L_i^{[a]} \not\ll L_k^{[c]}$ . Corollary 4.2 and the fact that  $L_i^{[a]} \longrightarrow L_j^{[b]}$  imply that  $L_i^{[a]} \ll L_j^{[b]}$  or  $L_i^{[a]} = L_j^{[b]}$ . This fact along with the fact that  $L_j^{[b]} \ll L_k^{[c]}$  implies that  $L_i^{[a]} \ll L_k^{[c]}$ . This contradicts that earlier assumption that  $L_i^{[a]} \not\ll L_k^{[c]}$ . Since  $\longrightarrow$  and  $\ll$  are transitive, the only other case is  $L_i^{[a]} \ll L_j^{[b]}$ and  $L_j^{[b]} \longrightarrow L_k^{[c]}$  but  $L_i^{[a]} \not\to L_k^{[c]}$  and  $L_i^{[a]} \not\ll L_k^{[c]}$ . We use the same reasoning as in the previous case to show that this case also cannot arise.

<u>total</u>: Consider any two label operations  $L_i^{[a]}$  and  $L_j^{[b]}$ . When  $i \neq j$  then  $L_i^{[a]}$  and  $L_j^{[b]}$  are ordered by  $\ll$ . When i = j then  $L_i^{[a]}$  and  $L_j^{[b]}$  are ordered by  $\longrightarrow$ .

Since  $\implies$  is irreflexive, antisymmetric, transitive and total, we can conclude that  $\implies$  is a *total* order.

#### **Lemma 4.4** $\beta$ using the order $\implies$ and choice function c satisfies axiom P0.

**Proof:** This follows immediate from the definition of c, the fact that  $\beta$  is well-formed, and the definition of the SNAP and UPDATE actions.

#### **Lemma 4.5** $\beta$ using the order $\Rightarrow$ and choice function c satisfies axiom P1.

**Proof:** In order to simplify the notation in this proof, we write  $L_i^{[a]} \ll L_j^{[b]}$  instead of  $(t_i^{[a]}, i) \ll (t_j^{[b]}, j)$ . From Lemma 4.3 we know that  $\Longrightarrow$  is a total order. Part *a* of **P1**, precedence, follows immediately from the definition of  $\Longrightarrow$ . For part *b* of **P1**, consistency, let  $S_i^{[a]}$  return  $\bar{o}_i$ . There are four cases to consider:

$$\begin{split} c(i,a,j) \neq 0 \quad \text{and} \quad c(i,a,k) \neq 0: \Rightarrow \text{ If } j < k \text{ in } \bar{o_i} \text{ then, by the definition of } \bar{o_i} \text{ in the SNAP}_i \\ \text{action, } L_j^{[c(i,a,j)]} \ll L_k^{[c(i,a,k)]}. \text{ By definition of } \Rightarrow \text{ this shows that } L_j^{[c(i,a,j)]} \implies L_k^{[c(i,a,k)]}. \\ & \leftarrow \text{ If } L_j^{[c(i,a,j)]} \implies L_k^{[c(i,a,k)]} \text{ then either } L_j^{[c(i,a,j)]} \longrightarrow L_k^{[c(i,a,k)]} \text{ or } L_j^{[c(i,a,j)]} \ll L_k^{[c(i,a,k)]}. \\ & \text{ When } L_j^{[c(i,a,j)]} \implies L_k^{[c(i,a,k)]} \text{ Corollary 4.2 and the fact that } j \neq k \text{ show that } L_j^{[c(i,a,j)]} \ll L_k^{[c(i,a,j)]} \ll L_k^{[c(i,a,k)]}. \end{split}$$

- c(i, a, j) = 0 and c(i, a, k) = 0: In this case the definition of c show that the  $t_j$  and  $t_k$  read by  $S_i^{[a]}(\text{SNAP})$  are equal to their initial values, which are 0. Now the definition of  $\bar{o}_i$  in the SNAP action shows that j < k in  $\bar{o}_i$  if and only if j < k.

- c(i, a, j) = 0 and  $c(i, a, k) \neq 0$ : Lemma 4.1 shows that  $(t_j^{[c(i, a, j)]}, j) \ll (t_k^{[c(i, a, k)]}, k)$ . Now the definition of  $\bar{o}_i$  in the SNAP action shows that j < k in  $\bar{o}_i$ .

- $c(i, a, j) \neq 0$  and c(i, a, k) = 0: Lemma 4.1 shows that  $(t_k^{[c(i, a, k)]}, k) \ll (t_j^{[c(i, a, j)]}, j)$ . Now the definition of  $\bar{\sigma}_i$  in the SNAP action shows that k < j in  $\bar{\sigma}_i$ .

#### **Lemma 4.6** $\beta$ using the order $\Rightarrow$ and choice function c satisfies axiom P2.

**Proof:** Consider  $S_j^{[a]}$  with c(j, a, i) > 0. By definition of c,  $L_i^{[c(j,a,i)]}(\text{UPDATE}) \Longrightarrow' S_j^{[a]}(\text{SNAP})$ . Hence  $S_j^{[a]} \nleftrightarrow L_i^{[c(j,a,i)]}$ . In order to prove that the second part of the axiom holds for  $\beta$ we assume that there exists  $L_i^{[b]}$  such that  $L_i^{[c(j,a,i)]} \longrightarrow L_i^{[b]} \longrightarrow S_j^{[a]}$ . This implies that  $L_i^{[c(j,a,i)]}(\text{UPDATE}) \Longrightarrow' L_i^{[b]}(\text{UPDATE}) \Longrightarrow' S_j^{[a]}(\text{SNAP})$ , which directly contradicts the definition of c. Now consider  $S_j^{[a]}$  where c(j,a,i) = 0. The definition of c shows that there exists no  $L_i^{[b]}(\text{UPDATE})$  such that  $L_i^{[b]}(\text{UPDATE}) \Longrightarrow' S_j^{[a]}(\text{SNAP})$ . Consequently, there exists no  $L_i^{[b]}$  such that  $L_i^{[b]} \longrightarrow S_j^{[a]}$ .

## **Lemma 4.7** $\beta$ using the order $\Rightarrow$ and choice function c satisfies axiom P3.

**Proof:** Consider  $S_i^{[a]} \to S_j^{[b]}$ , where c(i, a, k) > 0. By definition of c,  $L_k^{[c(i,a,k)]}(\text{UPDATE}) \Longrightarrow' S_i^{[a]}(\text{SNAP}) \Longrightarrow' S_j^{[b]}(\text{SNAP})$ . Now the definition of c and the fact that  $c(i, a, k) \neq c(j, b, k)$  imply that c(i, a, k) < c(j, b, k). When c(i, a, k) = 0 the fact that  $c(i, a, k) \neq c(j, b, k)$  immediately shows that c(i, a, k) < c(j, b, k).

### **Lemma 4.8** $\beta$ using the order $\implies$ and choice function c satisfies axiom P4.

**Proof:** Since  $S_i^{[a]} \to L_j^{[b]}$ ,  $S_i^{[a]}(SNAP) \Longrightarrow' L_j^{[b]}(SNAP)$ . Furthermore, the definition of c and the fact that c(i, a, k) > 0 imply that  $L_k^{[c(i,a,k)]}(UPDATE) \Longrightarrow' S_i^{[a]}(SNAP)$ . Consequently,  $L_k^{[c(i,a,k)]}(UPDATE) \Longrightarrow' L_j^{[b]}(SNAP)$ . Now Lemma 4.1 implies that  $(t_k^{[c(i,a,k)]}, k) \ll (t_j^{[b]}, j)$ . Therefore the definition of  $\Longrightarrow$  implies that  $L_k^{[c(i,a,k)]} \Longrightarrow L_j^{[b]}$ .

**Lemma 4.9** If a behavior  $\beta$ , where  $\beta \in fairbehs(UCTSS)$ , has a well-formed-input, then  $\beta$  is well-formed and response-live.

**Proof:** Notice by inspecting the *precondition* clauses in the code of Figure 1 that for any equivalence class  $C_i$  of *part*(UCTSS), there is always at most one action enabled. Furthermore each action remains enabled until it is executed. Consequently, the actions must be executed in the sequence in which they are enabled. Furthermore, in a fair execution each enabled action will eventually be executed.

Now consider any fair execution that has a well-formed-input. The precondition-effects code in Figure 1 shows that the following sequence of actions is executed in response to a BEGINSCAN<sub>i</sub> input action:  $SNAP_i(\bar{t}_i, \bar{v}_i)$  and  $ENDSCAN_i(\bar{o}_i, \bar{v}_i)$ . In response to a BEGINLABEL<sub>i</sub>(val<sub>i</sub>) input action, the following sequence of actions is executed:  $SNAP_i(\bar{t}_i, \bar{v}_i)$ ,  $UPDATE_i((t_i, v_i), (nt_i, val_i))$ , and  $ENDLABEL_i$ . Also, no actions of  $C_i$  are enabled between the execution of an  $ENDSCAN_i(\bar{o}_i, \bar{v}_i)$ or  $ENDLABEL_i$  action and the next execution of a  $BEGINSCAN_i$  or  $BEGINLABEL_i(val_i)$  action. Inspection of these action sequences and the definitions of well-formed-preserving and responselive, immediately shows that UCTSS is well-formed-preserving and response-live.

We now have the necessary lemmas to show that UCTSS solves CTSS.

Lemma 4.10 UCTSS solves CTSS.

**Proof:** By inspection exsig(UCTSS) = exsig(CTSS). In order to show that  $fairbehs(UCTSS) \subseteq behs(CTSS)$  we consider any behavior  $\beta$  such that  $\beta \in fairbehs(UCTSS)$ . If  $\beta$  does not have a well-formed-input, then  $\beta \in behs(CTSS)$  trivially. So, assume that  $\beta$  has a well-formed-input. Now Lemma 4.9 shows that  $\beta$  is well formed. Define an order  $\Longrightarrow$  and a choice function c as in Definition 4.2 and Definition 4.3 respectively. Now, Lemma 4.4, Lemma 4.5, Lemma 4.6, Lemma 4.7, and Lemma 4.8 show that  $\beta$ ,  $\Longrightarrow$  and c satisfy axioms **PO-P4**. Hence  $\beta \in behs(CTSS)$ .

## 5 A Bounded Concurrent Timestamp System

In this section we present our bounded implementation of a concurrent timestamp system, BCTSS. BCTSS differs from UCTSS in three ways: the structure of the labels, the order between labels, and the manner in which NEWLABEL; determines new labels. In all other aspects BCTSS

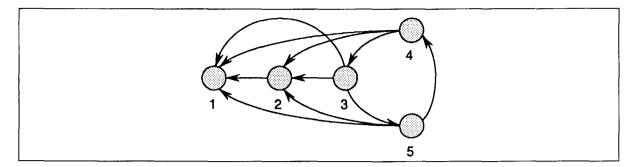

Figure 4: A graphical illustration of the  $\prec_{\mathcal{A}}$  order between the elements of  $\mathcal{A} = \{1 \dots 5\}$

and UCTSS are identical. Recall that a label in UCTSS is an element of  $\Re^+$ . In BCTSS, labels are taken from a different domain. In order to construct the new domain we introduce the set  $\mathcal{A} = \{1 \dots 5\}$ . We define the order  $\prec_{\mathcal{A}}$  and the function NEXT on the elements of  $\mathcal{A}$ .

$$1 \prec_{\mathcal{A}} 2, 3, 4, 5; \quad 2 \prec_{\mathcal{A}} 3, 4, 5; \quad 3 \prec_{\mathcal{A}} 4; \quad 4 \prec_{\mathcal{A}} 5; \quad 5 \prec_{\mathcal{A}} 3.$$

The graph in Figure 4 represents  $\prec_{\mathcal{A}}$ , where  $a \prec_{\mathcal{A}} b$  iff there is a directed edge from b to a.

NEXT(k) =

$$\begin{cases} k+1 & \text{if } k \in \{1, 2, 3, 4\} \\ 3 & \text{if } k = 5 \end{cases}$$

A BCTSS label is an element of  $\mathcal{A}^{n-1}$ , where *n* is the number of processes in the system. We refer to elements of  $\mathcal{A}^{n-1}$  using array notation. Specifically, the  $h^{th}$  digit of label  $\ell$  will be denoted by  $\ell[h]$ . Since we have redefined the label type, we must specify the order that is to be used between elements of  $\mathcal{A}^{n-1}$  for the  $\ll$  order in the SNAP<sub>i</sub> action. The order between elements of  $\mathcal{A}^{n-1}$  is represented by the symbol  $\prec$  and will be a lexicographical order based on  $\prec_{\mathcal{A}}$ .

**Definition 5.1** ( $\prec$  order)  $\ell_i \prec \ell_j$  iff there exists  $h \in \{1 \dots n-1\}$  such that  $\ell_i[h'] = \ell_j[h']$  for all h' < h and  $\ell_i[h] \prec_{\mathcal{A}} \ell_j[h]$ .

**Example 5.1**  $4 \dots 4.5.2 \prec 4 \dots 4.3.1$

**Lemma 5.1** If  $\ell_1$  and  $\ell_2$  are elements of  $\mathcal{A}^{n-1}$  then exactly one of the following is true:  $\ell_1 \prec \ell_2$ ,  $\ell_2 \prec \ell_1$ , or  $\ell_1 = \ell_2$ .

**Proof:** If  $a, b \in A$ , then by definition of  $\prec_A$  exactly one of the following is true:  $a \prec_A b$ ,  $b \prec_A a$  or a = b. The lemma now follows since  $\prec$  is a lexicographical order defined by  $\prec_A$ .

We define the following notation and functions for BCTSS labels:

**Definition 5.2** ( $\stackrel{h}{=}$  equivalence relation) For any  $h \in \{0 \dots n-1\}, \ell_1 \stackrel{h}{=} \ell_2$  iff  $\ell_1[h'] = \ell_2[h']$  for all  $h' \leq h$ . Note that  $\ell_1 \stackrel{n=1}{=} \ell_2$  implies that  $\ell_1 = \ell_2$ .

**Definition 5.3** (NEXTLABEL) For any  $h \in \{1 \dots n-1\}, \ell' = \text{NEXTLABEL}(\ell, h)$  iff  $\ell' \stackrel{h-1}{=} \ell$ ,  $\ell'[h] = \text{NEXT}(\ell[h])$  and  $\ell'[h'] = 1$  for all  $h' \in \{h + 1 \dots n-1\}$ .

**Definition 5.4** (CYCLE) For any  $h \in \{1 \dots n-1\}, \ell' \in CYCLE(\ell, h)$  iff  $\ell' \stackrel{h-1}{=} \ell$  and  $\ell'[h] \in \{3, 4, 5\}.$

**Lemma 5.2** A set  $\mathcal{L}$  of labels is not totally ordered by  $\prec$  iff there exist  $\ell_1, \ell_2, \ell_3 \in \mathcal{L}$  and  $h \in \{1 \dots n-1\}$  such that  $\ell_1 \stackrel{h=1}{=} \ell_2 \stackrel{h=1}{=} \ell_3$  and  $\{\ell_1[h], \ell_2[h], \ell_3[h]\} = \{3, 4, 5\}.$

**Proof:**  $\Rightarrow$  The  $\prec$  ordering on  $\mathcal{L}$  is irreflexive by definition and antisymmetric by Lemma 5.1. Therefore, it must be that transitivity does not hold. Specifically there exist  $\ell_1, \ell_2, \ell_3 \in \mathcal{L}$  such that  $\ell_1 \prec \ell_2 \prec \ell_3$ , and  $\ell_1 \not\prec \ell_3$ . By Lemma 5.1 it cannot be that  $\ell_1 = \ell_3$ , therefore  $\ell_3 \prec \ell_1$ . Since  $\prec$  is a lexicographical order, there must exist  $h \in \{1 \dots n - 1\}$  such that  $\ell_1 \stackrel{h=1}{=} \ell_2 \stackrel{h=1}{=} \ell_3$  and  $\ell_1[h] \prec_{\mathcal{A}} \ell_2[h] \prec_{\mathcal{A}} \ell_3[h]$  and  $\ell_1[h] \not\prec_{\mathcal{A}} \ell_3[h]$ . Now by definition of  $\mathcal{A}$ ,  $\{\ell_1[h], \ell_2[h], \ell_3[h]\} = \{3, 4, 5\}.$

$\Leftarrow By definition of \mathcal{A} we can conclude without loss of generality that <math>\ell_1[h] \prec_{\mathcal{A}} \ell_2[h] \prec_{\mathcal{A}} \ell_3[h]$ and  $\ell_1[h] \not\prec_{\mathcal{A}} \ell_3[h]$ . Since  $\ell_1 \stackrel{h-1}{=} \ell_2 \stackrel{h-1}{=} \ell_3$  and  $\prec$  is a lexicographical order,  $\ell_1 \prec \ell_2 \prec \ell_3$ , and  $\ell_1 \not\prec \ell_3$ . Hence,  $\ell_1, \ell_2$ , and  $\ell_3$  are not totally ordered.

We now define some functions on the states of BCTSS. In order to reason about the states of the system we introduce the notation b.x to refer to the variable x in state b. For a state band any label  $\ell$  in state b:

**Definition 5.5** (AGREE) For any

$$h \in \{0 \dots n-1\}$$

, AGREE $(b,\ell,h) = \{j \mid b,t_j \stackrel{h}{=} b,\ell\}$ .

**Definition 5.6 (NUM)** For any

$$h \in \{0 \dots n-1\}$$

,  $\text{NUM}(b.\ell, h) = |\text{AGREE}(b.\ell, h)|$ .

**Definition 5.7 (NUM**<sub>i</sub>) For any

$$h \in \{0 \dots n-1\}$$

,  $\text{NUM}_i(b.\ell, h) = |\text{AGREE}(b.\ell, h) - \{i\}|$ .

**Definition 5.8 (choice vector)** A choice vector for state b is any vector  $(b.\ell_1...b.\ell_n)$  such that  $b.\ell_i \in \{b.t_i, b.nt_i\}$  for each i.

```

\begin{aligned} & \text{FULL}_{i}(h), h \in \{1 \dots n-1\} \\ & \text{if } \text{NUM}_{i}(t_{max}, h) \geq n-h \\ & \text{then return } (true) \\ & \text{else return } (false) \end{aligned}

\begin{aligned} & \text{NEWLABEL}_{i}(\bar{t_{i}}) \\ & \text{if } i \neq i_{max} \\ & \text{then } h' \leftarrow \min h \in \{1 \dots n-1\} \text{ such that } \text{FULL}_{i}(h) = true \\ & \text{return } (\text{NEXTLABEL}(t_{max}, h')) \end{aligned}

```

Figure 5: Code for  $NEWLABEL_i$  of BCTSS

**Definition 5.9** (TOT) TOT(b) = true iff the set of values in every choice vector is totally ordered by  $\prec$ ; otherwise TOT(b) = false.

Recall that the second difference between UCTSS and BCTSS is the  $\ll$  order that is used in  $SNAP_i$ . We define  $\ll$  for BCTSS lexicographically.

**Definition 5.10 (**

$$\ll$$

order) ( $\ell_i$ ,  $i$ )  $\ll$  ( $\ell_i$ ,  $j$ ) iff either  $\ell_i \prec \ell_i$  or  $\ell_i = \ell_i$  and  $i < j$ .

In any state b in which  $TOT(b) = true, \ll$  defines a total order.

We now define  $b.t_{max}$  and  $b.i_{max}$  for a state, b, in which TOT(b) = true. Consider the choice vector  $(b.t_1 \dots b.t_n)$ . Since TOT(b) = true, there must exist  $i \in \{1 \dots n\}$  such that, for all  $j \neq i$  and  $j \in \{1 \dots n\}$ ,  $b.t_j \leq b.t_i$ . Let  $b.t_{max} = b.t_i$ . Let  $b.i_{max}$  be the largest index j such that  $b.t_j = b.t_{max}$ .

The final difference between BCTSS and UCTSS is in the code for NEWLABEL<sub>i</sub>. Recall that in UCTSS, NEWLABEL<sub>i</sub> nondeterministically picks a real number that is larger than  $t_{max}$ . In BCTSS, NEWLABEL<sub>i</sub> also picks the new label based on  $t_{max}$ . In states in which TOT(b) = true,  $b.t_{max}$  and  $b.i_{max}$  are defined. We let NEWLABEL<sub>i</sub> be a no-op for states in which TOT(b) = false. In Section 6 we will show that TOT(b) = true for all reachable states. When  $i_{max}$  is defined and  $i \neq i_{max}$ , NEWLABEL<sub>i</sub> finds the minimum h such that at least n - h t-labels, excluding  $t_i$ , agree with the prefix of  $t_{max}$  up to and including the  $h^{th}$  digit. Then the new label is the same as  $t_{max}$  for the first h - 1 digits, it differs from  $t_{max}$  at the  $h^{th}$  digit based on the function NEXT, and its remaining digits are equal to 1. The code for NEWLABEL<sub>i</sub> of BCTSS is given in Figure 5.

NEWLABEL<sub>i</sub> finds the minimum integer h such that  $\text{FULL}_i(h)$  returns true. We now show that such an h exists in  $\{1 \dots n-1\}$ . The code that finds h is executed only when  $i \neq i_{max}$ . Notice that  $\text{NUM}_i(t_{max}, n-1) \geq 1$  when  $i \neq i_{max}$ , hence  $\text{FULL}_i(n-1) = true$ .

The initial values for the labels in BCTSS are:  $t_i = nt_i = 1^{n-1}$ ,  $\bar{o_i} = (1 \dots n)$ ,  $\bar{v_i} = (v_o \dots v_o)$ ,  $\bar{t_i} = (1^{n-1} \dots 1^{n-1})$ ,  $v_i = val_i = v_o$ ,  $op_i = NIL$ , and  $pc_i = NIL$ .

## 6 Invariants

For use in the simulation proof we define the following invariants:

**Theorem 6.1** If b is a reachable state of BCTSS then, for all  $i \in \{1...n\}$ :

- I: TOT(b) = true.

- II: If  $i = b.i_{max}$  then  $b.t_i = b.nt_i$ .

- III: If  $b.t_{max} \prec b.nt_i$  then there exists  $h \in \{1 \dots n-1\}$  such that  $b.nt_i = \text{NEXTLABEL}(b.t_{max}, h)$ .

- IV: If  $b.nt_i \leq b.t_{max}$  then for any  $h \in \{1 \dots n-1\}$ , if  $b.t_i \stackrel{h}{=} b.t_{max}$  then  $b.nt_i \stackrel{h}{=} b.t_{max}$ .

- V: For any  $h \in \{1...n-1\}$ , if  $b.nt_i \in CYCLE(b.t_{max}, h)$  then  $b.t_i \stackrel{h-1}{=} b.t_{max}$ .

- *VI:* For any  $h \in \{1..., n-1\}$ ,

- a: if  $b.nt_i = \text{NEXTLABEL}(b.t_{max}, h)$  then  $\text{NUM}_i(b.t_{max}, h-1) \ge n-h$ . b: if  $b.t_{max}[h] \ne 1$  then  $\text{NUM}(b.t_{max}, h-1) \ge n-h+1$ .

I, II, and III are used in the simulation proof. We use an induction argument to show that all reachable states of BCTSS satisfy these invariants. The purpose of invariants IV - VI is to strengthen the induction hypothesis enough so that I can be proven. The only action that can cause invariant I to be violated is  $SNAP_i$  when  $op_i = LABEL_i$ . Specifically, we must show that the new  $nt_i$  picked by  $NEWLABEL_i$  does not introduce any cycles in the  $\prec$  order of the t-labels and nt-labels. Since the  $NEWLABEL_i$  code can examine the all of the t-labels, the code can be written to avoid any cycles involving  $nt_i$  and the t-labels. However, the  $NEWLABEL_i$  code cannot examine the local nt-labels of the other processes. In order to show that cycles that include  $nt_i$  and nt-labels are avoided, invariants IV and V are used to limit the possible values of the nt-labels based on the corresponding t-labels.

For example invariant IV implies that  $nt_i \stackrel{h}{=} t_i$  when  $t_i \stackrel{h}{=} t_{max}$  for all  $nt_i \leq t_{max}$ . If  $nt_i$  is in the cycle at level h, in other words  $nt_i[h] \in \{3,4,5\}$ , then invariant V states that  $nt_i \stackrel{h=1}{=} t_i$ . Now assume that NEWLABEL<sub>i</sub> picks  $nt_i = \text{NEXTLABEL}(t_{max}, h)$ . Then the code for NEWLABEL<sub>i</sub>, using the function FULL<sub>i</sub>, limits the number number of t-labels that are  $\stackrel{h=1}{=} t_{max}$  and consequently the number of t-labels that are  $\stackrel{h=1}{=} nt_i$ . Now invariant V can be used to limit the number of nt-labels that could, by being in the cycle at level h, cause a cycle to occur with the new  $nt_i$ .

Invariant III gives information about the structure of *nt*-labels that are  $\succ t_{max}$ . This information is used to determine how the new  $nt_i$  is ordered with respect to any *nt*-labels that are  $\succ t_{max}$ . Finally invariant VIb is used to prove invariant V, and invariant VIa is used to prove VIb. If a new label  $nt_i$  is picked in the cycle at level h then it must be that  $t_{max}[h] \neq 1$ ; hence VIb applies. VIb says that  $\text{NUM}(t_{max}, h - 1) \geq n - h + 1$ . The code for  $\text{NEWLABEL}_i$ insures that  $\text{NUM}_i(t_{max}, h - 1) < n - h + 1$ . Thus it must be the case that  $t_i \stackrel{h=1}{=} t_{max}$ . This is precisely what is required to prove invariant V.

The proof of Theorem 6.1 uses induction. It depends on a series of lemmas, one for the initial state and one for each action in the inductive step.

**Lemma 6.2** The initial state b of BCTSS, satisfies invariants I - VI.

**Proof:** This follows from the fact that  $b.t_i = b.nt_j = 1^{n-1}$  for all  $i, j \in \{1...n\}$ .

**Lemma 6.3** Let b be a state of BCTSS that satisfies I - VI. If  $(b, \pi, b')$  is a step of BCTSS where  $\pi \in \{\text{BEGINSCAN}_k, \text{ENDSCAN}_k(\bar{o_k}, \bar{v_k}), \text{BEGINLABEL}_k(val_k), \text{ENDLABEL}_k\}$  for any k, then b' satisfies I - VI.

**Proof:** None of the *t*-labels or *nt*-labels change as a result of  $\pi$ . This suffices to show that b' satisfies I - VI.

**Lemma 6.4** Let b be a state of BCTSS satisfying I - VI. If  $(b, UPDATE_k((t_k, v_k), (nt_k, val_k)), b')$  is a step of BCTSS for any k, then b' satisfies I - VI.

**Proof:** The proof is divided into a series of claims. By invariant I for state b,  $b.t_{max}$  and  $b.i_{max}$  are defined. We split the argument into two cases:  $k = b.i_{max}$  and  $k \neq b.i_{max}$ . Consider  $k = b.i_{max}$  first.

Claim 6.4.1 If  $k = b.i_{max}$ , then b' satisfies I - VI.

**Proof:** By invariant II for state b,  $b.t_k = b.nt_k$ . Thus, none of the *t*-labels or *nt*-labels change for BCTSS. This suffices to show that b' satisfies I - VI.

So assume that  $k \neq b.i_{max}$  for the remainder of the proof.

Claim 6.4.2 If  $k \neq b.i_{max}$  then I is true in b'.

**Proof:** Assume for a contradiction that TOT(b') = false. Since TOT(b) = true and  $t_k$  is the only label that changes, the choice vector whose values are not totally ordered must include  $b'.t_k$ . Now consider the same choice vector except that we substitute  $b'.nt_k$  for  $b'.t_k$ . Since  $b'.t_k = b'.nt_k$ , this new choice vector's values are also not totally ordered. Since none of the labels in this new choice vector change as a result of the action, the same choice vector must not have had its values totally ordered in state b. However this contradicts the assumption that TOT(b) = true.

Having proved invariant I we now know that  $b'.i_{max}$  and  $b'.t_{max}$  are defined. The proof for II - VI is subdivided into the following two cases:  $b.nt_k \leq b.t_{max}$  and  $b.t_{max} \prec b.nt_k$ . Assume first that  $b.nt_k \leq b.t_{max}$ .

Claim 6.4.3 If  $k \neq b.i_{max}$  and  $b.nt_k \leq b.t_{max}$  then  $b'.t_{max} = b.t_{max}$  and  $b'.i_{max} = b.i_{max}$  or  $b'.i_{max} = k$ .

**Proof:** Let  $z = b.i_{max}$ , then  $b.t_z = b.t_{max}$  and  $z \neq k$ . We show first that  $b'.t_i \leq b.t_z$  for all *i*. First consider  $i \neq k$ . Since  $t_k$  is the only label that changes,  $b'.t_i = b.t_i$ . Therefore, the fact that  $b.t_i \leq b.t_z$  implies that  $b'.t_i \leq b.t_z$ . Now let i = k. As a result of the action,  $b'.t_i = b.nt_i$ . By assumption  $b.nt_i \leq b.t_z$ , so  $b'.t_i \leq b.t_z$ . Since  $z \neq k$ ,  $t_z$  does not change, so we can conclude that  $b'.nt_i \leq b'.t_z$  for all *i*. This implies that  $b'.t_z = b'.t_{max}$ . The following identity now establishes the first part of the claim:  $b.t_{max} = b.t_z = b'.t_z = b'.t_{max}$ . Let  $S = \{i|b.t_i = b.t_{max}\}$  and  $S' = \{i|b'.t_i = b'.t_{max}\}$  Then,  $b.i_{max} = MAX(S)$  and  $b'.i_{max} = MAX(S')$ . Since  $t_k$  is the only t-label that changes and  $b'.t_{max} = b.t_{max}$ , S' = S or  $S' = S - \{k\}$  or  $S' = S \cup \{k\}$ . When S' = S then MAX(S') = MAX(S). Let  $z = b.i_{max}$ . Since  $k \neq b.i_{max}$ , the definition of  $b.i_{max}$  shows that  $z \in S$  and k < z when  $k \in S$ . Consequently, when  $S' = S - \{k\}$  then MAX(S') = MAX(S). Finally, when  $S' = S \cup \{k\}$  then MAX(S') = MAX(S) or MAX(S') = k. This shows that  $b'.i_{max} = b.i_{max}$  or  $b'.i_{max} = k$ .

Claim 6.4.4 If  $k \neq b.i_{max}$  and  $b.nt_k \leq b.t_{max}$  then  $\text{NUM}(b'.t_{max}, h) \geq \text{NUM}(b.t_{max}, h)$  and  $\text{NUM}_i(b'.t_{max}, h) \geq \text{NUM}_i(b.t_{max}, h)$  for all i and h.

**Proof:** The Claim follows immediately if we show that  $AGREE(b'.t_{max}, h) \supseteq AGREE(b.t_{max}, h)$ . Suppose  $i \in AGREE(b.t_{max}, h)$ . If  $i \neq k$ , then since  $t_i$  does not change and, by Claim 6.4.3,  $t_{max}$  does not change,  $i \in AGREE(b'.t_{max}, h)$ . Now consider i = k. By definition of AGREE,  $b.t_i \stackrel{h}{=} b.t_{max}$ . Since  $b.nt_i \leq b.t_{max}$ , IV for state b implies that  $b.nt_i \stackrel{h}{=} b.t_{max}$ . As a result of the action  $b'.t_i = b.nt_i$ , so  $b'.t_i \stackrel{h}{=} b.t_{max}$ . This fact along with the fact that  $t_{max}$  does not change implies that  $i \in AGREE(b'.t_{max}, h)$ .

**Claim 6.4.5** If  $k \neq b.i_{max}$  and  $b.nt_k \leq b.t_{max}$  then b' satisfies II - VI.

**Proof:** We proceed with a case analysis. Consider any  $i \in \{1 \dots n\}$  and  $h \in \{1 \dots n-1\}$ .

- II: Suppose  $i = b'.i_{max}$ . By Lemma 6.4.3, i = k or  $i = b.i_{max}$ . First consider i = k. As a direct consequence of the action,  $b'.t_i = b'.nt_i$ . Now consider  $i = b'.i_{max}$  where  $i \neq k$ . In this case II holds for b' since  $t_i$  and  $nt_i$  do not change, and II holds for b.

- III: III holds for b' since  $t_{max}$  and  $nt_i$  do not change, and III holds for b.

- IV: First consider i = k. As a consequence of the action  $b'.t_i = b'.nt_i$ . Hence,  $b'.t_i \stackrel{h}{=} b'.t_{max}$ implies that  $b'.nt_i \stackrel{h}{=} b'.t_{max}$  for all h. Now consider  $i \neq k$ . Since IV holds in state b, and  $t_{max}$ ,  $t_i$  and  $nt_i$  do not change, IV holds for state b'.

- V: First consider i = k. b'.nt<sub>i</sub> ∈ CYCLE(b'.t<sub>max</sub>, h) and the definition of CYCLE imply that b'.nt<sub>i</sub> <sup>h-1</sup> b'.t<sub>max</sub>. As a consequence of the action, b'.t<sub>i</sub> = b'.nt<sub>i</sub>. Hence, b'.t<sub>i</sub> <sup>h-1</sup> b'.t<sub>max</sub>. Now consider i ≠ k. In this case V is true in b' since t<sub>i</sub>, nt<sub>i</sub>, and t<sub>max</sub> do not change and V is true in b.

VI: Since  $nt_i$  and  $t_{max}$  do not change,  $b'.nt_i = \text{NEXTLABEL}(b'.t_{max}, h)$  implies that  $b.nt_i = \text{NEXTLABEL}(b.t_{max}, h)$ , and  $b'.t_{max}[h] \neq 1$  implies that  $b.t_{max}[h] \neq 1$ . By Claim 6.4.4,  $\text{NUM}(b'.t_{max}, h) \geq \text{NUM}(b.t_{max}, h)$  and  $\text{NUM}_i(b'.t_{max}, h) \geq \text{NUM}_i(b.t_{max}, h)$ . Hence, VI holds for state b' since it holds for state b.

Claim 6.4.5 shows that II - VI hold when  $b.nt_k \leq b.t_{max}$ . For the remainder of the proof assume that  $b.t_{max} \prec b.nt_k$ .

## Claim 6.4.6 If $k \neq b.i_{max}$ and $b.t_{max} \prec b.nt_k$ then $b'.t_{max} = b'.t_k$ and $b'.i_{max} = k$ .

**Proof:** We proceed by showing that  $b'.t_i \prec b'.t_k$  for all  $i \neq k$ . From the definition of  $t_{max}$  and the assumption that  $b.t_{max} \prec b.nt_k$ , we know that  $b.t_i \preceq b.t_{max} \prec b.nt_k$ . Let  $z = b.i_{max}$  then  $b.t_z = b.t_{max}$  and  $z \neq k$ . Since  $k \neq z$ ,  $k \neq i$ , and  $b.t_z = b.t_{max}$ , there exists a choice vector that includes the values  $b.t_i, b.t_{max}$ , and  $b.nt_k$ . Since TOT(b) = true, the values in this choice vector are totally ordered. Hence,  $b.t_i \leq b.t_{max} \prec b.nt_k$  implies that  $b.t_i \prec b.nt_k$ . As a result of the action  $b.nt_k = b'.t_k$  and  $t_i$  does not change. Therefore,  $b.t_i \prec b.nt_k$  implies that  $b'.t_i \prec b'.t_k$ .

The following Claim lists some of the properties of  $b'.t_{max}$ .

**Claim 6.4.7** If  $k \neq b.i_{max}$  and  $b.t_{max} \prec b.nt_k$  then there exists  $h' \in \{1 \dots n-1\}$  such that:

- 1.  $b'.t_{max} = b'.t_k = b'.nt_k = b.nt_k = \text{NEXTLABEL}(b.t_{max}, h').$

- 2.  $b'.t_{max}[h] = 1$  for all h > h'.

- 3. For all  $i, b'.nt_i \stackrel{h'}{=} b'.t_{max}$  implies that  $b'.nt_i = b'.t_{max}$ .

- 4. There exists no  $i \neq k$  such that  $b'.t_i \stackrel{h'}{=} b'.t_{max}$ .

- 5.  $\operatorname{NUM}(b'.t_{max}, h) \ge \operatorname{NUM}(b.t_{max}, h)$  and  $\operatorname{NUM}_i(b'.t_{max}, h) \ge \operatorname{NUM}_i(b.t_{max}, h)$  for all i and all h < h'.

**Proof:** By invariant III for state b and the assumption that  $b.t_{max} \prec b.nt_k$ , we conclude that  $b.nt_k = \text{NEXTLABEL}(b.t_{max}, h')$  for  $h' \in \{1 \dots n-1\}$ . Fix h'.

1: By Claim 6.4.6  $b'.t_{max} = b'.t_k$ . The fact that  $b'.t_k = b'.nt_k = b.nt_k$  is a direct consequence of the action  $UPDATE_k((t_k, v_k), (nt_k, val_k))$ . Finally, we have already shown that  $b.nt_k = NEXTLABEL(b.t_{max}, h')$ .

2: This follows directly from the definition of NEXTLABEL.