MIT/LCS/TR-286

2 A.

**6**

A.

and Alasta Alast

. .

100

1998

140

"方得"。

1

Clear.

A SIMULATION ENVIRONMENT NOL SCHOOL

Margaret Ann St. Pierre

December 1986

This blank page was inserted to preserve pagination.

# A Simulation Environment for Schema

by

Margaret Ann St. Pierre

Copyright © 1986 Massachusetts Institute of Technology

Support for this research was provided by the Defense Advanced Research Projects Agency of the Department of Defense under Contract No. N00014-80-C-0822.

2

# A Simulation Environment for Schema

by

Margaret Ann St. Pierre

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degrees of Master of Science and Electrical Engineer

# Abstract

In present day circuit design, many independent simulation tools are available for analyzing circuits at various levels of detail. This thesis presents a framework to tie these tools into the Simulation Environment in Schema, an integrated CAD system. The framework easily incorporates additional simulators, serves as a foundation upon which to build new analysis tools, and provides the ability for mixed-mode simulation. The Simulation Environment is composed of common data representations, a Generic Simulator, and a single user interface. A common representation for topological, model, and waveform data objects facilitates a uniform interface to the user and to all CAD tools. The Generic Simulator coordinates the flow of data objects between each simulator and the user or analysis tool.

Thesis Supervisor:Professor Richard ZippelTitle:Associate Professor of Electrical Engineering and Computer Science

Key Words and Phrases: CAD, VLSI, simulation

# Acknowledgments

#### I would like to thank:

My thesis advisor, Rich Zippel, for the inspiration, focus, and encouragement that made this thesis possible, for fathering the famous ski resorts upon which this thesis work was implemented, and for providing me with quiet officespace.

Brian Williams for many stimulating discussions and suggestions along the way.

Jeff Arnold, Randy Davis, Steve Heller, and Jerry Roylance for comments on early drafts of this thesis.

George Clark and Mike MacDonald for giving unity to Schema.

My friends back at the Schema Chalet.

Moses Ma, Peter Nuth, and Pete Osler for interesting non-technical discussions.

Jim Restivo for faithfully escorting me to and beyond the finish line.

My family for their love and support throughout my many years of academia.

# **Table of Contents**

| Chapter One: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1.1 Motivation</li> <li>1.2 Design Goals <ol> <li>1.2.1 Integrating Simulation Tools</li> <li>1.2.2 Building Analysis Tools</li> <li>1.2.3 Mixed-mode Capability</li> </ol> </li> <li>1.3 Overview of Thesis</li> </ul>                                                                                                                                                                                                                                                                                                                                                     | 7<br>9<br>9<br>10<br>10<br>10                                                                                              |

| Chapter Two: Design Methodology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 12                                                                                                                         |

| <ul> <li>2.1 Simulation Domain</li> <li>2.2 Design Strategy</li> <li>2.3 What is a Simulation Environment?</li> <li>2.3.1 Common Representation</li> <li>2.3.1.1 Objects</li> <li>2.3.1.2 Object Types</li> <li>2.3.1.3 Appropriate Types</li> <li>2.3.2 The Generic Simulator</li> <li>2.3.2.1 Internal Simulation</li> <li>2.3.2.2 External Simulation</li> <li>2.3.3 Uniform Interface</li> <li>2.3.4 Accomplishing the Design Goals</li> <li>2.4.1 Hierarchical Organization</li> <li>2.4.2 Constraint Network</li> <li>2.4.3 Creation on Demand</li> <li>2.5 Summary</li> </ul> | 12<br>14<br>14<br>16<br>16<br>16<br>17<br>18<br>19<br>20<br>21<br>20<br>21<br>21<br>21<br>22<br>22<br>23<br>24<br>24<br>24 |

| Chapter Three: Topology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25                                                                                                                         |

| <ul> <li>3.1 Module Definition <ul> <li>3.1.1 Uniform Representation</li> <li>3.1.2 Module Interconnection</li> <li>3.1.3 Module Definition Creation</li> <li>3.1.4 Uniform User Interface</li> </ul> </li> <li>3.2 Defining New Module Types <ul> <li>3.2.1 Simple Modules</li> <li>3.2.2 Compound Modules</li> <li>3.2.3 Abstract Modules</li> </ul> </li> <li>3.3 Defining New Module Operations</li> <li>3.4 Summary</li> </ul>                                                                                                                                                  | 25<br>25<br>25<br>28<br>29<br>30<br>30<br>30<br>31<br>32<br>33                                                             |

| Chapter Four: Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 34                                                                                                                         |

| 4.1 Uniform Representation                                  | 34 |

|-------------------------------------------------------------|----|

| 4.2 Uniform User Interface                                  | 35 |

| 4.3 Defining New Model Types                                | 35 |

| 4.3.1 Models Without State                                  | 36 |

| 4.3.2 Models With State                                     | 37 |

| 4.4 Defining New Model Operations                           | 37 |

| 4.5 Summary                                                 | 38 |

| Chapter Five: Waveforms                                     | 39 |

| 5.1 Uniform Representation                                  | 40 |

| 5.2 Uniform User Interface                                  | 41 |

| 5.3 Display Types and Waveform Types                        | 42 |

| 5.3.1 Analog Waveforms                                      | 42 |

| 5.3.2 Binary Waveforms                                      | 44 |

| 5.3.3 Defining New Displays and New Waveform Types          | 45 |

| 5.4 Mixed-Mode Capability                                   | 45 |

| 5.5 Summary                                                 | 46 |

| Chapter Six: Generic Simulator                              | 47 |

| 6.1 Uniform User Interface                                  | 47 |

| 6.2 Initiation Phase                                        | 48 |

| 6.3 Initialization Phase                                    | 48 |

| 6.3.1 Locating Appropriate Modules                          | 49 |

| 6.3.2 Interconnection of Appropriate Modules                | 49 |

| 6.3.3 Locating Appropriate Waveforms                        | 50 |

| 6.3.4 Attaching Appropriate Waveforms                       | 50 |

| 6.3.4.1 Input Waveforms                                     | 50 |

| 6.3.4.2 Output Waveforms                                    | 51 |

| 6.3.4.3 Mapping Waveforms onto Nodes                        | 51 |

| 6.3.4.4 Mapping Waveforms onto Pins                         | 52 |

| 6.3.5 Locating Appropriate Models                           | 53 |

| 6.4 Execution Phase                                         | 55 |

| 6.4.1 Internal Simulation                                   | 55 |

| 6.4.2 External Simulation                                   | 56 |

| 6.5 Completion Phase                                        | 56 |

| 6.6 Summary                                                 | 57 |

| Chapter Seven: Discussion                                   | 58 |

| 7.1 Summary                                                 | 58 |

| 7.2 Implementation: The Simulation Environment Layer        | 58 |

| 7.3 Future Work: The Concurrent Mixed-Mode Simulation Layer | 59 |

| 7.4 Conclusion                                              | 60 |

| References                                                  | 61 |

# **Table of Figures**

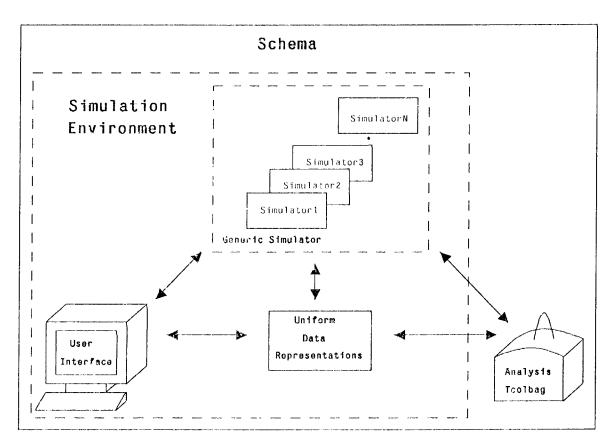

| Figure 2-1: Simulation Environment in Schema.                                           | 15 |

|-----------------------------------------------------------------------------------------|----|

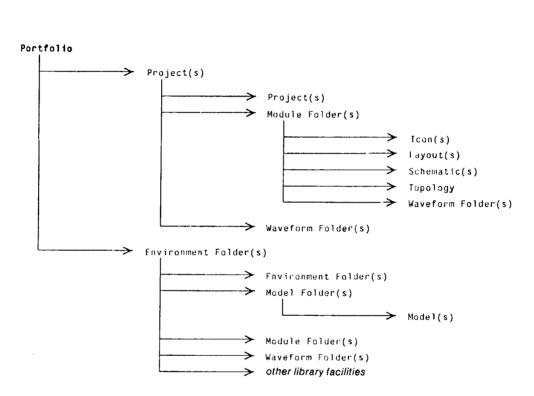

| Figure 2-2: Hierarchical organization of Schema.                                        | 23 |

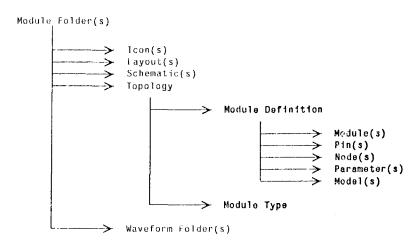

| Figure 3-1: The topology and its placement in the hierarchical organization of Schema.  | 26 |

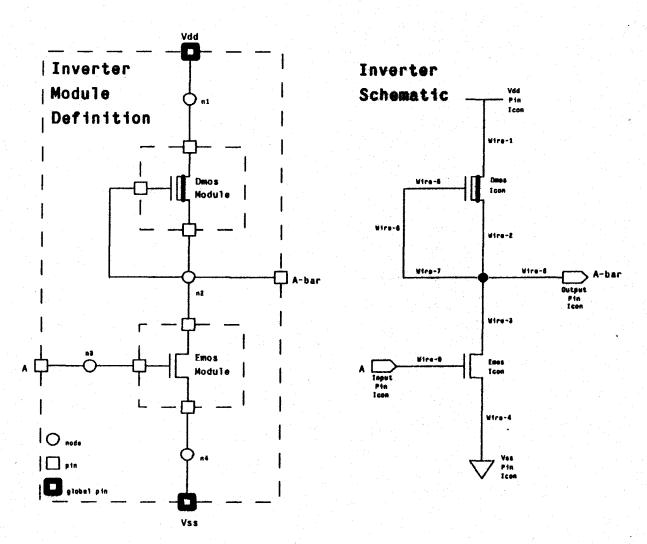

| Figure 3-2: Inverter module definition and corresponding schematic presentation.        | 27 |

| Figure 4-1: Models and their placement in the hierarchical organization of Schema.      | 35 |

| Figure 5-1: Waveforms in the hierarchical organization of Schema.                       | 39 |

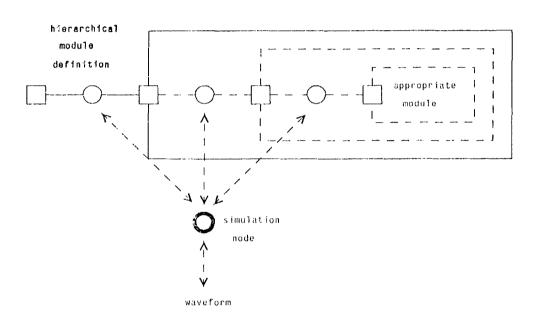

| Figure 6-1: Mapping of a single simulation node onto electrically equivalent nodes of a |    |

| hierarchical module definition.                                                         |    |

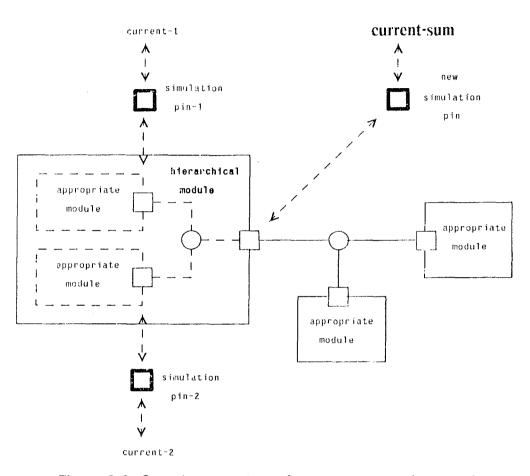

| Figure 6-2: Summing current waveforms, current-1 and current-2, to produce              | 54 |

| current-sum for pin of a hierarchical module.                                           |    |

# **Chapter One**

# Introduction

Circuit design requires the assistance of a comprehensive range of computer aided design (CAD) tools, many of which either currently exist or are under development. Individually, each tool addresses a specific task in the design process. As an *integrated* collection, however, the tools *share data and tasks* across all stages of the design process. Unfortunately, no one system has effectively integrated the collection into a single design environment.

Research on such an environment is presently underway at M.I.T. with the development of Schema [Zippel 85]. Schema research focuses on providing a software environment for easily integrating all CAD tools necessary for design and allowing the effortless building of new tools into the existing system. One area of major interest in Schema and of circuit design in general is simulation. Fatal design errors are detected and circuit performance is measured by simulating the operation of electronic designs. In this way, simulation invaluably contributes to the success of high-performance circuit designs and is a vital component of any CAD system.

This thesis presents a Simulation Environment for Schema following in the footsteps of the integrated software design environment established in Schema.

# **1.1** Motivation

Many simulators have been developed to satisfy different design needs using a single modeling level of circuit abstraction. Often the designer is overwhelmed by the need to learn the operation of and to manually recode circuit descriptions for each individual simulator. In addition, cutput waveforms associated with one particular circuit module's simulation must be interpreted and manually translated for use as input to some other interconnected module's simulation. Because of the massive time investment required, this process is typically omitted altogether.

The recent trend has been towards mixed-mode simulation whereby different levels of simulation are consolidated into one software package. At the high end, the Sable [Hill 79, Hill 80]

system combines behavioral, register transfer, and gate level descriptions. Similarly, Themis [Doshi 84] addresses simulation at the behavioral, register transfer, logic, and switch levels. Both simulators deal exclusively in the digital domain, however; neither includes circuit, timing, or linear level models, which are critical to the design of high-performance circuits. On the low end, concurrent circuit, timing, and logic analyses are illustrated in both the Diana [Arnout 78, Antognetti 84] and Splice [Newton 78, Newton 79] systems. In addition, the second generation Motis [Chawla 75, Fan 77, Chen 84, Antognetti 84] program combines timing, switch, and logic level simulators into one software package, running on a single mainframe; accuracy is reduced by omitting the detailed transistor models available in a circuit level simulator such as Spice2 [Nagel 75, Cohen 76].

These and others [Nestor 82, Thomas 83, Borrione 83, Lanthrop 85] are attempts to combine simulators using a range of modeling levels into a single software program. One disadvantage of this single system approach is a loss in *computational efficiency*. With increasing integrated circuit complexity, the computational power required for simulating very large circuits becomes a major bottleneck to the design effort. Even the use of the most advanced hardware and software technology inevitably results in extensive execution times for a single system. Expensive design effort is halted while waiting upon simulation results. Another cost is incurred from discarding old, yet still usable simulators to invest in software recoding for a mixed-mode system. For example, in an effort to provide an integrated computer aided design system for Sandia, a substantial amount of manpower was invested in understanding, recoding, and debugging undocumented industry and university software programs [Daniel 82].

With the accelerated advancement of today's technology, new simulators are continually being developed using state-of-the-art hardware technology, and more efficient, optimized, and sophisticated algorithms. Dramatic speed improvements are achievable with special-purpose hardware, such as the Yorktown Engine [Pfister &2] and the Logic Simulation Machine [Abramovici &3], and highly parallel algorithms, such as Prsim [Arnold &5] and Msplice [Deutsch &4] designed specifically for multi-processor systems.

Simulation alone cannot guarantee the success of today's high performance circuits. In conjunction with simulation, *analysis tools* are an essential ingredient of the design process. Analysis tools operate on simulation data This data may pertain to one simulation, multiple simulations, or ultimately different simulation levels. Performance evaluation, verification of

8

simulation results against specifications, and circuit partitioning for different levels of simulation are just a sampling of invaluable analysis tools. Analysis tools also instigate simulations. An analysis tool may schedule a series of simulations to compare the performance of different designs or the behavior of a single design in different operating regimes.

Each analysis tool is simple to build, yet creating a simulator and user interface for each is a major undertaking. In effect, the existence of the analysis tool alone is not justified. For example, mathematical operations on waveforms are useful for analyzing circuit simulation results. For instance, power consumption over time amounts to a simple multiplication of waveforms, yet without a graphical user interface and a simulator interface, the tool is unusable. The designer would be forced to manually enter the simulation data points - a tedious, error-prone, and time-consuming task - as well as interpret the numerical output data.

### 1.2 Design Goals

A framework is essential to tie simulation tools into a common environment. This thesis presents such a framework: *A Simulation Environment for Schema*. The framework is designed to easily integrate simulation tools, to serve as a foundation for building new analysis tools, and to provide mixed-mode capability. The following sections detail each of these design goals.

#### **1.2.1 Integrating Simulation Tools**

The Simulation Environment is designed with the ability to readily integrate new as well as currently existing simulation tools. Simulation of all modeling levels may be easily incorporated; this includes tools exploiting each of the various transistor modeling levels and the simulators that address the more abstract circuit representations. Without slowing down the user's design effort, simulation can be *distributed* to another local process or remote engine that can efficiently run the simulation. Distributing the effort among whatever engines are currently available, and potentially least loaded, enhances the overall computational power of the designer's environment. Furthermore, because a large amount of time, money, and effort went into developing and maintaining the existing simulation tools, they could remain constantly in use - greatly enhancing computational power. Adding new simulators allows the environment to keep pace with the rapid development of new hardware and software simulation engines.

#### 1.2.2 Building Analysis Tools

The Simulation Environment could serve as a foundation for building an unlimited number of powerful analysis tools. Automatic partitioning algorithms can be developed for partitioning large-scale circuits into a collection of blocks to be individually simulated at different modeling levels. Another tool could schedule a series of simulations for each block to verify that it meets specifications. Additionally, small analysis tools could be designed to compare the results of different simulations or to perform operations on simulation output. Comparison and evaluation of the performance of new simulators could even be executed by an analysis tool.

#### 1.2.3 Mixed-mode Capability

*Mixed-mode* refers to transforming the output data from one module's simulation for use as input to an interconnected module's simulation, where each module may be modeled at different levels of detail. For example, certain portions of a design may require the accuracy of a circuit simulation, while for other less critical portions, a less exact switch or logic level simulation is most appropriate. Both require simulation, yet using different simulators. With the mixed-mode capability, the Simulation Environment transforms the output analog waveforms from the circuit simulation into logic waveforms for use in the switch or logic level simulation, and vice versa.

# **1.3 Overview of Thesis**

Chapter 2 opens with a brief overview of the types of simulators available. This naturally leads into a discussion of the goals of the Simulation Environment and the approach taken to achieve them. Next each component of the Simulation Environment is briefly described: the uniform data representations, a Generic Simulator, and a common user interface. The chapter closes with a discussion of the techniques available in Schema that are useful to the Simulation Environment.

The circuit topology, models, and waveforms are the data required for simulation. Their uniform representations and user interface are discussed in Chapters 3, 4, and 5, respectively. When integrating additional simulators or building new analysis tools, only new data types and local operations need to be defined as described in the latter sections of each chapter.

Chapter 6 describes the role of the Generic Simulator in the Simulation Environment. The

57

#### Chapter 1

Generic Simulator contains the simulation tools of the environment and generically interfaces them to the objects in the environment, to the user, and to the analysis tools. This chapter presents each step of the Generic Simulation Process.

Chapter 7 concludes with a summary of the Simulation Environment for Schema recounting the properties achieved. Suggestions for possible future analysis tools are cited. These tools could be easily built on top of the Simulation Environment in Schema.

# **Chapter Two**

# **Design Methodology**

The currently available simulators are reviewed with respect to input and output data required for each. Next, a design strategy is developed to tie these simulators into a single Simulation Environment. Each component of the Simulation Environment is defined along with its corresponding role in the simulation process. And finally, the implementation of the Simulation Environment within Schema is presented.

### 2.1 Simulation Domain

Many simulators have been developed to satisfy different design needs throughout the various stages of the design process. This section briefly described the different kinds of simulators in use today. Notably, each simulator utilizes different algorithms, accepts input such as a circuit description, excitation signals and perhaps some modeling parameters, and ultimately produces output data.

*Circuit simulators* provide the most detailed level of simulation; node voltages and branch current waveforms are calculated and plotted. *General-purpose* circuit simulators, such as Spice2 [Nagel 75, Cohen 76] and Astap [Weeks 73], apply general algorithms for non-linear static, linear ac, and non-linear transient analyses. Circuits may contain capacitors, resistors, inductors, mutual inductors, voltage and current sources, and a wide range of nonlinear active devices including diodes, bipolar junction transistors (BJTs), junction field-effect transistors (JFETs), and metal-oxide-semiconductor (MOS) field-effect transistors (FETs). Each semiconductor device is modeled with a set of process parameters. Spice2, for example, has three built-in types of MOS device models: Shichman and Hodges, analytical, and semi-empirical models. At this level of detail, circuit simulators are generally cost effective for circuits with a few hundred devices or less. Execution time can be increased by replacing analytic device models with simplified table look-up models relating device current to terminal voltages. These general-purpose circuit simulators are largely independent of technology. If simulation algorithms are tailored to specific technologies or applications, substantial speed improvements can be achieved. To take advantage of the unilateral nature of MOS devices, *relaxation-based* circuit simulation [Dumlugol 83, Newton 84] algorithms provide up to a twofold increase in simulation speed over generalpurpose circuit simulators.

The *linear-model simulator* Rsim [Terman 83] represents MOS transistors as resistors in series with a voltage-controlled switch. This model provides logical and approximate timing information. Logic behavior is determined by a fast event-driven algorithm; transition times depend upon on effective transistor resistance, and interconnect and gate capacitance. Using this simplified linear model, networks containing up to 50,000 transistors may be simulated. Instead of node voltages and branch currents, discrete logic states at network nodes are used.

Switch-level simulators such as Mossim [Bryant 81] and Esim [Terman 83] model MOS transistors as a network of on/off switches. This model captures the logical properties of a circuit while ignoring many of the detailed electrical issues. A switching network is most appropriate for simulating the bidirectional nature of MOS transistors. Furthermore, since so little modeling information is retained for each transistor, this type of simulator is able to handle larger scale designs. Signals are typically represented in terms discrete logic states in unit-delay time sequence.

A simplification of the switch-level simulator is the unidirectional *gate-level logic simulator*, which uses NOT, AND, OR, NAND, and other combinational logic gates, and state-preserving components such as flip-flops and counters. This simulator solves simple boclean equations to obtain the output state of the logic components. Time may be in unit delay intervals or variable delay, which more closely models continuous time. Unfortunately, not all MOS gate-level elements, specifically pass transistors, are unidirectional in nature, and thus are not suitable for gate-level simulation.

Register-transfer level simulators [Hafer 83, Lewke 83] deal with the overall structure and architecture of a design. Modules, such as full adders and systolic arrays, are specified by procedural descriptions. Because they simulate more abstract modules and their representation of signals is somewhat courser than in the logical case, register-transfer level simulators are usually over an order of magnitude faster than gate-level simulators for the same circuit.

At the highest level of abstraction, behavioral or functional simulators are used at the initial

design phase to verify the algorithms of the abstract system to be implemented. In contrast to the register-transfer level simulator, the actual structure of the circuit is not necessary for this type of simulation.

# 2.2 Design Strategy

The first question to answer when developing a new system is "What are the design goals of our system?". The Simulation Environment ties together the simulators needed by all phases of the circuit design process. More specifically, the Simulation Environment in Schema provides (1) simple extensibility for incorporating additional simulators, (2) a foundation for building and integrating new analysis tools, and (3) the capability to perform mixed-mode simulation. These are the major design goals of the Simulation Environment.

A *uniform interface* is a natural consequence of the aforementioned design goals. This can be viewed from two perspectives. For the *designer* of CAD software, a uniform CAD interface facilitates additional simulation tools as well as providing the groundwork upon which to build new analysis tools. For the *user* of CAD software, a common interface eliminates the unnecessary task of learning the operation of each individual tool.

The question remaining is "What approach or design strategy leads to these desired properties?". Common data representations make it possible to create a uniform interface to the user, the simulators, and the analysis tools. The following sections describe the Simulation Environment in Schema, and how this approach achieves the design goals.

### 2.3 What is a Simulation Environment?

The major components of the Simulation Environment are: a Generic Simulator, common data representations, a single user interface. Figure 2-1 depicts the interactions of each component within Schema. The *Generic Simulator* coordinates the flow of information between the simulation initiator and the individual simulators. The medium for information flow is a *common data representation*, and finally the *user interface* provides a slick graphical interaction with the underlying data structures.

The Generic Simulator acts as an interactive guide in the Generic Simulation Process:

Figure 2-1: Simulation Environment in Schema.

- 1. The user interacts with the Simulation Environment by way of the user interface. Analysis tools interact directly with the Simulation Environment. Once the appropriate input data has been entered, simulation is initiated by the user or by an analysis tool. At this time the initiator chooses a specific simulator from among a rich variety of available simulators and selects a specific region of a circuit for simulation.

- 2. The Generic Simulator initializes input data for simulation. This may require a translation of the input data to the form required by the selected simulator. Prior to execution the Generic Simulator interactively notifies the initiator in the event of any ambiguities, inconsistencies, or undefined quantities.

- 3. The simulation is performed.

- 4. The Generic Simulator interprets the output data and transforms it into a common representation. The results are then presented to the user, again via the user interface, or are made directly available to the analysis tools.

The following sections take a closer look at each component and its role in the development stages of the Simulation Environment. The final section discusses the contribution of each piece toward the design goals.

#### 2.3.1 Common Representation

#### 2.3.1.1 Objects

For electronic simulators, typical *input* data comprise circuit topology, modeling parameters, and excitation signals; typical *output* data are the resulting waveforms. Thus, the basic entities or *objects* the Simulation Environment must supply to the Generic Simulator are *circuit topologies, models,* and *waveforms.* Determining what objects exist is the first task in designing the Simulation Environment.

For each object to be accepted by a simulator, a corresponding object in the Simulation Environment is defined. Within Schema, a circuit design is made up of components called *modules*. Modules and their interconnections are supplied by the circuit *topology*. Each module may contain some local *model* information. For example, transistor modules may have threshold voltages or logic gates may have propagation delays as part of their model. And finally, signals are the *waveforms* associated with the input to and the output from simulators. In general, these objects represent the data essential for simulation, and thus essential to the Simulation Environment.

#### 2.3.1.2 Object Types

The next task is to further subdivide the types of topology, model, and waveform objects required in the Simulation Environment. *This subdivision is dictated by the types of objects each simulation tool simulates.* A transistor, for example, has a non-linear, linear, and switch model; thus, these model types should be made available in the Simulation Environment. Similarly a circuit-level simulator accepts topological modules including resistors, capacitors, transistors, and waveforms such as exponential or piece-wise linear voltages and currents. The subdivision of topological, model, and waveform types is explored further in Chapter 3, Chapter 4, and Chapter 5, respectively.

There is an overlap in the types of topological, model, and waveform objects accepted by

each simulator. An example of a topological module is the transistor. Although circuit, linear, and switch level simulators all simulate the transistor, it is not necessary to define a different transistor object in the Simulation Environment for each individual simulator that simulates it. *The objects defined in the Simulation Environment are the union of the object types that could possibly be simulated by any of the simulation tools.* This is the key idea behind a common representation for data objects in the Simulation Environment. The user interface, the Generic Simulator, and the analysis tools built into or integrated on top of the Simulation Environment all interact with these uniform data objects.

#### 2.3.1.3 Appropriate Types

Of course, not all objects defined in the Simulation Environment will be accepted by each simulator. A logic level simulator for instance does not simulate capacitor modules, and exponential voltage waveforms. Thus, associated with each simulator is a specific set of *appropriate module, model,* and *waveform types*. These represent the types of objects each simulator accepts. Incorporating a new simulator requires the specification of a set of appropriate module, model, and waveform types.

While some simulators handle different types of modules, other simulators share some of the same types of modules. Circuit, linear, and switch-level simulators all have the MOS transistor as an *appropriate module type*. But each of these simulators uses a different model for the MOS transistor module type. A major feature distinguishing one kind of simulator over another is the models it associates with its modules. For any given appropriate module type, there may be one or more *appropriate model types*. For the circuit simulator Spice2, no model is expected for modules of type resistor, yet for the MOS transistor, three model types are possible.

Simulator selection also restricts the *appropriate waveform types*: different signals are required for different simulators. Voltage and current waveforms are expected for a circuit-level analysis, and binary waveforms are required for switch or logic level analysis. To support the mixed-mode capability of the Simulation Environment, if signals of one type can be transformed into another type acceptable to a specific simulator, these types are also part of the simulator's set of appropriate waveform types. If a transformation operation on a binary signal can produce a voltage signal for a circuit simulation, then binary as well as the voltage signals are appropriate signal types for a circuit simulation. In summary, the object types in the Simulation Environment are the union of the types of objects handled by the different simulators. As every simulator does not accept all types of objects defined in the Simulation Environment, a set of appropriate types are associated with each simulator.<sup>1</sup>

#### 2.3.2 The Generic Simulator

The Generic Simulator is made up of many simulators, and treats each component simulator as a *black box*. It is only responsible for supplying input to and obtaining output from the black box. Thus the Generic Simulator need never know about the internal workings of each component simulator. From outside the Generic Simulator, the user and the analysis tools perceive the Generic Simulator as a black box. Furthermore they never need to interact with the simulators within the Generic Simulator.

The Generic Simulator interactively coordinates the flow of topology, model, and waveform objects between the simulation initiator and each individual simulator. This entails obtaining the input data from the user or analysis tool, supplying the data in the representation required for the simulator, invoking simulation execution, interpreting the resulting output data, and placing the output data into the Simulation Environment for future analysis.

The Generic Simulator interacts with two kinds of simulators: internal and external. An *Internal Simulator* directly manipulates the data objects present within the Simulation Environment, in much the same way an analysis tool built on top of the Simulation Environment would. In this case, the simulation initiator has the opportunity to *interactively control* simulation execution; output signals can be monitored in real time. On the other hand, an *external simulator* creates its own data structures. External simulators typically exist on a remote processor(s) using a separate address space. Computationally intensive simulations are sent off to special-purpose hardware or multiprocessor systems without inhibiting the speed of the Simulation Environment's current process. The combination of internal and external simulation offers the advantages of both strategies and permits a large degree of flexibility in simulation.

The Generic Simulator expects the objects in the Simulation Environment to perform cer-

<sup>&</sup>lt;sup>1</sup>The sets of appropriate types are not necessarily static. As low-level simulation results are summarized into models of more abstract modules for use in higher-level simulations, the modules and their corresponding models may be appended to the set of appropriate types.

tain tasks, or *operations*. The operation actually invoked depends on the type of object being asked to perform the operation, yet the object type is irrelevant to the Generic Simulator. The same operation can mean different things depending on the type of the object. This technique is known as *data-directed programming* [Abelson 85]. The following two sections present a more detailed look at both internal and external simulators and what operations are required for each kind of simulation tool.

#### 2.3.2.1 Internal Simulation

Internal simulators have direct access to the objects in the Simulation Environment. Each object involved in the simulation is delegated responsibility for delivering some local information about itself or performing some computation using this information. To do this, specific simulation operations are defined for each appropriate object type handled by the selected simulation routine. For example, the NAND and NOR model types each have their own boolean operation for a logic level simulation.

Internal simulation becomes a layer of these simulation routines where each general algorithm stands alone as an independent, modular unit. Common algorithms could then be shared over different simulators. For example, relaxation-based simulators and asynchronous logic simulators both exploit the inactivity of the circuit by using selective-trace and event-driven algorithms. One routine could serve both simulators. Other generic algorithms are useful for other parts of Schema. The matrix manipulation routines used for the general-purpose circuit simulator may also be useful in handling graphics.

A generic layer of operations on objects would ideally complement this layer of simulation routines. These operations are similarly shared over different simulation algorithms as well as other components of Schema. For instance, most types of waveforms have a generic internal-value operation which calculates and returns a value given a specific point in time. This is a very common operation used not only by circuit level simulators, but also by display routines and analysis tools. One generic operation is defined for each waveform type to satisfy the needs of all potential callers.

19

#### 2.3.2.2 External Simulation

Prior to an External Simulation, each object in the Simulation Environment requiring simulation must be transformed into the appropriate external representation, usually a textual description language understandable by the simulator. The description is then sent to a separate address space where the simulator builds its own internal data structures for the simulation. If the simulator exists on a remote processor(s), the description is sent via the local network or file system. After simulation execution, the output data must be interpreted and transformed into data objects in the Simulation Environment.

Input transformations are instigated by the Generic Simulator, yet are actually performed by the object itself. As in the Internal Simulation case, the particular operator invoked will depend upon the type of object being transformed. A transistor object requires a very different transformation operator than that of an exponential waveform. Furthermore, because there is exactly one representation for the transistor object in the Simulation Environment and possibly many simulators that use this type of object, there may be many transformation operators defined for it -- potentially one for each external tool that simulates the transistor. A switch-level simulator for example, requires a different transistor representation than a circuit-level simulator and thus a different transformation operator. In the case of output data, the Generic Simulator must however supply a parser to extract the output information and to create the data objects within the Simulator.

For both types of simulators, each object has a certain set of operations that it must perform. The Generic Simulator need never know the implementation details of these operations, and each object need not know about the internal workings of the Generic Simulator. The individual simulators, the Generic Simulator, and each object in the Simulation Environment are all perceived as black boxes. Their internal structure and operations are essentially hidden and isolated from each other. *The Generic Simulator can be designed independent of the type of objects it is simulating.* It is *generic* in the true sense of the word. Thus, for the Generic Simulator to perform its task, coordinating the flow of objects within the Simulation Environment, it must simply know what operation to perform and on which object to perform it.

#### 2.3.3 Uniform Interface

The user and the analysis tools interact only with the data objects and the Generic Simulator. Because of the black-box quality of the Generic Simulator, the user and the analysis tools do not interact with the individual simulators.

The analysis tools built on top of the Simulation Environment have *direct* access to the uniform data structures in the Simulation Environment, and thus can interact with the objects in much the same way as an internal simulator. Thus the interface to the topology, model, and waveform objects, as well as the Generic Simulator is simple; the analysis tools need only know the operations defined for each. By just knowing the operations for accessing output waveform objects and the operations for telling the Generic Simulator to halt the simulation process, an analysis tool can interactively monitor the execution of an internal simulation the moment erratic waveform behavior develops.

The user *indirectly* interacts with both the data representations and the Generic Simulator through a graphical interface. The Generic Simulator interface amounts to a well-defined series of textual, or menu-driven commands. The designer is thus spared the burden of learning the operation of each individual simulator; instead, a working knowledge of the Generic Simulator is sufficient. Schematics, layouts, and icons serve as a graphical presentations of the topology. The correspondence between the graphical presentations and the topology is dealt with further in Chapter 3. Models have a simple menu-driven interface. Waveforms have display objects which have the ability to represent themselves graphically to the user; these are discussed in Chapter 5.

#### 2.3.4 Accomplishing the Design Goals

A common representation for data is equivalent to defining a set of object types and a set of operations that can be performed on those types. These types provide the uniform interface which enables us to achieve our design goals. Interfacing new CAD tools requires only local additions to the environment. Integrating an additional simulator may require new object types and a set of operations for each type of object the simulator handles. A new object type is defined for the Simulation Environment only if the simulator actually simulates an object not yet defined in the environment. Adding an internal simulator may also necessitate the modular addition of general simulation algorithms along with some object operations. For an external simulator, a set of transformation operators and an output parser are necessary. Building new analysis tools

requires only a working knowledge of the objects in the environment, the operations that can be performed on them, and the operations that are available for the Generic Simulator. Because waveform objects are represented uniformly in the Simulation Environment, output signals from one simulation can be used as input to another simulation; the mixed-mode property is a direct result of the uniform data structures. With the different levels of simulation, a type transformation operation may be necessary. This is explored further in Chapter 5. In summary, all design goals can be accomplished through the local addition of new objects and operations on those objects.

### 2.4 Implementation in Schema

The Simulation Environment is implemented in Schema. In this section, a brief overview of Schema's hierarchical organization, constraint network, and creation on demand techniques are all described. In subsequent chapters, we shall see how these strategies tie directly into the Simulation Environment.

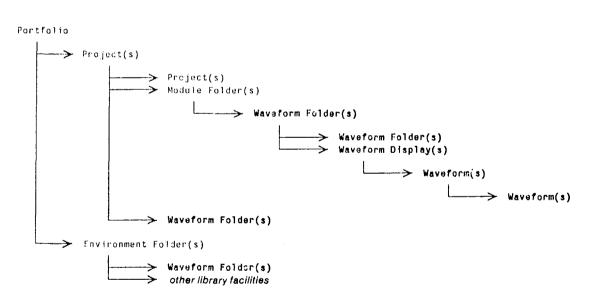

### 2.4.1 Hierarchical Organization

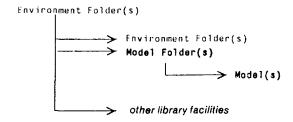

Schema is organized hierarchically as shown in Figure 2-2 where each part in the hierarchy may contain subparts. The root of the hierarchy is the Portfolio which has subparts called *Projects*, and *Environment folders*. Projects serve as an organizational mechanism for grouping together other Projects and Module folders. Environment folders supply the designer with standard libraries. A *Module folder*<sup>2</sup> contains the electronic circuit design; it has *lcon*, *layout*, *schematic*, *topology*, and *waveform folder* parts. The user's graphical interface to the topology is mainly through the schematic, layout, and icon presentations. And finally, waveform folders hold collections of waveform specifications, simulation stimuli, and simulation results. This partitioning allows the user to concentrate on one given hierarchical level of design at any particular time. Hierarchical organization is an essential strategy in controlling the complexity of large scale designs.

Each object in the Simulation Environment naturally fits into the hierarchical organization of Schema. The circuit topology and simulation waveforms are parts of Module folders. Because a

<sup>&</sup>lt;sup>2</sup>Module folders and modules are different entities; for historical reasons, they were incorrectly named. Modules are components of the topology; the topology is a component of the module folder.

model may be shared over many modules, models are collected into folders located directly in the user's environment. In later chapters, we shall see how each of the objects also naturally conforms to this hierarchical representation.

Figure 2-2: Hierarchical organization of Schema.

#### 2.4.2 Constraint Network

Objects may contain *parameters*. Relationships called *constraints* are held between these parameters. A transistor has local width, length, and shape-factor parameters where the width is constrained to be the length multiplied by the shape factor. All constraint relationships are specified in a global *constraint network*. This permits constraints between the parameters of different objects. Complex timing relationships between the parameters of many different waveforms can be captured in the constraint network.

This technique is primarily useful for the *automatic propagation of constraints* through local computation. Modifying one waveform's parameter automatically propagates to those waveforms constrained to it. In the event of far-reaching effects, constraint propagation saves the designer from the tedious and time-consuming process of manual updates. Analysis, synthesis, and reasoning tools can also make use of the constraint network in transistor sizing or circuit verification, for example.

#### 2.4.3 Creation on Demand

*Creation on demand* is the technique of creating an object's internal structure only when it is needed. In the meantime, the external environment only knows the object exists; typically this is done by knowing the name of the object. Creation on demand applies equally over all objects in the hierarchy. Once the internal data structure has been created, its internal parts likewise need not be created until required. For example, if the designer is interested in only in one specific module folder in a large hierarchy of projects and module folders, then it is only necessary to create the parents of the desired module, beginning with the designer's Portfolio. This technique has the advantage of saving valuable memory space and subsequent garbage collection time - a substantial savings when dealing with large-scale designs.

# 2.5 Summary

The Simulation Environment provides a uniform CAD interface, a consistent user interface, and mixed-mode capability by using a common representation for simulation data objects: circuit topologies, models, and waveforms. The Generic Simulator coordinates the flow of these objects between each simulator and the simulation initiator. The data objects, the Generic Simulator, and the user interface together make up the Simulation Environment as implemented in Schema.

# **Chapter Three**

# Topology

The *topology* contains the interconnection information of a circuit design. The structure of a topology deviates from the general hierarchical organization of Schema in that it does not contain subparts. Instead, the topology has a *module definition* and a *module type*. The *module definition* is used for the simulation of the current topology. The first half of the chapter concentrates on the module definition: its uniform representation, submodule interconnection, and user interface. The module definition defines a new *module type*. The basic module types as well as techniques for creating new module types and operations are examined in the remaining half of the chapter.

# 3.1 Module Definition

#### 3.1.1 Uniform Representation

The module definition contains submodules, pins, nodes, parameters, and models. The submodules may also have submodules. In this way, modules fit naturally into the hierarchical organization of Schema, as shown in Figure 3-1. Together, the submodules, pins, and nodes specify the electrical connectivity information. Parameters name quantities which are tied to Schema's constraint network. Models are discussed in detail in Chapter 4. The topology, as all objects in the Simulation Environment, has a uniform representation.

#### **3.1.2 Module Interconnection**

Module interconnection, an essential piece of electrical information, is accomplished with *pins*, *nodes*, and *global pins*. A *pin* is a module's interface to the outside world. Transistor modules for example contain four pins: gate, source, drain, and body. Modules are interconnected by attaching their pins to *nodes*. And finally, a *global pin* is a special pin seen by all modules spanning the hierarchy. It may connect through a common node to any module pin. Global pins are used mainly for supply voltages such as Vdd and Vss.

Figure 3-1: The topology and its placement in the hierarchical organization of Schema.

Each module *pin* knows (1) the nodes connected to internal modules, *inodes*, (2) the nodes to which external modules connect, *enodes*, (3) its direction, and (4) its parent module. In Figure 3-2, the inverter module has four pins associated with it: A, A-bar, Vdd, and Vss - of which the latter two are global pins. They all have nodes that connect to the pins of internal modules. Pin A has an internal node n3, no nodes connected externally, the direction *input*, and a parent, the inverter module. The gate pin of the enhancement mode eMOS module has no nodes internally connected, but does have an external node n3, the direction, *input*, and the eMOS module as a parent.

Each node knows all the pins attached to it and the internal pins for which it is the internal node. Node n2 is attached to pin A-bar of the inverter module, the gate and drain pins of the depletion mode dMOS module, and the drain pin of the eMOS module. Pin A-bar is the internal pin for which n2 is the internal node.

1

STREET, STREET,

# Figure 3-2: Inverter module definition and corresponding schematic presentation.

#### 3.1.3 Module Definition Creation

Prior to initiating a simulation, a module definition must be available. If the definition does not exist, it is initially created from the most recent graphical schematic or layout presentation. A module definition may however already exist from some other simulation. In this case, if it is not up to date with the latest version of the presentation, it is updated. This section describes the process of creating or updating a module definition from the presentation.

The presentation is given responsibility for creating or updating the module definition. If the definition is nonexistent, a dummy module object is created for the definition; it initially has no submodules, pins, or nodes. Then for each part in the presentation, a *topological correspondent* is created in the module definition, if none exists. Topological correspondents are submodules, pins, or nodes in the module definition; the module definition is updated accordingly.

A schematic presentation for example, is composed of icons and wires that contain placement and display information. Pin icons, module icons, and wires in the schematic have topological correspondents of pins, modules, and nodes respectively, in the module definition. A schematic for the inverter is shown in Figure 3-2. Wire-2, Wire-3, Wire-5, Wire-6, Wire-7, and Wire-8 of the inverter schematic all have node n2 of the inverter definition as their topological correspondent. The Input Pin Icon and eMOS Icon have topological correspondents of Pin A, and the eMOS module, respectively. Associated with each icon is a set of display pins used to connect wires. These display pins are not shown graphically, yet they do have topological correspondents in the module definition. The eMOS-Icon has three display pins, each of which has a topological correspondent - the gate, source, and drain pins.

The module definition is created at the top level; the submodules and their interconnections are created. The internal structure of each submodule is only created on demand. Once this top-level module definition has been generated, it may be saved in a topology save file for future use. When the file is read in during a new Schema session, the module definition is not created, but rather a new module type is defined. In this case, it is not necessary to create the definition from the presentation; the definition can be simply created from the module type.

#### 3.1.4 Uniform User Interface

The module definition is visually transparent to the user. The user indirectly communicates with the objects in the topology's module definition via the graphical schematic or layout presentation. During the simulation process, the presentation is used as a *read-only* medium for extracting or modifying electrical information in the module definition. Because each display object has a topological correspondent in the module definition, the user can easily access electrical information. Similarly, each part in the module definition has a presentation correspondent. In this way, the parts of the module definition may report back to the user.

The presentation is a flat structure, whereas the topology is hierarchical. The correspondence between the module definition and the presentation is only for the top-level modules in the hierarchical definition. This presents two problems when the user tries to examine the electrical information in the lower level modules. First of all, the only topological components accessible to the user are those having a correspondent in the presentation. Any parts of submodules in the module definition do not have presentations associated with them. Secondly, these parts may not even exist. When the module definition is first created, only the top level objects and their interconnections may exist.

These problems are solved with the *zoom-in* facility. Suppose an inverter icon is a part of the user's current presentation, and the user wishes to set the length and width parameters of the transistors inside the inverter module. Further suppose the inverter module is not fully created, *i.e.*, the transistors do not yet exist. The zoom-in facility finds the layout or schematic presentation from the module folder of the inverter icon, and makes it visible to the user as a read-only reference for examining the submodules of the inverter module. In order to examine the transistor submodules of the inverter, the inverter must first create its submodules. During the creation process, a correspondence is set up between the inverter's presentation and the module instance in the same manner as before. The advantage to this strategy is a single schematic or layout presentation is useful for all modules of the same type - not just the module definition.

# 3.2 Defining New Module Types

A new module type is defined from the module definition, or from a textual description stored in the topology's save file. The type is used to create a separate copy of the module definition for use as a part in some other module. When the type is created, operations are automatically defined to enable an object of the new *module type* to create its own parameters, constraints, submodules, pins, and internal interconnections. Three basic module types are available: simple, compound, and abstract.

#### 3.2.1 Simple Modules

Simple Module Types do not contain submodules. They may, however, have pins, parameters, and constraint relationships, which are generated as soon as an object of this type is created. Examples of simple modules include the resistor, capacitor, dMOS and eMOS transistors, and inverter, NAND, NOR, XOR, OR, and AND logic gates. These types are mainly defined in the designer's environment. Another distinguishing feature of simple modules is they typically have no schematic, only an icon. The following examples depict simple module type definition for the resistor and eMOS transistor.

```

(defmodule resistor simple

(resistance) ; parameter definition

(pins p+ p-)) ; pin definitions

(defmodule eMOS simple

(width length shape ; parameter definitions

source-area source-perimeter

drain-area drain-perimeter)

(pins gate t1 t2 body)

(c* (>> width) ; constraint between parameters

(>> shape)

(>> length)))

```

#### 3.2.2 Compound Modules

Compound Module Types have submodules; and thus, can be hierarchically structured. As with simple modules, pins, parameters, and constraints are all generated when an object of this type is first created. Pin creation is particularly important at this point; external modules can then connect to this module without knowing the internal structure of the module. The submodules and their internal interconnections are created only upon demand. The type associated with each

user-defined topology is usually a compound module type. An example of an inverter module type follows:

```

(defmodule inverter general

()

(global-pins Vdd Vss)

(pin a input)

(pin a-bar output)

(module pulldown eMOS)

;submodule definitions

(module pullup dMOS)

(connect (>> t2 pullup)

; internal connections

(>> Vdd)

(connect (>> t1 pulldown)

(>> Vss)

(connect (>> gate pulldown)

(>> a-bar))

(connect (>> t1 pullup)

(>> gate pullup)

(>> t2 pulldown)

(>> a-bar))

```

### 3.2.3 Abstract Modules

Abstract Module Types are generalizations of a class of module types with similar characteristics. For example, there are many module types that have two pins, such as the resistor, capacitor, and inverter. The abstract module type, Two-Pin-Device, captures this notion. (defmodule\_two-pin-device\_abstract

| defindure two pri | αυδιίαςι        |

|-------------------|-----------------|

| ()                | ;no parameters  |

| (pins p+ p-))     | ;pin definition |

The resistor can now inherit this abstract type, and thus implicitly includes two pins. This is known as *type inheritance*. The previously-defined simple module type, resistor, is redefined as follows.

```

(defmodule resistor simple

(resistance)

(includes two-pin-device)) ;inherits two pins

```

Another abstract module, MOS, captures the general characteristics of MOS transistors including width, length, and shape parameters. Additionally, a constraint is placed between these parameters.

```

(defmodule MOS abstract

(width length shape

source-area source-perimeter

drain-area drain-perimeter)

(pins gate t1 t2 body)

(c* (>> width)

(>> shape)

(>> length)))

```

This abstract module is then used to define specific types of transistors, such as eMOS and dMOS, with these implicit parameters and constraints. Type inheritance greatly simplifies the type definition.

```

(defmodule eMOS simple

()

(includes MOS)) ;inherits MOS characteristics

```

## 3.3 Defining New Module Operations

A layer of general, all-purpose accessors and operations is currently defined for topological objects. This layer is independent of any particular simulator and thus is useful not only to the Generic Simulator, but to any tool requiring access to topological information. One very basic operation gives modules the ability to create their own submodules if they have not yet been created. Another operation permits a module definition to dump its data structure in such a way that a module type is defined when the dump forms are evaluated. Other localized operations may be easily incorporated.

Because a general layer of operations on topological objects currently exists, integrating additional internal simulators does not require the addition of a new operators. For an external simulator, however, a transformation operation must be defined to translate the data objects in the environment into a textual description for the simulator. For each module type the simulator accepts, a new transformation operation is defined. Simple transformation operations for creating a Spice2 input deck are shown below.

```

(defmethod (resistor :spice-deck) (stream)

(format stream "R~D ~D ~D ~F~%"

(simulation-resistor-number self)

(simulation-node-number (>> p+))

(simulation-node-number (>> p-))

(>> resistance)))

(defmethod (MOS :spice-deck) (stream)

(format stream "M~D ~D ~D ~D ~D ~A W=~D L=~D~%"

(simulation-MOS-number self)

(simulation-ncde-number (>> t2))

(simulation-node-number (>> gate))

(simulation-node-number (>> t1))

(simulation-node-number (>> body))

(send (send self :get-model) :name)

(>> width)

(>> length))

```

Notice a single operation is defined for a whole class of MOS devices. In other words, this operation is performed on all modules that have the abstract MOS type; this includes eMOS module type redefined above. Thus, not only is the type inherited, but the operations defined on the type are also inherited.

### 3.4 Summary

A topology contains a module definition and a type. The module definition is the topological object used in simulation. It is uniformly represented within the hierarchical organization of Schema. It is initially created from a presentation and serves to define the module type. In this way, new types and their operators can be easily integrated into the Simulation Environment. The simple addition of new types and their operators facilitates extensibility to both Internal and external simulators.

# **Chapter Four**

# Models

Because simulators *model* the behavior of real devices, models play a vital role in the simulation of circuit designs. In the Simulation Environment, a model may be associated with each module being simulated. Models contain many of the electrical quantities required in simulation. The uniform representation, the user interface, and the basic types of models are all discussed in this chapter.

### 4.1 Uniform Representation

Models are not hierarchical; they do not contain other models. Instead, models have parameters such as threshold voltages and oxide thicknesses for circuit level transistor models, and setup times, propagation delays and hold times for logic-level models. These parameters are not the associated with the constraint network. In the hierarchical organization of Schema, models applicable to a particular type of module are collected into a *model folder*. Similarly, model folders for different modules are grouped into *environment folders* as shown in Figure 4-1. At any one level in the environment folder hierarchy, there is at most one model folder for each module type.

It is interesting to note that model folders and their respective models are kept separate from the module folder for which apply. Rather models and model folders are classified by environment, and the information contained in the module folder is shared over all the environments. In this way, environments can be configured by a particular fabrication process, for example. By simply switching environments, a new set of models corresponding to a different fabrication process can be used. The major advantage to this approach is that circuits can be designed independent of the fabrication process, or indeed, any other technological division.

Figure 4-1: Models and their placement in the hierarchical organization of Schema.

## 4.2 Uniform User Interface

The user interface to creating new model folders and models is simply menu-driven and self-explanatory. If the model folder for the module to be modeled does not exist, a new module folder is first created. A new model is generated by selecting any one of the currently defined model types for the chosen module type. Furthermore, the user is free to modify any of the parameters of the newly-created model.

### 4.3 Defining New Model Types

In the Simulation Environment, each newly-defined model type must specify both a module type for which it is applicable and a list of parameters. A default value, a short documentation string, and a dimension accompany each parameter definition.

While a model type corresponds to exactly one module type, each module type may correspond to several different models. The MOS transistor is a prime example of a module having many model types: switch, linear, shichman and hodges, analytical, and semi-empirical models. Each model type may produce several individual model objects. There may, for example, be special models for worst-case speed, worst-case power, and worst-case noise margin.

Two basic types of models exist: models without state and models with state. Models

without state may be shared by modules of a common type, but models with state may not be shared. Modules may require the use of both kinds of models; some parameters may be shared over many devices of the same type, whereas other parameters refer to the local state of the device<sup>3</sup>. The following two sections describe each model type and explain how to define new model types.

#### 4.3.1 Models Without State

Modules of the same type share a common model without state. The obvious advantage to this approach is a savings in memory space because only one copy of the model is generated. This does not imply that *all* devices of a common type must share the same model. This mechanism just facilitates a sharing of a common model. Some modules of a common type may require one shared model without state, while others of the same type may require a different model without state.

Models without state are useful to both external simulators and internal simulators. In a logic level simulation, all NAND gates in the circuit may share common values for transition times along with a common boolean operation. In this case, a single shared model without state is useful to all modules of type NAND, regardless of whether the logic level simulator is an external or internal simulator.

For the abstract module type MOS defined in Chapter 3, a abstract Spice2 model is defined as follows:

```

(define-model MOS spice-MOS ()

(vt0 0.0 "Zero bias threshold voltage" :voltage)

(kp 2.0e-5 "Transconductance" :current-per-voltage-squared)

(gamma 0.0 "Bulk threshold parameter" :sqrt-voltage)

(phi 0.6 "Surface potential" :voltage)

...)

```

The new model type is called spice-MOS and its parameters are those that are used over all three MOS device models defined in Spice2. A spice-MOS-analytical model type can now be defined with the additional parameters required for simulating an analytical model. Since this new model includes the spice-MOS model, all of its parameters will also be included.

<sup>&</sup>lt;sup>3</sup>This case has not yet been dealt with explicitly. Either the two separate models could both be cached in the module, or another type could be defined having local state along with a pointer to the shared model.

```

(define-model MOS spice-MOS-analytical (spice-MOS)

(lambda 0.0 "Channel length modulation" :inverse-voltage)

(ucrit 1.0e4 "Crit field mobility degrad" :voltage-per-length)

...)

```

And finally, this abstract model is used to define a general model for the eMOS module. The model restricts the channel type to n-channel, while also including all the abstract characteristics of the spice-MOS-analytical and spice-MOS model types.

```

(define-model eMOS spice-eMOS-analytical (spice-MOS-analytical)

(channel-type "Channel-type" :value nMOS))

```

#### 4.3.2 Models With State

As the name implies, a model with state stores information relating to the current state of the module, such as charge, binary state, and local variable bindings. Internal simulators use models with state to temporarily store simulation data. The Q parameter of the logic-D-flip-flop model and the state parameter of the Rsim-MOS model are recalculated for each event or clock cycle of the simulator.

```

(define-model-with-state D-flip-flop logic-D-flip-flop

(Q "Current state" :values '(L H X)))

(define-model-with-state MOS Rsim-MOS ()

(state "Current state" :values '(on off unknown weak))

(rstatic-min "Minimum static resistance" :resistance)

(rdynlow "Dynamic low resistance" :resistance)

...)

```

An implementation of Rsim also requires an initial determination of the effective static and dynamic resistances of each MOS device. These parameters are calculated one time only from the local parameters of each module and are reused over many simulations. To sum up, the parameters of a model with state may depend on the model's local state and the module's local properties.

### 4.4 Defining New Model Operations

Defining operations for models is a very powerful tool for promoting modularity in internal simulation design as well as in integrating additional external simulators. For internal analysis tools, models perform certain operations such a drain current calculations, boolean functions,

#### Chapter 4

and behavioral-level procedures. For external simulators, transformation operations can be defined similar to those defined on modules.

# 4.5 Summary

Models have parameters which hold the electrical information required during simulation. Models are located in the designer's environment and are cached in the module prior to simulation. The cached model is then available for future simulations. Two basic types of models exist in the Simulation Environment: models with and without state. New models and operations can be built out of these basic types.

# **Chapter Five**

# Waveforms

Waveforms embody any type of excitation or response signal used in the simulation and analysis of electronic circuits. In the Simulation Environment, the uniform waveform representations are patterned after the input and output signals of simulators. This chapter briefly examines these uniform representations and how they fit into the overall hierarchical framework of Schema. Then an introduction to the uniform user interface leads naturally into a discussion of the display types, their associated waveform types and operations, and the usefulness of the constraint mechanism. And finally, type conversions are discussed with respect to the mixedmode property of the Simulation Environment.

Figure 5-1: Waveforms in the hierarchical organization of Schema.

# 5.1 Uniform Representation

Waveforms are the uniform mechanism for communication among modules in the Simulation Environment. The means of organizing and grouping waveforms, *waveform folders*, the means of displaying waveforms, *waveform displays*, and the actual *waveforms objects* themselves, provide the mechanism for fitting waveforms into the hierarchical organization of Schema as shown in Figure 5-1. This section gives a brief overview of each, along with its dedicated purpose in the Simulation Environment. This background, in combination with a discussion on the applicability of the constraint network in the waveform domain, lays the foundation for the implementation details presented in the remaining sections.

In the hierarchy of Schema, *waveform folders* are parts of projects, module folders, and environment folders. As a project part, a waveform folder serves as a medium for capturing many of the simulation stimuli, *e.g.*, clocks, control signals, and waveform specifications that are shared between the simulations of different modules. As a module-folder part, a waveform folder contains waveform information pertaining just to the module. Waveform folders that are project and module parts are generic and thus may be shared by many different environments. And finally, as an environment folder part, a waveform folder holds simulation results. In the same way that models are associated with a particular environment, so are the waveforms resulting from simulations that use those models. Allowing waveform folders at many levels in the hierarchy permits a large degree of modularity in organizing the waveforms of very large circuit designs.

Waveform folders contain other waveform folders as well as *waveform displays* as parts. As the name implies, a waveform display object holds the information required for a visual display to the user. A display object, for example, could contain information regarding maximum and minimum axis amplitudes, horizontal and vertical scaling, and dimensional units. This information is conveniently useful to display routines defined for the objects.

One level deeper in the hierarchy, waveform displays hold a ordered set of *waveform* parts. These parts represent the actual signal values. In keeping with the hierarchical structure of parts, waveforms may also have waveform parts. Waveforms are ordered in increasing value along the x-axis to guarantee fast searching through parts.

Constraints may be placed among parameters internal to a waveform, between the waveform parts of a common display object, or across waveform parts of different display objects.

A ramp has parameters of initial-x, final-x, and delta-x. In this case, delta-x is numerically constrained to be equal to the difference between the final-x and the initial-x parameters. This is an example of a constraint placed on parameters *internal* to a waveform.

Another constraint may be tied *between* parameters of waveform parts in a common display object. In a sequence of ramps, the initial-x parameter of each ramp part of a display object is constrained to be equal to the final-x of waveform part preceding it. This constraint, in conjunction with the aforementioned internal constraint imposed upon each individual ramp, makes it possible to achieve simple shifting operations along the *x*-axis. Changing one parameter locally propagates the constraints to shift all waveform parts of the display object to the right or left along the *x*-axis.

Finally, constraints may be placed *across* waveforms parameters in different display objects. This is especially valuable when specifying complicated timing relationships between input signals. Consider a typical dynamic random-access memory chip where read, early-write, write, read-write/read-modify-write, page-mode read, page-mode write, and Ras-bar-only refresh cycle timing relationships each occupy a full page in the standard MOS memory data book. Local constraint propagation to achieve global consistency over the numerous complicated timing relationships associated with very large performance circuits is a very valuable asset to the circuit designer of today.

### 5.2 Uniform User Interface