#### MIT/LCS/TR-355

## DATA STRUCTURE MANAGEMENT IN A DATA FLOW COMPUTER SYSTEM

Bhaskar Guharoy

May 1985

## Data Structure Management in a Data Flow Computer System

Bhaskar Guharoy

May 1985

#### © Bhaskar Guharoy 1985

The author hereby grants to M.I.T. permission to reproduce and distribute copies of this thesis document in whole or in part.

MASSACHUSETTS INSTITUTE OF TECHNOLOGY Laboratory for Computer Science Cambridge, MA 02139 This empty page was substituted for a blank page in the original document.

#### **Abstract**

# DATA STRUCTURE MANAGEMENT IN A DATA FLOW COMPUTER SYSTEM by Bhaskar Guharoy

Submitted to the Department of Electrical Engineering and Computer Science on May 28, 1985 in partial fulfillment of the requirements for the Degree of Master of Science

VIM is an experimental computer system being developed at MIT for supporting functional programming. The execution mechanism of the computer is based on data flow. This thesis presents mechanisms for managing data structures in this system. The thesis also develops a methodology for designing computers, which is based on successive refinement of formal models of the computer.

A formal model L1 of the abstract architecture of VIM is first developed. The behaviour of this model is described by its operational semantics; L1 is the specification of VIM. L1 is then refined to model hierarchical physical storage consisting of main memory and disk. This refined model is called L2. The unit of storage allocation and of data transfer between main store and disk is a chunk. The thesis proposes a new data structure called VIM-tree which is a tree of chunks. Data structures in VIM (arrays and records) are stored on VIM-trees. VIM-trees allow efficient applicative operations on data structures and permit a large amount of sharing. A reference count mechanism is proposed to perform automatic storage reclamation. Special care is taken to handle operations in L2 on data structures containing *early-completion queues* and *suspensions*, which are distinctive features of VIM. A base language for this machine is outlined in the thesis.

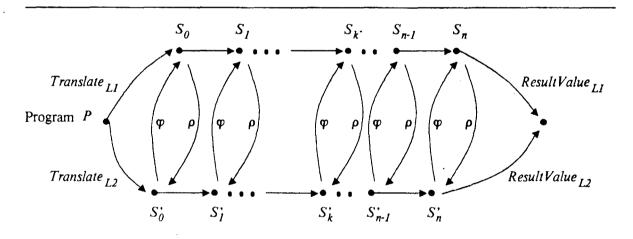

The models L1 and L2 are then shown to be equivalent for the proposed base language. The equivalence is proved by exhibiting a McGowan mapping between the states of the two models during the execution of a program writen in the base language.

Thesis Supervisor: Jack B. Dennis

Professor of Electrical Engineering and Computer Science

**Keywords:** - VIM, Dataflow Graphs, Functional Languages, Structure Management, Hierarchical Storage, Heaps, Tree structures, Early-Completion Structures, Suspensions, Streams, Machine Equivalence, VIMVAL Compilation.

This empty page was substituted for a blank page in the original document.

## Acknowledgments

There are many people who contributed, directly or indirectly, to the writing of this thesis. I wish to thank Jack Dennis for providing encouragement and support during the long period of gestation of this thesis. Thanks to Suresh Jagannathan for being ever ready to listen to my ideas and coming up with constructive criticism. Much of the formal model L1 was developed jointly with Suresh.

My sincere thanks to David Culler for being such a wonderful friend. Thanks to Sara Mayeno for allowing me to cook for her whenever I visited her and David. Steve Heller provided much of the fun and laughter. My thanks to Keshav Pingali for the many interesting discussions I had with him. Thanks to Andy Boughton, Guang-Rong Gao, Vinod Kathail, Greg Papadopoulos, Earl Waldin and all the other members of CSG and FLA who make the laboratory such a fun place to work in.

My family has always been very encouraging and I cherish their enthusiasm and interest in my work. Finally, my thanks to Marcela for making me finally go crazy, in the right way, and for being the perfect partner in goofiness.

The woods are lovely, dark and deep But I have promises to keep And miles to go before I sleep And miles to go before I sleep.

> "Stopping by woods on a snowy evening" Robert Frost.

This empty page was substituted for a blank page in the original document.

.4

This empty page was substituted for a blank page in the original document.

## **Table of Contents**

| Chapter One: Introduction                                                                                                                                                                                                                                                                                                            | 1                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| <ul><li>1.1 The VIM Project</li><li>1.2 Background and Previous Work</li><li>1.3 Outline of the Thesis</li></ul>                                                                                                                                                                                                                     | 2<br>3<br>6                                |

| Chapter Two: The Val Interpretive Machine                                                                                                                                                                                                                                                                                            | 8                                          |

| <ul> <li>2.1 The VIMVAL Language</li> <li>2.2 An Example Program in VIMVAL</li> <li>2.3 The VAL Interpretive Machine — VIM <ul> <li>2.3.1 Function Application</li> <li>2.3.2 Early-Completion Queues</li> <li>2.3.3 Suspensions and Streams</li> </ul> </li> <li>2.4 Operational Model for VIM - L1</li> <li>2.5 Summary</li> </ul> | 8<br>9<br>12<br>13<br>17<br>19<br>21<br>38 |

| Chapter Three: Operational Semantics of VIM with Storage                                                                                                                                                                                                                                                                             | 40                                         |

| 3.1 Arrays and VIM-trees 3.2 Operational semantics of L2 3.3 Discussion                                                                                                                                                                                                                                                              | 44<br>45<br>68                             |

| Chapter Four: Equivalence of L1 and L2                                                                                                                                                                                                                                                                                               | 70                                         |

| 4.1 Proof of Equivalence of L1 and L2 4.2 Discussion                                                                                                                                                                                                                                                                                 | 71<br>81                                   |

| Chapter Five: A Base Language for VIM                                                                                                                                                                                                                                                                                                | 82                                         |

| <ul> <li>5.1 The Let expression</li> <li>5.2 Conditional Expression</li> <li>5.3 The Tagcase Expression</li> <li>5.4 Function Application and Returns</li> <li>5.5 Stream Producers and Consumers</li> <li>5.6 Discussion</li> </ul>                                                                                                 | 82<br>83<br>84<br>86<br>87<br>90           |

| Chapter Six: Conclusion and Scope for Further Work                                                                                                                                                                                                                                                                                   | 92                                         |

This empty page was substituted for a blank page in the original document.

## Chapter One

### Introduction

In recent years data flow computer systems have been the focus of vigorous research, especially in the context of high speed scientific computations. In addition to higher speed, the data flow model of computation appears to provide a more robust programming environment than is available on conventional systems. The VIM project of the Computation Structures Group at MIT is aimed at examining the issues involved in implementing a modern, general-purpose computing environment based on the principles of dataflow that can effectively support such diverse computational applications as database systems, logic programming, etc. The ideas about the VIM system have evolved over the years, drawing much from the works of Dennis [9, 10, 11], Patil [31] and Weng [38].

The VIM system will support functional programming and the execution mechanism is based on data flow. In the world of functional programming all values are treated as mathematical values. This implies that the traditional view of data structures (arrays and records) as *modifiable* entities is no longer valid — the system must operate so that the user gets the view that a new structure is created from the old one whenever required. In a simplistic implementation, this would lead to a proliferation of copies of data structures, each differing from the others in only a small number of values. It is recognized that sharing of common elements among structures would reduce both the amount of copying and the storage space required to run the program. Various proposals have been made to implement data structures in data flow systems; none of them can be called definitive solutions. Applicative languages are also side-effect free languages and the language constructs provided in the functional language for VIM does not allow the creation of circular structures. Therefore, reference-counted memory management becomes an attractive alternative to traditional mark-and-sweep methods for garbage collection. This thesis proposes a representation for data structures that greatly reduces the amount of copying and describes a reference count mechanism for storage reclamation.

In most currently proposed functional language architectures, an implicit assumption is that the

program and the data which the program operates upon are all located in the main memory<sup>1</sup>. VIM has a two-level physical hierarchy of storage consisting of a large, slow disk and a smaller, faster main store. Values in the main-memory can be accessed immediately while values which are resident in the disk must be read into the main memory first.

The problem of storage reclamation on systems with large address spaces is a prickly one; the strategy for garbage collection in VIM is based on reference counting. The architecture of VIM modelled in this thesis consists of a single processor, some main store and disk store. The principal source of parallelism in the single-processor version of VIM stems from the concurrency in the processing of instructions and disk activities.

#### 1.1 The VIM Project

The goal of the VIM project is to develop a computing environment which supports functional programming and provides a large address space and automatic storage reclamation. A two-level physical storage has been chosen to reduce the cost of physical memory. The primary vehicle for programming on this system will be the VimVal language, a functional language that is an extension of the language VAL developed by Ackerman and Dennis [1, 26, 27]. The criteria that have guided the design of the new language are that it should have the following characteristics.

- It should be sufficiently expressive in that it provides language constructs to the programmer to express most application programs that he needs to, without having to appeal to some features of the underlying architecture that are not evidenced in the language.

- A program consists of one or more modules. Modules must be independently compilable. All the independently compiled modules of a program are linked prior to execution by a linker.

- The language must be strongly typed, *i.e.*, if the compiler and the linker certify the program to be legally typed then the program will not encounter any type errors at the time of execution of the program.

- The language must provide constructs to express computations on streams.

<sup>&</sup>lt;sup>1</sup>The models proposed by Dennis and Weng have a two-level physical storage,

- Non-determinacy must be expressible in the language.

- Higher-order functions must be permitted.

Programs written in VIMVAL will be run on a data flow processor with hierarchical storage. The conceptual framework for the machine was described in [38]. As currently envisioned, the VIM system consists of a single processing element and a two-level physical storage consisting of main memory and disk.

#### 1.2 Background and Previous Work

A number of projects have aimed at providing a coherent and structured programming environment within the framework of a multiprocessing system. Of principal interest from the perspective of this thesis are the Hydra/C.mmp system, the Cm\* computer and the SYMBOL computer.

The Hydra/C.mmp was an experimental multiprocessor system [39]. Capabilities were adopted as a mechanism for providing a large and uniform address space and also to control accesses to shared data structures. However, the system fell short of providing a truly integrated interface between the capability architecture and the programming language. The task of processor management was left largely in the hands of the user. The user had to ensure the correct usage of shared data structures by the use of appropriate locking and synchronization primitives, with a resultant decrease in the programmability of the system [23]. However, in spite of these shortcomings the Hydra/C.mmp system represented a significant advance in programmability over the multiprocessor systems then existing.

The Cm\* [34, 35] was also a capability based architecture consisting of a large number of processors and memory modules. An underlying goal of the Cm\* project was to develop a system that would be scalable, i.e., the computing power of the system would grow in proportion to the number of processors in the system. However, this effort too left the issue of processor management as a user responsibility. Also, since the cost of a memory access was proportional to the distance of the memory cell from the processor, the task of organizing the program so that the number of non-local memory references would be minimal was left to the programmer [22].

The Mu project [18] at MIT was aimed at assessing the importance of programmability in multiprocessor organizations. Though the theoretical framework appears to provide a better working environment than in Cm\* and C.mmp, the system was still unable to provide an elegant way of avoiding the need for explicit synchronizaton mechanisms for shared data that could be updated independently by the processors. It became clear from Halstead's work that the language supported by a multiprocessor is critical to the usability of the system. The difficulty of programming on a multiprocessor can be alleviated if the user can write programs without having to worry about task scheduling, process synchronization and hazards such as read-before-writes, such chores being taken care of by the underlying system automatically.

The SYMBOL computer system [8, 29] was a language based multiprocessor system that allowed the user to program without having to worry about low level considerations like mapping the tasks onto the processors. Each of the processors had a very specific task; however, the task division was so rigid that it ruled out the possibility of scaling the system. Also, the various processors did not aim at solving a single problem in parallel. There was a processor dedicated to compilation, one to memory management, one to I/O management, one that actually executed the compiled program, etc. The parallelism in this system resulted from the fact that memory management, input-output and actual processing could be done in parallel. There was no facility in the system whereby multiple processors could concurrently execute a compiled program.

The SYMBOL was not a true multiprocessor since it was unable to support parallel execution of a program exhibiting a lot of computational parallelism. However, many of the ideas it introduced were far ahead of the times. It was one of the first processors to specialize the memory architecture to support structure memory. The memory representations of data were specialized to reflect the type of data, allowing operations to be performed on such typed data more efficiently. Significant amount of specialized hardware was developed to allow structure operations to be executed fast — a revolutionary approach, considering the cost of hardware in that period.

One of the seminal contributions of the SYMBOL system is that it viewed that the design of the memory management system was an integral part of the multiprocessor system design. The memory management mechanism provided primitives which could support high-level memory abstractions such

as stacks, queues, lists and strings. A specialized processor performed the memory management tasks, exemplifying the philosophy of static load distribution that so characterized the system.

In spite of its failings, the SYMBOL system, which predated the other projects discussed above by a number of years, presented a pointer to the direction in which the development of programming environments for multiprocessor systems ought to proceed — an architecture based on a high-level language that provided a very uniform, integrated environment for programming.

Among the various general purpose computing environments available on modern systems, the one on the Lisp machines deserve special mention. Lisp machines are language-based uniprocessors designed at Massachusetts Institute Technology [24, 28, 32, 33, 36]. They provide a uniform programming environment; there is no distinction between the command language used for interaction with the system and the principal programming language supported (Lisp), the hardware is tailored for processing Lisp primitives, high level data structures such as lists and arrays are regarded as data types even at the machine architecture level, and mechanisms for storage reclamation constitute an integral part of the system design.

Lisp machines provide a very large address space which can be effectively used to support a uniform addressing scheme for all objects created in the system. However, the necessity of explicitly "loading" a file containing an object residing in secondary storage before the object can be used detracts from the uniform addressability feature. Once the file is loaded, the object may be placed on the disk by the memory manager; references to this object are handled by the system so that its actual placement in the memory hierarchy is transparent to the user. Ideally, the user should never have to worry about whether the object is in the primary storage or in the secondary; given the name of the object, the system should automatically resolve the references to the object appropriately. In the VIM system, there is no concept of a file — all data structures are persistent in that they continue to exist across sessions, until there exist no references to the structure in the system, in which case they are discarded. This strategy obviates the necessity of "loading" files.

The storage reclamation scheme adopted by the Lisp machine is a variant of the mark and sweep strategy. The process of marking and sweeping the address space starts when the system runs out of storage. In the Lisp machine, the process of garbage collection is overlapped with the processing of

other tasks in the system. This overlap is achieved by frequent switching of the task of reclamation with other activities. In conventional systems (von Neumann derived architectures), the switching of tasks involves the execution of substantial amounts of code to save the state, reducing the efficiency of the process of switching. The data flow model of program execution allows such switching to be performed with only a small overhead. In mark-and-sweep garbage collection, the time required to reclaim storage is proportional to the size of the address space over which the reclamation is to be performed. By constrast, the time required to reclaim the storage occupied by an object by reference-count based reclamation schemes is proportional to the size of the storage occupied by the reclaimed objects.

#### 1.3 Outline of the Thesis

The design of the VIM architecture espouses the following philosophy. An architecture should be developed by successive refinement, starting from an abstract mathematical specification. The extensions and refinements at each of specification are designed to permit more efficient implementation of the machine. By proving that all the models are equivalent<sup>2</sup>, one can largely eliminate the unexpected behaviours that one encounters when designing a system in an *ad hoc* basis. This type of top-down approach is especially important to the design of multiprocessor systems, since the possibility for errors of omission and commission is so much greater.

The design of the VIM system started with the design of the language VIMVAL which conformed to the aims outlined earlier. VIMVAL programs are compiled into programs in a base language, a preliminary version of which was proposed by Dennis and Stoy in 1982; a refinement of the base language is presented in this work.

In this thesis, first the operational semantics of an abstract model for VIM is described. The model, called L1, is the basis for specifying the behaviour of VIM, and is a set theoretic characterization of the abstract machine. The execution model is defined by a non-deterministic state-transition function. The set of instructions in this abstract model is an extension of that proposed by Dennis and Stoy. Chapter 2 gives a brief description of the VIMVAL language and then presents the formal model

<sup>&</sup>lt;sup>2</sup>A naive notion of equivalence may be that the models produce the same results. A formal notion of equivalence for the various models of Vim will be defined in chapter 4

Ll.

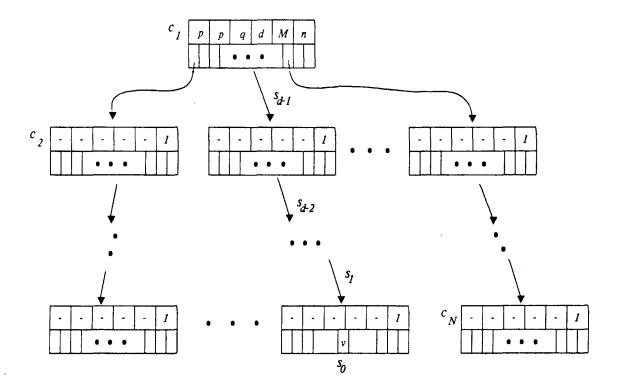

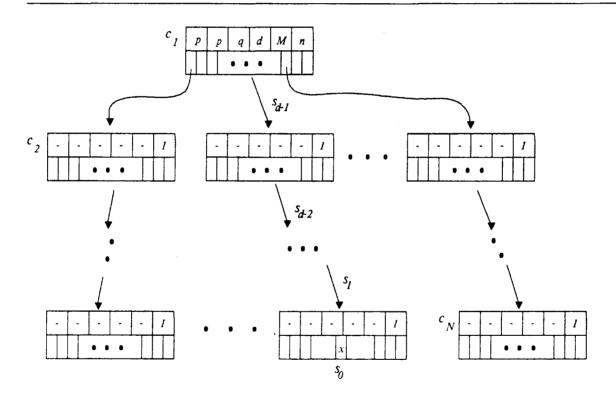

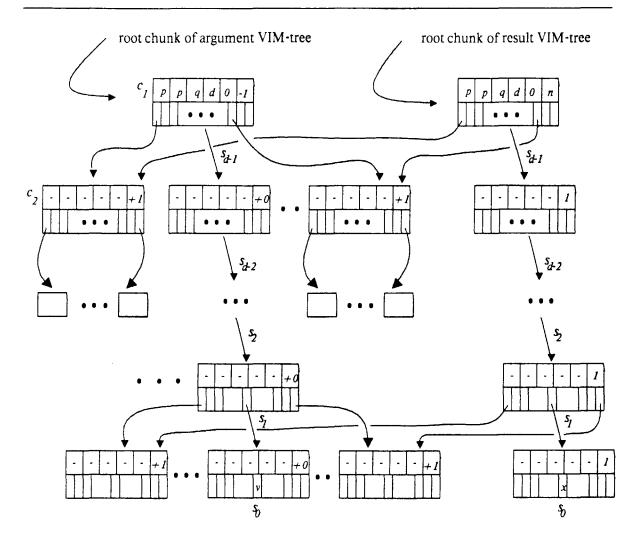

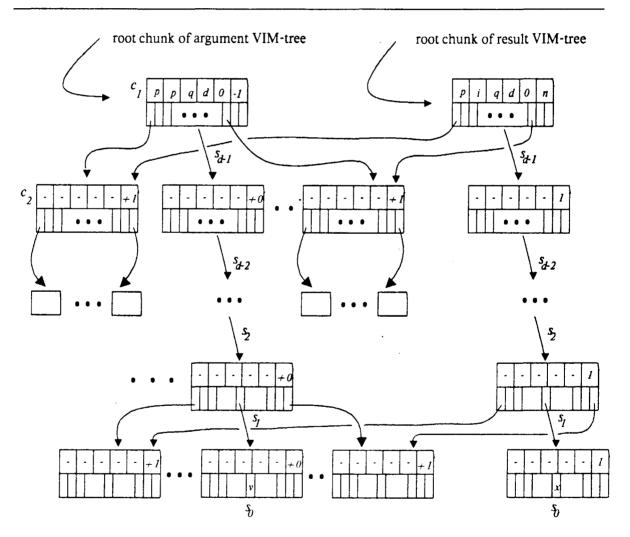

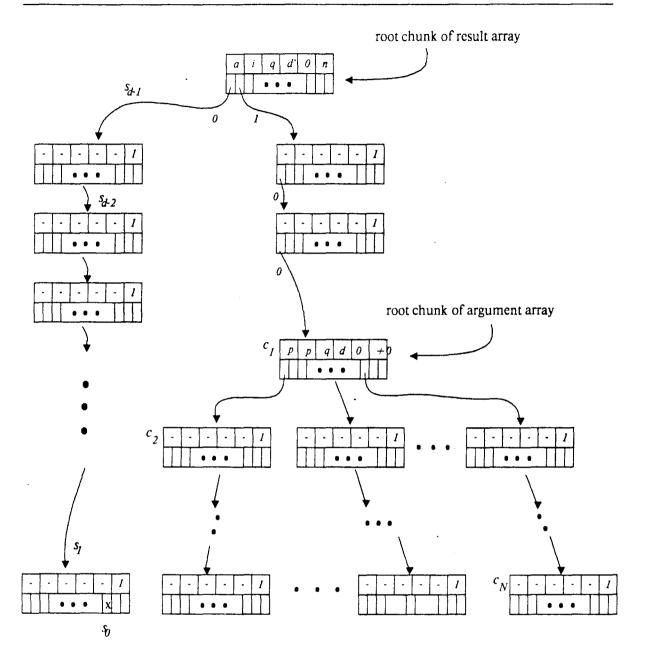

The operational model L2 is a refinement of L1 and is obtained by adding the notion of storage. In this model, structure values (such as arrays and records) which were modelled as elements of sets in L1 are viewed as stored values. L2 models a system with a hierarchically organized physical memory consisting of main store and disk. Storage consists of a large collection of equal sized chunks, each of which is an ordered set of words. Structure values are stored in trees of chunks, thus permitting sharing of information. L2 models a strategy for storage reclamation based on a reference count mechanism. The operational semantics of this model is presented in chapter 3.

In accordance with our proposal of designing by refinement, we must next demonstrate that the L2 satisfies the specifications of L1. This is shown by proving that the two machines are computationally equivalent. A formal definition of equivalence is developed in Chapter 4 and the proof of the equivalence of L1 and L2 is presented.

The base language for the machine, which is the target language of the compiler for VIMVAL, is described in Chapter 5. Essentially, the data flow graphs are such that when the computation of a program terminates, the reference counting mechanism would guarantee that if a structure becomes inaccessible in L1, the corresponding element in L2 would have reference count of zero and would thus be reclaimed.

The thesis concludes with a discussion of the relationship between L2 and its physical realization, and a brief list of related problems which are beyond the scope of this thesis and need further investigation.

### Chapter Two

## The Val Interpretive Machine

The goal of the VIM project is the design and development of a computer system that supports functional programming well. The architecture of the computer is based on data flow principles and the data flow model of program execution is well suited for interpreting functional languages.

The functional language supported by VIM is VIMVAL, which has evolved from VAL. VIMVAL is a textual language and a brief description of it is given in the first section. VIMVAL programs are compiled into programs in the base language, which consists of a set of data flow graph schemata. Translation from VIMVAL to the base language is straightforward since each construct in VIMVAL corresponds to a graph schema in the base language.

Programs in the base language are executed by interpreting the data flow instructions which are the nodes in the data flow graph for the program. Section 2.3 gives an informal description of some of the distinctive mechanisms used in VIM. The operational semantics of the abstract model L1 is presented in section 2.4. The model is the specification of VIM and all implementations of VIM must meet the specifications.

#### 2.1 The VIMVAL Language

The programming language for the VIM system is the VIMVAL, an applicative language which is a revision and an extension of the Val programming language. The extensions include the addition of stream-types, free variables, recursion and mutual recursion, and higher order functions. A type inference mechanism guarantees type safety even if most type declarations are absent. Type inference is also used to provide polymorphic functions.

The data types of ViMVai, fall into two classes — *simple* types and *structure* types. The simple types include the familiar types integer, real, boolean, character and null. The structure types include array-types, record-types, distinguished unions, stream-types, and functions.

Functions are first-class objects. They may be passed as arguments to and returned as results from functions, and they may be built into data structures. The body of a function definition is an expression. Evaluation of an expression yields a single value or a tuple of values. Forms of expressions include the conditional expression, the tagcase expression, and the function invocation. There is no form of expression for expressing iteration, use of recursion being preferred.

#### 2.2 An Example Program in VIMVAL

A program in VIMVAL consists of one or more modules. Each module has a header specifying its interface, type declarations, function definitions and one expression which constitutes the body of the module. An example module is shown in Figures 1 and 2. Figure 1 illustrates how the user may define a new data type *List*, which represents a list of integers. The example module defines three simple operations on objects of type *List*. Figure 2 illustrates the use of streams in the language. The functions *car*, *cdr* and *cons* defined by the example programs have the same meaning as in Lisp. The function *ListToStream* creates a stream of integers when it is given a list of integers. *SumOfStream* sums up the elements of a stream of integers.

A module written in VIMVAL defines a function that may be invoked from within another module or by a user command to the system. A module may contain function definitions — these may be invoked only from within the module unless they are explicitly exported by incorporating them into data structures sent out as module results. The body of a module may use names that are not defined bound to values by definitions in the module. These *free* names must be bound to other modules before the module may be run.

Within a module, type declarations precede the function definitions and the body. Within a function, the type declarations must precede the expression that constitutes the body of the function. An array  $\Delta$  of integers is declared as follows.

A: array[integers] = array(1, 100)

The elements of the array are initially undefined. select(A, i) returns the *Value* of the ith element of the array. append(A, i, v) creates a new array which is identical to the array A except that the value of the ith element of the new array is v.

```

module returns record[head, tail, tuple: function]

type List = oneof[emptylist:nil;

atom: integer;

pair: record[first, second: List]]

function car (L:List) returns List;

tagcase L

tag emptylist: error;

tag atom: error;

tag pair : L.first;

endtag

endfun

function cdr (L: List) returns List;

tagcase L

tag emptylist: error;

tag atom: error;

tag pair: L.second;

endtag

endfun

function cons (L1, L2: List) returns List;

make List[pair: record[first:L1, second: L2]]

endfun

record[head:car, tail:cdr, tuple:cons]

endmodule

```

Figure 1: An example program in VIMVAL.

```

The definition of a record-type is of the form type Pair = record[first, second : List]

```

Records of type Pair have two fields named left and right. The operation

```

record[first : v1, second : v2]

```

constructs a record where vI and v2 are of type List. Record fields are accessed by the select operation, for instance

L.first

yields the value of the kji field of L, which must be of type List in which the tag is pair. Tagged unions are used where different choices of representation are appropriate for different cases of a value. For example, the type List is a tagged union.

```

function ListToStream (L:List, C:List) returns stream[integer]

tagcase L

tag empty: tagcase C

tag empty: stream[];

tag atom : affix(C, stream[]);

tag pair: ListToStream(car(L), cdr(L))

tag atom: affix(L, ListToStream(car(L), cons(cdr(L), C);

tag pair: ListToStream(car(L), cons(cdr(L), C))

endtag

endfun;

function SumOfStream(S:stream[integer]) returns integer;

if isempty(S) then 0

else first(S) + SumOfStream(rest(<math>S))

endif

endfun;

Figure 2: Continuation of the example.

```

type List = oneof [emptylist : nil; atom : integer; pair : record [first, rest : List]]

where the subtypes are distinguished by the tags *emptylist*, *atom* and *pair*. **make**[*atom* : 0] creates a oneof in which the tag field is *atom* and the associated value is 0. A case expression is used to access values of a **oneof** type:

```

tagcase L

tag emptylist: exprl;

tag atom: expr2;

tag pair: expr3

endtag

```

A stream is a sequence of values, all of the same type, that are passed in succession, one-at-a-time between functions. The operations defined on streams are [], first, rest, affix and empty. [] produces an empty stream. first(S) produces the first element of the stream S. The result of rest(S) is the stream left after removing the first element of S. affix(v, S) is the stream whose first element is v and whose remaining elements are the stream S. The result of empty(S) is true if S is an empty stream, false otherwise.

#### 2.3 The Val Interpretive Machine - Vim

The abstract architecture of VIM uses data driven program execution. A program in the base language consists of one or more functions, each represented by an acyclic, directed data flow graph. The nodes of the graph are the instructions and the arcs between the nodes specify the data dependencies among the instructions. Arcs connecting two nodes may be of two types — value arcs and signal arcs. Values are carried on tokens along the directed value arcs of the graph. A function template is an array of the instructions which belong to the data flow graph corresponding to a function definition in VIMVAL. The size of the array is equal to the number of instructions in the data flow graph and the indexing of the array starts from 1. Instructions are identified by their array indices within a function template.

In VIM, iteration is modelled as recursion, and the chosen method for implementing recursion avoids the use of cyclic graphs<sup>3</sup>. Instead, each function application uses a fresh copy of the graph represented by the function template, the copy being called an *activation template*. An instruction is *enabled* or ready for *firing* when a value is available on each input value arc, and a signal has been received on each signal arc. Note that it may happen that some instructions in a template<sup>4</sup> will receive values but will never fire because no signal will ever arrive. In chapter 5 we give rules of graph construction to ensure that this does not happen; otherwise, the storage reclamation scheme will be unable to reclaim all possible structures, leading to degraded memory utilization.

A salient characteristic of VIM is that no arc is ever reused — at most one value or signal will be sent from one instruction to another along a value or signal arc of an activation template, respectively. This is assured by the acyclic nature of the data flow graphs and by the property that each function application produces a new activation template. This is quite different from the data flow models used by the U-Interpreter [2] or the Static Data Flow machine [14, 12]. In the static data flow machine, the data flow graph does not change during program execution. The creation of function activations provides a very natural way of implementing recursion in VIM. VIM is similar to the static machine in that instructions have special fields for holding the operand values. This is quite unlike the mechanism

<sup>&</sup>lt;sup>3</sup> Furner uses cyclic graphs to implement recursion in [37].

<sup>&</sup>lt;sup>4</sup>We shall use "template" instead of "activation template" whenever there is no cause for confusion.

used in the U-interpreter where the value is stored in an associative store. Function application in ViM expands the execution graph due to the creation of activation templates; the graph contracts whenever a function terminates and the activation is discarded. In the U-interpreter function application results in the creation of a new context, which is a part of the tags on values.

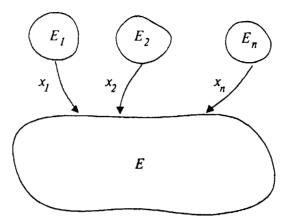

Another feature of VIM which distinguishes it from other data flow models such as the U-interpreter or the Static data flow machine is the *heap*. VIM maintains a heap in which all objects except scalars that enter into computation are held. Scalar values are stored in the operand fields of the instructions, and passed around among the instructions on the tokens. The kinds of objects held by the heap include function templates, closures, early-completion queues (described below) and data structures (arrays, records, etc.). Each object on the heap has a unique identifier which permits its selection from among all objects in the heap. Conceptually, the heap is a multi-rooted, directed acyclic graph in which an arc signifies that the target object is a component of its superior.

A distinctive feature of VIM is the set of mechanisms designed to support aspects of the VIMVAL language; in particular, these include support for function application and tail recursion and computation on streams. These mechanisms are described informally below; a formal description of the mechanisms will be presented in the next section.

#### 2.3.1 Function Application

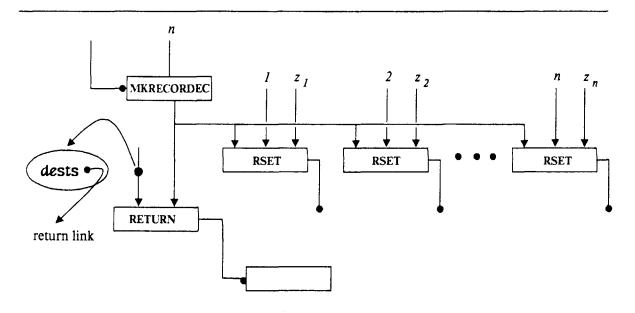

Function applications are made by the APPLY instruction, which requires two operands — a function closure for the function to be applied, and a data structure containing argument values. The first element of the closure is the uid of the function template which is to be applied; the rest of the closure contains information defining the binding of any free variables of the function. The APPLY instruction creates an *activation* of the function by copying the function template. It then sends the closure, the argument structure and the return link to the first operand of the first three instructions in the activation template, respectively. The return link consists of the uid of the calling activation and the uid of the destination list of APPLY.

Instructions of the activation are then executed according to the data flow firing rule until the RETURN instruction is enabled. The RETURN instruction uses the return link to send the result of the

function invocation to the recipients. Due to the presence of early-completion structures the RETURN instruction may not be the last instruction to execute in the activation. A separate RELEASE instruction releases the storage occupied by the activation template.

The following notation will be used for drawing data flow graphs. The nodes of a function template are instructions drawn as rectangular boxes. The value arcs connect from bottoms to tops of instruction boxes and convey data values. The signal arcs convey signals that perform control functions such as the release of function templates. The signal arcs connect from right sides to left sides of instruction boxes. Numerals at the left corner of instruction boxes denote the index of the instruction in the activation. A Greek letter next to an instruction box corresponds to the address of the instruction, consisting of the uid of the activation template and the index of the instruction. An open box with two or more values or signals is the merge operator. The graphs are arranged such that exactly one *Value* or signal will arrive at a merge box. This is merely a notational convenience; in VIM, the signal count and operand counts are set such that the merge occurs naturally.

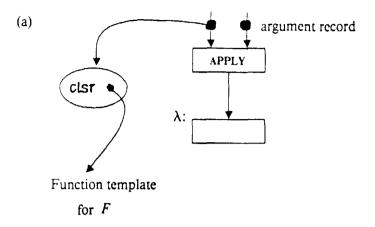

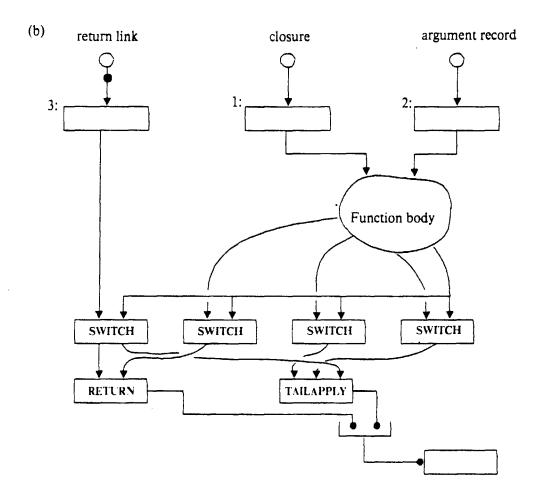

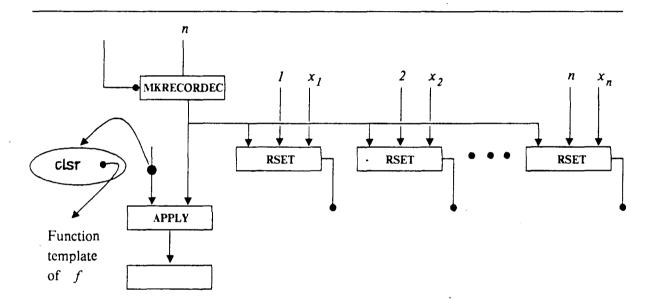

Figure 3(a) shows a data flow graph which causes a function activation.  $\lambda$  is the address of the destination instruction of APPLY, which is sent to the third instruction of the activation created by APPLY. Figure 3(b) shows a typical function template. The RETURN instruction receives the destination list consisting of the address  $\lambda$ ; when it receives the result computed by the function body, it sends the result to the instructions whose addresses are listed in the return link and sends a signal to a RELEASE instruction.

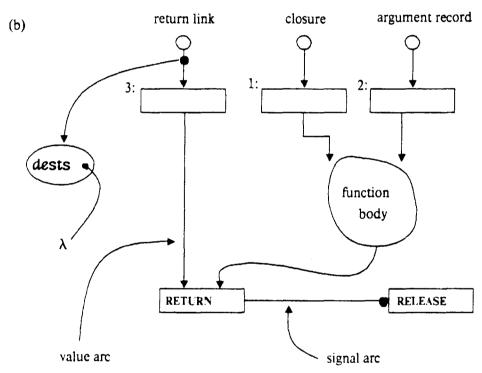

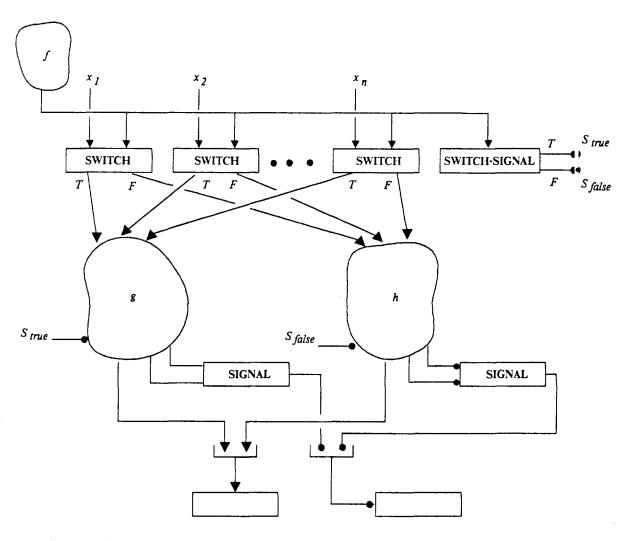

In many cases the value returned by a function f is computed directly by a tail-recursive application of f, as shown in Figure 4. In this situation the result to be returned by the caller is exactly that returned from the callee, and the reactivation of the caller is unnecessary. The TAILAPPLY instruction in VIM implements this. It also causes a function activation but is different from APPLY; it has an extra operand, a return link which it passes to the callee instead of generating a new one; also, it sends signals to the instructions whose indices are in the destination list of the TAILAPPLY instruction.

Figure 4(a) shows the TAHLAPPLY instruction and illustrates the operands that it needs. Figure 4(b) shows a typical template corresponding to a tail-recursive function. The SWITCH instruction takes two operands: if its second operand, which must be boolean, is true then the first operand is sent to all

Figure 3: (a) shows the data flow graph for function invocation. (b) Data flow graph of a typical function template.  $\lambda$  is the address of the destination of APPI Y: it is a pair consisting of the uid of the calling activation and the index of the instruction in the template.

the destinations of SWITCH whose addresses are marked **true** in its destination list and if it is false then the first operand is sent to the destinations marked **false**. The function body determines if no further applications are to occur, in which RFILRN is activated, otherwise the TAILAPPLY instruction is enabled.

Figure 4: (a) The TAILAPPLY instruction. (b) Typical data flow graph for the body of a tail-recursive function.

#### 2.3.2 Early-Completion Queues

In computations involving data structures, concurrency is increased if a data structure can be made available for access before all the component values have been computed. If instructions are required to receive all their operands before their application, as is usual for the execution of data flow programs, this concurrency of creating and accessing a data structure is not possible.

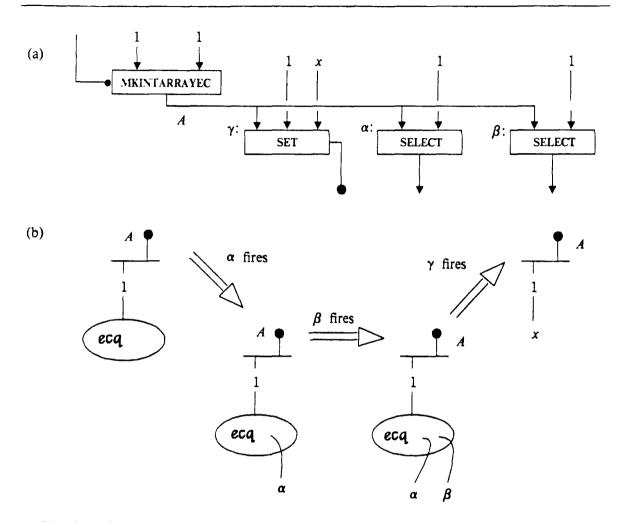

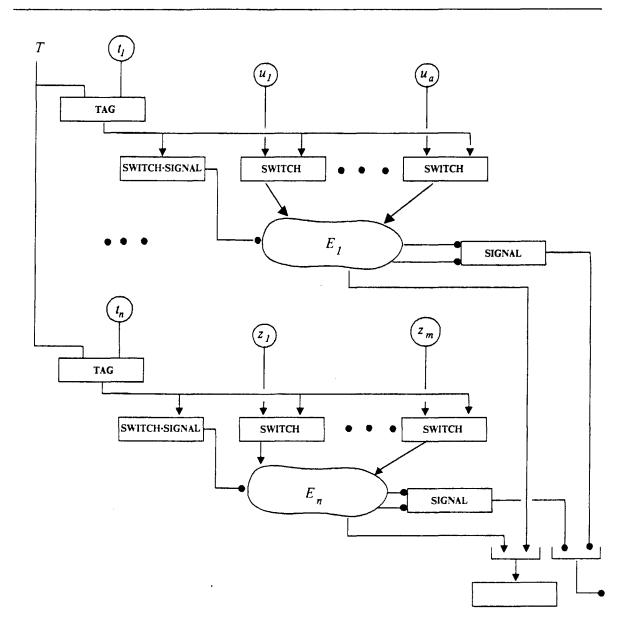

In VIM there is a special facility called early-completion queue (abbreviated EC-queue) to permit structures to be created before the values of all the components are available. Arrays will be used to describe the early-completion mechanism informally (figure (5). The behaviour of structures containing EC-queues is specified by the state-transition rules of the MKINARRAYEC, SELECT, APPEND and SET instructions.

An EC-queue is a collection of addresses of instructions. MKINARRAYEC creates an array in which all the elements are EC-queues, all initially empty. This shell of the structure is passed onto consumers of the data structure, and also to producers which replace the EC-queues by values using the SET instruction. If a SELECT tries to access an element which is an EC-queue, its address is added to the EC-queue and the instruction is removed from the set of enabled instructions. Eventually, a SET instruction replaces the EC-queue by a *Value* and adds the addresses of the instructions in the EC-queue to the set of enabled instructions. When these instructions are attempted for execution again, they would read the value, as desired. Structures with EC-queues provide a powerful mechanism for synchronisation, and is an effective solution to the read-before-write problem [4].

Figure 5 illustrates the early-completion mechanism. Figure 5(a) shows a data flow graph which creates an array of one element which is an empty EC-queue. The array is sent to two consumers whose addresses are  $\alpha$  and  $\beta$ , and to a set instruction  $\gamma$ . Figure 5(b) shows how the contents of the array changes when the instructions  $\alpha$ ,  $\beta$  and  $\gamma$  fire in sequence. If  $\gamma$  fires first, then  $\alpha$  and  $\beta$  can access the value in the usual manner; the erstwhile presence of the EC-queue does not affect subsequent accesses after it is replaced.

The early-completion mechanism makes it possible to allow function applications to begin execution before the values of all their arguments have been computed. This is done by packaging the arguments into a record of FC-elements. Similarly, the result values, if there are more than one, may be

returned as a structure of EC-elements so each may be available to the caller without waiting for all the results to be evaluated.

Figure 5: (a) Data flow graph showing producer-consumer relationship for structure containing EC-queue. (b) The contents of the array under the firing of  $\alpha$ ,  $\beta$  and  $\gamma$  in sequence. First, the firing of  $\alpha$  causes  $\alpha$  to be added to the EC-queue, which was empty. Next  $\beta$  attempts to access the element and also gets added to the EC-queue. Eventually when x is computed, the SET fires. It replaces the EC-queue with x and adds  $\alpha$  and  $\beta$  to the set of enabled instructions.

The semantics of arrays with ecqueues is very similar to the semantics of *I-structures*, which were proposed by Arvind and Thomas [5]. An I-structure is a linear contiguous data structure; an element of an I-structure can be written into at most once. Reads occurring before an element has been written into are deferred until the arrival of the value. The *futures* construct of Halstead [19] is also of similar flavour.

#### 2.3.3 Suspensions and Streams

Stream structures are an attractive language feature since they permit the producer and consumers of the stream to operate concurrently. VIM provides a special mechanism for efficient implementation of streams. A stream is represented in VIM as a chain of records of two elements, each of which is an EC-queue; the first element contains an element of the stream and the second element is a pointer to the rest of the stream. In a completely data driven evaluation of a stream, the producer would proceed at its own pace and generate the values to construct the stream. The consumer process accesses the elements of the stream at its own rate, waiting whenever it encounters an EC-queue until the value is supplied.

The problem with this scheme is that it allows the producer to get arbitrarily far ahead of the consumer process. If the consumer needs only a part of stream then substantial computation performed by the producer may wasted. In particular, if streams are evaluated in a data driven manner, then infinite streams cannot be supported on VIM. So streams are produced in a data driven manner, allowing the user to write programs in VIMVAL which deal with potentially infinite streams.

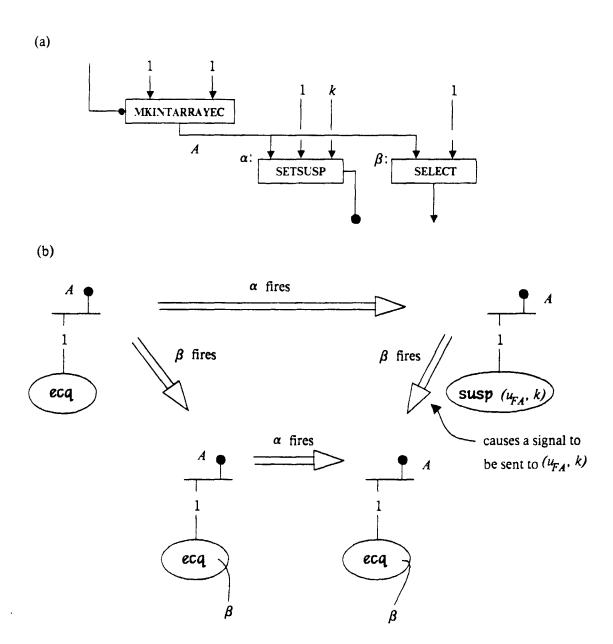

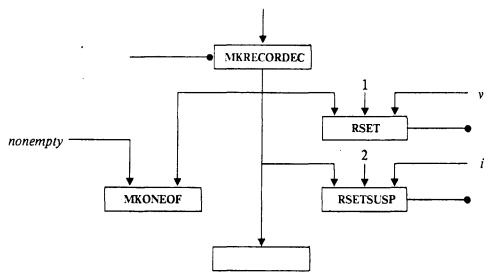

VIM uses *suspensions* to implement demand-driven evaluation of streams. Suspension mechanisms have been used to implement infinite data structures by Henderson [20], Friedman and Wise [16], etc. In VIM, a suspension contains the address of an instruction, consisting of the uid of the activation template of the instruction and its index in the template. When a SELECT instruction tries to access an element which is a suspension, the suspension is replaced by an EC-queue containing the address of the SELECT and a signal is sent to the instruction whose address is found in the suspension. The signalled instruction eventually causes the EC-queue to be eventually replaced by a value and the SELECT instruction gets the value it was trying to access.

Figure 6(a) shows the creation of an array whose only element is an EC-queue. If SETSUSP fires before SELECT, it finds an empty EC-queue and replaces it by a suspension. When SELECT executes, the suspension is replaced by an EC-queue containing the address  $\beta$  of SELECT and a signal is sent to the instruction indicated in the suspension. If SELECT fires first, it is enqueued in the EC-queue; SETSUSP executes, finds a non-empty EC-queue, and simply sends a signal. The graph is arranged such that the arrival of the signal initiates a computation that ultimately enables a SEL instruction. The SET instruction replaces the EC-queue in this array by a value and services the EC-queue by adding the set of

instructions whose addresses are in the EC-queue to the set of enabled instructions.

Figure 6: (a) Creation of an array with a suspension element. (b) Effect of firing of SELECT and SETSUSP instructions in different orders.

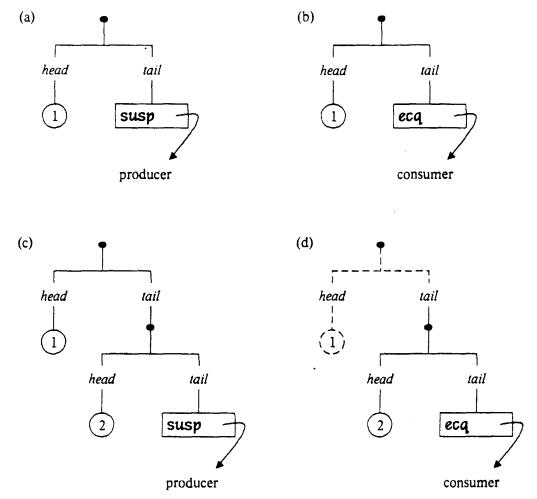

The use of suspensions for generating the elements of a stream is shown in Figure 7. The records

which constitute the stream have two fields which are named *head* and *tail*. The stream consists of successive integers. Figure 7(a) shows an initial stream whose first element is 1 and the tail component is a suspension. When a consumer  $\alpha$  tries to access the tail of the stream, the suspension is replaced by an EC-queue containing the address of the consumer (7(b)). A signal is sent to the suspended instruction which causes the EC-queue to be replaced by new record whose *head* component contains the next element of the stream and the tail component is a suspension (7(c)). The consumer which tries to access the rest of this stream in turn replaces the suspension by an EC-queue. If there are no consumers which have pointers to the beginning of the stream then the element at the front may be abandoned (7(d)). Suspensions can also be used to advantage for evaluating the elements of arrays in a demand driven manner. The main benefit in doing this would be that array elements which are never read need not be computed, thus reducing the amount of computation performed.

The rest of the chapter gives a mathematical specification of VIM. The operational semantics of the instructions of VIM are presented. The specification will be called L1 in this thesis. L1 will serve as the basis for the development of an operational model for VIM in which storage is modelled; that model will called L2.

#### 2.4 Operational Model for Vim - L1

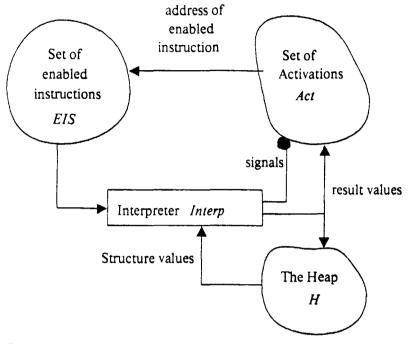

The VIM interpreter has two components: a function *Interp* and *State*. *Interp* takes two arguments - a *State* and an enabled instruction (defined later) and produces a new *State* of the machine. The following notation will be used in the thesis. Sets are denoted by bold font, elements of sets (which may themselves be sets) are denoted by italicised letters and names are indicated in a distinctive font. Thus, This is a set, *This*  $\in$  This and **This** is a name.

The actions of the interpreter are described by state transition rules. A programming language-ish description is used to specify the rules for mapping a set to another set. Mathematical notations such as set unions and differences are used wherever convenient. A rule *F* is expressed as follows:

Define  $F(A, (i, j), v) \equiv$ ... body of the rule

The definitions may be recursive.

Figure 7: Demand-driven generation of stream elements. (a) Stream element: the producer is awaiting a demand. (b) The consumer demands the next stream element. (c) The producer generates one stream element and suspends itself. (d) The consumer abandons the previous element and demands another.

$VIM = \langle Interp, State \rangle$  where

*Interp*: State × EIS → State

State =  $Act \times H \times EIS$ ,

$Act = U \rightarrow Function$

$H = U \rightarrow ST$

U =the set of all unique identifiers.

EIS = the set of all enabled instructions, described later.

Act is the set of all activations; an activation is created by the invocation of a function. The heap H contains all structure values and function templates, early-completion queues (discussed later),

Figure 8: The abstract VIM architecture

function closures and the instructions. Each element on the heap has a unique identifier (uid). Only scalar values and uids are sent on tokens from one data flow actor to another; data structures always reside on the heap.

Scalar values are tagged.

```

Scalars = Integers \cup Reals \cup Booleans \cup Character \cup Null Integers = {int} \times ({undef} \cup the set of all integers)

Reals = {real} \times ({undef} \cup the set of all reals)

Booleans = {bool} \times ({undef} \cup the set of characters in the machine.)

Character = {char} \times ({undef} \cup the set of characters in the machine.)

Null = {null} \times {nil, undef}

```

The set ST describes the elements which reside on the heap. Elements of different types are distinguished by their tags.

$$ST = (\{arr\} \times (Array \cup \{undef\})) \cup (\{fn\} \times Function)$$

$$\cup (\{ecq \times ECQ\}) \cup (\{inst\} \times Instruction) \cup \{dests\} \times Dests$$

$$\cup (\{clsr\} \times Clsr)$$

Array = [Integers  $\rightarrow$  (U  $\cup$  Scalars  $\cup$  SUSP], Integers being the set of integers.

Function =  $[N \rightarrow Instruction]$ , N being the set of natural numbers.

An early-completion element (EC-element) is a tuple (u, i) where u is the uid of a function activation and i is the index of an instruction in the activation. An early-completion queue is a collection of such EC-elements.

$$ECE = U \times N$$

.

Thus  $(u, k) \in ECE$  where u corresponds to the uid of a function activation and N is the index of the instruction in the activation template.

The EC-queue is a collection of elements of ECE. All EC-queues are members of the set ECQ which is defined below. The notation  $\mathfrak{P}(N)$  denotes the powerset of the set N.

$$ECQ = \mathfrak{P}(ECE)$$

A suspension is a member of the set SUSP specified by:

$$SUSP = \{susp\} \times (U \times N)$$

An instruction is a seven-tuple:

Instruction = OPS

$$\times$$

(U  $\cup$  Scalars)<sup>3</sup>  $\times$  N  $\times$  N  $\times$  U

OPS is the set of opcodes, the next three elements of the tuple refer to the operands, the fifth and sixth elements of the tuple are the operand count and the signal count and the last element is the unique identifier of the list of destinations. Fach destination of an instruction is the index of the instruction to which the result is to be sent. The result may be a value or a signal. For  $l \in I$ , the elements of the tuple will be denoted by the  $\mathbb{N}$  notation. Thus, l.opcode is the first element of the tuple, l.op1, l.op2 and l.op3 refer to the second through fourth elements of the tuple, l.opcnt, l.sigcnt and l.destlist denote the fifth through seventh elements of the tuple.

A destination of an instruction consists of the the address of the instruction to which the result is

to be sent, and the operand which is to receive the result value. **op1**, **op2** and **op3** denote the first, second and third operand fields in an instruction, respectively. If the result is a signal then no operand number is required. The destination also specifies if the result is to be sent unconditionally or conditionally. For all instructions except for SWITCH, the results of instructions (both values and signals) are sent to the destinations unconditionally.

Dests =

$$\Re(D)$$

D = {unconditional, true, false}  $\times$  N  $\times$  {op1, op2, op3, signal}

Clsr is the set of closure records. The operator (APPLY, TAILAPPLY, STREAM-APPLY) which cause a function activation take a closure as the first argument. The first component of the closure is the uid of a function template; that uid corresponds to the function which is to be called.

Clsr =

$$[(\{FunctionToApply\} \cup M) \rightarrow (U \cup Scalars]]$$

where  $C(FunctionToApply) \in U$  such that  $H(u) \in (\{fn\} \times Function)$ .

An enabled instruction is an element of  $EI \subseteq U \times N$ . An instruction I becomes enabled when I. Opent and I. Sigent both become zero. The set of enabled instructions describes the collection of instructions which are ready to executed because they have received an operand on each of the operand arcs and a signal on each of the signal arcs. The set of enabled instructions is:

$$EIS = \mathfrak{P}(EI)$$

The function *Choice* selects an element from a set of enabled instruction. The instruction is then interpreted by the function *Interp*. Thus *Choice* is our scheduler:

Choice : EIS

$$\rightarrow$$

EI

Functions AddToHeap and DeleteFromHeap add and delete elements from the heap. AddToAct and DeleteFromAct which

$$AddToHeap: H \times U \times ST \rightarrow H$$

AddToHeap(H, u, v) produces a new function H such that:

$$(\forall u' \neq u [H(u') = H(u')])$$

and  $H(u) = V$

$DeleteFromHeap: \mathbf{H} \times \mathbf{U} \times \mathbf{ST} \rightarrow \mathbf{H} \ DeleteFromHeap(H, u, V)$  produces a new heap H such that the domain of H is the domain of H without the element u.

H such that

$$(\forall u' \neq u[H(u') = H(u')])$$

AddToHeap(H, u, v) creates a new heap which contains, in addition to the associations between uids and objects in H, a new association between u and v. DeleteFromHeap(H, u, v) creates a new heap which does not contain the uid u in its domain.

Similarly, *AddToAct* and *DeleteFromAct* create new activation sets by adding an activation to and deleting an activation from the current set of activations.

```

AddToAct: Act \times U \times Function \rightarrow Act

DeleteFromAct: Act \times U \times Function \rightarrow Act

```

Function SendResult is used to dispatch the result of an instruction I to a destination instruction. SendResult models the following actions: the result is stored in the appropriate operand field of the destination instruction, and the operand count and signal count fields are decremented accordingly. Since we are dealing with a mathematical representation of instructions and function activations, this updating is modelled by producing new values that reflect the changes. Thus,  $\Gamma$  is the destination instruction after it receives the result, FA' is the new new value of FA with the updated  $\Gamma$  and Act' is the same as Act except that the ith instruction of activation FA has received some operand (or signal).

```

SendResult: Act \times EIS \times U \times D \times [[{value} \times (U \cup Scalars)] \cup {signal}] \rightarrow Act \times EIS

```

```

define SendResult(Act, EIS, u_{FA}, (dc, i, opnum), result) \equiv

let

FA = Act(u_{FA}), \qquad \% \ FA \ is \ an \ activation \ template.

I = FA(i) \qquad \% \ I \ is \ the \ ith \ instruction \ in \ the \ activation \ template.

in

AddToAct(DeleteFromAct(Act, u_{FA}, FA), u_{FA}, FA'),

if (f.opcnt = 0) \land (f.sigcnt = 0) \ then \ EIS \cup \{(u_{FA}, i)\}

else EIS

endif

endlet

where

FA'(j) = FA(j), \qquad j \neq i.

= f. \qquad i = i.

```

```

and I' ∈ Instruction,

I'.opcode = I.opcode,

I'.op1 = if opnum ≠ op1 then I.op1 else t where result = (value, t)

I'.op2 = if opnum ≠ op2 then I.op2 else t where result = (value, t)

I'.op3 = if opnum ≠ op3 then I.op3 else t where result = (value, t)

I'.opcnt = if opnum ∈ {op1, op2, op3} then I.opcnt else I.opcnt - 1

I'.sigcnt = if opnum = signal then I.sigcnt-1 else I.sigcnt

I'.destlist = I.destlist

```

The function *SendToDestinations* sends the result of an instruction to all the destinations of the instruction. It is a simple tail-recursive function which uses *SendResult* repeatedly to send the value or signal to the destination.

```

SendToDestinations: Act \times EIS \times U \times \mathfrak{P}(D \times ([\{value\} \times (U \cup Scalars)] \cup \{signal\}) \rightarrow Act \times EIS

define SendToDestinations (Act, EIS, u, DestValue) \equiv

if DestValue = \{\} then Act, EIS

else

let ((dc, d, opnum), V) = e where e \in DestValue

in

if V = signal then

SendToDestinations

(SendResult(Act, EIS, u, (dc, d, signal), Signal), DestValue - \{e\})

else

SendToDestinations

(SendResult(Act, EIS, u, (dc, d, opnum), v), DestValue - \{e\})

endif

endlet

endif

```

Execution of a program on VIM is initiated by the invocation of a function in the base language. The execution terminates when there are no more enabled instructions. The execution loop may be summed as:

```

define MainLoop (State) ≡

let (Act, H, EIS) = State

in

if FIS = {} then halt

else MainLoop(Interp(State, Choice(EIS)))

endif

endlet

```

The interpreter is defined by the function Interp and Choice is a function which selects an element from the set of enabled instructions. This instruction is interpreted by Interp in the context of the current state of the machine; the result of the execution of the instruction is a new state. Choice is the scheduler in VIM since it makes the choice of the instruction which is to be executed. Choice(EIS) where  $EIS \in EIS$  is the address of an enabled instruction.

```

Interp: State \times Choice(EIS) \rightarrow State where State = Act \times H \times EIS.

```

It is pertinent to point out that VIM is a non-deterministic state transition system; any one of the enabled instructions could be selected for execution and the final result of the computation is independent of the order of execution of the enabled instructions.

The following notation is used to denote that the new state (Act', H', EIS') is produced when the instruction e is interpreted by Interp in the state (Act, H, EIS).

```

(Act, H, EIS) \vdash (Act', H', EIS') on e.

```

Now we can define the interpreter by specifying the state transitions for each of the opcodes. The state transitions for some of the more interesting instructions will be presented below; these serve as the model for specifying the transition rules for the rest of the instruction set. The body of *Interp* is a big conditional statement; the branches of the conditional are based on the opcodes of the instruction being executed. Some general comments are in order here. The result of an instruction is sent to its indicated destinations unconditionally, unless it is a SWITCH instruction.

```

define Interp(State, (u_{FA}, k_{FA})) \equiv

let

FA = Act(u_{FA}), \quad \% the function activation

I = FA(k_{FA}), \quad \% the instruction

\{(dc_1, d_1, opnum_1), (dc_2, d_2, opnum_2), ..., (dc_n, d_n, opnum_n)\} = I.destlist

\% the destinations of the instruction I.

in

if I.opcode = Set then ...

elseif I.opcode = APPLY then ...

endif

endlet

```

The specification of the state transition rules for some of the interesting and representative

instructions of VIM will be the subject of the rest of this chapter. Each conditional statement of the form "if I.opcode = ... then " is an arm of the big conditional statement in Interp above. Thus, the names Act, H, EIS,  $u_{FA}$ ,  $k_{FA}$ ,  $(dc_1, d_1, opnum_1)$ , ...,  $(dc_n, d_n, opnum_n)$  will have the same bindings as indicated in the body of Interp shown above.

Let us begin with the simple instruction IADD which adds two integers. The operands are read from the operand fields of the instruction and the result of the addition is *sum*. This value is sent to the listed destinations. Observe that the heap remains unchanged.

```

if I.opcode = IADD then let  (int, m) = I.op1,   (int, n) = I.op2,   sum = m + n,   Act', EIS' =   SendToDestinations(Act, EIS, u_{FA}, \{((unconditional, d_1, opnum_1), \alpha_1), ..., \\ ((unconditional, d_n, opnum_n), \alpha_n)\})  in  Act',   H,   EIS - \{(u_{FA}, k_{FA})\}  endlet endif

```

where  $\alpha_i \in \{(value, sum), signal\}$

The actions of the interpreter for instructions such as ISUB, IMUL, IDIV, IGT, ILT, etc. are very similar and will not be described.

The instructions which operate on structures produce a new heap. The operations on one type of structures — arrays — are described here; the actions of *Interp* for instructions which operate on record and one of types are very similar and are not presented. The array instructions of interest which are discussed below are: MKARRAYINT, MKARRAYINTEC, SELECT, APPEND, SET and SETSUSP.

MKARRAYINT takes two integer operands (m and n) and adds an array with bounds (m, n) to the heap. All the elements of the array are undefined. The uid of the new array is sent as the result to the destinations, along with signals if necessary.

```

if //opcode = MKINTARRAY then let (\textbf{int}, p) = I.\textbf{op1}, (\textbf{int}, q) = I.\textbf{op2}, \qquad \% \ p \ and \ q \ are \ integers, \ p < q. u_v = a \ \text{new uid in U}, Act', EIS' = SendToDestinations(Act, EIS, u_{FA}, \{((\textbf{unconditional}, d_1, opnum_1), \alpha_1), ..., ((\textbf{unconditional}, d_n, opnum_n), \alpha_n)\}) in Act', AddToHeap(H, u_v, (\textbf{arr}, ([p, q] \rightarrow undef))), EIS' - \{(u_{FA}, k_{FA})\} endlet endif \text{where } \alpha_i \text{ is either } (\textbf{value}, u_v) \text{ or } \textbf{signal}.

```

The instruction MKINTARRAYEC works quite similarly except that the elements of the array are all early-completion queues, all empty.

The APPEND instruction takes three operands — an array A, an index i and a value x. It creates a new array A' which is identical to A except that the i th element of A' has value x. It is important to be very careful while performing APPEND operations on arrays with EC-elements. If some elements in A are EC-elements then the corresponding elements of A' would also be EC-elements. When a SET instructions replaces an EC-element in A by a value, this value must be forwarded to the corresponding elements in structures which were created by APPEND on A. There may be a cascade of value-forwarding precipitated by this since the values may also have to be forwarded to arrays created by APPENDs on structures derived from A. Since suspensions are potential sites for EC-queues, APPEND operations on arrays containing suspensions introduces a similar need for Value forwarding. This thesis adopts a simple alternative to the value-forwarding discipline outlined above. An APPEND instruction is executed provided that there are no EC-elements or suspensions in the array on which the operation is to be performed. If there is any EC-element in the array then there is no change in the state of the machine: the APPEND instruction remains in the set of enabled instructions and will be selected for execution at some future time.

```

if Lopcode = APPEND then

let

u = Iop1

(arr, A) = H(u),

(int, i) = i.op2,

x = 1.003,

u' = \text{new uid from } \mathbf{U}

Act', EIS' =

SendToDestinations(Act, EIS, u_{FA}, \{((\textbf{unconditional}, d_1, opnum_1), \alpha_1), ..., ((\textbf{unconditional}, d_n, opnum_n), \alpha_n)\})

in

if |\{i : A(i) \in U \times \{(\{ecq\} \times ECQ) \cup (\{susp\} \times SUSP)\}\}| = 0 then

AddToHeap(H, u', A'),

EIS' - \{(u_{FA}, k_{FA})\}

else

Act,

H

EIS

endif

endlet

where A'(j) = A(j)

j = i.

= x

```

and where  $\alpha_i$  is either (value, u') or signal.

SELECT requires two operands — the uid of an array A and an integer i, and in the simplest case (the element being accessed is neither an early-completion structure nor a suspension) returns the value associated with the element of A that has index i. The behaviour of the interpreter is more complex when such is not the case. The state transition is specified below, and the discussion on early-completion elements and suspensions follows. The special value est is used for indicating the end of a stream.

```

if I.opcode = SELECT then

let

u = I.op1),

\% (u_r (arr, A)) \in H

(arr, A) = H(u),

% i must be an integer

(int, i) = I.op2,

t = A(i)

in

if t = (u_v, (ecq, Q)) then

Act,

AddToHeap(DeleteFromHeap(H, u_{v}, (\textbf{ecq}, Q)), u_{v}, (\textbf{ecq}, Q \cup \{(u_{FA}, k_{FA})\})))

EIS - \{(u_{FA}, k_{FA})\}

elsif t = (u_{v}, (Susp, (u', k'))) then

let Act', EIS' = SendResult(Act, EIS, u', (unconditional, k', signal)), signal))

in

Act',

AddToHeap(DeleteFromHeap(H, u_v (susp, u', k')), u_v (ecq, u_{FA}, k_{FA})),

EIS' - \{(u_{FA}, k_{FA})\}

endlet

else

let x =

Act', EIS' =

SendToDestinations(Act, EIS, u_{FA}, \{((unconditional, d_1, opnum_1), \alpha_1), ..., a_1\})

((unconditional, d_n, opnum, \alpha_n))

in

Act',

Н,

EIS' - \{(u_{FA}, k_{FA})\}

endlet

endif

where \alpha_i = \text{either (value, } x) \text{ or signal.}

```

```

if l.opcode = SET then

let

u_1 = I.0p1

(\operatorname{\mathsf{arr}}, A) = H(u_1),

\% (u_r (art, A)) \in H

(int, j) = I.op2,

% i must be an integer

\% v \in Scalars \cup U

v = 1.003.

\% where the uids must be of records, arrays, oneofs.

t = A(i)

% t = (u, (ecq, Q))

Act', EIS' =

SendToDestinations(Act, EIS, u_{FA}, \{((\textbf{unconditional}, d_1, opnum_1), \alpha_1), ...,

((unconditional, d_n, opnum, \alpha_n))

in

Act'.

% the new set of activations.

AddToHeap(DeleteFromHeap(H, u_1, (arr, A)), u_1, (arr, A')),

% the new heap reflects the fact that the ith element

% of the array with uid u has value v.

(EIS - \{(u_{FA}, k_{FA})\}) \cup Q

% The new EIS' includes the instructions whose addresses were in the

% EC-queue. (u_{FA}, k_{FA}) is the address of the current instruction,

\% which is removed from the set of enabled instructions. When the value

% becomes available, this instruction will be added back to the set of enabled

% instructions.

endlet

endif

where A(j) = A(j),

j \neq i

j=i.

```

The use of EC-elements in data structures permits the construction of a data structure before the values of all the components have been computed. Suspensions allow demand driven computation. A suspension is a tagged triple — a tag SUSP, the uid u of some function activation, and i the index of an instruction in the activation. The instruction SETSUSP takes three arguments: an array A, an integer  $v_1$  which is an index of the array, and another integer  $v_2$  which is the index of an instruction in the template of the SETSUSP instruction. SETSUSP sets the  $v_1$ th element of the array to a suspension of the form (SUSP,  $u_{FA}$ ,  $v_2$ ) where  $u_{FA}$  is the uid of the activation template of the SETSUSP. When a SELECT tries to access the element, the suspension is replaced by an EC-queue which contains the address of the SELECT and a signal is sent to the instruction whose address is found in the suspension. The graph is so arranged that the arrival of the signal enables the instruction ( $u_{FA}$ ,  $v_2$ ), which initiates the computation of the value of the element.

```

if I.opcode = SETSUSP then

u_1 = I.op1

(\tilde{\mathbf{arr}}, A) = H(u_1),

\% (u_p, (arr, \Lambda)) \in H

(int, v_1) = I.op2

% (v, must be an integer

(int, v_{\gamma}) = l.op3

% (v, must be an integer

(u', (\mathbf{ecq}, Q) = A(i)

\% A(i) must be an early-completion queue.

Act', EIS' =

SendToDestinations(Act. EIS, u_{FA}. {((unconditional, d_1, signal), signal), ...,

((unconditional, d_n, signal), signal)})

in

if |Q| = 0 then

\% put a suspension in the ith element of the structure with uid u ,

AddToHeap(DeleteFromHeap(H, u_1, (art, A), u_1, (art, A'))),

EIS' - \{(u_{FA}, k_{FA})\}

where A'(j) = (\text{if } j \neq v_1 \text{ then } A(j) \text{ else } (SUSP, (u_{FA}, v_2))

else

\% just send a signal to the instruction whose index is v_{m{	au}}

let Act", EIS" =

SendResult(Act', EIS', u_{EA}, (unconditional, v_2, signal), signal)

in

Act",

Н,

EIS \cdot \{(u_{FA}, k_{FA})\}

endlet

endif

endlet

endif

```

The SWITCH operator is used to implement the conditional graph schema. It takes two operands — a value  $v_1$  and a boolean b. The condition fields of the destinations of the SWITCH operator must have values either true or false. If b is true, then  $v_1$  is sent to the destinations which are marked true, otherwise they are sent to the destinations marked false. The destinations (true,  $d_{tl}$ , opnum<sub>tl</sub>), ..., (true,  $d_{tp}$ , opnum<sub>tp</sub>) denote the destinations to which the first operand must be sent if the second operand is true; otherwise the first operand is sent to the destinations (false,  $d_{fl}$ , opnum<sub>fl</sub>), ..., (false,  $d_{fl}$ , opnum<sub>fl</sub>).

```

if

1.0000de = SWITCH then

u_1 = I.0p1

(bool, b) = 1.002.

% b must be a boolean value.

(true, d_{II}, opnum<sub>II</sub>), .... (true, d_{Ip}, opnum<sub>IP</sub>), (false, d_{II}, opnum<sub>II</sub>), .... (false, d_{II}, opnum<sub>II</sub>) = I.destlist, Aci', ElS' =

if b then

SendToDestinations(Act, EIS, u_{FA}, \{((dc_{tI}, d_{tI}, opnum_{tI}), \alpha_{tI}), ..., ((dc_{tp}, d_{tp}, opnum_{tp}), \alpha_{tp})\})

else

SendToDestinations(Act, EIS, u_{FA}, {((dc_{fI}, d_{fI}, opnum<sub>fI</sub>), \alpha_{fI}), ..., ((dc_{fq}, d_{fq}, opnum<sub>fQ</sub>), \alpha_{fq})})

endif

in

Act',

Η,

EIS - \{(u_{FA}, k_{FA})\}

endlet

endif

```

The SWITCH-SIGNAL operator is very similar. It takes a boolean operand; if the operand has true value then it sends signals to the destinations tagged **true**, otherwise it sends signals to the destinations marked **false**.

The SIGNAL instruction requires no operands; it becomes enabled when it receives a signal on each of the signal arcs incident on it. The result of executing the instruction is a signal which is sent to the destinations listed in the **dests** field of the instruction. The state transition rule for the SIGNAL instruction is very simple and will not be specified here.

```

if I.opcode = APPLY then

let

\%\;(u_{p}\;\text{(clsr, C)})\in H \%\;(u_{p}\;\text{(rec, R)})\in H

(clsr, C) = H(I.op1),

u_{\gamma} = I.0p2

% (u_r, fn, F)) \in H, u_r = C(Function To Apply)

\tilde{F} = H(C(FunctionToApply)),

u' = a new uid from U,

Act' = AddToAct(Act, u', F),

Act", EIS" =

SendResult

(SendResult

(SendResult

(Act', EIS, u', (unconditional, 1, op1), (value, u_1)),

% function closure.

u', (unconditional, 2, op2), (value, u_2)),

% arguments

u', (unconditional, 3, op1), (value, L'aestlist))

% return link.

Act", H, EIS' - \{(u_{FA}, k_{FA})\}

endlet

endif.

```

The function closure, argument structure and the return link are sent to the first operand of the first, second and third instruction in the activation template of the called function. A RETURN instruction in the called function will send the result of the function application to the destinations of APPLY.

The TAILAPPLY instruction is used whenever tail-recursive function application is performed. It sends the closure, argument structure and the return link to the first operand of the first three instructions in the called activation. It then sends a signal to each of its destinations.

```

if I.opcode = TAILAPPLY then

let

(clsr, C) = H(l.op1),

\% (u,, (CLST, C)) \in H, the closure

\% (u_n, (\text{Tec}, R)) \in H, the arguments

u_1 = 1.0p2

u_{2} = 1.0p3

% (u_r (dests, Destinations) \in H, the return link

\vec{F} = H(C(FunctionToApply)),

% (u_r (fn, F)) \in H, u_r = C(Function To Apply)

u' = a new uid from U.

Aci' = AddToAci(Aci, u', F),

Act", EIS" =

SendResult

(SendResult

(SendResult

(Act', EIS, u', (unconditional, 1, op1), (value, u_1)),

% function closure.

u', (unconditional, 2, op2), (value, u_2)),

% arguments

u', (unconditional, 3, op1), (value, u_2)),

% return link.

Act", EIS" =

SendToDestinations(Act. EIS. u_{FA}, {((unconditional, d_1, signal), signal), ...,

((unconditional, d_{x}, signal), signal)})

in

Act",\,H,\,EIS" \cdot \{(u_{FA},\,k_{FA})\}

endlet

endif

```

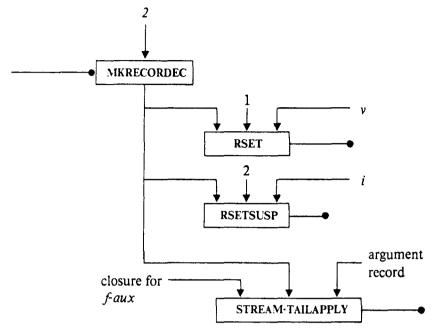

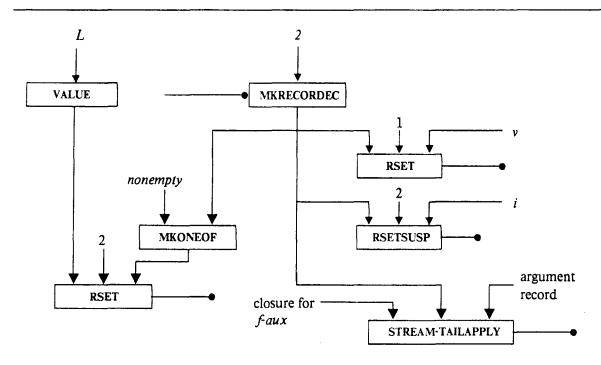

STREAM-TAILAPPLY is another instruction for function application and is used for tail-recursive evaluation of streams. It takes three arguments — a function closure which contains the stream producer, a record which will contain the next element of the stream, and the argument record. Its semantics are very similar to that of TAILAPPLY and it sends signals to the destinations listed in its **dests** field. The compilation of functions which generate streams and use this instruction is discussed in chapter 5.

The RETURN instruction is responsible for sending the result of a function activation to the caller. It requires two operands — a return link and a value. It constructs the addresses of the instructions which are to receive the result of the function invocation from the return link and sends the value to each of those destinations. In addition, it sends signals to those instructions in its own activation whose indices appear in the destination list of RETURN.

```

if opcode = RETURN then

let

\{dc_1, d_1, opnum_1\}, ..., (dc_p, d_p, opnum_p)\} = H(I.op1),

% the list of destinations to which the value computed

% by the function must be forwarded

u_v = 1.0p2

% the value to be returned

Act', EIS, =

SendToDestinations(Act. EIS, u_{FA}, {((unconditional, d_1, signal), signal), ...,

((unconditional, d_n, signal), signal)}),

Act", EIS" =

SendToDestinations(Act, EIS, u_{FA}, \{((unconditional, d_1, opnum'_1), \alpha_1), ..., \alpha_1\})

((unconditional, d_p, opnum, ), \alpha_p))

in

Act".

Н.

EIS · {(u_{EA}, k_{EA})}

endlet

endif

```

The data flow graph of a function is arranged so that RELEASE is the last instruction to be enabled and executed in the activation. The effect of the instruction is to remove the activation it belongs to from the set of current activations in the system. In a "real" system, this would amount to the release of the storage occupied by the activation template to the pool of free storage in the system.

```

if opcode = RELEASE then

DeleteFromAct(Act,u_{FA}, FA)

H,

EIS - \{(u_{FA}, k_{FA})\}

where FA is the activation template associated with u_{FA}.

endif

```

#### 2.5 Summary

In the preceding section a formal specification of VIM was given by defining its operational semantics. A brief description of the functional language VIMVAL was given, and some example programs illustrated some features of the language. Some of the key features of VIM were described informally. Next, we developed a formal model of the abstract machine for VIM. An interpreter for executing the data flow instructions was defined. The operational semantics of the data flow instructions of the machine were presented. The state transition rules for operations on early-completion structures and suspensions were formalised.

1, 3

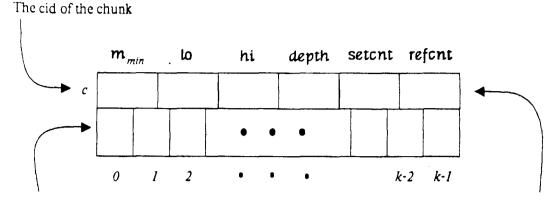

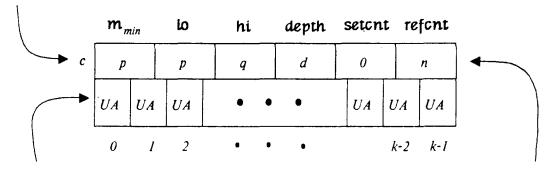

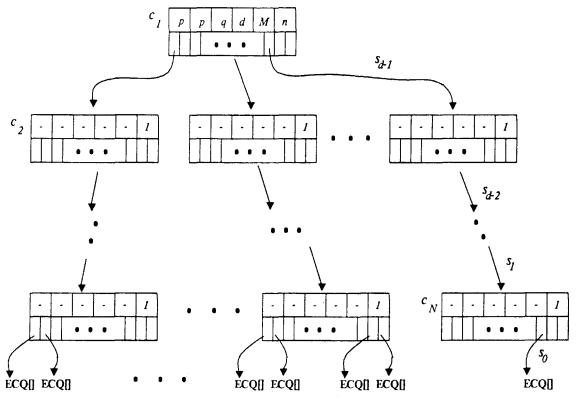

This operational model is gailed T1 194 (1991) the specification of VIM. The next chapter defines the operational semantics of L2, in which the machine L1 is refined to include a model for storage operational semantics of L2, in which the machine L1 is refined to include a model for