### MIT/LCS/TR-351

and the second second

1

-

「あってい

PLANET ALL TANK AND A

# THE COMPLEXITY OF GRAPH LAYOUT

Sandeep N. Bhatt

October 1985

This blank page was inserted to preserve pagination.

### THE COMPLEXITY OF GRAPH LAYOUT AND CHANNEL ROUTING FOR VLSI

by

### SANDEEP NAUTAM BHATT

S.B. Massachusetts Institute of Technology (1978)

S.M. Massachusetts Institute of Technology (1980)

Submitted to the Department of Electrical Engineering and Computer Science in Partial Fulfillment of the Requirements for the Degree of

DOCTOR OF PHILOSOPHY

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

February 1984

© Massachusetts Institute of Technology 1984

Key Words: VLSI graph layout, Bifurcators, Divide-and-Conquer, Fault-tolerance, Wire delay, Restructurable design, Channel routing, density, flux, approximation algorithm This empty page was substituted for a blank page in the original document.

### Acknowledgements

To Charles Leiserson for his constant encouragement and guidance. He taught me how to express myself, and gave me confidence in my abilities. I was fortunate to collaborate with Charles and with Tom Leighton, and to share in their boundless enthusiasm, unrelenting flow of ideas, and friendship. Thanks also to Shafi Goldwasser for graciously agreeing to serve on my thesis committee at the last minute.

To Ron Rivest for his support and gentle guidance through my years in graduate school, and for inspiring me to pursue research in algorithms. Mike Sipser and Christos Papadimitriou stimulated my interest in theory further, Mike with his characteristic knack of making every argument appear beautiful, and Christos with his natural ebullience.

Life would have been deadly dull without my fellow sufferers Keshav, Varghese, and Vinod. Steve Trilling kept up my morale with his endless repertoire of one-liners. This document would never have been prepared without all his help. Benny Chor, Stavres Cosmadakis and John Mitchell made even technical discussions pleasant. Arline, Andy, Flavio and Ray helped maintain my sanity over the years.

To Inna for her warm and steadfast friendhip, and to Susan Landau and Neil Immerman who have helped me in so many ways.

It has been my good fortune to be part of so many families. The Schecters and the Lymans and Mumpuc have been wonderfully supportive and warm. Thank you for being so special.

To Ravin and Swati who will always be concerned.

To Papaji and Mummy who make everything worthwhile.

# TABLE OF CONTENTS

|    | Abstract                                      | 2 |

|----|-----------------------------------------------|---|

|    | Acknowledgements                              | 3 |

|    | Table of contents                             |   |

| 1. | PERSPECTIVE                                   | 6 |

|    | 1.1 The complexity of VLSI graph layout       | 8 |

|    | 1.2 The complexity of channel routing         |   |

|    | 1.3 Overview                                  |   |

|    |                                               |   |

| 2. | ISSUES IN VLSI GRAPH LAYOUT                   | 3 |

|    | 2.1 The layout model                          | 3 |

|    | 2.2 Elementary bounds on layout area          | 4 |

|    | 2.3 Layouts based on separator theorems       | 5 |

|    | 2.4 Eight VLSI graph layout problems          |   |

|    |                                               |   |

| 3. | LAYOUTS FOR TREES                             | 4 |

|    | 3.1 Layouts for complete binary trees         | 5 |

|    | 3.2 Layouts for arbitrary binary trees        | 8 |

|    | 3.3 Planar layouts for trees                  | 1 |

|    | 3.4 The complexity of minimizing edge lengths | 5 |

|    | 3.5 Assembling complete trees                 |   |

|    | 3.6 Collinear layouts and two-color bisectors |   |

|    | 3.7 Assembling arbitrary trees                |   |

|    |                                               |   |

| 4. | THE GENERAL FRAMEWORK                         | 6 |

|    | 4.1 Combinatorial lemmas                      | 7 |

|    | 4.2 Decomposition trees and bifurcators       | l |

|    | 4.2.1 Special cases                           | 3 |

|    | 4.3 Balanced decomposition trees              |   |

|    | 4.4 Embeddings in the tree of meshes          |   |

|    | 4.5 Layouts for the tree of meshes            |   |

|    |                                               |   |

| 5. | SOLVING THE LAYOUT PROBLEMS                   | 3 |

.

| 6. | THE CHANNEL ROUTING PROBLEM                           | 2 |

|----|-------------------------------------------------------|---|

|    | 6.1 Manhattan routing within channels                 | 3 |

|    | 6.2 Bounds on channel width                           | 5 |

|    | 6.3 Bounds for other wiring models                    | 7 |

| 7. | AN APPROXIMATION ALGORITHM FOR MANHATTAN ROUTING 7    | 9 |

|    | 7.1 Channel flux                                      | } |

|    | 7.2 An approximation algorithm for top-to-bottom nets | 2 |

|    | 7.3 Running time analysis                             | ) |

|    | 7.4 The channel routing algorithm                     | ) |

| 8  | CONCLUSIONS, EXTENSIONS AND OPEN PROBLEMS             | 3 |

| 0, | 8.1 Problems in graph layout                          |   |

|    |                                                       |   |

|    | 8.2 Problems in channel routing                       | , |

|    | BIBLIOGRAPHY                                          | ) |

5

•

.

#### CHAPTER 1

## Perspective

Advances in integrated circuit technology have had a revolutionary impact on computer system design. A chip today integrates far greater sophistication and computing power than ever before. Fabrication processes have progressed rapidly so that chips with one million components are a reality, and enthusiasts predict chips with upto one hundred million components within a decade. Indeed, it is expected that if ion beam etching techniques become viable for "printing" chips directly, then minimum feature sizes would drop by a factor of ten, thus allowing a hundred-fold increase in the number of components on a chip.

More significantly, the new technology encourages custom design of special purpose integrated systems for solving very large scale sophisticated problems. No longer is it necessary to use a single conventional architecture for solving diverse problems. Instead, the computational structure of a problem may be mapped directly into hardware. This has shifted the emphasis from searching for algorithms, necessarily convoluted to suit a given architecture, to efficient hardware design suited to individual problems.

While this emphasis on greater design flexibility has opened up new directions in computing, a number of difficult problems must be addressed before the emerging technologies can be effectively exploited. Probably the most significant development in easing the awesome task of designing and implementing large systems has been the standardization of design rules and the widespread use of standard building blocks. The design methodology expounded by Mead and Conway [55], and the development of building blocks such as gate-arrays, PLA's, and ROM's has helped shift the emphasis in circuit design from the exclusive domain of electronics to a higher, more functional level, where aspects of circuit layout may be treated in purely

#### PERSPECTIVE 7

geometrical terms.

This thesis examines various aspects of the circuit layout problem. We address questions such as: why is circuit layout difficult, what properties of a circuit critically determine the quality of its layout, and what kinds of heuristics can help solve layout problems efficiently? These questions are motivated by the need for general techniques for laying out very large circuits. Such basic issues must be addressed before building any automatic or computer-aided design and layout system.

Although the circuit layout problem is not new, progress has been painfully slow. The proliferation of diverse technologies and concerns has only exacerbated the layout problem. On the one hand we desire to minimize layout area, signal delays, and power dissipation, while on the other hand we need to increase reliability by increased redundancy. In addition we require that custom circuits be assembled using standard configurable or restructurable chips as building blocks. It is not at all clear whether these different requirements are compatible or necessarily contradictory.

Part I presents a general theory for VLSI graph layout. Not only does the theory identify structural properties of circuits that critically determine the quality of layouts, but also provides techniques for solving various layout problems. Perhaps the most significant result that emerges is a general framework for solving diverse problems in a simple and uniform manner. In particular, the unified framework provides a layout technique which is suitable for custom layout, and at the same time is efficient with regard to area, delay, and fault-tolerance. Part I consists of Chapters 2 through 5.

Part II examines the channel routing problem. Algorithms for channel routing form the basis of many existing automatic layout systems. Although this problem has received wide attention over the last decade and a number of heuristic algorithms have been proposed, none of these is guaranteed to always determine efficient routings. Approaching this problem from a theoretical viewpoint, we characterize completely the properties that make channel routing difficult. Moreover, we provide a novel, linear-time algorithm that is always guaranteed to find near-optimal solutions. Chapters 6 and 7 constitute Part II of this thesis.

#### 8 PERSPECTIVE

Although the two parts of the thesis investigate different problems, they share a common underlying philosophy. We begin with a theoretical characterization of the properties that make the problems difficult. In the next step, algorithmic techniques are developed for exploiting these properties to solve the problems. Although the results in their present form are primarily theoretical in nature, the techniques provide new insights and approaches for VLSI layout. It is likely that some of the techniques can be adapted for use in practice.

The remainder of this chapter discusses the two parts of the thesis in more detail, and concludes with an outline of the thesis.

#### 1.1. The Complexity of VLSI Graph Layout

In recent years a number of interconnection networks have been proposed for solving diverse problems. For example, one- and two-dimensional arrays of processors are naturally suited to vector and matrix computations [50]. Binary trees are particularly attractive because of their logarithmic depth and have been proposed for a variety of applications including raster graphics [27], databases [75], and direct execution of applicative programming languages [54]. The mesh of trees [19, 44, 57] combines arrays and trees in an elegant manner. By virtue of their sophisticated structure, networks such as the shuffle-exchange network [73], cube-connected cycles network [63], and fast-fourier transform network [76], in which recursive algorithms are programmed conveniently in a natural manner, are computationally more versatile and powerful than the simpler array structures.

Can we exploit the power of sophisticated networks in VLSI? This question becomes increasingly important as problem sizes, and the number of processors increase. It might be relatively simple to fit a thousand processor array on one chip, but can we fit a thousand processor shuffle-exchange network on one chip? Moreover, even if the shuffle-exchange network fits, will its performance, determined by the clockperiod or longest delay, be comparable to the array? To answer such questions, and to compare the relative merits of different networks, it is necessary to develop a general theory for VLSI graph layout.

Research in layout theory was initiated by Thompson [79, 80] who proposed a formal model

for VLSI graph layout and investigated area-time tradeoffs for computing certain functions. Using information-transfer arguments, he obtained strong lower bounds on the layout areas of graphs such as the shuffle-exchange and cube-connected cycles graphs. Subsequently, Leiserson [49, 50] and Valiant [83], focussing on the problem of minimizing layout area, independently developed a divide-and-conquer layout strategy for general classes of graphs. Using elegant combinatorial arguments, Leighton [40, 41] showed that the bounds of Leiserson and Valiant were the best possible in that each class contained graphs for which the bounds were, upto constant factors, optimal. For some graphs however, the bounds were very weak.

Layout area is not the only consideration in choosing one layout over a multitude of possible layouts. In practice, we desire to fabricate *small, inexpensive*, and *easily testable* chips which compute *quickly* and *reliably*. A large number of important engineering issues need to be considered in fulfilling these (possibly conflicting) requirements.

Propagation delays across long wires critically affect the performance of a circuit layout. In pipelined or systolic systems, long delays determine the clockperiod and overall performance of the system. Since propagation delay can be reduced by decreasing wire length, it is important to make the longest wire in the layout as short as possible. Another way to reduce the propagation delay across a long wire is by increasing the size of the transistor that drives the wire; by carefully adjusting transistor sizes to match wire lengths, the clockperiod can be dramatically reduced. Since wire delays determine the efficiency of a chip, it is imperative that techniques to minimize delay be developed within a general theory for VLSI layout.

Fault tolerance is another important design consideration. Fabrication processes are prone to errors so that every wafer invariably contains a small number of defects. Even if a wafer contains a number of defective processors, it may still be possible to use the wafer by configuring wires around the defective processors. This may, for example, be performed by laser restructuring techniques [64]. This ability to wire together processors selectively has considerable impact on sytem design. For example, how should a thousand processor wafer be designed so that a two-dimensional array can be realized using all the good processors, no matter how the defective processors are distributed?

Another major concern is the problem of assembling large systems. Researchers have

#### 10 PERSPECTIVE

proposed networks with as many as one million processing elements [54]. Such systems are clearly too large to fit on a single chip. Whenever any system is larger than a single chip, it is necessary to partition the system among several chips which can be assembled at the printed circuit (or chip carrier) level. What is the most effective way to partition a large system among several chips? This question is pressing because although fabrication technology has been advancing at a rapid pace, the technology for packaging chips has been crawling in comparison: current projections indicate as many as one hundred million components per chip but not more than two hundred off-chip pin connections.

The economics of fabrication technology dictates that it is expensive to make one chip, but cheap to make many copies. For this reason, manufacturers of custom chips have been encouraged to make configurable designs such as gate-arrays, ROM's, and PLA's. The entire chip is manufactured, except for one mask. Given a desired configuration of the chip, a final layer of metallization connects up the circuitry in that way. Most of the design and fabrication costs are thus factored over several chips. Similarly, restructuring techniques allow a chip to be modified after fabrication. For example, "diode-busting" is used to configure PROM's (programmable read only memory) after fabrication. More recent and exciting is the prospect of "laser welding" by which connections between wires can be either made or broken after fabrication by high-intensity laser beams. Such techniques further encourage configurable design of VLSI chips. Thus, we are led to consider how to design efficient layouts which may be configured to realize, for example, arbitrary binary trees or arbitrary rectangular arrays.

Motivated by the engineering issues outlined above, Part I develops a general framework for VLSI graph layout. Within this framework all the diverse concerns mentioned above are dealt with in an efficient and uniform manner. The framework is based on a divide-and-conquer strategy for graph layout which differs significantly from the divide-and-conquer strategy of Leiserson [49, 50] and Valiant [83]. The improved strategy is based on the notion of graph bifurcators introduced by Leighton [42], and provides universally close bounds on important cost functions such as layout area and propagation delay. The results of Part I are based on the papers of Bhatt and Leiserson [8, 9], and Leighton [42]. In addition, the results of Chapters 4 and 5 appear in [7].

#### 1.2. The Complexity of Channel Routing

Although the graph layout problems considered in Part I provide new insights and paradigms for VLSI layout, they are nonetheless abstractions of layout problems encountered in practice. Part II focuses on a specific problem confronting current automatic layout systems.

Channel routing plays a central role in automated layout systems. Most layout systems proceed by first placing modules on a chip, and then wiring together terminals on different modules that should be electrically connected. To solve the latter wiring problem, the chip is heuristically partitioned into a set of rectangular channels, and each channel is assigned a set of wires which are to pass through it. This effectively reduces a difficult "global" wiring problem to a set of disjoint (and presumably easier), "local" channel routing subproblems.

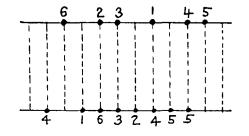

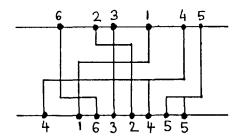

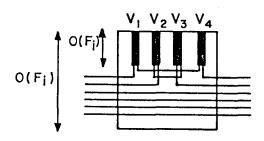

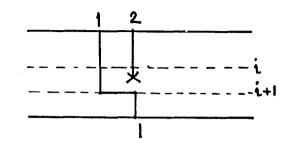

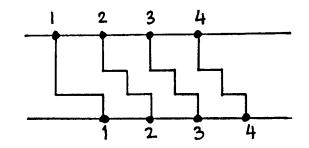

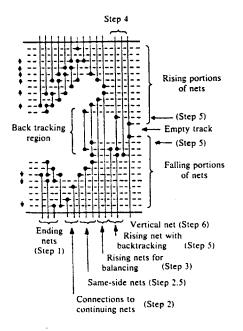

An instance of the channel routing problem is specified by a set of terminals located at fixed positions on two horizontal tracks. Each set of terminals with the same label constitutes a net which must be electrically connected by wires running in horizontal tracks and vertical columns. Figure 1.1 shows a channel with six nets. Horizontal and vertical wire segments are placed on two different layers of interconnect. The objective is to wire up all nets in a way that minimizes the channel width, which is the number of horizontal tracks used for wiring. For example, Figure 1.2 shows a minimum width wiring of the channel in Figure 1.1.

The channel routing problem has been intensively studied for over a decade, and many heuristic algorithms have been proposed for solving the problem [1, 2, 11, 12, 18, 20, 21, 34, 35, 36, 38, 51, 60, 62, 67, 68, 81, 84]. Recently, Szymanski [77] showed that the general problem is NP-complete, and with Yannakakis [78] showed that the problem is NP-complete even when every wire connects exactly two terminals. This might explain why the fast heuristic algorithms developed thus far either produce arbitrarily bad solutions in many cases and/or completely fail on other instances.

Part II of the thesis presents a linear-time algorithm which *always* produces a near-optimal solution. This algorithm is based on the key notion of channel flux which is introduced in Chapter 7. The algorithm originally appears in a paper by Baker, Bhatt, and Leighton [3].

Figure 1.1: A channel with six nets.

Figure 1.2: A minimum width routing.

#### 1.3. Overview

The next four chapters are devoted to VLSI graph layout, and form Part I of the thesis. Chapter 2 outlines Thompson's model for VLSI layout, reviews previous research, and describes important layout problems in a formal setting. Chapter 3 focuses on layouts for the simplest of networks: binary trees. In addition to presenting new layouts with improved bounds on edge lengths, the complexity of producing optimal layouts is examined. The new layout strategy motivates the paradigm for general graph layout presented in Chapter 4. Finally, Chapter 5 shows how the new layout paradigm can be used to efficiently solve the important layout problems of Chapter 2.

Part II of the thesis consists of Chapters 6 and 7. Chapter 6 describes the channel routing problem, its use in automatic layout systems, and briefly reviews previous research. Chapter 7 introduces the concept of channel flux and presents a linear-time approximation algorithm for Manhattan routing.

In conclusion, Chapter 8 summarizes the major results of both parts and outlines a number of important, unresolved problems.

#### CHAPTER 2

## Issues in VLSI Graph Layout

The first three sections of this chapter introduce the layout model developed by Thompson [79, 80] and briefly review previous research in VLSI graph layout. In particular, we discuss the layout strategy of Leiserson [49] and Valiant [83] and note that bounds on layout area based on separator theorems can be very different from the actual minimum layout area. The remainder of this chapter is devoted to formalizing a number of layout questions motivated by engineering considerations.

#### 2.1. The Layout Model

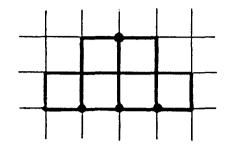

In order to cast VLSI layout problems within a mathematical framework, Thompson [79, 80] developed a formal model for VLSI graph layout. The model is based on, and is consistent with, the VLSI design rules established by Mead and Conway [55]. It is also similar to the widely used Manhattan wiring model. In the *Thomspon grid model*, a layout for a graph is characterized as an embedding within a *two-dimensional grid*. A *two-dimensional grid* is a collection of horizontal and vertical *tracks* spaced apart at unit intervals. A layout for a graph G is specified by an *embedding* which assigns nodes of G to points in the grid where horizontal and vertical tracks intersect, together with an (incidence-preserving) assignment of the edges of G to *paths* in the grid. The paths of the layout are restricted to follow along grid tracks and are not allowed to overlap for any distance (although a vertical path segment may cross a horizontal path segment). In addition, the paths may not cross nodes to which they are not adjacent. For obvious reasons, we restrict our attention to graphs in which no node has degree

Figure 2.1: A layout for  $K_4$ .

greater than four. As an example, Figure 2.1 shows a layout for the complete graph on four nodes.

*Remark.* The results of this thesis extend to variants and generalizations of the Thomspon grid model. For example, graphs with bounded valence greater than four may be laid out by mapping each node to a region of the grid, instead of a single grid point. The results are also applicable to networks with large processors. Techniques for dealing with large processors are described more fully in Chapter 5.

#### 2.2. Elementary Bounds on Layout Area

Although there are a variety of important engineering considerations in choosing one layout for a graph over other possible layouts, the best understood, and perhaps the most desirable cost measure to minimize is *layout area*. The area of a layout is most naturally defined as the area of the "bounding-box" around the layout, and equals the product of the number of vertical tracks and the number of horizontal tracks that contain a node or wire segment of the graph. For example, the layout of Figure 2.1 has area 15. This is not the minimum possible; there is another layout with area 9.

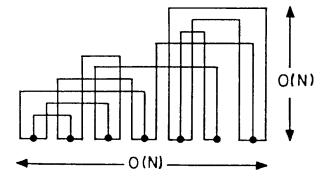

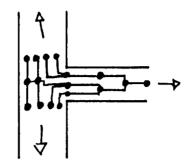

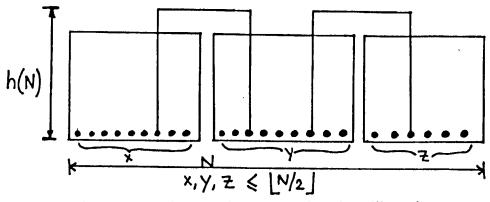

How much area does an N-node graph require? Clearly, the area cannot be less than the number N of nodes. On the other hand, by embedding nodes at equally spaced intervals along a line, and using a distinct horizontal track for each edge (as shown in Figure 2.2), it is clear that the area required for an N-node graph is no greater than  $O(N^2)$ . These bounds are independent of the structure of the graph and hold for all N-node graphs. In general, however, the minimum area needed to lay out a graph depends on the graph.

15

Figure 2.2: Every N-node graph can be laid out in  $O(N^2)$  area.

Thompson [79, 80] identified bisection width as an important property of graphs that affects minimum layout area. The bisection width of an N-node graph is the minimum number of edges which must be removed from the graph in order to disconnect it into two subgraphs each of size at least  $\lfloor N/2 \rfloor$ . Thompson showed that, up to a constant factor, the layout area can be no less than the square of the bisection width. Therefore, if the bisection width for a graph is known, a lower bound on area can be easily computed. By showing that certain computationally powerful graphs such as the shuffle-exchange graph have large bisection width, Thompson showed that these graphs require large area. In fact, Thompson extended this observation to obtain area-time tradeoffs for computing certain functions.

Leighton [40, 41] identified crossing number as another general property that affects layout area. The crossing number of a graph is defined as the minimum number of edge crossings in any drawing of the graph in the plane. It is easy to see that the crossing number of a graph is a lower bound on layout area. Using more sophisticated arguments for special graphs, Leighton also directly obtained lower bounds on *total wire length* (the sum of the lengths of the wires in a layout), which of course is a lower bound on layout area. These techniques are heavily dependent on the recursive structure of the special graphs and are generalized in [7].

#### 2.3. Layouts Based on Separator Theorems

Leiserson [49, 50] and Valiant [83] investigated general properties that provide effective upper bounds on layout area. They independently developed a divide-and-conquer strategy for graph layout and showed, for example, that every N-node tree can be laid out in O(N) area and that every N-node planar graph can be laid out in  $O(N \lg^2 N)$  area. Their technique is based on the notion of separator theorems for graphs.

Definition: A class of graphs which is closed under the subgraph relation is said to have an f(x)-separator theorem if there exist constants a and b where  $0 < a \le 1/2$  and b > 0such that every N-node graph in the class can be partitioned (by the removal of at most bf(N) edges of the graph) into disjoint subgraphs having a'N and (1-a')N nodes where  $a \le a' \le 1-a$ .

Given a class of graphs for which a separator theorem is known (e.g., trees have a 1separator theorem [52] and planar graphs have a  $\sqrt{x}$ -separator theorem [53]), it is possible to construct a layout for any N-node graph in the class by using a simple divide-and-conquer approach. For example, Leiserson [49, 50] proved the following upper bounds on layout area.

| $x^{lpha}$ -separator theorem | Layout Area      |

|-------------------------------|------------------|

| lpha < 1/2                    | O(N)             |

| lpha=1/2                      | $O(N \lg^2 N)$   |

| lpha>1/2                      | $O(N^{2\alpha})$ |

*Remark.* The layout procedure assumes that a complete recursive decomposition of the graph is given. If a complete decomposition is not given, then there is no known polynomial time algorithm which achieves the upper bounds on area. This severely limits the applicability of separator-based layout strategies to classes of graphs (such as trees or planar graphs) for which decompositions are easily computed.

How good are the preceding area bounds? Thompson [79, 80] and Leighton [40, 41] showed that none of the bounds can be improved. More precisely, they showed that within each class there is a graph for which the bound is optimal. But this does not mean that the bounds are optimal for every graph within a class. In fact, while the bounds are *existentially* optimal, they are not *universally* optimal. For example, an N-node square grid can be laid out in area linear in N, but since the minimum separator theorem for the class of square grids is  $\sqrt{x}$ , the best bound obtainable by separator-based layouts is  $O(N \lg^2 N)$ , which is off by a factor of  $O(\lg^2 N)$  from the optimal. Of course, since N-node graphs require area at least N, the bounds for graphs with  $x^{\alpha}$ -separator theorems,  $\alpha < 1/2$ , are asymptotically universally optimal.

For graphs with larger separator theorems, the discrepancy between the minimum layout area and that given in the table can be much worse. Consider, for example, the N-node graph  $S_N$  which consists of  $N/\lg N$  disjoint  $\lg N$ -node expander graphs. An m-node expander graph has the property that every subset of k nodes is linked by  $\Theta(\min(k, m-k))$  edges to the m-knodes outside the subset.<sup>\*</sup> The bisection width of such a graph is  $\Omega(m)$ , and hence the minimum separator theorem is  $\Theta(x)$ . The existence of trivalent graphs that satisfy this definition has been known for a long time [28, 31]. In fact, almost all trivalent graphs satisfy this definition. Since each  $\lg N$ -node expander graph can be trivially laid out in  $O(\lg^2 N)$  area, the layout area of  $S_N$  is no greater than  $O(N \lg N)$ . However, Leighton [42] showed that the minimum separator theorem for the class of graphs  $S_N$  exceeds  $\Omega(x/\lg^2 x)$ , so that the area bound from the table above is  $O(N^2/\lg^4 N)$ , which is much worse than the optimal bound of  $O(N \lg N)$ .

Remark. Any class of graphs closed under the subgraph relation and containing  $S_N$  must also contain expander graphs. Hence, the minimum separator theorem (as defined earlier) for the class is  $\Theta(x)$ . Instead of defining separator theorems for classes of graphs closed under the subgraph relation, it is more convenient (and general) to define separators for individual graphs in terms of the subgraphs produced by its recursive decomposition. Using the less restrictive (but more useful) definition, it is possible to show that  $S_N$  has an  $O(N/\lg N)$ -separator. The lg N-node expander graphs are split in the upper levels of the decomposition and never appear intact as subgraphs in the lower levels of the decomposition. Leighton [42] proved that even using the most liberal definition, the minimum separator for  $S_N$  is at least  $\Omega(N/\lg^2 N)$ . Any bound on layout area for  $S_N$  based on the minimum separator can therefore be no less than  $\Omega(N^2/\lg^4 N)$ .

Thus, while the divide-and-conquer strategy based on separator theorems gives existentially

<sup>\*</sup>The original definition of expander graphs is slightly different from that given here. We adopt this minor variant because it allows nodes of degree no greater than three.

optimal bounds, the bounds can be unacceptably poor in a universal sense. It was the discovery of such large discrepancies that led to the search for an alternative framework for VLSI layout. Within the new framework presented in Chapter 4 we shall see how these large discrepancies are overcome.

#### 2.4. Eight VLSI Graph Layout Problems

As mentioned earlier, there are many important considerations in choosing one layout over a multitude of other possible layouts. The problems in this section are motivated by some engineering concerns fundamental to circuit design and layout. Though not exhaustive, this list covers most of the theoretical issues studied recently. Many of the problems are known to be NP-Complete. The emphasis throughout this thesis is the development of a general unifying framework for dealing with diverse issues in a uniform manner. Within the framework, solutions to some problems are reasonably close to optimal. For other problems, good heuristics are developed or suggested, and general bounds obtained.

#### **Problem 1.** Given a graph G, produce an area-efficient layout for G.

As mentioned before, minimizing area is a critical concern in VLSI circuit layout. In addition to the work on area-efficient layouts described in the previous section, Dolev, Leighton, and Trickey [22] have shown that determining the minimum layout area of a forest of trees is NP-Complete.

# **Problem 2.** Given a graph G, produce an area-efficient layout for G with minimax edge length.

Besides area, speed is another critical factor in chip performance. Signals do not propagate instantaneously across wires, and the longer the wire, the longer the propagation delay. In pipelined or systolic systems, the effect of propagation delays is even more dramatic. The maximum delay determines the clockperiod, and hence the throughput, of the system. To maximize throughput we need to minimize the maximum delay. In short, we must produce layouts so that the longest edge is as short as possible. The minimum, over all layouts, of the length of the longest edge is called the minimax edge length.

Paterson, Ruzzo and Snyder [59] studied the problem of minimizing edge lengths for complete binary trees. They showed that the minimax edge length of an N-node complete binary tree is  $\Theta(\sqrt{N}/\lg N)$ . Adopting a different strategy based on separator theorems, the next chapter presents a general technique for bounding the maximum edge length of arbitrary trees, while Chapters 4 and 5 extend the techniques to general graphs. The next chapter also shows that minimizing the edge lengths of trees is NP-complete.

# **Problem 3.** Given a graph, produce an area-efficient layout in which each wire has bounded delay in the capacitive model.

Although it is certainly true that propagation delay across a wire depends on the length of the wire, there has been little consensus on how fast propagation delay grows as a function of wire length. Thompson [79, 80] assumes propagation delay to be constant, independent of wire length. This might seem unreasonable given the ultimate speed-of-light limitation which indicates that the delay increases linearly with length. The speed-of-light limitation, however, greatly exaggerates the importance of wire delay in determining the speed of circuits. Mead and Conway [55] take into account some of the electrical characteristics of interconnections on MOS integrated circuits, and emphasize the role of wire *capacitance* in determining propagation delay. Recent analysis by Bilardi, Pracchi, and Preparata [10] strongly supports the belief that capacitive effects play the predominant role in determining the speed of MOS circuits.

In a capacitive model, each wire is assumed to present a purely *capacitive load* to the transistor that drives a signal across the wire. This load is proportional to the length of the wire plus the area of the transistor that receives the signal. The delay is proportional to this load divided by the area of the driving transistor. By increasing the size of the driving transistor it is therefore possible to bound the propagation delay, independent of the length of the wire. A second well-known technique for reducing delay across a long wire is to "ramp" the wire with a geometrically increasing series of inverters [55]. The number of intermediate drivers, and hence the delay, is logarithmic in the length of the wire, but an attractive feature is that this process can be carried out without the need to resize the original transistors in the

circuit.

Of course, increasing the size of one transistor or introducing new transistors might force some wires to be stretched to avoid the enlarged transistor area. In other words, decreasing the delay across one wire might force an increase in delay over other wires. Leiserson [47] and Mehlhorn [56] independently posed the question of whether or not the transistors in a layout could be resized so that every wire in the layout has constant propagation delay. Ramachandran [65] investigated the problem of introducing intermediate drivers along long wires to decrease delays, but under the constraint that the topology of the layout remain unchanged. With the restriction that wires can not be rerouted, she showed that logarithmic delay can be achieved, but at the expense of squaring the layout area in the worst case. We allow the layout topology to be changed, and obtain significantly better results.

#### **Problem 4.** Given a graph G, produce a layout for G with few wire crossings.

An undesirable feature of layouts is the presence of a large number of wire crossings. When two wires cross, they must be on different layers. For faster operation, and less power dissipation, it is advantageous to maximize the total amount of wiring on a layer of low resistance, e.g. the metal layer, while minimizing the wiring on a layer of high resistance, e.g. the polysilicon layer. The net wiring on one layer may be reduced by laying wires on that layer only just before and after two wires cross. If the number of wire crossings is small, the number of contact-cuts which connect wire segments on different layers is small so that the area of the layout is not blown up by the contact cuts which occupy large area. In addition, long wires that are crossed by many other wires are susceptible to cross-talk when all the crossing wires simultaneously carry the same signal.

The crossing number of a graph is defined to be the minimum number of wire crossings in any drawing of the graph on the plane. Leighton [40, 41] proved upper and lower bounds on crossing numbers and then used the results to find bounds on layout area. Garey and Johnson [29] showed that determining the crossing number of bipartite graphs is NP-Complete.

#### **Problem 5.** Given a graph, produce an area-efficient regular layout for the graph.

Some design methodologies, most notably gate-arrays, require that processors be located at fixed positions on a chip. In gate-arrays the processors are placed in a grid pattern with uniform spacing between processors adjacent along every row and column. Such layouts are said to be *regular*. An important advantage of this design restriction is its flexibility: even if the size of every processor is increased, the wiring between processors remains unaffected and the total area remains proportional to the *sum* of the wire area (as computed with unit-size processors) and the processor area. This is because only the  $\sqrt{N}$  rows and columns containing the *N* unit-size processors need to be expanded to accomodate the non-unit-size processors. In non-regular layouts, *every* row and column might have to be expanded since there might be a node in every row and in every column. Increasing the linear dimension of the processors by a factor of *s* could result in an  $\Theta(s^2)$  increase in layout area.

Previous divide-and-conquer layout strategies do not produce regular layouts. Hence, they are not useful in laying out circuits with non-unit-size processors. A good strategy for producing regular layouts would solve the nagging problem of how to cope with variable-size processors.

# **Problem 6.** Design area-efficient chips that can be configured to realize a large number of graphs.

Because it is expensive to make one chip but cheap to make many copies, manufacturers of custom chips have been encouraged to make *configurable* designs such as gate-arrays, ROM's and PLA's. In such designs, the entire chip is prefabricated except for one layer. The customer then specifies a configuration for the chip, and the final layer of metalization connects up the circuitry in that particular way. Hence, most of the design and fabrication costs can be factored over many custom chips. Similarly, the fast emerging laser-restructuring technology [64] provides another economical way to customize chips after fabrication is complete. Laser restructuring allows connections between wires to be made or broken after the chip has been fabricated. In either case, it is desirable to design layouts that can be configured from one of a few basic patterns. **Problem 7.** On a wafer which has arbitrarily distributed defective cells, realize a given graph on the good cells.

In any fabrication process, it is expected that some of the processing cells will be defective. In a two-dimensional array of cells on a wafer in which defective cells are arbitrarily distributed, it may still be possible to use the wafer by configuring wires around the defective cells. This may, for example, be performed by laser restructuring techniques [64]. Given this ability to isolate defective cells, it is important to consider how a graph may be realized on the remaining good cells. This problem has received considerable attention recently [33, 45, 69]. The problem is similar to the general graph layout problem in the Thompson model but with the important restriction that nodes of the circuit can only be mapped to a restricted set of nodes in the grid.

# **Problem 8.** Given a graph G, assemble G using the minimum number of copies of a single chip having few external pin connections.

A number of very large networks have been proposed in recent years for implementing priority queues [48], for searching [5], for direct execution of applicative programming languages [54], and for recognizing regular expressions [26]. Some of these networks are too large to fit on a single chip. For example, the tree-structured network of [54] is envisioned to contain as many as one million processing elements. Clearly, such networks must be partitioned over many interconnected chips, so that each chip realizes a small portion of the network.

The technology for packaging chips severely limits the number of external pin connections on a chip. While chips with over a million components are forseeable in the near future, no one predicts a chip with over two hundred external pin connections. This poses a pressing problem in assembling large networks of processors.

Even if a network could be partitioned so that each portion has only a few external connections, it would be economically infeasible to design each chip individually. For instance, it would be prohibitively expensive to design one thousand different chips, each containing a thousand processing elements, to assemble a network of one million processors. For this reason, it is necessary to assemble large systems using copies of a few configurable or restructurable chips. The next chapter presents one solution to the problem of assembling large tree structures using copies of a single, area-efficient, restructurable chip with few external pin connections.

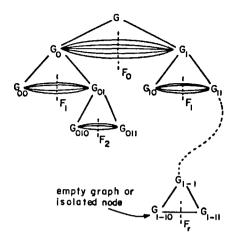

Within the new framework, efficient solutions are provided for each of these problems. In fact, a single layout simultaneously solves many of these problems efficiently. The framework provides a two-step strategy for solving these problems. First, the graph to be laid out is embedded within a very special network called the *tree of meshes*. For the tree of meshes it is possible to solve all these problems efficiently. In the second step, therefore, a good layout for the tree of meshes also solves these problems for the embedded graph.

#### CHAPTER 3

# Layouts for Trees

A binary tree may not be the best multiprocessor organization, but it has been proposed by many researchers for a variety of reasons. For example, a complete binary tree can be the major component of a priority queue resource [48] and of a smart-memory raster graphics system [27]. A complete binary tree can also serve as a hardware structure for searching [5], for databases [75], or for direct execution of applicative programming languages [54]. Browning [15] proposes a complete binary tree for general-purpose multiprocessing, and two systems based on her ideas are being built at Caltech and Bell Laboratories.

Attention is also directed to binary trees which are not complete. Floyd and Ullman [15] show that strings described by a regular expression can be recognized by processing elements organized as the parse tree of the regular expression. Foster and Kung [25] have a similar scheme based on the simple configurable layout developed by Leiserson [50]. There are other proposals, for example [58, 74], of machine organizations that, while not trees, are nevertheless tree-like.

We shall not debate the merits of the various tree machines here, but shall confine ourselves to understanding their physical organization. In this regard trees are particularly attractive because of their simple interconnection structure. Not only can trees be laid out efficiently, but good layouts for trees also suggest efficient ways to lay out general graphs. Moreover, problems that are intractable for trees are also intractable in general. Thus, by investigating layouts for trees we stand to learn more about general graph layout.

In the following section we examine two well-known layouts for complete binary trees and present a better layout which minimizes (asymptotically) both area as well as maximum edge

length. These bounds are extended to arbitrarily structured trees in Section 3.2, and to planar layouts for trees in Section 3.3. Computing the minimum edge length exactly is shown to be NP-complete in Section 3.4. Section 3.5 describes Leiserson's [50] assembly of large complete trees using multiple copies of a single chip with only four external pin connections. Section 3.6 introduces and examines the *two-color bisection* problem for arbitrary trees. Section 3.7 presents one way to assemble large arbitrarily structured trees using the minimum number of copies of a single restructurable chip with few pins.

#### 3.1. Layouts for Complete Binary Trees

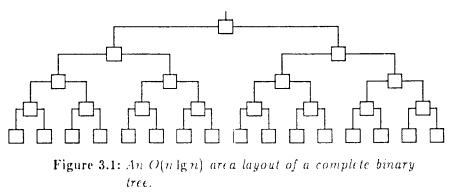

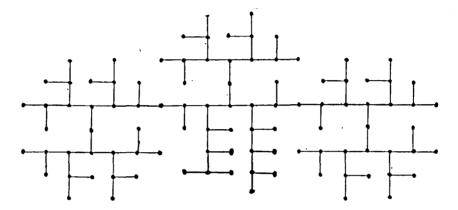

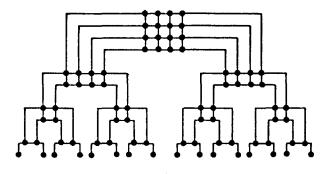

In addition to their usefulness in speeding up computation time by allowing both parallelism and pipelining, complete binary trees are attractive also because they can be laid out efficiently. Figure 3.1 shows the naive layout of a complete binary tree. Since the height of an N-leaf tree is  $\lg N$ , and the N leaves are spread out over a line of length 2N, it follows that the area of the layout is  $2N \lg N$ . Furthermore, the longest edges are at the top level and their length is  $\frac{1}{2}N$ .

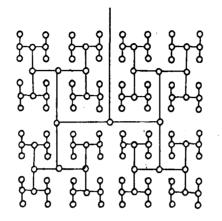

The familiar H-tree layout in Figure 3.2 was originally proposed by Mead and Rem [55]. In contrast to the naive layout which, in a sense is one-dimensional, this layout exploits both dimensions symmetrically. If S(N) is the side of the layout, then we have that S(1) = 1 and more generally,

$$S(N) = 2S(N/4) + 1,$$

which yields  $S(N) = 2\sqrt{N} - 1$ . Consequently, the area of the layout is no greater than 4N. The longest edges are again at the top level, and their length is no more than  $\frac{1}{2}\sqrt{N}$ .

Figure 3.2: The H-tree layout of a complete binary tree.

The H-tree layout asymptotically minimizes area but not maximum edge length. Paterson, Ruzzo, and Snyder [59] demonstrated a linear-area layout with maximum edge length  $O(\sqrt{N}/\lg N)$ . In any layout there are two nodes which are distance  $\sqrt{N}$  apart; moreover, these two nodes are connected by a path containing no more than  $2\lg N$  tree edges. It follows then that at least one of these edges must have length at least  $\sqrt{N}/2\lg N$ . Thus, the layout of [59] asymptotically minimizes area as well as maximum edge length. Unfortunately, however, the layout technique of [59] does not extend to more general graphs. The remainder of this section demonstrates another layout with asymptotically optimal area and maximum edge length. The following section generalizes our technique to arbitrary trees and, the next chapter to general graphs.

To illustrate our technique, consider the layout of Figure 3.3 in which the nodes at the second and third levels of the tree have been brought closer to the root so that all edges within the top four levels are of equal length. This "averaging" of edge lengths reduces the maximum edge length from  $\frac{1}{2}\sqrt{N}$  to  $\frac{5}{12}\sqrt{N}$ . Of course, the layout is stretched in the middle in order to accomodate two edges instead of one. This increases the area of the layout, but only slightly, from 4N to  $4N + 6\sqrt{N}$ .

This averaging operation can be carried out further down the tree so that many levels are brought closer towards the root. In order to space top levels of the tree closely together, we embed these levels within an H-channel structure shown in Figure 3.4. This structure is

Figure 3.3: The H-tree layout with shorter edges at the top

Figure 3.4: The H-channel structure.

obtained by taking the H-tree layout of a complete binary tree and blowing up the layout in both dimensions by a suitable factor. The details of the embedding are described next.

**Theorem 3.1.** An N-node complete binary tree can be embedded in linear area with maximum edge length  $O(\sqrt{N}/\lg N)$ .

**Proof.** To layout a complete binary tree with N leaves, start with the H-tree layout of a complete binary tree with  $\lg^2 N$  leaves which has area  $4 \lg^2 N$  and maximum edge length  $\frac{1}{2} \lg N$ . Blow up this layout in either dimension by a factor  $\alpha \sqrt{N} / \lg N$ , where  $\alpha$  is a constant specified later. The area of the layout becomes  $4\alpha^2 N$  and the longest channel has length  $\frac{1}{2}\alpha\sqrt{N}$ .

#### 28 LAYOUTS FOR TREES

Next, lay the root at the centre of the H-channel structure and place the second level nodes at distance  $\beta \sqrt{N}/\lg N$  from the root on either side. Once again,  $\beta$  is a constant specified later. Place lower levels of the tree as shown in Figure 3.4, with successive levels spaced equally apart. At every corner of the H-channel structure, bisect the tree so that the subtrees embedded within the two substructures are of equal size. Finally, in the lowest level channels lay out the remaining subtrees in the H-tree manner.

We must ensure that every channel is wide enough to accomodate all the nodes in any level embedded within it, and also that the II-tree layouts in the final step fit within the lowest level channels. To satisfy these conditions, let us first calculate the total number of tree levels embedded in all but the lowest level channels. The total length of all channels encountered from the centre of the layout to the end of a terminal channel does not exceed the quantity  $2\alpha\sqrt{N}$ . Since the distance between successive tree levels is  $\beta\sqrt{N}/\lg N$ , the number of tree levels embedded is bounded by  $(2\alpha/\beta) \lg N$ . The total number of tree nodes within any one of these levels is therefore no greater than  $N^{2\alpha/\beta}$ . If  $2\alpha/\beta < 1/2$  then the number of nodes in any level is asymptotically less than the width of a channel which equals  $\beta\sqrt{N}/\lg N$ . The first condition is therefore satisfied by having  $\alpha < \beta/4$ .

To ensure that the H-tree layouts at the final step fit within the final channel, it suffices to check that the dimensions of the layout are smaller than the dimensions of the channel. The size of a subtree embedded within a final-level channel cannot be more than  $N/\lg^2 N$  because the tree is split into half at each corner. The side of the H-tree layout is no greater than  $2\sqrt{N}/\lg N$ . By choosing  $\alpha > 2$ , the side of the channel is guaranteed to be larger than a side of the H-tree layout. Therefore, by choosing  $\alpha > 2$  and  $\beta > 4\alpha$ , we see that the layout can be completed. Finally, the area is linear in N and the maximum edge length is bounded by  $O(\sqrt{N}/\lg N)$ .

#### 3.2. Layouts for Arbitrary Binary Trees

One property of complete binary trees crucial to the layout of Theorem 3.1 is that a complete binary tree can be bisected into two equal size subtrees simply by removing the root.

At every corner in the II-channel structure, a forest of complete trees is bisected into two equal halves, each "growing" in opposite directions. This controls the size of every subgraph at the final level so that a standard layout fits within a final-level channel.

Arbitrarily structured binary trees are only slightly harder to bisect. Any N-node binary tree can be separated into two components, each with no more than  $\lfloor \frac{2}{3}N \rfloor + 1$  nodes, by removing a single edge [52]. (The worst-case occurs for the four-node tree in which one node is adjacent to three others.) Either of the two components might be a forest, but the same result applies to forests, so that the binary tree can be split recursively. By recursively splitting the larger component, a tree can be bisected by cutting at most  $O(\lg N)$  edges, or by removing the nodes incident to these edges. The  $O(\lg N)$  bound follows because the subgraphs decrease geometrically in size with each cut.

The property that all trees have small bisections was used by Leiserson [49, 50] and Valiant [83] to show that all trees have linear-area layouts. We strengthen this result to show that the maximum edge length of any N-node tree is bounded by  $O(\sqrt{N}/\lg N)$ . The details of the layout are described in the following Theorem.

**Theorem 3.3.** Every N-node tree can be embedded in linear area with maximum edge length  $O(\sqrt{N}/\lg N)$ .

**Proof.** As before, begin with the II-tree layout of a complete binary tree with  $\lg^2 N$  leaves, and blow up the layout in either dimension by a factor  $\alpha \sqrt{N}/\lg N$ , where  $\alpha$  is a constant specified later. The area of the layout becomes  $4\alpha^2 N$  and the longest channel has length  $\frac{1}{2}\alpha\sqrt{N}.$

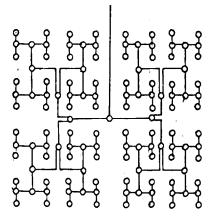

Find a set of  $O(\lg N)$  nodes which bisect the tree and locate them at the center of the layout. Place nodes of the tree in breadth-first levels starting with the bisector set as the roots of the search, so that consecutive levels are distance  $\beta \sqrt{N} / \lg N$  apart ( $\beta$  is a constant specified later). At every corner of the II-channel structure, bisect the remaining forest of subtrees so that the subforests embedded within the two substructures are of equal size. Add the new bisector set to the set of nodes from the previous breadth-first level, as shown in Figure 3.5. In the new channel, start with the updated set as the root of a breadth-first search and repeat

29

Figure 3.5: Inserting new bisector sets at every corner.

the procedure used before. Finally, in the lowest level channels lay out the remaining subtrees using the standard divide-and-conquer layout of Leiserson [49, 50] or Valiant [83].

As before, we need to ensure that every channel is wide enough to accomodate all the nodes embedded within any level, and also that the layouts in the final step fit within the lowest level channels.

Let us first calculate a crude upper bound on the total number of nodes embedded in any one breadth-first level. This quantity is certainly less than the total number of nodes embedded in all but the final-level channels. To bound the latter quantity, suppose that nodes in each bisector set within the H-channel structure are pulled in to the center of the layout, and the remaining nodes placed in breadth-first levels until the final-level channels. Bringing all the bisector sets towards the center can only increase the number of nodes in all but the final-level channels. Since an N-node tree has a bisector of size  $O(\lg N)$ , the total number of nodes within the union of all bisector sets is bounded by:

$$O\left(\sum_{i=0}^{2\lg \lg N} 2^i \lg \frac{N}{2^i}\right) = O(\lg^3 N).$$

The total length of all channels encountered from the centre of the layout to the end of a final-level channel does not exceed  $2\alpha\sqrt{N}$ . Since the distance between successive tree levels is  $\beta\sqrt{N}/\lg N$ , the number of tree levels embedded within the H-channel is bounded by  $(2\alpha/\beta)\lg N$ . Starting with  $O(\lg^3 N)$  nodes as the roots of a breadth-first search, the number of nodes encountered in  $(2\alpha/\beta)\lg N$  levels cannot exceed  $O(N^{2\alpha/\beta}\lg^3 N)$ . Since every node embedded within the H-channel must be in one such breadth-first level, the previous quantity also bounds the total number of nodes within the H-channel structure. By choosing  $2\alpha/\beta < 1/2$ , or  $\alpha < \beta/4$ , we see that the width of a channel asymptotically exceeds the number of nodes in any level within the channel. Therefore, the first condition is satisfied by having  $\alpha < \beta/4$ .

To ensure that the layouts at the final step fit within a final-level channel, it suffices to check that the dimensions of a layout generated by the Leiserson-Valiant strategy are smaller than the dimensions of the channel. Their layout of an x-node tree is linear in x, i.e., bounded by  $\gamma x$ , for all x and some constant  $\gamma$ . In the layout described above, the size of a forest embedded within a final-level channel cannot be more than  $N/\lg^2 N$  because the tree is split into half at each corner. The side of a layout at the final level is no greater than  $\sqrt{\gamma N}/\lg N$ . By choosing  $\alpha > \sqrt{\gamma}$ , the side of the channel is guaranteed to be larger than a side of the H-tree layout. Therefore, by choosing  $\alpha > \sqrt{\gamma}$  and  $\beta > 4\alpha$ , we see that the layout can be completed. Finally, the area is linear in N and the maximum edge length is bounded by  $O(\sqrt{N}/\lg N)$ .

#### 3.3. Planar Layouts for Trees

It is sometimes necessary to produce layouts in which distinct edges do not cross one another. Planar layouts have the advantage that only one layer of interconnect is required; by using a low-resistance metal layer, the resulting circuit is not only faster, but also dissipates less power. Many current automatic layout systems reserve a single layer of interconnect for special purposes such as, for example, power and ground connections. In such cases, it is necessary to find good planar layouts. Needless to say, the underlying connection scheme must be planar.

Planar layouts may require much more area than non-planar layouts. In particular, Valiant [83] demonstrated an N-node planar graph for which every planar layout occupies at least  $\Omega(N^2)$  area and has edges of length  $\Omega(N)$ . On the other hand, Leiserson [49, 50] and Valiant [83] showed that every N-node planar graph can be laid out in  $O(N \lg^2 N)$  area with edges of length  $O(\sqrt{N} \lg N)$  in Thompson's layout model, which allows distinct wires to cross.

Valiant [83] further showed that every tree has a linear-area planar layout. In other words, the planarity restriction does not affect the asymptotic area requirements of trees. But what

#### 32 LAYOUTS FOR TREES

about edge length? Intuitively, the length of a wire can be reduced by taking a short-cut across another wire, instead of going around it. So, an important question is whether the planarity requirement affects the maximum edge length for trees.

Although the layout of Section 3.2 has linear area, and asymptotically optimal edge length in the worst-case, it is not guaranteed to be planar. However, Ruzzo and Snyder [70] showed that this layout could be transformed into a planar layout without increasing edge length asymptotically. The details of their transformation are fairly complicated; in the following Theorem, we present a simpler transformation.

# **Theorem 3.4.** Every N-node tree has a linear-area planar layout with maximum edge length $O(\sqrt{N}/\lg N)$ .

**Proof.** The layout proceeds exactly as in the proof of Theorem 3.3, with particular attention paid to the way a bisector set is chosen and to the ordering of nodes within the set. In particular, if a forest of x nodes has to be separated from an N-node tree,  $x \leq \lfloor N/2 \rfloor$ , then it suffices to remove at most  $\lceil \lg x \rceil$  nodes. The key fact is that these nodes can be chosen from a single path in the tree. This path induces a natural linear ordering on the set of nodes removed.

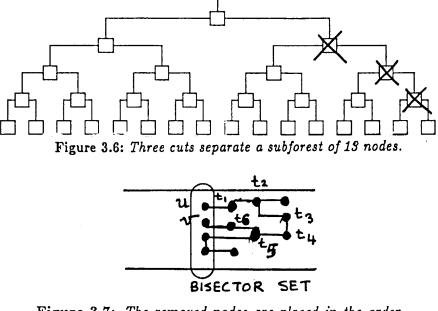

To see this, consider a binary tree rooted at a node of degree either one or two. It is always possible to choose such a root, and if the remainder of the tree is drawn in levels then every internal node has at most two sons. Label each node in the tree by the size of the subtree rooted at that node and below it. Pick any node whose label is no less than x, and both of whose sons have labels less than x. Mark this node. If its label equals x then we have found a node whose removal separates a subtree of the required size. Otherwise, one of its sons must have a label  $y \ge \lfloor x/2 \rfloor$ , while the other son has label no less than x - y - 1. Recursively mark nodes in the subtree rooted at the second son so that the removal of the marked nodes separates a forest of size x - y - 1. It is easily seen that the marked nodes lie along a path of the original tree. Moreover, the removal of all marked nodes separates a component of size exactly x. Finally, since the first node separates a component of size at least  $\lfloor x/2 \rfloor + 1$ , it follows that no more than  $\lceil \lg x \rceil$  nodes are marked. Figure 3.6 illustrates this procedure.

Figure 3.7: The removed nodes are placed in the order of occurrence along the path.

Given a tree, use the above procedure to find a set of nodes which bisect the tree, and lie along a path. Place these nodes at the center of the layout in the same order in which they are encountered along the common path. Next, find all nodes adjacent to the bisector set and place them on either side as before. However, the ordering of nodes in these breadth-first levels is chosen as follows: for each pair of nodes u, v that are placed next to each other in the bisector set, if the path connecting them is  $u, t_1, t_2, \ldots, t_k, v$ , then place nodes  $t_1$  and  $t_k$  next to each each other in the second level, as shown in Figure 3.7. The orderings of nodes on either side of the center again satisfy the condition that nodes connected by a path in the forest embedded on that side appear in the order in which they are encountered along the common path.

By placing nodes in every level in the same order in which they lie along a common path within the forest still to be embedded, it is easy to guarantee that the layout is planar inside the channel (see Figure 3.7). All that remains is to guarantee that the layout can be made planar at every corner when new bisector sets are added to a level.

When the end of a channel is reached, the situation is as shown in Figure 3.8. Nodes  $u_1, u_2, \ldots, u_n$  are those in the last level of the channel. The subgraph which remains to be embedded is a forest of subtrees. The *n* nodes can be grouped according to which subtree they

Figure 3.8: To bisect a forest of trees, only one tree need be separated.

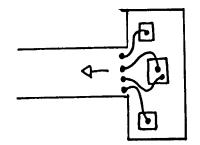

Figure 3.9: Nodes in the final level may be connected to their subtrees without crossovers.

belong to, nodes in the same subtree being adjacent within the ordering. To bisect this forest, it suffices to split only one of these subtrees: order the subtrees top-down and pick the lowest one so that the subforest above it contains at most one-half of all nodes in the forest. Split the subtree this node belongs to into two components as required so that the original forest is bisected. By laying out the next breadth-first level and the new bisector nodes as in Figure 3.8, we see that in each of the two lower-level channels the nodes within the same subtree are ordered in the order in which they are encountered along a common path.

Repeating this process further down the H-channel structure, we see that the layout is free of wire crossings. To complete the layout, within the final-level channels we use Valiant's [83] linear-area planar layouts for each remaining subtree. Edges from these subtrees to nodes in the last breadth-first level of the penultimate channel can be inserted without crossovers as shown in Figure 3.9. This completes the planar layout.

35

## 3.4. The Complexity of Minimizing Edge Lengths

Thus far we have only showed that every tree can be laid out with maximum edge length bounded by  $O(\sqrt{N}/\lg N)$ . While this bound is asymptotically optimal for some trees such as the complete binary tree, it is way off for others. For example, a two-ended string with every node connected only to its immediate neighbors can be trivially laid out with every edge of length one, independent of the number of nodes.

This motivates the problem: it Given a tree, produce a layout with minimax edge length. In this section we show that determining the minimax edge length is computationally intractable. The results are quite discouraging – even the problem of deciding if a given tree can be laid out with all edges of unit length is NP-complete.

**Theorem 3.5.** Given a tree T, deciding whether or not T has a layout with unit length edges is NP-complete.

**Proof.** Observe that the problem is clearly in NP; it is easy to guess a layout and verify that no edge has length greater than one. It remains to show that the problem is NP-hard.

The known NP-complete problem used in the reduction is the NOT-ALL-EQUAL 3CNFSAT problem [29, 72] stated below.

**NOT-ALL-EQUAL 3CNFSAT:** Given a boolean formula  $\phi$  in 3CNF (conjunctive normal form with three literals per clause), does there exist a truth assignment which satisfies  $\phi$  such that each clause contains at least one false literal?

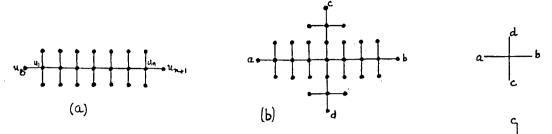

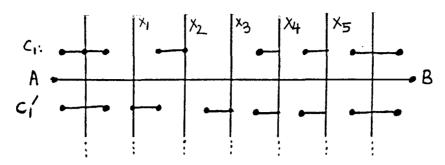

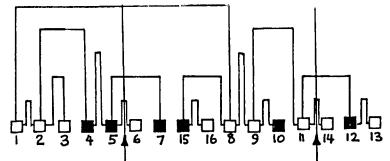

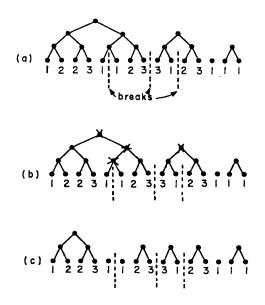

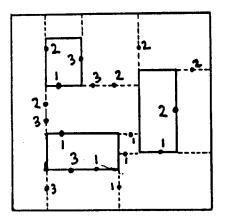

Given a formula  $\phi$  in 3CNF, we construct a graph G with the property that G can be laid out with all edges of unit length *iff*  $\phi$  is an instance of NOT-ALL-EQUAL 3CNFSAT, i.e.,  $\phi$  can be satisfied with at least one false literal per clause. The graph G is constructed from elementary components termed "lines" (Figure 3.10). The crucial property of a line is its rigidity, meaning that in any layout with unit-length edges, nodes  $u_1, \ldots, u_n$  must be lined up either horizontally or vertically. Figure 3.10 shows how to connect two lines so that the resulting graph can be laid out in only two ways (ignoring rotations).

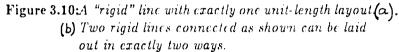

Let  $x_1, \ldots, x_n$  be the variables, and  $C_1, \ldots, C_m$  be the clauses of  $\phi$ . The basic "skeleton"

Figure 3.11: The skeleton of the transformation. Each column represents a variable, while each clause is associated with two rows that are mirror images with respect to the x-axis.

of G is shown in Figure 3.11. For each  $j, 1 \leq j \leq m$ , the distances (number of intermediate nodes)  $\alpha_i - C_{ji}, \alpha_i - C'_{ji}$  are all equal. The line  $u_i - v_i$  corresponds to variable  $x_i$ , and the two ways of embedding it with respect to the A-B axis correspond to assigning  $x_i$  true or false.

Thus far, there are  $2^n$  possible ways of laying out G with unit length edges, each corresponding to a truth assignment to the variables of  $\phi$ . Next, we encode within G the "structure" of  $\phi$  as described below.

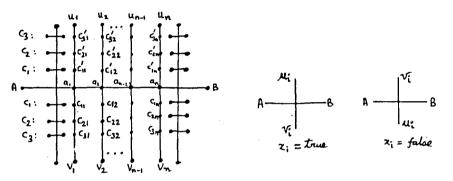

Let clause  $C_j$  be denoted  $l_{j_1} \vee l_{j_2} \vee l_{j_3}$ . If  $l_{j_i}$  is positive  $(x_i)$  add a "striker" at node  $C_{j,j_i}$ . Otherwise, if  $l_{j_i}$  is negative  $(\overline{x}_i)$  add a striker at node  $C'_{j,j_i}$ . Finally, for every  $k \neq j_1, j_2, j_3$ , add strikers both at  $C_{j,k}$  and at  $C'_{j,k}$ . For example, if  $C_1 = x_1 \vee \overline{x}_2 \vee x_3$ , the strikers are added as shown in Figure 3.12.

Think of a node without a striker as a "hole". The rows  $C_j$  and  $C'_j$  together share three holes, and 2n - 3 strikers. Because of the boundary constraints at the sides, no more than n - 1 of these strikers may lie on any side of the A - B axis. In other words, for each clause

Figure 3.12:In any unit-length layout each row contains at least one hole; this corresponds to an instance of NAE-3CNFSAT.

Figure 3.13: A binary tree which has a unique (upto rotations) unit-length layout.

there must be at least one hole on either side of the axis in a unit-length layout. For each clause, a hole "above" the axis implies a truth assignment which makes the clause true, while a hole "below" the axis implies at least one false literal within the clause. Therefore, there is a unit-length layout if and only if the formula is satisfiable with at least one false literal per clause. In short, G has a unit-length layout iff  $\phi$  is an instance of NOT-ALL-EQUAL 3CNFSAT. Since the reduction is easily carried out in polynomial time, the theorem follows.

In the above reduction, many nodes had degree four. We may strengthen the result to binary trees with maximum degree 3. A rigid line may be implemented by stringing together binary trees as shown in Figure 3.13. It is not hard to show that the structure is rigid; the key property is that the complete binary tree on 31 nodes has a unique (up to rotations) unit-length layout. This yields the following result.

E

Corollary 3.6. Given a binary tree, deciding whether or not it has a layout with unitlength edges is NP-complete.

#### 3.5. Assembling Complete Trees

Whenever any system is larger than a single chip, it is necessary to partition it among separate chips which can be assembled at the printed circuit (or chip carrier) level. What is the most effective way to partition a large binary tree among several chips?

This question is pressing because although integrated circuit technology has been advancing at a rapid pace, the technology for packaging chips has been crawling in comparison. Packaging technology severely restricts the number of external connections to an integrated circuit. While the number of components per chip is expected to reach one hundred million, no one forsees chips with more than two or three external pin connections.

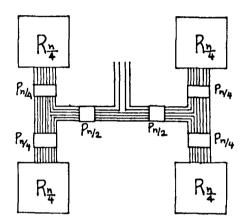

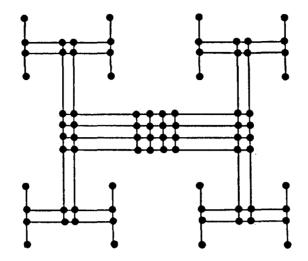

This section presents Leiserson's scheme [50] for assembling complete binary trees using one kind of chip with only four external pin connections. This chip has been used in tree-machine projects at Caltech and Bell Laboratories [16]. We review this scheme here for its simplicity and because the general scheme developed in Section 3.7 is based on similar ideas.

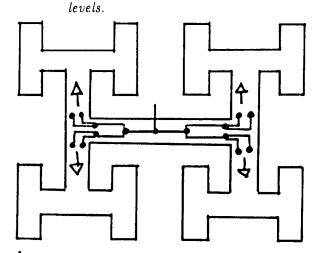

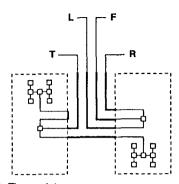

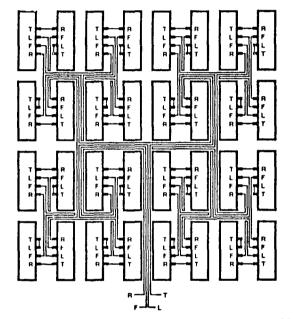

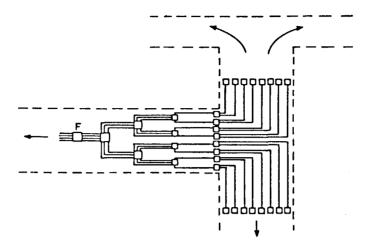

Figure 3.14 shows how arbitrarily large complete binary trees can be built out of a single chip that has only four off-chip connections. Each chip contains one internal node of the tree, and the remainder of the chip is packed as full as possible with an H-tree layout. The internal node requires three off-chip connections (denoted F, R, and L in the figure) for its father, right son, and left son. The H-tree requires only one off-chip connection (denoted T) to its father.

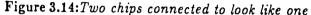

To interconnect two chips, the unconnected internal node of one of the two chips is selected as the father of the two II-trees. In Figure 3.14 the internal node on the left has been chosen for this purpose. The R pin on this chip is connected to its own T pin, and the L pin is connected to the T pin on the other chip. Considered as a unit, the combined two chips now have the same structure as a single chip — three connections to an internal node and one to the root of a complete binary tree. The pair of chips can be similarly combined with another pair to produce a quadruple of chips, which can in turn be combined, and so forth. Figure 3.15 shows

Figure 3.15:A large complete binary tree assembled using many copies of the same chip.

a large complete binary tree which has been wired up in this recursive fashion.

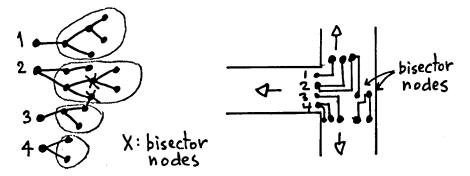

Unlike the assembly for complete trees, configurable or restructurable designs are required for assembling arbitrary binary trees. The reason is simple: a single fixed chip with N processors can realize only one N-node binary tree. In order to realize every N-node binary tree, either a new mask must be designed for each tree, or else connections on the chip must be restructured (for example, by laser) after fabrication. Given the ability to restructure wires on a chip, we ask: Is there an area-efficient restructurable chip with N processors and m pins (m << N) which can be used to assemble every binary tree, independent of its size? This question is affirmatively answered in Section 3.7. The solution depends heavily on the results of the next section which considers the problem of partitioning a binary tree into subforests of size N so that every subforest has at most  $O(\lg N)$  edges connected to nodes in other subforests. The solution to this problem leads directly to the restructurable chip design of Section 3.7.

#### 3.6. Collinear Layouts and Two-color Bisectors

This section introduces the notion of two-color bisectors for trees. Two-color bisectors are a natural extension of graph bisectors, and will be critically used in partitioning graphs for layout. In this section we show how to use two-color bisectors to partition an arbitrary tree into subforests of size N so that every subforest has at most  $O(\lg N)$  edges connected to nodes in other subforests. Bounds on the size of two-color bisectors are obtained from collinear layouts developed by Bentley and Leiserson [50].

Definition. Suppose that an N-node graph G has b black nodes and w white nodes. A twocolor bisector for G is a set of edges whose removal bisects G into two subgraphs each of size at least  $\lfloor N/2 \rfloor$ , and such that each contains at least  $\lfloor b/2 \rfloor$  black and  $\lfloor w/2 \rfloor$  white nodes.

**Theorem 3.7.** Every N-node forest of binary trees has a two-color bisector of size no greater than  $2 \lg N$ .

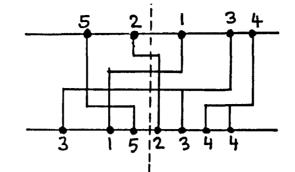

**Proof.** Following Bentley and Leiserson [50], construct a collinear layout for the forest as follows. By removing one edge, separate the forest into two subforests so that neither contains no more than  $\lfloor \frac{2}{3}N \rfloor + 1$  nodes [52]. If either component contains more than  $\lfloor N/2 \rfloor$  nodes, separate it into two smaller components using the one-separator theorem again. Next, recursively construct collinear layouts for each subforest, and place these layouts side-by-side along the baseline. Finally, as shown in Figure 3.16, connect the two (or three) subforests by

Figure 3.16: The recursive construction of a collinear layout.

routing the separator edges on distinct vertical tracks and along a common horizontal track. (For two components this is trivial since only edge is routed; for three components, place the subforest connected to both other subforests in the middle as shown.) For each node there are three vertical tracks to accomodate edges incident to that node.

The height of the layout is determined by a simple recurrence relation. Let h(N) be the height of the layout, so that h(1) = 0, and in general,

$$h(N) \leq h(\lfloor N/2 \rfloor) + 1.$$

A straightforward calculation yields  $h(N) \leq \lg N$ .

Thus far we have ignored the coloring on the nodes. Suppose there are b black nodes and N-b white nodes. Consider a "window" which overlaps  $\lfloor N/2 \rfloor$  consecutive nodes, and place it over the leftmost  $\lfloor N/2 \rfloor$  nodes. If more than  $\lfloor b/2 \rfloor$  black nodes fall within the window, slide the window one position to the right. Observe that by sliding the window on position, the number of black nodes within the window changes by at most one. Furthermore, by sliding the window all the way to the right, less than  $\lfloor b/2 \rfloor$  black nodes would fall within the window. Consequently, there must be an intermediate placement of the window (see Figure 3.17) in which exactly  $\lfloor b/2 \rfloor$  black nodes and exactly  $\lfloor (N-b)/2 \rfloor$  white nodes are contained within the window. (Such a placement can be obtained in linear time.)

Draw vertical lines through the endpoints of the window in the position obtained above. The edges of the forest intersecting these lines form a two-color bisector of the forest. The size of this two-color bisector is no more than twice the height of the layout; in other words, the size of the two-color bisector is no more than  $2 \lg N$ .

Figure 3.17: At some point, a window of size n/2 slid along the baseline must contain half the black and half the white nodes.

For our purpose the following variant of two-color bisectors is appropriate. Suppose each node of an N-node forest is assigned a weight from a *bounded* set  $\{1, 2, ..., k\}$  of weights. We wish to bisect the forest into two equal-size subforests whose total weights differ by at most k. How many edges need be cut? Adapting the argument for two-color bisectors to this variant in a straightforward manner shows again that  $2 \lg N$  cuts suffice.

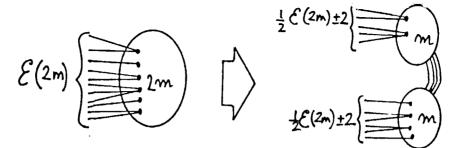

Having obtained bounds on the size of two-color bisectors for forests, we wish to use them for partitioning an arbitrary binary tree into subforests of size at most N so that every subforest has  $O(\lg N)$  edges connected to nodes in other subforests. This result is established in the following Theorem.

**Theorem 3.8.** Every N-node binary tree can be partitioned into  $\lceil N/M \rceil$  subforests, each of size at most M, such that no subforest has more than 4lgM + 8 edges connected to nodes in other subforests.

**Proof.** First bisect the tree into two subforests, each of size at least  $\lfloor N/2 \rfloor$ , by cutting no more than  $\lg N$  edges. Split each subforest recursively as follows: For each node in a recursively split component of size m assign a weight equal to the number of edges incident to that node and which were cut at a previous level. Since the degree of a node is at most three, the weight assigned to a node is at most 2. From the argument following Theorem 3.7, there is a weighted bisector of size no greater than  $2\lg m$  for the component. This weighted bisector divides the number of external connections almost equally (the difference is at most two) between the subcomponents of sizes  $\lfloor m/2 \rfloor$  and  $\lfloor m/2 \rfloor$ . As seen in Figure 3.18, the number

42

ASSEMBLING ARBITRARY TREES

Figure 3.18: To keep the number of external connections to all subcomponents small when a component is bisected, the external connections must be evenly divided between the subcomponents.

of external connections into either of the new subcomponents is no more than the size of the weighted bisector plus one-half the number of external connections into the component just split (plus two). This recursive decomposition terminates when each component has size at most M. Letting  $\mathcal{E}(m)$  be the number of external connections into any component of size m, we have  $\mathcal{E}(N) = 0$ , and

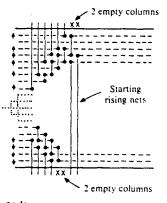

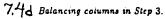

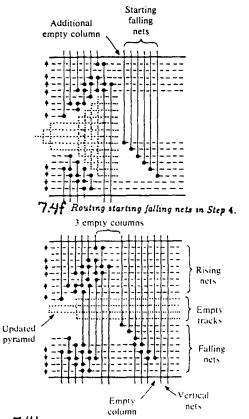

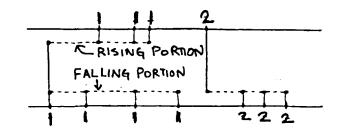

$$\mathcal{E}(m) \leq \frac{1}{2}\mathcal{E}(2m) + 2\lg(2m) + 2.$$