FOUNDATIONS OF A THEORY OF SPECIFICATION

Section & Section of

FOR DISTRIBUTED SYSTEMS

Eugene W. Stark

This blank page was inserted to preserve pagination.

# Foundations of a Theory of Specification for Distributed Systems

by

# Eugene William Stark

B.E.S. The Johns Hopkins University (1977)

S.M. Massachusetts Institute of Technology (1980)

Submitted to the Department of Electrical Engineering and Computer Science in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

at the

# MASSACHUSETTS INSTITUTE OF TECHNOLOGY

August, 1984

Copyright Massachusetts Institute of Technology 1984

Signature of Author\_\_

Department of Electrical Engineering and Computer Science August 24, 1984

Certified by\_\_\_\_

Prof. Nancy A. Lynch, Thesis Supervisor

Accepted by

Prof. Arthur C. Smith, Chairman., E.E.C.S. Department Committee on Graduate Students

# Foundations of a Theory of Specification for Distributed Systems by

Eugene William Stark

Submitted to the

Department of Electrical Engineering and Computer Science on August 24, 1984 in partial fulfillment of the requirements for the Degree of Doctor of Philosophy.

## Abstract

This thesis investigates a particular approach, called *state-transition specification*, to the problem of describing the behavior of modules in a distributed or concurrent computer system. A state-transition specification consists of: (1) a state machine, which incorporates the safety or invariance properties of the module, and (2) validity conditions on the computations of the machine, which capture the desired liveness or eventuality properties. The theory and techniques of state-transition specification are developed from first principles to a point at which it is possible to write example specifications, to check the specifications for consistency, and to perform correctness proofs using the specifications. The utility of the techniques is demonstrated through examples.

Major contributions of the thesis include: (1) the definition of a semantic model that incorporates *hierarchy of abstraction* and *modular decomposition* as fundamental notions; (2) specification and proof techniques that amoothly handle both safety and liveness properties; (3) techniques that use liveness properties stated in *rely-/guarantee-condition* form to obtain simple proofs of correctness; (4) an interesting and useful notion of consistency for specifications involving liveness properties.

Keywords: state-transition specification, verification, concurrency, hierarchy, modularity, temporal logic, safety, liveness, rely/guarantee conditions

Thesis Supervisor: Nancy A. Lynch

Title: Associate Professor of Computer Science and Engineering

# Acknowledgements

I am deeply indebted to my thesis adviser, Nancy Lynch, but for whom this thesis would likely never have been completed. Nancy read many, many difficult drafts of this work with enthusiasm and promptness that went far beyond the mere call of duty. She always seemed to manage not only to identify the most troublesome portions of each draft, but to make insightful suggestions for improvement as well. I am also grateful to John Guttag, Barbara Liskov, and Albert Meyer for their suggestions on improving the presentation. Discussions with Bill Weihl helped to formulate ideas during the early stages.

In an entirely different category are my parents, Joan S. Stark and William L. Stark, Jr., who made it seem natural that I should seek and complete graduate education, and whose love and support during this endeavor I cannot adequately acknowledge. Julian Stanley of Johns Hopkins made it possible for me to pursue the undergraduate portion of my education at an accelerated rate.

Finally, I would like to thank the chessplayers at Au Bon Pain in Harvard Square for providing a much-needed diversion during the past year.

# CONTENTS

| 1. Introduction                                          | 6         |

|----------------------------------------------------------|-----------|

| 1.1 Scope of the Thesis                                  | 7         |

| 1.2 An Example                                           |           |

| 1.3 Outline of the Thesis 1                              |           |

| 1.4 Related Work 1                                       |           |

| 2. Framework for a Theory of Specification 3             | 8         |

| 2.1 Interfaces, Observations, and Behaviors              | 38        |

| 2.2 Abstraction, Decomposition, and Interconnection 4    | 41        |

| 2.3 Specification, Implementation, and Correctness 4     | 13        |

| 3. State-Transition Specifications                       | 5         |

| 3.1 Subset Specifications 4                              | <b>16</b> |

| 3.2 Machines and Computations 4                          |           |

| 3.3 Properties of Histories 5                            | 50        |

| 3.4 State-Transition Specifications                      | 52        |

| 3.5 The Correctness Theorem 5                            | 54        |

| 3.6 Possibilities Mappings 5                             | <b>58</b> |

| 3.7 Rely-/Guarantee-Conditions6                          | Ю         |

| 4. The Synchronizer Implementation                       | 6         |

| 4.1 Notation 6                                           | 36        |

| 4.2 Specification of the Synchronizer Module             | 37        |

| 4.3 Specification of the Synchronizer Component Module 6 | <b>9</b>  |

| 4.4 Correctness of the Synchronizer Implementation       | ′3        |

|                                                          |           |

| 5. Consistency of Specifications                    | ;2         |

|-----------------------------------------------------|------------|

| 5.1 I/O-Systems 8                                   | 83         |

| 5.2 I/O-Behaviors and I/O-Consistency               | <b>B</b> 7 |

| 5.3 Machine Characterization of I/O-Behaviors       |            |

| 5.4 Examples of I/O-Behaviors                       | 97         |

| 5.5 Composition of I/O-Behaviors                    | 07         |

| 5.6 Alternative Classes of Computable Behaviors 11  | 10         |

| 6. A Completeness Result 11                         | 2          |

| 6.1 Specification Domains 11                        | 12         |

| 6.2 Locally J-Consistent Subset Specifications 11   | 16         |

| 6.3 Well-Formedness Properties of Specifications 11 | 17         |

| 6.4 The Completeness Theorem 12                     | 20         |

| 7. Conclusion 12                                    | 3          |

| 7.1 Summary 12                                      | 23         |

| 7.2 Ideas for Future Work 12                        |            |

| Appendix I. Formal Specification and Proof 13       | 6          |

| I.3 Event/State Algebras 13                         | 37         |

| I.4 Description of Event/State Algebras 14          | 40         |

| I.5 Implementation Algebras 14                      | 44         |

| I.6 Proof Techniques 14                             | 46         |

| 1.7 Rely-/Guarantee-Condition Proof Techniques 14   | 49         |

| I.8 I/O-Consistency Proof Technique 15              | 50         |

| Appendix II. Additional Examples                    | 2          |

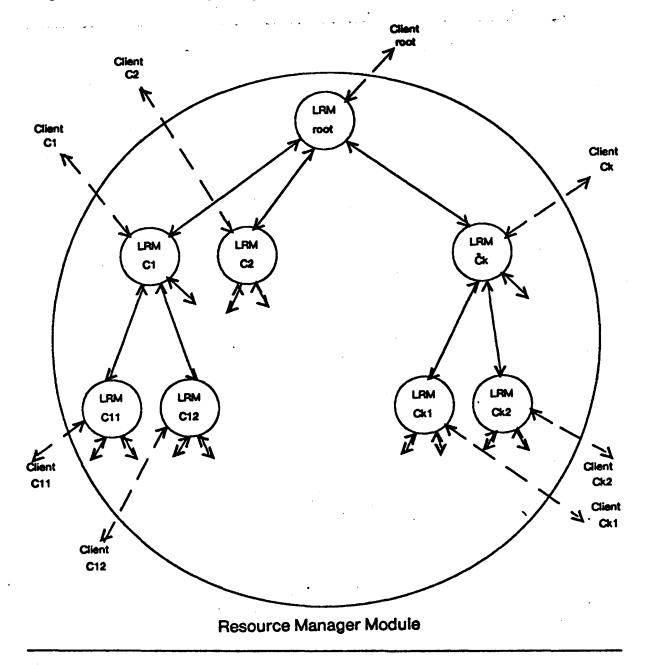

| II.9 A Distributed Resource Management Algorithm 15 | 53         |

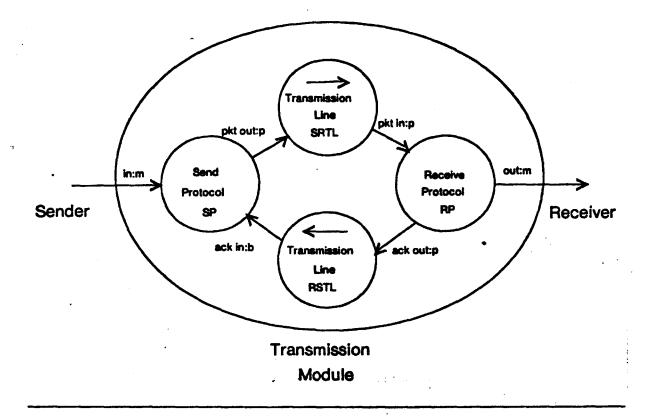

| II.10 A Message Transmission System                 |            |

| Appendix III. Index of Definitions 20               | 2          |

\*..,.

•••

# 1. Introduction

The purpose of this thesis is to investigate a particular approach, called *state-transition specification*, to the problem of describing the behavior of modules in a concurrent or distributed computer system. In the state-transition approach, the desired behavior is described in terms of a kind of state machine whose computations generate records of event occurrences, called *observations*. A state-transition specification consists of two parts: (1) the definition of the state machine, which incorporates the "safety" or invariance properties of the module, and (2) the definition of some *validity conditions* on the computations of the machine, whose purpose is to capture the desired module "liveness" or eventuality properties. A state-transition specification defines a set of "acceptable" observations, namely the observations produced by valid computations of the state machine. A module behavior satisfies such a specification if the module behavior contains only acceptable observations.

The idea of describing module behavior with the help of state machines is not new, having already been proposed in various forms by other authors, [e.g. Parnas72, Yonezawa77, Lamport83]. However, previous work seems to be concerned primarily with *how* to write module specifications, and *how* to use proof rules to prove the correctness of implementations. The important issues of what constitutes the *meaning* of a specification, and what it *means* for an implementation to be correct, have not received satisfactory treatment. As a result, it is impossible to answer important questions such as: "What rules are *sound* for proving the correctness of an implementation," and "When is a specification *consistent*?"

This thesis improves upon previous work by systematically developing the theory and techniques of specification from "first principles" to a point at which it is possible to write example specifications, to prove implementations correct, and to check specifications for consistency. The theory incorporates an underlying semantic model within which one can formulate language-independent definitions of the notions of "implementation" and "correctness." The meaning of state-transition specifications is defined in terms of the model, and all proof techniques are shown to be sound with respect to the model. The major contributions of this thesis are:

(1) The definition of a semantic model that incorporates hierarchy of abstraction and modular decomposition as fundamental notions.

(2) Specification and proof techniques that smoothly handle both safety and liveness properties.

(3) Techniques that use liveness properties stated in *rely-/guarantee-condition* form to obtain simple proofs of correctness.

(4) An interesting and useful notion of consistency for specifications involving liveness properties.

(5) Illustration of the utility of the ideas developed through specifications, implementations, and correctness proofs for three examples:

(a) a synchronizer module, which is implemented by a ring-structured network of synchronizer component modules,

(b) a resource management module, which is implemented by a tree-structured network of local resource manager modules,

(c) a message transmission module, which is implemented by unreliable transmission line modules, a send protocol module, and a receive protocol module, which together obey the alternating bit protocol.

## **1.1 Scope of the Thesis**

A specification is a piece of text whose purpose is to describe the desired operation of a module in a computer system. Specifications form an integral part of a "top-down" design method in which design proceeds by the successive decomposition of a module to be implemented into a collection of interacting component modules [Liskov79, Wirth71]. The purpose of specifications in such an approach is to serve as a contract between the user and the implementer of a module. This helps to limit complexity by permitting a system to be decomposed into modules of reasonable size, such that each module depends only upon the specifications, and not the implementations, of the modules with which it interacts.

To permit the possibility of rigorous reasoning about specifications, a specification language should be given a formal semantics in terms of an underlying mathematical *semantic domain*. In this thesis, we use the term *behavior* to refer to the elements of a semantic domain, since the purpose of these elements is to serve as a mathematical

model of the behavior of a portion of a real-world computer system. The semantics of a specification language describe how each specification denotes a set of behaviors that *satisfy* the specification. If the semantics of a programming language are defined so that each important program fragment denotes a behavior, then it is possible to derive syntactic rules for proving that (the denotations of) program fragments satisfy (the denotations of) specifications. The purpose of this thesis is not to propose particular formal specification or programming languages, but rather to investigate a collection of language-independent semantic concepts upon which particular specification and programming languages might be based. We therefore assume that specification and programming languages can have their meanings defined in terms of behaviors, and do not concern ourselves with the precise method by which this is accomplished.

In this thesis, we are concerned with concurrent or distributed systems. By this we mean systems that are most naturally viewed as a collection of independent, communicating modules, such that effects of concurrent operation of the various modules form a significant part of the description of system behavior. This thesis is primarily concerned with the concurrency aspect of distributed computing; while the model and techniques do not rule out the possibility of treating other aspects such as node crashes and network failures, no special structure to deal with these problems is included. The techniques of this thesis have been developed primarily with the idea that they would be applied to the problem of describing and reasoning about distributed algorithms. The examples presented are of this kind.

## 1.2 An Example

In this section, an example specification problem will be used to introduce informally the fundamental ideas about specification on which this thesis is based.

## **1.2.1 The Synchronizer Module**

Consider the following scenario: A number of processes in a computer system require the use of a single resource to accomplish their respective tasks; however, because of limitations inherent in the resource, at most one process can be allowed to access the resource at any instant of time. To enforce this restriction, a synchronizer module is introduced, and the processes, which we will refer to as the user processes, are required to obtain permission from the synchronizer module before accessing the

-8-

resource. It is the job of the synchronizer module to produce correct synchronization of the user processes' accesses to the resource. Our problem is to describe precisely the synchronizer module behaviors that are "acceptable" in the sense that they always produce "correct synchronization." This precise description is the specification of the synchronizer module.

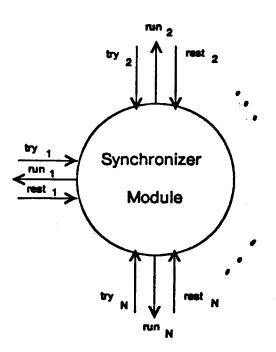

When a user process desires to access the resource, it issues a *try* request to the synchronizer module. The user process is then supposed to wait until it receives a *run* response from the synchronizer module. When the user process is finished using the resource, it issues a *rest* response to the synchronizer module. We can capture these decisions in diagrammatic form as shown in Figure 1, in which the synchronizer module is depicted as a circle, and the possible requests and responses are drawn as arcs incident on and exiting from the circle, respectively. We assume that there are a total of N user processes accessing the synchronizer module, and have used a subscripted process number to distinguish the requests and responses corresponding to different processes.

# Fig. 1. The Synchronizer Module

The set of all possible requests and responses for the synchronizer module can be thought of as an "alphabet" or "syntax" for describing the interaction of the synchronizer module with its environment. We call this set the *interface* of the synchronizer module, and refer to its elements as *events*. By observing the synchronizer module during an execution, we can obtain a record of the events that occurred during the execution. We call this record of event occurrences an *observation*, and assume that it takes the form of a finite or infinite sequence of events.

By fixing the interface of the synchronizer module to be a particular set of events, we determine a universe of possible observations. We next consider how to describe which observations in this universe are "acceptable." We must include in our description the idea that at most one user process at a time may access the resource. Also, we wish to require that the synchronizer module be *fair* in the sense that every *try* request by a user process is eventually answered by a *run* response, if it is possible to do so without violating the mutual exclusion property.

A natural way of describing which observations are acceptable is through the use of *conceptual states*. With this technique, we imagine that at any instant of time the synchronizer is in one of a number of possible internal states. These states may or may not have anything to do with the actual internal state of the synchronizer module; they are merely a tool for describing its observable behavior. After defining the set of initial states, we then describe for each event the preconditions required for that event to occur, and how the conceptual state of the synchronizer changes as a result of the occurrence of that event.

The conceptual state of the synchronizer module at any instant of time is a vector that tells for each user process what the synchronizer module thinks that user is currently doing with respect to the resource, based on the requests and responses that have occurred so far. The possibilities are that the user is either trying to obtain permission to access the resource (trying), is actively using the resource (running), is done using the resource (resting), or has failed to correctly follow the protocol (error).

1. The formal definition of observation used in this thesis is slightly more complicated than a finite or infinite sequences of events (see Chapter 2). This is done for technical reasons that are unimportant for the present, informal discussion.

Initially, the synchronizer module believes that each user process is resting. The state changes and preconditions are as follows: a *try* event for a process causes the state of that process to change to "trying" if it was previously resting, and to "error" otherwise; a *run* event for a process can occur only if that process is trying and no processes are currently running, and causes the state for that process to change to "running;" a *rest* event for a process causes the state of that process to change to "running;" a *rest* event for a process causes the state of that process to change to "resting" if it was previously running, otherwise to "error."

A particular observation for the synchronizer module satisfies the description of the previous paragraph if to each finite prefix of the observation we can assign a conceptual state in such a way that each state change satisfies the conditions enumerated in the previous paragraph. For example, assuming there are only two user processes, the observation

try, try, run, rest, run, rest,

satisfies the conditions above since we can assign internal states as follows:

However, the observation

try, try, run, run, rest, rest,

does not represent a correct functioning of the synchronizer module since

<resting, resting> try, <trying, resting> try, <trying, trying> run, <running, trying>

run, <running, running> rest, <resting, running> rest,

# <resting, resting>,

which is the only assignment of states that satisfies the state change requirements, has the property that the precondition for the  $run_2$  event is not satisfied by the state <running, trying>. We will use the term "history" to refer to an observation that has been annotated with states.

The state-transition description above tells us a significant amount about what are the correct observations of the synchronizer module, but it does not say everything that should be said. In particular, the requirement that every request by a user process should eventually be satisfied, if possible, is not captured by the state-transition description. Informally, the reason is that a state-transition description captures only properties of histories that are "local" in the sense that they involve only adjacent states, whereas the fairness property we would like is a "global" property that involves possibly widely separated portions of the history. If the conceptual state technique is to work, we must find some way to state global properties in a form compatible with the statement of the local properties. In Chapter 4 it will be shown how global properties can be expressed in the language of *temporal logic*.

A specification of the synchronizer module via the conceptual state approach therefore consists of a state-transition description of the local properties that must be satisfied by acceptable observations, plus a description of additional global properties satisfied by such observations. A particular synchronizer module behavior is said to *satisfy* the synchronizer module specification if it contains only acceptable observations.

#### 1.2.2 Implementation, Abstraction, and Composition

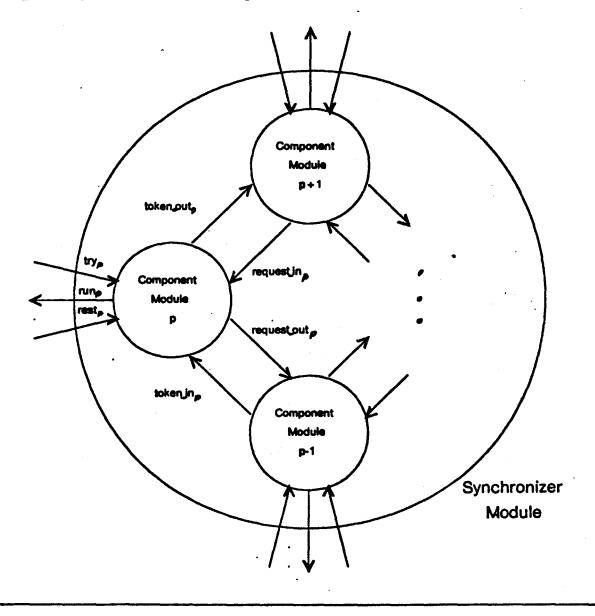

Now let us consider how the synchronizer module might be implemented. A possible organization is shown in Figure 2. In Figure 2, the synchronizer module is shown to be composed of a number of "synchronizer component" modules connected in a ring-like fashion. Each synchronizer component module interacts with exactly one user process and with its neighboring synchronizer component modules. The implementation operates as follows: There is a single conceptual token that circulates around the ring in the clockwise direction. A synchronizer component module must possess the token whenever it grants its associated user permission to access the resource. In addition to the *try*, *run*, and *rest* events with which communication with the user is accomplished, a synchronizer component module may pass the token to its clockwise neighbor with a *token\_out* event, may request the token from its counterclockwise neighbor with a *request\_out* event, and may accept a request from its clockwise neighbor with a *request\_in* event.

We resolve the implementation relationship between the synchronizer component modules and the synchronizer module into two separate operations on systems: a *composition* operation, which takes a number of component modules and combines them into a larger system, and an *abstraction* operation, which takes the larger system and throws away internal details that are not of interest in the more abstract view. In the synchronizer example the composition operation takes a collection of synchronizer

Fig. 2. Implementation of the Synchronizer Module

component modules and connects them into a ring network, and the abstraction operation throws away the details of the internal communication between the component modules, saving only the events that make up the interface with the user processes.

# **1.2.3** Correctness of an Implementation

Suppose we are given a specification for the synchronizer module, and specifications for each of the synchronizer component modules. Each specification determines a set of behaviors that satisfy it. The implementation is "correct" with respect to these specifications if, no matter what behaviors we "plug in" for the synchronizer component modules, as long as each component behavior satisfies its specification, then the resulting synchronizer module behavior, constructed from the components via the operations of composition and abstraction, satisfies the synchronizer module specification.

# 1.2.4 Summary

The ideas presented in this section can be summarized as follows:

(1) Every module in a system has a well defined *interface*, which is the syntax with which it interacts with other modules in the system.

(2) An interface defines a universe of observations, which are records of operation that might be produced by a module with that interface. These observations constitute the possible "functionings" of the module. The set of all observations that can be produced by a particular module instance serves as the *behavior* of that module instance.

(3) A module can be specified by describing a set of "acceptable" observations. A module behavior "satisfies" such a specification if it contains only acceptable observations.

(4) An implementation of an abstract module in terms of a collection of component modules consists of a *composition operation* for combining component module behaviors to form a "composite" behavior, and an *abstraction operation* for deleting information from the composite behavior to obtain a behavior of the abstract module.

(5) An implementation is correct with respect to given specifications if, whenever we apply the composition operation of the implementation to a collection of behaviors that satisfy the component module specifications, and then apply the abstraction operation of the implementation to the resulting composite behavior, we obtain a behavior that satisfies the abstract module specification.

# **1.3 Outline of the Thesis**

This thesis is an attempt to elaborate and make more precise the ideas illustrated informally in the previous section. In particular, an attempt will be made to answer the questions:

(1) What is an appropriate mathematical framework that adequately captures the notions of interface, observation, composition, abstraction, implementation, specification, and correctness discussed above? (Chapter 2)

(2) How can we translate, in a natural and systematic way, an intuitive understanding of the function to be performed by a module into a precise specification? (State-Transition Specifications, Chapter 3)

(3) Once we have obtained such a specification, how can we be sure that it says something meaningful? (*Consistency* of specifications, Chapter 5)

(4) How can we show, in a systematic way, that a particular implementation of an abstract module by a collection of component modules is correct with respect to given specifications? (*Correctness Proofs*, Chapters 3, 4, Appendix II)

(5) What general principles can we learn about how to organize specifications and proofs of correctness? (*Rely/Guarantee-Conditions*, Chapters 3, 4, Appendix II)

(6) How might the specification and proof techniques developed in this thesis be formalized to permit the use of mechanical aids? (*Event/State Algebras*, Appendix I).

This thesis is organized as follows: Chapter 2 introduces formal definitions of the notions of interface, observation, abstraction, composition, implementation, and correctness. Some of the modeling choices embodied in these definitions are discussed.

In Chapter 3, the basic definitions of Chapter 2 are used to define formally the notion of a state-transition specification. The main result of Chapter 3 is the Correctness Theorem (Theorem 3.9), which shows how the structure of state-transition specifications can be exploited to obtain a systematic method for performing correctness proofs. Secondary results of Chapter 3 (Lemma 3.11, Lemma 3.12) suggest how the proof method embodied in the Correctness Theorem can be further systematized if module liveness specifications are expressed in terms of rely-/guarantee-conditions.

Chapter 4 applies the theory of Chapters 2 and 3 to the synchronizer example. The complete specifications of the synchronizer and synchronizer component modules are presented, and the synchronizer implementation is proved correct with respect to these specifications. The language of *temporal logic* is used as a notation for expressing liveness properties.

Chapter 5 is concerned with finding an appropriate notion of consistency of specifications that include nontrivial liveness properties. Intuitively, a specification ought to be consistent if and only if it is satisfiable by some behavior. However, if by the term "behavior" we mean "arbitrary set of observations," then we obtain a notion of consistency that is much too liberal. To obtain stronger notions of consistency, we must restrict our attention to "realizable" or "computable" behaviors. Chapter 5 introduces a particular class of computable behaviors, the "I/O-behaviors," that is based on an underlying model of asynchronous concurrent computation called "I/O-systems." The corresponding notion of "I/O-consistency" is found to be useful for distinguishing between "obviously realizable" and "obviously unrealizable" liveness specifications. Chapter 5 develops a technique for proving state-transition specifications to be I/O-consistent and applies this technique to examples.

In Chapter 6 a kind of completeness result is proved (the Completeness Theorem, Theorem 6.4), which gives sufficient conditions under which a correct implementation has a proof by the Correctness Theorem. The statement and proof of Theorem 6.4 uses in a crucial way the existence of a "specification domain," which is a class of behaviors, like the I/O-behaviors, with certain closure properties.

Finally, Chapter 7 summarizes what has been accomplished and suggests avenues for future investigation.

Additional important material is contained in Appendices I, II, and III. Appendix I provides a formal semantics for the temporal logic language used informally in Chapters 4-6, and shows the correctness and consistency proof techniques developed in the thesis can be formalized within this language. Appendix II considers two additional examples: a distributed resource management system, and a reliable message transmission system based on the alternating bit protocol. Both of these systems are specified and proved correct using the techniques developed in the main body of the thesis. Appendix III is an index of definitions.

# 1.4 Related Work

The rather large body of work related to this thesis can be divided roughly into the following categories:

(1) Specification of sequential programs/abstract data types.

(2) Models of distributed/concurrent computation.

(3) Temporal logic specification techniques.

(4) Specification of communication protocols.

(5) Other distributed/concurrent system specification techniques.

Each of these categories will be discussed below. Further discussion is included at appropriate points in this thesis.

# 1.4.1 Specification of Sequential Programs/Abstract Data Types

Work in the area of specification of sequential programs can be classified into two categories: that concerned with the specification of the *function* to be performed by a program or program fragment, and that concerned with the specification of the *data types* manipulated by a program.

#### Sequential Program Function Specification

Specification of the function to be performed by a program or program fragment is a problem that must be addressed by any work on program correctness. In the sequential case, the semantics of a programming language assigns to each program fragment (statement, procedure, etc.) some mathematical object (denotation) representing the effect of executing that fragment. Typically, (see, e.g. [Jones81]) this denotation takes the form of a partial function or a binary relation on program states. A specification for a program fragment consists of some properties that must be satisfied by the denotation of that fragment.

Often function specifications are expressed in the form of Floyd/Hoare partial correctness assertions (PCA's) [Floyd67, Hoare69], consisting of a precondition and a postcondition, which are predicates on states. A program fragment satisfies a PCA if, whenever execution of the fragment is begun in a state satisfying the precondition, then execution will terminate only in a state satisfying the postcondition. Thus, if binary relations are used as denotations of fragments, a PCA is satisfied by any relation *R* such

that if  $\langle q, r \rangle \in R$  and q satisfies the precondition of the PCA, then r satisfies the postcondition.

Besides being convenient for specifying the function that must be satisfied by a program fragment, partial correctness assertions can be used to construct a formal deductive system for reasoning about the behavior of program fragments. For a good overview of these "Hoare logics" of programs, see [Apt81].

The partial correctness assertion technique has been generalized with some success to systems of concurrent processes [e.g. Owicki76]. However these techniques suffer from a lack of modularity in the sense that there is no notion of the behavior of a single process in isolation. Thus it is possible to specify the function of a complete parallel program, but not the behavior of its constituent processes. Although a logic of partial correctness assertions is used to prove that the behavior of a program satisfies its specification, the truth of PCA's associated with one process cannot be determined, except within the context of the PCA's for all other processes.

Partial correctness assertions are capable of expressing only safety properties of the form: "Whenever control is at point *P*, then relation *R* holds on the program variables. In general, one is interested in liveness specifications as well. For sequential programs, often the only liveness specifications of interest are statements that the program is guaranteed to terminate under certain conditions. Liveness properties of this simple form can be handled by incorporating termination into PCA's, as in Dijkstra's calculus of "weakest preconditions" [Dijkstra76], or by techniques completely outside of PCA's, such as Floyd's well-founded set technique [Floyd67]. For distributed or concurrent programs, it is almost always the case that more general liveness properties than simple termination are of interest, and these require alternative techniques.

#### **Data Type Specification**

The problem of describing the data objects manipulated by a program, especially the user-defined data objects, is usually referred to as "specification of abstract data types." There are actually two quite different problems that are addressed in the literature on abstract data type specification: the specification of *immutable* abstract data types, whose objects do not change their state during execution, and the specification of *mutable* abstract data types, whose objects have changeable state. Specification of immutable abstract data types is the problem of describing and reasoning about static collections of values, functions, and relations. Usually a collection of interdependent immutable abstract data types is identified with the mathematical notion of a *heterogeneous algebra*, and algebras are described either axiomatically, as in [Guttag78, Goguen78, Kapur80], or via set-theoretic constructions, as in [Abrial80]. Specification of mutable abstract data types, on the other hand, can be thought of as the problem of describing and reasoning about the dynamic behavior of a collection of objects that can be manipulated using a limited set of procedures [Guttag80, Wing83]. Berzins [Berzins79] models a mutable abstract data type as a kind of *state machine*, which describes how the states of the mutable data objects evolve as a result of the invocation of the procedures.

The problem of specifying *immutable* abstract data types is not addressed by this thesis. In fact, the specification and proof techniques presented in this thesis assume as a prerequisite the ability to describe heterogeneous algebras and to perform reasoning about such algebras once they have been described. On the other hand, the problem of specifying *mutable* abstract data types can be viewed as a special case of the general problem of module specification considered in this thesis, by thinking of a mutable abstract data type in terms of a "type manager" module, which encapsulates the objects of the data type and which performs manipulations on these objects in response to requests by the environment. Viewed in this way, the purpose of a mutable abstract data type specification is to describe the correct "observations" for the type manager module. The notion of observation appropriate here is that of a history of "events," where each event records either a request for the type manager to perform some manipulation on the objects, or a reply indicating the results of some previously requested manipulation.

## **1.4.2 Models of Concurrent Computation**

Quite a number of models have been proposed for investigating concurrent and distributed computer programs [Brock83, Hoare81b, Hoare81a, Greif75, Hewitt77, Kahn74, Keller76, Lynch81, Pratt82, Rounds81]. In this thesis as well, specific assumptions are made about how to model the behavior of such systems. It is necessary to make these assumptions to reach a point at which concrete example specifications can be written and correctness proofs performed. However, a conscious

effort has been made to assume no more structure than is necessary for the results of this thesis. An attempt has been made to identify a few fundamental concepts that are required of *any* model, if it is to serve as a semantic foundation for the theory of specification developed here.

The fundamental concepts identified in this thesis are the notions of *interface*, *observation*, *behavior*, *abstraction*, and *composition*. These concepts, which have already been informally discussed, are given formal definitions in Chapter 2. In this section, we will briefly review the features of a number of extant models of concurrency and attempt to identify the notions of event, interface, observation, behavior, abstraction, and composition used here with corresponding notions in each of the models. We will also be interested in whether each model is suitable as a semantic basis for a specification language -- in particular, whether the model can model is useful for specifications involving liveness properties.

#### Kahn-MacQueen Processes

A rather elegant model of concurrent computation is the stream processing model of Kahn [Kahn74] and Kahn and MacQueen [Kahn77]. In this model, a process communicates with its environment through a collection of named *channels*. A process uses each channel either as an *input* channel or an *output* channel, but never as both. During execution, a process can read input values from input channels and emit output values on output channels. We can imagine observing a process throughout an entire execution and recording the sequence of values transmitted on each channel. Such a sequence of values, which can be either finite or infinite, is called a *stream*. A process is modeled by a *continuous function* from tuples of input streams to tuples of output streams. The notion of continuity used here is derived from the fact that streams under the prefix ordering form a partially ordered set which is complete under limits of increasing chains. Processes are *deterministic* in the sense that to each input tuple *I*, there is precisely one output tuple *O* that can be produced by a particular process, when that process is supplied with input *I*. This is a consequence of the fact that processes are modeled by functions.

In the stream processing model, the sets of input and output channels used by a process serve as the interface of that process. The role of an observation of a process is played by a pair  $\langle I, O \rangle$ , where I is a tuple of streams corresponding to the input

channels, and O is a tuple of streams corresponding to the output channels. The usual identification of a function with its graph permits us to view a process behavior f as the set of all observations of the form  $\langle I, f(I) \rangle$ .

A process network describes how to compose a collection of processes to form a composite system. Formally, a process network defines a kind of fixed point construction that maps a collection of component process behaviors to a behavior for the composite network. These fixed point constructions comprise the composition operations. The composition operations used by Kahn and MacQueen include features of both composition and abstraction as defined here, in the sense that once two processes have been connected by a communication channel, the stream of values transmitted over that channel is no longer of interest, and is ignored.

The Kahn/MacQueen model is unsuitable for the purposes of this thesis because it is incapable of representing processes with nondeterministic behavior.

# Nondeterministic Process Nets

There have been several attempts to generalize the stream processing model of Kahn and MacQueen to incorporate nondeterminism. One such attempt is reported by Brock in [Brock83] (superseding the earlier version [Brock81] by Brock and Ackermann), where references to other attempts are given. In [Brock83], it is shown that the straightforward attempt to generalize the model of Kahn and MacQueen by permitting process behaviors to be *relations*, rather than functions, is doomed to failure. Intuitively, the reason is that the behavior of nondeterministic processes depends, in general, on the relative orders in which inputs are received and outputs produced. In essence, Brock's approach is to replace the </, O> observations used by Kahn and MacQueen by scenarios. Scenarios include, in addition to the streams of values transmitted on each of the channels, a partial ordering that records some of the information concerning the temporal order in which values were transmitted. The behavior of a process is defined to be the set of all scenarios that the process can produce in its various executions. Brock shows how composition operations on scenario sets can be defined, in analogy to the operations on continuous functions defined by Kahn and MacQueen.

Pratt's [Pratt82] "repackages" Brock's model into a general framework for modeling processes and their composition, in which the behavior of a process is represented by the set of all *traces* (partially ordered multisets of events) it is capable of producing. As in the models of Kahn/MacQueen and Brock, the interface of a process can be identified with the set of all events in which the process can participate. The notion of trace plays the role of an observation. The notion of the *restriction* of a trace to a subset of its events is used to define composition of process behaviors. Restriction mappings on traces play essentially the same role in Pratt's model as decomposition maps play in the model of this thesis.

The models of Brock and Pratt admit the possibility of infinite scenarios or traces, and therefore do not a priori rule out the possibility of modeling processes that satisfy nontrivial liveness properties. However, this possibility is not addressed by either Brock or Pratt. Since we are interested in modeling processes with liveness properties, the models of Brock and Pratt are not suitable in their present state of development.

# **Communicating Sequential Processes**

An important class of models of concurrency [Francez79, Hoare81a, Hoare81b, Rounds81] has been developed through attempts to give a formal semantics to the language of "Communicating Sequential Processes" (CSP) defined in [Hoare78]. In each of these models, the behavior of a process describes the traces (finite sequences of communication events) in which the process is willing to participate as it executes. The set of all events in which a process can ever participate plays the role of the interface of that process. The notion of a trace plays the role of an observation. Although the particular notion of process behavior is different for different models, each of the models of CSP contains a collection of algebraic operations on process behaviors, which are used to define the meaning of the various constructs of CSP. In particular, each model has some sort of "restriction" or "hiding" operations, which cause events to be deleted from a process behavior, and some sort of "relabeling" operations, which allow events of a process to be renamed. These operations are used for essentially the same purpose as the abstraction operations used in this thesis. Each model also has one or more "composition" operations (composition by intersection, composition by interleaving, or a mixture of the two) corresponding to the composition operators of this chapter, whose effect is to combine process behaviors in various ways.

The important considerations for models of CSP derive from a feature peculiar to that language. A CSP process can *refuse* to communicate with its environment. If a CSP process refuses to perform any of the communications offered by its environment, then *deadlock* is the result. The different definitions of process behaviors in the various models of CSP arise from attempting to deal with (or to ignore) the subtleties of refusals and nondeterminism.

In [Hoare81b], a process behavior is a prefix-closed set of traces, which can be viewed equivalently as a behavior of the kind defined in this thesis. There are operations in [Hoare81b] for deleting and renaming the events of a process. These operations are examples of the abstraction operators used in this thesis. Process behaviors are composed by the parallel composition operator ||, which is defined as follows: If A is the behavior of a process with interface E and B is the behavior of a process with interface F, then A || B is the set of all traces u formed from events in E U F such that the restriction of u to E is in A and the restriction of u to F is in B. This notion of composition is a particular example of the composition operators defined in this thesis.

Hoare, Brookes, and Roscoe [Hoare81a] extend the work of [Hoare81b] to deal with the problems of refusals and nondeterminism. They do this by permitting behaviors to be more highly structured objects than just sets of traces. In particular, a behavior is a set of pairs  $\langle s, X \rangle$ , where *s* is a trace, and X is a set of events that can be refused by the process after the trace *s* has been produced. Although they use a single universal set of events for all processes, we can imagine designating the set of all events that actually appear in a process as the interface of that process. As in the model of [Hoare81b], traces play the role of observations. There are "concealment" operators for deleting events, and "inverse image" operators that permit renaming of events. There are no "direct image" operators, apparently because they are not as well behaved as the inverse image operators. Two kinds of parallel composition operations are defined: composition by *intersection*, in which events of the component processes are connected, and composition by *interleaving*, in which the events of the components remain independent.

Rounds and Brookes [Rounds81] attempt to justify and extend the work of [Hoare81a] in the following way: A definition of process behaviors is made that includes somewhat more information than that of [Hoare81a], and is based on supposedly more

fundamental intuitive considerations. A number of algebraic operations, including composition and abstraction, are defined on behaviors. A notion of "observable equivalence" of behaviors is defined, and is shown to be a congruence. The quotient of the algebra of behaviors with respect to this congruence is then shown to be isomorphic to the model of [Hoare81a], thus providing evidence that this model exactly captures the externally observable properties of processes.

There seem to be problems associated with the use of models of CSP as a semantic basis for specification languages. These problems center around the following two questions: (1) Do traces represent a "complete" record of execution of a process, or simply some finite portion of such a record? (2) What is the meaning of a liveness specification such as "eventually event a will occur," if a process can be placed in an environment that refuses to permit the occurrence of event a?

With respect to question (1), it is difficult to see how the designers of the CSP models could have intended traces to represent complete observations. This is because in general a complete observation will be infinite, but the CSP models provide no method for extracting infinite traces from behaviors. Without a distinction between complete and incomplete observations, we have no way to determine whether a particular CSP process satisfies a liveness specification. It is clearly ridiculous to require that a specification such as "eventually event<sup>'</sup>a will occur" be satisfied by all "incomplete" as well as all "complete" observations.

Question (2) arises from a desire to "assign the blame" for an unsatisfied liveness specification, either to a process or its environment. If a process can always be placed in an environment that can prevent the occurrence of event *a*, then the only reasonable conclusion we can draw is that the specification "eventually *a* will occur" is too strong (i.e. inconsistent). However, it is not clear how to weaken such a specification so that it can be regarded as consistent.

The above problems associated with the models of CSP have been avoided here as follows: First, it is assumed here that the observations in a behavior represent *complete* records of execution. Second, we accept the obvious conclusion that the specification "eventually a will occur" is inconsistent with respect to a model (such as the model of [Hoare81b]) that admits the possibility of refusals. Instead of trying to find ways to weaken specifications like this so that they can be regarded as consistent even in the face of refusals, though, we construct a model in which refusals are not allowed. This is the idea behind the I/O-behaviors constructed in Chapter 5 of this thesis.

## Calculus of Communicating Systems

Rather similar to the models of CSP discussed above is the "Calculus of Communicating Systems," (CCS) of [Milner80]. As in CSP, the notions of a communication event and a sequence of communication events are the fundamental concepts for describing the behavior of a process. The role of a process interface is played, in CCS as in CSP, by the set of communication events in which the process is capable of participating. The CCS notion of an observation is a sequence of events; in contrast to CSP, CCS admits the possibility of infinite observations.

To represent the behavior of a process, Milner introduces the notion of a communication tree whose paths represent all possible complete histories of communication for a process. In a communication tree there can be multiple arcs emanating from a single node, labeled with with the same communication event, and arcs can be labeled with the special symbol  $\tau$ , which represents an internal action of a process not associated with any communication event. Communication trees therefore contain more information about a process than just a simple set of traces. In fact, communication trees contain more information about a process than can be detected through composition with other processes. Milner addresses this problem by defining several notions of "observable equivalence" of communication trees, and shows that these relations are congruences for an algebra of processes whose operations include operations of composition and abstraction. He suggests that the class of process behaviors be obtained by forming the quotient of the algebra of communication trees with respect to one of these congruences. He is unable to reach a conclusion, though, as to which of the congruences is "best," or to give explicit characterizations (not involving quotient constructions) of the quotient algebras.

Although communication between two processes in CCS, as in CSP, is *synchronized* in the sense that it is represented by the simultaneous occurrence of communication events for the participating processes, communication in CCS is unlike that in CSP in the sense that a CCS process cannot prevent another process from performing an event. This is because the definition of the composition operation in CCS states that, if process A can perform an event a, and process A' can perform the

"complementary" event a', then the composition  $A \parallel A'$  can perform either a, or a', or the communication represented by the simultaneous occurrence of both a and a'.

The fact that observations can be infinite in CCS raises the question of whether it is possible to define CCS processes that satisfy interesting liveness properties. However, it seems that this possibility is ruled out by Milner's composition operation. Milner's composition operation is "unfair" in the sense that there are paths in the communication tree corresponding to the composition of two processes along which only one of the component processes gets to run. This means that no process can satisfy a specification of the form: "eventually a will occur," in an environment that has the capability of producing an infinite observation.

#### Actors

One of the earlier event-based models of computation is the actor model [Greif75, Hewitt77]. An actor system consists of a collection of primitive computing agents (actors), that communicate by passing messages. A computation for an actor system is a partially ordered set of events, where an event marks the arrival of a message at its target. Receipt of a message *activates* the target actor, and may cause additional messages to be issued. The partial order represents a kind of temporal "precedes" relationship between events, formed by taking the transitive closure of the union of the "causes" relation and the "arrival" ordering, the latter of which linearly orders all events with the same target. Hewitt and Baker [Hewitt77] postulate certain laws that must be satisfied by the various orders.

The actor model was originally applied [Greif75] to the specification of synchronization problems such as the mutual exclusion and readers/writers problem. The specifications are written as axioms that constrain the possible computations of a system. The language used, although not formally defined, is essentially a propositional calculus in which the propositions are of the form " $e \rightarrow e'$ ," which means that event e must precede event e' in any computation of a system satisfying the specification. Although no notion of state was used in the specifications, the language has nevertheless sufficient expressive power to handle several important examples.

Subsequent work concentrated on applying the actor model to the specification of more complex systems, both distributed and centralized [Yonezawa77]. In contrast to the work of Greif, Yonezawa's specifications have a decidedly state-transition flavor,

and although proponents of the actor model consistently argue that global state is not a well-defined notion for distributed systems, the "situations" used in Yonezawa's correctness proofs appear to be just such global states.

In the actor model, the notion of an actor is generally defined by informal axioms and description, which are insufficient to answer the question: "What *is* an actor?" We must know the answer to this question if we wish to obtain a meaningful notion of the collection of all actors that satisfy a given specification, and to show the validity of rules for deriving consequences of specifications of actor systems. The question of what actors are has only recently been dealt with by Clinger [Clinger81], who defines actors and their computations directly in terms of set-theoretic constructs. It is interesting to note that, although actor enthusiasts like to point out that viewing computations as partially ordered sets of events captures "true" concurrency better than linearly ordered computations, Clinger shows that the laws of Hewitt and Baker are in fact equivalent to the existence of a global linear ordering of events in a computation.

To relate the actor model to the model used in this thesis, we can attempt to identify notions of interface, observation, behavior, abstraction, and composition in the actor model. There seems to be no obvious notion of the interface of an actor. The notion of a partially ordered set of events plays the role of an observation. Roughly speaking, Clinger defines the behavior of an actor to be a function that describes the actor's response (i.e. its state change and message transmissions) to the receipt of a message. Although we can imagine composing a collection of independent actors into a composite system, there seems to be no formal notion in the actor model corresponding to such an operation. As mentioned above, the existence of the arrival ordering prevents the definition of an abstraction operation.

The actor model has certain defects that render it unsuitable for a theory of specification. The major difficulty is that the actor model does not support abstraction of systems in a uniform way. There are notions of an actor and a system of actors, but no way to view a system abstractly as a single actor. The artificial "arrival ordering," imposed on all events that occur at a single actor, is the primary feature that prevents abstraction from being defined in a reasonable way. Another reason is the fact that every message must contain the name of its target actor, since this means that it is never possible to completely suppress the internal structure of an actor system.

#### Lynch/Fischer Processes

In the model of distributed computation proposed by Lynch and Fischer [Lynch81], the primitive objects are *variables* and *processes*, and *systems of processes*. A variable is a mailbox-like container for values, and a process is a kind of state machine that can perform input and output on variables. A system of processes consists of a collection of processes that communicate through variables. The variables of a system of processes are partitioned into *external* and *internal* variables. There is a kind of composition operation that combines a collection of systems of processes to form a larger system. There is also a kind of abstraction operation that transforms some of the external variables of a system into internal ones.

A correspondence between Lynch and Fischer's model and the model of this thesis can be established, if the notion of an event is identified with Lynch and Fischer's notion of a "variable action." A variable action describes the change in the value of a variable resulting from a single execution step. The interface of a system of processes is the set of all variable actions it can perform. The behavior of a system of processes is, as Lynch and Fischer define, the set of all finite and infinite sequences of variable actions the system is capable of performing. To view Lynch and Fischer's operation of composition of systems of processes as a special case of the composition operators defined here, it is necessary to account for the requirement that the actions on a single variable in the computation of a system have consistent values. This is easily accomplished if variables are thought of as active entities with an interface and a behavior. The interface of a variable is the set of all variable actions that can be performed on it. The behavior of a variable is the set of all variable actions the value written in the immediately preceding variable action.

In terms of modeling power, the model of this thesis and that of Lynch and Fischer appear equivalent. Lynch and Fischer's model is certainly capable of handling nondeterminism and liveness properties. The main advantage of the model of this thesis over that of Lynch and Fischer is that the former contains fewer primitive concepts. It is not necessary to draw distinctions between variables, processes, and systems of processes, and the definitions of composition and abstraction are simplified by avoiding these distinctions.

# 1.4.3 Temporal Logic Specification

Several authors [Hailpern80, Lamport83, Schwartz81] have proposed the use of temporal logic as a specification language and a vehicle for expressing correctness proofs. The use of temporal logic as a specification language evolved gradually from its use as an assertion language, that is, as a language for expressing properties of program executions [Pneuli77, Lamport80]. There is a subtle difference, though, between the semantics appropriate for temporal logic used as an assertion language and temporal logic used as a specification language. This difference, which has not been explicitly addressed in the literature.can be summarized as follows: Whereas temporal formulas as assertions express properties of single computations of a fixed program, temporal formulas as specifications express properties of the set of computations of an undetermined program. Stated another way, whereas a model for a temporal formula used as an assertion about a fixed program is a single computation of that program, a model for a temporal formula used as a specification is the set of all computations that can be produced by some program. This distinction has important ramifications for what notion of consistency is appropriate in each case. A temporal formula used as an assertion about the computations of a fixed program is consistent if and only if there exists a computation of that program that satisfies the formula. A temporal formula used as a specification is consistent if and only if there exists a program, all of whose computations satisfy the formula.

Another important issue that is not addressed explicitly in literature on temporal logic specification is the ability to specify a single module in isolation from particular program context.<sup>1</sup> The notion of a program module satisfying a specification in isolation *must* be meaningful if specifications are to effect the beneficial separation between module use and implementation. Since extant work does not include the notion of the meaning of a specification in isolation, there has been no discussion of the following important question: How can we combine independent module specifications to perform

<sup>1.</sup> Recent work [Barringer83], performed independently of the work described in this thesis, has begun to address some of the same issues, in particular: (1) temporal specifications express properties of *sets* of computations, rather than single computations, (2) specifications should have meaning that is independent of an enclosing context.

a proof of correctness? In particular, in what common language can the proof of correctness be expressed, and what deductions in this language are sufficient to imply the correctness of the implementation?

Among the papers on temporal specification of concurrent program modules, the approach developed by Lamport [Lamport83] contemporarily with work on this thesis, results in specifications that appear most similar to the state-transition specifications described here. In Lamport's approach, a specification consists of three parts: (1) A list of *state functions*, which define salient features of the program state; (2) A list of *initial conditions*, which represent assumptions on the initial values of the state functions; (3) A list of *properties*, which constitute the main body of the specification, and which can be viewed as standing for a collection of temporal logic formulas. The properties are of two kinds: *safety properties* and *liveness properties*. Safety properties describe the state transitions that are *permissible* for a program satisfying the specification, and liveness properties describe situations under which transitions are *required*.

The way one writes a specification in Lamport's approach is quite similar to the way one writes state-transition specifications as described in this thesis. At the semantic level, though, Lamport's approach seems rather different. The difference can be summed up briefly as follows: In Lamport's work, specifications for program modules play the role of assertions about the computations of a complete program in which the module appears. Whether or not a particular program module satisfies a specification can only be determined in such a context. In the framework presented in this thesis, whether a program module satisfies a specification can be determined without reference to any contextual information.

The meaning of the state functions used in Lamport's approach is obscure. Lamport says that state functions in a specification "should describe information that must be contained in the program state of any real implementation." This statement apparently implies that the value of the state functions is part of the observable behavior of the module being specified, and in this sense is just as important a part of a module specification as the relationship between the arguments passed and results returned from an invocation of an operation on the module. Choosing state functions that provide too detailed a view of the internal operation of a module can result in overspecification, since an implementer wishing to satisfy the specification is constrained to include enough information in the state so that the state functions can be

#### defined.

This thesis resolves the problem of overspecification by introducing the notion of an *interface*. By defining a module interface, one fixes a particular class of module instances (i.e. the behaviors of that interface) which serves as a domain of discourse for the temporal specifications. In this thesis, a module interface is a set of events. An interface does *not* contain any notion of module state. States are used merely as a device for increasing the expressive power of the specification language to permit the desired properties of observations to be expressed in a convenient and natural way. Since states are not part of the module interface, the state set in a state-transition specification can be chosen on the basis of convenience, without danger of overspecification.

Schwartz and Melliar-Smith have also proposed the use of temporal logic as a specification language. In [Schwartz80], specifications are developed for the alternating bit communication protocol. Appearing in these specifications are uninterpreted symbols such as "InQ" and "OutQ." These symbols, like the state functions used by Lamport, are evidently intended to refer to portions of the state that must be identifiable in any program satisfying the specifications. Schwartz and Melliar-Smith present collections of temporal axioms which they claim completely characterize the send and receive processes supporting the alternating bit protocol. There is little basis for this claim, since it is impossible to determine what a process is, much less determine whether the specifications characterize a particular process or class of processes.

The axioms presented by Schwartz and Melliar-Smith involve complicated derived temporal operators such as "latches-unfil," which make the resulting specifications quite difficult to understand. The specifications have an *ad hoc* flavor, and it is difficult to obtain insight into how specifications for different examples would be obtained. In contrast, the state-transition approach discussed in this thesis suggests a systematic way of proceeding from an intuitive conception of the desired module behavior to a precise specification. Schwartz and Melliar-Smith present no proof that their send and receive process specifications correctly implement the service specification for the alternating bit protocol. Experience gained from the examples presented in this thesis suggests that specifications that have not been used in a proof of correctness are quite likely to contain errors.

Hailpern and Owicki [Hailpern80] propose a style of temporal logic specification that is different from the styles of Lamport and of Schwartz and Melliar-Smith. Hailpern and Owicki also use the alternating bit protocol as an example to illustrate their approach to specification. In addition to symbols representing components of the internal states of processes in the system, Hailpern and Owicki introduce the notion of a *history variable*, whose value at any instant of time represents the entire history of communication between two processes up until that instant of time. They state explicitly that history variables are simply a descriptive tool, and are not intended to be implemented. History variables appear to be quite useful for writing high-level, nonprocedural specifications. For example, the safety properties satisfied by a transmission line could be expressed by stating that the history of messages delivered is always a prefix of the history of messages sent.

The state-transition approach to specification presented in this thesis takes the history variable idea to its logical conclusion, by allowing arbitrarily structured history information (in the form of states), to be introduced into a specification, together with operations for manipulating this information. This can be done differently for each specification, without change to the underlying semantic model. For example, the specification of the reliable transmission module presented in Chapter 6 uses the notion of the history of all messages input to the reliable transmission module. In the specification of the send protocol module in Chapter 6 it is convenient to define the notion of "the history of all messages for which acknowledgements have been received." This history is a subhistory of the history of *all* messages transmitted by the send protocol module, and would not be directly accessible in the model of Hailpern and Owicki.

# **1.4.4 Specification of Communication Protocols**

The problem of specification of communication protocols has received a good deal of attention, and can be viewed as a special case of the more general problem, investigated here, of specification of modules in a distributed system. Two surveys of the protocol specification literature, written from different vantage points, can be found in [Sunshine78] and [Hailpern81].

- 32 -

Of the numerous papers on protocol specification and verification, that of Bochmann [Bochmann78] appears to be most directly relevant to this thesis. Bochmann models a system as a collection of finite-state machines that affect each other through coupled state transitions. This is highly analogous to the definition, given here, of composition of behaviors by identifying events. Bochmann also has a notion of abstraction by ignoring uninteresting transitions, which matches the concept of abstraction of behaviors used here.

Schwabe [Schwabe81a, Schwabe81b] exploits the analogy between the instantaneous state of a communication protocol and a value of an abstract data type, to translate state-transition specifications of protocols into equational axioms that define an abstract data type. This translation enables him to verify correctness properties of communication protocols using an automated verifier (AFFIRM) originally intended for proving properties of abstract data types. However, only certain kinds of correctness properties can be stated and proved using his technique. In particular, liveness properties cannot be handled. Schwabe pays little attention to the semantics of his specifications, leaving some ambiguity as to what objects satisfy a specification, and what consitutes correctness of a protocol.

It is interesting that the notions of hierarchy and modularity of systems, and the prerequisite concept of the interface of a system with its environment, are much more prominent in the literature on protocol specification than they are in the literature on specification in general. In protocol specification, a system is viewed as a nested set of layers: the bottom level corresponds to the communication hardware, and each layer provides an abstract service to the next higher layer. The top level implements the service provided to the "end user." Typically the service provided by a level can be viewed as an abstract communication network connecting two users, which often have an asymmetric sender/receiver relationship. Higher levels of abstraction are implemented by interposing protocol processes between the users and the communication service provided by the next lower level. The interface between the users and a service comprises the set of operations (e.g. open connection, send message), they can perform. A distinction is drawn between the specification of an abstract service provided to a user (the service specification) and a description of the protocol processes (the protocol specification).

- 33 -

There are only a few specific correctness properties of interest for communication protocols: freedom from deadlock, completeness (i.e. definedness of the protocol in every reachable state), progress, and stability in the face of unexpected perturbations of the protocol. These properties are certainly also of interest for more general kinds of distributed systems. All verification techniques in the communication protocol literature are ultimately based on representing the protocol processes and abstract communication media as finite-state machines, constructing а combined state-transition graph for the implementation, and performing various analyses on this graph. The state-transition approach to specification and verification is a natural generalization of this technique. It should be noted, however, that the machines used in the state-transition specifications in this thesis are not necessarily finite-state, and that reachability analysis of a system is performed by proving predicates to be invariant, rather than by explicit construction of the combined state-transition graph. This means that the proof techniques discussed in this thesis need not be subject to the combinatorial explosion problem often referred to in the literature on protocol verification.

#### 1.4.5 Other Concurrent System Specification Techniques

Chen [Chen81, Chen82] develops a concurrent system specification language called EBS (Event-Based Specification Language), and gives specifications for a number of examples, including the alternating bit protocol. The EBS language can be thought of as a generalized version of the language used in [Greif75] to specify various synchronization problems. An EBS specification expresses properties of an event history, which is a partially ordered set of events. The EBS notion of an event history corresponds to the notion of an observation used in this thesis.

Chen's work seems to be motivated by a number of the same concerns that motivated this thesis. In particular, Chen discusses the distinction between the user's view and the designer's or implementer's view of a system, and introduces a notion of interface to capture the way in which a system interacts with its environment. In Chen's approach, a module interface consists of a collection of *ports*. There is a notion of module interconnection by identifying ports, which is reminiscent of the composition operations used in this thesis. Chen's work does not, apparently, include a notion of behavior, or the idea that a module specification has meaning except with respect to a complete program context. Chen does not have a semantic definition of the correctness of an implementation from which the soundness of proof techniques can be derived. Rather, the notion of correct implementation seems to be identified with the notion of logical consequence.

An interesting property of Chen's specifications is that they tend to be "orthogonal." An orthogonal specification is a specification that is composed of a collection of independent subspecifications. For example, Chen defines a number of different properties of a reliable transmission system, such as "no loss of messages," "no duplication of messages," and "no erroneous messages." It is not obvious how the state-transition technique presented in this thesis could support the writing of specifications with a comparable orthogonality property.

The Gypsy system [Good79, Good82] has some capability for the specification and verification of distributed systems. In the Gypsy model, a distributed system is viewed as a collection of independent processes that communicate through message buffers. Specifications of the communication function performed by a process are expressed in terms of properties of "buffer histories," which represent the sequences of messages transmitted on, or received from message buffers. Gypsy seems capable of handling only safety properties.

Correctness proofs in Gypsy are performed by deriving a collection of verification conditions from annotated program text, and then proving the validity of these verification conditions using a semi-automatic theorem prover. Evidently the validity of the verification conditions is taken as the definition of correctness; the literature shows no attempt to justify the sufficiency of the verification conditions in terms of any fundamental model of computation. Reasoning about the behavior of a system of processes in Gypsy is done in terms of relationships between buffer histories. The approach appears similar to Hailpern and Owicki's history variable approach.

An outgrowth of the Gypsy work is the work of DiVito [DiVito82], which is concerned with the description and mechanical verification of communication protocols. DiVito's specifications contain liveness properties only, and are expressed in a decision table style that captures much the same information as the definitions of state-transition relations presented in this thesis. The purpose of DiVito's work seems to be to quickly reach a point at which experimentation with mechanical verification is

possible. His focus is primarily on linguistic issues, rather than their semantics.