#### **A Switch-Level Simulation Model**

for

#### **Integrated Logic Circuits**

by

#### **Randal Everitt Bryant**

© Massachusetts Institute of Technology, 1981

March, 1981

This research was supported in part by the Department of Energy under contract number DE-AC02-79ER10473, and in part by the United States Air Force under contract number AFOSR F49620-80-C-0073.

Massachusetts Institute of Technology Laboratory for Computer Science

Cambridge

E

Massachusetts 02139

This blank page was inserted to preserve pagination.

### A Switch-Level Simulation Model

#### March 10 for Alaban H

## Integrated Logic Circuits

fant hat he an a harren

en an an 1944 an an tha an tha an thair. Agus an tha an tha an tha an tha 1947 tha tha

Massachusetts 02139

a ser sit at and a sit as a set of

and the second second

and the second second

by

# Randal Everitt Bryant

© Massachusetts Institute of Technology, 1981

March, 1981

#### This research was supported in part by the Department of Energy under contract number DE-AC02-79ER10473, and in part by the United States Air Force under contract number AFOSR E49620-80-Cc0073.

and the second second states and a state of the

and the state of the second second

Massachusetts Institute of Technology Laboratory for Computer Science

#### Cambridge

al a granget

#### A Switch-Level Simulation Model for Integrated Logic Circuits

#### Randal Everitt Bryant

by set of the set of the

Submitted to the Department of Electrical Engineering and Computer Science on March 31, 1981 in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

#### Abstract

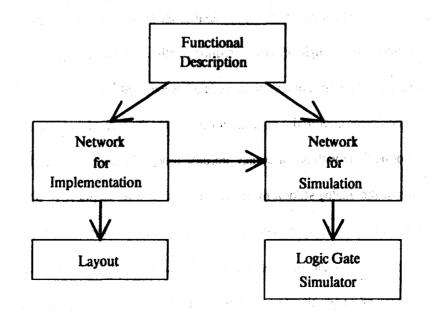

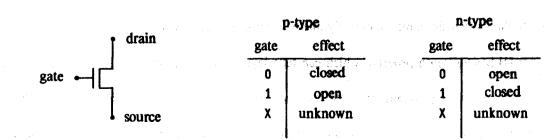

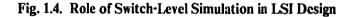

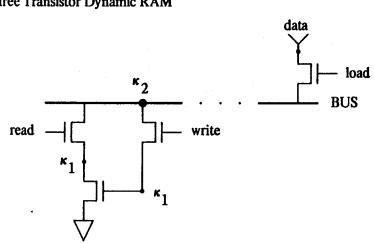

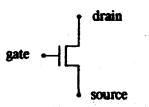

Switch-level simulators model a metal oxide semiconductor (MOS) large scale integrated (LSI) circuit as a network of transistor "switches". They can simulate many aspects of MOS circuits which cannot be expressed in the Boolean logic gate model, such as bidirectional pass transistors, dynamic storage, and charge sharing. Furthermore, the logic network can be extracted directly from the mask specification by a relatively straightforward computer program. Unlike analog circuit simulators, however, the nodes are assigned discrete states 0, 1, and X (for unknown), and the transistors are assigned discrete states "open", "closed", and "unknown". As a consequence, switch-level simulators operate at speeds comparable to logic gate simulators.

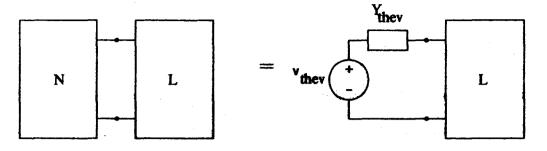

In this thesis, a formal model of switch-level networks is developed. The networks in this model may contain transistors of different strengths and types, as well as nodes of different sizes and types, and hence the logical behavior of a wide variety of ratioed, complementary, and ratioless designs can be expressed. In keeping with the concept of a *logic* model, however, both the transistor strengths and the node sizes may take on only discrete values, and electrical behavior is modeled in a highly idealized way. The operation of a network is characterized by its *target state* for etion, which for a particular state of the network yields the logic states which the nodes would eventually reach if all transistors were held fixed in their initial states. This characterization abstracts away the rate at which nodes approach their target states and the voltages through which they pass but provides adequate detail for many simulation and analysis techniques. The target state function can be defined in terms of an abstraction called *logic signals*, where a logic signal gives a composite description of the network at some node much as a Thevenin equivalent network gives a composite description of a linear network at some port.

Logic signals can be formalized into a simple, discrete algebra with operations describing the effects of performing some elementary network transformations. A technique for finding the target state of an arbitrary switch-level network can be derived by utilizing concepts from abstract algebra and lattice theory. This technique leads to an algorithm for a switch-level simulator which improves on previous algorithms in its generality, speed, and simplicity. Furthermore, the mathematical formulation provides a means for proving useful properties about the simulation method, and opens up further areas of application for the switch-level model.

#### Thesis Supervisor: Jack B. Dennis

Title: Professor of Electrical Engineering and Computer Science

Keywords: Switch-level simulation, logic simulation, computer-aided design, large scale integration.

#### Acknowledgments

I would like to thank Professor Jack B. Dennis for his continued intellectual and financial support during my graduate studies. He has taught me the value of defining a problem in terms of a set of simple, but often untraditional concepts upon which the solution can be based. Other present and past members of the Computation Structures Group have greatly contributed to this environment including Professor Arvind, Clement Leung, Dean Brock, Bill Ackerman, Andy Boughton, Narinder Singh, Sheldon Borkin, and Ken Weng.

My introduction to integrated circuit design was provided by Ms. Lynn Conway of Xerox PARC, and she has provided valuable encouragement of my research efforts. As a Teaching Assistant for Professor Jonathon Allen, I began serious work in this area, and his course provided a test facility for my simulator. The students in this course showed remarkable patience and enthusiasm. Both Professor Allen and Professor Paul Penfield have provided continued interest and encouragement in my work and served as readers for this thesis.

Much of the development of switch-level simulation has occurred through the efforts of Chris Terman and Clark Baker. My work has benefitted greatly from their ideas and experiences. The VLSI design communities at MIT and at other institutions have also provided a strong, motivating force for these developments.

The following people also assisted me by reading earlier drafts of this thesis: Dean Brock, Chris Terman, Clark Baker, and Wayne Gramlich.

This research was supported in part by the Department of Energy under contract number DE-AC02-79ER10473, and in part by United States Air Force Contract AFOSR F49620-80-C-0073.

# Contents

| 1.    | Introd | kaction                                           |

|-------|--------|---------------------------------------------------|

|       | 1.1    | The Boolean Gate Model                            |

|       | 1.2    | Analog and Hybrid Simulators 14                   |

|       | 1.3    | Switch-Level Simulators 15                        |

|       | 1.4    | An Abstract Model for MOS LSI                     |

| . ·   | 1.5    | Relation to Relay Networks                        |

|       | 1.6    | Outline of Thesis                                 |

|       | 1.7    | Notation 23                                       |

| 2.    | The S  | witch-Level Network Model 24                      |

| 1     | 2.1    | Introduction 24                                   |

|       | 2.2    |                                                   |

|       | 2.3    | Network Structure 24<br>Network Representation 29 |

|       | 2.4    | Logic States                                      |

|       | 2.5    | Network State                                     |

|       | 2.6    | The Target State Function                         |

| 5.57  | 2.7    | Specification of the Target State                 |

|       | 2.8    | Relation to Actual Circuits                       |

| · · · | 2.9    | Comparison to Other Switch-Level Models           |

|       | 2.10   | Derivation of the Switch-Level Network            |

|       | 2.11   | Summary                                           |

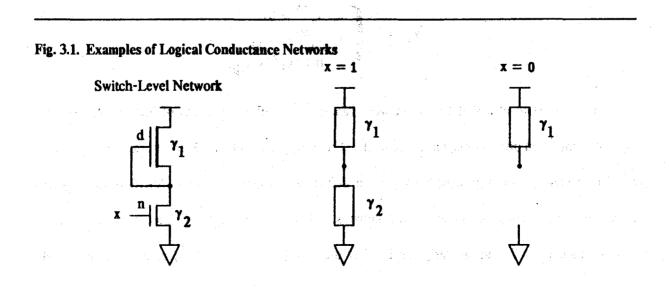

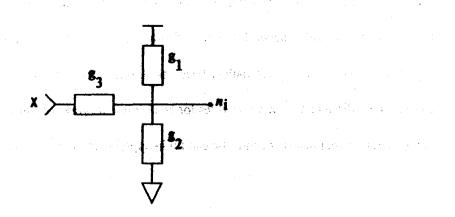

| 3.    | Logica | al Conductance Networks                           |

|       | 3.1    | Introduction                                      |

|       | 3.2    | Properties of the Electrical Model                |

|       | 3.3    | Simplification of the Target State Definition     |

|       | 3.4    | Rational Functions                                |

|       | 3.5    | Equivalent Networks                               |

|       | 3.6    | Logical Conductance                               |

|       | 3.7    | Properties of Logical Conductance Networks        |

|       | 3.8    | Summary                                           |

1

| 4. | Logic                 | c Signals                                                |  |  |  |  |  |

|----|-----------------------|----------------------------------------------------------|--|--|--|--|--|

|    | 4.1                   | Introduction                                             |  |  |  |  |  |

|    | 4.2                   | Definition                                               |  |  |  |  |  |

|    | 4.3                   | Rules for Logic Signals                                  |  |  |  |  |  |

|    | 4.4                   | The Steady State Signals                                 |  |  |  |  |  |

|    | 4.5                   | Constraints on the Steady Steady State Signals           |  |  |  |  |  |

|    | 4.6                   | Specification of the Steady State Signals                |  |  |  |  |  |

|    | 4.7                   | Signal Blocking                                          |  |  |  |  |  |

|    | 4.8                   | Conclusion                                               |  |  |  |  |  |

| 5. | An A                  | lgebra of Logic Signals                                  |  |  |  |  |  |

|    | 5.1                   | Introduction                                             |  |  |  |  |  |

|    | 5.2                   | General Definitions                                      |  |  |  |  |  |

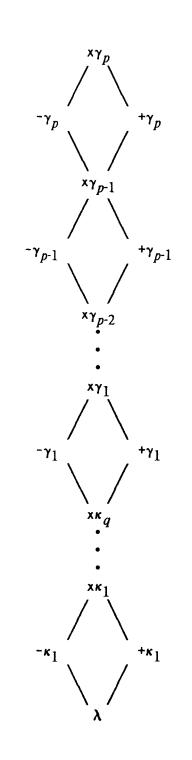

|    | 5.3                   | The Algebra of Signal Strengths                          |  |  |  |  |  |

|    | 5.4                   | The Algebra of Signal States                             |  |  |  |  |  |

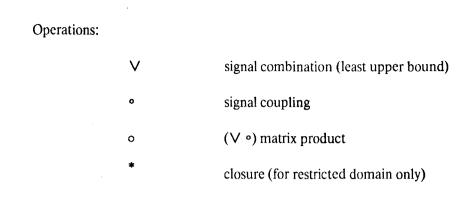

|    | 5.5                   | The Algebra of Signals                                   |  |  |  |  |  |

|    | 5.6                   | Summary                                                  |  |  |  |  |  |

| 6. | Com                   | putation of the Target State                             |  |  |  |  |  |

|    | 6.1                   | Introduction                                             |  |  |  |  |  |

|    | 6.2                   | Ine larget State Equation                                |  |  |  |  |  |

|    | 6.3                   | The Steady State Signal Equation                         |  |  |  |  |  |

|    | 6.4                   | Solution for Restricted Logical Conductance Networks 121 |  |  |  |  |  |

|    | 6.5                   | Solution for General Logical Conductance Networks        |  |  |  |  |  |

|    | 6.6                   | The Target State                                         |  |  |  |  |  |

|    | 6.8                   | Properties of the Target State                           |  |  |  |  |  |

|    | 6.9                   | Summary 141                                              |  |  |  |  |  |

| 7. | Simulation Algorithms |                                                          |  |  |  |  |  |

|    | 7.1                   | Introduction                                             |  |  |  |  |  |

|    | 7.2                   | Complexity Model                                         |  |  |  |  |  |

|    | 7.3                   | Sparse and Incremental Equations                         |  |  |  |  |  |

|    | 7.4                   | Unit Delay Simulation Algorithm                          |  |  |  |  |  |

|    | 7.5                   | Pseudo Unit Delay Simulation Algorithm                   |  |  |  |  |  |

|    | 7.6                   | Comparison to Other Switch-Level Simulators              |  |  |  |  |  |

|    | <b>7.7</b>            | Mixed-Level Simulation                                   |  |  |  |  |  |

|    | 7.8                   | Performance of MOSSIM 166                                |  |  |  |  |  |

|    | 7.9                   | Summary 169                                              |  |  |  |  |  |

- 5 -

|                | Timing Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 170                                   |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

|                | 8.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                         |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |

|                | 8.2 Simulation Timing Models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                         |

|                | 8.3 Analysis of Timing by Ternary Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>x</b> .                              |

|                | 8.4 Toward a Simulator for Self-Timed Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | •<br>                                   |

|                | 8.5 Summary 185                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |

| 9.             | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 186                                   |

|                | 9.1 Final Thoughts 186                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ·                                       |

|                | 9.2 Suggestions for Further Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | · · ·                                   |

| Apper          | dix I. Multi-Port Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 194                                   |

|                | I.1 Introduction 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |

|                | I.2 Port Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | * .                                     |

|                | I.3 The Effect of a Variable Resistor 197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                         |

|                | I.4 The Effect of Connecting Two Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                         |

| Apper          | dix II. Proofs of Results in Chapter 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 202                                   |

|                | II.1 Passive Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                         |

|                | II ? Theorem (A Strategy of the strategy of th           |                                         |

|                | II.3 Corollary 6.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                         |

|                | II.4 Theorem 6.5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - 1 - |

|                | II.5 Theorem 6.7. Sater not o mail hand a margar interior in a constant 214                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . (                                     |

|                | n frantski provinski se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                         |

| Refere         | nces (1998) and a second s<br>The second s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | . , 216                                 |

| Biogra         | phical Note                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 219                                   |

| - <b>0</b> - • |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |

|                | e de la companya de<br>Nome de la companya d                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | •                                       |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |

|                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                         |

|                | ,如此,我们就是我们的问题。""你们就是我们的问题。"<br>第二章                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                         |

|                | an a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |

|                | o a consetto da especifica e da consetto<br>obrectivato e Marakhas e escendores<br>freccias <b>francià la</b> degla e editaria Alberto e consetto e consetto e consetto e consetto e consetto e consetto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                         |