S.B., Massachusetts Institute of Technology (1964)

## SUBMITTED IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE OF

MASTER OF SCIENCE

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

August, 1968

Signature of Author Department of Electrical Engineering, August 30, 1968

Certified by

Accepted by Chairman, Departmental Committee on Graduate Students

#### IMPLEMENTING MULTI-PROCESS PRIMITIVES IN A MULTIPLEXED COMPUTER SYSTEM

by

#### ROBERT LEE RAPPAPORT

Submitted to the Department of Electrical Engineering on August 30, 1968, in partial fulfillment of the requirements for the Degree of Master of Science.

#### ABSTRACT

In any computer system primitive functions are needed to control the actions of processes in the system. This thesis discusses a set of six such process control primitives which are sufficient to solve many of the problems involved in parallel processing as well as in the efficient multiplexing of system resources among the many processes in a system. In particular, the thesis documents the work performed in implementing these primitives in a computer system, the Multics system, which is being developed at Project MAC of M.I.T. During the course of work that went into the implementation of these primitives, design problems were encountered which caused the overall design of the programs involved to go through two iterations before the performance of these programs was deemed acceptable. The thesis discusses the way the design of these programs evolved over the course of the work.

THESIS SUPERVISOR: Jerome Howard Saltzer TITLE: Assistant Professor of Electrical Engineering

#### ACKNOWLEDGEMENT

During the course of the work documented in this thesis several people contributed ideas which were incorporated into the work. In particular, I would like to thank Michael Spier, Peter Schicker, and Robert Daley all of whom have been contributors of ideas as well as critics of my ideas. Also, I would especially like to thank my thesis supervisor, Prof. J.H. Saltzer, on whose earlier work this thesis is based, and to whom I am deeply indebted. The time and effort he has expended discussing numerous subjects with me, over the last three years, have been greatly appreciated.

Lastly, and most importantly, I would like to thank my wife Paula and my little Shelley who make it all worthwhile.

Robert Rappaport August, 1968

# CONTENTS

.

| ABSTRACT<br>ACKNOWLEDGEMENT |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                          |

|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| I.                          | INTRODUCTION<br>1. Scope of thesis                                                                                                                                                                                                                                                                                                                                                                                                                | 7<br>10                                                  |

| II.                         | SEGMENTATION, PAGING, AND FILE SYSTEMS<br>1. Segmentation and Paging<br>2. Hierarchical File System<br>3. Files and Segments<br>4. Segment and Page Faults                                                                                                                                                                                                                                                                                        | 15<br>15<br>21<br>22<br>27                               |

| III.                        | PROCESSES AND TRAFFIC CONTROL<br>1. Block and Wakeup<br>2. Time Sharing, Pre-emption and Reschedule<br>3. Stop, Start and Istop<br>4. Conditions and Events                                                                                                                                                                                                                                                                                       | 29<br>30<br>35<br>37<br>38                               |

| IV.                         | <ul> <li>EVOLUTION OF THE TRAFFIC CONTROLLER</li> <li>1. Original Traffic Controller Implementation</li> <li>2. Reworking the Original Implementation</li> <li>3. Interlocking Changes</li> <li>4. Changes in Wakeup Scheme</li> <li>5. Changes to Loading Scheme</li> <li>6. Block-Wakeup Facility Environment</li> <li>7. Design of New PWN Facility</li> <li>8. Loading and Unloading of Processes</li> <li>9. Block and Scheduling</li> </ul> | 48<br>49<br>55<br>56<br>59<br>60<br>62<br>67<br>73<br>80 |

| v.                          | <ul> <li>PROCESS CREATION AND DESTRUCTION</li> <li>1. Introduction</li> <li>2. Intersegment Linkage in Multics</li> <li>3. Address Spaces in Multics</li> <li>4. Basic Process Creation</li> <li>5. Process Destruction</li> <li>6. Dynamic Linking in New Processes</li> </ul>                                                                                                                                                                   | 83<br>83<br>84<br>86<br>88<br>92<br>93                   |

| VI.                         | ANALYSIS, SUMMARY AND CONCLUSIONS<br>1. Traffic Controller - Before<br>2. Traffic Controller - After<br>3. Process Creation - Before and After<br>4. Targets<br>5. Conclusions                                                                                                                                                                                                                                                                    | 98<br>98<br>100<br>102<br>103<br>105                     |

| APPENDIX I<br>APPENDIX II   |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 108<br>119                                               |

| REFERENCES                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 133                                                      |

.

# ILLUSTRATIONS

· · · · · ·

£,

ſ

ł

| 1 Implementation of segmentation             | 19  |

|----------------------------------------------|-----|

| 2 Segmentation and paging                    | 20  |

| 3 Hierarchical File System                   | 23  |

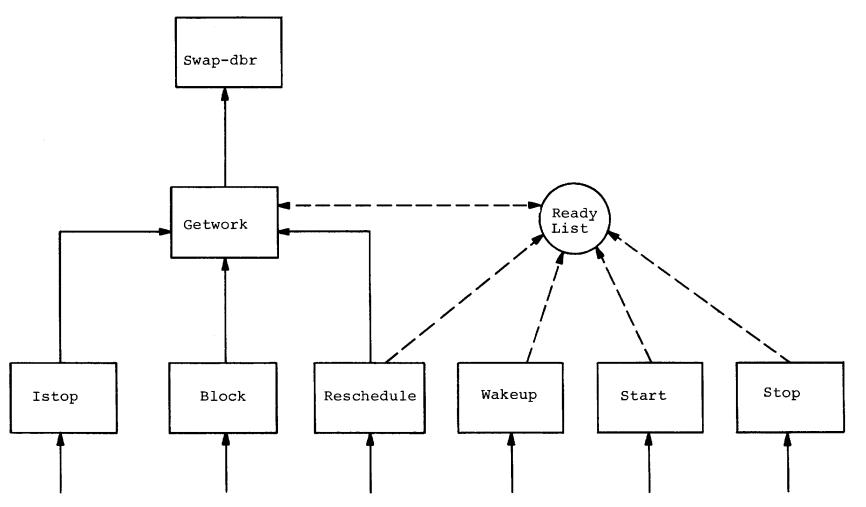

| 4 Block diagram of simple Traffic Controller | 32  |

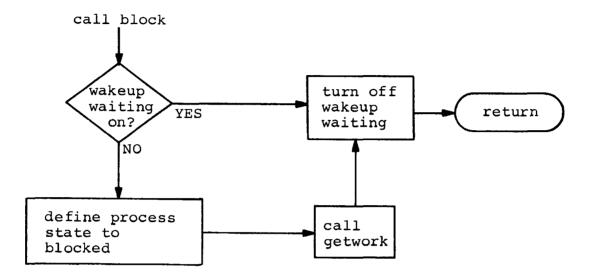

| 5 Block and Wakeup                           | 36  |

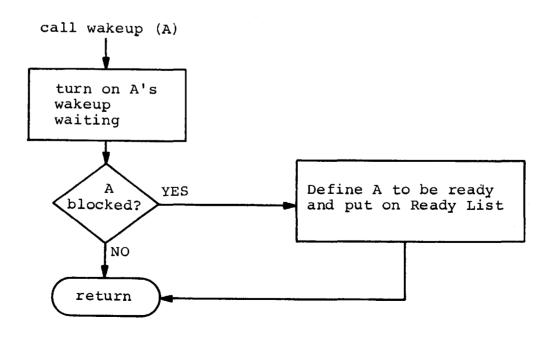

| 6 Execution state transitions                | 39  |

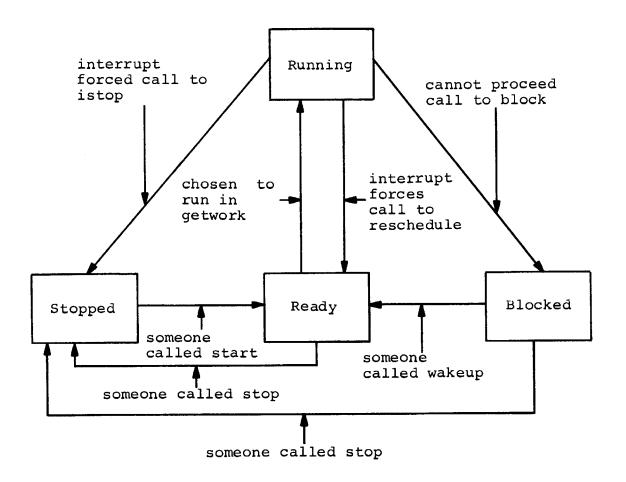

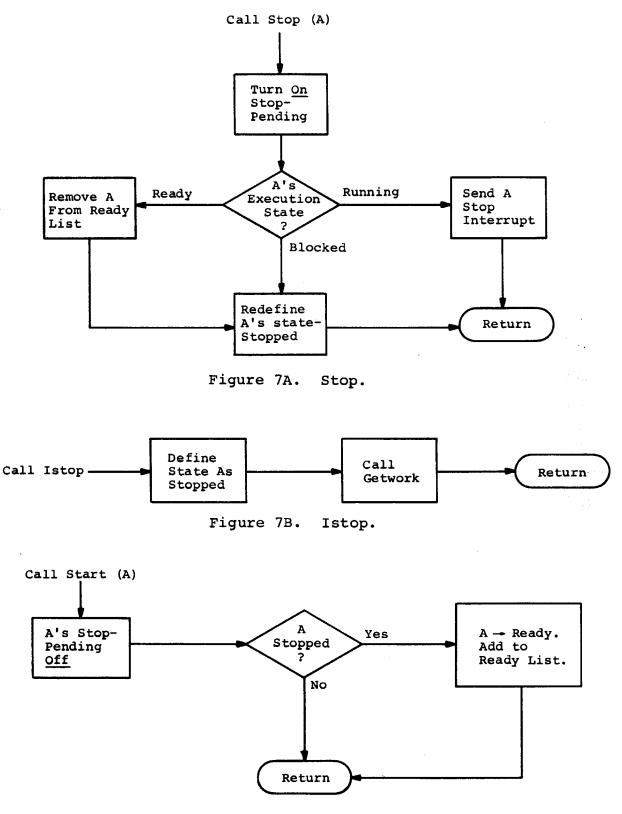

| 7 Stop, Istop, and Start                     | 40  |

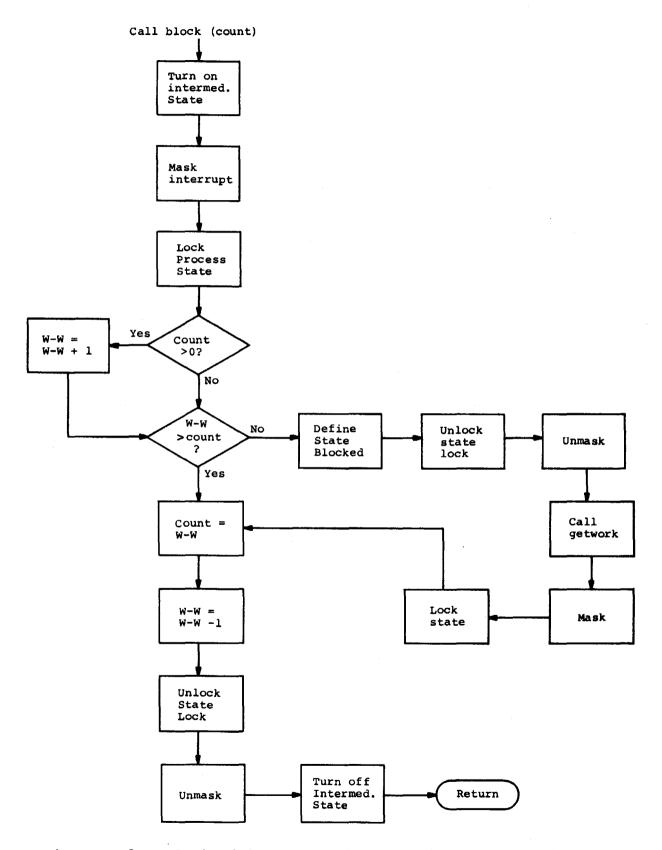

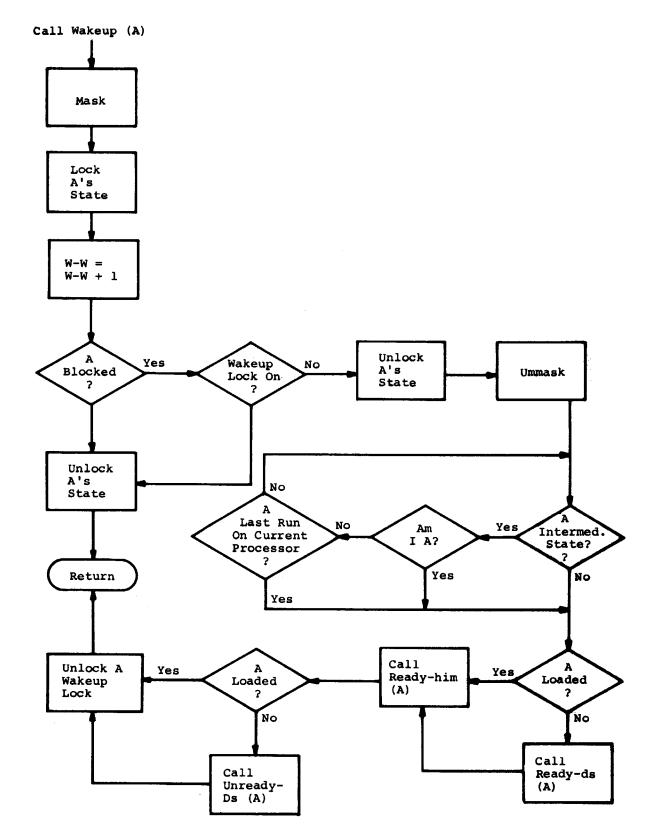

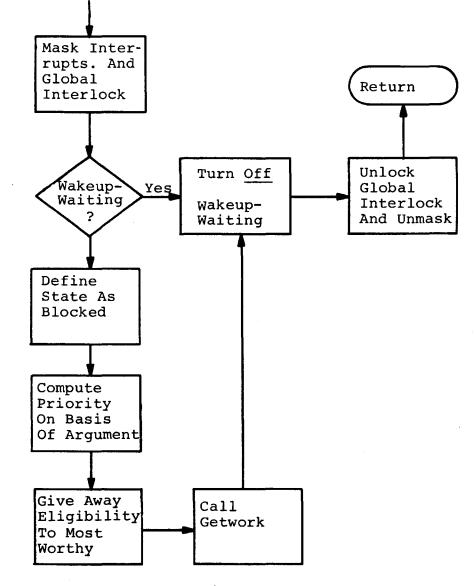

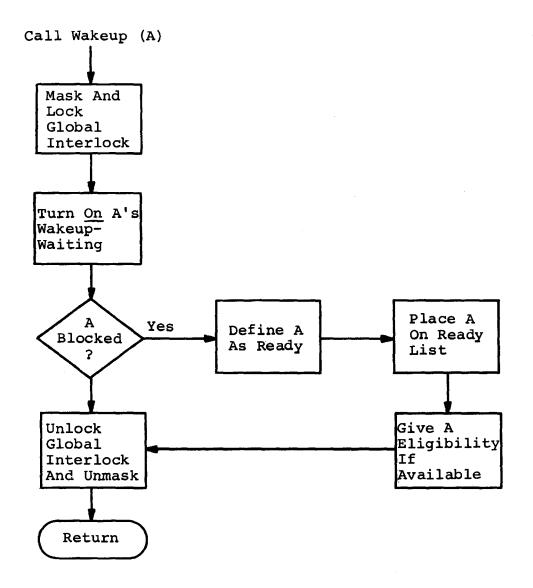

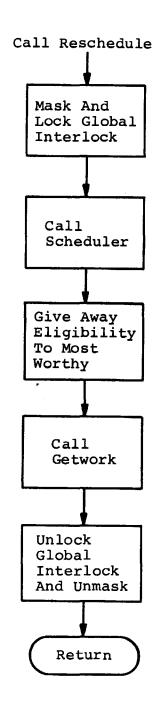

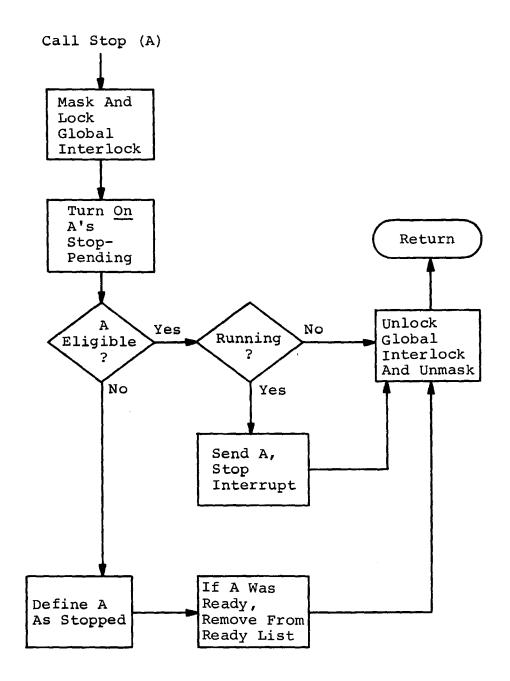

| I.1 Block                                    | 109 |

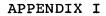

| I.2 Wakeup                                   | 110 |

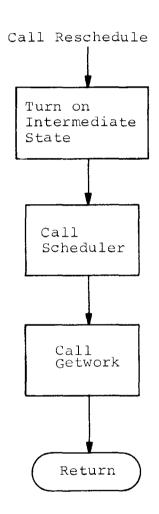

| I.3 Reschedule                               | 111 |

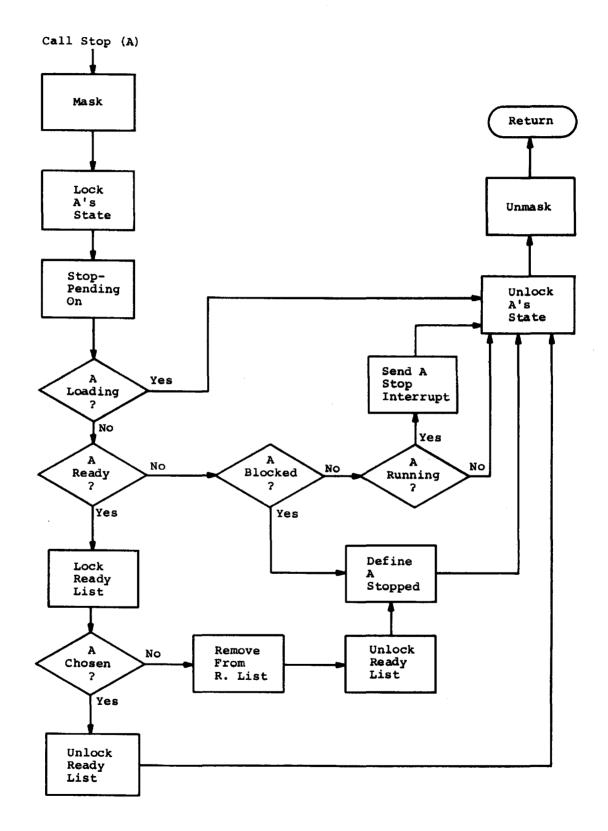

| I.4 Stop                                     | 112 |

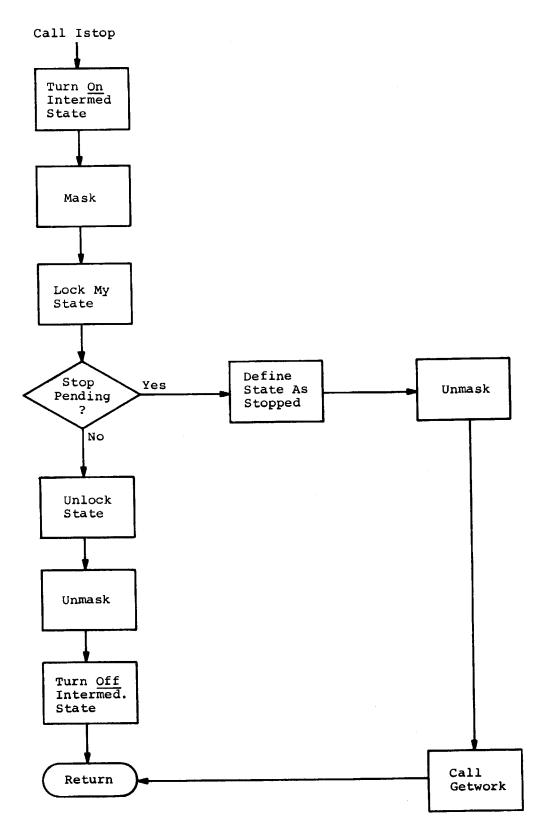

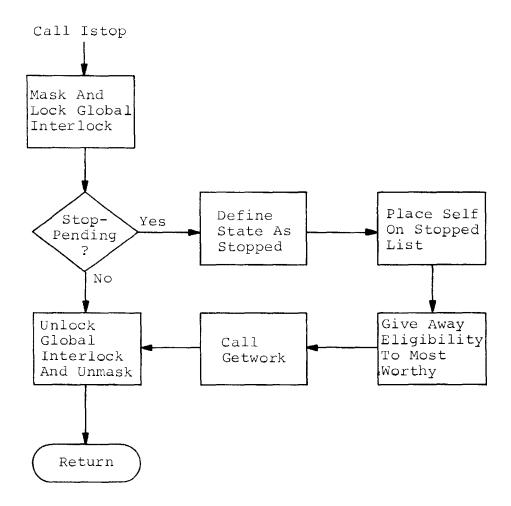

| I.5 Istop                                    | 113 |

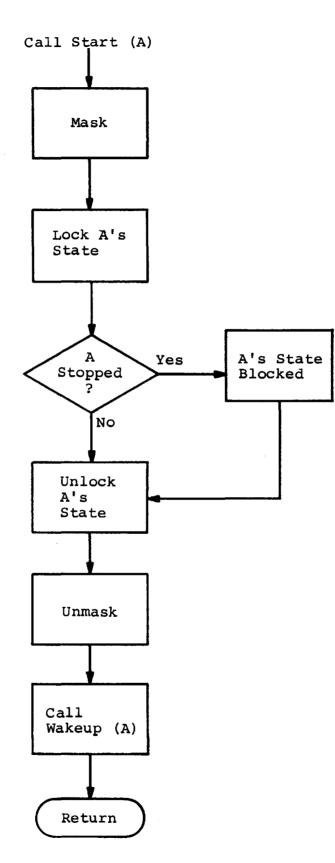

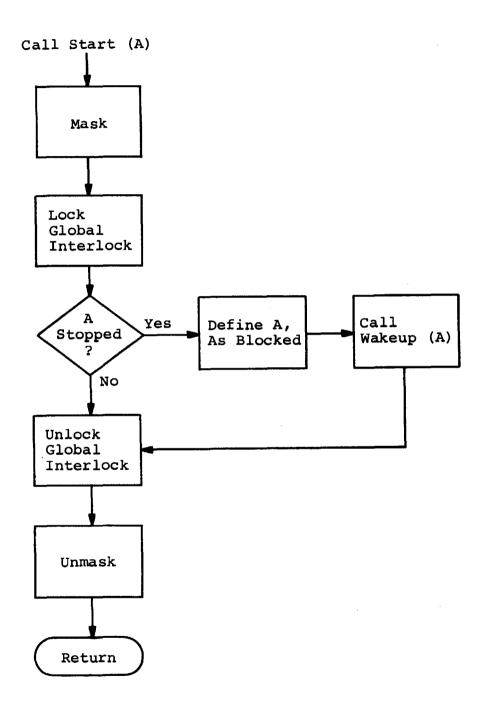

| I.6 Start                                    | 114 |

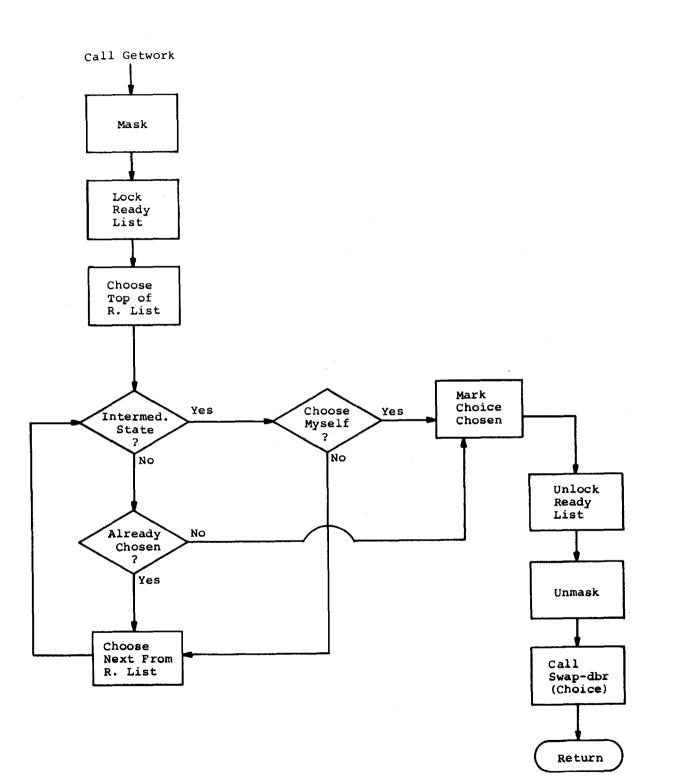

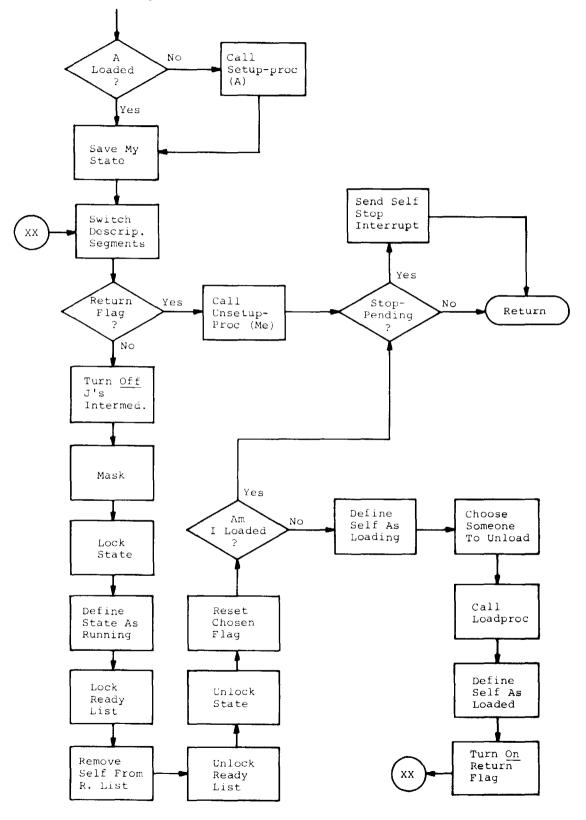

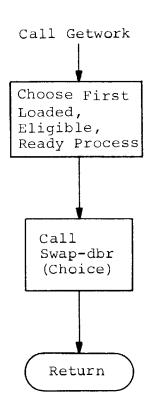

| I.7 Getwork                                  | 115 |

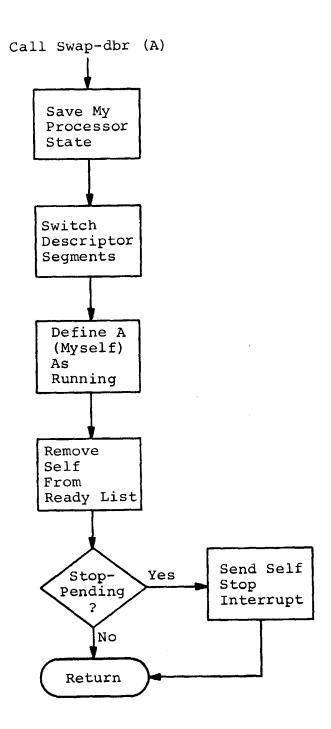

| I.8 Swap-dbr                                 | 116 |

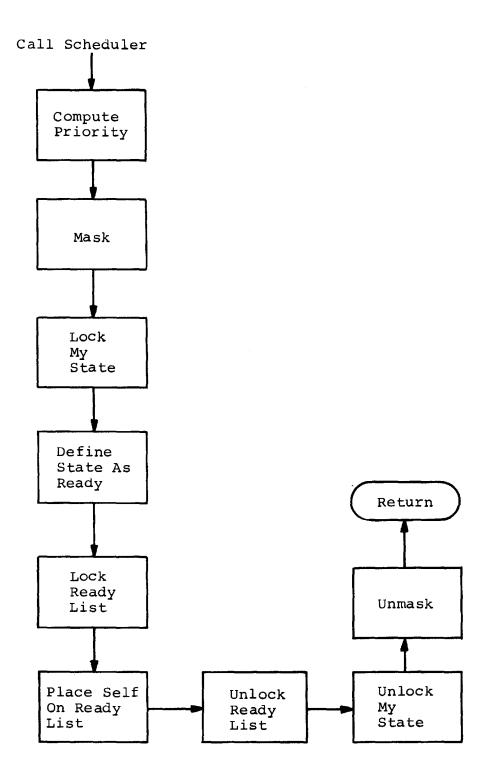

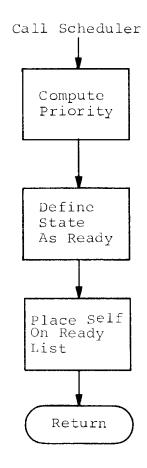

| I.9 Scheduler                                | 117 |

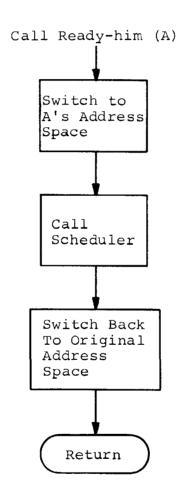

| I.10 Ready-him                               | 118 |

| II.1 Block                                   | 120 |

| II.2 Wakeup                                  | 121 |

| II.3 Reschedule                              | 122 |

| II.4 Stop                                    | 123 |

| II.5 Istop                                   | 124 |

| II.6 Start                                   | 125 |

| II.7 Getwork                                 | 126 |

| II.8 Swap-dbr                                | 127 |

| II.9 Scheduler                               | 128 |

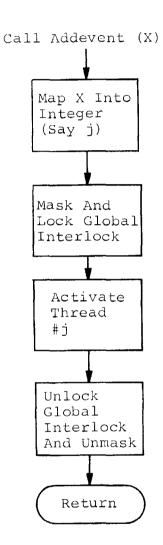

| II.10 Addevent                               | 129 |

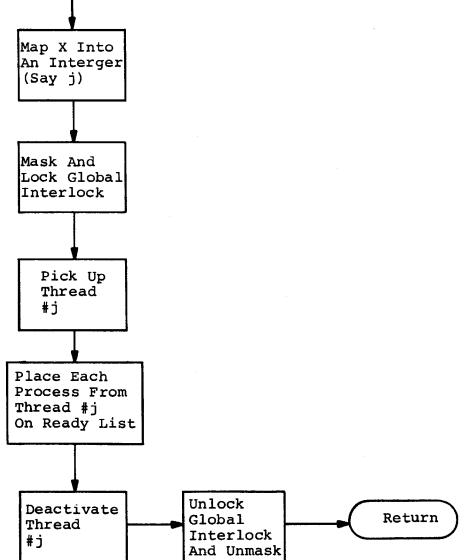

| II.11 Notify                                 | 130 |

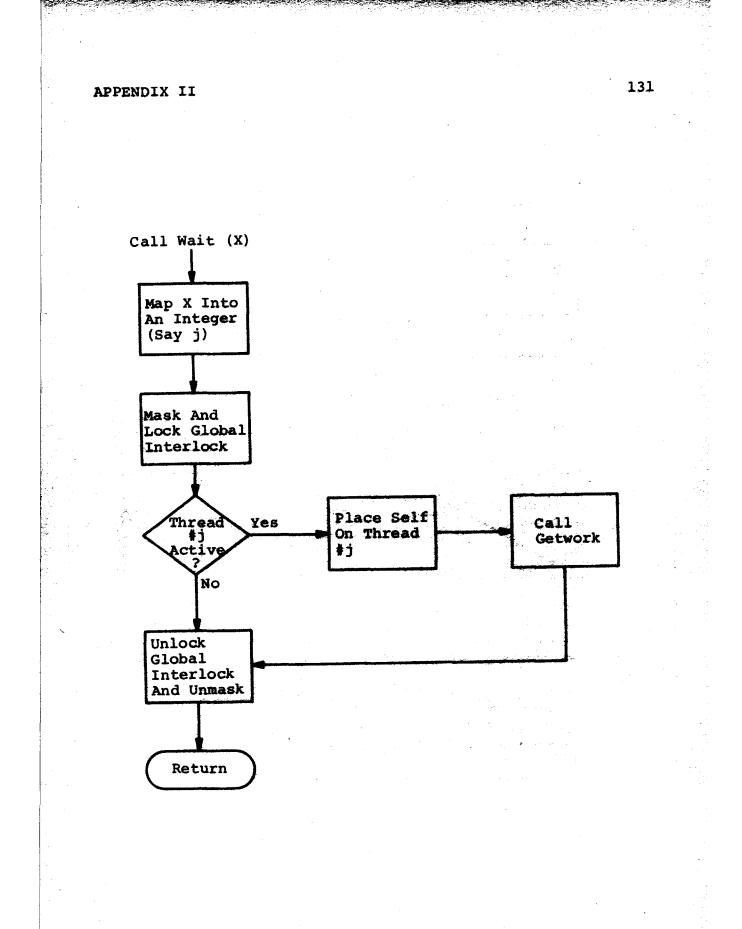

| II.12 Wait                                   | 131 |

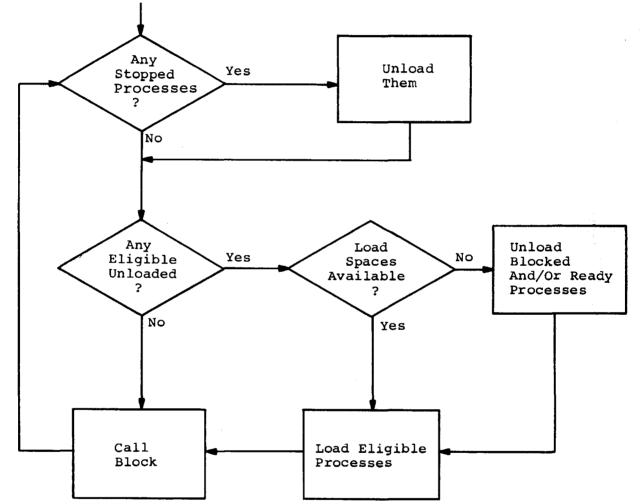

| II.13 Loader-daemon-driver Program           | 132 |

# Implementing Multi-Process Primitives in a Multiplexed Computer System

## CHAPTER ONE

## Introduction

A computer system is a vehicle in which various tasks or processes are executed. In all computer systems, at least two primitive process control functions exist. These are:

- The ability to create or introduce new processes.

We will call this the process creation primitive.

- 2. The ability to forceably halt the execution of a process. This ability rests in some force or power outside the process (possibly in another process). We will call this the process destruction primitive.

In a sense these two functions are implemented implicitly in the hardware of the computer system. The first is implemented in the hardware that allows information to be input into a "cold" machine. The second is implemented by the existence of a switch to turn off the electric power. Clearly most computer systems provide more elaborate implementations of these primitives however sight should not be lost of the fact that their implementation is

inherent in the nature of a computer system.

In addition to the above two primitives most systems for reasons of efficiency and convenience provide a third primitive function:

3. The ability for a process to declare that it has finished and ought to be terminated. We will call this the suicide primitive.

Many traditional computer operating systems are based on just these three primitive functions. Processes are begun using the process creation function and run until they either declare themselves finished (suicide function) or until someone or something decides that they should be terminated (process destruction). These three primitives in a system allow for the specification and implementation of serial (non parallel) computations in that system.

J.H. Saltzer in his thesis, "Traffic Control in a Multiplexed Computer System", (reference number 1 in the bibliography) proposed four additional primitives, one of which includes the suicide primitive. They are:

1. The block primitive which includes suicide.

- 2. The wakeup primitive.

- 3. The <u>reschedule</u> primitive (originally named restart by Saltzer).

4. The <u>stop</u> primitive (originally named quit by Saltzer).

These four primitives make up what Saltzer calls the Process Exchange.

The first of these, block, provides the ability for a process to declare itself unable to continue execution until some event has taken place. The wakeup primitive allows one process to signal another process about the occurrence of an event and thereby cause the return to execution of a blocked process. In a system without the wakeup primitive, block is synonomous with suicide. As Saltzer states, the block and wakeup functions are all that are necessary to solve the "intrinsic" problems associated with simple parallel processing.

The third of these primitives, reschedule, is intended to help solve the problem of processor multiplexing among the many processes in a system. This primitive allows a process to schedule future execution after it has had its execution forceably pre-empted. This primitive coupled with the ability to force pre-emption of executing processes allows a system to share a limited number of hardware processors among many processes.

The fourth of the Process Exchange primitives, stop, allows one process to forceably halt the execution of another process while leaving the halted process in such a state that continued execution is possible, at the discretion of the process that ordered the halt. Stop is

#### INTRODUCTION

basically a refined or narrowed form of the process destruction primitive. One can think of using this primitive as part of the implementation of the process destruction primitive, however stop has additional uses. For example, one could imagine stopping a process in order to examine various data items to determine whether everything was in order. For this reason stop should be kept distinct from process destruction.

The four Process Exchange primitives form a logical group distinct from the creation and destruction primitives in that the former functions deal only with actual processes (i.e., already created and not yet destroyed) and they therefore have no knowledge of how or why processes are created or destroyed. This allows us to discuss them more or less independently.

## Scope of Thesis

i

The existence of these six primitives in a system provide the capability to solve many of the problems involved with parallel processing and the efficient multiplexing of system resources among many processes. For the past several years work has been progressing, at Project MAC of M.I.T., on the design and implementation of a computer system in which these six process control primitives are available. The system is known as the "Multics" system (the name Multics being an acronym for Multiplexed Information and Computing Service). In such a

#### INTRODUCTION

system the efficiency of the modules which implement the six primitives have a profound effect on the overall performance of the entire system. In a system such as the Multics system, in which segmentation and paging have been implemented, and which is designed to support many processes concurrently, primitives such as block and wakeup can be expected to be invoked many times per second. Also in а system supporting many processes, new processes can be expected to be created frequently while older ones are being constantly destroyed. Clearly the efficiency of the modules which implement these functions are of utmost importance to system performance.

The thesis presented here covers the work involved in designing an effective implementation for the six primitives in Multics and in actually implementing them in the system. During the course of the work the implementation went through two iterations. The first implementation provided working versions of these primitives however performance performed tests on these modules showed them to be unacceptably slow in execution. With insight and lessons learned from working on this original implementation, ways were found to redesign the modules so that the second iteration of the implementation brought the performance of these modules into acceptable limits. The thesis report discusses the problems encountered in implementing the modules and shows how the implemented modules evolved over the course of the work. The discussion is divided into five

chapters (chapters 2 through 6).

of these chapters (chapter 2) The first is an introduction and review of the concepts involved in the ideas of a two dimensional addressing scheme (segmentation) and a large hierarchical file system. The background for the material presented in this chapter may be found in several published papers listed in the bibliography (references 2, 3, and 4) and cited in the text.

The second such chapter serves as a review and updating of the ideas involved in parallel processing and the multiplexing of hardware processors and primary addressable memory among many users. In major part this chapter is a review of the basic ideas presented in Saltzer's thesis, however several new concepts are introduced as well.

The next chapter (chapter 4) is a discussion of how the current design and implementation of the Process Exchange primitives in Multics evolved. For reasons of efficiency and performance several changes have been made in the internal structure of the Process Exchange although the user interface to the facility remains as originally designed. The changes include changes to the dynamic "loading" scheme, whereby information necessary for a running process is brought into primary memory, and also the addition of specially tailored versions of the block and wakeup functions (named the wait and notify functions respectively) to be used exclusively by the file system of Multics. The original block and wakeup remain as the user interface to

the Process Exchange. The wait and notify functions were originally file system functions which served as the file system interface to the Process Exchange. They were absorbed into the Process Exchange because of the high volume of traffic from the file system and the need for fast efficient processing of this traffic.

Chapter five is a discussion of the problems involved in process creation and destruction. It includes a definition of a process (an address space and a processor stateword) and a discussion of how one goes about defining an address space that contains a minimum set of primitive functions needed by a new process so that it can continue to expand its address space by itself. Among this minimum set are the Process Exchange primitives, a "map" primitive that allows a process to add things to its address space and a "linker" primitive that allows a process to refer by name to addresses in its space or to names not currently in the Included in this discussion is the address space. presentation of how the process creation mechanism evolved during the implementation work.

The sixth and final chapter of the thesis is a summary which includes the results of performance analysis tests performed on the implemented programs and a discussion of the importance of these figures to overall Multics performance. Specifically, minimum standards of acceptability for the primitives are put forward and the implemented primitives are compared to these standards to ascertain whether their performance is acceptable. Also included in this chapter is a discussion of what was learned in the course of implementing these programs. In particular, the hypothesis is put forward that without a well structured theory of computer systems which allows one to design optimum systems from scratch, such design problems as were encountered here are more or less inevitable.

#### CHAPTER TWO

Segmentation, Paging, and File Systems

## Segmentation and Paging

Segmentation is a device to allow hardware processors, in a computer system, to look at addressable memory as if it were a matrix. Each row of such a matrix is known as a segment. The four primary motivations for segmentation are:

- 1. Segmentation along with paging (as we shall see below) provide a simple way for a system to simulate the presence of a very large amount of primary addressable storage (i.e., in terms of current hardware, core storage) to user programs.

- 2. Segmentation, by segregating address spaces into distinct units, offers a handy way to organize a hardware protection scheme so as to permit differing access attributes to different parts of an address space. For example, some segments in an address

#### CHAPTER TWO

Segmentation, Paging, and File Systems

# Segmentation and Paging

Segmentation is a device to allow hardware processors, in a computer system, to look at addressable memory as if it were a matrix. Each row of such a matrix is known as a segment. The four primary motivations for segmentation are:

- 1. Segmentation along with paging (as we shall see below) provide a simple way for a system to simulate the presence of a very large amount of primary addressable storage (i.e., in terms of current hardware, core storage) to user programs.

- 2. Segmentation, by segregating address spaces into distinct units, offers a handy way to organize a hardware protection scheme so as to permit differing access attributes to different parts of an address space. For example, some segments in an address space can be marked as "read only" and in this way the segments can be protected from errors and/or maliciousness.

- 3. Segmentation also allows for the sharing of procedure and data segments between address spaces.

- 4. Each segment of an address space may be individually expanded in length as storage needs change dynamically. This allows a user to expand data areas without relocating or overflowing other data areas.

Addresses in a segmented environment are ordered pairs of integers. The first element of such an ordered pair refers to the segment (i.e., which row of the matrix) and the second element refers to the relative word number in that segment (i.e., which column in the row selected). For example, a valid address in such an environment would be the ordered pair (16,29) which would be interpreted as word number 29 of segment number 16.

Segmentation can be implemented in several ways. On the General Electric 645 computer, on which the Multics system is being implemented, segmentation is implemented by special purpose hardware in each processor. This hardware allows a processor to look at a standard linear array of physical memory as if it were a matrix. The scheme makes use of an array of "descriptors", one per segment, which point to and "describe" the segment. This array of descriptors is known as a descriptor segment. All addresses (i.e., ordered pairs) generated by a processor are handled in the following way. The segment number of the address is

#### SEGMENTATION AND PAGING

used as an index into the descriptor segment (array of descriptors) to find the descriptor for the referenced segment. Part of this descriptor is a pointer to the base of the segment. In order to obtain the desired word of the segment, the word number part of the address is added to this base address. The processor is able to find the base of the descriptor segment because of a special purpose register in the processor which points to the base of the descriptor segment. This register is known as the Descriptor segment Base Register (DBR for short).

The way in which the descriptors describe their segments is by containing information as to the length of the given segment, and its access (e.g., readable, or writeable, or executable, etc.). The descriptor may also indicate that the given segment is not currently in core memory. It is through this last trait that the system can simulate a large addressable memory. Only a few segments need be kept in core memory at any time. The descriptors of segments not in core indicate that they are absent from core and references to these missing segments cause the processor to recognize a fault condition upon reference to the corresponding descriptor word. Upon recognition of the fault condition the processor automatically branches to a "missing segment fault" handler subroutine which retrieves the missing segment, updates the segment's descriptor word and restarts the processor operation at the point of the fault. In this way, the user of the system, who doesn't see

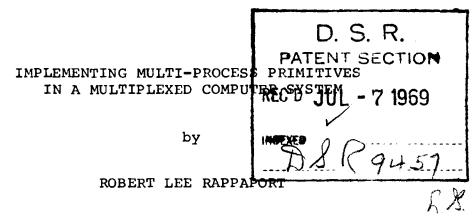

this faulting mechanism, is allowed to see a huge addressable memory. Figure 1 shows a descriptor segment, pointed to by a DBR register and itself containing descriptors for several segments, some of which indicate the absence of the segments. Note that the descriptor segment may contain a descriptor for the descriptor segment itself, meaning that this segment may appear in the address space defined by the descriptor segment.

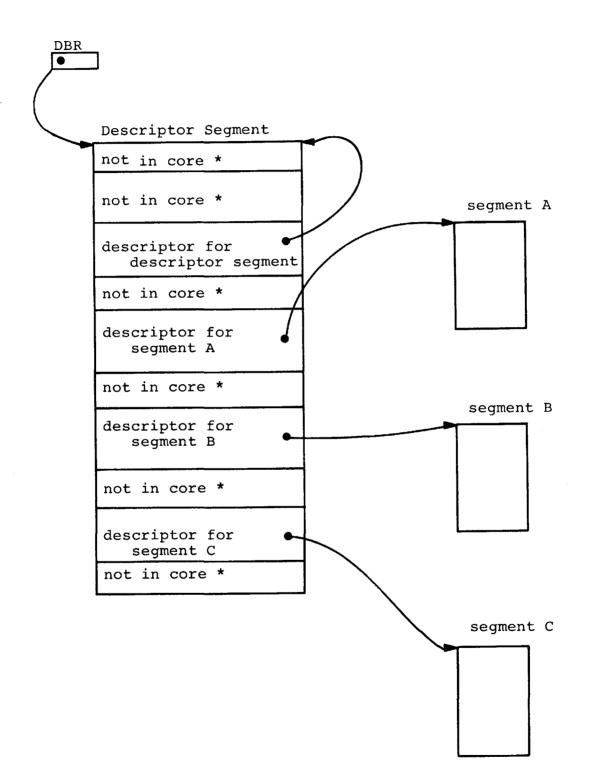

The above implementation implies that a segment be assigned to a contiguous block in core memory. If the segments themselves are potentially large, this would mean having to allocate large contiguous blocks of memory to individual segments. Such a requirement might necessitate needless movement of segments in core memory whenever new segments are brought into memory. A solution to this problem would be to break segments into smaller uniform sized blocks, called pages, and to force references to segments to be indirected through a second level "array of descriptors", called a page table. In this scheme, the descriptors for segments point to page tables for the segments rather than to the bases of the segments. The page tables then point at the individual pages of the segments. Figure 2 illustrates these ideas. Notice that here the descriptor segment is itself divided into pages and that the DBR register that was pointing to it in the previous figure now points to its page table. The above scheme requires only page tables to be stored in contiguous locations in

# Figure 1. Implementation of segmentation

#### SEGMENTATION AND PAGING

core memory, however since page tables are orders of magnitude smaller than segments this need not be a problem. Note also that page tables themselves, although instrumental in implementing the virtual memory, are not "in" the virtual memory and cannot be addressed directly, since they do not reside in any segment of the space. Just as descriptor words may indicate that a particular segment is not in core memory, page table words may indicate that a particular page is not in core. The absence of several pages is indicated in figure 2.

For the reader interested in more background material on segmentation and paging, he is referred to two papers. The first is by J.B. Dennis of M.I.T. and is entitled "Segmentation and the Design of Multiprogrammed Computer Systems". It was published in the Journal of the ACM in October 1965. The second paper is co-authored by E.L. Glaser, formerly of M.I.T., and J.F. Couleur and G.A. Oliver of the General Electric Company. The paper is entitled "System Design of a Computer for Time Sharing Applications", and it was presented at the Fall Joint Computer Conference These two papers are references 2 and 3 of 1965. respectively, in the bibliography that follows this thesis.

## Hierarchical File System

By a file system we mean a mechanism by which we systematically keep track of blocks of data. In a typical file system, we might find entries for each logically

distinct block of information (file). The respective entries, and therefore, the files, are accessed by name. In such an entry we might record the physical location of the file, its length, a list of authorized users, etc.

and a second second

The simple file system provided a computation by a descriptor segment, which maintains an array of core memory addresses, does not suffice when it proves impossible to maintain all information in core. The file system which we briefly describe below is organized around a mechanism, known as a <u>directory</u>, which in function, is very similar to a descriptor segment. A directory, which is itself a file in the system, maintains an array of entries which point to other files in the system. Some, all or none of the files pointed to by a directory may themselves be directories.

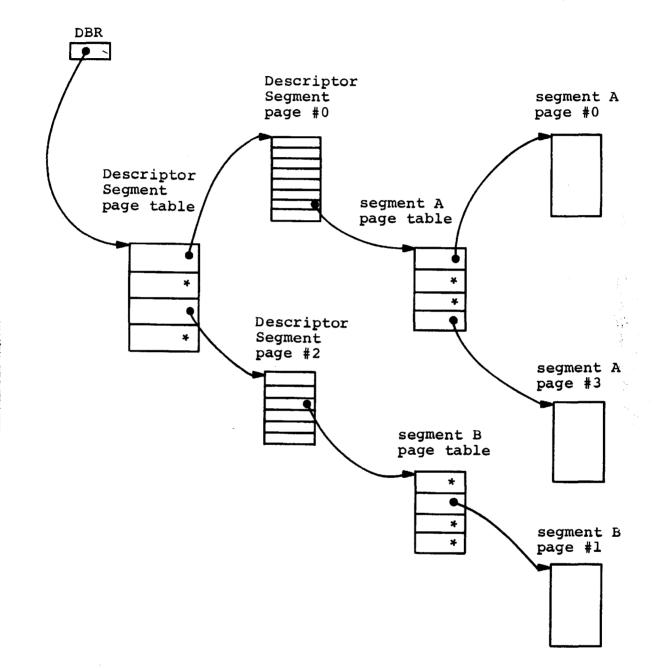

Figure 3 illustrates the hierarchical structure of our file system. In the diagram, circles represent files which happen to be directories while rectangles represent non-directory files. The lines drawn between directories and the files represent the entries in the directories for the files. As can be seen, the file system has as its base, the directory at the top of the picture. This directory is known as the Root directory.

Within a single directory, all the entries (and therefore the associated files) have different names and the name of a file in the system is a combination of the name of the directory in which the file lives (the parent directory) and the file's entry name within this directory. The

Figure 3. Hierarchical File System

syntactic rule we will use to form names of the files will be to concatenate the name of the parent directory and that of the file, separating them by the special character " ". Therefore, the name of file "A" listed in directory "B" will be "B A". Similarly, the name of the parent directory is formed from the name of its parent and its entry name in its parent directory. Since all names within a directory are different, we then see each file in the entire system has a unique name made by combining the entry names of all the directories on the unique path from the root of the tree structured file system to the respective file. Such a name will be known as a "tree name". In the figure, the tree name of the file labeled "1" is "A B A".

To the above file system we will add one additional This feature is the ability to create a special feature. entry in a directory (known as a link) which describes a file already contained in some directory (possibly the same one) in the system. A link serves as a shortcut to a file located somewhere else in the hierarchy of files and serves to give the illusion that the file pointed at by the link actually resides in the directory containg the link. Links can be implemented simply by having the directory entry corresponding to the link contain the complete name (e.q., tree name) of the file.

The addition of links to the file system adds no new capabilities to the system, however it facilitates the ease with which the file system may be used. For example, it may

ł

#### HIERARCHICAL FILE SYSTEM

be desired to maintain the illusion that a particular file exists in a number of different directories. Links make this possible without the cost of maintaining duplicate copies of the file. With links, we can see that there may be several "paths" from the root directory to a particular file. It is desirable to have a name analogous to the tree name which includes links. Such a name will be known as a "pathname".

## Files and Segments

The memory space defined by the hierarchical file system is the global memory space of the entire computer system and this space is always maintained by the system. The memory space defined by a descriptor segment in the computer system, is a subspace of the global space which is of interest to one or more computations (i.e., processes). It is a subspace in the sense that all of the data contained in it (that is addressable in it) can also be addressed directly in the global space, providing suitable pathnames are used. That is to say that the address space defined by a descriptor segment is formed by mapping several files into the segments of the space. For several reasons we will choose to map each distinct file into a distinct segment. These reasons include the fact that this simple mapping procedure means that files (segments) need not be "relocated" or "loaded" when mapped into segments.

To accomplish this mapping between files and segments, a data base is maintained for each descriptor segment defined address space in the system. This data base, known as the <u>Known Segment Table</u> (KST) of the address space serves to record the correspondences made between files and segments in the address space. That is, the KST maintains information such as: file "X Y Z" is mapped into segment #q. With such a data base available, it is clear that the KST serves as the principal piece of data at the time of a missing segment fault.

Let us now look at the mechanisms by which files are mapped into segments and the mechanisms by which the mappings are kept track of. Let us assume that we wish to map the file with pathname "X Y Z" into our address space. To do this we need merely locate the file in secondary storage and assign an unused segment number to it. Locating the file in secondary storage amounts to searching its parent directory for the appropriate entry. However, to search this directory, the directory (itself a file in the hierarchy) must be mapped into a segment, if it had not been previously. Similarly the parent's parent must also be mapped into a segment. If the root directory is guaranteed to be a segment in the address space then the procedure has a finite end. Implicit in the above steps is that a record is being maintained in the KST that file "X" has been mapped into segment #i, file "X Y" has been mapped into segment #j, and file "X Y Z" has been mapped into segment #k. In this

way we will remember where to find segments (files) "X" and "X Y", when we want to map "X Y W" into our address space.

Several things should be noticed about the information contained in the KST. The KST contains the names of each of the segments in the address space and the segment numbers by which they are addressed. In this way we can see that the KST effectively defines the address space. Also, the KST maintaining a correspondence between pathnames and segment numbers, defines exactly the same space that would be defined by a directory appended to the File System Hierarchy which contained a link for each segment in the space. Effectively the KST serves as such a directory and the analogue of a link name for a particular file is the associated segment number assigned when a file is mapped into the space.

As was mentioned at the beginning of this section, one of the prime motivations for segmentation is the ease with which segments (files) can be shared between computations. This can be seen by the fact that the same file may be mapped into any number of address spaces in just the same way that many directories can have links to the same file.

## Segment and Page Faults

In a manner analogous to the way an address space keeps track of its known segments, the system must keep track of which segments are currently active (i.e., have page tables in core memory). These records are kept in the Active

Segment Table (AST) which is a system wide table (i.e., it appears in each address space). Each active segment has an AST entry and this entry effectively serves as the current up-to-date copy of this segment's directory entry. At the time of a missing page fault on a page of an active segment, its AST entry serves as the principal piece of data since this entry contains the information as to where the missing page is located in secondary storage.

Now we can conceptually trace the sequence of events that occurs at the time of missing segment and pages faults. At the time of the missing segment fault the KST is scanned to determine which segment (file) was accessed. An AST entry is then established for the segment (if not already existent) and a page table consisting entirely of missing page faults is constructed. The descriptor word for this segment is then made to point to this page table. On any subsequent reference to the segment a missing page fault will be incurred which will make use of this AST entry to locate and bring into core the appropriate page.

For the reader interested in reading further about the concepts involved in maintaining an hierarchical file system, a paper by R.C. Daley of M.I.T. and P.G. Neumann of the Bell Telephone Laboratories is recommended. The paper, "A General-Purpose File System for Secondary Storage", was presented at the Fall Joint Computer conference of 1965 and this paper is reference number 4 in the bibliography.

#### CHAPTER THREE

## Processes and Traffic Control

A process can be defined as an address space and a set of machine conditions (processor state). Intuitively we can think of a process as simply a program in execution (i.e., a program being executed by a processor). In our discussion the address space of a process is defined by a descriptor segment (which is in turn defined by a KST) and the processor state is the state of the processor executing the process. The machine conditions include, by definition, at least the value of a descriptor segment base register, an instruction pointer register and a current stack frame pointer (see below). They might also include the contents of accumulators, index registers, etc. There is no inherent reason to limit the number of processes executing in a single address space however throughout this thesis, in the interest of simplicity we will impose the limitation of one process to an address space. Of course many of the segments in any particular address space will be shared segments which appear in many or all other spaces.

Along with shared segments each address space contains several per-process (or at least per address space) data segments. Among these are the previously mentioned KST and

one or more so-called "stack" segments. Stacks (call stacks, pushdown stacks, etc.) are areas in which procedures allocate blocks of space (frames) for the storage of temporary variables, contents of registers, and return points. Stacks are composed of frames which are threaded together. Each procedure of a program that has been entered (called) but has not yet returned has an associated stack frame which was allocated upon entry to the procedure. Α pointer to the current stack frame is part of the processor state and the above mentioned threading mechanism allows one to locate "older" or previously allocated frames. The current stack frame and all previously allocated and still active stack frames comprise the relevant history of the process. In our discussion we will assume the existence of a system-wide table (i.e., a shared segment which appears in each and every address space) known as the Process Table which has an entry for each process. The contents of an entry in the Process Table include the identification of the process and various other data items, the need for which will be developed as we go along.

## Block and Wakeup

As was mentioned above, a process is a program in execution. In most computing systems, in an attempt to achieve more efficient usage of system hardware, it is generally profitable to maintain more processes than processors. In particular most processes reach points in

their execution when they have no real need for a processor. For example, a process may have no need for a processor until an I/O operation is complete or a page is brought back to core, or perhaps until another process has completed a computation. In order to maintain the fiction of a process as always being in execution, Saltzer introduced the concept of a pseudo-processor which is the repositor of the state associated with а process. The processor pseudo-processor assigned to a process (there is a one to one relationship between pseudo-processors and processes) is "always executing" its process. When a process is actually in execution by a processor, its pseudo-processor state is contained in the state of the hardware processor. When a running period of time its process stops for а pseudo-processor state must be maintained until the next time the process executes.

Granted that it is desirable to maintain more processes than processors a mechanism must be found for handling the orderly switching of processors between the processes of the system. The Traffic Controller (of which the Process Exchange is an important part) introduced by Saltzer, will serve as our model. In the following refer to figure 4 (Program Structure of Simple Traffic Controller).

As mentioned above, from time to time a running process (i.e., one currently in execution) decides that it has no further need of a processor for the time being. The process declares this by issuing a call to the system primitive

. . . . . . .

Figure 4. Block Diagram of Simple Traffic Controller. Solid Lines Indicate Closed Subroutine Calls Whereas Dashed Lines Indicate Data Flow.

#### BLOCK AND WAKEUP

function known as block. The purpose of the call to block is to give the processor away to some other process which can make effective use of it. In order to be able to identify processes which can make use of a processor, a shared data base, known as the Ready List, is maintained which lists all the processes which currently desire the use of a processor. (The Ready List will be implemented by a thread running through the Process Table linking the entries of processes desiring a processor.) Subroutine getwork, called by block, makes the selection of a process from the Ready List and then itself calls subroutine swap-dbr. The purpose of swap-dbr is to record the state of the current pseudo-processor (i.e., the current state of the processor itself) and load into the processor the state of the pseudo-processor associated with the process chosen from the Ready List. (Note, that having saved the pseudo-processor state of the process which called block, we will be able to resume its execution at a later time.) Now with the processor executing the newly chosen process, we return to the point at which this process stopped executing some ago. A process that has given up a processor by calling block is said to be in the blocked state, while a process which is executing is said to be in the running state, and a process on the Ready List is said to be in the ready state.

التومحا الجريهي المحاطين

The only needed piece now, is a mechanism whereby a blocked process may become ready. This facility is provided by the system primitive known as wakeup. When a process

A CONTRACTOR OF A CONTRACTOR OF

(process A for example) discovers some event that has occurred which is of interest to some other process (say process B) process A calls wakeup passing as an argument the process identification of process B. The function of wakeup is to place process B on the Ready List and redefine its execution state to the ready state, if process B is currently blocked. The current state of B (running, blocked, or ready) is maintained in the Process Table entry for B.

The dynamic operation of a simple system containing the block and wakeup primitives can be visualized. Running processes would execute until they reached points from which they could not immediately continue. They would call block to give away their processors to processes which were listed for them on the Ready List. Wakeup, when called on behalf of a blocked process would change the state of this process to the ready state and would append the process to the Ready List to await the appearance of a processor. Wakeup, when called on behalf of a running or a ready process would have no discernible effect.

A potential race condition would exist if block and wakeup were implemented exactly as described above. Consider the case where process A decides to call block if a particular condition is not met. Process A tests the condition, finds it is not met and proceeds to call block. Before A reaches block, process B reverses the state of the condition that A was waiting for and calls wakeup for A.

Because A is running (on the way to calling block) the call to wakeup has no effect. A meanwhile reaches block gives away its processor possibly forever.

This race condition can be resolved by having wakeup set on a switch or flag belonging to the process on whose behalf wakeup was called, no matter what state the process was in at the time of the call. If this had been the case in our example above, process A would have discovered the switch set <u>on</u> by process B's call to awaken A and A could have returned from block immediately instead of giving away its processor. This per-process switch will be known as the "wakeup-waiting" switch and will be maintained in the Process Table entry of each process.

Given this discussion we can present flow diagrams (see figure 5) for each of the subroutines discussed and understand their use and relationship.

## Time Sharing, Pre-emption and Reschedule

In attempting to satisfy the processor requirements of a large number of processes in a system, it is necessary to have the ability to temporarily halt or interrupt the execution of a running process in order to give its processor to a more "worhty" process. This ability can be realized by using a hardware mechanism, an interrupt, and a software mechanism, an interrupt handling subroutine. The meaning of this interrupt to a running process will be that it has used up its current allotment of processor time and

-----

Figure 5a. Flow diagram of block.

Figure 5b. Flow diagram of wakeup.

#### TIME SHARING AND RESCHEDULE

that the process should prepare to give up control of the processor. This interrupt will be known as the timer-runout interrupt.

The interrupt handling subroutine, known as <u>reschedule</u>, is similar in function to block, except that reschedule schedules future processor use for the process and places the process onto the Ready List directly, in addition to calling getwork to give away the processor.

One can imagine the changes in execution state that a process might go through. A running process may go blocked waiting for I/O or it may go into the ready state because it ran out of time. Similarly, a blocked process may enter the ready state as a result of a call to wakeup and a ready process may enter the running state as a result of being chosen to run by subroutine getwork.

# Stop, Start and Istop

The ability to forceably halt the execution of a possibly run away process is essential. This ability is provided by primitive <u>stop</u>. Subroutine stop, called with one argument, effectively forces the process identified by the argument to call (or appear to call) subroutine <u>istop</u> and thereby enter the <u>stopped</u> state. Once in this state the process is dormant. It does not execute and calls to wakeup for it have no effect. The only way to bring the process back to "life" is for come other process to call procedure start. Istop and start are very similar to block and wakeup

$= \left\{ \left| \frac{1}{2} \left| \frac{1}{2} \right| + \frac{1}{2} \left| \frac{1}{2} \left|$

in function, differing only in the execution states with which they deal. Figure 6 gives a picture of process execution state transitions including the stopped state. The method by which subroutine stop actually brings a process to a halt, depends on the execution state of the process to be stopped, at the time of the call to stop. Stop operates by first turning on a flag in the Process Table entry of the process to be stopped (stop-pending flag) and then testing to see whether the process is currently running, ready, blocked or stopped. If the process is running, an interrupt is sent to the processor on which the process is executing. The interrupt will cause the process. to call istop. If the process is ready or blocked, stop redefines the state to stopped and (if necessary) removes it from the Ready List. If the process is stopped at the time of the call, clearly nothing need be done. The stop-pending flag is of use as a running process to be stopped may be masked against stop interrupts. Figure 7 contains flow diagrams of stop, start, and istop.

# Conditions and Events

As has been mentioned. the Traffic Controller primitives, block and wakeup, allow a process to relinquish a processor when the process cannot proceed with its execution. The reason that a process cannot proceed is that "conditions" one or more are not satisfied. An understanding of the concept of a "condition" and the

38

and the second second

Figure 6. Execution state transitions

Figure 7C. Start

closely related idea of an "event" are useful when trying to understand the problems involved in implementing the Traffic Controller primitives.

A condition is a discrete valued function of one or more variables. The variables which make up the domain of condition are functions of time which makes the the condition also a function of time. The value of the condition at a point in time is known as the state of the condition. The state of a condition can only change at discrete instances of time and the state of the condition remains constant in the intervals between these discrete instants. Finally, an event is said to occur whenever a condition changes state.

An example of a condition is the function defined on a particular word of memory which is equal to zero whenever the word is equal to zero and equal to one otherwise. That is, if we denote the word by W and the condition by C, then:

$$C(W) = 0$$

if  $W = 0$

Whenever the value of C goes from one to zero or from zero to one, an event occurs. If the value of W changes without changing the value of C, (e.g., W goes from 3 to 4) no event for condition C occurs. However this change in the value of W might denote an event for some other condition defined on W.

Another example of a condition is the condition defined to be equal to one whenever a particular page of a particular segment is in core memory and zero otherwise. To be more precise, this condition is a function of the page table word for the page and is equal to one if the page table word indicates the page is in core and is equal to zero if the page table word contains a fault or if the page table word itself does not exist (segment not active).

In general computations and processes are interested in the states of conditions and they are interested in events only in so far as the events indicate the current states of conditions. For example, given a condition that changes state (from zero to one) once and only once for all time the fact that an event of the condition has occurred, tells us implicitly that the state of the condition for all time after the event has occurred is equal to one. Whereas, given a condition capable of changing its state after each unit of time, the occurrence of an event does not insure the future state of the condition for anything but one unit of time. Using the above examples we can divide the set of conditions into two classes: simple conditions -those whose current states can be implied by a given observer from knowledge of a single event that has occurred in the past (not necessarily the last) and complex conditions -- those whose current states can only be ascertained by a given observer by explicit testing. A particular condition may be a simple one, to one observer, and very complex to another.

It is possible to analyze conditions to see where this inherent property of simplicitly or complexity comes from.

#### CONDITIONS AND EVENTS

Briefly, a condition is a simple condition to a particular observer if the observer is the only one who can control the state of the condition. If others can independently cause the condition to change state then the condition is complex to the observer.

The Traffic Controller primitives block and wakeup, provide processes with the ability to wait until events communicate the occurrence of events. occur and to Processes wait for events to occur by calling block and they signal other processes that events have occurred by calling wakeup. A process calls block to wait for an event of a condition whenever the state of the condition is such that the process cannot proceed. The rationale behind this is that after an event has occurred, the condition is more likely to satisfied. Of course if the condition is a simple one, it will be satisfied after the event with certainty.

As an example of the above ideas let us consider an algorithm that one might use in implementing a procedure that is used to interlock data. In a system making use of shared data bases, it is sometimes necessary to limit access to some of the data to one process at a time. This is done using so-called "interlocks". An interlock is a word (or a group of words) associated with a particular data base that serves as a flag to warn processes whether the shared data base is currently being accessed. By convention when the value of the interlock is non-zero, the data is being manipulated whereas when the value of the interlock is zero,

the data is not being accessed. A process locks the data base by storing a non-zero value into the lock, at a time when the lockword is equal to zero. This operation can be done if hardware is available which allows a processor to read the lockword and store into it if and only if the word is zero. By convention the non-zero value that a process stores in a lockword is its own process identification. After a process is finished with a data base. it stores а zero into the lockword, thereby opening the data base up to be used by others. The locker procedure will be called with one argument: a pointer to the word serving as the lockword and the locker does not return until the lockword contains the value of the caller's process identification. From the point of view of the caller to the locker, the caller is not willing to proceed with the computation until the value of the lockword is equal to the process identification of the caller. We can define a condition that describes this situation. This condition is a function of the value of the lockword (denoted by L in the following). We will name the condition F and define the function as follows:

####

This condition is a simple one since only this process will ever place this process identification into the lockword (i.e., set F(L) = 1) and then subsequently place a zero in the lockword (i.e., set F(L) = 0) after the data base is no longer needed. Before the call to the locker, the process

#### CONDITIONS AND EVENTS

$\sum_{i=1}^{n-1} (i-1) = 0$

<u>knows</u> that the state of F is zero since the process executing in a serial fashion knows that it has not locked the data. Upon return from the locker, the process knows that the lockword has been locked and that F(L) = 1. Return from the locker can be considered the signalling of an event in the condition F to the caller of the locker. This condition is a simple to the caller, therefore it can determine the state of F.

Inside the locker procedure condition F is of little interest. The locker is interested in storing the value of the caller's identification in the lockword if the current value of the lockword is zero. In other words, the locker is interested in the condition, G, defined on the lockword, L, in the following manner:

# $\begin{array}{rcl} 1 & \text{if } L = 0 \\ G(L) = & & \\ 0 & \text{otherwise} \end{array}$

Condition G is a complex condition, to the caller, since other processes are capable of changing the state of G (by storing their process identifications in L, for example). Therefore the only way that the locker can be positive that the condition G prevails is to test it explicitly (by means of the special hardware described which will store into the lockword only if the word is zero before the store). Basically, the locker is programmed as a loop waiting for the lockword to go to zero whereupon the caller' identification will be stored and a return will be executed.

Instead of looping, more efficient use can be made of the processor by making use of the Traffic Controller primitives and giving the processor away whenever the locker finds the lockword already locked. That is, if a process executing in the locker finds the particular lockword locked to another process (state of condition G = 0) the former process should somehow pass its name (identification) to the latter process and then call block. After the latter process unlocks the data base (i.e., causes state of G = 1), it can pick up the list of all the process identifications passed to it (including that of the former process above) and call wakeup for each and every such process signal to them of the occurrence of the event in condition G. Upon return from block our original process will again test condition G and attempt to lock the lockword if it equals zero. If the lockword is again locked to someone else, we again pass the process identification to the current process which has the lock set and call block again.

Another example of how conditions are defined and used is seen in the way I/O operations are usually handled. In the case of input, a buffer is assigned into which data will be read. Associated with the buffer is a flag that is set to zero before the input operation is begun and then set to one after the input operation is ended. The simple condition:

I(F) = F

#### CONDITIONS AND EVENTS

where F denotes the flag, is the condition that the process waiting for the input is interested in. The process could loop waiting waiting for condition I to change state or it could block to wait for the event of I's changing state to occur.

A third and final example of an interesting condition is the one associated with the residence in core of a page. Each time a processes accesses a page, it must explicitly test the condition by referring to the page indirectly through the page table word. The process (through its processor) may never take for granted the fact that the page is located at a particular place in memory. When a needed page is not in core, the process waits for an event to occur associated with the particular condition defined on the page table word, knowing that after at least one such event has occurred it is more likely that the page will be in core.

#### CHAPTER FOUR

#### Evolution of the Traffic Controller

Hindsight shows that in designing the original implementation of the Traffic Controller several assumptions and policy decisions were made. These include:

- 1. It is always "desirable" to allow processes to do as much as possible by themselves. That is, among other things, processes should "load" (the idea of a loaded process will be defined later) themselves and schedule themselves.

- 2. The interlock strategy to be followed in the Traffic Controller would be to use numerous interlocks, rather than a single global interlock that limits access to the Traffic Controller to one process at a time. Such a strategy would permit numerous processes to execute in the Traffic Controller simultaneously and prevent the Traffic Controller from becoming a bottleneck.

- 3. The user interface to the Traffic Controller (i.e., the block-wakeup primitives) should remain ignorant of the various "customers" of these primitives. This was done in an effort to remain modular.

#### TRAFFIC CONTROLLER EVOLUTION

Performance analysis tests of the Multics system containing the original Traffic Controller showed that each of the above decisions was very costly for various reasons. As a result, a reworked implementation of the Traffic Controller was prepared and this second implementation was shown to be a marked improvement over the earlier version. Appendix I contains flow charts of the subroutines of the original implementation. It is not necessary for the reader to understand each step of each program. Rather these flow charts are meant only as a basis of comparison for the flow charts of Appendix II wherein the final implementation is illustrated. The remainder of this chapter describes why the Traffic Controller evolved in this way.

# Original Traffic Controller Implementation

The traffic Controller originally implemented was basically the one described in Saltzer's thesis. There was major point of difference between them and the one difference was motivated by a logical problem that is not mentioned in the thesis presentation. This problem is known as the "lost wakeup" problem and it arises from the fact that the block primitive has two distinct customers in Multics (the user program and the basic file system) and that the memory provided by the wakeup-waiting switch is not sufficient to keep these customers from interfering with each other. The wakeup-waiting switch, as defined by Saltzer, is capable of remembering whether any wakeups have

been received since the last (chronologically) call to block by a process. Since at any time while executing in user programs a process may experience missing page or segment faults which result in "concealed" calls to block, the last logical call to block by a process (i.e., the last time a user program called block) is not always equivalent to the last chronological call to block. An example will clarify this point.

Suppose process "A" cannot proceed with its execution until condition X is met. A takes the following steps:

1. Test if condition X is met. If yes go on to step 4.

2. Call block since condition X has not been met.

3. Go to step 1 to test again.

4. Continue..

Suppose further that process A completes the test in step 1, finds that condition X is not met and proceeds to step 2. While executing step 2, (i.e., calling block) but before step 2 is complete, process A experiences a missing page fault that results in a call to block from within the missing page fault handling subroutine. Having called block, process A gives up its processor until some time after the next call to wakeup. However, in this case, suppose that two wakeups are received before process A resumes its computation: the wakeup signaling an event in condition X and the wakeup signaling the arrival of the

# ORIGINAL IMPLEMENTATION

missing page. These two wakeups leave the wakeup-waiting switch on however upon return to the caller of block (i.e., the page fault handler) the switch is turned off. Since the page has been retrieved, process A resumes its execution of step 2 above and completes the call to block. In this case block finds the wakeup-waiting switch off even though an event in condition X has been signaled. The reason is that the last logical call to block, which occurred before the execution of step 1, was not the last chronological call to block.

The way that this problem was solved in the original implementation of the Traffic Controller involved two steps. First a wakeup-waiting count was substituted for the wakeup-waiting switch. Second, in addition to wakeup incrementing this count on each call, block was also given the ability to selectively increment the count in special cases. The change to wakeup was trivial, the count was incremented instead of the switch being turned on. The change to block was more fundamental. Block was provided with an argument that was used in the following way:

1. Arg = 0.

2. Test is condition is met. If yes go to step 5.

3. Call block (Arg).

4. Go to step 2.

# 5. Continue...

Whenever block returned, the value of Arg was set equal to the value of the wakeup-waiting count prior to its being decremented by block. If a process returned from block and upon testing the condition in step 2 found it had still not been met the recall to block would transmit a non-zero value of Arg to block. Block would notice this and interpret this to mean that a caller to block received a return when in fact its condition had not been met. Therefore the wakeup-waiting count should be incremented by 1, in order not to lose track of the wakeup that was decremented by the incorrect return from block. After having incremented the count the value of the count is compared to the value of Arg (which was the value of the count at the time of the last logical call to block). If the count is greater than Arg, wakeups have been received since the last logical call to block and return should be immediate whereas if the count is equal to Arg, no wakeups have been received since the last logical call and the process should give the processor away.

Other known solutions to the lost wakeup problem exist. One such solution would, in fact, allow the block primitive to be implemented in exactly the way described by Saltzer. This solution, however, would force some users of the block-wakeup facility to exercise the facility in a slightly different way than has been previously stated. Specifically all those procedures, using block which <u>might</u> be invoked because of a fault condition (e.g., the missing page fault handler) would be required to turn <u>on</u> the wakeup-waiting switch, explicitly, after each successful return from block. That is, such procedures would be required to use the following algorithm to go blocked.

1. Test if condition is met. If yes go to step 4.

2. Call block.

3. Go to step 1.

4. Turn on wakeup-waiting switch and continue.

Use of this algorithm would solve the lost wakeup problem because concealed calls to block would <u>always</u> result in the wakeup-waiting switch being left <u>on</u>. This algorithm would also mean that many returns from block would be in cases where wakeups had not been received, but rather that page faults occurred between two logical uses of block.

One other difference between the Traffic Controller described by Saltzer and the original implementation is that the implemented one had an elaborate interlocking mechanism which allowed any number of processes to be executing in the Traffic Controller simultaneously. This meant that several intermediate execution states (i.e., in addition to the ready, running, blocked, and stopped states) had to be defined and detectable. An example of such a state is the state that occurs after a process defines itself to be ready (in reschedule) but before it can give away the processor in swap-dbr. Another such state occurs after a ready process has been chosen to run (by some other process executing in getwork) but before it is actually given control of a processor. In the flowcharts presented in Appendix I the reader sees all the logical complication introduced by this strategy. (It is not necessary to understand the interlocking mechanism for one to continue reading and therefore the reader is advised not to laboriously pore over these flow charts to gain such an understanding.)

A further point should be mentioned before proceeding. loaded process is defined as one that has enough Α information in core memory so that the process can be given a processor. Operationally in Multics, this means the process has, in core storage, a descriptor segment and also another segment known as the Process Data Segment (PDS) concealed which contains a special stack (known as the This stack is only used, by a process, when stack). executing procedures which cannot tolerate page faults. An example of such a procedure is the page fault handler procedure. The strategy, with regard to unloaded processes, adopted in the original Traffic Controller was that processes were to "load themselves". That is, when called upon to switch to an unloaded process, an interim descriptor segment and an interim PDS were created for the unloaded process and this process was switched to and made to use these interim segments. The process was forced to branch to subroutines (process bootstrap module) which recreated the original descriptor segment and retrieved the original PDS

to core storage. Having thereby loaded itself the process then switched from its interim segments to its actual segments and discarded the interim versions.

This approach to the problem of loading processes actually solves the problem not by allowing the process to load itself, but rather by effectively creating a new process manifested by the interim segments, which accomplish the loading. This new process however executes in the address space of the unloaded process.

Finally, one may notice references in the flow charts of Appendix I to programs not mentioned previously in the text. All of these programs are ones which disappear from the second implementation. They include ready-him (see figure I.10) which implemented the ability to switch to a process' address space in order that the process schedule itself at the time the process was awakened; setup-proc (and unsetup-proc) used to create (and destroy) an interim process; and ready-ds (and unready-ds) used to create (and destroy) an interim descriptor segment for a blocked, unloaded process that was awakened.

# Reworking the Original Implementation

The performance of the original implementation of the Traffic Controller in action was analyzed and found to be deficient in several ways. In the first case it was too slow in execution. In the second case, the size of the programs (which were required to be permanently resident in

#### REWORKING ORIGINAL IMPLEMENTATION

Several logically independent core storage) was large. improvements were incorporated in the second iteration of Traffic Controller which improved performance the However since these improvements are substantially. logically independent they are presented as if they were implemented in a serial manner, one by one, instead of all at once. This allows us to discuss them independently and to understand the motivations behind each of the changes.

# Interlocking Changes

From just a casual perusal of the flow charts in Appendix I, one can see that a large portion of each flow chart is devoted to implementing the complicated interlock strategy. In point of fact, more than 30 per cent of the machine instructions in the original Traffic Controller were there for this purpose alone. For this reason and for several others, a simple strategy was incorporated into the second implementation. The simplified scheme works as follows. Only one processor is ever allowed to execute in the Traffic Controller at any one time. This is accomplished by the use of a single global interlock. Since a processor can be forced to attempt to call subroutine wakeup by the receipt of an external interrupt to the processor, all interrupts must be masked by the processor executing inside the Traffic Controller to prevent a processor from looping forever on a lock that it had set itself. The scheme is implemented by providing code at each

### INTERLOCKING CHANGES

external entry into the Traffic Controller, whereby the processor masks itself and then attempts to lock the global interlock. If the interlock is already locked, the processor loops, waiting for it to become available. Use of this strategy does away with the need to worry about intermediate execution states of processes, since these states are now invisible behind the global interlock.

As was mentioned above, there are several valid reasons for abandoning the complex interlock strategy. The first one is that the complex strategy costs alot and buys little. The only gain experienced from this strategy is that the Traffic Controller is prevented from being a bottleneck that processors continually bang into. A paper presented to the conference of the Association for Computing national Machinery in August of 1968, by Stuart Madnick (reference number 5), discusses this problem of processor time wasted in looping on global interlocks. Madnick's conclusions show that in a system with a small number of processors (e.q., five or less) the probability of encountering a locked interlock is roughly proportional to the number of processors in the system and to the fraction of time that a processor spends executing such interlocked code, compared That is, if processors on average to total execution time. spend two per cent of their time executing such interlocked code and if the system contains three processors, then approximately six per cent of the time a processor will encounter such an interlock locked. Since the Multics

system currently contains only two processors (and can never have more than seven due to hardware limitations) it seems though the Traffic Controller even with a qlobal as interlock, is in no danger of becoming a bottleneck. Secondly, use of the complex scheme means that extra code is executed on each pass through the Traffic Controller. As stated above, approximately 30 per cent of the original code was devoted to implementing the complex strategy. Since there are no loops to speak of, in these programs, we can assume that the average running time of Traffic Controller programs was increased by approximately 30 per cent as a result of the extra code. The simple strategy tends to increase the average running time of the Traffic Controller by locking out processors for periods of time, however as . stated above, until we introduce a large number of processors into the system, this increase in average running time does not approach this 30 per cent figure. Therefore the only possible motivation for the complex scheme is not justified in our case.

The second major problem with the complex scheme is in maintaining it. Even minor changes to Traffic Controller modules mean that the interlock strategy would have to be scrutinized to assure that no bugs had been introduced. Because of the complexity of the scheme, such scrutinization is difficult and would effectively rule out changes to the Traffic Controller once it was "completely debugged".

58

ŧ

Summarizing these reasons, we see that the original scheme suffered from:

- Wasted space devoted to instructions realizing the complex interlock strategy.

- 2. Wasted time spent executing the above instructions.

- 3. Difficulty in maintaining and debugging this scheme.

- 4. No real need for such a scheme.

#### Changes in Wakeup Scheme

Τn the flow charts of Appendix I presented for subroutine wakeup and ready-him, we see that calls to wakeup for blocked processes result in a processor switch to the address space of the blocked process in order to call the scheduler in that address space. The original motivation for such a strategy was that each process could potentially have its own scheduler procedure and that such a scheduler could most sensibly make any decisions necessary in the address space of the process. For example, private data bases of that address space could be used in arriving at decisions. However, the decisions that must be made in awakening a blocked process (such as where in the Ready List the process should be inserted, what priority, etc.) need not be made at the time of the call to wakeup. They can be made at the time that the process puts itself into the blocked state and the data can be left in a shared data

base. Then at the time of the wakeup no decisions need be made. The process need merely be placed on the Ready List at the point indicated by the data left behind. In this way the work (and the expense) associated with switching address spaces at the time of wakeups can be dispensed with.

This revised strategy brings savings in two ways. First two subroutines disappear: ready-him and ready-ds. Second, the time spent in awakening blocked processes (particularly unloaded ones) is decreased. This revision meant minor changes to block and wakeup. In block this revision amounts to computing the priority to be given the process when it is awakened. The criteria for making this decision will be ignored for the present. In wakeup the change amounts to having wakeup directly place the awakened process on the Ready List at the appropriate place.

# Changes to Loading Scheme

The next major logical change to the Traffic Controller comes in the area of loading processes. in the original implementation, unloaded processes loaded themselves when they were chosen to run by subroutine getwork. The process choosing the unloaded process to run had to provide the unloaded process with an interim descriptor segment and an interim PDS in order for the unloaded process to be able to load itself. That is, the choosing process had to effectively create a new process that would perform the work of loading the unloaded process. In addition, the unloaded

process, once switched to, had to choose a candidate for unloading (i.e., a loaded process to be unloaded) if by loading itself, the number of loaded processes would cross a threshold. This scheme had several drawbacks.

- 1. Some of the procedures involved in process loading were required to be always resident in core because these procedures were called directly by the Traffic Controller at a time when page faults could not be tolerated. These procedures included the file system procedures which prepared the interim segments and discarded them after use (setup-proc and unsetup-proc).

- 2. During the execution of process loading, the loading process ties up twice as much core storage as does an ordinary process. It has two descriptor segments (interim and real) and it has two PDS segments (interim and real).

- 3. The above solution for the loading problem means that loading decisions be made during execution of the Traffic Controller, in getwork and swap-dbr specifically. In a Traffic Controller using a global interlock strategy, serious bottleneck situations could develop if such decisions involved much computation.

above loading scheme Once it is observed that the effectively creates (and later destroys) a new process for each loading operation, a more efficient solution to the problem immediately comes to mind. Why not provide a system process dedicated to loading and unloading other processes? The revised Traffic Controller makes use of such a special system process devoted to loading and unloading processes. This special process, referred to as the "loader-daemon" process, spends its life executing in a loop. Whenever the loader-daemon is awakened, this process peruses the Traffic Controller data bases, makes decisions as to whom to load and unload and actually performs the loading and unloading. The loader-daemon then calls block before perusing the data bases again. The mechanism whereby the loader-daemon is periodically awakened and the actual algorithms whereby the loading decisions are made will be ignored for now and will be presented in a later section. The consequences of the revised loading scheme to the modules of the Traffic Controller are manifested in the immense simplification to subroutine swap-dbr.

### Block-Wakeup Facility Environment

The block-wakeup primitives provide the capability whereby one process can signal a second process about the occurrence of an event of a condition that this second process is interested in. The extra mechanism that must be provided before such a facility becomes useful is the

#### BLOCK-WAKEUP FACILITY ENVIRONMENT