#### COMPUTER DESIGN FOR ASYNCHRONOUSLY REPRODUCIBLE MULTIPROCESSING

bу

## EARL CORNELIUS VAN HORN, JR.

- S.B., Massachusetts Institute of Technology 1961

- S.M., Massachusetts Institute of Technology 1963

## SUBMITTED IN PARTIAL FULFILLMENT OF THE

REQUIREMENTS FOR THE DEGREE OF

DOCTOR OF PHILOSOPHY

at the

MASSACHUSETTS INSTITUTE OF TECHNOLOGY September, 1966

| Signature of   | Author     |              | arl!U          | m Ho      | ukr.     |

|----------------|------------|--------------|----------------|-----------|----------|

|                | Department | of Electric  | al Engineering | g, August | 22, 1966 |

| Certified by   | 7          |              | ach B          | Jens      | mi_      |

|                |            | _ 7          |                | Thesis S  | pervisor |

| Accepted by_   | Three      | 5.           | Gran           |           | -        |

| - <del>-</del> | Chairman.  | Departmental | Committee on   | Graduate  | Students |

#### COMPUTER DESIGN FOR ASYNCHRONOUSLY REPRODUCTBLE MULTIPROCESSING

bу

#### EARL CORNELIUS VAN HORN, JR.

Submitted to the Department of Electrical Engineering on August 22, 1966, in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

#### ABSTRACT

A concept is presented for designing either a computing system, or a programming language system, so that the following problem is avoided: during a multiprocess computation in which several processes communicate. and in which the relative timing of the performance of the processes is arbitrary, the output produced by the computation might not be a function of only the initial computation state, i.e., of only the inputs and initial program of the computation. The design concept for avoiding this problem is explained by defining an apparently new class of abstract machines called machines for coordinated multiprocessing, or MCM's. Processes are coordinated in an MCM by means of a count matrix, which may be modified by actions of processes, and which determines the processes enabled to proceed at any instant. Remarks are made to suggest that a computing facility which behaves like an MCM can be both constructed and programmed at reasonable cost. It is proved that every MCM has the properties of output functionality and output assuredness. Output functionality means that each symbol in every output stream is a function only of the initial computation state. Output assuredness means that for each output stream the maximum number of symbols produced in the stream, or the fact that the number of such symbols has no upper bound, is a function only of the initial computation state.

Thesis Supervisor: Jack B. Dennis

Title: Associate Professor of Electrical Engineering

#### Preface

The Thesis discusses three broad topics: (1) a problem encountered in some contemporary computing systems, (2) a concept for designing a computing system in order to solve this problem, and (3) a proof that the concept presented does indeed solve the problem.

The problem concerns multiprocessing. Multiprocessing occurs whenever a computing system is programmed by a single user in a manner that allows more than one sequence of actions to be performed for him simultaneously. Suppose information is transmitted among such sequences of actions, and suppose the relative timing of the performance of these sequences is not under user control. The problem to which the Thesis is addressed is that in these circumstances the output produced for a user by the performance of such sequences might not be a function of only the inputs and initial program that are specified by the user. A more precise statement of the problem and a discussion of the problem's origin and significance are the subjects of Chapter I.

A concept for designing a computing system in order to avoid the problem just mentioned has been discovered. An attempt has been made to capture the essence of this design concept by describing, in Chapter II, a class of abstract machines called machines for coordinated multiprocessing, or MCM's for short. A preview of the structure of an MCM is given near the beginning of Chapter II.

Chapter III discusses the feasibility of constructing and programming a computing system whose internal structure can be placed into correspondence with the structure of an appropriately chosen MCM.

In Chapters IV and V it is proved that the problem mentioned above does not arise in an MCM. Conclusions and suggestions for future research are presented in Chapter VI.

The Thesis might be of interest to three groups: (1) those concerned with designing the hardware and supervisory software of computing systems, (2) those concerned with designing programming language systems, i.e., programming languages and compilers for these languages, and (3) those concerned with the theory of automata. primary orientation of the Thesis is toward the design of the hardware and supervisory software of a computing system. The Thesis is also relevant, however, to the design of programming language systems, in two respects. First, the programming of a computing system constructed along the lines to be discussed, although shown in the Thesis to be feasible, presents an interesting challenge both to programmers, and to the designers of programming language systems. Second, by employing the design concept to be discussed, it is possible to develop for any computer a programming language system having the property that if a user interacts with the computer only by means of the language system, the user will never encounter the problem mentioned above. Finally, the Thesis is relevant to automata theory, because it appears that the class of machines called MCM's has not been studied before.

Although the Thesis as a whole is oriented toward the area of computer engineering practice, the topics and methods of Chapters II, IV, and V are characteristic of the area of automata theory. The techniques of automata theory have been employed in the Thesis for three reasons. First, the essence of the design concept that has been discovered is

captured more effectively in a description of an abstract machine than in a description of a hypothetical computing system; in a description of the latter kind the essence of the design concept would tend to be obscured by irrelevant detail. Second, by expressing the design concept in terms of the structure of an abstract machine, the nature of an apparently new phenomenon is made readily available for study and comparison with other concepts in the theory of automata. Third, the mathematical language and techniques used in automata theory allow the presentation of highly rigorous proofs of facts that, although intuitively satisfying, have turned out to be slippery to verify by means of logic.

For the reasons just mentioned, the Thesis may be said to stand both in the area of computer engineering practice, and in the area of automata theory. As with any interdisciplinary work, the technical jargon of one area might not be readily understood by those working in the other area. An effort has been made, therefore, to explain technical terms not common to both fields, and to avoid locutions likely to be misleading.

The doctoral research program which led to the present Thesis began with an inquiry into the possibility of analyzing quantitatively the problems of storage allocation in computing systems. This inquiry led to a search for ways of characterizing the structural aspects of computing systems, particularly multiprogrammed computing systems. The present research topic, in turn, resulted from an effort to describe the properties of those events which constitute the execution of a single program within a multiprogrammed system.

I should like to acknowledge gratefully the support of M.I.T.'s Project MAC\*, the activities of which stimulated my search toward the present research topic. The presentation of ideas in the Thesis has been substantially improved as a result of comments and suggestions by Professors R. McNaughton, R. Y. Kain, and F. J. Corbató. I am grateful to my advisor, Professor Jack B. Dennis, not only for his assistance on technical matters, but also for his unswerving confidence in my abilities. Finally, to my wife, Sandra, I extend special thanks for the typing of the manuscript, and for her encouragement and devotion.

Earl Van Horn

<sup>\*</sup>Work reported herein was supported in part by Project MAC, an M.I.T. research program sponsored by the Advanced Research Projects Agency, Department of Defense, under Office of Naval Research Contract Number Nonr-4102(01).

"We cut up and organize the spread and flow of events as we do, largely because, through our mother tongue, we are parties to an agreement to do so, not because nature itself is segmented in exactly that way for all to see."

Benjamin Lee Whorf

# Contents

| Abstract                                              | ii  |

|-------------------------------------------------------|-----|

| Preface                                               | 111 |

| Introductory Quotation                                | vii |

| List of Figures                                       | xii |

|                                                       |     |

| Chapter I. Contemporary Multiprocessing               | 1   |

| Introduction                                          | 1   |

| Single-Process Programs                               | 1   |

| Multiprocess Programs                                 | 3   |

| The Computation State                                 | 5   |

| Computing Facilities                                  | 5   |

| Arbitrarily-Timed Cooperative Multiprocessing         | 8   |

| Output Functionality                                  | 9   |

| Lurking Bugs                                          | 12  |

| Lurking Bug Effects                                   | 15  |

| Contemporary Procedure Steps for Multiprocessing      | 16  |

| An Example of a Lurking Bug                           | 19  |

| Chapter II. A Machine for Coordinated Multiprocessing | 23  |

| Introduction                                          | 23  |

| Preview                                               | 24  |

| Cells                                                 | 27  |

| Transactions                                          | 29  |

| Get Transactions                                      | 32  |

| Put Transactions                                      | 34  |

| Procedure Steps                                       | 35  |

| Reading and Writing                                   | 36  |

| Outputting                                            | 37  |

| The Scheduler                                         | 38  |

| The Count Matrix                                      | 39  |

| The Enable Set                                        | 41  |

| Nomenclature for Cells                                | 42  |

|     | The Choice Collection for Gets and Puts                  | 43            |

|-----|----------------------------------------------------------|---------------|

|     | Send, Done, and Bye Transactions                         | <u> 14.14</u> |

|     | The Choice Collection                                    | 47            |

|     | Scheduling Strategies                                    | , 47          |

|     | Specifying A Well-Defined MCM                            | 48            |

|     | Coordination of Processes                                | 49            |

|     | Tabulation of MCM Properties                             | 56            |

| Chi | apter III. A Facility That Behaves Like an MCM           | 61            |

|     | Purpose                                                  | 61            |

|     | Method                                                   | 62            |

|     | Dynamic Allocation                                       | 64            |

|     | Overview of VM                                           | 64            |

|     | A Viewpoint toward Secondary Storage References          | 65            |

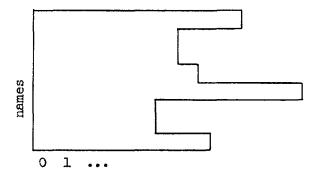

|     | Introduction to Segments                                 | 68            |

|     | Segments                                                 | 69            |

|     | Clerks                                                   | 71            |

|     | Input Devices                                            | 71            |

|     | Output Devices                                           | 73            |

|     | Control Matrix Elements                                  | 73            |

|     | A Sketch of VM's Operation                               | 76            |

|     | Coordination Procedure Steps                             | 77            |

|     | An Example Matrix Manipulation Again                     | 79            |

|     | Introduction to the Correspondence between VM and an MCM | 83            |

|     | The Cluster Corresponding to a Segment                   | 85            |

|     | The Cluster Corresponding to a Clerk                     | 85            |

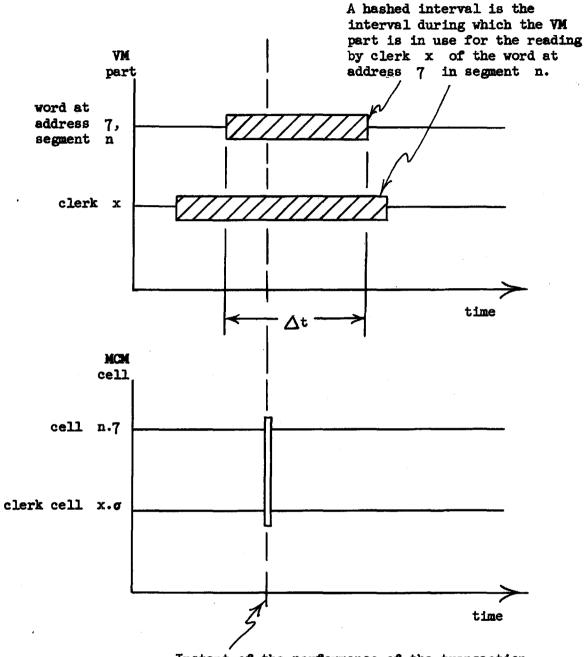

|     | Performance Correspondences                              | 87            |

|     | The Cluster Corresponding to an Input Device             | 88            |

|     | The Cluster Corresponding to an Output Device            | 93            |

|     | The Cluster Corresponding to an Unused Name              | 94            |

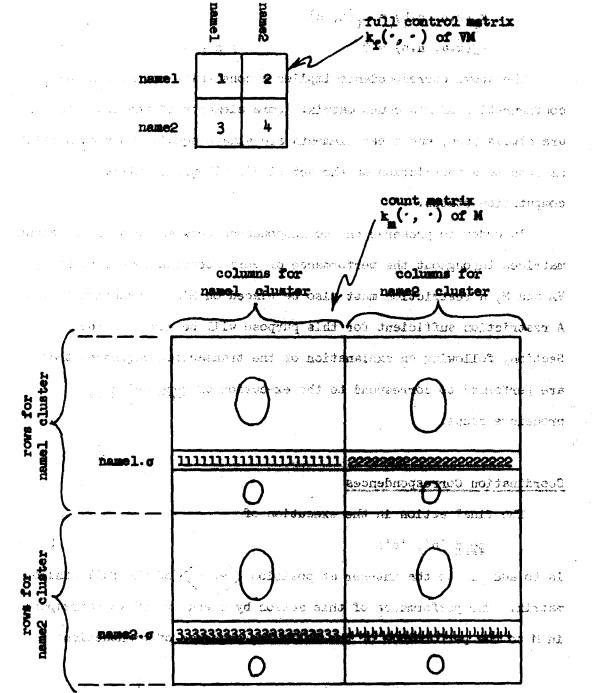

|     | The Correspondence between Control and Count Matrices    | 94            |

|     | Coordination Correspondences                             | 96            |

|     | Mrs. Mining Convergedance                                | ΩQ            |

| Creation and Deletion Correspondences                               | 104           |

|---------------------------------------------------------------------|---------------|

| Epilogue for the Correspondence between VM and M                    | 104           |

| The Problem of Choosing Names                                       | 105           |

| Naming Conventions Suggested to Facilitate<br>Creation and Deletion | 106           |

| Creation and Deletion Procedure Steps                               | נננ           |

| Another Example Macro Expansion                                     | 114           |

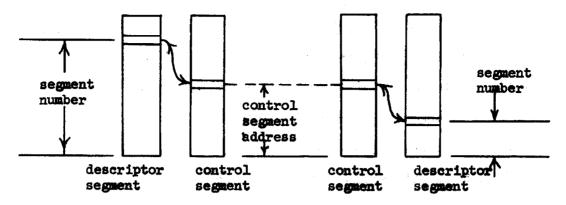

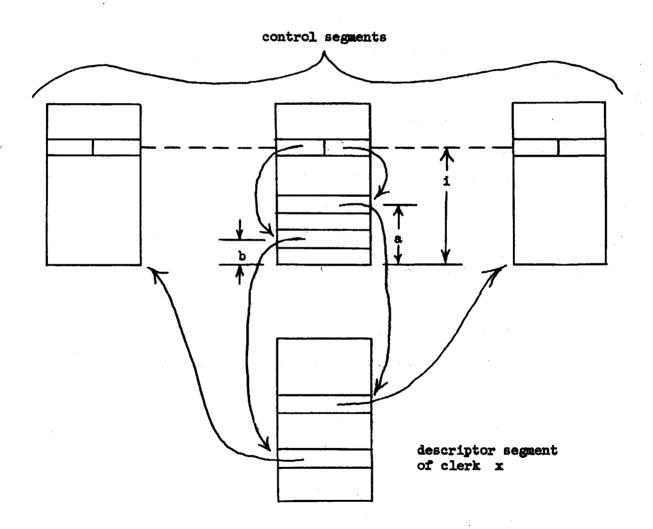

| Control Matrix Implementation                                       | 125           |

| Chapter IV. The Output Functionality of an MCM                      | · <b>13</b> 6 |

| Introduction                                                        | 136           |

| Specialization to a Single Arbitrary MCM                            | <b>13</b> 6   |

| The Run as a Formal Description of a Computation                    | 137           |

| The History Array of a Run                                          | 140           |

| Statement of the Functionality Theorem                              | 145           |

| The Augmented Array                                                 | 146           |

| Introduction to the Proof                                           | 148           |

| The Inductive Formulation                                           | 149           |

| The Initial Step                                                    | 150           |

| Beginning the Inductive Step                                        | 150           |

| Facts and Nomenclature about Augmented Arrays                       | 153           |

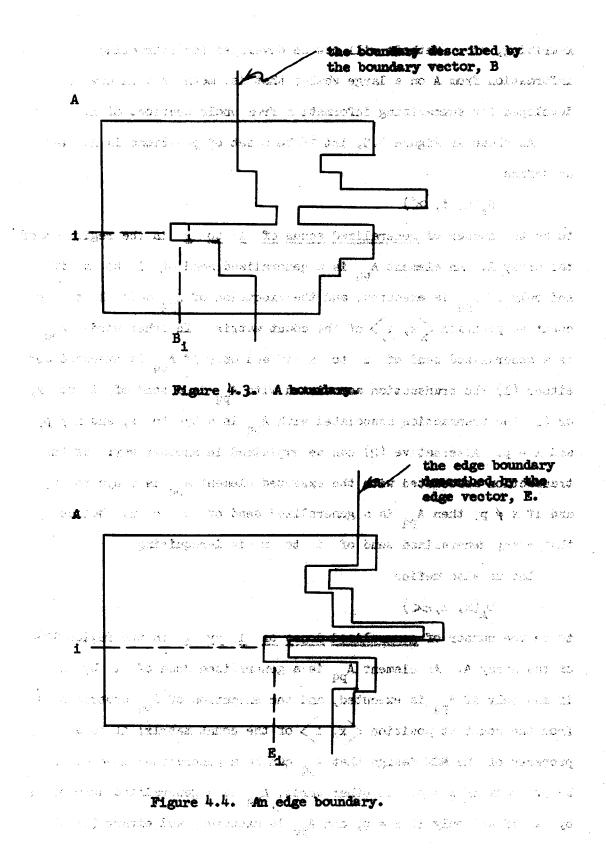

| Boundaries                                                          | 156           |

| The Count Matrix at the Conclusion of a Prefix Run                  | 156           |

| Resuming the Proof                                                  | 161           |

| The First Stage                                                     | 163           |

| The Second Stage                                                    | 179           |

| The Third Stage                                                     | 180           |

| Chapter V. The Output Assuredness of an MCM                         | 193           |

| Introduction                                                        | 193           |

| Specialization to a Single Arbitrary MCM                            | 193           |

| Types of Computations                                               | 194           |

| The Traces of an Initial Computation State                          | 195           |

| The Limit Vector of a Trace                                         | 197           |

| Statement of the Assuredness Theorem                        | 197         |

|-------------------------------------------------------------|-------------|

| The Formulation                                             | <b>19</b> 8 |

| The Construction                                            | 199         |

| The Contradiction                                           | 206         |

| Chapter VI. Conclusions and Suggestions for Future Research | 216         |

| Introduction                                                | 216         |

| Asynchronous Reproducibility                                | 216         |

| The Conditional Nature of Asynchronous Reproducibility      | 217         |

| Repeatable Input Streams                                    | 218         |

| State Input Streams                                         | 219         |

| The Hang-Up Phenomenon                                      | 220         |

| Ownership                                                   | 222         |

| Questions of Necessity                                      | 224         |

| Toward a Science of Computer Design                         | 226         |

| Appendix A. The Non-Redundancy of Bye Transactions          | 228         |

| Appendix B. Well-Defined MCM's                              | 231         |

| Appendix C. Summary of Notation                             | 233         |

| References                                                  | 235         |

| Biographical Note                                           | 237         |

# List of Figures

| 1.1. | Example of output-nonfunctional multiprocessing                                           | דנ  |

|------|-------------------------------------------------------------------------------------------|-----|

| 1.2. | Lurking bug destroying output functionality                                               | 13  |

| 1.3. | Flow-chart of a contemporary multiprocess program                                         | 20  |

| 2.1. | An MCM having three cells                                                                 | 26  |

| 2.2. | Additional properties of the MCM having three cells                                       | 31  |

| 2.3. | Typical count matrix configuration of the MCM having three cells                          | 40  |

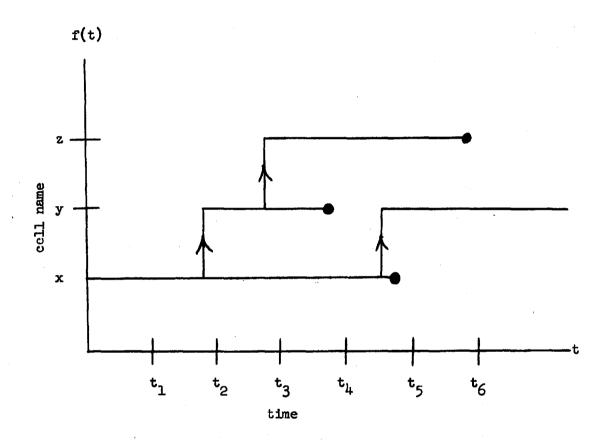

| 2.4. | Locus of read capabilities for a cell i in an example of process coordination             | 51  |

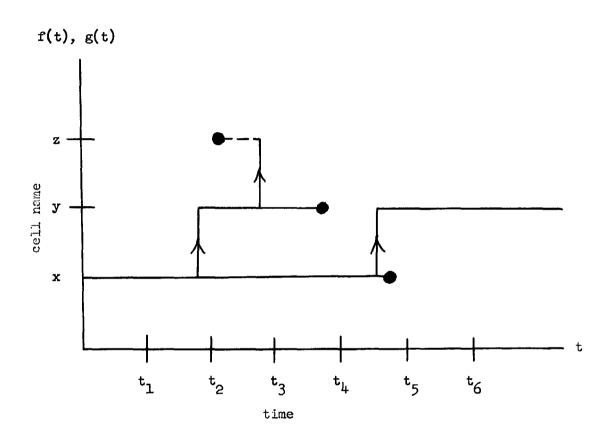

| 2.5. | Locus of counts for a cell i in a variation of the example of Figure 2.4                  | 54  |

| 2.6. | Locus of counts for a cell i in a variation of<br>the example of Figure 2.4               | 55  |

| 2.7. | The enabling rules                                                                        | 59  |

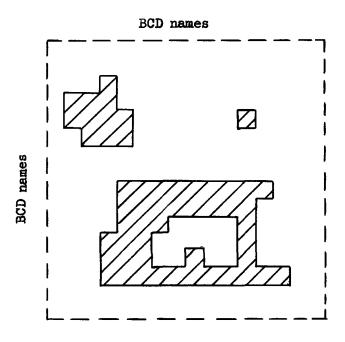

| 3.1. | A typical control matrix                                                                  | 74  |

| 3.2. | A typical set of existing control matrix elements                                         | 74  |

| 3.3. | Part of the control matrix upon entry into an example program                             | 81  |

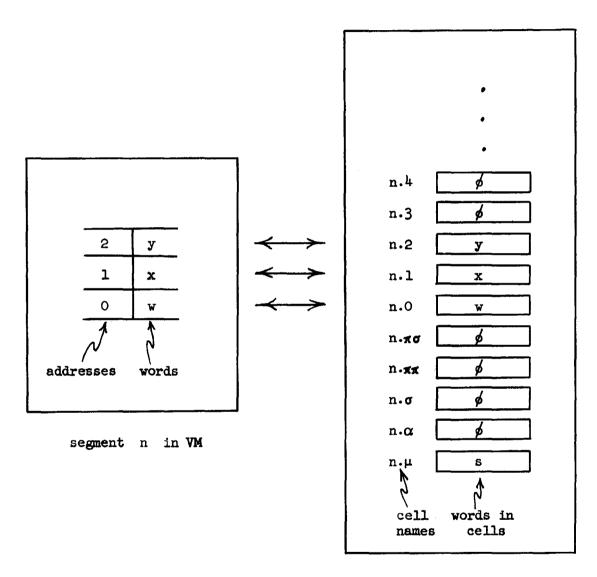

| 3.4. | The cluster corresponding to a segment                                                    | 86  |

| 3-5- | Correspondence between a full control matrix and a count matrix                           | 95  |

| 3.6. | The performance in M of the transaction that corresponds to a read action in VM           | 100 |

| 3.7. | Permission rules for several actions of a clerk in VM                                     | 103 |

| 3.8. | Segment numbers and the control segment address of a segment n in a two-clerk computation | 128 |

| 3.9.  | List structure linking clerks having read capability for a segment                                 | 128 |

|-------|----------------------------------------------------------------------------------------------------|-----|

| 4.1.  | Three typical history arrays                                                                       | 142 |

| 4.2.  | The environment of the inductive step                                                              | 152 |

| 4.3.  | A boundary                                                                                         | 157 |

| 4.4.  | An edge boundary                                                                                   | 157 |

| 4.5.  | A set of positions in an augmented array                                                           | 159 |

| 4.6.  | A boundary and the set of positions to its left                                                    | 159 |

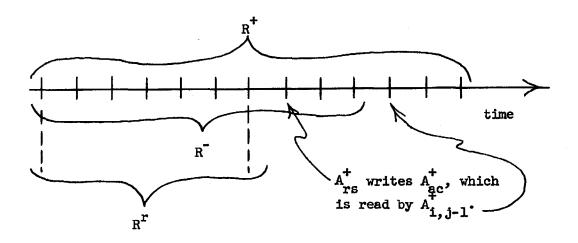

| 4.7.  | Four runs                                                                                          | 164 |

| 4.8.  | Principal boundaries used in the proof of the second case of the inductive step                    | 165 |

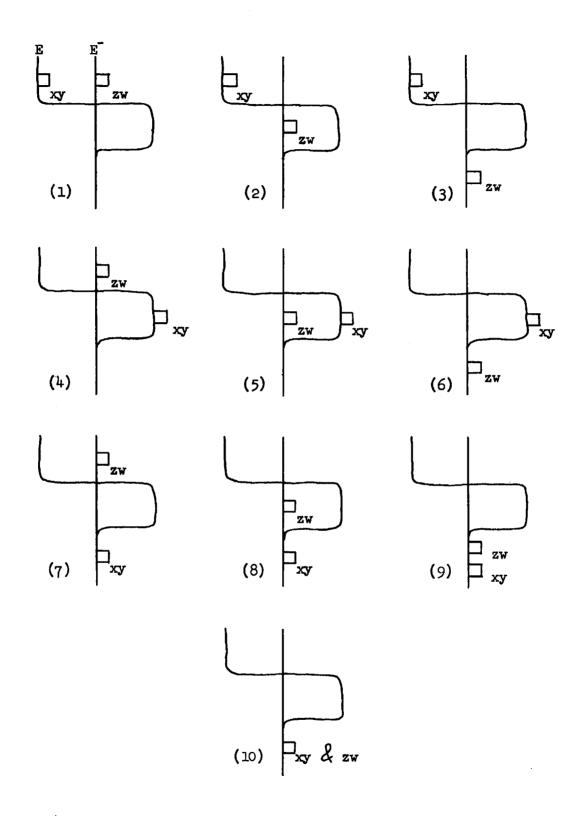

| 4.9.  | The ten possibilities in the proof of the first stage of the second case of the inductive step     | 166 |

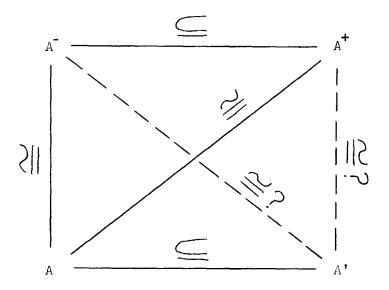

| 4.10. | Asymmetry in the environment of the inductive step                                                 | 169 |

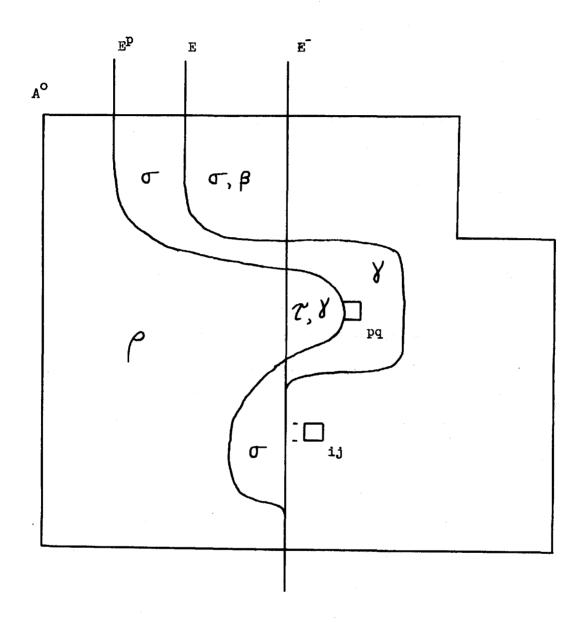

| 4.11. | Boundaries used in the demonstration that there are no i-requiring elements in $\gamma$            | 172 |

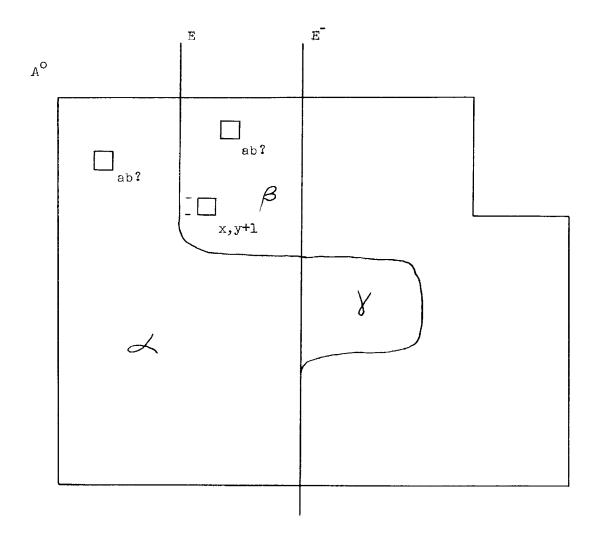

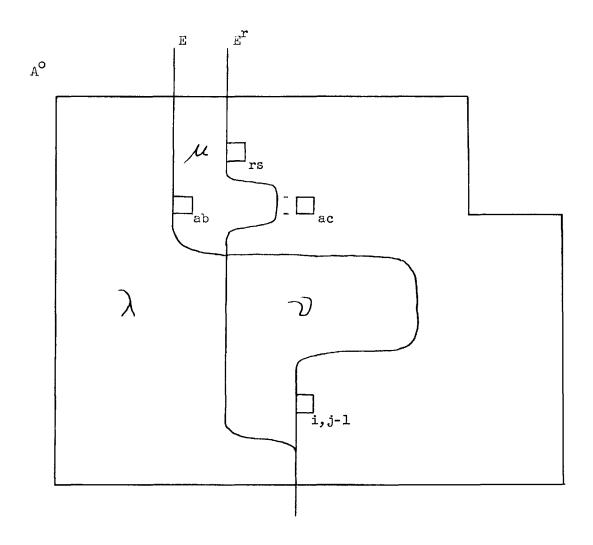

| 4.12. | Possible locations of Ao ab                                                                        | 176 |

| 4.13. | Boundaries used in the demonstration for possibilities (1) and (3) that A is executed              | 177 |

| 4.14. | The three possibilities in the proof of the third stage of the second case of the inductive step   | 182 |

| 4.15. | Possible locations of Ars                                                                          | 184 |

| 4.16. | Principal boundaries used in the proof of the third stage of the second case of the inductive step | 185 |

| 4.17. | The regions $\lambda$ , $\mu$ , and $\nu$                                                          | 186 |

| 4.18. | Boundaries used in the demonstration that there are no a-requiring elements in $\gamma$            | 188 |

| 4.19. | Six runs                                                                                           | 189 |

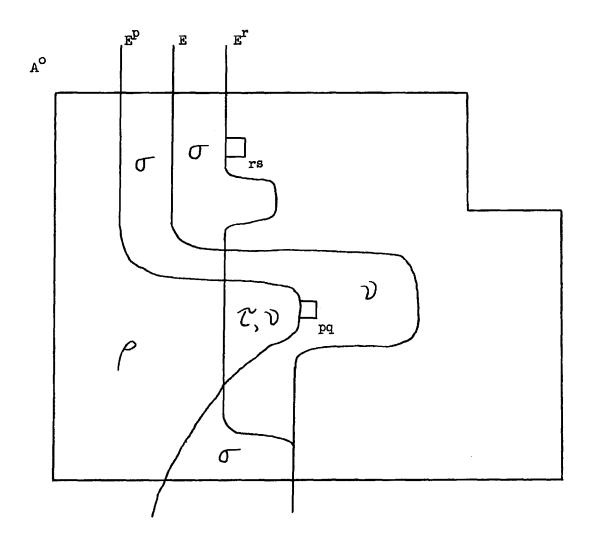

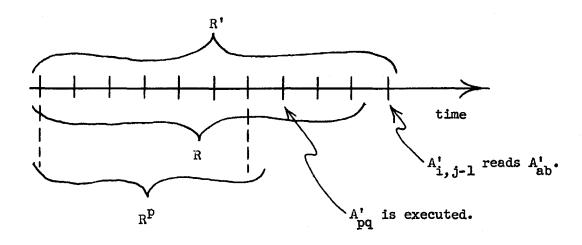

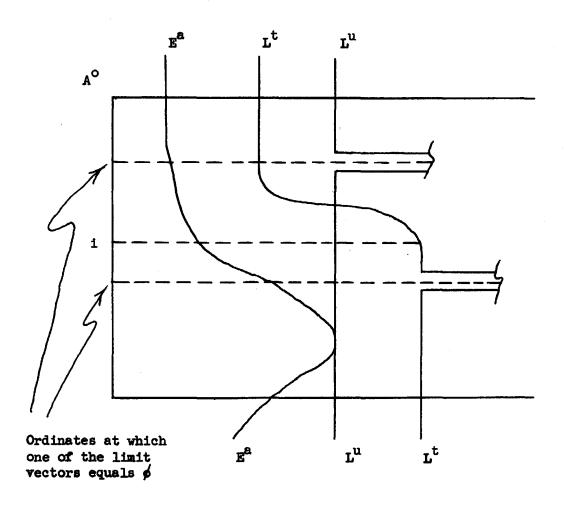

| 5.1.  | The houndaries E. L. and Lu                                                                        | 202 |

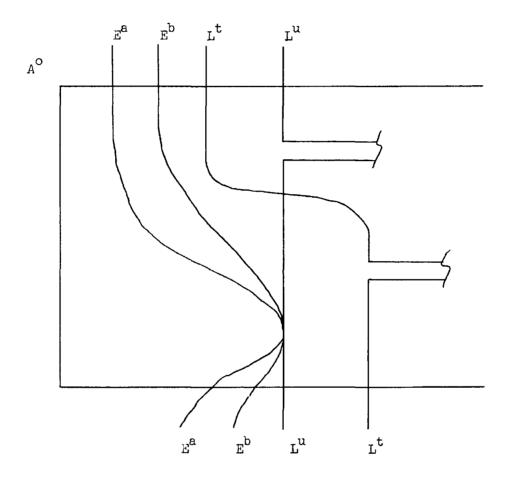

| 5.2. | Position of the desired E <sup>b</sup> boundary                                   | 203 |

|------|-----------------------------------------------------------------------------------|-----|

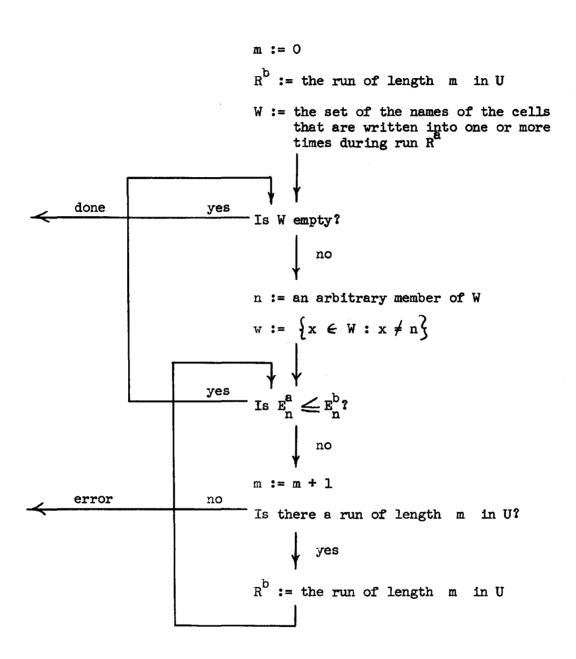

| 5•3• | Flow-chart of an algorithm for finding R                                          | 204 |

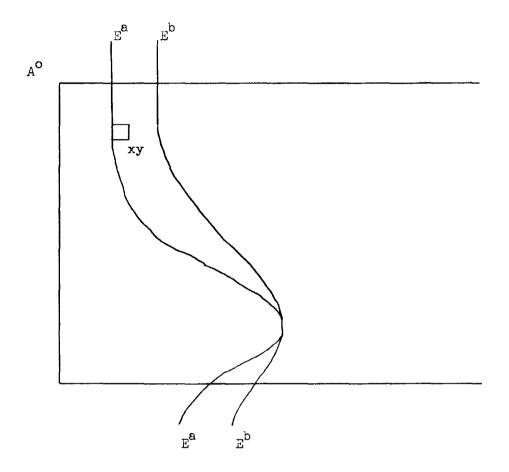

| 5.4. | The element A <sub>Xy</sub>                                                       | 207 |

| 5.5. | The Ea and E boundaries redrawn                                                   | 209 |

| 5.6. | The E <sup>p</sup> boundary                                                       | 212 |

| A.1. | Events of interest in the demonstration of the non-redundancy of bye transactions | 230 |

#### Chapter I

## Contemporary Multiprocessing

#### Introduction

This Chapter presents an explanation of selected problems and issues associated with contemporary multiprocessing. The explanation is organized to achieve two specific goals: (1) the establishment of a certain outlook, or viewpoint, toward the phenomenon of multiprocessing, in order to provide a base for the discussions in subsequent Chapters, and (2) the statement of the particular difficulties whose solutions are sought in subsequent Chapters. Thus Chapter I serves as an introduction for the Thesis as a whole.

The Chapter begins by introducing, through the use of examples, the notion of a <u>single-process program</u>. Next the notion of a <u>multiprocess program</u> is defined as a generalization of the notion of a single-process program, and multiprocessing is explained to be a phenomenon that involves the execution of a multiprocess program. Next some additional concepts are defined, and finally several problems and issues associated with contemporary multiprocessing are discussed in depth.

### Single-Process Programs

A program is a recipe for transforming an initial set of values into a final set of values; for example, the following program tells

how to find the largest value present in the list of numbers,

$x_1, x_2, \ldots, x_n$

- 1. Make i be 1.

- 2. Make j be 1.

- 3. If i = n then the answer is  $x_{i}$ .

- 4. Subtract  $x_i$  from  $x_{i+1}$  and remember the result.

- 5. If the result is positive then add 1 to j.

- 6. Add 1 to 1.

- 7. Go to step 3.

This program is composed of seven <u>procedure steps</u>, and the set of values to which the program refers is the set of quantities named i, j, n, and  $x_1, x_2, \dots, x_n$ .

One can imagine execution of the above program by a <u>clerk</u>, which passes from one procedure step to the next, obeying the directions encountered at each step. Between procedure steps a clerk might remember information within itself; for example, between steps (4) and (5) of the above program the clerk retains the result of the subtraction performed at step (4). In general, a procedure step might direct a clerk to modify either the clerk's own information, or the value set, or both.

The sequence of actions that a clerk performs in executing a program is called a <u>process</u> [11, 26].\* The above program is called a <u>single-process</u> <u>program</u>, because it directs the activity of exactly one clerk.

Numbers in square brackets refer to items in the list of references, which follows the Appendices.

The simplest kind of digital computer, having one arithmetic unit and one memory unit, executes single-process programs. The arithmetic unit of such a computer can act as a clerk; then the state word of the arithmetic unit is clerk information, and each word in the memory unit is value set information.

#### Multiprocess Programs

A <u>multiprocess</u> <u>program</u> is a set of procedure steps that directs the activities of two or more clerks. Since each <u>processing unit</u>, such as an arithmetic unit or i/o channel, of a computing system can act as a clerk, then any program permitting the simultaneous operation of processing units is an example of a multiprocess program.

One reason for specifying a computational activity in the form of a multiprocess program is that such a program can indicate an absence of sequencing constraints among portions of an activity by explicitly permitting several clerks to act simultaneously. Such permissions for simultaneity are desirable because they allow a system to perform a computational activity more rapidly than if the activity had to be performed sequentially.

Two examples of <u>systems for multiprocessing</u>, i.e., systems that can execute multiprocess programs, are the IBM 7090 [17], and the DEC PIP-1 [23]. In the 7090, the data channels and the arithmetic unit

A typical arithmetic unit state word includes program counter, instruction register, and accumulator information. Additional remarks on state words are given by Conway [3].

can execute separate processes simultaneously: the procedure steps executed in the data channel processes are drawn from a set of "channel commands". In the PDP-1, the single-channel sequence break hardware switches the arithmetic unit between a main process and an interrupt process.

The term "multiprocessing" is often used to describe systems having more than one processing unit. Nevertheless, when "multiprocessing" is used in this contemporary sense, it is the author's suspicion that many of the problems actually being discussed might be more effectively studied as problems of multiprocess programming rather than as problems of the simultaneous use of physically distinct processing units. For this reason, the term "multiprocessing" is used throughout the Thesis to refer to a programmer's specification of potential multiple activity. and not to refer to a particular method for carrying out such a specification. For example, suppose a multiprocess program is written to direct the activities of two clerks. If two processing units are available, they might execute the program together, each unit playing the role of one of the program's clerks. On the other hand, if only one processing unit is available, it might play the role of now one clerk and then the other, alternating back and forth between the two clerks according to some arbitrary scheduling strategy. Multiprocessing occurs in both of these situations, because in both cases a multiprocess program is being executed.

#### The Computation State

An execution of either a single-process program or a multiprocess program is called a <u>computation</u>. At an instant during a computation, the <u>computation state</u> is denoted by the information contained in the clerks and value set of the program being executed. For example, during the execution of the single-process program mentioned at the beginning of this Chapter, the computation state at some instant is denoted both by the information contained within the executing clerk, and also by the information held in the value set, i.e., held in the quantities i, j, n, and  $x_1, x_2, \ldots, x_n$ . A system performing a computation exhibits a succession of computation states: each transition from one computation state to the next is caused by one or more processing units, each playing the role of one of the program's clerks.

In practice, four kinds of information are encoded into a computation's initial state: (1) the procedure steps of a program, (2) the initial values of the program's internal quantities, (3) the information initially held in the program's clerks, and (4) the input symbols to be read during the program's execution. In other words, the initial computation state holds, of the information controlling a computation's performance, just that portion which a user can specify either explicitly, or implicitly through the use of programs and data prepared by others.

#### Computing Facilities

Many discussions to be presented in the Thesis concern the manner in which a computing system might execute an individual program. A fact

that might complicate these discussions is the fact that some computing systems can be simultaneously in the midst of executing two or more programs; such systems are said to be <u>multiprogrammed</u> [10]. The notion of a computing <u>facility</u> is introduced so that the manner in which an individual program is executed can be easily discussed without regard to whether the executing system is multiprogrammed.

A computing facility is a perhaps time-varying collection of hardware that executes at most one single-process or multiprocess program at a time. Every computing system provides at least one facility, but a computing system that is multiprogrammed can provide several facilities simultaneously. For example, a typical configuration of the CTSS system [14] provides 24 facilities. A user gains access to one of these facilities when he identifies himself to the system by "logging in".

In providing a facility, a computing system provides (1) input units by means of which a user can specify an initial computation state, (2) processing and storage units that can perform a computation beginning from such an initial computation state, and (3) output units that can produce for a user during such a computation one or more output streams, i.e., sequences of output symbols. An example of the production of three output streams is the writing of symbols on a typewriter, a printer, and a card punch unit.

An improved understanding of the way in which a computing system provides a facility can be achieved by studying some of the details of the way in which a computing system executes a program. A program refers to, or directs the activities of, a set of objects: each object to

which a program refers is either a clerk, a value set quantity, an input device, or an output device. During the execution of a program, it is appropriate for the role of each object referred to by the program to be played by a specific and distinct physical unit. Nevertheless, there need not exist such a fixed correspondence between program objects and physical units. In particular, the role of a program object might be played by a succession of physical units, and during occasional intervals the role of an object might not be played by any unit.

To provide a physical unit as part of a facility is to provide a physical unit to play the role of one of the objects referred to by the program the facility is executing. As was mentioned, each physical unit of a facility might be provided either continuously or intermittently. Thus, when a computing system provides one or more facilities, the system allocates its available physical units among the objects that are referred to by the programs the facilities are executing. In general, this allocation is time-varying, i.e., dynamic; dynamic allocation results in several distinct correspondences between physical units and program objects as time progresses.

An example of dynamic allocation is found in the previously mentioned PDP-1 system. When the single facility provided by the PDP-1 executes a program that uses the single-channel sequence break feature, the PDP-1's memory unit is permanently allocated to hold the program's value set, but the PDP-1's arithmetic unit is dynamically allocated by the sequence break hardware to carry out alternately the activities of the program's main clerk and interrupt clerk. Other examples of dynamic allocation are found in the CTSS system. Here the central processing unit and the main

memory unit are allocated dynamically among the clerks and the value set quantities, respectively, that are referred to in the programs of several facilities.

#### Arbitrarily-Timed Cooperative Multiprocessing

Clerks executing a multiprocess program are said to <u>cooperate</u> [11] whenever information is transmitted among them; such transmissions take place either through the internal memories of the clerks, or through the program's value set. Cooperative multiprocessing is assumed throughout the present study: a facility might allow inter-clerk cooperation, and a multiprocess program might direct such cooperation.

A multiprocess program is executed in an <u>arbitrarily-timed</u> manner just when there is at least one computation state for which the set of the program's clerks accomplishing the transition to the next computation state is at least partially determined by influences other than the current computation state. If a program's execution is arbitrarily-timed, then knowledge of the current computation state generally does not imply knowledge of the next computation state, because the next computation state can depend on the set of the program's clerks that happen to accomplish the next computation state transition.

An <u>arbitrarily-timed</u> facility is one that might execute a multiprocess program is an arbitrarily-timed manner. A facility might be arbitrarily-timed because of slight variations in the speeds of autonomous processing units, because of replacement of one system component by another of different speed, because of variations in the duration of 1/o activity,

or, perhaps most significantly, because of the scheduling strategy of a multiprogrammed system. Arbitrarily-timed facilities are assumed throughout the present study.

#### Output Functionality

A facility is <u>output-functional</u> just when each symbol produced in every output stream is a function only of the initial computation state.

An alternate description of an output-functional facility gives two intermediate definitions. A facility is (S, i, j)-output-definite just when S is an initial computation state and each S-initiated computation producing a j-th symbol in output stream i produces the same j-th symbol in output stream i. A facility if S-output-definite just when it is (S, i, j)-output-definite for each output stream, i, and each positive integer, j. Finally, a facility is output functional just when it is S-output-definite for each initial computation state, S.

Many contemporary facilities are S-output-definite only if S belongs to some proper subset of the initial computation states; such facilities require a user desiring output functionality to begin each of his computations from one of the S-output-definite initial computation states.

The present study describes methods for making the S-output-definite subset of a facility's initial computation states equal to the set of all the facility's initial computation states, so that computations will produce deterministic outputs regardless of programming mistakes or

improper input data. In Chapter II an abstract machine for coordinated multiprocessing is described, and a proof is given in Chapter IV that a facility which behaves like such a machine is an output-functional facility.

The following two examples show that, in the absence of interclerk coordination constraints such as will be proposed, cooperative

multiprocessing performed by an arbitrarily-timed facility is

nondeterministic in a way that can permit the symbol at some position

in an output stream to depend on factors other than the initial

computation state. In the first example, two clerks are ready to write

different symbols into the same output stream. If the clerks' order of

execution is arbitrary, then either symbol can appear as the next

symbol in the output stream.

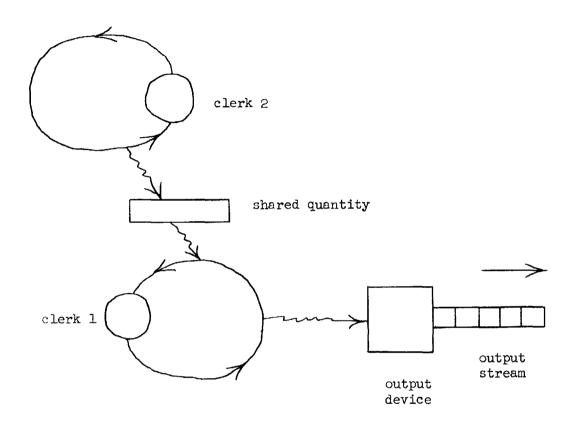

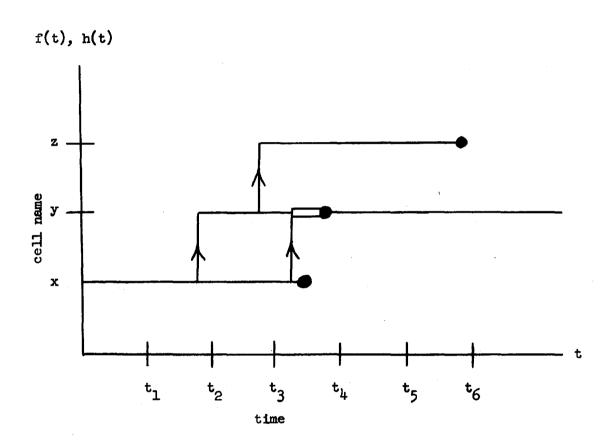

The second example is depicted in Figure 1.1. Suppose a clerk computes each of a stream of output symbols using only a result that a second clerk computes and stores as a shared quantity. If the first clerk stops for an arbitrary time while the second clerk continues execution, then an arbitrary number of symbols might be omitted from the output stream. On the other hand, if the second stops and the first continues, then some particular symbol might appear in the output stream an arbitrary number of times.

No one ever questions the output functionality of facilities that execute only single-process programs, because single-process computing is inherently deterministic. Unfortunately, the term "computer" has been associated for so many years with single-process computing that users sometimes expect any apparatus bearing the stamp "computer" to

Figure 1.1. Example of output-nonfunctional multiprocessing.

exhibit a functional relationship between initial state and output streams. Thus the term "multiprocess computer" has a deterministic connotation, which is often misleading.

#### Lurking Bugs

As mentioned previously, many contemporary facilities for multiprocessing appear <u>output-nonfunctional</u> to their users. This lack of output functionality has not substantially hindered the development of computing applications, because programmers have been able to recognize the effects of arbitrary execution timing, and have been able to isolate these effects from the output streams of computations. For instance, a programmer might have introduced into the example of Figure 1.1 an interlock quantity to be tested by each clerk before the clerk proceeded with the reading or writing of the shared data quantity.

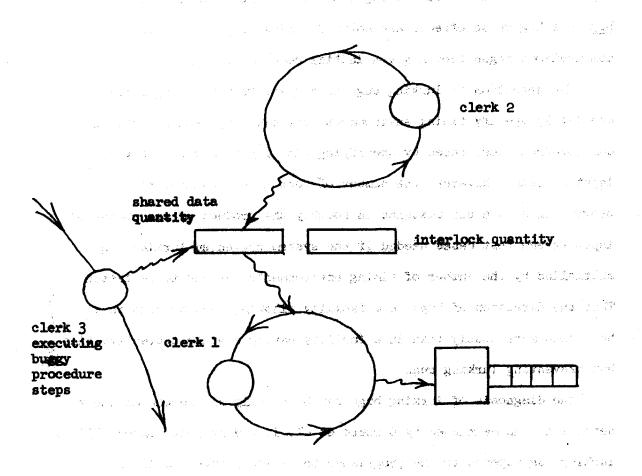

The seeking of deterministic outputs through the skillful programming of an output-nonfunctional facility is undesirable because the detection and the diagnosis of programming mistakes, i.e., bugs, are much more difficult in an output-nonfunctional facility than in an output-functional facility. The issues are best understood by considering again the example of Figure 1.1 in which two clerks cooperate using shared data and interlock quantities. As shown in Figure 1.2, suppose a bug in the procedure steps being executed by a third clerk causes the third clerk to change the value of the data quantity shared by clerks one and two. During some computations from a given initial state, this change does not affect the output stream, because at the instant of the change, clerk one has already read the shared data quantity's current

and from the control of the control

"我们的是有什么,我们们的,我们的人,我们的人,我们的经验,我们也没有一个人的人,我们就是一个人

green the company of the company of the contract the contract of the contract

gradina in the company of the gradient of the strong and strong strains of the strong of the strains and

and the state of t

Figure 1.2. Lurking bug destroying output functionality.

value and clerk two has not yet set the next value. During other computations from the same initial state, the change does affect the output stream, because at the instant of the change, the current value of the shared data quantity has not yet been read by clerk one. The bug in the procedure steps being executed by clerk three is a <u>lurking bug --</u> a bug whose effects are noticed during only some of the computations begun from a given initial computation state.

The detection of lurking bugs is easiest when the programmer can completely specify timing environments for his computations; then he can construct test cases by specifying timing environments as well as input streams. However, the number of test cases required to debug a program in such a circumstance is roughly the product of the number of input stream test cases needed if the system prevented lurking bugs multiplied by the number of timing environments desired to be tested. Thus the detection of bugs in a facility allowing lurking bugs is at best much more costly than in a facility having similar characteristics but preventing lurking bugs.

The diagnosis of lurking bugs can be equally as onerous as their detection. As mentioned by Corbato et al. in a different context [5], a lurking bug appears to the programmer to be indistinguishable from transient hardware failure. Breakpoints, dynamic dumps, traces, and other diagnostic tools all require the re-running of a computation at least once and possibly several times to isolate a bug into progressively smaller sections of a program. Unless the programmer can reproduce the timing environment of the computation in which a bug was detected, the programmer must choose between two alternatives: he can insert his diagnostic tools into the program and continue to run computations until

Providence shows the bug to him again, or he can try to diagnose using the program listing, the computation's output, and a dump of the final computation state. Both of these alternatives are costly as well as discouraging.

#### Lurking Bug Effects

The example of Figure 1.2 shows how a lurking bug's effect can be the destruction of output functionality. Such a lurking bug effect, i.e., the production of arbitrary output from identically-initiated computations, is called a <u>non-functionality</u> effect.

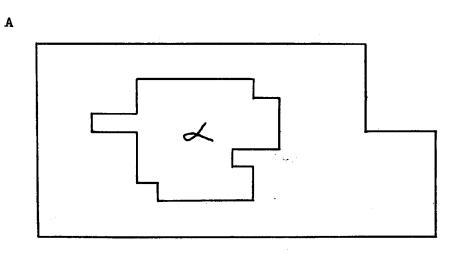

Another lurking bug effect, called a <u>noncompletion</u> effect, is the arbitrary curtailment of the production of output from identically initiated computations. An individual lurking bug might cause either a nonfunctionality effect, or a noncompletion effect, or both.

The following example describes a lurking bug causing a noncompletion effect. Suppose a bug in the procedure steps being executed by a clerk causes the clerk to change the procedure code being executed by a second clerk. During some computations from a given initial state, the second clerk has already executed the changed code, and so the change does not affect the second clerk's periodic execution of an output procedure step. During other computations from the same initial state, the second clerk executes the changed code, and thereupon begins executing a loop of procedure steps that excludes the output step the clerk would otherwise have periodically executed. The bug in the procedure steps being executed by the first clerk is a lurking bug that causes a noncompletion effect.

Facilities for multiprocessing that behave like the abstract machine to be described in Chapter II are proved in Chapter IV to prevent nonfunctionality effects. In Chapter V, such facilities are also proved to prevent noncompletion effects.

#### Contemporary Procedure Steps for Multiprocessing

To allow comparison between contemporary facilities for multiprocessing and the facilities to be discussed in subsequent Chapters, several types of procedure steps used in contemporary multiprocess programs are now described. In the next Section, procedure steps of some of these types are used in an exemplary program, into which a typing error could introduce a lurking bug.

The first type of procedure step is <u>fork</u> [1, 3, 10]. Execution of the step

#### fork e;

creates a clerk that will start execution at the label e, and causes the clerk that executed the fork to pass to the next procedure step. The creation of a clerk means that there is an additional clerk participating in the computation; an immediately recruited processing unit might play the role of the new clerk, or a new entry might be placed in a list, called a ready list [10, 26], of clerks whose roles ought to be played.

Execution of the step

# quit;

[10] deletes the executing clerk. The deletion of a clerk means that

there is one less clerk participating in the computation; the processing unit that had played the role of a clerk being deleted might either join a pool of available processing units, or begin playing the role of the highest priority clerk on a ready list.

One of several schemes for programming the cooperation of simultaneously existing clerks is the scheme reported on by Dijkstra [11] involving semaphore quantities. Execution of the step

V s;

adds one to a semaphore quantity, s, using an uninterruptible incrementmemory instruction. Execution of the step

Ps;

causes the executing clerk to act as if it executed the following program:

- 1. If s is greater than zero then go to step 3.

- 2. Cease activity until s becomes greater than zero.

- 3. Subtract 1 from s without interruption.

If several clerks are at step (2) for s when s becomes greater than zero, then just one of these clerks, which is selected according to a priority discipline, proceeds to step (3).

Procedure steps of the types  $\underline{V}$  and  $\underline{P}$  are useful for directing the cooperation between a clerk producing data and a clerk receiving data, such as the clerks of Figure 1.1. In this application the semaphore quantity indicates the number of data values ready for consumption in a variable length buffer.

Y and P procedure steps can also be used to restrict a <u>critical</u>

section of a program's procedure steps to execution by one clerk at a

time. Each critical section is preceded by a  $\underline{\underline{\mathbf{P}}}$  and followed by a  $\underline{\underline{\mathbf{V}}}$ , both referring to the section's unique semaphore quantity, which will only take the values 1 and 0.

Dijkstra has shown that critical section control can be achieved without using a procedure step whose execution requires uninterruptible read-alter-write action [12, 20]. The construction is so complicated, however, that it is mainly of theoretical interest.

Similar to the actions performed by P and V when used for critical section control are the actions of lockout in the D825 system [13], lock and unlock discussed by Dennis and Van Horn [10], and obtain and release described by Anderson [1]. Each procedure step of these types acts on a binary semaphore quantity that is associated with a data quantity specified by the procedure step.

As described by Conway [3], execution of the step

## join c;

subtracts 1 from c without interruption. If the result is negative or zero, the clerk proceeds to the next step; otherwise the clerk is deleted. The initial value of the quantity c is the number of clerks that must execute the join in order for one of them to proceed to the step following the join.

Dennis and Van Horn [10] describe a join similar to Conway's join, but which specifies a label to which a clerk should transfer rather than quit.

#### An Example of a Lurking Bug

To exemplify the use of some of the types of procedure steps described in the previous section, as well as to allow the illustration of a lurking bug, the following program is presented, which tells how to compute the expression

$$(AB)^{-1}((CD)(AB))$$

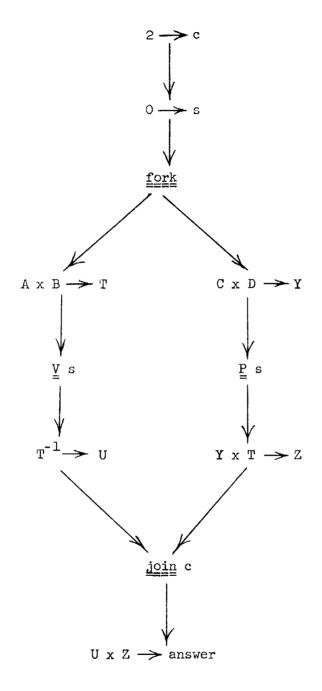

where A, B, C, and D are n by n matrices, and AB is assumed non-singular. The language in which the program is written is similar to the Algol language [2]. The join appearing at the label "last" is a Conway-type join. A flow-chart representation of the program is given in Figure 1.3.

```

array T, U, Y, Z[1:n, 1:n];

<u>begin</u>

integer c, s;

c := 2;

s := 0;

fork parpro;

matrix multiply (A) times: (B) into: (T);

¥ s;

matrix inverse of (T) into:(U);

goto last;

matrix multiply (C) times:(D) into:(Y);

parpro:

Ps;

matrix multiply (Y) times: (T) into: (Z);

last:

<u>join</u> c;

matrix multiply (U) times:(Z) into:(answer);

<u>end</u>

```

Figure 1.3. Flow-chart of a contemporary multiprocess program.

A clerk enters the program by passing to the symbol begin. The following activity ensues when exactly one clerk enters the program. First the entering clerk causes a new clerk to start execution at the label "parpro". Then the entering clerk, after computing the product AB, executes a V telling the parpro clerk that AB has been formed. Next the entering clerk inverts AB. The parpro clerk, after computing CD, \* delays at a P until AB is available. Then the parpro clerk computes (AB)(CD). Finally, the two clerks join, and the last to arrive computes the final answer.

Consider the effect of a typographical error on this program: suppose that

Ps;

had been inadvertently typed as

Pc;

If the execution timing were such that the entering clerk proceeded all the way to the <u>loin</u> before the parpro clerk reached the P, then a correct result would be obtained; otherwise an unreproducible incorrect result

Applying the Algol rule of procedure body replacement to the above program, the simultaneous execution by both clerks of the procedure "matrix multiply" occurs as if each clerk executed a separate copy of the procedure. The need for separate copies of the procedure in an implementation can be avoided, however, through the use of <u>pure procedure</u> programming techniques [4], in which programs, instead of directing their own modification, direct the modification of data quantities <u>private</u> to each executing clerk [10].

could be expected. In particular, if the program were tested using a facility in which as many actions as possible were performed in one process before any actions were performed in another, then the effects of the typographical error would be hidden during debugging, but might be discovered on an application in which simultaneous processing occurred.

### Chapter II

# A Machine for Coordinated Multiprocessing

# Introduction

This Chapter delineates a class of machines called machines for coordinated multiprocessing, or MCM's for short. An MCM is abstract, in the same sense that a Turing machine [8] or a finite automaton [24] is abstract. In principle, it is possible to construct an MCM; indeed, the structure and functioning of an MCM are best understood by imagining the existence of an actually constructed physical device. Nevertheless, it is desirable to keep in mind that an MCM is abstract, because an application of an MCM need not involve the MCM's straightforward construction as a physical device.

Although an extended discussion of MCM applications is postponed until Chapter III, it is useful to see examples of how an MCM can be applied in ways that do not constitute its straightforward construction. One example is the simulation of an MCM on a digital computer through the use of interpretive software. Another example is the use of an MCM as a model for analyzing, from an individual user's point of view, the behavior of a computing system's hardware and supervisory software. This last example can be expressed in another way: just as a CTSS [14] facility appears to a user like a virtual machine very similar to an IBM 7094, so also might some facility behave as if it were an actually constructed MCM.

In Chapter III, techniques and examples are presented to suggest that a facility which behaves like an MCM can be useful, and can be both constructed and programmed at reasonable cost. In Chapters IV and V, it is proved that nonfunctionality lurking bug effects and noncompletion lurking bug effects, respectively, do not occur in an MCM. That is, it is proved in these two Chapters that identically initiated MCM computations never produce arbitrary output, and that the production of output from identically initiated MCM computations never is arbitrarily cut short. The questions treated in Chapters III, IV, and V concern the sufficiency of an MCM for achieving various goals; questions concerning the necessity of an MCM remain open.

### Preview

One of the purposes underlying the formulation of the MCM concept has been to bridge the gap, or provide a way station as it were, between the simplicity of automata theory and the complexity of contemporary computing systems. Specifically, the structure of an MCM is complex compared to the structure of a Turing machine or a finite automaton, but is clean and symmetrical compared to the structure of a contemporary computing system.

During the presentation of the details of MCM structure and operation, the reader may find it helpful to have in mind a broad framework upon which to sort out the details as they arrive. The following paragraphs establish this framework by mentioning the components of an MCM, and by indicating how these components work together to perform computations.

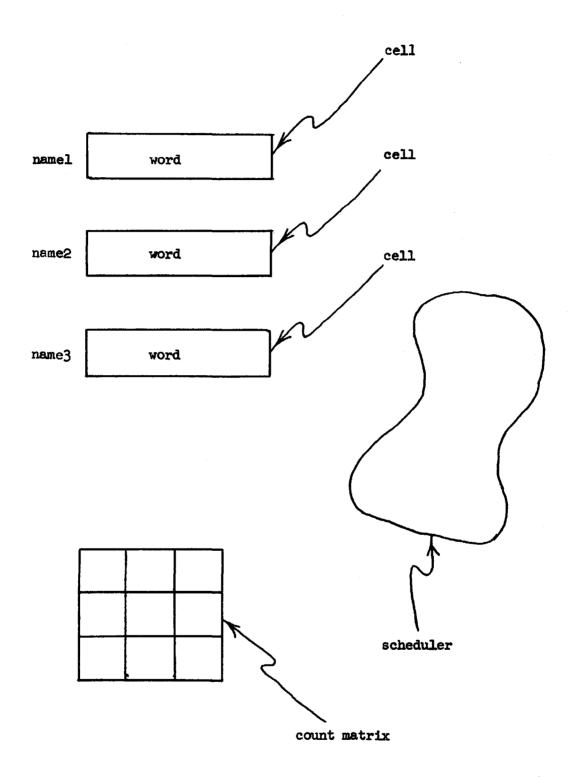

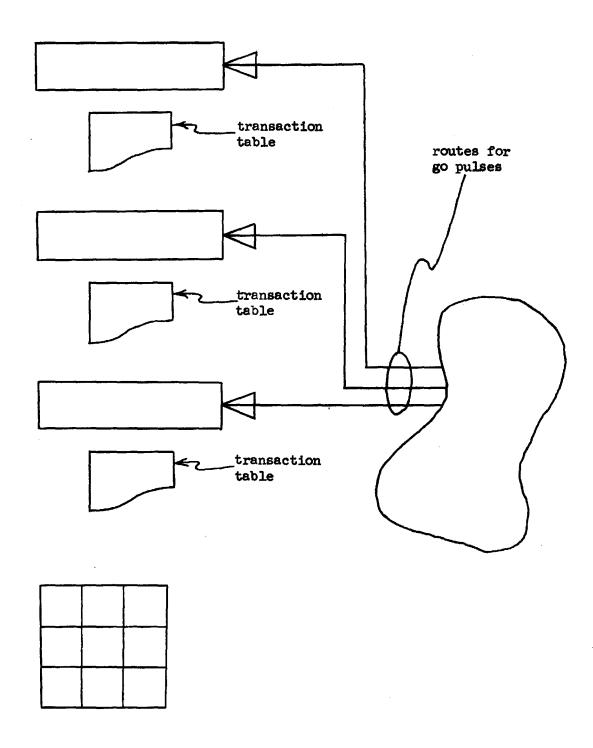

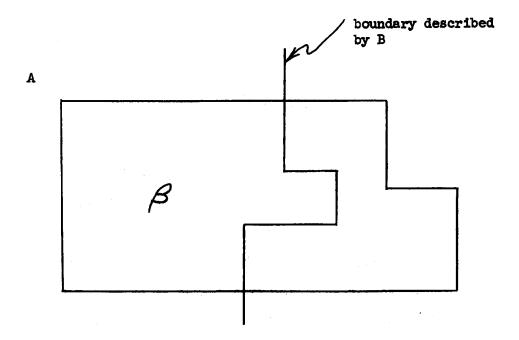

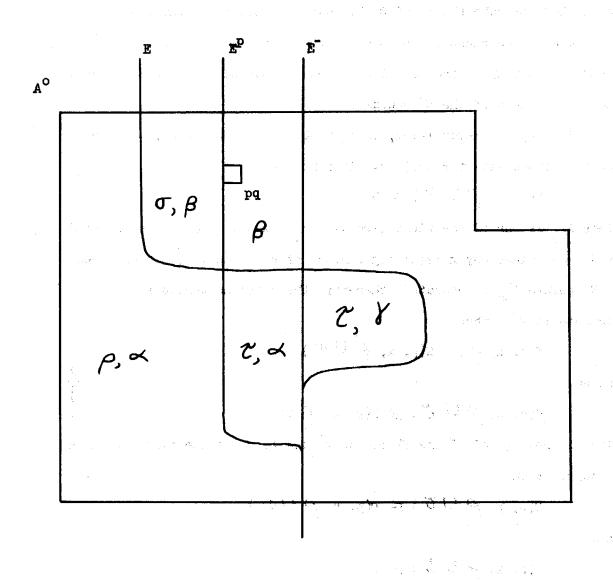

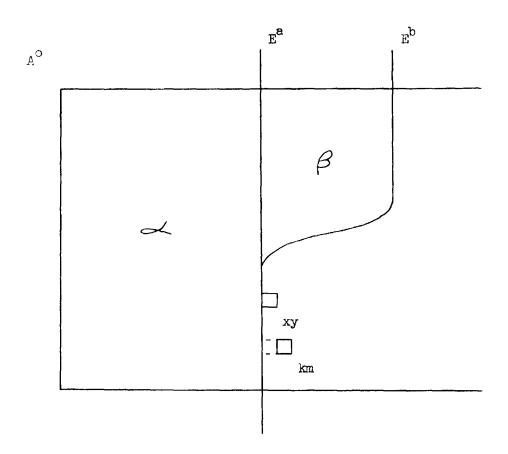

An MCM consists of a collection of cells, a scheduler, and a count matrix; Figure 2.1 shows an MCM with three cells. A cell might act like a main memory register of a contemporary computing system, or a cell might act like a processing unit of such a system. That is, a cell might store information passively, or a cell might actively perform a process. In performing a process, a cell performs a sequence of basic actions called transactions; in performing an individual transaction, a cell might read from or write into another cell, or might change an element of the count matrix.

The <u>computation state</u> of an MCM is denoted by the information contained in the MCM's cells and count matrix. During the performance of a <u>computation</u>, an MCM takes on a succession of computation states: each transition from one computation state to the next is accomplished by the simultaneous performance of single transactions by one or more cells.

The cells that are to accomplish each computation state transition are selected by the scheduler. The scheduler's selection of such cells is affected by the immediately preceding computation state, and perhaps also by the unpredictable influences that make a facility for multiprocessing be arbitrarily-timed.

As was mentioned, a cell performing a transaction might change the count matrix. The count matrix, in turn, affects the scheduler's selecting of the cells that are to perform transactions. This loop of cause and effect -- from cells to count matrix to scheduler to cells --

Figure 2.1. An MCM having three cells.

is the mechanism by which the activities of the cells are coordinated in order to prevent nonfunctionality and noncompletion lurking bug effects.

The author does not know of a contemporary facility for multiprocessing that behaves like an MCM in every respect. Nevertheless, there seems to be a certain similarity between MCM's and contemporary facilities, no doubt because the MCM concept grew out of an effort to model such facilities. Specifically, the cells of an MCM function in a way that is in many respects similar to the behavior of the processing units and main memory registers of a contemporary facility. Moreover, the scheduler of an MCM functions in a way that is somewhat similar both to the behavior of a supervisory computation that schedules processing units among programs to be executed, and to the behavior of electronic hardware that disciplines a queue of processing units awaiting access to a main memory unit. The count matrix of an MCM, however, does not appear to be similar to any feature of a contemporary facility.

# Cells

A cell is unusual in that it can model either an active device like a processing unit, or a passive device like a memory register. A cell that models an active device is called a <u>clerk</u> cell, and a cell that models a passive device is called a <u>value</u> cell. A clerk cell performs a process that is a sequence of transactions, and a value cell stores information passively. As shown in Figure 2.1, the state of a cell is denoted by a word, and each cell is designated by a unique name.

It was mentioned that no contemporary facility is known that behaves like an MCM in every respect. Nevertheless, in order to understand the

properties of the cells that occur in MCM's, it will be useful to observe how a collection of such cells might model the processing units and main memory registers of, say, an IBM 7090. Such a collection might contain 32,768 + 9 cells: one value cell to hold each memory word, one clerk cell to hold each data channel state word, and one clerk cell to hold the central processing unit state word. These cells might be named: 0, 1, ..., 32767, A, B, ..., H, CPU.

The state of an MCM's collection of cells can be described by means of a table in which the name of each cell is associated with the word held by the cell. Since each name is unique, such a table defines a single-valued function, called a content function, that takes the name of a cell into the word held by the cell; for example, if  $c(\cdot)$  is the content function denoting some state of the 7090 cells described above, then the memory word at location 5 is c(5), and the state word of channel B is c(B). If  $c(\cdot)$  is a content function and x is a name, then the word c(x) is called the content of cell x. As an MCM passes from one computation state to the next, its collection of cells takes on a succession of states, each distinct state being described by a different content function.

An interesting property of an MCM is that the designation of a cell as either a clerk cell or a value cell can be a function of time. In this respect, the cells of the 7090 model mentioned above are not typical of MCM cells in general. Although each cell of the 7090 model is for all time either a clerk cell or a value cell, the general case is that a cell might alternate between clerk and value status as time progresses.

This alternation of cells between clerk and value status is similar to the alternation of modules between active and non-active roles in an abstract iterative computer described by Holland [16].

The clerk or value status of a cell is determined at any instant solely from the count matrix, in a manner to be described later. A clerk cell is changed into a value cell, or a value cell is changed into a clerk cell, by making an appropriate change in the count matrix.

# Transactions

It was mentioned that the process each clerk cell performs is a sequence of basic actions called transactions. A clerk cell's performance of an individual transaction generally involves an interaction between the clerk cell and its environment. For example, suppose the CPU cell of the 7090 model mentioned above executes a store-accumulator instruction that does not specify indirect addressing. This execution is a sequence of two transactions: the first transaction reads from a value cell the encoded store-accumulator instruction, and the second transaction writes into perhaps some other value cell the accumulator information held in the CPU cell. These two transactions are of the types get and put, respectively. Gets, puts, and transactions of three other types are explained later in detail.

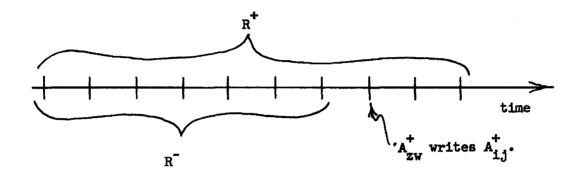

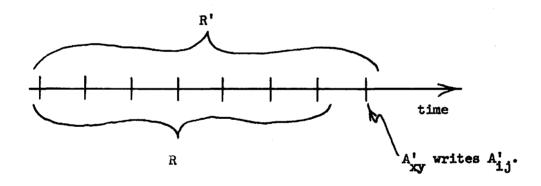

Each computation state transition is accomplished by the simultaneous performance of single transactions by one or more clerk cells. After the scheduler has selected the clerk cells that are to carry out a computation state transition, the scheduler simultaneously transmits a single go pulse to each clerk cell that has been selected. Upon receipt

of a go pulse a clerk cell performs, not a series of transactions, but exactly one transaction; specifically, a clerk cell performs exactly one transaction when and only when it receives a go pulse. The scheduler's operation, which will be described later, is such that only clerk cells receive go pulses.

When a clerk cell receives a go pulse, the transaction the cell performs is determined both by the cell's identity, and by the cell's content. For example, during the previously mentioned store-accumulator execution, the first transaction performed by the CPU cell is determined both by the fact that the cell is the CPU cell rather than, say, the B cell, and by the fact that the content of the cell has cycle information saying that an instruction fetch activity is to take place next.

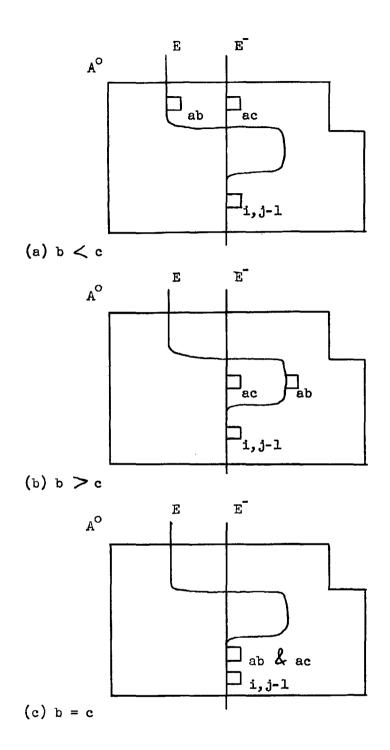

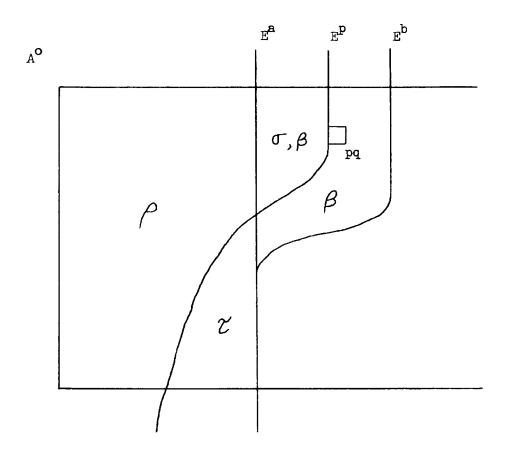

As shown in Figure 2.2 for the MCM of Figure 2.1, a cell's identity determines a transaction table, within which the cell's content determines a transaction. Specifically, in a cell's transaction table each possible content of the cell is associated with the type and parameters of a transaction; that is, if a cell might hold any one of n words, then there are exactly n word-transaction pairs in the cell's transaction table. At any instant, the transaction associated in this way with a cell's content is the transaction the cell would perform if it were to receive a go pulse at that instant. In other words, if the content of a cell is a certain word, and one wishes to know the transaction the cell would perform upon receipt of a go pulse, one need only look up the word in the cell's transaction table in order to obtain the type and parameters of the desired transaction.

Figure 2.2. Additional properties of the MCM having three cells.

Every cell has a transaction table, because, in general, every cell is potentially a clerk cell. A cell's transaction table is permanently associated with the cell; in other words, a cell's transaction table does not vary with time. In the 7090 model, the transaction table of the CPU cell describes the wired-in properties of the 7090 central processing unit -- in the same way that the state transition table of a sequential machine describes certain wired-in properties of the machine.

# Get Transactions

The first transaction of the previously mentioned store-accumulator execution is of the type get. A typical get transaction is described in a transaction table as follows.

get of i replace f(·) (2.1)

The two parameters of a get are its operand name, such as i in (2.1), and its replacement function, such as f(·) in (2.1). In performing

and its <u>replacement function</u>, such as  $f(\cdot)$  in (2.1). In performing the transaction described by (2.1), a clerk cell reads the content of cell i, evaluates the function  $f(\cdot)$  with this content as argument, and causes itself to hold the result of this evaluation. For example, suppose  $c(\cdot)$  denotes the state of a collection of cells at some instant, and suppose (2.1) is the transaction that corresponds to c(x) in clerk cell x's transaction table. If at this instant clerk cell x receives a go pulse, then clerk cell x will be caused to hold the word f(c(i)).

The performance of a get by clerk cell x changes the content of clerk cell x from some word, A, to some word, B. Let us review the way in which the word B is determined. First, the name x determines a

transaction table. Second, the word A determines in this table a particular transaction -- in this case a get whose parameters are, say i and  $f(\cdot)$ . Third, the content of cell i is used as the argument of  $f(\cdot)$  to determine the word B.

As noted above, the first transaction of the previously mentioned store-accumulator execution is a get. This get is determined by the word W that is held in the CPU cell just before the get's performance. The get's operand name is W's instruction location counter information, and the content of the cell named by this operand name is the encoded store-accumulator instruction. If the get's replacement function is evaluated with the encoded instruction as argument, the function yields for placement in the CPU cell a word X consisting of (1) instruction register information denoting the encoded instruction's operation part, (2) storage register information denoting the encoded instruction's address part, (3) cycle information saying that an instruction execution activity is to take place next, (4) instruction location counter information denoting a name numerically one greater than the name denoted by W's instruction location counter information, and (5) other information, such as accumulator and index register information, identical to the corresponding information of W. In other words, the replacement function of the get associated with W tells how the word X, which replaces W, depends on the encoded instruction.

The above example illustrates that in practice the state of a processing unit is usually the state of a collection of several information-storing elements, such as flip-flops or ferrite cores. When a processing unit performs a get, not every information-storing

element need change state. In fact, the replacement function of some particular get may be such that the states of certain elements never change during the get's performance, regardless of the word read as operand. Thus the performance of a get may involve a change in only "part of" the word held in a processing unit. For present purposes, it will be convenient to think of the performance of a get as always changing the "entire" word held in a processing unit, and recognize that a get's performance might actually change the state of only some of a unit's information storing elements. In fact, for understanding the formal properties of an MCM, one may think of a word, not as a string of digits denoting states of separate elements, but as one symbol selected from some alphabet; with the latter point of view it is meaningless to speak of replacing "part of" a word.

# Put Transactions

The second transaction of the previously mentioned store-accumulator execution is of the type put. A typical <u>put</u> transaction is described in a transaction table as follows.

put of i with v replace w (2.2)

The three parameters of a put are its operand name, such as i in (2.2), its operand word, such as v in (2.2), and its replacement word, such as w in (2.2). In performing the transaction described by (2.2), a clerk cell causes itself to hold the word w, and causes cell i to hold the word v; if the clerk cell and cell i are the same cell, then the clerk cell causes itself to hold w, and v is ignored. For example, suppose c(·) denotes the state of a collection of cells at some

instant, and suppose (2.2) is the transaction that corresponds to c(x) in clerk cell x's transaction table. If at this instant clerk cell x receives a go pulse, then clerk cell x will be caused to hold the word w, and, if i is not equal to x, cell i will be caused to hold the word v.

As noted above, the second transaction of the previously mentioned store-accumulator execution is a put. This put is determined by the word X that is held in the CPU cell just before the put's performance. The put's operand name is X's storage register information. The put's operand word, which is the word to be placed in the cell named by the operand name, is X's accumulator information. The put's replacement word, which is the word to be placed in the CPU cell, is a word consisting of (1) cycle information saying that an instruction fetch activity is to take place next, and (2) other information identical to the corresponding information of X.

#### Procedure Steps

A program may be stored within a subset of an MCM's cells. When an MCM holds a program in this way, each procedure step of the program is encoded into one or more words, and each word is held by a distinct cell. For example, the previously mentioned 7090 model might hold a program that has as one of its procedure steps the previously mentioned storeaccumulator instruction; this instruction is a procedure step that is encoded into exactly one word.

The execution of a procedure step begins with the performance of a get whose operand name is the name of a cell holding an encoded procedure

step word. A procedure step execution might consist only of the performance of such a get, or a procedure step execution might consist of the performance of such a get followed by the sequential performance of one or more transactions, each of which might be either (1) a get whose operand name is the name of a cell holding an encoded procedure step word, or (2) a transaction, of any of the five types, whose performance is requested by the procedure step itself. For example, a program for the 7090 model might contain procedure steps such as:

(1) a transfer-on-minus instruction, whose execution is the performance of a single get, (2) a store-accumulator instruction with indirect addressing, whose execution is the performance of a sequence of two or three gets followed by a put, and (3) a convert-by-replacement-from-the-MQ instruction, whose execution is the performance of a sequence of some number of gets from 1 through 256.

### Reading and Writing

When one says that some cell reads another cell, the notion of "reading" is fairly clear from contemporary usage. Nevertheless, it is desirable to have a more precise notion of what it means to read a cell. In the MCM design as introduced thus far, the notion of reading is applicable in two contexts. The first application is intuitive: a clerk cell performing a get reads from the cell named by the get's operand name. The second application is more subtle: a clerk cell performing either a get or a put reads from itself, because the clerk cell's content just before the performing of the get or put determines the particular get or put to be performed. Based on these examples, a

definition of the notion of reading may be given: a clerk cell x that is performing a transaction <u>reads</u> from a cell i just when x senses the content of i in order to help determine x's performance of the transaction.

Similar remarks may be made concerning the notion of "writing".

In the MCM design as introduced thus far, the notion of writing is applicable in two contexts. The first application is intuitive: a clerk cell performing a put writes into the cell named by the put's operand name. The second application is more subtle: a clerk cell performing either a get or a put writes into itself. Based on these examples, a definition of the notion of writing may be given: a clerk cell x writes into a cell i just when x causes a new word to be held by i, where the new word might or might not be the same as the word previously held by i.\*

# Outputting

An explanation can now be given of the method by which an MCM produces output symbols. Some of an MCM's cells are <u>output</u> cells; the designation of a cell as an output cell does not vary with time, and is in addition to the time-varying designation of the cell as either a clerk cell or a value cell. There is a one-to-one correspondence between the output cells of an MCM and the output streams that are produced when the

<sup>\*</sup>The concepts of reading and writing described here are no doubt the same as the concepts analyzed by Maurer in his discussion of the "input regions" and "output regions" of computer instructions [21].

MCM performs a computation. Whenever a word is written into an output cell, the word is not only caused to be held by the cell, but also is produced as the next symbol in the cell's output stream.

### The Scheduler

At any instant when no transactions are being performed, the computation state of an MCM is denoted by the information contained in the MCM's cells and count matrix. When an MCM performs a computation, the MCM takes on a succession of computation states: each transition from one computation state to the next is accomplished by the simultaneous performance of single transactions by one or more clerk cells.

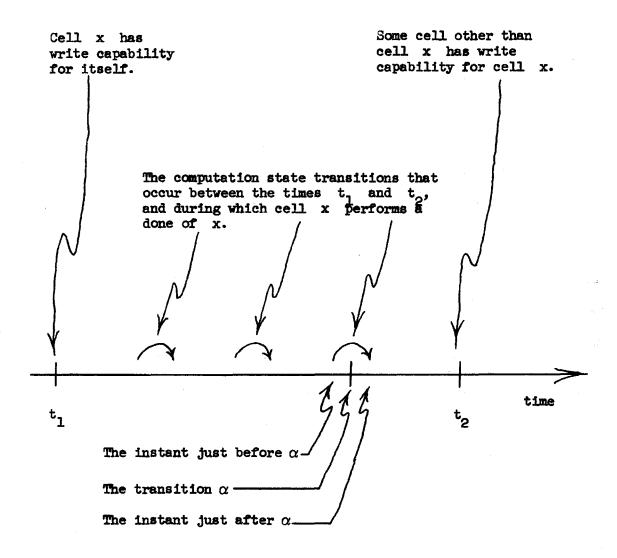

The set of clerk cells that accomplish a computation state transition is selected by the scheduler on the basis of the immediately preceding computation state, the transaction tables, and perhaps on the basis of unpredictable influences. In making such a selection, the scheduler behaves as if it carried out in sequence the following three activities: (1) the determination of an enable set, which is a set of names of enabled clerk cells, (2) the determination of a choice collection, which is a collection of subsets of the enable set, and (3) the selection of a member of the choice collection. The selected member of the choice collection is a set of names of cells; it is to these cells that the scheduler transmits simultaneous go pulses in order to initiate a computation state transition. The scheduler's activities are described later in more detail.

The performance of a <u>computation</u> proceeds as follows. At an instant when no transactions are being performed, i.e., when some computation state prevails, the scheduler selects a set of clerk cell names in the manner outlined above and transmits one go pulse simultaneously to each of the cells named in the set. After the transactions triggered by these go pulses are finished, a new computation state prevails. At a subsequent instant, the activity is repeated, i.e., the scheduler again selects and sends pulses to clerk cells, which then accomplish a transition to still another computation state. The succession of computation states produced in this way begins from an initial computation state specified by a user.

The second secon

# The Count Matrix

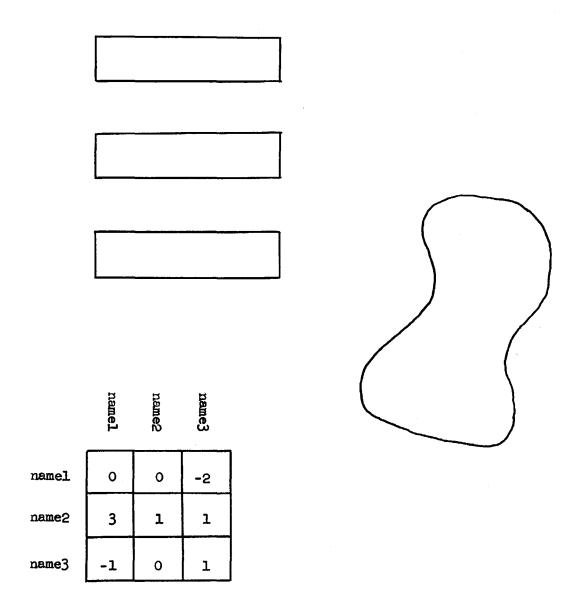

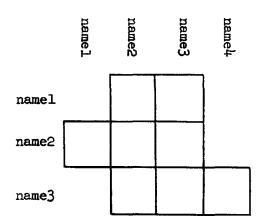

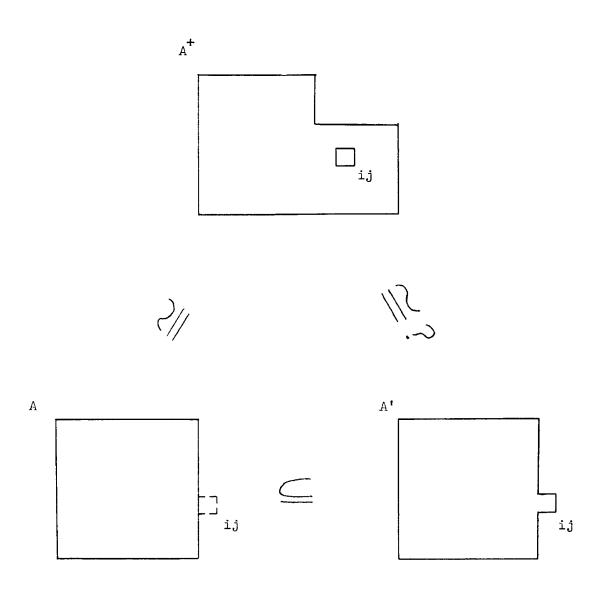

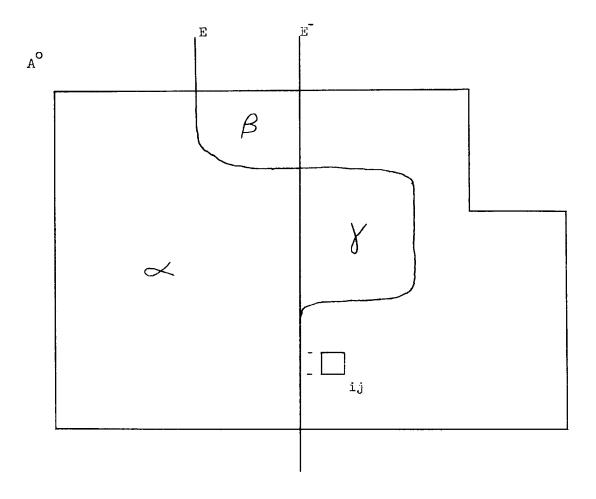

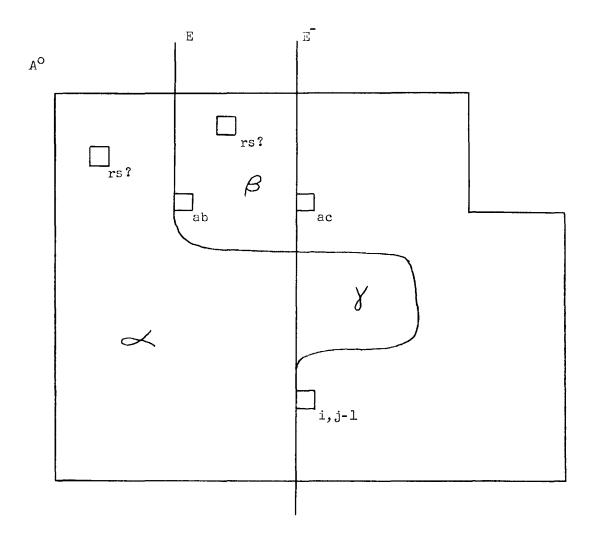

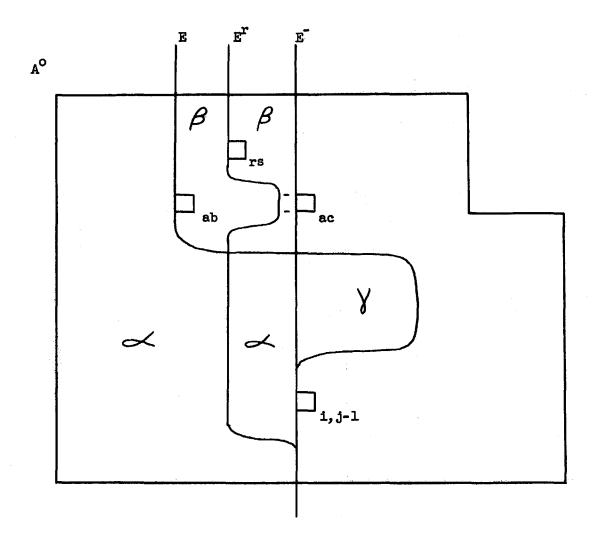

In determining an enable set, the scheduler refers to the count matrix. If an MCM contains n cells, then the MCM's count matrix is an n by n matrix. Each element of a count matrix is an integer, called a count, that can be positive or negative.

The information contained at some instant in an MCM's count matrix allows statements to be made such as, "cell x has read capability for cell i", and "cell x has write capability for cell i". Cell x has read capability for cell i just when the count at row x and column i of the count matrix is greater than zero. Cell x has write capability for cell i just when cell x is the only cell that has read capability for cell i. The capabilities of the cells of the MCM shown in Figure 2.3 are the following: name2 has read capability for name3, name2 has write capability for both itself and name1,

Figure 2.3. Typical count matrix configuration of the MCM having three cells.

and name3 has read capability for itself. The significance of the fact that a cell has a read capability for another cell is explained in the following Section.

### The Enable Set

At any instant between computation state transitions, the scheduler's enable set is just the set of names of those cells that are enabled clerk cells. In order to decide whether a particular cell is an enabled clerk cell, the scheduler first examines the cell's content and transaction table in order to discover the transaction the cell would perform if it were to receive a go pulse; then the scheduler makes its decision for the examined cell by applying the enabling rule for the discovered transaction. The enabling rules for gets and puts are described below. The enabling rules for transactions of the other three types will be described as these types are introduced.

The enabling rule for a get is the following: a cell that would perform a get upon receipt of a go pulse is an enabled clerk cell just when the cell has both write capability for itself, and read capability for the cell named by the get's operand name. In the example of Figure 2.3, suppose the name2 cell would perform a get of name3 upon receipt of a go pulse; then the name2 cell is an enabled clerk cell.

The enabling rule for a put is the following: a cell that would perform a put upon receipt of a go pulse is an enabled clerk cell just when the cell has both write capability for itself, and write capability for the cell named by the put's operand name. In the example of

Figure 2.3, suppose the name2 cell would perform a put of name1 upon receipt of a go pulse; then the name2 cell is an enabled clerk cell.

For gets and puts, the notions of reading and writing correspond in a simple way to the notions of read capability and write capability, respectively; this correspondence is seen in the following restatement of the above enabling rules. A cell that would perform either a get or a put upon receipt of a go pulse is an enabled clerk cell just when the cell has read capability for each cell it would read, and has write capability for each cell it would write.

# Nomenclature for Cells