MAC-TR-18 (THESIS)

MASSACHUSETTS INSTITUTE OF TECHNOLOGY

Project MAC

AN ANALYSIS OF TIME-SHARED COMPUTER SYSTEMS

bу

Allan Lee Scherr

June 1965

### AN ANALYSIS OF TIME-SHARED COMPUTER SYSTEMS

bу

# ALLAN LEE SCHERR

- S.B., Massachusetts Institute of Technology (1962)

- S.M., Massachusetts Institute of Technology (1962)

SUBMITTED IN PARTIAL FULFILIMENT

OF THE REQUIREMENTS FOR THE

DEGREE OF DOCTOR OF

PHILOSOPHY

at the

MASSACHUSETTS INSTITUTE OF

TECHNOLOGY

JUNE, 1965

| Signature of Author                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | allantee Sien                                          |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|----|

| Digital of industrial                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Department of Electrical Engineering                   | ne |

| Certified by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | May 14, 1965                                           | 5  |

| Joseph System Control of the Control | Thesis Superviso                                       | 01 |

| Accepted by                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | man 3. Shaff                                           |    |

| nedepood of this is a second                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Chairman, Departmental Committe<br>on Graduate Student |    |

This empty page was substituted for a blank page in the original document.

#### ABSTRACT

"An Analysis of Time-Shared Computer Systems"

Allan Lee Scherr

Submitted to the Department of Electrical Engineering in partial fulfillment of the requirement for the degree of Doctor of Philosophy.

Some of the aspects of the operation of time-shared, interactive computer systems are analyzed. The emphasis is on the reaction of hardware systems to the demands that its users make upon it. Simply stated, the problem is to characterize both time-shared systems and their users in order to be able to predict the performance of the two operating together. Portions of this problem include the specification and measurement of user characteristics, the development and verification of both simulation and mathematical models for time-shared systems, and the specification and measurement of performance metrics for such systems. The user and some of the performance measurements were made on Project MAC's "Compatible Time-Sharing System" (CTSS).

First, simulation models are used to study the effects of changing small details in the operation of CTSS-like systems. Then, a continuous-time Markov process model is derived to predict the performance of a broad class of systems. Throughout, the CTSS data are used as a basis for comparison with model predictions. In order to be able to take measurements and to build models, many definitions of commonly used time-shared system terminology are made precise.

Thesis Supervisor: Herbert M. Teager Title: Associate Professor of Electrical Engineering

DEDICATED TO THE SCHERRS, KRATZMARS, AND KAHNS

### **ACKNOWLEDGEMENTS**

The author would like to express his deep appreciation to Professor Herbert M. Teager who has served not only as thesis supervisor, but also has been a friend and a source of inspiration and guidance since the author's early undergraduate days.

Thanks are also due to the thesis readers, Professors Ronald A. Howard and Chung L. Liu, for their criticism and evaluation of the thesis research.

Many friends and colleagues at Project MAC contributed in a great variety of ways to the completion of the research. The author would particularly like to thank: Professors D.C. Carroll, R.M. Fano, and M. Greenberger; Messrs. P. Clermont, P. Denning, G. Everest, G. Gorry, T. Johnson, M. Jones, L. Kanodia, R. Mills, D. Ness, F. Russo, A. Saltalamacchia, L. Selwyn, M. Wantman, and D. Wilde. In addition, thanks are due to G.A. Maley and J. Ever of the IBM Corporation.

Finally, the author would like to express his sincere thanks to his parents and aunt, without whose aid and encouragement none of this would have been possible; and to his understanding wife Marsha, who was a constant source of inspiration.

Work reported herein was supported (in part) by Project MAC, an MIT research project sponsored by the Advanced Research Projects Agency, Department of Defense under Office of Naval Research Contract NONR-4102(01). Reproduction in whole or in part is permitted for any purpose of the United States Government.

# TABLE OF CONTENTS

| SECTIO                   | ON                  |                                                                        | PAGE                             |

|--------------------------|---------------------|------------------------------------------------------------------------|----------------------------------|

| DEI<br>ACI<br>TAI<br>LI: | KNOW<br>BLE<br>ST O | CT<br>TION<br>LEDGEMENTS<br>OF CONTENTS<br>F ILLUSTRATIONS<br>F TABLES | i<br>ii<br>iii<br>v<br>vii<br>ix |

| I                        | IN                  | TRODUCTION                                                             | 1                                |

| II                       | тн                  | E CTSS ENVIRONMENT                                                     | 5                                |

|                          | Α                   | The Composite Interaction Model                                        | 7                                |

|                          | В                   | Limitations and Possible Extensions of the User Model                  | 18                               |

|                          | С                   | The Reliability of the Data                                            | 26                               |

|                          | D                   | Changes in the System Reflected by User Characteristics                | 30                               |

| III                      |                     | DELING TIME-SHARED SYSTEM HARDWARE<br>D SOFTWARE                       | 31                               |

|                          | A                   | The CTSS Model                                                         | 33                               |

|                          | В                   | Variations of the CTSS Model                                           | 40                               |

|                          | С                   | The Need for a New Simulation System                                   | 43                               |

|                          | D                   | Continuous-Time Markov Model for CTSS-like Systems                     | 46                               |

|                          | E                   | Markov Model for Multiple-Processor, Time-Shared Systems               | 52                               |

| IV    | ANALYSIS OF MODEL PREDICTIONS                                                                                                                                                                                                      | 55                                            |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

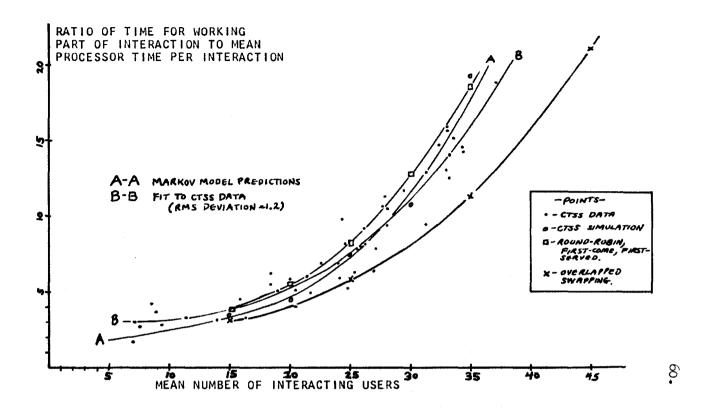

|       | A Response Time vs. the Number of Users                                                                                                                                                                                            | 59                                            |

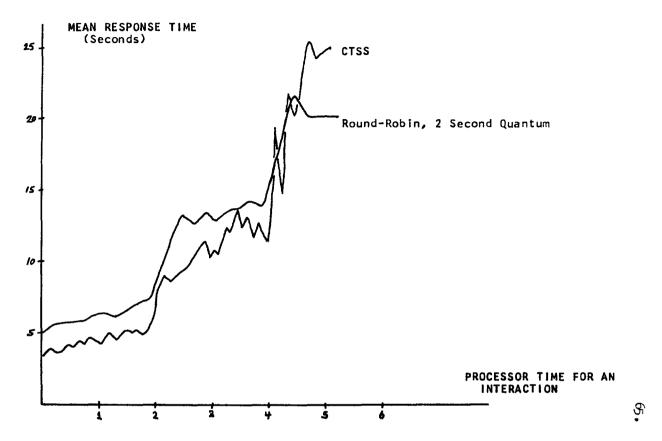

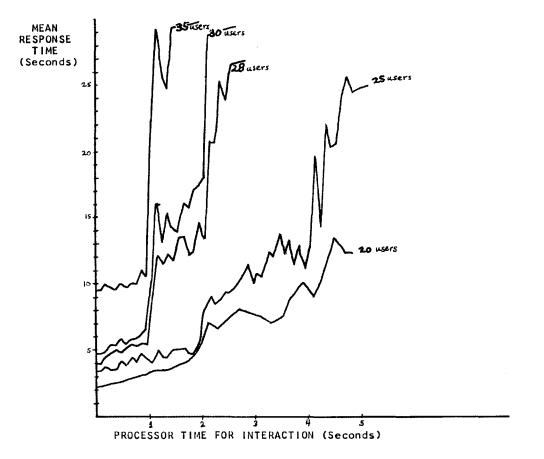

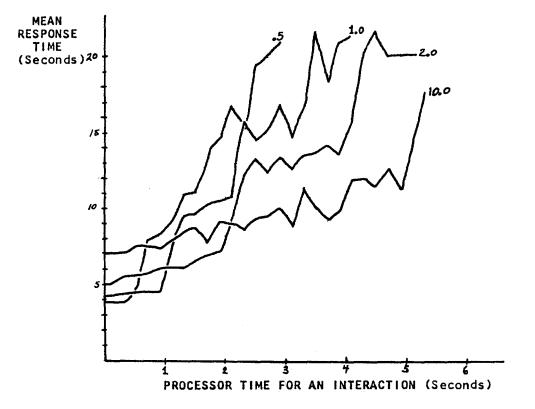

|       | B Scheduling Policy and Response Time<br>Distributions                                                                                                                                                                             | 64                                            |

|       | C Hardware Usage                                                                                                                                                                                                                   | 72                                            |

|       | D Multiple Systems                                                                                                                                                                                                                 | 77                                            |

|       | <pre>1 Equal Capacity, Parallel Multiple     Systems 2 "Polymorphic" Systems 3 Serial Multiple Systems</pre>                                                                                                                       | 79<br>83<br>94                                |

| V     | CONCLUSIONS                                                                                                                                                                                                                        | 96                                            |

| APPE  | NDIX A - DESCRIPTION OF CTSS                                                                                                                                                                                                       | 111                                           |

|       | 1 The CTSS Hardware<br>2 The CTSS Software                                                                                                                                                                                         | 111<br>117                                    |

| APPEN | IDIX B - ADDITIONAL CTSS DATA                                                                                                                                                                                                      | 130                                           |

| APPEN | DIX C - THE SIMULATION PROGRAMMING SYSTEM                                                                                                                                                                                          | 134                                           |

|       | <pre>1 Organization of a Simulation 2 Systems Variables 3 Timing of Events 4 Element Specification-Form and Restrictions 5 Examples of Element Specification 6 The Simulation Operating System 7 Simulation Element Listings</pre> | 135<br>138<br>140<br>143<br>146<br>149<br>154 |

| BIBLI | OGRAPHY                                                                                                                                                                                                                            | 177                                           |

| BIOGE | АРНУ                                                                                                                                                                                                                               | 178                                           |

### LIST OF ILLUSTRATIONS

| Figure |                                                                                                                                                   | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|------|

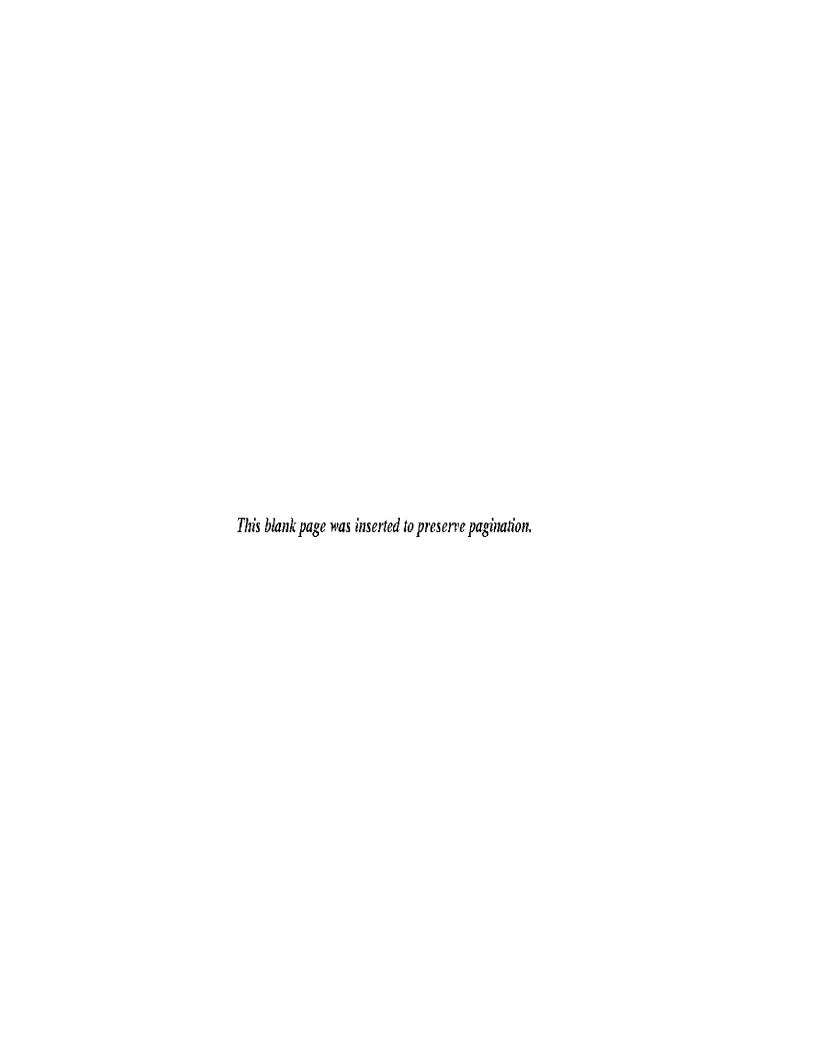

| 1      | Probability Density of Time for Console Part of Interaction ("Think Time")                                                                        | 10   |

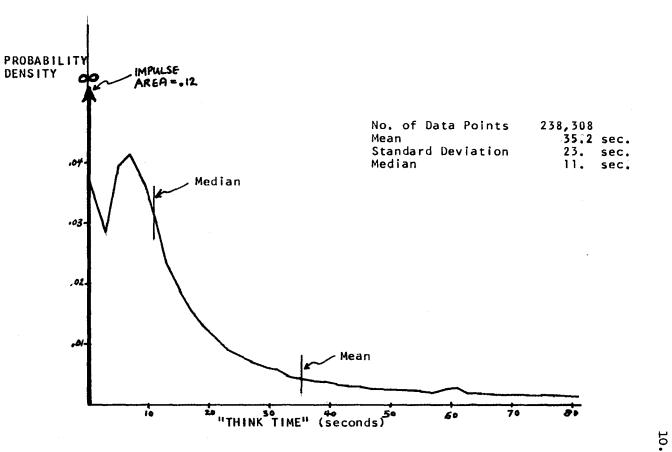

| 2      | Probability Density of Interactions per Command                                                                                                   | 13   |

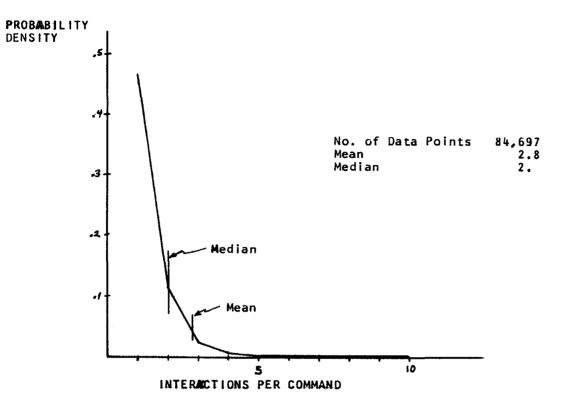

| 3      | Probability Density of Program Sizes                                                                                                              | 15   |

| 4      | Probability Density of Processor Time per<br>Interaction                                                                                          | 17   |

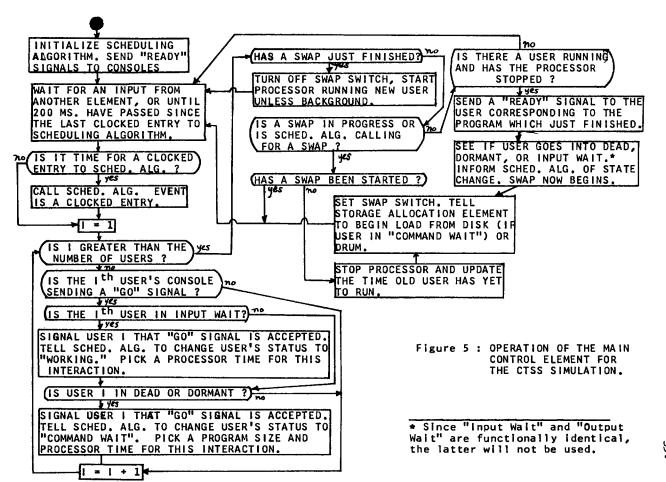

| 5      | Operation of the Main Control Element for the CTSS Simulation                                                                                     | 35   |

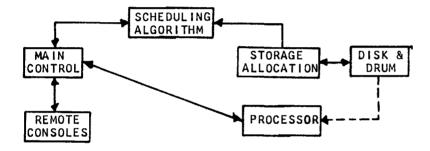

| 6      | Interconnection of Elements in CTSS Simulation                                                                                                    | 38   |

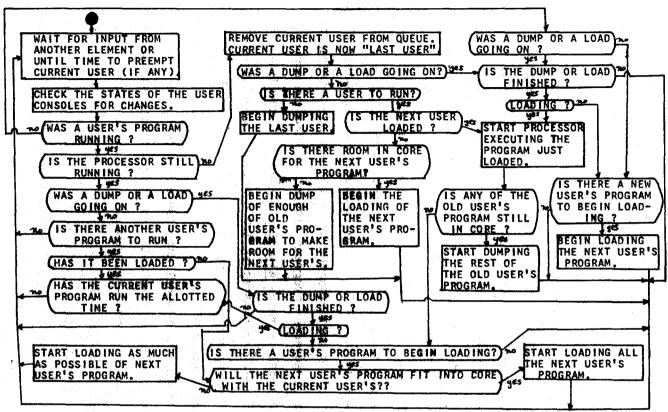

| 7      | Operation of the Main Control Element for A Time-<br>Sharing System with Overlapping Swapping and<br>Processing                                   | 42   |

| 8      | Ratio of Mean Time for Working Portion of Interaction (Response Time) to Mean Processor Time per Interaction vs. Mean Number of Interacting Users | 60   |

| 9      | Mean Response Time vs. Processor Time per Interaction<br>for CTSS and Round-Robin (Quantum = 2 seconds)<br>Scheduling, 25 Users                   | 65   |

| 10     | Mean Response Time vs. Processor Time per Interaction for CTSS                                                                                    | 66   |

| 11     | Mean Response Time vs. Processor Time per Interaction<br>for Various Quanta in Round-Robin, First-Come-First-<br>Served Scheduling (25 Users)     | 67   |

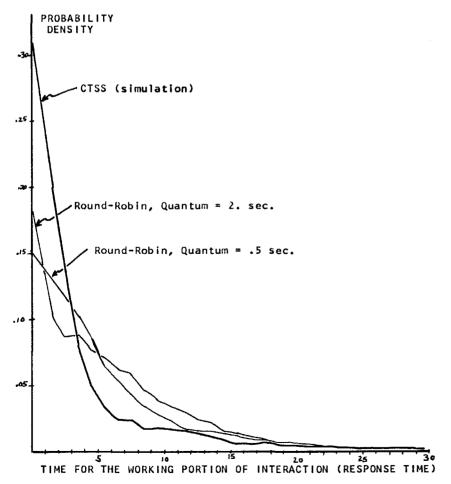

| 12     | Probability Density of Response Time per Interaction                                                                                              | 70   |

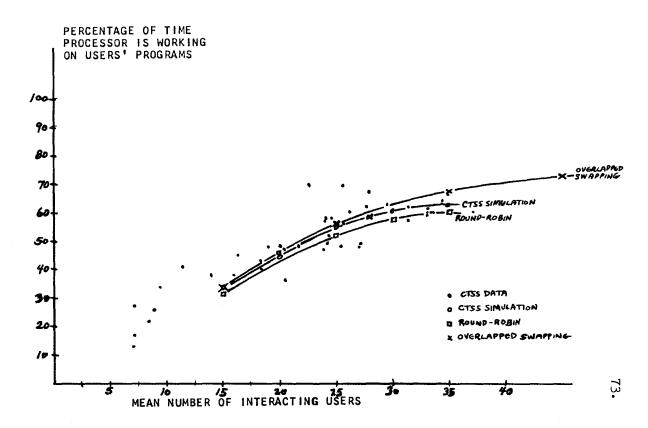

| 13     | Percentage Usage of Processor for Users' Programs vs. Mean Number of Interacting Users                                                            | 73   |

# LIST OF ILLUSTRATIONS (CONT.)

| igur | re                                                                                               | Pag |

|------|--------------------------------------------------------------------------------------------------|-----|

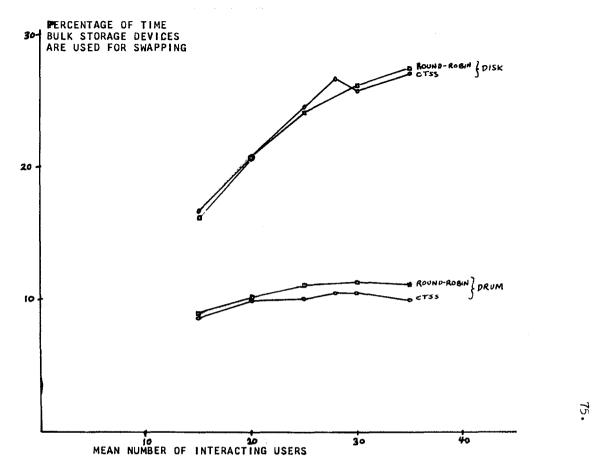

| 14   | Usage of Bulk Storage Devices for Swapping vs. Mean<br>Number of Interacting Users               | 75  |

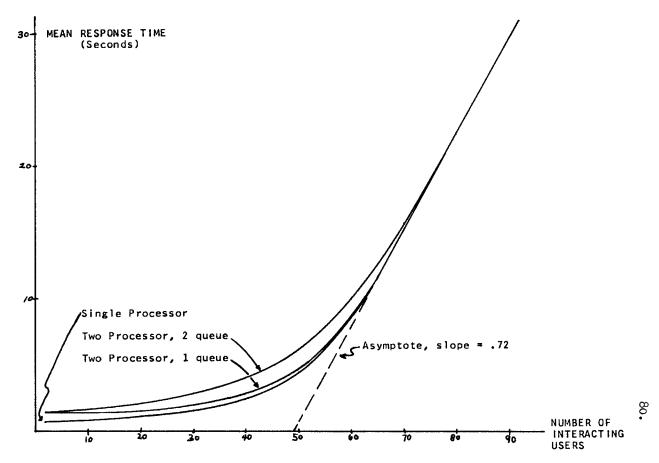

| 15   | Mean Response Time vs. Number of Users for Three<br>Multiple Systems with Equal Capacity         | 80  |

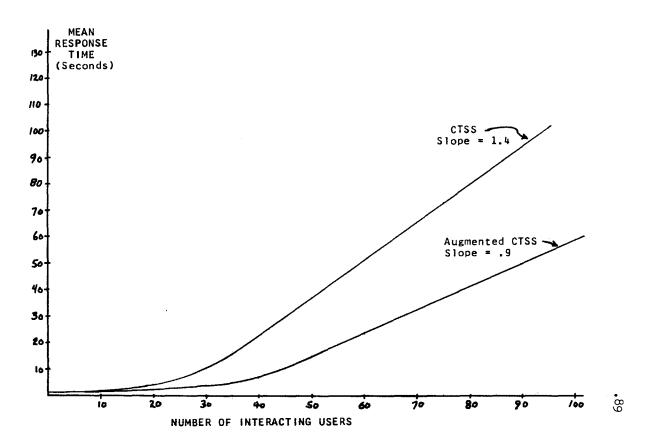

| 16   | Mean Response Time vs. Number of Interacting Users for CTSS and "Augmented" CTSS                 | 89  |

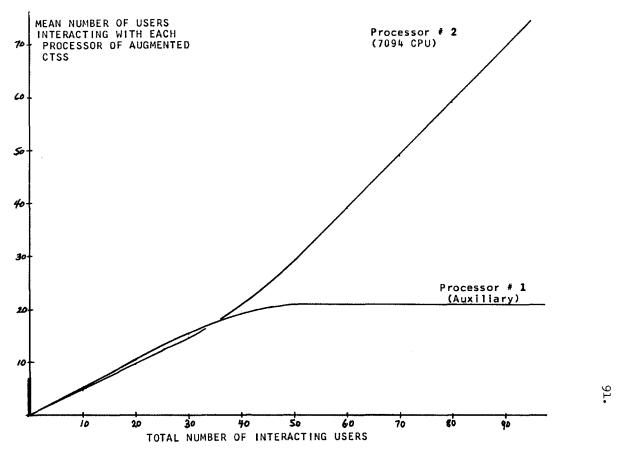

| 17   | Mean Number of Users Interacting with Each Processor of Augmented CTSS vs. Total Number of Users | 91  |

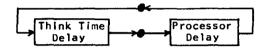

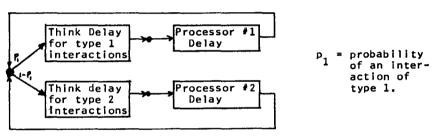

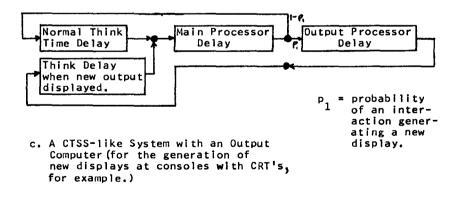

| 18   | Delay Networks for Some Interactive Systems                                                      | 102 |

# LIST OF TABLES

| Table |                                          | Page |

|-------|------------------------------------------|------|

| 1     | Parameters of Various Interaction Models | 23   |

| 2     | Steady-State Probabilities               | 131  |

| 3     | Mean Occupancy Times (seconds)           | 132  |

| 4     | Relative Frequency of Command Usage      | 133  |

This empty page was substituted for a blank page in the original document.

### I. INTRODUCTION

Computer systems which are able to serve a single user in a conversational or interactive manner have been in existence for relatively many years. Lately, for economic and other reasons, interactive computer systems have been implemented to simultaneously serve many users. At any given time in the operation of such a system, some portion of the interacting users may require particular programs to be executed. The function of the computer system is to execute these programs in such a way as to provide "reasonable" service to each user's requirement. A widely-used technique for providing this type of service is called "time-sharing", and consists of executing each user's program in some order, for some time, not necessarily to completion. Typically, a particular user's program will be allowed to use a processor for a period of time, will be stopped so that another user's program can run, and then at some later time will be continued from the point where it was stopped. In order to be able to continue a program, its status must be saved when it is stopped and restored when it is resumed. At the point in time when one user's program is stopped and another's resumed, the status of the former must be saved and that of the latter restored. This process is called "swapping". In

general, the status of a program consists of the state of the processor as well as a copy of every instruction in the program.

The primary aim of the research reported here is to develop techniques and models for the analysis of a broad class of interactive, time-shared computer systems. The emphasis is on the reaction of a hardware system to the demands made upon it by its users. Segments of the overall problem include: the specification of a model for and the measurement of user behavior, the development and verification of both mathematical and simulation models of time-shared systems, and the specification and measurement of performance metrics for time-shared systems. The user and some of the performance measurements were made on Project MAC's "Compatible Time-Sharing System" (hereafter referred to as "CTSS", see CORBATO, 1962 and SALTZER, 1965).

The model development is divided into two phases. First, simulation models are used to study in detail the effects of small changes in the operation of CTSS-like systems. Then, continuous-time Markov processes are used to model more general classes of time-shared systems. Throughout, the CTSS measurements are used as a basis of comparison with the model predictions.

The primary result obtained is that it is possible

to successfully model users of interactive computer systems and the systems themselves with a good degree of accuracy using relatively simple models. Moreover, many of the results obtained and most of the techniques developed are applicable to the analysis of a broad class of interactive systems. This fact is established and discussed in the Conclusions (Section V).

Since human users are an integral part of any interactive system, no real progress can be made in the analysis of the performance of such systems until the behavior of its users is established. The CTSS user characteristics were measured and modeled and are presented in Section II. The user model is represented as being the composite of the models for users working on a "mix" of different tasks. Thus, to a certain extent, models for a different type of user than those studied can be generated by using a different task mix.

The models for the hardware-software time-shared systems are divided into two classes, (Section III). First, simulation models are used to study three systems: (1) CTSS, (2) CTSS modified by the replacement of its scheduling procedure by a simple round-robin, and (3) a time-shared system using the CTSS hardware but using some multi-programming techniques to improve hardware efficiency. Using the operation of these simulation models, detailed measurements

are made of several performance parameters and hardware usage (Section IV). Where possible, simulation results are also compared to actual CTSS measurements for verification.

A simple continuous-time Markov model for single and multiple processor time-shared systems is derived for the purpose of predicting the mean of one of the performance measures, (Section III). The accuracy of the values predicted by these models is established by comparing them to the CTSS measurements. Then, using the Markov models, several examples of multiple-processor time-shared systems are investigated, (Section IV).

The Conclusions (Section V) discuss the generality of the techniques and models used as well as the specific results obtained. It is shown that a broad class of systems has been covered by the techniques presented, the extension of these techniques to other systems is discussed, and observations are made about the operation of CTSS-like systems.

#### II. THE CTSS ENVIRONMENT

The CTSS environment consists of approximately 250 users whose individual load on the system varies from nearly zero up to the equivalent of several hours of IBM 7094 time per month. The model of this environment consists of a description of what a single user does during an elementary operation at his console, the interaction. Simply stated, an interaction consists of the user requesting and then receiving service from the system. The usual form of an interaction is the user's thinking, typing input at his remote console, waiting for a response from the system, and finally watching output. From the point of view of the time-shared system, the user may be thought of as being in one of two states: either the user is waiting for the system to respond, or the system is waiting for the user. Since the function of a time-shared system is to execute programs at the request of its users, these states may be rephrased as: either the system does or does not have a program to execute for a particular user. An interaction can now be precisely defined as the events occurring between two successive exits from the state in which the system has a program to execute for the user.

The primary purpose for the development of a user model is its incorporation into models of complete time-shared systems. The most important requirement for these models is that they reproduce the activities of a real system during several hours of operation. These models will be required to faithfully reproduce distributions of service times, hardware usage, etc. Fidelity of the model's minute-to-minute operation is of secondary importance.

In this section, the user interaction model is completely described, next the inherent compromises with reality in the model are discussed, and finally the limitations on this type of model are outlined. It is assumed that the reader has some knowledge of the operation and hardware configuration of CTSS. However, Appendix A describes the operation of this system in detail sufficient to enable understanding of the remainder of this report.

The data presented in this section was taken between December 29, 1964 and February 4, 1965, during 112 hours of weekday 9:00 A.M. to 5:00 P.M. operation. Approximately 80,000 commands were monitored. The day-to-day changes in the data were slight, and there was stability in the system as well as user behavior for the duration of the monitoring. A more detailed discussion of these considerations appears at the end of this section.

# A. The Composite Interaction Model

The two states of the user during an interaction have a definite correspondence to the six user states internal to CTSS. The part of the interaction during which the system has a program to execute for the user corresponds exactly to the "Working" state and the "Command Wait" state. This portion of the interaction will be called "the working part of the interaction". The other part of the interaction corresponds to the "Dead", "Dormant", "Input Wait", and "Output Wait" states, and will be called "the console part of the interaction". This name is due to the fact that the time which the user spends in this part of the interaction is primarily determined by console operations. Exit from either the Dead or Dormant states is caused by the user completing a line of input which is interpreted as a command by the CTSS supervisory program. A line of input for the program serving the user terminates the Input Wait period. Output Wait lasts until the console output buffers empty.

The event marking the transition from the working part of one interaction to the console part of the next is the completion of the program serving the user. The nature of this completion determines what happens during the following console portion. The program may require

input from the console, it may have attempted to add to an already full output buffer, or it may terminate. In addition, a program may enter the Dormant state for a program-specified period of time. The subsequent transition from the console part to the working part occurs at the end of this "sleeping" period. A program-generated command will be considered as a new interaction with a zero console portion.

Thus, one transition can be tied to the event of a program's finishing, the other, usually to an event at the console (i.e., end of an input line or output buffers at a certain level). The importance of the other console events, i.e., the beginning and end of output, the beginning of input, etc., to the operation of the system is slight. Moreover, the volume of inputoutput is negligible. Even fifty consoles transmitting or receiving at fifteen characters per second yield a total rate of only 750 characters per second. This figure is a maximum; the average rate on CTSS is closer to 100 to 150 characters per second. Furthermore, there is no relation of these other console events to anything of importance within the system. For example, output started during the working part of the interaction usually overlaps into the console part. Naturally, higher data rate consoles, based on devices other than keyboards and typewriters, are possible but will not be considered. Appendix B contains statistics describing console input-output. No further separation of console I/O and the time the user spends thinking, etc. will be made; and, in fact, all of these activities will be lumped under the term "thinking".

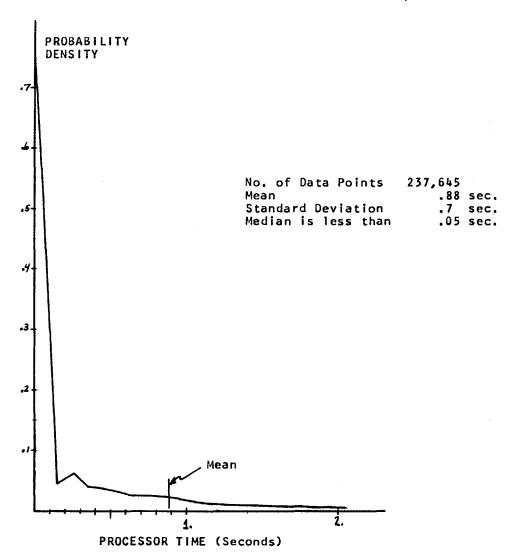

The description of the user during the console part of an interaction is simply the elapsed time from start to finish of this portion and the specification of the cause of the last program completion. will be specified by a probability distribution. nature of the program completion marking the beginning of the console portion indicates what the user is doing during this portion. It is necessary to know, for example, whether a new program will be started, i.e., a new command, or the old one continued, etc. The distribution of the time a user requires for the console part of the interaction is shown in Figure 1. The mean value of this time was determined to be 35.2 seconds. The following table shows the relative probabilities for the various reasons that a user is in the console part of an interaction. These probabilities are generally not independent from interaction to interaction, as will be seen.

Figure 1: PROBABILITY DENSITY OF TIME FOR CONSOLE PART OF INTERACTION ("THINK" TIME)

| Activity during console part of interaction               | Probability |

|-----------------------------------------------------------|-------------|

| User typing the next command (Dead or Dormant             | •23         |

| User typing program input (Input Wait)                    | •58         |

| Program waiting for output buffers to empty (Output Wait) | •05         |

| Program "sleeping" (Dormant)                              | .01         |

| Program-generated command                                 | .12         |

The time distribution shown in Figure 1 can be divided into several different phenomena. The impulse of area .12 at time zero represents the zero console time required for program-generated commands. The high probability between zero and two seconds is caused primarily by the easily typed, trivial responses, such as merely a carriage return, in Input Wait. A user is in Dead or Dormant (typing a command) for at least three seconds. This is due to the fact that a user must wait until a "ready" message is typed (ten to fifteen characters taking approximately one second) and then type the several characters constituting the command word. The line of input for Input Wait, however, may consist of only a carriage return character. The second highprobability area at around seven seconds is due to users making non-trivial responses at their maximum rate. Superimposed onto these maxima is an extensive uniformly distributed time caused by both the responses which require the user to stop to think and the time that a user is in the Output Wait state.

An important statistic about the nature of the user's activity during the console part of the interaction is whether or not a new command is coming next. In addition, it is important to know whether or not the user is in the Dead or Dormant state (i.e., whether or not a core-image is being saved on the drum). Figure 2 shows the distribution of the number of interactions per command. Note that the probability of having another interaction of a command is not independent of the number of interactions per command is 2.8. The ratio of entries to Dead versus Dormant is .8 to .2.

During the time a user is in the working portion of the interaction he is loading the system. The amount of time that the user remains in this state is determined by how much of a load the system is already carrying (in the form of other users working) and the amount of work this user requires. A user's loading during the working part of an interaction will be described by two parameters: the amount of processor time required by the user's program during the interaction and the size of the program. The size of the program determines how long it will take

Figure 2 : PROBABILITY DENSITY OF INTERACTIONS PER COMMAND

for the system to swap the user's program in and out of core memory and/or how many other user's programs are able to fit simultaneously into a core memory with it. Ordinarily, the size of a user's program remains constant for the duration of the command. The user's program may change size in CTSS, but this will be ignored in the model. The probability distribution of program size, shown in Figure 3, reflects measurements made at the end of a command, i.e., on the program's entry to either the Dead or Dormant state. The average program size was determined to be  $6.3 \times 10^3$  words. The parameter of processor time was chosen to reflect the user's processing requirements because of its simplicity. Because there is no significant overlapping of processor and channel operation in CTSS, the processor runs at a nearly constant rate. The time that a user requires the processor for an interaction includes any overhead computation needed by the system and access and transmission times for the user's program to access the disk storage. Swapping time is not included in the processor time since it is a function of the time-shared system and not of the user. System overhead includes scheduling and the continuous processing of console input. These functions are almost uniformly distributed, degrading the processor's execution rate by almost a constant. Disk storage is used by the user's

Figure 3 : PROBABILITY DENSITY OF PROGRAM SIZES

programs much in the same way as tapes are used on a conventional batch-processed system. The breakdown between overhead computation, disk usage, and normal computation will be discussed later. The distribution of processor time per interaction is shown in Figure 4 and has a mean of .88 seconds.

There is really no need to know anything more about a user's processing needs than the amount of time required. Typically, a program receives control of the processor for about two to four seconds at a time. During this period, several hundreds of thousands of instructions will be executed. Clearly if the structure of second-to-second operation is not important, no instruction mixes, etc. are required. However, if channel operation overlaps processor operation to the extent that the rate of instruction execution is affected, or if multiple, special-purpose processors are used in a time-shared system, information concerning instruction mixes, command types, etc. is desirable. Such information is discussed next.

Figure 4: PROBABILITY DENSITY OF PROCESSOR TIME PER INTERACTION

### B. Limitations and Possible Extensions of the User Model

In order to develop the interaction model, many simplifications of reality have had to be made. The following paragraphs discuss these simplifications and attempt to justify them from CTSS data and other reasoning. Some possible expansions of the interaction model are discussed. In addition, the effects of these simplifications on the behavior of the model are outlined.

The first simplification is to consider all users as equal in the sense that all are representable by the same model. The interaction model tends to average out the differences between individual users. However, since there may be as many as thirty or forty consoles being used simultaneously and since there is a considerable turnover in this user population (approximately 30 per cent per hour), no significant long-term errors should result. The model will also tend to smooth out the effects of users working in bursts. That is, users sometimes have flurries of activity, working at a high rate, followed by periods of comparitive inactivity.

The next simplification is that there is no dependence of the model on the total number of users sharing the system. Data shows that user loading, as reflected by the time in the console part of the interaction and the processor time per interaction, is relatively insen-

sitive to the number of users sharing the system. Moreover, there has been very little drift in the means of the user parameters during the two months that the data was taken. Changes in the system tend to effect these user parameters, and such changes will be discussed later.

The choice of the interaction to be the basis for the model can be defended in several ways. First of all, the interaction is an operation which is of great interest to the user. The response time of the system to a line of input from the user is an important parameter of a time-shared system. In fact, it is one of the few, welldefined, measurable performance parameters available. This response time determines the basic rate at which the user can operate. Moreover, data has shown that the count of the number of interactions per hour is a stable, reliable measure of how much the user or the system is accomplishing. Counts of commands per hour are much less reliable and have greater deviations from the mean. fact remains, however, that users working on different tasks behave differently. A task is defined as the interactions comprising a sequence of commands of the same type from start to finish. The various purposes of the user's operation can be reflected by a modification of the parameters of the basic interaction model. Thus, different interaction models can be used for different types of command sequences. In addition, information describing the length of command sequences in interactions per task and/ or commands per task is required to complete the specification. In this way, users can be modeled by selecting a task type for each, using the corresponding interaction model for the number of commands or interactions specified by the appropriate distribution, and then switching tasks. The concept of a task is useful for returning some of the fine structure to the operation of the interaction model and for deriving a new composite interaction model with a different "mix" of tasks.

The expansion of the interaction model, as outlined above, will first involve the definition of the task types. The approximately 75 CTSS commands will be divided into five types, and then the parameters for the interaction model for each type will be presented and discussed. The first type of task is (disk) File Manipulation. In terms of conventional batch-processed systems, File Manipulation is usually carried out by hand or by tabulating equipment. The CTSS commands which correspond to this type of task print the contents of a file, combine files, split files, list the names of the files in a user's directory, delete files, copy files, etc. A complete listing of these commands is given in Appendix B. File Manipulation commands are characterized by usually consisting of a single inter-

action and requiring little processor time.

The second type of task is that of Program Input and Editing. Commands of this type are used for the generation and modification of disk files which contain the MAD, FAP, FORTRAN, etc. source programs written by the user. These commands are characterized by many interactions and very little processor time per interaction. Commands which generate disk files from console input for purposes such as memoranda, etc. are not included in this category. The third type of task is that of Program Running and Debugging. These commands cause files corresponding to binary decks to be loaded and linked by a conventional BSS loader. Also included are commands to start and stop these programs, to initiate debugging traces of their operation, to examine the registers of a program or the state of the processor, etc. Commands of this type are characterized by a moderate number of interactions and more processor time per interaction than any of the previous types. The fourth type is that of Program Compilation and Assembly. These commands generate binary deck files from the source language files, and are characterized by usually having just one interaction and requiring the most processor time per interaction.

and the state of t

The fifth and final type is "Miscellaneous" and consists of the unclassifiable commands. Included in this

type are the commands which save and resume core-images of programs in the process of running. Also included are commands to generate commands, a command which will cause the commands listed in a disk file to be executed, the memoranda generating commands, etc.

Table I presents the parameters of the various interaction models for each task. In addition, information describing the relative frequency of each type of task is given. This data was gathered concurrently with the composite interaction model statistics.

TABLE 1

|                                                                     | File<br>Manipu-<br>lation | Program In-<br>put and<br>Editing | Program<br>Running<br>and Debug. | Assembly and Compilation | Misc. |

|---------------------------------------------------------------------|---------------------------|-----------------------------------|----------------------------------|--------------------------|-------|

| Command<br>Probability                                              | .36                       | •15                               | .12                              | •09                      | •29   |

| Interaction<br>Probability                                          | .16                       | • 32                              | - 14                             | • 04                     | • 34  |

| Interactions per Command (Avg.                                      | ) 1.3                     | 6.3                               | 3.0                              | 1.4                      | 3.4   |

| Avg. Duration of<br>Console Portion<br>of Interaction<br>(Sec.)     | 52.                       | 33.                               | 38.                              | 25.                      | 29.   |

| Avg. Processor<br>Time per Inter-<br>action (Sec.)                  | 1.1                       | 0.4                               | 1.5                              | 3•4                      | 0.6   |

| Prob. of Activity<br>During Console<br>Portion of Inter-<br>action: |                           |                                   |                                  |                          |       |

| Typing Command                                                      | .61                       | .10                               | •29                              | •54                      | .12   |

| Program-generated<br>Command                                        | .18                       | .06                               | .04                              | .16                      | .18   |

| Input Wait                                                          | •02                       | .84                               | .61                              | .16                      | .65   |

| Output Wait                                                         | .18                       | .00                               | •05                              | .04                      | •03   |

| "Sleeping"                                                          | •00                       | .00                               | •02                              | .10                      | •02   |

| Avg. Interac-<br>tions per Task                                     | 2.8                       | 10.7                              | 5.8                              | 1.7                      | 6.3   |

| Proportion of Processor use                                         | .21                       | •15                               | • 25                             | .16                      | . 24  |

| Proportion of user's total time                                     | .22                       | .27                               | .18                              | .06                      | •28   |

The shapes of the individual distributions for the parameters of the different tasks are very similar to those of the composite model.

No data on program sizes was taken to go with Table 1, but it is fairly easy to estimate the program sizes of most of the command types. A breakdown of the usage of individual commands is also given in Appendix B.

Since there are differences between the time a user takes to type a command, the time he takes to type a line of input to a program, etc., the question might be asked if the time in the console part of the interaction can be predicted from the mix of typed commands, Input Waits, Output Waits, etc. The answer is generally that such a prediction cannot be made, although the mix is some indication. For example, it turns out that there are significant differences in the distributions of time in Dead or Dormant for File Manipulation commands and Program Running and Debugging commands. Perhaps the best explanation of these differences is that the user requires different thinking times for different command input lines. Some commands are easy to remember and require no arguments; others require a complicated argument string.

The loss of fine structure in the operation of the model amounts to a smoothing of the peaks in user activity. Of course, using the task model will return some of this

structure, but the model is unlikely to reproduce every detail. The effects of users getting "into phase" with each other is still possible with the interaction models, but not likely. This phenomenon occurs when many users require service at the same time and is self-perpetuating. That is, as more and more users begin waiting, service for the individual user is reduced; and there is time for more users to reach the point where they require service. Thus, users tend to fall into step with each other; many working at the same time, many thinking at the same time. With the composite interaction model, this phenomenon will occur with one basic frequency. If the task model is used, a frequency corresponding to each task type will appear. In reality, there are many sub-frequencies to this rise and fall of the number of users in the working part of the interaction.

#### C. The Reliability of the Data

During the period that this data was taken, the hardware configuration of CTSS remained nearly constant. The software system was virtually the same throughout. Several commands were added to the system, but their usage did not amount to one per cent of the interactions. The day-to-day user characteristics did not change very much. During the 47 different time periods that the data was taken, there were only one or two instances of really unusual behavior (i.e., unusually short times for the console portion of the interaction and high processor times per interaction). The average of the means obtained during each period for the console part of the interaction time was 34.2, the median was 34, and the standard deviation was 5 seconds. This compares with the mean time for the console portion for all of the data of 35.0. These figures include data taken during the evening and on weekends! In fact, no significant differences were noted between the user parameters for weekend and evening operation and prime-time operation. The mean time for the console portion for prime-time only was 35.2, for evening and weekend operation, 32 seconds. What makes this so surprising is that on non-prime-time the average number of users sharing the system was approximately 10, whereas for prime-time this average was nearly 28. Moreover, there was no measurable correlation between the variation of the times for the console portion of an interaction with time, time of day, or the number of users interacting with the system.

For processor time per interaction, the average of the 47 means was .92, the median was .93, and the standard deviation was .15 seconds. Here again, this data includes both prime-time and weekend and evening operation. This compares with the overall mean of prime-time operation of .88 seconds of processor time per interaction and the non-prime-time mean of .94. The biggest difference between prime- and non-prime-time operation turned out to be in the standard deviation of the means from separate periods. The evening and weekend user data tended to be much more erratic. With regard to the mix of interaction types, there was no significant correlation of the probability of a particular type of interaction with time, time of day, number of users interacting with the system, level of service, etc. The standard deviation about the mean probabilities for interactions of types one through five were .16, .16, .28, .31, and .19 of the means, respectively.

This data was taken by a program written to run as part of the CTSS Supervisory Program. The data-taking

program was entered each time the Scheduling Algorithm was entered and thus was able to determine the exact time of user state changes. The data gathering added negligibly to the overhead computations of the system and in no other way affected the operations of the users being monitored. Typically, the periods monitored amounted to several hours, but several periods were as short as one hour and some as long as eight hours. Due to the fact that there was a strict limit on the size of the data-gathering program, some important parameters could not be measured. This is the primary reason why the program size distribution was gathered during a separate interval.

Overhead computation can be thought of as degrading the effective operating rate of the processor as seen by the user. Overhead computation primarily involves scheduling and the processing of input characters from the remote consoles. Every 200 milliseconds, the processor is stopped and control is transferred to the CTSS Supervisory Program for these purposes. Therefore, this overhead can be considered as being uniformly distributed since users are generally interrupted for these functions many times. Rough measurements show that CTSS, operating with 30 users, has an approximate overhead of five percent. That is, a program requiring one second of IBM 7094

processor time under non-time-shared operation, requires approximately 1.05 seconds on CTSS. As previously stated, all processor time measurements include this overhead. Also included is user programs' use of the disk (not to be confused with loading commands from the disk) as a tape-like, input-output device. Data taken over the summer of 1964 by T. Hastings, formerly of the M.I.T. Computation Center Programming Staff, indicates that the average program accesses (i.e., reads or writes) approximately 1500 disk words per interaction.

# D. Changes in the System Reflected by User Characteristics

Changes in the time-shared system itself certainly have an effect on the behavior of the users. For example, if a heavy scheduling penalty is placed on the users of large programs, the average program size will decrease. In fact, over the summer of 1964, data taken by Hastings indicated that the average program size dropped from 9,000 to 6,000 words in the space of three months because of just such a scheduling policy. The addition of new commands, which may supplant older ones but operate in a different manner, will obviously affect the users characteristics.

#### III. MODELING TIME-SHARED SYSTEM HARDWARE AND SOFTWARE

This section describes models which represent timeshared hardware-software systems. The models will range

in generality from CTSS-like systems up to idealized,

multiple-processor, time-shared systems. Simulation

models which represent systems close to CTSS will be used

to predict distributions for response times, processor

usage, disk usage, saturation, etc., whereas more general,

mathematical models will be used for the prediction of

the mean values for some of these parameters. The level

of detail incorporated into these models will match that

of the interaction model. That is, individual instructions,

data words, and disk tracks will not be considered. The

models will be based on processor time for an interaction,

transmission time for a block of words from disk to corememory, etc.

The first model developed matches CTSS. The very same Scheduling Algorithm and storage allocation scheme will be used. Next, a simple, first-come, first-served, round-robin scheduling procedure will be substituted. Then, a model which incorporates multi-programming techniques with the CTSS hardware configuration will be developed. Finally, a simple continuous-time Markov model will be used to represent both single-processor and multiple-processor time-shared systems.

As was stated in the Introduction, the first three models to be developed are of the simulation type. Simulation models are required because the level of detail necessary to handle some of the features studied is beyond the scope of mathematically tractable models. Markov models cannot, in general, be used to represent processes where other than random queueing is used. Queueing Theory models are not usable for processes where the arrival rates of service requests are a function of the service rate. Furthermore, the addition of pre-emptive scheduling complicates the mathematics beyong the point where models can even be formulated.

In order that efficient simulations can be written using a convenient notation, a special simulation programming language and operating system were designed. The language itself is fairly straightforward and about as readable as any of the algebraic programming languages. A discussion of the problem will be found later in this section, and a complete description of this simulation language and operating system will be found in Appendix C along with listing of the simulation programs for the models presented here.

### A. The CTSS Model

The CTSS hardware-software simulation model consists of six interacting sub-programs. These are:

- The actual CTSS Scheduling Algorithm (see Appendix A).

- (2) The Console element which simulates the users' finishing the console portion of the interaction, waiting for the completion of the working part, etc. This element is based on the data taken in Section II for the composite interaction model.

- (3) The Main Control element which informs the Scheduling Algorithm of changes in user status, starts and stops the processor, initiates swapping. It does the former at the direction of the user element, the latter two at the direction of the Scheduling Algorithm.

- (4) The Storage Allocation element which directs the detailed operation of swapping. It controls the disk and drum storage elements, causing programs to be loaded and dumped in accordance with the "onion skin algorithm" used in CTSS.

- (5) The Processor element which is started and stopped by the Main Control element.

(6) The Bulk Storage element which simulates both drum and disk storage, controlled by the Storage Allocation element.

The user-simulating element is based on the composite interaction model developed in Section II. An array of values indicating the status of each user is kept. When a user first enters the console part of an interaction, the amount of time he will "think" is drawn from a distribution fitting the one in Figure 1. After this time elapses, a signal is sent to the Main Control element placing the user into the Working status. When a "finish" signal is received from the Main Control element, the process is repeated.

The Main Control element has several functions:

(1) to enter the Scheduling Algorithm every 200 milliseconds for the basic timing event, (2) to inform the Scheduling Algorithm of user status changes using the six CTSS user states, (3) to control the starting and stopping of the processor and the swapping process under the direction of the Scheduling Algorithm. An informal flow chart of this element is shown in Figure 5. Using the distributions presented in Section II, the Main Control element selects a program size and internal state for the user in the console portion of an interaction. Likewise, when a user enters the Working portion of an interaction, a program

size and processor time are selected.

The Storage Allocation element is activated whenever a swap is to occur. Given the size and identification of the program to be loaded and a "map" of the current contents of the core memory, this element causes the proper disk and drum activity to load this program. Using the CTSS "onion skin algorithm", only as much of the contents of the core memory is dumped as is required to make room for the incoming program. All dumping is done with the drum. Since all programs are loaded from location zero, there can be only one complete program in core at a time. However, there also may be many partial sections of other programs in core. In CTSS, the number of these partially-dumped programs is limited to four. Naturally, whenever a program is loaded which is already partially in core, only the part that is missing is transmitted from the drum. In addition to the transmission of the actual programs, each swap is accompanied by the dumping and loading (with the drum) of the processor status and disk file status of the outgoing and incoming programs. This transmission consists of approximately 500 words in each direction.

The Processor element is started by being given the number of instructions to be executed. If it is stopped, it supplies the number of instructions actually executed. If it finishes, it informs the Main Control element. The

Bulk Storage element simulates the disk and drum systems. The number of words to be transmitted is supplied along with the type of unit (disk or drum), and the element signals when the transmission is completed. For the drum, a rotational delay uniformly distributed between zero and 17.2 milliseconds is used with a transmission time of 8.4 microseconds per word (IBM 7320A drum). The disk is simulated as having a head positioning delay of either 50, 120, or 180 milliseconds with probabilities of .033 , .134 , and .833 respectively. The rotational delay is distributed uniformly between zero and 34 milliseconds, and the transmission time is 66.6 microseconds per word. Since up to 9320 (20 "tracks") words may be read without repositioning the read/write heads of the disk, some assumption must be made about the organization of the programs on the disk. Data has shown that approximately 80 per cent of the programs loaded from the disk come from files which are arranged optimally on the disk, i.e., on adjacent tracks. The remainder of these files come from the user's file area (i.e., they are RESUME class programs, see Appendix B) and were determined to be arranged less optimally, approximately 650 words being obtained per seek.

The interconnection of these elements is shown in Figure 6. Since CTSS does not overlap the operation of

Figure 6: INTERCONNECTION OF ELEMENTS IN CTSS SIMULATION

(Dotted lines show connections for overlapped use of processor and disk or drum.)

the drum, disk, and processor, there is no interference at the core memory for accesses. Thus, there is no need to represent the core memory in the CTSS simulation.

#### B. Variations of the CTSS Model

The first variation to be considered is a change in the Scheduling Algorithm. Instead of the multiplequeue arrangement used by CTSS, a simple, first-come, first-served, round-robin procedure will be used. The time interval during which users! programs are given "bursts" of processor time will be a constant and not variable as in CTSS. The length of the burst will also be referred to as the "quantum time". In operation, a list of all of the users in the working state will be kept, and programs will be given bursts of processor time in the order that they are in this list. As users' programs finish, they are removed from the list; users whose programs have just received a burst of processor time are removed from the front and placed at the end of this list. In both cases, the remaining programs are moved toward the front. Programs newly entering the working status are added to the end.

The final model to be simulated will represent a system in which swapping and processor operation are overlapped. While a program is being run by the processor, the program which was running previously is dumped and the next program to run is loaded. Since loading and dumping cannot occur simultaneously, there must be room in the core memory for at least two complete user programs—

the program being executed and the program being dumped or loaded. Should two programs intended to run in sequence not fit together in the core memory, the processor must be stopped to complete the swapping. This procedure is shown in detail in the informal flow chart of Figure 7. While a program is running, all or as much as will fit of the next program to run is loaded. After the quantum time (two seconds) is up, the swap is completed if the next program could not be completely loaded; and then this program is started. A dump of the stopped program is then begun, and the process is repeated. Scheduling is done strictly on the basis of program size, with a simple algorithm used to sort programs in an attempt to maximize the number of adjacent programs fitting together in memory.

A model in which <u>all</u> disk operation (including its use by user programs as an I/O device) is overlapped with processor operation is being undertaken by Mr. Donald Widrig of the staff of Project MAC. His simulation will use the same user model and simulation system developed and used here. A more detailed study of bulk storage device operation in a multi-programmed system is being carried out by Mr. Peter J. Denning, also of the staff of Project MAC, as an S.M. thesis. The results of both these studies will not be available in time to be discussed in this report.

Figure 7: OPERATION OF THE MAIN CONTROL ELEMENT FOR A TIME-SHARED SYSTEM WITH OVERLAPPED SWAPPING AND PROCESSING.

The second of the second second second

42

## C. The Need for a New Simulation System

There exist dozens of different types of simulation programming systems. Among these are many special-purpose as well as several general-purpose systems. At this time, there exists no special-purpose simulation programming language specifically for use with models of digital computer systems. The general-purpose languages, such as SIMSCRIPT, GPSS, etc., all have faults which render them unsuitable for this type of work. Since SIMSCRIPT (MARKOWITZ, 1963) and GPSS (IBM, 1963) are perhaps the most widely used of the general-purpose languages, they will be discussed in more detail. The basic objections to these languages are that: (1) their notation is not convenient for the description of digital systems, (2) they are inefficient in their use of computer time, and (3) their basic timing structure is not well matched to the structure of the digital systems being simulated.

SIMSCRIPT is an event-based language. That is, the simulation is described, event by event, with small programs, one per event. Each event program (or sub-program) must specify the times for the events following it. Conditional scheduling of an event is extremely difficult. The notation is an augmented version of FORTRAN, which is acceptable; but this organization does not take advantage of the modularity of digital systems. SIMSCRIPT's list

of coming events may grow to an indeterminately large size, but in a computer system there are only as many coming events as there are independent elements. In SIMSCRIPT it is difficult to distinguish the events associated with a particular physical element. Thus, the modification of such an element is frequently not easily accomplished. Finally, SIMSCRIPT is very difficult to learn, there are no real provisions for automatic tracing and other debugging aids, it is inefficient, and it is not available for on-line use with CTSS.

On the other hand, GPSS is organized around the flow of information through a system. A fairly inconvenient block diagram notation is used. Again, it is difficult to express and take advantage of modularity in GPSS. It is also extremely inefficient from the standpoint of computer time because it is executed interpretively, not compiled into machine language. The use of canned, machine language routines is, therefore, difficult. It is available as a command with CTSS, but is rarely used, despite the fact that quite a lot of simulation is being done at Project MAC. Furthermore, GPSS is difficult to learn.

As opposed to the above disadvantages, the simulation programming system used here and described in detail in Appendix C is easy to learn, has great modularity, has

automatic debugging features, is moderately efficient, and, it is felt, is very well suited to the simulation of digital computer systems. This new language is now being used by several people at Project MAC who learned it in approximately two or three hours of instruction. The language is based on MAD, and each physical element in a system to be simulated corresponds to a conventional MAD subroutine. Built-in traces of the activities of a running simulation can be started or stopped at any time by the programmer, special post-mortems are available which print the state of the simulation at any point, and real-time interaction with the simulation from a CTSS remote console is possible.

### D. Continuous-Time Markov Model for CTSS-like Systems

A simple continuous-time Markov process will be used to represent the operation of a single processor, timeshared system. The primary reasons for developing such a model are to compare its predictions with those of the simulation models and with the actual CTSS data and to extend its usage to more complex systems. The basis for this model is the interaction model for the CTSS user, described in Section II. The states of the Markov process representing a system with n users will correspond to the number of users in the working part of the interaction. That is, state j being occupied will indicate that j users are in the working portion of an interaction. Thus, the Markov process will have (n+1) states. order to use a continuous-time Markov process, the distributions of processor time per interaction and the duration of the console portion of the interaction must be exponential. The mean time for the console portion will be T; the mean processor time per interaction, P. In this development, P will include the necessary swap time per interaction since in CTSS swapping is not overlapped with computation, and the processor stands idle while swapping occurs. The time-shared aspect of the operation of CTSS will be idealized in that no overhead will be associated with additional users waiting for service. The processor

will be considered as switching from program to program at an infinite rate with no loss of efficiency. Thus if there are currently j users waiting for service (i.e., in the working part of an interaction), the rate of exit to the state where (j+1) users are waiting for service is  $(\frac{n-j}{\eta})$ ; that is, (n-j) users are in the console portion of the interaction. The rate of exit to the state where there are (j-1) users is  $(\frac{1}{p})$ . This implies that each of the j users is receiving  $(\frac{1}{3})$  of the processor's capacity. That is, each user is finishing at a rate of  $(\frac{1}{4P})$  and any one of the j users is finishing at a rate of  $(\frac{1}{p})$ . The rate matrix (HOWARD, 1960, p. 92 ff.) A, is shown below. An expression for the steady-state probabilities is found; expressions for the average number of users waiting for service and the mean ratio of waiting time to processor time are derived.

Let  $T = \{\pi_0, \pi_1, \pi_2, \dots, \pi_n\}$  be the vector of the steady-state probabilities of occupancy. Then,

$$\prod A = 0 .$$

The equations for the  $\pi$ 's are:

$$-\frac{n}{T}\pi_{0} + \frac{1}{P}\pi_{1} = 0$$

$$\frac{n}{T}\pi_{0} - \frac{1}{P}\pi_{1} - \frac{n-1}{T}\pi_{1} + \frac{1}{P}\pi_{2} = 0$$

etc.

yielding

$$\pi_1 = n_{\overline{T}}^P \pi_0$$

$$\pi_2 = n(n-1) \left(\frac{P}{T}\right)^2 \pi_0$$

etc.

In general,

$$\pi_{1} = \frac{n!}{(n-1)!} (\frac{P}{T})^{1} \pi_{0}$$

.

Making use of the fact that  $\sum_{i=0}^{n} \pi_{i} = 1$ , the following equation results:

$$1 = \pi_0 [1 + n_{\overline{T}}^P + n(n-1)(\frac{P}{T})^2 + \dots + \frac{n!}{(n-1)!} (\frac{P}{T})^{\frac{1}{2}} + \dots + n!(\frac{P}{T})^n]$$

Letting  $\frac{P}{T} = r$  , and solving for  $\pi_0$  :

$$\pi_0 = \frac{1}{\sum_{j=0}^{n} \frac{n!}{(n-j)!} r^j}$$

Thus

$$\pi_{i} = \frac{\prod_{j=0}^{n!} r^{j}}{\sum_{j=0}^{n!} \frac{n!}{(n-j)!} r^{j}}.$$

$\boldsymbol{\pi}_{\mathrm{O}}$  is the steady-state probability that the processor is idle.

Now, let W be equal to the mean length of time a user spends in the working part of the interaction (i.e., the mean response time). Let Q be the average number of users waiting for service. Then

$$\overline{Q} = n \frac{W}{W+T} = \sum_{i=0}^{n} i\pi_{i}$$

and

$$Q = \frac{\sum_{i=0}^{n} \frac{in!}{(n-i)!} r^{i}}{\sum_{i=0}^{n} \frac{n!}{(n-i)!} r^{i}} = n \frac{W}{W+T}$$

Solving for W;

$$W = \frac{\sum_{i=0}^{n} \frac{ir^{i}}{(n-i)!}}{\sum_{i=0}^{n} \frac{r^{i}}{(n-i-1)!}} T$$

Dividing both sides by P and using the definition of r:

$$\frac{W}{P} = \frac{\sum_{i=0}^{n} \frac{ir^{i}}{(n-i)!}}{r \sum_{i=0}^{n} \frac{r^{i}}{(n-i-1)!}}$$

Expressed in terms of  $\pi_0$ ,

$$\frac{W}{P} = \frac{n}{(1-\pi_O)} - \frac{1}{r}$$

or

$$W = \frac{nP}{(1-\overline{v_0})} - T .$$