|   |   |   |   | D | I | Μ | Ε | N | S | Ι | 0 | N |   | 6 | 8 | Ø | Ø | Ø |   |   |   |   |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| S | Y | S | Т | Ε | М |   | R | Е | F | Е | R | Е | N | С | Е |   | Μ | A | N | U | A | L |

| М | i | с | r | 0 |   | С | r | a | f | t |   | С | 0 | r | р | 0 | r | a | t | i | 0 | n |

6 8 Ø - Ø Ø Ø 1 - 2 Ø Ø

PRELIMINARY

#### NOTICE

\_\_\_\_\_

Micro Craft Corporation reserves the right to make improvements in the product described in this manual at any time and without notice.

#### DISCLAIMER OF ALL WARANTIES AND LIABILITY

MICRO CRAFT CORPORATION MAKES NO WARRANTIES, EITHER EXPRESS OR IMPLIED, WITH RESPECT TO THIS MANUAL OR WITH RESPECT TO THE SOFTWARE DESCRIBED IN THIS MANUAL, ITS QUALITY, PERFORMANCE, MERCHANTIBILITY, OR FITNESS FOR ANY PARTICULAR PURPOSE. MICRO CRAFT CORPORATION SOFTWARE IS SOLD OR LICENSED "AS IS." THE ENTIRE RISK AS TO ITS QUALITY AND PERFORMANCE IS WITH THE BUYER. SHOULD THE PROGRAMS PROVE DEFECTIVE FOLLOWING THEIR PURCHASE, THE BUYER (AND NOT MICRO CRAFT COPPORATION, ITS DISTRIBUTOR, OR ITS RETAILER) ASSUMES THE ENTIRE COST OF ALL NECESSARY SERVICING, REPAIR, OR CORRECTION AND ANY INCIDENTAL OR CONSEQUENTIAL DAMAGES. IN NO EVENT WILL MICRO CRAFT CORPORATION BE LIABLE FOR DIRECT, INDIRECT, INCIDENTAL, OR CONSEQUENTIAL DAMAGES RESULTING FROM ANY DEFECT IN THE SOFTWARE, EVEN IF MICRO CRAFT CORPORATION HAS BEEN ADVISED OF THE POS-SIBILITY OF SUCH DAMAGES. SOME STATES DO NOT ALLOW THE EXCLUSION OR LIMITATION OF IMPLIED WARRANTIES OR LIABILITY FOR INCIDENTAL OR CONSE-QUENTIAL DAMAGES, SO THE ABOVE LIMITATION OR EXCLUSION MAY NOT APPLY TO YOU.

This manual is copyrighted. All rights are reserved. This document may not, in whole or in part, be copied, photocopied, translated, or reduced to any electronic medium or machine readable form without prior consent, in writing, from Micro Craft Corporation.

Copyright 1983 by Micro Craft Corporation

Micro Craft Corporation 4747 Irving Blvd. Dallas, Texas 75247 (214) 630-2562 Additional copies of this manual may be ordered from your DEALER by using the MICRO CRAFT part number 680-0001-200.

> Ask your DEALER also for a free brochure with a complete list of a Micro Craft manuals and products

> > MICRO CRAFT CORPORATION Customer Support Department 4747 Irving Blvd. Dallas, Texas 75247

|                                                                    | _                                                                                                                                                  | TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pg.<br>Pg.                                                         | 1<br>3                                                                                                                                             | INTRODUCTION<br>WELCOME                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.        | 10<br>10<br>10<br>10<br>10                                                                                                                         | CHAPTER 1 - OVERVIEW<br>POWER SUPPLY<br>MAIN BOARD<br>KEYBOARD<br>KEYBOARD<br>KEYBOARD INTERFACE<br>CRT<br>PROCESSOR<br>MEMORY<br>I/O<br>EXPANSION SLOTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg.<br>Pg. | 15<br>15<br>15<br>16<br>16<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>22<br>22<br>22<br>23<br>23<br>24<br>25<br>26<br>27<br>27<br>28<br>29<br>31 | CHAPTER 2 - HARDWARE<br>POWER SUPPLY<br>MAIN BOARD<br>J1 - POWER<br>J2 - RESET SWITCH ASSEMBLY<br>J3 - KEYBOARD<br>J4 - VIDEO OUTPUT<br>J5 - MINI STANDARD DISKETTE CONNECTOR (34 Pin)<br>J6 - PARALLEL PRINTER PORT<br>J7 - STANDARD DISKETTE CONNECTOR (50 Pin)<br>J8 - RS-232C INTERFACE<br>J9 - GAME CONTROL (A/D)<br>J10 - SPEAKER<br>J11 - LIGHT PEN<br>J12 - NOT USED AND NOT PHYSICALLY PRESENT<br>J13 - AUTO LINE FEED<br>J14 - AUXILIARY VIDEO<br>KEYBOARD<br>KEYBOARD<br>KEYBOARD INTERFACE<br>PRINTER OUTPUT<br>RS-232<br>REAL TIME CLOCK<br>CRT<br>SPEAKER<br>DISK DRIVES<br>MC68000<br>INTERRUPTS<br>MEMORY<br>EXPANSION SLOTS<br>CO-PROCESSORS<br>CHAPTER 3 - MEMORY ALLOCATION |

| Pg.<br>Pg.<br>Pg.                                                  | 33<br>33                                                                                                                                           | MEMORY CIRCUITRY<br>MEMORY MAP<br>USES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Pg. 37  | CHAPTER 4 - CP/M-68K, CPMBIOS, and ROMBIOS       |

|---------|--------------------------------------------------|

| Pg. 39  | FLOW                                             |

| Pg. 39  | ADDITIONAL CALLS                                 |

| Pg. 40  | FUNCTION 256 - Change DIskette Drive Format      |

| Pg. 41  | FUNCTION 257 - Read Diskette Drive Format        |

| Pg. 42  | FUNCTION 258 - Set the Physical Parameter Table, |

|         | Set the CP/M Disk Parameter Table, or            |

|         | Set the Disk Interlace Table                     |

| Pg. 43  | TERMINAL ATTRIBUTES                              |

| Pg. 43  | CONTROL FUNCTIONS                                |

| Pg. 43  | ESCAPE SEQUENCES                                 |

| Pg. 44  | ROMBIOS                                          |

| Pg. 44  | ROMBIOS FUNCTIONS                                |

| Pg. 45  | INPUT/OUTPUT                                     |

|         |                                                  |

| APPENDI | CES                                              |

| Pg. A-l | TOOL-KIT                                         |

| Pg. B-l | KEYBOARD CODES                                   |

| Pg. C-l | ASCII CODES                                      |

|         |                                                  |

- Pg. D-1EXPANSION SLOT PINOUTSPg. E-1DIRECT I/OPg. F-1ROMBIOS

# INTRODUCTION

### WELCOME TO THE DIMENSION 68000

You are now the owner of the most powerful most compatible, most flexible micro computer available in the world today. You, also, may be assured that the designers of Dimension 68000 intend that the statement above will be true for many years to come!

This manual is a tool for gaining an in-depth understanding of the operation of the DIMENSION 68000. It is NOT a tutorial. It is a collection of facts and other data. CHAPTER 1

OVERVIEW

-

The DIMENSION 68000 system is made up of several functional components or systems. Those systems are:

- The Power Supply

- The Main Board

- The Keyboard

- The CRT Interface

- The Processor (CPU)

- The Memory

- The I/O (Input/Output)

- The Expansion Slots

- The Floppy Disks and Controllers

These systems, together, handle all of the operations that are performed by the DIMENSION  $68000\,.$

This manual often gives directional instructions for the location, by the user, of various systems, parts, and components. In this manual, all directional instructions will refer to the orientation depicted in the view (looking down on the top) below:

The directions "Front" and "down" are towards the diskette drives and the reset switch. The directions "back" and "up" are away from the drives and toward the REAR PANEL.

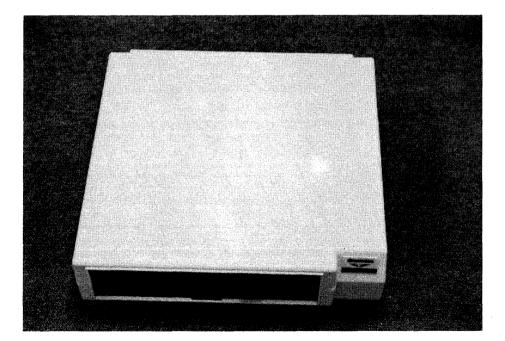

To remove the top cover from the system unit of the DIMENSION 68000, use the following steps:

- TURN OFF the POWER

- TURN the system unit over (upside down)

- USING a PHILLIPS HEAD SCREWDRIVER, LOOSEN the SIX (6) SCREWS that are holding the top cover. These screws are NOT removable from the bottom cover of the system unit. The screws are designed to be held captive in the bottom cover so that they will not be lost.

- With the loosened cover still in place, TURN the system unit back over (right side up)

- LIFT off the top cover

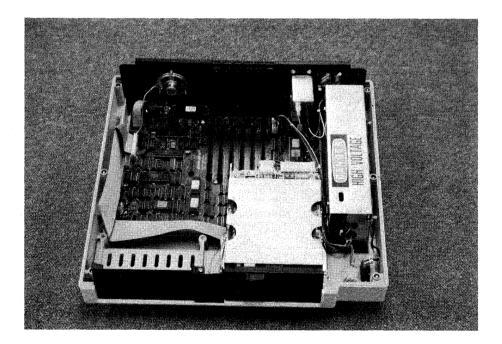

Looking down upon the system unit (with the top cover removed), the system unit looks like the picture below.

The POWER SUPPLY

The POWER SUPPLY is enclosed in the metal cover on the right side inside the system unit. It supplies +5 VDC @ 8 A., +12 VDC @ 2.5 A., and -12 VDC @ 2 A. It is a high-frequency "switching"-type power supply.

The MAIN BOARD

The MAIN BOARD is the large printed circuit board which takes up most of the bottom of the case of the system unit. The MAIN BOARD is the actually the computer.

On the MAIN BOARD are the integrated circuits, components, and the expansion slots. The microprocessor (or "brain") of the DIMENSION 68000 is the Motorola (or equivalent) MC68000L8 device. The 68000 has an addressing capacity of 16 M Bytes. The MAIN BOARD can have up to 512 K Bytes of RAM (Random Access Memory) in 128 K Byte increments.

Also, on the MAIN BOARD are 8 K Bytes of ROM (Read Only Memory). The ROM is used to hold the system MONITOR and the ROMBIOS.

The six long peripheral slots that are toward the middle back of the MAIN BOARD can each hold a card. The cards can be any one of the following types:

- An Emulator Card (examples; Z-80, 8086, and 6512)

- A Memory Expansion Card

- A Hard Disk Controller

- A Peripheral Controller

- A Peripheral Device

The KEYBOARD System

The Keyboard system is composed of two parts; the Keyboard and the Keyboard Interface.

The Keyboard

The Keyboard unit, that plugs into the back of the DIMENSION 68000 system unit, is a microprocessor controlled assembly that is capable of handling in excess of 30 characters per second. The Keyboard assembly transmits the characters, that are typed in, to the DIMENSION 68000 system using the following characteristics:

- 30 characters/second

- 8 bit characters

- ASCII (American Standard Code for Information Interchange) encoding

- asynchronous transmission

CHAPTER 1

Page 10

#### The Keyboard Interface

The Keyboard Interface circuitry receives the characters from the Keyboard assembly. The asynchronous transmission technique adds a "start" bit and adds a "stop" bit to each character, and then transmits the character, with the added bits, in a serial mode, from the Keyboard assembly to the Keyboard Interface. The Keyboard Interface removes the added "start" and "stop" bits from each character received, and converts the character from a serial mode to a parallel mode. This is implemented using one serial channel of the Signetics 2681 Dual Universal Asynchronous Receiver/Transmitter (DUART) chip.

### The CRT Interface

The CRT Interface provides a video output signal for the connection of a CRT or other video display device. The CRT interface supplies a video signal with the following characteristics:

- RS-170 compatible signal

- Composite video (sync + video)

- Capable of COLOR and MONOCHROME operation

#### The Processor (CPU)

The Processor (or CPU - Central Processing Unit) is a Motorola MC68000 (or equivalent) microprocessor integrated circuit (or chip). The Motorola MC68000 device is internally a 32 Bit microprocessor. The MC68000 has 16 Bit wide data paths.

#### The Memory

There are two (2) types of memory in the DIMENSION 68000; RAM (Random Access Memory) and ROM (Read Only Memory). The Main Board can hold 128 K Bytes, 256 K Bytes, 384 K Bytes, or 512 K Bytes of RAM. The amount of RAM can be expanded from 512 K Bytes up to 16 M Bytes by using memory expansion cards. There are 8 K Bytes of ROM.

The I/O (Input/Output)

The I/O (Input/Output) for the DIMENSION 68000 system unit consists of the following devices:

- The Keyboard Interface

- The CRT Interface

- The Diskette Drives

- The Parallel Printer Port

- The RS-232C Interface

- The Game Control Interface

Optionally, there can be connectors on the rear panel to connect the following:

- Additional Mini (5 1/4", 3 1/2", 3 1/4", etc.) Diskette Drives - Additional 8 Inch (Full Size) Diskette Drives (up to four total)

The Expansion Slots

There are six (6) Expansion Slots inside the system unit. The Expansion Slots provide the capability to plug in various types of cards. Some of the types of cards are:

- Emulator Card(s)

- Hard Disk Interface Card

- RS-232 Ports Card(s) 8 ports per card

- Analog/Digital Interface Card(s)

512 K Byte RAM Memory Cards

It is expected that, in the future, Micro Craft Corporation and other manufacturers will be providing many types of cards to plug into the Expansion Slots.

## CHAPTER 1

SYSTEM REFERENCE MANUAL

### CHAPTER 2

HARDWARE

- 1

The POWER SUPPLY

The POWER SUPPLY for the DIMENSION 68000 is a high-frequency "switching"-type unit. It supplies the following voltages and currents:

+5 VDC +,- 1% @ 8 Amps +12 VDC +,- 5% @ 2.5 Amps -12 VDC +,- 5% @ 2 Amps

These voltages are supplied to the MAIN BOARD and to the Disk Drives. Power supplied to the MAIN BOARD is available to the Expansion Slots, and to the Game Control connector (J9) on the MAIN BOARD.

The POWER SUPPLY requires 115 VAC @ 3 Amps (MAX.) to operate. The POWER SUPPLY for the DIMENSION 68000, optionally, may be configured to operate from 220 VAC power. The POWER SUPPLY input power, whether 115 VAC or 220 VAC, must be of a frequency in the range of from 50 Hz. to 400 Hz. The input power to the POWER SUPPLY is filtered for RFI (Radio Frequency Interference). The input power to the POWER SUPPLY also has power line surge suppression applied.

The MAIN BOARD

The MAIN BOARD has the Expansion Slots, the integrated circuits (including the 68000 microprocessor), the components, and the connectors that link the MAIN BOARD to the POWER SUPPLY, the Keyboard, etc. The connectors on the MAIN BOARD are detailed below.

J1 - POWER

MAIN BOARD

| 456          | PIN | USAGE   | The Connector Necessary      |

|--------------|-----|---------|------------------------------|

|              |     |         | to Mate With the Connector   |

| /            | 1   | +5 VDC  | on the MAIN BOARD is made    |

| 000          | 2   | GROUND  | using a MOLEX P/N Ø3-Ø9-1Ø64 |

| 1            | 3   | +12 VDC | recepticle and MOLEX         |

|              | 4   | +5 VDC  | P/N 02-09-1118 pins          |

|              | 5   | GROUND  | (or the equivalent).         |

| ++           | 6   | -12 VDC |                              |

| 123          |     |         |                              |

| Top View of  |     |         |                              |

| Connector on |     |         |                              |

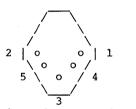

| ++    | +       | PIN      | USAGE     | The      |

|-------|---------|----------|-----------|----------|

| 11    |         |          |           | to       |

| 0     | 1       | 1        | RESET     | on       |

| 11    |         | 2        | GROUND    | P/N      |

| 10    | 2       | 3        | NORMAL    | equ      |

| 11    | 1       | 4        | LED POWER | <b>1</b> |

| 1 0   | 3       |          |           |          |

|       |         |          |           |          |

| 0     | 4       |          |           |          |

|       | -       |          |           |          |

|       |         |          |           |          |

| ++=== | т<br>1  |          |           |          |

|       | iew of  | The PAIN |           |          |

|       | ctor on | indicate | ès        |          |

| MAIN  | BOARD   | pin l.   |           |          |

|       |         |          |           |          |

5

The Connector Necessary to Mate With the Connector on the MAIN BOARD is a MOLEX P/N 22-26-9041 (or the equivalent).

J3 - KEYBOARD

PIN USAGE --- ----1 SIGNAL FROM KEYBOARD 2 3 4 GROUND

+5 VDC POWER

TO KEYBOARD

The Connector Necessary to Mate With the Connector at rear of SYSTEM UNIT is a 5 PIN, "DIN"-type, MALE

View of Front of Connector at rear of SYSTEM UNIT

#### J4 - VIDEO OUTPUT

|   | PIN     | USAGE  | The Connector Necessary    |

|---|---------|--------|----------------------------|

|   |         |        | to Mate With the Connector |

| 0 | Center  | SIGNAL | on the REAR PANEL is an    |

|   | Outside | GROUND | RCA type MALE              |

## J5 - MINI STANDARD DISKETTE CONNECTOR (34 Pin)

| ++             | PIN | USAGE      | The Connector Necessary    |

|----------------|-----|------------|----------------------------|

| [++]           |     |            | to Mate With the Connector |

| 0 0  ]         | 1   | GROUND     | on the MAIN BOARD is an    |

| 0 0            | 2   |            | ANSLEY P/N 609-34000 (or   |

| 0 0            | 3   | GROUND     | the equivalent)            |

| 0 0            | 4   |            | <b>_</b> ,                 |

| 0 0            | 5   | GROUND     |                            |

| 00             | 6   | DRSEL 3 *  | NOTE: An * after a signal  |

| 0 0 ++         | 7   | GROUND     | name indicates that        |

|                | 8   | INDEX*     | the logic for that         |

| 00             | 9   | GROUND     | signal is inverted,        |

|                | 10  | DRSEL Ø *  | that is to say that        |

| 0 0 ++         | 11  | GROUND     | the signal is active       |

| 0 0            | 12  | DRSEL 1 *  | on a "Ø" instead of        |

| 0 0            | 13  | GROUND     | a "1".                     |

| 0 0 0          | 14  | DRSEL 2 *  |                            |

| 0 0            | 15  | GROUND     |                            |

| 00             | 16  |            |                            |

| 00 01          | 17  | GROUND     |                            |

| ++             | 18  | M DIR *    |                            |

| ++             | 19  | GROUND     |                            |

| View of the    | 2Ø  | M STEP *   |                            |

| Connector on   | 21  | GROUND     |                            |

| the MAIN BOARD | 22  | M W DATA * |                            |

|                | 23  | GROUND     |                            |

| The PAINT DOT  | 24  | WR ENA *   |                            |

| indicates      | 25  | GROUND     |                            |

| pin l          | 26  |            |                            |

| -              | 27  | GROUND     |                            |

|                | 28  |            |                            |

|                | 29  | GROUND     |                            |

|                | ЗØ  | RD DATA    |                            |

|                | 31  | GROUND     |                            |

|                | 32  | M HEAD *   |                            |

|                | 33  | GROUND     |                            |

|                | 34  |            |                            |

|                |     |            |                            |

## J6 - PARALLEL PRINTER PORT

| PIN                   | USAGE                          |

|-----------------------|--------------------------------|

| 1                     | STROBE*                        |

|                       | DØ*                            |

| 2<br>3<br>4<br>5<br>6 | DI*                            |

| 4                     | D2*                            |

| 5                     | D3*                            |

| 6                     | D4*                            |

| 7                     | D5*                            |

| 8                     | D <b>6*</b>                    |

| 9                     | D <b>7</b> *                   |

| 10                    | ACKNLG*                        |

| 11                    | RDY*                           |

| 12                    | Not Connected<br>Not Connected |

| 13                    | Not Connected                  |

| 14                    | AUTO LINE FEED                 |

| 15                    | Not Connected                  |

| 16                    | Not Connected                  |

| 17                    | GROUND                         |

| 18                    | Not Connected                  |

| 19                    | GROUND                         |

| 2Ø                    | GROUND                         |

| 21                    | GROUND                         |

| 22                    | GROUND                         |

| 23                    | GROUND                         |

| 24                    | GROUND                         |

| 25                    | GROUND                         |

| 26                    | GROUND                         |

| 27                    | GROUND                         |

| 28                    | GROUND                         |

| 29                    | GROUND                         |

| 30                    | GROUND                         |

| 31                    | INIT*                          |

| 32                    | Not Connected                  |

| 33<br>34              | GROUND                         |

| 34<br>35              | Not Connected<br>Not Connected |

| 35                    | Not Connected                  |

| 20                    | Not Connected                  |

\*

The Connector Necessary to Mate With the Connector on the REAR PANEL is an Amphenol 36 Pin "Blue Ribbon" type

NOTE: An \* after the signal name indicates that the logic for that signal is inverted, that is to say that the signal is active on a "0" instead of a "1".

## J7 - STANDARD DISKETTE CONNECTOR (50 Pin)

|                                                            | PIN<br>1<br>2<br>3<br>4<br>5                                                                             | USAGE<br><br>GROUND<br>M LOW C *<br>GROUND<br>MOTOR OFF Ø *<br>GROUND                                                                                                     | The Connector Necessary<br>to Mate With the Connector<br>on the MAIN BOARD is an<br>ANSLEY P/N 609-5000 (or<br>the equivalent)                                                |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>0 0<br>++<br>0 0<br>0 0 | 6<br>7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16                                               | MOTOR OFF 1 *<br>GROUND<br>MOTOR OFF 2 *<br>GROUND<br>2 SIDED *<br>GROUND<br>GROUND<br>M HEAD *<br>GROUND                                                                 | NOTE: An * after a signal<br>name indicates that<br>the logic for that<br>signal is inverted,<br>that is to say that<br>the signal is active<br>on a "0" instead of<br>a "1". |

|                                                            | 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25<br>26                                                 | GROUND<br>M HEAD LD *<br>GROUND<br>INDEX *<br>GROUND<br>MOTOR OFF 3 *<br>GROUND<br>DR SEL Ø *                                                                             |                                                                                                                                                                               |

| ++<br>View of the<br>Connector on<br>the MAIN BOARD        | 27<br>28<br>29<br>30<br>31<br>32                                                                         | GROUND<br>DR SEL 1 *<br>GROUND<br>DR SEL 2 *<br>GROUND<br>DR SEL 3 *                                                                                                      |                                                                                                                                                                               |

| The PAINT DOT<br>indicates<br>pin 1                        | 33<br>34<br>35<br>36<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>44<br>45<br>46<br>47<br>48<br>49<br>50 | GROUND<br>M DIR *<br>GROUND<br>M STEP *<br>GROUND<br>M W DATA *<br>GROUND<br>WR ENA *<br>GROUND<br>TK ØØ *<br>GROUND<br>W PROT *<br>GROUND<br>RD DATA<br>GROUND<br>GROUND |                                                                                                                                                                               |

## J8 - RS-232C INTERFACE

| 1  |      | PIN<br>1<br>2<br>3<br>4<br>5<br>6 | USAGE<br>GROUND<br>XMIT DATA<br>RECV DATA<br>"MARK"<br>NOT USED | The Connector Necessary<br>to Mate With the Connector<br>on the REAR PANEL is a<br>25 PIN, "D Subminiature"<br>type MALE (DB25P) |

|----|------|-----------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

|    | 0    | 7                                 | NOT USED<br>GROUND                                              | NOTE: "MARK" indicates a<br>high logic signal                                                                                    |

|    | 0    | 8                                 | DCD                                                             | (+12 VDC)                                                                                                                        |

|    | 0    | 8<br>9<br>1Ø                      |                                                                 |                                                                                                                                  |

|    | 0    | 10                                |                                                                 |                                                                                                                                  |

|    | 0    | 11                                |                                                                 |                                                                                                                                  |

|    | 0    | 12                                |                                                                 |                                                                                                                                  |

|    | 0    | 13                                |                                                                 |                                                                                                                                  |

|    | 0    | 14                                |                                                                 |                                                                                                                                  |

|    | 0    | 15                                |                                                                 |                                                                                                                                  |

|    | 0    | 16                                |                                                                 |                                                                                                                                  |

|    | 0    | 17                                |                                                                 |                                                                                                                                  |

|    | 0    | 18                                |                                                                 |                                                                                                                                  |

|    | 0    | 19                                |                                                                 |                                                                                                                                  |

|    | 0    | 2Ø                                | "MARK"                                                          |                                                                                                                                  |

|    | 0    | 21                                |                                                                 |                                                                                                                                  |

|    | 0    | 22                                |                                                                 |                                                                                                                                  |

|    | 0/25 | 23                                |                                                                 |                                                                                                                                  |

| 13 | 0/   | 24                                |                                                                 |                                                                                                                                  |

|    | /    | 25                                |                                                                 |                                                                                                                                  |

View of Connector on REAR PANEL J9 - GAME CONTROL (A/D)

| 1    |                | PIN | USAGE         | The Connector Necessary<br>to Mate With the Connector |

|------|----------------|-----|---------------|-------------------------------------------------------|

| _    | 0 \ 9          | 1   | +5 VDC        | on the REAR PANEL is a                                |

|      | 0              | 2   | SW l (Bit Ø)  | 15 PIN, "D Subminiature"                              |

|      | 0              | 3   | POT 1 (Bit 4) | type MALE (DB15P)                                     |

|      | 0              | 4   | GROUND        |                                                       |

|      | 0              | 5   | GROUND        |                                                       |

|      | 0              | 6   | POT 2 (Bit 5) |                                                       |

|      | 0              | 7   | SW 2 (Bit 1)  |                                                       |

|      | 0              | 8   | +5 VDC        |                                                       |

|      | 0              | 9   | +5 VDC        |                                                       |

| 1    | 0              | 10  | SW 3 (Bit 2)  |                                                       |

|      | 0              | 11  | POT 3 (Bit 6) |                                                       |

|      | 0              | 12  | GROUND        |                                                       |

|      | o / 15         | 13  | POT 4 (Bit 7) |                                                       |

| 8    | 0/             | 14  | SW 4 (Bit 3)  |                                                       |

|      |                | 15  | +5 VDC        |                                                       |

| View | w of Connector |     |               |                                                       |

| on I | REAR PANEL     |     |               |                                                       |

,

J1Ø - SPEAKER

-

| +++               |     |   | PIN | USAGE         | The Connector Necessary      |  |  |

|-------------------|-----|---|-----|---------------|------------------------------|--|--|

|                   |     |   |     |               | to Mate With the Connector   |  |  |

| 0                 |     | 1 | 1   | +5 VDC        | on the MAIN BOARD is a MOLEX |  |  |

| 1                 | 11  |   | 2   | SIGNAL        | P/N 22-26-9021 (or the       |  |  |

| 0                 |     | 2 |     |               | equivalent).                 |  |  |

| +                 | -++ |   |     |               |                              |  |  |

| View of Connector |     |   | The | PAINT DOT     |                              |  |  |

| on MAIN BOARD     |     |   | ind | licates pin l |                              |  |  |

The Connector Necessary to Mate With the Connector on the MAIN BOARD is a MOLEX P/N 22-26-9041 (or the

equivalent).

-

| J11 | - | LIGHT | PEN |

|-----|---|-------|-----|

| JTT | - | LIGHT | PLN |

| +                               | + | ŧ | PIN       | USAGE         |  |

|---------------------------------|---|---|-----------|---------------|--|

|                                 |   | _ |           |               |  |

|                                 | 0 | 1 | 1         | RESET         |  |

|                                 |   |   | 2         | GROUND        |  |

|                                 | 0 | 2 | 3         | NORMAL        |  |

|                                 | 0 | 3 | 4         | LED POWER     |  |

|                                 |   | 5 |           |               |  |

|                                 | 0 | 4 |           |               |  |

|                                 |   | - |           |               |  |

| +++                             |   |   |           |               |  |

| View of Connector The PAINT DOT |   |   | PAINT DOT |               |  |

| on MAIN BOARD                   |   |   | ind       | licates pin l |  |

J12 - NOT USED AND NOT PHYSICALLY PRESENT

J13 - AUTO LINE FEED

-

| ++   | -+        | PIN     | USAGE          | The Connector Necessary      |

|------|-----------|---------|----------------|------------------------------|

|      |           |         |                | to Mate With the Connector   |

| 0    | 1         | 1       | LOGIC "1"      | on the MAIN BOARD is a MOLEX |

|      | }         |         | (+5 VDC BFFRD) | P/N 22-26-9031 (or the       |

| 0    | 2         | 2       | CONTROL LINE   | equivalent).                 |

|      |           | 3       | GROUND         |                              |

| 0    | 3         |         | (LOGIC "Ø")    |                              |

|      | (         |         |                |                              |

| ++   | -+        |         |                |                              |

| View | of Connec | tor The | PAINT DOT      |                              |

| view or | Connector | THE PAINT | DOT   |

|---------|-----------|-----------|-------|

| on MAIN | BOARD     | indicates | pin l |

J14 - AUXILIARY VIDEO

|     | -          |              |     |                 |                              |

|-----|------------|--------------|-----|-----------------|------------------------------|

| +   | • <b>+</b> | +            | PIN | USAGE           | The Connector Necessary      |

|     |            | J            |     |                 | to Mate With the Connector   |

|     | 0          | 1            | 1   | +5 VDC          | on the MAIN BOARD is a MOLEX |

| - 1 | 1          |              | 2   | SIGNAL          | P/N 22-26-9031 (or the       |

|     | 0          | 2            |     | (Signal is      | equivalent).                 |

| - 1 |            |              |     | NOT Adjustable) |                              |

|     | 0          | 3            | 3   | GROUND          |                              |

|     |            |              |     |                 |                              |

| +   | ++         | +            |     |                 |                              |

| v   | 'iew d     | of Connector | Th  | e PAINT DOT     |                              |

| c   | n MAI      | IN BOARD     | in  | dicates pin l   |                              |

A schematic of the MAIN BOARD is included in the APPENDICES.

The KEYBOARD System

The Keyboard system is composed of two parts; the Keyboard and the Keyboard Interface.

The Keyboard

The Keyboard is a microprocessor controlled assembly that is capable of handling in excess of 30 characters per second. The Keyboard transmits characters to the DIMENSION 68000 system using the following character-istics:

- 30 characters/second

- 8 bit characters

- ASCII (American Standard Code for Information Interchange) encoding

e

- asynchronous transmission

- Power required = +5 VDC at 250 mA.

- Rollover = 2 key

- Special Keys =

The Keyboard Interface

The Keyboard Interface receives the characters from the Keyboard assembly. The asynchronous transmission that is used between the Keyboard and the Keyboard Interface adds a "start" bit and a "stop" bit to each character. The Keyboard Interface removes the added "start" and "stop" bits from each character received.

Memory Mapped Locations

FFC401 = Keyboard Mode Register

FFC403 = Keyboard Status

FFC405 = Keyboard Interface Command Register

FFC407 = Keyboard Data

FFC409 = Auxilliary Command Register

A list of the keys, on the keyboard, and the codes that each key generates is included in the KEYBOARD CODES APPENDIX. Also, a detailed description of the keyboard and the keyboard interface is included in the DIRECT I/O APPENDIX.

The Keyboard Interface, the Printer, the RS-232C Interface, and the Real Time Clock are all handled by a Signetics (or equivalent) 2681 type Dual Universal Asynchronous Receiver / Transmitter (DUART) integrated circuit (chip).

SYSTEM REFERENCE MANUAL

#### The PRINTER OUTPUT

The PRINTER OUTPUT is handled through the DUART chip that is described above. The PRINTER OUTPUT is unusual in that the user writes the character to be printed to the SET OUTPUT Register, and then writes the character to the RESET OUTPUT Register.

Memory Mapped Locations

FFC41B = Printer Port Configuration Register

FFC41B = Printer Port Status

FFC41D = Printer Port Data SET Register

FFC41F = Printer Port Data RESET Register

The AUTO LINE FEED \* signal is strappable for either enabling the auto line feed function or disabling it. This strapping is done at J13 on the MAIN BOARD. The strapping options for J13 are discussed above under the topic MAIN BOARD.

A detailed discussion of the printer port is contained in the DIRECT I/O APPENDIX.

The RS-232 Interface

The RS-232C Interface is handled through the DUART chip that is described above. The RS-232 Interface is capable of handling bit-per-second rates of from 75 BPS to 19.2 KBPS. (It is not proper to speak of Baud rate on an RS-232 Interface. Baud rate is properly defined as the number of signalling changes per second on a telephone or telegraph communications line. Baud rate is normally considered to be the signalling changes per second between modems. Baud rate and bit rate are not always the same.)

- Memory Mapped Locations

FFC409 = Auxilliary Control Register FFC40B = Interrupt Mask Register FFC411 = Mode Registers (1 and 2) FFC413 = Clock Select Register FFC413 = Status Register FFC415 = Command Register FFC417 = Output Data Register FFC417 = Input Data Register FFC418 = Input Port for DCD

A detailed discussion of the RS-232C interface is contained in the DI-RECT I/O APPENDIX. The REAL TIME CLOCK

The REAL TIME CLOCK is handled through the DUART chip that is described above. Neither the ROMBIOS nor the CP/M BIOS use interrupts, and therefore they do not use the REAL TIME CLOCK.

- Memory Mapped Locations

FFC409 = Auxilliary Control Register

FFC409 = Input Port Change Register

FFC40B = Interrupt Mask Register

FFC40B = Interrupt Status Register

FFC40D = Counter/Timer Upper Register (Most Significant Byte)

FFC40F = Counter/Timer Lower Register (Least Significant Byte)

A detailed discussion of the REAL TIME CLOCK is contained in the DIRECT I/O APPENDIX.

The CRT Interface

The CRT Interface provides a video output signal to connect a CRT or other video display device. The CRT interface supplies a video signal with the following characteristics:

- EIA RS-170 compatible signal

- (EIA = Electronic Industries Association)

- NTSC Positive Composite Color Video

- (NTSC = National Television Standards Committee)

- Capable of COLOR and MONOCHROME operation

- Adjustable output level (Ø to 1 Volt Pk to Pk)

The tint of the color signal is adjustable by means of a trimmer capacitor that is located on the MAIN BOARD. Also, there is potentiometer that is used to adjust the level of the output signal that is routed to the main video connector on the rear panel.

On the MAIN BOARD is an auxiliary video connector which is described above. The signal available on the auxiliary video connector is an NTSC compatible positive video signal. The black level is about 0.75 Volts, the white level is about 2.0 Volts, and the sync tip level is 0 Volts. The output level is NOT adjustable, and the output is NOT protected against short circuits.

- Memory Mapped Locations

FF8001 = CRT Controller Register Address Selection Register

FF8003 = CRT Controller Addressed Register Data

FF8005 = Display Buffer Address High Byte

FF8009 = CRT Display Write Mode Register

FF800A = Reset CRT Controller

A detailed description of the CRT Interface is included in the DIRECT I/O APPENDIX.

#### The SPEAKER

The SPEAKER is inside the case of the system unit. It is driven by half of a 74LS74 flip-flop through a Darlington amplifier circuit. The SPEAKER connection is described above. The SPEAKER used is a one. It is an 8 ohm unit.

The SPEAKER is controlled by a soft switch. The switch can put the cone of the SPEAKER into the "in" position or the "out" position. This switch operates in the same fashion as a TOGGLE switch. Each time a program references the memory address associated with the SPEAKER switch, the speaker will change state: move from "in" to "out" or from "out" to "in". Each time the state of the SPEAKER is changed, a tiny "click" is produced. By referencing the address of the SPEAKER switch very frequently and continuously, a program can cause the generation of a steady tone from the speaker. A program can reference the address of the SPEAKER switch by performing either a "read" or a "write" to that address.

- Memory Mapped Locations FFC800 = Speaker Toggle Address

The SPEAKER is also described in the DIRECT I/O APPENDIX.

The DISK DRIVES

The DISK DRIVES that are standard on the DIMENSION 68000 are half height, 5 1/4 inch, double-sided, double-density, half-steppable, 40 track diskette drives. They are capable of storing up to 400 KBytes of data.

Optionally available, are 80 track diskette units that are capable of storing up to 800 KBytes. As well as 8 inch diskette drives, 3 1/2 inch diskette drives, and 3 1/4 inch diskette drives.

The controller for the diskettes is the NEC uPD765A integrated circuit.

- Memory Mapped Locations FFDØØ1 = Diskette Controller Status FFDØØ3 = Data Register FFDØØ5 = Control Register

Further information is available in the PINOUT APPENDIX and the DIRECT I/O APPENDIX. A detailed description of the controller is available in the NEC DATA SHEET for the uPD765A.

The MC68000

The MC68000 microprocessor used in the DIMENSION 68000 is an 8 MHz. device. It has 16 bit wide data paths (but all of the internal architecture is 32 bits wide). The 68000 chip has the following registers:

8 DATA REGISTERS that are 32 bits wide 7 ADDRESS REGISTERS that are 32 bits wide 1 USER STACK POINTER that is 32 bits wide 1 SUPERVISOR STACK POINTER that is 32 bits wide 1 PROGRAM COUNTER that is 32 bits wide 1 STATUS REGISTER that is 16 bits wide

The 68000 allows 5 data types:

Bits BCD Digits (4 bits/BCD Digit - 1 BCD DIGIT = 1 Nybble) Bytes (8 bits) Words (16 bits) Long Words (32 bits)

The 68000 has the capability of directly addressing 16 MBytes of memory. There are 14 addressing modes on 61 basic instructions for over 1000 total instruction types.

For a detailed discussion of the 68000 microprocessor, see the MOTOROLA MC68000 USER'S MANUAL.

INTERRUPTS

The DIMENSION 68000 comes with six maskable levels of interrupts and one non-maskable interrupt level. The maskable interrupt levels are levels 1, 2, 3, 4, 5, and 6. The non-maskable interrupt level is level 7. Level 1 is the lowest priority and level 7 is the highest priority. The DUART (which is described above) is set by the hardware circuitry to be the non-maskable interrupt on priority level 7. The DUART has the capability to mask for interrupts the Keyboard, the RS-232, the Printer, and the Real Time Clock. All of the interrupts on the DIMENSION 68000 utilize the Autovector type of interrupt processing.

The Autovector processing computes the interrupt vector number (in hex) by the following formula:

VECTOR NUMBER = (PRIORITY-LEVEL +  $\emptyset$ 24)

The above formula gives the interrupt vector number in hexadecimal. The Autovector processing computes the location of the interrupt vector (in hex) by the following formula:

VECTOR LOCATION = VECTOR NUMBER \* 4

SYSTEM REFERENCE MANUAL

The location of the vector address contains the address of an interrupt routine. The following chart shows the assignments for priority level, vector number, and vector address for the DIMENSION 68000.

| DEVICE | PRIORITY<br>LEVEL<br>(decimal) | VECTOR<br>NUMBER<br>(decimal) | LOCATION OF<br>VECTOR ADDRESS<br>(hex) |

|--------|--------------------------------|-------------------------------|----------------------------------------|

|        |                                |                               |                                        |

| SLOT 6 | 1                              | 25                            | Ø64                                    |

| SLOT 5 | 2                              | 26                            | Ø68                                    |

| SLOT 4 | 3                              | 27                            | Ø6C                                    |

| SLOT 3 | 4                              | 28                            | Ø7Ø                                    |

| SLOT 2 | 5                              | 29                            | Ø74                                    |

| SLOT 1 | 6                              | 30                            | Ø78                                    |

| DUART  | 7                              | 31                            | Ø7C                                    |

. . . . . . . .

Additionally, there are exception vectors. Vectors Ø and 1 are taken as a pair and not as two separate vectors. The following chart shows the assignments for the vector number, the vector address, and its usage.

| VECTOR<br>NUMBER<br>(decimal)           | VECTOR<br>ADDRESS<br>(hex) | ASSIGNMENT                              | USED BY |

|-----------------------------------------|----------------------------|-----------------------------------------|---------|

| ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                            |                                         |         |

| Ø                                       | ØØØ                        | Reset: Initial Supervisor Stack Pointer | BOOT    |

|                                         | ØØ4                        | Reset: Initial Program Counter          |         |

| 2                                       | ØØ8                        | Bus Error                               | CP/M    |

| 3                                       | ØØC                        | Address Error                           | CP/M    |

| 4                                       | Ø1Ø                        | Illegal Instruction                     | CP/M    |

| 5                                       | Ø14                        | Zero Divide                             | CP/M    |

| 6                                       | Ø18                        | CHK Instruction                         | CP/M    |

| 7                                       | ØlC                        | TRAPV Instruction                       | CP/M    |

| 8                                       | Ø2Ø                        | Privelege Violation                     | CP/M    |

| 9                                       | Ø24                        | Trace                                   | CP/M    |

| 10                                      | Ø28                        | Line 1010 Emulator                      | CP/M    |

| 11                                      | Ø2C                        | Line llll Emulator                      | CP/M    |

| 12 - 24                                 | 030-060                    | NOT USED                                | NO USER |

| 32 - 255                                | Ø80-3FF                    | NOT USED                                | NO USER |

|                                         |                            |                                         |         |

#### MEMORY

The DIMENSION 68000 memory is byte addressable. Each memory address has associated with it an additional bit that is used for emulation trapping. If a memory address is accessed, and the emulation trap bit is on, then the emulation strobe bit, on the bus and at the slots, is toggled.

The DIMENSION 68000 can address up to 16 MBytes of memory. This is made possible by the use of a 24 Bit wide address.

The DIMENSION 68000 memory has, in its associated circuitry, bus arbitration logic. The bus arbitration priorities are:

| HIGHEST | CRT CONTROLLER | R CIRCUITRY |

|---------|----------------|-------------|

|         | EXPANSION SLOT | r 6         |

|         | EXPANSION SLOT | r 5         |

|         | EXPANSION SLOT | r 4         |

|         | EXPANSION SLOT | r 3         |

|         | EXPANSION SLOT | r 2         |

|         | EXPANSION SLOT | r 1         |

| LOWEST  | MC68000 CPU    |             |

#### EXPANSION SLOTS

Each EXPANSION SLOTS can accept a plug in card. Each slot directly connects to the system's bus. A detailed discussion of the connections for the EXPANSION SLOTS is contained in the EXPANSION SLOT PINOUT APPENDIX.

Each EXPANSION SLOT has four signals that are unique to that slot. They are:

| - | BOARD | ENABLE      | FROM | SYSTEM |

|---|-------|-------------|------|--------|

| - | BOARD | REQUEST     | то   | SYSTEM |

| - | BOARD | ACKNOWLEDGE | FROM | SYSTEM |

| - | BOARD | INTERRUPT   | то   | SYSTEM |

The Micro Craft Corporation supplies an expansion slot board prototyping kit. This kit contains a prototyping board, a set of expansion slot board drawings, data regarding the signals available on the expansion slot connector, and data about the DIMENSION 68000 system circuitry.

### CO-PROCESSORS

The DIMENSION 68000 has been designed to allow the simultaneous use of more than one processor. All of the emulator cards have a microprocessor chip on them. This makes all of the emulator cards, co-processors. Some other possible co-processor uses are: - an array processor

- a mathematical floating point processor

- a mathematical multiply and divide processor

- a specific machine emulator

- an intelligent device controller

СНАРТЕК З

MEMORY ALLOCATION

#### MEMORY CIRCUITRY

The MEMORY CIRCUITRY contains bus arbitration logic circuitry and emulation trapping circuitry. The bus arbitration logic circuitry is designed to give to the CRT Controller circuitry the highest priority. The next highest priority to EXPANSION SLOT 6, then, EXPANSION SLOTS 5, 4, 3, 2, and 1. The lowest priority is the MC68000 CPU.

The emulation trapping circuitry for the memory is implemented by including in the memory design an additional bit with each byte of memory. The additional bit is used as an emulation trapping flag. If the bit is on for a specific byte, and that byte is accessed, then the emulation circuitry causes the emulation strobe bit in the system bus to be pulsed. This does NOT hold true for accesses by the CRT Controller circuitry, NOR does it hold true for accesses by the MC68000 CPU.

#### MEMORY MAP

The DIMENSION 68000 memory contains both Read Only Memory (ROM) and Random Access Memory (RAM). The system memory is allocated as follows.

| ADDRESS             | FUNCTION                                            |

|---------------------|-----------------------------------------------------|

|                     |                                                     |

| ************ INTERR | UPT VECTORS ************************************    |

| ØØØØØØ              | RESET - Initial Stack Pointer                       |

| 000004              | RESET - Initial Program Counter (PC)                |

| 000008              | BUS ERROR                                           |

| ØØØØØC              | ADDRESS ERROR                                       |

| 000010              | ILLEGAL INSTRUCTION                                 |

| 000014              | DIVIDE BY Ø                                         |

| 000018              | CHECK INSTRUCTION                                   |

| ØØØØ1C              | TRAPV INSTRUCTION                                   |

| ØØØØ2Ø              | PRIVILEGE INSTRUCTION                               |

| 000024              | TRACE                                               |

| 000028              | OPCODE 1010 EMULATION                               |

| ØØØØ2C              | OPCODE 1111 EMULATION                               |

| 000030 - 00005F     | Reserved                                            |

| 000060              | SPURIOUS INTERRUPT                                  |

| 000064              | LEVEL 1 INTERRUPT                                   |

| 000068              | LEVEL 2 INTERRUPT                                   |

| ØØØØ6C              | LEVEL 3 INTERRUPT                                   |

| 000070              | LEVEL 4 INTERRUPT                                   |

| 000074              | LEVEL 5 INTERRUPT                                   |

| 000078              | LEVEL 6 INTERRUPT                                   |

| ØØØØ7C              | LEVEL 7 INTERRUPT - DUART - Keyboard, Printer, etc. |

| 000080 - 0000BF     | TRAP VECTORS                                        |

| 0000C0 - 0000FF     | Reserved                                            |

| ADDRESS                            | FUNCTION                                                      |

|------------------------------------|---------------------------------------------------------------|

| ****                               | HERAL CONTROLLER BOOT RAM *********************************** |

| ØØØ1ØØ - ØØØ113                    | CONTROLLER 1                                                  |

| 000114 - 000127                    | CONTROLLER 2                                                  |

| ØØØ128 - ØØØ13B                    | CONTROLLER 3                                                  |

| ØØØ128 - ØØØ13B<br>ØØØ13C - ØØØ14F |                                                               |

|                                    | CONTROLLER 4                                                  |

| ØØØ15Ø - ØØØ163                    | CONTROLLER 5                                                  |

| 000164 - 000177                    | CONTROLLER 6                                                  |

|                                    | VED PERIPHERAL RAM ***********************************        |

| ØØØ178 - ØØØ19B                    | MONITOR RESERVED LOCATIONS                                    |

| ØØØ19C                             | TOP OF RAM                                                    |

| 0001A0 - 0001A7                    | ADDRESS of ROM BASED RESET VECTOR                             |

| 0001A8 - 0001CB                    | CRT PARAMETER TABLE                                           |

| ØØØ1CC - ØØØ1E5                    | BOOT DISK PARAMETER TABLE                                     |

| ØØØ1E6 - ØØØ1E9                    | SYSTEM CONFIGURATION WORD                                     |

| ØØØ1EA - ØØØ1ED                    | ADDRESS OF TEXT SCREEN TABLE                                  |

| ØØØ1EE - ØØØ1F1                    | ADDRESS OF KEYBOARD TABLE                                     |

| ØØØ1F2 - ØØØ1F5                    | ADDRESS of GRAPHICS CHARACTER SET #1 TABLE                    |

| ØØØ1F6 - ØØØ1F9                    | ADDRESS of GRAPHICS CHARACTER SET #2 TABLE                    |

| ØØØ1FA - ØØØ1FD                    | ADDRESS OF PRESENT SCREEN TABLE                               |

| ØØØlFE                             | INTERRUPT MASK FOR 2861 I/O CHIP                              |

| ØØØlFF                             | END OF RESERVED PERIPHERAL RAM                                |

|                                    | RAM AREA **********************************                   |

| ØØØ2ØØ - ØØ119F                    | NORMAL (80 x 50) SCREEN TEXT AREA                             |

| ØØ12ØØ - Ø1FFFF                    | MINIMUM SYSTEM USER RAM                                       |

| 001300                             | Start of CP/M-68K TRANSIENT PROGRAM AREA                      |

| Ø10000 - Ø1FFFF                    | Co-Processor RAM Area, During Emulation (Min)                 |

| Ø10000 - 07FFFF                    | Co-Processor RAM Area, During Emulation (Max)                 |

| Ø20000 - FEFFFF                    | Expanded User RAM Area                                        |

|                                    | VED AREAS ************************************                |

| FFØØØØ - FF1FFF                    | Basic Processor ROM Area (ROMBIOS and MONITOR)                |

| FF2000 - FF7FFF                    | Reserved Area (Graphics RAM)                                  |

|                                    | /OUTPUT REGION ************************************           |

| FF8000 - FF87FF<br>FF8800 - FF8FFF | slot 1                                                        |

|                                    |                                                               |

| FF9000 - FF97FF<br>FF9800 - FF9FFF | Slot 2                                                        |

| FFAØØØ - FFA7FF                    | Slot 3<br>Slot 4                                              |

|                                    | Slot 5                                                        |

| FFA8ØØ - FFAFFF<br>FFBØØØ - FFB7FF | Slot 6                                                        |

|                                    |                                                               |

| FFB8ØØ – FFBFFF                    | Reserved<br>Reserved                                          |

| FFCØØØ - FFC3FF                    |                                                               |

| FFC400 - FFC7FF                    | Keyboard/Printer/Modem/Real Time Clock                        |

| FFC800 - FFCBFF                    | Speaker                                                       |

| FFCCØØ - FFCFFF                    | Game Control                                                  |

| FFDØØØ - FFD3FF                    | Floppy Disk<br>Emulation Controllor                           |

| FFD400 - FFD7FF                    | Emulation Controller                                          |

| FFD8ØØ - FFDBFF                    | Reserved                                                      |

| FFDCØØ - FFDDFF                    | ROM Toggle                                                    |

| FFDEØØ - FFDFFF                    | Reserved                                                      |

| FFEØØØ - FFFFFF                    | Reserved                                                      |

#### USES

The USES for the DIMENSION 68000 system memory are described by the above memory map. Some of the descriptions will be further amplified here.

The area from FFØØØØ to FFIFFF comprise the ROMBIOS area. This name is a combination of ROM and BIOS, where BIOS is short for Basic Input / Output System. The ROMBIOS provides the routines for I/O and for the DIMENSION 68000 system MONITOR. The MONITOR is a collection of routines that are used to "boot" the system and to communicate with the Keyboard and the CRT.

Each interrupt vector is a location in memory that contains the address of a software routine (or a ROMBIOS routine) that handles the interrupt that is associated with that specific location. The interrupt vectors are used by CP/M, by the EXPANSION SLOTS, and by the DUART which handles the Keyboard, the Printer Port, the RS-232 Interface, and by the Real Time Clock.

The highest address of the RAM varies depending on the amount of RAM that is installed. The following chart shows the relationship between the amount of memory installed and the highest address in RAM.

| ľ |

|---|

|   |

| 3 |

| • |

|   |

|   |

|   |

|   |

|   |

|   |

16 MB FEFFFF

SYSTEM REFERENCE MANUAL

CHAPTER 4

.

CP/M-68K, CPMBIOS, AND ROMBIOS

#### FLOW

The CP/M-68K operating system is basically composed of three parts; the Console Command Processor (CCP), the Basic Disk Operating System (BDOS), and the Basic Input / Output System (BIOS). The CCP handles the commands that are typed in from the console (or are entered from a submit file) such as DIR, or SUB.

The BDOS handles the functions such as file access, drive access, system/program control, and exceptions. The BDOS partially handles character Input/Output (I/O) functions.

The largest part of the character I/O handling and all of the basic I/O handling is performed by the CP/M BIOS. The CP/M BIOS accesses the I/O functions that are provided in the DIMENSION 68000 Read Only Memory BIOS (ROMBIOS). The ROMBIOS actually controls the I/O controllers and I/O devices.

The CP/M operating system is described more fully in the CP/M-68K Operating System User's Guide and it the CP/M Operating System Programmer's Guide. Both manuals are from Digital Research, Inc. Digital Research, Inc., is the company that developed CP/M and it is the company that licenses the use of CP/M.

# ADDITIONAL CALLS

There is a list of the CP/M-68K functions in the CP/M Operating System Programmer's Guide. The Micro Craft Corporation has added three additional functions to the CP/M-68K operating system for use on the DIMEN-SION 68000 computer. The additional functions are presented in the following pages.

```

FUNCTION 256: Change Diskette Drive Format

Entry Parameters:

Register D\emptyset \cdot W = 1\emptyset\emptysetH = 256 (decimal)

Register Dl.W = New Disk Drive Unit Number

where \emptyset = Drive A:

1 = Drive B:

2 = Drive C:

3 = Drive D:

4 = \text{Drive E:}

5 = Drive F:

6 = Drive G:

7 = Drive H:

Register D2.W = New Disk Drive Format

where \emptyset = null

1 = Std 40 track

2 = Std 80 track

3 = IBM single side (CPM 86) 8 sector

4 = IBM double side (CPM 86) 8 sector

5 = TRS 80

6 = KayPro

7 = Cromemco

8 = Osborne

9 = IBM 3740 8 Inch Single Side, Density

A = TRS 16 Double Side, Density

B = User Defined

Returned Values:

```

NONE

```

Page 41

```

```

FUNCTION 257: Read Diskette Drive Format

Entry Parameters:

Register D\emptyset.W = 1\emptysetIH = 257 (decimal)

Register D1.W = Disk Unit Number

where \emptyset = Drive A:

1 = Drive B:

2 = Drive C:

3 = Drive D:

4 = Drive E:

5 = Drive F:

6 = Drive G:

7 = Drive H:

Returned Values:

Register DØ.W = Selected Drive Type

where \emptyset = \text{null}

1 = Std 40 track

2 = Std 80 track

3 = IBM single side (CPM 86) 8 sector

4 = IBM double side (CPM 86) 8 sector

5 = TRS 80

6 = KayPro

7 = Cromemco

8 = Osborne

9 = IBM 3740 8 Inch Single Side, Density

A = TRS 16 Double Side, Density

B = User Defined

```

Page 42

```

FUNCTION 258: Set the Physical Parameter Table,

Set the CP/M Disk Parameter, or

Set the Disk Interlace Table

______

Entry Parameters:

Register D\emptyset.W = 1\emptyset2H = 258 (decimal)

Register D1.W = Command Select

where \emptyset = Ignore

1 = Set Physical Parameters

(DPRMTX 16 words)

2 = Set CP/M Disk Parameter Block Table

(DPBX 8 words)

3 = Set Interlace Table

(XLTX 64 words)

Register D2.L = Table Address

Returned Values:

```

1 .

NONE

## TERMINAL ATTRIBUTES

The DIMENSION 68000 CP/M BIOS has been augmented to provide a set of "ESCAPE SEQUENCES" that will handle various screen functions on the CRT display. Also, several "CONTROL" screen functions have been implemented. The following charts list the "ESCAPE SEQUENCES" and the "CONTROL" functions. These functions are accessed by outputting the code or codes through the CP/M "CONOUT" function.

CONTROL FUNCTIONS

------

ASCIT

HEY

| HEX   |              |             |

|-------|--------------|-------------|

| VALUE | FUNCTION     |             |

|       |              |             |

| в1    | Clear Screen |             |

| Ø7    | Bell         |             |

| в7    | Home         |             |

| 91    | Cursor Up    |             |

| 92    | Cursor Left  |             |

| 93    | Cursor Right |             |

| 94    | Cursor Down  | (Line Feed) |

|       |              |             |

v

ESCAPE SEQUENCES (Escape plus the hex value listed)

| пбл   | ASCII |                            |

|-------|-------|----------------------------|

| VALUE | CODE  | FUNCTION                   |

|       |       |                            |

| 48    | Н     | Home Cursor                |

| 3D    | =     | Position Cursor            |

| 76    | v     | Clear Screen & Home Cursor |

| 41    | Α     | Cursor Up                  |

| 42    | В     | Cursor Down                |

| 43    | С     | Cursor Right               |

| 44    | D     | Cursor Left                |

| 4B    | К     | Erase End of Line          |

| 4A    | J     | Erase End of Page          |

| 78    | х     | Clear End of Line          |

| 79    | У     | Clear End of Page          |

| 63    | С     | Turn On Cursor Flag        |

| 64    | d     | Turn Off Cursor Flag       |

| 65    | е     | Turn On Inverse Flag       |

| 66    | f     | Turn Off Inverse Flag      |

|       |       |                            |

#### ROMBIOS

The CP/M functions operate by performing calls to the appropriate routines in the ROMBIOS. ROMBIOS is an acronym for the ROM Based Input / Output System. The usage of the ROMBIOS is fully described in the ROM-BIOS Appendix to this manual. A chart showing the ROMBIOS functions is included to illustrate the contents of the ROMBIOS.

ROMBIOS FUNCTIONS

\_\_\_\_\_\_

= Initialize CRT Controller 1 = Output a character to the screen 2 3 = Clear the TEXT screen 4 = Read a key stroke 5 = Get keyboard status 6 = Boot from disk 7 = Start the built-in monitor 8 = Read selected disk drive status 9 = Select disk drive and turn motor ON 10 = Deselect disk drive and turn motor OFF 11 = Seek to selected disk track 12 = Seek to track Ø and recalibrate disk - rezero 13 = Seek to track and read a sector 14 = Seek to track and write a sector 15 = Seek to track and format a track 16 = Format the entire disk 17 = Read the sector ID information 18 = Read the disk status 19 = Reserved $2\emptyset$  = Reserved 21 = Read Printer Status 22 = Output a character to Printer Interface 23 = Position CRT cursor 24 = Read character at present CRT cursor location 25 = Clear Graphics Screen 26 = Set graphics color 27 = Plot X, Y point28 = Reserved29 = Read color at designated point 30 = Output Character to CRT with No Control Characters INPUT / OUTPUT

To fully appreciate the functions supplied in the ROMBIOS, requires a knowledge of the actual input and output circuitry used inside the DIM-ENSION 68000 computer. A detailed discussion of the programming requirements for the input and the output circuitry is included in the DIRECT I/O Appendix to this manual. CHAPTER 5

СР/М-68К

### BDOS AND BIOS

The CP/M operating system is composed of two parts; the Basic Disk Operating System (BDOS) and the Basic Input / Output System (BIOS). The BDOS is that part of the operating system that is independent of the Input/Output.

The BIOS is that part of the operating system that is concerned with Input/Output. The BIOS for the DIMENSION 68000 system uses the ROMBIOS as much as is possible. The CP/M BIOS includes a table that handles diskettes and also handles the RS-232 port. The label that has been assigned to that table is "drivetb". Following is a description of the "drivetb" table.

TABLE OFFSETS

| OFFSET | LENGTH  | DESCRIPTION                              |

|--------|---------|------------------------------------------|

|        |         | ~~~~~~                                   |

| +Ø     | l byte  | Number of Disk types                     |

| +1     | l byte  | DUART reset RS-232 command               |

| +2     | l byte  | DUART select RS-232 command              |

| +3     | l byte  | DUART set 9600 bits per second           |

| +4     | l byte  | DUART set no parity/8 bits               |

| +5     | l byte  | DUART set normal/l stop bit              |

| +6     | l byte  | RS-232 XON/XOFF flag                     |

| +7     | l byte  | Old Track Number                         |

| +8     | 1 byte  | Old Physical Sector Number               |

| +9     | l byte  | New Track Number                         |

| +10    | l byte  | New Sector Number                        |

| +11    | 4 bytes | New DMA Address                          |

| +15    | l byte  | Old Disk Unit                            |

| +16    |         | Retry Count                              |

| +17    | 4 bytes | Save Location for the Dl register        |

| +2Ø    | l byte  | Save Location                            |

| +21    | l byte  | Save Location                            |

| +22    | 2 bytes | Drive                                    |

| +24    |         | Warm Boot Flag                           |

| +26    |         | Number of Memory Regions = 1             |

| +28    | 4 bytes | Starting Address of the Memory Region(s) |

| +32    | 4 bytes | Ending Address of the Memory Region(s)   |

Page 52

## ADDITIONAL CALLS

The DIMENSION 68000 version of CP/M has three functions added to the normal CP/M calls. The functions are:

```

256 - Change Diskette Drive Format

Entry Parameters:

Register D\emptyset.W = 1\emptyset\emptysetH = 256 (decimal)

Register Dl.W = New Disk Drive Unit Number

where \emptyset = Drive A:

1 = Drive B:

2 = Drive C:

3 = Drive D:

4 = Drive E:

5 = Drive F:

6 = Drive G:

7 = Drive H:

Register D2.W = New Disk Drive Format

where \emptyset = null

1 = Std 40 track

2 = Std 80 track

3 = IBM single side

4 = IBM double side

5 = TRS 80

6 = KavPro

7 = Cromemco

8 = Osborne

9 = IBM 3740 8 Inch Single Side, Density

A = TRS 16 Double Side, Density

B = User Defined

Returned Values:

Register DØ.W

257 - Read Diskette Drive Format

Entry Parameters:

Register D\emptyset.W = 1\emptyset1H = 257 (decimal)

Register Dl.W = Disk Unit Number

where \emptyset = Drive A:

1 = Drive B:

2 = Drive C:

3 = Drive D:

4 = Drive E:

5 = Drive F:

6 = Drive G:

7 = \text{Drive H}:

```

Retruned Values: Register DØ.W

```

258 - Set the Physical Parameter Table,

Set the CP/M Disk Parameter, or

Set the Disk Interlace Table

_____

Entry Parameters:

Register D\emptyset.W = 1\emptyset2H = 258 (decimal)

Register Dl.W = Command Select

where \emptyset = Ignore

1 = Set Physical Parameters

(DPRMTX 16 words)

2 = Set CP/M Disk Parameter Block Table

(DPBX 8 words)

3 = Set Interlace Table

(XLTX 64 words)

Register D2.L = Table Address

Returned Values:

Register DØ.W

```

TERMINAL ATTRIBUTES

The DIMENSION 68000 CP/M BIOS has been augmented to provide a set of "ESCAPE SEQUENCES" that will handle various screen functions on the CRT display. Also, several "CONTROL KEY" screen functions have been implemented. The following charts list the "ESCAPE SEQUENCES" and the "CON-TROL KEY' functions.

CONTROL KEYS \_\_\_\_\_ HEX KEYS TO VALUE PRESS FUNCTION \_\_\_\_\_ \_\_\_\_ \_\_\_\_\_ Bl Alt l Clear Screen Bell F8 Alt 7 Ø7 в7 Home Alt End 1 Cursor Up Alt Dwn 2 Cursor Left Alt Pgd 3 Cursor Right Alt Lft 4 Cursor Down 91 92 93 94 (Line Feed) -----

To generate the escape code (27Hex) Press CTRL plus the '" key

ESCAPE SEQUENCES (Escape plus the key value listed)

| HEX<br>VALUE | KEYS TO<br>PRESS | FUNCTION                   |

|--------------|------------------|----------------------------|

| 48           | Н                | Home Cursor                |