7300 Processing Unit Design Description Manual Volume 3: Dedicated Resources 2501.003

Computer System

Products

February 1973 Edition

Memorex Corporation Santa Clara, California 95052

Requests for copies of Memorex publications should be made to your Memorex representative or to the Memorex branch office serving your locality.

This publication is provided for informational purposes. Contact Memorex for the latest periodic enhancement.

A readers' comments form is provided at the back of this publication. If the form has been removed, comments may be addressed to the Memorex Corporation, Publications Dept., Santa Clara, California 95052.

© 1973, MEMOREX CORPORATION

# 7300 Processing Unit Design Description Volume 3, Dedicated Resources

This volume provides Memorex Field Engineers with logic design descriptions for the 7300 Processing Unit's dedicated resources: Basic Data Channels 1 and 2 and integrated card device adapters, Integrated File Adapter (IFA) and Integrated Communications Adapter (ICA).

The three sections that comprise this volume are a part of the continuum of sections that make up the four volume, 7300 Processing Unit Design Description Manual. The four volumes are organized as follows:

#### Volume 1, Overview (2501.001)

Section 1. A general description of the 7300 Processing Unit.

#### Volume 2, Shared Resources (2501.002)

- Section 2. A detailed description of main storage, control, timing and arithmetic parts of the 7300 Processing Unit.

- Section 3. A detailed description of the formats, characteristics and implementation of the micro instructions associated with the 7300 Processing Unit.

## Volume 3, Dedicated Resources (2501.003)

- Section 4. A detailed description of the two basic data (selector) channels for the 7300 Processing Unit.

- Section 5. A detailed description of the Integrated Communications Adapter (ICA) for the 7300 Processing Unit.

- Section 6. A detailed description of the Integrated File Adapter (IFA) for the 7300 Processing Unit.

## Volume 4, Power System (2501.004)

Section 7. A detailed description of the 7300 Processing Unit power system.

#### NOTE

Because Volume 1 provides an overview of the 7300 Processing Unit, it should always be used as an introduction to the other volumes in the set.

# TABLE OF CONTENTS

| Section |                                            | Page |

|---------|--------------------------------------------|------|

| 4       | BASIC DATA CHANNELS (BDC)                  | 4-1  |

|         | Introduction                               | 4-1  |

|         | Basic Data Channels                        | 4-1  |

|         | General Description                        | 4-1  |

|         | Channel Configuration                      | 4-1  |

|         | Channel Requirements                       | 4-2  |

|         | Selection Loop Continuity                  | 4-2  |

|         | Addressing                                 | 4-6  |

|         | Command Byte                               | 4-6  |

|         | Status Information                         | 4-7  |

|         | Sense Information                          | 4-9  |

|         | Signal Interlock Summary                   | 4-9  |

|         | Basic Data Channel Control Instructions    | 4-10 |

|         | Logic Description                          | 4-11 |

|         | Block Diagram                              | 4-11 |

|         | Register Functions                         | 4-11 |

|         | Bus Out Register (BOR)                     | 4-11 |

|         | Bus In Register (BIR)                      | 4-11 |

|         | Tag Out Register (TOR)                     | 4-15 |

|         | Channel Control Register (CCR)             | 4-16 |

|         | Byte Count Register (BCR)                  | 4-18 |

|         | Channel Signals                            | 4-19 |

|         | Operational Sequences                      | 4-24 |

|         | Initial Selection                          | 4-27 |

|         | Adapter or Control Unit-Initiated Sequence | 4-28 |

|         | Short Busy Sequence                        | 4-30 |

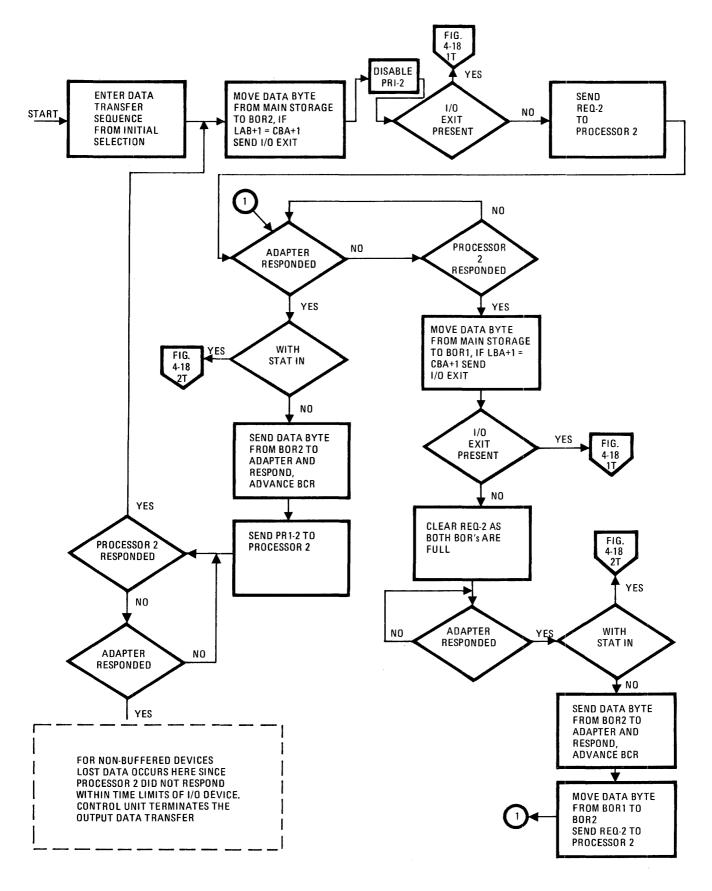

|         | Data Transfer Sequence                     | 4-31 |

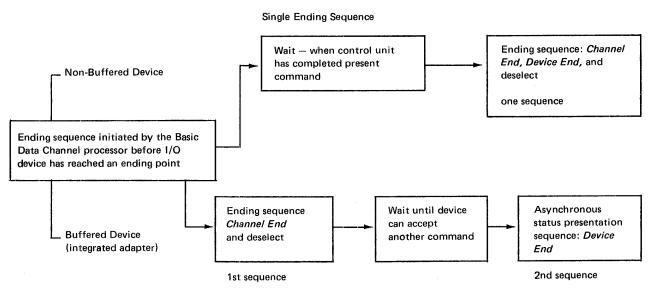

|         | Ending Sequences                           | 4-31 |

|         | Processor-Initiated                        | 4-32 |

|         | Double Ending Sequence                     | 4-32 |

|         | Single Ending Sequence                     | 4-32 |

|         | Adapter or Control Unit-Initiated          | 4-33 |

|         | Sequence Controls                          | 4-33 |

|         | Suppress Status                            | 4-33 |

|         | Command Chaining                           | 4-33 |

|         | Interface Disconnect                       | 4-33 |

|         | Selective Reset                            | 4-33 |

|         | System Reset                               | 4-34 |

|         | Stack Status                               | 4-34 |

|         | Stop                                       | 4-34 |

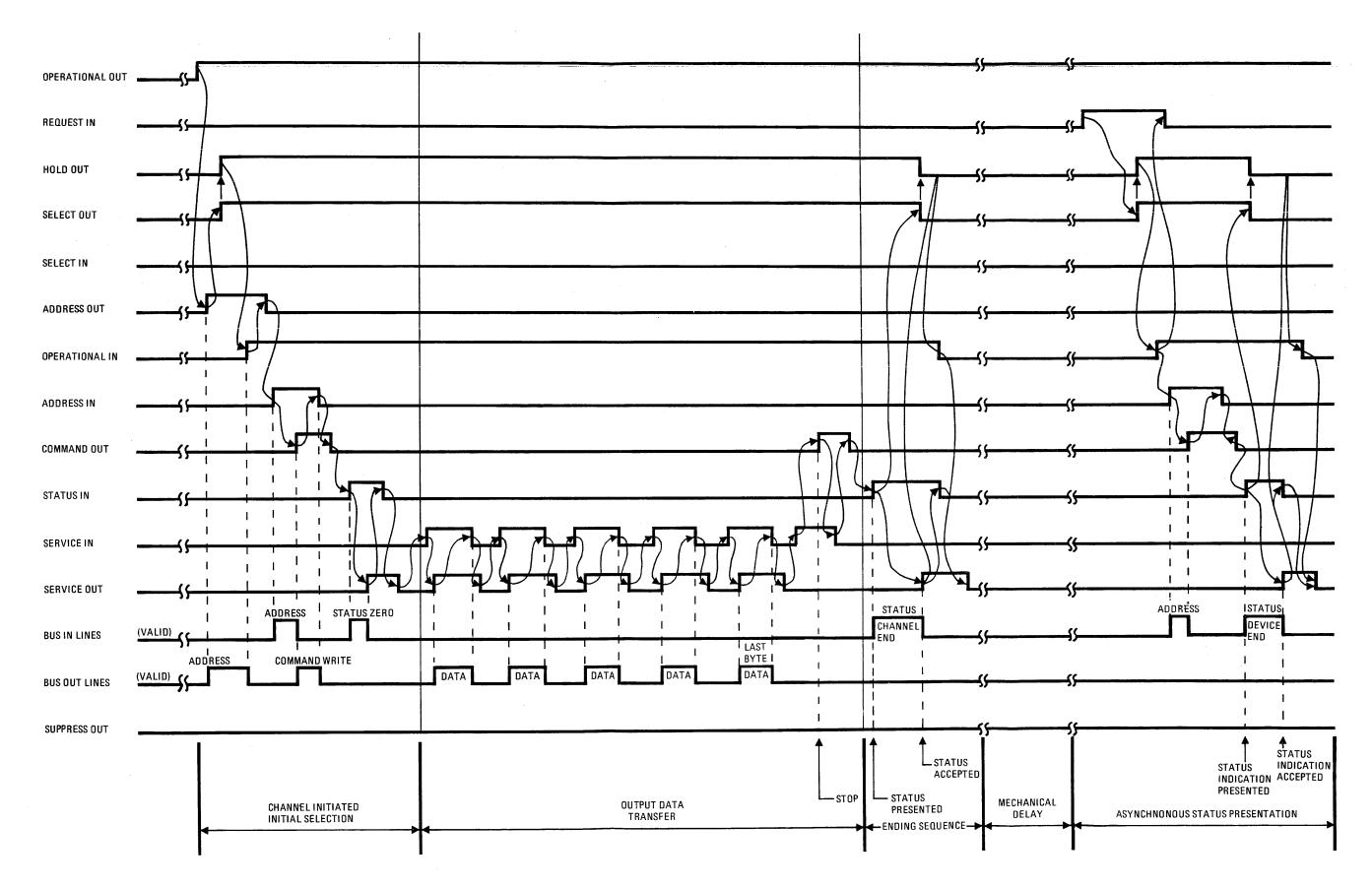

|         | Data Transfer Operations                   | 4-34 |

|         | Software Operation                         | 4-34 |

|         | Hardware Operation                         | 4-34 |

V.

# Section

| Hardware Input Operation                 | 4-35 |

|------------------------------------------|------|

| Processor Not Busy When Adapter Responds | 4-35 |

| Processor Busy When Adapter Responds     | 4-40 |

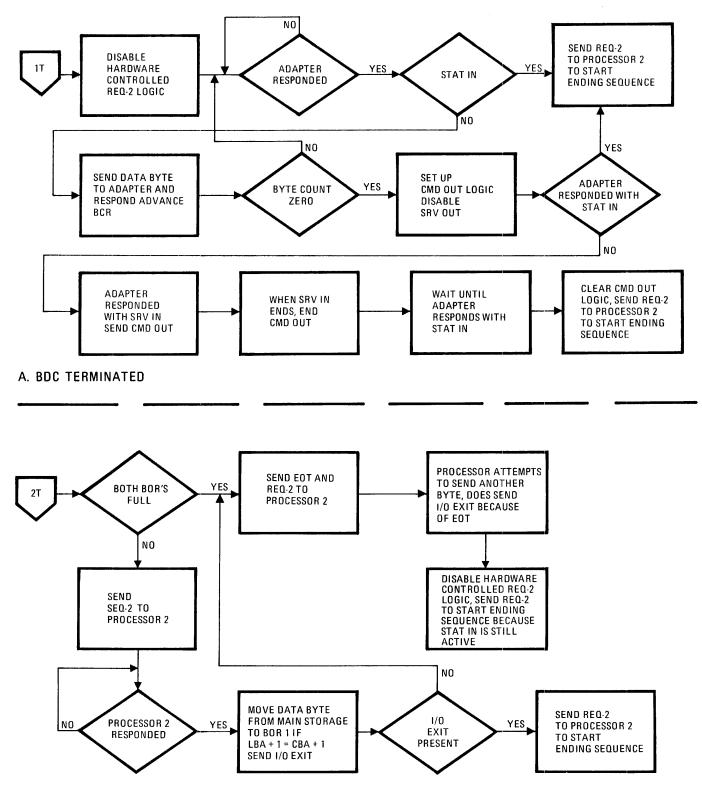

| BDC Terminated Transfer                  | 4-40 |

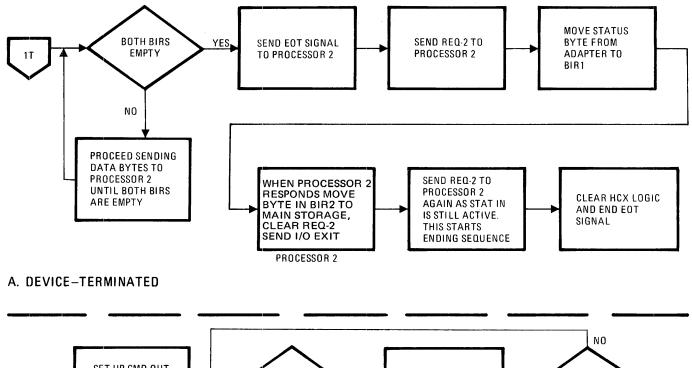

| Device-Terminated Transfer               | 4-40 |

| Assembly/Disassembly Option              | 4-43 |

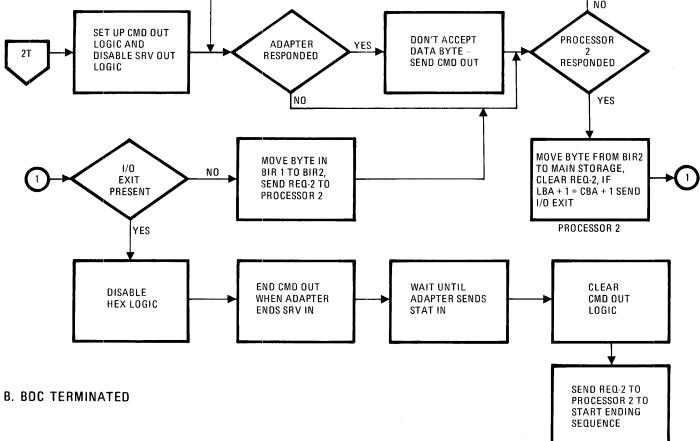

| Hardware Output Operations               | 4-46 |

| Processor-Terminated Transfer            | 4-51 |

| Device Terminated Transfer               | 4-51 |

| Data Chaining                            | 4-51 |

| High-Speed Transfer                      | 4-51 |

| Integrated Card Reader Adapter (ICRA)    | 4-53 |

| General Description                      | 4-53 |

| Reader Commands                          | 4-56 |

| Status Information                       | 4-56 |

| Sense Information                        | 4-57 |

| Data Formats                             | 4-57 |

| Logic Description                        | 4-58 |

| Bus Out                                  | 4-58 |

| Bus In                                   | 4-58 |

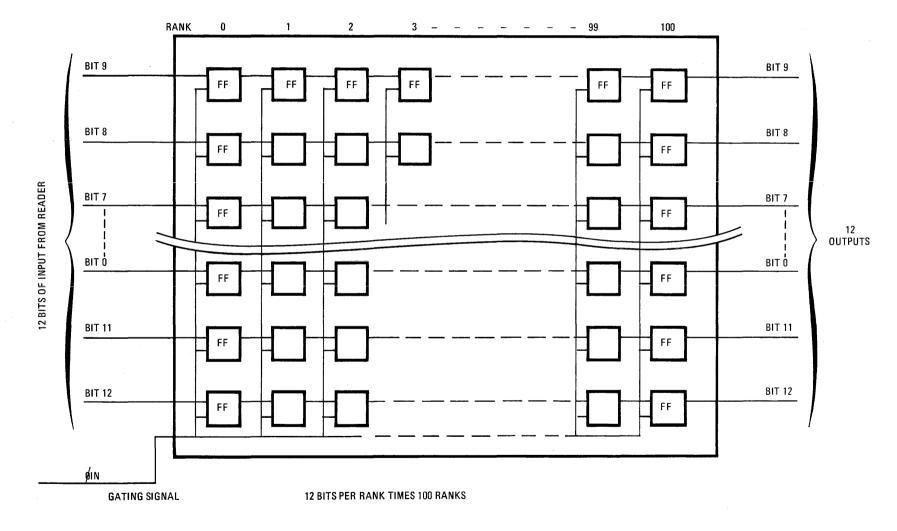

| Buffer Register                          | 4-60 |

| Sense Logic                              | 4-60 |

| Status Logic                             | 4-64 |

| Reader Interface Logic                   | 4-64 |

| Tag Line Control                         | 4-64 |

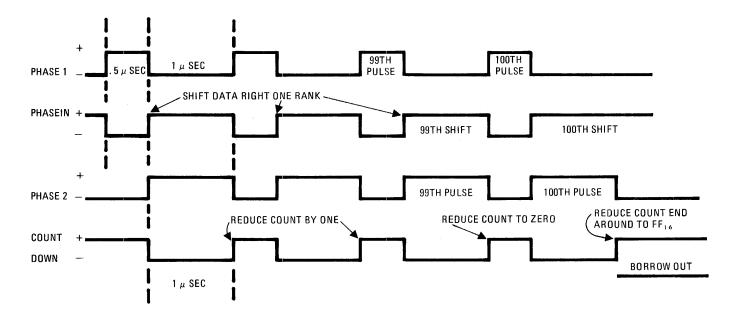

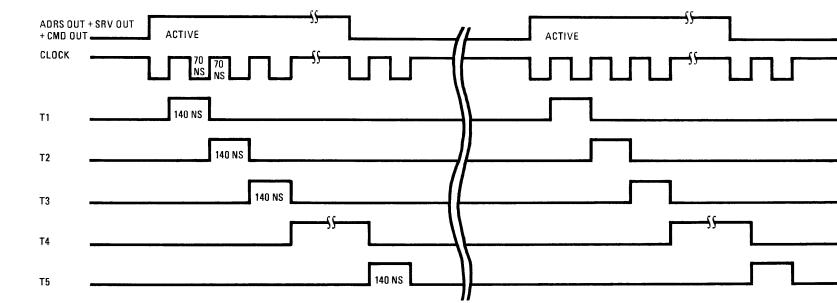

| Tag Line Timing Chain                    | 4-65 |

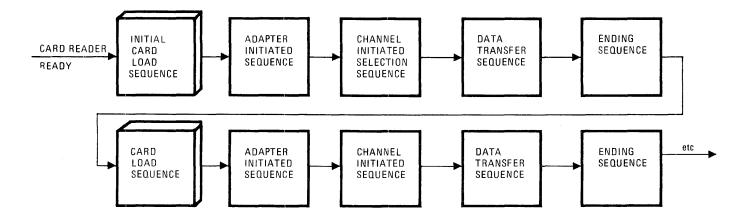

| Operating Sequences                      | 4-67 |

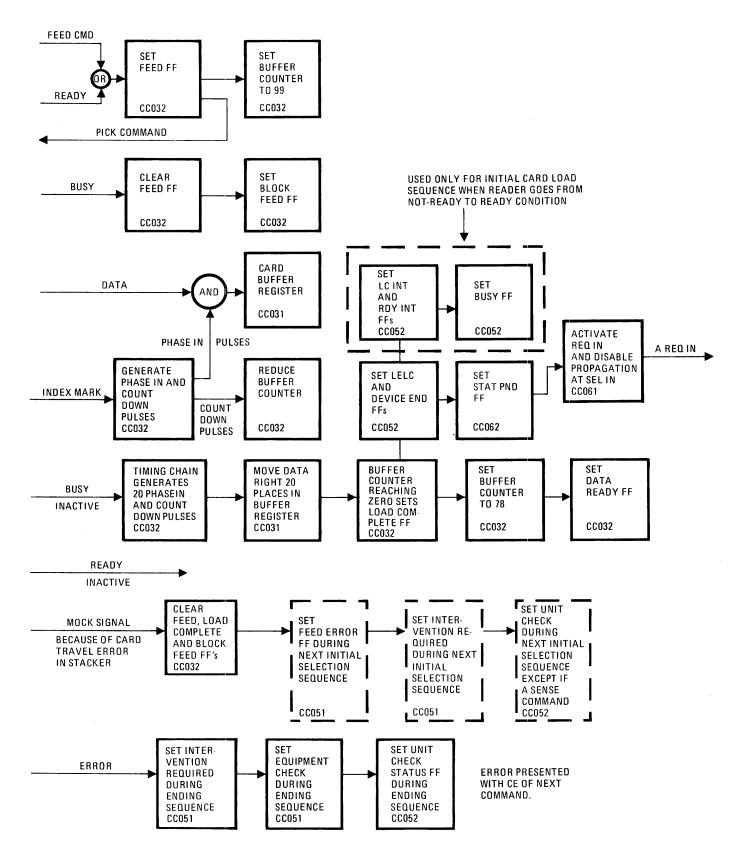

| Card Load Sequence                       | 4-67 |

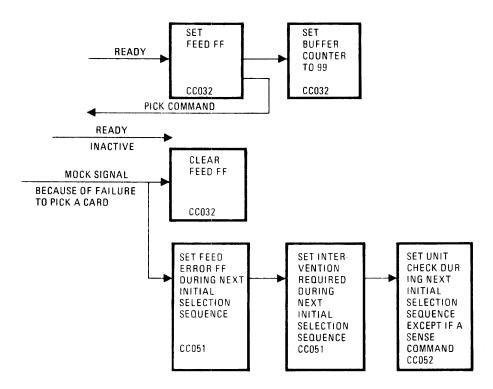

| Initial Card Load                        | 4-67 |

| Reader Error Signals                     | 4-69 |

| Single Card Read                         | 4-69 |

| Adapter-Initiated Sequence               | 4-69 |

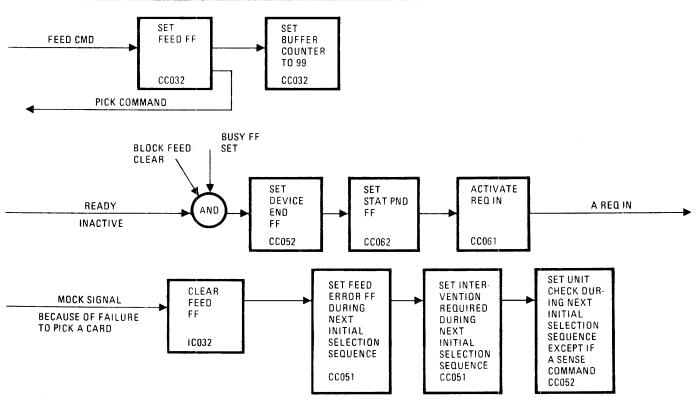

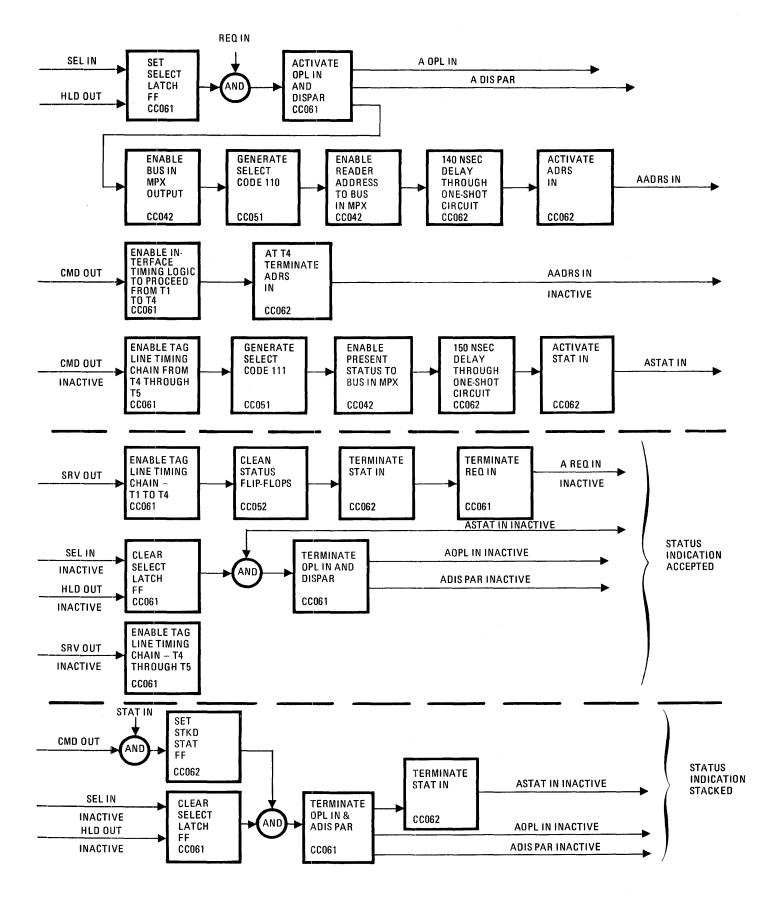

| Initial Selection                        | 4-69 |

| Address                                  | 4-72 |

| Command                                  | 4-72 |

| Status                                   | 4-72 |

| Data Transfer Sequence                   | 4-72 |

| Ending Sequence                          | 4-76 |

| Processor-Terminated Input               | 4-76 |

| Status Indication Accepted               | 4-76 |

| Status Indication Stacked                | 4-79 |

| Adapter-Terminated Transfer              | 4-79 |

| Next Card Preparation                    | 4-79 |

| Card-Image Read                          | 4-79 |

| -                                        |      |

,

Section

| Page |  |

|------|--|

|      |  |

| Initial Selection                      | 4-79  |

|----------------------------------------|-------|

| Data Transfer                          | 4-82  |

| Ending Sequence                        | 4-82  |

| Non-Motion Commands                    | 4-82  |

| No-Operation Command                   | 4-86  |

| Test I/O Command                       | 4-86  |

| Sense Command                          | 4-86  |

| Control Storage Logic                  | 4-86  |

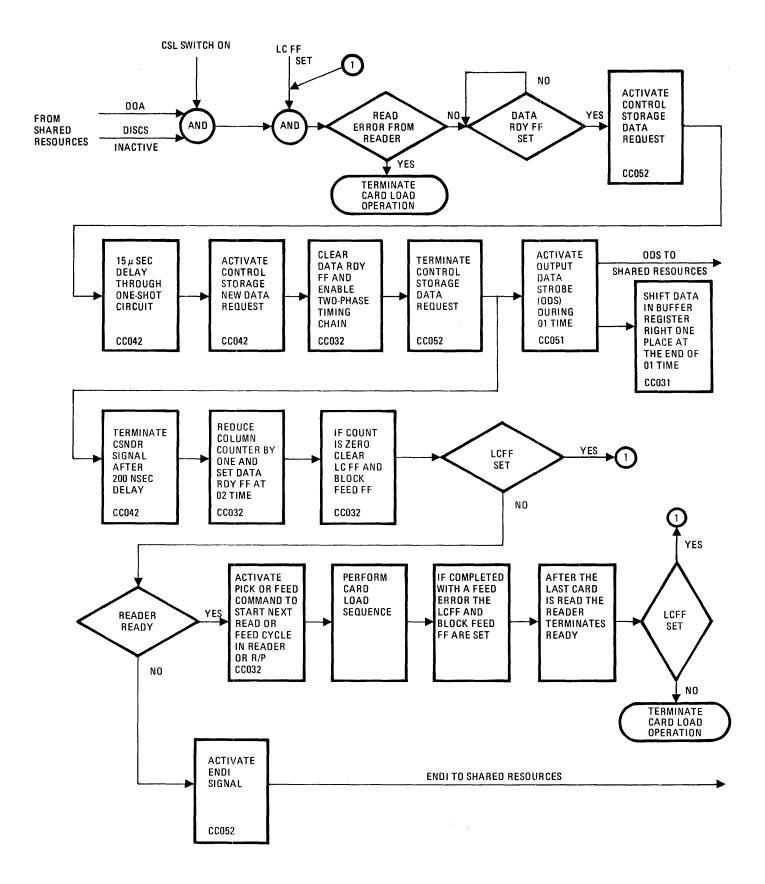

| Initial Card Load                      | 4-87  |

| CSL Operation                          | 4-87  |

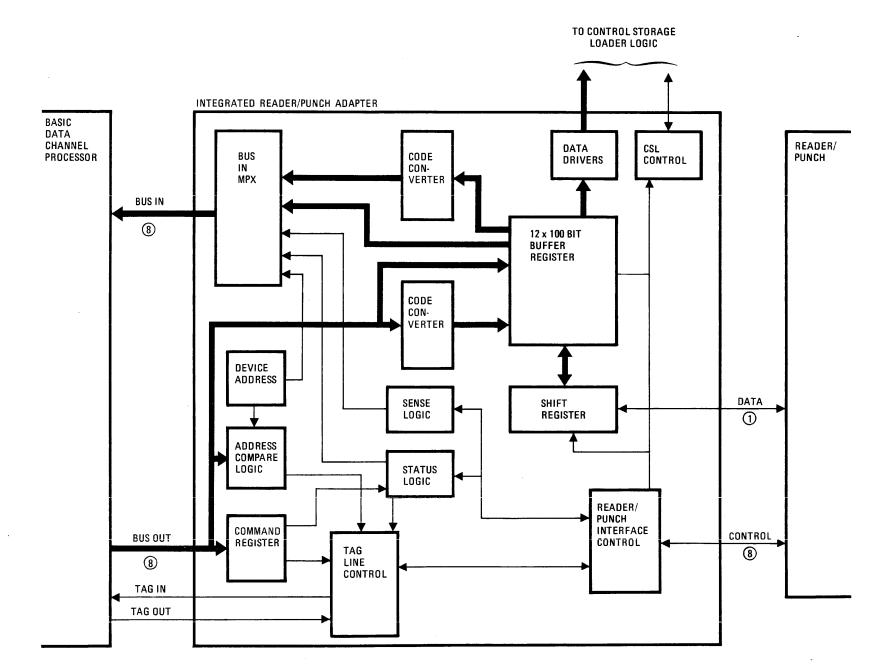

| Integrated Reader/Punch Adapter (IRPA) | 4-89  |

| General Description                    | 4-89  |

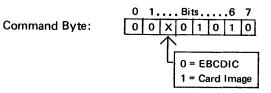

| Commands                               | 4-89  |

| Status Information                     | 4-92  |

| Sense Information                      | 4-92  |

| Data Formats                           | 4-92  |

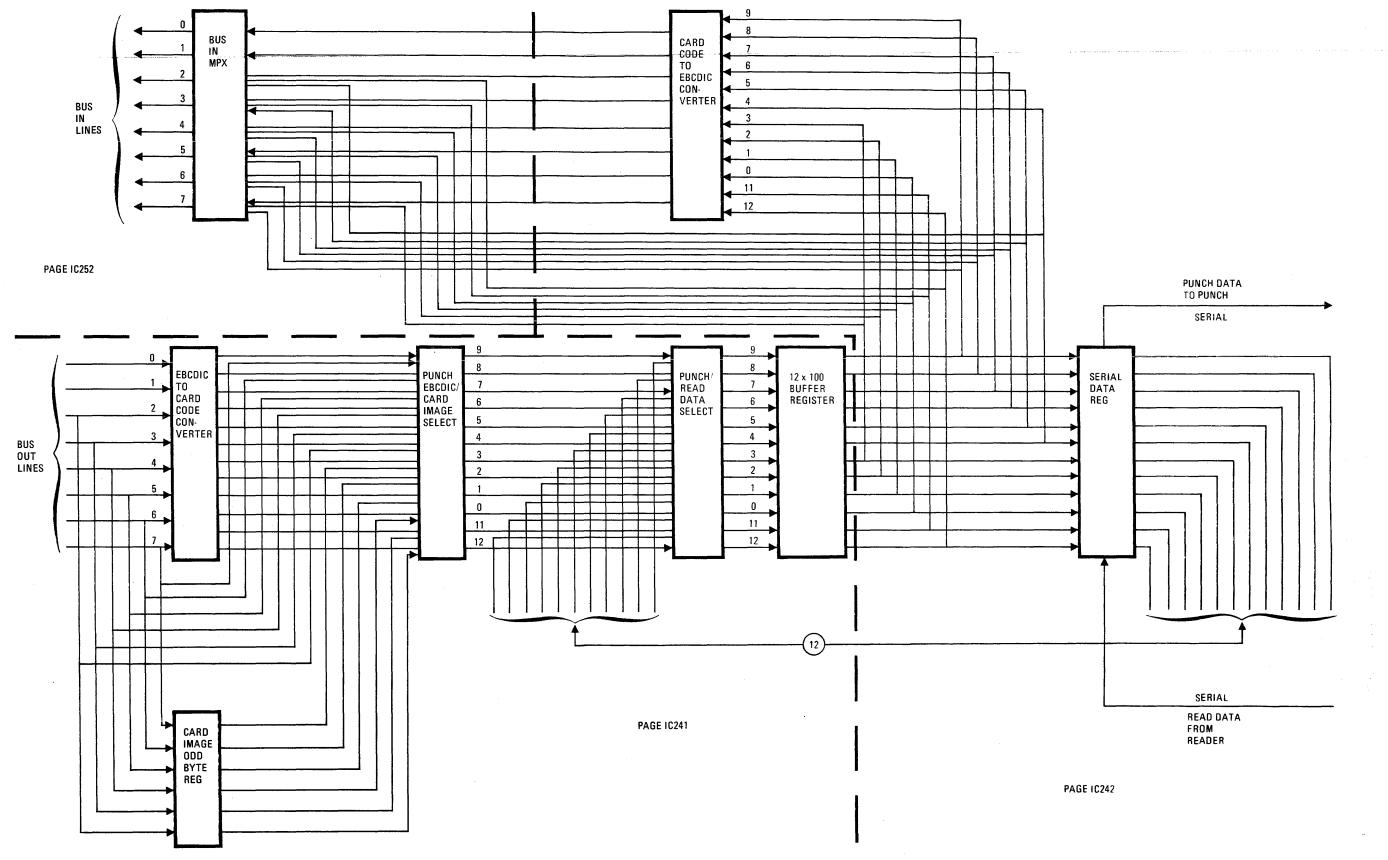

| Logic Description                      | 4-92  |

| Reader/Punch Data                      | 4-92  |

| Buffer Register                        | 4-92  |

| Sense Logic                            | 4-94  |

| Status Logic                           | 4-94  |

| Reader/Punch Interface Logic           | 4-94  |

| Serial Data Transfer                   | 4-94  |

| Two-Phase Timing Chain                 | 4-95  |

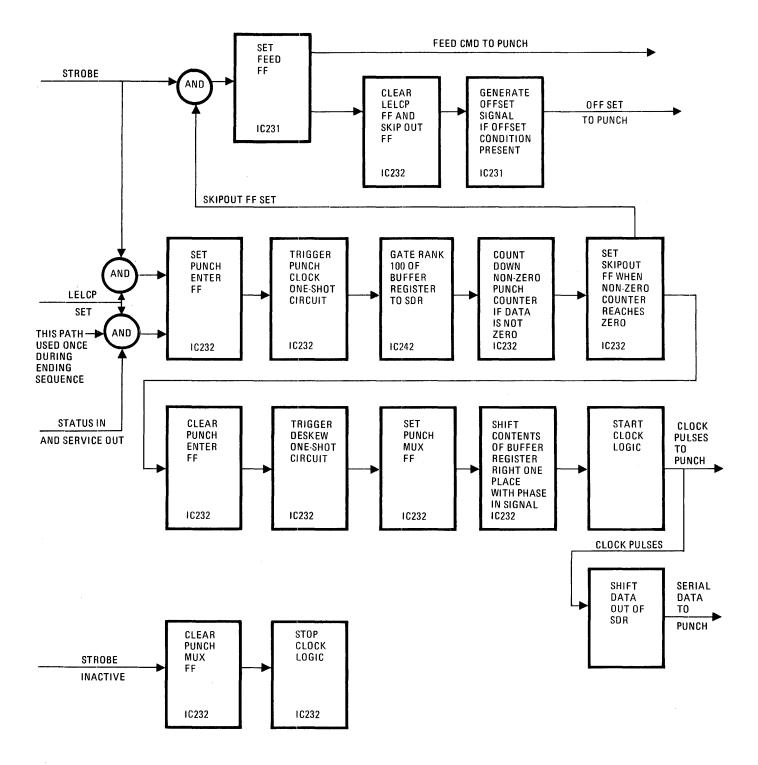

| Punch Control Logic                    | 4-96  |

| Tag Line Control                       | 4-96  |

| Tag Line Timing Chain                  | 4-96  |

| Operating Sequences                    | 4-96  |

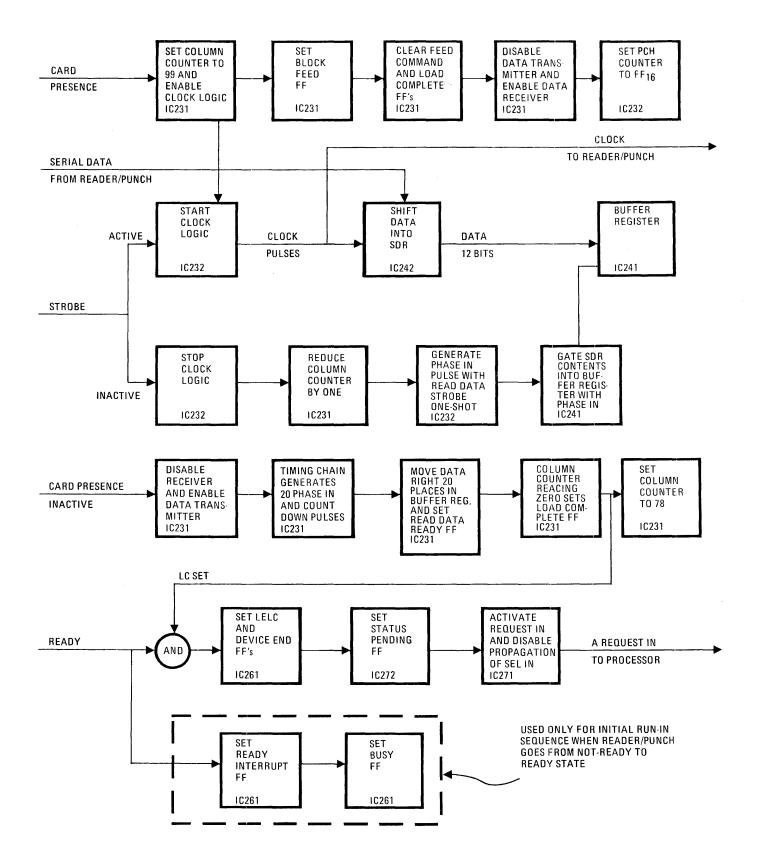

| Initial Run-In                         | 4-96  |

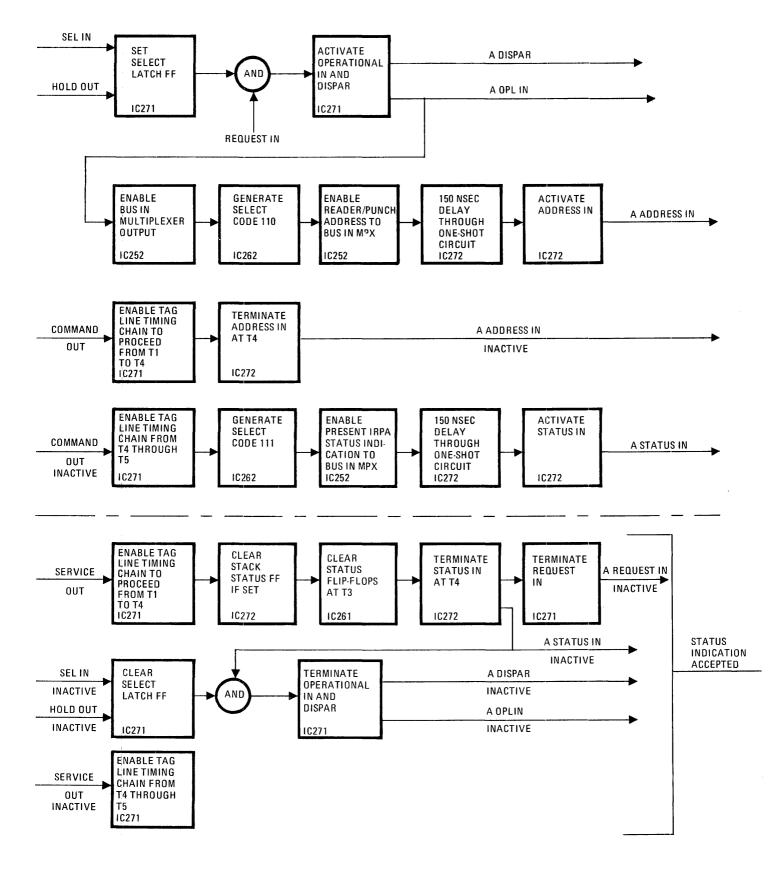

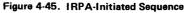

| Adapter Initiated Sequence             | 4-99  |

| Initial Selection                      | 4-99  |

| Data Transfer Sequence                 | 4-99  |

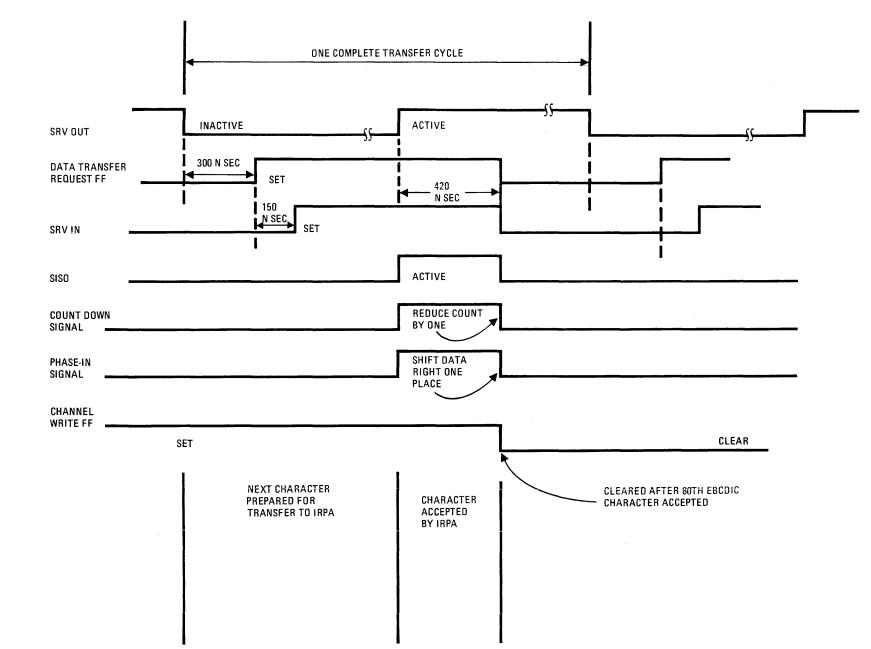

| EBCDIC Data Transfer to Channel        | 4-101 |

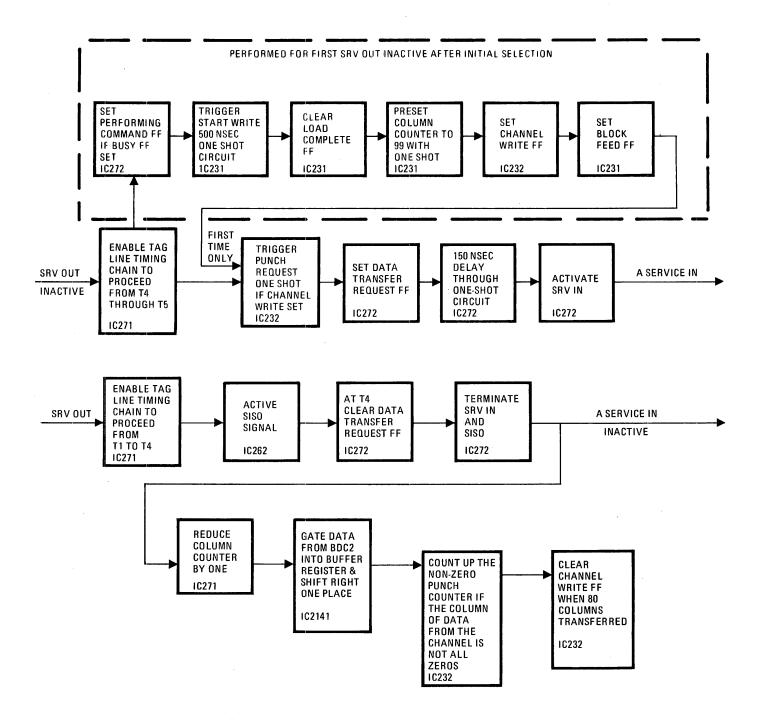

| EBCDIC Data Transfer From Channel      | 4-102 |

| Card-Image Data Transfer to Channel    | 4-105 |

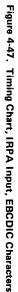

| Card-Image Data Transfer From Channel  | 4-105 |

| Ending Sequence                        | 4-106 |

| Terminated Input                       | 4-106 |

| Status Accepted                        | 4-106 |

| Status Stacked                         | 4-106 |

| Processor-Terminated Output            | 4-106 |

| Adapter Terminated                     | 4-109 |

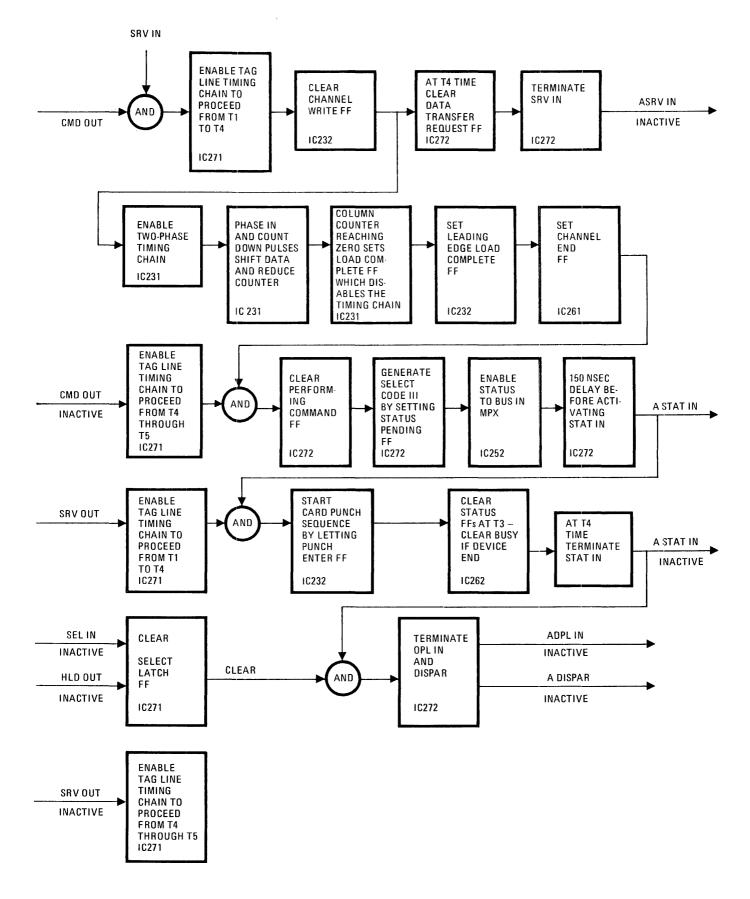

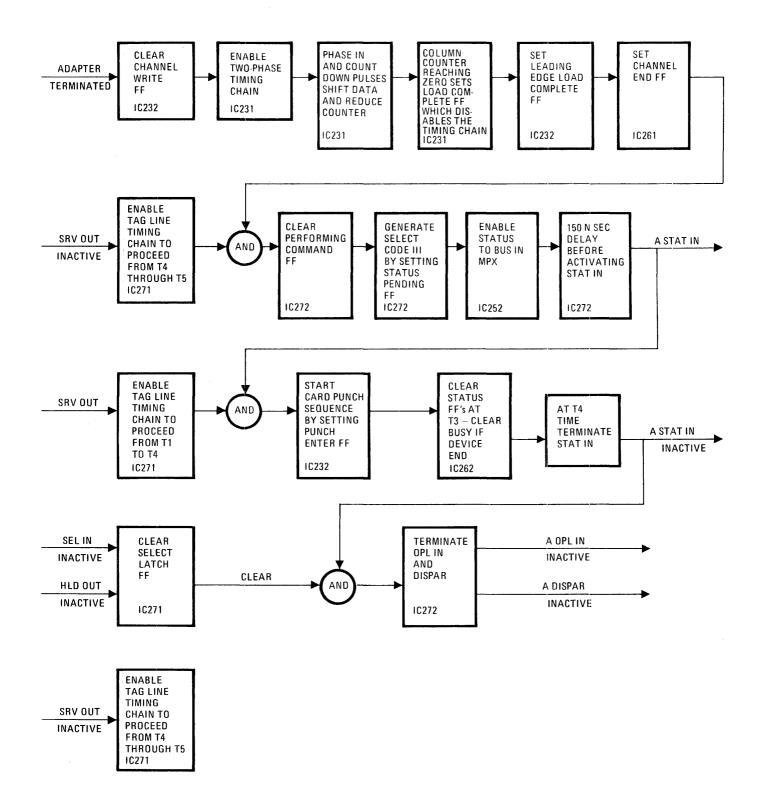

| Card Punch Sequence                    | 4-109 |

| Non-Motion Commands                    | 4-112 |

|                                        |       |

| <u>Section</u> |                                         | Page  |

|----------------|-----------------------------------------|-------|

|                | Error Handling                          | 4-112 |

|                | Control Storage Load                    | 4-112 |

| 5              | INTEGRATED COMMUNICATIONS ADAPTER (ICA) | 5-1   |

| 6              | INTEGRATED FILE ADAPTER (IFA)           | 6-1   |

|                | Introduction                            | 6-1   |

|                | Capabilities                            | 6-1   |

|                | Characteristics                         | 6-1   |

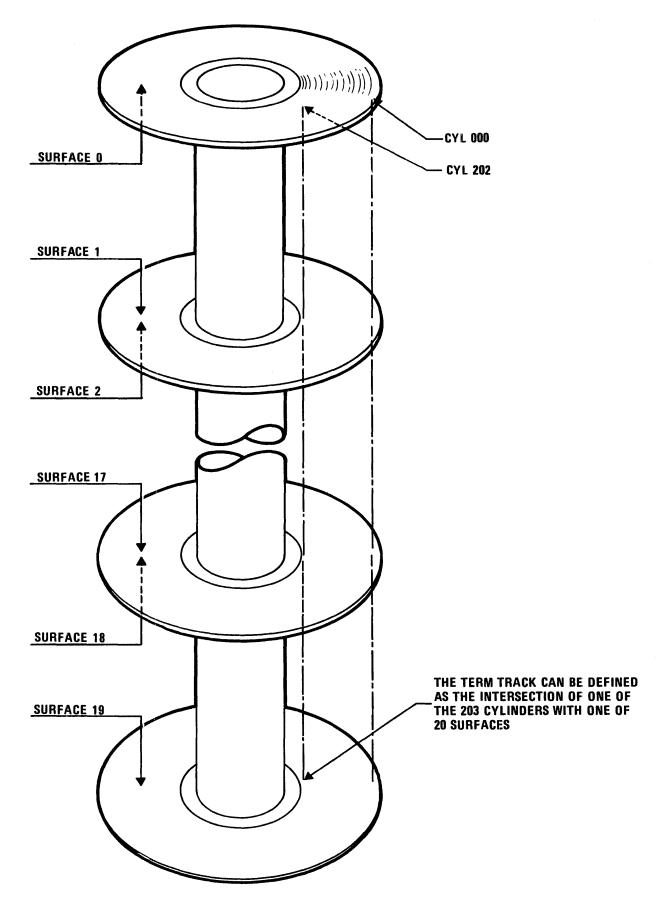

|                | Disc Organization                       | 6-1   |

|                | Basic Drive Operations                  | 6-3   |

|                | First Seek                              | 6-3   |

|                | Seek Other than First Seek              | 6-3   |

|                | Head Selection                          | 6-3   |

|                | Write                                   | 6-3   |

|                | Read                                    | 6-3   |

|                | Reset/Load                              | 6-3   |

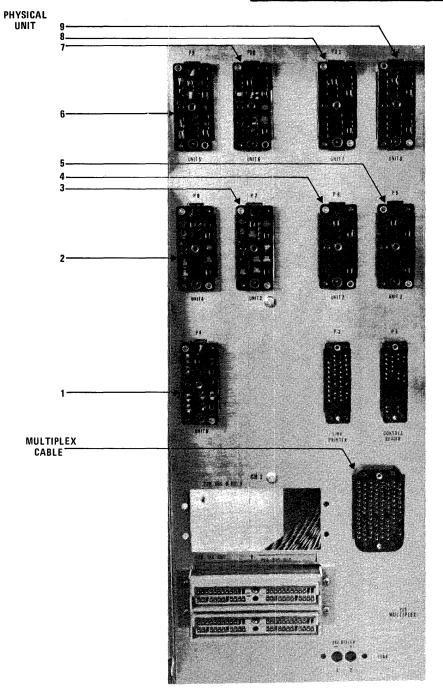

|                | Physical Description                    | 6-3   |

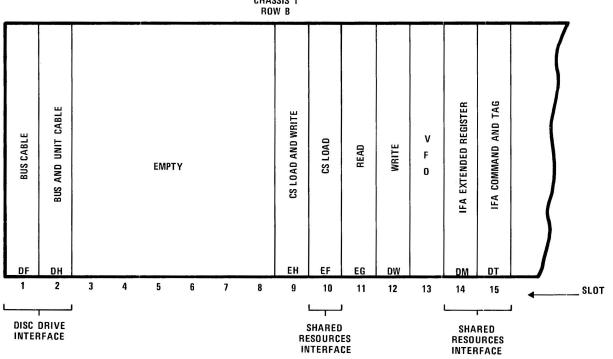

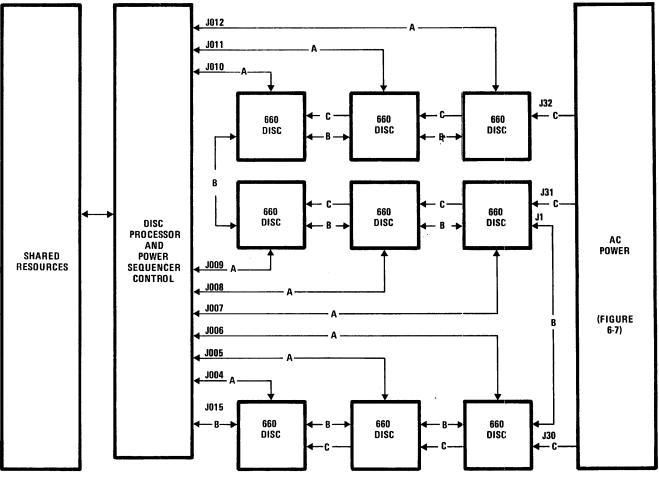

|                | Hardware Placement                      | 6-3   |

|                | Drive Logic Cabling                     | 6-6   |

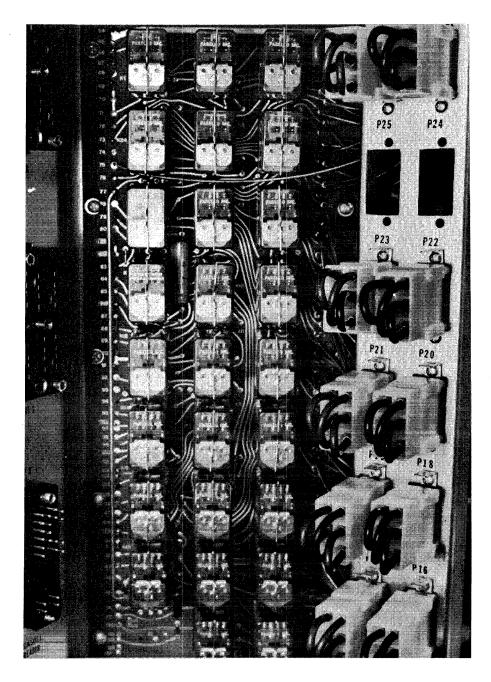

|                | I/O Connector Panel                     | 6-7   |

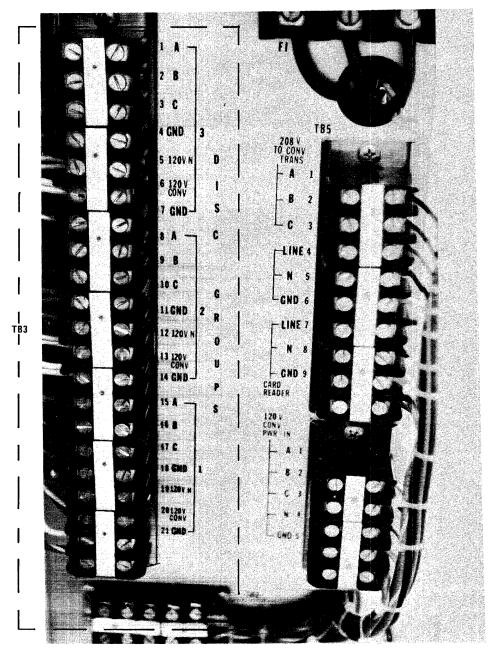

|                | Power Cabling                           | 6-8   |

|                | Power Interface                         | 6-8   |

|                | Cable Lengths                           | 6-9   |

|                | Electrical Specifications               | 6-9   |

|                | Operational Description                 | 6-10  |

|                | Command Structure                       | 6-10  |

|                | Machine Language Instructions           | 6-10  |

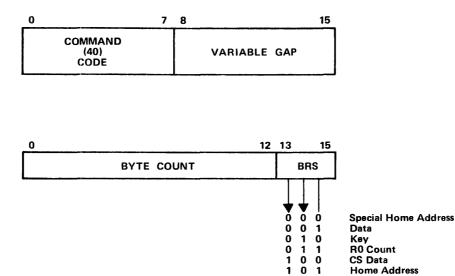

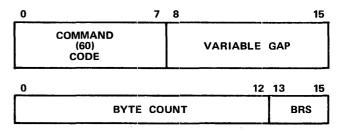

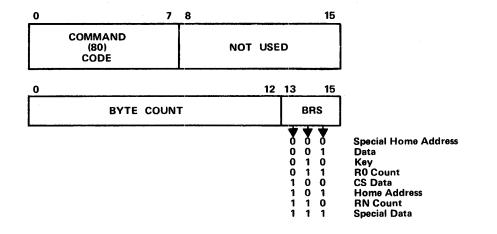

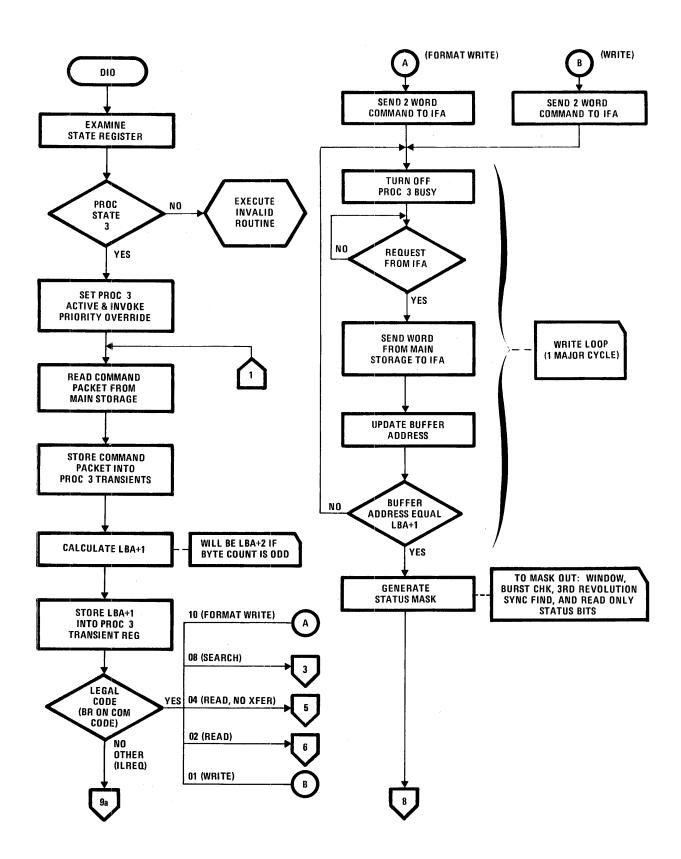

|                | Disc Input/Output (DIO)                 | 6-10  |

|                | Output to I/O Register (OUT)            | 6-12  |

|                | Input from I/O Register (INP)           | 6-12  |

|                | IFA Commands                            | 6-12  |

|                | IFA Commands Specified by OUT MLI       | 6-12  |

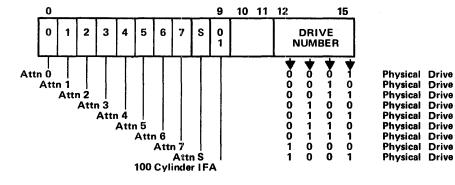

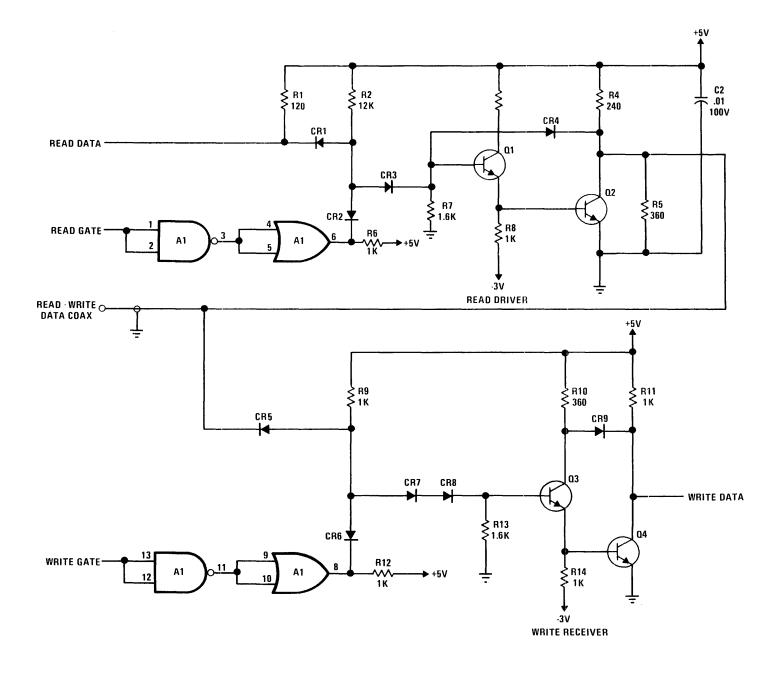

|                | Select Drive Command                    | 6-13  |

|                | Diagnostic Commands                     | 6-13  |

|                | Control Commands                        | 6-13  |

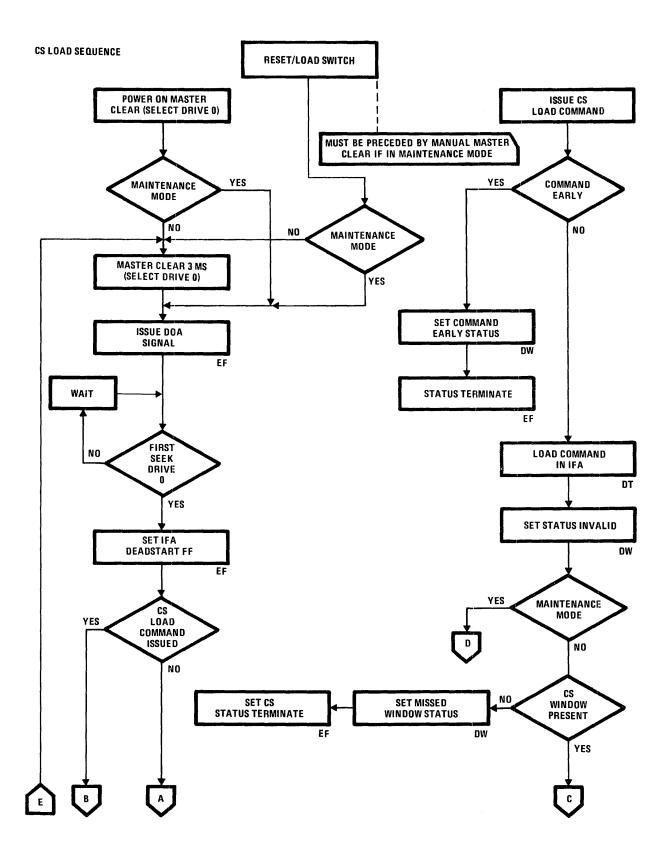

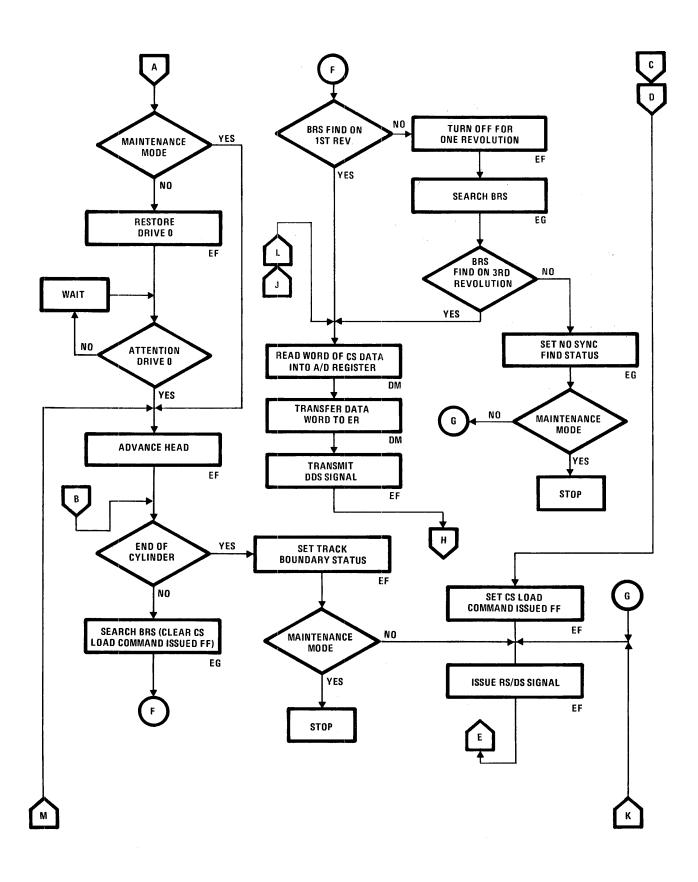

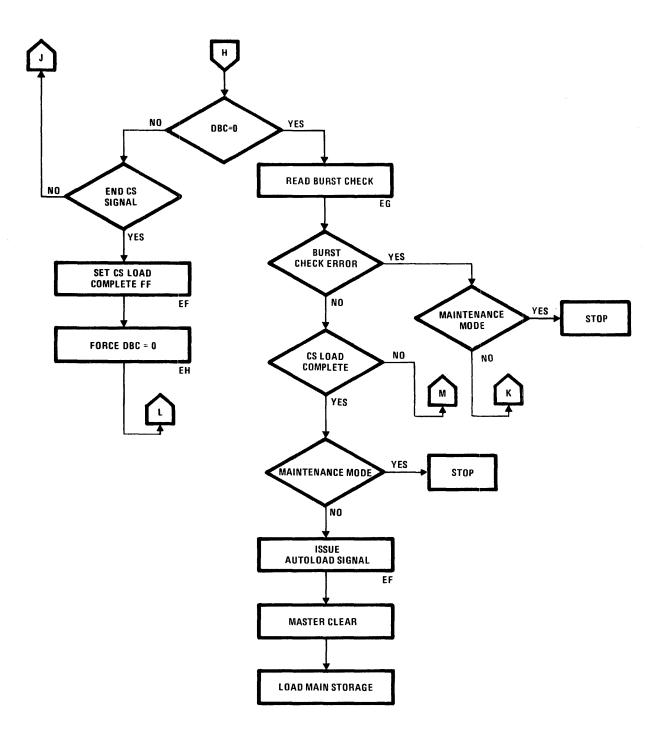

|                | CS Load Command                         | 6-14  |

|                | Write Hardware Status Command           | 6-14  |

|                | Write Other Status Commands             | 6-15  |

|                | IFA Commands Specified by DIO MLI       | 6-15  |

|                | Write Command                           | 6-15  |

|                | Format Write Command                    | 6-16  |

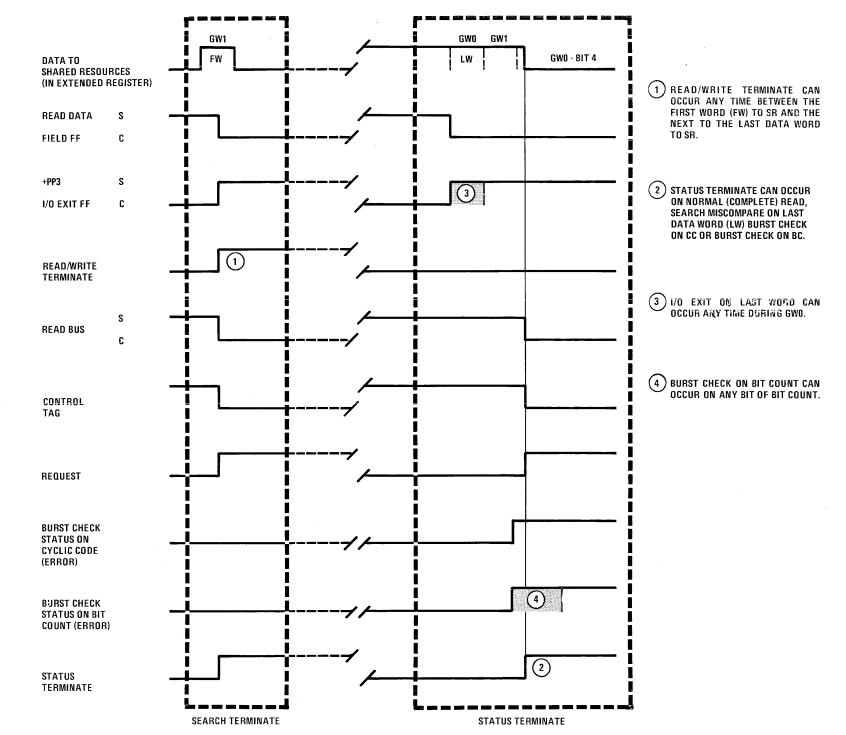

|                | Read Command                            | 6-16  |

| Section                               | Page |

|---------------------------------------|------|

| Read Without Transfer Command         | 6-17 |

| Search Command-Packet                 | 6-17 |

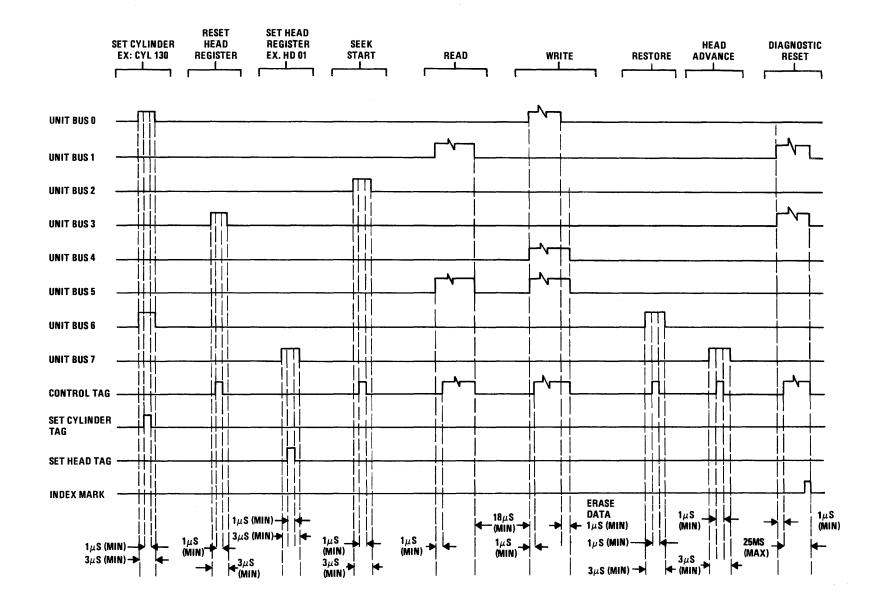

| Command Timing                        | 6-17 |

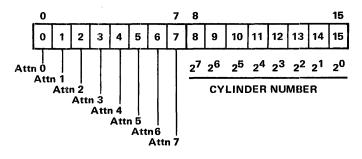

| Seek to a Specified Cylinder and Head | 6-19 |

| Read                                  | 6-19 |

| Write                                 | 6-19 |

| Head Advance                          | 6-20 |

| Restore                               | 6-20 |

| Reset Attention                       | 6-20 |

| Diagnostic Reset                      | 6-20 |

| Load CS                               | 6-20 |

| IFA Status Responses                  | 6-21 |

| Disc Status                           | 6-22 |

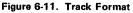

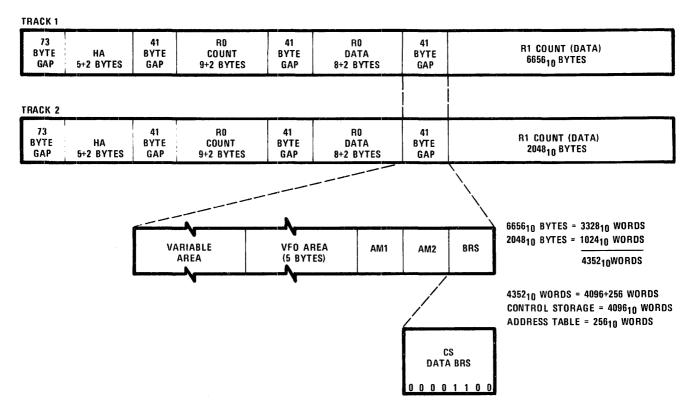

| Standard Track Format                 | 6-23 |

| Home Address Field                    | 6-24 |

| Record Zero                           | 6-24 |

| Data Records                          | 6-24 |

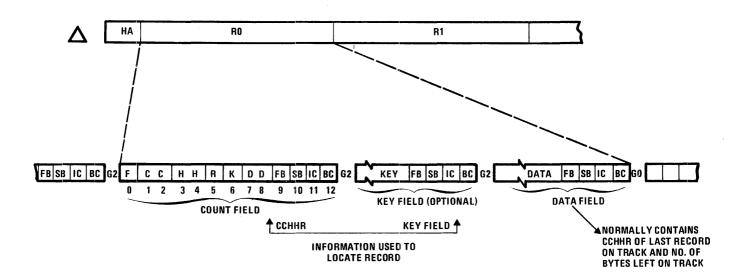

| Gaps                                  | 6-24 |

| Special Track Format for CS Load      | 6-27 |

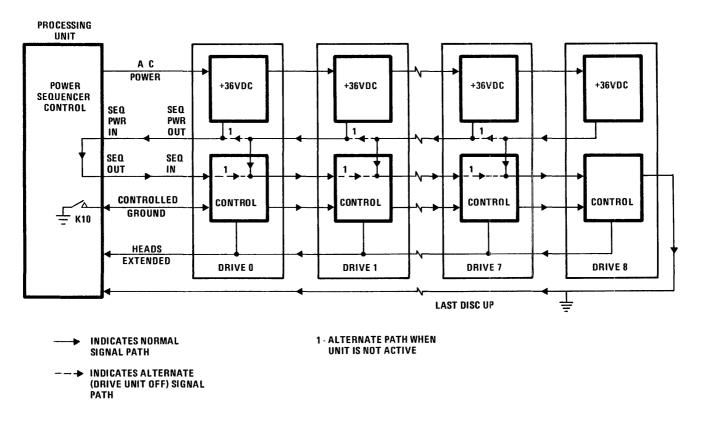

| Power Sequencing                      | 6-27 |

| First Seek                            | 6-28 |

| Power Down                            | 6-28 |

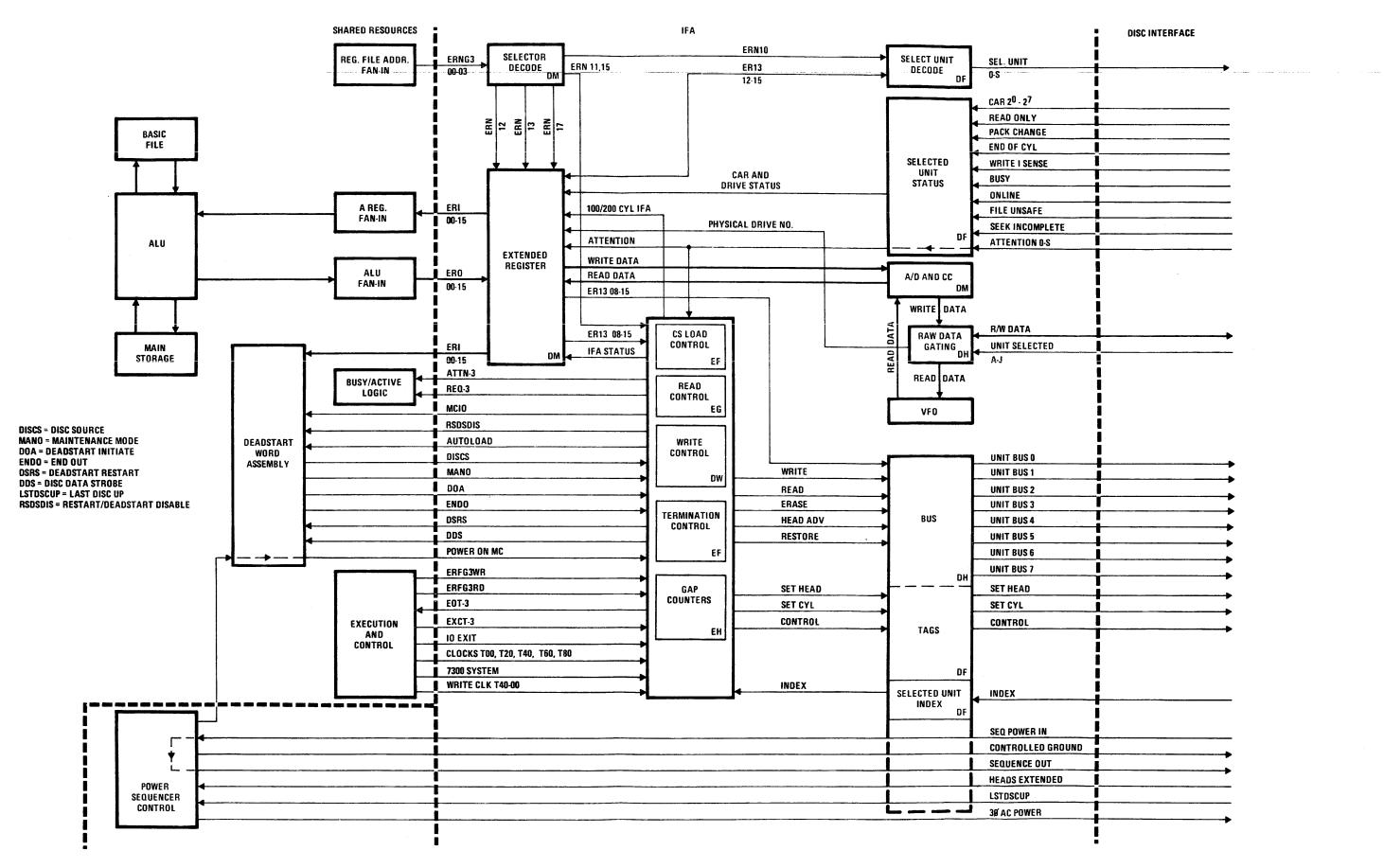

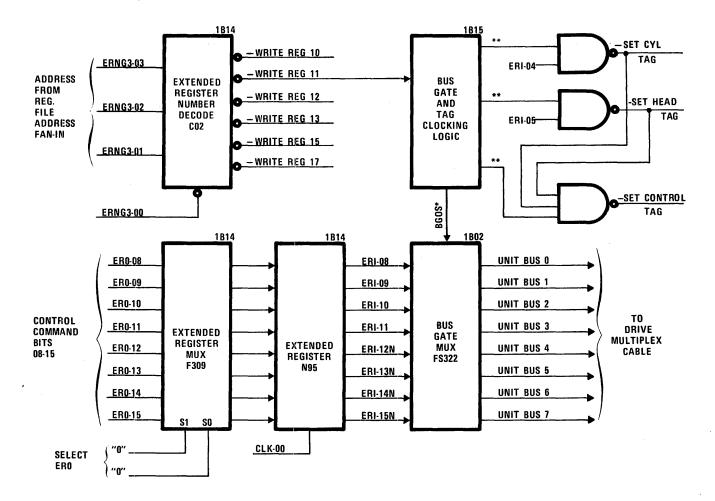

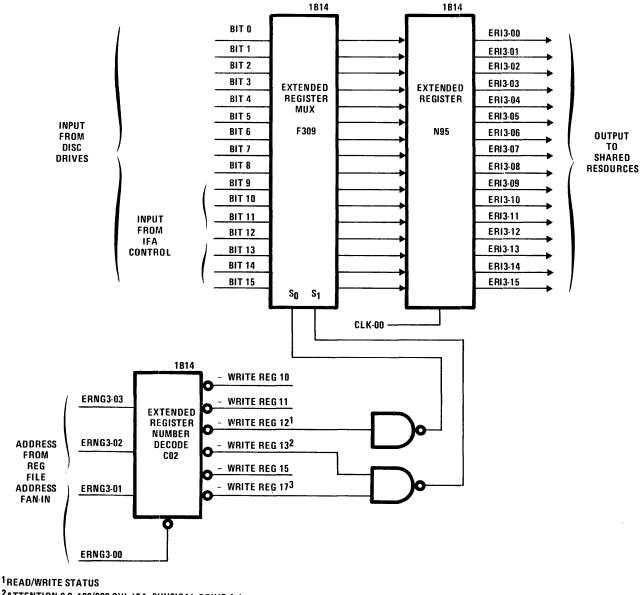

| Functional Logic Description          | 6-29 |

| Shared Resources Interface            | 6-29 |

| Drive Interface                       | 6-35 |

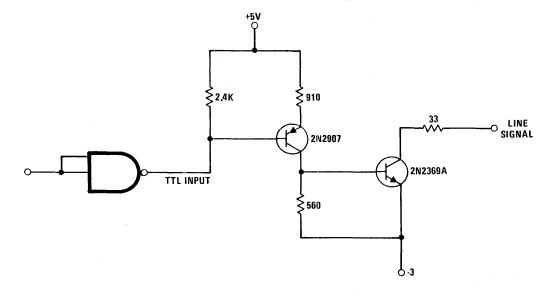

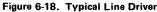

| Disc Line Drivers                     | 6-35 |

| Disc Line Receivers                   | 6-35 |

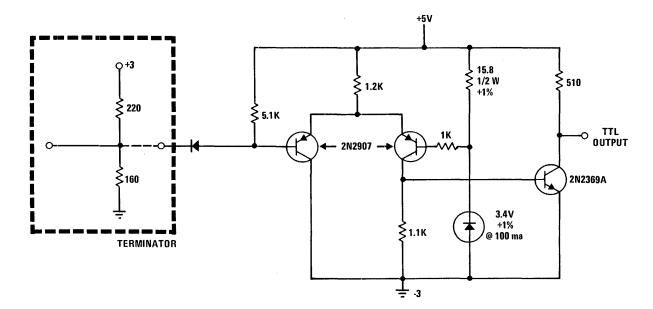

| Disc Read/Write Multiplexer           | 6-36 |

| Drive Interface Lines                 | 6-37 |

| Drive Selection Logic                 | 6-40 |

| Control Commands Logic                | 6-41 |

| Request Status Logic                  | 6-42 |

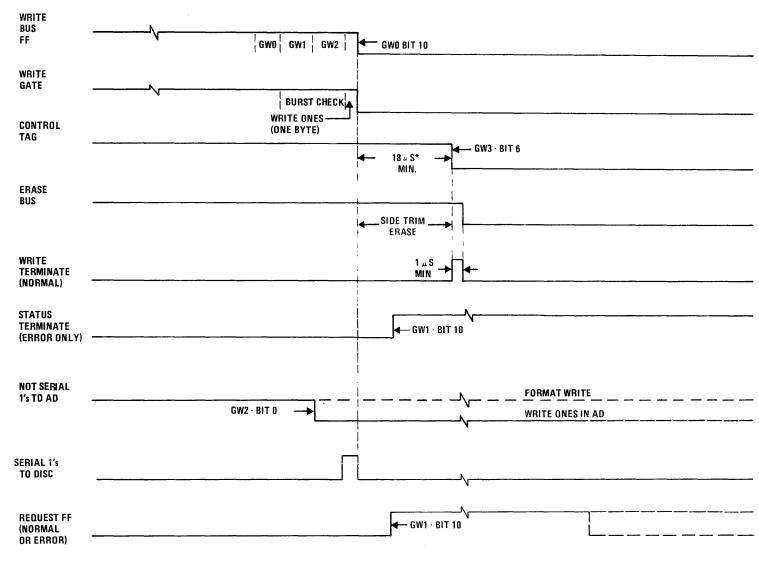

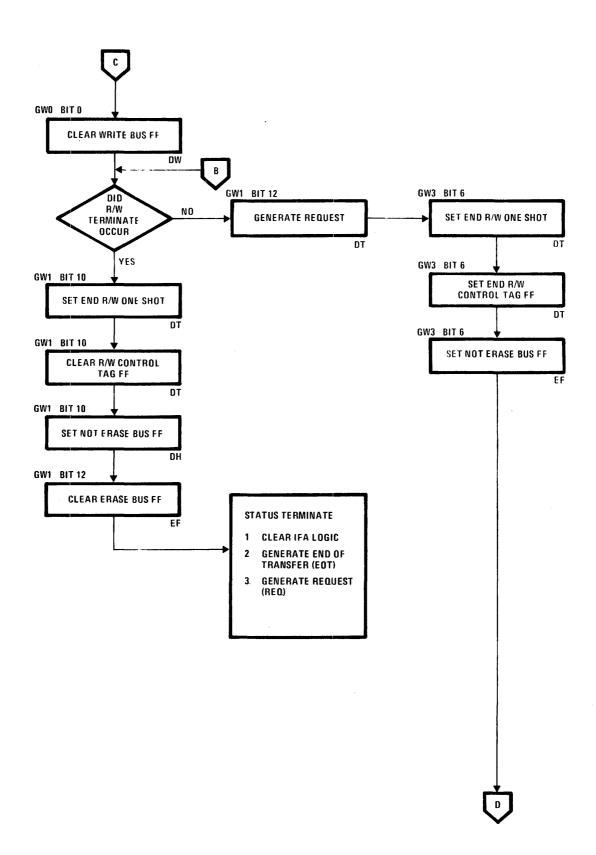

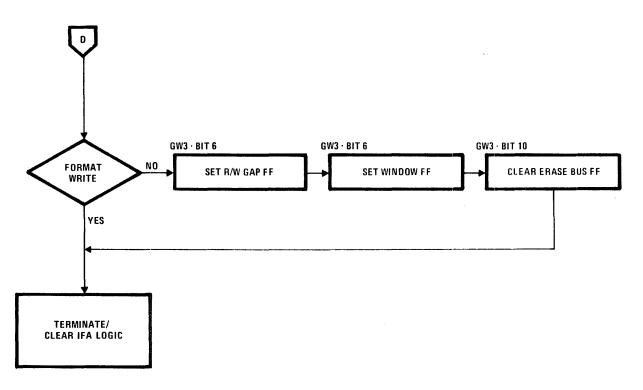

| Read/Write Control Logic              | 6-43 |

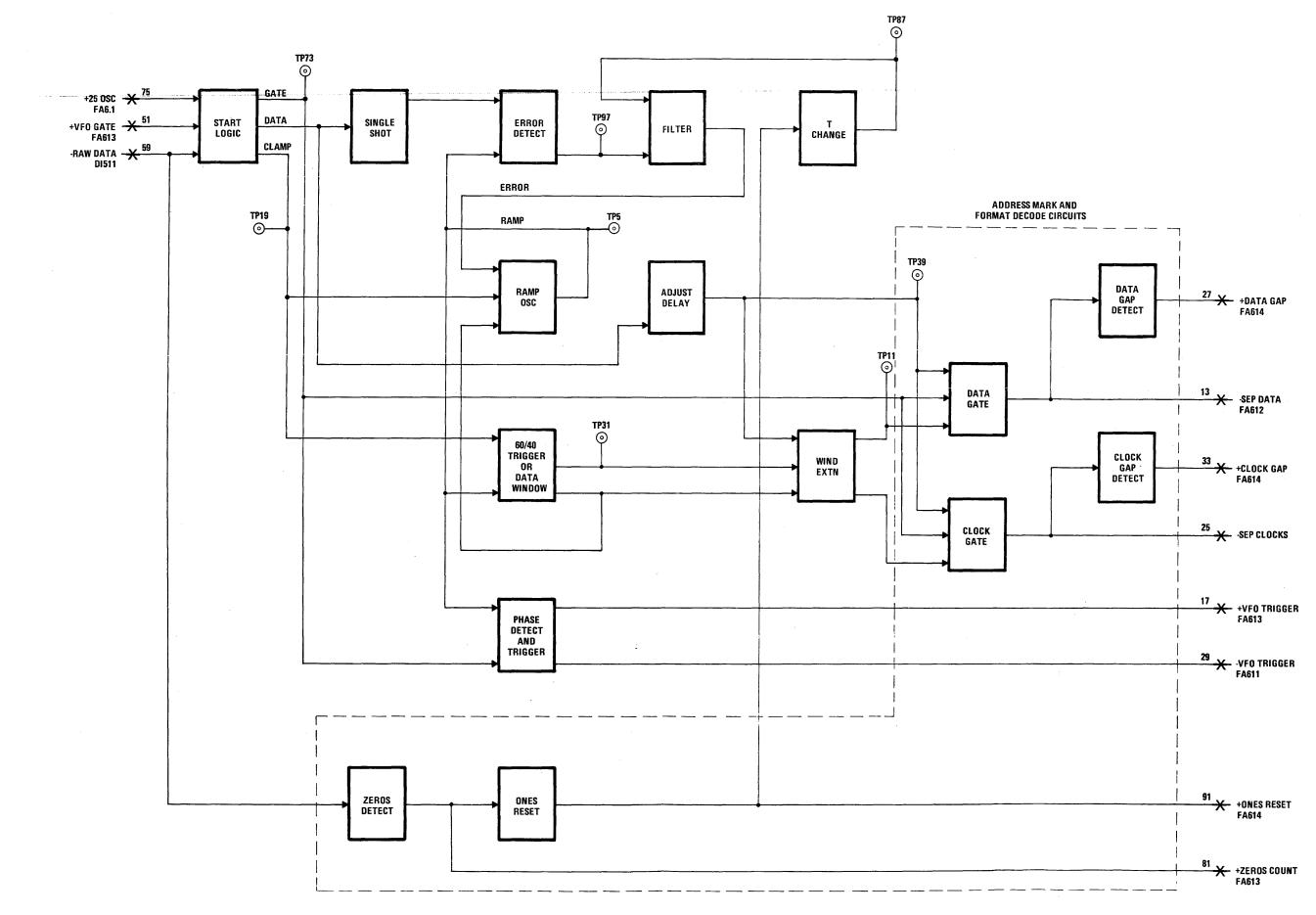

| Data Detection                        | 6-68 |

# LIST OF TABLES

| Table      |                                                             | Page |

|------------|-------------------------------------------------------------|------|

| 4-1        | EDNC2 Dit Assignment: Store Migra Instruction               | 4-10 |

| 4-1        | ERNG3 Bit Assignment: Store Micro-Instruction               | 4-10 |

| 4-2<br>4-3 | ERNG3 Bit Assignment: Load Micro-Instruction                | 4-15 |

| 4-3<br>4-4 | Tag Out Register                                            | 4-16 |

|            | ERO Bit Assignment in Channel Control Register              | 4-18 |

| 4-5        | CCR and Status Bit Assignment (ERI)                         | 4-19 |

| 4-6        | Tag In Signal Usage                                         | 4-13 |

| 4-7        | Initial Selection                                           |      |

| 4-8        | Adapter Initiated                                           | 4-29 |

| 4-9        | Short Busy                                                  | 4-30 |

| 4-10       | Channel Initiated Ending                                    | 4-32 |

| 4-11       | Hardware Controlled Input Data Transfer                     | 4-36 |

| 4-12       | Hardware Assembly Mode Input Data Transfer                  | 4-44 |

| 4-13       | Hardware Controlled Data Transfer (Output)                  | 4-49 |

| 4-14       | Bus In MPX Select Codes                                     | 4-60 |

| 6-1        | Power Connections                                           | 6-9  |

| 6-2        | Extended Register Addressing                                | 6-12 |

| 6-3        | Variable Gap Byte Entries                                   | 6-16 |

| 6-4        | Instruction Selection                                       | 6-29 |

| 6-5        | Signals from Shared Resources                               | 6-29 |

| 6-6        | Signals to Shared Resources                                 | 6-31 |

| 6-7        | Bus Line Signals to the Drives from IFA                     | 6-37 |

| 6-8        | Bus Line Signals to the Drives from Power Sequencer Control | 6-38 |

| 6-9        | Bus Line Signals to IFA from the Drives                     | 6-38 |

| 6-10       | Bus Line Signals to Power Sequencer Control from the Drives | 6-39 |

| 6-11       | Unit Line Signals to/from Each Drive                        |      |

| 6B1        | Bus Cable (Multiplex)                                       | 6B-1 |

| 6B2        | Unit Cable (Simplex)                                        | 6B-3 |

|            | - · · · · · · · · · · · · · · · · · · ·                     |      |

# LIST OF FIGURES

| Figure       |                                                      | Page         |

|--------------|------------------------------------------------------|--------------|

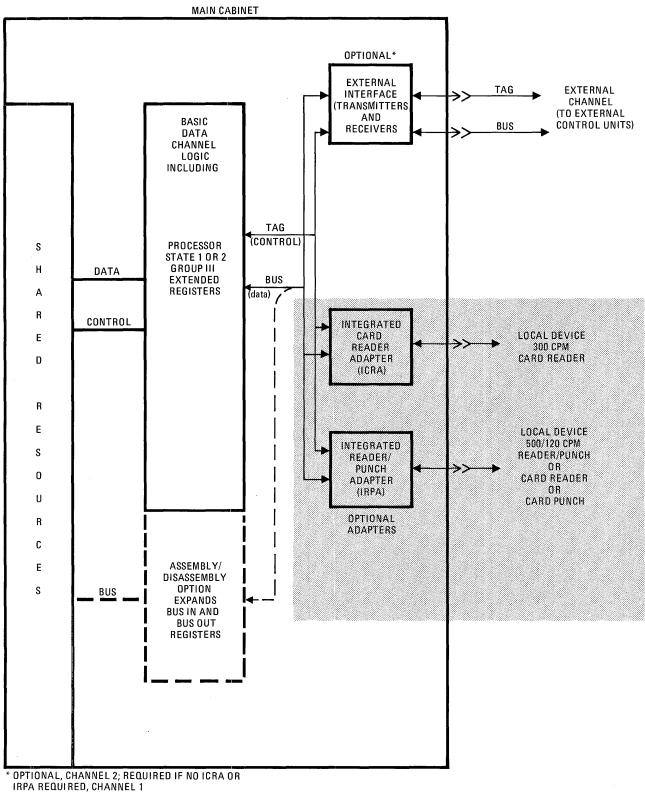

| 4-1          | Basic Data Channel Processor Configuration           | 4-3          |

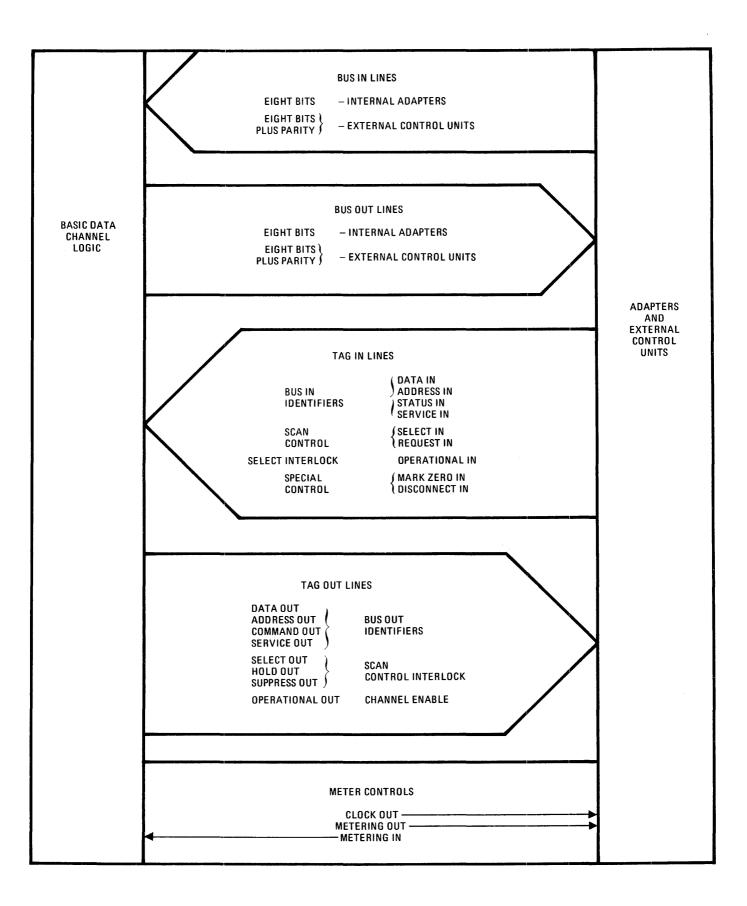

| 4-2          | BDC Common Signal Lines                              | 4-4          |

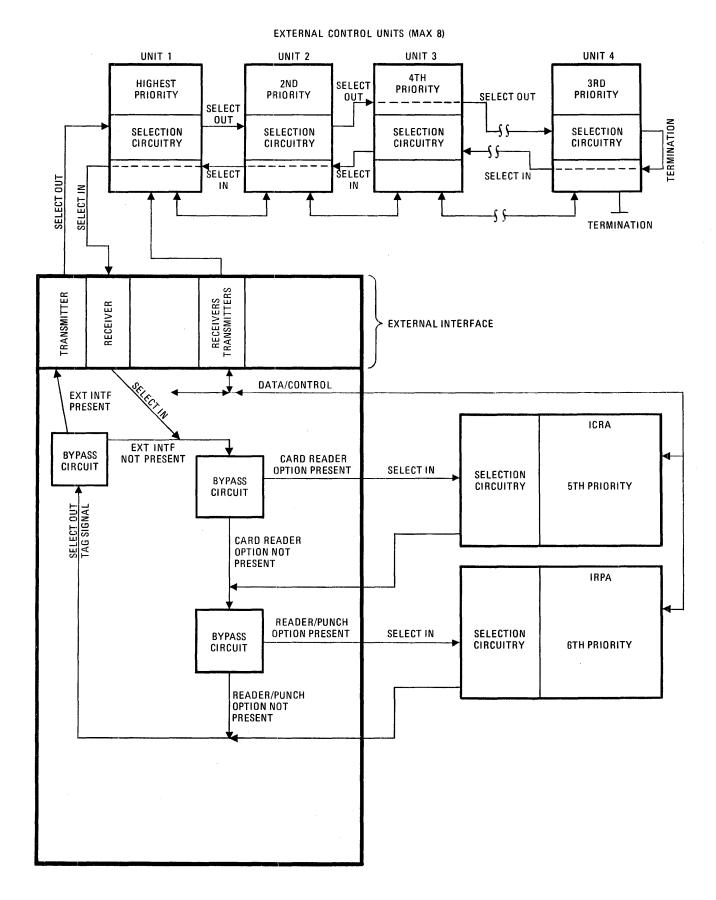

| 4-3          | BDC Interconnection Diagram                          | 4-5          |

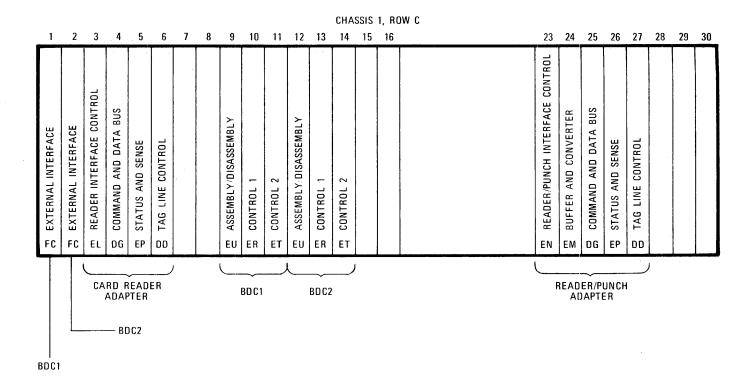

| 4-4          | Printed-Circuit Module Placement                     | 4-6          |

| 4-5          | BDC Processor Block Diagram                          | 4-12         |

| 4-6          | Bus Out Configuration                                | 4-13         |

| 4-7          | Bus In Configuration                                 | 4-14         |

| 4-8          | Byte Count Register Configuration                    | 4-19         |

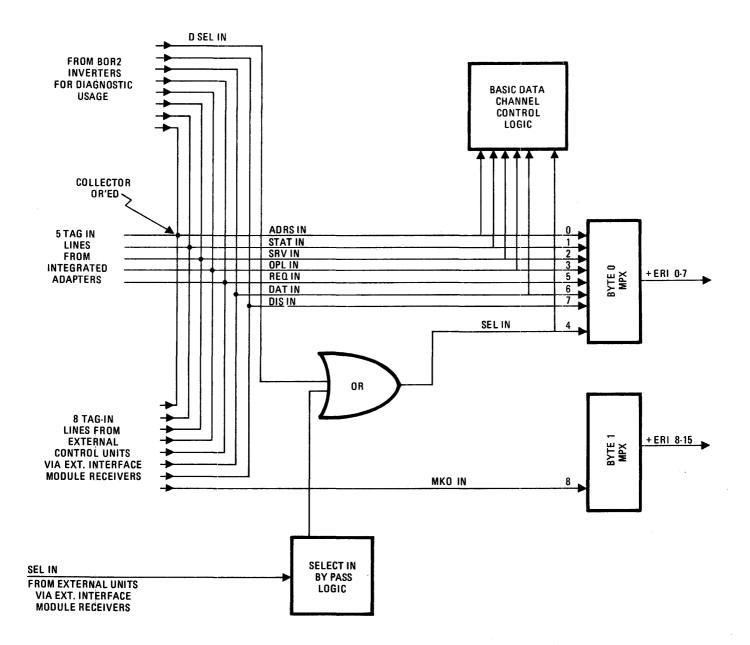

| 4-9          | Tag In Line Configuration                            | 4-20         |

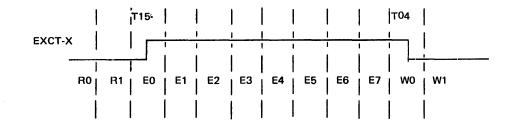

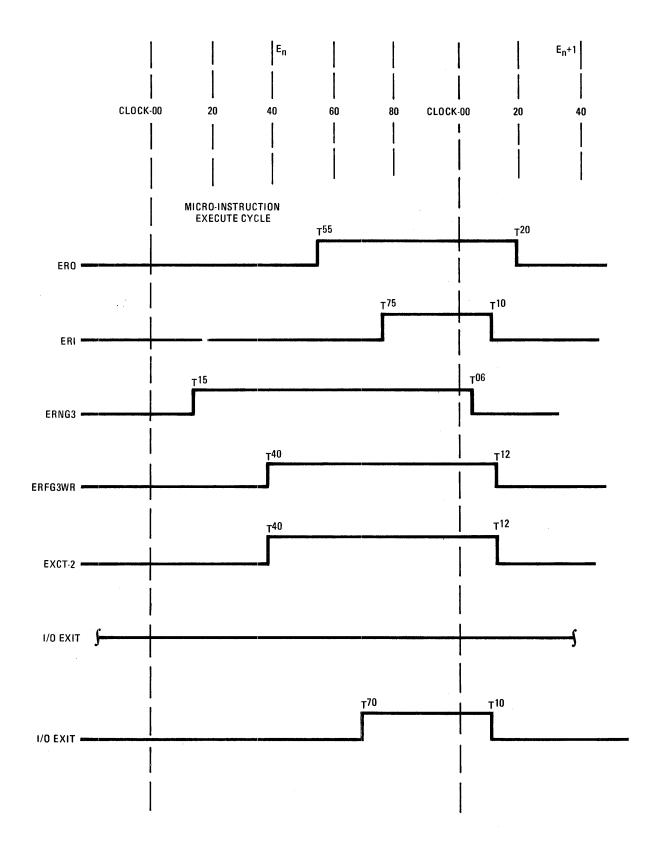

| 4-10         | Timing Relationship, Minor Cycle to Signal           | 4-23         |

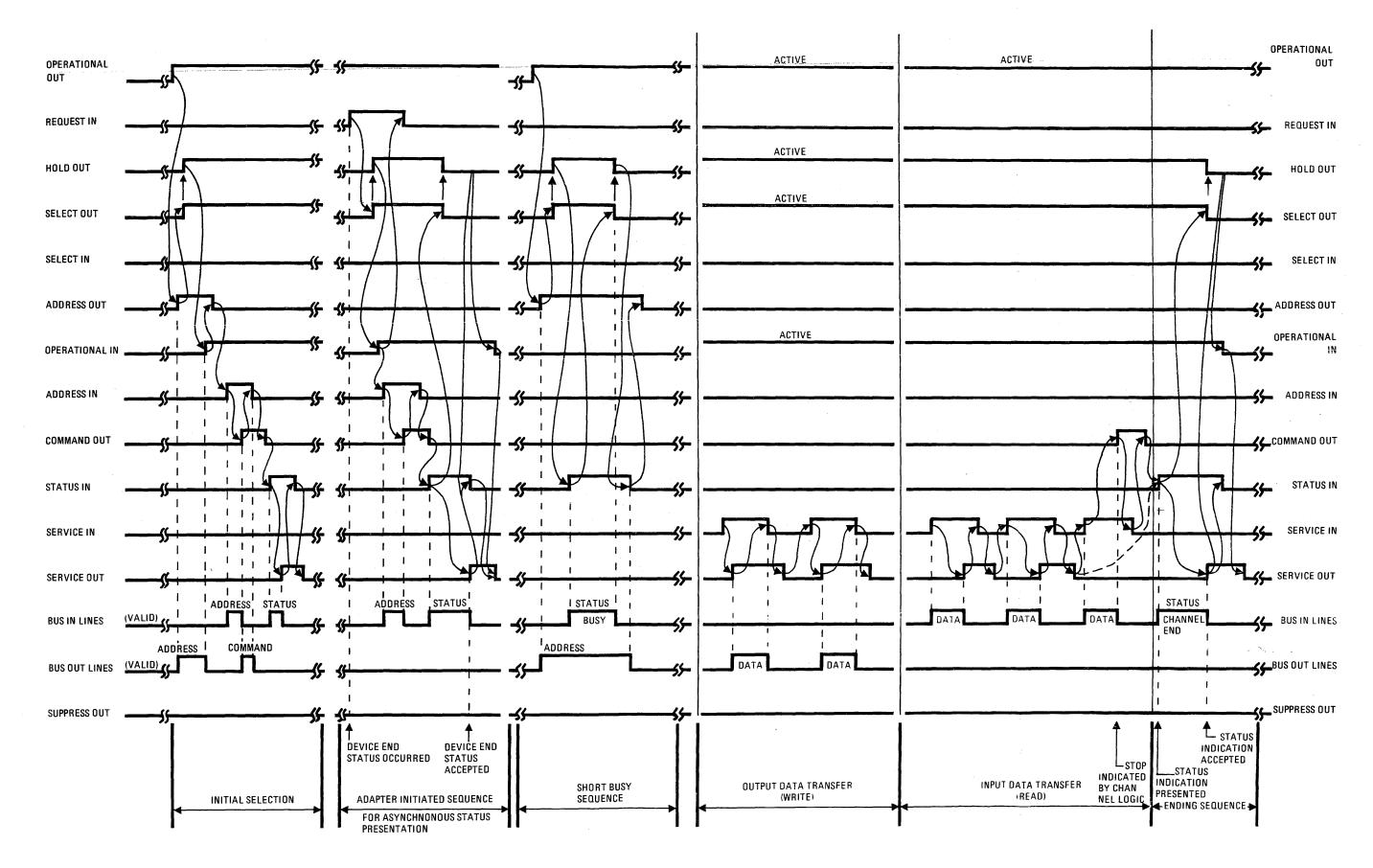

| 4-11         | BDC Operational Sequences                            | 4-25         |

| 4-12         | SIO Initial Selection Sequence                       | 4-37         |

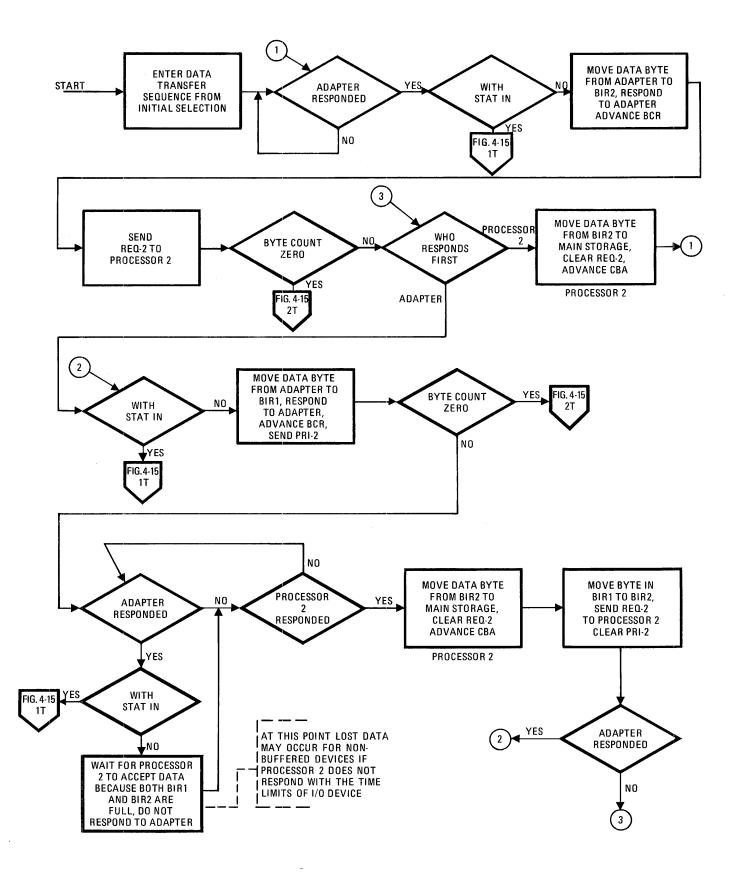

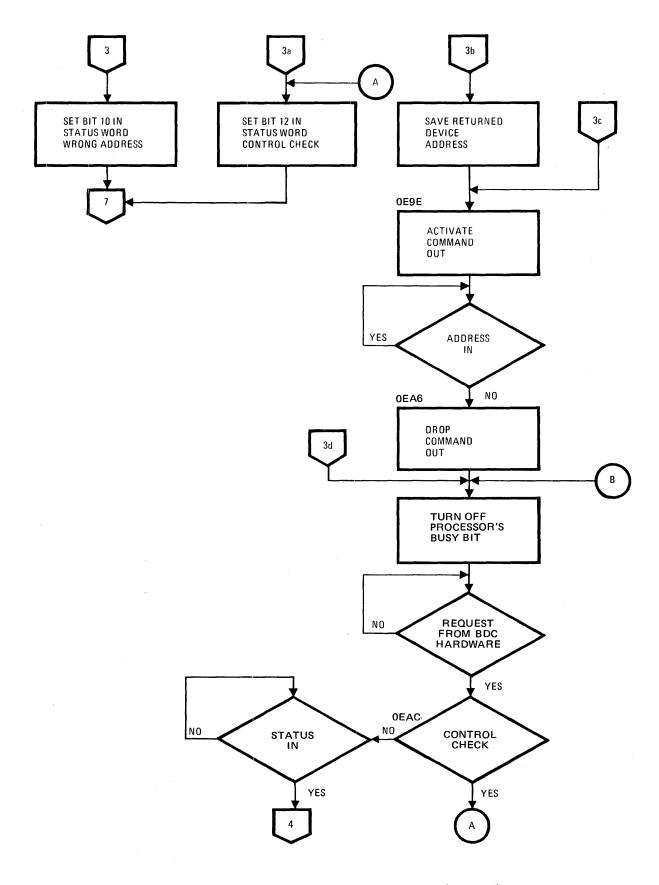

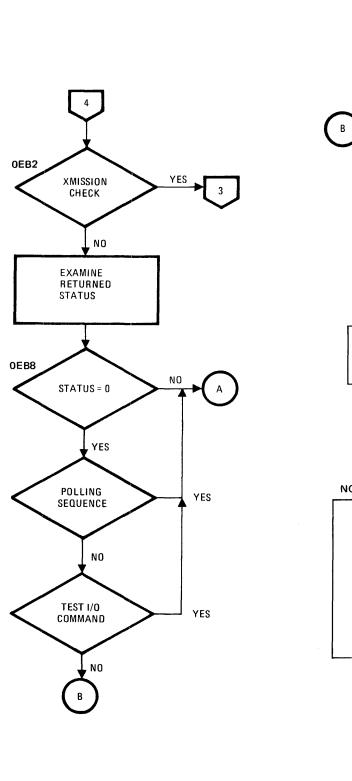

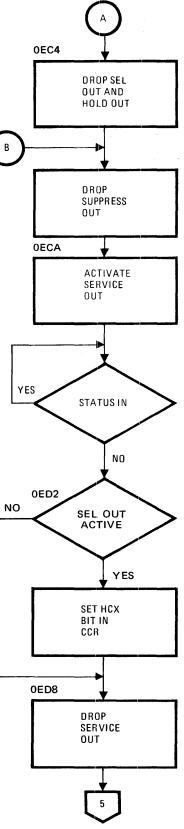

| 4-13         | Flowchart, Input Data Transfer                       | 4-39         |

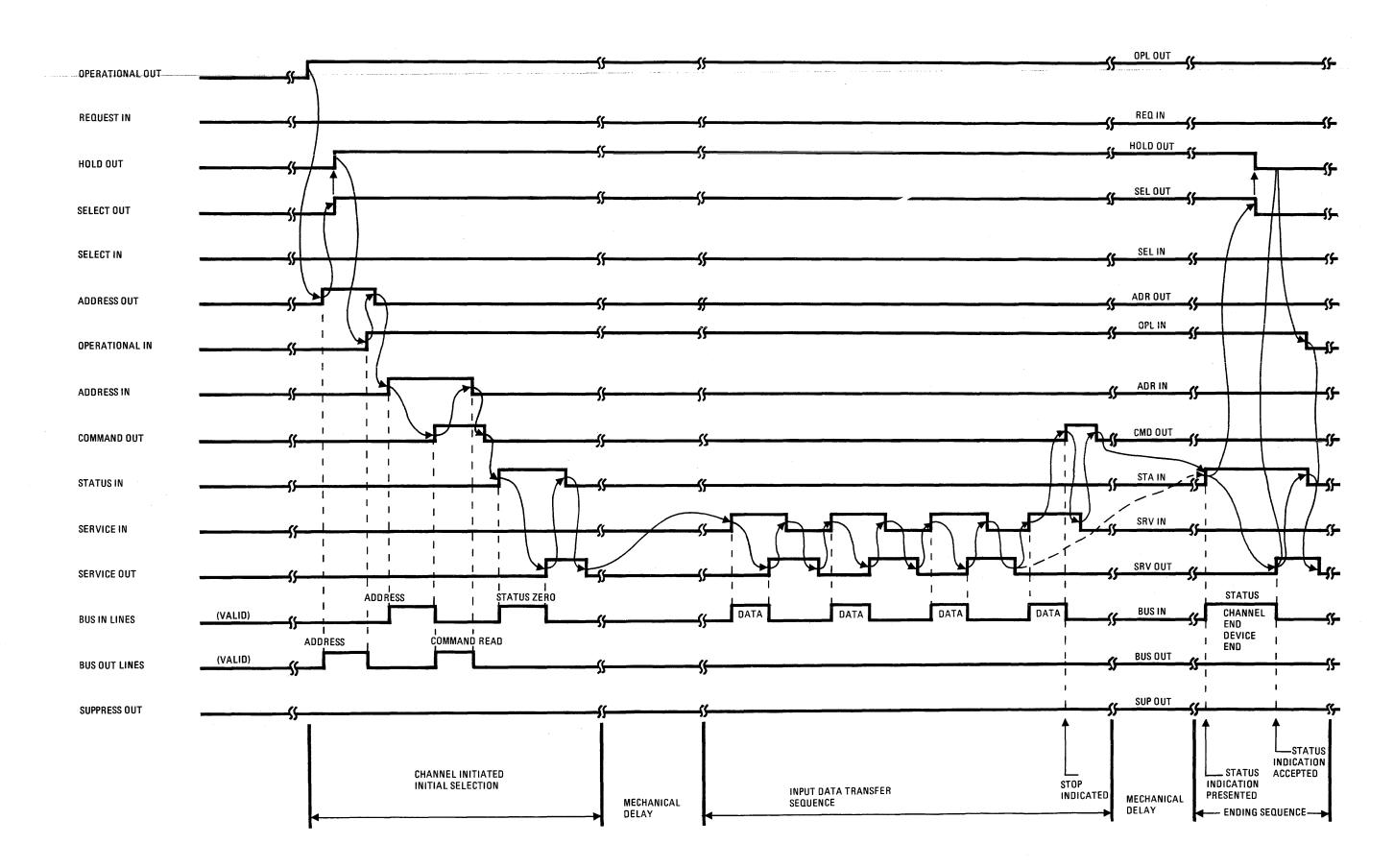

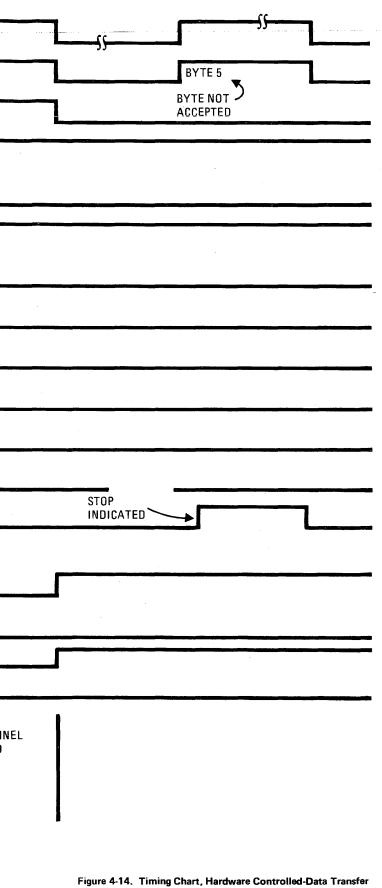

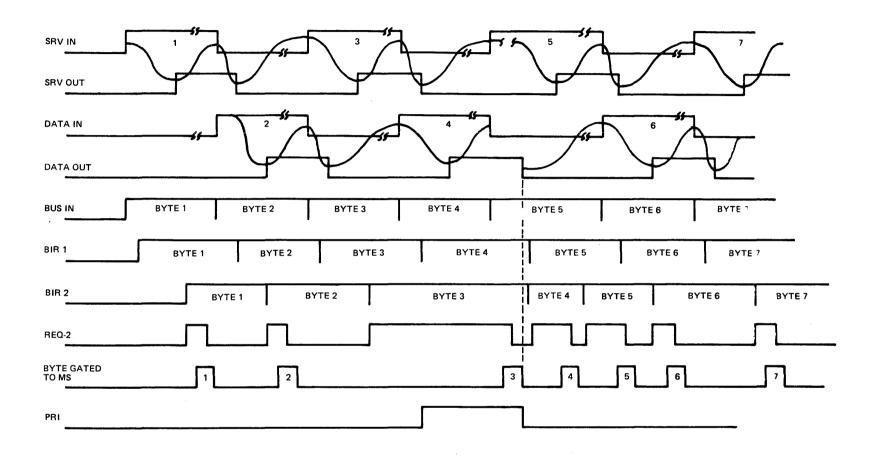

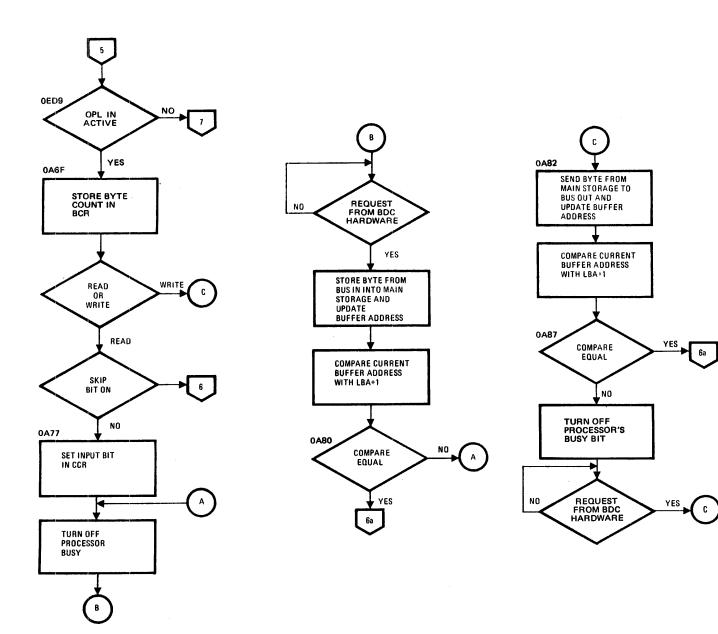

| 4-14         | Timing Chart, Hardware Controlled-Data Transfer      | 4-41         |

| 4-15         | Flowchart, Hardware Transfer Termination             | 4-45         |

| 4-16         | Selector Mode Output Sequence                        | 4-47         |

| 4-17         | Flowchart, Hardware-Controlled Output Data Transfer  | 4-50         |

| 4-18         | Flowchart, Hardware Output Termination               | 4-52         |

| 4-19         | Timing Chart, High-Speed Input Transfer              | 4-54         |

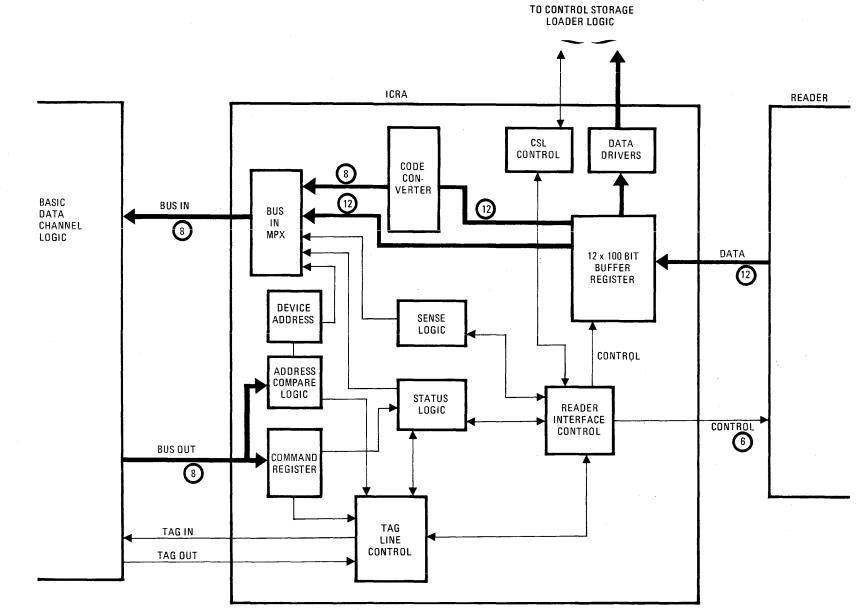

| 4-20         | ICRA Block Diagram                                   | 4-55         |

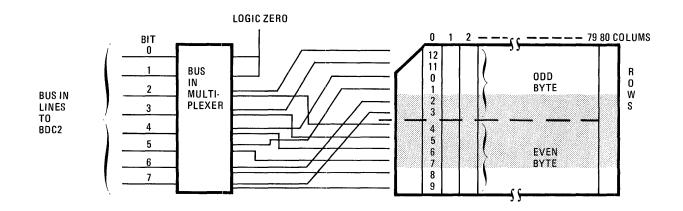

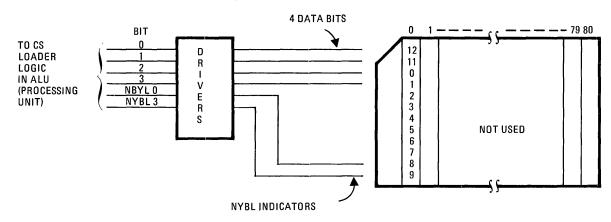

| 4-21         | Card Data Formats                                    | 4-59         |

| 4-22         | Data Paths, Adapter – BDC Processor                  | 4-61         |

| 4-23         | Adapter Buffer Register                              | 4-63         |

| 4-24         | Adapter Timing Chain Output                          | 4-65         |

| 4-25         | Timing Chart, Adapter Tag Line                       | 4-66         |

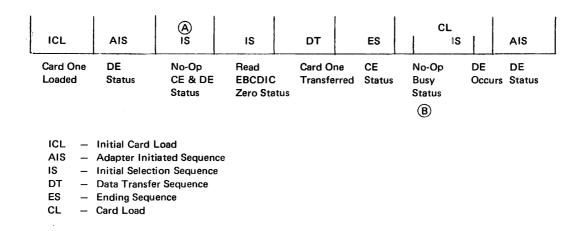

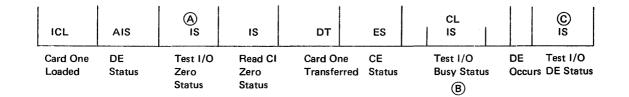

| 4-26         | ICRA Operating Sequences                             | 4-67         |

| 4-27         | ICRA Card Load Sequence                              | 4-68         |

| 4-28         | Card Load Attempt Sequences                          | 4-70         |

| 4-29         | ICRA-Initiated Sequence                              | 4-71         |

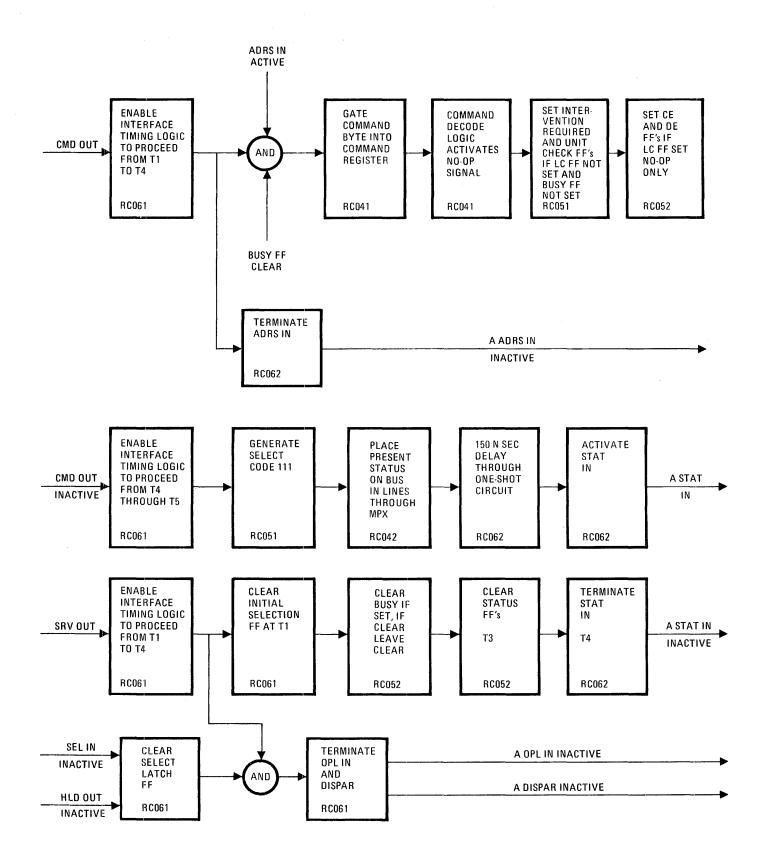

| 4-30         | Adapter Initial Selection Sequence                   | 4-73         |

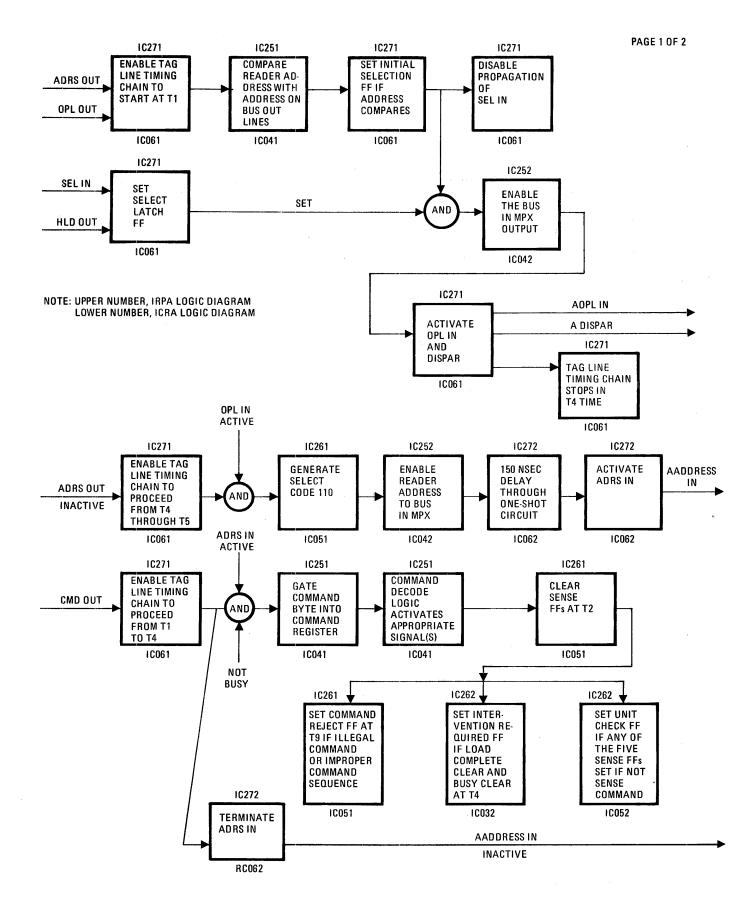

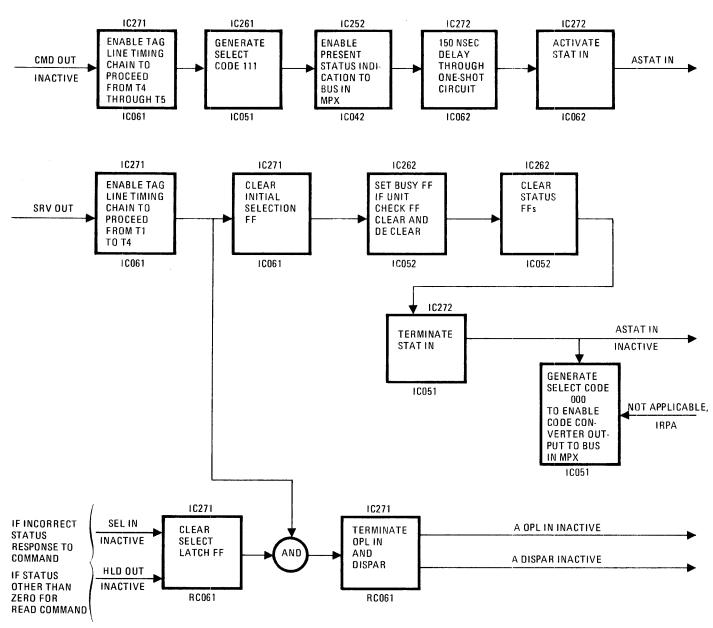

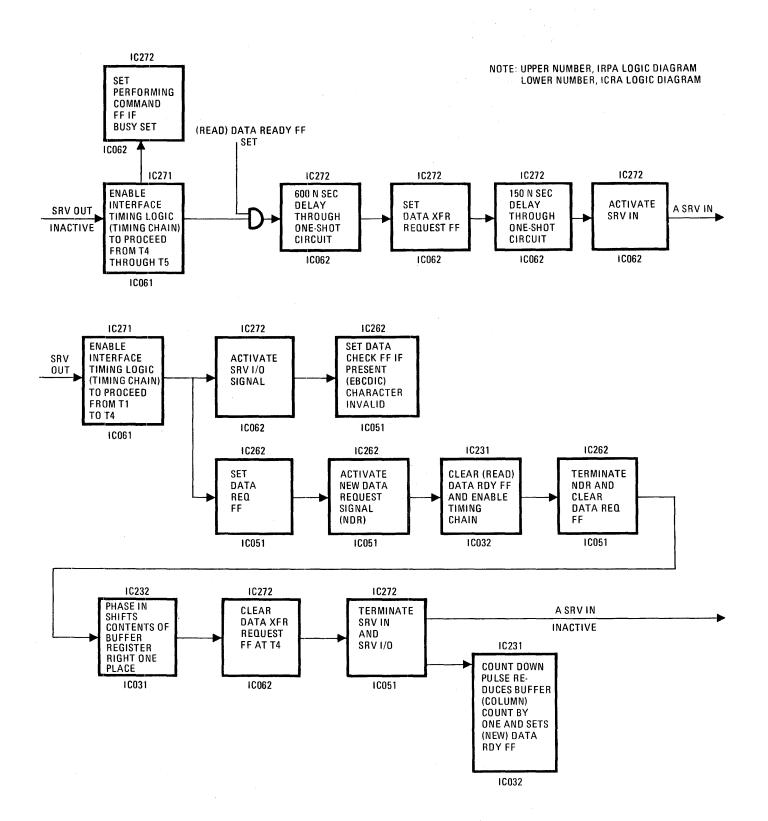

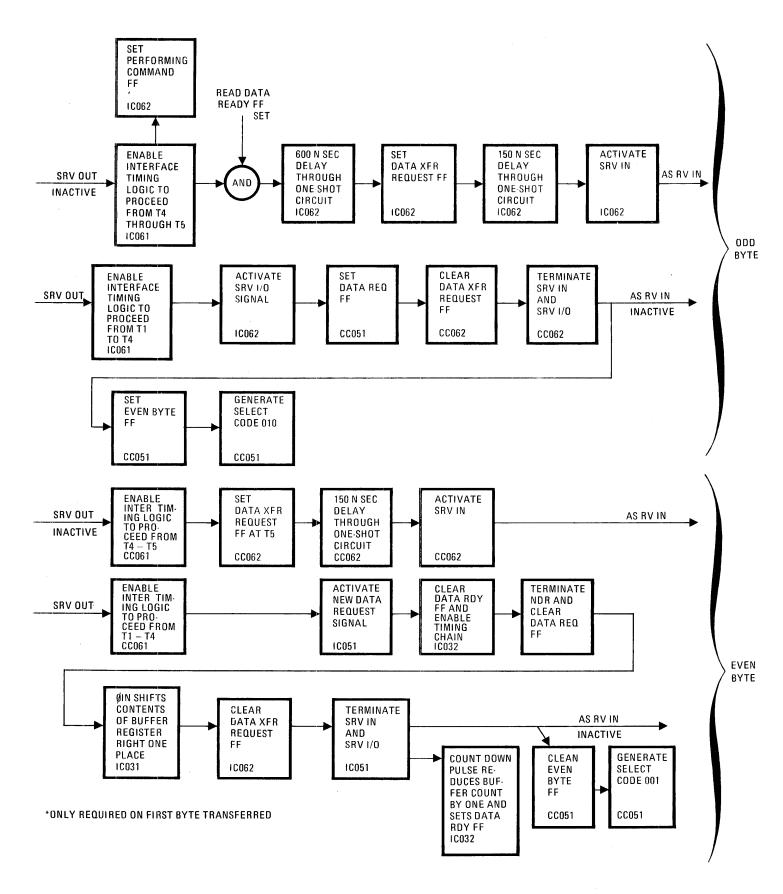

| 4-31         | Data Transfer Events for One EBCDIC Character        | 4-75         |

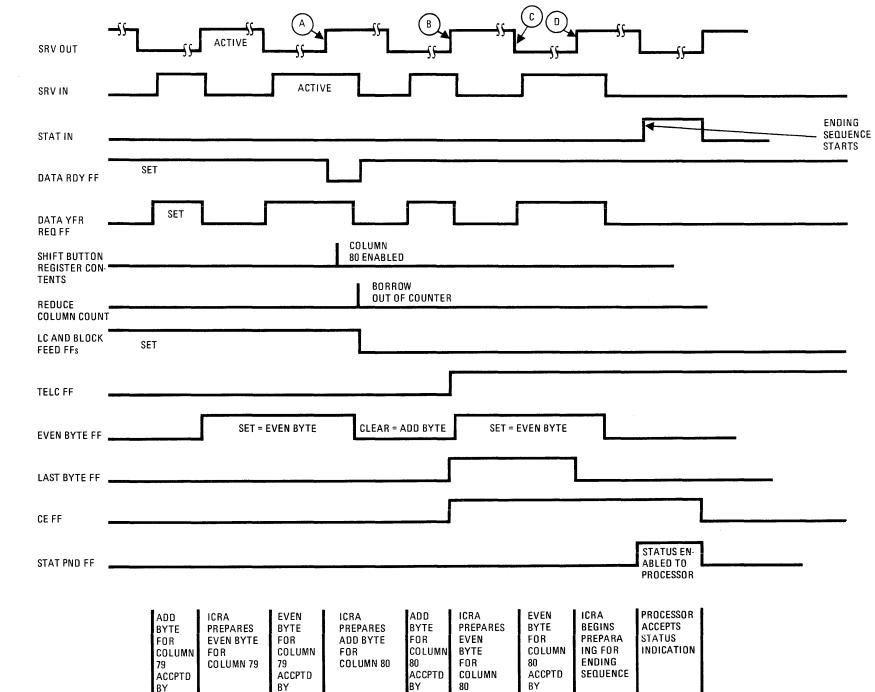

| 4-32         | Timing Chart, Transfer of One EBCDIC Character       | 4-77         |

| 4-33         | Adapter Input Ending Sequence                        | 4-78         |

| 4-34         | Timing Chart, Adapter-Terminated Sequence            | 4-80         |

| 4-35         | Adapter Error Handling                               | 4-81         |

| 4-36         | ICRA Card Image Data Transfer Sequence               | 4-83         |

| 4-37         | Timing Chart, Adapter Termination of Card Image Read | 4-84         |

| 4-38         | ICRA No-Operation and Test I/O Sequences             | 4-85         |

| 4-39         | Flowchart, Control Storage Operation                 | 4-88         |

| 4-40         | IRPA Block Diagram                                   | 4-90         |

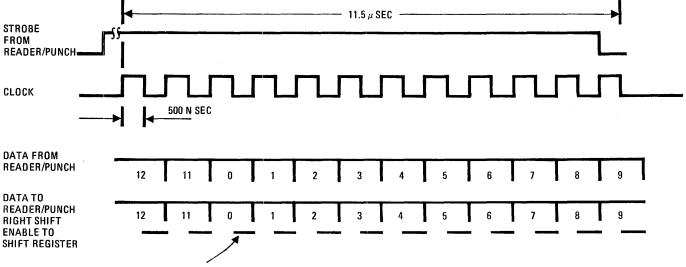

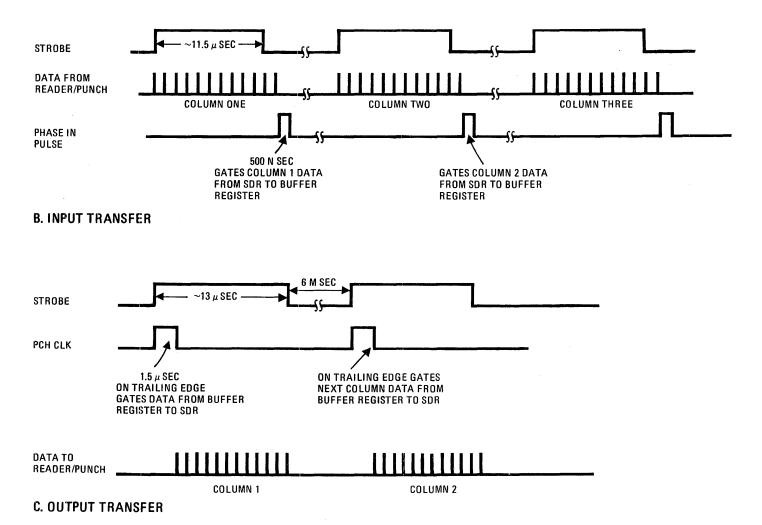

| 4-40         | Timing Chart, IRPA Transfers                         | 4-90         |

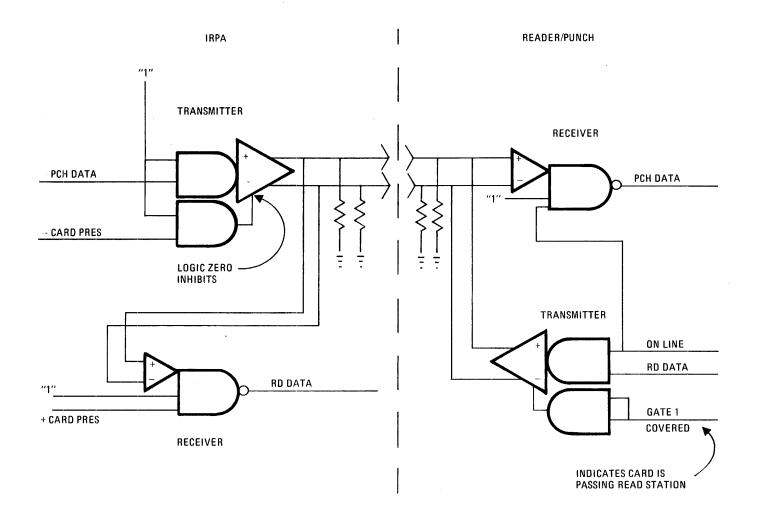

| 4-41         | IRPA Data Line Configuration                         | 4-93         |

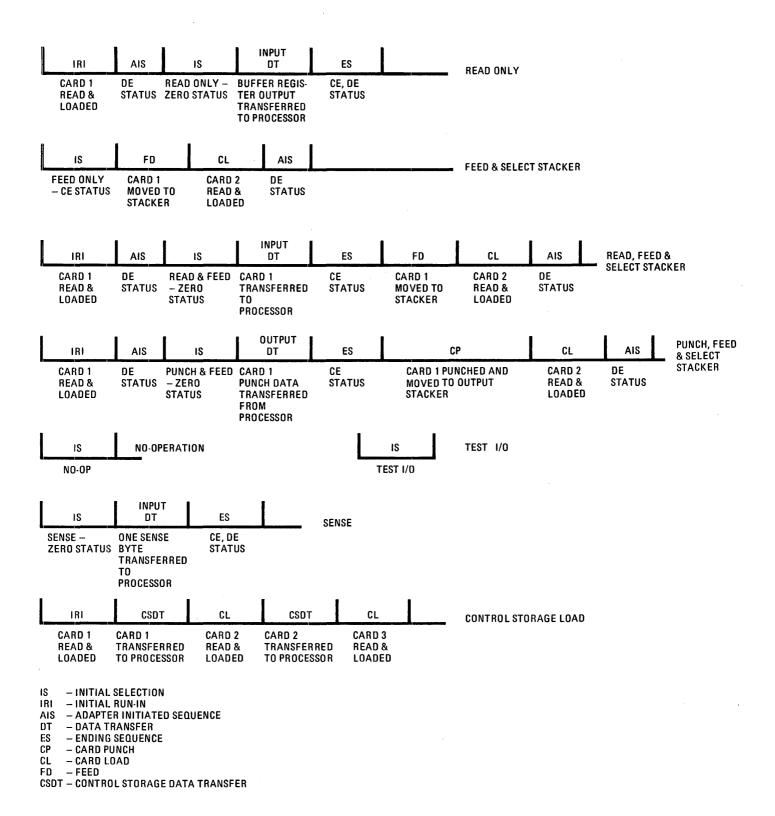

| 4-42         | IRPA Operating Sequences                             | 4-95         |

| 4-43<br>4-44 |                                                      | 4-97<br>4-98 |

| 4-44         | IRPA Card Load Sequence                              | 4-90         |

# LIST OF FIGURES (Continued)

| Figure |                                                        | Page  |

|--------|--------------------------------------------------------|-------|

| 4-45   | IRPA-Initiated Sequence                                | 4-100 |

| 4-46   | IRPA Output Transfer Sequence for One EBCDIC Character | 4-103 |

| 4-47   | Timing Chart, IRPA Input, EBCDIC Characters            | 4-104 |

| 4-48   | IRPA Card-Image Output Transfer Sequence               | 4-107 |

| 4-49   | Processor-Terminated Output Ending Sequence            | 4-108 |

| 4-50   | Adapter-Terminated Output Ending Sequence              | 4-110 |

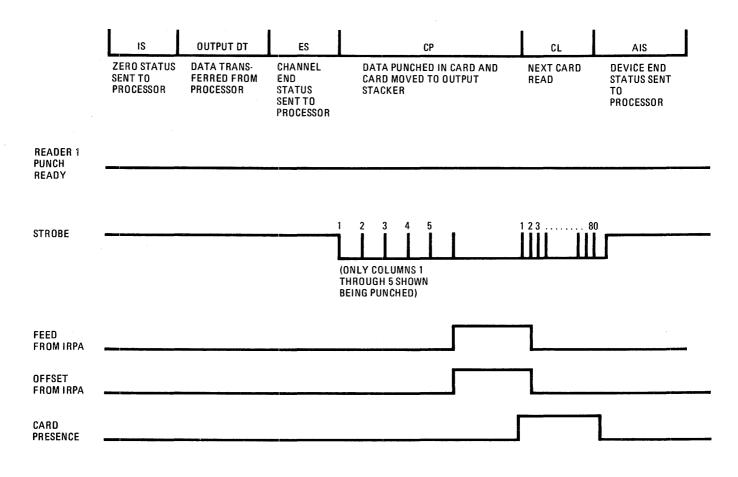

| 4-51   | Timing Chart, Punch Sequences                          | 4-111 |

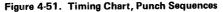

| 4-52   | Card Punch Sequence                                    | 4-113 |

| 4-53   | Relationship of Error Occurrence and Indications       | 4-114 |

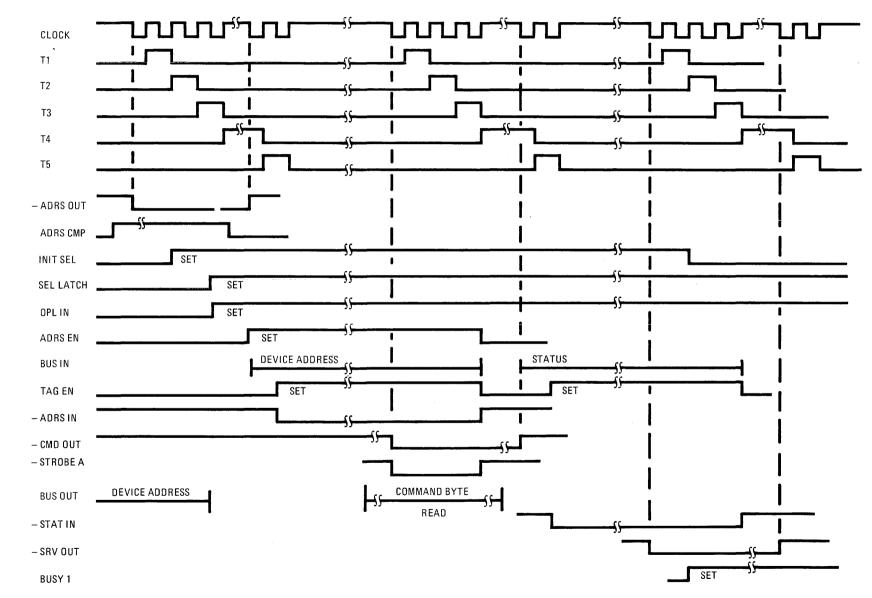

| 4-A1   | Initial Selection Timing                               | 4-A1  |

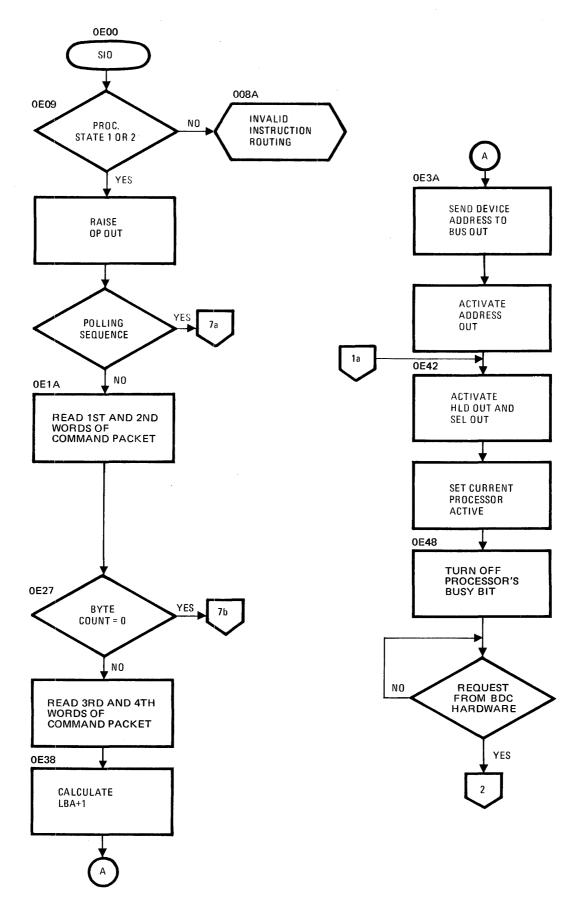

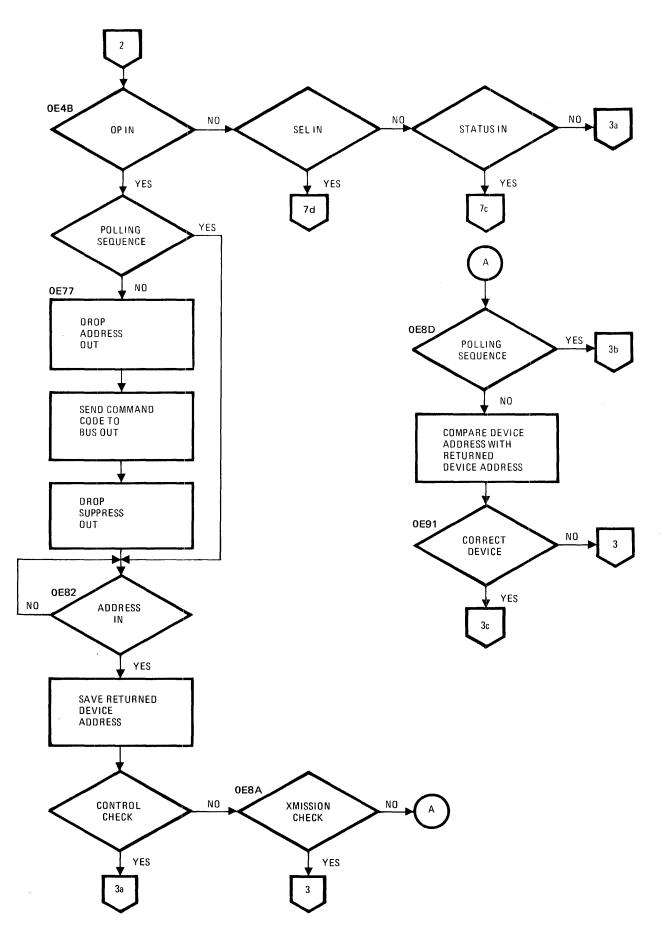

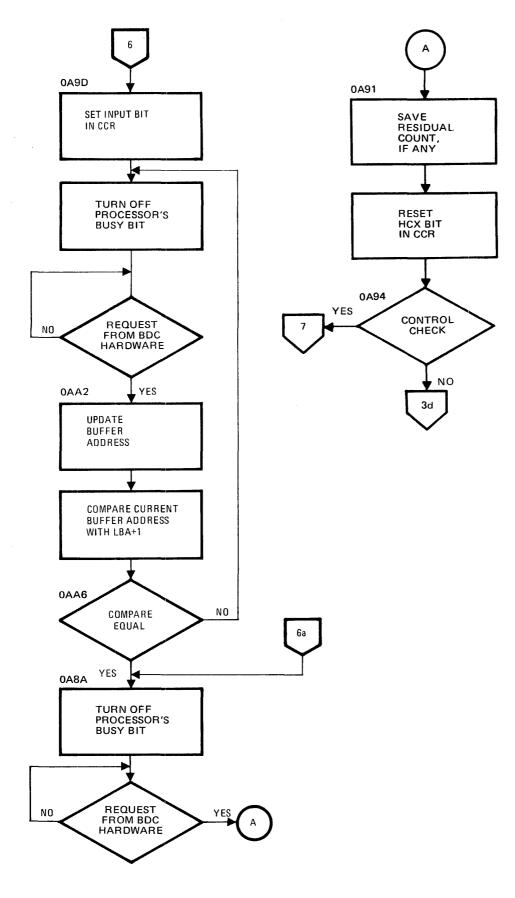

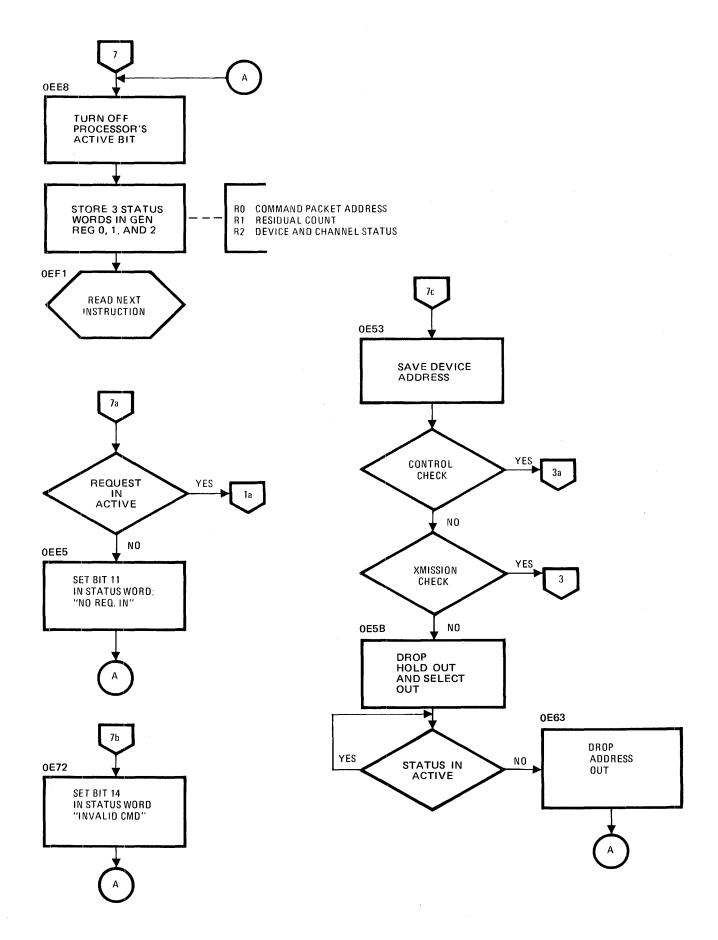

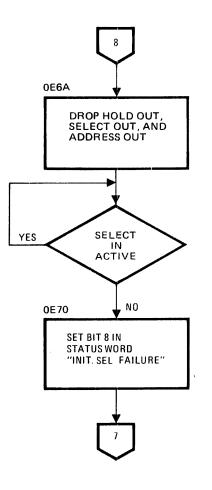

| 4-B1   | Flowchart, SIO Micro-Instruction Routing               | 4-B1  |

| 6-1    | Disc Organization                                      | 6-2   |

| 6-2    | Integrated File Adapter Hardware Placement             | 6-4   |

| 6-3    | IFA Card Type and Locations                            | 6-4   |

| 6-4    | Power Sequencer Control                                | 6-5   |

| 6-5    | Cable Connections                                      | 6-6   |

| 6-6    | I/O Connector Panel                                    | 6-7   |

| 6-7    | Power Distribution                                     | 6-8   |

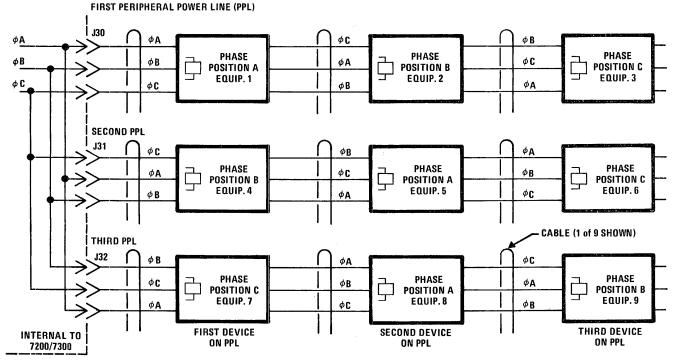

| 6-8    | Phase Rotation                                         | 6-9   |

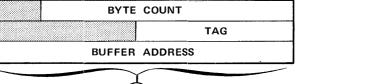

| 6-9    | DIO Command Packets                                    | 6-11  |

| 6-10   | Disc Operation Timing                                  | 6-18  |

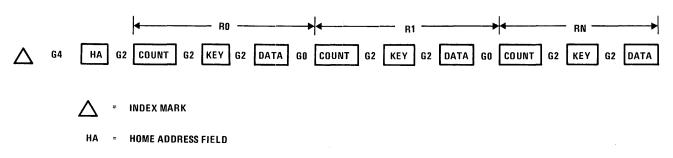

| 6-11   | Track Format                                           | 6-23  |

| 6-12   | Home Address                                           | 6-24  |

| 6-13   | Record Zero                                            | 6-25  |

| 6-14   | Gaps                                                   | 6-26  |

| 6-15   | Special Track Format for CS Load (Drive Zero)          | 6-27  |

| 6-16   | Power Sequencing Control Lines                         | 6-28  |

| 6-17   | IFA Signal Exchange                                    | 6-33  |

| 6-18   | Typical Line Driver                                    | 6-35  |

| 6-19   | Typical Line Receiver and Terminator                   | 6-35  |

| 6-20   | Read/Write Data Input                                  | 6-36  |

| 6-21   | Drive Selection                                        | 6-40  |

| 6-22   | Control Commands                                       | 6-41  |

| 6-23   | Request Status                                         | 6-42  |

| 6-24   | Write Terminate                                        | 6-44  |

| 6-25   | Read Terminate                                         | 6-45  |

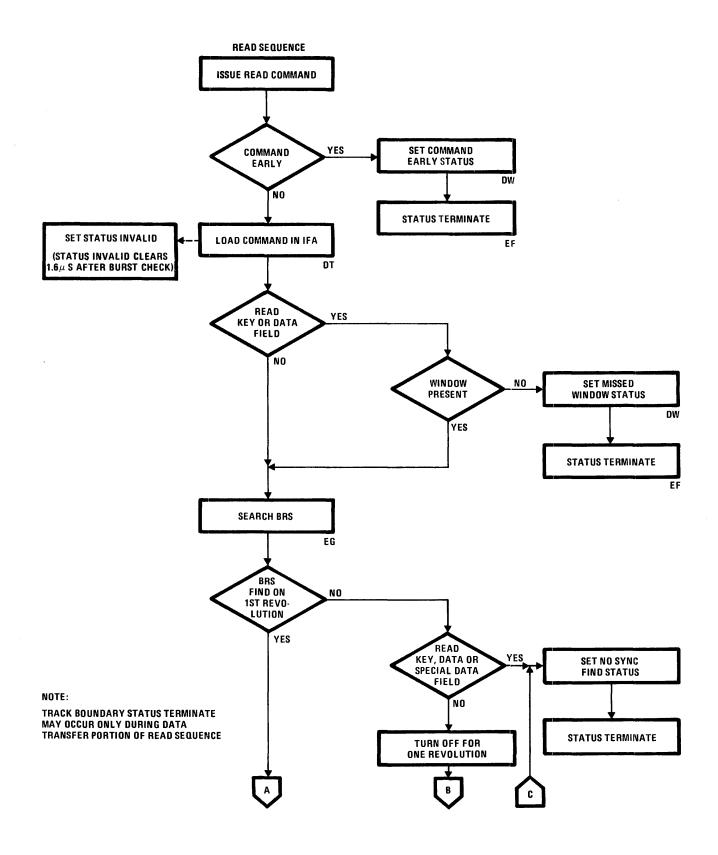

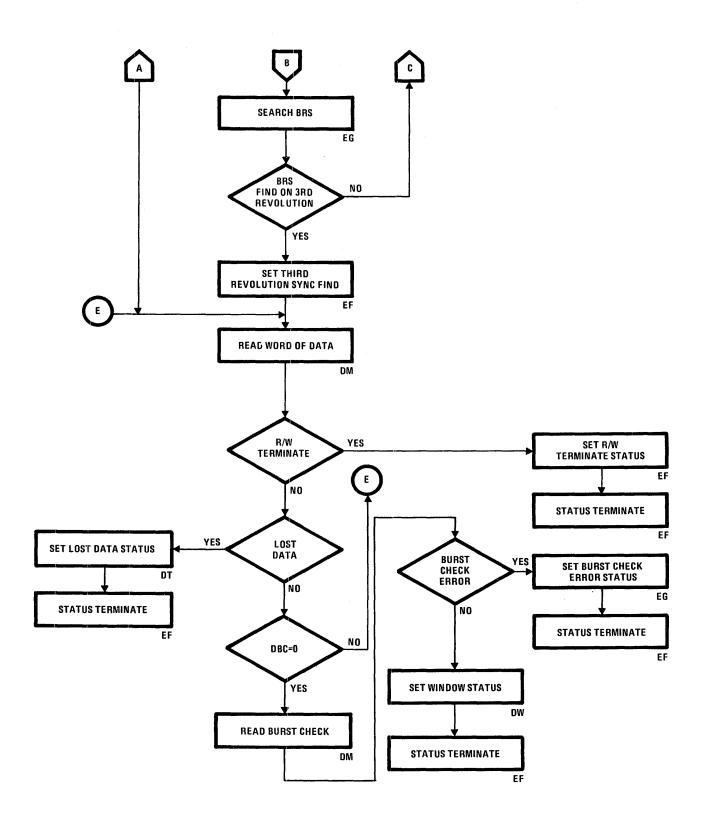

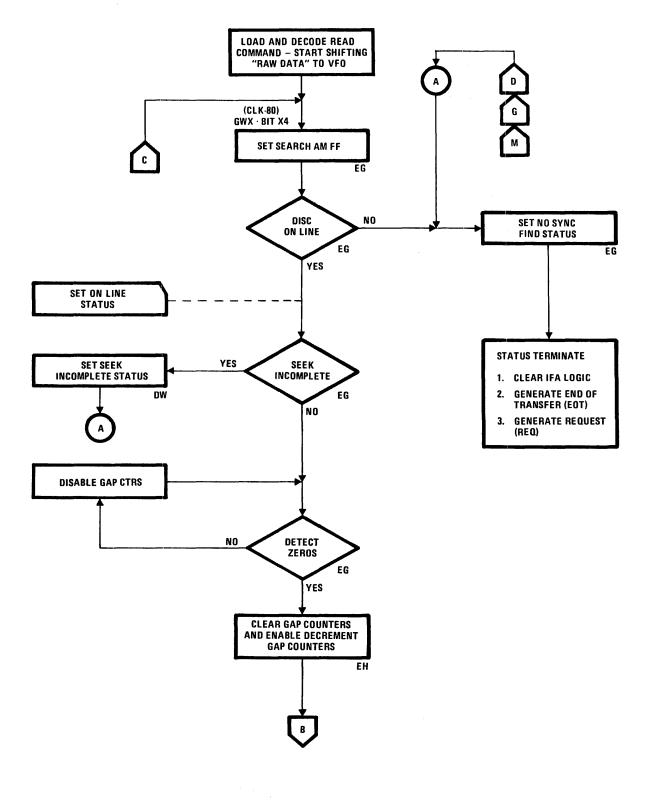

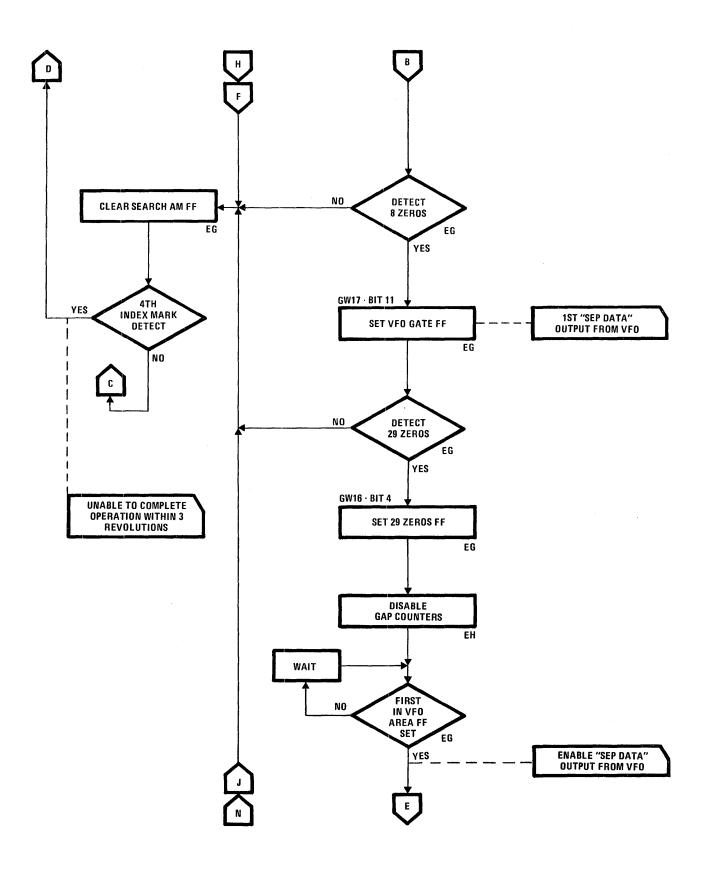

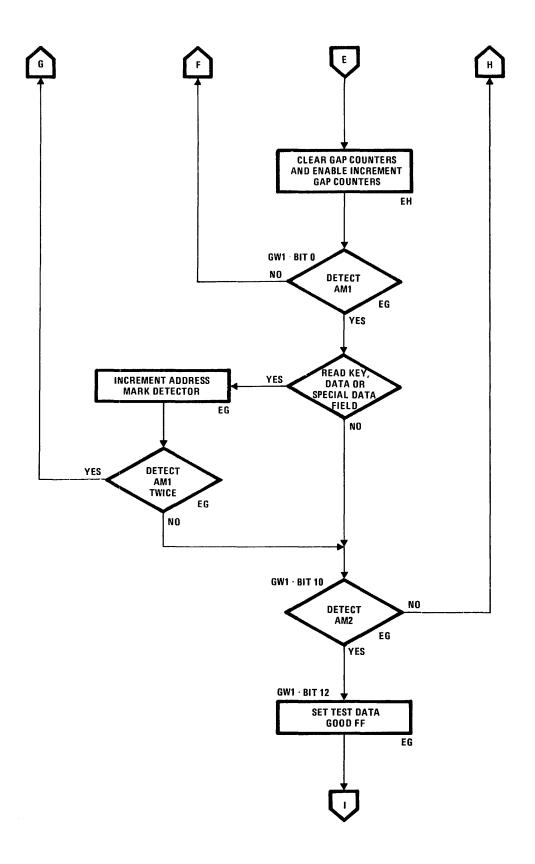

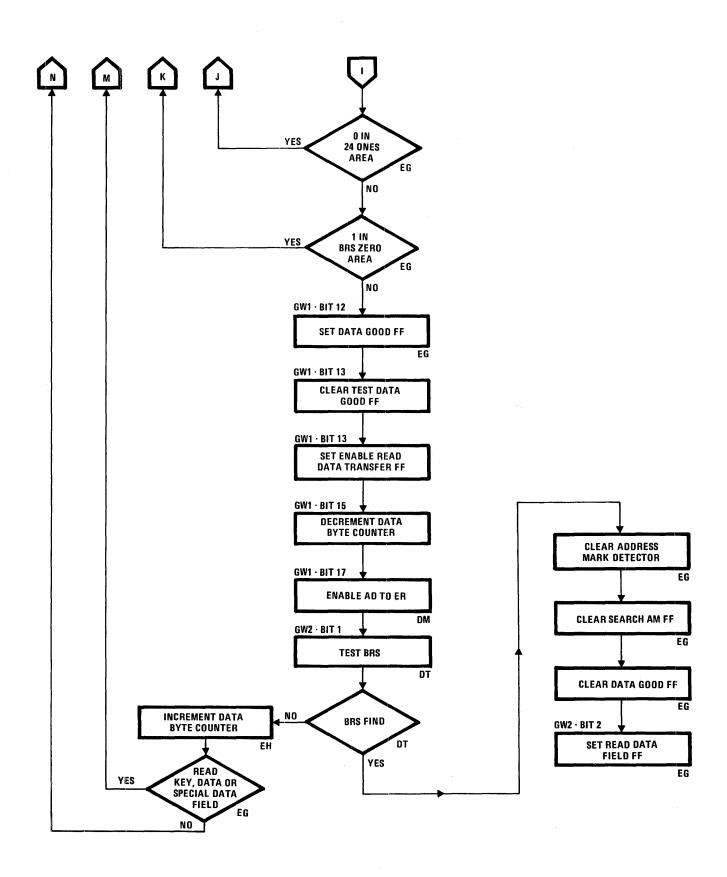

| 6-26   | Read Sequence                                          | 6-46  |

| 6-27   | Load Read Command                                      | 6-38  |

| 6-28   | Search BRS                                             | 6-50  |

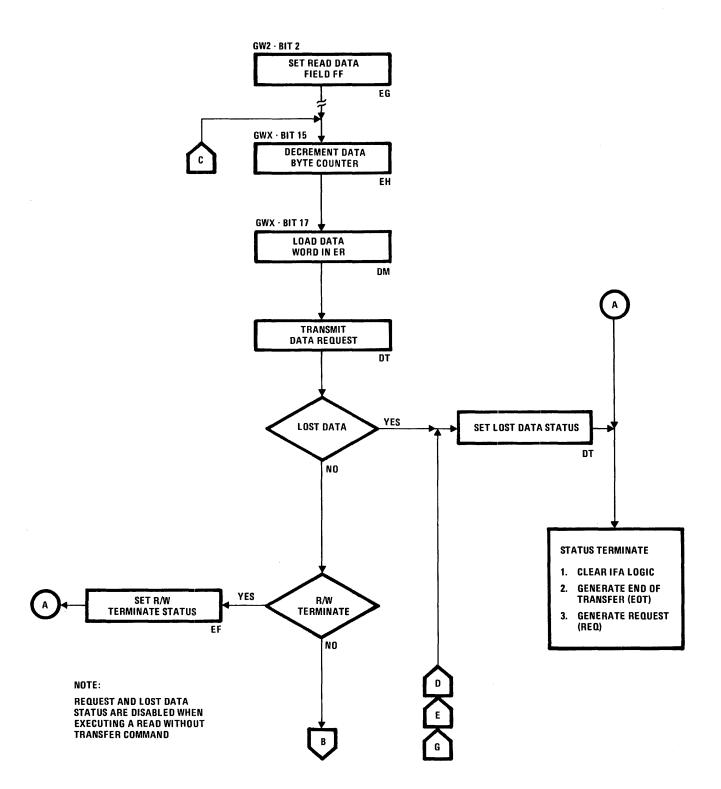

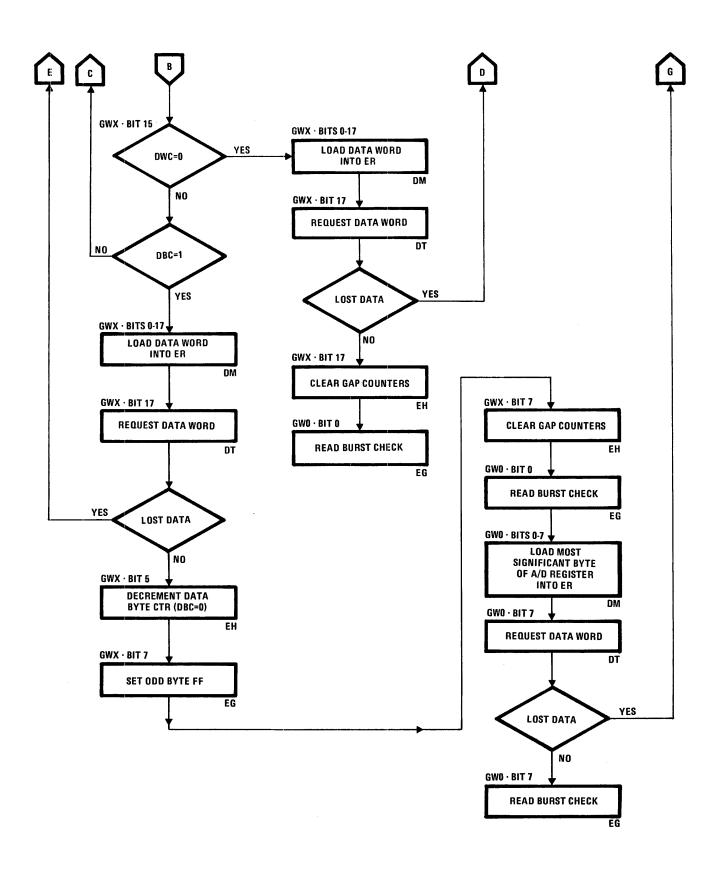

| 6-29   | Read Data Transfer                                     | 6-54  |

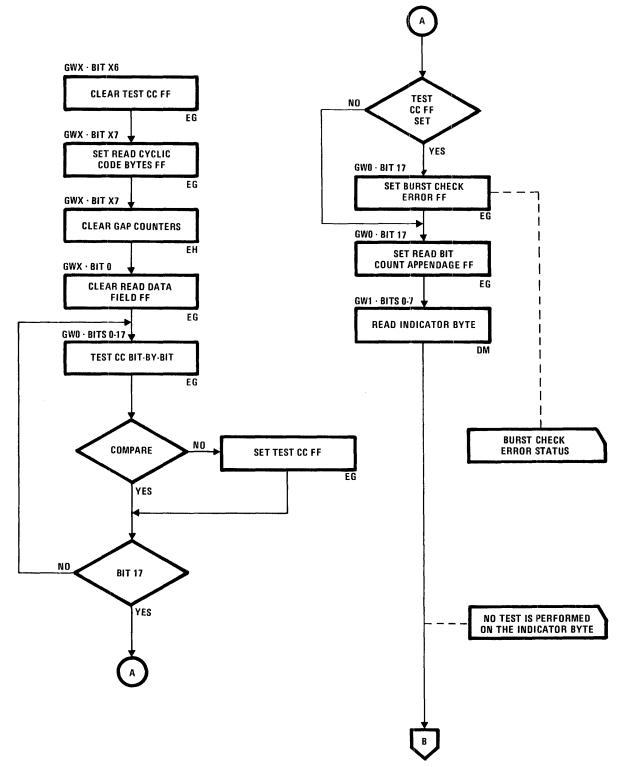

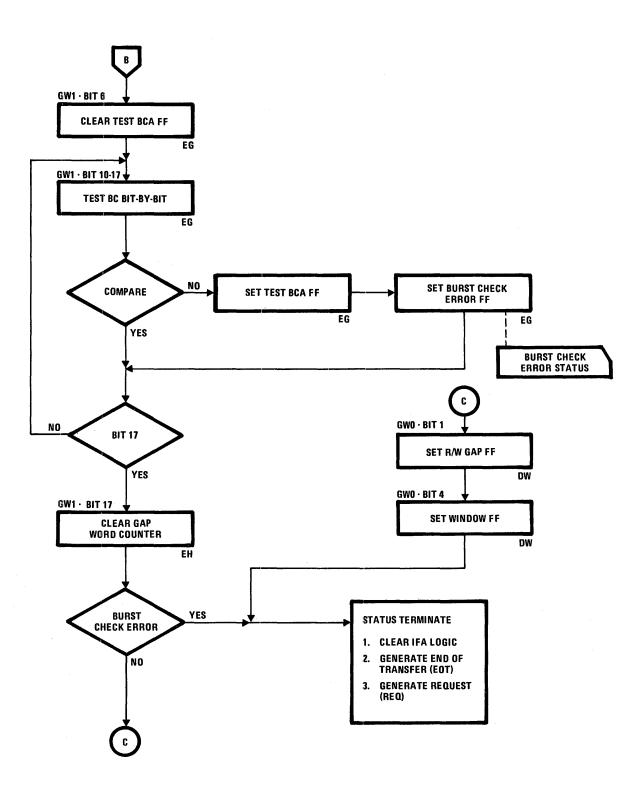

| 6-30   | Read Burst Check                                       | 6-56  |

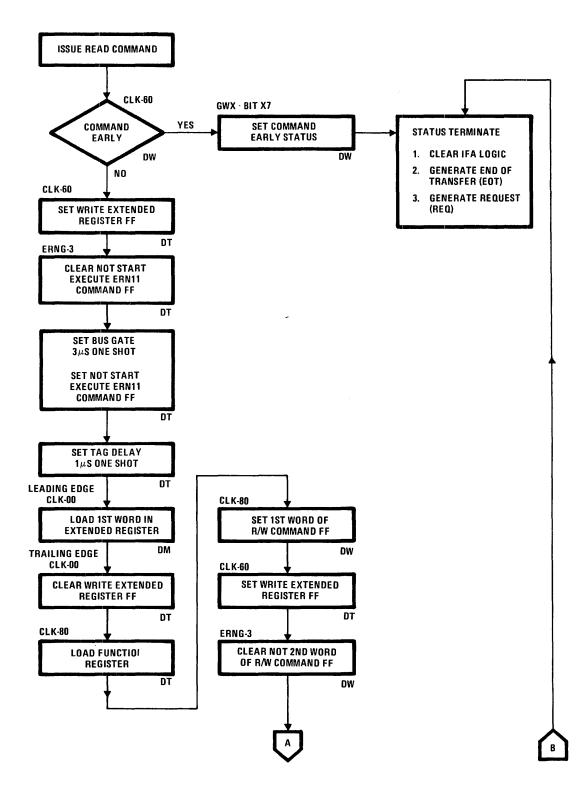

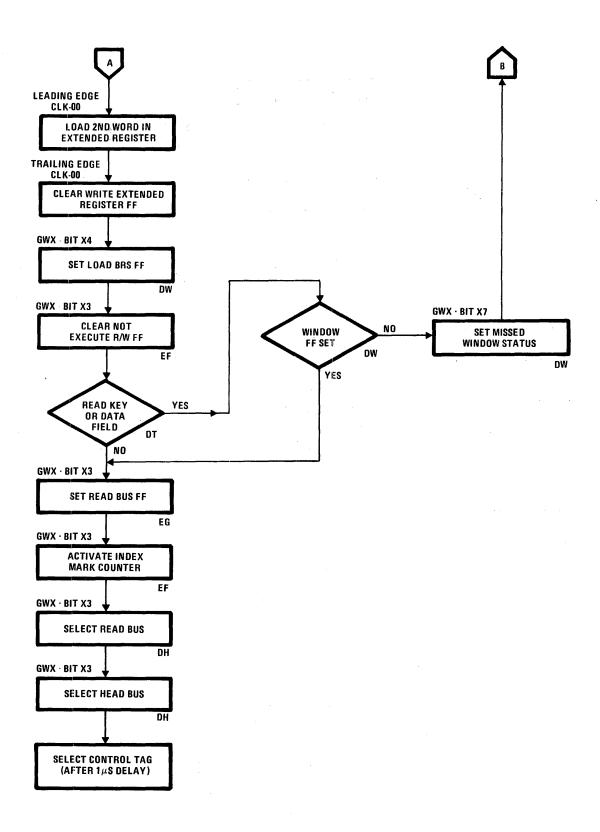

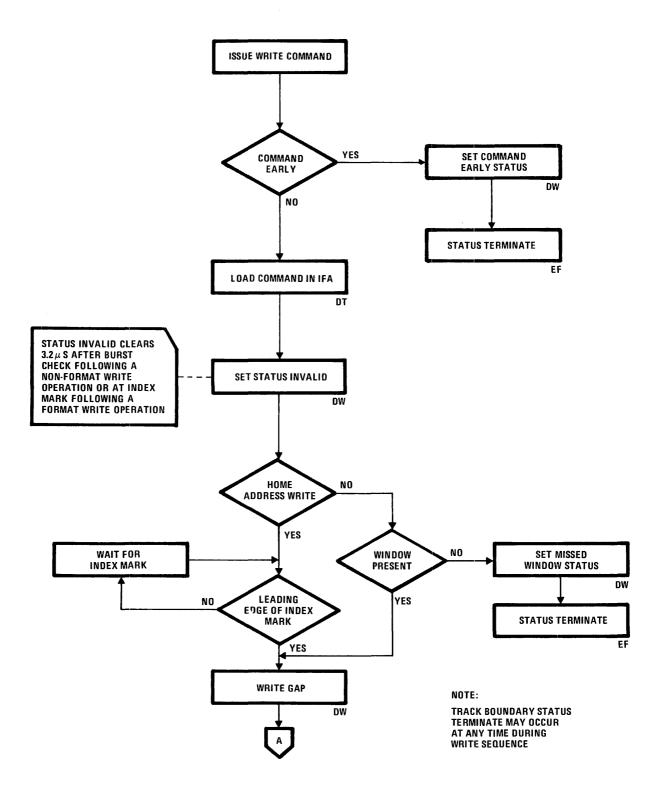

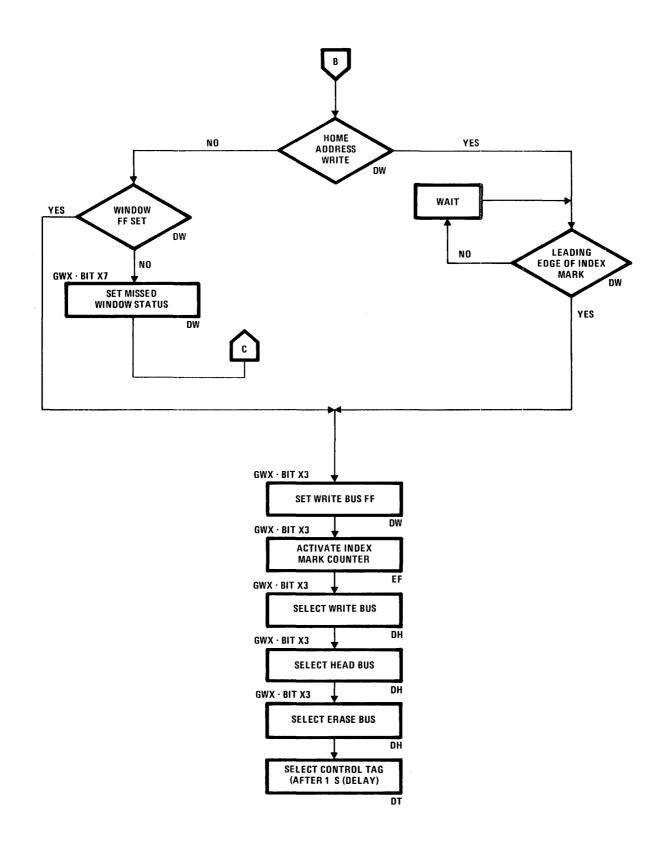

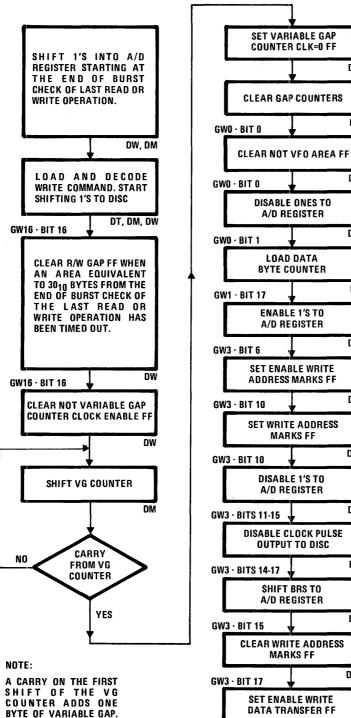

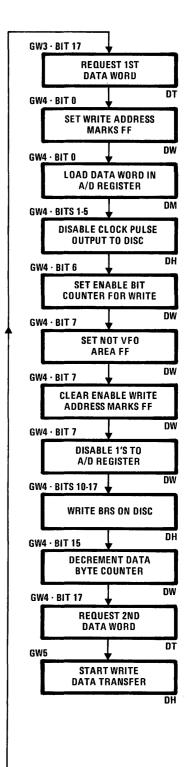

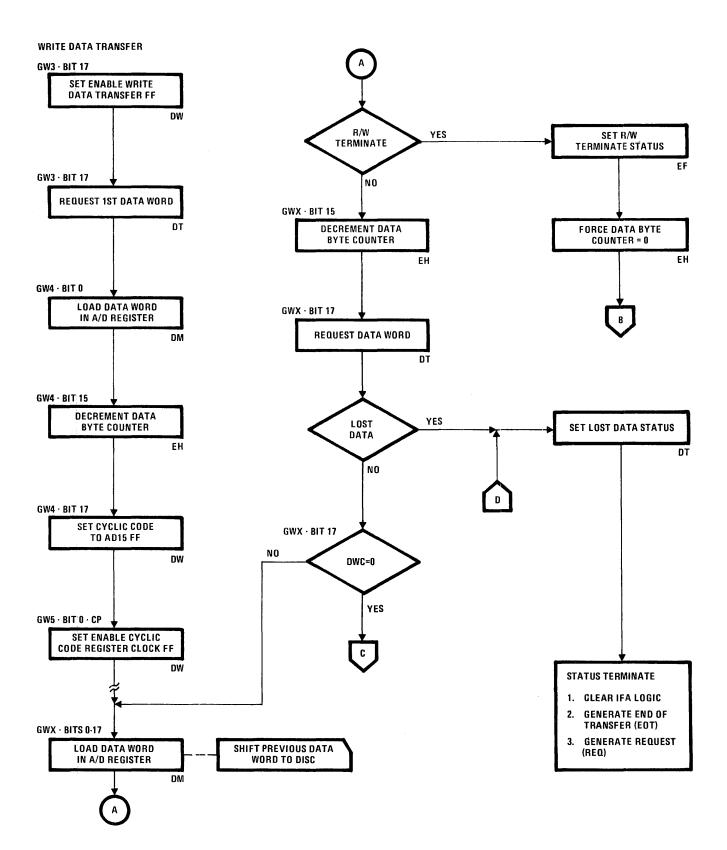

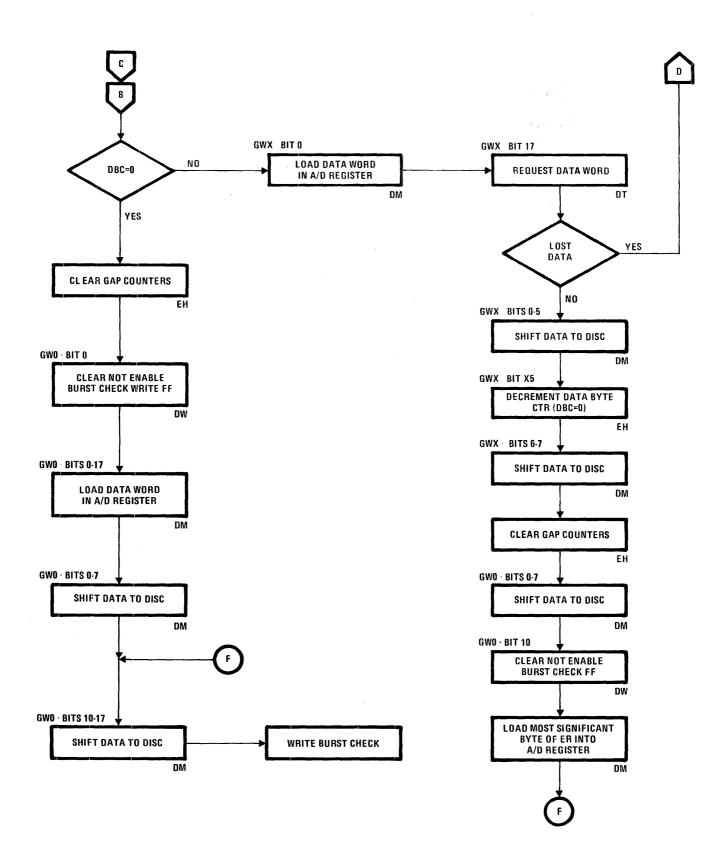

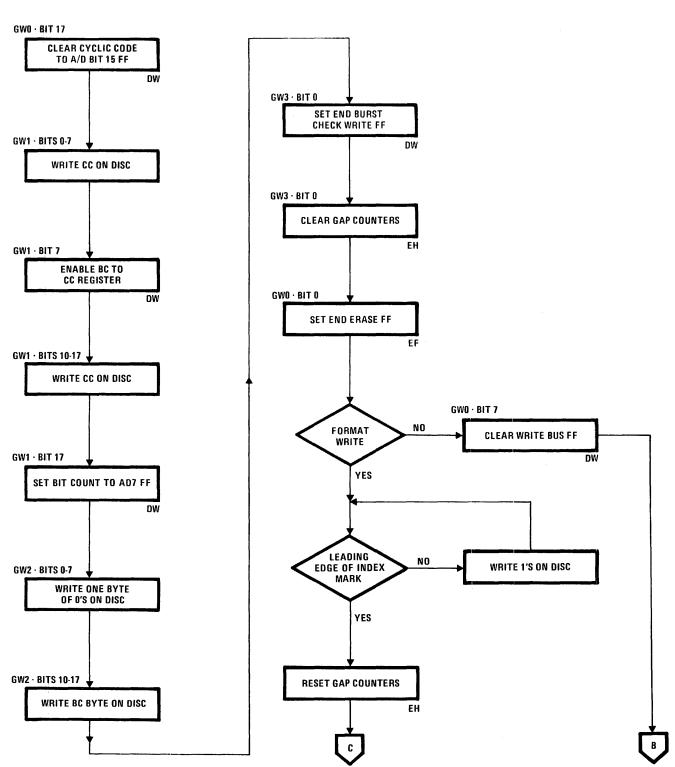

| 6-31   | Write Sequence                                         | 6-58  |

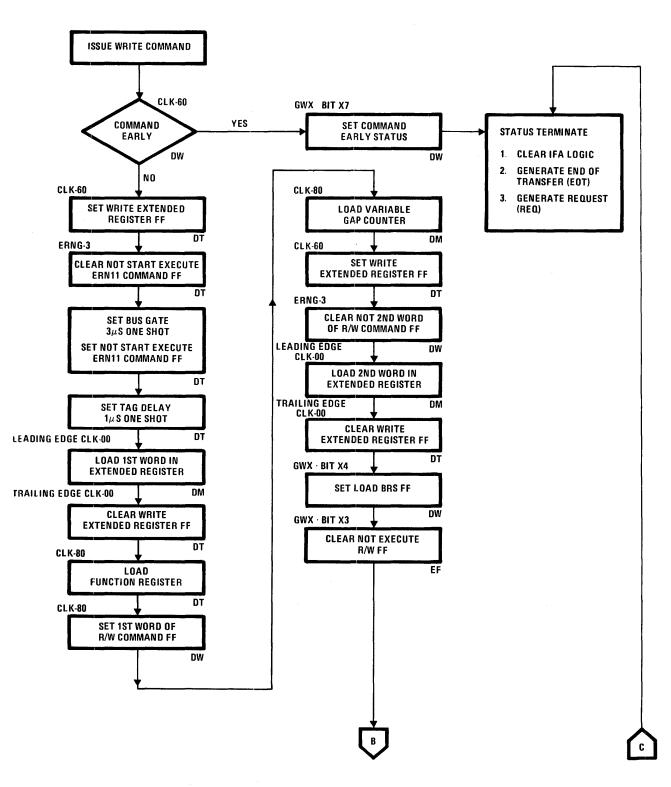

| 6-32   | Load Write Command                                     | 6-61  |

| 6-33   | Write Gap                                              | 6-63  |

# LIST OF FIGURES (Continued)

| Figure |                                                               | Page |

|--------|---------------------------------------------------------------|------|

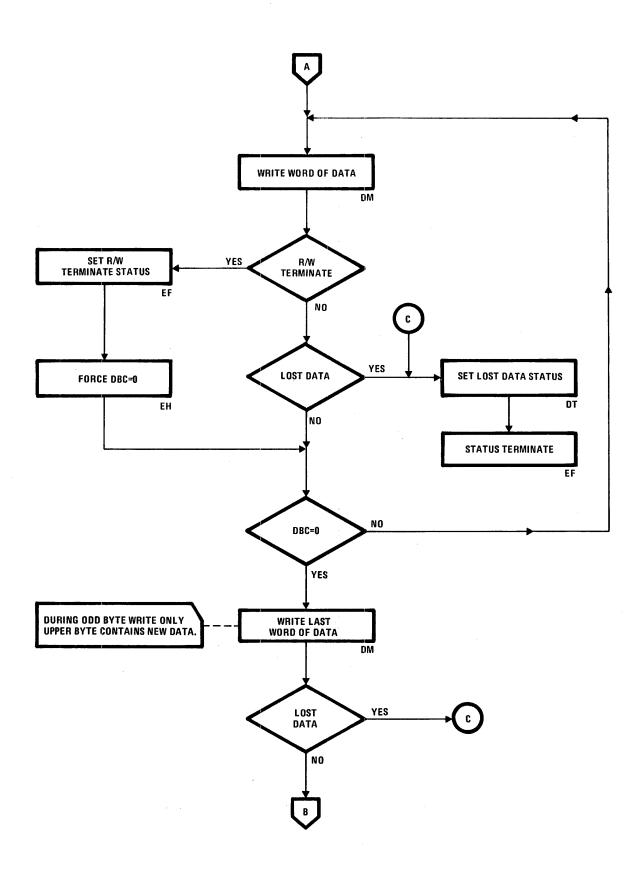

| 6-34   | Write Data Transfer                                           | 6-64 |

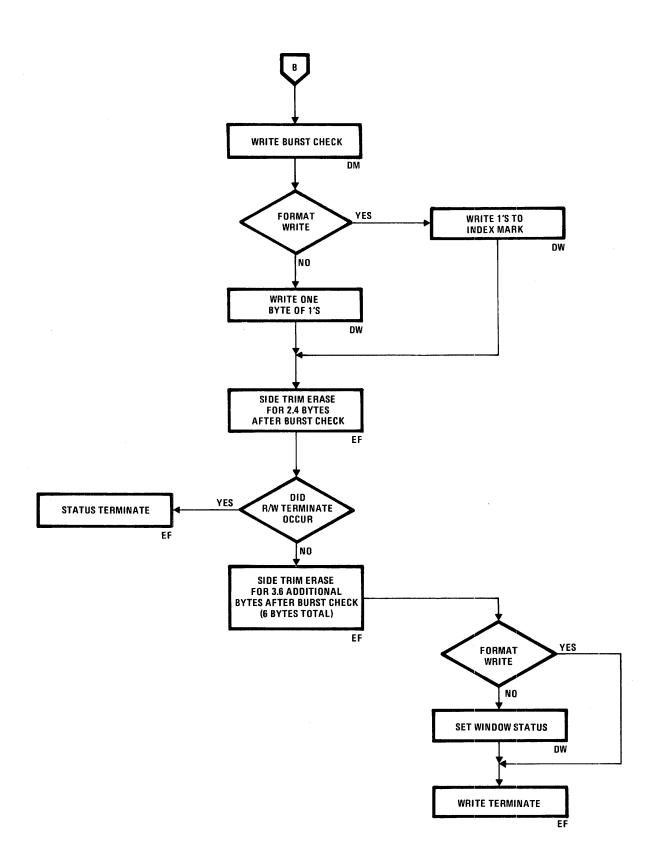

| 6-35   | Write Burst Check                                             | 6-66 |

| 6-36   | VFO Block Diagram                                             | 6-71 |

| 6-37   | Write Timing 1 (Start)                                        | 6-73 |

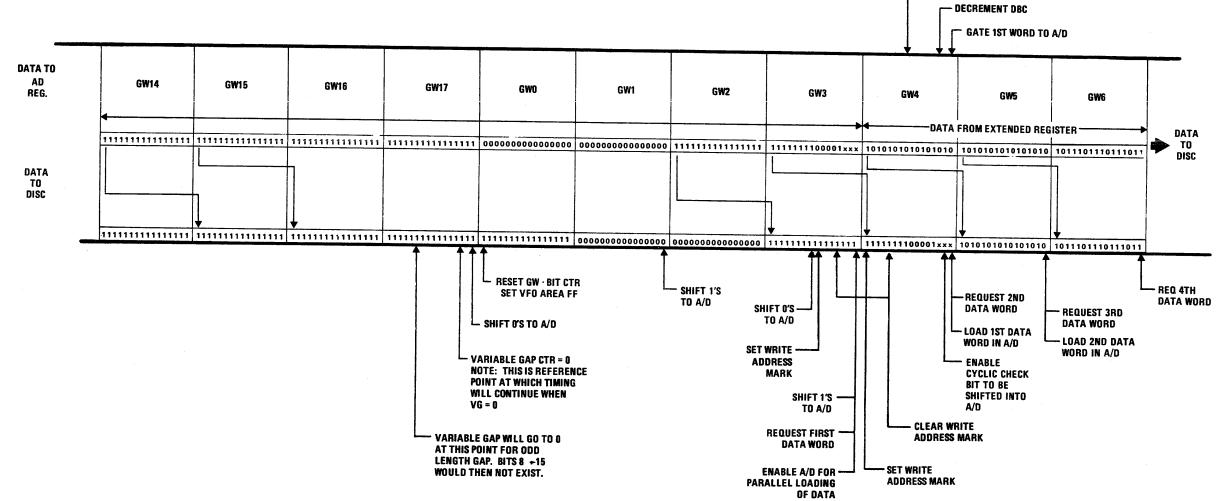

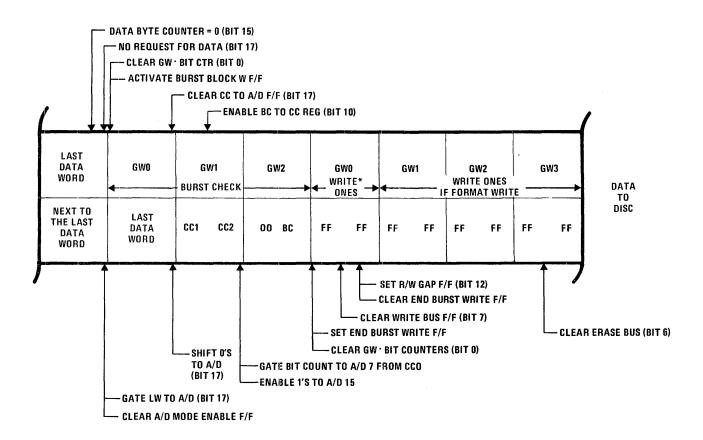

| 6-38   | Write Timing 2 (End)                                          | 6-75 |

| 6-39   | Odd Byte Write Timing                                         | 6-75 |

| 6-40   | Read Timing                                                   | 6-77 |

| 6-41   | Odd Byte Read Timing                                          | 6-79 |

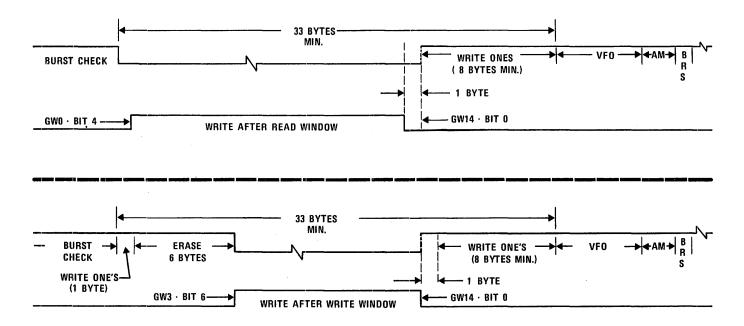

| 6-42   | Write After Read/Write After Write Ones Generation and Window | 6-79 |

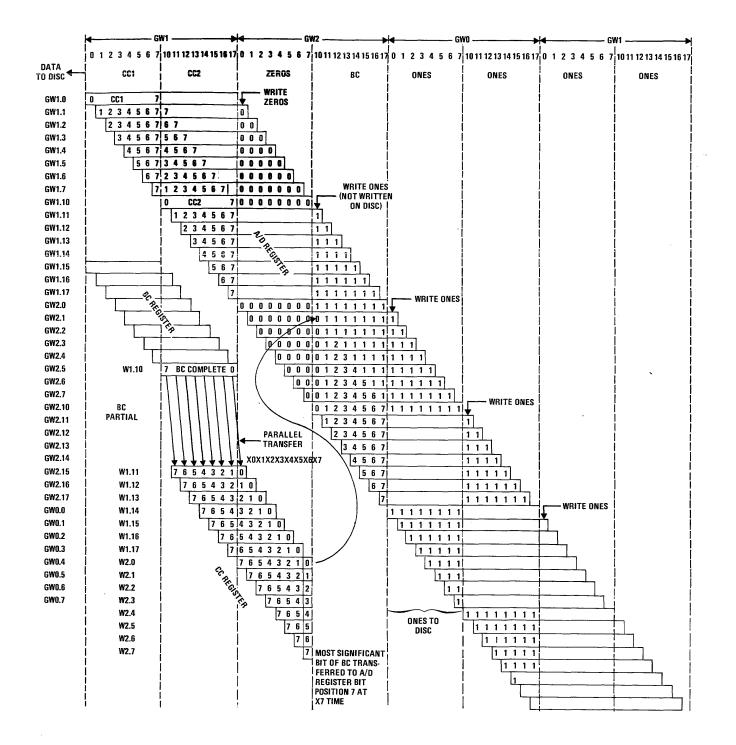

| 6-43   | Write CC and BCA                                              | 6-83 |

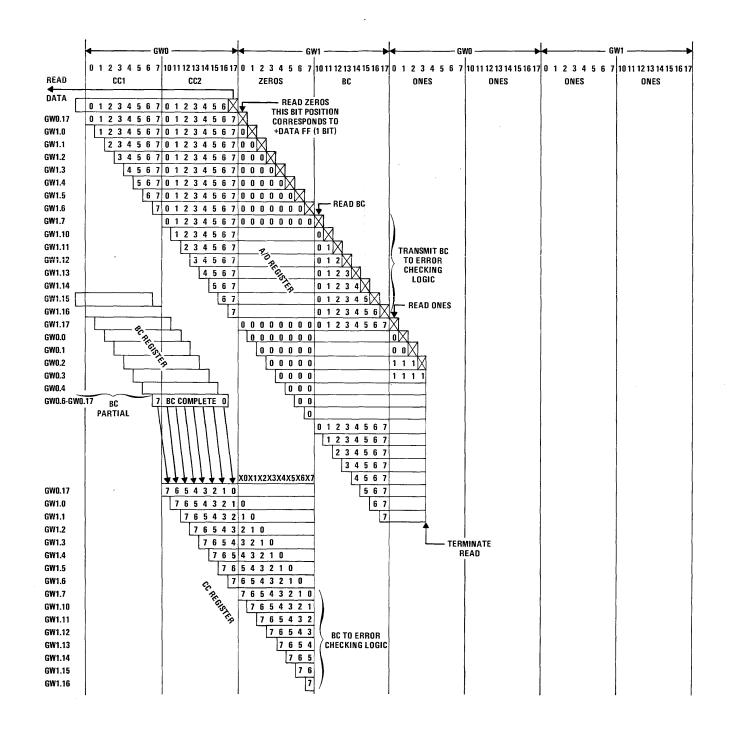

| 6-44   | Read CC and BCA                                               | 6-83 |

| 6-45   | Generate Cyclic Code                                          | 6-85 |

| 6-46   | Read Cyclic Code                                              | 6-86 |

| 6-47   | Generate BCA                                                  | 6-86 |

| 6-48   | Read Bit Count                                                | 6-87 |

| 6-49   | CS Load/MS Load Procedure                                     | 6-87 |

| 6-50   | CS Load Sequence                                              | 6-88 |

| 6A1    | Disc ML1 Flow Diagram                                         | 6A-1 |

# 4. BASIC DATA CHANNELS (BDC)

# INTRODUCTION

These processors' dedicated resources include the Basic Data Channel (BDC) logic (as a minimum), providing interface and control circuitry for communication with various peripheral equipments. Processor 2 circuitry also includes the Integrated Card Reader Adapter (ICRA) and the Integrated Reader/Punch Adapter (IRPA). The processor-state logic, functional capabilities, and characteristics of the two processor states are identical; the difference between them is that of the integrated adapters, absent in the BDC1 processor, and present in the BDC2 processor.

Both channels can communicate in the selector-channel mode with peripheral devices having external controllers. For BDC1, this is the only configuration possible; for BDC2, external assignments may be optional, depending upon the configuration.

Both the integrated adapters and external controllers contain the logic necessary to operate the I/O devices and to adapt device characteristics to the BDC format.

The processor-state logic, of which BDC logic is a principal control component, operates with the following characteristics:

- Only one I/O device is selected at a time.

- Once an I/O device is selected, it stays selected until a block of data (or, if data chaining is specified, a sequence of data blocks) is transferred.

- During basic data channel transfers, other devices may be executing operations not requiring basic data channel activity.

The processor states, in conjunction with the basic data channel logic, can perform the following operations with respect to adapters and control units connected to the channel.

• Select a device, dictate the device operation, and initiate and control the data transfer and termination under BDC2 software control.

- Select a device, dictate the device operation, allow the basic channel logic to initiate and maintain control of the data transfers (hardware operation).

- Respond to a device-initiated request, scan all devices, and determine (in order of priority) which device generated the request (polling).

- Select and read status indications from each I/O device.

- Perform data "turn-around" transfers within the basic data channel logic for diagnostic testing.

The basic data channels each have the following characteristics:

- 8-bit byte data transfers

- 16-bit data transfers to/from main storage when the Assembly/Disassembly option is present

- Parity generation and checking logic

- Basic data channel status indication logic

- Modular design

- Diagnostic capabilities

- Maximum data rate of 1110K bytes (7300) or 555K bytes (7200) per second.

- Hardware and software control of interface signals

- Ability to communicate with up to eight IBM 360/370 compatible external control units

# **BASIC DATA CHANNELS**

#### **GENERAL DESCRIPTION**

## **Channel Configuration**

The interconnection and positional relationship of the basic data channel logic, shared resources,

integrated adapters, local I/O devices, and external control units is shown in Figure 4-1. The tag lines (control) determine whether the information transferred on the parallel bus lines is data, status, address, or command information.

The start and termination of signals between the basic data channel logic and the control units and adapters are response-interlocked; that is, termination of one signal depends upon the initiation of a response signal. Interlocking allows channel communications with control units having different circuit speeds and data rates.

The integrated adapters and external control units communicate with the channel logic over a group of common signal lines. The common signal designation and the direction of travel are shown in Figure 4-2. Two cables carry all the common signal lines to the external control units. All the common signal lines are connected in parallel except the Select In and Select Out lines which are connected in a serial selection loop (see Figure 4-3). Each external control unit's selection circuitry is either in series with the Select In or the Select Out line. Regardless of which selection line is controlled by the selection circuitry, the control unit simply passes the other of the two selection signals to the next unit. Each control unit or adapter will disable the selection loop when selected, or will forward the selection signal to the next unit when not selected. This selection loop configuration and the channel logic provide two important features: polling and priority.

Polling enables the processor state program to select and service the control unit(s) and adapter(s), in order of priority, when an I/O operation has been requested by one or more control units or adapters. The priority scheme utilizes the fact that the external control units may be electronically connected into the Select Out or the Select In line with priority levels determined by their placement in this selection loop. For example, unit one in Figure 4-3 has the highest priority because it is connected first on the Select Out line and bypasses the Select In line, but it could become 4th in priority by being connected instead to the Select In line and bypassing the Select Out line.

The integrated adapters are always connected to the Select In line in the order of priority shown in Figure 4-3.

The Basic Data Channel logic and Integrated Adapter logic are contained on printed-circuit modules located in chassis one, row "C". The specific number of PC modules and their designation, location and function are shown in Figure 4-4. The basic data channel logic requires only two PC modules; the Assembly/Disassembly option is contained on an additional module, as is the External Interface logic.

# **Channel Requirements**

Control units and adapters connected to the Basic Data Channel must be compatible with the BDC requirements as described in the following paragraphs.

A complete selection loop is required regardless of the number of control units or adapters in the loop. External control units within the cabling chain may be bypassed and the integrity of the selection loop maintained by disconnecting the cables from a unit and mating the cable ends together. The last physically connected unit in the external cabling chain may be removed, temporarily, for maintenance purposes, and the selection loop integrity retained by disconnecting the two cables and two terminators from the unit and then mating the cable ends and terminators. The basic data channel logic routes the SELECT OUT signal to either the external control units (EXT INTF present) or to the integrated adapters. The channel bypass logic directs the SELECT IN signal to those adapters present. In BDC1, the SELECT IN signal received back from the EXT INTF receiver passes straight through the bypass logic since integrated adapters are not present, thus maintaining the selection loop (Figure 4-3).

A control unit, while in an off-line mode, must gate all of its line transmitters off to prevent interference with communications between the channel logic and the other control units and adapters. Likewise, a control unit in the power-off state must not interfere with the Basic Data Channel operation.

# Selection Loop Continuity

While in the off-line mode, each control unit must provide selection loop continuity by electrically bypassing the SELECT OUT signal. Each control unit must ensure that the method of bypassing the SELECT OUT signal in the power-off state does not interfere with the propagation of the SELECT OUT signal.

Each control unit must also ensure that SELECT OUT signal discontinuities, which may occur when another control unit on the external channel is powering up or down, do not affect the propagation of the SELECT OUT signal. One method of accomplishing this is by the use of a latch circuit. The latch is turned on by ANDing the SELECT OUT/IN signal and the HOLD OUT signal. The latch is turned off by the termination of the HOLD OUT signal. The latch circuit is in series with the control unit selection circuitry, providing a constant SELECT OUT/IN signal within the control unit, and therefore to the following control units, regardless of variations in the incoming SELECT OUT/IN signal.

The integrated adapters also ensure SELECT OUT signal continuity by the use of a similar latch circuit.

Figure 4-2. BDC Common Signal Lines

Figure 4-3. BDC Interconnection Diagram

Figure 4-4. Printed-Circuit Module Placement

#### Addressing

An eight-bit address is used to select the adapters, control units and I/O devices. The adapters and single device external control units are assigned a unique eight-bit address in the range of 0 through 255. The address is assigned to a control unit or adapter at the time of installation.

Multiple I/O devices controlled by one control unit are assigned addresses within a contiguous number set. The higher-order bit positions of the address within a set identify the control unit, and the lower-order bit positions identify the device.

Adapters and control units respond to their address whether their respective device is ready or not-ready. A not-ready condition is indicated by the *Unit Check* bit in the Status Byte and the *Intervention Required* bit in the sense byte.

If none of the adapters or control units recognize an address, the SELECT OUT signal returns as the SELECT IN signal. The addressed device appears as non-operational, which indicates one or more of the following conditions:

- the unit is not installed.

- the unit is in the off-line mode.

- the unit is in a power-down state.

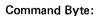

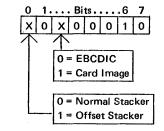

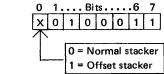

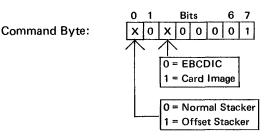

#### Command Byte

The Command Byte comprises eight bits of command information placed on the Bus Out lines. The Command Byte is decoded by the addressed adapter or control unit only during aBDC processor-initiated selection sequence. The low-order bit positions indicate the basic type of operation, and the high-order bit positions are a modification code for expanding basic operations at the adapter or I/O device.

The particular modifier and operation codes for external control units are specified in the appropriate equipment publication. The integrated adapter operation codes are detailed in the appropriate sections of this manual.

The Command Byte bit designations for the basic operations are listed below:

| Command       |    |   | Bit | Ро | siti | on | 5 |   |

|---------------|----|---|-----|----|------|----|---|---|

| *****         | 0  | 1 | 2   | 3  | 4    | 5  | 6 | 7 |

| Test I/O      | 0  | 0 | 0   | 0  | 0    | 0  | 0 | 0 |

| Sense         | M  | Μ | Μ   | Μ  | 0    | 1  | 0 | 0 |

| Read Backward | M  | М | Μ   | Μ  | 1    | 1  | 0 | 0 |

| Write         | M  | М | Μ   | Μ  | Μ    | Μ  | 0 | 1 |

| Read          | M  | Μ | Μ   | Μ  | Μ    | Μ  | 1 | 0 |

| Control       | ΙM | Μ | М   | Μ  | Μ    | М  | 1 | 1 |

M = Modifier Bit

- The *Read* command initiates the transfer of data from the control unit or adapter to the processor logic. The data is obtained from the recording media of the selected I/O device.

- The *Read Backward* command also initiates data transfer to the channel as does the *Read* command. With the *Read Backward* command, the data bytes are transferred from the adapter or control unit in reverse order to that of the *Read* command.

- The *Write* command initiates the transfer of data from the processor logic to the adapter or control unit.

- The *Control* command initiates a function or operation in the adapter or control unit as determined by the modifier bits. A *Control* command may use second level addressing requiring several bytes of data to complete the control operation, or it may initiate film advance as in the MEMOREX Model 1603 Microfilm Printer.

A *Control* command with all-zero modifier bits performs no operation at the adapter or control unit but does allow time for certain control units to check conditions before releasing the channel processor.

• The Sense command proceeds as does a *Read* command, only the data transferred is obtained from the selected sense points within the unit rather than from a record source.

A Sense command with all-zero modifiers is a basic Sense command to all adapters and control units and will not initiate any operation other than sensing. The basic Sense command to an available control unit is accepted even though the addressed device is in a not-ready state.

• The *Test 1/O* command requests status information from the addressed adapter or control unit. If status information is available, the status bits are placed on the Bus In lines to the channel logic. If no outstanding status information is available, a zero Status Byte is placed on the Bus In lines (see Status Information). If the selected adapter or control unit is still performing the previous operation, status information is not available and, as such, only the *Busy* bit is presented as status information.

A *Test I/O* command byte during a processor-initiated selection sequence does not initiate an operation as do the other Command Byte codes.

#### **Status Information**

The information on the Bus In lines is a Status Byte when the STAT IN signal is active. The Status Byte shows the status indications of the control unit or adapter whose address appeared on the Bus In lines when ADRS IN was active. During the short-busy sequence when no ADRS IN signal occurs, it is assumed that the status information pertains to the addressed control unit, device, or adapter.

The timing and causes of the status information for the external control units is specified in the appropriate equipment publications.

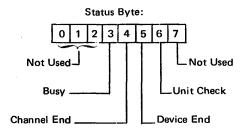

The Status Byte has the following format on the channel Bus In lines.

| <b>Bit Position</b> | Designation      |

|---------------------|------------------|

| Р                   | Parity           |

| 0                   | Attention        |

| 1                   | Status Modifier  |

| 2                   | Control Unit End |

| 3                   | Busy             |

| 4                   | Channel End      |

| 5                   | Device End       |

| 6                   | Unit Check       |

| 7                   | Unit Exception   |

Once the status indication is accepted by the processor, it is cleared and not presented again. The Status Byte is transferred to the channel in the following situations:

- To indicate the initial-selection status.

- To indicate the *Channel End* status at the termination of data transfer.

- To indicate the *Device End* and associated conditions to the processor logic. The I/O device remains busy during an operation until the processor accepts the *Device End* status indication.

- To indicate *Control Unit End* or *Device End* status which signals that a control unit or device that was busy had been interrogated and is now free.

- To indicate any previously stacked status when allowed to do so.

- To indicate any externally initiated status to the channel (*Attention* and/or *Device End* because of not-ready-to-ready transition).

The following is a brief description of the Status Byte bit meanings.

• Attention: This state is generated when some asynchronous condition occurs in the

I/O device. Attention is not associated with initiation, execution, or termination of any input/output operations, but may occur with Device End.

- Status Modifier: This bit is used by control units in the following situations:

- 1) During an initial selection sequence control, units unable to provide current status-in response to a *Test I/O* command present the *Status Modifier* bit alone.

- 2) Shared control units present the *Status Modifier* bit with the *Busy* bit during initial selection sequence to differentiate a busy control unit from a busy device.

- 3) Control units designed to recognize special ending conditions (Search Equal on a disk) present the Status Modifier bit with Device End when the condition occurs.

- 4) Control units capable of requesting a retry of a command, in order to recover from a transient error, or because the state of the control unit or device prevented the execution of the command when it was previously issued present the Status Modifier bit with Channel End and Unit Check and Mark In tag line.

- Control Unit End: These conditions are provided only by shared control units or control units with multiple I/O devices, and only when one or both of the following conditions occur:

- 1) The control unit was interrogated while it was in the busy state.

- 2) The control unit detected an unusual condition while busy, but after Channel End was accepted.

- Busy: This can occur only during a Basic Data Channel-initiated selection sequence, and indicates that the control unit or adapter cannot execute the command because a previously initiated operation is being executed or because outstanding status conditions exist. An operation is being executed from status acceptance during initial selection until *Device End* acceptance.

Busy is indicated to Test I/O only if a previously initiated operation is still being executed and no end status is available.

• Channel End: This is caused by the completion of the data transfer portion of an input or output operation. Each operation causes only one *Channel End* status.

For the adapters, the *Channel End* condition occurs on completion of the data transfer between the adapter buffer and the channel. During Control operations, *Channel End* is usually generated after the control information is transferred to the control unit or adapter; although for short operations it may be delayed until end of the operation. Operations that do not involve data transfer provide the *Channel End* condition during the initial selection sequence (immediate commands).

- Device End: This is caused by the completion of an I/O operation at the I/O device; it indicates overall completion of the current operation. Each I/O operation causes only one *Device End* condition. It is generated either simultaneously with the *Channel End* or presented later.

- Unit Check: This situation indicates the I/O device, control unit, or adapter has detected an unusual condition that is detailed by the information available to a *Sense* command. An error condition causes the *Unit Check* indication only when it occurs during execution of a command or during some activity associated with an I/O operation.

Unless the command is designed to cause Unit Check (such as Rewind And Unload on magnetic tape), it is not indicated if the command is properly executed even though the device has become not-ready during, or as a result of, the operation. Similarly, Unit Check is not indicated if the command can be executed with the device not-ready.

If, during an initial selection sequence, the device detects that the command cannot be executed, *Unit Check* is presented to the processor and it appears without *Channel End, Control Unit End*, or *Device End*. Such unit status indicates that no action has been taken at the *Device In* response to the command.

• Unit Exception: This means that the I/O device detected an unusual condition such as end-of-file. This code has only one meaning for any particular command and type of I/O device. A *Sense* operation is not required as a response to the acceptance of a *Unit Exception* condition.

A Unit Exception condition can be generated only when the I/O device is executing an I/O operation, or when the device is involved with some activity associated with an I/O operation and the condition is of immediate significance. If a device detects a Unit Exception condition during the initial-selection sequence, it is presented without *Channel End*, *Control Unit End*, or *Device End*.

## Sense Information

This information is presented in response to a *Sense* command during a BDC-initiated selection sequence. (See *Sense* under Command Byte.) The information provided by a basic sense operation is more detailed than that supplied by the Status Byte. The Sense Bytes, for example, may describe reasons for the *Unit Check* indication in the Status Byte or may indicate when a device is in the not-ready state.

All sense information significant to the use of the I/O device is usually provided in the first two Sense Bytes. The amount and meaning of the sense information is peculiar to each type of I/O device and is specified in the appropriate equipment publication.

The sense information from the last I/O operation or control unit action is cleared by the next command addressed to that control unit, provided the *Busy* bit was not set in the *Initial Selection* Status Byte and the command is addressed to the device that causes the sense. The commands *Sense, Test I/O* or *No-Operation,* presented to that device, will not clear the sense information.

Sense information may also be generated or changed as a result of asynchronous actions of the device.

A command code with invalid parity causes the sense information to be replaced with the new sense information which contains Bus Out Check.

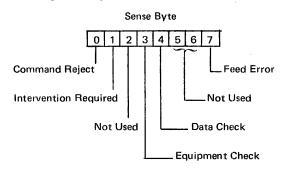

The first six bits of the first sense byte have the same designation for all I/O devices:

| Bit Position | Description           |  |  |

|--------------|-----------------------|--|--|

| 0            | Command Reject        |  |  |

| 1            | Intervention Required |  |  |

| 2            | Bus Out Check         |  |  |

| 3            | Equipment Check       |  |  |

| 4            | Data Check            |  |  |

| 5            | l Over Run            |  |  |

- The Command Reject condition occurs when the device receives a command it is not designed to execute, receives a command it cannot execute because of its present state, or recognizes an invalid sequence of commands.

- Intervention Required is generated when the last operation could not be executed because of a condition that requires intervention at the I/O device. This bit indicates conditions such as an empty magazine (hopper) in a card punch or a lack of paper in the printer.

*Intervention Required* is also turned on when the addressed device is in the not-ready state, is in a test mode, or is not connected to the control unit.

- Bus Out Check results when the external control units receive a Data Byte or a Command Byte with invalid parity. Invalid parity in an output Data Byte does not cause the operation to be terminated prematurely, whereas invalid parity in a Command Byte does prevent command execution.

- Equipment Check indicates detection of an equipment malfunction in the adapter, control unit or I/O device. It stops transmission and terminates the operation prematurely.

- Data Check is generated when invalid data has been detected by the control unit during the reading of data from the record source. The control unit forces correct parity on the data sent to the processor logic via the external channel. During writing operations Data Check indicates invalid data may have been recorded at the I/O device. Data Check causes premature termination only when the errors prevent meaningful continuation of the operation.

- Overrun results when the processor logic fails to respond on time to a request for service from a non-buffered adapter or a control unit operating with a moving medium. On an output operation, Overrun indicates the data recorded on the device may be invalid. This normally stops data transfer and terminates the operation in the same manner as a Stop sequence control (discussed later).

*Overrun* conditions also occur during command chaining when the I/O device receives the new command too late.

# Signal Interlock Summary

The following list of direct-current interlocking signal rules must be adhered to by all adapter and control units using either Basic Data Channel.

- 1. No more than one bus-in identifier may be active at any given time, except for the possible overlap of DAT IN and SRV IN.

- 2. A bus-in identifier may become active only when all bus-out identifiers are inactive, except during the short-busy or high speed data transfer sequences.

- 3. A bus-in identifier may go inactive only after the activation of a responding bus-out identifier, except for STATUS IN in the short busy sequence.

- 4. OPERATIONAL IN cannot go active unless OPERATIONAL OUT is active, and must terminate if OPERATIONAL OUT terminates.

- 5. OPERATIONAL IN cannot terminate until either:

- SELECT OUT ends, and a bus-out identifier is active in response to the last bus-in identifier of any sequence.

- OPERATIONAL OUT terminates.

- an interface-disconnect control signal is given.

- 6. During an interface-disconnect operation ADDRESS OUT is the only signal which may be active with other bus-out identifiers.

- 7. None of the outgoing common signals lines, except SUPPRESS OUT, have meaning when OPERATIONAL OUT is inactive.

- 8. SELECT OUT can go active only if OPERATIONAL IN and SELECT IN are inactive.

- 9. SERVICE OUT, DATA OUT and COMMAND OUT can go active only in response to an active bus-in identifier.

- 10. A D D R E S S O U T for a processor-initiated selection sequence can go active only if SELECT IN and SELECT OUT are inactive in the processor logic.

- 11. Once ADDRESS OUT has become active for the interface disconnect operation it must not end until OPERATIONAL IN terminates.

- 12. Once ADDRESS OUT and SELECT OUT have become active during a processor-initiated selection sequence, ADDRESS OUT must stay active until after SELECT IN or OPERATIONAL IN becomes active (or if in a short-busy response, until after STATUS IN goes inactive).

# **Basic Data Channel Control Instructions**

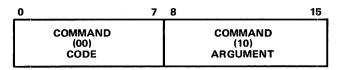

The three machine-language instructions (MLI's) used by the processor state to communicate with the I/O devices via the Basic Data Channel processor logic are as follows:

- Input from I/O register (INP)

- Output to I/O register (OUT)

- System I/O (SIO)

These instructions deal with the processor state's Extended register file, Group III, which comprises the five registers residing in the Basic Data Channel logic.

The microprograms which implement the above MLI's use Store Register and Load Register micro-instructions in communicating with the extended registers. Store Register micro-instructions transfer information from a shared resources register to one or more of the Extended registers in the BDC logic. The Load Register micro-instructions transfer information from the extended registers in the BDC logic to a shared resources register.

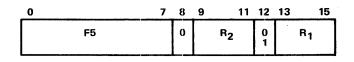

The 4-bit  $R_2$  portion of the *INP* and *OUT* instruction is the Extended register designator. This 4-bit designation is sent out through the I-O register select logic as Extended Register Number Group Three (ERNG3) bits 00, 01, 02 and 03.

The SIO instruction does not contain an Extended register designator at the machine-language level. The micro-instructions within the SIO microprogram contain the Extended register numbers required.

The five Extended registers in the Basic Data Channel logic are selected using an ERNG3 bit-oriented scheme. The relationship between the ERNG3 bits of a store-register micro-instruction and the Basic Data Channel register(s) selected is shown in Table 4-1.

Table 4-1. ERNG3 Bit Assignment: Store Micro-Instruction

|    | ERNG3 Bits |    |    | Extended File Register Written    |

|----|------------|----|----|-----------------------------------|

| 00 | 01         | 02 | 03 | (Destination)                     |

| 0  | 0          | 0  | 1  | Tag Out Register (TOR)            |

| 0  | 0          | 1  | 0  | Channel Control Register<br>(CCR) |

| 0  | 1          | 0  | 0  | Bus Out Register (BOR)            |

| 1  | 0          | 0  | 0  | Byte Count Register<br>(BCR)      |

| 1  | 1          | 1  | 1  | TOR, CCR, BOR and BCR             |

| 0  | 0          | 0  | 0  | None                              |

A Load Register micro-instruction transfers information from four Basic Data Channel registers and the Tag In lines. The registers and/or lines read are selected by the ERNG3 bits as shown in Table 4-2.

Table 4-2. ERNG3 Bit Assignment: Load Micro-Instruction

|    | ERNG3 Bits |    |    | Extended File Registers Read |  |

|----|------------|----|----|------------------------------|--|

| 00 | 01         | 02 | 03 | (Source)                     |  |

| X  | х          | 0  | 0  | Bus In Register (BIR)        |  |

| ×  | х          | 0  | 1  | TAG IN Lines and TOR         |  |

| ×  | х          | 1  | 0  | CCR                          |  |

| x  | х          | 1  | 1  | BCR                          |  |

# LOGIC DESCRIPTION

# **Block Diagram**

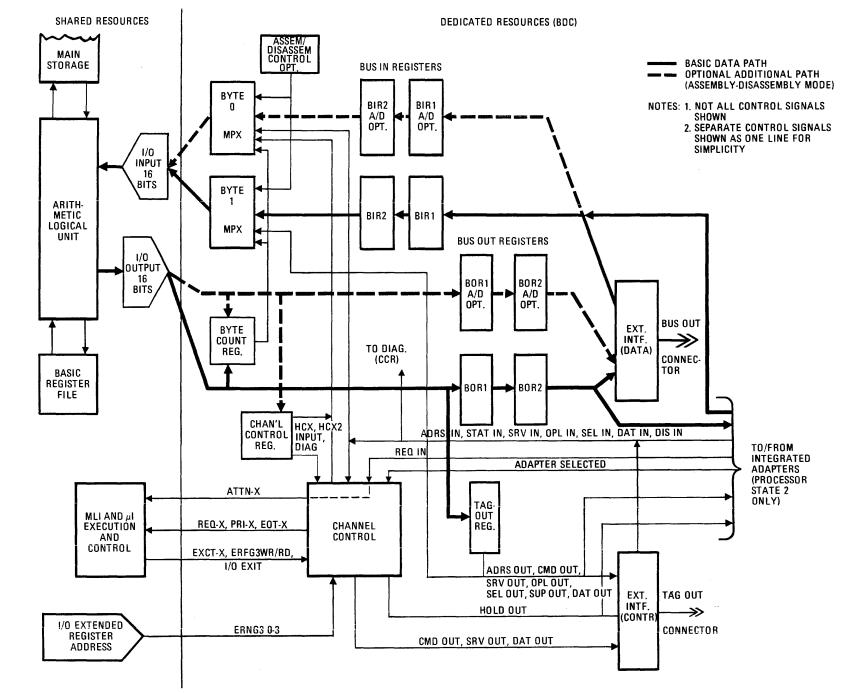

The logic for a Basic Data Channel processor state contains two 8-bit data-handling registers (Bus Out and Bus In); two control registers (Channel Control and Tag Out); two 8-bit multiplexers (Byte 0 and Byte 1); a 16-bit Byte Count register; and associated control logic as shown in the block diagram (Figure 4-5). The signal relationships and data paths between the shared resources, the Basic Data Channel logic, and the adapters and external control units are also shown.

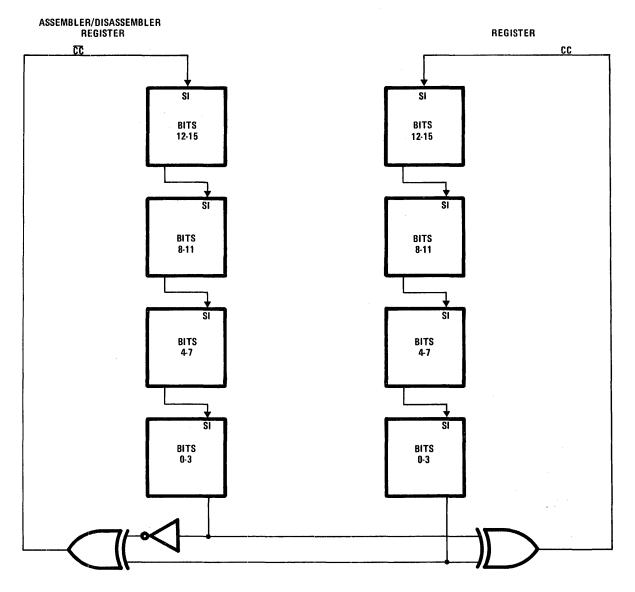

The expansion of the Bus In and Bus Out registers and data paths for the Assembly/Disassembly option is indicated by the shaded area. This option also expands the Channel Control register by adding the Assembly/Disassembly flip-flop.

# **Register Functions**

### Bus Out Register (BOR)

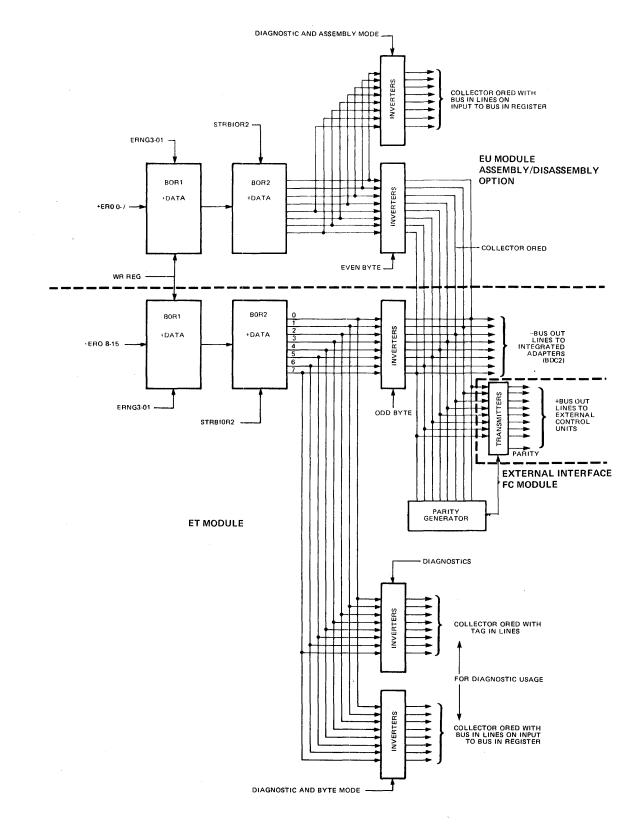

Information placed in the BOR originates in either a processor state's Basic register file or main storage and is transferred via lines 8 through 15 of the Extended Register Output (ERO) data path (Figure 4-6), when the Assembly/Disassembly option is not present. The contents of the BOR are interpreted by the adapters and control units as *device address, command,* or *data* as directed by individual Tag Out lines.

The BOR is a double rank register with each rank consisting of two 4-bit register MSI elements. The input clocking to the first rank (BOR1) is the WRITE REGISTER (WR REG) signal. It is enabled only when extended register number group 3, bit position one (ERNG3-01) is set. The contents of rank one is gated into rank two (BOR2) by STRBIOR2 signal generated by the control logic. The eight BOR2 outputs are enabled through a rank of inverters to the integrated adapters (BDC2) and the transmitters on the external interface board, with the ODD BYT signal. The ODD BYT signal is produced by the BYT MD signal which is always active when the Assembly/Disassembly option is not present.

A parity bit is also generated and sent to the external control units via the EXT INTF module. The PARITY Bus Out signal is used to maintain odd parity (an odd number of 1's including parity bit) on the nine Bus Out lines. The parity generating element monitors the BOR2 contents and places a logic 1 or a logic 0 on the Parity Bus Out line depending on the number of logic 1's contained in the BOR2.

Information placed in the BOR is transferred from the shared resources using all sixteen ERO data paths, when the Assembly/Disassembly option is present (Figure 4-6). The BOR becomes a sixteen-bit double-rank register utilizing the same enables and clocking signals. The sixteen BOR2 outputs are enabled through a rank of inverters to the integrated adapters (BDC2) and the transmitters on the external interface board one byte at a time.

The Odd Byte flip-flop, on the Extended register board, is used to control enabling by the BDC processor logic. The Odd Byte flip-flop stays set (enabling odd byte) during all sequences except the hardware-controlled data transfer sequences. During this sequence the Odd Byte flip-flop changes state after each byte transfer, thus alternately enabling odd (bits 8-15) and even (bits 0-7) bytes. Of course this only happens when the Assembly/Disassembly option is present and the Assembly/Disassembly Mode flip-flop in the Channel Control register is set. When the Assembly/Disassembly Mode flip-flop is clear (BYT MD) and the option is present the BDC1 still performs straight byte transfers just as though the option were not present.

# Bus In Register (BIR)

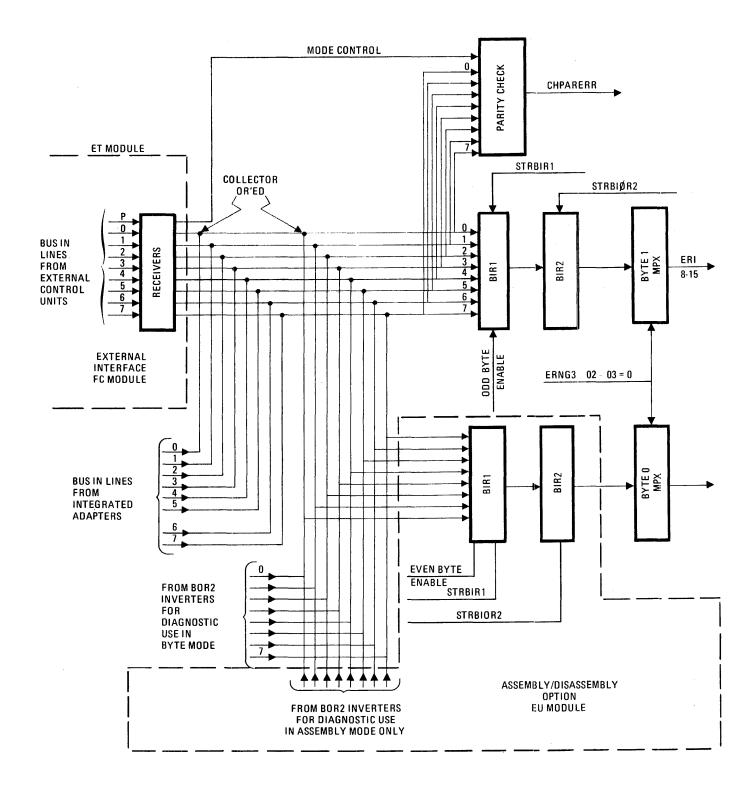

The BIR is also a double-rank register with each rank consisting of two 4-bit register MSI elements when the Assembly/Disassembly option is not present. The register inputs are clocked into rank one (BIR1) by the STR BIR1 signal when the odd byte enable is present. BIR information can indicate status, device address, or data as determined by a specific Tag In line.

Figure 4-7 is a functional block diagram of the bus-in configuration. The BIR inputs connect directly to the eight Bus In lines from the integrated adapters and to eight of the Bus In Line Receivers on the external interface module. The BOR2 output is also connected through one stage of inversion to the BIR1 input and is enabled only during diagnostic operations.

The eight BIR input lines also connect to the parity check element inputs. The PARITY Bus In signal from the external control units controls the parity check mode. When the PARITY Bus In signal is a logic 1, it places the parity checker in the even mode, checking for an even number of 1's on the BIR1 inputs. Conversely, if the PARITY Bus In signal is a logic 0, it places the parity checker in the odd mode, checking for an odd number of 1's.

The parity check element monitors the nine Bus In lines, checking for an odd number of 1's, and indicates a parity error, when detected, with the CHANNEL PARITY ERROR (CHPARERR) signal.

The contents of BIR1 are gated into BIR2 by the STRBIOR2 signal generated by the control logic. Information leaving the BIR2 is selected via the Byte One multiplexer for the Extended register input (ERI) bits 8 through 15. The BIR2 output is selected when Extended Register Number Group Three bit positions 2 and 3 are clear.

Figure 4-5. BDC Processor Block Diagram

Figure 4-6. Bus Out Configuration

Figure 4-7. Bus In Configuration

The BIR also becomes a 16-bit double-rank register when the Assembly/Disassembly option is present (Figure 4-7). The eight bits of information from the integrated adapters or from the external interface module are clocked into both halves of rank 1 by the STR BIR1 signal. Into which half of the BIR the information is enabled is controlled by the Odd Byte flip-flop. During data transfer sequences the Odd Byte flip-flop changes state after each data transfer, thus alternately enabling the data into the odd byte (bits 8-15) and the even byte (bits 0-7) halves of the register.

The Odd Byte flip-flop is controlled by the hardware data transfer logic on the ER board. As with the BOR, the Odd Byte flip-flop is set for all sequences except the data transfer. Therefore, the even byte (0-7) half of the BIR is only used during data transfers, provided the Assembly/Disassembly option is present and the Assembly/Disassembly Mode flip-flop in the CCR is in the *assembly* state (set).

All sixteen bits of information from BIR2 are selected via the input multiplexers and placed on the ERI 0-15 data paths to the shared resources during data transfer sequences. The BOR2 output which is added when the Assembly/Disassembly module is present is also connected to the BIR input for use during diagnostic operations in the assembly mode.

### **Tag Out Register (TOR)**

The TOR (logic page 1C14) consists of two 4-bit register MSI elements, the same as BOR1. The TOR input is clocked by the WRITE REGISTER (WR REG) signal, but is enabled only when ERNG3-03 is present. TOR inputs connect to the ERO bits 8-15 through one stage of inversion. Seven of the eight TOR FF's hold bus-out identification, interlock and scan control information. The TOR bit assignment is listed in Table 4-3.

| Bit<br>Position | Title              | Abbreviation | Function                           |

|-----------------|--------------------|--------------|------------------------------------|

| 8               | Address Out        | ADRS OUT     | Bus Out ID                         |

| 9               | Command Out        | CMD OUT      | Bus Out ID                         |

| 10              | Service Out        | SRV OUT      | Bus Out ID                         |

| 11              | Operational<br>Out | OPL OUT      | Channel<br>Enable and<br>Interlock |

| 12              | Select Out         | SEL OUT      | Scan Control                       |

|                 | Hold Out           | HLD OUT      | Scan Control                       |

| 13              | Suppress Out       | SUP OUT      | Scan Con-<br>trol and<br>Interlock |

| 14              | Data Out           | DAT OUT      | Bus Out ID                         |

| 15              | Not Used           |              |                                    |

Table 4-3. Tag Out Register

All TOR outputs (except SEL OUT) connect directly to the integrated adapters and through the external interface module transmitters to the external control units. The Basic Data Channel control logic also utilizes the TOR information during operational sequences. The contents of the TOR may also be routed through the Byte One Multiplexer to the ERI lines 8 through 15.

The following paragraphs provide a brief definition of the TAG OUT signals. An in-depth discussion of the channel logic usage of the TAG OUT signals and Tag In lines is included in the operational sequences presentation.

- Address Out: This signal indicates the information on the Bus Out lines is an I/O device address and all adapters and control units are to decode it.

- Command Out: This signal is sent to the selected adapter or control unit during initial selection to indicate that the Bus Out lines contain a command byte. During other sequences this signal is sent in response to three of the TAG IN signals: in response to ADRS IN it means *proceed*, in response to STAT IN, it means *stack status*, and in response to SRV IN or DAT IN, it means *stop*.

- Service Out: This signal is sent to the selected adapter or control unit in response to SRV IN or STAT IN signals. A SERVICE OUT signal indicates the processor has accepted or presented data or has accepted status information.

# NOTE

The COMMAND OUT, SERVICE OUT and DATA OUT Tag Out signals are also controlled by the channel control logic as well as by the TOR (page 1C13).

- Operational Out: With exception of SUP OUT, all signals from the processor logic to the adapters and control units are valid only while the OPERATIONAL OUT signal is present.

- Select Out: This line, which connects via a serial selection loop to all adapters and control units, is made active during an initial selection sequence or poll sequence. The SELECT OUT signal allows an adapter or control unit to be selected during an initial selection sequence or poll sequence by sending an OPERATIONAL IN signal to the channel logic.

The Select Out line connects to both the external interface module and to the bypass

logic (page 1C1302) where its signal is enabled to the Integrated Card Reader Adapter (ICRA) if the external interface option (external interface module) is not present. If the option is present (EXTINFOP signal low) the SEL IN signal from the external interface module receiver is enabled to the ICRA as the EXT INTF SEL IN signal. The SEL IN back from the ICRA is enabled to the next adapter (Integrated Reader/Punch Adapter (IRPA) if that option is present). If the ICRA were not present the SEL IN signal would be routed directly to the IRPA. The SEL IN signal is routed to all options present and finally arrives on the SEL IN Tag In line if OPERATIONAL IN is not made active by a control unit or adapter.

- Hold Out (HLD OUT): This signal, in conjunction with the latch circuits in the external control units and adapters, performs three distinct functions:

- 1. During selection sequences HLD OUT is ANDed with SEL OUT, in each control unit and adapter, to validate SEL OUT propagation.

- 2. During data transfer sequences, it ensures SEL OUT continuity (see Select Out).

- 3. When going inactive, it clears the serial select loop by clearing the Select-Out latch in all control units and adapters in parallel.

Once HLD OUT becomes inactive, it may not become active again for 4 microseconds.

The control logic (page 1C1401) monitors the *Sel Out* bit of the TOR and generates the HLD OUT signal when the SEL OUT signal is active.

When the SEL OUT signal goes inactive the HLD OUT signal is also deactivated and cannot be activated by SEL OUT again for 4 microseconds. The HLD OUT signal is disabled by the N121 one-shot circuit, which produces a 4-microsecond logic 0 on the Q output each time the SEL OUT signal goes inactive.

- Suppress Out: This signal is used both alone and in conjunction with the other tag out lines to provide the following special functions: *suppress data, suppress status, command chaining,* and *selective reset.* Each of these functions will be described in subsequent sections.

- Data Out: This signal is sent to the selected adapter or control unit in response to DAT IN and indicates the channel has accepted or presented the data byte. Because of signal

turn-around time on the cables, the DAT OUT and DAT IN signals are used in conjunction with and overlap the SRV IN and SRV OUT signals during the hardware controlled data transfer operation to increase the data transfer rate. The control logic only uses the DAT OUT-DAT IN signals with external control units that are equipped to handle it.

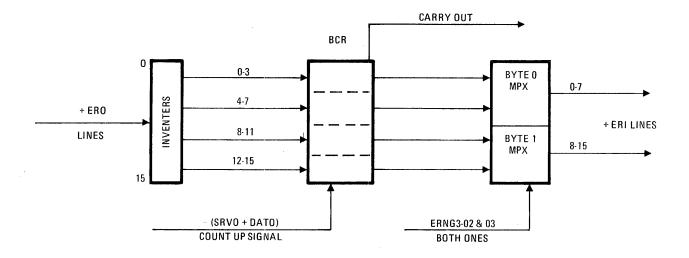

# Channel Control Register (CCR)

The CCR consists of six edge-triggered flip-flops, five located in the Basic Data Channel logic on the Extended register (ER) module, and one contained on the optional Assembly/Disassembly (EU) module. The CCR receives its information from the processor state via ERO bits 0 through 3 and 7. The REGISTER CLOCKING signal is generated by ANDing the WR Reg FF output pulse with ERNG3-02.

Outputs from the CCR connect directly to the processor control logic with each flip-flop directing a specific channel operation. The ERO bit assignment for the CCR is shown in Table 4-4. Bit 0 connects directly to the HCX FF and through one stage of inversion to the HCX2 FF (page 1C13 Loc). When the CCR is clocked with bit 0 set, the HCX FF sets and the HCX2 FF clears. This is the required state of the two flip-flops when beginning a hardware-controlled data transfer.

Table 4-4. ERO Bit Assignment in Channel Control Register

| Bit<br>Position | Title                             | Abbreviation |

|-----------------|-----------------------------------|--------------|

| 0               | Hardware Controlled<br>Transfer   | нсх          |

|                 | Hardware Controlled<br>Transfer 2 | HCX2         |

| 1               | Input                             | INPUT        |

| 2               | Diagnostic                        | DIAG         |

| 3               | Data Chaining                     | DAT CHNG     |

| 7               | Assembly/Disassembly<br>Mode      | ASMDASMD     |

The following is a definition of the CCR flip-flop usage.

• Hardware Controlled Transfer: The adapter or control unit initiates each data byte transfer. In response, with HCX set, the channel logic deskews the data, generates or checks parity, initiates the correct response to the control unit or adapter, and requests data transfer to or from the shared resources. The processor program transfers the data, updates the storage address and compares the updated address with the last address plus one.

- Hardware Controlled Transfer 2: While set, this flip-flop enables rank 1 to rank 2 of both the BIR and BOR, thus effectively making them single-rank registers. When clear, the HCX2 FF forces the channel control logic to gate data from rank 1 to rank 2 of the BOR and BIR. The HCX2 FF is cleared at the same time the HCX FF is set. The cleared state of the FF, therefore, is defined as +HCX2.

- Input: This flip-flop controls the direction of byte transfers. When set, it indicates an input operation and enables the control logic to gate data into the BIR1 during the input (read) operation. The Input FF, when cleared, indicates an output (write) operation.

## NOTE

The *Input* bit position in the CCR must be set during the processor state's last major cycle prior to the start of an input hardware controlled transfer operation.

- Diagnostic: With the Diag FF set and OPL OUT and SUP OUT signals absent (page 1C14), the information in the BOR2 is placed on the Tag In lines and at the input to the BIR1. The BIR is loaded, when the proper Tag In lines are activated, by setting the appropriate bit positions in the BOR. The basic data channel diagnostic feature provides information turn-around for register operational checks and limited control sequence simulation.

- Data Chaining: This FF set inhibits the clearing of the HCX FF, in the CCR, by the I/O Exit FF output at the end of each data segment transfer. This allows the processor state to set up control for the next data s e g m e n t a n d to initiate the hardware-controlled transfer again without the channel logic losing control of the data transfer sequence.

- Assembly-Disassembly Mode: The flip-flop determines whether the data transferred to/from main storage will be one byte or two bytes wide. When it is set, the hardware data transfer logic is allowed to assemble and disassemble bytes in the BIR and BOR and to perform two-byte-wide transfers to and from main storage. When it is clear, the input-output operations are performed in the one-byte-wide mode.

The state of the CCR FF's along with channel logic status information is selected via both multiplexers and routed to the ERI lines when ERNG3-02 is high

and ERNG3-03 is low. Table 4-5 indicates the ERI bit assignment during a *Load Register* micro-instruction with the CCR selected.

The channel status bits indicate such things as sequence termination conditions, parity error, interlock signal errors, external control unit status and assembly/disassembly (EU) module presences.

- Control Check: This flip-flop, when set, indicates the existence of too many active TAG IN or TAG OUT signals. The Cntl Chk FF (page 1C13) becomes set when OPL IN and SEL IN are active at the same time, or when any two of the signals ADRS IN, STAT IN, or SRV IN/DAT IN are active at the same time. It also is set for a channel error; that is, when the BDC processor logic and/or software via the TOR activate CMD OUT and SRV OUT or DAT OUT at the same time. The Cntl Chk FF is cleared by the CHANNEL CLEAR (CH CLR) signal which is present any time the BDC processor logic is not active: OPL OUT inactive and not in a diagnostic state. This CH CLR signal clears all channel logic control flip-flops. channel status flip-flops, and the HCX, -HCX2 and Dat Chng FF's in the CCR,

- Transmission Check: The Xmn Chk FF, when set, indicates a parity error on the byte of information received from an external control unit. The Xmn Chk FF (page 1C13 Loc) is clocked each time the BUS IN signals are gated into the BIR1, if the channel is not communicating with an integrated adapter. The CHPAR ERR signal controlled by the parity check element (page 1C14) determines if the Xmn Chk FF will set when clocked.

Any time one of the integrated adapters is communicating with the channel logic it activates the ADAPTER SELECTED signal. This signal disables the clocking gate to the Xmn Chk FF, thus not allowing parity error indications on information transferred from integrated adapters.

The Xmn Chk FF is precleared when an interface disconnect sequence is performed, or by CMD OUT active, by SRV OUT active, or by the CH CLR signal.

Illegal Length: This flip-flop, when set, indicates that the CMD OUT signal was used, in response to either SRV IN or DAT IN, to terminate the data transfer. CMD OUT is used to indicate *stop* to the control unit or adapter when the channel logic has determined all the data has been transferred (byte count=0). The Illegal Length Channel Status flip-flop and the byte count in the Byte Count register indicates the type of data transfer termination as listed below:

Illegal Length Set = Processor terminated the data transfer before device was ready to.

Illegal Length Clear and byte count zero = Both the processor logic and device terminated data transfer at same time.

Illegal Length Clear and byte count not zero = Device terminated data transfer before processor logic was ready to.

- Assembly/Disassembly Mode: The state of this flip-flop indicates whether the processor logic is in the one-byte-wide or two-byte-wide transfer mode: when set, it indicates two-byte; when clear, it indicates one-byte.

- Mark Zero In: This Tag In Line is activated by an external control unit requesting command retry via the MKO IN signal.

- Assembly/Disassembly Option Present: This channel status line is active when the ASMDASOP (EU module) is present.

| Source                       | ERI Bit<br>Position             | Title                               | Abbreviation |

|------------------------------|---------------------------------|-------------------------------------|--------------|

| CCR 0                        | 0                               | Hardware Coantrolled Transfer       | нсх          |

| 1                            | 1                               | Input                               | INPUT        |

| 2                            | 2                               | Diagn ostic                         | DIAG         |

| 3                            | 3                               | Data Chaining                       | DAT CHNG     |