MLSI-BA11-200X/300X SERIES OF CHASSIS ASSEMBLIES AND BASIC BOX SYSTEMS

For use with DEC<sup>TM</sup> LSI-11<sup>TM</sup> Computers

INSTRUCTION MANUAL

1

H

1

# MLSI-BA11-200X/300X SERIES OF CHASSIS ASSEMBLIES AND BASIC BOX SYSTEMS

For use with DEC<sup>TM</sup> LSI-11<sup>TM</sup> Computers

**INSTRUCTION MANUAL**

## Document Part Number: 80033664 Document Revision Level: A

### Copyright © 1986 by MDB Systems, Inc. All rights reserved. Printed in U.S.A.

This document, as well as all subject matter disclosed herein, is a proprietary item of which MDB Systems, Inc. retains the exclusive rights of reproduction, manufacture, and sale. Permission for further disclosure must be granted in writing by MDB Systems, Inc. The information supplied in this document is subject to change without notice.

#### WARNING

This equipment generates, uses, and may emit radio frequency energy. If not installed in accordance with the information provided in this instruction manual, it may cause interference to radio communications. It has been tested and found to comply with the limits for a Class A computing device pursuant to Subpart J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference when operated in a commercial environment. Operation of this equipment in a residential area is likely to cause interference, in which case the user, at his own expense, may be required to take whatever measures are necessary to correct the interference.

The postage-prepaid READER'S COMMENTS page at the end of this instruction manual requests the user's critical evaluation to assist us in preparing future documentation.

DEC and LSI-ll are registered trademarks of Digital Equipment Corporation.

Price: \$10.00

## TABLE OF CONTENTS

## CHAPTER 1 GENERAL DESCRIPTION

| 1.1 | Scope of Manuall-1     |

|-----|------------------------|

| 1.2 | Reference Documents1-1 |

| 1.3 | Product Overviewl-2    |

CHAPTER 2 Q-BUS BACKPLANE CONFIGURATION

| 2.1   | Introduction2-1                      |

|-------|--------------------------------------|

| 2.2   | MLSI-BP84-E-F/R                      |

| 2.2.1 | 22-Bit Addressing Capability2-3      |

| 2.2.2 | Q-Bus Termination2-3                 |

| 2.3   | System Expansion2-3                  |

| 2.4   | DEC-Compatible Modules2-4            |

| 2.5   | Q-bus Backplane Interface Signals2-5 |

CHAPTER 3 SWITCH/INDICATOR CONTROL PANEL

| 3.1   | Introduction                   |

|-------|--------------------------------|

| 3.2   | Switch/Indicator Control Panel |

| 3.3   | Theory of Operation            |

| 3.3.1 | AC Voltage Detector            |

| 3.3.2 | DC Voltage Detector            |

| 3.3.3 | Run Indicator                  |

| 3.3.4 | Halt Control                   |

| 3.3.5 | Line Time Clock                |

| 3.4   | PSM Adjustment Procedures      |

CHAPTER 4 THE POWER SUPPLY

| 4.1   | Introduction                          |

|-------|---------------------------------------|

| 4.2   | The Power Supply                      |

| 4.3   | AC Power Connection                   |

| 4.4   | AC Input Power Conversion             |

| 4.4.1 | Chassis Conversion4-3                 |

| 4.4.2 | Power Supply Conversion4-4            |

| 4.4.3 | Power Sequencing Module Conversion4-4 |

## CHAPTER 5 REAR CABLE DISTRIBUTION PANEL ASSEMBLY

| 5.1 | Introduction                  | .5-1 |

|-----|-------------------------------|------|

| 5.2 | Rear Cable Distribution Panel | 5-1  |

## TABLE OF CONTENTS (continued)

| CHAPTER                  | 6 RECOMMENDED PLACEMENT OF MODULES |

|--------------------------|------------------------------------|

| 6.1<br>6.2<br>6.3<br>6.4 | General                            |

| CHAPTER                  | 7 MAINTENANCE AND REPAIR           |

| 7.1<br>7.2               | Maintenance                        |

|                          |                                    |

| CHAPTER                  | 8 BASIC BOX SYSTEMS                |

| 8.1<br>8.2               | Introduction                       |

## LIST OF TABLES

## Table

| 1-1 | MLSJ-BAll-200X/300X Series Model Designations1-3      |

|-----|-------------------------------------------------------|

| 2-1 | DEC-Compatible Module Dimensions                      |

| 2-2 | Q-Bus Backplane Interface Signals                     |

| 3-1 | Function of Control Panel Switches and Indicators 3-3 |

| 4-1 | Power Supply Specifications4-1                        |

| 8-1 | Basic Box Systems8-1                                  |

## LIST OF ILLUSTRATIONS

# Figure

Page

| 2-1 | MLSI-BPA84-E-F/R Backplane Configuration          | .2-2  |

|-----|---------------------------------------------------|-------|

| 2-3 | DEC-Compatible Module Pin Assignments             | . 2-4 |

| 3-1 | Switch/Indicator Control Panel                    | . 3-2 |

| 3-2 | PSM Power-Up/Power-Down Timing Diagram            |       |

| 3-3 | Power Sequencing Module, Simplified Block Diagram |       |

| 5-1 | Rear Cable Distribution Panel Assembly            |       |

| 6-1 | Recommended Module Placement                      |       |

| 8-1 | Rear Cable Distribution Panel Assembly            | .8-3  |

## CHAPTER 1

#### GENERAL DESCRIPTION

## 1.1 SCOPE OF MANUAL

This instruction manual provides a general description of the MLSI-BAll Series of Chassis Assemblies which are to be used with the Digital Equipment Corporation LSI-ll family of Q-bus computers.

Included in this manual are descriptions of the backplane/card guide assembly, power fail sequencing circuitry, the power supply, use of the rear distribution panel, and recommended placement of system modules. Also provided are assembly drawings and schematic diagrams to aid in troubleshooting.

## 1.2 REFERENCE DOCUMENTS

Before configuring a Q-bus-based computer system, it is highly recommended that the you become familiar with LSI-11 operation and Q-bus architecture. The following reference documents may be used in conjunction with this instruction manual to ensure an adequate understanding of system operation.

- DEC Microcomputers and Memories Handbook

- DEC Microcomputer Processor Handbok

- DEC Microcomputer Interfaces Handbook

- DEC Peripherals Handbook

## 1.3 PRODUCT OVERVIEW

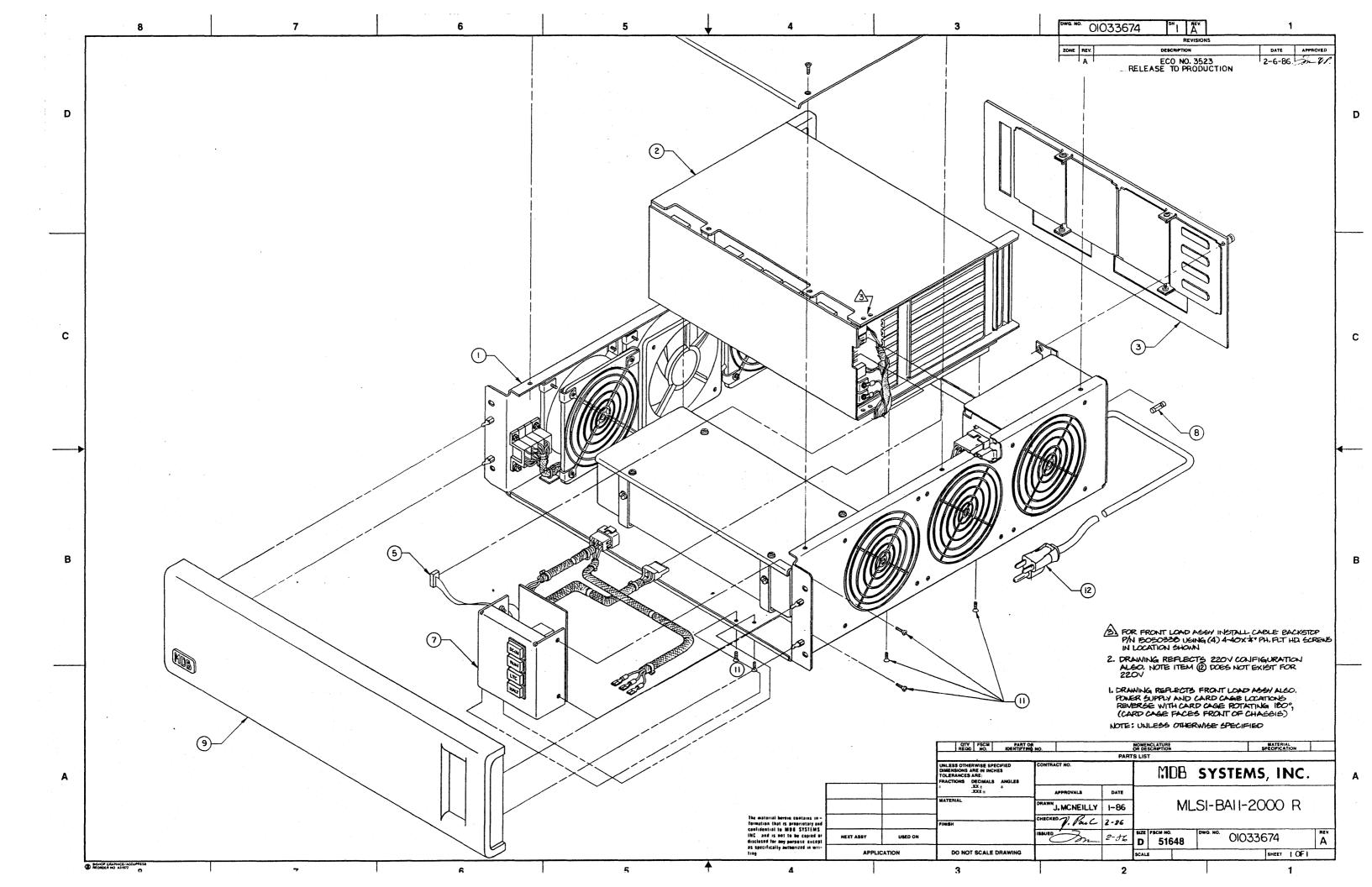

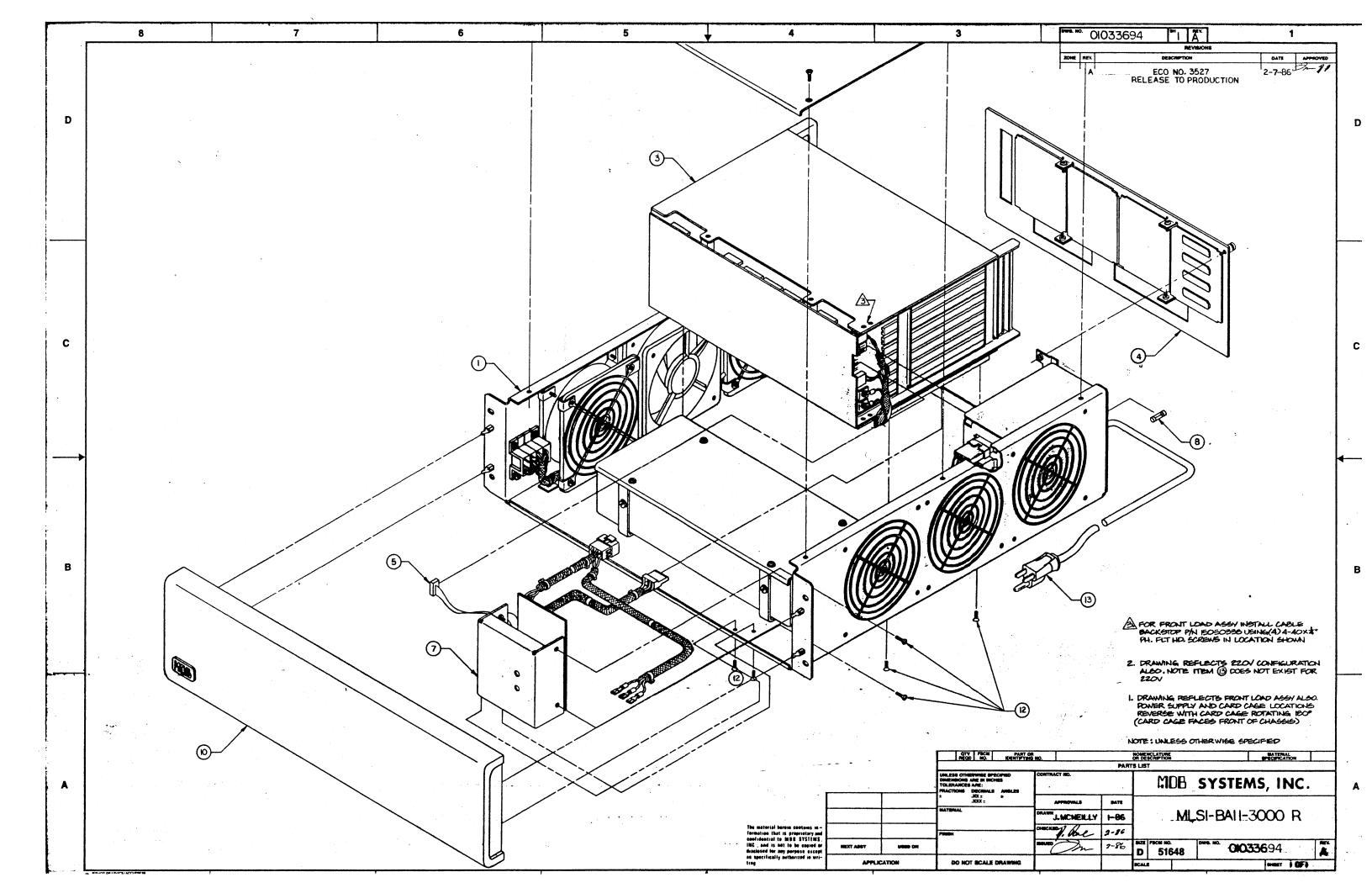

The MLSI-BAll Series consists of front or rear-loading system chassis assemblies which may be used with Q-bus-based microprocessors and associated interface modules. (Refer to Table 1-1 for a complete list of MLSI-BAll Model Designations.)

Included with each chassis in the MLSI-BAll Series is a removable front panel and a backplane/card guide assembly with 22-bit addressing capability and factory installed removable Q-bus termination. The backplane can accommodate sixteen (16) dual-size modules, eight (8) quad-size modules, or a user-selected combination of both dual and quad modules.

Also included is a triple output regulated switching power supply which provides +5V dc at 37 amps, +12V dc at 4 amps, and -12V dc at 1 amp. The chassis are also equipped with three cooling fans which provide 300 cfm of air circulation.

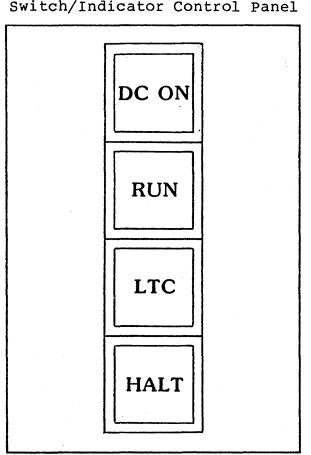

The Switch Control Panel located on the chassis front panel contains three illuminated push-button switches (DC ON, LTC, and HALT) and one indicator (RUN) which manipulate and monitor certain operational functions of the system. The switch panel provides integral ON/OFF power fail sequencing.

The Rear Cable Distribution Panel facilitates the connection of cables between modules installed in the system backplane and user peripheral devices. Cable connections are made internally at the distribution panel bulkhead connectors, with external interface cables installed from the panel to the peripheral devices.

Also mounted on the rear chassis panel is a rocker style AC power ON/OFF circuit breaker switch. AC input power is accomplished by means of a removable 8-foot line cord which is connected to the line filter/voltage selector.

The chassis assembly can be easily mounted in a standard 19-inch RETMA-type cabinet. Slide or rack mounting assemblies may be used.

The overall dimensions of the MLSI-BAll-200X/300X Series of Chassis Assemblies are as follows:

- Height: 5.25 inches (13.34 cm)

- Width: 19.00 inches (48.26 cm)

- Depth: 18.00 inches (45.72 cm)

- Weight: 30.00 pounds (13.60 kg)

Table 1-1 provides a complete list of the various configurations of the MLSI-BA11-200X/300X Series.

| Model Number     | AC Input Power    | Module Loading |

|------------------|-------------------|----------------|

| MLSI-BA11-2000-F | 110 VAC, 50/60 Hz | Front          |

| MLSI-BAll-2000-R | 110 VAC, 50/60 Hz | Rear           |

| MLSI-BA11-2002-F | 220 VAC, 50/60 Hz | Front          |

| MISI-BA11-2002-R | 220 VAC, 50/60 Hz | Rear           |

Table 1-1 MLSI-BA11-2000 Model Designations

MLSI-BA11-3000 Model Designations

| Model Number     | Model Number AC Input Power |       |

|------------------|-----------------------------|-------|

| MLSI-BA11-3000-F | 110 VAC, 50/60 Hz           | Front |

| MLSI-BA11-3000-R | 110 VAC, 50/60 Hz           | Rear  |

| MLSI-BA11-3002-F | 220 VAC, 50/60 Hz           | Front |

| MLSI-BA11-3002-R | 220 VAC, 50/60 Hz           | Rear  |

AC Input Power is also commonly referred to as 115 VAC and 230 VAC.

#### CHAPTER 2

#### Q-BUS BACKPLANE CONFIGURATION

### 2.1 INTRODUCTION

This chapter describes the backplane/card guide assembly utilized in the MLSI-BAll Series of Chassis Assemblies. Designated the MISI-BPA84-E-F/R, the backplane is wired for standard LSI-11 Q-bus signals, and is equipped with full 22-bit addressing capability. The assembly is also provided with full-length card guides to ensure maximum support for the modules installed in the backplane.

Provided in this chapter is information pertaining to the configuration and use of the MLSI-BPA84-E Backplane/Card Guide Assembly, and a complete list of Q-bus signals.

#### 2.2 MLSI-BPA84-E-F/R BACKPLANE CARD GUIDE ASSEMBLY

The MISI-BPA34-E-F/R Backplane Card Guide Assembly is a pre-wired, multilayer, printed circuit LSI-11 backplane which provides sixteen (16) dual or eight (8) quad standard Q-bus slots. These slots will accommodate a total of 16 dual-size modules, 8 quad-size modules, or a user-selected combination of both dual and quad modules.

For example, a quad-size LSI-11/23-PLUS CPU (KDF11-BA) and 14 dual-size modules may be installed in the backplane. The backplane may also be used with LSI-11/23 (KDF11-AA), LSI-11/2 (KD11-HA), or LSI-11 (KD11-F) microprocessors.

The overall dimensions of the MLSI-BPA84-E-F/R Backplane Card/Guide Assembly are as follows:

NOTE

Since all slots have 22-bit addressing, KDJ11-BF and PMI memory must not be installed in the back-plane.

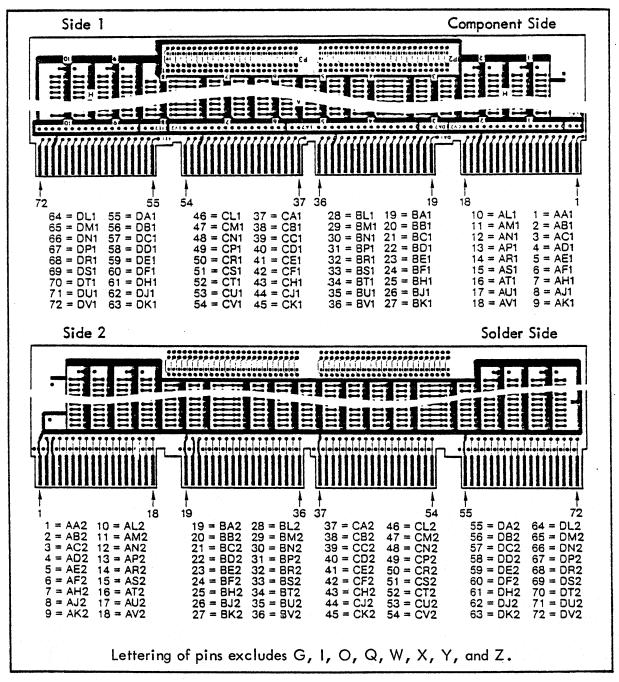

The MLSI-BPA84-E Backplane will accommodate sixteen dual-size, eight quad-size DEC-compatible modules, or a user-selected combination of both. Figure 2-3 provides pin assignments for DEC-compatible modules, and Table 2-1 lists required module dimensions.

Figure 2-3 DEC-Compatible Module Pin Assignments

| Module Size | Height           | Width             |

|-------------|------------------|-------------------|

| Quad        | 8.42" (21.40 cm) | 10.44" (26.50 cm) |

| Dual        | 8.42" (21.40 cm) | 5.20" (13.20 cm)  |

| Single      | 8.42" (21.40 cm) | 2.44" ( 6.20 cm)  |

Table 2-1 DEC-Compatible Module Dimensions

## 2.5 Q-BUS BACKPLANE INTERFACE SIGNALS

Table 2-2 lists and defines signals present at the LSI-ll Q-bus backplane/module interface. Most Q-bus signals are active (true) when at a low level (0 volts), and are inactive (false) when at a high level (+3 volts). However, bus signals BDCOK H and BPOK H are active when high, and are noted as such in the following table.

For more detailed information regarding interface signals and timing, refer to the DEC Microcomputers and Memories Handbook or Microcomputer Processor Handbook.

| g and BuckPlance Incollage Bighaits |           |                                                                                |  |

|-------------------------------------|-----------|--------------------------------------------------------------------------------|--|

| Bus Pin                             | Mneumonic | Description                                                                    |  |

| AAl (CAl)                           | BIRQ5 L   | Priority Level 5 Interrupt<br>Request.                                         |  |

| ABl (CBl)                           | BIRQ6 L   | Priority Level 6 Interrupt<br>Request.                                         |  |

| ACl (CCl)                           | BDAL16 L  | Extended address bit 16.                                                       |  |

| ADl (CDl)                           | BDAL17 L  | Extended address bit 17.                                                       |  |

| AEl (CEl)                           | SSPARE    | Spare pin, not assigned on<br>the backplane; available<br>for user connection. |  |

| AFl (CFl)                           | SRUN L    | Run light signal.                                                              |  |

| AHl (CHl)                           | SRUN L    | Run light signal.                                                              |  |

Table 2-2 Q-bus Backplane Interface Signals

| Bus Pin   | Mneumonic | Description                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AJl (CJl) | GND       | Signal ground.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| AKl (CKl) | MSPAREA   | Maintenance spare. Normally<br>connected to bus pin ALl<br>(CLl) on the backplane.                                                                                                                                                                                                                                                                                                 |  |  |

| ALl (CLl) | MSPAREA   | Maintenance spare. Normally<br>connected to bus pin AK1<br>(CK1) on the backplane.                                                                                                                                                                                                                                                                                                 |  |  |

| AM1 (CM1) | GND       | Signal ground.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| AN1 (CN1) | BDMR L    | Direct Memory Access (DMA)<br>Request. Asserted by a de-<br>vice to request control of<br>the bus (bus mastership).<br>If the processor is not the<br>bus master, nor asserting<br>BSYNC L, it grants bus mas-<br>ter status to the reques-<br>ting device by asserting<br>the signal BDMGO L. The<br>requesting device responds<br>by negating BDMR L and as-<br>serting BSACK L. |  |  |

| APl (CPl) | BHALT L   | Processor Halt. A device<br>will cause the processor to<br>halt normal program execu-<br>tion by asserting BHALT L.                                                                                                                                                                                                                                                                |  |  |

| ARl (CRl) | BREF L    | Memory Refresh. When BREF L<br>is asserted, the processor<br>will perform a memory re-                                                                                                                                                                                                                                                                                             |  |  |

|           |           | fresh that forces all dy-<br>namic memory devices to be<br>activated for each BSYNC L/<br>BDIN L bus transaction.                                                                                                                                                                                                                                                                  |  |  |

| AS1 (CS1) | + 12B     | + 12 V dc battery power.                                                                                                                                                                                                                                                                                                                                                           |  |  |

| ATI (CTI) | GND       | Signal ground.                                                                                                                                                                                                                                                                                                                                                                     |  |  |

Table 2-2 Q-bus Backplane Interface Signals (continued)

| Bus Pin   | Mneumonic | Description                                                                                                                                                                                                                                                                                                               |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUl (CUl) | PSPARE    | Power spare, not assigned.<br>This pin is not recommended<br>for use.                                                                                                                                                                                                                                                     |

| AVl (CVl) | + 5B      | + 5 V battery power.                                                                                                                                                                                                                                                                                                      |

| AA2 (CA2) | + 5V      | + 5 V dc power.                                                                                                                                                                                                                                                                                                           |

| AB2 (CB2) | - 12V     | - 12 V dc power.                                                                                                                                                                                                                                                                                                          |

| AC2 (CC2) | GND       | Signal ground.                                                                                                                                                                                                                                                                                                            |

| AD2 (CD2) | + 12V     | + 12 V dc power.                                                                                                                                                                                                                                                                                                          |

| AE2 (CE2) | BDOUT L   | Data Output. Implies that<br>valid data is available on<br>bus lines BDAL00 L through<br>BDAL15 L and, with refer-<br>ence to the bus master de-<br>vice, that an output trans-<br>fer is in process. The<br>slave device that responds<br>to the BDOUT L signal must<br>assert BRPLY L to complete<br>the data transfer. |

| AF2 (CF2) | BRPLY L   | Reply. Asserted in response<br>to BDIN L or BDOUT L. The<br>signal indicates that input<br>data is available on the<br>BDAL bus, or that output<br>data has been accepted from<br>the bus.                                                                                                                                |

| AH2 (CH2) | BDIN L    | Data Input. When BSYNC L is<br>asserted, BDIN L indicates<br>an input transfer from the<br>active bus master. When the<br>signal BSYNC L is not as-<br>serted, it implies that an<br>interrupt operation is in<br>process.                                                                                                |

Table 2-2 Q-bus Backplane Interface Signals (continued)

| Bus Pin   | Mneumonic | Description                                                                                                                                                                                                                                                                        |  |  |

|-----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| AJ2 (CJ2) | BSYNC L   | Synchronize. Asserted by<br>the bus master device when<br>it has placed an address on<br>bus lines BDAL00 L through<br>BDAL21 L.                                                                                                                                                   |  |  |

| AK2 (CK2) | BWTBT L   | Write/Byte. Controls the<br>bus cycle in either of two<br>ways, as follows:                                                                                                                                                                                                        |  |  |

|           |           | 1. Asserted with leading<br>edge of BSYNC L to in-<br>dicate that an output<br>sequence will follow<br>(DATO or DATOB).                                                                                                                                                            |  |  |

|           |           | <ol> <li>Asserted, while BDOUT L<br/>is asserted, for byte<br/>addressing in a DATOB<br/>cycle.</li> </ol>                                                                                                                                                                         |  |  |

| AL2 (CL2) | BIRQ4 L   | Priority Level 4 Interrupt<br>Request.                                                                                                                                                                                                                                             |  |  |

| AM2 (CM2) | BIAKI L   | Interrupt Acknowledge. This<br>signal is asserted by the<br>processor in response to<br>the signal BIRQ L. Causes<br>the device to put an inter-<br>rupt vector on the bus.                                                                                                        |  |  |

| AN2 (CN2) | BIAKO L   | Interrupt Acknowledge Out.<br>Normally asserted to the<br>device having the next-<br>lower priority on the in-<br>terrupt daisy-chain, and<br>appears at BIAKI L input to<br>the device. If the module<br>stores an interrupt request<br>BIAKO L is negated at the<br>next device. |  |  |

Table 2-2 Q-bus Backplane Interface Signals (continued)

| Bus Pin   | Mneumonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AP2 (CP2) | BBS7 L    | Bank 7 Select. Indicates<br>that the address on the bus<br>is for the upper 4K bank.<br>When BSYNC L is asserted,<br>BBS7 L will remain active<br>until the addressing of the<br>bus cycle is completed.                                                                                                                                                                                                                                                                                                                                                                                          |

| AR2 (CR2) | BDMGI L   | DMA Bus Grant Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| AS2 (CS2) | BDMGO L   | DMA Bus Grant Output. This<br>processor-generated signal<br>is daisy-chained through<br>all DMA devices on the bus.<br>When asserted, the signal<br>BDMGI L grants bus master<br>status to the DMA device<br>requesting the bus that has<br>the highest priority. If a<br>higher-priority DMA device<br>has no active bus request,<br>BDMGO L passes from that<br>device to the BDMGI L input<br>of the next DMA device. If<br>the higher-priority device<br>has an active bus request,<br>that device inhibits its<br>BDMGO L output. A DMA de-<br>vice requests the bus by<br>asserting BDMR L. |

| AT2 (CT2) | BINIT L   | Initialize. This signal is<br>generated by the processor<br>during a power-up or reset<br>operation. BINIT L clears<br>all devices on the I/O bus.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AU2 (CU2) | BDAL00 L  | Bit 0. One of the data/ad-<br>dress bus lines used to<br>transfer all address and<br>data information. This sig-<br>nal is bidirectional.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| AV2 (CV2) | BDAL01 L  | Bit l. Data/Address bit.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

Table 2-2 Q-bus Backplane Interface Signals (continued)

## Q-BUS BACKPLANE CONFIGURATION

| Bus Pin   | Mneumonic | Description                                                                                                                                                                    |  |  |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| BAl (DAl) | BDCOK H   | DC Power OK. Asserted when<br>the system dc voltage level<br>is suitable for reliable<br>system operation. BDCOK H<br>is active when high.                                     |  |  |

| BBl (DBl) | ВРОК Н    | AC Power OK. Asserted when<br>primary power is within<br>limits assuring reliable<br>system operation. BPOK H<br>is active when high.                                          |  |  |

| BCl (DCl) | BDAL18 L  | Bit 18. One of the ex-<br>tended address bus lines<br>used to transfer address<br>information.                                                                                 |  |  |

| BD1 (DD1) | BDAL19 L  | Extended address bit 19.                                                                                                                                                       |  |  |

| BEl (DEl) | BDAL20 L  | Extended address bit 20.                                                                                                                                                       |  |  |

| BFl (DFl) | BDAL21 L  | Extended address bit 21.                                                                                                                                                       |  |  |

| BHl (DHl) | SSPARE    | Special spare pin that is<br>not assigned; available for<br>user connection.                                                                                                   |  |  |

| BJl (DJl) | GND       | Signal ground.                                                                                                                                                                 |  |  |

| BKl (DKl) | MSPAREB   | Maintenance spare. Normally<br>connected to bus pin BL1<br>(DL1) on the backplane.                                                                                             |  |  |

| BLl (DLl) | MSPAREB   | Maintenance spare. Normally<br>connected to bus pin BKl<br>(DKl) on the backplane.                                                                                             |  |  |

| BMl (DMl) | GND       | Signal ground.                                                                                                                                                                 |  |  |

| BN1 (DN1) | BSACK L   | Bus Grant Acknowledge. This<br>signal is asserted by a DMA<br>device in response to the<br>processor's BDMGO L signal,<br>indicating that the device<br>is now the bus master. |  |  |

Table 2-2 Q-bus Backplane Interface Signals (continued)

| Bus Pin   | Mneumonic | Description                                                                                                                                                                                     |  |  |  |

|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| BPl (DPl) | BIRQ7 L   | Priority Level 7 Interrupt<br>Request.                                                                                                                                                          |  |  |  |

| BRl (DRl) | BEVNT L   | External Event Interrupt<br>Request. Using BEVNT L,<br>Line Time Clock interrupts<br>occur every 16 2/3 msec for<br>a 60 Hz line frequency, and<br>every 20 msec for a 50 Hz<br>line frequency. |  |  |  |

| BSl (DSl) | + 12B     | + 12 V battery power.                                                                                                                                                                           |  |  |  |

| BTl (DTl) | GND       | Signal ground.                                                                                                                                                                                  |  |  |  |

| BUl (DUl) | PSPARE    | Power spare, not assigned.<br>This pin is not recommended<br>for use.                                                                                                                           |  |  |  |

| BVl (DVl) | + 5V      | + 5 V dc power.                                                                                                                                                                                 |  |  |  |

| BA2 (DA2) | + 5V      | + 5 V dc power.                                                                                                                                                                                 |  |  |  |

| BB2 (DB2) | - 12V     | - 12 V dc power.                                                                                                                                                                                |  |  |  |

| BC2 (DC2) | GND       | Signal ground.                                                                                                                                                                                  |  |  |  |

| BD2 (DD2) | + 12V     | + 12 V dc power.                                                                                                                                                                                |  |  |  |

| BE2 (DE2) | BDAL02 L  | Bit 2. One of the data/ad-<br>dress bus lines used to<br>transfer all address and<br>data information. This sig-<br>nal is bidirectional.                                                       |  |  |  |

| BF2 (DF2) | BDAL03 L  | Bit 3. Data/Address bit.                                                                                                                                                                        |  |  |  |

| BH2 (DH2) | BDAL04 L  | Bit 4. Data/Address bit.                                                                                                                                                                        |  |  |  |

| BJ2 (DJ2) | BDAL05 L  | Bit 5. Data/Address bit.                                                                                                                                                                        |  |  |  |

| BK2 (DK2) | BDAL06 L  | Bit 6. Data/Address bit.                                                                                                                                                                        |  |  |  |

| BL2 (DL2) | BDAL07 L  | Bit 7. Data/Address bit.                                                                                                                                                                        |  |  |  |

Table 2-2 Q-bus Backplane Interface Signals (continued)

| Bus Pin   | Mneumonic | Description               |  |  |  |

|-----------|-----------|---------------------------|--|--|--|

| BM2 (DM2) | BDAL08 L  | Bit 8. Data/Address bit.  |  |  |  |

| BN2 (DN2) | BDAL09 L  | Bit 9. Data/Address bit.  |  |  |  |

| BP2 (DP2) | BDAL10 L  | Bit 10. Data/Address bit. |  |  |  |

| BR2 (DR2) | BDAL11 L  | Bit ll. Data/Address bit. |  |  |  |

| BS2 (DS2) | BDAL12 L  | Bit 12. Data/Address bit. |  |  |  |

| BT2 (DT2) | BDAL13 L  | Bit 13. Data/Address bit. |  |  |  |

| BU2 (DU2) | BDAL14 L  | Bit 14. Data/Address bit. |  |  |  |

| BV2 (DV2) | BDAL15 L  | Bit 15. Data/Address bit. |  |  |  |

Table 2-2 Q-bus Backplane Interface Signals (continued)

#### CHAPTER 3

#### SWITCH/INDICATOR CONTROL PANEL

## 3.1 INTRODUCTION

This chapter describes the proper operation, function, and adjustment of the Switch/Indicator Control Panel utilized in the MLSI-BAll Series of Chassis Assemblies.

#### 3.2 SWITCH/INDICATOR CONTROL PANEL

The Switch/Indicator Control Panel is a complete subassembly consisting of a printed circuit board (MLSI-PSM23 Power Sequencing Module), switches and lighted indicators, and a mounting panel.

The Control Panel manipulates the operation of the Micro/ll system by use of switches. It monitors, via lighted displays, certain operational functions of the system including DC ON, RUN, LTC, and HALT. In addition, the Power Sequencing Module continuously monitors power supply voltages to ensure reliable computer operation.

The MLSI-PSM23 is designed to monitor AC line voltage and DC power and cause a power-down sequence to occur if the voltages fall below the following parameters:

| AC Voltage | +12 VDC | +5 VDC |

|------------|---------|--------|

|            |         |        |

| 98 V       | 11.3 V  | 4.6 V  |

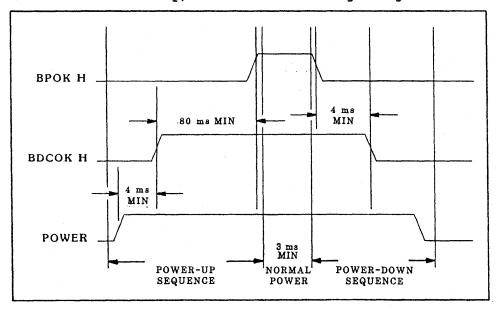

Upon detection of voltages outside of the specified parameters, the Power Sequencing Module will initiate a power-down sequence as shown in Figure 3-2, indicating voltage abnormalities.

The Switch/Indicator Control Panel is electrically connected to the power supply and the chassis backplane via removable flat cables. The Power Sequencing Module requires dc power from the power supply, as follows:

- +5 volts dc at 51 milliamps

- +12 volts dc at 1.2 milliamps

Figure 3-1 shows the location of the Control Panel switches and indicators. Table 3-1 lists and defines the function of each switch and indicator on the panel.

Figure 3-1 Switch/Indicator Control Panel

|          |    |         | Table | 3-1      |     |            |

|----------|----|---------|-------|----------|-----|------------|

| Function | of | Control | Panel | Switches | and | Indicators |

| Switch/Lamp        | Position                                                                                                                                                                               | Function                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DC ON*             | On<br>(Lamp On)                                                                                                                                                                        | When the DC ON switch is<br>depressed, a power-down<br>sequence is initiated,<br>which, in turn, causes the<br>CPU to assert the signal<br>BINIT L on the bus (Q-bus<br>is initialized). When the<br>DC ON switch is released,<br>a power-up sequence is<br>initiated. The illuminated<br>DC ON lamp indicates that<br>AC and DC voltages are at<br>acceptable levels. |

|                    | (Lamp Off)                                                                                                                                                                             | When the DC ON indicator<br>is off, it indicates that<br>AC and DC voltages are not<br>at acceptable levels, and<br>a power fail sequence is<br>initiated.                                                                                                                                                                                                             |

| RUN<br>(Lamp only) | Lamp On<br>When the RUN indicato<br>illuminated, it signi<br>that the processor is<br>cuting a program. The<br>indicator turns off<br>microseconds after pro<br>execution is completed |                                                                                                                                                                                                                                                                                                                                                                        |

|                    | Lamp Off                                                                                                                                                                               | When off, the indicator<br>signifies that the CPU is<br>not executing programs.                                                                                                                                                                                                                                                                                        |

| LTC                | On<br>(Lamp On)                                                                                                                                                                        | When the LTC switch is de-<br>pressed and locked, the<br>Line Time Clock feature is<br>activated, asserting and<br>negating the BEVNTL inter-<br>rupt line at a 50 Hz or 60<br>Hz rate.                                                                                                                                                                                |

|                    | Off<br>(Lamp Off)                                                                                                                                                                      | Disables the switchable<br>LTC feature. (This switch<br>does not effect the pro-<br>grammable LTC on the CPU.                                                                                                                                                                                                                                                          |

| Switch/Lamp | Position          | Function                                                                                                                                                                                                                                                                                                                                                             |

|-------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HALT        | On<br>(Lamp On)   | When the HALT switch is<br>depressed and locked, the<br>signal BHALT L is asserted<br>on the bus by the Control<br>Panel. This switch halts<br>execution of the current<br>program without powering-<br>down the system. The pro-<br>cessor executes the ODT<br>microcode and a single<br>instruction for each "P"<br>keystroke on the console<br>terminal keyboard. |

|             | Off<br>(Lamp Off) | Negates the signal BHALT L<br>to allow the processor to<br>resume normal program exe-<br>cution.                                                                                                                                                                                                                                                                     |

Table 3-1 Function of Control Panel Switches and Indicators (cont.)

\* The function of the DC ON switch may be altered slightly by reconfiguring a jumper on the MLSI-PSM23 module. As configured at the factory (jumper B-C installed), the DC ON switch will function as described in Table 3-1. However, if jumper B-C is removed and jumper A-C is installed, the DC ON switch may be used to toggle the BDCOK H line ONLY, and will have no effect upon the BPOK H line. Consequently, a normal power-up sequence will NOT be initiated when the DC ON switch is activated. The reason for this particular configuration is that some controllers initialize when the signal BDCOK H is encountered.

#### NOTE

The HALT and LTC indicators do not specify a halt or line time clock activity that has been asserted on the bus by another module. These Switch Control Panel indicators represent only a HALT or LTC activity that has been directly asserted by the Power Sequencing Module/Switch Control Panel.

## 3.3 THEORY OF OPERATION

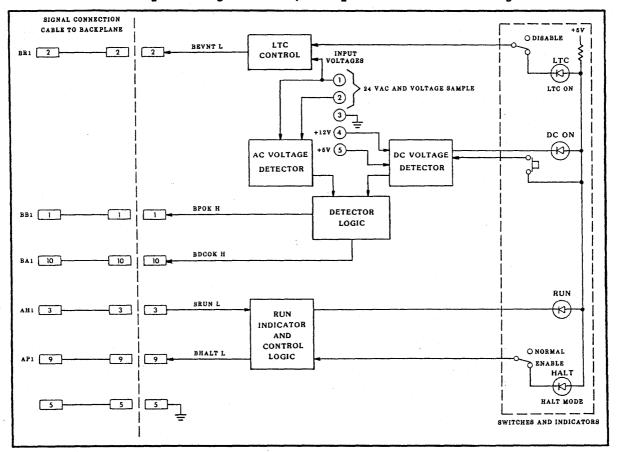

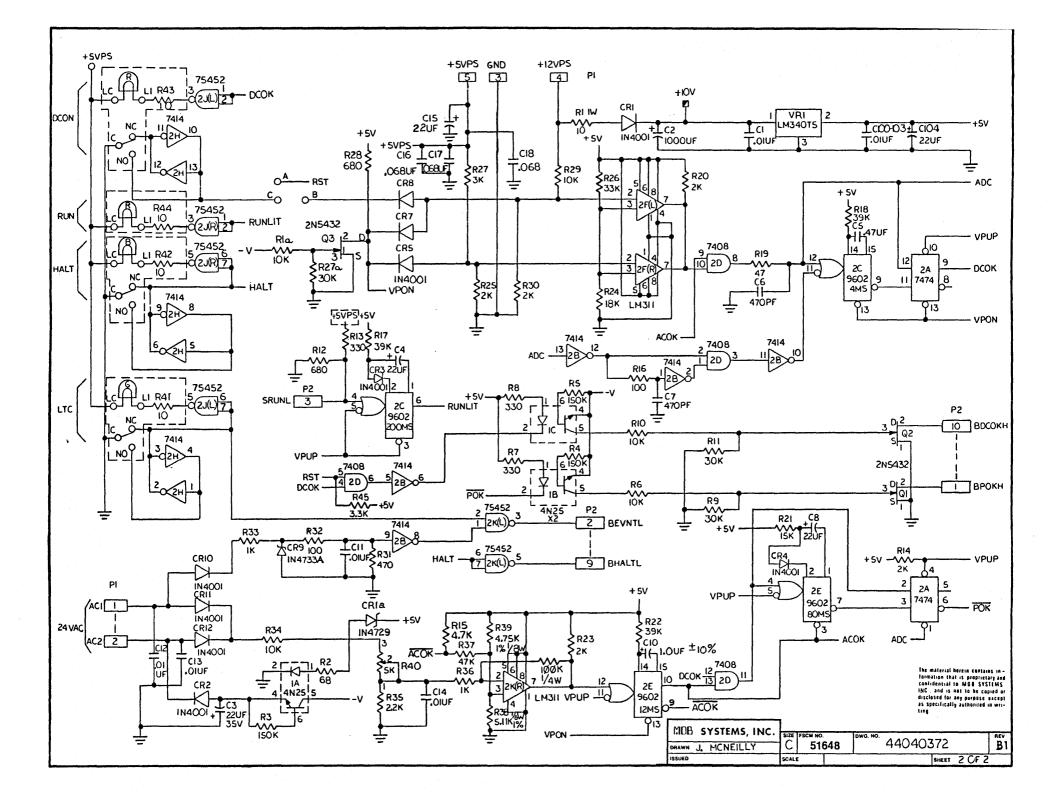

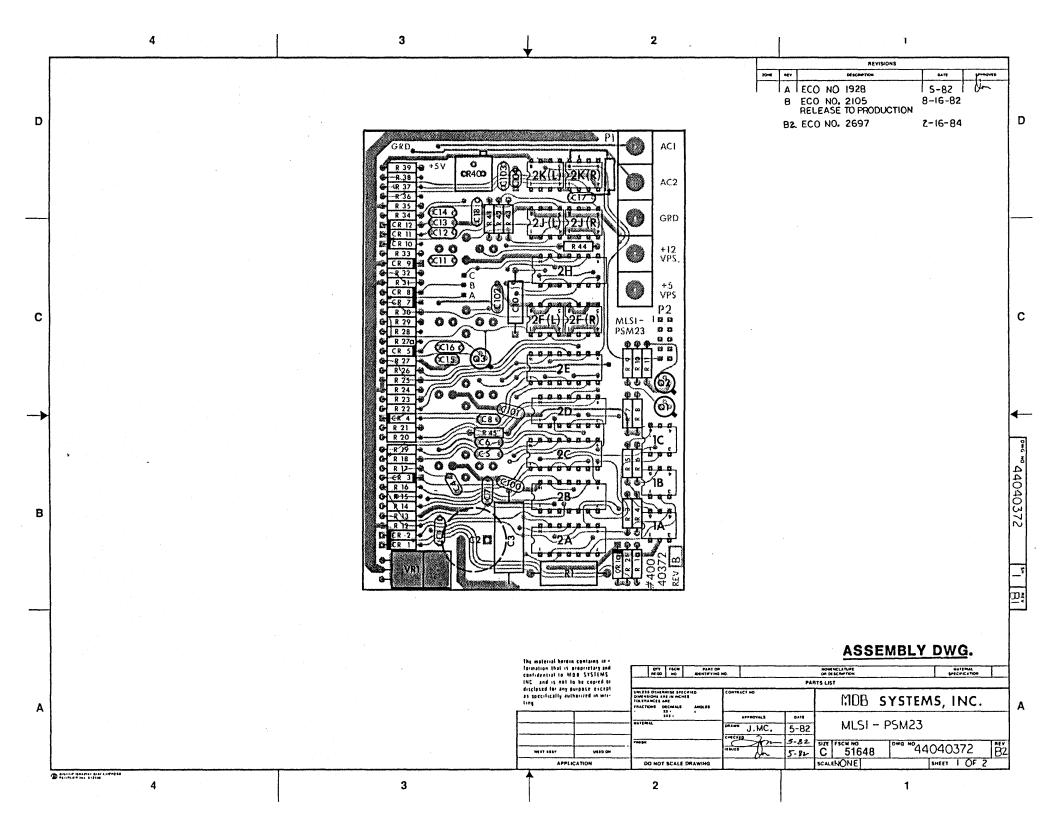

The following paragraphs describe the theory of operation of the Power Sequencing Module in terms of logic diagram #44040372 contained at the end of this manual.

#### 3.3.1 AC Voltage Detector (BPOK H)

After AC power is turned on, a 24 VAC reference voltage originating from a transformer mounted within the power supply enclosure (AC1, AC2) is rectified and the resulting half-cycles appear at voltage comparator 2K(R). This circuit compares the sample AC voltage with a 2.4V or 2.6V reference at 2K(R)-3.

The first, and subsequent half-cycles of the normal line voltage sample causes the output of comparator 2K(R) to be a pulse having an interval of 8.35-milliseconds. This is one-half the AC input line frequency at 60 Hz. (A 50 Hz input would have a pulse interval of 10-milliseconds.) This pulse triggers a re-triggerable one-shot having a period of 12-milliseconds.

The resulting signal ACOK is ANDed with DCOK and triggers an 80-millisecond one-shot. After the 80-millisecond period, the output of this one-shot clocks the POK flip-flop, asserting the signal BPOK H to indicate normal AC voltage levels.

#### 3.3.2 DC Voltage Detector (BDCOK H)

The +12V dc and +5V dc supply bus voltages are monitored by voltage comparators 2F(R) and 2F(L), which compare the bus voltage with a 1.8 volt reference at 2F-3. If the voltage on the +5V dc bus falls below 4.6V dc, or if the +12V dc bus falls below 11.3V dc, the output of 2F(R) or 2F(L) goes low and clears POK flip-flop 2A. This causes optical isolator 1B to stop conducting, which enables FET Ql to conduct, which deasserts the signal BPOK H.

When POK goes low, a pulse appears at 2C-11, which triggers 2C (4-millisecond one-shot). After 4-milliseconds, DCOK deasserts, causing optical isolator 1C to stop conducting which, in turn, causes FET Q2 to conduct and deassert the signal BDCOK H.

Upon power-up, the output of comparator 2F(R) and 2F(L) go high and are ANDed with ACOK, triggering 2C. After the 4-millisecond delay, DCOK is set, which applies BDCOK H to the bus via the optical isolator and FET.

The DC ON indicator is illuminated by the assertion of the signal DCOK.

Figure 3-2 is a simplified timing diagram which illustrates the PSM power-up/power-down sequence in relation to the AC and DC Voltage Detectors.

Figure 3-2 PSM Power-Up/Power-Down Timing Diagram

#### 3.3.3 RUN Indicator

Whenever the processor is in the RUN mode and executing programs, a train of pulses having intervals of 3 to 5 milliseconds appears on the SRUN L line. These pulses trigger a re-triggerable one-shot having a period of 200-milliseconds. While the pulses are present, and for 200-milliseconds after the pulses are removed, the RUNLIT line remains asserted to illuminate the RUN indicator on the Control Panel.

200 msec after the processor is placed in the HALT mode, or power is turned off, the one-shot reverts to its stable state, causing the RUNLIT line to deassert and turn off the RUN indicator.

### 3.3.4 HALT Control

When the HALT switch on Control Panel is set to the normal position (switch out, indicator off), the signal BHALT L is deasserted on the bus and the processor is free to resume normal program execution.

When the switch is depressed and locked (indicator on), the signal BHALT L is asserted on the bus, placing the system in the HALT mode and causing the processor to execute the console ODT mode.

#### NOTE

In the HALT mode, the processor will continue to execute memory refresh operations and respond to DMA requests.

The cross-coupled inverters 2H-8 and 2H-6 remove the effects of switch bounce when the HALT switch is operated.

#### 3.3.5 Line Time Clock

The Power Sequencing Module can enable the generation of the signal BEVNT L as a periodic interrupt at the frequency of the AC input power source (i.e., 50 Hz or 60 Hz). This serves as the Line Time Clock signal.

One side of a 24 VAC voltage reference is half-wave rectified by CR10 and shaped by components CR9, Cll, and R31, creating a pulse that occurs every 16 2/3 msec for a 60 Hz line frequency, and every 20 msec for a 50 Hz line frequency. This pulse is applied to driver 2K(L), creating the signal BEVNT L.

When the LTC switch on the Control Panel is set to the normal position (LTC disabled, indicator off), the signal BEVNT L is always high. When the LTC switch is depressed and locked, the Line Time Clock is enabled and the LTC indicator is illuminated.

The cross-coupled inverters 2H-1 and 2H-4 remove the effects of switch bounce when the LTC switch is operated.

Figure 3-3 illustrates the general functional organization of circuitry on the MLSI-PSM23 module.

Figure 3-3 Power Sequencing Module, Simplified Block Diagram

#### 3.4 PSM ADJUSTMENT PROCEDURES

The Power Sequencing Module is calibrated and adjusted at the factory prior to shipment; therefore, no periodic checks or adjustments are required. However, should the module or individual components ever need to be replaced in the field, it may be necessary to readjust the AC and DC voltage monitoring circuits. Adjustment procedures are described in the following paragraphs.

The following test equipment is required to perform adjustments on the Power Sequencing Module:

1. AC/DC Voltmeter (Digital preferred).

2. AC Variable Transformer (Variac or equivalent).

With the appropriate test equipment, adjust the Power Sequencing Module as follows:

- 1. Remove all printed circuit boards from the backplane assembly.

- 2. Connect the AC line cord from the chassis to the AC variable transformer.

- 3. Connect the AC voltmeter across the variable transformer output.

- Apply AC power to the chassis and adjust the variable transformer to 98 VAC for a 115 VAC input voltage (185 VAC for a 230 VAC input voltage).

- 5. At this time, the DC ON indicator on the Switch Control Panel may or may not be lighted. If the indicator is off, adjust potentiometer R40 on the MLSI-PSM23 module until the DC ON turns on.

- 6. Then, adjust R40 again until the DC ON indicator just goes out.

- 7. Check the voltmeter to verify that the AC voltage is at 98 volts +.2V or -.5V when the DC ON indicator turns off. (For 230 VAC operation, the AC voltage observed on the voltmeter should be 185 volts ±.5V.)

- 8. Then, adjust the AC voltage up to 106 volts ±.5V (201 volts ±1V for 230 VAC operation). At this voltage, the DC ON indicator should illuminate, and should remain lighted as the AC voltage is adjusted to approximately 115 volts (230 volts for 230 VAC operation).

## CHAPTER 4

## THE POWER SUPPLY

## 4.1 INTRODUCTION

This chapter provides a description of the power supply utilized in the MLSI-BAll Series of Chassis Assemblies. Also included are necessary procedures for converting the chassis for an AC input voltage different from that configured at the factory.

## 4.2 THE POWER SUPPLY

The power supply is a regulated switching power supply which provides three dc output voltages. Refer to the power supply schematic diagram (#99-0013-001) contained at the end of this instruction manual for details. Power supply specifications are provided in Table 4-1.

| Output Voltage   | +5V dc    | +12V dc    | -12V dc    |

|------------------|-----------|------------|------------|

| Current          | 37 amps   | 4 amps     | l amp      |

| Line Regulation  | 0.2 %     | 0.2 %      | 0.2 %      |

| Load Regulation  | 0.2 %     | ±0.5 %     | ±0.5 %     |

| Ripple and Noise | 50 mV P-P | 100 mV P-P | 100 mV P-P |

Table 4-1 Power Supply Specifications

Table 4-1 Power Supply Specifications (continued)

| Input Voltage:                                | 90 - 132 VAC   | 180 - 264 VAC       |

|-----------------------------------------------|----------------|---------------------|

| Input Frequency: 47 - 440 Hz                  |                |                     |

| Operating Temperature: 0 - 50 degrees Celsius |                |                     |

| Height: 2.50" (6                              | .60 cm) Width: | : 5.00" (8.25 cm)   |

| Length: 13.50" (40                            | .40 cm) Weight | : 5.5 lbs. (2.5 kg) |

The power supply is factory-configured for the required input voltage, either 115 VAC or 230 VAC, depending upon the model designation specified at the time of order. (Refer to Table 1-1 for a complete list of the available MLSI-BAll Series Model Designations.)

The power supply is protected by a fuse and circuit breaker which is integral to the AC ON/OFF switch. These items are all located on the rear panel of the system chassis. For use with 115 VAC input voltage, the fuse is rated for 5.0 amperes; for use with 230 VAC input voltage, the fuse is rated for 2.5 amperes.

In addition to the protective input fuse on the chassis rear panel, the power supply is provided with a completely self-contained 5.0 amp fuse, which is used for either 115 VAC or 230 VAC input voltage.

#### IMPORTANT NOTES

- 1. For proper voltage operation, the power supply must always be connected to the Power Sequencing Module, which serves as the essential voltage load for the power supply.

- 2. To ensure that the power supply will regulate properly at ±12V dc, the system load must be enough to draw a minimum of 3.0 amps at +5V dc. If the load is insufficient, the DC ON indicator will extinguish after a period of time.

- 3. The 115/230 VAC jumper (located near the AC terminal block) must be removed from the power supply when used for 230 VAC operation, and must be installed for 115 VAC operation.

## 4.3 AC POWER CONNECTION

An AC input power connector is located on the rear of the chassis box. Simply plug the provided power cord to the AC input connector and to an appropriate AC receptable.

Apply AC power to the MLSI-BAll chassis by placing the AC ON/OFF rocker-style switch on the rear of the chassis in the ON position.

#### 4.4 AC INPUT POWER CONVERSION

If necessary to configure the MLSI-BAll Series chassis for operation with an AC input voltage different from that configured at the factory, perform the conversion procedures outlined in the following paragraphs.

#### 4.4.1 Chassis Conversion

To convert the MLSI-BAll Series chassis from 115 VAC to 230 VAC input power (or from 230 VAC to 115 VAC), perform the following:

- 1. Locate the AC input connector on the rear of the chassis assembly. Situated beside the AC input connector is the fuse compartment, containing a voltage selector printed circuit board and a protective fuse.

- 2. Remove the AC line cord from the power connector.

- 3. Slide the transparent window (covering the fuse compartment) to the left (open position).

- 4. Move the FUSE PULL lever to its left-most position. This causes the protective fuse to be released from the fuse holder.

- 5. Insert a pointed tool (such as a small screwdriver) into the hole in the small voltage selector PCB mounted in the fuse compartment and remove the PCB.

- 6. The voltage selector PCB contains the markings "120" and "240" to specify the AC input voltage ("120" = 115 VAC and "240" = 230 VAC). Position the voltage selector PCB as required for the AC input voltage to be used, and reinstall it in the fuse compartment. For 115 VAC operation, the "120" must be up and visible when the PCB is inserted in the compartment. For 230 VAC operation, the "240" must be up and visible when

installed. DO NOT turn the voltage selector PCB upside-down.

- Once the voltage selector PCB is installed properly, move the FUSE PULL lever back to its original position (to the right).

- Insert an appropriate protective slow-blow fuse in the fuse holder. The fuse should be rated for 5 amps when used with 115 VAC input voltage, and 2.5 amps when used with 230 VAC input voltage.

- 9. Close the transparent sliding window and reconnect an appropriate AC power cord, making sure the plug is compatible with either 115 VAC or 230 VAC.

#### 4.4.2 Power Supply Conversion

In addition to the necessary modifications on the rear of the chassis, the MLSI-BAll power supply must also be modified for the required AC input voltage. Simply remove the power supply top cover and remove the 115/230 VAC jumper from the power supply for 230 VAC operation, and install the jumper for 115 VAC operation. The 115/230 VAC jumper is located beside the power supply AC terminal block.

### 4.4.3 Power Sequencing Module Conversion

The Power Sequencing Module (MLSI-PSM23) must also be adjusted for the required AC input voltage. The necessary adjustments for 115 VAC and 230 VAC operation are described in paragraph 3.4. The "B" size option plates are removed for utilization of DEC's DZV11 or DLV11-J, or MDB's MLSI-DLV11-J and DMA Systems Modules such as the MLSI-F-DR11-W, MLSI-F-DR11-B, and MLSI-F-DRV11-B.

The two "B" size option plates and the adapter bracket in locations "A/B" and "Cl/C2" can be removed as one unit to accommodate MDB's 8-port or 16-port DZ11 multiplexor distribution panels (MLSI-F-DZ11-A and MLSI-F-DZ11-E, respectively).

The "D" size option plate is removed to accommodate disk or tape controllers (i.e., MLSI-F-RM11, MLSI-F-TM11, MLSI-F-TS11).

Consult the factory or an MDB Systems sales representative for a complete listing of modules which may be used with the Rear Cable Distribution Panel.

#### CHAPTER 6

#### RECOMMENDED PLACEMENT OF MODULES

## 6.1 INTRODUCTION

This chapter describes the recommended placement of modules in a standard MLSI-BA11-2000 system chassis. Prior to configuring an LSI-ll-based computer system, you should become familiar with the operation and bus architecture of the LSI-ll family of computers by referring to the DEC Microcomputers and Memories Handbook or Microcomputer Processor Handbook.

User discretion is advised in the configuration of an appropriate computer system. The examples discussed in this chapter are recommendations only.

Also included in this chapter is information pertaining to chassis installation and the initial power-up sequence.

#### 6.2 RECOMMENDED MODULE PLACEMENT

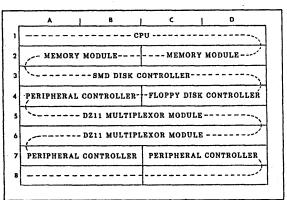

Figure 6-1 shows a recommended placement of DEC-compatible modules in the MLSI-BPA84-E Backplane/Card Guide Assembly.

Figure 6-1 Recommended Module Placement

#### RECOMMENDED PLACEMENT OF MODULES

PAGE 6-2

#### NOTE

The chassis is shown as viewed from the front (module-loading) side with the component sides of the modules facing upward.

The dashed lines indicate the Q-bus priority daisy chain. Priority for modules depends upon closeness to the processor; that is, the modules installed closest to the CPU have a higher interrupt priority than the modules that follow. However, if a module with four-level interrupt capability is used, it may be installed in any backplane slot and still retain its preassigned interrupt priority level.

The CPU should always be installed in the first slot of the backplane. In Figure 6-1, a quad-size CPU (i.e., LSI-11/23-PLUS) is installed in slot 1.

Memory modules might be installed as shown. The memory module in slot 2 C-D is the first module in position to receive the Q-bus signals after the CPU.

A Direct Memory Access (DMA) module, such as the SMD Disk Controller and the Floppy Disk Controller in the example provided, should follow the memory modules in the priority sequence.

After the DMA devices, programmed I/O devices, such as the MLSI-F-DZ11 8-port multiplexor, might be installed.

Following the multiplexor modules, your system configuration might require the installation of peripheral controller modules (i.e., MLSI-F-LP11).

The final backplane slot (8 A-B) may be utilized for a variety of applications. For system expansion, a Backplane Jumper/Cable Assembly (MLSI-BCV2A/B) or Bus Repeater Assembly (MLSI-DB11-R) may be installed. Note that the Bus Repeater should be used if the total number of modules in the system exceeds twenty dc bus

If no system expansion is required, the Terminator should be retained, leaving the backplane slot available for the installation of a functional module, such as the peripheral controller shown in the example.

#### NOTE

If necessary to leave an open slot in the priority daisy chain sequence, a Bus Grant Continuity Card (MLSI-BGC or equivalent) must be inserted in the "A" and "C" portion only of the vacant location. These devices transfer the DMA and Interrupt Bus Grant to the next module in the daisy chain.

### 6.3 CHASSIS INSTALLATION

The MLSI-BAll Series of Chassis Assemblies can be easily slide or rack mounted in a standard 19-inch RETMA-type rack or cabinet. Front retaining flanges are predrilled on the chassis to accommodate machine screws for chassis retention.

To facilitate the optional slide mounting of the chassis (MLSI-SMO), all chassis are equipped with factory-drilled holes with tapped, self-clenching fasteners (PEM nuts) installed. Provided at the end of this manual is a drawing showing installation of the chassis slide mount option.

#### PRECAUTIONARY NOTES

- 1: For chassis that are not mounted on slides, it is recommended that the chassis be supported on rails to preclude damage to the front retaining flanges.

- 2. It is recommended that the chassis be removed from the cabinet before shipping to prevent possible damage. In addition, all modules should be removed from the chassis prior to shipping and reinstalled at the destination site.

- 3. Three cooling fans which provide 300 cfm air circulation are located on the side panel of the chassis. Proper air circulation is vital to reliable system cooling and operation. To preclude overheating and possible system damage, DO NOT restrict air flow through the chassis assembly.

# 6.4 CHASSIS POWER-UP SEQUENCE

After all modules are installed as recommended or required, and the necessary cables are securely connected. apply power to the chassis assembly by placing the AC ON/OFF rocker-style switch on the rear of the chassis in the ON position. When the system is configured for the ODT mode, the following power-up sequence should occur when power is initially applied to the chassis:

- 1. The DC ON indicator on the Switch/Indicator Control Panel should illuminate and remain in this state. When lighted, this indicator signifies that AC line voltage and DC power are acceptable for reliable system operation.

- The RUN indicator should flash momentarily and then turn off. (If the RUN indicator remains illuminated in the ODT mode, a malfunction exists in the system.)

- 3. The LTC switch is normally disabled at the factory before shipment; therefore, the LTC indicator should be off when the system is powered-up for the first time. To enable line time clock interrupts, simply depress the LTC switch, which causes the indicator to light.

- 4. The HALT indicator should not be illuminated upon system power-up (the switch should be out). If the indicator is lighted (switch in), it signifies that the system is in the HALT mode and the normal power-up sequence is inhibited. To disable the HALT mode and enable the system to operate freely, simply press and release the HALT switch.

## NOTE

In certain processor bootstrap modes, the chassis assembly may perform a power-up sequence different from the one described above. Refer to appropriate DEC documentation for additional information.

# CHAPTER 7

# MAINTENANCE AND REPAIR

# 7.1 MAINTENANCE

In the event of apparent malfunction, refer to the schematic diagrams and assembly drawings contained in the following pages. Check to make sure that all connectors are secure and that control panel switches are properly set.

Repair the chassis assembly using appropriate skills, techniques, and materials. If you wish MDB Systems to repair the chassis, contact the Customer Service Department and request a Return Material Authorization (RMA) number. After return authorization is obtained, pack the chassis assembly carefully, along with your best evaluation of trouble symptoms, and ship it, prepaid, to MDB Systems, Inc.

# 7.2 DRAWINGS

The following pages contain schematic diagrams and assembly drawings which may be useful in maintaining and repairing the chassis assembly.

## CHAPTER 8

# REAR CABLE DISTRIBUTION PANEL ASSEMBLY FOR MDB BASIC BOX SYSTEMS

## 8.1 INTROUCTION

This chapter describes the function and configurations of the MLSI-BAll-200X Rear Cable Distribution Panel Assembly supplied with the Basic Box Systems listed in Table 8-1.

#### Table 8-1

| MDB MODEL NO.            | CPU<br>TYPE | CPU<br>SIZE | BOOTSTRAP<br>CHIP | MEMORY<br>CAPACITY | MEMORY<br>SIZE | NUMBER OF<br>SERIAL<br>PORTS | NUMBER OF<br>UNUSED<br>SLOTS |

|--------------------------|-------------|-------------|-------------------|--------------------|----------------|------------------------------|------------------------------|

| MLSI-S1-11/23 + 200X-F/R | KDF11-BA    | QUAD        | MXV11-A2          | 256 KB             | DUAL           | 2                            | 1 Dual, 6 Quad<br>or 13 Dual |

| MLSI-S2-11/23 + 200X-F/R | KDF11-BA    | QUAD        | MXV11-A2          | 512 KB             | DUAL           | 2                            | 1 Dual, 6 Quad<br>or 13 Dual |

| MLSI-S3-11/23 + 200X-F/R | KDF11-BA    | QUAD        | MXV11-A2          | 1 MB               | DUAL           | 2                            | 1 Dual, 6 Quad<br>or 13 Duai |

| MLSI-S4-11/23 + 200X-F/R | KDF11-BA    | QUAD        | MXV11-A2          | 2 MB               | DUAL           | 2                            | 1 Dual, 6 Quad<br>or 13 Dual |

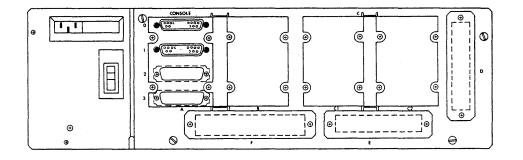

# 8.2 REAR CABLE DISTRIBUTION PANEL

The Rear Cable Distribution Panel Assembly facilitates the connection of cables between modules installed in the system backplane and user peripheral devices. Cable connections are made internally at the distribution panel bulkhead connectors, with external interface cables installed from the panel to the peripheral devices.

## NOTE

To reduce radiated noise, shielded interface cables should be used. (Shielded cables may be purchased from MDB Systems, obtained from other sources, or supplied by the user.)

# REAR DISTRIBUTION PANEL FOR BOX SYSTEMS

As supplied from the factory, the Rear Cable Distribution Panel contains a dual-port EIA RS-232-C Distribution Board with two male 25-pin bulkhead connectors (A0 and A1). Connectors A0 and A1 are provided for the connection of two internal mass terminated 10-conductor flat cables from the serial port connectors of a module installed in the backplane.

For example, since an LSI-11/23-PLUS processor is used, the cables may be installed from the CPU serial line unit (SLU) connectors (J1 and J2) to A0 and A1, respectively, of the RS-232-C Distribution Board.

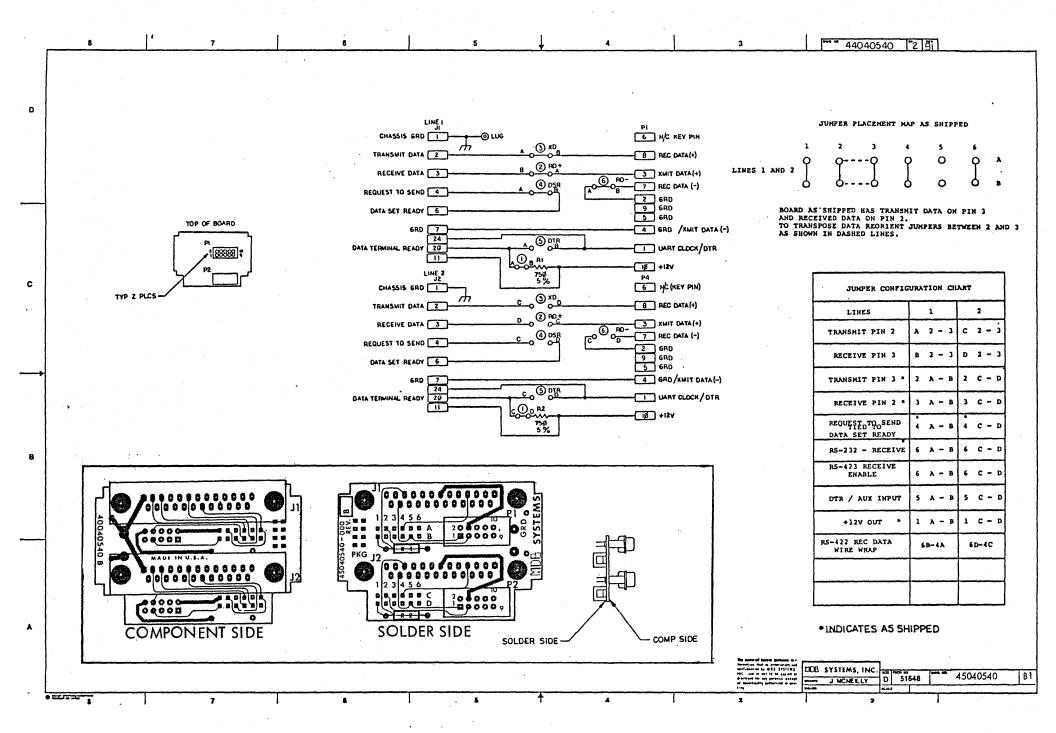

Each port of the RS-232-C Distribution Board is configured at the factory for Transmit Data on pin 3, Receive Data on pin 2. In effect, this configuration provides a limited "null-modem" cable capability, thereby minimizing the number of different types of cables required for various applications. You may reconfigure the board, via jumper plugs, for the standard RS-232-C capability; that is, with Transmit Data on pin 2 and Receive Data on pin 3.

The required jumper settings for RS-232-C and "null-modem" configurations are shown below. The jumper connections shown under Jl are for the console serial line unit (line 0), and those listed under J2 are for the secondary serial line unit (line 1).

|               | RS-23 | 32-C  | Null Modem                                          |       |  |  |

|---------------|-------|-------|-----------------------------------------------------|-------|--|--|

|               |       |       | while must seem while some time this seem time time |       |  |  |

| Signal        | Jl    | J2    | Jl                                                  | J2    |  |  |

|               |       |       |                                                     |       |  |  |

| Transmit Data | A2-A3 | C2-C3 | A2-B2                                               | C2-D2 |  |  |

| Receive Data  | B2-B3 | D2-D3 | A3-B3                                               | C3-D3 |  |  |

## Factory-configuration

The board may also be configured to provide EIA RS-423-compatible signals for Transmit and Receive Data. It also contains provisions to operate with a DEC DLV11-KA and allows the use of an external clock.

For additional jumper information, a schematic diagram (#44040540) and an assembly drawing (#45040540) of the RS-232-C Distribution Board are provided at the end of this manual.

The design of the Rear Cable Distribution Panel also provides for future system expansion. The panel can accommodate a wide variety of MDB modules as well as DEC modules with cable kits. Figure 8-1 is a pictorial view of the Rear Cable Distribution Panel Assembly.

Refer to Chapter 5 for further details.

# Figure 8-1

# Rear Cable Distribution Panel Assembly

|   |                                               |                                        |   | <b>*</b>                                                                                                           |                                                                                                                             | -                        |                        | 1. State 1. |                           |

|---|-----------------------------------------------|----------------------------------------|---|--------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| Γ |                                               |                                        |   |                                                                                                                    |                                                                                                                             |                          | r                      | REVISIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                           |