# MAC 16 OPTIONS REFERENCE MANUAL (INTERIM)

November 1969

## **FOREWORD**

This document is an interim manual containing Engineering design data. Information in this manual is supplemented, and in some instances, superceded, by information available in the following manuals:

MAC 16 Reference Manual

MAC 16 Interface Manual

MAC 16 Computer Maintenance Manual

# TABLE OF CONTENTS

| Section     | $\underline{	ext{Title}}$                   | Page |

|-------------|---------------------------------------------|------|

| FOREWORD    |                                             | iii  |

| SECTION I   | MAC 16 PROCESSOR OPTIONS                    | 1-1  |

|             | MAC 16 Processor Options                    | 1-3  |

|             | Multiply/Divide Option                      | 1-13 |

|             | Multiplex Data Channel, MDC                 | 1-15 |

|             | ICB Interface Module                        | 1-35 |

|             | Memory Interleave Channel, MIC              | 1-37 |

|             | Programmed Data Channel, PDC                | 1-49 |

| SECTION II  | MAC 16 MEMORY OPTIONS                       | 2-1  |

|             | MAC 16 Memory Options                       | 2-3  |

|             | DMA/ Controller Interface                   | 2-13 |

| SECTION III | MAC 16 DEVICE CONTROLLER OPTIONS            | 3-1  |

|             | MAC 16 Device Controller Options            | 3-3  |

|             | YAD Teletypewriter Controller               | 3-13 |

|             | RAD HSPT Controller                         | 3-21 |

|             | External Data Input Channel (EDIC)          | 3-31 |

|             | External Data Output Channel (EDOC)         | 3-35 |

|             | DCA, DCB, Disc./Drum Controller             | 3-39 |

|             | Line Printer Controller                     | 3-45 |

|             | CRC Card Reader Controller                  | 3-51 |

|             | Magnetic Tape Controller, 9 Track           | 3-55 |

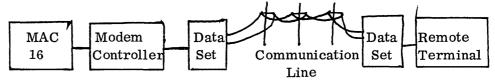

|             | Systems Description of Data Modem           | 3-65 |

|             | YAM Modem I/O Buffer                        | 3-81 |

|             | YHS High Speed Synchronous Modem Controller | 3-91 |

## TABLE OF CONTENTS (continued)

| Section    | <u>Title</u>                      | Page |

|------------|-----------------------------------|------|

| SECTION IV | MAC 16 HARDWARE OPTIONS           | 4-1  |

|            | MAC 16 Hardware Options           | 4-3  |

| SECTION V  | CARD SLOT ASSIGNMENTS FOR OPTIONS | 5-1  |

|            | Option Slot Assignments           | 5-3  |

|            | Main Frame Option Configurations  | 5-7  |

## SECTION I

MAC 16 PROCESSOR OPTIONS

#### MAC 16 PROCESSOR OPTIONS

#### PROCESSOR OPTIONS

Processor options consist of add on features that improve the performance of the computer. They are provided with the addition of Printed Circuit (PC) cards and wired PC connectors in the computer's mainframe. Card slots 1-7, 10 and 11 are used for these options. This is summarized in Table 1.

## Multiply/Divide -MD or -ME

This option provides two new instructions: MPY and DIV. Refer to page 3-14 of the Computer Reference Manual. The instruction execution time for Divide is now 14 microseconds instead of 13 microseconds as given in the manual.

In case of an overflow on Multiply (when minus one is squared) and Divide (when divisor is less than or equal to the dividend), the operands are not modified and the overflow indicator is set "on."

The Multiply/Divide option is located in card slots 4 and 5 (-MD) or slots 1 and 2 (-ME). It is a separate high speed arithmetic unit contained on two logic cards. The MPU card contains control logic and the MPR card contains registers and a full-adder.

#### Multiplex Data Channel - MCl to -MC5

This option provides hardware control of data communication with up to 16 device controllers. A set of two I/O control words for each device controller is held within fixed locations in memory. One control word specifies block length of the data in characters or words, and the other specifies memory address of data and defines the mode of communication. In the character mode of data communication the Multiplex Data Channel, MDC, packs or unpacks characters. The MDC provides system data rates up to 200 KC in the multiplex mode

Table 1. Processor Options

| Option                 | Designator       |                        |            |

|------------------------|------------------|------------------------|------------|

| Multiply/Divide        | -MD              | MPR, MPU               | 4,5        |

| Multiplex Data Channel |                  |                        |            |

| Interrupts l and 3     | -MCl             | MDU, MDR, LAD-4        | 3, 4, 5    |

| Interrupts 1, 3 to 7   | -MC2             | MDU, MDR LAD-8         | 3, 4, 5    |

| Interrupts 8 to 15     | -MC3             | MDU, MDR, LAD-8        | 3, 4, 5    |

| Interrupts 1, 3 to 15  | -MC4             | MDU, MDR, LAD-16       | 3, 4, 5    |

| Interrupts 8 to 23     | -MC5             | MDU, MDR, LAD-l6       | 3, 4, 5    |

| Interrupts 4, 8, 16    | -14              | LAD-4                  | ll (basic) |

|                        | -18, -116        | LAD-8, LAD-16          | 11         |

| Interrupts 20, 24, 32  | -l20, -l24, -l32 | LAD-16                 | 11         |

|                        |                  | LAD-4, LAD-8 or LAD-16 | 7          |

| Interrupts 36, 40, 48  | -136, -140, -148 | LAD-16                 | 11         |

|                        |                  | LAD-l6                 | 7          |

|                        |                  | LAD-4, LAD-8 or LAD-16 | 2          |

| Interrupts 52, 56, 64  | -152, -156, -164 | LAD-16                 | 11         |

|                        |                  | LAD-16                 | 7          |

|                        |                  | LAD-16                 | 2          |

|                        |                  | LAD-4, LAD-8 or LAD-16 | 1          |

| Line Driver            | -LD              | ICB-l                  | 6          |

| Line Receiver          | -LR              | ICB-2                  | 1          |

| Cable Driver           | -GD              | GAD                    | 6          |

| Cable Receiver         | -GR              | GAR                    | 1          |

| Bootstrap, TTY         | -BT              | BAD-T                  | 10         |

| Bootstrap, HSPT        | -BH              | BAD-H                  | 10         |

| Memory Interleave      | -MI              | none                   | none       |

and a data rate of 333 KC in the burst mode for a single controller.

Device Controllers that are controlled by the MDC are connected to the computer via the Programmed Data Channel, PDC, in the normal manner with one exception. That is, service request lines from the controllers are connected to a priority level logic card, LAD, that is a part of the MDC. This card may have a four, eight or sixteen level interrupt assembly depending upon the number of device controllers that are connected to the MDC.

Each device controller that is controlled by the MDC also must be assigned an interrupt level in the Central Processor Unit, CPU. A set of five, standard interrupt level assignments have been made and are summarized in Table 2.

The five interrupt assignments depend upon the number of device controllers that are controlled by the PDC and on the number of CPU interrupts that are provided.

- -MCl, The MDC controls one or two device controllers. The CPU contains the basic four interrupts, -l4. The MDC uses CPU interrupt levels l and 3. Priority two can be used if standard I/O service request is modified.

- -MC2, The MDC controls from one to six device controllers. The CPU contains eight interrupts, -18. The MDC uses CPU interrupt levels 1, 3, 4 to 7. Priority two can be used if standard I/O service request is modified.

- -MC3, The MDC controls from one to eight device controllers. The CPU contains sixteen interrupts, -ll6. The MDC uses CPU interrupt levels 8 to 15.

- -MC4, The MDC controls from one to fourteen device controllers. The CPU contains sixteen interrupts, -ll6. The MDC uses CPU interrupt levels 1, 3, to 15. Priority two can be used if standard I/O service request is modified.

- -MC5, The MDC controls from one to sixteen device controllers. The CPU contains at lease 24 interrupts, -124. The MDC uses CPU interrupt levels 8 to 23.

Table 2. MDC Option Configuration

|                                                  |                        | MDC O-tio         | - D:                                  |                                             |                                       |

|--------------------------------------------------|------------------------|-------------------|---------------------------------------|---------------------------------------------|---------------------------------------|

|                                                  | MDC Option Designators |                   |                                       |                                             |                                       |

|                                                  | -MCl                   | -MC2              | -MC3                                  | -MC4                                        | -MC5                                  |

| CPU Interrupts                                   | l or 2                 |                   | ollers on MI                          | <u> </u>                                    | 17-10                                 |

|                                                  | 1 or 2                 | l to 6            | 1 to 8                                | l to l4                                     | l to l6                               |

| 0 - not available to<br>MDC                      |                        |                   |                                       |                                             |                                       |

| 1                                                | 1                      | 1                 |                                       | 1                                           |                                       |

| 2 - available to MDC if standard I/O is modified | (2)                    | (2)               |                                       | (2)                                         |                                       |

| 3                                                | 3*                     | 3                 |                                       | 3                                           |                                       |

| 4<br>5<br>6<br>7                                 |                        | 4<br>5<br>6<br>7* |                                       | 4<br>5<br>6<br>7                            |                                       |

| 8<br>9<br>10<br>11<br>12<br>13<br>14             |                        |                   | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7* | 8<br>9<br>10<br>11<br>12<br>13<br>14<br>15* | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7* |

| 16<br>17<br>18<br>19                             |                        |                   |                                       |                                             | 8<br>9<br>10<br>11                    |

| 20<br>21<br>22<br>23                             |                        |                   |                                       |                                             | 12<br>13<br>14<br>15*                 |

<sup>\*</sup> Highest level may not be available if power fail safe option is included.

The MDC consists of three PC cards: MDU, MDR and a LAD. They occupy slots 3, 4 and 5. MDU provides control logic and MDR provides register logic. The LAD card is a regular processor interrupt level PC card.

Interrupt Expansion -14, -18, -116, -120, -124, -132, -136, -140, -148, -152, -156, -164.

The basic MAC 16 contains four interrupt levels, -14. They are provided on one PC card, LAD. This card has three assemblies: four interrupts, eight interrupts and sixteen interrupts. Each interrupt represents a flip flop within the computer's Program Level Register, L. An interrupt signal may set its corresponding flip flop in this register at any time that the computer is "on."

Interrupt expansion up to 20, 24, or 32 requires a second LAD card in slot 11.

Interrupt expansion up to 36, 40, or 48 requires a third LAD card in slot 2, and expansion to 52, 56 or 64 requires a fourth LAD card in slot 1.

It is occasionally necessary for LEC to provide receiver gates and external connections for external interrupt signals. Up to ll interrupt signals can be interfaced by the service request logic provided on an LD or GD option module. These would be used by controllers which are interconnected to the CPU via the External PDC. Other remote interrupt signals may require special termination and if so, special options can be provided for these cases.

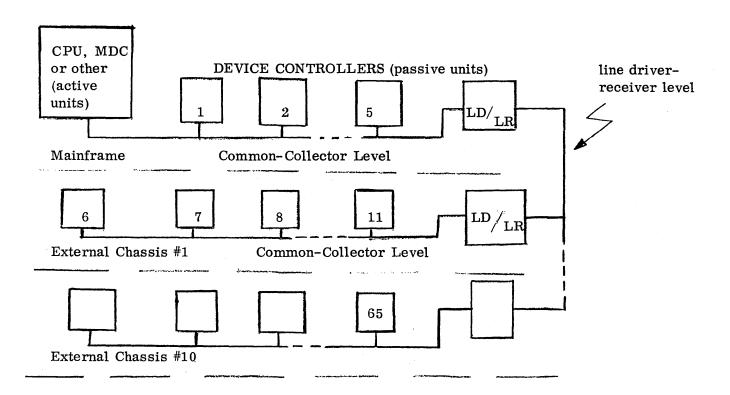

## Line Driver -LD and Line Receiver -LR

A logic card called ICB is available in two assemblies: as a line driver and as a line receiver. The Line Driver option is wired into slot six. It provides long line drive on the PDC interface. It can drive up to 50 feet of twisted pair cable and can drive up to three line receivers. The Line Receiver option is only an external chassis option.

Line Drivers and Line Receivers are required when MAC 16 device controllers are provided in an external chassis. A PDC cable set (three connectors with 41 pin Winchester connectors) are required for the interconnect. Cables are not included with the -LD or \_LR options.

They are ordered separately.

The -LD and -LR options include a set of external cable connectors in their chassis.

It is not necessary to sell a line receiver with a line driver if the customer wishes to connect directly to the line driver. The interface is the same as the PDC except that all signals are inverted.

A complete description of the line driver and line receiver options is available in the MAC 16 Computer Interface Manual. Also see entries S-29, SS-30, SS-31 of the Computer Project Notebook.

## Cable Driver -GD and Cable Receiver -GR

This option is similar to the Line Driver option, -LD, except that more drive is provided with discrete components instead of TTL, IC components. The Cable Driver option can drive up to 200 feet of PDC cable.

The cable driver option is provided with a PC card called GAD which is wired into slot 6. It has the same pin assignments as the ICB card that is used for the -LD option. The -GD option also provides three 4l pin external connectors for the PDC cables.

The Cable Receiver option, -GR, that is available for an external chassis is provided with a second PC card called GAR. The same PDC cables that connect line drivers and line receivers are used for interconnect.

#### Bootstrap, TTY -BT

This option is the provision of a read-only, diode memory of 64 words. A bootstrap program is provided that can be automatically entered into the computer's memory and executed. The program will read a paper tape from the Teletype reader. The paper tape may be punched with any program in the bootstrap format.

It is easy to modify this fixed program by location of diodes on a matrix. Therefore, the option can be used for special functions.

#### Bootstrap, HSPT -BH

This is the provision of the same diode memory in slot 10 as the -BT option.

The fixed program is modified to read paper tape from the HSPT Reader. This option requires that the HSPT Controller (-HC) option is also included.

#### Memory Interleave -MI

As presently defined this option does not include hardware; and is, therefore, a MAC 16 capability. It is the capability to suspend the computer at the end of its current instruction and to obtain control of the processor. It is the same capability that is used to provide the Multiplex Data Channel (-MC) and Multiply/Divide (-MD) options.

A special controller could be developed by the customer to take advantage of this capability. This controller could be used to access memory or processor registers. This controller should be located in slots 1, 2, 3, 4 or 5 replacing the -MC and -MD options. Location of the special Memory Interleave Controller in the mainframe is important to minimize wire lengths.

A complete description of this feature is being prepared for the MAC 16 Computer Interface Manual.

#### Combination Options

Different wire lists are required for different combinations of Processor Options. This difference occurs in the "daisy-chaining" of the PDC interface. The PDC is always wired to connector A of slot 8. The Line (Cable) Driver, (-LD), Multiplex Data Channel (-MC) and Multiply Divide (-MD) options also connect to the PDC interface. All connections to the PDC are pin for pin on connector A.

In order to minimize wire lists for combination options, the line (cable) driver, connector A will always be wired in whenever any one or all of the three options -LD (or -GD), -MC, -MD are designated.

The Multiply/Divide option (-MD) occupies slots 4 and 5 when the MDC option is not provided. If it is provided, the Multiply/Divide (-ME) cards occupy slots 1 and 2.

Figure 1 represents the PDC interface wiring for mainframe options.

Figure 1. PDC Mainframe Connections

| PROCESSOR                                                                                 | CARD SLOTS |     |     |     |     |             |              |             |

|-------------------------------------------------------------------------------------------|------------|-----|-----|-----|-----|-------------|--------------|-------------|

| OPTIONS                                                                                   | l          | 2   | 3   | 4   | 5   | 6           | 7            | 8           |

| Line (Cable) Driver Card: Wiring: -LD                                                     |            |     |     |     |     | -I.D<br>ICB | TTY-I<br>YAD | -HC<br>RAD  |

| Multi/Div. Only                                                                           |            |     |     |     |     |             |              |             |

| or Mult/Div. & Line Drive                                                                 | <br>       |     |     | MPR | MPU | ICB         | YAD          | RAD         |

| -MD or -LD/MD                                                                             |            |     |     |     |     |             |              | <del></del> |

| Mpx Data Chan. or<br>Mpx. Data Chan. and<br>Line Driver<br>-MC or -LD/MC                  |            |     | MDU | MDR | LAD | ICB         | YAD          | RAD         |

| Mult/Div and Mpx Data Chans or Mult/Div, Mpx. Data Chan and Line Drvr -ME/MC or -LD/ME/MC | MPR        | MPU | MDU | MDR | LAD | ICB         | YAD          | RAD         |

#### MULTIPLY/DIVIDE OPTION

The multiply and divide calling sequences for software, and the entries for hardware multiply and divide are defined below. Any software generated using these entries may operate on any MAC-16, whether it contains the hardware multiply/divide option or not.

The calling sequences (entries) are:

Multiply:

multiplicand in A register

MPY

JMM MPY

PTR multiplier

PTR least sig half of product

(return) - most sig half of product in A register

(return) - most sig half of product in A register

software timing:  $\sim$  350  $\mu$  sec average  $\sim$  700  $\mu$  sec worst case

hardware timing: 10 microseconds

Divide:

most sig half of dividend in A register DIV

JMM DIV

PTR least sig half of dividend (also R)

PTR divisor

(return) - quotient in A register

hardware timing: 13 microseconds

software timing: $\sim$ 800  $\mu$  sec

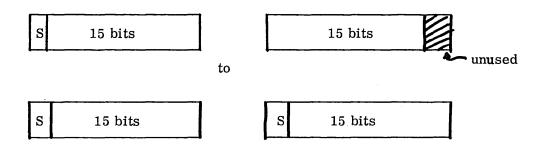

The double word fixed-point format is changed from

## MULTIPLEX DATA CHANNEL, MDC

| 1.0 | SYST | rem des              | ESCRIPTION                |                             |  |  |

|-----|------|----------------------|---------------------------|-----------------------------|--|--|

| 1.1 |      | Operation of the MDC |                           |                             |  |  |

|     |      | 1.1.1                | Channel C                 | Channel Control Words       |  |  |

|     |      |                      | 1.1.1.1                   | Memory Address              |  |  |

|     |      |                      | 1.1.1.2                   | Block Length                |  |  |

|     |      |                      | 1.1.1.3                   | Mode Field                  |  |  |

|     |      | 1.1.2                | Executive                 | Page                        |  |  |

|     |      |                      |                           | Control Word Locations      |  |  |

|     |      |                      | 1.1.2.2                   | Priority Level Assignment   |  |  |

|     |      |                      | 1.1.2.3                   | · ·                         |  |  |

|     |      | 1.1.3                | MDC System Configurations |                             |  |  |

|     |      |                      | 1.1.3.1                   | Device Controller Options   |  |  |

|     |      |                      | 1.1.3.2                   |                             |  |  |

|     |      |                      | 1.1.3.3                   | Multiple Device Controllers |  |  |

|     |      | 1.1.4                | System Operation with MDC |                             |  |  |

|     |      |                      | 1.1.4.1                   |                             |  |  |

|     |      |                      | 1.1.4.2                   | •                           |  |  |

|     |      |                      | 1.1.4.3                   | G                           |  |  |

|     |      |                      | 1.1.4.4                   | Burst Mode                  |  |  |

|     |      |                      | 1.1.4.5                   |                             |  |  |

|     | 1.2  | I/O Inst             | tructions                 |                             |  |  |

|     |      | 1.2.1                | ECO and                   | ESI                         |  |  |

|     |      |                      | 1.2.1.1                   | Command and Status Format   |  |  |

|     |      |                      | 1.2.1.2                   | ECO Device Selection        |  |  |

# 1.2.2 EDI and EDO

1.2.3 EAI

## 1.3 Program Requirements

- 1.3.1 Rules for Programming

- 1.3.1.1 Interrupt Inhibit in CPU

- 1.3.1.2 Interrupt Inhibit in Device Controller

|     |      |         | 1.3.1.3      | Sensing Status                           |

|-----|------|---------|--------------|------------------------------------------|

|     |      |         | 1.3.1.4      | Halting The CPU                          |

|     |      |         |              |                                          |

|     |      | 1.3.2   | The Active   |                                          |

|     |      |         | 1.3.2.1      | Idle State                               |

|     |      |         | 1.3.2.2      | Quiescent State                          |

|     |      | 1.3.3   | A Typical N  | MDC Driver Routine                       |

| 2.0 | CON  | TROLLE  | R DESCRIPT   | TION                                     |

|     | 2.1  | Logic D | escription   |                                          |

|     | -• - | 2.1.1   | Registers    |                                          |

|     |      |         | 2.1.1.1      | C Register                               |

|     |      |         | 2.1.1.2      | B Register                               |

|     |      |         | 2.1.1.3      | L Register                               |

|     |      |         | 2.1.1.0      | 1 liegibioi                              |

|     |      | 2.1.2   | Service Rec  | quests                                   |

|     |      | 2.1.3   | Algorithm    |                                          |

|     |      | 2.1.4   | Control Sta  | tes                                      |

|     |      | 2.1.5   | Control Fli  | p Flops and Signals                      |

|     |      | 2.1.6   | Micro-ops    |                                          |

|     |      |         | 2.1.6.1      | Micro-ops CPU                            |

|     |      |         | 2.1.6.2      | Micro-ops MDC                            |

|     |      | 2.1.7   | Instruction  |                                          |

|     |      | 2.1.8   | Address Ge   | eneration                                |

|     |      |         | 2.1.8.1      | Executive Page Address                   |

|     |      |         | 2.1.8.2      | Device Address                           |

|     | 9 9  | Hondayo | re Configura | tion.                                    |

|     | 2.2  | 2. 2. 1 | Cards        | tion                                     |

|     |      | 4.4.1   | 2. 2. 1. 1   | MDR                                      |

|     |      |         | 2.2.1.2      | MDU                                      |

|     |      |         | 2.2.1.3      | LAD-MDC                                  |

|     |      |         | 2. 2. 1. 0   |                                          |

| •   |      | 2.2.2   | Wiring       |                                          |

|     |      |         | 2.2.2.1      | CPU Clock and Timing Signals             |

|     |      |         | 2.2.2.2      | Micro-ops                                |

|     |      |         | 2.2.2.3      | Interconnects                            |

|     |      |         | 2.2.2.4      | PDC Bus                                  |

|     |      |         | 2.2.2.5      | Service Requests from Device Controllers |

|     |      |         | 2226         | Service Requests to CDII Priority Level  |

2.2.3 Test Points

#### 1.0 SYSTEM DESCRIPTION

The Multiplex Data Channel, MDC, is a MAC 16 option that will control data communication between the computer's memory and up to 16 device controllers connected to the Program Data Channel, PDC. The MDC control consists of accessing the data word, controlling the I/O transfer with the device controller, and monitoring the length of the record. The MDC does automatically with hardware what is normally accomplished in an interrupt service routine with software. Thus, by cutting the program overhead in I/O operations, the MDC facilitates greater overall data and throughput rates. The MDC will operate with any device controller that has a standard PDC interface.

Maximum data rates with the MDC are 200KC in the normal mode of operation and 333 KC in the burst mode. Both Input and Output devices may be accommodated in any combination; and, character devices may have their data packed and unpacked automatically. Devices may be assigned a relative priority according to system requirements, and a unique interrupt occurs automatically at the end of each record transfer.

#### 1.1 Operation of the MDC

Up to 16 device controllers on the PDC may operate with the MDC if their unique Service Request signals are wired to the MDC hardware option instead of to program level interrupts. This will allow the MDC hardware to respond to a service request instead of requiring an interrupt service routine response. When the MDC detects a service request it will respond by automatically forcing the computer into an idle state between instructions, during which time the memory is accessed for address and block length, and the data is transferred to or from memory. In normal mode, the program automatically resumes execution until the next service request; and when the entire record has been transferred, the MDC will send a service request to the CPU that will cause a priority interrupt, thus informing the program of completion.

#### 1.1.1 Channel Control Words

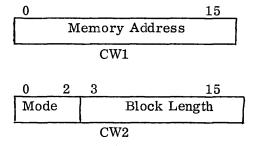

Associated with each device controller are two control words, CW1 and CW2, previously stored in memory by the program. CW1 provides a 16 bit memory address of the data to be transferred. CW2 provides a 13 bit block length field and a 3 bit mode field. The word formats are as follows:

CW1 is incremented upon each word transferred and the block length is decremented each service request. Eight modes of operation are specified in the mode field, combinations of input or output, normal or burst, and word or byte.

## 1.1.1.1 Memory Address

CW1 is initialized before an I/O operation with a starting address. During the I/O operation CW1 will contain the address of the next data to be accessed and after the I/O operation is complete it will contain the address of the last data accessed plus 1.

#### 1.1.1.2 Block Length

The block length field of CW2 is initialized before the I/O operation with the number (binary) of bytes or words to be transferred. During the I/O operation it will contain the number of bytes or words yet to be transferred and after the I/O operation is complete the block length field will normally contain zeros. If the record was terminated early, the block length will contain the number of words or bytes not transferred.

#### 1.1.1.3 Mode Field

Bits 0 to 2 of CW2 provide 8 communication modes. The logic of the MDC examines these three bits to control its operation.

| Bit | _0_    | _1_   |

|-----|--------|-------|

| 0   | Output | Input |

| 1   | normal | burst |

| 2   | byte   | word  |

The 8 modes are summarized as follows:

MDC COMMUNICATION MODES SELECTED BY CW2

| CW2 Bits |                      |                                                                                                                                                                                                                                                                                                 |

|----------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 1 2    | Mode                 | Operation                                                                                                                                                                                                                                                                                       |

| 0 0 0    | Output, Normal, Byte | Obtain a word from memory address CW1. If bit position 15 of CW2 (block length) is a one, transmit the right byte and increment CW1. If bit position 15 of CW2 is a zero, transmit the left byte. Decrement CW2. Return CW1 and CW2 to memory.                                                  |

| 0 0 1    | Output, Normal, Word | Obtain a word from memory address CW1.  Transmit this word. Increment CW1. Decrement CW2. Return CW1 and CW2 to memory.                                                                                                                                                                         |

| 0 1 0    | Output, Burst, Byte  | Obtain a word from memory address CW1. If bit position 15 of CW2 (block length) is a one, transmit the right byte and increment CW1. If bit position 15 of CW2 is a zero, transmit the left byte. Decrement CW2. Hold CW1 and CW2 for the next service request from the same device controller. |

| 0 1 1    | Output, Burst, Word  | Obtain a word from memory address CW1.  Transmit this word. Increment CW1. Decrement CW2. Hold CW1 and CW2 for the next service request from the same device controller.                                                                                                                        |

| 1 0 0 | Input, Normal, Byte | Receive a byte on data input lines 7 to 15. If position 15 of CW2 (block length) is a one, insert this byte into the right half of memory address CW1 and increment CW1. If bit position 15 of CW2 is a zero, insert this byte into the left half of memory address CW1, Decrement CW2. Return CW1 and CW2 to memory.                                       |

|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 0 1 | Input, Normal, Word | Receive a word (up to 16 bits) on the data input lines. Write this word into memory address CW1. Decrement CW2. Increment CW1. Return CW1 and CW2 to memory.                                                                                                                                                                                                |

| 1 1 0 | Input, Burst, Byte  | Receive a byte on data input lines 7 to 15. If bit position 15 of CW2 is a one, insert this byte into the right half of memory address CW1 and increment CW1. If bit position 15 of CW2 is a zero, insert this byte into the left half of memory address CW1. Decrement CW2. Hold CW1 and CW2 for the next service request from the same device controller. |

| 1 1 1 | Input, Burst, Word  | Receive a word (up to 16 bits) on the data input line. Write this word into memory address CW1. Decrement CW2. Increment CW1. Hold CW1 and CW2 for the next service request from the same device controller.                                                                                                                                                |

#### 1.1.2 Executive Page

The fixed memory locations of channel control words is in the Executive Page, where each of the 16 possible device controllers is associated with a program priority level. The two channel control words CW1 and CW2 may be conveniently stored and examined by the program, and an end of record interrupt can automatically direct program flow to a terminating routine. The program levels assigned to MDC device controllers is a system variable, but in most cases, levels 8-23 will be assigned. The degree of priority assigned to each device controller will match the corresponding program priority level.

#### 1.1.2.1 Control Word Locations

In the set of 4 locations associated with each program priority level, the MDC control words occupy 2 locations as shown:

| Word | Program | $\underline{\mathbf{MDC}}$ |

|------|---------|----------------------------|

| 0    | P       | (P)                        |

| 1    | X       | CW1                        |

| 2    | Α       | CW2                        |

| 3    | Status  | (Status)                   |

While an MDC device controller is active, words 1 and 2, (normally X and A), will be accessed by the MDC to determine memory address, block length, and mode. Words 0 and 3, (P and Status) will not be accessed by the MDC.

#### 1.1.2.2 Priority Level Assignment

Usually program priority levels 8-23 will be assigned to MDC device controllers. The corresponding locations in the executive page for each of the 16 device controllers is shown in the table.

| Program<br>level |      | Executive Page Locations |      |      |            | Relative<br>device |

|------------------|------|--------------------------|------|------|------------|--------------------|

| Dec.             | Hex. | (P)                      | CW1  | CW2  | (Status)   | priority           |

|                  |      |                          |      |      |            |                    |

| 8                | 08   | 0020                     | 0021 | 0022 | 0023       | 0                  |

| 9                | 09   | 24                       | 25   | 26   | 27         | 1                  |

| 10               | 0A   | 28                       | 29   | 2A   | 2B         | 2                  |

| 11               | 0B   | 2C                       | 2D   | 2E   | 2F         | 3                  |

| 12               | 0C   | 0030                     | 0031 | 0032 | 0033       | 4                  |

| 13               | 0D   | 34                       | 35   | 36   | 37         | 5                  |

| 14               | 0E   | 38                       | 39   | 3A   | 3B         | 6                  |

| 15               | 0 F  | 3 C                      | 3D   | 3E   | 3F         | 7                  |

| 16               | 10   | 0040                     | 0041 | 0042 | 0043       | 8                  |

| 17               | 11   | 44                       | 45   | 46   | 47         | 9                  |

| 18               | 12   | 48                       | 49   | 4A   | 4B         | 10                 |

| 19               | 13   | 4C                       | 4D   | 4E   | 4 <b>F</b> | 11                 |

| 20               | 14   | 0050                     | 0051 | 0052 | 0053       | 12                 |

| 21               | 15   | 54                       | 55   | 56   | 57         | 13                 |

| 22               | 16   | 58                       | 59   | 5A   | 5B         | 14                 |

| 23               | 17   | 5C                       | 5D   | 5E   | 5 <b>F</b> | 15                 |

#### 1.1.2.3 MDC Interrupt

At the termination of an I/O operation a complete record has been buffered in or out. The MDC detects either that the block length has been counted down to zero or that the device has terminated the record. It then sends a service request to the program priority level associated with that device controller. When an interrupt at that level occurs, the registers in the executive page will be loaded into the CPU's operating registers as if a normal interrupt had occurred. The CPU will begin execution of a program at P, where the necessary stop commands should be executed. To activate a new buffer, this program level should be left before initializing the control words again and starting the device.

#### 1.1.3 MDC System Configurations

The MDC may satisfy a variety of system configurations, from a few I/O devices to many. A few device controllers may be used or 16 maximum, all of which may be actively buffering data simultaneously. Each device controller may have from 1 to 16 I/O devices for a maximum of 256 devices but only 1 device per device controller may be active at a time. A variety of device addresses may be assigned depending upon program priority level assignments. And, device controllers may be fully duplexed for both input and output as long as both modes do not operate in simultaneous buffers.

#### 1.1.3.1 Device Controller Options

The MDC may operate with any number of device controllers, from 1 to 16, by selectively wiring in those service requests and program priority levels desired. The various options possible are as follows:

| <u>Option</u> | Number of Device Controllers | Hardware Required |

|---------------|------------------------------|-------------------|

| 1             | 1 only                       | MDC, MDR          |

| 2             | from 1 to 4                  | MDU, MDR, LAD-4   |

| 3             | from 1 to 8                  | MDU, MDR, LAD-8   |

| 4             | from 1 to 16                 | MDU, MDR, LAD-16  |

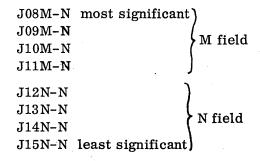

## 1.1.3.2 Device Address

The program priority levels assigned to MDC device controllers determines at least 4 bits of device address that must be assigned. In the simple case, if the MDC is assigned levels 0-15, the device controllers must have addresses X0-XF (Hex), where the decoding of X by a device controller is arbitrary. In particular, since the standard levels assigned are 8-23, the device addresses assigned are 08-17 (Hex). In this case 5 bits of address are predetermined and only 3 bits are arbitrary. The alternate device address assignments for the standard wiring are: 28-37, 48-57, 68-77, 88-97, A8-B7, C8-D7, or E8-F7. In any case, device controllers are assigned a set of 16 consecutive addresses with the 4 or 5 least significant bits determined by level assignment.

## 1.1.3.3 Multiple Device Controllers

If a controller has more than one device attached to it, the arbitrary bits of the device address identify the particular device. ECO and ESI instructions will use the full 8 bit device address to select or sense the device. Device controllers may accept commands for inactive devices (such as rewind tape) while another is actively transferring data with the MDC as long as service requests associated with those commands can be selectively inhibited.

## 1.1.4 System Operation with MDC

Initializing a buffer for a device controller connected to the MDC is analogus to PDC operation. Constants are stored (P, CW1 and CW2) and a command is issued to the device. Once initialized, the buffer continues automonously until an interrupt occurs. Additional buffers may be initialized at any time and normal programmed I/O to a non-MDC device is allowed in both interrupt and non-interrupt modes. All active devices will be transferring data over the same I/O data bus (PDC) on a time shared basis. Maximum data rates through the MDC are a function of certain system variables which affect the response time to a service request; i.e., longest instruction being executed, relative priority of device controllers, number of devices active on the MDC, etc. Certain free running devices require quick program response to the termination of a buffer.

## 1.1.4.1 Initializing a Buffer

Storing P, CW1, and CW2, does not in itself start the I/O operation with the MDC. The device controller must be issued a command to start (input or output) with interrupts allowed. The MDC will not react until the first service request is raised by the device controller, indicating a request for data. If the block length of CW2 is non-zero the MDC will attempt a data transfer with the device.

If the block length is zero (failure to initialize CW2), the MDC will not attempt to transfer data, but send a service request (interrupt) to the CPU; and because the device controller did not transfer data, the device service request will remain active. For this reason the control words must be properly initialized before the ECO command to allow interrupts is executed.

## 1.1.4.2 Terminating a Buffer

An interrupt from an MDC device calls for either of two actions, reinitialization of the buffer or the termination. Terminating consists of stopping the device and inhibiting interrupts (service requests). This command must be issued before another service request is raised or the MDC will begin cycling on zero block length. The minimum time from the last service request to the time when a stop command can be executed is 25 microseconds.

#### 1.1.4.3 Data Rates, Response Times

Maximum data rate in the normal mode is 200KC, either for words or bytes, one device or 16 devices. The 200KC figure comes from the fact that 5 1-microsecond cycles are required for each word or byte transferred. If there is more than one device active on the MDC, the maximum rate must be shared on a relative priority basis. Device controllers must have adequate buffering to hold data for the length of time it takes the MDC to service all devices of a higher relative priority plus the maximum possible response time to the first service request. The maximum possible response time is the execution time of the longest instruction being executed plus 1 cycle. (Shift-15 is 5+1 = 6 microseconds, hardware Divide is 13+1 = 14 microseconds). With 16 devices active, the device controller of the lowest relative priority must be able to hold data 5x16+14=94 microseconds, or longer. Without data buffer registers this device could transfer data no faster than about 10KC. In fact, devices of higher priority with rates higher than 12.5KC would degrade the maximum data rate of the lowest even further. In general, the system determines the maximum data rate for a device on a given priority. The MDC will not detect a timing error if it occurs but most device controllers are designed to do so, making the information available in the controller's status word.

#### 1.1.4.4 Burst Mode

If the burst mode is designated in CW2 for any device on the MDC, no program execution will occur after the first service request from that device. Usually, the burst mode will be used with those devices that have a long start or search time followed by a high data rate. Rates of any other active device – either MDC or normal PDC – must be less than the total block transfer time of the burst device. The maximum data rate for the burst device itself is 333KC, with increments of 1 microsecond added for waiting on rates less than that.

#### 1.1.4.5 Unknown Record Lengths

The MDC will input from devices that have unknown record lengths, magnetic tape, for example. The records may be read in either the burst or normal mode. Termination of the data transfer will be under the control of the device controller, which will sense the end of the record and not acknowledge the next data transfer. The block length in CW2 would have been initialized with some number greater than the length of the record (8, 191 words or bytes maximum); and, after the termination the block length in CW2 (or A) will be a number equal to the original block length less the actual length of the record, less the number of "extra" service requests that the controlle requires to terminate. The memory address in CW1 (or X) will be the address of the last word

or byte of the record increased by the number of extra service requests.

#### Example:

A device controller will issue one extra service request at the end of a 10 character record. When the MDC attempts to input on the last service request, the device controller will not acknowledge. The I/O operation is performed in the normal and byte mode. The contents of CW1 and CW2 are:

|     | Before            | After |

|-----|-------------------|-------|

| CW1 | $010\overline{0}$ | 0106  |

| CW2 | 800F              | 8004  |

The contents of memory will be:

| 0100 | no change | 1st   | 1        |

|------|-----------|-------|----------|

| 101  | 2nd       | 3rd   |          |

| 102  | 4th       | 5th ( | bytes of |

| 103  | 6th       | 7th   | record   |

| 104  | 8th       | 9th   |          |

| 105  | 10th      | zeros |          |

| 106  | no cha    | nge   |          |

| 107  |           |       |          |

| 108  |           |       |          |

| -    | -1        |       |          |

The number of extra service requests following the last character of a record is a characteristic of the device controller. The MDC only knows to terminate the data transfer by detecting no acknowledge. If there are any more service requests after the one that was not acknowledged the block length and memory address will be counted for each.

#### 1.2 I/O Instructions

The four I/O Instructions, EDO, EDI, ECO, and ESI may be used with any device controller connected to the MDC. Programming with these instructions should be as if the device controller were operating in inhibited interrupt mode. In most cases, only the ECO and ESI instructions are used in programming a device on the MDC. EDO and EDI may be executed, but only if the special requirements of a device controller need them.

#### 1.2.1 ECO and ESI

ECO. Used to allow interrupt and start device before the I/O operation, and after the I/O operation, to stop the device and inhibit the interrupt. The ECO may be used for any other special functions required by the device controller.

ESI. Used to sense the status of a device controller. The ESI should not be executed while an I/O operation is in progress because data may be lost.

#### 1, 2, 1, 1 Command and Status Formats

The format of commands and status will be as defined in the description for a particular device controller. Communication using an ECO or ESI is through the A Register, as normally.

#### 1.2.1.2 ECO Device Selection

If a device controller on the MDC controls more than one device, the ECO instruction may serve the purpose of selecting which device is to transfer data.

#### 1.2.2 EDI and EDO

The EDI or EDO instructions may be executed to transfer a final data word after the I/O operation is complete, if the device controller so requires. For example, after stopping a paper tape reader one or two more characters may be read (depending upon timing). An EDI (in inhibited interrupt mode) will input a character into the A Register if the device controller is ready to input.

#### 1.2.3 EAI

The EAI instruction serves no useful function to devices connected to the MDC. Device controllers will not be wired to respond to an EAI.

#### 1.3 Program Requirements

The primary difference between programming for MDC I/O and programmed I/O is that the MDC transfers data asynchronously with respect to program decision logic. It is necessary to completely input a record before making decisions on the data, for example; and on output, the full record must have been operated upon before a buffer is initiated to send it to a device. If so desired, incoming data can be monitored by observing the progress of a buffer. The control words CW1 and CW2 may be read to find the address of the last data to be input. And computation of an output record may likewise be in process if it is known that the computation will proceed faster than the output device will accept data. But more typically, programs are written such that buffers are traded back and forth - computation proceeding upon one record while the next is being buffered in or out. In going back and forth between buffers the program must execute a buffer turn around, which may or may not limit the data rate. In a real time situation where data is input, computed upon, and output, the critical time may be buffer turn around, and it may be necessary to stop a device between records.

## 1.3.1 Rules for Programming

The following rules should be observed for programs using devices on the MDC.

#### 1.3.1.1 Interrupt Inhibit in CPU

Interrupts should be allowed in the CPU. If interrupts are inhibited in the CPU the end of record interrupt from a device on the MDC may be missed or delayed. Otherwise, the Inhibit Interrupt does not affect the normal transfer of data.

#### 1.3.1.2 Interrupt Inhibit in Device Controller

Interrupts (service requests) should be allowed in device controllers actively transferring data with the MDC. No data will be transferred (by the MDC) if the device interrupt is inhibited. In those inactive devices on the MDC that normally request data when at rest (example: HSPT Punch) the device interrupts should be inhibited. If not, the MDC will attempt to service the device.

#### 1.3.1.3 Sensing Status

An ESI to a device actively transferring data with the MDC should not be executed or data will be lost. Status may be sensed before and after the data transfer as normally.

#### 1.3.1.4 Halting the CPU

The CPU should not be halted when a buffer is active. Since the MDC requires the internal CPU clock, a halt will cause the MDC to lose data, and the device may not be properly stopped at the end of its current record.

#### 1.3.2 The Active Buffer

An MDC buffer is made active by allowing a device controller to send service requests to the MDC. The MDC reacts to any service request in same manner; i.e., by accessing CW1 and CW2 for that device and attempting a transfer of data. The idle state only occurs after the completion of the current instruction so allowances should be made for devices with high data rates. An active buffer will remain active until the interrupt is inhibited in the device controller.

#### 1.3.2.1 The Idle State

The MDC will cause an idle state at the end of an instruction, at the end of the 6 microsecond transition from one priority level to another, or during the quiescent state. The idle state will not be entered after a single cycle instruction. If hardware MPY/DIV is installed the idle state will not be entered until the MPY or DIV instruction has completed execution. If an MDC service request is pending at the same time a higher level program priority is set, the idle state for the MDC will be entered first.

#### 1.3.2.2 Quiescent State

The MDC will service active buffers in the quiescent state. If a priority interrupt occurs in the quiescent state while the MDC is servicing a device, the new program level will not be entered until the service has finished. Since in the quiescent state new program levels may be entered while the interrupts are inhibited in the CPU, the termination of a buffer will always cause an interrupt.

## 1.3.3 A Typical MDC Driver Routine

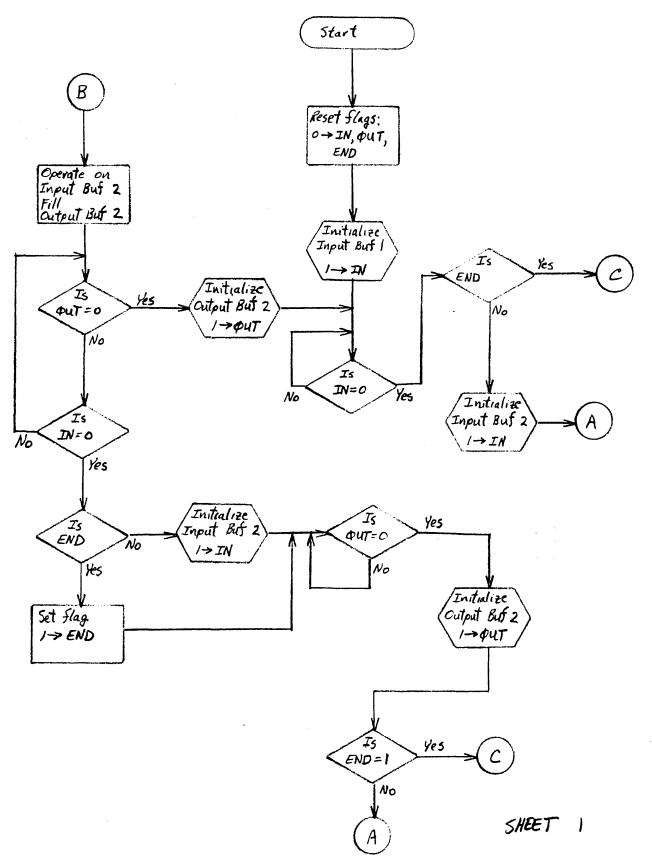

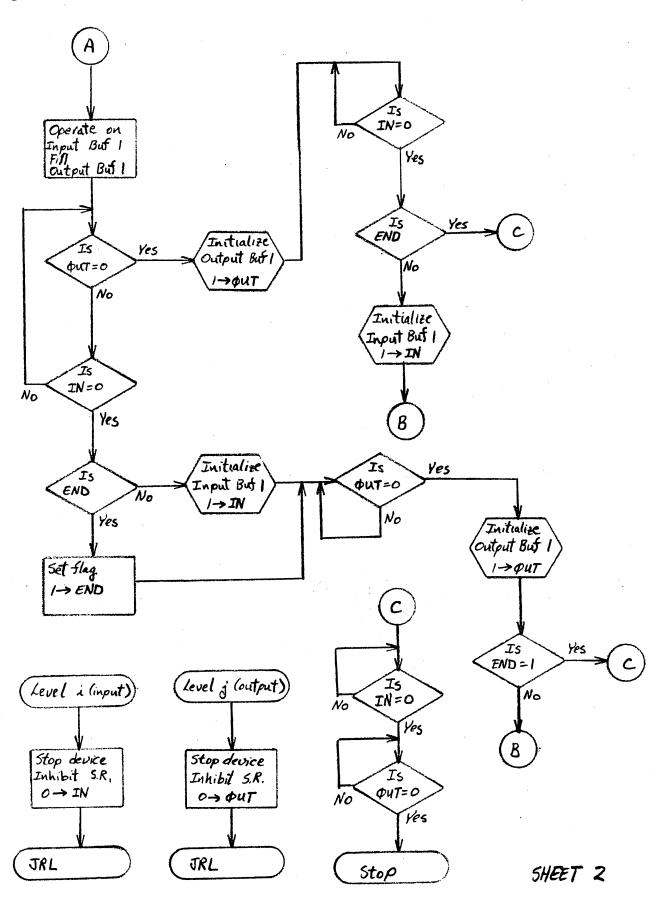

A typical use of the MDC might be to operate on a stream of data. In this type of operation the CPU may be required to (1) input a record (a line or card image), (2) operate on the record, and (3) output a record.

Without knowing anything about the execution times of each of the three operations, a driver routine can be written for the MDC that will maximize the overlap. A method of alternating buffers is suggested here. In this scheme the CPU is operating on record N, while inputting record N+1 and outputting record N-1. Four buffer areas are required for data: two input buffers and two output. Two flags are required: a flag for the input device and a flag for the output device. Each flag is set when the buffer for that device is initialized and reset when the buffer is finished. Assume that while operating on record N, neither its source area (where the record was input) nor its destination area (where the record will be later output) can be used until the operation on that record is finished. Then if record N+1 is completely input the input buffer for record N+2 may not be initialized until the operation on record N has finished. Likewise, if record N-1 has been completely output, the output buffer for record N may not be initialized until the operation on record N has finished. In the program level for each device, the CPU should stop the device, inhibit service requests, and reset the device flag. Initialization for the next buffer will be in the main part of the routine after the operation on the current record has finished and after the respective flag of each device has been reset. It will consist of storing the control words, starting the device, allowing the service request, and setting the flag. Since it is not known which device, input or output, will finish before the other, the looping on flags reset will have to be split into two paths. Also, assuming the last record will be some kind of an END record, provision must be made for preventing any additional records being input if not desired. The use of a stop flag is suggested. A flow chart for this hypothetical driver is shown.

#### 2.0 CONTROLLER DESCRIPTION

The MDC consists of three standard size PC cards installed in the CPU main frame and wired into the back panel nest. Other options may be required to work in conjunction with the MDC, such as a second LAD board (providing up to 32 priorities) and various combinations of I/O device controllers. In general, each system with an MDC will be slightly different. Supplementary documentation will be provided to completely define a given installation.

## 2.1 Logic Description

Logic of the MDC can be described in the following bread areas: registers, service requests, algorithm, control states, control flip flops, micro-ops, instruction decode, and address generation. For more complete details refer to the block diagram, flow chart, and logic diagram.

#### 2.1.1 Registers

The MDC contains three registers, a data register (C), a register for CW2 (B), and a priority register (L) for service requests. C and B are located on the register board MDR and L is located on LAD-MDC.

## 2.1.1.1 C Register

C holds the data word during an input or output operation. It is a full 16 bit register constructed of D-type flip flops. The data path into C is from the CPU function bus. The outputs of C are gated onto the PDC data bus, either a full 16 bit word or the left 8 bit byte onto the right byte position.

#### 2.1.1.2 B Register

B holds Control Word 2 which contains the mode bits (Input/Output, Burst/Normal, and Word/Byte) and the Block Length. The data paths into and out of B is via the CPU function bus. Associated with bits 3-15 of B is a binary down counter. The mode bits are not affected by the counter.

#### 2.1.1.3 L Register

Service Requests are remembered in the dual rank L Register which determines priority of devices. Each of 16 possible service requests directly sets a flip flop in the upper rank of L, and the upper rank is transferred to the lower rank once each machine execution cycle. The lower rank is encoded into a 4 bit device number which is held in 4 flip flops during the idle state.

## 2.1.2 Service Requests

If any of the 16 flip flops is set in the lower rank of L, the signal SERV-P indicates to the MDC logic that an idle request should be initiated. Once the MDC is in the idle state, however, SERV-P is ignored and only the service request corresponding to the device number is used. The device number is decoded into 16 decode gates, which are in turn, anded with the corresponding service request, and ored together to form a signal called selected service request SSRA-P. Associated with the selected service request are two flip flops, SSR and KSR, that provide the logic with a signal HSRA-P which is essentially the selected service request synchronized with the input/output control lines, JEDI-N and JEDO-N. This logic differentiates between an old service request and a new one for a selected device while ignoring service requests from other devices.

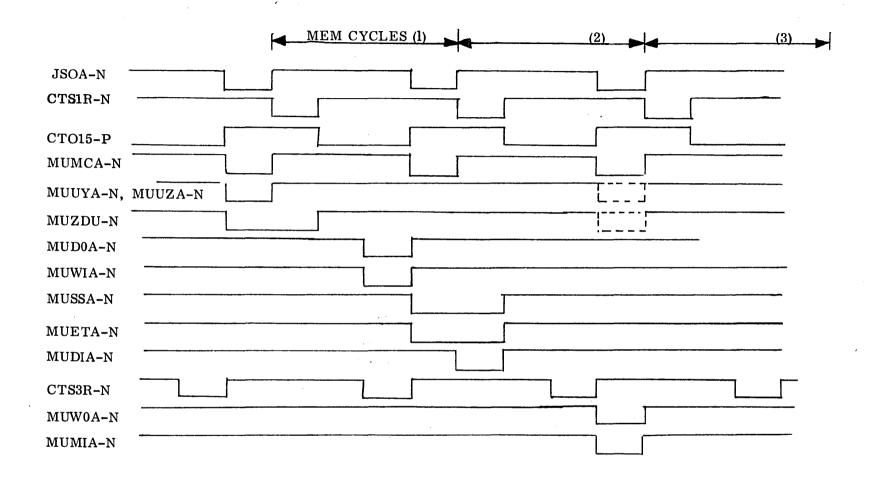

#### 2.1.3 Algorithm

The algorithms for input and output are slightly different. Both use the same set of control states, but in a different sequence. For details of the algorithm see the flow chart. Briefly, the sequence of machine cycles is as follows:

- 1) Access CW2 and transfer contents to B.

- 2) Access CW1 and transfer contents to W. Decrement B13-15 if not zero.

- 3) If input, increment W and store in CW1. If output, access W and transfer the contents to C.

- 4) If input, store data in W. If output, increment W and store in CW1.

- 5) Store B in CW2.

Variations and qualifications of this algorithm of course depend upon the modes burst/normal and word/byte. And further, the sequence will be qualified by device acknowledge.

#### 2.1.4 Control States

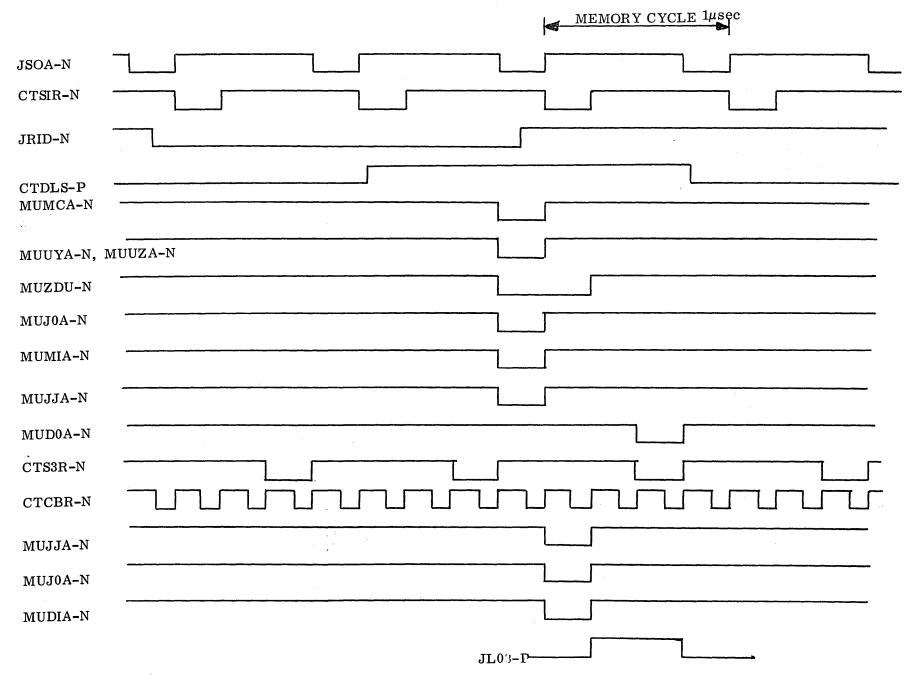

The MDC algorithm is controlled by 7 flip flops, one per control state. Each state is a full 1 microsecond machine cycle and includes slots S0, S1, S2, and S3. Transition from one control state to another is on the trailing edge of S3. The function of each control state is as follows:

| State   | Function_                         |

|---------|-----------------------------------|

| A       | Access CW2 (Read cycle)           |

| В       | Access CW1 (Read cycle)           |

| C       | Access CW1 (Store cycle)          |

| D       | Access data (Read or store cycle) |

| ${f E}$ | Access CW2 (Store cycle)          |

| F       | Extra output cycle                |

| X       | Wait cycle (Burst mode)           |

## 2.1.5 Control Flip Flops and Signals

The following is a list of control flip flops in the MDC and their function.

| FF  | Function                               |

|-----|----------------------------------------|

| KEO | Data Out control line. Same as JEDO-N. |

| KEI | Data In control line. Same as JEDI-N.  |

| KAQ | Acknowledge. Set by JACK-N.            |

| KID | Idle request. Same as JRID-N.          |

The following is a list of control signals. These signals are identical to bits 0, 1, 2, and 15 of CW2.

| Sig. I | <u>Function</u>         | Bit |

|--------|-------------------------|-----|

| KIOA-P | Input = 1, Output = $0$ | 0   |

| KBNA-P | Burst = 1, $Normal = 0$ | 1   |

| KWBA-P | Word = 1, Byte = $0$    | 2   |

| KRLA-P | Right = 1, Left = $0$   | 15  |

## 2.1.6 Micro-Ops

Micro-ops in the MDC can be put into two groups, (1) those that cause micro-operations in the CPU, and (2) those that cause micro-operations within the MDC. Each is listed here with its function.

## 2.1.6.1 Micro-Ops CPU

| Mnemonic | Function         |

|----------|------------------|

| MUMCA-N  | Memory cycle     |

| MUUYA-N  | Read left byte   |

| MUUZA-N  | Read right byte  |

| MUZDU-N  | Clear D Register |

| MUMXP-N  | LP5-0 to M08-13  |

| MUM14-N  | 1 to M14         |

| MUM15-N  | 1 to M15         |

| 3 # T    | Ti hara da Mi    |

| MUMIA-N  | F bus to M       |

| MUWIA-N  | F bus to W       |

| MUWOA-N  | W to O bus       |

| MUDIA-N  | F bus to D       |

| MUDOA-N | D to O bus                       |

|---------|----------------------------------|

| MUJJA-N | Inhibit A to PDC                 |

| MUJOA-N | PDC to O bus                     |

| MURLA-N | O bus right to F bus left        |

| MULLA-N | Inhibit O bus left to F bus left |

| MUSSA-N | Adder to F bus                   |

| MUETA-N | 1 to Adder Carry-In              |

#### 2.1.6.2 Micro-Ops MDC

|   | Mnemonic | Function                       |

|---|----------|--------------------------------|

|   | EORL-P   | End of record Service Request  |

|   | MHLA-N   | L upper to L lower             |

|   | MZLH-P   | Clear L upper                  |

|   | REBF-P   | B to F bus                     |

|   | RCBD-P   | Count B down                   |

|   | RCZB-N   | Clear B, Clear decoded L lower |

|   | RELL-P   | C left to PDC left (byte)      |

|   | RERR-P   | C right to PDC right (byte)    |

| ~ | RELR-P   | C left to PDC right (byte)     |

|   | RCFC-P   | F bus to C                     |

|   | RCFB-P   | F bus to B                     |

|   | MFLA-P   | Set decoded L lower            |

|   | RCSF-P   | Set Device Number Flip Flops   |

# 2.1.7 Instruction Decode

The MDC must anticipate the end of an instruction to set the first control state A. Bits 0-7 of the I register are decoded by the MDC to provide a signal HSAJ-P that will be true for those instructions terminating execution in the TEA state. The "double execute" class of instructions will not cause state A to be set until TEB state. Likewise, the Shift instructions will not set the A state until the shift count has been counted down to zero. The instruction decode for hardware MPY or DIV are not included in the MDC instruction decode since they must first enter the idle state under their own control before terminating execution. After MPY or DIV at least one more instruction will be executed before control state A can be set.

#### 2.1.8 Address Generation

From the 4 device number flip flops two addresses must be generated, the address in the executive page of either CW1 or CW2, and the Device Address of the device controller being serviced.

## 2.1.8.1 Executive Page Address

The MDC transfers an executive page address into the M register via the same path that the CPU uses to access program level registers. This transfer path is mechanized as a two port entry into M08-13 by a set of gates in the MDC. The signal HMEM-P selects either the program level register LP0-5 or the device number flip flops FF0-3 according to whether the MDC is initiating a memory cycle or not. The device number flip flops are wired to generate the proper address for the executive words corresponding to the program priority level assigned to each device controller. Bits 14 and 15 of M are set by micro-ops.

#### 2.1.8.2 Device Address

Once a device controller on the MDC is assigned a particular program priority level 4 or 5 bits of the device address are determined. The remaining bits of the device address may be assigned 1's or 0's by wiring ground to certain pins. The device address is ored onto the 8 address lines of the PDC only during an MDC service of the device.

# 2.2 Hardware Configuration

Only one basic hardware configuration of the MDC can exist but slight variations may be tailored to different system requirements. Most variations will be differences in back panel wiring affecting priority level assignment, device address, etc. A few systems may use a LAD-8, LAD-4, or no LAD. Here again only minor wiring differences will occur. For the following discussion, the standard MDC system is assumed.

#### 2.2.1 Cards

The MDC option consists of three standard size printed circuit cards MDR, MDU, and LAD-MDC. These cards must be installed for the CPU to function. Other LAD cards may be required to expand the number of program levels but these are considered a separate option.

#### 2.2.1.1 MDR

The MDR board contains the MDC registers. It is installed in location 4 and contains 66 integrated circuits. Maximum power consumption is 1.13A of +5V.

#### 2.2.1.2 MDU

The MDU board contains the MDC micro-ops, It is installed in location 3 and contains 74 integrated circuits. Maximum power consumption is 1.46A of +5V.

# 2.2.1.3 LAD-MDC

The LAD-MDC board contains the service request priority register. It is installed in location 5 and contains 57 integrated circuits. Maximum power consumption is 1.1A of +5V.

## 2.2.2 Wiring

The MDR, MDU, and LAD-MDC boards are installed in the CPU main frame and connected to the back panel wire nest by point-to-point wiring. No other special connectors are involved except those required for I/O device controllers. The wires may be broken down into 6 groups:

(1) CPU clock and timing signals, (2) Micro-ops, (3) Interconnects, (4) PDC bus, (5) Service Requests from controllers, and (6) Service Requests to CPU priority level.

## 2.2.2.1 CPU Clock and Timing Signals

This group of wires includes the clocks CA, CB, the slots S0-3, certain control states, and other internal CPU signals. The mnemonics are the identical four letter mnemonic as used in the CPU logic, preceded by a C. Fan out for these signals is provided on the MDU board.

#### 2.2.2.2 Micro-Ops

This group of signal wires originate on the MDU and go to the CPU where they drive the CPU micro-ops. They are typically tied collector drivers. The mnemonics are the same as the micro-op they drive, but preceded by a M.

#### 2.2.2.3 Interconnects

This group of wires are interconnections between the MDR, MDU, and LAD-MDC boards. They are four letter mnemonics.

#### 2, 2, 2, 4 PDC Bus

The PDC data bus and control signals are bussed onto the MDU and MDR boards on the standard pins. Their four letter mnemonic begins with a J. Typically the signals are tied collector circuits. From the MDC they may be jumpered to another device controller or to a line driver/receiver board.

#### 2.2.2.5Service Requests from Device Controllers

There is one service request per device controller, 16 possible, and they are wired up to the LAD-MDC and MDR. The four letter mnemonics are called out in the MDC prints as SR\_\_\_\_, but in the various device controllers they may have different mnemonics. Normally, the service requests go to a CPU LAD board, so if a device controller is to be changed from normal PDC operation to MDC operation, the wire must be physically moved.

# 2.2.2.6 Service Requests to CPU Priority Level

These wires, 16 possible, go from the MDR board to a LAD board in the CPU. The four letter mnemonic begins with JL. Not all of them may be wired in, depending upon the I/O configuration. Unused priority levels in the CPU must be grounded, but in the MDC an unused service request driver may be left unterminated.

#### 2.2.3 Test Points

Most significant signals are available for probing on the back panel connectors, A and B. None are available on the test connector C.

#### ICB INTERFACE MODULE

The ICB module design provides for two complementary configurations: ICB-CPU Driver; ICB-I/O Receiver. The CPU Driver is used within the computer to drive and to receive from the external PDC cables. The I/O Receiver provides the capability to interface to the PDC cables to form an I/O bus identical to the internal CPU PDC.

The following characteristics apply to both ICB configurations.

- 1. Driving Element an SN7440N with a series 68 ohm resistor.

- 2. Receiving Element any of SN7400 family or equivalent.

- 3. Cable Length up to 50 feet.

- 4. Loading

- a. One to three SN7400 loads

- b. If a fourth load is required, a resistor of  $3900 \pm 2\%$  must be placed between the input of the receiving gate and ground.

- 5. Signal Delay

- a. Cable insertion delay is 1.5 nsec per foot.

- b. Gate pair delay is 55 nsec (20/35).

NOTE: For additional information on the ICB Interface Module refer to the MAC 16 Interface Reference Manual.

#### MEMORY INTERLEAVE

## GENERAL

The MAC 16 is provided with an optional high data rate input-output channel called the Multiplex Data Channel, MDC. The MDC will service up to sixteen input-output device controllers on a priority demand basis. Data communication is controlled by sixteen pairs of pre-stored control words that specify the type of communication, block length and memory address. The control words are located in fixed memory locations. The types of communication that may be selected are in-out, burst or single datum and byte or word. Maximum communication rates are 200KC in the non burst mode or 333KC in the burst mode.

The MDC functions by temporarily placing the processor into an "idle" state at the end of its current instruction. It then takes control of the processor's memory word register (D Register), memory address register (M Register) and memory control lines in order to access memory. The MDC also uses other hardware functions of the processor to modify control words.

This "external" control and access to the MAC 16 Processor is available to the user who wishes to design an input-output channel that satisfies his own system requirements better than those functions of the multiplex Data Channel. This report specifies the available signals and connector pins and describes the logic design requirements for this special device.

This device is called the Memory Interleave Channel. If it is provided with its own hardware memory address register, it may interleave memory cycles in-between processor instructions at a burst rate of up to one megacycle. Data may be either read or written into memory. Control for packing eight bit bytes into a 16 bit word is provided. Access to all memory (up to 65D) is possible.

In general, the Memory Interleave Channel may be designed to be as complex as is required. If it provides a memory address, it can load it into the processor's internal M register, and initiate a memory cycle. Data to be written is then loaded into the processor register, or, data to be read is output from the D Register near the end of the cycle. Special input signals are provided for manipulating the register transfers and initiating the memory cycle. These control signals are referred to as micro-operations. Also provided are timing signals derived from the computer's internal clocking source. The timing signals are combined with the Memory Interleave Channel's own logic to generate the micro-operations at the proper time. Memory cycles are interleaved between instructions and sharing the processor's D and M Registers does not interfere with program execution other than to temporarily suspend processing.

The Memory Interleave Channel may be initialized with starting address via the Programmed Data Channel (PDC) or a starting address may be stored in memory at a specific location. If an address is stored in memory the interleave channel may use the processor's internal parallel adder to increment it once for each word transferred. The block length may also be stored in memory, but there are no provisions available for internally counting the block length down to zero.

# Memory Interleave Page 2

Likewise provisions for comparing a terminating address to the current address would have to be mechanized externally in the Memory Interleave Channel. When the block of I/O data has been completely transferred, the Memory Interleave Channel may communicate with the program by setting a priority interrupt. Up to 64 levels of interrupt are available as a separate option. For details of interfacing to the PDC refer to the MAC 16 I/O Interface Manual.

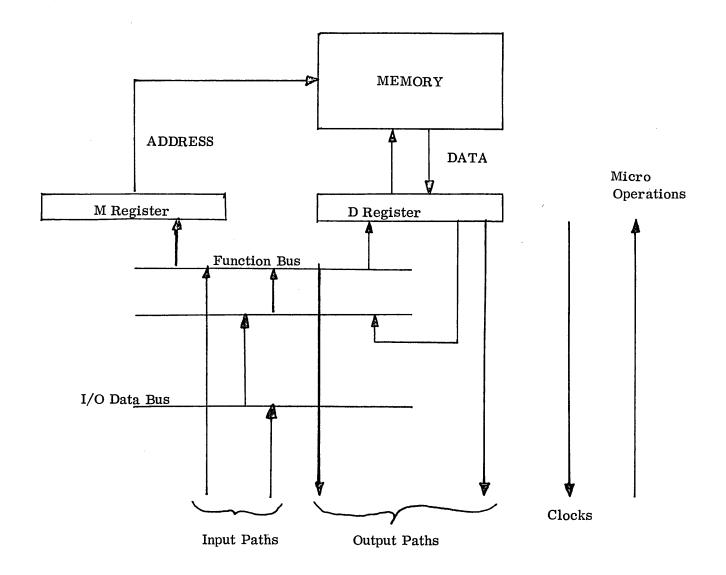

# MEMORY INTERFACE

Four data paths are provided for interfacing to memory, two input and two output. These paths are "fan-in" and "fan-out" pins of four parts of the processor. This is shown in the following diagram. The data paths are as follows:

- 1. Function Bus Input. Data may be loaded into either the M or D Registers via this path, however, packing of byte data must be performed externally.

- 2. I/O Data Bus Input. This is the standard PDC data bus, but data may be input only. Byte data may be packed into the D Register and address may enter the M Register.

- 3. Function Bus Output. The D Register may be output via this path, but micro-operations for unpacking byte data are not available.

- 4. D Register Output. The actual D Register is available for output. The earliest possible access is via this path.

#### CIRCUIT INTERFACE REQUIREMENTS

Circuits to be used throughout are TTL integrated circuits series 7400 or equivalent. All input signals are to be open collector (7401 or 7405) with only one driving source. (Collector resistors are not required at the source since they are already installed at the destination). Output signals are typical 7400 series outputs and should not be loaded by more than one 7400 series load, or equivalent.

The electronics is to be mounted on three MAC 16 standard size PC boards and installed in the MAC 16 mainframe where back panel wiring should be kept to a minimum. The three card slots of the MDC may be used. If the Memory Interleave Channel is not wired into the processor's mainframe, it must be located within 18 inches of the available interface pins. Clock signals provided for timing should not go through more than two inverterpair delays from interface out to interface in.

The logic conventions in the MAC 16 are as follows:

(Mnemonic) - N means negative polarity. A logic true is a low signal.

(Mnemonic) - P means positive polarity. A logic true is a high signal.

#### IDLE REQUEST AND RESPONSE

Since the computer is normally executing instructions and accessing memory, the Memory Interleave Channel must first request an idle state before initiating a memory cycle. The following signal, a flip flop to be provided by the Memory Interleave logic, causes the computer to assume an idle state:

MEMORY INTERLEAVE CHANNEL

| Signal                                                                                  | Connector | Pin | <u>Name</u>       | Description                                              |

|-----------------------------------------------------------------------------------------|-----------|-----|-------------------|----------------------------------------------------------|

| JRID-N                                                                                  | A 15      | 25  | Idle Request.     | A flip flop to be set and reset by the "SO" clock pulse. |

| JSOA-N                                                                                  | A08       | 63  | "SO" clock pulse. | 250 nanosecond pulse provided for timing.                |

| No memory cycles should be started until the computer has responded with the following: |           |     |                   |                                                          |

| JIDL-N                                                                                  | A12       | 53  | Idle Response.    | A flip flop indicating computer is in an idle state.     |

To release the computer from an idle state, the idle request flip flop, JRID-N, should be reset on the "SO" clock pulse of the last memory cycle desired.

# Idle Request Timing

The delay between the idle request and the time the computer goes into an idle state is variable depending on the instruction being executed and machine state. The quickest response would be 1 microsecond. The longest delay would be the execution time of the longest instruction. (Shift, with N=15 is 5 microseconds, Divide is 13 microseconds). An idle request will not be honored after a single cycle instruction.

# Quiescent State

The Memory Interleave Channel may cycle the memory while the computer is in the quiescent state. An idle request is required as above, the computer will not respond by going into the idle state. As long as the idle request is active the computer will be locked up in the quiescent state and the memory may be cycled. Quiescent state is determined by the following signal:

CTQSS-P B13 70 Quiescent state

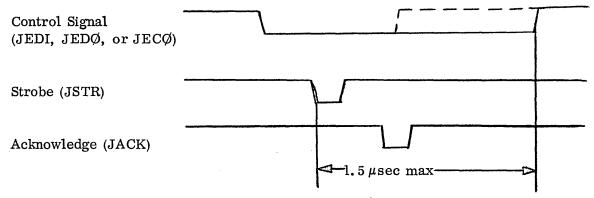

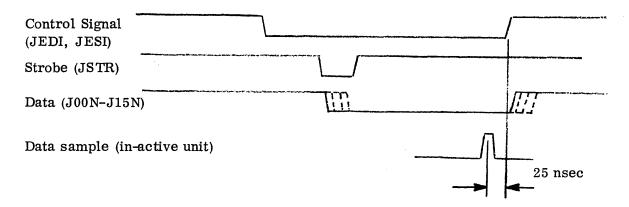

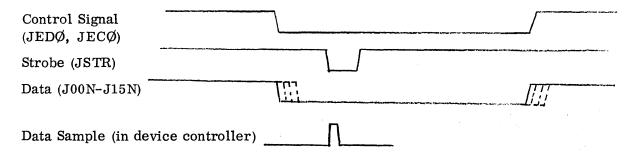

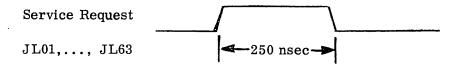

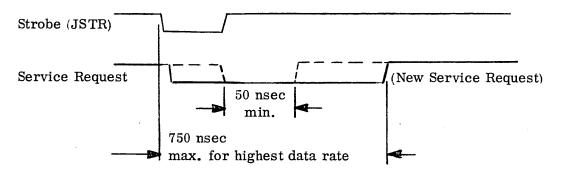

## Idle Request In A Machine With Hardware Multiply/Divide