# FREEDOM<sup>™</sup> 100 Maintenance Manual

**Liberty Electronics**

## Change Notice #1

July 29, 1983

## Freedom 100 Maintenance Manual Errata and Changes

- 1. Replace pages Int-7 and Int-8.

- Add the Appendices section entitled "The Self-Test Mode" after page Int-8.

- 3. Note that all references to P 401, P 402, P 403, P 404, P 405, and P 406 on pages PWR-1, PWR-2, PWR-3, and MTC-1 should be changed to B 401, B 402, B 403, B 404, B 405 and B 406 respectively.

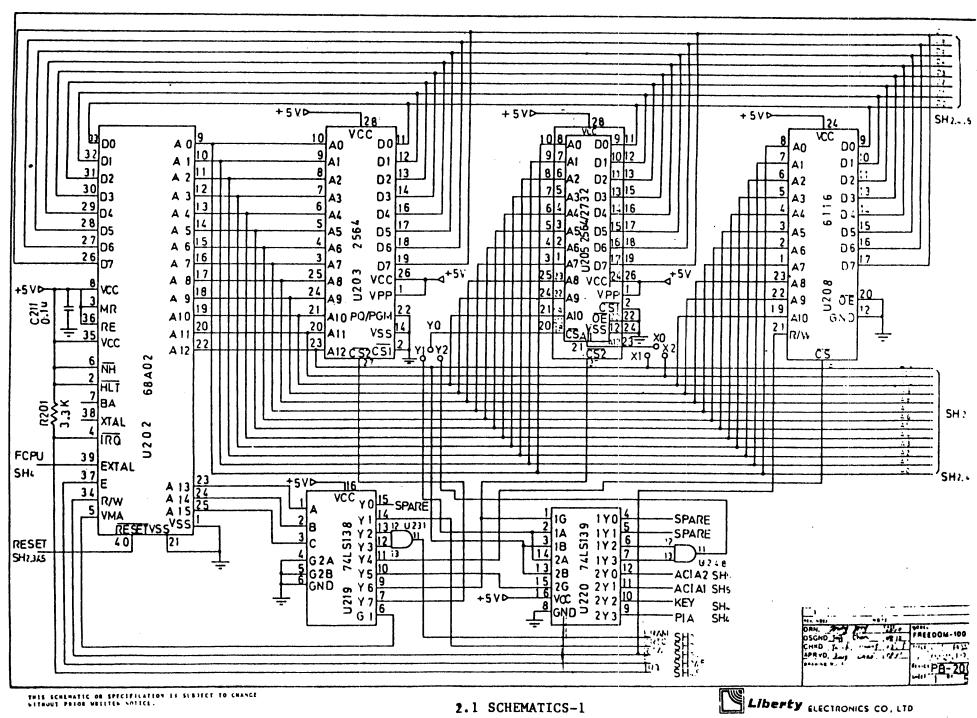

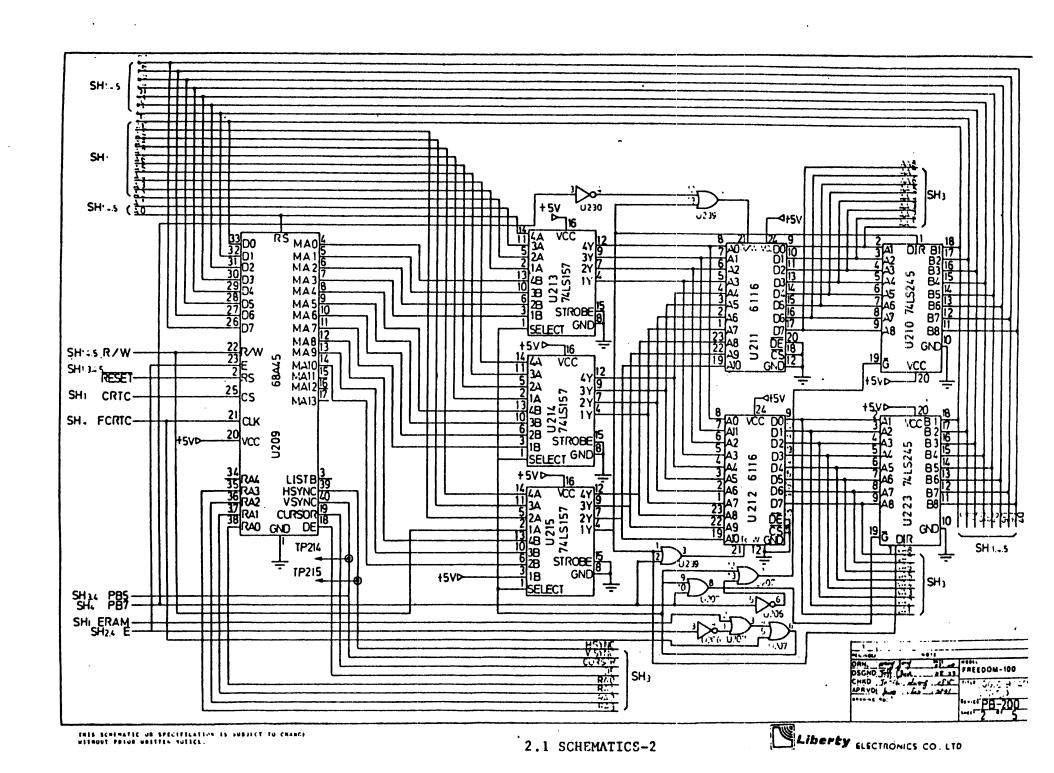

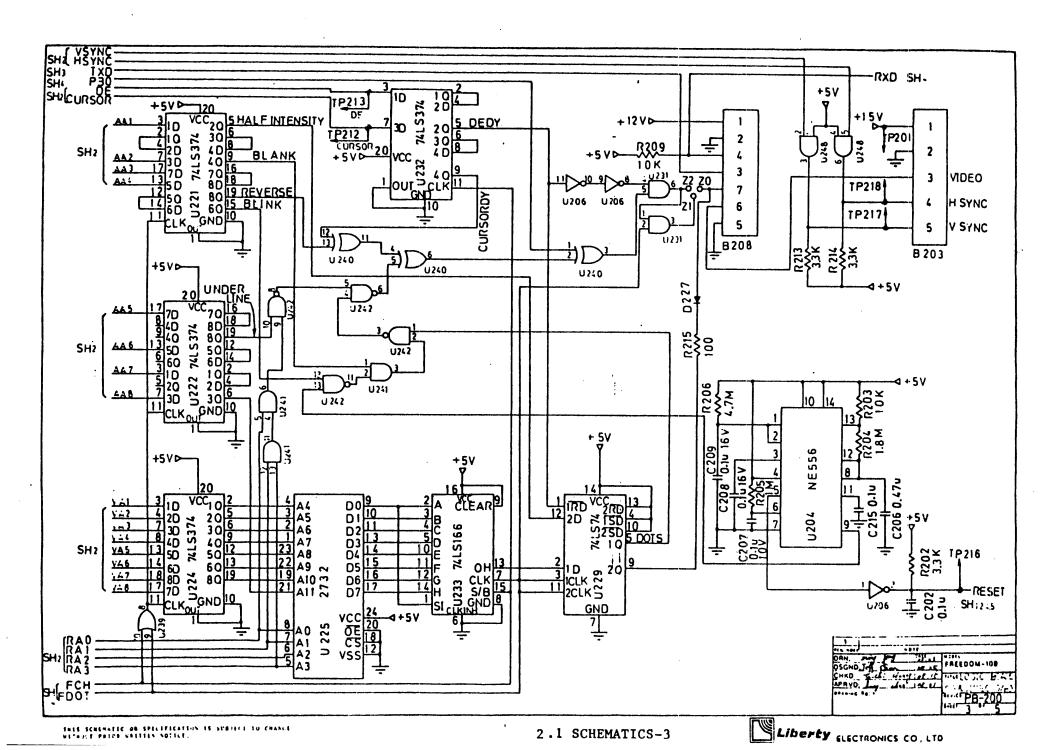

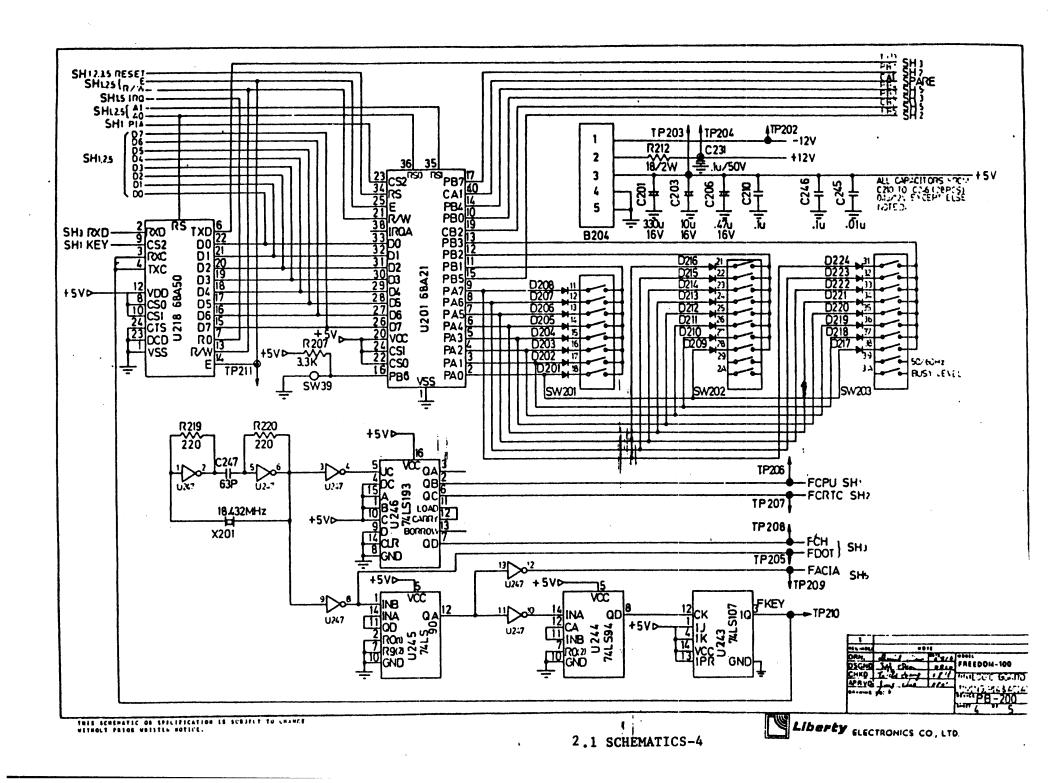

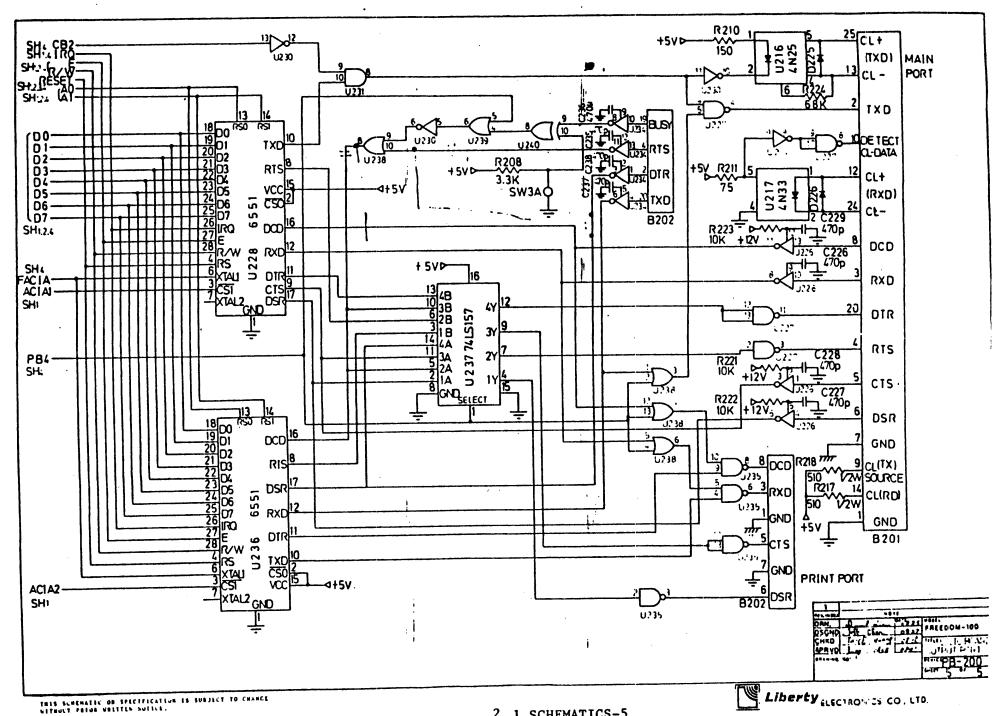

- 4. Replace appendices -C- schematics "The Main Logic Board" schematics, 2.1-1 through 2.1-5

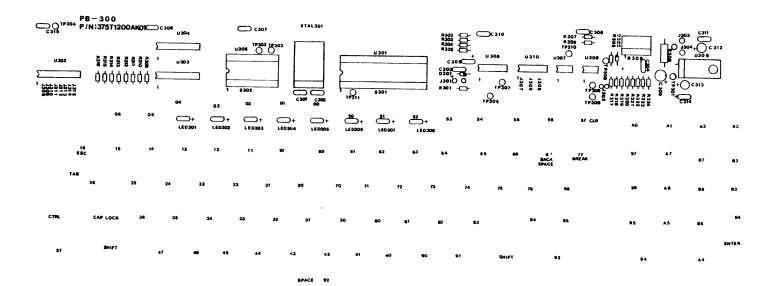

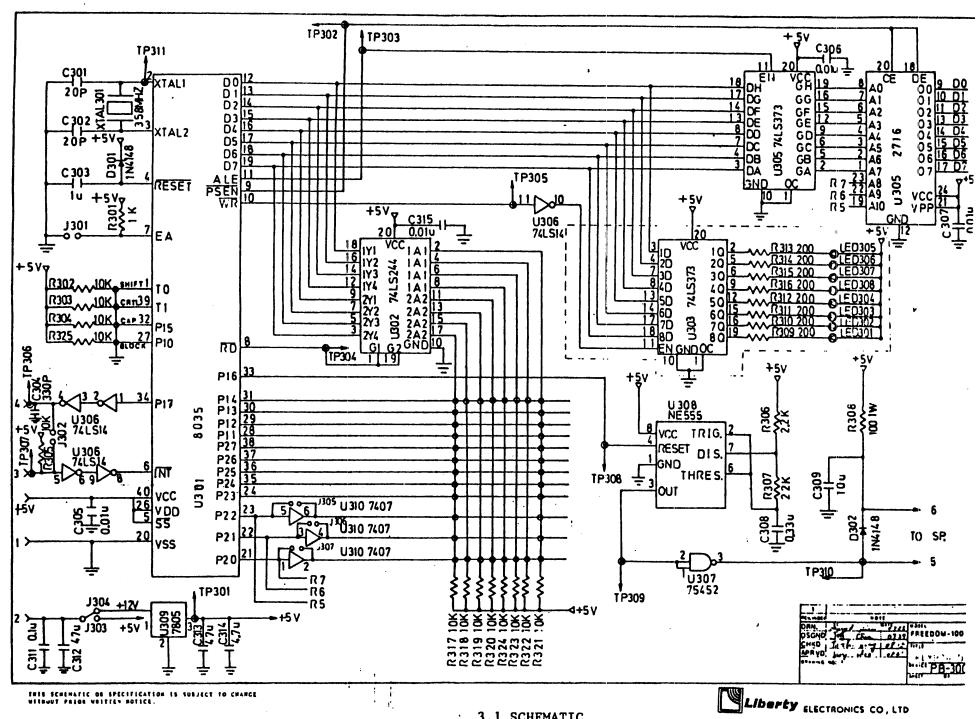

- Replace appendices -D schematics "The Keyboard" schematics,

3.1

- 6. Insert the parts list after page 2 of the part list which includes a parts listing for the monitor board.

All rights reserved. No part or all of this document may be reproduced in any form without the express permission of Liberty Electronics. Printed in the U.S.A. Copyright Liberty Electronics, 1982.

### SUBSCRIPTION REGISTRATION

With the purchase of your Freedom  $^{TM}$ 100 Maintenance Manual you are entitled to all updates for one year at no additional charge. Please provide us with the following information to register your manual for these updates.

| Company Name:      |  |  |  |  |

|--------------------|--|--|--|--|

| Your Name:         |  |  |  |  |

| Mail Stop:         |  |  |  |  |

| Address:           |  |  |  |  |

| City/State:        |  |  |  |  |

| Date Received:     |  |  |  |  |

| Liberty Invoice #: |  |  |  |  |

|                    |  |  |  |  |

Please Mail to:

Liberty Electronics USA 625 Third Street San Francisco, CA 94107

ATTN: Service Department

## TABLE OF CONTENTS

| SECTION |                                                    | PAGE           |

|---------|----------------------------------------------------|----------------|

| 0       | INTRODUCTION                                       |                |

|         | Scope of this Manual                               | INT-1          |

|         | WARNING                                            | INT-1          |

|         | Components                                         | INT-1          |

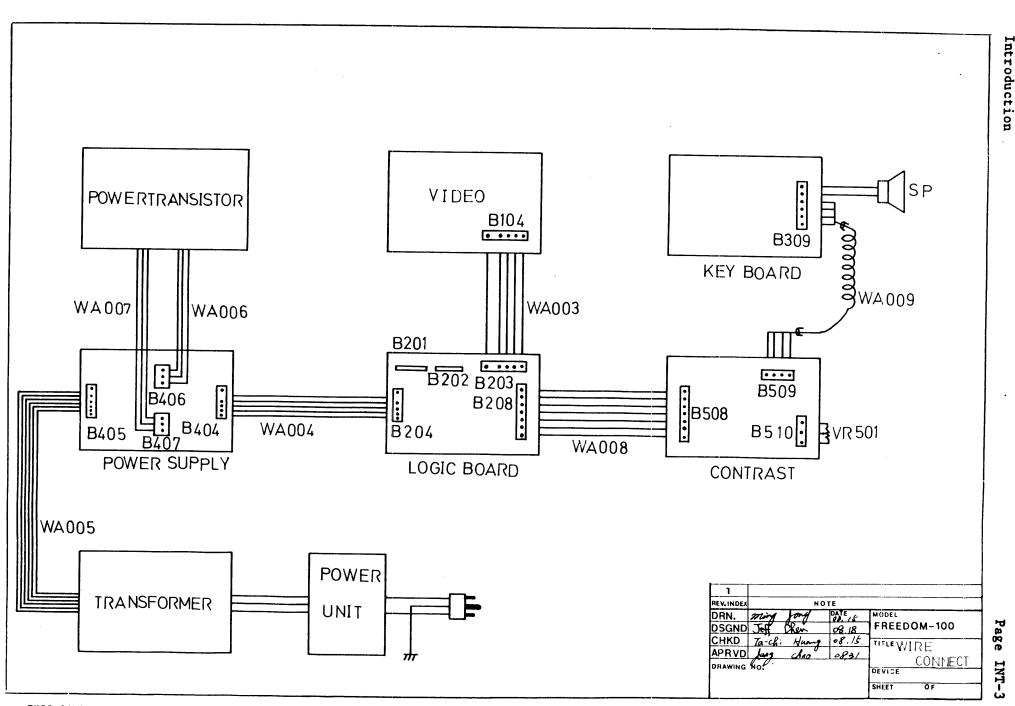

|         | Block Diagram                                      | INT-3          |

|         | Interconnections                                   | INT-4          |

|         | Theory of Operation                                | INT-5          |

|         | Terminal Operation<br>Data Paths                   | INT-5          |

|         | Quick Check-out                                    | INT-6<br>INT-7 |

| 1       | THE VIDEO BOARD                                    |                |

|         | Theory of Operation                                | VID-1          |

|         | Video Signal                                       | V1D-1          |

|         | Vertical Synch                                     | VID-1          |

|         | Horizontal Synch                                   | VID-1          |

| •       | Miscellaneous Controls                             | VID-2          |

|         | Troubleshooting                                    | VID-2          |

|         | Components                                         | VID-2          |

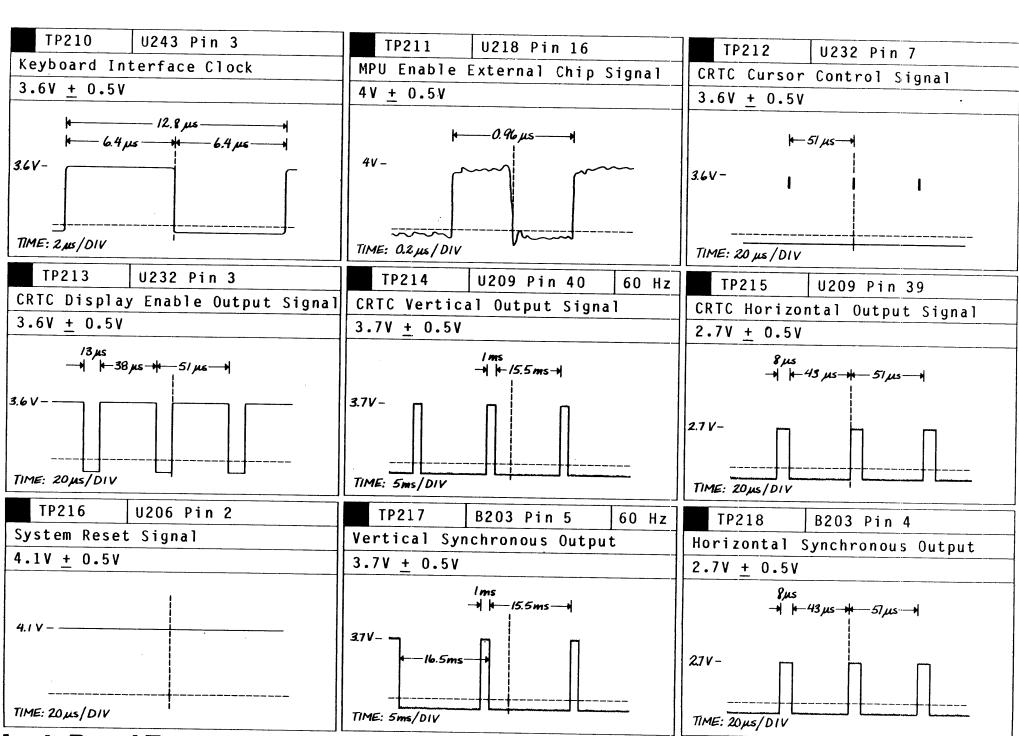

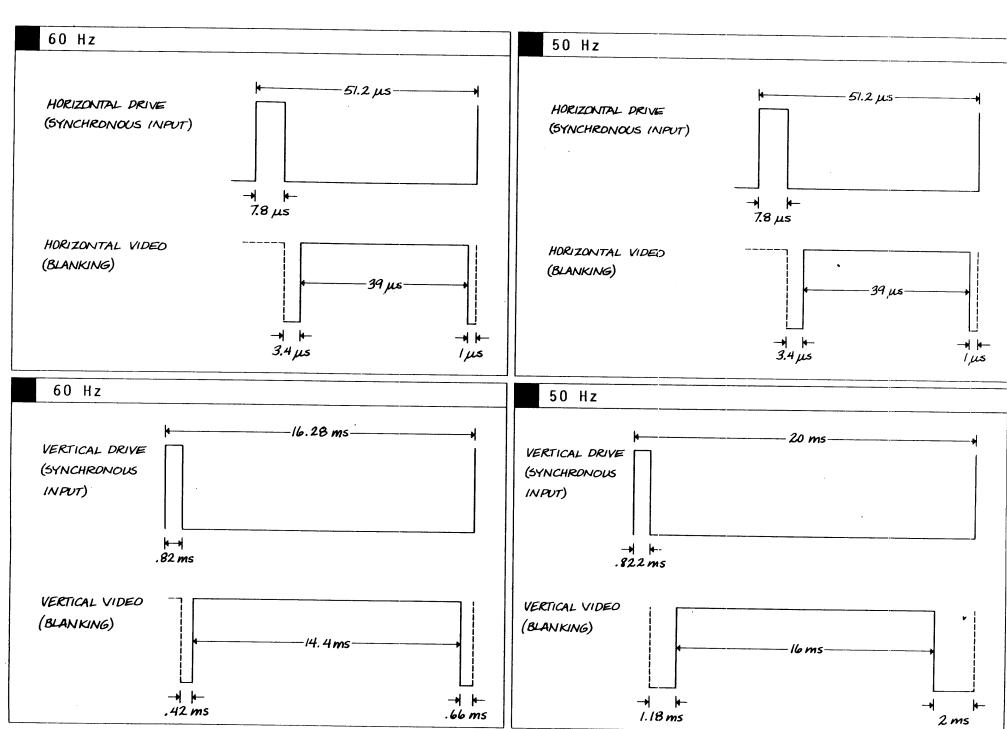

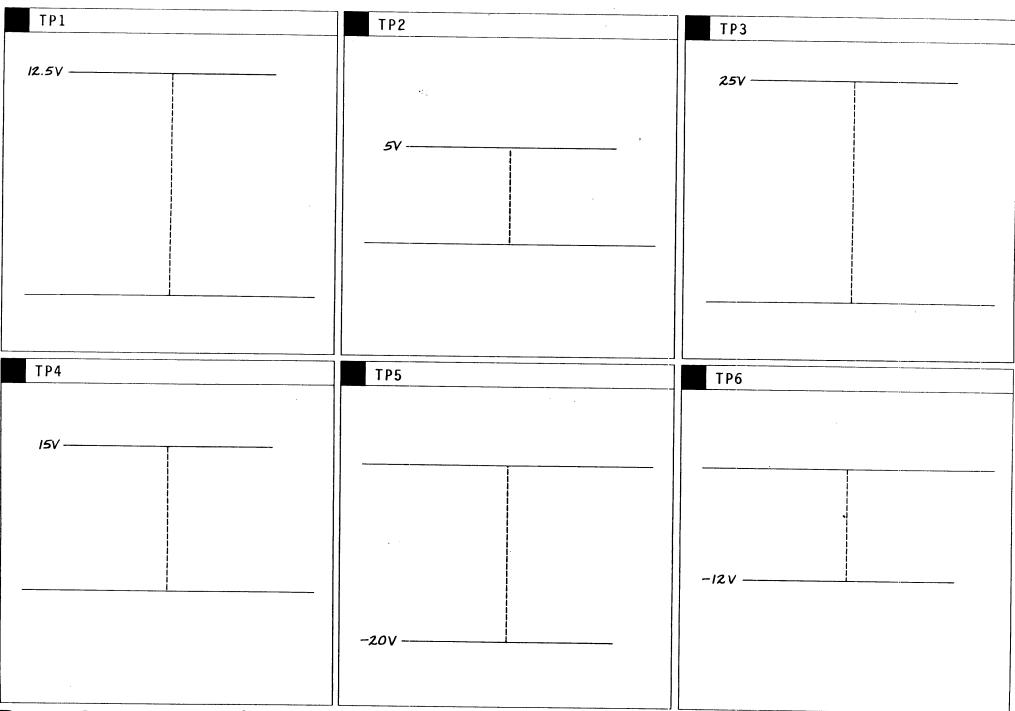

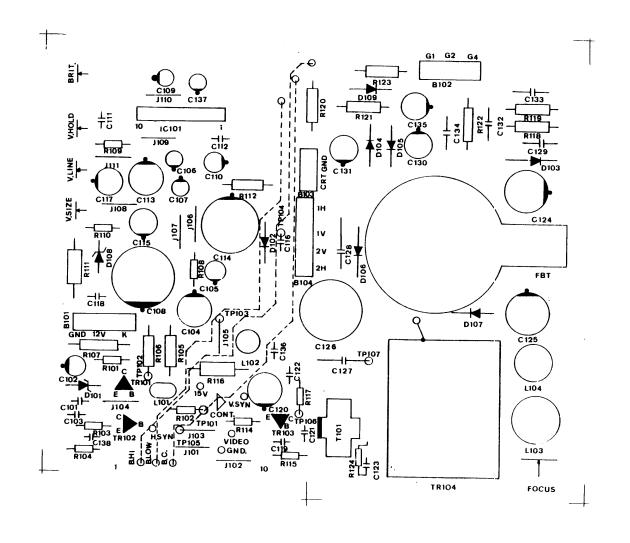

|         | Test Points, Typical Waveforms & Signal Levels     | VID-6          |

| 2       | THE MAIN LOGIC BOARD                               |                |

|         | Theory of Operation                                | MLB-1          |

|         | Test Points, Typical Waveforms                     |                |

|         | & Signal Levels                                    | MLB-1          |

| 3       | THE KEYBOARD                                       |                |

|         | Theory of Operation Test Points, Typical Waveforms | KYB-1          |

|         | & Signal Levels                                    | KYB-1          |

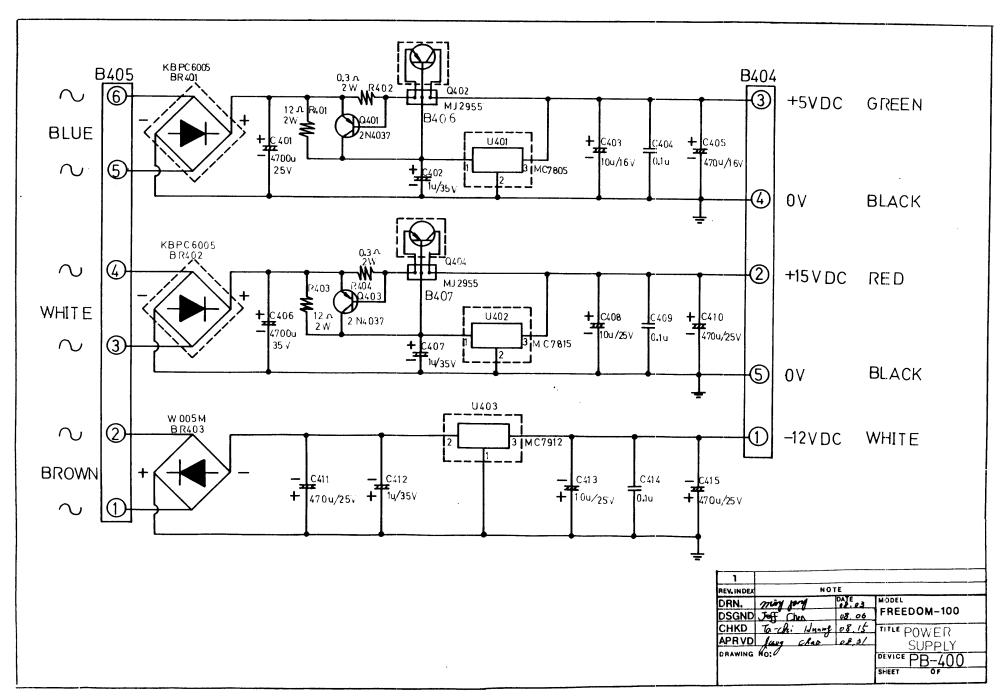

| 4       | THE POWER SUPPLY                                   |                |

|         | Theory of Operation                                | PWR-1          |

|         | Troubleshooting                                    | PWR-1          |

|         | Components                                         | PWR-1          |

|         | Test Points, Typical Waveforms                     |                |

|         | & Signal Levels                                    | PWR-3          |

## 5 -- MAINTENANCE

| The Monitor Unit       | MTC-1 |

|------------------------|-------|

| General                | MTC-1 |

| Replacing the CRT tube | MTC-1 |

| The Keyboard Unit      | MTC-2 |

## APPENDICES

- A -- Freedom 100 User Manual

- B -- The Video Board Layout Schematic

- C -- The Main Logic Board Layout Schematic

- D -- The Keyboard Layout Schematic

- E -- The Power Supply Layout Schematic

- F -- Parts List

- G -- Key Component Data Sheets

#### INTRODUCTION

## Scope of this Manual

This Manual presents details of the circuitry and data paths of the Freedom<sup>tm</sup> 100 Video Display Terminal, along with information on typical waveforms and signal levels, to allow service personnel to troubleshoot and repair the terminal, as needed. Familiarity with the Freedom<sup>tm</sup> 100 User's Manual is assumed.

While every effort has been made to assure that the information contained herein is accurate and up to date, Liberty Electronics reserves the right to make engineering changes and appropriate parts substitutions without prior notice in the interests of increased and improved performance.

#### > > > > WARNING < < < <

## CRITICAL COMPONENT WARNING:

SERVICEMAN WARNING: This product contains components which are critical for X-Radiation Safety. See Service Manual for proper replacement. Normal 2nd Anode Voltage is 12 KV at Zero beam current, AC 120V input, and must MOT exceed 13 KV under any operating conditions. To measure 2nd Anode Voltage, use High Impedance meter. Connect (-) to chassis, use a High Voltage lead from (+) to 2nd Anode.

## Components of the Freedom tm 100 Terminal

### <u>External</u>

From an outside viewpoint, the Freedom 100 consists of two units: The Monitor Unit, containing the CRT, power supply, and control circuits; and the Keyboard Unit, containing the physical keyboard, its decoding circuitry, and circuits for communicating with the Monitor Unit.

The Keyboard and Monitor Units are connected by a coiled telephone handset cord with 7,62 mm (0.3 in) male plugs at each end. Power is supplied via a 3-wire grounded cord, terminated by a U.S. NEMA standard plug (which may be replaced to suit local power system requirements).

Communications with a Host computer or modem and a printer are provided via asynchronous RS-232 communication via two female DB-25 receptacles on the rear of the Monitor Unit. Controls are provided on the Monitor Unit for Power ON/OFF, Contrast, and setting operating parameters.

### Internal

Internally, the Freedom 100 consists of:

→ A Transformer and Voltage Selector Switch for converting 115V or 230V AC mains power to 10.5V AC, 16.7V AC, and 21.3V AC.

- $\Rightarrow$  A Power Supply board, with rectifiers and voltage regulators, to produce +5V, +15V, and -12V DC [regulated to  $\pm 10\%$ ].

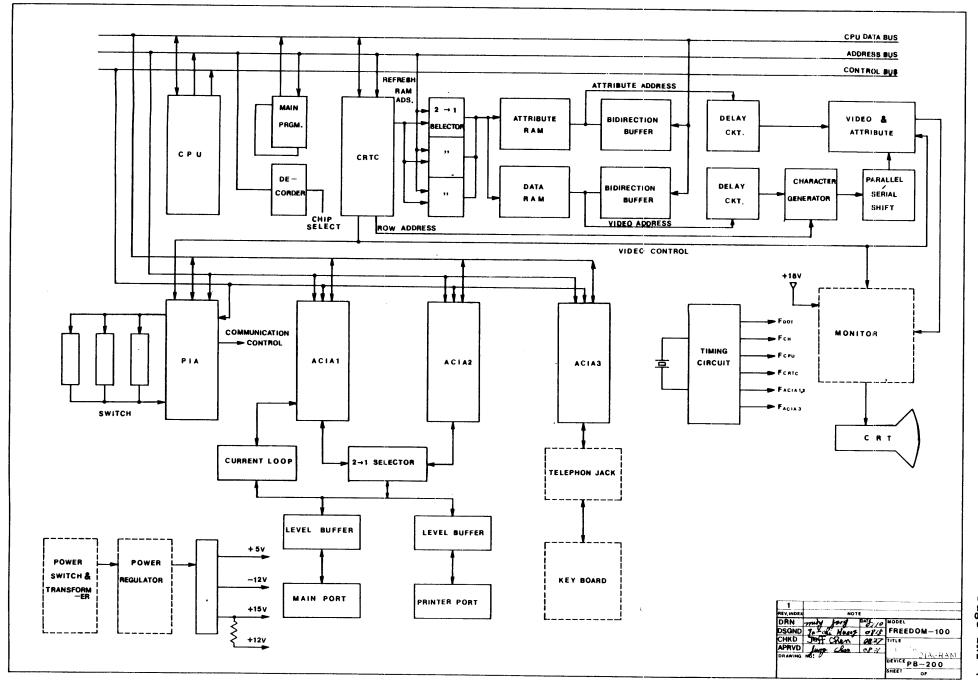

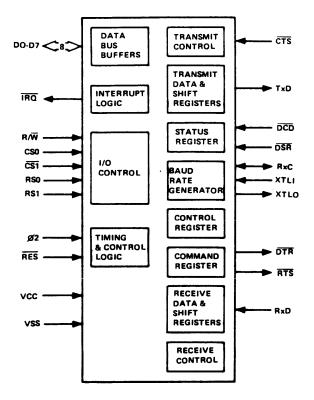

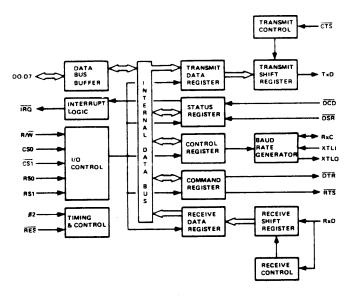

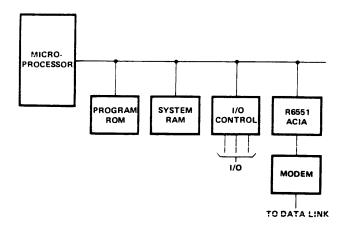

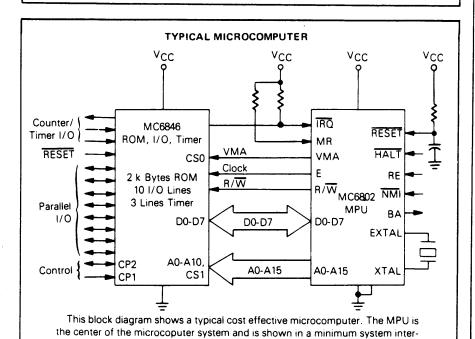

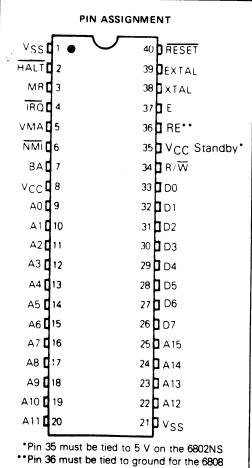

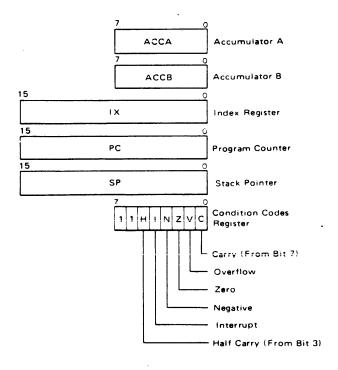

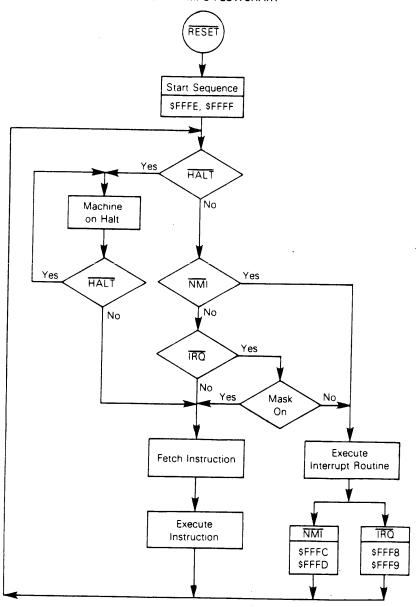

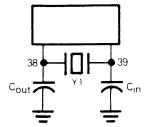

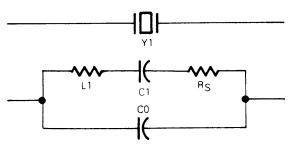

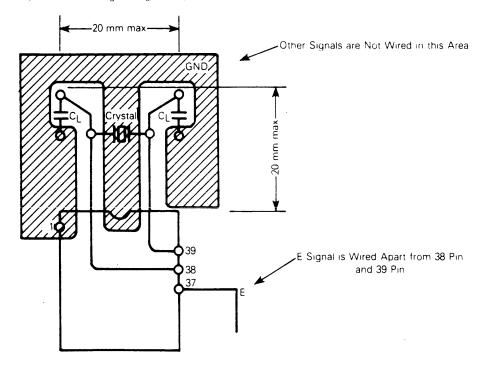

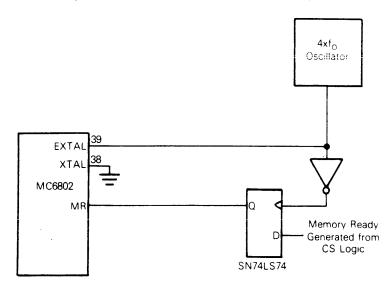

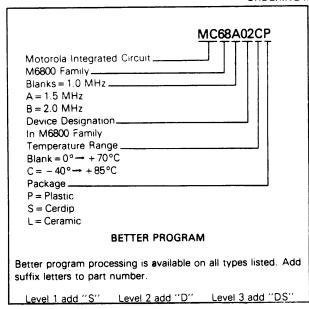

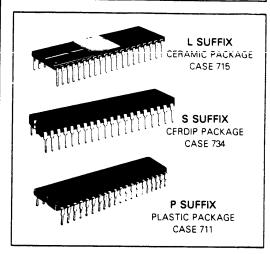

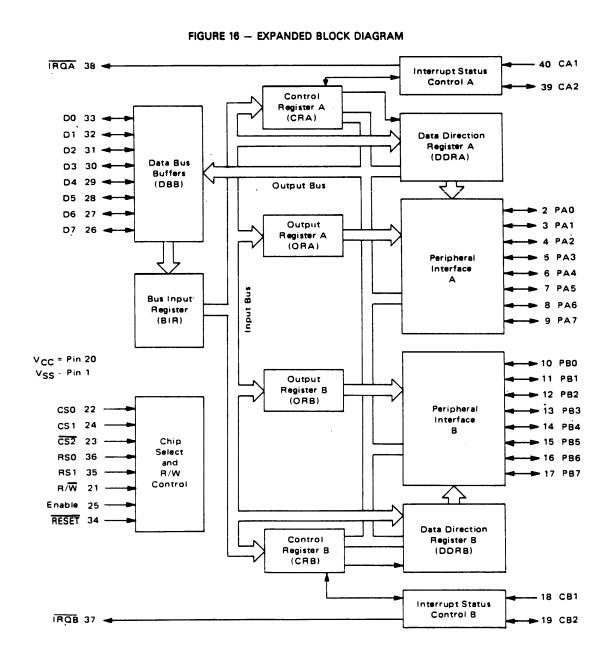

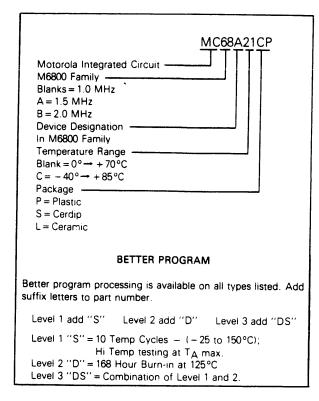

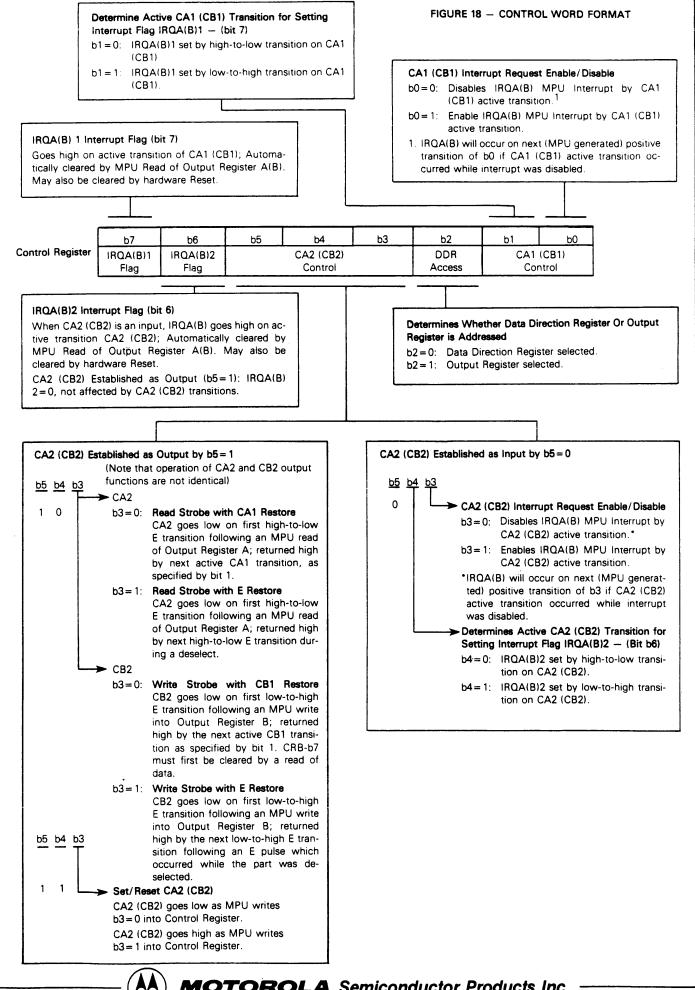

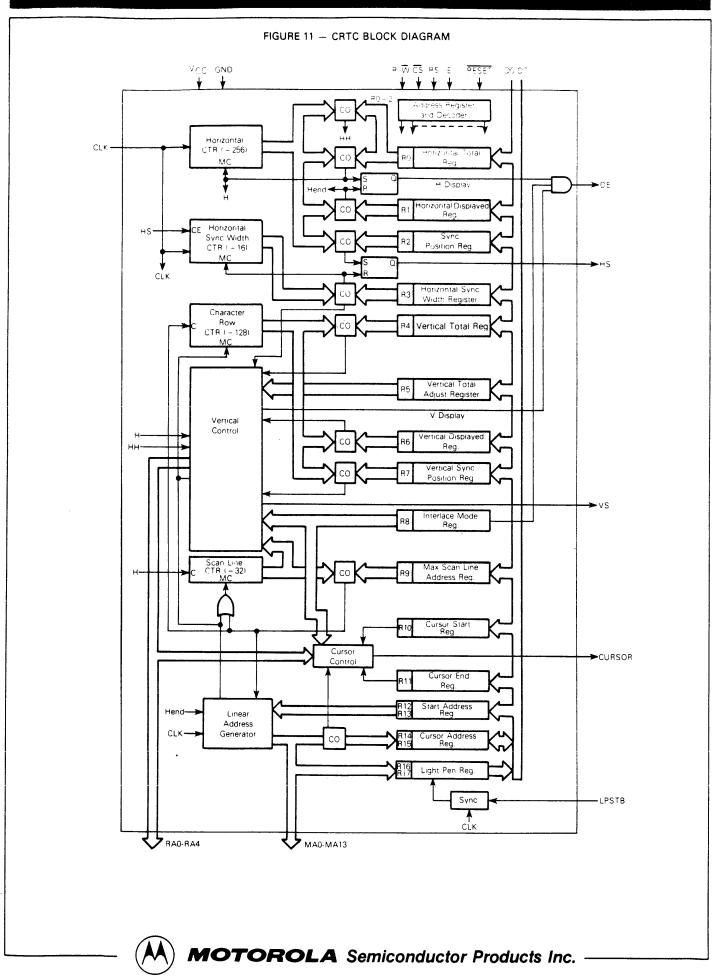

- → A Main Logic Board, with a 68A02 Microprocessor, 16k of EPROM-resident firmware, 2k of character storage RAM, 4k of attribute and control storage RAM, a 68A45 CRT Controller, a 68A21 PIA, one 6850 and two 6851 ACIAs for Keyboard, Host and Printer communications, respectively, as well as miscellaneous control and sequencing logic.

- → A Video Control board, to convert Horizontal and Vertical synch pulses to the proper waveforms for controlling CRT raster scan, and circuitry to control pixel display. Connection is made via cables to a 12" diagonal CE745129 VRA tube (or equivalent) for actual display.

- → A small Contrast control and connector board, having a rotating potentiometer for contrast control, and a female RJ-11 receptacle for the Keyboard connector cord.

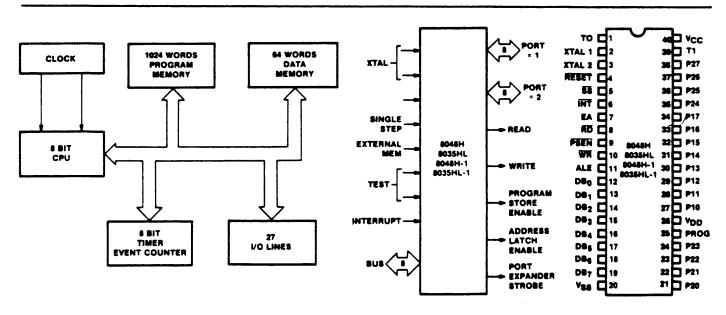

- → A Keyboard, with a 93-key switch-matrix keyboard, decoded by an 8035 stand-alone microcomputer, which generates RS-232 signals by toggling one output line under the control of on-chip software, and receives RS-232 data via software use of interrupts.

Introduction Page INT-5

## Theory of Operation

### Terminal Operation

The Freedom 100 CRT Terminal is designed to be an inexpensive and convenient data-entry and console device for a wide range of computer and data applications.

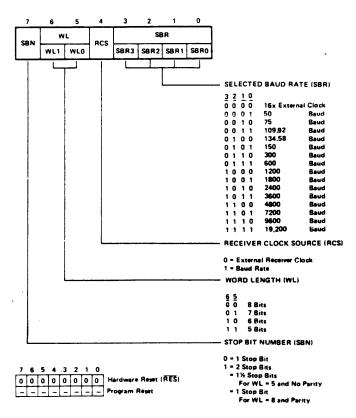

The Freedom 100 will normally be connected to a Host computer system, either directly or via MODEM, by asynchronous RS-232 or 20ma current loop, through the Host connector on the rear of the Monitor Unit. The terminal's on-board firmware allows it to communicate with the Host in Full or Half Duplex, Block Mode (transmitting a screen full of data at once, instead of character-at-a-time), or strictly Local mode (no outside communication). Communication rates range from 110 to 19,200 baud.

A subsidiary Printer port, also located on the rear of the Monitor Unit, allows the Freedom 100 to be connected to any ASCII printer with an RS-232 serial interface. Baud rates from 100 to 19,200 are available. The terminal provides two basic modes for printer operation:

<u>Simultaneous Mode</u> -- all characters transmitted from the Host are displayed on the monitor, and also sent to the Printer

Buffer Mode -- characters from the Host are buffered internally in the Freedom 100, and sent to the Printer without being displayed on the monitor

The Freedom 100's 16k of on-board firmware provides 93 basic commands, as well as numerous options, for setting operating parameters. These commands can be sent by the operator from the Keyboard, or by the Host through the Host port. The commands and their effects are documented in the Freedom 100 User's Manual.

Introduction Page INT-6

#### <u>Data Paths</u>

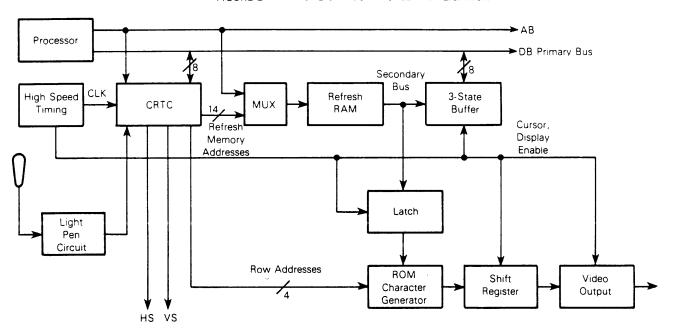

The Freedom-100's Main Logic Board receives serial Asynchronous RS-232C character data from either the Host Port or the Keyboard. This character data is stored in a 2k-byte Display RAM. Character data from the display RAM is sent continuously to the Video display circuitry, where it is processed by a Character generating ROM, combined with attribute data from a separate 2k-byte Attribute RAM, and sent to the CRT for display.

If the Freedom 100 is in Full Duplex Mode, all character data received from the keyboard is immediately transmitted to the Host brough the Host Port, but is not displayed on the CRT.

If it is in Half Duplex Mode, character data received from the keyboard is displayed on the CRT in addition to being transmitted to the Host.

In either Mode, XON/XOFF protocols are used in communicating with the Host.

If it is in Simultaneous (Transparent) Print Mode, character data received from either the Host or the Keyboard is displayed on the CRT and transmitted to the Printer Port.

If it is in Buffered Print Mode, character data received from the Host is transmitted directly to the Printer Port (with XON/XOFF handshaking) without being displayed on the CRT.

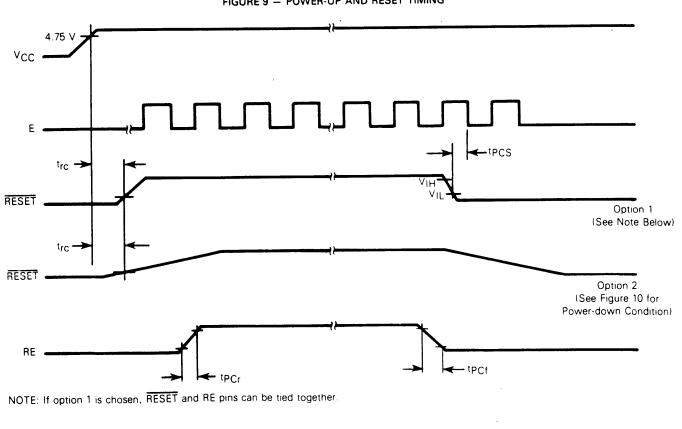

## Quick Check-out

To check out the operation of the Freedom 100 quickly, and isolate problems:

- 1) The logic operation of the Freedom 100 can be checked by putting the unit in self test mode. A description of this test follows this diagnostic procedure.

- 2) Check for 115V AC or 230V AC on the primary (input) leads of the Power Transformer.

- a) If found, go to Step 4

- b) Check the fuse, power switch and power select switch.

- 3) Check the secondary (output) leads for 10.6V AC on blue, 21.3V AC on white, and 16.7V AC on brown.

- a) if OK, go to Step 4

- b. Replace power transformer

- 4) Disconnect cable from Power Supply to Main Logic Board (B404 -- B204). Check B404 for:

Pin 1 - -12V DC +0.5V Pin 2 - +15V DC +0.5V Pin 3 - +5V DC +0.25V Pins 4 & 5 Ground

If OK, replace cable to Main Logic Board (B404 -- B204), to step 6.

5) Disconnect cable to power transistors (B406, 407). Check connectors for:

B406 Pin 1 - 15.1V DC Pin 2 - 29.8V DC Pin 3 - 29.9V DC

B407 Pin 1 - 5.1V DC Pin 2 - 14.3V DC Pin 3 - 14.4V DC

- a) If OK, check U401 through U403 and capacitor.

- b) Check Bridge Rectifiers BR401, BR402, BR403, and transistors 0401 and 0403.

- 6. Check voltage on B404 again. If OK, go on to Step 8.

- 7. Check Power Transistor voltages:

Q402 Base - 10.6V DC Collector - 5.1V DC Emitter - 11.4V DC Introduction Page INT-8

Q404 Base - 24.6V DC Collector - 15.1V DC Emitter - 25.2V DC

- a) If OK, check U401 through U403 and capacitor.

- b) Replace transistor(s).

- 8) Disconnect cable from Main Logic Board to Video Board (B203 -- B104). Check signal levels and typical waveforms on Connector B203.

- 9) Disconnect cable to Contract Board (B208 -- B508). Check signal levels and typical waveforms on Connector B208.

- a) If OK, reconnect cable to Contrast Board (B208 -- B508), go to Step 10.

- b) Check all test points on Main Logic Board for proper signal levels and typical waveforms, then isolate and replace defective parts.

- 10) Disconnect cable connecting Keyboard to Contast Board (B509 -- B309). Check Contrast Board for defective parts and broken traces.

- a) If OK, reconnect cable to Keyboard connector (B509 --B309) and go to Step 11.

- b) Replace Contrast Board.

- 11) Check signal levels and typical waveforms at B309 on Keyboard PC board.

- a) If OK, check all test points on Keyboard for signal levels and typical waveforms. Isolate and replace defective components.

- b) Replace coiled telephone handset cord.

- 12) END.

## Self Test Mode

The self test mode is a good mechanism for initial burn-in to find problems and subsequent testing after maintenance. To enter the self test mode set up the terminal as follows.

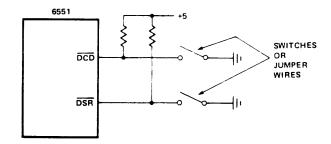

- 1. Prepare the main RS-232C port by placing a jumper from pin 2 to pin 3 to allow loop-back.

- 2. Prepare the Auxiliary RS-232C port by placing a jumper from pin 2 to pin 3 and from pin 4 to pin 6 to allow loop-back.

- 3. Prepare dipswitches as follows.

- A. Reading the dipswitches from left to right set the first bank of 10 switches to the up position with the exception of switch number 9.

- B. Set the next bank of switch in the down position.

- C. Set the remaining bank of switches to the up position.

- 4. Enter the self test mode by entering an "ESC V" from the keyboard.

At this point the screen and attribute memory will be exercised. A special status line will appear at the bottom of the screen. This will supply information for diagnosis. The status line appears as follows:

Ø Z.Y E=nnnn P=mmmm UUUUUUUU XXDDDDDDDD XUUUUUUUU M= A= K=

Where:

Z.Y is the revision of firmware nnnn is the ME eprom check sum mmmmm is the MP eprom check sum

U - represents up on dipswitches

D - represents down on dipswitches

X - not connected

M - represents the main port

A - represents the auxiliary port

K - represents the keyboard port

- A. If everything is fine with logic and firmware the screen will constantly change and the status line will appear as shown above.

- B. If an eprom is not inserted correctly of data corruption has occured, the eprom where this occured will be framed in "?" on the status line.

- C. If a dipswitch is suspected of not working it can be determined by toggling the dipswitches while in self-test to see if they register on the status line.

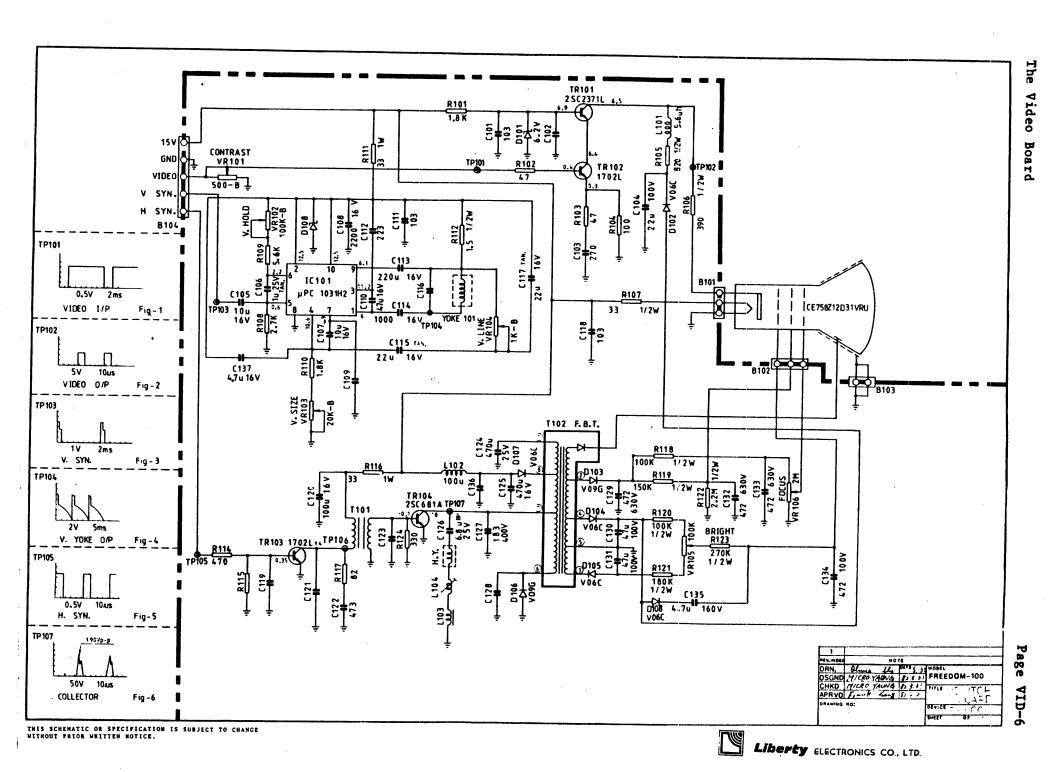

## The Video Board

## Theory of Operation

## <u>Video</u> Signal

The Video Signal is essentially an ON/OFF signal, which determines whether a particular pixel position on the face of the CRT will be illuminated or not by the scanning electron beam. It is generated by the video circuitry on the Main Logic Board, and received via Pin 3 of Connector B103 on the Video Board. It is amplified and pulse-formed by Transistors TR101 and TR102, and fed to the gate of the CRT tube through Pin 1 of Connector B101.

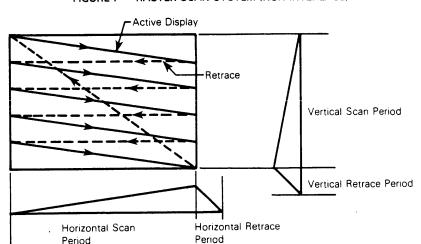

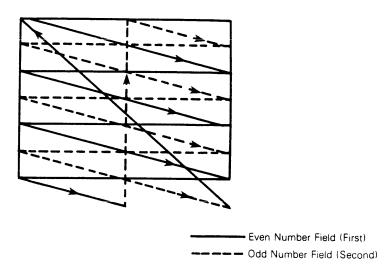

### Vertical Synch

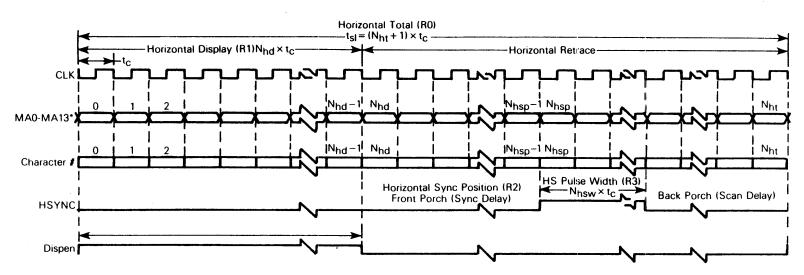

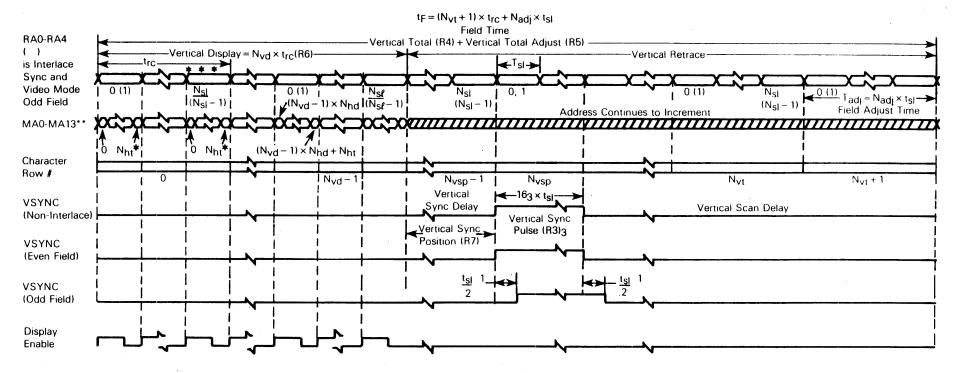

The Vertical Synchronization signal is generated by the CRT Controller chip on the Main Logic Board, and reaches the Video Board via Pin 4 of Connector Bl03. It is used by IC101 (muPC 1031 H2) to reset the beam of the CRT to the top of the screen in preparation for a scan. After pulse-shaping by IC101, it is used to control the Vertical Deflection Yoke (Y101) to position the beam correctly.

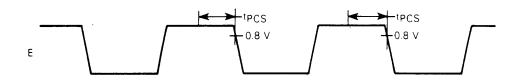

## Horizontal Synch

The Horizontal Synchronization Signal is also generated by the CRT Controller chip on the Main Logic Board, and reaches the Video Board via Pin 6 of Connector B103. It controls the rate at which the beam scans the face of the CRT from side to side. After being amplified and pulse-shaped by TR103 and TR104, it is fed to the Horizontal Yoke and the Fly-Back Transformer (T102) to produce scan lines on the face of the CRT tube.

## Miscellaneous Controls

Variable Resistors (Potentiometers) are provided to control:

Vertical Hold Vertical Size Vertical Linearity Focus Brightness The Video Board Page VID-2

## Troubleshooting

#### Components

I) Make sure that the power is **OFF.** Look at the Video Board, and check for obvious physical problems:

Broken Wires

Loose connectors

Broken connector parts

Dirt or dust

Overheated or burned parts

Correct problems and recheck before going on.

- II) Remove the Video Board from the Freedom 100, and give it a thorough look, both front and back.

- A) Are you sure the power is off? Turn it OFF.

- B) CAREFULLY ground the Anode lead from the CRT tube. A heavy jumper from the Anode lead connection at the Flyback Transformer to chassis ground is the best bet -- the Anode may be at any voltage up to 12kV!

- C) Disconnect the Anode lead.

- D) Disconnect B104 (connector to Main Logic Board)

- E) Disconnect Bl01 (connector to CRT tube)

- F) Disconnect B102 (connector to small PCB on CRT tube)

- G) Disconnect B103 (CRT tube grounding strap)

- H) Remove the screws which hold it in the Monitor Unit.

- I) Lift out the board, carefully.

- J) Check all of the components for burns, overheating, leaks, etc.

- K) Check for broken or missing components.

- L) Check for cracked or broken traces, solder bridges or cold solder joints.

- M) Carefully re-install Video Board, remembering to put the holding screws back in, and tighten them down.

- N) Re-connect B101, B102, B103, B104, and the CRT Anode lead.

- 0) Turn ON power, wait for the CRT tube to warm up.

- P) Enter a random assortment of letters and numbers via the keyboard. (If nothing happens, check Keyboard and Main Logic Board)

## Q) Adjust:

Contrast,

Brightness,

Focus,

Horizontal Hold,

Vertical Hold,

Vertical Linearity, and

Vertical Size

#### III) Malfunctions

## A) No Video Signal

- 1) Check that the Contrast control knob at the front of the Monitor Unit is turned up (clockwise).

- 2) Check for +15V on Pin 1, Connector B104, and at base of TR101. If not found, check Main Logic Board and Power Supply.

- 3) Check for Video Signal at TP101 (base of TR102). If not found, check Pin 3 of Connector B104.

- a) If signal found, check VR101 (contrast control pot on small PCB at front of Monitor Unit) and R102. Replace as necessary.

- b) If not found, check Main Logic Board.

- 4) Check for Video signal at TP102. If found, go to Step 9.

- 5) Check collector of TR102 for 6.4V, base for 0.4V, and emitter for 0.3V.

- a) If signal found, go to Step 5.

- b) If not found, isolate collector to check for pin being pulled down.

- c) Check R103, R104, C103. Replace as necessary.

- d) Check/replace TR102.

- 6) Check TP102 (collector of TR101) for 6.5V, base for 6.9V, and emitter for 6.4V.

- a) If signal found, go to Step 6.

- b) Check R101, C101, D101, C102. Replace as necessary.

- c) Isolate collector to check for pull-down. If no signal, check/replace TR101.

- d) Check L101, R105, C104, D102, and Brightness circuitry connected to Pins 3, 4, & 5 of Flyback Transformer. Replace as necessary.

The Video Board Page VID-4

- 7) Check Pin 1 of Connector B101.

- a) If signal found, go to step 6).

- b) Check R106. Replace as necessary.

- $\,$  8) Check R107 and C118 for short, open or solder bridges. Replace/repair as necessary.

- 9) Check circuitry connected to Pin 2 of Flyback Transformer -- D103, C129, R118, R119, R122, C132, C133, VR106. Replace/repair as necessary.

- 10) Check CRT tube for open circuit in Cathode. Replace as necessary.

## B) No Vertical Deflection

- 1) Is the power ON? Turn it on.

- 2) Check connection between R111 and R101 for +15V relative to ground. If not found, check Pin 1, Connector B104 for +15V. If not found, check Main Logic Board and Power Supply Board.

- 3) Are all of the connectors from the Video Board to the Main Logic board and the CRT tube actually connected? Wiggle them to make sure.

- 4) Check Test Point TP103 for Vertical Synch signal from the Main Logic Board. If no signal, check Main Logic Board.

- a) If signal found, go to Step 5.

- b) Check C105, C106, and R108. Replace as necessary.

- 5) Check TP104 for Vertical deflection signal from IC101. If no signal, test or replace IC101.

- 6) Check Vertical Yoke (Y101) for broken wires. If found to be open circuit, replace Yoke.

- 7) Check cathode of CRT tube for open circuit.

- 8) If all of the above are OK, check diodes, resistors, potentiometers, and capacitors in the vertical timing circuit for shorts, broken wires, or internal open circuits.

## C) No Horizontal Deflection

- 1) Check connection between R116 and L102 for +15V relative to ground. If not found, check Pin 1, Connector B104 for +15V. If not found, check Main Logic Board and Power Supply Board.

- 2) Check TP105 for Horizontal Synch signal from Main Logic

Board. If no signal, check Main Logic Board. If signal does not agree with illustration of typical signal, check R114, and check TR103 for 0.35V on base, 14V on collector, and Ground on emitter.

- 3) Check TP106 (collector of TR103)

- a) If signal found, go to Step 3).

- b) Check collector of TR103.

- c) If signal found, isolate collector of TR103 to see if signal is being pulled down by R116, R117, C121, or C122. Also check T101. Replace as necessary.

- d) Test/replace TR103

- 4) Check TP107 (collector of TR104)

- a) If signal found, go to Step 5).

- b) Check base of TR104 for -0.1V, collector for 18V, and emitter for ground. Also check T101. Replace as necessary.

- c) If signal found, isolate collector of TR104 to see if signal is being pulled down. Replace components as necessary.

- d) Test/replace TR104.

- 5) Check for open circuit between Horizontal Yoke and ground. Check Horizontal Yoke, L103, L104 (adjustable), C127 and C126. Replace as necessary.

- 6) If all of above are OK, check all components in Horizontal Deflection circuitry, including connections to the Flyback Transformer, for shorts, opens, or corroded wires.

- 7) Check CRT Tube, replace as necessary.

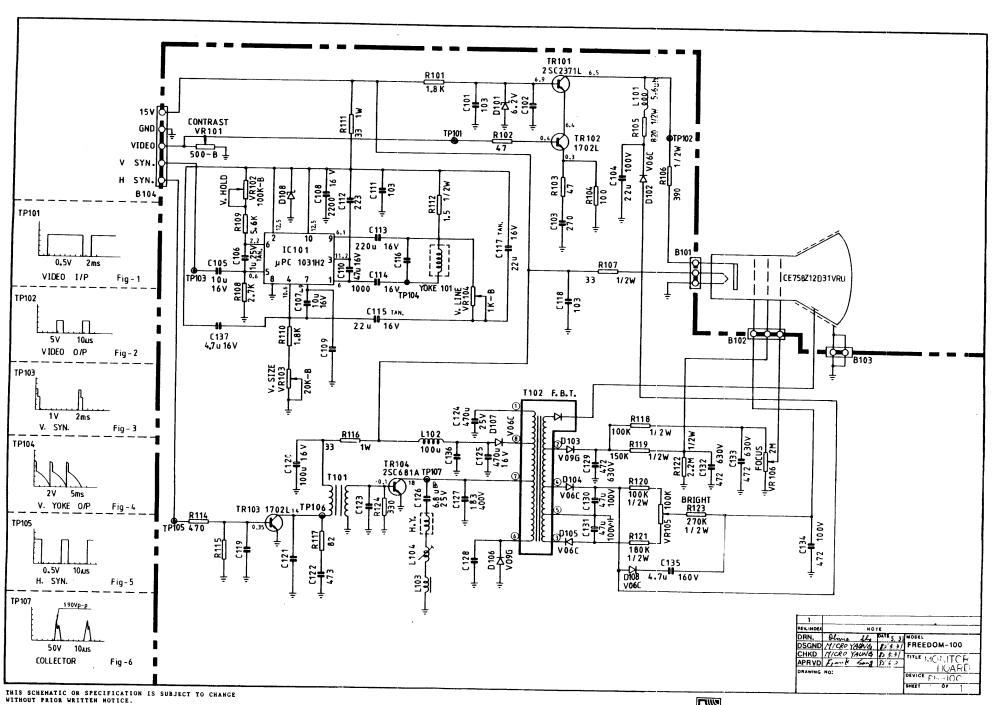

## The Main Logic Board

### Theory of Operation

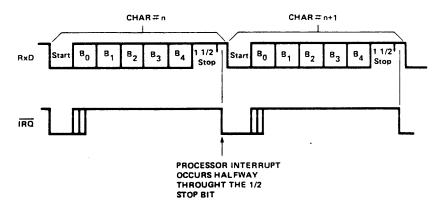

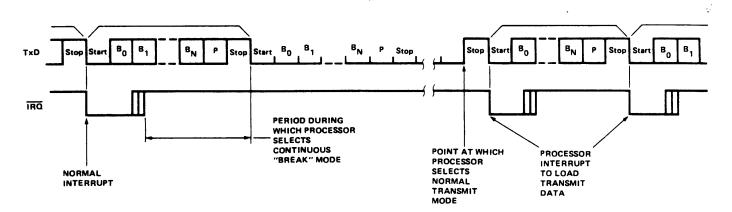

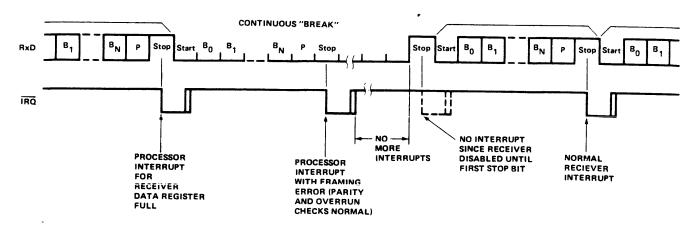

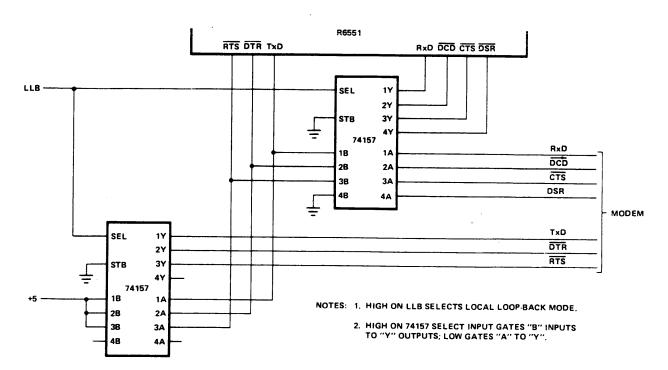

Serial character data from the Host reaches the Main Logic board via Pin 3 of Connector B201, and is directed to Pin 12 (RXD) of U228 (6551 ACIA).

Serial data from the keyboard reaches the Main Logic Board via Pin 4 of Connector B208, and is directed to Pin 2 (RxD) of U218 (68A50 ACIA).

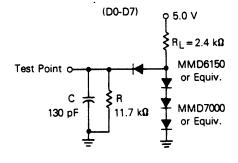

The ACIAs convert the serial data to 8-bit parallel data on their output pins (DO - D7) which are connected to Lines DO - D7 of the CPU Data Bus.

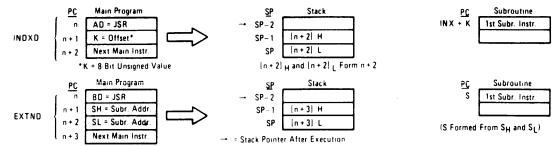

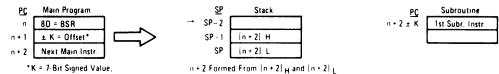

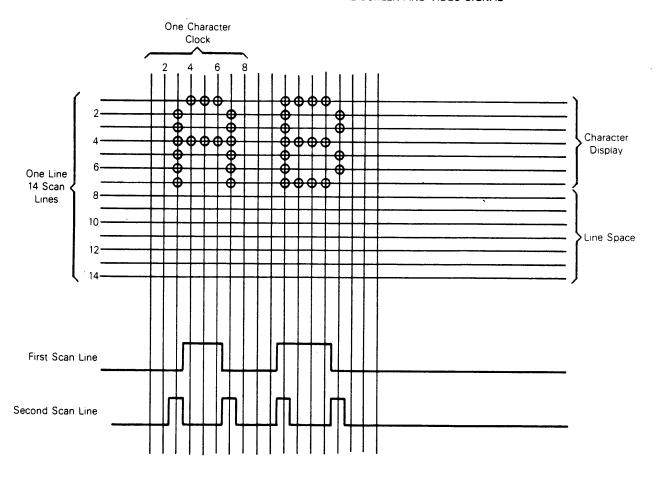

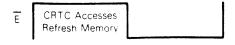

The 68A02 Microprocessor accepts the data and re-transmits it on the Data Bus to the display memory, U212 (2k x 8 RAM). From the memory, it is later transmitted via U223 (Octal Transciever) to U224 (Octal Latch). It is then ready for transmission to U225 (2732 Character Generator EPROM).

If the Freedom 100 is in Full Duplex Mode, the character data is also sent to U228 (ACIA) for transmission to the Host via Pin 2 of Connector B201. In Half Duplex, Block and Local Modes, data is not transmitted to the Host.

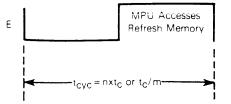

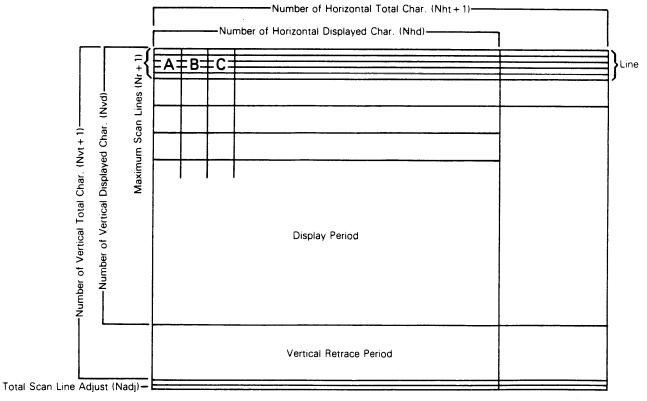

U209 (68A45 CRT Controller) controls Display refresh, as it withdraws character data from the Character Generator EPROM (U225). It also takes care of painting the cursor on the CRT screen.

Output from the Character Generator goes to U236 (74LS166 Shift Register), where it is converted into a serial bit stream. This serial bit stream represents the sequence of pixels which must be turned ON to display one line on the CRT screen. Freedom 100 characters are displayed in a  $7 \times 9$  dot block within a  $9 \times 12$  dot matrix.

The serial data from U233 is combined at U229 (74LS74 Dual D Flip-FLop) with Attribute data from U211 (2k x 8 DRAM) gated through U221 & U222 (Octal Latches) to produce the Video Data output signal, which is transmitted on Pin 3 of Connector B203 to the Video Board.

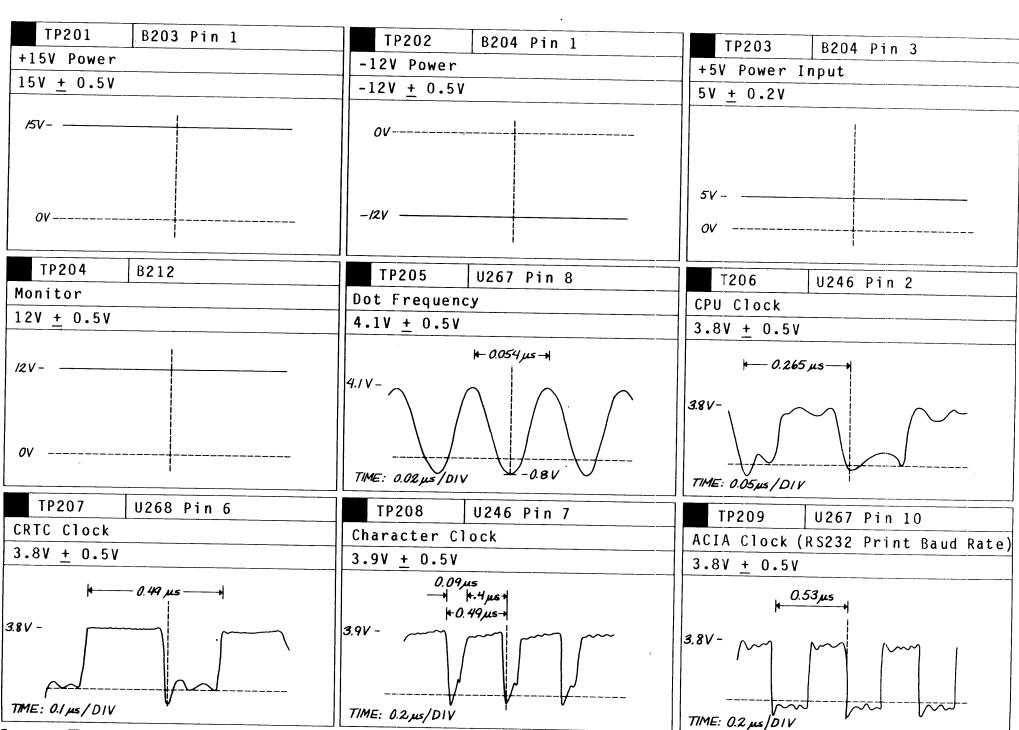

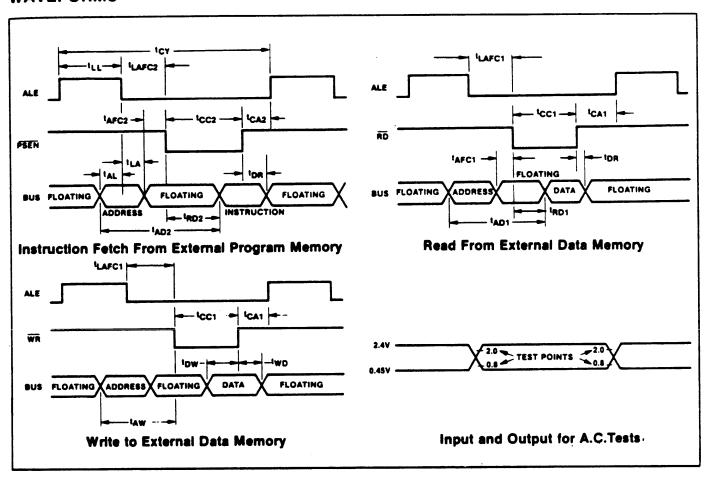

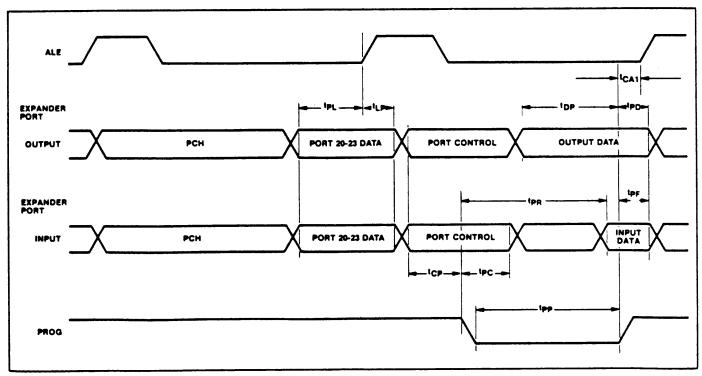

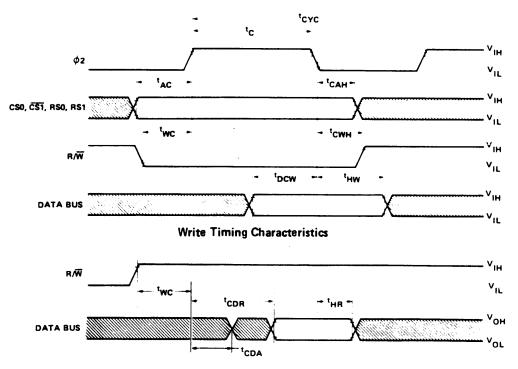

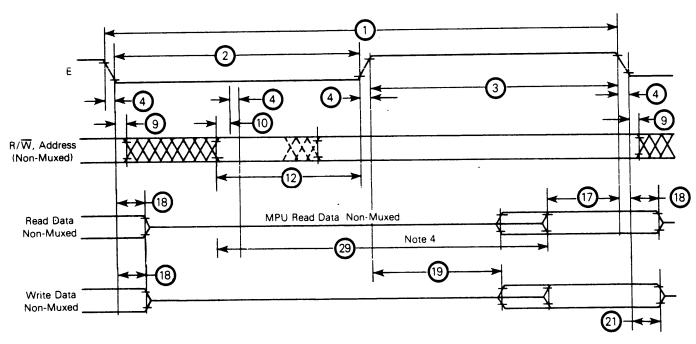

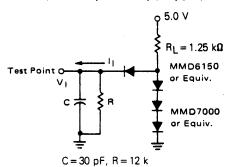

## Test Points, Typical Waveforms, & Signal Levels

See the attached drawings and schematics

**Logic Board Test Points**

**Logic Board Test Points**

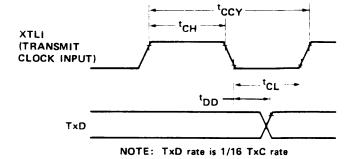

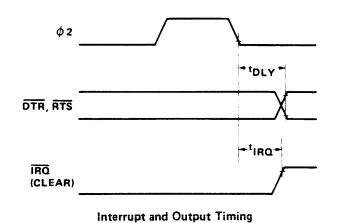

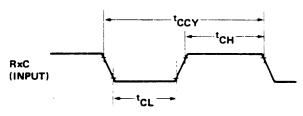

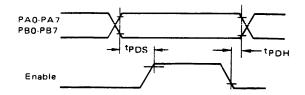

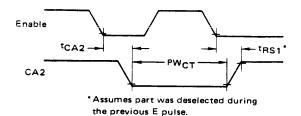

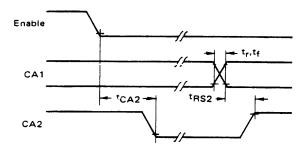

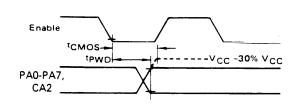

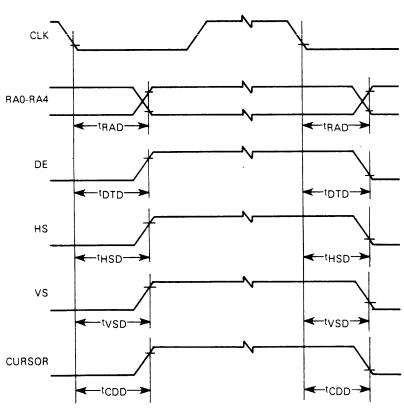

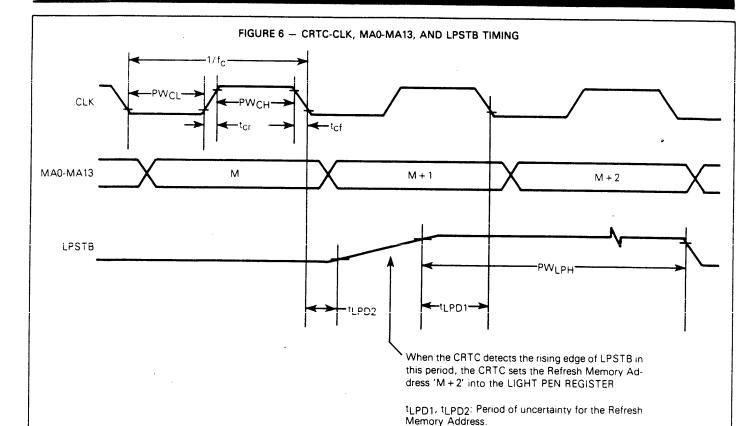

**Logic Board Output Timing**

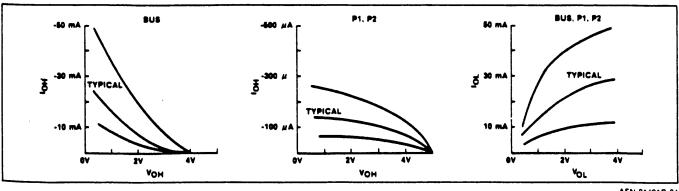

## The Keyboard

## Theory of Operation

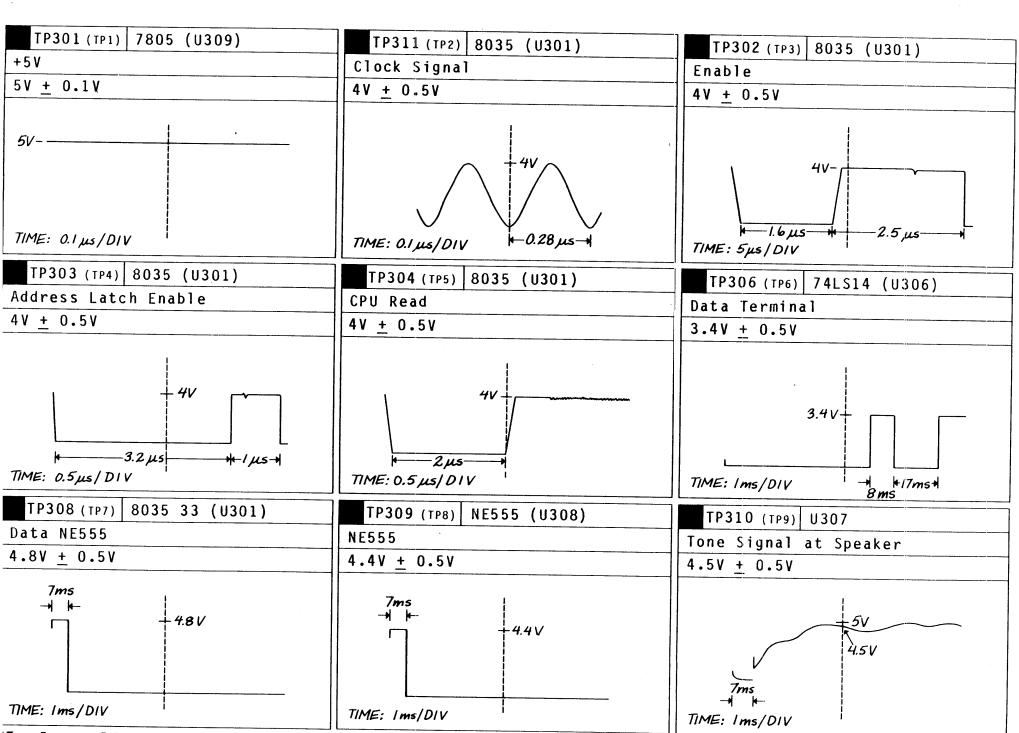

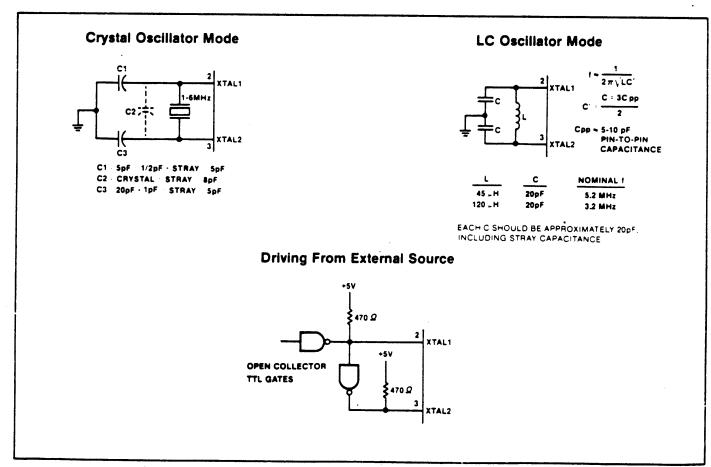

The Freedom 100 Keyboard consists of an 8 x 12 matrix, 89 nodes of which are actually connected to key switches, decoded under software control by an 8035 Microprocessor with a crystal-controlled clock frequency of 3.58 MHz.

The <SHIFT>, <CTRL>, <CAPS LOCK> and <BLOCK> keys are separately decoded by Input Pins TO, T1, P15, & P10, respectively.

All 8 rows of the matrix are normally pulled up to +5V by 10k resistors, and are connected to the inputs of a 74LS244 inverting Octal Buffer. When a key is pressed, the Row line is connected to one of 12 Column lines connected to Input Pins 21 - 24, 28 - 31, and 35 - 38 of the 8035 (P 11 - 14 & P 20 - 27).

To read a key, the 8035 strobes data onto its data bus by bringing  $\underline{RD}$  (Pin 8) low, enabling the Octal Buffer. Rows 0 - 7 are mapped to D0 -  $\overline{D7}$  (Pins 12 - 19). The 8035 then reads Column Data from the Input Pins to determine which key has been depressed.

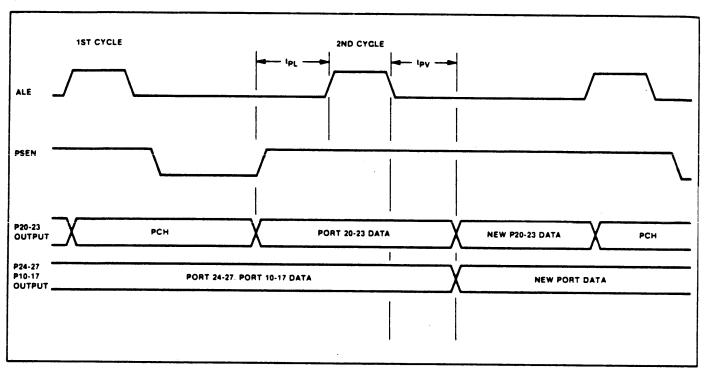

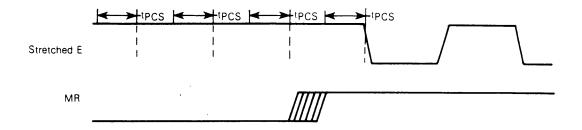

The 8035 uses external Program Memory, stored in a 2k x 8 UV EPROM (2716). It uses a multiplexed Address/Data Bus, first putting the Address on the bus, then strobing the address data into an Octal Latch (U304, 74LS373) with a 1 microsecond pulse on the ALE line (Pin 11). The outputs of the Octal Latch are connected to the address inputs of the EPROM. The 8035 then strobes the EPROM by bringing PSEN (Pin 9) low for 1.6 microsec. One byte of program data is then put onto the Data Bus.

The 8035 can access a total of 8 256-byte pages in this way by specifying the page number on P20 - P22 (Pins 21 - 23). These pins are also used for keyboard decoding, but interference is precluded by adroit use of timing.

The Freedom 100 keyboard has an on-board 8-0hm speaker for audio signalling (ASCII <BELL> character, operator attention, etc.) which is connected to the output of U308 (a NE 555 timer). The 555 puts out a 7 ms pulse, and is controlled by the 8035, which strobes P16 (Pin 33) under software control at a rate sufficient to produce either a high or low tone. The low tone is used in the key-click option to signal that a key has been pressed.

The keyboard also contains a 7805 Voltage Regulator to convert +12V power received from the Monitor Unit to +5V, which is used internally.

## Test Points, Typical Waveforms & Signal Levels

See the attached drawings and schematics

**Keyboard Test Points**

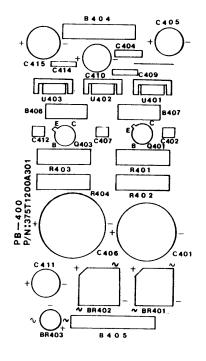

## The Power Supply

## Theory of Operation

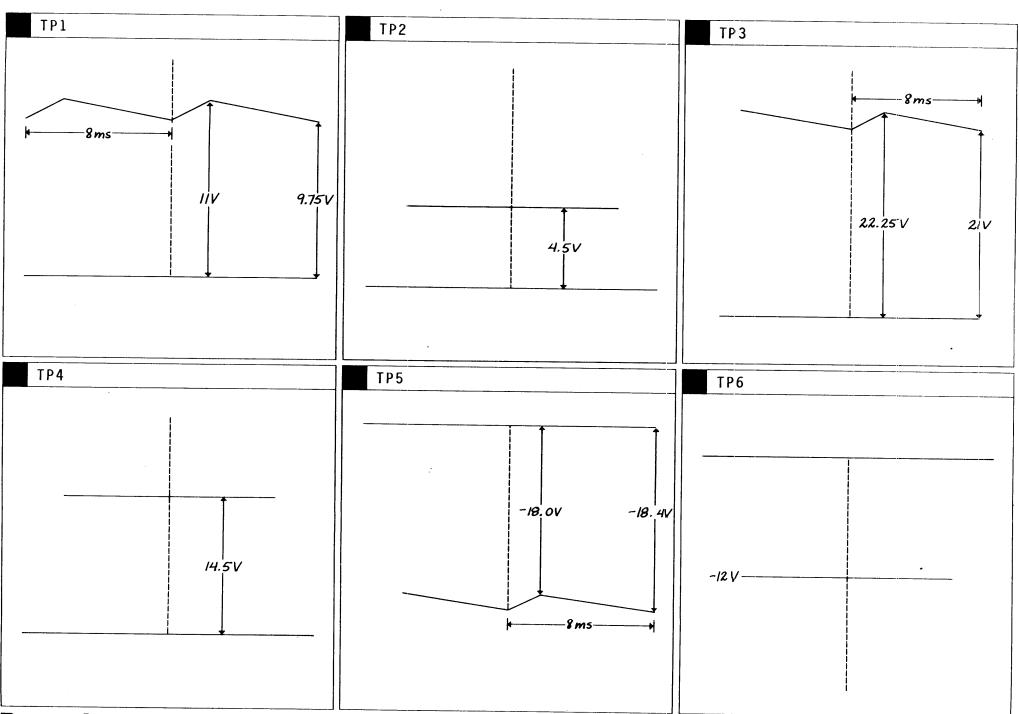

The Freedom 100 Power Supply consists of a 3-wire grounded power cord, an ON/OFF switch, a fuseholder with a  $\frac{1}{2}$  A fuse, a voltage level select switch, a 115/230 V (Primary) transformer, whose 3 secondary windings produce: 10.6V AC, 21.3V AC, and 16.7V AC, as well as a power regulator board.

The Power Regulator Board gets 16.7V AC via Pins 1 & 2 of Connector P405, which is rectified to unfiltered -15.0V RMS by BR401 (Full-Wave Rectifier, W005M or equiv.), filtered and voltage limited to -12V DC, 1.5 A, by U403 (MC7912 or equiv.), which is output on Pin 1 of P404.

Pins 3 & 4 receive 21.3V AC, which is rectified to an unfiltered 19.2V RMS by BR402 (Full-wave rectifier, KBPC6005 or equiv.), voltage-limited by U402 (MC7815) to 15V DC, 1.5 A, and output on Pin 2 of P404. Pin 5 is the 0V reference ground for this power line.

Pins 5 & 6 receive 10.6V AC, which is rectified to an unfiltered 9.5V RMS by BR401 (KBPC6005 or equiv.), voltage limited to +5V DC, 1 A by U401 (MC7805 or equiv.) and output on Pin 3 of Connector P404. Pin 4 is the 0V reference ground for this power line.

## Troubleshooting

## Components

- I) Visual Check.

- A) Turn power OFF and disconnect power cord from mains socket.

- B) Visually check all wiring and components for signs of heat, burning, leakage or breakage.

- C) Using ohmmeter, check Power cord for open circuit (all 3 wires). Check ON/OFF switch for proper operation. Check fuse for open circuit. Check voltage selector switch for proper operation. Check transformer for open circuits (both primary and secondary windings).

- D) Disconnect P405 (connector to transformer) and P406 (connector to Main Logic Board). Disconnect P402 (connector to Power Transistors on heat sink).

- E) CAREFULLY discharge all capacitors on the Power Supply Board.

- F) Carefully remove Power Supply Board, unscrewing and saving any holding screws.

- G) Inspect both sides of Board for damaged or burnt components, broken or corroded wires, broken traces, solder bridges, cold solder joints, etc.

- H) Carefully replace Power Supply Board, tightening down all holding screws. Replace Connectors P402, P404, and P405.

- I) Plug in Unit and turn ON power.

- J) Check secondary (output) leads for:

Blue lead - 10.6V AC

White lead - 21.3V AC

Brown lead - 16.7V AC

Replace Power Transformer if necessary.

## II) Voltage Problems

#### A) No +5V DC

- 1) Check Pins 5 & 6 of P405 for 10.6V AC. If not found, check transformer.

- 2) Check across C401 (electrolytic) for 15V DC. If not found, replace BR401 (full wave rectifier) and/or Capacitor C401.

- 3) Check for ground at Pin 4 of P404, Pin 2 of U401, and negative pole of C401, C402, C403, C405, and at C404. If not found, locate and repair broken trace.

- 4) Check capacitors for short circuit, check R401 and R402 for open circuit.

- 5) Remove and check Q402 (power transistor) using transistor checker. Replace or repair wiring as necessary.

- 6) Isolate and test Q401 with transistor checker. Replace as necessary.

- 7) Remove and test U401. Replace as necessary.

#### B) No +12V DC

- 1) Check Pins 3 & 4 of P405 for 21.3V AC. If not found, check transformer.

- 2) Check across C406 (electrolytic) for 30.1V DC. If not found, replace BR402 (full wave rectifier) and/or Capacitor C406.

- 3) Check for ground at Pin 5 of P404, Pin 2 of U402, and negative pole of C406, C407, C408, C410, and at C409. If not found, locate and repair broken trace.

- 4) Check capacitors for short circuit, check R403 and R404 for open circuit.

- 5) Remove and check Q404 (power transistor) using transistor checker. Replace or repair wiring as necessary.

- $\,$  6) Isolate and test Q403 with transistor checker. Replace as necessary.

- 7) Remove and test U402. Replace as necessary.

### B) No +15V DC

- 1) Check Pins 1 & 2 of P405 for 16.7 V AC. If not found, check transformer.

- 2) Check across C411 (electrolytic) for 15.0V DC. If not found, replace BR403 (full wave rectifier) and/or Capacitor C411.

- 3) Check for ground at Pin 1 of U403, and negative pole of C411, C412, C413, C415, and at C414. If not found, locate and repair broken trace(s).

- 4) Check capacitors for short circuit.

- 5) Remove and test U403. Replace as necessary.

## Test Points, Typical Waveforms, & Signal Levels

See the attached drawings and schematics

Power Supply Board (Loaded)

Maintenance Page MTC-1

#### Maintenance

## The Monitor Unit

#### <u>General</u>

The exterior of the Monitor Unit should be cleaned periodically with a damp cloth to remove accumulated dirt and grime. Be careful, however, in cleaning the face of the CRT screen, since it is covered with a Nylon antiglare screen. This screen is relatively fragile, and will not withstand heavy pressure or vigorous scrubbing motions.

Approximately every 6 months to 1 year, the housing of the Monitor Unit should be removed by a competent service technician, and the circuitry inspected for collected dust or particulate matter, possible corrosion, or loose connections. Vacuum as necessary, and replace or clean parts, and check signal levels before reassembling the case.

It is recommended that signal levels and waveforms at all defined Test Points be checked whenever the Monitor Unit case is opened.

Starting with the Power Supply, check signal levels at Connectors P405 and P404, then Test Points TP401 - TP406.

Next, test the Main Logic Board, beginning with P204, and continuing with TP201 through TP218, in order.

Next, test the Video Board, beginning with PlO3, and continuing with TP101 through TP107, in order.

## Replacing the CRT tube

## > > > > WARNING < < < <

## CRITICAL COMPONENT WARNING:

SERVICEMAN WARNING: This product contains components which are critical for X-Radiation Safety. See Service Manual for proper replacement. Normal 2nd Anode Voltage is 12 KV at Zero beam current, AC 120V input, and must NOT exceed 13 KV under any operating conditions. To measure 2nd Anode Voltage, use High Impedance meter. Connect (-) to chassis, use a High Voltage lead from (+) to 2nd Anode.

Maintenance Page MTC-2

## The Keyboard Unit

Like the Monitor Unit, the Keyboard Unit should be cleaned periodically with a damp cloth to remove accumulated dirt and grime. Be careful not to get water on the keyboard itself, since this would cause electrical shorting and possible damage.

It is recommended that the Keyboard Unit be opened and the keys, PC board and case be vacuumed or blown out with oil- and moisture-free compressed air every 3 to 6 months, since it is exposed to environmental contamination -- dust, dirt, hair, cigarette ashes, spills, paper shreds and dust, etc.

While the Keyboard Unit is being cleaned, it is recommended that signal level and waveform checks on the circuitry be performed.

First check signal levels and waveforms on the pins of Connector 308, the proceed with Test Points TP301 through TP311, in order.

Variance of more than 15% in signal level, or significant deviations from the illustrated waveforms will indicate that detailed troubleshooting of the associated circuitry should be performed.

## APPENDICES

- A -- FREEDOM 100 USER MANUAL

- B -- THE VIDEO BOARD

Layout

Schematic

- C -- THE MAIN LOGIC BOARD

Layout

Schematics

- D -- THE KEYBOARD

Layout

Schematic

- E -- THE POWER SUPPLY

Layout

Schematic

- F -- PARTS LIST

- G -- KEY COMPONENT DATA SHEETS

## THE VIDEO BOARD

Layout and Schematics

| REV. IN DEAL                     |       |     | ) T E |       |                       |

|----------------------------------|-------|-----|-------|-------|-----------------------|

| DRN.<br>DSGND<br>CHKD<br>APR VO. | i for | 124 | DATE  |       | DOM-10G<br>DNITOR PCB |

|                                  |       |     |       | SHEET | PB-100                |

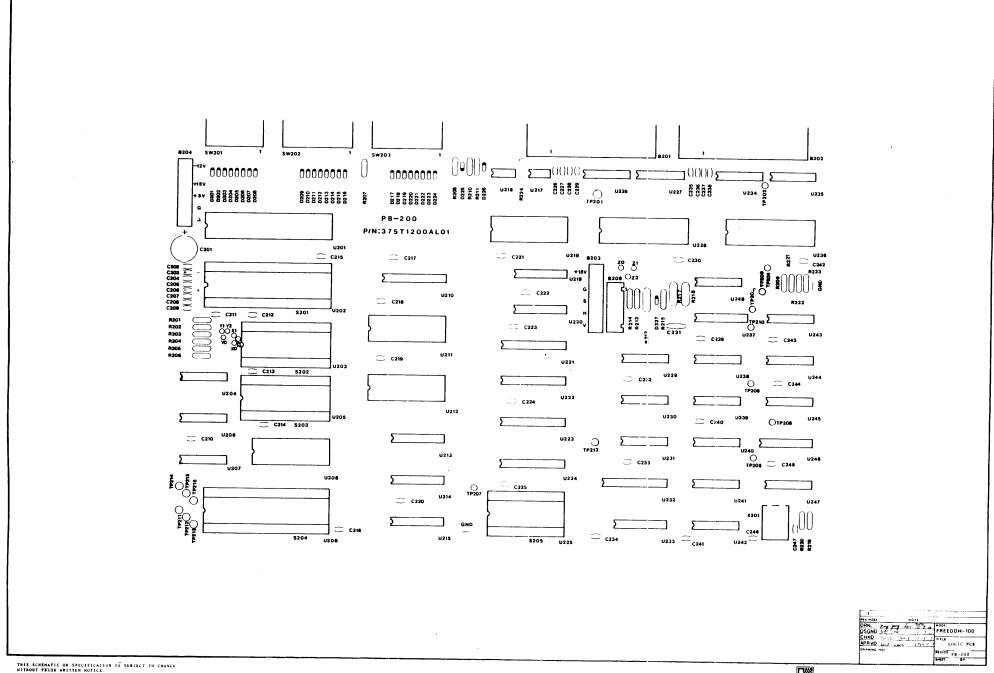

### THE MAIN LOGIC BOARD

Layout and Schematics

#### APPENDIX D

#### THE KEYBOARD

Layout and Schematics

DRN. STATE MODEL

DRN. STATE MODEL

FREEDOM-10-3

CHND STATE

FREEDOM-

#### THE POWER SUPPLY

Layout and Schematics

| 1<br>i∈Carnocx            |                                | <br>V Daha Maria                      |

|---------------------------|--------------------------------|---------------------------------------|

| OSGND                     | and the same                   | FREEDOM-100                           |

| CHKD<br>APRVD.<br>⊇∾∧∧ ча | Jenne Honge in<br>Jenne Hausen |                                       |

|                           |                                | DEV CE<br>1'L-100 1'K-500<br>SHELL OF |

### PARTS LIST

|                  |                |                      | Generic                | Component           |

|------------------|----------------|----------------------|------------------------|---------------------|

| Part             | #              | Desc.                | Desc.                  | Location            |

|                  |                |                      | *                      |                     |

|                  | 0000-0         | CPU                  | 68A02                  | U202                |

|                  | 0000-0         | ACIA                 | 68A50                  | U218                |

|                  | 0000-0         | CRTC                 | 68A45                  | U209                |

|                  | 0000-0         | PIA                  | 68A21                  | U201 ·              |

|                  | 0000-0         | ACIA                 | 6551                   | U228,236            |

|                  | 0001-0         | Static Ram           | 6116                   | U208,211,212        |

|                  | 0000-0         | EPROM                | 2564                   | U203                |

|                  | 0000-0         | EPROM                | 2732                   | U205,225            |

|                  | 0004-0         |                      | 74LS00                 | U242                |

|                  | 0005-0         |                      | 74LS04                 | U206,230,247        |

| 237140           |                |                      | 74LS08                 | U231,241            |

| 23/140           | 0001-0         |                      | 74LS32                 | U207,238,239        |

| 2271/6           | 2002 0         |                      | 74LS74                 | U229                |

| 237140           | 0003-0         |                      | 74LS86                 | U240                |

| 0071/0           | 2006 0         |                      | 74LS90                 | U245                |

| 237140           |                |                      | 74LS92                 | U 2 4 4             |

| 237140           |                |                      | 74LS107                | U243                |

| 237160           |                |                      | 74LS138                | U219                |

|                  | 0005-6         |                      | 748139                 | U220                |

| 237160           | 0003-0         |                      | 74LS157                | U213,214,           |

| 227160           | 004            |                      |                        | 215,237             |

| 237160           | 004-0          |                      | 74LS166                | U233                |

|                  |                |                      | 74LS374                | U221,222            |

| 227160           | 000            |                      | 7/                     | 224,232             |

| 237160           |                |                      | 74LS193                | U246                |

| 237200           |                |                      | 74LS245                | U210,223            |

| 235060<br>235140 |                |                      | 4N33                   | U216,217            |

| 235140           |                |                      | MC1488                 | U227,235            |

| 271140           |                | v <sup>r</sup>       | MC1489                 | U226,234            |

| 3502-1           |                |                      | NE 556                 | U204                |

| 3302-1           | 1004           | Resistor<br>Resistor | 180HM2W.J              | R212                |

|                  |                | Kesistor             | 5100HM                 | R217,218            |

| 3194-1           | 4753           | Resistor             | 1/2 W.J<br>4.7M.1/4W.J | D 106               |

| 3194-1           |                | Resistor             | 1.8M.1/4W.J            | R206                |

| 3194-1           |                | Resistor             | 1.6M.1/4W.J            | R204<br>R205        |

| 3194-1           |                | Resistor             | 3.3K.1/4W.J            |                     |

|                  |                | NC515C01             | 3.3K.1/4W.5            | R201,202<br>207,208 |

|                  |                |                      |                        | 209,211             |

|                  |                |                      |                        | 213,214             |

| 3194-1           | 2743           | Resistor             | 570K.1/4W.J            | R203                |

| 3194-1           |                | Resistor             | 1.2K.1/4W.J            | R210                |

| 3194-1           |                | Resistor             | 2200HM.1/4W.J          | R219,220            |

| 3194-1           |                | Resistor             | 1000HM.1/4W.J          | R215,220            |

| 42-T11           | -              | Capacitor            | 330uf/16v              | C201                |

| 49-K11           |                | Capacitor            | 10uf/16v               | C203                |

|                  | - <del>-</del> | Capacitor            | 0.47uf/16v             | C206                |

|                  |                | Capacitor            | 0.luf/50v              | C231                |

|                  |                | Capacitor            | 0.1uf/12v              | C202,204            |

|                  |                | -                    | • •                    | 205,207             |

|                  |                |                      |                        | •                   |

|               |                    |                                  | 208,209<br>210,211<br>212,213<br>214,215<br>216,217<br>218,219<br>220,221<br>222,223<br>224,225<br>230,232<br>233,234<br>239,240<br>241,242<br>243,244 |

|---------------|--------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|               |                    |                                  | 210,211                                                                                                                                                |

|               |                    |                                  | 212,213                                                                                                                                                |

|               |                    |                                  | 214,215                                                                                                                                                |

|               |                    |                                  | 216,217<br>218,219                                                                                                                                     |

|               |                    |                                  | 220,221                                                                                                                                                |

|               |                    |                                  | 222,223                                                                                                                                                |

|               |                    |                                  | 224,225                                                                                                                                                |

|               |                    |                                  | 230,232                                                                                                                                                |

|               | •                  |                                  | 233,234                                                                                                                                                |

|               |                    |                                  | 239,240                                                                                                                                                |

|               |                    |                                  | 241,242                                                                                                                                                |

|               |                    |                                  | 243,244                                                                                                                                                |

|               |                    |                                  | 246                                                                                                                                                    |

| /1 702/710    | Capacitor          | $0.01 \mathrm{uf}/50 \mathrm{v}$ | C245                                                                                                                                                   |

| 41-K234710    | Capacitor          | 470pf/50v                        | C226,227                                                                                                                                               |

|               |                    |                                  | 228,229                                                                                                                                                |

|               |                    |                                  | 235,236                                                                                                                                                |

| 41-K23680C    | Canaditar          | 60 E / E O                       | 237,238                                                                                                                                                |

| 1120-00010    | Capacitor<br>Diode | 68pf/50v<br>1N4148               | C247                                                                                                                                                   |

| 382GA00000001 | Crystal            | 18.432MH2                        | D201-227<br>X201                                                                                                                                       |

| 377410018001  | Dip SW             | 8 pin piano                      | SW201                                                                                                                                                  |

|               | 21p 3.1            | type                             | 3 W Z O I                                                                                                                                              |

| 37741001A001  | Dip SW             | 10 pin piano                     |                                                                                                                                                        |

|               | •                  | type                             | SW202,203                                                                                                                                              |

| 3786125H001   | D Connector        | 25 pin right                     | ,200                                                                                                                                                   |

|               |                    | angle                            | B201,202                                                                                                                                               |

| 1603-00004    |                    | 5 pin RTB-                       | ,                                                                                                                                                      |

|               |                    | 1.5-5                            | B203,204                                                                                                                                               |

|               | Post Connector     | MICRO 7 pin                      | -                                                                                                                                                      |

|               |                    | JST                              | B208                                                                                                                                                   |

| 3781140P0001  | IC Socket          | 40 pin                           | S201,204                                                                                                                                               |

| 3781128P001   | IC Socket          | 28 pin                           | \$202,203                                                                                                                                              |

| 3781124P001   | IC Socket          | 24 pin                           | S 2 0 5                                                                                                                                                |

| 275712004700  | Jumper             | 62.5m/m                          | X • 4                                                                                                                                                  |

| 375T1200AL00  | PCB                |                                  | PB-200                                                                                                                                                 |

| Monitor Poord |                    |                                  |                                                                                                                                                        |

Monitor Board

| Part #                        | Desc.              | Generic<br>Desc. | Component<br>Location                |

|-------------------------------|--------------------|------------------|--------------------------------------|

| 3A2B1M1200017                 | 12" CRT Tube       | 758Z12D31VRU     | V01                                  |

| 15300000024175                | Transistor         | 2SC681A          | TR104                                |

| 1330000020PH6                 | Transistor         | 1702L            | TR102, TR103                         |

| 1530000016NE8                 | Transistor         | 2SC2371L         | TR101                                |

| 1120000001Œ6                  | Diode              | V06C(1N4003)     | D102, D104, D105, D107               |

| 1140620500NE7                 | Zener              | 6.2V             | D101                                 |

| 213100001NE04                 | V. IC              | uPC1031H2        | 1C101                                |

| 3525R6J0E0011                 | Coil               | 5.6cH +5%        | 1101                                 |

| 352101K0G0014                 | Coil               | 100u +10%        | 1102                                 |

| 3621007000014                 | Coil               | 3 - 16uH         | 1103                                 |

| 356070MG00014                 | Coil               | 7uH              | 1104                                 |

| 39C1211200112                 | D. Yoke            |                  | Yoke 01                              |

| 398412P000018                 | Driver Transformer |                  | T101                                 |

| 396B2M1200216                 | Flyback            |                  | T102                                 |

| 1110000004RE2                 | Diode              | FR155            | VD106                                |

| 375T1200AM001                 | PCB                |                  | PCB01                                |

| 11100000044E5                 | Diode              | RCP15J           | VD103                                |

| 4C22022500024                 | 2P Assembly Wire   | 250 m/m (Mini)   | CN01                                 |

| 4052064500014                 | 6P Assembly Wire   |                  | Sock 01                              |

| 4C22042500020                 | 4P Assembly Wire   | 250 m/m (Mini)   | Q104                                 |

| 4022053500018                 | 5P Assembly Wire   | 350 m/m (Mini)   | QN05                                 |

| 3784102P00017                 | 2P Base            | •                | Base 03                              |

| 3784103P00011                 | ' 3P Base          | •                | Base 01, 02                          |

| 3784104P00014                 | 4P Base            |                  | Base 04                              |

| 441024050A771                 | Lead Wire          | 50 m/m           | W01<br>Л01, Л02, Л03, Л04, Л05       |

| 48R50000001                   | Jump Wire          | 10m/m            | 1101, 1102, 1103, 1109, 1110<br>1111 |

| 311R21R5JHC11                 | Resistor           | 1.5 CHM 1/2W J   | R112                                 |

| 311R2330JHC15                 | Resistor           | 33 CHM 1/2W J    | R107                                 |

| 31501330JHC16                 | Resistor           | 33 CHM IW J      | R116, R111                           |

| 311R4470JHC16                 | Resistor           | 47 CHM 1/4W J    | R102, R103                           |

| 311R4331_HC13                 | Resistor           | 330 OHM 1/4W J   | R124                                 |

| 311R4560JHCL5                 | Resistor           | 56 CHM 1/4W J    | R117                                 |

| 311R436WHC17                  | Resistor           | 100 OHM 1/4W J   | R104                                 |

| 311R410LHC11                  | Resistor           | 390 CHM, 1/2W J  | R106                                 |

| 311R239LHC11<br>311R447LJHC11 | Resistor           | 470 CHM 1/4W J   | R114                                 |

| 311R2122JHC15                 | Resistor           | 1.2K 1/2W J      | R105                                 |

| 311R2560JHC11                 | Resistor           | 56 CHM 1/2W J    | R124                                 |

| 311R4182.IHC11                | Resistor           | 1.8K 1/4W J      | R110, R101                           |

| 311R4272JHC10                 | Resistor           | 2.7K 1/4W J      | R108                                 |

| 311R4562JHC14                 | Resistor           | 5.6K 1/4W J      | R109                                 |

| 311R2104JHC17                 | Resistor           | 100K 1/2W J      | R118                                 |

| 311R2154JHC15                 | Resistor           | 150K 1/2W J      | R119, R120                           |

| 311R2184JHC16                 | Resistor           | 180K 1/2W J      | R121                                 |

| 311R2274JHC15                 | Resistor           | 270K 1/2W J      | R123                                 |

|                               | Resistor           | 2.2M 1/2W J      | R122                                 |

| 311R2225JHC11                 | RESIDUL            |                  |                                      |

|                               |                    |                  | 9<br>3                               |

| Part #                   | Desc.             | Generic _<br>Desc.       | Component<br>Location |

|--------------------------|-------------------|--------------------------|-----------------------|

| 321B5B52B0016            | Variable Resistor | 16¢ 500B                 | VR101                 |

| 32785B13V2011            | Variable Resistor | 8ø 1K V Type             | VR104                 |

| ; 32785B24V <b>3</b> 019 | Variable Resistor | 86 20K V Type            | VR103                 |

| 32785B15V3010            | Variable Resistor | 86 100K V Type           | VR102, VR105          |

| ! 327D1B26V3017          | Variable Resistor | 15\$ 2M                  | VR106                 |

| `33750027LJSL3           | Capacitor         | 270PF/50V                | C103                  |

| 338500103H0B2            | Capacitor         | 10000PF/50V <u>+</u> 20% | C101                  |

| 336101472J020            | Capacitor         | 4700PF/100V              | C134                  |

| 336601472K039            | Capacitor         | 4700PF/600V              | C129, C132, C13       |

| 336500223K014            | Capacitor         | 22000PF/50V              | C112                  |

| 336401183K036            | Capacitor         | 18000PF/400V             | C127                  |

| 3385004732084            | Capacitor         | 47000PF/50V +80,-20%     | C122                  |

| 334250010KC13            | Capacitor         | luF/25V `                | C106                  |

| 3331014R7TG14            | Capacitor         | 4.7uF/100V +100,-10%     | C130, C131            |

| 333160100TG17            | Capacitor         | 10uF/16V +100,-10%       | C105, C107            |

| 3312506R8MG13            | Capacitor         | (BP) 6.8uF/25V           | C126                  |

| 333101220TG11            | Capaction         | 22uF/100V +100,-10%      | C104                  |

| 333160470TG10            | Capacitor         | 47uF/16V +100,-10%       | C110                  |

| 334160220KG16            | Capacitor         | 22uF/16V                 | C117, C115            |

| 333160221TG15            | Capacitor         | 220uF/16V +100,-10%      | C113                  |

| :3331602R2TG18           | Capacitor         | 2.2uF/16V +100,-10%      | C120                  |

| 333250471TG14            | Capacitor         | 470uF/25V +100,-10%      | C124                  |

| 333160471TG15            | Capacitor         | 470uF/16V +100,-10%      | C125                  |

| 333160102TG18            | Capacitor         | 1000uF/16V +100,-10%     | C114                  |

| 333160222TG11            | Capaction         | 2200uF/16V +100,-10%     | C108                  |

| 3331604R7TC12            | Capacitor         | 4.7uF/16V +100,-10%      | C1.37                 |

#### Keyboard

| 231400001-0<br>233240002-0<br>237140000-0<br>237200000-0<br>237200001-0<br>237080000-0<br>271080000-0 | CPU<br>EPROM         | 8035<br>2716<br>74LS14<br>74LS244<br>74LS373<br>SN75452<br>NE555 | U301<br>U305<br>U306<br>U302<br>U304<br>U307<br>U308                   |

|-------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------|------------------------------------------------------------------------|

| 215030001-0                                                                                           | Regulator IC         | 7805                                                             | U309                                                                   |

| 3194-12233                                                                                            | Resistor             | 22K.1/4W.J                                                       | R307                                                                   |

| 3194-11033                                                                                            | Resistor             | 10K.1/4W.J                                                       | R302,303<br>304,305<br>317,318<br>319,320<br>321,322<br>323,324<br>325 |

| 3194-12223                                                                                            | Resistor             | 2.2K.1/4W.J                                                      | R306                                                                   |

| 3194-11023                                                                                            | Resistor             | 1K.1/4W.J                                                        | R301                                                                   |

| 3501-31014                                                                                            | Resistor             | 1000HM.1W.J                                                      | R308                                                                   |

|                                                                                                       | Capacitor            | 47uf/16v                                                         | C312,313                                                               |

| 42-K12100C                                                                                            | Capacitor            | 10uf/16v                                                         | C309                                                                   |

|                                                                                                       | Capacitor            | 4.7uf/16v                                                        | C314                                                                   |

| 49-K11109D                                                                                            | Capacitor            | luf/16v                                                          | C303                                                                   |

|                                                                                                       | Capacitor            | 0.luf/12v                                                        | C311                                                                   |

| 49-K11107C                                                                                            | Capacitor            | 0.01uf/50v                                                       | C305,306<br>C307,310                                                   |

| 41-K23333C                                                                                            | Connector            | 0.022.5/50                                                       | 315                                                                    |

| 41-K23333C                                                                                            | Capacitor            | 0.033uf/50v                                                      | C308                                                                   |

| 41-K23331C<br>41-J30220C                                                                              | Capacitor            | 330Pf/50v                                                        | C304                                                                   |

| 1127-00002                                                                                            | Capacitor<br>Crystal | 22Pf/50v<br>3.58MHZ                                              | C301,302                                                               |

| 1127-00002                                                                                            | Diode                |                                                                  | X301                                                                   |

| 3781140P0001                                                                                          | IC Socket            | 40 Pin                                                           | D301,302<br>S301                                                       |

| 3781124P001                                                                                           | IC Socket            | 24 Pin                                                           | S301                                                                   |

| 39A020R16801                                                                                          | Speaker              | 0.16W.8ohm                                                       | SP301                                                                  |

| 37K020K10001                                                                                          | Wafer                | GPin Micro90                                                     | 31301                                                                  |

|                                                                                                       | Walci                | Degree JST                                                       | в309                                                                   |

| 377920040001                                                                                          | Keyboard             | Key Top + Key                                                    | <b>D</b> 307                                                           |

| 3,200.10001                                                                                           | ney board            | SW. + Plate                                                      | KB301                                                                  |

| 375T1-200AK00                                                                                         | PCB                  | ow . IIacc                                                       | PB300                                                                  |

|                                                                                                       |                      |                                                                  | 12000                                                                  |

| Power Supply                                                                                          |                      | _                                                                |                                                                        |

| 215030000-0                                                                                           | Regulator IC         | 7805                                                             | U401                                                                   |

| 215030001-0                                                                                           | Regulator IC         | 7815                                                             | U402                                                                   |

| 215030002-0                                                                                           | Regulator IC         | 7912                                                             | U403                                                                   |

| 131000000015B                                                                                         | Tr                   | 2N40373                                                          | Q401,403                                                               |

|              |              |                  | The second secon |

|--------------|--------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15100000008M | Tr           | MJ2955           | Q402,404                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 11200000015  | BR           | KBPCG005         | BR401,402                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 11200000016G | BR           | W005M            | BR 403                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |