# V/Ethernet 3207 Hawk

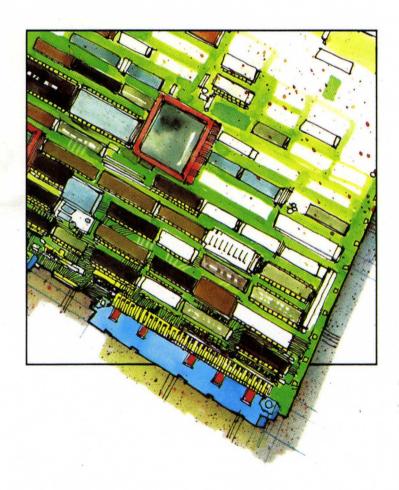

High-performance VMEbus Ethernet Communications Controller

# V/Ethernet 3207 Hawk

High-performance VMEbus Ethernet Communications Controller

# V/Ethernet 3207 Hawk LOCAL AREA NETWORK CONTROLLER FOR ETHERNET USER'S GUIDE

| Document Number  | UG-0750-000-X0H   |

|------------------|-------------------|

| Revision         | XOH               |

| Follows Revision | XOG               |

| Release Date     | November 20, 1987 |

#### **COPYRIGHT NOTICE**

No part of this publication may be stored in a retrieval system, transmitted, or reproduced in any way, including, but not limited to photocopy, photograph, electronic or mechanical, without prior written permission of INTERPHASE CORPORATION. Information in this user document supersedes any preliminary specifications and/or data sheets that may have been made available. Every effort has been made to supply accurate and complete information. However, Interphase Corporation assumes no responsibility for its use. In product addition, Interphase reserves the right to make improvements without prior notice. Such improvements may include, but are not limited to, command codes and error codes.

Information pertaining to the AMD LANCE chip is reprinted with permission: Copyright<sup>©</sup> Advanced Micro Devices, Inc., October, 1986. Reprinted with permission of copyright owner. All rights Reserved.

#### FOR ASSISTANCE IN USING THE V/ETHERNET 3207 OR ANY OTHER INTERPHASE PRODUCT CALL:

#### INTERPHASE CUSTOMER SERVICE DEPARTMENT (214) 919-9000

IN THE UNITED KINGDOM CALL: (869) 321222

#### UPDATE

### ТО

# V/ETHERNET 3207 USER'S GUIDE

(UG-0750-000-XOH, Rev. B)

March 28, 1989

The following 2-page update contains information which either supplements or supersedes information in the user's guide (UG-0750-000-XOH). The user's guide itself is located immediately following the update.

# UPDATE

# ΤO

# V/Ethernet 3207 User's Guide

## UG-0750-000-XOH, Rev. B

#### ADDENDUM - Released, March 28, 1989

The following information will be included in the next revision of the V/Ethernet 3207 Disk Controller User's Guide.

### ACCESS TO THE DUAL PORT RAM

This section is a clarification of how jumpers JA4, JA8, JA9 and JA12 work in conjunction with each other to access the 256K dual port RAM.

The two functional blocks of the system that can access the 256K dual port RAM are the LANCE chip and VMEbus master. The following tables illustrates the jumpers to be set in order to detect parity errors. To configure the board properly, a selection for VMEbus and/or LANCE access generated errors must be made.1

#### VMEbus ACCESS GENERATED ERRORS

| *Jumpers    | <u>Pins</u> | Error Description                        |

|-------------|-------------|------------------------------------------|

| JA4 and JA9 | 1++2        | Parity error causes BERR                 |

|             | 2⇔3         | User detects parity error by polling BSR |

# LANCE ACCESS GENERATED ERRORS

| *Jumpers     | Pins | Error Description                                                                    |

|--------------|------|--------------------------------------------------------------------------------------|

| JA8 and JA12 | 1⇔2  | Parity error on LANCE read causes<br>LANCE "MERR" error and subsequent<br>interrupt. |

|              | 2⇔3  | User detects parity error by polling BSR.                                            |

\*Set both jumpers for proper configuration.

## 2 V/Ethernet 3207 UPDATE

# ERRATA

Pages 57 - 59. Factory Default jumper settings for JA4, JA8, JA9 and JA12 were miss labelled. The corrections are as follows:

| JA4  | 1 - 2 | DTACK timing for VMEbus initiated transfers is slow. This is for use when parity errors are reported to the VMEbus master as VMEbus error (BERR) (see JA8, JA12)Factory Default.                                                   |

|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | 2 - 3 | DTACK timing for VMEbus initiated transfers is fast. This is preferred when parity errors are sensed by polling board status register (BSR) (see JA8, JA12).                                                                       |

| JA8  | 1 - 2 | Enable special parity error reporting. LANCE cycle parity<br>errors will cause a memory error (CSR0 bit 11) (See JA4,<br>JA12)Factory Default.                                                                                     |

|      | 2 - 3 | Disable special parity error reporting (See JA4, JA12).                                                                                                                                                                            |

| JA9  | 1 - 2 | Enable VMEbus reporting of parity error using BERR signal-<br>-Factory Default.                                                                                                                                                    |

|      | 2 - 3 | Disable VMEbus reporting of parity error using BERR signal.<br>(NOTE: VMEbus BERR is asserted only on parity errors<br>detected during V/Ethernet 3207 bus accesses. LANCE<br>induced parity errors do not generate VMEbus BERRs.) |

| JA12 | 1 - 2 | This is set if parity errors are being reported to the LANCE as memory errors (See JA4, JA8)Factory Default.                                                                                                                       |

|      | 2 - 3 | This setting is preferred if parity errors are sensed by polling board status register (See JA4, JA8).                                                                                                                             |

Page 66. The title to Table A-2 was labelled incorrectly, it should read as followed:

"Table A-2: VMEbus Connector P2 Signal Descriptions (DASH 0 Only)\*"

Page 67. The title to Table A-3 was labelled incorrectly, it should read as followed:

"Table A-3: VMEbus Connector P2 Signal Descriptions (DASH 1 Only)\*"

# TABLE OF CONTENTS

# 1 INTRODUCTION TO THE V/Ethernet 3207 HAWK

| OVERVIEW                     | 1 |

|------------------------------|---|

| NETWORK PERFORMANCE FEATURES | 1 |

| LANCE Pipeline               | 2 |

| OPERATION                    | 3 |

| SUMMARY OF FEATURES          | 4 |

2 PROGRAMMING OF THE V/Ethernet 3207

| INTRODUCTION                   | 7  |

|--------------------------------|----|

| ADDRESSING                     | 8  |

| COLLISION DETECTION            | 8  |

| ERROR REPORTING/DIAGNOSTICS    | 9  |

| BUFFER MANAGEMENT              | 9  |

| INTERRUPT HANDLING             | 10 |

| PROGRAMMING                    | 11 |

| Programming Sequence           | 12 |

| Control and Status Registers   | 12 |

| Accessing CSRs                 | 13 |

| Ring Access Mechanism in LANCE | 13 |

| SILO Operation                 | 13 |

| FOR FURTHER INFORMATION        | 14 |

3 FUNCTIONAL DESCRIPTION OF THE V/Ethernet 3207

| INTRODUCTION<br>BOARD CONTROL REGISTER (BCR)<br>BOARD STATUS REGISTER (BSR)<br>INTERRUPT VECTOR REGISTER (IVR)<br>ETHERNET ADDRESS REGISTER (EAR)<br>The Serial Nonvolatile RAM<br>REGISTER DATA PORT (RDP)<br>REGISTER ADDRESS PORT (RAP) | 15<br>20<br>22<br>23<br>24<br>24<br>24<br>29<br>29 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| REGISTER ADDRESS PORT (RAP)                                                                                                                                                                                                                | 29                                                 |

# TABLE OF CONTENTS (cont.)

# 3 FUNCTIONAL DESCRIPTION OF THE V/Ethernet 3207 (Cont.)

|                                         | ~~ |

|-----------------------------------------|----|

| CONTROL AND STATUS REGISTERS            | 30 |

| Control and Status Register 0 (CSR0)    | 30 |

| Control and Status Register 1 (CSR1)    | 35 |

| Control and Status Register 2 (CSR2)    | 36 |

| Control and Status Register 3 (CSR3)    | 36 |

| INITIALIZATION BLOCK                    | 37 |

| Mode Register                           | 38 |

| Physical Address Register (PADR)        | 40 |

| Logical Address Filter (LADRF)          | 41 |

| Receive Descriptor Ring Pointer (RDRP)  | 42 |

| Transmit Descriptor Ring Pointer (TDRP) | 43 |

| DESCRIPTOR RINGS                        | 46 |

| Receive Message Descriptor 0 (RMD0)     | 46 |

| Receive Message Descriptor 1 (RMD1)     | 46 |

| Receive Message Descriptor 2 (RMD2)     | 48 |

| Receive Message Descriptor 3 (RMD3)     | 48 |

| Transmit Message Descriptor 0 (TMD0)    | 49 |

| Transmit Message Descriptor 1 (TMD1)    | 49 |

| Transmit Message Descriptor 2 (TMD2)    | 51 |

| Transmit Message Descriptor 3 (TMD3)    | 51 |

|                                         |    |

# 4 INSTALLATION OF THE V/Ethernet 3207

| CABLING         | 53 |

|-----------------|----|

| Dash 0 Version  | 53 |

| Dash 1 Version  | 53 |

| SWITCH SETTINGS | 53 |

| JUMPER SETTINGS | 57 |

| INSTALLATION    | 59 |

|                 |    |

# TABLE OF CONTENTS (cont.)

# 5 SPECIFICATIONS OF THE V/Ethernet 3207

| VMEbus SPECIFICATIONS        | 61 |

|------------------------------|----|

| ENVIRONMENTAL SPECIFICATIONS | 61 |

| ELECTRICAL SPECIFICATIONS    | 61 |

| MECHANICAL SPECIFICATIONS    | 61 |

# APPENDICES

# Appendix A

| Connector Pin-outs<br>Connector P1 Signal Description<br>Connector P2 Signal Description (DASH 1)<br>Connector P2 Signal Discription (DASH 0)<br>Transceiver Connector Pin Assignments | 65<br>65<br>66<br>67<br>68 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| Appendix B                                                                                                                                                                             |                            |

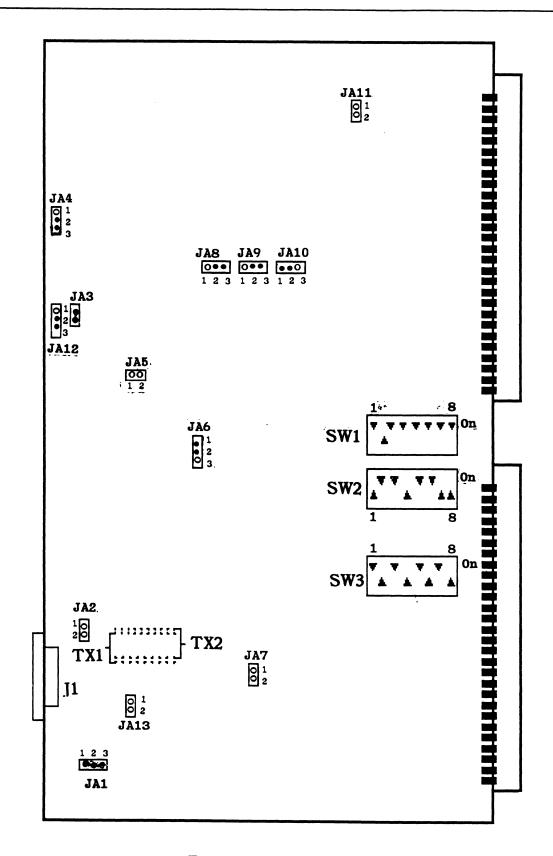

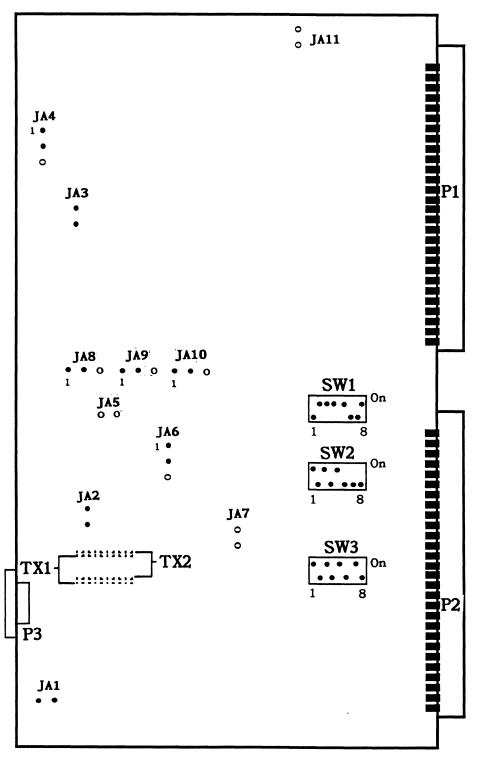

| V/Ethernet 3207 Board Layout for Artwork Rev. X0B<br>Jumper Configuration for Artwork Rev. X0B                                                                                         | 75<br>76                   |

| GLOSSARY OF TERMS                                                                                                                                                                      | 71                         |

| INDEX                                                                                                                                                                                  | 79                         |

# ILLUSTRATIONS

| FIGURE 1  | - CONTROL/STATUS & DATA STRUCTURES.17/18 |

|-----------|------------------------------------------|

| FIGURE 2  | - V/Ethernet 3207 BLOCK DIAGRAM19        |

| FIGURE 3  | - BOARD CONTROL REGISTER FORMAT20        |

| FIGURE 4  | - BOARD STATUS REGISTER FORMAT22         |

|           | - INTERRUPT VECTOR REGISTER FORMAT23     |

| FIGURE 6  | - \CONTROL STATUS REGISTER FORMAT30      |

|           | - MODE REGISTER FORMAT                   |

| FIGURE 8  | - RMD 1 FORMAT                           |

| FIGURE 9  | - TMD 1 FORMAT                           |

| FIGURE 10 | - TMD 3 FORMAT                           |

| FIGURE 11 | - BOARD LAYOUT                           |

| FIGURE 12 | - SAMPLE SWITCH BLOCK SETTINGS55         |

| FIGURE 13 | - SWITCH BLOCK RECORD                    |

# TABLES

| TABLE | 1          |   | PROGRAMMABLE REGISTERS1        | 15 |

|-------|------------|---|--------------------------------|----|

| TABLE | 2          |   | ADDITIONAL LANCE REGISTERS1    | 6  |

| TABLE | 3          | - | INTERRUPT VECTOR SETTINGS2     | 21 |

| TABLE | 4          | - | SERIAL NOVRAM INSTRUCTION SET2 | 25 |

| TABLE | 5          |   | INITIALIZATION BLOCK           | 37 |

| TABLE | Α1         | - | VMEbus P1 CONNECTOR SIGNALS    | 55 |

| TABLE | A2         | - | P2 CONNECTOR SIGNALS (DASH 1)6 | 56 |

| TABLE | <b>A</b> 3 | - | P2 CONNECTOR SIGNALS (DASH 0)6 | 57 |

| TABLE | Α4         |   | TRANSCEIVER CONNECTOR SIGNALS  | 58 |

### PREFACE

This User's Guide is intended to be a reference document for users who already have a general understanding of Ethernet and IEEE 802.3 compatible local area networks and a general knowledge of the VME standard. The V/Ethernet 3207 Hawk uses the Am7990 LANCE chip from Advanced Micro Devices to control many of the data transfer functions on the network. This document does not attempt to fully explain all of the LANCE. Instead, where more information may be necessary, the user may wish to consult the Am7990 LANCE and the Am7992B SIA (Serial Interface Adapter) data sheets from Advanced Micro Devices.

The following information is provided in this user's guide:

| Section 1 - | Introduction | to the | V/Ethernet | 3207 |

|-------------|--------------|--------|------------|------|

|-------------|--------------|--------|------------|------|

- Section 2 Programming of the V/Ethernet 3207

- Section 3 Functional Description of the V/Ethernet 3207

- Section 4 Installation of the V/Ethernet 3207

- Section 5 Specifications of the V/Ethernet 3207

- Appendix A Connector Pin-outs

Glossary

Index

For more detailed explanations of specific operations or features of the V/Ethernet 3207 Hawk, call us at INTERPHASE. We would be happy to answer any questions!

# INTERPHASE CORPORATION APPLICATIONS ENGINEERING DEPARTMENT (214) 350-9000

#### IN THE U.K. CALL (0296) 435661

## SECTION 1

## INTRODUCTION TO THE V/ETHERNET 3207 HAWK

#### **OVERVIEW**

The V/Ethernet 3207 Hawk is a VMEbus Local Area Network Controller for Ethernet and other IEEE 802.3 compatible networks. Designed to be used primarily in a single user, workstation environment, the V/Ethernet 3207 Hawk provides cost effective control of layers one and two of the seven-layer ISO/OSI model of data communications. Layers three and above of the protocol are referred to software running on the host CPU. While this minimal approach does use some host CPU computing power, it also creates several significant advantages over the direct effect of a low cost Ethernet connection.

This approach gives the system designer great latitude in implementing the optimum tradeoff between protocol sophistication and network efficiency. The continuing evolution of various implementations of the OSI model, plus the need to support existing TCP/IP, XNS, and ISO-IP low-level protocols as well as NFS and RFS applications, requires the flexibility and maintainability only found in host resident software. Indeed, any disadvantage of referring the upper layers of the protocol to the host becomes increasingly less significant as host CPUs become faster and more powerful. Thus, by not having a general purpose microprocessor on-board, the V/Ethernet 3207 Hawk provides both a degree of flexibility and a price performance ratio not found in other approaches.

#### NETWORK PERFORMANCE FEATURES

The V/Ethernet 3207 Hawk utilizes the combination of an Am7990 Local Area Network Controller for IEEE-802.3/Ethernet (LANCE), an Am7992B Serial Interface Adapter (SIA) and 256 Kbytes of dual ported RAM. The dual ported RAM is configured as transmit and receive ring buffers, with the number of buffers in each ring under programmatic control via Ring Descriptor Tables. Ring Descriptor Tables also identify each buffer (transmit or receive) and indicate the buffer owner (the LANCE or the host CPU). Both the host CPU (via the VMEbus) and the LANCE have access to the full 256 Kbyte buffer. The host CPU sends data across the network by writing it into the RAM and receives data by reading it from the RAM. To the host CPU, the dual ported RAM appears as fast access, 16- or 32-bit wide, system memory. The inherent queuing mechanism of the transmit and receive ring buffers decouples system timing from network timing and vice versa. Thus, VMEbus timing cannot degrade network performance and neither can host CPU response time.

#### LANCE Pipeline

The Ethernet interface on the V/Ethernet 3207 Hawk consists of the LANCE chip and the SIA (Serial Interface Adapter) from AMD. The LANCE is a 10 Mbit/sec device, optimized to perform the link-level Ethernet protocol. This includes the CSMA/CD network access, on-chip DMA, error reporting, packet handling and local bus interface functions. The SIA provides Manchester II encoding/decoding of the serial bit stream and translation of the TTL I/O of the LANCE into differential I/O for the transceiver.

The operation of the SIA is controlled by the LANCE and the LANCE is controlled The LANCE is programmed through registers in Short I/O space of by the host. the V/Ethernet 3207 Hawk and through data and control structures in the 256 Kbytes of dual ported RAM. The LANCE has an internal 48-byte data SILO which it services from the dual port RAM (by filling from the RAM or emptying into the RAM). The LANCE does this with DMA bursts of up to eight words. In conventional architectures, the LANCE is tightly coupled either to the local bus (local memory) or to the system bus interface. The result is that it monopolizes the bus (either the local bus or the system bus, depending upon the architecture) during the entire eight word transfer. This takes a minimum of 4.8 microseconds even with zero wait state (200 nanosecond or better) memory.

The V/Ethernet 3207 Hawk resolves this problem by including a LANCE PIPELINE between the LANCE and the dual port memory. The LANCE PIPELINE enables the V/Ethernet 3207 Hawk to interleave VMEbus accesses to the dual port RAM (and refresh cycles) with LANCE accesses, even though the LANCE "thinks" it has total control of the memory for eight cycles. Thus, there is no critical timing between the VMEbus and the LANCE. And there is no monopolizing of the dual port RAM by the comparatively slow DMA of the LANCE. The data and control structures that reside in the 256 Kbytes of dual port RAM can be accessed by the host over the VMEbus at any time.

2

The data structures include ownership bits to indicate which device (host or LANCE) can write to a structure, so this does not change the software interface. But it does have a profound effect on the way the system performs because it decouples the LANCE and the internal bus (and thus it decouples the LANCE and the VMEbus), and it minimizes the bus bandwidth requirements of the LANCE. These are two of the important performance considerations that give the V/Ethernet 3207 Hawk such an outstanding price performance ratio.

#### **OPERATION**

The 256 Kbytes of on-board buffer RAM contain both the Transmit and Receive Data Buffers as well as the Transmit and Receive Ring Descriptor Tables for the LANCE chip. For each entry in either the Receive Ring Descriptor Table (RRDT) or the Transmit Ring Descriptor Table (TRDT) there is a corresponding Receive or Transmit Data Buffer. Each entry in either table includes an owner bit to indicate whether the data buffer is currently under control of the host CPU or the LANCE.

To send an Ethernet frame, or sequence of frames, the host simply puts the data into the first available buffer in the transmit ring (i.e. the first transmit buffer that is owned by the host). The host then writes the packet byte count to that buffer's entry in the TRDT and sets the owner bit in the TRDT to indicate to the LANCE chip that the buffer is ready to be transmitted.

When the LANCE finds that it owns this transmit buffer, it formats the data into a standard Ethernet packet and transmits it over the network. At the completion of the transmit operation, the LANCE chip clears the owner bit in the TRDT and generates an interrupt that gets passed to the host CPU. After reading a register in the LANCE chip to determine the cause of the interrupt, the host accesses the TRDT to determine the status of the transmit operation.

The low level details of a receive operation are similarly attended to by the hardware on the V/Ethernet 3207 Hawk. When a packet with this node's Ethernet Node Address is received over the network, data is transferred into the on-board buffer and an interrupt is generated on the VMEbus.

The host CPU reads a set of status registers in the LANCE chip to determine the cause of the interrupt. If the interrupt was caused by the completion of a packet reception, then the host accesses that buffer's entry in the RRDT to determine the status of the operation and to obtain the packet byte count for the received packet. Once the host CPU has moved the data, it resets the owner bit in the RRDT to free the buffer for the reception of another packet.

### SUMMARY OF FEATURES

- Supports IEEE 802.3 Ethernet or Cheapernet Transceivers

- Network Access Independent of Host Response Time

- Network Performance Independent of VMEbus Timing

- Ethernet Node Address Stored in Nonvolatile Memory

- 256 Kbytes of Fast Access Dual Ported Memory accessible to both the LANCE and the VMEbus

- LANCE PIPELINE maximizes VMEbus performance

- Software Configurable Transmit Ring Buffer (from 2 to 128 buffers) for Automatic Transmit Queuing

- Software Configurable Receive Ring Buffer (from 2 to 128 buffers) for Automatic Receipt of Multiple Frames

- Software Programmable Interrupt Levels (1 of 7)

- Software programmable interrupt vector

- UNIX<sup>®</sup> Driver support

- Software Drivers on a Variety of Distribution Media

- Provides Flexibility in Implementing the Optimum Tradeoff between Protocol Sophistication and Network Efficiency

- Slave Data Transfers 16- and 32-bit data, 24- and 32-bit address, address modifiers: supervisory or non-privileged, standard or extended data access (3D, 39, 0D, 09)

- Slave Control/Status Transfers (Short I/O Space) 16-bit data, 16-bit address, address modifiers: supervisor or non-privileged, short access (2D, 29)

- Single Double-height VMEbus Board

- Superior Price Performance Ratio

UNIX is a registered trademark of AT&T Bell Laboratories.

## SECTION 2

### PROGRAMMING OF THE V/ETHERNET 3207 HAWK

#### INTRODUCTION

This section provides a summary of V/Ethernet 3207 programming considerations that will help you optimize your Ethernet activity when you write a driver. The Am7990 Ethernet controller chip (LANCE) is responsible for much of the V/Ethernet 3207 activity, as such, it is highly recommended that the user also read the LANCE technical manual. To receive a copy of it, call the Interphase Applications Engineering Department at (214) 350-9000.

The LANCE has four internal control and status register (CSR0, CSR1, CSR2, and CSR3) which are used for various functions such as loading the initialization block address, selecting different programming modes, and indicating status conditions. The host communicates with the LANCE during the initialization phase by loading the starting address of the Initialization Block into two of these internal control registers. During normal operation, the host communicates directly with the LANCE for demand transmission and periodically to read the status bits following interrupts. All other transfers to/from the dual ported RAM are automatically handled by the LANCE as DMA and are controlled indirectly by the host through the transmit and receive descriptor ring pointers.

Interrupts to the host are generated by the LANCE upon six different events:

- Completion of its initialization routine

- Reception of a packet

- Transmission of a packet

- Transmitter timeout error

- Missed packet

- Memory error

The cause of the interrupt is ascertained by reading CSR0. Bit six of CSR0 (INEA) enables or disables interrupts to the host. The method in which the V/Ethernet 3207 handles interrupts is explained in Section 3 of this user's guide.

The basic operation of the LANCE consists of two distinct modes: transmit and receive. In the transmit mode, the LANCE directly accesses data in the transmit

buffer. It prefaces the data with a preamble and a sync pattern. It also calculates and appends a 32-bit CRC. This packet is then ready for transmission to the Am7992B SIA. On transmission, the first byte of data loads into the 48-byte SILO. The LANCE then begins to transmit preamble while simultaneously loading the rest of the packet into the SILO for transmission.

In the receive mode, packets are sent via the SIA to the LANCE. the packets are loaded into the 48-byte SILO for preparation of automatic downloading into the buffer memory. A CRC is calculated and compared with the CRC appended to the data packet. If the calculated CRC does not agree with the packet CRC, an error bit is set.

#### ADDRESSING

Packets can be received using three different destination addressing schemes: physical, logical, and promiscuous.

The physical scheme does a full comparison of the 48-bit destination address in the packet with the node address that was programmed into the LANCE during initialization.

There are two types of logical address. One is a group-type mask where the 48bit address in the packet is put through a hash filter to map the 48-bit physical address into one of 64 logical groups. If any of the 64 groups have been preselected as the logical address, then the 48-bit address is stored in main memory. At this time, a look up is performed to compare the 48-bit incoming address with the prestored 48-bit logical address. This mode can be useful if sending packets to all of a particular type of device simultaneously (e.g., send a packet to all file servers or all printer servers). The second logical address is a broadcast address where all nodes on the network receive the packet.

The last receive mode of operation is the promiscuous mode. In this mode a node will accept all packets on the coax regardless of destination address.

#### COLLISION DETECTION

The Ethernet CSMA/CD network access algorithm is implemented completely within the LANCE. In addition to listening for a clear coax before transmitting, Ethernet handles collisions in a predetermined way. Should two or more transmitters attempt to access the coax at the same time, they will collide and the data on the coax will be garbled. The transmitting nodes listen while they transmit, detect the collision, and then continue to transmit for a predetermined length of time to "jam" the network and ensure that all nodes have recognized the collision. The transmitting nodes then delay a random amount of time according to the Ethernet "truncated binary backoff algorithm," so the colliding nodes do not try to repeatedly access the network at the same time. Up to 16 attempts to access the network are made by the LANCE before reporting back an error due to excessive collisions.

## ERROR REPORTING/DIAGNOSTICS

Extensive error reporting is provided by the LANCE. Error conditions reported relate either to the network as a whole or to data packets. Network-related errors are recorded as flags in the CSRs and are examined by the host CPU following an interrupt. Network-related errors include:

- Babbling transmitter

- Transmitter attempting to transmit more than 1518 data bytes

- Collision

- Collision detection circuitry nonfunctional

- Missed packet

- Insufficient buffer space

- Memory timeout

- Memory response failure

Packet-related errors are written into descriptor entries corresponding to the packet. Packet-related errors include:

- CRC

- Invalid data

- Framing

- Packet did not end on a byte boundary

- Overflow/Underflow

- Abnormal latency in servicing a DMA request

- Buffer

- Insufficient buffer space

The LANCE performs several diagnostic routines which enhance the reliability and integrity of the system. These include a CRC logic check and two loopback modes (internal and external). Errors may be introduced into the system to check error detection logic. A Time Domain Reflectometer (TDR) is incorporated in the LANCE to help system designers locate faults in the Ethernet cable. Shorts and opens manifest themselves in reflections which are sensed by the TDR.

### BUFFER MANAGEMENT

A key feature of the V/Ethernet 3207 is the flexibility and speed of communication between the LANCE and the host through the 256 kbytes of dual ported RAM. The basic organization of the buffer management is a circular queue of tasks in memory called descriptor rings.

9

There are separate descriptor rings to describe transmit and receive operations. up to 128 tasks can be queued up on a descriptor ring awaiting execution by the LANCE. Each entry in a descriptor ring holds a pointer to a data memory buffer and an entry for the length of the data buffer. Data buffers can be chained or cascaded to handle a long packet in multiple data buffer areas. The LANCE searches the descriptor rings in a "lookahead" manner to determine the next empty buffer in order to chain buffers together or to handle back-to-back packets. As each buffer is filled, an "own" bit is reset, allowing the host processor to process the data in the buffer.

Buffer management is accomplished through message descriptors organized in ring structures in memory. Each message descriptor entry is four words long. There are two rings allocated for the LANCE: a Receive Ring and a Transmit Ring. The LANCE is capable of polling each ring for buffers to either empty or fill with packets to or from the channel. The LANCE is also capable of entering status information in the descriptor entry with which it is currently working.

The location and length of the descriptor rings are specified in the Initialization Block, accessed by the LANCE during the initialization procedure. Writing a '1' into the STRT bit of CSRO will cause the LANCE to start accessing the descriptor rings and enable it to send and receive packets.

The LANCE communicates with a host device through the ring structures in memory. Each entry in the ring is either "owned" by the LANCE or the host. There is an ownership bit (OWN) in the message descriptor entry. Mutual exclusion is accomplished by a protocol which states that each device can only relinquish ownership of the descriptor entry to the other device; it can never take ownership and no device can change the state of any field in any entry after it has relinquished ownership.

#### INTERRUPT HANDLING

The V/Ethernet 3207 hardware can generate an interrupt request on any one of the seven possible VMEbus interrupt request lines. The interrupt level (i.e., interrupt request line) is selected by setting bits in the V/Ethernet 3207 Board Control Register (BCR). The interrupt request bits should, however, only be changed only when an interrupt request condition is not imminent. To ensure that the interrupt request condition does not occur, LANCE interrupts can be disabled by clearing the INEA bit in CSR0 (bit 6).

The LANCE can generate a VMEbus interrupt for any of six different occurrences: packet reception, packet transmission, initialization done, memory error, babbling transmitter, and missed packet. When any one of these situations occurs, the Interrupt Flag and the Interrupt Enable bit are both set in CSR0, the LANCE interrupt logic will assert the external interrupt output and the host will then initiates an IACK cycle on the VMEbus.

Typical interrupt handling procedures will clear the condition that originally causes an internal LANCE interrupt. But if a second interrupting condition occurs while the first condition is being serviced, the internal LANCE hardware does not ensure that every attention condition will generate a high-to-low transition on the LANCE interrupt output; thus not every interrupt will be serviced. Therefore, additional V/Ethernet 3207 hardware is used to handle simultaneous interrupts.

Between the LANCE interrupt output and the VMEbus request line is an enable, or mask, function. This interrupt mask function performs two tasks. First, after an interrupt request is presented to the VMEbus interrupt logic, subsequent interrupt requests are not presented because of the original LANCE attention situation. Second, if more than one interrupting condition occurs simultaneously within the LANCE, the V/Ethernet 3207 is able to present multiple interrupt requests to the VMEbus interrupt logic.

Once the LANCE asserts its interrupt output, a single request is passed on to the VMEbus request logic. After the interrupt handling procedures, including clearing of the LANCE internal interrupt source are complete, the V/Ethernet 3207 interrupt mask must be re-enabled before any subsequent interrupts from the LANCE are passed to the VMEbus interrupt request logic.

The Interrupt Enable bit in the Board Control Register resets the on-board interrupt circuitry after each interrupting condition. Therefore, this bit should be the last bit set before returning from the interrupt handling routine.

#### PROGRAMMING

The LANCE operates in an environment that includes close coupling with the 256 Kbytes of dual ported RAM and the host. The LANCE is programmed by a combination of registers and data structures resident within the LANCE and in memory. There are four Control and Status Registers (CSRs) within the LANCE which are programmed by the HOST device. Once enabled, the LANCE has the ability to access memory locations to acquire additional operating parameters.

The LANCE has the ability to do independent buffer management as well as transfer data packets to and from the Ethernet. There are three memory structures that reside within the dual ported RAM that are accessed by the LANCE.

The Initialization Block: it occupies 12 words in contiguous memory starting on a word boundary. It contains the operating parameters necessary for device operation. The Initialization Block is comprised of six entries:

- Mode of operation

- Physical address

- Logical address mask

- Location of Receive and Transmit Descriptor Rings

- Number of entries in Receive and Transmit Descriptor Rings

Receive and Transmit Descriptor Rings: these are two ring-structures, one each for incoming and outgoing packets. Each entry in each ring is four words long, and each entry must start on a longword boundary. The descriptor rings are comprised of the following information:

- Address of a data buffer

- Length of a data buffer

- Status information associated with the data buffer

*Data Buffer*: it is made up of contiguous portions of memory reserved for packet buffering. Data buffers may begin on arbitrary byte boundaries.

#### Programming Sequence

In general, the programming sequence of the LANCE may be summarized as:

- 1. Programming the LANCE CSRs by a host device to locate an Initialization Block in memory. The byte control, byte addressing, and address latch enable modes are defined here also.

- 2. The LANCE loads itself with the information contained in the Initialization Block.

- 3. The LANCE accesses the descriptor rings for packet handling.

### CONTROL AND STATUS REGISTERS

There are four Control and Status Registers (CSRs) resident within the LANCE. The CSRs are accessed through two registers in Short I/O space, address port (RAP) and data port (RDP).

#### Accessing the Control and Status Registers

The CSRs are read (or written) in a two-step operation. The address of the CSR to be accessed is written into the address port (RAP). During a subsequent transaction, the data being read from (or written to) the data port (RDP) is read from (or written to) the CSR selected in the RAP.

#### RING ACCESS MECHANISM IN THE LANCE

Once the LANCE is initialized through the Initialization Block and started, the Host and the LANCE communicate via Transmit and Receive rings for packet transmission and reception.

These are two sets of pointers into the dual ported RAM (four 16-bit registers per set, corresponding to the four entries in each descriptor) maintained in the LANCE. The first set points to the current buffer, and they are working registers which are used for transferring the data for the packet. The second set contains the pointers to the next buffer in the ring which the LANCE obtained from the lookahead operation.

There are three types of ring access in the LANCE. The first type is when the LANCE polls the rings to own a buffer. The second type is a lookahead operation. The LANCE does a lookahead between the time that it is transferring data to and from the SILO; this lookahead is only done once. The third type of ring access is a data chaining operation. The LANCE tries to own the next descriptor in the ring when it clears the OWN bit for the current buffer.

#### SILO Operation

The SILO provides temporary buffer storage for data being transferred between the parallel bus I/O pins and the serial bus I/O pins of the LANCE. The capacity of the SILO is 48 bytes.

For transmit operations, data is loaded into the SILO under LANCE internal microprogram control. The SILO has to have at least 16 bytes available before the LANCE requests the dual port RAM access. The LANCE will start sending the preamble (if the line is idle) as soon as the first byte is loaded into the SILO from memory. Should the transmitter be required to back off, there could be up to 32 bytes of data in the SILO ready for transmission. Reception has priority over transmission during the time that the transmitter is backing off.

For receive operations, data is loaded into the SILO from the serial input shift register during reception. Data leaves the SILO under microprogram control. The LANCE microcode will wait until there are at least 16 bytes of data in the SILO before initiating a transfer into dual port RAM. The preamble (including sync) is not loaded into the SILO.

#### PARITY CHECKING

The V/Ethernet 3207 has a 32-bit wide internal DRAM array that has four possible sources of parity errors (i.e., one parity error for each byte of DRAM). When a parity error occurs, a bit in a latch is set and subsequently read through the Board Status Register. And by periodically polling the bits in the latch, parity errors can be easily reported.

Also, the V/Ethernet 3207 can be configured (via hardware jumpers) to modify the manner in which the DRAM read cycle is terminated. Depending on the source of the read cycle, the parity error is terminated in one of two ways. For a VMEbus-originated DRAM read cycle, the cycle is terminated by returning BERR instead of DTACK. For a LANCE-originated DRAM read cycle, the cycle is terminated by forcing a Memory Error (MERR).

One important aspect of parity error reporting that is easy to overlook is the time it takes to check parity. If the V/Ethernet 3207 is configured such that the DTACK and READY signals are blocked (refer to Section 4 for specific hardware jumper configuration), the generation of DTACK or READY is delayed for approximately 30 nanoseconds to allow the parity check process to complete. The reporting of parity errors to VMEbus and LANCE may be programmed independently of each other.

The PERR CLR bit in the Board Control Register is used to clear any parity errors, regardless of origination, that are "remembered" in the Board Status Register.

## FOR FURTHER INFORMATION

The following topics are discussed in more detail in the Am7990 LANCE data sheet from Advanced Micro Devices, Inc.:

Transmit Ring Buffer Management Receive Ring Buffer Management Frame Formatting Framing Errors (Dribbling Bits) Collision Detection and Collision JAM Receive-based Collisions Transmit-based Collisions Collision/Microcode Interaction Time Domain Reflectometry Heartbeat Cyclic Redundancy Check (CRC) Loopback Serial Transmission Serial Reception

The LANCE performs these functions on-board the V/Ethernet 3207 Hawk as outlined in the data sheet. Since the V/Ethernet 3207 is designed around the Am7990 Local Area Network Controller from Advanced Micro Devices, it is highly recommended that the user also read the LANCE technical manual. Call the Interphase Applications Engineering Department at (214) 350-9000 for a copy.

# **SECTION 3**

# FUNCTIONAL DESCRIPTION OF THE V/Ethernet 3207 HAWK

#### **INTRODUCTION**

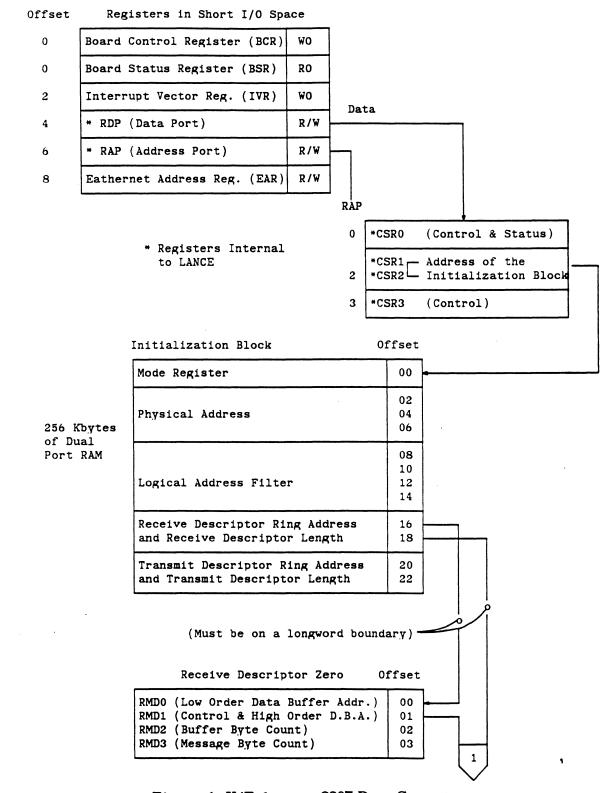

The V/Ethernet 3207 Hawk is a VMEbus slave device whose control and status registers are accessed through five locations in the Hawk's 256 bytes of Short I/O space. Data and extended control/status information not available in the registers is passed through 256 Kbytes of dual ported RAM that appears as fast access system memory.

There are six registers that are accessed through five contiguous word locations in Short I/O space. They are listed below:

| Register Name             | Mnemonic | Offset<br>into<br>Short I/O | Туре       |

|---------------------------|----------|-----------------------------|------------|

| Board Control Register    | (BCR)    | 0                           | Write Only |

| Board Status Register     | (BSR)    | 0                           | Read Only  |

| Interrupt Vector Register | (IVR)    | 2                           | Write Only |

| Register Data Port *      | (RDP)    | 4                           | Read/Write |

| Register Address Port *   | (RAP)    | 6                           | Read/Write |

| Ethernet Address Register | (EAR)    | 8                           | Read/Write |

## Table 1 - Programmable Registers

\* these are LANCE registers

There are four additional registers inside the LANCE itself that are accessed by setting the register number in the RAP and then reading or writing to the RDP. They are as follows:

## Table 2 - Additional LANCE Registers

| Register Name/Mnemonic                | Register |

|---------------------------------------|----------|

| – register usage                      | Number   |

| CSR0 - (control/status)               | 0        |

| CSR1 - (initialization block address) | 1        |

| CSR2 - (initialization block address) | 2        |

| CSR3 - (control)                      | 3        |

The remainder of the control/status information and all of the data structures reside within the 256 Kbytes of dual port, on-board RAM. The Initialization Block Address in CSR1 and CSR2 point to the 24-byte Initialization Block in RAM. It in turn points to a Receive Ring Descriptor Table (RRDT) and to a Transmit Ring Descriptor Table (TRDT). Individual entries in the RRDT then point to individual Receive Data Buffers and entries in the TRDT point to Transmit Data Buffers. Once initialized, the LANCE maintains the two sets of Ring Descriptor Tables that keep track of where the data buffers are and what their status (ownership) is.

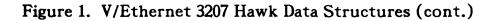

Figure 1 is a Control/Status and Data Structure Diagram showing the relationship of the various hardware registers and the data structures within the 256 Kbytes of dual ported RAM.

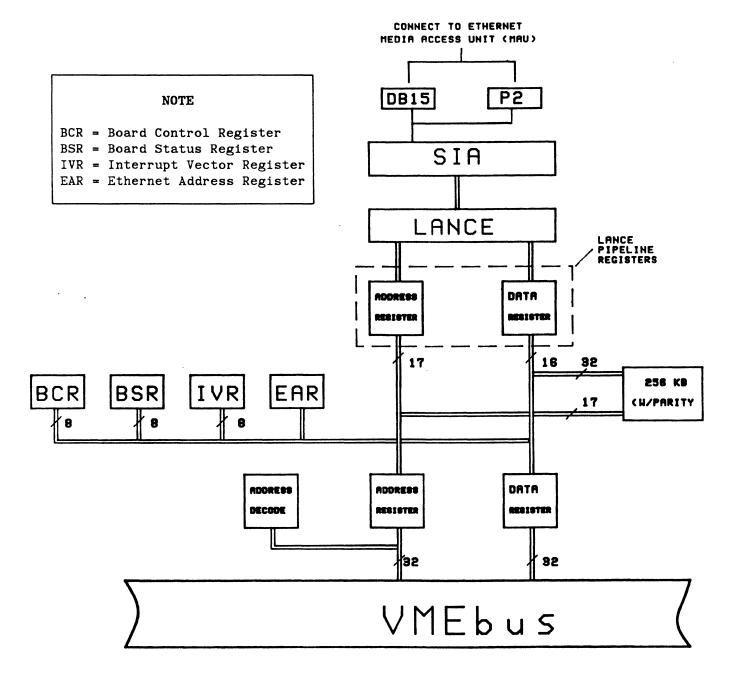

Figure 2 is a simplified Functional Block Diagram of the V/Ethernet 3207 Hawk. It shows the relationship of the hardware blocks and the major address and data paths.

Figure 1. V/Ethernet 3207 Data Structures (Continued on next page.)

: : Receive Descriptor n Offset n+ 0 RMD 0 RMD 1 n+ 1 RMD 2 n+ 2 RMD 3 n+ 3 Receive Data Buffer Buffer 0 Buffer n Offset Transmit Descriptor 0 TMD 0 (Low Order Buffer Address) 0 TMD 1 (Control/High Order Addr.) 1 TMD 2 (Buffer Byte Count) 2 TMD 3 (Status) 3 Transmit Descriptor n Offset TMD 0 n+ 0 TMD 1 n+ 1 TMD 2 n+ 2 TMD 3 n+ 3 Transmit Data Buffer

1

Buffer n

Figure 2. V/Ethernet 3207 Simplified Block Diagram

#### BOARD CONTROL REGISTER - BCR - (Write Only)

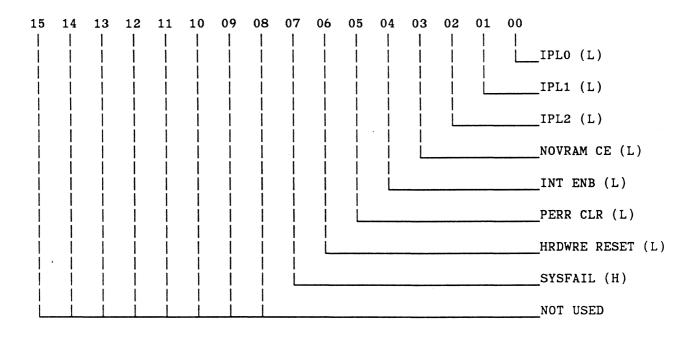

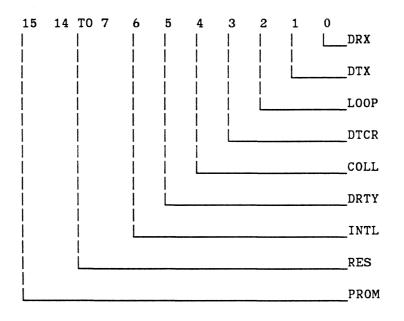

The Board Control Register contains the bits that are used by the host CPU to initiate commands to the V/Ethernet 3207. It also contains the bits required to indicate the condition of the V/Ethernet 3207 to the CPU. The Board Control Register is a write only register in Short I/O space with an address offset of 000. The format of the Board Control Register is shown in Figure 3 below.

Bits 15-8: Not Used.

Bit 7: SYSFAIL - SYSTEM FAILURE: This bit is used to drive the SYSFAIL\* signal on the VMEbus (if enabled by hardware jumper JA 11) during a hardware or software reset. If this bit is set to'1', the VMEbus SYSFAIL line is set and the status indicator on the front panel is red, if this bit is cleared to '0', the SYSFAIL line is cleared and the status indicator is green. The V/Ethernet 3207 sets this bit to '1' when System Reset or Hardware Reset is performed.

Bit 6: HRDWRE RESET - HARDWARE RESET: When this bit is cleared to '0', it causes a hardware reset of the V/Ethernet 3207. This is the

equivalent of driving the SYSRESET signal on the VMEbus. Once this bit is cleared, the board will be busy for 15 microseconds. There is no need to set this bit to '1' once it is cleared.

- Bit 5: PERR CLR PARITY ERROR CLEAR: This bit is cleared to '0' to reset the parity error bits in the BSR after a parity error has been detected. In addition, this bit should be cleared to '0' during initialization to clear the parity bits in the BSR. There is no need to set this bit to '1' once it is cleared.

- Bit 4: INT ENB\* INTERRUPT ENABLE: This bit is cleared to '0' to reset the on-board interrupt circuitry after an interrupting condition. This enables the next interrupt to be posted. This bit should be cleared as the last action of the interrupt service routine. In addition, this bit should be cleared to '0' during initialization. There is no need to set this bit to '1' once it is cleared.

- Bit 3: NOVRAM CE\* NONVOLATILE RAM CHIP ENABLE: This bit must be cleared to '0' when reading from or writing to the V/Ethernet 3207 nonvolatile RAM. It must remain clear ('0') during the entire read or write cycle. Upon completion of the read/write, this bit must be set to '1'. The V/Ethernet 3207 sets this bit to '1' when System Reset or Hardware Reset is performed..

- Bits 2-0: IPL0-2\* INTERRUPT VECTOR LEVEL: These three bits set the bus interrupt level (level one through seven). Table 3 below shows the bit settings and the corresponding interrupt level that is indicated.

|         |   | IPL2 | IPL1 | IPL0 |

|---------|---|------|------|------|

| Level 7 | 7 | 0    | 0    | 0    |

| Level 6 | 5 | 0    | 0    | 1    |

| Level 5 | 5 | 0    | 1    | 0    |

| Level 4 | 1 | 0    | 1    | 1    |

| Level 3 | 3 | 1    | 0    | 0    |

| Level 2 | 2 | 1    | 0    | 1    |

| Level   | 1 | 1    | 1    | 0    |

Table 3 - Interrupt Vector Settings

Level 0 (1,1,1) indicates that no interrupts are specified. The V/Ethernet 3207 sets IPLO, IPL1 and IPL2 to '1' (interrupt level zero) when System Reset or Hardware Reset is performed.

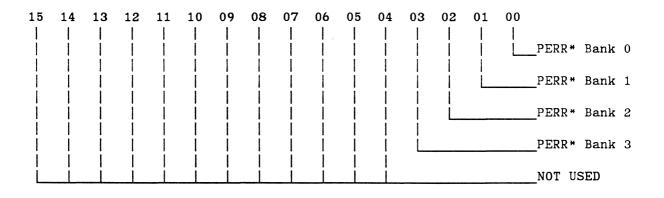

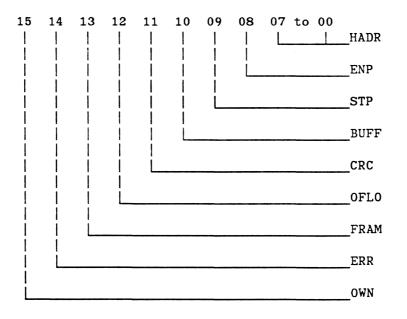

# BOARD STATUS REGISTER - BSR - (Read Only)

The Board Status Register is used to indicate when a parity error has occurred in the on-board RAM. This register is a read only register in Short I/O space with an address offset of 000. The following figure illustrates the format of the Board Status Register.

- Bits 15-4: Not Used.

- Bits 3-0: PERR PARITY ERROR. These are active low signals. A '1' indicates no error and a '0' indicates an error.

#### -NOTE-

The Board Status Register indicates any parity errors that occur on the V/Ethernet 3207. It cannot differentiate between parity errors that occur during a VMEbus access and parity errors that occur as a result of a LANCE access.

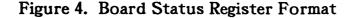

# INTERRUPT VECTOR REGISTER - IVR - (Write Only)

The Interrupt Vector Register contains the interrupt vector used to respond to the VMEbus Interrupt Acknowledge cycle. It consists of a unique 8-bit user defined vector. This register is a write only register in Short I/O space with an address offset of 002 (hex). The following figure illustrates the format of the Interrupt Vector Register.

# Figure 5. Interrupt Vector Register Format

Bits 15-8: Reserved (Clear to '0'.)

Bits 7-0: IVEC - INTERRUPT VECTOR.

## ETHERNET ADDRESS REGISTER - EAR - (Read/Write)

The Ethernet Address Register is used for reading and writing to the 256-bit (sixteen 16-bit words) nonvolatile RAM. The EAR is a one-word register with the least significant bit (D0) reserved for reading and writing to the 256-bit serial nonvolatile RAM. The EAR is a read/write register in Short I/O space with an address offset of 008 (hex).

The serial 256-bit nonvolatile RAM is composed of a 16 X 16 static RAM, overlaid bit for bit with a nonvolatile EEPROM array. The serial nonvolatile RAM is controlled through an 8-bit instruction register that is also accessed serially through the Ethernet Address Register.

### The Serial Nonvolatile RAM

To enable the serial nonvolatile RAM for any data accesses, bit 3 in the Board Control Register (NOVRAM CE - active low) must be set to a '0'. And then before a write operation can be performed, the Write Enable Latch (internal to the nonvolatile RAM) must be set by shifting in a Set Write Enable Latch (WREN) instruction. Then the Write Data into RAM (WRITE) instruction is shifted in, one bit at a time, starting with the MSB. Finally, the 16 bits of data are shifted in. (Data should also be shifted in the MSB first.)

After the data is shifted into the RAM, a Store RAM Data EEPROM (STO) instruction must be shifted in to move the data from the RAM to the EEPROM. This complete cycle must be repeated three times to store the 48-bit Ethernet Node Address in the EEPROM. After the last WRITE operation has been performed, a Reset Write Enable Latch (WRDS) instruction must be shifted in, and then the NOVRAM CE bit in the BCR must be set to a '1'. This disables further write operations.

It should be noted that the Ethernet Address Register is preprogrammed at the factory with an Ethernet node address (assigned by Xerox), so unless the user wants to change that address, there is no need to write to this register.

Once the Ethernet Node Address is in the EEPROM, it will be retained for more than 100 years, or until it is overwritten. To read any data back from the 256-bit serial nonvolatile RAM, the NOVRAM CE bit in the BCR must be cleared to '0'. The data must then be read from the EEPROM to the RAM with a Recall EEPROM Data into RAM (RCL) instruction. Once the data is in the RAM, it can then be shifted out, one bit at a time, through the EAR with a Read Data from RAM (READ) instruction. After the last READ operation has been performed, the NOVRAM CE bit in the BCR must be set to a '1'. This disables further READ operations. Because of a data/shift pulse anomaly, the data does not shift out in the same order that it was shifted in. If data was shifted in MSB first, then the data will be shifted out correctly ordered but rotated to the left one position (see below).

| 15 |    |    |    |    |    |   | 8 | 7 |   |   |   |   |   |   | 0  |

|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|----|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0  |

|    |    |    |    |    |    |   |   |   |   |   |   |   |   |   |    |

| 15 |    |    |    |    |    |   | 8 | 7 |   |   |   |   |   |   | 0  |

| 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | 15 |

It is the responsibility of the host CPU not only to shift the data in and out, but also to order the data correctly before attempting to use it.

| Table 4                           | Table 4: Serial Nonvolatile RAM Instruction Set |                                                                |  |  |  |  |  |  |

|-----------------------------------|-------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|

| Instruction<br>M                  | Format<br>SB LSI                                | Operation<br>3                                                 |  |  |  |  |  |  |

| WRDS                              | 0XXXX111                                        | Reset Write Enable Latch (Disables WRITE and STO)              |  |  |  |  |  |  |

| STO                               | 0XXXX110                                        | Store RAM Data in EEPROM                                       |  |  |  |  |  |  |

| WRITE                             | 0AAAA100                                        | Write Data into RAM Address AAAA                               |  |  |  |  |  |  |

| WREN                              | 0XXXX011                                        | Set Write Enable Latch (Enables WRITE and STO)                 |  |  |  |  |  |  |

| RCL                               | 0XXXX010                                        | Recall EEPROM Data into RAM                                    |  |  |  |  |  |  |

| READ                              | 0AAAA00X                                        | Read Data from RAM Address AAAA                                |  |  |  |  |  |  |

| X = Don't Care<br>A = Address Bit | Note:                                           | The NOVRAM instruction data is sent by shifting the MSB first. |  |  |  |  |  |  |

The V/Ethernet 3207 NOVRAM occupies 256 bytes. The first three words (48 bits) are used for the Physical Ethernet Address. (Bit zero of the physical address is always forced to '0'). The following four words (64 bits) are used for the Logical Ethernet Address. (Bit zero of the logical address is always forced to '1'). The remaining nine words (144 bits) of the NOVRAM space is reserved.

The sample code on the following three pages illustrates a typical implementation of NOVRAM access using the "C" programming language.

#define HBC\_NOV\_RAM 0x0008 /\* novram enable bit in BLCSR \*/ 1\* \* Novram "Opcode" masks (inverted due to 74AS646's) \*/ #define WRD\_NOVRAM0xE0#define STO\_NOVRAM0x60#define SLP\_NOVRAM0xA0#define WRT\_NOVRAM0x20 /\* Reset write enable latch

/\* Store ram to eeprom **\*/** \*/ /\* Novram into low power mode \*/ /\* Writes word from location x\*/

#define WRE\_NOVRAM

0xC0

/\* Set write enable latch

\*/

#define RCL\_NOVRAM

0x40

/\* Recall eeprom data into ram\*/

#define RDE\_NOVRAM

0x00

/\* Reads word from location x \*/

/ \* \* BOARD Register Access Macros \*1 //

#define WRT\_BDCSR\_OR(x) hwk->hwk\_hwkaddr->board\_csr=board\_csr\_image| =x

#define WRT\_BDCSR\_AND(x) hwk->hwk\_hwkaddr->board\_csr=board\_csr\_image&=x

#define DELAY(x) for (counter = x; counter >0; counter--)

#define NOVRAM\_CMD(c.a) for(1=0;i<8; hwk\_novram=((c| (a<<1))>>i), i++);

DELAY(HW\_DELAY) DELAY(HW DELAY) \* reset write enable latch (disables writes and stores) • nr\_wtdis() WRT\_BDCSR\_AND ( "HBC\_NOV\_RAM ); /\* set novram chip enable bit \*/ NOVRAM\_CMD(WRD\_NOVRAM,0); /\* send opcode \*/ WRT\_BDCSR\_OR ( HBC\_NOV\_RAM ); /\* clear novram chip enable bit\*/ return(OK); Y \* store novram ram data into eeprom +/ nr\_store() ( WRT\_BDCSR\_AND ( ~HBC\_NOV\_RAM ); /\* set novram chip enable bit \*/

NOVRAM\_CMD(STO\_NOVRAM,0); /\* send opcode \*/

WRT\_BDCSR\_OR ( HBC\_NOV\_RAM ); /\* clear novram chip enable bit\*/

return(OK); return(OK); 3

```

1*

* places novram into SLEEP lower power mode

+/

nr_sleep()

WRT_BDCSR_AND ( ~HBC_NOV_RAM ); /* set novram chip enable bit */

NOVRAM_CMD(SLP_NOVRAM,0); /* send opcode */

WRT_BDCSR_OR ( HBC_NOV_RAM ); /* clear novram chip enable bit*/

{

return(OK);

1

1.

* writes 16 bits to the novram at location ×

*/

nr_write(addr,data)

register u_short addr,data;

{

register unsigned short val = 0,

mask = 0x8000;

register unsigned int whit;

/*

* Write novram

WRT_BDCSR_AND ( ~HBC_NOV_RAM ); /* enable novram with image*/

NOVRAM_CMD ( WRT_NOVRAM, addr ); /* send write novram opcode*/

•

* Put 16 bits one at a time to the novram

*/:

for (wbit=0; wbit<16; wbit++) { /* put 16 bits

*/

(mask&data) ? (hwk_novram=1) : (hwk_novram=0);

(mask&data) ? (hwk_novram=1) . [] == _____

mask = mask >>1; /* one bit at a time

*/

DELAY( HW_DELAY );

/* until done

.... * /

}

WRT_BDCSR_OR ( HBC_NOV_RAM ); /* disable novram with image*

1

]*

* set write enable latch (enables writes and stores)

*1

```

```

nr_wten()

/* set novram chip enable bit */

/* send opcode */

/* clear novram chip enable bit*/

return(OK);

}

1*

* recall eeprom data into ram

*1

nr_recall()

WRT_BDCSR_AND ( ~HBC_NOV_RAM ); /* set novram chip enable bit */

NOVRAM_CMD(RCL_NOVRAM,0); /* send opcode */

WRT_BDCSR_OR ( HBC_NOV_RAM ); /* clear novram chip enable bit*/

return(OK);

return(OK);

3

* reads 16 bits from the novram at location x

*/

nr read(addr)

register u_short addr;

register unsigned short val = 0, mask = 0x04000;

register unsigned int whit;

WRT_BDCSR_AND ( •HBC_NOV_RAM ); /* enable novram with image*/

NOVRAM_CMD ( RDE_NOVRAM, addr ); /* send read opcode */

/×

* Get 16 bits one at a time from the novram

* We wrote bit 15 first, so we read bit 14 first, bit 15 last.

*1

for (wbit=0; wbit<15; wbit++) (</pre>

*/

/* get bits 14 thru 0

/* and build data

: #1

(hwk_novram & 0x01) ? (val=(val mask)):(val=(val&(~mask)));

mask = mask>>1;

DELAY( HW DELAY ):

*/

3

/* until done

/* get blt 15 */

(hwk_novram & 0x01) ? (val=(val| 0x8000)):(val=(val&0x7FFF));

DELAY ( HW_DELAY );

WRT_BDCSR_OR ( HBC_NOV_RAM ); /* disable novram with image*/

return (val); /* return word value read */

```

# **REGISTER DATA PORT - RDP - (Read/Write)**

The Register Data Port is used to read or write data to or from the four Control/Status Register (CSR0--CSR3) in the LANCE. It is a 16-bit Read/Write register in Short I/O space with an address offset of 004 (hex).

The particular CSR connected to the RDP is determined by the register number in the Register Address Port (RAP). CSR1, CSR2, and CSR3 are accessible only when the STOP bit of CSR0 (bit 02) is set. If the STOP bit is not set while attempting to Read CSR1, CSR2, CSR3, undefined data will be returned. If it is not set on a Write, the operation will be ignored. RAP is cleared by a HRDWRE RESET or a VMEbus SYSRESET.

# **REGISTER ADDRESS PORT - RAP - (Read/Write)**

The Register Address Port is used to specify which of the four Control/Status Registers (CSRs) in the LANCE is connected to the RDP. The RAP is a Read/Write register in Short I/O space with an address offset of 006 (hex)

Bits 15 through two of the Register Address Port are reserved and must be set to zero. Bits one and zero are used to select the CSR number which is accessed through the RDP. The CSRs are selected as follows:

| Bit 1 | Bit 0 | CSR Selected |

|-------|-------|--------------|

| 0     | 0     | CSR0         |

| 0     | 1     | CSR1         |

| 1     | 0     | CSR2         |

| 1     | 1     | CSR3         |

To access a CSR, its address (number) must be written into the RAP during a bus slave transaction. During a subsequent bus slave transaction, the data being read from (or written to) the RDP is read from (or written to) the CSR selected in the RAP. Once written, the address in RAP remains unchanged until it is rewritten or cleared by HRDWRE RESET or VMEbus SYSRESET.

#### NOTE -

All four Control and Status Registers in the LANCE (CSR0, CSR1, CSR2, CSR3) are Read/Write.

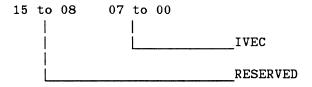

# CONTROL AND STATUS REGISTERS

### Control and Status Register Zero - CSR0 (Read/Write)

Each bit of CSR0 is delineated in the following subsection. The format of the register is detailed in Figure 6 below.

### Figure 6. Control Status Register Zero (CSR0)

Bit 15 ERR: ERROR summary is set by the "OR" of BABL, CERR, MISS, and MERR. ERR remains set as long as any of the error flags are true. ERR is read only, writing to it has no effect. It is cleared by HRDWRE RESET or VMEbus SYSRESET, by setting the STOP bit, or by clearing the individual error flags.

#### -NOTE-

Babble (bit 14), Missed Packet (bit 12), Memory Error (bit 11), Receive Interrupt (bit 10), Transmit Interrupt (bit 9), and Initialization Done (bit 8) all create a VMEbus interrupt if and only if the following conditions are met:

| INTR | (CSR0 | bit 7   | ) is | set |  |

|------|-------|---------|------|-----|--|

| INEA | (CSR0 | bit $6$ | is   | set |  |

Interrupt Vector Level is greater than zero (i.e., BCR bits 2..0 are not 1,1,1) Bit 14 BABL: BABBLE is a transmitter timeout error. It indicates that the transmitter has been on the channel longer than the time required to send a packet of the maximum length. It will be set after 1519 data bytes have been transmitted. The V/Ethernet 3207 will continue to transmit until the whole packet is transmitted or until there is a failure before the whole packet is transmitted. A VMEbus interrupt is generated as specified in the note on page 30. After the interrupting condition has been cleared, the VMEbus interrupt must be enabled by writing a '0' to INT ENB\* (BCR bit 4).

BABL is Read/Clear only and is set by the LANCE and cleared by the host writing a '1' into the bit; writing a '0' has no effect. It may also be cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit.

Bit 13 CERR: COLLISION ERROR indicates that the collision input to the LANCE failed to activate within two microseconds after a chip-initiated transmission was completed. The collision after transmission is a transceiver test feature. This function is also known as a "heartbeat" or SQE (Signal Quality Error) test.

> CERR is Read/Clear only and is set by the LANCE. It is cleared by the host writing a '1' into the bit; writing a '0' has no effect. It is also cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit. A CERR error will not cause an interrupt to be generated.

Bit 12 MISS: MISSED PACKET is set to indicate a loss of data when the receiver loses a packet because it does not own any receive buffers. SILO overflow is not reported since there is no receive ring entry in which to write the status. MISS is invalid in internal loopback mode. A VMEbus interrupt is generated as specified in the note on page 30. After the interrupting condition has been cleared, the VMEbus interrupt must be enabled by writing a '0' to INT ENB\* (BCR bit 4).

> MISS is a Read/Clear only bit and is set by the LANCE and is cleared by the host writing a '1' to the bit; writing a '0' has no effect. It is also cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit.

Bit 11 MERR: MEMORY ERROR is set when the LANCE is the internal bus master and has not received Ready within 25.6 microseconds after asserting the address on the DAL (Data/Address Lines of the LANCE) lines. When a Memory Error is detected, the receiver and transmitter are turned off (CSR0, TXON = 0, RXON = 0). A VMEbus interrupt is generated as specified in the note on page 30. After the interrupting condition has been cleared, the VMEbus interrupt must be enabled by writing a '0' to INT ENB\* (BCR bit 4).

During normal operation, the buffers between the LANCE and the 256 Kbyte RAM prevent the LANCE from ever generating a Memory Error. If however, Memory Parity is enabled (hardware jumper JA8), and if there is a parity error on a LANCE memory read, then the hardware will force the LANCE to generate a Memory Error. This in turn can generate an interrupt to the host, et cetera. This is the only condition that should ever generate a Memory Error.

MERR is a Read/Clear only bit and is set by the LANCE and is cleared by the host writing a '1' to the bit; writing a '0' has no effect. It is also cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit.

Bit 10 RINT: RECEIVER INTERRUPT is set when the LANCE updates an entry in the Receive Descriptor Ring for the last buffer received or reception is stopped due to a failure. A VMEbus interrupt is generated as specified in the note on page 30. After the interrupting condition has been cleared, the VMEbus interrupt must be enabled by writing a '0' to INT ENB\* (BCR bit 4).

> RINT is a Read/Clear only bit and is set by the LANCE and is cleared by the host writing a '1' to the bit; writing a '0' has no effect. It is also cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit.

Bit 9 TINT: TRANSMITTER INTERRUPT is set when the LANCE updates an entry in the Transmit Descriptor Ring for the last buffer sent or transmission is stopped due to a failure. A VMEbus interrupt is generated as specified in the note on page 30. After the interrupting condition has been cleared, the VMEbus interrupt must be enabled by writing a '0' to INT ENB\* (BCR bit 4).

> TINT is a Read/Clear only bit and is set by the LANCE and is cleared by the host writing a '1' to the bit; writing a '0' has no effect. It is also cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit.

Bit 8 IDON: INITIALIZATION DONE indicates that the LANCE has completed the initialization procedure started by setting the INIT bit. When IDON is set, the LANCE has read the Initialization Block from memory and stored the parameters. A VMEbus interrupt is generated as specified in the note on page 30. After the interrupting condition has been cleared, the VMEbus interrupt must be enabled by writing a '0' to INT ENB\* (BCR bit 4).

> IDON is a Read/Clear only bit and is set by the LANCE and is cleared by the host writing a '1' to the bit; writing a '0' has no effect. It is also cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit.

Bit 7 INTR: INTERRUPT FLAG is set by the "OR" of BABL, MISS, MERR, RINT, TINT, and IDON.

A VMEbus interrupt will be generated if INTR is set, if INEA (CSR0, bit 6) is '1', and if the BCR (bits 2--0) contains an Interrupt Vector Level other than 0 (1,1,1). INTR is Read only; writing to this bit has no effect. INTR is cleared by HRDWRE RESET or VMEbus SYSRESET, by setting the STOP bit, or by clearing the condition that caused the interrupt.

After the interrupting condition (BABL, MISS, MERR, RINT, TINT, or IDON) has been cleared, the VMEbus interrupt must be enabled by writing a '0' to INT ENB\* (BCR bit 4).

- Bit 6 INEA: INTERRUPT ENABLE allows the LANCE to generate a VMEbus interrupt when the interrupt flag is set. INEA is Read/Write and is automatically cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit. If INEA is '1', if the BCR (bits 2--0) contains an Interrupt Vector Level other than level 0 (1,1,1), and if interrupts have been enabled via the INT ENB\* (BCR bit 4) when the INTR (CSR0 bit 7) is set, a VMEbus interrupt will be generated.

- Bit 5 RXON: RECEIVER ON indicates that the receiver is enabled. RXON is set when STRT is set if DRX is '0' in the Mode word of the Initialization block. (The LANCE must be initialized before RXON can be set.) RXON is cleared in two circumstances: when IDON is set via the INIT bit and DRX is '1' in the Mode word of the Initialization block, or when a memory error (MERR) occurs. RXON is Read only; writing this bit has no effect. RXON is also cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit.

Bit 4 TXON: TRANSMITTER ON indicates that the transmitter is enabled. TXON is set when STRT is set if DTX is '0' (DTX is in the Mode word of the Initialization block) and the INIT bit has been set. TXON is cleared when IDON is set and DTX is '1' in the Mode word or an error such as MERR, CFLO, or BUFF has occurred during transmission.

TXON is Read only; writing to this bit has no effect. TXON is cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit.

Bit 3 TDMD: TRANSMIT DEMAND, when set, causes the LANCE to access the Transmit Descriptor Ring without waiting for the polltime interval to elapse. TDMD does not have to be set to transmit a packet; it merely hastens the V/Ethernet 3207's response to a Transmit Descriptor Ring entry insertion by the host.

> TDMD is Write with '1' only and cleared by the microcode after it is used. It may read as a '1' for a short time after it is written because the microcode may have been busy when TDMD was set. It is also cleared by HRDWRE RESET or VMEbus SYSRESET or by setting the STOP bit. Writing a '0' to this bit has no effect.

Bit 2 STOP: STOP disables the LANCE from all external activity when set. STOP also clears the LANCE internal logic. Setting STOP is the equivalent of asserting Bus Reset on the LANCE. Bus Reset is a hardware reset pin on the LANCE. STOP is asserted directly by the host by HRDWRE RESET (BCR bit 6) or by the VMEbus SYSRESET signal. The LANCE remains inactive and STOP remains set until the STRT or the INIT bit is set. If STRT, INIT, and STOP are all set simultaneously, STOP will override the other bits and only STOP will be asserted.

> STOP is Read/Write with '1' only and is also set by Reset. Writing a '0' to this bit has no effect. STOP is cleared by setting either the INIT or STRT bits. If STOP has been set, CSR1, CSR2, and CSR3 should be reloaded prior to setting STRT.

Bit 1 STRT: START enables the LANCE to send and receive packets, perform local memory access and manage the buffers. The STOP bit must be set prior to setting the STRT bit. Setting STRT clears the STOP bit (CSR1, CSR2, and CSR3 should be reloaded prior to setting STRT). If STRT and INIT are set together, the INIT function will be executed first.

STRT is Read/Write with '1' only. Writing a '0' into this bit has no effect. STRT is cleared by HRDWRE RESET or VMEbus SYSRESET, or by setting the STOP bit.

Bit 0 INIT: INITIALIZE, when set, causes the LANCE to begin the initialization procedure and access the Initialization Block. The STOP bit must be set prior to setting the INIT bit. Setting INIT clears STOP. If STRT and INIT are set together, the INIT function will be executed first.

INIT is Read/Write with '1' only. Writing a '0' into this bit has no effect. INIT is cleared by HRDWRE RESET or VMEbus SYSRESET, or by setting the STOP bit.

## Control and Status Register 1 - CSR1 (Read/Write)

CSR1 is selected when RAP bits one and zero are '0,1' respectively. It is Read/Write, and accessible only when the STOP bit of CSR0 is '1'. The contents of CSR1 are not preserved after a HRDWRE RESET or VMEbus SYSRESET, or when the STOP bit (CSR0 bit 2) is set.

Bits 15 through one of CSR1 indicate the low order 16 bits of the address of the first word (lowest address) of the Initialization Block. Bit zero of CSR1 is reserved and must be '0'.

### Control and Status Register 2 - CSR2 (Read/Write)

CSR2 is selected when RAP bits one and zero are '1,0' respectively. It is Read/Write, and accessible only when the STOP bit of CSR0 is '1'. The contents of CSR2 are not preserved after a HRDWRE RESET or VMEbus SYSRESET, or when the STOP bit (CSR0 bit 2) is set.

Bits 15 through eight of CSR2 are reserved. Bits seven through zero indicate the high order eight bits of the address of the first word (lowest address) of the Initialization block.

#### Control and Status Register 3 - CSR3 (Read/Write)

CSR3 is selected when RAP bits one and zero are '1,1'. It is the mechanism through which the LANCE defines the Bus Master Interface. CSR3 is Read/Write and accessible only when the STOP bit of CSR0 is '1'. The contents of CSR3 are not preserved after a HRDWRE RESET or VMEbus SYSRESET, or when the STOP bit (CSR0 bit 2) is set.

- Bits 15--3 RESERVED These bits are reserved and must be set to '0'.

- Bit 2 BSWP FOR THE V/Ethernet 3207 TO FUNCTION PROPERLY, THIS BIT MUST BE SET TO '1'.

- Bit 1: ACON FOR THE V/Ethernet 3207 TO FUNCTION PROPERLY, THIS BIT MUST BE SET TO '0'.

- Bit 0: BCON FOR THE V/Ethernet 3207 TO FUNCTION PROPERLY, THIS BIT MUST BE SET TO '0'.

# INITIALIZATION BLOCK

Operating parameters are defined during the initialization procedure which includes reading the Initialization Block in memory. The 24-bit address of the Initialization Block must be written into CSR1 and CSR2 prior to setting INIT. The Initialization Block is read by the LANCE when INIT (CSR0 bit 00) is set. The INIT bit should be set before, or concurrent with, the STRT bit to insure proper initialization, and subsequently, proper operation. After the LANCE has read the Initialization Block, IDON (Initialization Done) is set, and a VMEbus interrupt is generated if INTR is set, if INEA (CSR0 bit 6) is '1', and if the BCR (bits 2--0) contains an Interrupt Vector Level other than 0 (i.e., 1,1,1). After the interrupting condition has been cleared, the VMEbus interrupt must be enabled by writing a '0' to INT ENB\* (BCR bit 4).

Table 5 shows the format of the Initialization Block. Each entry is described in more detail following the table.

| Address | (hex)<br>Offset |   | Contents                       |

|---------|-----------------|---|--------------------------------|

| IADR    | +00             | > | MODE REGISTER                  |

| IADR    | +02             | > | PADR BITS 00 THROUGH 15        |

| IADR    | +04             | > | PADR BITS 16 THROUGH 31        |

| IADR    | +06             |   | PADR BITS 32 THROUGH 47        |

| IADR    | +08             | > | LADRF BITS 00 THROUGH 15       |

| IADR    | +0A             | > | LADRF BITS 16 THROUGH 31       |

| IADR    | +0C             | > | LADRF BITS 32 THROUGH 47       |

| IADR    | +0E             | > | LADRF BITS 48 THROUGH 63       |

| IADR    | +10             | > | RDRA BITS 00 THROUGH 15        |

| IADR    | +12             | > | RLEN & RDRA BITS 16 THROUGH 23 |

| IADR    | +14             | > | TDRA BITS 00 THROUGH 15        |

| IADR    | +16             | > | TLEN & TDRA BITS 16 THROUGH 23 |

|         |                 |   |                                |

# Table 5 - Initialization Block

Following the description of the Initialization Block, a sample program listing is provided to further illustrate the structure and use of the Initialization Block.

### MODE REGISTER

The Mode Register allows the V/Ethernet 3207's operating parameters to be altered. Normally, the Mode Register is clear (all zeros).

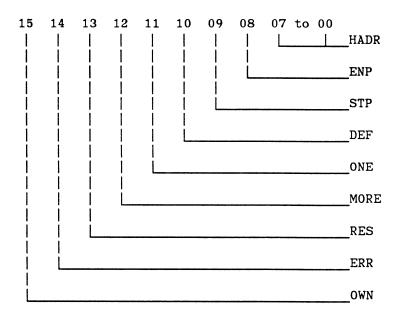

Figure 7. Mode Register Format

- Bit 15 PROM: PROMISCUOUS mode is selected by setting this bit to '1'. In this mode, all incoming packets are accepted, regardless of the Ethernet node address.

- Bits 14--7 RES: RESERVED. These bits are reserved.

- Bit 6 INTL: INTERNAL LOOPBACK is used with the LOOP bit to determine where the loopback is to be done. If this bit is '1' and LOOP is '1', internal loopback is selected; if this bit is '0' and LOOP is '1', external loopback is selected. Internal loopback allows the V/Ethernet 3207 to receive its own transmitted packet. Since this represents full duplex operation, the packet size is limited to between eight and 32 bytes. Internal loopback in the LANCE is operational only when the packets are addressed to the node itself.

The LANCE will not receive any packets externally when it is in internal loopback mode.

External loopback allows the LANCE to transmit a packet through the SIA transceiver cable out to the Ethernet coax. Packet sizes must be between eight and 32 bytes (inclusive) long for valid external loopback operation. External loopback is used to determine the operability of all circuitry and connections between the LANCE and the coaxial cable. Multicast addressing in external loopback is valid only when DTCR is '1' (user must append the four-byte CRC). In external loopback mode, the LANCE also receives packets from other nodes. INTL is only valid if LOOP is '1', otherwise it is ignored.

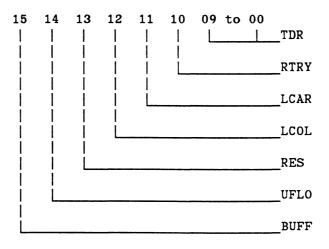

- Bit 5 DRTY: DISABLE RETRY, when set to '1', specifies that only one attempt will be made to transmit a packet. If there is a collision on the first transmission attempt, a Retry Error (RTRY) will be reported in Transmit Descriptor 3 (TMD3).

- Bit 4 COLL: FORCE COLLISION allows the collision logic to be tested. The V/Ethernet 3207 must be in internal loopback mode for COLL to be valid. If COLL is '1', a collision will be forced during the subsequent transmission attempt. This will result in 16 total transmission attempts with a Retry Error (RTRY) reported in TMD3.

- Bit 3 DTCR: DISABLE TRANSMIT CRC, when '0', will cause the transmitter to generate and append a CRC to the transmitted packet. When DTCR is '1', the CRC logic is allocated to the receiver and no CRC is generated.

During loopback, if DTCR is '0', a CRC is generated on the transmitted packet but it will not be checked by the receiver since the CRC logic is shared and cannot generate and check CRC at the same time. The generated CRC will be written into memory with the data and can be checked by the host software.

If DTCR is '1' during loopback, the host software must append a CRC value to the transmit data. The receiver will check the CRC on the received data and report any errors.