# COMMON ASSEMBLY LANGUAGE (CAL/32) Reference Manual

OS/32 Version R08-03 and higher

48-050 F01 R03

MANUAL UPDATE PACKAGE COVER SHEET

| MANUAL TITLE:          | COMMON ASSEMB<br>Manual | LY LANGUAGE/32 | (CAL/32) | Reference |

|------------------------|-------------------------|----------------|----------|-----------|

| PUBLICATION<br>NUMBER: | 48-050                  | OLD REVISION   | LEVEL:   | F00 R03   |

NEW REVISION LEVEL: F01 R03

This package of affected pages updates the current version of the subject manual. New features, as well as changes, deletions and additions to information in this manual are indicated by change bars in the page margins. Please discard the indicated old pages and replace or insert them with the supplied new pages.

| OLD PAGES                               | NEW PAGES                                                                                                                                                                                                                                                                                                                     |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                         | Title Sheet/Disclaimer, F01<br>R03                                                                                                                                                                                                                                                                                            |

| Sheets i through v, F00 R03             | Sheets i through v, F01 R03                                                                                                                                                                                                                                                                                                   |

|                                         | Sheets vii through xii, F01<br>R03                                                                                                                                                                                                                                                                                            |

| Sheet vii, F00 R03                      | Sheet xiii, FOl RO3                                                                                                                                                                                                                                                                                                           |

| Sheets 1-1 through 1-17, F00  <br>  R03 | Sheets 1-1 through 1-18, F01<br>R03*                                                                                                                                                                                                                                                                                          |

| Sheet 5-3, F00 R03                      | Sheet 3-19, F01 R03<br>Sheet 3-20, F01 R03<br>Sheet 3-25, F01 R03<br>Sheet 3-26, F01 R03<br>Sheet 3-26, F01 R03<br>Sheet 3-27, F01 R03<br>Sheet 3-28, F01 R03<br>Sheet 3-35, F01 R03<br>Sheet 3-36, F00 R03<br>Sheet 3-58, F01 R03<br>Sheet 3-63, F00 R03<br>Sheet 3-64, F01 R03<br>Sheet 3-66, F01 R03<br>Sheet 5-3, F01 R03 |

|                                         | Sheet 5-4, FOO RO3<br>Sheets IND-1 through IND-6,<br>FO1 RO3                                                                                                                                                                                                                                                                  |

\* Due to the time-consuming task of updating manuals, this chapter is being reissued for your convenience.

# TABLE OF CONTENTS

| SYNTAX CONVENTIONS | vii  | I |

|--------------------|------|---|

| PREFACE            | xiii | 1 |

### CHAPTERS

| 1 | BASIC CONCEPTS                              |                                                                                                                        |                                 |

|---|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------|

|   | 1.1                                         | INTRODUCTION                                                                                                           | 1-1                             |

|   | 1.2<br>1.2.1                                | THE PROCESSOR<br>Temporary Storage (Registers)                                                                         | 1-1<br>1-4                      |

|   | 1.2.2<br>1.2.3<br>1.2.3.1<br>1.2.4<br>1.2.5 | Program Status Word (PSW)<br>Input/Output (I/O) Interface<br>Main Memory<br>Software Relocation<br>Hardware Relocation | 1-5<br>1-6<br>1-6<br>1-6<br>1-7 |

|   | 1.3<br>1.3.1<br>1.3.2                       | Register and Indexed Storage (RX)                                                                                      | 1-7<br>1-7                      |

|   | 1.3.3<br>1.3.4                              | Instructions<br>Register and Immediate (RI) Instructions<br>Short Form (SF) Instructions                               | 1-8<br>1-9<br>1-9               |

|   | 1.4<br>1.4.1<br>1.4.2                       | Register and Indexed Storage One (RX1)                                                                                 | 1-10<br>1-10                    |

|   | 1.4.3<br>1.4.4                              | Instructions<br>Register and Indexed Storage Two (RX2)<br>Instructions<br>Register and Indexed Storage Three (RX3)     | 1-11<br>1-11                    |

|   | 1.4.4<br>1.4.5<br>1.4.6<br>1.4.7<br>1.4.8   | Instructions<br>Register and Immediate One (RII) Instructions                                                          |                                 |

|   | 1.5<br>1.5.1<br>1.5.2<br>1.5.3              | VARIATIONS ON INSTRUCTION FORMATS                                                                                      | 1-17<br>1-17<br>1-18<br>1-18    |

i

|

# CHAPTERS (Continued)

| 2 | SYMBOLIC                               | REPRESENTATION                                                                                                                                                                                                                                                                                                                                   |                                                              |

|---|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

|   | 2.1                                    | INTRODUCTION                                                                                                                                                                                                                                                                                                                                     | 2-1                                                          |

|   | 2.2                                    | SYMBOLS AND EXPRESSIONS                                                                                                                                                                                                                                                                                                                          | 2-1                                                          |

|   |                                        | SYMBOLS AND THEIR VALUES<br>Implicit Symbols<br>Global Symbols                                                                                                                                                                                                                                                                                   | 2-3<br>2-3<br>2-5                                            |

| 3 | THE SOUR                               | CE PROGRAM                                                                                                                                                                                                                                                                                                                                       |                                                              |

|   | 3.1                                    | INTRODUCTION                                                                                                                                                                                                                                                                                                                                     | 3-1                                                          |

|   | 3.2                                    | COMMENT STATEMENTS                                                                                                                                                                                                                                                                                                                               | 3-1                                                          |

|   |                                        | INSTRUCTION STATEMENTS<br>Fixed Format Source Programming<br>Free Format Source Programming                                                                                                                                                                                                                                                      | 3-2<br>3-2<br>3-3                                            |

|   | 3.4.3<br>3.4.3.1<br>3.4.3.2<br>3.4.3.3 | COMMON ASSEMBLY LANGUAGE/32 (CAL/32)<br>INSTRUCTION REPRESENTATION<br>Name Field<br>Operation Field<br>Operand Field<br>Register-to-Register (RR) Instructions<br>Register and Indexed Storage (RX) Instructions<br>Register and Immediate (RI) Instructions<br>Register and Indexed Storage/Register and<br>Indexed Storage (RXRX) Instructions | 3-4<br>3-5<br>3-6<br>3-6<br>3-7<br>3-8<br>3-9                |

|   | 3.5<br>3.5.1<br>3.5.2<br>3.5.3         | COMMON ASSEMBLY LANGUAGE/32 (CAL/32)<br>MACHINE INSTRUCTIONS<br>Usual Branch Mnemonics for the 3280, 3280E<br>MPS, and Micro3200 Systems<br>CAL/32 Machine Instructions for 3280, 3280E<br>MPS, and Micro3200 Systems<br>Instructions for the Input/Output<br>Processor (IOP)                                                                    | 3-11<br>3-25<br>3-27<br>3-29                                 |

|   |                                        | Equate (EQU) Instruction<br>External, Entry, Weak External, Weak<br>Entry and Data Entry (EXTRN, ENTRY,                                                                                                                                                                                                                                          | 3-30<br>3-30<br>3-30                                         |

|   |                                        | WXTRN, WNTRY and DNTRY) Instructions<br>Include (INCLD) Instruction<br>Data Definition Instructions<br>Define Storage (DS, DSH and DSF) Instruction<br>Define Constant (DC and DCF) Instruction<br>Hexadecimal Constants<br>Integer Constants<br>Address Constants                                                                               | 3-33<br>3-36<br>3-37<br>3-37<br>3-39<br>3-40<br>3-42<br>3-44 |

| 3.6.2.6                      | Floating Point Constants                                                                                                                                                                                                                                                                                                                 | 3-46        |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 3.6.2.7                      | Character Constants                                                                                                                                                                                                                                                                                                                      | 3-47        |

| 3.6.2.8                      | Decimal String Constants                                                                                                                                                                                                                                                                                                                 | 3-47        |

| 3.6.3                        | Define Pute (DP) Instruction                                                                                                                                                                                                                                                                                                             | 3-50        |

| 3.0.3                        | Define byte (DD) instruction                                                                                                                                                                                                                                                                                                             | 2-50        |

| 3.6.4                        | Define List (DLIST) Instruction                                                                                                                                                                                                                                                                                                          | 3-51        |

| 3.6.5                        | Define Command (DCMD) Instruction                                                                                                                                                                                                                                                                                                        | 3-52        |

| 3.6.6                        | Location Counter (LOC) Instructions                                                                                                                                                                                                                                                                                                      | 3-52        |

| 3.6.6.1                      | Floating Point Constants<br>Character Constants<br>Decimal String Constants<br>Define Byte (DB) Instruction<br>Define List (DLIST) Instruction<br>Define Command (DCMD) Instruction<br>Location Counter (LOC) Instructions<br>Pure (PURE) Instruction                                                                                    | 3-52        |

| 3.6.6.2                      | Impure (IMPUR) Instruction                                                                                                                                                                                                                                                                                                               | 3-53        |

| 3.6.6.3                      |                                                                                                                                                                                                                                                                                                                                          | 3-53        |

| 3.6.6.4                      |                                                                                                                                                                                                                                                                                                                                          | 3-54        |

|                              |                                                                                                                                                                                                                                                                                                                                          | 3-54        |

| 3.6.6.5                      |                                                                                                                                                                                                                                                                                                                                          |             |

| 3.6.6.6                      | Conditional No Operation (CNOP) Instruction                                                                                                                                                                                                                                                                                              | 3-55        |

| 3.6.7                        | Assembler Control Instructions                                                                                                                                                                                                                                                                                                           | 3-56        |

| 3.6.7.1                      | Target (TARGT) Instruction                                                                                                                                                                                                                                                                                                               | 3-56        |

| 3.6.7.2                      | End (END) Instruction                                                                                                                                                                                                                                                                                                                    | 3-56        |

| 3.6.7.3                      | Copy Library (CLIB) Instruction                                                                                                                                                                                                                                                                                                          | 3-57        |

| 3.6.7.4                      | Copy (COPY) Instruction                                                                                                                                                                                                                                                                                                                  | 3-57        |

| 3 6 7 5                      | File Conv (FCOPV) Instruction                                                                                                                                                                                                                                                                                                            | 3-58        |

| 3.0.7.5                      | Conditional No Operation (CNOP) Instruction<br>Assembler Control Instructions<br>Target (TARGT) Instruction<br>End (END) Instruction<br>Copy Library (CLIB) Instruction<br>Copy (COPY) Instruction<br>File Copy (FCOPY) Instruction<br>Lower-Case (LCASE) Instruction<br>No Lower-Case (NLCASE) Instruction<br>Pause (PAUSE) Instruction | 3 50        |

| 3.0./.0                      | Lower-Case (LCASE) Instruction                                                                                                                                                                                                                                                                                                           | 3-59        |

| 3.6././                      | NO LOWER-Case (NLCASE) Instruction                                                                                                                                                                                                                                                                                                       | 3-59        |

| 3.6.7.8                      | Pause (PAUSE) Instruction                                                                                                                                                                                                                                                                                                                | 3-59        |

| 3.6.7.9                      | Squeeze (SQUEZ and NOSQZ) Instructions                                                                                                                                                                                                                                                                                                   | 3-60        |

| 3.6.7.10                     | Squeeze Related (ERSQZ and NORX3) Instructions                                                                                                                                                                                                                                                                                           | 3-63        |

| ~ ~                          |                                                                                                                                                                                                                                                                                                                                          |             |

|                              | Instructions                                                                                                                                                                                                                                                                                                                             | 3-64        |

| 3 6 7 12                     | Scratch (SCDAT) Instruction                                                                                                                                                                                                                                                                                                              | 3-64        |

| $3 \cdot 0 \cdot 7 \cdot 12$ | Sequence Checking (SQCHK and NOSEQ)<br>Instructions<br>Scratch (SCRAT) Instruction<br>Pass Pause (PPAUS) Instruction<br>Message (MSG) Instruction<br>Batch Assembly (BATCH and BEND) Instructions                                                                                                                                        | 2           |

| 3.0.7.13                     | Pass Pause (PPAUS) Instruction                                                                                                                                                                                                                                                                                                           | 3-05        |

| 3.6./.14                     | Message (MSG) Instruction                                                                                                                                                                                                                                                                                                                | 3-65        |

| 3.6.7.15                     | Batch Assembly (BATCH and BEND) Instructions                                                                                                                                                                                                                                                                                             | 3-65        |

|                              | Unreferenced Externals (UREX and NUREX)                                                                                                                                                                                                                                                                                                  |             |

|                              | Instructions<br>Assembly Performance (HPM and NHPM)<br>Instructions                                                                                                                                                                                                                                                                      | 3-66        |

| 3.6.7.17                     | Assembly Performance (HPM and NHPM)                                                                                                                                                                                                                                                                                                      |             |

|                              | Instructions                                                                                                                                                                                                                                                                                                                             | 3-66        |

| 3 6 7 18                     | 16-Bit Object Code (CAL and NOCAL)                                                                                                                                                                                                                                                                                                       |             |

| 3.0.7.10                     | Instructions                                                                                                                                                                                                                                                                                                                             | 3-67        |

| 2 6 9                        |                                                                                                                                                                                                                                                                                                                                          | 3-67        |

| 3.0.0                        | Conditional Assembly Instructions                                                                                                                                                                                                                                                                                                        | 3-07        |

| 3.6.8.1                      | Compound Conditional (IFx, ELSE and ENDC)                                                                                                                                                                                                                                                                                                |             |

|                              | Instructions                                                                                                                                                                                                                                                                                                                             | 3-67        |

| 3.6.8.2                      | Simple If (IF) Instruction                                                                                                                                                                                                                                                                                                               | 3-71        |

| 3.6.8.3                      | Do (DO) Instruction                                                                                                                                                                                                                                                                                                                      | 3-72        |

| 3.6.9                        |                                                                                                                                                                                                                                                                                                                                          | 3-73        |

| 3.6.9.1                      |                                                                                                                                                                                                                                                                                                                                          | • • •       |

| 3.0.3.1                      | Instructions                                                                                                                                                                                                                                                                                                                             | 3-73        |

| 2602                         |                                                                                                                                                                                                                                                                                                                                          | 5-75        |

| 3.6.9.2                      | •                                                                                                                                                                                                                                                                                                                                        |             |

|                              | Instructions                                                                                                                                                                                                                                                                                                                             | 3-75        |

|                              | Listing Control Instructions                                                                                                                                                                                                                                                                                                             | 3-77        |

| 3.6.10.1                     | Listing Identification (PROG and TITLE)                                                                                                                                                                                                                                                                                                  |             |

|                              | Instructions                                                                                                                                                                                                                                                                                                                             | 3-77        |

| 3.6.10.2                     | Format Control (LCNT, EJECT, SPACE and                                                                                                                                                                                                                                                                                                   |             |

| –                            | WIDTH) Instructions                                                                                                                                                                                                                                                                                                                      | 3-77        |

| 3.6.10.3                     | Content Control Instructions                                                                                                                                                                                                                                                                                                             | 3-78        |

| 3.6.11                       | Auxiliary Processing Unit (APU) and NAPU                                                                                                                                                                                                                                                                                                 | 5.0         |

| 7 • V • T T                  | Options                                                                                                                                                                                                                                                                                                                                  | 3-81        |

|                              | oberoup.                                                                                                                                                                                                                                                                                                                                 | <b>JO</b> T |

|                              |                                                                                                                                                                                                                                                                                                                                          |             |

1

ł

I

4

5

|

| 3.7                     | ASSEMBLY LISTING                                                                                                                     | 3-81              |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| COMMON MC               | DDE PROGRAMMING                                                                                                                      |                   |

| 4.1                     | INTRODUCTION                                                                                                                         | 4-1               |

| 4.2                     | ADDRESS OPERATION INSTRUCTIONS                                                                                                       | 4-1               |

| 4.3                     | COMMON MODE IMMEDIATE OPERATIONS                                                                                                     | 4-3               |

| 4.4<br>4.4.1<br>4.4.1.1 | Data Definition Instructions                                                                                                         | 4-3<br>4-4        |

|                         | Instruction                                                                                                                          | 4-4               |

| 4.4.1.2<br>4.4.2        | Define Address Length Storage (DAS)<br>Instruction<br>Assembler Control (CAL and NOCAL) Instructions                                 | 4-4<br>4-5        |

| 4.5                     | MIXED MODE COMPUTATIONS                                                                                                              | 4-5               |

| 4.6                     | GLOBAL SYMBOLS                                                                                                                       | 4-6               |

| 4.7                     | SPECIAL INSTRUCTIONS                                                                                                                 | 4-8               |

| COMMON AS               | SSEMBLY LANGUAGE/32 (CAL/32) OPERATING<br>IONS                                                                                       |                   |

| 5.1                     | INTRODUCTION                                                                                                                         | 5-1               |

| 5.2                     | OPERATING INSTRUCTIONS FOR ESTABLISHING<br>COMMON ASSEMBLY LANGUAGE/32 (CAL/32) AS A<br>TASK                                         | 5-1               |

| 5.3<br>5.3.1<br>5.3.2   | COMMON ASSEMBLY LANGUAGE/32 (CAL/32) START<br>OPTIONS<br>High Performance Method (HPM) Assembly<br>Assigning Logical Units           | 5-3<br>5-7<br>5-9 |

| 5.3.3                   | Starting Common Assembly Language/32 (CAL/32)<br>Using Command Substitutions (CSS)<br>Common Assembly Language/32 (CAL/32) Assembler | 5-11              |

|                         | End of Task (EOT) Codes                                                                                                              | 5-13              |

# APPENDIXES

| A | COMMON | ASSEMBLY LANGUAGE/32 (CAL/32) ERROR CODES | A-1 |

|---|--------|-------------------------------------------|-----|

| В | OBJECT | CODE FORMAT                               | B-1 |

| $ \begin{array}{c} 1-1\\ 1-2\\ 1-3\\ 1-4\\ 1-5\\ 1-6\\ 1-7\\ 1-8\\ 1-9\\ 1-10\\ 1-11\\ 1-12\\ 1-13\\ 1-14\\ 1-15\\ \end{array} $ | Configuration of a Typical Uniprocessing System<br>Configuration of a Typical Multiprocessing System<br>Configuration of a Typical 3280/Micro3200 System<br>RR Format (16-Bit)<br>RX Format (16-Bit)<br>RI Format (16-Bit)<br>SF Format (16-Bit)<br>RX1 Format (32-Bit)<br>RX1 Format (32-Bit)<br>RX2 Format (32-Bit)<br>RX3 Format (32-Bit)<br>RI1 Format (32-Bit)<br>RI2 Format (32-Bit)<br>SF Format (32-Bit)<br>SF Format (32-Bit)<br>RXRX Format (32-Bit) | $1-2 \\ 1-2 \\ 1-3 \\ 1-8 \\ 1-9 \\ 1-9 \\ 1-10 \\ 1-11 \\ 1-11 \\ 1-12 \\ 1-13 \\ 1-14 \\ 1-14 \\ 1-15 $ |

|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 3-1                                                                                                                              | Comment Statement Column Positioning                                                                                                                                                                                                                                                                                                                                                                                                                           | 3-2                                                                                                       |

| 3-2                                                                                                                              | Source Program Sequence Identification                                                                                                                                                                                                                                                                                                                                                                                                                         | 3-2                                                                                                       |

| 3-3                                                                                                                              | Instruction Statement Positioning (Fixed Format)                                                                                                                                                                                                                                                                                                                                                                                                               | 3-3                                                                                                       |

# TABLES

| 3-1 | SUMMARY OF CAL/32 MACHINE INSTRUCTIONS AND    |            |

|-----|-----------------------------------------------|------------|

|     | MNEMONICS                                     | 3-12       |

| 3-2 | CAL/32 MACHINE INSTRUCTIONS AND MNEMONICS FOR |            |

|     | THE 3200MPS FAMILY OF PROCESSORS              | 3-20       |

| 3-3 | SUMMARY OF CAL/32 MACHINE INSTRUCTIONS AND    |            |

|     | MNEMONICS FOR THE SERIES 3211 PROCESSORS      | 3-21       |

| 3-4 | EXTENDED BRANCH MNEMONICS                     | 3-23       |

|     | USUAL EXTENDED BRANCH MNEMONICS FOR THE       |            |

|     | 3280, 3280E MPS, AND MICRO3200 SYSTEMS        | 3-25       |

| 3-6 | SUMMARY OF CAL/32 MACHINE INSTRUCTIONS AND    |            |

|     | MNEMONICS FOR 3280, 3280E MPS, AND MICRO3200  | 3-27       |

|     | SYSTEMS                                       |            |

| 3-7 | SUMMARY OF CAL/32 MACHINE INSTRUCTIONS AND    |            |

| 5 7 | MNEMONICS FOR IOPS                            | 3-29       |

| 3-8 | CONSTANT TYPES                                | 3-40       |

| 5.0 | CONDIMIT TITLD                                | 5 40       |

| 4-1 | COMMON MODE ADDRESS OPERATIONS                | 4-1        |

|     |                                               |            |

| 5-1 | MEMORY REQUIREMENTS FOR HPM                   | 5-1        |

|     | HPM MEMORY UTILIZATION                        | 5-8        |

|     |                                               | 5-8        |

| 5-4 | CAL/32 LOGICAL UNITS                          | 5-9        |

| 5-4 | CAL/ 52 LOGICAL UNITS                         | 5-9        |

| B-1 | 32-BIT LOADER ITEM DEFINITIONS                | B-2        |

|     | 16-BIT LOADER ITEM DEFINITIONS                | B-2<br>B-4 |

| D-2 | TO-DII POWDER TIEW DEFINITIOND                | D-4        |

INDEX

IND-1

48-050 F00 R03

v

I

1

#### SYNTAX CONVENTIONS

#### GENERAL SYNTAX RULES

These rules clarify the syntax of the commands in this document. Refer to these conventions when interpreting the command syntax.

Multiple commands may appear on one line, but each one must be separated by a semicolon (;). When multiple commands are entered on the same line, they are executed sequentially. If an error occurs, any subsequent commands on the line are ignored.

If the first character of any command input is an asterisk (\*), the remainder of that line is considered to be a comment and is not executed. It is copied to the system log device if logging is active.

In a batch environment, continue parameters by entering a comma as the last character and continuing the parameters on the following line.

#### Statement Syntax Conventions

The following conventions are used in all statement, command, and instruction formats. They point out differences between information that must be entered exactly as shown and that which denotes information provided by the user. However, when entering this information, upper- or lower-case can be used.

Underlining points out the mnemonic of the entry and means that at least the underlined portion must be entered. If an entry is not underlined at all, the entire entry must be entered.

#### PAUSE

Commands and parameters are represented in upper-case and must be entered as shown.

#### DELETE actno

Variables are represented in lower-case and denote information provided by the user:

#### ACCOUNT n

Punctuation must be entered exactly as shown.

#### 48-050 F01 R03

Commas separate parameters and substitute for missing positional parameters:

LIST [actno, [, actno<sub>2</sub>]]

Commas preceding braces inside brackets must be entered if one of the optional parameters is chosen:

$$\frac{PRIVILEGE}{actno_1 [-actno_2]} \left[, \left\{ \begin{array}{c} priv_1 [, priv_2] \\ \star \end{array} \right\} \right]$$

Commas inside brackets must be entered if the optional parameter is chosen:

```

EOU [NOSAVE], UNPROTECT]

```

An ellipsis represents an indefinite number of parameters or range of parameters:

IOTAB (classno, classid [, iocount]), ..., (classno, classid [, iocount])

Brackets represent optional parameters:

ENCRYPT [fd]

Braces represent required parameters of which one must be chosen:

$$\text{log} \left\{ \begin{matrix} \text{ON} \\ \\ \text{OFF} \end{matrix} \right\}$$

Shading represents default options:

ERRMODE EQU

$$\begin{cases} 0 \\ 1 \end{cases}$$

An equals sign associates a parameter with its keyword:

#### Upper- and Lower-Case Characters

All commands and parameters can be entered in either upper- or lower-case. Parameters that are retained internally (such as task identifiers) are translated to uppercase. Subsequent displays show the uppercase version.

## Decimal and Hexadecimal Numbers

The OS/32 commands use decimal rather than hexadecimal numbers for most numeric operands. One exception is addresses, which are expressed in hexadecimal. Numeric operands are always integers except for the SET SYS and TCOM commands, and the segment size increment field of the LOAD command where the decimal point is permissible. Leading zeros can be omitted in numeric operands, whether decimal or hexadecimal.

#### Task Identifiers

Task identifiers must consist of 1 to 8 alphanumeric characters; the first character must be alphabetic. Valid task identifiers are:

TASK3

MAX

Х

**T997XY25**

Examples of invalid task identifiers are:

| 34TASK | First | character | is | not | alphabetic |

|--------|-------|-----------|----|-----|------------|

|--------|-------|-----------|----|-----|------------|

- T43.2 Contains a nonalphanumeric character

- TASK12345 Contains more than eight characters

The background task has the special identifier .BG[nnnnn].

48-050 F01 R03

# File Descriptors

Many of the command formats in this manual require the user to enter a file descriptor (fd). File descriptors are entered in the following format:

#### Format:

[{voln:}

[filename] [.[ext]]

[actno]

dev:

[file class]

### **Parameters:**

- voln: is the name of the disk volume on which the file resides. It may be from one to four characters long. The first character must be alphabetic and the remaining alphanumeric. This parameter need not be specified. If this parameter is not specified, the default user volume is used. When voln is not specified, the colon separating voln and filename must not be entered.

- dev: is a 1- to 4-character device name. The first character must be alphabetic and the remaining alphanumeric. A colon must follow the device name, and neither the filename or the extension is entered.

- filename is the name of a file and is from one to eight characters long. The first character must be alphabetic and the remaining alphanumeric. If a filename is specified when a device mnemonic is specified as dev:, the filename is ignored.

- .ext is a 1- to 3-character alphanumeric string preceded by a period (.) specifying the extension to a filename. If the period and extension are omitted, a default extension is appended to the filename, if appropriate for that particular command; otherwise, it remains blank. If the period is specified and the extension is omitted, the default is a blank extension.

- is a decimal number ranging from 0 to 65,535 actno specifying the account number associated with the file. Account numbers 1 through 65,535 (excluding 255) are used by MTM. Account 255 for number is reserved the MTM administrator. Account number 0 is used for system files and is the default for all operator commands.

- file class is the class name of the file and consists of one character. The class names are:

- /P for private file

- /G for group file

- /S for system file

The file class can be specified by a terminal user or the system operator. If the system operator specifies /P, /G, or /S, the operation is performed to account 0 only.

#### Examples:

In the following example, PACK: is the volume name, CAL is the filename, .TSK is the extension name and 0 is the account number.

PACK:CAL.TSK/0

In the following example, CONV is the filename, and .CAL is the extension name with a default account number on the default volume.

CONV.CAL

In the following example, all filenames beginning with CGG as the first three characters and ending with the extension GG are requested.

CGG-.\*GG Possible filenames are:

| CGG1.AGG     | CGG12.AGG    | CGG123.AGG |

|--------------|--------------|------------|

| CGG1.BGG     | CGG12.BGG    | CGG123.BGG |

| CGG1.CGG     | CGG12.CGG    | CGG123.CGG |

| •            | •            | •          |

| •            | •            | •          |

| CGG12345.XGG | CGGABCDE.ZGG | CGG.YGG    |

In the following example, CAL is the filename with a default extension, default account number, and default volume.

CAL

In the following example, M300: is the volume name, and MAR is the filename with a default extension and default account number.

M300:MAR

In the following example, CARD: is the device mnemonic.

CARD:

#### PREFACE

This manual describes the Common Assembly Language/32 (CAL/32). Chapter 1 is an introduction to the basic concepts of the assembler, central processing unit (CPU) and main memory. Also described are the instruction formats for 16- and 32-bitmachines, as well as variations in the formats. Chapter 2 introduces assembly language symbolic representation and describes symbolic values. Chapter 3 defines the source program and contains a list of machine instructions, mnemonics and detailed descriptions of assembler instructions. Common mode programming and common mode operations are explained in Chapter 4. CAL/32 operating instructions are listed in Chapter 5.

Appendix A contains CAL/32 error codes. Appendix B describes the 16- and 32-bit object code formats.

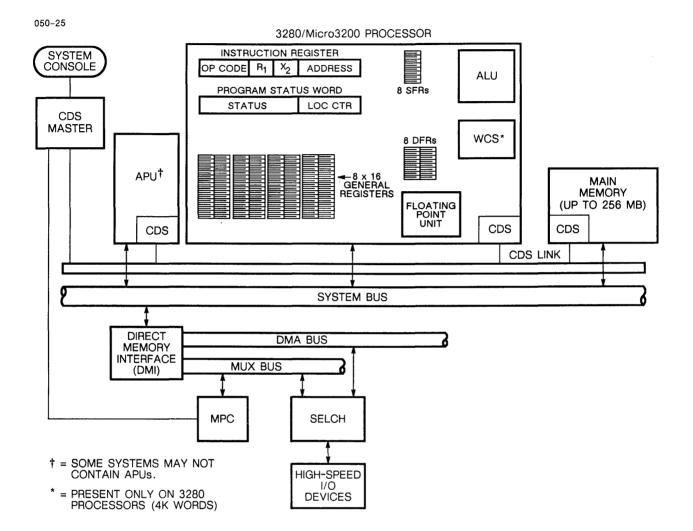

The F01 R03 version of the manual presents a model of a typical 3280/Micro3200 System in Chapter 1. Chapter 3 presents a 16-bit value mode for the EXTRN instruction. The chapter also provides additional information concerning the SCRAT instruction.

This manual is intended for use with the OS/32 R08-03 software release and higher.

#### CHAPTER 1 BASIC CONCEPTS

#### 1.1 INTRODUCTION

Like all assemblers, Common Assembly Language/32 (CAL/32) simplifies the direct control of the processor by providing the programmer with a way of representing actual machine operations in an easily understood symbolic form. Assemblers translate symbolic representations of machine instructions into binary form to be executed by the processor. CAL/32 also includes such features as relocation, segmentation, complex data definitions, and expression analysis. CAL/32 can run on any 32-bit processor and produce machine code for any 32-bit processor.

Because assembly language programming is so close to actual machine operations, it is essential that the assembly language programmer have a good understanding of system architecture. This chapter contains introductory architectural descriptions for uniprocessing systems and multiprocessing systems. See the appropriate Processor User Manual or Instruction Set Reference Manual for more detailed information.

#### 1.2 THE PROCESSOR

The main components of a processor are the central processing unit (CPU) and main memory. All processors, whether in a uniprocessing or a multiprocessing system, are stored-program, multiregister machines.

There are four iterations of the processor:

1

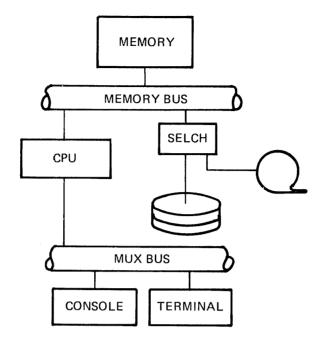

- A standard processor for a uniprocessing system. Figure 1-1 depicts the configuration of a typical uniprocessing system.

- A CPU in a multiprocessing system.

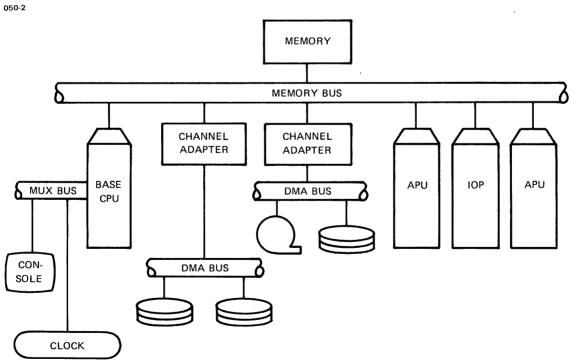

- Up to nine auxiliary or input/output processing units | (attached processors) in a multiprocessing system. Figure 1-2 | depicts the configuration of a typical multiprocessing system.

- Figure 1-3 shows a typical 3280/Micro3200 system.

050-1

TYPICAL UNIPROCESSOR

Figure 1-1 Configuration of a Typical Uniprocessing System

Figure 1-2 Configuration of a Typical Multiprocessing System

48-050 F01 R03

Figure 1-3 Configuration of a Typical 3280/Micro3200 System

In addition to the standard tasks performed by the operating system in a uniprocessing system, the operating system in a multiprocessing system:

- controls all auxiliary processing units (APUs)

- monitors all activity in the multiprocessing system,

- services all APU exceptions,

- dispatches application tasks created for existing CPUs or the CPU in the 3200MPS Family of Processors, and

- dispatches tasks to the APUs and IOPs for execution in the 3200MPS Family of Processors.

The function of an APU is to execute tasks concurrently with the CPU and other APUs. The function of the IOP is to handle all input/output (I/O) devices configured under it, thereby relieving the CPU of I/O overhead.

1.2.1 Temporary Storage (Registers)

All processors have some amount of temporary storage that can be used as accumulators or index registers. There are three types of temporary storage:

- General-purpose registers (GR)

- Single precision floating point registers (SFR)

- Double precision floating point registers (DFR)

All processors have at least one set of 16 general-purpose registers. In the 16-bit processors, each general-purpose register holds 16 bits; in the 32-bit processors, each holds 32 bits. General-purpose registers can be used for integer arithmetic, address arithmetic, logical operations, and character operations. Floating point registers are used only for floating point arithmetic operations. Processors with floating point registers have either eight single precision registers or eight double precision registers. The single precision registers hold 32 bits. The double precision registers hold 64 bits.

For a multiprocessing system, there are up to ten sets of registers; one for each of the nine APUs that can be part of the system, plus a set in the CPU; (i.e., ten processors each having 16 general register sets, eight SFRs, and eight DFRs).

#### 1.2.2 Program Status Word (PSW)

The PSW defines the current state of a processing unit. The uniprocessing system has one current PSW. Since the 3200MPS Family of Processors consists of multiple processors, there is one current PSW for each processor. The PSW consists of three major parts:

- Status descriptor

- Condition code (CC)

- Location counter (LOC)

Individual bits and bit fields within the status descriptor portion of the PSW define the current state of interrupts and various hardware features of the processor. By setting or resetting bits within the status descriptor, the programmer can enable or disable such interrupts as I/O, arithmetic fault, and machine malfunction (MMF). On those processors with multiple sets of general-purpose registers, a field in the status descriptor defines which set is currently in use. Programmers writing user level programs, as opposed to operating system or stand-alone programs, cannot directly access the status descriptor. In this case, the operating system maintains control of interrupts and registers.

The CC provides a means of controlling program flow, based on the results of instruction execution. As certain instructions are executed, the value in the CC changes to indicate the nature of the result. For example, if an operation produces a zero result, the CC may be changed to a zero value. With branch instructions, the programmer can test the value in the CC and branch or not, depending on that value. Not all instruction executions affect the CC. See the appropriate processor reference manual for more details.

The LOC controls the order of instruction execution. Normally, the processor executes instructions sequentially and uses the LOC to keep track of where the instructions are in main memory, then fetches the instruction from the memory location specified by the address contained in the LOC. It increments the LOC by the length of the instruction, executes the instruction and fetches the next instruction. Branch instructions, when executed, change the contents of the LOC and, thereby, affect the branch.

In 32-bit machines, the PSW contains 64 bits; the least significant 24 bits are reserved for the LOC. In 16-bit machines, the PSW contains 32 bits; the least significant 16 bits are reserved for the LOC.

# 1.2.3 Input/Output (I/O) Interface

The execution of certain machine instructions allows the programmer to control external devices and to cause the transfer of data between external devices and main memory or registers. The actual programming of I/O operations is very much dependent upon the hardware of both the processor and the peripherals. I/O instructions are restricted to operating systems and stand-alone programs. User programs can communicate with I/O devices through facilities provided by the operating system.

# 1.2.3.1 Main Memory

To the assembly language programmer, main memory appears as a block of contiguous storage locations. The smallest unit of memory the programmer can access is the byte (eight bits). The programmer can also access halfwords (two bytes), fullwords (four bytes), and doublewords (eight bytes). Each byte in memory is accessed by a unique address. Memory addresses start with zero and are incremented by one for each succeeding byte. Memory addresses in the 32-bit processors always consist of 24 bits. In the 16-bit processors, memory addresses consist of 16 bits. When accessing bytes, any memory address within the limits of the particular hardware configuration is considered valid. Halfwords must be accessed with halfword addresses. Fullwords must be accessed with addresses that are multiples of four. Doublewords must be accessed with addresses that are multiples of eight.

#### 1.2.4 Software Relocation

Programs written in CAL/32 can be absolute or relocatable. An absolute program is one whose origin (starting location) is specified at assembly time as being at a fixed halfword location in memory. Subsequent addresses within the program, whether referring to instructions or data, are fixed at assembly time. For execution, absolute programs must always be loaded into memory at the location specified as the origin. This type of programming is useful in stand-alone applications and some operating system situations. A user program written with absolute addresses is relocatable, but the addresses that are used refer to their absolute values relative to task address 0. It is the actual location of this task, 0, which is relocatable.

Relocatable programs can be loaded for execution beginning at any halfword location in memory. The origin of a relocatable program is assumed to be relocatable zero. The CAL/32 output for this type of program specifies all addresses in the program as relative displacements from the origin. At link time, the linkage editor resolves all addresses within the program by adding a relocation value (the actual memory address for the start of the program) to the relative addresses supplied by CAL/32. Relocation applies only to addresses within the program. Relocatable programs can contain absolute data.

# 1.2.5 Hardware Relocation

Some processors and their operating systems support hardware relocation and segmentation. Programs prepared for these systems start out as relocatable. A linkage editor processes the relocatable output from CAL/32 to link in any needed subprograms. The output of this process is an absolute program that, because of the relocating hardware, can be loaded beginning at any memory address that is a multiple of 256 for memory access controller (MAC) machines, 2,048 for memory address translator (MAT) machines, or 4,096 for virtual address translator (VAT) machines. At run-time, the relocating hardware adds the required relocation value to all addresses supplied by the program. This relocating hardware also provides for program segmentation, where the program is divided into pieces that can be loaded into noncontiguous blocks of memory.

CAL/32 supports segmentation by allowing the programmer to divide the program into pure and impure segments. The pure segment of a program consists of machine instructions and constant data and cannot be modified at run-time. (The operating system and the hardware prevent modification.) The impure segment consists of the data base which can be modified at run-time. Programs prepared as pure and impure segments can be shared (executed concurrently) by several users. Only one copy of the pure segment resides in memory during execution while there is one copy of the impure segment for each user.

#### 1.3 INSTRUCTION FORMATS (16-BIT)

The 16-bit processors have four types of machine instructions: register-to-register (RR), register and indexed storage (RX), register and immediate (RI) and short form (SF). The following abbreviations illustrate the instruction formats:

- OP Operation

- Rl First operand register

- R2 Second operand register

- N A 4-bit immediate value

- X2 Second operand index register

- A2 Second operand direct address

- 12 Second operand immediate value

Most instructions require two operands, the first of which is contained in a register. The result usually replaces the contents of the first operand register. Exceptions to these rules are noted in Section 1.5.

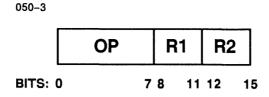

#### 1.3.1 Register-to-Register (RR) Instructions

RR instructions cause operations to take place between operands contained in registers. RR instructions are 16 bits long, as shown in Figure 1-4.

Figure 1-4 RR Format (16-Bit)

The first eight bits of the instruction define the operation. The next four bits identify the first operand register. The final four bits identify the second operand register. In most RR instructions, the specified operation takes place between the contents of the first operand register and the contents of the second operand register. The result of the operation replaces the contents of the first operand register.

### 1.3.2 Register and Indexed Storage (RX) Instructions

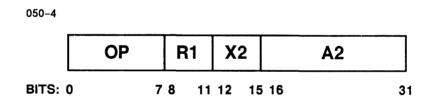

RX instructions cause an operation to take place between a first operand, contained in a register, and a second operand, located in main memory. These instructions require 32 bits, as shown in Figure 1-5.

Figure 1-5 RX Format (32-Bit)

The first eight bits define the operation. The next four bits identify the first operand register and the next four bits identify an optional index register. The remaining 16 bits specify an address in main memory. The operation takes place between the contents of the first operand register and the contents of the memory location specified. The actual address of the second operand is determined by adding the contents of the index register to the contents of the address field. If the index field of the instruction contains zero, no indexing takes place. In most cases, the result of the operation replaces the contents of the first operand register.

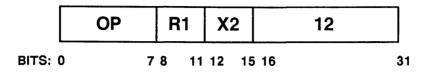

# 1.3.3 Register and Immediate (RI) Instructions

RI instructions cause operations to take place between the contents of a register and the contents of an immediate field embedded in the instruction itself. They are 32 bits long, as shown in Figure 1-6.

050-5

Figure 1-6 RI Format (32-Bit)

The first eight bits specify the operation; the next four bits identify the first operand register; the next four bits identify an optional index register; the final 16 bits are the immediate value. The first operand is the contents of the first operand register. The second operand is obtained by adding the contents of the index register to the contents of the immediate field. If the index field contains zero, no addition takes place. The result of the operation usually replaces the contents of the first operand register.

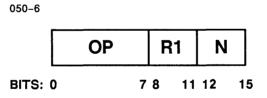

#### 1.3.4 Short Form (SF) Instructions

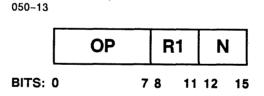

SF instructions are variations on the RI instructions in which the second operand is small enough to be expressed in four bits. SF instructions require 16 bits, as shown in Figure 1-7.

Figure 1-7 SF Format (16-Bit)

The first eight bits indicate the operation. The next four bits identify the first operand register and the 4-bit immediate field. The next four bits contain the immediate value. Operations take place between the contents of the first operand register and the 4-bit immediate operand. The result of the operation usually replaces the contents of the first operand register.

#### 1.4 INSTRUCTION FORMATS (32-BIT)

The 32-bit processors recognize seven different types of instructions. They are: RR, three variations on RX, two variations on RI, and SF. The following abbreviations are used to illustrate instruction formats:

| OP  | Operation                            |

|-----|--------------------------------------|

| Rl  | First operand register               |

| R2  | Second operand register              |

| N   | A 4-bit immediate value              |

| X2  | Second operand single index register |

| D2  | Second operand displacement          |

| FX2 | Second operand first index register  |

| SX2 | Second operand second index register |

| A2  | Second operand direct address        |

| 12  | Second operand immediate value       |

| Ll  | Length of first operand string       |

| L2  | Length of second operand string      |

Most instructions require two operands. The first is the contents of a register. The result of the operation usually replaces the contents of the first operand register. Exceptions to these rules are noted in Section 1.5.

# 1.4.1 Register-to-Register (RR) Instructions

The format and function of these instructions are the same as for the 16-bit processors. They cause operations to take place between operands contained in registers and they require 16 bits. These instructions are shown in Figure 1-8.

050--7

|       | OP |     | <b>R1</b> |    | R2 |    |

|-------|----|-----|-----------|----|----|----|

| BITS: | 0  | 7 8 | 8         | 11 | 12 | 15 |

Figure 1-8 RR Format (32-Bit)

The first eight bits specify the operation. The next four bits identify the first operand register and the last four bits identify the second operand register. The processor performs the indicated operation between the contents of the first operand register and the contents of the second operand register. In most RR instructions, the result replaces the contents of the first operand register.

# 1.4.2 Register and Indexed Storage One (RX1) Instructions

RX1 instructions define an operation between the contents of a register and the contents of a main memory location. They require 32 bits, as shown in Figure 1-9.

050-8

Figure 1-9 RX1 Format (32-Bit)

The first eight bits define the operation. The next four bits identify the first operand register and the next four bits identify the optional index register. The next two bits, 16 and 17, must be zeros. The next 14 bits constitute a direct program address in a range from 0 to 16,383.

The address of the second operand is obtained by adding the contents of the index register to the contents of the 14-bit address field. If the index register field contains zero, this addition does not take place and the contents of the address field are used as the address. The operation takes place between the contents of the first operand register and the contents of the specified memory location. The result usually replaces the contents of the first operand register.

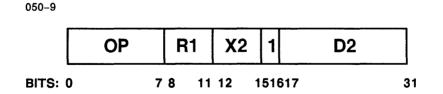

#### 1.4.3 Register and Indexed Storage Two (RX2) Instructions

RX2 instructions define operations between the contents of a register and the contents of a location in main memory. RX2 instructions are like the RX1 instructions; they require 32 bits. They differ from the RX1 instructions in the method of calculating the second operand address. See Figure 1-10.

Figure 1-10 RX2 Format (32-Bit)

The first eight bits define the operation; the next four bits identify the first operand register and the next four bits identify the optional index register. The next bit, 16, must be a one. The remaining 15 bits are treated as a signed integer in two's complement notation. Bit 17 is the sign bit which, if one, indicates a negative quantity, and if zero, indicates a positive quantity.

The address of the second operand is obtained in two steps.

- The signed integer, with sign bit extended to produce a 32-bit integer, is added to the contents of the index register.

- 2. This intermediate result is added to the value in the incremented LOC. The result is truncated to 24 bits.

If the index register field is zero, the first addition does not take place. The indicated operation takes place between the contents of the first operand register and the contents of the specified memory location. The result usually replaces the contents of the first operand register.

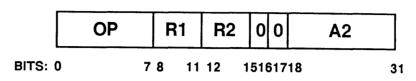

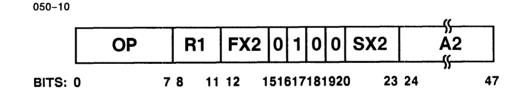

1.4.4 Register and Indexed Storage Three (RX3) Instructions

RX3 instructions are analogous to the RX instructions in the 16-bit processors. They call for operations between the contents of a register and the contents of an indexed memory location and require 48 bits. See Figure 1-11.

Figure 1-11 RX3 Format (32-Bit)

The first eight bits specify the operation; the next four bits identify the first operand register and the next four bits identify the optional first index register. Bit 16 must be zero. Bit 17 must be one. Bits 18 and 19 must be zero. The next four bits identify the optional second index register. The final 24 bits contain a direct memory address. The address of the second operand is obtained by adding the contents of the first index register to the contents of the second index register. This intermediate result is then added to the contents of the direct address field, and the final result is truncated to 24 bits.

If either of the index register fields contains zero, that level of indexing does not take place. If both are zero, no indexing takes place. In most RX3 instructions, the operation takes place between the contents of the first operand register and the contents of the specified memory location. The result usually replaces the contents of the first operand register.

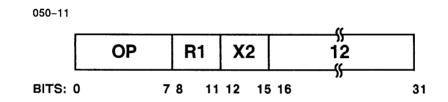

#### 1.4.5 Register and Immediate One (RII) Instructions

RIl instructions are similar to the RI instructions in the 16-bit processors. They specify operations that take place between the contents of a register and the contents of a field that is part of the instruction. They require 32 bits, as shown in Figure 1-12.

Figure 1-12 RIL Format (32-Bit)

The first eight bits indicate the operation. The next four bits identify the first operand register and the next four bits identify an index register. The final 16 bits are the immediate value. The second operand is obtained by extending the contents of the immediate field to 32 bits, by propagating the sign bit and then adding this quantity to the contents of the index register. If the index register field is zero, no addition takes place and the extended immediate value is the second operand. The operation takes place between the contents of the first operand register and the immediate value. The result usually replaces the contents of the first operand register.

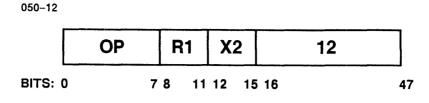

# 1.4.6 Register and Immediate Two (RI2) Instructions

RI2 instructions are similar to the RI1 instructions except that the immediate field contains a 32-bit value and the instruction itself requires 48 bits. See Figure 1-13.

Figure 1-13 RI2 Format (32-Bit)

The first eight bits define the operation. The next four bits identify the first operand register. The next four bits identify the optional index register. The final 32 bits are the immediate value. The second operand is obtained by adding the contents of the index register to the contents of the immediate field. If the index register field is zero, no addition takes place and the immediate value is the second operand. The operation takes place between the contents of the first operand register and the immediate value. The result usually replaces the contents of the first operand register.

# 1.4.7 Short Form (SF) Instructions

SF instructions are similar to the SF instructions in the 16-bit processors. They specify operations between the contents of a register and the contents of an immediate field whose value is small enough to be expressed in four bits. These instructions require 16 bits, as shown in Figure 1-14.

Figure 1-14 SF Format (32-Bit)

The first eight bits define the operation. The next four bits identify the first operand register. The next four bits are the immediate field. The operation then takes place between this value and the contents of the first operand register. The result usually replaces the contents of the first operand register.

# 1.4.8 Register and Indexed Storage/Register and Indexed Storage (RXRX) Instructions

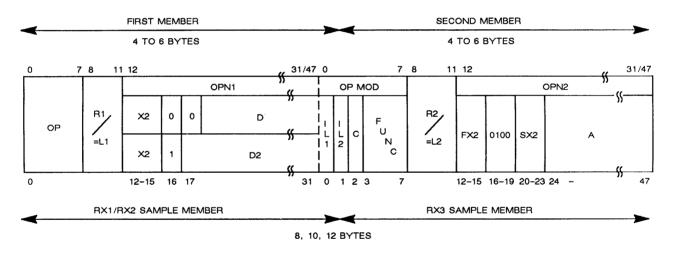

RXRX instructions resemble a pair of adjacent RX instructions, but represent one cohesive string-processing instruction. An RXRX instruction is comprised of two instruction members. Each member can be any one of the RX1, RX2, or RX3 machine formats, independent of the other member's format. For example, the first instruction member might be of the RX1 format and the second instruction member might be of the RX3 format, yielding a 10-byte RXRX instruction. Thus, an RXRX instruction length might range from 8, 10, or 12 bytes.

The first eight bits of the first instruction member, OP, specify the operation class. The particular RXRX operation is specified by the contents of the operation-modifier (OP-MOD) field in the first eight bits of the second instruction member. OP-MOD is actually generated by the assembler according to the specific RXRX operation mnemonic and the R1/L1 or R2/L2 fields programmed by the user in source code. See Figure 1-15.

050-14

Figure 1-15 RXRX Format (32-Bit)

The next four bits in the first instruction member, Rl/Ll, identify either Rl, the string's length-specifying register or Ll, the string's actual length. The user specifies to the assembler whether the value in the Rl/Ll field is a register or an immediate value. The Rl/Ll field is assumed to be a register unless an equal sign (=) precedes the Ll source expression. In machine format, the ILl field is set when the =Ll source field specifies an immediate value as length. The IL2 field in machine format is reset when the Rl field is used to specify a register that contains the string's length. When the length is an immediate value, its value may range from 0 through 15. When the length is in a register, the register may contain a length that ranges from 0 through exponent 2 -1. A length of 0 indicates a null string.