# COMMON ASSEMBLY LANGUAGE/32 (CAL/32)

Reference Manual

OS/32 version 8.2 or higher

48-050 F00 R03

The information in this document is subject to change without notice and should not be construed as a commitment by Concurrent Computer Corporation. Concurrent Computer Corporation assumes no responsibility for any errors that may appear in this document.

The software described in this document is furnished under a license, and it can be used or copied only in a manner permitted by that license. Any copy of the described software must include any copyright notice, trademarks, or other legends or credits of Concurrent Computer Corporation and/or its suppliers. Title to and ownership of the described software and any copies thereof shall remain in Concurrent Computer Corporation and/or its suppliers.

The licensed program described herein may contain certain encryptions or other devices which may prevent or detect unauthorized use of the Licensed Software. Temporary use permitted by the terms of the License Agreement may require assistance from Concurrent Computer Corporation.

Concurrent Computer Corporation assumes no responsibility for the use or reliability of the software on equipment that is not supplied by Concurrent Computer Corporation.

© 1979, 1981, 1983, 1984, 1985, 1986 Concurrent Computer Corporation — All Rights Reserved

Concurrent Computer Corporation, 2 Crescent Place

Oceanport, New Jersey 07757

Printed in the United States of America

# NOTICE

THIS MANUAL CONTAINS REFERENCES TO THE EXTENDED MEMORY AND THE MULTIPROCESSOR VERSION OF THE 3280 SYSTEM WHICH WERE NOT AVAILABLE FOR THE OS/32 8.2 SOFTWARE RELEASE.

FOR FURTHER INFORMATION OR ASSISTANCE CONCERNING THESE PRODUCTS, PLEASE CONTACT YOUR LOCAL CONCURRENT COMPUTER CORPORATION SALES REPRESENTATIVE.

# TABLE OF CONTENTS

| PRE | FACE                                                        |                                                                                                                                                                                                                     | vii                                    |

|-----|-------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|     |                                                             |                                                                                                                                                                                                                     |                                        |

|     |                                                             |                                                                                                                                                                                                                     |                                        |

| CHA | PTERS                                                       |                                                                                                                                                                                                                     |                                        |

|     |                                                             |                                                                                                                                                                                                                     |                                        |

| 1   | BASIC CO                                                    | NCEPTS                                                                                                                                                                                                              |                                        |

|     | 1.1                                                         | INTRODUCTION                                                                                                                                                                                                        | 1-1                                    |

|     | 1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.3.1<br>1.2.4<br>1.2.5 | THE PROCESSING UNIT Temporary Storage (Registers) Program Status Word (PSW) Input/Output (I/O) Interface Main Memory Software Relocation Hardware Relocation                                                        | 1-1<br>1-3<br>1-4<br>1-5<br>1-5<br>1-5 |

|     | 1.3<br>1.3.1<br>1.3.2                                       | INSTRUCTION FORMATS (16-BIT) Register-to-Register (RR) Instructions Register and Indexed Storage (RX) Instructions Register and Immediate (RI) Instructions                                                         | 1-6<br>1-6<br>1-7<br>1-8               |

|     | 1.3.4<br>1.4<br>1.4.1<br>1.4.2                              | Short Form (SF) Instructions  INSTRUCTION FORMATS (32-BIT)  Register-to-Register (RR) Instructions  Register and Indexed Storage One (RX1)                                                                          | 1-8<br>1-9<br>1-9                      |

|     | 1.4.3                                                       | Instructions Register and Indexed Storage Two (RX2) Instructions Register and Indexed Storage Three (RX3)                                                                                                           | 1-10                                   |

|     | 1.4.5<br>1.4.6<br>1.4.7<br>1.4.8                            | Instructions Register and Immediate One (RII) Instructions Register and Immediate Two (RI2) Instructions Short Form (SF) Instructions Register and Indexed Storage/Register and Indexed Storage (RXRX) Instructions | 1-11<br>1-12<br>1-12<br>1-13           |

|     | 1.5<br>1.5.1<br>1.5.2<br>1.5.3                              | VARIATIONS ON INSTRUCTION FORMATS<br>Conditional Branch Instructions<br>Branch and Link Instructions<br>Other Variations                                                                                            | 1-16<br>1-16<br>1-17<br>1-17           |

48-050 F00 R03

# CHAPTERS (Continued)

| 2 | SYMBOLIC                           | REPRESENTATION                                                                                                                                                                                                                                                                                                        |                                                      |

|---|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

|   | 2.1                                | INTRODUCTION                                                                                                                                                                                                                                                                                                          | 2-1                                                  |

|   | 2.2                                | SYMBOLS AND EXPRESSIONS                                                                                                                                                                                                                                                                                               | 2-1                                                  |

|   | 2.3<br>2.3.1<br>2.3.2              | SYMBOLS AND THEIR VALUES Implicit Symbols Global Symbols                                                                                                                                                                                                                                                              | 2-3<br>2-3<br>2-5                                    |

| 3 | THE SOURCE                         | CE PROGRAM                                                                                                                                                                                                                                                                                                            |                                                      |

|   | 3.1                                | INTRODUCTION                                                                                                                                                                                                                                                                                                          | 3-1                                                  |

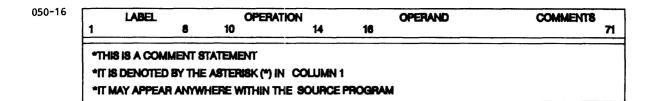

|   | 3.2                                | COMMENT STATEMENTS                                                                                                                                                                                                                                                                                                    | 3-1                                                  |

|   | 3.3<br>3.3.1<br>3.3.2              | INSTRUCTION STATEMENTS Fixed Format Source Programming Free Format Source Programming                                                                                                                                                                                                                                 | 3-2<br>3-2<br>3-3                                    |

|   | 3.4.3.1<br>3.4.3.2                 | COMMON ASSEMBLY LANGUAGE/32 (CAL/32) INSTRUCTION REPRESENTATION Name Field Operation Field Operand Field Register-to-Register (RR) Instructions Register and Indexed Storage (RX) Instructions Register and Immediate (RI) Instructions Register and Indexed Storage/Register and Indexed Storage (RXRX) Instructions | 3-4<br>3-4<br>3-5<br>3-6<br>3-6<br>3-7<br>3-8        |

|   | 3.5.1<br>3.5.2<br>3.5.3            | COMMON ASSEMBLY LANGUAGE/32 (CAL/32) MACHINE INSTRUCTIONS Usual Branch Mnemonics for the 3280 System CAL/32 Machine Instructions for 3280 System Instructions for the Input/Output Processor (IOP)                                                                                                                    | 3-11<br>3-25<br>3-27<br>3-29                         |

|   | 3.6<br>3.6.1<br>3.6.1.1<br>3.6.1.2 | ASSEMBLER INSTRUCTIONS Symbol Definition Instructions Equate (EQU) Instruction External, Entry, Weak External, Weak Entry and Data Entry (EXTRN, ENTRY,                                                                                                                                                               | 3-30<br>3-30<br>3-30                                 |

|   | 3.6.2.4                            | WXTRN, WNTRY and DNTRY) Instructions Include (INCLD) Instruction Data Definition Instructions Define Storage (DS, DSH and DSF) Instruction Define Constant (DC and DCF) Instruction Hexadecimal Constants Integer Constants Address Constants                                                                         | 3-33<br>3-36<br>3-37<br>3-37<br>3-40<br>3-42<br>3-44 |

ii 48-050 F00 R03

# CHAPTERS (Continued)

| 3.6.2.6          | Floating Point Constants                                                              | 3-46             |

|------------------|---------------------------------------------------------------------------------------|------------------|

| 3.6.2.7          | Character Constants                                                                   | 3-47             |

| 3.6.2.8          | Decimal String Constants                                                              | 3-47             |

| 3.6.3            |                                                                                       | 3-50             |

| 3.6.4            | Define List (DLIST) Instruction                                                       | 3-51             |

| 3.6.5            |                                                                                       | 3-52             |

| 3.6.6            | Location Counter (LOC) Instructions                                                   | 3-52             |

| 3.6.6<br>3.6.6.1 | Pure (PURE) Instruction                                                               | 3-52             |

| 3.6.6.2          | Impure (IMPUR) Instruction                                                            | 3-53             |

| 3.6.6.3          |                                                                                       | 3-53             |

| 3.0.0.3          | Absolute (ABS) Instruction                                                            | 3-54             |

| 3.0.0.4          | Absolute (ABS) Instruction                                                            |                  |

| 3.6.6.5          | Align (ALIGN) Instruction                                                             | 3-54             |

| 3.6.6.6          |                                                                                       |                  |

| 3.6.7            |                                                                                       | 3-56             |

|                  |                                                                                       | 3-56             |

|                  | End (END) Instruction                                                                 | 3-56             |

|                  | Copy Library (CLIB) Instruction Copy (COPY) Instruction File Copy (FCOPY) Instruction | 3-57             |

|                  | Copy (COPY) Instruction                                                               | 3-57             |

| 3.6.7.5          | File Copy (FCOPY) Instruction                                                         | 3-58             |

| 3.6.7.6          | Lower-Case (LCASE) Instruction                                                        | 3-59             |

| 3.6.7.7          | No Lower-Case (NLCASE) Instruction                                                    | 3-59             |

| 3.6.7.8          | Pause (PAUSE) Instruction                                                             | 3-59             |

| 3.6.7.9          | Squeeze (SQUEZ and NOSQZ) Instructions                                                | 3-60             |

|                  | Squeeze Related (ERSQZ and NORX3) Instructions                                        |                  |

|                  | Sequence Checking (SQCHK and NOSEQ)                                                   |                  |

|                  | Instructions                                                                          | 3-64             |

| 3.6.7.12         |                                                                                       | 3-64             |

|                  |                                                                                       | 3-65             |

|                  | Message (MSG) Instruction                                                             | 3-65             |

|                  | Batch Assembly (BATCH and BEND) Instructions                                          | 3-65             |

|                  | Unreferenced Externals (UREX and NUREX)                                               | 5 05             |

| 3.0.7.10         | Instructions                                                                          | 3-66             |

| 3 6 7 17         | Assembly Performance (HPM and NHPM)                                                   | 3-00             |

| 3.0.7.17         | Instructions                                                                          | 3-66             |

| 2 6 7 10         |                                                                                       | 3-00             |

| 3.6.7.18         | 16-Bit Object Code (CAL and NOCAL)                                                    | 2 (7             |

| 2 6 2            | Instructions                                                                          | 3-67             |

|                  | Conditional Assembly Instructions                                                     | 3-67             |

| 3.6.8.1          |                                                                                       |                  |

|                  | Instructions                                                                          | 3-67             |

|                  | Simple If (IF) Instruction                                                            | 3-71             |

|                  | Do (DO) Instruction                                                                   | 3-72             |

| 3.6.9            | Instructions for Data Structures Structure Definition (COMN, STRUC and ENDS)          | 3-73             |

| 3.6.9.1          |                                                                                       |                  |

|                  | Instructions                                                                          | 3-73             |

| 3.6.9.2          | Structure Initialization (BDATA and BORG)                                             |                  |

|                  | Instructions                                                                          | 3-75             |

| 3.6.10           | Listing Control Instructions                                                          | 3-77             |

| 3.6.10.1         | Listing Identification (PROG and TITLE)                                               |                  |

|                  | Instructions                                                                          | 3-77             |

| 3.6.10.2         | Format Control (LCNT, EJECT, SPACE and                                                |                  |

|                  | WIDTH) Instructions                                                                   | 3-77             |

| 3.6.10.3         | Content Control Instructions                                                          | 3-78             |

|                  | Auxiliary Processing Unit (APU) and NAPU                                              | - · <del>-</del> |

| _ , , , ,        | Options                                                                               | 3-81             |

48-050 F00 R03 iii

# CHAPTERS (Continued)

|      | 3.7       | ASSEMBLY LISTING                                                                                                                                                | 3-81              |

|------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4    | COMMON MO | DDE PROGRAMMING                                                                                                                                                 |                   |

|      | 4.1       | INTRODUCTION                                                                                                                                                    | 4-1               |

|      | 4.2       | ADDRESS OPERATION INSTRUCTIONS                                                                                                                                  | 4-1               |

|      | 4.3       | COMMON MODE IMMEDIATE OPERATIONS                                                                                                                                | 4-3               |

|      | 4.4.1     | COMMON MODE ASSEMBLER INSTRUCTIONS Data Definition Instructions Define Address Length Constant (DAC)                                                            | 4-3<br>4-4        |

|      |           | Instruction Define Address Length Storage (DAS)                                                                                                                 | 4-4               |

|      |           | Instruction Assembler Control (CAL and NOCAL) Instructions                                                                                                      | 4-4<br>4-5        |

|      | 4.5       | MIXED MODE COMPUTATIONS                                                                                                                                         | 4-5               |

|      | 4.6       | GLOBAL SYMBOLS                                                                                                                                                  | 4-6               |

|      | 4.7       | SPECIAL INSTRUCTIONS                                                                                                                                            | 4-8               |

| 5    | COMMON AS | SSEMBLY LANGUAGE/32 (CAL/32) OPERATING IONS                                                                                                                     |                   |

|      | 5.1       | INTRODUCTION                                                                                                                                                    | 5-1               |

|      | 5.2       | OPERATING INSTRUCTIONS FOR ESTABLISHING COMMON ASSEMBLY LANGUAGE/32 (CAL/32) AS A TASK                                                                          | 5-1               |

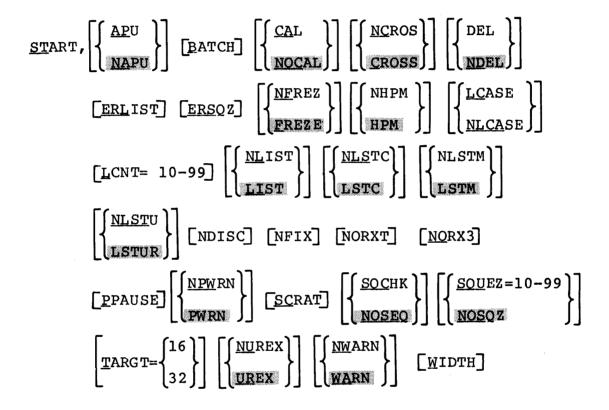

|      |           | COMMON ASSEMBLY LANGUAGE/32 (CAL/32) START OPTIONS High Performance Method (HPM) Assembly Assigning Logical Units Starting Common Assembly Language/32 (CAL/32) | 5-3<br>5-7<br>5-9 |

|      | 5.3.4     | Using Command Substitutions (CSS) Common Assembly Language/32 (CAL/32) Assembler End of Task (EOT) Codes                                                        | 5-11<br>5-13      |

| APPE | ENDIXES   |                                                                                                                                                                 |                   |

| A    | COMMON AS | SSEMBLY LANGUAGE/32 (CAL/32) ERROR CODES                                                                                                                        | A-1               |

| В    | OBJECT CO | DDE FORMAT                                                                                                                                                      | B-1               |

iv 48-050 F00 R03

# **FIGURES**

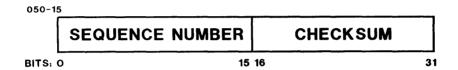

| 1-1<br>1-2<br>1-3<br>1-4<br>1-5<br>1-6<br>1-7<br>1-8<br>1-9<br>1-10<br>1-11<br>1-12<br>1-13 | Configuration of a Typical Uniprocessing System Configuration of a Typical Multiprocessing System RR Format (16-Bit) RX Format (16-Bit) RI Format (16-Bit) RR Format (32-Bit) RX1 Format (32-Bit) RX2 Format (32-Bit) RX3 Format (32-Bit) RI1 Format (32-Bit) RI2 Format (32-Bit) SF Format (32-Bit) RX7 Format (32-Bit) RX7 Format (32-Bit) RX7 Format (32-Bit) | 1-2<br>1-2<br>1-7<br>1-7<br>1-8<br>1-8<br>1-9<br>1-10<br>1-11<br>1-12<br>1-13<br>1-13 |     |

|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|-----|

| 3-1                                                                                         | Comment Statement Column Positioning                                                                                                                                                                                                                                                                                                                             | 3-2                                                                                   | 1   |

| 3-2<br>3-3                                                                                  | Source Program Sequence Identification Instruction Statement Positioning (Fixed Format)                                                                                                                                                                                                                                                                          | 3-2<br>3-3                                                                            | -   |

| TABLES                                                                                      |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                       | •   |

| 3-1                                                                                         | SUMMARY OF CAL/32 MACHINE INSTRUCTIONS AND MNEMONICS                                                                                                                                                                                                                                                                                                             | 3-12                                                                                  |     |

| 3-2                                                                                         | CAL/32 MACHINE INSTRUCTIONS AND MNEMONICS FOR THE 3200MPS FAMILY OF PROCESSORS                                                                                                                                                                                                                                                                                   | 3-12                                                                                  | 1   |

| 3-3                                                                                         | SUMMARY OF CAL/32 MACHINE INSTRUCTIONS AND MNEMONICS FOR THE SERIES 3211 PROCESSORS                                                                                                                                                                                                                                                                              | 3-21                                                                                  | •   |

| 3-4                                                                                         | EXTENDED BRANCH MNEMONICS                                                                                                                                                                                                                                                                                                                                        | 3-23                                                                                  |     |

| 3-5                                                                                         | USUAL EXTENDED BRANCH MNEMONICS FOR THE 3280 SYSTEM                                                                                                                                                                                                                                                                                                              | 3-25                                                                                  | 1   |

| 3-6                                                                                         | SUMMARY OF CAL/32 MACHINE INSTRUCTIONS AND                                                                                                                                                                                                                                                                                                                       | 2 27                                                                                  |     |

| 3-7                                                                                         | MNEMONICS FOR 3280 SYSTEM SUMMARY OF CAL/32 MACHINE INSTRUCTIONS AND                                                                                                                                                                                                                                                                                             | 3-27                                                                                  | 1   |

| 3-8                                                                                         | MNEMONICS FOR IOPS CONSTANT TYPES                                                                                                                                                                                                                                                                                                                                | 3-29<br>3-40                                                                          | ı   |

| 4-1                                                                                         | COMMON MODE ADDRESS OPERATIONS                                                                                                                                                                                                                                                                                                                                   | 4-1                                                                                   |     |

| 5-1                                                                                         | MEMORY REQUIREMENTS FOR HPM                                                                                                                                                                                                                                                                                                                                      | 5-1                                                                                   |     |

| 5-2                                                                                         | HPM MEMORY UTILIZATION                                                                                                                                                                                                                                                                                                                                           | 5-8                                                                                   | - 1 |

| 5-3                                                                                         | ASSEMBLY PERFORMANCE IMPROVEMENT USING HPM                                                                                                                                                                                                                                                                                                                       | 5-8                                                                                   | - 1 |

| 5-4                                                                                         | CAL/32 LOGICAL UNITS                                                                                                                                                                                                                                                                                                                                             | 5-9                                                                                   | İ   |

| B-1                                                                                         | 32-BIT LOADER ITEM DEFINITIONS                                                                                                                                                                                                                                                                                                                                   | B-2                                                                                   |     |

| B-2                                                                                         | 16-BIT LOADER ITEM DEFINITIONS                                                                                                                                                                                                                                                                                                                                   | B-4                                                                                   |     |

|                                                                                             |                                                                                                                                                                                                                                                                                                                                                                  |                                                                                       |     |

| INDEX                                                                                       |                                                                                                                                                                                                                                                                                                                                                                  | IND-1                                                                                 | -   |

48-050 F00 R03 v

#### **PREFACE**

This manual describes the Common Assembly Language/32 (CAL/32). Chapter 1 is an introduction to the basic concepts of the assembler, central processing unit (CPU) and main memory. Also described are the instruction formats for 16and machines, as well as variations in the formats. Chapter 2 introduces assembly language symbolic representation describes symbolic values. Chapter 3 defines the source program and contains a list of machine instructions, mnemonics and detailed descriptions of assembler instructions. Common mode programming and common mode operations are explained in Chapter CAL/32 operating instructions are listed in Chapter 5.

Appendix A contains CAL/32 error codes. Appendix B describes the 16- and 32-bit object code formats.

The F00 R03 version of this manual includes descriptions of new machine instructions for use with the 3280 System.

Included in this release of OS/32 is a new START option that assembles user created source programs over sixty percent faster than the standard method of assembly. A description of the high performance method (HPM) of assembly is found in Chapter 5. Included in this section is a description concerning optimization of the CAL/32 assembler.

The 3200MPS Family of Processors features identified throughout the manual are applicable to the 3200MPS Family of Processors only. This manual is intended for use with the OS/32 R08.2 software release and higher.

48-050 F00 R03 vii

|  | • |  |

|--|---|--|

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

|  |   |  |

# CHAPTER 1 BASIC CONCEPTS

#### 1.1 INTRODUCTION

Like all assemblers, Common Assembly Language/32 (CAL/32) simplifies the direct control of the processor by providing the programmer with a way of representing actual machine operations in an easily understood symbolic form. Assemblers translate symbolic representations of machine instructions into binary form to be executed by the processor. CAL/32 also includes such features as relocation, segmentation, complex data definitions and expression analysis. CAL/32 can run on any 32-bit processor and produce machine code for any 32-bit processor.

Because assembly language programming is so close to actual machine operations, it is essential that the assembly language programmer have a good understanding of system architecture. This chapter contains introductory architectural descriptions for uniprocessing systems and multiprocessing systems. See the appropriate Processor User Manual or Instruction Set Reference Manual for more detailed information.

#### 1.2 THE PROCESSOR

The main components of a processor are the central processing unit (CPU) and main memory. All processors, whether in a uniprocessing or a multiprocessing system, are stored-program, multiregister machines.

There are three iterations of the processor:

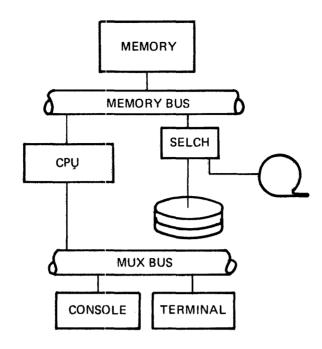

- A standard processor for a uniprocessing system. Figure 1-1 depicts the configuration of a typical uniprocessing system.

- A CPU in a multiprocessing system.

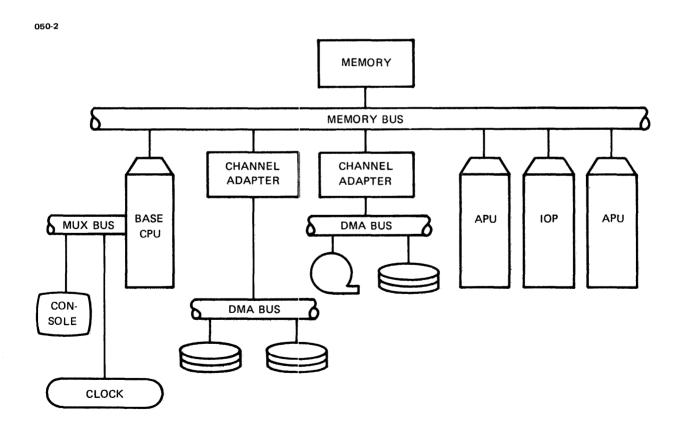

- Up to nine auxiliary or input/output processing units (APUs or IOPs) in a multiprocessing system. Figure 1-2 depicts the configuration of a typical multiprocessing system.

48-050 F00 R03 1-1

Figure 1-1 Configuration of a Typical Uniprocessing System

Figure 1-2 Configuration of a Typical Multiprocessing System

In addition to the standard tasks performed by the operating system in a uniprocessing system, the operating system in a multiprocessing system

- controls all APUs,

- monitors all activity in the multiprocessing system,

- services all APU exceptions,

- dispatches application tasks created for existing CPUs or the CPU in the 3200MPS Family of Processors, and

- dispatches tasks to the APUs and IOPs for execution in the 3200MPS Family of Processors.

The function of an APU is to execute tasks concurrently with the CPU and other APUs. The function of the IOP is to handle all input/output (I/O) devices configured under it, thereby relieving the CPU of I/O overhead.

# 1.2.1 Temporary Storage (Registers)

All processors have some amount of temporary storage that can be used as accumulators or index registers. There are three types of temporary storage:

- General-purpose registers

- Single precision floating point registers (SPFPR)

- Double precision floating point registers (DPFPR)

All processors have at least one set of 16 general-purpose registers. In the 16-bit processors, each general-purpose register holds 16 bits; in the 32-bit processors, each holds 32 bits. General-purpose registers can be used for integer arithmetic, address arithmetic, logical operations and character operations. Floating point registers are used only for floating point arithmetic operations. Processors with floating point registers have either eight single precision registers, or eight single precision registers and eight double precision registers. The single precision registers hold 32 bits. The double precision registers hold 64 bits.

For a multiprocessing system, there are up to ten sets of registers; one for each of the nine APUs that can be part of the system, plus a set in the CPU; (i.e., ten machines each having 16 general register sets, eight SPFPR and eight DPFPRs).

#### 1.2.2 Program Status Word (PSW)

The PSW defines the current state of a processing unit. The uniprocessing system has one current PSW. Since the 3200MPS Family of Processors consists of multiple processors, there is one current PSW for each processor. The PSW consists of three major parts:

- Status descriptor

- Condition code (CC)

- Location counter (LOC)

Individual bits and bit fields within the status descriptor portion of the PSW define the current state of interrupts and various hardware features of the processor. By setting or resetting bits within the status descriptor, the programmer can enable or disable such interrupts as I/O, arithmetic fault and machine malfunction. On those processors with multiple sets of general-purpose registers, a field in the status descriptor defines which set is currently in use. Programmers writing user level programs, as opposed to operating system or stand-alone programs, cannot directly access the status descriptor. In this case, the operating system maintains control of interrupts and registers.

The CC provides a means of controlling program flow, based on the results of instruction execution. As certain instructions are executed, the value in the CC changes to indicate the nature of the result. For example, if an operation produces a zero result, the CC may be changed to a zero value. With branch instructions, the programmer can test the value in the CC and branch or not, depending on that value. Not all instruction executions affect the CC. See the appropriate processor reference manual for more details.

The LOC controls the order of instruction execution. Normally, the processor executes instructions sequentially and uses the LOC to keep track of where the instructions are in main memory, then fetches the instruction from the memory location specified by the address contained in the LOC. It increments the LOC by the length of the instruction, executes the instruction and fetches the next instruction. Branch instructions, when executed, change the contents of the LOC and, thereby, affect the branch.

In 32-bit machines, the PSW contains 64 bits; the least significant 24 bits are reserved for the LOC. In 16-bit machines, the PSW contains 32 bits; the least significant 16 bits are reserved for the LOC.

1-4 48-050 F00 R03

### 1.2.3 Input/Output (I/O) Interface

The execution of certain machine instructions allows the programmer to control external devices and to cause the transfer of data between external devices and main memory or registers. The actual programming of I/O operations is very much dependent upon the hardware of both the processor and the peripherals. I/O instructions are restricted to operating systems and stand-alone programs. User programs can communicate with I/O devices through facilities provided by the operating system.

#### 1.2.3.1 Main Memory

To the assembly language programmer, main memory appears as a block of contiguous storage locations. The smallest unit of memory the programmer can access is the byte (eight bits). The programmer can also access halfwords (two bytes), fullwords (four bytes) and doublewords (eight bytes). Each byte in memory is accessed by a unique address. Memory addresses start with zero and are incremented by one for each succeeding byte. Memory addresses in the 32-bit processors always consist of 24 bits. In the 16-bit processors, memory addresses consist of 16 bits. When accessing bytes, any memory addresses within the limits of the particular hardware configuration is considered valid. Halfwords must be accessed with halfword addresses. Fullwords must be accessed with addresses that are multiples of four. Doublewords must be accessed with addresses that are multiples of eight.

#### 1.2.4 Software Relocation

Programs written in CAL/32 can be absolute or relocatable. An absolute program is one whose origin (starting location) is specified at assembly time as being at a fixed halfword location in memory. Subsequent addresses within the program, whether referring to instructions or data, are fixed at assembly time. For execution, absolute programs must always be loaded into memory at the location specified as the origin. This type of programming is useful in stand-alone applications and some operating system situations. A user program written with absolute addresses is relocatable, but the addresses that are used refer to their absolute values relative to task address 0. It is the actual location of this task, 0, which is relocatable.

Relocatable programs can be loaded for execution beginning at any halfword location in memory. The origin of a relocatable program is assumed to be relocatable zero. The CAL/32 output for this type of program specifies all addresses in the program as relative displacements from the origin. At link time, the linkage editor resolves all addresses within the program by adding a relocation value (the actual memory address for the start of the program) to the relative addresses supplied by CAL/32. Relocation applies only to addresses within the program. Relocatable programs can contain absolute data.

48-050 F00 R03 1-5

#### 1.2.5 Hardware Relocation

Some processors and their operating systems support hardware relocation and segmentation. Programs prepared for these systems start out as relocatable. A linkage editor processes the relocatable output from CAL/32 to link in any needed subprograms. The output of this process is an absolute program that, because of the relocating hardware, can be loaded beginning at any memory address that is a multiple of 256 for memory access controller (MAC) machines or 2,048 for memory address translator (MAT) machines. At run-time, the relocating hardware adds the required relocation value to all addresses supplied by the program. This relocating hardware also provides for program segmentation, where the program is divided into pieces that can be loaded into noncontiguous blocks of memory.

CAL/32 supports segmentation by allowing the programmer to divide the program into pure and impure segments. The pure segment of a program consists of machine instructions and constant data and cannot be modified at run-time. (The operating system and the hardware prevent modification.) The impure segment consists of the data base which can be modified at run-time. Programs prepared as pure and impure segments can be shared (executed concurrently) by several users. Only one copy of the pure segment resides in memory during execution while there is one copy of the impure segment for each user.

#### 1.3 INSTRUCTION FORMATS (16-BIT)

The 16-bit processors have four types of machine instructions: register-to-register (RR), register and indexed storage (RX), register and immediate (RI) and short form (SF). The following abbreviations illustrate the instruction formats:

- OP Operation

- Rl First operand register

- R2 Second operand register

- N A 4-bit immediate value

- X2 Second operand index register

- A2 Second operand direct address

- 12 Second operand immediate value

Most instructions require two operands, the first of which is contained in a register. The result usually replaces the contents of the first operand register. Exceptions to these rules are noted in Section 1.5.

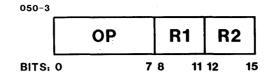

#### 1.3.1 Register-to-Register (RR) Instructions

RR instructions cause operations to take place between operands contained in registers. RR instructions are 16 bits long, as shown in Figure 1-3.

1-6 48-050 F00 R03

Figure 1-3 RR Format (16-Bit)

The first eight bits of the instruction define the operation. The next four bits identify the first operand register. The final four bits identify the second operand register. In most RR instructions, the specified operation takes place between the contents of the first operand register and the contents of the second operand register. The result of the operation replaces the contents of the first operand register.

## 1.3.2 Register and Indexed Storage (RX) Instructions

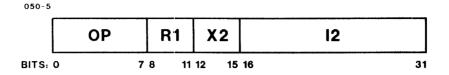

RX instructions cause an operation to take place between a first operand, contained in a register, and a second operand, located in main memory. These instructions require 32 bits, as shown in Figure 1-4.

Figure 1-4 RX Format (32-Bit)

The first eight bits define the operation. The next four bits identify the first operand register and the next four bits identify an optional index register. The remaining 16 bits specify an address in main memory. The operation takes place between the contents of the first operand register and the contents of the memory location specified. The actual address of the second operand is determined by adding the contents of the index register to the contents of the address field. If the index field of the instruction contains zero, no indexing takes place. In most cases, the result of the operation replaces the contents of the first operand register.

#### 1.3.3 Register and Immediate (RI) Instructions

RI instructions cause operations to take place between the contents of a register and the contents of an immediate field embedded in the instruction itself. They are 32 bits long, as shown in Figure 1-5.

Figure 1-5 RI Format (32-Bit)

The first eight bits specify the operation; the next four bits identify the first operand register; the next four bits identify an optional index register; the final 16 bits are the immediate value. The first operand is the contents of the first operand register. The second operand is obtained by adding the contents of the index register to the contents of the immediate field. If the index field contains zero, no addition takes place. The result of the operation usually replaces the contents of the first operand register.

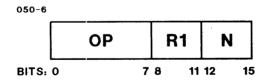

#### 1.3.4 Short Form (SF) Instructions

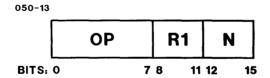

SF instructions are variations on the RI instructions in which the second operand is small enough to be expressed in four bits. SF instructions require 16 bits, as shown in Figure 1-6.

Figure 1-6 SF Format (16-Bit)

The first eight bits indicate the operation. The next four bits identify the first operand register and the 4-bit immediate field. The next four bits contain the immediate value. Operations take place between the contents of the first operand register and the 4-bit immediate operand. The result of the operation usually replaces the contents of the first operand register.

1-8 48-050 F00 R03

#### 1.4 INSTRUCTION FORMATS (32-BIT)

The 32-bit processors recognize seven different types of instructions. They are: RR, three variations on RX, two variations on RI, and SF. The following abbreviations are used to illustrate instruction formats:

OP Operation R1 First operand register R2 Second operand register N A 4-bit immediate value X2 Second operand single index register Second operand displacement D2 FX2 Second operand first index register SX2 Second operand second index register Second operand direct address **A2** 12 Second operand immediate value Ll Length of first operand string Length of second operand string L2

Most instructions require two operands. The first is the contents of a register. The result of the operation usually replaces the contents of the first operand register. Exceptions to these rules are noted in Section 1.5.

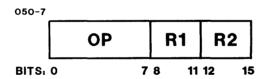

### 1.4.1 Register-to-Register (RR) Instructions

The format and function of these instructions are the same as for the 16-bit processors. They cause operations to take place between operands contained in registers and they require 16 bits. These instructions are shown in Figure 1-7.

Figure 1-7 RR Format (32-Bit)

The first eight bits specify the operation. The next four bits identify the first operand register and the last four bits identify the second operand register. The processor performs the indicated operation between the contents of the first operand register and the contents of the second operand register. In most RR instructions, the result replaces the contents of the first operand register.

48-050 F00 R03 1-9

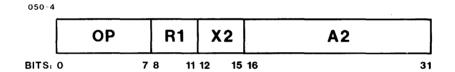

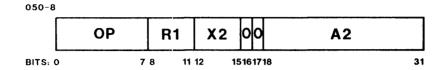

#### 1.4.2 Register and Indexed Storage One (RX1) Instructions

RX1 instructions define an operation between the contents of a register and the contents of a main memory location. They require 32 bits, as shown in Figure 1-8.

Figure 1-8 RX1 Format (32-Bit)

The first eight bits define the operation. The next four bits identify the first operand register and the next four bits identify the optional index register. The next two bits, 16 and 17, must be zeros. The next 14 bits constitute a direct program address in a range from 0 to 16,383.

The address of the second operand is obtained by adding the contents of the index register to the contents of the 14-bit address field. If the index register field contains zero, this addition does not take place and the contents of the address field are used as the address. The operation takes place between the contents of the first operand register and the contents of the specified memory location. The result usually replaces the contents of the first operand register.

#### 1.4.3 Register and Indexed Storage Two (RX2) Instructions

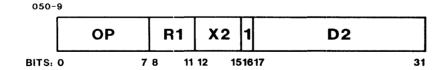

RX2 instructions define operations between the contents of a register and the contents of a location in main memory. RX2 instructions are like the RX1 instructions; they require 32 bits. They differ from the RX1 instructions in the method of calculating the second operand address. See Figure 1-9.

Figure 1-9 RX2 Format (32-Bit)

The first eight bits define the operation; the next four bits identify the first operand register and the next four bits identify the optional index register. The next bit, 16, must be a one. The remaining 15 bits are treated as a signed integer in two's complement notation. Bit 17 is the sign bit which, if one, indicates a negative quantity, and if zero, indicates a positive quantity.

The address of the second operand is obtained in two steps.

- 1. The signed integer, with sign bit extended to produce a 32-bit integer, is added to the contents of the index register.

- 2. This intermediate result is added to the value in the incremented LOC. The result is truncated to 24 bits.

If the index register field is zero, the first addition does not take place. The indicated operation takes place between the contents of the first operand register and the contents of the specified memory location. The result usually replaces the contents of the first operand register.

#### 1.4.4 Register and Indexed Storage Three (RX3) Instructions

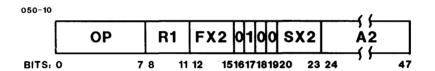

RX3 instructions are analogous to the RX instructions in the 16-bit processors. They call for operations between the contents of a register and the contents of an indexed memory location and require 48 bits. See Figure 1-10.

Figure 1-10 RX3 Format (32-Bit)

The first eight bits specify the operation; the next four bits identify the first operand register and the next four bits identify the optional first index register. Bit 16 must be zero. Bit 17 must be one. Bits 18 and 19 must be zero. The next four bits identify the optional second index register. The final 24 bits contain a direct memory address.

The address of the second operand is obtained by adding the contents of the first index register to the contents of the second index register. This intermediate result is then added to the contents of the direct address field, and the final result is truncated to 24 bits.

If either of the index register fields contains zero, that level of indexing does not take place. If both are zero, no indexing takes place. In most RX3 instructions, the operation takes place between the contents of the first operand register and the contents of the specified memory location. The result usually replaces the contents of the first operand register.

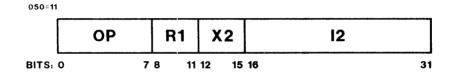

#### 1.4.5 Register and Immediate One (RII) Instructions

RIl instructions are similar to the RI instructions in the 16-bit processors. They specify operations that take place between the contents of a register and the contents of a field that is part of the instruction. They require 32 bits, as shown in Figure 1-11.

Figure 1-11 RII Format (32-Bit)

The first eight bits indicate the operation. The next four bits identify the first operand register and the next four bits identify an index register. The final 16 bits are the immediate value. The second operand is obtained by extending the contents of the immediate field to 32 bits, by propagating the sign bit and then adding this quantity to the contents of the index register. If the index register field is zero, no addition takes place and the extended immediate value is the second operand. The operation takes place between the contents of the first operand register and the immediate value. The result usually replaces the contents of the first operand register.

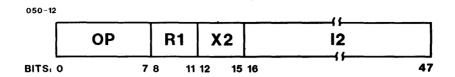

#### 1.4.6 Register and Immediate Two (RI2) Instructions

RI2 instructions are similar to the RI1 instructions except that the immediate field contains a 32-bit value and the instruction itself requires 48 bits. See Figure 1-12.

Figure 1-12 RI2 Format (32-Bit)

The first eight bits define the operation. The next four bits identify the first operand register. The next four bits identify the optional index register. The final 32 bits are the immediate value. The second operand is obtained by adding the contents of the index register to the contents of the immediate field. If the index register field is zero, no addition takes place and the immediate value is the second operand. The operation takes place between the contents of the first operand register and the immediate value. The result usually replaces the contents of the first operand register.

#### 1.4.7 Short Form (SF) Instructions

SF instructions are similar to the SF instructions in the 16-bit processors. They specify operations between the contents of a register and the contents of an immediate field whose value is small enough to be expressed in four bits. These instructions require 16 bits, as shown in Figure 1-13.

Figure 1-13 SF Format (32-Bit)

The first eight bits define the operation. The next four bits identify the first operand register. The next four bits are the immediate field. The operation then takes place between this value and the contents of the first operand register. The result usually replaces the contents of the first operand register.

48-050 F00 R03 1-13

# 1.4.8 Register and Indexed Storage/Register and Indexed Storage (RXRX) Instructions

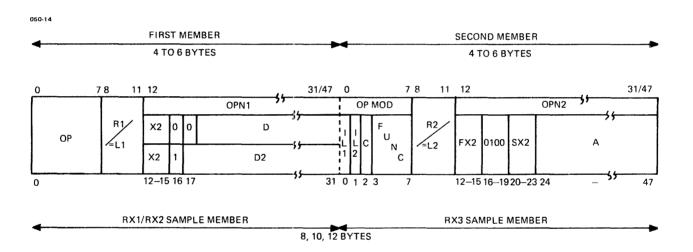

RXRX instructions resemble a pair of adjacent RX instructions, but represent one cohesive string-processing instruction. An RXRX instruction is comprised of two instruction members. Each member can be any one of the RX1, RX2 or RX3 machine formats, independent of the other member's format. For example, the first instruction member might be of the RX1 format and the second instruction member might be of the RX3 format, yielding a 10-byte RXRX instruction. Thus, an RXRX instruction length might range from 8, 10 or 12 bytes.

The first eight bits of the first instruction member, OP, specify the operation class. The particular RXRX operation is specified by the contents of the operation-modifier (OP-MOD) field in the first eight bits of the second instruction member. OP-MOD is actually generated by the assembler according to the specific RXRX operation mnemonic and the R1/L1 or R2/L2 fields programmed by the user in source code. See Figure 1-14.

Figure 1-14 RXRX Format (32-Bit)

The next four bits in the first instruction member, Rl/Ll, identify either Rl, the string's length-specifying register or Ll, the string's actual length. The user specifies to the assembler whether the value in the Rl/Ll field is a register or an immediate value.

1-14 48-050 F00 R03

The Rl/Ll field is assumed to be a register unless an equal sign (=) precedes the Ll source expression. In machine format, the ILl field is set when the =Ll source field specifies an immediate value as length. The IL2 field in machine format is reset when the Rl field is used to specify a register that contains the string's length. When the length is an immediate value, its value may range from 0 through 15. When the length is in a register, the register may contain a length that ranges from 0 through exponent  $2^{24}$  -l. A length of 0 indicates a null string.

The remaining bits, 12 through 31 or 12 through 47, of the first instruction member, OPN1, contain the address/location of the lowest addressable byte of a string or its storage location. The field, OPN1, is then similar to the indexed address portion of an RX1, RX2 or RX3 machine format.

The first eight bits of the second instruction member, OP-MOD, are an operation-modifier field containing OPN1's length indicator, IL1, in bit 0; OPN2's length indicator, IL2, in bit 1; a special circumstances bit, C, in bit 2, and in bits 3 through 7, FUNC, the specific function code of the general operation class, OP. As described above, IL1 and IL2 are determined by the assembler. The special circumstances bit, C, and function code, FUNC, are determined by the assembler from the operation-mnemonic. The C bit is used by some RXRX instructions to indicate that the result of the operation will be forced positive.

The next four bits, bits 8 through 11, of the second instruction member, R2/L2, identify either R2, this string's length-specifying register or L2, the string's actual length. Again, the user specifies in source format to the assembler whether the value in the R2/L2 field is a register or an immediate value. The R2/L2 source format field is assumed to be a register unless an equal sign (=) precedes the L2 source expression. In machine format, IL2 is set when the =L2 field is used to specify an immediate value. IL2 is reset when R2 is used to specify a register. When the length is an immediate value, expressed as =L2, its value may range from 0 through 15. When the length is in a register, its value may range from 0 through exponent  $2^{24}$  -1. A zero length indicates a null string.

The remaining bits, 12 through 31 or 12 through 47, of the second instruction member, OPN2, contain the address/location of the lowest addressable byte of a second member's string. Both OPN1 and OPN2 are similar in format to the indexed address portion of an RX1, RX2 or RX3 machine format. The particular format of either OPN1 or OPN2 is selectively generated by the assembler, independently, according to the user source program.

In RX1 machine format, bits 16 and 17 are zero. Bits 12 through 15 identify the index register, X2, the contents of which are added to the absolute 14-bit value, D, to formulate the string's address.

48-050 F00 R03 1-15

In RX2 machine format, bit 16 is set. Bits 12 through 15 identify the index register, X2, the contents of which are added to the 15-bit displacement value, D2, to formulate the string's address.

In RX3 machine format, bits 16 through 19 are 0100 binary. Bits 12 through 15 identify the first index register, FX2 and bits 20 through 23 identify the second index register, SX2. The contents of both are added to the 24-bit address value, A, to formulate the string's address.

#### NOTES

- 1. When the first member's OPN1 represents the string's address in RX2 format, the displacement value, D2, is relative to the end address of the first instruction member, not to the end of the full RXRX instruction.

- 2. When the second member's OPN2 represents the string's address in RX2 format, the displacement value is relative to the end of the second instruction member, which is also the end of the full RXRX instruction.

#### 1.5 VARIATIONS ON INSTRUCTION FORMATS

Not all instructions follow the preceeding instruction formats.

Instructions may also have the following formats:

- Fields are redefined

- Instructions require two operands

- Instructions do not change the first operand

- Instructions change the second operand

- Instructions change neither operand

#### 1.5.1 Conditional Branch Instructions

Conditional branch instructions use formats that resemble RR, RX and SF instructions. However, the interpretation of the fields differs from the standard, as does the actual operation. In all conditional branch instructions, the first operand identification is interpreted as a mask that is ANDed with the condition code. If the result of this test indicates that the branch is to be taken, then the second operand address is the location to which the processor must go to obtain the next instruction.

1-16 48-050 F00 R03

In the RR instructions, the second operand register contains the branch address. In the RX instructions, the branch address is obtained by one of the standard methods for obtaining second operand addresses. In the SF instructions, the immediate field is interpreted as a halfword displacement, either forward or backward, from the current LOC. The branch address is obtained by adding or subtracting this quantity from the current LOC.

#### 1.5.2 Branch and Link Instructions

These instructions facilitate branching to and returning from subroutines. They use formats similar to RR and RX where the first operand register is the link register. Before the branch is taken, the address of the next memory location following the branch instruction is placed in this register. In the RR instructions, the branch location is the contents of the second operand register. In the RX instruction, the branch address is obtained by one of the usual methods for obtaining second operand addresses.

#### 1.5.3 Other Variations

Some instructions change the second operand rather than the first. Most notable among these are the store instructions and the instructions that add the contents of a register to the contents of a memory location.

Test instructions and compare instructions change neither operand. The indicated operation takes place between the two operands, but neither is changed. The result of the operation is indicated by the condition code.

Certain other instructions, such as Load PSW and Simulate Interrupt, do not always require a first operand. In addition, all of the I/O instructions do not follow the general rules. For detailed information on how these instructions work, see the appropriate Processor Reference Manual.

48-050 F00 R03 1-17

|  |  | • |  |

|--|--|---|--|

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

|  |  |   |  |

# CHAPTER 2 SYMBOLIC REPRESENTATION

#### 2.1 INTRODUCTION

When writing assembly language programs, the programmer uses meaningful symbols to represent the binary language interpreted by both Common Assembly Language/32 (CAL/32) and the processor. Symbols consist of printable ASCII characters, either singly or in combination. CAL/32 recognizes the complete set of printable ASCII characters. However, depending on the context, there can be restrictions on the use of the complete set. See Chapter 3 for further details.

#### 2.2 SYMBOLS AND EXPRESSIONS

Symbols represent addresses, register identifiers, absolute values, operation identifiers and constants. Examples of symbols are:

A LOOP BXLE PART1 REG5 16

Symbols can be combined to form expressions. The arithmetic operators: add, subtract, multiply and divide are represented in CAL/32 by the symbols: +, -, \* and /. They combine with other symbols to form arithmetic expressions. Examples of these arithmetic expressions are:

A+B LAST-FIRST\*TWO A-16

Blanks and parentheses are not permitted within an expression. For example, the following sequence would not be interpreted by CAL/32 as an expression.

A - B \* (C + D)

48-050 F00 R03

Depending on the context, CAL/32 might misinterpret the symbols, generate incorrect code and fail to detect the error. Where CAL/32 can recognize the error, it generates an error message.

The evaluation of expressions takes place from left to right with no rules of precedence. Thus, CAL/32 evaluates the expression:

LAST-FIRST\*TWO

by subtracting the value of FIRST from the value of LAST, and multiplying this result by the value of TWO.

Logical expressions consist of symbols joined by the logical operators AND and inclusive OR. They are represented in CAL/32 by the symbols & and !. Examples of logical expressions are:

X&Y!A CHAR&NULL

Logical expressions are evaluated from left to right with no rules of precedence. Blanks and parentheses are not permitted in logical expressions.

Mixed expressions are formed by combining logical and arithmetic operators. For example:

A-B!TWO

CAL/32 evaluates this expression by first subtracting the value of B from the value of A and then ORing the result with the value of TWO. Mixed expressions are like arithmetic and logical expressions in that blanks and parentheses are not allowed and the method of evaluation is from left to right with no rules of precedence.

Symbols represent either absolute or relocatable quantities. At assembly time, relocatable quantities have a value equal to their displacement from some fixed point within the program, usually but not necessarily, the origin or starting location. At load time, the relocatable quantity is replaced by an absolute quantity whose value is calculated by adding the relocation value to the relocatable quantity. Absolute quantities are known to the assembler at assembly time and are not changed at load time.

The operations: multiply, divide, AND and OR are permitted only between absolute data. The plus and minus operators can be used on mixed data. The results of such operations are:

2-2 48-050 F00 R03

| Absolute + Absolute       | Absolute    |

|---------------------------|-------------|

| Absolute - Absolute       | Absolute    |

| Relocatable + Relocatable | Invalid     |

| Relocatable - Relocatable | Absolute    |

| Relocatable + Absolute    | Relocatable |

| Relocatable - Absolute    | Relocatable |

| Absolute + Relocatable    | Relocatable |

| Absolute - Relocatable    | Invalid     |

#### 2.3 SYMBOLS AND THEIR VALUES

OPERATION

By definition, certain symbols used in CAL/32 programming have implicit values; that is, the value of the symbol is determined by the way in which it is expressed and used. Examples of this kind of symbol are the decimal, hexadecimal and character symbols used as operands in instructions. There are also global symbols in CAL/32. These symbols have preset values that cannot be redefined by the programmer. The programmer can define the value of a symbol explicitly by using the equate statement. This section covers the use of implicit and global symbols. Chapter 3 covers the explicit use and definition of symbols.

RESULT

# 2.3.1 Implicit Symbols

When used in the correct context, a string of decimal digits is automatically assigned the actual value of the number represented by the string. For example, the expression:

#### A+14

has a value that the assembler determines by adding the quantity 14 to the value A, which must be defined by some other means.

CAL/32 also recognizes the implicit value of special character strings the programmer uses to represent decimal, hexadecimal and character values. These strings are made up of a single letter that indicates the particular type, followed by a group of characters enclosed in apostrophes that represents the value. The code characters are:

| CODE<br>CHARACTER | T         | YPE         |

|-------------------|-----------|-------------|

| Н                 | Halfword  | decimal     |

| F                 | Fullword  | decimal     |

| X                 | Halfword  | hexadecimal |

| Y                 | Fullword  | hexadecimal |

| С                 | Character | r           |

Decimal numbers consist of an optional sign (+ or -) followed by decimal digits representing the actual value. Commas are not allowed in the representation. Halfword decimal values can be represented by one to five decimal digits, with a range from -32,768 to +32,767. Fullword values can be represented by one to ten decimal digits, with a range from -2,147,483,648 to +2,147,483,647. CAL/32 converts these decimal numbers into two's complement binary integers. Examples of decimal symbols, with their internal representation expressed in hexadecimal notation, are:

| SYMBOL    | VALU | JE   |

|-----------|------|------|

| H'125'    | 007D |      |

| H'32765'  | 7FFD |      |

| H'+32765' | 7FFD |      |

| H'-15'    | FFF1 |      |

| F'123123' | 0001 | EOF3 |

| F'1'      | 0000 | 0001 |

| F'-2'     | FFFF | FFFE |

Hexadecimal symbols consist of the X or Y type code followed by a string of hexadecimal digits enclosed in apostrophes. Halfword symbols can use from one to four digits. Fullword symbols can use from one to eight digits. Leading zeros are not required and the value is right justified. Examples of hexadecimal symbols are:

| SYMBOL | VALUE |      |  |

|--------|-------|------|--|

| X'F'   | 000F  |      |  |

| X'D4E' | OD4E  |      |  |

| Y'030' | 0000  | 0030 |  |

| Y'A'   | 0000  | 000A |  |

| Y'0'   | 0000  | 0000 |  |

Character symbols consist of one to four ASCII characters enclosed in apostrophes and preceded by the type code C. Characters are right justified, with zero fill. Depending on the context, either a halfword or a fullword results. Examples of character symbols are:

| SYMBOL  | VALUE<br>(HALFWORD) | VALUE<br>(FULLWORD) |      |

|---------|---------------------|---------------------|------|

| C'*1    | 002A                | 0000                | 002A |

| C'12'   | 3132                | 0000                | 3132 |

| C'AB'   | 4142                | 0000                | 4142 |

| C'1234' | 3334                | 3132                | 3334 |

In the last example, where a halfword value was generated, only the right-most two characters were used. Where the context dictates a halfword and a longer string is used, a truncation error results. One final type of implicit assignment occurs in the use of symbols as statement identifiers. Where a symbol is used in the name field of a statement, it is automatically assigned a value equal to the value of the current location counter (LOC). This type of assignment is covered in Chapter 4.

#### 2.3.2 Global Symbols

Six symbols recognized by CAL/32 have predetermined values. They are:

ADC LADC PURETOP IMPTOP ABSTOP

The use of these symbols is somewhat restricted and they cannot be redefined by the programmer.

In programs written for 32-bit processors, the address length constant (ADC) always has a value of 4, the length of an address constant in bytes. (In 32-bit processors, addresses must be contained in fullwords, even though the actual address is only 24 bits in length.) In programs for which CAL/32 is to generate 16-bit code, the ADC has the value of 2. In programs written for 32-bit processors, the log (base 2) of the address length constant (LADC) always has a value of 2. In programs for 16-bit processors, the LADC always has a value of 1. Both of these symbols, the ADC and the LADC, are used most frequently in common mode programming. See Chapter 4.

The symbols PURETOP, IMPTOP, and ABSTOP have values equal to:

PURETOP The next available location in the pure segment

IMPTOP The next available location in the impure segment

ABSTOP The next available location in the absolute segment

Because these values change during assembly, the symbols must be used carefully. They can be used as second operand identifiers in machine instructions and as operands in assembler instructions where they are treated as address values. They cannot be used in assembler instructions that control the LOC.

48-050 F00 R03 2-5

The asterisk symbol (\*), used as an operand rather than an operator in an expression, always has a value equal to the value of the current LOC. Throughout the assembly process, CAL/32 maintains a LOC analogous to the hardware LOC contained in the central processing unit (CPU). Depending on the organization of the program, this LOC can contain any one of several values. For 32-bit programs, the LOC may point to the current location in the absolute segment, the pure segment or the impure segment. For 16-bit assemblies, the LOC may point to the current absolute location or the current relocatable location.

#### NOTE

While processing within block data programs, common block definitions or structure definitions, LOC has an absolute nonrelocatable value. This value is equivalent to the offset from the beginning of the block, common or structure definition to the current location.

2-6

# CHAPTER 3 THE SOURCE PROGRAM

## 3.1 INTRODUCTION

The source program consists of a set of assembly language statements that perform the following functions:

- Specify the operations to be performed by the processor

- Define the constants and storage areas for the program