Publication Number 29-215

INFORMATION CONTAINED IN THIS MANUAL IS SUBJECT TO DESIGN CHANGE OR PRODUCT IMPROVEMENT

xy hisre.

© INTERDATA INC., 1970 All Rights Reserved Printed in U.S.A. • September 1970

### QUICK REFERENCE INDEX

To aid in quickly locating a particular chapter, the index marks on the edge of this page are aligned with similar marks on the first page of each chapter.

| Chapter 1  | INTRODUCTION                             |  |

|------------|------------------------------------------|--|

| Chapter 2  | SYSTEM DESCRIPTION                       |  |

| Chapter 3  | INSTRUCTION FORMATS AND ADDRESSING MODES |  |

| Chapter 4  | INSTRUCTION REPERTOIRE                   |  |

| Chapter 5  | INPUT/OUTPUT (I/O) SYSTEM                |  |

| Chapter 6  | MEMORY SYSTEM                            |  |

| Chapter 7  | CONTROL PANEL                            |  |

| Chapter 8  | PERIPHERAL DEVICES                       |  |

| Chapter 9  | CONFIGURATION AND INSTALLATION PLANNING  |  |

| Chapter 10 | BASIC MODEL 1 PROGRAMMING                |  |

| Chapter 11 | MODEL 1 SOFTWARE                         |  |

## **MODEL 1 USER'S MANUAL**

| Chapter |              |                                                                                                                                                                                                                                                                                                                                                                                 | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | INTRODUCTION |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|         | 1.1          | General Features                                                                                                                                                                                                                                                                                                                                                                | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | 1.2          | Memory                                                                                                                                                                                                                                                                                                                                                                          | 1-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | 1.3          | Input/Output<br>1.3.1 Multiplexor Bus<br>1.3.2 Direct Memory Access Channel (DMAC)                                                                                                                                                                                                                                                                                              | 1-1<br>1-1<br>1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|         | 1.4          | Control Options                                                                                                                                                                                                                                                                                                                                                                 | 1-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         | 1.5          | <ul> <li>Peripherals</li> <li>1.5.1 Digital Multiplexor</li> <li>1.5.2 Intertape System</li> <li>1.5.3 Mini Disc System</li> <li>1.5.4 Magnetic Tapes</li> <li>1.5.5 Data Communications Equipment</li> <li>1.5.6 Paper Tape Equipment</li> <li>1.5.7 Card Reader</li> <li>1.5.8 System Modules</li> <li>1.5.9 Conversion Equipment</li> <li>1.5.10 Other Interfaces</li> </ul> | $1-3 \\ 1-3 \\ 1-3 \\ 1-3 \\ 1-3 \\ 1-3 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 \\ 1-4 $ |

|         | 1.6          | Software<br>1.6.1 Assembler<br>1.6.2 Model 1 Text Editor<br>1.6.3 Model 1 Debug<br>1.6.4 Model 1 Loader<br>1.6.5 Model 1 Diagnostics<br>1.6.6 Model 1 Monitor<br>1.6.7 Model 3, 4, 5/Model 1 Assembler<br>1.6.8 Model 1 Simulator                                                                                                                                               | 1-4<br>1-5<br>1-5<br>1-5<br>1-5<br>1-5<br>1-6<br>1-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|         | 1.7          | Customer Support<br>1.7.1 Field Service<br>1.7.2 Training Center<br>1.7.3 Systems Engineering                                                                                                                                                                                                                                                                                   | 1-6<br>1-6<br>1-6<br>1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|         | 1.8          | Interchange                                                                                                                                                                                                                                                                                                                                                                     | 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2       | SYST         | 'EM DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

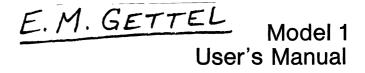

|         | 2.1          | General Block Diagram Description                                                                                                                                                                                                                                                                                                                                               | 2-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|         |              | <ul> <li>2.1.1 Program Status Word (PSW)</li> <li>2.1.2 Page Buffer Register (PBR)</li> <li>2.1.3 Page Address Register (PAR)</li> <li>2.1.4 Byte Address Register (BAR)</li> </ul>                                                                                                                                                                                             | 2-2<br>2-2<br>2-2<br>2-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

~

#### Chapter

|   |      | <ul> <li>2.1.5 Memory Data Register (MDR)</li> <li>2.1.6 Instruction Register(IR)</li> <li>2.1.7 Accumulator Register (AR)</li> <li>2.1.8 Interrupt Queue Register (IQR)</li> <li>2.1.9 Interrupt Mask Register (IMR)</li> <li>2.1.10 Serial Input/Output Port</li> <li>2.1.11 Multiplexor I/O Bus</li> <li>2.1.12 Memory Bus</li> <li>2.1.13 Memory Modules</li> </ul> | 2-2<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-4<br>2-5 |

|---|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

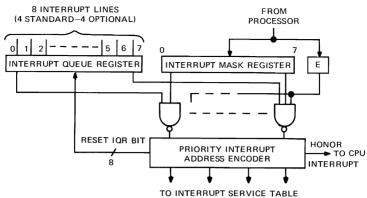

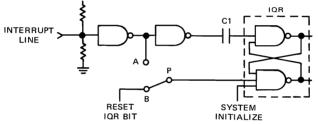

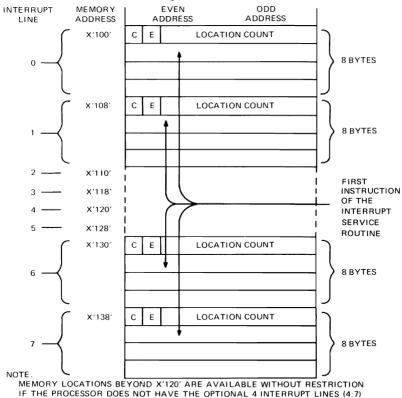

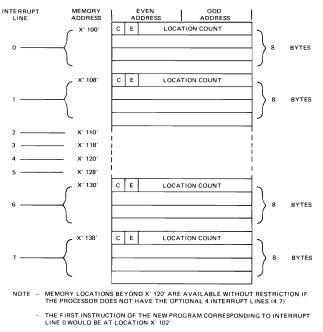

|   | 2.2  | Interrupts<br>2.2.1 Introduction<br>2.2.2 Block Diagram<br>2.2.2.1 Interrupt Queue Register (IQR)<br>2.2.2.2 Interrupt Mask Register (IMR)<br>2.2.2.3 Interrupt Enable (E) Bit<br>2.2.2.4 Interrupt Service Table<br>2.2.3 General Notes on Interrupts                                                                                                                  | 2-5<br>2-5<br>2-6<br>2-6<br>2-7<br>2-7<br>2-8<br>2-9                      |

| 3 | INST | RUCTION FORMATS AND ADDRESSING MODES                                                                                                                                                                                                                                                                                                                                    | 3-1                                                                       |

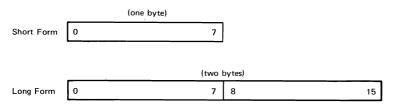

|   | 3.1  | Introduction                                                                                                                                                                                                                                                                                                                                                            | 3-1                                                                       |

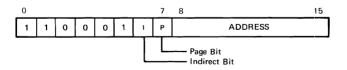

|   | 3.2  | Instruction Formats<br>3.2.1 A Register/Carry Format<br>3.2.2 Input/Output Format<br>3.2.3 Command Format<br>3.2.4 Shift/Rotate Instruction Format<br>3.2.5 Immediate Format<br>3.2.6 Memory Reference Format                                                                                                                                                           | 3-2<br>3-2<br>3-3<br>3-3<br>3-3<br>3-4<br>3-4                             |

|   | 3.3  | Addressing Modes<br>3.3.1 Direct Addressing Mode<br>3.3.2 Indirect Addressing Mode<br>3.3.3 Auto-Indexing                                                                                                                                                                                                                                                               | 3-4<br>3-5<br>3-6<br>3-7                                                  |

|   | 3.4  | Addressing Mode Summary                                                                                                                                                                                                                                                                                                                                                 | 3-9                                                                       |

| 4 | INST | RUCTION REPERTOIRE                                                                                                                                                                                                                                                                                                                                                      | 4-1                                                                       |

|   | 4.1  | Introduction                                                                                                                                                                                                                                                                                                                                                            | 4-1                                                                       |

|   | 4.2  | <ul> <li>A Register-Carry Instructions</li> <li>4.2.1 Add One to A AO</li> <li>4.2.2 Test and Skip TS</li> <li>4.2.3 Complement A CA</li> <li>4.2.4 Add A to A with Carry Out AA</li> <li>4.2.5 Clear Accumulator CLR</li> </ul>                                                                                                                                        | 4-1<br>4-2<br>4-3<br>4-3<br>4-3<br>4-4                                    |

| Chapter |     |         |                                      | Page         |

|---------|-----|---------|--------------------------------------|--------------|

|         |     | 4.2.6   | No Operation NOP                     | 4-4          |

|         |     | 4.2.7   | Set Carry SC                         | 4-4          |

|         |     | 4.2.8   | Reset Carry RC                       | 4-4          |

|         |     | 4.2.9   | Complement Carry CC                  | 4-5          |

| 4       | 4.3 | Shift/H | Rotate Instructions                  | 4-5          |

|         |     | 4.3.1   | Shift SH                             | 4-6          |

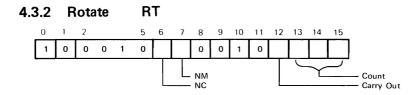

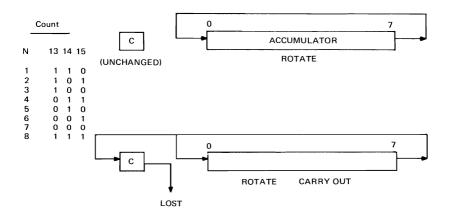

|         |     | 4.3.2   | Rotate RT                            | 4-8          |

| 4       | 4.4 | -       | Output Instructions                  | 4-9          |

|         |     |         | Address ADR                          | 4-10         |

|         |     | 4.4.2   | Output Command OC                    | 4-10         |

|         |     |         | Write Data WD                        | 4 - 10       |

|         |     | 4.4.4   | Write Data and Skip WDS              | 4-11         |

|         |     | 4.4.5   | Acknowledge AK                       | 4-12         |

|         |     | 4.4.6   | Sense Status SS                      | 4-12         |

|         |     | 4.4.7   | Read Data RD                         | 4 - 12       |

|         |     | 4.4.8   | Read Data and Skip RDS               | 4-12         |

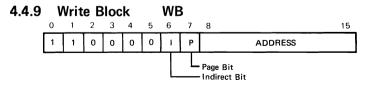

|         |     | 4.4.9   | Write Block WB                       | 4-13         |

|         |     | 4.4.10  | Read Block RB                        | 4-14         |

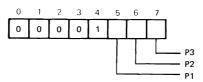

|         |     | 4.4.11  | Pulsed I/O PI0 P1, P2, P3            | 4-15         |

| 4       | .5  | Comm    | and Instruction                      | 4-16         |

|         |     | 4.5.1   | Command C                            | <b>4-1</b> 6 |

| 4       | .6  |         | liate Instructions                   | 4-18         |

|         |     |         | Load Immediate LI                    | 4-19         |

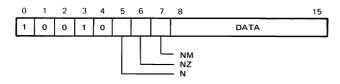

|         |     |         | And Immediate NI                     | 4-20         |

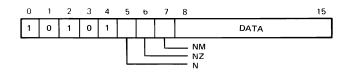

|         |     |         | OR Immediate OI                      | 4-20         |

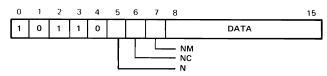

|         |     |         | Exclusive OR Immediate XI            | 4-20         |

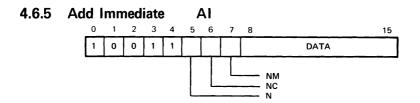

|         |     |         | Add Immediate AI                     | 4-21         |

|         |     | 4.6.6   | Subtract Immediate SI                | 4-21         |

| 4       | .7  |         | ry Reference Instructions            | 4-21         |

|         |     | 4.7.1   | Branches                             | 4-22         |

|         |     |         | 4.7.1.1 Branch B                     | 4-23         |

|         |     |         | 4.7.1.2 Direct In Page Zero          |              |

|         |     |         | (Bits 6 and $7 = 00$ )               | 4-23         |

|         |     |         | 4.7.1.3 Direct In Current Page       |              |

|         |     |         | (Bits 6 and $7 = 01$ )               | 4-23         |

|         |     |         | 4.7.1.4 Indirect through Page Zero   |              |

|         |     |         | (Bits 6 and $7 = 10$ )               | 4-23         |

|         |     |         | 4.7.1.5 Indirect through the Current |              |

|         |     |         | Page (Bits 6 and $7 = 11$ )          | 4-24         |

|         |     | 4.7.2   |                                      | 4-24         |

|         |     |         | 4.7.2.1 Direct In Page Zero          |              |

|         |     |         | (Bits 6 and $7 = 00$ )               | 4-24         |

/

#### Chapter

5

|      |         | 4.7.2.2 Direct In ( | <del>-</del>         | 4-24   |

|------|---------|---------------------|----------------------|--------|

|      |         | 4.7.2.3 Indirect th |                      | 4-23   |

|      |         | 4.7.2.4 Indirect th | and $7 = 10$ )       | 4-23   |

|      |         |                     | its 6 and $7 = 11$ ) | 4-25   |

|      | 4.7.3   | Arithmetic and Log  |                      | 1 20   |

|      |         | Reference Instru    | -                    | 4-25   |

|      |         | 4.7.3.1 Add A       |                      | 4-27   |

|      |         | 4.7.3.2 Subtract S  |                      | 4-27   |

|      |         | 4.7.3.3 Exclusive   | OR X                 | 4-28   |

|      |         | 4.7.3.4 OR O        |                      | 4 - 28 |

|      |         | 4.7.3.5 AND N       |                      | 4-29   |

|      |         | 4.7.3.6 Store ST    |                      | 4 - 29 |

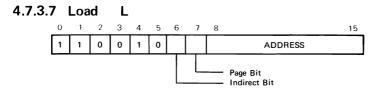

|      |         | 4.7.3.7 Load L      |                      | 4 - 29 |

|      |         | 4.7.3.8 Increment   | and Skip on          |        |

|      |         | Not Zer             | o ISN                | 4 - 30 |

|      |         | 4.7.3.9 Increment   | and Skip on          |        |

|      |         | Zero ISZ            |                      | 4-30   |

|      | 4.7.4   | Bit Operation Memo  | ory Reference        |        |

|      |         | Instructions        |                      | 4-30   |

|      |         | 4.7.4.1 AND BIT     |                      | 4-31   |

|      |         | 4.7.4.2 OR BIT O    | В                    | 4-32   |

| INPU | JT/OUT  | PUT (I/O) SYSTEMS   |                      | 5-1    |

| 5.1  | Introdu | ction               |                      | 5-1    |

| 5.2  | I/O Sys | tem Block Diagram   | Analysis             | 5 - 1  |

|      | 5.2.1   | Multiplexor Channe  | 1                    | 5 - 1  |

|      |         | Selector Channel    |                      | 5-6    |

|      |         |                     | Bus Interface (UMBI) | 5-11   |

|      | 5.2.4   | Direct Memory Cor   | mection              | 5-11   |

| 5.3  | Input/C | utput Instructions  |                      | 5-11   |

|      | 5.3.1   | Introduction        |                      | 5-11   |

|      | 5.3.2   | Address ADRS        |                      | 5 - 13 |

|      | 5.3.3   | Output Command C    | DC                   | 5-14   |

|      | 5.3.4   | Write Data WD       |                      | 5-15   |

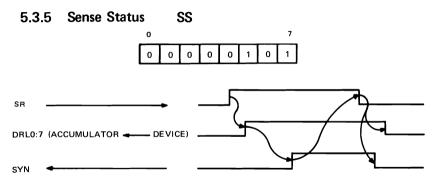

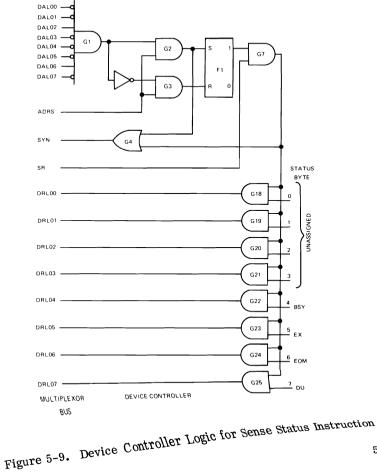

|      | 5.3.5   | Sense Status SS     |                      | 5 - 17 |

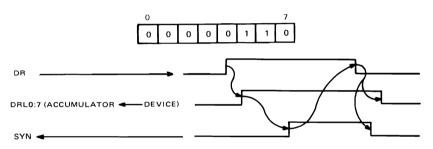

|      |         | Read Data RD        |                      | 5-18   |

|      |         | Acknowledge AK      |                      | 5-19   |

|      |         | Read Data and Skip  |                      | 5 - 21 |

|      |         | Write Data and Skip | WDS                  | 5-23   |

|      | 5.3.10  | Read Block RB       |                      | 5-24   |

|      | 5.3.11  | Write Block WB      |                      | 5-25   |

•

Chapter

|   | 5.4 | Device Controller Logic Design                              | 5-25       |

|---|-----|-------------------------------------------------------------|------------|

|   |     | 5.4.1 Multiplexor Channel                                   | 5-25       |

|   |     | 5.4.2 Device Controller Addressing                          | 5-28       |

|   |     | 5.4.3 Data and Status Input                                 | 5-30       |

|   |     | 5.4.4 Data and Command Output                               | 5-32       |

|   |     | 5.4.5 Interrupt Control                                     | 5-32       |

|   |     | 5.4.6 Multiplexor Channel Wiring                            | 5-37       |

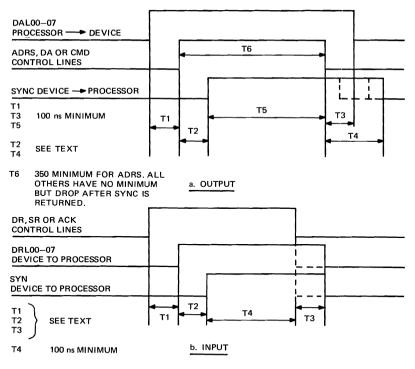

|   |     | 5.4.7 Multiplexor Channel Timing                            | 5-37       |

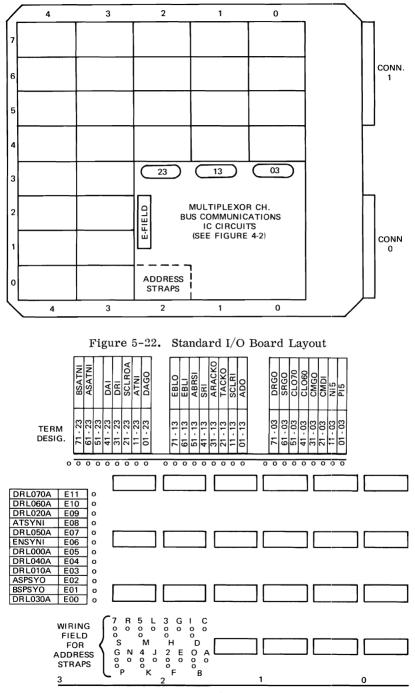

|   | 5.5 | Standard I/O Board                                          | 5-39       |

|   |     | 5.5.1 Introduction                                          | 5-39       |

|   |     | 5.5.2 Communications Logic                                  | 5-39       |

|   |     | 5.5.3 Wire-Wrap Facilities                                  | 5-39       |

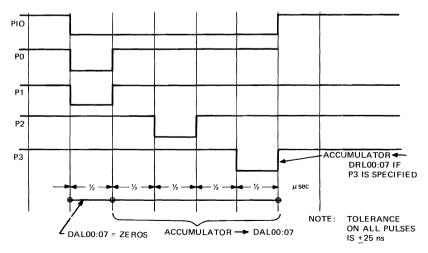

|   | 5.6 | Pulsed Input/Output                                         | 5-41       |

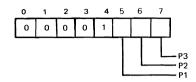

|   |     | 5.6.1 Pulsed I/O Instruction                                | 5-44       |

|   |     | 5.6.2 Use of the Pulsed I/O Instruction                     | 5-45       |

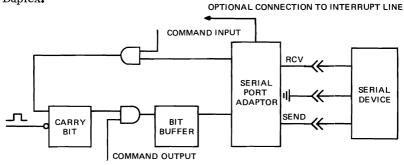

|   | 5.7 | Serial Input/Output Port                                    | 5-46       |

|   |     | 5.7.1 Operation With a Teletypewriter                       | 5-47       |

|   |     | 5.7.2 Operation With a Device Different                     |            |

|   |     | From a Teletypewriter                                       | 5-48       |

| 6 | MEN | AORY SYSTEM                                                 | 6-1        |

|   | 6.1 | Introduction                                                | 6-1        |

|   | 6.2 | Core Memory Modules                                         | 6-2        |

|   | 6.3 | Read-Only-Memory Module                                     | 6-3        |

|   | 6.4 | Parity Option                                               | 6-3        |

|   | 6.5 | Memory Bus                                                  | 6-4        |

|   | 0.0 | 6.5.1 Priority On The Memory Bus                            | 6-6        |

|   |     | 6.5.2 Interfacing to the Memory Bus                         | 6-7        |

|   |     | 6.5.3 Memory Bus Timing                                     | 6-12       |

| 7 | CON | TROL PANEL                                                  | 7-1        |

|   | 7.1 | Introduction                                                | 7-1        |

|   | 7.2 |                                                             | 7-1        |

|   | 1.4 | Standard Control Panel Description<br>7.2.1 Indicator Lamps | 7-1<br>7-1 |

|   |     | 7.2.2 Data Switches                                         | 7-3        |

|   |     | 7.2.3 Control Switches                                      | 7-3        |

|   |     | 7.2.4 Key Operated Security Lock                            | 7-3<br>7-4 |

|   |     |                                                             |            |

|   | 7.3 | Control Panel Operating Procedures                          | 7-4        |

Page

| Chapter |      |                                                                        | Page |

|---------|------|------------------------------------------------------------------------|------|

|         | 7.4  | Control Panel Programming                                              | 7-7  |

|         | 7.5  | Auto-Control Panel                                                     | 7-7  |

| 8       | PERI | PHERAL DEVICES                                                         | 8-1  |

|         | 8.1  | Introduction                                                           | 8-1  |

|         | 8.2  | Peripheral Devices                                                     | 8-1  |

|         |      | 8.2.1 Teletypewriters                                                  | 8-1  |

|         |      | 8.2.2 Paper Tape and Card Equipment                                    | 8-1  |

|         |      | 8.2.3 Magnetic Storage Systems                                         | 8-2  |

|         |      | 8.2.4 System Modules                                                   | 8-3  |

|         |      | 8.2.5 Digital Input/Output Multiplexor                                 |      |

|         |      | Equipment                                                              | 8-4  |

|         |      | 8.2.6 Data Communications Equipment,<br>Character Buffered Half Duplex |      |

|         |      | Line Adapter                                                           | 8-5  |

|         |      | 8.2.7 Conversion Equipment                                             | 8-5  |

|         | 8.3  | Teletype (With Teletype Controller) Operation                          |      |

|         |      | and Programming                                                        | 8-7  |

|         |      | 8.3.1 Device/Controller Description                                    | 8-7  |

|         |      | 8.3.2 Power Control                                                    | 8-9  |

|         |      | 8.3.3 Status and Commands                                              | 8-9  |

|         |      | 8.3.4 Device Number                                                    | 8-9  |

|         |      | 8.3.5 Interrupts                                                       | 8-11 |

|         |      | 8.3.6 Initialization                                                   | 8-11 |

|         |      | 8.3.7 ASR-35 Features                                                  | 8-11 |

|         |      | 8.3.8 Paper Tape Reader                                                | 8-11 |

|         |      | 8.3.9 Paper Tape Punch                                                 | 8-13 |

|         |      | 8.3.10 Data Formats                                                    | 8-14 |

|         |      | 8.3.11 Program Examples                                                | 8-15 |

|         | 8.4  | High Speed Paper Tape Reader/Punch                                     |      |

|         |      | Operation and Programming                                              | 8-16 |

|         |      | 8.4.1 Introduction                                                     | 8-16 |

|         |      | 8.4.2 General Description                                              | 8-16 |

|         |      | 8.4.3 Status and Command                                               | 8-18 |

|         |      | 8.4.4 Interrupts                                                       | 8-20 |

|         |      | 8.4.5 Initialization                                                   | 8-20 |

|         |      | 8.4.6 Punch Power Controls                                             | 8-20 |

|         |      | 8.4.7 Mode Switching                                                   | 8-21 |

|         |      | 8.4.8 Device Number                                                    | 8-23 |

|         | 8.5  | Card Reader Operation and Programming                                  | 8-23 |

|         |      | 8.5.1 General Description                                              | 8-23 |

|         |      | 8.5.2 Operator Controls                                                | 8-24 |

#### Chapter

9

10

|      | 8.5.2         | 2.1 POWER                | 8-24         |

|------|---------------|--------------------------|--------------|

|      | 8.5.2         |                          | 8-24         |

|      | 8.5.2         | 2.3 Read START           | 8-24         |

|      | 8.5.2         | 2.4 Read STOP            | 8-24         |

|      | 8.5.3 Status  | s Indicator Lights       | 8-24         |

|      | 8.5.3         |                          | 8-24         |

|      | 8.5.3         |                          | 8-25         |

|      | 8.5.3         |                          | 8-25         |

|      | 8.5.3         |                          | 8-25         |

|      | 8.5.3         |                          | 8-25         |

|      | 8.5.3         |                          | 8-25         |

|      | 8.5.3         |                          | 8-25         |

|      | 8.5.3         |                          | 8-25         |

|      |               | s and Command Bytes      | 8-25         |

|      |               | Format                   | 8-25         |

|      |               | lization                 | 8-27<br>8-27 |

|      |               | ator Procedures          | 8-27         |

|      |               | ramming                  | 8-27         |

|      | 0.0.0         |                          | 0 21         |

| CON  | FIGURATION A  | ND INSTALLATION PLANNING | 9-1          |

| 9.1  | Introduction  |                          | 9-1          |

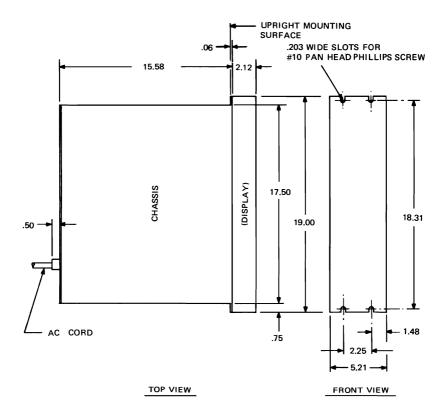

| 9.2  | Basic Process | or Chassis               | 9-1          |

| 9.3  | Expansion Cha | ssis                     | 9-1          |

| 9.4  | Decorator Cov | er                       | 9-2          |

| 9.5  | Line Power Re | equirements              | 9-2          |

| 9.6  | Regulated Pow | rer                      | 9-3          |

| 9.7  | Configuration | Power Requirements       | 9-3          |

| 9.8  | Configuration | Constraints              | 9-4          |

| 9.9  | Installation  |                          | 9-4          |

| BASI | C MODEL 1 PR  | OGRAMMING                | 10-1         |

| 10.1 | Introduction  |                          | 10-1         |

|      |               | Aodel 1                  | 10-1         |

|      |               | rammable Registers       | 10-1         |

|      | U             | metic/Logical Unit       | 10-1         |

|      |               | omplement Notation       | 10-2         |

|      | 10.1.5 Hex N  | lotation                 | 10-2         |

| 10 2 | Addressing Te | chniques                 | 10-3         |

| 10.2 | muressing le  | ounques                  | T0-9         |

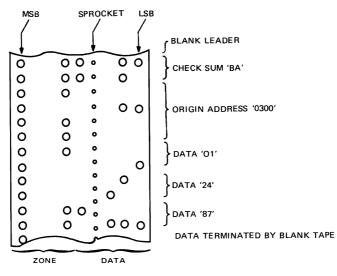

#### Chapter Page 10.3 Memory Organization 10 - 510.4 Basic Programming Examples 10 - 810.4.1 Moves 10 - 810.4.2 Multiple Precision Arithmetic (Triple Precision Example) 10 - 9Subroutine Linkage (Use of the 10.4.3 BAL Instruction) 10 - 1010.4.4 Auto-Indexing/Auto-Skip 10 - 1110.4.5 Condition Checks and Comparison 10 - 1210.4.6 I/O Programming 10 - 1310.4.6.1 Parallel I/O 10 - 1310.4.6.2 Interrupt Mode 10 - 1410.4.6.3 Non-Interrupt Mode 10 - 1510.4.6.4 Serial I/O 10 - 1710.4.7 Power Fail and Restart Programming 10 - 2010.4.8 Bit Instructions 10 - 2110 - 2310.5 Software and Program Usage 10.5.1 Model 1 Software Summary 10 - 2310.5.2 Model Tape Formats 10 - 2310.5.3 Loading Procedure and Core Usage 10 - 2410.5.4 User Program Relocation in the Model 1 10 - 2511 MODEL 1 SOFTWARE 11-1 11.1 Model 1 Assembler 11 - 111.1.1 Introduction 11-1 11.1.2 Assembly Listing 11-2 11.1.3 The Assembler Language 11 - 411.1.3.1 Source Statements 11-4 11.1.3.2 Instruction Statement Format 11-8 **11.1.4** Machine Instruction Format 11-11 11.1.4.1 Short Format Instructions 11-11 11.1.4.2 Memory Referenced Instructions 11-11 11.1.4.3 Immediate Instructions 11 - 1211.1.5 Pseudo-Ops 11-13 11.1.5.1 Symbol Definition 11 - 1311.1.5.2 Data Definition 11-13 11.1.5.3 Assembler Control Instructions 11 - 1511.1.5.4 Summary of Assembler

Instructions

11 - 16

| Chapter |      |                  |                                                         | Page    |

|---------|------|------------------|---------------------------------------------------------|---------|

|         |      | 11.1.6<br>11.1.7 | Input Format<br>Operating Instructions for the          | 11-17   |

|         |      |                  | Model 1 Assembler                                       | 11-17   |

|         |      |                  | 11.1.7.1 General Description                            | 11-17   |

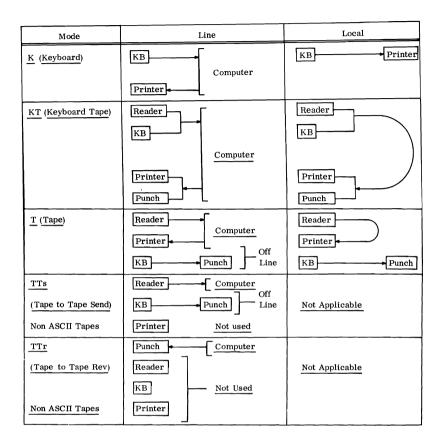

|         |      |                  | 11.1.7.2 Configuration                                  | 11-18   |

|         |      |                  | 11.1.7.3 Tape Format                                    | 11.18   |

|         |      |                  | 11.1.7.4 Loading Procedures                             | 11-18   |

|         |      |                  | 11.1.7.5 Device Selection                               | 11-18   |

|         |      |                  | 11.1.7.6 Operating Procedures                           | 11-19   |

|         |      |                  | 11.1.7.7 Symbol Table Size<br>11.1.7.8 NO-PRINT and NO- | 11-20   |

|         |      |                  | PUNCH Options                                           | 11-20   |

|         | 11.2 |                  | In-Core Loader                                          | 11 - 21 |

|         |      | 11.2.1           | Introduction                                            | 11-21   |

|         |      | 11.2.2           | -                                                       | 11 - 21 |

|         |      | 11.2.3           | Device Definition Table                                 | 11-23   |

|         | 11.3 |                  | General Loader                                          | 11-24   |

|         |      | 11.3.1           | Introduction                                            | 11 - 24 |

|         |      | 11.3.2           | Loader Features                                         | 11 - 24 |

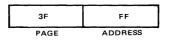

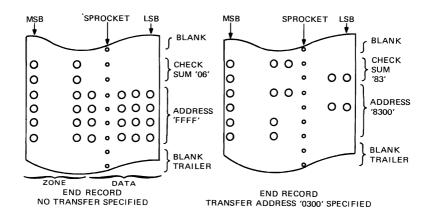

|         |      | 11.3.3           | Standard Loader Format                                  | 11 - 25 |

|         |      | 11.3.4           | Loader Tape Format                                      | 11 - 27 |

|         |      | 11.3.5           | Operating Procedures                                    | 11 - 27 |

|         | 11.4 | The Mod          | lel 1 Unloader                                          | 11-28   |

|         | 11.5 | Hexadec          | imal Debug Program Description                          |         |

|         |      | (DBUC            | G)                                                      | 11-28   |

|         |      | 11.5.1           | Introduction                                            | 11-28   |

|         |      | 11.5.2           | Terminology                                             | 11 - 28 |

|         |      | 11.5.3           | Configuration                                           | 11-30   |

|         |      | 11.5.4           | Tape Format                                             | 11-30   |

|         |      | 11.5.5           | Features Available in DBUG                              | 11-30   |

|         |      | 11.5.6           | Description of Operations                               | 11-30   |

|         |      |                  | 11.5.6.1 Cell Examination and                           |         |

|         |      |                  | Modification                                            | 11-30   |

|         |      |                  | 11.5.6.2 Program Control                                | 11-32   |

|         |      | 11.5.7           | Loading Procedures                                      | 11-34   |

|         | 11.6 |                  | Text Editor Program Description                         | 11-35   |

|         |      | 11.6.1           | Introduction                                            | 11 - 35 |

|         |      | 11.6.2           | Program Structures                                      | 11 - 35 |

|         |      |                  | 11.6.2.1 Operating Modes                                | 11-35   |

|         |      |                  | 11.6.2.2 Basic Unit                                     | 11-36   |

|         |      |                  | 11.6.2.3 Line Addressing                                | 11-36   |

|         |      |                  | 11.6.2.4 Command Formats                                | 11 - 36 |

| Chapter |                               | Page    |

|---------|-------------------------------|---------|

|         | 11.6.2.5 Commands             | 11 - 37 |

|         | 11.6.2.6 Command Examples     | 11 - 41 |

|         | 11.6.2.7 Errors               | 11 - 42 |

| 11.6.3  | Operating Procedures          | 11-43   |

|         | 11.6.3.1 Loading              | 11-43   |

|         | 11.6.3.2 I/O Device Selection | 11 - 43 |

|         | 11.6.3.3 Starting Location    | 11 - 44 |

|         | 11.6.3.4 Tape Format          | 11-44   |

|         | 11.6.3.5 Text Buffer Size     | 11-44   |

Clay Archer

### **ILLUSTRATIONS**

| Figure      |                                                                     | Page   |

|-------------|---------------------------------------------------------------------|--------|

| 2-1         | Model 1 Block Diagram                                               | 2-3    |

| 2-2         | Model 1 Interrupt Lines and Associated Hardware                     | 2-7    |

| 2-3         | Interrupt Service Table                                             | 2-8    |

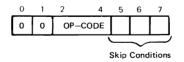

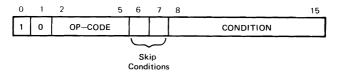

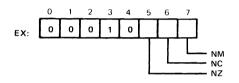

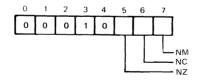

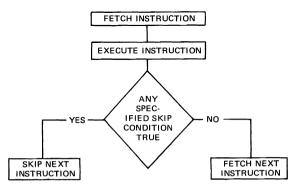

| 3-1         | Skip Examples                                                       | 3-2    |

| 3-2         | Pages in the Memory System                                          | 3-5    |

| 3-3         | Flow Chart - Direct Addressing Mode                                 | 3-6    |

| 3-4         | Flow Chart - Indirect Addressing Mode                               | 3-7    |

| 3-5         | Auto Indexing                                                       | 3 - 8  |

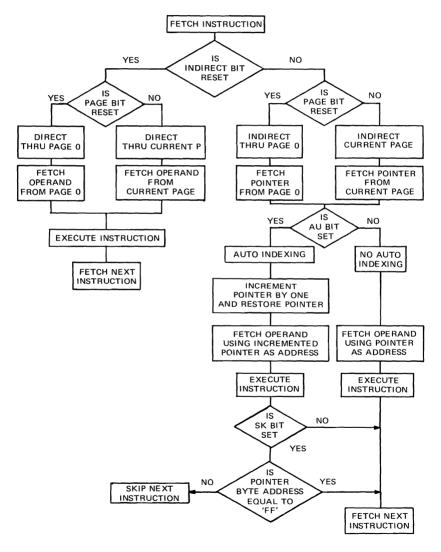

| 3-6         | Flow Chart - Addressing Modes/Auto Indexing                         | 3-9    |

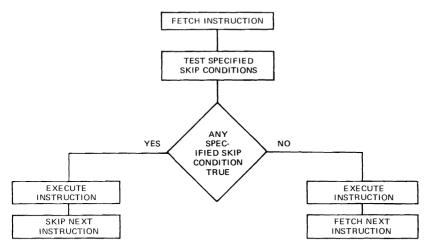

| 4-1         | Flow Chart - A Register/Carry Instruction                           | 4-2    |

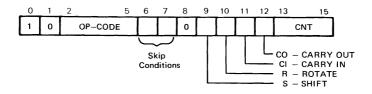

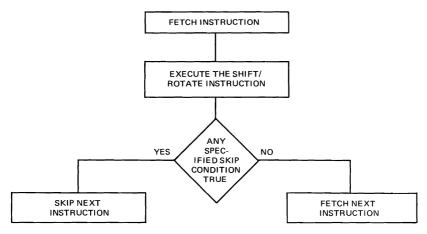

| 4-2         | Shift/Rotate Instruction                                            | 4 - 5  |

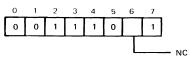

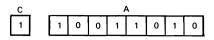

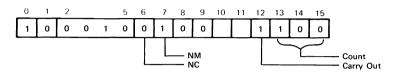

| 4-3         | Example of Shift Instruction                                        | 4-6    |

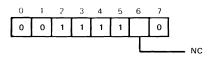

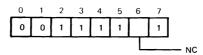

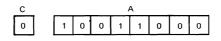

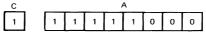

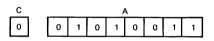

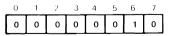

| 4-4         | Example of Rotate Instruction                                       | 4-8    |

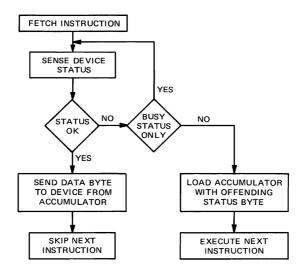

| 4-5         | Write Data and Skip Flow Chart                                      | 4-11   |

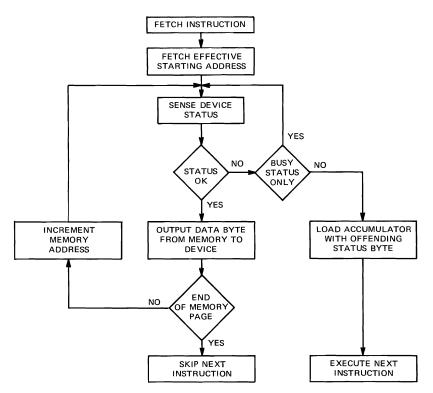

| 4-6         | Write Block Flow Chart                                              | 4-14   |

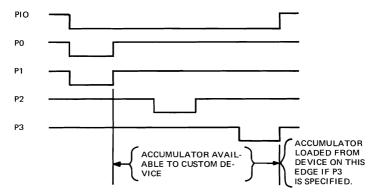

| 4-7         | Pulsed I/O Timing                                                   | 4-15   |

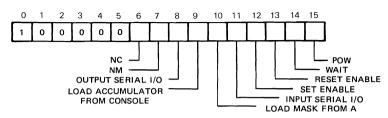

| 4-8         | Example of Command Instruction                                      | 4-16   |

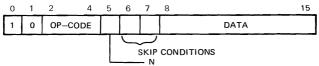

| 4-9         | Immediate Instructions Flow Chart                                   | 4-19   |

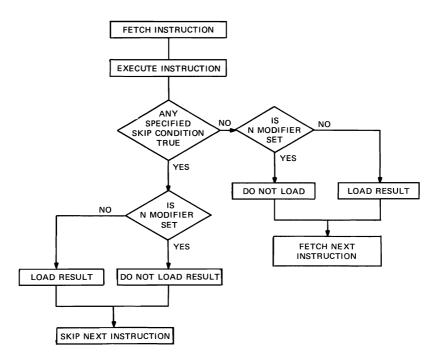

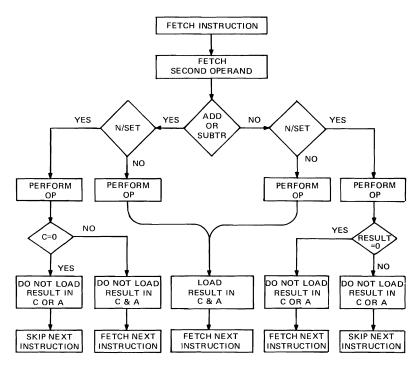

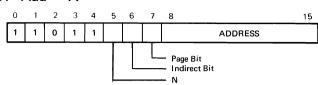

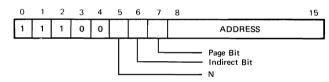

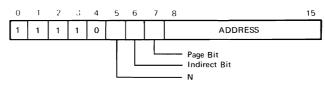

| 4-10        | Arithmetic and Logical Memory Reference<br>Instructions, Flow Chart | 4-26   |

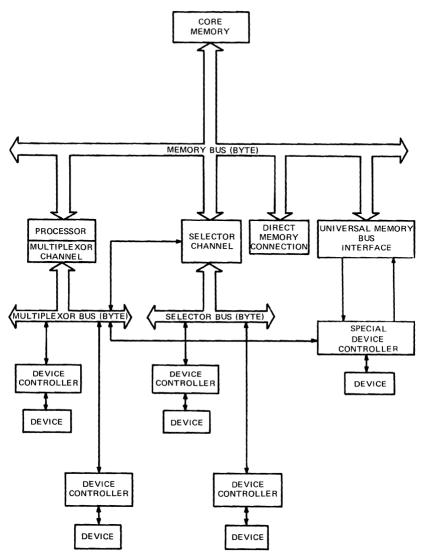

| 5-1         | Systems Interface, Block Diagram                                    | 5-4    |

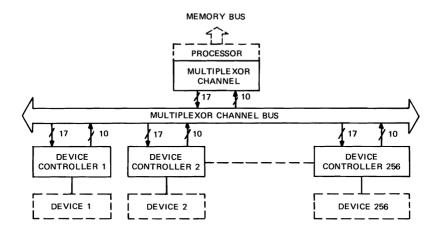

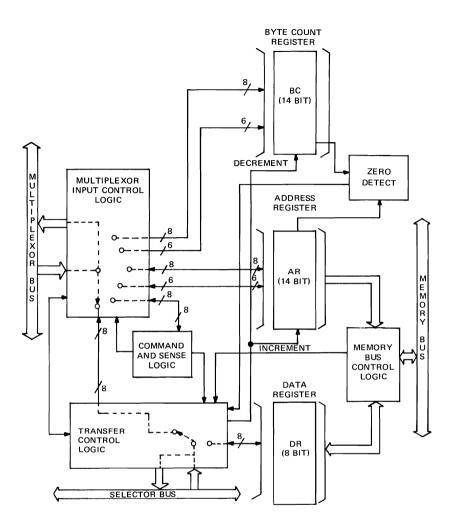

| 5-2         | Multiplexor Channel, Block Diagram                                  | 5-5    |

| 5-3         | Selector Channel, Block Diagram                                     | 5-7    |

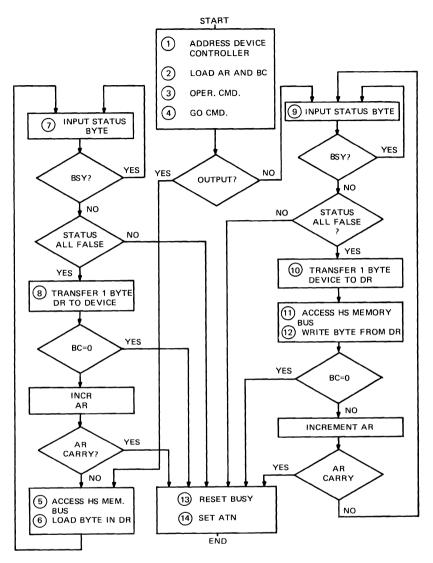

| <b>5-</b> 4 | Selector Channel, Flow Chart                                        | 5-9    |

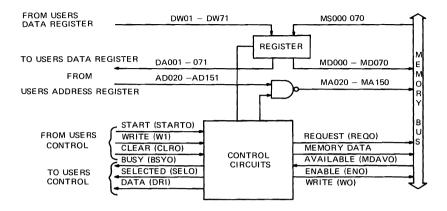

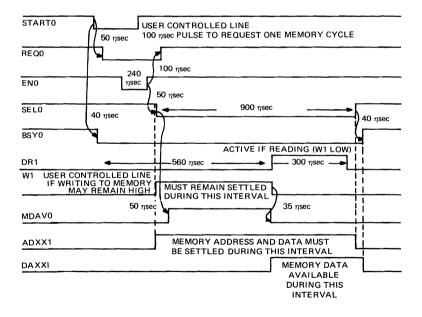

| 5-5         | Universal Memory Bus Interface, Block Diagram                       | 5 - 12 |

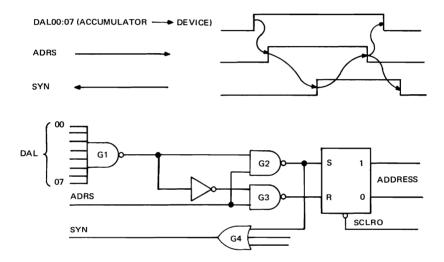

| 5-6         | Device Controller Logic for the Address Instruction                 | 5 - 13 |

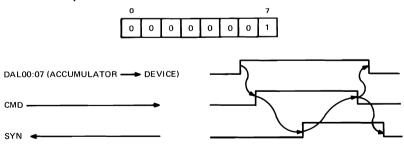

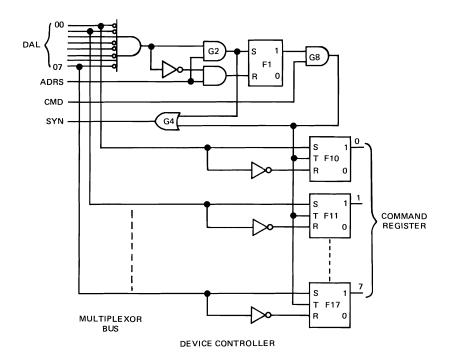

| 5-7         | Device Controller Logic for the Output Command                      |        |

|             | Instruction                                                         | 5 - 15 |

| 5-8         | Device Controller Logic for the Write Data                          | 5 10   |

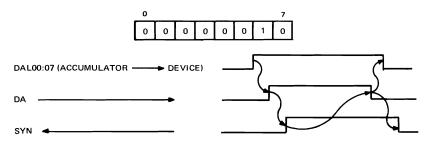

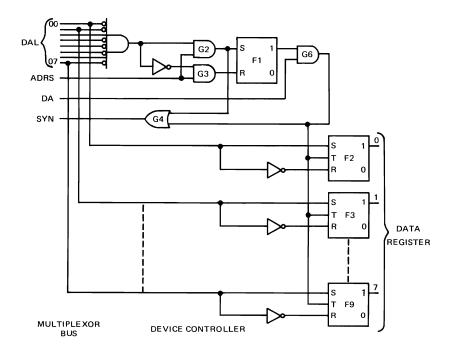

| 5 0         | Instruction                                                         | 5-16   |

| 5-9<br>5 10 | Device Controller Logic for Sense Status Instruction                | 5-17   |

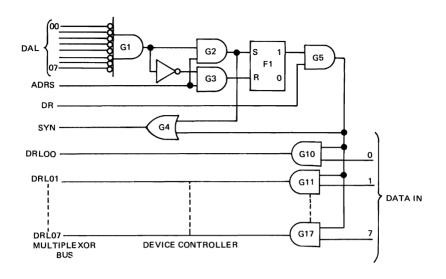

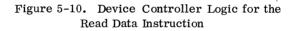

| 5-10        | Device Controller Logic for the Read Data                           | 5 10   |

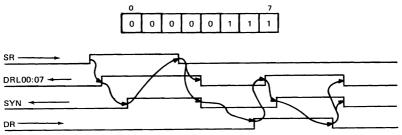

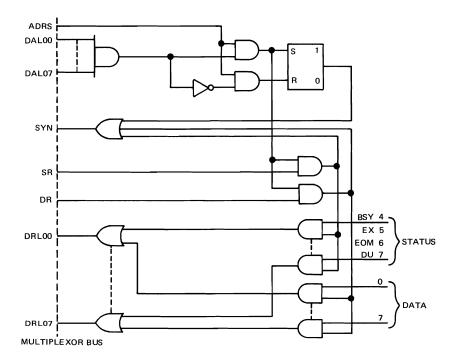

| 5-11        | Instruction<br>Device Controller Logic for the Acknowledge          | 5-19   |

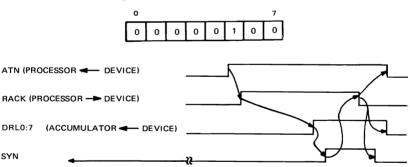

| 0 11        | Interrupt Instruction                                               | 5-20   |

| 5-12        | Device Controller Logic                                             | 5-22   |

| 5-13        | Device Controller Logic                                             | 5-24   |

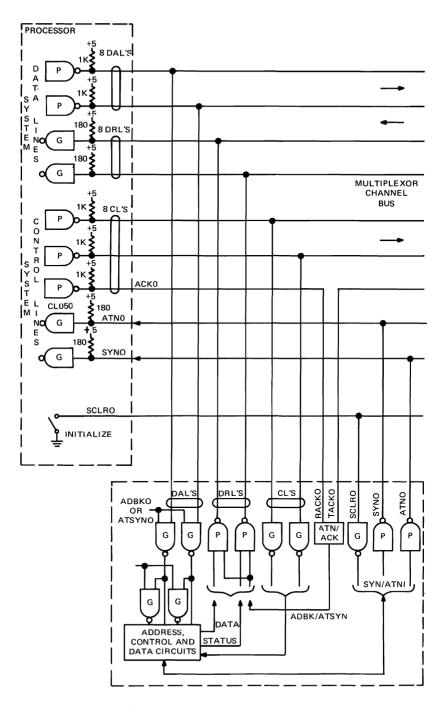

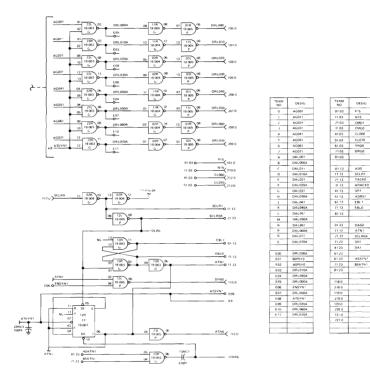

| 5-14        | I/O Bus Communication Circuits, Logic Diagram                       | 5-27   |

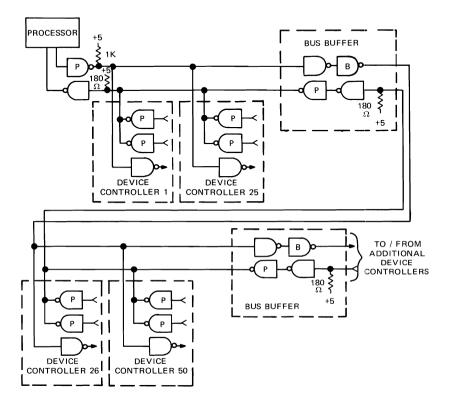

| 5-15        | Multiplexor Channel Bus Buffers                                     | 5-28   |

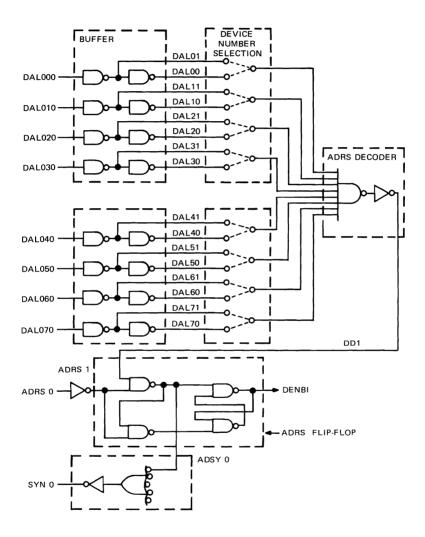

| 5-16        | Device Addressing, Logic Diagram                                    | 5-29   |

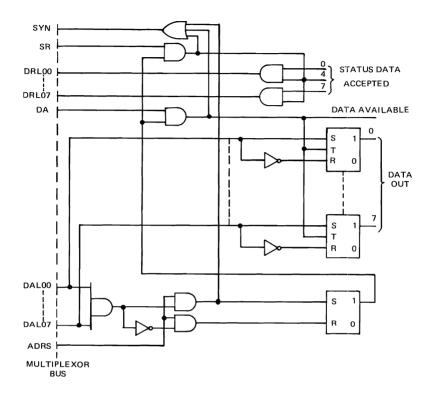

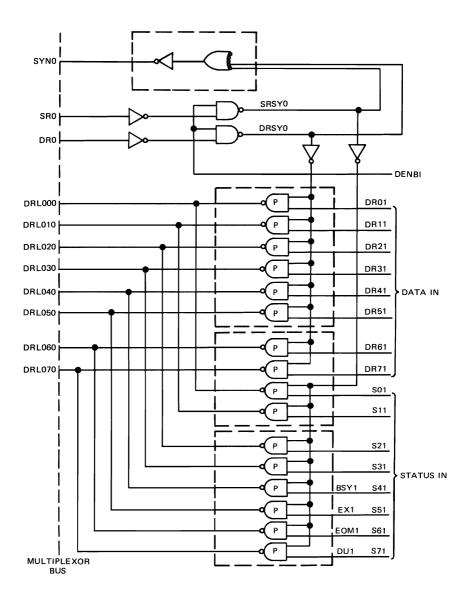

| 5-17        | Data and Status Input, Logic Diagram                                | 5-31   |

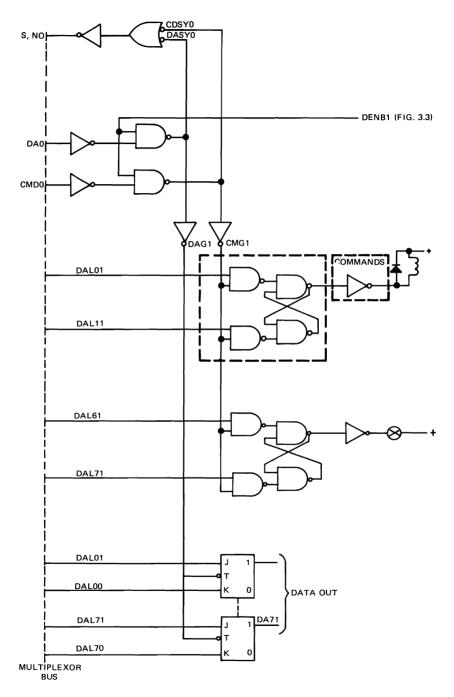

| 5-18        | Data and Command Output, Logic Diagram                              | 5-33   |

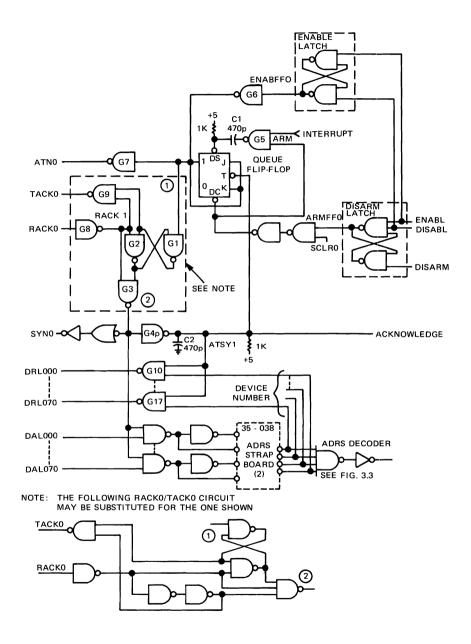

| 5-19        | Interrupt Control, Logic Diagram                                    | 5-34   |

|             | ·····                                                               |        |

## ILLUSTRATIONS (Cont)

| Figure                                               |                                                                                                                                                                                                                                               | Page                                                                                   |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 5-20                                                 | Typical Universal Expansion Slot Wiring                                                                                                                                                                                                       | 5-36                                                                                   |

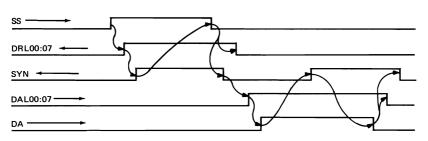

| 5-21                                                 | Multiplexor Channel Timing                                                                                                                                                                                                                    | 5-38                                                                                   |

| 5-22                                                 | Standard I/O Board Layout                                                                                                                                                                                                                     | 5-40                                                                                   |

| 5-23                                                 | Standard I/O Board Field Layout                                                                                                                                                                                                               | 5-40                                                                                   |

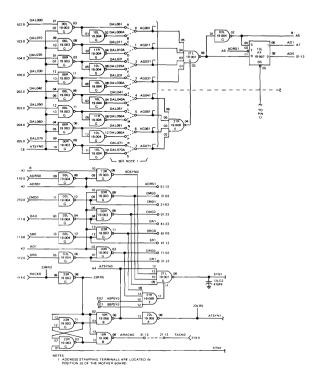

| 5-24                                                 | Standard I/O Board Schematic (Sheet 1 of 2)                                                                                                                                                                                                   | 5-42                                                                                   |

| 5-24.                                                | Standard I/O Board Schematic (Sheet 2 of 2)                                                                                                                                                                                                   | 5-43                                                                                   |

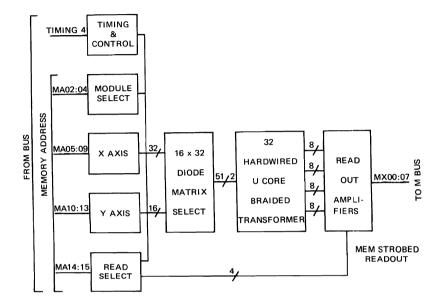

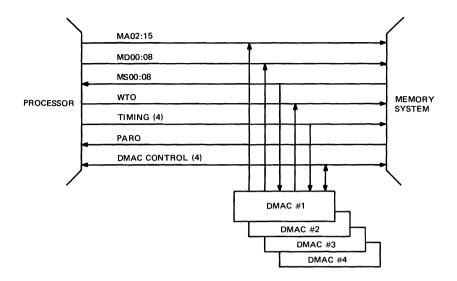

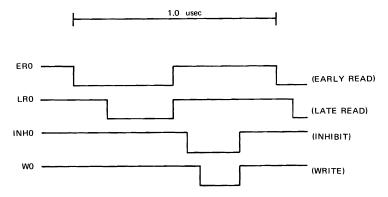

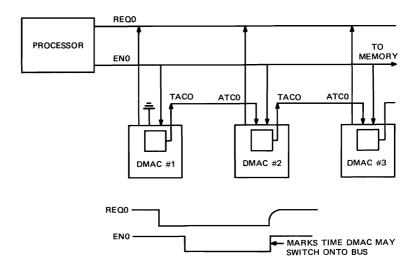

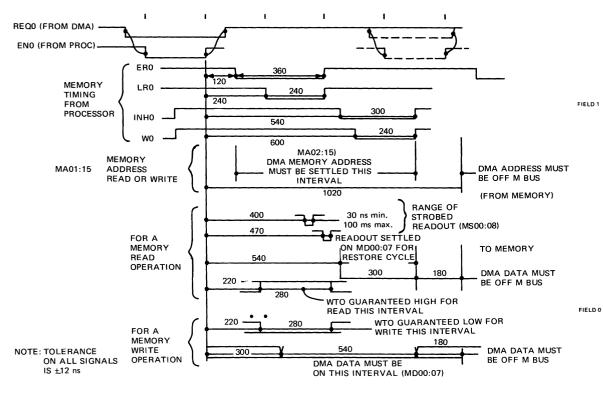

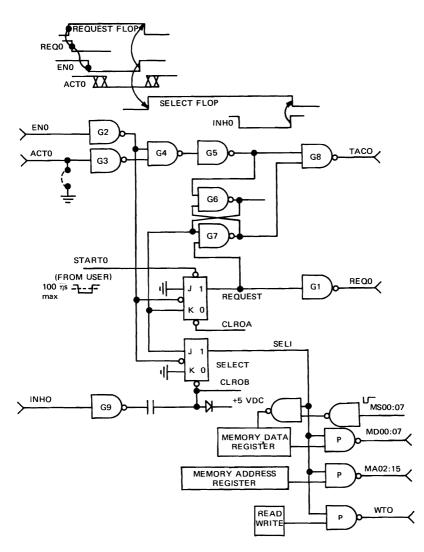

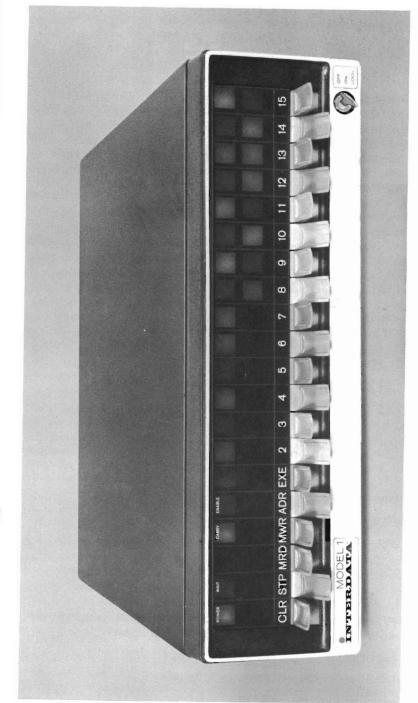

| 6-1<br>6-2<br>6-3<br>6-4<br>6-5<br>6-6<br>6-7<br>7-1 | Model 1 Memory System<br>Core Memory Module<br>ROM Module 2048 by Eight-Bit<br>Model 1 Memory System Diagram<br>Example of Memory Bus Priorities<br>Model 1 Memory Bus Timing<br>Daisy-Chain Select Request Circuits<br>Model 1 Control Panel | $ \begin{array}{r} 6-1 \\ 6-3 \\ 6-4 \\ 6-5 \\ 6-7 \\ 6-9 \\ 6-10 \\ 7-2 \end{array} $ |

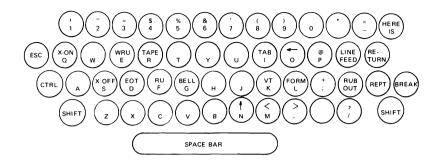

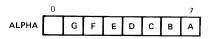

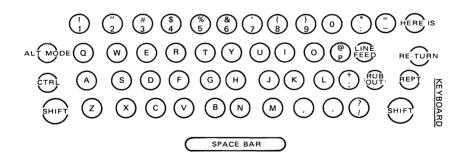

| 8-1                                                  | Teletype Keyboard Layout                                                                                                                                                                                                                      | 8-9                                                                                    |

| 8-2                                                  | Punch Power                                                                                                                                                                                                                                   | 8-21                                                                                   |

| 8-3                                                  | Data Byte Format                                                                                                                                                                                                                              | 8-27                                                                                   |

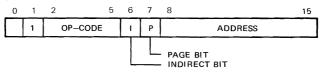

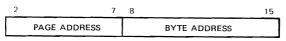

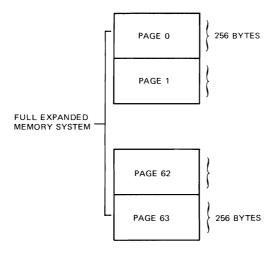

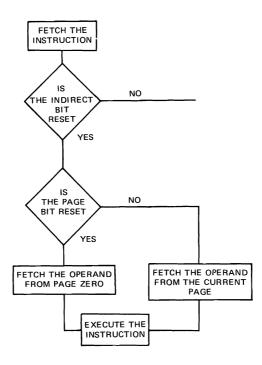

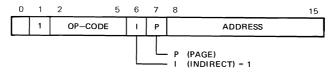

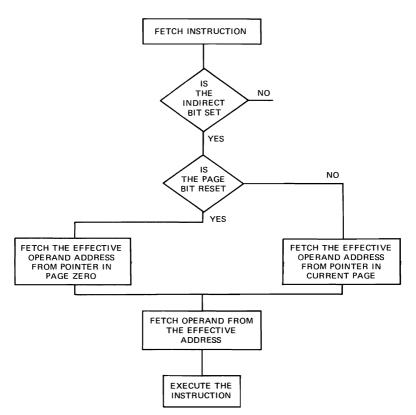

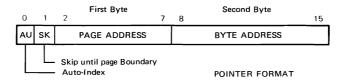

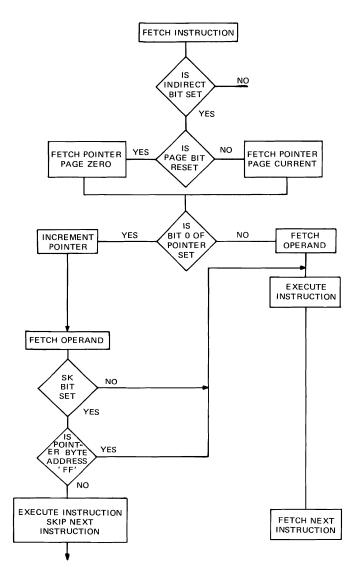

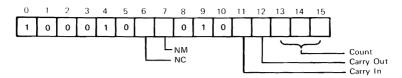

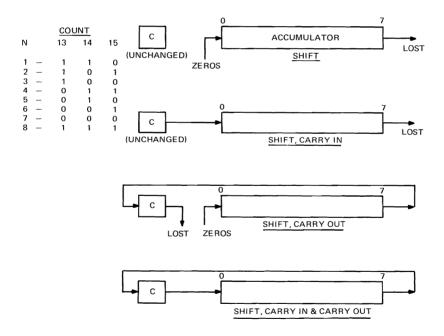

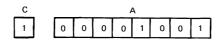

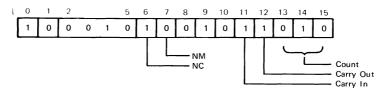

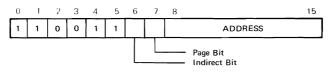

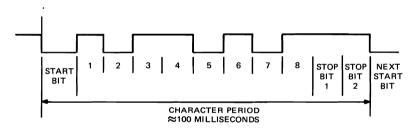

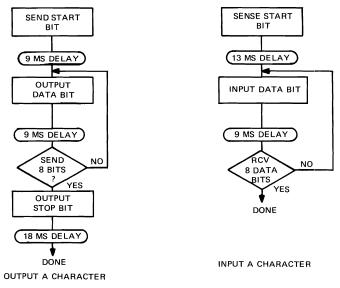

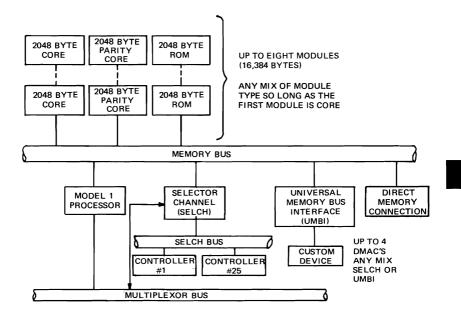

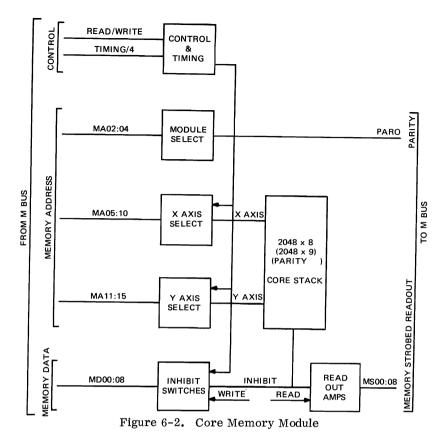

| 9-1                                                  | Model 1 Outline Drawing                                                                                                                                                                                                                       | 9-2                                                                                    |