## iSBC 016A/032A/064A/028A/056A™ RAM BOARD HARDWARE REFERENCE MANUAL

Manual Order Number: 143572-001

| REV. | <b>REVISION HISTORY</b> | PRINT<br>DATE |

|------|-------------------------|---------------|

| -001 | Original Issue          | 7/81          |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

|      |                         |               |

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| ВХР    | Intel           | Megachassis |

|--------|-----------------|-------------|

| CREDIT | Intelevision    | Micromap    |

| i      | Intellec        | Multibus    |

| ICE    | iRMX            | Multimodule |

| iCS    | iSBC            | PROMPT      |

| im     | iSBX            | Promware    |

| Insite | Library Manager | RMX/80      |

| Intel  | MCS             | System 2000 |

|        |                 | ŬPI         |

|        |                 | µScope      |

and the combination of ICE, iCS, iRMX, iSBC, iSBX, MCS, iMMX or RMX and a numerical suffix.

This manual provides general information, preparation for use, principles of operation, and service information for the iSBC 016A/032A/064A/028A/056A RAM Board. Supplementary information is provided in the following documents.

- Peripheral Design Handbook, Order No. 9800676.

- Intel Multibus Specification, Order No. 9800683.

## CHAPTER 1 GENERAL INFORMATION

| GENERAL INFORMATION | PAC | ЭE  |

|---------------------|-----|-----|

| Introduction        |     | 1-1 |

| Description         |     | 1-1 |

| Modes of Operation  |     | 1-2 |

| Equipment Supplied  |     | 1-2 |

| Specifications      |     | 1-2 |

# CHAPTER 2 PREPARATION FOR USE

| Introduction                   | 2-1    |

|--------------------------------|--------|

| Unpacking and Inspection       | 2-1    |

| Installation Considerations    | 2-1    |

| Power Requirements             | 2-1    |

| Cooling Requirements           | 2-1    |

| Interfacing Requirements       | 2-1    |

| Jumper Configurations          | 2-8    |

| Memory Address Jumper          |        |

| Configuration                  | 2 - 10 |

| Megabyte Page Address          |        |

| Select Jumpers                 | 2-11   |

| 4k Boundary Select Jumpers     | 2 - 12 |

| RAM Board Address              |        |

| Configuration Examples         | 2-13   |

| Delayed/Advanced WRITE         |        |

| Jumper Configuration           | 2-14   |

| Parity Flag Register Address   |        |

| Jumper Configuration           | 2-14   |

| Battery Back-Up/Memory Protect |        |

| Jumper Configuration           | 2-15   |

| Board Installation             | 2-15   |

|                                |        |

#### **CHAPTER 3**

| CHAPTER 3       |                    |

|-----------------|--------------------|

| PROGRAMMING     | <b>INFORMATION</b> |

| Testus de etter |                    |

| Introduction                | 3-1 |

|-----------------------------|-----|

| Port Address                | 3-1 |

| Parity Flag Register Format | 3-1 |

#### **CHAPTER 4**

| PRINCIPLES OF OPERATION          | PAGE |

|----------------------------------|------|

| Introduction                     | 4-1  |

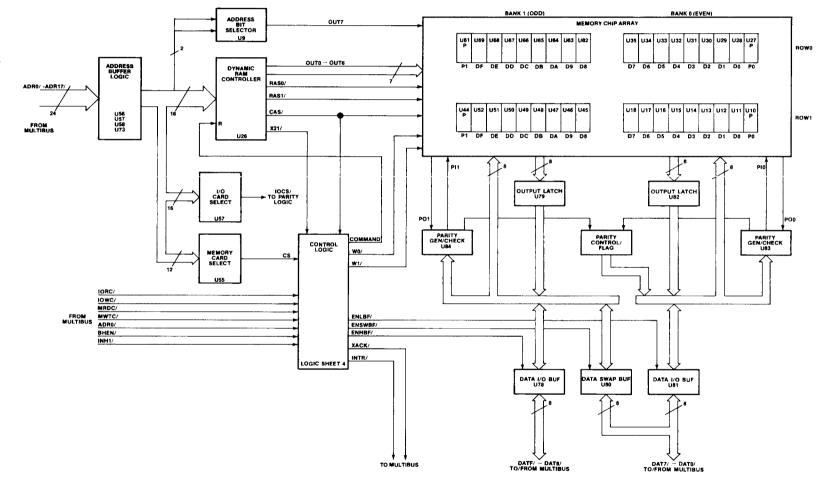

| Functional Description           | 4-1  |

| Dynamic RAM Controller           |      |

| Dynamic RAM Controller Interface | 4-3  |

| Address Buffers                  |      |

| Address Decode Logic             | 4-4  |

| Memory Array                     | 4-4  |

| Data I/O Buffers                 | 4-4  |

| Parity Generation/Checking Logic | 4-4  |

| Control Logic                    | 4-5  |

| Detailed Circuit Analysis        | 4-5  |

| Addressing and Data Routing      | 4-6  |

| Memory Partitioning              |      |

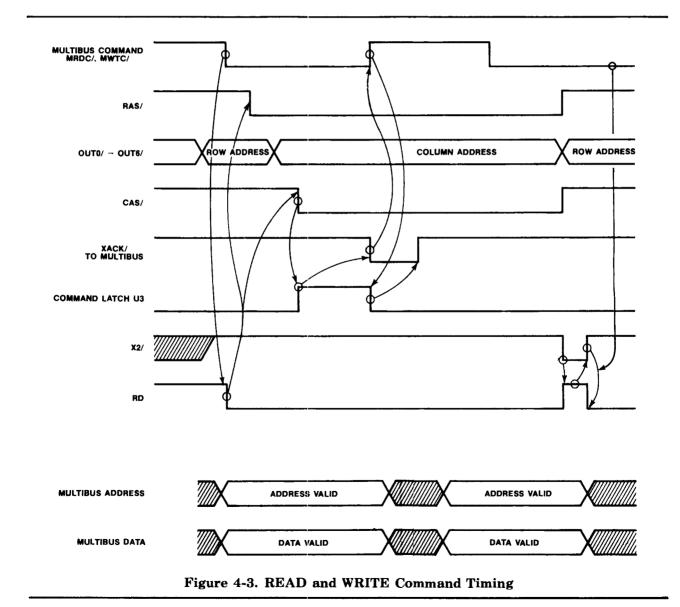

| Memory READ Command              | 4-7  |

| Memory WRITE Command             |      |

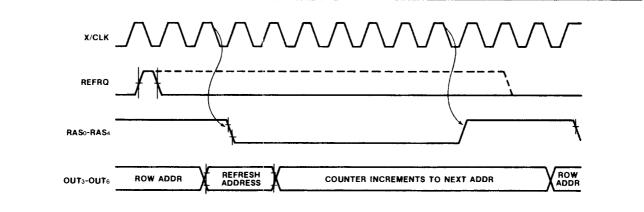

| REFRESH Command                  |      |

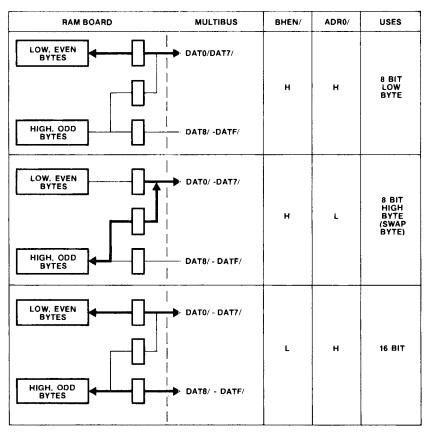

| Data Transfer Modes              | 4-9  |

| Even Byte Transfer Operation     | 4-9  |

| Odd Byte Transfer Operation      |      |

| 16-bit Transfer Operation        |      |

| Transfer Acknowledge Operation   | 4-10 |

| Inhibit Operation                | 4-10 |

| Memory Protect Operation         | 4-11 |

| Parity Circuitry Operation       | 4-11 |

| Parity Test Circuitry Operation  |      |

| Interrupt Request Logic          | 4-13 |

# CHAPTER 5 SERVICE INFORMATION

| Introduction                  | 5-1 |

|-------------------------------|-----|

| Service and Repair Assistance | 5-1 |

| Replaceable Parts             | 5-1 |

| Service Diagrams              | 5-1 |

## TABLES

| TABL | E TITLE                         | PAGE |

|------|---------------------------------|------|

| 1-1. | Specifications                  | 1-2  |

| 2-1. | Power Consumption/Heat          |      |

|      | Dissipation                     | 2-1  |

| 2-2. | P1 Connector Pin Assignment     | 2-2  |

| 2-3. | P1 Connector Signal Description | 2-3  |

| 2-4. | P2 Connector Pin Assignment     | 2-3  |

| 2-5. | P2 Connector Signal Description | 2-4  |

| 2-6. | DC Signal Characteristics for   |      |

|      | P1 Connector                    | 2-4  |

| 2-7. | AC Signal Characteristics for   |      |

|      | P1 Connector                    | 2-5  |

| 2-8. | Compatible User-provided        |      |

|      | P1 and P2 Connectors            | 2-8  |

| 2-9. | Jumper Functions                | 2-8  |

#### TABLETITLEPAGE

| 2-10. | Jumper Configuration              |

|-------|-----------------------------------|

|       | (as shipped) 2-9                  |

| 2-11. | Megabyte Page Select Jumpers 2-12 |

| 2-12. | 4k Boundary Jumper Configuration  |

|       | Examples 2-12                     |

| 2-13. | Maximum Starting 4k Boundary 2-13 |

| 2-14. | I/O Addresses Line Enables        |

|       | for Parity Flag Register 2-14     |

| 2-15. | I/O Port Address Selection 2-14   |

| 4-1.  | Memory ARRAY Organization 4-6     |

| 4-2.  | Data Transfer Modes 4-9           |

| 5-1.  | Replaceable Parts 5-2             |

| 5-2.  | Manufacturer Codes 5-3            |

## **ILLUSTRATIONS**

#### FIGURE TITLE PAGE

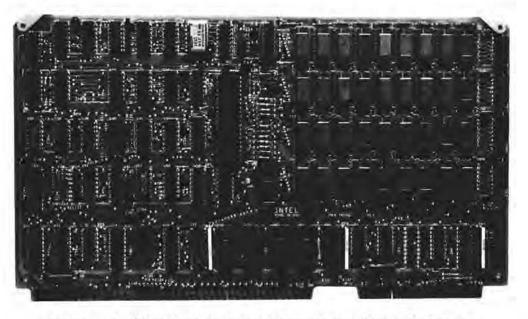

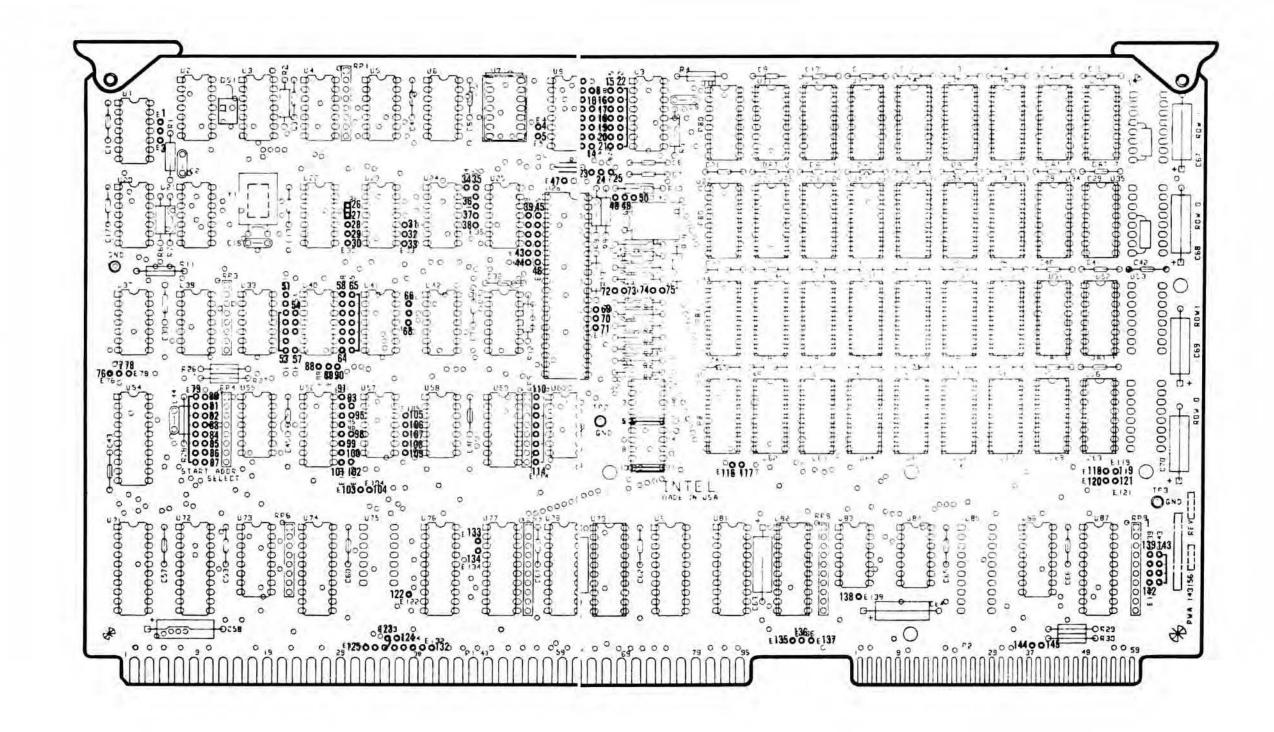

| 1-1. | iSBC 016A/032A/064A/028A/056A    |

|------|----------------------------------|

|      | RAM Boards 1-1                   |

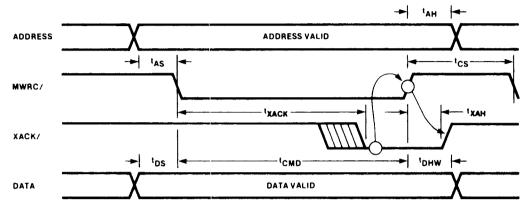

| 2-1. | Multibus Timing For Memory READ  |

|      | and Memory WRITE operations 2-6  |

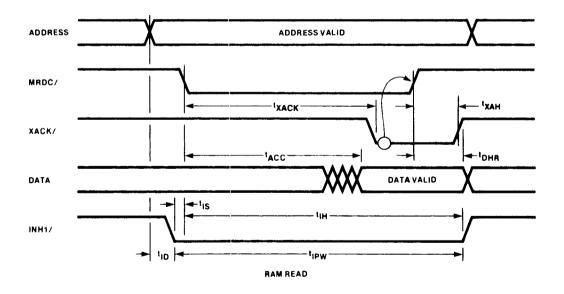

| 2-2. | Multibus Timing For I/O READ and |

|      | I/O WRITE operations 2-7         |

| 2-3. | Memory Address Jumper            |

|      | Location Diagram 2-10            |

| 2-4. | Address Selection                |

|      | Jumper Configuration 2-11        |

| 2-5. | Address Jumper                   |

|      | Configuration Example 2-13       |

| 3-1. | Parity Flag Register Format 3-1  |

| 4-1. | iSBC 016A/032A/064A/028A/056A    |

|      | RAM Boards Block Diagram 4-2     |

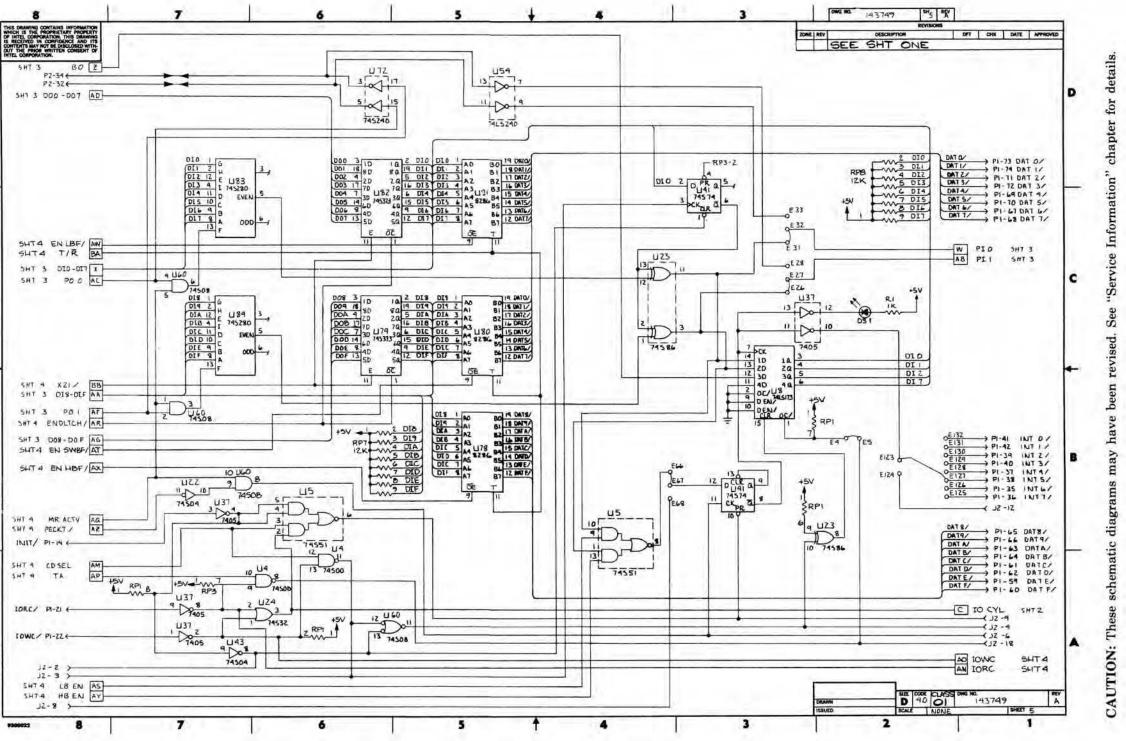

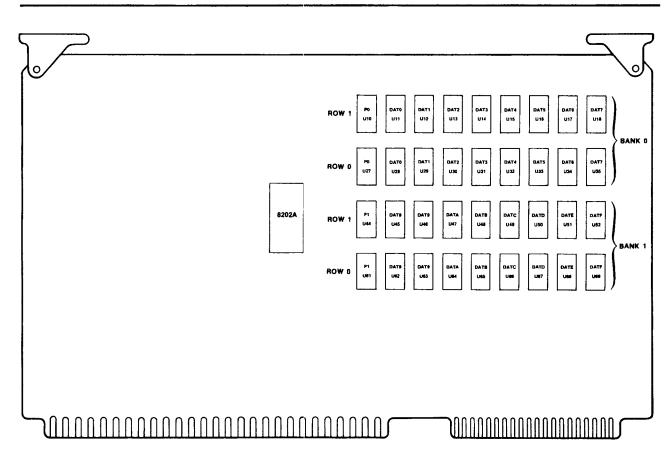

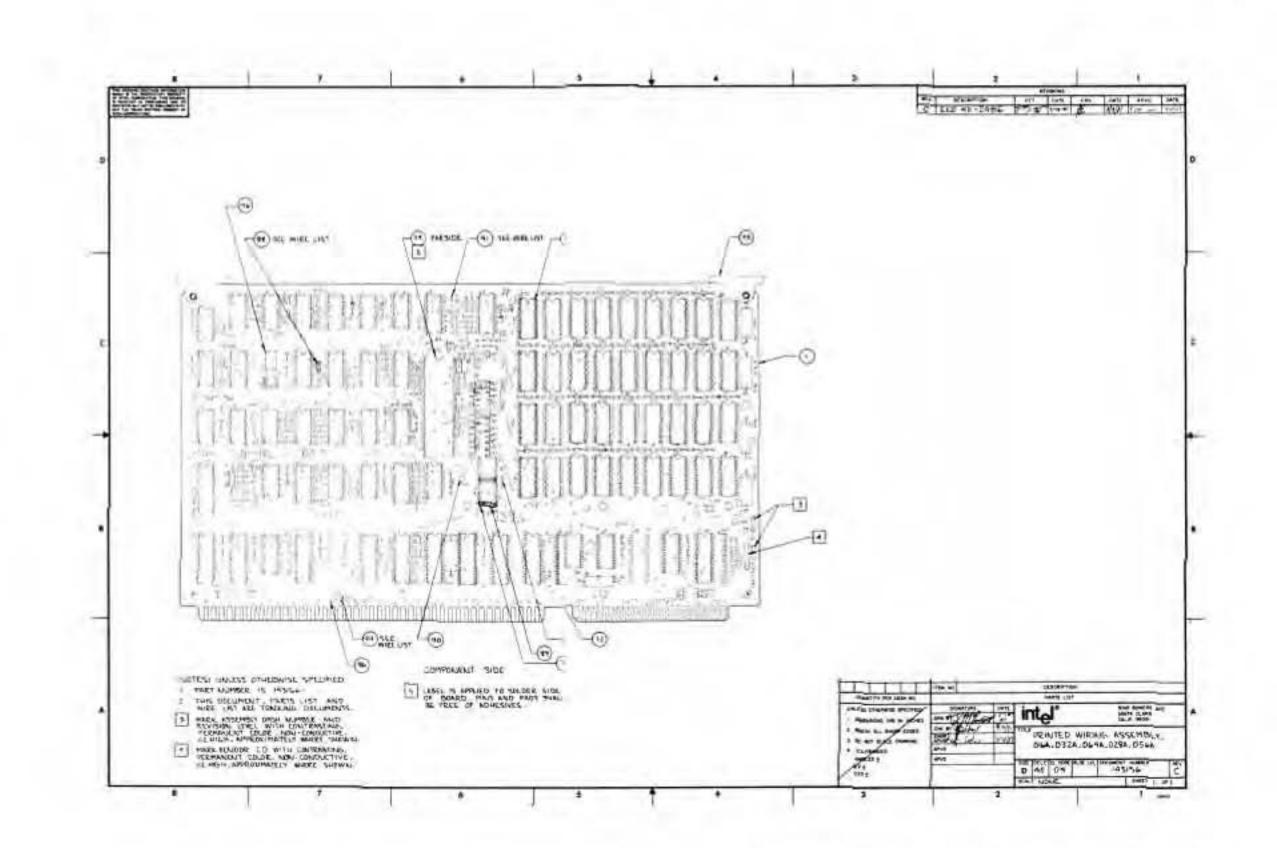

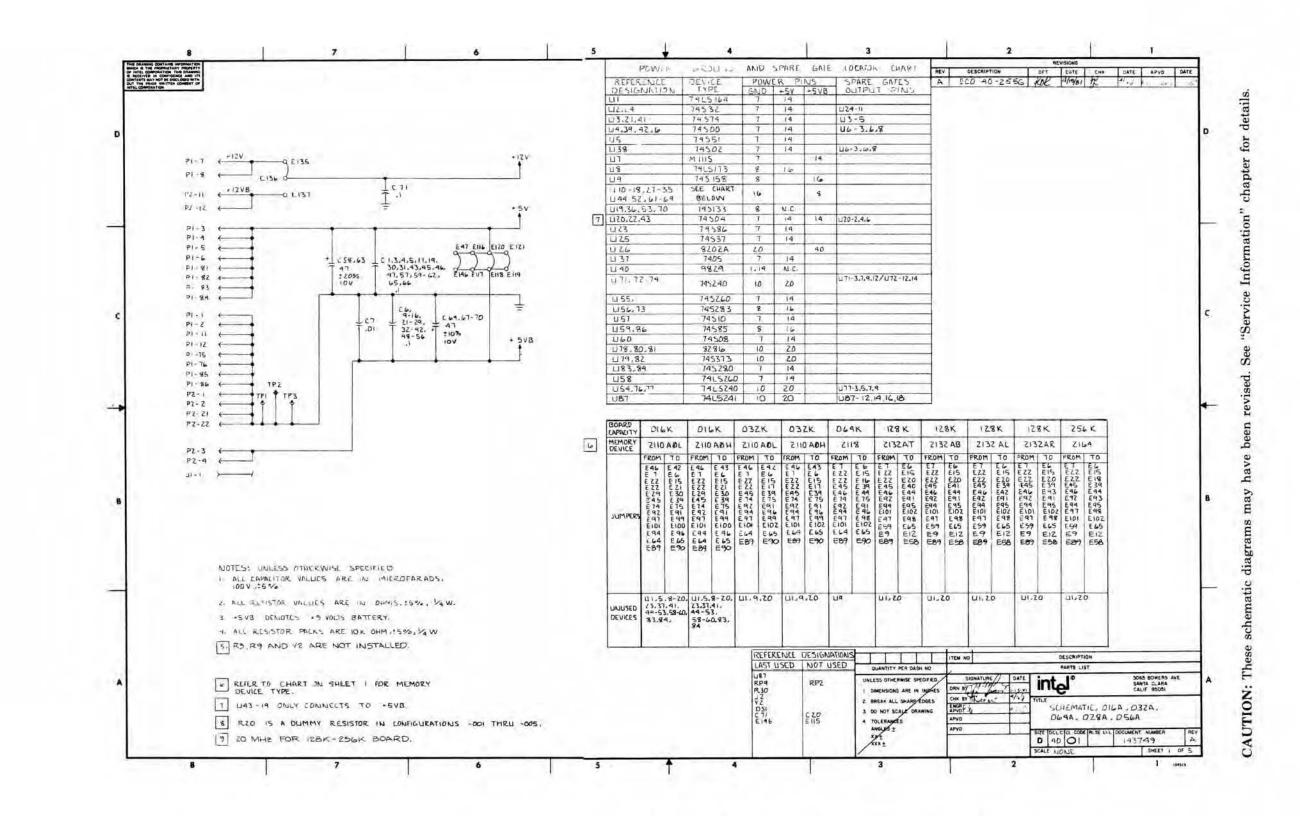

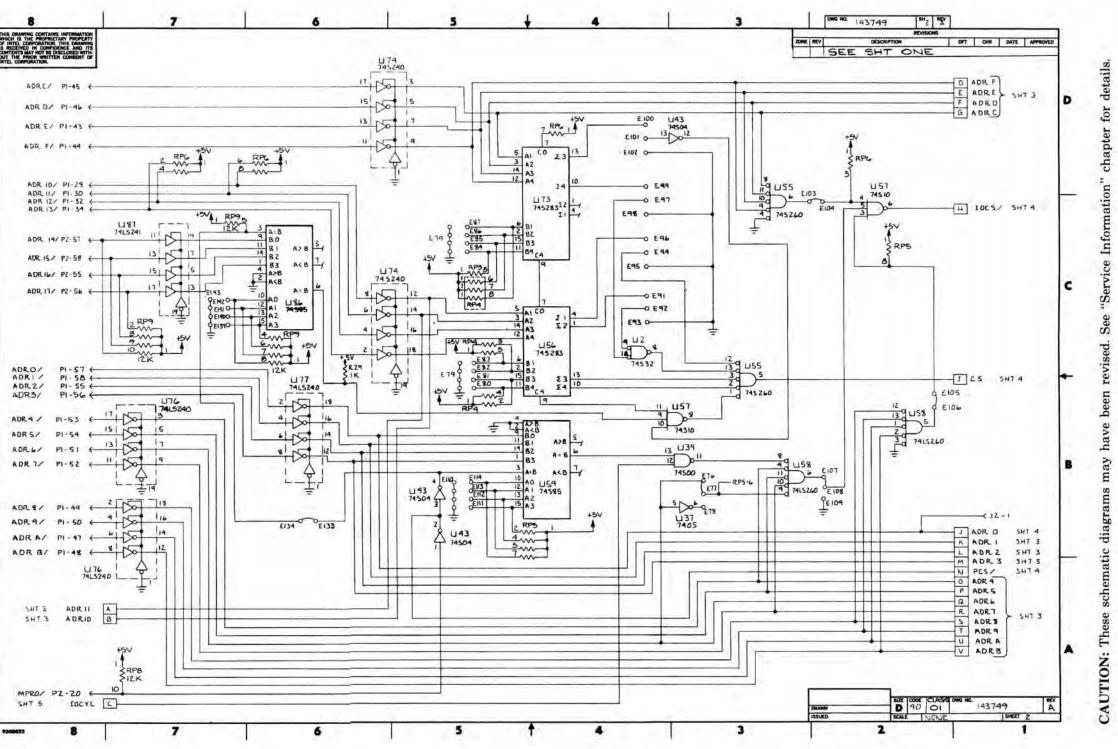

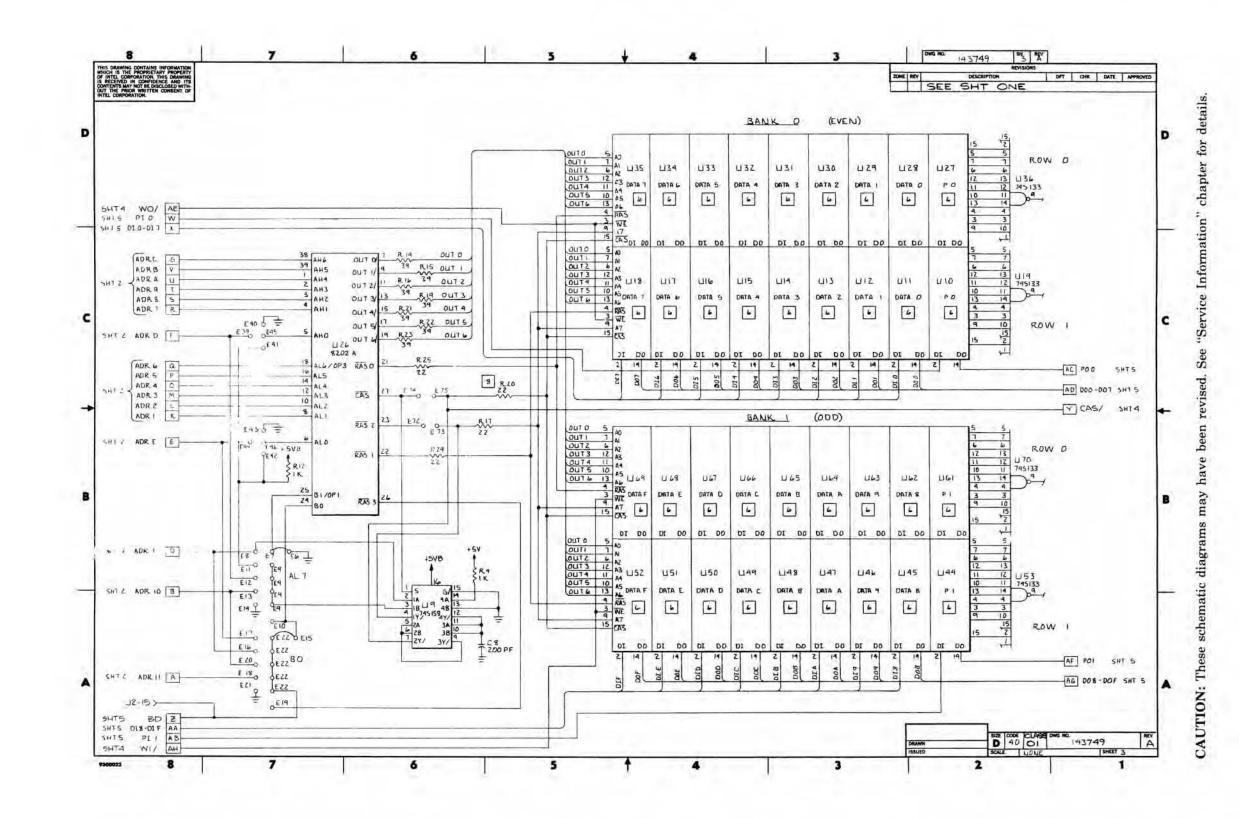

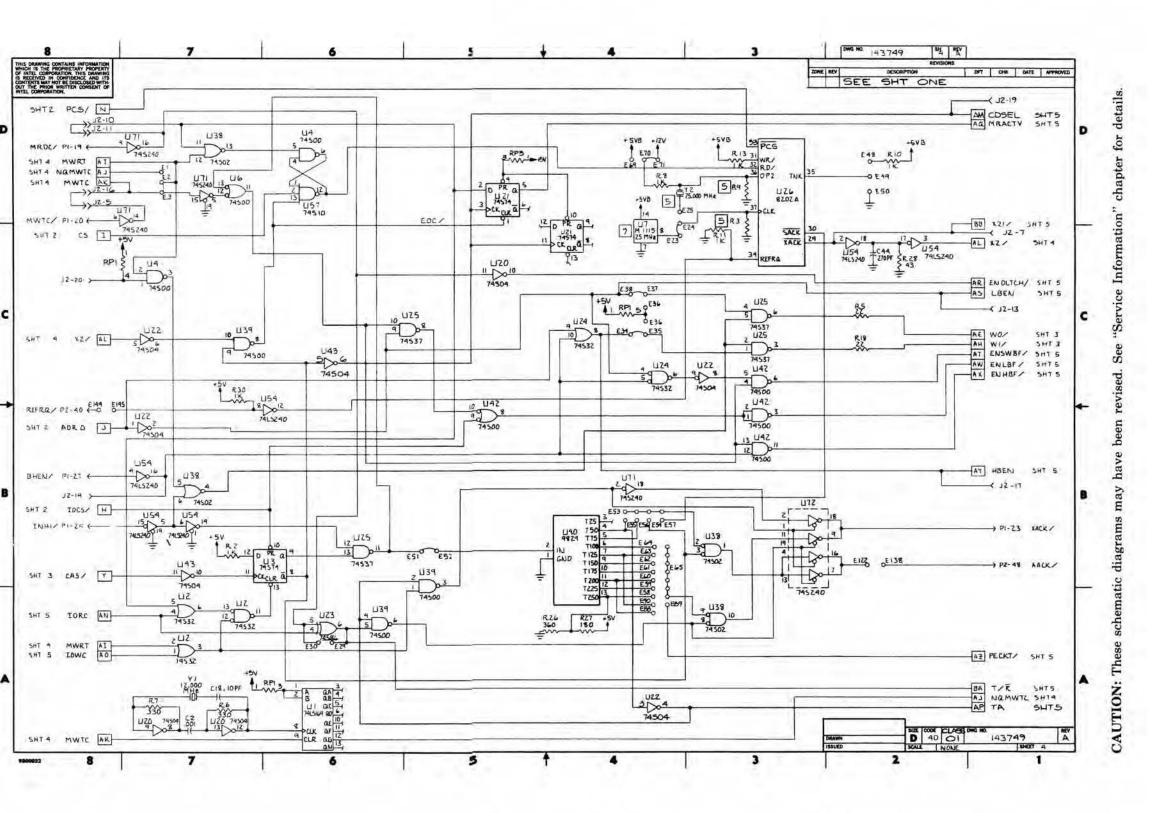

#### FIGURE TITLE PAGE **4**·2. Memory Array Layout ..... 4-5 4-3. **READ** and WRITE Command Timing ..... 4-7 4-4. External REFRESH Command Timing ..... 4-8 Jumper Location Diagram ..... 5-5 5-1. iSBC 016A/032A/064A/028A/056A 5-2. **RAM** Boards Parts Location Diagram ..... 5-7 5-3. iSBC 016A/032A/064A/028A/056A RAM Boards Schematic Diagram ..... 5-9

## CHAPTER 1 INTRODUCTION

#### **1-1. INTRODUCTION**

The iSBC 016A/032A/064A/028A/056A Random Access Memory (RAM) Boards provide a dynamic memory storage capacity of 16k, 32k, 64k, 128k, and 256k bytes, respectively, for use with all Intel iSBC 80/86 Series Single Board Computers and Intel 80/86 Series Microcomputer Systems. These RAM boards interface directly with the bus master via the Multibus interface and differ only in memory capacity and memory array configuration. This manual provides a general introduction, preparations for use, principles of operation, and service requirements for each of the configurations of the RAM board.

The iSBC 016A/032A/064A/028A/056A RAM boards are designed to allow quick, easy, and inexpensive expansion of RAM storage facilities within an Intel Multibus-compatible System. On-board refresh circuitry initiates periodic RAM refresh cycles to maintain the integrity of the RAM data. An optional auxiliary bus connector may provide battery backup power for the RAM and the refresh circuits. The RAM boards are direct replacement products for the iSBC 016/032/064 RAM Boards. Figure 1-1 shows a typical example of the iSBC 016A/032A/064A/028A/ 056A RAM Boards.

#### **1-2. DESCRIPTION**

The RAM boards consist of components that are mounted onto a single printed circuit board (as shown in figure 1-1) that is physically and electrically compatible with the Multibus standards as outlined in the *Intel Multibus Specification*. The capacity of the RAM boards varies depending on the type of memory devices installed on the boards; Intel 2110 (8,192 by 1 bit), Intel 2118 (16,384 by 1 bit), Intel 2132 (32,768 by 1 bit), or Intel 2164 (65,536 by 1 bit) RAM chips. The capacity of each version of the RAM board is as follows:

| Type of RAM Board   | Quantity of Chips | Type of Chips | Memory Capacity |

|---------------------|-------------------|---------------|-----------------|

| ISBC 016A RAM Board | 16                | 2110          | 16k bytes       |

| ISBC 032A RAM Board | 36                | 2110          | 32k bytes       |

| ISBC 064A RAM Board | 36                | 2118          | 64k bytes       |

| ISBC 028A RAM Board | 36                | 2132          | 128k bytes      |

| ISBC 056A RAM Board | 36                | 2164          | 256k bytes      |

Figure 1-1. iSBC 016A/032A/064A/028A/056A<sup>™</sup> RAM Boards

The design of the RAM boards allows operation within either an 8-bit or a 16-bit system. On-board jumpers are used to establish a RAM base address and to define page address boundaries. The RAM base address serves as a select address for the board. More information on jumper configurations is presented in Chapter 2 of this manual.

All of the RAM boards (except for the iSBC 016A RAM board) are equipped with a parity generating and checking feature that provides data handling and storage integrity verification for the RAM boards. The result of the parity check performed on a READ operation is stored within an internal I/O register on the RAM boards and accessible to the Multibus interface via an I/O READ operation. The RAM boards are equipped with an LED that provides a visual indication if a parity error does occur.

All electrical connections to and from the RAM boards are implemented via edge connectors P1 and P2. Connector P1 (86-pin) provides the interface to the Multibus structure and accommodates the power and signal lines including the address and data busses. The P2 connector (60-pin) accommodates the auxiliary power lines and upper address lines.

#### **1-3. MODES OF OPERATION**

The iSBC 016A/032A/064A/028A/056A RAM boards are capable of operation with any 8- or 16-bit iSBC board operating as the Multibus master. Board modifications are not required to convert a RAM board from 8- to 16-bit system operation. More details of the data transfer sequence are contained in Chapter 4 of this manual.

#### **1-4. EQUIPMENT SUPPLIED**

The RAM boards are shipped with a current revision of the schematic drawing that should be placed into this manual.

#### 1-5. SPECIFICATIONS

Table 1-1 lists the specifications and requirements for the iSBC 016A/032A/064A/028A/056A RAM boards.

| BOARD CAPACITY:                                                                                                      |                                                                                                                                                                                                                  |

|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iSBC 016A RAM Board:<br>iSBC 032A RAM Board:<br>iSBC 064A RAM Board:<br>iSBC 028A RAM Board:<br>iSBC 056A RAM Board: | 16,384 bytes or       8,192 words         32,768 bytes or       16,384 words         65,536 bytes or       32,768 words         131,072 bytes or       65,536 words         262,144 bytes or       131,072 words |

| MULTIBUS INTERFACE:                                                                                                  | All versions of the RAM board are fully compatible with the Multibus Specification.                                                                                                                              |

|                                                                                                                      | ADDRESS SELECTION:                                                                                                                                                                                               |

| Page Address:                                                                                                        | User configured jumpers allow assignment of memory into one of 16 possible<br>megabyte pages of memory address space.                                                                                            |

| 4k Boundary Address:                                                                                                 | User configured jumpers allow assignment of the starting address of memory to one of 256 possible 4k boundaries.                                                                                                 |

| ACCESS TIME:                                                                                                         |                                                                                                                                                                                                                  |

| Read:<br>Write:                                                                                                      | 406 nanoseconds (maximum for 016A, 032A, 064A)<br>343 nanoseconds (maximum for 016A, 032A, 064A, 028A)<br>See table 2-7                                                                                          |

| CYCLE TIMES:                                                                                                         |                                                                                                                                                                                                                  |

| Read:<br>Write:<br>Refresh:<br>PHYSICAL CHARACTERISTICS:                                                             | 608 nanoseconds (maximum for 016A, 032A, 064A, 028A)<br>608 nanoseconds (maximum for 016A, 032A, 064A, 028A)<br>608 nanoseconds (maximum for 016A, 032A, 064A, 028A)<br>See table 2-7                            |

| Width:                                                                                                               | 30.48 cm (12.00 inches)                                                                                                                                                                                          |

| Length:<br>Thickness:                                                                                                | 17.15 cm (6.75 inches)<br>1.27 cm (0.50 inch)                                                                                                                                                                    |

| Weight:                                                                                                              | 400 gm (14.0 ounces)                                                                                                                                                                                             |

| POWER REQUIREMENTS:                                                                                                  |                                                                                                                                                                                                                  |

| Power Consumption:                                                                                                   | 24 Watts maximum (see table 2-1)<br>10 Watts typical                                                                                                                                                             |

| Power Supply Voltage:                                                                                                | +5 volts at 4.0 amps (maximum)<br>2.0 amps (typical)                                                                                                                                                             |

| ENVIRONMENTAL SPECIFICATIONS:                                                                                        |                                                                                                                                                                                                                  |

| Operating Temperature:                                                                                               | 0 to 55°C (32 to 130°F)                                                                                                                                                                                          |

| Operating Humidity:                                                                                                  | Tc 90% (without condensation)                                                                                                                                                                                    |

Table 1-1. Specifications

## CHAPTER 2 PREPARATION FOR USE

#### **2-1. INTRODUCTION**

This chapter provides instructions for preparing the iSBC 016A/032A/064A/028A/056A RAM Boards for use in a user-defined environment. Included in this chapter are instructions on unpacking and inspection, installation considerations, jumper configurations, battery back-up configuration, and board installation information. It is advisable that the contents of Chapter 4 be fully read and understood before beginning the configuration and installation procedures contained in this chapter.

#### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent be present when the carton is opened. If the carrier's agent is not present when the carton is opened and the contents of the carton are damaged, keep the carton and the packing material for the agent's inspection.

For repair to a product damaged in shipment, contact the Intel Technical Support Center to obtain a Return Authorization Number and further instructions. A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

It is suggested that the salvageable shipping cartons and packing material be saved for future use in the event that the product must be shipped.

#### 2-3. INSTALLATION CONSIDERATIONS

Installation considerations such as power, cooling, physical size requirements, and interfacing requirements are outlined in the following paragraphs.

#### **2-4. POWER REQUIREMENTS**

The power requirements for the RAM boards depend on the type and quantity of RAM chips installed onto the RAM boards. Table 2-1 lists the various current requirements for each configuration of the RAM boards.

In all cases, the "A" versions of the RAM boards require more +5 volt current than their earlier-model counterparts. Ensure that the current requirements of the RAM boards are within the limits of your system's capability. Failure to do so could result in damage to the power supply.

#### 2-5. COOLING REQUIREMENTS

The heat dissipation for the RAM boards varies with the configuration of the board; table 2-1 shows the maximum power dissipation for each configuration. Adequate circulation of air must be provided to prevent a temperature rise above  $55^{\circ}$ C ( $130^{\circ}$ F). The system chassis units available from Intel include fans that provide adequate intake and exhaust of ventilating air.

| Table 2- | 1. Powe   | r Consump | otion/ |

|----------|-----------|-----------|--------|

| Heat 1   | Dissipati | on (maxim | um)    |

| Configuration   | Power<br>Requirements | Heat<br>Dissipation    |

|-----------------|-----------------------|------------------------|

| iSBC 016A board | 16.5 W                | 247 gc/m<br>(1.00 BTU) |

| iSBC 032A board | 17.3 W                | 299 gc/m<br>(1.21 BTU) |

| iSBC 064A board | 17.3 W                | 299 gc/m<br>(1.21 BTU) |

| iSBC 028A board | 24.0 W                | 341 gc/m<br>(1.38 BTU) |

| iSBC 056A board | 24.0 W                | 341 gc/m<br>(1.38 BTU) |

#### 2-6. INTERFACING REQUIREMENTS

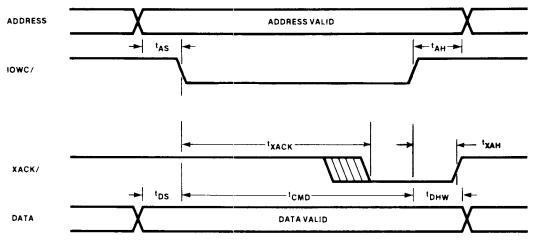

The iSBC 016A/032A/064A/028A/056A RAM Boards are designed for installation into a standard Intel iSBC cardcage or into an Intel Microcomputer Development System chassis. As shown in figure 1-1, the 43/86-pin edge connector (P1) on the RAM boards provides interfacing to the Multibus structure. Table 2-2 lists the pin assignments for the P1 connector and table 2-3 lists a description of the function of each signal. Edge connector P2 on the RAM boards is an optional 30/60-pin connector providing the external RAM refresh signal, the upper memory address bits, parity bits for each byte of a data word, battery backup signals, and memory protection signals for the RAM boards. Table 2-4 lists the pin assignments for connector P2 and table 2-5 lists a description of each signal function on the P2 interface. Notice that the RAM boards require the use of a P2 connector if the memory is to reside anywhere other than on megabyte page 0; the upper address lines must be made available to the RAM boards. The ac and dc characteristics of the RAM boards are listed in tables 2-6 and 2-7, respectively. The ac characteristics listed in table 2-6 are further defined by figure 2-1 which shows the system timing requirements for a Memory WRITE and Memory READ operation, and by figure 2-2 which shows the system timing requirements for an I/O WRITE and I/O READ operation.

|                                   |                                              | (COMPONENT SIDE)                                                              |                                                                                     |                                              | (C                                                                   | IRCUIT SIDE)                                                                             |

|-----------------------------------|----------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------------------------|

|                                   | PIN                                          | MNEMONIC                                                                      | DESCRIPTION                                                                         | PIN                                          | MNEMONIC                                                             | DESCRIPTION                                                                              |

| POWER<br>SUPPLIES                 | 1<br>3<br>5<br>7<br>9<br>11                  | GND<br>+5V<br>+5V<br>GND                                                      | Signal GND<br>+5Vdc<br>+5Vdc<br>Reserved<br>Signal GND                              | 2<br>4<br>6<br>8<br>10<br>12                 | GND<br>+5V<br>+5V<br>GND                                             | Sig GND<br>+5Vdc<br>+5Vdc<br>Reserved<br>Signal GND                                      |

| BUS<br>CONTROLS                   | 13<br>15<br>17<br>19<br>21<br>23             | MRDC/<br>IORC/<br>XACK/                                                       | Reserved<br>Reserved<br>Reserved<br>Mem Red Cmd<br>I/O Read Cmd<br>XFER Acknowledge | 14<br>16<br>18<br>20<br>22<br>24             | INIT/<br>MWTC/<br>IOWC/<br>INH1/                                     | Reset<br>Reserved<br>Reserved<br>Mem Write Cmd<br>I/O Write Cmd<br>Inhibit 1 Disable RAM |

| BUS<br>CONTROLS<br>AND<br>ADDRESS | 25<br>27<br>29<br>31<br>33                   | BHEN/                                                                         | Reserved<br>Byte High Enable<br>Reserved<br>Reserved<br>Reserved                    | 26<br>28<br>30<br>32<br>34                   | AD10/<br>AD11/<br>AD12/<br>AD13/                                     | Reserved<br>Address<br>Bus                                                               |

| INTERRUPTS                        | 35<br>37<br>39<br>41                         | INT6/<br>INT4/<br>INT2/<br>INT0/                                              | Parallel<br>Interrupt<br>Requests                                                   | 36<br>38<br>40<br>42                         | INT7/<br>INT5/<br>INT3/<br>INT1/                                     | Parailei<br>Interrupt<br>Requests                                                        |

| ADDRESS                           | 43<br>45<br>47<br>49<br>51<br>53<br>55<br>57 | ADRE/<br>ADRC/<br>ADRA/<br>ADR8/<br>ADR6/<br>ADR4/<br>ADR2/<br>ADR0/          | Address<br>Bus                                                                      | 44<br>46<br>48<br>50<br>52<br>54<br>56<br>58 | ADRF/<br>ADRD/<br>ADRB<br>ADR9/<br>ADR7/<br>ADR5/<br>ADR3/<br>ADR1/  | Address<br>Bus                                                                           |

| DATA                              | 59<br>61<br>63<br>65<br>67<br>69<br>71<br>73 | DATE/<br>DATC/<br>DATA/<br>DAT8/<br>DAT6/<br>DAT6/<br>DAT4/<br>DAT2/<br>DAT0/ | Data<br>Bus                                                                         | 60<br>62<br>64<br>66<br>68<br>70<br>72<br>74 | DATF/<br>DATD/<br>DATB/<br>DAT9/<br>DAT7/<br>DAT5/<br>DAT3/<br>DAT1/ | Data<br>Bus                                                                              |

| POWER<br>SUPPLIES                 | 75<br>77<br>79<br>81<br>83<br>85             | GND<br>+5V<br>+5V<br>GND                                                      | Signal GND<br>Reserved<br>Reserved<br>+5Vdc<br>+5Vdc<br>Signal GND                  | 76<br>78<br>80<br>82<br>84<br>84<br>86       | GND<br>+5<br>+5V<br>GND                                              | Signal GND<br>Reserved<br>Reserved<br>+5Vdc<br>+5Vdc<br>Signal GND                       |

Table 2-2. P1 Connector Pin Assignment

Table 2-8 contains a list of compatible connectors that a user may install into a standard Intel iSBC cardcage for interface to the P2 connector on the RAM boards. If the system does not require any of the signals provided on the P2 connector, the compatible P2 connector need not be installed.

| Signal                       | Functional Description                                                                                                                                                                                                                                                                             |

|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR0/ ADRF/<br>ADR10/-ADR13/ | Address. These 20 lines transmit the address of the memory location or I/O port to be accessed. For mem-<br>ory access, ADR0/ (when active) enables the even byte bank (DAT0/-DAT7/) on the Multibus; i.e., ADR0/ is<br>active for all even addresses. ADR13/ is the most significant address bit. |

| BHEN/                        | Byte High Enable. When active low, enables the odd byte bank (DAT8/-DATF/) onto the Multibus.                                                                                                                                                                                                      |

| DAT0/-DATF/                  | Data. These 16 bidirectional data lines transmit and receive data to and from the addressed memory location or I/O port. DATF/ is the most significant bit. For data byte operations, DAT0/ - DAT7/ is the even byte and DAT8/-DATF/ is the odd byte.                                              |

| INH1/                        | Inhibit RAM. For system applications, allows iSBC dual port RAM addresses to be overlayed by ROM/PROM or memory mapped I/O devices. This signal has no effect on local CPU access of its dual port RAM.                                                                                            |

| INT0/-INT7/                  | Interrupt Request. These eight lines transmit interrupt Requests to the appropriate interrupt handler. INTO has the highest priority.                                                                                                                                                              |

| IORC/                        | I/O Read Command. Indicates that the address of an I/O port is on the Multibus address lines and that the output of that port is to be read (placed) into the Multibus data lines.                                                                                                                 |

| IOWC/                        | I/O Write Command. Indicates that the address of an I/O port is on the Multibus address lines and that the contents on the Multibus data lines are to be accepted by the addressed port.                                                                                                           |

| MRDC/                        | Memory Read Command. Indicates that the address of a memory location is on the Multibus address lines<br>and that the contents of that location are to be read (placed) on the Multibus data lines.                                                                                                |

| MWTC/                        | Memory Write Command. Indicates that the address of a memory location is on the Multibus address lines and that the contents on the Multibus data lines are to be written into that location.                                                                                                      |

| XACK/                        | Transfer Acknowledge. Indicates that the address memory location has completed the specified read or write operation. That is, data has been placed onto or accepted from the Multibus data lines.                                                                                                 |

| Table 2-3. | P1 | Connector | Signal | Description |

|------------|----|-----------|--------|-------------|

|------------|----|-----------|--------|-------------|

| <b>Table 2-4.</b> | P2 Connector | Pin Assignment |  |

|-------------------|--------------|----------------|--|

|          | (COMPONENT SIDE) |                 |          | (CIRCUIT SIDE)                          |                              |  |

|----------|------------------|-----------------|----------|-----------------------------------------|------------------------------|--|

| PIN      | MNEMONIC         | DESCRIPTION     | PIN      | MNEMONIC                                | DESCRIPTION                  |  |

| 1        | GND              | Signal GND      | 2        | GND                                     | Signal GND                   |  |

| 3        | GVB              | +5V Battery     | 4        | GBV                                     | +5V Battery                  |  |

| 5        |                  | Reserved        | 6        |                                         |                              |  |

| 7        |                  |                 | 8        |                                         |                              |  |

| 9        |                  | Reserved        | 10       | Reserved                                |                              |  |

| 11       |                  |                 | 12       |                                         |                              |  |

| 13       |                  |                 | 14       | Reserved                                |                              |  |

| 15       |                  |                 | 16       |                                         |                              |  |

| 17       |                  |                 | 18<br>20 | MPRO/                                   | Mamaru Brataat               |  |

| 19<br>21 | GND              | Signal GND      | 20       | GND                                     | Memory Protect<br>Signal GND |  |

| 23       |                  | Signal GIVD     | 24       | GIND                                    | Signal CIND                  |  |

| 25       | 1                |                 | 26       |                                         |                              |  |

| 27       |                  |                 | 28       |                                         |                              |  |

| 29       |                  |                 | 30       |                                         |                              |  |

| 31       |                  |                 | 32       | PO0                                     | Parity Bit (Byte 0)          |  |

| 33       |                  |                 | 34       | PO1                                     | Parity Bit (Byte 1)          |  |

| 35       |                  |                 | 36       |                                         |                              |  |

| 37       |                  |                 | 38       |                                         |                              |  |

| 39       |                  |                 | 40       |                                         |                              |  |

| 41       | RFQST/           | REFRESH REQUEST | 42       | 1                                       |                              |  |

| 43       |                  |                 | 44       |                                         |                              |  |

| 45       |                  |                 | 46       | Reserved                                |                              |  |

| 47       |                  |                 | 48       |                                         |                              |  |

| 49<br>51 |                  |                 | 50<br>52 |                                         |                              |  |

| 53       |                  |                 | 54       |                                         |                              |  |

| 55       | ADR17/           | ADDRESS         | 56       | ADR16/                                  | ADDRESS                      |  |

| 57       | ADR16/           | BUS             | 58       | ADR14/                                  | BUS                          |  |

| 59       |                  | 200             | 60       | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | 200                          |  |

| Signal        | Functional Description                                                                                                                                                                  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADR14/-ADR17/ | Address. These address lines select one of 16 megabytes of memory space to be accessed.                                                                                                 |

| MPRO/         | Memory Protect. This externally generated signal prevents the the memory and I/O on the RAM boards from recognizing and responding to a subsequent command from the Multibus interface. |

| PO0/,PO1/     | Parity Bits. These parity bits are generated by the RAM boards for each data word when enabled; PO0/ for the even byte and PO1/ for the odd byte of data.                               |

| RFQST/        | Refresh Request. This signal provides the Dynamic RAM Controller with an externally generated timing signal for generation of RAM refresh.                                              |

Table 2-5. P2 Connector Signal Description

| Signal                   | Parameter                                    | Test Conditions                               | Minimum    | Maximum                          | Units                         |

|--------------------------|----------------------------------------------|-----------------------------------------------|------------|----------------------------------|-------------------------------|

| MRDC/                    | VIL<br>VIH<br>IIL<br>IIH<br>CL               | VIN=0.45V<br>VIN=2.4V                         | 2.0        | 0.8<br>-0.4<br>50<br>7           | ν<br>ν<br>mA<br>μA<br>pF      |

| MWTC/                    | VIL<br>VIH<br>IIL<br>IIH<br>CL               | VIN=0.5V<br>VIN=2.4V                          | 2.0        | 0.8<br>-0.4<br>50<br>7           | ν<br>ν<br>mA<br>μA<br>pF      |

| IORC/<br>IOWC/           | VIL<br>VIH<br>IIL<br>IIH<br>CL               | VIN=0.4V<br>VIN=2.7V                          | 2.0        | 0.8<br>-1.6<br>40<br>7           | ν<br>ν<br>mA<br>μA<br>pF      |

| INIT/                    | VIL<br>VIH<br>IIL<br>IIH<br>CL               | VIN=0.4V<br>VIN=2.4V                          | 2.0        | 0.8<br>-1.6<br>40<br>7           | ν<br>ν<br>mA<br>μA<br>pF      |

| AACK/<br>XACK/           | VOL<br>VOH<br>CO                             | IOL=64mA<br>IOH=-3mA                          | 2.4<br>300 | 0.55                             | V<br>V<br>pF                  |

| INHI/                    | VIL<br>VIH<br>IIL<br>IIH<br>CL               | VIN=0.4V<br>VIN=2.4V                          | 2.0        | 0.8<br>-0.2<br>20<br>7           | V<br>V<br>mA<br>μA<br>pF      |

| ADR0/<br>ADR17/<br>BHEN/ | VIL<br>VIH<br>IIL<br>IIH<br>CL               | VIN=0.45V<br>VIN=2.4V                         | 2.0        | 0.8<br>-0.4<br>50<br>7           | V<br>MA<br>µA<br>pF           |

| DAT0/<br>DATF/           | VIL<br>VIH<br>IIL<br>IIH<br>CL<br>VOL<br>VOH | VIN=0.45V<br>VIN=2.4V<br>IOL=32mA<br>IOH=-5mA | 2.0        | 0.8<br>-0.4<br>100<br>24<br>0.45 | ν<br>mA<br>μA<br>pF<br>ν<br>ν |

Table 2-6. DC Signal Characteristics for P1 Connector

| Signal | Parameter                      | Test Conditions      | Minimum        | Maximum              | Units                    |

|--------|--------------------------------|----------------------|----------------|----------------------|--------------------------|

| MPRO/  | VIL<br>VIH<br>IIL<br>IIH<br>CL | VIN=0.4V<br>VIN=2.4V | 2.0            | 0.8<br>-2<br>50<br>7 | ν<br>ν<br>mA<br>μA<br>pF |

| INT0/  | VOL<br>VOH<br>CL               | IOL=16mA             | Open Collector | 0.4<br>18            | V<br>pF                  |

#### Table 2-6. DC Signal Characteristics for P1 Connector (Continued)

Table 2-7. AC Signal Characteristics for P1 Connector

| Parameter | Description                                                  | Minimum | L         | Maximum |      |  |

|-----------|--------------------------------------------------------------|---------|-----------|---------|------|--|

|           |                                                              | All     | 016A-064A | 028A    | 056A |  |

| AS        | Address Set-up Time                                          | 50      |           |         |      |  |

| tDS       | Write Data Set-up Time Memory                                | -100    |           |         |      |  |

|           | Write Data Set-up Time I/O                                   | 0       |           |         |      |  |

| tAH       | Address Hold Time                                            | 0       |           |         |      |  |

| tDHW      | Write Data Hold Time                                         | 0       |           |         |      |  |

| tDXL      | Read Data Set-up Time to XACK                                | 0       |           |         |      |  |

| tDHR      | Read Data Hold Time                                          | 0       |           | 60      |      |  |

| tAXAH     | Acknowledge Hold Time                                        | 0       |           | 55      |      |  |

| tXACK     | Acknowledge Time: Memory Read Cycle                          |         | 406       | 500     | 570  |  |

|           | Acknowledge Time: Memory Write Cycle                         |         | 343       | 343     | 363  |  |

|           | Acknowledge Time: I/O Read Cycle                             | 1       | 238       | 330     | 370  |  |

|           | Acknowledge Time: I/O Write Cycle                            |         |           | 185     |      |  |

| tID       | Inhibit Delay From Address                                   |         |           | 150     |      |  |

| tCS       | Command Separation                                           | 50      |           |         |      |  |

| tIS       | Inhibit Set-up Time to CMD                                   |         |           | -100    |      |  |

| tACC      | Command to Data Valid                                        |         | 357       | 402     | 447  |  |

| tIH       | Inhibit Hold Time after CMD                                  | 850     |           |         |      |  |

| tCY       | Cycle Time Memory                                            |         | 608       | 608     | 653  |  |

|           | Cycle Time I/O Read                                          |         | 268       | 340     | 360  |  |

|           | Cycle Time I/O Write                                         |         |           | 235     |      |  |

| tINIT     | INIT Pulse Width                                             | 50      |           |         |      |  |

| tCYD      | Cycle Time of Non-Qualified Write                            |         | 1200      | 1200    | 1200 |  |

| tRD       | Refresh Delay Time                                           |         | 480       | 480     | 540  |  |

| tRI       | Refresh Interval                                             | 10.56µs |           | 14.4µs  |      |  |

| tNQDS     | Write Data Delay from Command<br>(Non qualified write cycle) |         | 600       |         |      |  |

RAM WRITE

A. WRITE TO I/O PORT

Figure 2-2. Multibus Timing For I/O READ and I/O WRITE operations

| Function                     | Pins  | Centers<br>(inches) | Connector<br>Type                           | Vendor          | Part Number                       |

|------------------------------|-------|---------------------|---------------------------------------------|-----------------|-----------------------------------|

| Multibus<br>Connector<br>P1  | 43/86 | 0.156               | Solder PCB                                  | ELFAB<br>VIKING | BS1562043PBB<br>2KH43/9AMK12      |

| FI                           |       |                     | Wire Wrap<br>(no ears)                      | EDAC<br>ELFAB   | 337-086-0540-201<br>BW1562D-43PBB |

|                              |       |                     | Wire Wrap<br>(with 0.128<br>mounting holes) | EDAC<br>ELFAB   | 337-086-540-202<br>BW1562A-43PBB  |

| Auxiliary<br>Connector<br>P2 | 30/60 | 0.100               | Wire Wrap                                   | EDAC<br>ELFAB   | 345-060-524-802<br>BS1020A-30PBB  |

| ΓZ                           |       |                     | With 0.128<br>mounting holes                | TI<br>VIKING    | H421121-30<br>3KH30/9JNK          |

|                              |       |                     | No Ears                                     | EDAC<br>ELFAB   | 345-060-540-201<br>BW1020D-30PBB  |

| Table 2-8. | Compatible | <b>User-provided</b> | P1 and | <b>P2</b> Connectors |

|------------|------------|----------------------|--------|----------------------|

|------------|------------|----------------------|--------|----------------------|

Notes:

1. Connector heights are not guaranteed to conform to OEM equipment.

2. Wire wrap pin lengths are not guaranteed to conform to OEM equipment.

3. Connector numbering convention may not agree with board connector.

#### 2-7. JUMPER CONFIGURATIONS

Jumper selection options available to a user of the RAM boards include megabyte page address selection, 4k boundary selection, parity enable/disable, external refresh request enable, interrupt level selection, and non-qualified memory write selection. The instructions for configuring each of these jumpers are provided in the following paragraphs; table 2-9 contains a list of the functions performed by each jumper and table 2-10 contains a list of the default jumper connections for each version of the RAM boards, as shipped.

| Table | 2-9. | Jumper | Functions |

|-------|------|--------|-----------|

|-------|------|--------|-----------|

| Jumper Number                                                                       | Version Used On              | Function                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------------------------------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1,E2,E3                                                                            | Used only in<br>064A version | ADVANCED/DELAYED WRITE SELECT. Connecting E2-E3 (the as-shipped configuration) enables operation in a DELAYED (normal) WRITE mode. Connecting E1-E2 enables the ADVANCED (NON-QUALIFIED) WRITE mode; the ADVANCED WRITE mode is required only for use with MDS 800 Development Systems and ICE 80 Emulators.             |

| E4,E5                                                                               | All versions<br>except 016A  | PARITY FLAG REGISTER OUTPUT ENABLE. When installed (the as-shipped condition), the jumper enables the Parity Flag Register to output the parity error location information onto the Multibus interface.                                                                                                                  |

| E26,E27,E28                                                                         | All versions<br>except 016A  | INPUT PARITY SELECT (BANK 1). Jumper E26-E27 (installed as-shipped)<br>enables on-board generation of a parity bit for a WRITE to memory bank 1<br>operation. Installation of jumper E27-E28 enables external generation of a parity<br>bit via the P2 connector.                                                        |

| E31,E32,E33                                                                         | All versions<br>except 016A  | INPUT PARITY SELECT (BANK 0). Jumper E31-E32 (installed-as-shipped)<br>enables on-board generation of a parity bit for a WRITE to memory bank 0<br>operation. Installation of jumper E32-E33 enables external generation of a parity<br>bit via the P2 connector.                                                        |

| E76,E77,E78,<br>E103,E104,<br>E105,E106,<br>E107,E108,E109,<br>E110 through<br>E114 | All versions                 | ENABLES FOR ON-BOARD I/O PORT ADDRESS SELECT. These jumpers allow user selection of the I/O port address at which the Parity Flag Register is accessed via the Multibus interface. As shipped, E103-E104, E105-E106, E107-E108, and E76-E77 are connected. Refer to tables 2-14 and 2-15 to verify proper configuration. |

| Jumper Number                                  | Version Used On | Function                                                                                                                                                                                                                                                       |

|------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E139<br>through<br>E143                        | All versions    | MEGABYTE PAGE SELECT. As shipped, all page select jumpers are removed, selecting megabyte page address 0XXXXXH; more information on configuration of the megabyte page address is contained in table 2-11.                                                     |

| E79<br>through<br>E87                          | All versions    | 4k MEMORY ADDRESS BOUNDARY SELECT. As shipped, the starting 4K boundary for the board is 000000 (no jumpers installed) on all RAM boards (except the iSBC 032A RAM Board which starts at 08000H). User configuration of the jumpers is outlined in table 2-12. |

| E116,E117,E120,<br>E121,E146,E47,<br>E118,E119 | All versions    | BATTERY BACK-UP ENABLE. As shipped, the jumpers ARE connected.<br>Removal of E146- E 47, E116-E117, E118-E120, and E119-E121 fully enables the<br>battery back-up option.                                                                                      |

| E144,E145                                      | All versions    | EXTERNAL REFRESH REQUEST ENABLE. This jumper is not installed at the factory, but may be added by a user requiring a refresh cycle that is generated from an external source.                                                                                  |

| E123<br>through<br>E132                        | All versions    | INTERRUPT REQUEST ENABLE. Jumper E123-E127 is factory installed to provide an interrupt request on INT5/ if a parity error is detected. Reconfiguration of the jumper will generate one of the Multibus interrupt request lines as follows: E123 E132          |

|                                                |                 | E123-E132 Generate INT0/<br>E123-E131 Generate INT1/<br>E123-E130 Generate INT2/<br>E123-E129 Generate INT3/<br>E123-E128 Generate INT4/<br>E123-E127 Generate INT5/                                                                                           |

|                                                |                 | E123-E126 Generate INT6/<br>E123-E125 Generate INT7/                                                                                                                                                                                                           |

| Table 2-9. Ju | umper Fu | nctions (C | ontinued) |

|---------------|----------|------------|-----------|

|---------------|----------|------------|-----------|

#### Table 2-10. Jumper Configuration (as shipped)

| Board Version                               | Default Jumper Configuration                                                                                                                                                                                               |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iSBC 016A board with 2110-4AOL RAM chips    | Connect E2-E3, E6-E7, E15-E22, E21-E22, E29-E30, E34-E35, E37-E38, E39-E45, E42-E46, E64-E65, E74-E75, E91-E92, E94-E96, E97-E99, E100-E101, E109-E108.                                                                    |

| iSBC 016A board with 2110-4AOH RAM chips    | Connect E2-E3, E6-E7, E15-E22, E21-E22, E29-E30, E34-E35, E37-E38, E39-E45, E43-E46, E64-E65, E74-E75, E91-E92, E94-E96, E97-E99, E100-E101, E109-E108, E123-E127.                                                         |

| iSBC 032A board with<br>2110-4AOL RAM chips | Connect E2-E3, E4-E5, E6-E7, E15-E22, E17-E22, E26-E27, E31-E32, E34-E35, E37-E38, E39-E45, E42-E46, E64-E65, E66-E67, E74-E75, E76-E77, E91-E92, E94-E96, E97-E99, E102-E101, E103-E104, E105-E106, E107-E108, E123-E127. |

| iSBC 032A board with<br>2110-4AOH RAM chips | Connect E2-E3, E4-E5, E6-E7, E15-E22, E17-E22, E26-E27, E31-E32, E34-E35, E37-E38, E39-E45, E43-E46, E64-E65, E66-E67, E74-E75, E76-E77, E91-E92, E94-E96, E97-E99, E102-E101, E103-E104, E105-E106, E107-E108, E123-E127. |

| iSBC 064A board with<br>2118-4 RAM chips    | Connect E2-E3, E4-E5, E6-E7, E15-E22, E16-E22, E26-E27, E31-E32, E34-E35, E37-E38, E39-E45, E44-E46, E64-E65, E66-E67, E74-E75, E76-E77, E91-E92, E94-E96, E97-E98, E101-E102, E103-E104, E105-E106, E107-E108, E123-E127. |

| iSBC 028A board with<br>2132A-20T RAM chips | Connect E2-E3, E4-E5, E6-E7, E15-E22, E20-E22, E26-E27, E31-E32, E34-E35, E37-E38, E40-E45, E44-E46, E61-E65, E66-E67, E76-E77, E91-E92, E94-E95, E97-E98, E101-E102, E103-E104, E105-E106, E107-E108, E123-E127, E9-E12.  |

| iSBC 028A board with<br>2132A-20B RAM chips | Connect E2-E3, E4-E5, E6-E7, E15-E22, E20-E22, E26-E27, E31-E32, E34-E35, E37-E38, E41-E45, E44-E46, E61-E65, E66-E67, E76-E77, E91-E92, E94-E95, E97-E98, E101-E102, E103-E104, E105-E106, E107-E108, E123-E127, E9-E12.  |

|                                             |                                                                                                                                                                                                                            |

| Board Version                               | Default Jumper Configuration, as shipped                                                                                                                                                                                  |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| iSBC 028A board with<br>2132A-20L RAM chips | Connect E2-E3, E4-E5, E6-E7, E15-E22, E20-E22, E26-E27, E31-E32, E34-E35, E37-E38, E39-E45, E44-E46, E61-E65, E66-E67, E76-E77, E91-E92, E94-E95, E97-E98, E101-E102, E103-E104, E105-E106, E107-E108, E123-E127, E9-E11. |

| iSBC 028A board with<br>2132A-20R RAM chips | Connect E2-E3, E4-E5, E6-E7, E15-E22, E20-E22, E26-E27, E31-E32, E34-E35, E37-E38, E39-E45, E44-E46, E61-E65, E66-E67, E76-E77, E91-E92, E94-E95, E97-E98, E101-E102, E103-E104, E105-E106, E107-E108, E123-E127, E9-E14. |

| iSBC 056A board with<br>2164A-25 RAM chips  | Connect E2-E3, E4-E5, E6-E7, E15-E22, E18-E22, E26-E27, E31-E32, E34-E35, E37-E38, E39-E45, E44-E46, E59-E65, E66-E67, E76-E77, E92-E93, E94-E95, E97-E98, E101-E102, E103-E104, E105-E106, E107-E108, E123-E127, E9-E13. |

Table 2-10. Jumper Configuration (as shipped) (Continued)

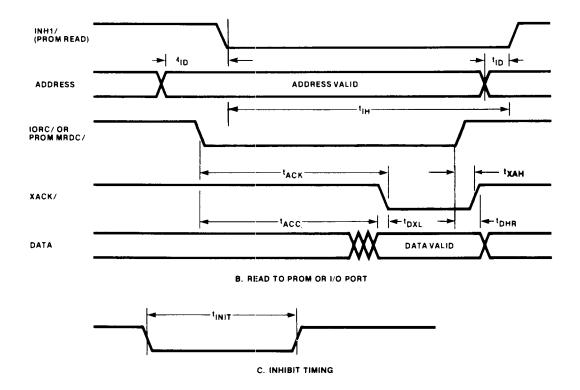

#### 2-8. MEMORY ADDRESS JUMPER CONFIGURATION

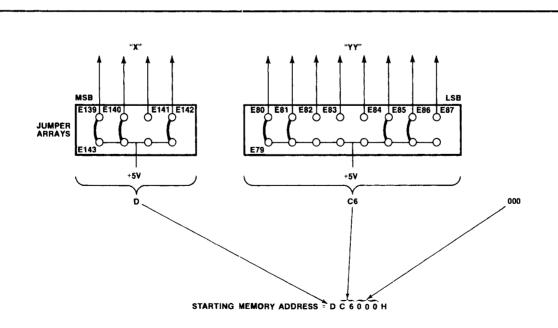

Configuration of the memory address jumpers is performed by placing the binary equivalent of the desired memory address into jumper matrices E79 through E87 and E139 through E143. Figure 2-3 shows the approximate location of the jumper matrices on the RAM boards. The starting memory address for the RAM boards is assigned in two steps:

- The first step in configuring the memory addresses for the RAM boards is to select one of 16 possible 1 megabyte pages in which the address space of the RAM boards will reside.

- The second step is to select a 4k boundary address (within the selected 1 megabyte page) to be the starting address of the on-board memory space.

Figure 2-3. Memory Address Jumper Location Diagram

In general terms, if the desired megabyte page address is "X" and the desired starting 4k boundary is "YY", then the starting address of the boards memory space is:

"X" (megabyte) + "YY" (4k bytes) = Starting Memory Address.

where "X" and "YY" are direct decodes of the jumpers present in the respective jumper matrices. (See Figure 2-5 for example.)

The formula contains the required megabyte page address (X) and the 4k boundary select address (YY). The combination of the 3 hexadecimal digits X and YY, when assembled into one number, provides the highest 12 bits of the memory address. Since the memory can be segmented only on 4k boundaries, the lowest 3 digits of each starting memory address must be 000. Each step for configuring the address select jumpers on the RAM boards is detailed further in the following paragraphs.

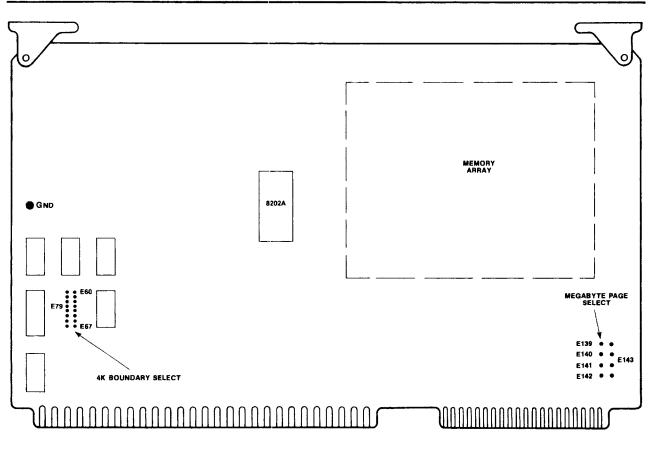

2-9. MEGABYTE PAGE ADDRESS SELECT JUMPERS. The iSBC 016A/032A/064A/028A/ 056A RAM Boards contain four user-configured jumpers that allow user selection of the megabyte page of memory in which the on-board memory resides; one of 16 possible 1 megabyte pages of the system memory address space. (Figure 2-4 shows the page address select jumpers (E139, E140, E141, E142, and E143) and the memory address lines (ADR14/, ADR15/, ADR16/, and ADR17) to which they are compared.

The page address select jumpers are configured as described in table 2-11. The jumper matrix decodes as a true binary representation of the actual megabyte page that is selected; E139 provides the most significant bit and E142 provides the least significant bit of the address. The presence of a jumper can be interpreted as a "1"; the absence of a jumper can be interpreted as a "0". As shipped from the factory, all RAM boards are configured to reside in megabyte page 0; i.e., all jumpers are removed.

### NOTE

The RAM boards cannot increment a memory address across a megabyte page boundary. The proper megabyte page boundary must be configured in the megabyte page address select jumpers.

Figure 2-4. Address Selection Jumper Configuration

| Address Space of the Board | Jumpers Required To Configure              |

|----------------------------|--------------------------------------------|

| 0 to 1Mb-1                 | None                                       |

| 1Mb to 2Mb-1               | E142-E143                                  |

| 2Mb to 3Mb-1               | E141-E143                                  |

| 3Mb to 4Mb-1               | E141-E143, E142-E143                       |

| 4Mb to 5Mb-1               | E140-E143                                  |

| 5Mb to 6Mb-1               | E140-E143, E142-E143                       |

| 6Mb to 7Mb-1               | E140-E143, E141-E143                       |

| 7Mb to 8Mb-1               | E140-E143, E141-E143, E142-E143            |

| 8Mb to 9Mb-1               | E139-E143                                  |

| 9Mb to 10Mb-1              | E139-E143, E142-E143                       |

| 10Mb to 11Mb-1             | E139-E143, E141-E143                       |

| 11Mb to 12Mb-1             | E139-E143, E141-E143, E142-E143            |

| 12Mb to 13Mb-1             | E139-E143, E140-E143                       |

| 13Mb to 14Mb-1             | E139-E143, E140-E143, E142-E143            |

| 14Mb to 15Mb-1             | E139-E143, E140-E143, E141-E143            |

| 15Mb to 16Mb-1             | E133-E143, E140-E143, E141-E143, E142-E143 |

Table 2-11. Megabyte Page Select Jumpers

2-10. 4k BOUNDARY SELECT JUMPERS. The iSBC 016A/032A/064A/028A/056A RAM Boards contain eight user-configured jumpers that assign the starting location for the memory space to any 4k address boundary (see note) within the 1 megabyte page. Figure 2-4 shows the 4k boundary select jumpers (E79 through E87) and the memory address lines (ADR13/ through ADRC/) to which the jumpers are compared.

The 4k boundary select jumper configurations are shown in table 2-12. The jumper matrix is decoded as

a true binary representation of the actual 4k boundary that is selected; E80 through E83 provide the most significant bit and E84 through E87 provide the least significant bit of the address. The presence of a jumper can be interpreted as a "1"; the absence of a jumper can be interpreted as a "0". As shipped from the factory, all versions except the iSBC 032A RAM Board are configured to 4k boundary X00000H, i.e., all jumpers are removed. The iSBC 032A RAM Board, as shipped, contains a jumper at E79-E83 to configure the 4k boundary select to 32k (address X08000H).

| Starting 4k Boundary <sup>e</sup>                                                                                                                                                                                                                                                                | Jumpers Required To Configure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| X00000H of the megabyte page<br>X01000H of the megabyte page<br>X02000H of the megabyte page<br>X03000H of the megabyte page<br>X04000H of the megabyte page<br>X05000H of the megabyte page<br>X06000H of the megabyte page<br>X07000H of the megabyte page                                     | None<br>E87-E79<br>E86-E79<br>E87-E79,E86-E79<br>E85-E79<br>E85-E79,E87-E79<br>E85-E79,E86-E79<br>E85-E79,E86-E79<br>E85-E79,E86-E79,E87-E79                                                                                                                                                                                                                                                                                                                                                                                               |

| <sup>7</sup><br>XC0000H of the megabyte page <sup>5</sup><br>XE0000H of the megabyte page <sup>4</sup><br>XF0000H of the megabyte page <sup>3</sup><br>XF8000H of the megabyte page <sup>2</sup><br>XFC000H of the megabyte page <sup>1</sup>                                                    | E80-E79,E81-E79<br>E80-E79,E81-E79,E82-E79<br>E80-E79,E81-E79,E82-E79,E83-E79<br>E80-E79,E81-E79,E82-E79,E83-E79,E84-E79<br>E80-E79,E81-E79,E82-E79,E83-E79,E84-E79,E85-E79                                                                                                                                                                                                                                                                                                                                                                |

| <ol> <li>The highest possible 4k boundary tha</li> <li>The upper digit (X) of each address is</li> </ol> | t does not cross a megabyte page boundary for an iSBC 016A board.<br>t does not cross a megabyte page boundary for an iSBC 032A board.<br>t does not cross a megabyte page boundary for an iSBC 064A board.<br>t does not cross a megabyte page boundary for an iSBC 028A board.<br>t does not cross a megabyte page boundary for an iSBC 028A board.<br>t does not cross a megabyte page boundary for an iSBC 056A board.<br>s the megabyte page select; refer to table 2-11 for actual values.<br>decode of 256 possible configurations. |

By modifying the 4k boundary select jumpers, the user may assign the memory space to start from any 4k byte boundary between 0 and 256.

### NOTE

The 4k boundary for the starting memory address should be selected such that the entire memory space of the RAM board fits onto the same 1 megabyte page of memory. Failure to do so will cause the off-page portion of memory to be inaccessible.

### NOTE

The memory on one RAM board must be assigned contiguously within a 1 megabyte page starting at a selected 4k boundary.

2-11. RAM BOARD ADDRESS CONFIGURA-TION EXAMPLE. The iSBC 016A/032A/064A/ 028A/056A RAM Boards must be assigned to the memory space so that all memory locations are accessible within the megabyte of memory space. This requires that the starting address for the lowest 4k byte segment be less than or equal to the addresses listed in table 2-13. To assign the memory segments to address space within the megabyte of on-board memory space, use the formula:

"X" (megabyte) + "YY" (4k bytes) = Starting Memory Address.

### NOTE

Banks 0 and 1 always operate as a pair; for a word operation, bank 0 holds the odd byte and bank 1 holds the even byte.

Table 2-13. Maximum Starting 4k Boundary

| RAM Board           | Maximum 4k<br>Boundary Selected |

|---------------------|---------------------------------|

| iSBC 016A RAM Board | XFC000H                         |

| iSBC 032A RAM Board | XF8000H                         |

| iSBC 064A RAM Board | XF0000H                         |

| iSBC 028A RAM Board | XE0000H                         |

| iSBC 056A BAM Board | XC0000H                         |

- a. Determine which megabyte page address to use, and convert it to hexadecimal. Then place the hexadecimal equivalent of the number (listed as "X" in the formula and in figure 2-5) into the jumper matrix; E139 is the MSB and E142 is the LSB (presence of a jumper equals a "1").

- b. Determine which starting 4k boundary to use, and convert it to hexadecimal. Then place the hexadecimal equivalent of the number (listed as "YY" in the formula and in figure 2-5) into the jumper matrix; E80 is the MSB and E87 is the LSB (presence of a jumper equals a "1").

Figure 2-5. Address Jumper Configuration Example

#### 2-12. DELAYED/ADVANCED WRITE JUMPER CONFIGURATION

Most systems operate in a Delayed (normal) WRITE mode. That is, the Memory WRITE Command is issued to the RAM board a minimum of 50 nanoseconds after the write data and memory address are placed on the Multibus interface. This is the normal mode of operation for the iSBC 016A/032A/ 064A/028A/056A RAM Boards. As shipped, each version of the RAM board contains a jumper connecting E2-E3 to enable the Delayed WRITE mode operation on the board.

For the iSBC 064A RAM Board, the Delayed WRITE mode operation can be eliminated and the Advanced WRITE (or non-qualified WRITE) mode can be enabled by removing the jumper E2-E3 and installing one at E1-E2. Systems requiring an Advanced WRITE mode are those that must receive a Memory WRITE Command from the bus master a maximum of 500 nanoseconds before the write data is placed onto the Multibus interface. The Advanced WRITE mode is required for operation with an MDS 800 Development System or an ICE 80 Emulator.

#### 2-13. PARITY FLAG REGISTER ADDRESS JUMPER CONFIGURATION

The configuration of jumpers E76, E77, E78, E103 through E108, and E110 through E114 determines the Multibus I/O port address at which the bus master can access the Parity Flag Register within the RAM boards. As shipped, the RAM boards contain jumpers to configure the Parity Flag Register I/O port address to 000FH. The jumpers allow the user a two part selection of the I/O port address:

- Jumpers E103 through E108 allow user selection of the number of bits of Multibus address to be considered in decoding the I/O port address required to access the Parity Flag Register; either 8-bits, 12-bits, or 16-bits. Refer to table 2-14 for the jumper connections.

- Jumpers E76, E77, E78, and E110 through E114 allow user selection of the state (active or inactive) of Multibus address lines ADR0/, ADR1/, ADR2/, ADR3/, and ADR6/ to generate the IOCS/ signal required to access the Parity Flag Register. Refer to table 2-15 for jumper connections.

#### Table 2-14. I/O Address Line Enables for Parity Flag Register

| Jumper Conn | ection Description                                                                                                                   |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

| E103-E104*  | Enable address lines ADRC/, ADRD/, ADRE/, and ADRF/ into the I/O port address decode logic when jumper installed.                    |

| E105-E106*  | Enable address lines ADR8/, ADR9/, ADRA/, and ADRB/ into the I/O port address decode logic when jumpe<br>installed.                  |

| E107-E108*  | Enable address lines ADR0/, ADR1/, ADR2/, ADR3/, ADR4/, ADR5/, ADR6/, and ADR7/ into the address decode logic when jumper installed. |

| E108-E109   | Disables the operation of the Parity Error Flag. (016A version only.)                                                                |

| Table | 2-15. | I/0 | Port | Address | Selection |

|-------|-------|-----|------|---------|-----------|

|-------|-------|-----|------|---------|-----------|

| Jumper                                                                              | Function                                                                                                                 |  |  |  |  |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| E76-E77 Installed*                                                                  | Enables the I/O port address decode when Multibus address line 6 (ADR6) is LOW. Jumper E107-<br>E108 must be installed.  |  |  |  |  |

| E77-E78 installed                                                                   | Enables the I/O port address decode when Multibus address line 6 (ADR6) is HIGH. Jumper E107-<br>E108 must be installed. |  |  |  |  |

| E110-E111 Installed                                                                 | Enables Multibus address line 3 (ADR3) into the I/O port address decode when LOW.                                        |  |  |  |  |

| E110-E111 Removed*                                                                  | Enables Multibus address line 3 (ADR3) into the I/O port address decode when HIGH.                                       |  |  |  |  |

| E110-E112 Installed                                                                 | Enables Multibus address line 2 (ADR2) into the I/O port address decode when LOW.                                        |  |  |  |  |

| E110-E112 Removed*                                                                  | Enables Multibus address line 2 (ADR2) into the I/O port address decode when HIGH.                                       |  |  |  |  |

| E110-E113 Installed                                                                 | Enables Multibus address line 1 (ADR1) into the I/O port address decode when LOW.                                        |  |  |  |  |

| E110-E113 Removed*                                                                  | Enables Multibus address line 1 (ADR1) into the I/O port address decode when HIGH.                                       |  |  |  |  |

| E110-E114 Installed                                                                 | Enables Multibus address line 0 (ADR0) into the I/O port address decode when LOW.                                        |  |  |  |  |

| E110-E114 Removed*                                                                  | Enables Multibus address line 0 (ADR0) into the I/O port address decode when HIGH.                                       |  |  |  |  |

| NOTE:<br>* indicates that the jumpers are installed at the factory before shipment. |                                                                                                                          |  |  |  |  |

#### 2-14. BATTERY BACK-UP/MEMORY PROTECT JUMPER CONFIGURATION

In systems employing a battery back-up memory protect feature, the user must provide and install a P2 connector for the Intel iSBC cardcage. Compatible connectors listed in table 2-8 include both soldered and wirewrapped types of connectors. Procure the required connector at a local electronic parts supplier.

When the P2 connector is secured into place, solder the battery back-up, memory protect, and address lines to the appropriate pins of the connector, as listed in table 2-4.

When battery back-up power is to be installed for use with the RAM boards, disconnect the system power from the RAM boards. Then remove the jumpers E146-E47, E116-E117, E118-E120, and E119-E120 to separate the +5 volt battery bus on connector P2 pins 3 and 4 from the Multibus +5 volt bus.

Always remove both battery back-up and system power from the RAM boards before installing or removing the boards from a system cardcage. Failure to do so could result in damage to the boards.

#### 2-15. BOARD INSTALLATION

The iSBC 016A/032A/064A/028A/056A RAM Boards are compatible with the Intel iSBC 604/614 Cardcage. In a single board computer based system, install the RAM board into any cardcage slot that is not wired for a dedicated function. Ensure that the auxiliary connector P2 (if used) is mated properly with the user installed connector.

### CHAPTER 3 PROGRAMMING CONSIDERATIONS

#### **3-1. INTRODUCTION**

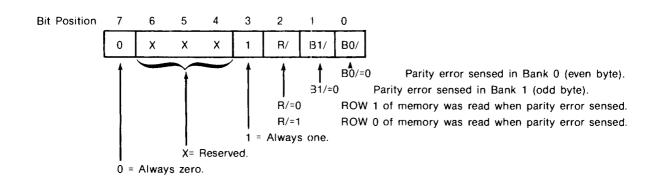

Data is written to and read from the RAM boards through normal Memory READ and Memory WRITE operations. However, the contents of the Parity Flag Register is accessed through I/O REAĐ and I/O WRITE operations. The following paragraphs provide a description of the Parity Flag Register. user selection of the quantity of Multibus address lines to be used in performing the selection and the state of address lines ADR0/, ADR1/, ADR2/, ADR3/, and ADR6/ that is required for the selection; the remaining Multibus address lines must be inactive.

#### **3-3. PARITY FLAG REGISTER FORMAT**