# inte

### THE I<sup>2</sup>ICE<sup>™</sup> INTEGRATED INSTRUMENTATION AND IN-CIRCUIT EMULATION SYSTEM USER'S GUIDE

Copyright 1985, Intel Corporation, All Rights Reserved Intel Corp., 3065 Bowers Ave., Santa Clara, CA 95051

## THE I<sup>2</sup>ICE<sup>™</sup> INTEGRATED INSTRUMENTATION AND IN-CIRCUIT EMULATION SYSTEM USER'S GUIDE

Order Number: 166298-001

Copyright 1985, Intel Corporation, All Rights Reserved Intel Corporation, 3065 Bowers Avenue, Santa Clara, California 95051

This equipment generates, uses, and can radiate radio frequency energy and if not installed and used in accordance with the instruction manual, may cause interference to radio communications. As temporarily permitted by regulation, it has not been tested for compliance with the limits for Class A Computing Devices pursuant to Subpart J of Part 15 of FCC rules, which are designed to provide reasonable protection against such interference. Operation of this equipment in a residential area is likely to cause interference in which case the user, at his own expense, will be required to take whatever measures may be required to correct the interference.

Additional copies of this manual or other Intel literature may be obtained from:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

Intel Corporation assumes no responsibility for the use of any circuitry other than circuitry embodied in an Intel product. No other circuit patent licenses are implied.

Intel software products are copyrighted by and shall remain the property of Intel Corporation. Use, duplication or disclosure is subject to restrictions stated in Intel's software license, or as defined in ASPR 7-104.9(a)(9).

No part of this document may be copied or reproduced in any form or by any means without prior written consent of Intel Corporation.

Intel Corporation makes no warranty for the use of its products and assumes no responsibility for any errors which may appear in this document nor does it make a commitment to update the information contained herein.

Intel retains the right to make changes to these specifications at any time, without notice.

Contact your local sales office to obtain the latest specifications before placing your order.

The following are trademarks of Intel Corporation and its affiliates and may be used only to identify Intel products:

| e        |

|----------|

| 0        |

| <b>U</b> |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

|          |

MDS is an ordering code only and is not used as a product name or trademark. MDS<sup>®</sup> is a registered trademark of Mohawk Data Sciences Corporation.

\* MULTIBUS is a patented Intel bus.

Copyright 1985, Intel Corporation, All Rights Reserved

# CONTENTS

#### inte<sup>r</sup> 🚥

#### Page

| Preface             | xi   |

|---------------------|------|

| Revision History    | xvii |

| Service Information | xix  |

#### CHAPTER 1 I²ICE™ SYSTEM OVERVIEW

| The Microcomputer Development Process                                |      |

|----------------------------------------------------------------------|------|

| Features of a Development System with an Emulator                    | 1-1  |

| Generalized Hardware Design Steps.                                   | 1-2  |

| Generalized Software Design Steps                                    | 1-2  |

| Hardware/Software Integration                                        | 1-3  |

| An Introduction to the I <sup>2</sup> ICE <sup>™</sup> System        |      |

| The Base Configuration of the I <sup>2</sup> ICE <sup>™</sup> System | 1-4  |

| I <sup>2</sup> ICE <sup>™</sup> System Options                       | 1-6  |

| I <sup>2</sup> ICE <sup>™</sup> System Accessories                   |      |

| Hardware Overview                                                    |      |

| The Instrumentation Chassis                                          | 1-8  |

| The Host Interface Board                                             |      |

| The Emulation Base Module                                            | 1-10 |

| System Interface Cables                                              | 1-11 |

| High-Speed Memory                                                    | 1-11 |

| Optional High-Speed Memory Board                                     | 1-11 |

| The Intel Logic Timing Analyzer (iLTA)                               |      |

| Emulation Personality Modules                                        | 1-11 |

| Software Overview                                                    |      |

| Software Environment                                                 | 1-12 |

| The I <sup>2</sup> ICE <sup>™</sup> System Command Language          | 1-14 |

|                                                                      |      |

| The I <sup>2</sup> ICE <sup>™</sup> System Host Disk(s)              | 1-15 |

| The I <sup>2</sup> ICE <sup>™</sup> System Error/Help Disk           |      |

| The I <sup>2</sup> ICE <sup>™</sup> System Probe Disks               |      |

| The I <sup>2</sup> ICE <sup>™</sup> System Diagnostic Disk           | 1-15 |

| The iLTA Disks                                                       | 1-16 |

| The PSCOPE-86 Disk                                                   |      |

| The I <sup>2</sup> ICE <sup>™</sup> System Tutorial Disk(s)          |      |

| I <sup>2</sup> ICE <sup>™</sup> System Specifications                |      |

| Host Requirements                                                    | 1-17 |

| System Performance                                                   | 1-18 |

| Emulation Clips                                                      |      |

| The Target System User Interfaces                                    | 1-19 |

| CHAPTER 2 GUIDE TO THE I <sup>2</sup> ICE <sup>™</sup> SYSTEM TUTORIAL   | Page |

|--------------------------------------------------------------------------|------|

| Tutorial Use                                                             |      |

| Invoking the Tutorial During Program Debugging                           | 2-2  |

| Deactivating the Tutorial                                                | 2-2  |

| Reactivating the Tutorial                                                | 2-2  |

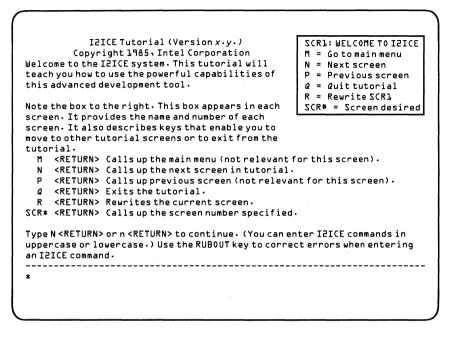

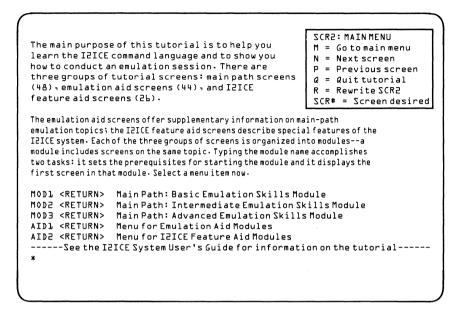

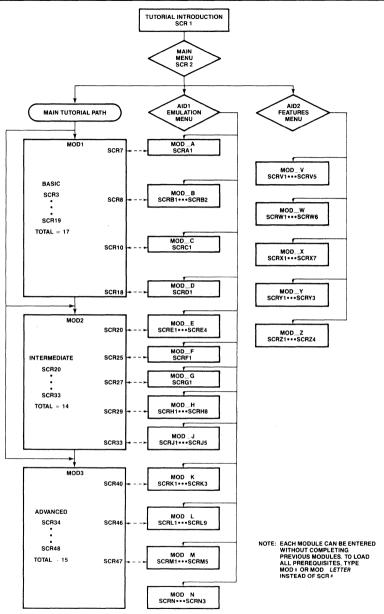

| Tutorial Screens and Structure                                           | 2-2  |

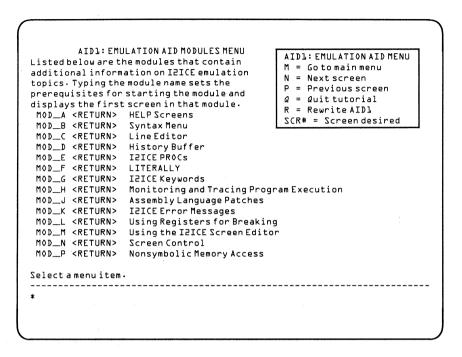

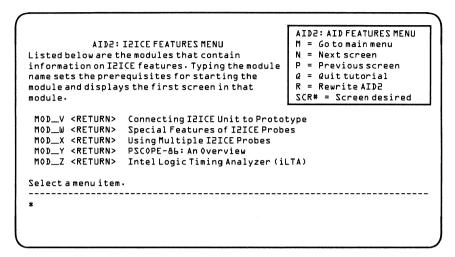

| Copies of Selected Tutorial Screens                                      | 2-4  |

| An Overview of the Tutorial Structure                                    |      |

| List of All Tutorial Screens                                             |      |

| Tutorial Index                                                           | 2-13 |

| Tutorial Program Listings                                                | 2-16 |

| Overview of the PL/M Tutorial Program                                    | 2-16 |

| PL/M Program Listing for the Two-Bug Version of the Change Maker Program |      |

| The ASM-86 Listing for the No-Bug Version of the Change Maker Program    | 2-21 |

| Sample Programs in C, FORTRAN, and Pascal                                |      |

| A Change Maker Program in C                                              |      |

| A Change Maker Program in FORTRAN                                        |      |

| A Change Maker Program in Pascal                                         | 2-33 |

#### CHAPTER 3 INTRODUCTION TO USING THE I<sup>2</sup>ICE<sup>™</sup> SYSTEM

| Invoking I <sup>2</sup> ICE <sup>™</sup> Software          | 3-1  |

|------------------------------------------------------------|------|

| Entering I <sup>2</sup> ICE <sup>™</sup> System Commands   | 3-3  |

| Extending a Command to Another Line                        |      |

| Aborting Commands                                          | 3-3  |

| Multiple Commands on a Line                                | 3-4  |

| Comments                                                   | 3-4  |

| The Command Line Editor                                    | 3-4  |

| The I <sup>2</sup> ICE <sup>™</sup> System Syntax Menu     | 3-4  |

| The I <sup>2</sup> ICE <sup>™</sup> Command History Buffer | 3-5  |

| String Handling                                            |      |

| Block Commands.                                            | 3-7  |

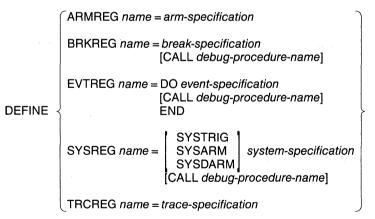

| Creating Debug Objects                                     | 3-8  |

| Creating a Debug Procedure                                 | 3-8  |

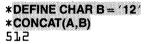

| Creating a LITERALLY Definition                            | 3-9  |

| Creating a Debug Register                                  | 3-9  |

| Creating a Debug Variable                                  | 3-9  |

| The I <sup>2</sup> ICE <sup>™</sup> Screen Editor          | 3-10 |

| Inserting Text                                             | 3-10 |

| Deleting and Moving Text.                                  | 3-11 |

| Viewing Text                                               | 3-11 |

| Overwriting Text                                           | 3-11 |

| Editing External Files                                     | 3-11 |

| Exiting the Screen Editor                                  | 3-12 |

| File Handling                                              | 3-12 |

| LIST Files                                                 | 3-12 |

| INCLUDE Files: The INCLUDE, PUT, and APPEND Commands       | 3-13 |

| The LOAD and SAVE Commands                                 | 3-14 |

| Memory Types                                               | 3-15 |

| Debug Variables                                            | 3-16 |

|                                                            |      |

#### Page

| Program Variables and Symbolic Debugging                 | 3-16 |

|----------------------------------------------------------|------|

| Program Variables and the PICE <sup>™</sup> Memory Types |      |

| Managing the Memory and I/O Spaces                       |      |

| The I <sup>2</sup> ICE <sup>™</sup> Memory Map           |      |

| Mapping Input/Output.                                    |      |

| Simulating I/O from the Console                          | 3_22 |

| Simulating I/O with a Debug Procedure                    |      |

| The Emulation Clips                                      |      |

| The Clipsin Lines                                        |      |

| The Clipsout Lines                                       |      |

| Emulating a Program.                                     |      |

| Preparing a Pascal Program                               |      |

| Compiling the Source File                                |      |

| Linking the Object File                                  |      |

| Locating the Link File.                                  |      |

| Creating a Submit File                                   |      |

| Getting Ready to Emulate                                 |      |

| Emulating Your Program.                                  |      |

| Breaking, Tracing, and Arming                            |      |

| The Example                                              |      |

| Emulating a User Program                                 |      |

| The Event Machines                                       |      |

| The Debug Registers                                      |      |

| Arm Registers                                            |      |

| Break Registers                                          |      |

| System Registers                                         |      |

| Trace Registers                                          |      |

| Event Registers                                          |      |

| Debug Registers Calling Debug Procedures                 |      |

| Interpreting the Trace Buffer.                           |      |

| The Timetag.                                             |      |

| The Pseudo-variable TRCBUS                               |      |

| Trace Buffer Information                                 |      |

| Hardware Slipping on a Breakpoint                        |      |

| Even Addresses, Odd Addresses, and Breaking.             |      |

| Word Writes to Even and Odd Addresses                    |      |

| Byte Writes to Even and Odd Addresses.                   |      |

| Word Reads from Even and Odd Addresses.                  |      |

| Byte Reads from Even and Odd Addresses                   |      |

| Moving the User Cable                                    |      |

|                                                          | 5-54 |

#### CHAPTER 4 THE I<sup>2</sup>ICE<sup>™</sup> SYSTEM PERSONALITY MODULES (PROBES)

| The 8086/8088 Probe                                          | 4-1 |

|--------------------------------------------------------------|-----|

| Hardware and Software Considerations for the 8086/8088 Probe | 4-2 |

| Address Wrap-Around.                                         | 4-2 |

| Break Information                                            | 4-3 |

| READY Signal Set-Up Time                                     | 4-4 |

| Request/Grant Line                                           | 4-4 |

|                                                                        | Page |

|------------------------------------------------------------------------|------|

| Non-Maskable Interrupt Line and Interrupt Line.                        | 4-4  |

| Non-Maskable Interrupts and Program Stepping                           | 4-4  |

| Synchronization between the Prototype and the Probe                    | 4-4  |

| User-Accessible Test Points                                            | 4-4  |

| Coprocessor Considerations                                             | 4-6  |

| Inability to Break when RESET Is Asserted                              | 4-6  |

| Getting a User NMI while in Emulation Mode                             | 4-6  |

| Using the I <sup>2</sup> ICE <sup>™</sup> System as a Signal Generator |      |

| 10-MHz 8086 Probe MAX Mode Operation                                   |      |

| Probe MIN Mode Operation                                               |      |

| Address/Data Bus Float                                                 |      |

| The 80186/80188 Probe                                                  | 4-7  |

| Hardware and Software Considerations for the 80186/80188 Probe         |      |

| Address Wrap-Around                                                    |      |

| Break Information                                                      | 4-9  |

| Mapping Considerations for the 80186/80188 Probe                       |      |

| Synchronization Between the Prototype and the Probe                    |      |

| User-Accessible Test Points                                            |      |

| User Socket                                                            |      |

| The 80286 Probe                                                        |      |

| Address Translation                                                    |      |

| 8086 Address Translation                                               |      |

| 80286 Address Translation                                              |      |

| Multitasking                                                           |      |

| Interrupts                                                             |      |

| Address Protection                                                     |      |

| Real Mode and PCHECK                                                   |      |

| Protected Mode and PCHECK                                              |      |

| Memory Mapping for the 80286 Probe                                     |      |

| Support for Processor Extensions                                       |      |

| Displaying 80286 Registers and Flags                                   |      |

| Real Mode and PCHECK = TRUE                                            |      |

| Real Mode and PCHECK = FALSE                                           |      |

| Protected Mode and PCHECK = TRUE                                       |      |

| Protected Mode and PCHECK = FALSE                                      |      |

| Hardware and Software Considerations for the 80286 Probe               | 4-20 |

| Hardware Slipping Past a Breakpoint                                    | 4-21 |

| High-Address Bits Override                                             | 4-22 |

| Issuing a Reset Command When an 80287 Is Present                       |      |

| Resetting the 80286 Chip and the 80286 Probe                           |      |

| Timing Differences Between the iAPX 286 and the 80286 Probe            |      |

| User Substrate Capacitor and +5 Volt Source                            |      |

| Tracing Considerations                                                 |      |

| User Socket                                                            |      |

| Synchronizing Emulation to an External Event                           | 4-25 |

|                                                  | Page |

|--------------------------------------------------|------|

| Using the Initialization Segment                 | 4-25 |

| Reading from and Mapping to Mapped Memory or I/O | 4-26 |

| Pascal-286 and FORTRAN-286 Array Size            | 4-26 |

#### CHAPTER 5 COPROCESSOR SUPPORT

| Mapping Restrictions When Using Coprocessors | 5-1 |

|----------------------------------------------|-----|

| The PHANG Pseudo-Variable                    |     |

| The 8087/80287 Numeric Data Processors       |     |

| The COENAB Pseudo-Variable                   |     |

| COENAB and an External Coprocessor.          | 5-3 |

| COENAB and an Internal Coprocessor           |     |

| The CPMODE Pseudo-Variable                   | 5-3 |

| The COREQ Pseudo-Variable                    | 5-4 |

| The GET87 Command                            | 5-4 |

#### CHAPTER 6 MULTIPLE-PROBE SYSTEMS

| I <sup>2</sup> ICE <sup>™</sup> System Units          |

|-------------------------------------------------------|

| Arming the I <sup>2</sup> ICE <sup>™</sup> System     |

| Asserting the System Break and Trace Lines            |

| Enabling I <sup>2</sup> ICE <sup>™</sup> System Units |

| Symbolic Support for Multiple Probes                  |

| Writing Debug Procedures for Multiple Probe Systems   |

| Synchronization Between Units                         |

| The 8086/8088 and 80186/80188 Probes                  |

| The 80286 Probe                                       |

#### APPENDIX A I<sup>2</sup>ICE<sup>™</sup> SYSTEM NON-HOST HARDWARE INSTALLATION

| The I <sup>2</sup> ICE <sup>™</sup> System Instrumentation Chassis Installation                  | A-1  |

|--------------------------------------------------------------------------------------------------|------|

| Emulation Base Module Installation                                                               | A-4  |

| Buffer Base Assembly Jumpering                                                                   | A-4  |

| Installing Personality Modules and User Cables                                                   | A-4  |

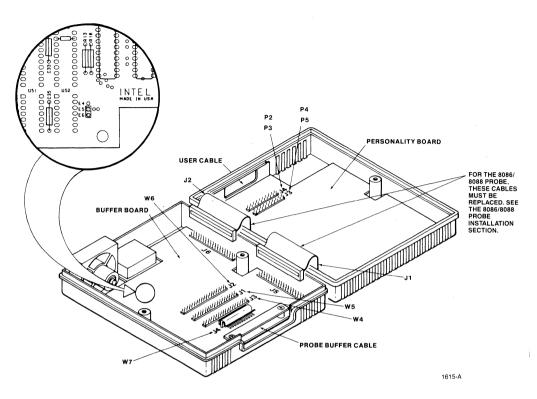

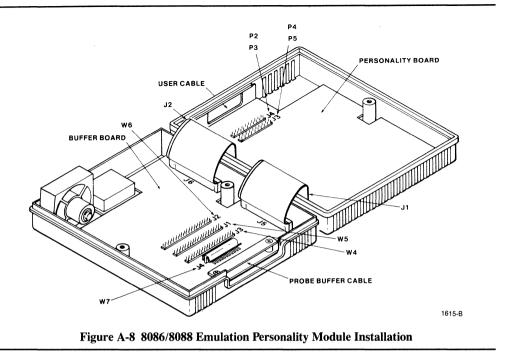

| Installing the I <sup>2</sup> ICE <sup>™</sup> System 8086/8088 Emulation Personality Module A   | A-4  |

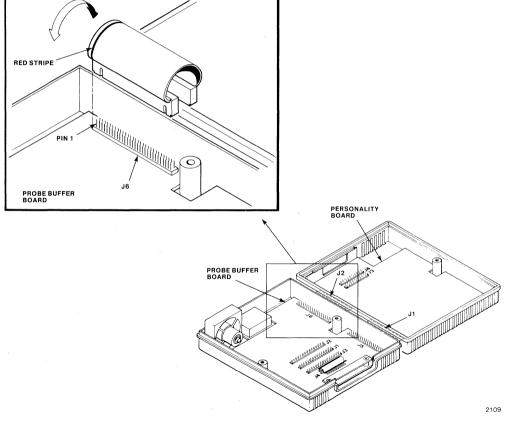

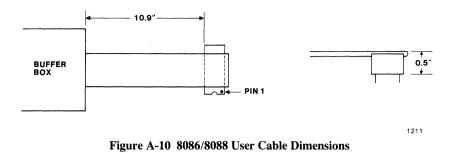

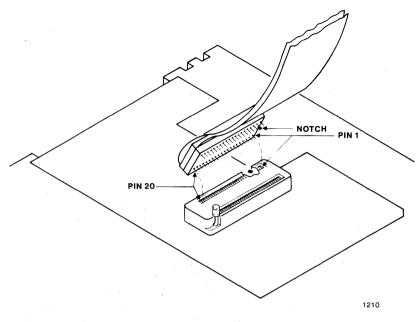

| Installing the 8086/8088 User Cable                                                              | A-10 |

| Installing the I <sup>2</sup> ICE <sup>™</sup> System 80186/80188 Emulation Personality Module A | A-11 |

| Installing the 80186/80188 User Cable                                                            | A-14 |

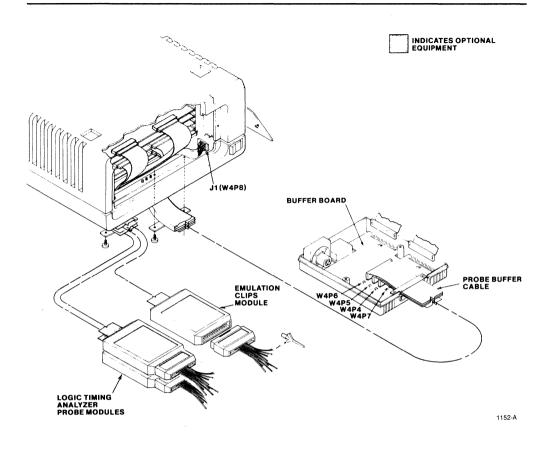

| Installing the I <sup>2</sup> ICE <sup>™</sup> System 80286 Emulation Personality Module         | A-16 |

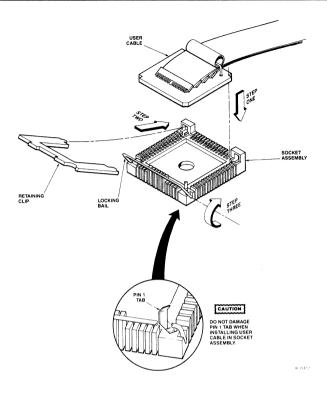

| Installing the 80286 User Cable                                                                  | A-16 |

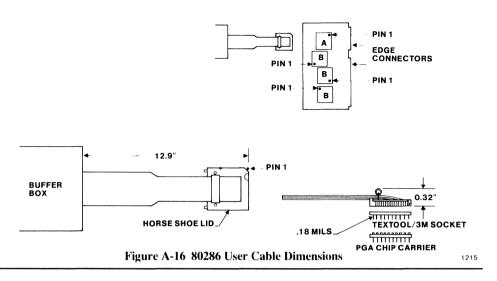

| Installing the Emulation Clips Module A                                                          | A-18 |

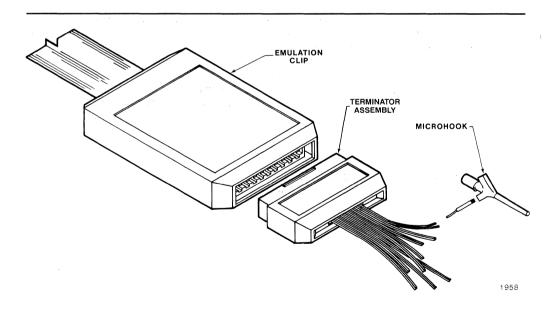

| Installing the iLTA Logic Timing Analyzer Option A                                               | A-20 |

| Host Installation Information                                                                    | A-20 |

# APPENDIX B CONFIGURING THE I<sup>2</sup>ICE<sup>™</sup> SYSTEM FOR NON-STANDARD HOST TERMINALS

| Creating a CRT File    | <b>B-1</b> |

|------------------------|------------|

| Configuration Commands | B-2        |

#### Glossary

#### Index

#### TABLES

| 1-1 | I <sup>2</sup> ICE <sup>™</sup> System Hardware Components                | 1-9  |

|-----|---------------------------------------------------------------------------|------|

| 1-2 | I <sup>2</sup> ICE <sup>™</sup> System Emulation Clips—DC Characteristics | 1-19 |

| 2-1 | Main Tutorial Path Screens                                                | 2-10 |

| 2-2 | Emulation Aid Module (AID1) Screens                                       | 2-11 |

| 2-3 | I <sup>2</sup> ICE <sup>™</sup> Feature Aid Module (AID2) Screens         | 2-12 |

| 3-1 | System Parameters Used with I/O Debug Procedures                          | 3-23 |

| 4-1 | 8086/8088 Segment Boundary Increments                                     | 4-3  |

| 4-2 | 80186/80188 Segment Boundary Increments                                   | 4-10 |

| 5-1 | Coprocessor Pseudo-Variable Interaction.                                  | 5-2  |

| A-1 | 8086/8088 Emulation Personality Module Jumper Configurations              | A-6  |

| A-2 | Jumpering for 8087 Support                                                | A-7  |

| A-3 | Intel Host Installation Appendixes                                        | A-21 |

| B-1 | The A Configuration Command Values                                        | B-3  |

| B-2 | The AF Configuration Command Values                                       | B-4  |

|     |                                                                           |      |

#### FIGURES

| 1-1 | Typical Microcomputer Development Process                                                       | 1-2  |

|-----|-------------------------------------------------------------------------------------------------|------|

| 1-2 | A Basic I <sup>2</sup> ICE <sup>™</sup> System                                                  | 1-5  |

| 1-3 | A Maximum Configuration I <sup>2</sup> ICE <sup>™</sup> System                                  | 1-7  |

| 1-4 | The I <sup>2</sup> ICE <sup>™</sup> System Debugging Capabilities                               | 1-13 |

| 2-1 | Tutorial Introductory Screen: SCR1                                                              |      |

| 2-2 | Tutorial Main Menu: SCR2                                                                        | 2-5  |

| 2-3 | Menu for the Emulation Aid Modules: AID1                                                        | 2-6  |

| 2-4 | Menu for the I <sup>2</sup> ICE <sup>™</sup> System Feature Modules: AID2                       | 2-7  |

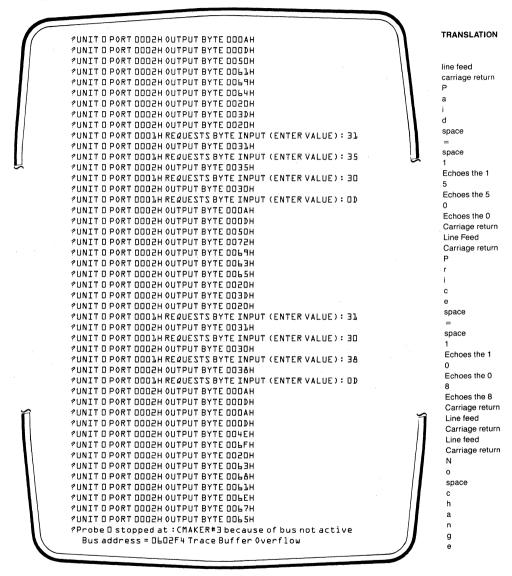

| 2-5 | Emulation Display for the Screens SCR12 Through SCR15                                           | 2-8  |

| 2-6 | Tutorial Structure.                                                                             |      |

| 3-1 | Sample Trace Buffer INSTRUCTIONS Display Showing the Data Write for Instruction #12             | 3-39 |

| 3-2 | Sample Trace Buffer Display in CYCLES Mode Showing Frames                                       |      |

|     | f 006-008 and f 00B                                                                             | 3-40 |

| 3-3 | Sample Trace Buffer Display in INSTRUCTIONS Mode for Emulation with the System<br>Register EVEN | 3-45 |

| 3-4 | Sample Trace Buffer Display in CYCLES Mode for Emulation with the System Register EVEN.         | 3-46 |

| 3-5 | Sample Trace Buffer Displays in Both Modes for Emulation with the System Register ODD           | 3-47 |

#### FIGURES (continued)

#### Page

| 3-6  | Sample Trace Buffer Displays in Both Modes for Emulation with the System Register EVENWORD              | 3-50 |

|------|---------------------------------------------------------------------------------------------------------|------|

| 3-7  | Sample Trace Buffer Displays in Both Modes for Emulation Using the Event Register ODDWORD.              | 3-52 |

| 3-8  | Sample Trace Buffer Displays in Both Modes for Emulation with the System Register EVENBYTE              | 3-53 |

| 3-9  | Sample Trace Buffer Displays in Both Modes for Emulation with the System Register ODDBYTE               | 3-55 |

| 4-1  | READY Signal Set-Up Time                                                                                | 4-5  |

| 4-2  | The GDT and the LDT                                                                                     |      |

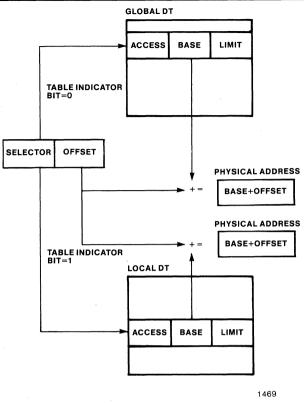

| 4-3  | 80286 Virtual Address Translation                                                                       | 4-16 |

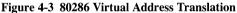

| 4-4  | The Segment Register and the Descriptor Tables                                                          | 4-17 |

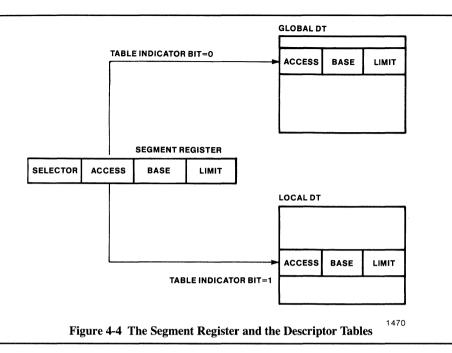

| 4-5  | Returning the Probe's Microprocessor to Real Mode                                                       | 4-23 |

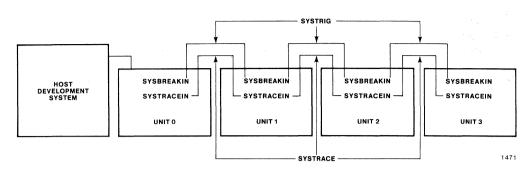

| 6-1  | A Multiple-Probe I <sup>2</sup> ICE <sup>™</sup> System                                                 | 6-2  |

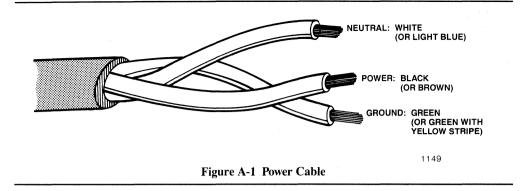

| A-1  | Power Cable                                                                                             |      |

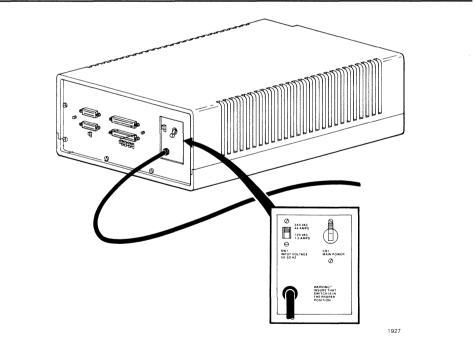

| A-2  | Circuit Breaker on the Rear Panel of the I <sup>2</sup> ICE <sup>™</sup> System Instrumentation Chassis | A-2  |

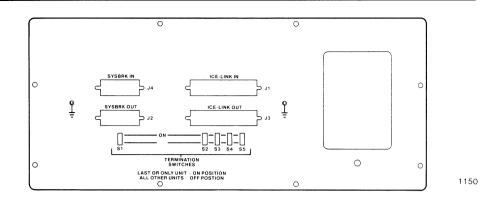

| A-3  | Termination Switches on the Rear Panel of the I <sup>2</sup> ICE <sup>™</sup> System Instrumentation    |      |

|      | Chassis                                                                                                 |      |

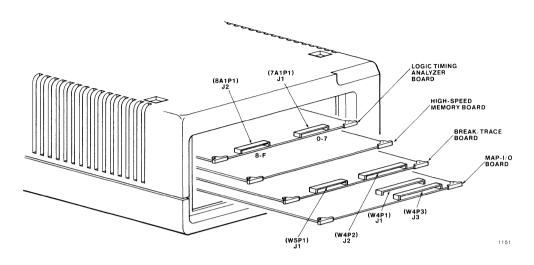

| A-4  | Instrumentation Chassis Boards                                                                          |      |

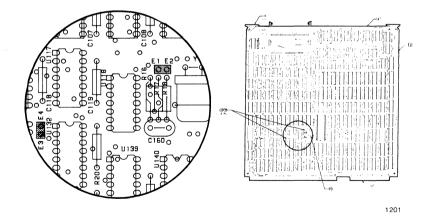

| A-5  | Jumper Positions on the Map-I/O Board                                                                   |      |

| A-6  | Jumper Positions on the Buffer Board                                                                    |      |

| A-7  | New Cable Installation for the 8086/8088 Probe                                                          |      |

| A-8  | 8086/8088 Emulation Personality Module Installation                                                     |      |

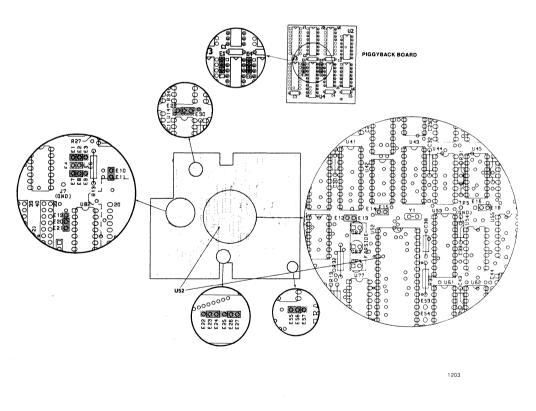

| A-9  | Jumper Positions on the 8086/8088 Personality Board                                                     | A-9  |

| A-10 | 8086/8088 User Cable Dimensions                                                                         |      |

| A-11 | The Correct Orientation of the 8086/8088 User Cable                                                     |      |

| A-12 | 80186/80188 and 80286 Emulation Personality Module Installation                                         | A-13 |

| A-13 | Jumper Positions on the 80186/80188 Personality Board                                                   |      |

| A-14 | 80186/80188 User Cable Dimensions                                                                       |      |

| A-15 | Connecting the 80186/80188 User Cable                                                                   |      |

| A-16 | 80286 User Cable Dimensions                                                                             |      |

| A-17 | Assembling the Emulation Clips Module.                                                                  |      |

| A-18 | Instrumentation Chassis Cables                                                                          | A-19 |

# PREFACE

inta' 🚥

This manual introduces Intel's Integrated Instrumentation and In-Circuit Emulation (I<sup>2</sup>ICE<sup>™</sup>) system. It assumes that you are familiar with the architecture of the iAPX 86, iAPX 88, iAPX 186, iAPX 188, and iAPX 286 microprocessors. It also assumes that you are familiar with the concept of in-circuit emulation.

- Chapter 1 describes the hardware/software design process and explains how the I<sup>2</sup>ICE system aids this design process. Chapter 1 also provides general information about the features and components of the I<sup>2</sup>ICE system, describes the hardware components of the I<sup>2</sup>ICE system, and describes the I<sup>2</sup>ICE system software packages.

- Chapter 2 provides an overview of the I<sup>2</sup>ICE system on-line tutorial and contains a listing of the program debugged during the tutorial session.

- Chapter 3 introduces the user to the I<sup>2</sup>ICE system. This chapter reinforces and augments information provided in the on-line tutorial. It explains symbolic debugging, I<sup>2</sup>ICE debug procedures, file handling, the I<sup>2</sup>ICE editor, and the single-line assembler. The chapter also contains a sample program that illustrates how to get the I<sup>2</sup>ICE system up and running; it describes how to set up and work with the I<sup>2</sup>ICE memory and I/O maps; and it describes how to set breakpoints and interpret the trace buffer.

- Chapter 4 is an overview of how the I<sup>2</sup>ICE system operates with the 8086/8088, 80186/80188, and 80286 personality modules (probes). This chapter also describes special considerations that pertain to each of the probes.

- Chapter 5 describes the special debugging aids offered by the I<sup>2</sup>ICE system for prototypes that use coprocessors and processor extensions.

- Chapter 6 describes the operation of I<sup>2</sup>ICE systems with more than one probe.

- Appendix A explains how to install I<sup>2</sup>ICE system hardware, except hardware that is installed on the host system.

- Appendix B shows how to configure the I<sup>2</sup>ICE system to run with non-standard terminals.

- Host Installation explain how to install the I<sup>2</sup>ICE system hardware in the host system and how to install the I<sup>2</sup>ICE system software.

- Glossary defines specific I<sup>2</sup>ICE system terms used in this manual.

Index

#### **Related Publications**

The following manuals contain additional information about the PICE system and its operating environment.

Copies of the publications listed are available through the Intel Literature Department.

#### I<sup>2</sup>ICE<sup>™</sup> System Publications Library

The following manuals are supplied (together with this manual) with the I<sup>2</sup>ICE system; they contain additional information about the I<sup>2</sup>ICE system and its operating environment. Copies of the publications listed are also available through the Intel Literature Department, located at the following address:

Literature Department Intel Corporation 3065 Bowers Avenue Santa Clara, CA 95051 (800) 548-4725

• *FICE™ Integrated Instrumentation and In-Circuit Emulation System* (data sheet), order number 210469.

This publication provides an overview of the FICE system. It describes the hardware and software, provides some general application information, and lists the system specifications. The data sheet is available through Intel sales offices as well as the Intel Literature Department.

*FICE™ Reference Manual*, order number 166302. This manual is the principle reference for the I<sup>2</sup>ICE command language. It includes descriptions of I<sup>2</sup>ICE commands and I<sup>2</sup>ICE topics that are not probe-specific.

- *PSCOPE-86 High-Level Program Debugger User's Guide*, order number 121790 [This manual is only supplied to users with Intel hosts.] The manual describes the operation of PSCOPE-86, a high-level language symbolic debugger. It includes a tutorial and invocation sections, a command dictionary, an error message listing, and configuration information for non-Intel terminals.

- *AEDIT Text Editor User's Guide*, order number 121756 This manual describes features and operation of the screen editor that is part of the I<sup>2</sup>ICE system software.

#### **Reference Publications**

The publications in the following sections are not supplied with the FICE system.

#### **Hardware Reference Publications**

- *Memory Components Handbook*, order number 210830. This catalog contains data sheets on the memory components manufactured by Intel Corporation.

- *Microsystems Components Handbook*, order number 230843 (two volumes). These handbooks contain data sheets on the microprocessor and peripheral products manufactured by Intel Corporation.

- OEM Systems Handbook, order number 210941. This catalog contains data sheets on integrated microcomputer systems, single-board computers, memory expansion boards, high-speed math boards (including the iSBC<sup>®</sup> 337 MULTIMODULE<sup>™</sup> board), peripheral controllers, communications controllers, digital I/O expansion and signal conditioning boards, industrial control series, and analog I/O expansion. It also contains data sheets on systems software, such as the iRMX<sup>™</sup> operating system.

- Development Systems Handbook, order number 210940. This catalog contains data sheets on microcomputer development systems (hardware and software), in-circuit emulators (including the I<sup>2</sup>ICE system), network development systems, system design kits, and third-party software.

- *iAPX 86/88, 186/188 User's Manual*, order number 210911. This manual contains product descriptions and operating instructions for 8-bit and 16-bit CPUs and support chips in the iAPX 86/88 and 80186/80188 families.

- *iAPX 186 High Integration 16-Bit Microprocessor* (data sheet), order number 210451. This publication provides an overview of the iAPX 186 microprocessor. It includes chip pinouts, a functional description, hardware, software, and timing specifications, and an instruction set summary.

- *iAPX 286/10 High Performance Microprocessor with Memory Management and Protection* (data sheet), order number 210253. This publication provides an overview of the iAPX 286/10 microprocessor. It includes chip pinouts, a functional description, chip architecture, hardware and timing specifications, and an instruction set summary.

- *iAPX 286 Hardware Reference Manual*, order number 210760. This manual is the hardware reference guide for iAPX 286 system designs.

- *iSBC® 337 MULTIMODULE™ Numeric Data Processor Hardware Reference Manual*, order number 142887.

This manual contains design and operation information on the iSBC 337 NDP MULTI-MODULE board. The manual includes installation, program interface, operation, and service information.

#### **Software Reference Publications**

• ASM-86 Language Reference Manual, order number 121703. This manual provides design and operating information about the ASM-86 assembly language. The manual provides an overview of the language, procedures for program structuring, information about data operation, and an appendix describing the 80186 instruction set.

- *iAPX 86/88 Family Utilities User's Guide*, order number 121616. This guide provides a full description of the utility commands that support 86/88 program development. It is intended for use with any language translator that generates object code compatible with the utility commands.

- 8087 Support Library Reference Manual, order number 121725. This manual provides design and operating information about the library of support utilities for the 8087 processor. It provides overviews of the support library, procedures for program structuring, and information on data operation.

- *iAPX 286 Programmer's Reference Manual*, order number 210498. This manual describes the iAPX 286 architecture and instruction set.

- *iAPX 286 Utilities User's Guide*, order number 121934. This guide provides a full description of the utility commands that support 286 program development. It is intended for use with any language translator that generates object code compatible with the utility commands.

- *iAPX 286 Operating Systems Writer's Guide*, order number 121960. This book is written for systems designers, operating system designers, and programmers using the Intel iAPX 286 microprocessor in its protected, virtual-address mode.

- *PL/M-86 Programming Manual*, order number 980466. This manual provides programming instructions for PL/M-86. It includes details on expressions and assignments, procedures, variables, and a sample program.

- *PL/M-86 User's Guide*, order number 121636.

- PL/M-286 User's Guide, order number 121945.

- Pascal-86 User's Guide, order number 121539.

- FORTRAN-86 User's Guide, order number 121570.

- *iC-86 Compiler User's Guide*, order number 122085. These guides provide introductory and overview information on the high-level languages supported by the I<sup>2</sup>ICE system. Each manual provides installation instructions, language information, compiler operating instructions, and information on interfacing to other software modules.

#### **Command Syntax**

The following syntax notation is used throughout the I<sup>2</sup>ICE manual set:

COMMANDS Command keywords appear in all uppercase letters. You must enter commands exactly as they appear, except that you may enter them in either uppercase or lowercase letters.

| elements           | Items for which you must substitute a value, expression, file name, etc., are in lowercase letters and italicized.                                                      |  |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| {menu}             | Braces indicate that you must select one and only one of the items in the enclosed menu.                                                                                |  |

| {menu}*            | Braces followed by an asterisk (*) indicate that you must select at least one of the items in the enclosed menu                                                         |  |

| [menu]             | Brackets indicate optional items of which you can select one and only one.                                                                                              |  |

| [menu]*            | Brackets followed by an asterisk (*) indicate optional items of which you can select more than one item.                                                                |  |

| punctuation        | You must enter punctuation other than braces ({ }) and brackets ([ ]) exactly as shown. For example, you must enter all the punctuation shown in the following command: |  |

| LIST:Fl:myprog.OOl |                                                                                                                                                                         |  |

| apostrophe         | If your terminal has two apostrophes (or single quotes), determine which one the I <sup>2</sup> ICE system accepts in command syntax.                                   |  |

| CTRL               | CTRL denotes the terminal's control key. For example, CTRL-C means enter C while pressing the control key.                                                              |  |

| REV. | <b>REVISION HISTORY</b> | DATE |

|------|-------------------------|------|

| -001 | Original Issue.         | 9/85 |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

|      |                         |      |

# SERVICE INFORMATION

intها 🚥

The best possible service for your Intel product is provided by Intel Customer Engineers. These trained professionals provide prompt, efficient, on-site installation, preventive maintenance, and corrective maintenance services required to keep your equipment in the best possible operating condition.

Intel Customer Engineers provides the service needed through a prepaid service contract or on an hourly charge basis. For further information, contact your local Intel sales office.

In Phoenix, Arizona, there is a technical information center that will connect you with the software support group for your particular Intel product.

Telephone (602) 869-INFO (4636)

When an Intel Customer Engineer is not available, contact the Intel Product Service Center.

United States customers can obtain service and repair assistance from Intel Corporation by contacting the Intel Product Service Center in their local area. Customers outside the United States should contact their sales source (Intel Sales Office or Authorized Distributor) for service information and repair assistance.

Before calling the Product Service Center, have the following information available:

- 1. The date you received the product.

- 2. The complete part number of the product (including dash number). On boards, this number is usually silk-screened onto the board. On other MCSD products, it is usually stamped on a label.

- 3. The serial number of the product. On boards, this number is usually stamped on the board. On other MCSD products, the serial number is usually stamped on a label mounted on the outside of the chassis.

- 4. The shipping and billing address.

- 5. If the Intel Product warranty has expired, a purchase order number is needed for billing purposes.

- 6. Be sure to advise the Center personnel of any extended warranty agreements that apply.

Use the following telephone numbers for contacting the Intel Product Service Center:

| Western Region: | (602) 869-4951 |

|-----------------|----------------|

| Midwest Region: | (602) 869-4392 |

| Eastern Region: | (602) 869-4045 |

| International:  | (602) 869-4862 |

Always contact the Product Service Center before returning a product to Intel for repair. You are given a repair authorization number, shipping instructions, and other important

information which helps Intel provide you with fast, efficient service. If you are returning the product because of damage sustained during shipment, or if the product is out of warranty, a purchase order is required before Intel can initiate the repair.

If available, use the original factory packaging material when preparing a product for shipment to the Intel Product Service Center. If the original packaging material is not available, wrap the product in a cushioning material such as Air Cap SD-240, manufactured by the Sealed Air Corporation, Hawthorne, N.J. Securely enclose it in a heavy-duty corrugated shipping carton, mark it "FRAGILE" to ensure careful handling, and ship it to the address specified by the Intel Product Service Center.

# I<sup>2</sup>ICE<sup>™</sup> SYSTEM OVERVIEW

inta **m**

Intel's Integrated Instrumentation and In-Circuit Emulation (I<sup>2</sup>ICE<sup>™</sup>) system offers real-time hardware and software emulation for designs using the iAPX 86, iAPX 88, iAPX 186, iAPX 188, and iAPX 286 microprocessor systems.

This chapter is an overview of the I<sup>2</sup>ICE system and its operating environment. It contains the following sections.

- The Microcomputer Development Process—this section reviews the role of an emulator in the microcomputer development process.

- An Introduction to the I<sup>2</sup>ICE<sup>™</sup> System—this section describes the I<sup>2</sup>ICE system configuration, options, and accessories.

- Hardware Overview

- Software Overview

- The I<sup>2</sup>ICE<sup>™</sup> System Command Language

- I<sup>2</sup>ICE<sup>TM</sup> System Specifications

#### **The Microcomputer Development Process**

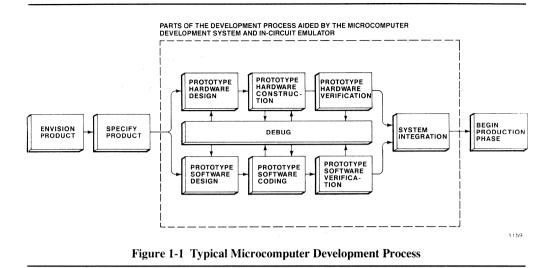

Designing a product that contains a microcomputer requires close coordination of two separate but highly dependent design efforts: hardware development and software development. These two development efforts can be accomplished independently, but it is more efficient to work on them together. Figure 1-1 illustrates a typical microcomputer development process, using a development system and an emulator.

#### Features of a Host Development System with an Emulator

A host development system with an emulator offers the following resources:

- A stand-alone computer

- Development software such as assemblers and compilers

- Prototype hardware interface

- Mapping capability

- Break and trace capability

#### **Generalized Hardware Design Steps**

Although the complexity of hardware design varies from one design to another, the general process is the same. The following sequence illustrates the advantage of using a development system with an emulator.

- Organize the hardware into logical blocks with well-defined inputs and outputs. Determine the CPU, RAM, ROM, I/O, board layout, and bus interface requirements.

- Build a hardware prototype.

- Test the interaction of the prototype hardware with proven software. The user program resides initially in either the host development system's memory or the emulator's memory. You can reassign the user program, memory block by memory block, to prototype memory as you verify the code and as prototype memory becomes available.

- Test, debug, and verify each prototype module.

#### **Generalized Software Design Steps**

Software design follows a process similar to hardware design as illustrated in the following sequence.

• Organize the software into logical blocks with well-defined inputs and outputs. Complete the specifications for the software control logic and integrated system performance.

- Program the software modules. Desk-check each module as it is completed. Name and store the software modules as files in the development system's memory. Assemble or compile the modules. Link and load the combinations that are ready to be tested.

- Emulate the program using an emulator to debug the software.

#### Hardware/Software Integration

When the hardware and software designs are complete, system integration is already in progress. The usefulness of a development system with an emulator extends into the integration and test phases.

When an emulator is connected to the prototype system through the microprocessor socket and emulator hardware probes, the emulator can emulate, test, and trace prototype system operation.

After testing the prototype, the host development system with an emulator can be used to verify the product in production test. Test procedures developed for final prototype testing can serve as the basis for production test routines. The same procedures developed for hardware debugging and production test can also be used to troubleshoot and repair failing products at a repair center.

#### An Introduction to the I<sup>2</sup>ICE<sup>™</sup> System

Intel developed the I<sup>2</sup>ICE system to address the requirements of designers who use Intel's iAPX microprocessors. The I<sup>2</sup>ICE system is a second-generation design tool that provides the following advantages:

- Full-speed, multiple microprocessor emulation

- Real-time emulation support for each of the iAPX microprocessors (86/88, 186/188, and 286)

- Software patching without recompiling or reassembling

- Extensive breakpoint capabilities

- Expanded logic analysis

The I<sup>2</sup>ICE system also offers the following features:

- Access to eight signals input from the prototype system and two signals output to the prototype system using the emulation clips. An additional output line is asserted when the I<sup>2</sup>ICE system breaks emulation, and another is asserted when the I<sup>2</sup>ICE system triggers a trace.

- An optional Intel Logic Timing Analyzer (iLTA) module which is a general-purpose, integrated, 16-channel, 100-MHz logic timing analyzer. With the mass storage provided by the host development system, you can store an unlimited number of scope displays for later analysis. Combined with the capabilities of the I<sup>2</sup>ICE system, the iLTA extends the range of development applications. [This option is not available for IBM PC hosts.]

- An optional high-speed (OHS) memory board. The I<sup>2</sup>ICE system provides up to 256K bytes of additional programmable wait-state RAM for each emulator. With the I<sup>2</sup>ICE system, you can specify zero wait-states for real-time emulation and simulate slow memories by inserting up to 15 wait states.

- Program memory mapping to high-speed (HS) memory (up to 32K-bytes) on the system map-I/O board, to OHS memory, or to host development system memory. [There is no mapping to IBM PC/AT or PC/XT host memory.]

- Multiprocessor debugging. The I<sup>2</sup>ICE system can control up to four emulators simultaneously.

- Coprocessor support, which provides debugging support for the 8087 numeric coprocessor and the 80287 numeric processor extension.

- Emulation flexibility. The iAPX 86/88 and 186/188 emulation personality modules (also called probes) each emulates two separate microprocessors. To change microprocessors, you need only change the personality module CPU chip and jumpers on the buffer and personality boards.

#### NOTE

Probe CPU chips must be provided by Intel. All probes use either bond-out chips or specially tested microprocessors.

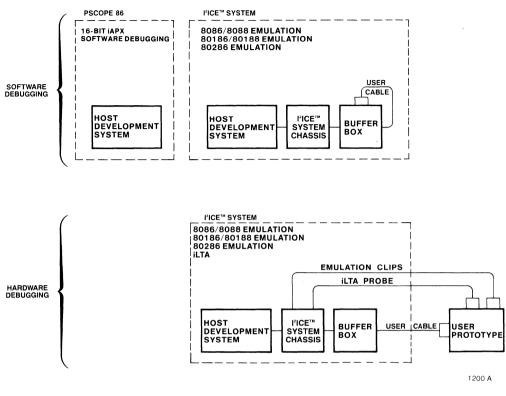

- Symbolic debugging support for programs written in assembly language, PL/M, C, Pascal, and FORTRAN by both PSCOPE-86 and the I<sup>2</sup>ICE system command language. With the symbolic debugging capabilities you can access variables and memory locations with user-defined names.

- Two programmable event machines that allow break and trace on simple and complex event sequences.

- A real-time trace buffer that displays trace information in either a disassembled-instruction format or a microprocessor bus-cycle format.

#### The Base Configuration of the I<sup>2</sup>ICE<sup>™</sup> System

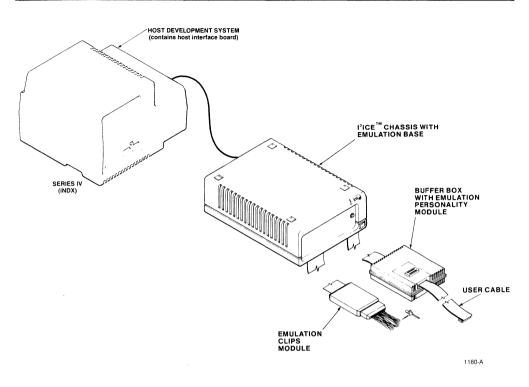

Figure 1-2 shows a basic single-chassis  $I^2ICE$  system. The base configuration is readily expandable to include a number of  $I^2ICE$  system options.

The base configuration of the I<sup>2</sup>ICE system contains the following hardware:

- The host interface board, which resides in the host development system and handles communication between the host development system and the I<sup>2</sup>ICE instrumentation chassis.

- The I<sup>2</sup>ICE instrumentation chassis, which contains the communications board and provides slots for up to four I<sup>2</sup>ICE system boards. The communications board connects to the host interface board. The chassis slots also hold the map-I/O board and the break/trace board.

- The map-I/O board, which contains high-speed RAM and the memory map. There are 32K bytes of high-speed RAM available to user programs through the memory map. The

Figure 1-2 A Basic I<sup>2</sup>ICE<sup>™</sup> System

rest of the on-board RAM contains I<sup>2</sup>ICE system software that implements probe-specific commands.

- The break/trace board, which contains two programmable event machines that implement the break and trace specifications.

- The emulation clips assembly, which enables the I<sup>2</sup>ICE system to assert signals to the prototype hardware and to read signals from the prototype hardware.

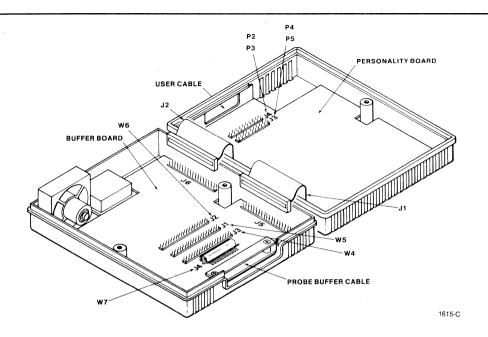

- The probe buffer box, which contains the buffer board and the personality board. The buffer board connects to the break/trace board and the map-I/O board in the instrumentation chassis. The personality board connects to the prototype hardware through the user cable.

- System cables, which connect the instrumentation chassis to the host development system and to the probe buffer box. The host/instrumentation-chassis cable is either 10 or 40 feet long.

The base configuration of the I<sup>2</sup>ICE system contains the following software.

- The I<sup>2</sup>ICE system host software, which implements the non-probe-specific I<sup>2</sup>ICE system commands. After the I<sup>2</sup>ICE system software is loaded, it resides in the host development system.

- The I<sup>2</sup>ICE system probe (personality module) software, which implements the probespecific I<sup>2</sup>ICE system commands. After the probe software is loaded, it resides in the map-I/O board.

- The I<sup>2</sup>ICE system diagnostic software.

- The PSCOPE-86 high-level language software debugger which runs in the host development system and does not emulate in real-time. It is loaded in place of the I<sup>2</sup>ICE system host software. [PSCOPE-86 is an option for the IBM PC hosts.]

- The I<sup>2</sup>ICE system tutorial software.

#### I<sup>2</sup>ICE<sup>™</sup> System Options

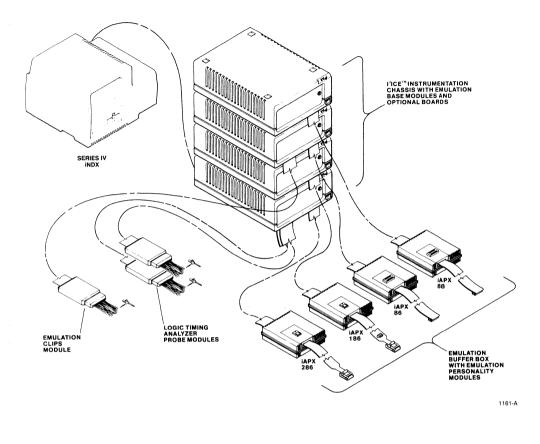

The I<sup>2</sup>ICE system is expandable. An I<sup>2</sup>ICE system can have up to four instrumentation chassis. Each chassis can emulate any of the five microprocessors. Each chassis provides up to 256K bytes of additional zero wait-state memory to user programs, and serves as a logic timing analyzer while retaining the basic I<sup>2</sup>ICE system functions.

Figure 1-3 shows the maximum configuration of an I<sup>2</sup>ICE system.

The I<sup>2</sup>ICE system options are as follows.

- The optional high-speed (OHS) memory board. This option increases the amount of I<sup>2</sup>ICE system memory available to user programs through the memory map. Each board adds 128K bytes of zero wait-state memory.

- The iLTA has all the features found in a stand-alone logic analyzer. In addition, the iLTA uses the mass storage and real-time breakpoint facilities of the I<sup>2</sup>ICE system. The iLTA monitors 16 channels at a maximum frequency of 100 MHz. [The iLTA system is not available for use with the IBM PC hosts.]

The iLTA hardware consists of one board, two probe pods, and test and hook-up accessories. Each instrumentation chassis can contain only one iLTA module, and the iLTA board must reside in the top slot.

The I<sup>2</sup>ICE system enables real-time emulation and debugging of up to four instrumentation chassis from a single host development system. A unit is composed of an instrumentation chassis, a probe buffer box, and an emulation clips pod. Each unit can emulate one of the five iAPX microprocessors. Optional high-speed memory residing in one chassis cannot be mapped into the emulation environment of another chassis.

Figure 1-3 A Maximum Configuration I<sup>2</sup>ICE<sup>™</sup> System

#### I<sup>2</sup>ICE<sup>™</sup> System Accessories

The I<sup>2</sup>ICE system accessories are as follows.

- An emulation clips assembly that consists of an emulation clips pod, an emulation clips cable, and an emulation clips terminator.

- Two logic probe pods (channels 0-7 and 8-F) that supplement the iLTA pods. Each pod can be ordered separately.

- Two iLTA terminator sets that supplement the terminator sets normally supplied with the iLTA. A 16-channel terminator set is used to hook-up to 16 separate signals. An 8-channel

terminator set is used for glitch detection and multi-threshold triggering. Each terminator set can be ordered separately.

• A microhook set that consists of 40 grabber clips (microhooks) that connect to wires belonging to the emulation clips terminator or to the iLTA terminators. The microhooks connect to individual leads of a dual in-line package (DIP). This set supplements the microhooks supplied with the emulation clips pod and the iLTA.

#### Hardware Overview

The hardware components of the FICE system are listed in Table 1-1 and discussed in the following sections.

#### **The Instrumentation Chassis**

The instrumentation chassis encloses a card cage and a backplane with four vacant slots. a switching power supply, and a communications board. As many as four chassis may be daisy-chained together in a fully-configured FICE system to allow multiprocessor emulation under the control of a single host development system.

Both the top and front covers of the instrumentation chassis are easily removed to allow access to system components. The four-slot card cage holds 12 in. by 12 in. (.30 m by .30 m) boards. Three fans on the side of the card cage provide cooling.

The internal switching power supply uses line power (110 or 220 VAC) to develop the regulated DC voltages used by the I<sup>2</sup>ICE system. (The host interface board obtains power from the host development system.) The power supply has five voltages: +5VDC (two voltages), -5.2VDC, +15VDC, and -15VDC.

The communications board is part of the rear panel of the instrumentation chassis. The board contains termination switches, rear panel connectors, and interface circuitry. The communications board handles communications with the host development system (using the host interface board). The communications board also provides the link between the I<sup>2</sup>ICE chassis in which it resides and other I<sup>2</sup>ICE chassis in the system. In multiple-chassis I<sup>2</sup>ICE systems, the communications board assigns sequential unit numbers (0 through 3) to each chassis.

#### The Host Interface Board

Each FICE system requires one host interface board. It resides in the host development system and controls up to four instrumentation chassis. For Intel hosts, the host interface board is a MULTIBUS® master board that makes possible direct memory access (DMA) to MULTIBUS board memory by the FICE system; for multiple-probe systems, the probes can share common MULTIBUS memory. IBM PC/AT and PC/XT hosts are provided with a PC-specific interface board that does not support MULTIBUS mapping.

#### Table 1-1 I²ICE™ System Hardware Components

| Instrumentation chassis Host interface board Emulation base module Break/trace board Map-I/O board Buffer base assembly Emulation buffer boare Probe buffer box base Probe buffer box cable Emulation clips assembly Emulation clips assembly Emulation clips cable Emulation clips assembly Emulation clips cable Emulation clips sod Emulation clips terminator Emulation clips somerohooks System cables Host/chassis cable (not needed for Model 800 and IBM PC hosts) Inter-chassis cable set (2 or 10 feet) Inter-chassis cable set (2 or 10 feet) Inter-chassis break cable High-speed memory board iLTA module (not available for IBM PC hosts) iLTA board External trigger wires iLTA demonstration card assembly Logic probe pod, channels 0-7 Logic probe pod, channels 0-7 Logic probe pod, channels 8-F Terminator set, 16-channel Microhook set (40 microhooks) 86/88 emulation personality board Selected 8088 CPU chip Selected                                                                                                                                                                                                                                                       | -<br>-                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| Emulation base module<br>Break/trace board<br>Map-I/O board<br>Buffer base assembly<br>Emulation buffer box dase<br>Probe buffer box base<br>Probe buffer box base<br>Probe buffer box cable<br>Emulation clips assembly<br>Emulation clips cable<br>Emulation clips cable<br>Emulation clips terminator<br>Emulation clips is microhooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis communications cable<br>Inter-chassis communications cable<br>Inter-chassis communications cable<br>Inter-chassis communications cable<br>Inter-chassis break cable<br>Optional high-speed memory board<br>iLTA module (not available for IBM PC hosts)<br>iLTA board<br>External trigger wires<br>iLTA demonstration card assembly<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 0-7<br>Digic probe pod, channels 8-F<br>Terminator set, 16-channel<br>Microhook set (40 microhooks)<br>86/88 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>86/88 personality board<br>Selected 8086 CPU chip<br>User system cable<br>186/188 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality board<br>Selected 8086 CPU chip<br>User system cable<br>286 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality board<br>Selected 80186 CPU chip<br>Selected 80286 CPU chip                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       |

| Break/trace board<br>Map-I/O board<br>Buffer base assembly<br>Emulation buffer box base<br>Probe buffer box cable<br>Emulation clips assembly<br>Emulation clips cable<br>Emulation clips cable<br>Emulation clips terminator<br>Emulation clips incrohooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Inter-chassis cable (20 or 10 feet)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis break cable<br>High-speed memory board<br>iLTA module (not available for IBM PC hosts)<br>iLTA board<br>External trigger wires<br>iLTA demonstration card assembly<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 8-F<br>Terminator set, 16-channel<br>Microhook set (40 microhooks)<br>86/88 emulation personality module<br>Probe buffer box cover<br>86/88 personality board<br>Selected 8088 CPU chip<br>Selected 80188 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 8                                                                                             |                                       |

| Map-I/O board<br>Buffer base assembly<br>Emulation tolifer board<br>Probe buffer box base<br>Probe buffer box cable<br>Emulation clips assembly<br>Emulation clips cable<br>Emulation clips terminator<br>Emulation clips microhooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Inter-chassis cable (10 or 40 feet)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis communications cable<br>Inter-chassis break cable<br>High-speed memory module<br>Optional high-speed memory board<br>iLTA module (not available for IBM PC hosts)<br>iLTA board<br>External trigger wires<br>iLTA demonstration card assembly<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 8-F<br>Terminator set, 16-channel<br>Microhook set (40 microhooks)<br>86/88 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>86/88 personality board<br>Selected 8088 CPU chip<br>Selected 8088 CPU chip<br>User system cable<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality board<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip                                                                                                                                                                         |                                       |

| Buffer base assembly<br>Emulation buffer board<br>Probe buffer box base<br>Probe buffer box cable<br>Emulation clips assembly<br>Emulation clips cable<br>Emulation clips cable<br>Emulation clips microhooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Internal host cable (not needed for Model 800 and IBM PC hosts)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis break cable<br>High-speed memory module<br>Optional high-speed memory board<br>iLTA module (not available for IBM PC hosts)<br>iLTA board<br>External trigger wires<br>iLTA demonstration card assembly<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 8-F<br>Terminator set, 16-channel<br>Microhook set (40 microhooks)<br>86/88 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>86/88 personality board<br>Selected 8088 CPU chip<br>Selected 8088 CPU chip<br>Selected 8088 CPU chip<br>User system cable<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>386/88 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>386/88 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>386 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>386 personality board<br>Selected 80188 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 80286 CPU chip<br>Selected 80286 CPU chip<br>Selected 80286 CPU chip                                                                                                                                                                                             |                                       |

| Emulation buffer board<br>Probe buffer box cable<br>Probe buffer box cable<br>Emulation clips assembly<br>Emulation clips cable<br>Emulation clips terminator<br>Emulation clips microhooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis cable memory board<br>iLTA module (not available for IBM PC hosts)<br>iLTA board<br>External trigger wires<br>iLTA demonstration card assembly<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 0-7<br>Sef&8 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>86/88 personality board<br>Selected 8088 CPU chip<br>Selected 8088 CPU chip<br>User system cable<br>186/188 personality board<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selecte                                                                                             |                                       |

| Probe buffer box base<br>Probe buffer box cable<br>Emulation clips pod<br>Emulation clips cable<br>Emulation clips cable<br>Emulation clips microhooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Interral host cable (not needed for Model 800 and IBM PC hosts)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis communications cable<br>Inter-chassis break cable<br>High-speed memory module<br>Optional high-speed memory board<br>iLTA module (not available for IBM PC hosts)<br>i ITA board<br>External trigger wires<br>i ITA demonstration card assembly<br>Logic probe assembly<br>Logic probe pod, channels 0-7<br>Logic probe pad, channels 8-F<br>Terminator set, 8-channel<br>Microhook set (40 microhooks)<br>86/88 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>86/88 personality board<br>Selected 8088 CPU chip<br>Selected 8088 CPU chip<br>User system cable<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>286 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>386/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>386/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>386/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>386 personality board asselected 803 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 80186 CPU chip<br>Selected 80266 CPU chip<br>Selected 80266 CPU chip                                                                                                                                                                                                                                                             |                                       |

| Probe buffer box cable<br>Emulation clips assembly<br>Emulation clips cable<br>Emulation clips cable<br>Emulation clips microhooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Inter-abasis cable (not needed for Model 800 and IBM PC hosts)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis communications cable<br>Inter-chassis break cable<br>High-speed memory module<br>Optional high-speed memory board<br>iLTA module (not available for IBM PC hosts)<br>iLTA board<br>External trigger wires<br>iLTA demonstration card assembly<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 8-F<br>Terminator set, 16-channel<br>Microhook set (40 microhooks)<br>86/88 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>86/88 personality board<br>Selected 8086 CPU chip<br>Selected 80186 CPU chip<br>Selected 8026 CPU chip                                                                                             |                                       |

| Emulation clips assembly<br>Emulation clips pod<br>Emulation clips terminator<br>Emulation clips microhooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Internal host cable (not needed for Model 800 and IBM PC hosts)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis break cable<br>High-speed memory module<br>Optional high-speed memory board<br>iLTA module (not available for IBM PC hosts)<br>iLTA board<br>External trigger wires<br>iLTA demonstration card assembly<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 8-F<br>Terminator set, 16-channel<br>Microhook set (40 microhooks)<br>86/88 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>86/88 personality board<br>Selected 8086 CPU chip<br>Selected 8086 CPU chip<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>286 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>186/188 personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>286 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>286 personality board<br>Selected 80186 CPU chip<br>Selected 80286 CPU chip                                   |                                       |

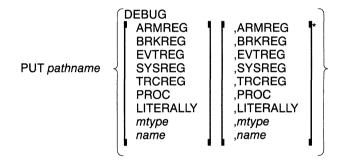

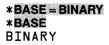

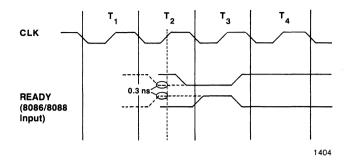

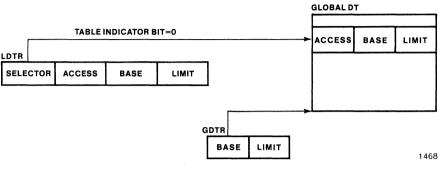

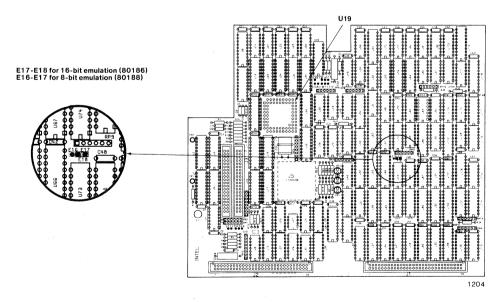

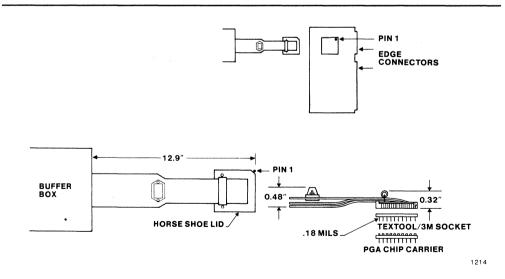

| Emulation clips pod<br>Emulation clips cable<br>Emulation clips microhooks<br>System cables<br>Host/chassis cable (10 or 40 feet)<br>Interal host cable (not needed for Model 800 and IBM PC hosts)<br>Inter-chassis cable set (2 or 10 feet)<br>Inter-chassis communications cable<br>Inter-chassis break cable<br>High-speed memory module<br>Optional high-speed memory board<br>iLTA module (not available for IBM PC hosts)<br>iLTA board<br>External trigger wires<br>iLTA demonstration card assembly<br>Logic probe pod, channels 0-7<br>Logic probe pod, channels 8-F<br>Terminator set, 16-channel<br>Terminator set, 40 microhooks)<br>86/88 emulation personality module<br>Probe buffer cover assembly<br>Buffer box cover<br>86/88 personality board<br>Selected 8086 CPU chip<br>Selected 8088 CP |                                       |