Instrumentation Laboratory

Theory of Operation

THE PIXEL 100/AP SERVICE MANUAL

# THE PIXEL 100/AP SERVICE MANUAL

I

THEORY OF OPERATION

Part No. 160451-00 Rev. 0

This is a preliminary document which may be subject to change without notice. The information contained herein is believed to be accurate and reliable; however, no responsibility is assumed by Instrumentation Laboratory Incorporated for its use; nor any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Instrumentation Laboratory Incorporated.

Copyright © 1982 Instrumentation Laboratory Incorporated. All rights reserved.

This publication, or parts thereof, may not be reproduced in any form by photographic, electrostatic, mechanical, or any other method, for any use, including information storage and retrieval.

# CONTENTS

Section 1 -- INTRODUCTION

| General                                      |

|----------------------------------------------|

| Physical Description                         |

| 1.1.1 Computer Module                        |

| 1.1.2 Terminal                               |

| 1.1.3 Optional Equipment and Peripherals 1-4 |

| Functional Description                       |

| 1.2.1 Processor/Memory Modules               |

| 1.2.2 I/O Interfaces and Devices 1-7         |

| 1.2.3 Bulk Storage Devices 1-7               |

| 1.2.4 Support Elements                       |

| Specifications                               |

|                                              |

# Section 2 -- THEORY OF OPERATION

| 2.0 | General  |              |        | •••           | •   | • • | • | • | <br>• | • | • | • | 2-1  |

|-----|----------|--------------|--------|---------------|-----|-----|---|---|-------|---|---|---|------|

| 2.1 | Input/Ou | itput Proces | sor M  | <i>l</i> odul | e.  | • • | • | • | <br>• | • | • | • | 2-2  |

|     | 2.1.1    | Overview .   |        |               | •   |     | • | • | <br>• | • | • | • | 2-2  |

|     | 2.1.2    | Functional   |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.1.3    | Block Diagr  | am.    |               | •   |     |   | • |       |   | • | • | 2-4  |

|     | 2.1.4    | Memory Open  | atior  | ns            | •   |     | • | • | <br>• | • | • | • | 2-11 |

|     | 2.1.5    | Bootstrap I  | Perfoi | rmanc         | e.  |     | • | • |       | • |   | • | 2-15 |

|     | 2.1.6    | Operations   |        |               |     |     |   |   |       |   |   |   |      |

| 2.2 | Attached | d Processor  | Modu]  | le            | •   | • • | • |   | <br>• |   |   |   | 2-18 |

|     |          | Overview .   |        |               |     |     |   |   |       |   |   |   |      |

|     |          | Functional   |        |               |     |     |   |   |       |   |   |   |      |

|     |          | Block Diagr  |        |               |     |     |   |   |       |   |   |   |      |

| 2.3 |          | Board        |        |               |     |     |   |   |       |   |   |   |      |

|     |          | Overview .   |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.3.2    | Functional   | Chara  | acter         | ist | ics |   | • | <br>• |   | • |   | 2-27 |

|     |          | Block Diagn  |        |               |     |     |   |   |       |   |   |   |      |

|     |          | Interface S  |        |               |     |     |   |   |       |   |   |   |      |

| 2.4 |          | ome Terminal |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.4.1    |              |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.4.2    | Functional   |        |               |     |     |   |   |       |   |   |   |      |

|     |          | Block Diagr  |        |               |     |     |   |   |       |   |   |   |      |

| 2.5 | Terminal |              |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.5.1    |              |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.5.2    | Functional   |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.5.3    | Block Diag   | am.    |               | •   |     |   | • |       |   |   |   | 2-38 |

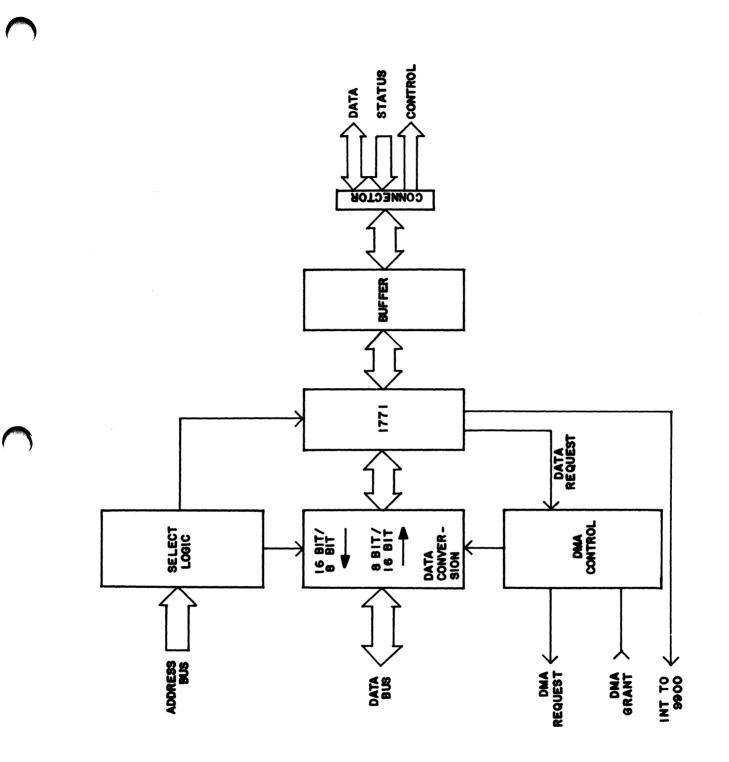

| 2.6 | Diskette | e Drive Cont | rolle  | er Bo         | ard |     |   |   | <br>• |   | • |   | 2-43 |

|     | 2.6.1    | Overview .   | • • •  |               | •   |     | • | • | <br>• |   | • |   | 2-43 |

|     | 2.6.2    |              |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.6.3    | Block Diag   |        |               |     |     |   |   |       |   |   |   |      |

|     | 2.6.4    | Diskette Da  |        |               |     |     |   |   |       |   |   |   |      |

|     |          |              |        |               |     |     |   |   |       |   |   |   |      |

| 2.7  | Diskette Drive                            | -52 |

|------|-------------------------------------------|-----|

|      | 2.7.1 Overview                            | -52 |

|      | 2.7.2 Functional Characteristics 2-       |     |

|      | 2.7.3 Block Diagram                       | -53 |

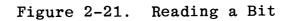

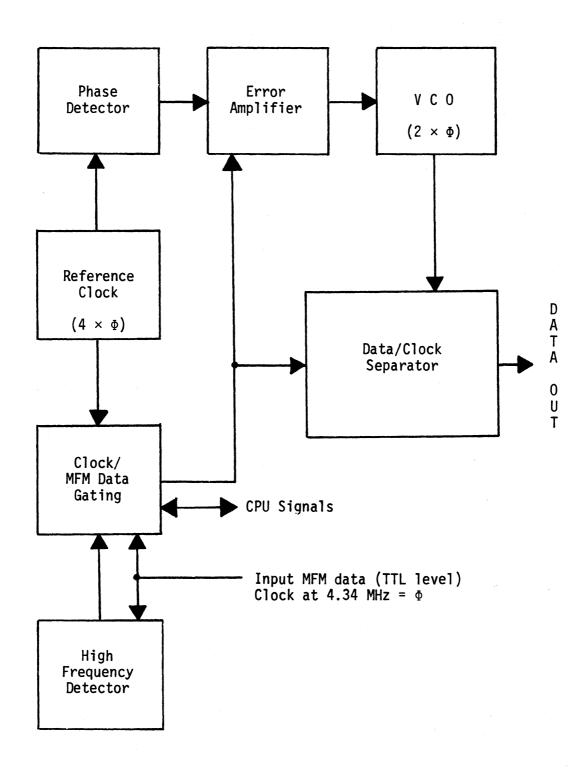

| 2.8  | Winchester Disk Drive Controller Board 2- |     |

|      | 2.8.1 Overview                            |     |

|      | 2.8.2 Functional Characteristics 2-       |     |

|      | 2.8.3 Block Diagram                       |     |

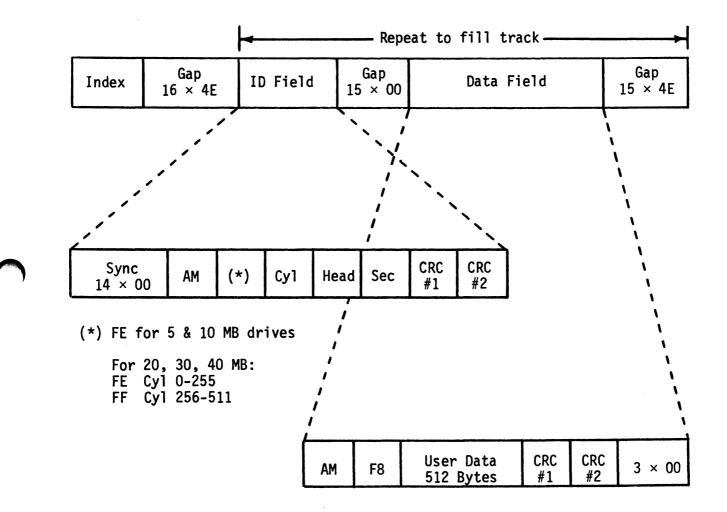

|      | 2.8.4 Winchester Recording Format 2-      |     |

| 2.9  | Winchester Disk Drive                     |     |

|      | 2.9.1 Overview                            |     |

|      | 2.9.2 Functional Characteristics          |     |

|      | 2.9.3 Block Diagram                       |     |

| 2.10 | Power Supply                              |     |

|      | 2.10.1 Overview                           |     |

|      | 2.10.2 Functional Characteristics 2-      |     |

| 2.11 | Backplane, Card Cage, and Housing         | -79 |

|      | 2.11.1 Overview                           | -79 |

|      | 2.11.2 Functional Characteristics         |     |

| 2.12 | Backplane Signals                         | -80 |

# FIGURES

| The Pixel $100/AP$                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Input/Output Processor Board         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9900 Microprocessor                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 9900 Virtual Memory Space Allocation | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                      | The Pixel 100/AP.1-2100/AP Modules.1-6Input/Output Processor Board.2-59900 Microprocessor2-6Clock Signals2-7Memory Read Cycle2-1Memory Write Cycle.2-19900 Virtual Memory Space Allocation.2-110P and Backplane Buses2-1Attached Processor Module2-2Serial Board.2-3Terminal.2-4CRT and Display Driver.2-4Keyboard Data2-4Diskette2-4FM Recording Technique.2-5Diskette Drive.2-5Writing a Bit2-5Winchester Disk Drive Controller2-5Winchester Recording Format2-6Winchester Drive Circuits2-6 |

# Section 1

# INTRODUCTION

# 1.0 GENERAL

The Pixel 100/AP is a general-purpose microcomputer manufactured by the Pixel Division of Instrumentation Laboratory, Inc., One Burtt Road, Andover, Mass. 01801.

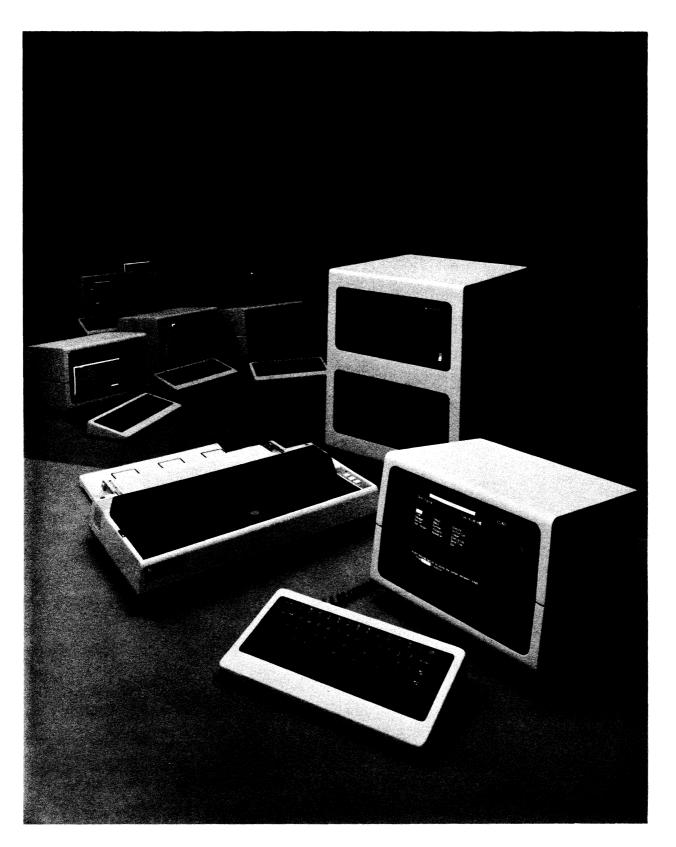

The 100/AP is illustrated in Figure 1-1.

Figure 1-1. The Pixel 100/AP

#### 1.1 PHYSICAL DESCRIPTION

The Pixel 100/AP system consists of:

- A computer module,

- One to eight terminals, and

- Various options and peripherals.

They are discussed individually in the sections which follow.

#### 1.1.1 Computer Module

Most of the 100/AP's circuitry is enclosed in a  $20" \times 21" \times 26\frac{1}{2}"$  (50.8 × 53.3 × 67.3 cm) metal housing. A card cage mounted inside the housing holds the 10" × 12" (25.4 × 30.5 cm) printed circuit card modules which include the processor and memory boards, controllers for mass storage and I/O, and the power supply. Mass storage devices (diskette and Winchester disk drives) mount underneath the card cage.

The front panel of the computer module contains an on/off switch, power light, and the diskette drive doors.

External devices may be connected to ports on the computer module's rear panel. Ports are provided for up to eight Pixel terminals, two parallel printers, and eight RS-232C serial devices. An AC line cord is also attached to the rear panel.

1.1.2 Terminal

The terminal consists of a cathode-ray tube (CRT) display and an alphanumeric keyboard. The display and keyboard are separate units connected by a flexible coiled cable. The terminal is connected to the computer module with a cable which plugs into the back panel of the CRT display and one of the terminal ports on the computer module's rear panel.

The display unit contains a power supply, a receiver board which serves as the interface between the terminal and the computer module, and a display driver. The receiver board also drives the audible signal, or "bell." The CRT features a direct-etched surface to reduce glare. It displays 25 eighty-character lines of  $9 \times 9$  dot-matrix characters. A contrast control, provided under the right side of the display screen, allows the operator to adjust the brightness of the displayed characters. The operator may also adjust the angle of the display by rotating the back foot of the display.

The rear panel contains an AC power cord and a rocker-type power switch. Two connectors are provided for connecting the terminal to the computer and the display to the keyboard.

1.1.3 Optional Equipment and Peripherals

The 100/AP system may be expanded and upgraded by adding extra terminals, additional mass storage devices, more main memory, and serial or parallel communication devices to the basic system configuration.

Additional positions are available in the card cage for printed circuit modules. Mounting and panel space for up to four disk drives, of which two may be diskette drives, is available.

# 1.2 FUNCTIONAL DESCRIPTION

The 100/AP system was designed according to a modular philosophy. Modular design means that the machine consists of a number of sub-assemblies, each with a specific function. It simplifies maintenance and repair, since a malfunction can usually be identified as a failure within a certain module or modules. It also simplifies system upgrading and expansion.

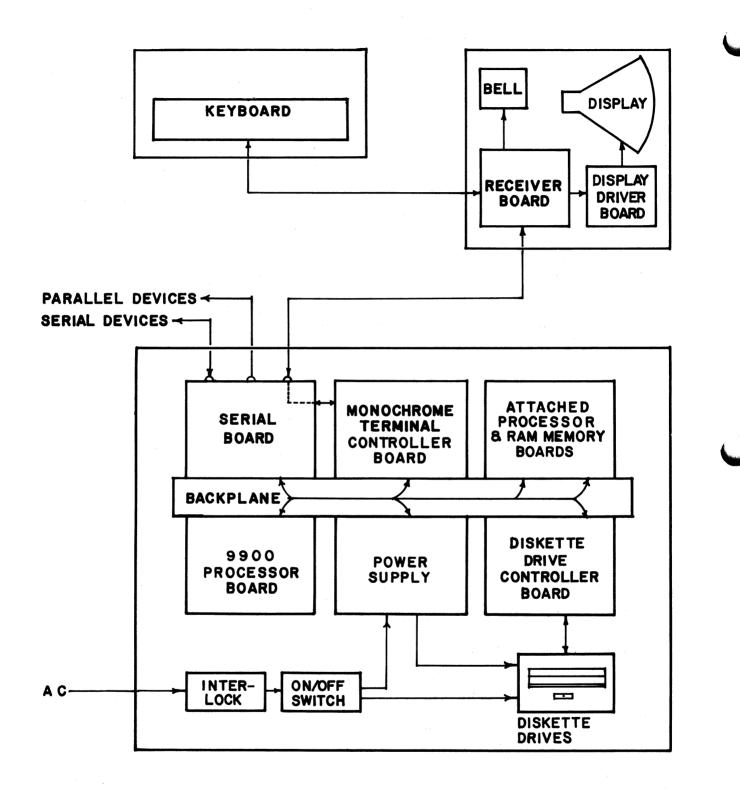

The various modules are interconnected as shown in Figure 1-2. Many of the modules are printed circuit cards which fit into the card cage inside the computer housing:

- Input/output processor board

- Attached processor board and RAM board(s)

- Serial board

- Monochrome terminal controller board(s)

- Diskette drive controller board

- Winchester disk drive controller board (optional)

- Power supply

The machine also includes these modules:

- Terminal(s), consisting of keyboard and display

- Diskette drive(s)

- Winchester disk drive(s) (optional)

- Backplane, card cage, and housing

# 1.2.1 Processor/Memory Modules

The processor/memory modules include the input/output processor board and the attached processor module. The attached processor module consists of one board which contains the attached processor and associated electronics, and one to six boards containing one Megabyte of RAM each.

The input/output processor, or IOP, serves as the central control processor for the 100/AP machine. Upon powerup, it performs the system bootstrap. It also coordinates data transactions between the system modules. It is supported by 128 kilobytes of dynamic RAM memory (256 kbytes optional).

The attached processor executes instuctions and processes data. Because the attached processor is unencumbered by housekeeping and I/O functions, it is able to process larger amounts of data than would otherwise be possible.

# Figure 1-2. 100/AP Modules

# 1.2.2 I/O Interfaces and Devices

The 100/AP supports input/output ports which allow communication with up to eight Pixel terminals, eight RS-232C serial devices, and two Centronics-compatible parallel printers. These ports are mounted on the serial board; they can be accessed through a cutout on the rear panel of the computer.

Serial and parallel communications are managed by the serial board, which acts as an interface between the I/O ports and the 100/AP's internal data paths and control lines. These interfaces are programmable—parameters such as baud rate, number of bits per character, number of stop bits, and parity are set by the system software and may be changed by the user as communication requirements change.

The Pixel terminals consist of a keyboard and video display. Video and sync outputs for the video displays, and buffers and interrupt logic for the keyboard data stream are provided by the monochrome terminal controller board(s). Each monochrome terminal controller board can control up to four terminals; by equipping the system with two of these controller boards, the maximum configuration of eight user terminals can be supported.

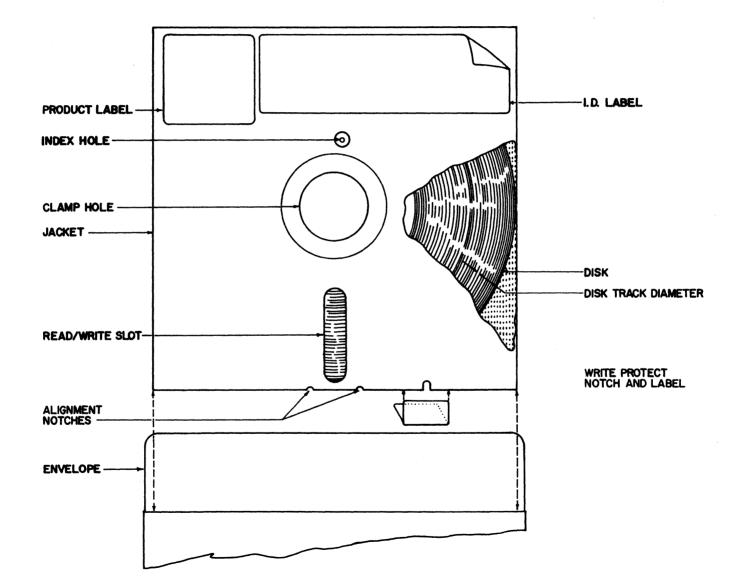

#### 1.2.3 Bulk Storage Devices

The 100/AP can be equipped with two different types of magnetic disk recording subsystems for bulk storage. Diskette drives record information on inexpensive, removable diskettes (also called "floppy disks"). Winchester disk drives store information on rigid, fixed disks housed in a sealed environment. Diskette drives provide 0.4 Megabytes of storage per diskette (single-density recording format); Winchester rigid disk drives are available in 5 Mbyte, 10 Mbyte, 20 Mbyte, 30 Mbyte, and 40 Mbyte nominal capacities.

A disk subsystem consists of a controller board and one or more drives. The controller board converts data from a format which can be stored on disk to a format which can be used by the processor, and vice versa. It also generates the necessary control and status signals. Controller boards plug into the computer backplane.

Drives spin the magnetic disks and locate, modify or read data with a magnetic read/write head. The 100/AP system can accomodate a total of four disk drives (diskette or Winchester). Of these four drives, two may be diskette drives. Most systems will include diskette drives: in a small system they function as the principal drive, and in a large system equipped with Winchester disk drives they function as a software loading and archival backup unit.

# 1.2.4 Support Elements

Support elements include the housing (described in Section 1.1), the card cage and the power supply.

The 14-position card cage houses the printed circuit card modules and guides them into the 100-contact connectors on the backplane. The backplane includes the data and address buses, power lines, and control signals used by the printed circuit card modules.

A switching-type power supply provides regulated power for the system.

# 100/AP CONFIGURATIONS

# CARD CAGE POSITIONS (14 total)

- Serial board (4-1-8) or Serial board (8-2-8)

- Power supply

- Monochrome terminal controller #0

- Monochrome terminal controller #1

- Input/output processor with 128K (256K) RAM

- Diskette drive controller (or empty slot)

- Winchester disk drive controller

- Attached processor board

- AP/memory board #0

- AP/memory board #1

- AP/memory board #2

- AP/memory board #3

- AP/memory board #4

- AP/memory board #5

## DISK DRIVES

- Diskette drive or Winchester disk drive

- Diskette drive or Winchester disk drive

- Winchester disk drive

- Winchester disk drive

# TERMINALS

- Terminal #0

- Terminal #1

- Terminal #2

- Terminal #3

- Terminal #4

- Terminal #5

- Terminal #6

- Terminal #7

- Notes: Additions to the basic configuration are shown in italics.

- 1) Terminals 4-7 require the second terminal controller.

# 1.3 SPECIFICATIONS

Mechanical

| Height: | 26.5 | in  | 67.3 | $\mathtt{cm}$ |

|---------|------|-----|------|---------------|

| Width:  | 20.0 | in  | 50.8 | cm            |

| Depth:  | 21.0 | in  | 53.3 | cm            |

| Weight: | 250  | lbs | 113  | kg            |

| Power Requirements |                                                                                                      |

|--------------------|------------------------------------------------------------------------------------------------------|

| Input voltage:     | 85-130 or 170-260 VAC                                                                                |

| Frequency:         | 47-63 Hz                                                                                             |

| Power:             | 1100 watts                                                                                           |

| Other:             | A three-wire grounded receptacle is required<br>for both the computer and terminal AC line<br>cords. |

| Environmental | Requirements     |             |

|---------------|------------------|-------------|

| Temperature:  | 32-95 °F         | 0-35 °C     |

| Humidity:     | 10-80% nonconder | nsing       |

| Altitude:     | 10,000 ft        | 3050 m      |

| RFI/EMI:      | Meets FCC class  | A standards |

# Section 2

# THEORY OF OPERATION

# 2.0 GENERAL

# This section contains functional descriptions and block-level discussions of the following modules:

# Processing Modules

- I/O processor (9900) module

- Attached processor (68000) module (and RAM boards)

# I/O Modules

- Serial board

- Monochrome terminal controller board

- Terminal

# Disk Subsystems

- Diskette drive controller board

- Diskette drive

- Winchester disk drive controller board

- Winchester disk drive

# Support Elements

- Power supply

- Backplane, card cage, and housing

Each subsection discusses one of these modules; an additional subsection describes the backplane-bus arrangement. Each subsection begins with a general overview of the module and a table of its functional characteristics; it goes on to a blockdiagram and a discussion based on the block diagram. Finally, some subsections contain other information important to the understanding of the module and the machine.

#### 2.1 INPUT/OUTPUT PROCESSOR MODULE

### 2.1.1 Overview

The input/output processor module, or IOP, is a single  $10 \times 12$ inch (25.4 × 30.5 cm) printed circuit board which contains the I/O microprocessor, associated support and interface electronics, dynamic RAM, and bootstrap ROM. The I/O microprocessor serves as the central control processor for the Pixel 100/AP system. It communicates with the attached processor module and the other system components via the backplane.

The IOP performs the I/O and housekeeping functions and processes faults for the attached processor (AP), leaving the AP free for data processing. The IOP also performs the bootstrapping function upon powerup.

In the Pixel 100 system, which lacks the attached processor module, the IOP also performs the central data processing functions. Section 2.1.6 of this manual will discuss the differences in this module's operation between the 100 and 100/AP systems.

The I/O microprocessor, a TMS 9900, is a single-chip NMOS device with 64 pins. It employs a 16-bit memory word and executes an advanced instruction set. Its memory-to-memory architecture allows faster response to interrupts and increased programming flexibility.

Support and interface circuitry, including timing generation, interrupt logic, and direct memory access control, is designed around 9900-family LSI components for reliability and low cost.

The IOP is supported by 128 kilobytes of  $64K \times 1$  dynamic RAM. An additional 128 kilobytes of RAM are available as an option. This memory is mounted on the IOP board itself, and should not be confused with the AP's 1 Megabyte RAM boards.

Bootstrap code is stored on 2  $2K \times 8$  EPROMs.

# 2.1.2 Functional Characteristics

Processor

Type:

TMS 9900

- Instruction types: Data transfer Arithmetic Compare Logical Shift Branch Control and I/O

- Object lengths: 16-bit word 8-bit byte

Interrupts: 16 prioritized interrupts Reset

Registers:

Buses:

16-bit bidirectional data bus 15-bit address bus

16 general registers Workspace register Program counter Status register

# Memory

| Type:           | 65,536 × 1 dynamic RAM                                     |

|-----------------|------------------------------------------------------------|

| Board capacity: | 128 kilobytes<br>256 kilobytes optional                    |

| Cycle time:     | Access: 150 nsec.<br>Read, modify, write: 280 nsec.        |

| Refresh period: | 2 milliseconds (128 kbytes)<br>4 milliseconds (256 kbytes) |

#### 2.1.3 Block Diagram

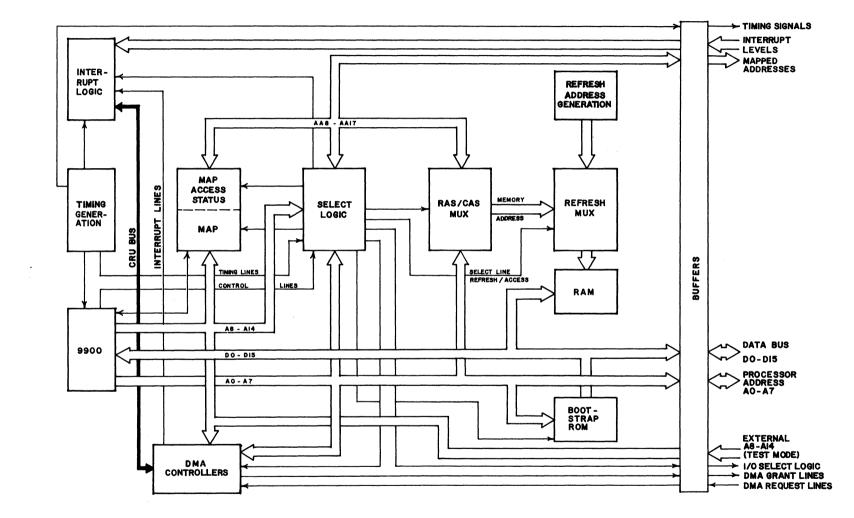

Figure 2-1 shows the principal components and interconnections of the I/O processor board. The board includes the 9900 micro-processor, support and interface components, and 128 or 256 kilobytes of RAM.

This section covers the following functional blocks and operations:

- 9900 microprocessor

- Timing generation

- Interrupt processing

- Data and address paths

- Direct memory access (DMA) control

- Communications register unit (CRU) operations

#### 9900 Microprocessor

The 9900 is an advanced 16-bit microprocessor (also called a central processing unit, or CPU) with minicomputer-like architecture and instructions. Operations are performed with a set of dedicated registers, an arithmetic logic unit (ALU), and instruction handling circuitry. These components are shown in Figure 2-2.

The 64 pins of the 9900 processor chip include a 15-bit address bus, a 16-bit data bus, and support and control lines. Support lines include three supply voltages (+5, -5, and +12 volts), a ground reference, and four clock phases. Bus control lines include read/write and memory enable signals, as well as the three CRU signals discussed below. Interrupt control lines accept interrupt requests and a four-bit interrupt level code from the interrupt logic. Memory control lines are provided for direct memory access (DMA) control, and for memory control during read/write operations. A pin is also provided for the RESET signal.

The 9900 is programmed by storing sets of instructions in memory. Instructions specify operations and the memory locations of operands. These operations include data transfer, arithmetic, compare, logical (boolean), bit shifting, program branching, and a number of control and input/output operations.

As the processor receives clock signals from the timing generation circuitry, it fetches an instruction, executes it, stores the result, fetches another instruction, and so on. While an Figure 2-1. Input/Output Processor Board

Address Bus Control Signals and Clock φ1-φ4 WP Timing CRU Signals CRU Logic PC and Control Control Instruction Register Interrupt Logic Interrupt Signals ALU Status Register Data Bus

2-6

C

C

instruction is being executed it is stored in a special register called the instruction register. Decode circuitry sets up the appropriate controls based on the contents of the instruction register. After an instruction is executed, a memory write cycle is performed to store the result of the operation at the desired location in memory.

The 9900 also provides 16 general-purpose registers implemented as blocks of memory called workspaces. Three special registers are provided to manipulate these workspaces and perform other functions during the execution of a program. The workspace pointer (WP) holds the address of the first word in the current workspace. The program counter (PC) is used to locate the next instruction to be executed. The status register (ST) consists of individual bits which are used as flags. These flags are set as a result of instructions and may be used as a basis for decision making during program execution.

# Timing Generation

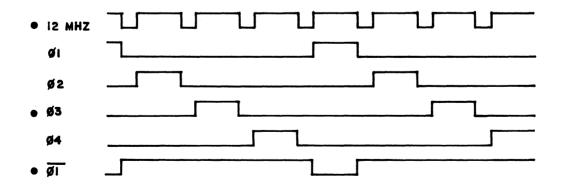

Timing generation is performed by a TMS 9904 clock generator/ driver chip. A 48 MHz crystal-controlled oscillator is divided to generate the four-phase timing signals required by the 9900. Phases 1 and 3 of the clock and a 12 MHz oscillator signal are supplied to the backplane for synchronous operations. (Note: the attached processor and the IOP run asynchronously.)

The output of the timing generator is shown in Figure 2-3.

• BACKPLANE SIGNALS

2 - 7

#### Interrupt Processing

The 9900 provides fifteen maskable interrupt levels in addition to the RESET function. An interrupt request processor chip receives the interrupt requests and signals the 9900 by asserting the interrupt request signal INTREQ. The interrupt processor provides a four-bit code corresponding to the level of the interrupt. RESET is given the highest priority, followed by interrupt requests generated by devices on the IOP board. Ten interrupt requests lines corresponding to the lowest-priority interrupt requests (INTO6..INT15) are provided on the backplane. Interrupt level assignments are shown in Table 2-1.

# Table 2-1 I/O Processor Interrupt Levels

- 01 Power failure

- 02 Memory parity error

03 Timer

- 04 DMA channels 0 and 1

- 05 DMA channels 2 and 3

- 06 (reserved)

- 07 Winchester disk drives

- 08 Diskette drives

- 09 Communications controller

10 Serial board

11 (reserved)

12 (reserved)

- 13 Attached processor errors

- 14 Terminals

- 15 Attached processor service request

#### Data and Address Paths

The principal data path on the I/O processor board is the 16-bit bidirectional tri-state data bus. A bidirectional buffer is used to connect the on-board data bus to the backplane data bus. The two buses are connected when the processor addresses the off board memory space or when a direct memory access transfer is performed. In all other cases the two buses are isolated. The individual bits of the data bus are numbered D0 through D15. D0 is the most significant bit.

The address buses include the processor address bus and the mapped address bus; they are discussed in more detail in Section 2.1.4 under "memory mapping." The address information is supplied to the backplane through buffers.

### DMA Controllers

Four direct memory access (DMA) channels are provided on the backplane. The DMA channels are used to provide a fast-response and high-transfer-rate coupling between processor RAM and certain high-speed peripheral devices (for example, diskette and Winchester disk drives).

DMA transfers are more efficient than other I/O operations because they are performed without CPU intervention. Other I/O operations usually require an interrupt routine for each word of data transferred. In a DMA transfer, the DMA controller holds the processor—causes it to stop execution and relinquish control of the data and address buses—and generates the signals necessary to transfer directly between the external device and memory.

DMA operations are controlled by two TMS 9911 DMA controller These channels chips which provide two DMA channels each. consist of request and grant lines-actual data transfers take place along the data bus. A peripheral device signals that it is ready for a transfer by asserting one of the request signals The DMA controller issues a hold signal to the DMARQO. DMARQ3. CPU. At the next available non-memory cycle, the processor relinquishes control of the data and address buses and issues a hold acknowledge signal. The DMA controller then signals the peripheral device by asserting one of the grant lines DMAGRO. DMAGR3. The DMA controller then supervises the direct transfer of data between the peripheral device and the processor RAM. When the transfer is complete, the DMA controller releases the hold signals and the processor resumes execution of its instructions.

DMA channel assignments are shown in Table 2-2.

Table 2-2 DMA Channel Assignments

| 0 Winchester | r disk drives |

|--------------|---------------|

|--------------|---------------|

- 1 Diskette drives

- 2 (reserved)

- 3 Communications controller

#### CRU Operations

The communications register unit (CRU) is a serial communication path used by the 9900 processor for a number of I/O operations, particularly those involving slower I/O devices.

The primary advantage of the CRU is economic; its data path is one bit wide, allowing chips with lower pin counts to be used. The CRU also provides a convenient alternate address path which is described more fully in Section 2.1.4.

The CRU data field consists of up to 4096 directly addressable input bits and 4096 directly addressable output bits. These bits can be addressed individually or in groups of 2 to 16 bits. Three signal lines—CRUIN, CRUOUT, and CRUCLK—are used to read and write bits of the CRU data field. The bits are specified by a portion of the processor address bus PA03..PA14 (on the backplane, these appear as A3..A7 and CA8..CA14). The processor instructions that drive the CRU can set, reset, or read any bit in the CRU data field or transfer between external memory and the CRU data field.

CRU data is sampled on CRUIN during input operations. During output operations, CRU data appears on the CRUOUT line and is strobed by CRUCLK.

CRU addresses  $000_{16}$  through  $300_{16}$  are reserved for the external CRU address space under the control of the EXTCRU line on the backplane. EXTCRU is asserted whenever one of the external CRU addresses appears on the processor address bus.

# 2.1.4 Memory Operations

# Read and Write

The processor begins a memory read or write cycle by asserting its memory enable signal,  $\overline{\text{MEMEN}}$ , on the second phase of a clock cycle. (On the backplane,  $\overline{\text{MEMEN}}$  is called  $\overline{\text{BMEMEN}}$ . It is connected to the processor signal via a buffer.)

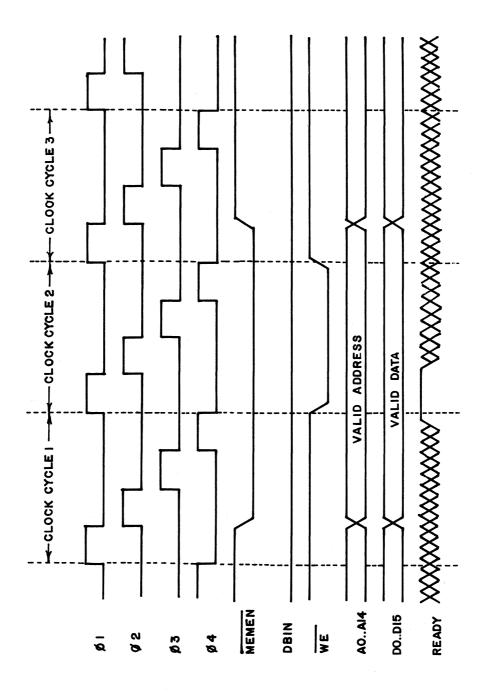

<u>A read</u> cycle is shown in Figure 2-4. The processor asserts <u>MEMEN</u> and DBIN (data bus in; on the backplane, BDBIN) on the second phase of the first clock cycle. If the memory device is ready at the first phase of the next clock cycle, the processor will read data from the data bus on the first phase of clock cycle 3. If the memory device is not ready (that is, if it has not asserted to READY signal), then the processor will enter a wait state for one clock cycle and sample READY again.

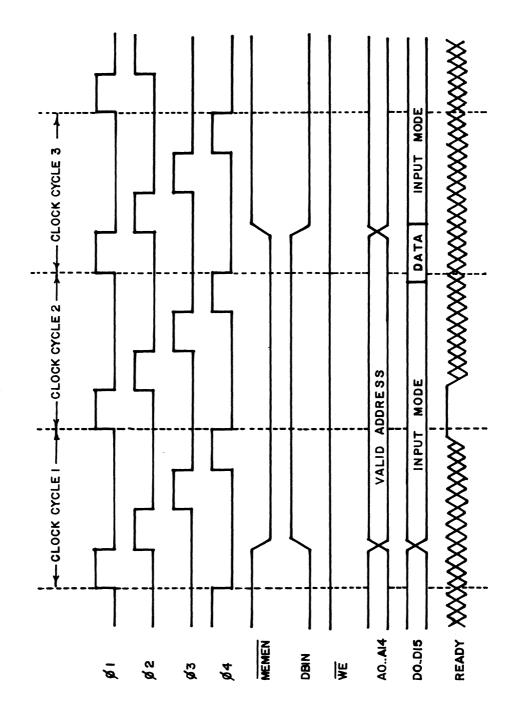

<u>A write cycle is shown in Firgure 2-5.</u> The processor asserts <u>MEMEN</u> and places a memory vector and valid data on the address and data buses respectively. At the beginning of the second clock cycle, the processor asserts  $\overline{WE}$  (write enable). If the memory device is READY, then the data is written during the second clock cycle. If the device is not READY, then the processor enters a one-cycle wait state as before.

#### Memory Mapping

The 9900 microprocessor's fifteen-bit address bus allows it to address directly 64 kilobytes of memory. Since the actual addressing requirements of the IOP are greater than 64 kilobytes (about eight times greater), provisions must be made to expand the addressing capabilities of the microprocessor. This is accomplished with the use of a memory map, a functional block constructed of very high speed (65 nsec.) static RAMs. The memory map stores arrays of pointers, which select windows within the address space for memory operations. In effect, the memory map accepts the 9900's 15-bit address and converts it into an 18-bit mapped address.

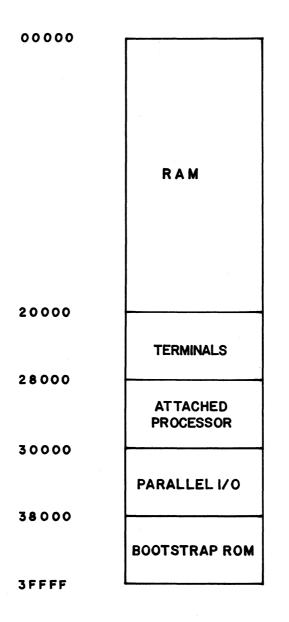

The eighteen bit mapped address allows the 9900 microprocessor to address eight 64 kilobyte memory spaces. Four spaces are assigned to the processor RAM, while the other four are assigned to bootstrap ROM and three external memory spaces: the terminals, the attached processor, and parallel I/O devices. The allocation of the mapped memory space—or "virtual" memory space—is shown in Figure 2-6.

Figure 2-5. Memory Write Cycle

Figure 2-6. 9900 Virtual Memory Space Allocation

2-14

There are two map images. One is used for running user programs, and the other is used for DMA transfers and operating system code.

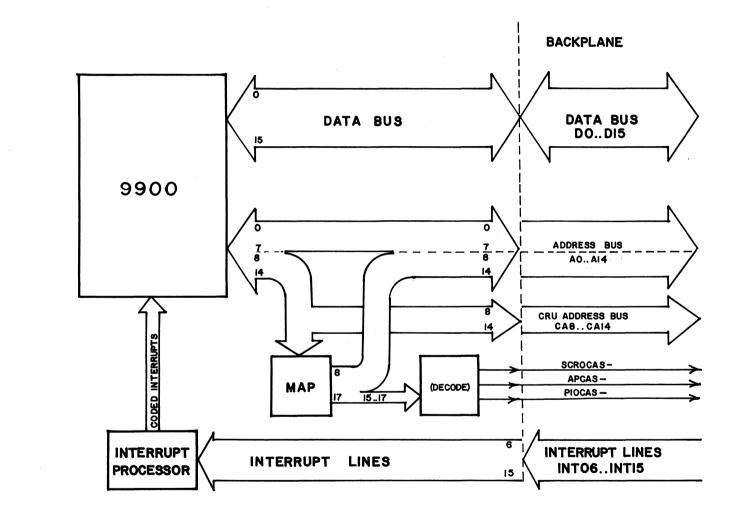

The memory-mapped design results in several different address paths on the IOP module and the backplane. These address paths, and some other important buses, are shown in Figure 2-7.

The processor address bus, that is, the fifteen lines directly connected to the microprocessor chip itself, is fifteen bits wide (PA00..PA14). Of these fifteen bits, the higher-order seven and lower-order eight are treated differently. The lowerorder eight bits PA00..PA07 are the same as the lower-order eight bits of the backplane address bus A00..A07.

The higher-order seven bits PA08..PA14 are fed into the memory map. The map's output consists of ten bits AA08..AA17. The higher-order three bits of the mapped address are then decoded into column address strobes for the processor RAM, bootsrtrap ROM, and the <u>externalmemory address select lines SCROCAS</u> (terminals), APCAS (attached processor), and PIOCAS (parallel I/O).

The fifteen bits of the backplane address consist of

the processor addresses  $PA00..PA07 \rightarrow A00..A07$ and the mapped addresses  $AA08..AA14 \rightarrow A08..A14$ .

For CRU operations, however, the unmapped processor addresses are required. The CRU address bus (CA08..CA14) on the backplane is equivalent to the higher-order portion of the processor address bus (PA08..PA14).

Thus, two complete address buses are available on the backplane: the fifteen-bit mapped address bus (A00..A14), which with the external select lines SCROCAS, APCAS, and PIOCAS is used for addressing external devices; and the fifteen-bit unmapped address bus (A00.A07..CA08..CA14) used for CRU operations.

#### 2.1.5 Bootstrap Performance

When the machine is powered up, or a  $\overrightarrow{\text{RESET}}$  signal is received, the IOP must perform a number of routines before loading the operating system which allows the user to use the system. This operation, bootstrapping, is executed from code stored in two 1024 × 8 EPROMS. The bootstrap code runs some diagnostics on the IOP board—it primarily makes sure that the 9900 and its

ſ

2-16

principal support components are operating properly—before initializing the system modules.

The reset operation which precedes bootstrapping causes the memory map to be disabled. The memory map outputs are pulled up; in other words, the map address is all ones. This address is assigned to the bootstrap EPROMs.

The 9900 fetches a reset vector from the memory map and begins to execute from the EPROMS. After the diagnostics have been run, some of the memory map is initialized to allow the EPROMs to continue to be addressed, and to set up addressing to the processor RAM. Once these initializations are complete, the map is enabled.

The diskette drive controller board, and the Winchester disk drive controller board (if present), are initialized. The system then continues to bootstrap from operating system code located on a system diskette. If an operating system diskette is not present, the system will check the Winchester drive(s) for the operating system code.

2.1.6 9900 Operations in the Pixel 100 Machine

The Pixel 100 machine differs from the 100/AP in that it does not contain the AP (attached processor) module or the RAM memory module(s) associated with the AP. It will not work with an AP operating system.

The 9900 processor module is therefore called upon to perform both control and data processing functions. From a hardware point of view, the attached processor is an external device which occupies 64 kilobytes of the virtual memory space. The only real hardware difference between the IOP's function in the two systems is the use of the memory space decoded by the APCAS line, and the operating system version.

It is possible to upgrade a Pixel 100 system by plugging the AP and AP memory boards into the extra positions in the card cage and booting an AP operating system. It is also possible to boot a Pixel 100 system operating system on a 100/AP machine; the system will simply ignore the AP and AP/memory boards. This operation is useful in isolating certain AP system failures.

## 2.2 ATTACHED PROCESSOR MODULE

## 2.2.1 Overview

The attached processor (AP) module consists of two to seven printed circuit boards. One of the boards, the "AP board," contains the attached processor and its associated support and interface circuitry. The other boards, "AP/memory boards," each contain up to one Megabyte of dynamic RAM memory.

The AP module is the principal data processor for the 100/AP system. The AP board communicates with the I/O processor via the backplane, and with the AP/memory boards through two sixty-conductor ribbon cables attached to the tops of the boards.

The attached processor is a 68000, a 64-pin single-chip microprocessor built using high-density NMOS techniques. It supports an object length of 32, 16, or 8 bits. It offers seventeen 32-bit data and address registers.

Support and interface electronics are fairly simple, since all of the input/output operations are handled by the I/O processor module.

Each AP/memory board contains 1 Megabyte of  $64K \times 1$  dynamic RAM. The system may be expanded to a maximum of 6 Megabytes of RAM, although the power requirements at this maximum configuration may limit the number of peripherals and options the machine is able to support.

# 2.2.2 Functional Characteristics

Processor

Type:

### 68000

Instruction types:

Data transfer Integer arithmetic Logical Shift and rotate Bit manipulation Binary coded decimal Program control

Addressing:

16 Megabyte direct addressing range 14 addressing modes Processor, cont'd

Object lengths: 32-bit long word 16-bit word 8-bit byte

Registers: Eight 32-bit data registers Seven 32-bit address registers Two 32-bit stack pointers One 32-bit program counter One 16-bit status register

Buses: 16-bit bidirectional data bus 32-bit address bus

# Memory

| Type:           | 65,536 × 1 dynamic RAM                              |

|-----------------|-----------------------------------------------------|

| Board capacity: | 1 Megabyte                                          |

| Cycle time:     | Access: 150 nsec.<br>Read, modify, write: 280 nsec. |

| Refresh period: | 4 millisec. maximum                                 |

#### 2.2.3 Block Diagram

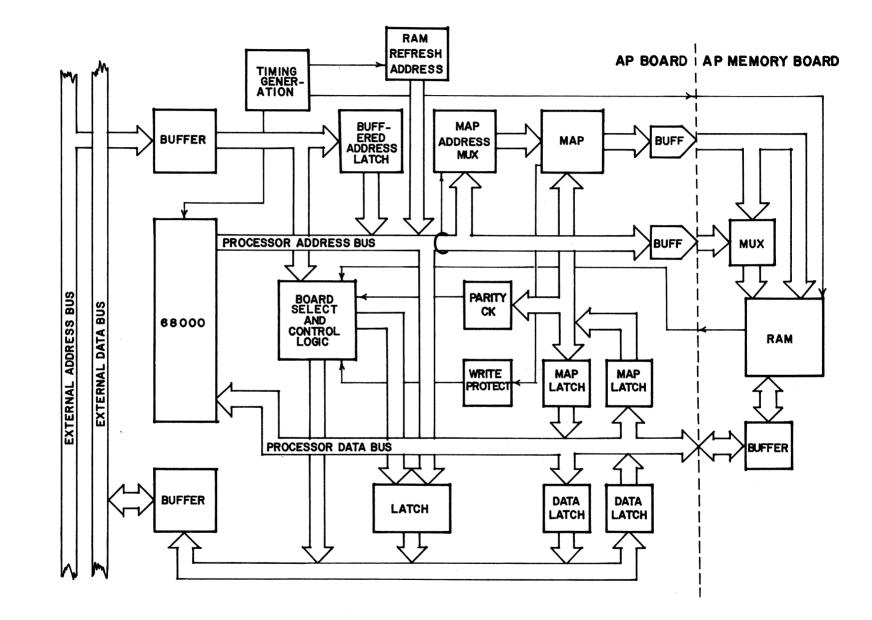

Figure 2-8 shows the principal components and data paths of the attached processor board. This board includes the 68000 microprocessor chip, some support components, the processor address and data paths, and the memory map.

This section will discuss the following:

- 68000 microprocessor

- Timing generation

- Memory operations

- Board select and control

- Data and address paths

#### 68000 Microprocessor

68000 microprocessor operations are similar to those of the I/O processor discussed in Section 2.1.3. Like the I/O processor, the 68000 operates with a set of dedicated registers, instruction handling circuitry, and an arithmetic logic unit. It is programmed by storing instructions in memory. As clock signals are received, the 68000 will fetch an instruction, execute it, store the result, fetch another instruction, and so on.

The 68000 chip has 64 pins, which perform the following functions:

- A 23-bit address bus, which provides the address for 68000 operations.

- A 16-bit bidirectional data bus.

- Bus control signals, including the address strobe  $\overline{AS}$ and a single read/write signal  $R/\overline{W}$ . The address strobe indicates that there is a valid address on the address bus, and  $R/\overline{W}$  identifies a data bus transfer as a read or write cycle.

- Bus arbitration control signals, which permit devices to request and receive control of the 68000 processor address and data buses.

- Interrupt control signals.

- System control signals, which indicate fault conditions and HALT or RESET the 68000.

Figure 2-8. Attached Processor Module

-

- Processor status codes, which indicate the processor state (user, supervisor, or interrupted) and the cycle type being executed.

- Support pins, including +5V, ground, and a single-phase clock input.

The 68000 performs operations on 8-bit bytes, 16-bit words, and 32-bit long words. Some instructions contain an explicitly coded operand-size specification, while others are designed to operate on certain data types.

These three data types can be stored in one of the eight general purpose data registers. A byte will occupy the lower order 8 bits, a word will occupy the lower order 16 bits, and a long word will occupy the entire 32 bits of space in the register.

The 68000 also supports seven address registers and two stack pointers (similar to the "workspace pointers in the 9900 microprocessor). These registers are 32 bits wide. The 32-bit program counter and 16-bit status register identify instructions to be executed and provide flags for decision-making, respectively.

The instruction set, specially designed to support high-level languages and to facilitate ease of programming form a set of tools to manipulate these registers and the external AP memory. Instructions contain two kinds of information: the type of function to be performed, and the locations of data on which to perform that function. The latter infomation is referred to as addressing information. The 68000 instruction set allows the program to address data in registers, at a specific address, or in certain specialized registers. Certain addressing types direct the processor to operate on information preceding or following certain information in memory.

The instructions perform the following functions:

• Data movement. Basic transfer and storage is provided by a move instruction, which allows the manipulation of both addresses and data. Data move instructions allow byte, word, and long word operands to be transferred from memory to memory, memory to register, register to memory, and register to register. Address move instructions allow word and long word operand transfers and ensure that only legal address manipulations are executed. Several special data movement instructions are also supported.

- Integer Arithmetic Operations. These include add, subtract, multiply and divide, as well as arithmetic compare, clear and negate.

- Logical Operations. These operations include and, or exclusive or, and not.

- Shift and Rotate. Shift and rotate operations in both directions are supported. Shift counts of zero to 63 bits can be specified in a data register; 1 to 7 can be explicitly coded in the instruction.

- Bit Manipulation Operations. These permit individual bits to be tested, set, cleared, or changed.

- Binary Coded Decimal Operations. These permit standard multiprecision arithmetic operations to be performed on four-bit binary-coded-decimal (BCD) data.

- Program/System Control Operations. These instructions are used to control the execution of programs and also permit the operating system to integrate the processor into a usable system.

#### Timing Generation

Timing signals for the 68000 microprocessor, as well as for RAM refresh, are generated by a 32 MHz crystal-controlled oscillator module. The 32 MHz signal is divided by four to provide the single 8 MHz clock signal required by the processor.

The attached processor and the I/O processor run asynchronously.

#### Memory Operations

The AP subsystem is supported by up to six Megabytes of dynamic RAM memory. AP/memory boards, which hold up to one Megabyte of RAM each, are connected to the AP through two 60-conductor ribbon cables which plug into connectors on the tops of the boards. Switches on each AP/memory board allow it to be identified as memoryØ through memory5.

The 68000 microprocessor is capable of addressing 16 megabytes of hardware address space. Since the AP/memory (at maximum configuration) consists of only 6 Megabytes, the 68000 processor address bus is translated through a memory map. While the I/O processor uses a memory map to accomodate a larger address space, the AP uses a memory map to accomodate a smaller address space.

The RAM memory shown in Figure 2-8 can be addressed in one of two ways: via the 68000 processor address bus or via the memory map. Addressing via the address bus is used for refresh, performed by the RAM refresh address circuitry and the timing generation section.

The RAM is normally addressed via the memory map. An address on the 68000 processor address bus is translated by the memory map into the shorter address actually used by the RAM. The 68000 then performs a memory read or write (specified by  $R/\overline{W}$ ) and the data are buffered onto the 68000 data bus.

The I/O processor can access a 64 kiloByte section of the AP's virtual memory space in order to transfer information from terminals, or processing state information. This memory space makes use of the AP's map to provide access to the entire memory space. Data latches permit the 68000 data bus information to be transferred onto the IOP's buffered data bus.

Data in the memory map are read or written via the map latches. A write-protect feature permits each page of the memory map to be protected against supervisor or user access, or both.

# Board Select and Control

Board select and control is the general name for the various circuits which select the attached processor board, read status words, process fault conditions, and issue interrupt requests between the processors.

The principal communication paths used for these operations are the (buffered) backplane address and data buses, the AP select line  $\overline{APCAS}$ , and the I/O processor read signal BDBIN.

The I/O processor treats the attached processor as an external memory device. The board is selected by means of the address bus and  $\overline{APCAS}$ . In addition, a portion of the parallel I/O virtual memory space decoded by  $\overline{PIOCAS}$  contains various control and status registers used by the IOP to control the AP. These registers include bits which give the status of some of the pins on the 68000 microprocessor chip, and are particularly useful in the case of AP faults.

The AP cannot process faults; a fault condition causes the AP to halt and set the appropriate bits of the fault words. These faults can include an error in the parity-protected RAM or memory map; page faults, which occur when the memory map output doesn't coincide with any real memory space; errors in the map's write protection system; and common errors such as spurious interrupts.

### Address and Data Paths

This section reviews the various data and address paths on the AP board. Please refer to the AP block diagram, Figure 2-8.

Of the six important paths on the AP board, two are associated with the 68000 microprocessor. These are:

- The processor address bus (labeled as such in the diagram). This contains the unmapped 68000 address. It is used as an input value to the memory map for all RAM addressing operations, and it is used directly by the RAM refresh logic for refresh.

- The processor data bus. All data to and from the RAM appear on this bus. It is also used to supply data to the memory map via two map latches.

Two paths are associated with the backplane data and address lines under the control of the I/O processor. These include:

- The IOP address bus (the output of the buffer connected to the external address bus in the diagram). This is used to access the virtual memory space assigned to the AP, decoded by the APCAS line. It is also used to obtain status and control words from the board control logic; this function is decoded by the PIOCAS line.

- The IOP data bus (the in/output of the buffer connected to the external data bus in the diagram). This is used for general data transfers between the AP subsystem and the rest of the computer. It is also used for transferring control and status words to the IOP.

Two paths are associated with the AP's memory map.

• The mapped address bus (output of the map block). This contains the mapped address used by the real RAM memory.

• The map data bus (the input to the map block from the map latches). This is used to read, modify, and write data in the memory map.

#### 2.3 SERIAL BOARD

#### 2.3.1 Overview

The serial board is the external communications interface for the 100/AP. The serial board plugs into the rearmost position in the card cage, in such a way that the I/O ports mounted on the serial board may be accessed through a cutout in the rear panel of the computer enclosure. The serial board is available with a maximum of eight Pixel terminal ports, eight serial ports conforming to RS-232C protocol, and two Centronicscompatible parallel ports.

The serial board communicates with the I/O processor via the backplane. Parallel and serial data are received and transmitted through programmable devices—parallel interfaces and UARTS—located on the serial board.

A ribbon cable connects the top of the serial board to the monochrome terminal controller board(s). This cable carries all of the signals required by the terminals. The serial board does not process or buffer these signals—it merely makes them available at the terminal connectors. (Note: if there are two monochrome terminal controllers, two top-cables are used.)

Board control and backplane interface logic is shared among all of the serial and parallel ports. A parallel interface or UART is assigned to each port.

2.3.2 Functional Characteristics

| Data ports:       | Four or eight EIA RS-232C serial ports<br>One or two parallel output ports<br>Eight Pixel terminal connectors |

|-------------------|---------------------------------------------------------------------------------------------------------------|

| Data format:      | (see Section 2.3.4)                                                                                           |

| Hardware options: | 4•1•8 or 8•2•8<br>(serial•parallel•terminal)                                                                  |

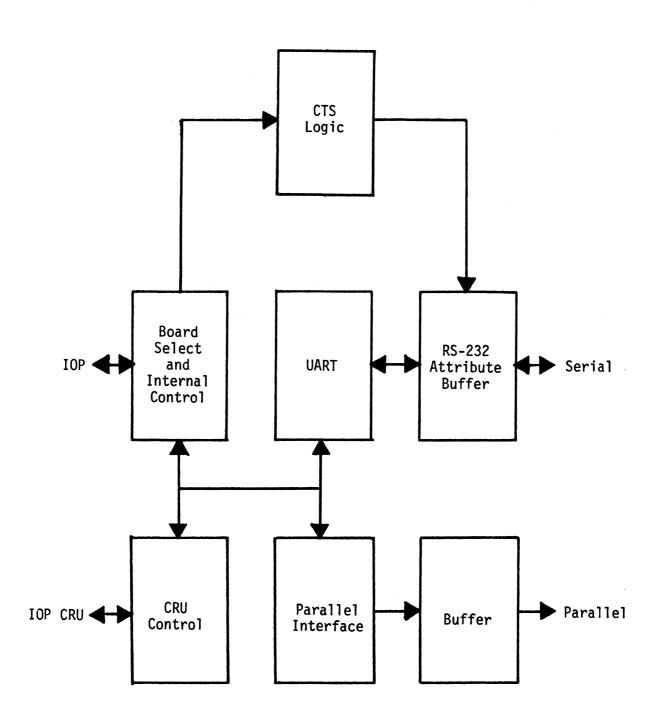

### 2.3.3 Block Diagram

Data paths and functional blocks for the serial board are shown in Figure 2-9. The serial board performs three basic functions:

- Select/internal control and CRU buffer

- Serial data transmission and reception

- Parallel data transmission

# Select/Internal Control and CRU Buffer

On-board control operations are performed by a TMS 9901 programmable interface device which communicates with the I/O processor via the backplane. CRU signals, the external CRU space select line EXTCRU, and the CRU address bus are buffered and used to select individual serial board devices. The interface also services device interrupts and generates a tenthlevel interrupt request on the backplane INT10 line.

The programmable interface occupies 32 bits of CRU address space, and the individual devices interfaced through the serial board occupy a total of 32 bits of CRU address space. The CRU concept and operations are described in Section 2.1.3.

Timing signals for the interface devices on the serial board is provided by dividing the backplane oscillator signal MHZ12 to 3 MHz. This signal is used by the interface devices for baudrate timing and device operation.

# Serial Data Transmission and Reception

Each serial port is controlled by a TMS 9902 universal asynchronous receiver/transmitter (UART). The transmission and reception parameters including baud rate, character size, number of stop bits, and parity are stored on programmable registers on the 9902 chip. Default parameters are set by the operating system when the machine is bootstrapped. These parameters may be changed by the user.

Buffered address lines 0 through 4 are used to select, process interrupts, and generate clear-to-send signals for each of the eight UARTs.

Figure 2-9. Serial Board

### Parallel Data Transmission

Each parallel data port is controlled by a TMS 9901 parallel interface. Transmission rate and other parameters are programmable; as with serial transmission, the parameters are set to default values when the system is bootstrapped, and they may be changed by the user.

Buffered address lines 0 and 3 are used to select and respond to interrupts for the two interfaces.

### 2.3.4 Interface Specifications

### RS-232C Serial Ports

Communication type: Asynchronous, bit serial full-duplex

Xmit/receive: Independently programmable rate 50 to 19,200 baud

Data Structure: Start bit (logic 0) 5 to 8 character length 1,  $1\frac{1}{2}$ , or 2 stop bits Odd, even or no parity

Line type:

Control signals:

EIA RS-232C protocol

Clear to send Request to send Data set ready

> Line control characters Flush buffer characters

Recommended mating connector:

Pixel p/n 160180-00 3M p/n 3485-1000 Parallel I/O Ports

Communication type: Parallel data out, 8-bit with strobe Centronics-compatible Positive or negative data Positive or negative data strobe

Line speed:

Programmable

Control signals:

Acknowledge Busy On Line Paper Out Fault Reset

Recommended mating Connector:

- Connector Pixel p/n 160131-00 AMP p/n 552138-1

- Strain relief cover Pixel p/n 160135-00 AMP p/n 552073-6

Terminal Ports

Communication type:

Recommended mating connector:

(Refer to Sections 2.4 and 2.5.)

Plug Pixel p/n 160363-01 AMP p/n 205204-4

Pins Pixel p/n 160365-00 AMP p/n 66506-9

### 2.4 MONOCHROME TERMINAL CONTROLLER BOARD

# 2.4.1 Overview

The monochrome terminal controller board multiplexes video, control, and memory operations for one to four separate Pixel terminals. The controller uses a memory mapped design which allows up to eight pages of text to be shared among the terminals. Complete and separate keyboard control, character generation, and video signals are provided for each terminal.

The Pixel machine can accomodate one or two monochrome terminal controller boards. With two controller boards installed, eight terminals can be used. Controller #0 supports terminals 0 through 3, and controller #1 supports terminals 4 through 7.

Each controller board plugs into the card cage, and is connected by a ribbon cable to one of the two connectors on top of the serial board. The terminal connectors are mounted on the serial board; they are accessible through a cutout in the rear panel of the computer enclosure.

### 2.4.2 Functional Characteristics

| Communication type: | 16.2 kHz horizontal sync<br>50/60 Hz vertical sync<br>12.247 MHz video signal<br>Bit serial data from keyboard<br>Bell control pulse                          |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Characters:         | 25 80-character line display area<br>Complete 7-bit ASCII character set<br>7 × 10 character matrix<br>Normal/reverse video<br>User-selectable blinking cursor |

| Keyboard receiver:  | Bit serial data, start and stop bits<br>8 bit word, even parity<br>2400 baud receive rate                                                                     |

| Bell control:       | User-selectable                                                                                                                                               |

| Hardware options:   | 50 or 60 Hz operation<br>Terminal controller #0 or #1                                                                                                         |

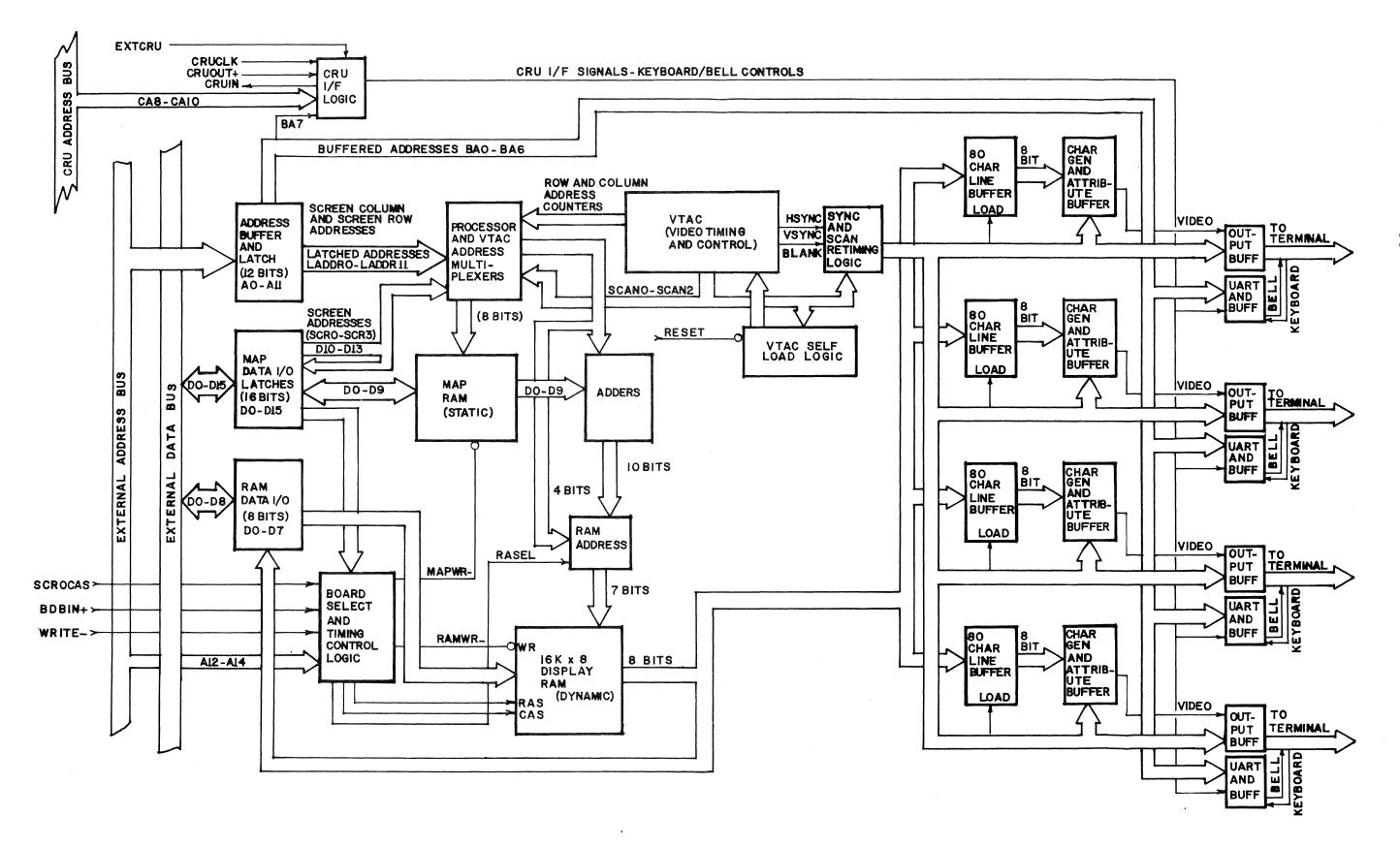

### 2.4.3 Block Diagram

A block diagram for the monochrome terminal controller board is provided in Figure 2-10. The controller is made up of five basic blocks:

- Processor interface

- Memory map and screen RAM

- Video control and addressing

- Video drive

- Keyboard receiver and bell control

#### Processor Interface

The processor interface includes board select, read/write control, and timing electronics. The interface controls the transfer of information between the external (backplane) and on-board buses with TTL latches.

The board is <u>selected</u> when the terminal external memory space select line <u>SCROCAS</u> is asserted and the external address bus bits 13 and 14 are zero. Address bit 12 is used to differentiate between operations involving controller board 0 and controller board 1.

When the board is selected, read/write signals from the backplane (BDBIN and  $\overline{WE}$ ) are used to operate the address and data latches shown in the block diagram.  $\overline{WE}$  is used to latch the address bus, the memory map and RAM during write operations, and BDBIN is used to latch the data bus during read operations.

Timing signals are generated by a 24.4944 MHz crystal oscillator. The oscillator signal controls a latch on a timing ROM; this is used to generate timing signals used by the various components of the board and column and row address strobes for the screen RAM.

#### Memory Map and Screen RAM

The terminal controller employs a memory-mapped design. The screen RAM (or display RAM) is a 16 kB  $\times$  8 array of dynamic RAM. The screen RAM stores 204 eighty-character lines of information in random order. The lines of information stored in the screen RAM are arranged by the memory map into the order in which they appear on the terminal screens.

2-34

The map is an array of static RAM. In addition to arranging the screen RAM data lines into display order, it is used for screen RAM refresh and for enabling or inhibiting actual screen display.

The map is divided into 16 sections called windows, numbered 0 through 15. Windows 0 through 3 are used for the four terminal screens. The terminal windows consist of a pointer which points to a line of blanks (used for retrace), and 25 pointers which correspond to the 25 lines of text on the display screen.

Windows 8 and 9 are used for refreshing the screen RAM. Writes to window 14 will turn the display off by disabling the horizontal sync signal, and writes to window 15 will turn the display on by enabling the horizontal sync signal. (Note: When the horizontal sync is disabled, power to the keyboard unit is disabled as well by the terminal's receiver board. Upon powerup, the horizontal sync is disabled to prevent screen trash from being displayed, and to prevent the keyboard from interfering with the system initialization.)

The other windows are reserved for future applications.

Screen RAM and map data may be modified by the I/O processor during the screen retrace; at other times the memory is busy transferring data into the line buffer and character generator for display on the user terminals.

#### Video Control and Addressing

The components responsible for video control and addressing include the video timing and control (VTAC) chip and its associated electronics, and the video multiplexing and RAM addressing circuitry. The purpose of these functional blocks is to transfer information from the screen RAMs to the actual screens.

The VTAC chip is a TMS 9927 video controller/timer, a programmable NMOS device. Parameters for the operation of Pixel terminals are stored on a self-load PROM; these parameters are loaded into the appropriate registers on the VTAC chip when the system is bootstrapped.

Raster-scan, row and column addresses from the VTAC are supplied to the processor and VTAC address multiplexers shown in the block diagram. This functional block generates an output character address which is sent to the adders. The line address from the map RAM is added to the character address from the VTAC; the result is used to select the desired character code which is stored in the screen RAM.

#### Video Drive

The video drive processes information from the display RAMs and sync and scan information from the VTAC to generate the video signals which actually control the CRT display. The output of this section consists of horizontal and vertical sync signals, which govern the CRT's electron gun movement, and a video signal, which turns the electron gun on and off to produce white dots on the CRT screen.

The basic blocks of the video drive include an  $80 \times 8$  shift register which serves as a line buffer, a character generator ROM which converts the character code into a dot-matrix character, and attribute buffers which generate the video signal and transmit it and the sync signals to the terminal.

Each terminal is assigned a complete and separate video drive section; there are four on each monochrome terminal controller board.

### Keyboard Receiver/Bell Control

The previous sections have dealt with the video ouput sections of the terminal controller board. Each controller board also includes four entirely separate keyboard and bell control sections. These functions are performed by TMS 9902 UARTS. The UARTS receive the keyboard serial data stream and transmit the bell signal, serving as the interface between the terminal and the I/O processor.

The interface with the processor is conducted via the CRU backplane signals and the CRU address bus. Keyboard data will also generate a fourteenth-level interrupt on the backplane INT14 line.

### 2.5 TERMINAL

# 2.5.1 Overview

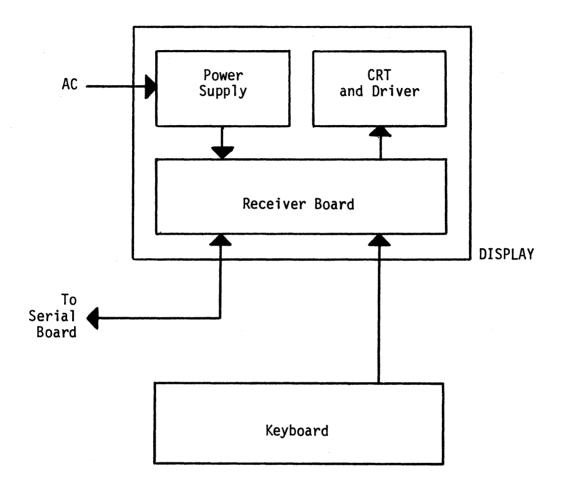

The terminal consists of a 25 line  $\times$  80 character cathode-ray tube (CRT) display, a typewriter-format keyboard, an audible signal (called a "bell"), and associated electronics. A cable connects the display to the computer module, and a four-conductor coiled cable connects the keyboard to the display.

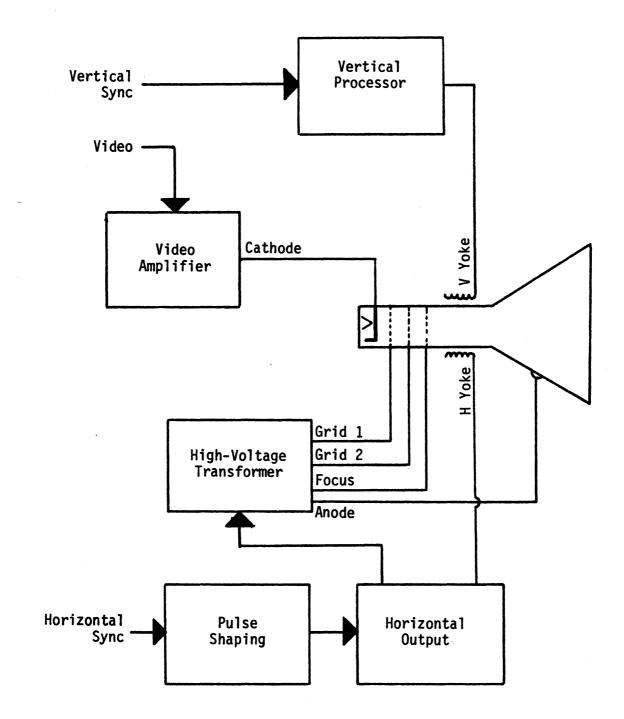

A receiver board and display driver are mounted inside the display housing. The receiver board buffers the sync and video signals sent by the monochrome terminal controller and drives the bell. The display driver drives the CRT display.

The keyboard is equipped with a scanner which converts key transitions into a stream of serial data. The data stream and power for the keyboard are supplied via the four-conductor cable.

An AC line cord mounted on the back of the display supplies power to an IC-regulated power supply which powers the entire terminal unit. A rocker-type on/off switch is also mounted on the rear panel. 120 or 220 volt AC supplies are accomodated by an internal jumper.

2.5.2 Functional Characteristics

| Video display:     | Raster-scan monochrome display<br>Grey phosphor<br>Direct etched (non-glare) CRT |

|--------------------|----------------------------------------------------------------------------------|

| User controls:     | Character intensity (contrast)<br>Screen angle                                   |

| Display area:      | 25 lines of 80 characters each                                                   |

| Keybo <b>ard</b> : | Standard typewriter keyboard with additional command and function keys.          |

| Audible tone:      | User-selectable                                                                  |

### 2.5.3 Block Diagram

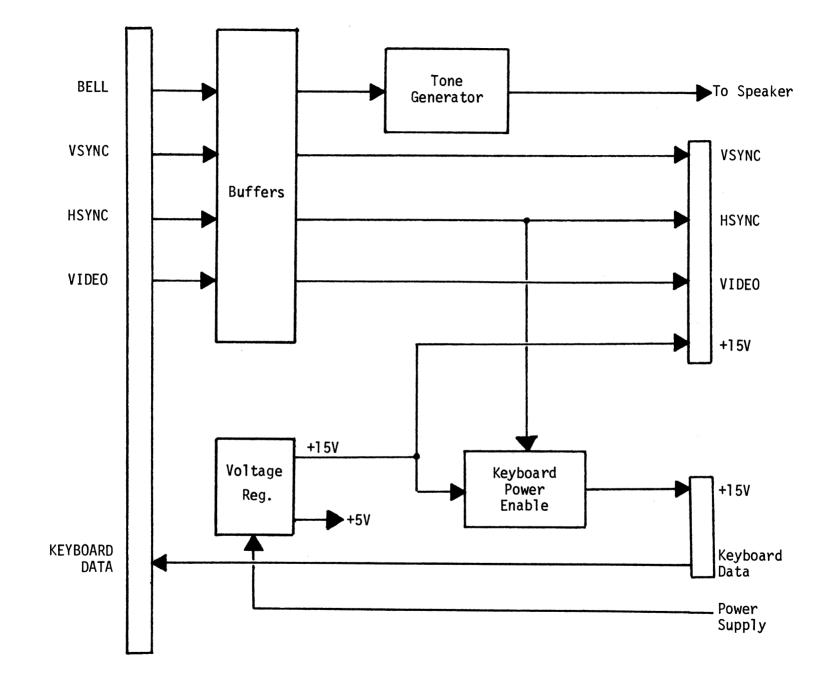

The main components of the terminal are the keyboard and the display, the latter consisting of a power supply, receiver board, display driver, bell, and CRT. These are interconnected as shown in Figure 2-11.

#### Receiver Board

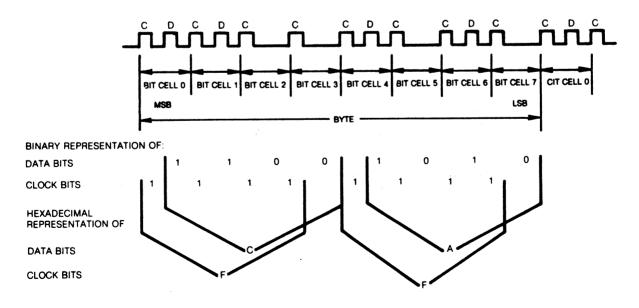

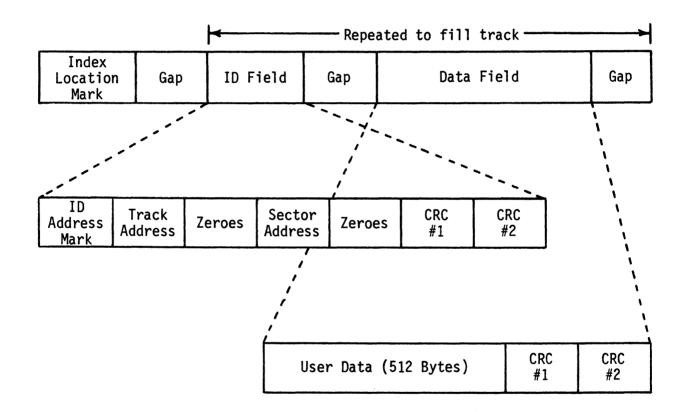

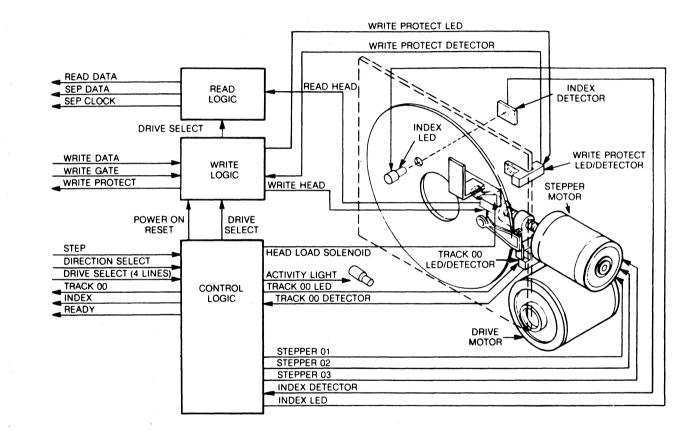

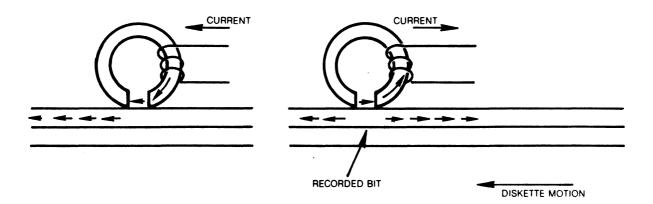

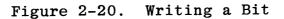

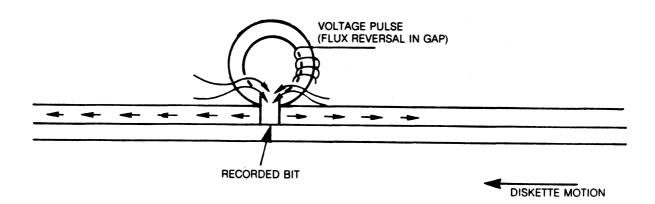

The principal components of the receiver board are shown in Figure 2-12.