IMSAI MANUFACTURING CORP. 14860 Wicks Boulevard San Leandro, CA 94577 (415) 483-2093 TWX: 910-366-7287

## IMSAI EUROPE

Europa Terrassen 8 Rue Jean Engling Dommeldange, Luxembourg 43-67-46 TWX: 1428

November, 1978

The information in this document is subject to change without notice and should not be construed as a commitment by IMSAI Manufacturing Corporation. IMSAI Manufacturing Corporation assumes no responsibility for any errors that may appear in this document.

# DISKETTE SYSTEM REFERENCE MANUAL

# Copyright (C) 1978, IMSAI Manufacturing Corporation

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of IMSAI Manufacturing Corporation.

The postage prepaid READER SUGGESTION form enclosed with this document requests the user's critical evaluation to assist us in preparing future documentation.

IMSAI Manufacturing Corporation 14860 Wicks Boulevard San Leandro, California 94577 All rights reserved worldwide.

# DISKETTE SYSTEMS REFERENCE MANUAL

# TABLE OF CONTENTS

| Section 1   | INTRODU                                | CTION                                                                                | DSK – 1                          |  |  |

|-------------|----------------------------------------|--------------------------------------------------------------------------------------|----------------------------------|--|--|

| Section II  | DISKETTE SYSTEMS, GENERAL              |                                                                                      |                                  |  |  |

|             | 2 - 1<br>2 - 1.1<br>2 - 1.2            | Components and Interface<br>Controller<br>Drive                                      | DSK – 2                          |  |  |

|             | 2 – 1.3<br>2 – 1.4                     | Media<br>Data Transfer Mechanism<br>Programmed Data Transfer                         | DSK - 3                          |  |  |

|             |                                        | Interrupt Driven Data Transfer<br>DMA Data Transfer                                  | DSK - 4                          |  |  |

|             | 2 - 2<br>2 - 2.1<br>2 - 2.2<br>2 - 2.3 | Formats and Encodation<br>Tracks and Sectors<br>Data Formats<br>Data Encodation      | DSK – 7<br>DSK – 9               |  |  |

|             | 2 – 2.4<br>2 – 2.5                     | Bit Cells<br>Synchronization<br>FM Synchronization<br>MFM Synchronization            | DSK – 12<br>DSK – 13<br>DSK – 14 |  |  |

|             | 2 - 3<br>2 - 3.1                       | Write and Read Processes<br>Access Conventions<br>Byte Commands and Command Strings  | DSK – 16<br>DSK – 17<br>DSK – 18 |  |  |

|             | 2 - 3.2                                | Access Schema<br>Read/Write Sequences<br>Write Operation                             | DSK - 20<br>DSK - 21             |  |  |

|             | 2 - 3.3                                | Read Operation<br>Error Handling                                                     | DSK - 22                         |  |  |

| Section III | IMSAI DISKETTE SYSTEMS                 |                                                                                      | DSK - 23                         |  |  |

|             | 3 - 1                                  | General                                                                              |                                  |  |  |

|             | 3 - 2<br>3 - 2.1                       | Configurations<br>Controllers<br>FIF Controller<br>MDIO Controller<br>DIO Controller |                                  |  |  |

|             | 3 - 2.2<br>3 - 2.3                     | Hardware Compatibilities<br>Format Compatibilities                                   | DSK – 24<br>DSK – 26             |  |  |

|            | 3 – 3<br>3 – 3 <b>.</b> 1 | Transactions<br>Byte Commands                                                                       | DSK – 32                                                 |

|------------|---------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------|

|            | 3 - 3.2                   | Command Strings<br>Byte Definitions                                                                 | DSK – 34                                                 |

|            | 3 - 3.3                   | Command Types<br>Accessing the Controller<br>Parameter Set Up                                       | DSK – 40                                                 |

|            |                           | Command Call<br>Status<br>Error Codes                                                               | DSK – 41<br>DSK – 42                                     |

|            | 3 – 4                     | System Initialization                                                                               | USK - 44                                                 |

| Section IV | FIF CON                   | ITROLLER                                                                                            | FIF – 1                                                  |

|            | 4 - 1                     | In troduction                                                                                       |                                                          |

|            | 4 – 2                     | Functional Description                                                                              |                                                          |

|            | 4 - 3                     | Data Transaction Processes                                                                          | FIF – 5                                                  |

|            | 4 - 4                     | User Guide                                                                                          | FIF - 7                                                  |

|            | 4 - 5<br>4 - 5.1          | Theory of Operation<br>Interface Master (IFM)<br>CPU                                                | FIF - 11                                                 |

|            | 4 - 5.2                   | Addressing<br>1/O<br>DMA Access<br>DMA Prioritization<br>Floppy Interface Board (FIB)<br>Addressing | FIF - 12<br>FIF - 13<br>FIF - 14                         |

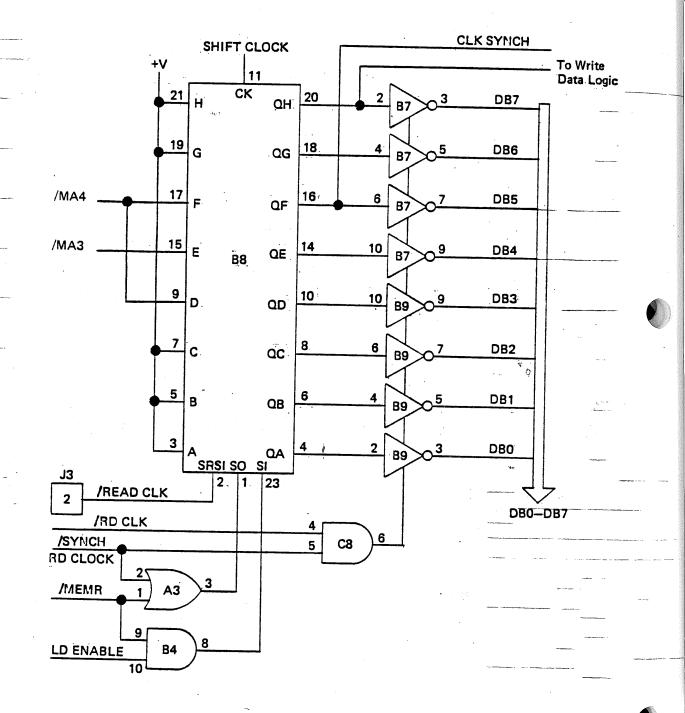

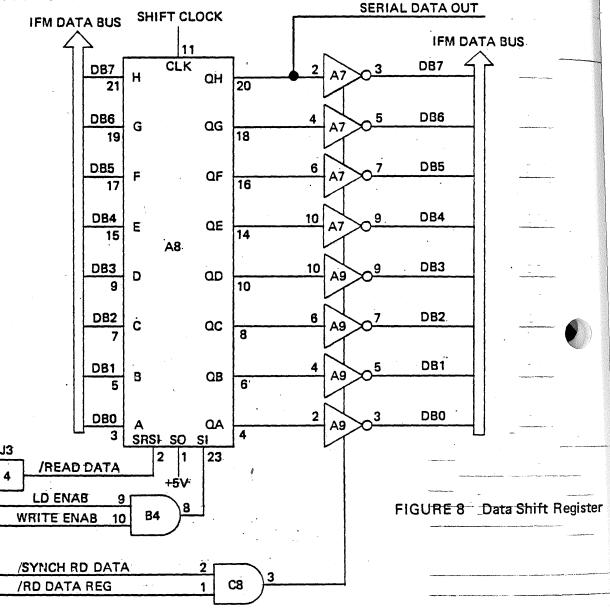

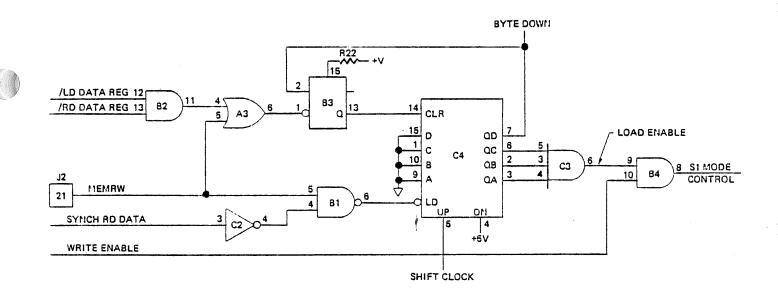

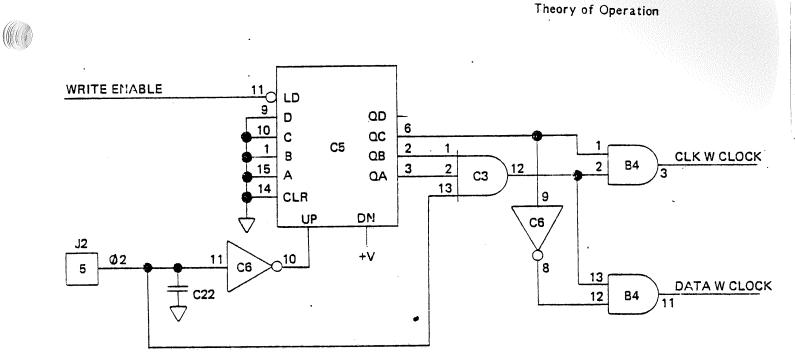

|            |                           | 'READY' Line Control<br>Clock S/R<br>Data S/R<br>Synchronization<br>Data Encoding                   | FIF - 17<br>FIF - 19<br>FIF - 21<br>FIF - 22<br>FIF - 23 |

|            | 4 - 6                     | Schematics and I/O Interconnect                                                                     | FIF - 24                                                 |

| Section V  | MDIO CONTROLLER           |                                                                                                     | MD10 – 1                                                 |

|            | 5 – 1                     | Introduction                                                                                        |                                                          |

|            | 5 - 2                     | Functional Description                                                                              | ~                                                        |

|            | 5 - 3                     | Data Transaction Processes                                                                          | MD10 - 5                                                 |

|            | 5 - 4                     | User Guide                                                                                          |                                                          |

|            | 5 - 5                     | Theory of Operation                                                                                 | MD10 - 8                                                 |

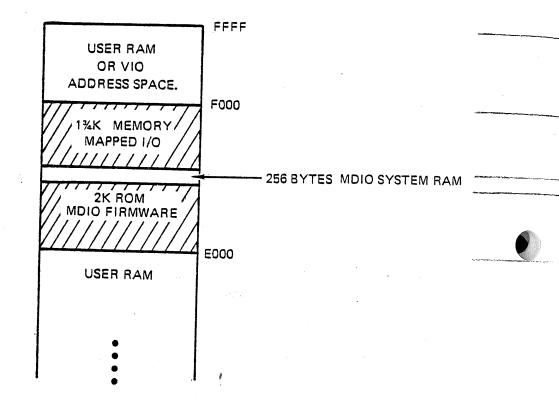

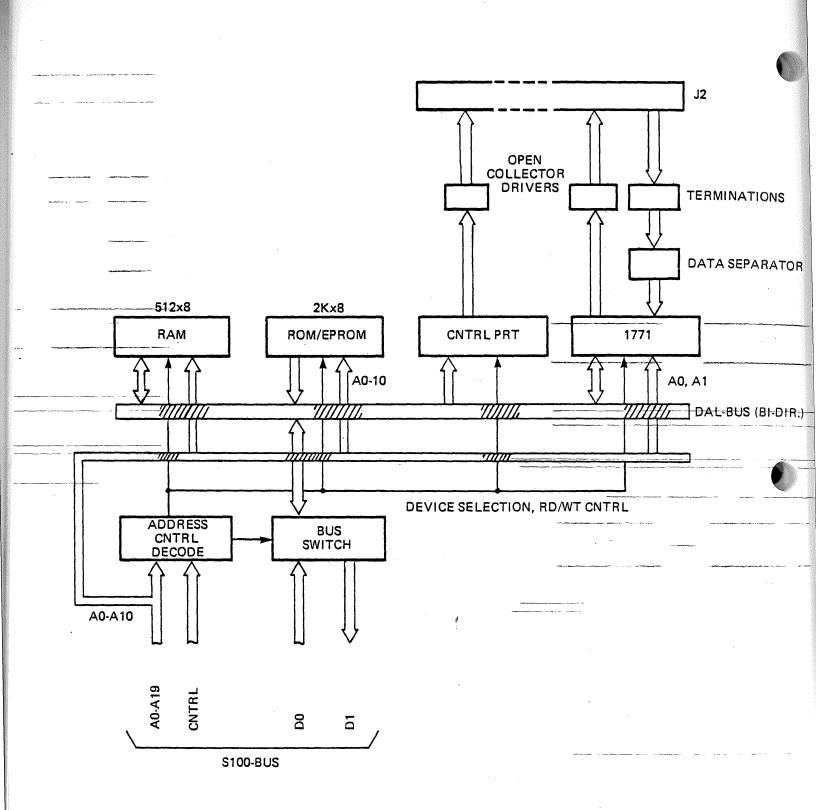

|    | 5 – 5.1  | Hardware Structure<br>Bus Organization |                      |

|----|----------|----------------------------------------|----------------------|

|    |          | Major Logic Blocks                     | MD10 - 9             |

|    | 5 - 5.2  | Addressing<br>Control Logic Timing     | MD10-11              |

|    | 5 - 5.2  | Write Operations                       |                      |

|    |          | Read Operations                        | MD10-12              |

|    | 5 - 5.3  | 1771 LSI Controller                    |                      |

|    | 5 - 5.4  | Use of 1771 'READY' Status Bit         |                      |

|    | 5 - 5.5  | Data Separator                         | MD10-15              |

|    | 5 - 6    | 1771 Data Sheet                        | MD10-18              |

|    | 5 – 7    | Schematic and I/O Interconnect         | MD10-19              |

| VI | DIO CONT | ROLLER                                 | DIO – 1              |

|    | 6 – 1    | Introduction                           |                      |

|    | 6 – 2    | Functional Description                 |                      |

|    | 6 – 3    | Data Transaction Processes             | DIO - 5              |

|    | 6 – 4    | User Guide                             | D10 - 6              |

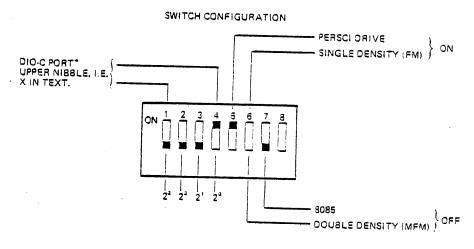

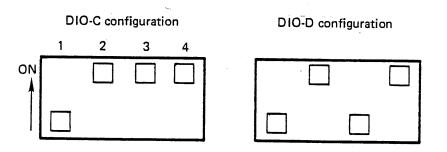

|    |          | D10-C                                  | DIO - 13             |

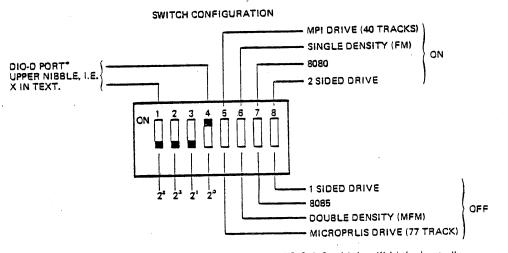

|    |          | DIO-D                                  | 010 - 13             |

|    | 6 - 5    | Theory of Operation                    | DIO - 20             |

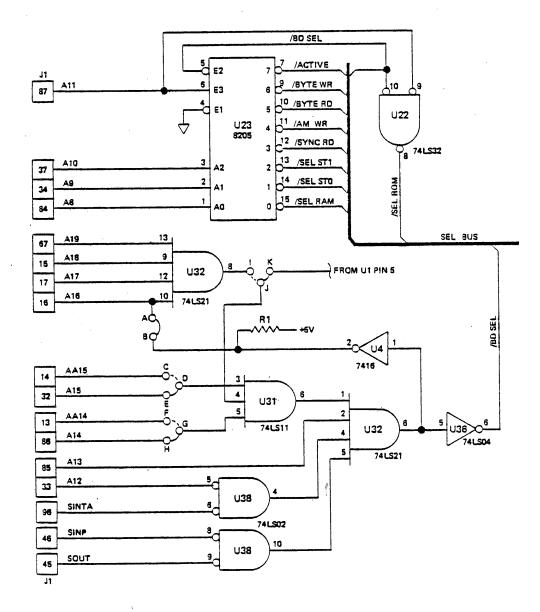

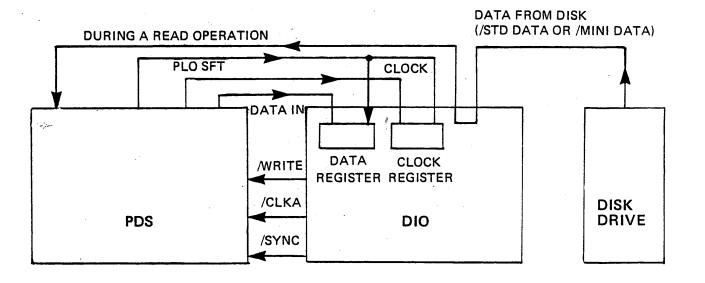

|    | 6 - 5.1  | Disk I/O Board (DIO)                   |                      |

|    | • •••    | Introduction                           |                      |

|    |          | DIO and PDS Interconnection            |                      |

|    |          | DIO Implementation                     | DIO - 21             |

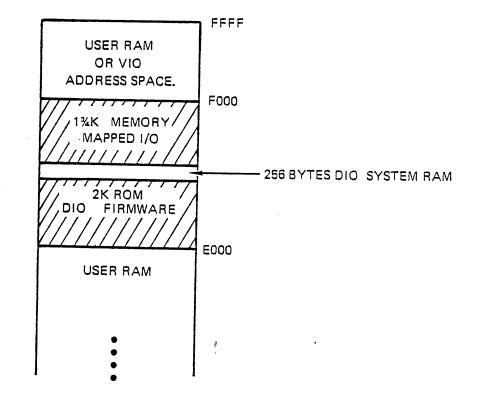

|    |          | Addressing                             | DIO - 22             |

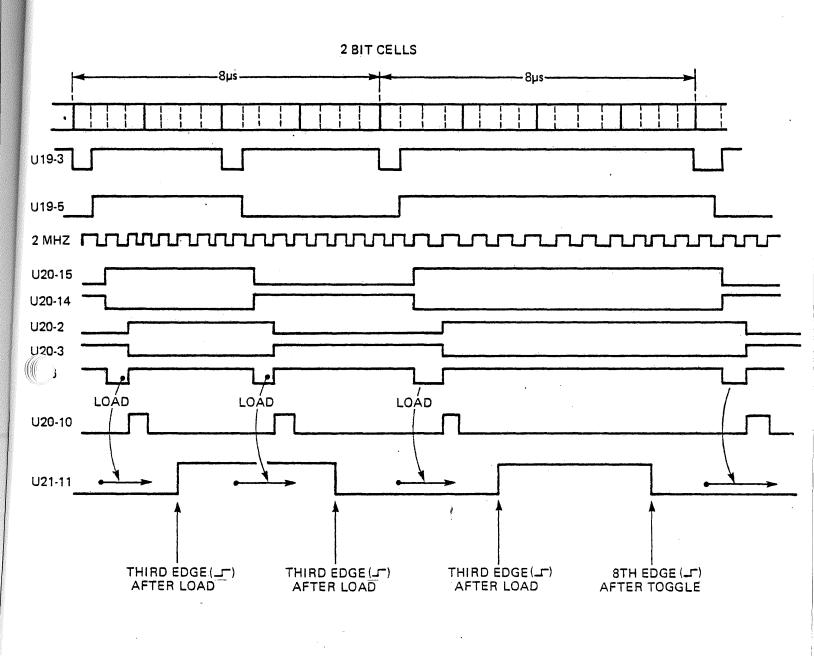

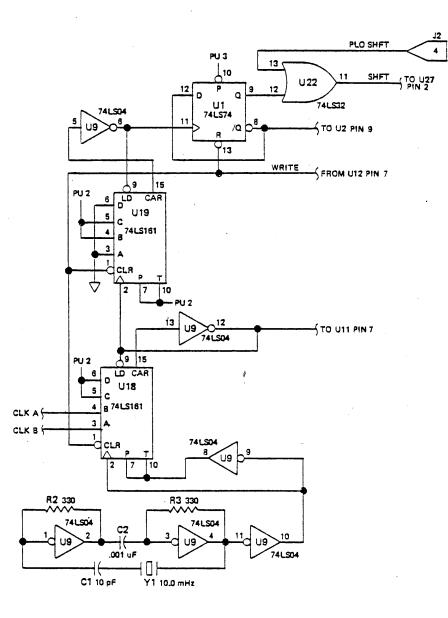

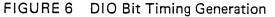

|    |          | Bit and Byte Timing                    | DIO - 23<br>DIO - 26 |

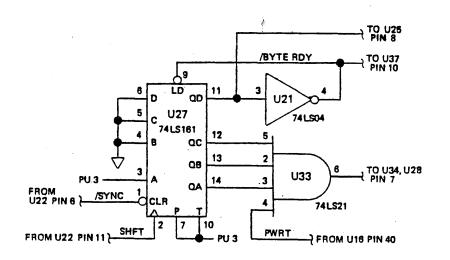

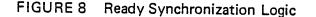

|    |          | 'READY' Line Synchronization           | DIO - 27             |

|    |          |                                        | 010 - 27             |

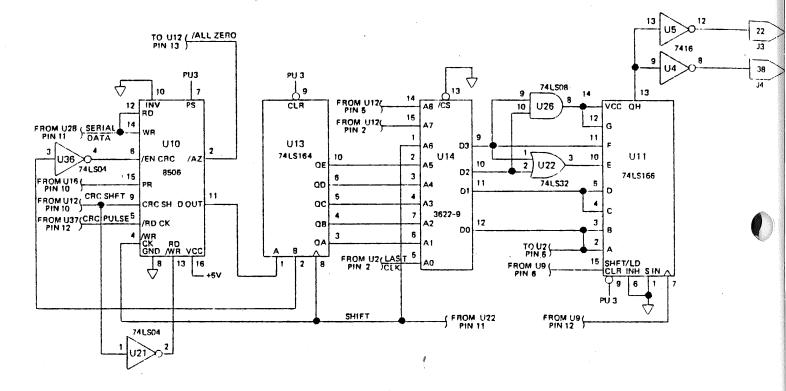

|    |          | AM Synchronization<br>CRC Generation   |                      |

|    |          | Write Precompensation                  | DIO - 29             |

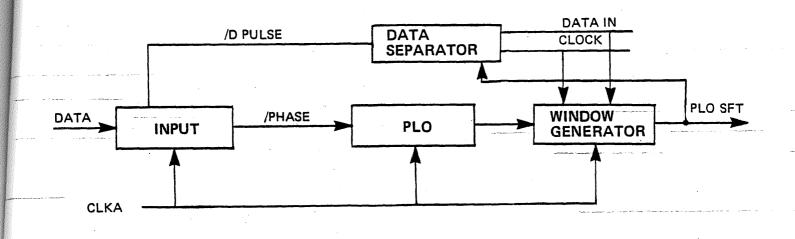

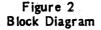

|    | 6 - 5.2  | Programmable Data Separator (PDS)      | DIO - 31             |

|    | 0 302    | Introduction                           |                      |

|    |          | PDS and DIO Interconnection            |                      |

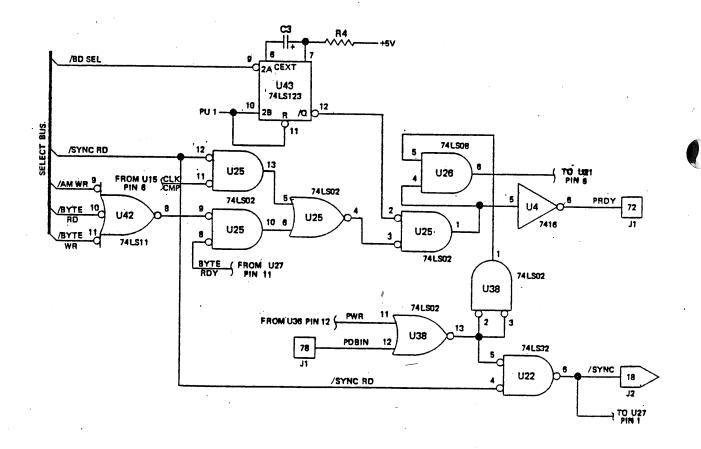

|    |          | Serial Input                           | DIO - 32             |

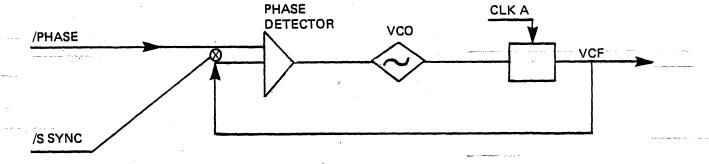

|    |          | VCO Channel                            | DIO - 33             |

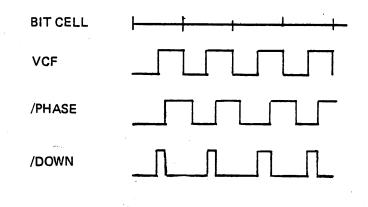

|    |          | Bit Framing                            | DIO - 37<br>DIO - 39 |

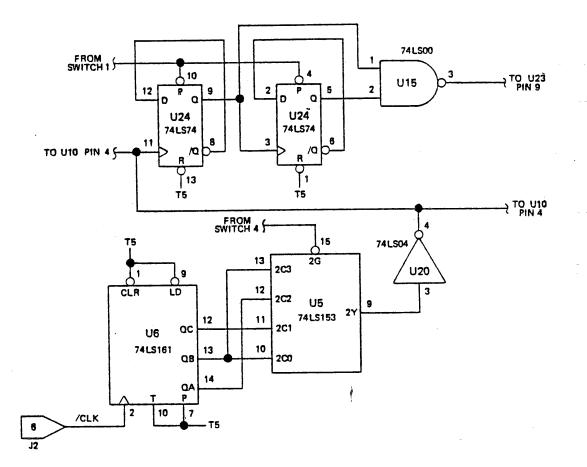

|    |          | Bit Synchronization                    | DIO - 39<br>DIO - 40 |

|    |          | Self Adjust Logic                      | 010 - 40             |

6 - 6

Section

Schematics and I/O Interconnect

D10 - 46

×

# INTRODUCTION DISKETTE SYSTEMS

#### Components and Interface

#### **1** INTRODUCTION

This volume discusses IMSA1 diskette systems hardware (for information on the diskette operating system software, refer to the IMDOS User's Manual). It starts off by reviewing the essential elements and operation of diskette storage systems and then proceeds to discuss IMSA1 disk system configurations and the diskette I/O protocol that governs all IMDOS diskette system transactions. This comprises the System Section that is common to all system configurations. The System Section is followed by sections of detailed technical descriptions of the individual IMSA1 diskette formatter/controllers available. Users who are primarily interested in learning about the diskette I/O protocol and how to use it may wish to skip section 2 and move on to section 3.

#### 2 DISKETTE SYSTEMS, GENERAL

#### 2 – 1 COMPONENTS AND INTERFACE

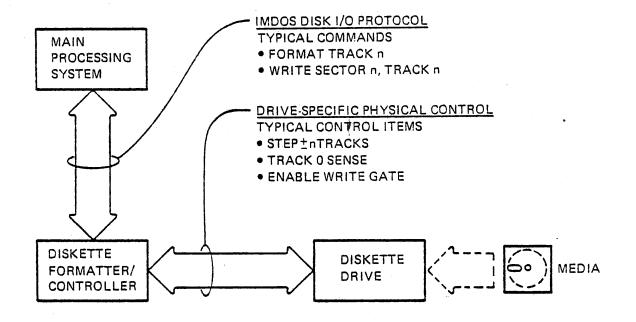

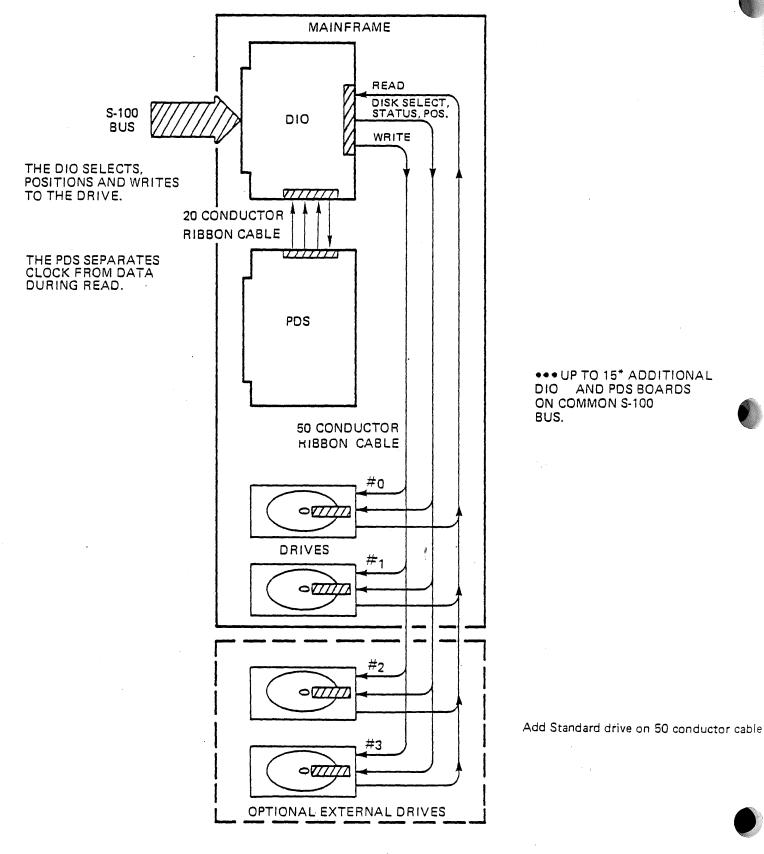

A diskette mass storage system typically consists of the three major elements shown in the block diagram of figure 1.

| 1)       | a controller |

|----------|--------------|

| 1)<br>2) | a drive      |

| 3)       | media        |

# FIGURE 1 Disk System, Functional Block Diagram

Components and Interface

## 2-1.1 CONTROLLER

The controller forms a bridge between the main processing system and the data storage mechanism. On the system end, it interfaces to the system bus structure and participates in the disk I/O protocol of the operating system. On the level of this system node, communications take place in the abstract world of data structures. The operating system (O/S) is oblivious to the physical details of the diskette drive mechanism and the recording media. It knows only of files that consist of multiple blocks of bytes which are identified by track and sector numbers (of which more, below), and of commands that facilitate the movement of data blocks to and from storage within the disk system. Central to the purpose of any controller is its ability to transform the high level O/S commands into the appropriate sequences of discrete steps that conform to the specific control requirements of the individual drive mechanism. On the peripheral end, the controller interfaces to the more elementary world of the drive mechanism.

## 2-1.2 DRIVE

The diskette drive contains the various electro-mechanical components and their associated control circuitry which a) rotate the diskette medium with a constant velocity, b) lower the read/write head onto and raise it off the medium, c) propel the head carriage assembly radially across the diskette surface, and d) detect a variety of special conditions in which some of the moving parts within the drive may find themselves. Among the special conditions that are detected in a typical drive, are a) read/write head positioning over Track-00, b) media hardware write protect interlock, c) diskette index hole passage past fixed point in drive, and the like.

Many of the activities within the drive mechanism are independent of one another and are controlled over dedicated lines. The on/off sequencing of these activities (such as drive motor on/off, head carriage stepping, head lowering and raising) is one of the three major tasks which the controller has to perform. The other two are a) FORMATing of the diskette and b) supervising the actual data transfer to and from the recording medium.

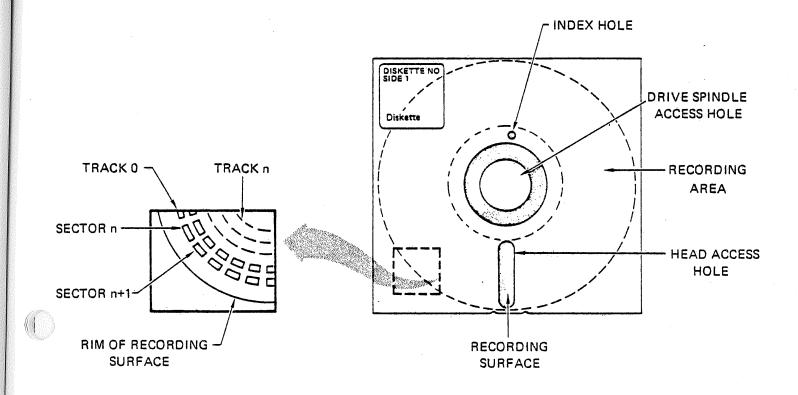

#### 2-1.3 MEDIA

Data is stored on the surface of a circular sheet that consists of a mylar base coated with an oxide that has magnetic properties especially suited for saturation recording. This sheet is contained within a protective envelope called a cartridge. The inner surfaces of this cartridge are lined with low friction material that offer minimal resistance to the rotating sheet. The cartridge typically has three openings through which the disk may be accessed by a) the read/write head, b) the drive spindle, and c) the photosensor which detects the passage of the index hole on the disk. Optionally, a diskette cartridge may also have a 'hardware write protect' notch. This serves a purpose similar to the knock-out tab on a tape cassette: Prevention of unintentional erasure of recorded data.

#### Components and Interface

Diskettes are sensitive to temperature and humidity variations and must be treated with great care. However, in routine utilization under normal ambient conditions, diskettes have proven to be quite rugged. Since the recording head is in contact with the medium during record or playback, it is important that the recording surface be kept free of dust particles and contaminants of any kind. A diskette that is not mounted in a drive should always be replaced in its dust jacket to prevent such contamination. For similar reasons, the diskette should only be handled by its jacket; and under no circumstances should the recording surface (exposed by the read/write head access slot) be touched.

# 2 – 1.4 TRANSFER MECHANISM

Data is transferred serially between the controller and the diskette drive. It is formatted and encoded in the controller prior to transcription to the recording medium, and it is decoded and decomposed to byte rendition prior to input to the main processing system.

Actual data transfer between the main processing system and the disk system (drive plus controller) may be designed to occur in three distinct forms:

1) 2) 3)

- Programmed Transfer

- Interrupt Driven Transfer Direct Memory Access (DMA) Transfer

## PROGRAMMED DATA TRANSFER

In a system, in which data is moved to and from mass storage by a program that executes in the main CPU for the duration of an I/O transaction, data movement is said to occur via Programmed Transfer. The program that performs the data transfer may be considered part and parcel of the diskette controller and often takes the form of firmware which resides within the hardware bounds of the controller.

1/O transactions are commonly initiated by subroutine calls from the O/S to this controller firmware. The CPU of the main processing system will continue to execute various segments of this firmware until completion of the disk 1/O transaction. Thus, the CPU is not available for other tasks during periods of disk 1/O activity. It is for reasons of this constraint that this form of mass storage data transfer is only found in single user, single task oriented systems.

#### INTERRUPT DRIVEN DATA TRANSFER

A diskette controller may be designed to make use of an existing interrupt structure in the main processing system. Such a structure effectively segments central processing time into discrete apertures, each dedicated to the execution of a program segment that services the particular interrupt level that is currently 'on line'.

In a system of this sort, the O/S initiates a disk I/O transaction by setting up the data transfer parameters for the interrupt level which is occupied by the mass storage subsystem and subsequently issuing a particular disk I/O command to the controller. The controller then releases the system CPU and proceeds to implement the O/S command with the required sequence of control steps. During this time interval, the system CPU is free to perform other tasks (such as attend to other users or tasks in a

multi-user/task environment). The controller will not interrupt the CPU again until it is either ready to transfer data to/from main memory or it has encountered an irrecoverable error condition. (Note: At present, no IMSAI controller uses this data transfer method)

#### DMA DATA TRANSFER

If the main processing system has the capability for direct memory access, then the diskette controller may be designed to make use of this capability. DMA structures frequently also make use of the interrupt structure for purposes of transaction initialization. But it is in the nature of the actual data transfer that a significant difference may be noted between a DMA-based system and either of the two discussed above.

In both the Programmed Transfer and the Interrupt Driven Transfer scheme, the system CPU is involved in the data transfer operation. Depending on serial data transfer rates between the controller and the drive, and whether the controller has its own intermediate data buffer, the system CPU may be required to dedicate its time to disk I/O data transfer operations for uninterruptible periods of considerable length. Such constraints can severely impact a system's capacity to service more than one user or to control real time processes.

A DMA structure alleviates this congestion by freeing the system CPU from direct involvement in the actual data transfer process. At the time of data transfer, the diskette controller requests and obtains control over the main memory bus long enough to transfer a byte (cycle stealing scheme), then immediately releases this bus to the main processing system. Though the system CPU will experience an overall slowdown in its program execution during times of disk I/O activity, it is never preempted from performing such program execution for extended periods of time.

### 2 – 2 FORMATS AND ENCODATION

#### 2 – 2.1 TRACKS AND SECTORS

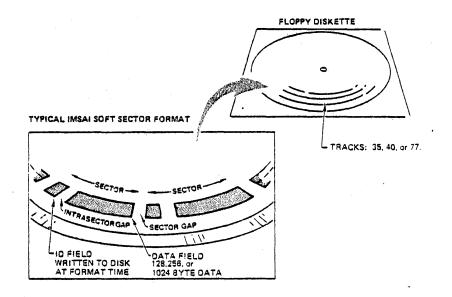

Unlike main memory RAM, in which each individual byte is uniquely identified by a single location within the system address space, a diskette mass storage system affords no such random access convenience on a byte level. Instead, data is stored bit-serially in segments of 128 bytes (or multiples of 128 bytes). These segments are known as sectors. A number of sectors are concatenated to form one continuous ring concentric about the center of the diskette. Such a ring is called a track. The diskette contains a number of such recorded tracks, each adjacent to another, radiating outward from the innermost track nearest the diskette center to the outermost track nearest the periphery of the diskette (see Figure 2).

Data is stored and retrieved one sector at a time. This is accomplished by positioning the read/write head over the appropriate track, locating the specific sector within that track, and updating the data field of the sector with new data (write operation) or reading the data field of the sector into main memory (read operation).

The read/write head passes over a particular track once per revolution of the diskette. An arbitrary track start/stop reference is established by the detection of the passage of an index hole past a sensing mechanism. Sectors are numbered in ascending order (starting with Sector 1) from this index reference all the way around the track.

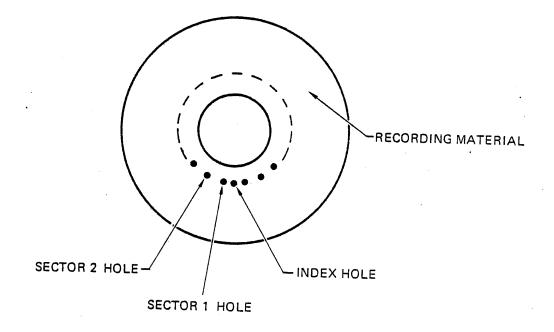

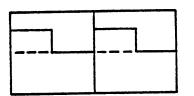

There are two distinct means of identifying successive sectors within a track. One makes use of sector holes which are equidistantly placed around the hub of the diskette in addition to the index hole; this is known as 'hard sectoring'. In this scheme each sector is identified by the number of sector holes that separate the sector from the start of the track (index). Such a diskette is shown in Figure 3 (Note: IMSAI does not make use of the hard sector technique).

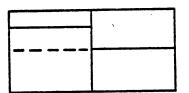

# FIGURE 3 Hard-Sector Formatting

The other method does away with these sector holes and employs identification fields that preface the data fields of the sectors; this is known as 'soft sectoring'. The identification fields contain track number and sector number information as well as synchronization patterns. This is the method depicted in Figure 4. Before an operating system can access a diskette mass storage system and store data on a soft-sectored magnetic medium, the diskette must be prepared so that the aforementioned identification fields partition the tracks into individual sector areas and identify these as described; this is known as FORMATing the diskette.

# FIGURE 4 Soft Sector Formatting

The length of the sector affects the maximum number of such sectors that may be placed on one track. Standard sector lengths are 128, 256 and 1024 bytes. Another factor that affects total number of sectors per track is the recording density. The recording density is a function of the data encodation and recording method used. This subject is treated in detail in the following subsections.

#### 2 – 2.2 DATA FORMATS

The particular organization of the data on a diskette is determined by the data formats that are used by the system. The format specifies the number of tracks on the diskette, the number of sectors on each track, the arrangement of synchronization and address mark patterns in the ID and data fields of each sector, the specific codes that constitute those unique patterns, and the arrangement of information regarding track number, sector number and sector length code.

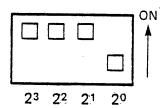

Some of the parameters regarding the specific format that is to be used on a particular drive at any particular time are maintained in a table located in the RAM memory of the controller. This table is loaded from the current settings of some hardware configuration options at the time of system initialization (following a reset condition). Some entries of this table may further be updated by one of the O/S utilities under user control; paramount among these is the selection of recording density. In the IMDOS O/S, the command file STAT.COM serves this function. The user is referred to the technical reference sub-section on the particular controller for details regarding the function and usage of these parameters.

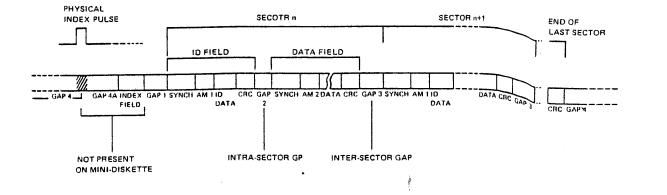

A typical sector format is shown in Figure 5. Each track contains one GAP1 immediately following the index reference. This index reference may one GAP1 physical index pulse from the drive (as is the case in mini-diskette formats), or it may gap of type GAP4A (as is the case in standard diskette formats). Sector 1 follows the gap which separates the last sector from the beginning of the track (i.e. Except for sectors are separated from adjacent sectors by a GAP3. Within each sector, the two

FIGURE 5 Typical Track Data Organization

The ID-field of a sector begins with a bit-synchronization sequence of hull bytes. Next comes the ID-field address mark (AM). This is followed by several bytes of ID also include information regarding diskette side selection (for future system expansion to incorporate double sided diskette drives). The two cyclical redundancy check (CRC) mathematical

#### Formats and Encodation

procedure which introduces an evenly distributed redundancy over the information field. It is by means of this information redundancy that a majority of possible errors are intercepted during read operations. Conversely, if no error is encountered by this error detection scheme, then data integrity may be assumed with a high degree of certainty.

The data field also begins with a bit-synchronization sequence of null bytes, followed by the data field address mark. The main body of data comes next, with the two CRC bytes for the data field bringing up the rear.

#### 2 – 2.3 DATA ENCODATION

Information is recorded on the magnetic surface of a diskette in the form of magnetic flux reversals that are induced by magnetic field reversals in the read/write head during a write operation. During a read operation, the recorded flux reversals induce electrical impulses in that same read/write head.

The significance of these flux reversals and their representative impulses is a function of the bit-serial data encodation process which the byte-parallel data undergoes in the disk controller prior to recording on the diskette.

During a read operation, the serial pulse stream undergoes a complementary decoding process in which the data is once again rendered in byte form. It is the unique physical characteristics of the magnetic recording process that dictate the preferred encodation of binary information.

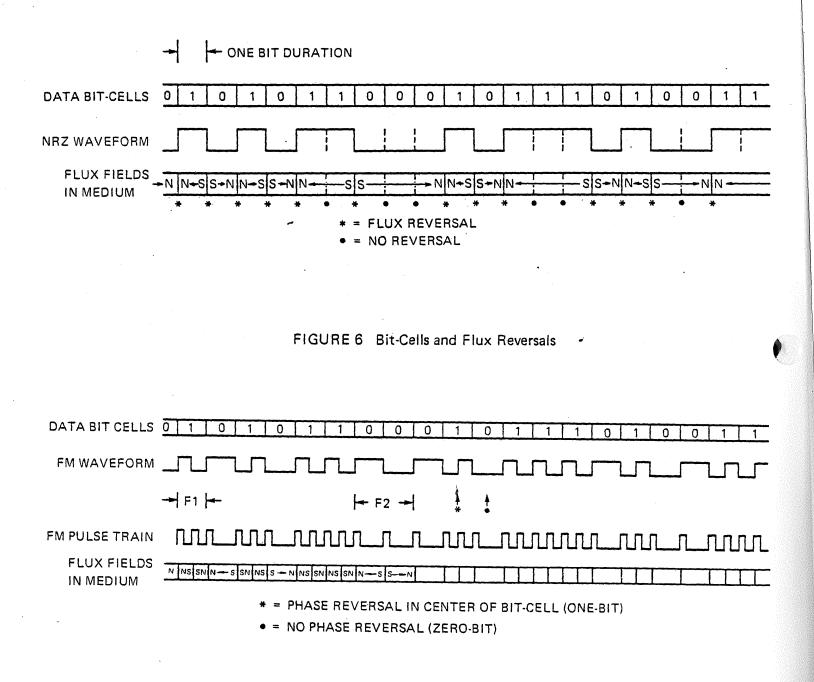

### 2 – 2.4 BIT CELLS

The simplest representation of serial binary data is in the form known as Non-Return to Zero (NRZ). Figure 6 shows a series of ONEs and ZEROs in NRZ. In this waveform, only the boundary condition that separates a ONE from a ZERO or vice versa produces a logical level change. Contiguous ONEs or ZEROs result in the extension over longer periods of time of the same logical level. In such bit sequences, the boundaries that delimit each bit-cell become imaginary and can only be inferred from the duration of a particular logical level (dashed lines in Figure 6).

The magnetic field reversals are coincident with reversals in logical level of the waveform that drives the write circuitry of the diskette drive. If serial data is presented to this circuitry in NRZ from, then the only flux reversals that would be recorded are those that represent logic level changes in the NRZ waveform. Sequences of contiguous ONEs or ZEROs would, therefore, contain no information regarding bit-cell boundaries. This is a major weakness of NRZ data recording on magnetic media.

FIGURE 7 FM Data Encodation

#### FM ENCODATION

The introduction of logic level transitions to signify bit-cell boundaries, and the adoption of the convention that the presence of a transition in the center of a bit-cell represents a ONE, while the absense of such a transition represents a ZERO, produces the data encodation method known as Frequency Modulation or FM. Figure 7 shows an equivalent FM representation of the bit sequence shown in NRZ form in Figure 6.

The recording mechanism will induce magnetic flux reversals for every logic level change in this FM waveform. As a result, each bit cell will be bounded by flux reversals, regardless of whether adjacent cells contain alternating ONEs and ZEROs or contiguous ONEs or ZEROs. This method is called FM because the resultant waveform contains two basic frequencies that are defined by the data rate and whose presence or absence is a function of the binary values of the bit stream that is encoded in this fashion. Each ONE bit cell is encoded by a complete cycle of F1. F1 is also the data rate. Each ZERO bit is encoded as one-half cycle of F2. The frequency of F1 is twice that of F2.

At the interface between the controller and the diskette drive, the FM encoded information is interchanged in the form of a pulse train rather than the FM waveform. This pulse train is also shown in Figure 7. Note that the frequency of flux reversals is  $2 \times F1$ .

The rules for FM encodation of serial binary data are, therefore:

1) Write data pulses in the center of ONE bit-cells

2) Write clock pulses at all bit-cell boundaries

FM data encodation has been known as Single Density recording since the advent of a Modified Frequency Modulation encodation technique which effectively doubles the amount of data that may be stored on any given stretch of magnetic medium at a specified velocity of linear travel. This technique is explained in the following section.

#### MFM ENCODATION

The FM recording technique is inefficient in that it requires two flux reversals for every ONE bit-cell. One of these is the actual reversal that specifies the logical value of the bit-cell (i.e. the flux reversal in the center of the bit-cell), the other forms the cell boundary with the next cell and provides bit synchronization clocking information.

If some of these clock pulses could be deleted at strategic locations in the bit stream where the characteristics of the surrounding data environment are sufficient to maintain bit synchronization, then the frequency of magnetic flux reversals would be lowered without undue degradation of recorded data integrity. Similarly, the recording frequency might then be increased until the frequency of magnetic flux reversals is, once again, that of the earlier FM process. This, in essence, is what is accomplished with the Modified FM (MFM) technique.

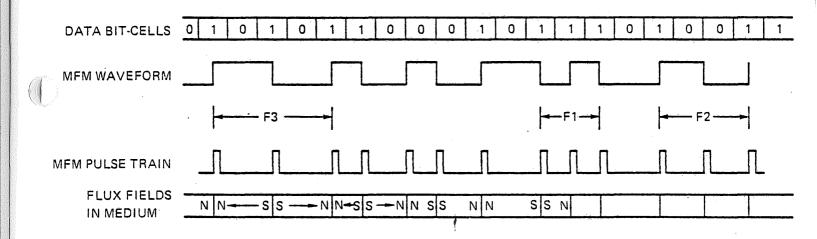

The rules for MFM encoding of serial binary data may be stated thus:

- 1) Write data pulses in the center of ONE bit-cells

- 2) Write clock pulses at the leading cell boundary if

Formats and Encodation

- a) the previous cell was a ZERO, and

- b) the current cell is a ZERO

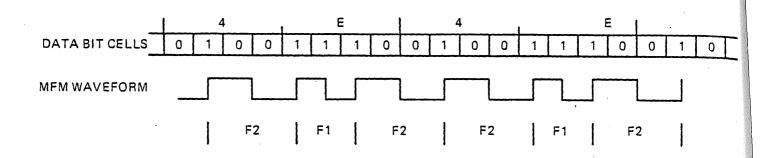

In MFM, the maximum frequency of flux reversal is equal to the data rate, while the F1 component is one-half of the data rate. Consequently, for any given rotational velocity of a diskette, twice as much data may be recorded in MFM on any given stretch of magnetic medium than is possible in FM. For this reason, the MFM encodation technique is also known as Double Density recording. Figure 8 shows the same serial data encoded in MFM. Note that this encoding scheme produces three basic frequency components, F1, F2 & F3, whose relationship may be expressed as follows: F1=2xF3; F2=1.5xF3.

## 2 – 2.5 SYNCHRONIZATION

During a read operation, the read/write head is positioned over the track that contains the desired sector of data. The head may or may not already be in contact with the recording surface of the diskette by the time it arrives at the destination track; in any event, the head will begin to pick up magnetic impulses from this track starting at some arbitrary and random location within the track.

The controller receives these pulses in electrical form and must make desisions regarding

Formats and Encodation 🗠

their significance in terms of phase and frequency relationships, clock and data pulse separation, and, on a higher level, in terms of synchronization sequences that permit it to identify the start and stop of the ID and DATA fields within each sector over which the head passes.

#### FM SYNCHRONIZATION

In FM encoded tracks, the various intra- and inter-sector gaps contain contiguous ONE-bits (but note exceptions, below). This constitutes a pulse stream at the F1 frequency. When traversing such a sequence, the controller may or may not be in bit synchronization and thus may not be certain with regard to the identity of clock and data pulses in this stream. The bit synchronization circuitry of the controller searches for a sequence of ZERO-bits in order to orient itself with respect to clock and data pulses. Once it has encountered such a sequence, it searches for an 1D address mark. In FM, this is a hex value of FE that differs from an ordinary data value of FE in that it is not encoded according to the standard FM encodation rules: some of its clock pulses have intentionally been deleted during the FORMATing of the diskette. Figure 9 shows the pattern for this address mark.

(It should be noted here that the MDIO uses ZERO-bits in gaps of the types GAP1,3 and 4, but uses ONE-bits in GAP2 and the trailing byte of the data field. The FIF employs ZERO-bits in all GAPs)

FIGURE 9 FM Address Mark

### Formats and Encodation

The recognition of this address mark signals to the controller that the succeeding bytes contain sector identification information. These bytes, in turn, are followed by the CRC bytes. A similar sequence of events takes place as the data field of the sector is traversed by the head.

During the data field update sequence in a sector write operation, the initial activation of the write current may glitch the magnetic medium in the region of GAP2. The exact location of this glitch varies from machine to machine, and may even vary from one write operation to the next. It is a function of a number of variables, primarily diskette drive speed variations. It may be stated that the purpose of GAP2 is to accommodate the aggregate dynamic range of these variables.

The spurious magnetic flux transition(s) which such a glitch may impart to the medium, can give rise to erroneous electrical pulses during playback. These, in turn, can derail the bit-synchronization which the controller had obtained while traversing the ID-field. It is for these reasons that the data field, too, starts with a bit-synchronization sequence of contiguous ZEROs.

At the conclusion of a write operation, the write current is turned off. As is the case with write current turn-on, turning it off may also induce spurious flux reversals in the recording medium. To ensure that this transient condition does not impact the trailing bits of the last data CRC byte, this turn-off is postponed until at least one byte after the last CRC byte.

Some controllers are designed to skip GAP2 during a read operation by counting off a fixed number of bytes and subsequently going into bit synchronization acquisition mode as the head enters the synchronization sequence of the data field. Others may rely on the fact that all Address Marks (AMs) are preceded by a certain number of ZERO-bytes and thus will not recognize an AM that is preceded by ONE-bits. In each case, however, the primary intent is the prevention of erroneous AM recognition. Similarly, the imposition of the criterion, that an AM must be preceded by a sequence of ZERO-bytes, also has the effect of reducing the frequency of false ID AM detection during sector search for both write and read operations. Whether or not a controller makes use of all the synchronization features of the recording format is a function of its implementation.

#### MFM SYNCHRONIZATION

MFM synchronization is not very different from that of FM. One of the adverse side effects incurred by going from FM to MFM is the considerable loss of clocking information on the recorded track. It will be remembered that the increase in data capacity per unit distance on a track was obtained at the cost of clock pulses. This imposes the requirement for tighter synchronization acquisition criteria in MFM.

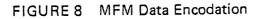

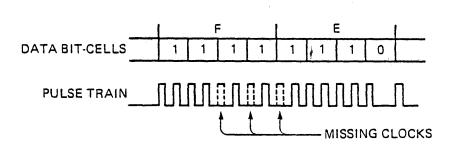

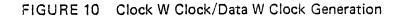

The bit-synchronization sequence is still a sequence of ZEROs, only now there are more of them (typically twice as many as in FM). But it is in the Address Mark detection that the major difference is to be found. Whereas a single byte of FEH with modified clock pattern suffices in FM, the Address Mark for MFM encoded data consists of four

bytes of which the first three are unique data/clock pulse patterns and the fourth byte is the actual Address Mark value with normal MFM encodation. Figure 10 shows the pulse train for the MFM 1D Address Mark. The first three bytes are A1H with a missing clock pulse as shown. This missing clock pulse is chosen such that the basic frequency contents of these patterns conforms with the F1, F2 & F3 components of conventionally MFM encoded data.

FIGURE 10 MFM Address Mark

Contiguous sequences of ONEs are indistinguishable from contiguous sequences of ZEROs encoded in MFM, except at boundary regions that separate two such sequences. It is for this reason that gaps are not filled with FFH sequences (as is the case in FM), but with sequences of another hex code which produces alternating groups of pulses at F1 and at F2, which, in turn, form an unbroken sequence of whole F1 and F2 lambdas (wavelengths). This code is 4EH, and the lambda sequence it generates is [..F1,F2,F2,F1,F2,F2,F1,F2,F2...], shown in Figure 11. Such a sequence is characterized by symmetrical 'peak shifting' during playback, and it aids in frequency tracking of the playback signal. It also makes possible the discernment of ID-field and data field synch sequences from GAP sequences.

Formats and Encodation Write and Read Processes

### FIGURE 11 MFM Inter- and Intra-Sector Gap Pattern

As is the case with FM, the turn-on and turn-off of the write current during write operations may induce erroneous AMs in GAP2 and GAP3 (i.e. preceding and following the data field). To disallow erroneous AM detection on subsequent sector search operations, a controller may enforce the requirement that the AM be preceded by ZERO-bytes. Since glitch-induced AMs will be embedded in 4EH sequences, they are readily recognized (and therefore ignored) as imposters. A further constraint is imposed by the requirement that three consecutive A1H AM bytes be preceded by these ZERO-bytes and followed by a normally MFM encoded FEH byte.

During a read operation, controllers may follow either of the two procedures already pointed out in the discussion on FM, above, to circumvent fallacious recognition of AMs in the vicinity of data fields.

The combined effect of all these constraints imposed upon the synchronization acquisition and retention process is the prevention of false synch acquisition and, in consequence of this, optimized data integrity and system reliability.

#### 2 – 3 WRITE AND READ PROCESSES

The discussion in the previous sections proceeded from the level of diskette system components down into the intricacies of patterns governing the magnetic encoding process. In the sections that follow, the higher level system interactions between a typical main processing system and the attached diskette system are discussed in terms of processes and the protocol that determines the particular form of their dynamic. Similarly, the sequences of operations that take place within the controller during typical read and write transactions are also presented in detail. Throughout this discussion, access conventions which characterize the diskette I/O protocol of IMSA1's IMDOS O/S serve as an example.

#### 2 – 3.1 ACCESS CONVENTIONS

Regardless of the data transfer mechanism that is employed in a disk system (be it programmed, interrupt driven, or DMA data transfer), the disk 1/O protocol usually

# DISKETTE SYSTEM Write and Read Processes

consists of these major components: Command Parameters Set Up, Disk System Call-Up, Command Execution (1: Sector Search, 2: Data Transfer), and Status Reporting. The particular mechanics of command, data, and status transfer between main system and disk system is dictated by the data transfer mechanism, however. Thus, in a DMA organization, the command parameters must be set up somewhere in system RAM out of which it is executed by the disk controller subsequent to a command call from the main system. In a programmed data transfer environment, these same command parameters might be forwarded to the data transfer firmware module via the system stack and/or some of the CPU registers.

The primary items that must be specified in any disk I/O transaction are a) type of operation (read or write, format, whatever), b) site of origin of data block to be moved elsewhere (RAM area, in the case of a write operation; drive/track/sector, in the case of a read operation), c) site of destination of data block to be moved, and d) special considerations (FM or MFM, sector length).

The disk 1/O protocol specifies the format of the data which conveys this information; it also specifies the sequence in which the entire disk 1/O transaction transpires.

In the discussion that follows, the basic structure of a typical disk access protocol and its associated formats is presented first, and then the typical sequence for a write and a read operation is detailed.

#### BYTE COMMANDS AND COMMAND STRINGS

Disk access commands may be categorized into the two classes of Set Up Commands and 1/O Commands. The former are executed to set up certain variables (write protect, write enable any drive; restore to track 00 any drive; modify Command String Address Array) and are called Byte Commands. The latter are executed to perform the actual data transfer to and from the disk system; these usually involve a number of parameters that are set up in system memory prior to the execution of what is known as a Command String.

The basic control element of any disk access is the byte code which is forwarded to the disk controller in the A-Register of the CPU during the execution of an instruction that accesses the controller. In the case of the MDIO and the DIO controllers, the control byte is conveyed via the execution of a CALL instruction to the controller firmware. The FIF controller, on the other hand, is accessed via the execution of an OUT instruction that addresses the FIF controller command port. For ease of discussion, all subsequent references to the controller access mechanism presumes the use of a DIO or an MDIO controller.

The control byte consists of two 4-bit fields that specify a) the type of command (upper nibble) and b) either the drive or drives specified for the operation (in the case of Byte Commands 2, 3 and 4), or the Command String Pointer (in the case of an 1/O Command). Distinction between Byte Command versus 1/O Command is made by setting the upper nibble to ZERO for an 1/O Command.

# DISKETTE SYSTEMS Write and Read Processes

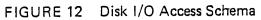

# ACCESS SCHEMA

The interrelationship of the Control Byte, Byte Command, String Pointer, and Command String within the environment of system main memory and diskette may be visualized as shown in Figure 12. The following paragraphs describe this interrelationship. The letters in brackets refer to the appropriate region within Figure 12.

·,

The Control Byte specifies either Byte Command or Command String execution [A]. Byte Command 1 is used to modify the contents of the Command String Address Array [B]. Command String execution is initiated by conveying the proper Control Byte in the A-Register via a CALL to the controller [C]. The controller uses the pointer to locate the start of the Command String residing somewhere in system RAM [D]. The first byte in this Command String identifies the type of command that is to be executed (Write Sector, Read Sector, Format Track, Verify Sector, Write Deleted Sector Mark) and the drive on which this action is to be performed [E]. The third byte specifies sector length, track number extension (0-255 or 256-511) and side selection (possible future expansion to double sided media) [F]. The fourth byte specifies the track, the fifth byte the sector that is involved in the transaction [G]. Bytes six and seven specify the start of the area in system main memory into or out of which data will be moved from or to the specified sector on the diskette [H]. Byte two is reserved for forwarding of the end-of-transaction status from controller to system.

All Command Strings require at least four bytes to specify the minimum set of parameters. The maximum number of parameter bytes that may compose a command string is seven. The complete Command String must be set up prior to the execution of the CALL to the controller. Variables that are controlled by Byte Commands, may be modified by these commands at any time between the execution of Command Strings.

#### 2 – 3.2 WRITE/READ SEQUENCES

First, the Command String has to be set up properly, and the Command String Address Array must reflect the starting location of this new Command String. Any one of the sixteen possible pointers may be used. Usually, the array is set up once early in the system initialization phase immediately following power-on, and individual pointer values are modified only rarely thereafter. That segment of the O/S which is responsible for disk I/O, has to make sure that the Command String is set up in alignment with the current value of whichever pointer it will specify during its CALL to the disk controller.

The Command String is composed according to the format already indicated in the previous section (ACCESS SCHEMA). Whether or not Command String bytes five through seven need to be set up depends on the type of command that is to be executed. Next, the Control Code is placed in the A-Register and the system executes a CALL instruction to a specified location within the disk controller firmware. This firmware examines the contents of the A-Register. If it detects a hex-ZERO value in the upper nibble, it interprets the lower nibble as a pointer number for the Command String Address Array. It looks up the 16-bit address value stored in the array location(s) specified by this pointer and uses this address to locate the start of the current Command String.

The Command String contains all the necessary parameters needed by the disk controller to perform a disk 1/O transaction. The first byte in this string identifies the Command String as either a write or a read operation, as well as the drive that is to be involved.

# DISKETTE SYSTEMS Write and Read Processes

# WRITE OPERATION

The controller issues a control sequence to the diskette drive which instructs this drive to

- 1) move the read/write head 'N' steps +/- from current location

- 2) lower the head onto the medium (if not already lowered)

- 3) perform a read operation

The controller then examines the pulse stream coming in from the drive and acquires bitand sector-synchronization (as described in earlier section on SYNCHRONIZATION).

After it has verified that the read/write head has successfully traversed the ID field of the sought after sector (Address Mark check OK, CRC computation OK) and is entering the intra-sector gap (GAP2), it counts off a specified number of bytes and turns on the write current.

The controller then proceeds to write the bit-synchronization sequence for the data field, the Address Mark, the data-field itself, followed by the CRC bytes and the end-of-record byte. Once this is done, the controller orders the write current to be turned off.

If the transaction was accomplished without indication of any error, the controller places a 01 value in byte two of the Command String to indicate an 'all's well' status. This code is also placed in the A-Register before the controller firmware completes its business by returning to the CALLer.

If an error indication was noted by the controller, then it will either forward an appropriate error code to the system, or it will repeat the execution of the Command String a specified number of times before giving up and indicating the requisite status to the system. The controller's response to error conditions varies with the error type encountered and is treated in another section, below (ERROR HANDLING).

The controller will perform a somewhat different sequence of operations when it is informed to FORMAT a track. In this case, the controller instructs the drive to position the read/write head over the specified track and lower the head. The controller next awaits the index pulse from the drive electronics which signals start of track. It then lays sector ID-fields and dummy DATA-fields from start to end of track in the format specified by the third byte in the Command String that is currently being executed.

#### READ OPERATION

The read operation differs only slightly from the write operation. The sequence that results in the positioning of the read/write head over the desired track and the identification of the proper sector within that track is the same as the one that is used in a write operation. After traversal of GAP2, the controller looks out for the bit-synchronization sequence and then the data field address mark (AM). Identification of AM leads to the subsequent readback of the data field into the system RAM region specified by bytes six and seven of the current Command String. Status reporting takes place as in a write operation.

Write and Read Processes

# 2 – 3.3 ERROR HANDLING

Error handling may be either in the simple form of reporting each encountered malfunction immediately back to the system, or in the form of a sophisticated error recovery procedure within the disk controller itself. The latter implementation relieves the main processing system of much of the housekeeping task that is involved in the handling of errors.

The controller may be equipped with enough intelligence (i.e. necessary firmware routines) to make a determination regarding the nature of the anomaly encountered during a disk I/O operation and to respond accordingly. There are several error classes, and from some of these the controller may recover on its own initiative. Some of these conditions are outlined below.

In all of the cases where a transaction reaches a point where a CRC error is discovered by the controller, the latter may be permitted to perform a number of 'retries'. During a retry, the controller executes the current Command String all over again. This procedure is based on the statistical fact that a majority of such errors are 'soft' errors which have a low but finite probability of occuring every time data is recovered from a magnetic medium. Inability to come up with an error-free data recovery after a specified number of retries produces the inference that there is something seriously wrong with the magnetic medium in the region occupied by the sector in question. In such cases, the controller will discontinue retries and report a 'hard' error to the system.

Another type of error from which the controller may recover on its own, is the case where track information in the sector ID-field does not match the specified target track number. In this case, the controller may be allowed to reposition the read/write head several times in an attempt to achieve a track number match; the assumption being that the head carriage control mechanism fails, on occasion, to correctly position the head as instructed.

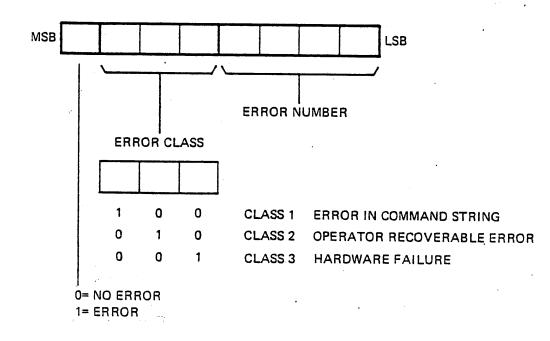

The remaining error types may be grouped into the three classes a) Command String Error, b) Recoverable System Error, and c) Hardware Error. The last class includes the previously described error conditions when these could not be corrected through retries by the controller. Command String Errors are usually the result of format errors in the Command String (track number too large, illegal command number, etc). Recoverable System Errors are those errors that may be corrected by altering a variable which currently disables an operation as specified by the Command String (hardware or software write protected diskette, drive not ready).

IMSAI DISKETTE SYSTEM

General

Configuration

## 3 IMSAI DISKETTE SYSTEMS

## 3-1 GENERAL

The IMSAI family of disk systems offers the user a wide variety of system configurations. Both standard and mini drive systems are available in several hardware arrangements ranging from simple expansion drive units with or without controller, to fully integrated computing systems. Drives may be combined with different types of controllers to form the desired configuration. Among these controllers is available a broad range of features, including single and double density recording for both mini and standard drives, capability for attachment of additional drives, and the incorporation of several controllers within one computer mainframe. IMSAI's powerful IMDOS multi-disk operating system supports all of these system configurations.

#### 3-2 CONFIGURATIONS

## 3-2.1 CONTROLLERS

The variety of disk system configurations is made possible by the flexibility of IMSA1 disk controllers. These are the FIF, the MDIO, and the DIO. Of the latter, several models provide multiple single and double density formats. The major features of these controllers are outlined below. Detailed descriptions of their operational characteristics may be found in the reference sections that follow this common front-end text.

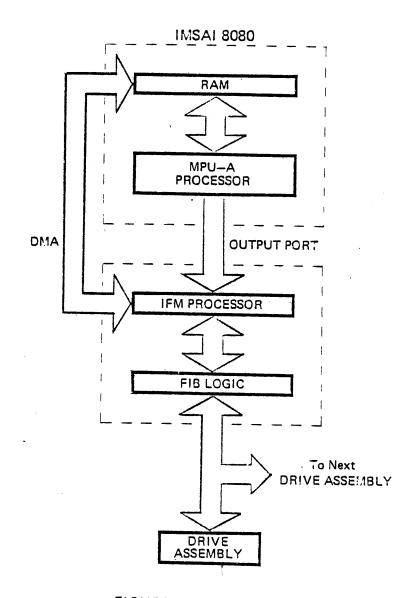

#### FIF CONTROLLER

The Floppy Interface consists of two S100 Bus printed circuit boards, the InterFace Master (IFM) and the Floppy Interface Board (FIB). It uses a data format that is fully compatible with the IBM 3740 format. The FIF attaches to a total of four standard diskette drives and supports single density recording (FM) only. The IFM contains a DMA-based data transfer mechanism that is organized around an internal 8080 microprocessor. The firmware program is contained in two (2) onboard 1K ROMs.

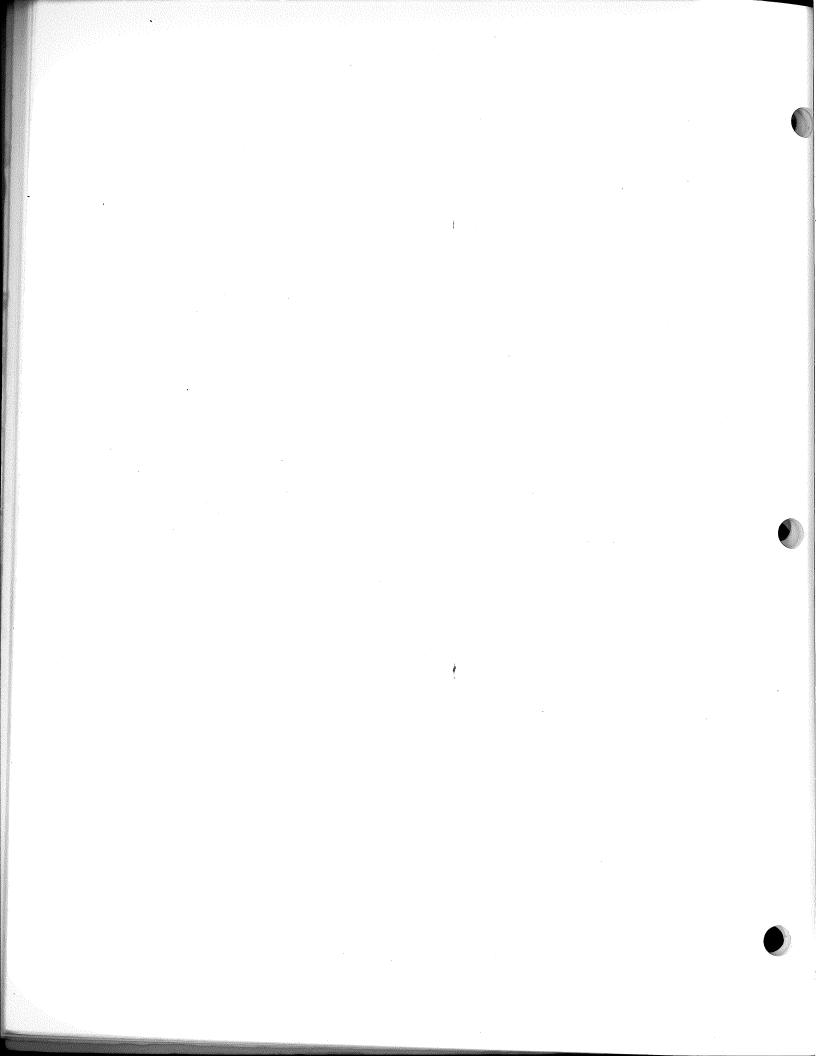

#### MDIO CONTROLLER

The MD1O is a single board diskette controller designed around an LSI floppy controller integrated circuit (1771). It attaches to a total of four mini-diskette drives and supports a single density format that is similar to the IBM 3740 format. The MD1O employs a Programmed Data Transfer mechanism and contains the diskette format/control firmware in an onboard 2K ROM/EPROM.

#### DIO CONTROLLER

The DIO is a two board controller consisting of a Disk I/O and a Programmable Data Separator printed circuit board. The DIO attaches to a total of four standard diskette drives and/or three (or four, depending on version) mini diskette drives, and supports both single and double density recording formats. The DIO comes in four versions, each with some unique features that are not available in the other versions.

#### IMSAI DISKETTE SYSTEM

Configuration

The DIO-A is the original version and supports the two early IMSAI data formats: Format I, the IBM 3740 compatible single density format, and Format V, a 128 bytes/sector double density format. DIO-A uses Format I for both standard and mini drives, Format V for standard drives only.

DIO-B is a variant of DIO-A which differs from the latter only in that it incorporates a different step rate for standard drives to provide compatibility with the CalComp 142.

NOTE: Both the DIO-A and B models have been replaced by the DIO-C.

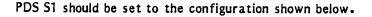

DIO-C supports the new single and double density formats and is designed to interface exclusively with standard drives. In addition to being backward compatible with the earlier Format I (though not  $\vee$ ), it also communicates in Formats II, III and I $\vee$ .

D10-D also supports the new formats and is designed to interface exclusively with mini drives. Up to four mini diskette drives may be attached to a D10-D.

3 – 2.2 HARDWARE COMPATIBILITIES

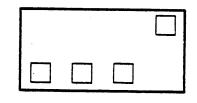

Though a variety of diskette drives, both mini and standard, may be attached to IMSA1 diskette formatter/controllers, the range of permissible controller/ drive configurations is delimited by both hardware and format compatibility constraints that arise from the specific characteristics of these system components. The matrix shown in Figure 13 indicates hardware compatibilities among the IMSA1 controllers and diskette drives of several manufacturers.

IMSAI DISKETTE SYSTEM

.

Configuration

#### STD MIN DRIVE TYPE SHUG 400 MICROP 1015 CONTROLLER DATA TRANSFER MODE CALCOMP PERSCI MPI 277 142 851 FIF DMA STD х MDIO PROG MIN Х х D10-C PROG STD Х Х D10-D PROG MIN X х

# FIGURE 13 Controller/Drive Compatibilities

LEGENDS:

MUTUALLY EXCLUSIVE DRIVE TYPES

STEP RATE JUMPER-SELECTABLE ( 12ms FOR MPI, 40ms FOR SHUG. ) IF JUMPERED FOR SHUG 400, MDIO WILL SUPPORT MIX OF SHUG & MPI, BOTH 35 TRACKS

DRIVE TYPE SWITCH SELECTABLE

MPI STEP RATE IS 5ms

USE WITH MPU-A ONLY

IMSAI DISKETTE SYSTEM Configuration

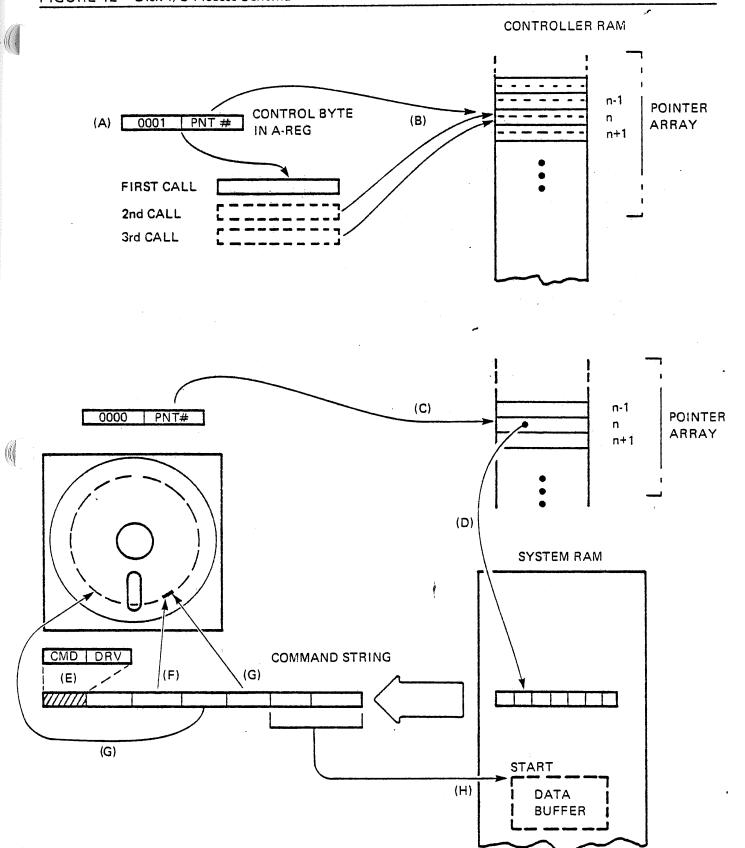

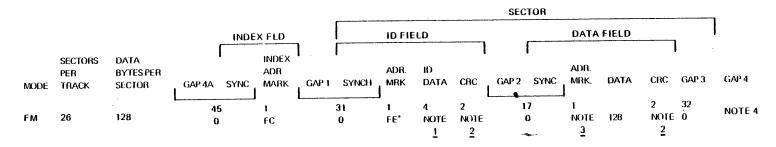

# 3-2.3 FORMAT COMPATIBILITIES

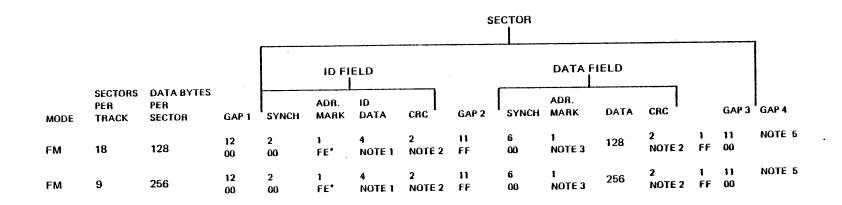

As was already indicated in the brief descriptions of IMSAI controllers, above, these controllers feature a range of data formats, not all of which are necessarily supported by each controller. Figure 14 shows a matrix in which format compatibilities are correlated with controller type and IMDOS versions. Note that IMDOS 2.05 (or later revision) supports all data formats used by DIO-C & DIO-D. Tables 1 through 4 show the field organization of the recording formats as they are utilized by the different controllers.

For details regarding media conversion techniques involving files created in systems utilizing DIO-A or DIO-B and to be transferred to systems utilizing DIO-C or DIO-D, the user is referred to the IMDOS User's Manual.

# IMSAI DISKETTE SYSTEM Configuration

# FIGURE 14 Format Compatibilities

ŝ

| CONTROLLER | FORMATS SUPPORTED<br>BY IMDOS VERSION |             |  |  |  |

|------------|---------------------------------------|-------------|--|--|--|

|            | 2.02                                  | 2.05        |  |  |  |

| FIF        | 1                                     | t.          |  |  |  |

| MDIO       | - 1                                   | F 11        |  |  |  |

| DIO-C      | I                                     | 1,11,111,1V |  |  |  |

| DIO-D      |                                       | 1,11,111,1V |  |  |  |

| FORMAT | DRIVE TYPE |        | DRIVE TYPE |                                   |  |  | RECORD | NOTES |

|--------|------------|--------|------------|-----------------------------------|--|--|--------|-------|

| FOF    | STD        | MIN    |            |                                   |  |  |        |       |

| 1      | 128/26     | 128/18 | SD         | IBM 3740 SD FORMAT, IMSAI DEFAULT |  |  |        |       |

| 11     | 256/15     | 256/9  | SD         | 2nd IBM 3740 SD FORMAT            |  |  |        |       |

| . 111  | 256/26     | 256/17 | 00 .       | IBM DD FORMAT 1, IMSAI DD DEFAULT |  |  |        |       |

| ١٧     | 1024/8     | 1024/5 | DD         | IBM DD FORMAT 2                   |  |  |        |       |

## TABLE 1

\* FM ID ADDRESS MARK CLOCK PATTERN = C7

NOTE 1: ID DATA CONTAINS FOLLOWING 4 BYTES

- 1) TRACK NUMBER (0-N)

- 2) ZERO

- 3) SECTOR NUMBER (0-N)

- 4) ZERO

- NOTE 2: CRC BYTES ARE GENERATED BY CCITT STD V41, STARTING WITH FIRST AM BYTE

- NOTE 3: FM DATA AM: F8H FOR 'DATA', F8H FOR 'DELETED DATA', CLOCK PATTERN = C7

- NOTE 4: TRAILING ZERO BYTES BETWEEN END OF LAST SECTOR AND INDEX

TABLE 2

\* FM ID ADDRESS MARK CLOCK PATTERN = C7

NOTE 1: ID DATA CONTAINS FOLLOWING 4 BYTES

1) TRACK NUMBER (0-N)

2) SIDE NUMBER (0 or 1)

3) SECTOR NUMBER (see also NOTE 4, below)

- 4) SECTOR LENGTH: 0 = 128, 1 = 256

- NOTE 2: CRC BYTES ARE GENERATED BY CCITT STD V41, STARTING WITH FIRST AM BYTE

NOTE 3: FM DATA AM: FB FOR 'DATA', F8 FOR 'DELETED DATA', CLOCK PATTERN = C7

NOTE 4: FOR PURPOSES OF SECTOR FORMAT RECOGNITION DURING SECTOR SEARCH BY 1771 LSI, THIS BYTE ALSO INCORPORATES SECTOR LENGTH SPECIFICATION:

NOTE 5:

DSK

I.

29

TRAILING ZERO BYTES BETWEEN END OF LAST SECTOR AND INDEX

#### TABLE 3

# DIO-C RECORDING FORMATS STANDARD DRIVE

|      |                         |                             |          |          |                       |          |          | SECTOR           |              |             |            |          |              |                |             |           |           |

|------|-------------------------|-----------------------------|----------|----------|-----------------------|----------|----------|------------------|--------------|-------------|------------|----------|--------------|----------------|-------------|-----------|-----------|

|      |                         |                             |          | INDE     | X FIELD               |          |          | I.D. F           | IELD         |             |            |          | DATA         | FIELD          |             |           | l         |

| MODE | SECTORS<br>PER<br>TRACK | DATA<br>BYTES PER<br>SECTOR | GAP 4A   | SYNC     | INDEX<br>ADR.<br>MARK | GAP 1    | SYNC     | ADR.<br>MARK     | I.D.<br>DATA | CRC         | GAP 2      | SYNC     | ADR.<br>MARK | DATA           | CRC         | GAP 3     | GAP 4     |

| FM   | 26                      | 128                         | 40<br>FF | 6<br>00  | 1<br>FC               | 26<br>FF | 6<br>00  | 1<br>FE*         | 4<br>NOTE 2  | 2<br>NOTE 3 | 11.<br>.FF | 6<br>00  | 1<br>NOTE 4  | 128<br>NOTE 6  | 2<br>NOTE 3 | 27<br>FF  | 247<br>FF |

| FM   | 15                      | 256                         | 40<br>FF | 6<br>00  | 1<br>FC               | 26<br>FF | 6<br>00  | 1<br>FE <b>*</b> | 4<br>NOTE 2  | 2<br>NOTE 3 | 11<br>FF   | 6<br>00  | 1<br>NOTE 4  | 256<br>NOTE 6  | 2<br>NOTE 3 | 42<br>FF  | 170<br>FF |

| MFM  | 26                      | 256                         | 80<br>4E | 12<br>00 | 4<br>NOTE 7           | 50<br>4E | 12<br>00 | 4<br>NOTE 1      | 4<br>NOTE 2  | 2<br>NOTE 3 | 22<br>4E   | 12<br>00 | 4<br>NOTE 5  | 256<br>NOTE 6  | 2<br>NOTE 3 | 64<br>4E  | 598<br>4E |

| MFM  | 8                       | 1024                        | 80<br>4E | 12<br>00 | 4<br>NOTE 7           | 50<br>4E | 12<br>00 | 4<br>NOTE 1      | 4<br>NOTE 2  | 2<br>NOTE 3 | 22<br>4E   | 12<br>00 | 4<br>NOTE 5  | 1024<br>NOTE 6 | 2<br>NOTE 3 | 116<br>4E | 654<br>4E |

\* FM ID ADDRESS MARK, CLOCK PATTERN = C7

NOTE 1: MFM ID ADDRESS MARK 3 BYTES OF A, CLOCK PATTERN = 0A

FOLLOWED BY 1 BYTE OF FE, NO MISSING CLOCK BITS

NOTE 2: ID DATA CONTAINS FOLLOWING 4 BYTES

1) TRACK NUMBER (O - N) 2) SIDE NUMBER (O OR 1) 3) SECTOR NUMBER (1 - N)

4) SECTOR LENGTH, 0 = 128 BYTES/SECTOR; 1 = 256 BYTES/SECTOR, 3 = 1024 BYTES/SECTOR

NOTE 3: CRC BYTES ARE GENERATED BY CCITT STANDARD V41, STARTING AT FIRST ADR. MARK BYTE

NOTE 4: FM DATA ADR. MARK: FB FOR DATA, FB FOR DELETED DATA CLOCK = C7

NOTE 5: MFM DATA ADR. MARK: 3 BYTES OF A1 CLOCK PATTERN = 0A, FOLLOWED BY FB (DATA) OR F9 (DELETED DATA), NO MISSING CLOCK BITS

NOTE 6: USER SPECIFIED DATA INITIALIZED TO 4E

NOTE 7: MFM INDEX ADR. MARK: 3 BYTES OF C2 (CLOCK PATTERN = 14), FOLLOWED BY 1 BYTE OF FC, NO MISSING CLOCK BITS

#### **DIO D RECORDING FORMATS MINI DRIVE**

|      |                         |                             |          |          | I. D.        | FIELD        |            |          |          | DATA         | FIELD         |            |           |           |

|------|-------------------------|-----------------------------|----------|----------|--------------|--------------|------------|----------|----------|--------------|---------------|------------|-----------|-----------|

| MODE | SECTOR:<br>PER<br>TRACK | S DATA BYT<br>PER<br>SECTOR |          | SYNC     | ADR.<br>MARK | I.D.<br>DATA | CRC        | GAP 2    | SYNC     | ADR.<br>MARK | DATA          | CRC        | GAP 3     | GAP 4     |

| FM   | 18                      | 128                         | 12<br>FF | 6<br>00  | 1<br>FE*     | 4<br>NOTE2   | 2<br>NOTE3 | 8<br>FF  | 6<br>00  | 1<br>NOTE4   | 128<br>NOTE6  | 2<br>NOTE3 | 10<br>FF  | 79<br>FF  |

| FM   | 9                       | 256                         | 40<br>Fe | 6<br>00  | 1<br>FF*     | 4<br>NOTE2   | 2<br>NOTE3 | 11<br>FF | 6<br>00  | 1<br>NOTE4   | 256<br>NOTE6  | 2<br>NOTE3 | 27<br>FF  | 241<br>FF |

| MFM  | 17                      | 256                         | 50<br>4E | 12<br>00 | 4<br>NOTE1   | 4<br>NOTE2   | 2<br>NOTE3 | 22<br>4E | 12<br>00 | 4<br>NOTE5   | 256<br>Note6  | 2<br>NOTE3 | 34<br>4E  | 216<br>4E |

| MFM  | 5                       | 1024                        | 50<br>4E | 12<br>00 | 4<br>NOTE1   | 4<br>NOTE2   | 2<br>NOTE3 | 22<br>4E | 12<br>00 | 4<br>NOTE5   | 1024<br>NOTE6 | 2<br>NOTE3 | 110<br>4E | 220<br>4E |

SECTOR

\* FM ID ADDRESS MARK, CLOCK PATTERN = C7

NOTE1: MFM ID ADDRESS MARK 3 BYTES OF A1, CLOCK PATTERN = 0A

FOLLOWED BY 1 BYTE OF FE, NO MISSING CLOCK BITS

NOTE2: ID DATA CONTAINS FOLLOWING 4 BYTES

- 1) TRACK NUMBER (0 N)

- 2) SIDE NUMBER (0 OR 1)

- 3) SECTOR NUMBER (1 N)

- 4) SECTOR LENGTH, 0 = 128 BYTES/SECTOR; 1 = 256 BYTES/SECTOR; 3 = 1024 BYTES/SECTOR

NOTE3: CRC BYTES ARE GENERATED BY CCITT STANDARD V41, STARTING AT FIRST ADR. MARK BYTE

NOTE4: FM DATA ADR MARK, FB FOR DATA, F8 FOR DELECTED DATA CLOCK = C7

NOTE5: MFM DATA ADR MARK: 3 BYTES OF A1 CLOCK PATTERN =0A, FOLLOWED BY FB (DATA) OR F9 (DELETED DATA), NO MISSING CLOCK BITS

# 3 – 3 TRANSACTIONS

In this section, the IMDOS disk I/O protocol is discussed in detail. Emphasis is placed on the expositon of command formats and error codes. The reader has already been introduced to these formats and the general disk access mechanism in sections, titled BYTE COMMANDS AND COMMAND STRINGS and ACCESS SCHEMA, above. Here the specific byte and string commands are explained and their formats defined.

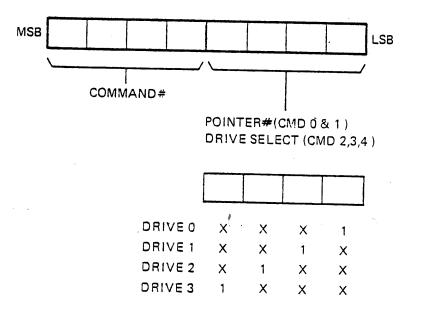

## 3 – 3.1 BYTE COMMANDS

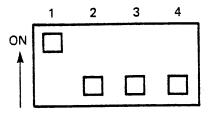

The Byte Command is an eight bit code structured so that the upper four bits contain the Byte Command Number and the lower four bits contain either a pointer number or a drive select number, depending on the Byte Command Number involved (see Figure 15).

# FIGURE 15 Byte Command Format

The Byte Commands are listed below according to the Byte Command Number (as defined above).

Transactions

#### COMMAND 0:

Execute Command String identified by pointer. The controller uses the lower four bits of the command code as a pointer into an array that contains sixteen 16-bit addresses. One of these 16-bit addresses (the one identified by the lower four bits in the command code) specifies the start of a string of bytes that comprises a Command String. This is the Command String that is to be executed. Note that prior to using this command type, the 16-bit address must have been initialized as required. This may be accomplished by the Byte Command described next.

## COMMAND 1:

This command instructs the controller firmware to expect two additional bytes from the calling program (by way of two additional calls). These two bytes constitute a 16-bit address that is to be placed into the pointer array at the location(s) specified by the lower four bits of the Command-1 byte.

COMMAND 2:

Restore Drive(s) instructs the controller to cause the read/ write head to be positioned over track-0 on any and all drive(s) specified by the lower four bits of this command code. The controller will take due notice of the drive(s) specified, and will perform the restore operation as first order of business the next time such drive(s) is (are) referenced by a Command String.

#### COMMAND 3:

This command sets software write protect flag(s) for drive(s) specified in the lower four bits of the command code. Note that the controller firmware presets all drives to Write Enabled during the initialization phase that follows system power-on; more of this later.

#### COMMAND 4:

This command resets software write protect flag(s) for drive(s) specified in the lower four bits of the command code.

#### COMMAND 5: (FIF only)

Software reset causes the IFM to jump to location 0000 and re-initialize. If drive 0 is ready, track 0 sector 1 will be read into location 0000 of system memory. This command can be used to effectively "cold start" the system.

NOTE: This command is implemented in REV. 4 and later firmware.

COMMANDS 6 – 15: (FIF only)

These commands perform no operation, except to reset interrupt if interrupt mode is being used. IMSAI standard RESET INTERRUPT command is COMMAND 15.

Transactions

#### COMMANDS 5 – 15: (MDIO and DIO)

Illegal commands. Controller returns with error code to system.

## POINTERS

The pointer is a number from 0 to 15 which points into an array that contains sixteen 16-bit addresses. Each of these addresses, in turn, points to the leading byte of a Command String that resides somewhere in system RAM. Byte Commands 0 and 1 interpret the lower four bits of the Byte Command Code as such a pointer into the Command String Address Array. Byte Command 1 is used to modify addresses within this array, while Byte Command 0 signals the order to execute the Command String whose starting address is (indirectly) specified by the lower four bits of the Byte Command 0 code.

During system initialization, the initialization entry point of the controller firmware is called by the operating system (or by BOOT, in case of a cold start). Among the many functions that are performed during this phase, the Command String Address Array is initialized to the following default values (hex):

| 0: 0080 | 4: 4000 | 8: 8000 | C: C000 |

|---------|---------|---------|---------|

| 1:1000  | 5: 5000 | 9: 9000 | D: D000 |

| 2: 2000 | 6: 6000 | A: A000 | E: E000 |

| 3: 3000 | 7: 7000 | B: B000 | F: F000 |

#### DRIVE SELECT NUMBERS

Byte Commands 2, 3 and 4 specify one or more drives with the lower four bits of the command code. The drives are bit-encoded, a ONE in any bit position signifying the selection of that particular drive. A command that does not specify at least one drive will be rejected with an error indication to the system.

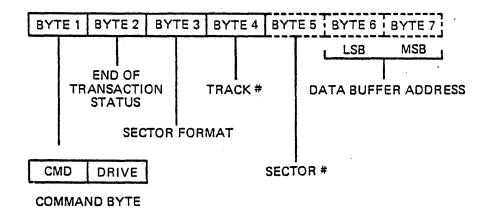

#### 3 – 3.2 COMMAND STRINGS

Command Strings are indirectly executable in that the exact operation to be performed is not specified in the code conveyed to the controller during the CALL. Instead, the Command String resides somewhere in system RAM in variable length format. The control code imparted to the controller during the CALL specifies the start address of this string by vectoring through the Command String Address Array. Controller firmware interprets the string and performs the specified operation.

Transactions

All Command Strings consist of at least four bytes of information and may include as many as seven. The definition of each of these bytes is given below. (See also Figure 16)

## BYTE 1 – Command Byte

This byte contains a command number in the upper hexadecimal digit and a drive select number in the lower digit. The operation of each Command Number is explained in the next section. A drive is selected if its corresponding bit is set. Commands that specify more than one drive are rejected with an error indication to the system.

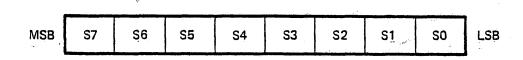

### BYTE 2 – Status Byte

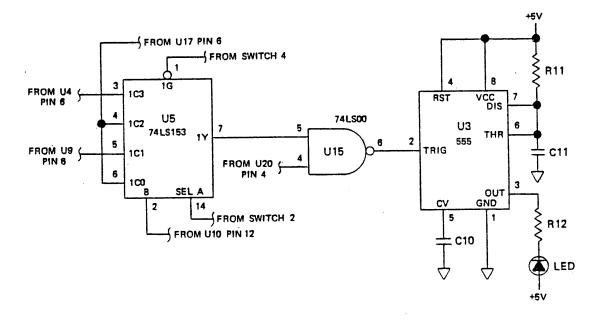

This byte indicates to the CALLer the status of the controller after completion of the last disk transaction. A hex value of 01H signifies successful completion. The MSB is set if an error condition had been encountered prior to completion of the operation. The same code that is placed into this byte location within the Command String is also forwarded to the system in the A-Register. The significance of the various codes is given in the subsection, titled ERROR CODES, below (see also Figure 17).

# IMSAI DISKETTE SYSTEM Transactions

iransactions

### BYTE 3 – Format & Extended Track

۰.

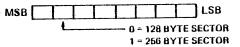

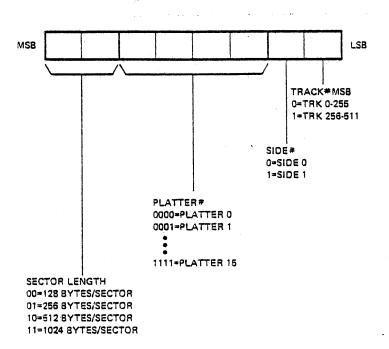

This byte consists of several single and multiple bit fields that specify a) MSB for extended track numbers (256-511), b) sector length, c) side select (for future expansion to double sided diskettes) and d) platter number (for future expansion to multi-platter fixed disk drives). Sector lengths that may be specified, are 128, 256 and 1024 bytes (see Figure 18).

## FIGURE 18 Command String Byte 3 Format

## BYTE 4 - Track Number

This byte specifies the track number which may be 0 through 76 for standard diskettes and 0 through 34, 39 or 76 for mini diskettes. MPI type B51 drives can accommodate 40, Micropolis-1015 77 tracks. Identification of what constitutes a legal track number specification is a function of controller type, drive type and format. Illegal track number specification in this byte is flagged and results in an error indication to the system.

#### BYTE 5 - Sector Number (when required)

This byte specifies the sector that will be involved in the disk 1/0 transaction. The legal sector numbers are:

1 to 18 for single density (SD) 128 byte sectors;

1 to 9 for SD 256 byte sectors;

1 to 17 for double density (DD) 256 byte sectors; and

1 to 5 for DD 1024 byte sectors when accessing mini diskettes.

1 to 26 for SD 128 byte sectors;

1 to 15 for SD 256 byte sectors;

1 to 26 for DD 256 byte sectors;

1 to 8 for DD 1024 byte sectors; and

1 to 58 for DD 128 byte sectors when accessing standard diskettes.

Applicability of these ranges of sector numbers and associated formats is governed by compatibility considerations involving the several IMSAI controller types and versions (see sections on hardware and format compatibility, above).

BYTE 6 & 7 - Memory Address (when required)

These two bytes specify the starting address of that contiguous block of memory locations within system RAM to or from which the specified sector is to be transferred. Byte 6 contains the least significant, byte 7 the most significant address byte. Specifying a value of EOH for byte 7 results in an error indication (start of address space occupied by the controller).

COMMAND TYPES

The individual Command String commands are identified by the value of the most significant hex digit of Byte 1 of a Command String. The definitions of these commands are given below by Command Number.

COMMAND 0 - Not used

COMMAND 1 - Write Sector

This command instructs the controller to write the data block whose starting address is specified by bytes 6 and 7 of the Command String, into the sector specified by byte 5, on the track specified by byte 4, according to the format called out in byte 3.

COMMAND 2 - Read Sector

The sector specified by byte 5, of length specified by byte 3, is read from the track called out in byte 4 of the Command String, and is written into the data buffer in system RAM whose starting address is specified by bytes 6 and 7 of the Command String.

Transactions

#### COMMAND 3 - Format Track

This command formats the track specified in byte 4, according to the format called out in byte 3 of the Command String. It encodes the appropriate number of sector 1D-fields, constructs dummy data fields and fills all intra- and inter-sector gaps with the required bit patterns. All data information previously contained in the specified track is eliminated.

#### COMMAND 4 - Verify Sector

This command informs the controller to read the specified sector and to check the validity of the CRC bytes. Byte 5 of the Command String specifies the sector of interest.

#### COMMAND 5 - Write Deleted Data Address Mark

Execution of this command results in the placement of a Deleted Data Address Mark in the data field of the sector whose number is specified in byte 5 of the Command String. The sector is located on the track specified by byte 4, and is of a length specified by byte 3 of the Command String.

#### COMMAND 6 - Configuration Check (FIF only)

This command causes the floppy controller to test for the presence of drives and return a bit map of the drives found. Only the drives indicated in the low order nibble of the command will be tested. Within 1 ms of issuing the command, the controller will return 40H in the status byte to indicate that the tests are in progress. When the operation is complete, the controller returns 2XH in the status byte where "X" is the map of drives tested and found.

NOTE: This command is implemented in REV. 4.0 and later firmware.

NOTE: Command 60H can be used to test for the presence of REV 4.0 or later firmware. No drives are tested but 40H and 20H are returned in the status byte as described above.

COMMANDS 7 - 11 (FIF only)

Commands 7 through 11 are identical with commands 1 through 5 and are used to read diskettes which have the logical and physical track address physically different. The logical track address to be used is always contained in the two bytes directly following the other command data called for in the COMMAND STRING (0-5). For example, if the basic command used just 4 bytes, then the logical track number would be in bytes 5 and 6. If the basic command used 7 bytes, then the logical track address number would be in bytes 8 and 9.

#### COMMANDS 5 - 15 (MDIO and DIO)

llegal commands. Controller returns with error code.

Transactions

## 3 – 3.3 ACCESSING THE CONTROLLER