# Contents

| 62PC DISK DRIVE AND ATTACHMENT 13-1   |

|---------------------------------------|

| INTRODUCTION                          |

| 62PC Disk Drive                       |

| Grounding                             |

| Subframe                              |

| Disk Enclosure and Spindle Brake 13-1 |

| Actuator Lock 13-1                    |

| Drive Motor Assembly                  |

| Attachment                            |

| Circuit Locations                     |

| DISK FORMAT                           |

| Cylinders                             |

| Tracks                                |

| Servo Track                           |

| Data Track                            |

| Guard Band                            |

| Landing Zone                          |

| Sectors                               |

| Data Recording                        |

| Reading and Writing Data              |

| DATA PROTECTION                       |

| Data Unsafe Conditions                |

| Not Ready                             |

| Power On and Power Off                |

| DATA FLOW                             |

| System I/O Channel Interface          |

| Common Adapter Interface              |

| State Counter                         |

| Controller                            |

| Buffer Storage                        |

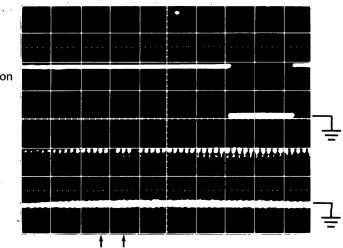

| Oscillator and Clocks                 |

| Disk Drive Interface                  |

| Write Data Flow                       |

| Read Data Flow                        |

| OPERATIONS                            |

| Operation Sequence                    |

| Read Id                               |

| Read Data                             |

| Read Diagnostic                       |

| Read Verify                           |

| Write ID                              |

| Write Data                            |

| Scan Equal, Scan High or Equal, Scan  |

| Low or Equal                          |

| Diagnostic Operations                     |

|-------------------------------------------|

| Load Seek Required Address Direct 13-19   |

| Load Seek Control Direct 13-19            |

| Sense File Direct                         |

| Sense File Diagnostic Sense Bytes         |

| 1, 2, and 3 ..................13-19       |

| Sense File Diagnostic Sense Bytes         |

| 1, 2, and 3 256 Sample Test 13-19         |

| Sense File Diagnostic Wrap 13-19          |

| Disk Speed Timing Diagnostic 13-19        |

| Timed Seek Diagnostic                     |

| Read Data with Data Repeat 13-19          |

| Read Common Adapter Buffer Storage 13-19  |

| Common Adapter File Control Block 13-20   |

| Loading and Sensing the Common Adapter    |

| File Control Block                        |

| Loading the Common Adapter File           |

| Control Block                             |

| Sensing the Common Adapter File           |

| Control Block 13-24                       |

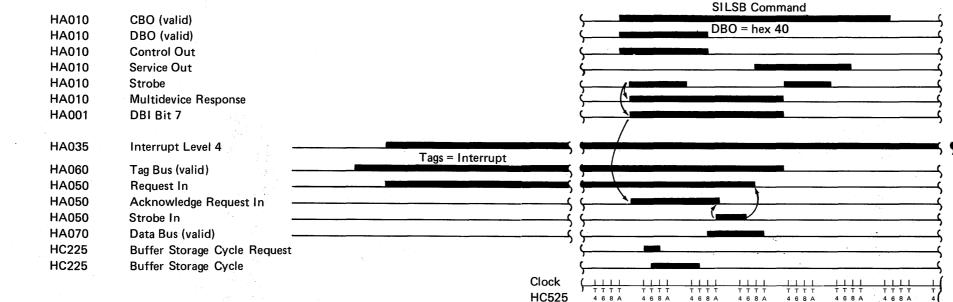

| Interrupts                                |

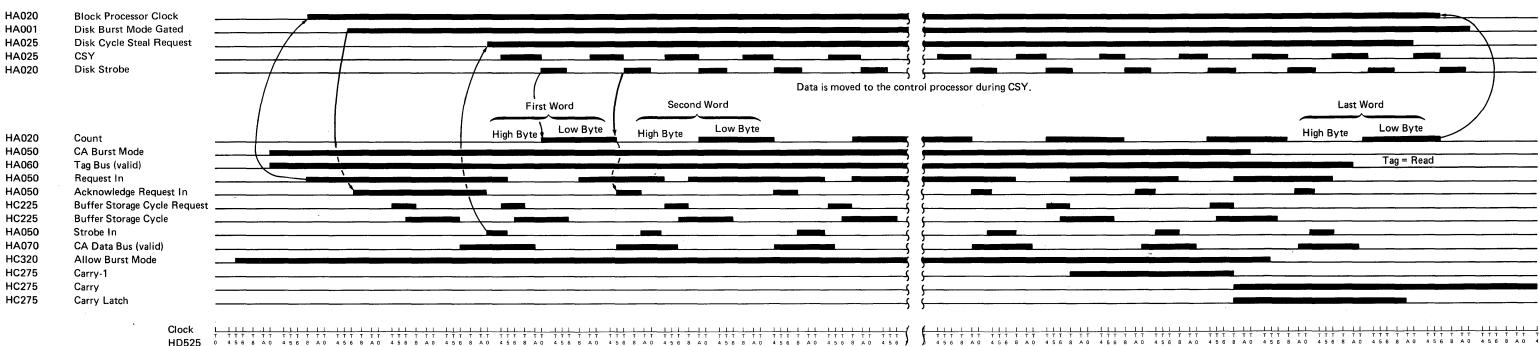

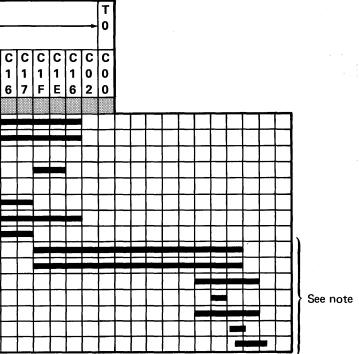

| Burst Mode Cycle Steal                    |

| Servo Tracks and Servo Track Follow 13-34 |

| Access Locating                           |

| Dedicated Servo                           |

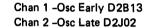

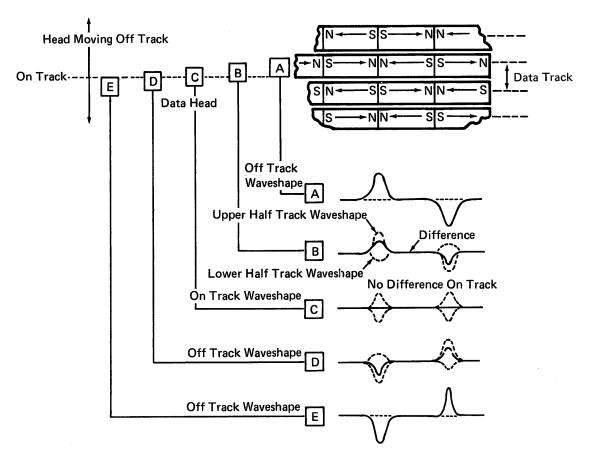

| Track Follow Waveshapes 13-38             |

| Sample Servo                              |

| Sample Servo Waveshapes                   |

| Access Operations                         |

| Starting the Operation                    |

| Performing the Operation                  |

| Seek Calibration Sequence                 |

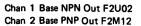

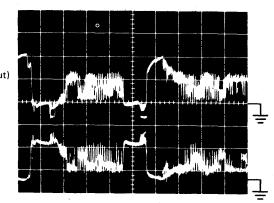

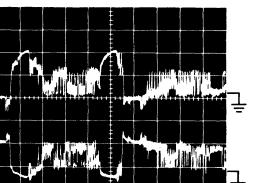

| Seek Waveshapes                           |

| Reading and Writing Data 13-47            |

| Head Selection                            |

| Writing Data                              |

| Reading Data                              |

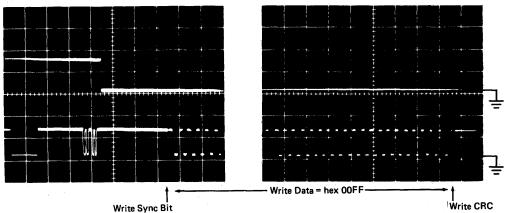

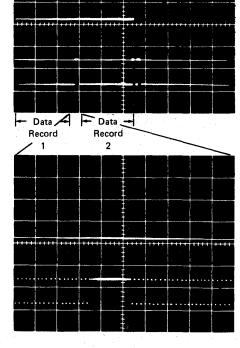

| Write Waveshapes                          |

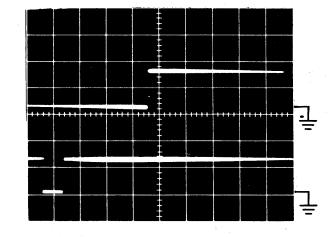

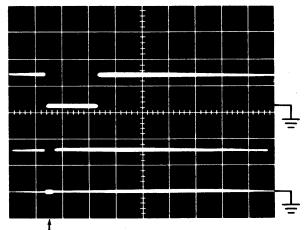

| Read Waveshapes                           |

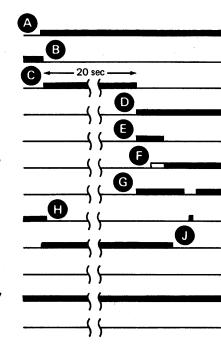

| Power On and Power Off Operations 13-54   |

| Power Sequence 13-54                      |

| Emergency Power Off                       |

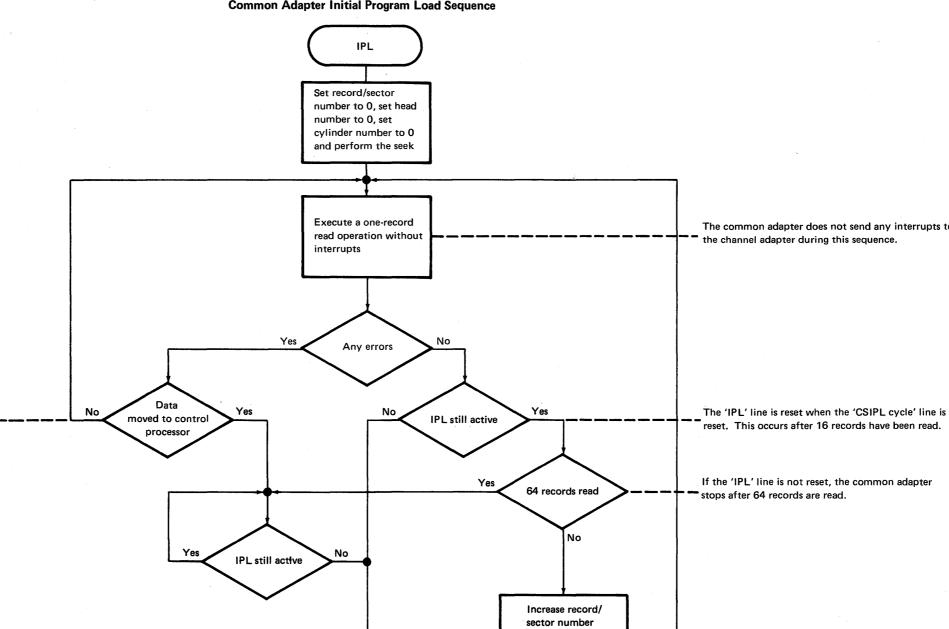

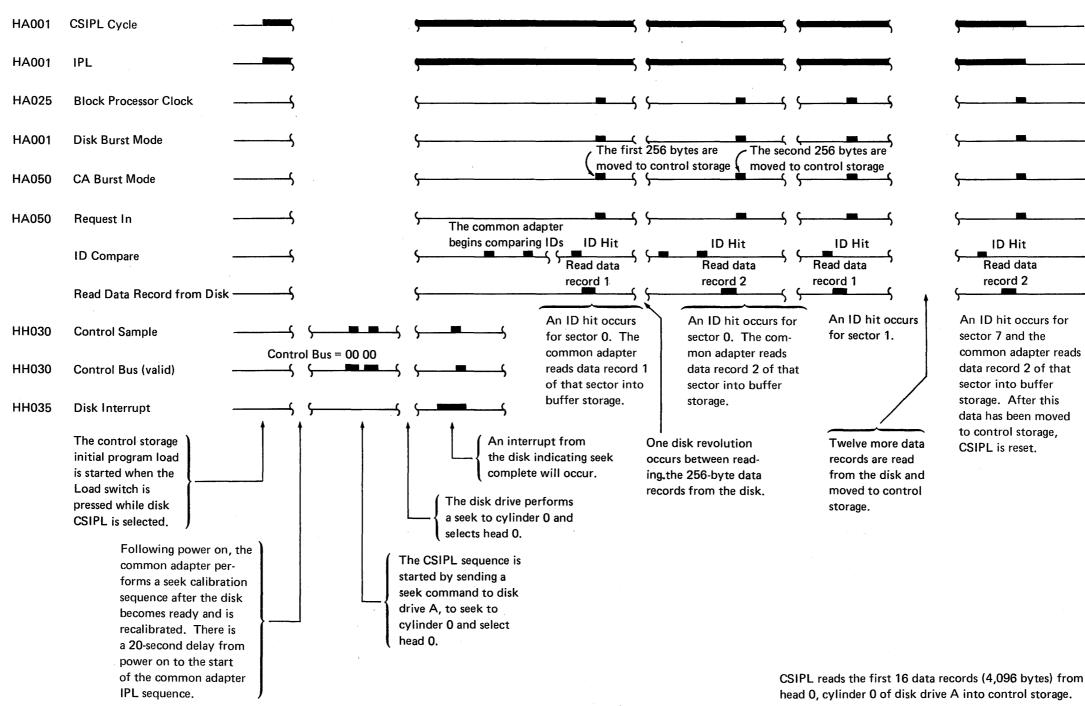

| Control Storage Initial Program Load 13-56  |

|---------------------------------------------|

| Common Adapter Initiation Program           |

| Load Operation                              |

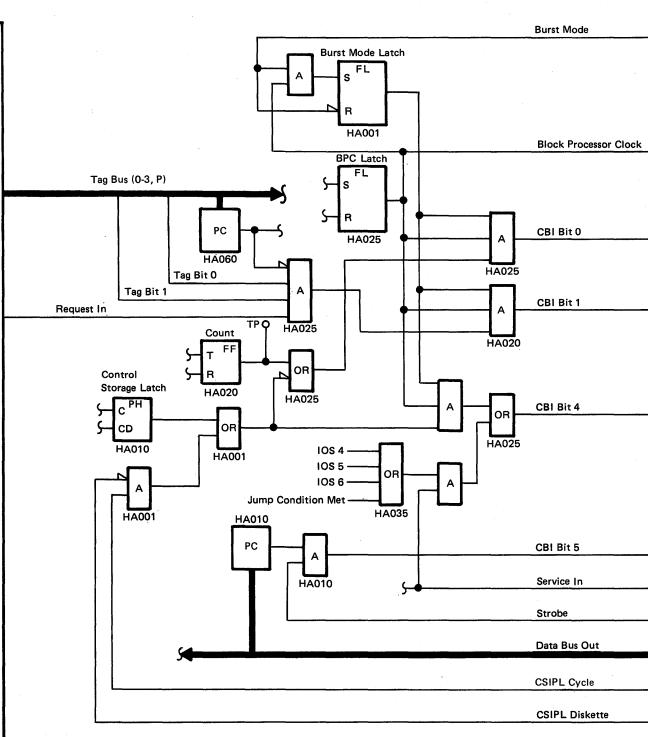

| Command Bus In                              |

| COMMANDS                                    |

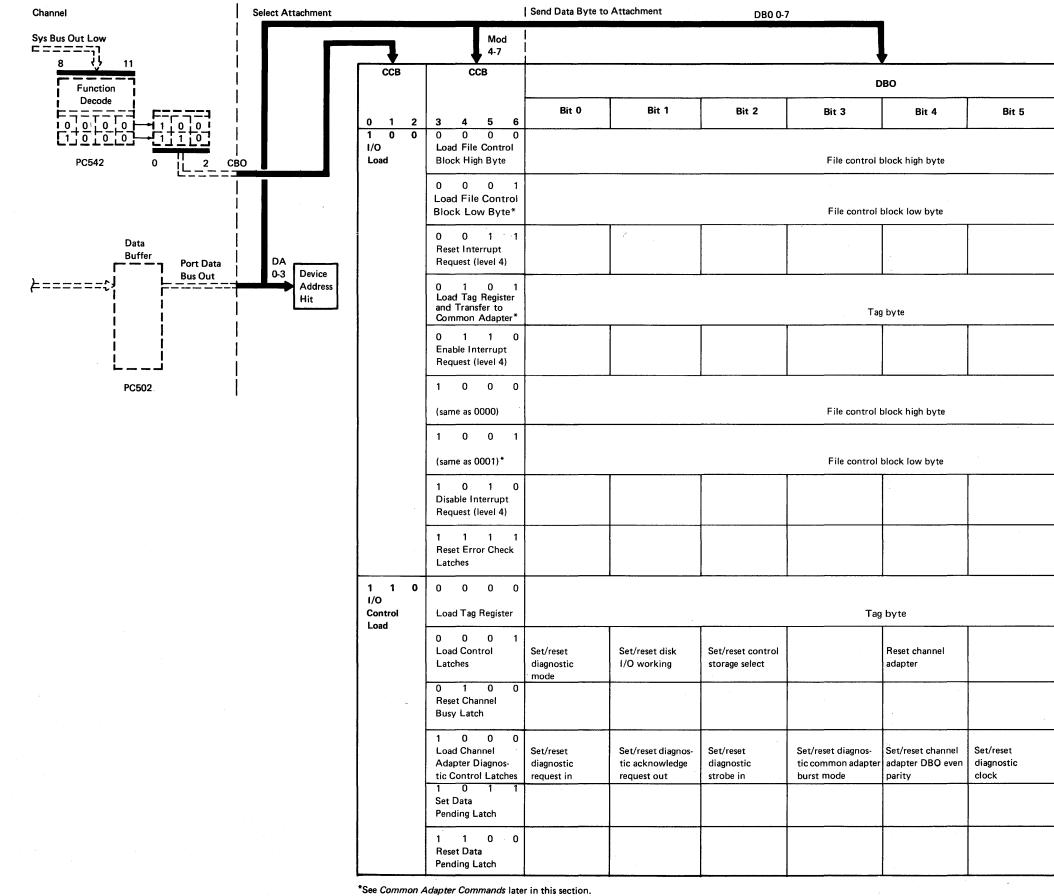

| I/O Load Command–I/O Control                |

| Load Command                                |

| I/O Sense Command–I/O Control               |

| Sense Command                               |

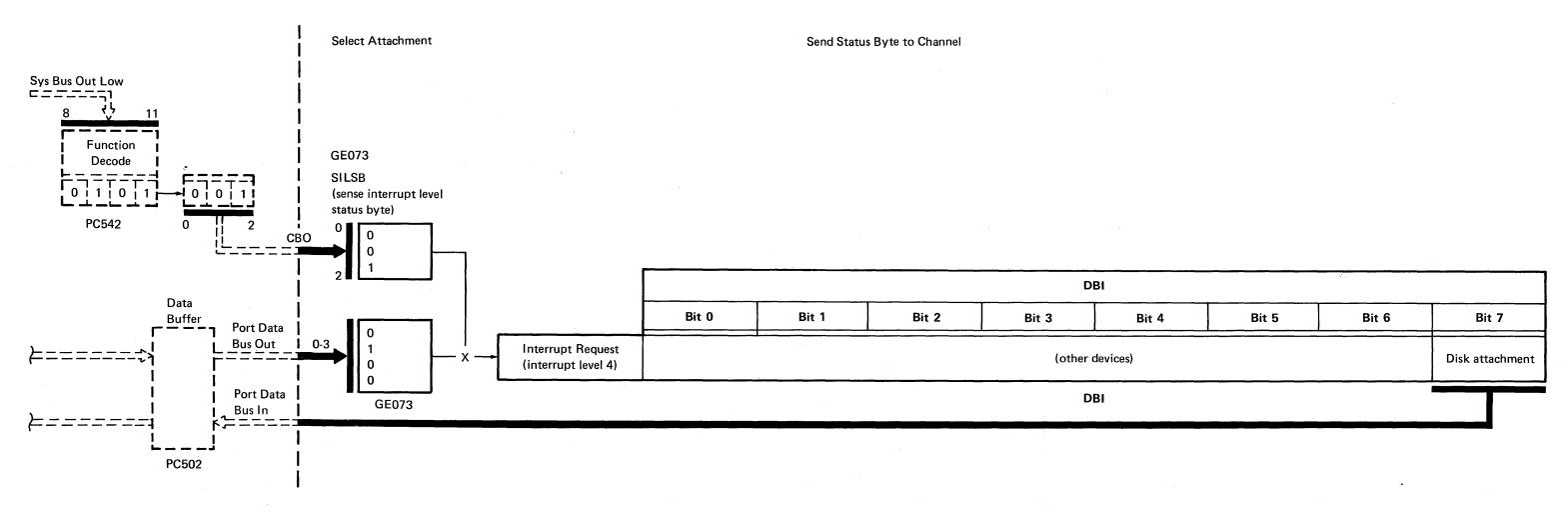

| Sense Interrupt Level Status Byte           |

| Command                                     |

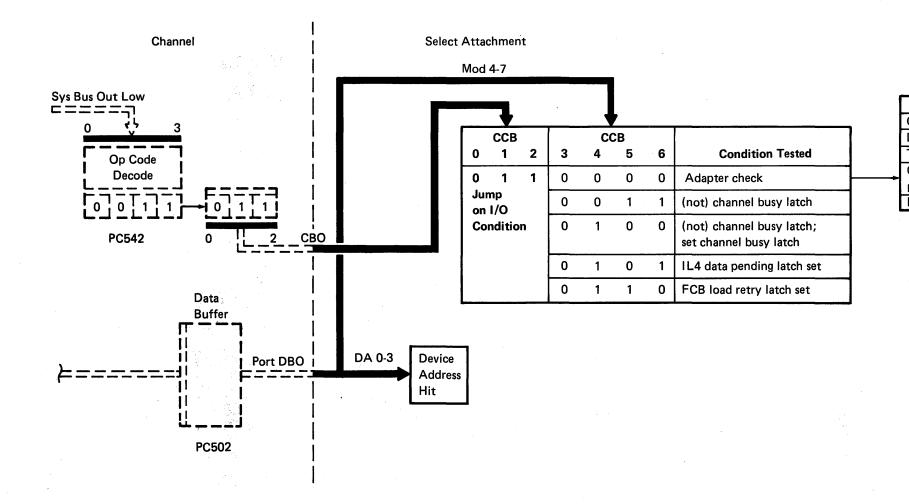

| Jump on I/O Condition Command               |

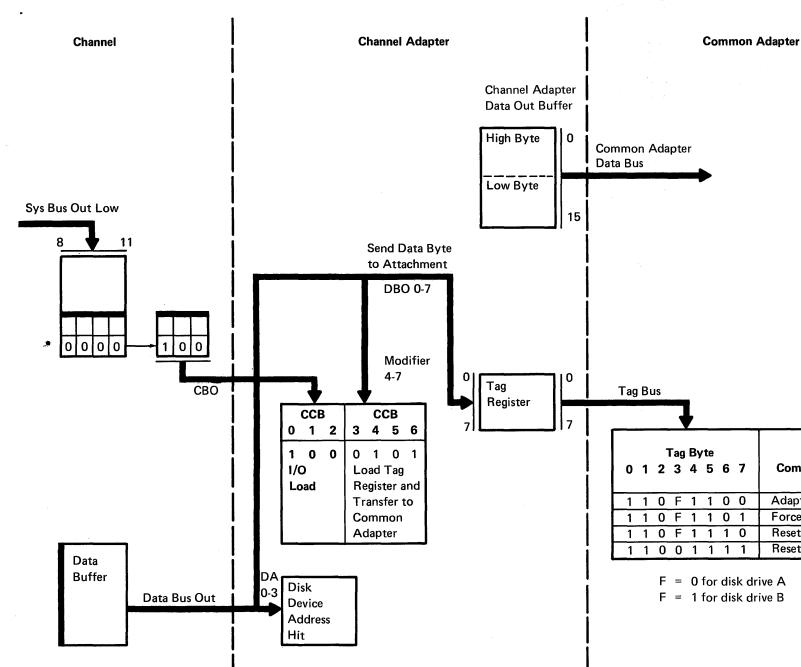

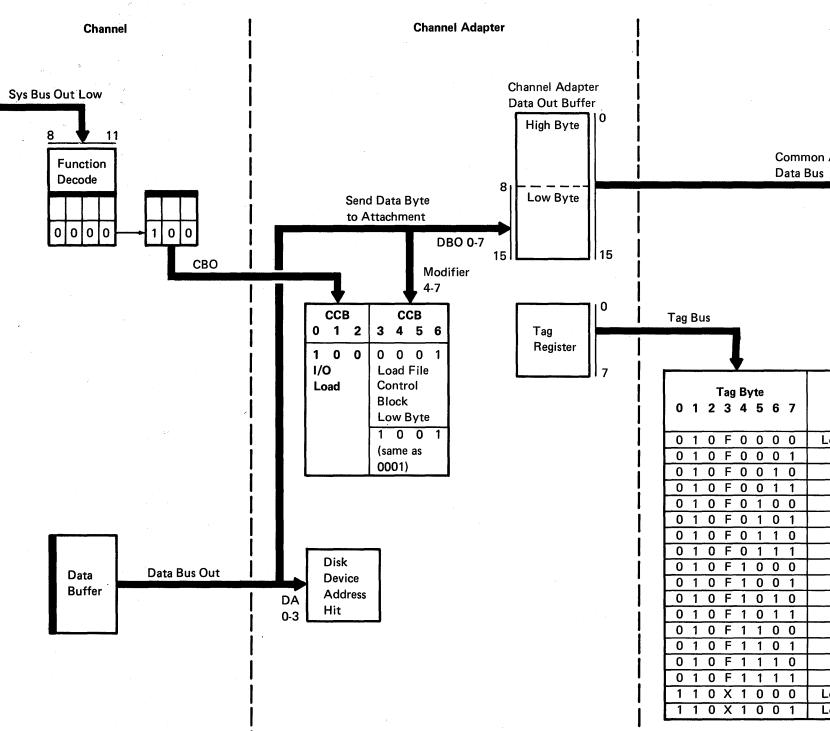

| Common Adapter Commands                     |

| Common Adapter Command Descriptions 13-69   |

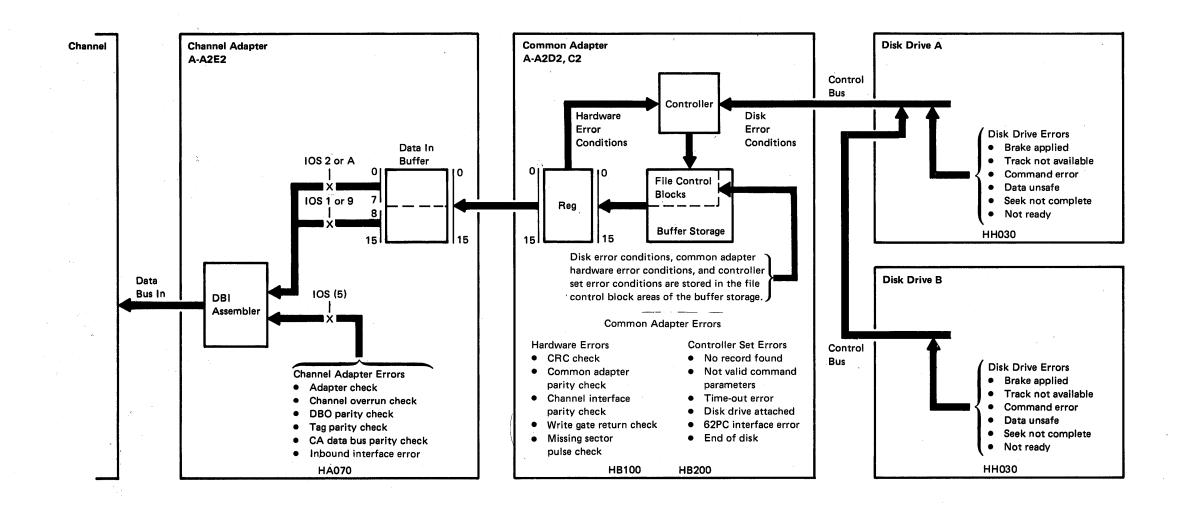

| ERROR CONDITIONS                            |

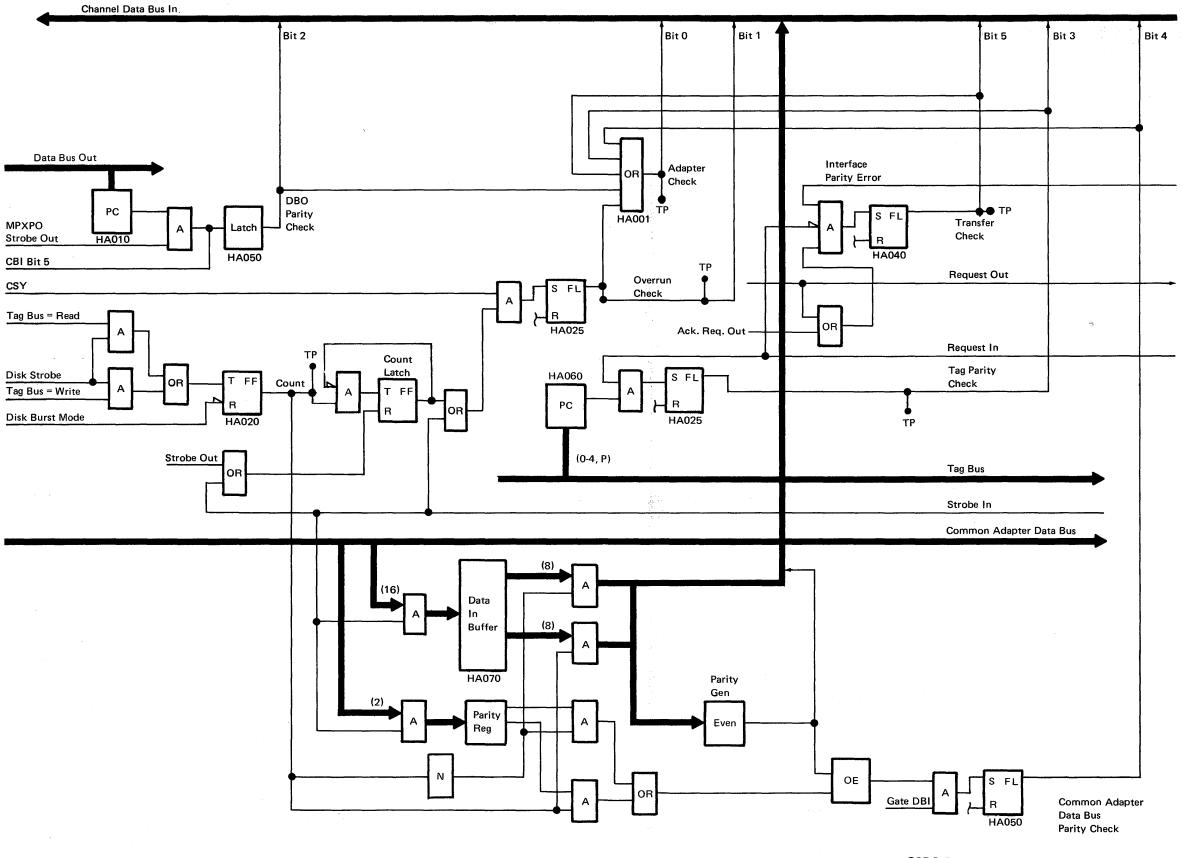

| Channel Adapter Sensed Errors               |

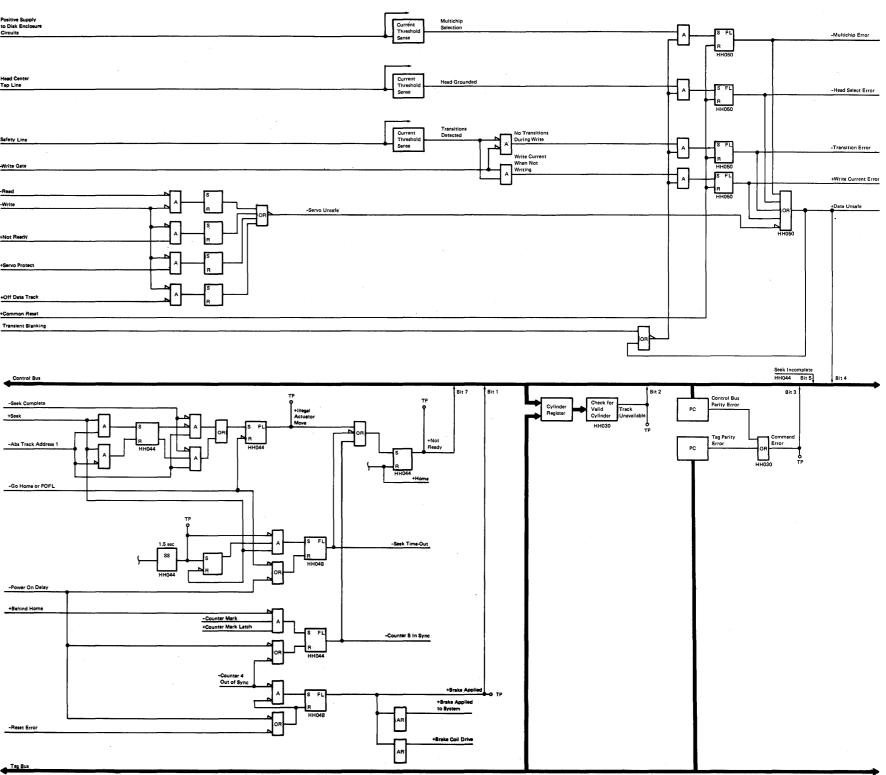

| Disk Drive Sensed Errors                    |

| Common Adapter Sensed Errors                |

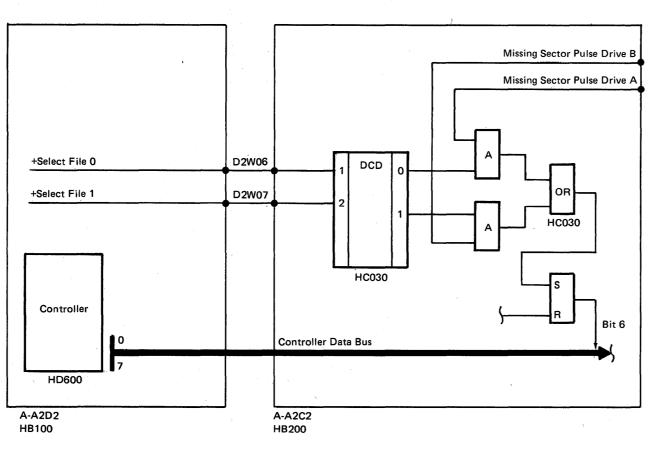

| INPUT/OUTPUT LINES                          |

| Lines Between the Channel and the Channel   |

| Adapter                                     |

| Lines Between the Channel Adapter and the   |

| Common Adapter                              |

| CA Data Bus (18 Lines, Bidirectional) 13-80 |

| Tag Bus (9 Lines)                           |

| Lines Between the Common Adapter and the    |

| 62PC Disk Drive                             |

| Dedicated Cable                             |

| Bus Cable                                   |

Contents for 62PC Disk Drive and Attachment

# INTRODUCTION

# 62PC Disk Drive

The 62PC disk drive has a data storage capacity of 63.9 megabytes. Installation of a second disk drive gives a total data storage capacity of 128.4 megabytes.

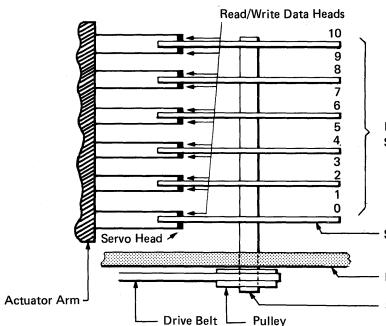

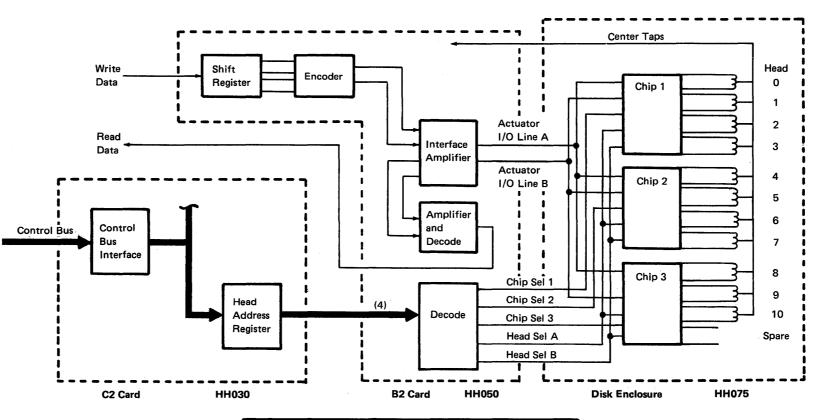

Each disk drive has six permanently installed magnetic disks. Data is written to and read from both sides of the disks by data heads attached to an actuator. Each disk drive has 11 data heads and one servo head. The disk data rate is one million bytes per second.

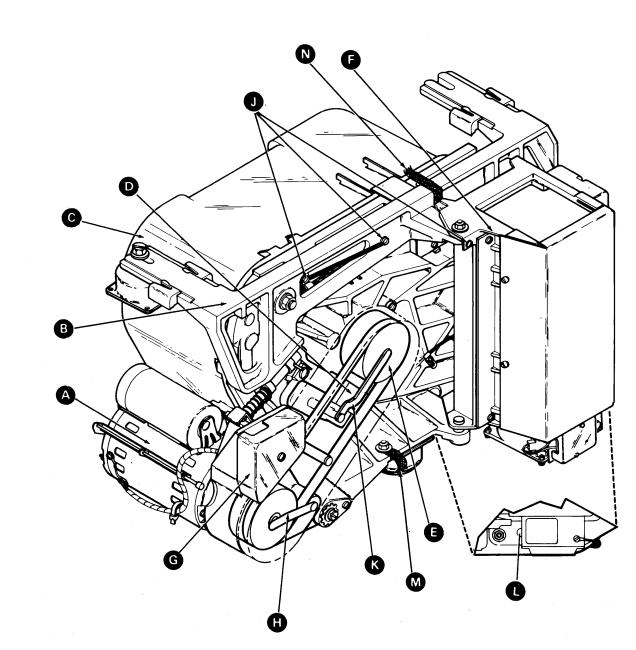

The disk drive contains a subframe B, disk enclosure C and spindle brake D, drive motor assembly (A), and a card gate (F). For a description of the card gate, see Circuit Locations later in this section.

#### Grounding

The disk drive board is grounded by the DC power cable **N** to the system DC ground. The card gate is grounded to the board (ground not shown). The disk enclosure and subframe are grounded to the gate by a wire or strap . The subframe is also grounded to the system frame by a strap M. The drive motor assembly **G** is grounded by the AC power cable to the system AC ground. The spindle 🚯 is grounded to the disk enclosure by the spindle antistatic brush **(K)**. The motor armature is grounded to the drive motor by the motor antistatic brush •

#### Subframe

The subframe is installed vertically in the system unit. Three shock mounts isolate the disk drive from the machine frame. The disk enclosure and spindle brake, the drive motor assembly, and the card gate are installed on the subframe.

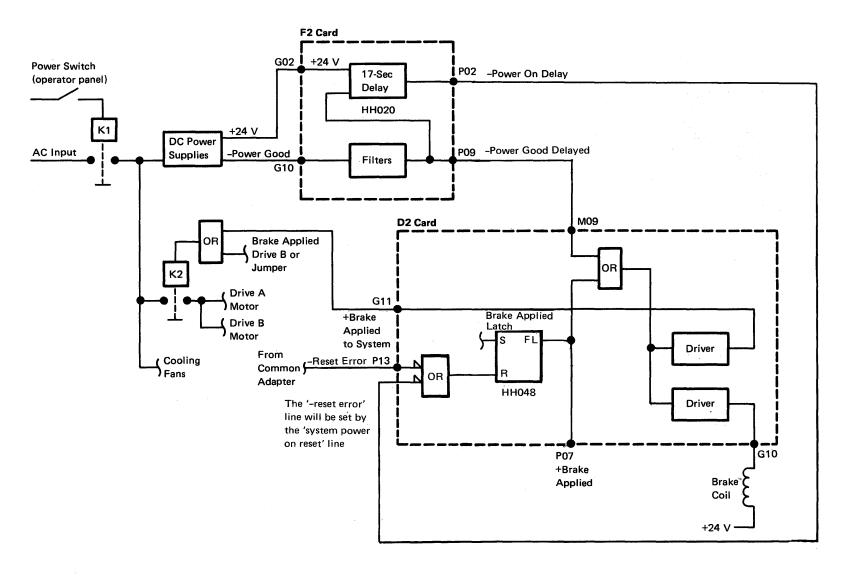

#### **Disk Enclosure and Spindle Brake**

The disk enclosure contains the following assemblies:

• The disk spindle assembly, which contains the disks installed on the disk spindle.

- The spindle brake, which is attached to the disk enclosure casting and quickly stops the disk when power is removed. This limits the time that the servo head and the data heads touch the disk when the disks are turning to prevent head or disk damage. The brake is de-activated when 24 Vdc is present on the brake coil.

- The actuator assembly, which contains the servo head, the data heads, and associated electronic circuits at one end of the actuator and a coil at the opposite end. Actuator movement and location is controlled by current applied to the coil.

Note: The disk enclosure is sealed at the factory and should not be opened in the field.

The disk enclosure has a closed-loop, air-moving system that uses blades on the spindle hub to continuously move air through an air filter. Another filter lets the air pressure remain equal as the disk is getting up to speed and as the temperature inside the disk enclosure changes.

#### Actuator Lock

When the actuator lock ( ) is turned clockwise as far as it will go, it is in the locked position. The lock prevents damage to the data heads during shipment, installation, or removal of the disk enclosure.

#### **Drive Motor Assembly**

The drive motor assembly contains the drive motor, pulley, and mounting frame. The assembly pivots on the subframe and a belt tensioner keeps the drive belt tight. The drive motor quickly starts the disk when power is turned on and turns the disk at 3,125 revolutions per minute. The motor has a manual thermal reset switch.

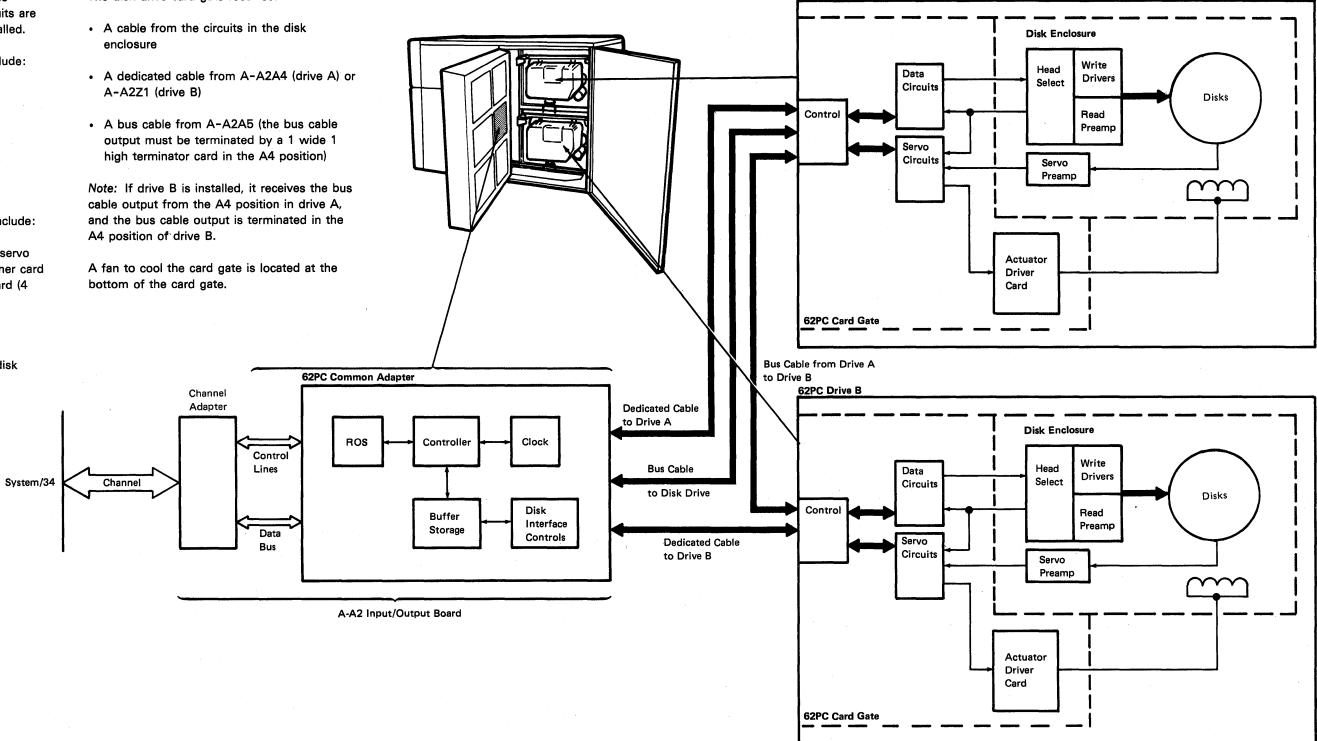

# Attachment

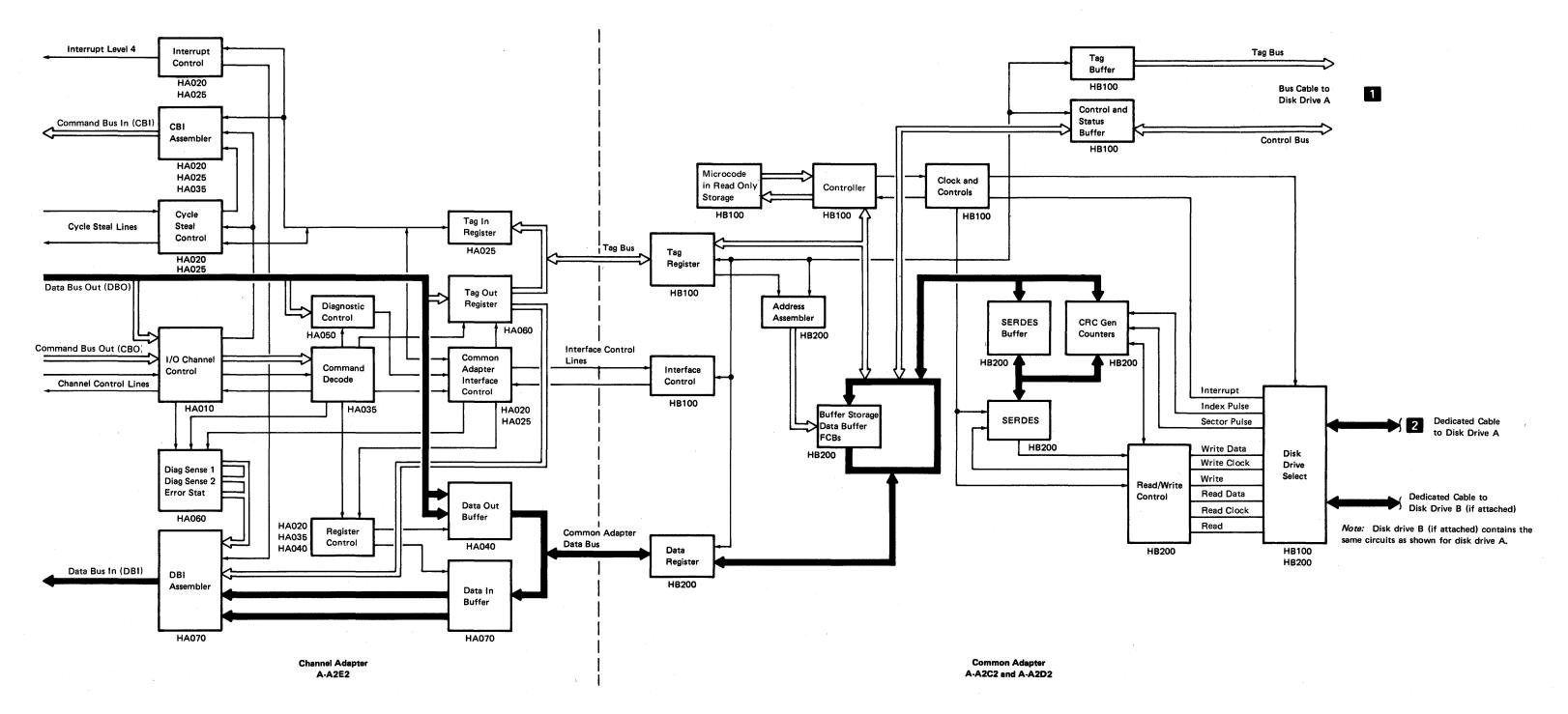

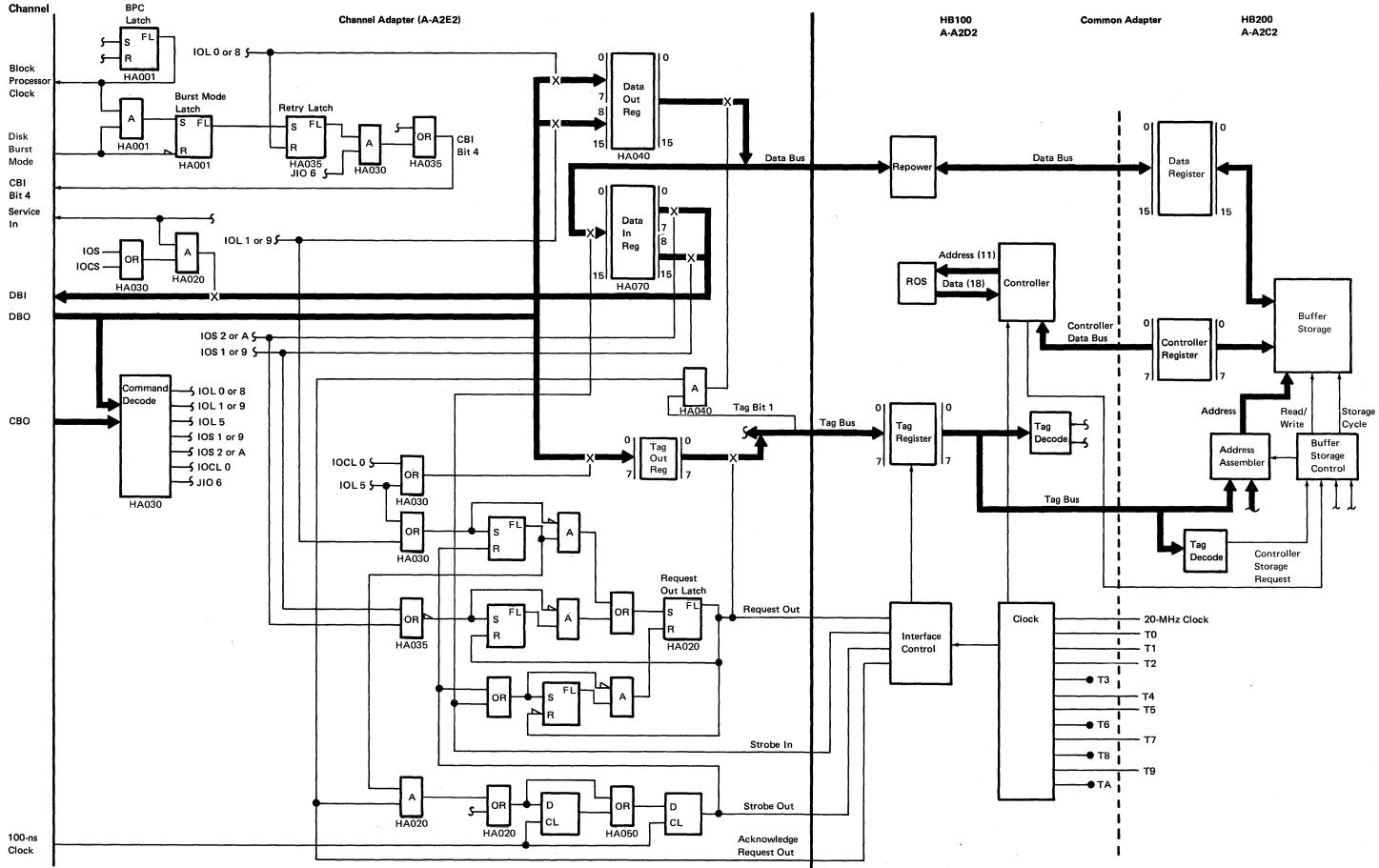

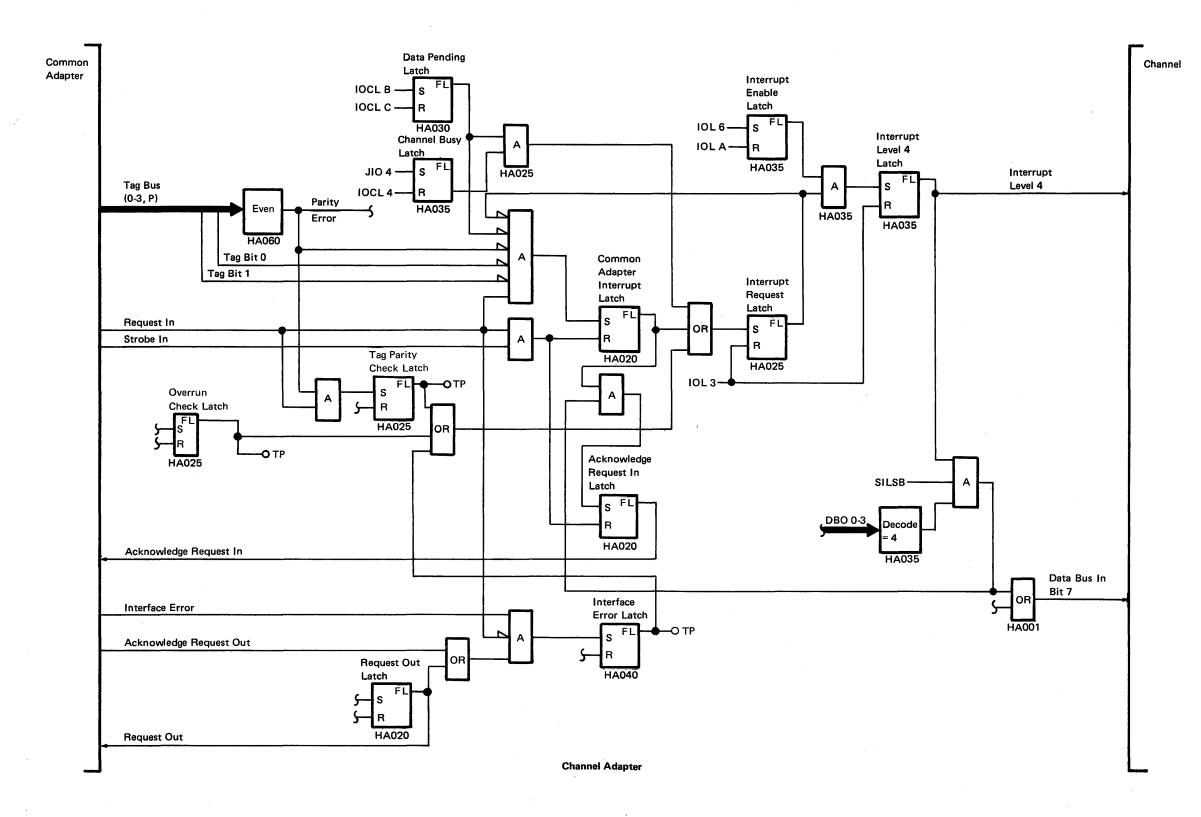

The disk drive attachment includes two adapters: the channel adapter and the common adapter.

- The channel adapter interfaces both to the system channel and to the common adapter. The channel adapter moves data and control information to and from the common adapter, and changes the data from 1-byte length on the system channel to 2-byte length on the common adapter interface. Interrupt level 4 and cycle steal control circuits are in the channel adapter.

- The common adapter executes the disk operations requested by the system. The common adapter controls access and data operations for one or two 62PC disk drives attached to the system. There are two common adapter cards. The channel interface card (A-A2D2) contains a microcontroller, microcode stored in read-only storage, an oscillator and clock circuits, and controls for the channel adapter/common adapter interface. The disk drive interface card (A-A2C2) contains the buffer storage, which is used to store control information and up to three sectors of data; the SERDES, which changes the 2-byte data to serial data; read and write control circuits; and controls for the common adapter/disk drive interface.

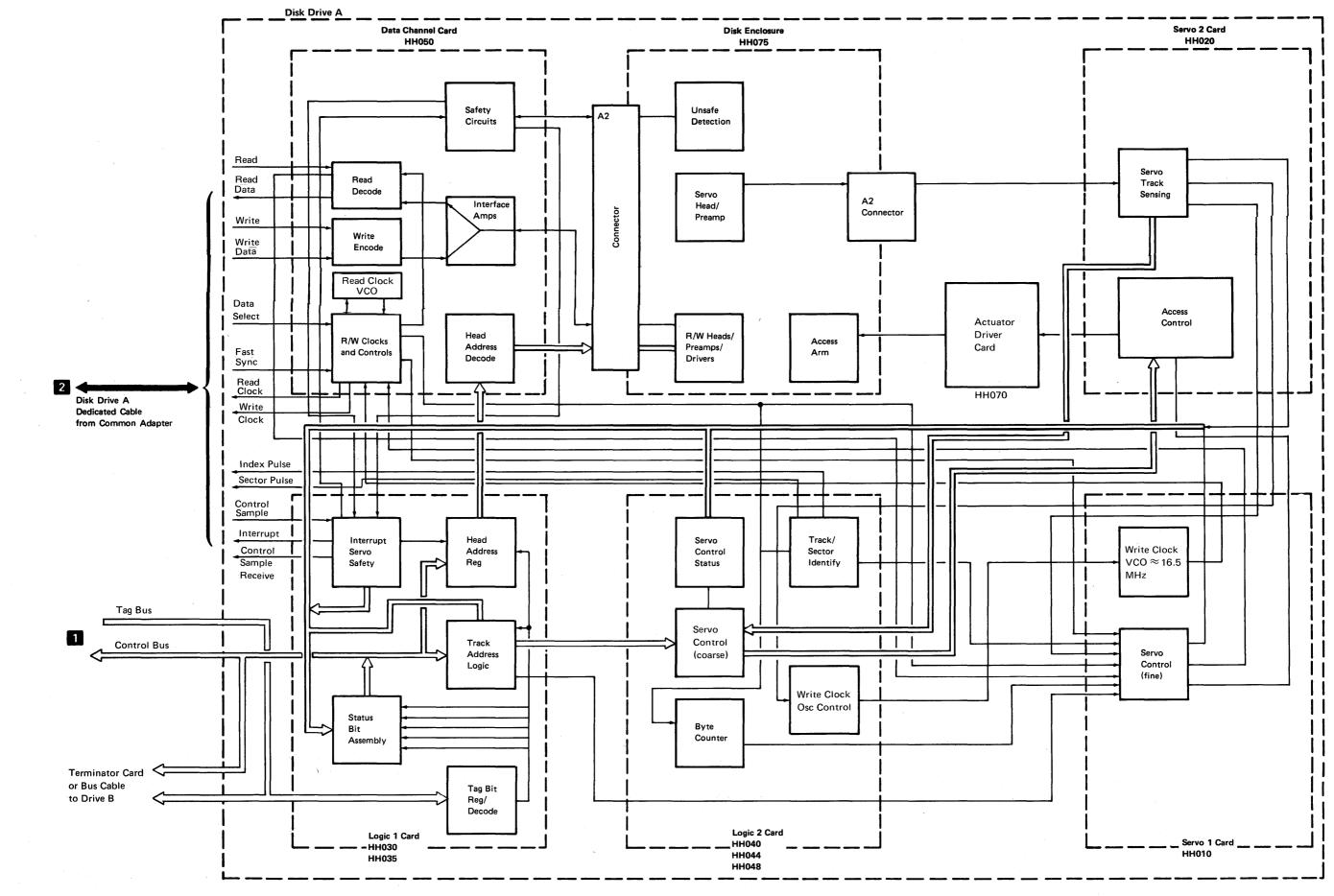

# **Circuit Locations**

The circuits for a disk drive are located in two separate areas: inside the disk enclosure and inside the card gate attached to the disk drive subframe. If a second disk drive is installed, it will have another set of the same circuits.

The attachment circuits are located on the A-A2 board. Additional attachment circuits are not needed if a second disk drive is installed.

The circuits inside the disk enclosure include:

- Read and write head selection

- · Read preamplifiers for each head

- · Write drivers for each head

- Servo preamplifier

The circuits in the disk drive card gate include:

- Two logic cards (4 wide 3 high), two servo cards (one card 4 wide 3 high, the other card 2 wide 3 high), and a data channel card (4 wide 2 high)

- A driver card for the actuator coil

Note: The card gate board is E-A1 for disk drive A and E-B1 for disk drive B.

The circuits on the A-A2 board include:

- The channel adapter card in A-A2E2

- The 62PC common adapter cards in A-A2D2 and A-A2C2 (these cards are connected by top card connectors)

The disk drive card gate receives:

enclosure

62PC Drive A

# **DISK FORMAT**

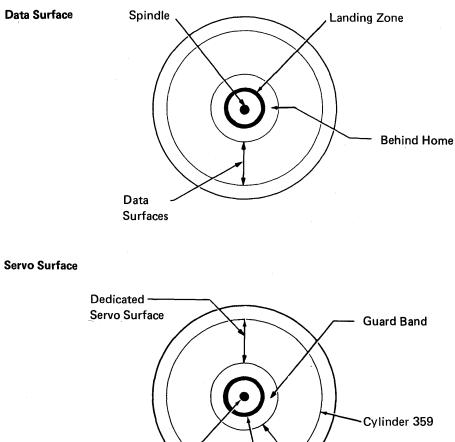

The disk surfaces are divided into cylinders, tracks, and sectors.

# Cylinders

A cylinder is the area that passes under all the data heads in one disk revolution. The 62PC disk drive has 358 data cylinders, 1 alternative cylinder, and 1 CE cylinder.

# Tracks

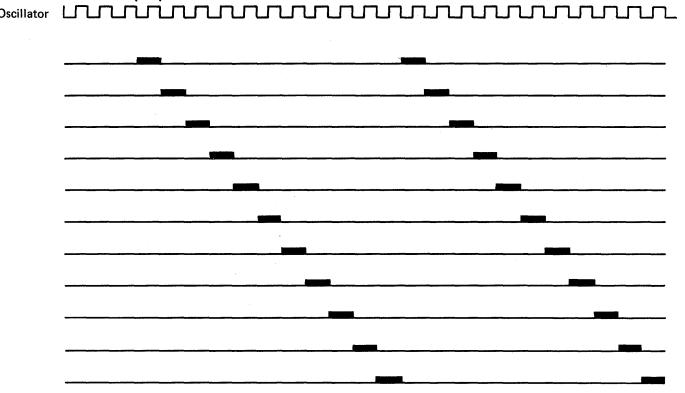

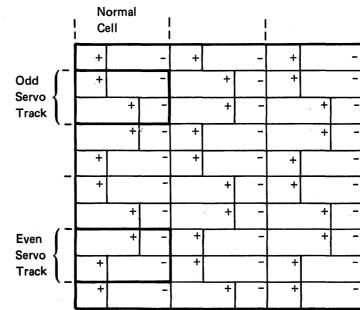

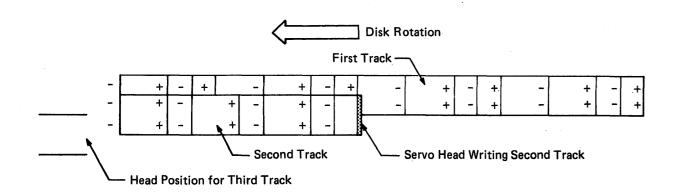

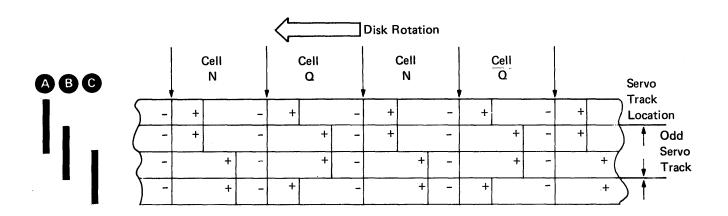

#### Servo Track

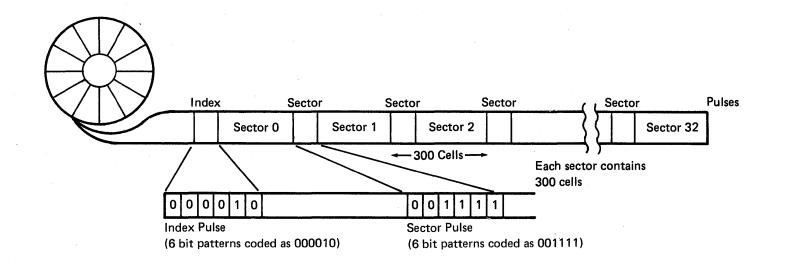

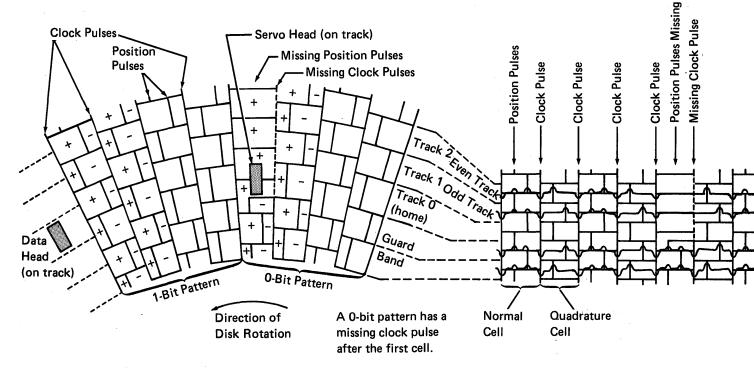

A servo track is the area that passes under the servo head in one disk revolution. There is one servo track on the dedicated servo surface for each cylinder. The servo tracks are patterns written on the disk at the factory. These patterns contain clock pulses and position pulses. The clock pulses are used to generate the write clock, and the position pulses are used to keep the heads over the specified track. Patterns of missing clock pulses are used to generate the index and sector pulses.

#### Data Track

A data track is the area that passes under a single data head in one disk revolution. The 62PC disk drive has 11 data tracks per cylinder. Each data track has a sample servo area, which contains additional servo information, at the start of each sector.

# **Guard Band**

The guard band is an area on the servo track surface that contains clock and position pulses, but does not have missing clock pulses to generate index or sector pulses. The behind home area on the data track surface is comparable to the guard band area.

#### Landing Zone

The landing zone is an area on all disk surfaces where the servo head and data heads are positioned (by a spring) when the disk drive is powered off, and when the disk drive is powered on until the disk is up to the correct speed. The landing zone is the area nearest the center of the disk.

| Disk capacity in megabytes  | 64.9 (Note 1)  |

|-----------------------------|----------------|

| Number of tracks            | 3,960 (Note 2) |

| Number of data heads        | 11             |

| Number of cylinders         | 360 (Note 3)   |

| Number of sectors per track | 33 (Note 4)    |

| Number of records per track | 64             |

| Bytes per record            | 256            |

#### Notes:

- 1. 63.9 megabytes available for customer use

- 2. 3,938 tracks for customer use

- 11 tracks reserved as alternative tracks 11 tracks reserved for CE use

- 3. 358 cylinders for customer use (cylinders 0 to 357, hex 0 to 165) 1 cylinder reserved as alternative cylinder (cylinder 358, hex 166)

- 1 cylinder reserved as CE cylinder (cylinder 359, hex 167)

- 4. 32 sectors available for customer use

Spindle

Cylinder 0

Landing Zone

Data Surfaces

Servo Surface

**Base Casting**

Spindle

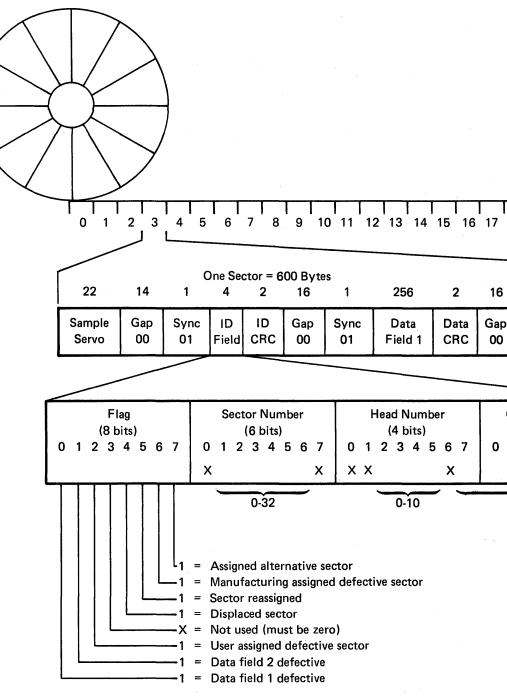

#### Sectors

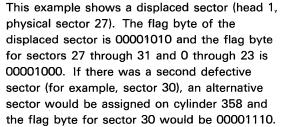

A sector is a division of a data track. Each data track is divided into 33 physical sectors, and each physical sector contains two data records. Only 32 of the physical sectors on each track are used for data storage. Therefore, there are 64 records for data storage on each track. Each record contains 256 bytes. Therefore, there are 16,384 bytes per track and 180,224 bytes per cylinder.

Each physical sector has an identification address that contains the cylinder, head, and sector numbers. This address is recorded in the identification field at the physical location of the sector on the disk. Each track has 33 identification fields.

Each of the 33 physical sectors is 600 bytes long and contains three main fields: the identification field and two data fields. Each data field contains a data record, and both records may be read or written after an ID hit. The records are numbered so that they may be operated on consecutively. Therefore, physical sector 0 (on head 0) contains records 0 and 1, physical sector 1 (on head 0) contains records 2 and 3, and so on. All 64 records on a track can be operated on in one revolution of the disk. Because a read or write operation can continue from one head to another head, the sectors for the next data head are delayed by a guarter revolution, or eight physical sectors, to permit time for head switching and for the servo circuits to become stable after the head switch.

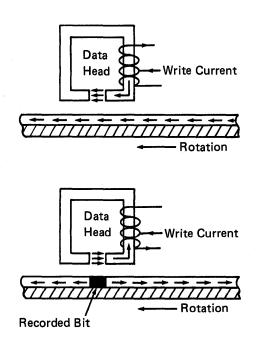

When the disks are assembled, each sector is tested. If a sector is damaged, an alternative sector is assigned for the damaged sector. Because only 32 of the 33 physical sectors on a track are used, the first damaged sector becomes the not used sector. On head 0, the 32 physical sectors that are used are numbered 0 through 31 sequentially, starting from the index pulse and skipping over the damaged sector, which is numbered 32. The damaged sector and all sectors located after it and before the next index pulse must have the displaced sector bit on in the identification field. If two or more sectors on a track are damaged, alternative sectors are assigned on the alternative cylinder. The identification field of the damaged sector contains the address of the alternative sector.

A sector that becomes damaged after the disk has been manufactured is assigned to the alternative cylinder. It becomes the not-used sector on the same track only when the sector fails during the disk initialize program.

Some areas of the disk are reserved. For more information, see the *Data Areas Handbook*.

X = Not used

*Note:* Flag bits 0 and 1 may be set in the ID field of an assigned alternative sector to indicate that the data written in the sector was obtained from a defective sector:

Bit 0 = 1 indicates that data field 1 was read with a CRC check.

Bit 1 = 1 indicates that data field 2 was read with a CRC check.

If the ID field of the defective sector was read with a CRC check, both bit 0 and bit 1 are set to 1. Flag bits 0 and 1 may also be set in the ID fields of sectors that were defective when the disk was manufactured, but these are ignored by the disk attachment.

| 7        | 18 19 2    | 20 21 22        | 23 24       | 1 I<br>25 | 26 27      | 28           | 29        | 30 | 31 | 32 |

|----------|------------|-----------------|-------------|-----------|------------|--------------|-----------|----|----|----|

| 6        | 1          | 256             | 2           | 7         |            | d Le<br>ytes | ngth<br>- |    |    |    |

| ар<br>)0 | Sync<br>01 | Data<br>Field 2 | Data<br>CRC | Gap<br>00 | Sam<br>Ser |              |           |    |    |    |

|                 |   |     |      |         |          | -        | -        |  |

|-----------------|---|-----|------|---------|----------|----------|----------|--|

| Cylinder Number |   |     |      |         |          |          |          |  |

| (9 bits)        |   |     |      |         |          |          |          |  |

| 1               | 2 | 3   | 4    | 5       | 6        | 7        |          |  |

|                 |   |     |      |         |          |          |          |  |

|                 |   | . ( | (9 t | (9 bits | (9 bits) | (9 bits) | (9 bits) |  |

0-359

| Sector Pulses                  |                      |                          |                      |                              |                                              |                         |

|--------------------------------|----------------------|--------------------------|----------------------|------------------------------|----------------------------------------------|-------------------------|

| .1                             | ndex                 |                          |                      |                              |                                              | Index                   |

|                                |                      |                          |                      |                              |                                              |                         |

|                                | ]                    | H                        | ead Settle Time—     |                              | →                                            |                         |

|                                | Ļ                    |                          |                      |                              |                                              |                         |

| Physical Sector ID – Head 0 32 | 00 01                | 02 03                    | 04 05                | 06 07 08                     |                                              | 31 32                   |

| Logical Record Position        | - 00 01 02 03        | 04 05 06 07              | 08 09 10 11          | 12 13 14 15 16               | 60 6 60 6                                    | 1 62 63                 |

|                                |                      |                          |                      |                              |                                              |                         |

| Head 1 32                      | 24 25<br>48 49 50 51 | 26  27    52  53  54  55 | 28 29<br>56 57 58 59 | 30 31 00<br>60 61 62 63 00   |                                              | 23 <u>32</u><br>5 46 47 |

|                                | 40 49 50 51          | 02 03 04 00              | 5 50 57 58 58        |                              | <u>5   01   02   03   04 )</u> <u>44   4</u> | 5 40 47                 |

| Head 2 32                      | 16 17                | 18 19                    | 20 21                | 22 23 24                     | 4 25 26 \ \14                                | 15 32                   |

|                                | 32 33 34 35          | 5 36 37 38 39            | 40 41 42 43          | 8 44 45 46 47 48             |                                              | 9 30 31                 |

|                                |                      |                          |                      |                              |                                              |                         |

| Head 3 32                      | 08 09<br>16 17 18 19 | 10 11<br>20 21 22 23     | 12 13<br>24 25 26 27 | 14 15 16<br>28 29 30 31 32   |                                              | 07 32                   |

|                                |                      |                          | 5 24 25 26 27        | 20 29 30 31 32               | 2 33 34 35 30                                | 3 14 15                 |

| Head 4 32                      | 00 01                | 02 03                    | 04 05                | 06 07 08                     | 8 09 10 30                                   | 31 32                   |

| •                              | 00 01 02 03          | 04 05 06 07              | 08 09 10 11          | 12 13 14 15 16               |                                              | 1 62 63                 |

|                                |                      |                          |                      |                              |                                              |                         |

| Head 5 32                      | 24 25<br>48 49 50 51 | 26  27    52  53  54  55 | 28 29                | 30 31 00<br>60 61 62 63 00   |                                              | 23 32                   |

| · · · · ·                      | 48 49 50 51          | 52 53 54 55              | 56 57 58 59          | 60 61 62 63 00               | 0 01 02 03 04 44 4                           | 5 46 47                 |

| Head 6 32                      | 16 17                | 18 19                    | 20 21                | 22 23 24                     | 4 25 26 14                                   | 15 32                   |

|                                | 32 33 34 35          |                          |                      |                              |                                              |                         |

| <b></b>                        |                      | ·····                    |                      |                              |                                              |                         |

| Head 7 32                      | 08 09                | 10 11                    | 12 13                | 14 15 16                     |                                              | 07 32                   |

|                                | 16 17 18 19          | 20 21 22 23              | 24 25 26 27          | 28 29 30 31 32               | 2 33 34 35 36 {12 1                          | 3 14 15                 |

| Head 8 32                      | 00 01                | 02 03                    | 04 05                | 06 07 08                     | 3 09 10 \ \30                                | 31 32                   |

|                                | 00 01 02 03          |                          |                      |                              |                                              |                         |

|                                |                      |                          | 1001001.01.1         |                              |                                              |                         |

| Head 9 32                      | 24 25                | 26 27                    | 28 29                | 30 31 00                     |                                              | 23 32                   |

|                                | 48 49 50 51          | 52 53 54 55              | 56 57 58 59          | 60 61 62 63 00               | 0 01 02 03 04 44 4                           | 5 46 47                 |

|                                |                      |                          |                      |                              |                                              |                         |

| Head 10 32                     | 16 17<br>32 33 34 35 | 18 19<br>36 37 38 39     | 20 21<br>40 41 42 43 | 22 23 24<br>3 44 45 46 47 48 |                                              | 15 <u>32</u><br>9 30 31 |

|                                | 02 03 04 30          | 1 20 27 20 28            | 140 41 42 43         | 40 40 47 40                  | 20 2 20 21 22 20 2                           |                         |

# **Data Recording**

#### **Reading and Writing Data**

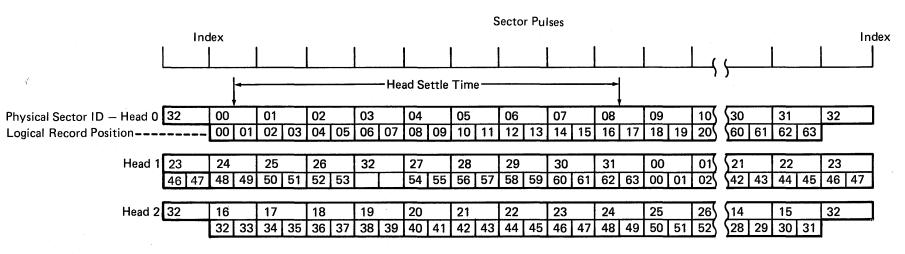

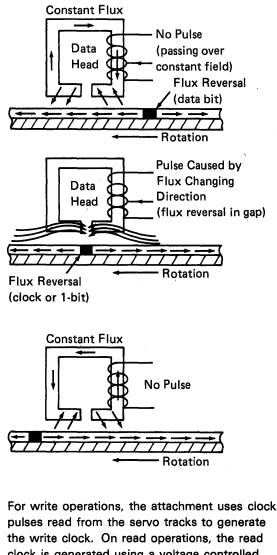

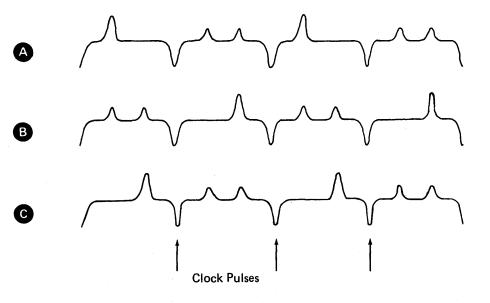

During a write operation, data is recorded by reversing the direction of the current in the coil, which reverses the direction of the magnetic flux in the data head gap. When the flux in the data head gap reverses, there is a magnetic change of direction on the disk surface. Each change of direction on the disk represents a recorded 0-bit or 1-bit.

During a read operation, when the disk surface is recorded in one magnetic direction, constant flux flows and the coil senses no output voltage. But, when a 180-degree horizontal flux change passes the gap, the flux through the ring and coil reverses and generates a voltage output pulse. The timing of these pulses indicates if a 0-bit or a 1-bit was written.

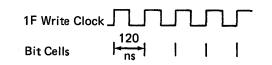

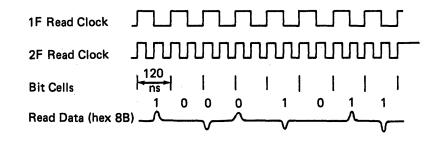

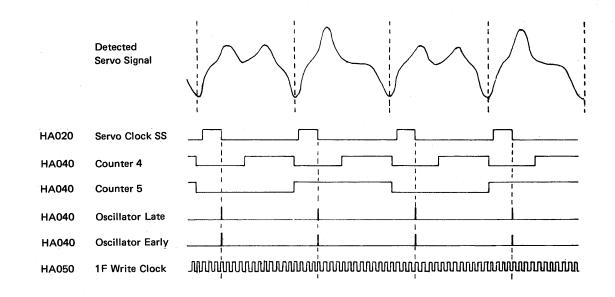

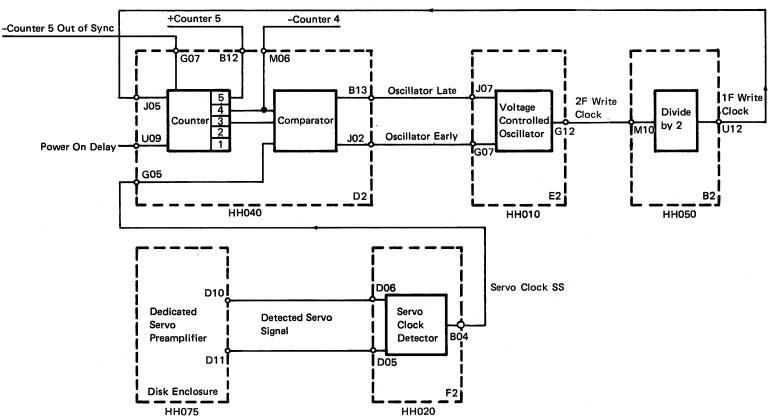

pulses read from the servo tracks to generate the write clock. On read operations, the read clock is generated using a voltage controlled oscillator synchronized with the data read from the disk.

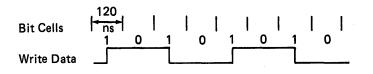

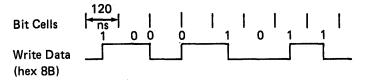

The time during which a data bit can be written is known as a bit cell. A bit cell is 120 nanoseconds long and is generated by the '1F write clock' line.

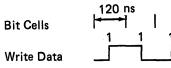

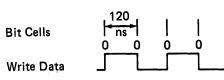

#### Writing 1-Bits and 0-Bits

One-bits are always written in the center of a bit cell.

With one exception, 0-bits are always written at the start of a bit cell.

The exception is when the 0-bit immediately follows a 1-bit. In this case, no bit is written and the 0-bit is represented by no magnetic change of direction during its bit cell time.

Both methods of writing 0-bits and the method of writing 1-bits can be shown when writing hexadecimal 8B.

Any data written is transmitted on the data transmission line from the disk drive card gate to the write circuits located on the actuator arm. For each change on the data transmission line, a 0-bit or 1-bit is written on the disk. These changes cause the current to be switched in the data head, which results in a change of magnetic direction on the disk.

#### **Reading Data Bits**

A voltage controlled oscillator generates the read clock when data is read from the disk drive. The oscillator is synchronized during the 16-byte gap field preceding the data field. The phase lock oscillator loop then keeps the oscillator in sync with the read data (1-bits and 0-bits) so the data can be decoded.

# DATA PROTECTION

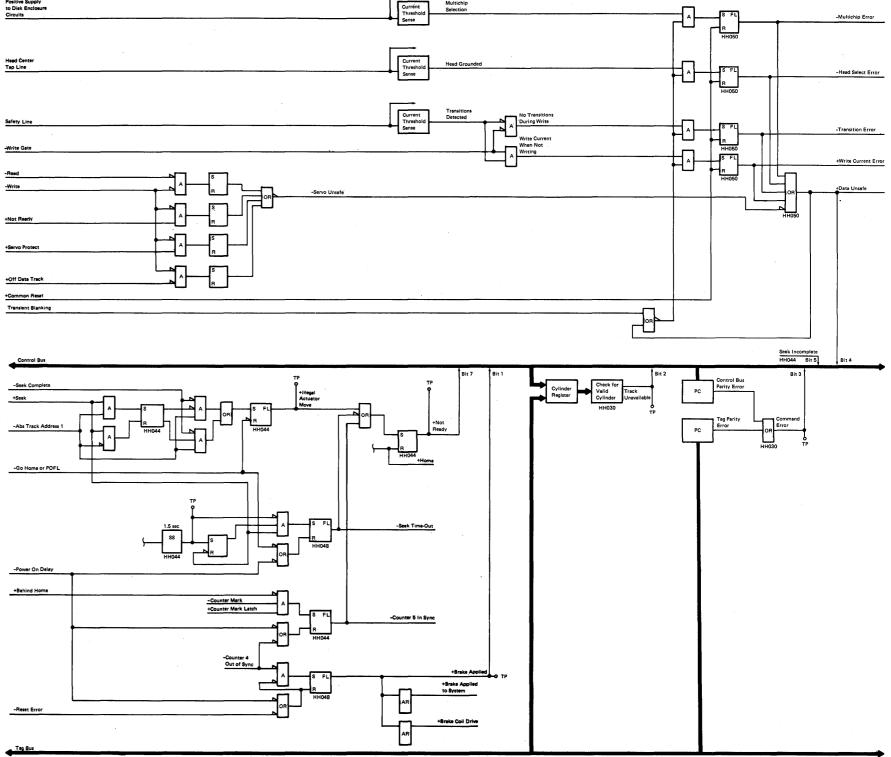

# **Data Unsafe Conditions**

To prevent data from being destroyed by accident, there are circuits to protect data by not permitting data to be written under unsafe conditions. These unsafe conditions are described in *Error Conditions* later in this section.

When any of these unsafe conditions occur, write current is turned off and the data head select lines are de-activated. The disk drive sends an interrupt to the common adapter, and all commands from the common adapter (except sense commands) are ignored until the condition is reset.

# Not Ready

Data cannot be written when the disk drive is not ready.

The 'not ready' latch is activated by the following:

- A seek time-out has occurred.

- The servo clock counter has lost synchronization.

- The 'illegal actuator move' line is active.

For more information, see *Error Conditions* later in this section.

# Power On and Power Off

During power on, the actuator is held against the inner stop until the disk is up to speed.

A correct power on will be followed within 25 seconds by an interrupt from the disk drive after the heads have moved to home (cylinder 0 head 1).

During a normal power off, the actuator is moved by a spring to the inner stop where it is held by a magnet. This locates the heads over the landing zone. The spindle brake is applied when its hold voltage is removed.

If a DC supply goes outside its limits, the system immediately removes all AC and DC voltages to decrease the possible loss of data. The actuator is moved to the inner stop as during a normal power off.

# **DATA FLOW**

The data flow in the disk attachment occurs across three interfaces:

- System I/O channel interface

- Common adapter interface

- Disk drive interface

62PC Disk Drive and Attachment 13-9

13

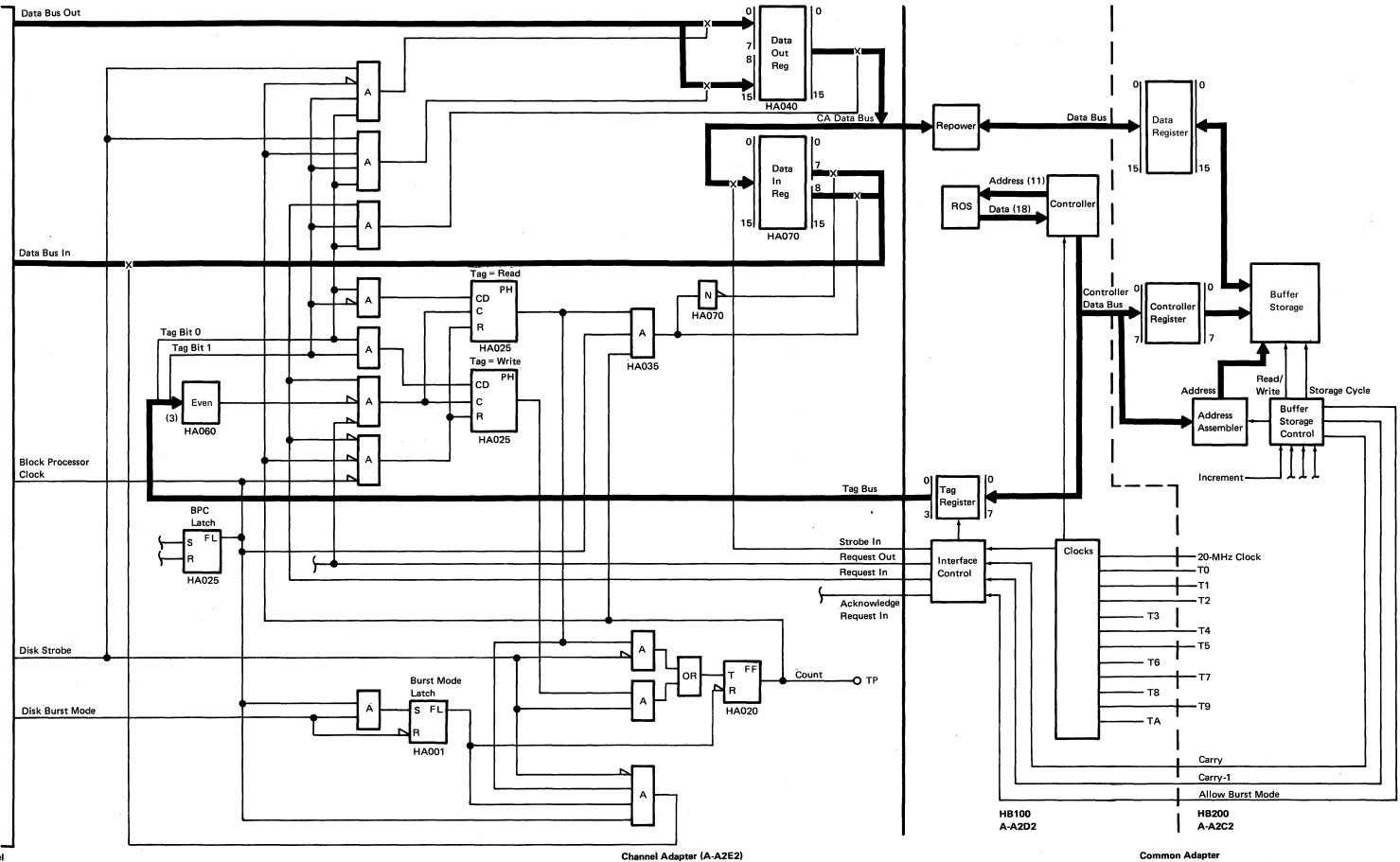

# System I/O Channel Interface

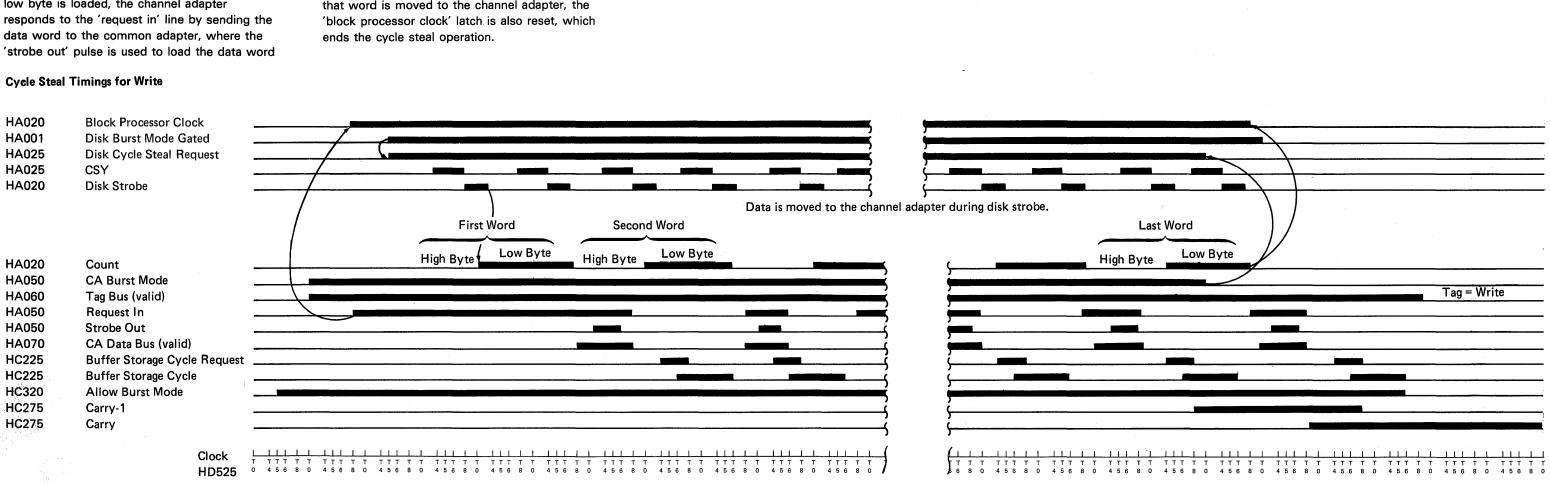

I/O instructions start the operations by using the DBO, the CBO, and the 'control out', 'service out', 'MPXPO strobe', and 'service in' control lines. Data is moved on the DBO for a write and on the DBI for a read. Cycle steal is used to move the data to and from the disk attachment. The 'block processor clock' and 'disk burst mode' lines are used to control the cycle steal operations.

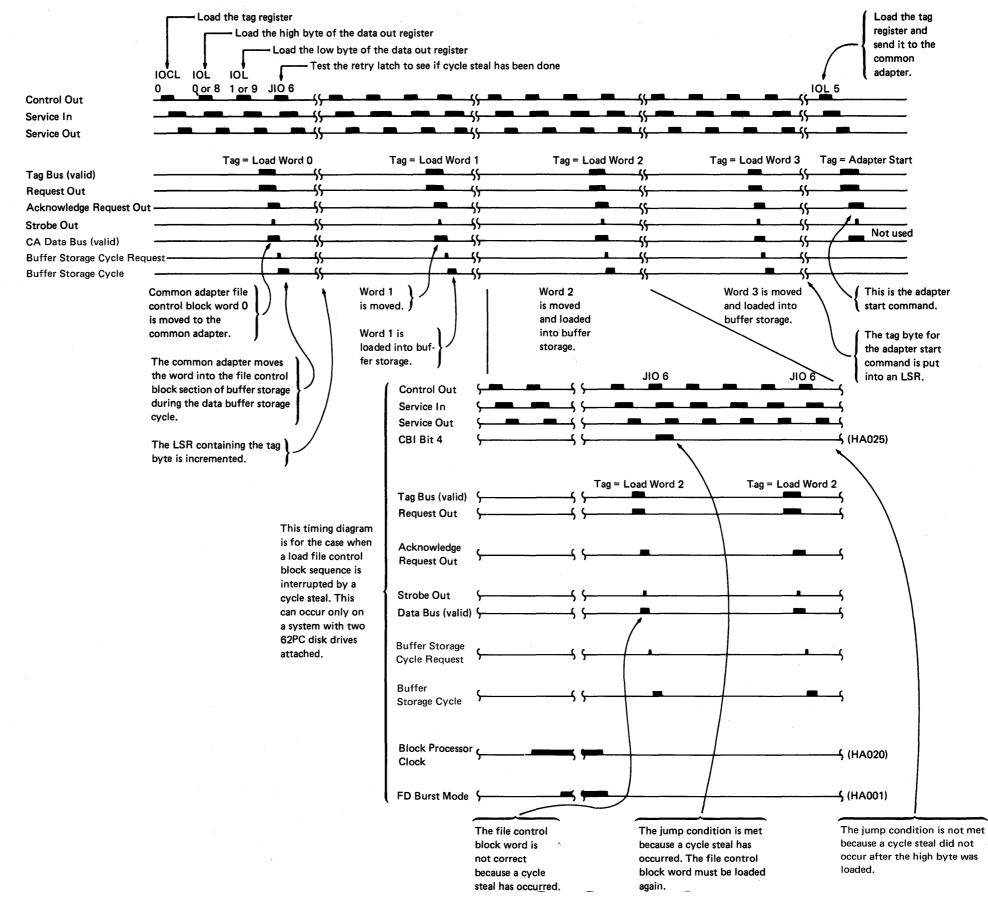

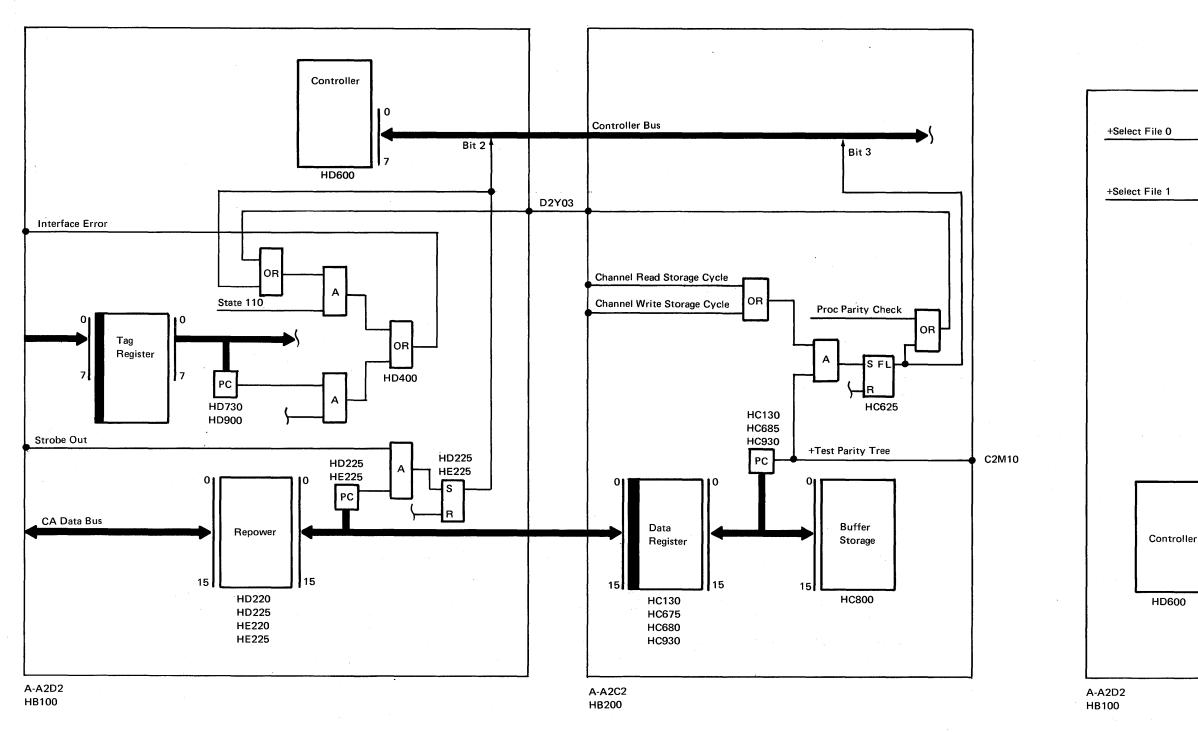

## **Common Adapter Interface**

Control information on the CA (common adapter) data bus starts the operations. The tag lines specify the information on the CA data bus and the 'request out', 'acknowledge request out', and 'strobe out' lines control the movement of this information.

Data is also moved on the CA data bus. The tag lines specify the direction of the data movement and the 'CA burst mode', 'request in', 'acknowledge request in', 'strobe in', and 'strobe out' lines control the movement of this data.

#### **State Counter**

The common adapter uses a 3-bit state counter to control data operations on the interface to the channel adapter. The state counter can change only 1 of its 3 bits each time it advances. The state counter starts at 0 and is advanced by the conditions on the interface lines and by internal timing pulses. The state counter is shown on timing charts later in this section to aid in understanding the logic, but the lines of the state counter cannot be probed.

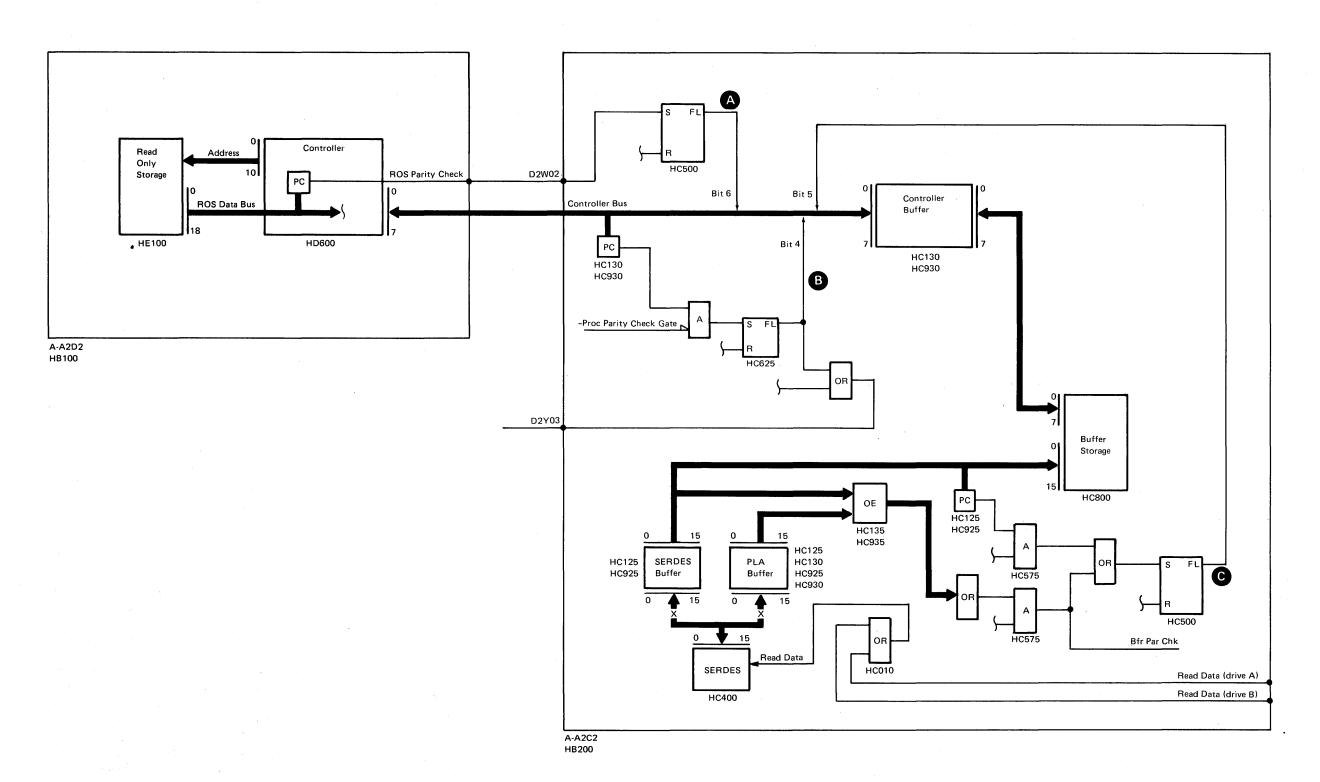

#### Controller

The common adapter has a controller which starts and executes all disk operations that are received from the control processor. The controller receives instructions from read-only storage (ROS), and uses a 9-bit controller bus and other internal control lines to send data or commands to a disk drive, to the channel adapter, or to buffer storage.

#### **Buffer Storage**

The common adapter buffer storage supplies temporary storage for data, commands, and status information. The buffer permits the controller to sense, to update, and to change the information while performing the control functions required for a specific operation. The buffer storage is divided into the following areas:

- ID compare field: This 4-byte field contains the ID of the sector for this operation. The contents of the ID compare field are compared to the IDs that are read from the disk. If the IDs are the same, an ID hit occurs.

- Controller work area: This 124-byte area is used by the controller as a work area.

- File control block(s): This area contains a 32-byte file control block (FCB) for each disk drive attached to the system. The FCB is used to store status and command information that is received from the control processor.

- Data buffers: These three 256-byte fields are used to store data that was read from or is to be written on the disk.

#### **Oscillator and Clocks**

TC W12 HD525 +T0

TC X02

TC W33

TC W32

**TC W28**

C2 S07

**TC Y11**

TC W30

NP

NP

NP

The common adapter has a 20-megahertz oscillator that generates eleven 50-nanosecond timing pulses. These timing pulses are used to sequence internal common adapter functions. Access to buffer storage is permitted during each sequence of timing pulses.

13

| Test Point | FSL<br>Page | Line Name         |   |

|------------|-------------|-------------------|---|

| TC Z33     | HD525       | 20-MHz Oscillator | ப |

+T1

HD525 +T2

HD525 +T3

HD525 +T4

HD525 +T5

HD525 +T6

HD525 +T7

HD525 +T8

HD525 +T9

HD525 +TA

→ 50 ns

- TC = Top card connectorC2 = A-A2C2 card

- NP = Cannot be probed

13-10

# **Disk Drive Interface**

The disk drive interface has two parts. The first part is used for access and sense commands and contains:

- A 9-bit control bus, which moves track addresses to the disk and senses status information from the disk.

- Four tag lines, which indicate the direction of the data and the type of data on the control bus.

- Two control lines (the 'control sample' and 'control sample received' lines), which control the movement of this data.

All of these lines, except for the 'control sample' line, are in the bus cable to the disk.

The second part of the disk drive interface is used for reading and writing data. The lines used to read and write data are located in the dedicated cable to the disk.

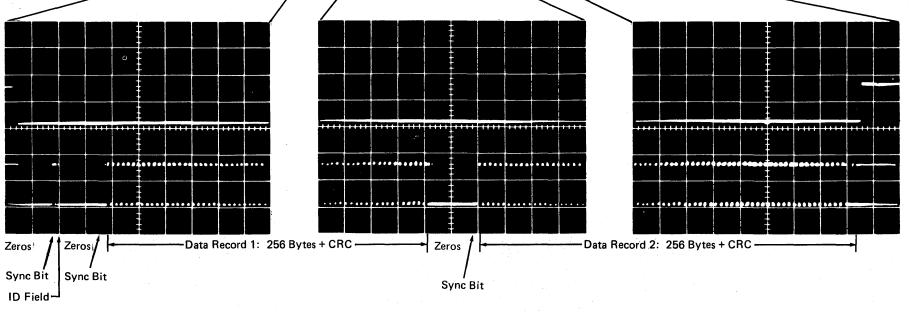

#### Write Data Flow

The data for a write operation is sent to the channel adapter on the DBO, and is loaded into the channel adapter data out buffer. Because the common adapter data bus is a 16-bit bus, 2 bytes of data from the DBO must be loaded into the data out buffer before data can be moved to the common adapter. In the common adapter, the data word is stored in the data register until it can be moved into buffer storage. The data is moved in blocks of 128 words, or 256 bytes, where each block is the data for one record on the disk. Data blocks may be moved immediately following each other until all three data buffers in buffer storage are full. When an ID hit occurs for the first sector to be written on the disk, the data is moved from buffer storage to the SERDES buffer, and then moved to the SERDES, where the data is serialized. The write data is moved to the disk drive under the control of the write clock. The data is written on the disk in synchronization with the write clock, which is controlled by the servo clock pulses on the dedicated servo surface.

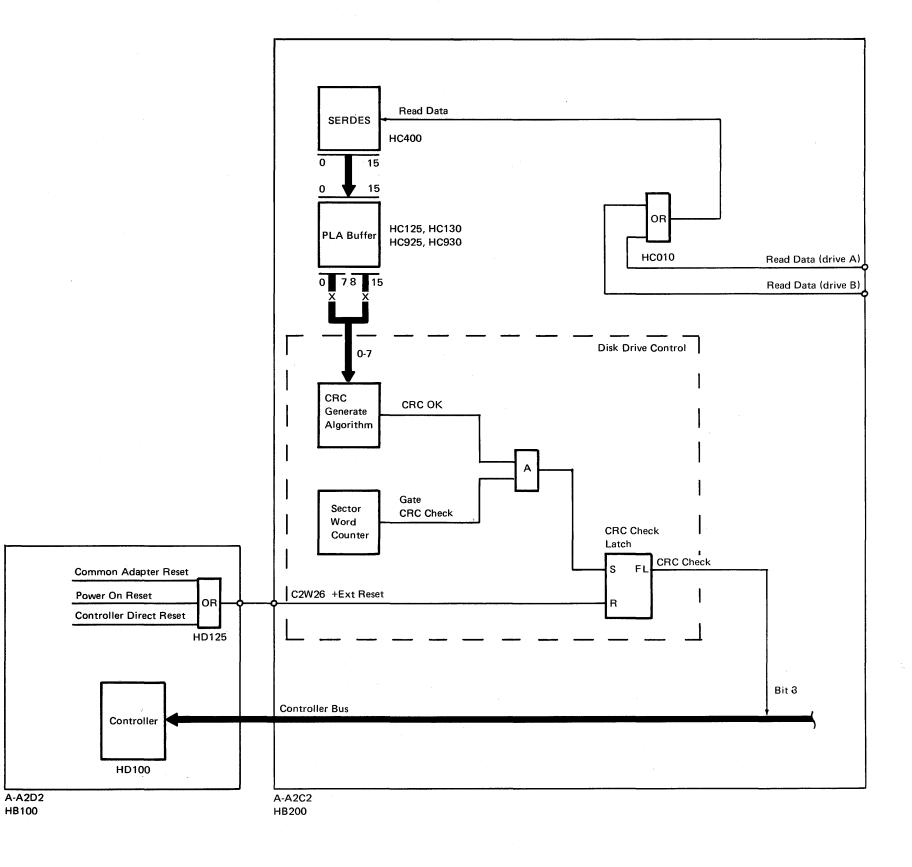

## **Read Data Flow**

When the 'read' line is active, the read clock is used to decode the data from the analog signals received from the disk. The read data circuits decode the pulses and send the serial data to the common adapter. This data is converted to word length in the SERDES and moved to the SERDES buffer until it can be moved into buffer storage. When a full sector has been moved to buffer storage, the common adapter starts to move the data in burst mode to the channel adapter, which starts the cycle steal operation when the 'disk burst mode' line becomes active. The data is converted to byte length in the channel adapter data in buffer, and is sent to the control processor on the DBI.

62PC Disk Drive and Attachment 13-11

13

# **OPERATIONS**

The disk drive and attachment perform the following data operations:

- Read ID

- Read data

- Read diagnostic

- Read verify

- Write ID

- Write data

- Scan equal

- · Scan high or equal

- · Scan low or equal

In addition, the special operations for diagnostic purposes are:

- Load seek required address direct

- · Load seek control direct

- · Sense file direct

- Sense file diagnostic sense bytes 1, 2, and 3

- Sense file diagnostic sense bytes 1, 2, and 3 256 sample test

- Sense file diagnostic wrap

- Disk speed timing diagnostic

- Timed seek diagnostic

- · Read data with data repeat

- Read common adapter buffer storage

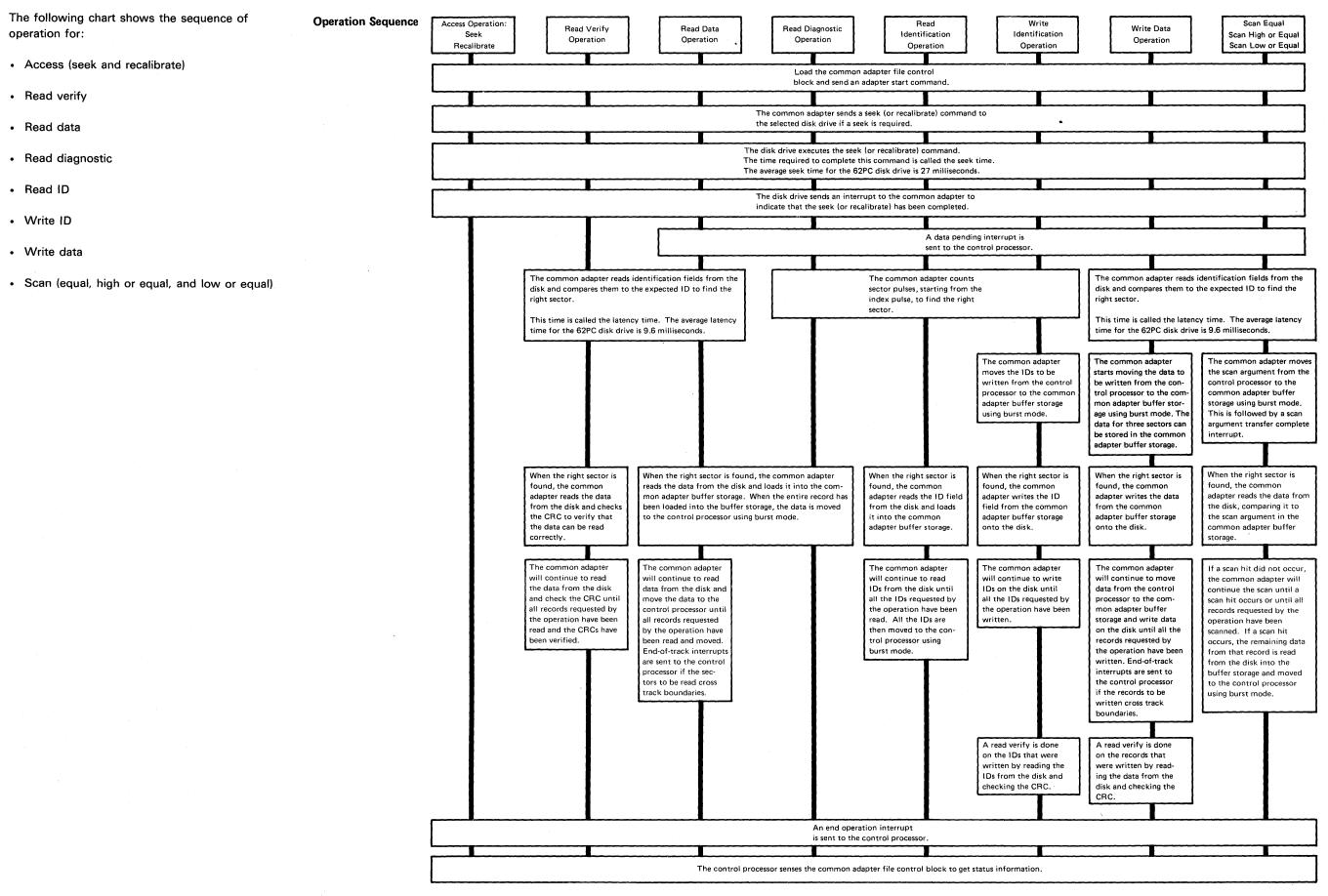

# **Operation Sequence**

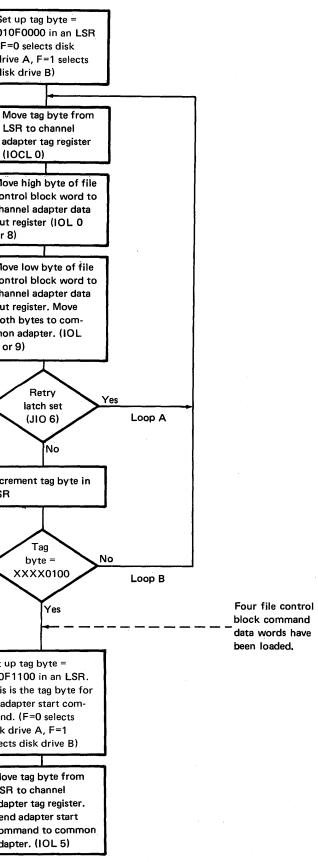

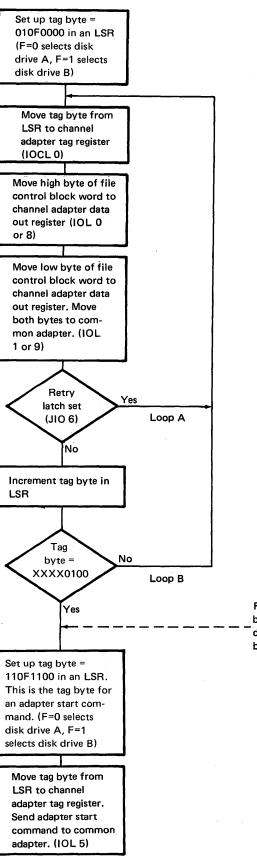

For each command received from the control storage program, the disk attachment (channel adapter and common adapter) and the disk drive perform an operation or operations. The sequence for these operations is:

- 1. Each operation is started by loading the common adapter file control block (FCB) for the requested disk drive. The FCB contains all the information needed by the common adapter to complete the operation. For more information, see Common Adapter File Control Block and Loading and Sensing the Common Adapter File Control Block later in this section.

- 2. An adapter start is sent to the common adapter. This instructs the common adapter to execute the operation contained in the FCB.

- 3. The common adapter controller executes the adapter start if no higher priority internal command than the adapter start is requested. During the operation, the common adapter can send interrupts to the channel adapter and move data between the channel adapter, common adapter, and disk drive. For more information, see *Interrupts* later in this section.

- 4. The common adapter indicates the operation is complete by sending an end operation interrupt to the control processor. If an error occurred, the operation may be terminated immediately and the end operation interrupt indicates an error condition. For more information, see Interrupts later in this section.

- Sense and status information is obtained by sensing the FCB. For more information, see Common Adapter File Control Block and Loading and Sensing the Common Adapter File Control Block later in this section.

#### Read ID

The ID fields on the disk are read for the read ID, read data, write data, and scan operations, but are sent to the control processor only on a read ID operation. The CRC of the ID field is checked every time the ID field is read, but a CRC error on an ID field is set only on a read ID operation. When ID fields are read during a read data, write data, or scan operation, a CRC check in the ID field of the desired sector causes a no-record-found error.

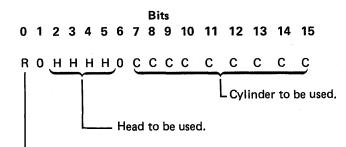

The read ID operation can read up to 33 IDs (one complete track). The record number or sector number in the FCB indicates the sector to be read starting from the index pulse. Because of the head switch delay, the sector following the index is not always sector 0 (for more information, see Sectors earlier in this section). If an error occurs during a read ID operation, the operation stops at the sector in error.

The read ID special operation is used to read IDs without stopping on the error. An ID of hexadecimal FFFFFFF is moved to the control processor to indicate a sector with an error.

The read ID extended operation is used if the ID field was written extended (64 bytes later than a normal ID) because of a failure on the disk at the normal ID location.

#### The command byte for a read ID operation is:

|                  | Bits |   |    |    |    |    |    |    |

|------------------|------|---|----|----|----|----|----|----|

|                  | 8    | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| Read ID          | 0    | 1 | 0  | 1  | 0  | 1  | 0  | 0  |

| Read ID Special  | 1    | 1 | 0  | 1  | 0  | 1  | 0  | 0  |

| Read ID Extended | 0    | 1 | 0  | 1  | 0  | 1  | 0  | 1  |

*Note:* If bit 12 is set to 1, the common adapter does not automatically perform a seek.

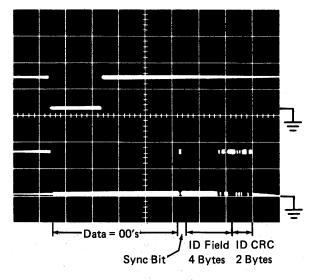

### Read ID

| Format           | Sample<br>Servo                           | Gap<br>(hex 00) | Sync<br>(hex 01)           | ID<br>FSHC                                                                        | ID CRC                                               | Gap<br>(hex 00)             |

|------------------|-------------------------------------------|-----------------|----------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------|

| Number of Bytes  | 22                                        | 14              | 1                          | 4                                                                                 | 2                                                    | 16                          |

| Sequence Counter | 0357 0                                    | <u>1</u>        |                            | 2                                                                                 |                                                      | 3                           |

|                  | Fine adjust of<br>data head over<br>track | Sync<br>clock   | Look<br>for<br>sync<br>bit | Read ID<br>and com-<br>pare with<br>ID com-<br>pare field<br>in buffer<br>storage | Read CRC<br>and com-<br>pare with<br>CRC<br>register | Read<br>circuit<br>recovery |

| -Index or        |                                           |                 |                            |                                                                                   |                                                      |                             |

### Read ID Extended

| Format   | <b>&gt;</b>               | Sample<br>Servo                           | Gap<br>(hex 00) | Sync<br>(hex 01)           | ID<br>FSHC                                                                        | ID CRC                                          | Gap<br>(hex 00)             |

|----------|---------------------------|-------------------------------------------|-----------------|----------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------|-----------------------------|

| Number o | f Bytes                   | 22                                        | 78              | 1                          | 4                                                                                 | 2                                               | 16                          |

| Sequence | Counter                   | 0357 0                                    | 1               |                            | 2                                                                                 |                                                 | 3                           |

|          |                           | Fine adjust<br>of data head<br>over track | Sync<br>clock   | Look<br>for<br>sync<br>bit | Read ID<br>and com-<br>pare with<br>ID com-<br>pare field<br>in buffer<br>storage | Read CRC<br>and compare<br>with CRC<br>register | Read<br>circuit<br>recovery |

| HH040    | -Index or<br>-Sector ■    | <b></b> (                                 |                 |                            | byte after                                                                        |                                                 |                             |

| HH050    | -Read                     |                                           |                 |                            | lock synchron                                                                     | ized twice                                      |                             |

| HH050    | -Fast Sync                |                                           |                 | for ext                    | tended ID                                                                         |                                                 | o                           |

| HH050    | Read Clock<br>Write Clock | Write<br>Clock                            | Data rea        |                            | Read Clock                                                                        | •                                               | Write<br>Clock              |

| HH050    | +Read Data                |                                           | commor          | n adapter                  | <u> </u>                                                                          |                                                 | ·                           |

| HC450    | +Sync Bit Found           |                                           |                 | (                          |                                                                                   |                                                 |                             |

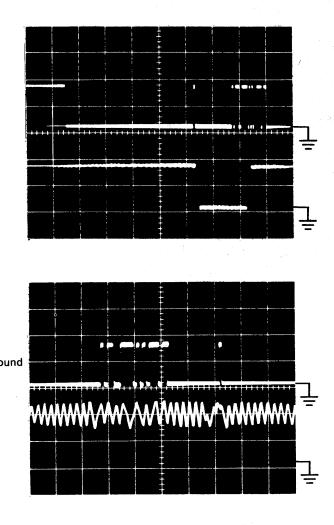

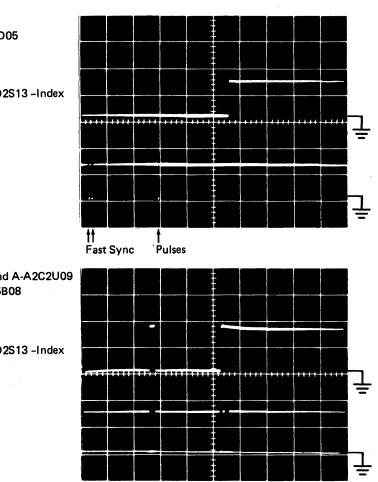

| HH040 | -Index or<br>-Sector      |                                                                                   | HH040 | -Index or<br>-Sector                  |

|-------|---------------------------|-----------------------------------------------------------------------------------|-------|---------------------------------------|

| HH050 | -Read                     | Read is selected 1 byte<br>after index or sector pulse<br>Read clock synchronized | HH050 | -Read                                 |

| HH050 | -Fast Sync 🔳              | by fast sync                                                                      | HH050 | -Fast Sync                            |

| HH050 | Read Clock<br>Write Clock | Clock used to gate bit ring<br>Write Read Clock Write<br>Clock Clock              | HH050 | Read Clock<br>Write Clock —— Wi<br>Cl |

| HH050 | +Read Data                | Data read from the disk is sent to the common adapter                             | HH050 | +Read Data                            |

| HC450 | +Sype Bit Found           |                                                                                   | HC450 | +Sync Bit Found                       |

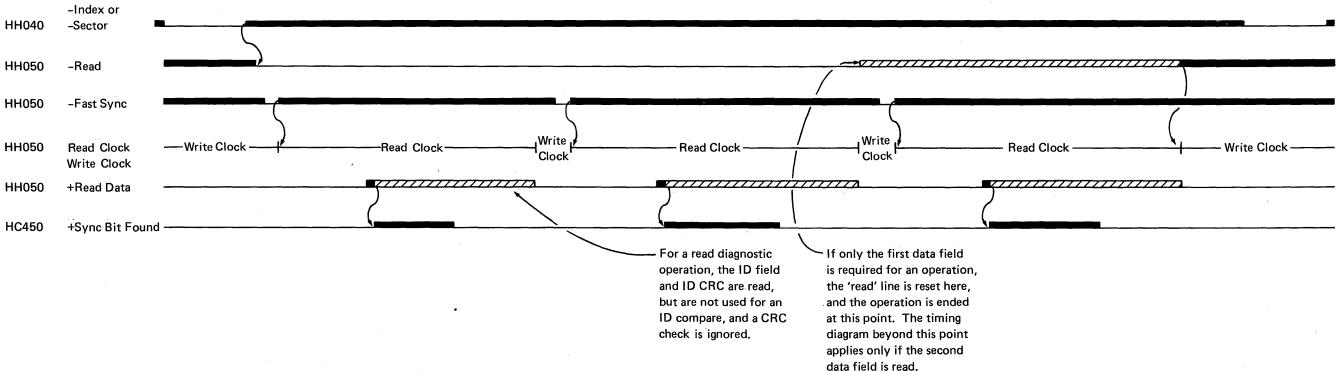

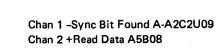

#### **Read Data**

The read data operation reads 256-byte data records from the data fields on the disk. One read data operation may read up to 256 consecutive records. The common adapter automatically performs seek operations to place the actuator at the correct track (if bit 12 of the command byte is 0). If the addressed sector has an alternative sector assigned, the common adapter performs a seek to the alternative cylinder and finds the alternative sector. The alternative sector is read and the actuator is returned to the original track if there are more sectors to be read by this operation. If a CRC check occurs, the operation ends with the sector in error, but that data is still moved to the control processor.

#### **Read Diagnostic**

The read diagnostic operation reads data from the disk without an identification field compare. The common adapter counts sector pulses, starting from the index, to find the correct sector.

In the read data operation, the data fields from a sector can be read only if an ID hit occurs. If an identification field becomes damaged after the data is written, an ID hit might not occur. The read diagnostic operation can then recover the data. This operation moves the data read from the disk to the control processor even if an error occurs during the read operation.

#### Read Data/Read Verify/Read Diagnostic/Scan High/Low/Equal

#### **Read Verify**

The read verify operation is the same as the read data operation, except that the data read from the disk is not moved to the control processor. This operation is used to verify that the data record being read from the disk can be read without an error.

| The command bytes diagnostic, and read |              |                   |    |                             | •: |    |    |    |

|----------------------------------------|--------------|-------------------|----|-----------------------------|----|----|----|----|

|                                        |              |                   |    | Bits                        |    |    |    |    |

|                                        | 8            | 9                 | 10 | 11                          | 12 | 13 | 14 | 15 |

| Read Data                              | 0            | 1                 | 0  | 1                           | 0  | 0  | 0  | 0  |

| Read Diagnostic                        | 0            | 1                 | 0  | 1                           | 0  | 1  | 1  | DF |

| Read Verify                            | 0            | 1                 | 0  | 1                           | 0  | 0  | 0  | 1  |

|                                        | DF<br>0<br>1 | = D<br>= d<br>= d | da | is figu<br>ta rec<br>e secc |    |    |    |    |

| Format           | Sample<br>Servo                           | Gap<br>(hex 00) | Sync<br>(hex 01)           | ID<br>FSHC                                     | ID CRC                                          | Gap<br>(hex 00) | Sync<br>(hex 01)           | Data Field 1                                          | Data<br>CRC                                     | Gap<br>(hex 00) | Sync<br>(hex 01)           | Data Field 2                                          | Data<br>CRC                                     | Gap<br>(hex 00)             | Sample<br>Servo                           |

|------------------|-------------------------------------------|-----------------|----------------------------|------------------------------------------------|-------------------------------------------------|-----------------|----------------------------|-------------------------------------------------------|-------------------------------------------------|-----------------|----------------------------|-------------------------------------------------------|-------------------------------------------------|-----------------------------|-------------------------------------------|

| Number of Bytes  | 22                                        | 14              | 1                          | 4                                              | 2                                               | 16              | 1                          | 256                                                   | 2                                               | 16              | 1                          | 256                                                   | 2                                               | 7                           | 22                                        |

| Sequence Counter | 0357 0                                    | 1               |                            | 2                                              |                                                 | 3               |                            | 4                                                     |                                                 | 5               |                            | 6                                                     |                                                 | 7                           |                                           |

|                  | Fine adjust<br>of data head<br>over track | Sync<br>clocks  | Look<br>for<br>sync<br>bit | Read ID<br>and compare<br>with field<br>in FCB | Read CRC<br>and compare<br>with CRC<br>register | Sync<br>clocks  | Look<br>for<br>sync<br>bit | Read data from<br>disk and store in<br>buffer storage | Read CRC<br>and compare<br>with CRC<br>register | Sync<br>clocks  | Look<br>for<br>sync<br>bit | Read data from<br>disk and store in<br>buffer storage | Read CRC<br>and compare<br>with CRC<br>register | Read<br>circuit<br>recovery | Fine adjust<br>of data head<br>over track |

figure shows the reading of one or two records from a sector on the disk. If only econd data field is to be read for an operation, the common adapter will read both data fields, but will not move the first record into buffer storage.

These timings apply to read data, read verify, read diagnostic, and scan operations.

#### Write ID

The write ID operation writes identification fields in sectors of the disk. This operation is used when a permanent error is found in a sector and the identification field must be written again to indicate that the sector is damaged, and to identify the location of the alternative sector to which the data has been moved. If the damaged area is within the identification field, the identification field can be written 64 bytes later than a normal ID, so that the ID will not be written on the damaged area (write ID extended).

The write ID operation can write up to 33 IDs (one complete track). The record number or sector number in the common adapter file control block (FCB) indicates the first sector to be written, starting from the index. If an error occurs during a write ID operation, the operation ends and that sector is indicated in the record or sector number byte of the FCB.

#### The command byte for a write ID operation is:

|                   |    |        |        | Bits  |    |    |    | ٠  |

|-------------------|----|--------|--------|-------|----|----|----|----|

|                   | 8  | 9      | 10     | 11    | 12 | 13 | 14 | 15 |

| Write ID          | 0  | 1      | 1      | 0     | 0  | 1  | 0  | RV |

| Write ID Extended | 0  | 1      | 1      | 0     | 0  | 1  | 1  | RV |

|                   | R٧ | / = re | ead ve | erify |    |    |    |    |

Note: If bit 12 is set to 1, the common adapter does not automatically perform a seek.

#### Write ID

#### Write ID Extended

| Format —  | <b>&gt;</b>            | Sample<br>Servo                           | Gap<br>(hex 00)                        | Sync<br>(hex 01)                    | ID<br>F S H C                   | ID CRC                   | Gap<br>(hex 00)              | Format                       | Sample<br>Servo                           | (        |

|-----------|------------------------|-------------------------------------------|----------------------------------------|-------------------------------------|---------------------------------|--------------------------|------------------------------|------------------------------|-------------------------------------------|----------|

| Number of | f Bytes ———            | <b>22</b>                                 | 14                                     | 1                                   | 4                               | 2                        | 16                           | Number of Bytes              | 22                                        |          |

| Sequence  | Counter>               | 0357 0                                    | 1                                      |                                     | 2                               |                          | 3                            | Sequence Counter>            | 0357 0                                    | L        |

|           |                        | File adjust of<br>data head<br>over track | Write<br>zeros<br>and<br>sync<br>clock | Write<br>sync<br>bit<br>(hex<br>01) | Write ID<br>and generate<br>CRC | Write<br>CRC             | Write<br>circuit<br>recovery |                              | File adjust of<br>data head<br>over track |          |

| HH040     | -Index or<br>-Sector ■ | ،<br>۱                                    |                                        |                                     |                                 |                          | •                            | -Index or<br>HH040 –Sector ■ | l                                         |          |

| HH050     | -Write                 |                                           | )                                      |                                     |                                 | _ / ···= · · · ···== ··· |                              | HH050 -Write                 |                                           | L        |

| HH050     | -Fast Sync             |                                           |                                        |                                     |                                 |                          |                              | ■ HH050 -Fast Sync           |                                           |          |

| HH050     | Write Clock            | <u></u>                                   |                                        |                                     |                                 |                          |                              | HH050 Write Clock            |                                           | <b>Z</b> |

| HH050     | -Write Data            |                                           |                                        |                                     | ·····                           |                          | 2                            | HH050 -Write Data            |                                           |          |

| Sample<br>Servo                           | Gap<br>(hex 00)                        | Sync<br>(hex 01)                    | ID<br>FSHC                      | ID CRC       | Gap<br>(hex 00)              |

|-------------------------------------------|----------------------------------------|-------------------------------------|---------------------------------|--------------|------------------------------|

| 22                                        | 78                                     | 1                                   | 4                               | 2            | 484                          |

| 0357 0                                    | 1                                      |                                     | 2                               |              | 3                            |

| File adjust of<br>data head<br>over track | Write<br>zeros<br>and<br>sync<br>clock | Write<br>sync<br>bit<br>(hex<br>01) | Write ID<br>and generate<br>CRC | Write<br>CRC | Write<br>circuit<br>recovery |

13-16

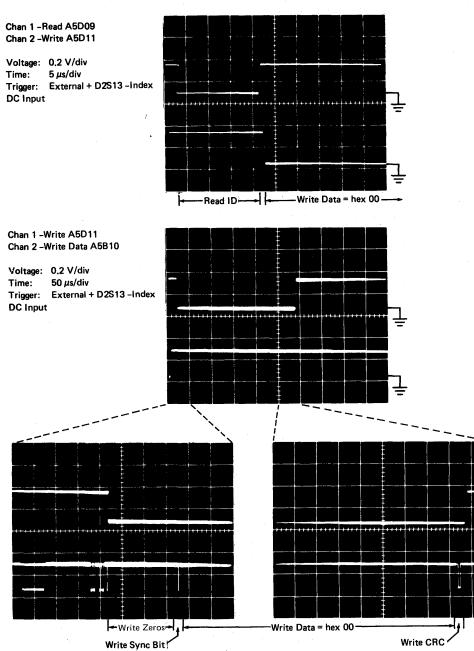

#### Write Data

The write data operation writes 256-byte data records to the data fields on the disk. Up to 256 consecutive records can be written by one write data operation. The common adapter automatically performs seek operations to place the actuator at the correct track (if bit 12 of the command byte is 0). If the addressed sector has an alternative sector assigned, the common adapter performs the seek to the alternative

cylinder and finds the alternative sector. The alternative sector is written and the actuator returns to the original track if there are more sectors to be written by this operation. If a CRC check occurs, the operation ends with the sector in error.

A read verify is done after a write operation to ensure that the data is written correctly, but the operation can be modified so that the read verify is not done. This operation can also be modified to write the same data to each data record.

| The command byte is: | for a | writ | e data         | oper | ation |    |    |    |

|----------------------|-------|------|----------------|------|-------|----|----|----|

|                      |       |      |                | Bits |       |    |    |    |

|                      | 8     | 9    | 10             | 11   | 12    | 13 | 14 | 15 |

| Write Data           | 0     | 1    | 1              | 0    | 0     | 0  | DR | RV |

|                      |       |      | epeat<br>ead v |      |       |    |    |    |

This figure shows the writing of the first or both data fields to a sector on the disk. If only the second data field is to be written for an operation, a dummy read is done on the first data field (see read data timings), and then the indicated timings for data field 2 apply.

| Format – |                            | Sample<br>Servo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Gap<br>(hex 00) | Sync<br>(hex 01)           | ID<br>FSHC                                           | ID CRC                                          | Gap<br>(hex 00)                         | Sync<br>(hex 01)     | Data Field 1                              | Data CRC             | Gap<br>(hex 00)                         | Sync<br>(hex 01)     | Data Field 2                                       | Data CRC             | Gap<br>(hex 00)              | Sample<br>Servo                           |

|----------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------------|------------------------------------------------------|-------------------------------------------------|-----------------------------------------|----------------------|-------------------------------------------|----------------------|-----------------------------------------|----------------------|----------------------------------------------------|----------------------|------------------------------|-------------------------------------------|

| Number o | f Bytes                    | 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 14              | 1                          | 4                                                    | 2                                               | 16                                      | 1                    | 256                                       | 2                    | 16                                      | 1                    | 256                                                | 2                    | 7                            | 22                                        |

| Sequence | Counter                    | 0357 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1               |                            | 2                                                    |                                                 | 3                                       |                      | 4                                         |                      | 5                                       |                      | 6                                                  |                      | 7                            |                                           |

|          |                            | Fine adjust<br>of data head<br>over track                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Sync<br>clocks  | Look<br>for<br>sync<br>bit | Read ID field<br>and compare<br>with field<br>in FCB | Read CRC<br>and compare<br>with CRC<br>register | Sync<br>clocks<br>and<br>write<br>zeros | Write<br>sync<br>bit | Write data on<br>disk and<br>generate CRC | Write CRC<br>on disk | Sync<br>clocks<br>and<br>write<br>zeros | Write<br>sync<br>bit | Write data on<br>disk. Develop<br>CRC              | Write CRC<br>on disk | Write<br>circuit<br>recovery | Fine adjust<br>of data head<br>over track |

| H040     | -Index or<br>-Sector ■     | <i>ـــــ</i> ر                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                            |                                                      |                                                 | 26,03                                   |                      | o                                         |                      | 20105                                   |                      |                                                    |                      |                              | L                                         |

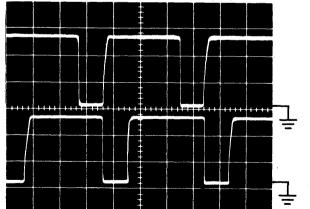

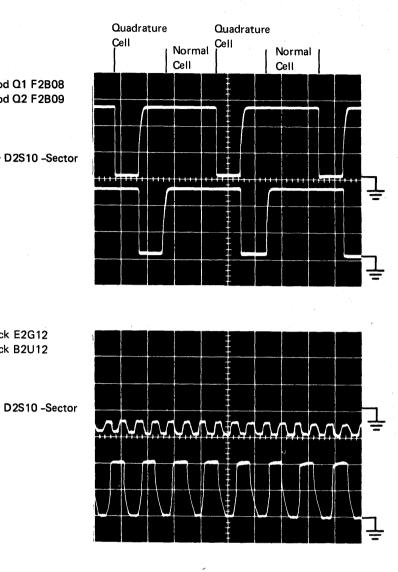

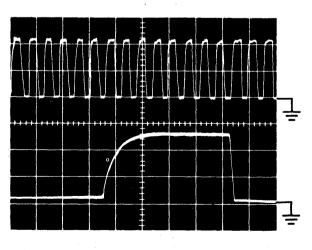

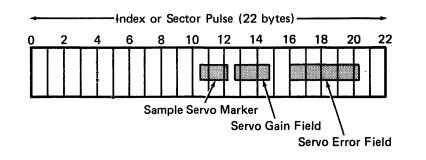

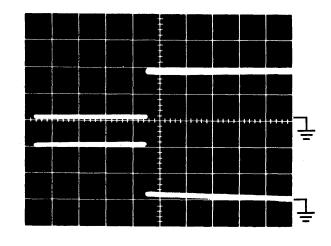

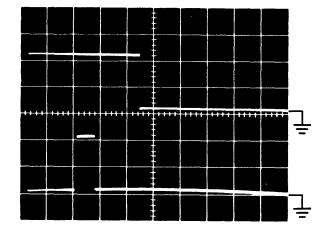

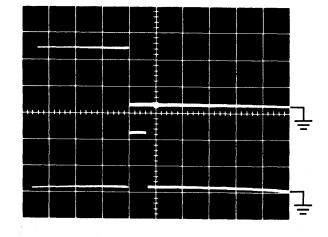

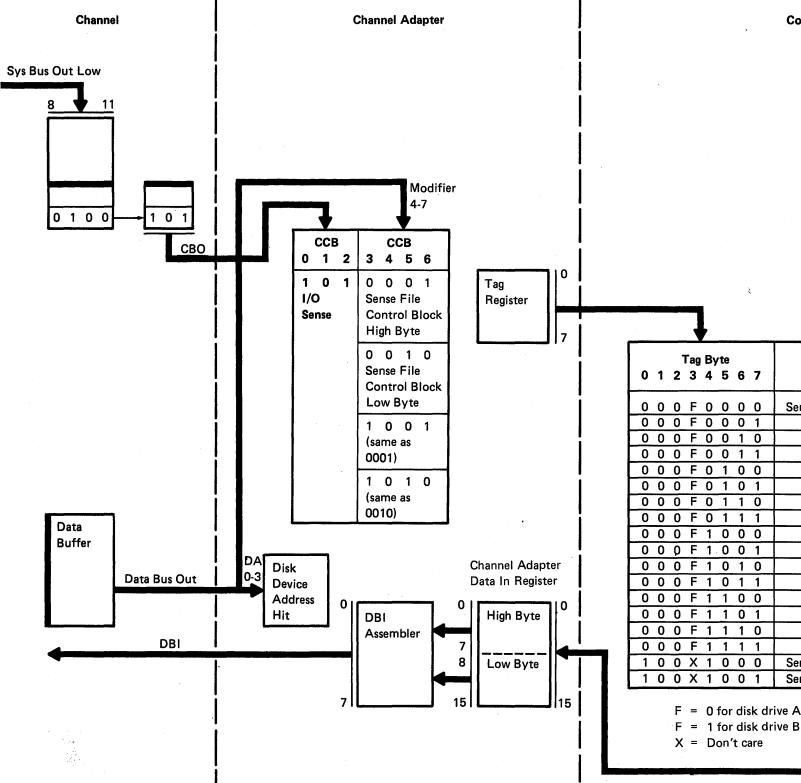

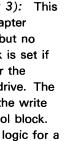

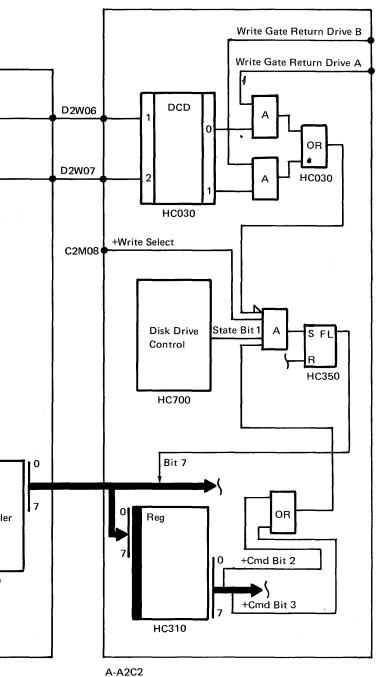

| HH050    | -Read ■                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | )               |                            | 21.8 μs                                              |                                                 |                                         |                      |                                           |                      |                                         |                      |                                                    |                      |                              |                                           |