# Contents

| DATA COMMUNICATIONS                             |                    |

|-------------------------------------------------|--------------------|

|                                                 | . 12-1             |

| Data Communications Systems                     | . 12-1             |

| Data Communications Networks                    |                    |

| Point-to-Point Network                          | . 12-1             |

| Multipoint Network                              | . 12-1             |

| Binary Synchronous Communications               | . 12-2             |

| BSC Message Format                              | . 12-2             |

| Transmit and Receive Storage Contents of        | 10 4               |

|                                                 |                    |

| EBCDIC, ASCII, and Line Control Characters      |                    |

| Synchronous Data Link Control                   | . 12-6             |

| Control Field Formats                           |                    |

|                                                 | . 12-7             |

| Primary Station Commands and Secondary          | 10.0               |

| Station Responses                               | . 12-8             |

| Examples of SDLC Commands and Responses         | . 12-9             |

| Systems Network Architecture                    |                    |

| SNA/SDLC Data Relationship                      | . 12-10            |

| Types of Network Addressable Units              |                    |

| Physical Configuration                          | . 12-10            |

|                                                 |                    |

| Modems and Interfaces                           |                    |

|                                                 | 12-20              |

|                                                 | 12-20              |

| Functional Units                                |                    |

| Adapter Controls                                |                    |

| System Level Interface                          |                    |

|                                                 |                    |

| Input/Output Blocks                             | . 12-28            |

| Operations                                      |                    |

| BSC Receive Only                                |                    |

| BSC Receive Initial Delayed (Multipoint)        |                    |

| BSC Receive Initial (Point-to-Point)            |                    |

| BSC Receive Initial (Multipoint)                |                    |

| BSC Transmit/Receive Overlay                    |                    |

| BSC Transmit/Receive Initial (Multipoint)       |                    |

| BSC Transmit/Receive                            |                    |

| BSC Transparent Operations                      | 12-36              |

| BSC Multipoint Operations                       |                    |

| SDLC Transmit Operations                        |                    |

|                                                 | . 12-39<br>. 12-42 |

| Commands                                        | . 12-42            |

|                                                 | 10 40              |

| Command                                         | . 12-42            |

|                                                 |                    |

| Load Time-out Clock and Registers               |                    |

| Load Timing Chart                               |                    |

|                                                 | . 12-48            |

| Sense Data, Registers, and Interrupt Conditions | 12-50              |

| Sense Data Timing Chart                         |                    |

| Sense Microinterrupt Level Timing Chart         |                    |

|                                                 | 12-03              |

| Error Conditions                           | -54 |

|--------------------------------------------|-----|

| Adapter Check                              |     |

| Data Set (Not) Ready                       | -55 |

| Abortive Disconnect                        |     |

| Receive Time-out                           |     |

| Invalid ASCII Character                    |     |

| Invalid Frame                              |     |

| Secondary SDLC Time-out (Inactivity        | •   |

| Timer)                                     | -55 |

| Primary SDLC Time-out (Idle Detect)        |     |

| and Nonproductive Timer)                   | -55 |

| Block/Frame Check Error                    |     |

| DBO Parity                                 |     |

| Diagnostics                                |     |

| Diagnostic Mode and Wrap Test 12-          |     |

| Internal Clock Feature                     |     |

| EIA/CCITT Line Adapter                     |     |

| MODEMS                                     |     |

| IBM 1200 BPS Integrated Modem              |     |

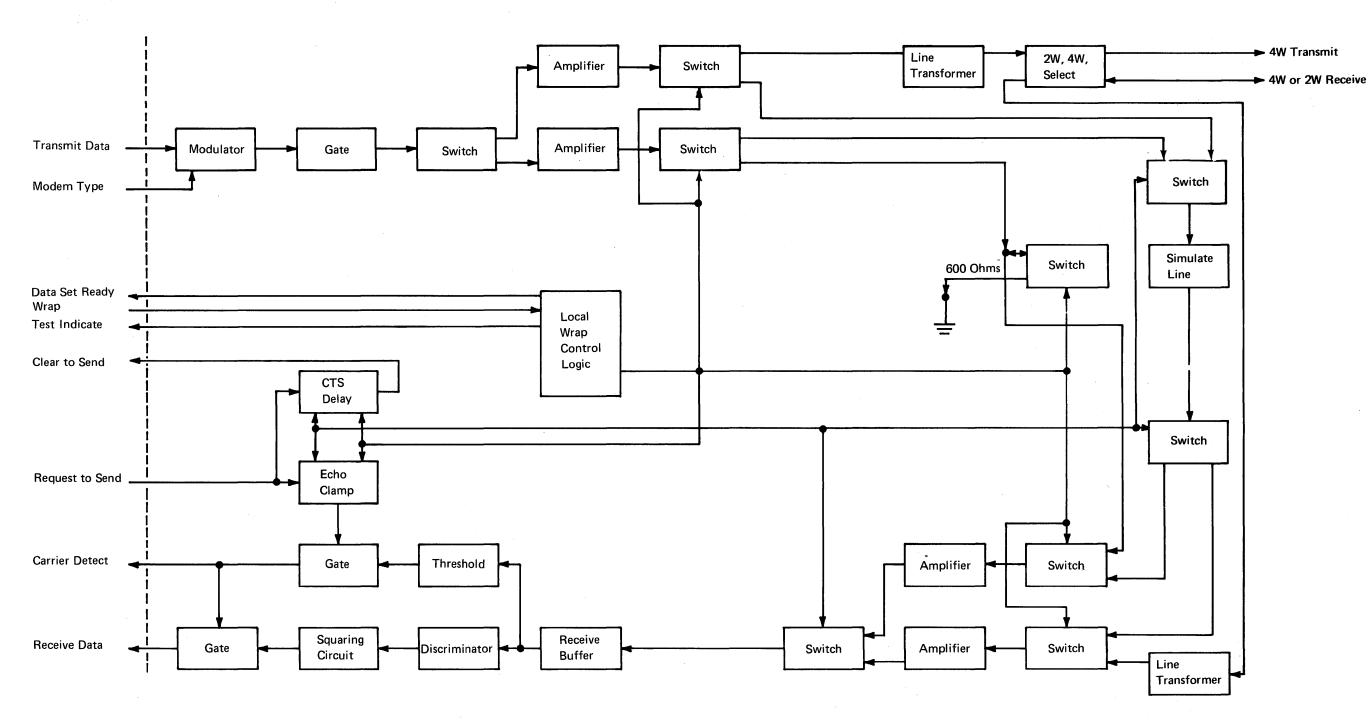

| Nonswitched Network Interface              |     |

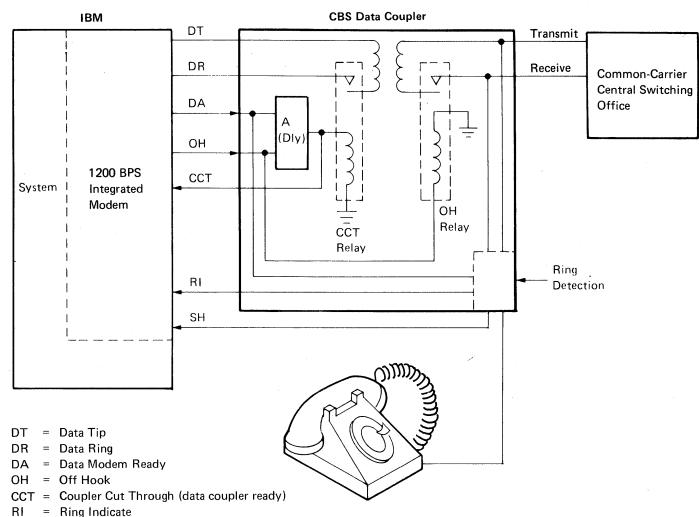

| Switched Network Interface                 |     |

| 1200 BPS Transmit Operations               |     |

| Receive Operations                         |     |

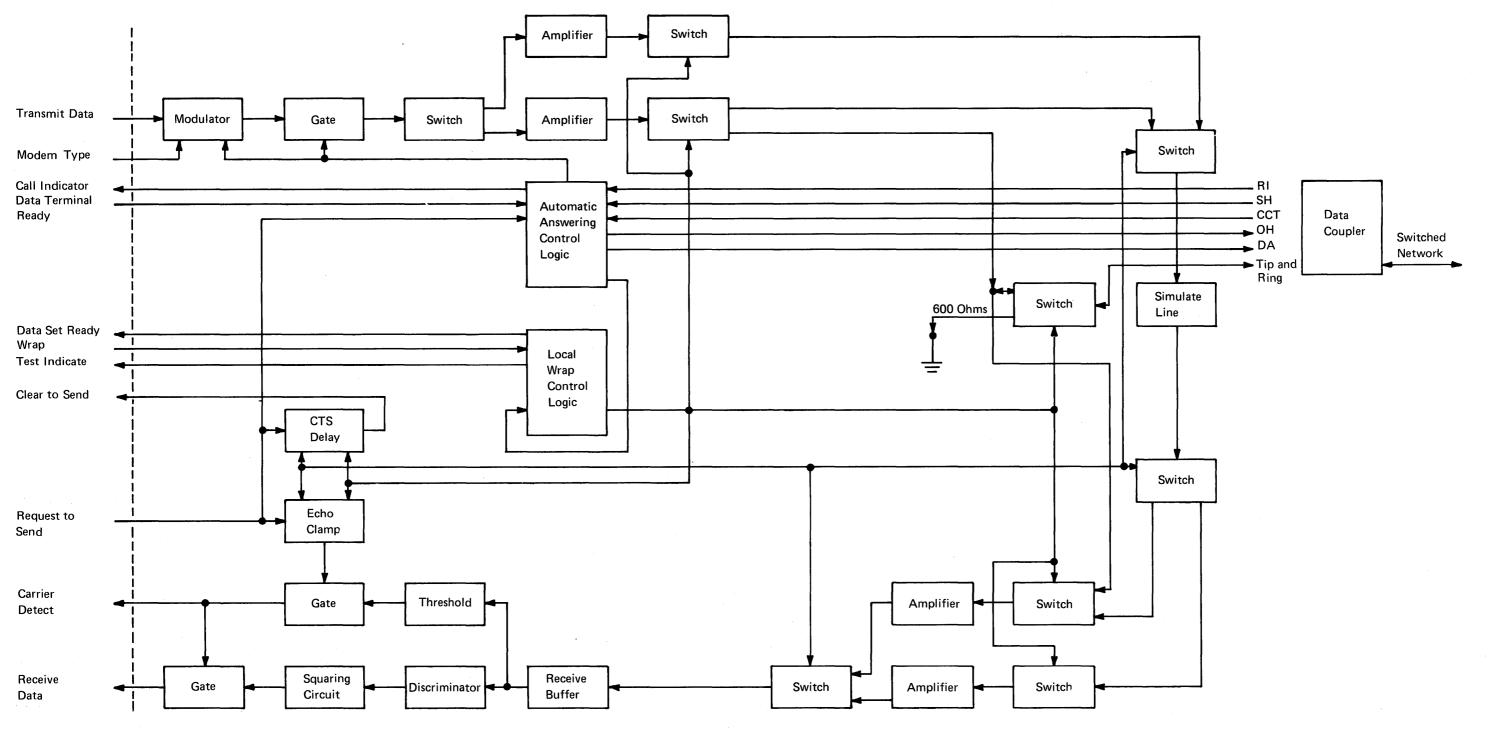

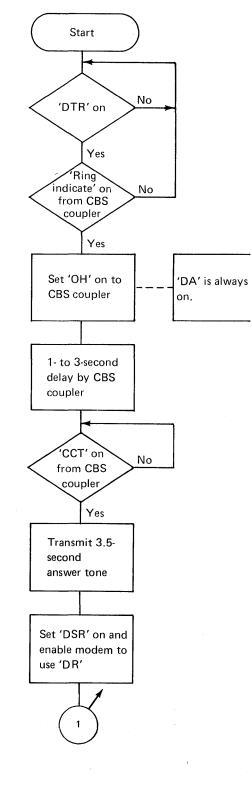

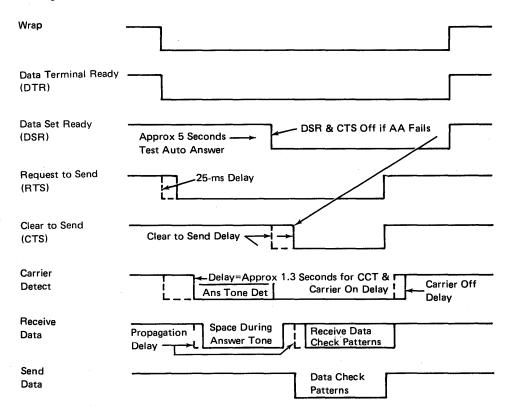

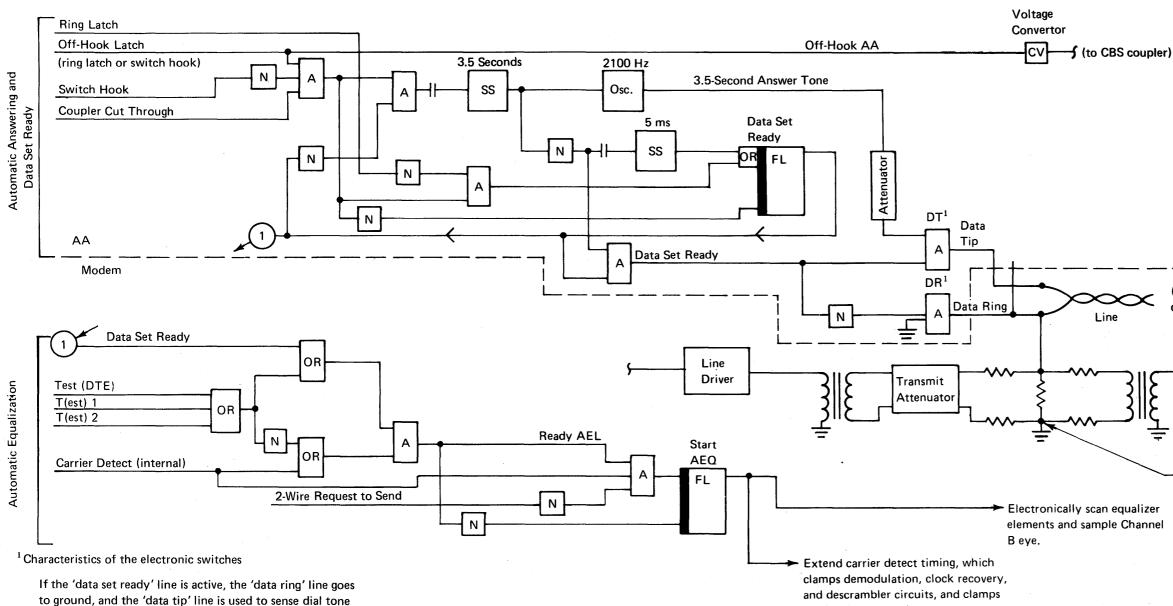

| Automatic Answering                        |     |

| 1200 BPS Integrated Modern Tests 12-       |     |

| Line Plate for Public Switched Network 12- |     |

| IBM 2400 BPS Integrated Modem 12-          |     |

| Operation                                  |     |

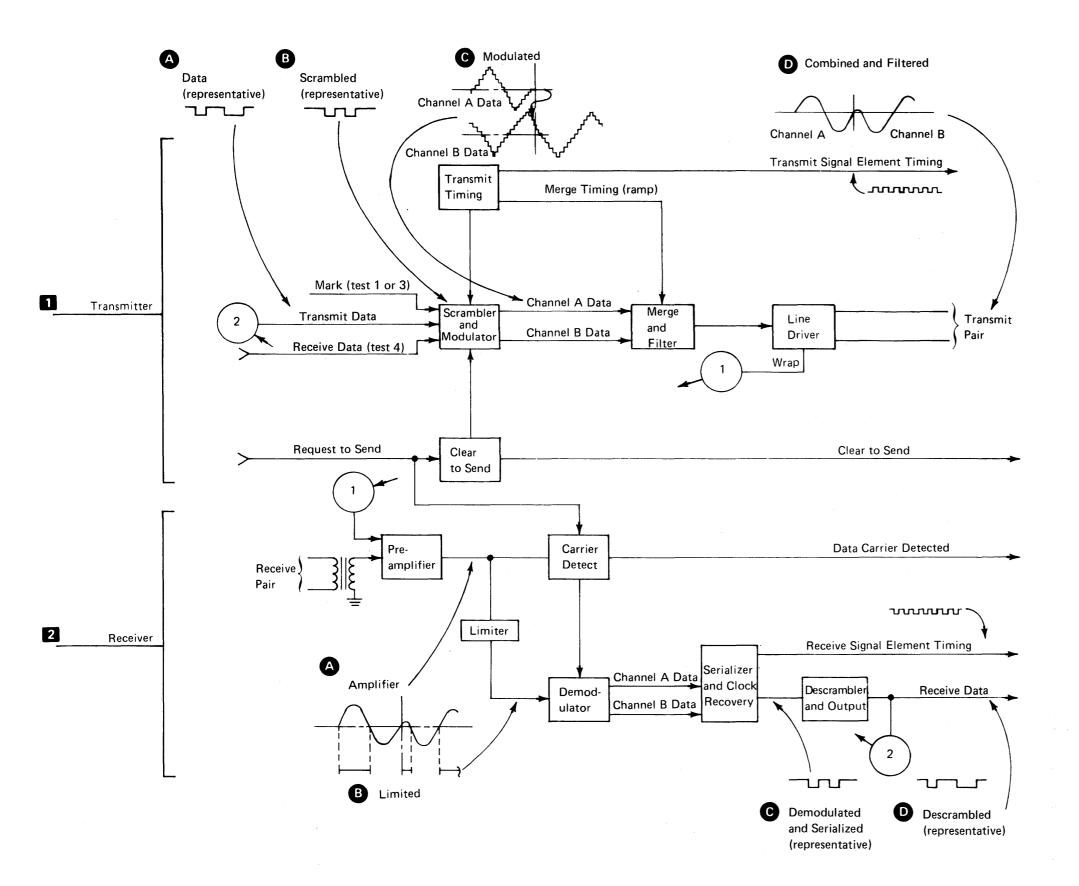

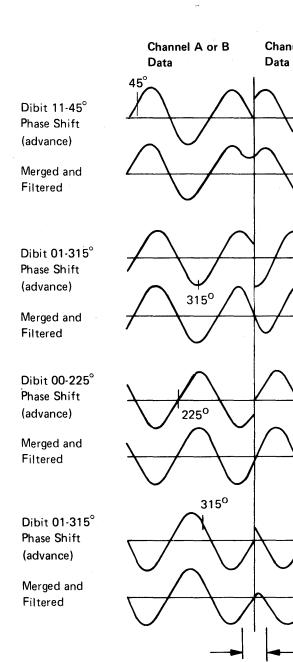

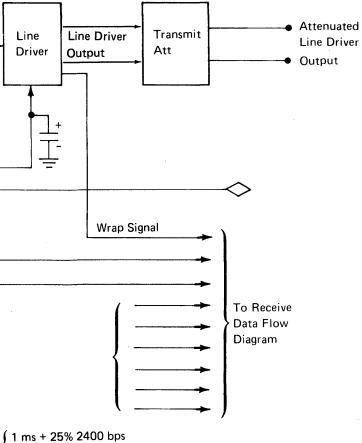

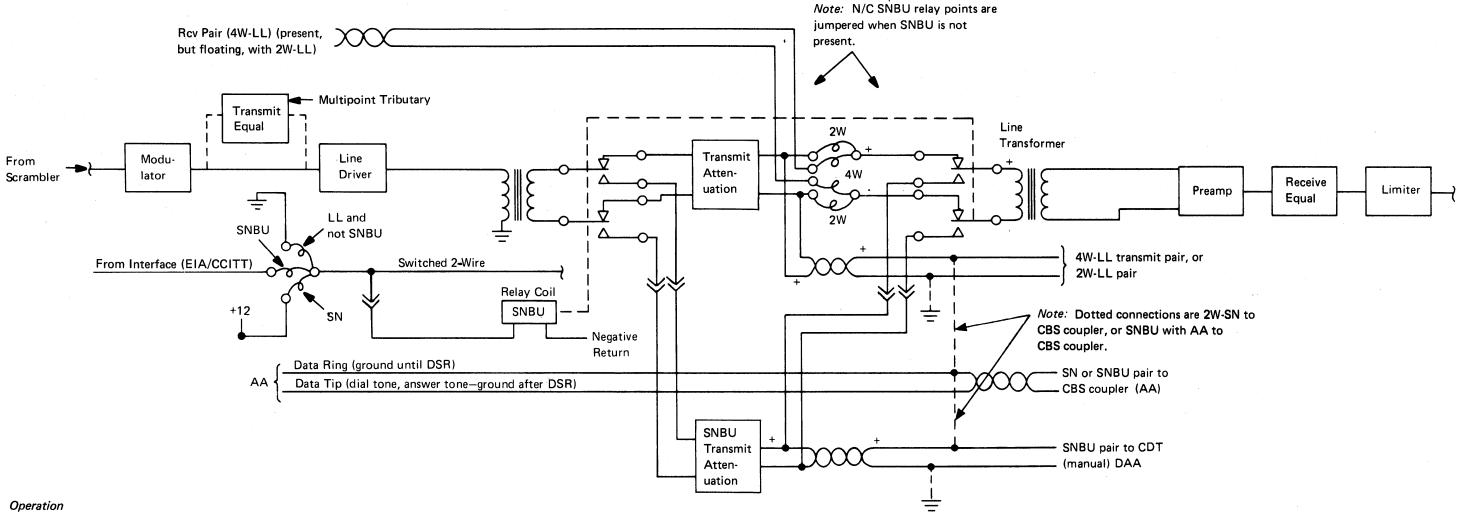

| 2400 BPS Transmit Data Flow                |     |

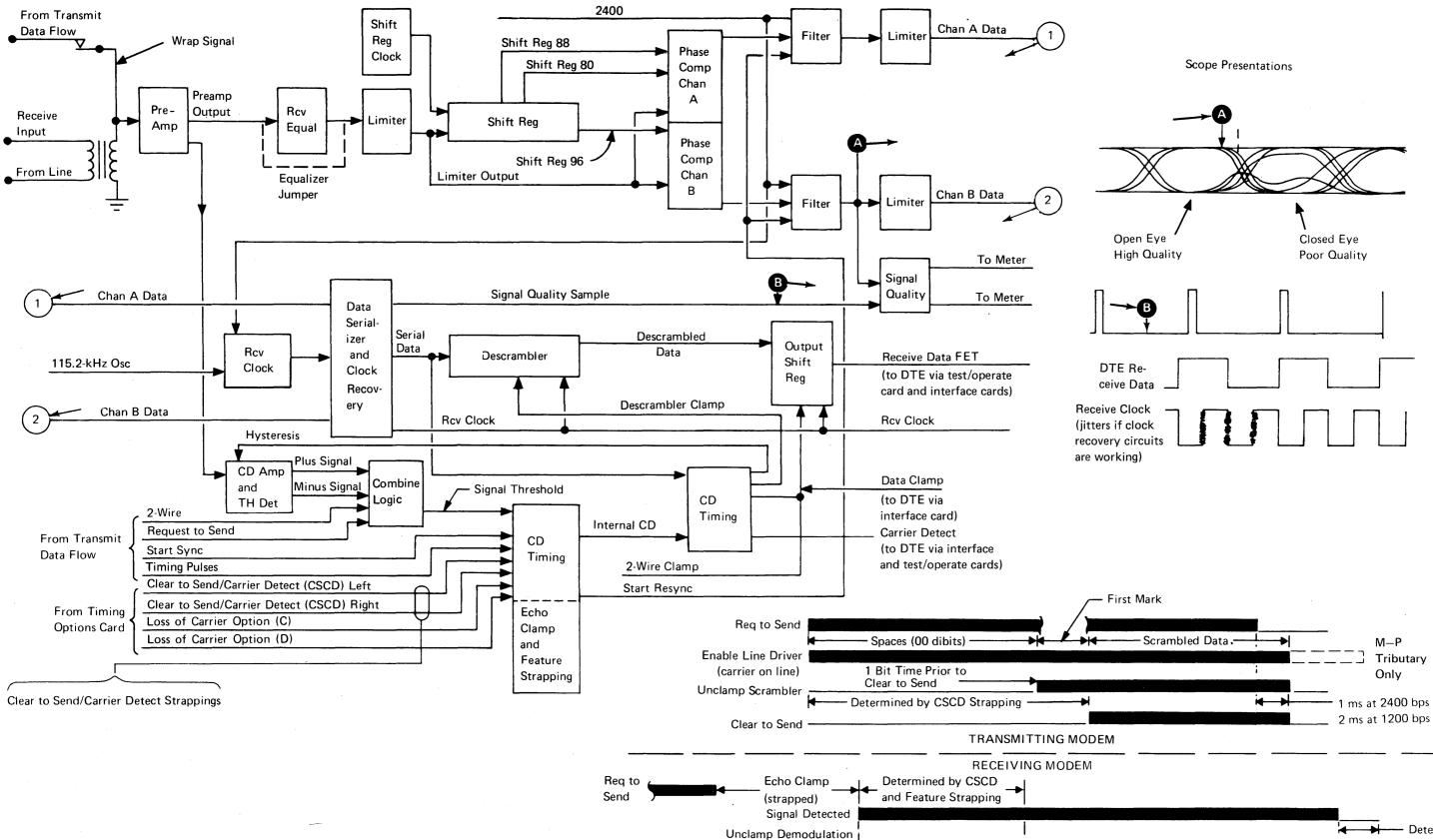

| 2400 BPS Receive Data Flow                 |     |

| Unclamp Demodulation Circuits              |     |

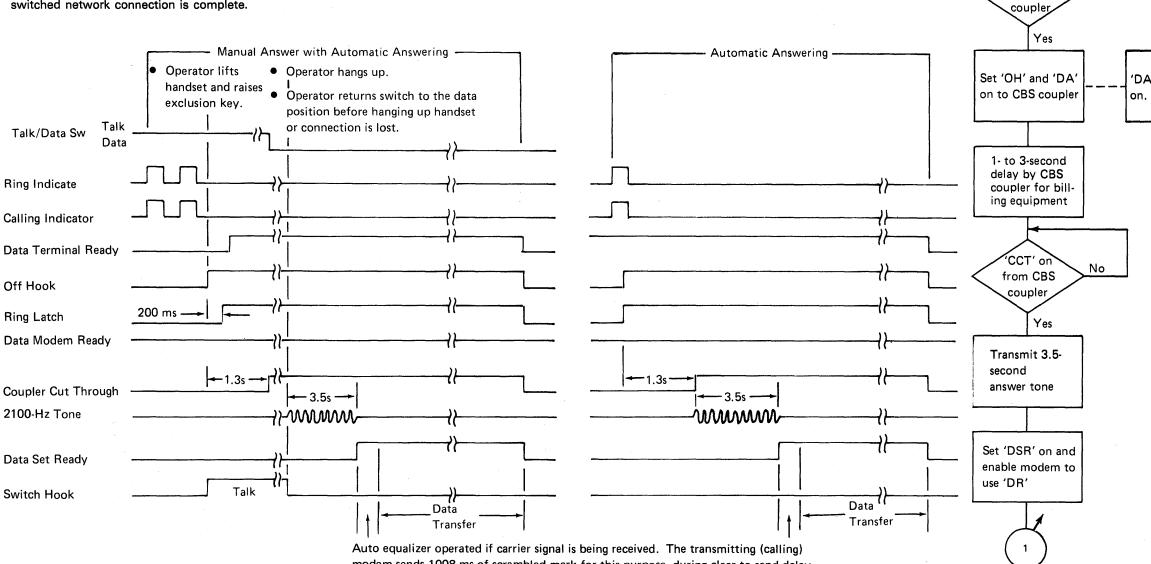

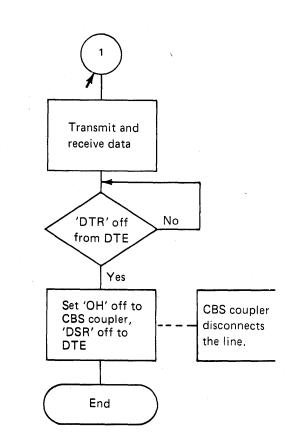

| Switched Network and Automatic Answering   | -/- |

| Operation                                  | 76  |

| 2400 BPS Integrated Modem with Switched    | -70 |

| Network and Automatic Answering 12-        | -77 |

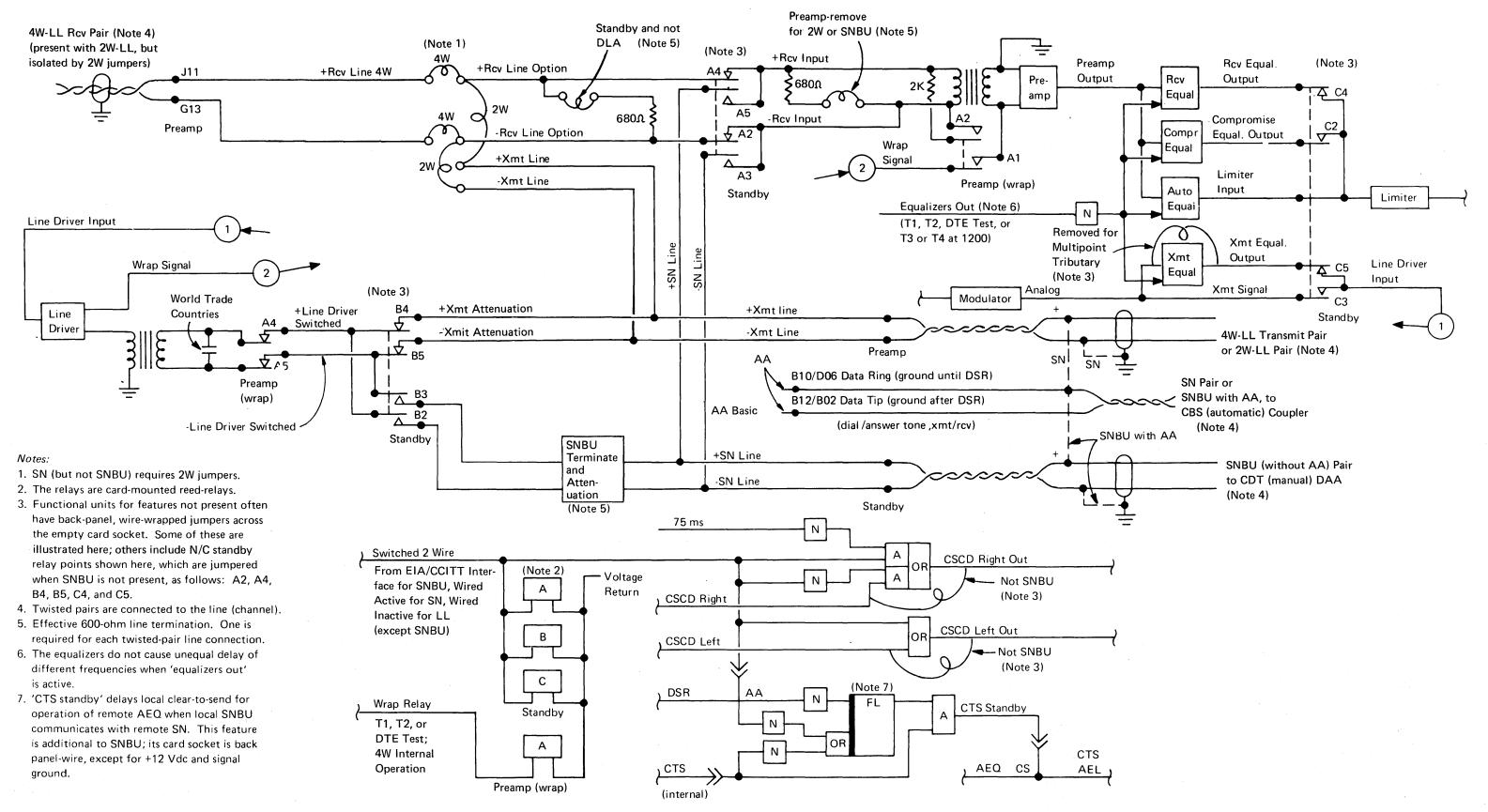

| Switched Network Backup (SNBU), Wrap,      | -// |

| and Line Connections                       | 70  |

| Switching and Jumpers for 2W/4W, SNBU,     | -/0 |

|                                            | 70  |

|                                            |     |

|                                            |     |

|                                            |     |

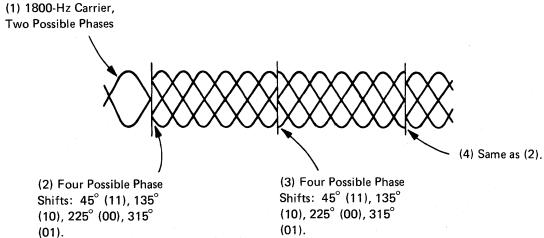

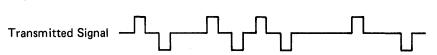

| Transmission Signal                        |     |

| Line Control Characters                    |     |

|                                            | -80 |

|                                            | -81 |

|                                            | -81 |

|                                            | -82 |

| Interface Lines                            | -03 |

|                                            |     |

# **Contents for Data Communications**

# **Data Communications**

# INTRODUCTION

# **Data Communications Systems**

Data communications (BSC or SDLC) is an optional feature that lets System/34 function as a primary station (SDLC only) or as a secondary station on a point-to-point or multipoint network.

Up to two communications features can be installed on the system.

The data communications feature can be connected to a half-duplex or full-duplex network. However, the communications feature operates only in a half-duplex mode; that is, data is transmitted in only one direction at a time. Data is transmitted or received serially-by-bit and serially-by-character over voice-grade switched or nonswitched data communications networks, or over switched or nonswitched public or private digital data lines.

The control processor controls the communications adapter system I/O instructions. Once a transmit or receive operation starts, the control storage program and the hardware execute the specified operation.

During transmit operations, each byte to be transmitted is sent to the communications adapter where data is transmitted 1 bit at a time to the modem (modulator/demodulator) or to the digital adapter. The modem or the digital adapter, in turn, sends the bit to the receiving station over the data communications network.

During receive operations, the communications adapter receives each bit from the modem or from the digital adapter and assembles the bits into bytes. Each byte of data is sent to the control processor as the result of a character microinterrupt.

# **Data Communications Networks**

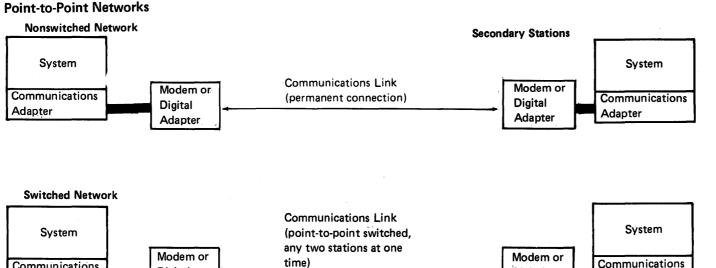

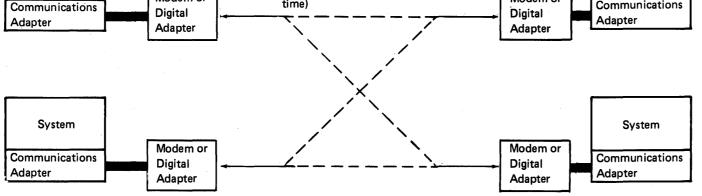

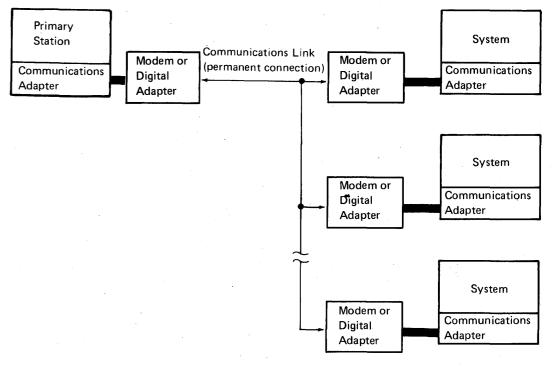

A data communications system using System/34 operates on a point-to-point network (switched or nonswitched) or as a secondary or control station (SDLC only) on a multipoint network.

# Point-To-Point Network

On a point-to-point network, all data transmissions are between two stations. If the network is a permanent connection (nonswitched), transmissions are always between the same two stations. If the network is a switched network, transmissions can be between any two stations in the network.

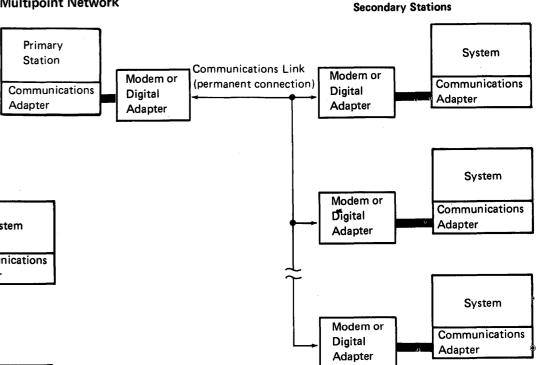

#### Multipoint Network

All stations in a multipoint network are permanently connected (nonswitched), and all data transmissions are between two stations-the primary (or multipoint control) station and an addressed secondary (or multipoint tributary) station.

# **Multipoint Network**

Data Communications 12-1

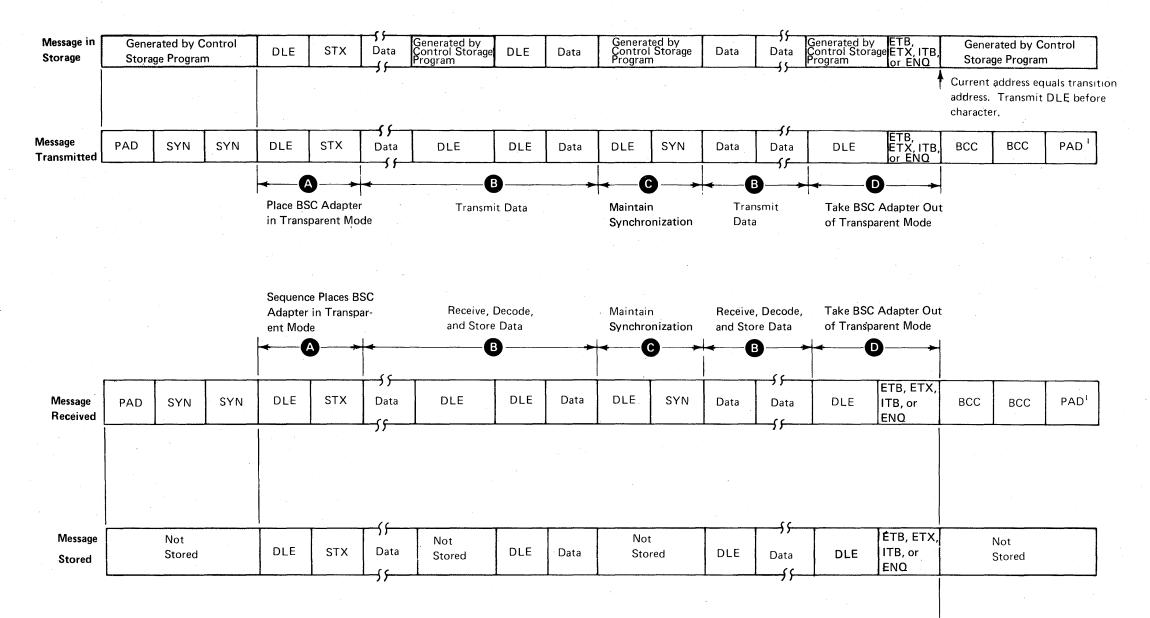

# **Binary Synchronous** Communications

Binary synchronous communications uses a message format and line control characters for transmitting and receiving data.

# **BSC Message Format**

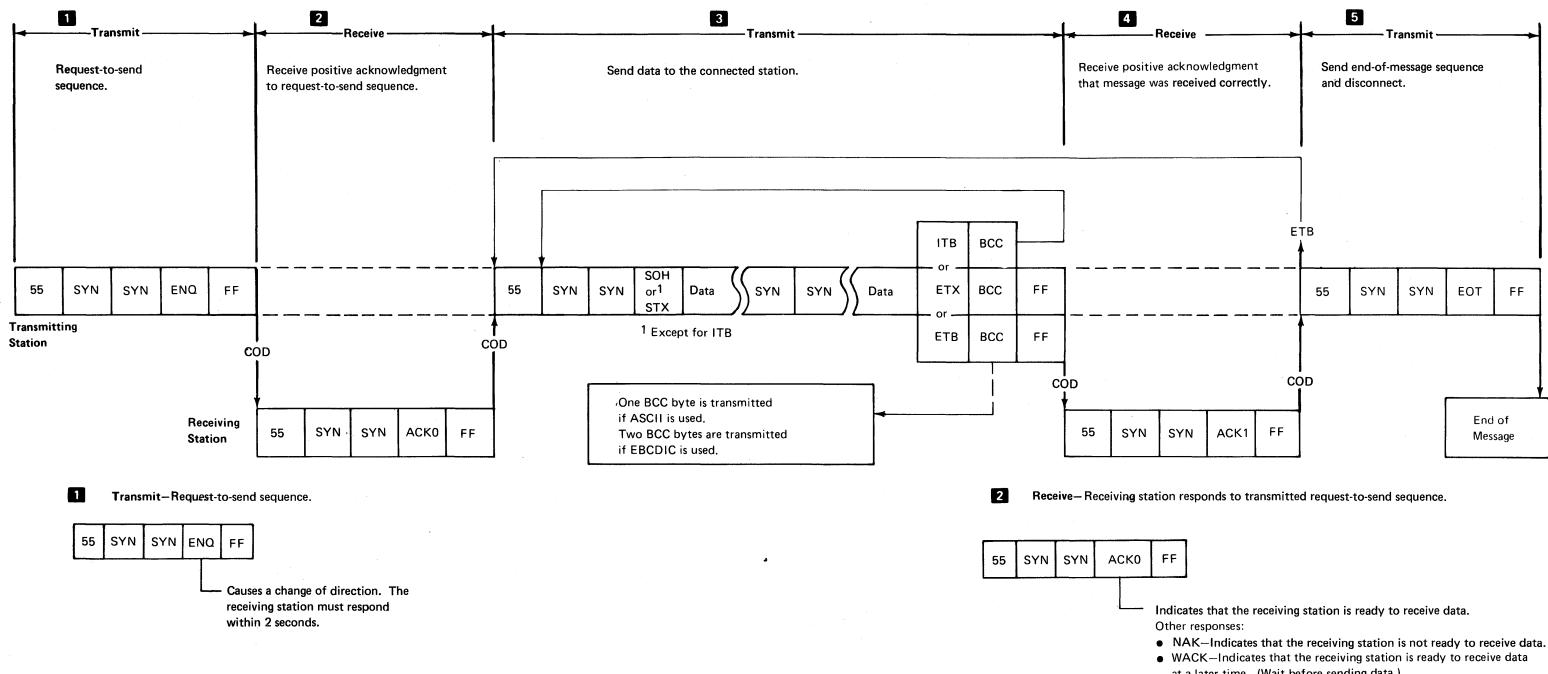

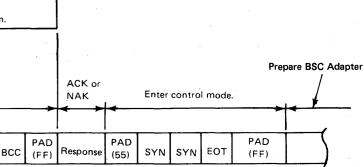

The BSC feature uses line control characters to transmit information over a data link. In addition, each message starts with a hex 55 character and 2 SYN bytes, and ends with a hex FF character. Some of the line control characters are described in the following figure, which shows typical message formats for transmit and receive operations.

- at a later time. (Wait before sending data.)

- No response-Receiving station did not respond to the request-tosend sequence. The transmitting station waits 3.25 seconds for a response from the receiving station.

# 3 Transmit—Send data to the connected station.

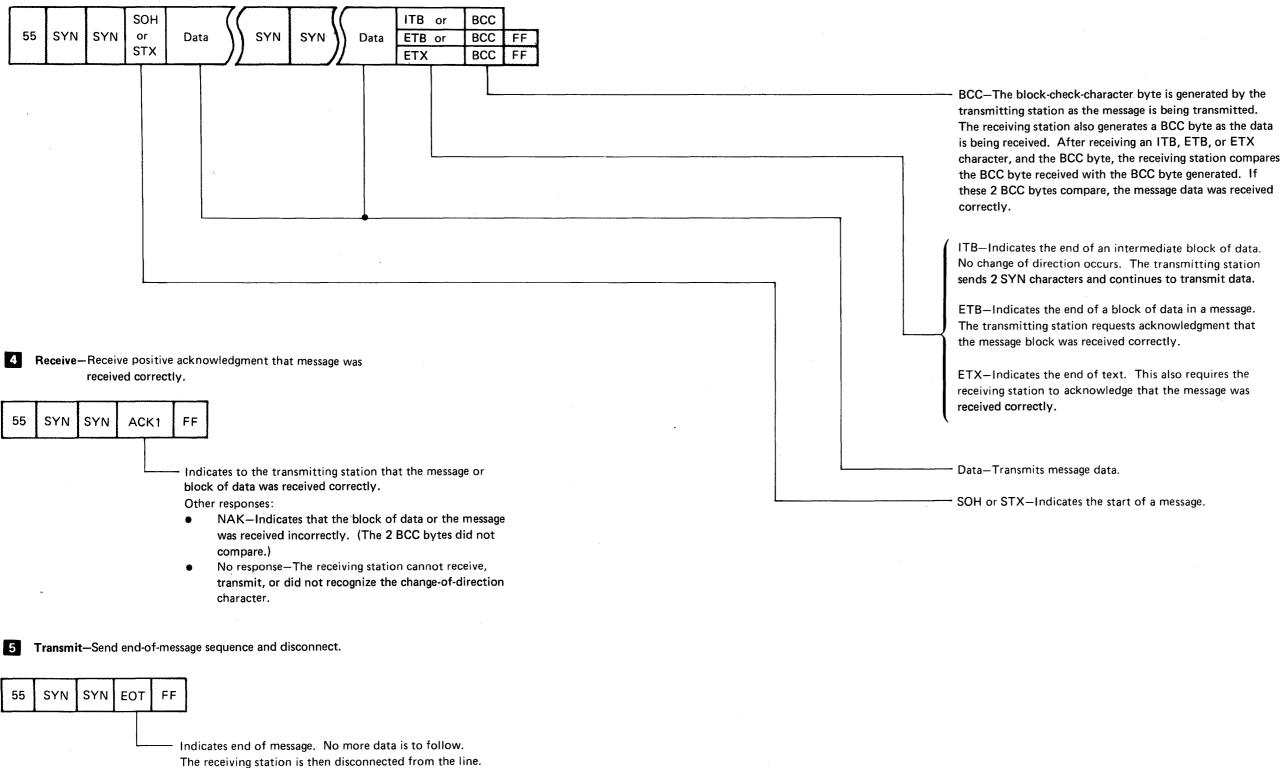

# Transmit and Receive Storage Contents of Message

Data from Main Storage

# EBCDIC, ASCII, and Line Control Characters

The following table gives the line control character codes for the BSC feature.

| Name                                                      | Mnemonic | EBCDIC          | ASCII   |

|-----------------------------------------------------------|----------|-----------------|---------|

| Start of header                                           | SOH      | SOH             | SOH     |

| Start of text                                             | STX      | STX             | STX     |

| End of text block <sup>1</sup>                            | ЕТВ      | ETB             | ЕТВ     |

| End of text <sup>1</sup>                                  | ETX      | ETX             | ETX     |

| End of transmission <sup>1</sup>                          | EOT      | EOT             | EOT     |

| Enquiry <sup>1</sup>                                      | ENQ      | ENQ             | ENQ     |

| Negative acknowledgment                                   | NAK      | NAK             | NAK     |

| Synchronous idle                                          | SYN      | SYN             | SYN     |

| Data link escape                                          | DLE      | DLE             | DLE     |

| Intermediate text block                                   | ITB      | IUS             | US      |

| Even acknowledgment <sup>1</sup>                          | ACK 0    | DLE (70)        | DLE 0   |

| Odd acknowledgment <sup>1</sup>                           | ACK 1    | DLE/            | DLE 1   |

| Wait before transmit-positive acknowledgment <sup>1</sup> | WACK     | DLE,            | DLE;    |

| Mandatory disconnect <sup>1</sup>                         | DISC     | DLE EOT         | DLE EOT |

| Reverse interrupt <sup>1</sup>                            | RVI      | DLE@            | DLE <   |

| Temporary text delay <sup>1</sup>                         | TTD      | STX ENQ         | STX ENO |

| Transparent start of text                                 | XSTX     | DLE STX         |         |

| Transparent intermediate text block                       | XITB     | DLE IUS         |         |

| Transparent end of text <sup>1</sup>                      | XETX     | DLE ETX         |         |

| Transparent end of text block <sup>1</sup>                | XETB     | DLE ETB         |         |

| Transparent synchronous idle                              | XSYN     | DLE SYN         |         |

| Transparent block cancel <sup>1</sup>                     | XENQ     | DLE ENQ         |         |

| Transparent TTD <sup>1</sup>                              | XTTD     | DLE STX DLE ENQ |         |

| Transparent DLE                                           | XDLE     | DLE DLE         |         |

# The following table gives the bit definitions for the EBCDIC characters.

|              |          |   |     | 00       |         |     |     | C          | 01         |                          |            | 1  | 10                           |             |          | 11   |                         |          |           |

|--------------|----------|---|-----|----------|---------|-----|-----|------------|------------|--------------------------|------------|----|------------------------------|-------------|----------|------|-------------------------|----------|-----------|

| Second He    | x Digit  |   | 00  | 01       | 10      | 11  | 00  | 01         | 10         | 11                       | 00         | 01 | 10                           | 11          | 00       | 01   | 10                      | 11       | Bits 0, 1 |

| Bits 4, 5, 6 | ô, and 7 |   | 0   | 1        | 2       | 3   | 4   | 5          | 6          | 7                        | 8          | 9  | A                            | В           | ¥        | D    | E                       | F        | Bits 2, 3 |

|              | 0000     | 0 | NUL | DLE      | DS      |     | SP  | &          |            |                          | 1          |    |                              |             | 1        | }    | $\overline{\mathbf{n}}$ | 0        | First Hex |

|              | 0001     | 1 | SOH | DC1      | sos     |     | t-  | 1          | 7 -        | f — ·                    | <b>1</b> a | j  | $\overline{\mathbf{\nabla}}$ |             |          |      | t —                     |          | 1         |

|              | 0010     | 2 | STX | DC2      | FS      | SYN | -   | - ·        | <b>—</b> – |                          | ь -        | k  | s                            |             | - в -    | ĸ    | s                       | 2        | 1         |

|              | 0011     | 3 | ETX | тм       |         |     |     |            | T          | †                        | c          | 1  | t -                          |             |          | L    | T                       | 3        | 1         |

|              | 0100     | 4 | PF  | RES      | BYP     | PN  | 1   | · · ·      | T -        |                          | d          |    | - <u> </u>                   |             |          | м    | Ū                       | 4        | 1         |

|              | 0101     | 5 | нт  | NL       |         | RS  |     | <u>⊢</u> − | <u> </u>   |                          | e          |    | $\overline{v}$               |             | Ē        | N    |                         | 5        | 1         |

|              | 0110     | 6 | LC  | BS       | EOB/ETB | UC  | 1   |            |            | <u>+</u>                 | ·          | 0  |                              | † <b></b> - | F        | 0    | W                       | 6        | 1         |

|              | 0111     | 7 | DEL |          | PRE/ESC | EOT | † - | ┣ ─        | †          | 1                        | g          | p  | ×                            |             | G        | - P  | X -                     | 7 -      | 1         |

|              | 1000     | 8 | GE  | CAN      |         |     | T - | Γ-         | T          | † — ·                    | h          | q  | V .                          |             | н        | ۵    | Y                       | 8        | 1         |

|              | 1001     | 9 | RLF | <u> </u> |         |     | Γ.  |            |            | $\Box \overline{\Sigma}$ |            | r  | Z                            |             |          | _ R_ | Z                       | 9        |           |

|              | 1010     | A | SMM | cc       | SM      |     | ¢   | 1          |            | :                        |            |    |                              | ļ           |          |      |                         | LVM      |           |

|              | 1011     | В | VT  | CU1      |         | CU3 | Ţ   | \$         | T .        | #                        | 1          |    |                              |             |          |      | <u> </u>                | F        | 1         |

|              | 1100     | c | FF  | IFS      |         | DC4 | <   | 1 -        | %          | @                        |            |    | 1—                           |             | $\int$   |      |                         | <u> </u> | 1         |

|              | 1101     | D | CR  | IGS -    | ENQ     | NAK | 1   | T) -       | <u> </u>   | † <del>-</del>           | 1          |    |                              | F           |          |      | T_`_                    | +        | 1         |

|              | 1110     | E | so  | IRS      | ACK     |     | + - | ┌;─        | $$         | =                        | 1          |    | 1 —                          |             | ŢŢ       |      | t —                     |          | 1         |

|              | 1111     | F | SI  |          | BEL     | SUB | Π - |            | † ?        |                          | <b>†</b>   |    | 1                            |             | <u> </u> | r —  |                         | EO       | 1         |

<sup>1</sup> IUS is the same as ITB.

The following table gives the bit definitions for the ASCII characters.

| _      |       | 7-       |            | >             | 0   | 0   | 0      | 0   | 1  | 1 | 1 | 1   |

|--------|-------|----------|------------|---------------|-----|-----|--------|-----|----|---|---|-----|

| Bit    | tions |          | - 6<br>• • |               | 0   | 0   | 1<br>0 | 1   | 0  | 0 | 1 | 1   |

|        |       | <u> </u> |            |               |     |     |        |     |    |   |   |     |

| 4<br>↓ | 3     | 2<br>↓   |            | Column<br>Row | 0   | 1   | 2      | 3   | 4  | 5 | 6 | 7   |

| 0      | 0     | 0        | 0          | 0             | NUL | DLE | SP     | 0   | @  | Р | • | Р   |

| 0      | 0     | 0        | 1          | 1             | SOH | DC1 | ! or I | 1   | A  | Q | а | q   |

| 0      | 0     | 1        | 0          | 2             | STX | DC2 | ''     | - 2 | B. | R | b | r   |

| 0      | 0     | 1        | 1          | 3             | ETX | DC3 | #      | 3   | C  | S | с | S   |

| 0      | 1     | 0        | 0          | 4             | EOT | DC4 | \$     | 4   | D  | Т | d | t   |

| 0      | 1     | 0        | 1          | 5             | ENQ | ΝΑΚ | %      | 5   | E  | U | е | · u |

| 0      | 1     | 1        | 0          | 6             | ACK | SYN | &      | 6   | F  | V | f | v   |

| 0      | 1     | 1        | 1          | 7             | BEL | ETB | ,      | 7   | G  | W | g | w   |

| 1      | 0     | 0        | 0          | 8             | BS  | CAN | (      | 8   | н  | X | h | ×   |

| 1      | 0     | 0        | 1          | 9             | нт  | EM  | )      | 9   | 1  | Y | i | Ŷ   |

| 1      | 0     | 1        | 0          | 10            | LF  | SUB | *      | 4   | J. | Z | j | z   |

| 1      | 0     | 1        | 1          | 11            | VT  | ESC | +      | ;   | К  |   | k | {   |

| 1      | 1     | 0        | 0          | 12            | FF  | FS  | ,      | <   | L  |   | t | I   |

| 1      | 1     | 0        | 1          | 13            | CR  | GS  | -      | =   | М  | ] | m | }   |

| 1      | 1     | 1        | 0          | 14            | SO  | RS  |        | >   | N  | ~ | n | ~   |

| 1      | 1     | 1        | 1          | 15            | SI  | US  | 1      | ?   | 0  |   | 0 | DEL |

|        |       |          | 1          | ••••••        |     |     |        |     |    |   |   |     |

- Bit 1 (the low-order bit) is transmitted first, bits 2-7 next, and a parity bit last.

1.1

# Synchronous Data Link Control

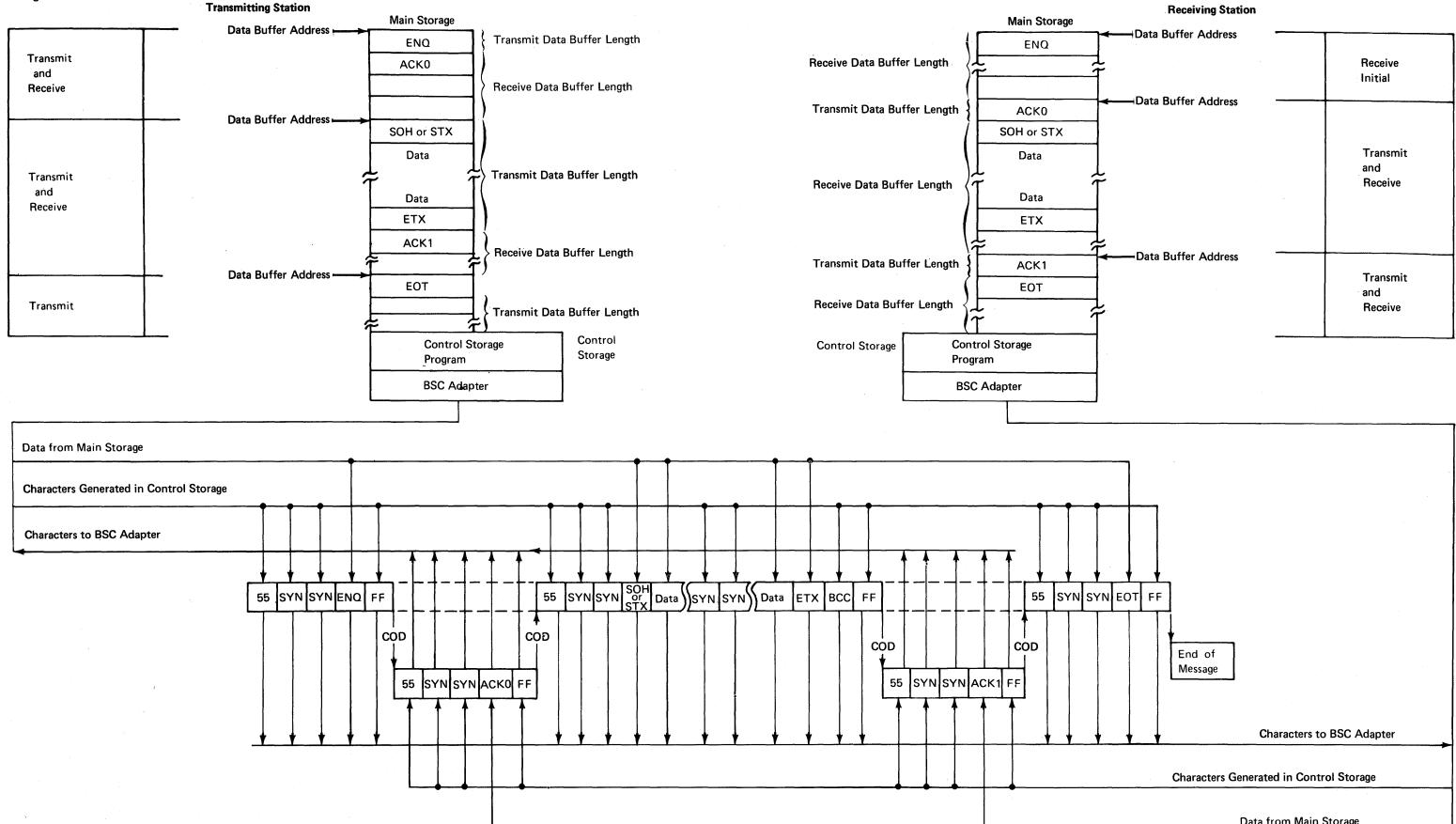

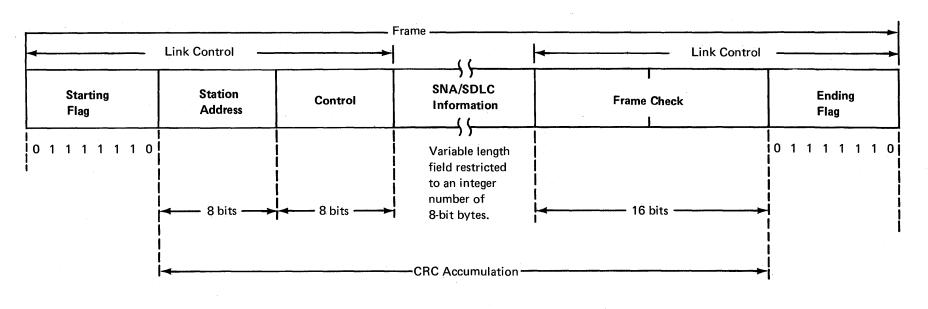

Synchronous data link control uses the frame format for transmitting every command, every response, and all information over the data link.

# Frame Format

Each frame contains a starting flag, a station address, a control field, an information field (optional), a frame check field, and an ending flag.

# Synchronization Bits A

This field, although not a part of the SDLC frame, is shown here because of its relationship with the frame. When the internal clock feature is used, the SDLC adapter inserts 2 additional synchronization bytes (hex 0000) into the data stream before the starting flag sequence. These 2 bytes are used to obtain or maintain synchronization of the clock following a line turnaround.

When modem clocking is used, the SDLC adapter inserts 1 byte (hex AA) into the data stream for synchronization. NRZI (zeros-complemented transition coding) may or may not be used with modem clocking. NRZI is described later in this section.

# Starting and Ending Flags B

In every SDLC frame, there are two flags (starting and ending) that have a binary configuration of 01111110. The starting flag starts all transmissions except when synchronization bits are needed, as described in A. The starting flag also starts transmission error checking. The ending flag ends the frame and transmission error checking. To identify the starting flag from the ending flag, the adapter (primary and secondary) assumes that a starting flag is followed by an 8-bit sequence that is a station address. Also, secondary stations can identify the starting flag if it is followed by the general address (1111111).

When more than one frame is transmitted, the ending flag of one frame can also be the starting flag of the next frame.

# Station Address C

The station address field is an 8-bit field that always identifies the secondary station. The primary station is never identified in the address field. If the System/34 is acting as a secondary station, in addition to recognizing its own address, it can also recognize the general address (1111111). The address field must be recognized before a frame can be received. The null address (00000000) is not a valid station address.

# Control D

This field is used for encoding the commands and responses needed to control a data link. As a secondary station, the control field is used for supervisory and nonsequenced responses. As a primary station, it uses the control field for supervisory and nonsequenced commands. Both stations use the control field for transferring information.

The control field, using bit 7 or bits 6 and 7, can select one of three formats—the information transfer, supervisory, or nonsequenced format. Each format is described under *Control Field Formats* with its associated commands and responses.

# Information 🕟

This field is not necessarily included in every frame, although a frame with the information transfer format usually contains an information field. Information fields are not allowed with some control field formats.

The information field is not restricted to any bit sequence, but it is restricted to an integer number of 8-bit bytes and by the buffering limits of the stations communicating with each other.

# Frame Check 🕞

All frames contain 2 bytes in the frame check field for the purpose of checking transmission accuracy. The CRC accumulation, started by the starting flag and ended by the ending flag, includes all bits in the station address, control, and information fields; the flags are not included.

CRC accumulation is performed on all frames at the transmitting and receiving stations. The transmitting station sends the binary complement of the CRC accumulation. The receiving station, having processed the CRC accumulation, should show a remainder of hex FOB8 if the transmission is error free.

*Note:* Inserted zeros are not included in the CRC accumulation.

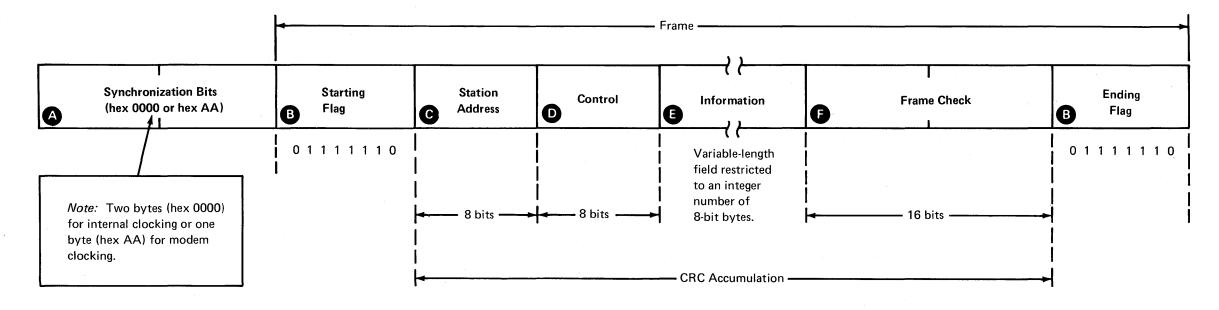

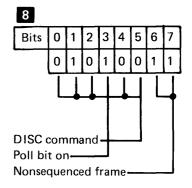

#### **Control Field Formats**

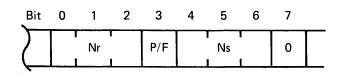

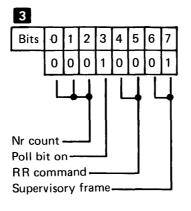

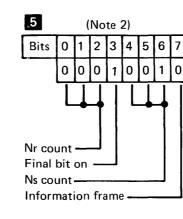

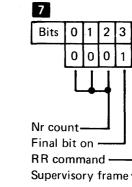

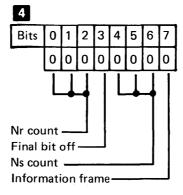

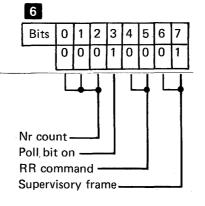

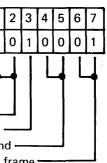

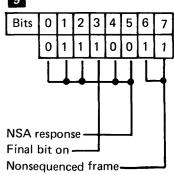

The control field uses bit 7 or bits 6 and 7 to identify the three control field formats-the information transfer, supervisory, and nonsequenced formats. All three formats use bit 3 as the poll/final (P/F) bit. A poll bit, sent by the primary station, permits the transmission of data from a secondary station. A secondary station sends a final bit when it has completed a transmission.

The Nr bits (bits 0 through 2 of the information transfer and supervisory formats) contain the sequence number of the next expected frame. The Ns bits (bits 4 through 6 of the information transfer format) contain the sequence number of the frames that have been sent. The remaining bits of the control field (for all three formats) are used to encode the commands and responses necessary to control a data link; the commands and responses are described on this page.

Information Transfer Format

The information transfer format is used for transferring information over a data link. The transmitting station increases its Ns count for each information frame it sends; the receiving station increases its Nr count for each valid sequenced frame it receives.

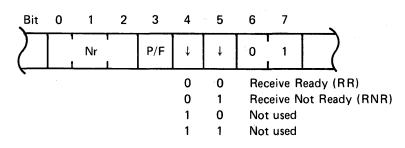

Supervisory Format

The supervisory format is used to acknowledge information frames, to request retransmission of information frames, and to report a busy condition. The commands and responses of the supervisory format are:

Receive Ready (RR)

This is a command or a response (sent by a primary station or by a secondary station), indicating that the originating station is ready to receive data. Receive ready also acknowledges information frames with sequence counts through Nr minus 1.

Receive Not Ready (RNR)

This is a command or a response (sent by a primary station or by a secondary station), indicating that the originating station has a busy condition and cannot receive additional information frames. Frames through Nr minus 1 are received.

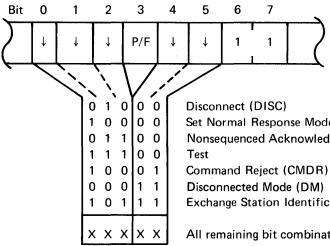

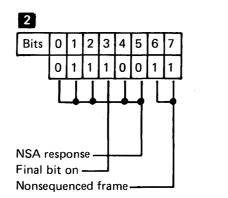

#### Nonsequenced Format

The nonsequenced format is used to perform data link control functions. The commands and responses of the nonsequenced format are:

- Disconnect (DISC)

- This command terminates normal response mode (NRM) and puts the receiving secondary station in normal disconnect mode (NDM). A System/34 that is acting as a secondary station should respond to the DISC command with an NSA (nonsequenced acknowledgment); it should then disable the adapter. No information field is permitted with the disconnect command.

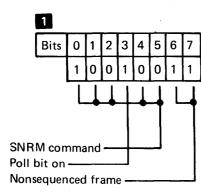

- Set Normal Response Mode (SNRM) This command puts the secondary station in normal response mode (NRM) by placing the receiving secondary station under control of the transmitting primary station. NSA (nonsequenced acknowledgment) is the expected response from the secondary station to an SNRM command. Transmissions are not allowed from a System/34 that is a secondary and is in normal response mode until it receives a frame with the poll bit on. The primary and secondary station Nr and Ns counts are reset to 0. The secondary station remains in normal response mode until it receives a DISC command.

- Nonsequenced Acknowledgment (NSA) This is an affirmative response to a DISC or SNRM command; it indicates that the command has been received.

- Set Normal Response Mode (SNRM) Nonsequenced Acknowledgment (NSA)

- Exchange Station Identification (XID)

All remaining bit combinations are not used.

Test

This is a command and a response. The primary station starts one round-trip transmission of test data to which a secondary station responds. The test data sent with the command is returned in the response from the secondary station. However, if the amount of test data is more than the amount of data that can be put into the receive buffer, only the control field is returned in the test response.

- Command Reject (CMDR) This is a response from a secondary station in NRM to indicate that a problem has been detected in a frame received with good frame check sequence. A CMDR response includes an information field that gives the reason for the rejected command.

- Disconnected Mode (DM) This is a response from a secondary station, indicating that it is in a disconnected state and that it wants an online status.

- Exchange Station Identification (XID) The primary station uses XID as a command to request station identification from a secondary station. The primary station also has the option of giving its own identification. An XID is the expected response to the XID command.

# Primary Station Commands and Secondary **Station Responses**

**Typical SDLC Sequence**

Each byte of every frame is either generated or analyzed by hardware, microcode, SDLC IOS, or SNA utility. The matrix shown at the right indicates with bullets (•) how each byte is generated or analyzed.

See the bottom of the page for bit descriptions of the nine control fields.

|                      | SNRM         | NSA     | RR          | Information – 2 Frames                                                                                    | RR          | RR                | DISC             | NSA              |

|----------------------|--------------|---------|-------------|-----------------------------------------------------------------------------------------------------------|-------------|-------------------|------------------|------------------|

| Primary Station      | FACFF<br>CCF |         | FACCFF<br>F | (Note 3)                                                                                                  | FACFF<br>F  |                   | FACFF<br>F<br>8  | 3                |

| Secondary<br>Station | N<br>o<br>t  | FACCCFF | N<br>o<br>t | F     A     C     I     I     F     F     A     C     I     I     F     F       4     5     5     5     5 | N<br>o<br>t | FACFFF<br>CC<br>7 | N<br>o<br>t<br>e | FACFF<br>CC<br>9 |

| Hardware             | • 1 •        | •       | • 1 •       | •                                                                                                         | • 1 •       | •                 | • 1 •            |                  |

| Microcode            | ••••         | •••••   | • • • • • • | •••••••••                                                                                                 | •••••       | • • • • •         | • • • • •        | • • • •          |

| SDLC IOS             | •            | •       |             |                                                                                                           |             |                   |                  | •                |

| SNA Utility          |              |         |             |                                                                                                           |             |                   |                  |                  |

# Notes:

1. System/34 microcode looks at the control byte to detect the poll/final bit only.

- 2. System/34 SDLC IOS turns on the final bit in the last information frame only if seven consecutive information frames are transmitted. If less than seven information frames are transmitted or a busy state exists for this line, the final bit is sent in a supervisory frame (RR or RNR) that follows the last information frame.

- 3. Most SNA users require that the primary station transmit the first information frame.

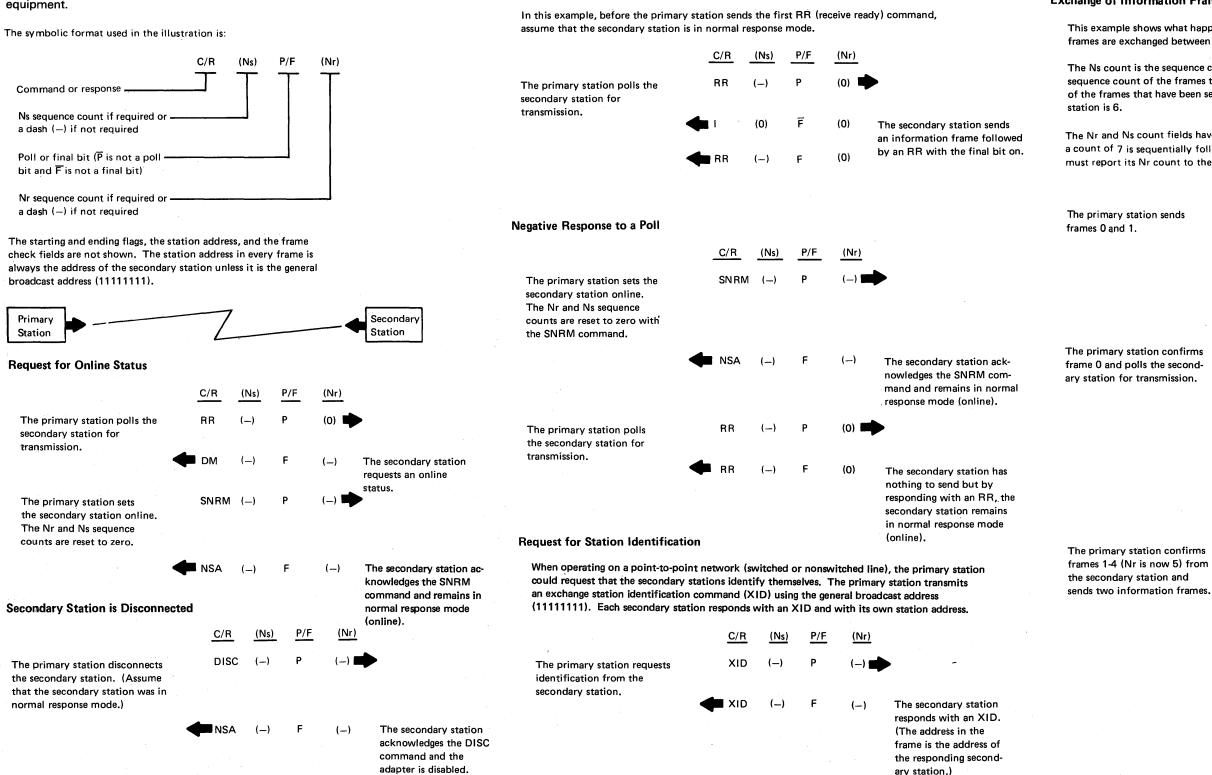

# Examples of SDLC Commands and Responses

The examples on this page show some of the more common commands and responses between the primary and secondary stations. The examples are for either point-to-point or multipoint networks using half-duplex equipment.

Primary

Station

Affirmative Response to a Poll

#### **Exchange of Information Frames**

Primary

Station

Secondary

Station

This example shows what happens to the sequence count fields at both stations when information frames are exchanged between the primary station and the secondary station.

The Ns count is the sequence count of the frames that have been sent. The Nr count is the sequence count of the frames that have been received plus 1. For example, if the sequence count of the frames that have been sent (Ns) by the secondary station is 5, the Nr count of the primary

The Nr and Ns count fields have a counting capacity of 8 and the counts can wrap around; that is, a count of 7 is sequentially followed by 0. Up to seven frame's can be sent before the receiving station must report its Nr count to the transmitting station.

|                                    | C/R        | <u>(Ns)</u> | P/F | <u>(Nr)</u> |                                                                                             |

|------------------------------------|------------|-------------|-----|-------------|---------------------------------------------------------------------------------------------|

| sends                              | I          | (0)         | P   | (0)         | •                                                                                           |

|                                    | I          | (1)         | Ρ   | (0)         | •                                                                                           |

|                                    | <b>4</b> 1 | (0)         | F   | (2)         | The secondary station confirms frames 0 and 1                                               |

|                                    | RR RR      | (_)         | F   | (2)         | from the primary station<br>and sends frame 0<br>followed by an RR                          |

| confirms<br>be second-<br>mission. | RR         | (_)         | Р   | (1)         | with the final bit on.                                                                      |

|                                    | <b>4</b>   | (1)         | F   | (2)         | The secondary station                                                                       |

|                                    | <b>4</b> I | (2)         | Ē   | (2)         | sends four information frames followed by an                                                |

|                                    | <b>4</b>   | (3)         | F   | (2)         | RR with the final bit on.                                                                   |

|                                    | <b>4</b>   | ((4)        | F   | (2)         |                                                                                             |

|                                    | 🗣 RR       | (_)         | F   | (2)         |                                                                                             |

| n confirms<br>ow 5) from           | 1          | (2)         | P   | (5)         | Notice that the Nr count of<br>the receiving station is one<br>greater than the Ns count of |

| on and<br>ion frames               | I          | (3)         | Ρ   | (5) 📫       | the transmitting station.                                                                   |

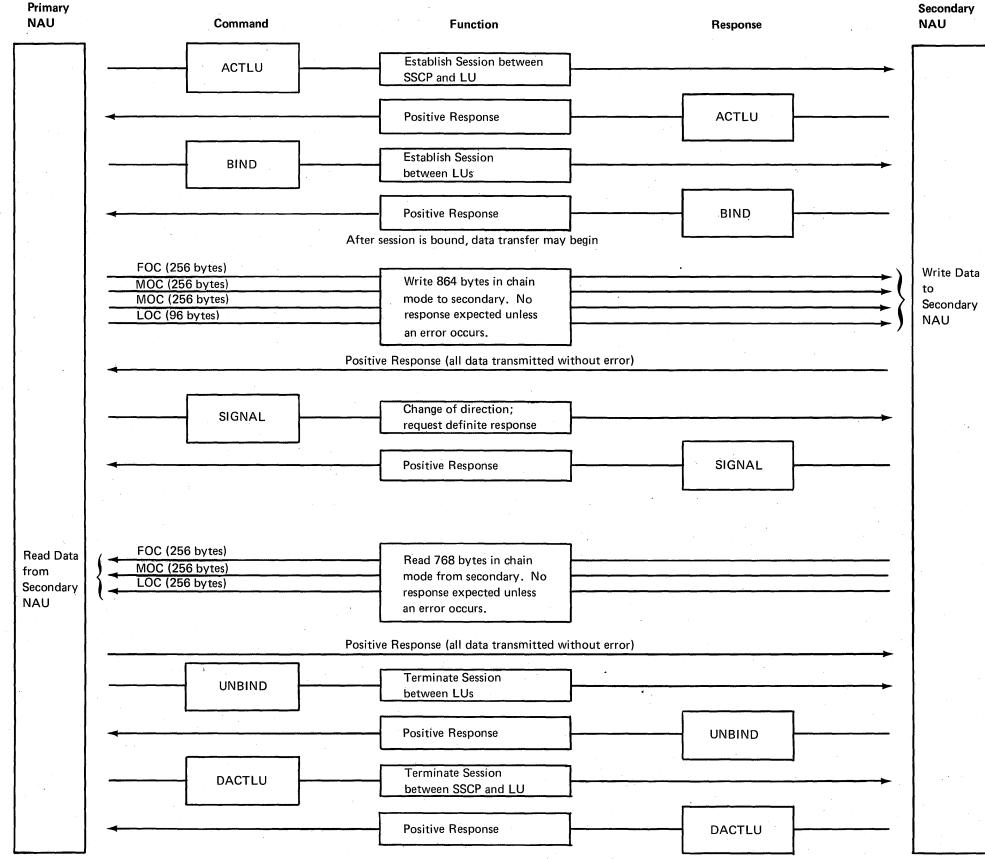

# Systems Network Architecture

| Systems network architecture (SNA) is the set<br>of protocols (requests and responses) that is<br>commonly understood by all the components in<br>the network that are used to transmit and<br>receive messages. | Primary NAU                           |                 | Secondary NAU |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|-----------------|---------------|

| receive messages.                                                                                                                                                                                                | 1                                     | XID             |               |

| SNA provides a way to:                                                                                                                                                                                           |                                       | XID             |               |

| Establish a communication session                                                                                                                                                                                | SDLC                                  | SNRM            |               |

| Handle a normal communication session                                                                                                                                                                            | (                                     | NSA             | · · · · · ·   |

| Allow interrupts                                                                                                                                                                                                 | ( -                                   |                 |               |

| • Terminate the communication session                                                                                                                                                                            | · · · · · · · · · · · · · · · · · · · | l (Nr, P, Ns)   |               |

|                                                                                                                                                                                                                  | ACTL⊎ (LSID = 0)                      | 1 ((1), 1, 103) | ► \           |

| SNA/SDLC Data Relationship                                                                                                                                                                                       | -                                     | I (Nr, F, Ns)   |               |

| All data that is transmitted in the information                                                                                                                                                                  | ACTLU (LSID = 1)                      | I (P)           |               |

| field of the SDLC frame is generated or<br>analyzed by SNA. Also, all SNA information                                                                                                                            | -                                     | (F)             |               |

| (transmission headers, request/response headers, request units) is handled as normal                                                                                                                             | BIND (LSID = 0)                       | I (P)           |               |

| data in the SDLC information field, and SDLC makes no distinction between these fields and                                                                                                                       |                                       | I (F)           |               |

| normal data.                                                                                                                                                                                                     |                                       |                 |               |

|                                                                                                                                                                                                                  | WRITE (LSID = 0)                      |                 |               |

|                                                                                                                                                                                                                  | •                                     |                 | > SNA         |

|                                                                                                                                                                                                                  | -                                     | I               | (             |

|                                                                                                                                                                                                                  | -                                     | RR (P)          |               |

|                                                                                                                                                                                                                  | -                                     | I (F)           |               |

|                                                                                                                                                                                                                  | UNBIND                                | I (P)           |               |

|                                                                                                                                                                                                                  |                                       | I (F)           | -             |

|                                                                                                                                                                                                                  | DACTLU                                | I (P)           |               |

|                                                                                                                                                                                                                  |                                       | I (F)           |               |

|                                                                                                                                                                                                                  | · · · · · · · · · · · · · · · · · · · | <               | /             |

DISC SDLC NSA

Typical SNA/SDLC Sequence

# Types of Network Addressable Units

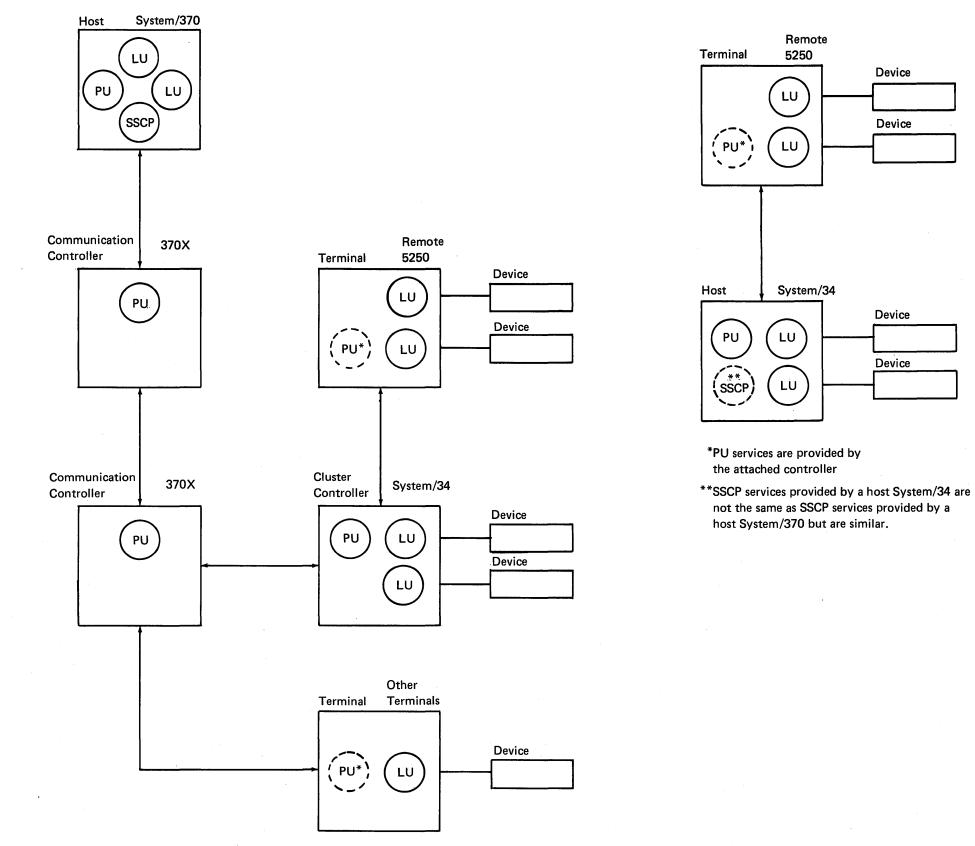

SNA defines three types of network addressable units (NAUs). The first type is the system services control point (SSCP). SSCP is responsible for the general management of the network (such as bringing up the network, establishing sessions, or recovering when a network component has failed to maintain contact). Some of the processes managed by SSCP are identified by commands from network operators who are responsible for the operation of the network. Other SSCP processes serve requests (for example, for sessions) from terminal operators.

The second type of NAU is the physical unit (PU). Each node in the network has an assoicated PU. (Communication controllers provide PU services for certain low-function, attached terminals as a boundary function.) The SSCP establishes a session with each PU in the network as a part of the bring-up process. This session is used to control the physical configuration and the communication system resources associated with the node and also to collect maintenance and operational statistics.

The third type of NAU is the logical unit (LU). The SSCP also establishes a session with each LU in the network as a part of the bring-up process. The LU is the port through which an end user has access to the SSCP-provided services such as session establishment. The LU is the port through which the end user also has access to presentation services provided by the communication system to support end user (or LU-LU) communication. A logical unit can support at least two concurrent sessions, one with the SSCP and one with another logical unit. Some LUs can support multiple sessions with other LUs. For example, in a remote work station environment the application program communicating with a remote 5250 is an LU capable of supporting multiple LU sessions (it can run more than one terminal).

There are three kinds of sessions among NAUs:

LU to LU

- LU to SSCP

- · PU to SSCP

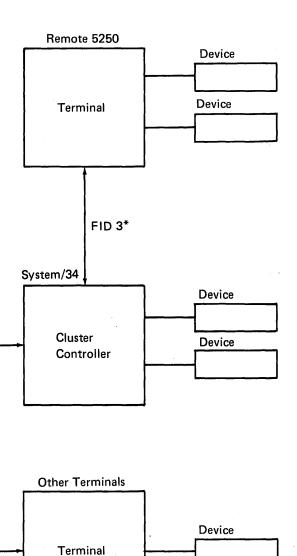

# **Physical Configuration**

The physical configuration of a network is defined in terms of four node types: host, communication controller, cluster controller, and tèrminal.

It should be noted that devices are physical assemblies that exist in the physical configuration. However, they do not have network addresses and do not exist in the configuration information used by the SSCP. Devices are physical resources that are controlled by the cluster controllers or terminals.

A host node is a facility that contains the system services control point in addition to executing application programs, managing data bases, and so forth.

A communication controller node is dedicated to the job of controlling communication lines (and related resources such as buffers) in addition to performing the functions related to supporting one or more subareas.

Cluster controller nodes support the attachment of a wide variety of devices to satisfy the needs of a broad range of end users. Cluster controllers have less network management capability than host nodes or communication controllers.

Terminal nodes have the least network management capability of all network nodes.

A communication controller node may provide two types of facilities: intermediate functions and boundary functions. A communication controller node providing an intermediate function routes messages to other subareas based on full network address processing. A communication controller node providing a boundary function converts a full network address (from the host) to a local address form for cluster controller or terminal nodes. Cluster controller and terminal nodes depend on the node to which they are attached for support in scheduling the data flow within a session.

# **Typical Large System Configuration**

,

| Device |  |

|--------|--|

|        |  |

| Device |  |

|        |  |

| v | Ī | C | )( | 9 |  |

|---|---|---|----|---|--|

|   |   |   |    |   |  |

De

| - |   |      |  |

|---|---|------|--|

| D | e | vice |  |

|   |   |      |  |

# Data Communications 12-11

# **SNA/SDLC Buffer**

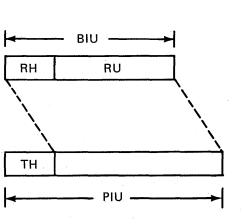

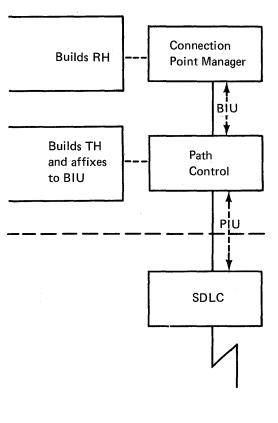

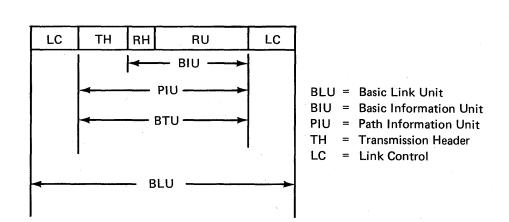

The SNA/SDLC (systems network architecture/synchronous data link control) buffer contains a transmission header (TH) field, a request/response header (RH) field, and a request/response unit (RU) field. Each field is discussed separately later in this section.

# Basic Information Unit

The basic unit passed between the connection point manager (CPMGR) and path control (PC) is the basic information unit (BIU). The BIU is made up of a request/response header (RH) built by the connection point manager and attached to the request/response unit (RU).

# Path Information Unit

A transmission header (TH) is attached to each BIU by path control. The TH contains control information required later by path control in handling the BIU. A TH plus a BIU is a path information unit (PIU).

# Basic Transmission Unit

The basic transmission unit (BTU) is the fundamental unit passed between path control and data link control (DLC). A BTU is made up of one or more path information units (PIUs). The term blocking is used to describe the generation of a BTU with more than one PIU. However, blocking is not used with System/34 and is not discussed here.

#### Basic Link Unit

The basic link unit (BLU) is the basic unit of transmission at the data link level; that is, in SDLC the BLU is one frame with the path information unit placed in the information field.

BLU is equal to SDLC Frame is equal to F, A, C, [PIU], FC, F.

# Relationship of TH, BIU, PIU, BTU, and BLU

A summary of the relationship of the TH, BIU, PIU, BTU, and BLU is shown below. Link control (LC) is the control information used by the data link. In the case of SDLC, the left LC would be F, A, C, and the right LC would be FC, F.

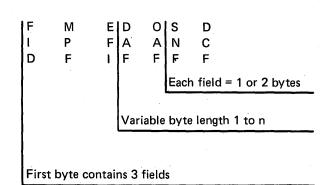

#### Transmission Header

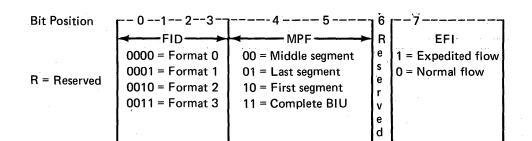

A transmission header (TH) is attached to each BIU that is handled by path control. The TH is made up of a variable number of bytes containing the format identification field (FID), the Mapping Field (MPF), and the expedited flow indicator (EFI), followed by a series of fields that define the associated BIU.

# **TH Format**

# FID = Format Identification Field

MPF = Mapping Field

EFI = Expedited Flow Indicator

DAF = Destination Address Field

- OAF = Origin Address Field

- SNF = Sequence Number Field

- DCF = Data Count Field

The bit configuration of the first byte of the TH is:

#### Format Identification Field

The format identification field (FID) is the first field of the transmission header. The FID is the 4 high-order bits (0-3) of the first byte in the TH. A detailed description of the 4 TH formats is presented later in this section.

# Mapping Field

The mapping field (MPF) is 2 bits (bits 4 and 5 of the first byte in the TH), which define the mapping of BIUs into PIUs for transmission.

The bit 4 and 5 settings indicate the following:

- 00 = Middle segment of a BIU 01 = Last segment of a BIU 10 = First segment of a BIU

- 11 = Complete BIU

#### Expedited Flow Indicator

The expedited flow indicator (EFI) determines whether the associated PIU is on the normal or expedited flow. Data on the normal flow must be processed in the order it was entered into the transmission subsystem. Data on the expedited flow may be moved ahead of data on the normal flow; however, within the expedited flow, processing order is maintained. The normal or expedited selection is made above the path control level and is passed as a parameter to path control.

The EFI is a 1-bit field, which is bit 7 of the first byte of the TH. It has the following meaning:

1 = Expedited flow 0 = Normal flow

# **Destination Address Field**

The destination address field (DAF) contains the address of the destination network addressable unit (NAU). The address will be in the form required by the receiving path control. The DAF may be from 1 bit to several bytes, depending on the FID. The DAF is always the destination NAU, and its position in the TH is fixed for any given FID.

#### Origin Address Field

The origin address field (OAF) contains the address of the originating NAU. The address will be in the form required by the receiving path control. The OAF may be from 1 bit to several bytes, depending on the FID. The OAF is always the address of the originating NAU, and its position in the TH is fixed for any given FID.

#### Sequence Number Field

The sequence number field (SNF) provides numeric identities for the associated BIU. The content of the SNF is generated by the origin connection point manager and is passed as a parameter to path control. Although the content may be either an actual sequence number or just an identification number, path control will use the SNF only as an identification number.

# Data Count Field

The data count field (DCF) contains a binary count of the number of bytes in the BIU associated with the header; the count does not include any of the bytes in the transmission header.

# TH Formats

There are four TH formats:

• TH Format 0 (communication controller node)

TH Format 0 is used between a host node and the communication controller node or between the communication controller node and pre-SNA devices. The remainder of the header fields for FID 0 are the same as those for FID 1 and are described in that section.

• TH Format 1 (communication controller node)

TH Format 1 is used between a host node and the communication controller node or between the communication controller nodes.

> FID 0: 0000 FID 1: 0001

Byte

| 0  | Format ID Field 1<br>Mapping Field<br>Reserved Bit<br>Expedited Flow Indicator | Reserved |  |  |  |  |

|----|--------------------------------------------------------------------------------|----------|--|--|--|--|

| 2  | Destination Address Field                                                      |          |  |  |  |  |

| 4  | Origin Address Field                                                           |          |  |  |  |  |

| 6  | Sequence Number Field                                                          |          |  |  |  |  |

| 8  | Data Count Field                                                               |          |  |  |  |  |

| 10 | Basic Information Unit                                                         |          |  |  |  |  |

• TH Format 2 (cluster controller node)

TH Format 2 is used by path control between cluster controller nodes and the attached communication controller nodes.

| Byte |                                                                                |                      |  |  |  |  |  |

|------|--------------------------------------------------------------------------------|----------------------|--|--|--|--|--|

| 0    | Format ID Field 2<br>Mapping Field<br>Reserved Bit<br>Expedited Flow Indicator | Reserved             |  |  |  |  |  |

| 2    | Destination Address Field                                                      | Origin Address Field |  |  |  |  |  |

| 4    | Sequence Number Field                                                          |                      |  |  |  |  |  |

| 6    | Basic Information Unit                                                         |                      |  |  |  |  |  |

• TH Format 3 (terminal node)

System/370 TH Format 3 is used by path control, between terminal nodes and their connecting nodes, to provide the boundary function. Host LSID FID 0/1 5 67 Byte 1 2 3 4 0 370X Local Address - - - - - -PU/LU SSCP/LU Communication Controller (with In FID 3, the DAF and OAF are replaced by 1 byte - the LSID. This intermediate replacement limits what the DAF/OAF can do. function) The LSID has three parts: FID 3: 0011 Byte • Bit 0 (SSCP/LU indicator) Format ID Field 3 0 Mapping Field Indicates if the FID 3 PIU is to be routed to or from the SSCP or an LU. Local Session ID FID 0/1 **Reserved Bit** 0 = SSCPExpedited Flow Indicator 1 = LU \* **Basic Information Unit** 2 370X • Bit 1 (PU/LU indicator) Indicates if the local address (bits 2-7) defines the PU or an LU in the Communication FID 3 NAU. FID 2\* Controller (with 0 = PU boundary 1 = LU function) • Bits 2 through 7 (local address) When the PU/LU indicator equals 1 (LU), bits 2-7 select one of 64 possible LUs in the FID 3 NAU. When the PU/LU indicator equals 0 (PU), bits 2-7 are reserved and must be set to zero.

\_\_\_\_\_

\*Only FID 2 and FID 3 are used by System/34 in SNA operations.

FID 3

# Request/Response Header

The request/response header (RH) field is 3 bytes long and is attached to each request unit (RU) as the RU passes through the connection point manager. It is possible that the RU that the RH is to be attached to will have a length of zero.

The format of the request header differs from that of the response header. The general format of each header is shown below.

#### **Control Fields in the Request Header Format**

Byte 0 Byte 1 Form of response requested Request RU type indicator Pacing Subsystem control indicator Format indicator Sense data included indicator Chaining control

# Byte 2

Change of direction control Begin-end bracket control Code selection indicator

# **Control Fields in the Response Header Format**

| Byte 0                        | Byte 1        |

|-------------------------------|---------------|

| Response                      | Response type |

| RU type indicator             | Pacing        |

| Subsystem control indicator   |               |

| Format indicator              |               |

| Sense data included indicator |               |

| Chaining control              |               |

|                               |               |

# Request/Response Unit

The request/response unit (RU) is the basic unit of information entering and leaving the transmission subsystem. It may contain commands that control the flow of data through the network, responses to commands, data, or acknowledgment of data.

There are two formats of the RU-the request format and the response format. The information that is placed in the RU and the format used are dependent on the function (command) being performed.

The RU is limited to 256 bytes in length including user data. If the RU is more than 256 bytes long, it must be divided into blocks of 256 bytes or less. This is called chaining. By setting the chain control bit in the request header (RH), SNA can determine which part is the first, middle, last, or only block of a chain.

# Session Control Request Units

The following is a list of request/response units (commands) used with session control:

- Activate physical unit (ACTPU)

- De-activate physical unit (DACTPU)

- Activate logical unit (ACTLU)

- De-activate logical unit (DACTLU)

- Bind session (BIND)

- Unbind session (UNBIND)

- Start data traffic (SDT)

- Clear (CLEAR)

- Request recovery (RQR)

- Set and test sequence numbers (STSN)

# Byte 2

Reserved

The following is a list of special request units (commands) used with network control. These RUs are special in the sense that they are allowed (under network control) to communicate through the common network using sessions established for other purposes.

- Logic unit status (LUSTAT)

- Signal (SIGNAL)

- Cancel (CANCEL)

- Request shutdown (RSHUTD)

- Request maintenance statistics error log (REQMS)

- Request test (REQTEST)

- Auto network shutdown (ANS)

- Auto network shutdown complete (ANSC)

- Prepare to switch (PREPS)

- Switch complete (SWICOM)

- Initialization complete (INITC)

Typical SNA LU/LU Session Sequence

Repeated as necessary while session is bound

# This page intentionally left blank

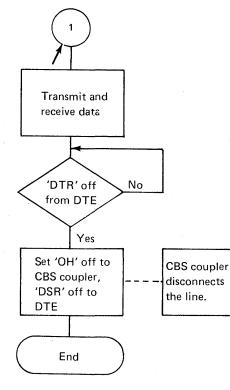

# Modems and Interfaces

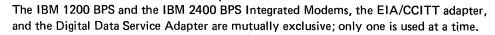

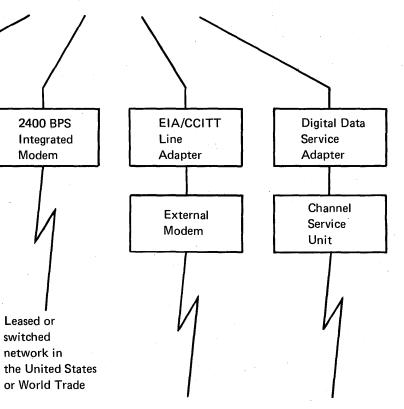

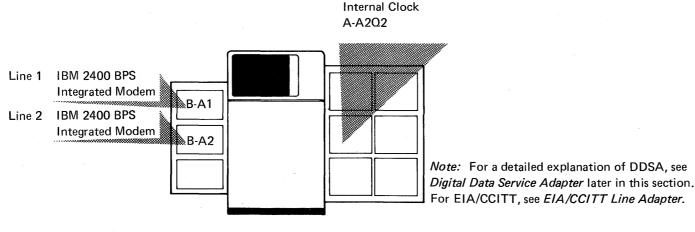

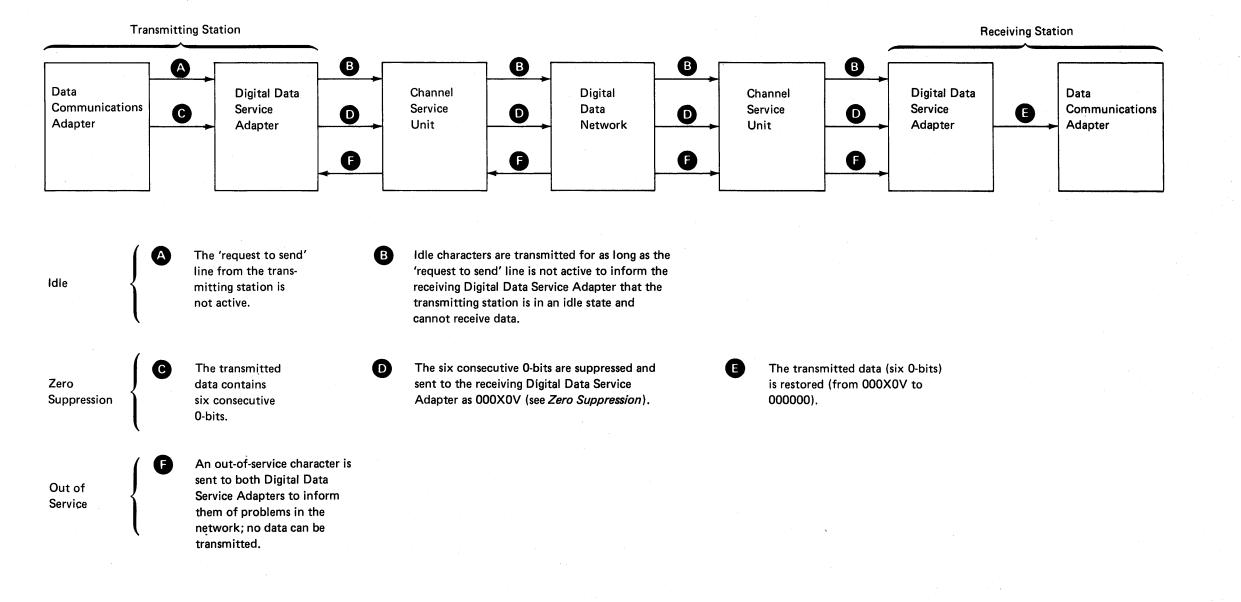

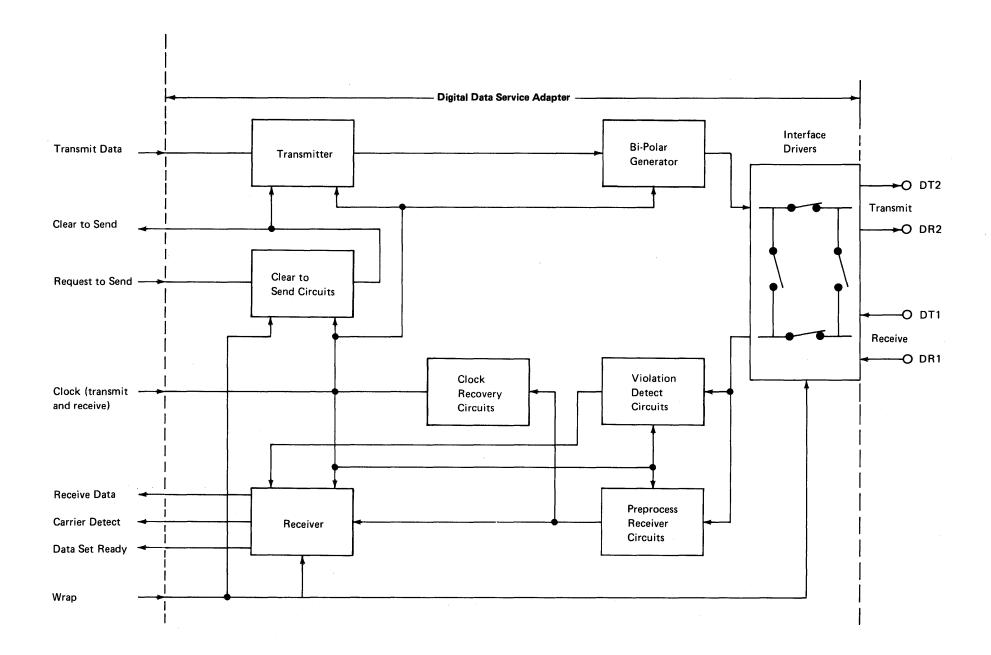

One of two modems (the IBM 1200 BPS Integrated Modem or the IBM 2400 BPS Integrated Modem) or the Digital Data Service Adapter can be installed in the system on each communication feature (line 1 and line 2). In addition, an external modem can be attached to the system by the EIA/CCITT (Electronic Industries Association/International Consultative Committee on Telegraph and Telephone) line adapter. All are described later in this section.

Communication lines 1 and 2 are not mutually exclusive; that is, the modem used on each line does not have to be the same type. If both adapters are operating at the same time, the sum total of the bit rate must not exceed 9,600 bps.

The IBM 1200 BPS and the IBM 2400 BPS Integrated Modems, the EIA/CCITT adapter, and the Digital Data Service Adapter are mutually exclusive; only one is used at a time.

# Data Communications 12-19

# COMMUNICATIONS ADAPTER

# **Data Flow**

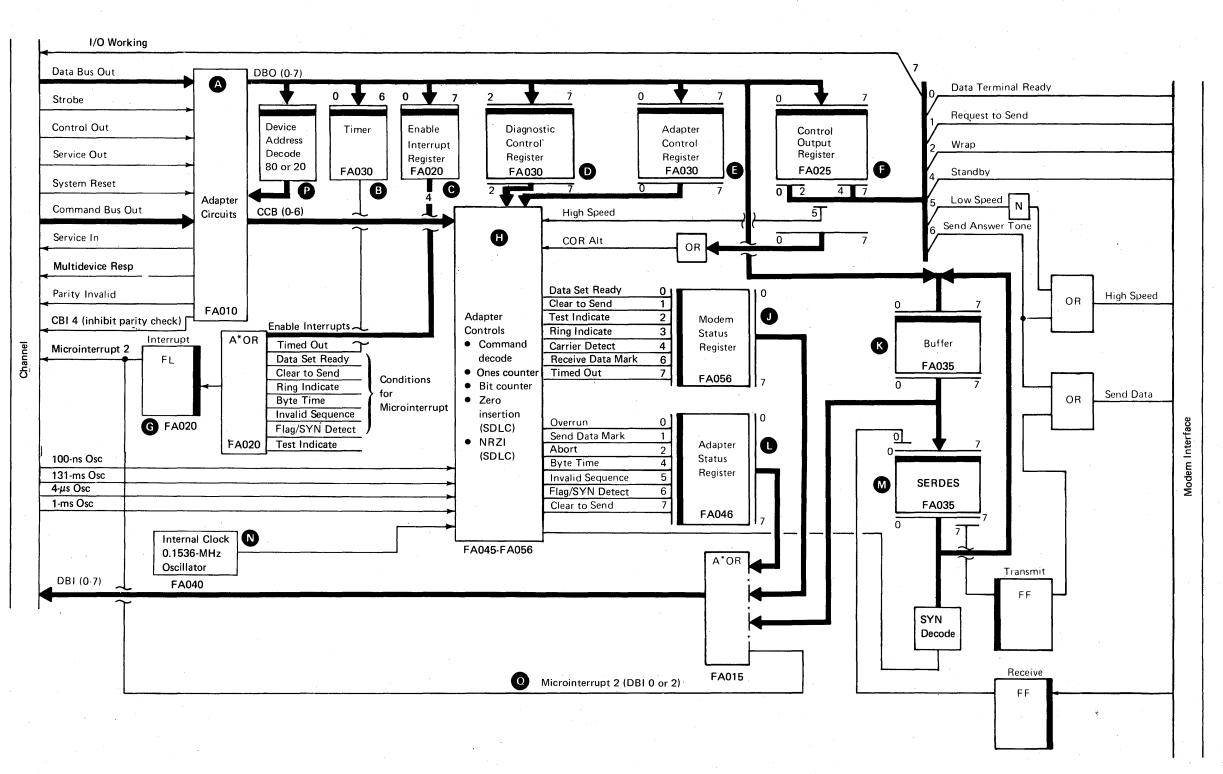

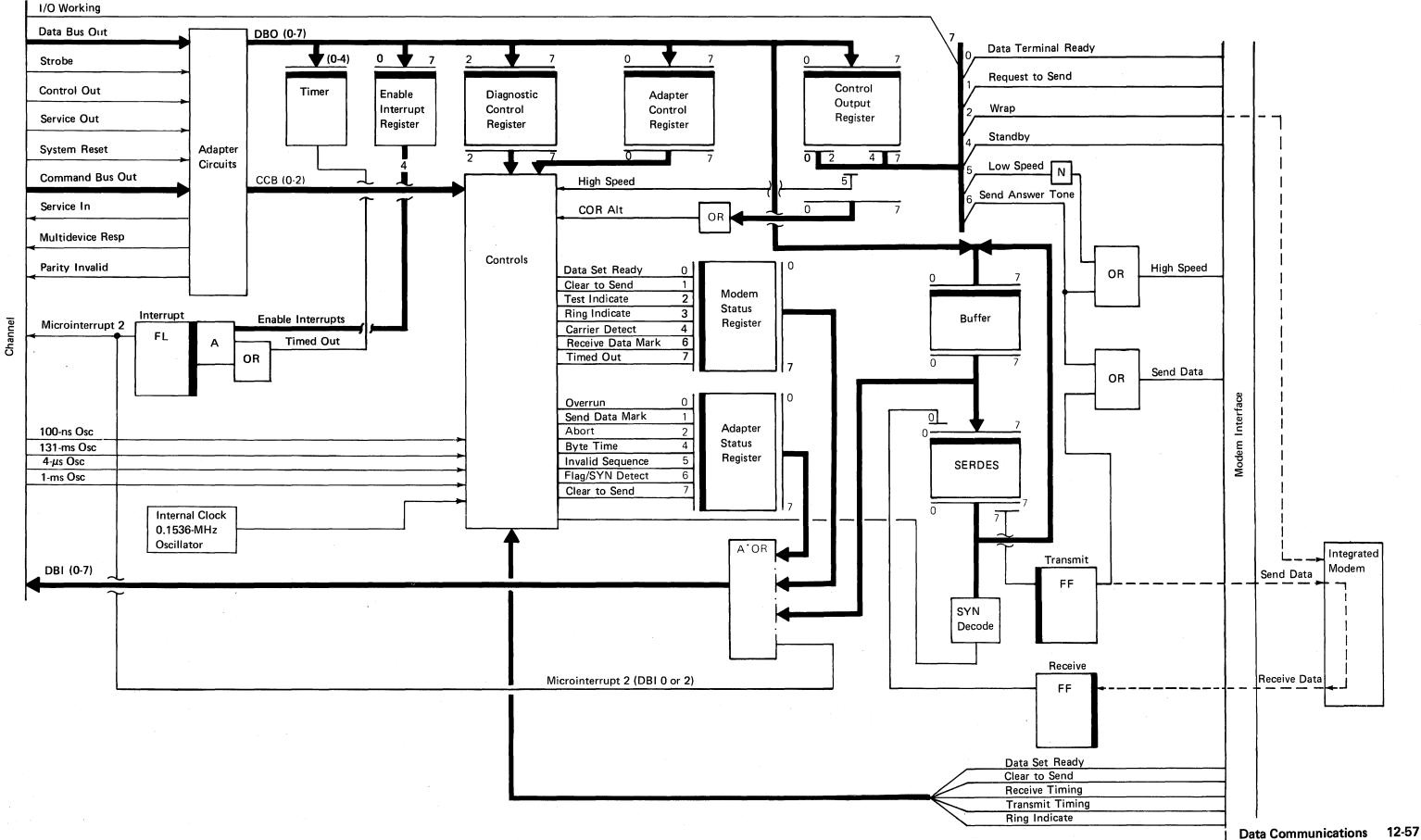

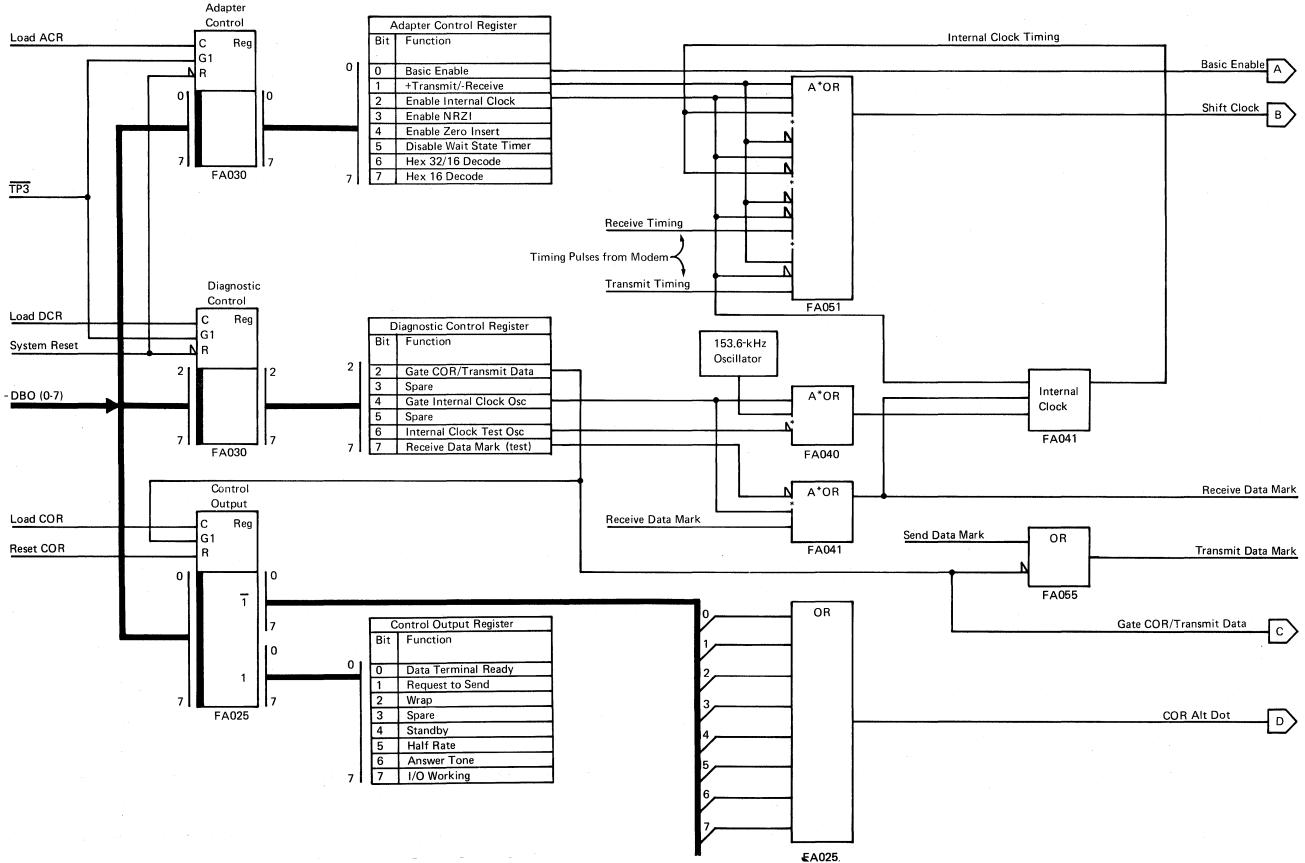

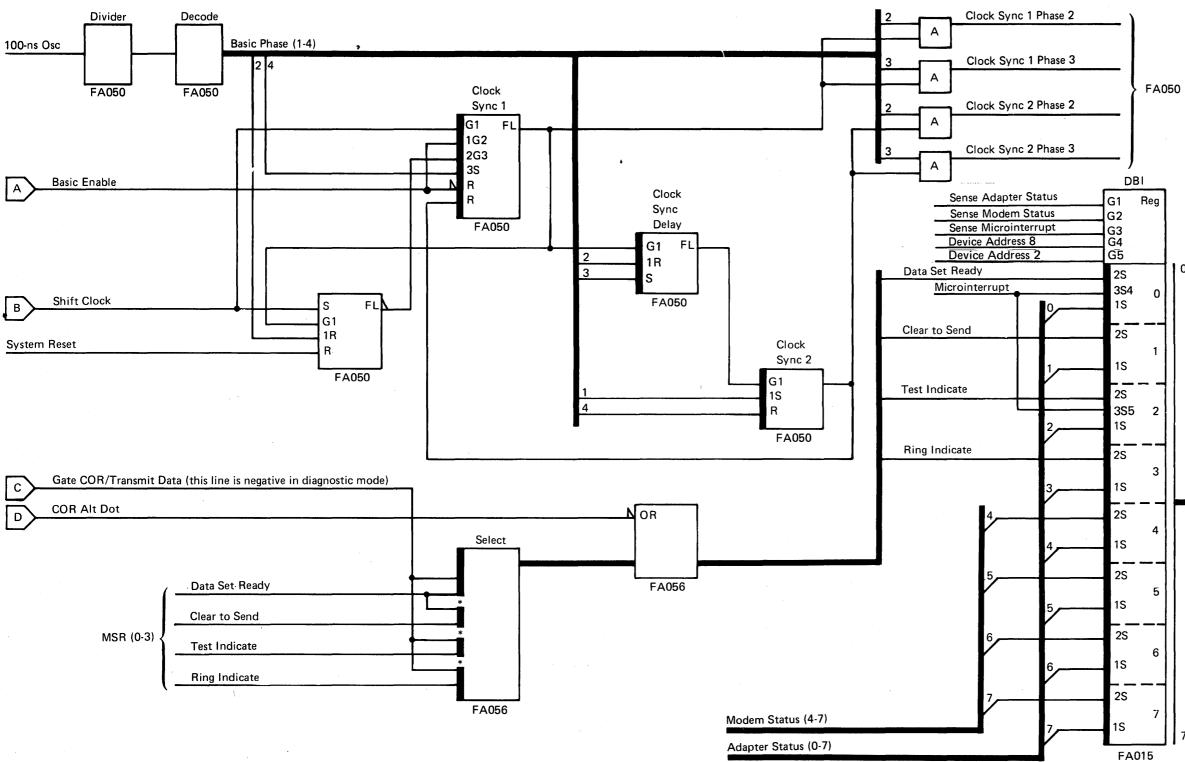

The data flow figure shows the functional units of the communications adapter. All functional units that are identified by an alphabetic character are described on the following seven pages. For a logic description of the functional units, see the appropriate FSL page. For example, see FSL page FA030 for a logic description of the adapter control register **E**.

12-20

# **Functional Units**

The functional units described here are shown in the data flow figure on the preceding page. As an example for all of the registers, a second-level diagram is shown for the adapter control register E.

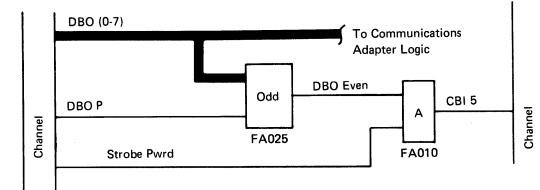

# Adapter Circuits 🗛

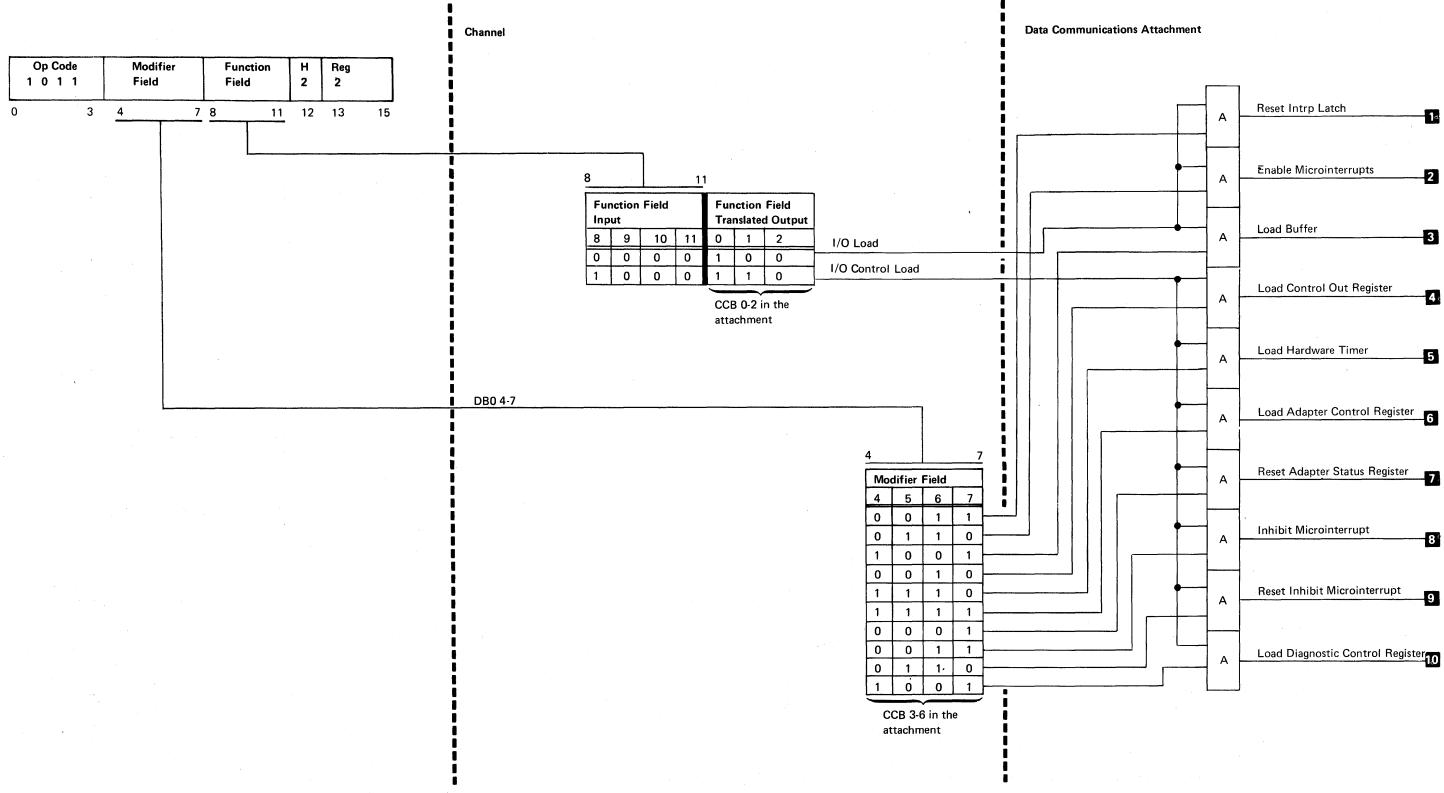

The adapter circuits:

- · Synchronize the adapter card with the channel

- Repower DBO

- Generate:

- A 7-bit channel command bus (CCB)

- Control lines used by the command decode to gate the CCB

- CBI bit 5 (bad DBO parity)

The adapter circuits let the channel communicate with the attachment through control lines and data buses. The 'control out', 'service out', and 'strobe' lines signal the adapter circuits when data is available on DBO or should be on DBI. The 'service in' and 'multidevice resp' lines signal the channel that the data on DBO has been received or that data is available on DBI.

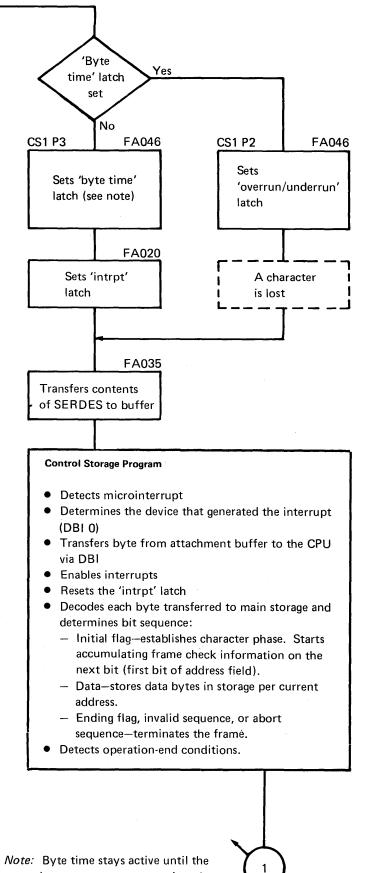

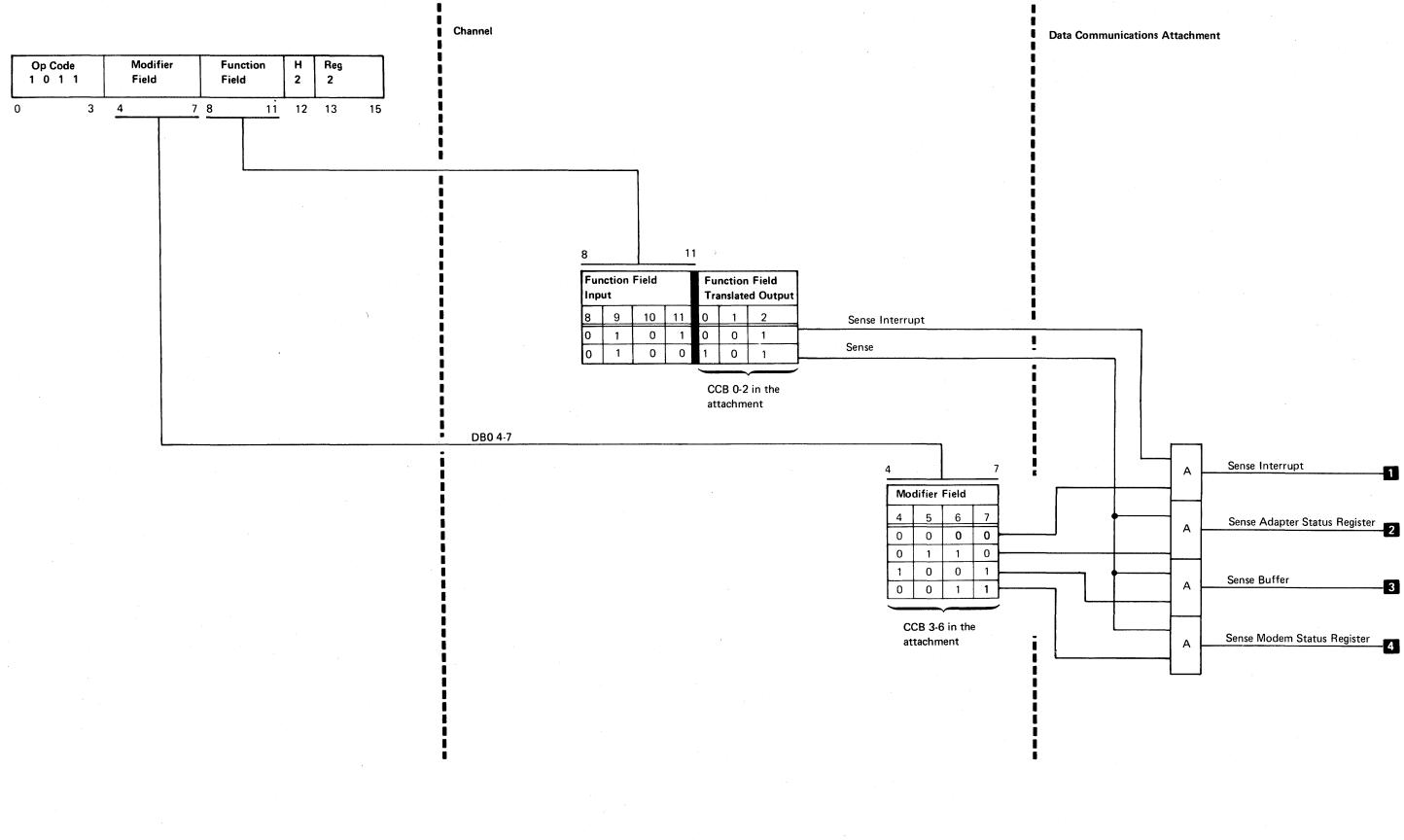

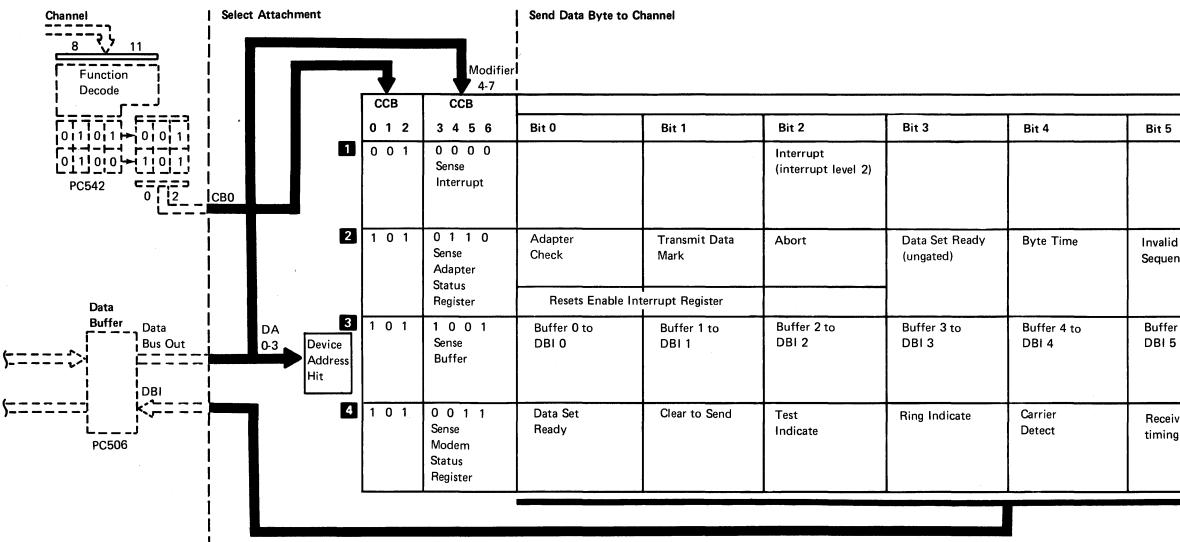

Data bus out (DBO) is a 9-bit bus (0 through 7 and parity) that performs one of two functions: (1) it supplies an I/O output instruction, or (2) it supplies data to the attachment during service out. On any I/O output instruction, DBO bits 4-7 contain the command modifier during control out. DBO bits 0-3 rely on the instruction type. For example, during control out of a sense microinterrupt, DBO bits 0-3 contain the attachment interrupt level address (1000). During control out of any I/O instruction other than sense microinterrupt, DBO bits 0-3 contain the attachment device address (1000).

Command bus out (CBO) is a 3-bit bus that specifies the type of I/O command to be executed. For the data communications adapter, these commands are:

- 000 = Not used

- 001 = Sense microinterrupt

- 010 = Not used

- 011 = Not used

- 100 = 1/0 load

- 101 = I/O sense

- 110 = I/O control load

- 111 = Not used

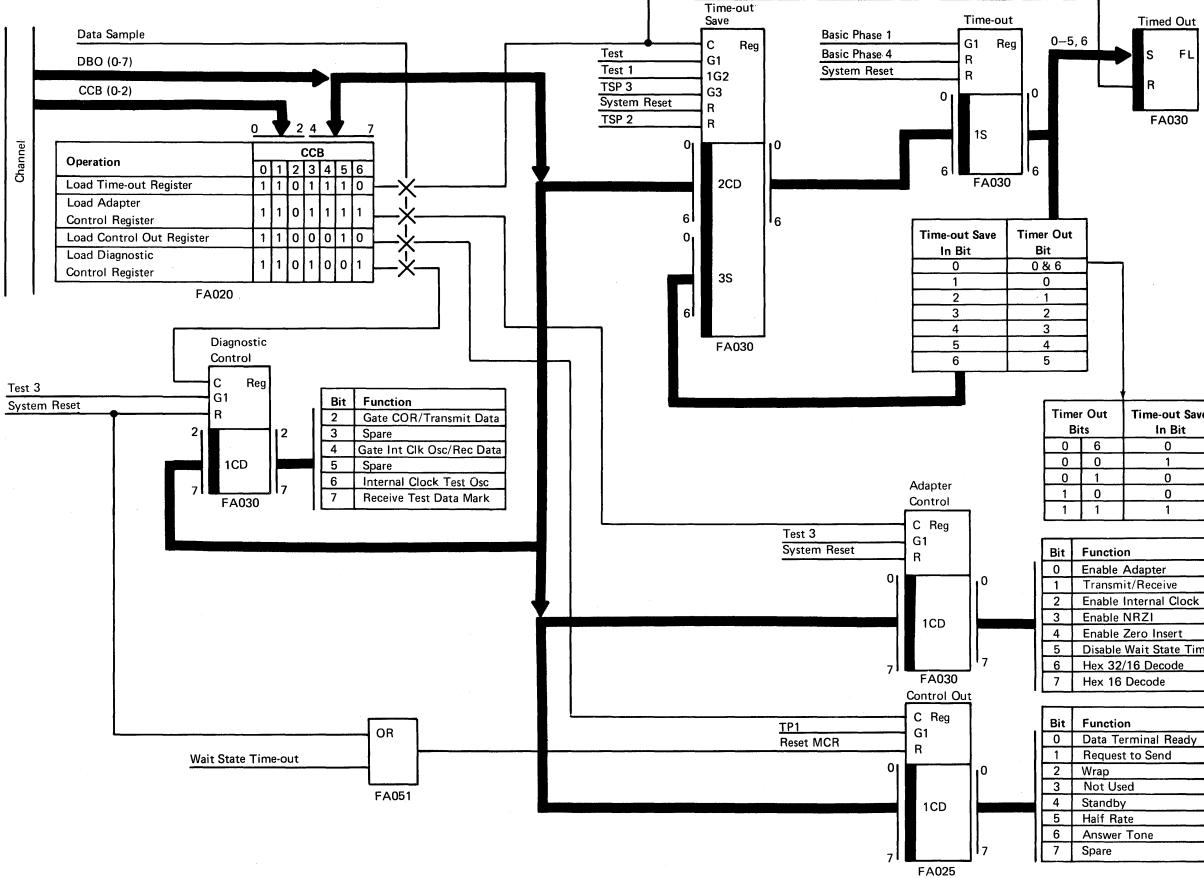

# Timer 🚯

A time-out value (maximum of 16 seconds) is loaded by an I/O control load instruction to start a time-out. A microinterrupt (level 2) occurs after the time-out to indicate that the selected time interval is complete. See Load Time-out Clock and Registers later in this section for a second-level diagram of the time-out register.

The following time-outs are used with BSC:

- A 1-second time-out generates an interrupt that the microcode uses to determine when 2 SYN characters are to be transmitted to maintain character phase at the receiving station.

- A 2-second time-out is used during transmit and receive operations. This 2-second time-out is provided to obtain a 2-second delay before transmitting a TTD or a WACK.

During receive operations with busy on, the operation is terminated if a 3.25-second time-out interrupt occurs when:

- Character sync is not established in 3.25 seconds.

- A continuous sync pattern is received for 3.25 seconds.

- No sync pattern is received for 3.25 seconds.

In a receive-initial, multipoint operation, the receive time-out causes the adapter to drop character phase if no sync pattern is received in 3.25 seconds.

For World Trade modems that do not generate answer tones, the BSC adapter holds a 3.25-second space condition on the 'send data' line with the 'request to send' line on. This is similar to an answer tone because it notifies the user that the connection is now complete.

The following time-outs are used with SDLC:

- Inactivity timer (secondary). A 32-second time-out to prevent long periods of inactivity that might result from an error condition.

- Idle detect and nonproductive timer (primary). The idle detect and nonproductive timer (3 seconds and 16 seconds, respectively) provide for error recovery when no response, or a response not recognized by System/34, is received to a poll.

#### Enable Interrupt Register C

The diagnostic control register is used during problem determination to check the communication circuits between the attachment and the modem. See Diagnostic Mode and Wrap Test later in this section for a second-level diagram of the diagnostic control register. The diagnostic lines and their associated DBO bits are: DBO Bit Diagnostic Line 0 Not used. **DBO Bit** Microinterrupt Source 1 Not used. 0 Data set ready: Indicates that the data set (modem) is ready to transmit or receive data. 2 Gate control output register: The control output register and transmit data are gated to the modem. Clear to send: Indicates that the 1 modem is ready to transmit data to 3 Not used. the communications network. 4 Gate internal clock oscillator: The 2 Test indicate: Indicates that the internal clock oscillator and receive modem is in test mode. data are gated to the attachment. 3 Ring indicate: Indicates that the 5 Not used. telephone is ringing. 6 Internal clock test oscillator: A 4 Byte time: Indicates that a byte of microcode-driven oscillator is data must be sent to the attachment supplied for testing. during transmit operations, or that a byte of data is ready to be sent to Receive test data mark: 7 the channel during receive Microcode-driven receive data is operations. supplied for testing.

Interrupts must be enabled before data is transmitted or received. The enable interrupt register is reset by the 'sense adapter status register' line. See Sense Data, Registers, and Interrupt Conditions later in this section for a second-level diagram of the enable interrupt reaister. The microinterrupts and their associated DBO bits are:

- - - Invalid sequence or abort: For SDLC, indicates that an invalid sequence (1111110) or an abort sequence (1111111) was received.

5

6

- Character sync: Indicates that a SYN character has been received for BSC, or that a flag sequence (01111110) has been received for SDLC.

- 7 Time-out interrupt: Indicates that the specified time interval in the hardware timer ends.

# Diagnostic Control Register D

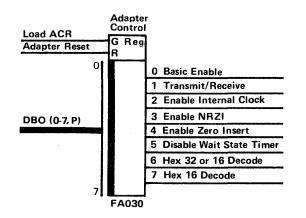

# Adapter Control Register 🗈

The adapter control register (ACR) is used to control the attachment. This register performs the following functions:

DBO Bit ACR Function

- 0 Basic enable: Enables the circuits to transmit or receive data.

- 1 Transmit/receive: Causes the adapter to enter transmit or receive mode.

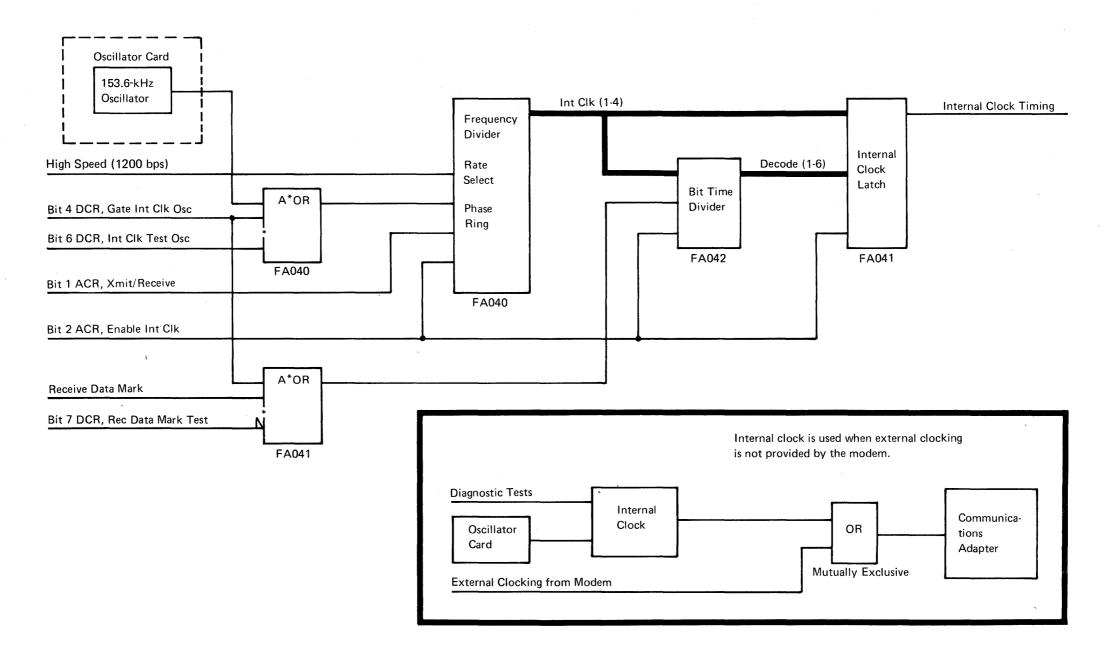

- 2 Enable internal clock: Enables the internal clock to supply transmit and receive timing pulses.

- 3 Enable NRZI: For SDLC, enables the NRZI circuits. The data transmitted or received is encoded or decoded in NRZI. When BSC is used, this bit disables the NRZI circuits.

- 4 Enable zero insert: For SDLC, lets the attachment insert a 0-bit after five consecutive 1-bits.

- 5 Disable wait state timer: Prevents the wait state time-out from resetting the control output register when the system clock stops.

- 6 If on, enables SYN decode in attachment for BSC; if off, transmits or receives flags for SDLC.

- Select ASCII: Selects ASCII SYN (instead of an EBCDIC SYN) if SYN is selected.

# Control Output Register F

0

1

2

3

5

6

7

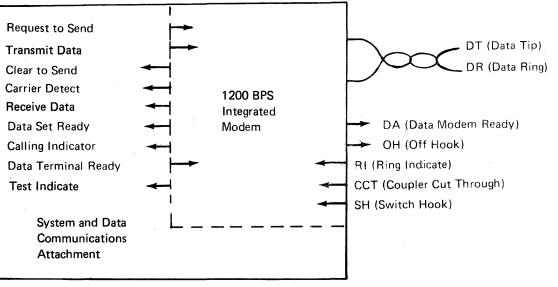

The control output register is reset by the 'system reset' line or at the end of the wait state timer. See *Load Time-out Clock and Registers* later in this section for a second-level diagram of the control output register. This register controls the attachment operations using the following bits:

#### DBO Bit Attachment Operation

- Data terminal ready: Indicates that the attachment is enabled.

- Request to send: Signals the modem to enter transmit mode.

- Wrap: Permits data to be sent through an IBM modem back through the receive circuits. The received data can then be compared with the transmitted data; this permits testing of the communications adapter and the IBM modem.

- Not used.

- 4 Standby: Causes IBM modems to select the switched network backup (SNBU) line.

- Low speed: Causes the modem and the internal clock to send or receive data at half rate.

- Send answer tone: Sends an answer tone; for modems that do not send an answer tone, forces high speed and sends data space.

- I/O working: Informs the control processor that microinterrupts might occur.

# Interrupt Latch G

The interrupt latch is set when the adapter needs a microinterrupt request. See Sense Data, Registers, and Interrupt Conditions later in this section for a second-level diagram of the interrupt latch.

# Controls 🕒

The controls contain the logic necessary for transmitting and receiving data. See Adapter *Controls* on the next page for a description of the control circuits.

#### Modem Status Register **D**

The modem status register contains the status of the modem; the status is sent to the channel. The modem status register is not a register but is shown as a register for purposes of the data flow.

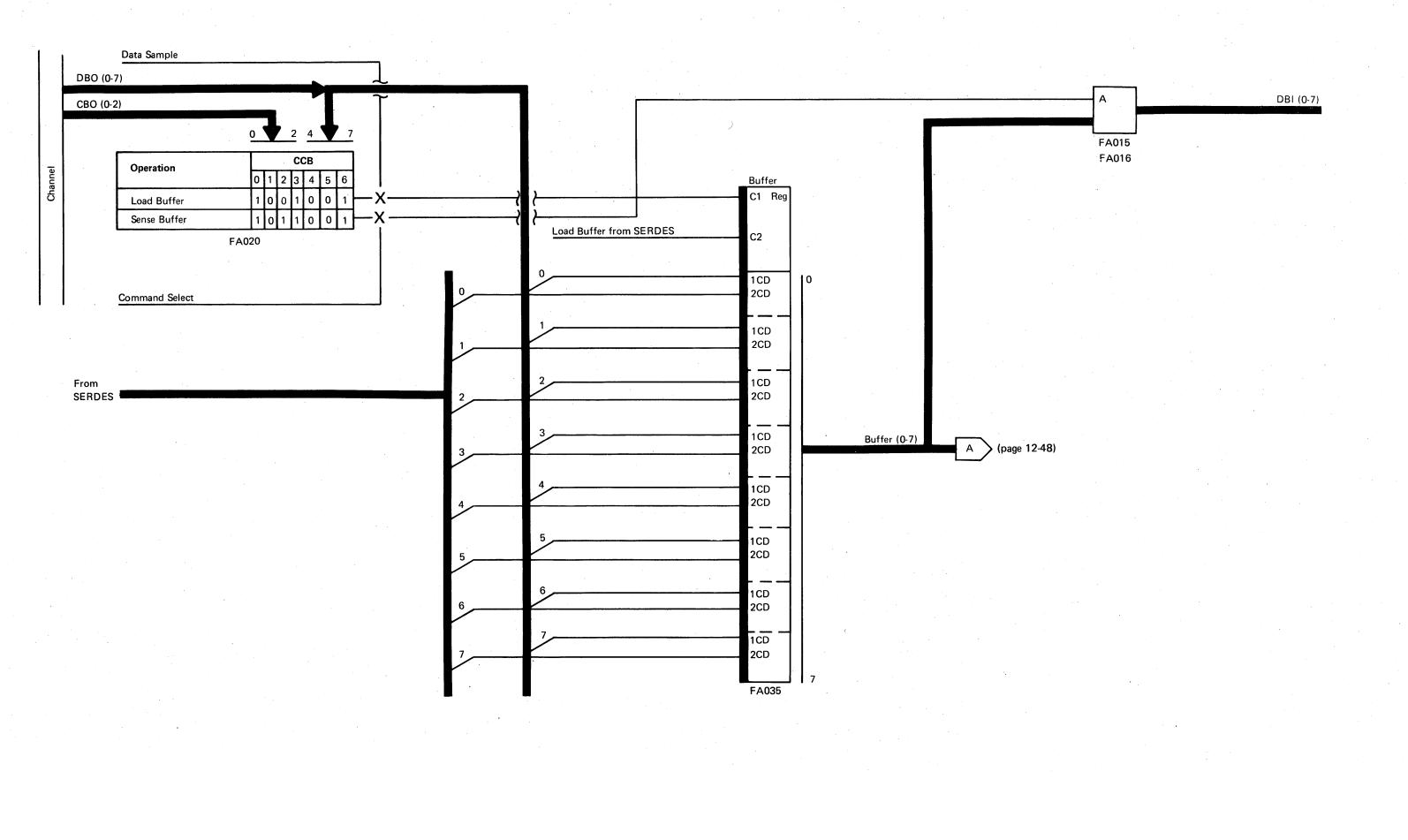

# Buffer K

The buffer contains (1) the data byte from main storage that is ready to be transmitted, or (2) the received data byte that is ready to be stored in main storage. See *Load/Sense Buffer* later in this section for a second-level diagram of the buffer.

#### Adapter Status Register 🚺

The adapter status register contains the status of the adapter; the status is sent to the channel. The adapter status register is not a register but is shown as a register for purposes of the data flow.

# SERDES M

During receive operations, the serializer/deserializer (SERDES) assembles the data received bit-by-bit into data bytes. During transmit operations, the SERDES sends the data byte to the transmit trigger.

# Oscillator N

The oscillator is used by the internal clock feature. The oscillator card is located in  $A-A2\Omega 2$ . Only one internal clock feature is required to supply internal clocking to either or both communication lines that require internal clocking.

#### Device Address P

The address switch on the adapter card is set to respond to a device address of 80 or 20. If one communication line is installed, address 80 should be used. If line 1 and line 2 are installed, and either line uses a data rate transfer speed greater than 4,800 bps, that line must use the device address of 80. The use of device address 80 by an adapter for a communication line configured as such will cause the use of the higher priority microcode and microinterrupt request bit.

# Microinterrupt Bit Q

If device address 80 is set in the address switch on the adapter card, microinterrupt request bit 0 (DBI 0) is used. If device address 20 is set on the adapter card, microinterrupt request bit 2 (DBI 2) is used. 12-22

12

# This page intentionally left blank.

.

# Data Communications 12-23

.

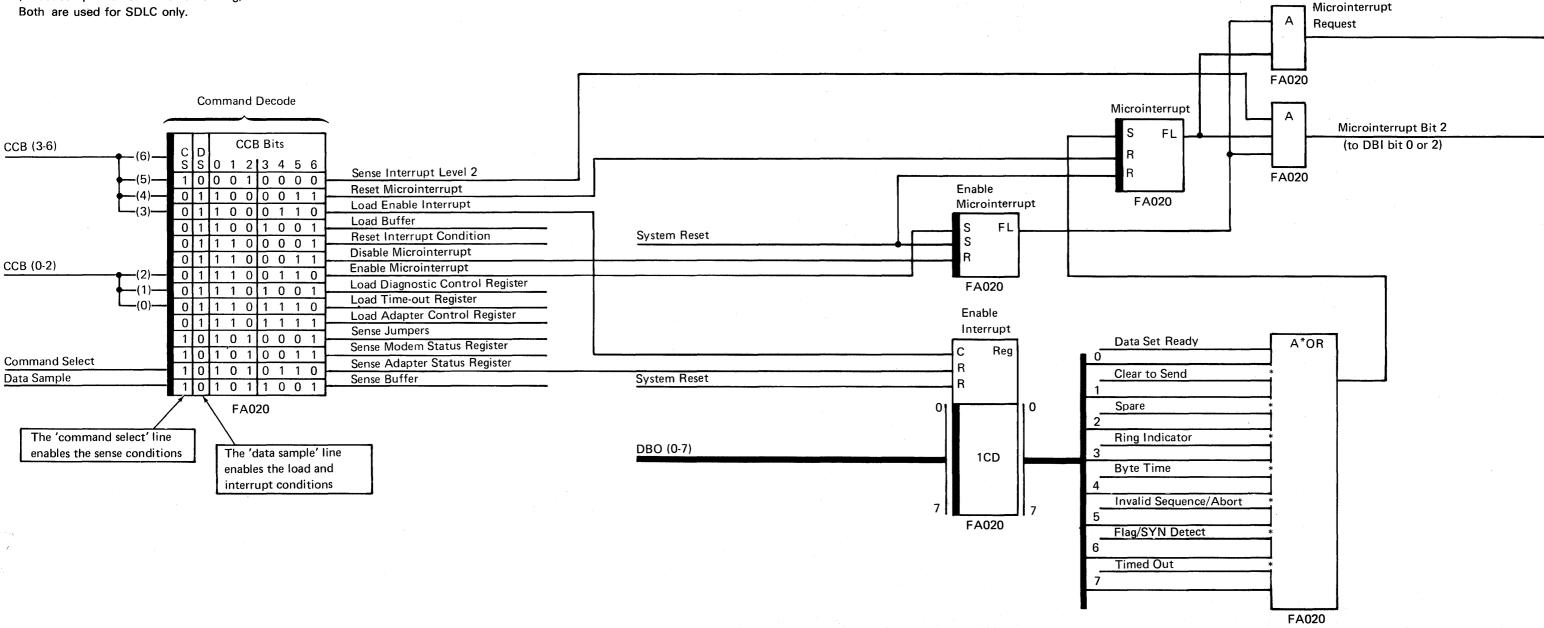

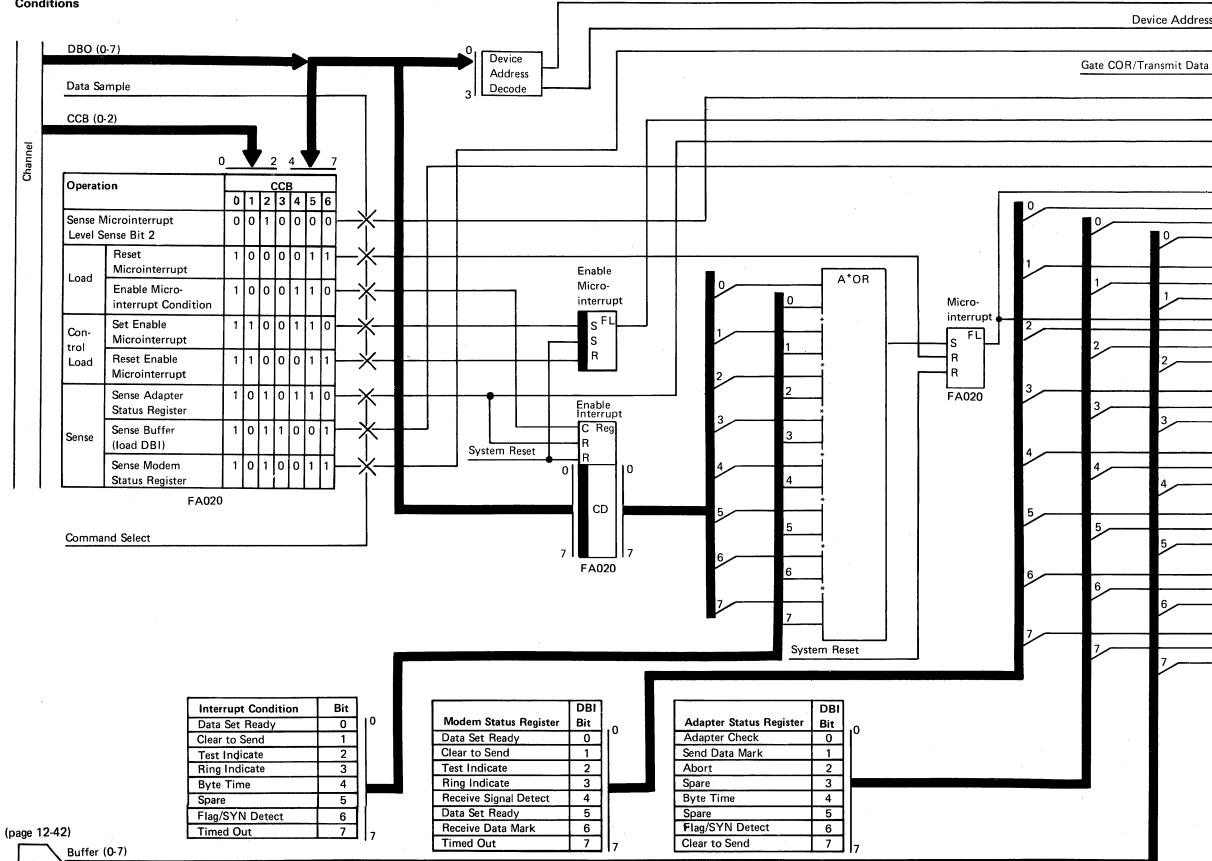

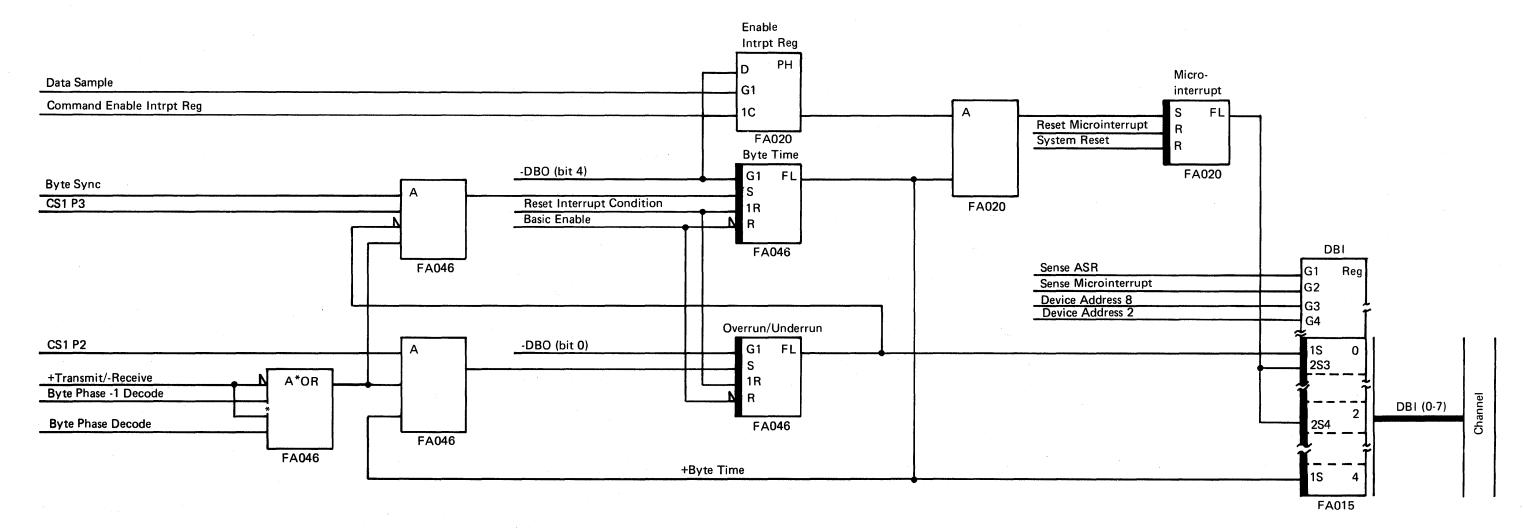

# Adapter Controls

The following pages show and describe the circuits contained in the *Controls* block (\*) on the data flow figure. Included in these circuits are:

- · Command decode.

- Ones counter.

- · Bit counter.

- Zero insertion and NRZI (zeros-complemented transition coding).

Both are used for SDLC only.

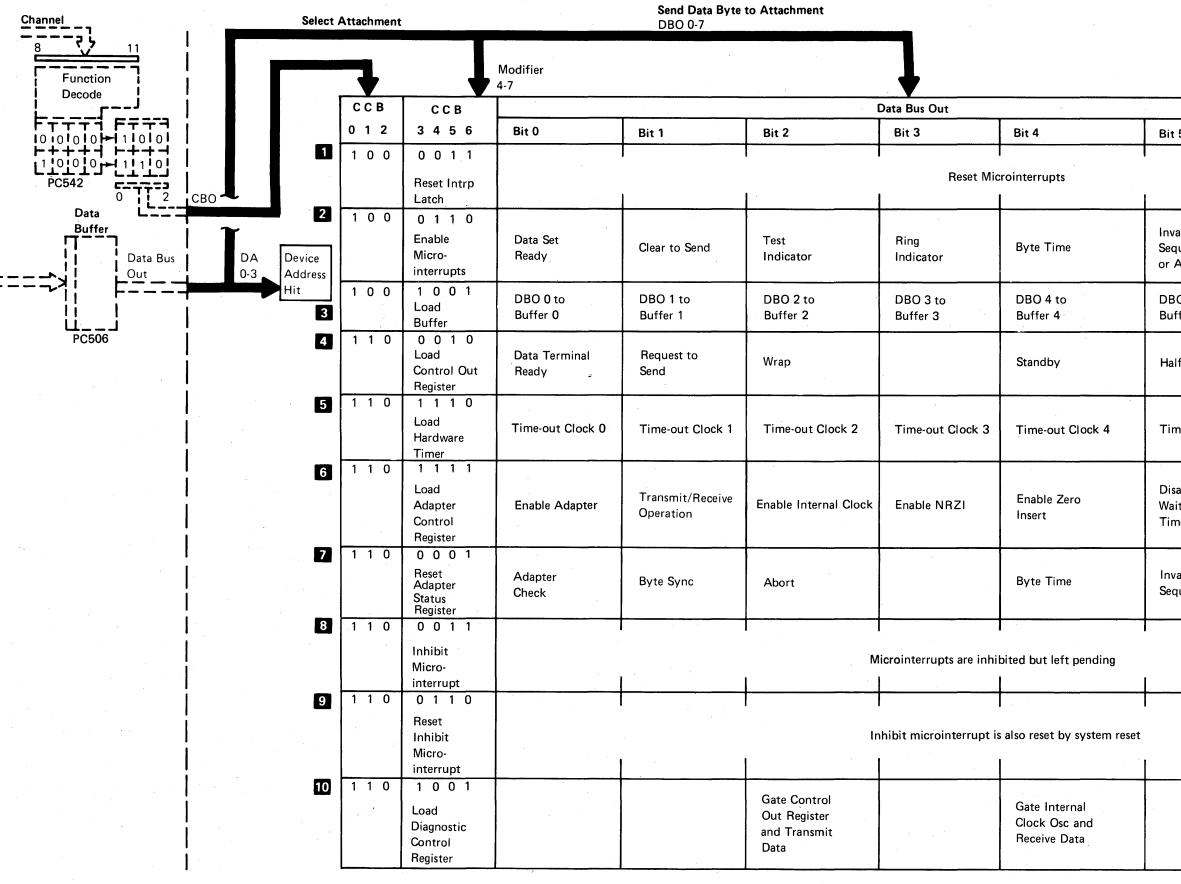

# Interrupts and Command Decode

The following figure shows the interrupt and command decode logic for the communications adapter. This logic is part of the adapter control and interrupt logic shown in the data flow figure. See the command decode logic block below for definitions of the CCB bits.

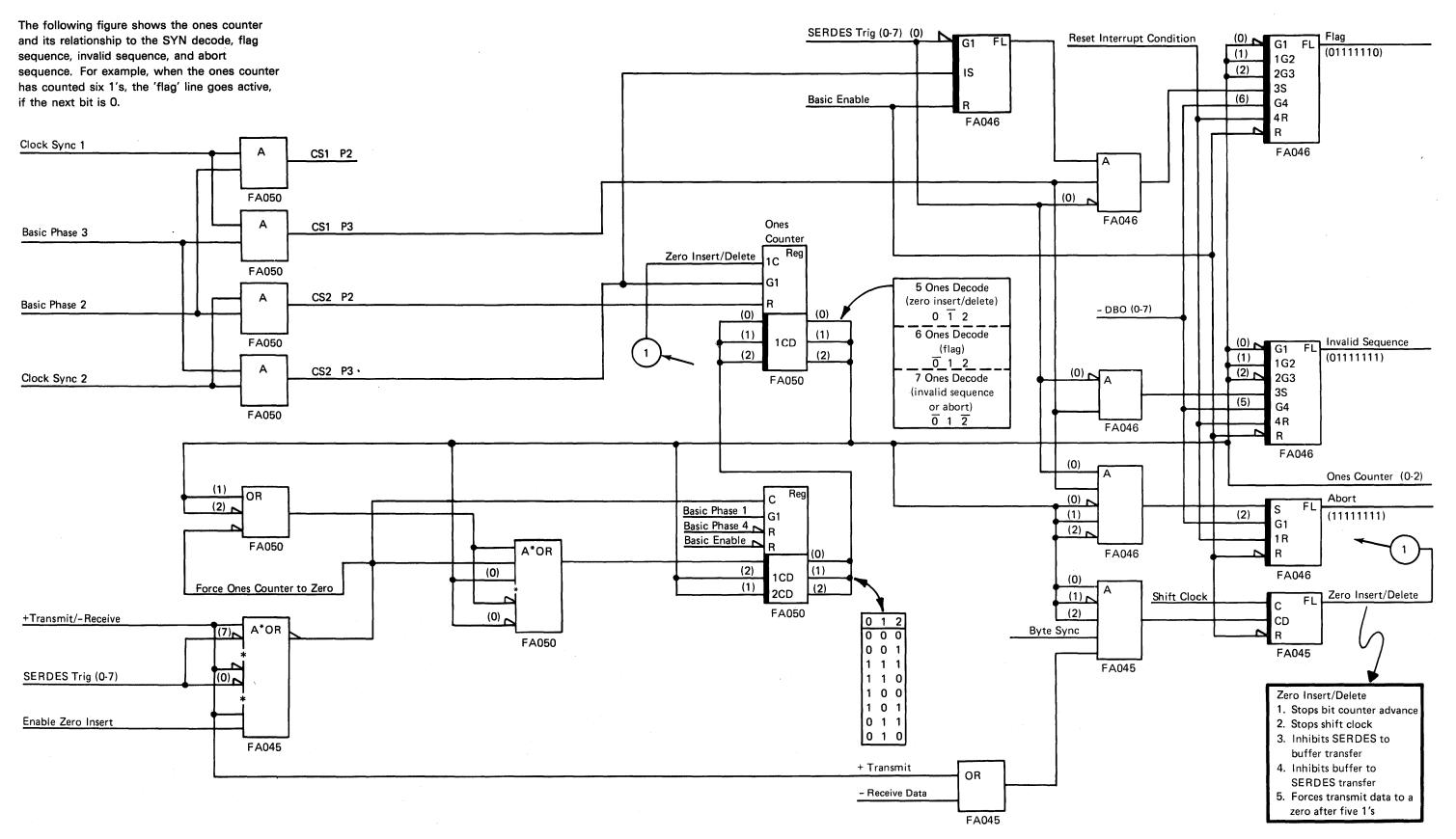

#### **Ones Counter**

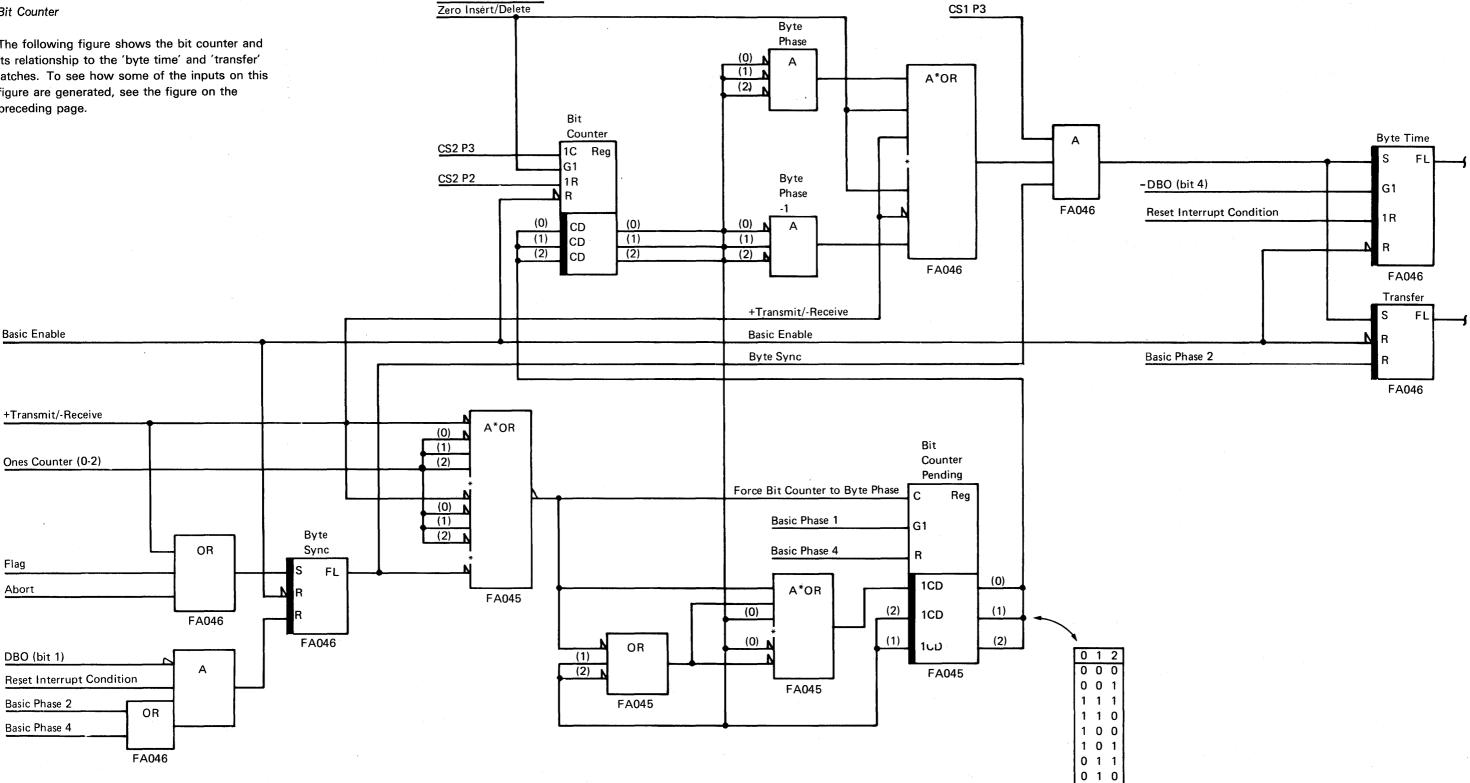

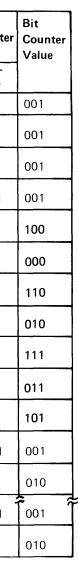

# Bit Counter

Basic Enable

Flag

Abort

DBO (bit 1)

The following figure shows the bit counter and its relationship to the 'byte time' and 'transfer' latches. To see how some of the inputs on this figure are generated, see the figure on the preceding page.

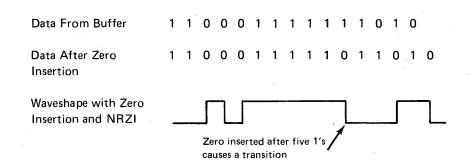

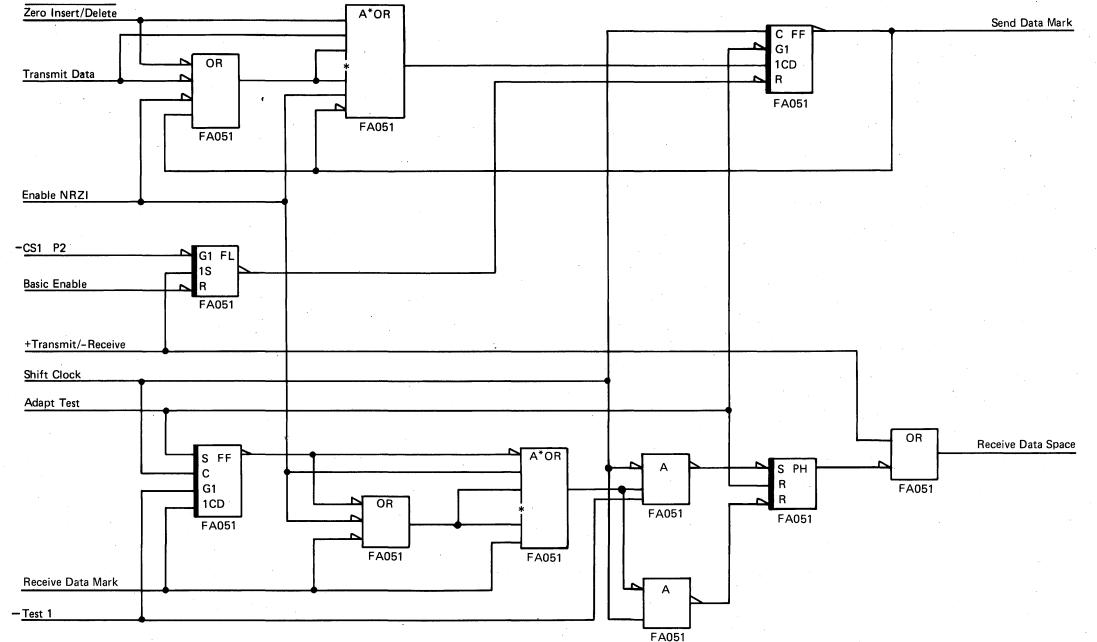

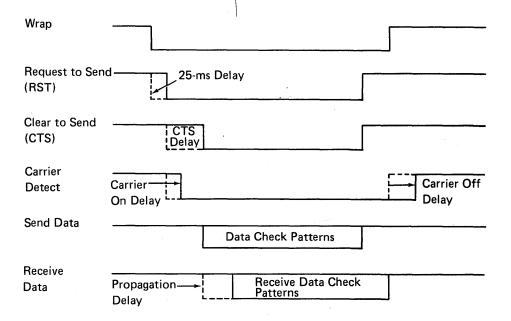

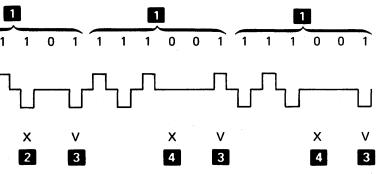

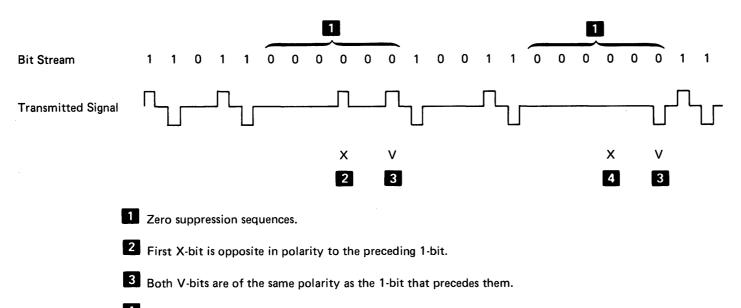

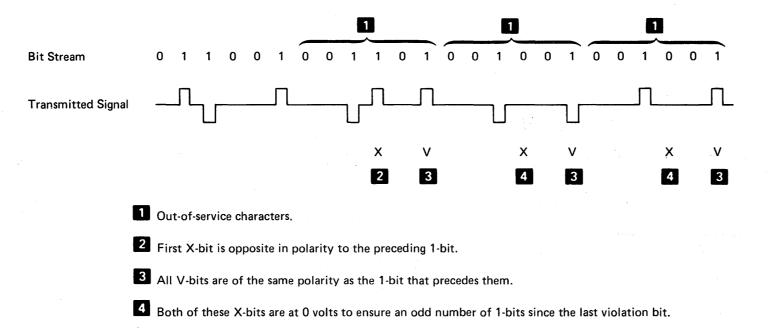

# Zero Insertion and NRZI

In data communications (SDLC only), NRZI is a method of encoding data; it prevents extended periods of transitionless data by complementing the state of the data when transmitting a 0-bit. Also, a transition must occur after the transmission of no more than five 1-bits (zero insertion/deletion adds a 0-bit after five consecutive 1-bits). The logic diagram and the following figure show how NRZI complements the state of the data when transmitting a 0-bit; the figure also shows that zero insertion inserts a zero after five 1-bits.

To maintain bit synchronization, NRZI must be used with nonsynchronous modems (needing the internal clock) and with those synchronous modems that are sensitive to transitionless bit streams.

If a synchronous modem is being used and its sensitivity to transitionless bit streams cannot be determined, contact the IBM marketing representative.

#### CAUTION

All DTEs (data terminal equipment) on the same data link must use the same encoding method (NRZI or non-NRZI). There is no communication between DTEs if the same method is not used.

# Data Communications 12-27

# System Level Interface

The system level interface includes a supervisor call input/output (SVC I/O) request instruction and an associated IOB. The supervisor call input/output request instruction places commands to the communications adapter on a aueue.

#### Queue

The system level interface has an assigned queue. Commands to the communications adapter are placed on this queue by the supervisor call input/output request instruction with index register 1 pointing to the IOB. The IOB is moved from the communication queue to the correct line queue (line 1 or line 2). As many commands as are needed can be placed on each line queue with an IOB associated with each supervisor call.

# Input/Output Blocks

Program operation of the communications adapter is executed by the input/output block (IOB) associated with the supervisor call input/output request instruction. More than one operation can be set up by queuing the IOBs. The IOB contains all information needed to carry out the operation. At the end of each operation, the completion code is set and the next operation on the queue is started. For definitions of each byte in the BSC and SDLC input/output blocks, see the Data Areas Handbook.

Attachment

functions

below the

character

level)

# SYSTEM LEVEL INTERFACE BETWEEN SYSTEM CODE AND ATTACHMENT

#### System Control Supervisor Call I/O Request Code Storage Program IOB Load Microinstruction Control Load Microinstruction Sense Interrupt Level Status Bit Sense Microinstruction (functions at (functions Microinterrupt

#### The system code:

• Uses the system level instructions during a transmit operation to format the message; the necessary control information (such as STX, ETX, and so on) is inserted into the message to be transmitted.

or above the

message level)

- Uses the system level instructions during a receive operation to process the data received.

- Is used to set up the starting conditions before issuing an SVC I/O request. The starting conditions consist of:

- Loading the data buffer address in the IOB.

- Issuing an SVC I/O request instruction to enable the adapter.

- Performs error recovery.

After an SVC I/O request instruction is issued, the microcode interface controls the execution of the specified operation (transmit or receive).

The control storage program:

Performs limited control character analysis (decodes STX, ETX, EOT, ACK0, and so on). For example, 55. SYN, or SOH places the BSC adapter in data mode which enables BCC checking.

between the

character leve

message level)

and the

Sense Data

- Inserts characters (such as SYN, BCC, pad, and so on) in the message as required.

- Generates the block check character (BCC).

- Compares the received block check character with the generated block check character to determine if the data was received correctly.

- Processes microinterrupts.

- Transfers data between main storage and the adapter.

- Updates the buffer addresses.

- Checks to determine if the buffer length has been exceeded.

- Processes microinterrupts.

- Compares for station address recognition.

Note: The above examples pertain only to BSC.

#### The attachment:

- Establishes and maintains bit phase.

- Generates microinterrupts.

- Provides clock pulses to synchronize the attachment with the modem.

- Detects DBO parity errors and character overrun conditions.

- Transmits data (serializes data).

- Receives data (deserializes data).

- Generates character microinterrupts.

# **Operations**

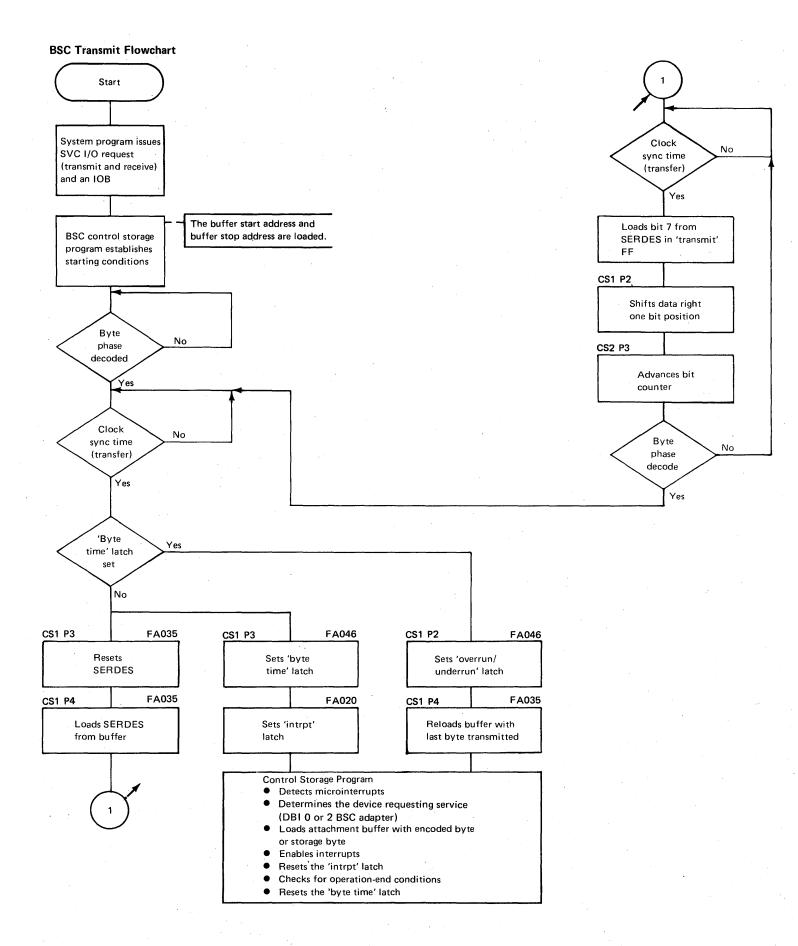

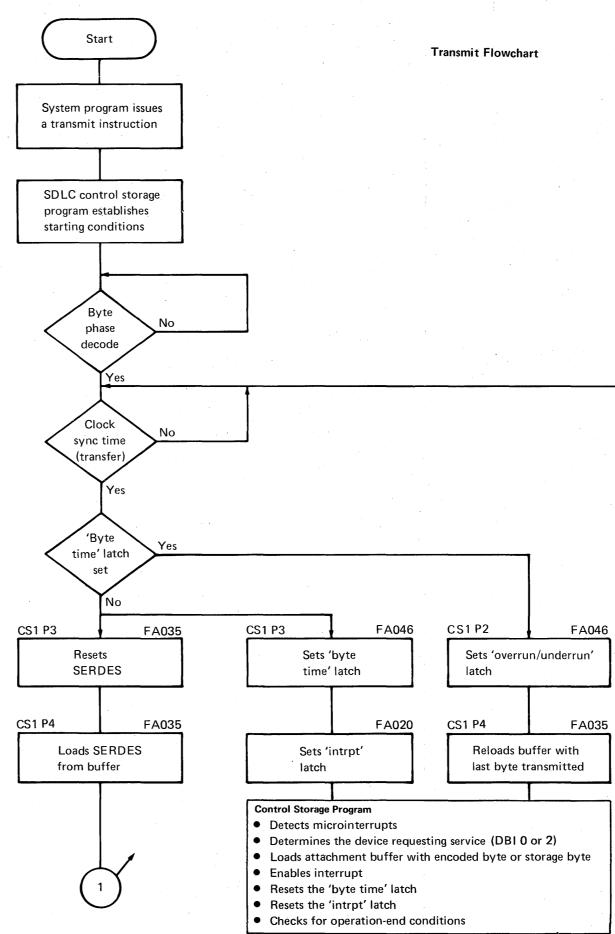

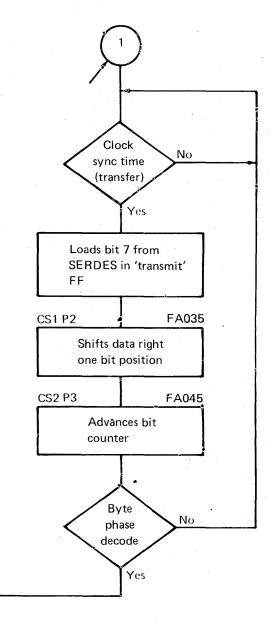

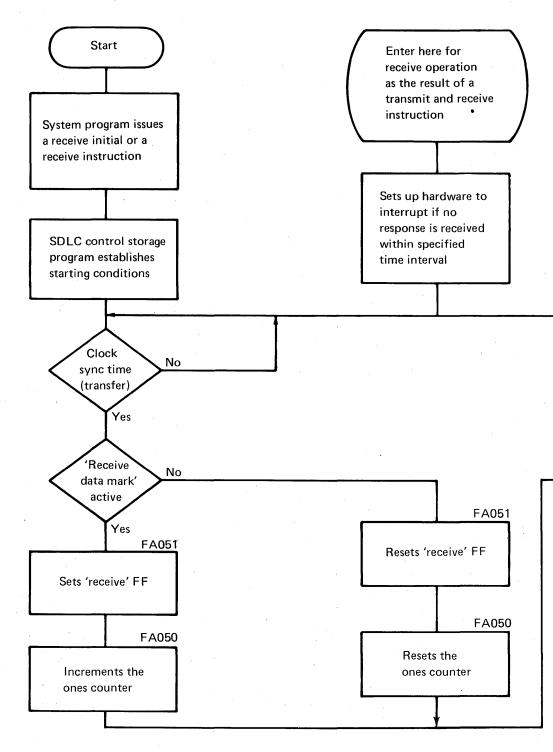

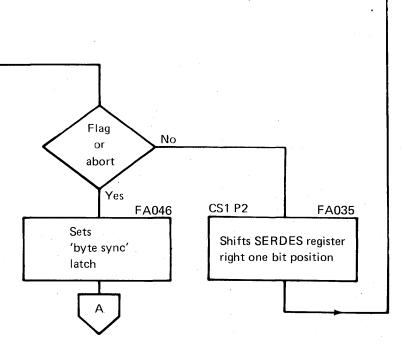

The operations for BSC and SDLC are described in Chapter 9 of the Functions Reference Manual. For each operation, the following paragraphs give (1) the command code (Q code), (2) the control storage objectives, and (3) the hardware objectives.

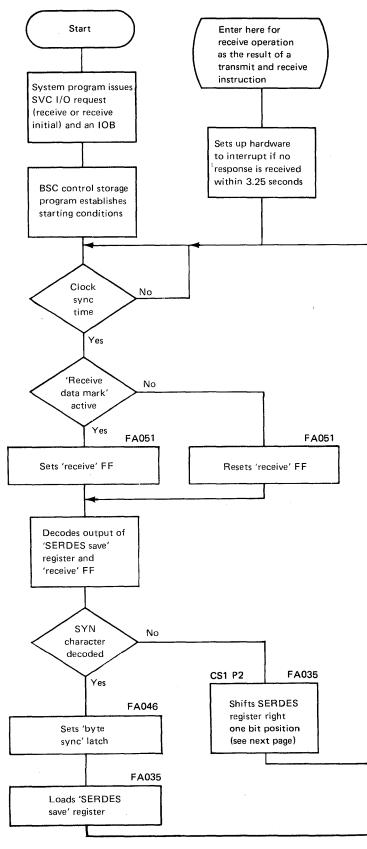

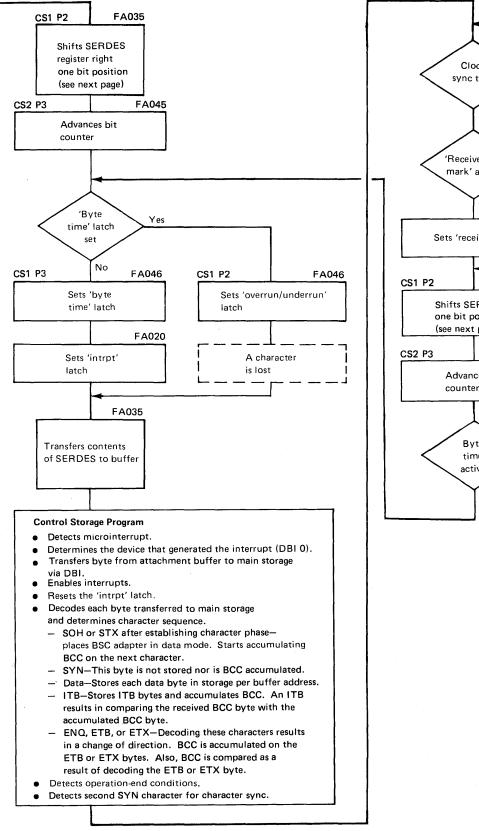

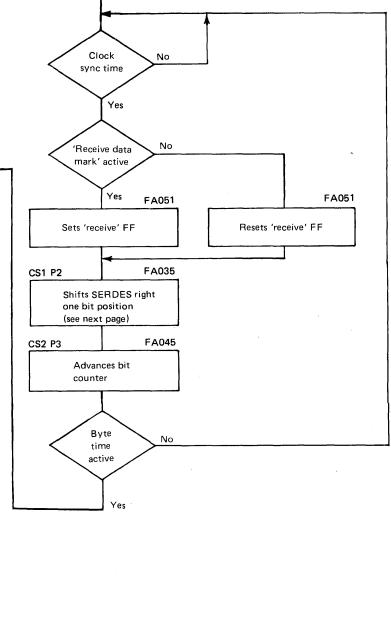

# **BSC Receive Only**

The Q-code for a BSC receive-only operation is hex 81.

Control Storage Program Objectives

The control storage program objectives for a receive-only operation are to:

- · Set up hardware and enable microinterrupts to indicate when byte time is complete. Byte time is complete when character phase is complete (2 SYNs have been sensed) and a character has been received. Byte time occurs for each character received.

- · Sense the second SYN character to complete character phase. (The first SYN character is sensed by hardware.)

- Set up hardware to enable a microinterrupt after a 3.25-second interval.

- · Store the data (including the second address byte) in main storage per the buffer address. The data is from the attachment buffer.

- Analyze each character to: - Set or reset data mode.

- Enter transparency mode. To enter transparency mode, receive DLE, STX sequence; to exit transparency mode, receive DLE ENQ, DLE ETX, DLE ETB, or DLE ITB.

- Sense change-of-direction character sequences.

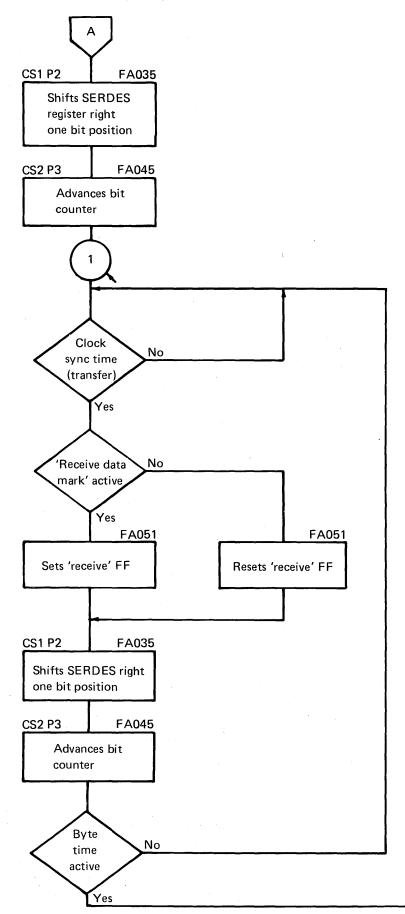

Decrease the receive buffer length.