## Contents

| WORK STATION ATTACHMENT                           |

|---------------------------------------------------|

| INTRODUCTION                                      |

| DATA FLOW                                         |

| FUNCTIONAL UNITS                                  |

| Channel Interface                                 |

| Controller Interface                              |

| Serial Interface                                  |

| SERIAL INTERFACE TO WORK STATIONS 11-6            |

| Data Transmissions                                |

| Phase Encoded Data 11-6                           |

| Predistorted and Distorted Data 11-7              |

| Differential Data                                 |

| Bit Synchronization 11-8                          |

| Frame Synchronization 11-8                        |

| Line Turnaround                                   |

| Typical Transmission Sequences 11-8               |

| Examples of Transmission Sequences 11-9           |

| Commands                                          |

| Frame Formats                                     |

| OPERATIONS                                        |

| Displaying a Message                              |

| Transmit and Receive Operations                   |

| Transmit Operation                                |

| Receive Operation                                 |

| COMMANDS                                          |

| I/O Load Command                                  |

| I/O Control Load Command                          |

| I/O Sense Command                                 |

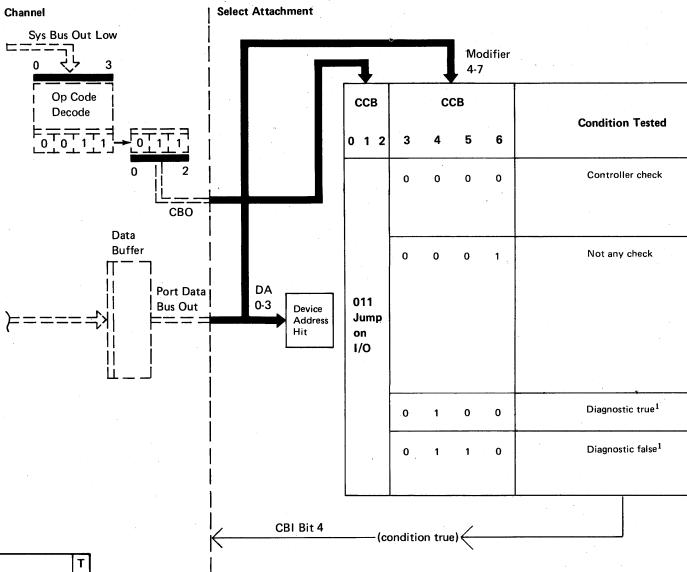

| Jump on I/O Command                               |

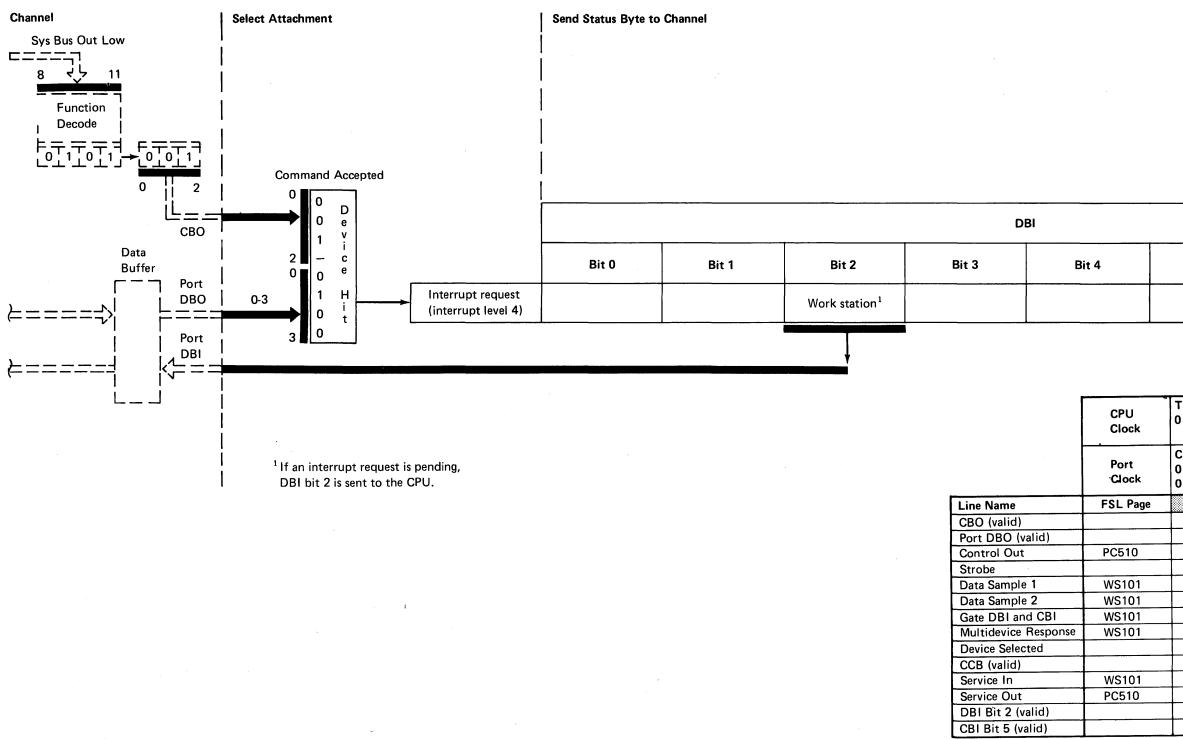

| Sense Interrupt Level Status Byte Command 11-23   |

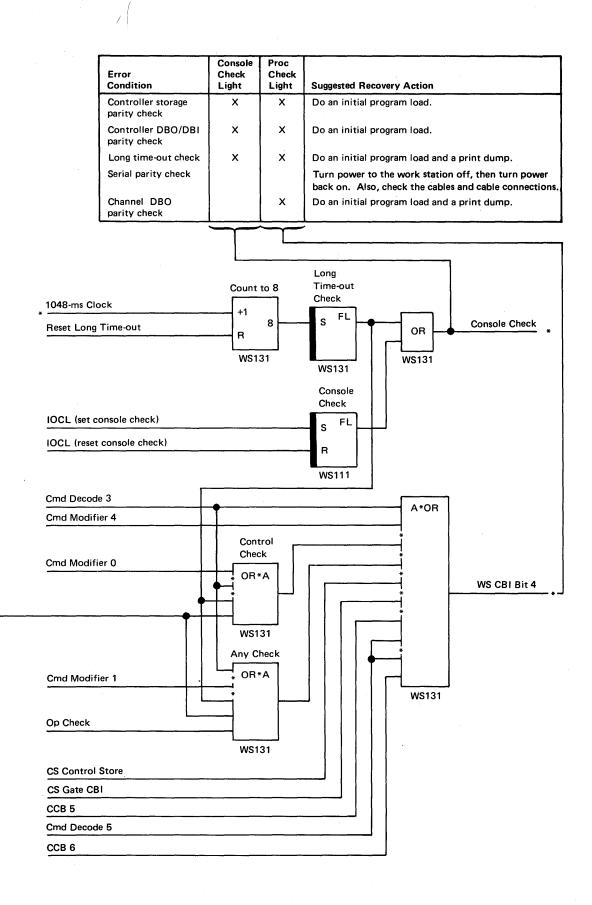

| ERROR CONDITIONS                                  |

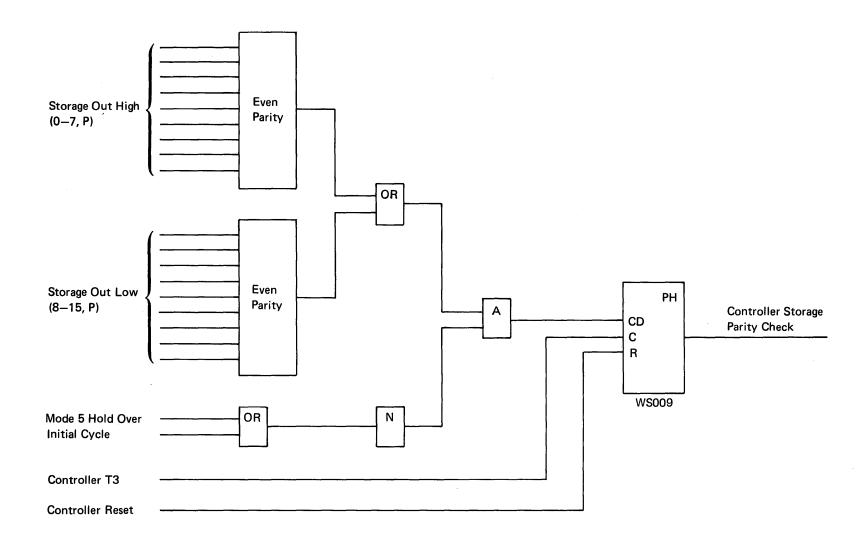

| Controller Storage Parity Check                   |

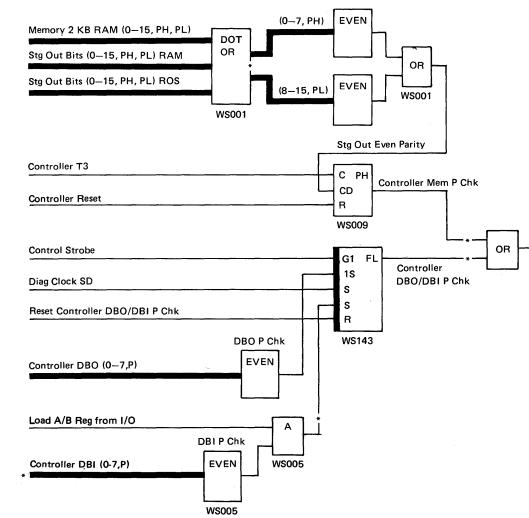

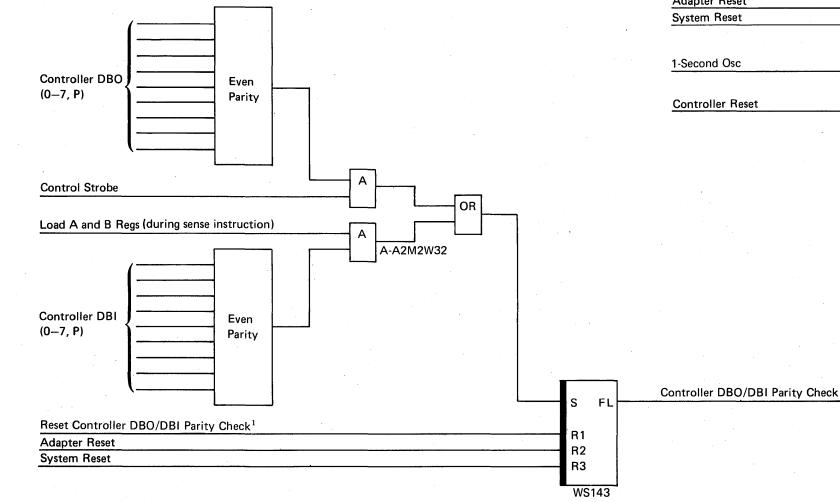

| Controller DBO/DBI Parity Check                   |

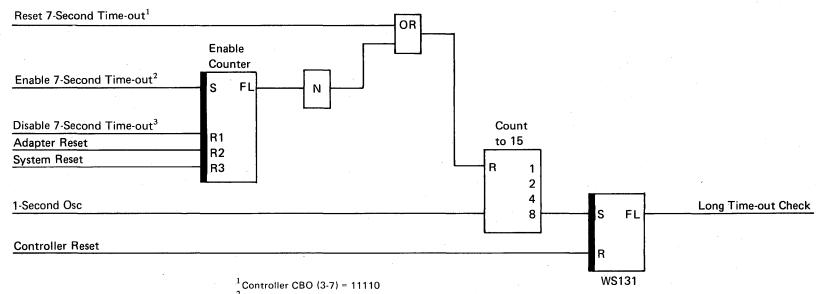

| Long Time-out Check                               |

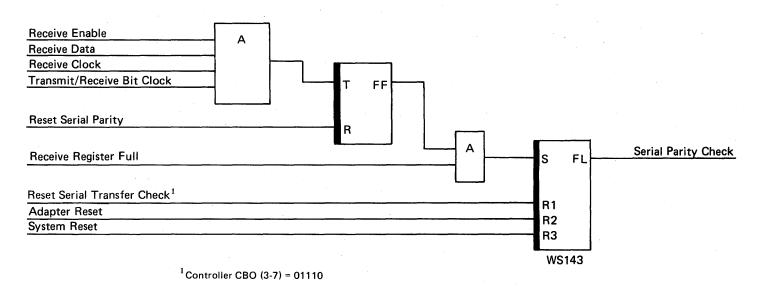

| Serial Parity Check                               |

| Work Station Controller Check (Any Check) . 11-28 |

| Channel DBO Parity Check                          |

| BASE CYCLE STEAL                                  |

| INPUT/OUTPUT LINES                                |

| INFUT/UUTFUT LINES                                |

ς.

**Contents for Work Station Attachment**

### **Work Station Attachment**

### INTRODUCTION

In System/34, the work station attachment controls from one to a maximum of eight work stations. One of the work stations, a 5251 Display Station or a 5252 Dual Display Station, is the system console and must be attached to System/34 on port 0. Then, at the customer's option, up to seven additional work stations can be attached to ports 1 through 3. These additional work stations can be either 5251 or 5252 Display Stations, 5256 Printers, or a combination of them.

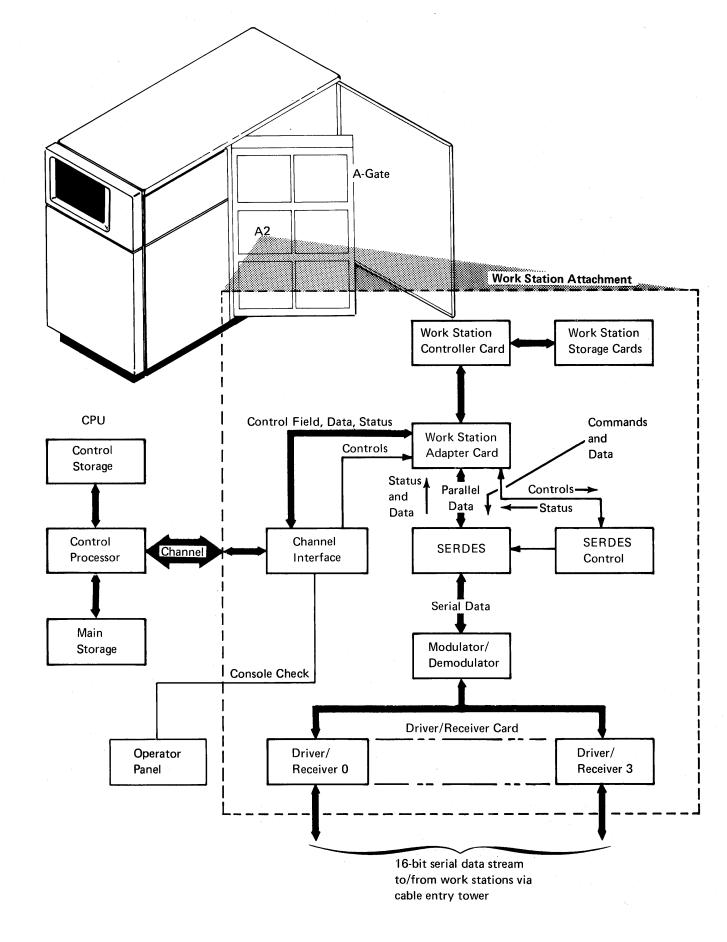

All work stations communicate with the attachment through a 16-bit serial data stream via twinaxial cables. For a description of the data stream, see *Serial Interface to Work Stations* later in this section.

The work station attachment circuits are located on the A-gate, A2 board, and include the following:

- Controller card in A-A2N2

- Adapter card in A-A2M2

- Driver/receiver card in A-A2R2

- Storage cards in A-A2P4 and A-A2Q4

- Feature storage card in A-A2R4 (optional)

- Four top card connectors

- One cable from A-A2V2 to the twinaxial cables attached to the cable entry tower

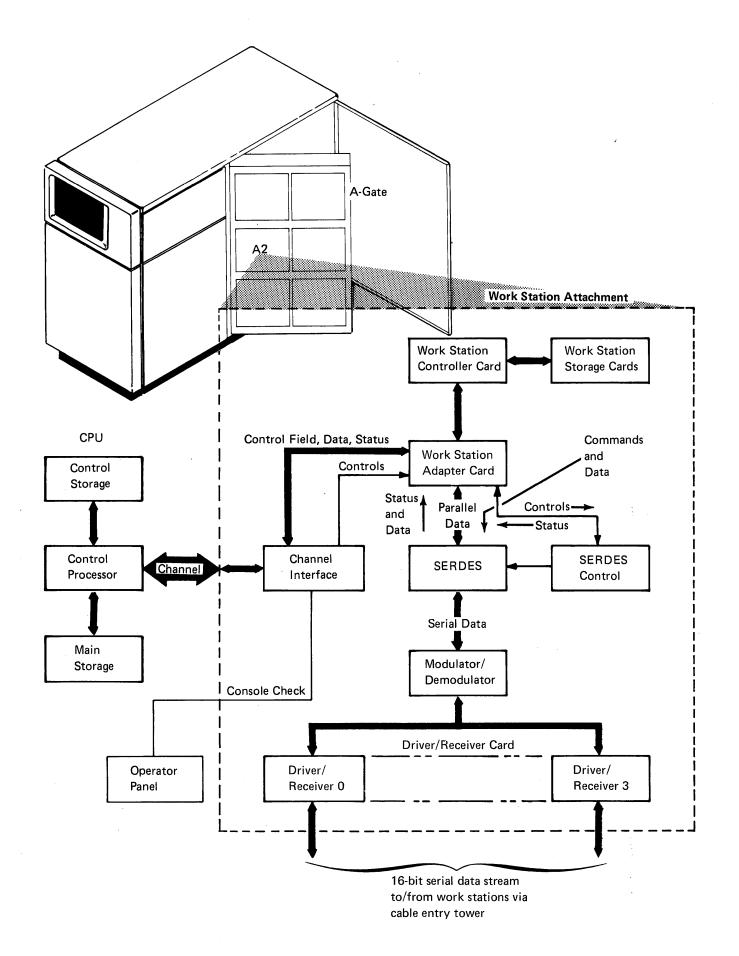

### DATA FLOW

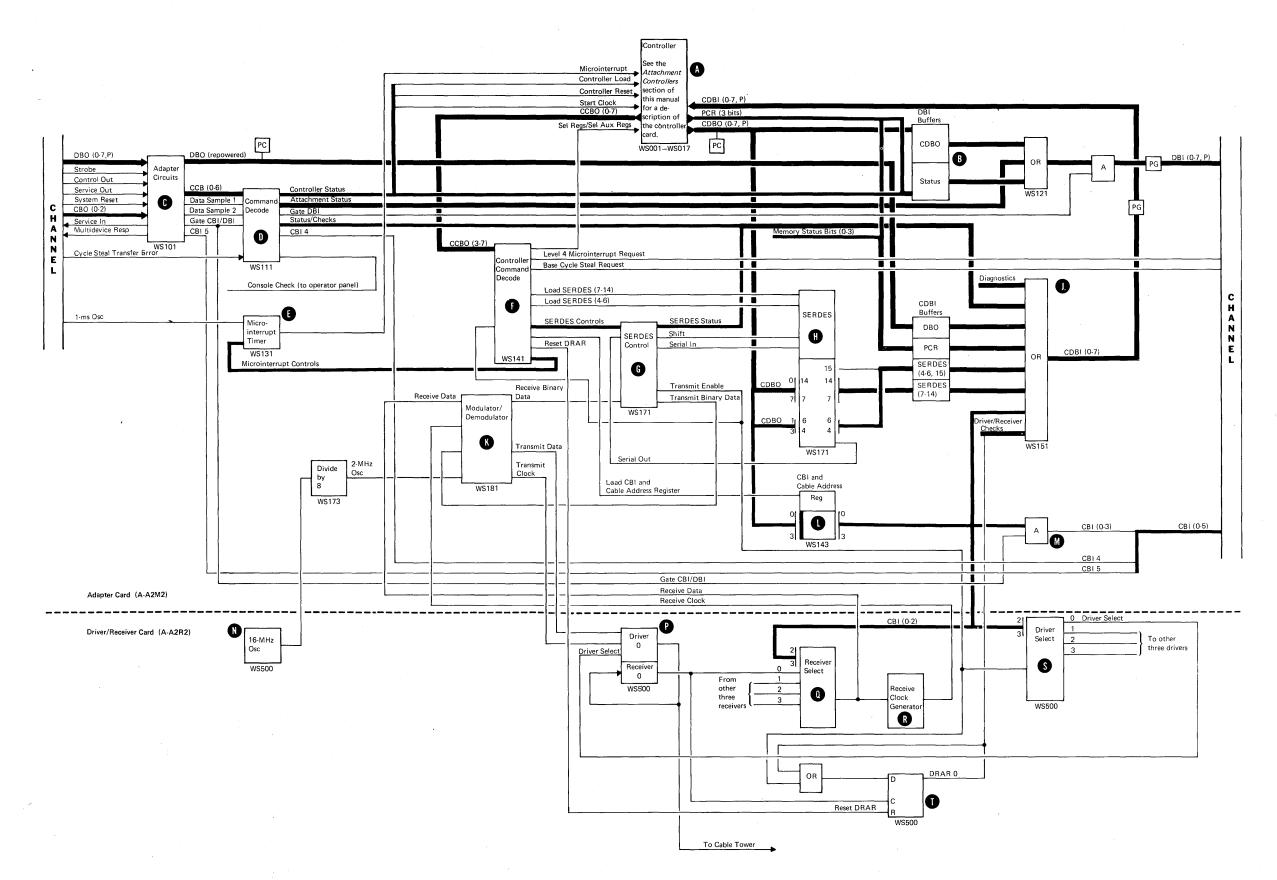

The functional units identified with an alphabetic character on this data flow figure are described on the following three pages. For a logic description of the functional units, see the appropriate FSL page. For example, see FSL page WS500 for a logic description of the driver/receiver circuits.

#### **FUNCTIONAL UNITS**

The functional units shown in the data flow figure on the preceding page are described in the following paragraphs. The controller signals A, the controller, and the storage signals are described in the Attachment Controllers section of this manual.

Two cards are shown in the data flow figure: the driver/receiver card (below the dashed line) and the adapter card (above the dashed line). The adapter card communicates with (1) the system through the channel, (2) the controller through the controller interface, and (3) the work stations through the serial interface.

#### **Channel Interface**

The channel communicates with the adapter card through an interface that includes the adapter circuits C, the command decode D, the DBI buffers and the DBI bus B, and the CBI bus M

#### Adapter Circuits 🕜

The adapter circuits:

- · Synchronize the channel with the adapter card

- Repower DBO

- Generate:

- A 7-bit channel command bus (CCB)

- Control lines used by the command decode to gate the CCB

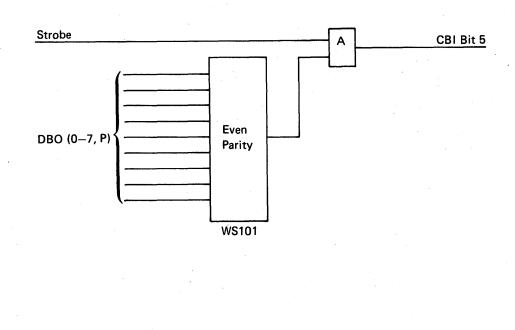

- CBI bit 5 (bad DBO parity)

The adapter circuits let the channel communicate with the attachment through control lines and data buses. The 'control out', 'service out', and 'strobe' lines signal the adapter circuits when data is available on DBO or should be on DBI. The 'service in' and 'multidevice resp' lines signal the channel that the data on DBO has been received or that data is available on DBI.

Data bus out (DBO) is a 9-bit bus (0 through 7 and parity) that performs one of two functions; (1) it supplies an I/O output instruction, or (2) it supplies data to the attachment during service out of a cycle steal operation. On any I/O output instruction, DBO bits 4-7 contain the command modifier during control out. DBO bits 0-3 rely on the instruction type. For example, during control out of the sense interrupt level status byte (SILSB) command, DBO bits 0-3 contain the attachment interrupt level address (0100). During control out of any I/O instruction other than SILSB, DBO bits 0-3 contain the work station attachment device address (1100). During control out of a cycle steal operation, DBO bits 0-3 contain an address (0001) forced by the channel.

Command bus out (CBO) is a 3-bit bus that specifies the type of I/O command to be executed. For the work station attachment, these commands are:

- = 000 Not used

- 001 = SILSB

- 010 = Base cycle steal

- Jump on I/O condition 011 =

- I/O load 100 =

- 101 = I/O sense

- 1/O control load 110 =

- Not used 111 =

#### Command Decode

The command decode logic decodes the commands on the channel command bus (CCB), which is a 7-bit bus generated by the adapter circuits. Bits 0-2 contain CBO bits 0-2 and bits 3-6 contain the command modifier bits from DBO bits 4-7 during control out. See Commands later in this section for a description of the commands decoded by this logic.

#### Data Bus In 🚯

Data bus in (DBI) is a 9-bit bus (0 through 7 and parity) that supplies data and status information to the channel. It contains:

- Data or sense information during I/O sense instructions

- Data during base cycle steal operations

- Sense information during SILSB instructions

The 'gate CBI/DBI' line from the adapter circuits activates the DBI bus, and CCB bits 5 and 6 determine what information is gated on the DBI bus. That information is:

- · Controller DBO during a sense controller DBO instruction or a base cycle steal operation

- · Controller status latches during a sense controller status instruction

- Attachment status and check conditions during sense check or sense attachment status instructions

#### Command Bus In M

Command bus in (CBI) is a 6-bit bus that supplies control information to the channel; it is activated during I/O instructions or during base cycle steal operations by the 'gate CBI/DBI' line from the adapter circuits.

CBI bits 0-3 supply control information to the channel during a base cycle steal operation through the following sequence of events:

- 1. A controller instruction, decoded in the controller command decode logic (E), generates the 'base cycle steal request' signal to the channel.

- The channel responds on command bus 2 out (CBO) with a base cycle steal (010).

- 3. A cycle steal operation is then executed as instructed by CBI bits 0-4.

| CBI Bits                                             |                                                                                                                                                                                                                             |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01234                                                | Function                                                                                                                                                                                                                    |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | Base cycle steal ser<br>Base cycle steal loa<br>Base cycle steal ser<br>Base cycle steal loa<br>Base cycle steal WI<br>Base cycle steal WI<br>Base cycle steal WI<br>Base cycle steal WI<br>Control storage<br>Main storage |

CBI bit 4, when active, has three functions:

- It specifies main storage or control storage during base cycle steal operations.

- · It signals the channel that DBI parity may not be valid.

- · It signals the channel that a condition tested for by a jump on I/O condition instruction is present.

CBI bit 5 is active when DBO even parity is sensed.

ense (WR not incremented) ad (WR not incremented) ense (WR incremented) ad (WR incremented) R4 on interrupt level 4 R5 on interrupt level 4 R6 on interrupt level 4 R7 on interrupt level 4

#### **Controller Interface**

In addition to the controller signals (A), the controller interface includes the 16-MHz oscillator N, the controller command decode **(F)**, the microinterrupt timer **(E)**, and the controller DBI buffers and controller DBI bus 0.

#### 16-MHz Oscillator 🔊

The 16-MHz oscillator is located on the work station driver/receiver card. It supplies a free-running clock to the work station controller card and to the 5211 Printer controller card (if the system has a 5211 Printer).

#### Controller Command Decode

The controller command decode logic decodes the controller instructions from bits 3-7 of the controller CBO (CCBO) bus. It also generates the 'level 4 microinterrupt request', 'base cycle steal request', and the SERDES control lines.

On input instructions, controller CBO bits 4-7 gate information on the controller DBI (CDBI) bus. On output instructions, the decode of the controller CBO bus causes the data byte on controller DBO (CDBO) to be gated into the DBI buffers **B**, the SERDES **H**, or the CBI and cable address register . The decode of the controller CBO bus is as follows.

| Controller CBO Bits<br>3 4 5 6 7 | Function                                                       | Comments                                                                               |

|----------------------------------|----------------------------------------------------------------|----------------------------------------------------------------------------------------|

| 0 0 0 0 0                        | Diagnostic load                                                |                                                                                        |

| 00001                            | Set level 4 microinterrupt request                             |                                                                                        |

| 0 0 0 1 0                        | Load SERDES                                                    | Bits 7-14                                                                              |

| 0 0 0 1 1                        | Load SERDES                                                    | Forces bits 0-2 to 000, initializes                                                    |

|                                  |                                                                | the parity bit (bit 3), loads bits<br>4-6, and forces the sync bit (bit<br>15) to a 1. |

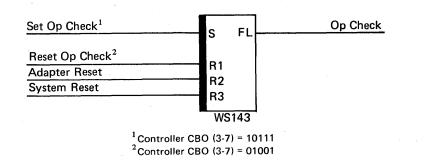

| 0 0 1 0 0                        | Diagnostic SERDES clock and set<br>controller DBO parity check |                                                                                        |

| 0 0 1 0 1                        |                                                                |                                                                                        |

| 0 0 1 0 1                        | Reset base cycle steal transfer error                          |                                                                                        |

| 0 0 1 1 0                        | Set base cycle steal request                                   |                                                                                        |

| 0 0 1 1 1                        | Reset command pending                                          | Leaded with DRO Hits 0.0                                                               |

| 01000                            | Load CBI and cable address register                            | Loaded with DBO bits 0-3                                                               |

| 01001<br>01010                   | Reset op check<br>Reset base cycle steal control storage       | Sets base cycle steal main storage                                                     |

| 0 1 0 1 1                        | Reset service required                                         | Sets base cycle stear main storage                                                     |

| 0 1 1 0 0                        | Set controller busy                                            |                                                                                        |

| 0 1 1 0 1                        | Reset controller DBO/DBI parity check                          |                                                                                        |

| 0 1 1 1 0                        | Reset serial transfer check                                    |                                                                                        |

| 0 1 1 1 1                        | Reset transmit enable                                          |                                                                                        |

| 10000                            | Set transmit enable                                            |                                                                                        |

| 1 0 0 0 1                        | Select aux regs                                                |                                                                                        |

| 10010                            | Select regs                                                    | Default case                                                                           |

| 10011                            | Reset controller busy                                          |                                                                                        |

| 10100                            | Reset receive enable                                           |                                                                                        |

| 10101                            | Set base cycle steal control storage                           | Resets base cycle steal main storage                                                   |

| 10110                            | Load DBI buffer                                                | Loaded with controller DBO bits 0-7                                                    |

| 10111                            | Set op check                                                   |                                                                                        |

| 1 1 0 0 0                        | Enable 7-second time-out                                       |                                                                                        |

| 1 1 0 0 1                        | Set receive enable                                             |                                                                                        |

| 1 1 0 1 0                        | Reset driver/receiver activity reg                             |                                                                                        |

| 1 1 0 1 1                        | Disable 7-second time-out                                      | Default case                                                                           |

| 1 1 1 0 0                        | Enable controller microinterrupt                               |                                                                                        |

| 1 1 1 0 1                        | Load microinterrupt timer                                      | Loaded with controller DBO bits 0-4                                                    |

| 1 1 1 1 0                        | Reset 7-second time-out                                        |                                                                                        |

| 1 1 1 1 1                        | Disable controller microinterrupt                              | Default case                                                                           |

| X 0 0 0 0                        | Sense SERDES                                                   | Bits 7-14                                                                              |

| X 0 0 0 1                        | Sense SERDES                                                   | Bits 0-6 and 15                                                                        |

| X 0 0 1 0                        | Sense checks                                                   |                                                                                        |

| X 0 0 1 1                        | Sense driver/receiver activity reg                             | Bits 0-3                                                                               |

| X 1 1 0 0                        | Sense diagnostic adapter status                                |                                                                                        |

| X 1 1 0 1                        | Sense 'not go' latch                                           | <b></b>                                                                                |

| X 1 1 1 0                        | Sense PCR                                                      | From controller DBI buffer                                                             |

| X 1 1 1 1                        | Sense channel DBO                                              | In controller DBI buffer                                                               |

#### Microinterrupt Timer

The microinterrupt timer is a 5-bit counter (counts down) that is loaded with a value from the controller DBO (CDBO) bits (0-4). It is decreased by a value of 1 every millisecond by a free-running, one-millisecond oscillator from the channel. When the timer has counted down to a value of 0 and if the 'enable microinterrupt' latch in the command decode logic is set, the 'microinterrupt' signal to the controller goes active.

| 1/0                                                          |                                |                                          |                                     |                                 |                           |                           |                           |                                 |

|--------------------------------------------------------------|--------------------------------|------------------------------------------|-------------------------------------|---------------------------------|---------------------------|---------------------------|---------------------------|---------------------------------|

| Sense                                                        |                                |                                          | Contro                              | ller DBI Bits                   | · · · · · · · · · · · ·   | -                         |                           |                                 |

| Command                                                      | 0                              | 1                                        | 2                                   | 3                               | 4                         | 5                         | 6                         | 7                               |

| Sense shift<br>register<br>(hex 00)                          | 7                              | 8                                        | 9                                   | 10                              | 11                        | 12                        | 13                        | 14                              |

| (110/ 00)                                                    |                                |                                          | SERDI                               | S Bits                          | l                         |                           |                           | L                               |

| Sense shift<br>register<br>(hex 01)                          | Set to<br>1                    | 4                                        | 5                                   | 6                               | 3                         | 15                        | Transmit<br>active        | Not end of<br>message           |

|                                                              |                                |                                          | SERDE                               |                                 |                           |                           |                           |                                 |

| Sense checks<br>(hex 02)                                     | Cycle<br>steal<br>request      | Controller<br>DBO/DBI<br>parity<br>check | Cycle<br>steal<br>transfer<br>error | Interrupt<br>level 4<br>request | Serial<br>parity<br>check | Service<br>required       | Command<br>pending        | Set to<br>1                     |

| Sense driver/<br>receiver<br>activity reg-<br>ister (hex 03) | 0                              | 1                                        | 2                                   | 3                               | 4                         | 5                         | 6                         | 7                               |

|                                                              |                                | ····                                     |                                     |                                 |                           |                           |                           |                                 |

| Sense<br>diagnostics<br>(hex OC)                             | Select<br>primary<br>registers | Sample<br>receive<br>disable             | Cycle<br>steal<br>main<br>storage   | Delayed<br>transmit<br>disable  | Cable<br>address<br>bit 0 | Cable<br>address<br>bit 1 | Cable<br>address<br>bit 2 | Cable<br>address<br>bit 3       |

| Sense 'go'<br>latch<br>(hex 0D)                              | These 3                        | bits are set t                           | o 0.                                | Not go                          | These (                   | 3 bits are set            | to 0.                     | Not go                          |

| Sense PCR<br>and memory<br>(hex 0E)                          | 0                              | 1                                        | 2                                   | 3                               | Nonzero                   | Carry                     | Zero                      | Controller<br>DBO/DBI<br>parity |

|                                                              |                                | Memory                                   | Status Bits                         |                                 |                           | PCR Bits                  |                           | check                           |

| Sense DBO<br>(hex 0F)                                        | 0                              | 1                                        | 2                                   | 3                               | 4                         | 5                         | 6                         | 7                               |

|                                                              |                                |                                          | DBO B                               | its 0-7                         |                           |                           |                           |                                 |

It is typical to have the timer set to some value such as 30, which causes the 'microinterrupt' signal to go active every 30 milliseconds. This signal forces the controller program to some routine, such as a poll, which in turn checks each keyboard for operator keystrokes.

#### Controller DBI

Controller DBI (CDBI) is a 9-bit bus (0 through 7 and parity) that supplies data and status information to the controller during a controller input instruction. The following table lists all of the data and status sent to the controller on controller DBI.

#### Serial Interface

System/34 communicates with the work stations through the work station serial interface. This interface includes the SERDES control **G**, the SERDES **H**, the modulator/demodulator **K**, the CBI and cable address register **L**, and the driver/receiver circuits **P**, **Q**, **R**, **S**, and **T**.

#### SERDES Control

The SERDES control signals from the controller command decode logic control the serial interface latches (located in SERDES control) by setting or resetting the 'transmit enable' and 'receive enable' latches. The SERDES control also contains a 'go' latch that synchronizes the controller with the serial interface. The 'go' latch is one of the bits of SERDES status gated to the controller on controller DBI **()**.

The SERDES control generates even parity on transmit operations and checks for even parity on receive operations. It also controls the SERDES shifting, reset, and gating of the SERDES parallel outputs to controller DBI on receive operations.

#### SERDES 🖪

The serializer/deserializer is a 16-bit shift register that is loaded with parallel data. It also has parallel outputs that are put into the controller DBI buffers when 16 bits have been shifted into the SERDES on a receive operation. Also on a receive operation, the 'serial in' data to SERDES is generated from the 'receive binary data' line by the SERDES control.

On transmit operations, the SERDES is loaded in parallel with controller DBO by a controller output instruction and the 'serial out' data to SERDES control becomes 'transmit binary data'.

The unit of information transmitted or received between the work stations and the attachment is a 16-bit serial frame. This frame is described under Serial Interface to Work Stations later in this section.

#### CBI and Cable Address Register 🚺

In addition to being used for base cycle steal operations, this 4-bit register uses bits 2 and 3 to select one of four driver/receivers for transmit or receive operations.

#### Driver/Receiver Circuits P, Q, R, S, and T

There are four driver/receivers **P** on the driver/receiver card: one for each twinaxial cable attached to the cable entry tower.

The outputs of the receiver select logic **Q** are always active, and they continuously represent the data on the cable selected by the cable address register. On receive operations, the following sequence occurs:

- The 'receive data' output from the receiver select logic feeds the modulator/demodulator (K) and the receive clock generator (R).

- 2. The 'receive clock' signal from the receive clock generator **R** is sent to the modulator/demodulator.

- 3. The modulator/demodulator generates 'receive binary data' and sends it to the SERDES control logic G.

The driver select logic **S** outputs, used on transmit operations, are gated by the 'transmit enable' line from the SERDES control. Then, the driver selected by the cable address register uses the 'transmit clock' and 'transmit data' lines from the modulator/demodulator to transmit serial data to the work station.

There is a clocked latch, called a driver/receiver activity register (DRAR) **1**, for each driver/receiver **P**. The latch is clocked by a transition on the receiver output. The data input to each latch comes from one of two sources: either the output of the latch itself, or the 'transmit enable' line from the SERDES control **G**. All driver/receiver activity registers are reset at the start of transmit operations (polls) to the work stations. The outputs of these registers are gated to CDBI for sensing.

### SERIAL INTERFACE TO WORK **STATIONS**

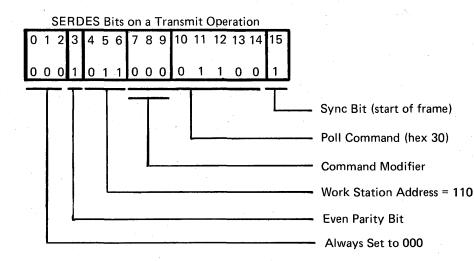

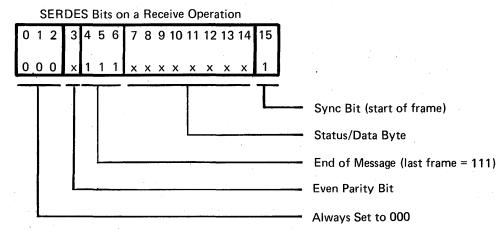

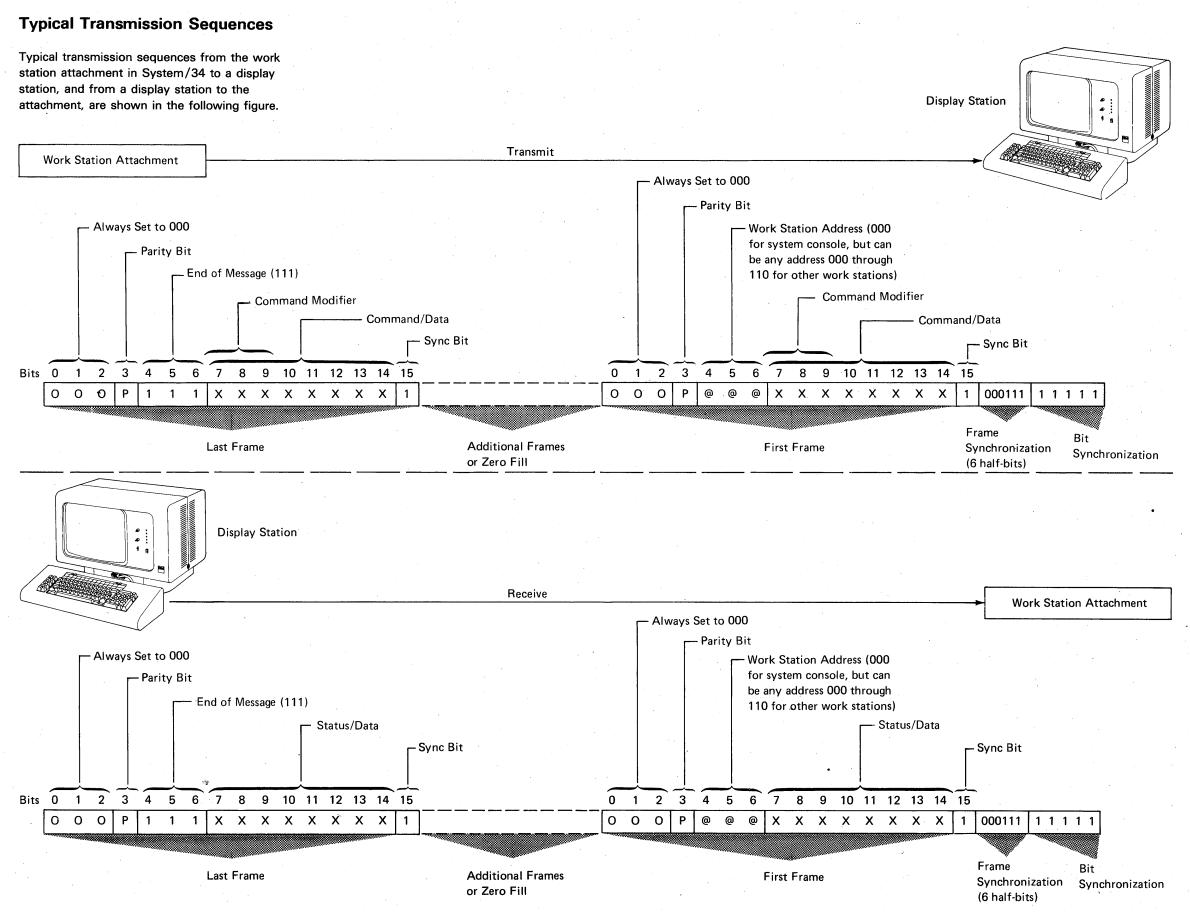

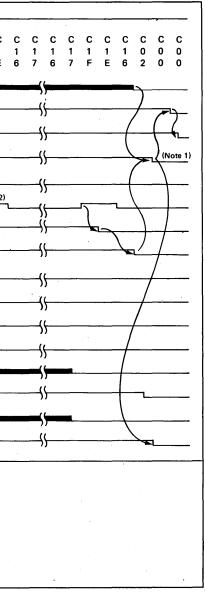

System/34 communicates with the work stations through a data stream frame. A frame, as shown in the following figure (for the last frame of typical transmit and receive operations) and described below, is 16 bits long. A frame is serially transmitted to, or received from, the work stations.

Note: Bits 4, 5, and 6 contain the work station address if the frame is not the last frame received from a work station.

| SERC | DES |

|------|-----|

| Bits |     |

15

14-7

6-4

#### Description

Bit 15 is the sync bit and the first bit of the frame. It is always active on transmit and receive operations. After the SERDES control logic senses the sync bit during a receive operation, it counts the next 15 bits going into SERDES. Then, the pulse to load the SERDES into the controller DBI buffers is generated.

These bits represent a data byte or a command byte on transmit operations and a data byte or a status byte on receive operations.

These bits represent the work station address (000 through 110) on transmit operations or receive operations. They also represent an end of message (111) for the last frame on transmit and receive operations.

This is an even parity bit that is generated on bits 3 through 15 on transmit and receive operations.

These bits are always set to 000 on transmit and receive operations.

#### Data Transmissions

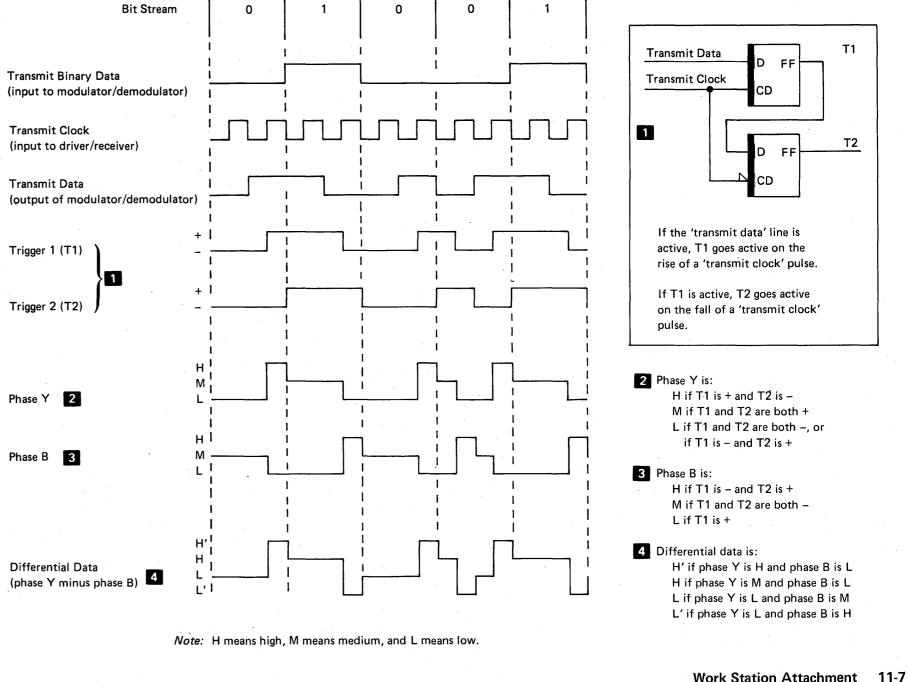

The data transmitted on the serial interface is described in the following paragraphs. Phase Encoded Data, Predistorted and Distorted Data, and Differential Data describe how the signal is generated. Bit Synchronization and Frame Synchronization describe the information transmitted before the first transmitted frame, and Line Turnaround describes the time between receive mode and transmit mode. Read all of this information before reading Operations later in this section.

#### Phase Encoded Data

The 'receive binary data' signal into the SERDES control (G in the Data Flow figure) and the 'transmit binary data' signal out of the SERDES control both have a frequency of 1 megahertz (1 microsecond per bit time). Each bit time contains phase encoded data on the

Bit Stream

Transmit (or receive) Binary Data

Transmit Data or Receive Data

2-0

3

'transmit data' or 'receive data' signal, as shown in the following figure. These two signals have each bit time divided into 2 half-bits to supply data integrity and noise detection on the serially transmitted data between System/34 and the work stations.

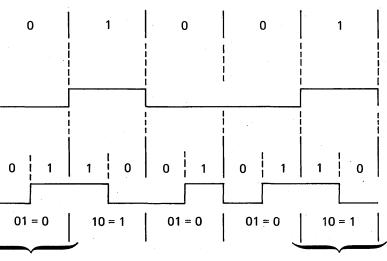

The 2 half-bits have a binary configuration of 10 for a logical 1, and a binary configuration of 01 for a logical 0. Binary configurations of 00 and 11 specify code violations. These code violations are used for the frame synchronization bits. When transmitting a logical 0 followed by a logical 1 (or a logical 1 followed by a logical 0), 2 consecutive half-bits must be at the same voltage level; that is, they

must be plus or minus.

The half-bits for a logical O are 01.

The half-bits for a logical 1 are 10.

#### **Predistorted and Distorted Data**

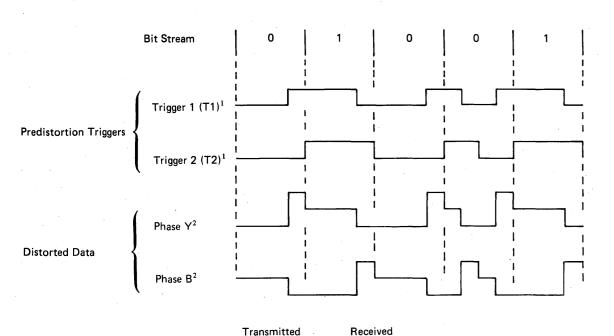

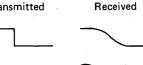

Each driver (P in the Data Flow figure) contains two triggers that apply a predistortion method to the 'transmit data' signal. This method supplies increased integrity on the serially transmitted data by generating trilevel voltage signals for phase Y and phase B (the two signal conductors of the twinaxial cable).

The generation of the trilevel signals is shown in the following figure. The bottom part of the figure compares transmitted and received bilevel signals to transmitted and received trilevel signals, respectively. Notice that by adding small pulses (predistortion/distortion) to the trilevel signal, the rise and fall times of the signal are greatly improved.

The transmission of the trilevel signals produces the four-level differential data because the work station hardware responds to the differential current flow between phase Y and phase B. The four-level differential data is described in the next paragraph.

#### **Differential Data**

The differential data includes phase Y and phase B data as transmitted on the twinaxial cable from System/34 to a work station, or from a work station to System/34.

When data is received from a work station, the receiver (P) in the Data Flow figure) subtracts the 'phase Y' signal from the 'phase B' signal to generate the four-level differential data

signal. The receiver select logic (0 in the Data Flow figure) then supplies the 'receive data' signal to the modulator/demodulator (K) in the Data Flow figure).

The following figure shows the relationship of the differential data signal to the signals that generate it. 2, 3, and 4 in the figure show how phase Y, phase B, and differential data are generated, respectively.

Bilevel

Trilevel

<sup>1</sup>The two triggers are in the driver/receiver. <sup>2</sup>Phase Y and Phase B are the two signals transmitted on the twinaxial cable.

#### **Bit Synchronization**

When commands or data are transmitted to a work station, the first frame in the bit stream is preceded by the bit synchronization bits and the frame synchronization bits. The bit synchronization bits contain five logical 1-bits (binary 1010101010, as described under Phase Encoded Data) that inform the work station to check for the frame synchronization bits.

#### **Frame Synchronization**

The frame synchronization bits follow the bit synchronization bits and precede the sync bit of the first transmitted frame. The frame synchronization bits include 3 half-bit 1's and 3 half-bit 0's. Therefore, in binary, the frame synchronization bits are 111000.

#### Line Turnaround

Work station line turnaround lasts from the time a work station (in receive mode) receives the last bit of a frame (bit 0) to the time the same work station goes into transmit mode and starts sending the bit synchronization bits. In the work stations, line turnaround occurs in a minimum of 15 microseconds to a maximum of 30 microseconds.

Attachment line turnaround lasts from the time the last bit of a frame (bit 0) is transmitted by the attachment (in transmit mode) to the time the attachment goes into receive mode and starts receiving the bit synchronization bits. Attachment line turnaround is less than 15 microseconds because the attachment must be ready to receive a frame from the work station in 15 microseconds (minimum time for work station line turnaround).

station attachment in System/34 to a display station, and from a display station to the attachment, are shown in the following figure.

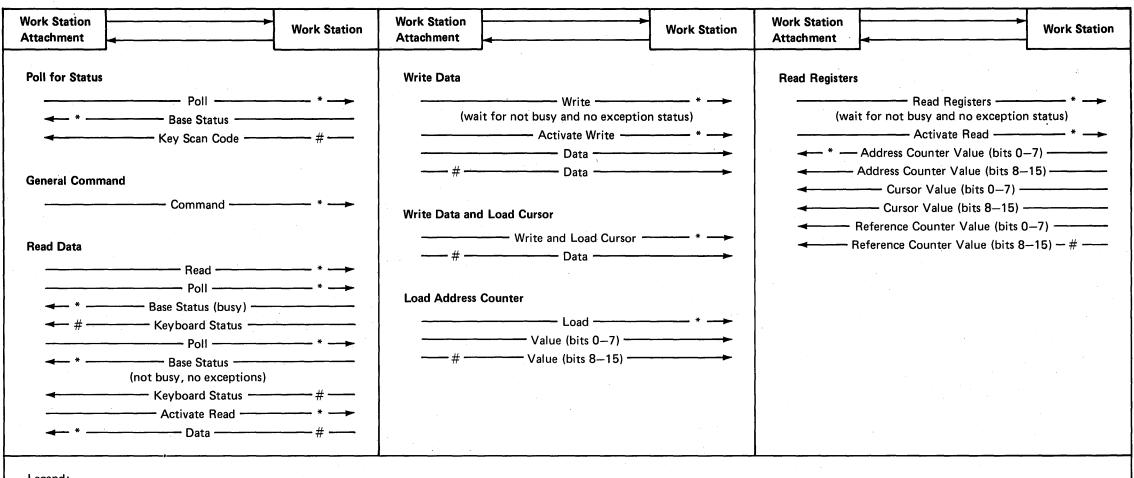

#### **Examples of Transmission Sequences**

The work stations never start a transaction to or from the work station attachment. Instead, the work station attachment starts all transactions via a command, and the work stations respond to the commands. For example, if the work station attachment issues an activate read command, the work station responds by returning data to the work station attachment. Information is passed between the work station attachment and the work stations in a half duplex mode; that is, information is sent in only one direction at a time. The following figure shows some of the typical commands sent to the work stations, and the information that is returned to the work station attachment.

#### Legend:

\* Bit synchronization and frame synchronization bits are generated by the work station attachment. These bits condition the work station to start receiving a command.

# Data stream terminating delimiter that ends the message and causes the work station to expect frame synchronization bits next. For example, under the Poll for Status command, the message ends as soon as the key scan code is sent to the work station attachment. Then, the work station can expect to receive the frame synchronization bits before receiving any other information. A 16-bit frame from the work station attachment to the work station.

A 16-bit frame from the work station to the work station attachment.

This page intentionally left blank.

#### Commands

The following table gives all the command names and the decode of bits 7 through 14 of the 16-bit frame. Bits 7, 8, and 9 are either the command modifier, or they are the device address. Bits 10 through 14 are always the command bits when the system sends a command to the work station. Only the valid command bit configurations are shown; all other bit configurations are reserved.

| Command Name               | De | odif<br>evice<br>Idre | ) | Cor | nma | and |    |          | Addressed<br>To       | Notes                                                       |

|----------------------------|----|-----------------------|---|-----|-----|-----|----|----------|-----------------------|-------------------------------------------------------------|

|                            | 7  | 8                     | 9 | 10  | 11  | 12  | 13 | 14       |                       |                                                             |

| Activate read              | 0  | 0                     | 0 | 0   | 0   | 0   | 0  | 0        | Base                  | Device address is specified by pre-                         |

| Activate write             | 0  | 0                     | 0 | l o | 0   | 0   | 0  | 1        | Base                  | ceding command.                                             |

| Clear                      | 0  | 0                     | 0 | 1   | 0   | 0   | 1  | 0        | Base                  |                                                             |

| EOQ delimiter              | 0  | 1                     | 1 | 0   | 0   | 0   | 1  | 0        | Base                  |                                                             |

| Insert character           | 0  | 0                     | 0 | 0   | 0   | 0   | 1  | 1        | Base                  |                                                             |

| Load address counter       | 0  | 0                     | 0 | 1   | 0   | 1   | 0  | 1        | Base                  |                                                             |

| Load cursor                | 0  | 0                     | 0 | 1   | 0   | 1   | 1  | 1        | Base                  |                                                             |

| Load reference<br>counter  | 0  | 0                     | 0 | 0   | 0   | 1   | 1  | 1        | Base                  |                                                             |

| Move data                  | 0  | 0                     | 0 | O   | 0   | 1   | 1  | 0        | Base                  |                                                             |

| Poll                       | ×  | х                     | X | 1   | 0   | 0   | 0  | 0        | Base                  | See note below for<br>a description of<br>bits 7, 8, and 9. |

| Read immediate field       | 0  | 0                     | 0 | 1   | 1   | 0   | 0  | -1       | Base                  | Activate required                                           |

| Read between limits        | 0  | 0                     | 0 | 1   | 1   | 0   | 1  | 0        | Base                  | Activate required                                           |

| Read registers             | 0  | 0                     | 0 | 1   | 1   | 1   | 0  | 0        | Base                  | Activate required                                           |

| Reset                      | 0  | 0                     | 0 | 0   | 0   | 0   | 1  | 0        | Base                  |                                                             |

| Search attribute           | 0  | 0                     | 0 | 0   | 0   | 1   | 0  | 0        | Base                  |                                                             |

| Search null                | 0  | 0                     | 0 | 1   | 0   | 1   | 0  | 0        | Base                  |                                                             |

| Set mode                   | Ū. | 0                     | 0 | 1   | 0   | 0   | 1  | 1        | Base                  |                                                             |

| Write control data         | 0  | 0                     | 0 | 0   | 0   | 1   | 0  | 1        | Base                  |                                                             |

| Write data and load cursor | 0  | 0                     | 0 | 1   | 0   | 0   | 0  | <b>1</b> | Base or<br>indicators |                                                             |

| Write immediate data       | 0  | 0                     | 0 | 1   | 1   | 1   | 0  | 1        | Base                  | Activate required                                           |

*Note:* Bits 7, 8, and 9 of the poll command have the following meaning:

• Bit 7 = Should be 0.

• Bit 8 = Resets the line parity check bit (bit 8 of a base response).

• Bit 9 = Acknowledge bit. Acknowledges that status has been received from the work station, and that status can be updated.

#### Frame Formats

The following figure shows the different formats for the 16-bit frame. In every format, bit 3 is shown as the parity (P) bit, and bit 15 is shown as the sync (S) bit. In the *Keyboard Response Format*, bit 7 is shown as the make/break (M/B) bit. In response to a poll command, the work station sends two frames of information. The first frame in the response informs the system of the work station's status. This first frame is shown below as the *Base Response Format*. The second frame in the response gives the key scan code, and is shown below as the *Keyboard Response Format*.

#### **Basic Format**

| 0 | 1    | 2 | 3 | 4 | 5                 | 6 | 7 | 8             | 9 | 10      | 11 | 12 | 13 | 14 | 15 |

|---|------|---|---|---|-------------------|---|---|---------------|---|---------|----|----|----|----|----|

|   | Fill |   | Ρ |   | Statior<br>Addres |   | D | Base<br>evice | D | Command |    |    |    |    | S  |

Data Word Format

| 0 | 1    | 2 | 3 | 4 | 5                 | 6 | 7 | 8 | 9 | 10     | 11      | 12 | 13 | 14 | 15 |

|---|------|---|---|---|-------------------|---|---|---|---|--------|---------|----|----|----|----|

|   | Fill |   | Ρ |   | Statior<br>Addres |   |   |   | D | ata Cł | naracte | er |    |    | S  |

#### **Base Response Format**

| 0                         | 1 | 2 | 3 | 4 | 5    | 6                   | 7 | 8           | 9 | 10               | 11 | 12         | 13 | 14 | 15 |

|---------------------------|---|---|---|---|------|---------------------|---|-------------|---|------------------|----|------------|----|----|----|

| Fill P Station<br>Address |   |   |   |   | Busy | Line<br>Par-<br>ity |   | Not<br>Used |   | ccepti<br>Status |    | Lev-<br>el | S  |    |    |

Determines new or old status from the work station ------

#### Keyboard Response Format

| Ő | 1      | 2 | 3 | 4 | 5                 | 6 | 7   | 8 | 9 | 10  | 11     | 12   | 13 | 14 | 15 |

|---|--------|---|---|---|-------------------|---|-----|---|---|-----|--------|------|----|----|----|

|   | Fill P |   | Р |   | Statior<br>Addres |   | M/B |   |   | Key | Scan ( | Code |    |    | S  |

#### **OPERATIONS**

As the following figure shows, the work station attachment contains a controller card, an adapter card, storage cards, and a driver/receiver card. All communications between the System/34 control processor, the work station controller, the work station adapter, and the work stations occur through the work station adapter card. For a description of the adapter card, see *Functional Units* earlier in this section.

The attachment controls:

- The movement of data and command information from the channel to the work stations

- The movement of data and status information from the work stations to the channel

- The Console Check light on the operator panel

The attachment also controls and processes keystrokes from the 5251 or 5252 Display Station(s) and control keys from the 5256 Printer(s).

The work station controller card is an important part of the work station attachment; when used with the work station input/output control handler (WSIOCH), it performs all work station control functions. This card is the same as the controller card for the 5211 Printer (the printer is optional). The card is described in the *Attachment Controllers* section of this manual.

The work station controller storage is both read-only storage and read/write storage. At system initial program load time, the processing unit I/O instructions cause the data on the channel to be put into the controller read/write storage. Then, the controller is started and the work station program is executed. This program causes the controller to perform the following functions:

- The controller controls the movement of commands and data to and from main storage and control storage and the work stations.

- The controller periodically polls all work stations and processes work station keystrokes and status conditions.

#### **Displaying a Message**

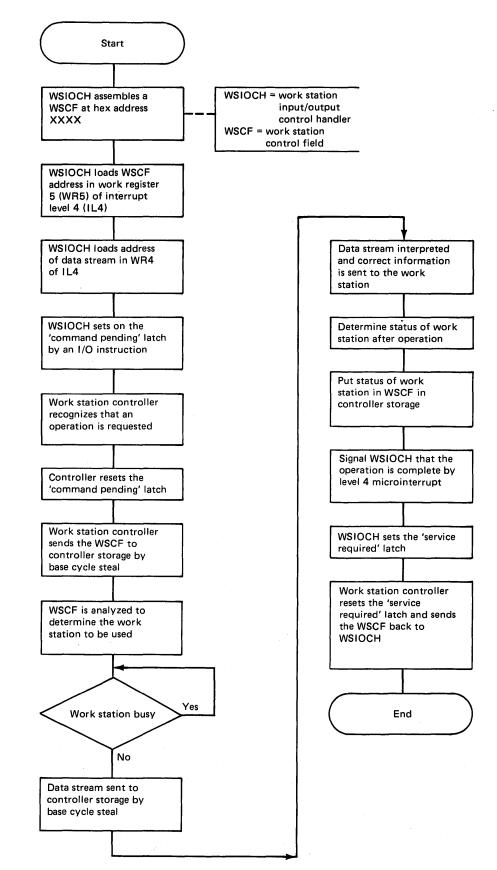

The flow chart on this page shows the operations needed for displaying a message on a 5251 Display Station. The sequence of events for displaying a message is:

- The work station input/output control handler (WSIOCH) in control storage sets a 'service required' latch in the attachment with an I/O instruction (through the channel) to signal the controller to send the work station control field back to WSIOCH.

- The controller samples the 'service required' latch; if it is active, the work station control field is sent back to WSIOCH by base cycle steal. Then, the 'service required' latch is reset and the work station controller interrupts the control processor on interrupt level 4.

- 3 Then WSIOCH does the following:

a. Assembles a work station control field in a fixed location of control storage.

- b. Loads work register 5 of interrupt level

- 4 with the address of the first byte of the work station control field.

- c. Loads work register 4 of interrupt level 4 with the address of the first byte of the main storage data stream associated with the work station control field.

- d. Sets the 'command pending' latch in the attachment with an I/O instruction (through the channel) to signal the controller that a work station control field and its associated data stream are prepared.

The controller:

4.

- a. Samples the 'command pending' latch and determines that an operation is to be performed.

- b. Receives the work station control field

1 byte at a time from the host by base cycle steal. The controller signals the processing unit to use work register 5 on interrupt level 4 as the starting address of the work station control field to be received and that the work station control field is in control storage.

- c. Analyzes the work station control field to determine the function to be performed and which work station is specified.

- d. Checks the work station status in the station parameter list to determine if the work station is able to receive the data stream.

- e. Receives the data stream from the host by base cycle steal. The controller signals the processing unit to use work register 4 of interrupt level 4 as the starting address of the data to be received and that the data is in main storage.

- f. Analyzes the data stream and sends the correct information to the work station through the serial interface.

- g. Communicates with the work station through the serial interface to determine the status of the work station after an operation; then, puts the status into the work station control field and sends the work station control field to the host by base cycle steal. Work register 5 on interrupt level 4 is used for this operation.

- h. Resets the 'command pending' latch and signals the WSIOCH routine with a level 4 microinterrupt that the operation is complete.

- WSIOCH gains control as the result of interrupt level 4 posting the action control word. WSIOCH finds that the work station control field contains a valid device address, and posts the terminal unit block complete.

11

#### **Transmit and Receive Operations**

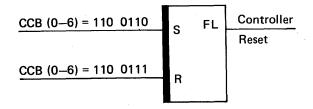

The work station attachment is either in transmit mode, receive mode, or idle mode (neither transmit nor receive mode). A system reset from the channel or an adapter reset (CCB bits 0 through 6 equal to 110 1100) in the attachment keeps the attachment in idle mode.

To keep the attachment in idle mode, either the 'system reset' signal or the 'adapter reset' signal resets the SERDES control (G in the Data Flow figure), and the SERDES (H). These reset lines also de-activate the outputs of the driver select logic s and disable the driver/receiver P when the attachment is in idle mode. Neither reset line is active in transmit mode or receive mode.

In the following descriptions of transmit and receive operations, the words controller instruction are followed, in parentheses, by five numbers. These five numbers are the decode of the controller CBO bits 3 through 7. See Controller Command Decode earlier in this section for the decode of these bits.

The descriptions of the transmit and receive operations contain circled alphabetic characters. These characters reference the Data Flow figure earlier in this section.

#### **Transmit Operation**

Before a transmit operation starts, the 'go', 'transmit enable', and 'receive enable' latches in the SERDES control G and the SERDES H are in a reset condition. To start a transmit operation, a controller instruction (01000) loads the cable address into the CBI and cable address register **()**. Another controller instruction (10000) sets the 'transmit enable' latch and, therefore, the SERDES is no longer in a reset condition. After the 'transmit enable' latch is set, the modulator/demodulator starts to generate the bit synchronization and frame synchronization bits. While these bits are being generated, another controller instruction (00010) causes controller DBO bits 0 through 7 to be loaded into the SERDES (bits 7 through 14) as the command or data byte. The SERDES bits are the same as the bits of the serially transmitted frame; that is, bit 0 of SERDES is bit 0 of the frame, bit 1 is bit 1, and so on.

After bits 7 through 14 of the SERDES are loaded, another controller instruction (00011) causes the new information on controller DBO bits 0 through 7 to be loaded into the remainder of SERDES. The SERDES control is then informed that the SERDES is now loaded with a full frame to be transmitted.

When the SERDES control senses the last frame synchronization bit, it uses the 'serial out' signal (starting with the sync bit) from the SERDES to generate the 'transmit binary data' signal, which is sent to the modulator/demodulator. The modulator synchronizes the 'transmit binary data' signal to the 'transmit clock' signal and then supplies the modulated 'transmit data' signal to the driver P. The driver selected (by the cable address register and the driver select logic (s) then generates a differential signal to represent a 1 for the sync bit and transmits this bit on the twinaxial cable.

To transmit the next 11 bits of the frame (bits 4 through 14), the SERDES control shifts the SERDES by 1 bit for each bit transmitted. Then, similar to the operations that occurred for the sync bit, the following occurs for each bit:

- 1. The SERDES control uses the 'serial out' signal to generate the 'transmit binary data' signal.

- 2. The modulator synchronizes the 'transmit binary data' signal to the 'transmit clock' signal and supplies the 'transmit data' signal to the driver.

- 3. The driver generates a differential signal to represent a 0 or a 1 on the twinaxial cable.

The parity bit (bit 3) is not shifted out of the SERDES as the first 12 bits were. Instead, the parity bit is generated by the parity latch in the SERDES control. This latch is reset when either the 'transmit enable' or the 'receive enable' signal is not active. Therefore, the latch is reset before the transmit operation starts but is set when the sync bit is sensed. Then, the latch is alternately reset or set by each 1-bit (for bits 4 through 14) on the 'transmit binary data' signal. After bit 4 has been transmitted, the condition (on or off) of the parity latch determines if the parity bit is 0 or 1. If the latch is on, the parity bit is 1; if the latch is off, the parity bit is 0. In either case, the parity bit generates even parity on bits 3 through 15 of the frame.

After the parity bit is generated, bits 0 through 2 (which are always 000) are generated by the SERDES control and are transmitted as the last 3 bits of the frame. When the frame has been transmitted, the SERDES control sets the 'go' latch, which causes 0-bits (fill bits) to be transmitted until the next frame is transmitted.

The controller senses that the 'go' latch is set and loads the next frame into the SERDES. When the SERDES is loaded, the SERDES control starts to transmit the new frame.

11-14

#### **Receive Operation**

Before a receive operation starts, the 'go', 'transmit enable', and 'receive enable' latches in the SERDES control **G** and the SERDES **H** are in a reset condition. Also, the driver part of the driver/receiver **P** is disabled.

In addition, the work station attachment must send a poll command to which the work station must respond. When the response from the work station is recognized by the work station attachment, the attachment can start to receive data.

To start a receive operation, a controller instruction (01000) loads the cable address into the CBI and cable address register . The output of the cable address register causes the receiver select logic • to select the output of the correct receiver. Another controller instruction (11001) sets the 'receive enable' latch. With this latch set:

- The SERDES is no longer reset, so the attachment can start to receive data.

- The modulator/demodulator **(K)** is enabled, and it starts checking for the bit synchronization and frame synchronization bits.

- After the frame synchronization bits are recognized, a frame (or frames) of data is (are) received as described in the following paragraphs.

The receiver part of the driver/receiver is always active, and it checks for the four-level differential signal received from the twinaxial cable (see *Differential Data* earlier in this section). Using the four-level differential signal as input, the receiver generates the binary 'receive data' signal.

The receive operation continues with the following sequence:

- The 'receive data' signal is gated through the receiver select logic to the receive clock generator

and to the modulator/demodulator.

- The output of the receive clock generator is gated to the modulator/demodulator as the 'receive clock' signal.

- The modulator/demodulator generates the 'receive binary data' signal (from the 'receive data' and 'receive clock' signals) and gates it to the SERDES control.

- The SERDES control gates the 'receive binary data' signal to the SERDES on the 'serial in' line.

The data on the 'serial in' line is shifted into SERDES 1 bit at a time, starting with bit 15 of the frame (the sync bit). Bit 14 is shifted in next, then bit 13, and so on. As the data is shifted in, the SERDES control checks for even parity on bits 3 through 15 (sync bit, data, work station address, and parity bit). Then the 3 fill-bits (000) are shifted into SERDES. The SERDES control senses when the SERDES is full (contains 16 bits) and causes the data in SERDES to be sent to the controller DBI buffer. The SERDES control also sets the 'go' latch to inform the controller that the controller DBI buffer contains a valid frame of data.

A controller instruction (X1101) is then issued to sense the condition of the 'go' latch. If the latch is set, two more controller instructions (X0000 and X0001) are issued to sense the contents of the SERDES. Then, assuming that the work station address bits (bits 4 through 6 of the frame) are not set to 111, the receive operation continues with the next frame.

Additional frames are received until bits 4 through 6 of the frame are set to 111, which indicates an end of message (the last frame sent on this receive operation). When the end of message is sensed, the 'receive enable' latch is reset. Also, the SERDES and the 'go' latch are held reset because neither the 'transmit enable' nor the 'receive enable' latch is set.

Note: The 'receive enable' latch is reset when the end of message is sensed so that any noise on the twinaxial cable cannot be sensed as the bit synchronization bits or the frame synchronization bits.

### COMMANDS

The work station attachment recognizes the following I/O immediate commands from the control processor:

- I/O load

- I/O control load

I/O sense

These commands are decoded from the function field (bits 8-11) and sent to the attachment on CBO bits 0-2. The format of the I/O immediate command is:

| 1 | 0 | 1 | 1 | Modifier |   | Function |    | H<br>2 | Re | g  |

|---|---|---|---|----------|---|----------|----|--------|----|----|

| 0 |   |   | 3 | 4        | 7 | 8        | 11 | 12     | 13 | 15 |

### I/O Load Command

| Channel<br>Sys Bus Out Low           | Select Attachment |              |                                                         | Send Data Byte to A<br>DBO 0-7 | Attachment |       |             |               |       |       |       |

|--------------------------------------|-------------------|--------------|---------------------------------------------------------|--------------------------------|------------|-------|-------------|---------------|-------|-------|-------|

|                                      |                   |              | Modifier<br>4-7                                         |                                |            |       |             |               |       |       |       |

| Function<br>Decode                   |                   | ССВ          | ССВ                                                     |                                |            |       | DE          | 30            |       |       |       |

| ╞╤╤╤╡╒╤╤╕<br>╚ <u>ᆠ</u> ᅆᆠᅆ <u>ᆠ</u> |                   | 012          | 3 4 5 6                                                 | Bit O                          | Bit 1      | Bit 2 | Bit 3       | Bit 4         | Bit 5 | Bit 6 | Bit 7 |

| 0   2                                |                   |              | 0 0 0 0<br>Set diagnostic mode                          |                                |            |       |             |               |       |       |       |

| СВО                                  |                   |              | 0 0 0 1<br>Reset diagnostic mode                        |                                |            |       |             |               |       |       |       |

| Data<br>Buffer                       |                   |              | 0 0 1 0<br>Diagnostic set cycle<br>steal transfer error |                                |            |       |             |               |       |       |       |

| Port Data<br>Bus Out                 |                   | 100<br>  1/0 | 0 0 1 1<br>Reset microinterrupt<br>request              |                                |            |       |             |               |       |       |       |

|                                      | Addres<br>Hit     | Load         | 0 1 0 0<br>Set microinterrupt<br>request                |                                |            |       |             |               |       |       |       |

|                                      |                   |              | 0 1 0 1<br>Load data buffer                             |                                |            |       | DBO Bits to | o Data Buffer |       |       |       |

|                                      |                   |              | 0 1 1 0<br>Disable microinterrupt<br>request            |                                |            | -     |             |               |       |       |       |

|                                      |                   |              | 0 1 1 1<br>Enable microinterrupt<br>request             |                                |            |       |             |               |       | · .   |       |

.

### I/O Load Command (continued)

| d (continued)        | CPU<br>Clock                          |   | Т<br>1      | 1 | Т<br>3 | 3 | 1. | 3 |     | • |             |   | Т<br>4 | Т<br>5 |   | Т<br>6<br>Е |             |             |   |             |   | Т<br>0      |   | P | lodi<br>ort<br>, 5, | DB | 0  | Port<br>DBO<br>Bit | Command                                  |

|----------------------|---------------------------------------|---|-------------|---|--------|---|----|---|-----|---|-------------|---|--------|--------|---|-------------|-------------|-------------|---|-------------|---|-------------|---|---|---------------------|----|----|--------------------|------------------------------------------|

|                      | Port<br>Clock                         | 0 | C<br>0<br>0 | 0 | 0      | 0 | 0  | 0 |     | 0 | C<br>0<br>6 | 1 | 1      | 1      | 1 | 1           | C<br>1<br>7 | C<br>1<br>F | 1 | C<br>1<br>6 | 0 | C<br>0<br>0 |   |   | 0                   |    |    |                    | Set diagnostic mod<br>Reset diagnostic m |

| Line Name            | FSL Page                              |   |             |   |        |   |    | İ |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   | 0 | 0                   | 1  | 0  |                    | Diagnostic set cycl                      |

| CBO (valid)          | · · · · · · · · · · · · · · · · · · · |   | T           |   |        |   |    | Ī | Ī   |   |             |   |        |        |   |             |             |             |   |             |   |             |   | Ŭ | Ŭ                   | •  | Ū  |                    | steal transfer error                     |

| Port DBO (valid)     | · · · · · · · · · · · · · · · · · · · |   | Ī           |   |        |   |    |   |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   |   |                     |    |    |                    |                                          |

| Control Out          | PC510                                 |   |             |   |        |   |    |   |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   | 0 | 0                   | 1  | 1  | 1                  | Reset microinterru                       |

| Strobe               |                                       |   |             |   |        |   |    |   |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   |   |                     |    |    |                    | request                                  |

| Data Sample 1        | WS101                                 |   |             |   |        |   |    |   |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   | 0 | · 1                 | 0  | 0  |                    | Set microinterrupt                       |

| Data Sample 2        | WS101                                 |   |             |   |        |   |    |   |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   |   |                     |    |    |                    | request                                  |

| Gate DBI and CBI     | WS101                                 |   | Γ           |   |        | Γ |    |   |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   |   | 1                   | ^  | 1  | 0.7                | l a d d da barter                        |

| Multidevice Response | WS101                                 |   |             |   |        | Ι | Γ  | Γ | · · |   |             |   |        |        |   |             |             |             |   |             |   |             |   | Ū | 1                   | U  | 1  | 0-7                | Load data buffer                         |

| Device Selected      |                                       |   |             |   |        |   |    | Γ |     |   |             |   |        |        |   |             |             | Ι.          |   |             |   |             |   |   |                     |    |    |                    |                                          |

| CCB (valid)          |                                       |   |             |   |        |   |    |   |     |   |             |   |        |        |   |             | Γ           |             |   |             |   |             | ļ | 0 | 1                   | 1  | 0  |                    | Disable microinter                       |

| Service In           | WS101                                 |   |             |   |        |   |    |   |     |   |             |   |        |        |   |             | Ι           |             |   |             |   |             |   |   |                     |    |    |                    | request                                  |

| Service Out          | PC510                                 |   |             |   |        |   |    |   |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   | 0 | 1                   | 1  | `1 |                    | Enable microinterr                       |

| CBI Bit 5 (valid)    |                                       |   |             |   |        |   |    |   |     |   |             |   |        |        |   |             |             |             |   |             |   |             |   | 5 | •                   | •  | •  |                    | request                                  |

| Action Taken                                                        | FSL<br>Page                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sets the 'diagnostic mode' latch                                    | WS111                                                                                                                                                                                                                                                                                                                                                                                    |

| Resets the 'diagnostic mode' latch                                  | WS111                                                                                                                                                                                                                                                                                                                                                                                    |

| Sets the 'cycle steal transfer error' latch for diagnostic purposes | WS111                                                                                                                                                                                                                                                                                                                                                                                    |

| Resets the 'microinterrupt request' latch                           | WS111                                                                                                                                                                                                                                                                                                                                                                                    |

| Sets the 'microinterrupt request' latch for diagnostic purposes     | WS111                                                                                                                                                                                                                                                                                                                                                                                    |

| Loads DBO bits 0-7 in the work station controller DBI buffer        | WS121                                                                                                                                                                                                                                                                                                                                                                                    |

| Resets the 'enable interrupt request' latch                         | WS111                                                                                                                                                                                                                                                                                                                                                                                    |

| Sets the 'enable interrupt request' latch                           | WS111                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                     | Sets the 'diagnostic mode' latch<br>Resets the 'diagnostic mode' latch<br>Sets the 'cycle steal transfer error' latch<br>for diagnostic purposes<br>Resets the 'microinterrupt request' latch<br>Sets the 'microinterrupt request' latch<br>for diagnostic purposes<br>Loads DBO bits 0-7 in the work station<br>controller DBI buffer<br>Resets the 'enable interrupt request'<br>latch |

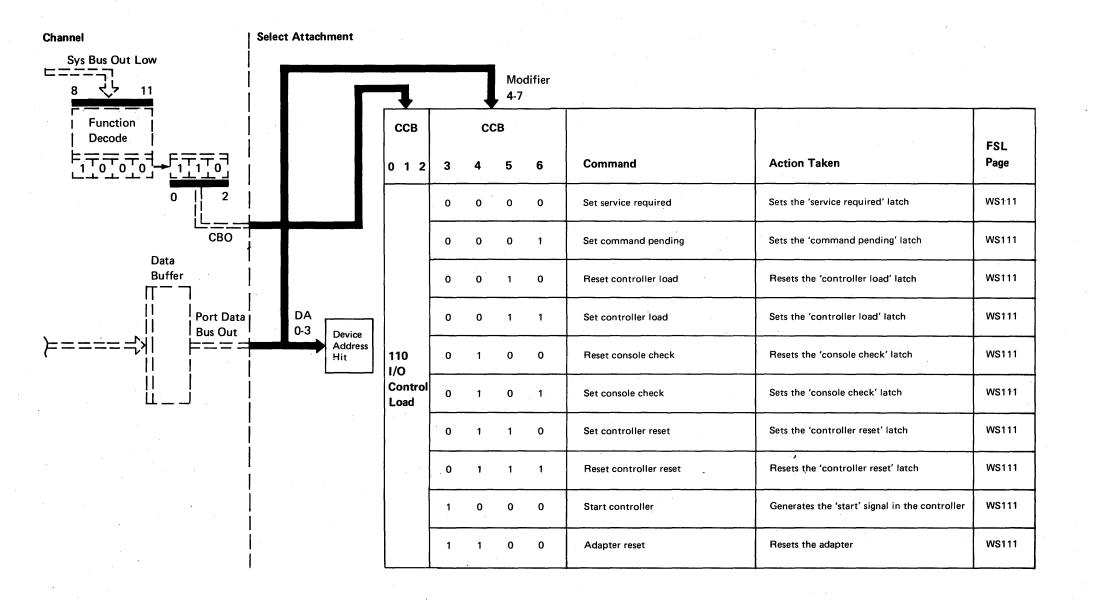

### I/O Control Load Command

The DBO bits are not used for any I/O control load commands.

# I/O Control Load Command (continued)

|                      | CPU<br>Clock  | Т<br>0      | T<br>1      | T<br>2      | Т<br>3      | T<br>3<br>A | T<br>3<br>B | T<br>3<br>E |             |             |   |             | Т<br>4      | Т<br>5      | Т<br>6      | T<br>6<br>E |             |   |   |   |             | Т<br>0      |

|----------------------|---------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|---|-------------|-------------|-------------|-------------|-------------|-------------|---|---|---|-------------|-------------|

|                      | Port<br>Clock | C<br>0<br>0 | C<br>0<br>0 | C<br>0<br>0 | C<br>0<br>0 | C<br>0<br>9 | C<br>0<br>3 | C<br>0<br>7 | C<br>0<br>F | C<br>0<br>E | 0 | C<br>1<br>2 | C<br>1<br>0 | C<br>1<br>8 | C<br>1<br>9 |             | C<br>1<br>7 | 1 | 1 | 1 | C<br>0<br>2 | C<br>0<br>0 |

| Line Name            | FSL Page      |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| CBO (valid)          |               | Τ           |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Port DBO (valid)     |               | T           |             |             | · .         |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Control Out          | PC510         |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Strobe               |               |             |             |             |             | н<br>-      |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Data Sample 1        | WS101         |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Data Sample 2        | WS101         |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Gate DBI and CBI     | WS101         |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Multidevice Response | WS101         |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Device Selected      | -             | T           |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| CCB (valid)          |               |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Service In           | WS101         | Ι           |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| Service Out          | PC510         |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

| CBI Bit 5 (valid)    |               |             |             |             |             |             |             |             |             |             |   |             |             |             |             |             |             |   |   |   |             |             |

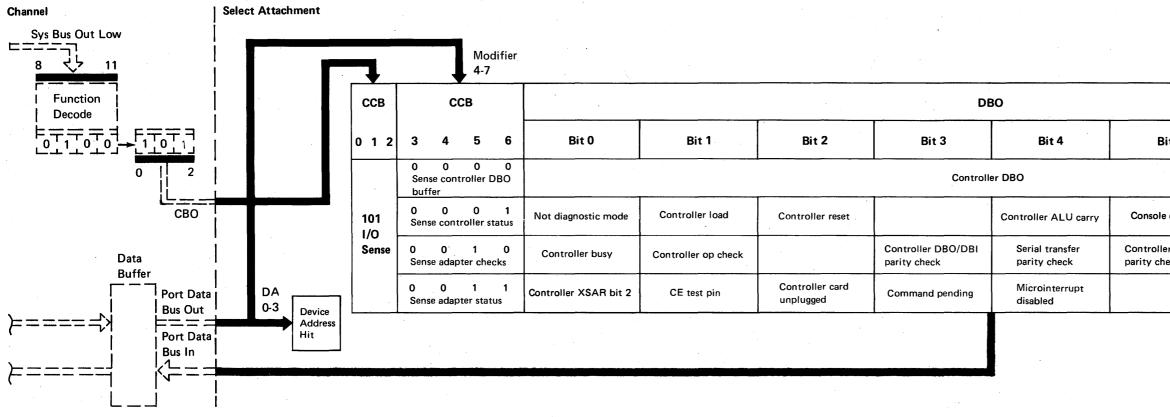

### I/O Sense Command

|                    |                       | •                         |

|--------------------|-----------------------|---------------------------|

| Bit 5              | Bit 6                 | Bit 7                     |