# Contents

| MAIN STORAGE PROCESSOR .                                           |     |   |   |   |   |   | . 3-1 |

|--------------------------------------------------------------------|-----|---|---|---|---|---|-------|

| DATA FLOW AND CLOCK                                                |     | • | • | • | • | • | . 3-2 |

| Data Flow                                                          |     | • |   |   |   |   | . 3-2 |

| Parity Checking and Generation .                                   |     |   |   |   |   |   |       |

| Clock                                                              |     |   | • | • |   |   | . 3-4 |

| OPERATIONS                                                         |     |   |   |   |   |   | . 3-6 |

| Instruction and Execution Cycles .                                 |     |   |   |   |   |   | . 3-6 |

| Sequential Instruction Execution                                   |     |   |   |   |   |   | . 3-6 |

| I/O Data Movement                                                  |     |   |   |   |   |   | . 3-6 |

| Instruction Formats                                                |     |   |   |   |   |   | . 3-6 |

| Instruction Fetch Operation                                        |     |   |   |   |   |   | . 3-8 |

| Addressing                                                         |     |   |   |   |   |   |       |

| Direct Addressing                                                  |     |   |   |   |   |   | 3-10  |

| Indexing                                                           |     |   |   |   |   |   | 3-10  |

| Indexing                                                           |     |   |   |   |   |   | 3-10  |

| INSTRUCTION EXECUTION                                              |     |   |   |   |   |   | 3-12  |

| Arithmetic Instructions                                            |     |   |   |   |   |   |       |

| Zero and Add Zoned (ZAZ)                                           |     |   |   |   |   |   |       |

| Add Zoned Decimal (AZ)                                             |     |   |   |   |   |   |       |

| Subtract Zoned Decimal (SZ)                                        |     |   |   |   |   |   |       |

| Recomplement Cycle                                                 |     |   |   |   |   |   |       |

| Add Logical Characters (ALC) .                                     |     |   |   |   |   |   |       |

| Subtract Logical Characters (SLC)                                  |     |   |   |   |   |   |       |

| Add to Register (A)                                                |     |   |   |   |   |   |       |

| Data Control Instructions                                          |     |   |   |   |   |   | 3-26  |

| Move Hexadecimal Character (MV                                     | /X) |   |   |   |   |   | 3-26  |

| Move Characters (MVC)                                              |     |   |   |   |   |   | 3-28  |

| Edit (ED)                                                          |     |   |   |   |   |   | 3-30  |

| Insert and Test Characters (ITC)                                   |     |   |   |   |   |   |       |

| Move Logical Immediate (MVI)                                       |     |   |   |   |   |   |       |

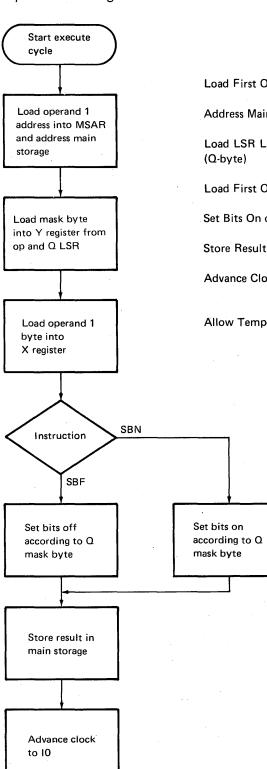

| Set Bits On Masked (SBN)                                           |     |   |   |   |   |   |       |

| Set Bits Off Masked (SBF)                                          |     |   |   |   |   |   |       |

| Store Register (ST)                                                |     |   |   |   |   |   |       |

| Load Register (L)                                                  |     |   |   |   |   |   |       |

| Load Address (LA)                                                  |     |   |   |   |   |   |       |

| Logical Instructions                                               |     |   |   |   |   |   |       |

| Compare Logical Immediate (CLI)                                    |     |   |   |   |   |   | 3-39  |

| Compare Logical Immediate (CLI)<br>Compare Logical Characters (CLC | )   |   |   |   |   |   | 3-40  |

| Test Bits On Masked (TBN)                                          |     |   |   |   |   |   | 3-42  |

| Test Bits Off Masked (TBF) .                                       |     |   |   |   |   |   |       |

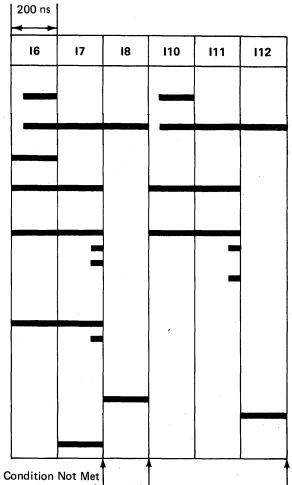

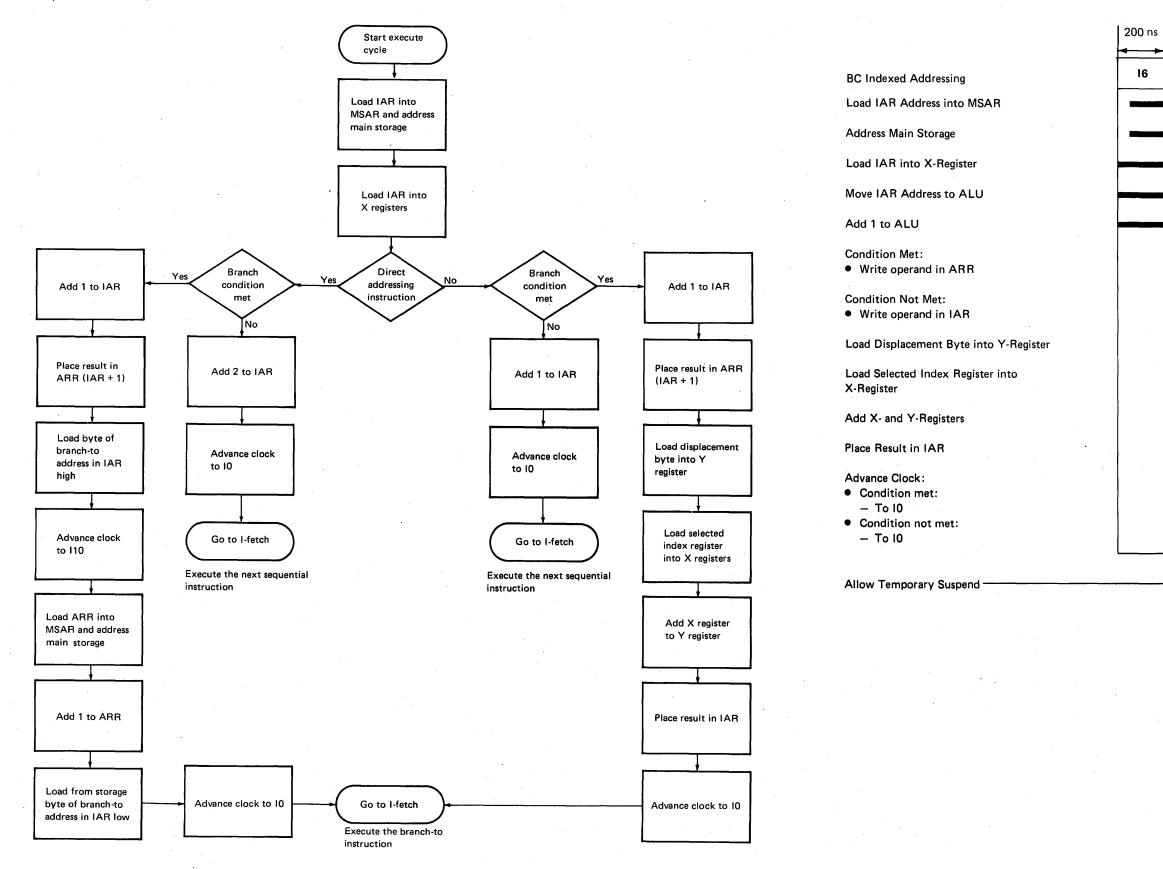

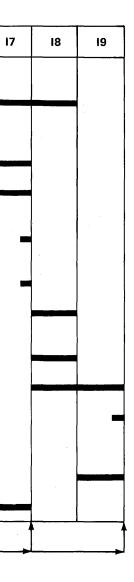

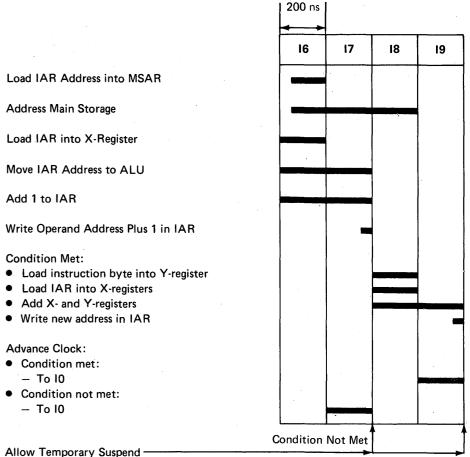

| Branch on Condition (BC)                                           |     |   |   |   |   |   |       |

| Command Instructions                       |    |   |   | 3-46 |

|--------------------------------------------|----|---|---|------|

| Jump on Condition (JC)                     |    |   |   | 3-46 |

| Load Program Mode Register (LPMR) .        |    |   |   | 3-47 |

| Supervisor Call (SVC)                      |    |   |   | 3-48 |

| FUNCTIONAL UNITS                           |    | ÷ |   | 3-50 |

| Main Storage                               |    |   |   | 3-51 |

| Main Storage Address Register              |    |   |   | 3-51 |

| Operation Register                         |    |   |   | 3-51 |

| Q-Backup Register                          |    |   |   | 3-51 |

| Q-Register                                 |    |   |   | 3-51 |

| X-Registers                                |    |   |   | 3-51 |

| Y-Register                                 | ۰. |   |   | 3-51 |

| Arithmetic and Logic Unit                  |    |   |   | 3-51 |

| Arithmetic and Logic Unit Parity Predict . |    |   |   | 3-51 |

| Incrementer or Decrementer                 |    |   |   | 3-51 |

| Decimal Correct                            | •  |   |   | 3-52 |

| Local Storage Register                     |    |   |   | 3-52 |

| Program Status Register                    |    |   |   | 3-53 |

| Status Byte Registers                      | •  |   | • | 3-54 |

| Status Byte 0 (Sense Only)                 |    |   | • | 3-54 |

| Status Byte 1 (Load Only)                  |    |   |   | 3-54 |

| Status Byte 2                              |    |   | • | 3-54 |

| Status Byte 3                              |    |   |   | 3-54 |

| Backup Mode Register                       |    |   |   | 3-54 |

| Configuration Control Register             |    |   |   | 3-54 |

| Address Compare Register                   |    |   | • | 3-54 |

| Address Translation                        |    |   |   | 3-55 |

| Address Translation Registers              |    |   |   | 3-55 |

| Program Mode Register                      |    |   |   | 3-55 |

| Control Mode Register                      |    |   |   | 3-55 |

| ERROR CONDITIONS                           |    |   |   | 3-56 |

| Main Storage Processor Checks              | ·  | · | • | 3-56 |

Contents for Main Storage Processor

# Main Storage Processor

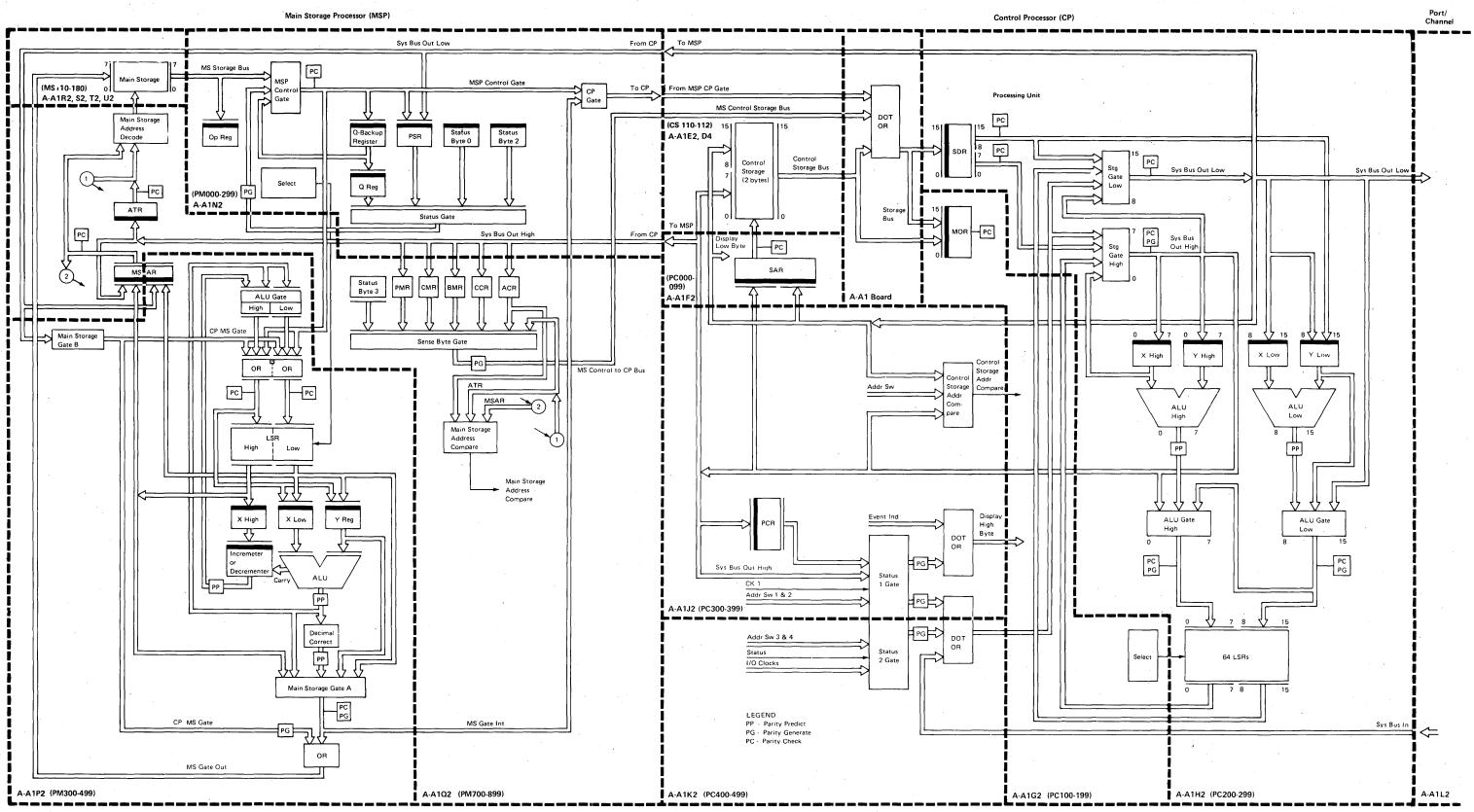

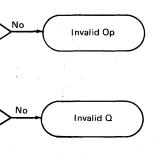

The combination of the control processor and associated control storage, the I/O interface, and the main storage processor and associated main storage makes up the System/34 processing unit. In System/34, the control processor controls the main storage processor.

The main storage processor is contained on five to eleven storage and processor logic cards. The number of cards is specified by the amount of main storage. Three cards are used for main storage processor and storage logic, and the other two to eight cards contain storage as follows:

- Five cards for 32K bytes of storage and processor logic

- Six cards for 48K bytes of storage and processor logic

- Seven cards for 64K bytes of storage and processor logic

- Nine cards for 96K bytes of storage and processor logic

- Eleven cards for 128K bytes of storage and processor logic

## DATA FLOW AND CLOCK

## **Data Flow**

Data flows serially through the main storage processor in 8-bit bytes (plus 1 parity bit), through an arithmetic and logic unit, and is distributed to the remaining functional units of the main storage processor.

#### Parity Checking and Generation

The main storage processor checks for missing or extra bits during data movement by checking for an odd number of bits after the move. The parity checking and parity generating points are shown in the data flow.

Parity predict circuits calculate the parity of the result of the arithmetic and logic unit operation. This calculated parity is compared against the parity generated. If there is a difference, a parity check occurs.

\*Data flow bus lines may not pass through FRUs as shown

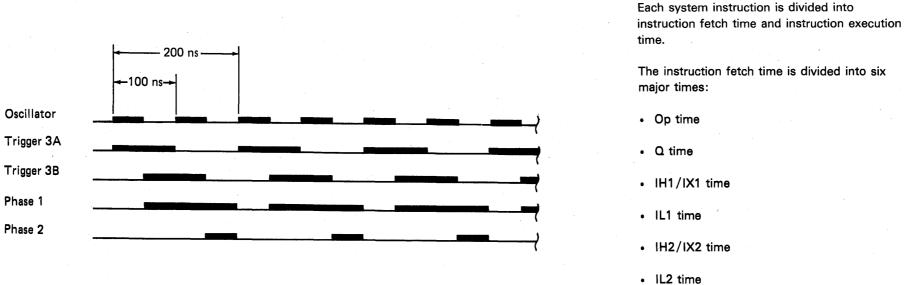

## Clock

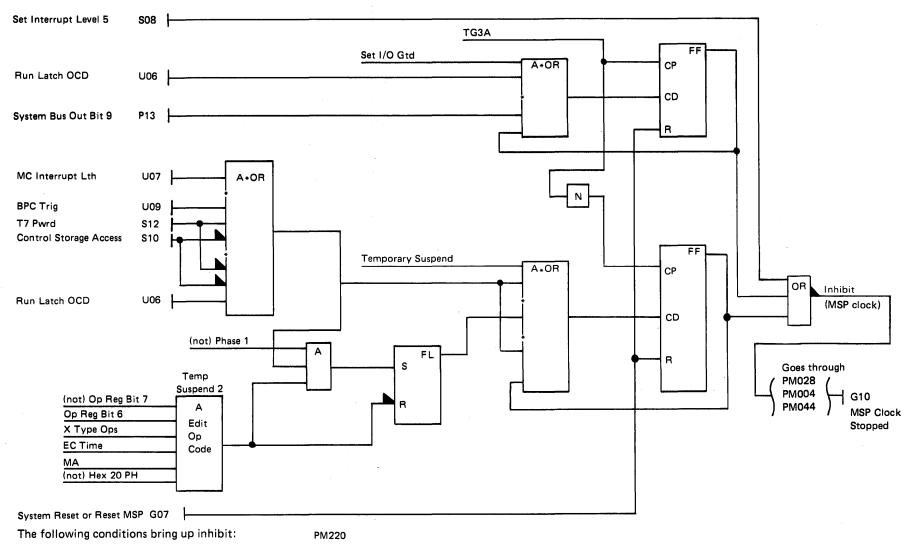

The main storage processor uses the free-running, 100-nanosecond oscillator (10 megahertz) from the control processor. The main storage processor generates its own clock times from this. The rise of the oscillator output causes trigger 3A to change condition, while the fall of the oscillator output causes trigger 3B to change condition. Triggers 3A and 3B generate phase 1 and phase 2 signals. Phase 1 is a 150-nanosecond signal that sets latches during the time the data is valid. Phase 2 is a 50-nanosecond signal that generates the local storage register write pulses.

|                    | •         |          |           |                                       |          |     |            |      | -      |           | μs       | ·                       |     |     |         |         | - |

|--------------------|-----------|----------|-----------|---------------------------------------|----------|-----|------------|------|--------|-----------|----------|-------------------------|-----|-----|---------|---------|---|

|                    | 200 ns    | <b> </b> |           |                                       |          |     |            |      |        | -         | 10       |                         |     |     |         |         |   |

|                    | <b></b>   | 1        |           |                                       |          |     |            |      | Ins    | struction | Fetch Ti | me                      |     |     |         | ·       |   |

| Major Time         | 4         | — Op —   |           |                                       | <u> </u> | •   | <b> </b> • | IH1, | /IX1 — |           |          | — IL1 —                 |     | +   | —– IH2/ | /IX2 —  |   |

| Cycle              | 10        | 11       | 12        | 13                                    | 14       | 15  | 16         | 17   | 18     | 19        | 110      | 111                     | 112 | 113 | 114     | 115     | 1 |

| Minor Time         | А         | в        | с         | A                                     | В        | с   | A          | В    | с      | D         | A        | В                       | с   | A   | в       | с       |   |

| Trigger 3A         |           |          |           |                                       |          |     |            |      |        |           | -        |                         |     |     |         |         |   |

| Phase 1            |           |          |           |                                       |          |     |            |      |        |           | -        |                         |     |     |         |         |   |

| Phase 2            |           |          | t         |                                       |          |     |            |      |        |           |          |                         |     |     |         |         |   |

| Trigger 0          |           | -<br>    |           |                                       |          |     |            | ·    |        |           | -        |                         |     |     |         |         |   |

| Trigger 1          |           |          | -         |                                       |          | -   |            |      |        |           |          |                         |     |     |         |         |   |

| Trigger 2          |           |          |           | <u>`</u>                              |          |     |            |      |        |           |          |                         |     |     |         |         |   |

| Trigger 3          |           | · .      |           | · · · · · · · · · · · · · · · · · · · | ·        |     |            |      |        |           |          | -                       |     |     |         |         |   |

| Trigger 4          | -         |          |           |                                       |          | · · |            |      |        |           |          | ·····                   |     |     | <u></u> |         |   |

| Trigger 5          |           |          |           |                                       | -        |     |            |      |        |           | -        | -                       |     |     |         |         |   |

| Trigger 6          |           |          | <br>      |                                       |          |     |            | -    |        |           |          | -                       |     |     |         |         |   |

| Trigger 7          |           |          |           | ;                                     |          |     | -          |      | -      |           |          |                         |     | •   |         | <u></u> |   |

| Trigger 8          | · · · · · |          |           |                                       |          |     |            |      | -<br>- |           |          |                         |     |     |         |         |   |

| Allow Clock Stop   |           |          |           | 1                                     |          |     |            | -    |        |           |          |                         |     | t   |         |         | 1 |

| (instruction depen | dent)     |          | · · · · · | • · · ·                               |          |     | <b>4</b>   | -    |        |           |          | · · · · · · · · · · · · |     | 1   |         |         |   |

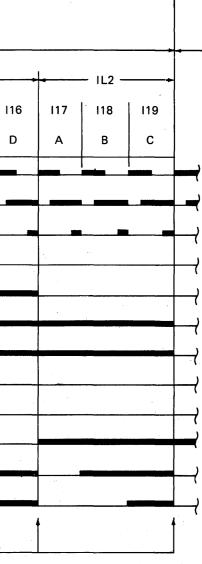

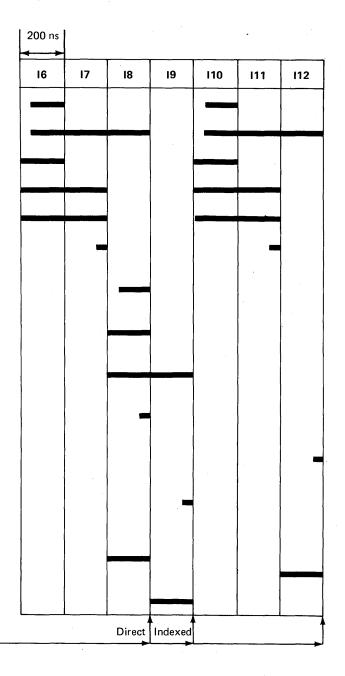

These times are twenty 200-nanosecond instruction cycles (I-cycles) that are numbered from IO through I19. These I-cycles fetch the instruction bytes. Three cycles are needed to fetch each byte from main storage. If indexing is needed, an additional cycle is taken so that the displacement byte can be added to the index register and the real address can be placed in the operation local storage register location.

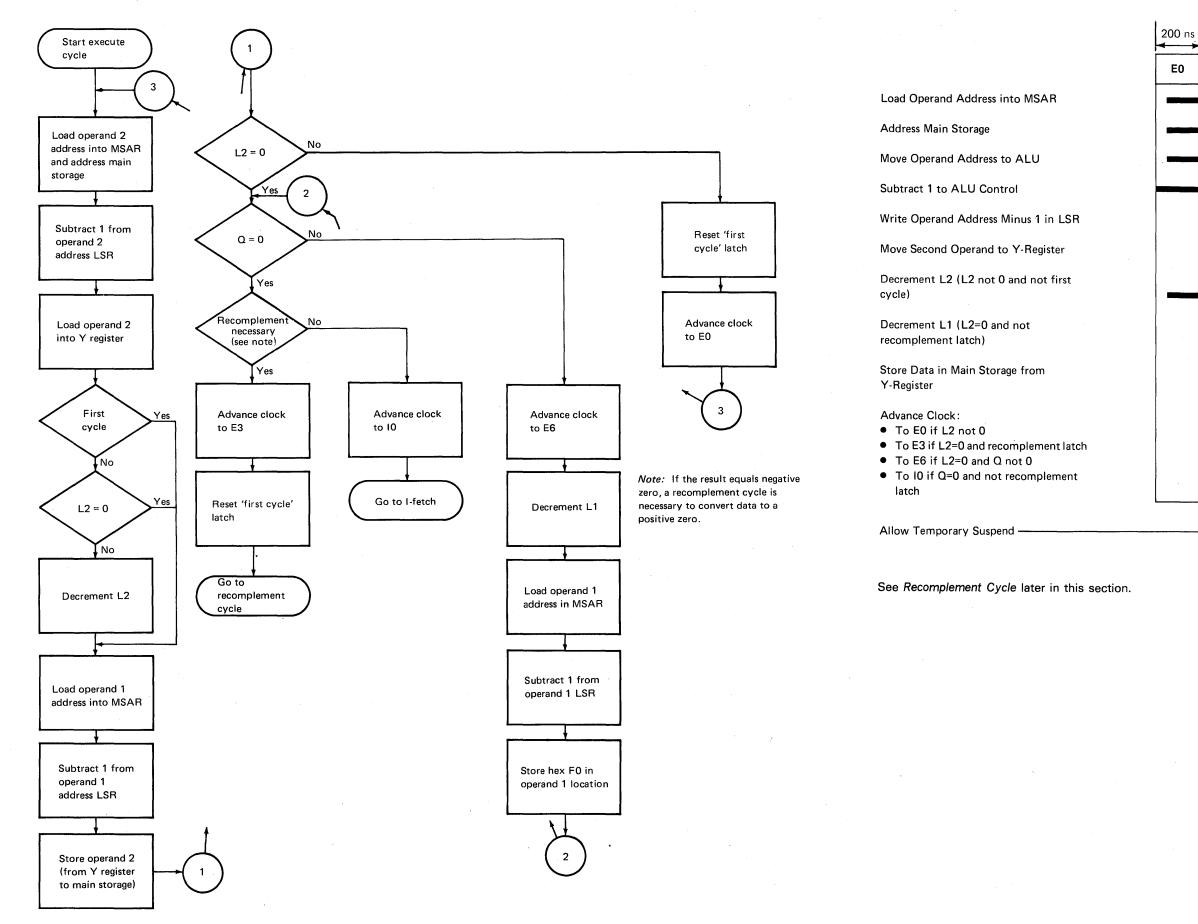

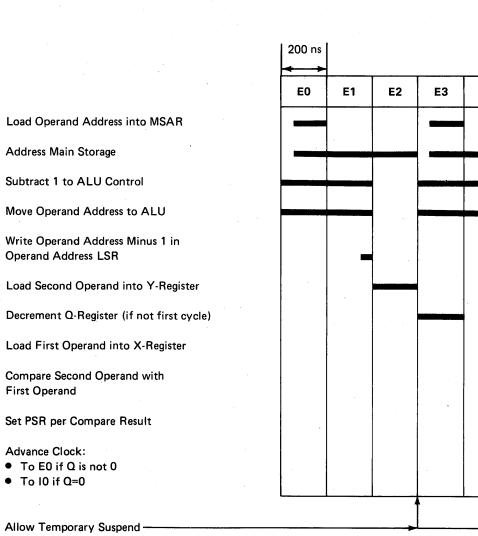

Go to 10 or to Execution Time The instruction execution time is divided into three major times: EA, EB, and EC. These times are ten 200-nanosecond execution cycles (E-cycles): three E-cycles for EA time, four E-cycles for EB time, and three E-cycles for EC time. During execution time, the operands are fetched from main storage and operated on as indicated by the instruction being executed.

Nine triggers are needed to divide the instruction fetch and instruction execution times into the needed cycles. The timing charts show how the cycle time and trigger 3A and trigger 3B work together. The output frequency from trigger 3A is one-half the oscillator frequency.

While an instruction is being executed, the main storage processor clock logic sets the clock to the needed cycle time. This permits skipping cycles or returning to a cycle in the major time. After instruction execution is complete, the clock logic is set to I0 time. Because the main storage processor clock can be stopped and started by the control processor, the clock inhibit logic permits stopping at specific points in the instruction fetch or instruction execution times. The times at which the clock can be stopped are determined by the instruction being fetched or executed.

The main storage processor clock can be stopped only at specific times because the control processor (1) must store the contents of the main storage processor registers while the main storage address register (MSAR) is being used by the control processor instruction, and (2) must return the contents before starting the main storage processor clock. The main storage processor stops only when a change in the MSAR can occur without affecting the system instruction execution.

|                                     |          |          |      |          | 2         | μs ——    |          |           |        | •  | 4              |

|-------------------------------------|----------|----------|------|----------|-----------|----------|----------|-----------|--------|----|----------------|

|                                     |          |          |      | Inst     | ruction E | Executio | n Time _ |           |        |    | Go to I0 or to |

|                                     | - 200 ns | <b> </b> |      |          |           | •        |          |           |        |    | Another E-Time |

| Major Time                          | •        | EA       |      | +        |           | EB ———   | •        | <b> -</b> | — EC – |    | -              |

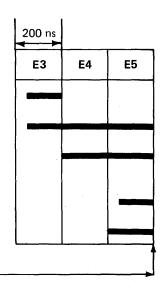

| Cycle                               | EO       | E1       | E2   | E3       | E4        | E5       | E5X      | E6        | E7     | E8 | i.             |

| Minor Time                          | A        | в        | c    | A        | в         | с        | D        | A         | в      | с  |                |

| Trigger 3A                          |          |          | <br> |          |           |          |          |           |        |    | 4              |

| Phase 1                             |          |          |      |          |           |          |          |           |        |    | -              |

| Phase 2                             | -        |          |      |          |           |          |          |           |        |    | •              |

| Trigger 0                           |          | ·····    |      | ļ        |           |          |          |           | ·      |    |                |

| Trigger 1                           |          |          |      | <u> </u> |           |          |          | <u> </u>  |        |    | -              |

| Trigger 2                           |          |          |      | <u> </u> |           |          | <u>.</u> |           |        |    | •              |

| Trigger 3                           |          |          |      |          |           |          | -        |           |        |    |                |

| Trigger 4                           |          | _        |      |          |           |          |          |           | ·      |    | · · · ·        |

| Trigger 5                           |          |          |      |          |           |          |          |           |        |    |                |

| Trigger 6                           |          |          |      |          |           |          | <b></b>  |           |        |    |                |

| Trigger 7                           |          |          |      | ļ        |           |          |          |           |        |    |                |

| Trigger 8                           |          |          |      |          |           |          |          |           |        |    |                |

|                                     |          |          |      | 1        |           |          | t        | t         | t      |    | t              |

| Allow Clock Sto<br>(instruction dep |          |          |      |          |           |          |          |           | _      |    | J              |

#### MSP Clock Control/Stop MSP Clock MSP Control Card A-A1N2

- End of MSP instruction (temp. suspend) and CP stopped

- MC interrupt and temporary suspend

- Main storage or MSP registers being accessed by the CP

3

## **OPERATIONS**

#### Instruction and Execution Cycles

The two types of machine cycles for the internal operation of the main storage processor are: instruction cycles (I-cycles) and execution cycles (E-cycles).

Instruction cycles read instruction bytes from main storage, and execution cycles execute the instruction.

Instruction cycles move the instruction bytes from main storage to the various registers needed to execute the instruction. If the instruction does not need any operands from main storage, the operation is completed without execution cycles. Instructions that do not need execution cycles are:

- Branch

- Jump

- Supervisor call

- Load address

Most operations need data from one or two main storage fields. Main storage holds the operands needed for working with these data fields. Execution cycles process the data fields.

## Sequential Instruction Execution

The main storage processor works step by step. Because of this, the instructions are placed in increasing main storage locations. Instruction sequence is maintained by keeping the address of the storage location in the instruction address register. The instruction address register is increased by 1 as each instruction byte is read from storage so that the next higher storage location can be addressed. This process continues until all the instruction bytes have been addressed. The instruction is then executed. After the instruction has been completed, the instruction address register addresses the next instruction from storage.

#### Branching

Branching permits the main storage processor to change the instruction sequence under specific conditions. Branching also permits changing the sequence of user program instructions. If the branch condition is met, the main storage processor places the address of the branch-to location in the instruction address register, which now becomes the location of the next branch instruction to be executed. By branching to a different storage location and skipping specific instructions, the sequence of the stored program is changed.

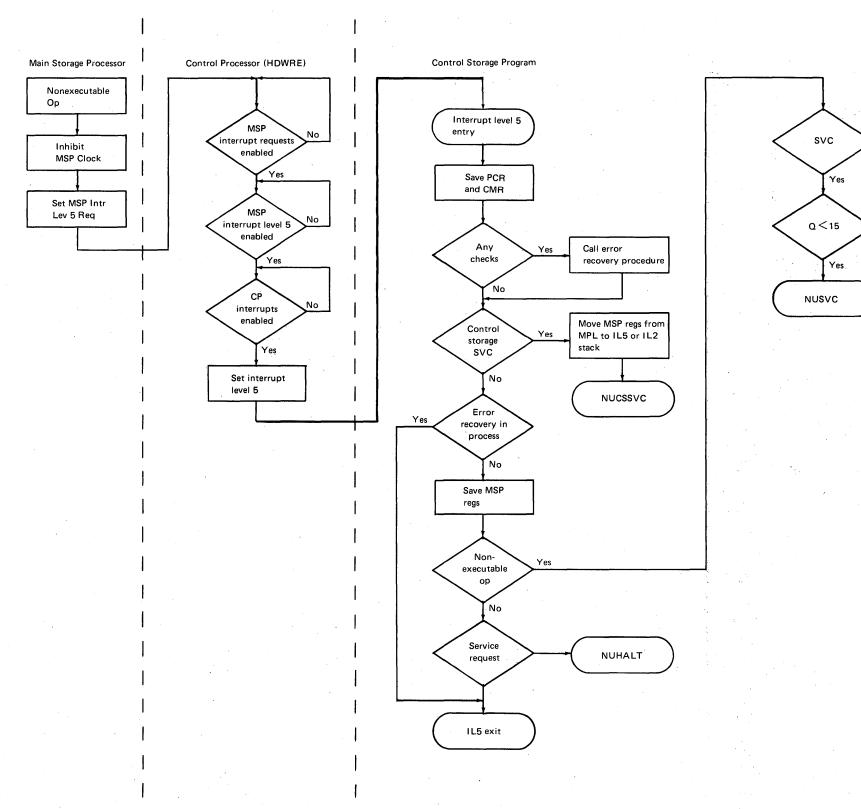

#### I/O Data Movement

The user program requests I/O data movement with a supervisor call (SVC) instruction. The SVC instruction sets interrupt level 5, if interrupt level 5 is enabled. When the control processor senses an SVC instruction from the main storage processor, the control processor determines which operation is requested by analyzing the constants stored in the main storage processor as a result of executing the SVC instruction. The control processor then controls all data movement between the main storage processor and the I/O devices.

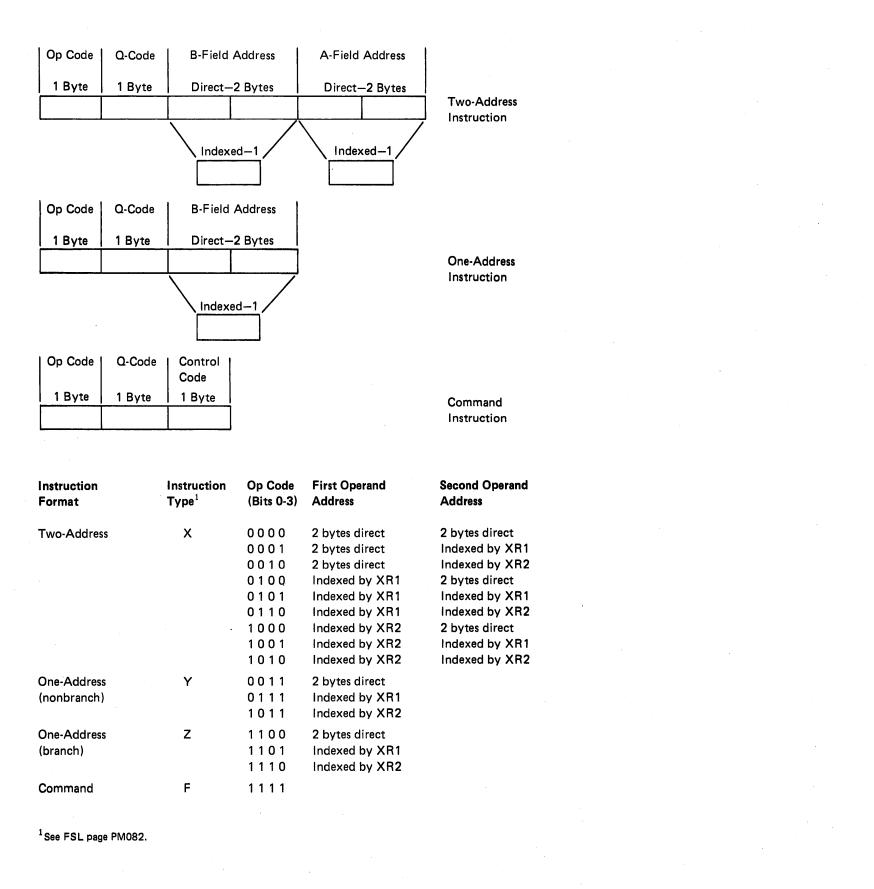

#### Instruction Formats

- The main storage processor performs three types of instructions:

- Two-address instructions

- One-address instructions

- Command instructions

Two-address instructions have two separate fields in main storage and, therefore, contain two addresses. Most one-address instructions have only one field in main storage and, therefore, contain only one address (the load address instruction contains the needed data instead of an address). Command instructions do not need main storage data fields at all and do not contain addresses.

Each instruction has an operation code and a Q-code. These codes are followed either by a control code or by one or two addresses. The length of the instruction is from 3 bytes to 6 bytes, as determined by the type of instruction and the type of addressing.

The first half-byte (bits 0-3) of the operation code determines the format of the instruction (one-address, two-address, and so on) and the method of addressing used. If all 4 bits are set to 1, the instruction is a command instruction. The bits are broken into two groups (bits 0-1 and bits 2-3). If both bits in either group are set to 1, the instruction is a one-address instruction; if neither group has both bits set to 1, the instruction is a two-address instruction. If only 1 bit is set to 1 in either of the groups in a two-address instruction, the address is indexed. The following instruction format chart shows the operation code bits and the number of bytes in the associated address.

The second half-byte (bits 4-7) of the operation code determines the operation. Use of the Q-code and the control code is controlled by the operation requested. The complete main storage instruction set is shown below under Instruction List.

| Opera-<br>tion | Instruction       |          |                      | Q-Code                    |

|----------------|-------------------|----------|----------------------|---------------------------|

| Туре           | Type <sup>1</sup> | Mnemonic | Operation            | Use                       |

| _              |                   |          |                      |                           |

| Two-           | X                 | ZAZ      | Zero and add         |                           |

| Address        |                   |          | zoned                |                           |

| •              | X                 | AZ       | Add zoned decimal    |                           |

|                | X                 | SZ       | Subtract zoned       |                           |

|                |                   |          | decimal              |                           |

|                | x                 | MVC      | Move characters      |                           |

|                | х                 | ALC      | Add logical          | Etald Ionath <sup>1</sup> |

|                |                   |          | characters /         | Field length              |

|                | Х                 | SLC      | Subtract logical     |                           |

|                |                   |          | characters           |                           |

|                | Х                 | CLC      | Compare logical      |                           |

|                |                   |          | characters           |                           |

|                | х                 | ED       | Edit                 |                           |

|                | х                 | ITC      | Insert and test      |                           |

|                |                   |          | characters           |                           |

|                | х                 | MVX      | Move hexadecimal     | Select a                  |

|                |                   |          | character            | half byte                 |

| One-           | Y                 | MVI      | Move logical         |                           |

| Address        |                   |          | immediate            | Immediate                 |

|                | Y                 | CLI      | Compare logical      | data                      |

|                |                   |          | immediate            |                           |

|                | Y                 | SBN      | Set bits on masked   |                           |

|                | Ŷ                 | SBF      | Set bits off masked  | Bit                       |

|                | Ŷ                 | TBN      | Test bits on masked  | selection                 |

|                | Ý                 | TBF      | Test bits off masked | 3010001011                |

|                | Ý                 | ST       | Store register       |                           |

|                | Y                 | L        | Load register        | Register                  |

|                | Y                 | A        | Add to register      | selection                 |

|                | Z                 |          | Load address         | Selection                 |

|                | Z                 |          | Branch on            | Branch                    |

|                | 2                 | BC       |                      |                           |

| · ·            | -                 | 01/0     | condition            | condition                 |

| Command        | F                 | SVC      | Supervisor call      | Part of syster            |

|                |                   |          |                      | support prog              |

|                | _                 |          | * .                  | product inter             |

|                | F                 | LPMR     | Load program         | Main storage              |

|                |                   |          | mode register        | processor reg             |

|                |                   |          |                      | selection                 |

|                | F                 | JC       | Jump on condition    | Branch condi              |

Legend for Instruction Type:

Instruction List

- F = Command instruction

- X = Two-address instruction (can be indexed by bits 0-3)

- Y = One-address instruction (can be indexed by bits 0 and 1)

- Z = One-address instruction (can be indexed by bits 2 and 3)

<sup>1</sup>See FSL page PM082.

3

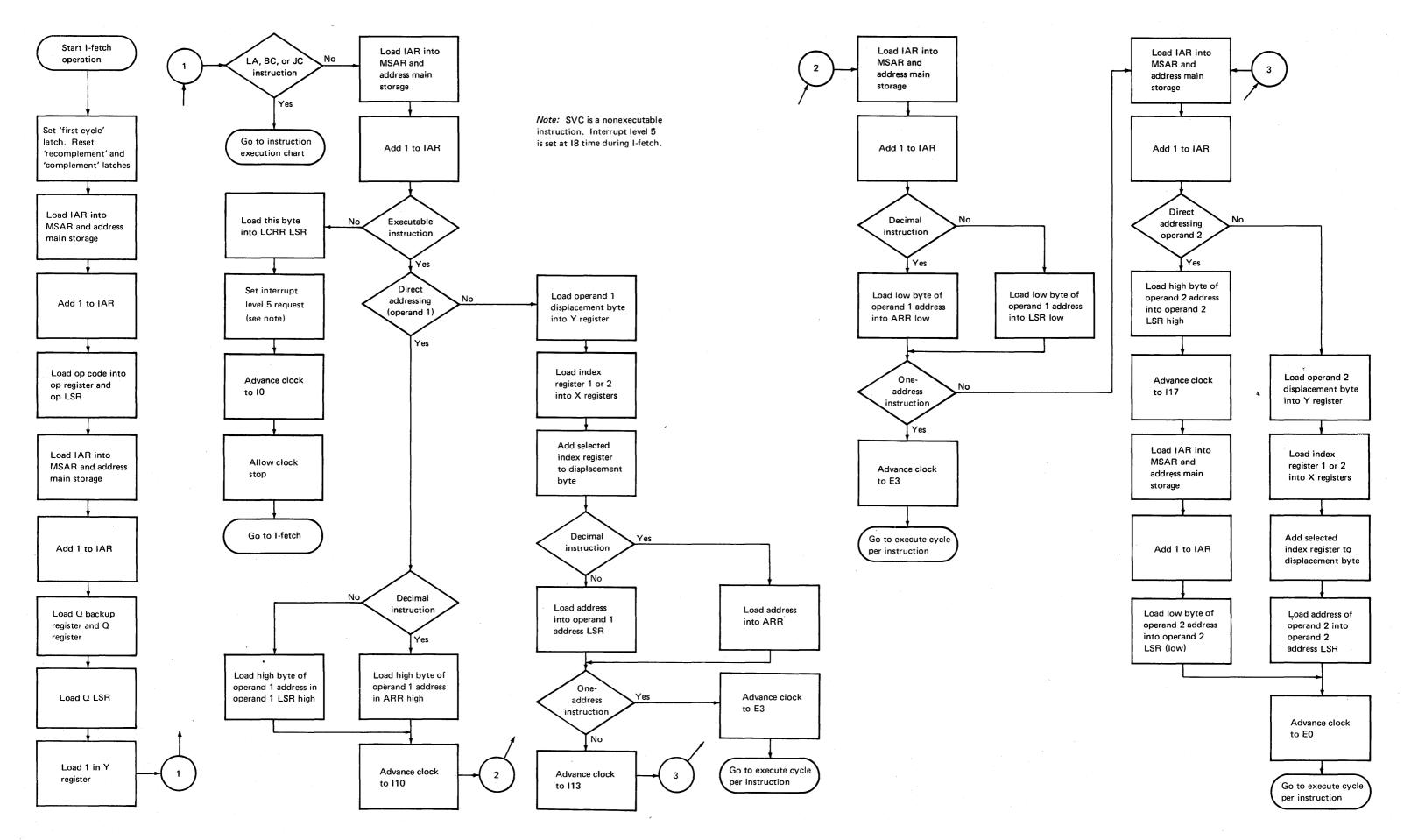

### **Instruction Fetch Operation**

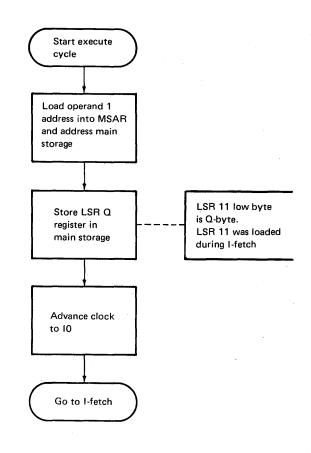

The instruction address register contains the address of the leftmost byte of the instruction. This byte specifies the operation to be performed. During the instruction fetch, the operation code byte is loaded in the operation register. The output of the operation register is decoded to determine the instruction and the type of addressing, if needed. One is added to the instruction address register. The second byte loaded during instruction fetch is the Q-byte. The Q-byte is loaded in the Q-backup register, the Q-register, and the Q-byte of the Op-Q local storage register.

Again, 1 is added to the instruction address register. The third byte read from main storage is a displacement byte, the first byte of the operand 1 address, or a control code. Note that 1 is added to the instruction address register after each storage cycle. The operations that follow the third storage cycle are controlled by the instruction and the type of addressing specified. Address calculations for indexed addresses are done during I-fetch and are stored in the main storage processor local storage registers for use during the execution cycles. However, some instructions do not need execution cycles. In such cases, the main storage processor clock is set to time IO and the next I-fetch cycle starts the next instruction. The I-fetch cycle:

- Loads the instruction op-code byte in the operation register and decodes the instruction

- Loads the Q-byte in the Q-backup register, Q-register, and Q-byte of the Op-Q local storage register

- Calculates and stores the addresses in the operand 1 and operand 2 local storage registers

- Loads the R-byte into the length count recall register (LCRR) local storage register stack for a nonexecutable instruction

- Calculates and stores addresses in the instruction address register and address recall register for branch-on-condition and jump-on-condition instructions.

3

## Addressing

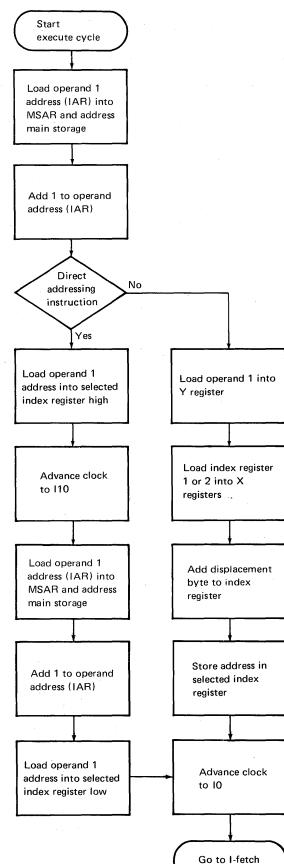

The main storage processor selects one of two types of addressing when executing instructions: direct addressing or indexed addressing.

Most addresses given in the instruction are for the location of the low-order (rightmost) byte of the field. Therefore, as the instruction is executed, the operand address local storage register is decreased to lower the main storage' address. An exception is the insert-and-test-characters instruction, which is executed from the high-order byte to the low-order byte. In this case, the operand address local storage register is increased in the same way that the instruction address register is increased during instruction fetch cycles.

#### **Direct Addressing**

Direct addressing needs a 2-byte address for each field selected by the instruction. The first address that follows the Q-byte in the instruction is the address of the result field or the first operand. In an instruction with two addresses, the second address is the source field (second operand) and the first operand field is used as both a source field and a result field. The first operand source field is changed during the instruction execution cycles. The second operand is not changed except when the two operands overlap.

#### Indexing

Indexing gives the user a method for changing addresses in a program without changing the instruction. An indexed address is a single byte in the instruction (third instruction byte). This single byte (displacement byte) is added to the contents of a 2-byte index register to form the operand address. This operand address is stored in the operand address local storage register.

#### Indexing is used to:

- Perform an instruction with an indexed address

- Add the index register to a constant

- · Branch to an address to execute the instruction at a different storage location

- · Perform an instruction or a series of instructions many times without using too many storage locations

Either of two index registers (XR1 or XR2) can be selected for indexing. The recognition of an indexed address and the selection of index registers are described under Instruction Formats earlier in this section.

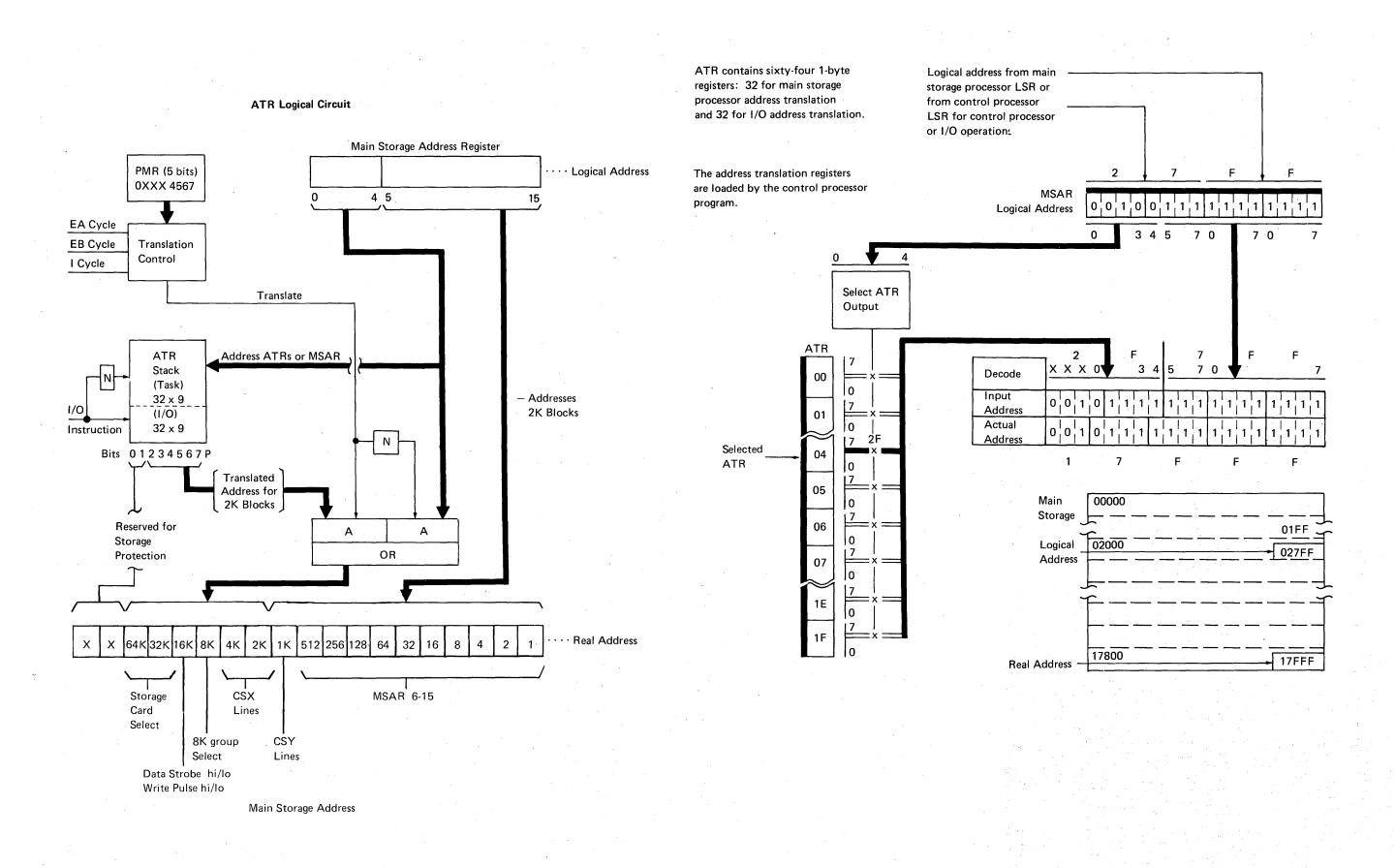

#### **Address Translation**

Address translation must be used to access any real address in main storage from 64K through 128K.

A user program, which is link-edited to load at one address, permits a different main storage address greater than 64K to be selected. The system operator does not have to keep track of which blocks of storage are available for program execution. For example, the system operator may need to execute a program that is link-edited for a 2K area of real addresses between hexadecimal 2000 and hexadecimal 27FF. Without address translation, the system operator cannot load the program until the specified 2K area is available. With address translation, the System Support Program Product updates the ATR with a 2K address block and issues a supervisor call instruction. The system then moves the program to the selected 2K area of main storage. The program is then executed using address translation, as if the program were in the specified 2K area. With address translation, the addresses specified by a user program become logical addresses and not real addresses.

During instruction and execution cycles, addresses are loaded into the main storage address register. The 11 low-order bits (5-7. 8-15) of the main storage address register contain an address inside a 2K area of storage. The 5 high-order bits (0-4) of the main storage address register select the output from the sixty-four 1-byte address translation registers. Note that 32 registers are used for main storage processor address translation and 32 registers are used for I/O address translation. The contents of the addressed address translation register are then sent to the main storage address decode logic. This decoded output is the real main storage address. This describes the operation for translate mode only. For nontranslate mode, the 5 high-order bits (0-4) of the main storage address register are used directly to obtain the real main storage address.

In the following address translation example, the logical addresses specified by the user program are between hexadecimal 2000 and hexadecimal 27FF. Assume that the only available 2K area of storage is between hexadecimal addresses 17800 and 17FFF. Therefore, the addresses must be translated. If an address of hexadecimal 27FF is the logical address, the real address is hexadecimal 17FFF.

In address translation, the main storage processor:

- · Loads the logical address into the main storage address register (hexadecimal 27FF).

- Selects the output from the selected address translation register bits 0-7, as instructed by bits 0-4 of the main storage address register and the main storage processor I/O selection circuits.

- Moves the contents of the address translation register to the main storage address decode logic. Here, the output of the address translation register and the 11 bits from the main storage address register are combined to generate the real address.

- · Generates the real address. The real address is hexadecimal 17FFF.

The address translation register is selected by the 5 high-order bits of the main storage address register. The address translation register must be loaded with the number of the 2K block of storage in which the program is loaded. In the above example, the program was loaded into the 47th 2K area of storage; therefore, hexadecimal 2F must be loaded into address translation register 4.

The following table shows the addresses in 2K areas for 32K bytes of storage. The hexadecimal address specified in any given ATR area number may be any 2K hexadecimal block (00-3F) and need not be in sequence.

| Area<br>Number<br>(Hex) | Starting<br>Address<br>(Hex) | Ending<br>Address<br>(Hex) |

|-------------------------|------------------------------|----------------------------|

| 00                      | 0000                         | 07FF                       |

| 01                      | 0800                         | OFFF                       |

| 02                      | 1000                         | 17FF                       |

| 03                      | 1800                         | 1FFF                       |

| 04                      | 2000                         | 27FF                       |

| 05                      | 2800                         | 2FFF                       |

| 06                      | 3000                         | 37FF                       |

| 07                      | 3800                         | 3FFF                       |

| 08                      | 4000                         | 47FF                       |

| 09                      | 4800                         | 4FFF                       |

| 0A                      | 5000                         | 57FF                       |

| 0B                      | 5800                         | 5FFF                       |

| 0C                      | 6000                         | 67FF                       |

| 0D                      | 6800                         | 6FFF                       |

| 0E                      | 7000                         | 77FF                       |

| 0F                      | 7800                         | 7FFF                       |

| Starting<br>Address<br>(Decimal) | Ending<br>Address<br>(Decimal) |

|----------------------------------|--------------------------------|

| 0000                             | 2047                           |

| 2048                             | 4095                           |

| 4096                             | 6143                           |

| 6144                             | 8191                           |

| 8192                             | 10239                          |

| 10240                            | 12287                          |

| 12288                            | 14335                          |

| 14336                            | 16383                          |

| 16384                            | 18431                          |

| 18432                            | 20479                          |

| 20480                            | 22527                          |

| 22528                            | 24575                          |

| 24576                            | 26623                          |

| 26624                            | 28671                          |

| 28672                            | 30719                          |

| 30720                            | 32767                          |

|                                  |                                |

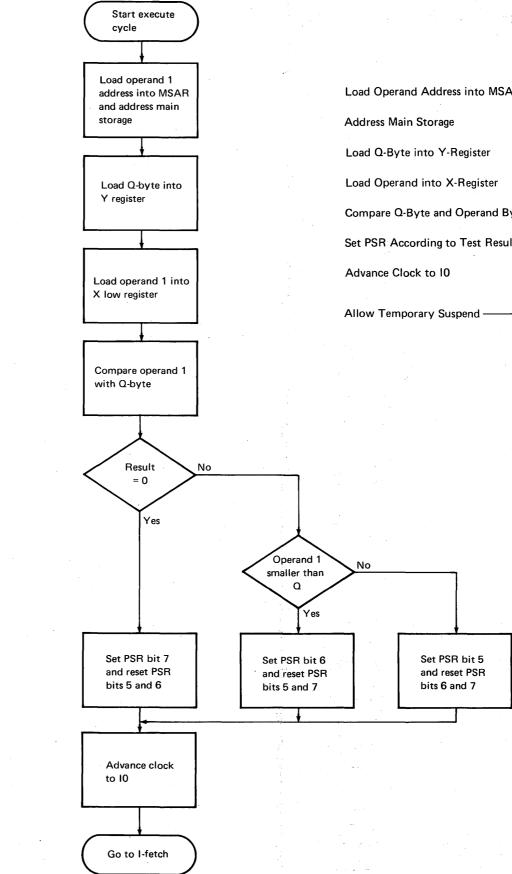

## **INSTRUCTION EXECUTION**

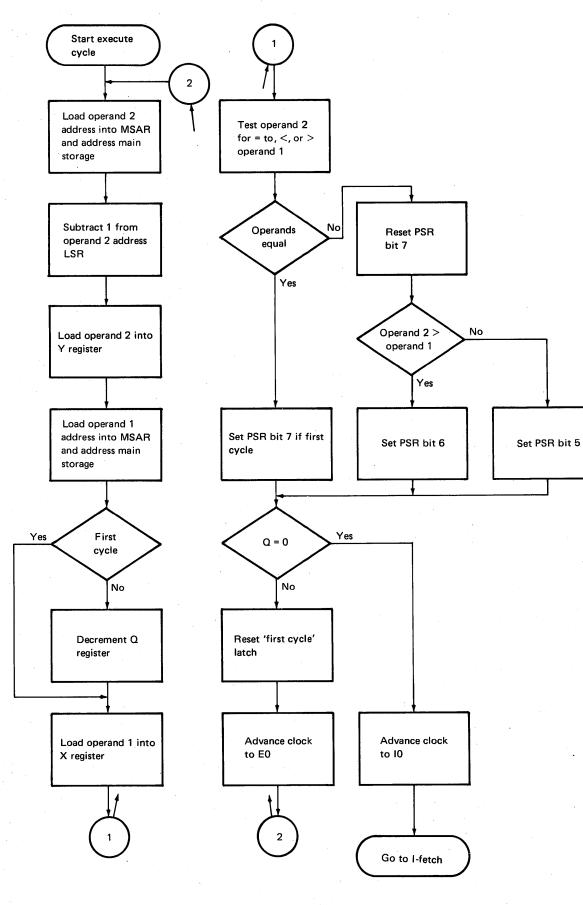

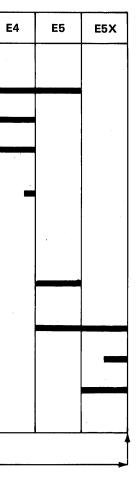

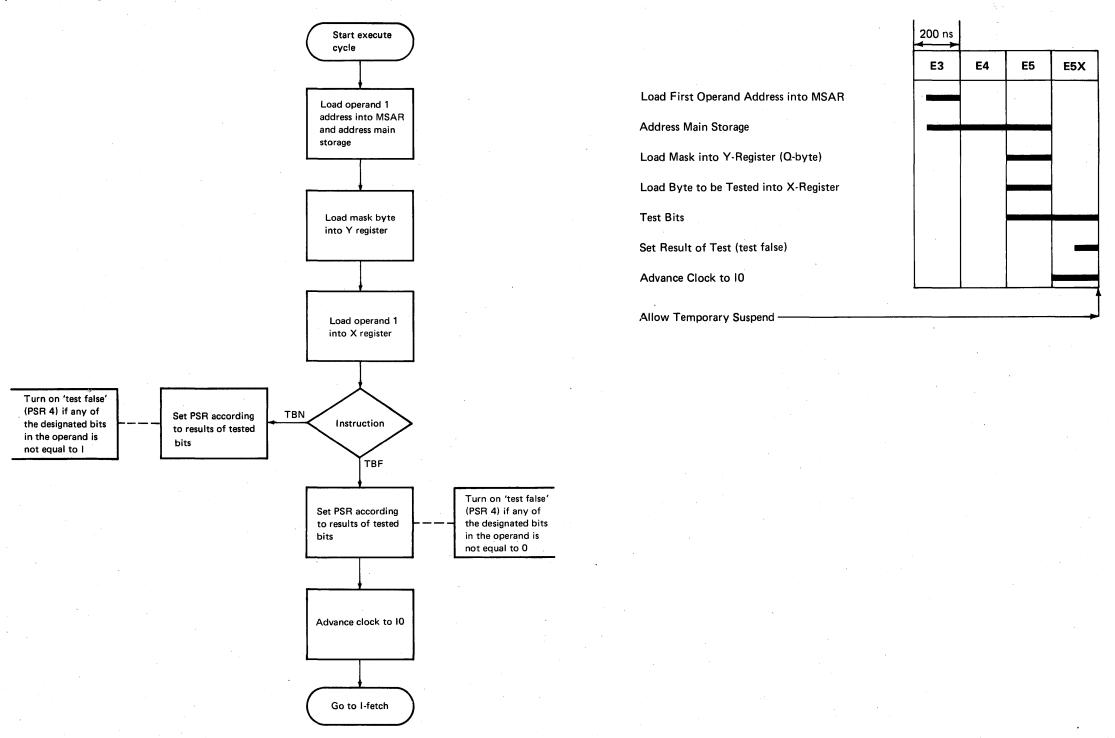

This section describes how each System/34 main storage instruction is executed. The method of describing how instructions are usually executed is:

- 1. Show the instruction format and operation codes.

- 2. Describe what the instruction does.

- 3. Show the program status byte settings.

- 4. Use a flowchart to show how the instruction is executed.

- 5. Use a timing chart to show the details of instruction execution.

The flowcharts and timing charts show the associated operation and machine timing.

Data flow and logical functions are controlled by selecting the proper gating lines in the main storage processor. These functions are shown on this page in appropriate charts.

Instructions for the main storage processor are divided into four groups:

- Arithmetic instructions

- Data control instructions

- Logical instructions

- Command instructions

| CP Gate Selection |                                                            |  |  |  |  |  |

|-------------------|------------------------------------------------------------|--|--|--|--|--|

| Bits<br>01        | Lines Gated Through                                        |  |  |  |  |  |

| 00                | No Input/Output Selected                                   |  |  |  |  |  |

| 01                | MSP Ctrl Gt (8-15, P)                                      |  |  |  |  |  |

| 10                | MS Gt Int (8-15,P)                                         |  |  |  |  |  |

| 11                | MSP Ctrl Gt ANDed with MS Gt Int                           |  |  |  |  |  |

| 1t_               | - +CP Gt Sel Bit 1 A1-P2J10<br>- +CP Gt Sel Bit 0 A1-P2J13 |  |  |  |  |  |

| MSP      | MSP X Y Selection |               |  |  |  |  |  |  |  |

|----------|-------------------|---------------|--|--|--|--|--|--|--|

| Bit<br>0 | XL                | YL            |  |  |  |  |  |  |  |

| 0<br>1   | LSR Gt<br>LSR     | LSR<br>LSR Gt |  |  |  |  |  |  |  |

----- +MSP XL, YL Select Bit A1-P2M07

| ALU                  | ALU Gate Selection                                       |                                      |  |  |  |  |  |  |

|----------------------|----------------------------------------------------------|--------------------------------------|--|--|--|--|--|--|

| Bits<br>01           | ALU Gt Hi                                                | ALU Gt Lo                            |  |  |  |  |  |  |

| 00<br>01<br>10<br>11 | Degate<br>ALU Lo<br>ALU Hi<br>ALU Hi/ALU Lo              | Degate<br>Degate<br>ALU Lo<br>ALU Lo |  |  |  |  |  |  |

|                      | +ALU Gt Sel Bit 1 A1-P2M12<br>+ALU Gt Sel Bit 0 A1-P2M13 |                                      |  |  |  |  |  |  |

| ALU         | ALU Control Selection                                                |                      |  |  |  |  |  |  |

|-------------|----------------------------------------------------------------------|----------------------|--|--|--|--|--|--|

| Bits<br>012 | ALU Function Lo                                                      | ALU Function Hi      |  |  |  |  |  |  |

| 000         | X and Y                                                              | X minus 1 plus carry |  |  |  |  |  |  |

| 001         | X or Y                                                               | X plus carry         |  |  |  |  |  |  |

| 010         | X or (not) Y                                                         | X minus 1 plus carry |  |  |  |  |  |  |

| 011         | X and (not) Y                                                        | X plus carry         |  |  |  |  |  |  |

| 100         | X minus 1 plus carry                                                 | X minus 1 plus carry |  |  |  |  |  |  |

| 101         | X plus Y plus carry                                                  | X plus carry         |  |  |  |  |  |  |

| 110         | X minus Y minus 1<br>plus carry                                      | X minus 1 plus carry |  |  |  |  |  |  |

| 111         | X plus carry                                                         | X plus carry         |  |  |  |  |  |  |

|             | -+ALU Func Sel Bit 2<br>-+ALU Func Sel Bit 1<br>-+ALU Func Sel Bit 0 | A1-P2P10             |  |  |  |  |  |  |

| LSR S                                                                                | election                                                                                                                                                                 |                                      |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Bits<br>0123                                                                         | Register Name                                                                                                                                                            |                                      |

| 0000<br>thru<br>0111<br>1000<br>1001<br>1010<br>1011<br>1100<br>1101<br>1110<br>1111 | Reserved<br>Operand 1 Addre<br>Operand 2 Addre<br>Instruction Addre<br>Operation Register<br>Index Register 1<br>Index Register 2<br>Address Recall R<br>Length Count Re | ess R<br>er/Q-<br>(XR<br>(XR<br>(XR2 |

|                                                                                      | +LSR Sel Bit 3<br>+LSR Sel Bit 2<br>+LSR Sel Bit 1<br>+LSR Sel Bit 0                                                                                                     | A<br>A<br>A<br>A                     |

| Main Storage Gate A Selection |                                                                            |  |  |  |

|-------------------------------|----------------------------------------------------------------------------|--|--|--|

| Bits<br>0123                  | Selection                                                                  |  |  |  |

| 0000                          | Control Processor Syster                                                   |  |  |  |

| 0001                          | Y Register                                                                 |  |  |  |

| 0010                          | LSR High                                                                   |  |  |  |

| 0011                          | LSR Low                                                                    |  |  |  |

| 0100                          | Zone = F, Numeric = De                                                     |  |  |  |

| 0101                          | Zone = D, Numeric = De                                                     |  |  |  |

| 0110                          | Not Used                                                                   |  |  |  |

| 0111                          | ALU                                                                        |  |  |  |

| 1000                          | Zone = F, Numeric = Y                                                      |  |  |  |

| 1001                          | Zone = D, Numeric = Y                                                      |  |  |  |

| 1001<br>1010<br>1011          | Not Used                                                                   |  |  |  |

| 1100                          | Zone = Y (8-11), Nume                                                      |  |  |  |

| 1101                          | Zone = Y (12-15), Nume                                                     |  |  |  |

| 1110                          | Zone = X (8-11), Nume                                                      |  |  |  |

| 1111                          | Zone = X (8-11), Nume                                                      |  |  |  |

|                               | -+MS Gt Sel Bit 3 A1-P                                                     |  |  |  |

|                               | -+MS Gt Sel Bit 2 A1-P<br>-+MS Gt Sel Bit 1 A1-P<br>-+MS Gt Sel Bit 0 A1-P |  |  |  |

|                               |                                                                            |  |  |  |

## **Arithmetic Instructions**

## ZERO AND ADD ZONED INSTRUCTION FORMAT

| Zero and | Add | Zoned | (ZAZ) |

|----------|-----|-------|-------|

|----------|-----|-------|-------|

This instruction moves data from operand 2, byte by byte starting with the rightmost byte, into the rightmost byte positions of operand 1. If operand 1 is longer than operand 2, the main storage processor fills the extra positions with high-order decimal zeros (hexadecimal F0).

The main storage processor sets the zone bits of all bytes, except the rightmost byte in operand 1, to hexadecimal F (binary 1111). The zone bits of the rightmost byte in operand 1 are set to:

- · Hexadecimal F if the value moved is either zero or positive

- Hexadecimal D (binary 1101) if the value moved is negative

**Condition Indicated**

#### Program Status Byte Settings

Bit

7

Name

| Operands            | Op Code<br>(hex) |       |      |                       | •                     | Addresses <sup>2</sup><br>ex) |           |

|---------------------|------------------|-------|------|-----------------------|-----------------------|-------------------------------|-----------|

|                     | Byte 1           | Byt   | :e 2 | Byte 3                | Byte 4                | Byte 5                        | Byte 6    |

| A1(L1),A2(L2)       | 04               | L1-L2 | L2-1 | Operand               | 1 address             | Operand 2                     | 2 address |

| A1(L1),D2(L2,R1)    | 14               | L1-L2 | L2-1 | Operand               | 1 address             | Op 2 disp<br>from XR1         |           |

| A1(L1),D2(L2,R2)    | 24               | L1-L2 | L2-1 | Operand               | 1 address             | Op 2 disp<br>from XR2         |           |

| D1(L1,R1),A2(L2)    | 44               | L1-L2 | L2-1 | Op 1 disp<br>from XR1 | Operand               | 2 address                     |           |

| D1(L1,R1),D2(L2,R1) | 54               | L1-L2 | L2-1 | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR1 |                               |           |

| D1(L1,R1),D2(L2,R2) | 64               | L1-L2 | L2-1 | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR2 |                               |           |

| D1(L1,R2),A2(L2)    | 84               | L1-L2 | L2-1 | Op 1 disp<br>from XR2 | Operand               | 2 address                     |           |

| D1(L1,R2),D2(L2,R1) | 94               | L1-L2 | L2-1 | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR1 |                               | -         |

| D1(L1,R2),D2(L2,R2) | A4               | L1-L2 | L2-1 | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR2 |                               |           |

<sup>1</sup>The Q-byte designates the operand length:

L1-L2 (4 bits) = the number of bytes in operand 1, minus the number of bytes in operand 2.

L2-1 (4 bits) = the number of bytes in operand 2, minus 1.

Maximum length of operand 1 is 31 bytes; maximum length of operand 2 is 16 bytes.

<sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

Equal Zero result Negative result 6 Low 5 High Positive result Decimal overflow Bit not affected 4 3 Test false Bit not affected 2 Binary overflow Bit not affected

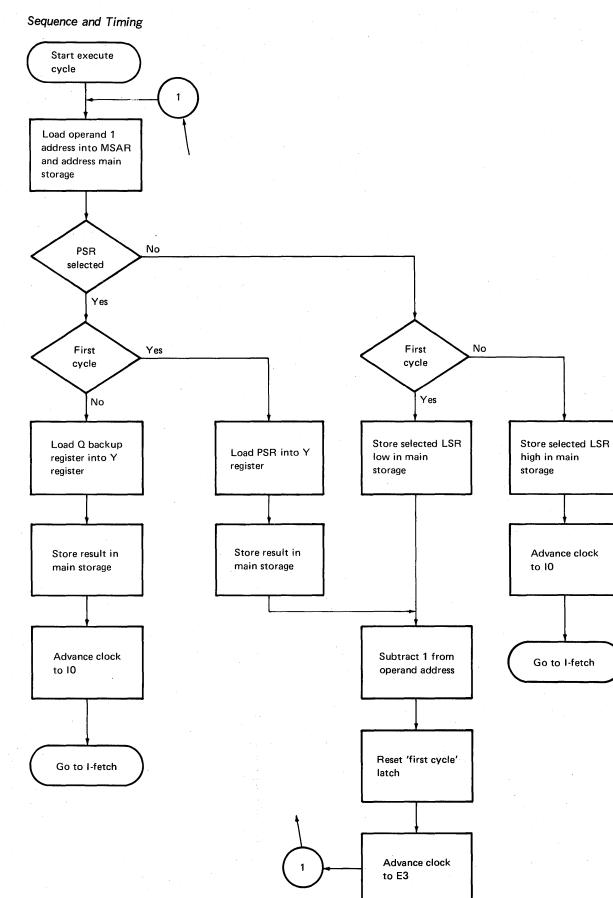

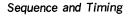

#### Sequence and Timing

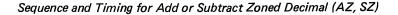

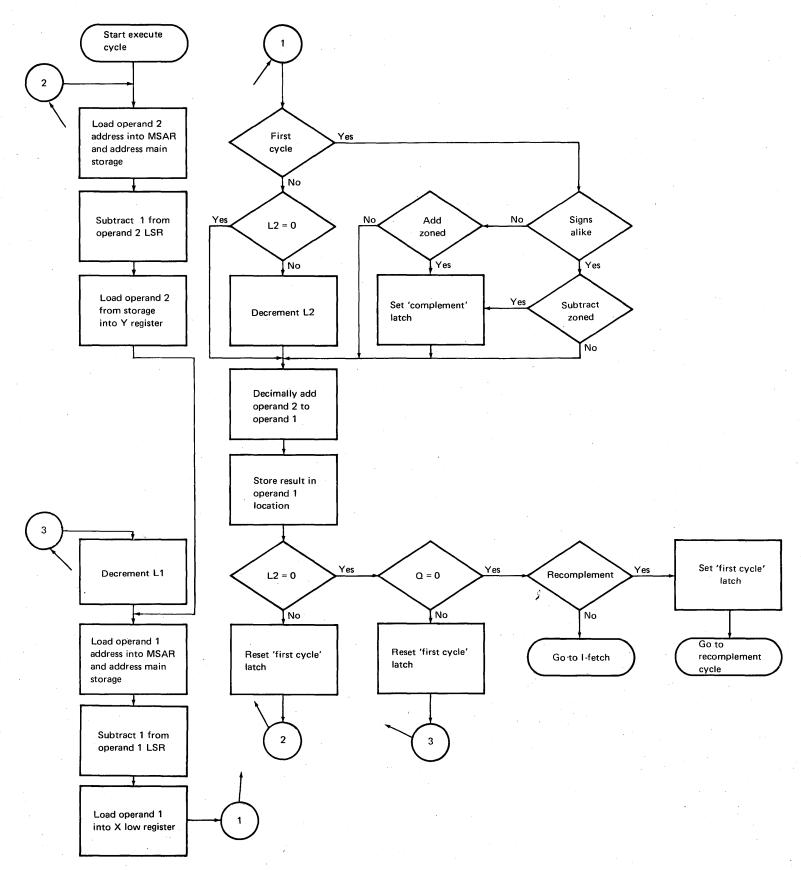

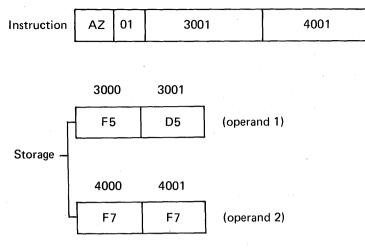

#### Add Zoned Decimal (AZ)

This instruction with algebraic results adds operand 2 to operand 1, byte by byte, and stores the result in operand 1. Both operands are executed as unpacked decimal numbers.

The main storage processor sets the zone bits of all bytes, except the rightmost byte in operand 1, to hexadecimal F (binary 1111). The zone bits of the rightmost byte in operand 1 are set to hexadecimal F if the result of the operation is either positive or zero, or to hexadecimal D (binary 1101) if the result is negative.

#### Program Status Byte Settings

| Bit | Name             | Condition Indicated                                    |

|-----|------------------|--------------------------------------------------------|

| 7   | Equal            | Zero result                                            |

| 6   | Low              | Negative result                                        |

| 5   | High             | Positive result                                        |

| 4   | Decimal overflow | Carry occurred from the leftmost position of operand 1 |

| 3   | Test false       | Bit not affected                                       |

| 2   | Binary overflow  | Bit not affected                                       |

See Recomplement Cycle later in this section.

Sequence and Timing See Subtract Zoned Decimal (SZ)

#### ADD ZONED DECIMAL INSTRUCTION FORMAT

| Operands            | Op Code Q-Byte <sup>1</sup><br>(hex) (hex) |        |      | Operand A<br>(he      |                       |                       |        |  |

|---------------------|--------------------------------------------|--------|------|-----------------------|-----------------------|-----------------------|--------|--|

|                     | Byte 1                                     | Byte 2 |      | Byte 3                | Byte 4                | Byte 5                | Byte 6 |  |

| A1(L1),A2(L2)       | 06                                         | L1-L2  | L2-1 | Operand               | 1 address             | Operand 2 address     |        |  |

| A1(L1),D2(L2,R1)    | 16                                         | L1-L2  | L2-1 | Operand               | 1 address             | Op 2 disp<br>from XR1 |        |  |

| A1(L1),D2(L2,R2)    | 26                                         | L1-L2  | L2-1 | Operand               | 1 address             | Op 2 disp<br>from XR2 |        |  |

| D1(L1,R1),A2(L2)    | 46                                         | L1-L2  | L2-1 | Op 1 disp<br>from XR1 | Operand               | 2 address             |        |  |

| D1(L1,R1),D2(L2,R1) | 56                                         | L1-L2  | L2-1 | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR1 |                       |        |  |

| D1(L1,R1),D2(L2,R2) | 66                                         | L1-L2  | L2-1 | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR2 |                       |        |  |

| D1(L1,R2),A2(L2)    | 86                                         | L1-L2  | L2-1 | Op 1 disp<br>from XR2 | Operand 2 address     |                       |        |  |

| D1(L1,R2),D2(L2,R1) | 96                                         | L1-L2  | L2-1 | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR1 |                       |        |  |

| D1(L1,R2),D2(L2,R2) | A6                                         | L1-L2  | L2-1 | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR2 |                       | ·      |  |

L2-1 (4 bits) = the number of bytes in operand 2, minus 1. Maximum length of operand 1 is 31 bytes; maximum length of operand 2 is 16 bytes.

<sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

L1-L2 (4 bits) = the number of bytes in operand 1, minus the number of bytes in operand 2.

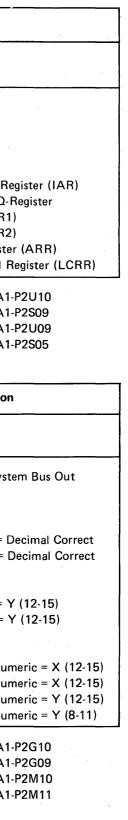

#### Subtract Zoned Decimal (SZ)

This instruction with algebraic results subtracts operand 2 from operand 1, byte by byte, and stores the result in operand 1. Both operands are executed as unpacked decimal numbers.

The main storage processor sets the zone bits of all operand 1 bytes, except the rightmost byte, to hexadecimal F (binary 1111). The zone bits of the rightmost byte in operand 1 are set to hexadecimal F if the result of the operation is either positive or zero, or to hexadecimal D (binary 1101) if the result is negative.

#### Program Status Byte Settings

| Bit | Name             | Condition Indicated                                          |

|-----|------------------|--------------------------------------------------------------|

| 7   | Equal            | Zero result                                                  |

| 6   | Low              | Negative result                                              |

| 5   | High             | Positive result                                              |

| 4   | Decimal overflow | Carry occurred from the<br>leftmost position of<br>operand 1 |

| 3   | Test false       | Bit not affected                                             |

| 2   | Binary overflow  | Bit not affected                                             |

#### SUBTRACT ZONED DECIMAL INSTRUCTION FORMAT

| Operands            | Op Code<br>(hex) | Q-Byte <sup>1</sup><br>(hex)<br>Byte 2 |      | · · · · ·             | Operand A<br>(he      |                       | •       |

|---------------------|------------------|----------------------------------------|------|-----------------------|-----------------------|-----------------------|---------|

|                     | Byte 1           |                                        |      | Byte 3                | Byte 4                | Byte 5                | Byte 6  |

| A1(L1),A2(L2)       | 07               | L1-L2                                  | L2-1 | Operand               | 1 address             | Operand 2             | address |

| A1(L1),D2(L2,R1)    | 17               | L1-L2                                  | L2-1 | Operand               | 1 address             | Op 2 disp<br>from XR1 |         |

| A1(L1),D2(L2,R2)    | 27               | L1-L2                                  | L2-1 | Operand               | 1 address             | Op 2 disp<br>from XR2 |         |

| D1(L1,R1),A2(L2)    | 47               | L1-L2                                  | L2-1 | Op 1 disp<br>from XR1 | Operand               | 2 address             |         |

| D1(L1,R1),D2(L2,R1) | 57               | L1-L2                                  | L2-1 | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR1 |                       |         |

| D1(L1,R1),D2(L2,R2) | 67               | L1-L2                                  | L2-1 | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR2 |                       |         |

| D1(L1,R2),A2(L2)    | 87               | L1-L2                                  | L2-1 | Op 1 disp<br>from XR2 | Operand 2 address     |                       |         |

| D1(L1,R2),D2(L2,R1) | 97               | L1-L2                                  | L2-1 | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR1 |                       |         |

| D1(L1,R2),D2(L2,R2) | A7               | L1-L2                                  | L2-1 | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR2 |                       |         |

L1-L2 (4 bits) = the number of bytes in operand 1, minus the number of bytes in operand 2. L2-1 (4 bits) = the number of bytes in operand 2, minus 1. Maximum length of operand 1 is 31 bytes; maximum length of operand 2 is 16 bytes. <sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

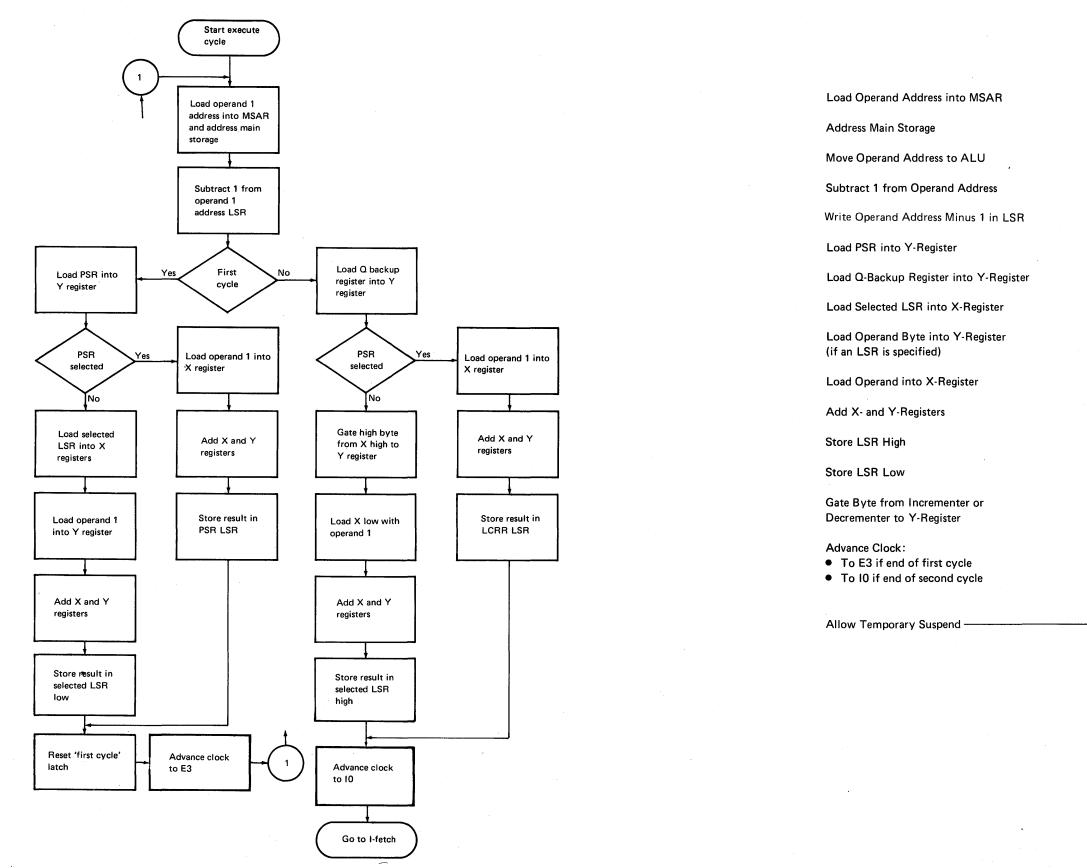

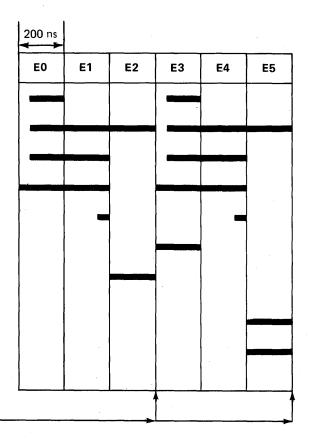

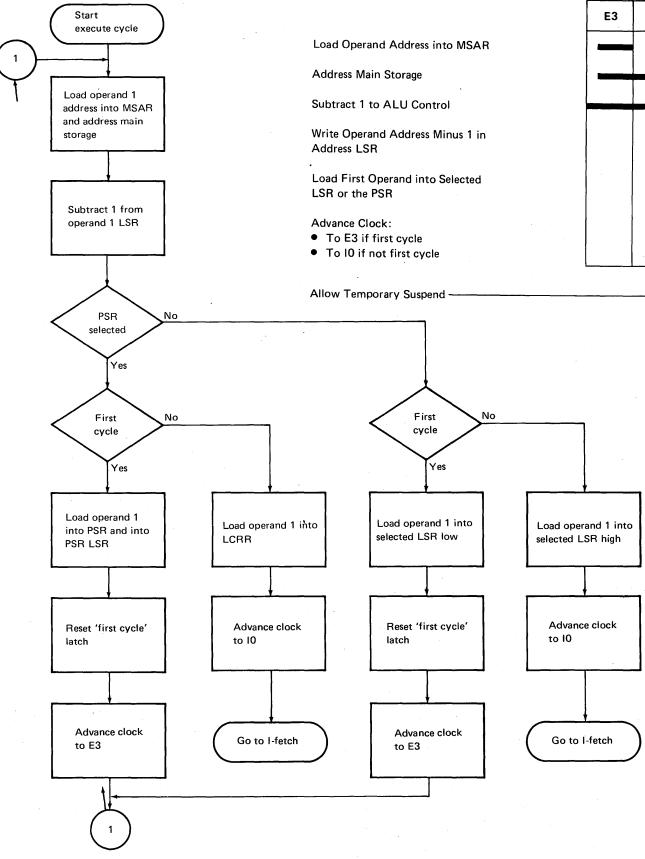

E0 Load Operand Address into MSAR Address Main Storage Move Operand Address to ALU Subtract 1 to ALU Control Write Operand Address Minus 1 in LSR Load Second Operand into Y-Register Decrement L1 (L2=0 and not first cycle) Decrement L2 (L2 not 0 and not first cycle) Load First Operand into X Low Decimal Add or Subtract Second Operand to or from First Operand Store Result in First Operand Location Advance Clock: • To E0 if L2 not 0 • To E3 if: L2=0 and Q not 0 and carry and not complement L2=0 and Q not 0 and not carry and complement Recomplement • To 10 if: - L2=0 and not carry and not complement

200 ns

- Q=0 and not recomplement latch

- L2=0 and carry and complement

Allow Temporary Suspend

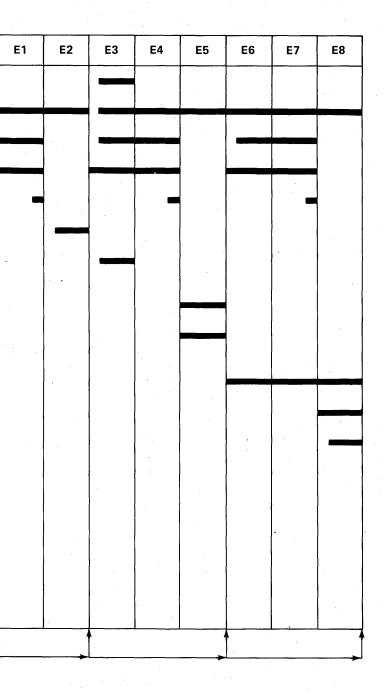

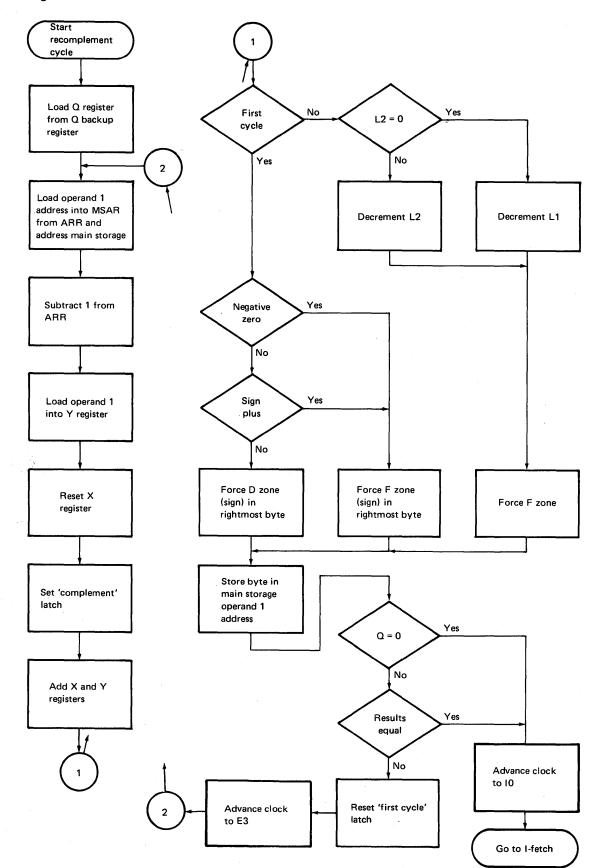

#### **Recomplement Cycle**

The zero and added zoned, add zoned decimal, and subtract zoned decimal instructions are the only instructions that use the recomplement cycle. The result of the decimal addition can be stored in the operand 1 location as a true value or as the complement of the true value. If the result is a true value, no recomplement cycle is necessary.

A recomplement cycle is necessary when:

- The result is negative zero or the stored result is in complement form.

- Operand 2 is complemented and there is no carry from the high-order byte after the algebraic addition.

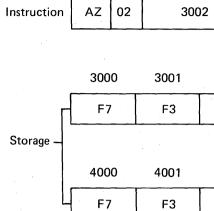

Op Q Operand 1 Address Operand 2 Address

#### Instruction Execution Chart

| After Cycle    | Q  | Complement | PSR 4 | Recomplement | Operand 1<br>in Storage | Next Clock |

|----------------|----|------------|-------|--------------|-------------------------|------------|

| I-Fetch        | 01 | Off        | xxx   | Off          | F5D5                    | E0         |

| 1              | 01 | On         | Off   | Off          | F5D8                    | EO         |

| 2              | 01 | On         | Off   | Off          | F7D8                    | E3         |

| Recomplement 1 | 01 | On         | Off   | On           | F7F2                    | E3         |

| Recomplement 2 | 00 | On         | Off   | On           | F2F2                    | 10         |

## Op Q Operand 1 A

#### Instruction Execution Chart

| After Cycle    | Q               | PSR 6<br>(Internal) | PSR 7 | Recomplement | Operand 1<br>in Storage | Next Clock |

|----------------|-----------------|---------------------|-------|--------------|-------------------------|------------|

| I-Fetch        | 02              | Off                 | On    | Off          | F7F3D5                  | E0         |

| 1              | 02              | On                  | On    | Off          | F7F3D0                  | EO         |

| 2              | 01              | On                  | On    | Off          | F7F0D0                  | E0         |

| 3              | 00              | On                  | On    | Off          | F0F0D0                  | F3         |

| Recomplement 1 | 02 <sup>1</sup> | Off                 | On    | On           | F0F0F0                  | 10         |

<sup>1</sup> Final Q = 2, therefore the 2 recomplement cycles are saved.

Example: Negative zero, recomplement cycle necessary.

*Note:* A recomplement cycle is necessary if there is no carry from the high-order byte; a recomplement cycle is not necessary if there is a carry from the high-order byte.

| Address Operand 2 Address |  |

|---------------------------|--|

|---------------------------|--|

| 4002 |

|------|

|      |

3002

D5

(operand 1)

## 4002

F5

(operand 2)

#### Sequence and Timing

den de la composition Composition de la comp

Load Q-Register (first cycle)

Load MSAR from ARR

Address Main Storage

Subtract 1 from ARR

Write New Address in ARR

Load First Operand Result Byte into Y-Register

Set Complement Latch

Move Complement Byte to Y-Register

Force F to Zone of First Byte if Negative Zero. Force D if Result is Negative. If Result is Plus, Do Not Change Sign.

Store Complemented Byte in Main Storage

Advance Clock:

- To E3 if Q not 0 and result not equal • To I0 if Q=0 or Q not 0 and result

- equal or ZAZ instruction

Reset First Cycle Latch

Allow Temporary Suspend -

3

This page intentionally left blank.

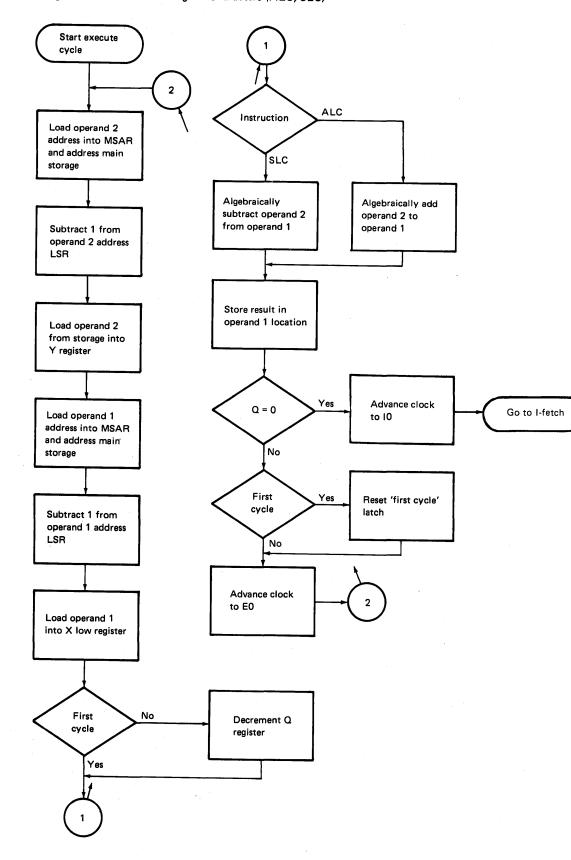

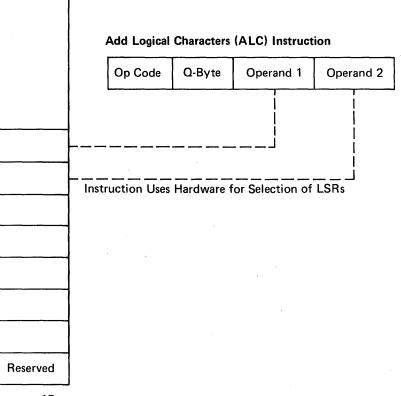

#### Add Logical Characters (ALC)

This instruction adds the binary number in operand 2 to the binary number in operand 1 and stores the result in operand 1. Both the operands and the result are executed as unsigned binary numbers.

#### Program Status Byte Settings

| Bit | Name             | Condition Indicated                                                  |

|-----|------------------|----------------------------------------------------------------------|

| 7   | Equal            | Zero result                                                          |

| 6   | Low              | No carry occurred from the<br>high-order byte and result<br>not zero |

| 5   | High             | Carry occurred from the<br>high-order byte and result<br>not zero    |

| 4   | Decimal overflow | Bit not affected                                                     |

| 3   | Test false       | Bit not affected                                                     |

| 2   | Binary overflow  | Carry occurred from the<br>high-order byte                           |

Sequence and Timing

See Subtract Logical Characters (SLC)

### ADD LOGICAL CHARACTERS INSTRUCTION FORMAT

| Operands          | Op Code<br>(hex) | Q-Byte <sup>1</sup><br>(hex) | Operand Addresses <sup>2</sup><br>(hex) |                       |                       |         |  |

|-------------------|------------------|------------------------------|-----------------------------------------|-----------------------|-----------------------|---------|--|

|                   | Byte 1           | Byte 2                       | Byte 3                                  | Byte 4                | Byte 5                | Byte 6  |  |

| A1(L1),A2         | OE               | L1-1                         | Operand                                 | 1 address             | Operand 2             | address |  |

| A1(L1),D2(,R1)    | 1E               | L1-1                         | Operand                                 | 1 address             | Op 2 disp from<br>XR1 |         |  |

| A1(L1),D2(,R2)    | 2E               | L1-1                         | Operand 1 address Op 2 disp from XR2    |                       |                       |         |  |

| D1(L1,R1),A2      | 4E               | L1-1                         | Op 1 disp<br>from XR1                   | Operand 2 address     |                       |         |  |

| D1(L1,R1),D2(,R1) | 5E               | L1-1                         | Op 1 disp<br>from XR1                   | Op 2 disp<br>from XR1 |                       |         |  |

| D1(L1,R1),D2(,R2) | 6E               | L1-1                         | Op 1 disp<br>from XR1                   | Op 2 disp<br>from XR2 |                       |         |  |

| D1(L1,R2),A2      | 8E               | L1-1                         | Op 1 disp<br>from XR2                   | Operand 2 address     |                       |         |  |

| D1(L1,R2),D2(,R1) | 9E               | L1-1                         | Op 1 disp<br>from XR2                   | Op 2 disp<br>from XR1 |                       |         |  |

| D1(L1,R2),D2(,R2) | AE               | L1-1                         | Op 1 disp<br>from XR2                   | Op 2 disp<br>from XR2 |                       |         |  |

ot bytes in either operand, minus 1. L1-1 Maximum length of each operand is 256 bytes; both operands must be the same length. <sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

#### Subtract Logical Characters (SLC)

This instruction subtracts the binary number in operand 2 from the binary number in operand 1 and stores the result in operand 1. Both the operands and the result are executed as unsigned binary numbers.

#### For example:

| Operand 1 | 0110 | 1101 |  |

|-----------|------|------|--|

| Operand 2 | 0111 | 1110 |  |

|           |      |      |  |

| Result    | 1110 | 1011 |  |

Program Status Byte Settings

#### CAUTION

The results of the program status byte are not reliable if they are selected.

|     | <u></u>          |                                                       |

|-----|------------------|-------------------------------------------------------|

| Bit | Name             | Condition Indicated                                   |

| 7   | Equal            | Zero result                                           |

| 6   | Low              | Operand 1 was smaller than operand 2 before execution |

| 5   | High             | First operand greater than second operand             |

| 4   | Decimal overflow | Bit not affected                                      |

| 3   | Test false       | Bit not affected                                      |

| 2   | Binary overflow  | Bit not affected                                      |

## SUBTRACT LOGICAL CHARACTERS INSTRUCTION FORMAT

| Operands          | ds Op Code Q-Byte <sup>1</sup> Operand Addresses <sup>2</sup><br>(hex) (hex) (hex) |        |                       |                       |                       |        |

|-------------------|------------------------------------------------------------------------------------|--------|-----------------------|-----------------------|-----------------------|--------|

|                   | Byte 1                                                                             | Byte 2 | Byte 3                | Byte 4                | Byte 5                | Byte 6 |

| A1(L1),A2         | 0F                                                                                 | L1-1   | Operand               | 1 address             | Operand 2 address     |        |

| A1(L1),D2(,R1)    | 1F                                                                                 | L1-1   | Operand               | 1 address             | Op 2 disp from<br>XR1 |        |

| A1(L1),D2(,R2)    | 2F                                                                                 | L1-1   | Operand               | 1 address             | Op 2 disp from XR2    |        |

| D1(L1,R1),A2      | 4F                                                                                 | L1-1   | Op 1 disp<br>from XR1 | Operan                | d 2 address           |        |

| D1(L1,R1),D2(,R1) | 5F                                                                                 | L1-1   | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR1 |                       | •      |

| D1(L1,R1),D2(,R2) | 6F                                                                                 | L1-1   | Op 1 disp<br>from XR1 | Op 2 disp<br>from XR2 | e                     |        |

| D1(L1,R2),A2      | 8F                                                                                 | L1-1   | Op 1 disp<br>from XR2 | Operan                | d 2 address           |        |

| D1(L1,R2),D2(,R1) | 9F                                                                                 | L1-1   | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR1 |                       |        |

| D1(L1,R2),D2(,R2) | AF                                                                                 | L1-1   | Op 1 disp<br>from XR2 | Op 2 disp<br>from XR2 |                       |        |

<sup>2</sup>The operands may overlap. Address operands by their rightmost bytes.

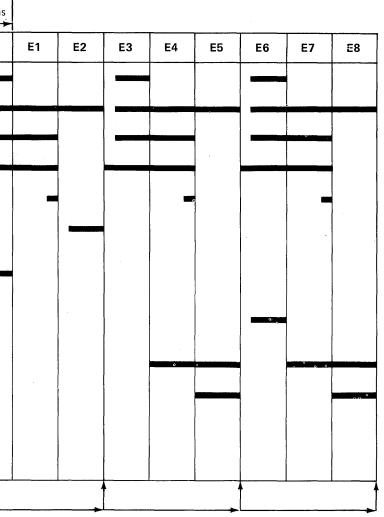

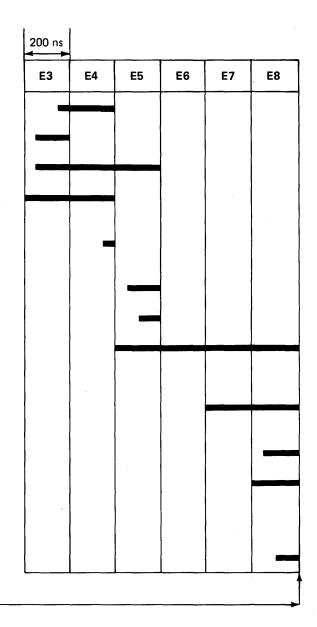

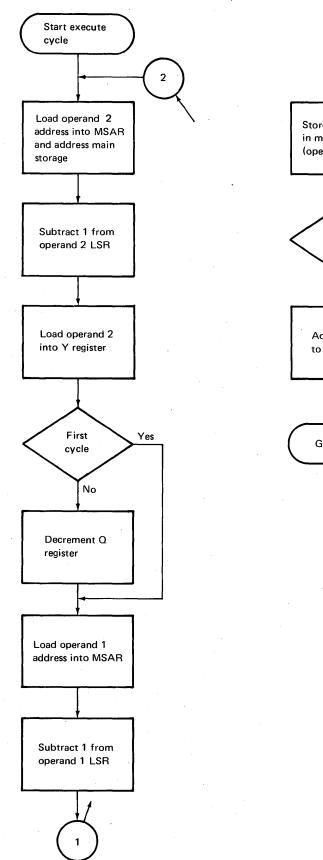

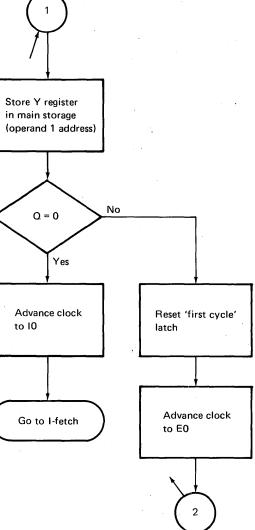

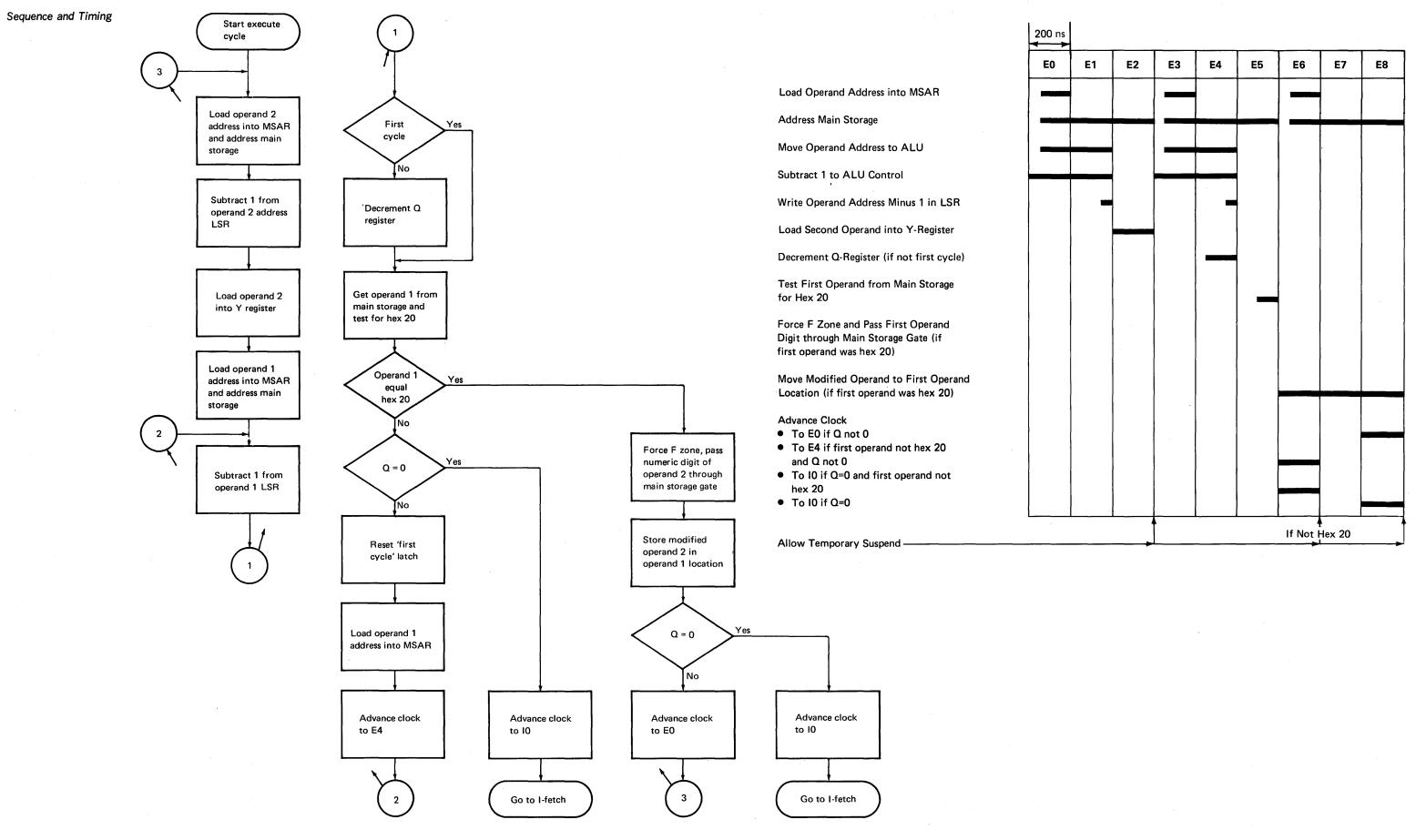

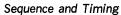

Sequence and Timing for Add or Subtract Logical Characters (ALC, SLC)

Load Operand Address into MSAR Address Main Storage Move Operand Address to ALU Subtract 1 to ALU Control Write Operand Address Minus 1 in LSR Decrement Q-Register (not first cycle) Load Second Operand into Y-Register Load First Operand into X Low Register Add/Subtract Operands Store Result in Main Storage Advance Clock: • To E0 if Q not 0 • To 10 if Q=0

Allow Temporary Suspend -

200 ns

E0

3

| E1 | E2 | E3 | E4 | E5                                     | E6 | E7 | E8 |

|----|----|----|----|----------------------------------------|----|----|----|

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    |                                        |    |    |    |

|    |    |    |    | ······································ |    |    | ]  |

#### Add to Register (A)

This instruction adds the binary number in operand 1 to the contents of the 2-byte register selected by the Q-byte and stores the result in the specified register. The Q-bytes used to specify various registers are:

| Q-Byte<br>(binary) | Q-Byte<br>(hex) | Register Specified                                 |

|--------------------|-----------------|----------------------------------------------------|

| 0000 0000          | 00              | None. The system ignores (no-ops) the instruction. |

| 0000 0001          | 01              | XR1.                                               |

| 0000 0010          | 02              | XR2.                                               |

| 0000 0100          | 04              | Program status register.                           |

| 0000 1000          | 08              | Address recall register.                           |

| 0001 0000          | 10              | Instruction address register.                      |

| 0010 0000          | 20              | Instruction address register.                      |

| 0100 0000          | 40              | Reserved; do not use.                              |

| 1000 0000          | 80              | Reserved; do not use.                              |

## Program Status Byte Settings

## CAUTION

Bit Name

Equal

Low

High

Test false

Binary overflow

7

6

5

4

3

2

The results of the program status byte are not reliable if they are selected.

**Condition Indicated**

No carry occurred from the

leftmost byte and result not

Carry occurred from the leftmost byte and result not

Carry occurred from the

Zero result

zero

zero

Bit not used

leftmost byte

Decimal overflow Bit not used

| (hex)  | Q-Byte <sup>1</sup><br>(binary) | (he                           | Address <sup>2</sup><br>x)                                            |

|--------|---------------------------------|-------------------------------|-----------------------------------------------------------------------|

| Byte 1 | byte 1 Byte 2 Byte 3            |                               | Byte 4                                                                |

| 36     | Rx                              | Operand <sup>2</sup>          | address                                                               |

| 76     | Rx                              | Op 1 disp<br>from XR1         |                                                                       |

| B6     | Rx                              | Op 1 disp<br>from XR2         |                                                                       |

|        | Byte 1<br>36<br>76              | Byte 1 Byte 2   36 Rx   76 Rx | Byte 1Byte 2Byte 336RxOperand 776RxOp 1 disp<br>from XR186BxOp 1 disp |

<sup>1</sup>Rx specifies the register whose contents are modified by the machine instruction.

<sup>2</sup>Operand 1 is a 2-byte field addressed by its rightmost byte; operand 2 is not used.

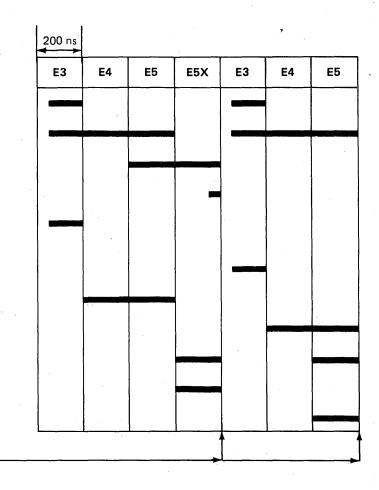

#### Sequence and Timing

| 200 ns |    |    |     |    |    |    |     |

|--------|----|----|-----|----|----|----|-----|

| E3     | E4 | E5 | Ę5X | E3 | E4 | E5 | E5X |

| (      |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    | 1  |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        |    |    |     |    |    |    |     |

|        | l  |    |     |    |    |    |     |

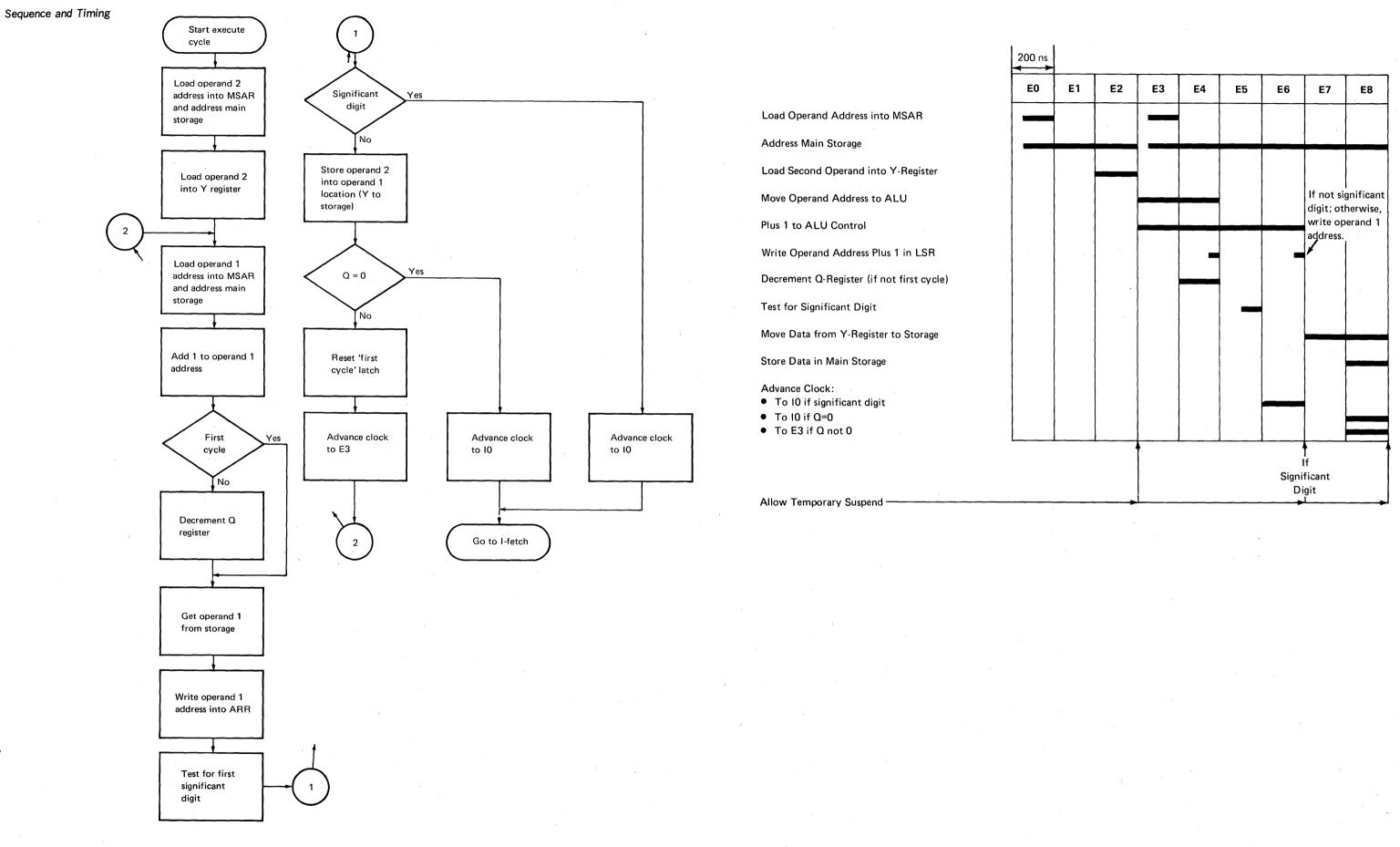

## **Data Control Instructions**

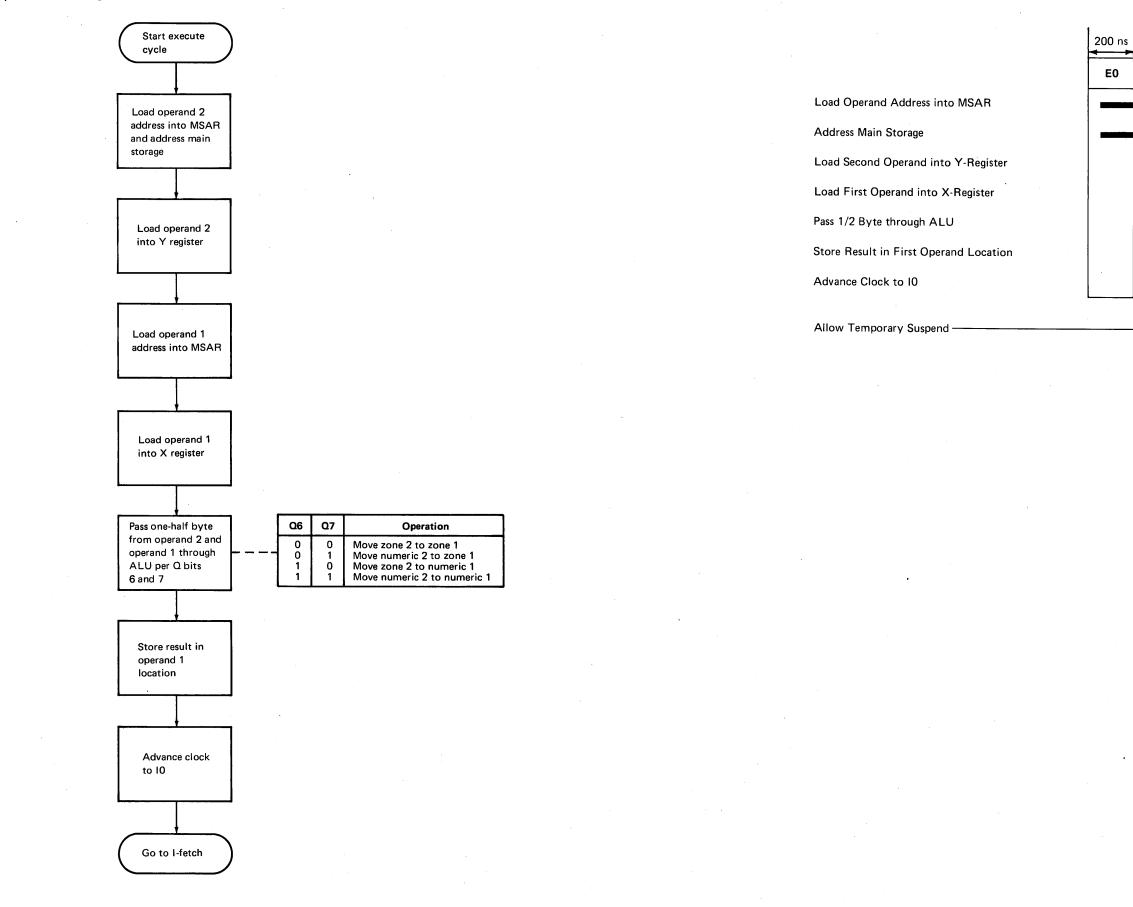

#### Move Hexadecimal Character (MVX)

This instruction moves the numeric part (bits 4-7) or the zone part (bits 0-3) of operand 2 to the numeric or zone part of operand 1, as specified by the Q-byte. The Q-byte codes are:

| Q-Byte<br>(binary) | Q-Byte<br>(hex) | Meaning                                                               |

|--------------------|-----------------|-----------------------------------------------------------------------|

| 0000 0000          | 00              | Move data from operand 2 zone portion to operand 1 zone portion       |

| 0000 0001          | 01              | Move data from operand 2 numeric portion to operand 1 zone portion    |

| 0000 0010          | 02              | Move data from operand 2 zone portion to operand 1 numeric portion    |

| 0000 0011          | 03              | Move data from operand 2 numeric portion to operand 1 numeric portion |

#### Program Status Byte Settings

This instruction does not affect the program status register.

#### MOVE HEXADECIMAL CHARACTER INSTRUCTION FORMAT

| Operands         | Op Code<br>(hex) | Q-Byte <sup>1</sup><br>(hex) | Operand Addresses <sup>2</sup><br>(hex) |                       |                       |           |

|------------------|------------------|------------------------------|-----------------------------------------|-----------------------|-----------------------|-----------|