# Contents

| CONTROL PROCESSOR                                |

|--------------------------------------------------|

| DATA FLOW AND CLOCKS                             |

| Data Flow                                        |

| Clocks                                           |

| System                                           |

| I/O Attachment and Controller                    |

| Storage                                          |

| OPERATIONS                                       |

| IPL-Customer User Programs                       |

| Control Storage Initial Program Load (CSIPL) 2-  |

| Main Storage Initial Program Load (MSIPL) 2-     |

| IPL Timing Sequence                              |

| Display Light Sequence (Byte 0)                  |

| Disk Operation                                   |

| Disk Sequence                                    |

| 62EH Disk Timing                                 |

| 62PC Disk Timing                                 |

| IPL-Customer SSP from Diskettes 2-1              |

| IPL-CE Diagnostics                               |

| Diskette CSIPL Diagnostic Sequence 2-1           |

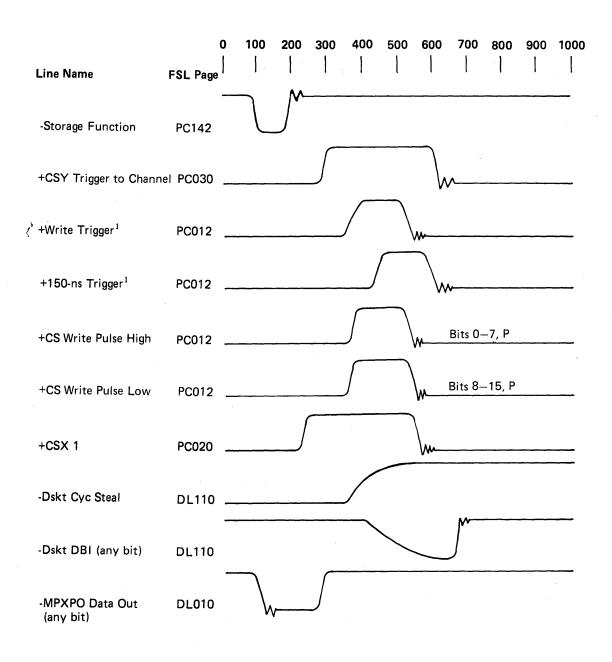

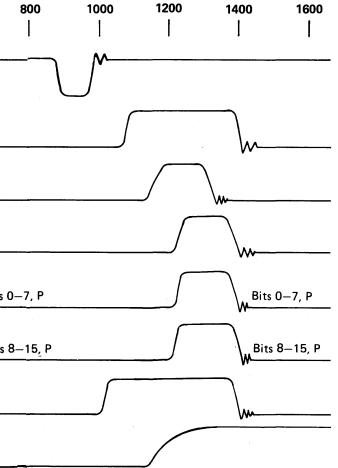

| Diskette Timing (Level 1 Attachment) 2-1         |

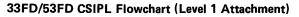

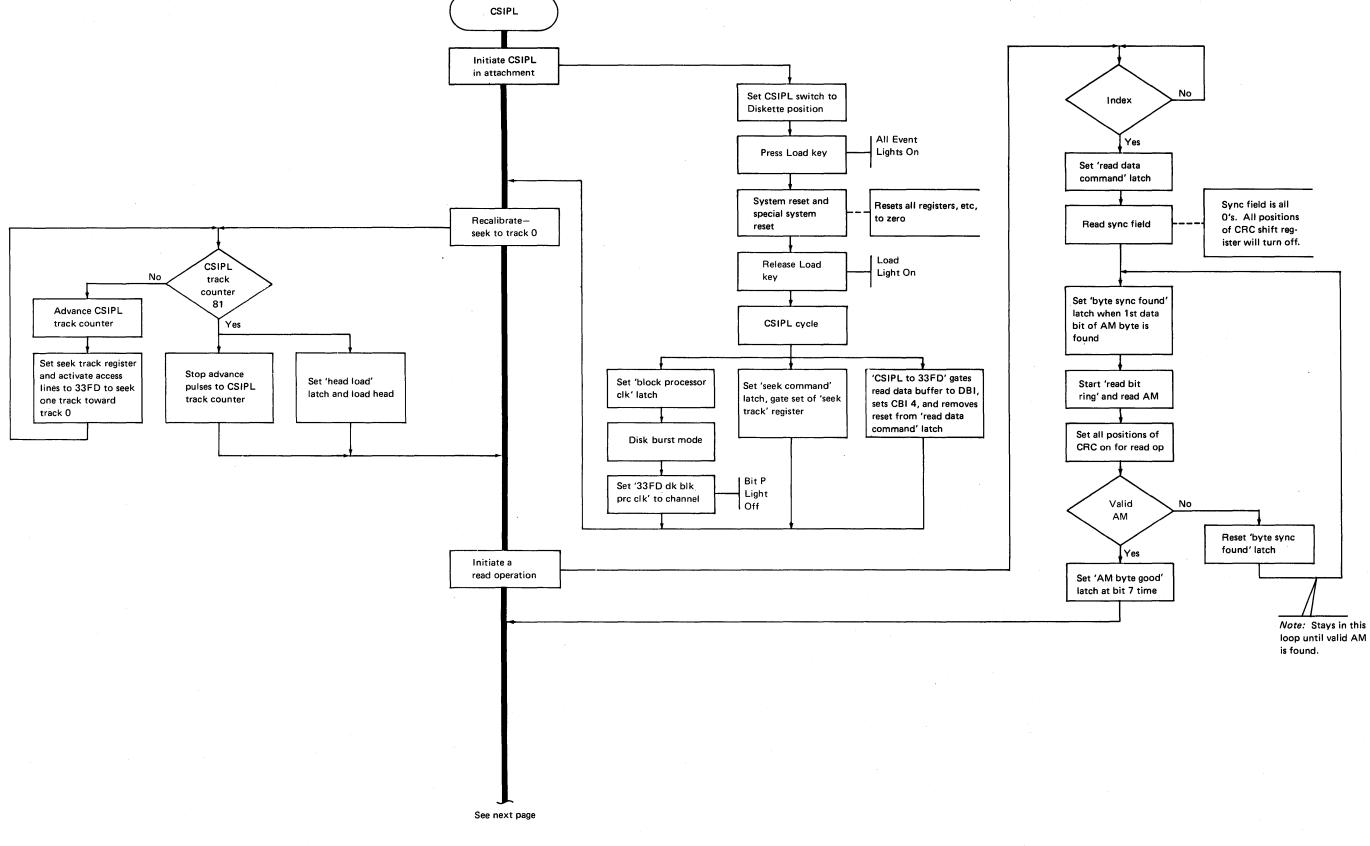

| 33FD/53FD CSIPL Flowchart (Level 1               |

| Attachment)                                      |

| Diskette Timing (Level 2 Attachment) 2-2         |

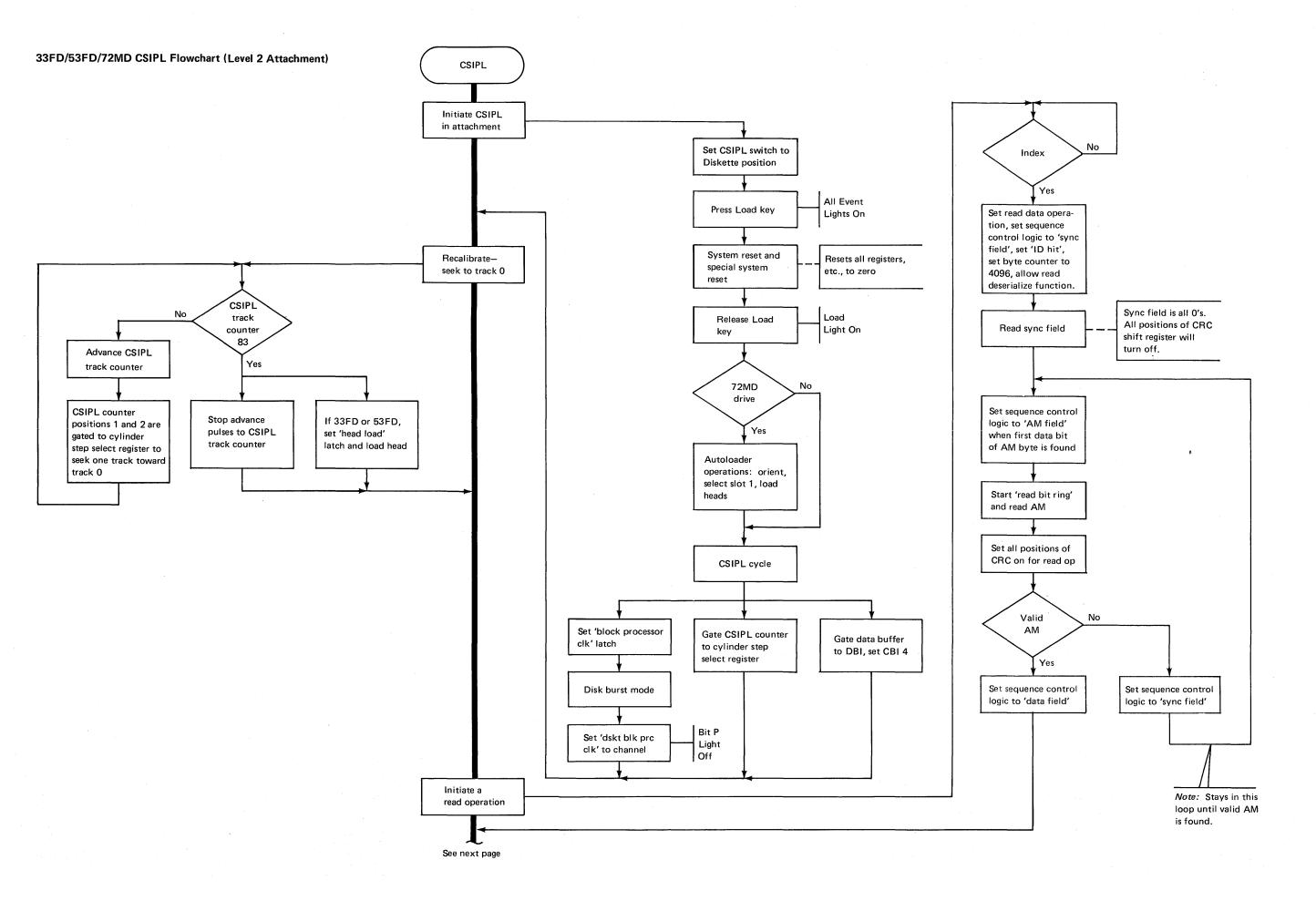

| 33FD/53FD/72MD CSIPL Flowchart (Level            |

| 2 Attachment)                                    |

| Error Indications                                |

| CSIPL Switch Options                             |

| Instructions                                     |

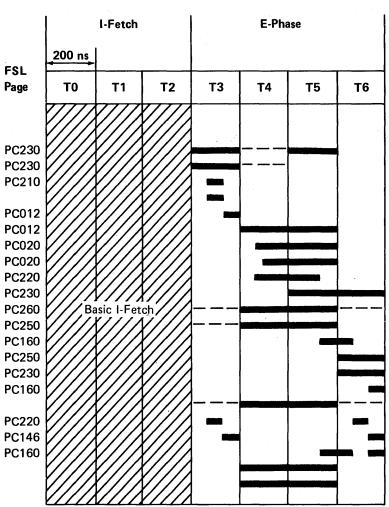

| Instruction Times                                |

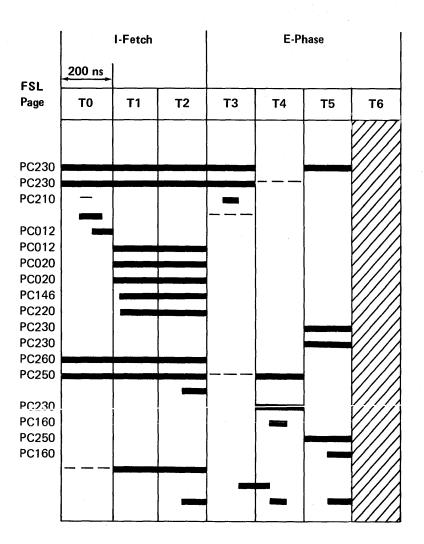

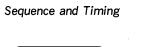

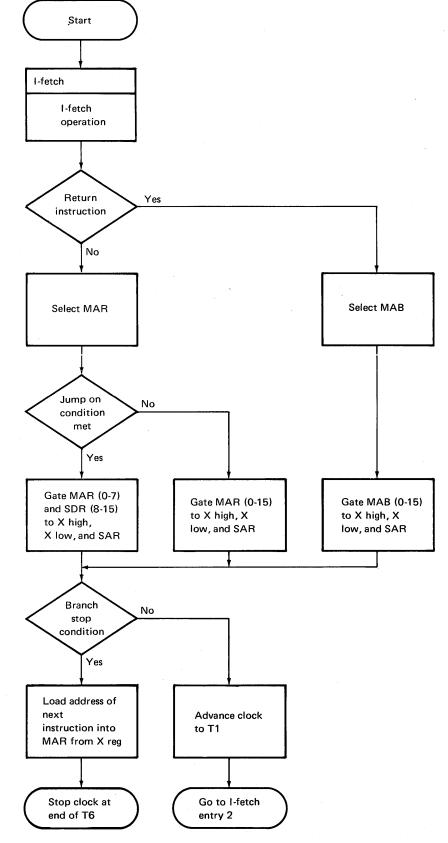

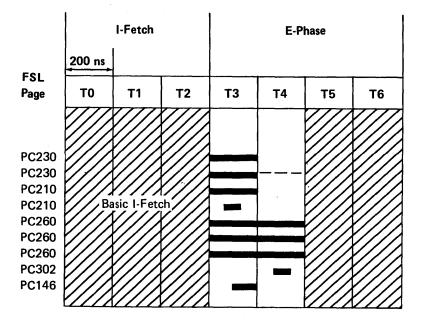

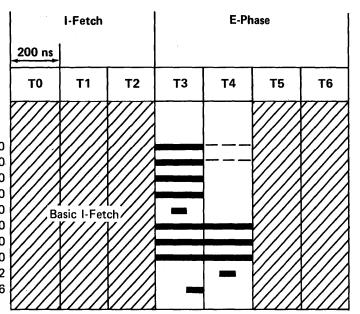

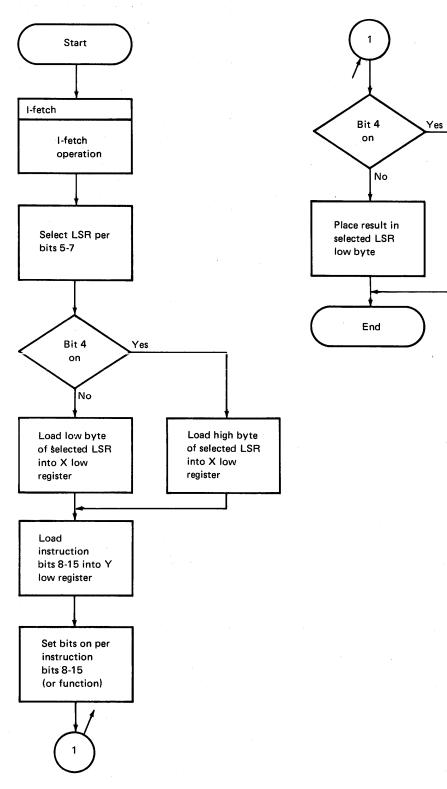

| Sequence and Timing                              |

| Routine Printout                                 |

| Mnemonic Listing                                 |

| INSTRUCTION EXECUTION                            |

| Signals, Gating Lines, and Logical Functions for |

| Timing Charts                                    |

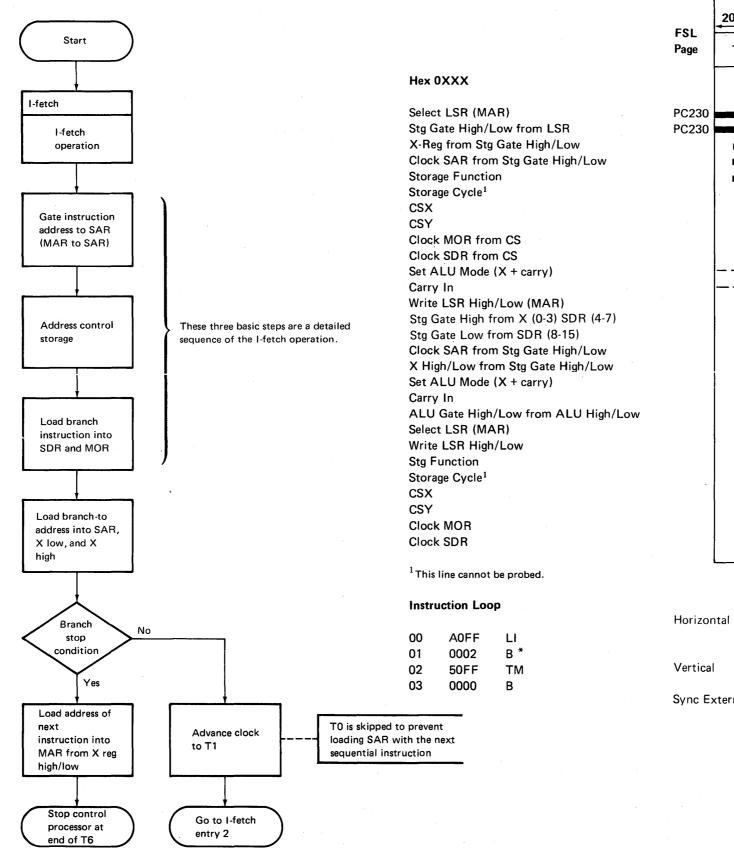

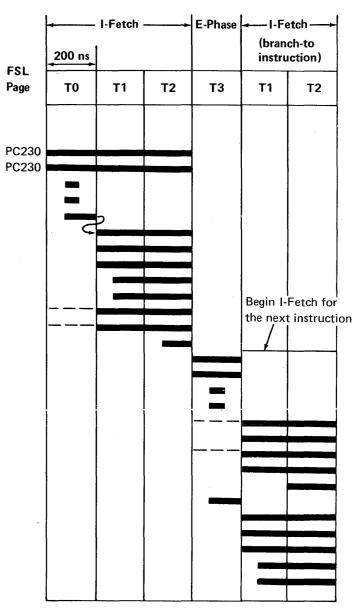

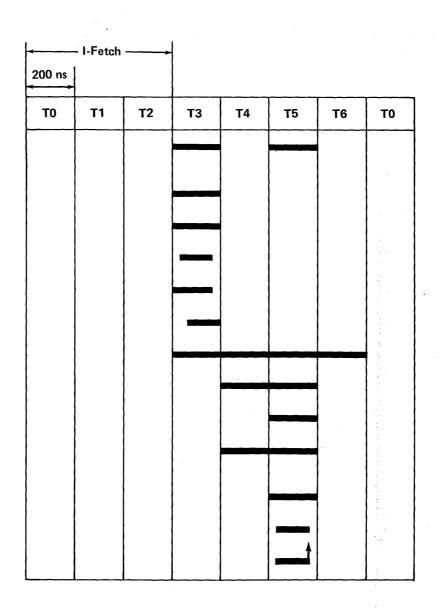

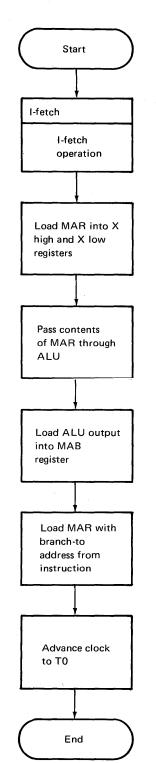

| Branch (B)                                       |

| Branch (Stop Condition) (B)                      |

| Branch and Link (BAL)                            |

| Jump on Condition (JC)                           |

| Jump on Condition (Stop Condition) (JC) 2-44     |

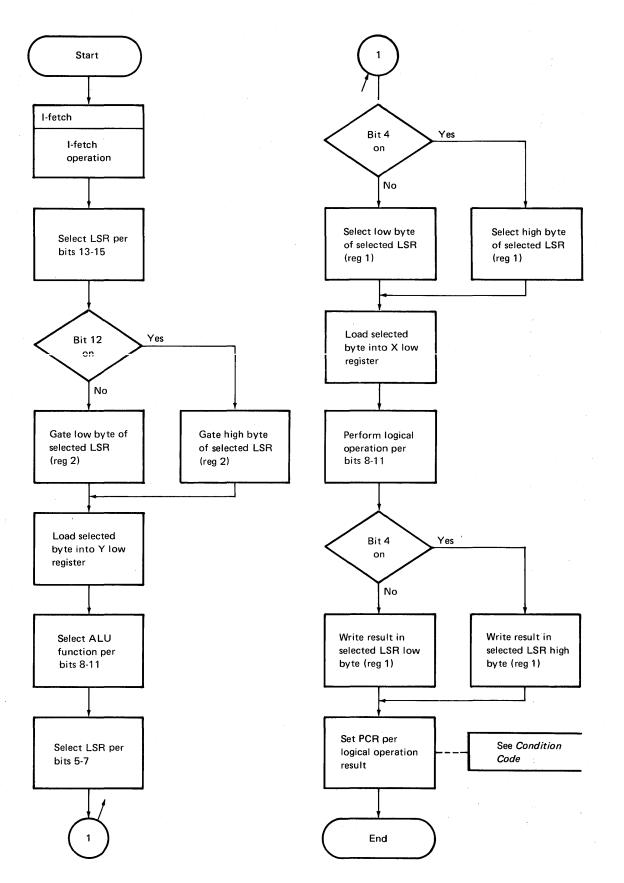

| Logical/Arithmetic 1 (XR, ZAR, OR, NCR, NR,  |       |

|----------------------------------------------|-------|

| OCR, DEC, ACYR, SR, AR, SCYR, INC)           | 2-42  |

| Condition Code for Logical Operations        | 2-42  |

| Condition Code for Arithmetic Operations     |       |

| Logical/Arithmetic Functions                 | 2-43  |

| Logical/Arithmetic 2 (XR, ZAR, OR, NCR, NR,  |       |

| OCR, DEC, ACYR, SR, AR, SCYR, INC)           | 2-46  |

| Condition Code for Logical Operations        | 2-46  |

| Condition Code for Arithmetic Operations     | 2-46  |

| Logical/Arithmetic Functions                 | 2-47  |

| Load Immediate (LI)                          | 2-50  |

| Compare Immediate (CI)                       | 2-52  |

| Subtract Immediate/Add Immediate (SI, AI)    | 2-54  |

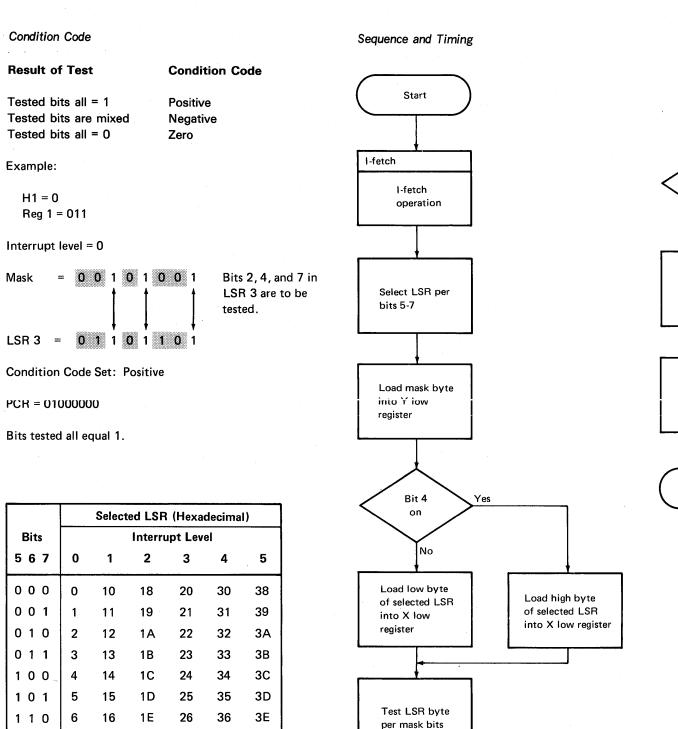

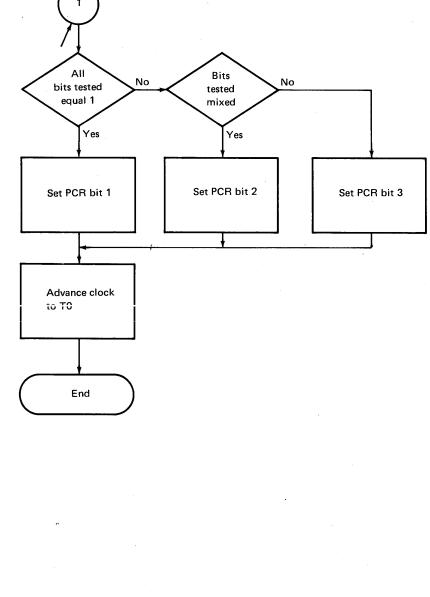

| Test Mask (TM)                               | 2-56  |

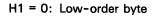

| Set Bits On (SBN)                            |       |

| Set Bits Off (SBF)                           |       |

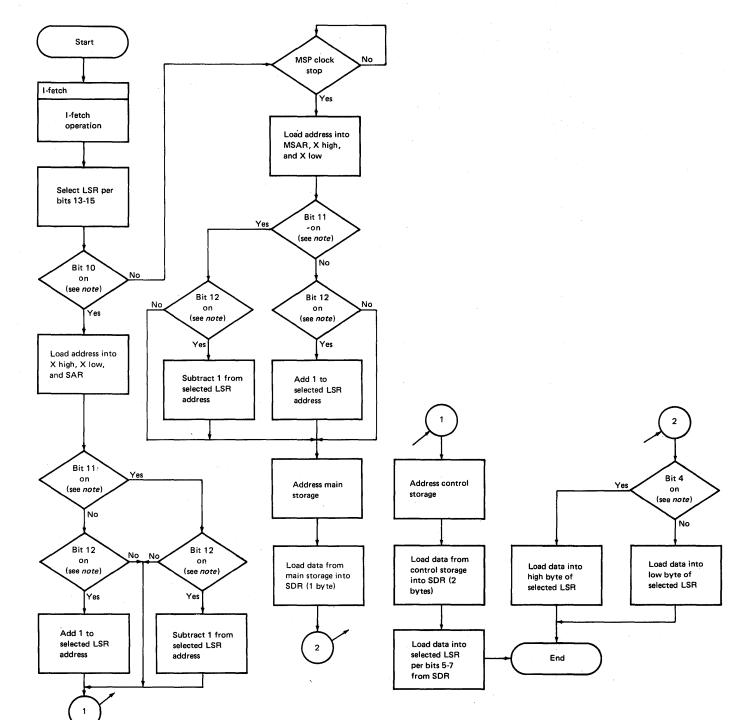

| Storage (LC, LM, STC, STM)                   | 2-63  |

| Instruction List                             | 2-63  |

| Main Storage Access by Control               |       |

| Processor                                    |       |

| Control Processor Control of MSAR            |       |

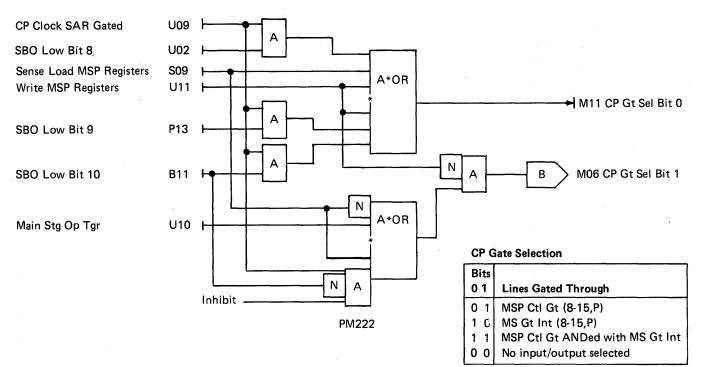

| MSP Bus Line Control                         | 2-68  |

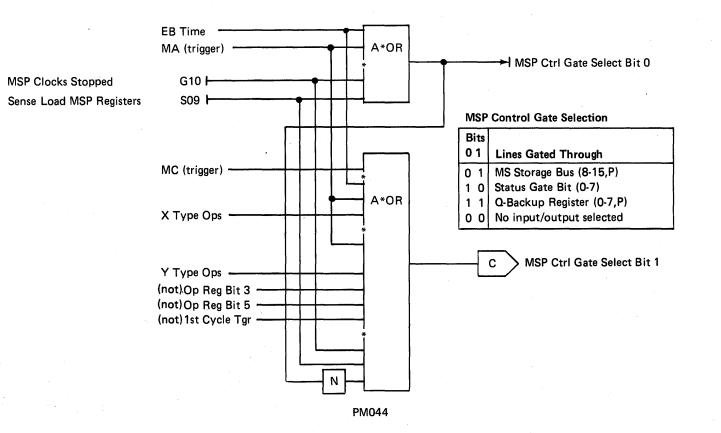

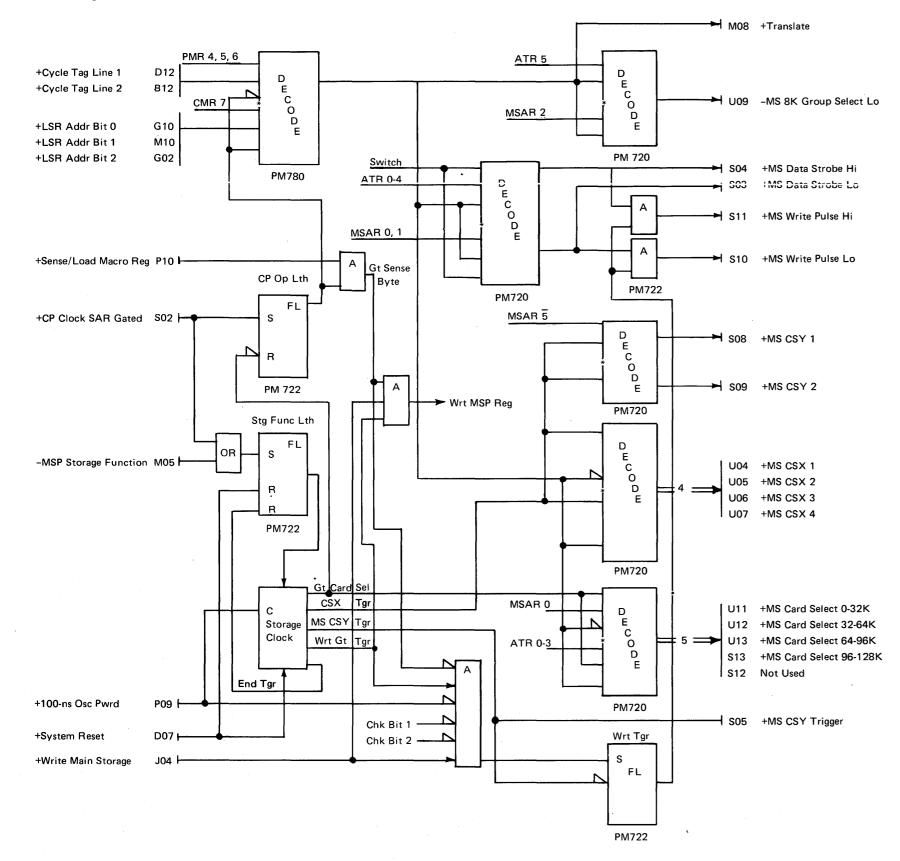

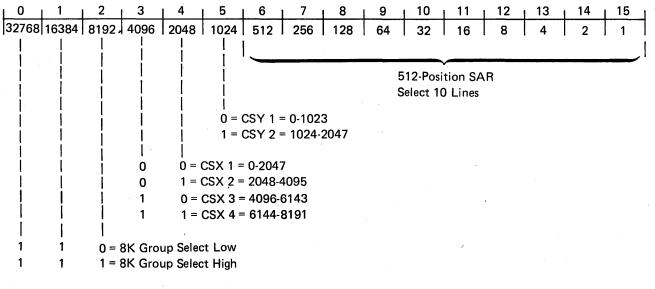

| Main Storage Address Decoding                | 2-69  |

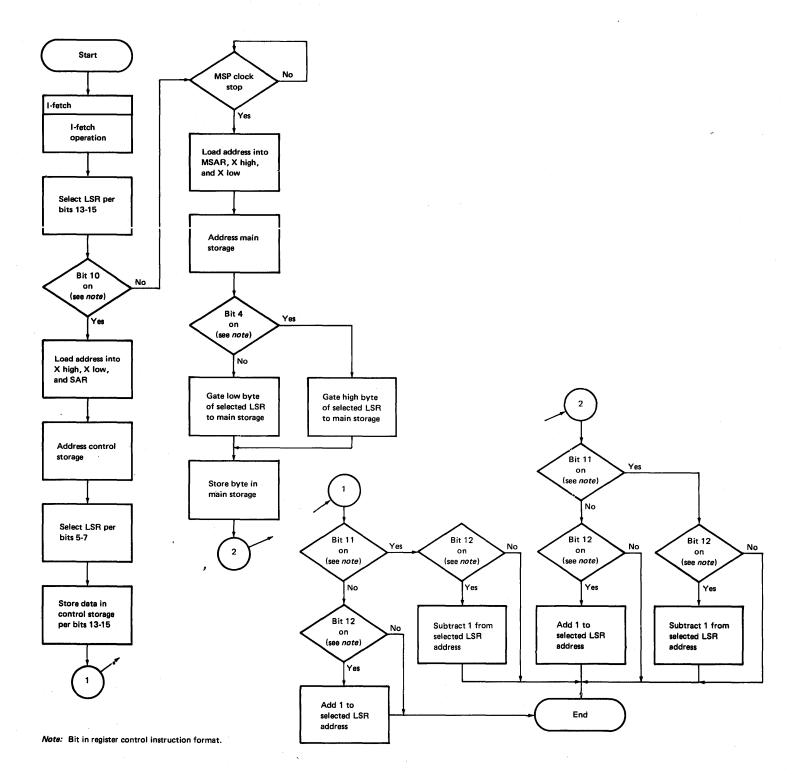

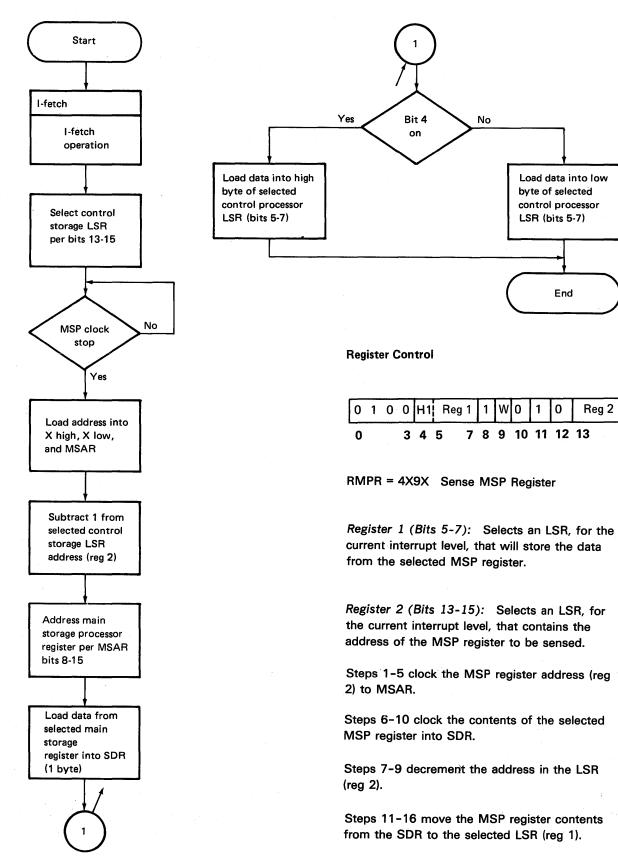

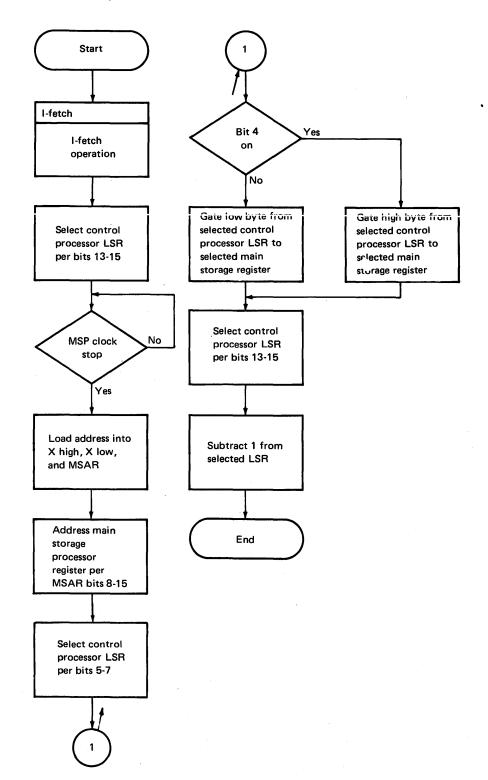

| Register Control (WMPR, RMPR)                | 2-73  |

| Instruction List                             | 2-73  |

| Storage Direct (L, ST)                       | 2-76  |

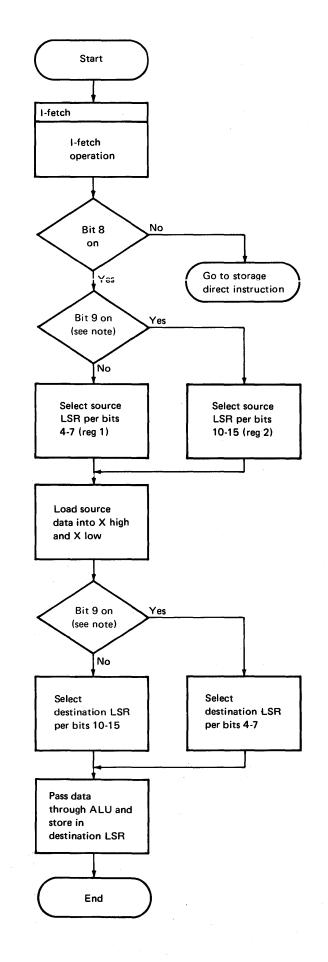

| Move Local Storage Register (MVR)            | 2-78  |

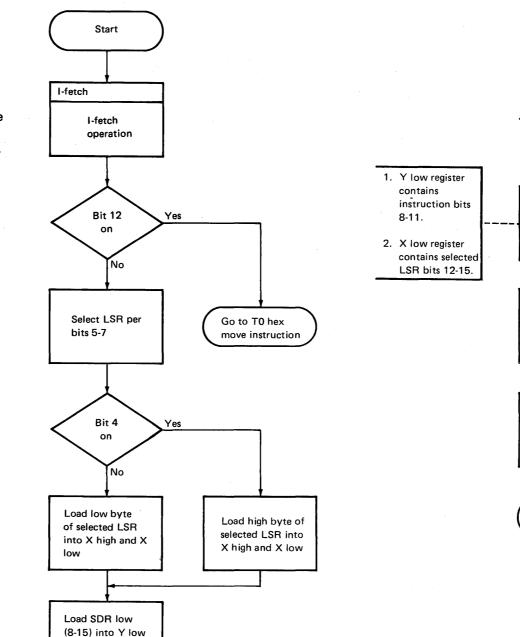

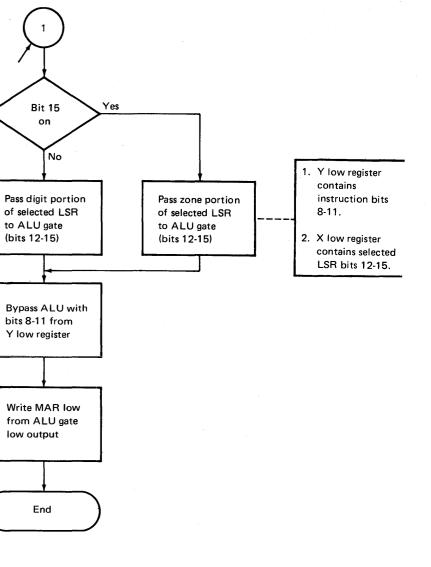

| Hexadecimal Branch (HBN, HBZ)                | 2-80  |

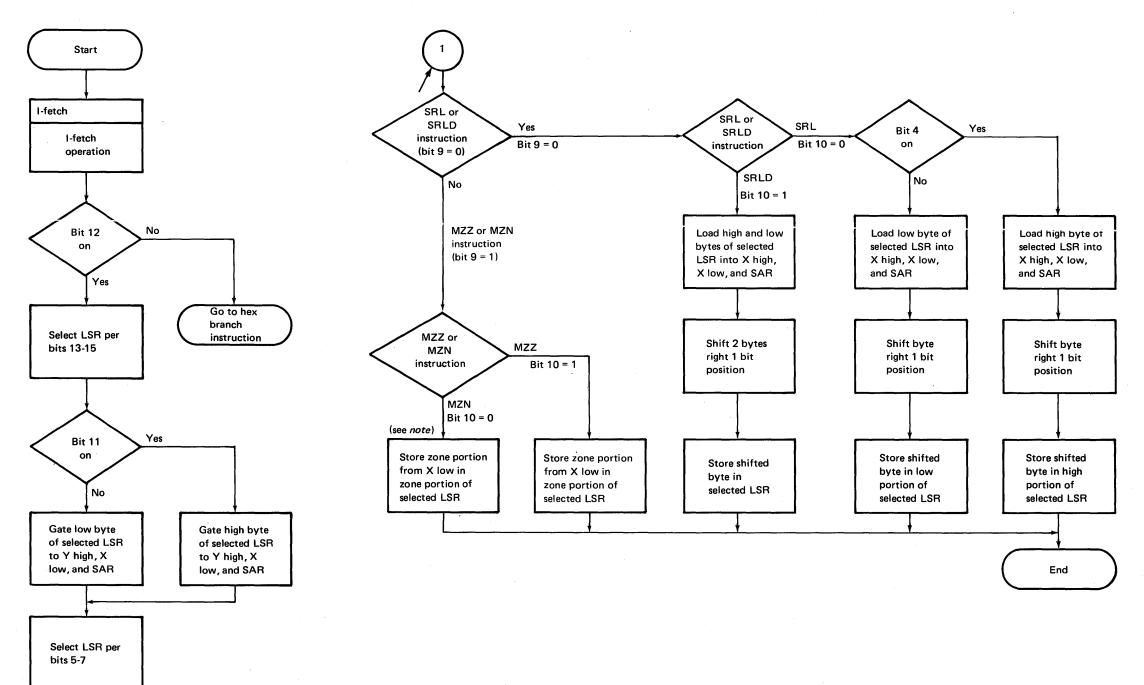

| Hexadecimal Move (SRL, SRLD, MZZ, MZN)       |       |

| I/O Immediate                                |       |

| I/O Load or I/O Control Load (IOL, IOCL)     |       |

| I/O Sense or I/O Control Sense (IOS, IOCS) . |       |

| Sense Interrupt Level Status Byte (SILSB)    |       |

| Control Processor Load Function (MPLF)       |       |

| Control Processor Sense (MPS)                | 2-99  |

| I/O Storage (WTCL, WTCH, RDCL, RDCH,         |       |

| WTM, RDM)                                    |       |

| Instruction List                             | 2-100 |

| •                                            | 2-104 |

|                                              | 2-108 |

| -                                            | 2-109 |

|                                              | 2-109 |

| Micro-Operation Register                     | 2-109 |

| X-Registers and Y-Registers                  | 2-109 |

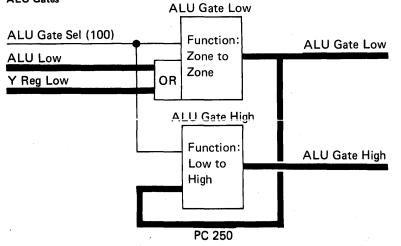

| Arithmetic and Logic Units                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Arithmetic and Logic Unit Gates                                                                                                                                                                                             |

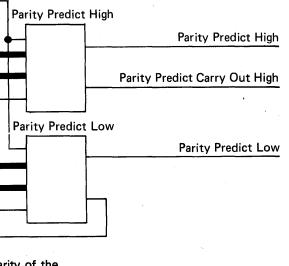

| Arithmetic and Logic Unit Parity Predict 2-111                                                                                                                                                                              |

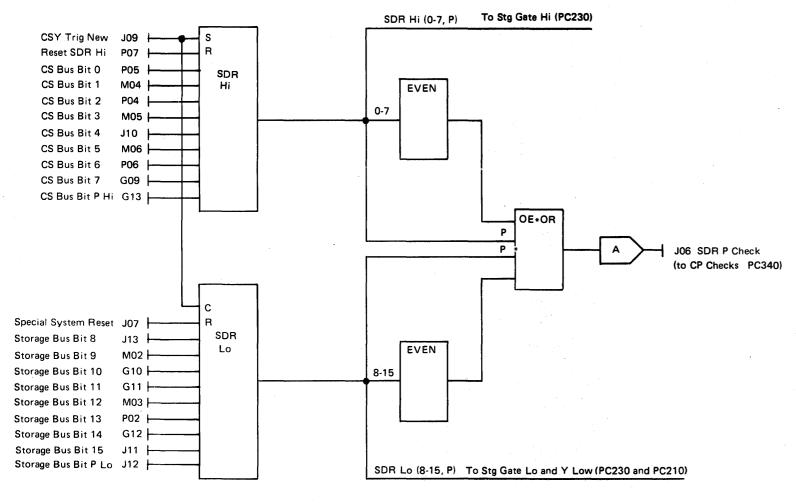

| Storage Data Register                                                                                                                                                                                                       |

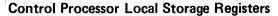

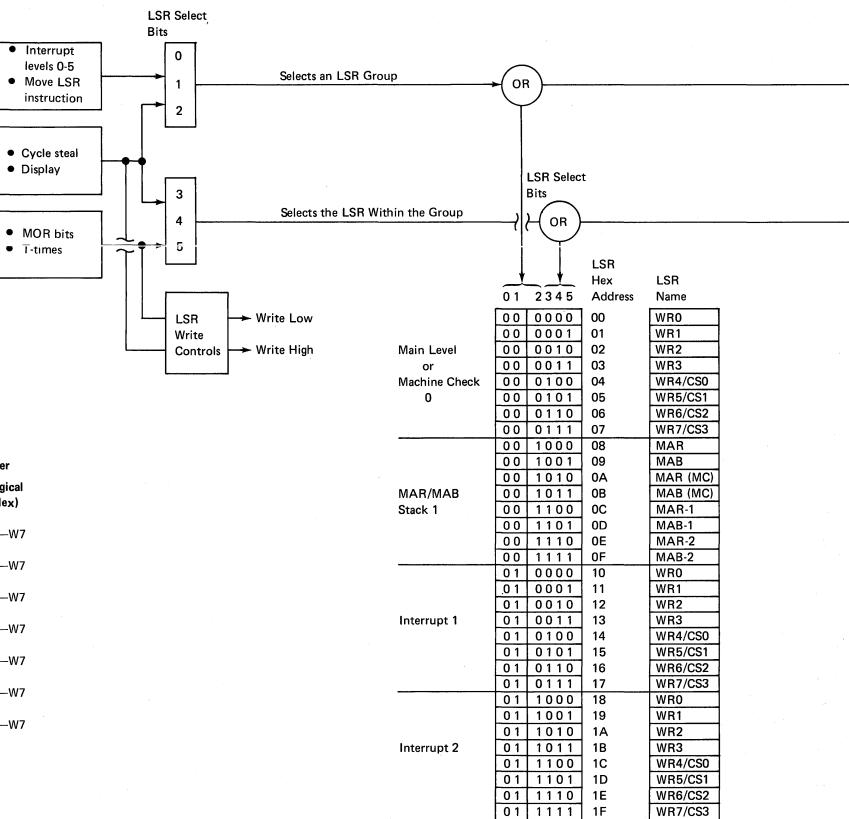

| Local Storage Registers                                                                                                                                                                                                     |

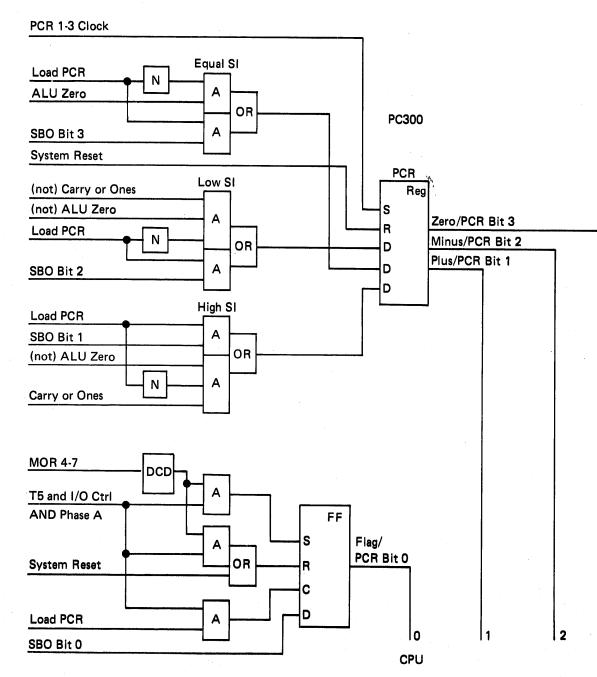

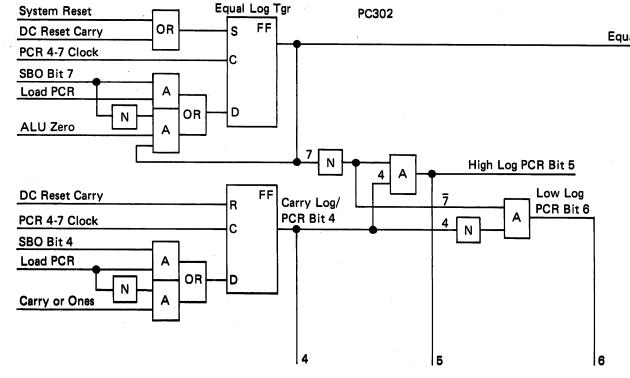

| Processor Condition Register                                                                                                                                                                                                |

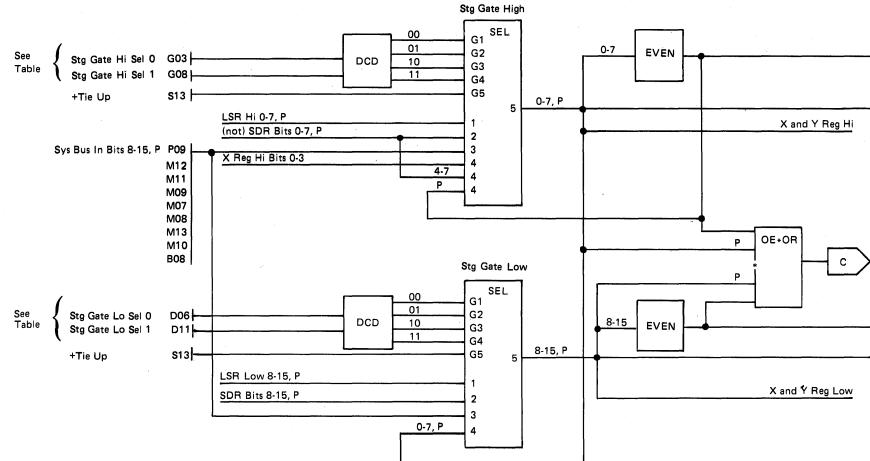

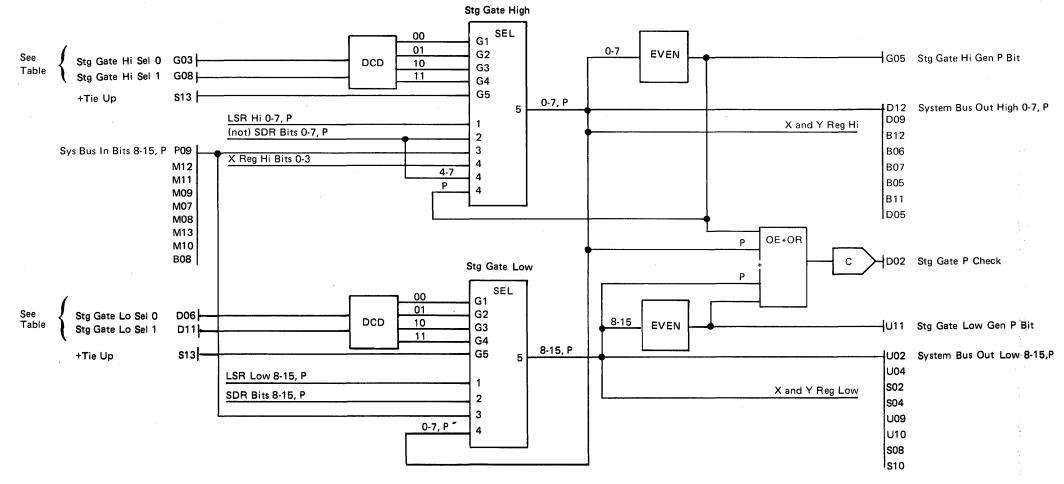

| Storage Gate High/Low                                                                                                                                                                                                       |

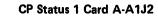

| Status 1 Gate                                                                                                                                                                                                               |

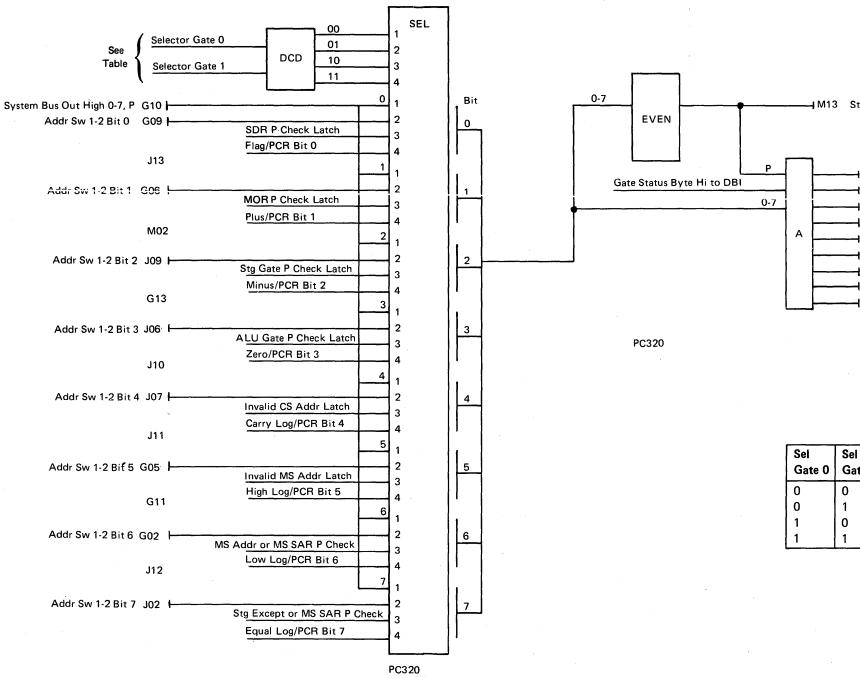

| Status 2 Gate                                                                                                                                                                                                               |

| ERROR CONDITIONS                                                                                                                                                                                                            |

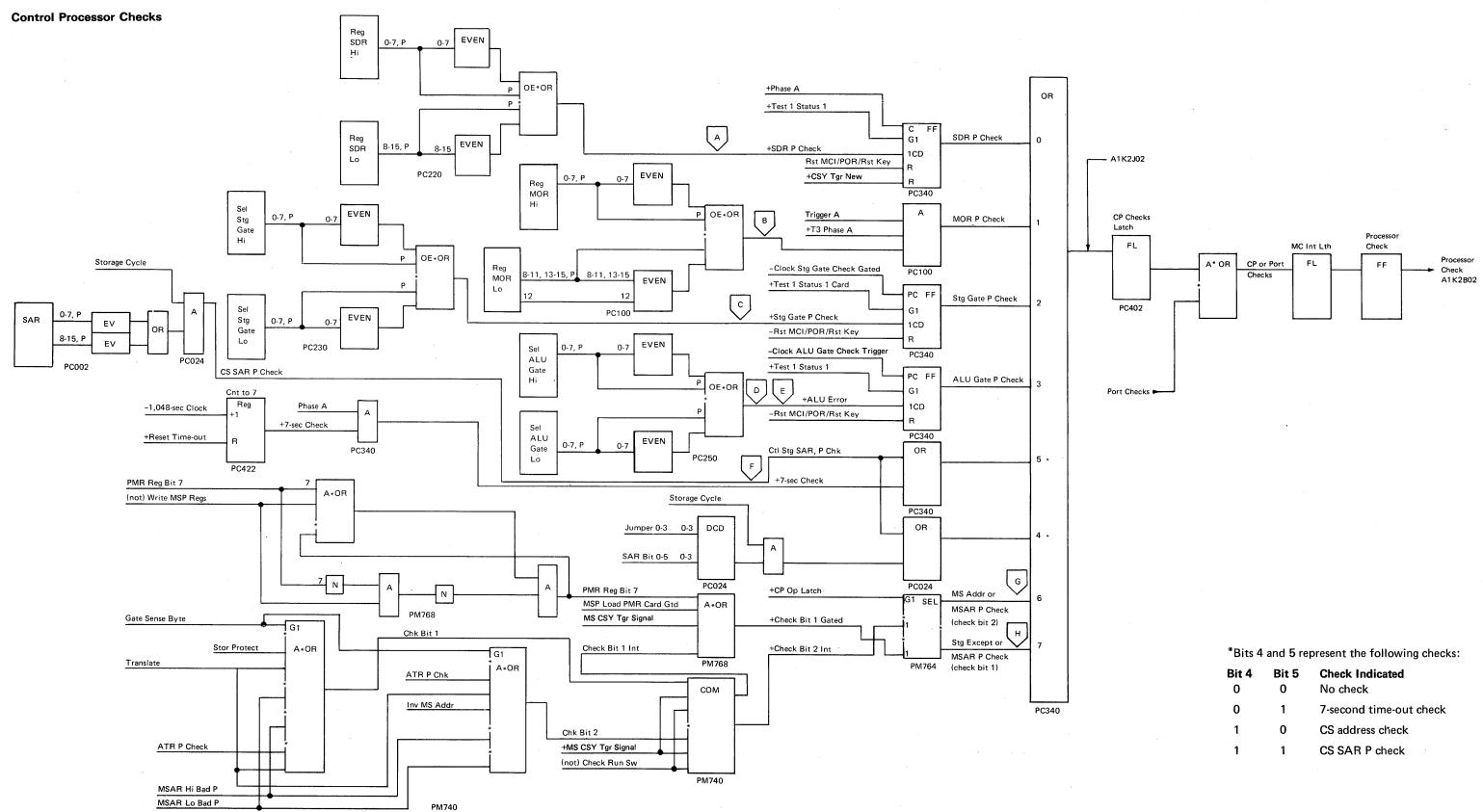

| Control Processor Checks                                                                                                                                                                                                    |

| Processor Errors                                                                                                                                                                                                            |

| Error Conditions (Second Level)                                                                                                                                                                                             |

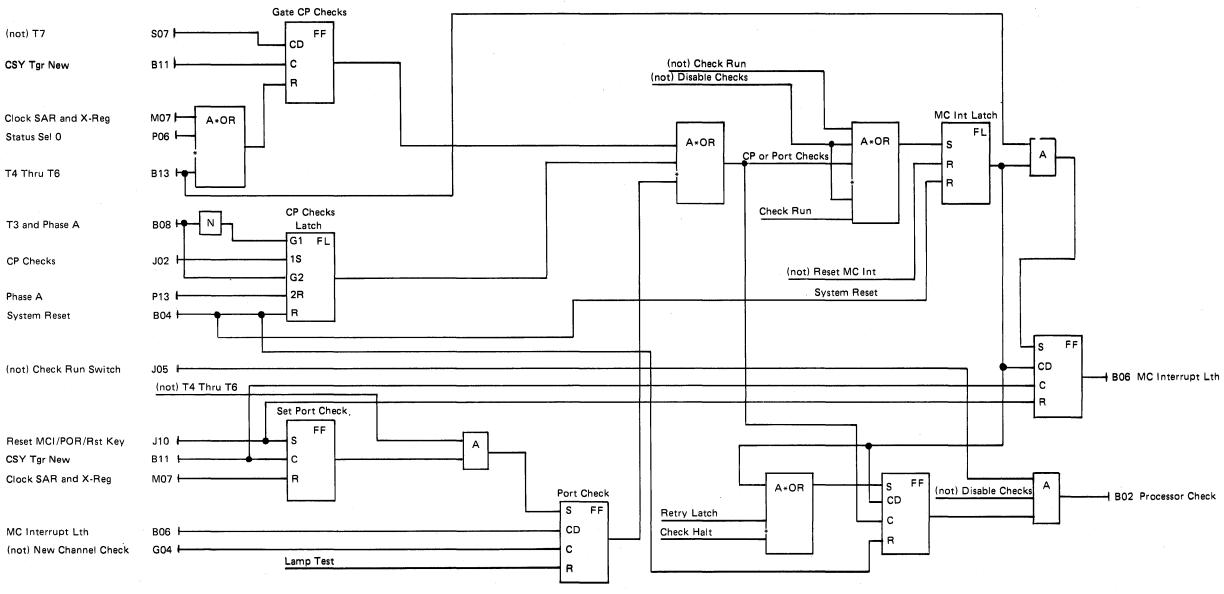

| Machine Check Interrupt and Processor                                                                                                                                                                                       |

| Check Generation                                                                                                                                                                                                            |

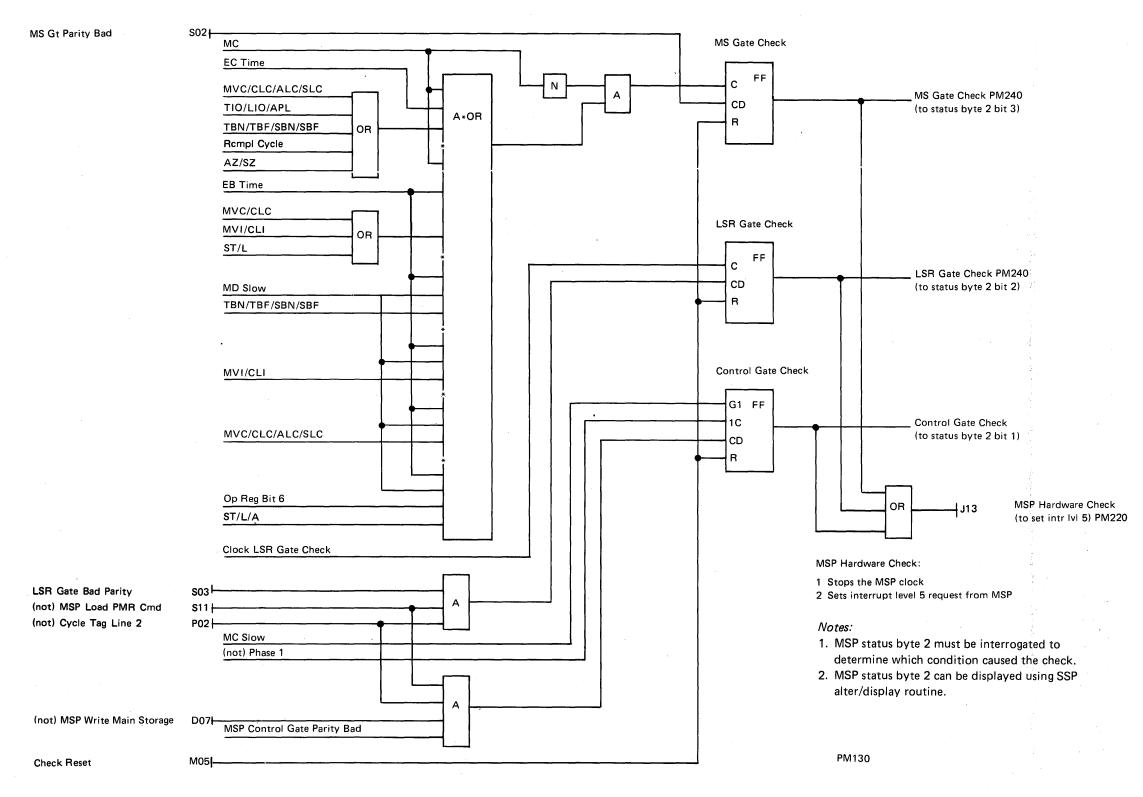

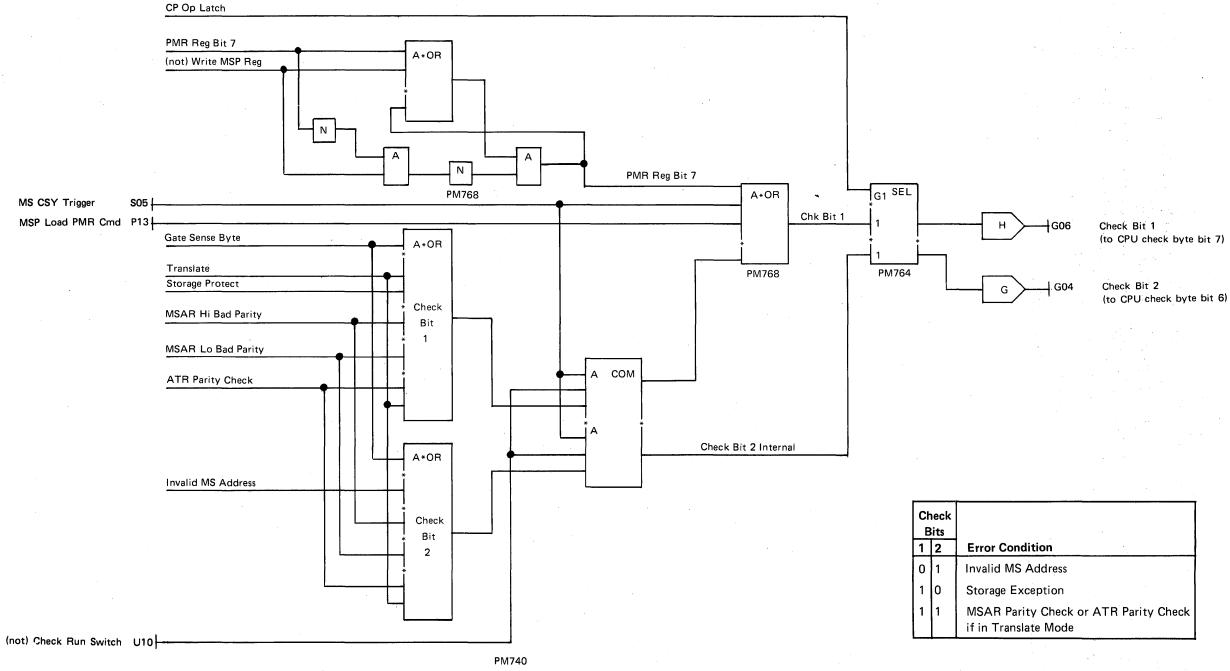

| MSP Hardware Checks                                                                                                                                                                                                         |

| Control Processor Checks                                                                                                                                                                                                    |

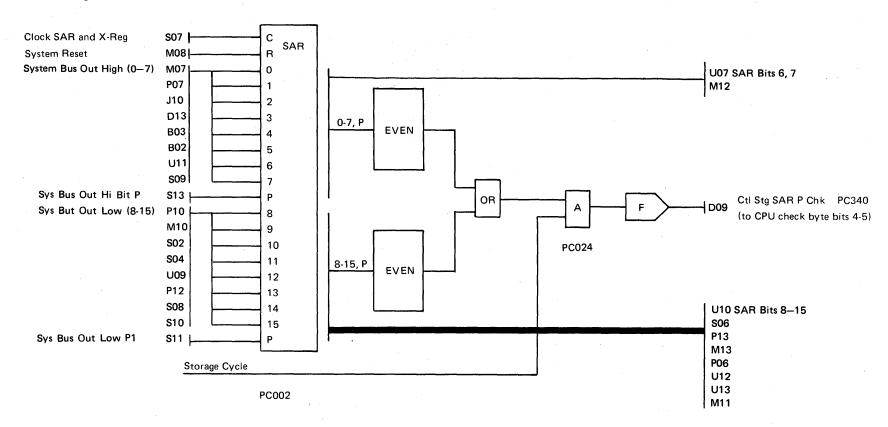

| SDR Parity Check Generation                                                                                                                                                                                                 |

|                                                                                                                                                                                                                             |

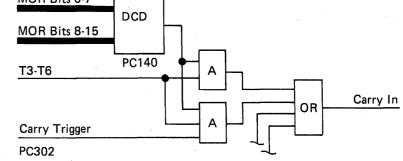

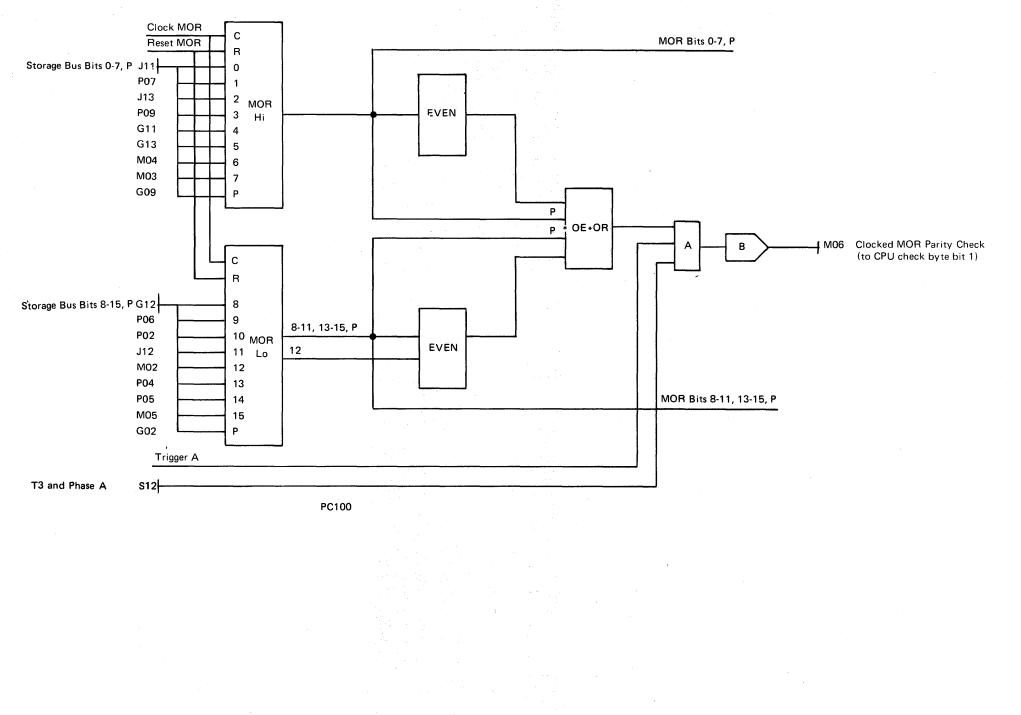

| MOR Parity Check                                                                                                                                                                                                            |

|                                                                                                                                                                                                                             |

| MOR Parity Check                                                                                                                                                                                                            |

| MOR Parity Check                                                                                                                                                                                                            |

| MOR Parity Check       2-124         Storage Gate High/Low Parity Check       2-125         and Generation       2-125                                                                                                      |

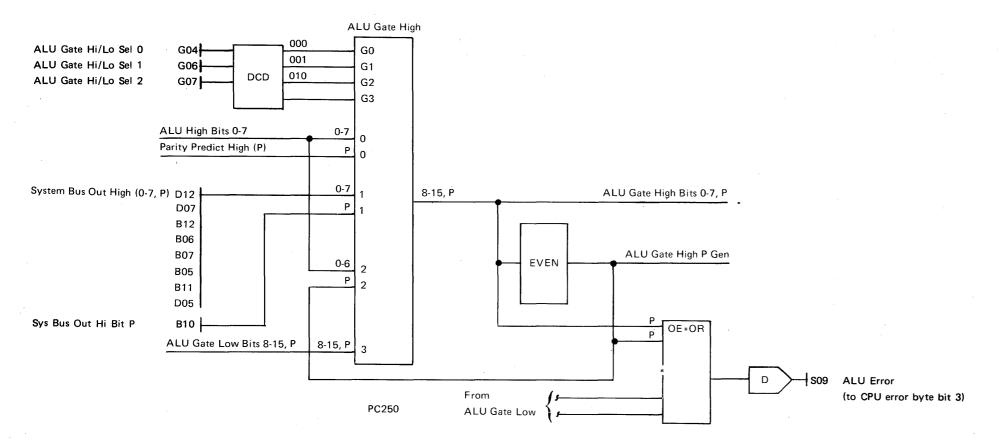

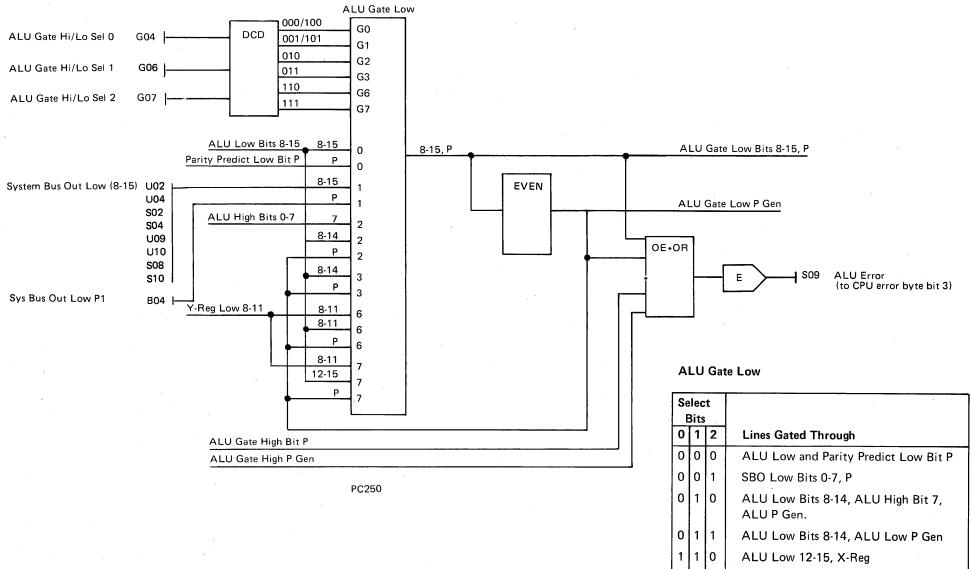

| MOR Parity Check       2-124         Storage Gate High/Low Parity Check         and Generation       2-125         ALU Gate High Parity Check and                                                                           |

| MOR Parity Check       2-124         Storage Gate High/Low Parity Check       2-125         and Generation       2-125         ALU Gate High Parity Check and       2-126         ALU Gate Low Parity Check and       2-126 |

| MOR Parity Check       2-124         Storage Gate High/Low Parity Check         and Generation       2-125         ALU Gate High Parity Check and         Generation       2-126                                            |

**Contents for Control Processor**

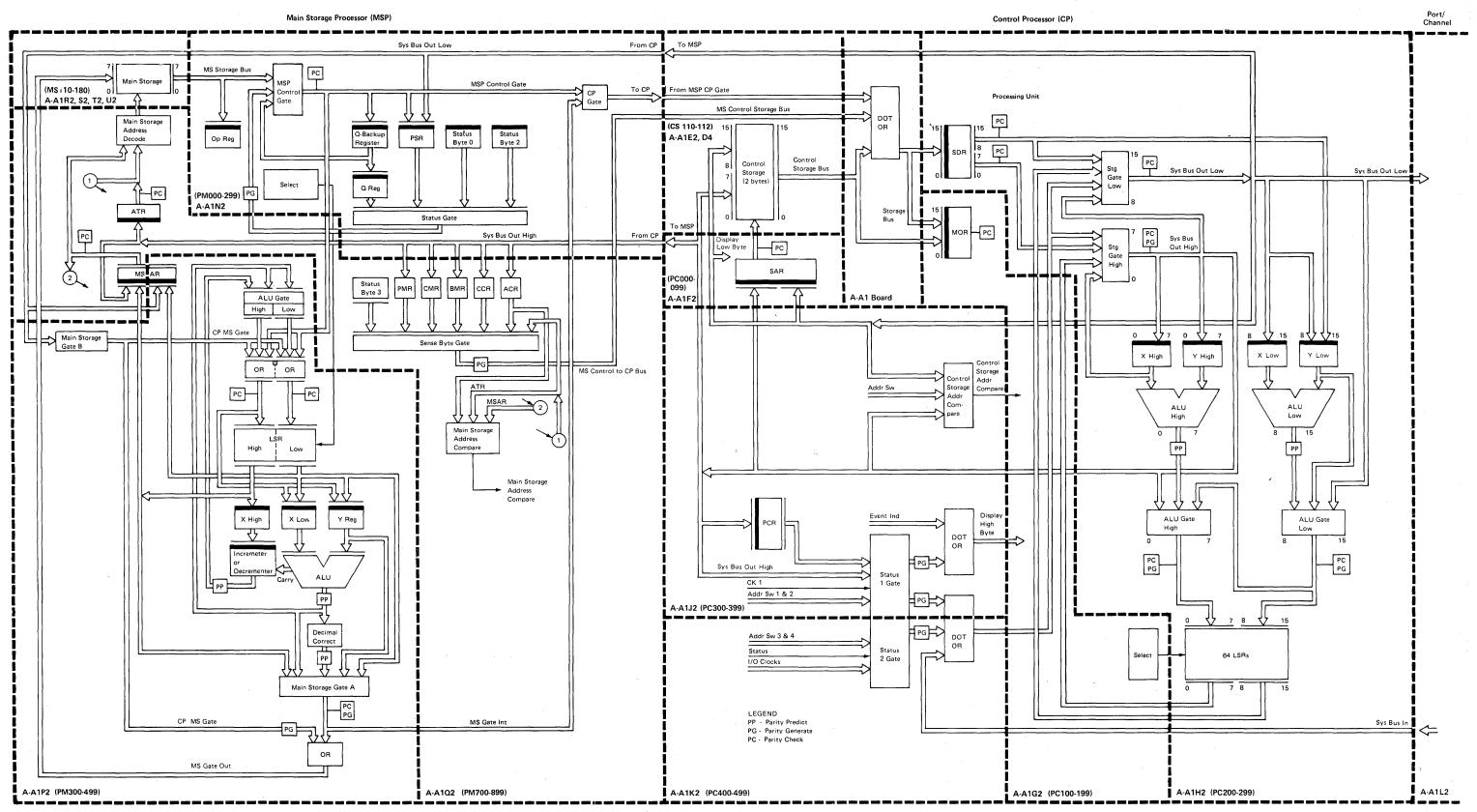

# **Control Processor**

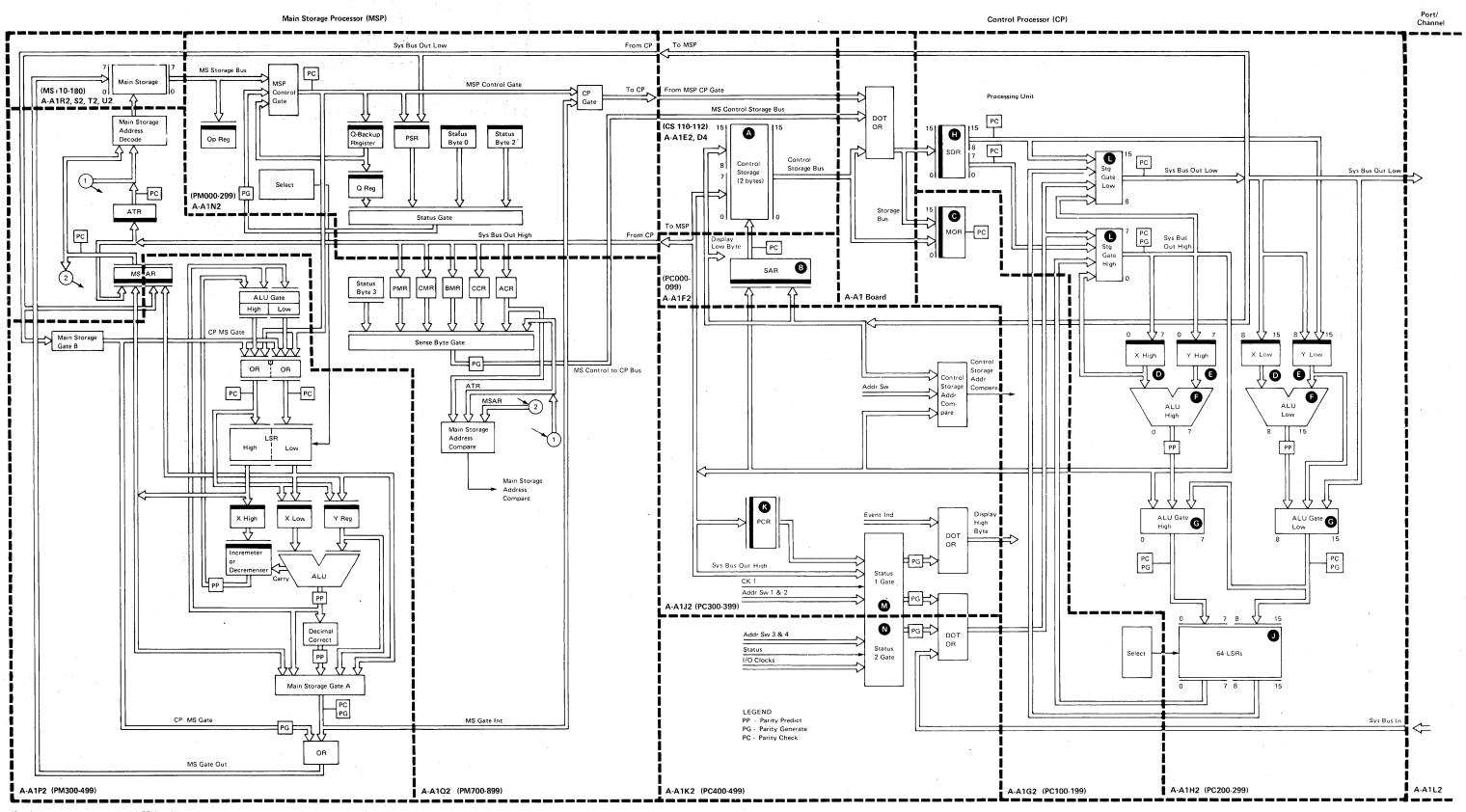

The control processor is made up of eight cards (16K-word storage positions that can be addressed): six cards for the processor and two cards for storage. The control processor:

- Controls system input/output (I/O) operations

- Controls assigning of tasks

- Moves data between the I/O devices and the main storage processor

- Handles some of the system control programming

- Moves data between the control processor and the I/O devices that use the channel

- Performs channel command functions (load and sense)

- Moves data between the control processor and the main storage processor

- Controls the main storage processor clock

Control storage contains 16K words; each word is 2 bytes long. Control storage can be addressed one word at a time. The control processor executes control storage instructions that are in control storage. The control processor functions are performed by the control storage program. The control storage program is loaded in control storage during the control storage initial program load (CSIPL) sequence. Control storage is loaded from the disk during normal operations or from the DIAGXX diskettes for diagnostic programs. The diagnostic programs control the routines and work done by transients that are not loaded at CSIPL time.

# DATA FLOW AND CLOCKS

# Data Flow

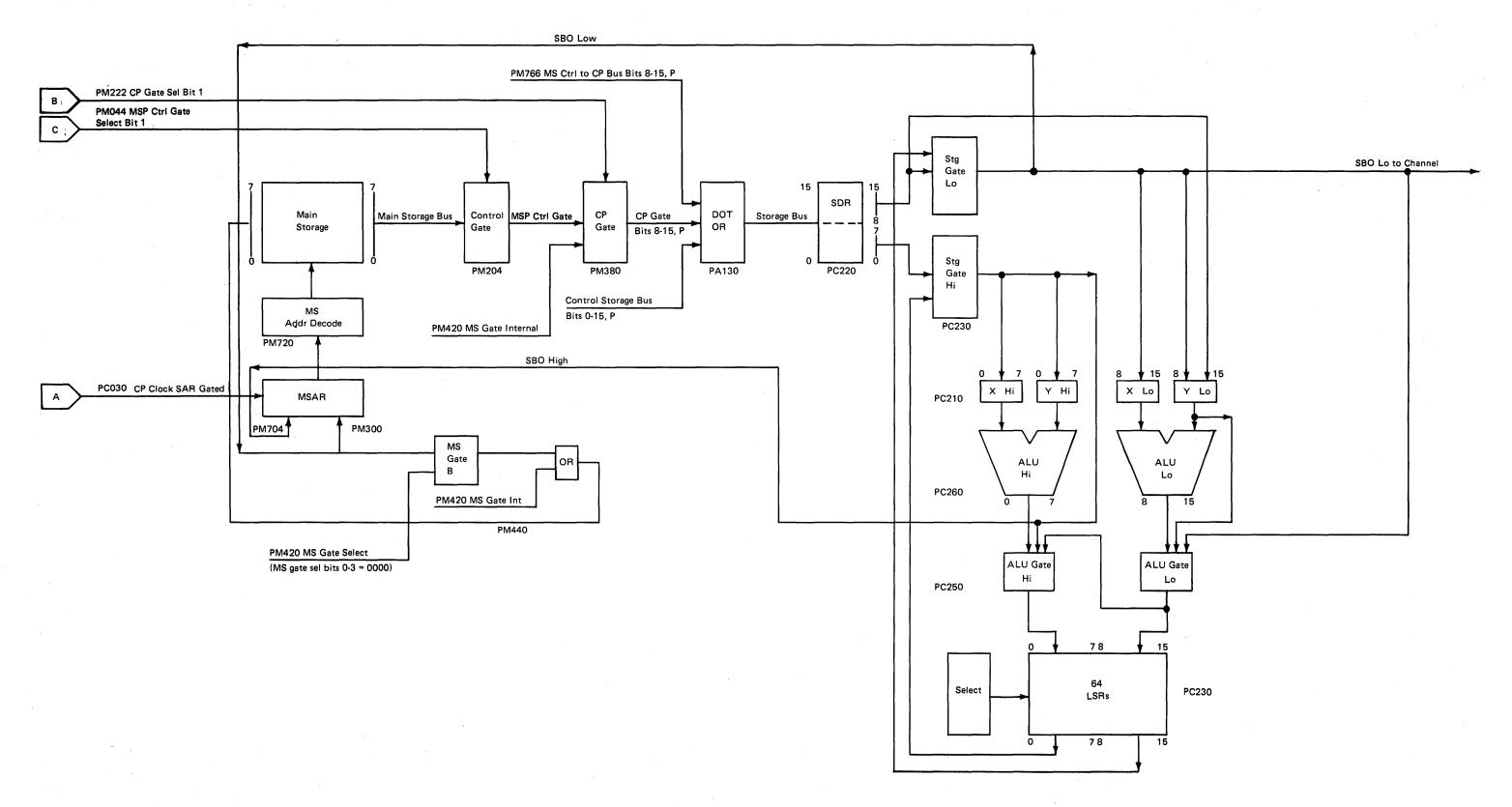

The control processor works with either 1 or 2 bytes of data at a time. The instruction being executed determines the number of bytes and the exact path of the data.

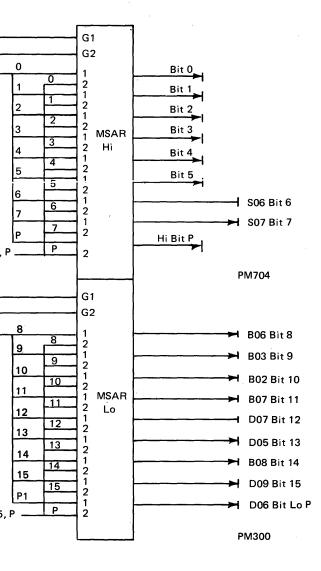

The 'system bus in' lines (channel SBI) from the channel are 1 byte wide plus parity (9 lines), but the byte can be either a high- or low-order byte in the control processor. If the data on the 'system bus in' lines is to be sent directly to the main storage processor, the control storage program sends 1 byte plus parity at a time. The control processor can also address main storage and main storage processor registers.

# Parity Checking

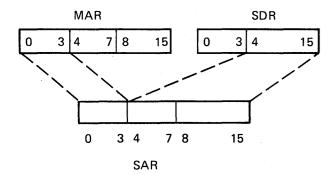

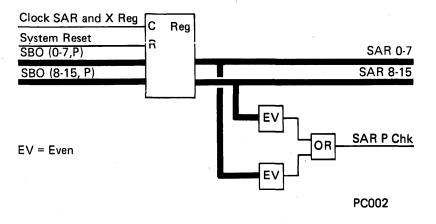

Odd parity by byte is maintained in the data flow. To ensure correct parity, System/34 has checking and generating stations. Parity is checked at the storage address register (SAR), storage data register (SDR), storage gates high and low, arithmetic and logic unit (ALU) gates high and low, micro-operation register (MOR), and on the channel data lines.

Parity generating stations are supplied for the status register, the control panel, switch bytes, and other internally generated data pertaining to the control processor (storage gate high and ALU gates high and low).

# **Default Conditions**

If no hardware conditions are specified for the control processor, the control processor has automatic selections and functions that are default conditions. The default conditions for the functional units in the control processor are as follows:

| Unit              | Default Selection |

|-------------------|-------------------|

| Storage gate high | LSR high          |

| Storage gate low  | LSR low           |

| ALU gate high     | ALU high          |

| ALU gate low      | ALU low           |

| ALU function      | X-register plus 1 |

\*Data flow bus lines may not pass through FRUs as shown

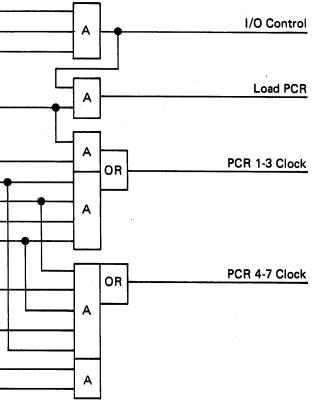

# Clocks

# System

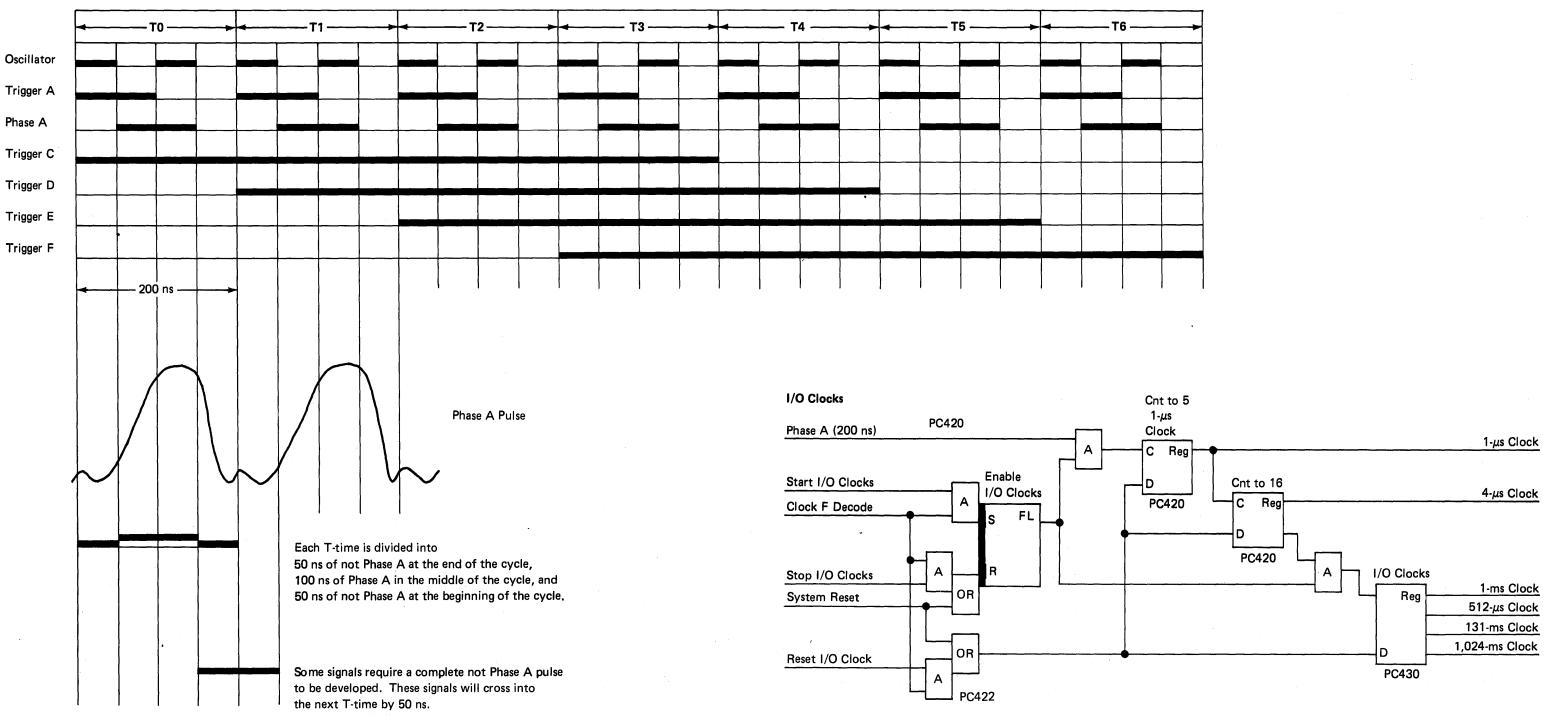

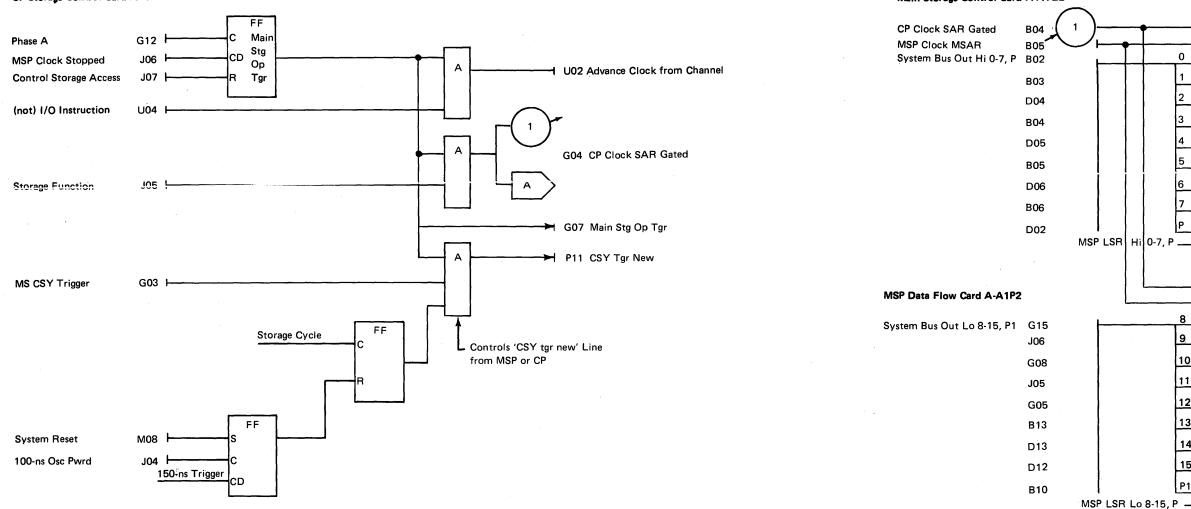

The control processor has a 100-nanosecond oscillator that runs continuously, supplying the 10-megahertz frequency needed for the clock pulses. The rise of this oscillator output causes

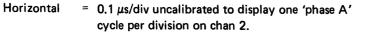

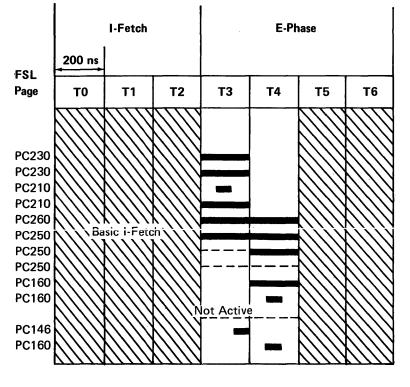

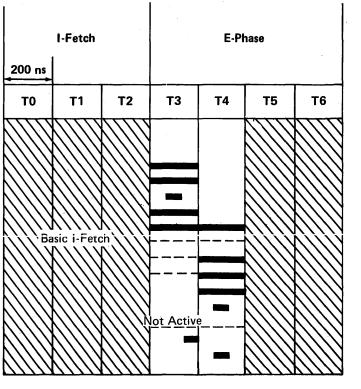

**T-Time and Phase A Relationship**

'trigger A' to change condition, while the fall of this oscillator output causes the 'phase A' line to change condition.

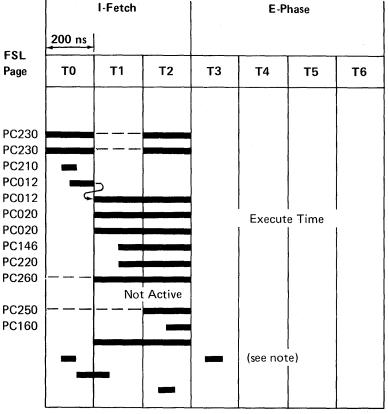

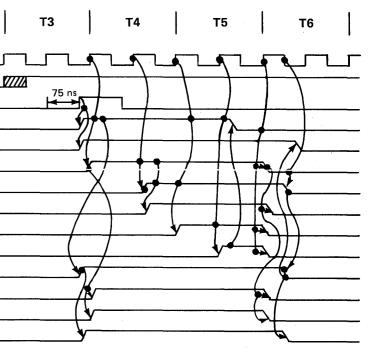

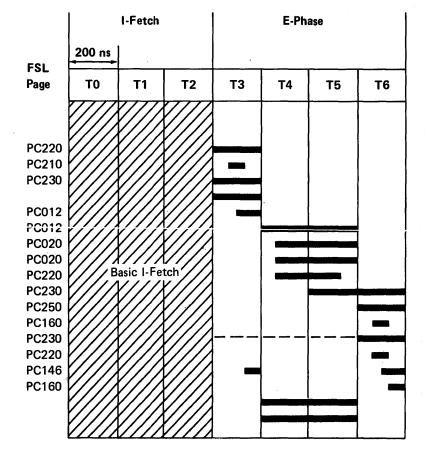

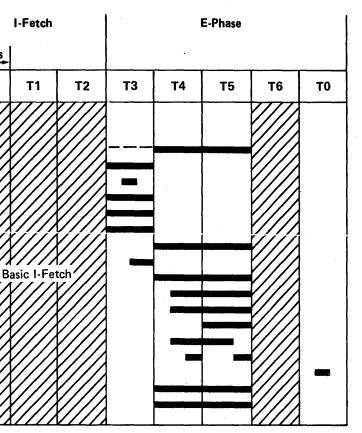

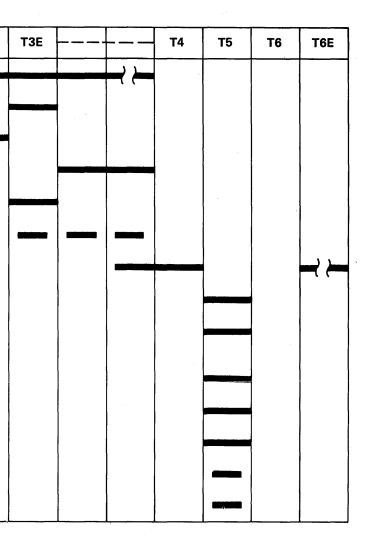

Four control processor clock triggers (C, D, E, and F) are decoded to determine control processor clock times T0 through T6.

When the current instruction is decoded, the control processor determines if some of the control processor clock times are needed and controls the gating of the triggers to skip the times that are not needed.

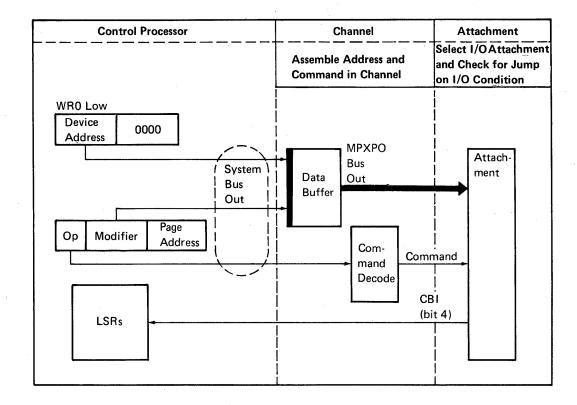

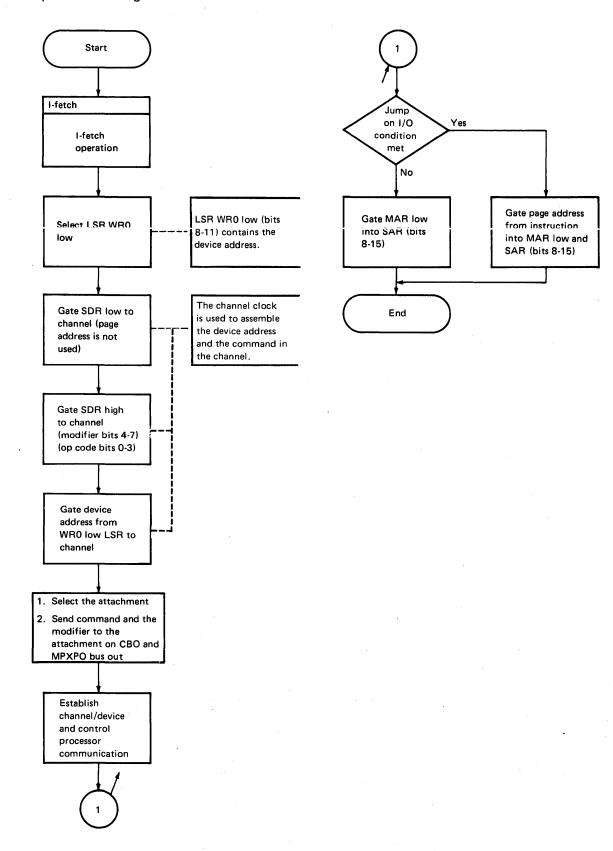

# I/O Attachment and Controller

The control processor has eight continuously running clocks that are used by the I/O attachments and controllers. Seven of these clocks can be stopped and started for diagnostic testing. The 100-nanosecond, free-running internal oscillator generates the 'phase A' line which, in turn, generates the other seven clocks. Clock triggers are used to count the time needed in the generation of the seven clocks. The times of the clocks are:

- 100 nanoseconds (oscillator)

- 1 microsecond

- 4 microseconds

- 1 millisecond

- 512 microseconds

- 16 milliseconds

- 131 milliseconds

- 1,024 milliseconds

These clocks, except for the 100-nanosecond oscillator, are sensed by the I/O immediate instruction. The clocks must be in a stop condition before a program can execute an I/O immediate instruction (B76R or B66R).

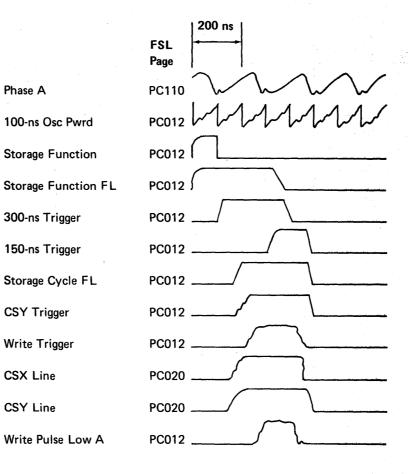

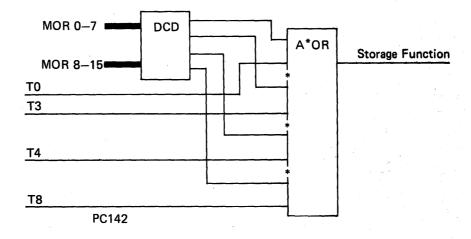

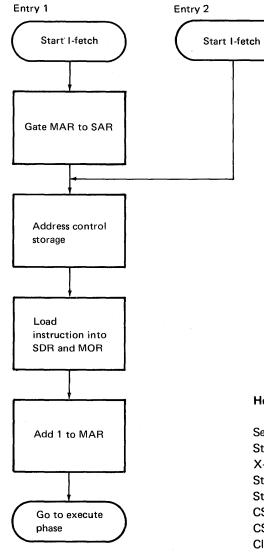

# Storage

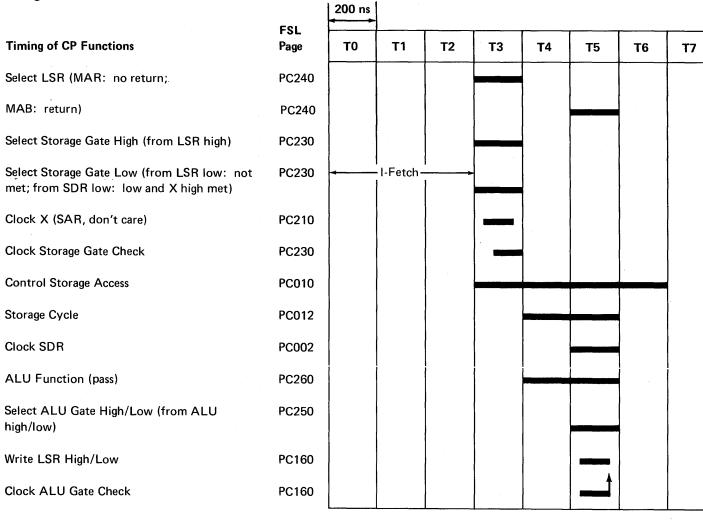

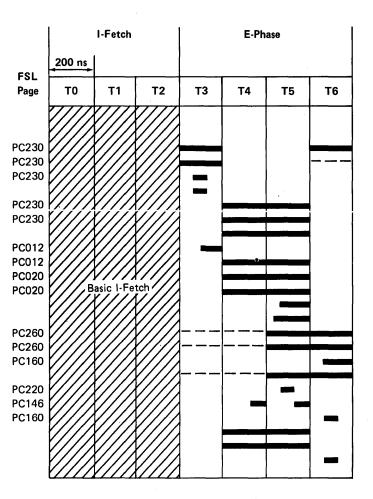

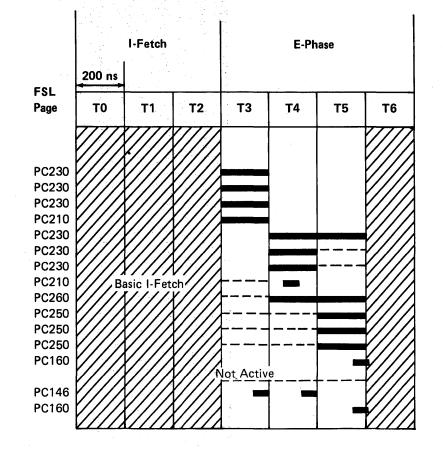

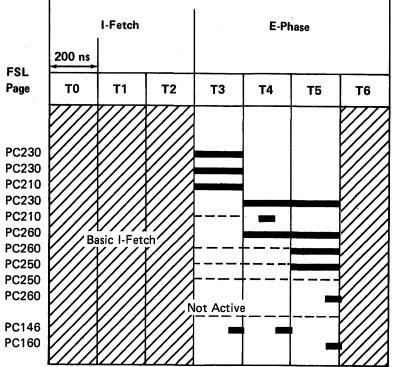

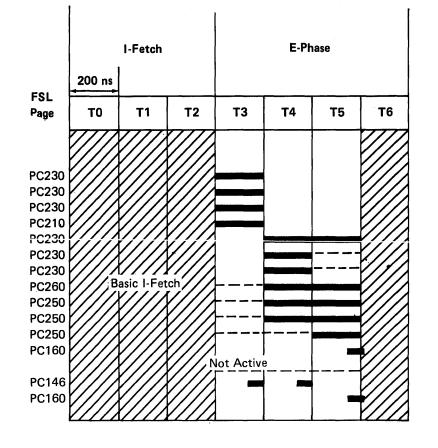

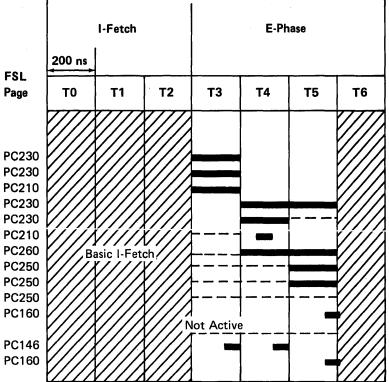

During instruction times T0 through T2, time T0 fetches the microaddress register (MAR) contents from the local storage register (LSR) stack and places this data into the storage address register (SAR). Time T0 also starts the storage clocks for the storage access. During times T1 and T2, storage is addressed to read the instruction.

The storage clocks are also used during burst-cycle-steal-mode operations and base-cycle-steal-mode operations. When an I/O device activates the 'disk/dskt block processor clock' line or the 'base cycle steal request' line, the control processor completes the instruction it is working on and then goes to the T7 condition where it is held until the 'disk/dskt block processor clock' line is not active. The rise of the 'disk/dskt (load) BC reg' line<sup>1</sup> while the 'disk/dskt block processor clock' line is active generates a 'storage cycle request' line which, in turn, generates time T8 (clock SAR and X reg); time T8 is then used to load the storage address in the main storage address register (MSAR) or control storage address register (SAR). After the operation is completed, the 'disk/dskt block processor clock' line is not active and the control processor clocks are permitted to run. (See Burst Cycle Steal Mode in the Channel section of this manual.) The control processor storage clocks can also control main storage. (See Control Processor and Main Storage Processor Communication in the Interrupts and Cycle Steal Requests section of this manual.)

# Storage Access Timings

# Storage Function

# **OPERATIONS**

# **IPL-Customer User Programs**

MSIPL Switch in Disk Position: CSIPL Switch in Disk Position: Initial program load (IPL) is completed in three major stages from the time the Load key is pressed until the SYSTEM CONSOLE message is displayed on the system console display screen. Loading is done from the disk. The three stages of IPL are as follows:

| IPL                                                                                                                                                                               |                                                                                                                                                                        |                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| CSIP                                                                                                                                                                              | L                                                                                                                                                                      | MSIPL                                                                                              |

| Stage 1                                                                                                                                                                           | Stage 2                                                                                                                                                                | Stage 3                                                                                            |

| Control storage is<br>loaded three times<br>to run diagnostic<br>routines and check<br>hardware circuits<br>(see Section 99 of<br>the 5340 System<br>Unit Maintenance<br>Manual). | The control storage pro-<br>gram loaded includes<br>IPL routines that overlay<br>stage 1 and are executed<br>(see the <i>Control Storage</i><br><i>Logic Manual</i> ). | Main storage initialization<br>is loaded in three phases<br>(see the SSP Logic Manual:<br>System). |

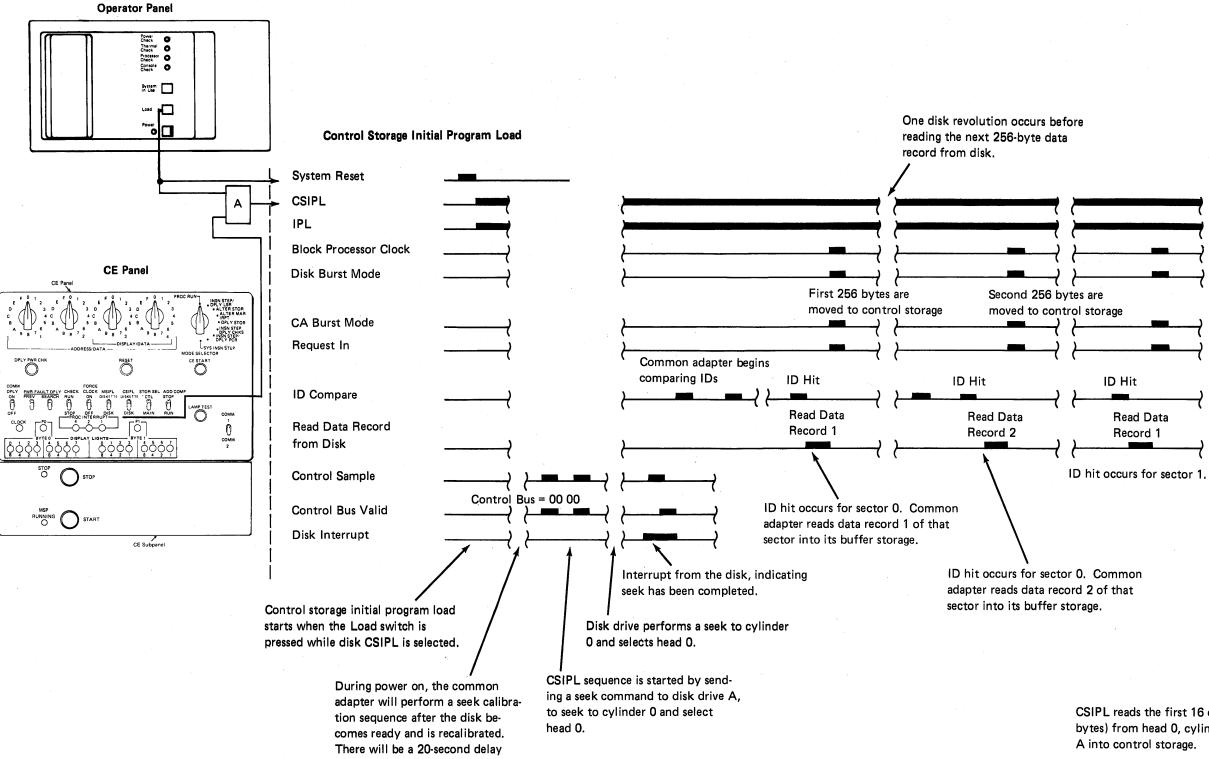

**Control Storage Initial Program Load (CSIPL)**

# Stage 1

Stage 1 of the control storage initial program load (CSIPL) sequence loads control storage three times and performs a basic system check of the control processor and I/O functions. Nine display lights (display byte 0, bits P0 and 0 through 7), and the Load light on the CE panel are set to on by pressing the Load key. These lights are reset to off at various stages of the CSIPL by both hardware and software as programs are loaded and executed.

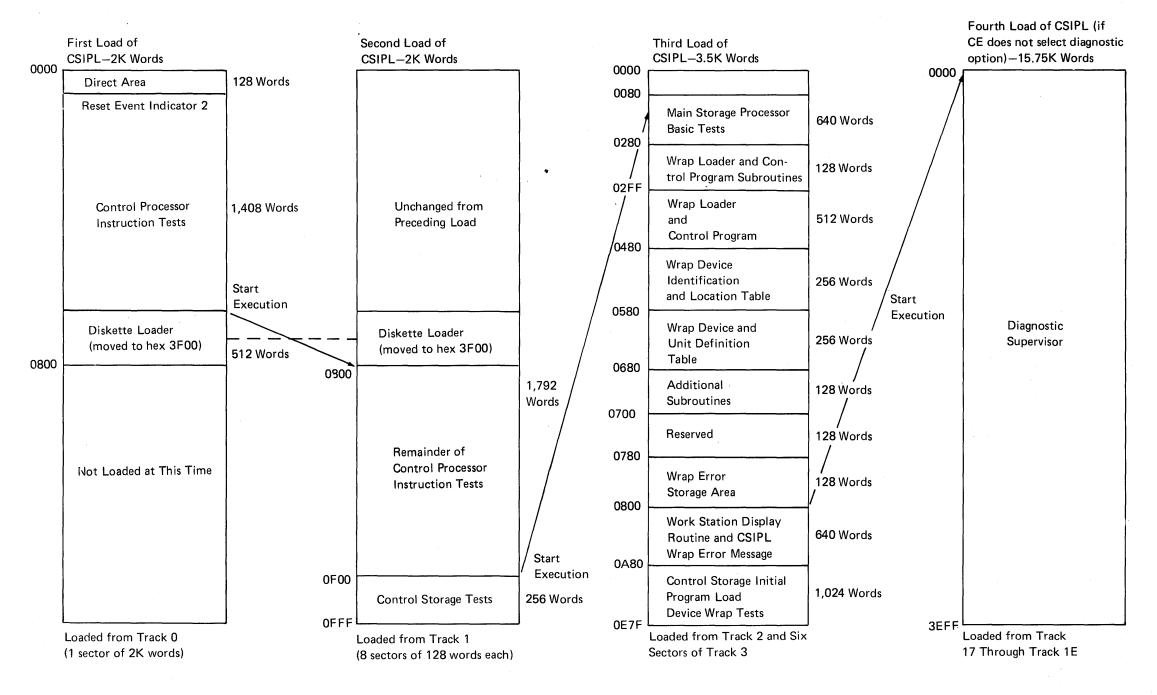

First Load: Load 16 sectors (2K words) that contain control processor diagnostic routines 1 through 19.

Then, perform the following tasks:

4

- 1. Load control storage from disk by a burst-cycle-steal-mode operation.

- 2. Load 2K words (4,096 bytes) into control storage at hexadecimal addresses 0000 through 07FF.

- 3. Reset the microaddress register (MAR) for machine check (local storage register hexadecimal 0A) to hexadecimal 0000 and execute any machine check log routines for control processor errors using interrupt level 0.

- 4. Software set the microaddress register (MAR) for main program level to hexadecimal 0292, branch to hexadecimal 00FF, and execute instructions for diagnostic routines 1 through 19.

If all tests run correctly, the following lights are reset to off in the sequence: bits PO, O, and 1 of display byte 0, the Load light, and bit 2 of display byte 0.

To indicate a failure, one or more of the following occur:

- The Processor Check light is set to on.

- Display byte 0 does not contain correct results.

- The system goes into a loop during CSIPL (display byte 0 lights show the sequence of advance).

See Error Indications or Display Light Sequence later in this section.

Second Load: Load 16 sectors (2K words) that contain control processor diagnostic routines 20 through 70.

Then, perform the following tasks:

- 1. Load control storage from disk by a burst-cycle-steal-mode operation.

- 2. Load 2K words (4,096 bytes) into control storage at hexadecimal addresses 0800 through OFFF.

- 3. Software set the microaddress register (MAR) for main program level to hexadecimal 0800 and execute instructions for diagnostic routines 20 through 70.

If all tests run correctly, bits 3 and 4 of display byte 0 are reset to off.

To indicate a failure, one or more of the following occur:

- · The Processor Check light is set to on.

- Display byte 0 does not contain correct results.

- The system goes into a loop during CSIPL (display byte 0 lights show the sequence of advance).

See Error Indications or Display Light Sequence later in this section.

Third Load: Load 28 sectors (3.5K words) that contain control processor diagnostic routines 71 through 79 and device wrap loader tests.

Then, perform the following tasks:

- 1. Load control storage from disk by a burst-cycle-steal-mode operation.

- 2. Load 3.5K words (7,168 bytes) into control storage at hexadecimal addresses 0080 through 0E7F.

- 3. Software set the microaddress register (MAR) to hexadecimal 0080 and execute instructions for diagnostic routines 71 through 79.

The wrap loader calls in each device wrap test and executes that test before it calls in the next wrap test.

If all tests run correctly, bits 5, 6, and 7 of display byte 0 are reset to off.

To indicate a failure, one or more of the following occur:

- The Processor Check light is set to on.

- The Console Check light is set to on.

- Display byte 0 does not contain correct results.

- · The system goes into a loop during CSIPL (display byte 0 lights show the sequence of advance).

- Error messages are stored in control storage at hexadecimal locations 07A0 through 07BF and may also appear on the system console display screen.

See Error Indications or Display Light Sequence later in this section.

### Stage 2

Stage 2 of the control storage initial program load (CSIPL) sequence loads the control storage program that contains the routines necessary to load:

- The work station controller program

- The printer controller program

- · The main storage nucleus initialization program (#MSNIP)

Then, perform the following tasks:

- 1. Load control storage from disk by a burst-cycle-steal-mode operation.

- Load 62 sectors (9.75K words) into 2 control storage at hexadecimal addresses 0000 through 26FF.

- 3. Software set the microaddress register (MAR) to hexadecimal 1E00 and the control processor takes control.

To indicate a failure, one or more of the following occur:

- · The Processor Check light is set to on.

- The Console Check light is set to on.

- Display byte 0 does not contain correct results.

- The system goes into a loop during CSIPL (display byte 0 lights show the sequence of advance).

- Error messages are stored in control storage at hexadecimal locations 07A0 through 07BF and may also appear on the system console display screen.

See Error Indications or Display Light Sequence later in this section.

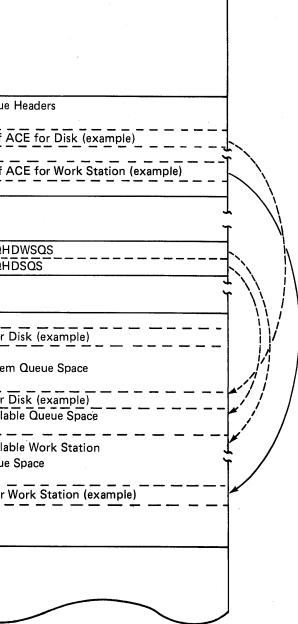

### Main Storage Initial Program Load (MSIPL)

## Stage 3

Initialization of main storage completes the hardware and software tasks necessary to load the System Support Program Product (SSP) and ready the system for customer user program requests. The initialization is performed in three phases.

Phase 1: The main storage module (#MSNIP) initializes main storage. This module is the basic first step for all other modules that will be used during the main storage initial program load (MSIPL) sequence. The main functions of #MSNIP are to:

- Initialize the system communications area

- Assemble the resident library format 1

- · Determine the bad main storage locations

- Initialize the transient/transfer control table

- Determine the disk addresses as needed

- · Set the command processor task control block (TCB) to indicate any bad 2K storage blocks

- Increase the size of the assign/free area to permit assigning of main storage

- · Load and pass control to software module #MSTWA (phase 2)

Phase 2: Software module #MSTWA initializes the task and work areas in main storage. The main functions of #MSTWA are to:

- Initialize the transfer control table for the resident routine

- Initialize the task work area index

- · Initialize the terminal unit blocks

- · Initialize the task work areas for each work station

- Assemble the device allocate table

- · Load and pass control to software module #MSIPL (phase 3)

Phase 3: This phase controls the last main storage initial program load (MSIPL) and includes a group of software modules under the control of software module #MSIPL. The main functions of #MSIPL are to:

- · Perform the main storage initial program load sign-on request

- Process the override information if necessary

- Initialize the print spool function

- · Complete the nucleus initialization

Before MSIPL is complete, the #MSIPL module updates the instruction address register (IAR) in the request block (RB) stack to pass control to the command processor resident router. The supervisor task attach transient then attaches a task control block (TCB) to run file rebuild. Control then passes to the control processor resident router. The IPL SIGN-ON message is displayed on the system console display screen while phase 3 is completing many of the last tasks.

Initial program load is complete when SYSTEM CONSOLE DISPLAY appears on the display screen or COMMAND DISPLAY appears at one of the work stations. The customer now has an operational system and can process job requests.

Errors that occur during main storage initial program load cause two types of not normal terminations (abends):

- · Task-associated abends do not stop the system (except for the command processor task), but a dump of main or control storage is written to disk and only the error task is terminated while other tasks continue.

- System-associated abends are so severe that they do not permit any task to continue. The system must be stopped immediately so the damage can be contained and diagnosed. Two types of processor checks that cause system-related abends are:

- Hardware generated—The specified error is shown in the command processor unit status word indicators. (Set the Mode Selector switch on the CE panel to the Dply Chks position.)

- Software generated-Activated by the System Support Program Product when an error occurs that cannot permit the operation to continue. (A display of selected local storage registers describes the error more fully.)

For detailed information on errors, see Appendix G. Troubleshooting Aids and Appendix I. Hardware Diagnostic Information in the Data Areas Handbook.

To run a complete test of the I/O devices, run the SYSTST program. SYSTST checks all the mechanical parts of all the I/O devices, the system program, and the I/O routines.

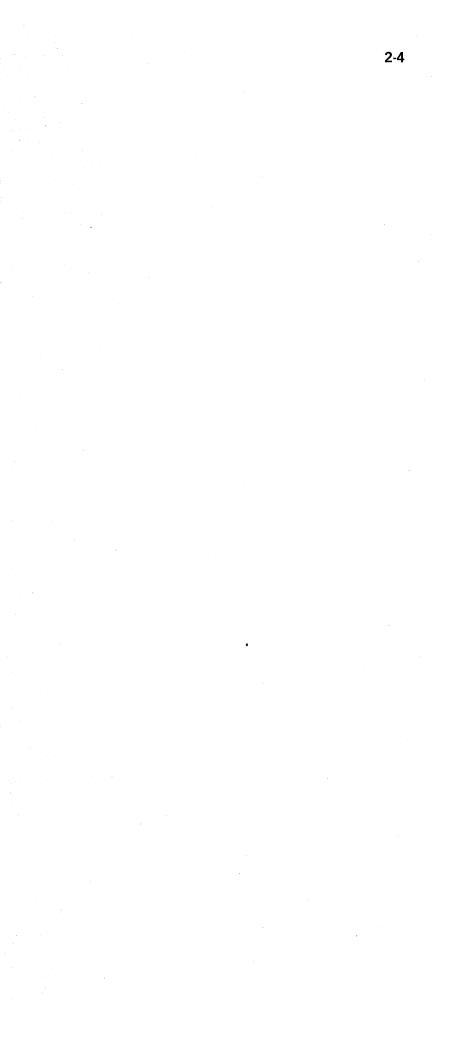

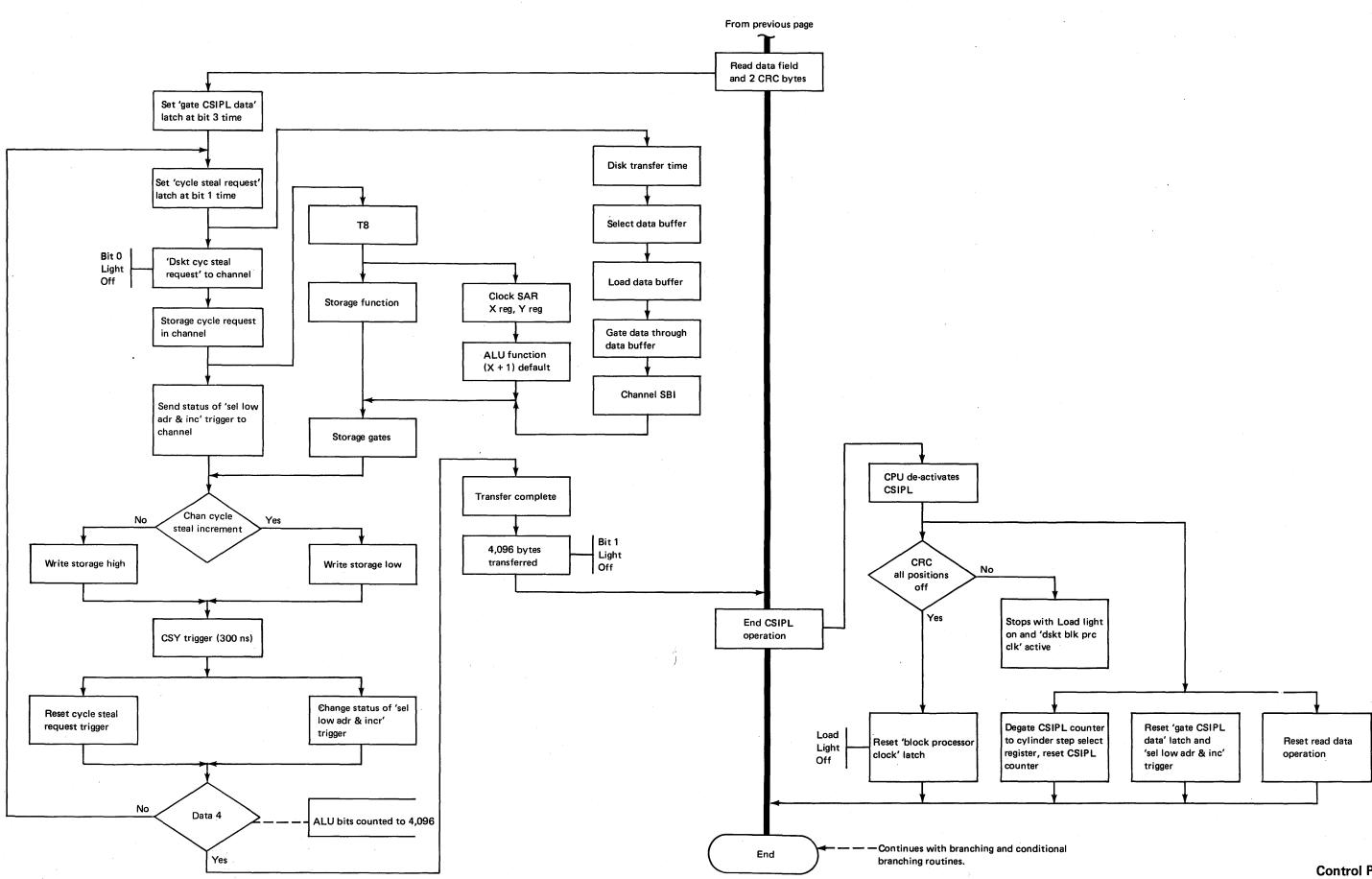

# **IPL Timing Sequence**

Pressing and releasing the Load switch starts the control storage initial program load (CSIPL) sequence and the Load light is set to on. The CSIPL, along with the ALU high 'data 4' and the '150-ns tgr' lines, causes the 'transfer complete' line to be activated.

| CSIPL Sequence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Load Pressed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Phase A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| System Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| (special) System Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| New CSIPL Cycle (to I/O)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| CSIPL Cycle (and) ALU High Data 4 (and)<br>150-ns Trigger (4,096 bytes transferred) <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Transfer Complete Latch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Run Latch OCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Block Processor Clock (BPC tgr) <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Load Indicator (light)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Data Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| CP Clocks Run <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| and the second states are set of the second states |

Note: The Load light continues to be set on if: (1) the block processor clock is not de-activated, (2) the disk is not ready, or (3) a processor check occurs.

<sup>1</sup> This line cannot be probed.

<sup>2</sup> The 'block processor clock' line is active as shown for 62EH disk drives. The line will be pulsing if 62PC disk drives are installed.

### **Display Light Sequence (Byte 0)**

The Load light and all nine display lights (display byte 0 on the CE panel) are set to on when the operator presses the Load switch. When the Load switch is released, the control storage initial program load (CSIPL) sequence starts and 2K words are moved into control storage (from either the disk or a diskette). At the end of the move of 2K words, the Load light is reset to off if no error was sensed. The lights are reset to off as described below as the sequence advances. If CSIPL is not completed, the lights that represent the part of CSIPL that was not completed continue to be set on. The Mode Selector switch must be in the Proc Run position for the lights to appear when set to on (clock running).

If during the CSIPL, the system has a processor check, and byte 0 bits P0, 0, 1, and 2 are reset to off, and either bit 3, 4, 5, 6, or 7 is set to on, this indicates that the control processor has failed in one of its bring-up diagnostic routines. To determine which routine failed (for routine numbers larger than 08), display work register 3 low. This register will contain the hexadecimal number that identifies the failing routine. See Section 99 of the 5340 System Unit Maintenance Manual for routine numbers.

Each light is reset to off and remains off as follows:

- **P0**<sup>1</sup> The adapter has received the 'load' signal and made active the 'disk/dskt block processor clock' signal to start data transmission by a burst-cycle-steal-mode operation. **O**<sup>1</sup> The first cycle steal request was received and data transmission was started (write trigger). 11 The transmission of 4,096 bytes of data was completed. The data transmission was Load<sup>1</sup> completed with no data check. 2 The branch and branch-on-condition routines have completed. Parity checks are reset during routine 2. 3 The second load of control storage was completed and the first instruction was executed. 4 The control storage test was run correctly. 5 The third load of control storage

- was completed and the first instruction was executed.

- 6 The main storage test ran correctly. Start executing the wrap loader control program.

7

The System Support Program Product or the diagnostic supervisor was loaded. After loading, the initial program load sequence is complete and the system is ready to run user programs or diagnostic programs.

<sup>1</sup>Reset by hardware controls. The other lights are reset by control storage instructions.

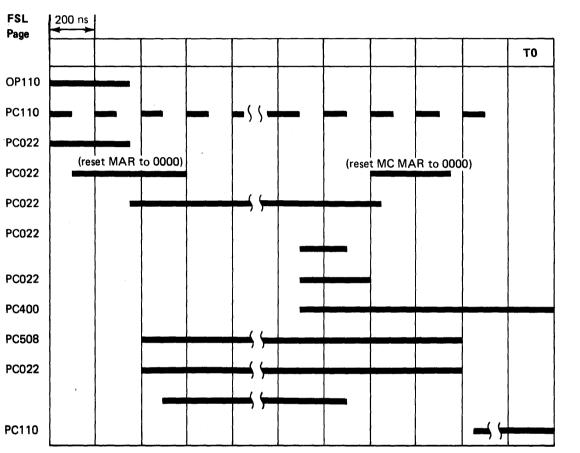

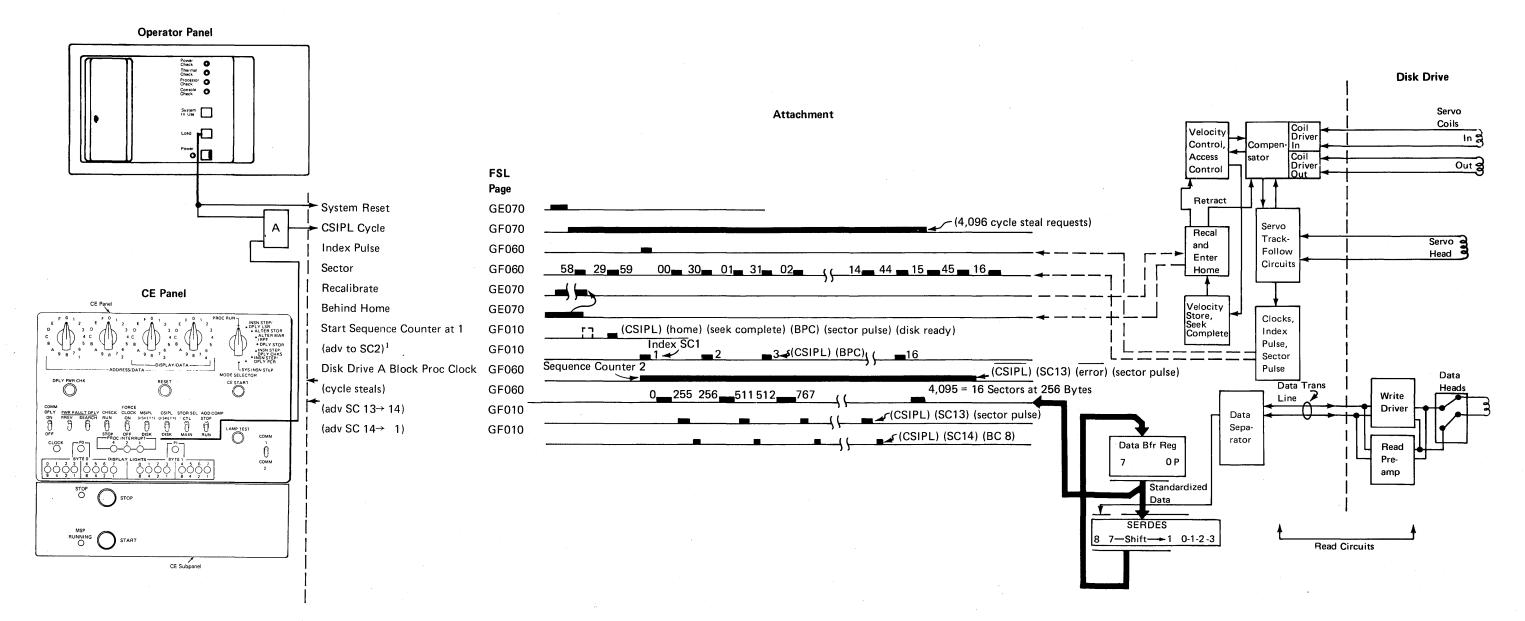

# **Disk Operation**

When the operator presses the Load switch, the control storage initial program load (CSIPL) sequence does three partial control storage loads. Then, it loads the control storage program from cylinder 0, track 1, sector 0-3B, and takes control at hexadecimal location 1E00 of control storage.

The control storage program has routines that load and control the main storage initialization along with loading the System Support Program Product.

First Load: Hardware loads 2K words into control storage at hexadecimal locations 0000 through 07FF. These words contain the following:

|                                                       | Words |

|-------------------------------------------------------|-------|

| Direct area (the unit definition table and addresses) | 128   |

| Control processor instruction tests                   | 1,408 |

| Disk loader                                           | 512   |

Second Load: The disk loader loads 2K words into control storage at hexadecimal locations 0800 through OFFF. These words contain the following:

|                                                  | Words |

|--------------------------------------------------|-------|

| Remainder of control processor instruction tests | 1,792 |

| Control storage tests                            | 256   |

Addresses (Hex) 0000-007F 0080-05FF 0600-07FF

Addresses (Hex)

0000-0EFF

0F00-0FFF

Third Load: The disk loader loads 3.5K words into control storage at hexadecimal locations 0080 through 0E7F. These words contain the following:

|   | And a second sec | Words     | Addresses (Hex) |

|---|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|

|   | Main storage processor<br>basic tests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 640       | 0080-027F       |

|   | Wrap loader and control program subroutines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 128       | 0280-02FE       |

|   | Wrap loader and control program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 512       | 02FF-047F       |

|   | Wrap device identification and location table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 256       | 0480-057F       |

|   | Wrap device and unit definition table                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 256       | 0580-067F       |

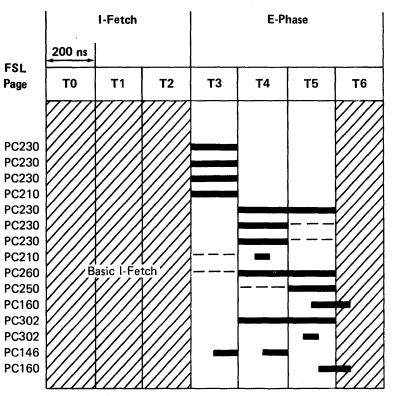

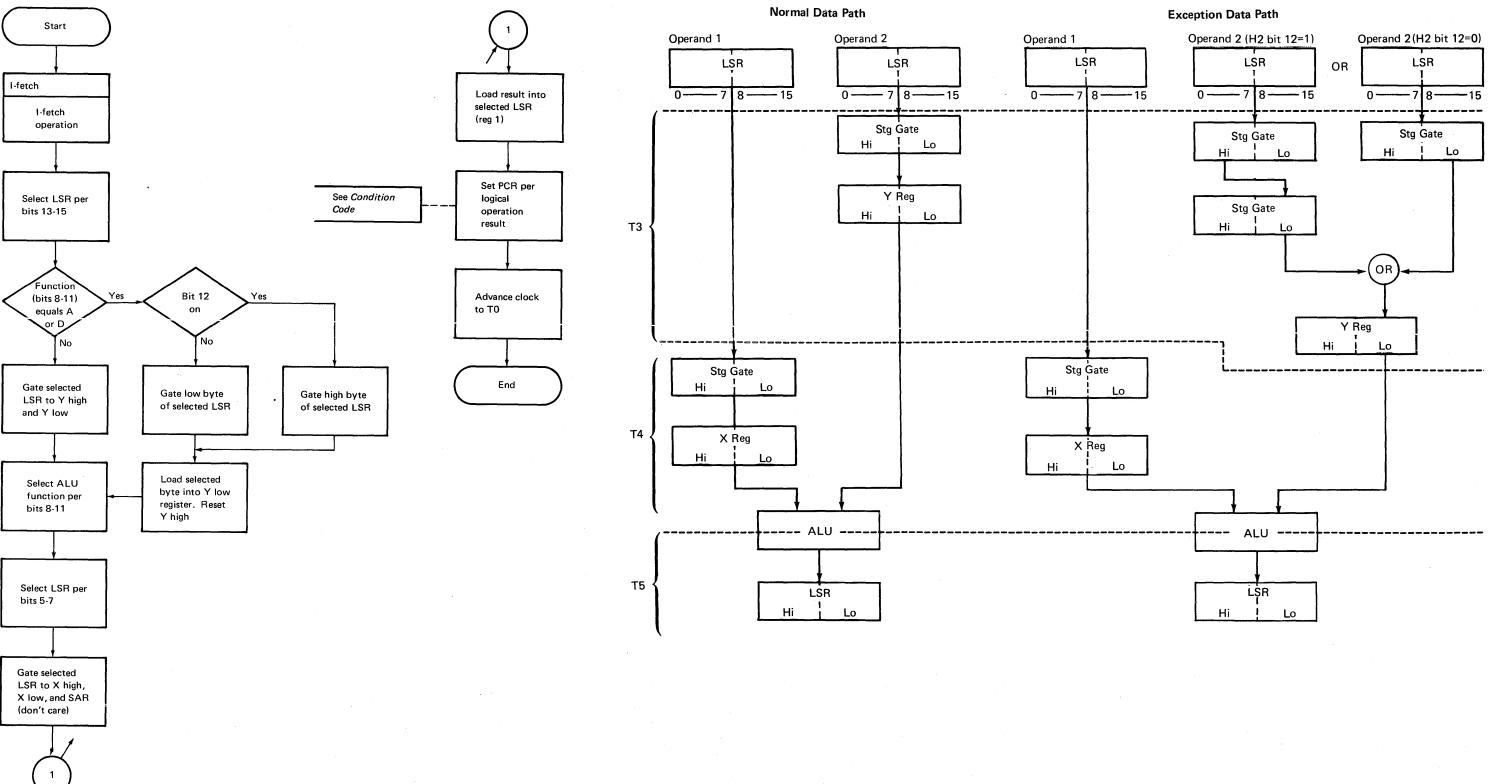

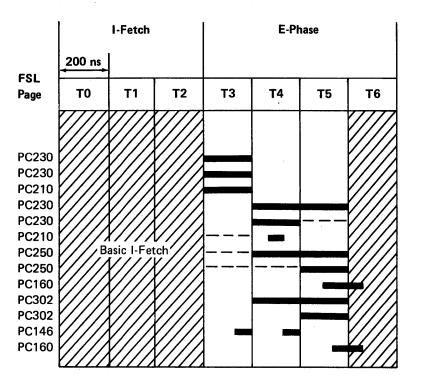

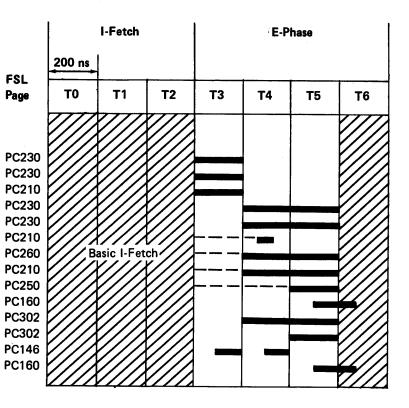

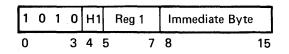

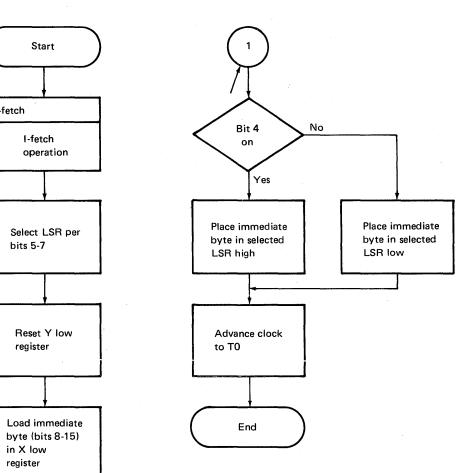

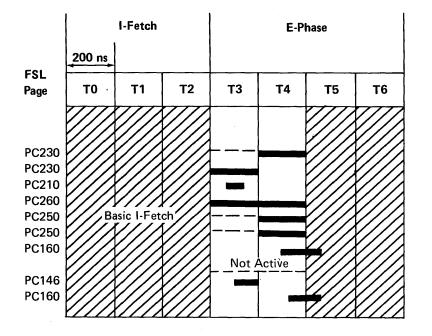

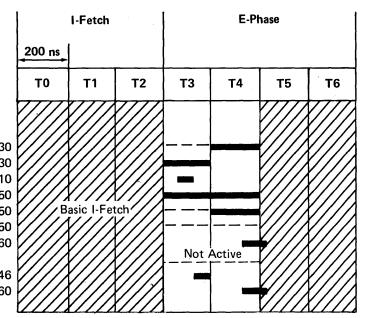

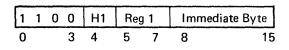

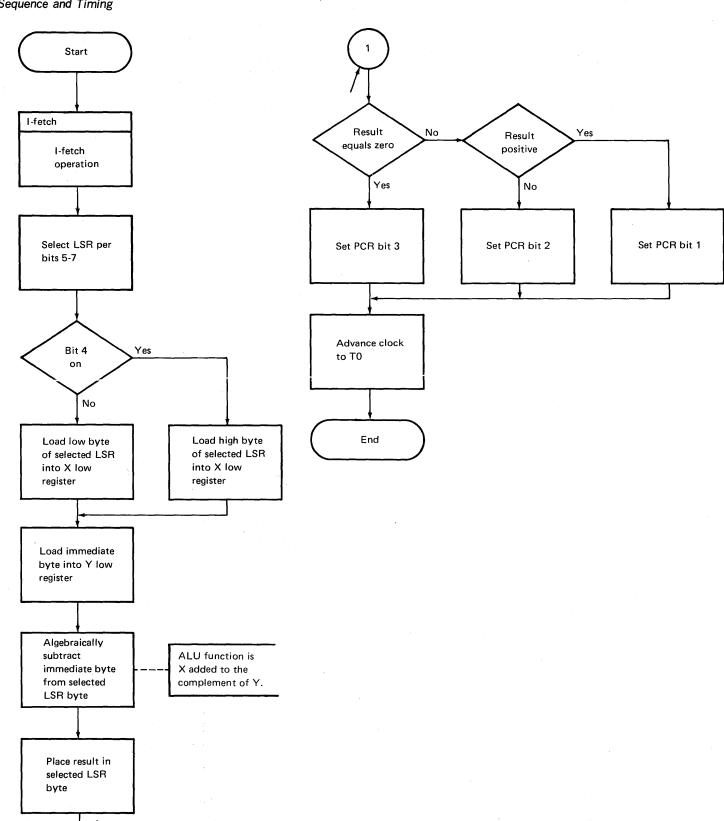

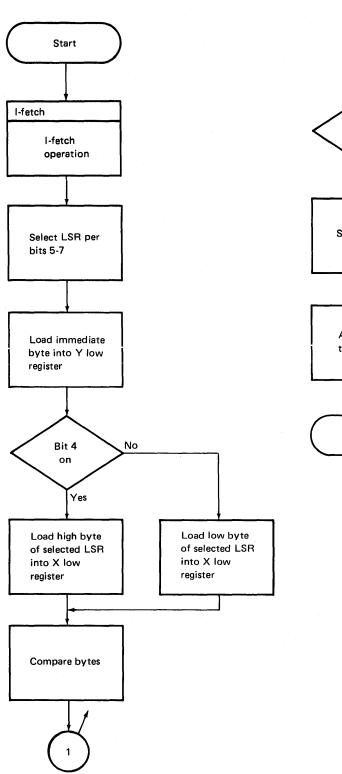

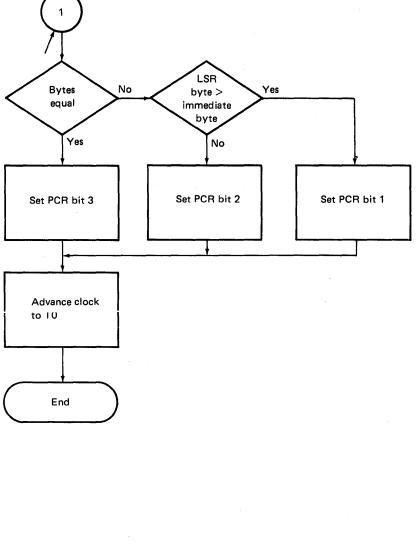

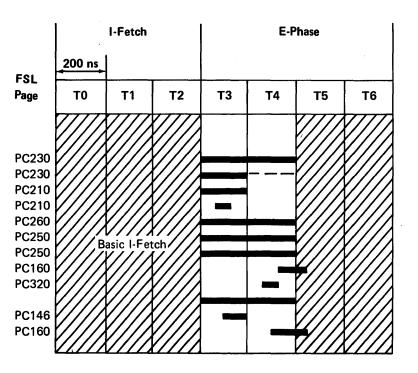

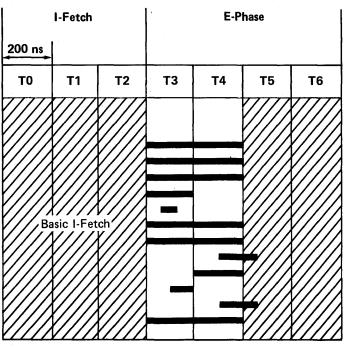

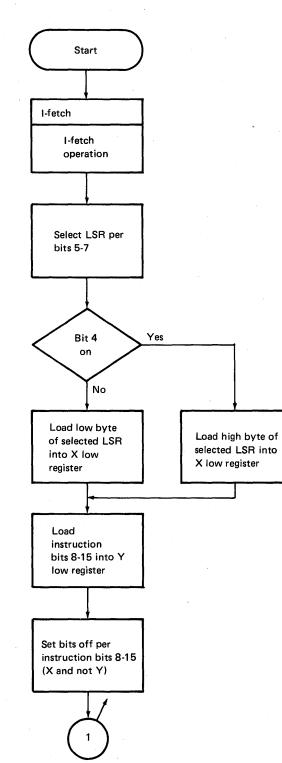

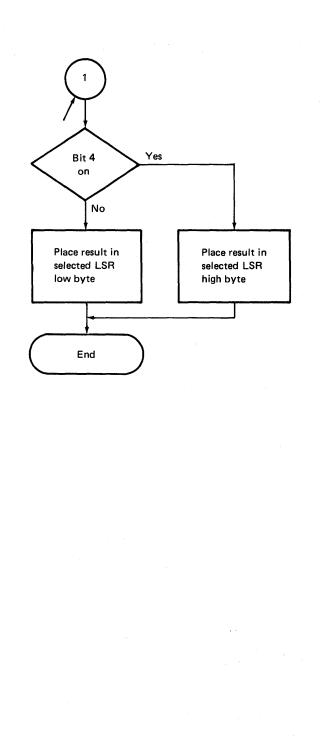

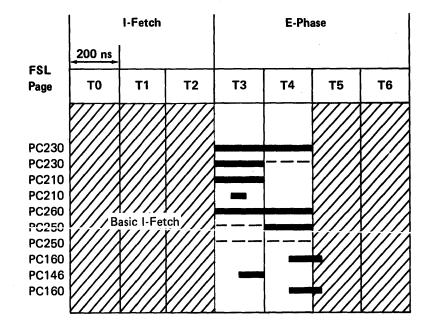

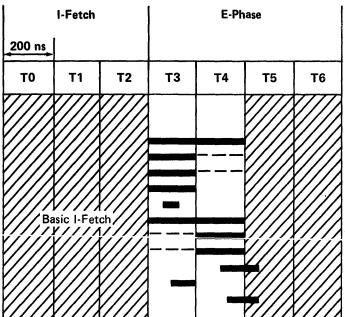

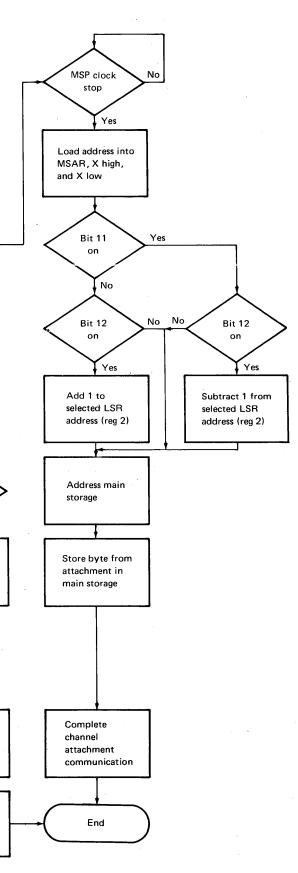

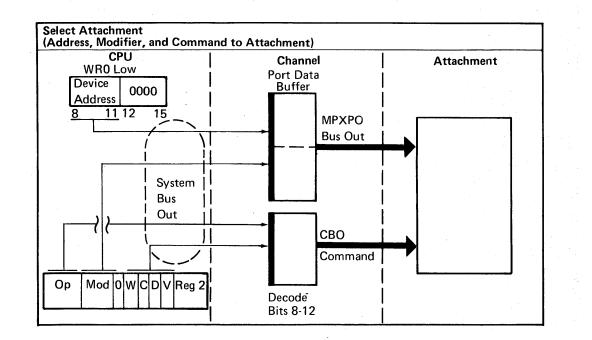

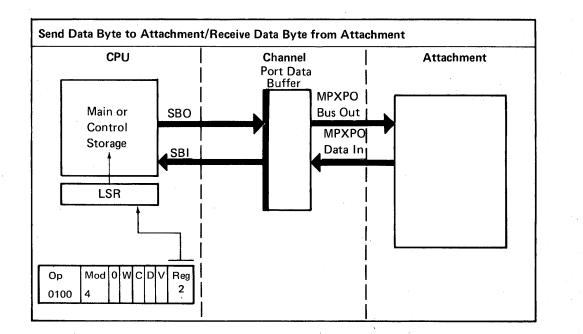

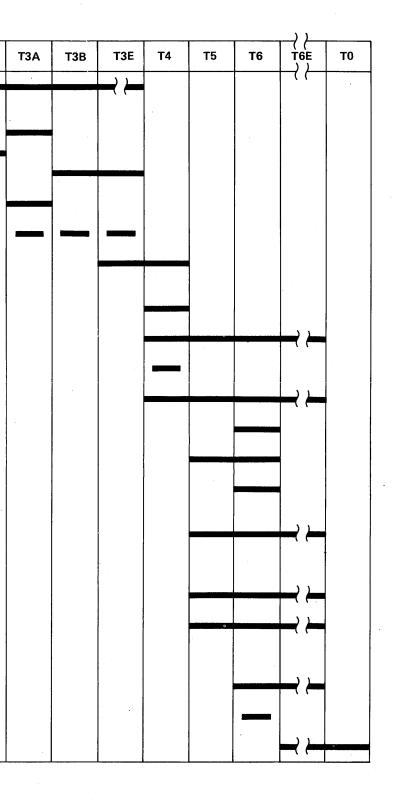

|   | Additional subroutines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 128       | 0680-06FF       |