### Contents

| ATTACHMENT CONTROLLER                       | . <b>16-1</b> |

|---------------------------------------------|---------------|

|                                             | . 16-1        |

| DATA FLOW                                   | . <b>16-2</b> |

| FUNCTIONAL UNITS                            |               |

| Processor-to-Processor Interface            |               |

| Control Processor Channel Adapter           |               |

| Command Bus out                             |               |

| Data Bus Out                                | 16-3          |

| Data Buffer                                 | 16-3          |

| Data Transfer Control                       | 16-3          |

| Command Bus In                              | 16-3          |

| Data Bus In                                 | 16-3          |

| Interrupt Request A Register                | 16-4          |

| Attachment Processor Channel Adapter        | 16-4          |

| Interrupt Request X and Y Register          | 16-4          |

| Attachment Processor Channel                | 16-5          |

| Attachment Processor Channel Controls       | 16-5          |

| I/O Data Bus In                             | 16-5          |

| I/O Command Bus In                          | 16-5          |

| I/O Command Bus Out                         | 16-5          |

| I/O Data Bus Out                            | 16-6          |

| Data Buffer                                 | 16-6          |

| Channel Register                            | 16-6          |

| Channel Check Register                      | 16-6          |

| Interrupt Timer                             | 16-6          |

| Interrupt Controls                          | 16-6          |

| 20 mHz Oscillator                           | 16-6          |

| Attachment Processor                        | 16-6          |

| Storage Controls                            | 16-6          |

| Micro Operation Register                    |               |

| Processor Checks Register                   |               |

| Controller Storage                          |               |

| X-Register and Y-Register                   |               |

| Arithmetic and Logic Unit                   |               |

| Storage Data Register                       |               |

| Local Storage Registers                     |               |

| Processor Condition Register                |               |

|                                             | 10 /          |

| PROCESSOR-TO-PROCESSOR INTERFACE            |               |

| OPERATIONS                                  | . 16-8        |

| Control Processor Commands                  |               |

| I/O Load Command                            |               |

| I/O Control Load Command                    |               |

| I/O Sense Command                           |               |

| Sense Interrupt Level Status Byte Command . |               |

| Schoe menupi Level Status byte Command .    | 10-14         |

| Attachment Processor Commands                                                                                                                                                                                                                                                                                                                                                                                      | 16-15                                                                                                                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I/O Load Command                                                                                                                                                                                                                                                                                                                                                                                                   | 16-15                                                                                                                                                                               |

| I/O Control Load Command                                                                                                                                                                                                                                                                                                                                                                                           | 16-17                                                                                                                                                                               |

| I/O Sense Command                                                                                                                                                                                                                                                                                                                                                                                                  | 16-19                                                                                                                                                                               |

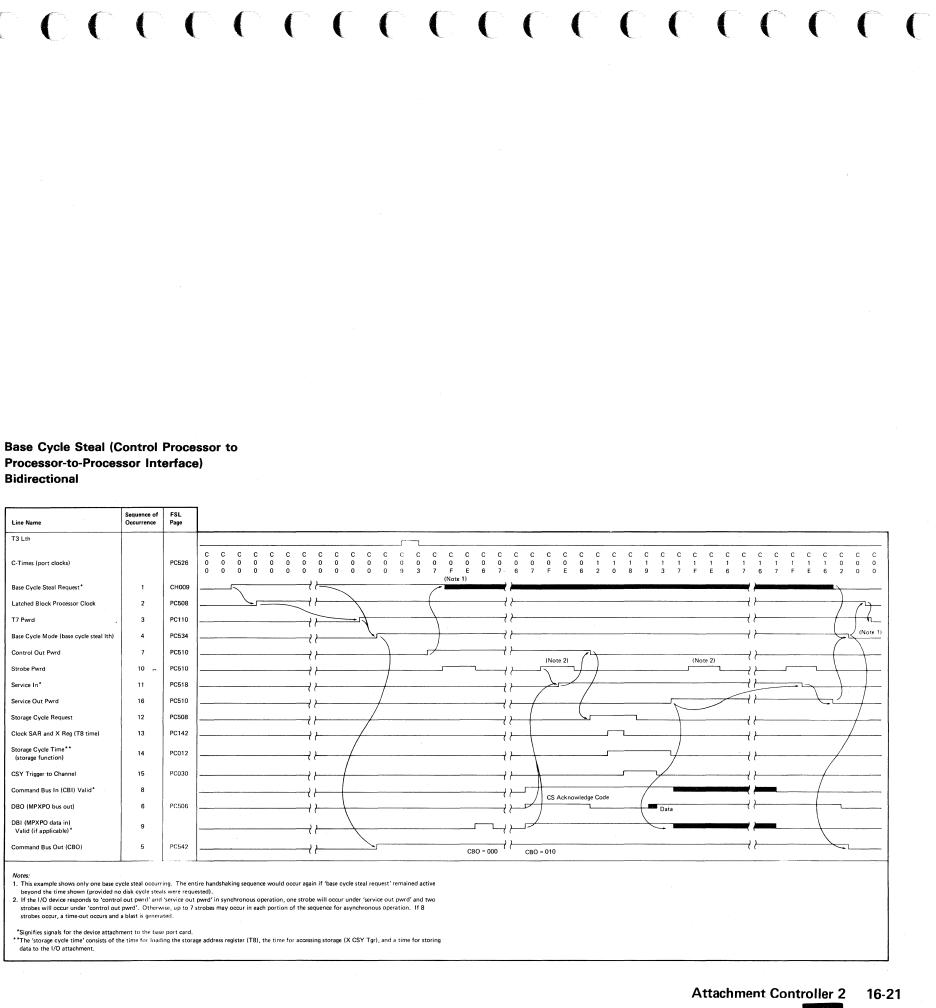

| Data Transfer Modes                                                                                                                                                                                                                                                                                                                                                                                                | 16-21                                                                                                                                                                               |

| Base Cycle Steal (Attachment Processor to                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                     |

| Processor-to Processor Interface)                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                     |

| Bidirectional                                                                                                                                                                                                                                                                                                                                                                                                      | 16-21                                                                                                                                                                               |

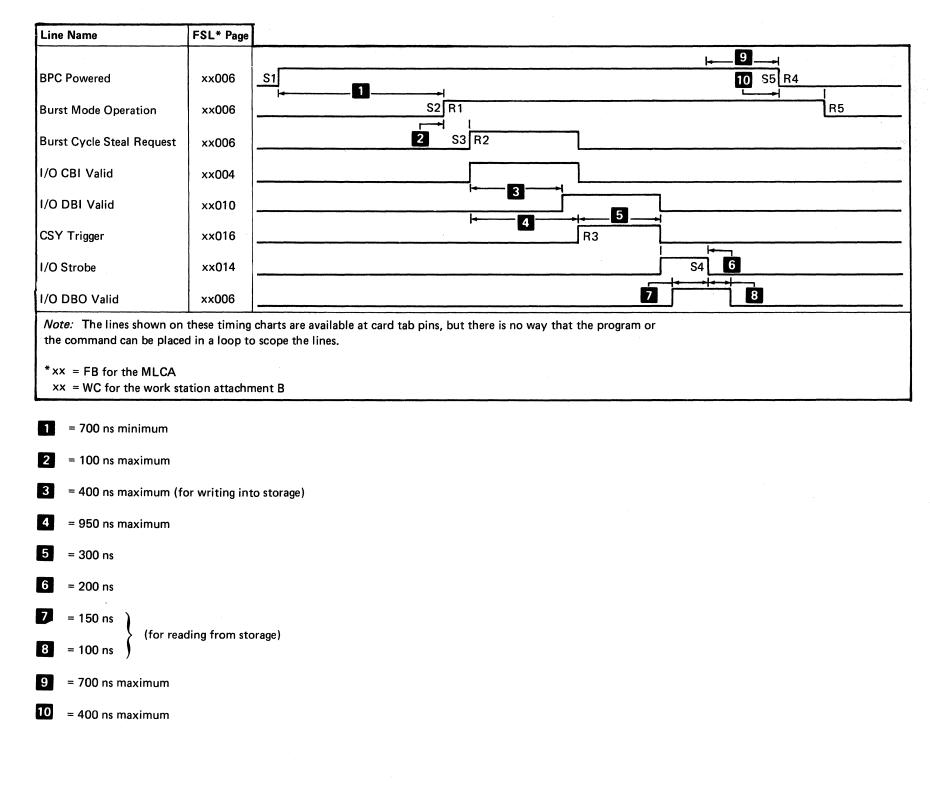

| Burst Cycle Steal (Attachment Processor to                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     |

| Processor-to- Processor)                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                     |

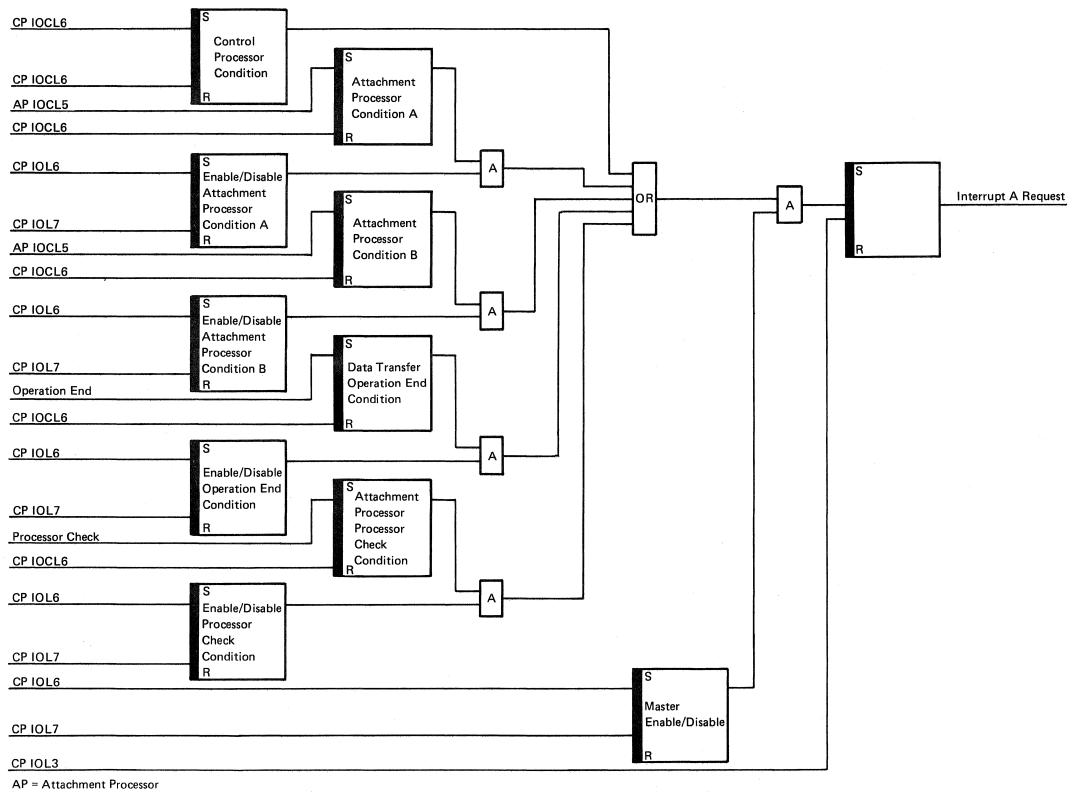

| Control Processor Interrupts                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                     |

| Attachment Processor Conditions                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

| Control Processor Condition                                                                                                                                                                                                                                                                                                                                                                                        | 16-23                                                                                                                                                                               |

| Hardware Conditions                                                                                                                                                                                                                                                                                                                                                                                                | 16-23                                                                                                                                                                               |

| Resetting the 'Interrupt A Request' Line                                                                                                                                                                                                                                                                                                                                                                           | 16-23                                                                                                                                                                               |

| Attachment Processor Interrupts                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

| Interrupt X Request                                                                                                                                                                                                                                                                                                                                                                                                | 16-25                                                                                                                                                                               |

| Control Processor Conditions                                                                                                                                                                                                                                                                                                                                                                                       | 16-25                                                                                                                                                                               |

| Attachment Processor Conditions                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

| Hardware Condition                                                                                                                                                                                                                                                                                                                                                                                                 | 16-25                                                                                                                                                                               |

| Resetting the 'Interrupt X Request' Line                                                                                                                                                                                                                                                                                                                                                                           | 16-25                                                                                                                                                                               |

| Interrupt Y Request                                                                                                                                                                                                                                                                                                                                                                                                | 16-27                                                                                                                                                                               |

| Resetting the 'Interrupt Y Request' Line                                                                                                                                                                                                                                                                                                                                                                           | 16-27                                                                                                                                                                               |

| ATTACHMENT PROCESSOR CHANNEL                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                     |

| OPERATIONS                                                                                                                                                                                                                                                                                                                                                                                                         | 10.00                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     |

| Commands                                                                                                                                                                                                                                                                                                                                                                                                           | 16-28                                                                                                                                                                               |

| Commands                                                                                                                                                                                                                                                                                                                                                                                                           | 16-28<br>16-28                                                                                                                                                                      |

| Commands                                                                                                                                                                                                                                                                                                                                                                                                           | 16-28<br>16-28<br>16-31                                                                                                                                                             |

| Commands                                                                                                                                                                                                                                                                                                                                                                                                           | 16-28<br>16-28<br>16-31<br>16-33                                                                                                                                                    |

| Commands       I/O Immediate         I/O Immediate       I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal       Interrupts                                                                                                                                                                                                                                                                            | 16-28<br>16-28<br>16-31<br>16-33<br>16-35                                                                                                                                           |

| Commands                                                                                                                                                                                                                                                                                                                                                                                                           | 16-28<br>16-28<br>16-31<br>16-33<br>16-35                                                                                                                                           |

| Commands       I/O Immediate         I/O Immediate       I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal       Interrupts                                                                                                                                                                                                                                                                            | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-35                                                                                                                                  |

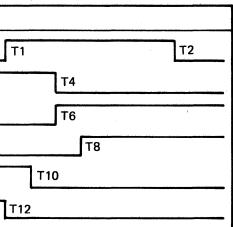

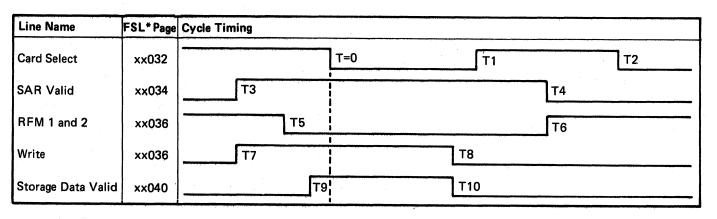

| Commands       I/O Immediate         I/O Immediate       I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal       Interrupts         Interrupts       Interrupts         Fixed-Interval Timer       Interrupts         STORAGE INTERFACE       Interrupts         Read Cycle       Interrupts                                                                                                           | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37                                                                                                         |

| Commands       I/O Immediate         I/O Immediate       I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal       Interrupts         Interrupts       Interrupts         Fixed-Interval Timer       Interrupts         STORAGE INTERFACE       Interrupts         Write Cycle       Interrupts                                                                                                          | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38                                                                                                |

| Commands       I/O Immediate         I/O Immediate       I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal       Interrupts         Interrupts       Interrupts         Fixed-Interval Timer       Interrupts         STORAGE INTERFACE       Interrupts         Write Cycle       Interrupts         Read Cycle       Interrupts         Refresh Cycles       Interrupts                              | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38                                                                                       |

| Commands       I/O Immediate         I/O Immediate       I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal       Interrupts         Interrupts       Interrupts         Fixed-Interval Timer       Interrupts         STORAGE INTERFACE       Interrupts         Write Cycle       Interrupts                                                                                                          | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38                                                                                       |

| Commands       I/O Immediate         I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal         Interrupts         Fixed-Interval Timer         STORAGE INTERFACE         Read Cycle         Write Cycle         Refresh Cycles         Adjusting Storage Size                                                                                                                                          | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-38<br>16-38<br>16-38                                                                                       |

| Commands                                                                                                                                                                                                                                                                                                                                                                                                           | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38<br>16-38<br>16-38                                                                     |

| Commands       I/O Immediate         I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal         Interrupts         Fixed-Interval Timer         STORAGE INTERFACE         Read Cycle         Write Cycle         Refresh Cycles         Adjusting Storage Size         BBO Parity Checks                                                                                                                | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38<br>16-38<br>16-38<br>16-38                                                            |

| Commands       I/O Immediate         I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal         Interrupts         Fixed-Interval Timer         STORAGE INTERFACE         Read Cycle         Write Cycle         Refresh Cycles         Adjusting Storage Size         DBO Parity Checks         Checks on the Attachment Processor Channel                                                             | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38<br>16-38<br><b>16-39</b><br>16-39<br>16-39                                            |

| Commands       I/O Immediate         I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal         Interrupts         Fixed-Interval Timer         STORAGE INTERFACE         Read Cycle         Write Cycle         Refresh Cycles         Adjusting Storage Size         BBO Parity Checks         Checks on the Attachment Processor Channel         Blast Condition                                     | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38<br>16-38<br>16-38<br>16-39<br>16-39<br>16-39<br>16-39                                 |

| Commands       I/O Immediate         I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal         Interrupts         Fixed-Interval Timer         STORAGE INTERFACE         Read Cycle         Write Cycle         Refresh Cycles         Adjusting Storage Size         DBO Parity Checks         Checks on the Attachment Processor Channel                                                             | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38<br>16-38<br>16-38<br>16-39<br>16-39<br>16-39<br>16-39                                 |

| Commands       I/O Immediate         I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal         Interrupts         Fixed-Interval Timer         STORAGE INTERFACE         Read Cycle         Write Cycle         Refresh Cycles         Adjusting Storage Size         BBO Parity Checks         Checks on the Attachment Processor Channel         Blast Condition                                     | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38<br>16-38<br>16-39<br>16-39<br>16-39<br>16-39<br>16-39                                 |

| Commands       I/O Immediate         I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal         Interrupts         Fixed-Interval Timer         STORAGE INTERFACE         Read Cycle         Write Cycle         Refresh Cycles         Adjusting Storage Size         DBO Parity Checks         Checks on the Attachment Processor Channel         Blast Condition         Attachment Processor Checks | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38<br>16-38<br>16-39<br>16-39<br>16-39<br>16-39<br>16-41<br>. <b>A-1</b>                 |

| Commands       I/O Immediate         I/O Storage (WTCL, WTCH, RDCL, RDCH)         Base Cycle Steal         Interrupts         Fixed-Interval Timer         STORAGE INTERFACE         Read Cycle         Write Cycle         Refresh Cycles         Adjusting Storage Size         DBO Parity Checks         Checks on the Attachment Processor Channel         Blast Condition         Attachment Processor Checks | 16-28<br>16-28<br>16-31<br>16-33<br>16-35<br>16-36<br><b>16-37</b><br>16-37<br>16-38<br>16-38<br>16-38<br>16-39<br>16-39<br>16-39<br>16-39<br>16-41<br>. <b>A-1</b><br>. <b>G-1</b> |

This page intentionally left blank.

### **Attachment Controller 2**

### INTRODUCTION

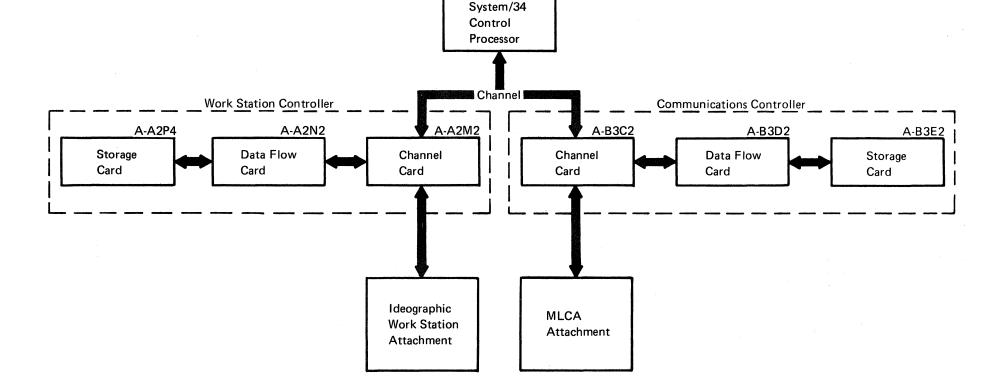

The Attachment Controller 2 is a double controller that is used with the ideographic work station feature and the MLCA (multiline communications adapter). The attachment controllers are located between the System/34 channel and the I/O attachments. The cards used for the attachment controllers and their locations are shown in the figure.

The channel cards connect the attachment controllers to the System/34 channel and supply the control logic and the lines that connect to the attachments.

The data flow cards contain the processing units and the storage interface.

The storage cards supply 32K of 2-byte words for the ideographic work station feature and 16K of 2-byte words for the MLCA.

Generally, the Attachment Controller 2 supplies:

- Sixteen-bit ALU and data flow

- Eight bits of data on both the DBI (data bus in) and the DBO (data bus out)

- Sixty-four, 16-bit general-purpose registers

- Five interrupt levels and branch and link

- Maintenance of odd-numbered parity throughout the data flow

- · Storage addressing lines for a maximum of 64K, 2-byte words

- · Cycle steal

- Addresses for a maximum of 14 I/O devices

Attachment Controller 2 16-1

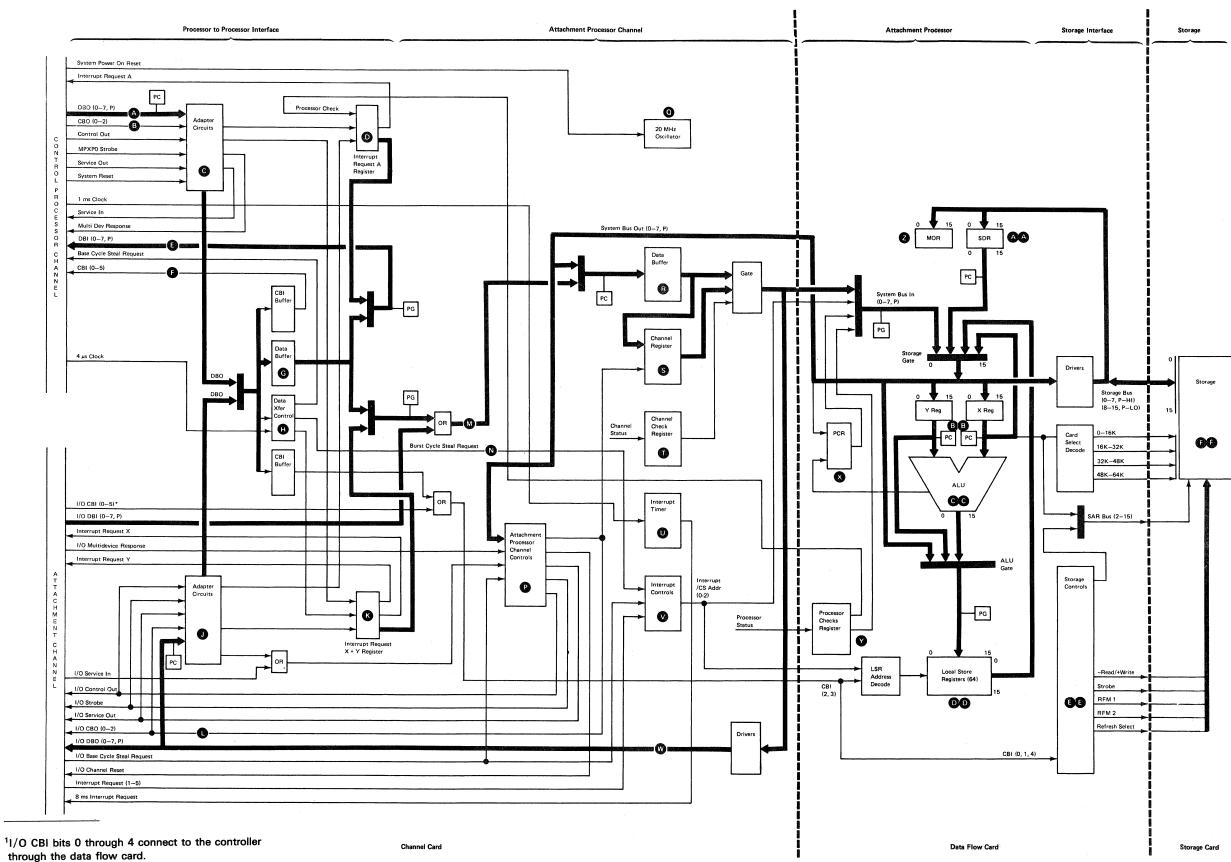

**DATA FLOW**

## $\begin{array}{c} \hline \end{array} \end{array}$

### **FUNCTIONAL UNITS**

### **Processor-to-Processor Interface**

The processor-to-processor interface is the logic that attaches the control processor to the attachment processor channel. This logic controls all communication between the control processor and the attachment processor. This communication is in the form of interrupts, data transfers, and I/O instructions. The processor-to-processor interface includes the control processor channel adapter circuits, the attachment processor channel adapter circuits, data buffers, data transfer controls, and interrupt request registers.

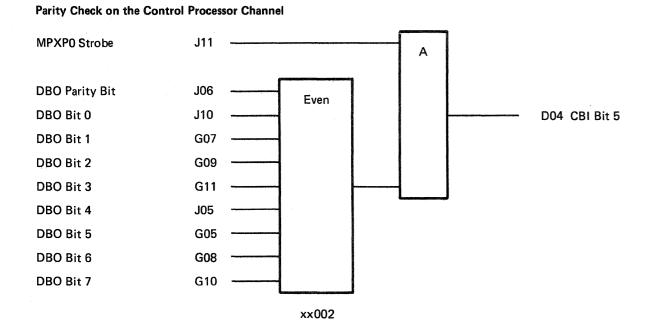

### Control Processor Channel Adapter

These circuits do the following:

- · Synchronize the control processor with the processor-to-processor interface

- Increase the power of the DBO

- · Check parity

- Decode device addresses

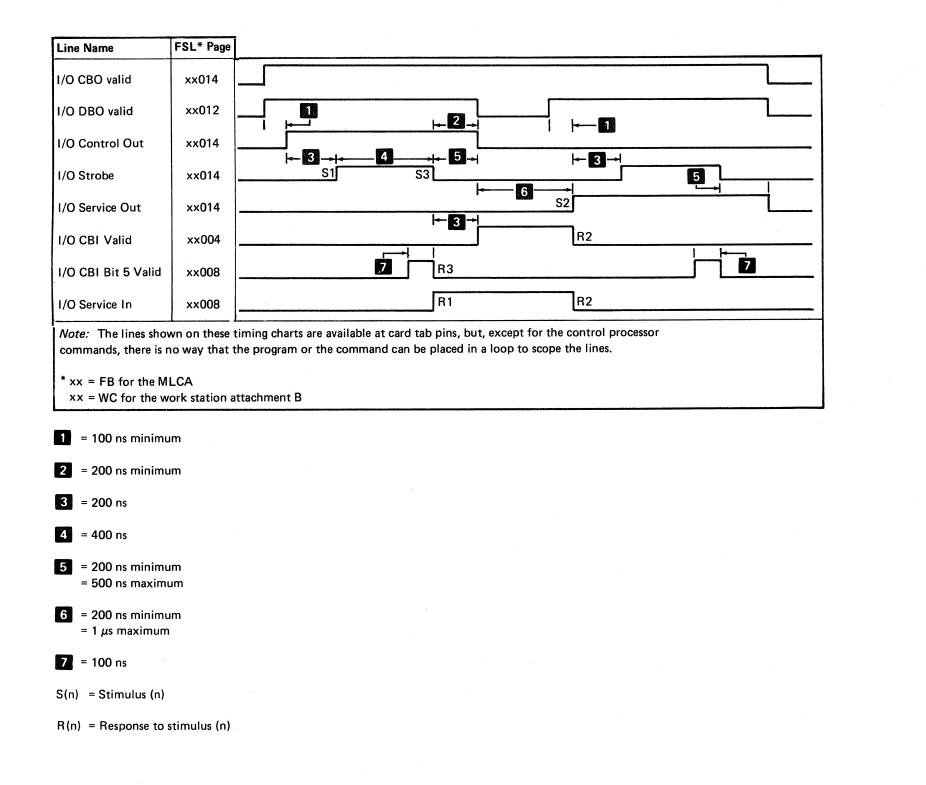

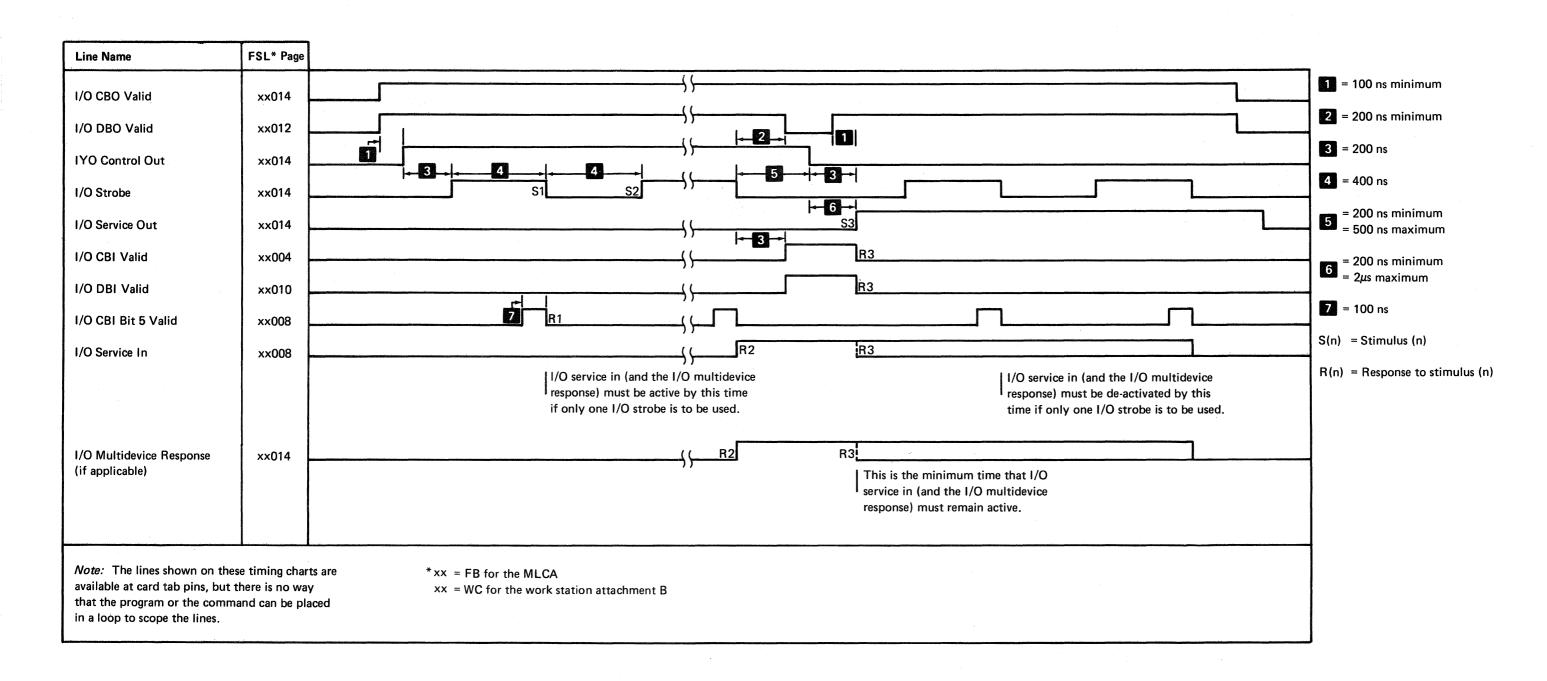

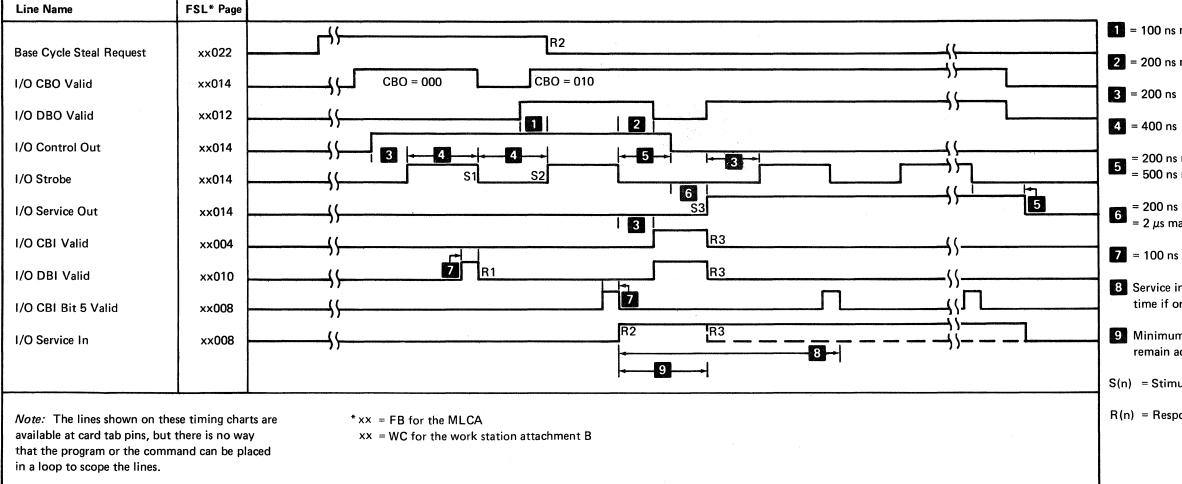

The control processor channel adapter circuits let the control processor channel communicate with the attachment processor through control lines and data buses. The 'control out', 'service out', and 'strobe' lines signal the adapter circuits when data is available on the DBO or when the data should be on the DBI. The 'service in' and 'multidevice response' lines signal the control processor channel that the data on the DBO has been received or that data is available on the DBI.

### Command Bus Out

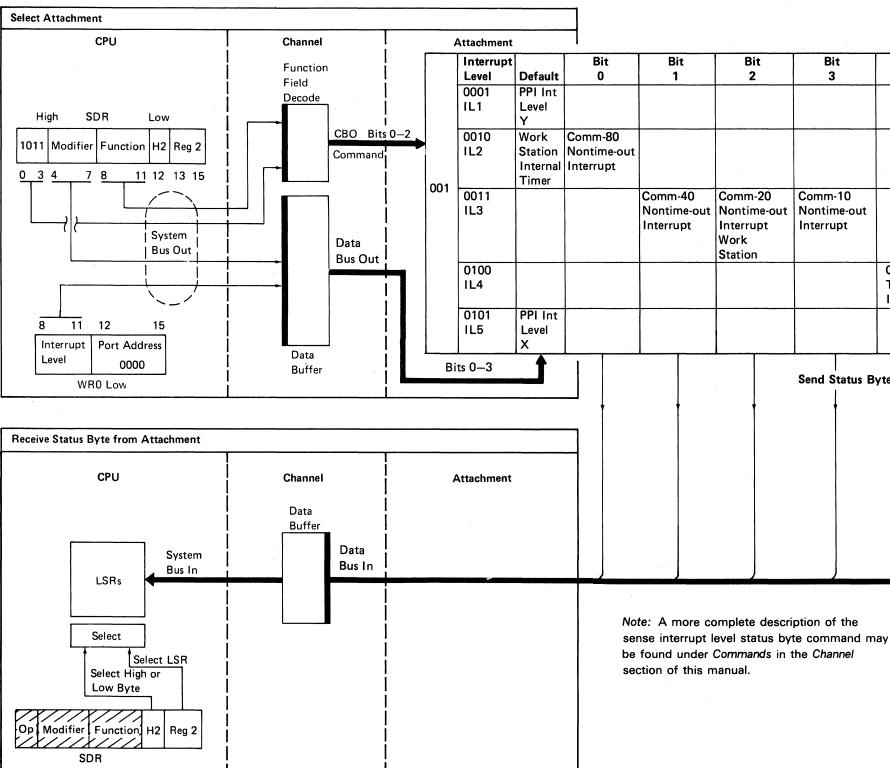

The command bus out (CBO) is a 3-bit bus that specifes the type of I/O operation to execute. The attachment controller commands are:

| Bits  |                                              |

|-------|----------------------------------------------|

| 012   | Command                                      |

| 000   | SCSSB (sense cycle steal status byte)        |

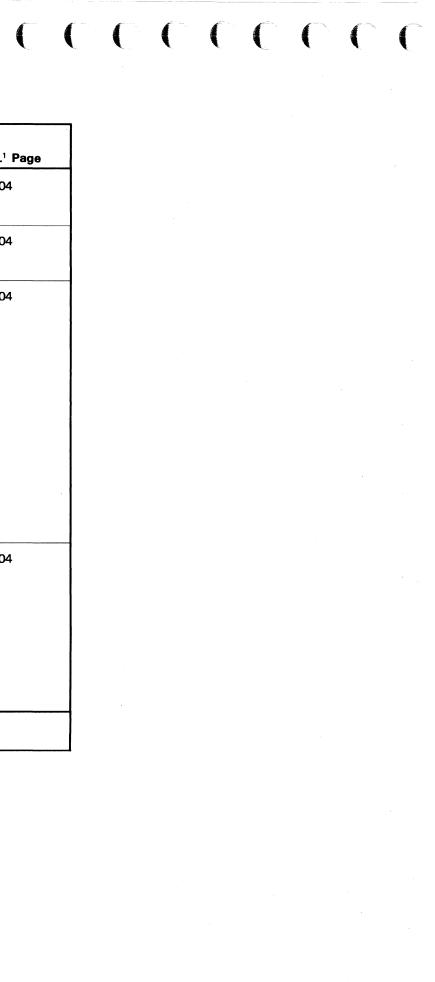

| 001   | SILSB (sense interrupt<br>level status byte) |

| 010   | CSACK (cycle steal<br>acknowledge)           |

| 011   | Not used                                     |

| 100   | I/O load                                     |

| 101   | I/O sense                                    |

| 1 1 0 | I/O control load                             |

| 111   | Not used                                     |

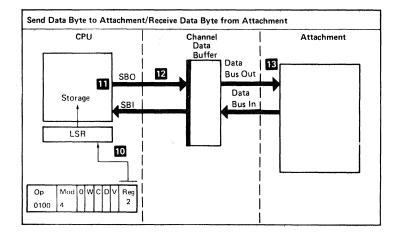

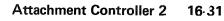

### Data Bus Out A

The data bus out (DBO) is a 9-bit bus (0 through 7, P) that is used in the following ways:

- · During control out of an SILSB command, DBO bits 0 through 3 contain the interrupt level.

- During control out of any I/O command other than SILSB. DBO bits 0 through 3 contain the device address and bits 4 through 7 contain the command modifier.

- During control out of a CSACK command, the DBO contains the cycle steal address of the device selected to perform the base cycle steal.

- During service out of an I/O load or I/O control load command, the DBO contains data.

- During service out of a CSACK command. the DBO contains data.

### Data Buffer G

The data buffer contains two 1-byte buffers that are used when moving data and status information between the control processor channel and the attachment processor channel.

### Data Transfer Control 田

The data transfer control logic controls the movement of data between the control processor and the attachment processor. The data is moved by single byte base cycle steal between the control processor and the processor-to-processor interface and moved by single byte burst cycle steal between the attachment processor and the processor-to-processor interface. The cycle steals are started by I/O commands from either processor.

The data transfer control logic contains the following:

- · A byte counter to control the number of bytes moved. This counter can be set to any value from 0 through 511.

- · A buffer full latch to indicate when a byte of data is in the data buffer. This latch signals the receiving processor that data is available.

- · A cycle steal pacer to control the speed of the data movement between the two processors. The 4-microsecond clock from the control processor is used to delay the base cycle steal requests to the control processor. The length of the delay is set by an I/O command to the processor-to-processor interface.

### Command Bus In

The command bus in (CBI) is a 6-bit bus that supplies control information to the control processor channel. The CBI bits have the following meanings:

| Bit  | Mea | ning |                             |

|------|-----|------|-----------------------------|

| 0    | 0   | =    | Base c<br>high by<br>increm |

|      | 1   | =    | Base c<br>low by<br>increm  |

| 1    | 0   | =    | Base c<br>sense             |

|      | 1   | =    | Base c<br>load              |

| 2, 3 | 00  | =    | Base c<br>WR4 o<br>level 4  |

|      | 01  | =    | Base c<br>WR5 c<br>level 4  |

|      | 10  | =    | Base c<br>WR6 o<br>level 4  |

|      | 11  | =    | Base c<br>WR7 o<br>level 4  |

| 4    | 0   | =    | Contro                      |

|      | 1   | =    | Main s                      |

| 5    | 1   | =    | Parity (<br>parity)         |

|      |     |      |                             |

The CBI is active during I/O commands and base cycle steal operations.

cycle steal yte (WR not nented)

cycle steal rte (WR nented)

cycle steal

cycle steal

cycle steal on interrupt

cycle steal on interrupt

cycle steal on interrupt

cycle steal on interrupt

ol storage

storage

error (even

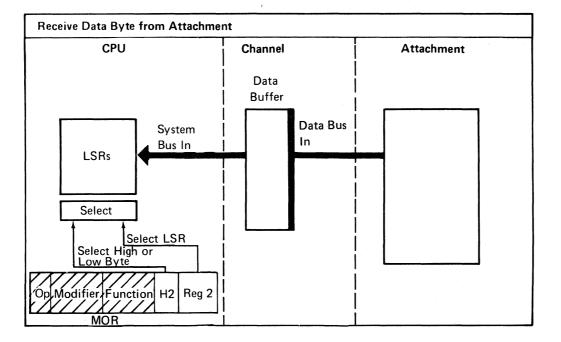

### Data Bus In 🚯

The data bus in (DBI) is a 9-bit bus (0-7, P) that is used in the following ways:

- During I/O sense commands, the DBI contains data or sense information.

- During base cycle steal operations, the DBI contains data.

- · During SILSB and SCSSB commands, the DBI contains sense information.

Attachment Controller 2 16-3

### Interrupt Request A Register D

The interrupt request A register supplies the 'interrupt request A' line to the control processor. This interrupt can be set by any of the following conditions:

- Attachment processor condition A, and attachment processor condition B. These conditions are set by the attachment processor and are anded with an enable/disable latch.

- Data transmission operation end condition. This condition is anded with an enable/disable latch and set by the processor-to-processor interface.

This interrupt indicates to the control processor that the data transfer byte counter has reached zero (the data transmission between the control processor and the attachment processor has completed).

- Attachment controller processor check condition. This condition is anded with an enable/disable latch and set by the attachment controller hardware. This interrupt indicates to the control processor that the attachment processor has stopped because of an error.

- · Control processor condition. This condition is set by the control processor for diagnostic purposes only.

### Attachment Processor Channel Adapter

These circuits do the following:

- Synchronize the attachment processor channel with the processor-to-processor interface

- Increase the power of the DBO

- Check parity

- Decode device addresses

The attachment processor channel adapter circuits let the attachment processor channel communicate with the control processor through control lines and data buses. These circuits control the execution of I/O commands and data transmissions from the attachment processor. The processor-to-processor interface receives and executes commands from the attachment processor. These commands are:

- I/O load

- I/O control load

- I/O sense

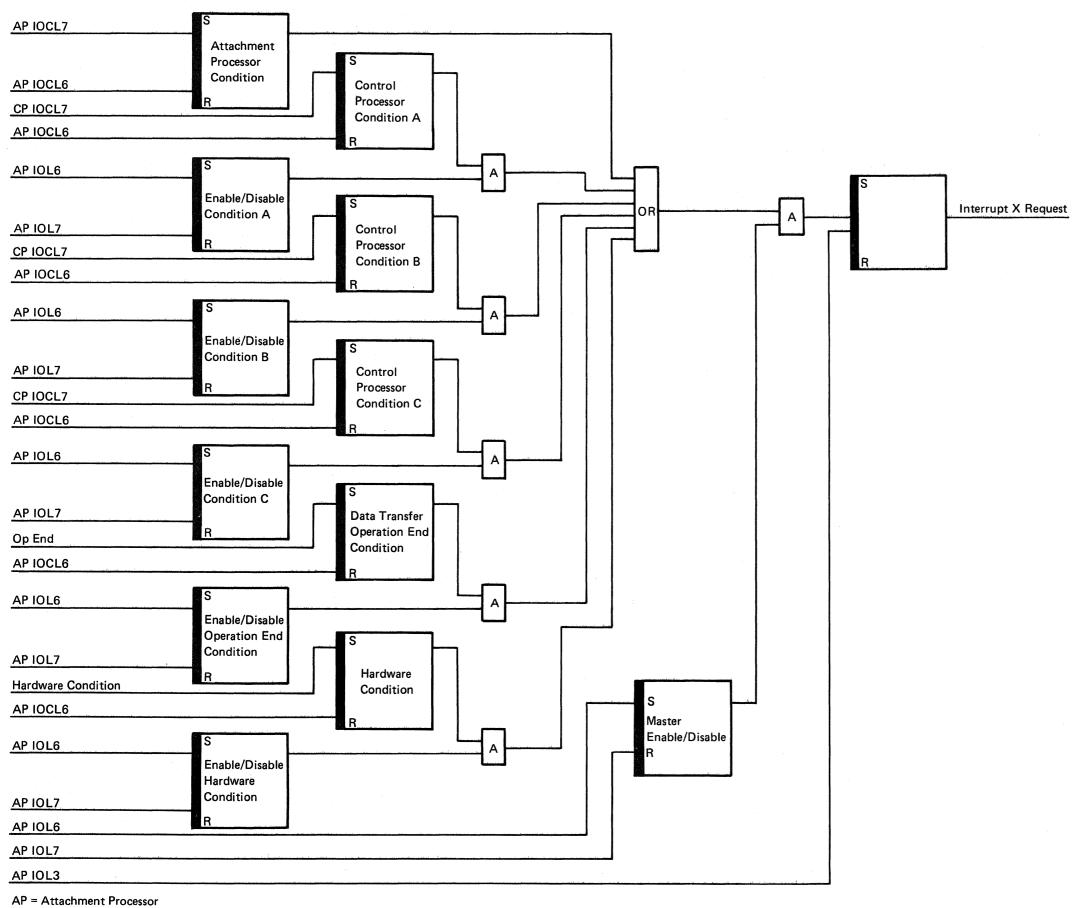

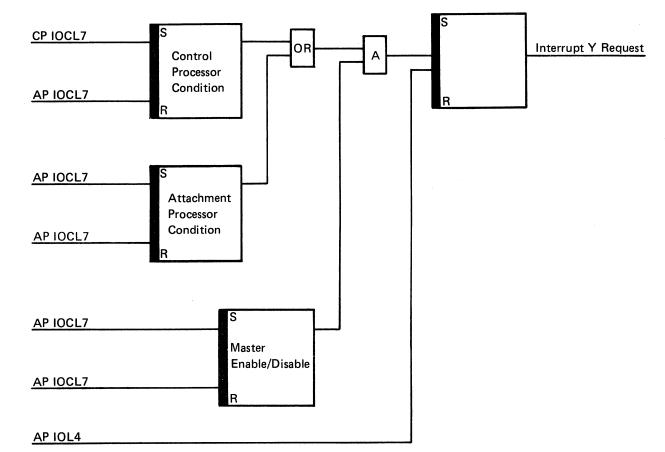

### Interrupt Request X and Y Register K

The interrupt request X and Y register supplies two interrupt requests to the attachment controller channel. The interrupt request X can be set by any of the following conditions:

- Control processor condition A, control processor condition B, and control processor condition C. These conditions are set by the control processor and are anded with enable/disable latches.

- · Data transmission operation end condition. This condition is anded with an enable/disable latch and set by the processor-to-processor interface hardware. This interrupt indicates to the attachment processor that the data transfer byte counter has reached zero (the data transmission between the control processor and the attachment processor has completed).

- Attachment processor condition. This condition is set by the attachment processor for diagnostic purposes only.

The interrupt request Y can be set by either of the following conditions:

- Attachment processor condition. This condition is set by the attachment processor.

- · Control processor condition. This condition is set by the control processor.

## $\begin{array}{c} \begin{array}{c} \hline \end{array} \end{array}$

### Attachment Processor Channel

The attachment processor channel contains the logic that moves the data and commands between the attachment processor, the attachment processor storage, the processor-to-processor interface, and the I/O device.

Odd-numbered parity is maintained on the channel data buses. Parity is checked at the output of the system bus out and the DBI gate.

The attachment processor channel circuits do the following:

- Move data between the attachment processor storage and the I/O device by using base cycle steal mode or I/O storage instructions.

- Move data between the attachment processor storage and the processor-to-processor interface by using burst cycle steal mode.

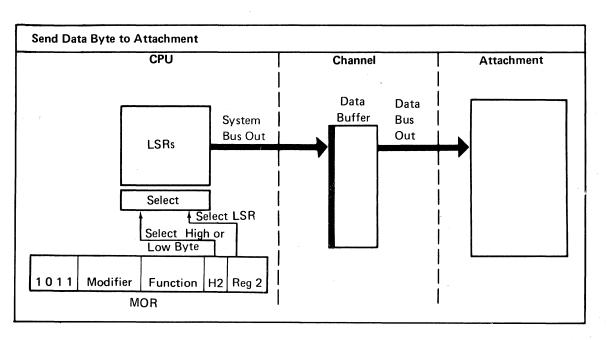

- Move data between the attachment processor local storage registers (LSRs) and the processor-to-processor interface or I/O device (I/O immediate instructions).

- Control the channel or I/O functions that may or may not include data movement (I/O control load and I/O control sense instructions).

The attachment processor channel supplies controls for the following:

- I/O instructions (immediate, storage, and iump)

- Interrupts (five levels)

- Burst cycle steal (processor-to-processor interface only)

- Base cycle steal (I/O devices)

Error detection

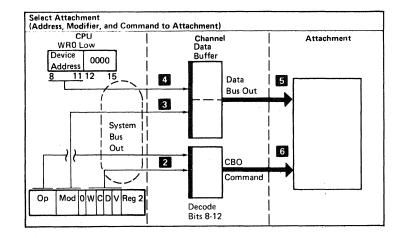

### Attachment Processor Channel Controls

The attachment processor channel, using the channel sequencer, controls the data transfer between the processor-to-processor interface and the I/O device attached to the channel. The logic controls the decode of the system bus out to generate the CBO bits.

The control lines function as follows:

- The 'I/O control out' line signals the attachment that the 'I/O DBO' and 'I/O CBO' lines are valid. When the 'I/O control out' and the 'I/O service out' lines are active at the same time, a blast condition is indicated, which forces all attachments off the channel.

- The 'I/O service out' line signals the attachment that the 'I/O DBO' lines are valid if data is being sent from the channel to the processor-to-processor interface or I/O device. If data is sent to the channel from an attachment, the 'I/O service out' line signals the processor-to-processor interface or I/O device that the channel has received the data.

- The 'I/O service in' line signals the channel that the command byte has been received by the attachment or that sense data on the 'I/O DBI' lines is valid.

### I/O Data Bus In M

The I/O data bus in (DBI) is a 9-bit bus (0-7, P) that is the result of the dot OR of the DBI from the processor-to-processor interface and the DBI from the I/O device. The I/O DBI supplies data and status information to the attachment processor channel. The I/O DBI contains:

- · Data or sense information during I/O sense instructions

- Data during cycle steal operations

- Sense information during SILSB and SCSID instructions

### I/O Command Bus In M

The I/O command bus in (CBI) is a 6-bit bus that supplies control information to the attachment processor channel. The CBI is the result of the dot or of the CBI from the processor-to-processor interface and the CBI from the I/O device. The bus is active during I/O instructions and cycle steal operations. Bits 0, 1, 2, and 3 of the I/O CBI control cycle steal and local storage register (LSR) selection. Bits 2 and 3 select the work register that contains the address where data is to be loaded or sensed for cycle steal operations.

The I/O CBI bits have the following meaning:

| Bit  |    |   |                                                                                                            |

|------|----|---|------------------------------------------------------------------------------------------------------------|

| 0    | 0  | = | Cycle steal high byte<br>(WR not<br>incremented)                                                           |

|      | 1  | = | Cycle steal low byte<br>(WR incremented)                                                                   |

| 1    | 0  | = | Cycle steal sense                                                                                          |

|      | 1  | = | Cycle steal load                                                                                           |

| 2, 3 | 00 | = | Select WR4 (see<br>note)                                                                                   |

|      | 01 | = | Select WR5 (see<br>note)                                                                                   |

|      | 10 | = | Select WR6 (see<br>note)                                                                                   |

|      | 11 | = | Select WR7 (see<br>note)                                                                                   |

| 4    | 1  | = | Required for cycle<br>steal operations and<br>indicates invalid DBI<br>parity during sense<br>instructions |

| 5    | 1  | = | DBO parity error<br>(even-numbered<br>parity)                                                              |

Note: These work registers are selected by interrupt level 1 during burst cycle steal mode and by interrupt level 4 during base cycle steal mode.

I/O Command Bus Out

The I/O command bus out (CBO) is a 3-bit bus that specifies the type of I/O operation to execute. The attachment processor commands are:

| Bits<br>0 1 2 | Command                         |

|---------------|---------------------------------|

| 000           | Sense cycle sidentification     |

| 001           | Sense interru<br>status byte (S |

| 010           | Cycle steal ac<br>(CSACK)       |

| 011           | I/O branch o                    |

| 100           | I/O load                        |

| 101           | I/O sense                       |

| 110           | I/O control lo                  |

| 111           | I/O control s                   |

|               |                                 |

steal (SCSID)

upt level SILSB)

icknowledge

on condition

load

sense

Attachment Controller 2 16-5

### I/O Data Bus Out 🕅

The I/O data bus out (DBO) is a 9-bit bus (0-7, P) that is used in the following ways:

- · During control out of an SILSB command, I/O DBO bits 0 through 3 contain the interrupt level.

- During control out of any I/O command other than SILSB, I/O DBO bits 0 through 3 contain the device address and bits 4 through 7 contain the command modifier.

- · During control out of a CSACK command, the I/O DBO contains the cycle steal address of the device selected to perform the base cycle steal.

- During service out of an I/O load or I/O control load command, the I/O DBO contains data.

- During service out of a CSACK command, the I/O DBO contains data.

### Data Buffer R

The attachment processor channel data buffer is used as an immediate storage register for all data that passes through the channel. The buffer is controlled by channel clocks and control lines.

### Channel Register S

The channel register is used for diagnostic purposes. During I/O instructions this register contains the attachment device address in bits 0 through 3 and the I/O command bus out in bits 5 through 7. During base cycle steal operations, the channel register stores the device ID of the I/O attachment. When an error occurs, this information can be stored in a local storage work register for later diagnostic use.

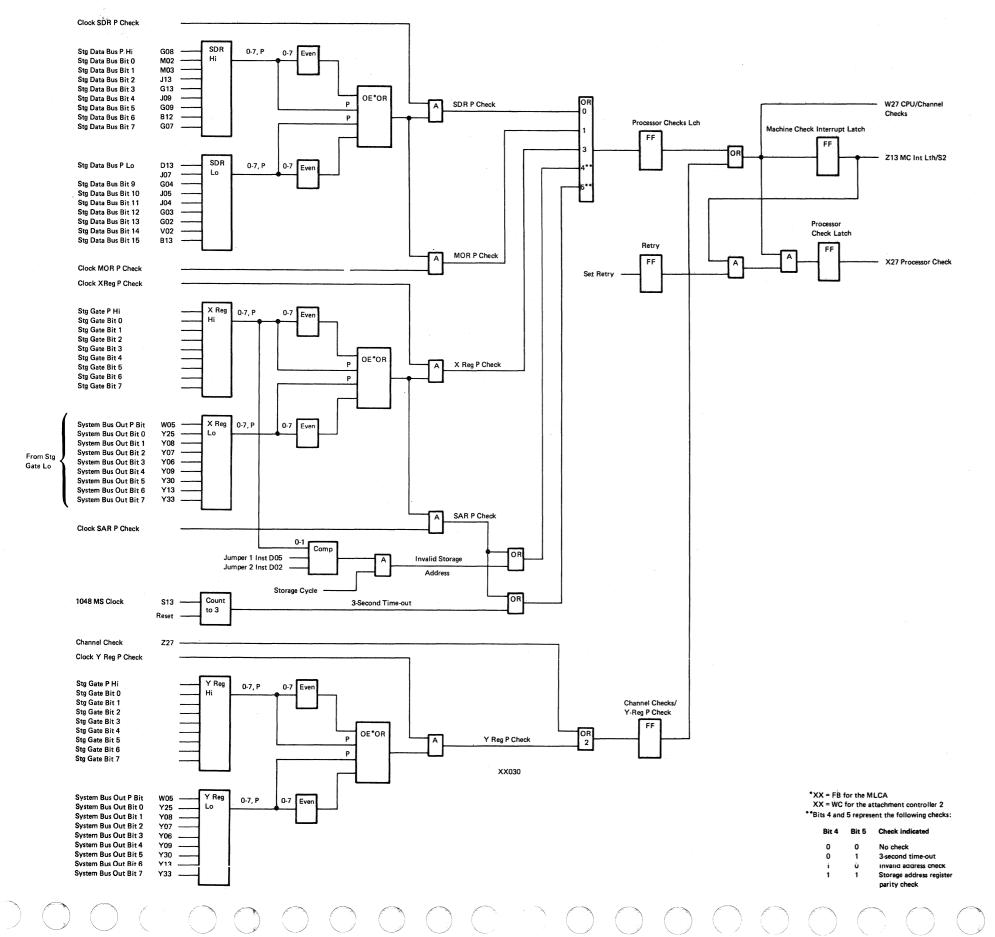

### Channel Check Register

The channel check register is an 8-bit register that stores the error status of the channel hardware. The information stored in this register can be moved to a local store work register for later diagnostic use.

The channel check register bits have the following meanings:

| Bit | Meaning                     |

|-----|-----------------------------|

| 0   | DBO parity check            |

| 1   | Invalid device address      |

| 2   | DBI parity check            |

| 3   | I/O time-out                |

| 4   | Not used                    |

| 5   | System bus out parity check |

Cycle steal operation (The check occured during a cycle steal operation.)

Not used

6

7

### Interrupt Timer 🕕

A fixed interval interrupt timer can be used to generate an interrupt request from the channel logic on 8-millisecond intervals. The 1-millisecond clock from the control processor channel is used to drive the interrupt timer. The timer interrupt request can be enabled, disabled, and reset by I/O instructions from the attachment processor.

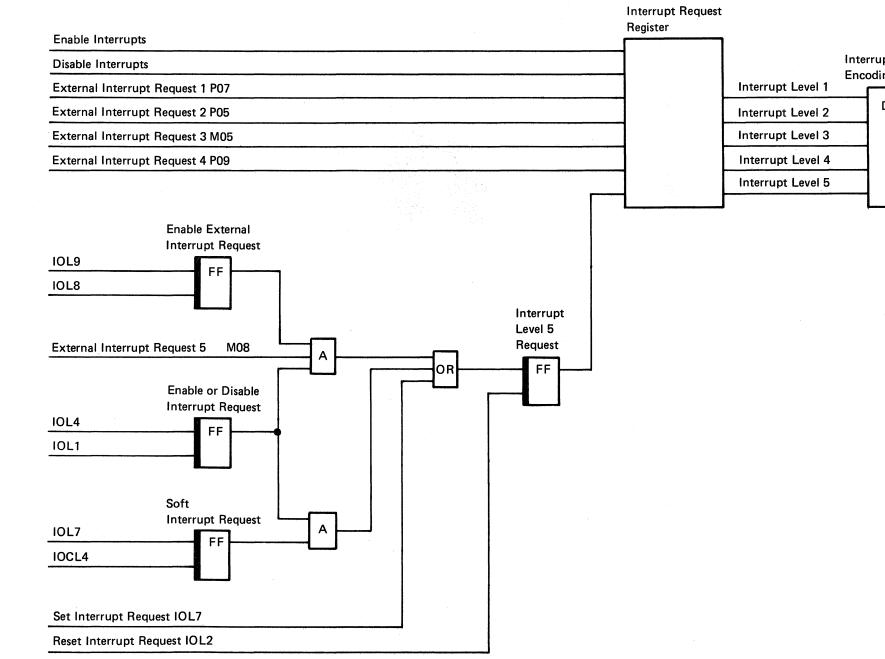

### Interrupt Controls 💽

The interrupt control logic controls the five levels of the interrupt request, the base cycle steal request from the I/O device, and the burst cycle steal request from the processor-to-processor interface.

The priority of interrupts is as follows:

- Interrupt level 0 processing (machine 1. check)

- 2. Burst cycle steal

- 3. Base cycle steal

- Interrupt level 1 processing 4

- 5. Interrupt level 2 processing

- 6. Interrupt level 3 processing

- 7. Interrupt level 4 processing

- 8. Interrupt level 5 processing

- 9 Main level processing

Interrupt level status can be stored in a local store work register for diagnostic use.

### 20 mHz Oscillator 🗿

The 20 mHz oscillator supplies the attachment processor two nonoverlapping clocks. Eight of these clocks are generated and used by the controller.

$\begin{array}{c} \begin{array}{c} \begin{array}{c} \end{array} \end{array}$

### Attachment Processor

The attachment processor can operate on either 1 or 2 bytes of data. The instruction that is being executed determines the number of bytes and the path of the data.

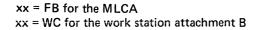

Odd-numbered parity by byte is maintained in the data flow. Parity generating stations are at the output of the status gate and the ALU gate. Parity is checked at the storage data register, the X-register, and the Y-register. Parity is also checked on the data going into the microoperation register (MOR) and the storage address register (SAR) bus. The MOR parity check is done by the storage data register (SDR) parity check logic and the SAR parity check is done when the storage address is loaded into the X-register.

### Storage Controls

The storage controls activate the prop signals for storage read/write operation These controls also contain a refresh a counter and refresh control logic that refresh the dynamic storage. The outp refresh address counter (7 bits) is gate storage address bus during refresh op

### Microoperation Register 2

The microoperation register is a 16-bit that holds each controller instruction as it is taken from storage. The instruction is decoded to control the data flow, for example, gate selection, arithmetic and logic unit operations, and local storage register selection.

### Processor Checks Register

The processor checks register stores the error status of the attachment processor. When a hardware error occurs in the attachment processor, a bit is set on in this register to indicate the error. If this error cannot be recovered from, an instruction is executed to activate the processor check line going to the interrupt request A register in the processor-to-processor interface. The processor-to-processor interface interrupts the control processor to indicate that the attachment processor has stopped. This register can be stored in an LSR work register by an I/O instruction for diagnostic use.

The processor checks register bits have the following meanings:

|                                       | Bit  | Meaning                                          |

|---------------------------------------|------|--------------------------------------------------|

| per control                           | 0    | SDR parity check                                 |

| ons.<br>address                       | 1    | MOR parity check                                 |

| is used to                            | 2    | Y-register parity check                          |

| put of the<br>ed to the<br>perations. | 3    | X-register parity check                          |

|                                       | 4    | Not valid storage address<br>or SAR parity check |

|                                       | 5    | 3-second time-out or SAR<br>parity check         |

| it register                           | 6, 7 | Not used                                         |

|                                       |      |                                                  |

### Controller Storage 🕞 🕞

Controller storage contains either 16K or 32K addresses of read/write storage; each address is 2 bytes wide. The storage cells within the controller storage are dynamic (the cells must be refreshed to maintain valid data).

The controller storage is loaded from the CP control storage or MSP main storage during IPL. When controller storage is loaded, it contains the microcode that is used to support the attachment.

### X-Register and Y-Register B B

These registers are two 1-byte registers (X-high, X-low, and Y-high, Y-low). The four registers form a buffer input to the arithmetic and logic unit (ALU). The X-high and Y-high registers are input to the ALU high, and the X-low and Y-low are input to the ALU low.

The X-registers are used as buffers for the base constants into the ALU and as a register for the 16-bit storage address.

The Y-registers are used as buffers for changing constants into the ALU.

### Arithmetic and Logic Units G G

The attachment processor contains two arithmetic and logic units (ALUs). ALU high uses bits 0 through 7 when 2-byte data fields are used. ALU low uses bits 8 through 15 when either 1-byte or 2-byte data fields are used. The ALUs always send 2 bytes of data to the local storage register (LSR) input bus. When 2 bytes are used in the ALU operation, both bytes (high and low) are placed on the LSR input bus and are, at the same time, written into bits 0 through 7 and bits 8 through 15 of the LSR. When the ALU output is only 1 byte, the byte is sent to both the high and low LSR input bus lines. In these cases, the instruction selects only 1 byte to be written into an LSR.

Any data sent to the ALU is first loaded into the X- and Y-registers. The X-registers supply the data for one operand, and the Y-registers supply the data for the other operand that is used in the current ALU operation. The instruction and its function determine if 1 or 2 bytes are affected by the ALU.

The ALU does arithmetic operations with two 16-bit words, one 16-bit word plus or minus one 8-bit byte, or one 8-bit byte plus or minus one 8-bit byte. The logical/arithmetic 1 instruction is used for 8-bit by 8-bit arithmetic operations. The logical/arithmetic 2 instruction is used for 16-bit by 16-bit arithmetic and 16-bit by 8-bit arithmetic operations.

Instructions that cause an increase or decrease of the X-register contents are executed by resetting the Y-high and Y-low registers and then forcing a carry in to the ALU. This causes only the X-register to be affected by the instruction.

### Storage Data Register \Lambda 🗛

The storage data register (SDR) is a 16-bit register that is an immediate buffer for all instructions and data bytes taken from storage. Each instruction is 2 bytes wide. The SDR high order bits (0 through 7) are gated through the storage gate to X-register high and Y-register high and then to the ALU. The SDR low order bits (8 through 15) are gated to X-register low and Y-register low and then to the ALU.

### Local Storage Registers D D

The attachment processor uses the local storage registers (LSRs) as:

- Data buffers and address registers for storage

- Operand registers for internal calculations

- I/O control registers that can be loaded from the I/O attachments or from which data can be sent to the I/O attachments

The local storage register stack contains sixty-four 16-bit registers. Bits 0 through 7 of each register are the high local storage register and bits 8 through 15 of each register are the low local storage register.

The 64 local storage registers are divided into six interrupt level groups with each group containing eight registers. Two of the eight register groups contain the microaddress registers (MAR) and microaddress backup registers (MAB), which supply the address pointers to the microcode for each interrupt level. The MAR contains the address of the next instruction to be executed. The MAB contains the return address when a branch and link instruction is executed. Interrupt level 0 and main program level share the same local storage register group.

### Processor Condition Register

The processor condition register (PCR) contains the processor conditions that are tested by the jump-on-condition instruction. The processor condition register is changed by system reset, program loading, or instructions that change register bits. These conditions are changed by the instructions that perform the add, subtract, test mask, compare immediate, subtract immediate, and R1-linked-with-R2 functions.

### PROCESSOR-TO-PROCESSOR INTERFACE OPERATIONS

### **Control Processor Commands**

The processor-to-processor interface recognizes the following I/O immediate commands from the control processor:

- I/O load

- I/O control load

- I/O sense

- Sense interrupt level status byte (SILSB)

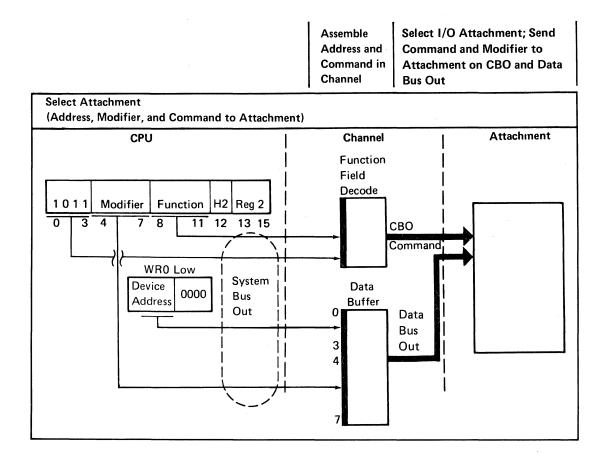

### I/O Load Command

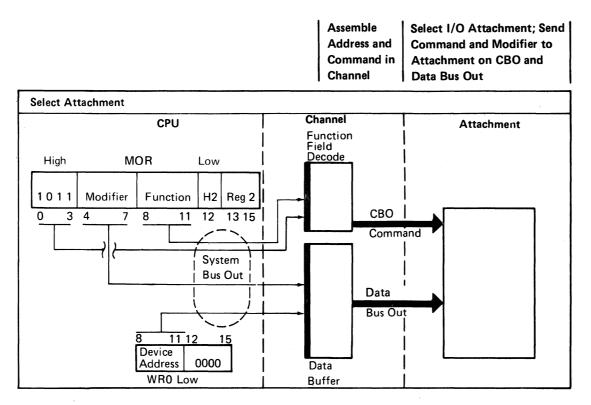

These commands are decoded from the function field (bits 8 through 11) and sent to the processor-to-processor interface on CBO bits 0 through 2. The format of the I/O immediate command is:

| 1 | 0 | 1 | 1 | Modifier | Function |    | H<br>2 | Reg | 3  |

|---|---|---|---|----------|----------|----|--------|-----|----|

| 0 |   |   | 3 | 4 7      | ' 8      | 11 | 12     | 13  | 15 |

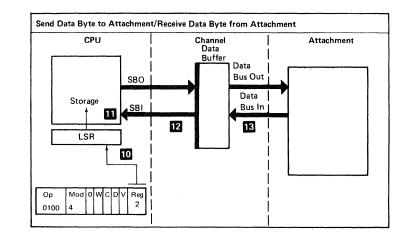

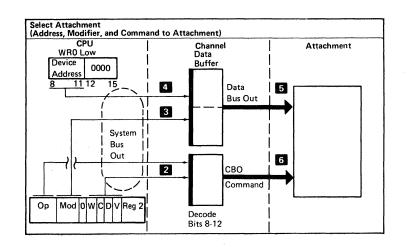

| Channel<br>Sys Bus Out Low   | Select Processor-to-Pro     | cessor Inte |                                                    | <mark>Send Data Byte t</mark><br>  DBO 0-7 | o Processor-to-Process | or Interface |              |                 |                                            |                               |                                                      |

|------------------------------|-----------------------------|-------------|----------------------------------------------------|--------------------------------------------|------------------------|--------------|--------------|-----------------|--------------------------------------------|-------------------------------|------------------------------------------------------|

| ⊑=<br>8 حل≻ 11<br>=          |                             | _           | Modifier<br>4-7                                    |                                            |                        |              |              | 1               |                                            |                               |                                                      |

| Function  <br>  Decode  <br> |                             | ССВ         | ССВ                                                |                                            |                        |              | C            | DBO             |                                            |                               |                                                      |

| ╞╤╤╤╡╒╤╤╕<br>╻╌╻╴╻╸<br>└╶┶╶┶ |                             | 012         | 3 4 5 6                                            | Bit 0                                      | Bit 1                  | Bit 2        | Bit 3        | Bit 4           | Bit 5                                      | Bit 6                         | Bit 7                                                |

| 0    2<br><br>CBO            | ╞╍╉╾╾┛                      |             | 0 0 0 0<br>Load CP CBI buffer                      |                                            |                        | CP CBI bit 2 | CP CBI bit 3 | CP CBI bit 4    | CP CBI bit 0                               | Select operation<br>end to CP | Select operation<br>end to attach-<br>ment processor |

| Data<br>Buffer               |                             |             | 0 0 0 1<br>Load data buffer 1                      |                                            |                        | • <b>-</b>   | DBO bits to  | o data buffer 1 |                                            | J.,                           | L.,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,               |

| Port Data                    | DA<br>0-3 Device<br>Address | 100<br>I/O  | 0 0 1 0<br>Load data buffer 2                      |                                            |                        |              | DBO bits to  | o data buffer 2 |                                            |                               |                                                      |

|                              | Hit                         | Load        | 0 0 1 1<br>Reset interrupt<br>level A request      |                                            |                        |              |              |                 |                                            |                               |                                                      |

|                              | <br> <br>                   |             | 0 1 0 1<br>Load attachment<br>processor CBI buffer | CBI bit 0                                  | CBI bit 1              | CBI bit 2    | CBI bit 3    |                 |                                            |                               | Data count bit 0                                     |

|                              | <br> <br>                   |             | 0 1 1 0<br>Enable interrupt<br>level A conditions  |                                            |                        |              | Condition B  | Condition A     | Attachment<br>processor<br>processor check | Cycle steal operation end     | Master<br>enable                                     |

|                              |                             |             | 0 1 1 1<br>Disable interrupt<br>level A conditions |                                            |                        |              | Condition B  | Condition A     | Attachment<br>processor<br>processor check | Cycle steal<br>operation end  | Master<br>disable                                    |

### I/O Load Command (continued)

|                      | CPU<br>Clock  | Т<br>0      | T<br>1      | T<br>2 | Т<br>3 | T<br>3<br>A | T<br>3<br>B | T<br>3<br>E |   |   |   |   | Т<br>4  | Т<br>5      | Т<br>6      | T<br>6<br>E |     |             |             |             | Т<br>0      |

|----------------------|---------------|-------------|-------------|--------|--------|-------------|-------------|-------------|---|---|---|---|---------|-------------|-------------|-------------|-----|-------------|-------------|-------------|-------------|

|                      | Port<br>Clock | C<br>0<br>0 | C<br>0<br>0 | 0      | 0      | 0           |             | 0           | 0 | 0 | 0 | 1 | 1       | C<br>1<br>8 | C<br>1<br>9 | 1           | 1   | C<br>1<br>F | C<br>1<br>E | C<br>0<br>2 | C<br>0<br>0 |

| Line Name            | FSL* Page     |             |             |        |        |             |             |             |   |   |   |   |         |             |             |             |     |             |             |             |             |

| CBO (valid)          | CH001         |             |             |        |        |             | 5. (2.1-1)  |             |   |   |   |   |         |             |             |             | 1.1 |             |             |             |             |

| Port DBO (valid)     | CH001         |             |             |        |        |             |             |             |   |   |   |   |         |             |             |             |     |             |             |             |             |

| Control Out          | CH002         |             |             |        |        |             |             |             |   |   |   |   |         |             |             |             |     |             |             |             |             |

| Strobe               | CH002         |             |             |        |        |             |             |             |   |   |   |   |         |             |             |             |     |             | 1           |             |             |

| Multidevice Response | xx002         |             |             |        |        |             |             |             |   |   |   |   | 2122/01 |             |             |             |     |             |             |             |             |

| Service In           | xx002         |             |             |        |        |             |             |             |   |   |   |   |         |             | 255.55      |             |     |             |             |             |             |

| Service Out          | CH002         |             |             |        |        |             |             |             |   |   |   |   |         |             |             |             |     |             |             |             |             |

| CBI Bit 5 (valid)    | xx002         |             |             |        |        |             |             |             |   |   |   |   |         |             |             |             |     |             |             |             |             |

\*xx = FB for MLCA

xx = WC for work station attachment B

| Modifier Port DBO<br>4 5 6 7 | Port<br>DBO Bit | Command                                 | Action Taken                                                                                  | FSL <sup>1</sup> |

|------------------------------|-----------------|-----------------------------------------|-----------------------------------------------------------------------------------------------|------------------|

| 0000                         | 2-7             | Load control<br>processor CBI buffer    | Loads the control<br>processor CBI buffer or<br>selects operation end                         | xx00             |

| 0001                         | 0-7             | Load data buffer 1                      | Loads control processor<br>DBO bits 0-7 into data<br>buffer 1                                 | xx00             |

| 0 0 1 0 0-7                  |                 | Load data buffer 2                      | Loads control processor<br>DBO bits 0-7 into data<br>buffer 2                                 | xx00             |

| 0011                         |                 | Reset interrupt level<br>A request      | Resets the interrupt level<br>A latch                                                         | xx00             |

| 0 0 1 1<br>0 1 0 1 0-3, 7    |                 | Load attachment<br>processor CBI buffer | Loads the attachment<br>processor CBI buffer and<br>the high-order bit of the<br>byte counter | xx00             |

| 0110 3-7                     |                 | Enable interrupt level<br>A conditions  | Sets the enable interrupt<br>latches for interrupt level A<br>request                         | xx004            |

| 0111                         | 3-7             | Disable interrupt<br>level A conditions | Resets the enable interrupt<br>latches for interrupt level A<br>request                       | xx004            |

|   | FSL <sup>1</sup> Page |  |

|---|-----------------------|--|

|   | xx004                 |  |

| • | xx004                 |  |

|   | xx004                 |  |

|   |                       |  |

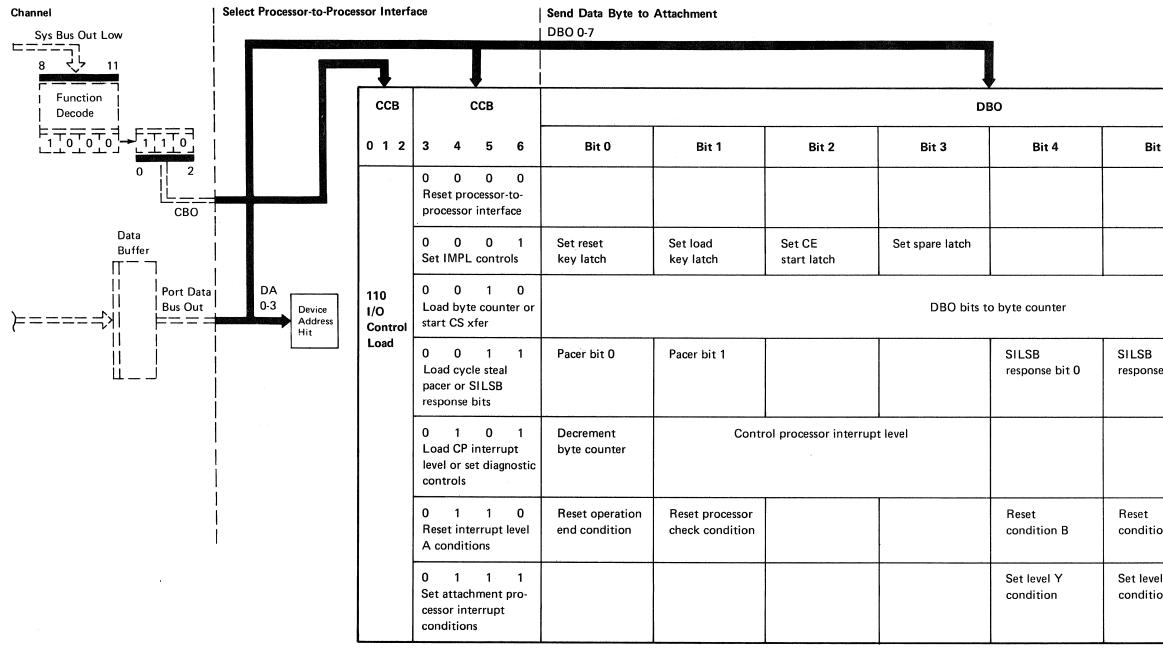

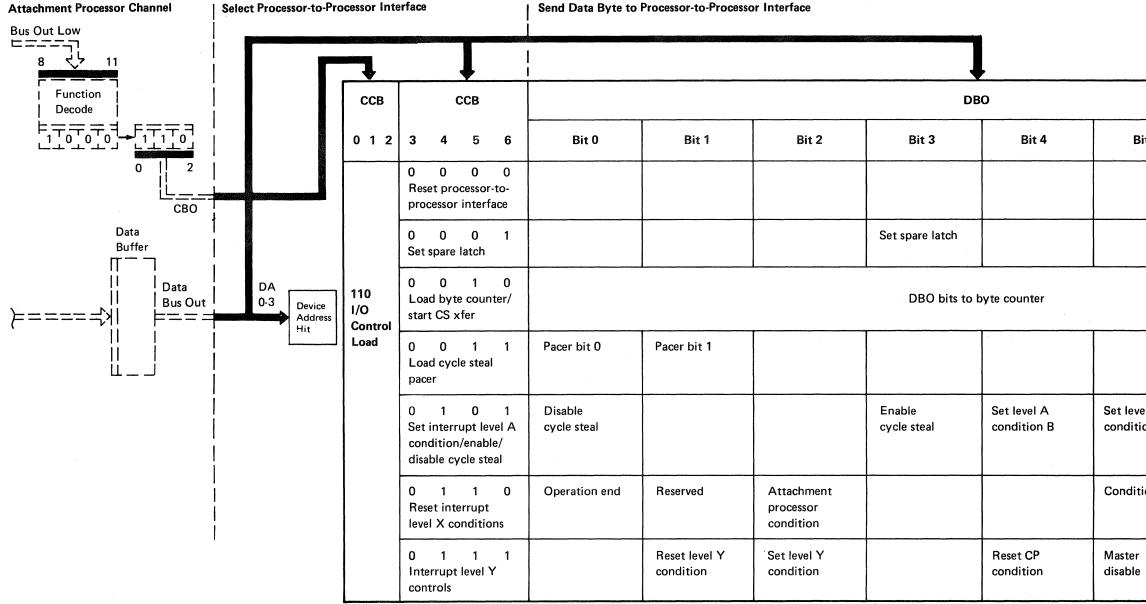

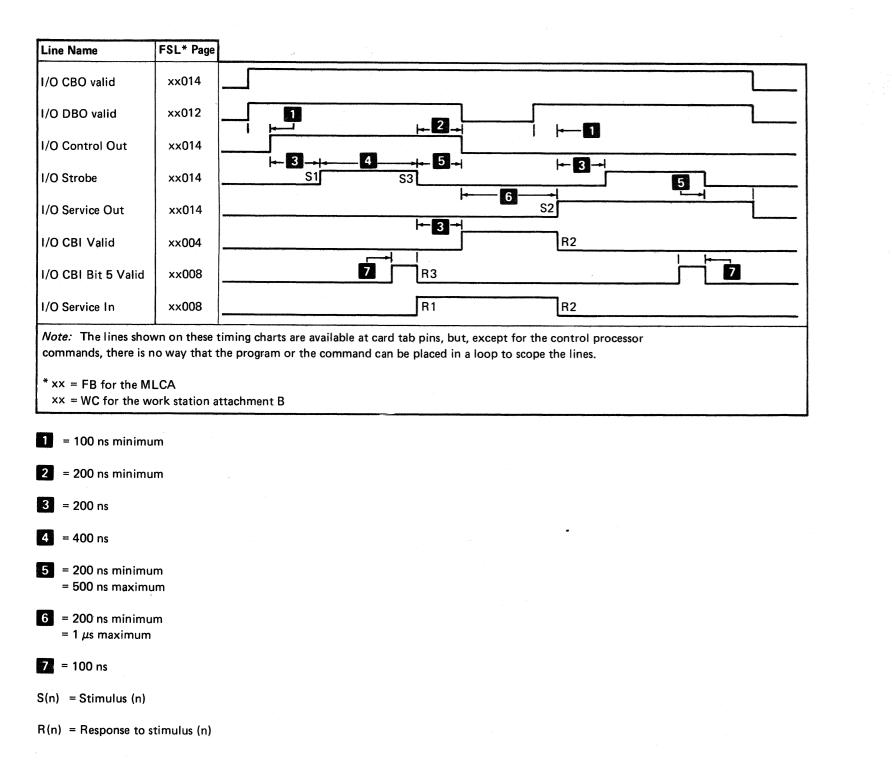

### I/O Control Load Command

| it 5          | Bit 6                                                                                                           | Bit 7                            |

|---------------|-----------------------------------------------------------------------------------------------------------------|----------------------------------|

|               |                                                                                                                 |                                  |

|               |                                                                                                                 |                                  |

|               |                                                                                                                 |                                  |

| se bit 1      | SILSB<br>response bit 2                                                                                         | SILSB<br>response bit 3          |

|               |                                                                                                                 | Set test mode                    |

| on A          | Diagnostic set<br>CP condition                                                                                  | Diagnostic reset<br>CP condition |

| el X<br>ion C | Set level X<br>condition B                                                                                      | Set level X<br>condition A       |

|               | 2 militar de la constante de la |                                  |

I/O Control Load Command (continued)

|                      | CPU<br>Clock  | Т<br>0      | Т<br>1      | T<br>2 | Т<br>3 | T<br>3<br>A | T<br>3<br>B | T<br>3<br>E |   |   |   | • | Т<br>4      | T<br>5      | Т<br>6 | T<br>6<br>E |   |   |             |             |             | Т<br>0      |

|----------------------|---------------|-------------|-------------|--------|--------|-------------|-------------|-------------|---|---|---|---|-------------|-------------|--------|-------------|---|---|-------------|-------------|-------------|-------------|

|                      | Port<br>Clock | C<br>0<br>0 | C<br>0<br>0 | -      |        |             | C<br>0<br>3 | 0           | 0 | 0 | 0 | 1 | C<br>1<br>0 | C<br>1<br>8 | 1      | C<br>1<br>3 | 1 | - | C<br>1<br>E | C<br>1<br>6 | C<br>0<br>2 | C<br>0<br>0 |

| Line Name            | FSL* Page     |             |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

| CBO (valid)          | CH001         |             |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

| Port DBO (valid)     | CH001         |             |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

| Control Out          | CH002         |             |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

| Strobe               | CH002         | T           |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

| Multidevice Response | xx002         |             |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

| Service In           | xx002         |             |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

| Service Out          | CH002         |             |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

| CBI Bit 5 (valid)    | xx002         |             |             |        |        |             |             |             |   |   |   |   |             |             |        |             |   |   |             |             |             |             |

\* xx = FB for MLCA

xx = WC for work station attachment B

| Modifier Port DBO<br>4 5 6 7 | Port<br>DBO Bit | Command                                                             | Action Taken                                                                                                                                                                                             | FSL <sup>1</sup> |

|------------------------------|-----------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 0000                         |                 | Reset processor-to<br>processor interface                           | Resets all latches and<br>registers in the processor-<br>to-processor interface,<br>except the device address<br>register, the CP interrupt<br>level register, and the<br>SILSB response bit<br>register |                  |

| 0001                         | 0-3             | Set IMPL controls                                                   | Sets the reset key latch,<br>the load key latch, the CE<br>start latch and the spare<br>latch                                                                                                            | xx00             |

| 0010                         | 0-7 -           | Load byte counter<br>and start cycle steal<br>transmission          | Loads DBO bits 0-7 into<br>the byte counter and starts<br>a cycle steal transmission                                                                                                                     | xx00             |

| 0011                         | 0, 1, 4-7       | Load cycle steal<br>pacer or SILSB<br>response bits                 | Loads DBO bits 0 and 1<br>into the cycle steal pacer<br>register and DBO bits 4-7<br>into the SILSB response<br>bit register                                                                             | xx00<br>xx00     |

| 0101                         | 0-3, 7          | Load CP interrupt<br>level and set<br>diagnostic controls           | Loads DBO bits 1-3 into<br>the CP interrupt level<br>register and activates the<br>processor-to-processor<br>diagnostic line                                                                             | xx00             |

| 0110                         | 0, 1, 4-7       | Reset interrupt level<br>A conditions                               | Resets condition latches<br>for interrupt level A<br>request                                                                                                                                             | xx00             |

| 0111                         | 4-7             | Set attachment<br>processor<br>programmable<br>interrupt conditions | Sets condition latches for interrupt levels X and Y                                                                                                                                                      | xx01             |

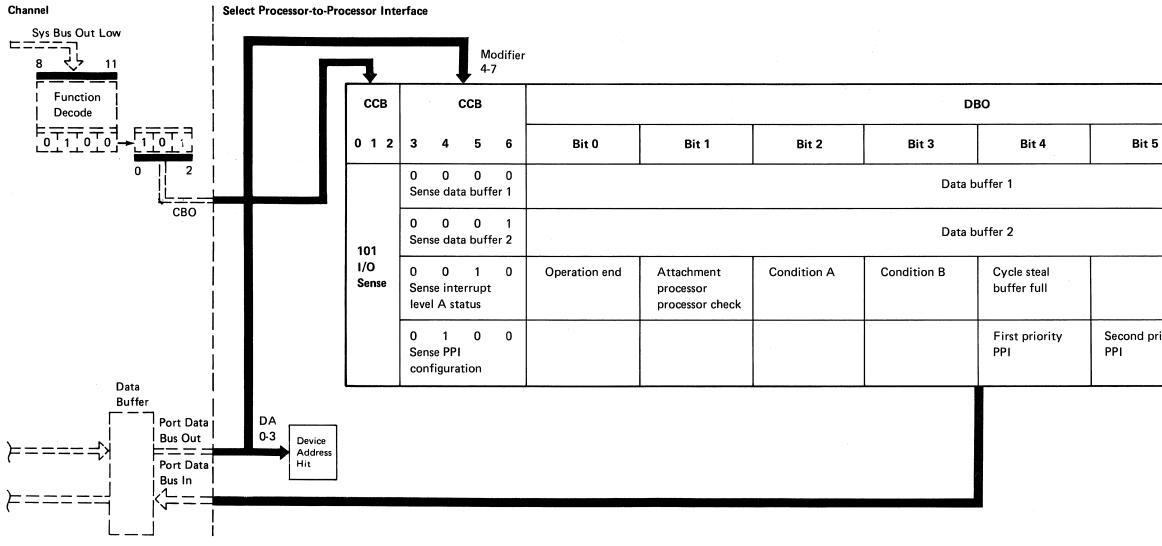

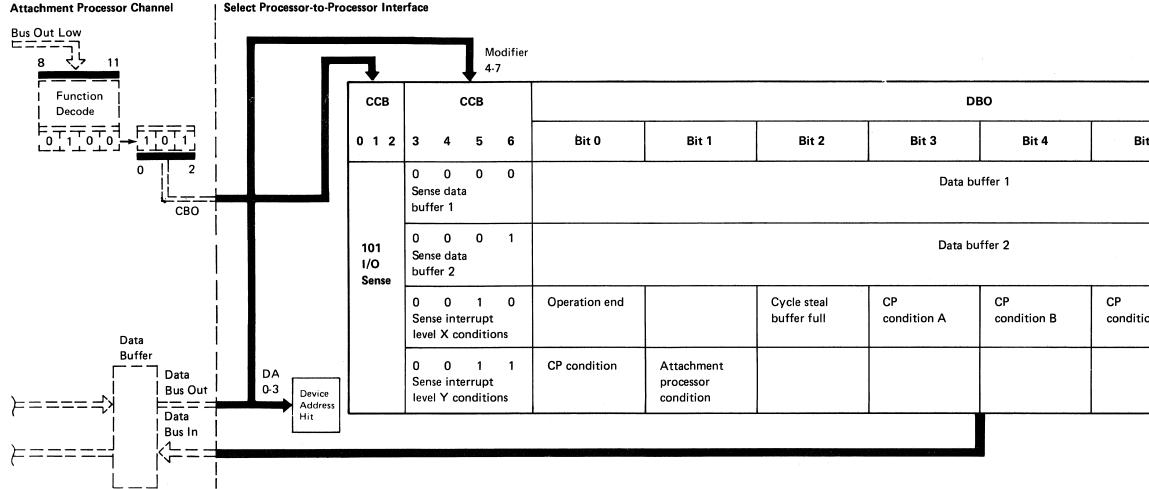

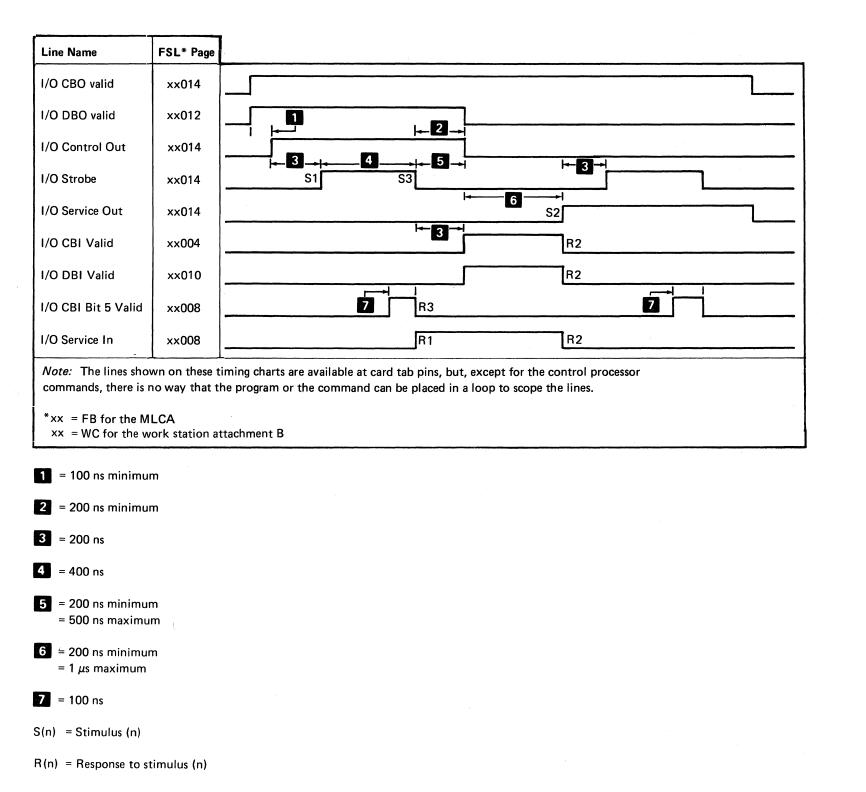

### I/O Sense Command

*Note:* **PPI** is processor-to-processor interface.

لا

| 5        | Bit 6                 | Bit 7                  |

|----------|-----------------------|------------------------|

|          |                       |                        |

|          |                       |                        |

|          | CP condition          |                        |

| oriority | Third priority<br>PPI | Fourth priority<br>PPI |

### I/O Sense Command (continued)

|                      | CPU<br>Clock  | Т<br>0      | T<br>1      | Т<br>2 | Т<br>3 | T<br>3<br>A | T<br>3<br>B | T<br>3<br>E |             |   |             |   | Т<br>4      | Т<br>5 | Т<br>6 | Т<br>6<br>Е |             |             |   |             |             | Т<br>0      |

|----------------------|---------------|-------------|-------------|--------|--------|-------------|-------------|-------------|-------------|---|-------------|---|-------------|--------|--------|-------------|-------------|-------------|---|-------------|-------------|-------------|