# Maintenance Library

SY31-0346-4

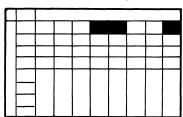

INTR CPU CHAN  $\mu$ IRPT  $\mu$ INSTR IMPL ERR HDL CNSL DISK 33FD PTR DISP KBD S-PTI

#### **PREFACE**

This manual contains theory information and diagrams for IBM System/32.

Other manuals to be used with this one are:

- IBM System/32 Operator's Guide, GC21-7591

- IBM System/32 Functions Reference Manual, GC21-9176

For maintenance information including checks, adjustments, removals, and replacements, see *IBM System/32 Maintenance Library, Introduction and Maintenance*, SY31-0373.

In addition, refer to the *IBM System/32 Diagnostic User's Guide* for further information on system diagnostics.

#### Fifth Edition (May 1977)

\*This is a major revision of, and obsoletes, SY31-0346-3. This edition adds theory and diagrams for the 285 line-per-minute belt printer, and 120 cps serial printer, and the 120 cps compatible printer attachments. All other changes are indicated by a vertical line at the left of the change. Changes are periodically made to the information herein; any such change will be reported in subsequent revisions or technical newsletters.

A Reader's Comment Form is at the back of this publication. If the form is gone, address your comments to IBM Corporation, Publications, Department 245, Rochester, Minnesota 55901.

## Contents

| INTRODUCTION TO IBM SYSTEM/32         | INTR-1 | Disk Drive Support CHAN-9                                      | Hex Branch μINSTR-26                             | CHECK RUN/STOP Switch                       | CNSL-7                 |

|---------------------------------------|--------|----------------------------------------------------------------|--------------------------------------------------|---------------------------------------------|------------------------|

| CPU Functional Units                  | INTR-3 | CBI Bit Description CHAN-9                                     | Condition Code                                   | CLOCK Light                                 | CNSL-7                 |

| Main Storage                          | INTR-3 | Port Checks CHAN-10                                            | Hex Move μINSTR-27                               | PWR FAULT DPLY Switch and DPLY              | CIVOL-7                |

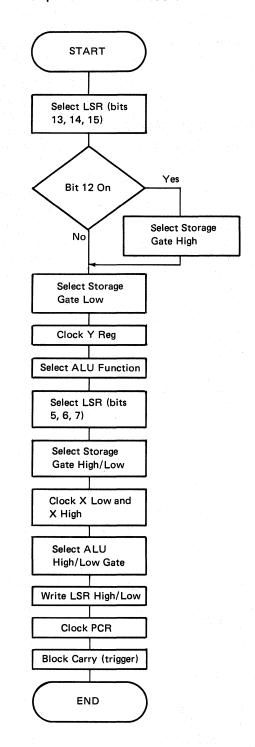

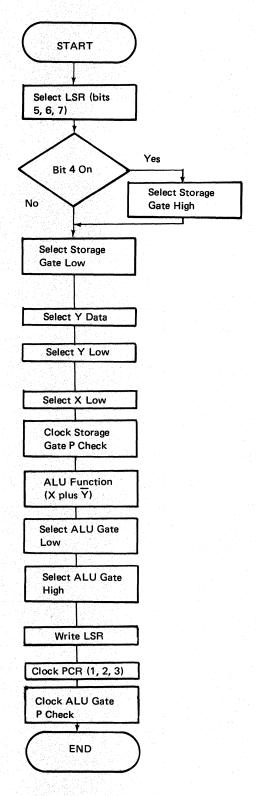

| Control Storage                       | INTR-3 | LSR Selection CHAN-12                                          | Condition Code                                   | PWR CHK Switch                              | CNCL 7                 |

| Storage Address Register (SAR)        | INTR-3 |                                                                | I/O IMMEDIATE                                    |                                             | CNSL-7                 |

| Micro Operation Register (MOR)        | INTR-3 | MICRO INTERRUPTS μIRPT-1                                       | I/O Load μINSTR-31                               | IMPL-IPL Switches                           | CNSL-7                 |

| Process Condition Register (PCR)      | INTR-3 | Level 0—Machine Check Interrupt µIRPT-1                        |                                                  | FORCE CLOCK ON/OFF Switch                   | CNSL-7                 |

| Storage Data Register (SDR)           | INTR-3 | Levels 1, 2, and 3—Disk Drive, Printer, Keyboard,              |                                                  | ADD COMP STOP/RUN Switch                    | CNSL-8                 |

| X and Y Registers                     | INTR-3 | BSCA/SDLC, and Mag Card Unit, Magnetic                         | Sense Interrupt Level Status Command . μINSTR-33 | Run Signal                                  | CNSL-9                 |

| Arithmetic Logical Unit (ALU)         | INTR-3 |                                                                | I/O Storage μINSTR-35                            |                                             |                        |

| Local Storage Registers (LSRs)        | INTR-4 |                                                                | Condition Code μINSTR-35                         | DISK DRIVE                                  | DISK-1                 |

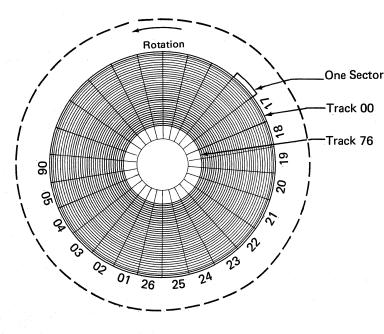

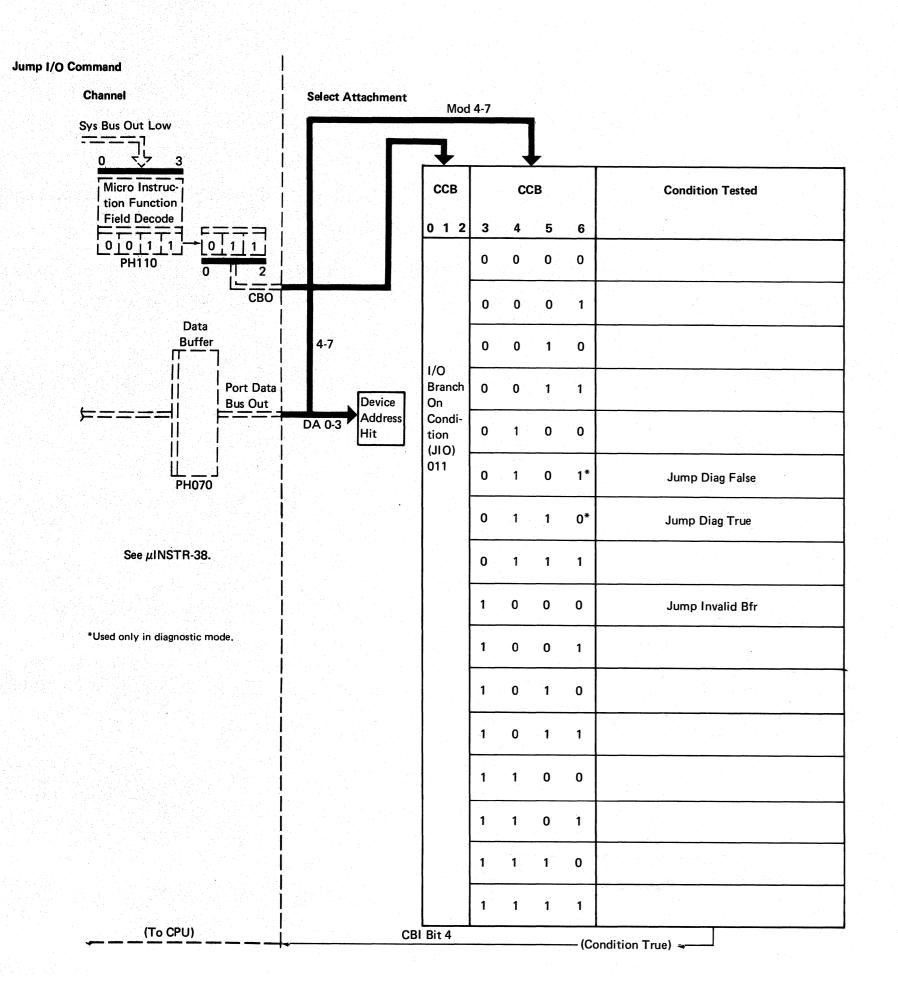

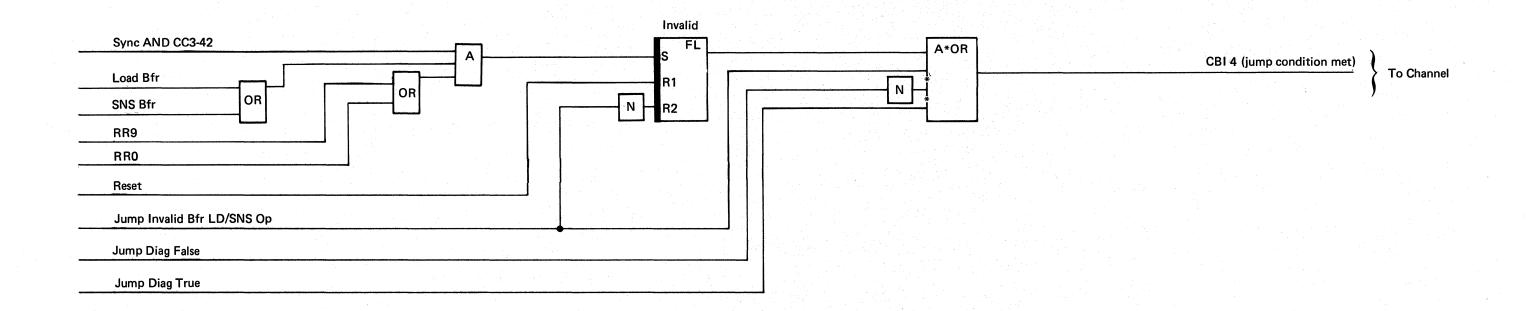

| Micro Interrupts                      | INTR-4 | Posting Interrupt Requests μIRPT-2 Interrupt Interface μIRPT-2 | I/O Branch On Condition μINSTR-38                | Data Tracks                                 | DISK-2                 |

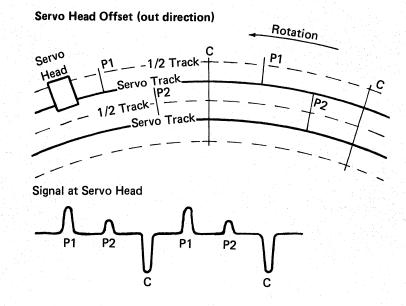

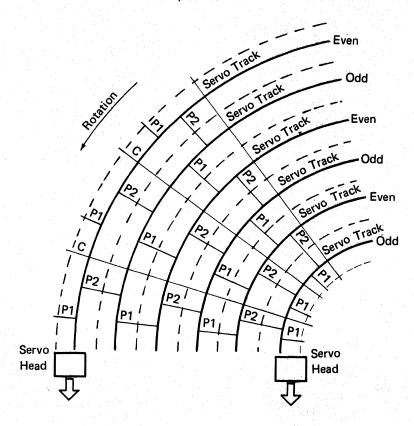

| System Checking and Parity Generation | INTR-5 | Interrupt Interface μIRPT-2                                    | Condition Code μINSTR-38                         | Servo Tracks                                | DISK-2                 |

|                                       | INTR-6 | MICO MICTOLICTICNIC                                            |                                                  | Landing Zone (LZ)                           | DISK-2                 |

| Retry and Error Logging               |        | MICRO INSTRUCTIONS μINSTR-1                                    | IMPL IMPL-1                                      | Guard Band (GB)                             | DISK-2                 |

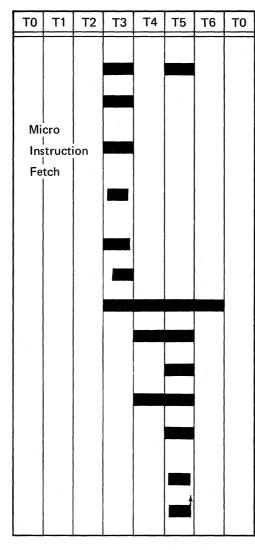

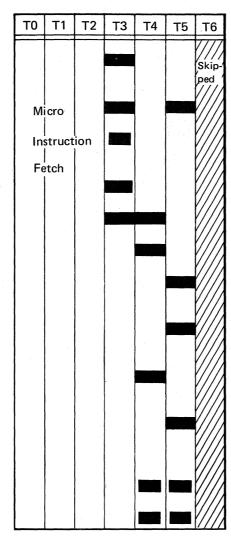

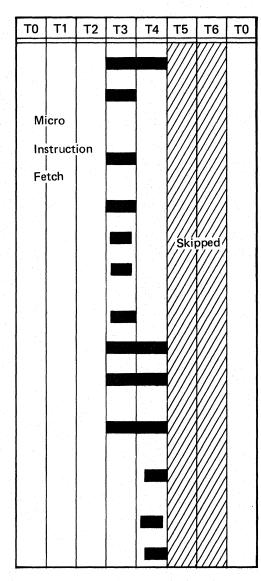

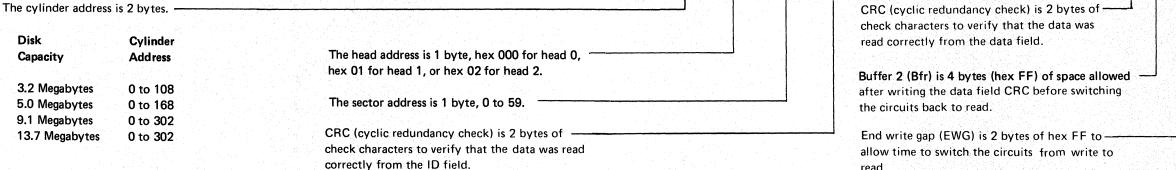

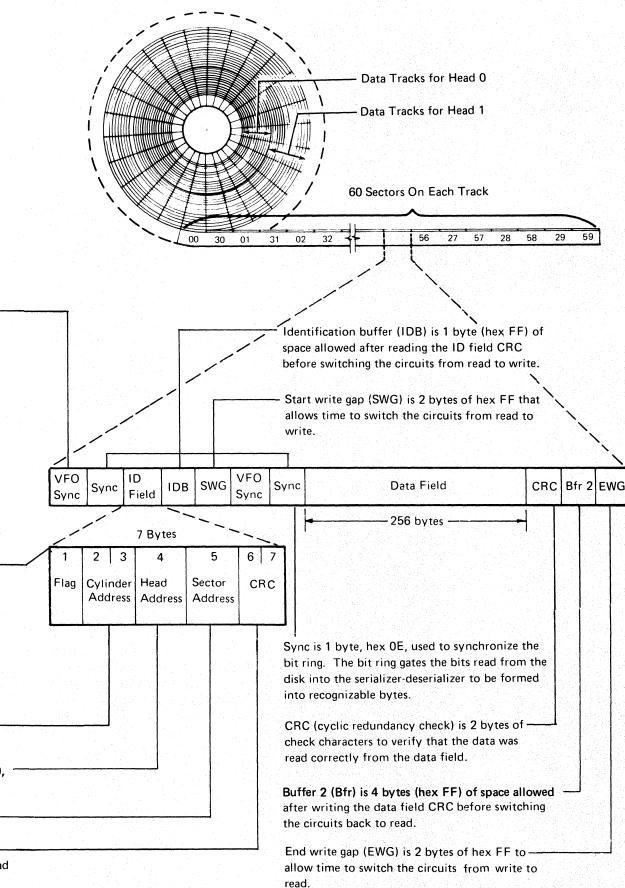

| Initial System Checkout               | INTR-6 | Micro Instruction Fetch μINSTR-1                               | IMPL Sequence (PN060) IMPL-1                     | Sector Format                               | DISK-3                 |

| DDOOCCOING HAUT                       | 00114  | Microlisting μINSTR-2                                          | Event Indicator Sequence IMPL-1                  | Data Recording                              | DISK-4                 |

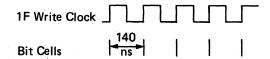

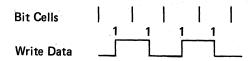

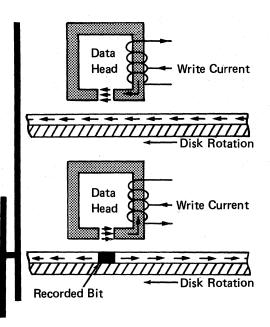

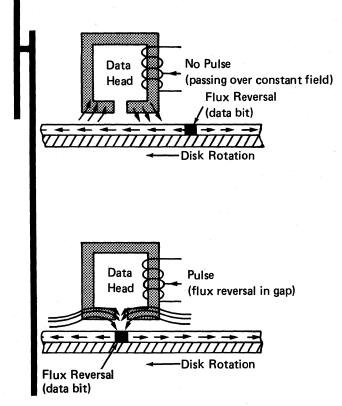

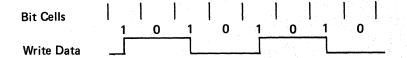

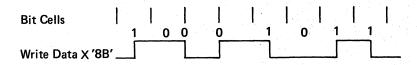

| PROCESSING UNIT                       | CPU-1  | Micro Instruction Mnemonics μINSTR-3                           | Disk IMPL Operation IMPL-2                       | Writing 1-Bits                              | DISK-4                 |

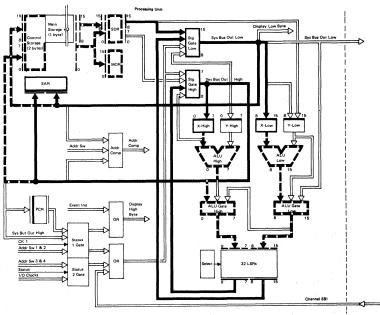

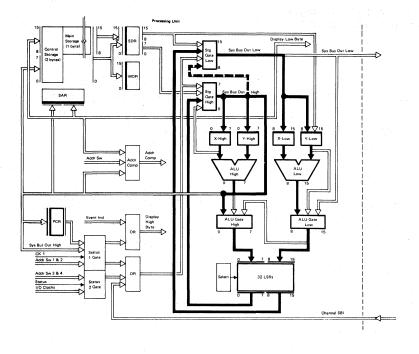

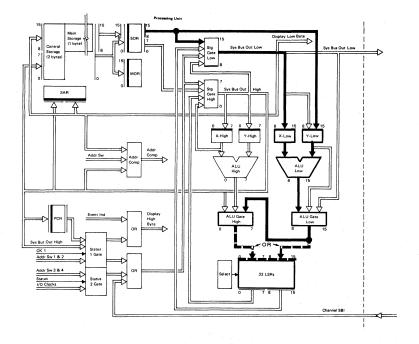

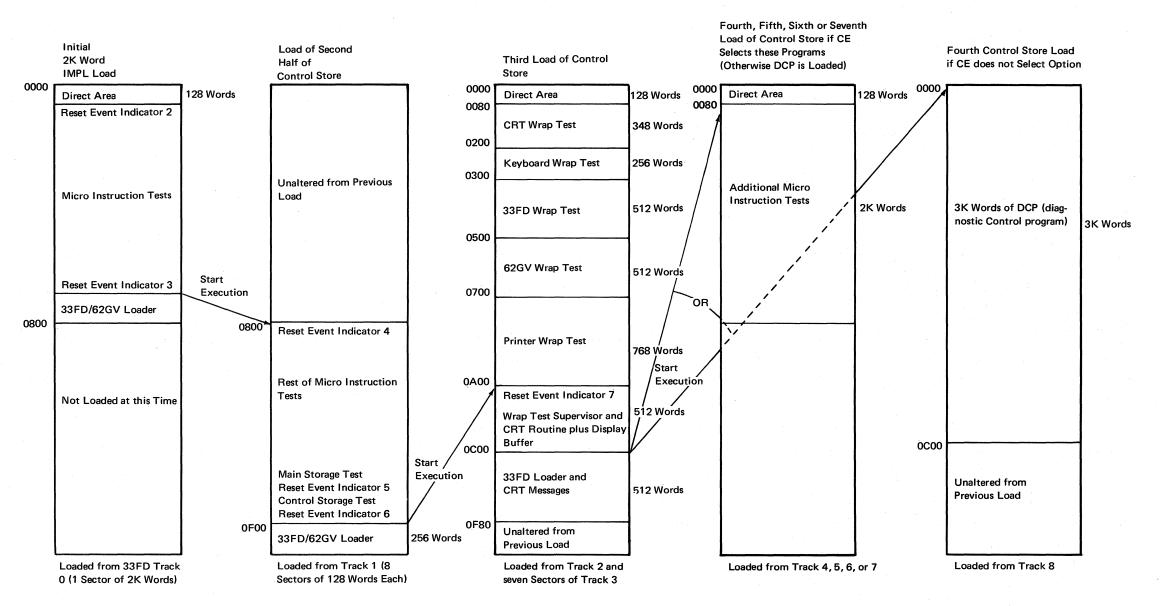

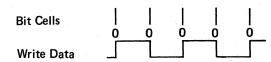

| CPU Data Flow                         | CPU-2  | Branch μINSTR-4                                                | 33FD CE Diskette IMPL Operation IMPL-3           | Writing 0-Bits                              | DISK-4                 |

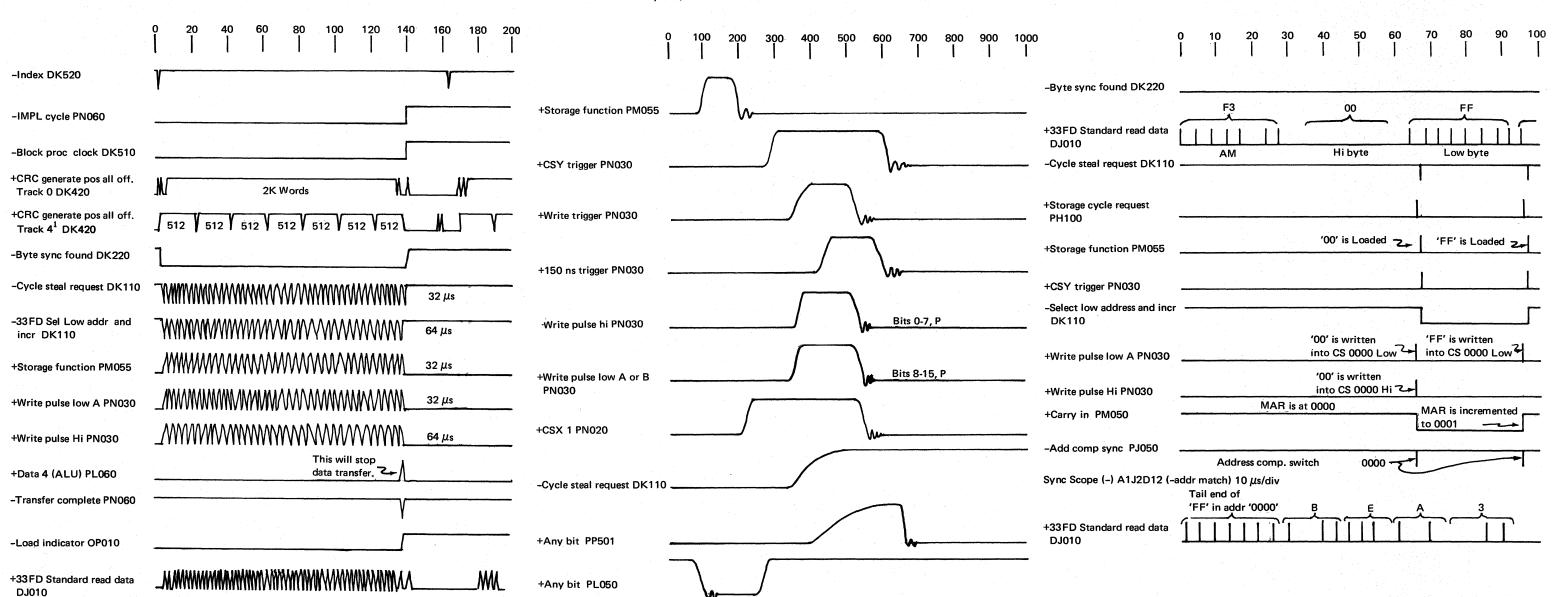

| Parity Checking                       | CPU-2  | Condition Code μINSTR-4                                        | 33FD IMPL Timing IMPL-4                          | Reading Data Bits                           | DISK-4                 |

| CPU Default Conditions                | CPU-2  | Branch (Stop Condition) μINSTR-5                               | Storage Cycle Function for 33FD IMPL . IMPL-4    | Seek Operation                              | DISK-5                 |

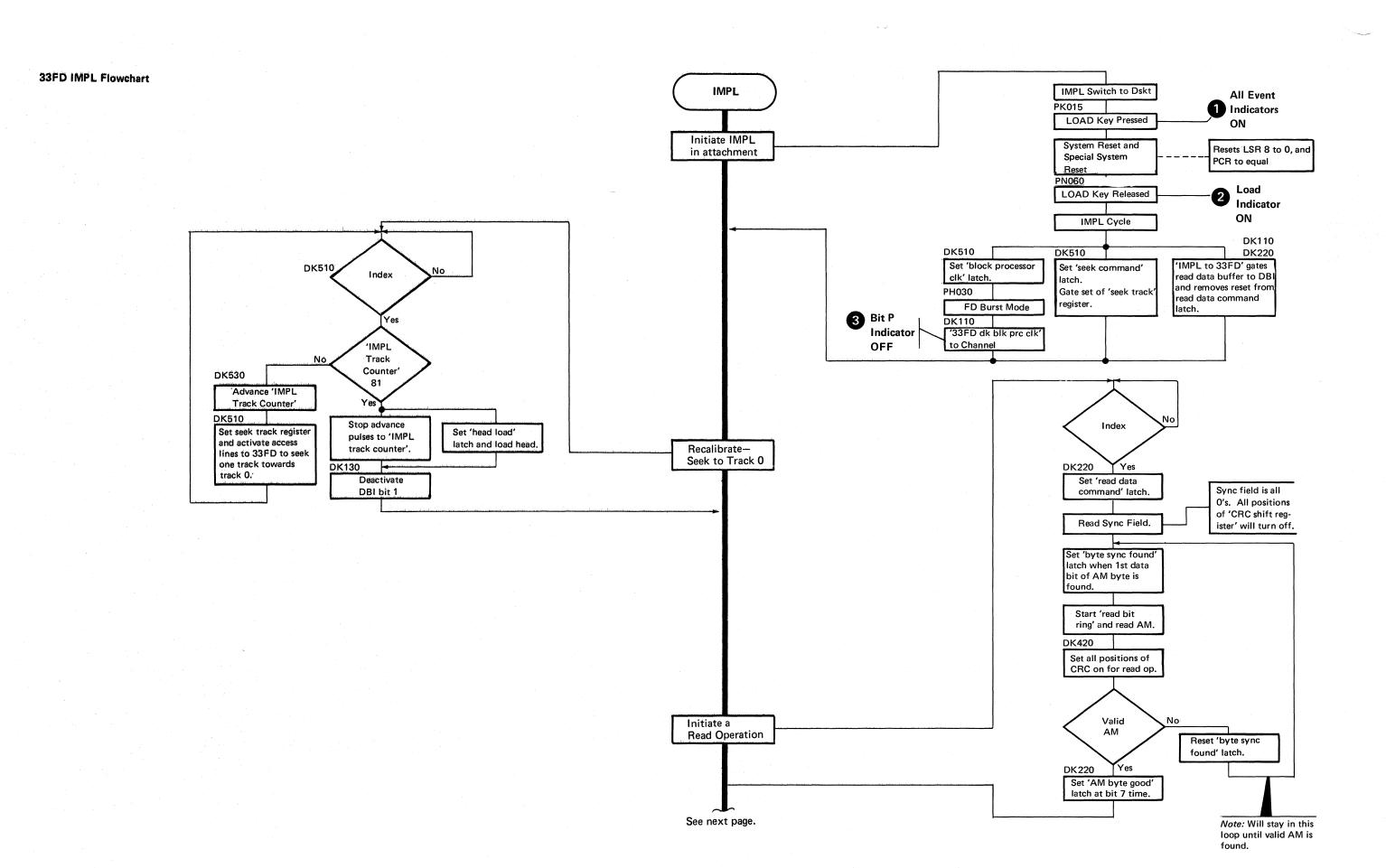

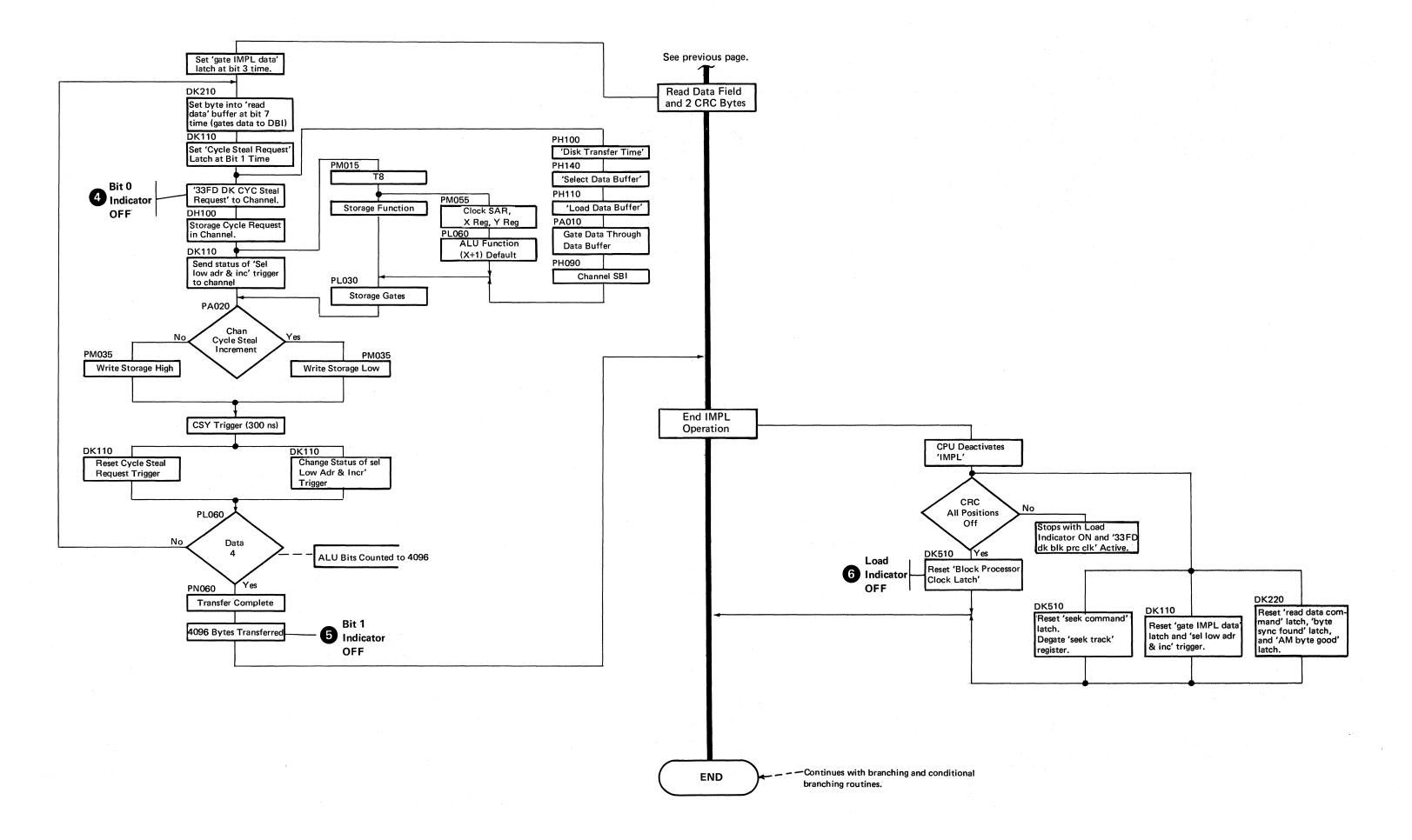

| CPU Functional Units                  | CPU-4  | Branch and Link $\mu$ INSTR-6                                  | 33FD IMPL Flowchart IMPL-5                       | Recalibrate Operation                       | DISK-5                 |

| ALU (PK060, PK070)                    | CPU-4  | Condition Code $\mu$ INSTR-6                                   | IMPL Error Indications IMPL-7                    | Behind Home                                 | DISK-5                 |

| ALU Gates                             | CPU-4  | Branch On Condition µINSTR-7                                   | Summary of IMPL Diagnostic Options IMPL-7        | Servo Track Following                       | DISK-6                 |

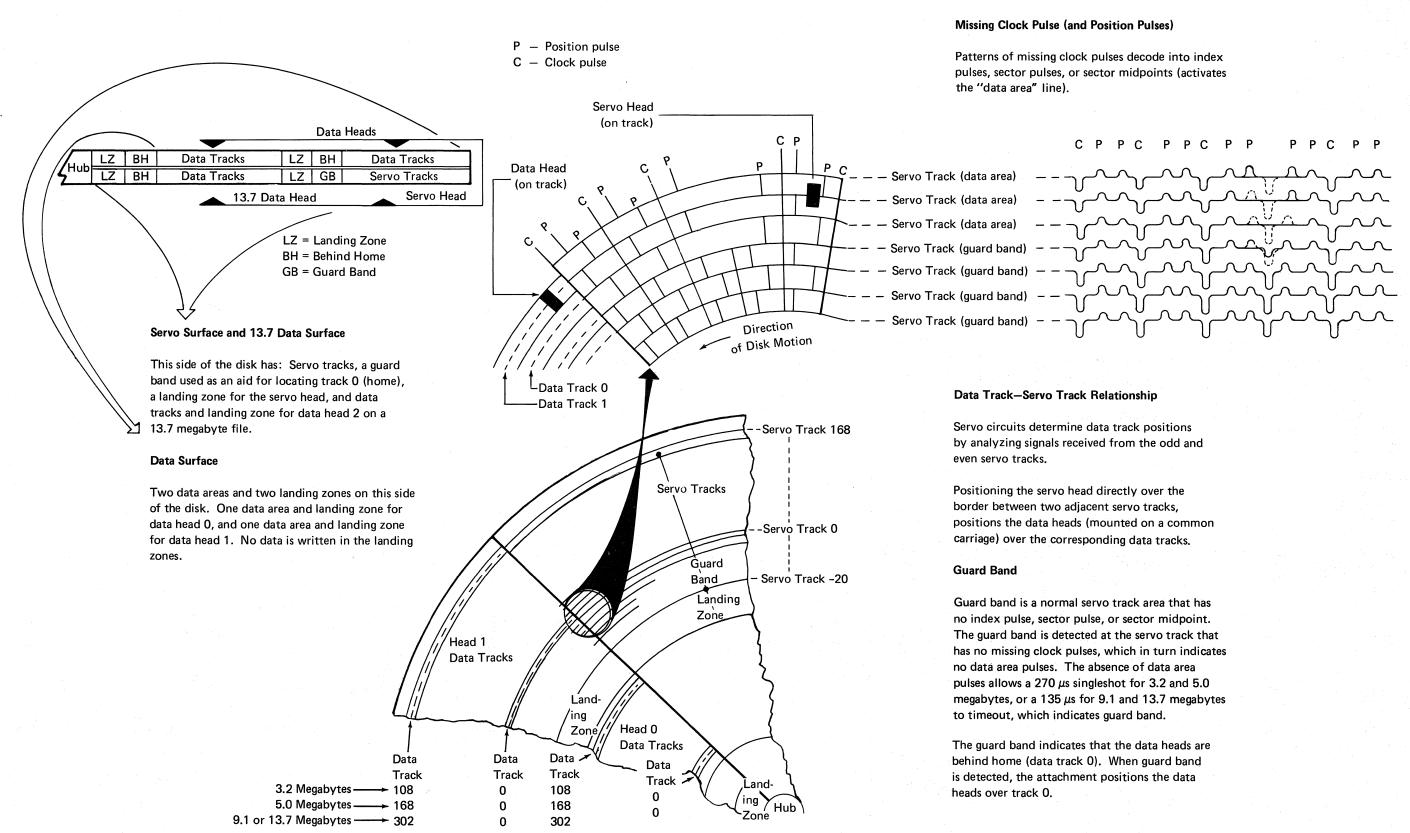

| Local Storage Registers               | CPU-5  | Condition Code μINSTR-7                                        |                                                  | Head Positioning and Disk Layout            | DISK-7                 |

| Micro Operation Register (MOR)        | CPU-5  | Branch On Condition (Stop Condition) . μINSTR-8                | ERROR HANDLING ERR HDL-1                         | Servo Surface and 13.7 Data Surface         | DISK-7                 |

| Storage Data Register (SDR)           | CPU-5  | Logical/Arithmetic 1 μINSTR-9                                  | CPU Checks ERR HDL-1                             | Data Surface                                | DISK-7                 |

| X-Registers                           | CPU-5  | Condition Code μINSTR-9                                        | Port Checks ERR HDL-1                            | Missing Clock Pulse (and Position Pulses) . | DISK-7                 |

| Y-Registers                           | CPU-5  | Logical/Arithmetic Functions μINSTR-10                         | Check Generation ERR HDL-2                       | Data Track-Servo Track Relationship         | DISK-7                 |

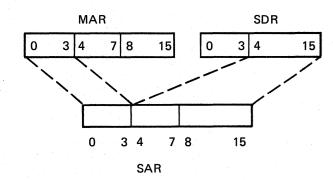

| Storage Address Register (SAR)        | CPU-5  | Logical/Arithmetic 2 μINSTR-12                                 | Check Halt ERR HDL-3                             | Guard Band                                  | DISK-7                 |

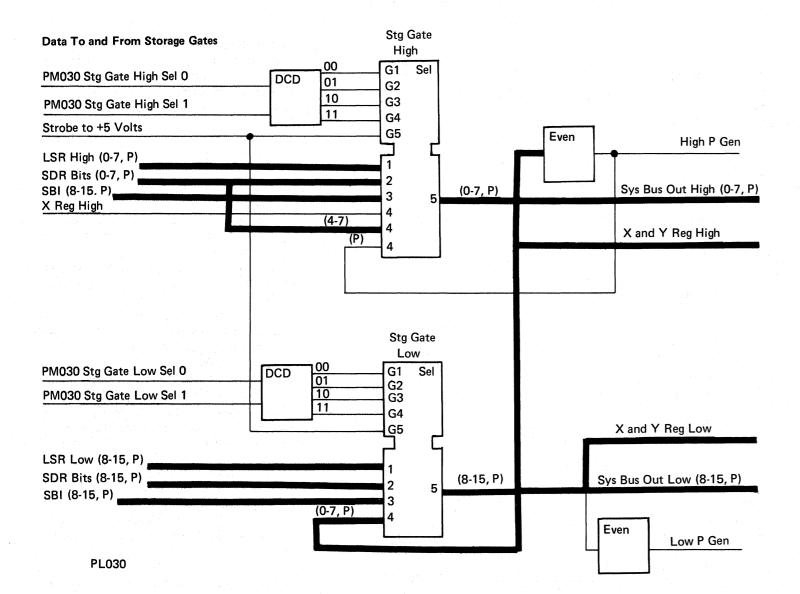

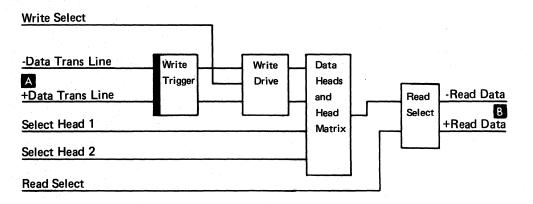

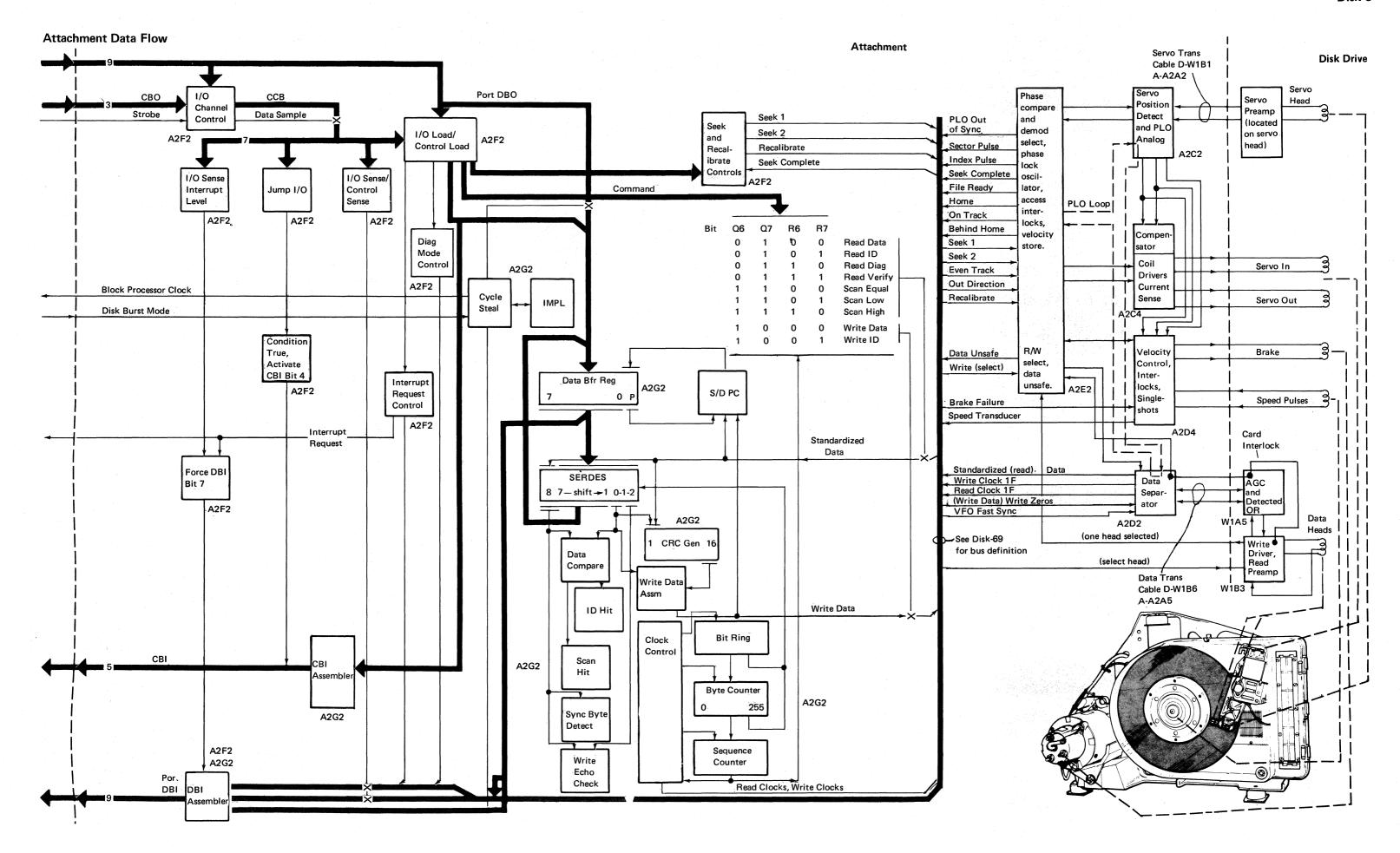

| Storage Gates                         | CPU-6  | Condition Code μINSTR-12                                       | Machine Check Interrupt Routine ERR HDL-4        | Attachment Data Flow                        | DISK-8                 |

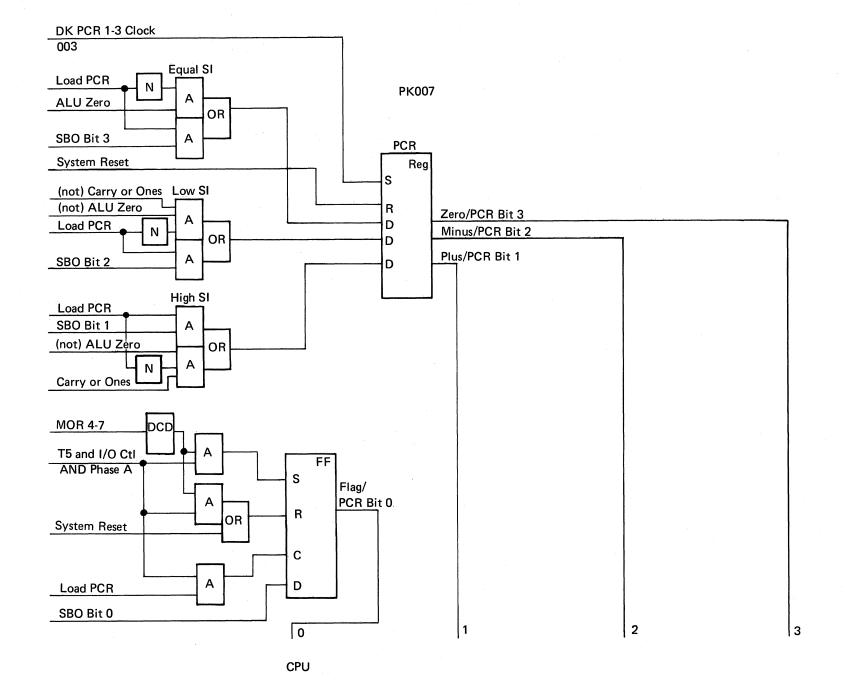

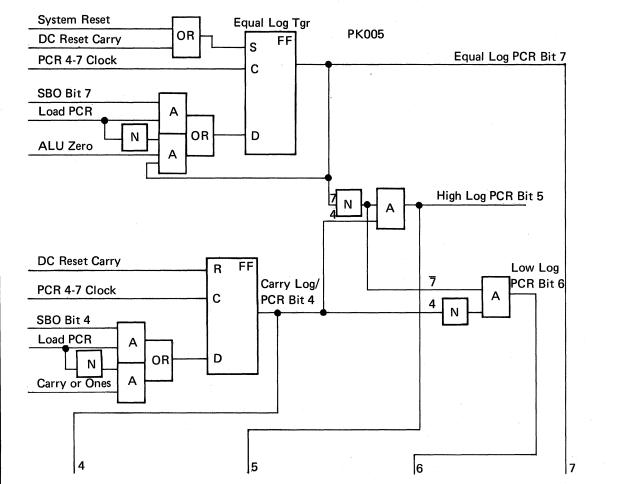

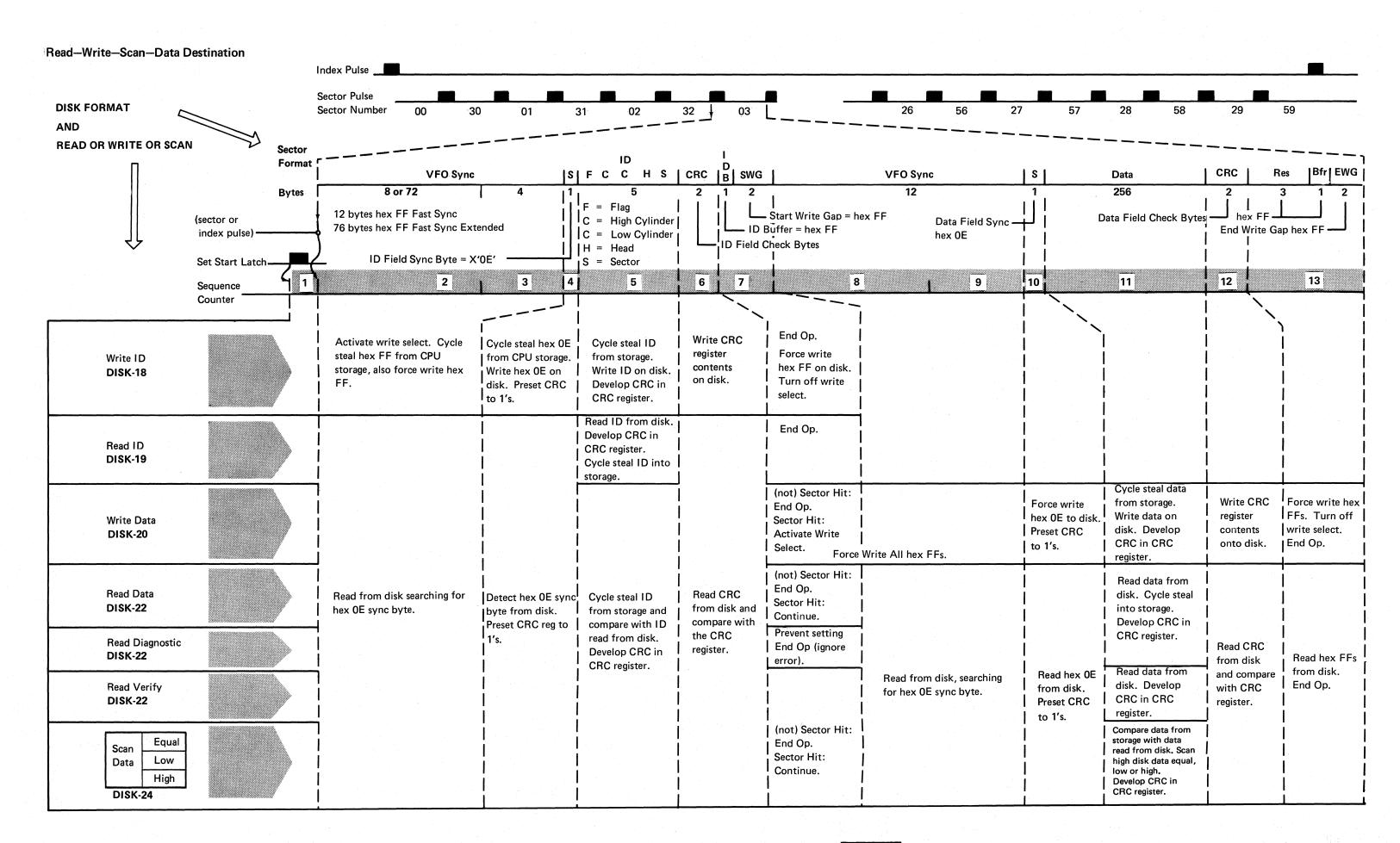

| Processor Condition Register (PCR)    | CPU-8  | Logical/Arithmetic Functions μINSTR-13                         | Error Logging ERR HDL-4                          | Read-Write-Scan Data Destination            | DISK-9                 |

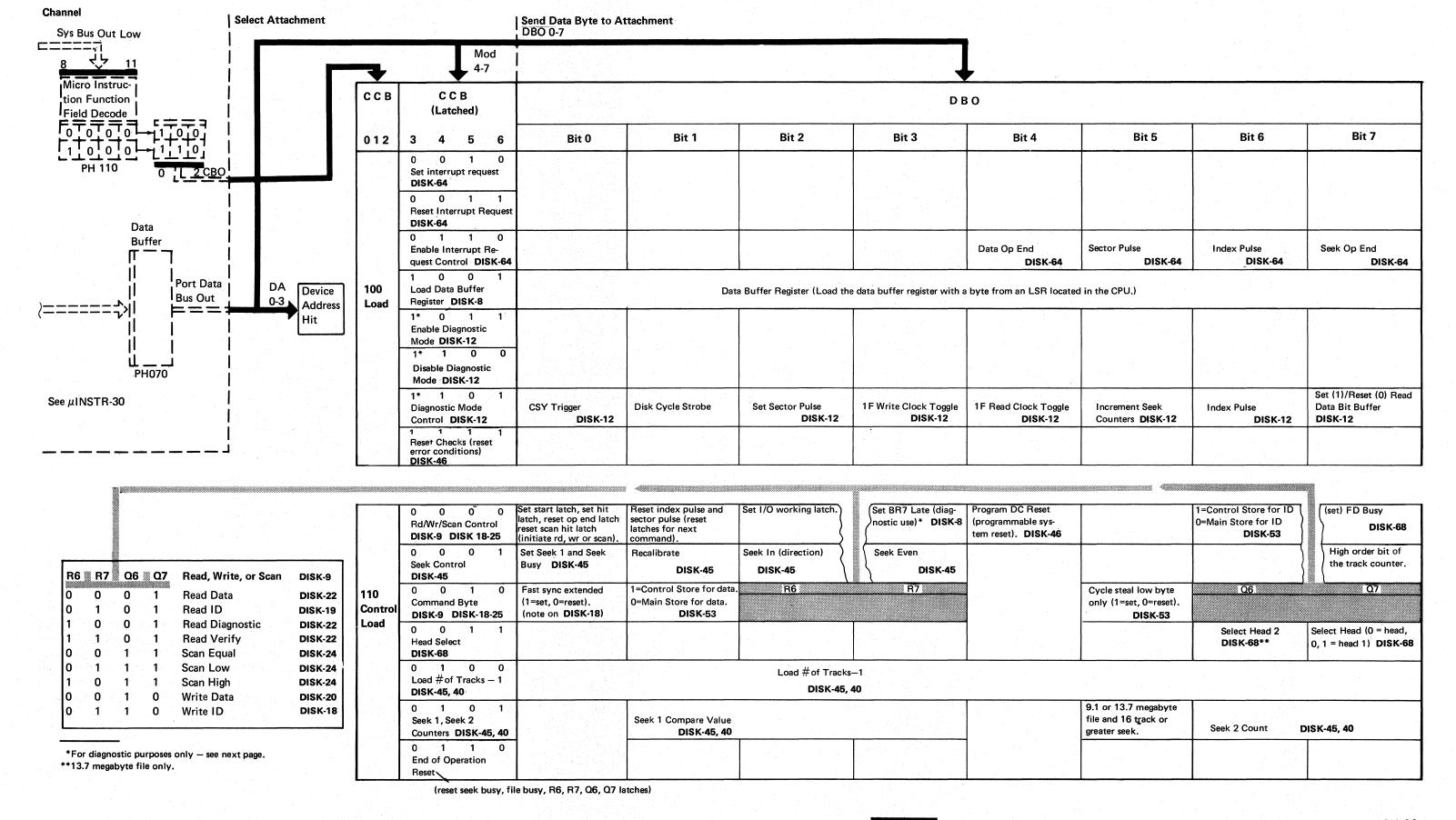

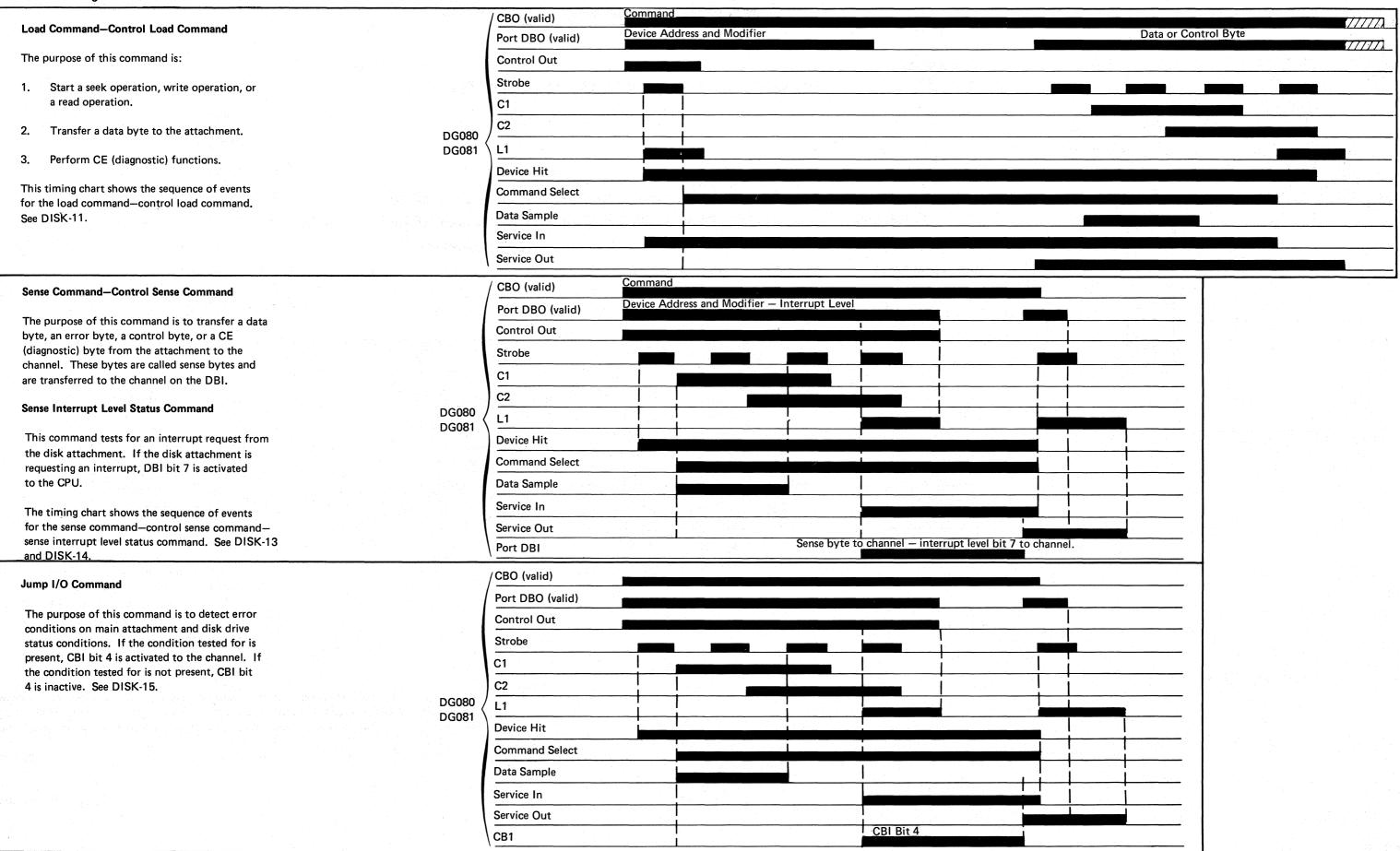

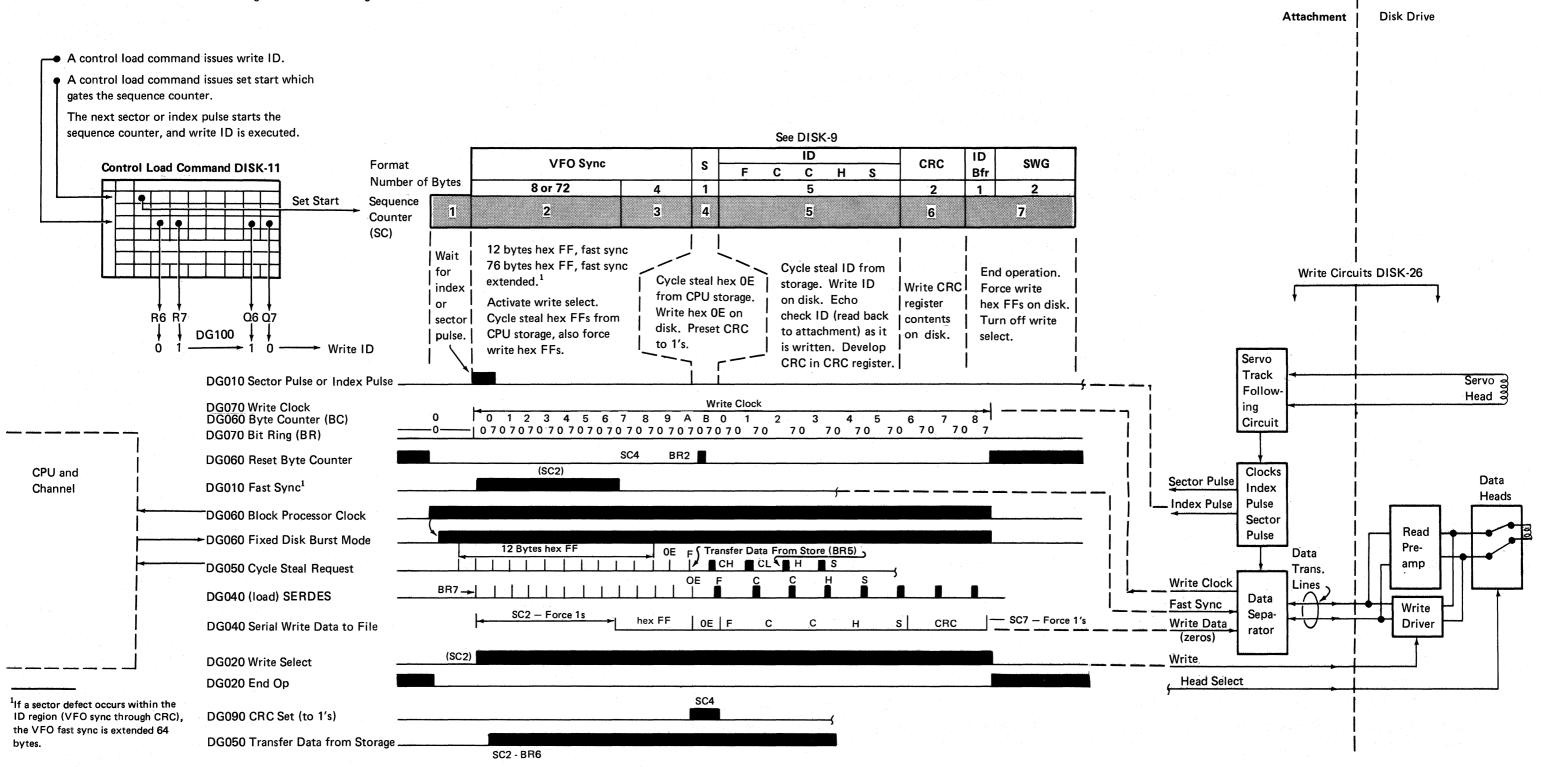

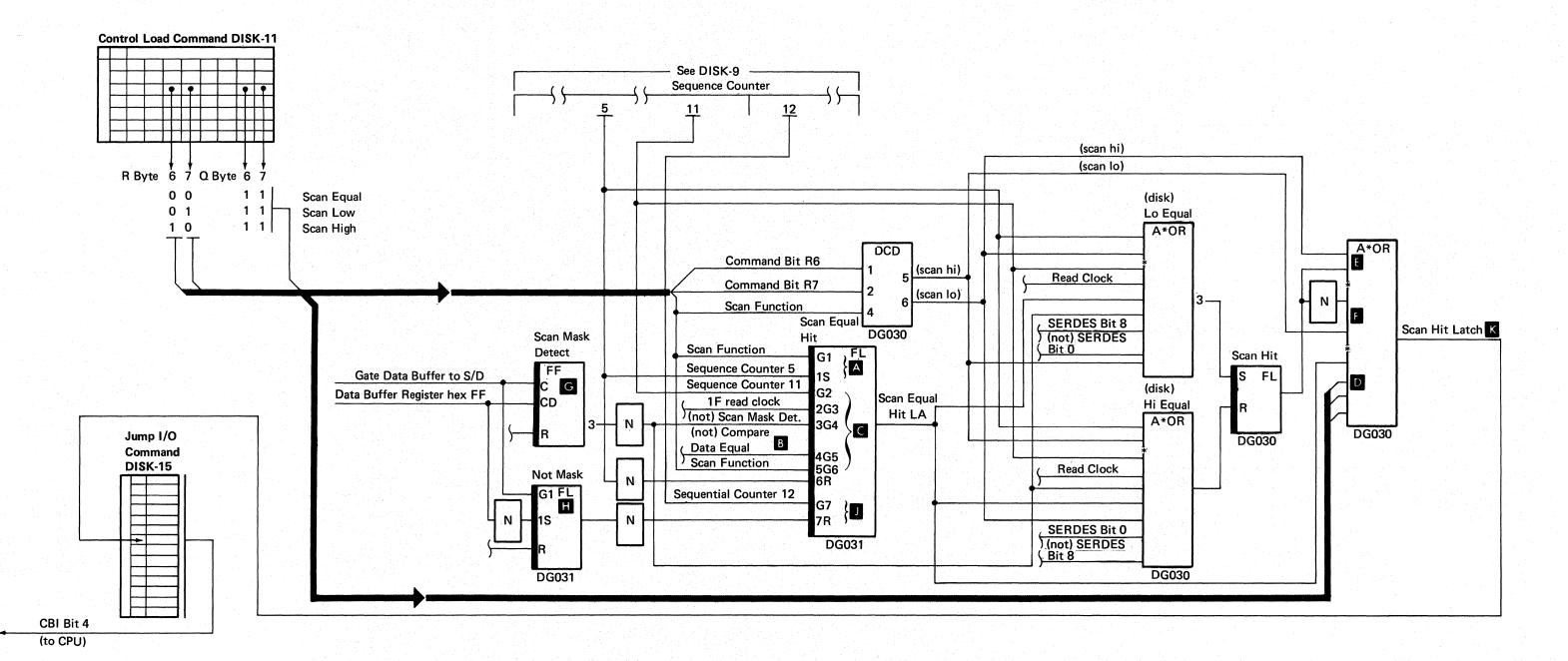

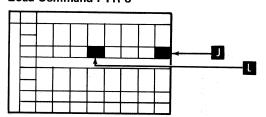

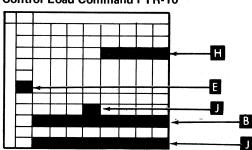

| Main Storage                          | CPU-10 | Immediate μINSTR-15                                            | Error Retry ERR HDL-4                            | Load Command—Control Load Command .         | DISK-11                |

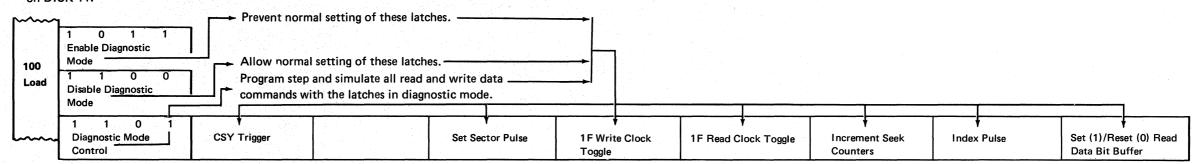

| Control Storage                       | CPU-10 | Condition Code                                                 |                                                  | Diagnostic Load                             | DISK-12                |

| Direct Area of Control Storage        | CPU-11 | Compare Immediate                                              | CONSOLE CNSL-1                                   | Diagnostic Mode                             | DISK-12                |

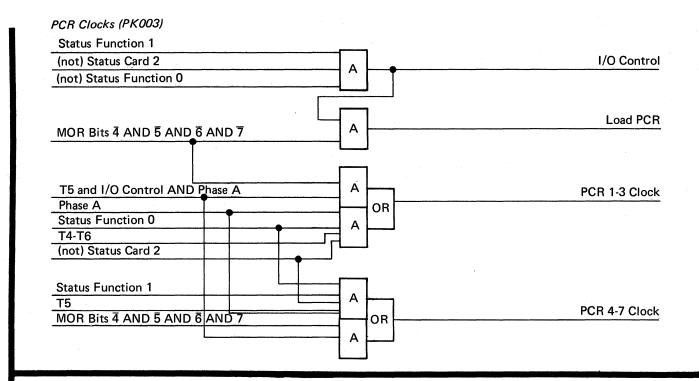

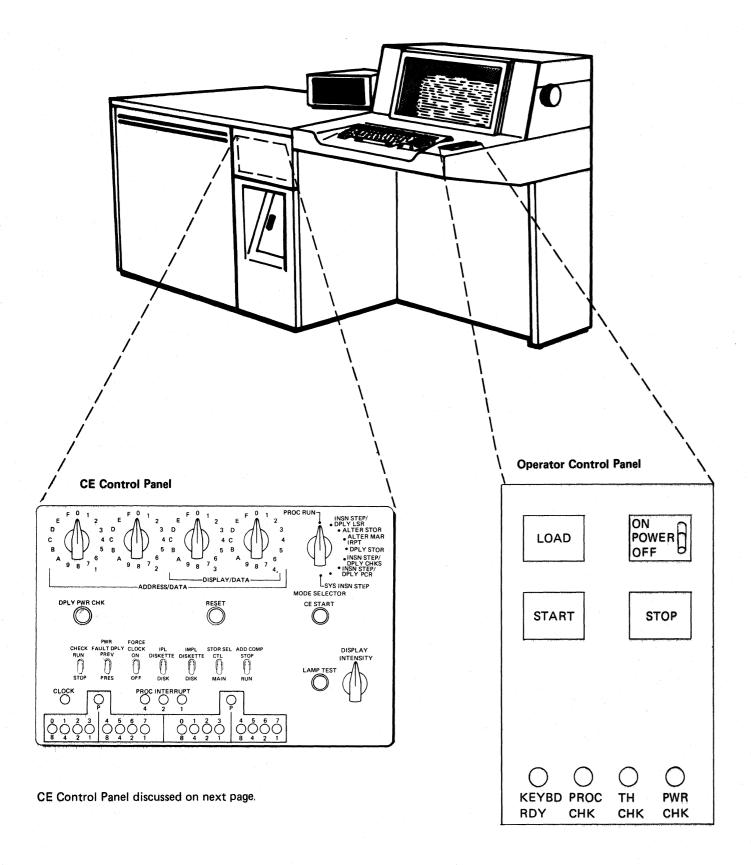

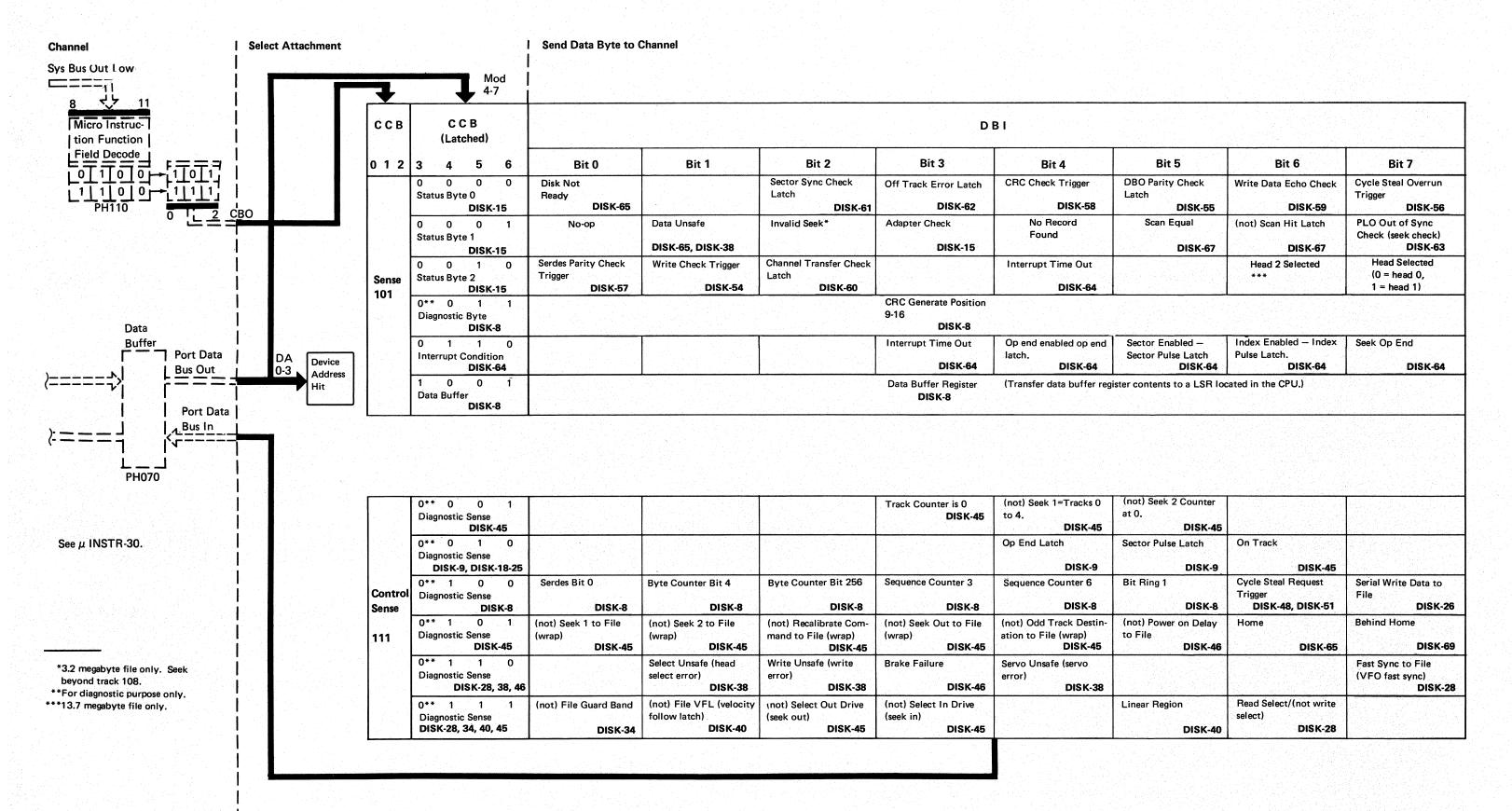

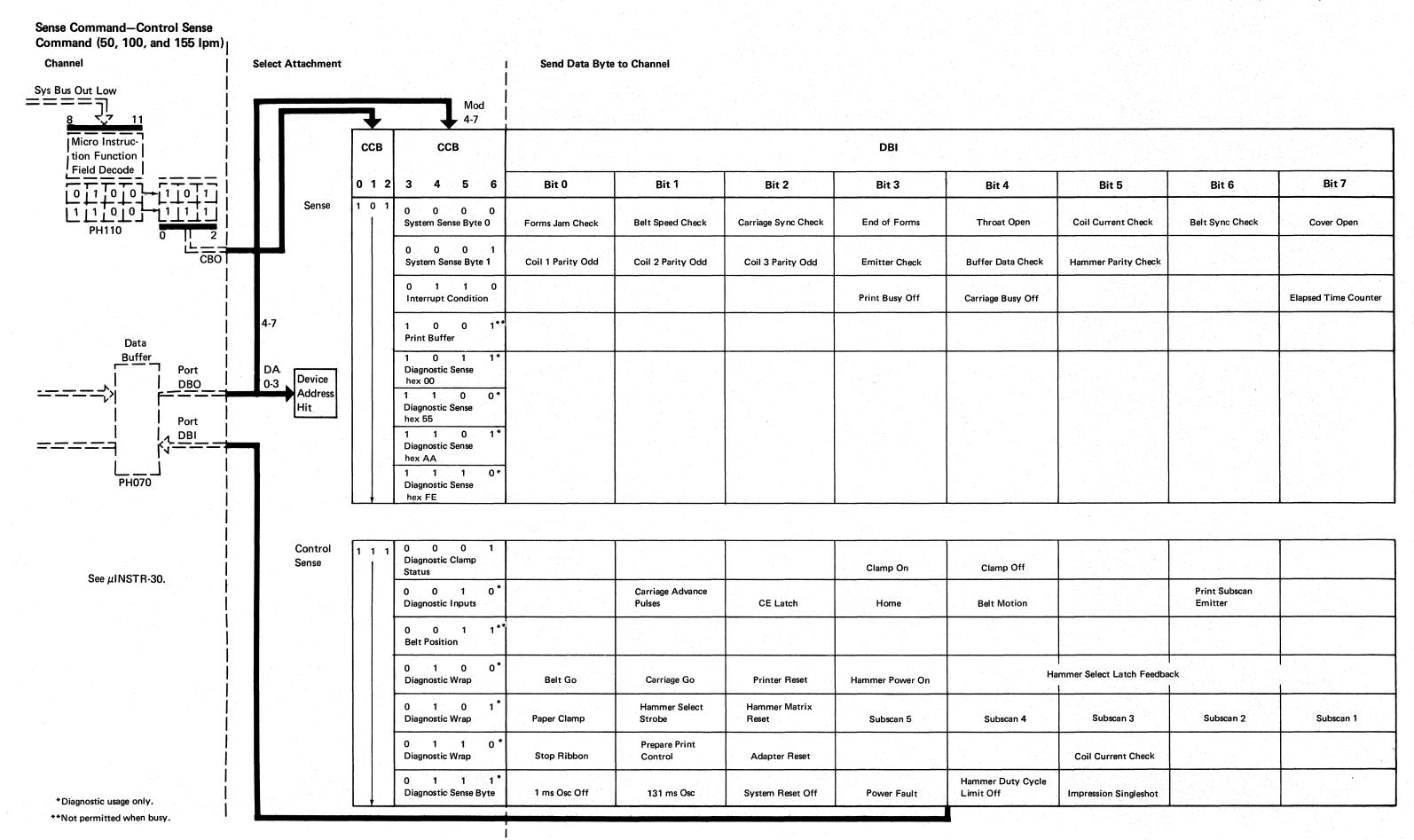

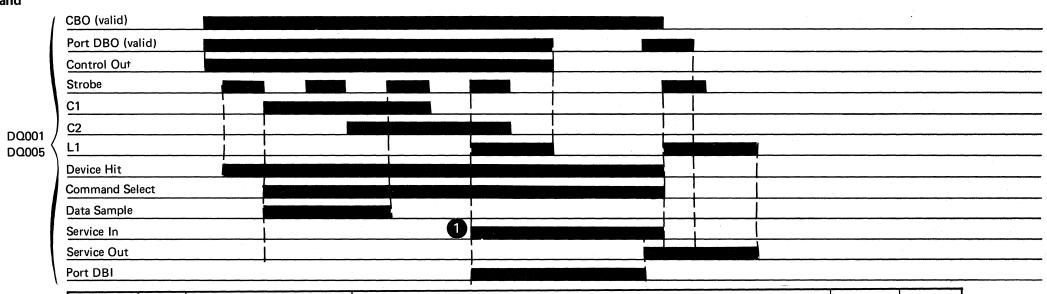

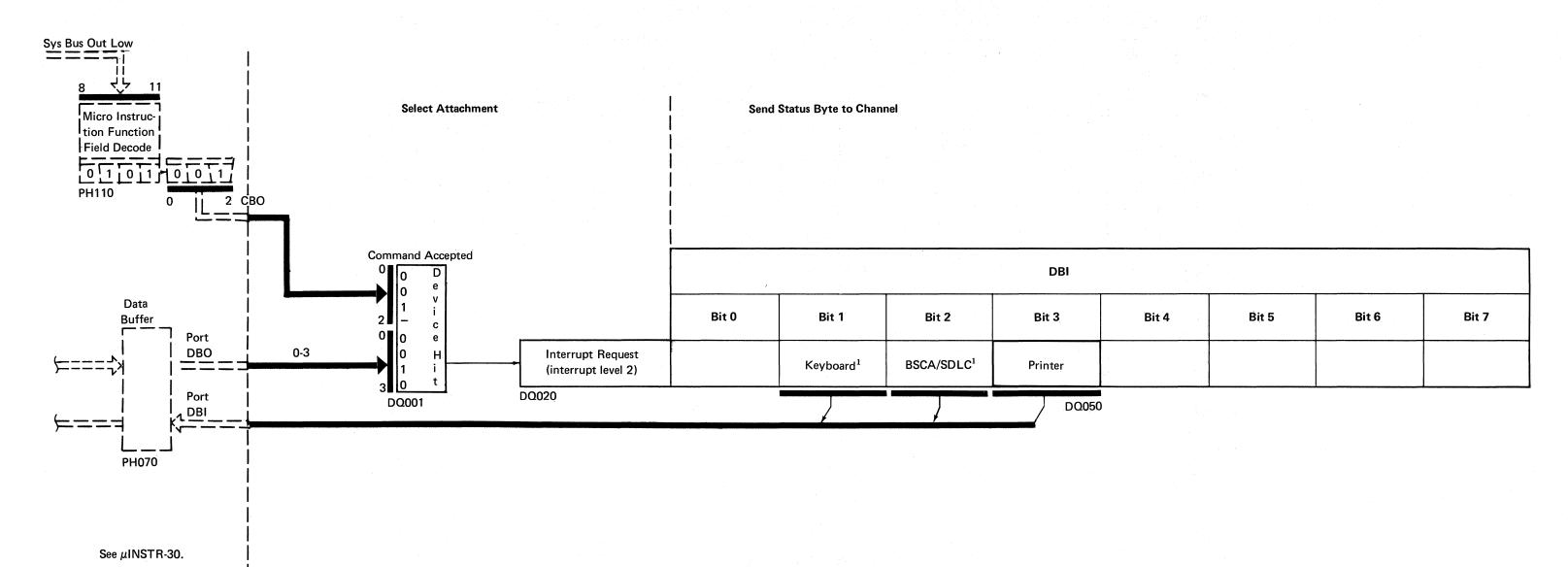

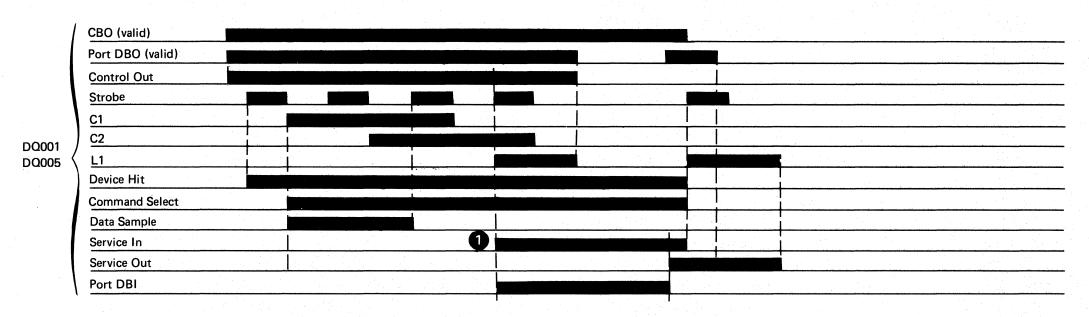

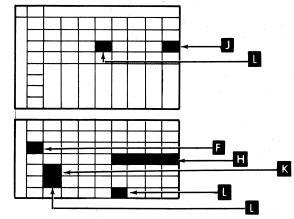

| CPU Clocks                            | CPU-12 | Condition Code μINSTR-16                                       | Operator Control Panel CNSL-1                    | Sense Command—Control Sense Command .       | DISK-13                |

| System Clocks                         | CPU-12 | Subtract Immediate                                             | Load Switch/Light (LOAD) CNSL-1                  | Sense Interrupt Level Status Command        | DISK-14                |

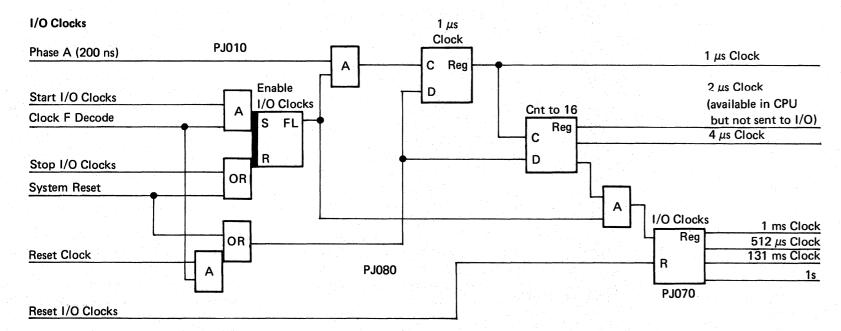

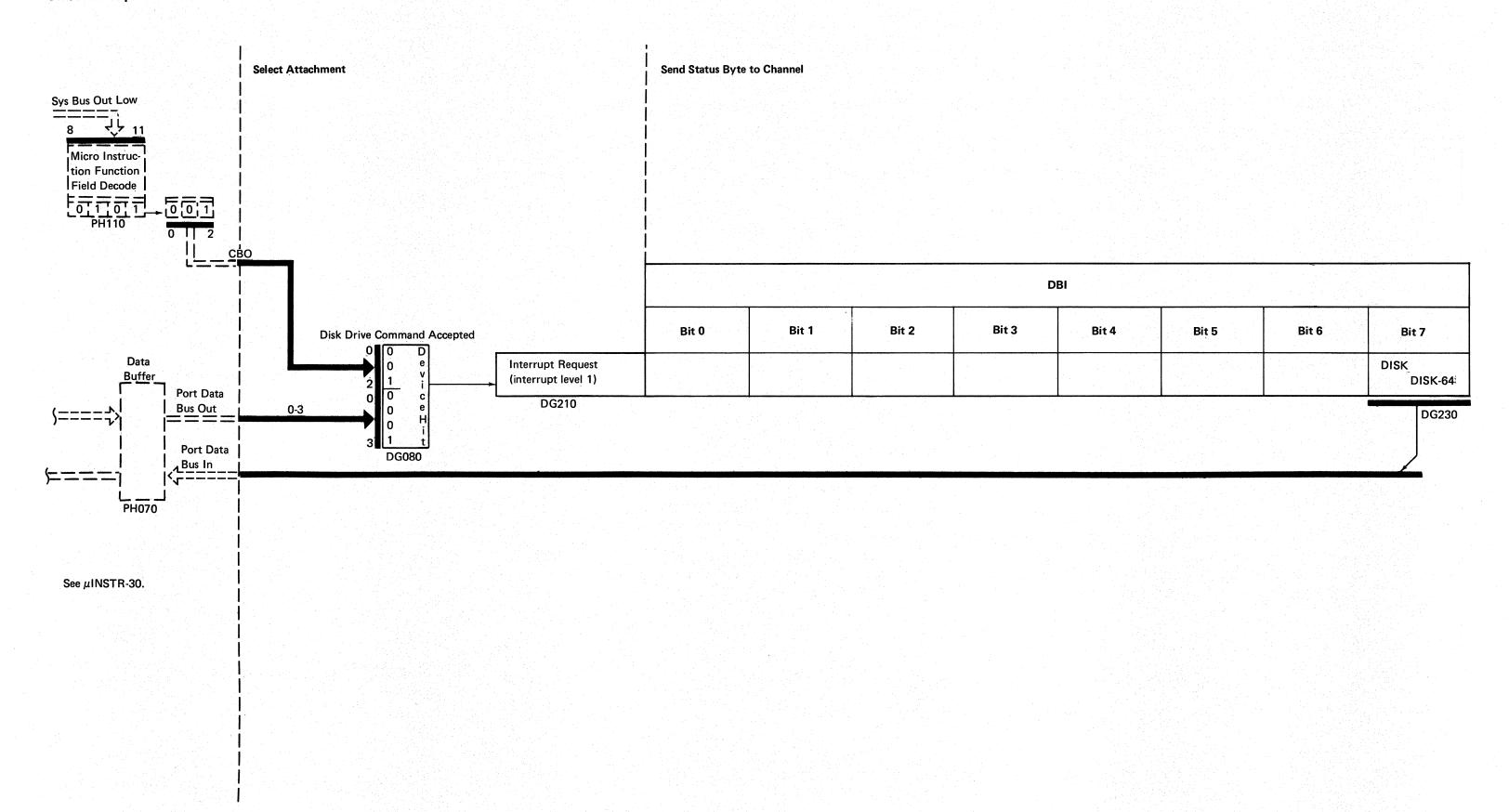

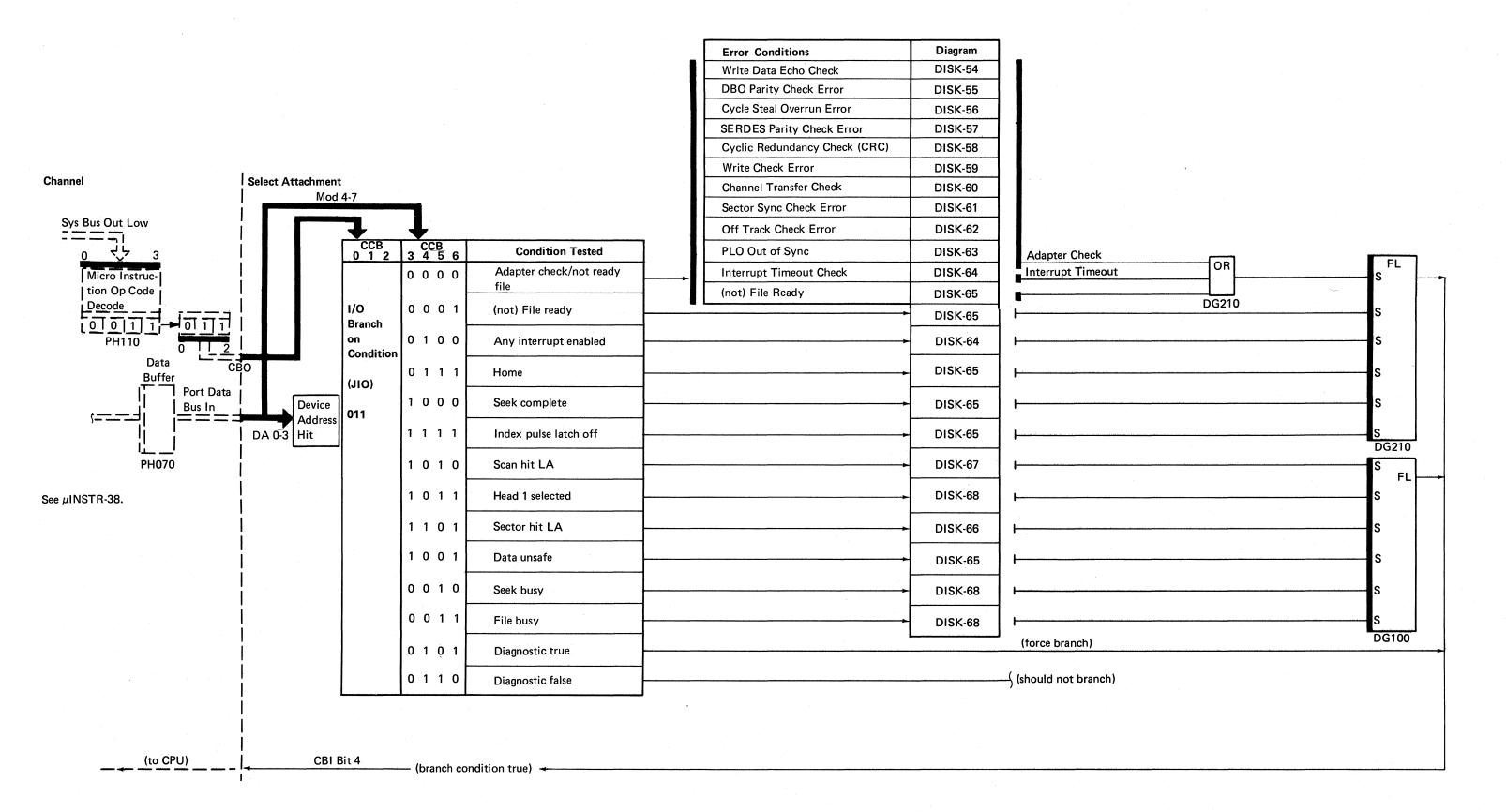

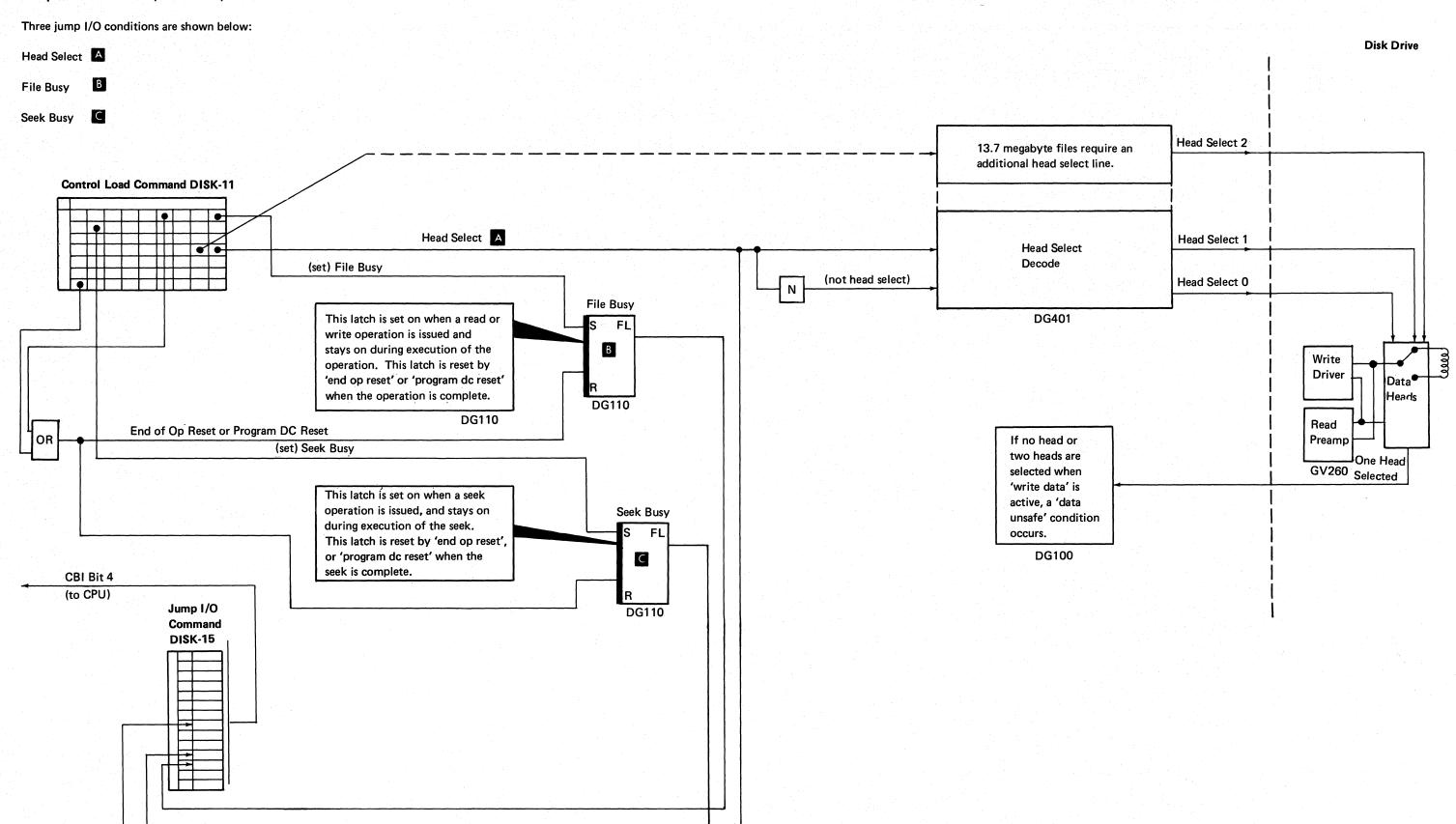

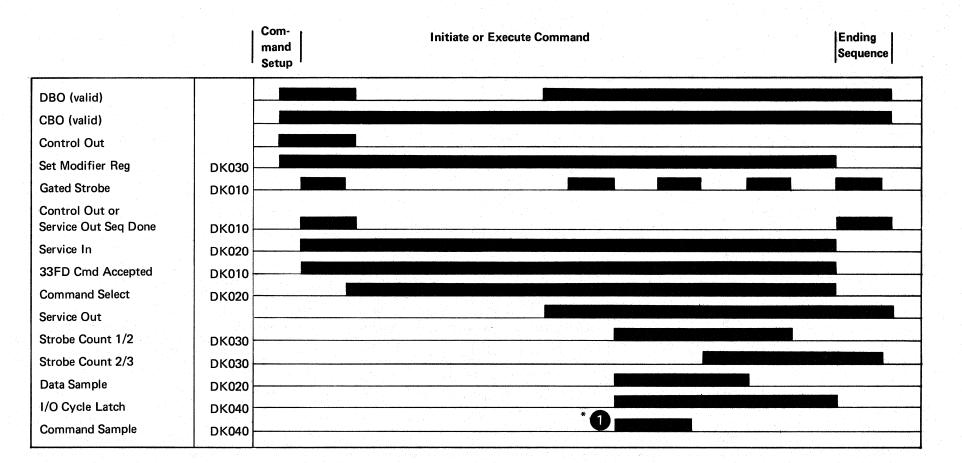

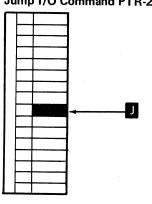

| I/O Clocks                            | CPU-12 | Condition Code                                                 | Start Switch/Light (START) CNSL-1                | Jump I/O Command                            | DISK-15                |

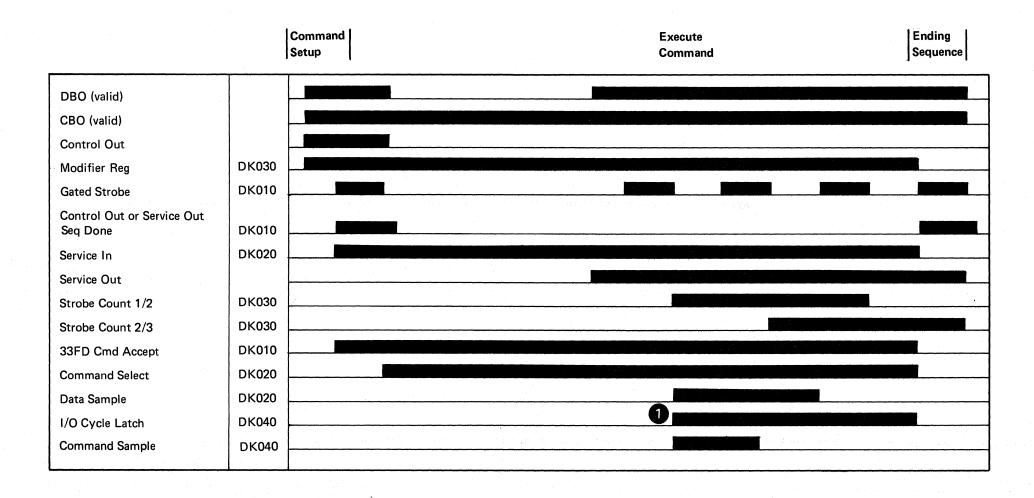

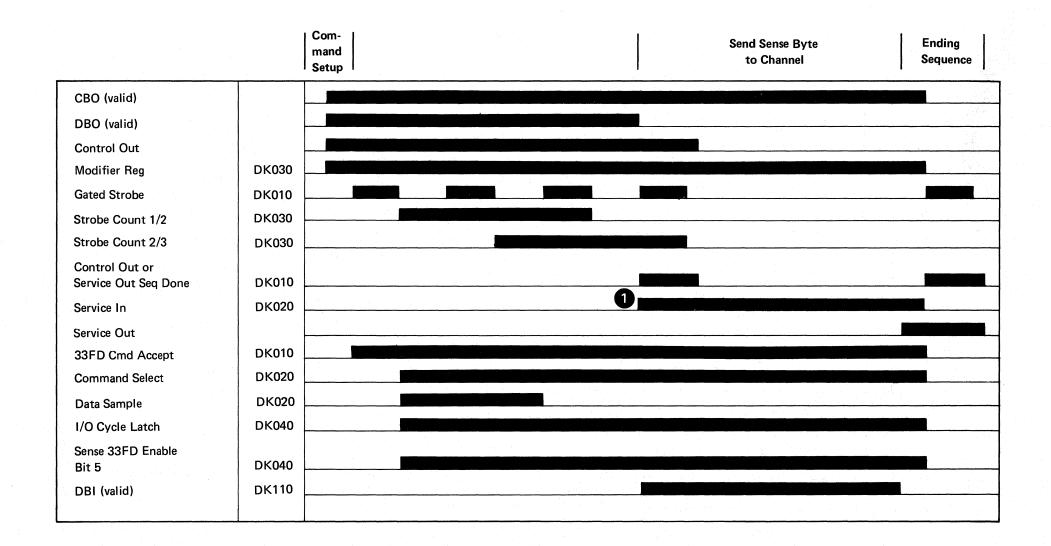

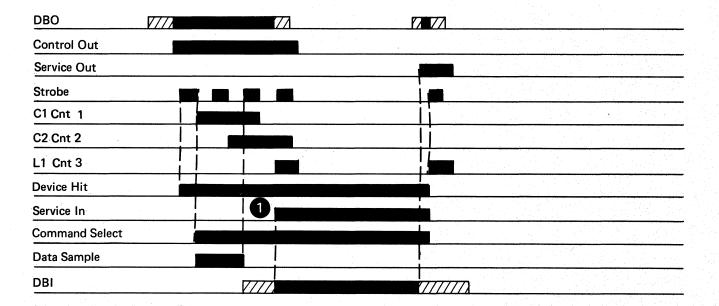

| Storage Clocks                        | CPU-12 | Test Mask μINSTR-18                                            | Keyboard Ready Light (KEYBD RDY) . CNSL-1        | Command Timing Charts                       | DISK-17                |

| Service Request                       | CPU-13 | Condition Code μINSTR-18                                       | Processor Check Light (PROC CHK) CNSL-1          | Load Command—Control Load Command           | DISK-17                |

| System Reset                          | CPU-13 | Set Bits On μINSTR-19                                          | Power On/Off Switch (POWER ON/OFF) CNSL-1        | Sense Command—Control Sense                 | A THAIR THAN I A STOCK |

|                                       |        | Condition Code μINSTR-19                                       | Stop Switch (STOP) CNSL-1                        | Command                                     | DISK-17                |

| CHANNEL                               | CHAN-1 | Set Bits Off μINSTR-20                                         | Power Check Light (PWR CHK) CNSL-1               | Sense Interrupt Level Status Command .      | DISK-17                |

| Channel Interfaces                    | CHAN-1 | Condition Code μINSTR-20                                       | Thermal Check Light (TH CHK) CNSL-1              | Jump I/O Command                            | DISK-17                |

| Main/Control Storage through CPU Data |        | Storage                                                        | CE Control Panel CNSL-2                          | Write Identifier (ID)                       | DISK-18                |

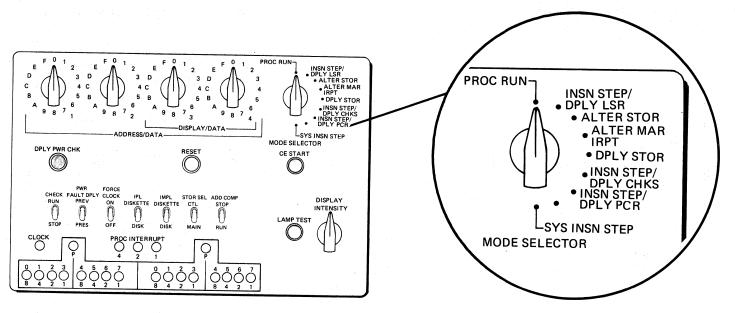

| Flow Interface                        | CHAN-1 | Condition Code μINSTR-21                                       | MODE SELECTOR Switch CNSL-2                      | Write ID                                    | DISK-18                |

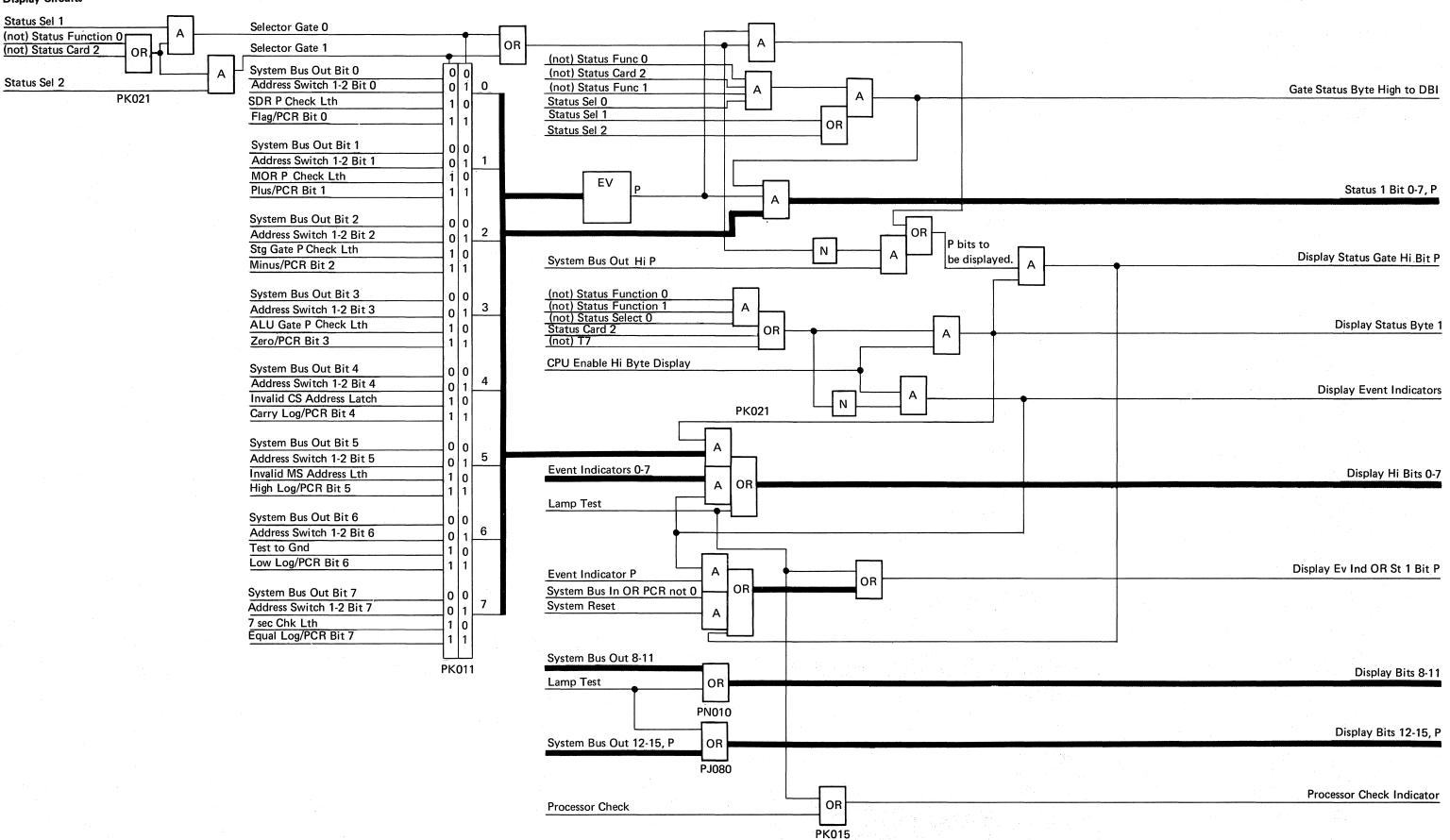

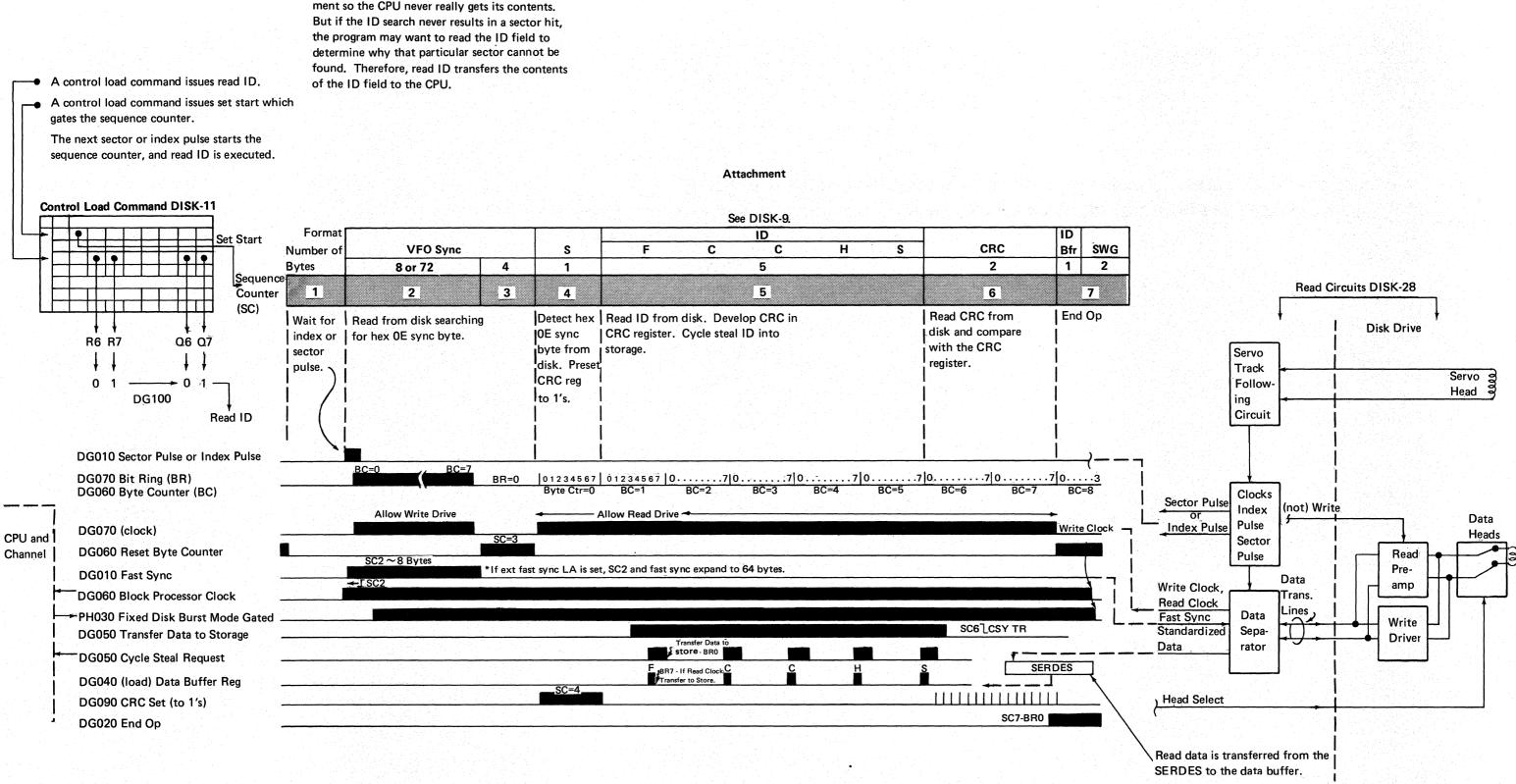

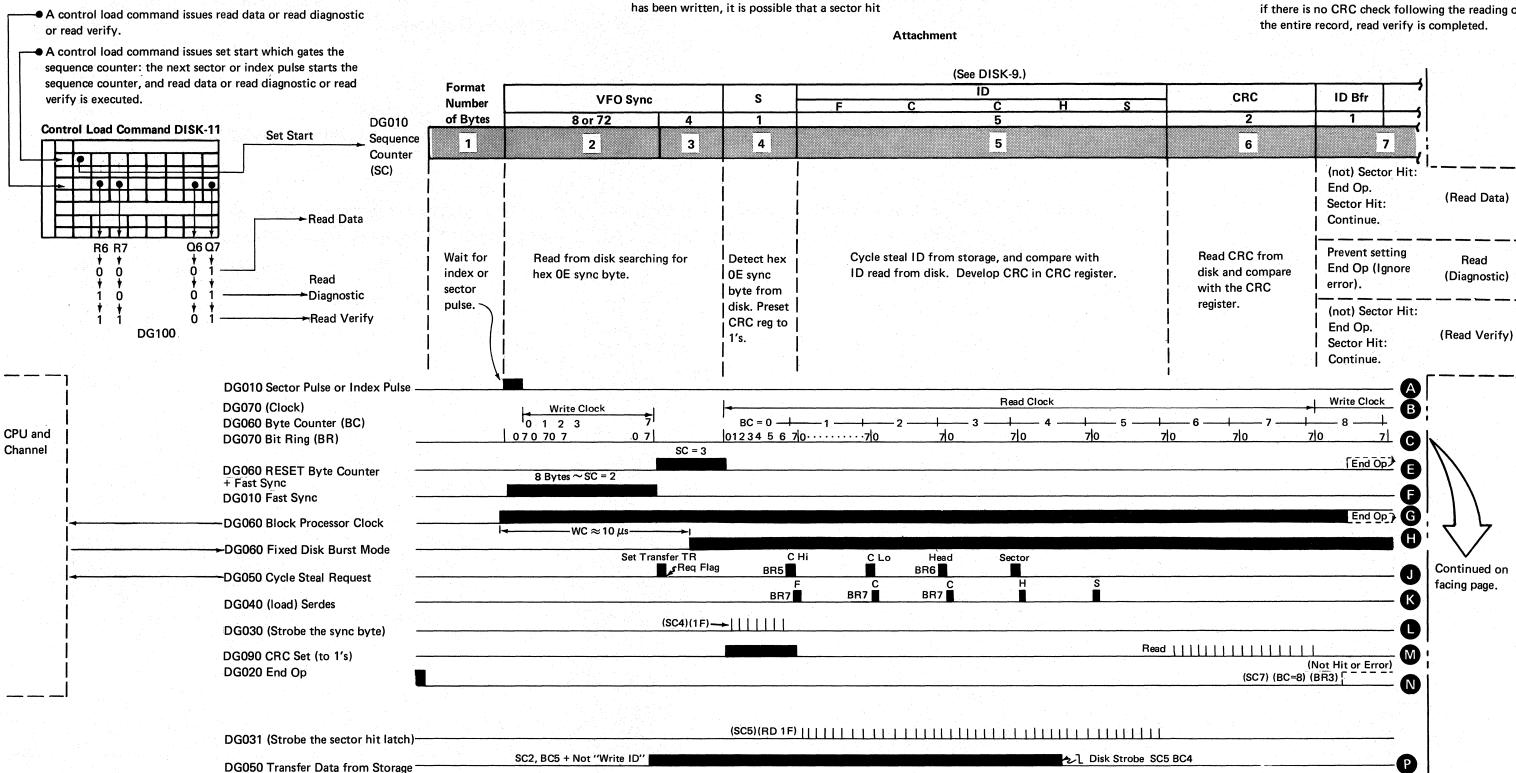

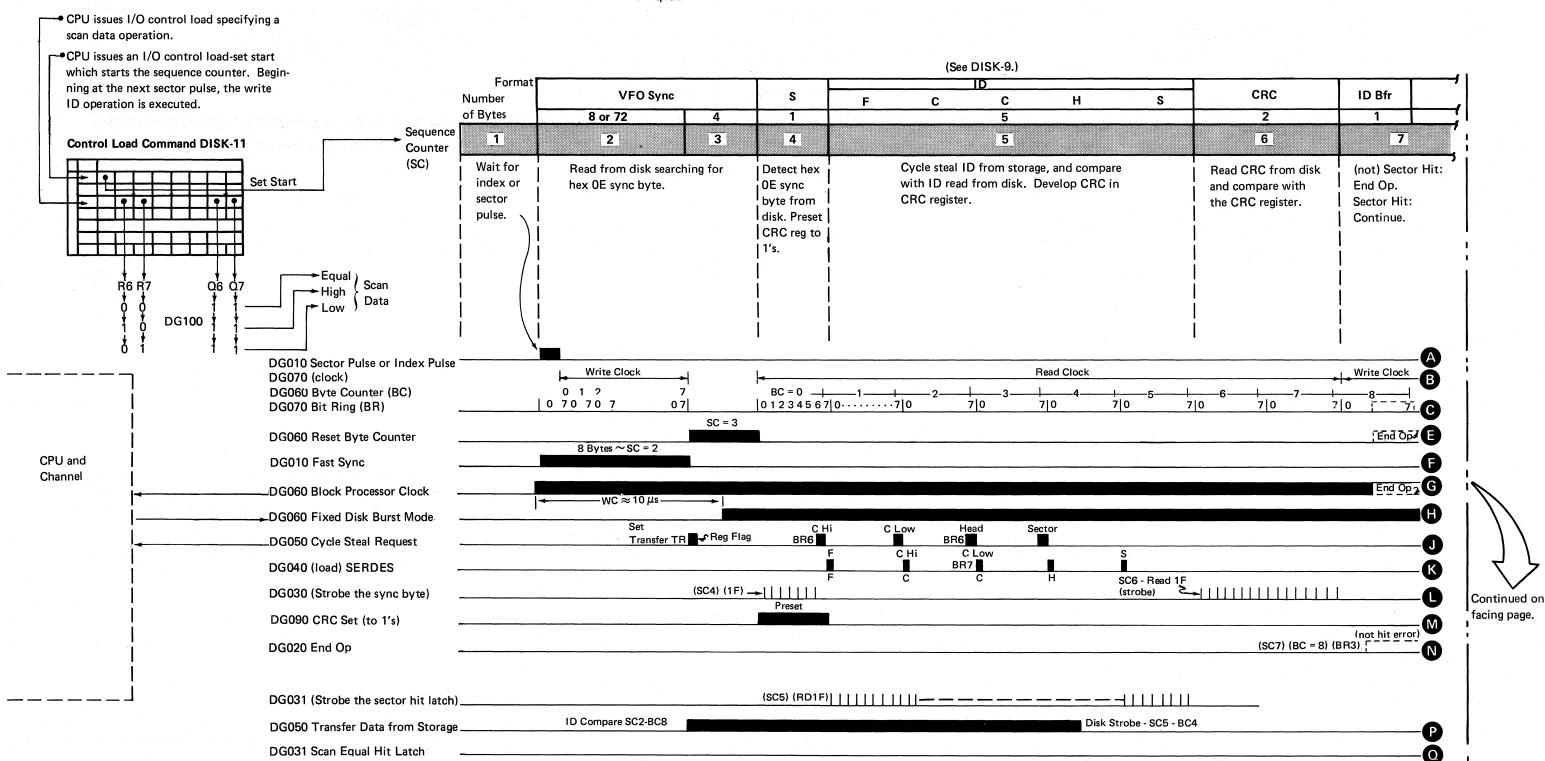

| CPU Data Flow and LSRs Interface      | CHAN-1 | Storage (Read)                                                 | Display Circuits CNSL-4                          | Read Identifier (ID)                        | DISK-19                |

| Disk Storage Interface                | CHAN-1 | Storage (Write)                                                | Address—Data—Display Switches CNSL-6             | Read ID                                     | DISK-19                |

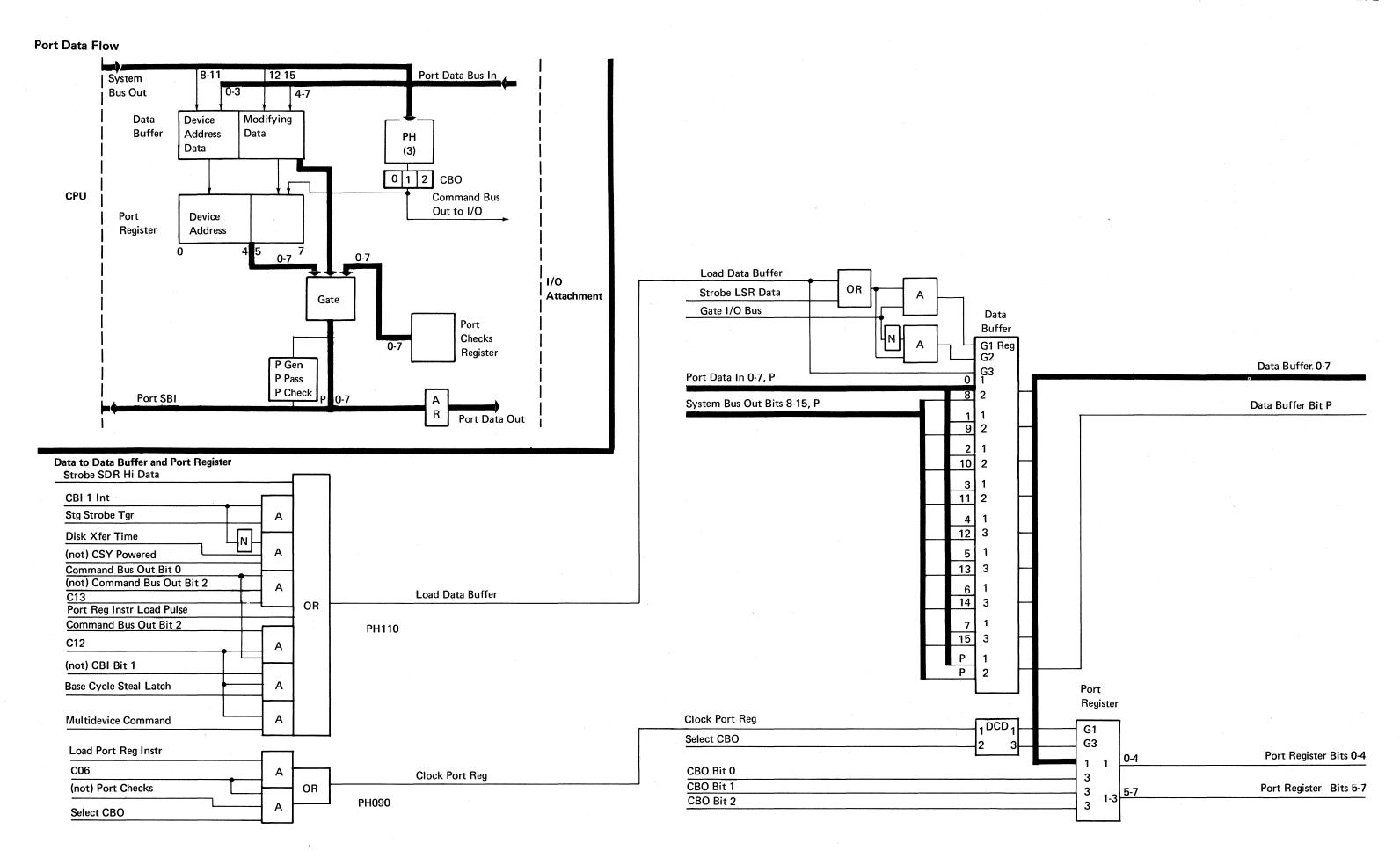

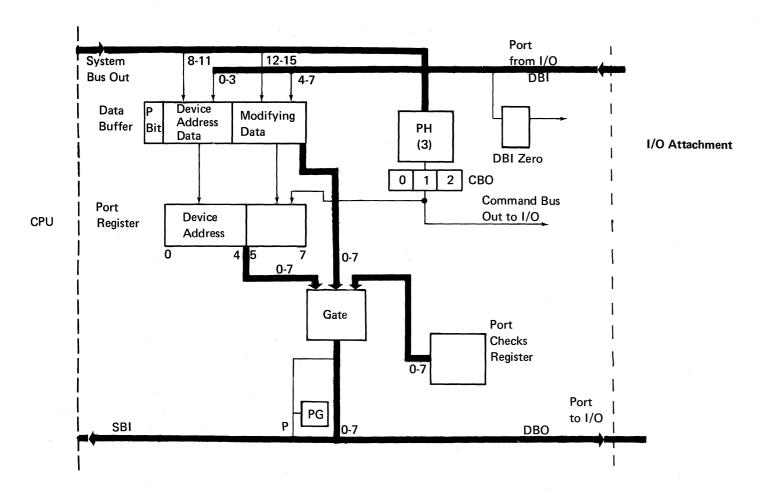

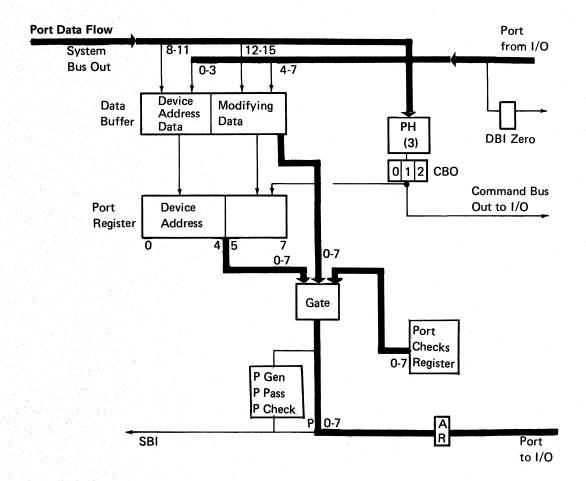

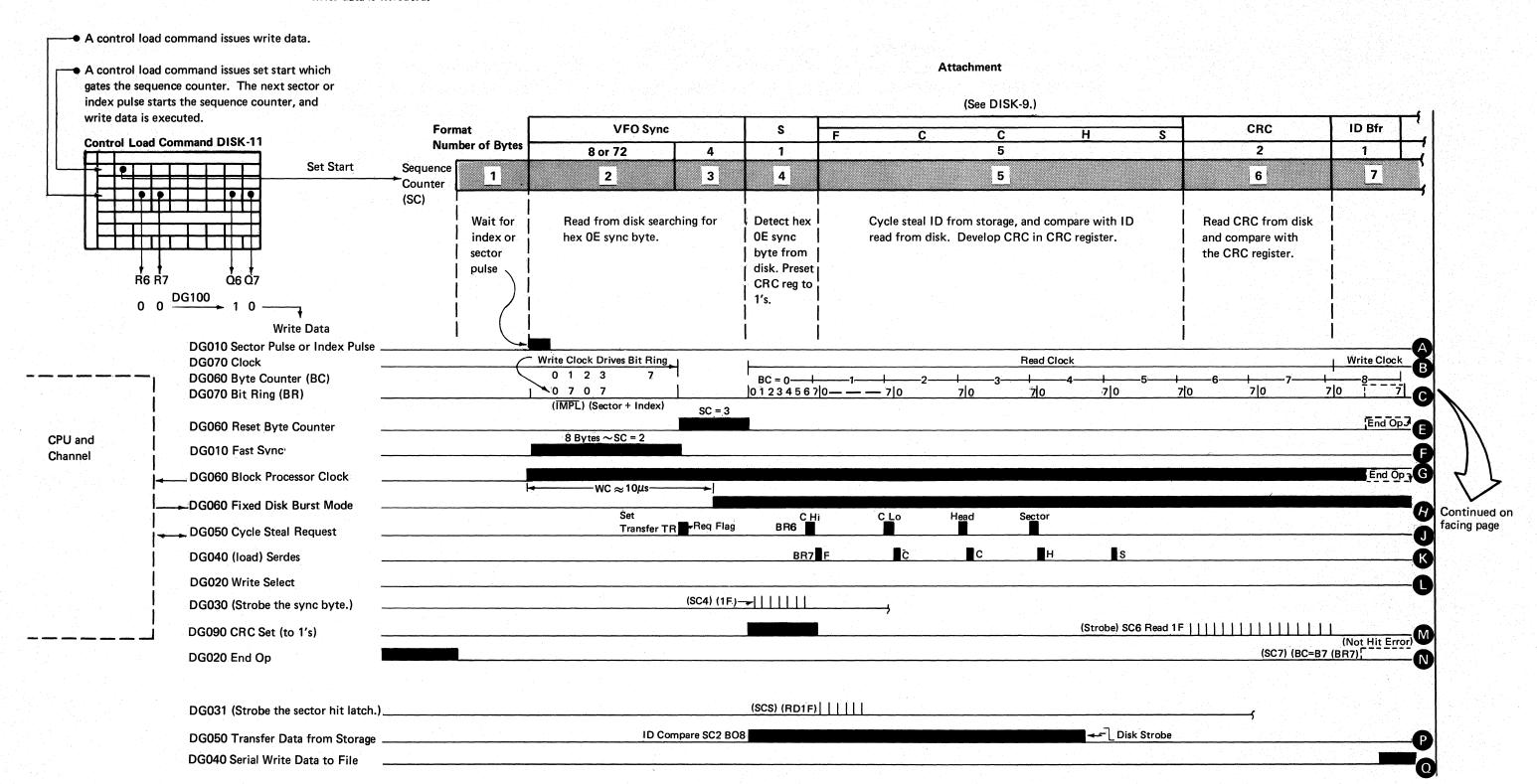

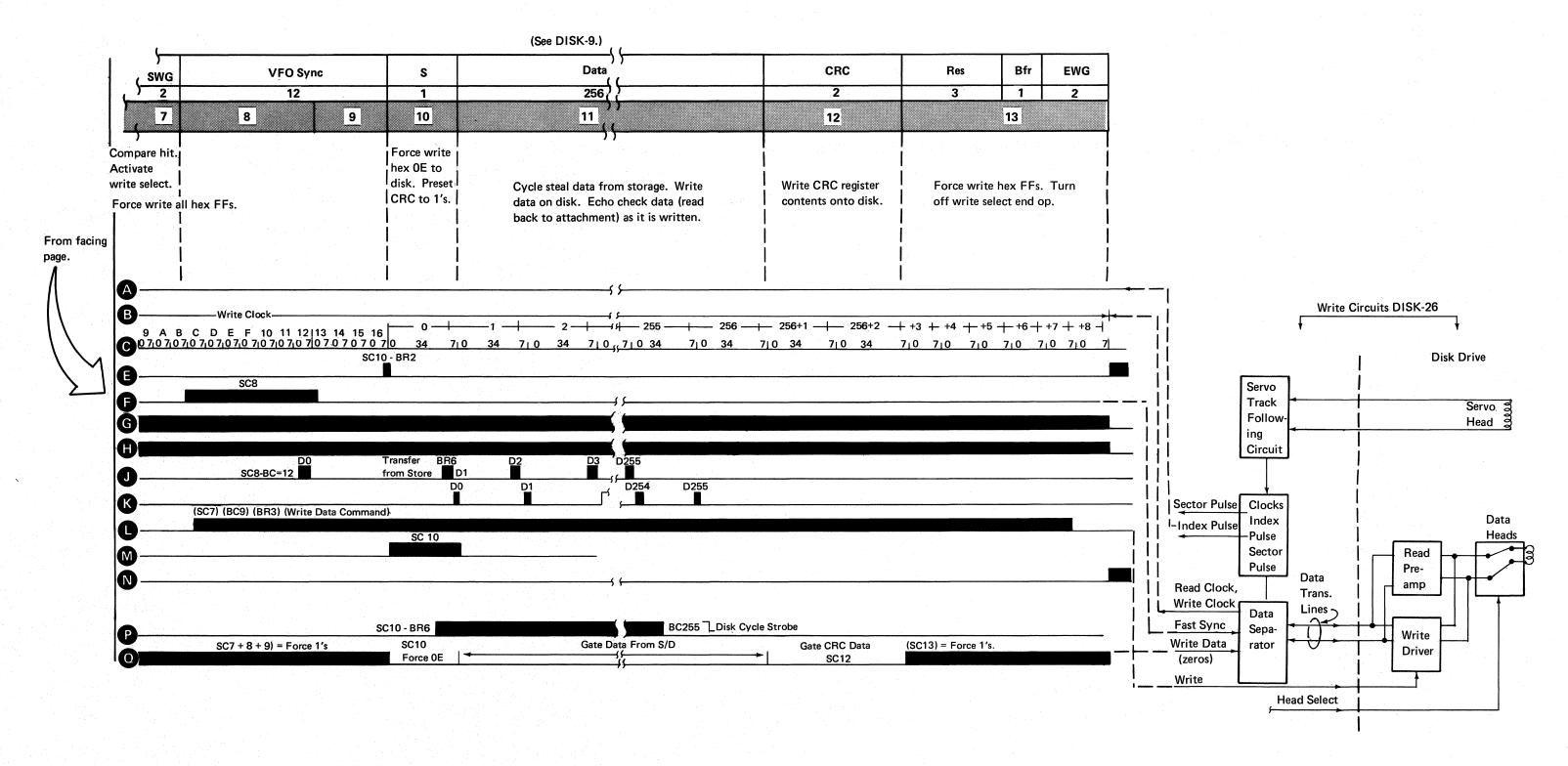

| Port Data Flow                        | CHAN-2 | Storage Direct                                                 | PROC INTERRUPT Lights CNSL-6                     | Write Data                                  | DISK-20                |

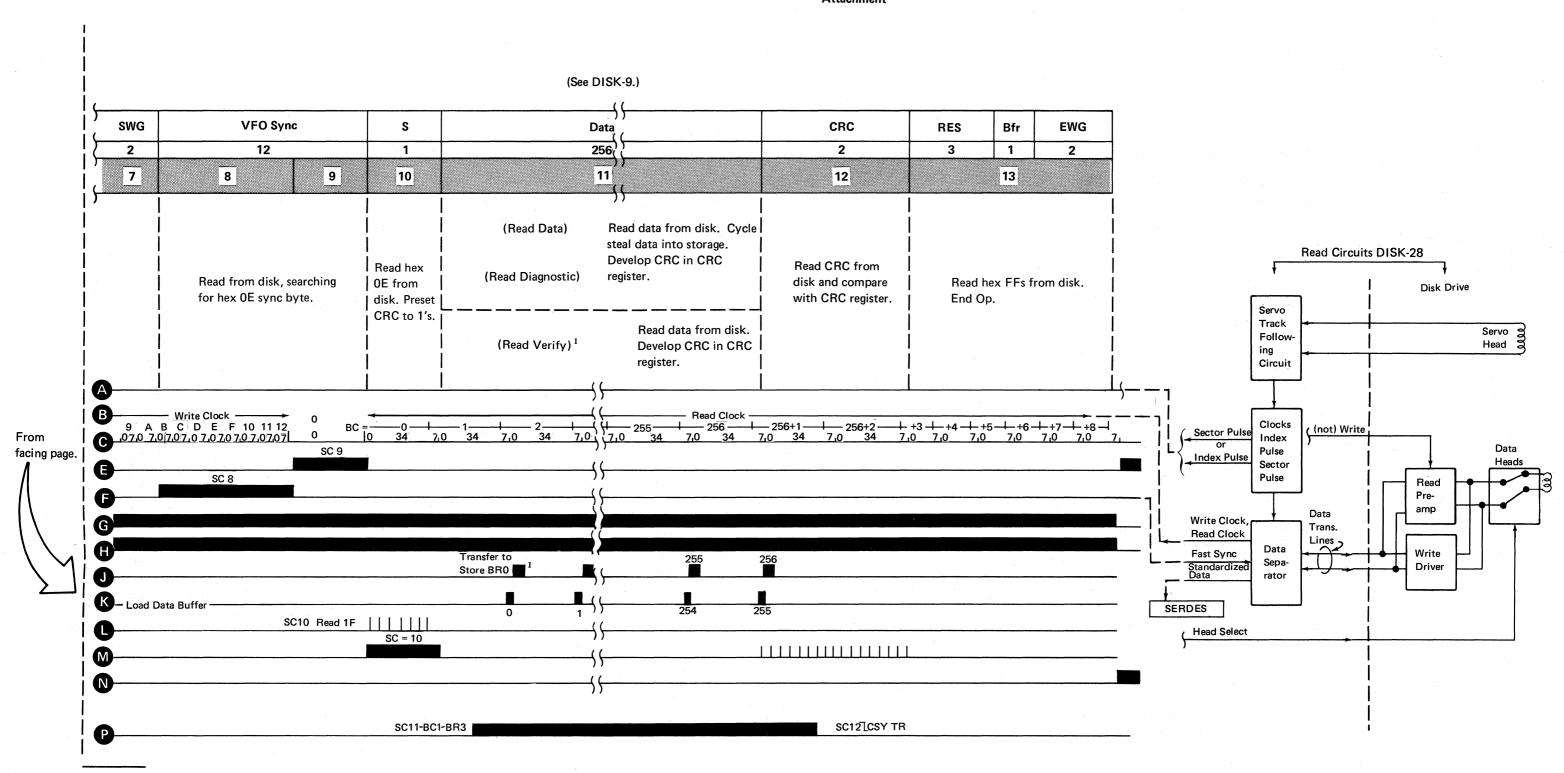

| Port Parity                           | CHAN-3 | Condition Code                                                 | RESET Switch CNSL-6                              | Read Data or Read Diagnostic or Read        | D101\-20               |

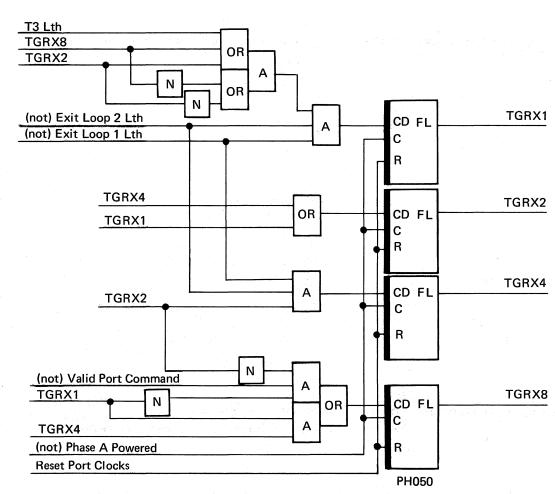

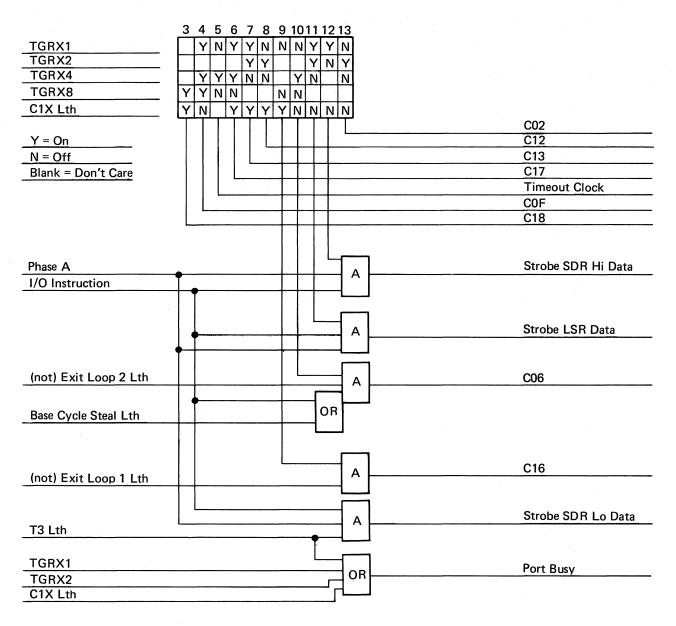

| Port Clocks                           | CHAN-4 | Read from Control Storage μINSTR-23                            | CE START Switch CNSL-6                           | Verify                                      | DISK-22                |

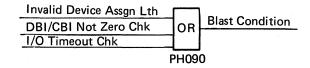

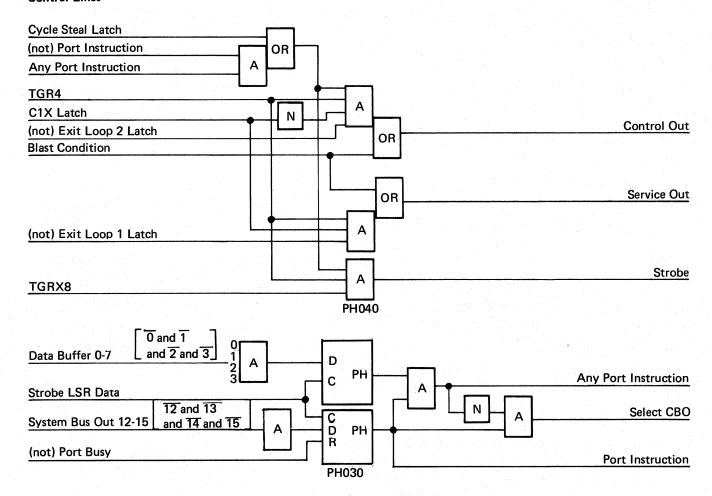

| Blast Condition (PH090)               | CHAN-6 | Write to Control Storage µINSTR-24                             | LAMP TEST Switch CNSL-6                          | Read Data                                   | DISK-22                |

| Controls                              | CHAN-7 | Move LSR μINSTR-25                                             | DISPLAY INTENSITY Control CNSL-6                 | Read Diagnostic                             | DISK-22                |

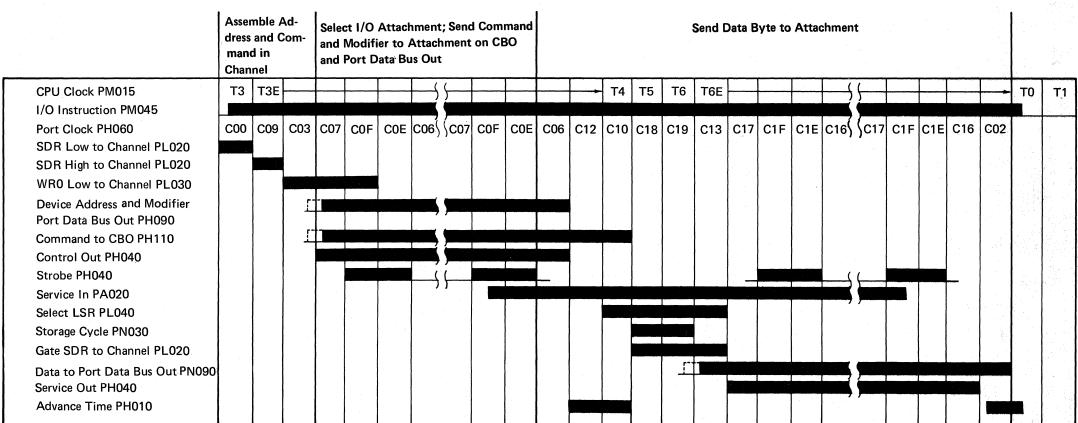

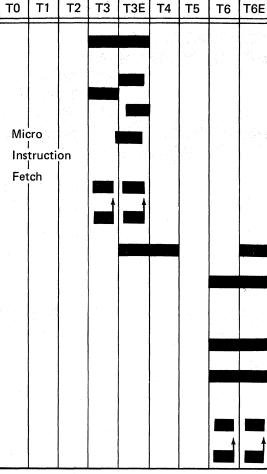

| I/O Instructions                      | CHAN-8 | Condition Code                                                 | Stor Sel Switch CNSL-6                           | Read Verify                                 | DISK-22                |

|                                       |        | Valid Reg1 Field Register Specification . μINSTR-25            |                                                  | riodo voriry                                | DION-ZZ                |

|                                       |        |                                                                |                                                  |                                             |                        |

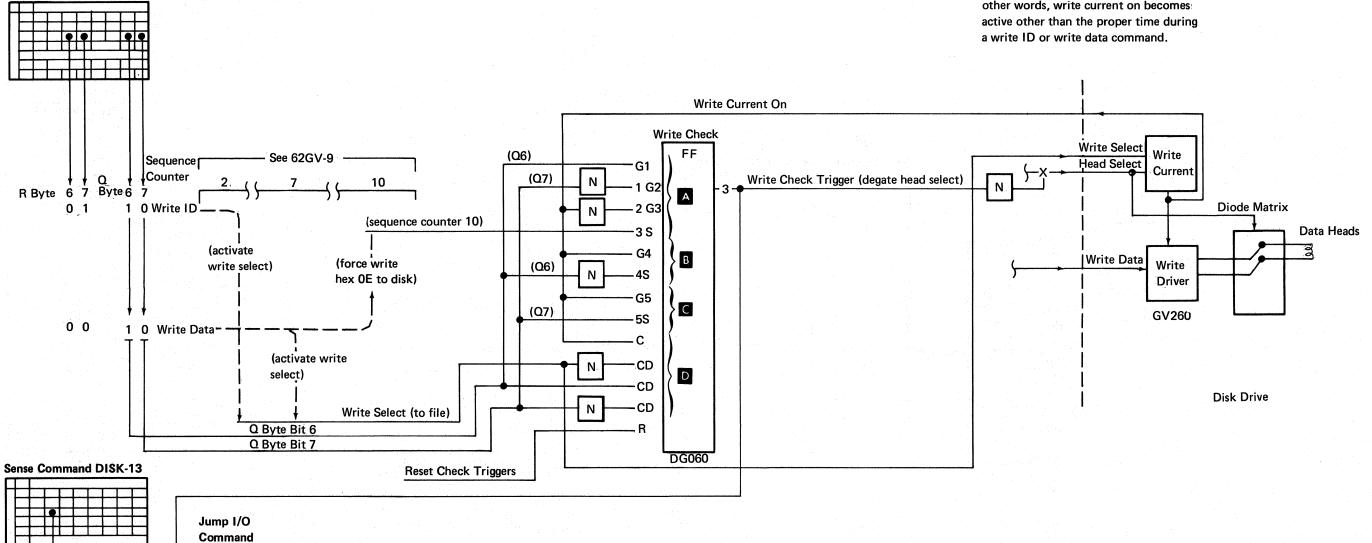

| Scan Data                                | DISK-24 | Write Check                            | DISK-59               | PRINTER                                                                                             | PTR-1   | Home Pulse (A)                                             | PTR-37 |

|------------------------------------------|---------|----------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------|---------|------------------------------------------------------------|--------|

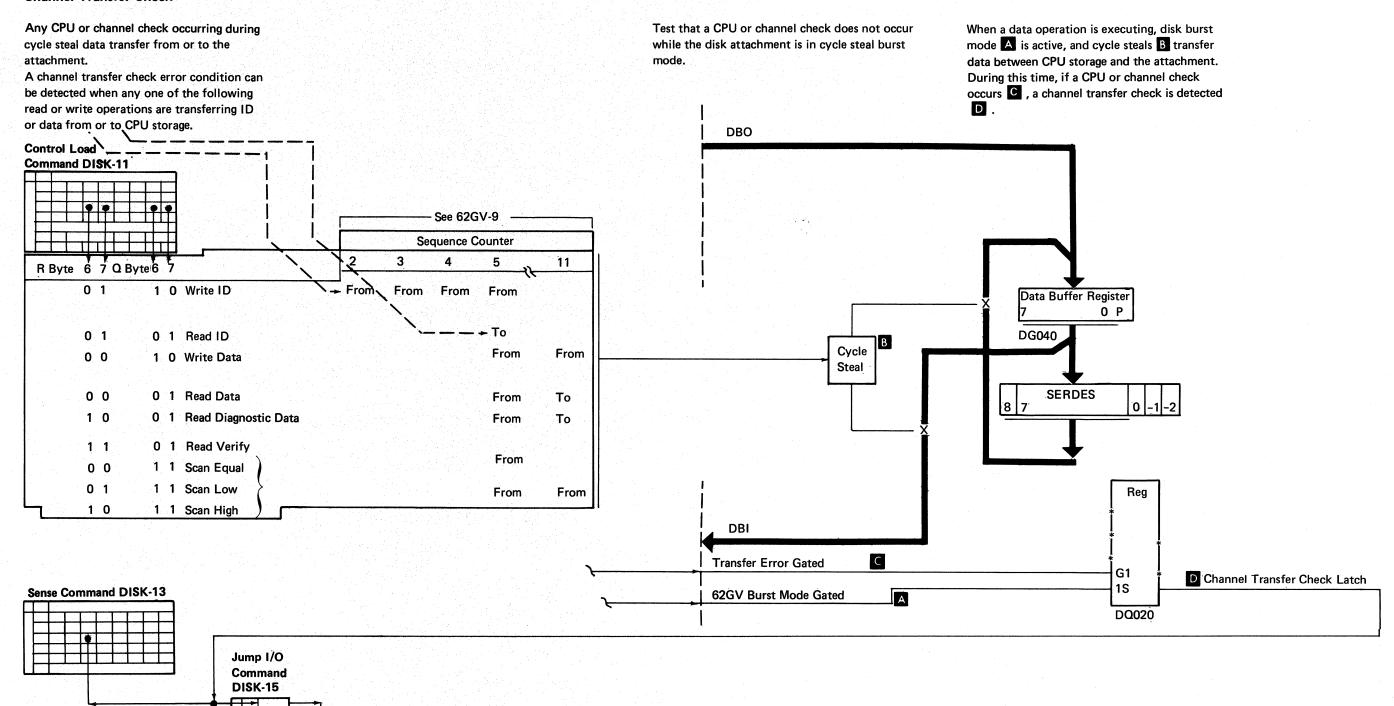

| Scan Data, Hi or Low, or Equal           | DISK-24 | Channel Transfer Check                 | DISK-60               | Circuitry Location                                                                                  | PTR-1   | Hammer Check 1-22 (also 23-44 and                          |        |

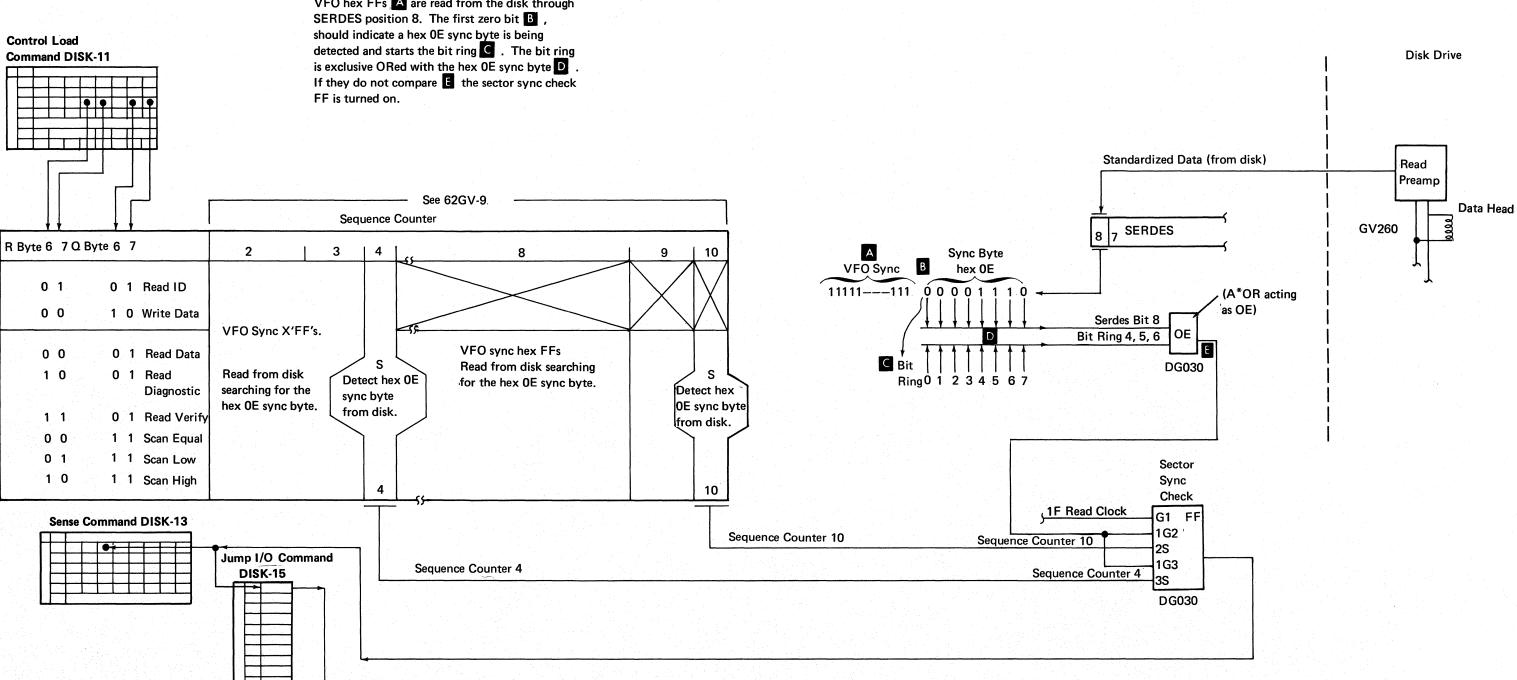

| Write                                    | DISK-26 | Sector Sync Check                      | DISK-61               | CPU/Attachment/Printer Operation                                                                    | PTR-3   | 45-66) (P)                                                 | PTR-37 |

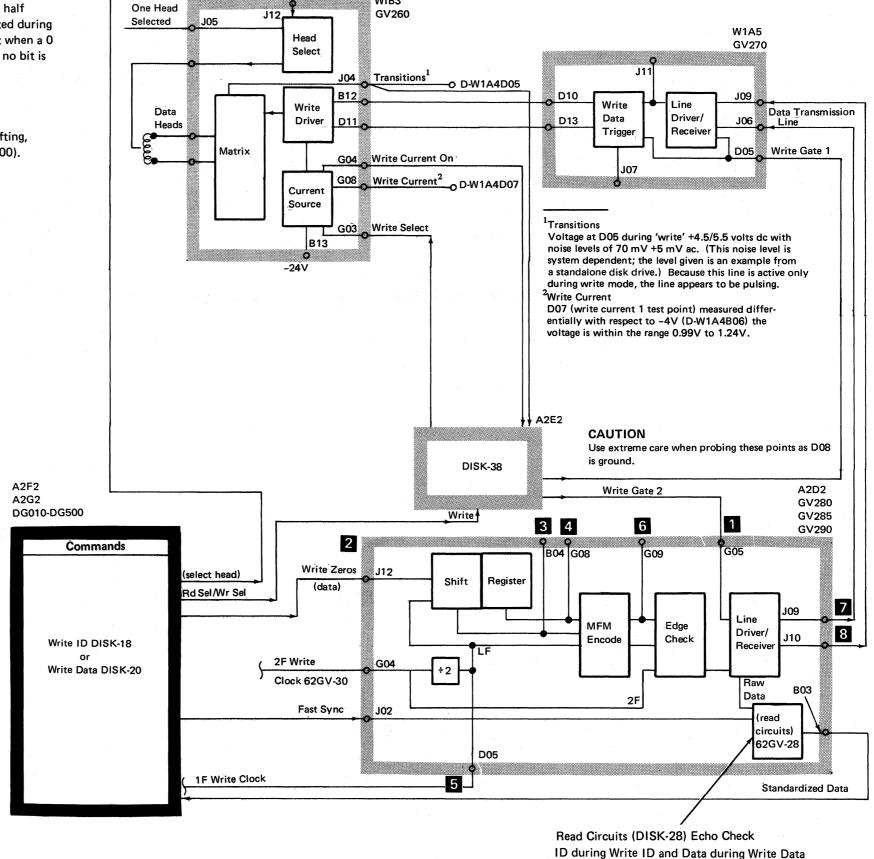

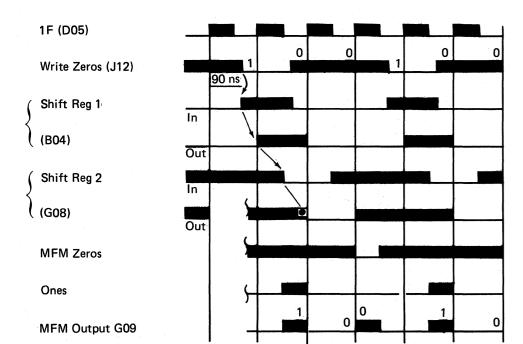

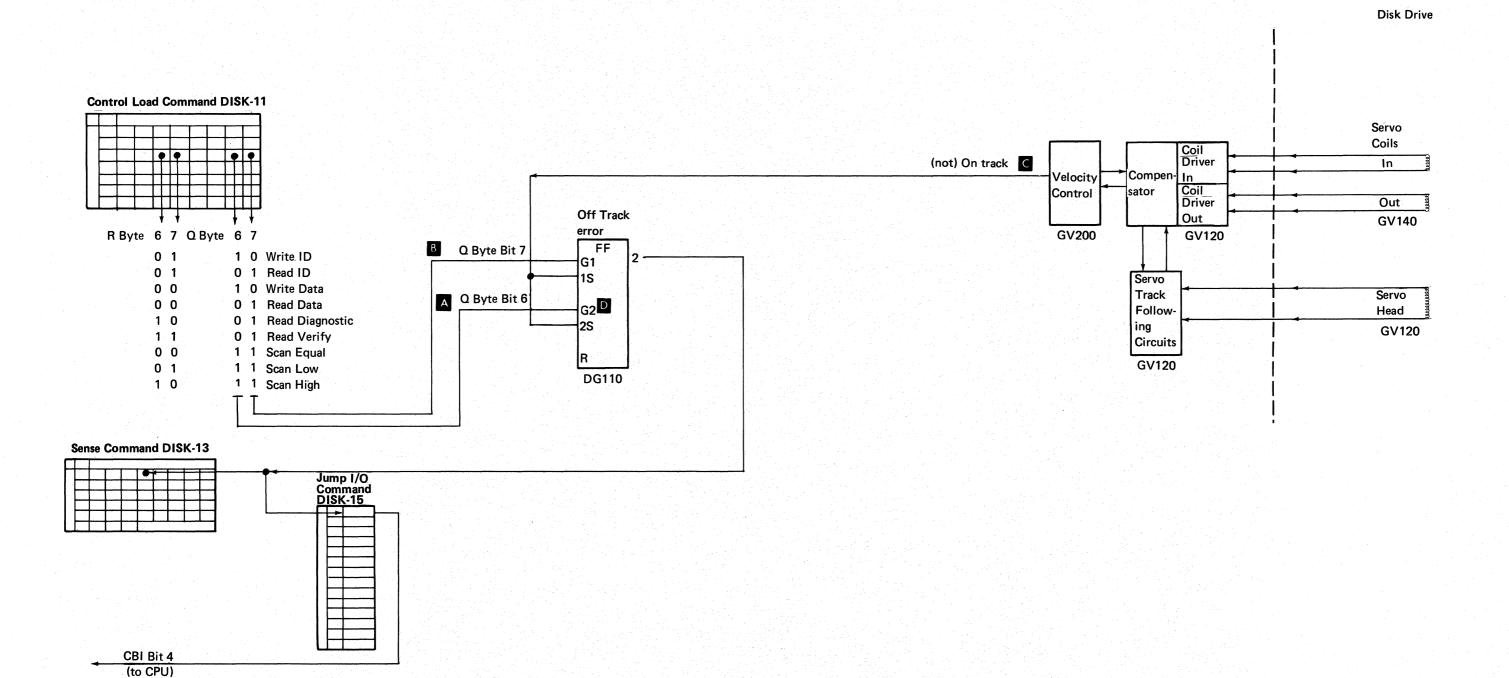

| Modified Frequency Modulation (MFM) .    | DISK-26 | Off Track Check                        | DISK-62               | Data Area                                                                                           | PTR-3   | Carriage Go (A)                                            | PTR-37 |

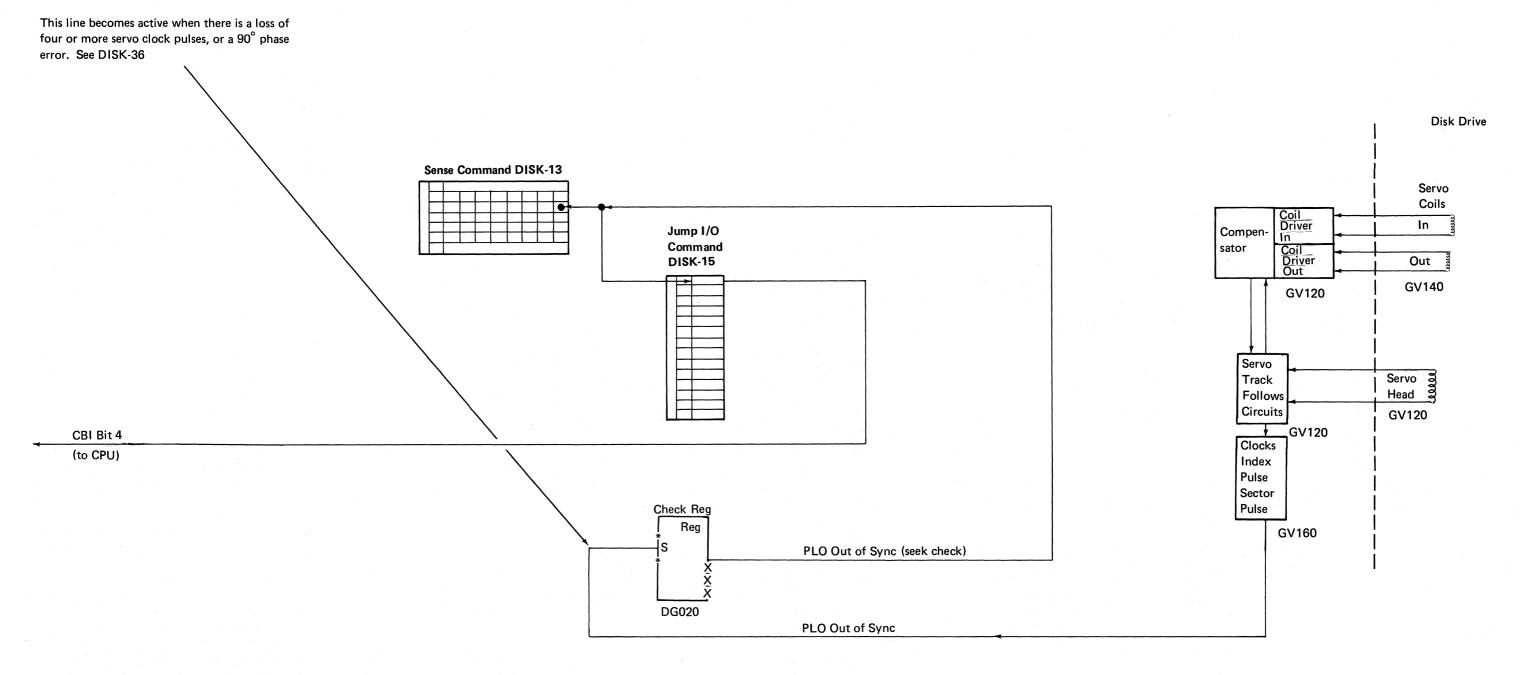

| MFM Encoding                             | DISK-26 | PLO Out of Sync                        | DISK-63               | Belt Image Area                                                                                     | PTR-3   | Stop Ribbon (A)                                            | PTR-37 |

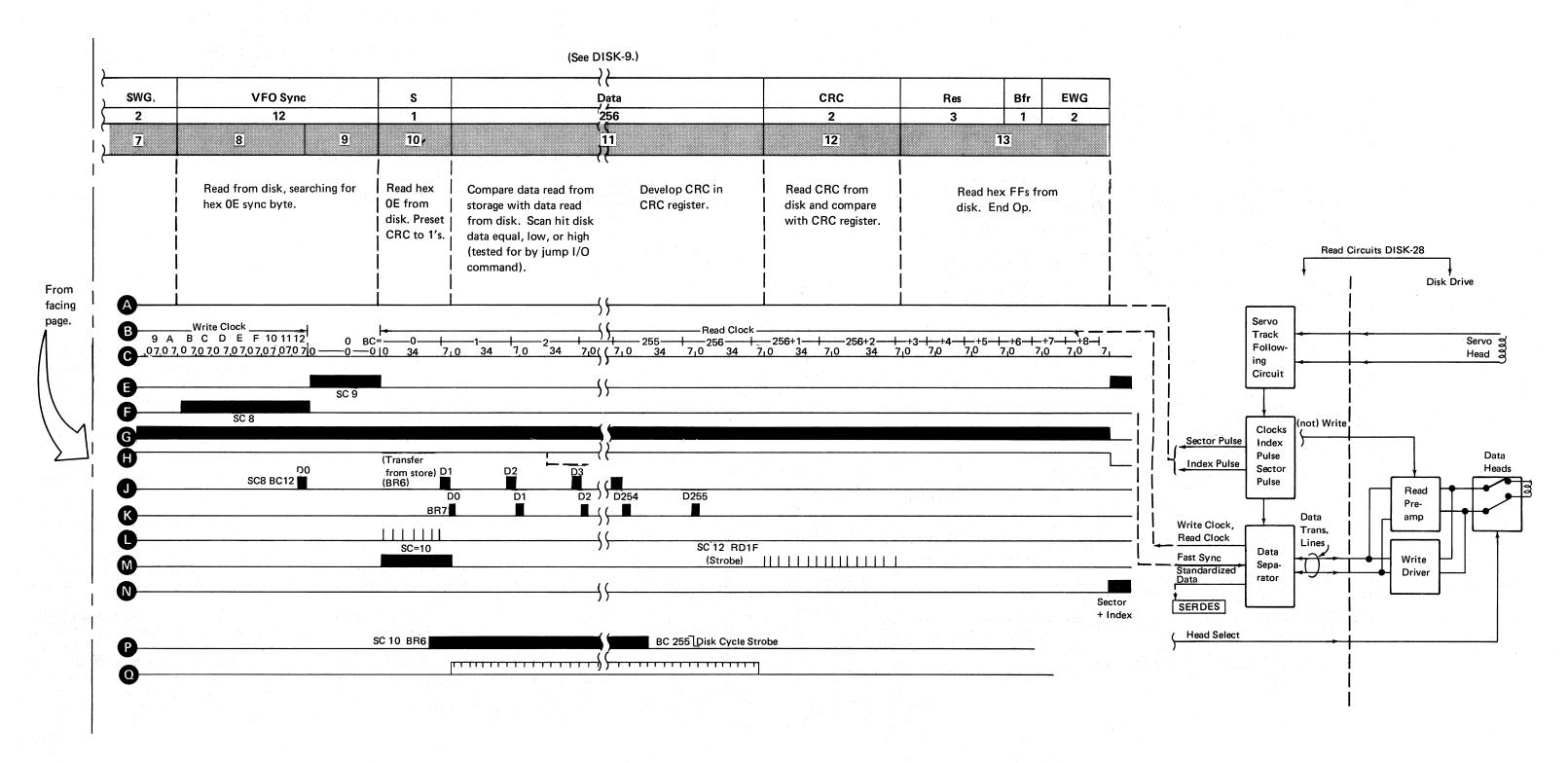

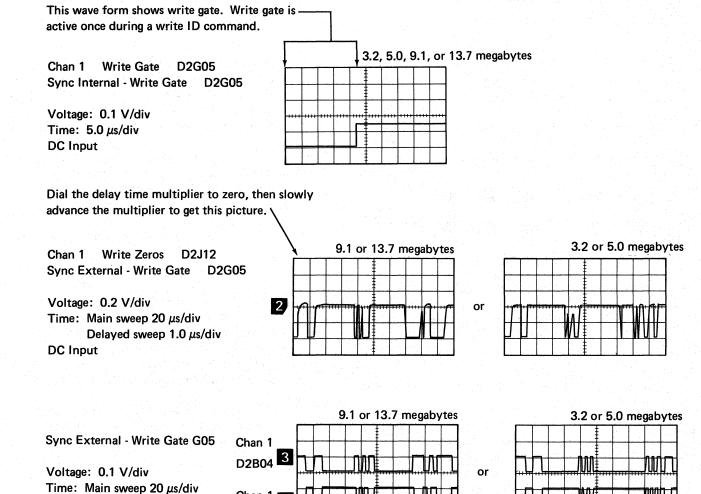

| Write ID and Write Data Waveforms        | DISK-27 | Interrupt Timeout Check                | DISK-64               | Forms Control                                                                                       | PTR-3   | Carriage Advance (P)                                       | PTR-37 |

| Read                                     | DISK-28 | JUMP I/O CONDITIONS                    | DISK-65               | End of Operation Interrupts                                                                         | PTR-3   | Printer Thermal Switch (P)                                 | PTR-37 |

| Read Circuits                            | DISK-28 | INPUT/OUTPUT AND SENSE LINES           | DISK-69               | Attachment Operation                                                                                | PTR-3   | 이 마음이 물로보다 이 아들은 왕이 된 물을 받은 장생들은 이 마이어를 보여 없는 그것 같습니다.     | PTR-37 |

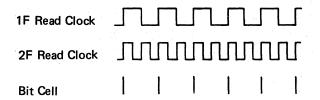

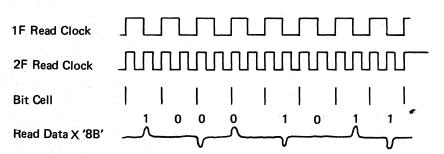

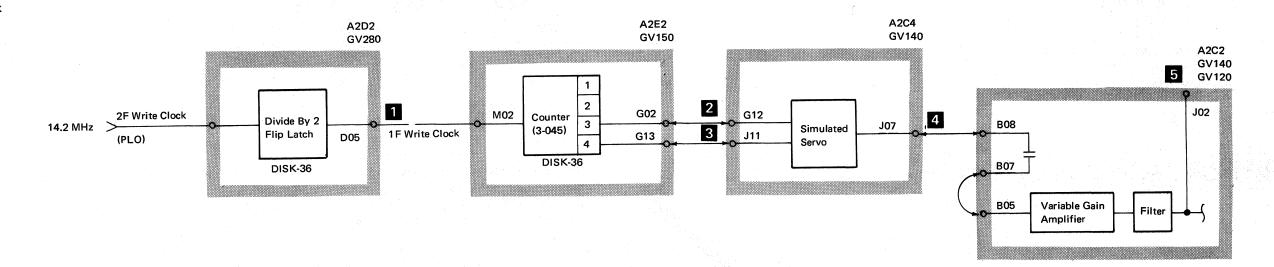

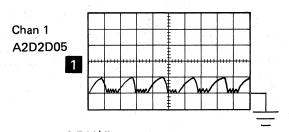

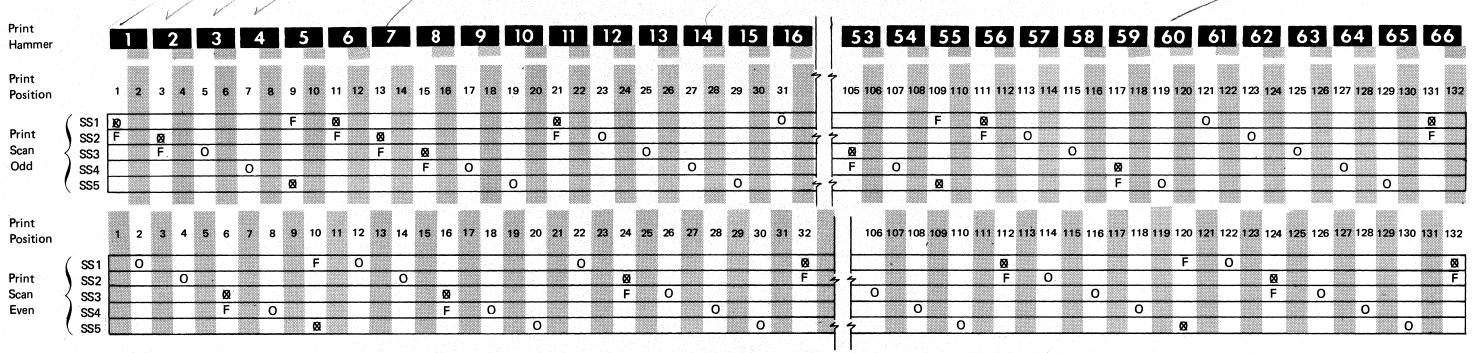

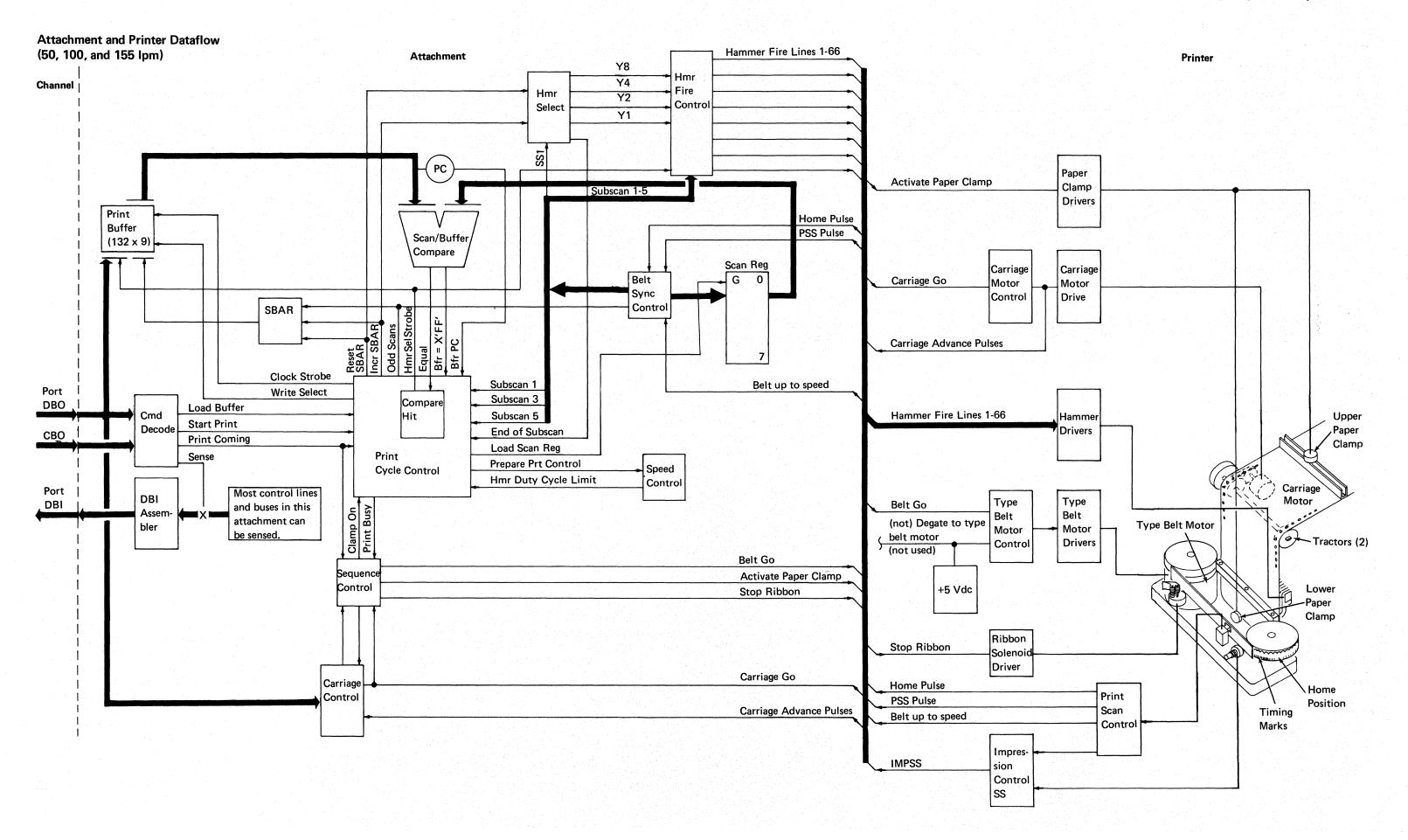

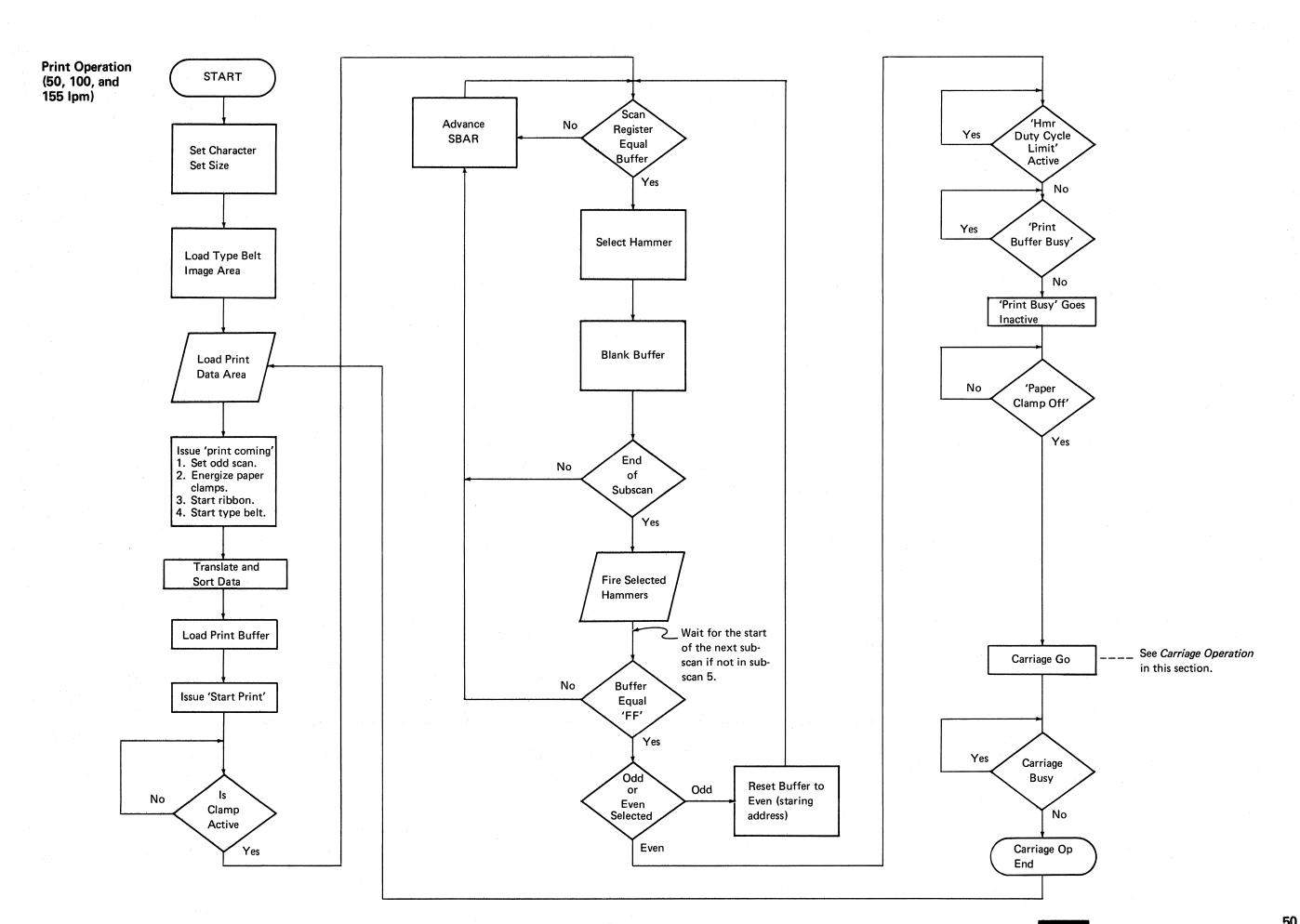

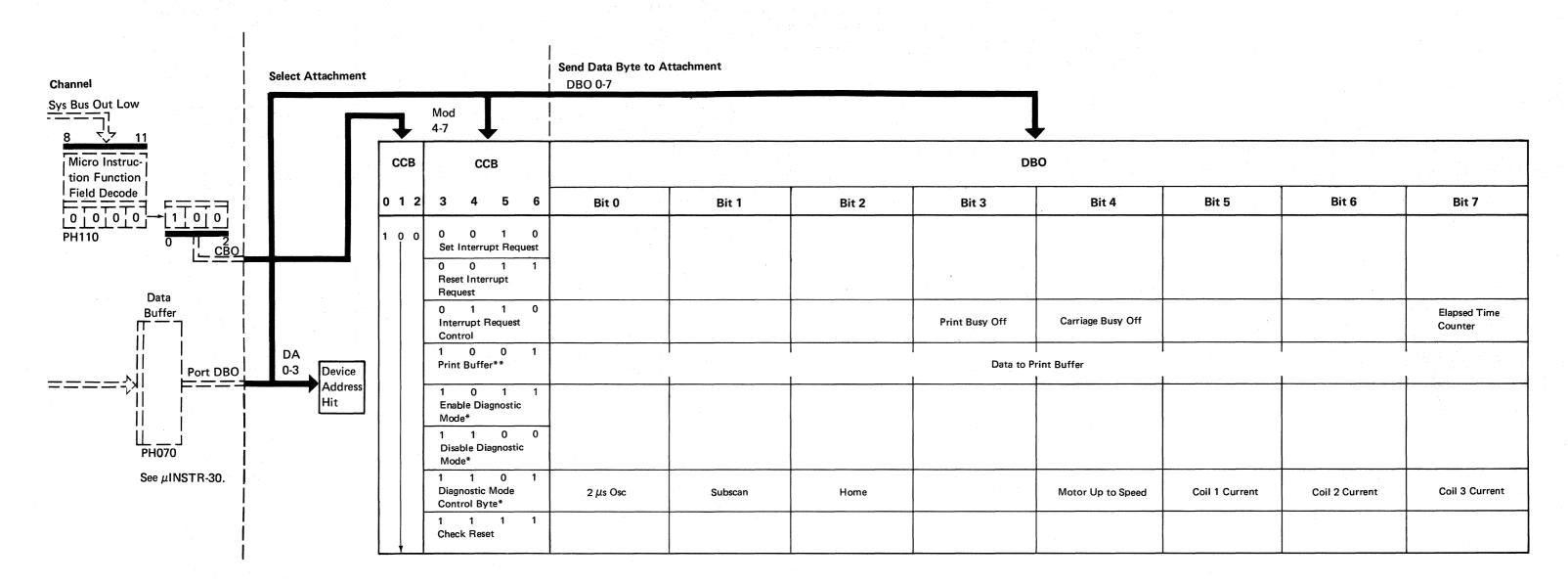

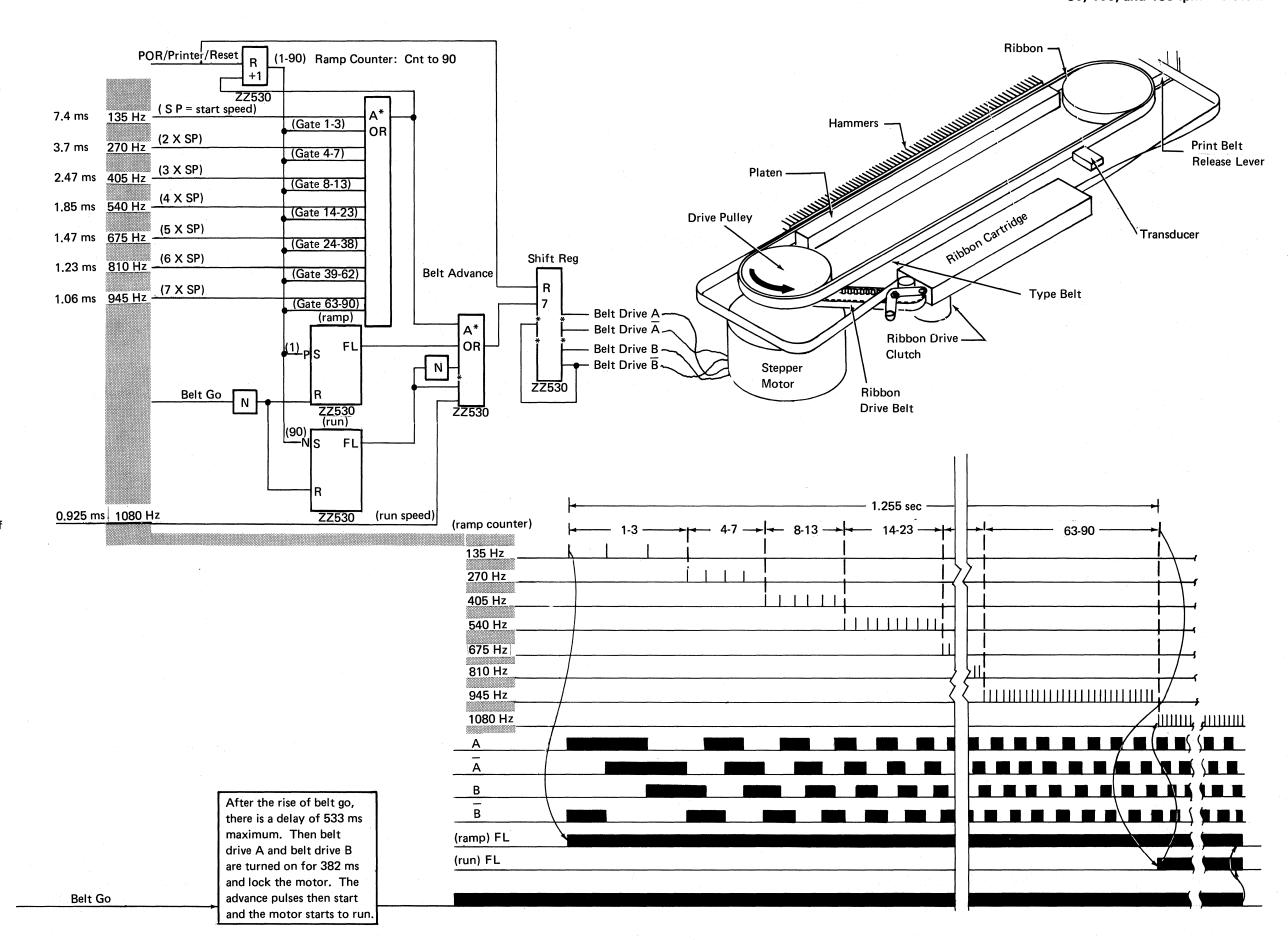

| Read Clock and Divide-by-Two Counter .   | DISK-28 |                                        |                       | Theory of Printing (50, 100, and 155 lpm)                                                           | PTR-4   | 이 많은 그리고 그리가 주요한 발전을 즐겁었다. 한국의 결과, 보기와 보기를 모르는 것이라고 되었다.   | PTR-37 |

| Read Clock Control                       | DISK-28 | 33FD DISKETTE DRIVE AND                |                       | Attachment and Printer Dataflow (50, 100,                                                           |         | 어머님들이 있으면 이 어느 있는데 그렇게 하는데 그 그들은 그 맛없이 아니는 사이를 하다 하다 때문에   | PTR-37 |

| Data/Read Clock Sync                     | DISK-28 | ATTACHMENT                             | 33FD-1                | and 155 lpm)                                                                                        | PTR-6   | 하실수 하다면 얼마라는 이상 사이가 되었다. 동안 하는데 생각하는 경기를 보냈어지고 이 아이들 때문 사람 |        |

| Data Latch and Standardized Data Latch . | DISK-28 | Diskette Format                        | 33FD-2                | Print Operation (50, 100, and 155 lpm)                                                              |         | Switch Assemblies                                          | PTR-37 |

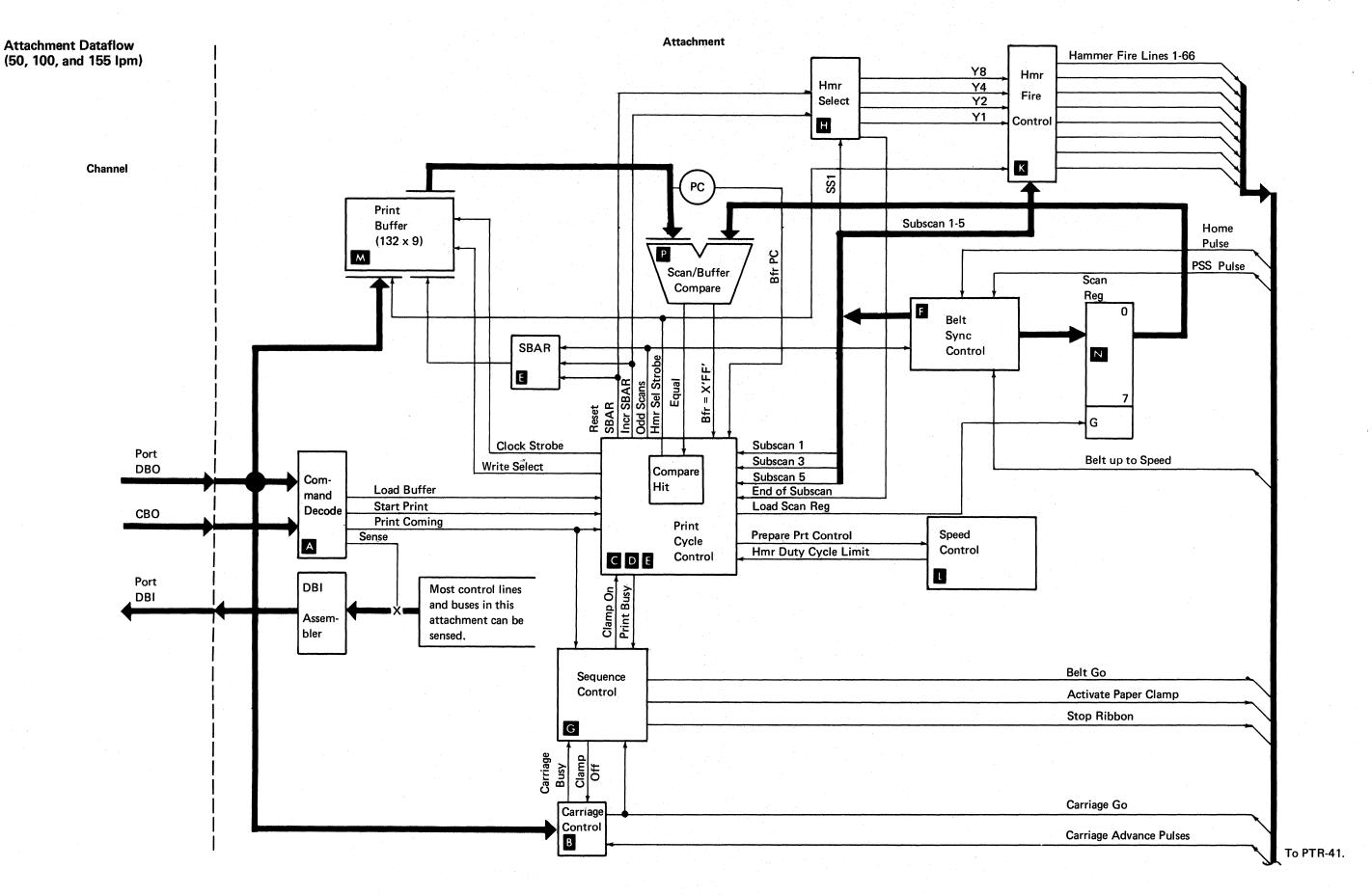

| Fast Sync                                | DISK-28 | Read/Write Circuit Principles          | 33FD-3                | 이 동네 가는 하는 그 불어난 사람이 되어 되어 되었다. 살아 되는 사람들이 되어 가장 하는 것이 되었다. 그는 그를 되어 되었다. 그는 그를 다 하는 것이 없다면 하는 것이다. | PTR-7   | Attachment Dataflow (50, 100, and                          | DTD 00 |

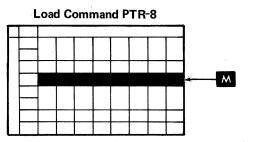

| Read ID and Read Data Waveforms          | DISK-29 |                                        | 33FD-3                | Load Command                                                                                        | PTR-8   | 155 lpm)                                                   | PTR-38 |

|                                          |         | Writing                                | 33FD-3                | Control Load Command                                                                                | PTR-10  | Attachment Functional Units (50, 100, and                  |        |

|                                          | DISK-30 | Reading                                | CARL CALL AND ALL AND | Sense Command—Control Sense Command                                                                 |         | 155 lpm)                                                   | PTR-39 |

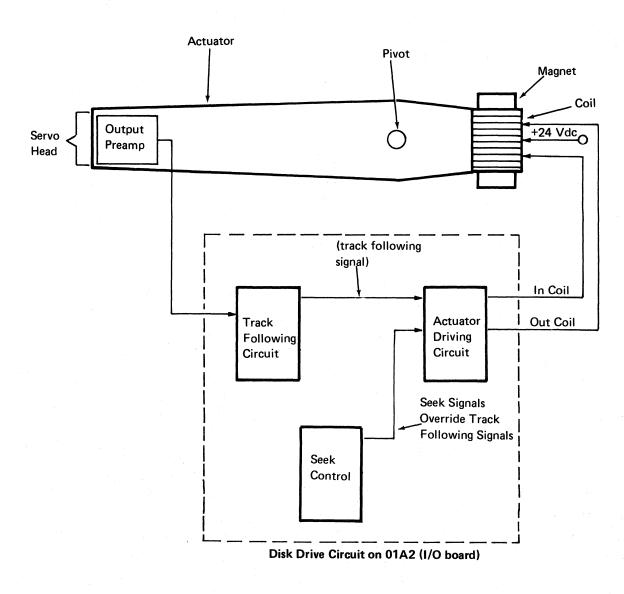

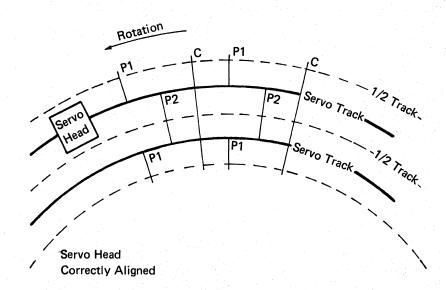

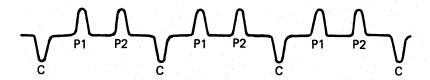

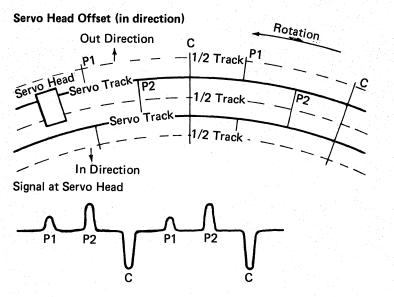

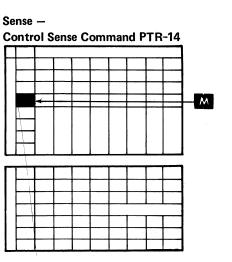

| Track Following Operation                | DISK-31 | Controls                               | 33FD-3                | (50, 100, and 155 lpm)                                                                              | PTR-14  | Printer Command Decode DQ020,                              |        |

| Track Following Waveforms                | DISK-31 | Data Representation                    | 33FD-3                | Sense Interrupt Level Status Command .                                                              | PTR-18  | 030,040                                                    | PTR-39 |

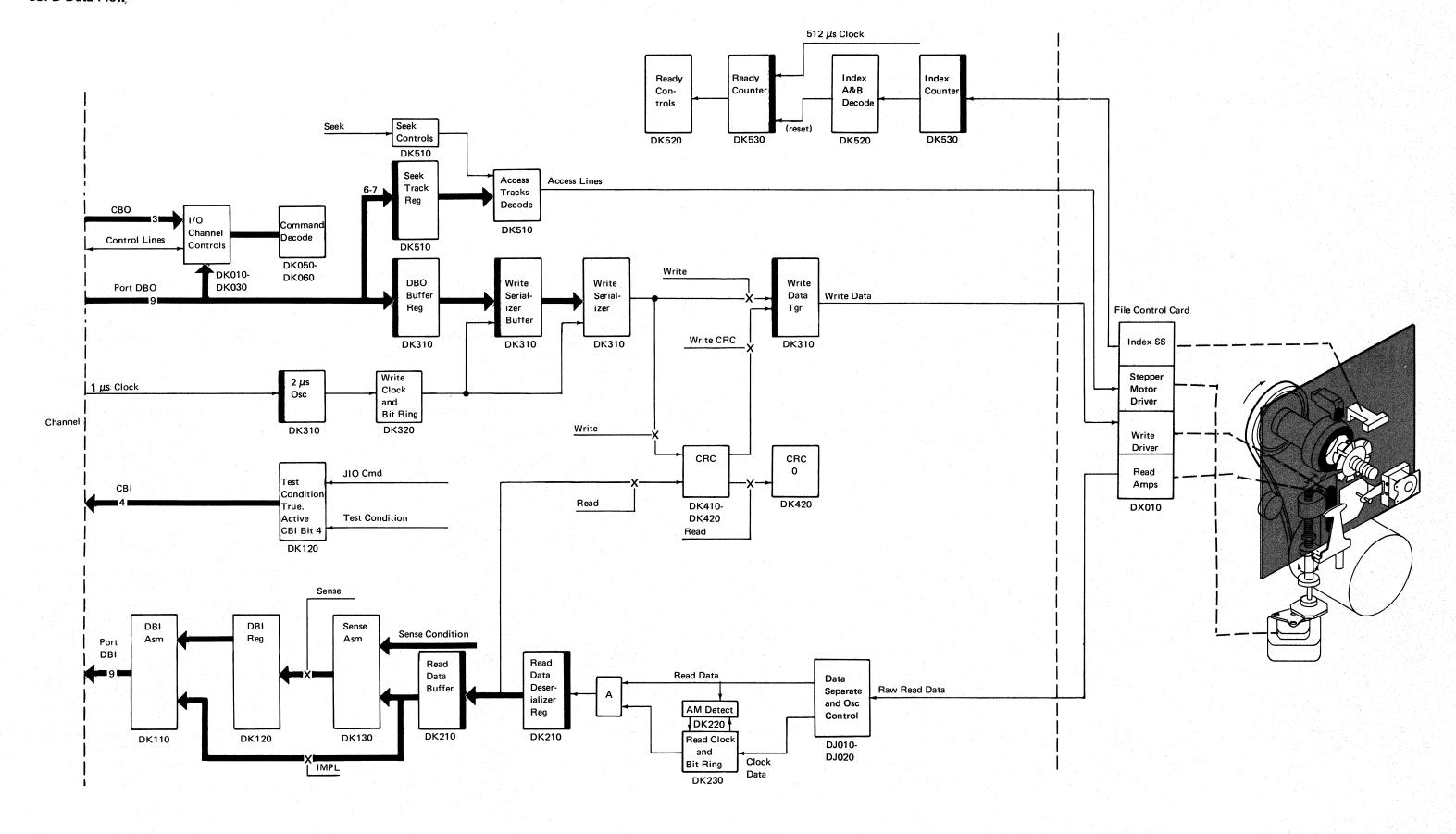

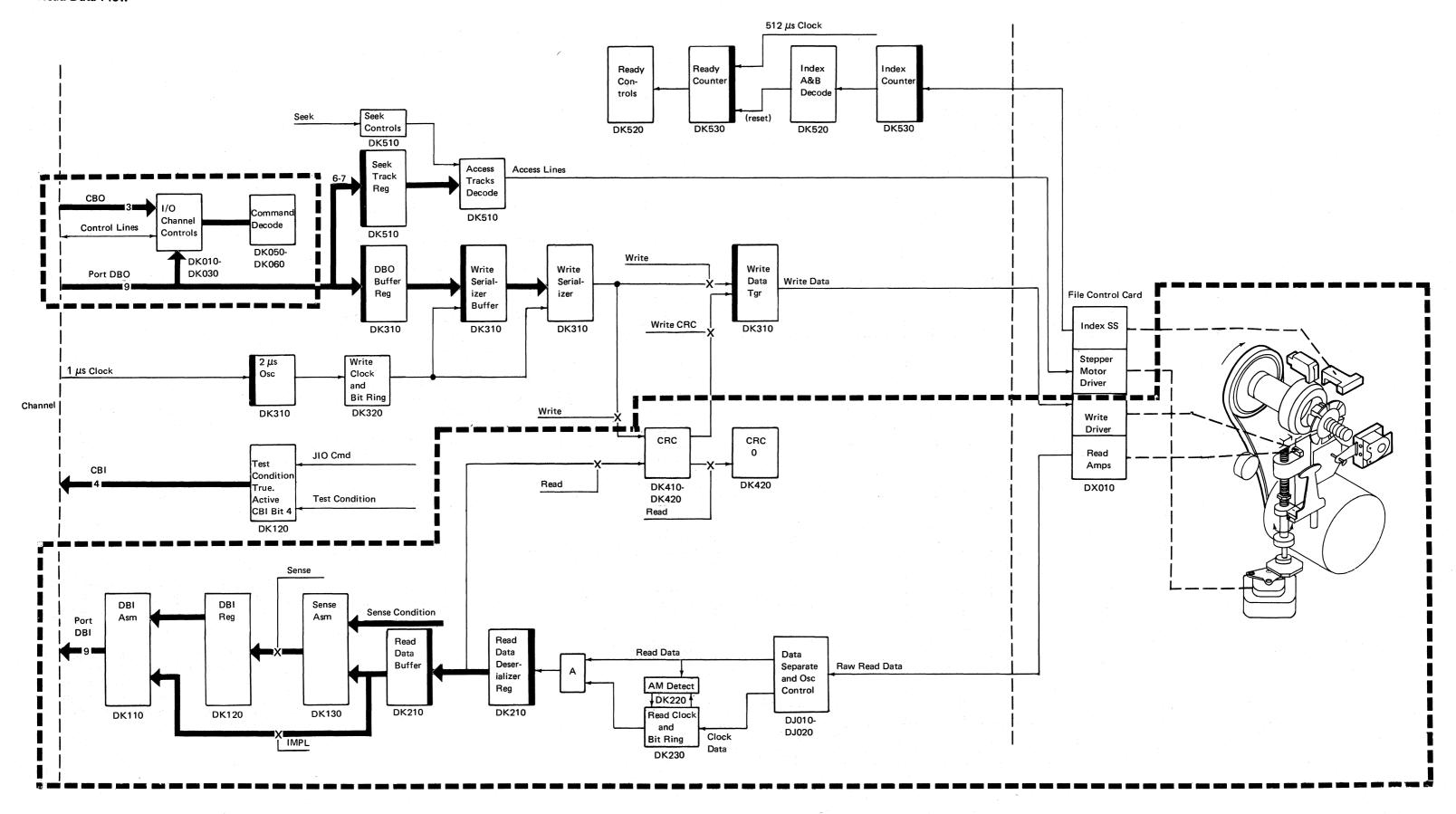

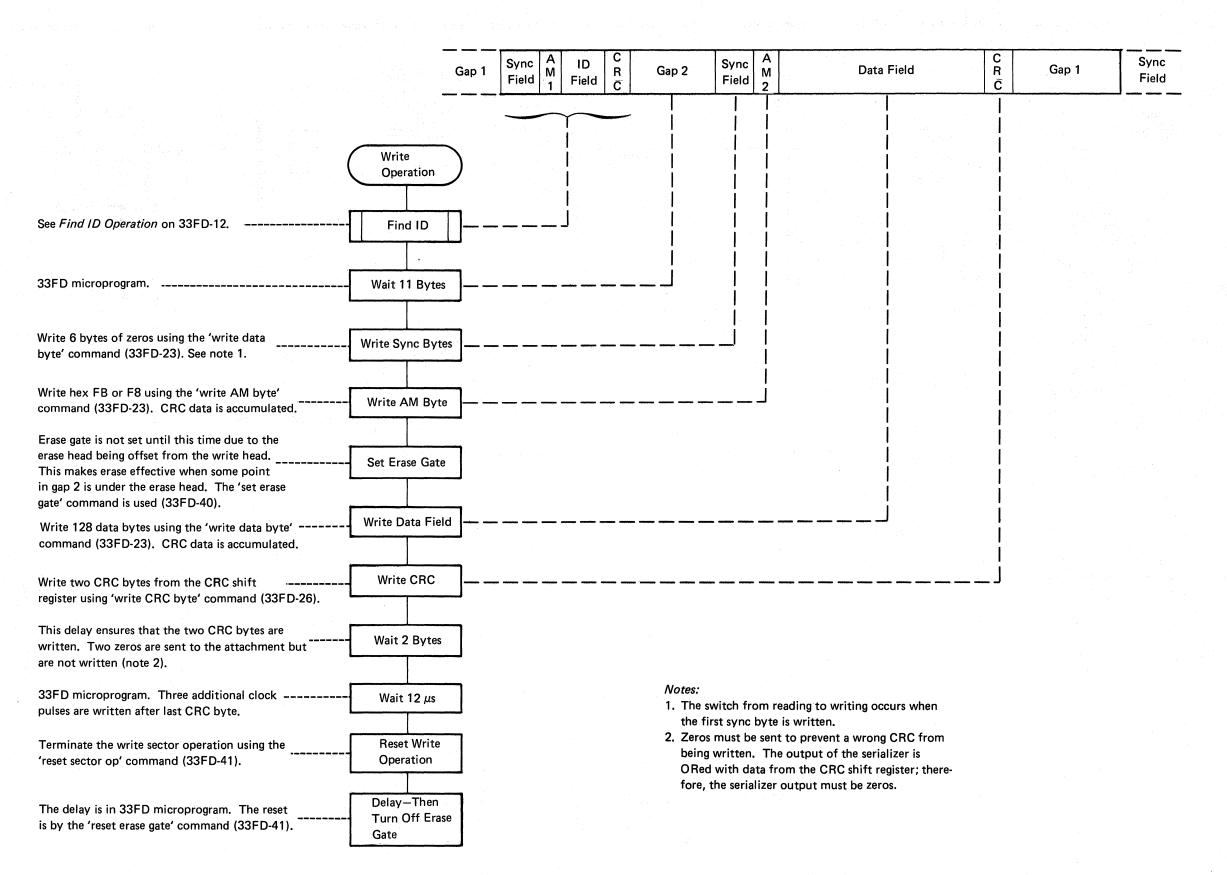

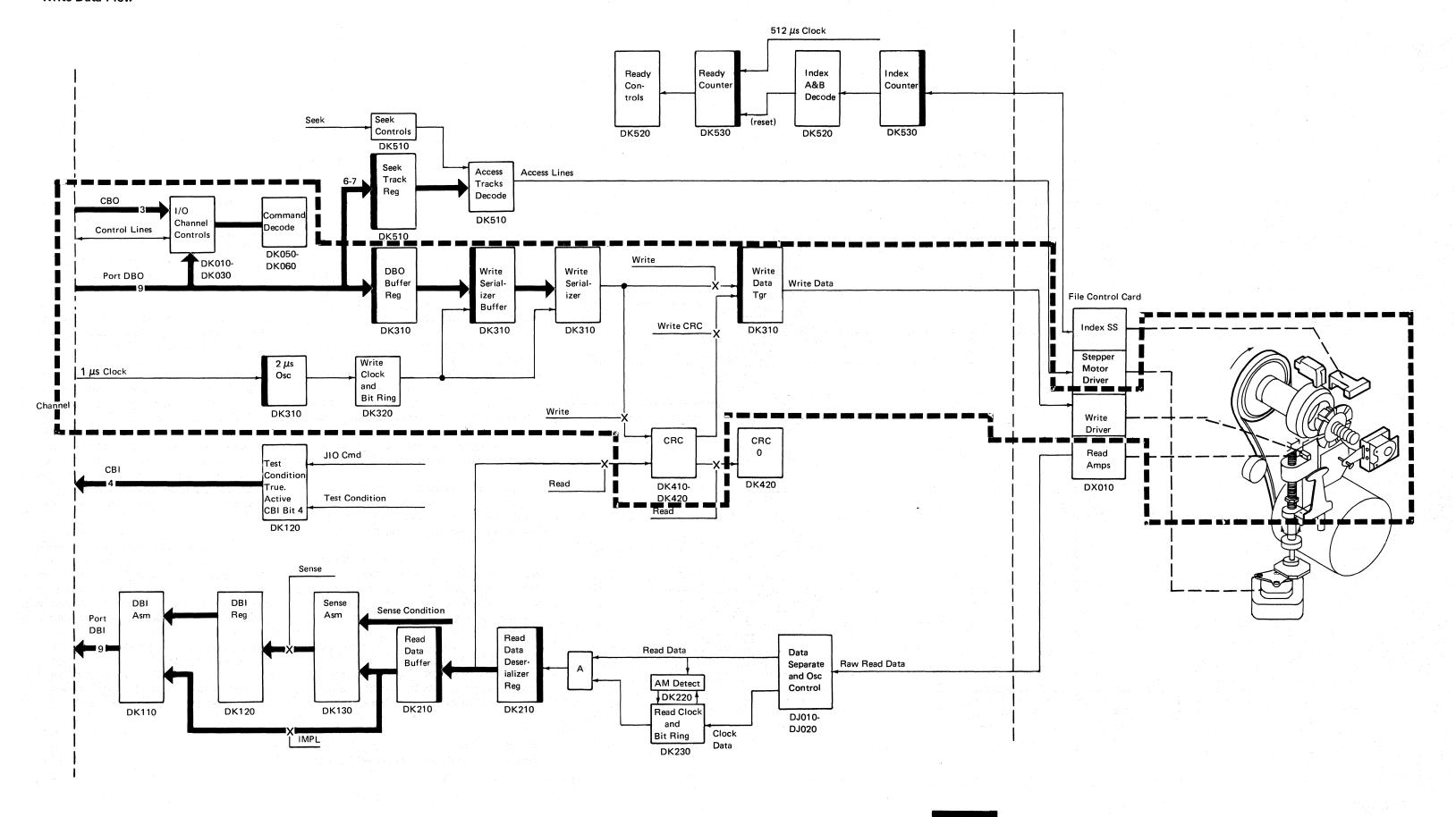

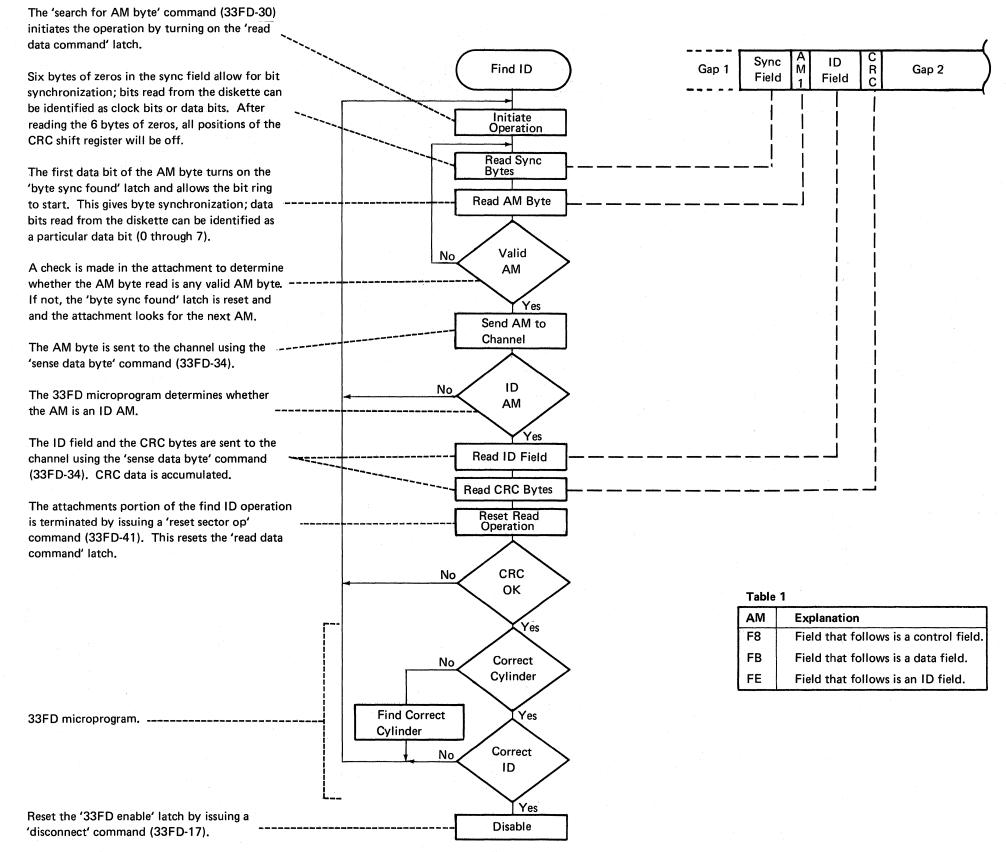

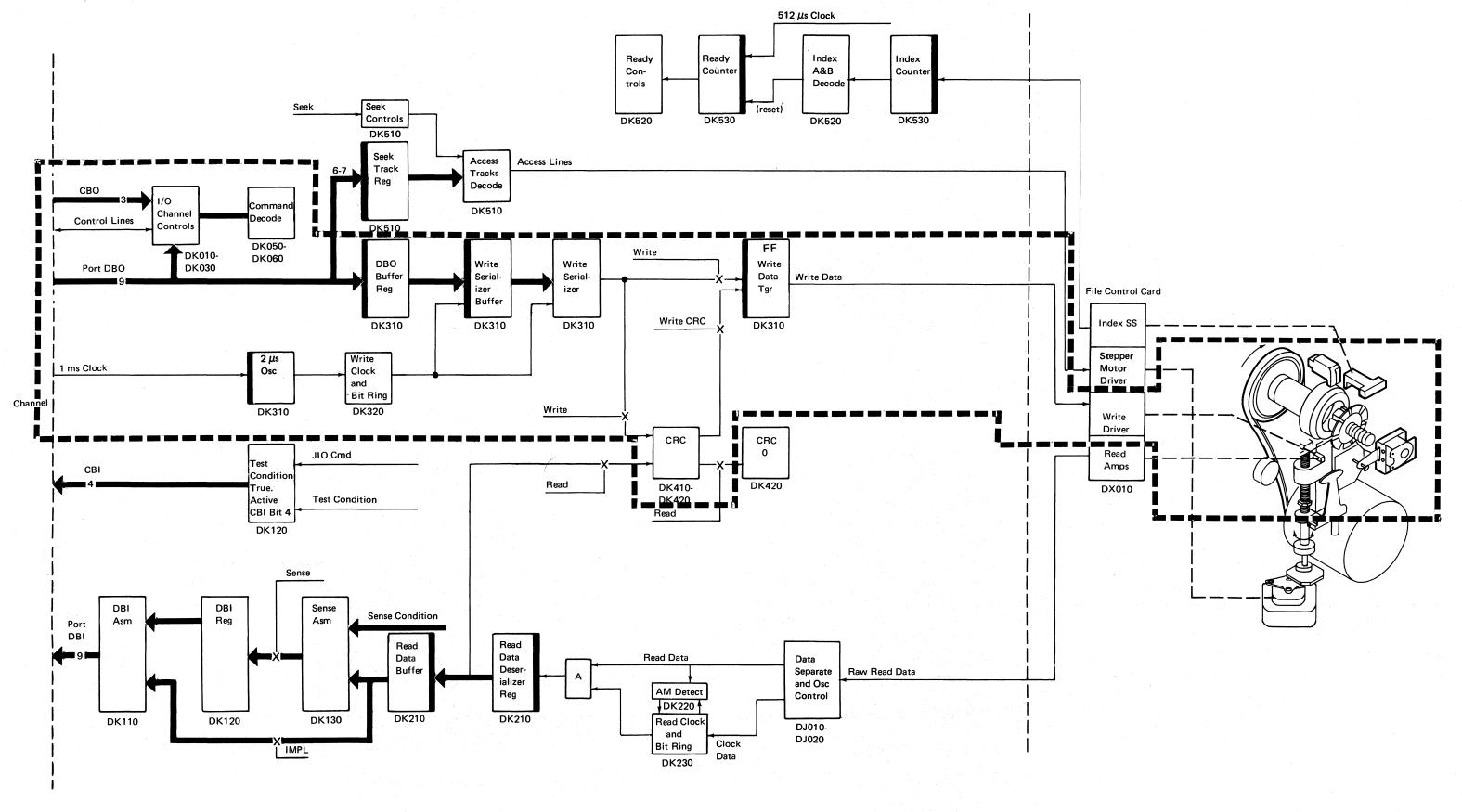

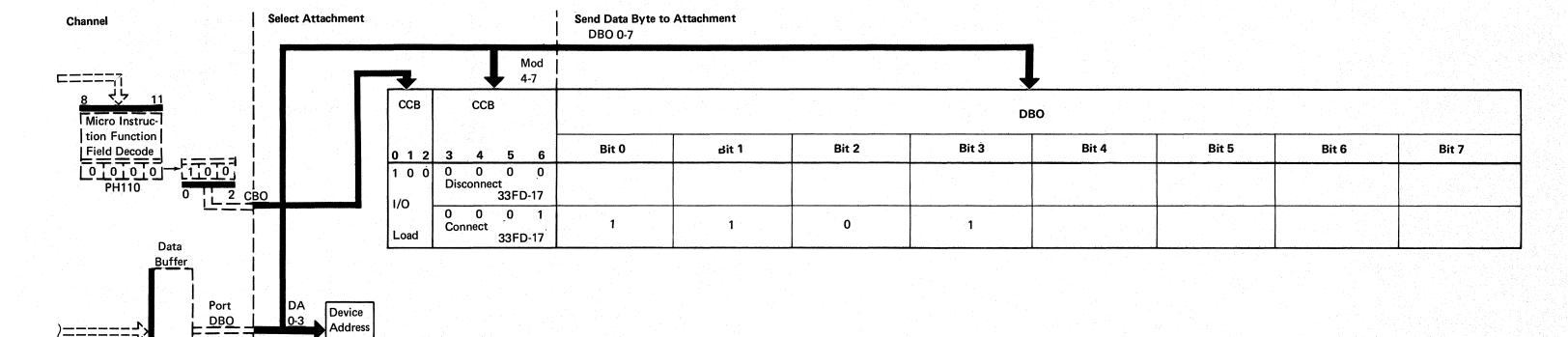

| Simulated Servo Test Procedure           | DISK-33 | 33FD Data Flow                         | 33FD-5                | Jump I/O Command                                                                                    | PTR-20  | Space Counter DQ100                                        | PTR-39 |

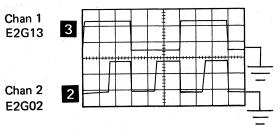

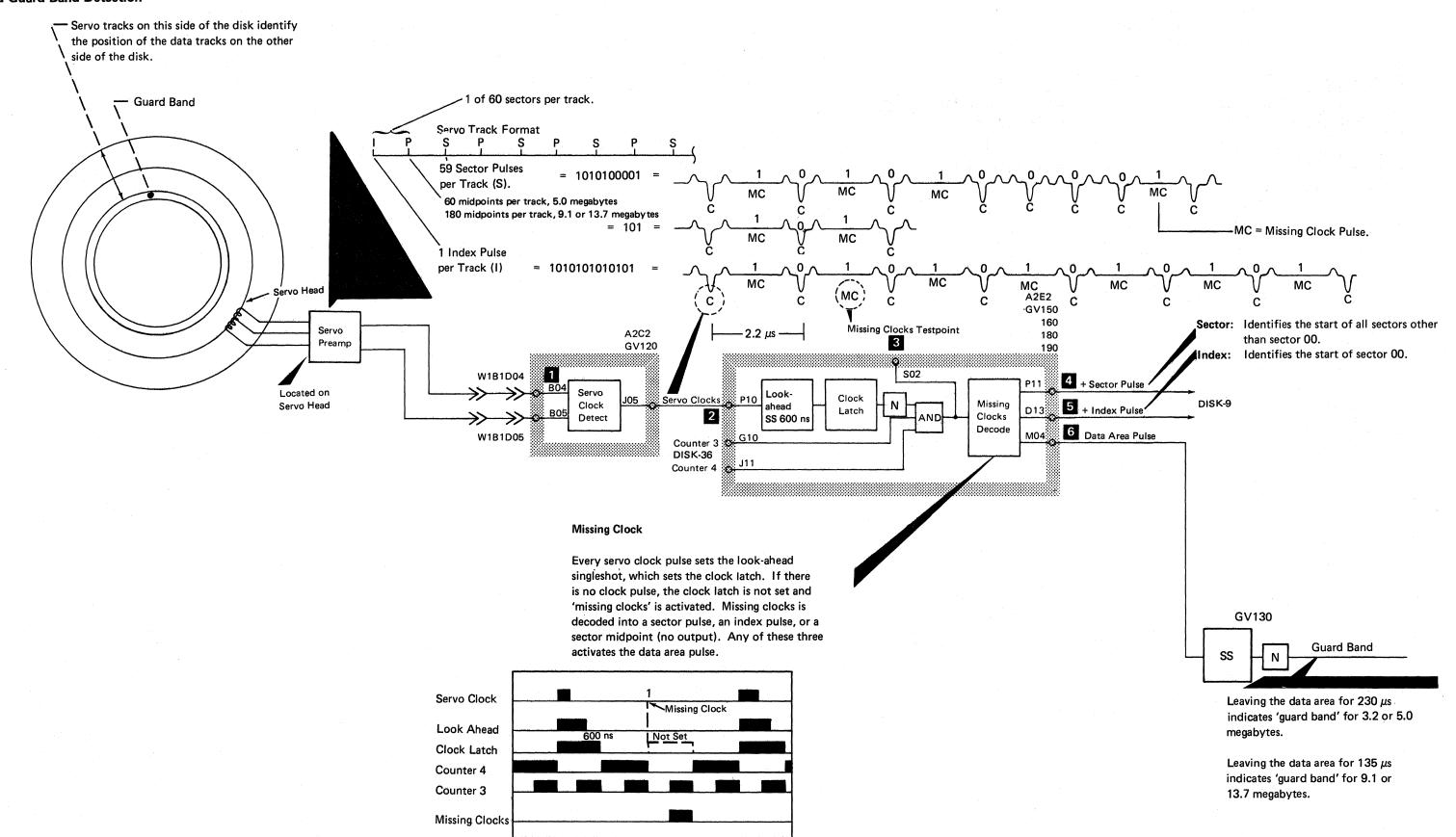

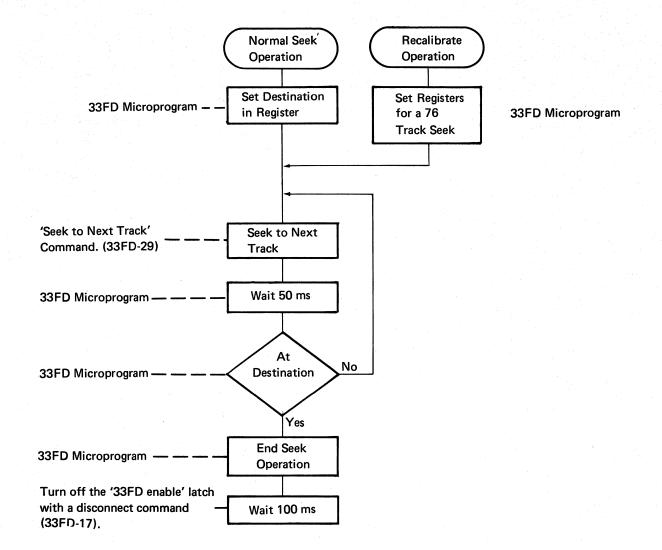

| Servo, Index and Sector Pulse, Data Area | •       | Seek Operations                        | 33FD-6                | Paper Clamps DQ240                                                                                  | PTR-23  | Scan Counter DQ160                                         | PTR-39 |

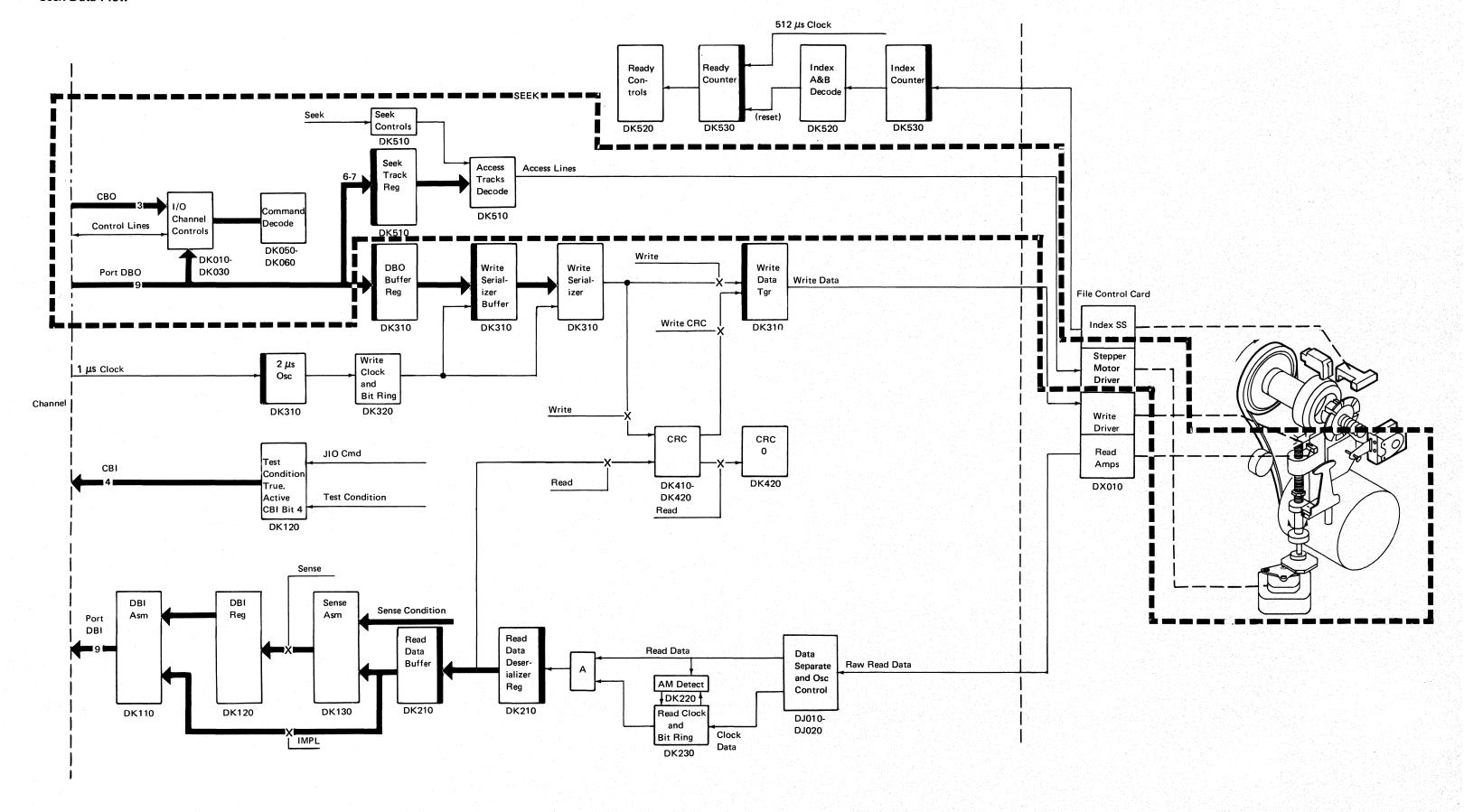

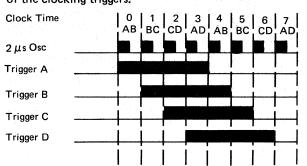

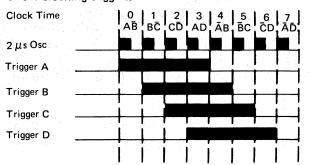

| and Guard Band Detection                 | DISK-34 | Seek Data Flow                         | 33FD-7                | Type Belt Start and Run (50, 100 and                                                                |         | Clocking Triggers DQ170                                    | PTR-39 |

| Missing Clock                            | DISK-34 | Read Operation                         | 33FD-8                | 155 lpm)                                                                                            | PTR-24  | Storage Buffer Address Register                            |        |

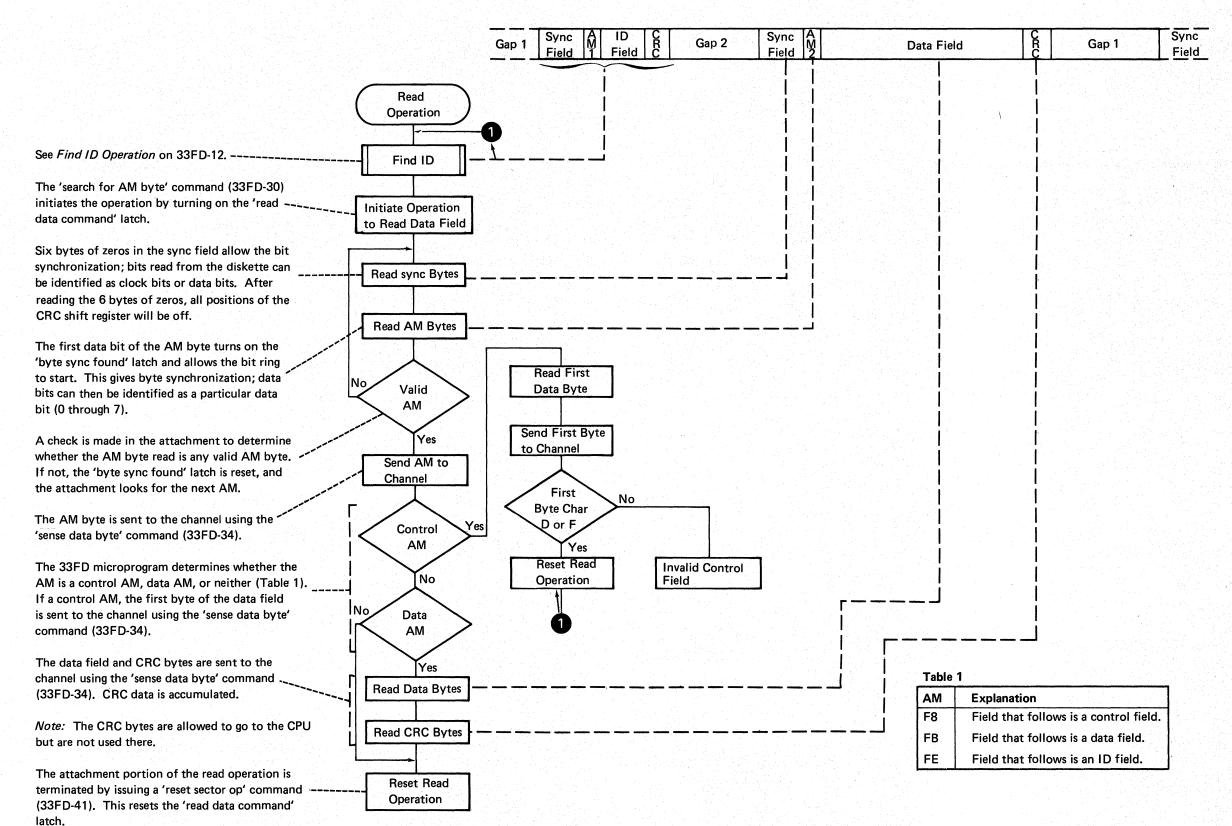

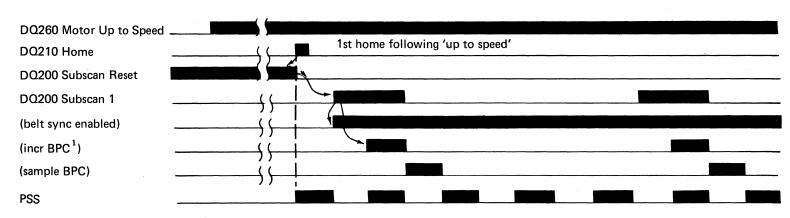

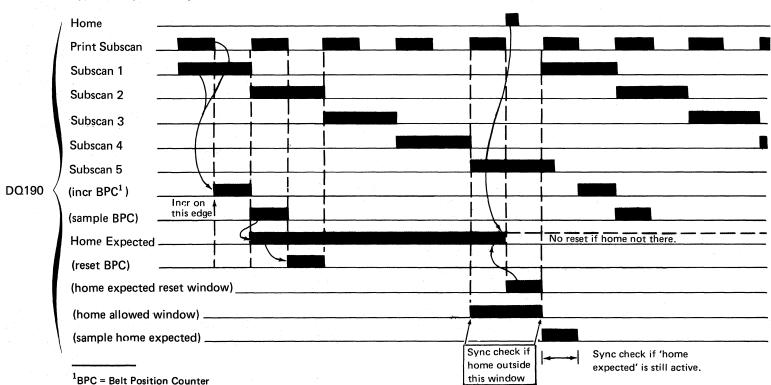

| Index and Sector Pulse and Data Area     | •       | Read Data Flow                         | 33FD-9                | Type Belt Sync Timing                                                                               | PTR-25  | (SBAR) DQ180                                               | PTR-39 |

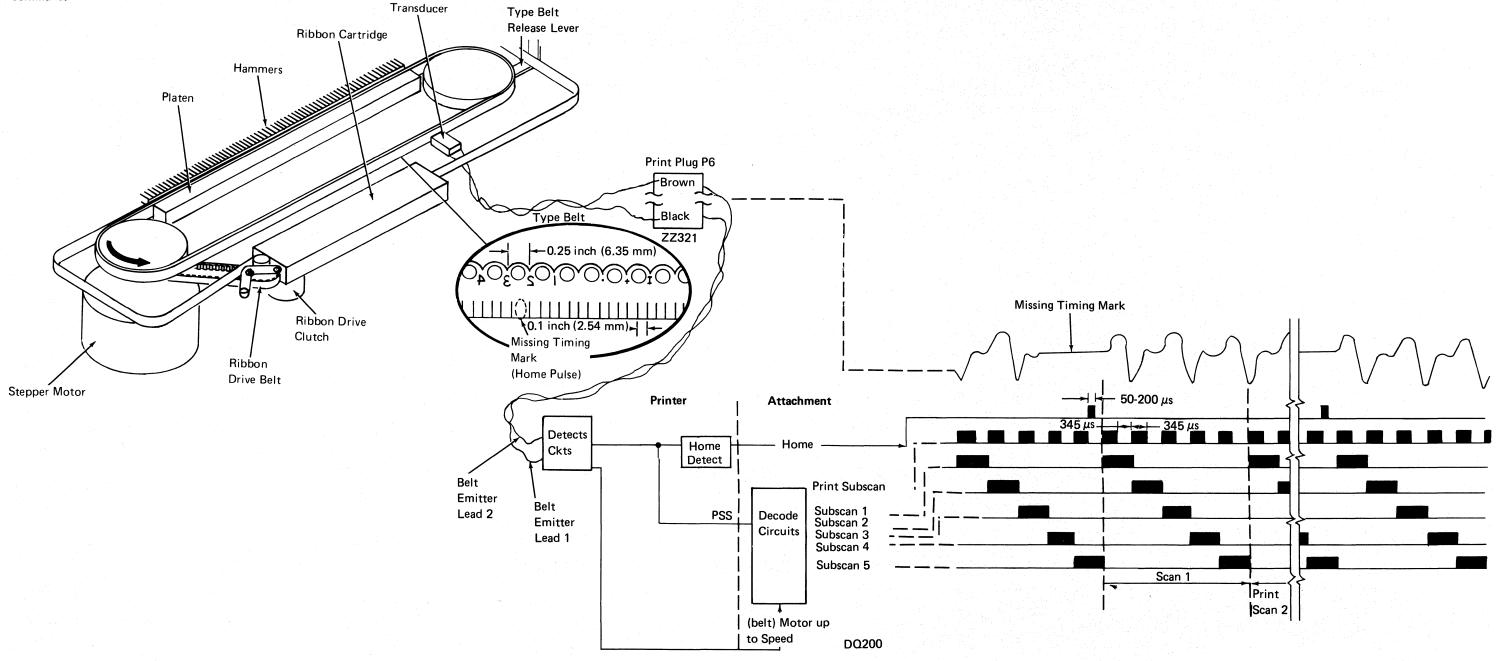

| Wave Forms                               | DISK-35 | Write Operation                        | 33FD-10               | Ribbon Drive/Type Belt Transducer (50, 100,                                                         |         | Belt Position Counter (BPC) DQ200                          | PTR-39 |

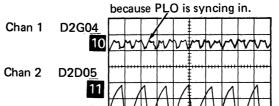

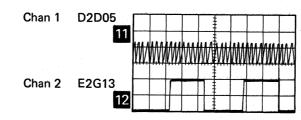

| Phase Locked Oscillator (PLO)            |         | Write Data Flow                        | 33FD-11               | and 155 (pm)                                                                                        | PTR-26  | Paper Clamp Timer DQ240                                    | PTR-39 |

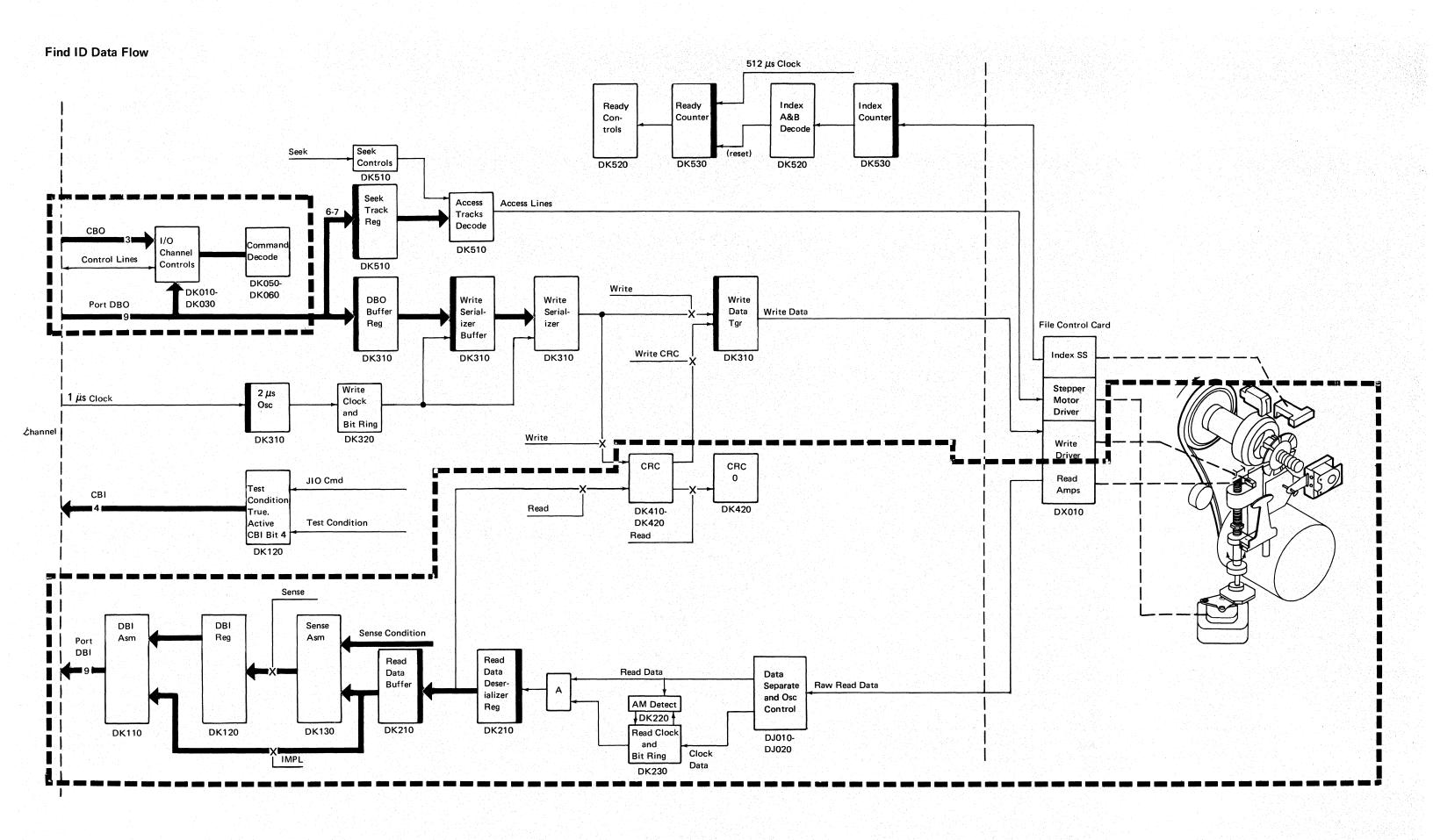

| Synchronization                          | DISK-36 | Find ID Operation                      | 33FD-12               | Ribbon Drive                                                                                        | PTR-26  | Hammer Select Control DQ290                                | PTR-39 |

| Synchronization After Power On           | DISK-36 | Find ID Data Flow                      | 33FD-13               | Type Belt Transducer                                                                                | PTR-26  | Elapsed Time Counter DQ300                                 | PTR-39 |

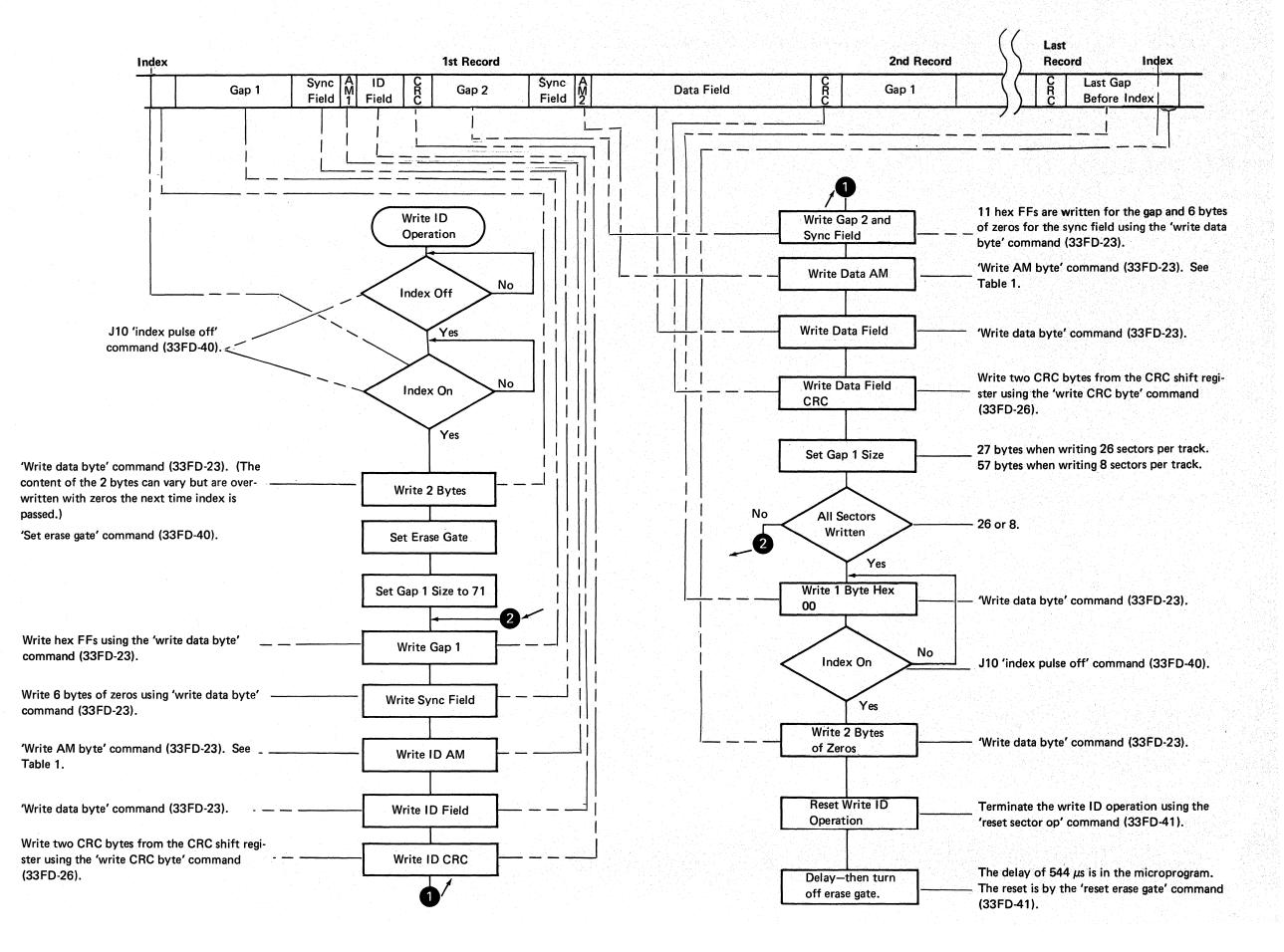

| PLO Out of Synchronization               | DISK-36 | Write ID Operation                     | 33FD-14               | Print Buffer Load DQ180 (50, 100, and                                                               |         | Hammer Fire Control (50, 100, and                          |        |

| Recalibrate                              | DISK-37 | Write ID Data Flow                     | 33FD-15               | 155 lpm)                                                                                            | PTR-27  | 155 lpm)                                                   | PTR-39 |

| Data Unsafe                              | DISK-38 | Load Command                           | 33FD-16               | Print Buffer Read DQ180 (50, 100, and                                                               |         | Printer Speed Control                                      | PTR-39 |

| DSF (Disk) Ready                         | DISK-39 | Sense Command                          | 33FD-18               | 155 lpm)                                                                                            | PTR-28  | Print Buffer DQ180                                         | PTR-40 |

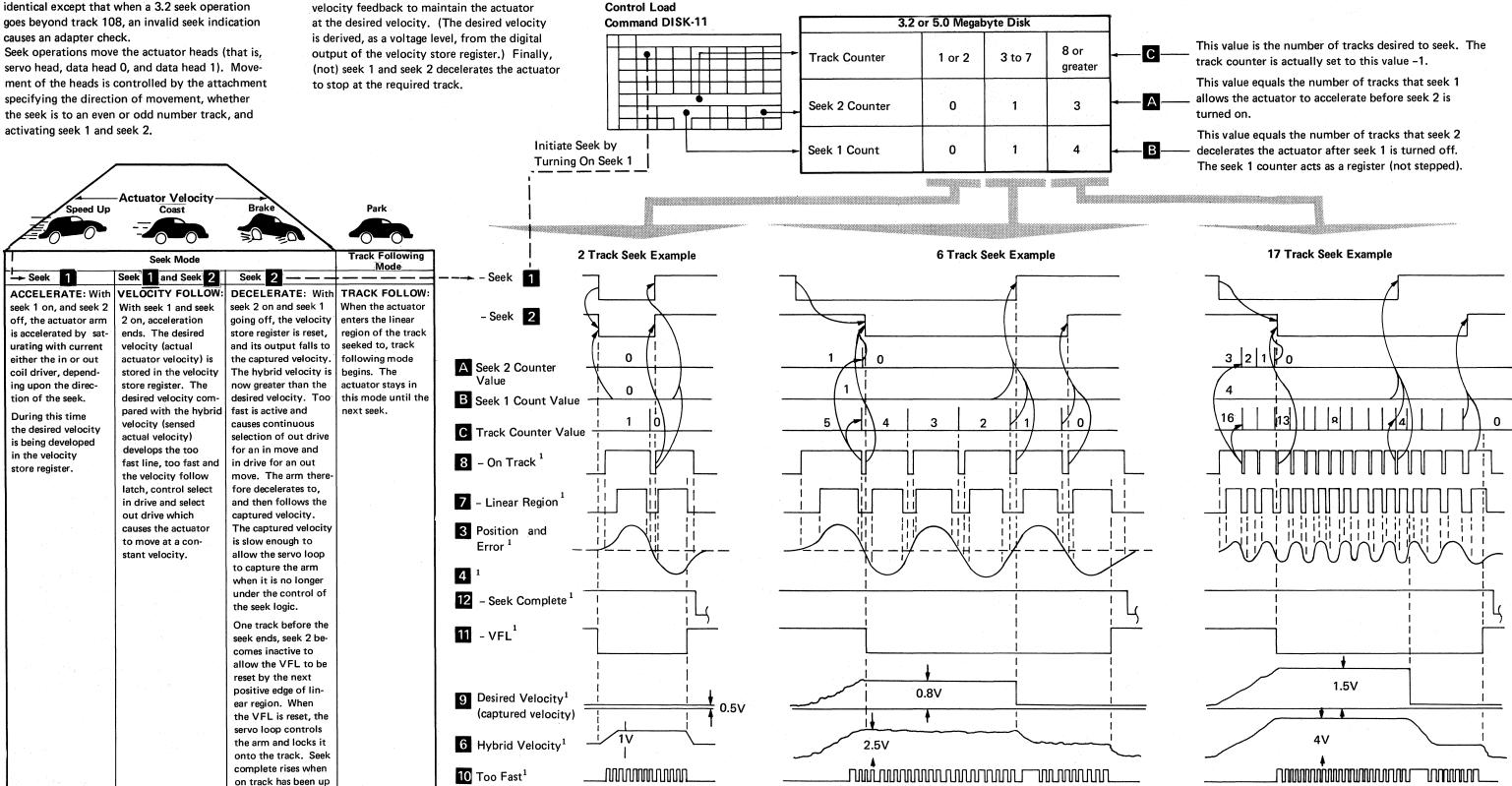

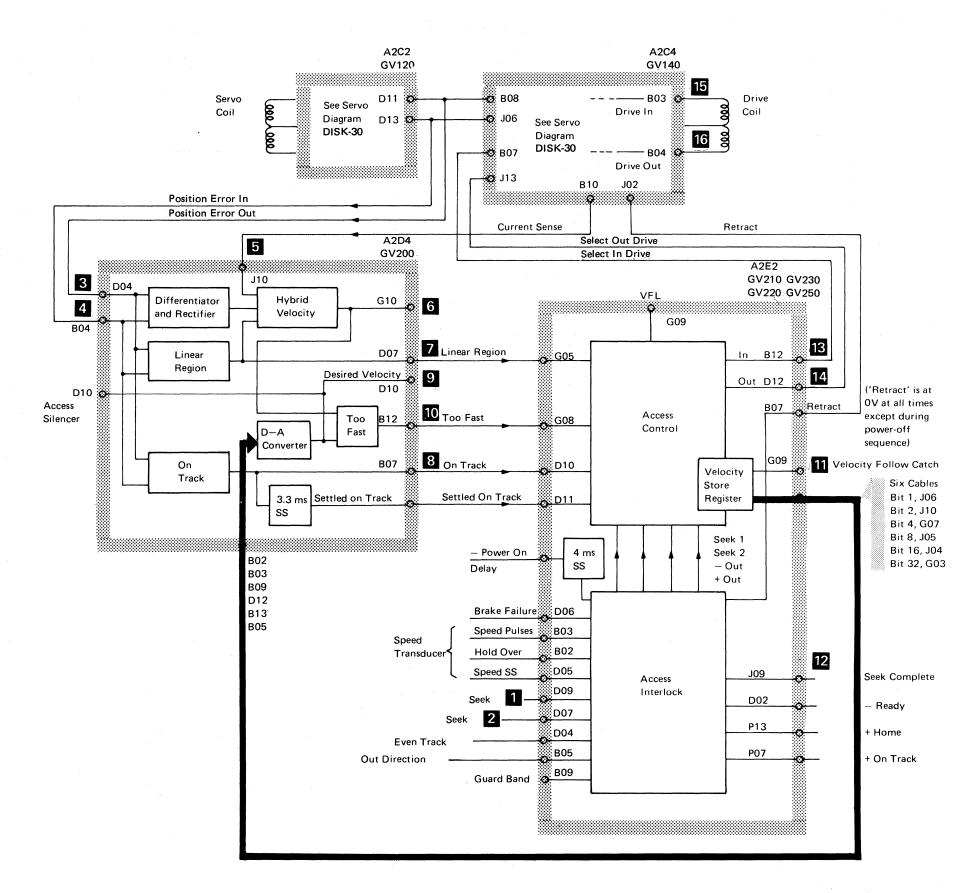

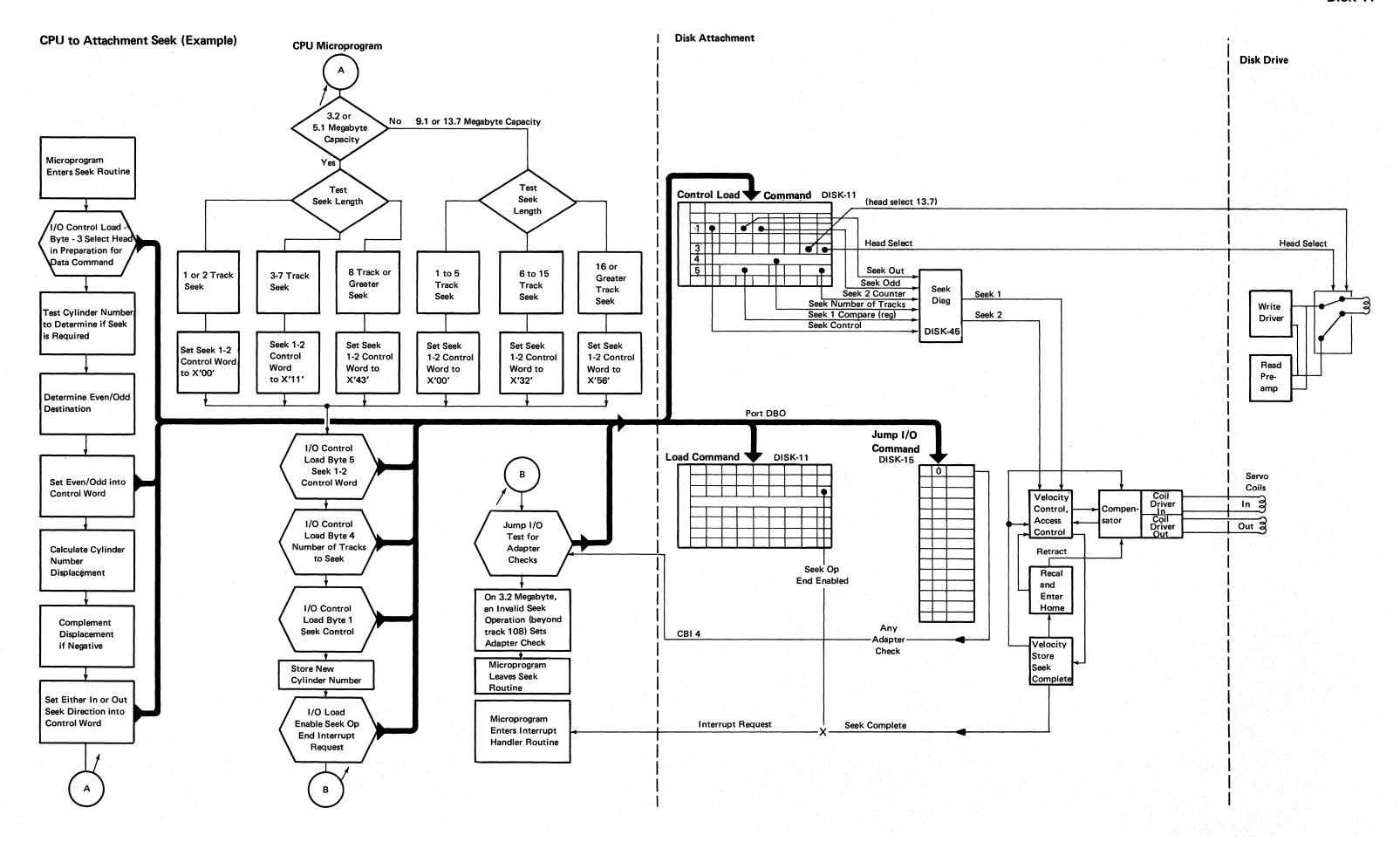

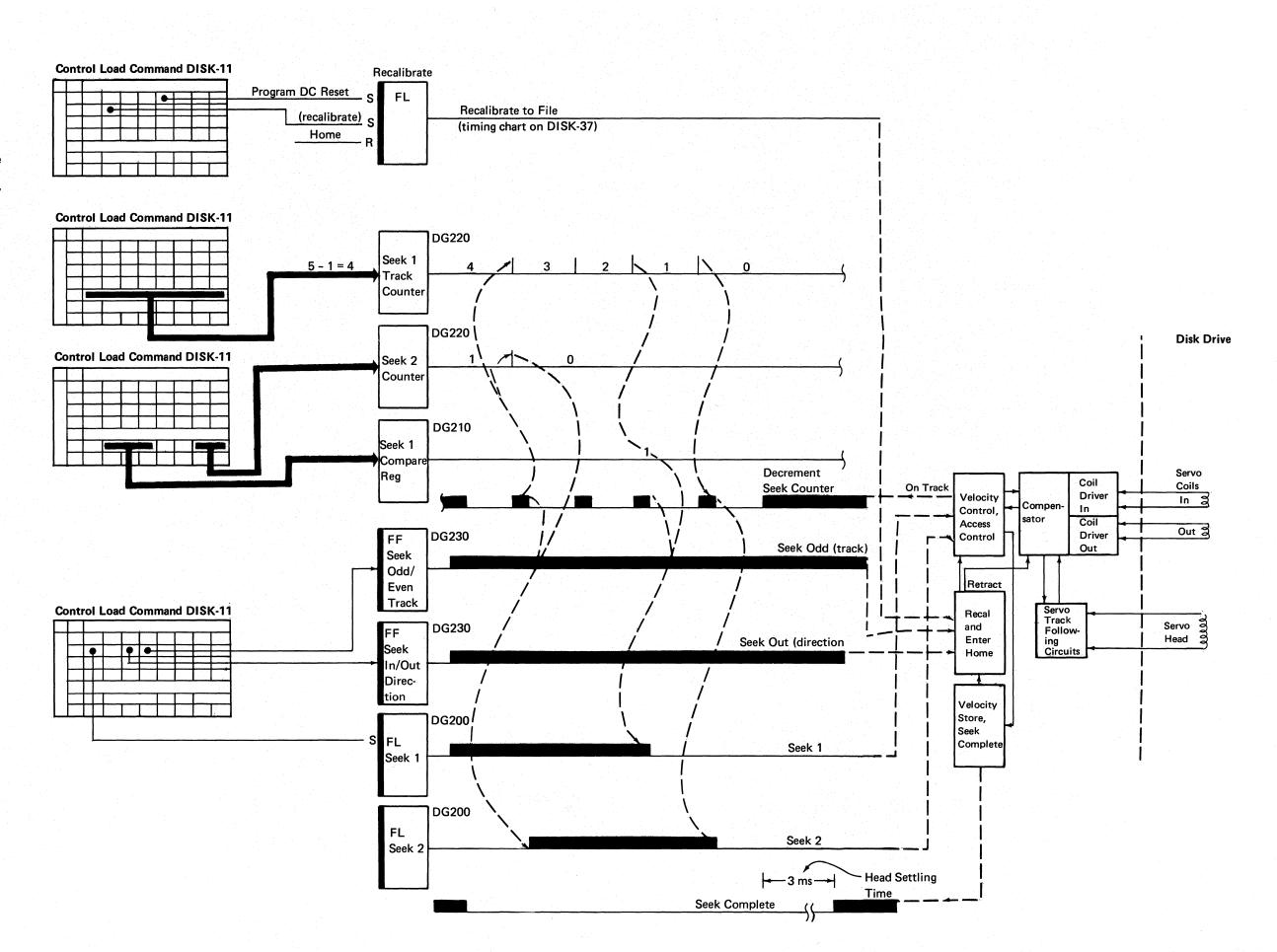

| Seek Operation                           | DISK-40 | Control Load Command                   | 33FD-20               | Hammer Selection and Firing (50, 100, and                                                           |         | Scan Register DQ200                                        | PTR-40 |

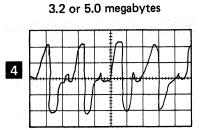

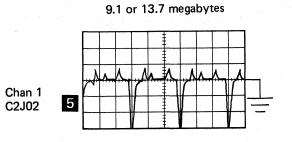

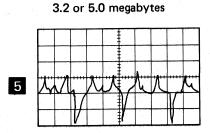

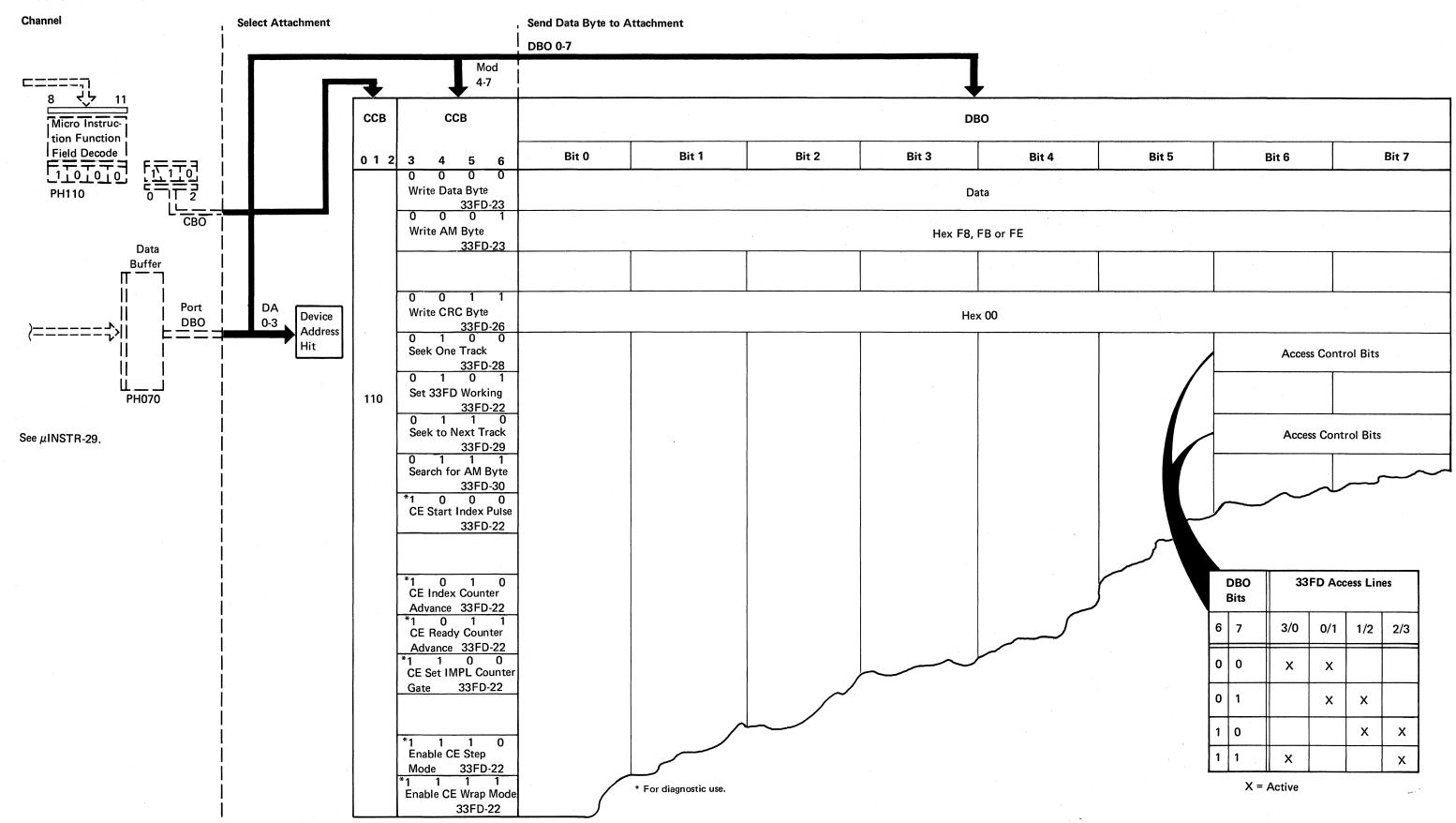

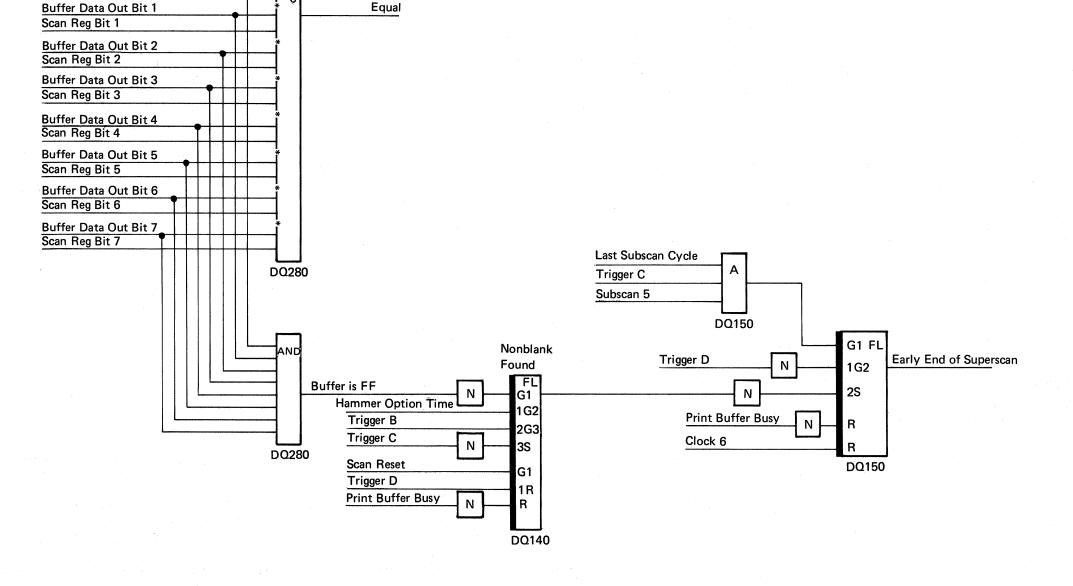

| 3.2 or 5.0 Megabytes                     | DISK-40 | Write Data Byte and Write AM Byte      | 33FD-23               | 155 lpm)                                                                                            | PTR-29  | Scan/Buffer Compare DQ280                                  | PTR-40 |

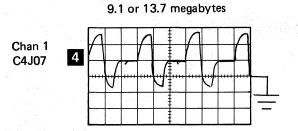

| 9.1 or 13.7 Megabytes                    | DISK-41 | Write CRC Byte                         | 33FD-26               | Hammer Latch Select (50, 100, and                                                                   | 111123  |                                                            | F1N-40 |

| Actuator Feedback During Seek            | DISK-42 | Seek One Track                         | 33FD-28               | 155 lpm)                                                                                            | PTR-30  | Printer Functional Units and Dataflow                      | DTD 41 |

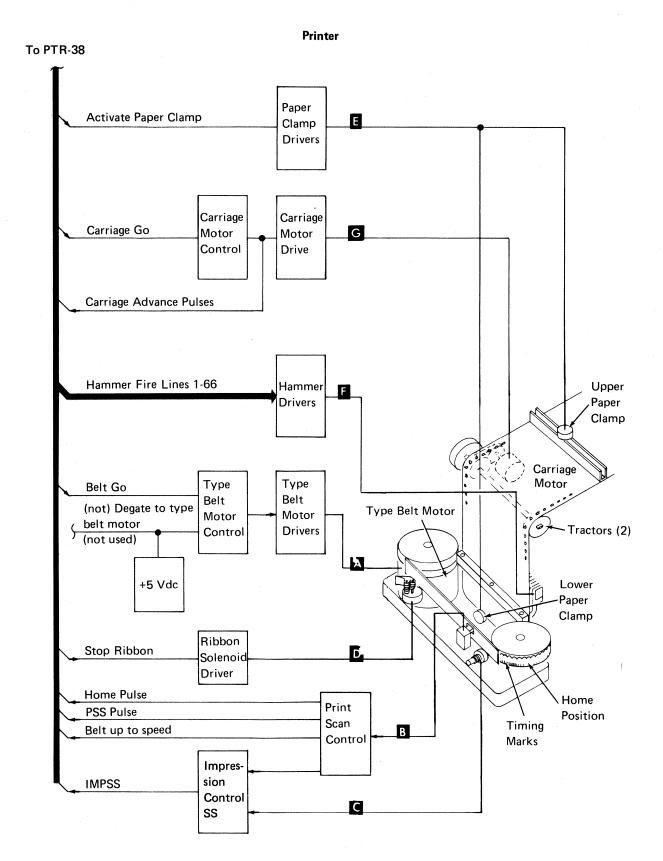

| Seek Wave Forms                          | DISK-43 | Seek to Next Track                     | 33FD-29               | Register Select (50, 100, and 155 lpm)                                                              | PTR-30  | (50, 100, and 155 lpm)                                     | PTR-41 |

| CPU to Attachment Seek (Example)         | DISK-44 | Search for AM Byte                     | 33FD-30               | 그렇게 됐다. 하는 사이를 가나와 하는 사람들이 가지 하는 사람들이 가장하는 사람들이 되었다. 하는 회사 사람                                       | FIN-30  | Type Belt Motor and Drive                                  | PTR-41 |

| Recalibrate and Seek Out (Example)       | DISK-45 | Control Sense                          | 33FD-32               | Hammer Select Strobe (50, 100, and                                                                  | DTD 20  | Home Pulse and Print-Subscan Pulse                         |        |

| D O /Off                                 |         | Jump I/O                               |                       | 155 lpm)                                                                                            | PTR-30  | Generation                                                 | PTR-41 |

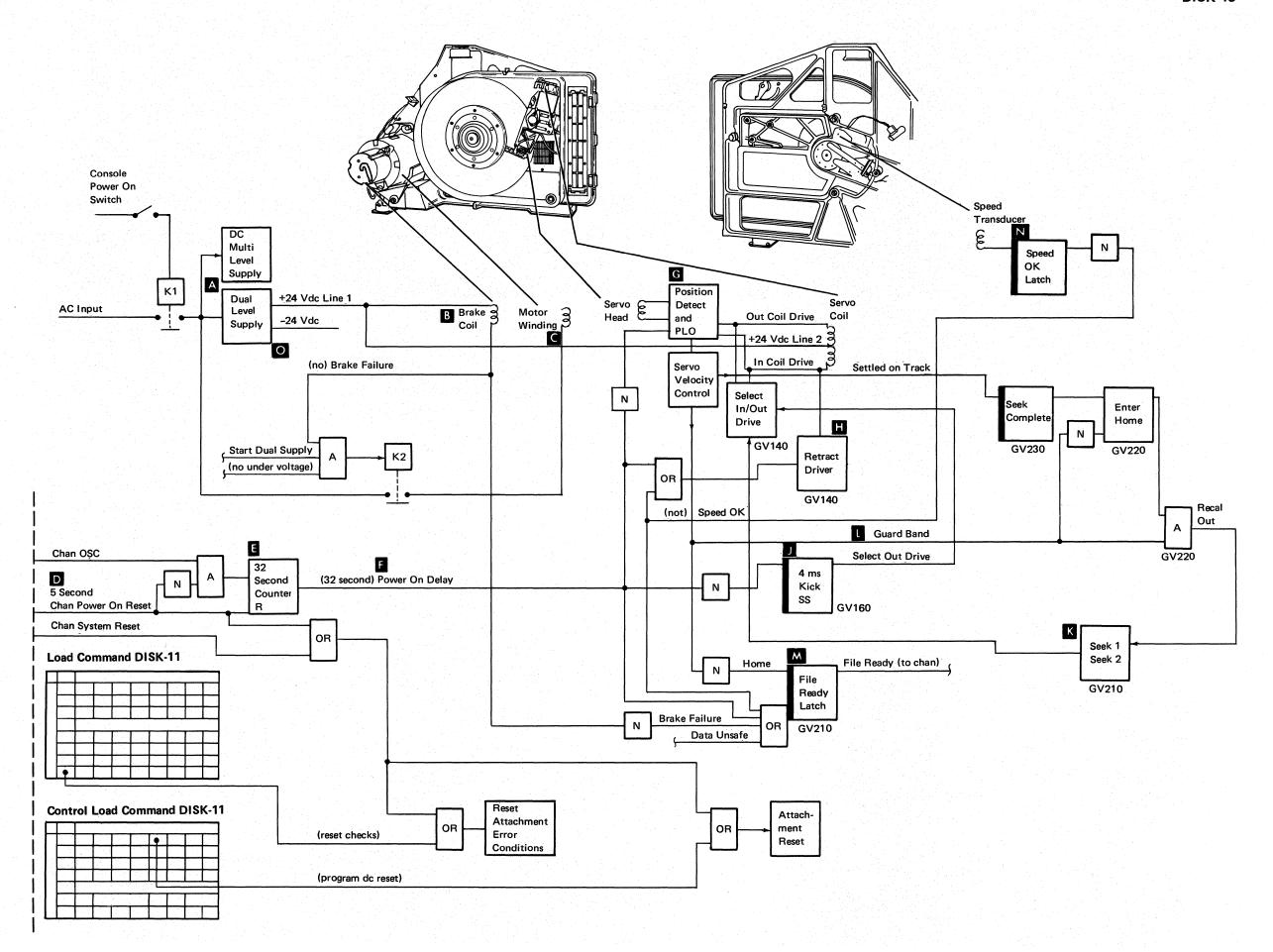

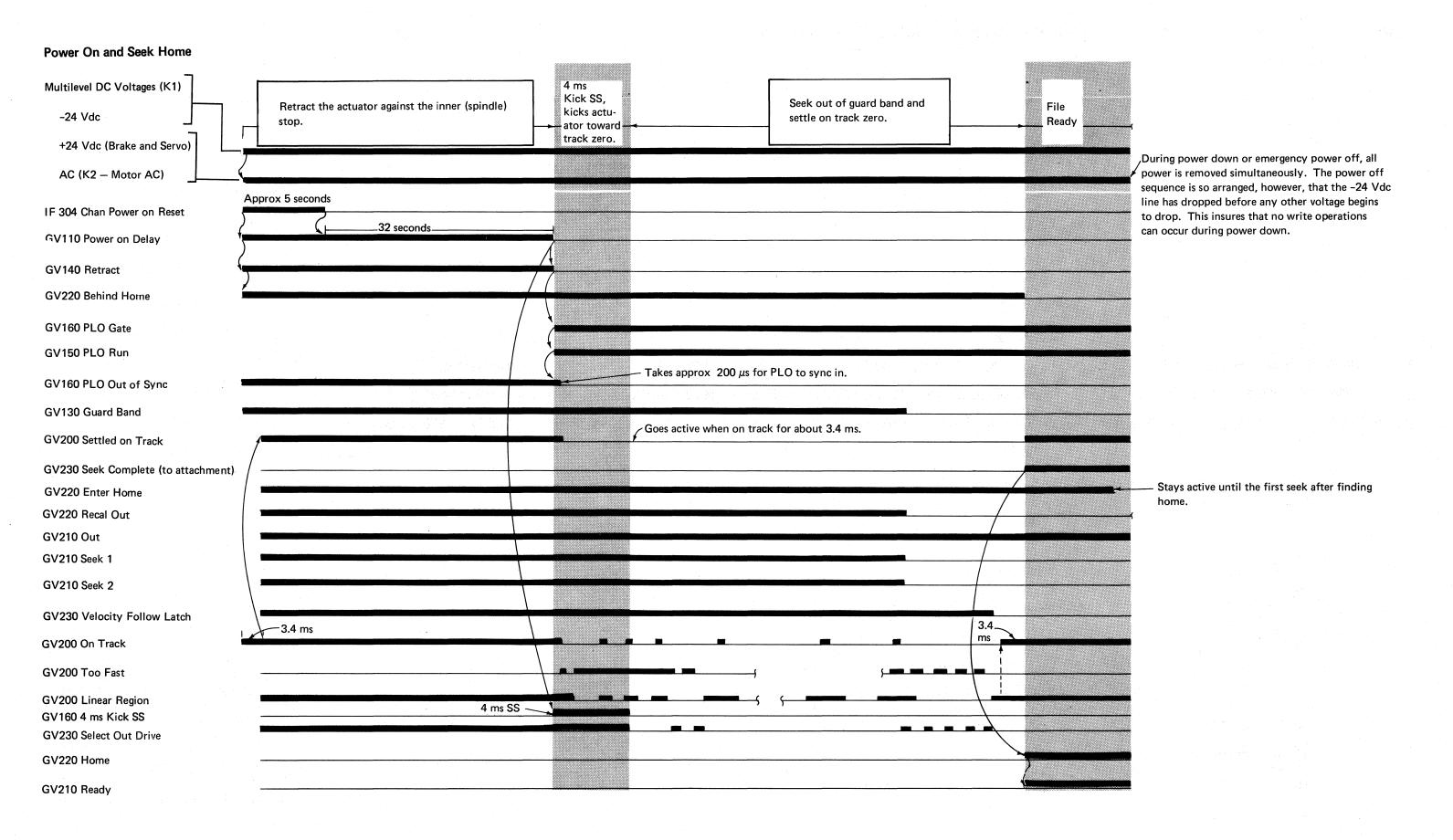

| Power On and Seek Home                   |         |                                        | 33FD-36               | Hammer Settling and Type Belt                                                                       |         |                                                            | PTR-41 |

| 0)(0) = 0== 1                            | DISK-47 | Error Conditions                       |                       | Synchronization (50, 100, and 155 lpm)                                                              | PTR-31  | Ribbon Drive                                               | PTR-41 |

|                                          | DISK-48 | 33FD Running Fast                      | 33FD-42               | Printer Speed Control                                                                               | PTR-32  | Paper Clamps                                               | PTR-41 |

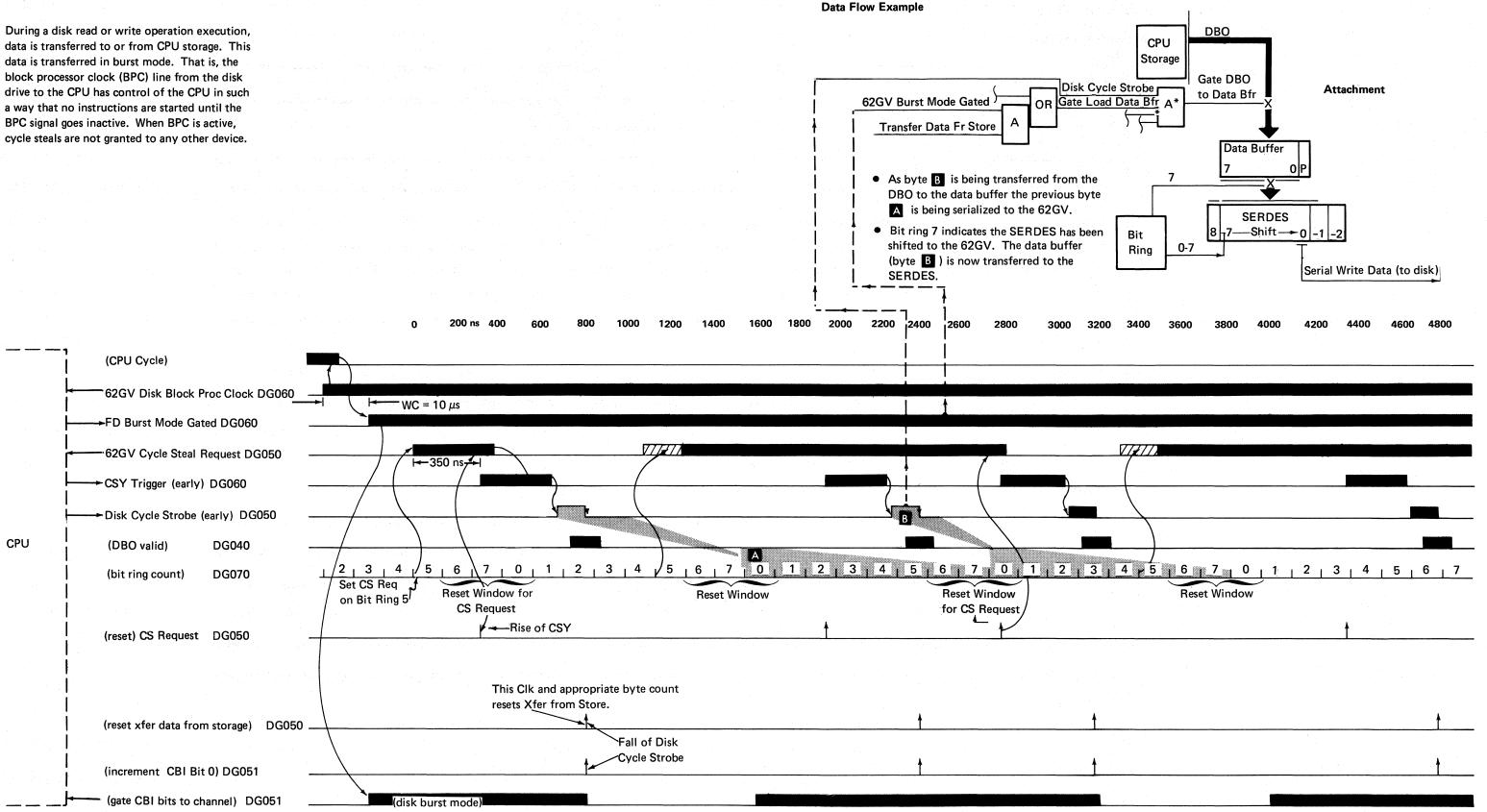

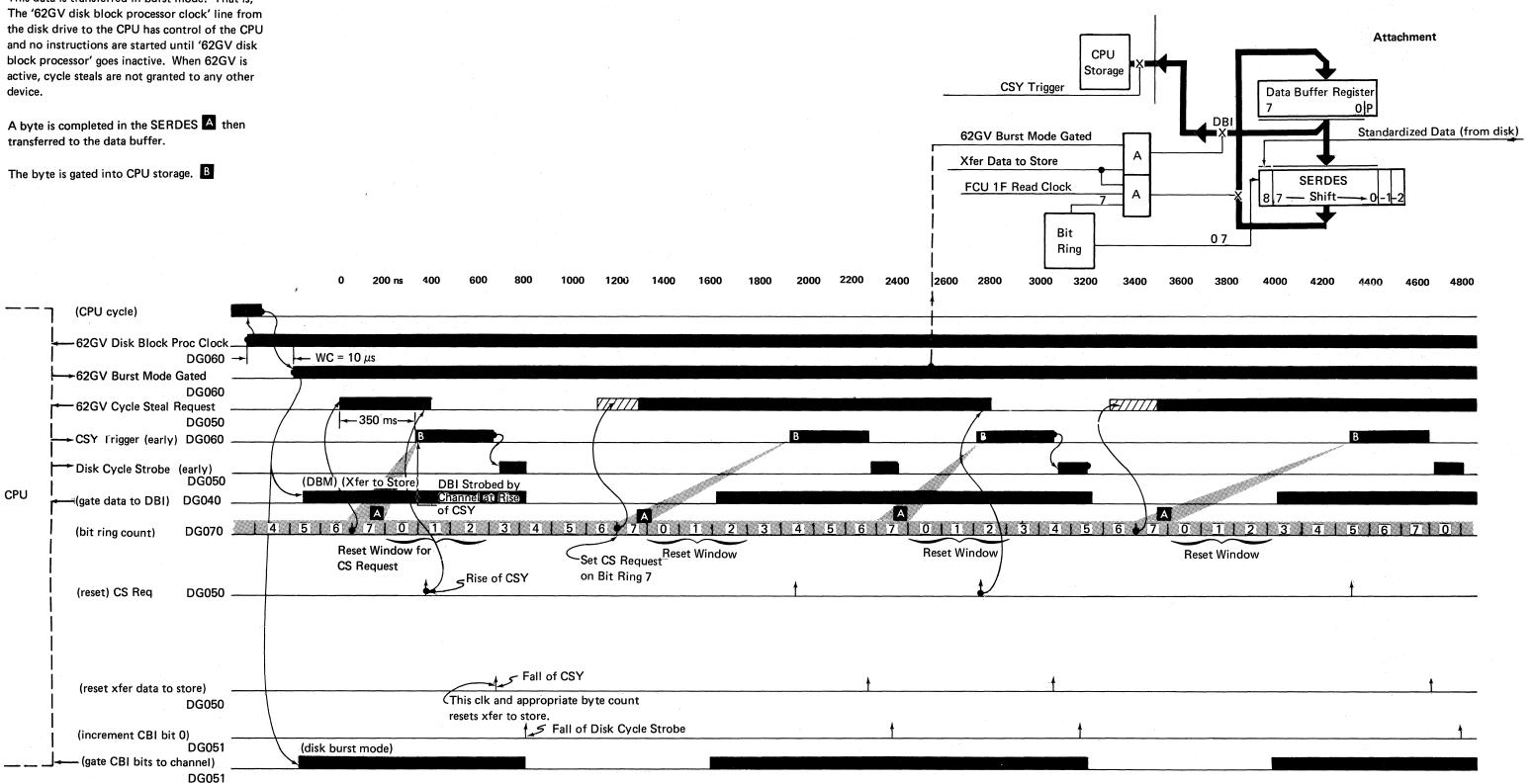

| Cycle Steal—CSY Early from CPU Storage . | DISK-48 | 33FD Not Ready                         | 33FD-42               | Carriage Operation (50, 100, and 155 lpm)                                                           | PTR-33  | Firing the Hammers                                         | PTR-41 |

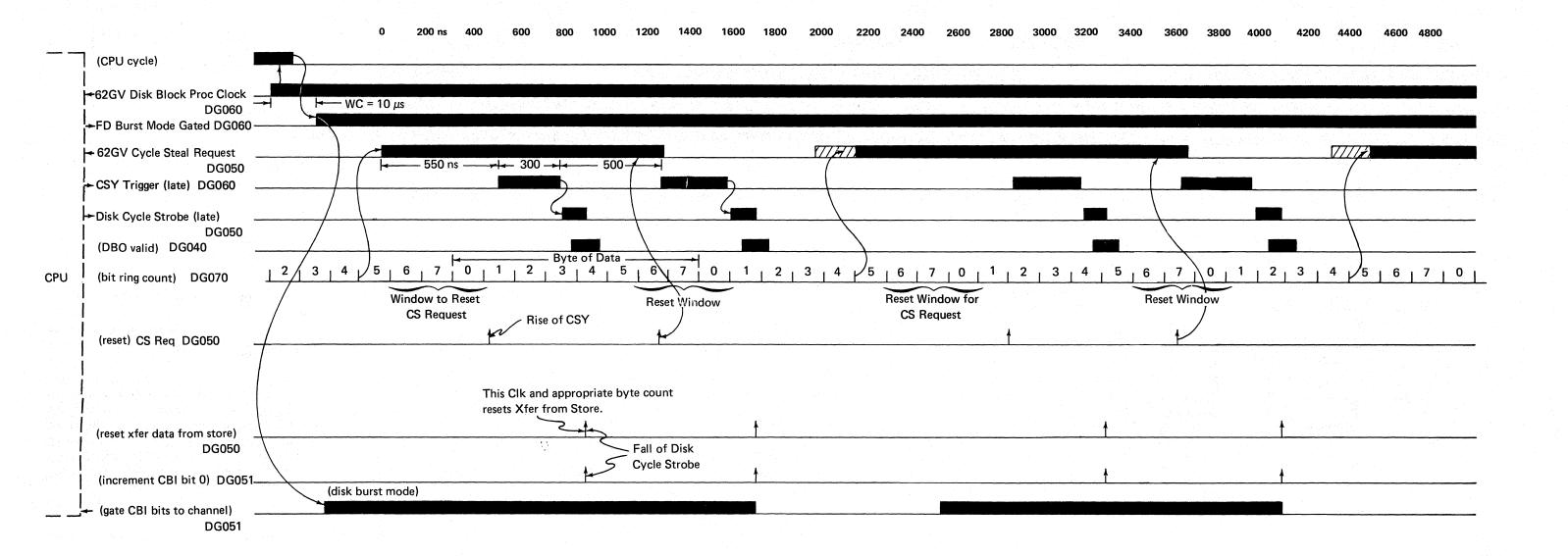

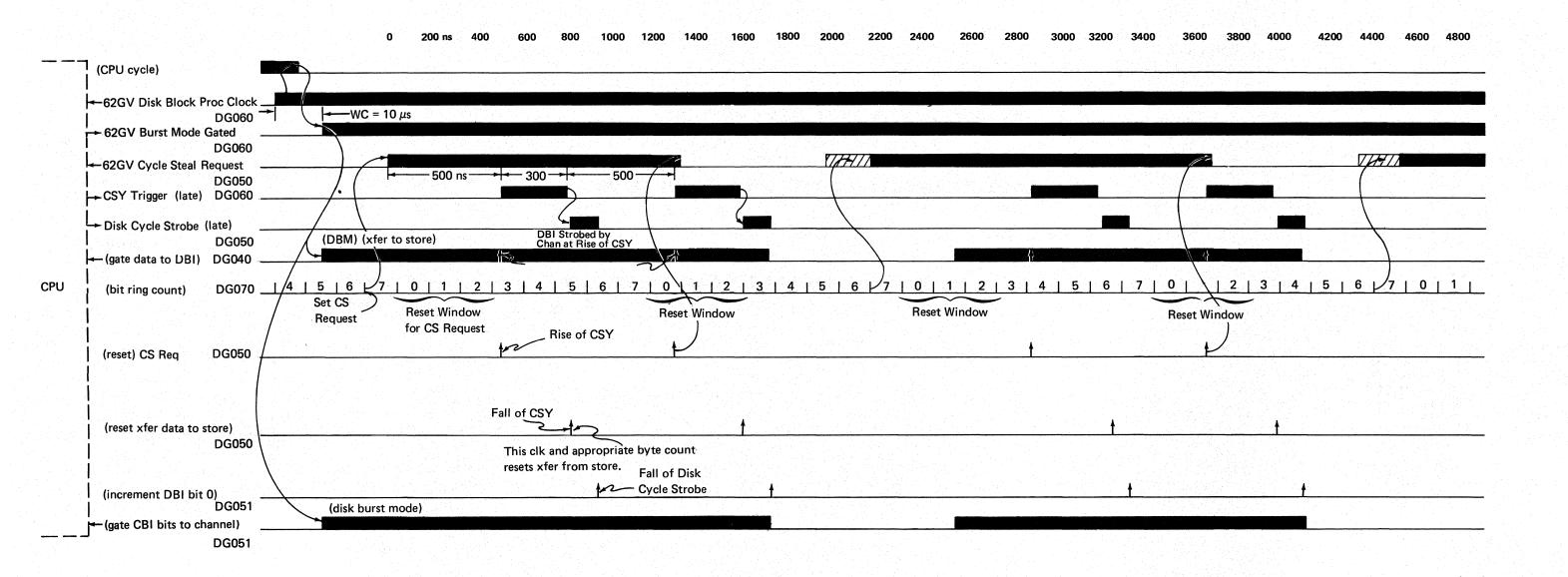

| Cycle Steal—CSY Late from CPU Storage    | DISK-49 | Read Overrun                           | 33FD-43               | Carriage Detent                                                                                     | PTR-33  | Carriage Spacing                                           | PTR-41 |

| Cycle Steal—CSY Early to CPU Storage     | DISK-50 | Write Overrun                          | 33FD-43               | Half Line Space Operation (50, 100, and                                                             |         | Error Conditions (50, 100, and 155 lpm)                    | PTR-43 |

| Cycle Steal—CSY Late to CPU Storage      | DISK-51 | Write Parity Check                     | 33FD-43               | 155 lpm)                                                                                            | PTR-34  | Unprintable Character                                      | PTR-43 |

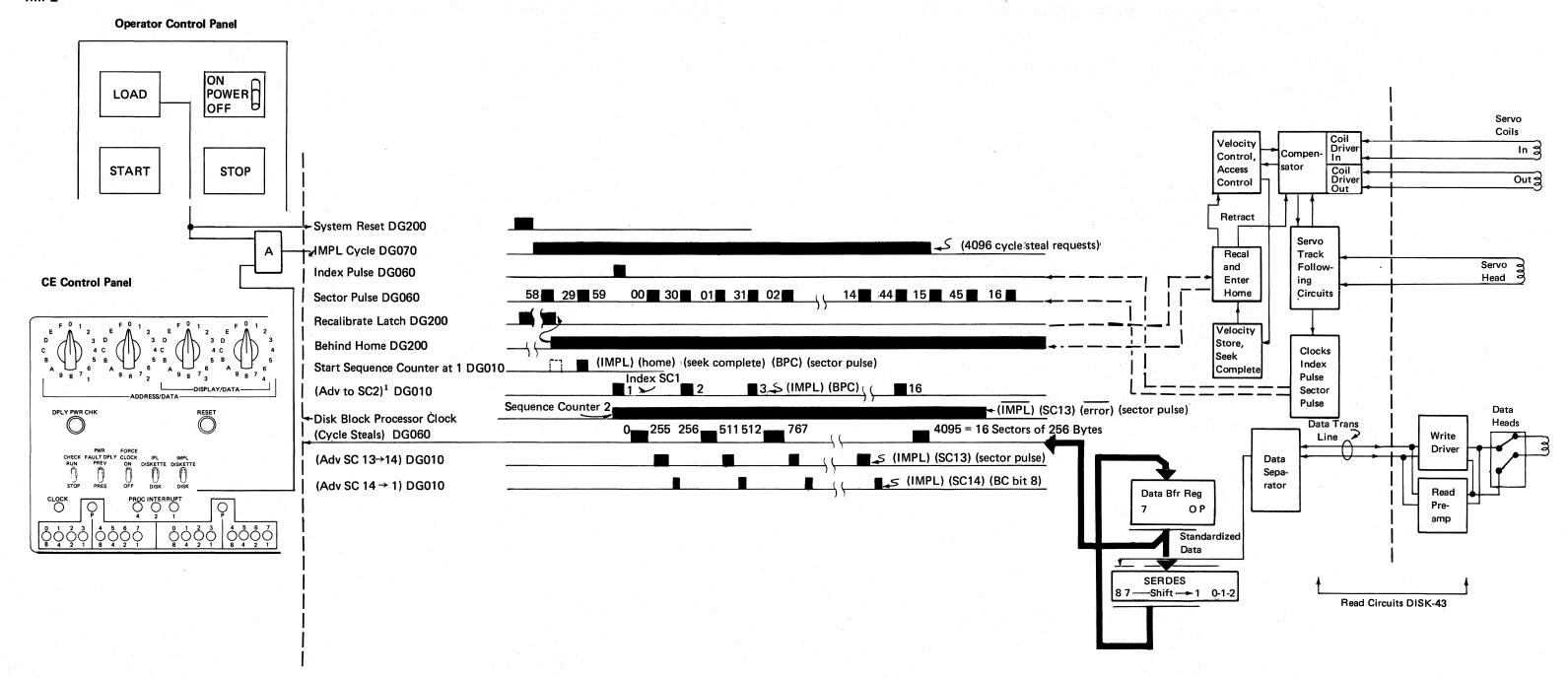

| INITIAL MICROPROGRAM LOAD (IMPL).        | DISK-52 | Write or Erase Gate Unsafe and Missing |                       | Input/Output Lines (50, 100, and                                                                    |         | Forms Jam Check/Belt Speed Check                           |        |

| IMPL                                     | DISK-52 | Erase Gate                             | 33FD-44               | 155 lpm)                                                                                            | PTR-36  | (50, 100, and 155 lpm)                                     | PTR-44 |

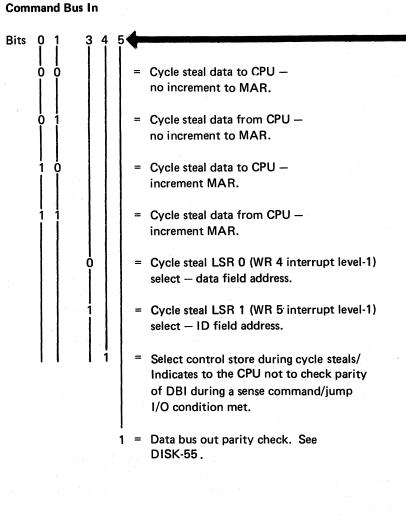

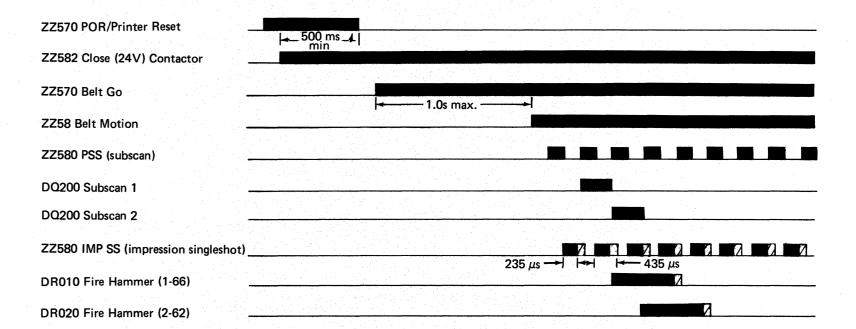

| COMMAND BUS IN (CBI)                     | DISK-53 | Missing Record                         | 33FD-45               | POR/Printer Reset (A)                                                                               | PTR-36  | Forms Jam Check                                            | PTR-44 |

| ERROR CONDITIONS                         | DISK-54 | Data Separator                         | 33FD-46               | Close (+24V) Contactor (A)                                                                          | PTR-36  | Belt Speed Check                                           | PTR-44 |

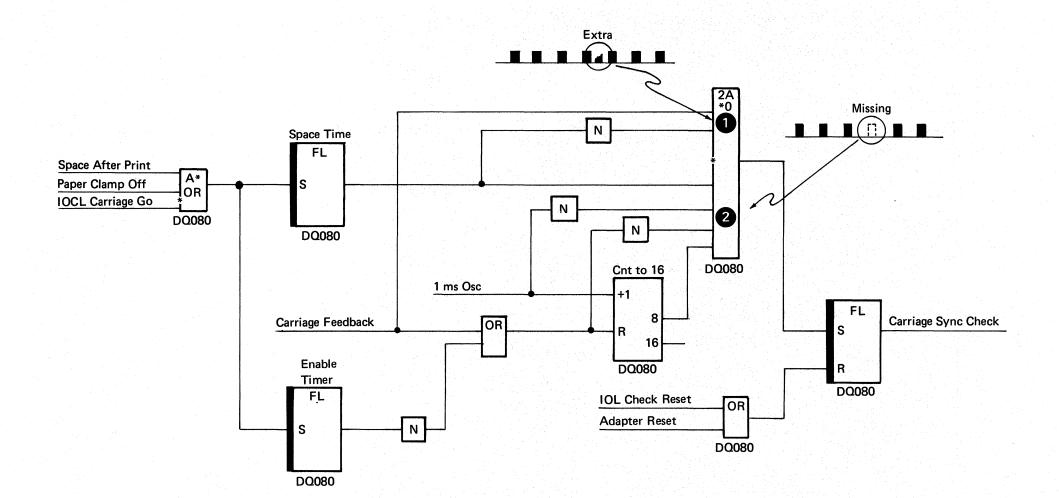

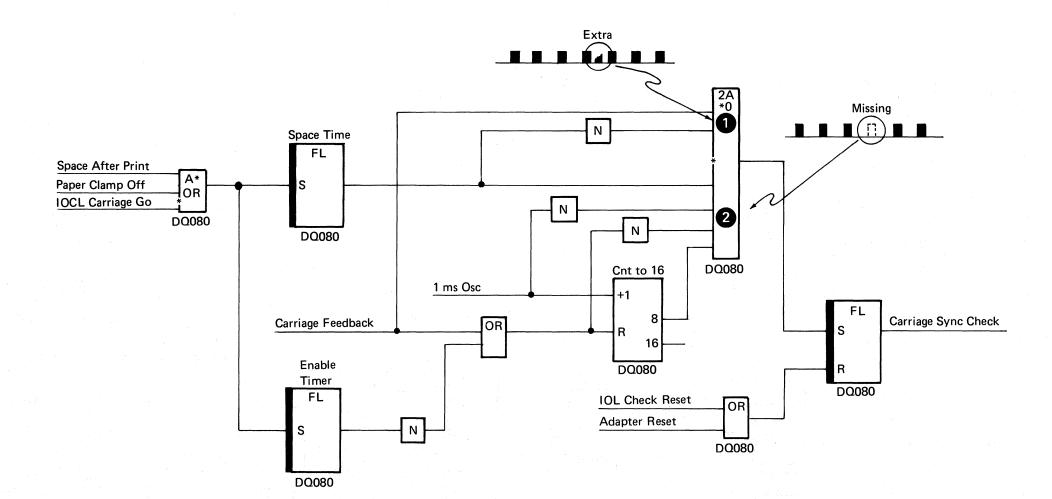

| Write Data Echo Check                    | DISK-54 | Index Counter                          | 33FD-47               | Belt Go (A)                                                                                         | PTR-36  | Carriage Sync Check                                        | PTR-45 |

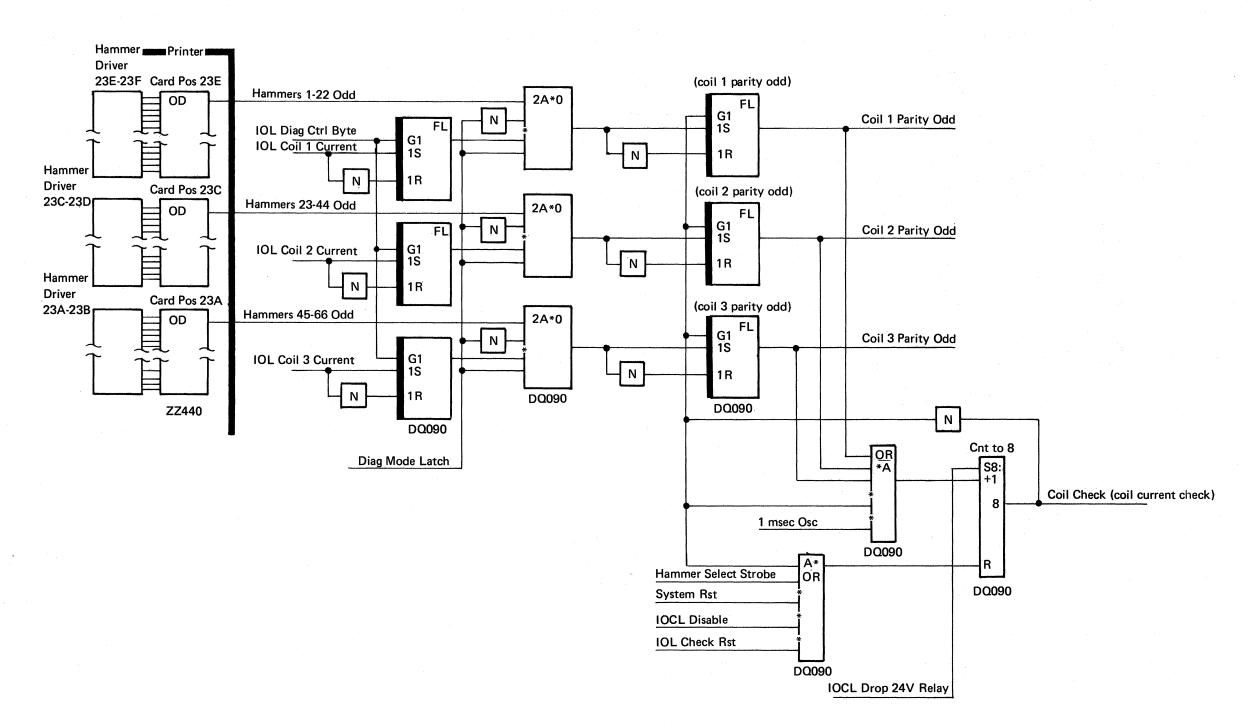

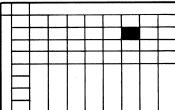

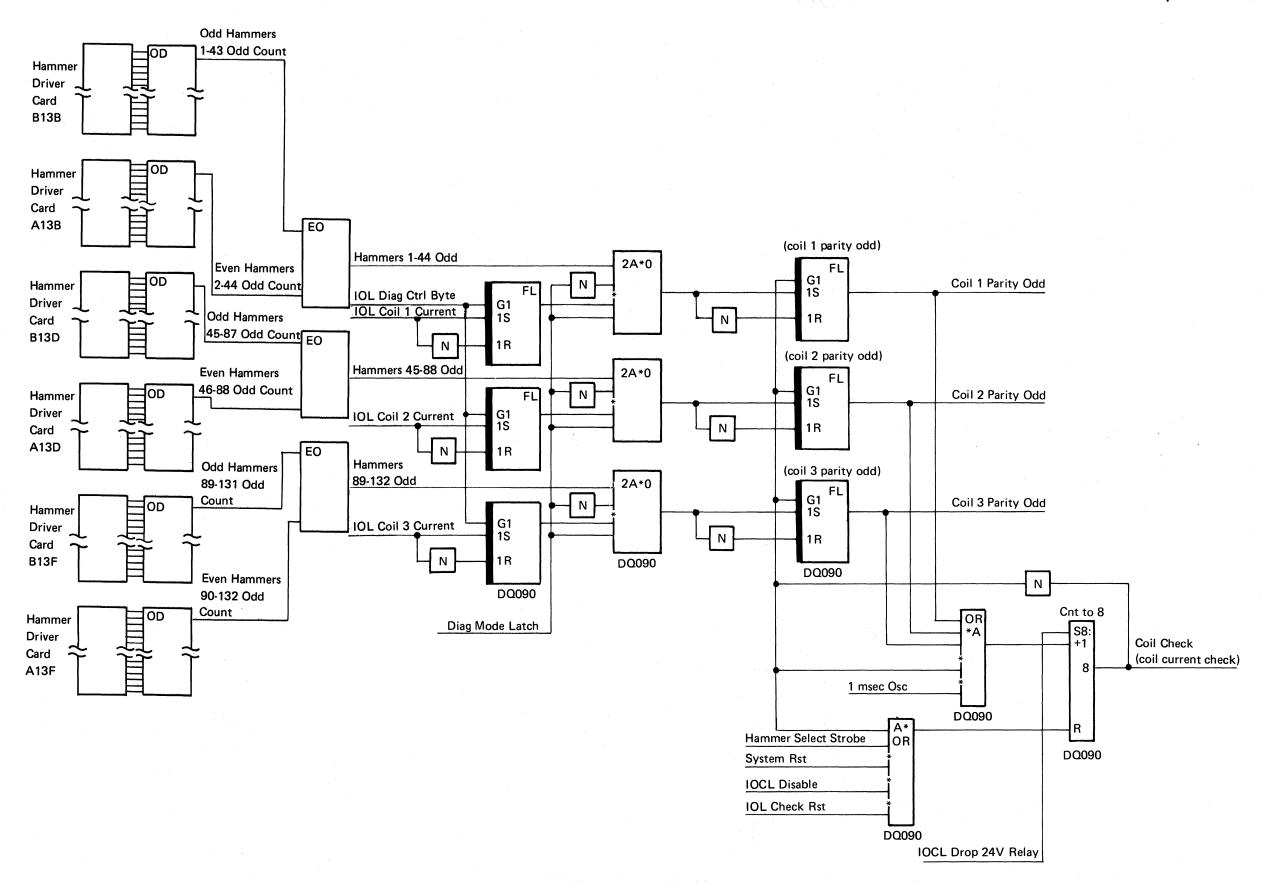

| DBO Parity Check                         | DISK-55 | Ready Counter                          | 33FD-47               | Belt Motion (P)                                                                                     | PTR-36  | Coil Current Check (50, 100, and                           |        |

| Cycle Steal Overrun Check                | DISK-56 | IMPL Counter                           | 33FD-47               | PSS (Subscan) (P)                                                                                   | PTR-36  | 155 (pm)                                                   | PTR-46 |

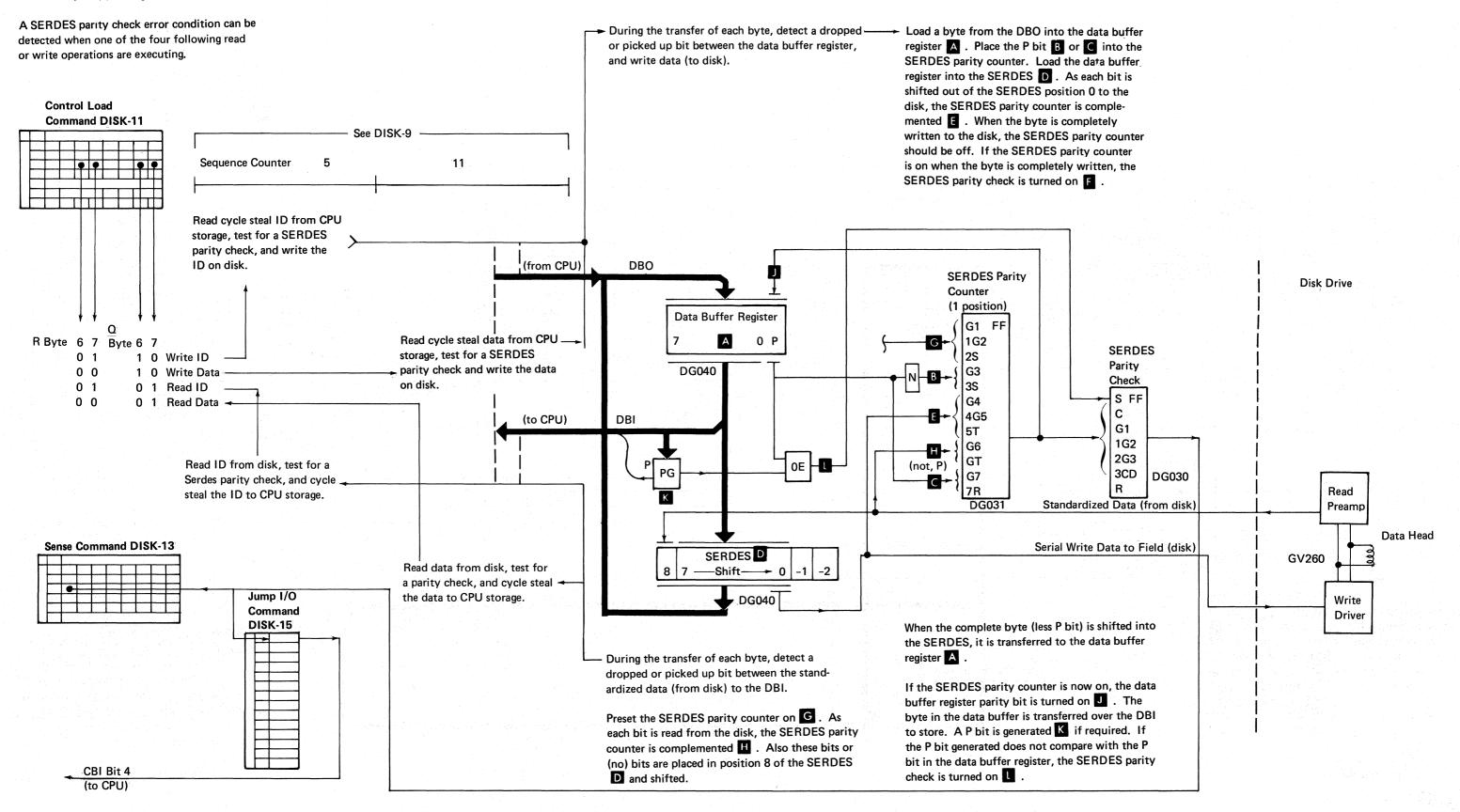

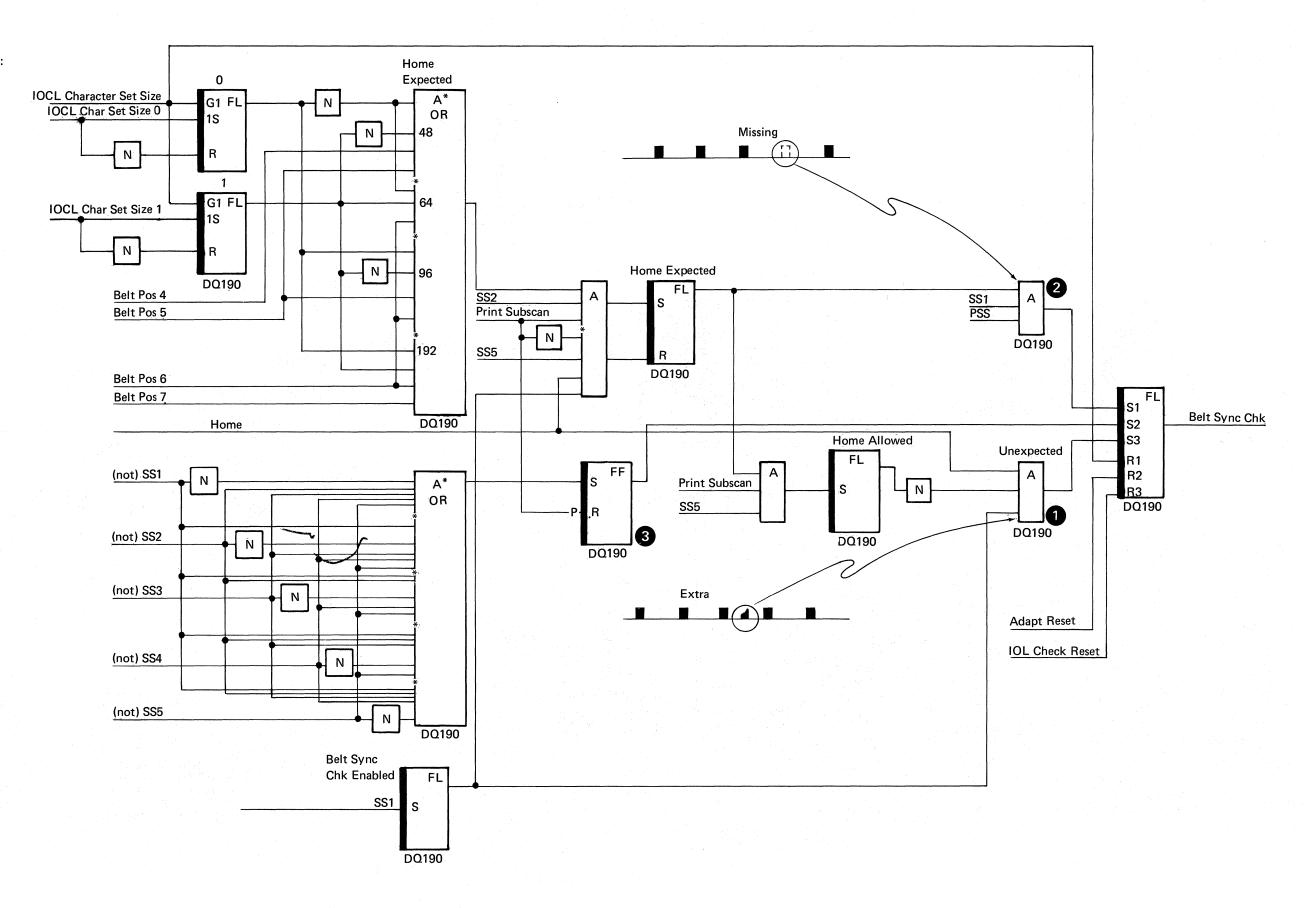

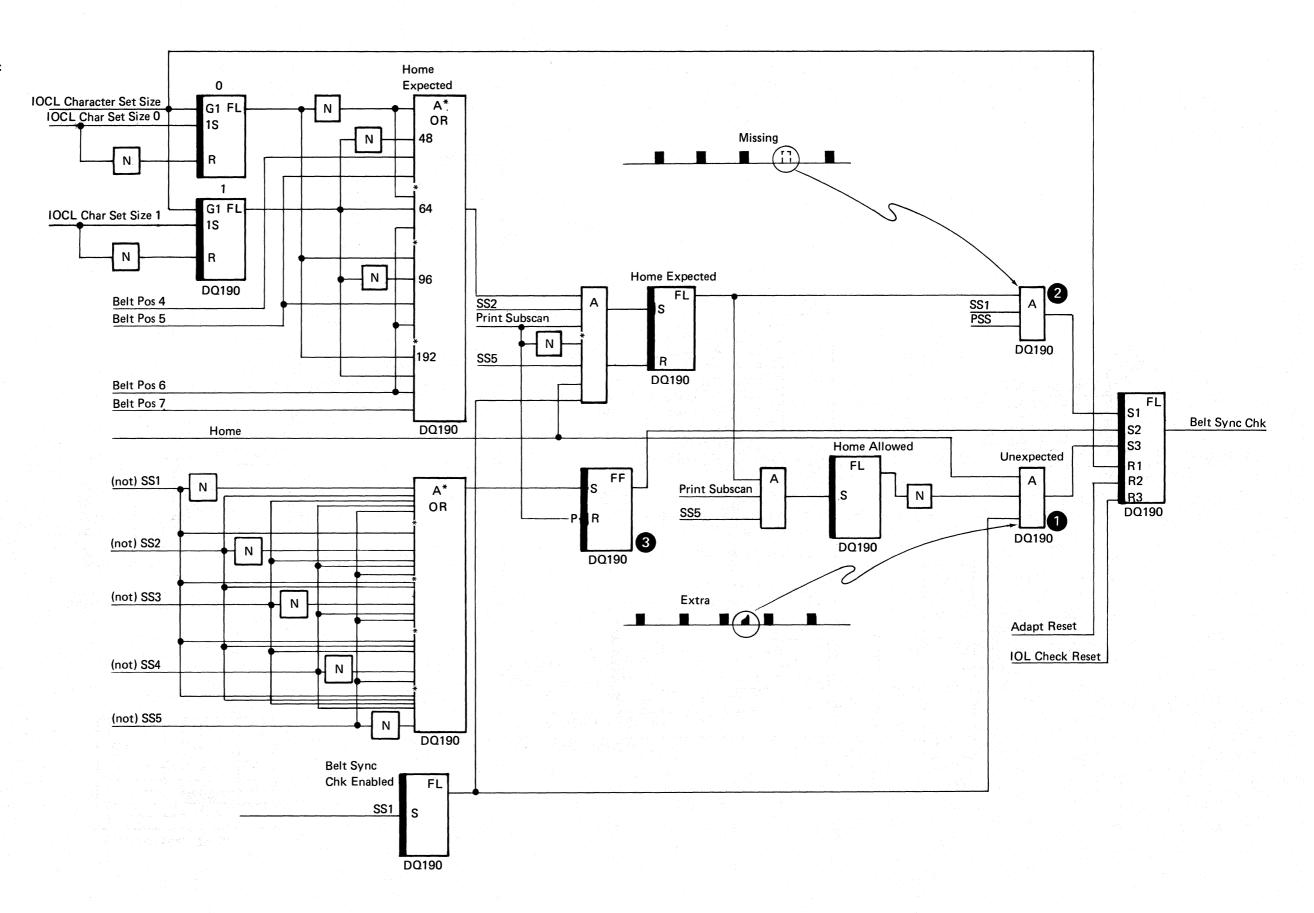

| SERDES Parity Check                      | DISK-57 | Write Clock and Write Bit Ring         | 33FD-48               | IMPSS (Impression Singleshot) (P)                                                                   | PTR-36  | Belt Sync Check                                            | PTR-47 |

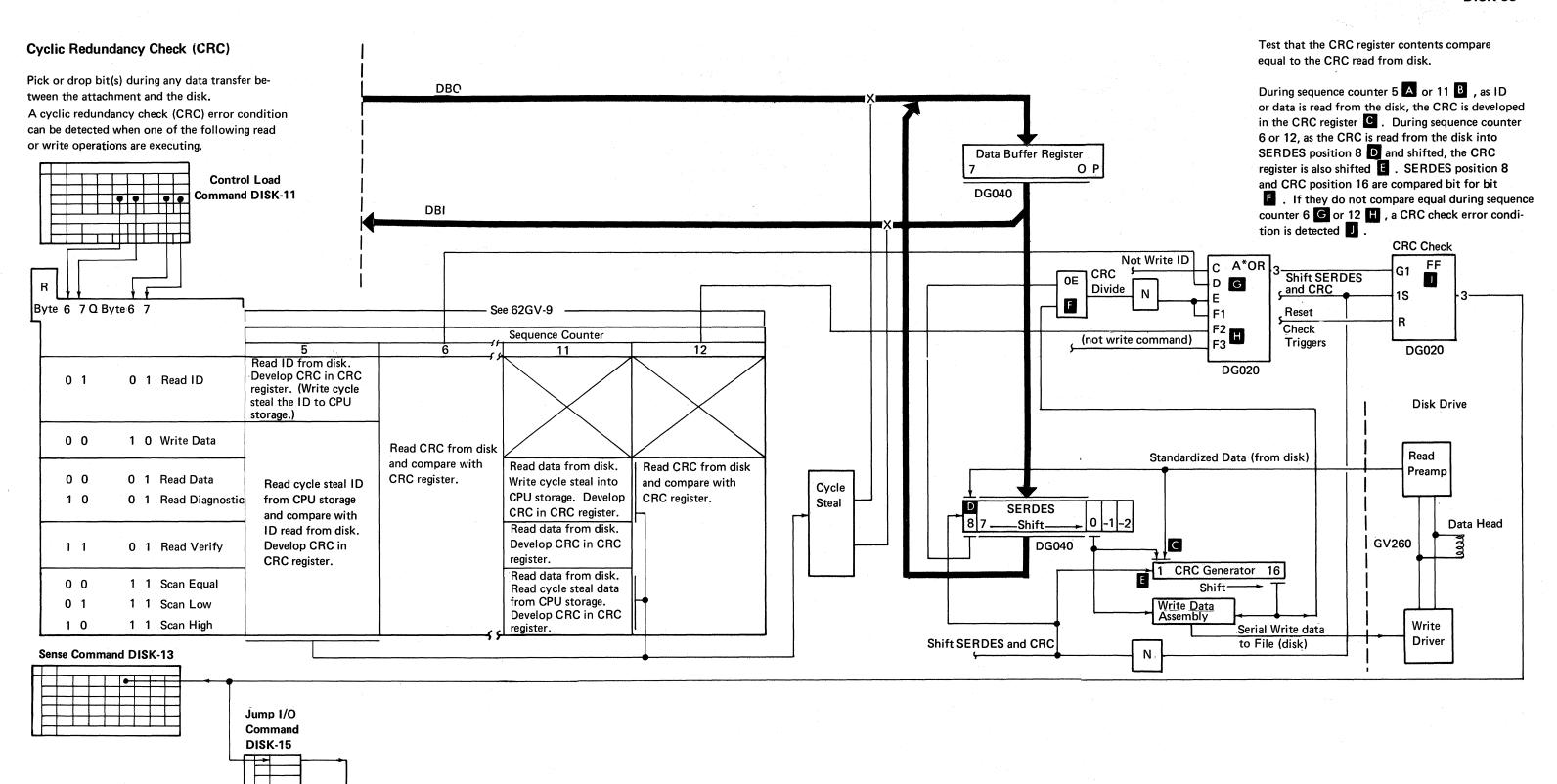

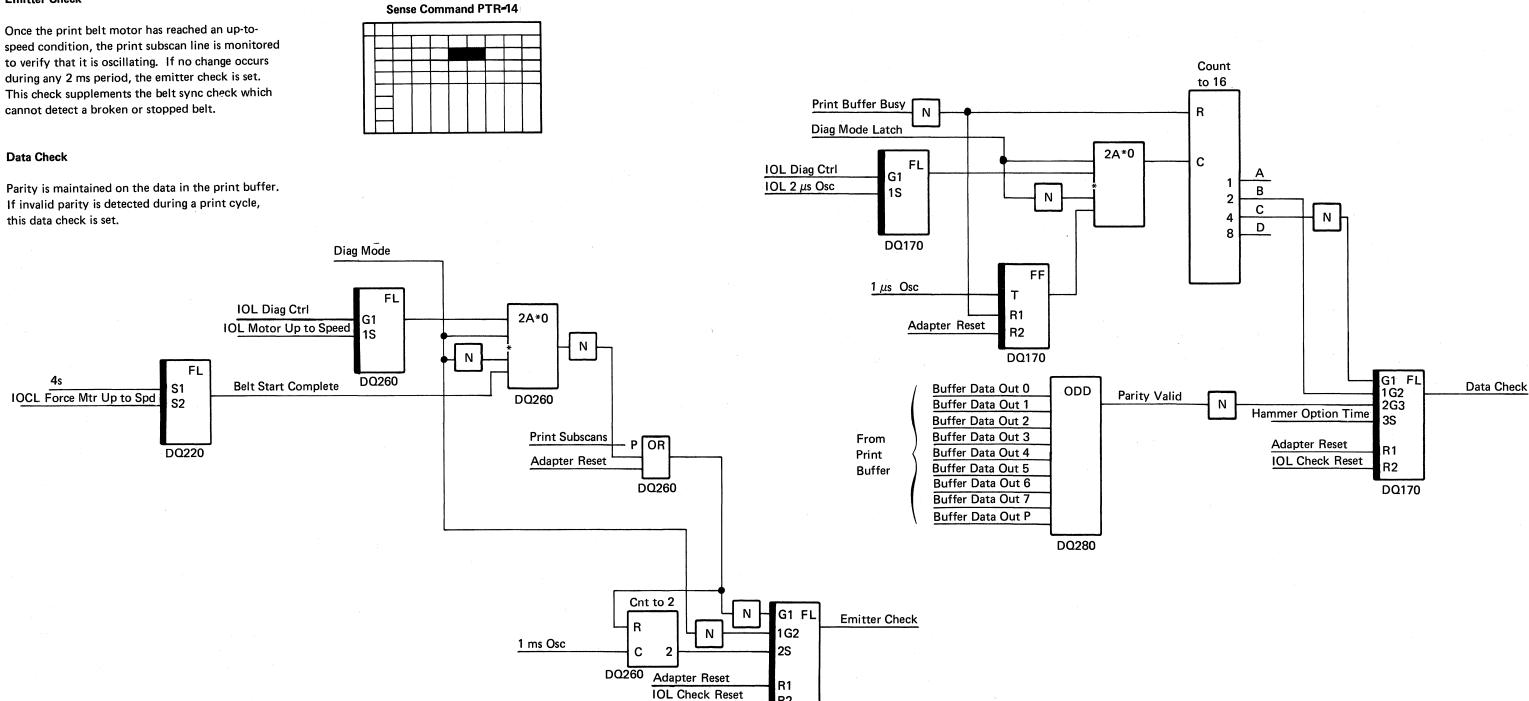

| Cyclic Redundancy Check (CRC)            | DISK-58 | Read Clock and Read Bit Ring           | 33FD-48               | Fire Hammer (A)                                                                                     | PTR-36  | Emitter Check/Data Check                                   | PTR-48 |

|                                          |         | CRC Shift Register                     | 33FD-49               | Activate Paper Clamps (A)                                                                           | PTR-37  |                                                            |        |

|                                          |         |                                        |                       | Montago i abei Olamba (A)                                                                           | 1111-07 | Emitter Check                                              | PTR-48 |

|                                         |          |                                                            |         |                                                     |          | 그는 그는 그는 그는 이 나라면 살아 있는 살아 한 말았다.         |                    |

|-----------------------------------------|----------|------------------------------------------------------------|---------|-----------------------------------------------------|----------|-------------------------------------------|--------------------|

| Data Check                              | PTR-48   | Carriage Advance (P)                                       | PTR-87  | DISPLAY SCREEN                                      | DISP-1   | Print Motor Drive                         | S-PTR-6            |

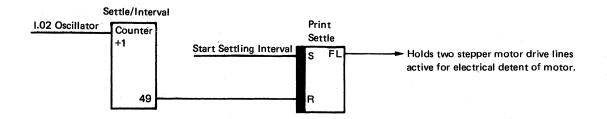

| Hammer Parity Check (50, 100, and       |          | Printer Thermal Switch (P)                                 | PTR-87  | Attachment Functions                                | DISP-1   | Settling Intervals                        | S-PTR-6            |

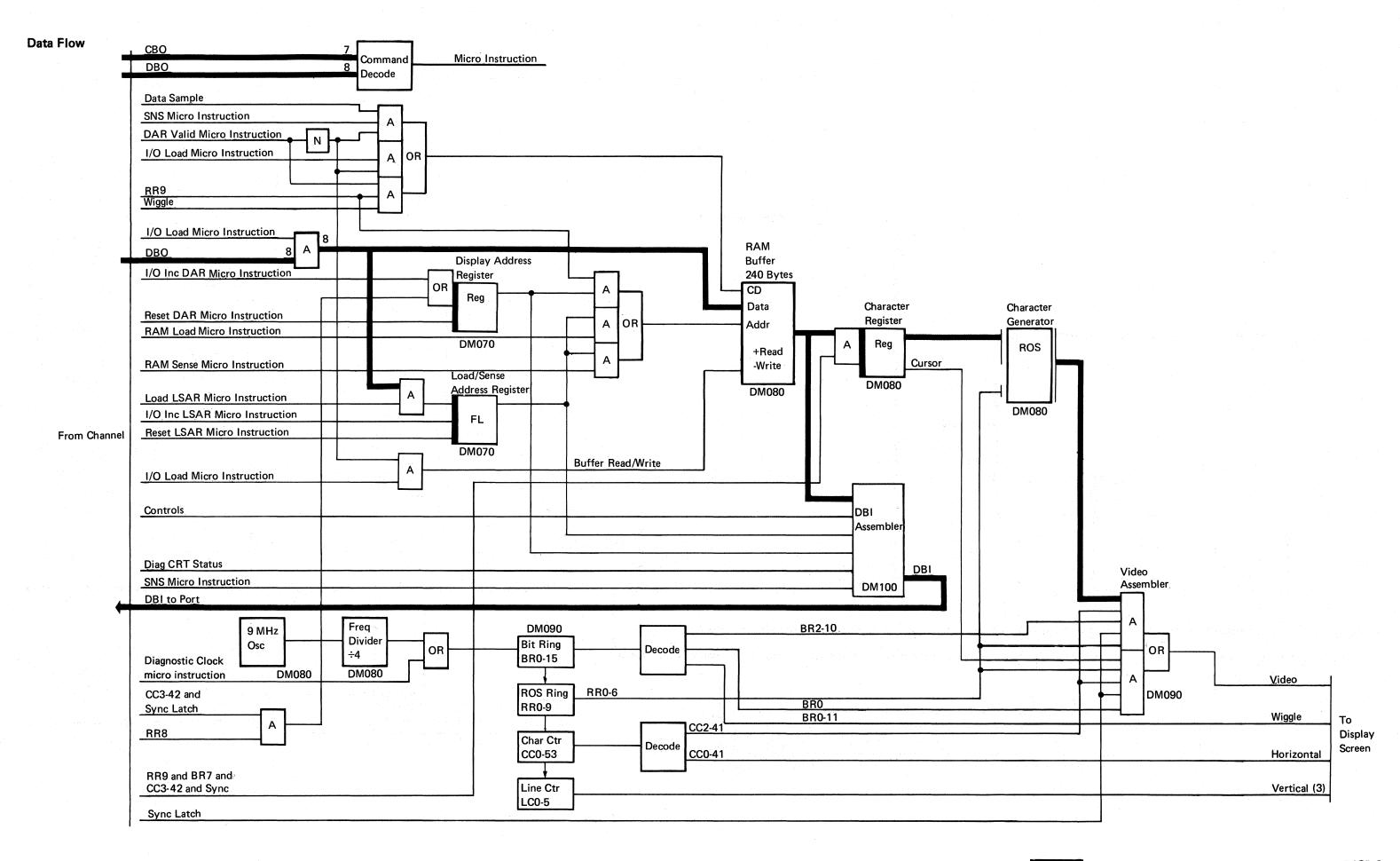

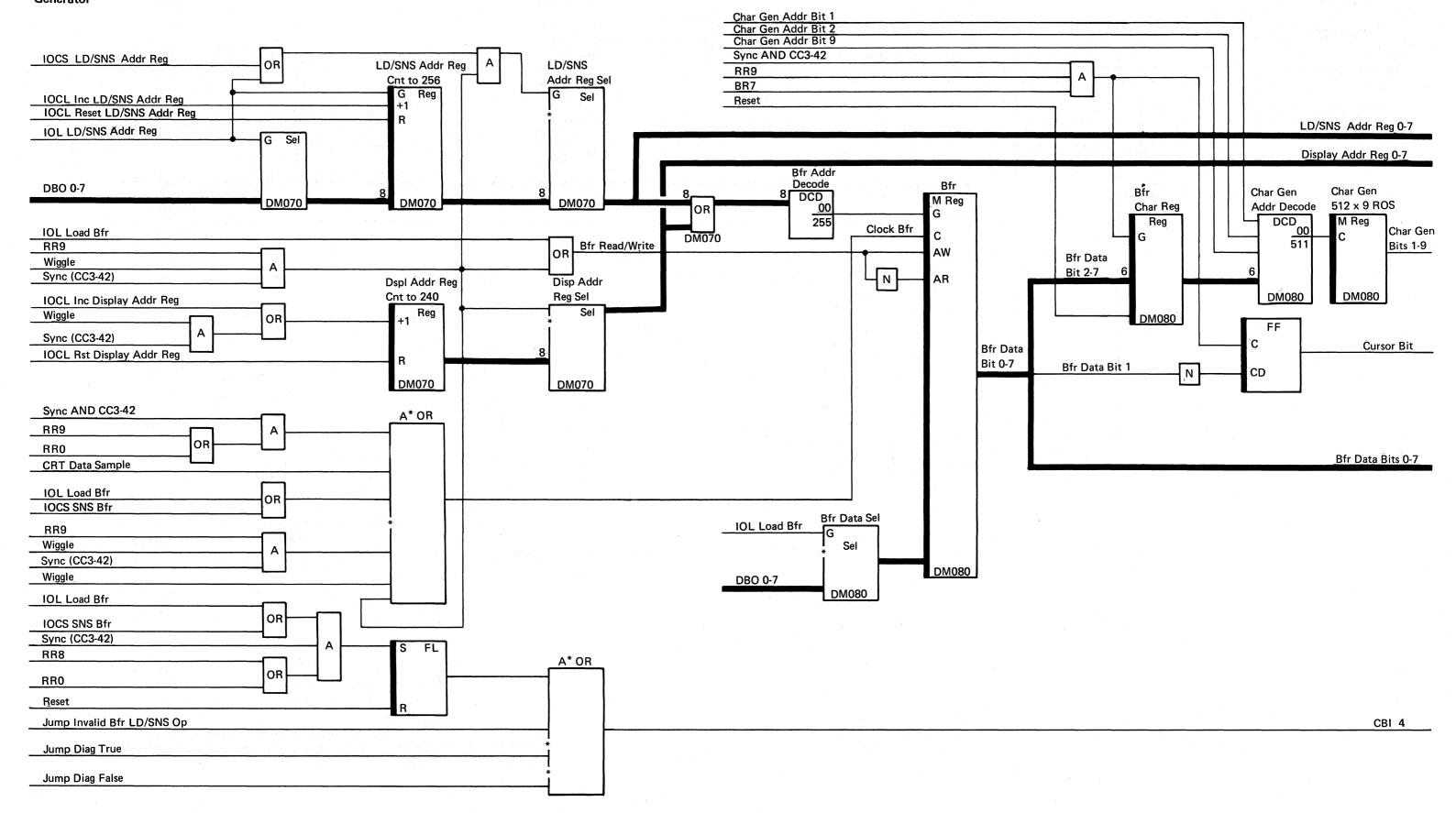

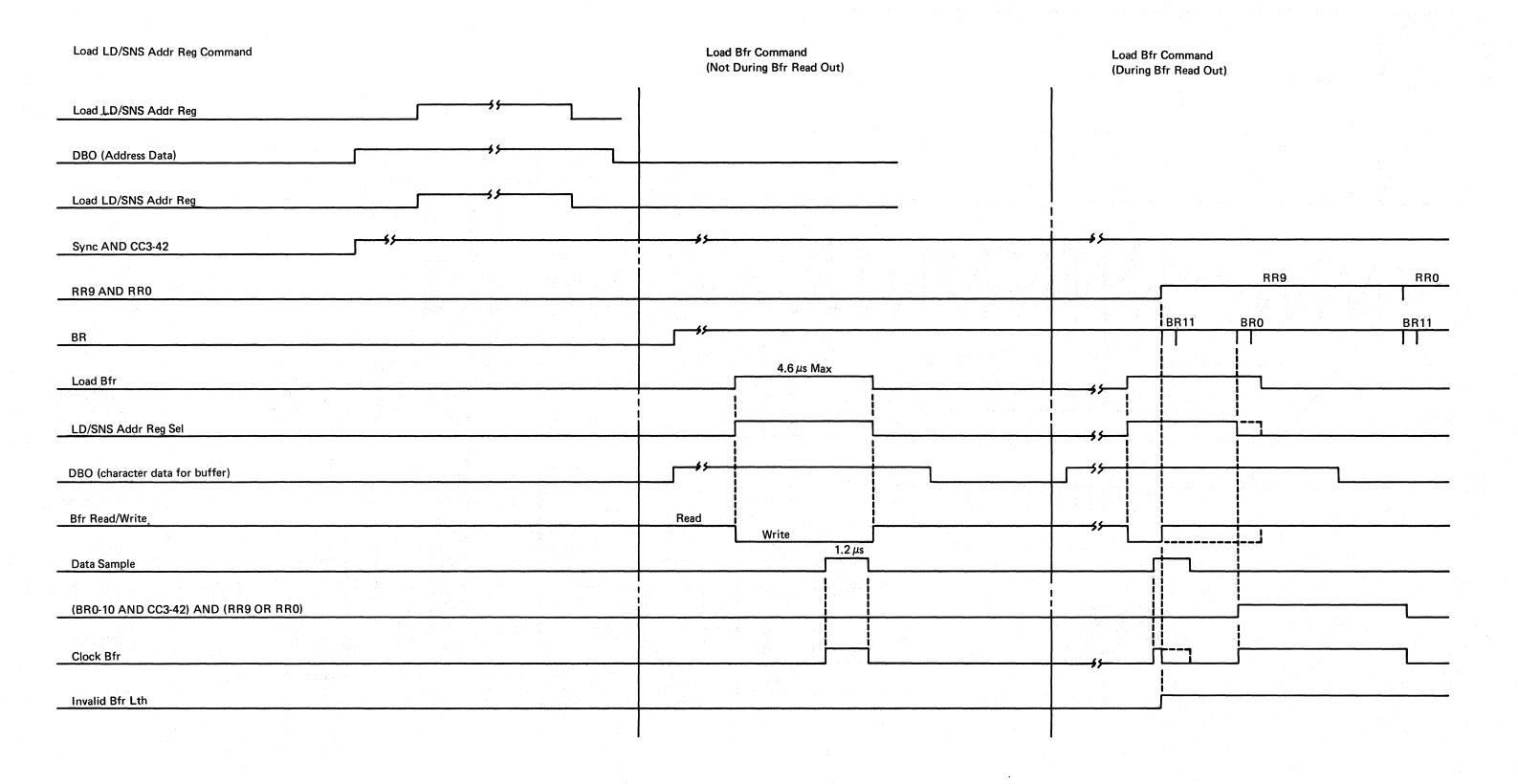

| 155 lpm)                                | PTR-49   | Cover Closed Switch (P)                                    | PTR-87  | Data Flow                                           | DISP-3   | Start Intervals                           | S-PTR-6            |

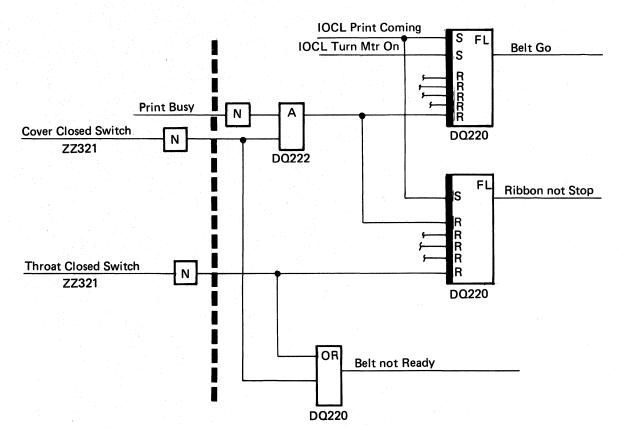

| End of Forms/Cover Closed/Throat Closed |          | Forms Sensed Switch (P)                                    | PTR-87  | LSAR/DAR, RAM Buffer Character                      |          | Up-to-speed Intervals                     | S-PTR-6            |

| (50, 100, and 155 lpm)                  | PTR-50   | Throat Closed Switch (P)                                   | PTR-87  | Generator                                           | DISP-4   | Stop Intervals                            | S-PTR-6            |

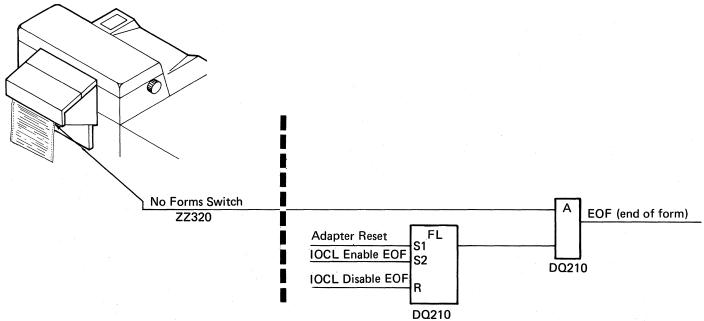

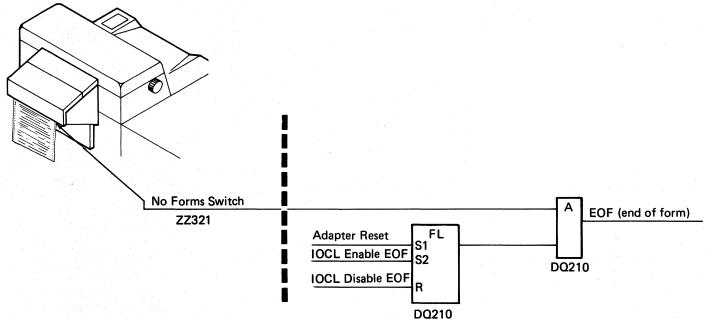

| End of Forms (EOF)                      | PTR-50   | Switch Assemblies                                          | PTR-87  | Loading Address in Address Register and             |          | Underscore                                | S-PTR-8            |

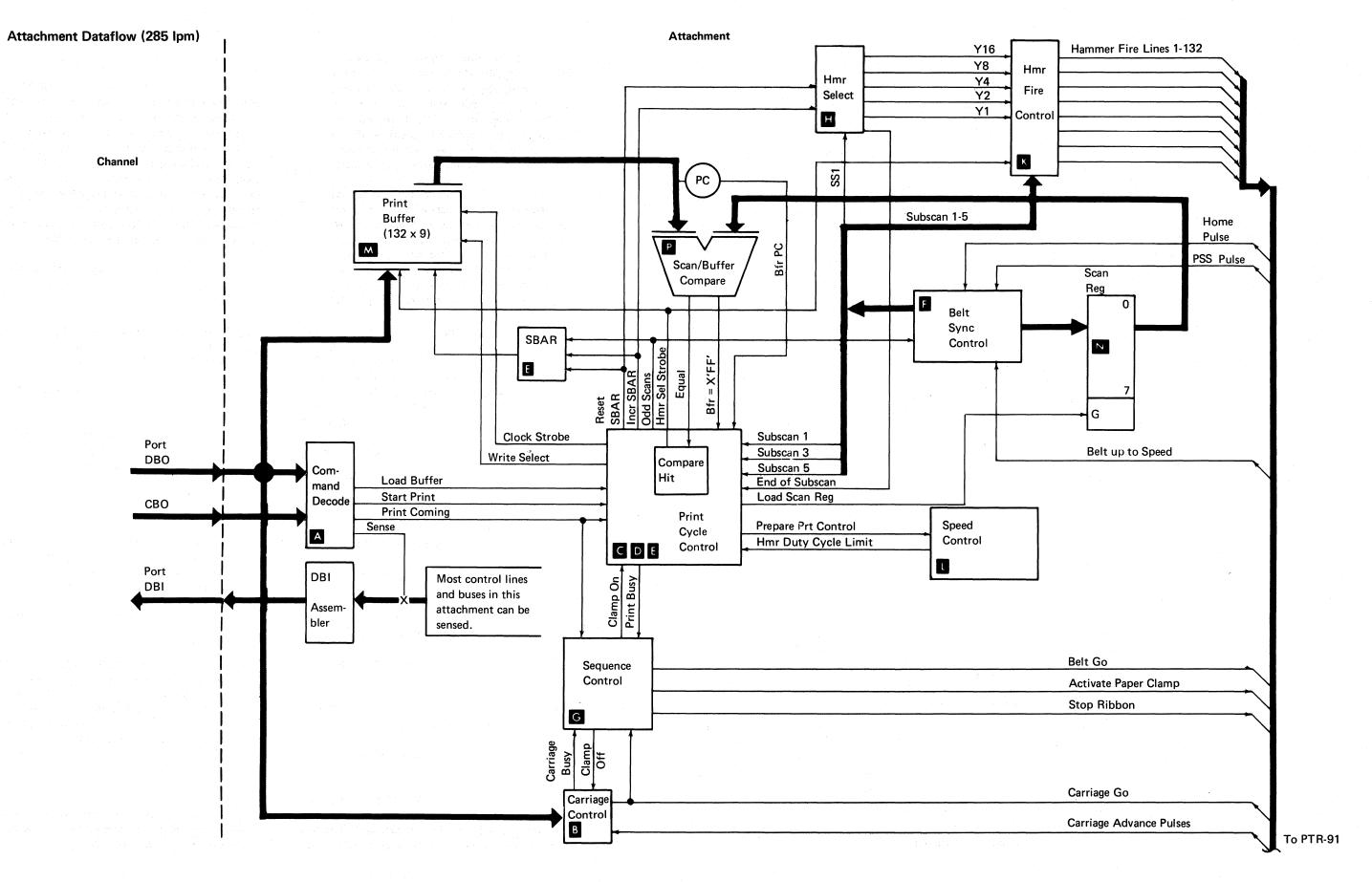

| Cover Closed                            | PTR-50   | Attachment Dataflow (285 lpm)                              | PTR-88  | 1 Byte of Data in RAM Buffer                        | DISP-5   | Head Restore                              | S-PTR-8            |

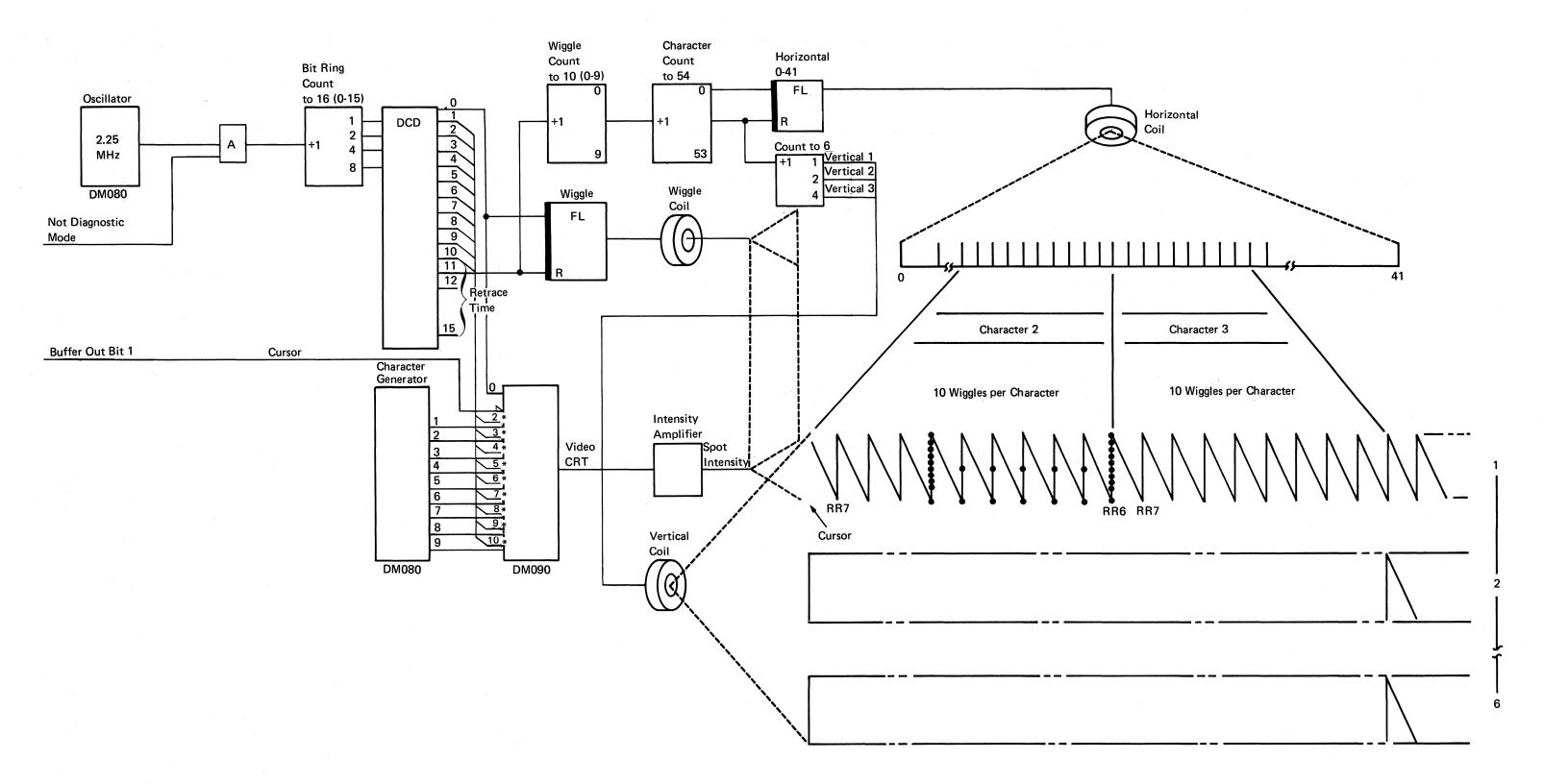

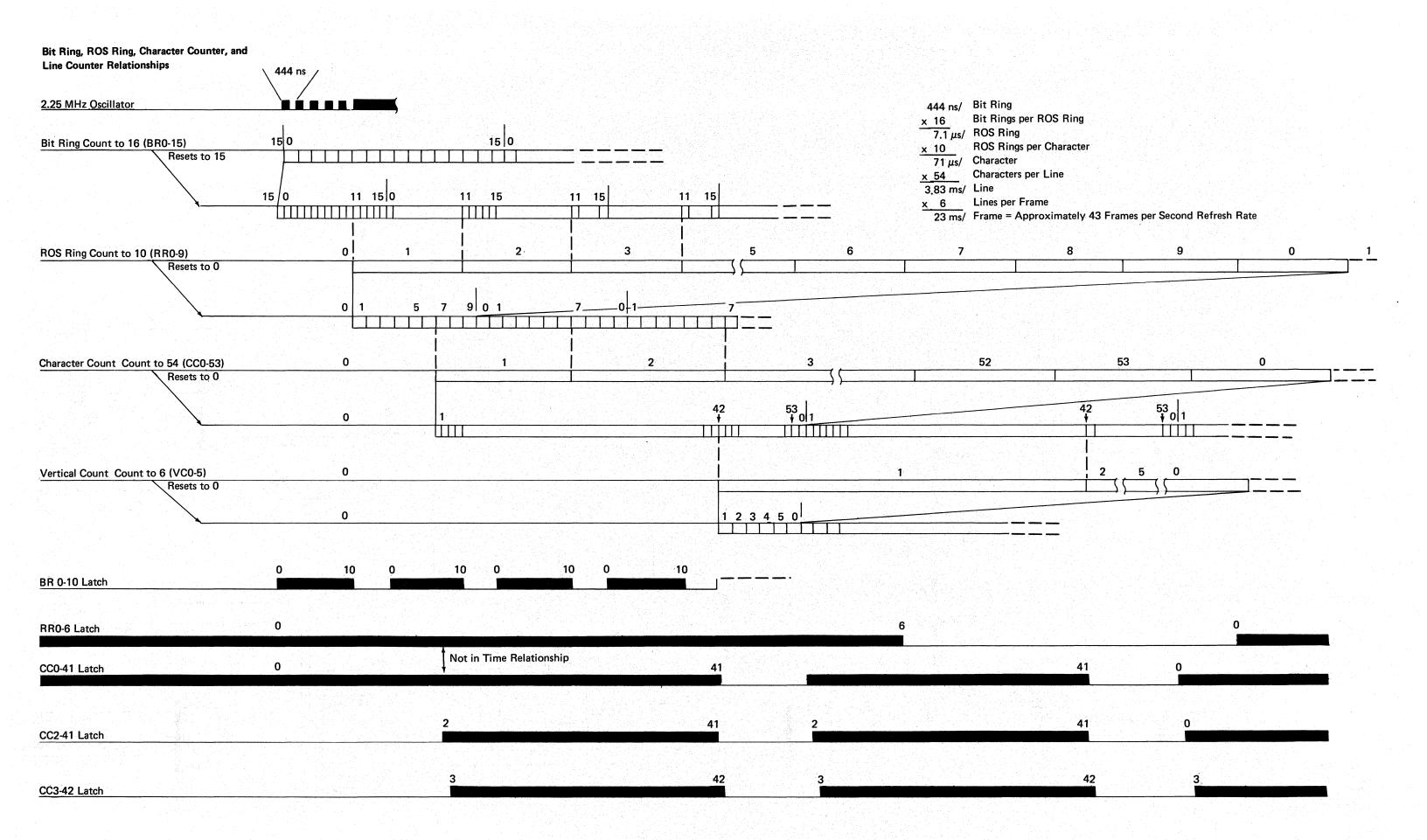

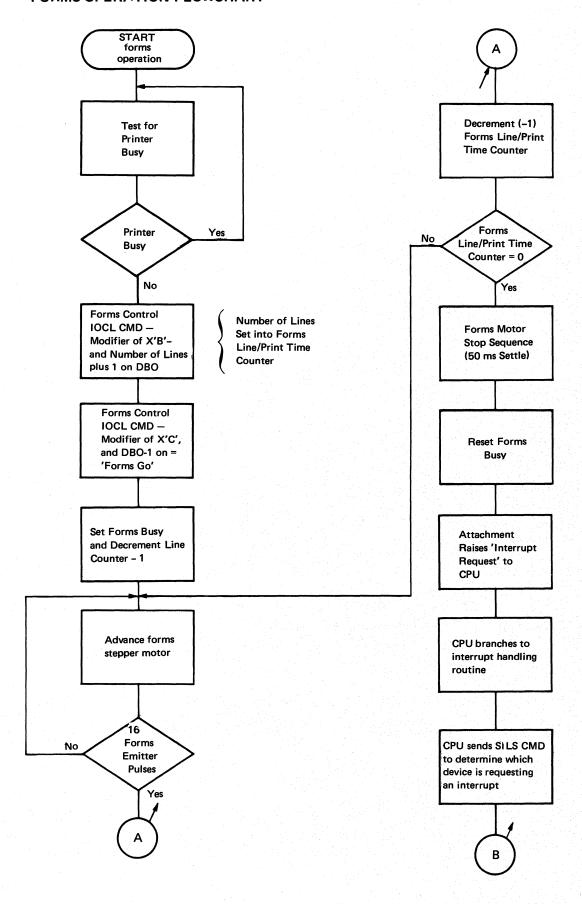

| Throat Closed                           | PTR-50   | Attachment-Functional Units (285 lpm)                      | PTR-89  | Character Display                                   | DISP-6   | FORMS OPERATION FLOWCHART                 | S-PTR-9            |

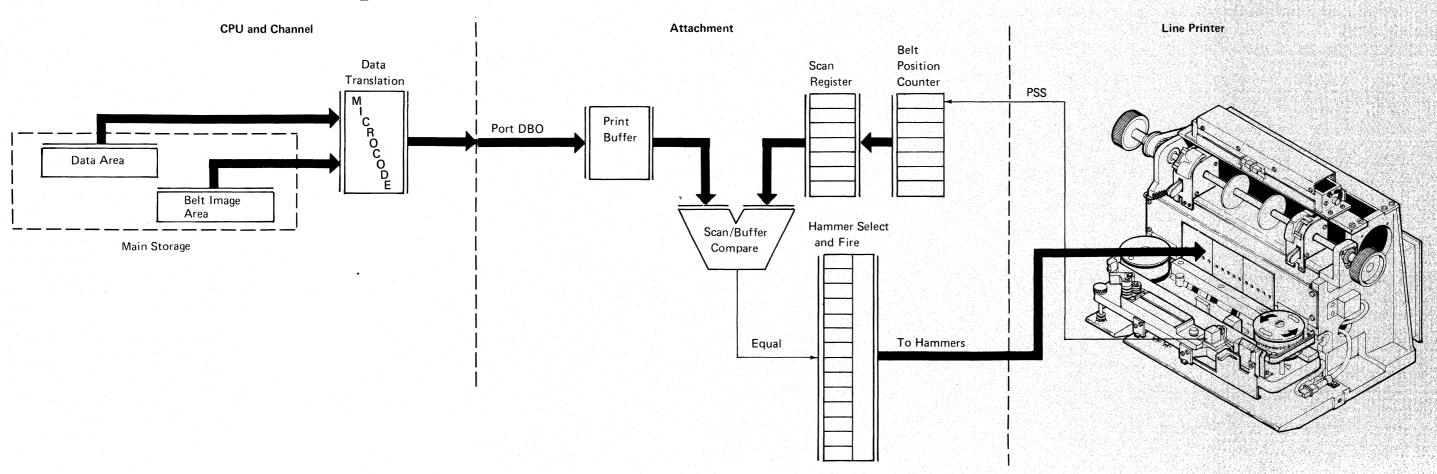

| CPU/Attachment/Printer Operation        | PTR-53   | Printer Command Decode DQ020,                              |         | Bit Ring, ROS Ring, Character Counter               |          | Moving the Forms                          | S-PTR-9            |

| Data Area                               | PTR-53   | 030, 040                                                   | PTR-89  | and Line Counter Relationships                      | DISP-7   | COMMANDS                                  | S-PTR-10           |

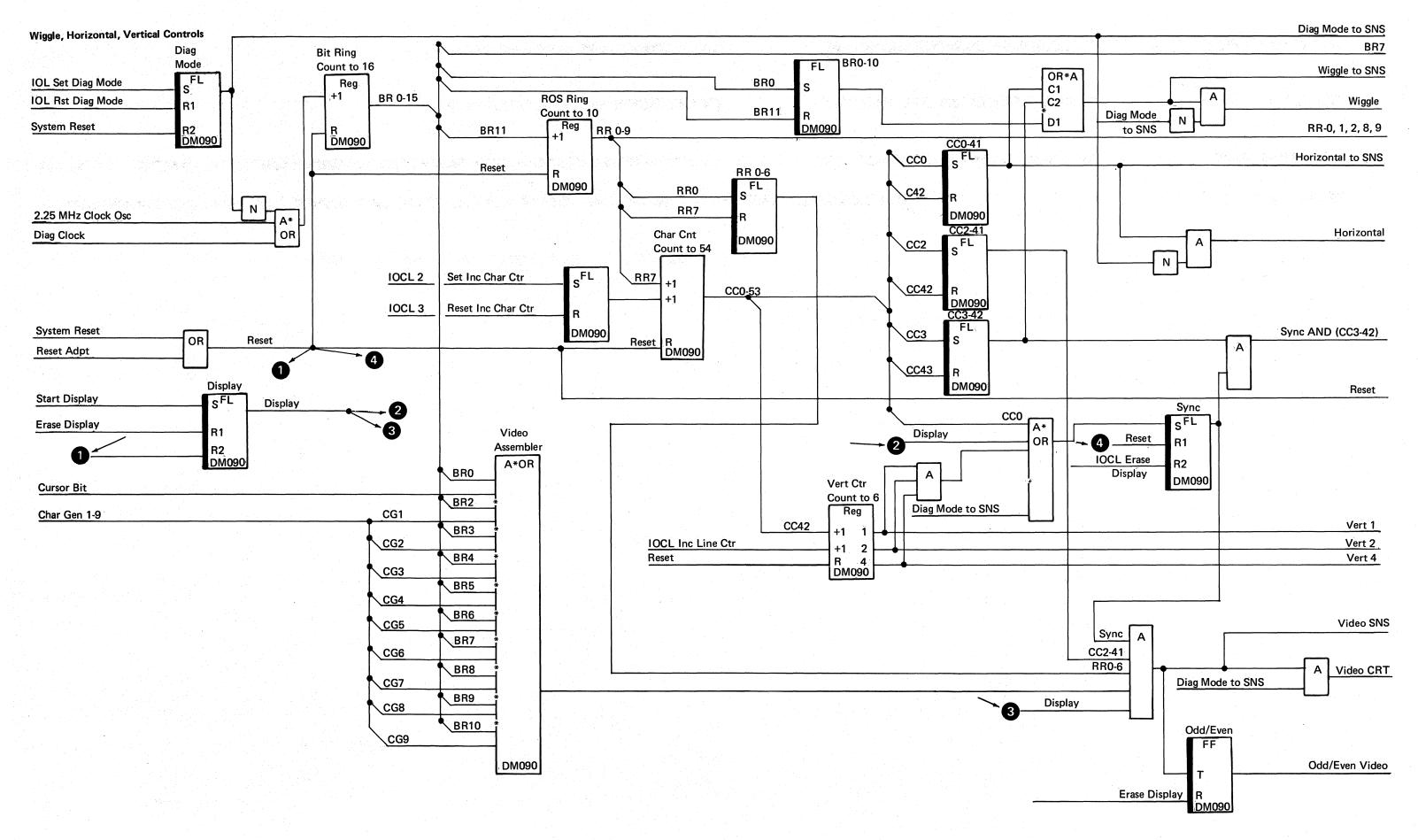

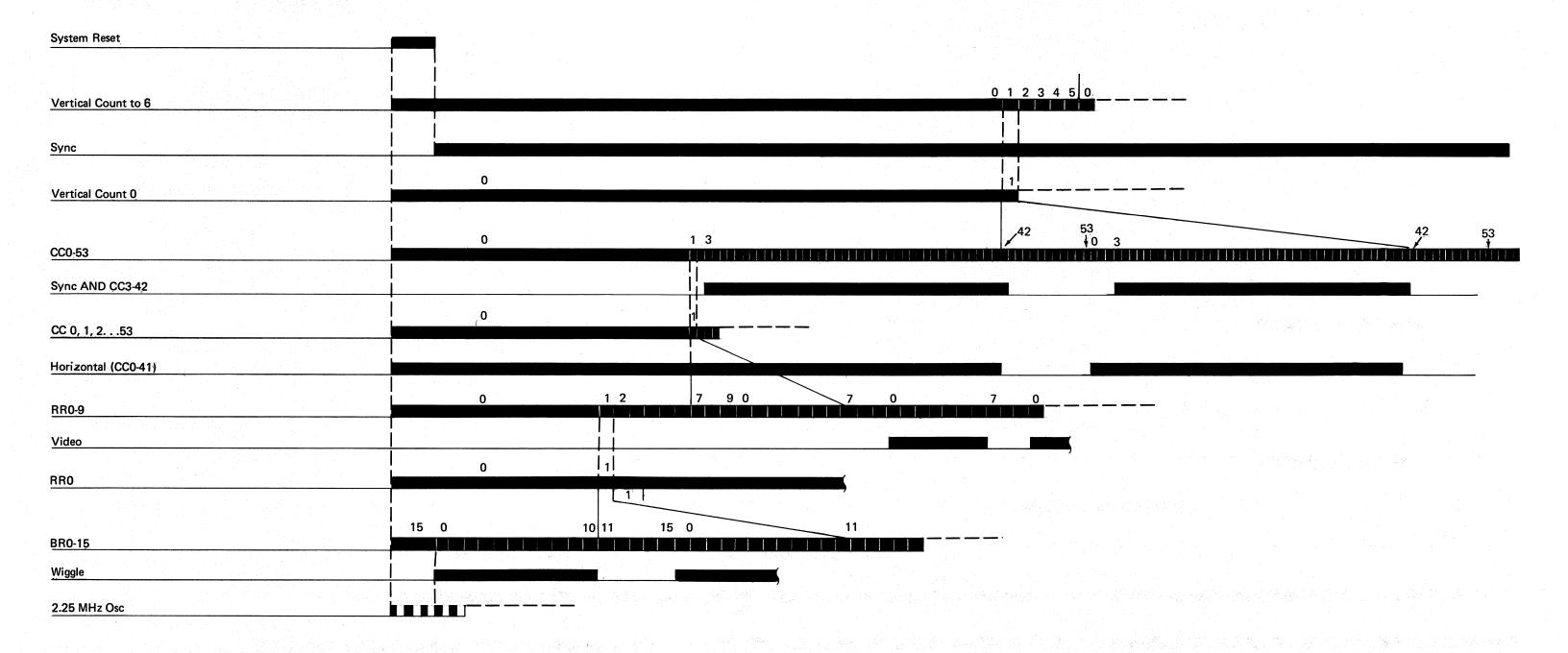

| Belt Image Area                         | PTR-53   | Space Counter DQ100                                        | PTR-89  | Wiggle, Horizontal, Vertical Controls               | DISP-8   | Load Command                              | S-PTR-10           |

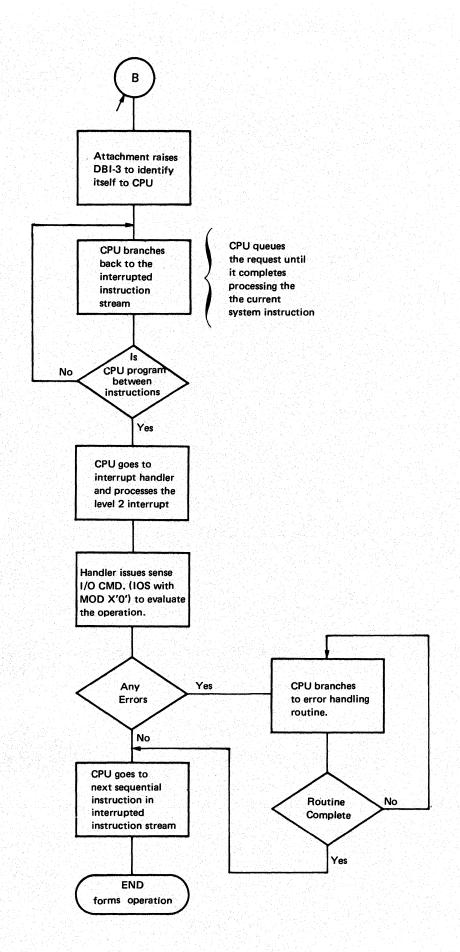

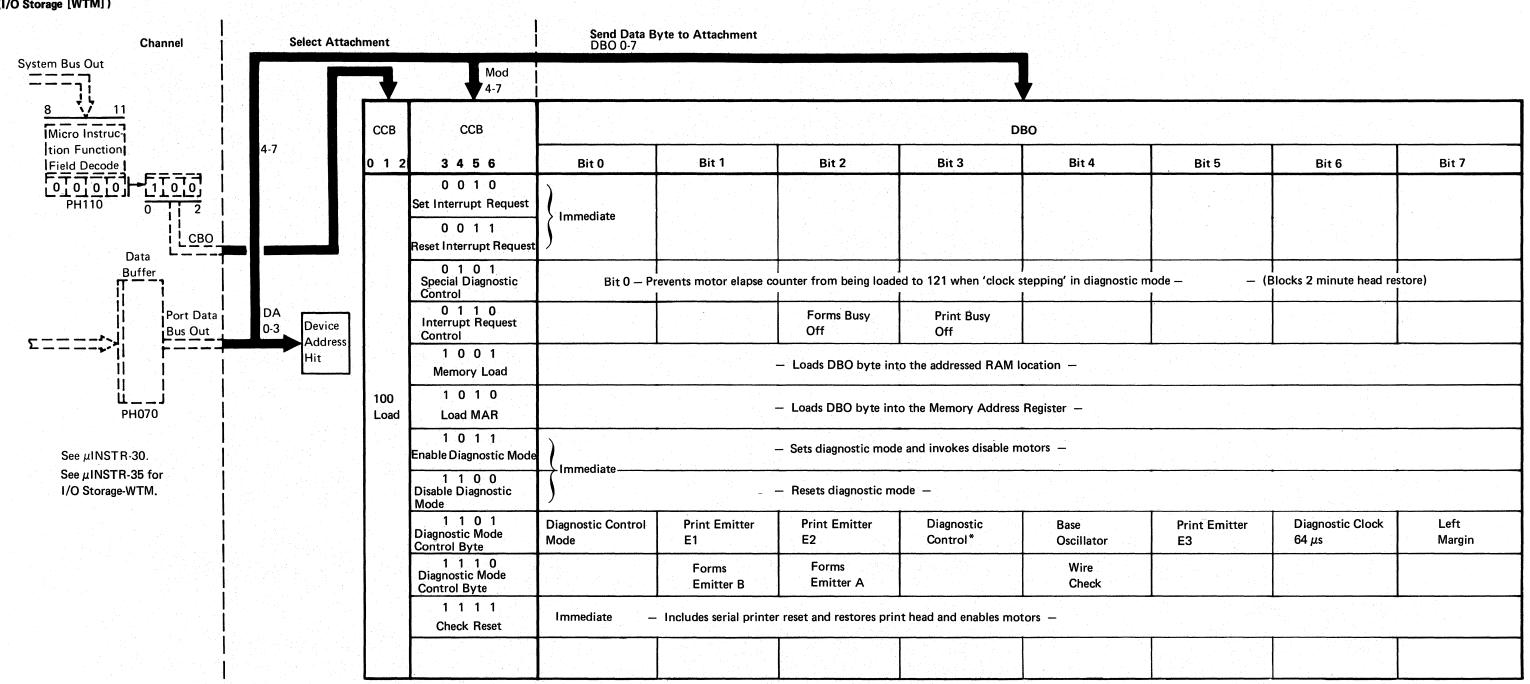

| Forms Control                           | PTR-53   | Scan Counter DQ160                                         | PTR-89  | Sync, Video, Wiggle, Horizontal                     | DISP-9   | I/O Load (IOL) (I/O Storage [WTM])        | S-PTR-10           |

| End of Operation Interrupts             | PTR-53   | Clocking Triggers DQ170                                    | PTR-89  | Display Buffer                                      | DISP-10  | Control Load Command                      | S-PTR-12           |

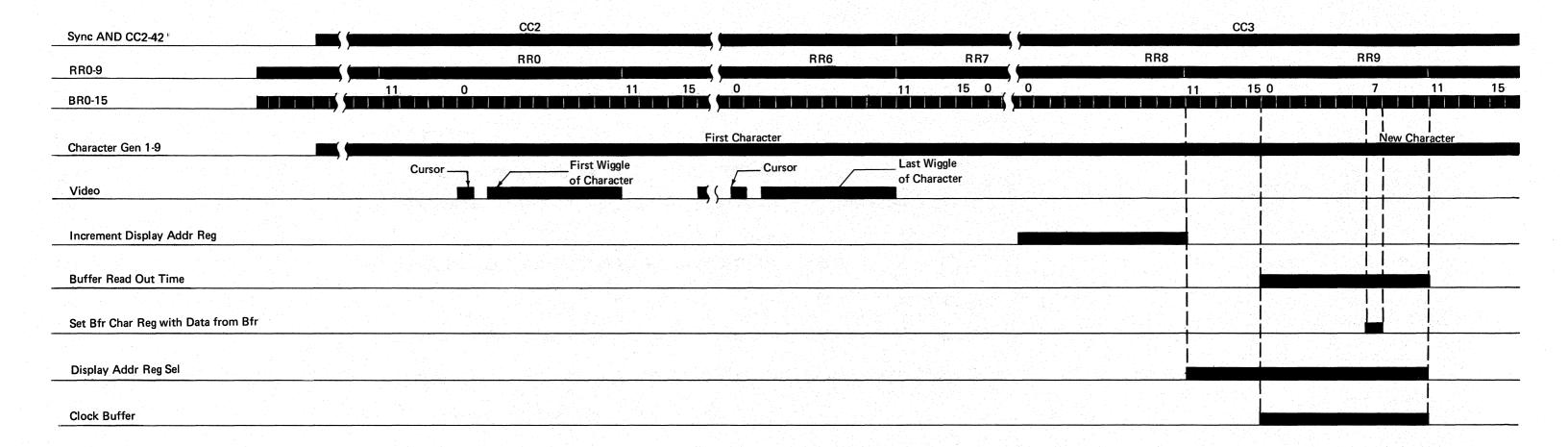

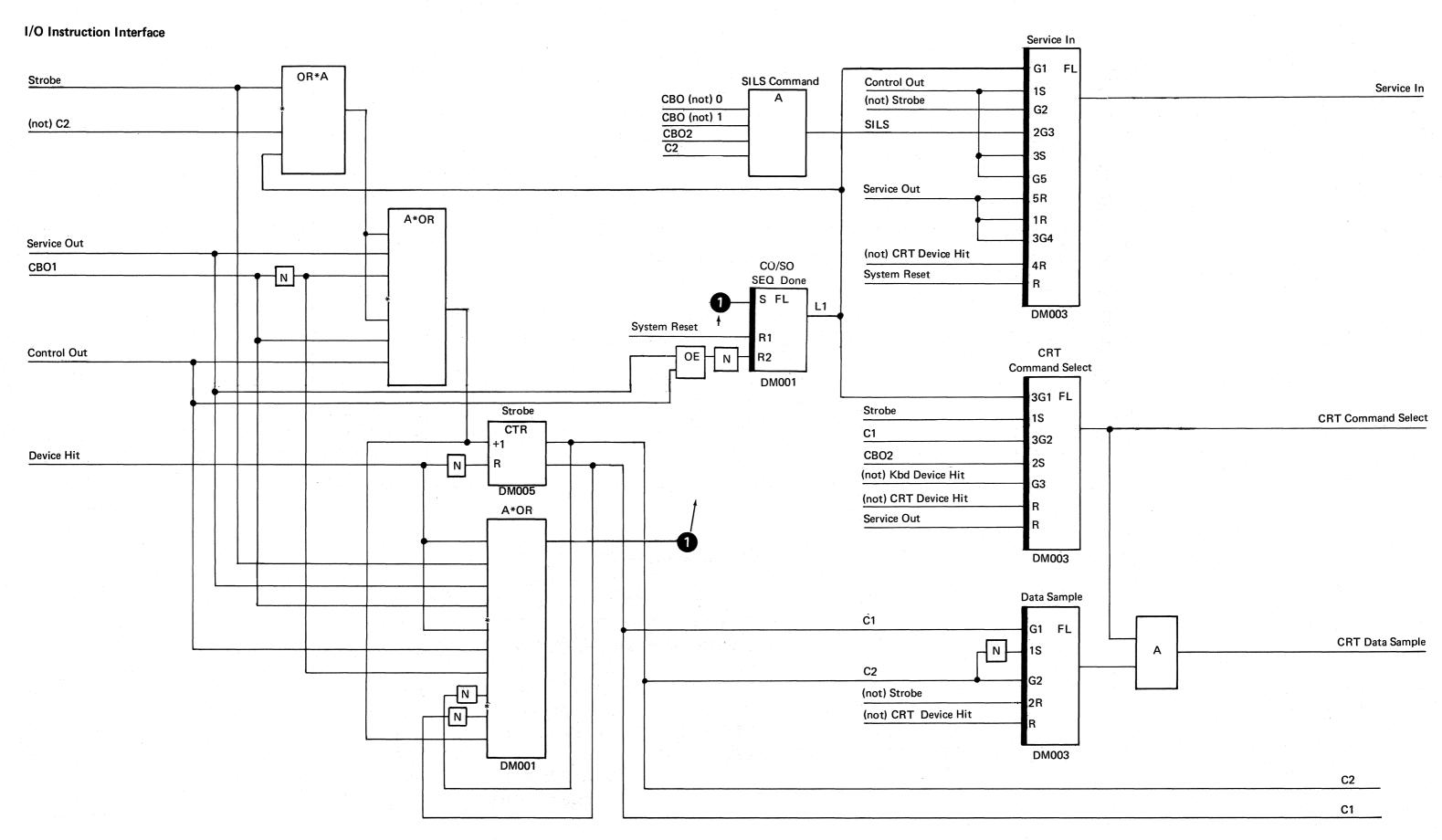

| Attachment Operation                    | PTR-53   | Storage Buffer Address Register                            |         | I/O Instruction Interface                           | DISP-11  | I/O Control Load (IOCL)                   | S-PTR-12           |

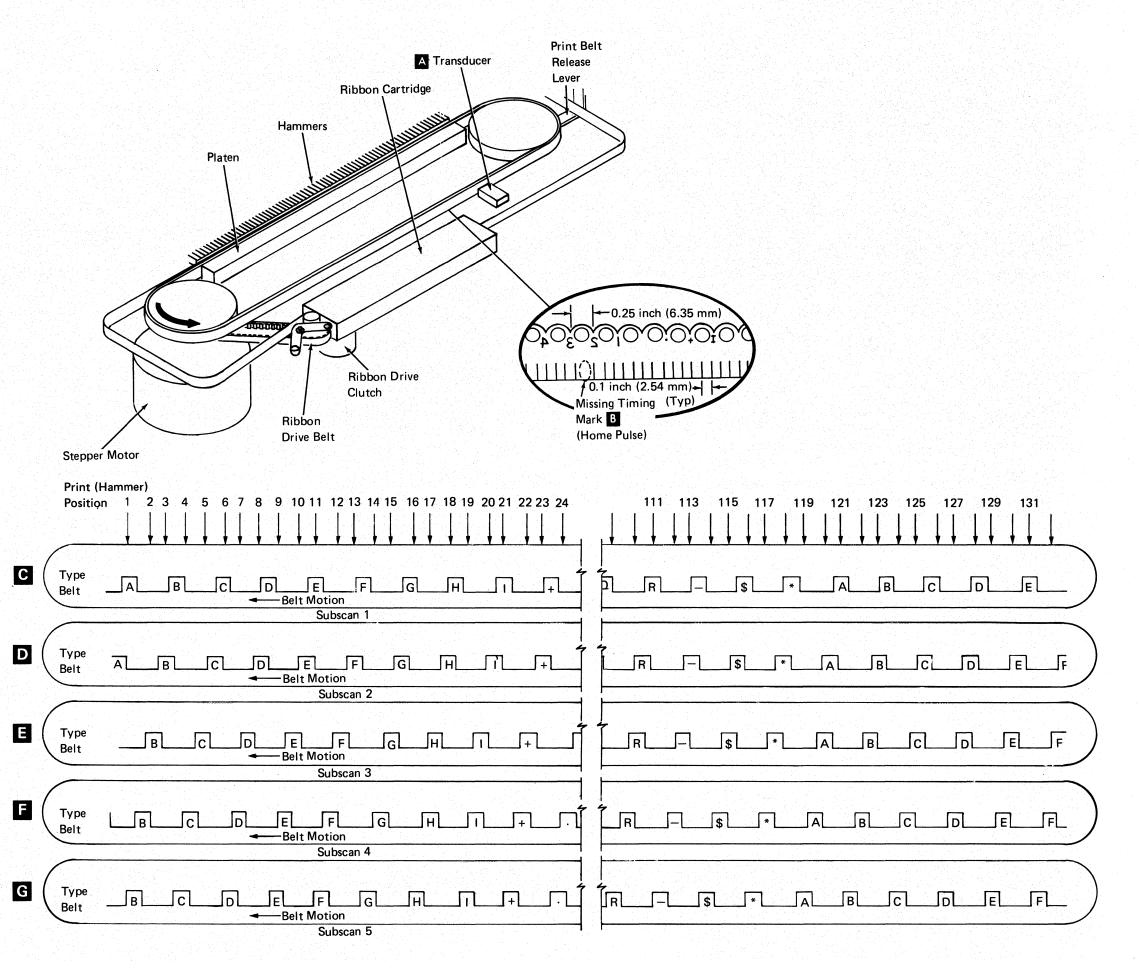

| Theory of Printing (285 lpm)            | PTR-54   | (SBAR) DQ180                                               | PTR-89  | Control Sense Command                               | DISP-12  | Sense Command                             | S-PTR-14           |

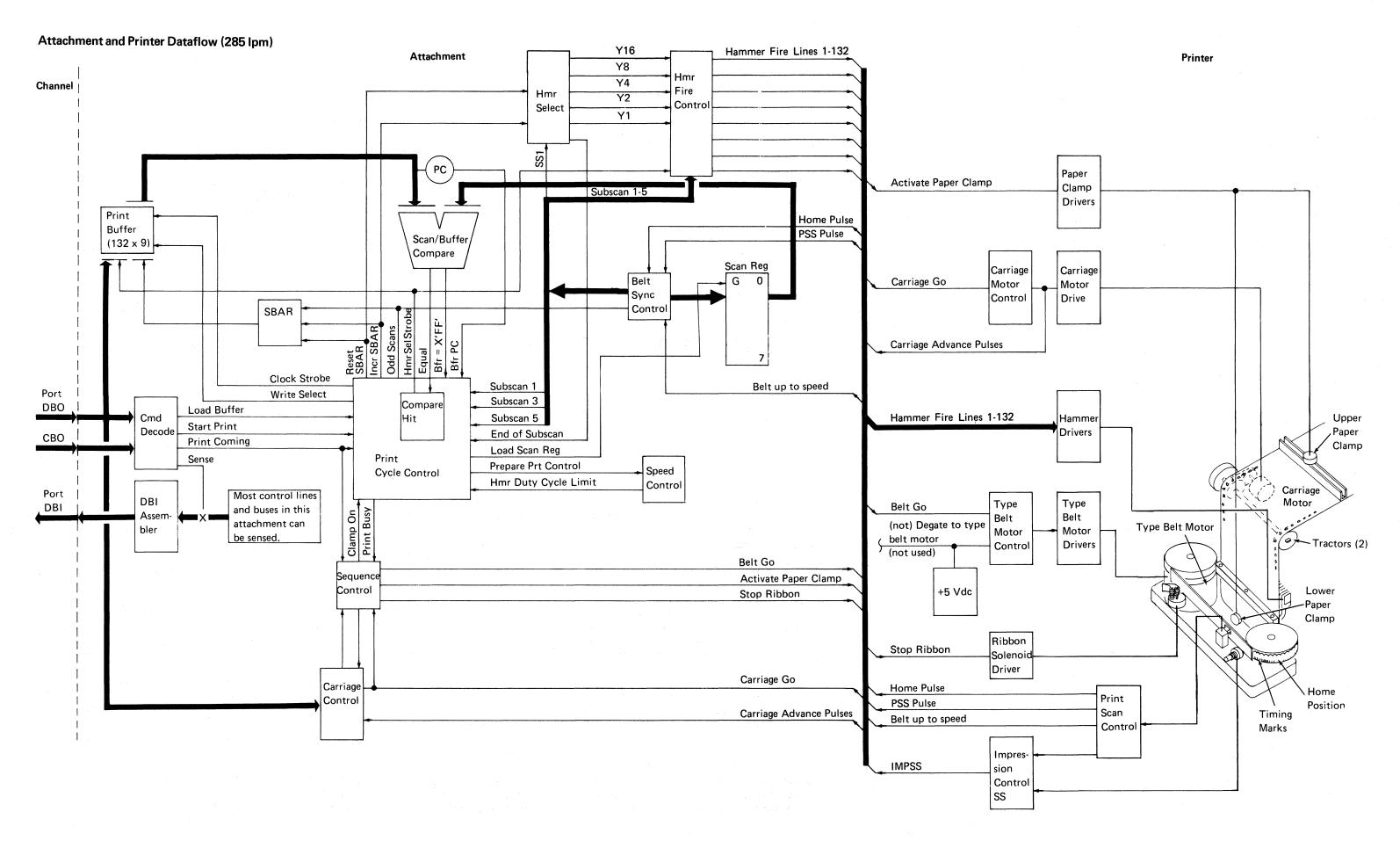

| Attachment and Printer Dataflow         |          | Belt Position Counter (BPC) DQ200 .                        | PTR-89  | Load, Control Load Timing                           | DISP-13  | I/O Sense (IOS)                           | S-PTR-14           |

| (285 lpm)                               | PTR-56   | Paper Clamp Timer DQ240                                    | PTR-89  | Load Command                                        | DISP-14  | Control Sense Command                     | S-PTR-16           |

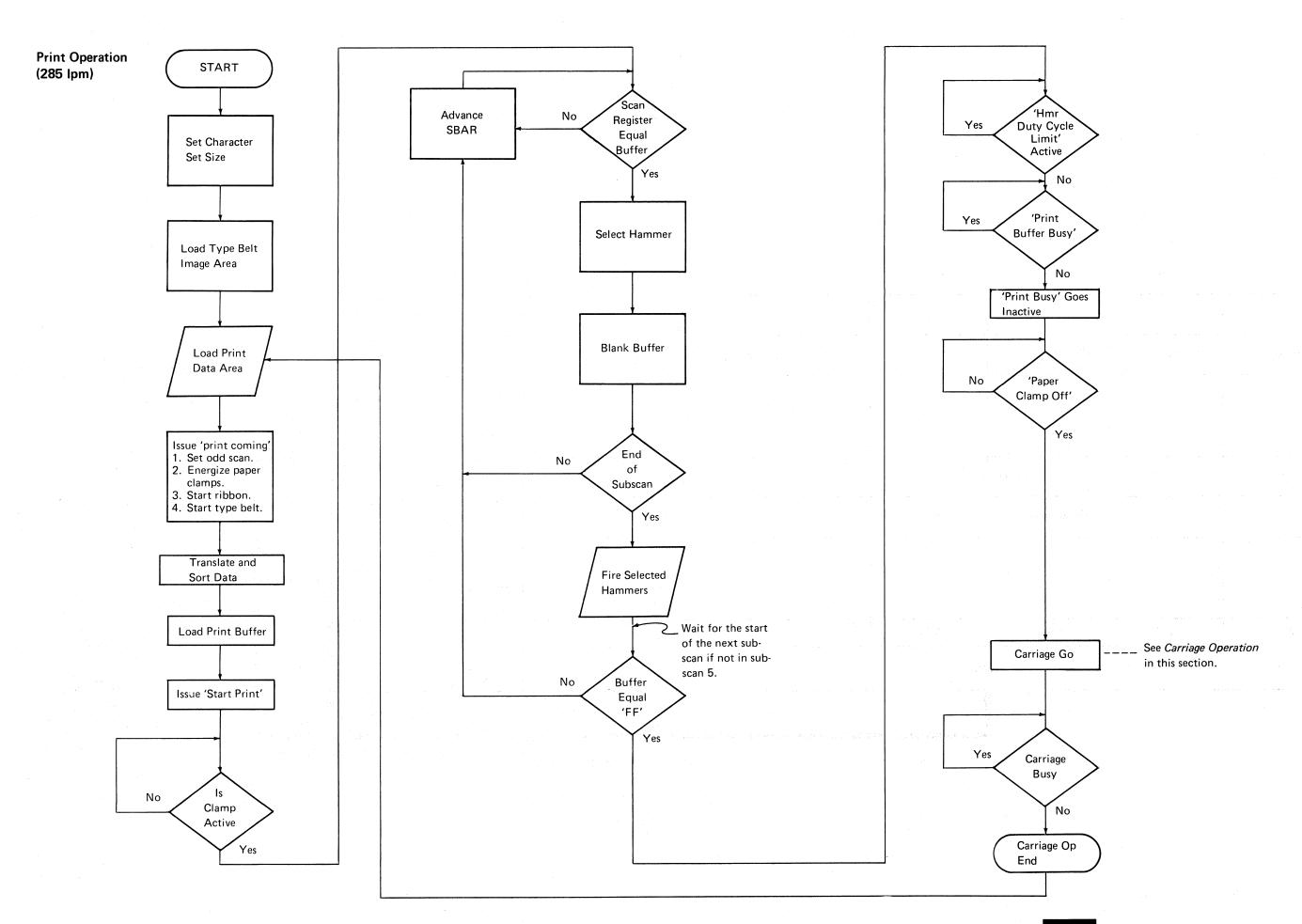

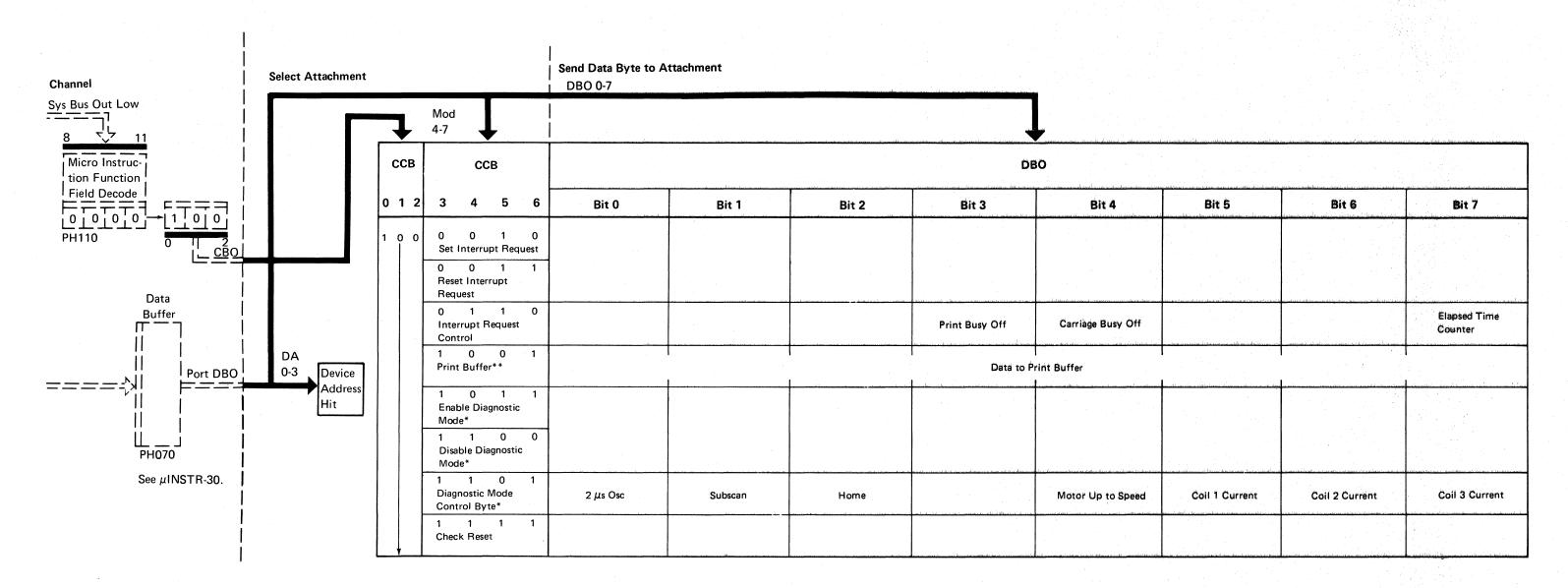

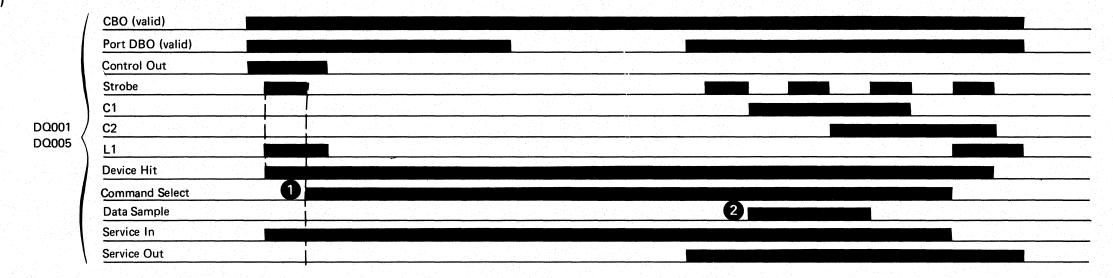

| Print Operation (285 lpm)               | PTR-57   | Hammer Select Control DQ290                                | PTR-89  | Control Load Command                                | DISP-16  | I/O Control Sense (IOCS)                  | S-PTR-16           |

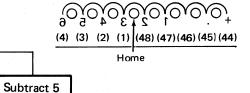

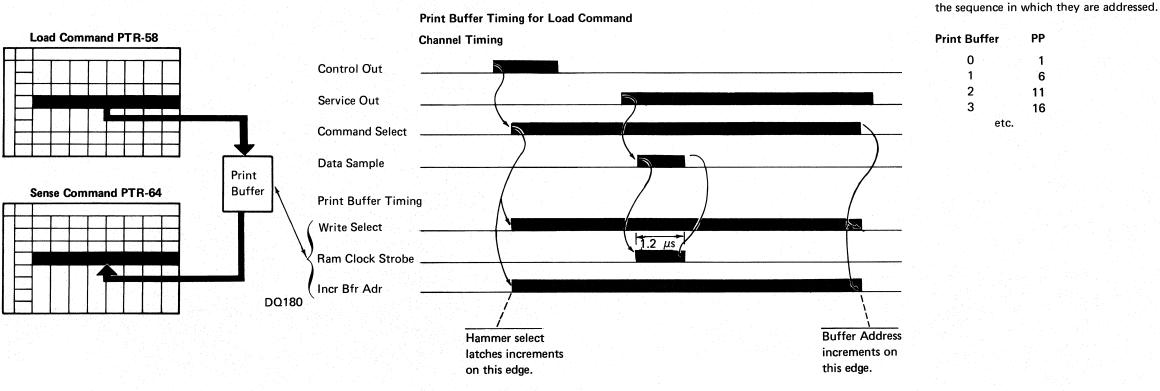

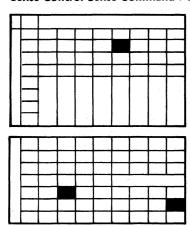

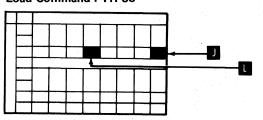

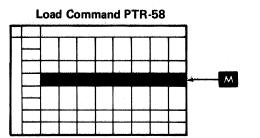

| Load Command                            | PTR-58   | Elapsed Time Counter DQ300                                 | PTR-89  | Timing for Sense, Control Sense, and                |          | Jump Command                              | S-PTR-18           |

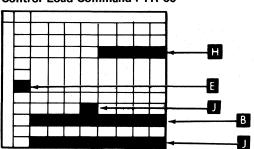

|                                         | PTR-60   | Hammer Fire Control (285 lpm)                              | PTR-89  | Jump Commands                                       | DISP-18  | Jump I/O (JIO)                            | S-PTR-18           |

|                                         | r 111-00 | 그는 이 문에 그리는데 그 그는 이 지절이 되지 않는데 되어 하는데 모모되다.                | PTR-89  | Sense Command                                       | DISP-19  | Sense Interrupt Level Status Byte (SILSB) | S-PTR-19           |

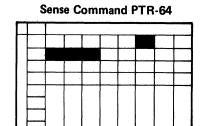

| Sense Command—Control Sense             | PTR-64   | 그는 그리고 가고 있다면 하는 그런 생활하는 모델 생활을 하는데 되다고 하다 하셨다면 하나 되었다.    | PTR-90  | Control Sense Command                               | DISP-21  | ATTACHMENT FUNCTIONAL UNITS               |                    |

| Command (285 lpm)                       | PTR-68   | 그렇게 되는 그 그리는 그 프로그램 가고 그는 그 그림을 받는 것이 하고 하루게 되었다. 모르게 되었다. | PTR-90  | Jump I/O Command                                    | DISP-24  |                                           | C DTD OO           |

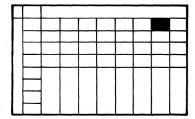

| Sense Interrupt Level Status Command    | PTR-70   | Scan Register DQ200                                        | PTR-90  | CBI 4 Function                                      | DISP-26  | (40/80 cps only)                          | S-PTR-20           |

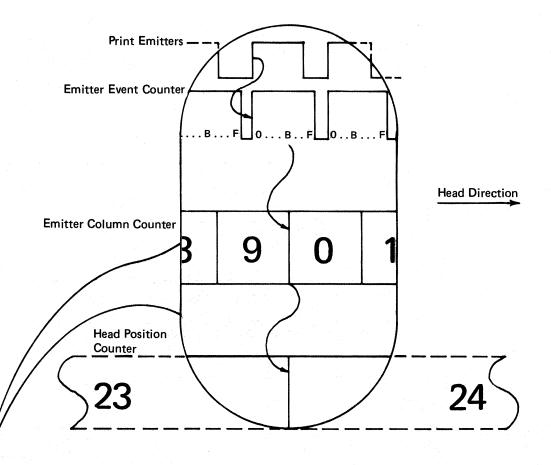

| Jump I/O Command                        | PTR-73   | Printer Functional Units and Dataflow                      | F1N-90  | ODI 4 I GILCONI                                     | D101 -20 | Print Emitter                             | S-PTR-20           |

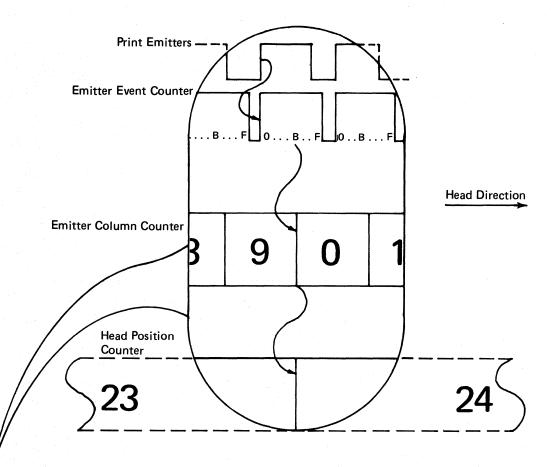

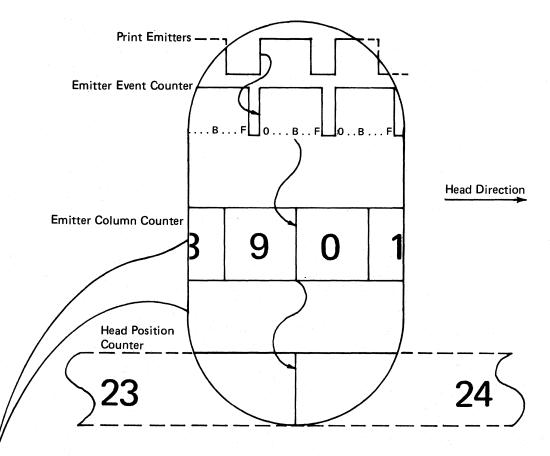

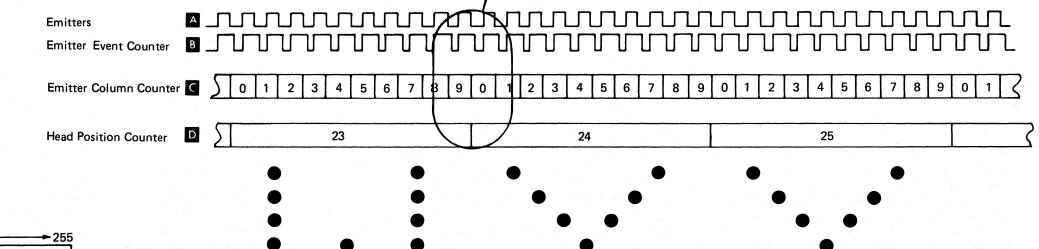

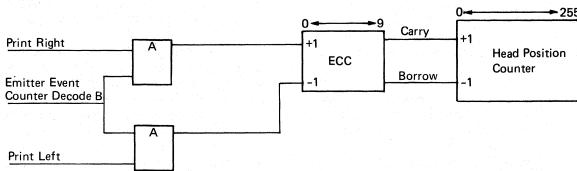

| Paper Clamps DQ240                      |          |                                                            | PTR-91  | KEYBOARD ATTACHMENT                                 | KBD-1    | Print Emitter Event Counter (FR114)       | S-PTR-20           |

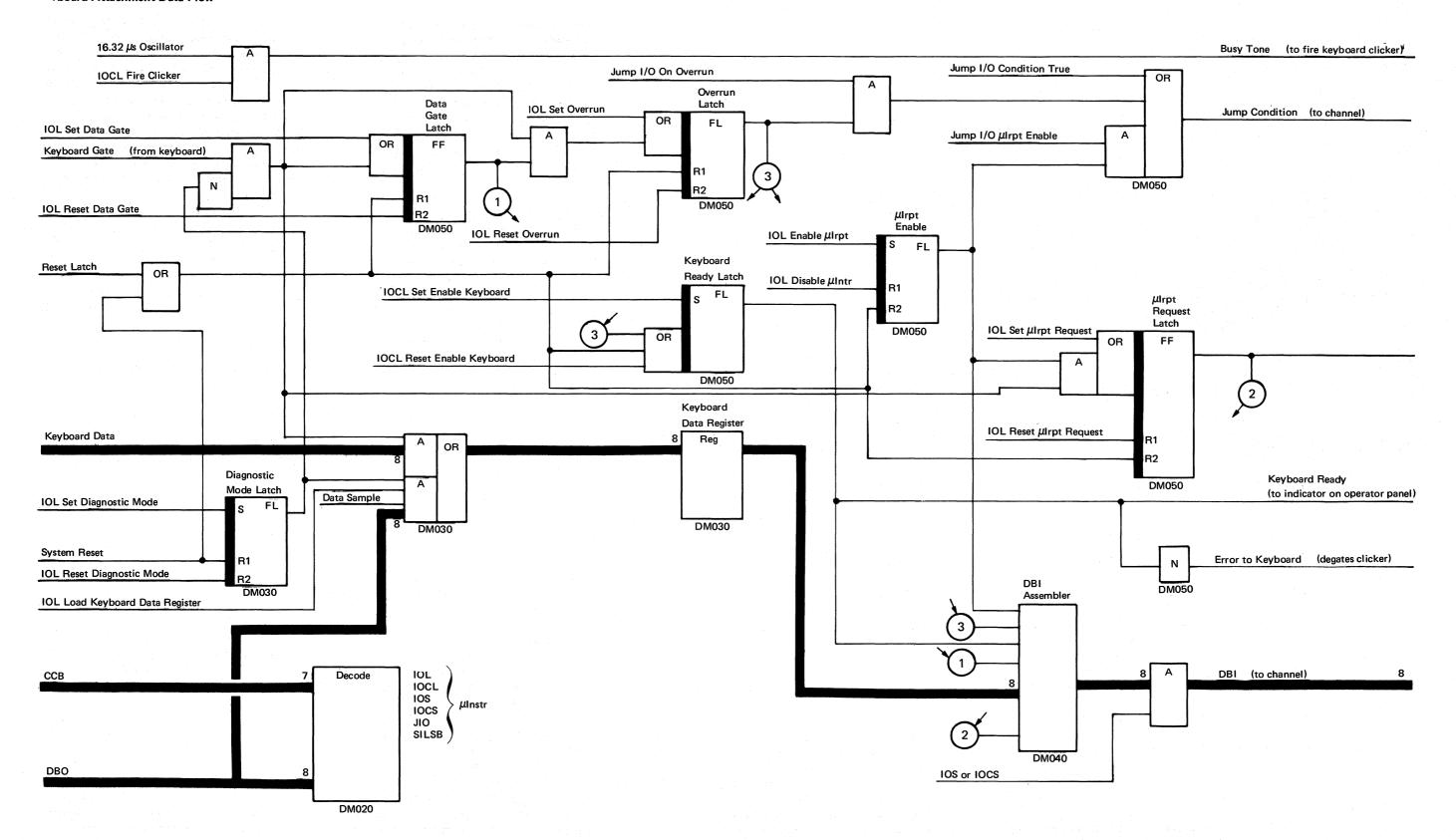

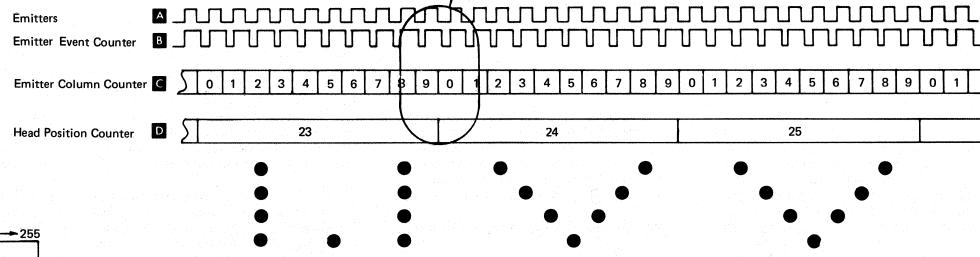

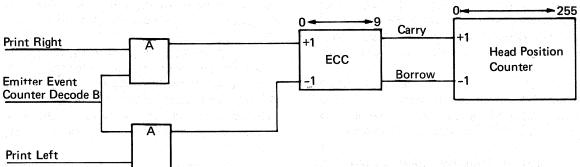

| Type Belt Start and Run (285 lpm)       | PTR-74   | (285 lpm)                                                  | PTR-91  | 어느 사람이 되었다면 가장으로 하게 들어 하는 것이 되었다. 그는 그는 것이 없습니다.    | KBD-1    | Emitter Column Counter [ECC] (FR112)      | S-PTR-20           |

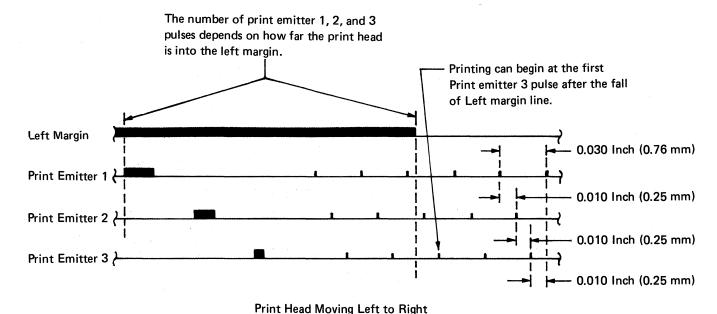

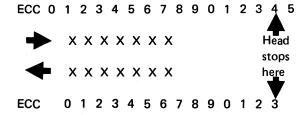

| Type Belt Sync Timing                   | PTR-75   | Type Belt Motor and Drive                                  | PIK-9I  | 경기 그렇게 하하하는데 그 아이는 아이는데 그는 그들은 그들이 그리지 않는데 그렇게 되었다. | KBD-1    | Printing Left to Right                    | S-PTR-20           |

| Ribbon Drive/Type Belt Transducer       | DTD 70   | Home Pulse and Print-Subscan Pulse                         | DTD 04  | Keyboard Attachment Data Flow                       | NDD-2    | Printing Right to Left                    | S-PTR-20           |

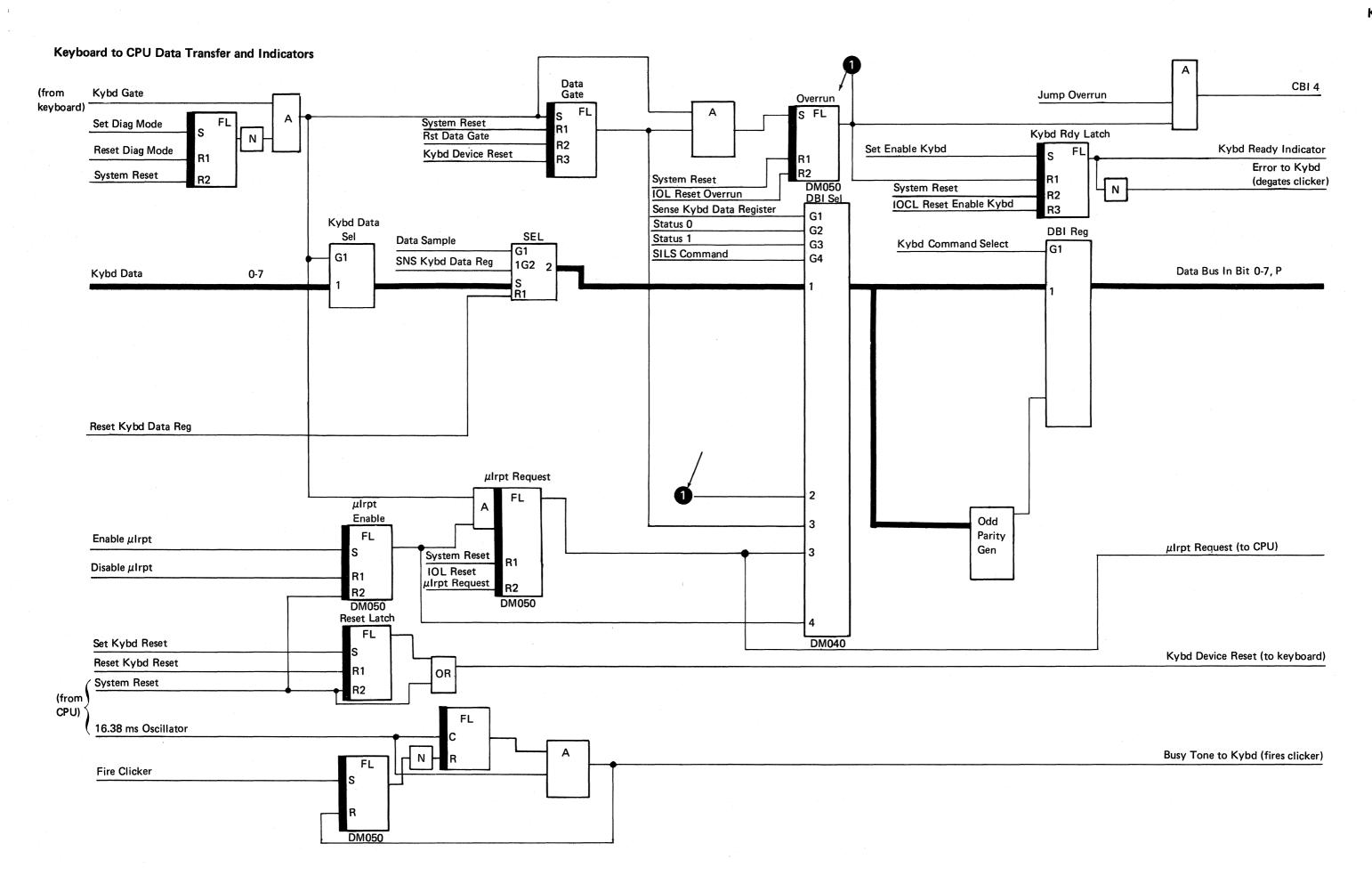

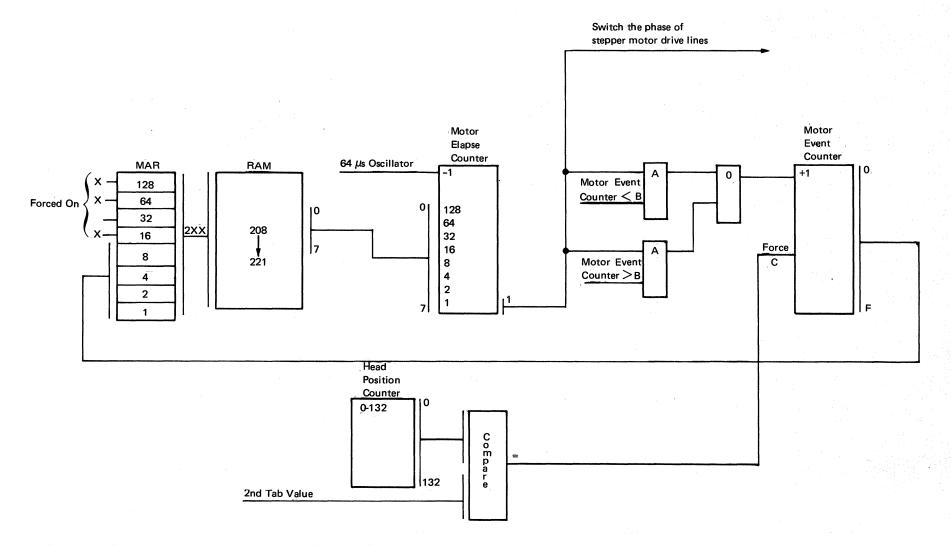

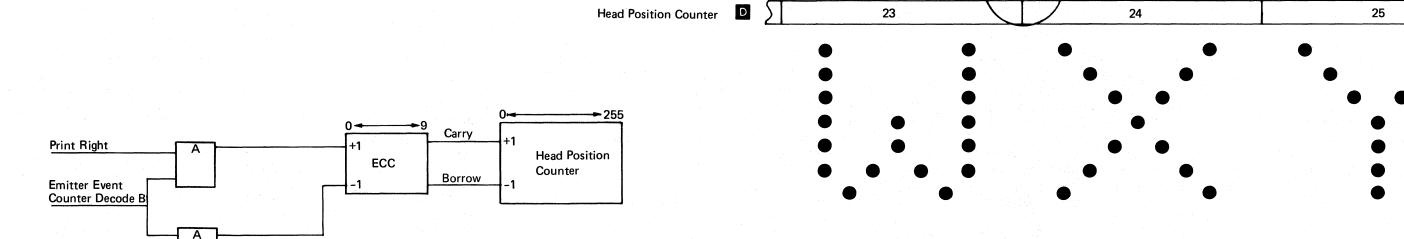

| (285 lpm)                               | PTR-76   | Generation                                                 | PTR-91  | Keyboard to CPU Data Transfer and                   | VDD 4    | Print Head Position Counter (FR112)       | S-PTR-21           |

| Ribbon Drive                            | PTR-76   | Forms Thickness Control                                    | PTR-91  | Indicators                                          | KBD-4    | Memory Address Register (FQ014)           | S-PTR-22           |

| Type Belt Transducer                    | PTR-76   | Ribbon Drive                                               | PTR-91  | I/O Instructions                                    | KBD-5    | Settle/Interval Counter (FR145)           | S-PTR-22           |

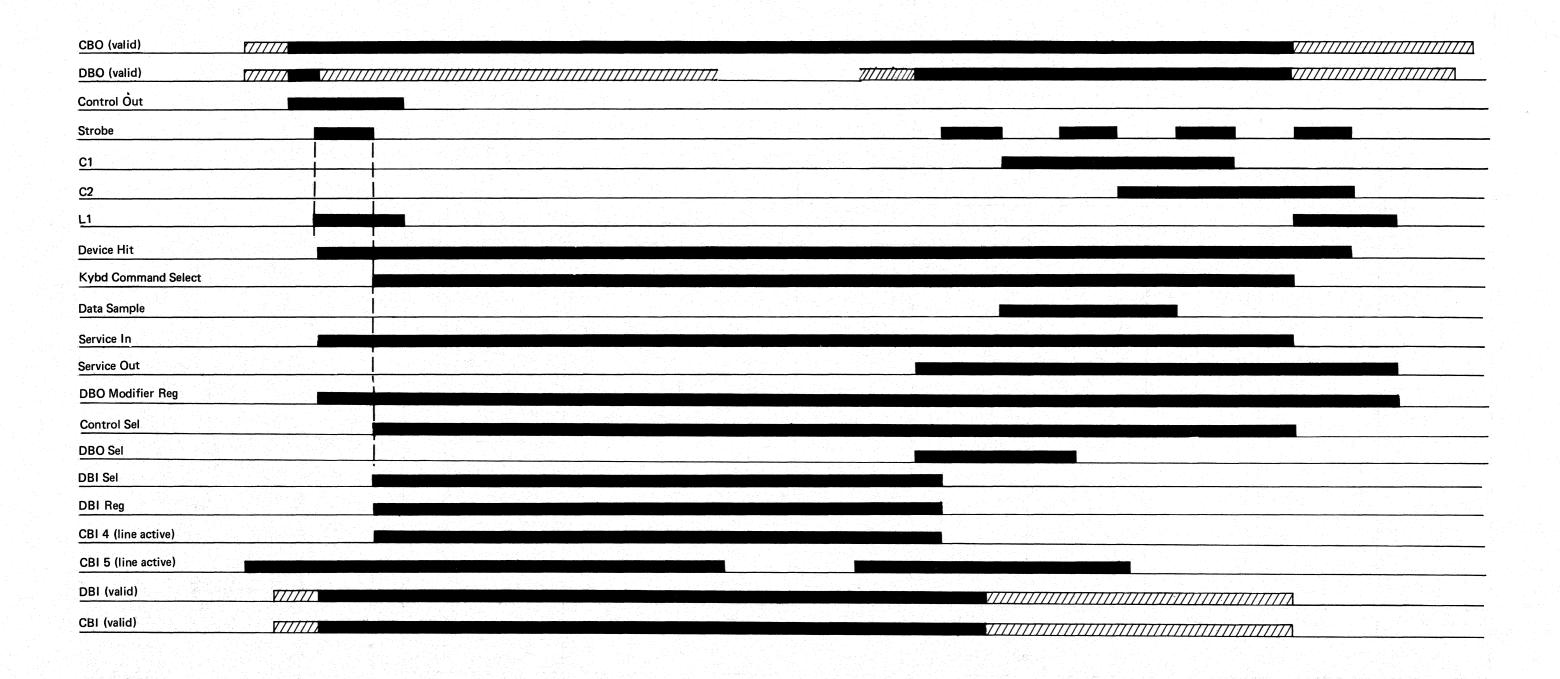

| Print Buffer Load DQ180 (285 lpm)       | PTR-77   | Paper Clamps                                               | PTR-91  | Load, Control Load Timing                           | KBD-5    | Print Motor Event Counter (FR123)         | S-PTR-22           |

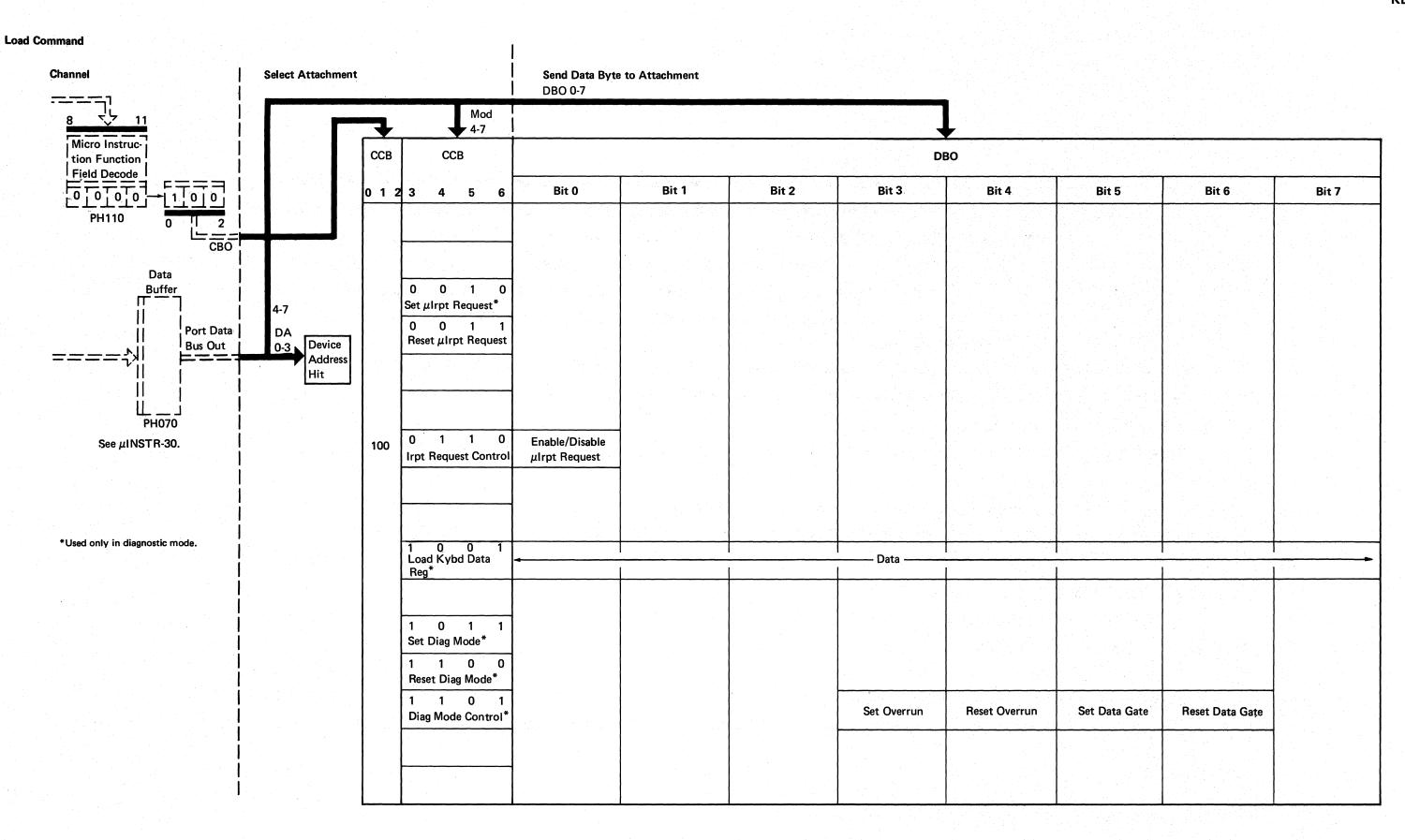

| Print Buffer Read DQ180 (285 lpm)       | PTR-78   | Firing the Hammers                                         | PTR-91  | Load Command                                        | KBD-6    | Print Motor Elapse Counter (FR127)        | S-PTR-22           |

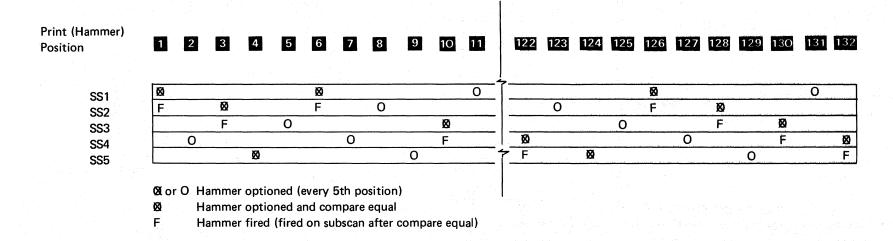

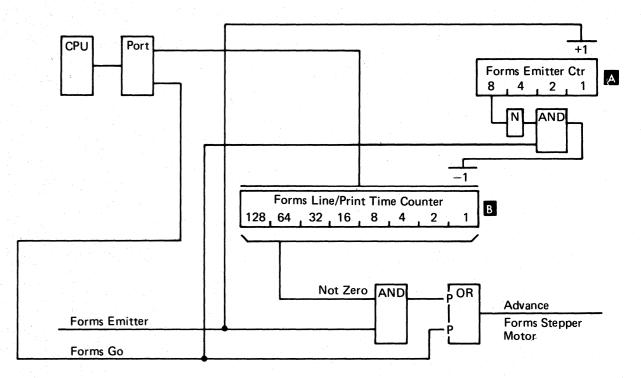

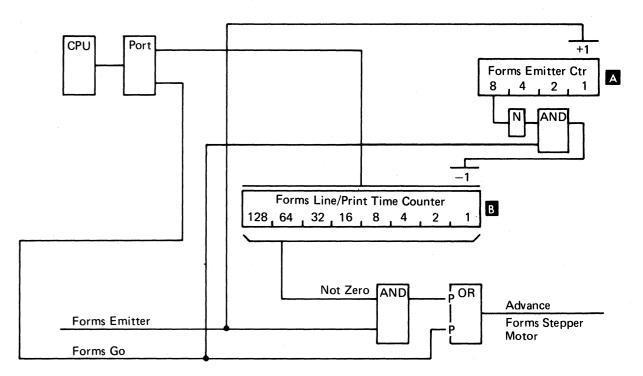

| Hammer Selection and Firing (285 lpm)   | PTR-79   | Carriage Spacing                                           | PTR-91  | Control Load Command                                | KBD-8    | Forms Emitter Counter (FR143)             | S-PTR-22           |

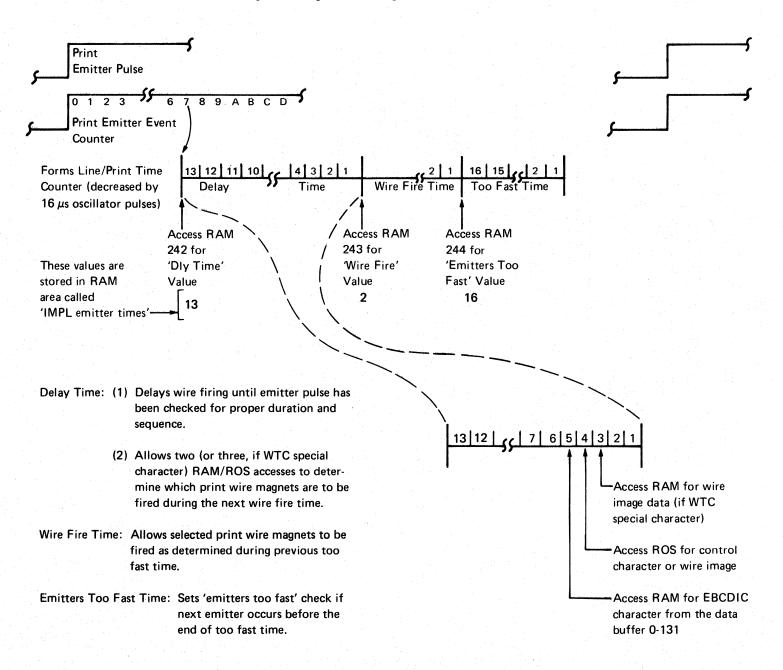

| Hammer Latch Select (285 lpm)           | PTR-80   | Error Conditions (285 lpm)                                 | PTR-93  | Sense, Control Sense, Jump I/O and                  | KDD 44   | Forms Line/Print Time Counter (FR130) .   | S-PTR-22           |

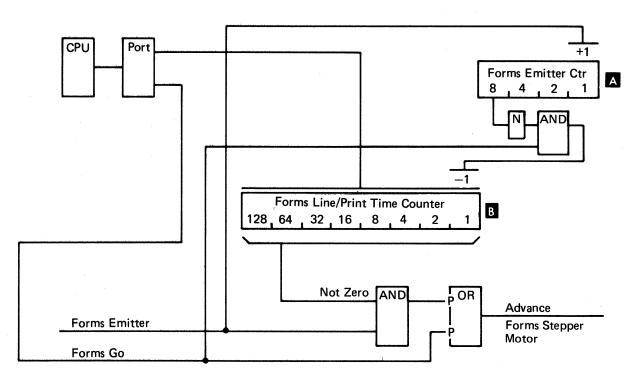

| Register Select (285 lpm)               | PTR-80   | Unprintable Character                                      | PTR-93  | SILSB Timing                                        | KBD-11   | Forms Operation                           | S-PTR-22           |

| Hammer Select Strobe (285 lpm)          | PTR-80   | Forms Jam Check/Belt Speed Check                           |         | Sense Command                                       | KBD-12   | Print Operation                           | S-PTR-23           |

| Printer Speed Control                   | PTR-82   | (285 lpm)                                                  | PTR-94  | Control Sense Command                               | KBD-14   | ATTACHMENT FUNCTIONAL UNITS               |                    |

| Carriage Operation (285 lpm)            | PTR-83   | Forms Jam Check                                            | PTR-94  | Jump I/O Command                                    | KBD-16   | (40/80 cps-120 compatible only)           | S-PTR-24           |

| Carriage Detent                         | PTR-83   | Belt Speed Check                                           | PTR-94  | Sense Interrupt Level Status Byte                   |          | Print Emitter                             | S-PTR-24           |

| Half Line Space Operation (285 lpm)     | PTR-84   | Carriage Sync Check                                        | PTR-95  | Command                                             | KBD-18   | Print Emitter Event Counter (FR214)       | S-PTR-24           |

| Input/Output Lines (285 lpm)            | PTR-86   | Coil Current Check (285 lpm)                               | PTR-96  | SILSB Command and (not) Keyboard                    |          | Emitter Column Counter [ECC] (FR212) .    | S-PTR-24           |

| POR/Printer Reset (A)                   | PTR-86   | Belt Sync Check                                            | PTR-97  | Interrupt Level                                     | KBD-20   | Printing Left to Right                    | S-PTR-24           |

| Close (+24V) Contactor (A)              | PTR-86   | Emitter Check/Data Check                                   | PTR-98  | CBI 4 Function                                      | KBD-21   | Printing Right to Left                    | S-PTR-24           |

| Belt Go (A)                             | PTR-86   | Emitter Check                                              | PTR-98  | Error Conditions                                    | KBD-22   | Print Head Position Counter (FR212)       | S-PTR-25           |

| Belt Motion (P)                         | PTR-86   | Data Check                                                 | PTR-98  | Keying Errors                                       | KBD-22   | Memory Address Register (FQ014)           | S-PTR-26           |

| PSS (Subscan) (P)                       | PTR-86   | Hammer Parity Check (285 lpm)                              | PTR-99  | Error Recovery                                      | KBD-22   | Settle/Interval Counter (FR245)           | S-PTR-26           |

| IMPSS (Impression Singleshot) (P)       | PTR-86   | End of Forms/Cover Closed/Throat Closed                    |         |                                                     |          | Print Motor Event Counter (FR223)         | S-PTR-26           |

| Fire Hammer (A)                         | PTR-86   | (285 lpm)                                                  | PTR-100 | SERIAL PRINTER                                      | S-PTR-1  | Print Motor Elapse Counter (FR227)        | S-PTR-26           |

| Activate Paper Clamps (A)               | PTR-87   | End of Forms (EOF)                                         | PTR-100 | INTRODUCTION                                        | S-PTR-1  | Forms Emitter Counter (FR243)             | S-PTR-26           |

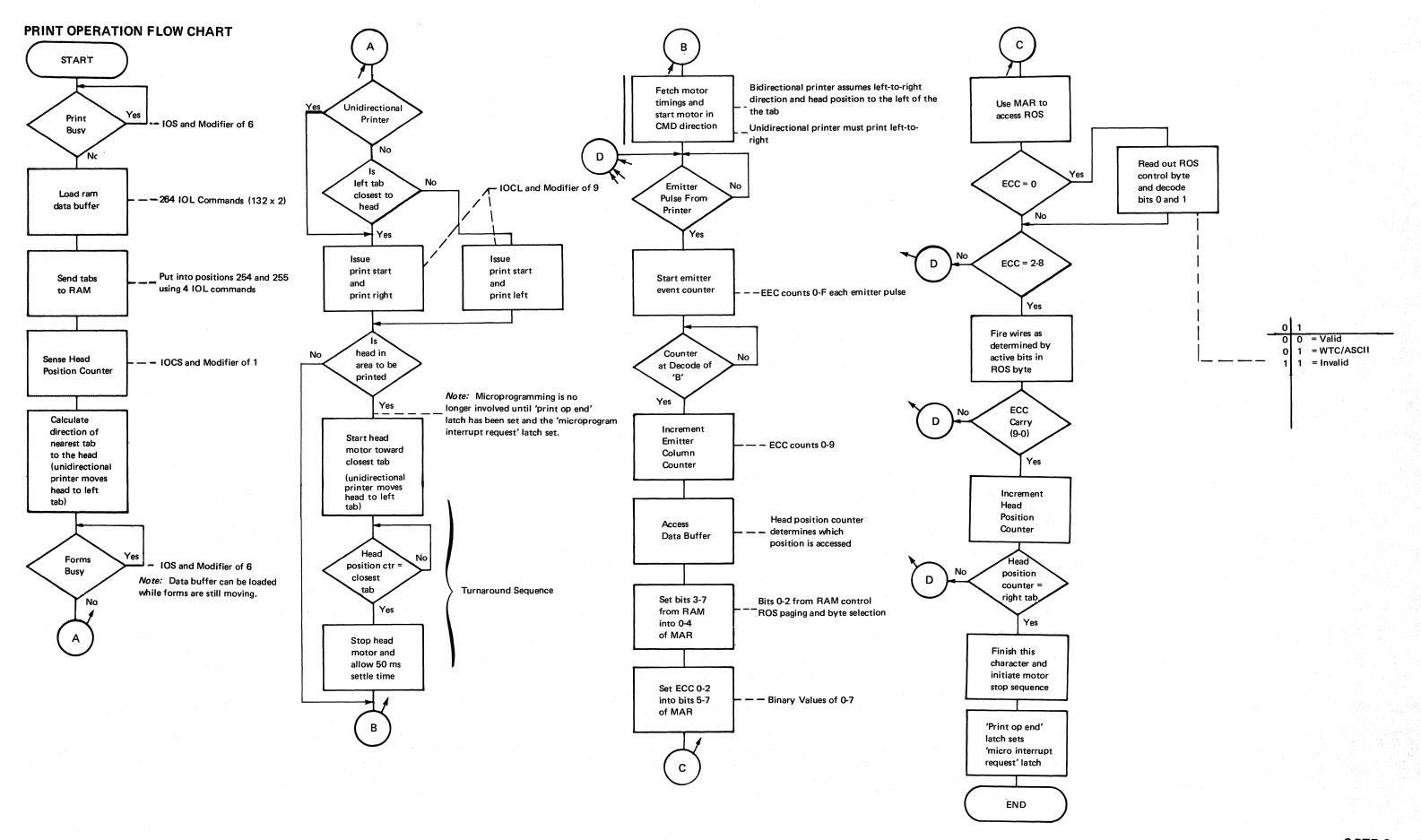

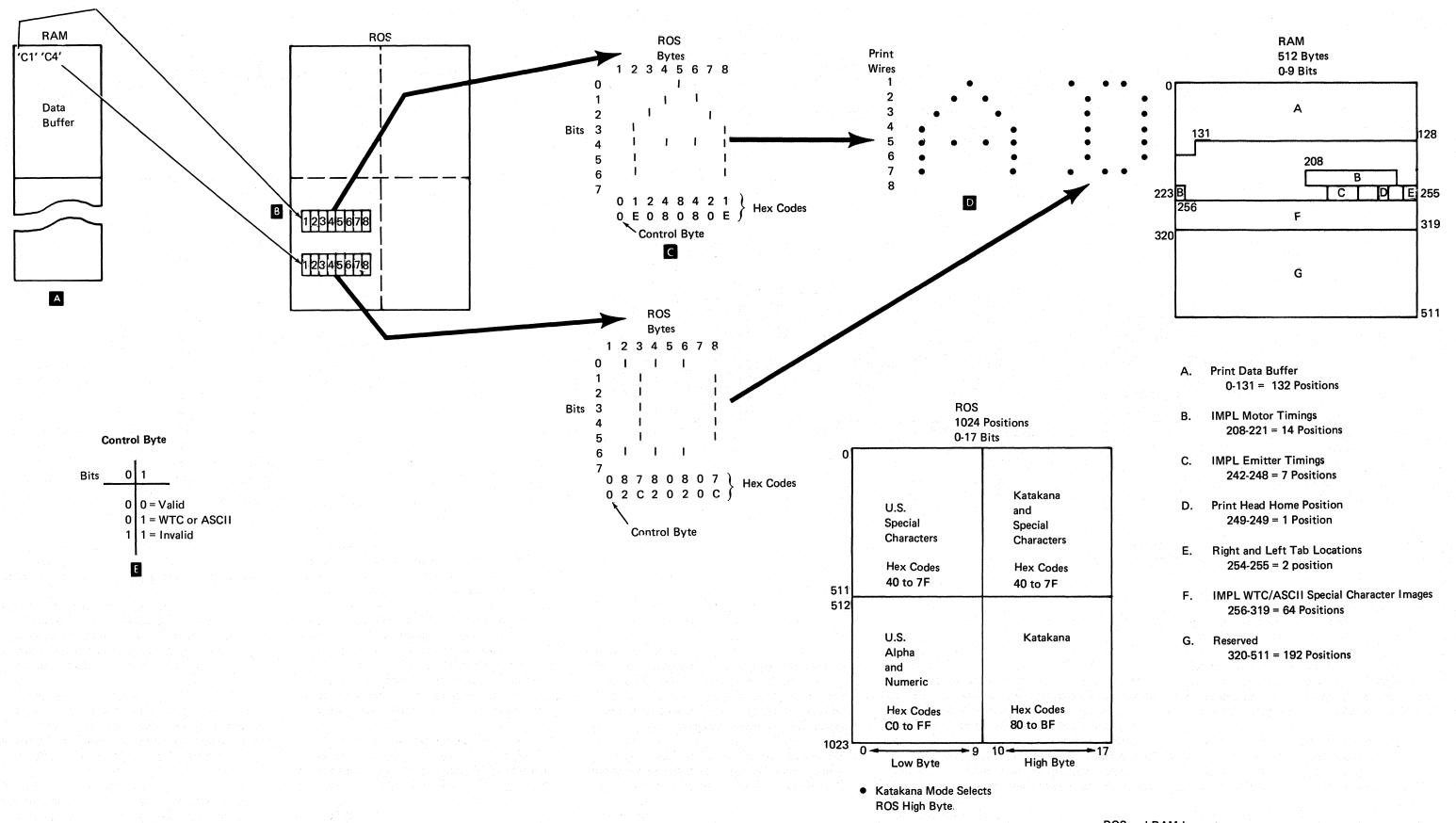

| Home Pulse (A)                          | PTR-87   | Cover Closed                                               | PTR-100 | PRINT OPERATION FLOW CHART                          | S-PTR-3  | Forms Line/Print Time Counter (FR230) .   | S-PTR-26           |

| Hammer Check 1-44, 45-88,               |          | Throat Closed                                              | PTR-100 | THEORY OF PRINTING                                  | S-PTR-4  | Forms Operation                           | S-PTR-26           |

| 89-132 (P)                              | PTR-87   |                                                            |         | Loading the Data Buffer                             | S-PTR-4  | Print Operation                           | S-PTR-27           |

| Carriage Go (A)                         | PTR-87   |                                                            |         | Positioning the Print Head                          | S-PTR-4  | ATTACHMENT FUNCTIONAL UNITS               |                    |

| Stop Ribbon (A)                         | PTR-87   |                                                            |         | Printing the Data from the Buffer                   | S-PTR-4  | (120 cps only)                            | S-PTR-28           |

|                                         |          |                                                            |         | 그림, 하고 이름을 보고 있다면서 가게 하는 물고 있다.                     |          | 는 이 그는 전 이번 등을 하셨다. 나를 잃어 사고하면 하다면 했다.    | 41.49 H.J. 37 H.J. |

| Print Emitter                           | S-PTR-28 |  |

|-----------------------------------------|----------|--|

| Print Emitter Event Counter (FR214)     | S-PTR-28 |  |

| Emitter Column Counter [ECC] (FR212) .  | S-PTR-28 |  |

| Printing Left to Right                  | S-PTR-28 |  |

| Printing Right to Left                  | S-PTR-28 |  |

| Print Head Position Counter (FR212)     | S-PTR-29 |  |

| Memory Address Register (FQ014)         | S-PTR-30 |  |

| Settle/Interval Counter (FR245)         | S-PTR-30 |  |

| Print Motor Event Counter (FR223)       | S-PTR-30 |  |

| Print Motor Elapse Counter (FR227)      | S-PTR-30 |  |

| Forms Emitter Counter (FR243)           | S-PTR-30 |  |

| Forms Line/Print Time Counter (FR230) . | S-PTR-30 |  |

| Forms Operation                         | S-PTR-30 |  |

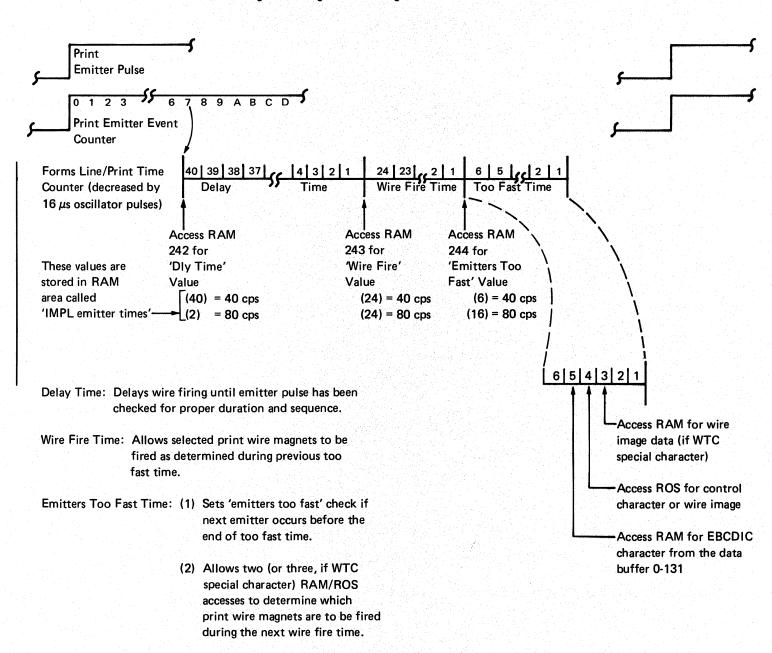

| Print Operation                         | S-PTR-31 |  |

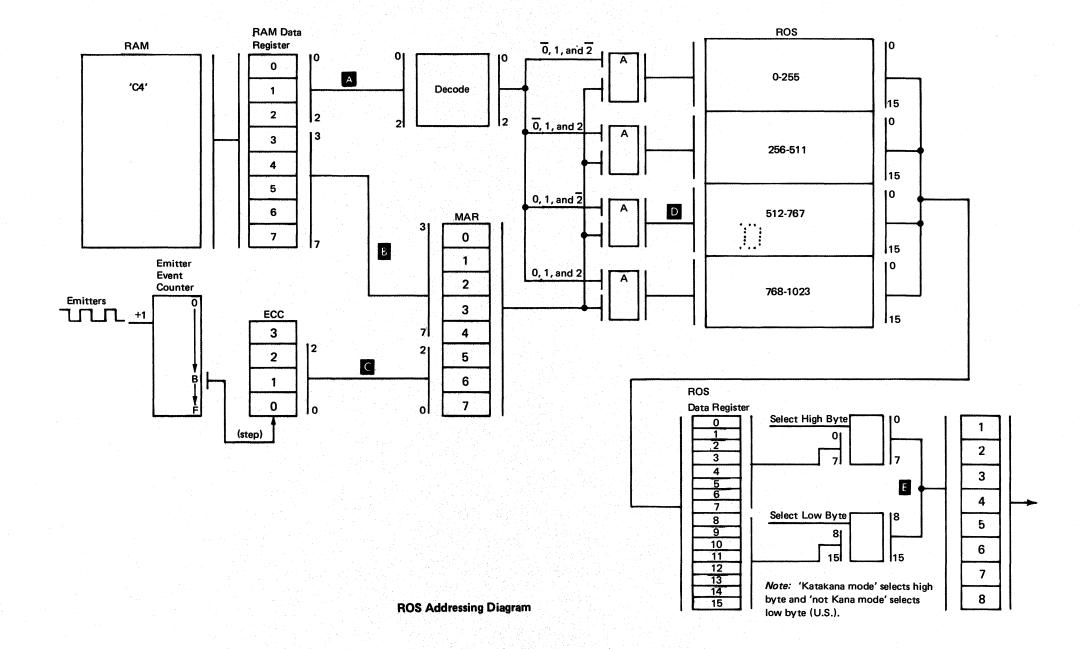

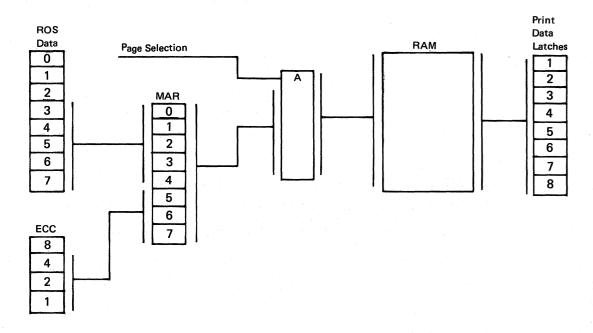

| ROS ADDRESSING                          | S-PTR-32 |  |

| WTC/ASCII/U.S. Special Character        |          |  |

| Addressing                              | S-PTR-33 |  |

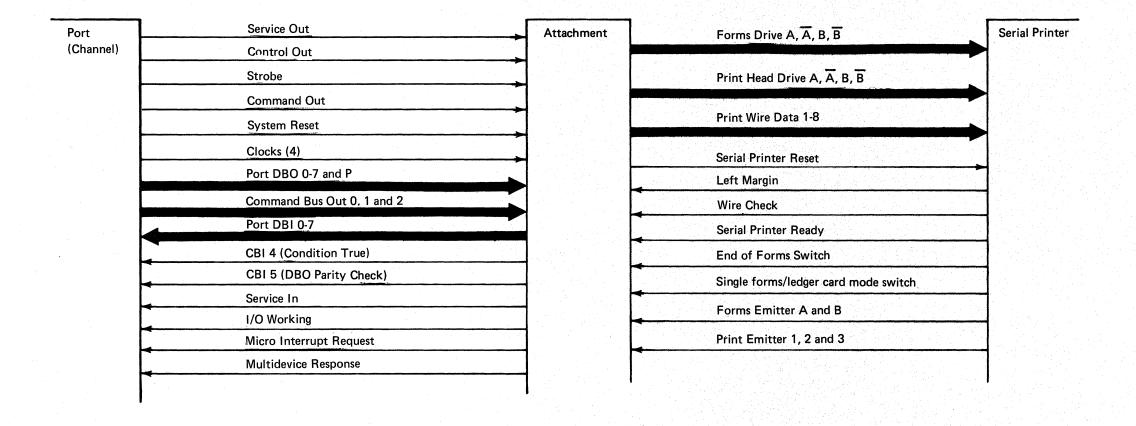

| INPUT/OUTPUT LINES                      | S-PTR-34 |  |

| ERROR CONDITIONS                        | S-PTR-35 |  |

| Byte 0, Bit 0 - Forms Hung Check        | S-PTR-35 |  |

| Byte 0, Bit 1 — Horizontal Check        | S-PTR-35 |  |

| Emitters Out of Order                   | S-PTR-35 |  |

| Print Head Hung                         | S-PTR-35 |  |

| Emitters Too Fast                       | S-PTR-35 |  |

| Memory Data Check                       | S-PTR-35 |  |

| Unprintable Character Check             | S-PTR-35 |  |

| Printer Not Ready                       | S-PTR-35 |  |

| Byte 0, Bit 2 — Forms Runaway Check     | S-PTR-35 |  |

| Byte 0, Bit 3 — End of Forms            | S-PTR-35 |  |

| Byte 1, Bit 0 — Printer Not Ready       | S-PTR-35 |  |

| Byte 1, Bit 1 — Wire Check              | S-PTR-35 |  |

| Byte 1, Bit 4 — Memory Data Check       | S-PTR-35 |  |

| Byte 1, Bit 6 — Unprintable Character   |          |  |

| Check                                   | S-PTR-35 |  |

|                                         |          |  |

| INDEX                                   | X-1      |  |

#### LIST OF ABBREVIATIONS

| μINSTR | micro instruction                      | FD   | disk drive                    |

|--------|----------------------------------------|------|-------------------------------|

| μIRPT  | microinterrupt                         | FET  | field effect transistor       |

| μιτι   | meromenape                             |      | neid effect transistor        |

| Adr    | address                                | GB   | guard band                    |

| AGC    | automatic gain control                 | gen  | generate/generator            |

| ALU    | arithmetic/logical unit                | 3    |                               |

| AM     | address mark                           | hmr  | hammer                        |

| ASCII  | American National Standard Code for    | Hz   | Hertz                         |

|        | Information Interchange                |      |                               |

|        |                                        | I/O  | input/output                  |

| ВС     | byte control                           | ID   | identification                |

| BFR    | buffer                                 | IMPL | initial microprogram load     |

| ВН     | behind home                            | IOB  | input/output block            |

| BI     | bidirectional                          |      |                               |

| BP     | belt position                          | KANA | Katakana                      |

| BPC    | block processor clock                  | KYB  | keyboard                      |

| BPC    | belt position counter                  | KYBD | keyboard                      |

| BR     | bit ring                               |      |                               |

| BSCA   | binary synchronous communications      | LM   | left margin                   |

|        | adapter                                | LSR  | local storage register        |

|        |                                        | Lth  | latch                         |

| C      | clock pause                            | LZ   | landing zone                  |

| CBI    | command bus in                         |      |                               |

| CBO    | command bus out                        | MAB  | micro address backup register |

| Chan   | channel                                | MAR  | memory address register       |

| CPS    | characters per second                  |      | microaddress register         |

| CPU    | processing unit                        | MCI  | machine check interrupt       |

| CRC    | cyclic redundancy check                | MCU  | Mag Card Unit                 |

| CRT    | cathode ray tube                       | mega | million                       |

| CS     | control storage                        | MFM  | modified frequency modulation |

| CS     | cycle steal                            | MOD  | modifier                      |

| CSILSW | control storage interrupt level status | MOR  | micro operation register      |

|        | word                                   | mtr  | motor                         |

| cmd    | command                                |      |                               |

| cnt    | count                                  | ор   | operation                     |

| ctrl   | control                                | OSC  | oscillator                    |

| ctr    | counter                                |      |                               |

|        |                                        | P    | position pulse                |

| DAR    | display address register               | PC   | parity check                  |

| DBI    | data bus in                            | PCR  | processor condition register  |

| DBO    | data bus out                           | PFN  | print fire number             |

| DCD    | decode                                 | PG   | parity generate               |

| DCP    | diagnostic control program             | Ph   | polarity hold                 |

| DE     | disk enclosure                         | PLO  | phase lock oscillator         |

| demod  | demodulator                            | POR  | power on reset                |

| diag   | diagram                                | PP   | parity predict                |

| DLY    | delay                                  | PP   | print position                |

|        |                                        | prt  | print                         |

| ECC    | emitter column counter                 | PSS  | print sub scan                |

| EOF    | end of forms                           | ptr  | printer                       |

| ERAP   | error recording and analysis procedure |      |                               |

|        |                                        |      |                               |

| RAM    | random access memory                |

|--------|-------------------------------------|

| rd     | read                                |

| req    | register                            |

| RIB    | request indicator byte              |

| ROS    | read only storage                   |

|        |                                     |

| SAR    | storage address register            |

| SBAR   | storage buffer address register     |

| SC     | sequence counter                    |

| SCP    | system control program              |

| SDLC   | system data link control            |

| sel    | select/selector                     |

| SERDES | serializer/deserializer             |

| sns    | sense                               |

| stg    | storage                             |

| svc    | supervisor call                     |

| SWG    | start write gap                     |

| sync   | synchronize                         |

| S3ILSW | system interrupt level status word  |

|        |                                     |

| tr     | trigger                             |

| TRA    | trigger A                           |

| TRC    | trigger C                           |

| TRD    | trigger D                           |

| TRE    | trigger E                           |

| TRF    | trigger F                           |

|        |                                     |

| UNI    | unidirectional                      |

| vert   | vertical                            |

| VFL    | velocity follow latch               |

| VFO    | variable frequency oscillator       |

| VIO    | variable frequency oscillator       |

| WC     | worst case                          |

| WR     | (N) H or L = work register (N) high |

|        | or low                              |

| WR     | work register                       |

| WTC    | World Trade Corp.                   |

|        |                                     |

|        |                                     |

Transfer

Xfer

### MICRO INSTRUCTION ABBREVIATIONS

| ACYR<br>AI<br>AR                                                 | add registers with carry<br>add immediate<br>add registers                                                                                                                                                                                                     |  |

|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| B<br>BAL                                                         | branch<br>branch and link                                                                                                                                                                                                                                      |  |

| CI                                                               | compare immediate                                                                                                                                                                                                                                              |  |

| DEC                                                              | decrement register by 1                                                                                                                                                                                                                                        |  |

| HBN<br>HBZ                                                       | hex branch numeric<br>hex branch zone                                                                                                                                                                                                                          |  |

| IOCL<br>IOCS<br>IOL<br>IOS<br>INC                                | I/O control load<br>I/O control sense<br>I/O load<br>I/O sense<br>increment register by 1                                                                                                                                                                      |  |

| JC JCY JE JFLG JH JIO JL JM JNH JNH JNH JNH JNP JO JP JSR JNZ JZ | branch on condition branch on carry branch on equal branch on flag branch on l/O condition branch on low branch on mixed branch on negative branch not equal branch not low branch not low branch not positive branch all ones branch not zero branch not zero |  |

| L<br>LA1<br>LA2<br>LC<br>LI<br>LM<br>LSAR                        | load direct to control storage<br>logical/arithmetic 1<br>logical/arithmetic 2<br>load from control storage<br>load immediate<br>load from main storage<br>load/sense address register                                                                         |  |

| MPL    | microprocessor load                       |

|--------|-------------------------------------------|

| MPLF   | microprocessor load for special functions |

| MPS    | microprocessor sense                      |

| MVR    | move LSR                                  |

| MZN    |                                           |

|        | move zone to numeric                      |

| MZZ    | move zone to zone                         |

| NCR    | AND complement                            |

| 000    | OB                                        |

| OCR    | OR complement                             |

| RDCH/L | I/O store to control storage high/low     |

| RDM    | I/O store to main storage                 |

| RETRN  | return                                    |

| SBF    | set bits off                              |

| SBN    | set bits on                               |

| SCYR   | subtract with borrow                      |

| SI     | subtract immediate                        |

| SILSB  | sense interrupt level status byte         |

| SLL    | shift left logical                        |

|        | <u> </u>                                  |

| SLLD   | shift left logical double                 |

| SR     | subtract registers                        |

| SRL    | shift right logical                       |

| SRLD   | shift right logical double                |

| ST     | store direct to control storage           |

| STC    | store to control storage                  |

| STM    | store to main storage                     |

| TM     | test mask                                 |

| WTCH/L | I/O load from/to control storage          |

|        | high/low                                  |

| WTM    | I/O load from/to main storage             |

| XR     | exclusive OR                              |

|        |                                           |

|        |                                           |

|        |                                           |

This page is intentionally left blank.

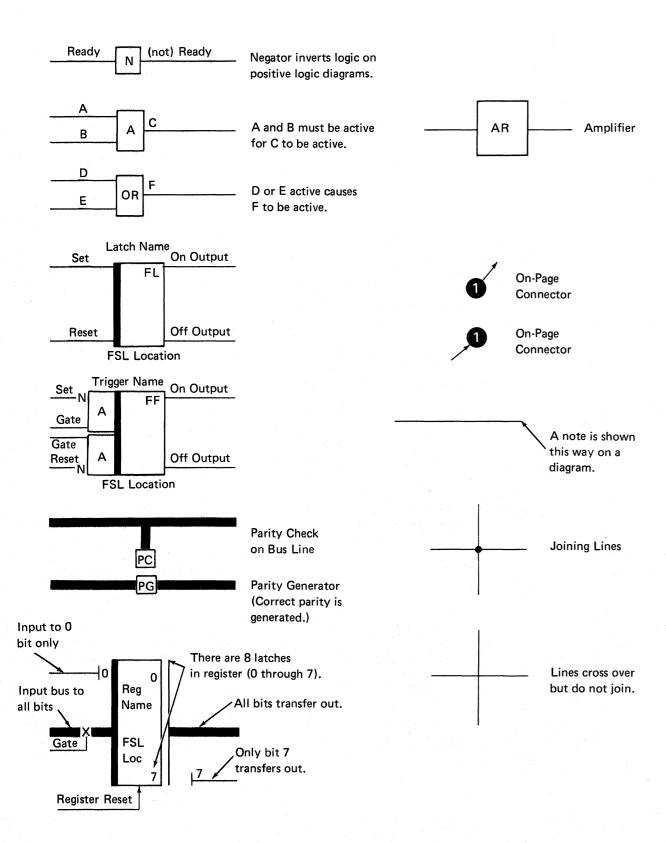

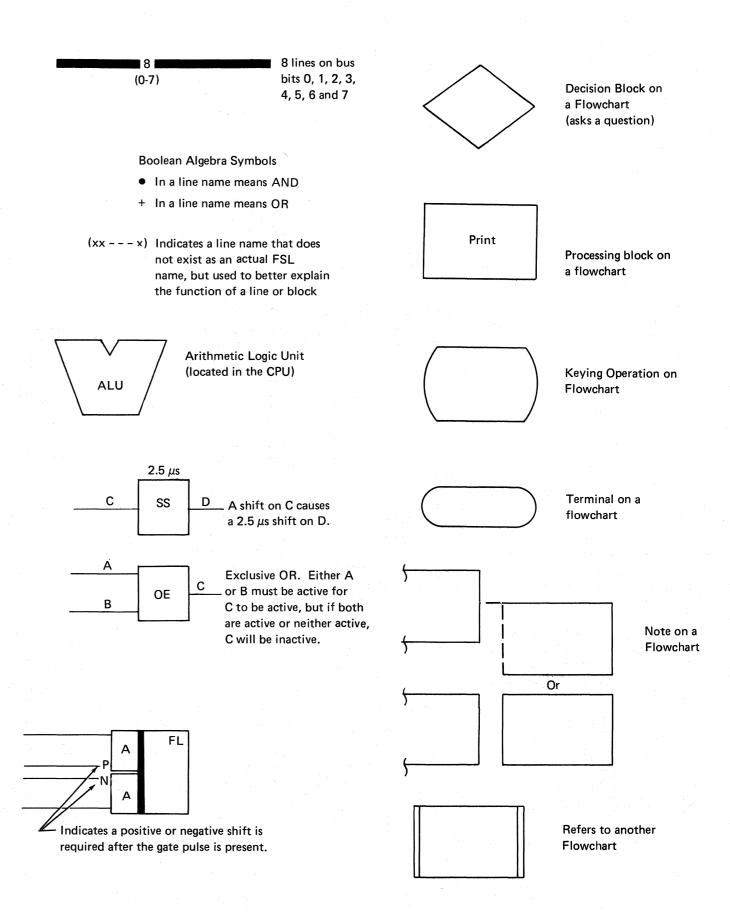

## Legend

#### **LEGEND-1**

#### Legend

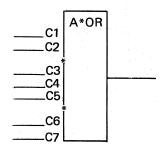

In this example three AND blocks feed an OR block. The three AND block functions are separated by asterisks.

The asterisk is a delimiter and separates groups of inputs

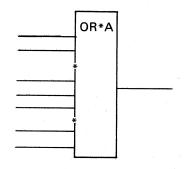

This is an example of three OR blocks feeding an AND block. The three OR block functions are separated by asterisks.

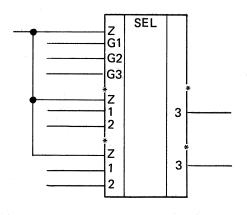

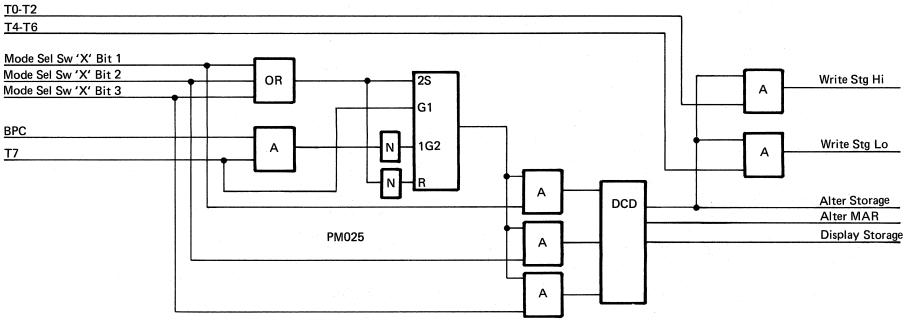

The selector block is a gating device. The upper section of the block contains the gates (G) and the lower section contains the gated data lines.

In this example gate 1 and gate 2 each control a set of input data lines.

Gate 3 controls both output lines.

Thus for data to pass through this block, it is necessary that one of the input gates (G1 or G2) be active, and the output gate (G3) must also be active.

This example of the selector also contains Z inputs. A Z input is used when a line is common to a number of functions. Thus if the input to Z is active and G3 is active, both output lines will be active.

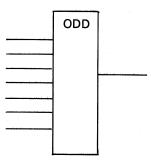

The output of the odd count block is active only when an odd number of inputs are active.

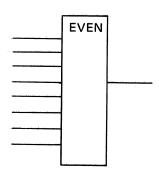

The output of the even count block is active when an even number of inputs are active.

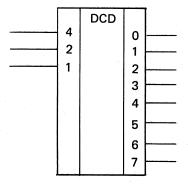

The decode translates a group of related inputs into a specific output. The inputs are numbered in binary progression; 1, 2, 4, 8 and so on. The number on the output equals the sum of the active inputs. For example, when the inputs to 4 and 1 are active, the 5 output will be active.

FL

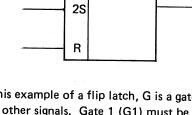

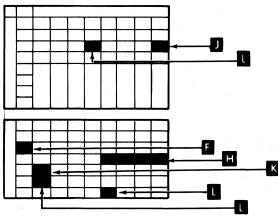

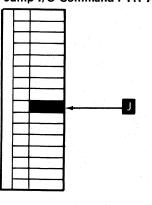

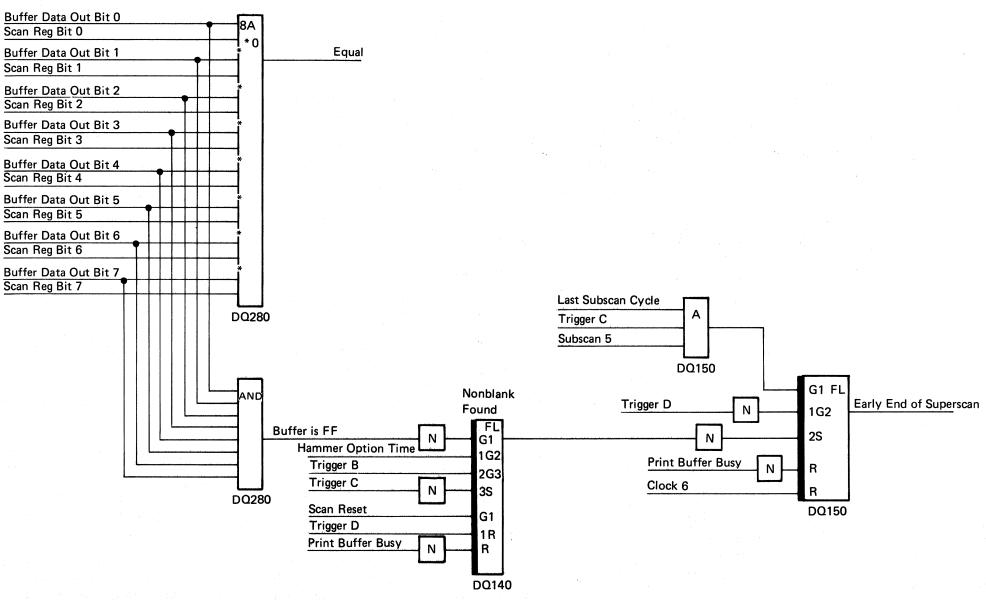

In this example of a flip latch, G is a gate used to gate other signals. Gate 1 (G1) must be active along with the input to gate 2 (G2) for gate 2 to become active.

The latch will turn on if gate 2 is active and the input to 2S becomes active.

When the R line is activated, the register will be reset.

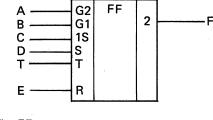

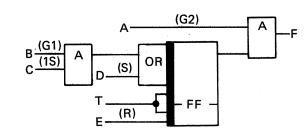

The FF trigger can be set with the S input and reset with the R input. A T (toggle) input can also be used to complement the current status of the trigger.

In this example there are 2 sets and 1 reset. The second set requires that gate 1 along with the input to 1S be active to turn the trigger on. Also in this example, gate 2 must be active to get an active output.

#### Legend

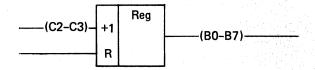

This example of a register illustrates bundled lines on both the input and output. The input contains 2 lines, C2 and C3, and an output that contains 8 lines, B0 through B7.

The + symbol indicates the register will be incremented by 1 when the input line becomes active. A minus symbol would indicate decrementing. The number following the + or - symbol indicates the amount of incrementing or decrementing.

When the R line is activated, the register will be reset.

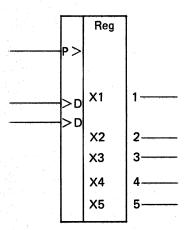

This is an example of a shift register. The symbol > indicates shift down while < would indicate shift up. In order to shift down by 1, the input to one of the > lines must be active and a shift must occur on the P> input.

The positions in the register are denoted by X1, X2, X3, and so on.

This page is intentionally left blank.

## Introduction to IBM System/32

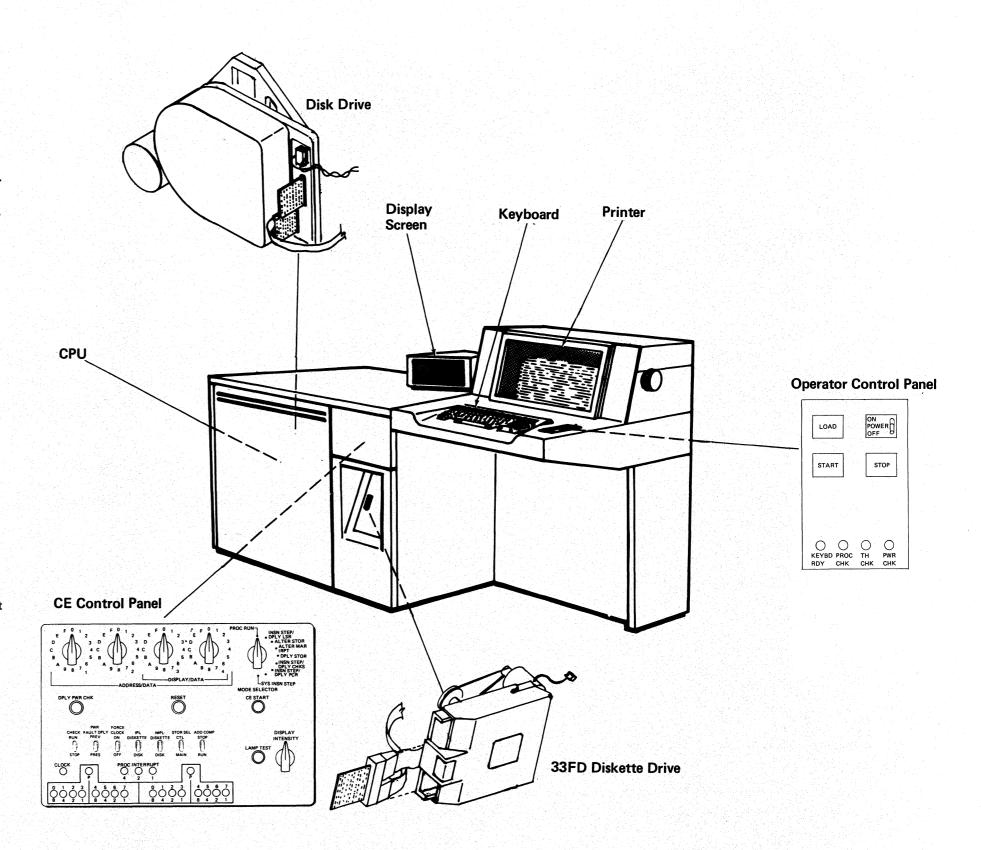

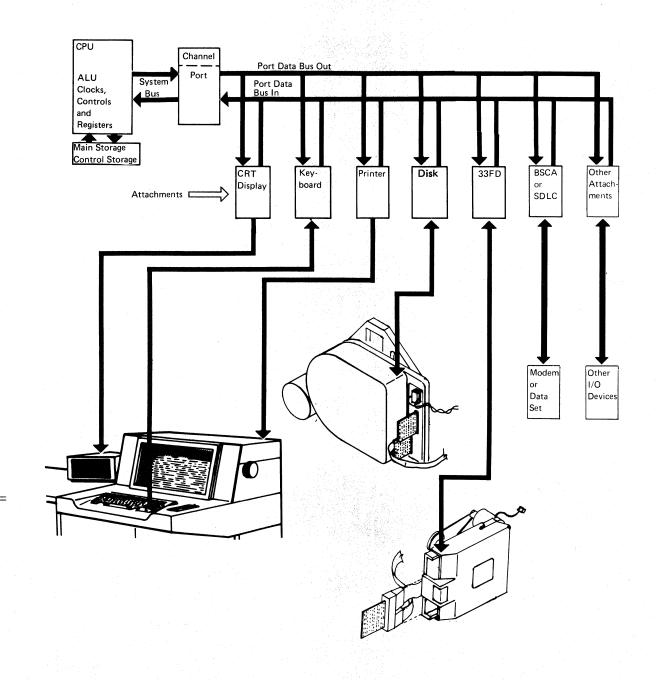

The IBM System/32 is a desk-sized business system with the following features:

- Programs are written in system language and executed by a machine language microprogram.

- Large storage capacity is provided by disk drive.

- Operating instructions and prompting messages are displayed.

- I/O and CPU errors are recorded and can be retrieved.

- Diagnostic programs are automatically run after the initial microprogram load.

- Whenever possible, conditions that caused errors are automatically retried.

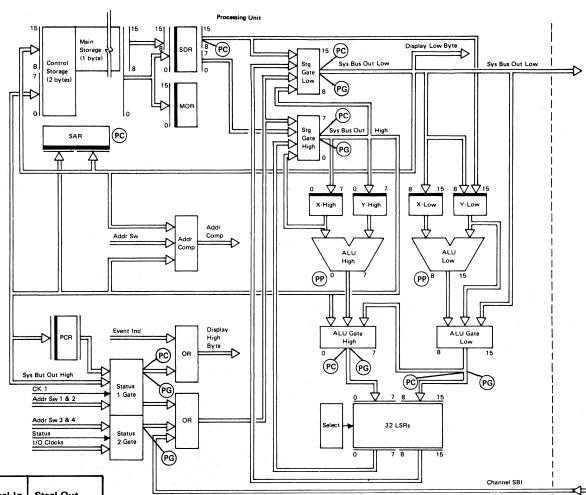

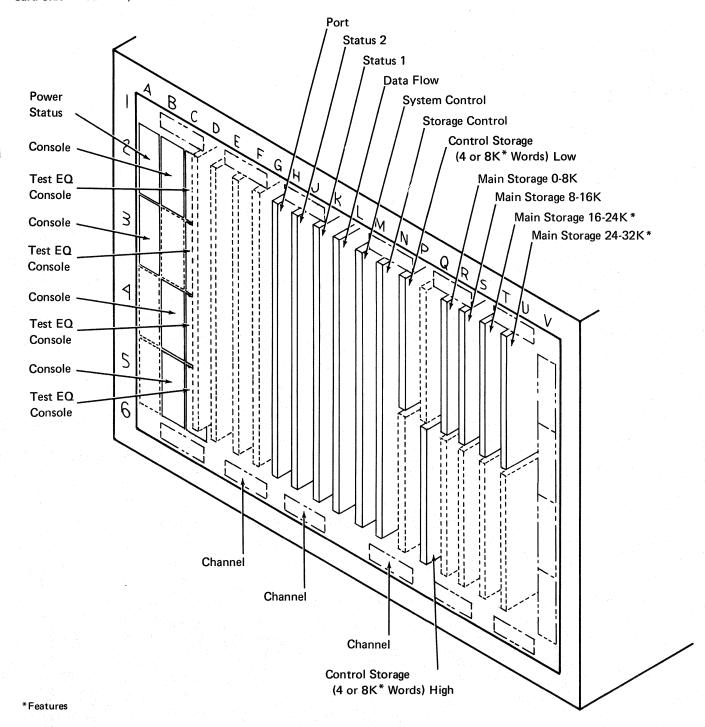

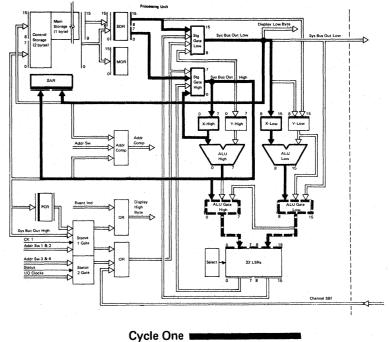

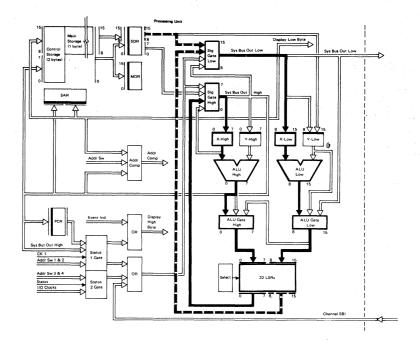

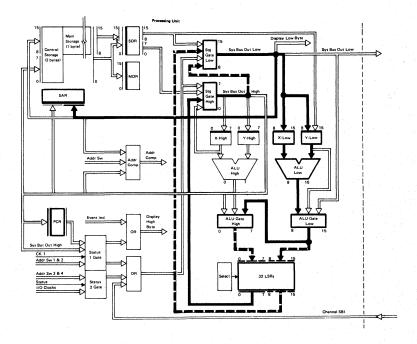

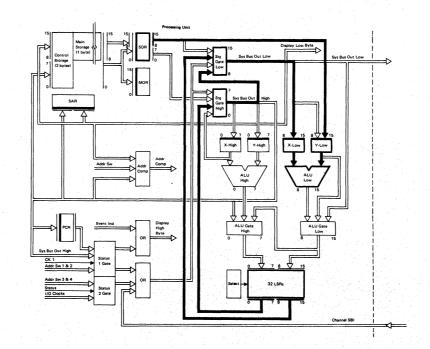

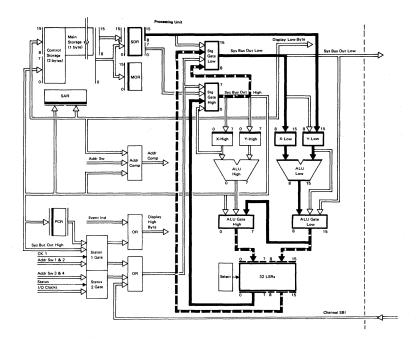

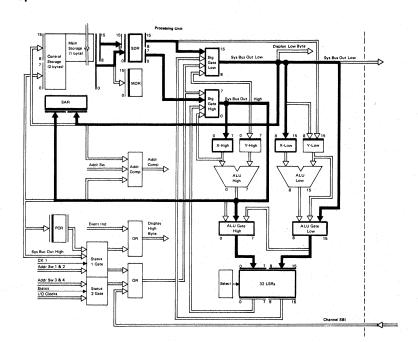

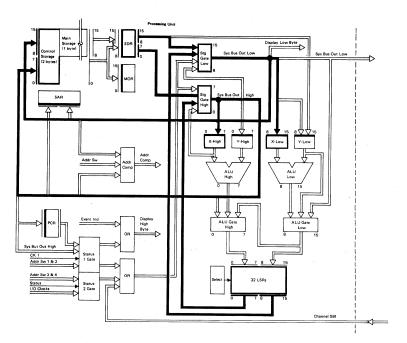

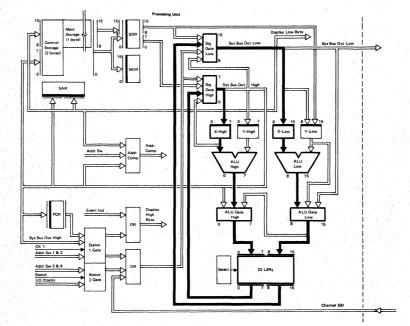

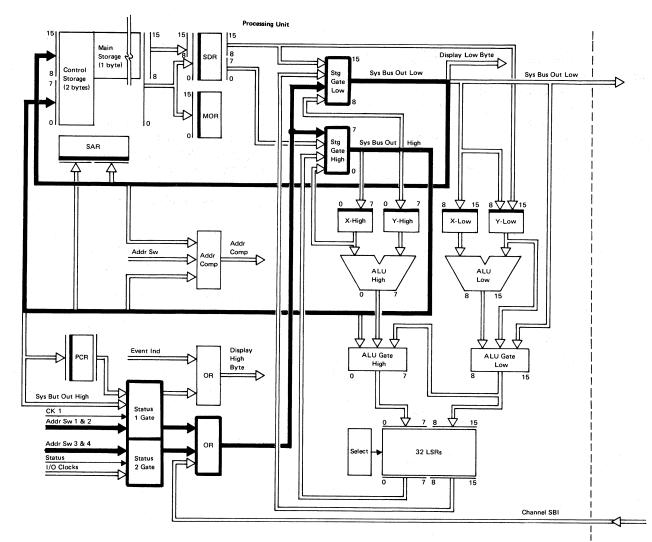

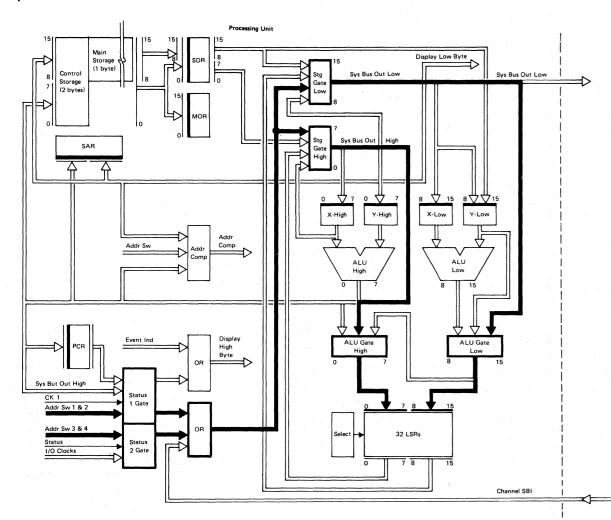

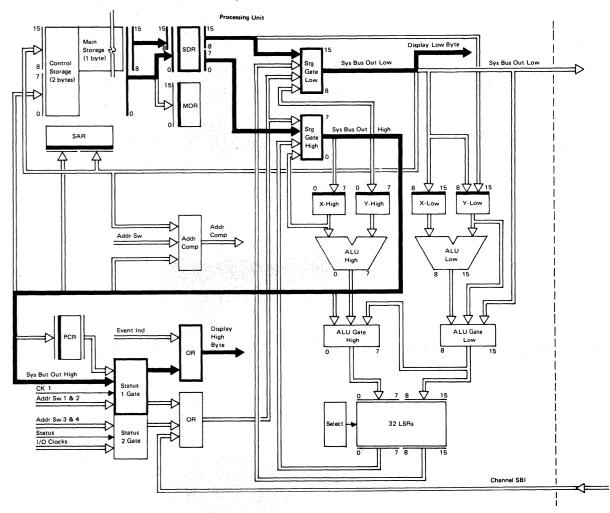

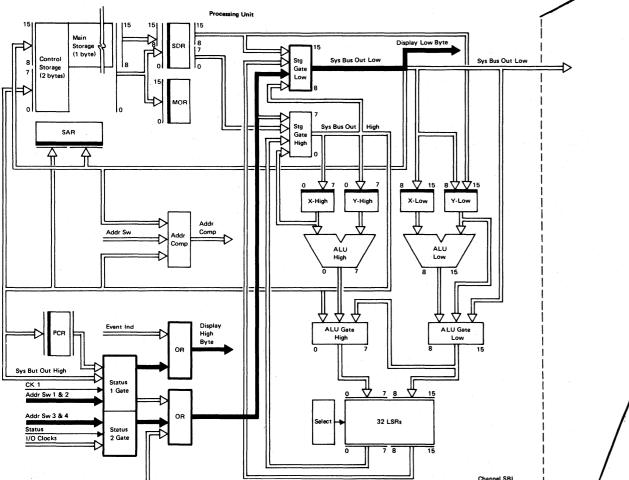

The CPU contains 16K, 24K, or 32K addressable positions of main storage and 4K or 8K addressable positions of control storage. Each position of main storage is one byte wide; each position of control storage is two bytes wide. FET technology is used for both main and control storage. The CPU also contains registers, gates, and ALUs that are controlled by the microprogram.

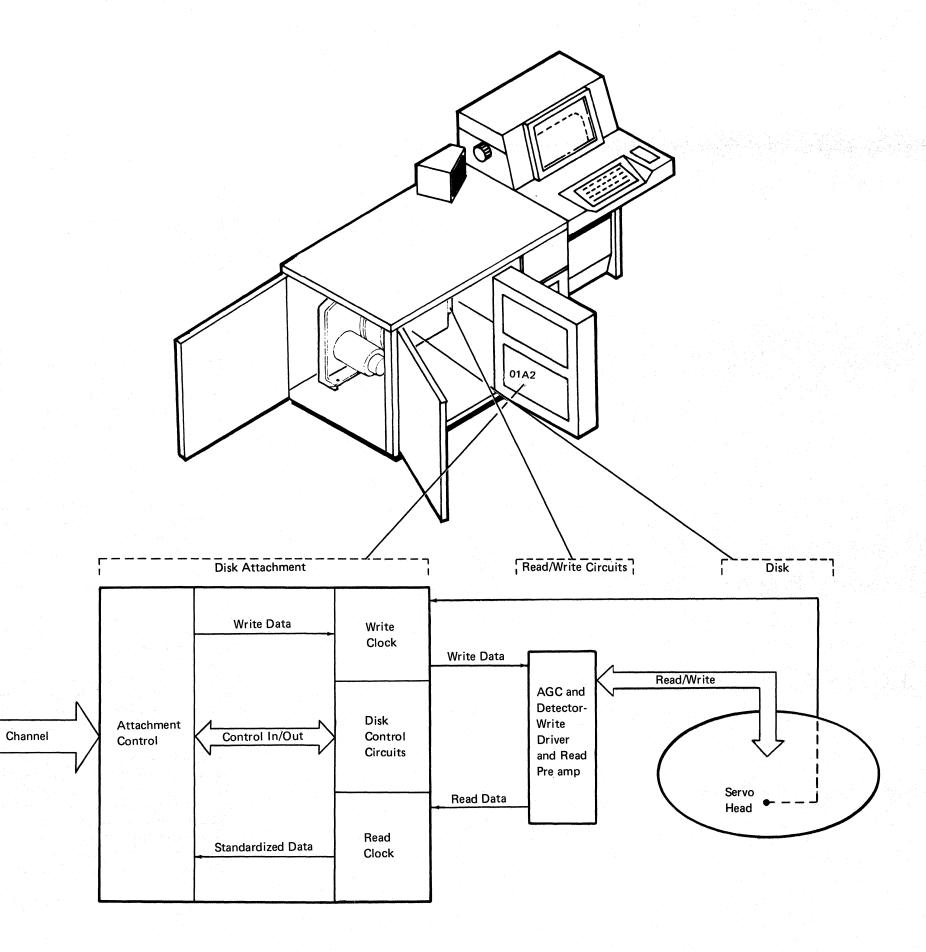

The disk drive is an integrated disk that provides 3.2, 5.0, 9.1, or 13.7 million bytes of accessible storage. In addition, various diagnostic programs reside on the disk.

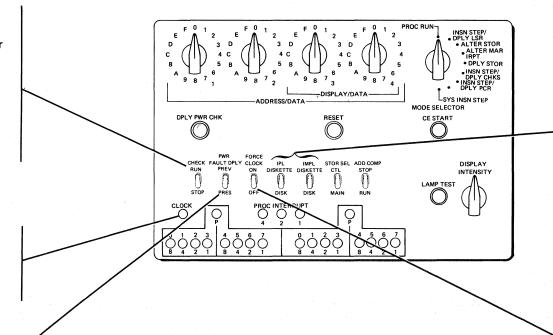

The CE control panel contains lights and switches used in the maintenance of the system.

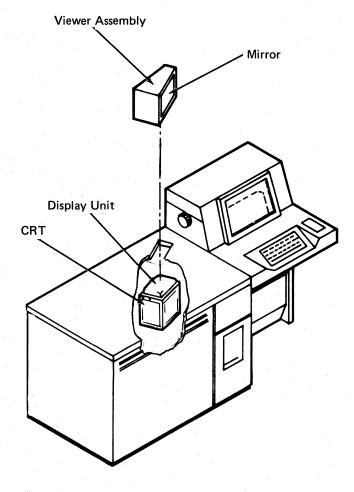

The display screen is used for operator prompting, job output, and other messages. Up to six lines of 40 characters-per-line can be displayed at one time.

The keyboard is used to control various system functions and as a data input device.

The IBM System/32 can be ordered with either the serial printer or the belt printer.

The serial printer has 132 print positions and uses a 64 character set. It is a 7 X 7 wire matrix printer. The serial printer has 132 print positions and uses a 64 character set. It is a 7 X 7 wire matrix printer. The serial printer is available in three models:

120 cps (characters per second) bidirectional

80 cps bidirectional

40 cps bidirectional

40 cps unidirectional

The two models of the 40 cps printer are identical. The attachment circuitry controls whether they print only left to right or in both directions.

The belt printer has 132 print positions and a 48, 64, or 96 character set. The printing speed is 50, 100, 155, or 285 lines per minute with a 48 character set.

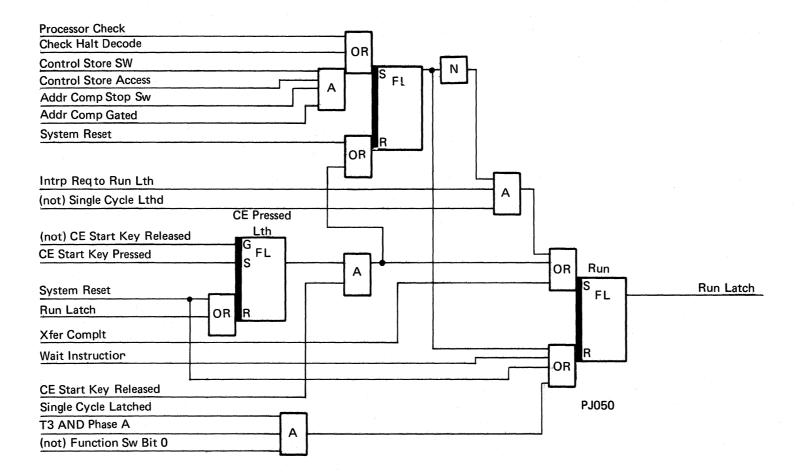

The operator control panel has switches to turn power off and on, start the loading of the diagnostic programs and control program, and start and stop the execution of system level instructions. Keyboard ready, processor check, thermal check, and power check lights are also included.

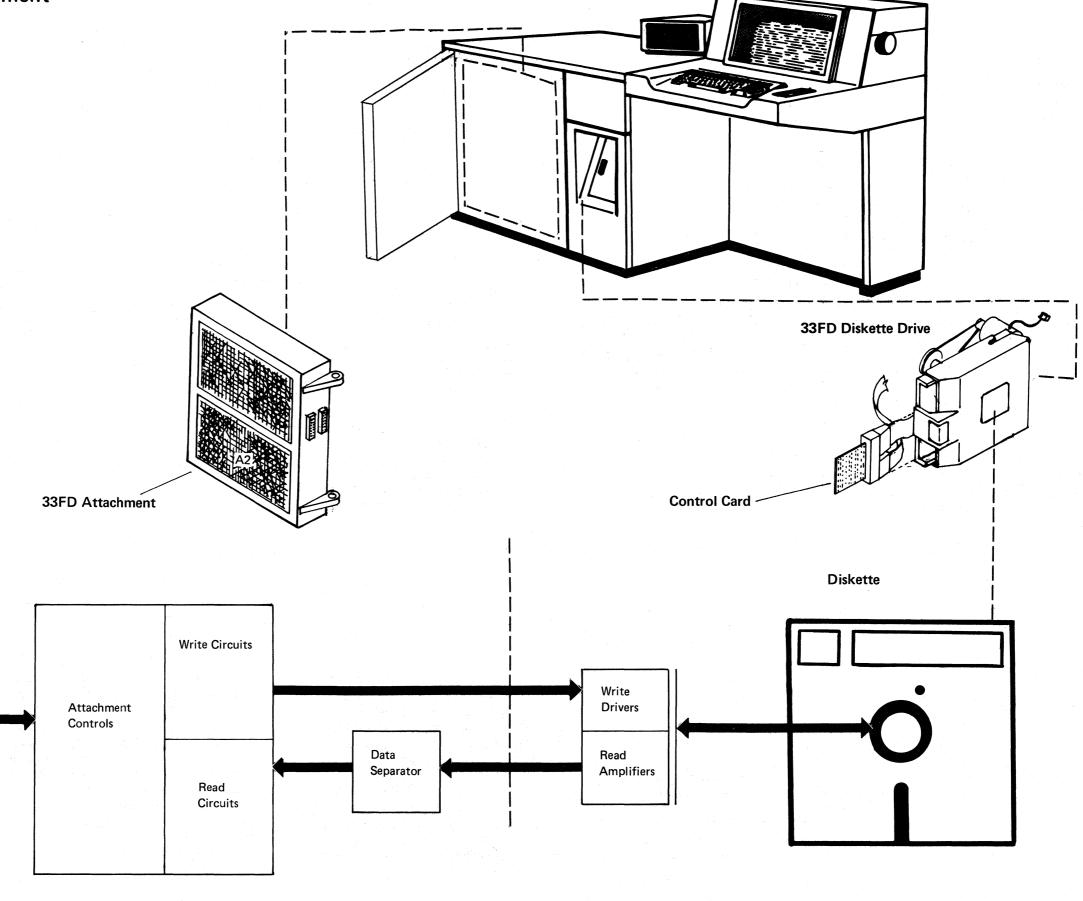

The 33FD diskette drive uses IBM diskettes as input and output to the system. Data can be entered on the diskettes by key entry devices such as the IBM 3740 Data Entry System. In addition, certain diagnostic programs reside on the diskettes.

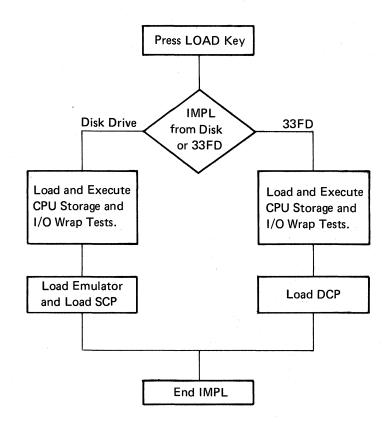

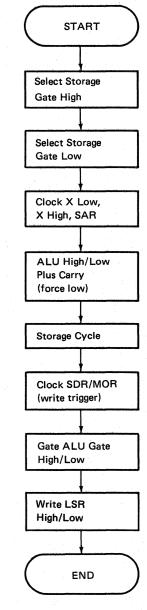

All the functions performed by the system are controlled by a microprogram which must be loaded into control storage before any processing can begin. This loading (initial microprogram load) is done from either the disk drive or the 33FD (CE only).

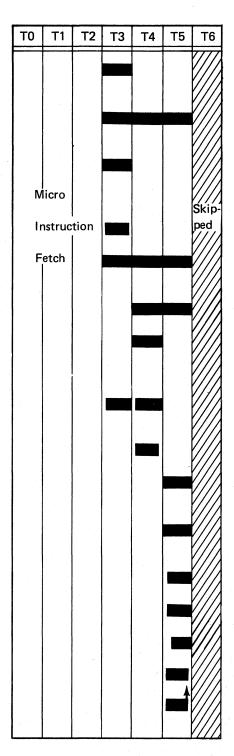

The microprogram processes system instructions, data in storage, and channel operations. The microprogram is composed of microroutines of varying sizes, each having a specific task to perform. Each microroutine is composed of bit-significant instructions that, in effect, are machine language instructions.

This page is intentionally left blank.

#### **CPU Functional Units**

#### Main Storage

Main storage contains 16K, 24K, or 32K addressable positions; each position is 1 byte wide.

#### **Control Storage**

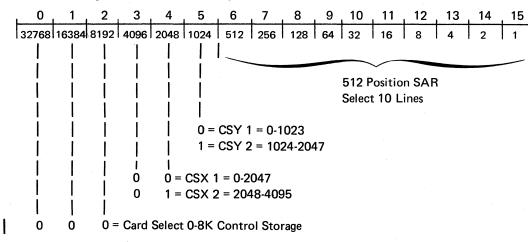

Control storage contains 4K addressable positions (8K positions on machines with the Control Storage Increment Feature); each position is 2 bytes wide. Control storage is loaded from the disk drive in a normal operation, or from the 33FD when running diagnostic programs. The loading of control storage occurs during the IMPL (initial microprogram load) sequence. When loaded, control storage contains the microprogram used to control the CPU and I/O devices.

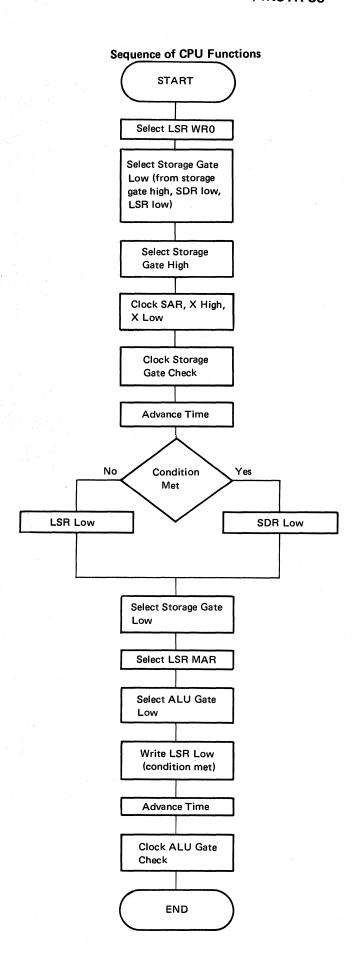

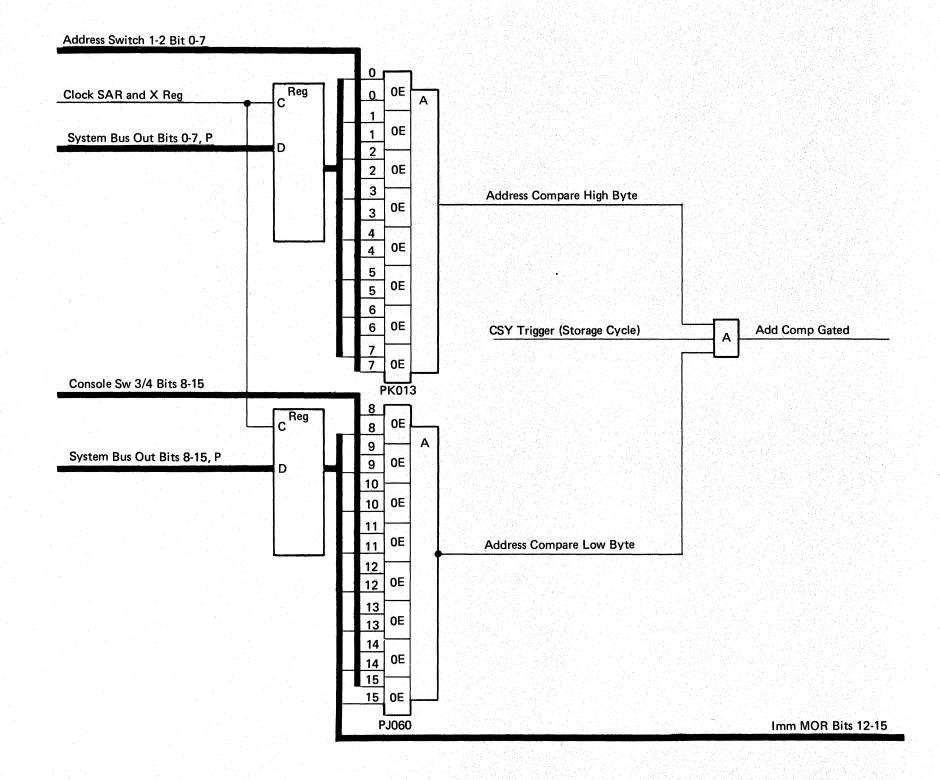

#### Storage Address Register (SAR)

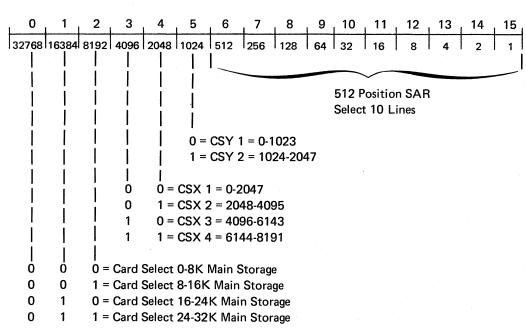

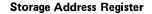

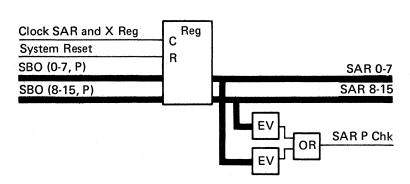

SAR is a 16-bit register used to address both main storage and control storage.

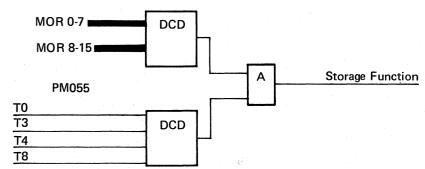

#### Micro Operation Register (MOR)

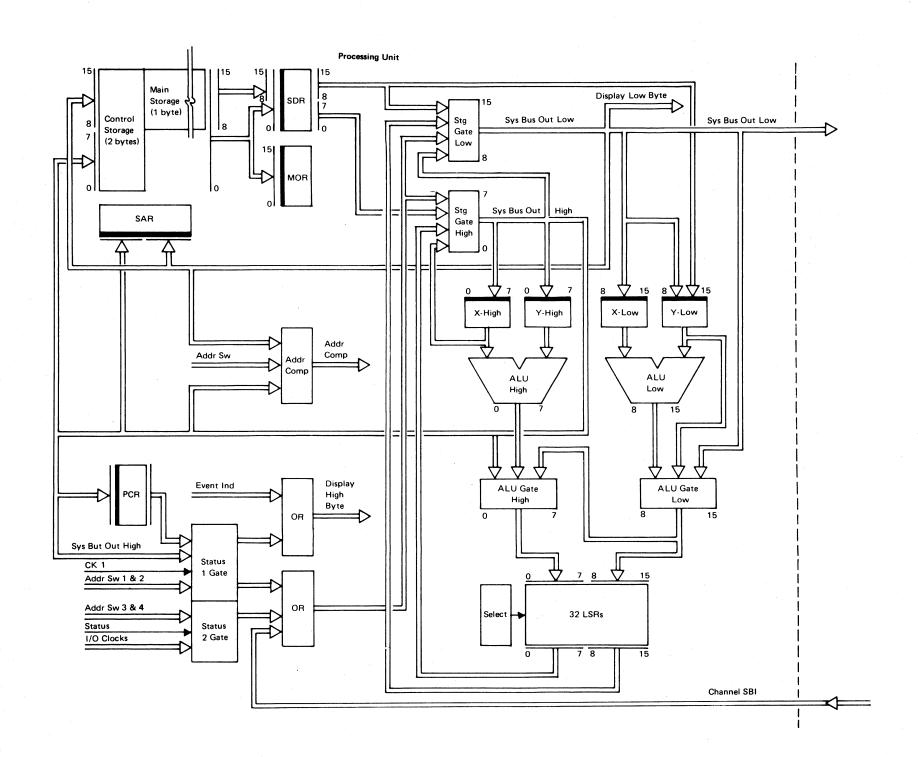

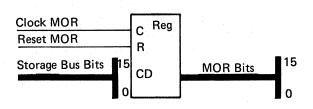

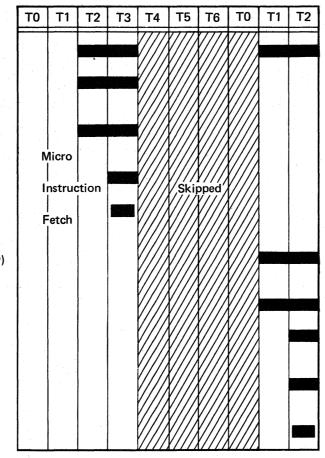

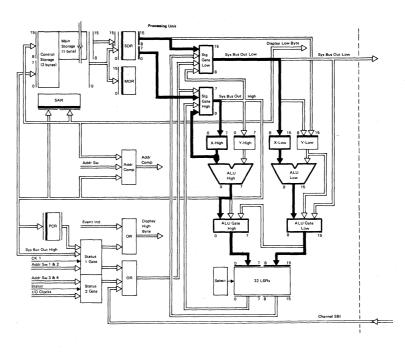

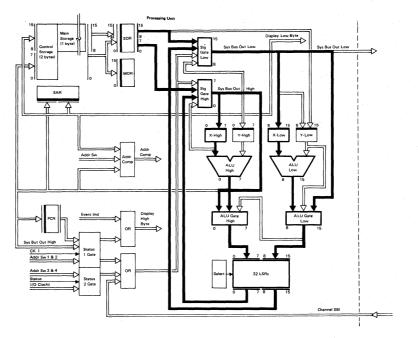

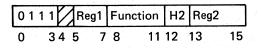

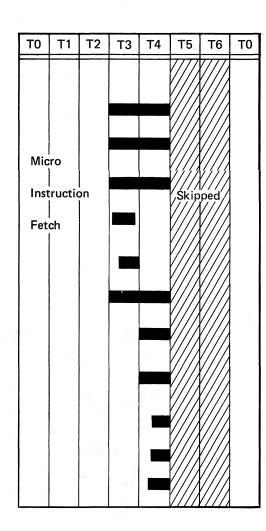

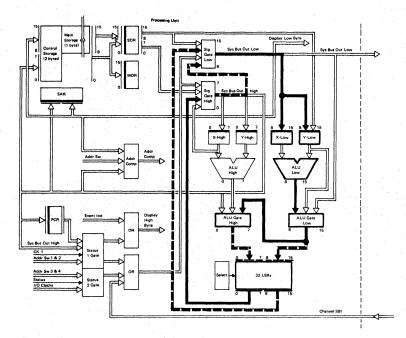

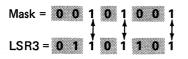

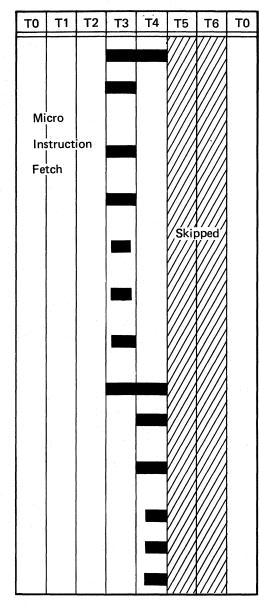

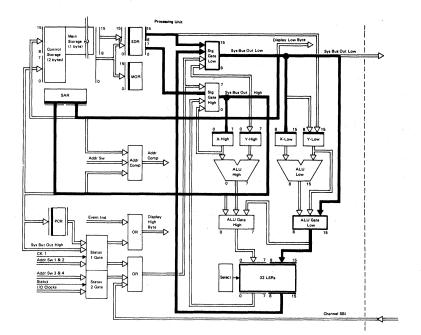

The MOR is a 16-bit register that holds each micro instruction as it is fetched from control storage. From here, the micro instruction is analyzed to control the data flow such as gate selection, ALU operation, LSR selection, etc.

#### **Process Condition Register (PCR)**

The PCR is an 8-bit register that contains information to be tested by branch instructions. For example, from the PCR, the result of a previous arithmetic instruction can be determined to be positive, negative, or zero. The PCR also contains results from compare or test mask instructions.

#### Storage Data Register (SDR)

The SDR is a 16-bit register that serves as an intermediate buffer for all micro instructions and data bytes fetched from storage. Each micro instruction, being 2 bytes wide, uses all 16 bit positions. Data from main storage, being only 1 byte wide, uses bit positions 8 through 15.

#### X and Y Registers

These four registers are 8-bit registers that serve as the buffer input for the two ALUs. The X-high and Y-high registers serve as input to ALU high while the X-low and Y-low registers serve as input to ALU low. The data for these registers comes from the local storage registers or the immediate data field of some micro instructions.

#### Arithmetic Logical Unit (ALU)

There are two ALUs in the system, ALU high and low. ALU high processes bits 0-7 when 2-byte data fields are involved. ALU low processes bits 8-15 when either 1-byte or 2-byte data fields are involved. The ALUs always present 2 bytes of data to the LSR input bus. When 2 bytes are involved in the ALU operation, both bytes (high and low) are placed on the LSR input bus and simultaneously written into bits 0-7 and bits 8-15 of the LSR. When the ALU output is only 1 byte, the byte is presented to both the high and low LSR input bus lines. In these cases, the micro instruction selects only 1 byte to be written into an LSR.

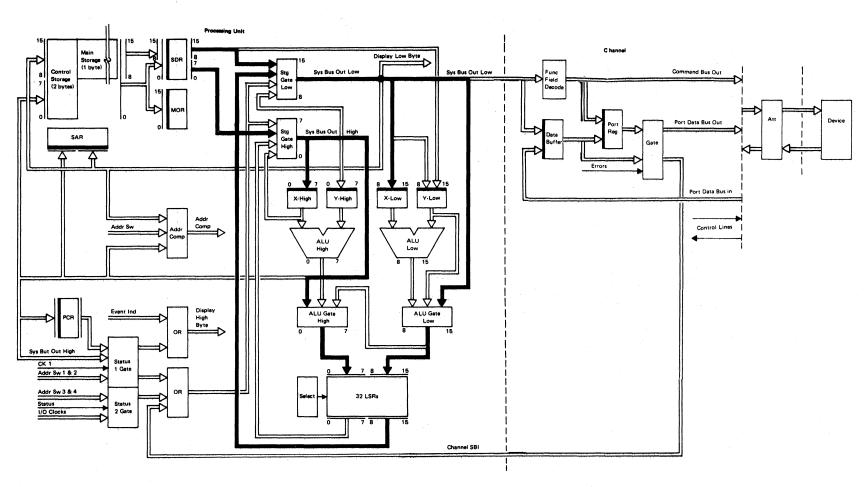

#### System Data Flow Through the Functional Units

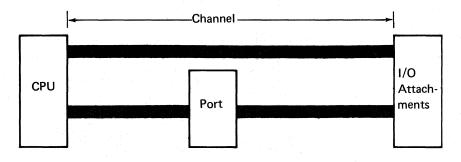

Note: Channel, as used in this system, refers to the internal interface between the processor and logic for control of I/O function. The channel contains a port through which part of this control passes.

#### Local Storage Registers (LSRs)

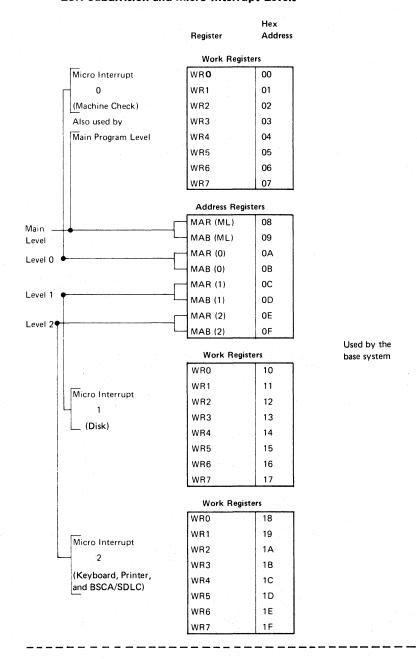

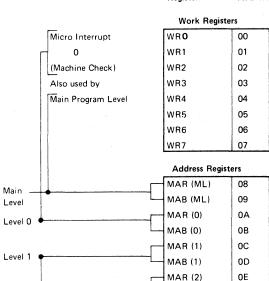

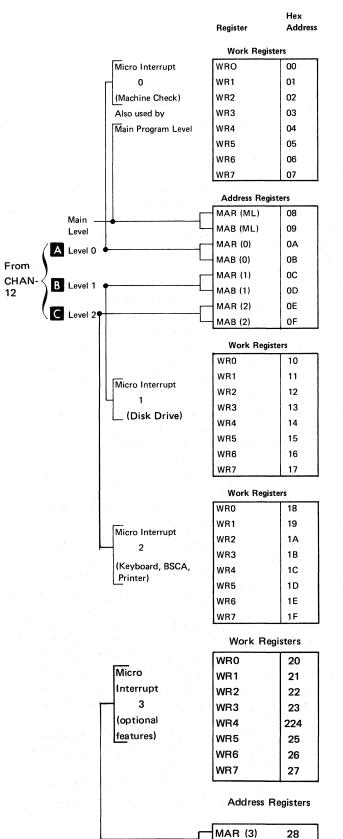

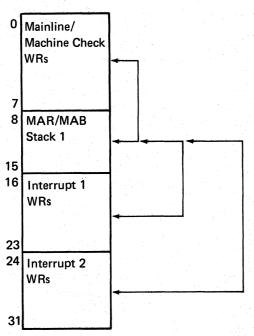

The LSR stack contains 64 LSRs; the first 32 are used by the base system and the remaining 32 are reserved for optional features. Each LSR contains 16 bits: bits 0-7 are the high LSR and bits 8-15 are the low LSR. The LSRs are called work registers (WR) and are used as data buffers and address registers for both main and control storage. In addition, the LSRs are used as operand registers for calculations and as I/O control data registers that can be loaded from or sent to the I/O attachments.

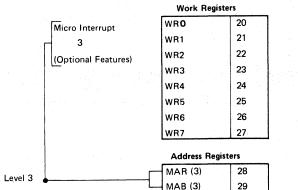

The first 32 LSRs are subdivided into four groups. The current micro interrupt level determines which group is used. The first group (hex address 00-07) is used by micro interrupt level 0 (machine check interrupt) and also by the main program level. The second group of LSRs (hex address 08-0F) contains the MAR/MAB (microprogram address register/microprogram address backup) stack. MAR contains the address of the next micro instruction to be executed. MAB contains the return address when a branch and link instruction is executed. The third group (hex address 10-17) is used by micro interrupt level 1 (disk drive), and the fourth group (hex address 18-1F) is used by micro interrupt level 2 (printer, BSCA, and keyboard).

Optional features use the remaining 32 LSRs. The first group (hex address 20-27) is used by micro interrupt level 3 as work registers. The second group (hex address 28-2F) contains the MAR/MAB for micro interrupt level 3 (hex address 28-29).

#### Micro Interrupts

The CPU handles micro instructions one at a time; one micro instruction is followed by the next sequential micro instruction. This sequence of execution of micro instructions can be changed by a branch instruction. This sequence can also be changed if the main level of processing or a micro interrupt level is interrupted by a higher micro interrupt level.

The system has six levels of micro interrupts, only level 0, level 1, level 2, and level 3 are used (levels 4 and 5 are reserved). Level 0 has the highest priority and level 3 the lowest micro interrupt priority. The display screen and 33FD cannot cause micro interrupts. Interrupts having a higher priority take precedence over those having a lower priority. For example, a micro interrupt on level 0 will interrupt the processing of a level 1, 2, or 3 micro interrupt.

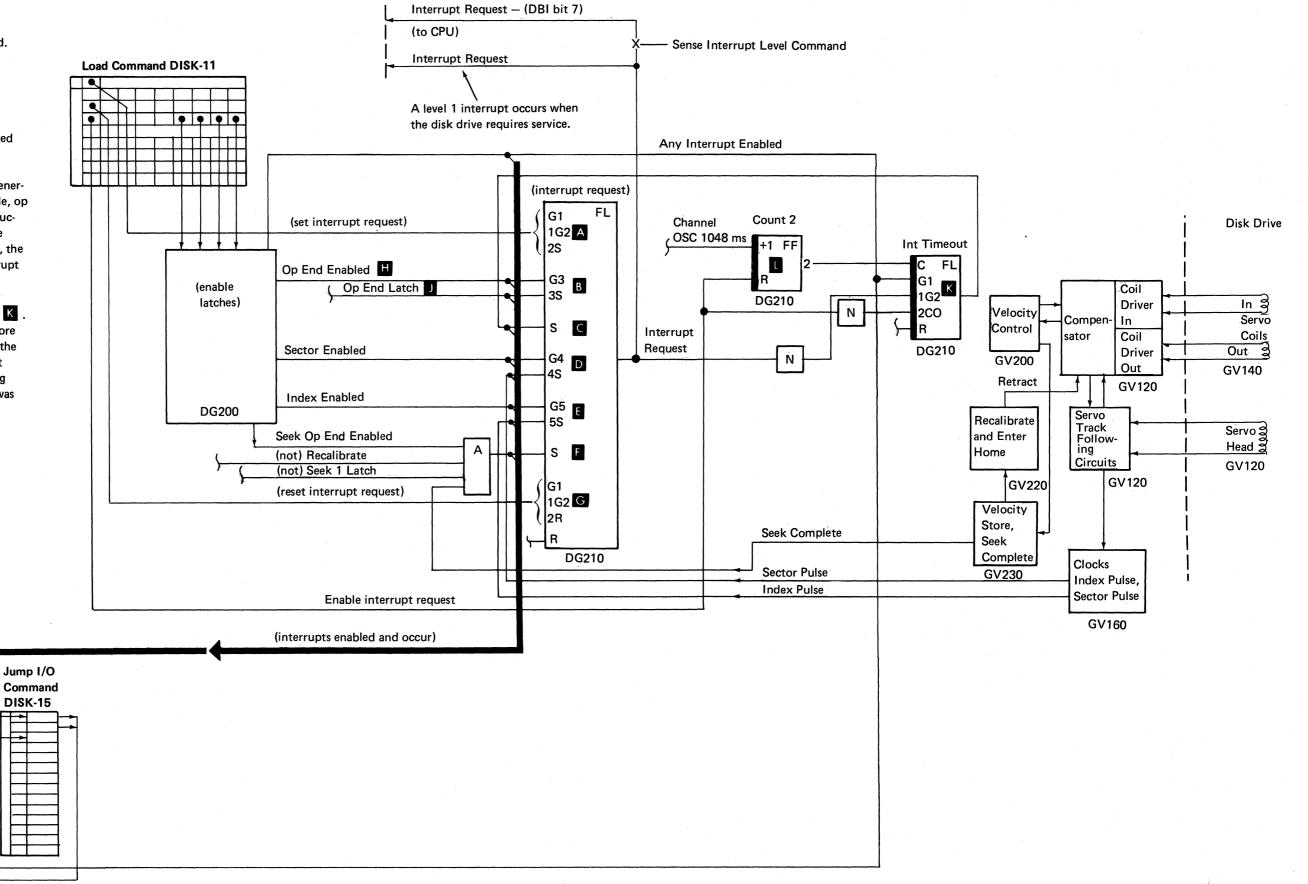

A machine check interrupt occurs whenever the system detects a CPU parity check, invalid address, or microprogram check. This micro interrupt can also be initiated by a port check. These checks are described on page CNSL-6. A level 1 interrupt occurs whenever the disk drive requires attention. The printer, BSCA, and keyboard operate on interrupt level 2. BSCA has highest priority, printer second, and the keyboard last.

Level 0, machine check interrupt, shares a set of work registers with the main level microroutines. Micro interrupt levels 1, 2, and 3 have a unique set of registers in the LSR stack. The set of LSRs for each micro interrupt level consists of:

- 8 16-bit work registers.

- 1 MAR (microprogram address register) used to store the address of the current micro instruction.

- 1 MAB (microprogram address backup) used to store the return address when a branch and link instruction is executed.

INTR-4

#### LSR Subdivision and Micro Interrupt Levels

Used by optional features

#### **System Checking and Parity Generation**

Various errors that occur in the system are recorded in the CPU error byte and in the port check byte. These errors can be displayed on the CE panel and are described on CNSL-6.

Odd parity (by byte) is maintained in the CPU data flow. To ensure correct parity, parity checking stations and parity generating stations are provided throughout the CPU.

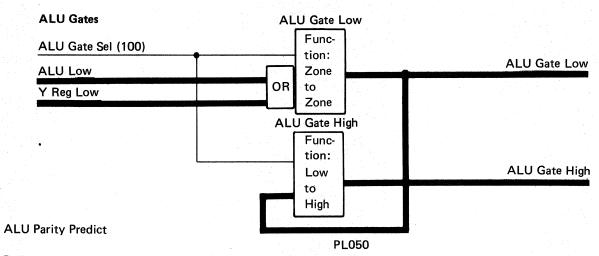

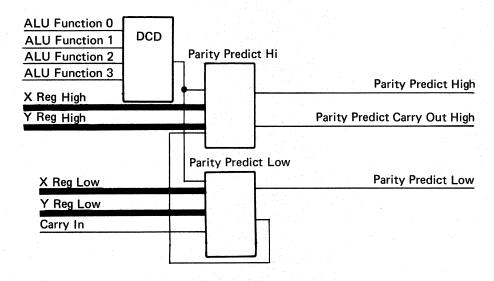

Parity predict circuits are used as a check on the ALU portion of the CPU. By analyzing the operation being performed and the input data, parity predict circuits predict whether the output of ALU will require a P-bit, and then generate the P-bit if required. The parity of the output of the ALU is compared to the output of the parity predict circuits to determine whether the ALU is working correctly.

Parity errors may be detected between the port and the CPU, or the port and an I/O attachment. Normally, the port operates in odd parity, however, some diagnostic programs use even parity.

#### Parity Checking and Generation in the CPU

|                             | IOCL | iocs                                        | Interrupt<br>Level Status | Steal In        | Steal Out                |

|-----------------------------|------|---------------------------------------------|---------------------------|-----------------|--------------------------|

| Channel                     | PG   | PC                                          | No PC, PG<br>in Channel   | PC              | PC from CPU<br>PG to DBO |

| Display                     | PC   | PG                                          | <u> </u>                  | N/A             | N/A                      |

| Keyboard                    | PC   | PG                                          |                           | N/A             | N/A                      |

| Printer<br>(Belt or Serial) | PC   | 1                                           |                           | N/A             | N/A                      |

| 33FD                        | PC   | PG on Data<br>Transfer<br>Only <sup>1</sup> |                           | PG <sup>2</sup> | N/A                      |

| Disk                        | PC   | PG on Data<br>Transfer<br>Only <sup>1</sup> |                           | PG              | PC                       |

| BSCA                        | PC   | PG                                          | _                         | N/A             | N/A                      |

PC - Parity Checked

Note: Attachments generate a parity bit on the DBI when responding to a jump I/O command whether or not the condition true response (CBI 4) is met.

PG - Parity Generated

<sup>&</sup>lt;sup>1</sup>Attachment activates CBI 4 line to CPU, which denotes that parity is not generated on DBI for transfers to the channel.

<sup>&</sup>lt;sup>2</sup>33FD cycle steals on IMPL only.

#### **Retry and Error Logging**

If errors occur during some operations, the operation is retried. Operations that cause errors while the emulator is analyzing system instructions and some operations that cause errors during the execution of the system instructions are retried at the system level.