# 64K-BIT READ-ONLY MEMORY

# MK36000(P/J/N)-4/5

#### **FEATURES**

- ☐ MK36000 8K x 8 Organization— "Edge Activated" \* operation (CE)

- □ Access Time/Cycle Time

| P/N       | Access | Cycle |

|-----------|--------|-------|

| MK36000-4 | 250ns  | 375ns |

| MK36000-5 | 300ns  | 450ns |

- ☐ Single +5V ± 10% Power Supply

- Standard 24 pin DIP (EPROM Pin Out Compatible)

### DESCRIPTION

The MK36000 is a new generation N-channel silicon gate MOS Read Only Memory, organized as 8192 words by 8 bits. As a state-of-the-art device, the MK 36000 incorporates advanced circuit techniques designed to provide maximum circuit density and reliability with the highest possible performance, while maintaining low power dissipation and wide operating margins.

The MK36000 utilizes what is fast becoming an industry standard method of device operation. Use of a static storage cell with clocked control periphery allows the circuit to be put into an automatic low power standby mode. This is accomplished by maintaining the chip enable (CE) input at a TTL high level. In this mode, power dissipation is reduced to typically 45mW, as compared to unclocked devices which

- Low Power Dissipation 220mW Max Active

- □ Low Standby Power Dissipation-45mWMax. (CE High)

- On chip latches for addresses

- ☐ Inputs and three-state outputs-TTL compatible

- Outputs drive 2 TTL loads and 100 pF

draw full power continuously. In system operation, a device is selected by the  $\overline{CE}$  input, while all others are in a low power mode, reducing the overall system power. Lower power means reduced power supply cost, less heat to dissipate and an increase in device and system reliability.

The edge activated chip enable also means greater system flexibility and an increase in system speed. The MK36000 features onboard address latches controlled by the  $\overline{\text{CE}}$  input. Once the address hold time specification has been met, new address data can be applied in anticipation of the next cycle. Outputs can be wire- 'OR'ed together, and a specific device can be selected by utilizing the  $\overline{\text{CE}}$  input with no bus conflict on the outputs. The  $\overline{\text{CE}}$  input allows the fastest access times yet available in 5 volt only

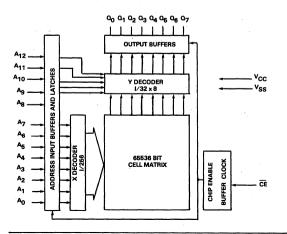

#### **FUNCTIONAL DIAGRAM (MK36000)**

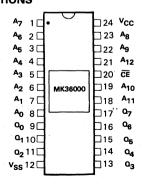

## PIN CONNECTIONS

#### **PIN NAMES**

| A <sub>0</sub> -A <sub>12</sub> | Address |

|---------------------------------|---------|

| $Q_0$ - $Q_7$                   | Outputs |

| Vcc                             | +5V     |

V<sub>SS</sub> GND CE Chip Enable

<sup>\*</sup> Trademark of Mostek Corporation

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Any Terminal Relative to VSS        | 1.0V to +7V    |

|------------------------------------------------|----------------|

| Operating Temperature T <sub>A</sub> (Ambient) | 0°C to +70°C   |

| Storage Temperature - Ceramic (Ambient)        |                |

| Storage Temperature - Plastic (Ambient)        | 55°C to +125°C |

| Power Dissipation                              |                |

<sup>\*</sup>Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operating sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# RECOMMENDED DC OPERATING CONDITIONS<sup>6</sup> $(0^{\circ}C \leq T_{A} \leq + 70^{\circ}C)$

| SYM             | PARAMETER             | MIN  | TYP | MAX | UNITS | NOTES |

|-----------------|-----------------------|------|-----|-----|-------|-------|

| V <sub>CC</sub> | Power Supply Voltage  | 4.5  | 5.0 | 5.5 | Volts | 6     |

| VIL             | Input Logic 0 Voltage | -1.0 |     | 0.8 | Volts |       |

| Viu             | Input Logic 1 Voltage | 2.0  |     | Vcc | Volts |       |

# D C ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 5V $\pm$ 10%) (0 °C $\leq$ T<sub>A</sub> $\leq$ + 70 °C)<sup>6</sup>

| SYM   | PARAMETER                                                | MIN | TYP | MAX | UNITS | NOTES |

|-------|----------------------------------------------------------|-----|-----|-----|-------|-------|

| ICC1  | VCC Power Supply Current (Active)                        |     |     | 40  | mA    | 1     |

| ICC2  | VCC Power Supply Current (Standby)                       |     |     | 8   | - mA  | 7     |

| II(L) | Input Leakage Current                                    | -10 |     | 10  | μΑ    | 2     |

| IO(L) | Output Leakage Current                                   | -10 |     | 10  | μΑ    | 3     |

| VOL   | Output Logic "O" Voltage<br>@ IOUT = 3.3mA               |     |     | 0.4 | volts |       |

| Vон   | Output Logic "1" Voltage<br>@ I <sub>OUT</sub> = -220 μA | 2.4 |     |     | volts |       |

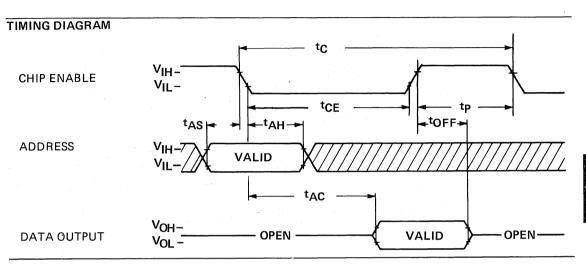

### A C ELECTRICAL CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%) (0^{\circ}C \le T_{A} \le +70^{\circ}C)^{6}$

| SYM  | DADAMETED                           | -4  |       | -5  |         | LINUTC | NOTES |

|------|-------------------------------------|-----|-------|-----|---------|--------|-------|

|      | PARAMETER                           |     | MAX   | MIN | MIN MAX |        |       |

| tC   | Cycle Time                          | 375 |       | 450 |         | ns     | 4     |

| tCE  | CE Pulse Width                      | 250 | 10000 | 300 | 10000   | ns     | 4     |

| tAC  | CE Access Time                      |     | 250   |     | 300     | ns     | 4     |

| tOFF | Output Turn Off Delay               |     | 60    |     | 75      | ns     | 4     |

| tAH  | Address Hold Time Referenced to CE  | 60  |       | 75  |         | ns     |       |

| tAS  | Address Setup Time Referenced to CE | 0   |       | 0   |         | ns     |       |

| tp   | CE Precharge Time                   | 125 |       | 150 |         | ns     |       |

#### NOTES:

- Current is proportional to cycle rate. I<sub>CCI</sub> is measured at the specified minimum cycle time. Data Outputs open.

- 2.  $V_{1N} = 0V$  to 5.5V ( $V_{cc} = 5V$ )

- 3. Device unselected; VOUT = 0V to 5.5V

- 4. Measured with 2 TTL loads and 100pF, transistion times = 20ns

- Capacitance measured with Boonton Meter or effective capacitance calculated from the equation:

- $C = \frac{\triangle O}{\triangle V} \text{ with } \triangle V = 3 \text{ volts}$

- A minimum 2msec time delay is required after the application of V<sub>CC</sub> (+5) before proper device operation is achieved. CE must be at VIH for this time period.

- 7. CE high.

# **CAPACITANCE**

$(0^{\circ}C \leq T_{\Delta} \leq 70^{\circ}C)$

| SYM | PARAMETER          | TYP | MAX | UNITS | NOTES |

|-----|--------------------|-----|-----|-------|-------|

| Cl  | Input Capacitance  | 5   | 8   | pF    | 5     |

| CO  | Output Capacitance | 7   | 15  | pF    | 5     |

### **DESCRIPTION** (Continued)

ROM's and imposes no loss in system operating flexibility over an unclocked device.

Other system oriented features include fully TTL compatible inputs and outputs. The three state outputs, controlled by the  $\overline{\text{CE}}$  input, will drive a minimum of 2 standard TTL loads. The MK36000 operates from a single +5 volt power supply with a wide  $\pm$  10% tolerance, providing the widest operating margins available. The MK36000 is packaged in the industry standard 24 pin DIP.

Any application requiring a high performance, high bit density ROM can be satisfied by the MK36000 ROM. This device is ideally suited for 8 bit microprocessor systems such as those which utilize the Z-80. It can offer significant cost advantages over PROM.

#### **OPERATION**

The MK36000 is controlled by the chip enable ( $\overline{CE}$ ) input. A negative going edge at the  $\overline{CE}$  input will

activate the device as well as strobe and latch the inputs into the onchip address registers. At access time the outputs will become active and contain the data read from the selected location. The outputs will remain latched and active until  $\overline{CE}$  is returned to the inactive state.

## **Programming Data**

MOSTEK is now able to utilize a wide spectrum of data input formats and media. Those presently available are listed in the following table:

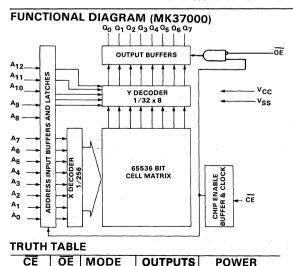

# 64K-BIT MOS READ-ONLY MEMORY

# MK37000 (P/J/N)-5

#### **FEATURES**

- ☐ Organization: 8K x 8 Bit ROM JEDEC Pinout

- □ Pin compatible with Mostek's BYTEWYDE™ Memory Family

- □ Access Time/Cycle Time

| P/N       | ACCESS | CYCLE |  |

|-----------|--------|-------|--|

| MK37000-5 | 300ns  | 450ns |  |

- ☐ Mask ROM replacement for MK2764 EPROM

- □ No Connections allow easy upgrade to future generation higher density ROMs

- □ Low power dissipation: 220mW max active, 45mW max standby

- ☐ CE and OE functions facilitate Bus control

#### DESCRIPTION

The MK37000 is a N-channel silicon gate MOS Read Only Memory, organized as 8192 words by 8 bits. As a state-of-the-art device, the MK37000 incorporates advanced circuit techniques designed to provide maximum circuit density and reliability with the highest possible performance, while maintaining low power dissipation and wide operating margins. The MK37000 is to be used as a pin/function compatible mask programmable alternative to the MK2764 8K x 8 bit EPROM. As a member of the Mostek BYTEWYDE

Memory Family, the MK37000 brings to the memory market a new era of ROM, PROM and EPROM compatibility previously unavailable.

Use of clocked control periphery and a standard static ROM cell makes the MK37000 the lowest power 64K ROM available. Active power is a mere 220mW while standby ( $\overline{\text{CE}}$  high) is only 45mW. To provide greater system flexibility an output enable ( $\overline{\text{OE}}$ ) function has been added using one of the extra pins available on the

|                            |    |      | and the second second     |          |

|----------------------------|----|------|---------------------------|----------|

| NC 1□                      | •  | 7    | □28 v <sub>cc</sub>       |          |

| A <sub>12</sub> 2          |    | 100  | □27 NC                    |          |

| A <sub>7</sub> 3 □         |    |      | □26 NC                    |          |

| <b>A</b> <sub>6</sub> 4 □  |    |      | □25 A <sub>8</sub>        |          |

| <b>A</b> <sub>5</sub> 5□   |    |      | □24 Ag                    |          |

| <b>A</b> <sub>4</sub> 6 □  | 11 |      | □23 A <sub>11</sub>       |          |

| A <sub>3</sub> 7□          |    |      | □22 <b>O</b> E            |          |

| A <sub>2</sub> 8□          |    |      | □21 A <sub>10</sub>       |          |

| A <sub>1</sub> 9□          |    |      | □20 <b>CE</b>             |          |

| A <sub>0</sub> 10 □        |    |      | ⊒19 <b>գ</b> շ            |          |

| <b>α</b> <sub>0</sub> 11 □ |    |      | ⊒18 դ <mark>6</mark>      |          |

| <b>α</b> <sub>1</sub> 12 □ |    |      | □17 <b>α</b> <sub>5</sub> |          |

| <b>a₂</b> 13 🗆             |    |      | □16 <b>0</b> 4            |          |

| • V <sub>SS</sub> 14 🗆     |    |      | □15 <b>α</b> <sub>3</sub> |          |

| PIN NAMES                  |    |      | 1                         |          |

| A0 - A12-Address           |    | NC - | No Co                     | nnection |

Chip Enable

Qn - Q7 - Outputs

ŌE -

Vcc -

$v_{SS}$  -

**Output Enable**

+5V supply Ground

PIN CONNECTIONS

X = Don't Care

CF